Patents

Literature

89results about How to "Eliminate parasitic capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

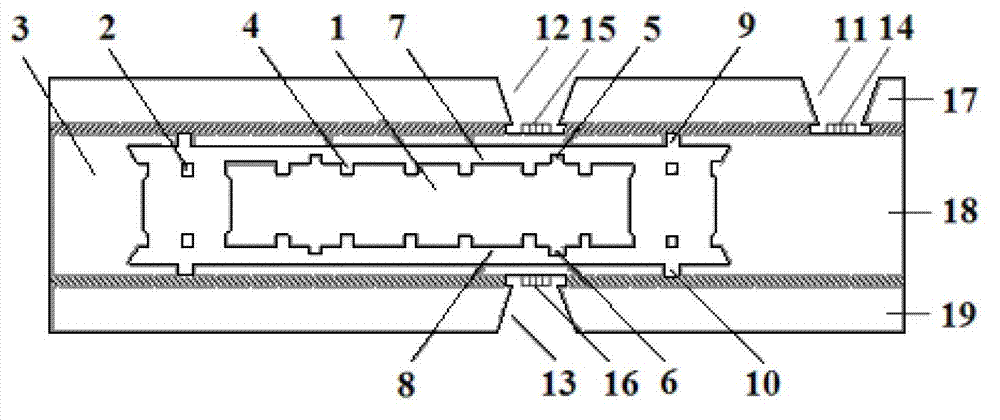

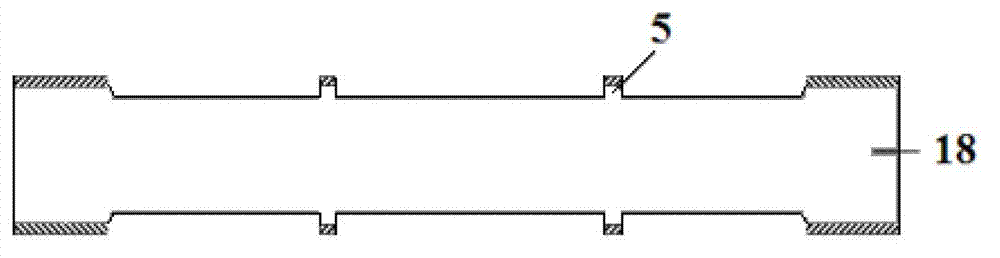

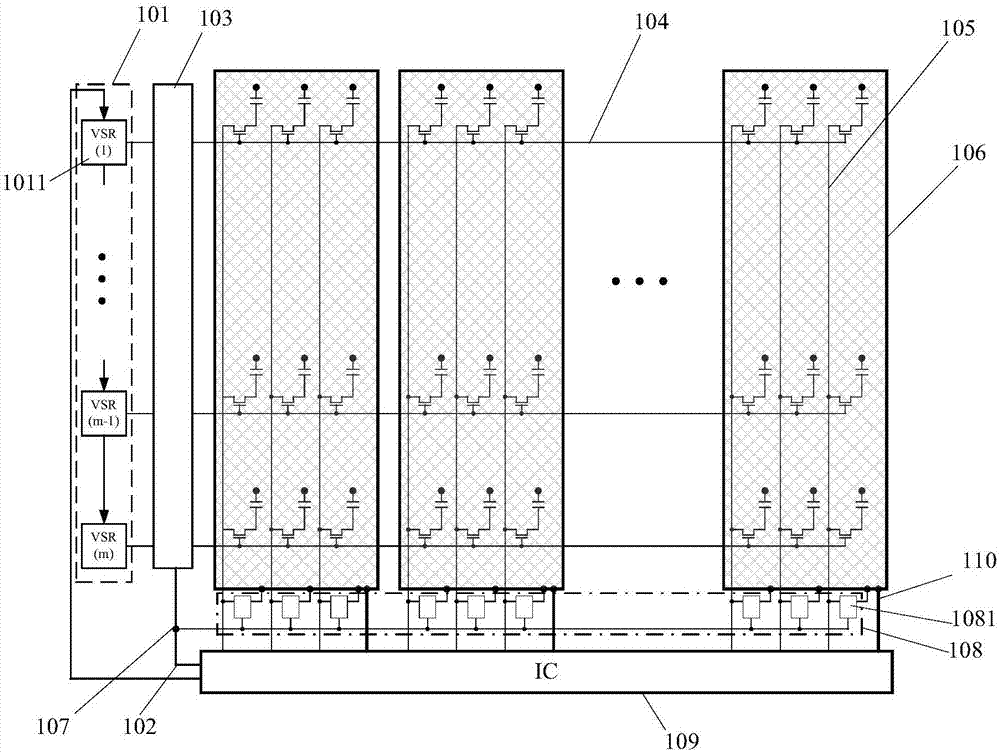

Organic electroluminescence touch control panel, driving method thereof and display device

ActiveCN104835454ARealize integrated touch functionImprove touch performanceStatic indicating devicesInput/output processes for data processingControl signalDisplay device

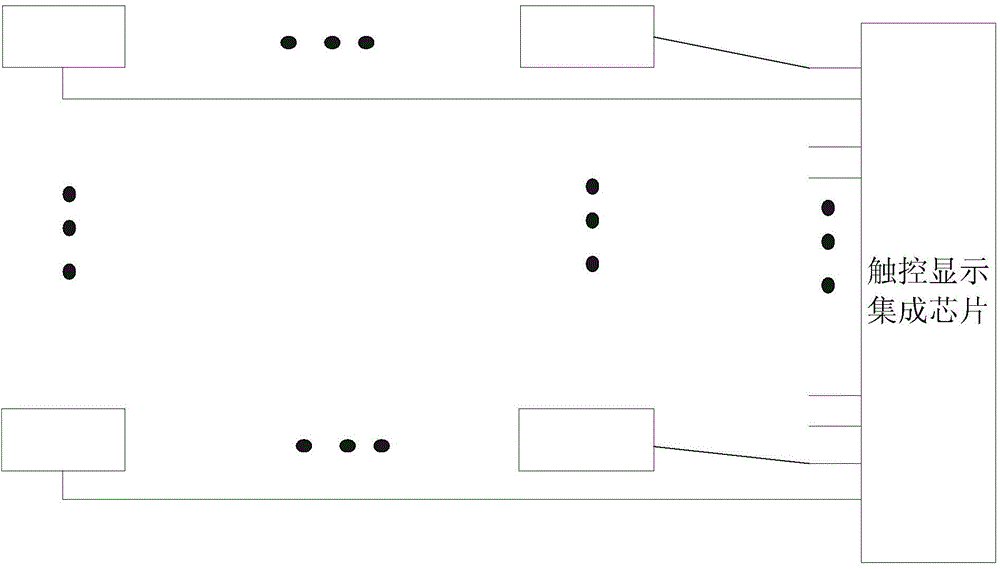

The invention discloses an organic electroluminescence touch control panel, a driving method thereof and a display device. On the basis that an original organic electroluminescence structure is not changed, a cathode layer of the organic electroluminescence structure is divided into multiple cathodes independent and insulated from each other, in the touch control stage, the cathodes serve as touch control electrodes to sense external touch control, touch control signals are transmitted to a touch control and display integrated chip via leads, and thus, the touch control function is integrated into organic electroluminescence display of a display panel; and in the reset stage, a pixel driving circuit is used to initialize a control end of a driving module; in the compensation stage, the threshold voltage of the driving module is compensated to avoid influence of the threshold voltage change of the driving module on the luminescence brightness of the organic electroluminescence structure; and in the touch control stage, signals of signal lines and external touch control signals sensed by the touch control electrodes are modulated synchronously to eliminate the parasitic capacitance of the touch control electrodes and improve the touch control performance of the touch control panel.

Owner:BOE TECH GRP CO LTD +1

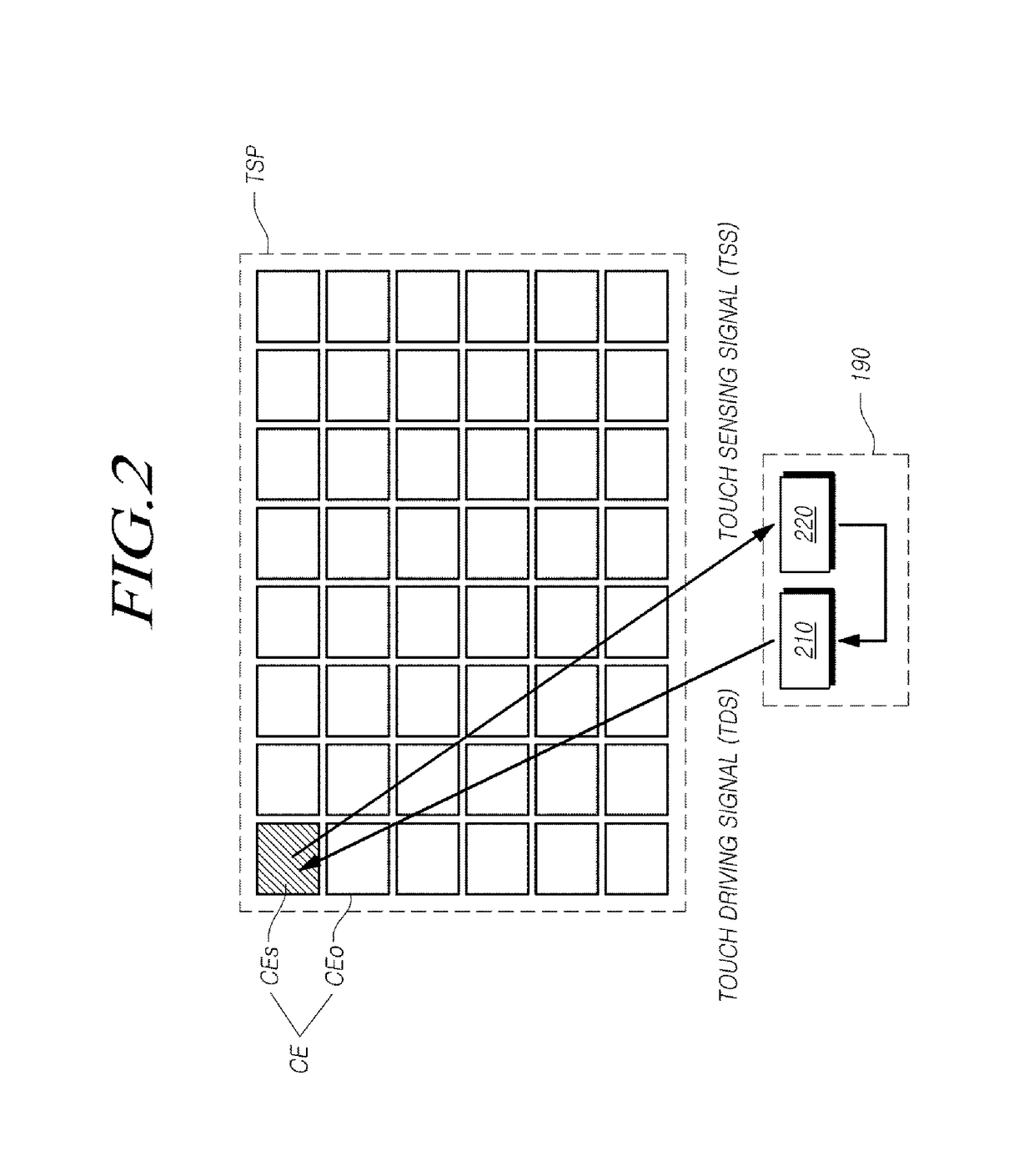

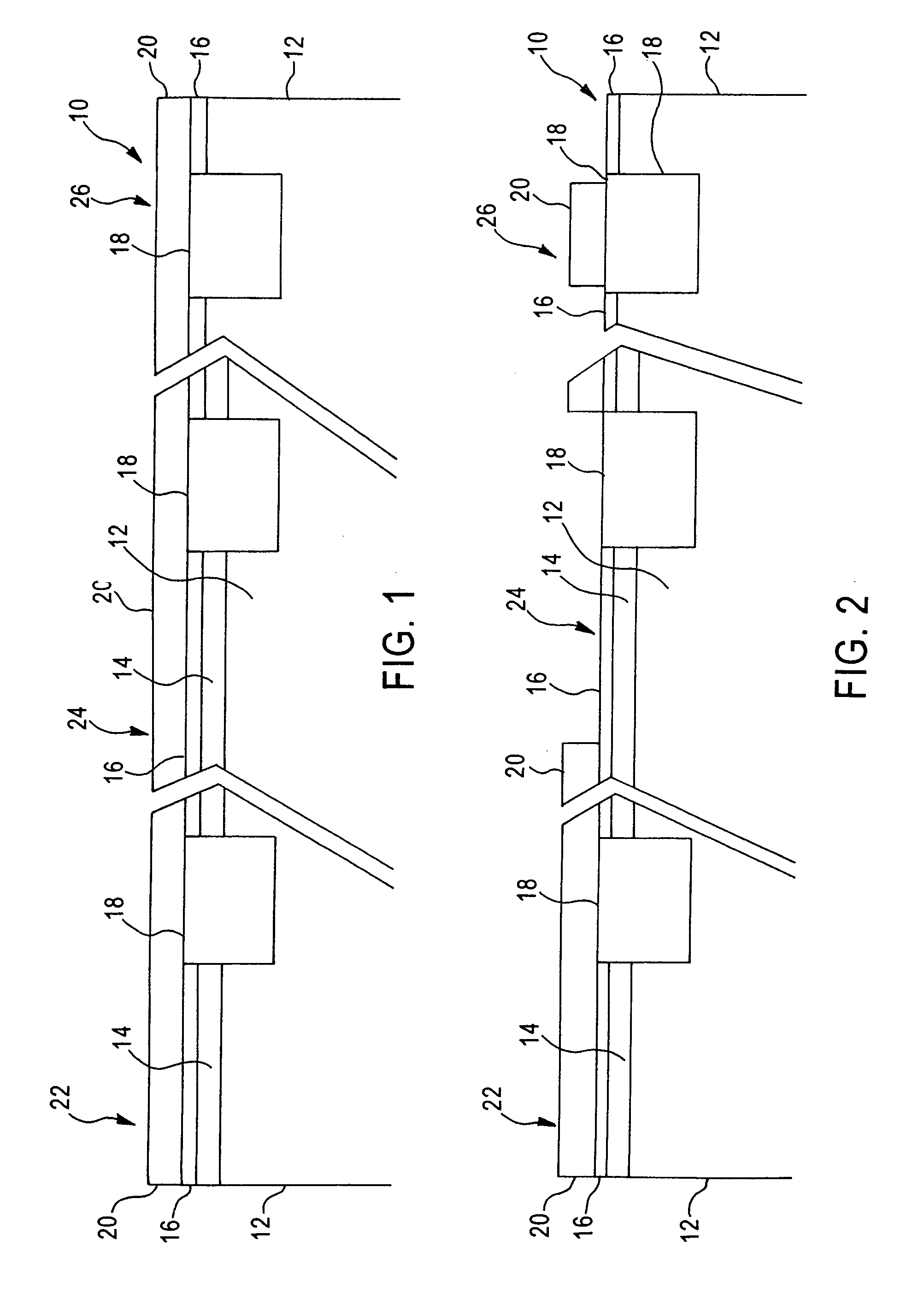

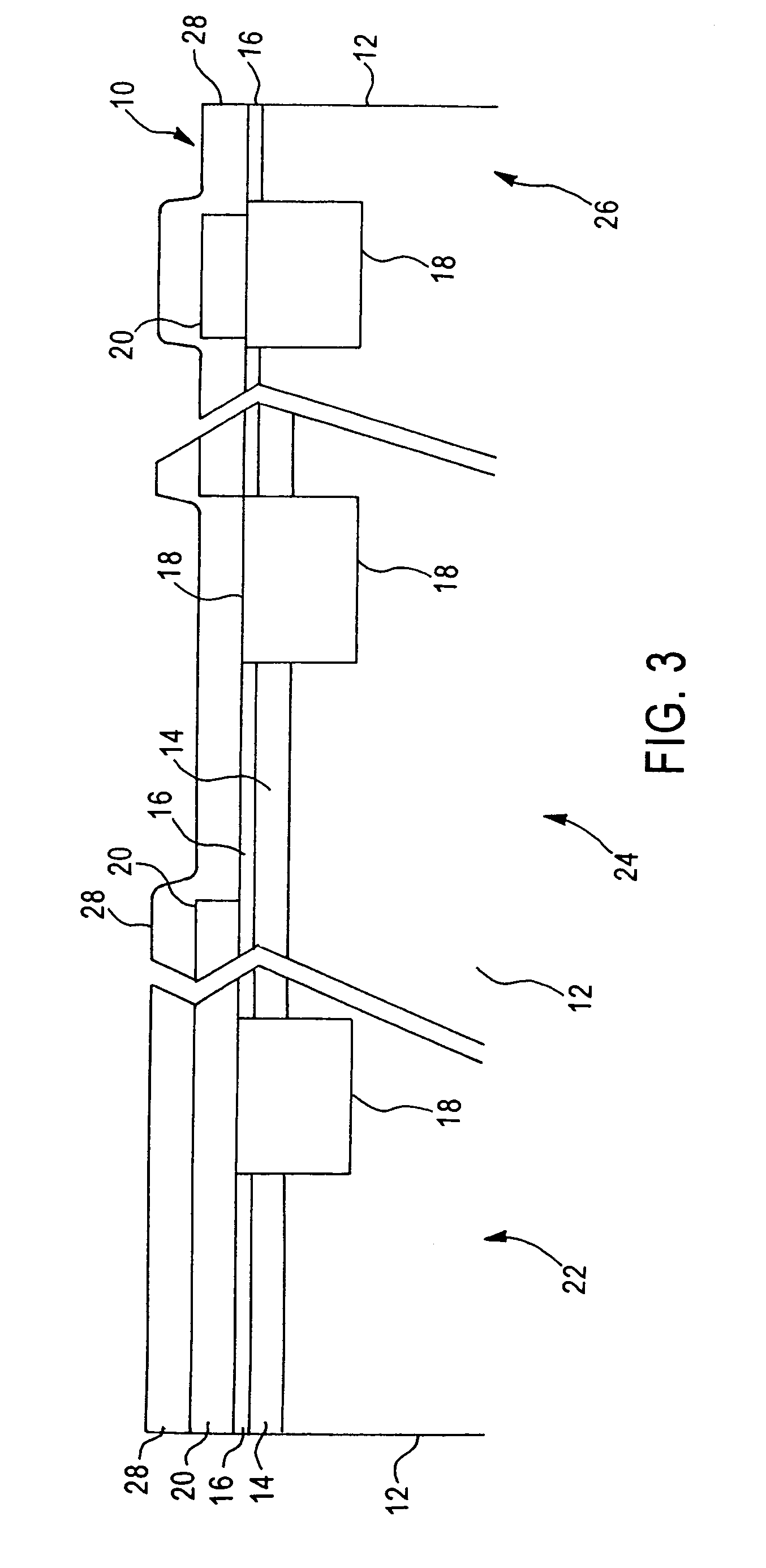

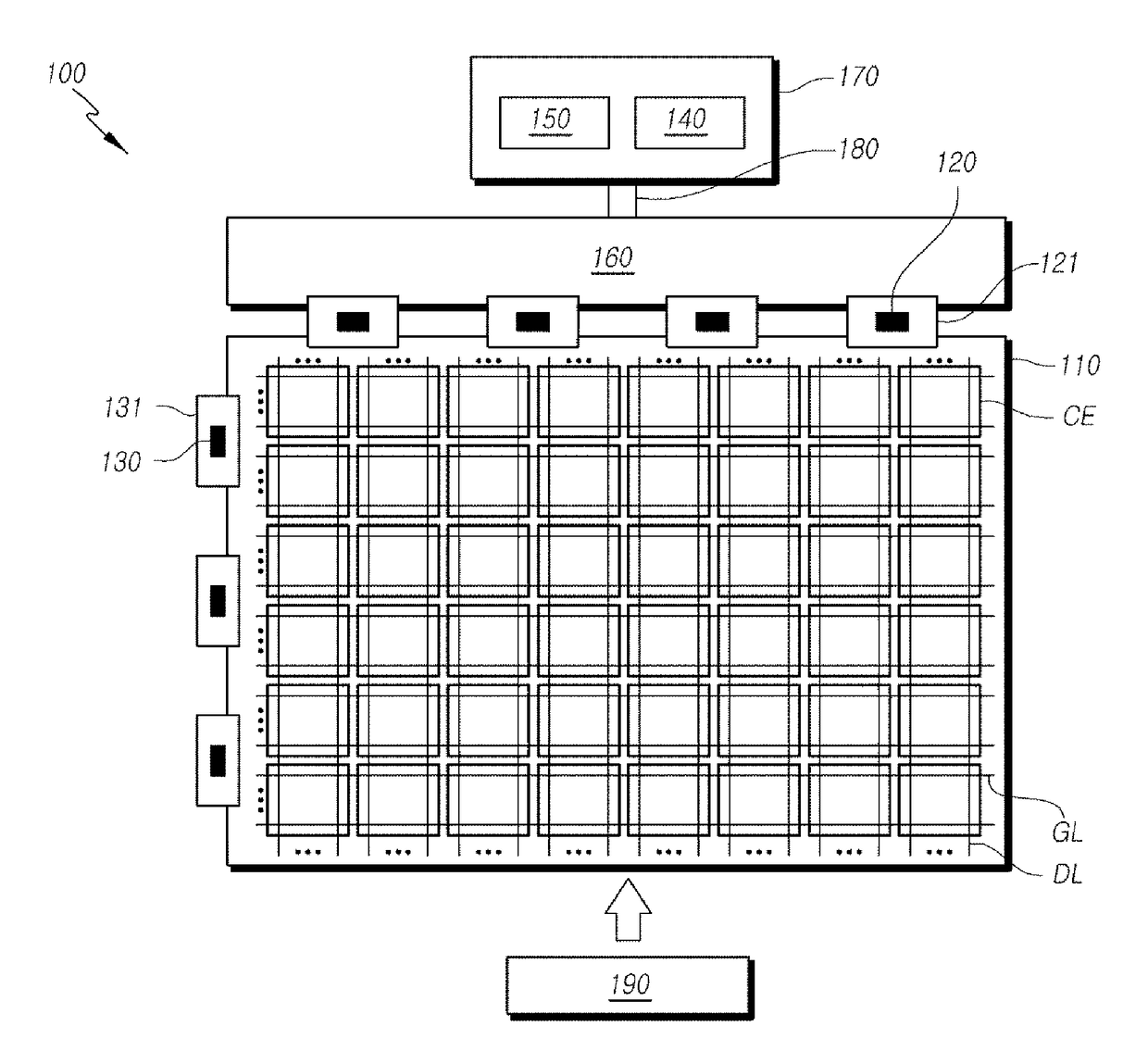

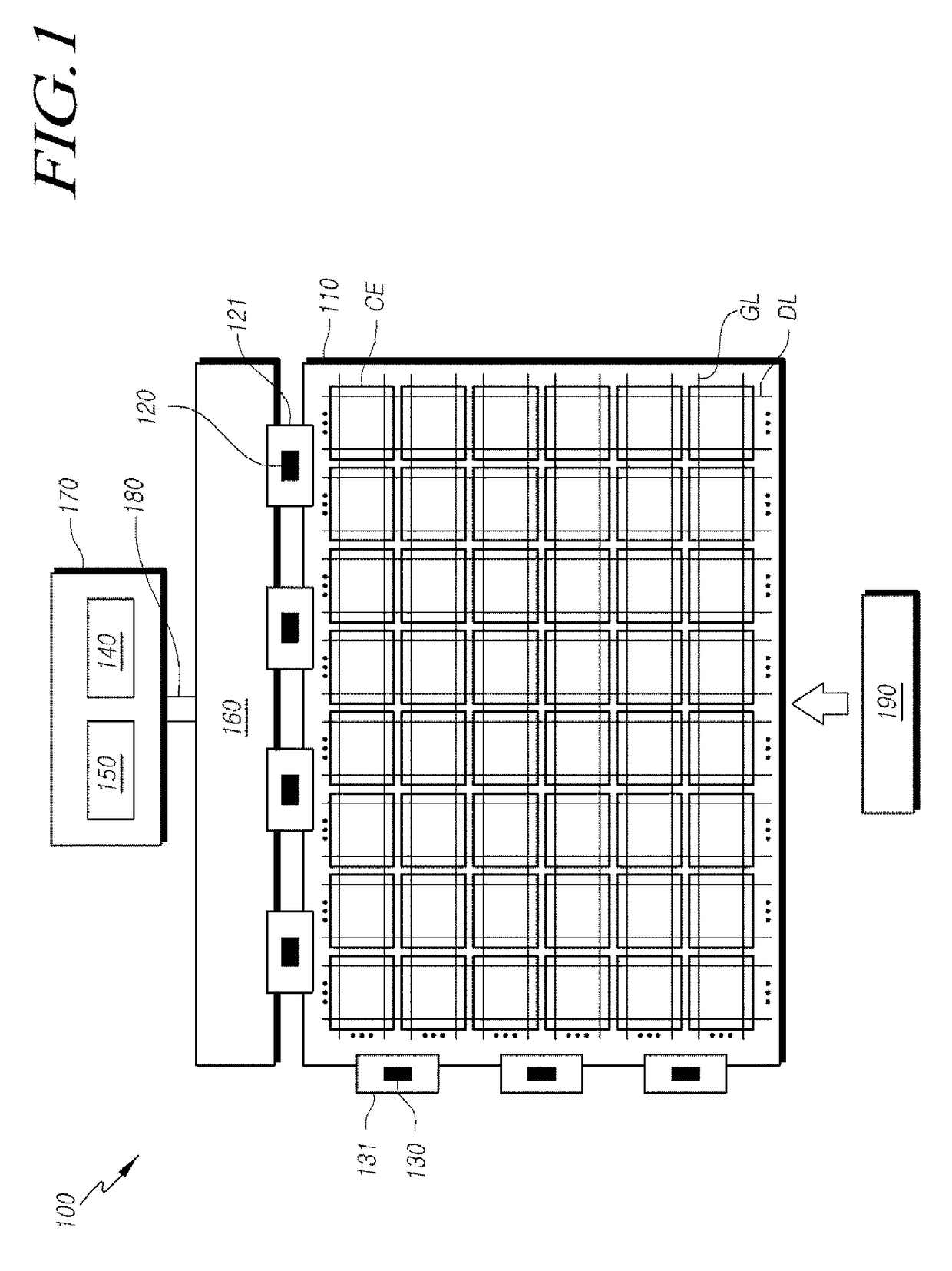

Signal Control Circuit, Power Control Circuit, Drive Circuit, Timing Controller, Touch System, and Touch Display Device and Driving Method Thereof

ActiveUS20170102825A1Eliminate parasitic capacitanceAvoid it happening againStatic indicating devicesNon-linear opticsDisplay deviceParasitic capacitance

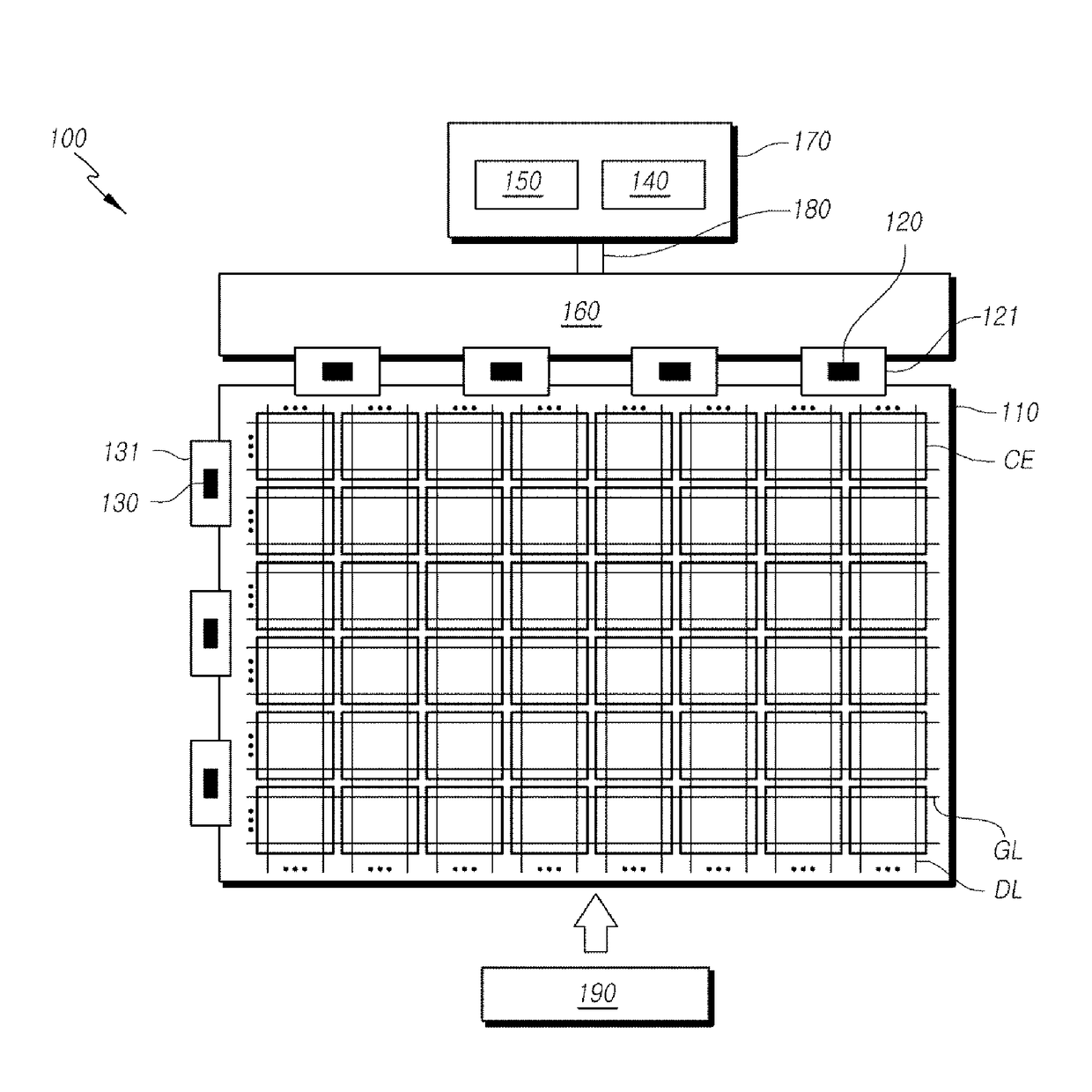

Exemplary embodiments of the present invention relate to a touch technology, and more specifically, to a signal control circuit, a power control circuit, a drive circuit, a timing controller, a touch system, and a touch sensitive display device and a driving method thereof that can simply swing various voltages in a display device for a touch mode period by using a modulated ground voltage obtained by swinging a ground voltage, thereby effectively providing touch driving and preventing unnecessary parasitic capacitance from being generated not only in an active area but also in all other areas.

Owner:LG DISPLAY CO LTD

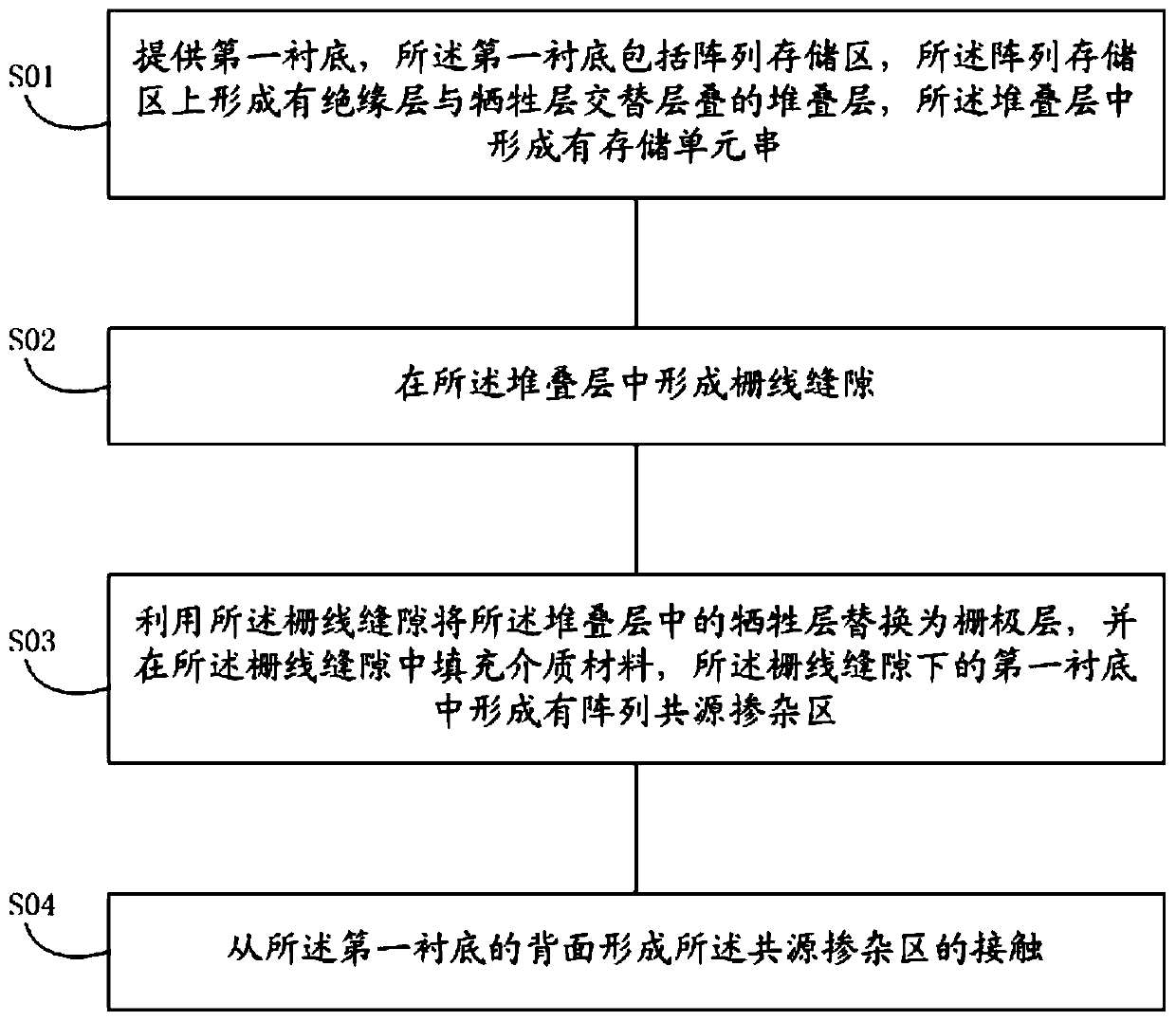

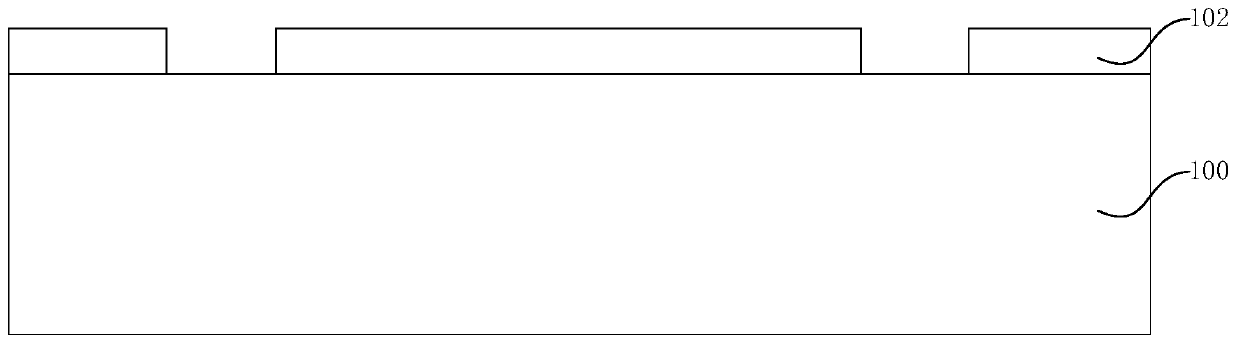

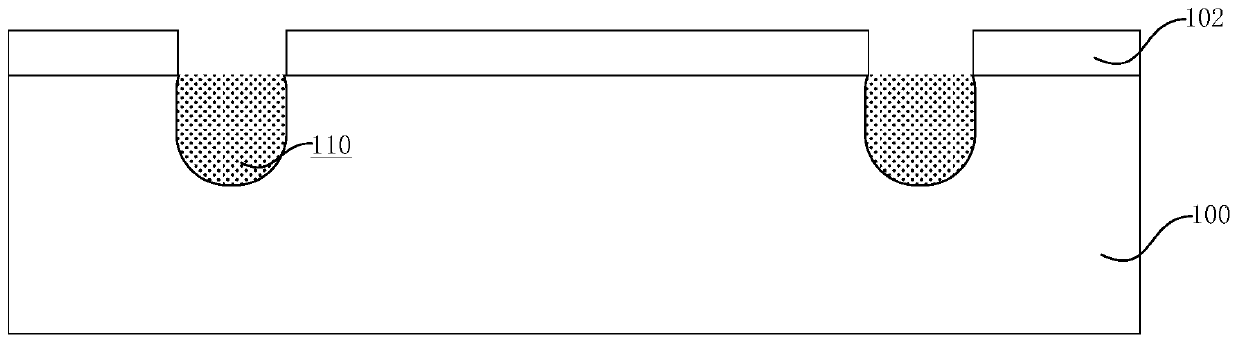

3D NAND storage device and manufacturing method thereof

PendingCN110246846AImprove performanceEliminate parasitic capacitanceSolid-state devicesSemiconductor devicesParasitic capacitorCapacitance

The invention provides a 3D NAND storage device and a manufacturing method thereof. After a stacked layer is formed, a sacrificial layer in the stacked layer is replaced with a gate layer by a gate line slit, secondly, a dielectric material is filled in the gate line slit, and an array co-source doped region is extracted from a back side of a substrate. The dielectric material is filled in the gate line slit, common source contact is formed on the back side of the substrate, a parasitic capacitor between the gate line slit and a word line is eliminated, breakdown between the word line and the common source contact is avoided, and device performance is improved.

Owner:YANGTZE MEMORY TECH CO LTD

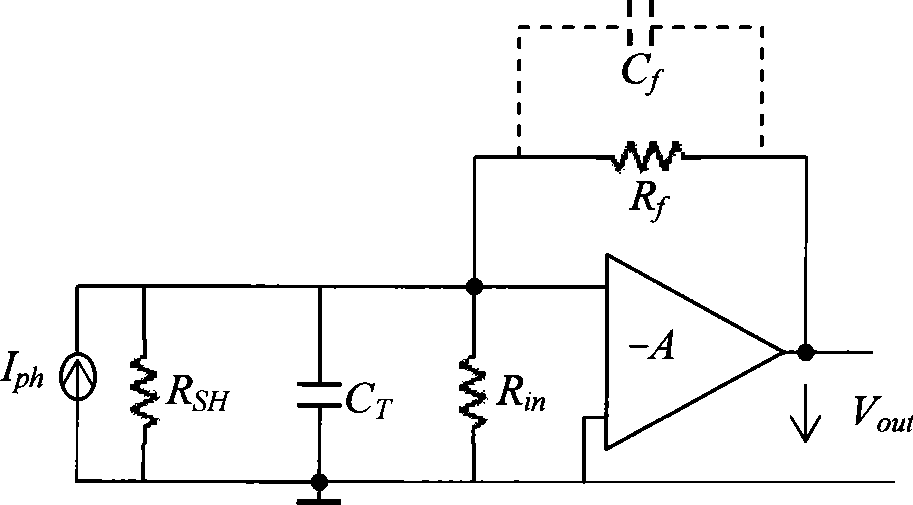

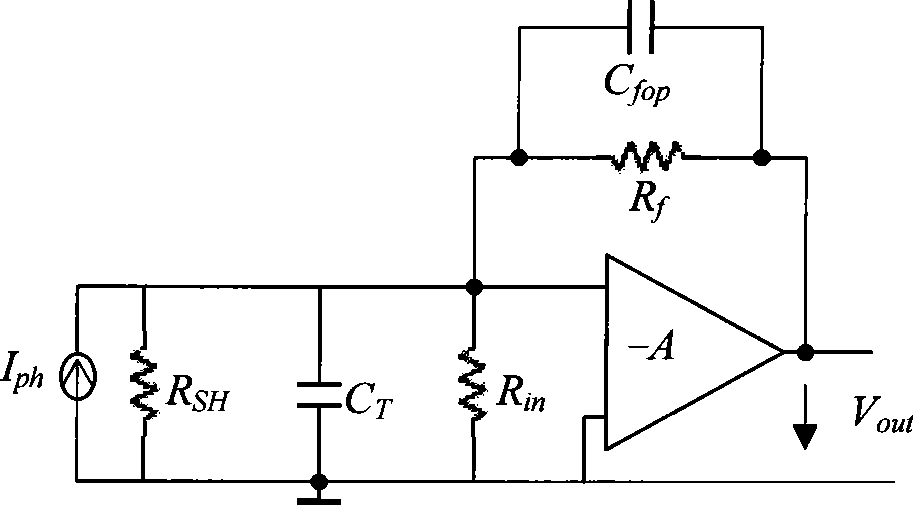

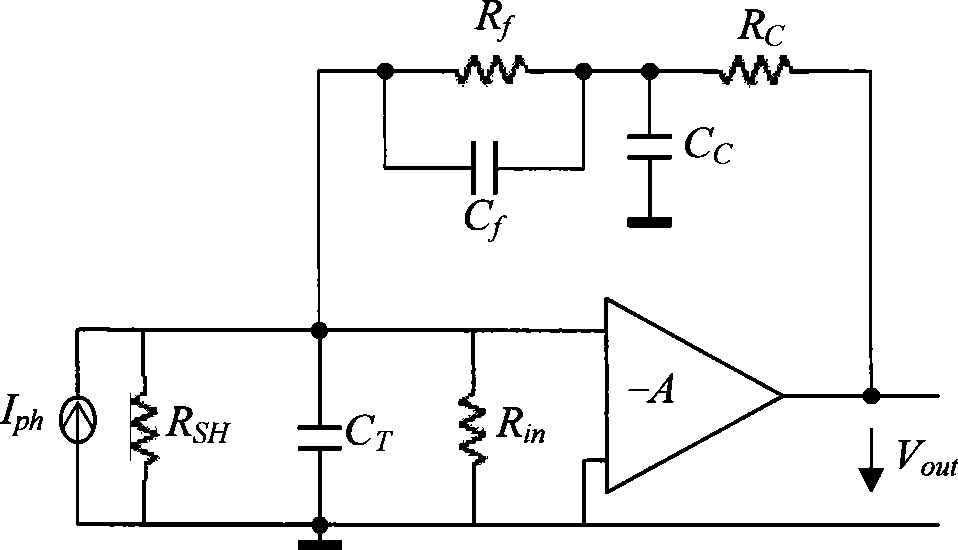

Trans-impedance amplifier with low noise and high gain-bandwidth product

ActiveCN101505140AWide signal bandwidthIncrease signal gainAmplifier modifications to reduce noise influenceAmplifiers controlled by lightCapacitanceLow noise

The invention provides an optical-receiver preamplifier for receiving analog or digital optical signals. The preamplifier comprises a high-gain amplifier A1, an input circuit, a negative-feedback impedor Zf, a low-gain amplifier A2 adjustable in gain and a feedback capacitor Cff, wherein the input circuit takes a photoelectric converter as a main component; the negative-feedback impedor Zf is connected with the reverse input end and the output end of the A1; the feedback capacitor Cff connects the output end of the A2 with the reverse input end of the A1; and the output end of the A1 can be directly connected with the input end of the A2 or can be connected with the input end of the A2 through a buffer. Output signals of the preamplifier are taken out from the output end of the A1 or the output end of the buffer, and can be directly subjected to subsequent signal processing or be further amplified and then subjected to subsequent signal processing.

Owner:CHINA ELECTRIC POWER RES INST +2

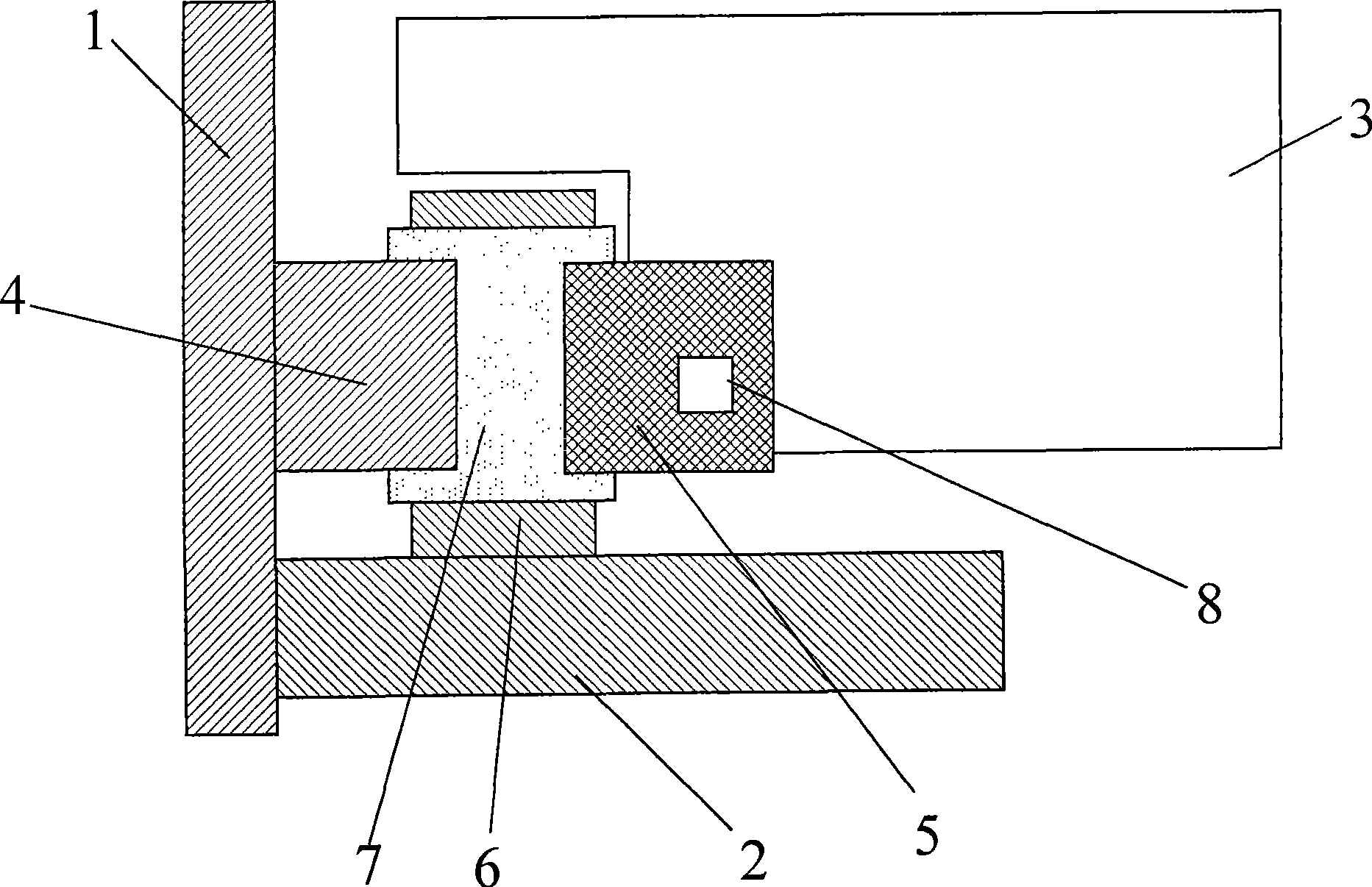

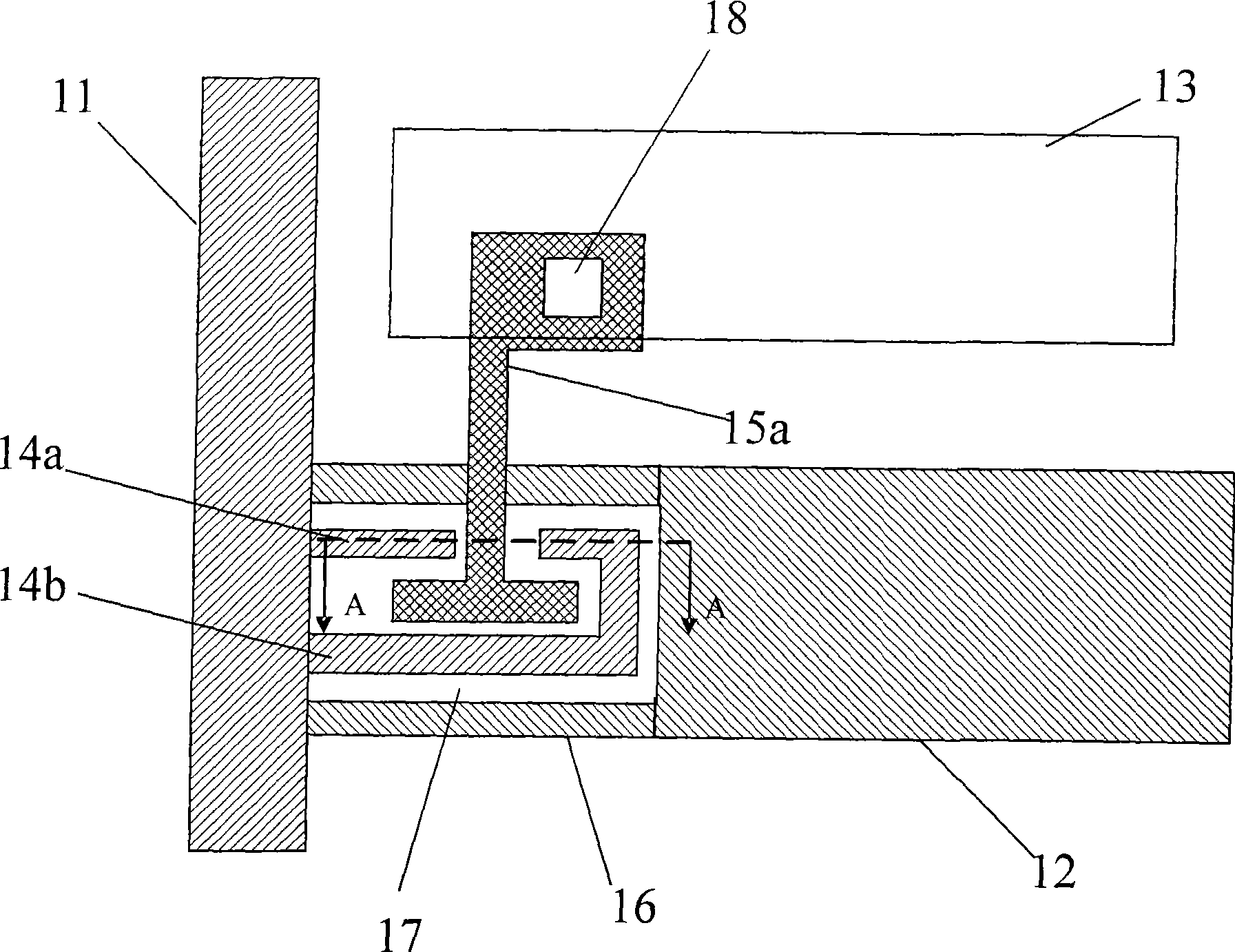

Double-surface pressing connecting through hole structure of printed-circuit board and machining method thereof

ActiveCN103458627AEliminate parasitic capacitanceImprove integrityElectrical connection printed elementsPrinted element electric connection formationTinningCopper plating

The invention discloses a double-surface pressing connecting through hole structure of a printed-circuit board and a machining method of the double-surface pressing connecting through hole structure of the printed-circuit board. The machining method comprises the following steps that a small hole A is drilled in the upper surface of a substrate in a depth-control mode; a pressing connecting hole B is drilled in the same position of the small hole A; the substrate is overturned; a small hole C is drilled in the surface opposite to the small hole A in a depth-control mode and is communicated with the small hole A; a pressing connecting hole D is drilled in the position of the small hole C; electroless copper plating, copper electroplating and tinning are carried out; a hole E is drilled in the position of the small hole A in a depth-control mode; the substrate is overturned; a hole F is drilled in the position of the small hole C in a depth-control mode; alkaline etching and tin stripping are carried out; part of a copper layer at each pressing connecting hole is thickened in a plating mode until the design requirement of a finished product is met, and finally the double-surface pressing connecting through hole structure is obtained. The double-surface pressing connecting through hole structure of the printed-circuit board and the machining method of the double-surface pressing connecting through hole structure of the printed-circuit board completely eliminate the stray capacitance among pressing connecting elements, facilitates the integrality of signal transmission and improves wire distribution density; the process is reasonable, the difficulty that plating layers of the middle small holes are eliminated in a drilling mode is largely lowered, and the diameter of the pressing connecting holes is made to be the smallest; the completeness of the plating layers on the walls of the pressing connecting holes is guaranteed, and the non-metallic middle small holes are achieved; copper wire defects in the holes are avoided.

Owner:SHANTOU ULTRASONIC PRINTED BOARD NO 2 FACTORY +1

Manufacturing method of semiconductor device and semiconductor device

InactiveUS20070221970A1Increase the number ofIncrease manufacturing costTransistorSemiconductor/solid-state device manufacturingSalicideMetal silicide

In a manufacturing process of a semiconductor device having a CMISFET, first, a silicon film and a first metal film made of a first metal are reacted with each other through heat treatment, thereby forming a gate electrode of a p-channel type MISFET and a dummy gate electrode of an n-channel type MISFET, which are formed of metal silicide. Subsequently, an insulating film is formed so as to cover the gate electrode but expose the dummy electrode, and then, a metal film formed of a second metal having a work function lower than that of the first metal. The metal film contacts with the dummy gate but not with the gate electrode due to the insulating film interposing therebetween. Thereafter, through heat treatment, the dummy gate electrode and the metal film are reacted with each other to form a gate electrode of the n-channel type MISFET.

Owner:RENESAS TECH CORP

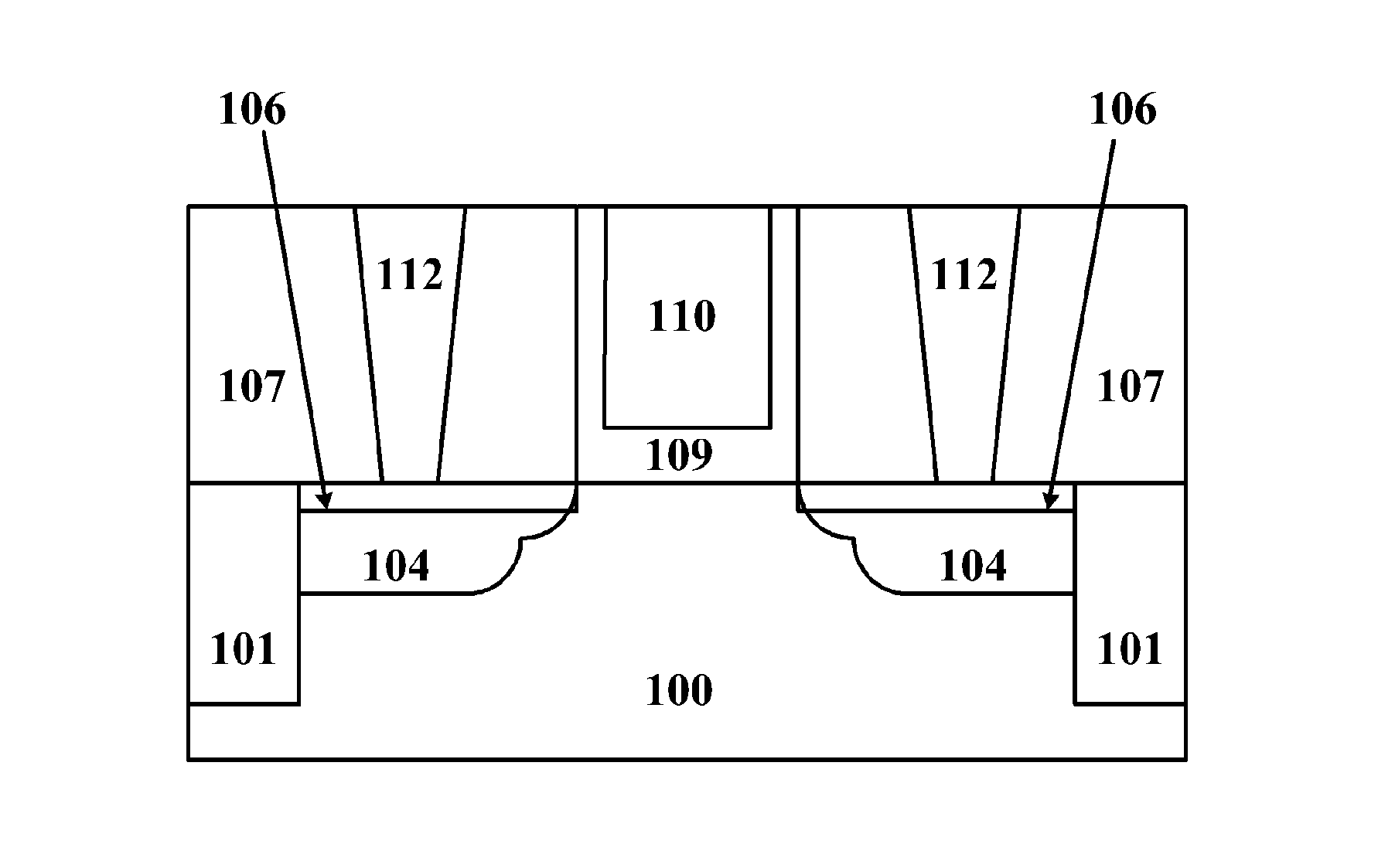

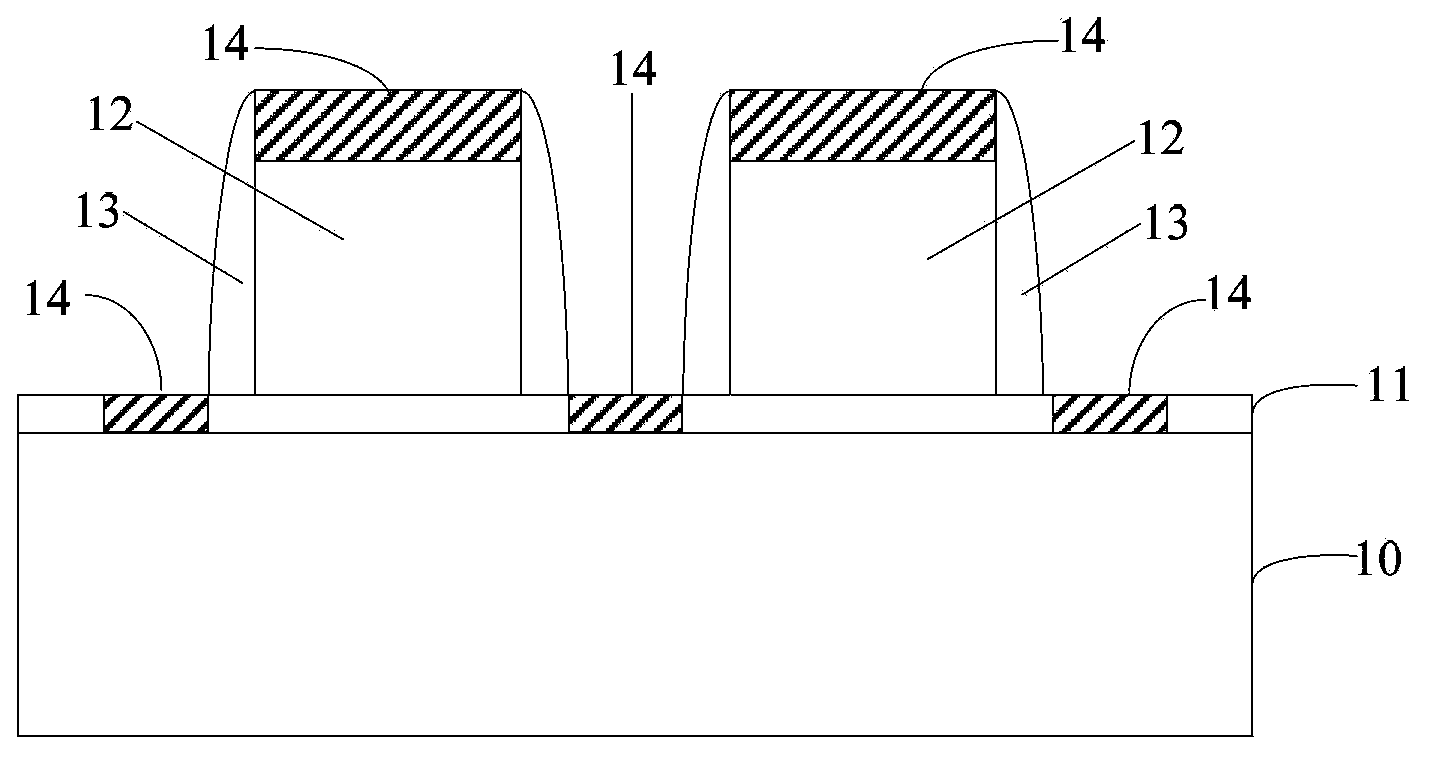

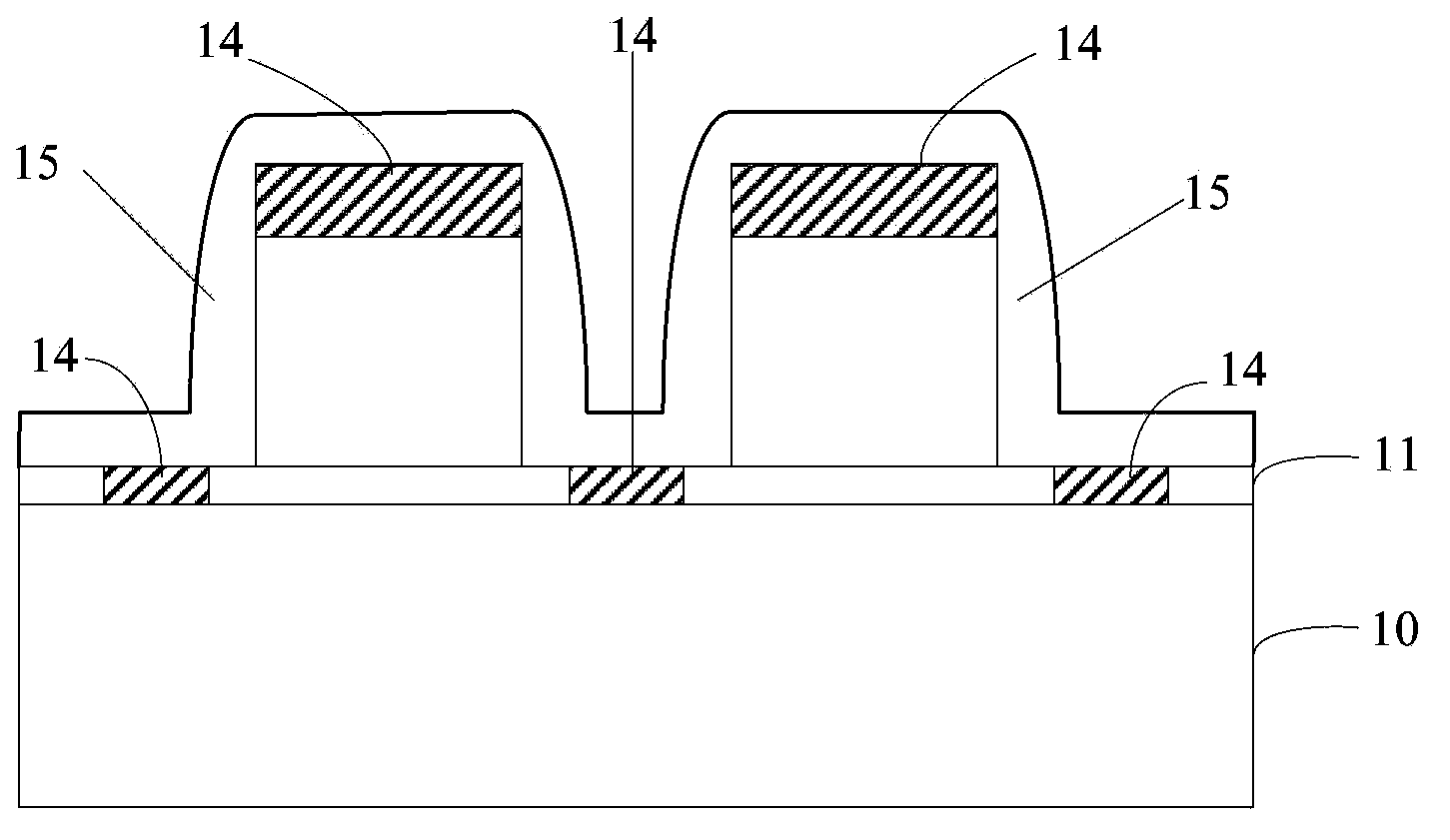

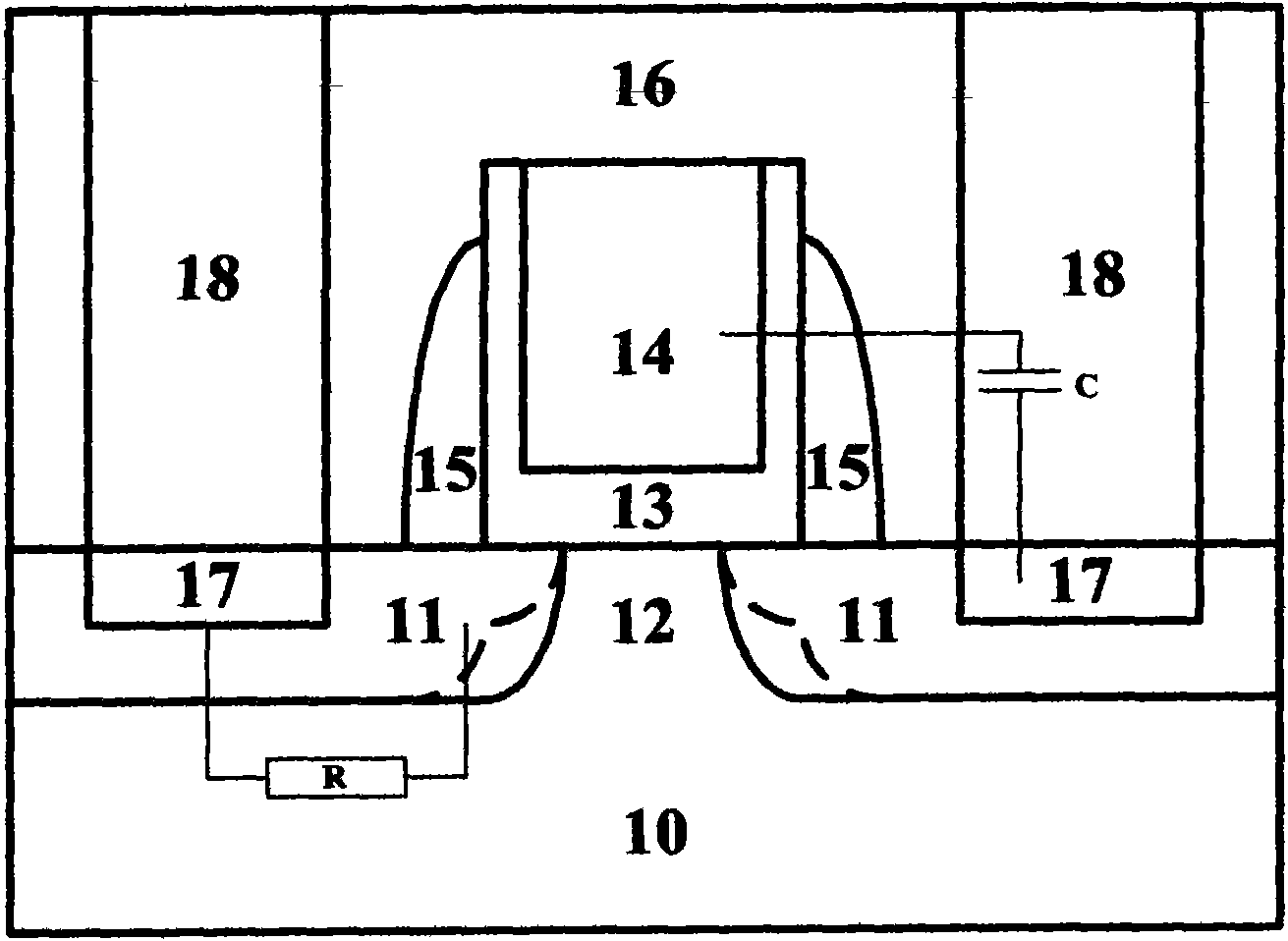

Semiconductor device and manufacturing method thereof

InactiveUS20120267706A1Reduced series resistanceReduce RC delaySolid-state devicesSemiconductor/solid-state device manufacturingMOSFETCapacitance

The invention discloses a novel MOSFET device and its implementation method, the device comprising: a substrate; a gate stack structure, on either side of which is eliminated a conventional isolation spacer; source / drain regions located in the substrate on opposite sides of the gate stack structure; epitaxially grown metal silicide located on the source / drain regions; characterized in that, the epitaxially grown metal silicide is in direct contact with a channel region controlled by the gate stack structure, thereby eliminating the high resistance region below the conventional isolation spacer. At the same time, the epitaxially grown metal silicide can withstand a second high-temperature annealing used for improving the performance of a high-k gate dielectric material, which further improves the performance of the device. The MOSFET according to the invention reduces the parasitic resistance and capacitance greatly and thereby decreases the RC delay, thus improving the switching performance of the MOSFET device significantly.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

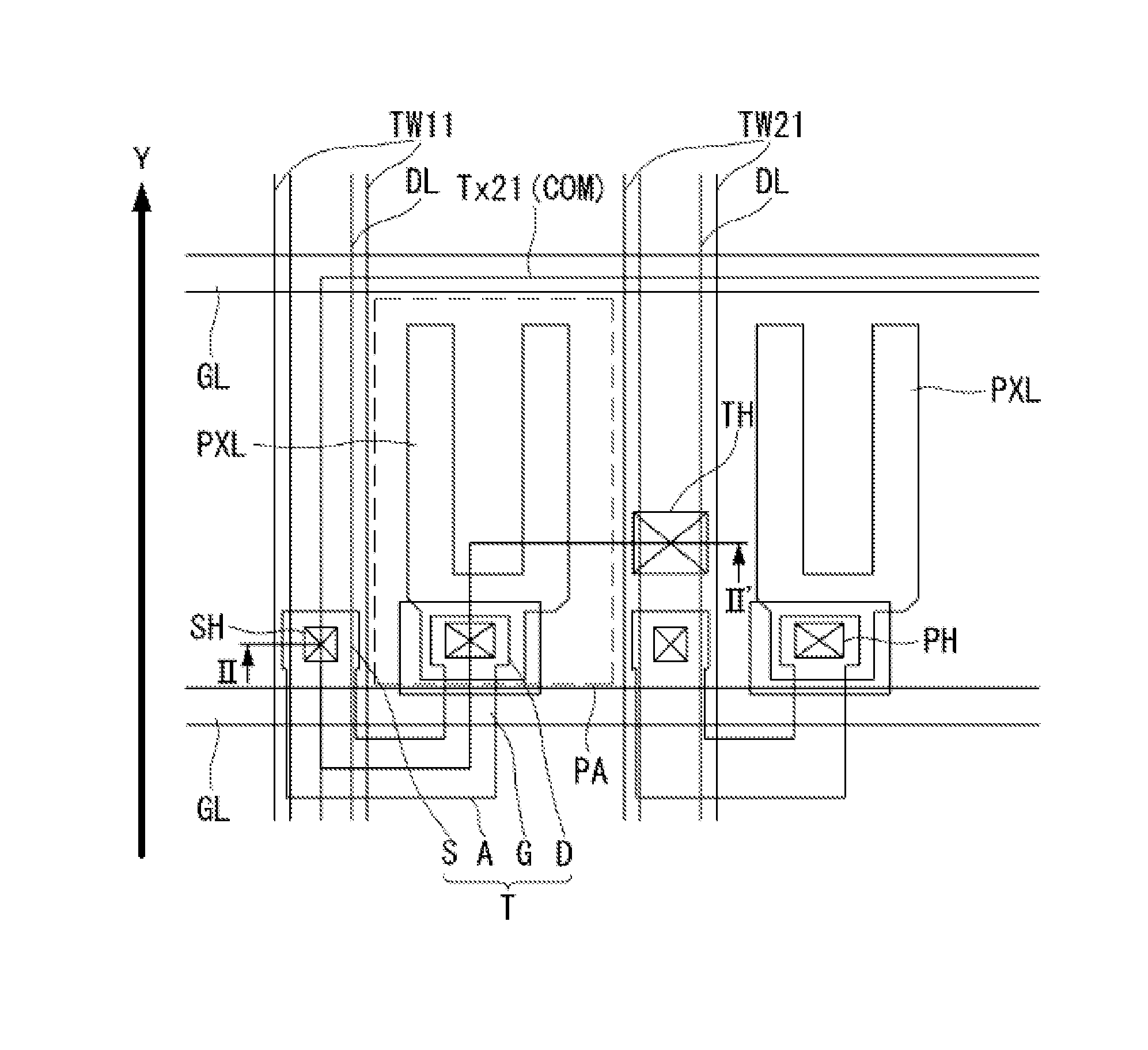

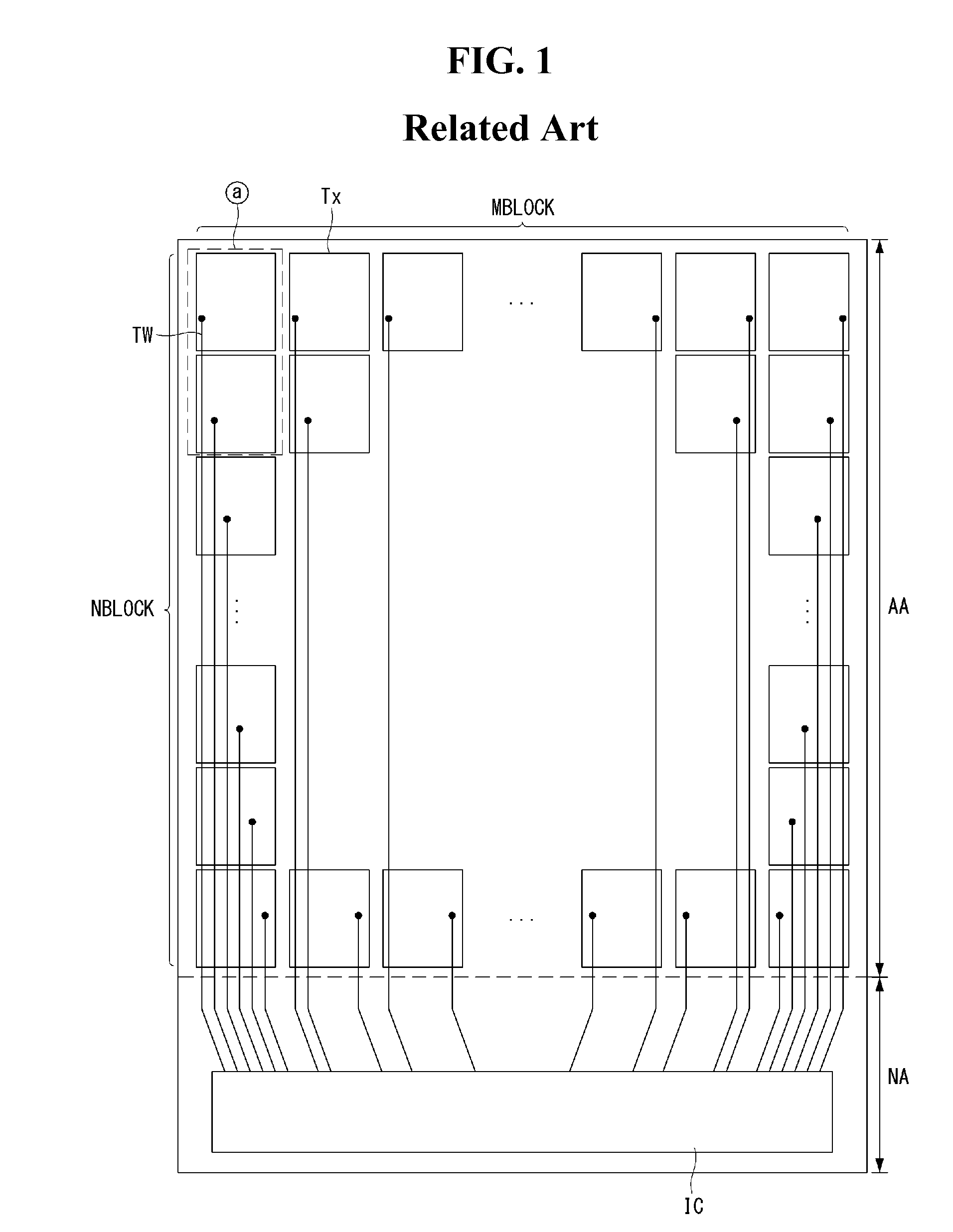

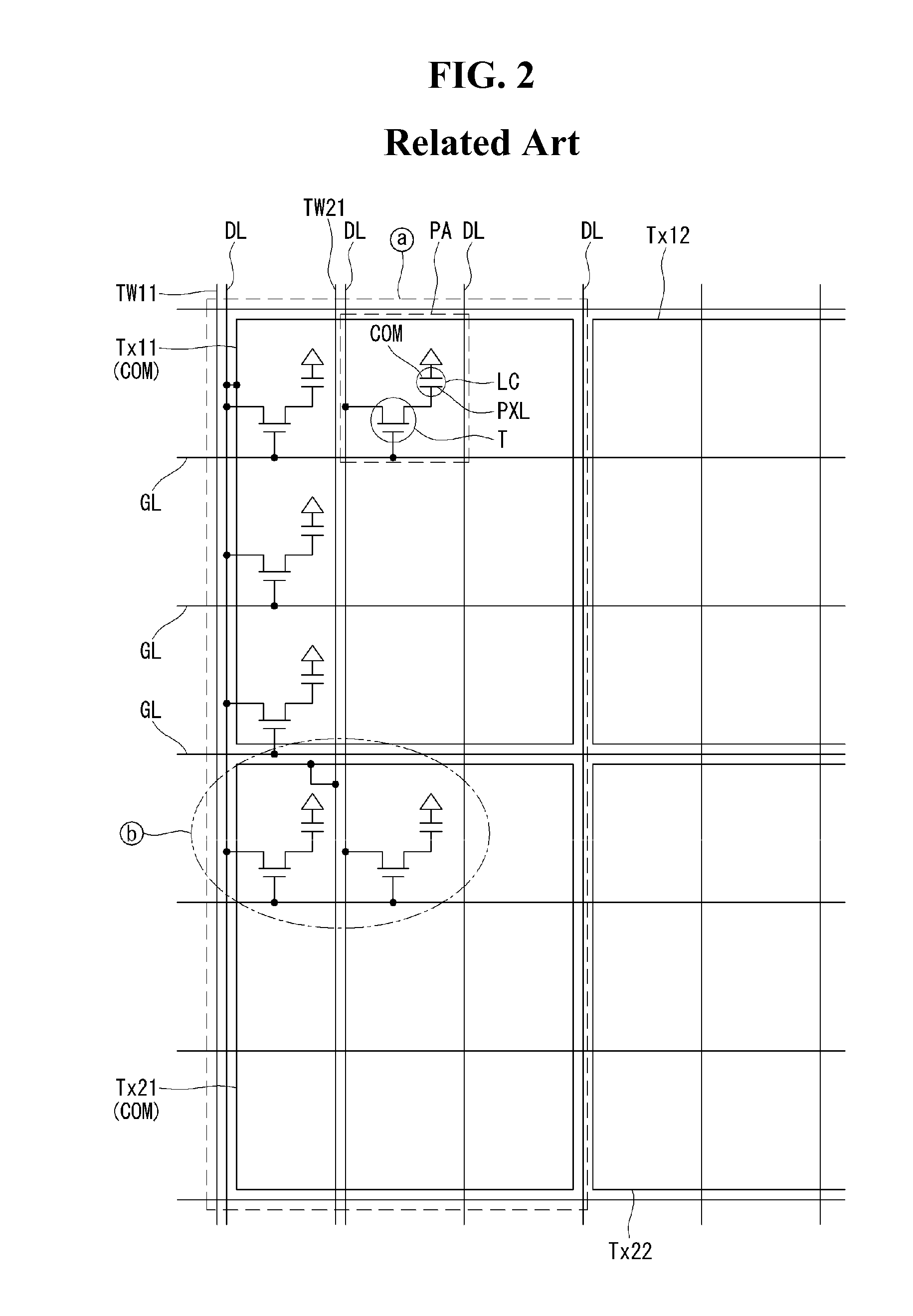

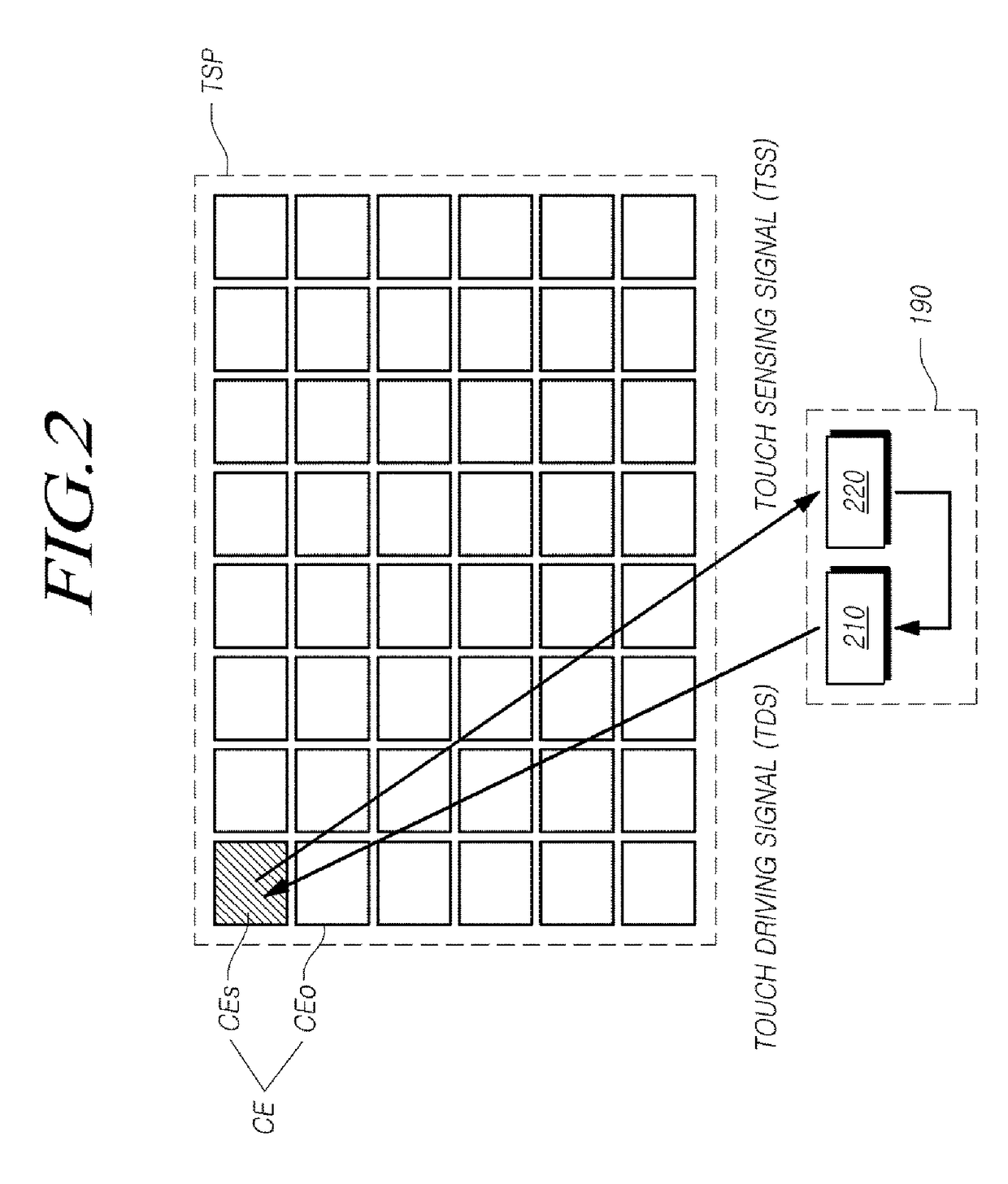

Ultra high resolution flat panel display having in-cell type touch sensor

ActiveUS20160188061A1Parasitic capacitanceImprove Sensing PerformanceStatic indicating devicesNon-linear opticsImage resolutionDisplay device

A display having a touch sensor comprises: a plurality of pixel areas disposed in a matrix manner on a substrate; a routing line running along a first direction on the substrate; a first passivation layer covering the routing line; a touch electrode covering the routing line and corresponding to a grouped pixel areas on the first passivation layer; a touch contact hole exposing some portions of the routing line by penetrating the touch electrode and the first passivation layer; a second passivation layer covering the touch electrode; a passivation contact hole exposing the touch contact hole and some portions of the touch electrode around the touch contact hole by penetrating the second passivation layer; and a touch terminal connecting the touch electrode and the routing line on the second passivation layer.

Owner:LG DISPLAY CO LTD

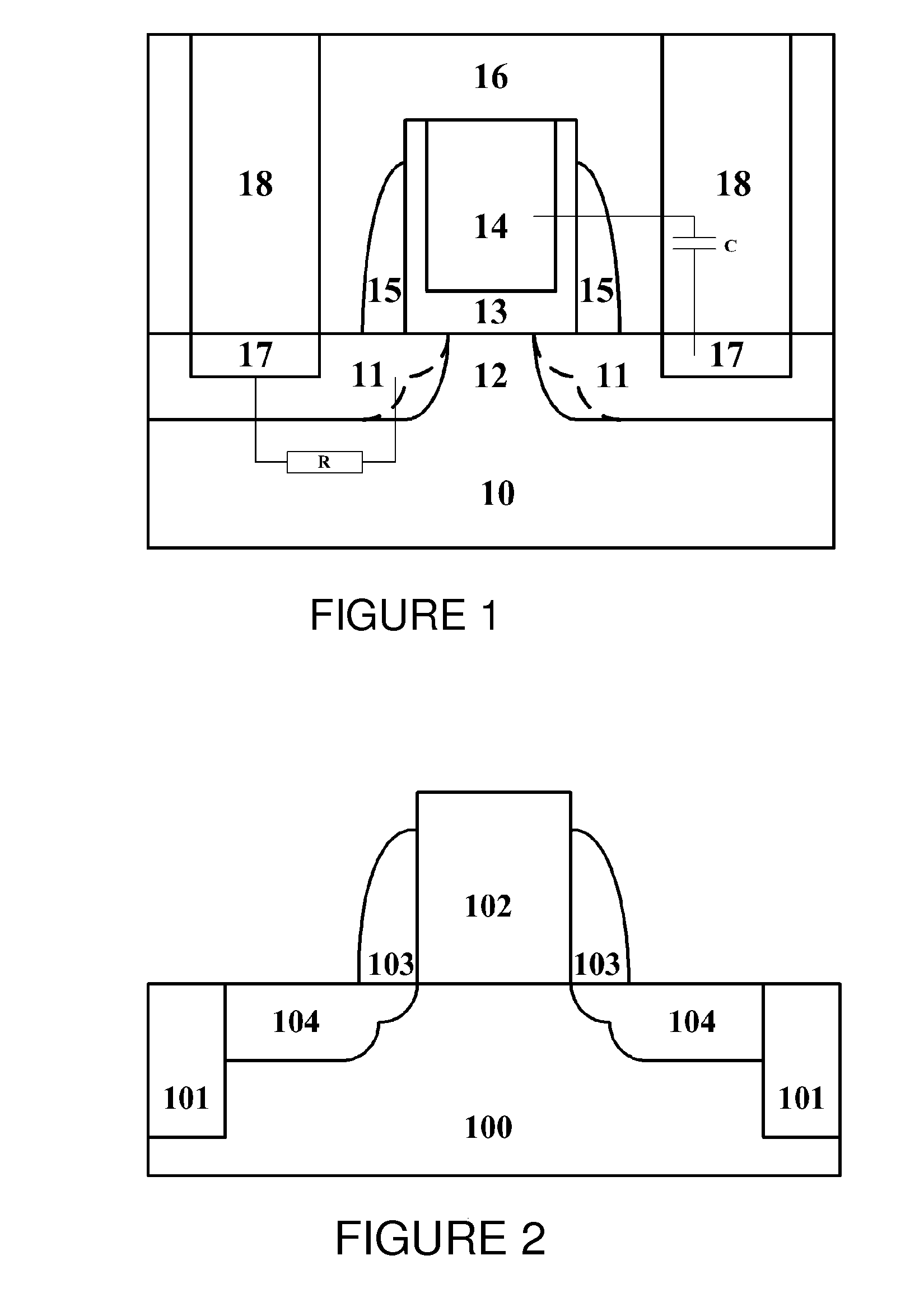

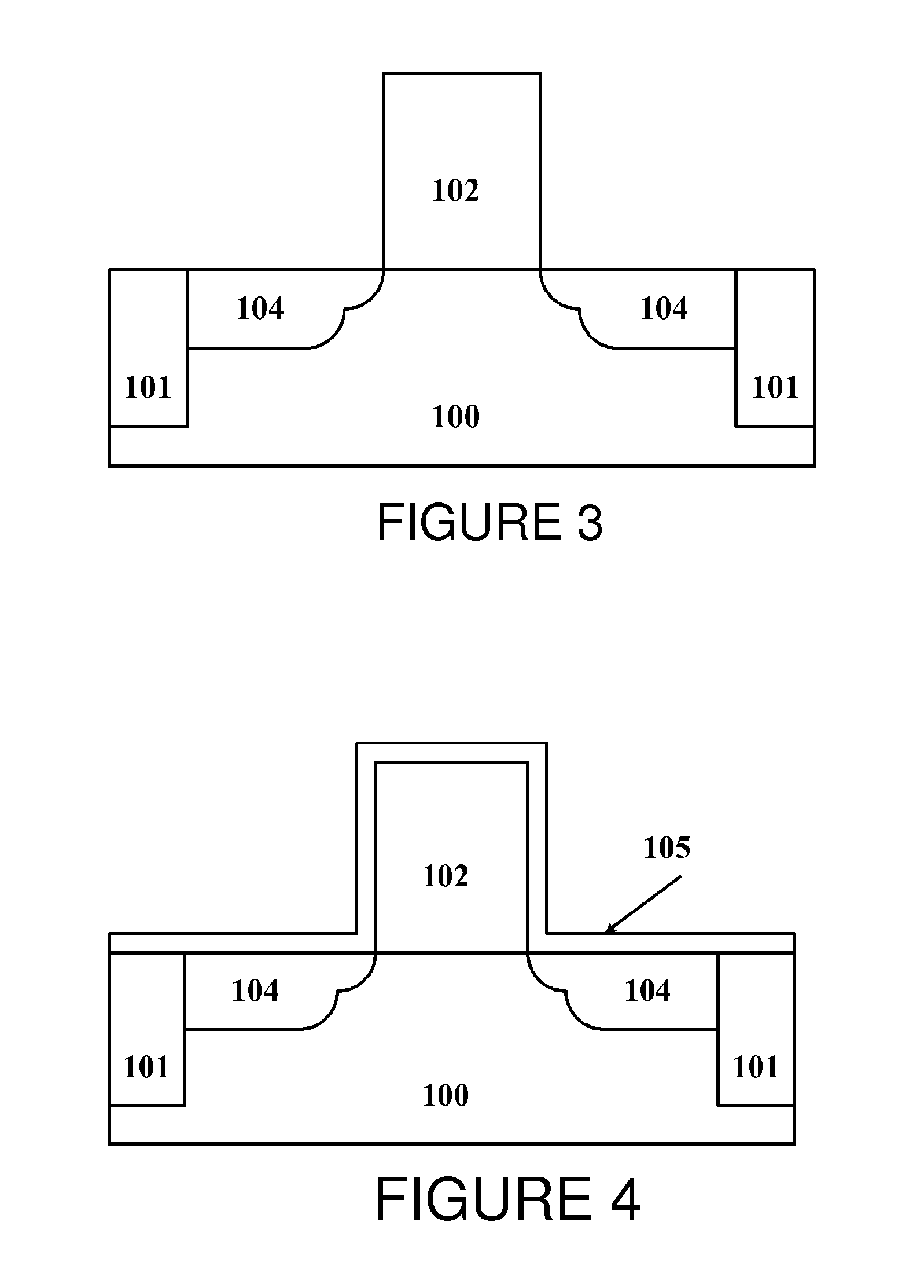

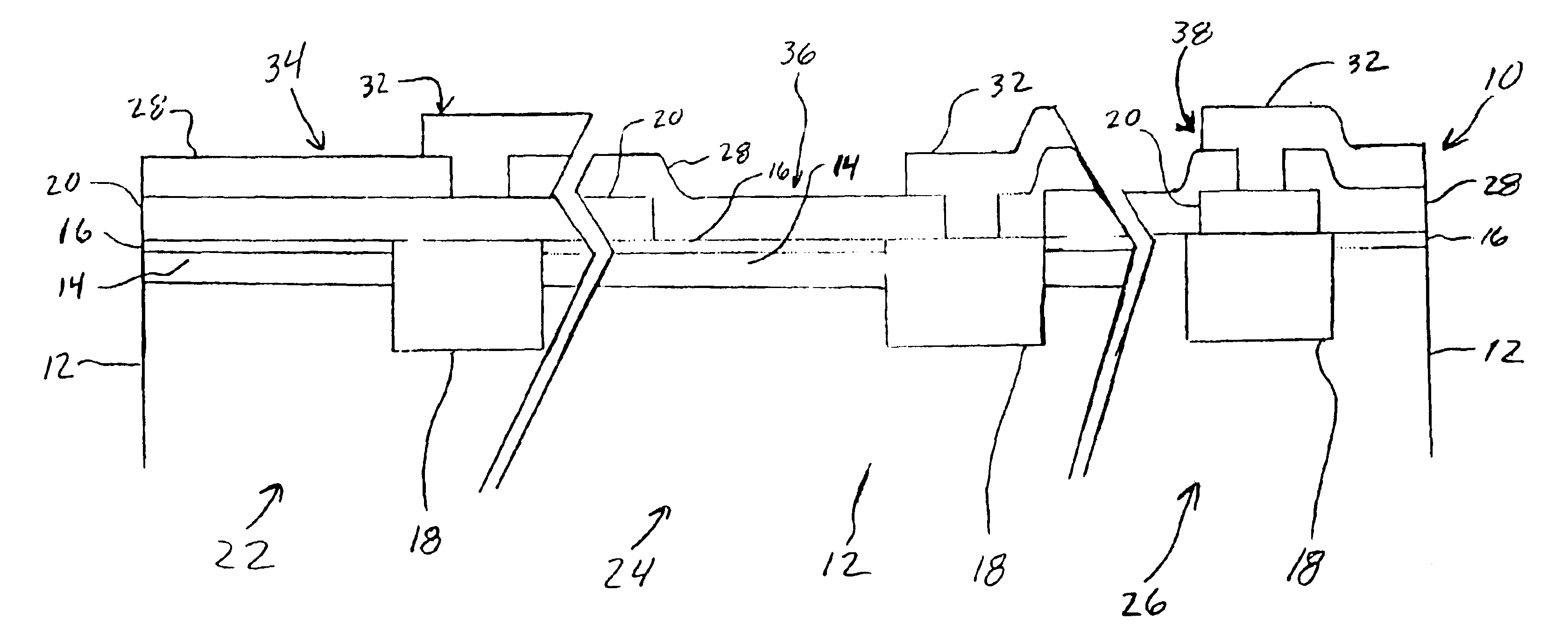

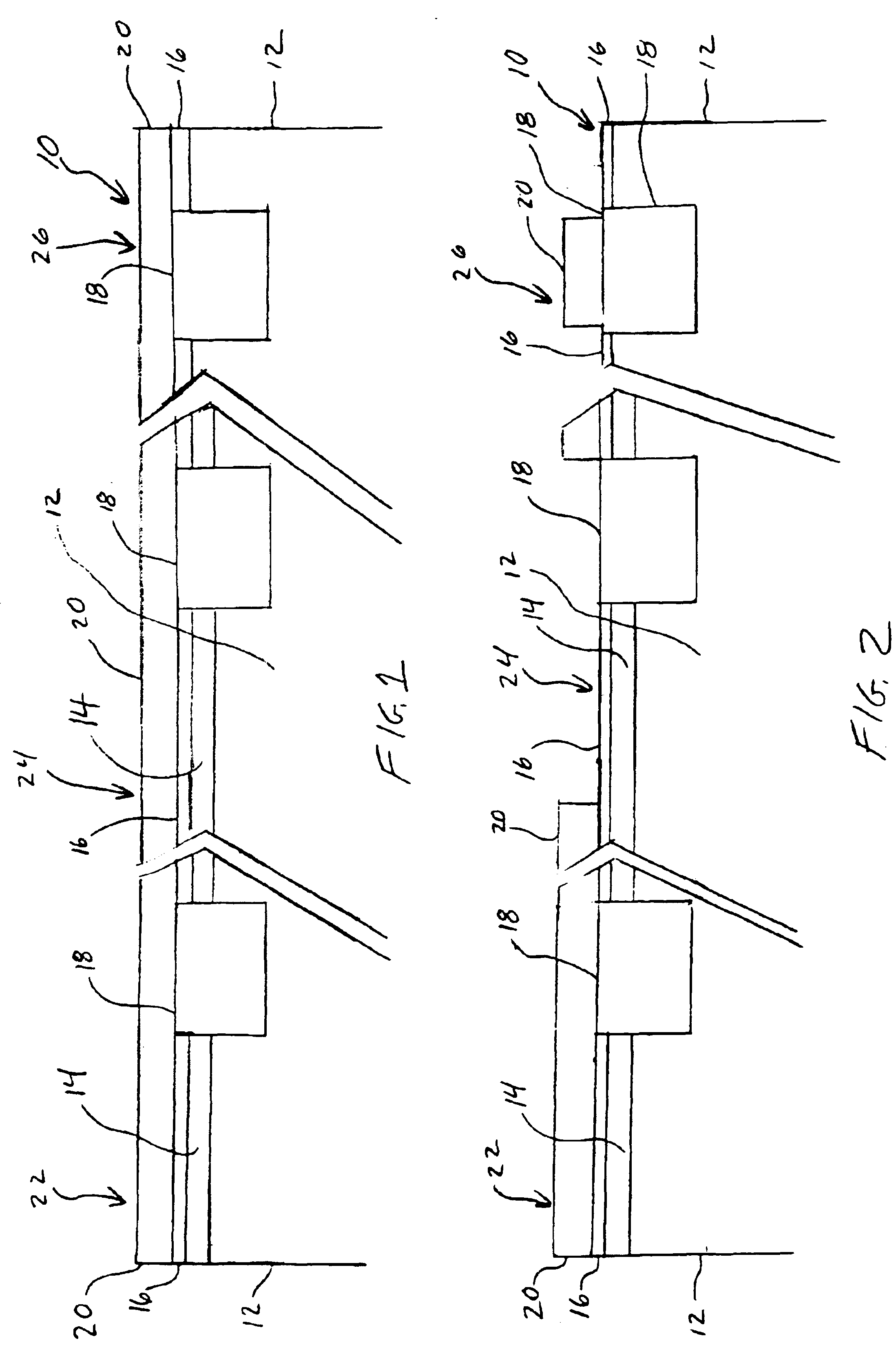

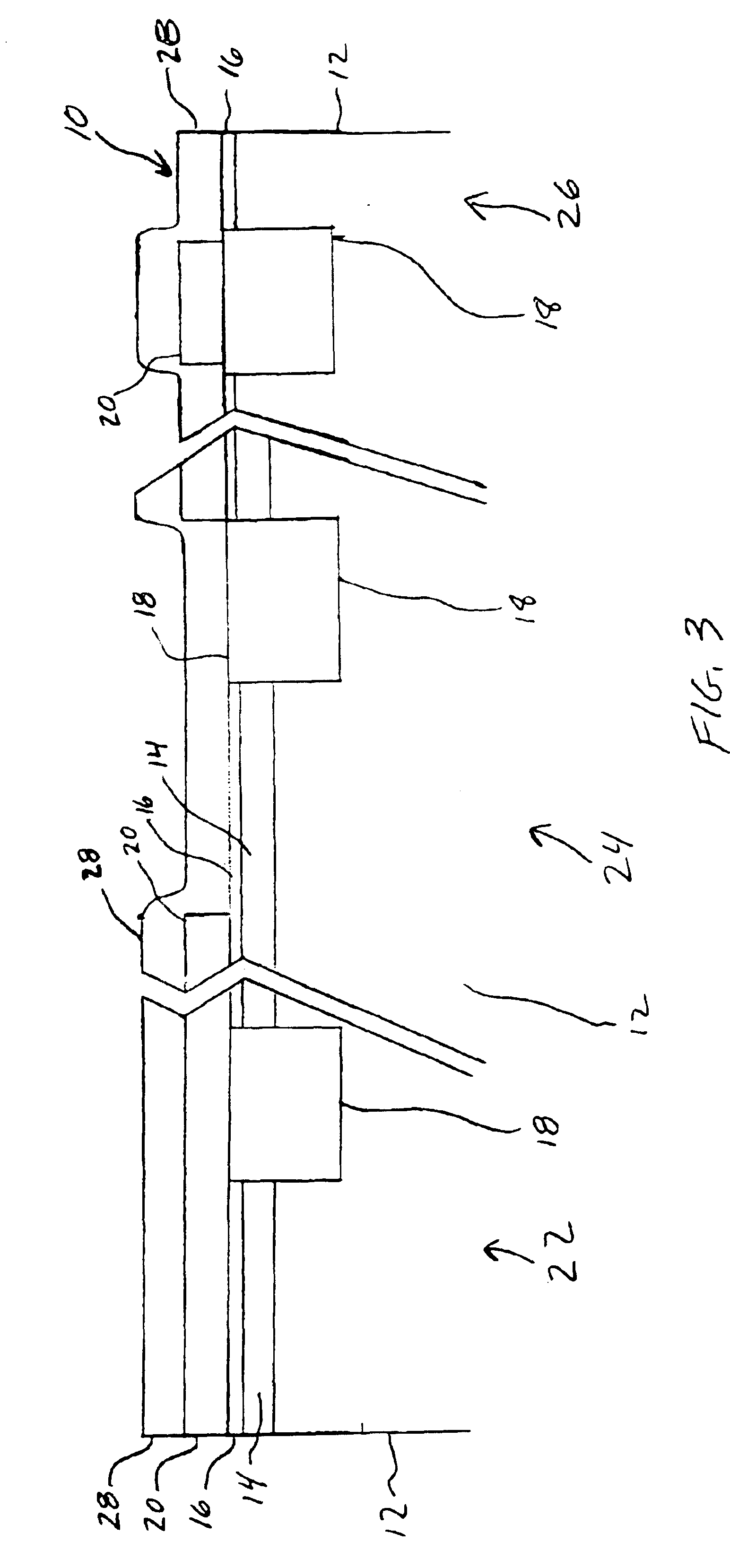

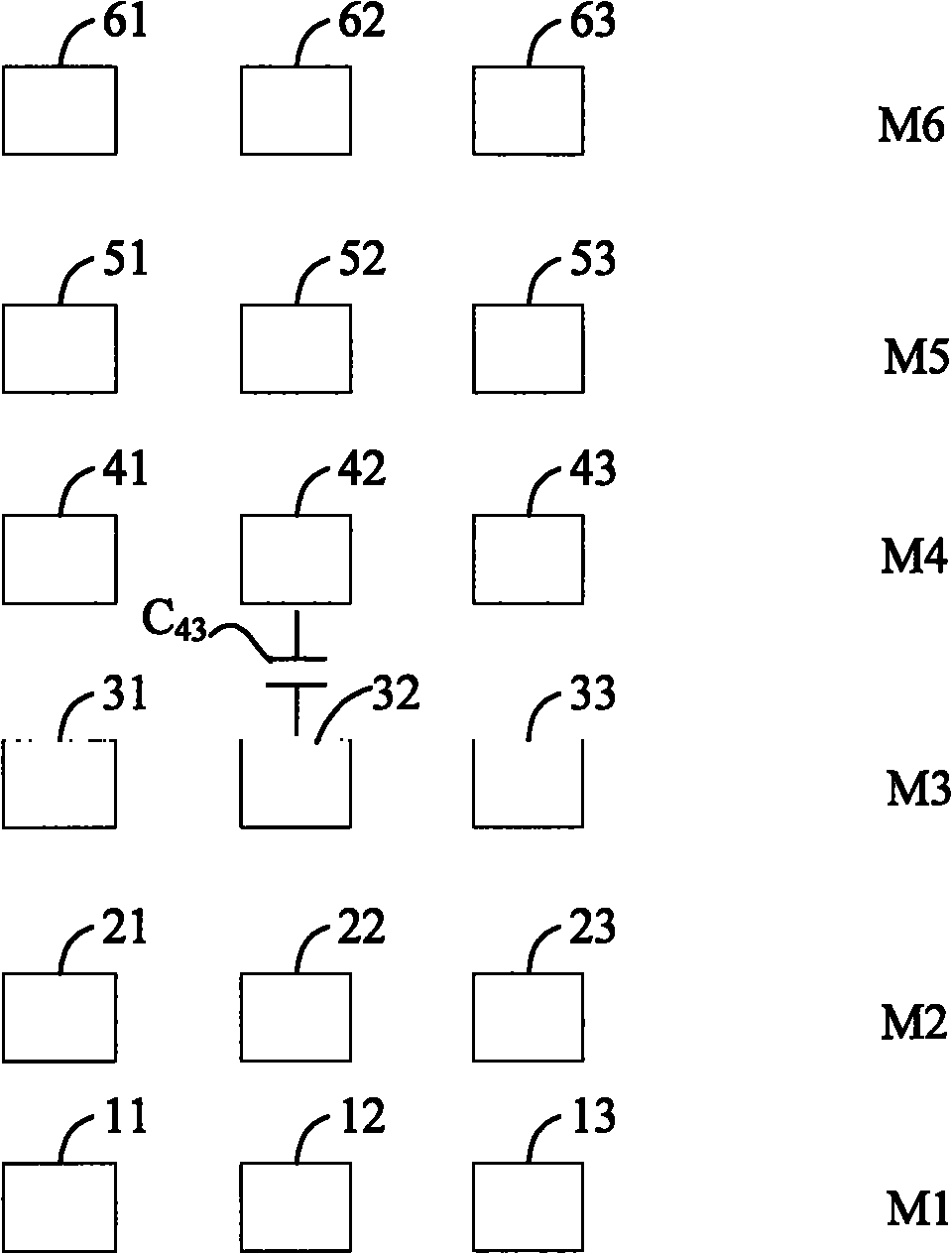

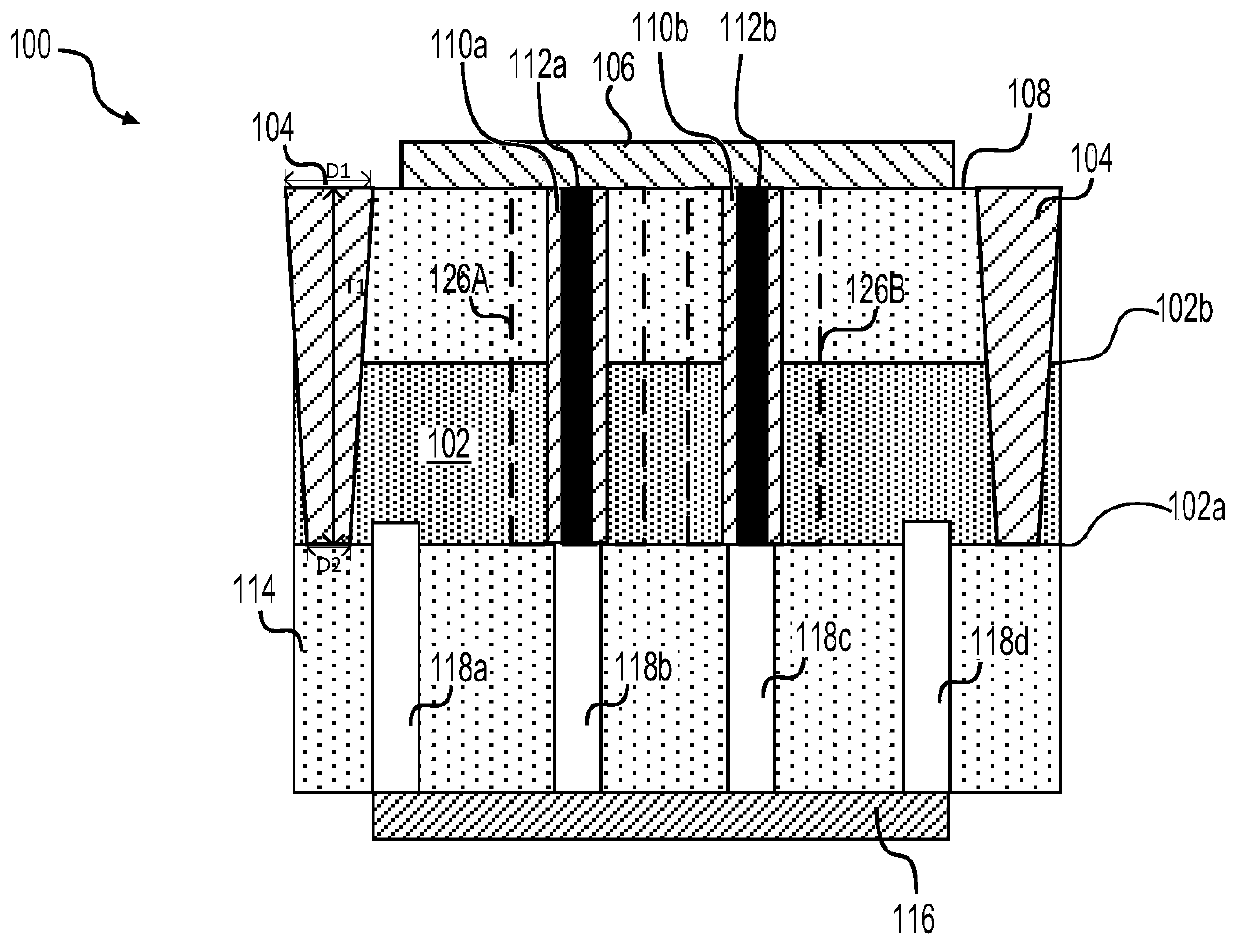

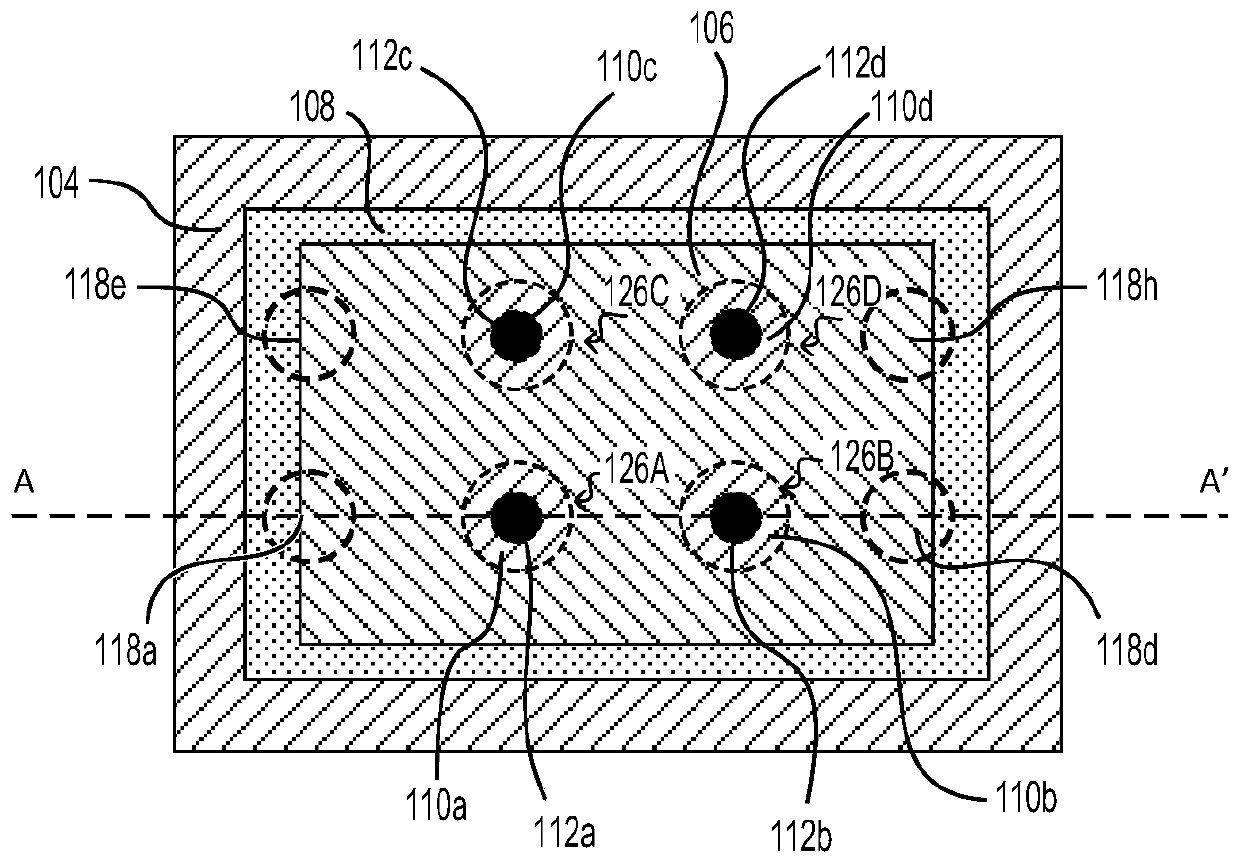

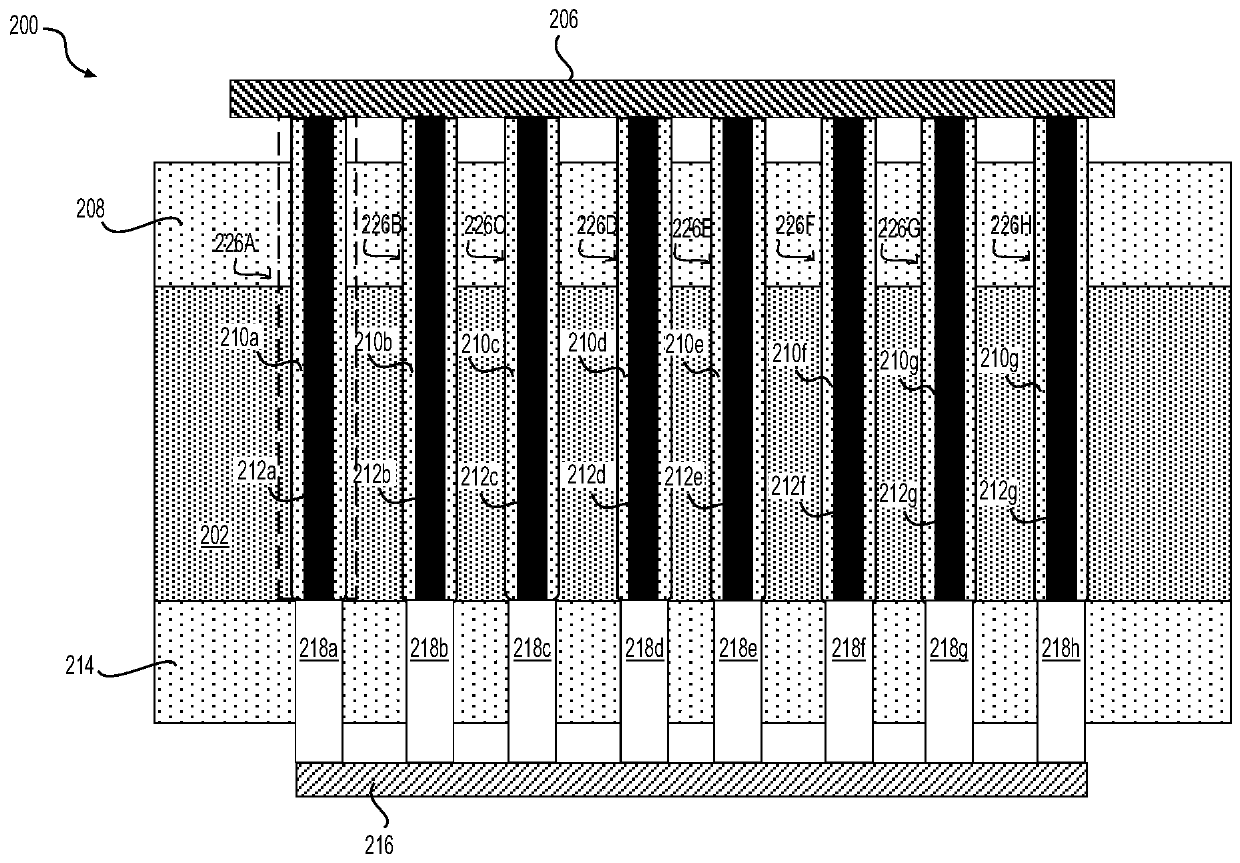

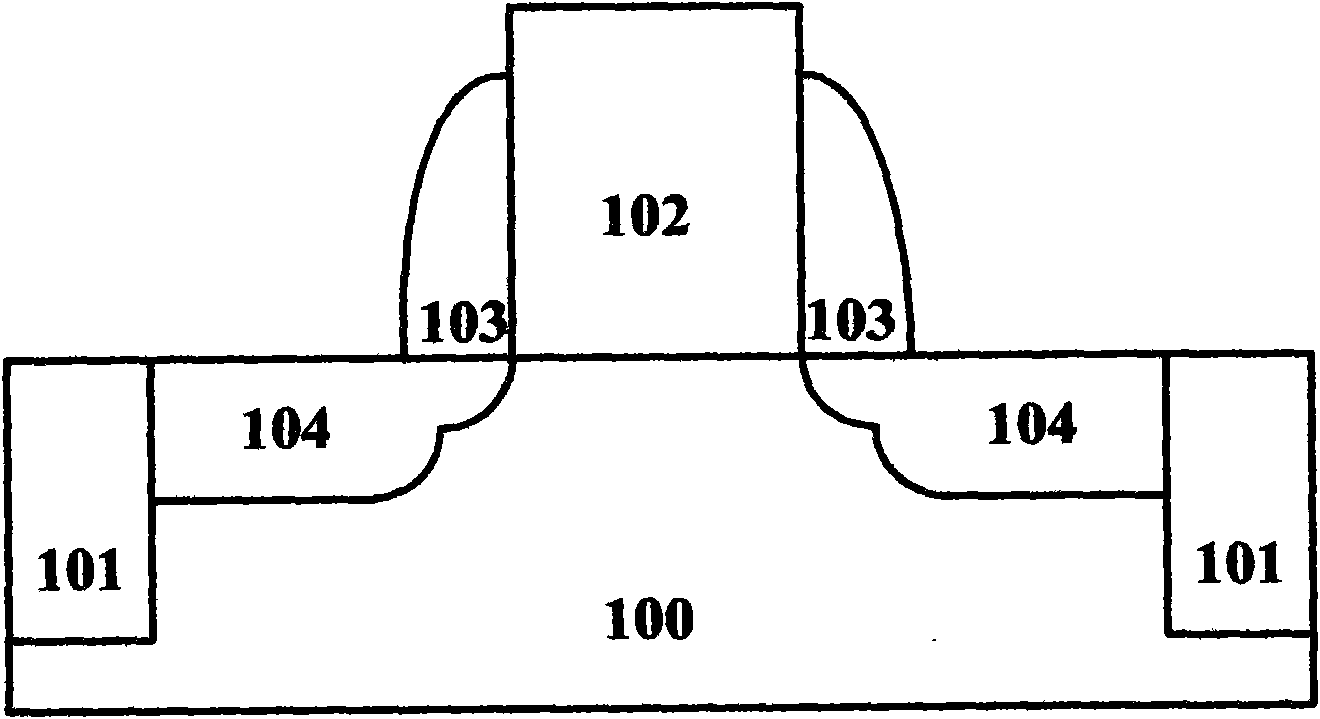

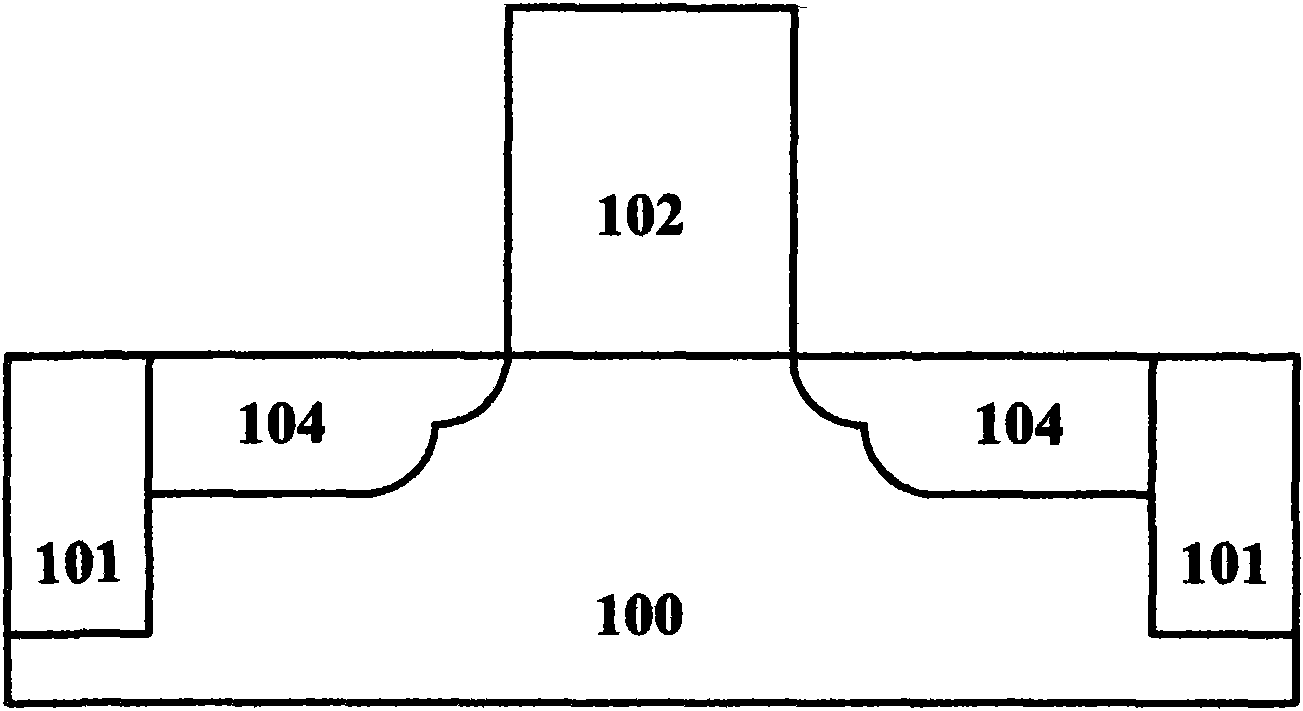

Array of gate dielectric structures to measure gate dielectric thickness and parasitic capacitance

InactiveUS6964875B1Eliminate parasitic capacitanceAccurate measurementSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsGate dielectricParasitic capacitance

Accurate determination of gate dielectric thickness is required to produce high-reliability and high-performance ultra-thin gate dielectric semiconductor devices. Large area gate dielectric capacitors with ultra-thin gate dielectric layers suffer from high gate leakage, which prevents the accurate measurement of gate dielectric thickness. Accurate measurement of gate dielectric thickness of smaller area gate dielectric capacitors is hindered by the relatively large parasitic capacitance of the smaller area capacitors. The formation of first and second dummy structures on a wafer allow the accurate determination of gate dielectric thickness. First and second dummy structures are formed that are substantially similar to the gate dielectric capacitors except that the first dummy structures are formed without the second electrode of the capacitor and the second dummy structures are formed without the first electrode of the capacitor structure. The capacitance, and therefore thickness, of the gate dielectric capacitor is determined by subtracting the parasitic capacitances measured at the first and second dummy structures.

Owner:GLOBALFOUNDRIES INC

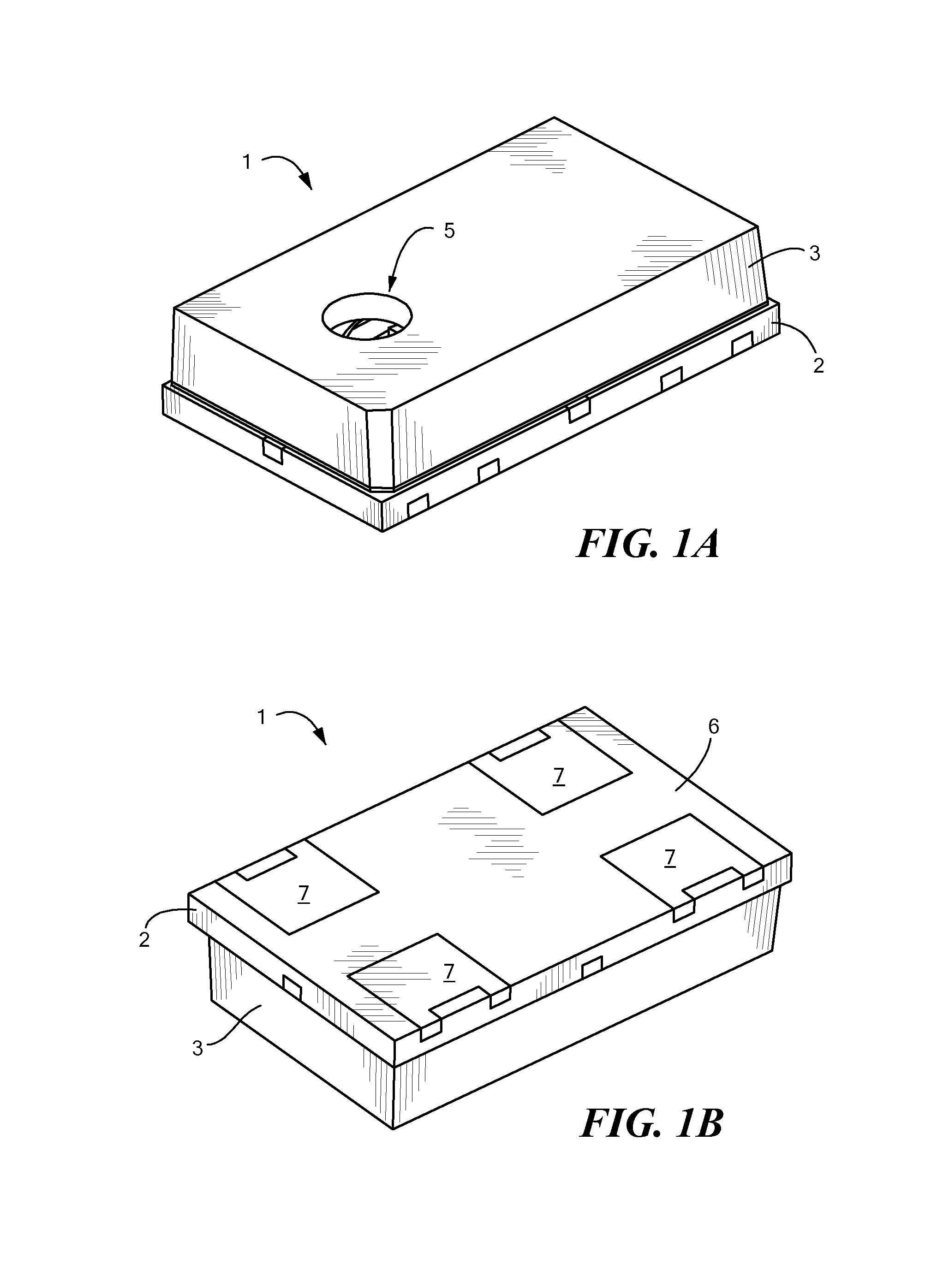

Micro-acceleration transducer capable of avoiding parasitic capacitance structure, and manufacturing method thereof

ActiveCN102928623ASimple structureGood dynamic responseAcceleration measurementWork performanceTransducer

The invention relates to a micro-acceleration transducer capable of avoiding a parasitic capacitance structure, which comprises a top electrode cover plate, a lower electrode cover plate and a mass block, wherein the top electrode cover plate and the lower electrode cover plate are respectively arranged at the upper end and the lower end of the mass block; the upper surface of the mass block is provided with an upper capacitance gap, and the lower surface of the mass block is provided with a lower capacitance gap; and the lower surface of the top electrode cover plate and the upper surface of the lower electrode cover plate are respectively provided with an isolation groove used for realizing isolation among a top electrode bonding pad, a middle electrode bonding pad and a lower electrode bonding pad. The micro-acceleration transducer is easy to manufacture, stable in working performance and wide in application.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

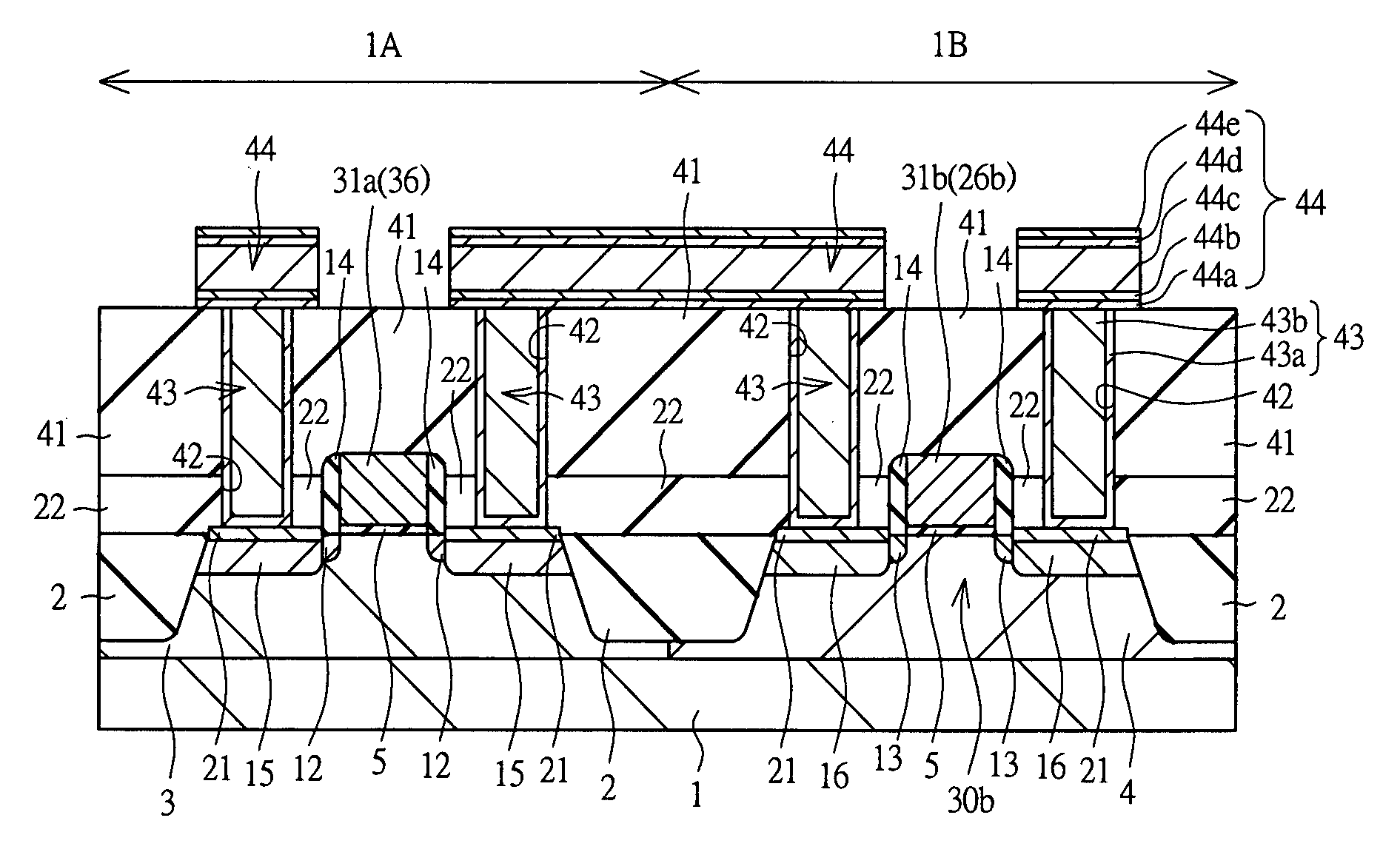

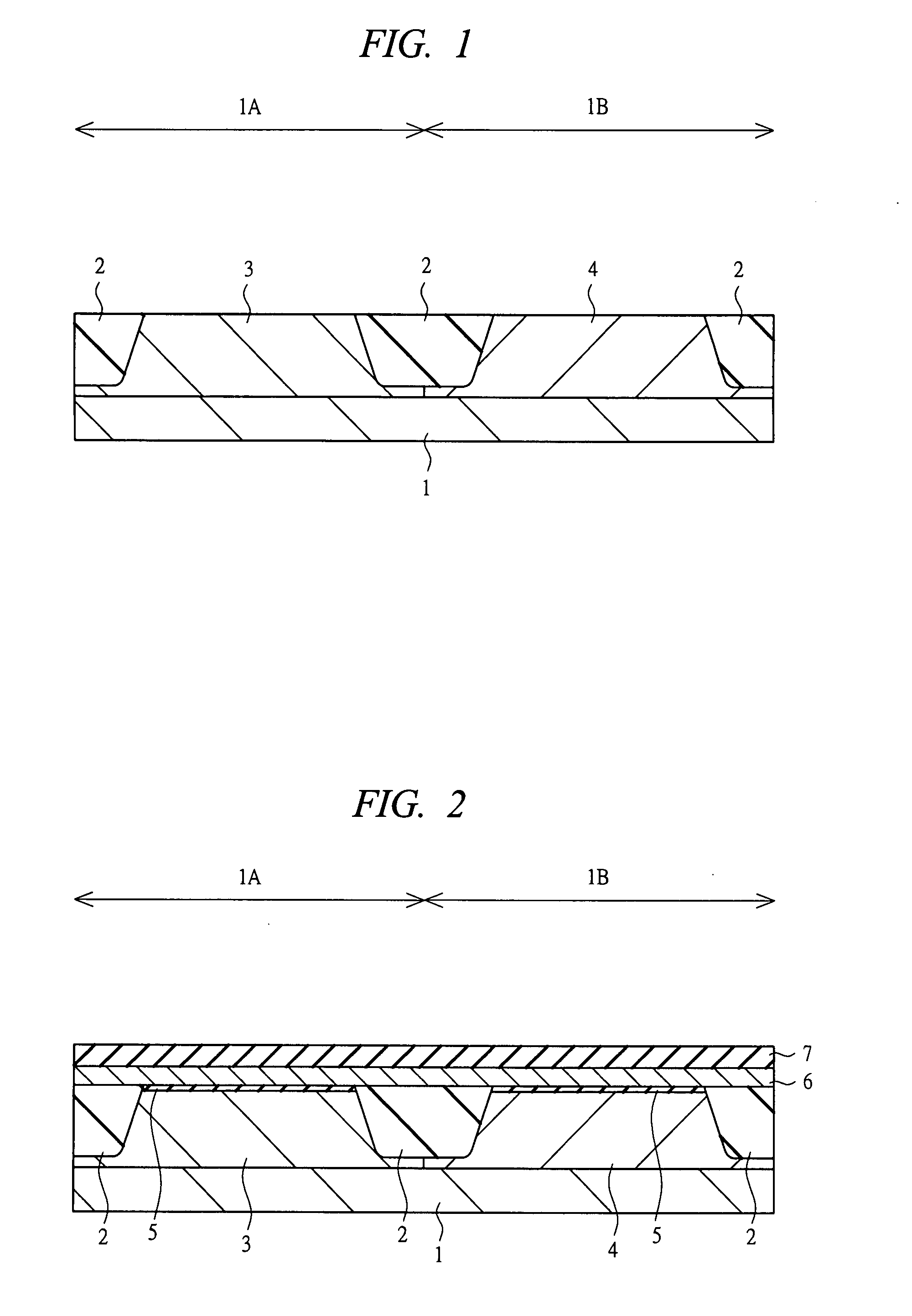

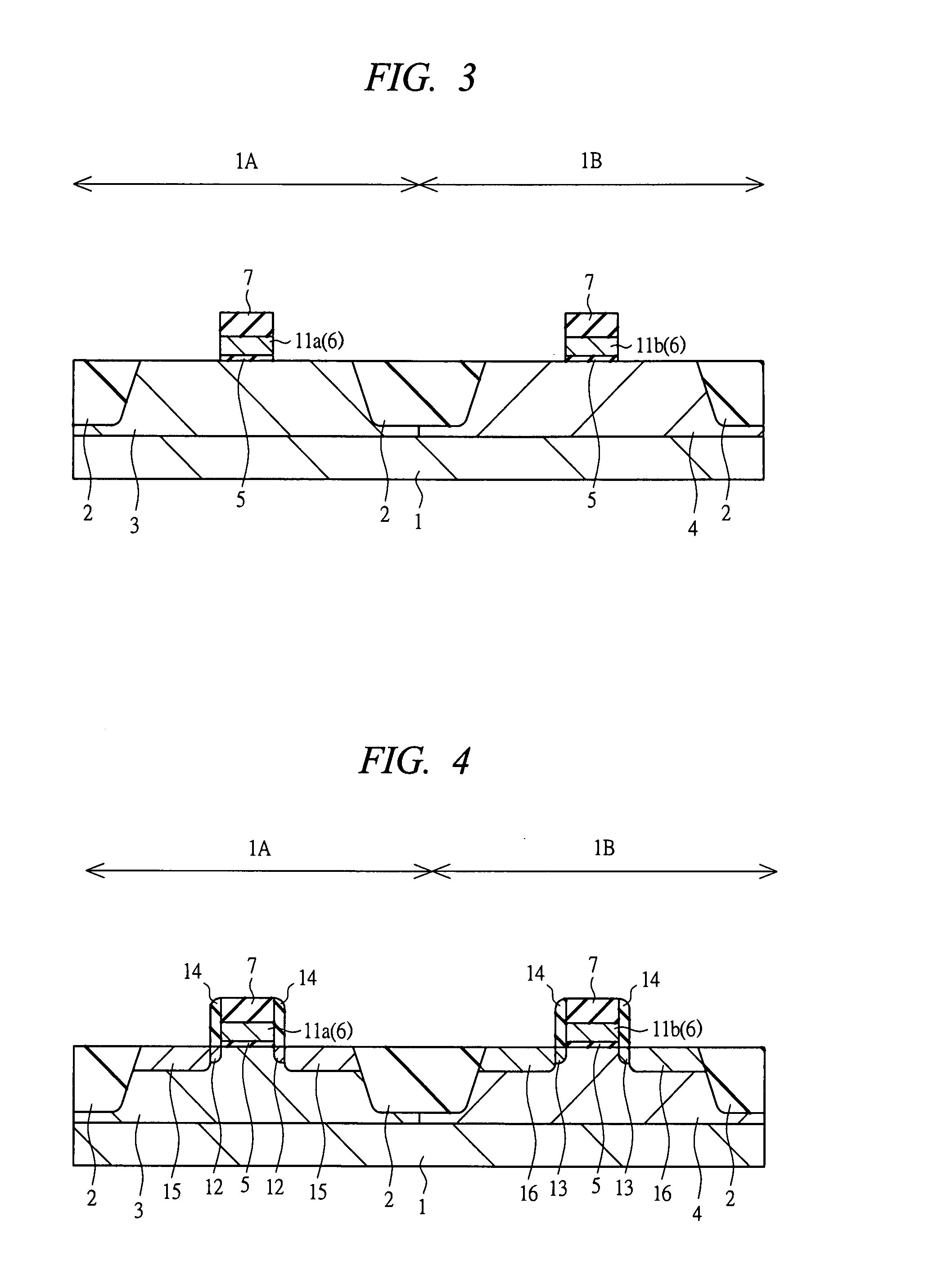

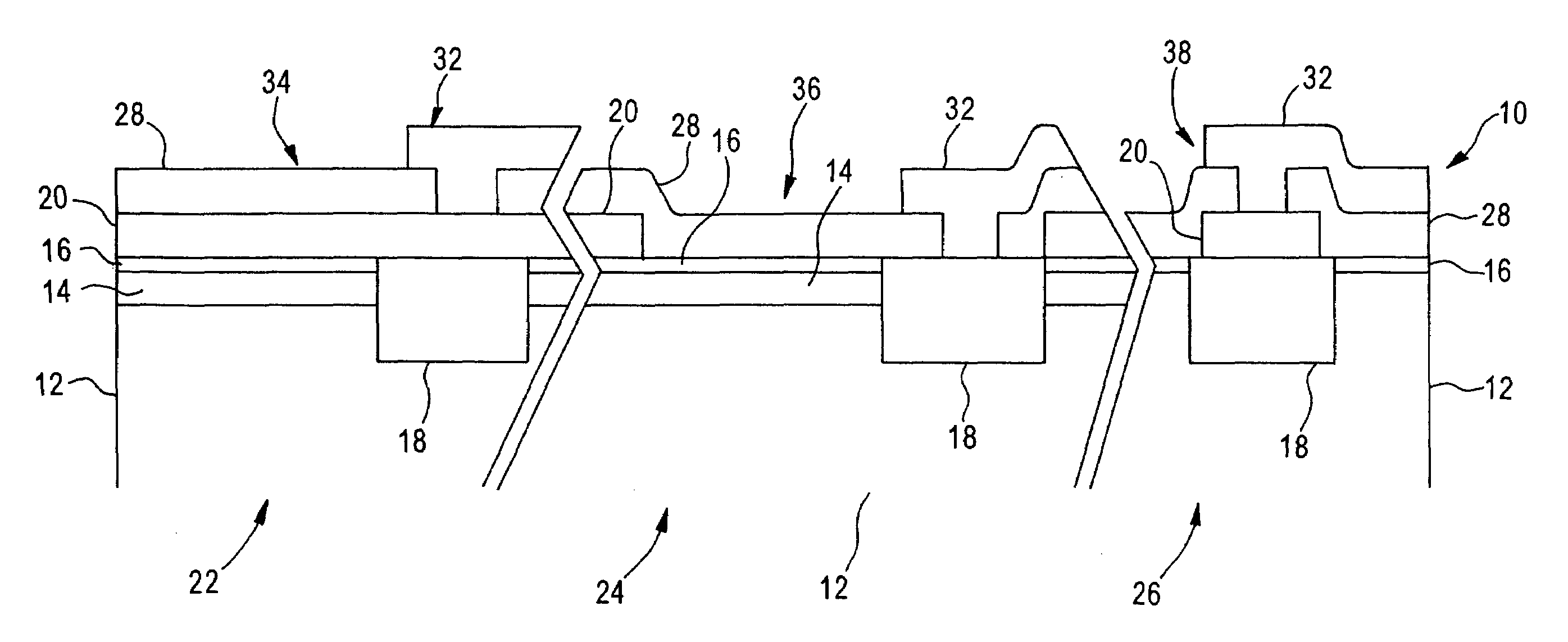

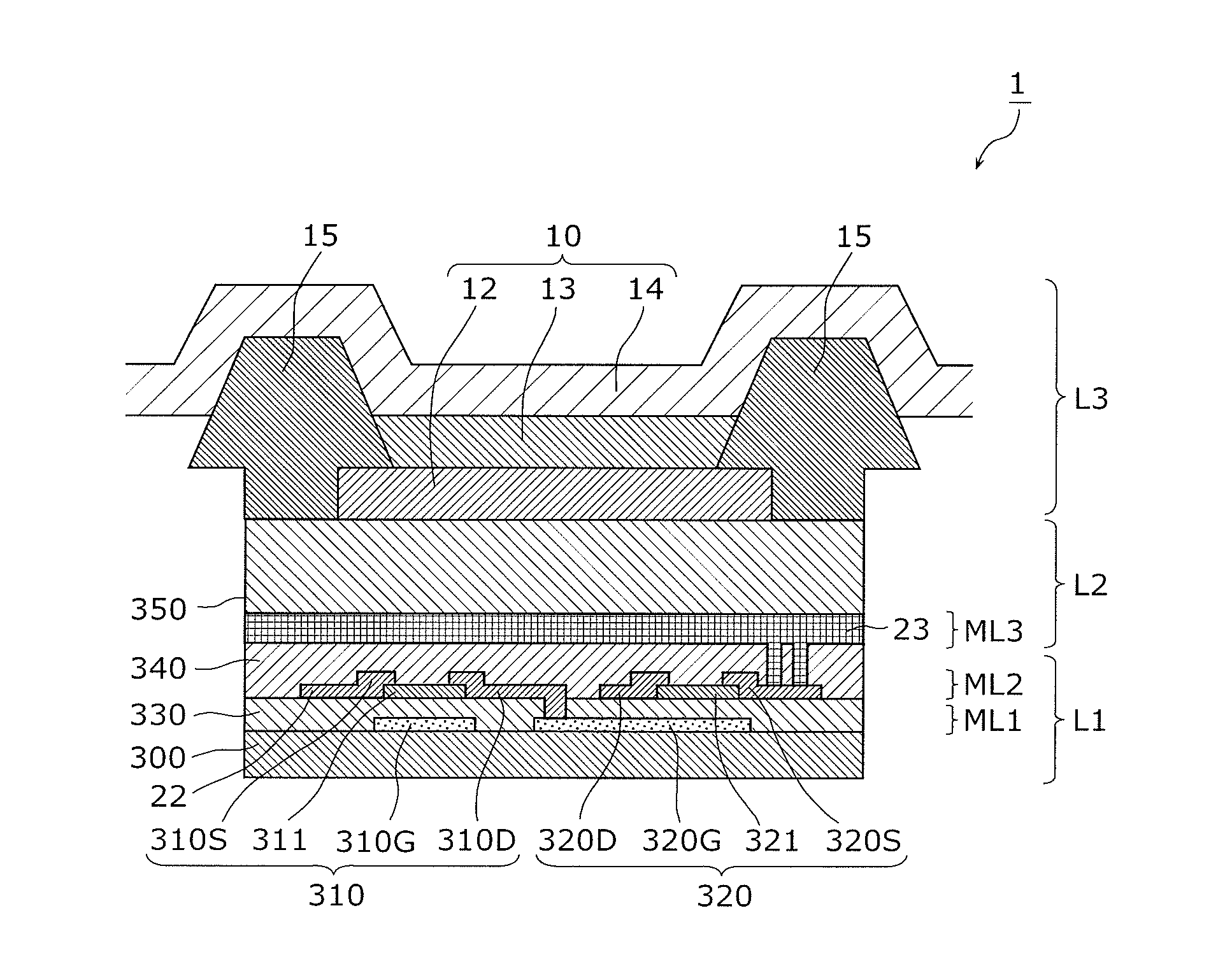

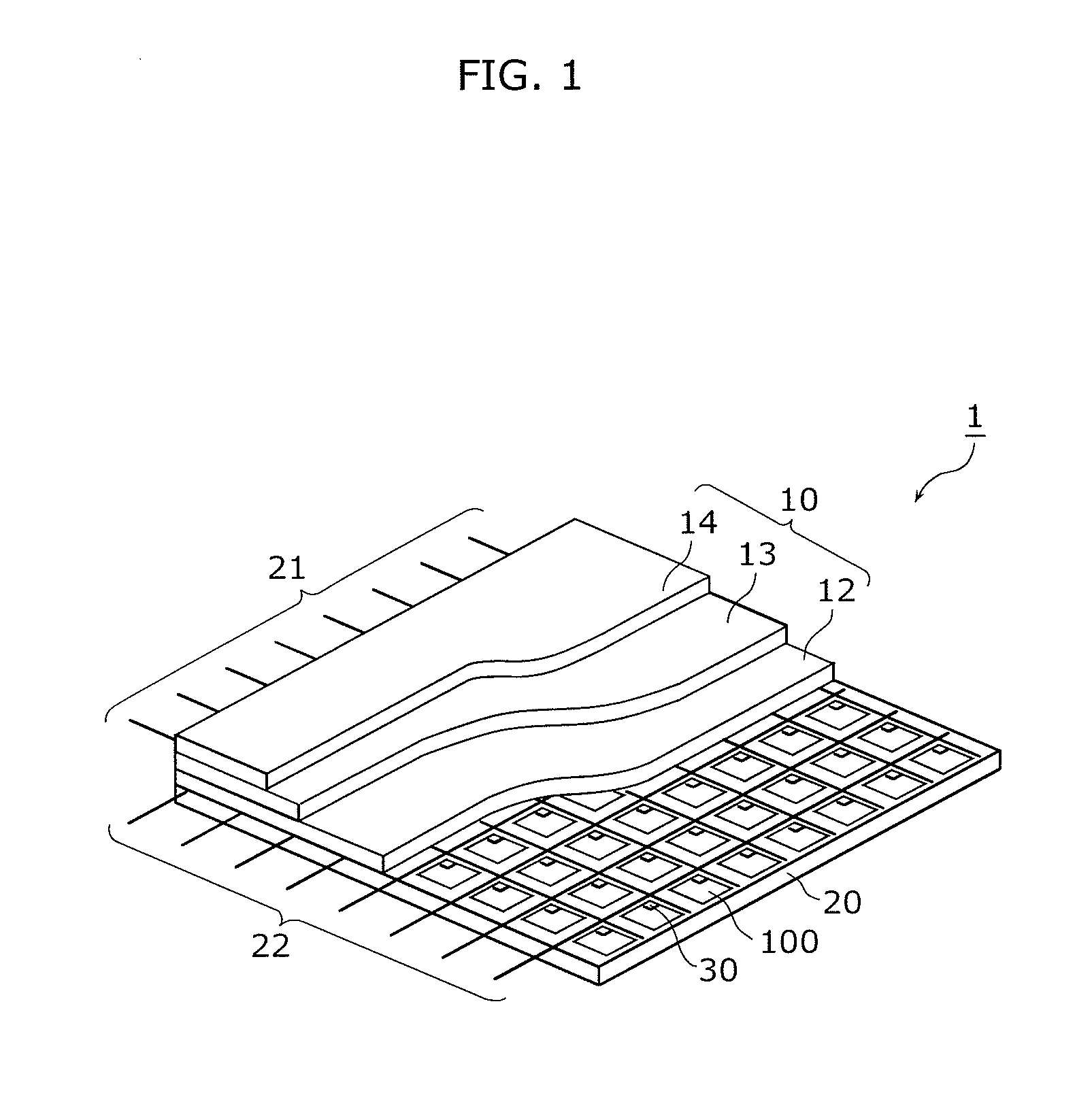

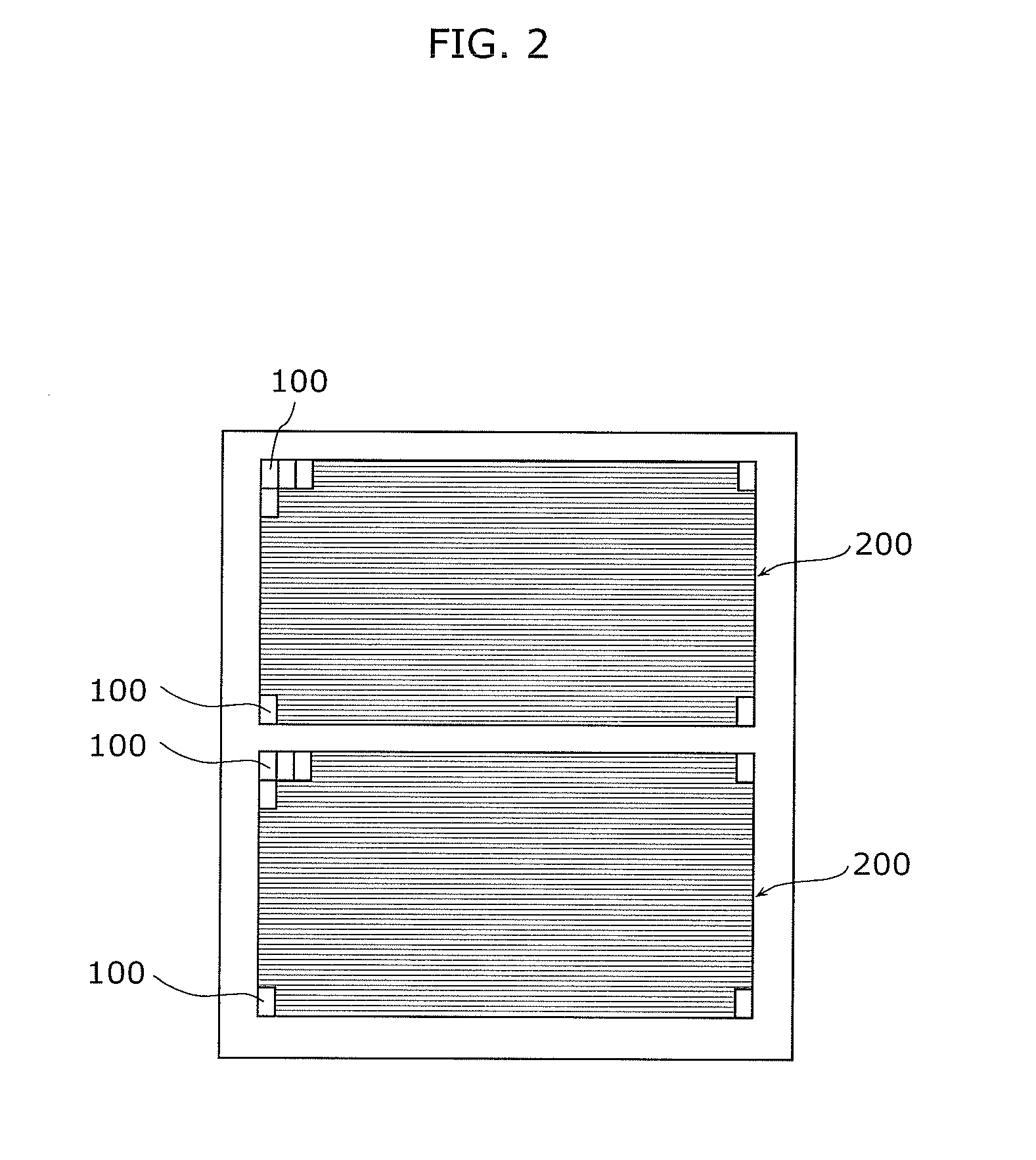

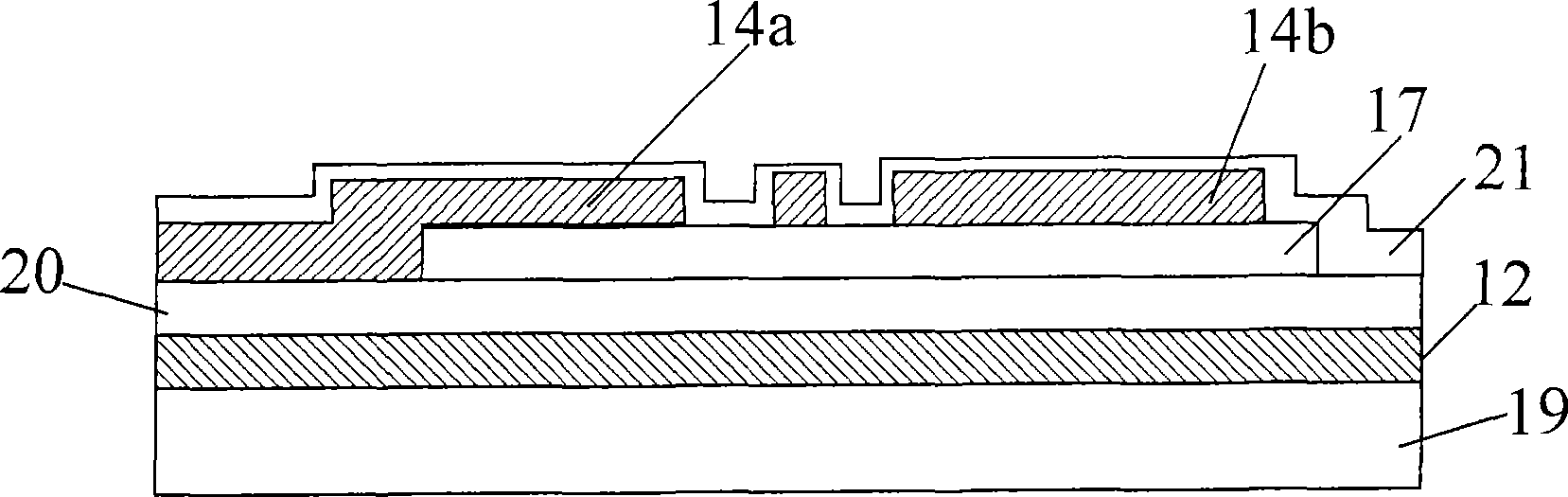

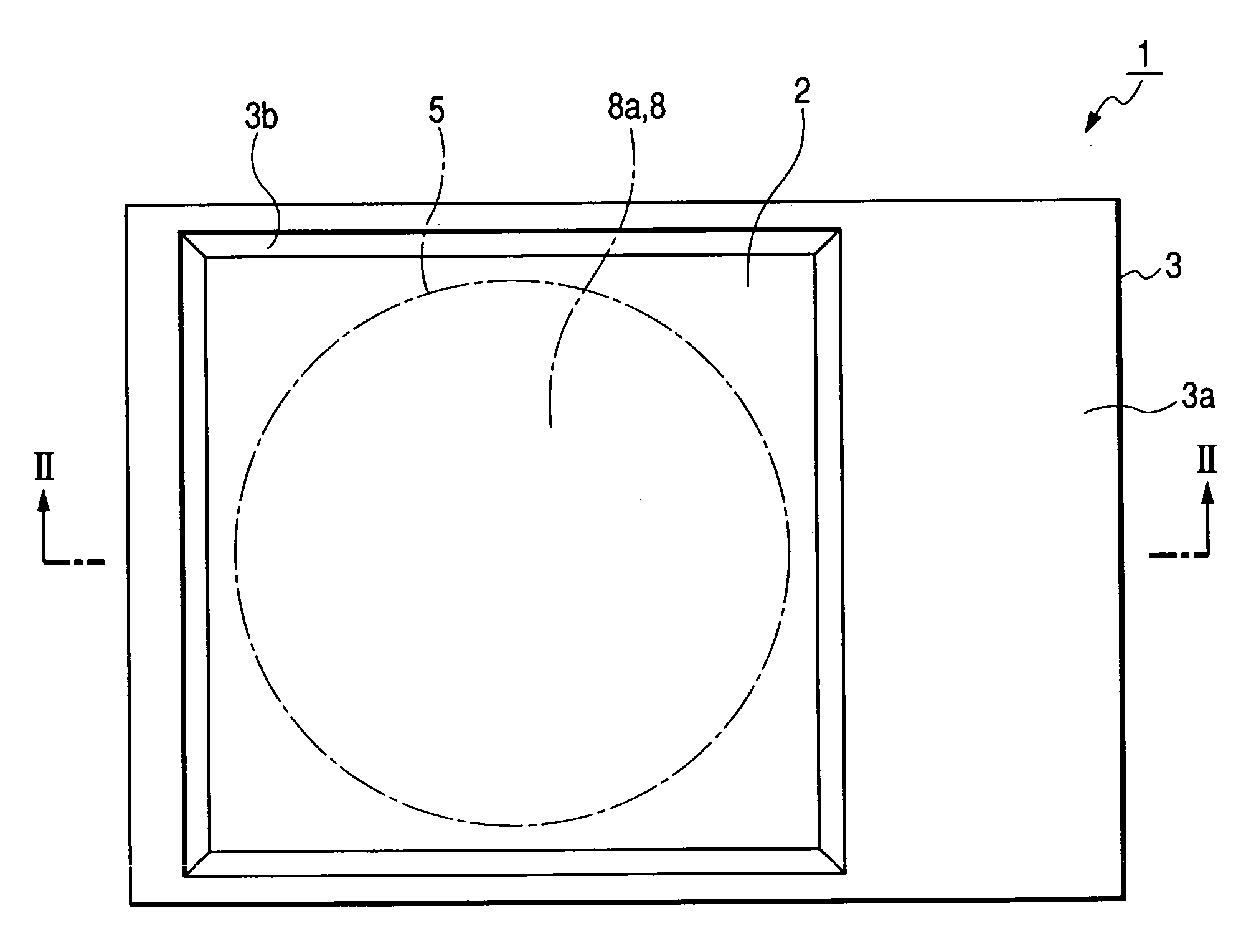

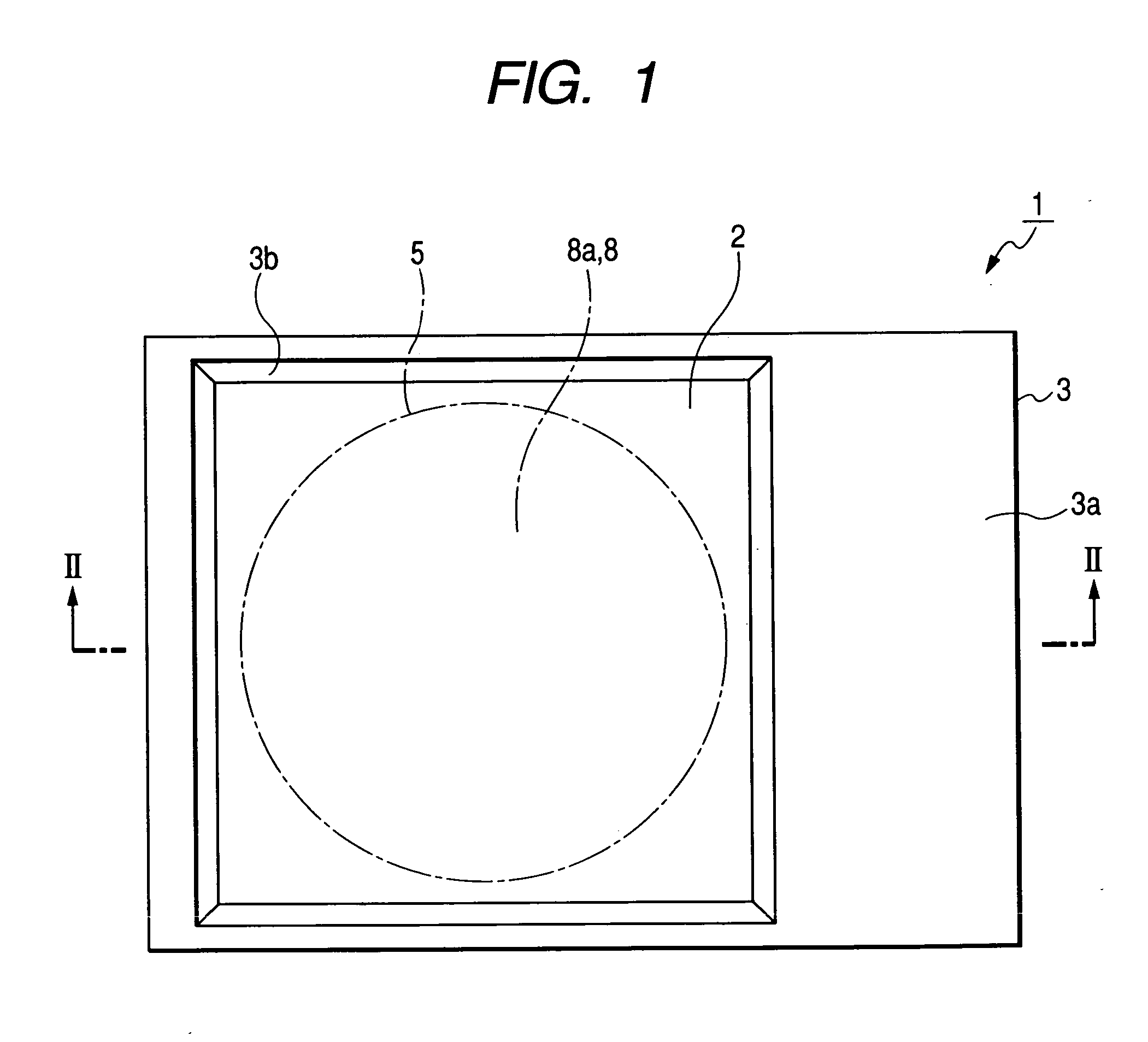

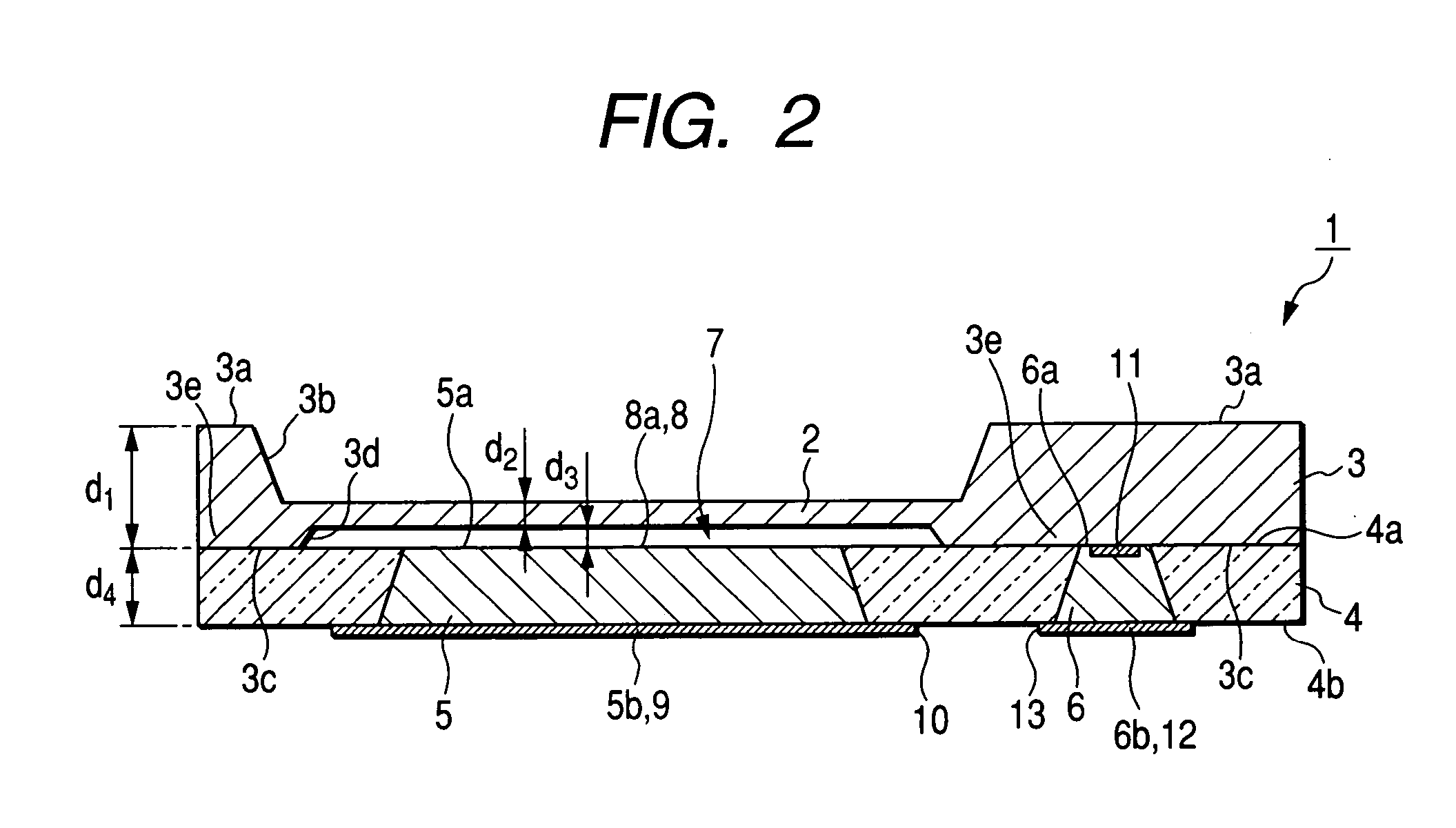

Thin-film semiconductor device for display apparatus, method for manufacturing thin-film semiconductor device for display apparatus, el display panel, and el display apparatus

ActiveUS20130082271A1Eliminate parasitic capacitanceFlatness be increaseSolid-state devicesSemiconductor/solid-state device manufacturingElectrically conductiveEngineering

A thin-film semiconductor device for a display apparatus according to the present disclosure includes: a gate electrode above a substrate; a gate insulating film above the gate electrode; a semiconductor layer on the gate insulating film; a first electrode above the semiconductor layer; a second electrode in a same layer as the first electrode; an interlayer insulating film covering the first electrode and the second electrode; a gate line above the interlayer insulating film; and a power supply line in a same layer as the gate line and adjacent to the gate line. Furthermore, the gate electrode and the gate line are electrically connected via a first conductive portion, and the second electrode and the power supply line are electrically connected via a second conductive portion.

Owner:JOLED INC

Signal Control Circuit, Power Control Circuit, Drive Circuit, Timing Controller, Touch System, and Touch Display Device and Driving Method Thereof

ActiveUS20170329167A1Eliminate parasitic capacitanceAvoid it happening againStatic indicating devicesNon-linear opticsDisplay deviceParasitic capacitance

Exemplary embodiments of the present invention relate to a touch technology, and more specifically, to a signal control circuit, a power control circuit, a drive circuit, a timing controller, a touch system, and a touch sensitive display device and a driving method thereof that can simply swing various voltages in a display device for a touch mode period by using a modulated ground voltage obtained by swinging a ground voltage, thereby effectively providing touch driving and preventing unnecessary parasitic capacitance from being generated not only in an active area but also in all other areas.

Owner:LG DISPLAY CO LTD

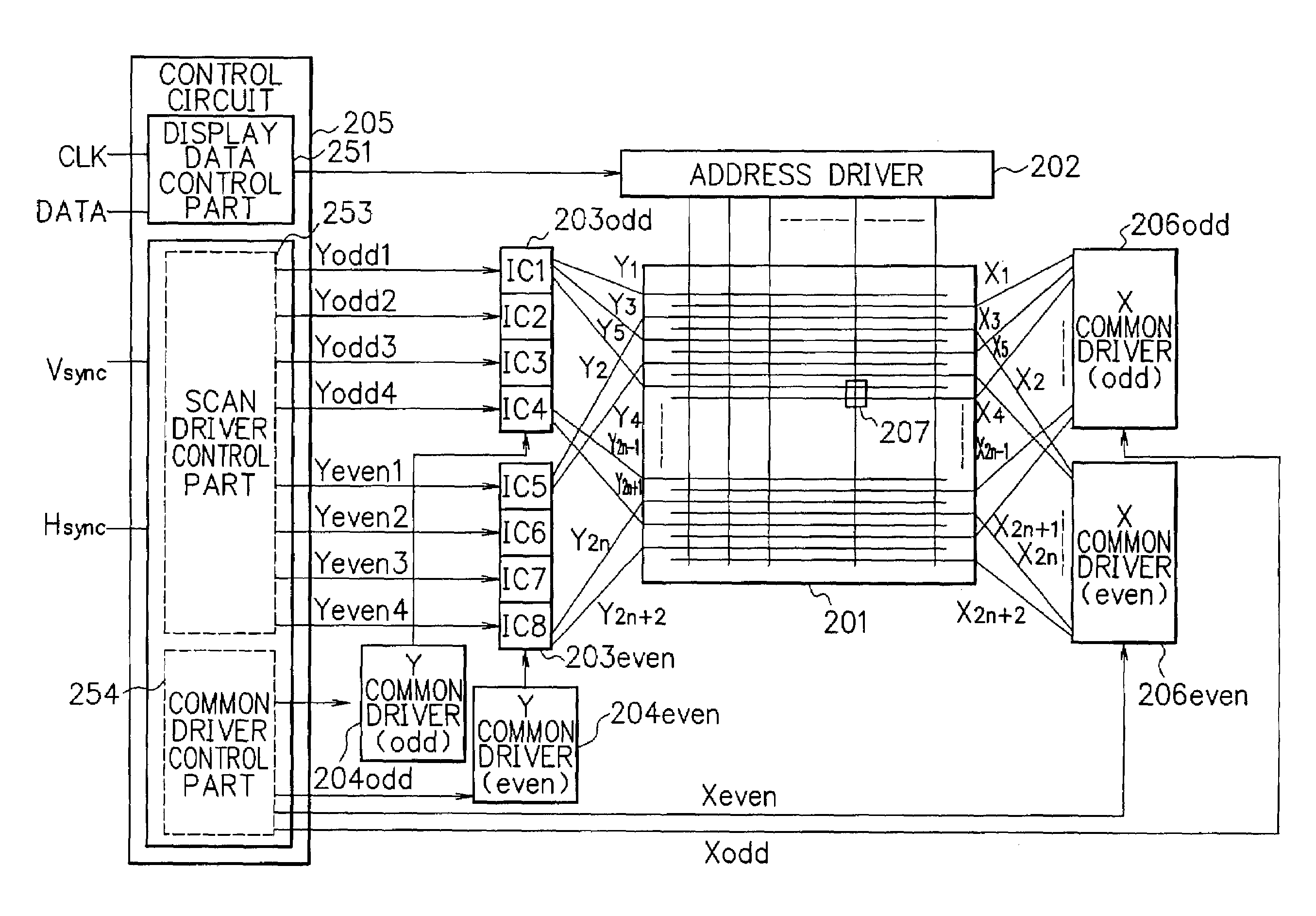

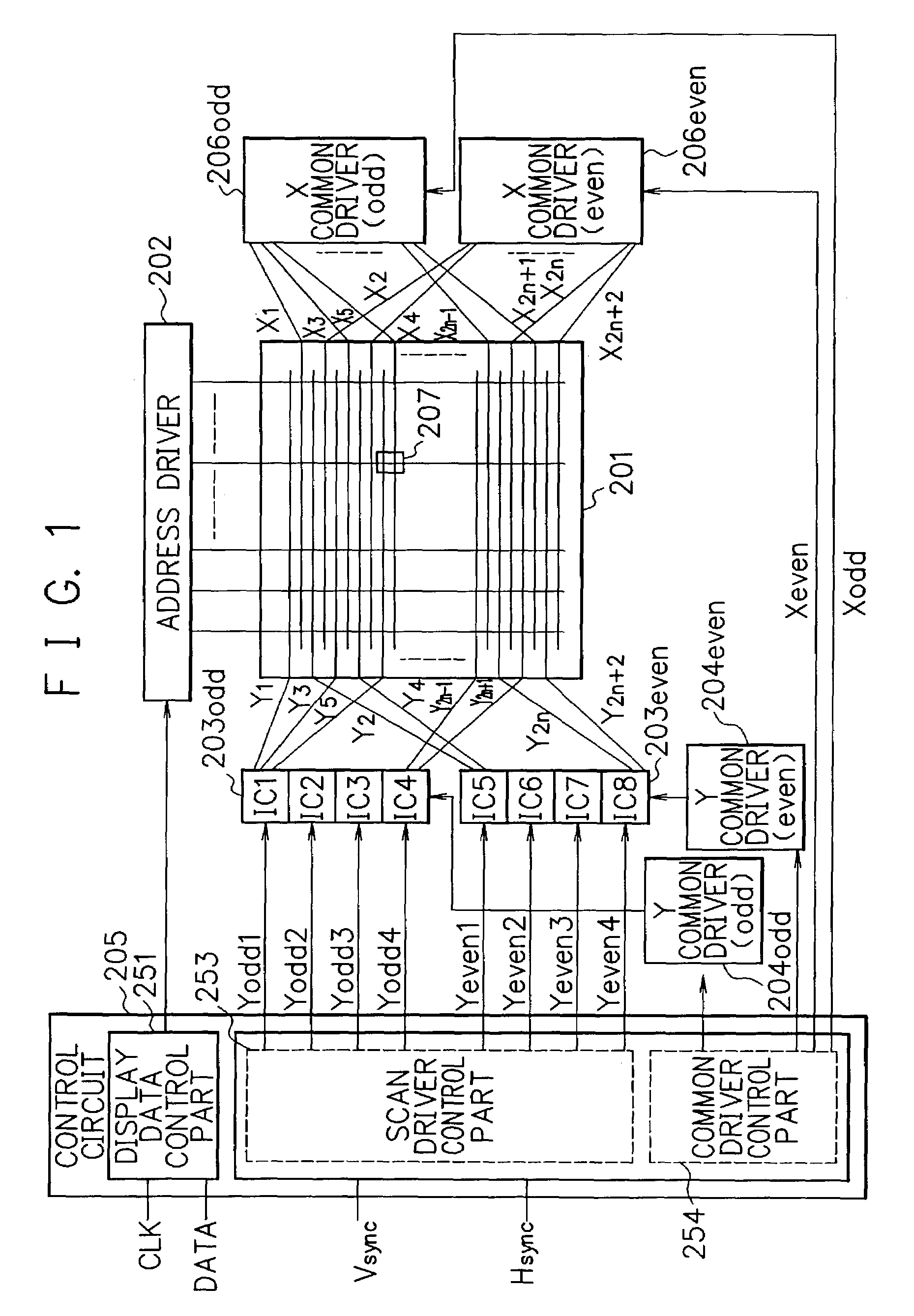

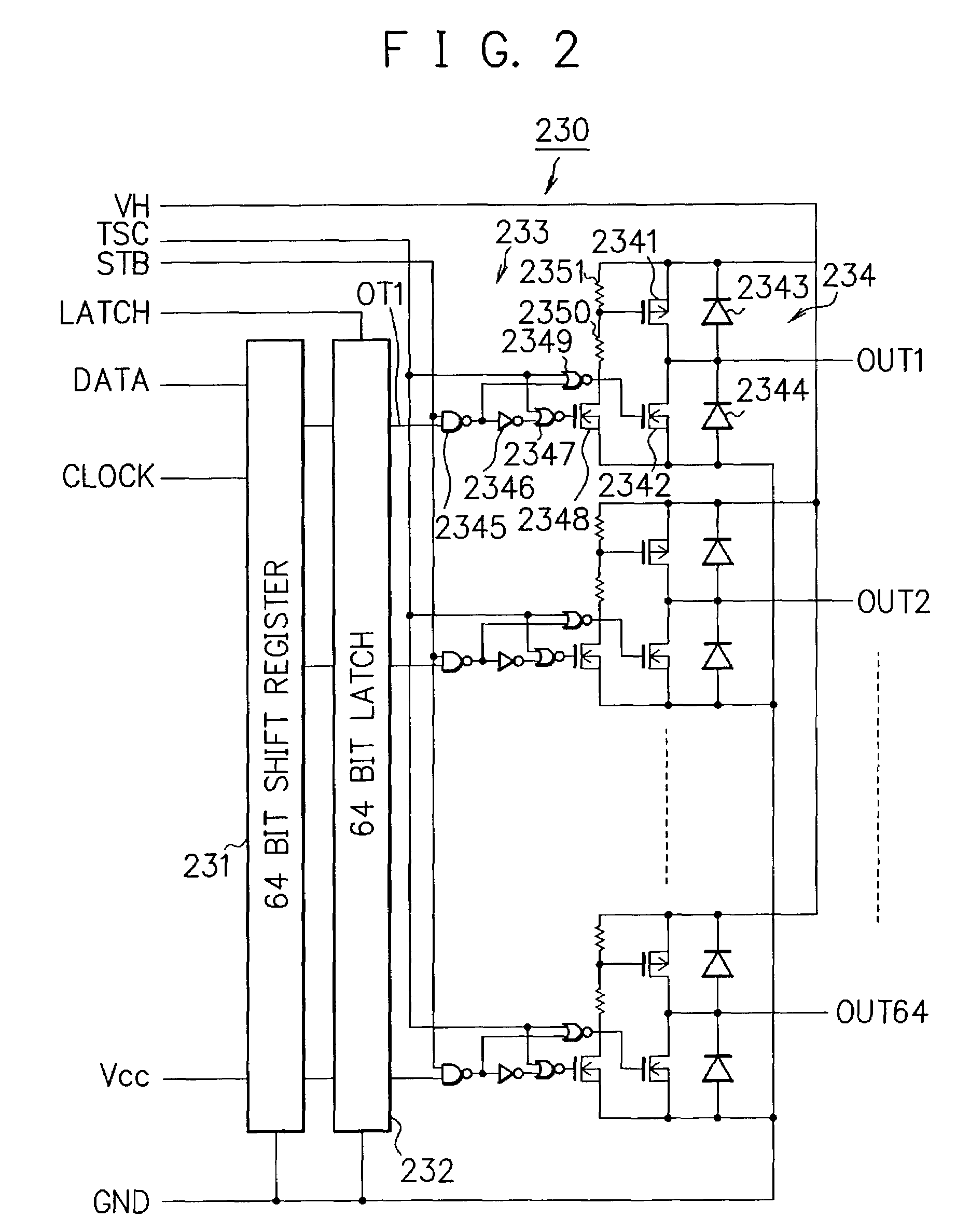

Display panel drive circuit and plasma display

InactiveUS7075528B2Reduce power consumptionImprovement in power recovery efficiencyCathode-ray tube indicatorsInput/output processes for data processingEngineeringOutput impedance

A display panel drive circuit having a plurality of first and second electrodes for connecting to a display panel, a first drive circuit for driving the first electrodes, and a second drive circuit for driving the second electrodes. The second drive circuit is connected to drive all or a part of a plurality of the second electrodes, or interrupted to increase output impedance.

Owner:HITACHI LTD

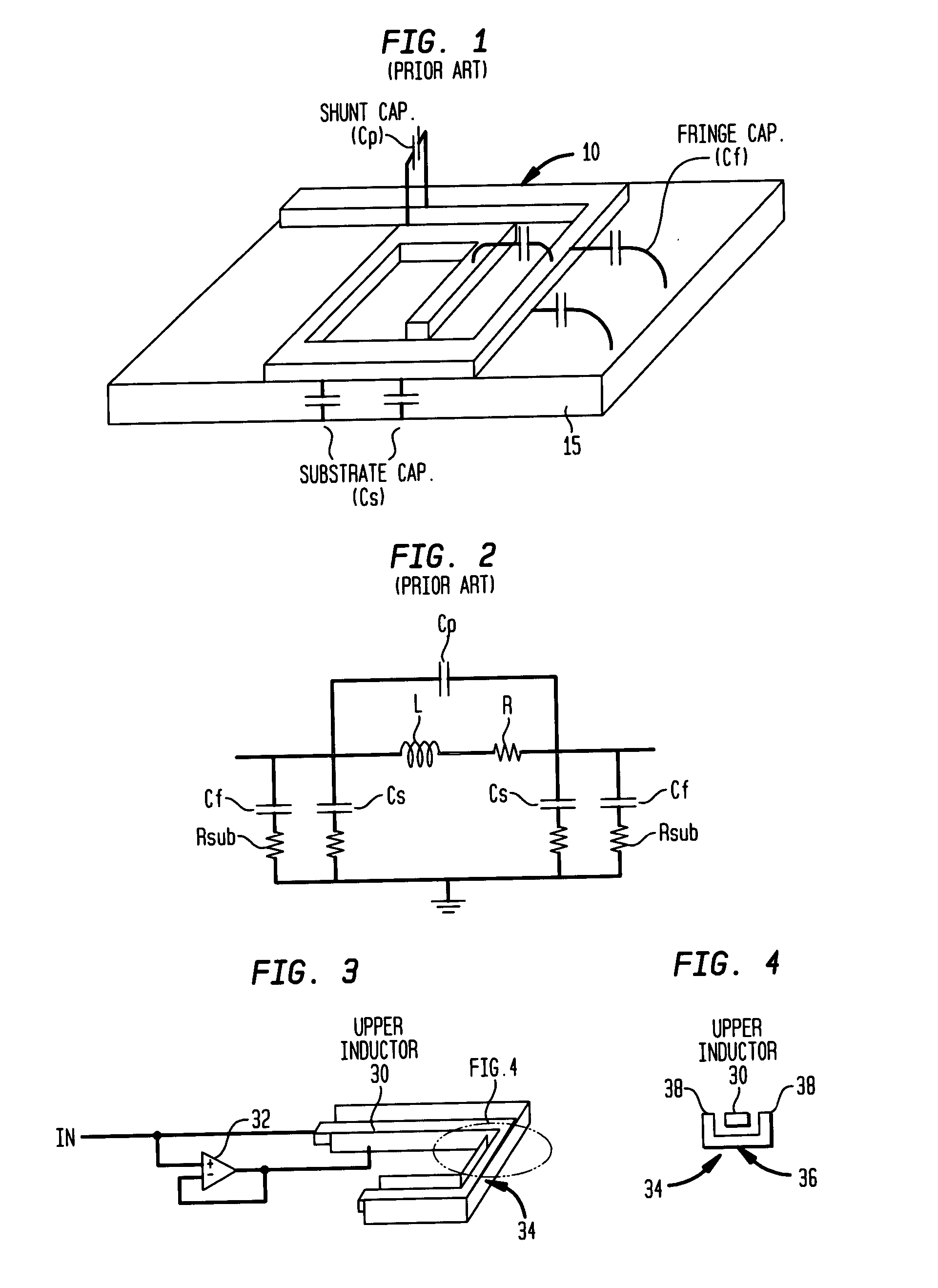

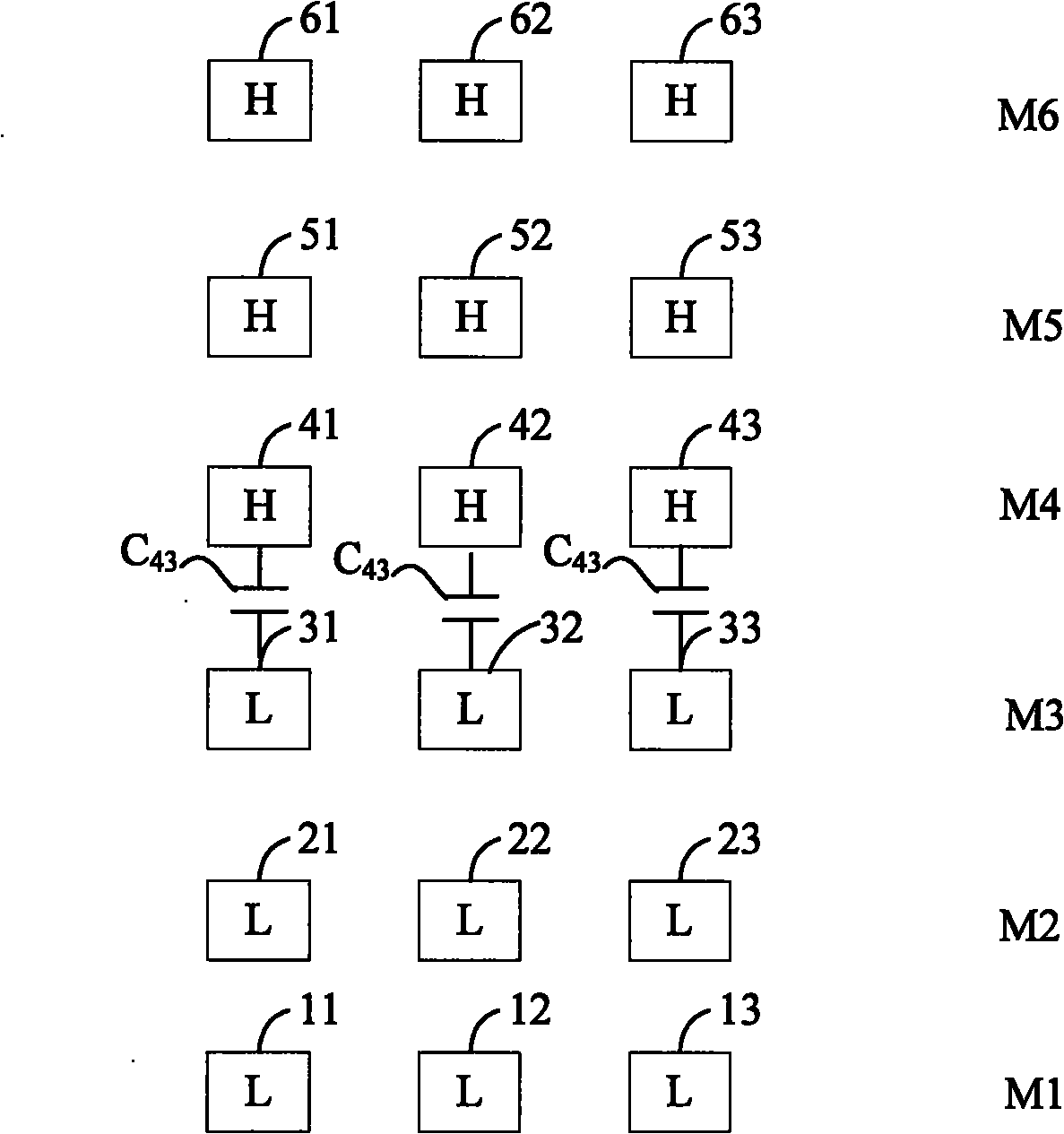

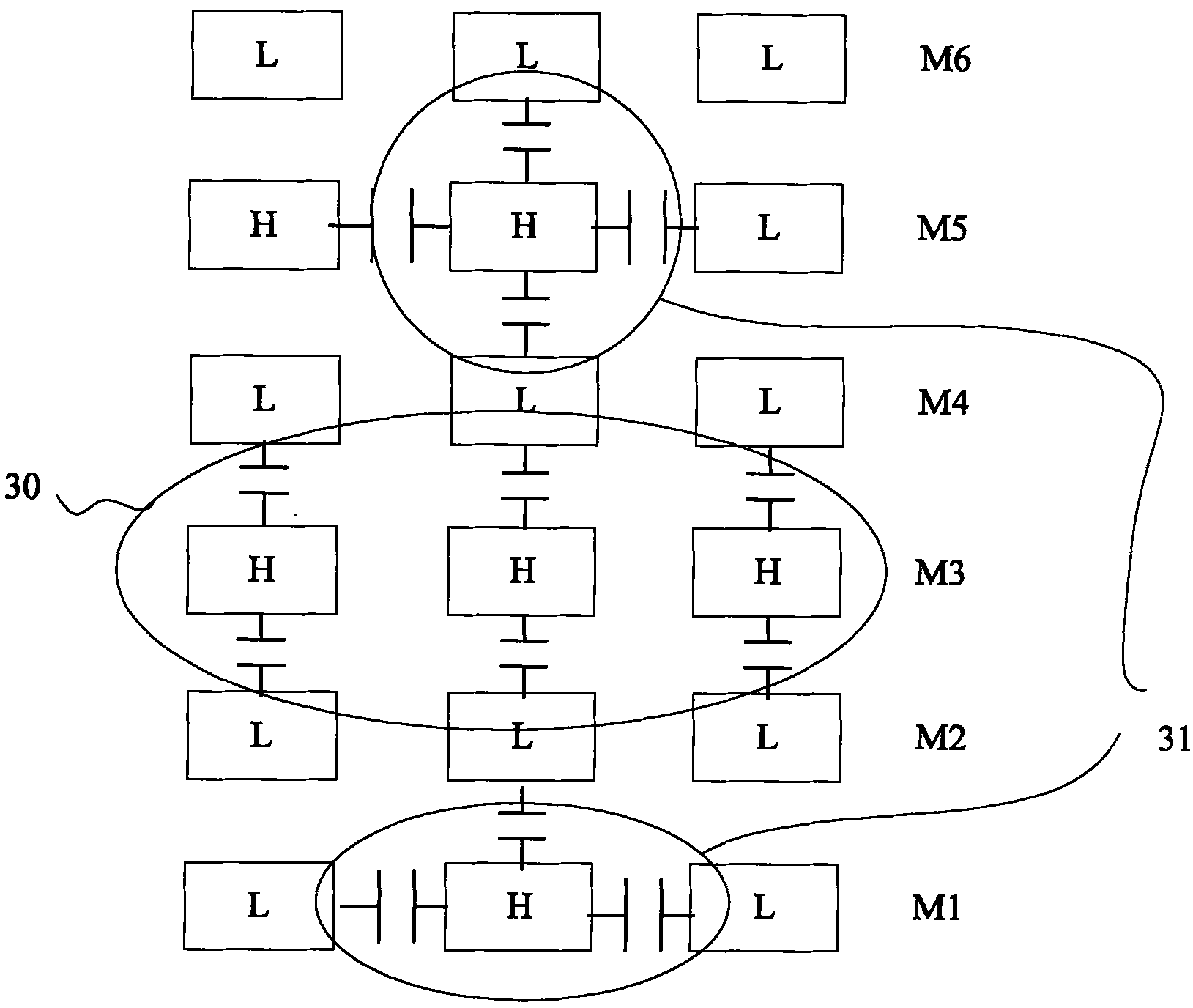

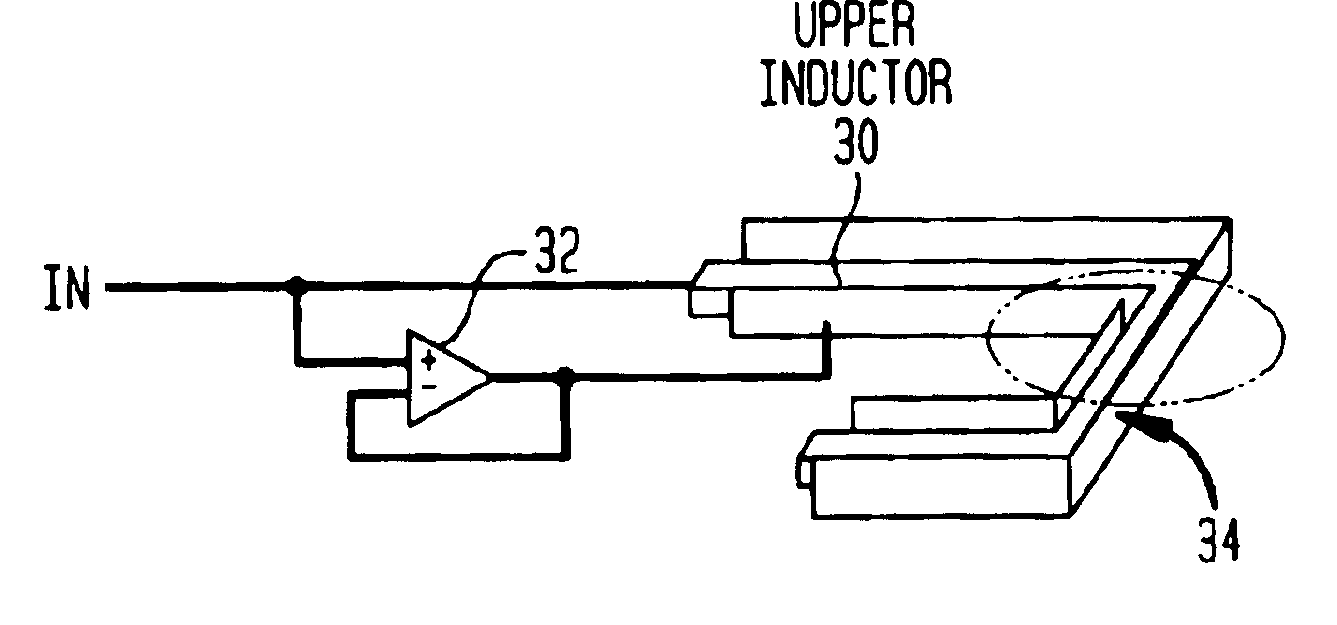

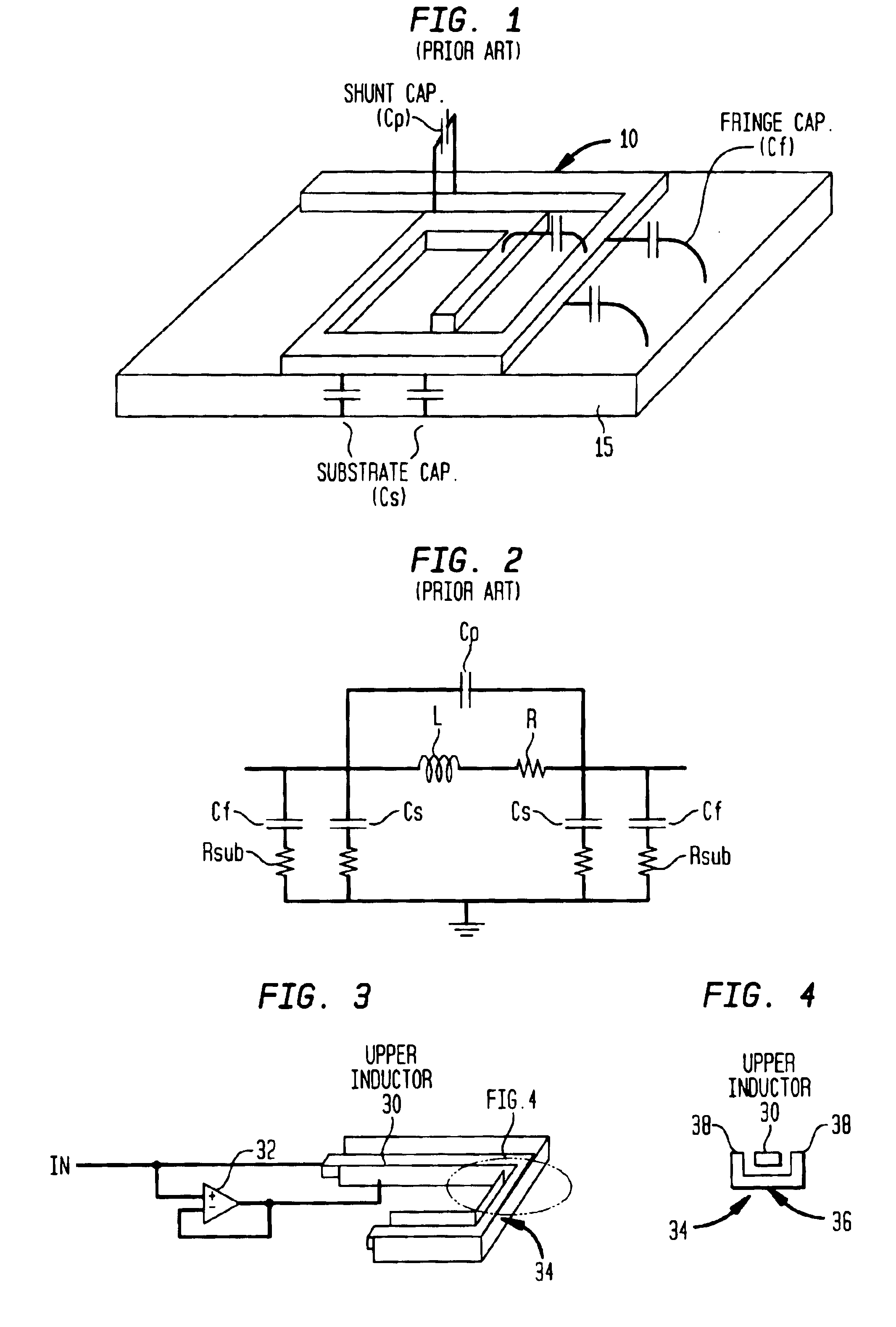

Three demensional dynamicaly shielded high-q BEOL metallization

InactiveUS20050034885A1Reduce the impactHigh QMagnetic/electric field screeningCross-talk/noise/interference reductionCapacitive couplingParasitic capacitance

Three dimensional dynamically shielded high quality factor (Q) BEOL metal elements, such as inductor elements, are disclosed. Three dimensional shielding structures for the BEOL elements reduce or eliminate parasitic substrate capacitive coupling between the BEOL element and the conductive substrate, and parasitic shunt capacitance coupling between different adjacent shunt sections of the BEOL element. The reduction or elimination of the parasitic capacitive components provides high Q BEOL metal elements such as inductor elements. The three dimensional shield structure includes a lower shield surface having a width greater than the width of the BEOL element, and opposed side shield surfaces which extend upwardly from opposite side edges of the lower shield surface, such that the three dimensional shield element forms a U shaped shield around the BEOL element. The three dimensional shield element is dynamically driven to the same electrical potential as the BEOL element, to substantially eliminate the metal element's parasitic capacitances.

Owner:IBM CORP

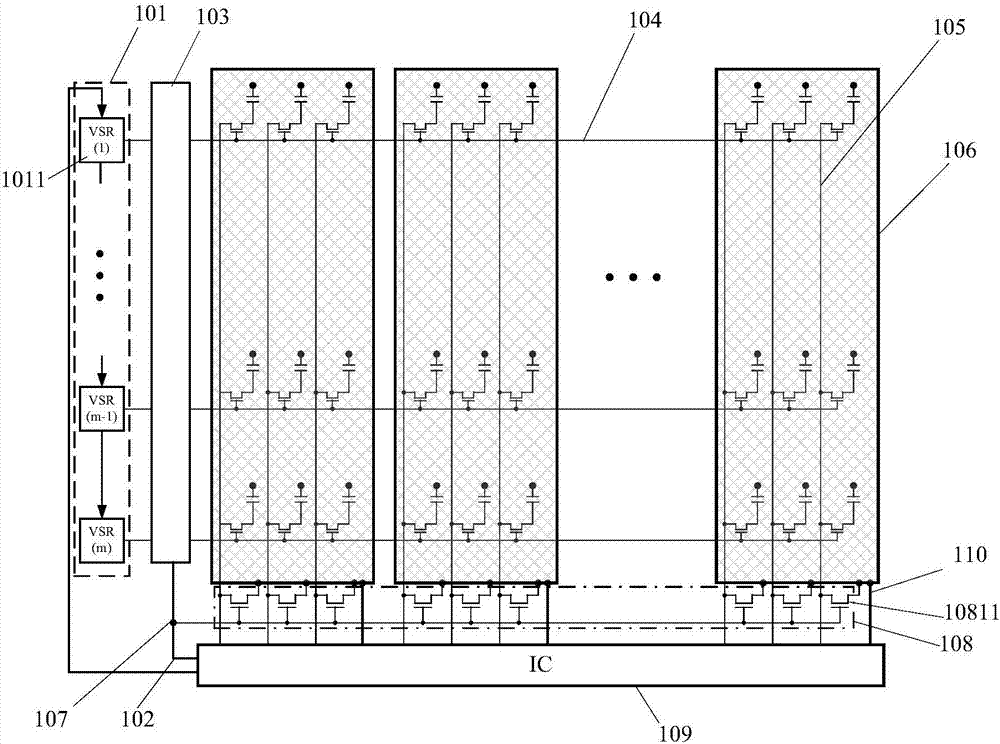

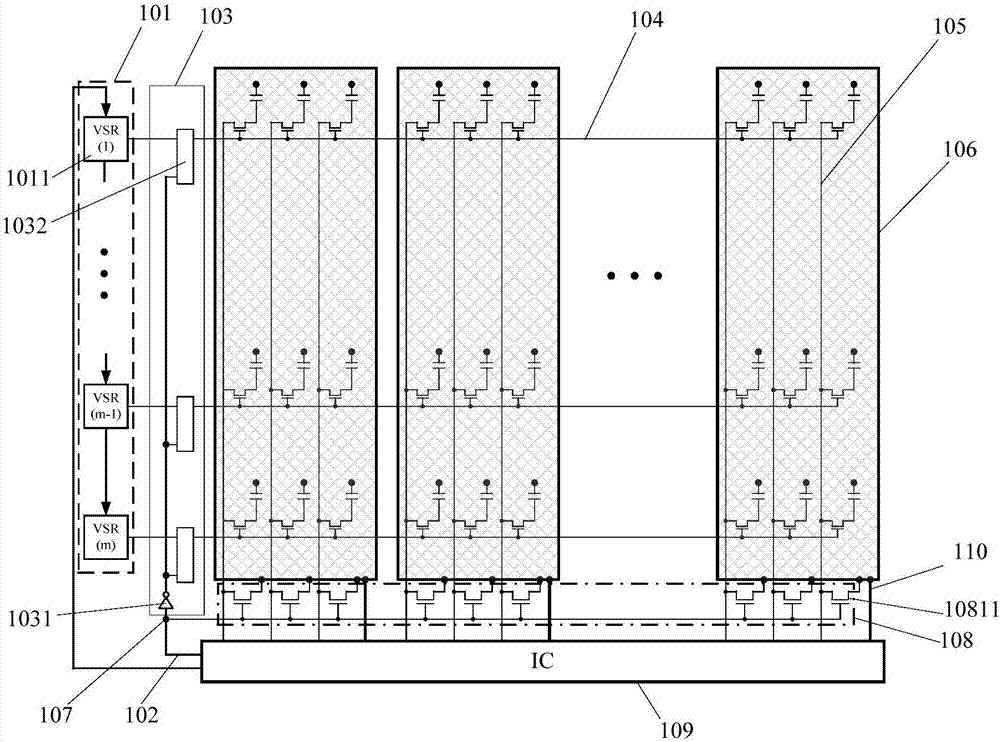

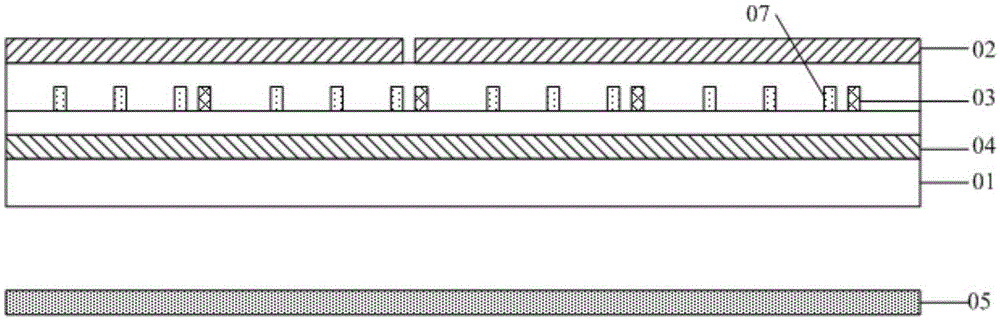

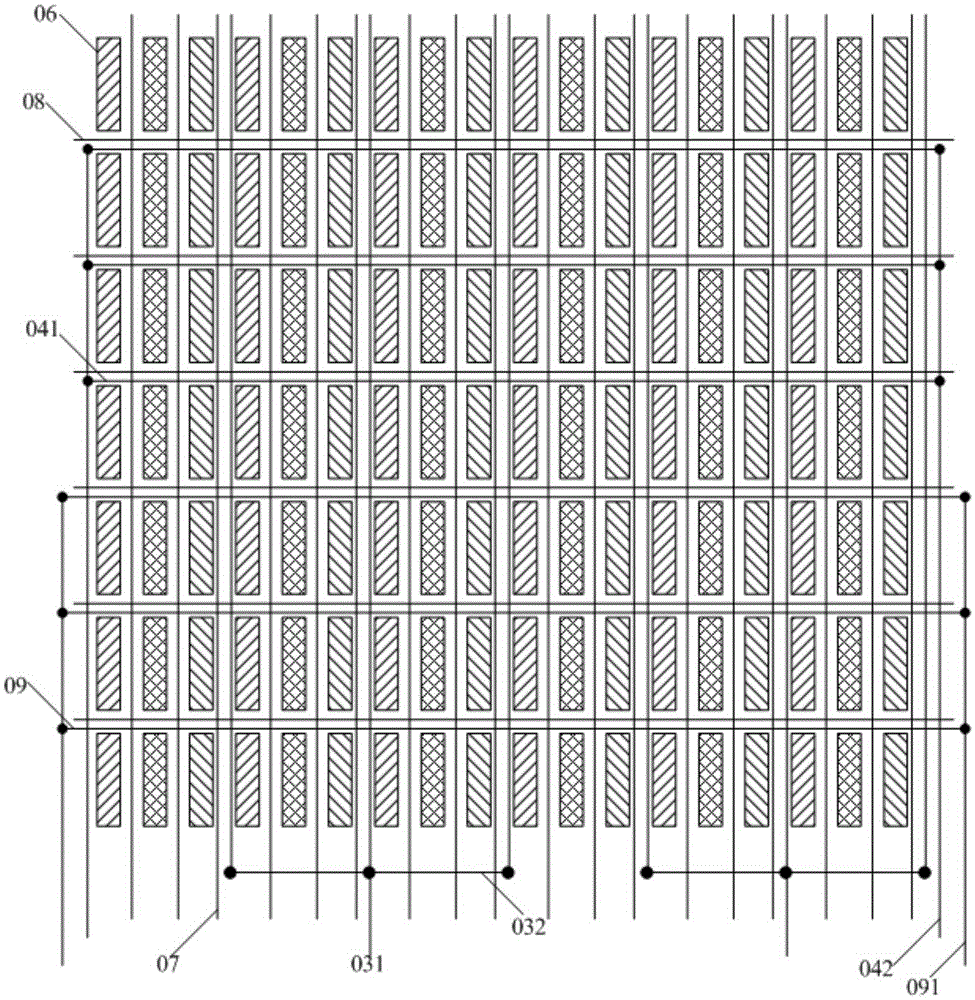

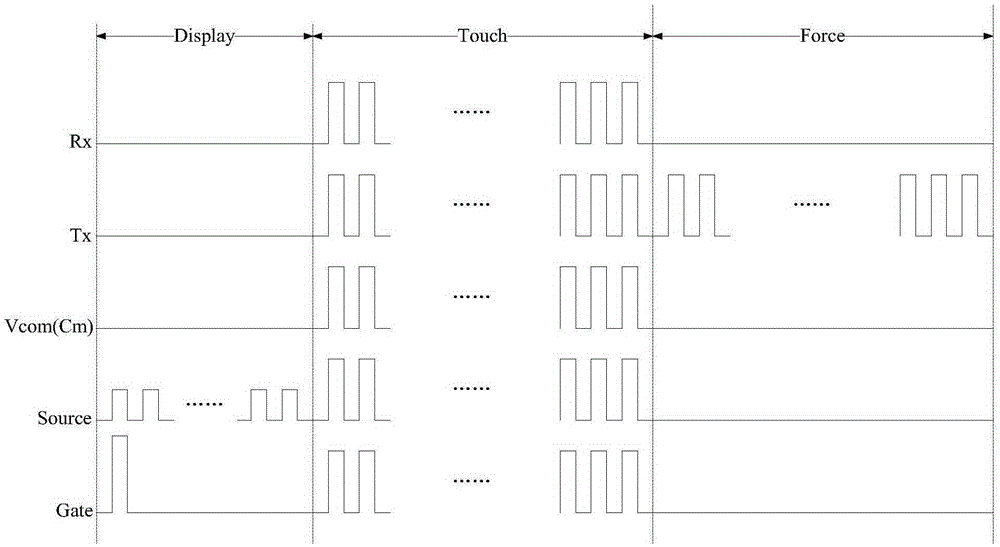

Touch display panel, driving method and touch display device

ActiveCN106959781AImprove signal detection accuracyEliminate parasitic capacitanceInput/output processes for data processingControl signalParasitic capacitance

The invention discloses a touch display panel, a driving method and a touch display device. The touch display panel comprises a shift circuit, a control signal line, a control circuit, multiple scanning lines, multiple data lines, multiple touch driving electrodes, a switching control signal end and a switching control switch unit. During a touch period of a frame cycle, all switching control switches are switched on under the control of a first control signal output by the switching control signal end, so that all the touch driving electrodes are electrically connected with at least one data line through at least one switching control switch; the control circuit enables the scanning lines to be suspended based on the first control signal output by the switching control signal end and a signal at the output end of the shift circuit. Through the touch display panel, coupling between devices on the touch display panel is lowered, stray capacitance between the scanning lines and other devices is eliminated, and the signal detection precision of the touch display panel is improved.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

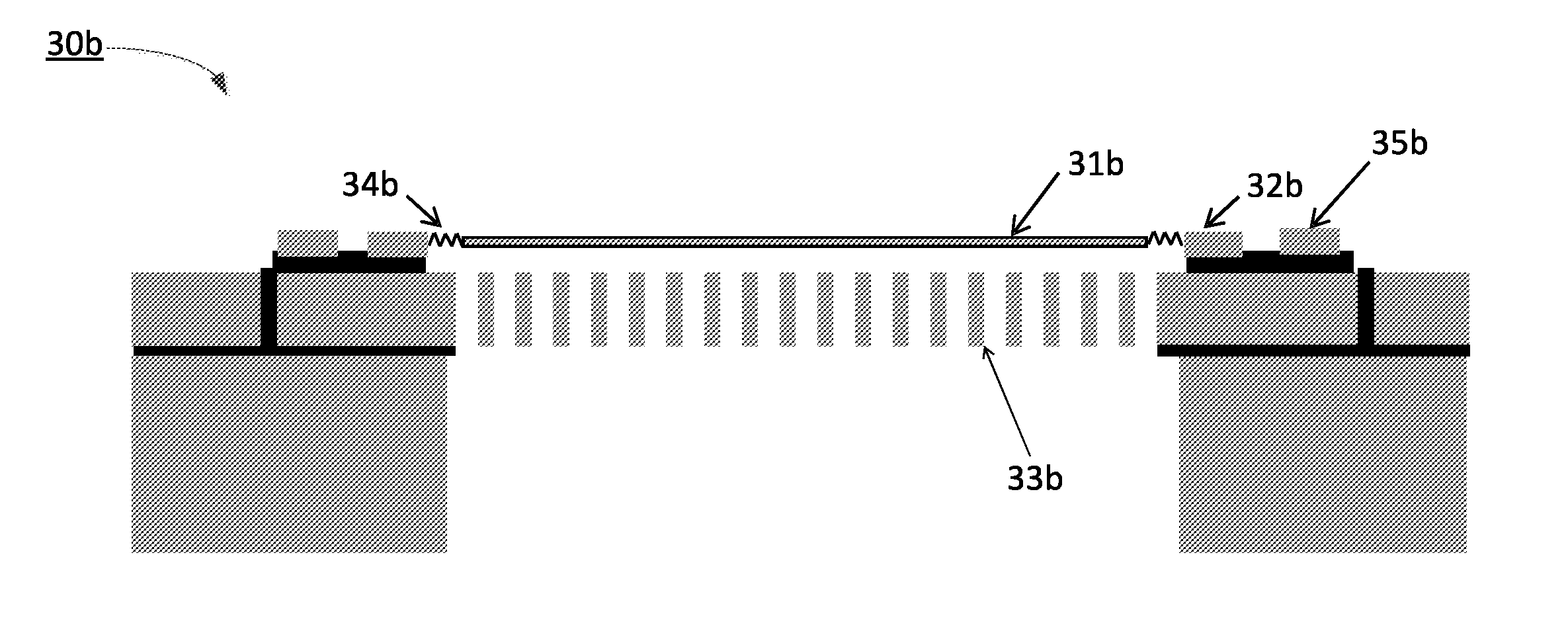

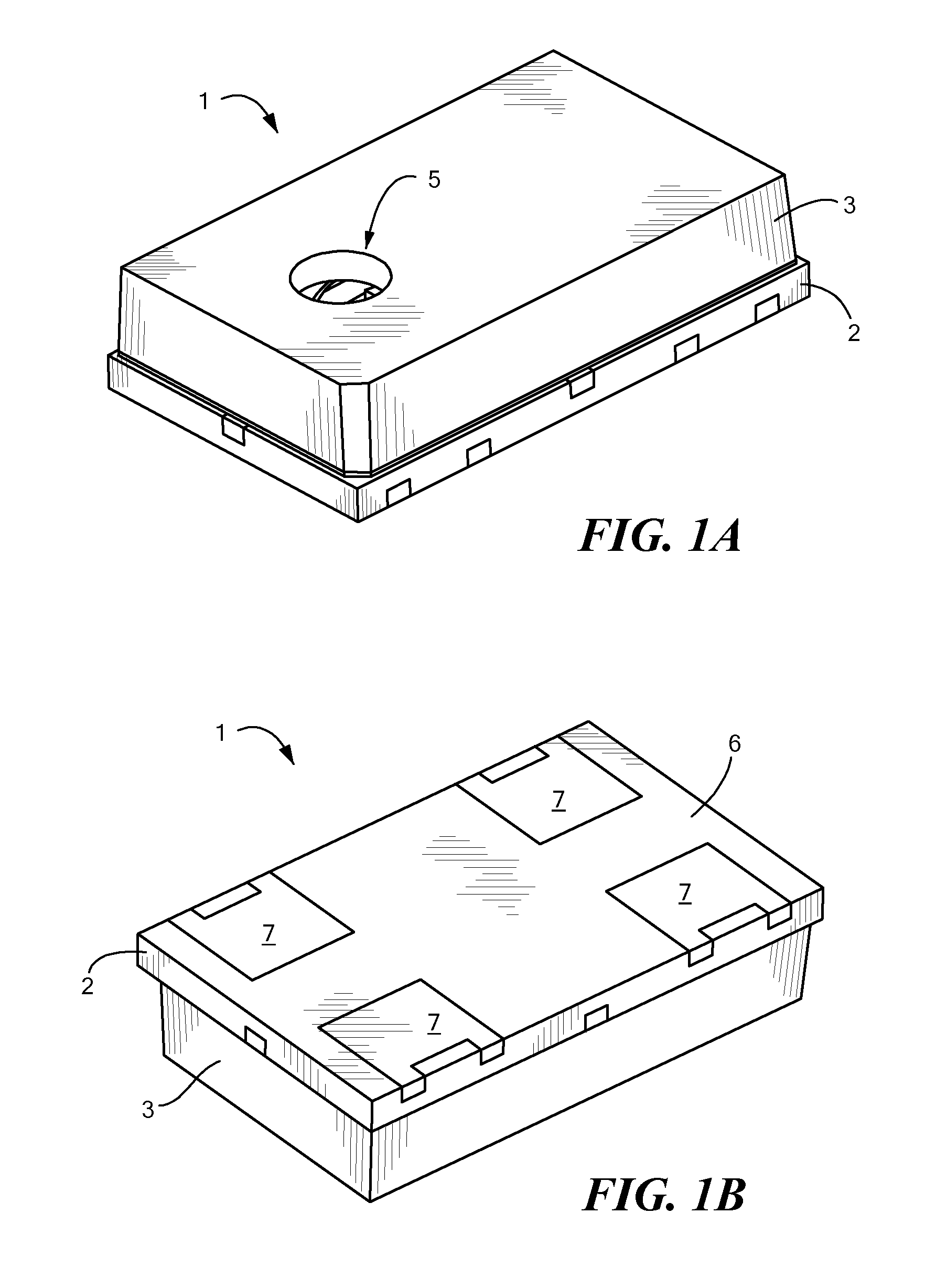

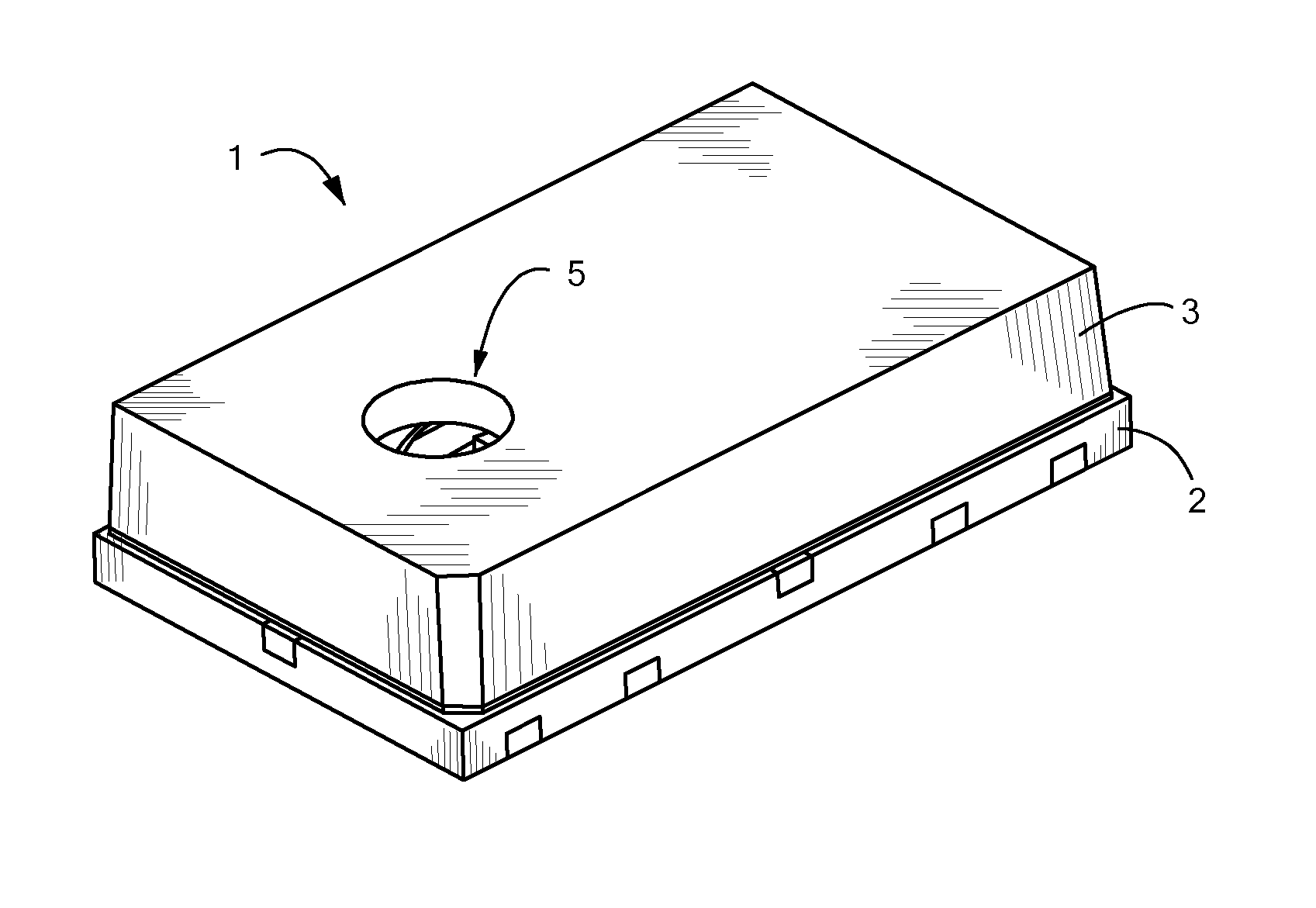

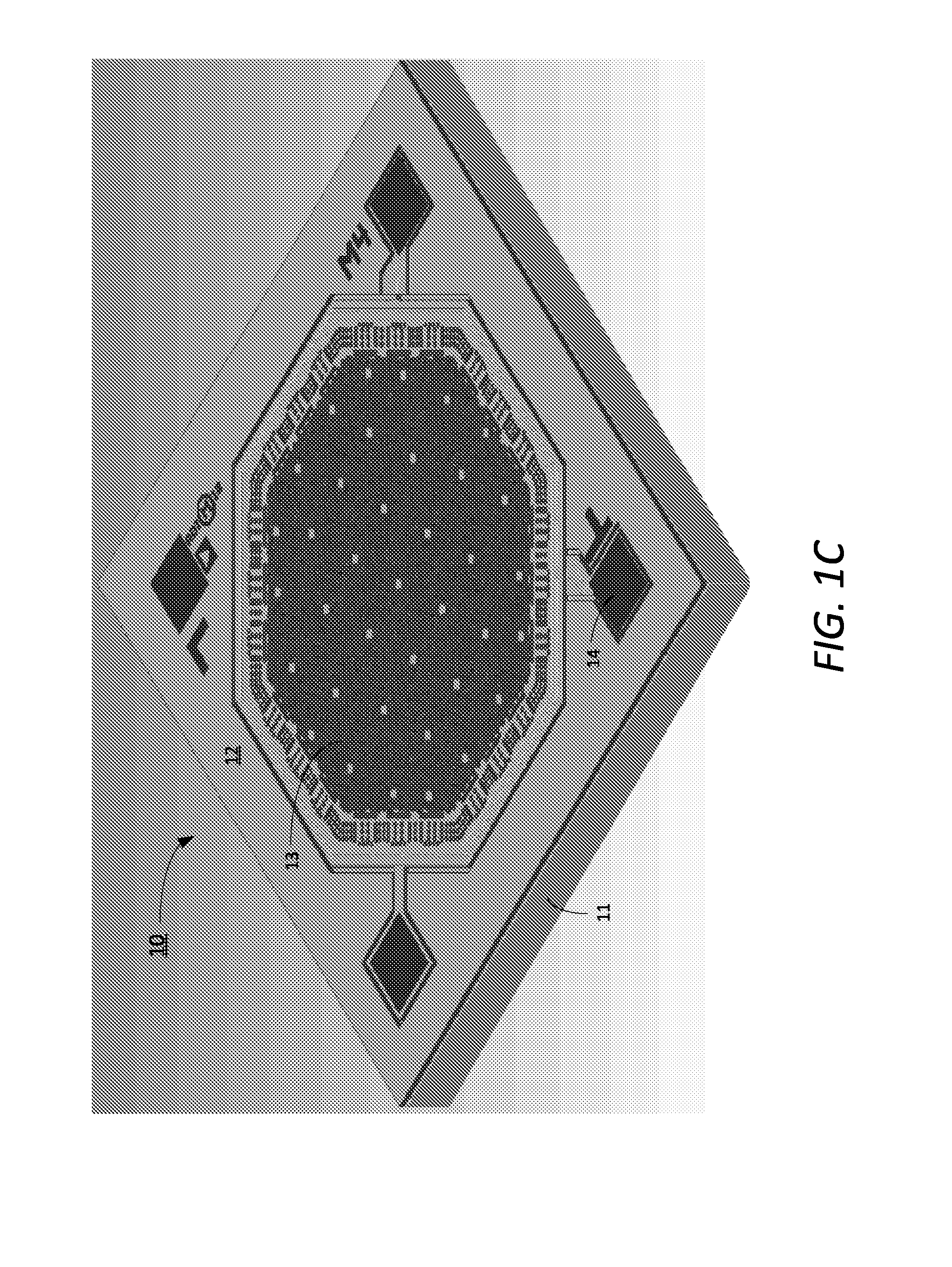

Microphone with parasitic capacitance cancelation

ActiveUS8755541B2Improve performanceEliminate parasitic capacitanceSemiconductor electrostatic transducersElectrostatic transducer microphonesElectricityParasitic capacitance

A microelectromechanical microphone and method of manufacturing the same are disclosed. The microphone has a moveable diaphragm and a fixed backplate that create a variable capacitance. A fixed anchor electrically coupled to the diaphragm has an electrode that measures the variable capacitance, but also measures an unwanted, additive, parasitic capacitance. Various embodiments include a reference electrode, manufactured in the same deposition layer as the diaphragm or anchor, that measures only the parasitic capacitance. A circuit is provided either on-chip or off-chip that subtracts the capacitance measured at the reference electrode from that measured at the anchor, thereby producing only the desired variable capacitance as output. Because the reference electrode is deposited at the same time as the diaphragm or anchor, only minimal changes are required to existing manufacturing techniques.

Owner:INVENSENSE

Electric conducting plug and forming method of electric conducting plug

ActiveCN103730433AAvoid corrosionContact won't happenSemiconductor/solid-state device detailsSolid-state devicesDielectric layerSemiconductor

The invention discloses an electric conducting plug and a forming method of the electric conducting plug. The forming method of the electric conducting plug comprises the steps that a semiconductor substrate is provided, a grid electrode is formed on the semiconductor substrate, a source region and a drain region are formed in the semiconductor substrate located on the two sides of the grid electrode respectively, a stress layer and an interlayer dielectric layer on the stress layer are formed on the semiconductor substrate, and the stress layer covers the grid electrode, the source region and the drain region; contact holes are formed in the interlayer dielectric layer and the stress layer; a liner layer is formed on the side walls of the contact holes; after the liner layer is formed, the contact holes are cleaned so as to eliminate polymers generated in the process that the contact holes are formed, the liner layer is used for preventing the stress layer from being corroded in the cleaning process of the contact holes, after the contact holes are formed, electric conducting materials are deposited in the contact holes, and the electric conducting plug is formed. Due to the liner layer, the stress layer is prevented from being corroded in the process that the polymers in the contact holes are cleaned later, contact of the grid electrode and the electric conducting plug is further prevented, and good performance of a semiconductor is guaranteed.

Owner:SEMICON MFG INT (SHANGHAI) CORP

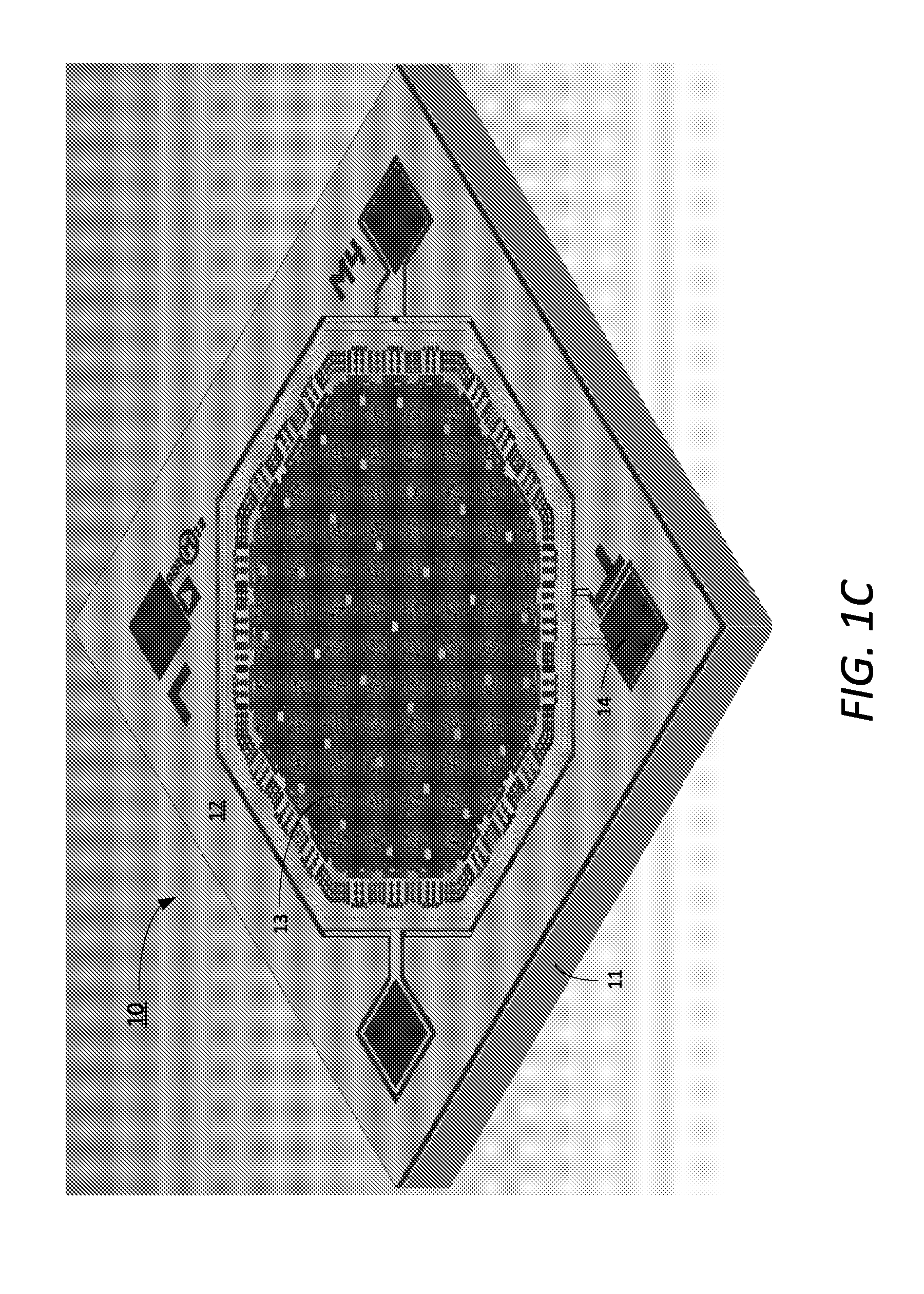

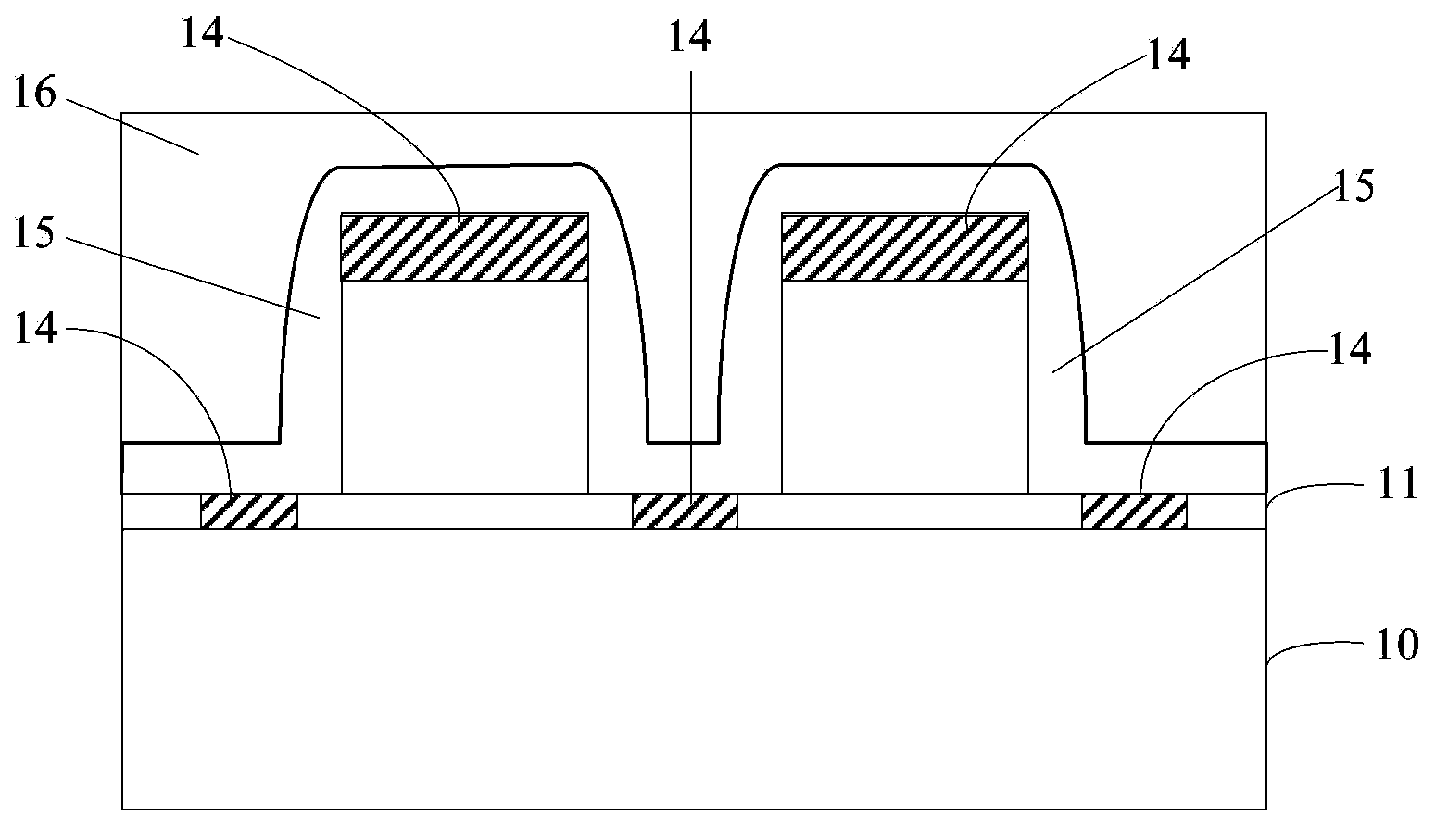

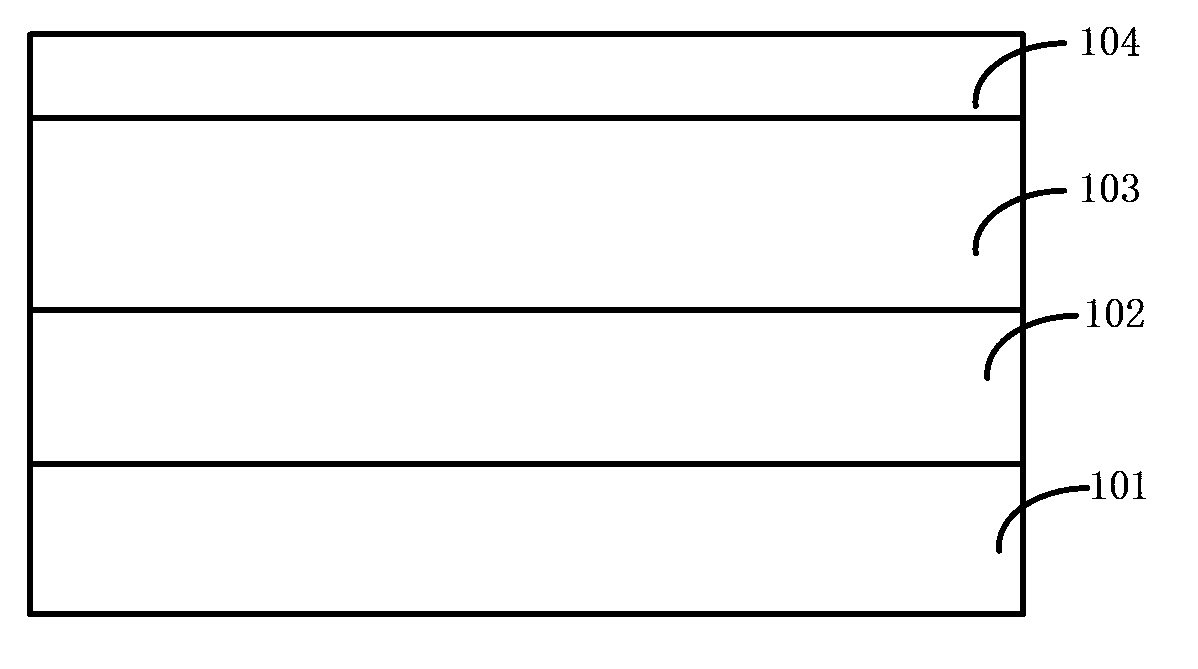

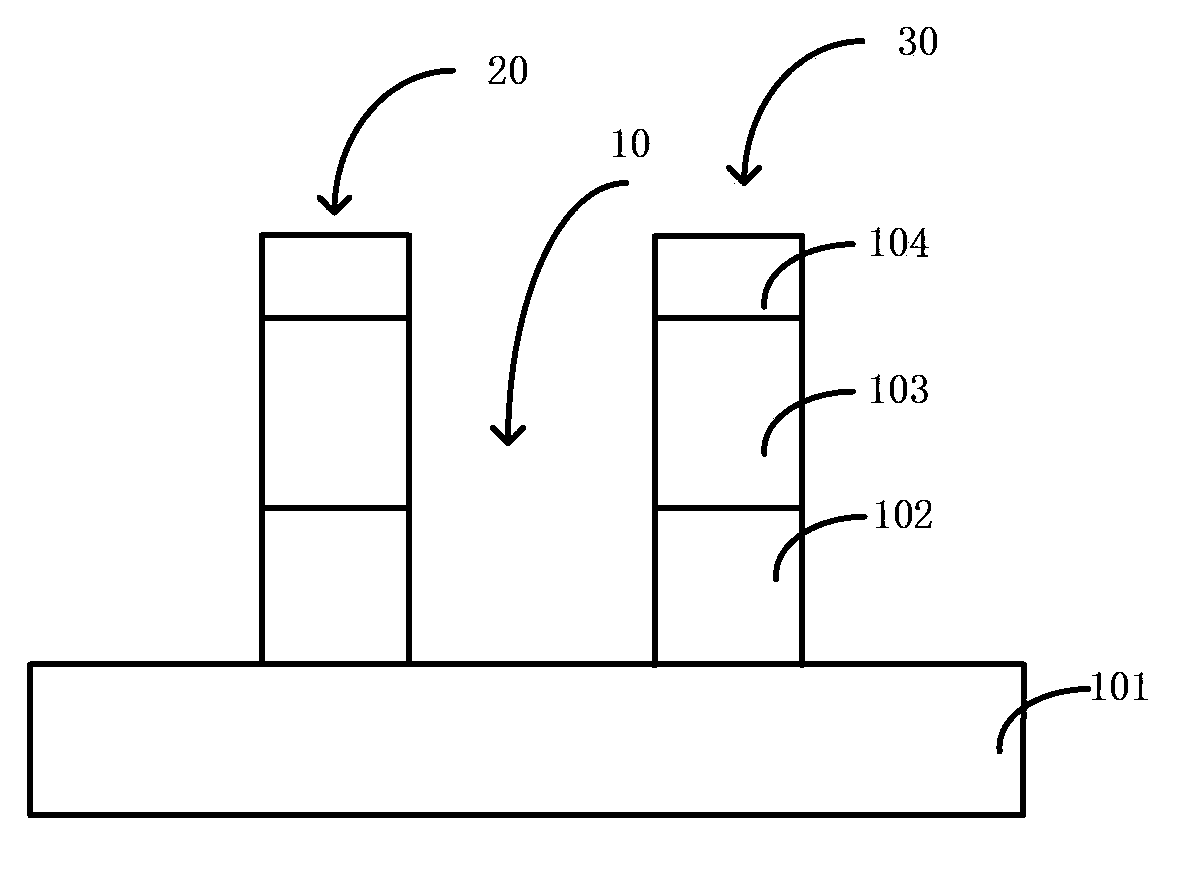

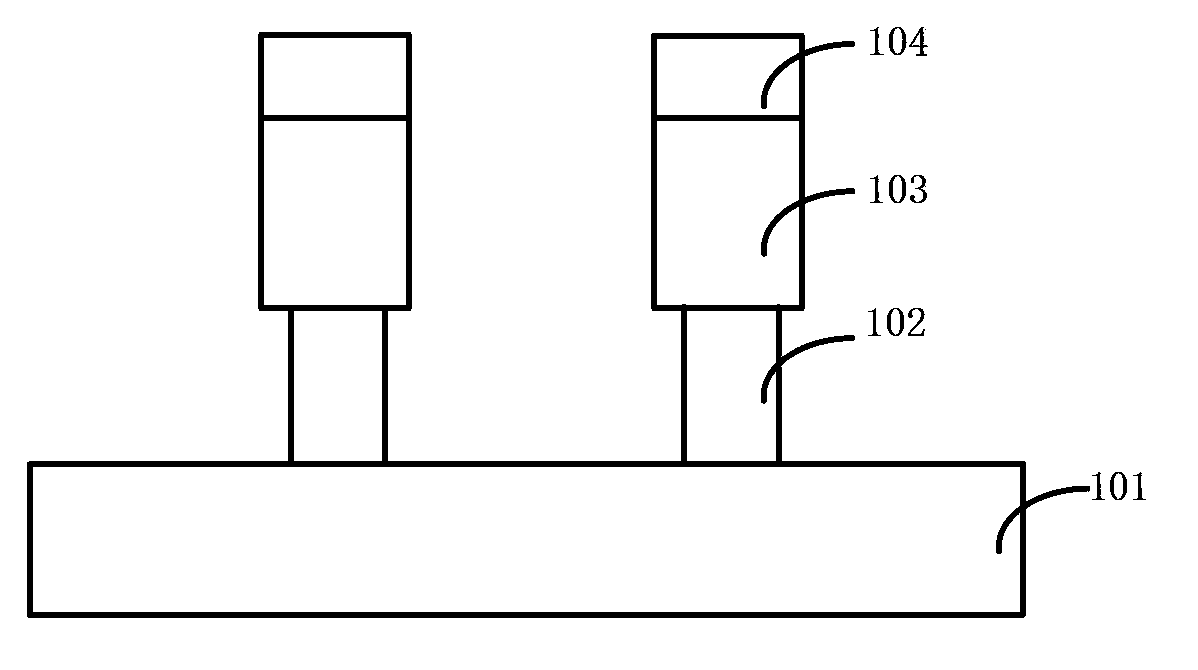

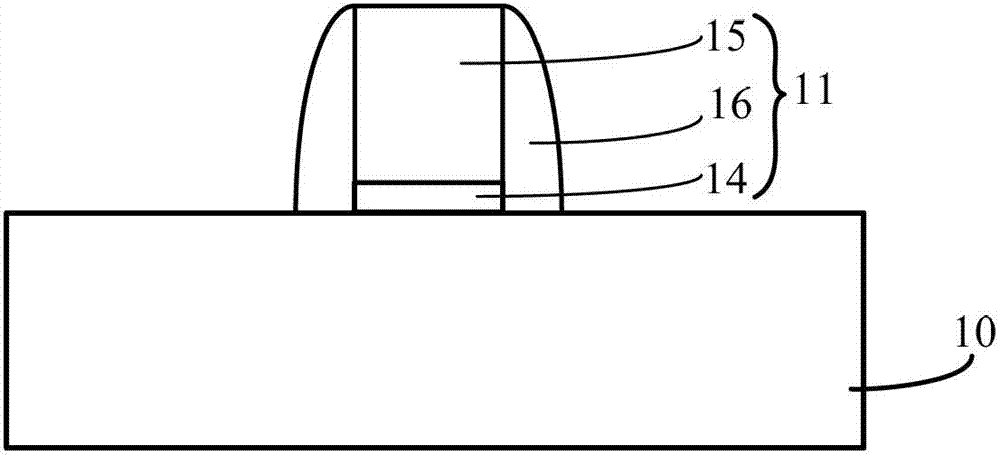

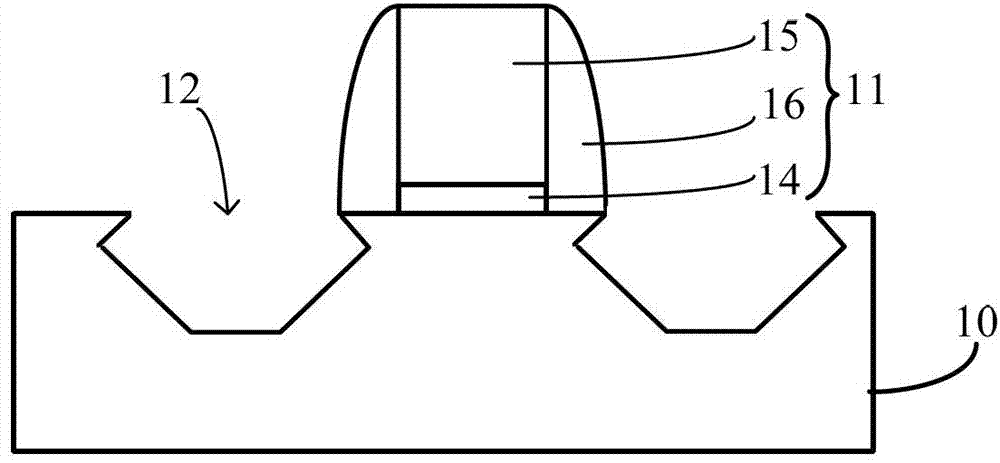

Semiconductor device with height-controllable fin and preparation method

ActiveCN103681275AGood static performanceEliminate parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceIsotropic etching

The invention relates to a semiconductor device with a height-controllable fin and a preparation method. The preparation method comprises the following steps: providing a semiconductor substrate; forming a first semiconductor material layer, a second semiconductor material layer and a hard mask layer on the substrate; etching the hard mask layer, a second semiconductor material layer and a first semiconductor material layer to form a trench and a fin pattern; performing isotropic etching to remove a part of the first semiconductor material layer in the fin pattern to form a virtual fin with reduced critical size; depositing dielectric layers to fill the trench and cover the fin pattern; etching the dielectric layers till the second semiconductor material layer below, in order to expose the second semiconductor material layer to form the fin. The preparation process of the fin is easy to control, and the obtained device is more stable.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Array of gate dielectric structures to measure gate dielectric thickness and parasitic capacitance

InactiveUS6841832B1Eliminate parasitic capacitanceAccurate measurementSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsGate dielectricParasitic capacitance

Accurate determination of gate dielectric thickness is required to produce high-reliability and high-performance ultra-thin gate dielectric semiconductor devices. Large area gate dielectric capacitors with ultra-thin gate dielectric layers suffer from high gate leakage, which prevents the accurate measurement of gate dielectric thickness. Accurate measurement of gate dielectric thickness of smaller area gate dielectric capacitors is hindered by the relatively large parasitic capacitance of the smaller area capacitors. The formation of first and second dummy structures on a wafer allow the accurate determination of gate dielectric thickness. First and second dummy structures are formed that are substantially similar to the gate dielectric capacitors except that the first dummy structures are formed without the second electrode of the capacitor and the second dummy structures are formed without the first electrode of the capacitor structure. The capacitance, and therefore thickness, of the gate dielectric capacitor is determined by subtracting the parasitic capacitances measured at the first and second dummy structures.

Owner:GLOBALFOUNDRIES INC

Capacity testing method

InactiveCN102169141AEasy to implementLow costResistance/reactance/impedenceCapacitanceCapacity value

The invention discloses a capacity testing method in a multi-layer interconnection system which is used for increasing the accuracy of capacity test. The method comprises the following steps: according to a test signal applying manner, applying test signals to all interconnected wires in the multi-layer interconnection system; after applying the test signals each time, testing the overall capacity value of the multi-layer interconnection system; and calculating a to-be-tested capacity value, according to the tested overall capacity value and the quantitative relation between the overall capacity value and the to-be-tested capacity value.

Owner:SHANGHAI RES INST OF MICROELECTRONICS SHRIME PEKING UNIV

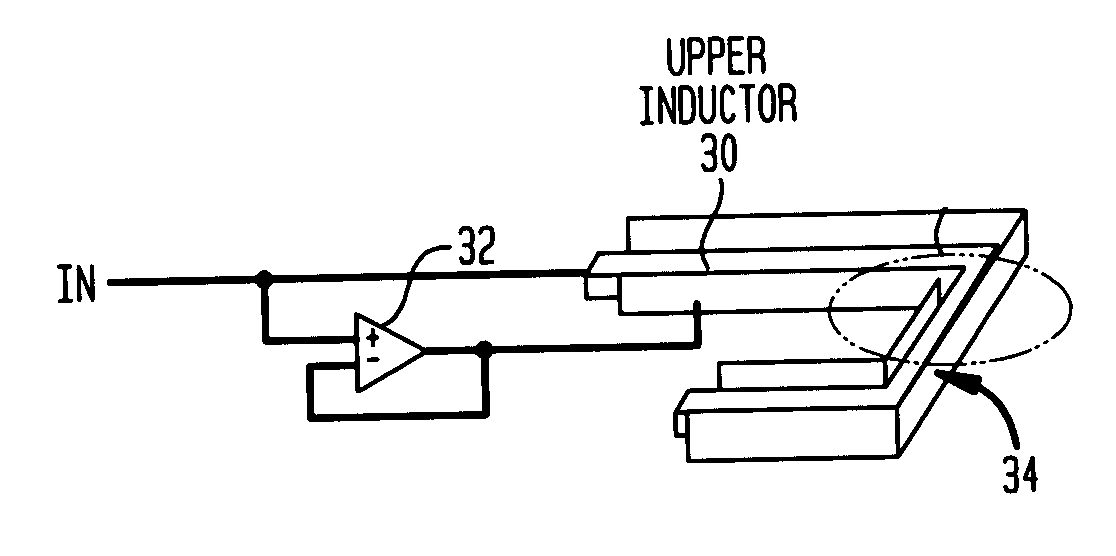

Three dimensional dynamically shielded high-Q BEOL metallization

InactiveUS6936764B2Reduce impactHigh QMagnetic/electric field screeningSemiconductor/solid-state device detailsCapacitive couplingParasitic capacitance

Three dimensional dynamically shielded high quality factor (Q) BEOL metal elements, such as inductor elements, are disclosed. Three dimensional shielding structures for the BEOL elements reduce or eliminate parasitic substrate capacitive coupling between the BEOL element and the conductive substrate, and parasitic shunt capacitance coupling between different adjacent shunt sections of the BEOL element. The reduction or elimination of the parasitic capacitive components provides high Q BEOL metal elements such as inductor elements. The three dimensional shield structure includes a lower shield surface having a width greater than the width of the BEOL element, and opposed side shield surfaces which extend upwardly from opposite side edges of the lower shield surface, such that the three dimensional shield element forms a U shaped shield around the BEOL element. The three dimensional shield element is dynamically driven to the same electrical potential as the BEOL element, to substantially eliminate the metal element's parasitic capacitances.

Owner:INT BUSINESS MASCH CORP

Novel through silicon contact structure and method of forming same

ActiveCN110036475AReduce/eliminate potential differenceEliminate potential differenceSemiconductor/solid-state device detailsSolid-state devicesDielectric layerSilicon

In the TSC structure, a first dielectric layer is formed over the first major surface of the substrate. The substrate includes opposing second major surfaces. A TSC is formed in the first dielectric layer and the substrate such that the TSC passes through the first dielectric layer and extends into the substrate. A conductive plate electrically coupled to the TSC is formed over the first dielectric layer. An isolation trench is formed in the substrate to surround the conductive plate and is spaced apart from the conductive plate. A second dielectric layer is formed on the second major surfaceof the substrate. A plurality of first through holes extending into the substrate and connected to the TSC are formed in the second dielectric layer. A plurality of second through holes extending intothe substrate but not connected to the TSC are formed in the second dielectric layer.

Owner:YANGTZE MEMORY TECH CO LTD

Microphone with Parasitic Capacitance Cancelation

ActiveUS20140072150A1Improve MEMS microphone performanceEliminate parasitic capacitanceSemiconductor electrostatic transducersLiquid/solution decomposition chemical coatingElectricityParasitic capacitance

A microelectromechanical microphone and method of manufacturing the same are disclosed. The microphone has a moveable diaphragm and a fixed backplate that create a variable capacitance. A fixed anchor electrically coupled to the diaphragm has an electrode that measures the variable capacitance, but also measures an unwanted, additive, parasitic capacitance. Various embodiments include a reference electrode, manufactured in the same deposition layer as the diaphragm or anchor, that measures only the parasitic capacitance. A circuit is provided either on-chip or off-chip that subtracts the capacitance measured at the reference electrode from that measured at the anchor, thereby producing only the desired variable capacitance as output. Because the reference electrode is deposited at the same time as the diaphragm or anchor, only minimal changes are required to existing manufacturing techniques.

Owner:INVENSENSE

Thin-film transistor and LCD device

InactiveCN101425542ASmall footprintReduce unused areaTransistorSolid-state devicesLiquid-crystal displayParasitic capacitance

The invention relates to a thin-film transistor and a liquid crystal display device using the thin-film transistor. The thin film transistor comprises a first drain electrode, a second drain electrode, a source electrode and a grid electrode, wherein a semi-close area is formed by the first drain electrode and the second drain electrode, and one end of the source electrode is positioned in the semi-close area. The thin-film transistor can reduce the parasitic capacitance generated between the source electrode and the grid electrode and improve the display quality of images.

Owner:SHANGHAI SVA LIQUID CRYSTAL DISPLAY

Capacitive pressure sensor

InactiveUS20060133006A1Eliminate parasitic capacitanceReduce parasitic capacitanceFluid pressure measurement by electric/magnetic elementsNon-mechanically variable capacitorsCapacitive pressure sensorLead electrode

A capacitive pressure sensor includes: a conductive silicon substrate having a diaphragm; an insulating substrate having a fixed electrode, the insulating substrate overlapping the conductive silicon substrate so as to be bonded thereto; and a sealed chamber formed between the diaphragm and the fixed electrode. A conductive silicon member is buried in a part of the insulating substrate, a portion of the conductive silicon member is exposed toward a surface of the insulating substrate facing the sealed chamber so as to form the fixed electrode, and another portion of the conductive silicon member is exposed toward the other surface of the insulating substrate not facing the sealed chamber so as to form a lead electrode of the fixed electrode.

Owner:ALPS ALPINE CO LTD

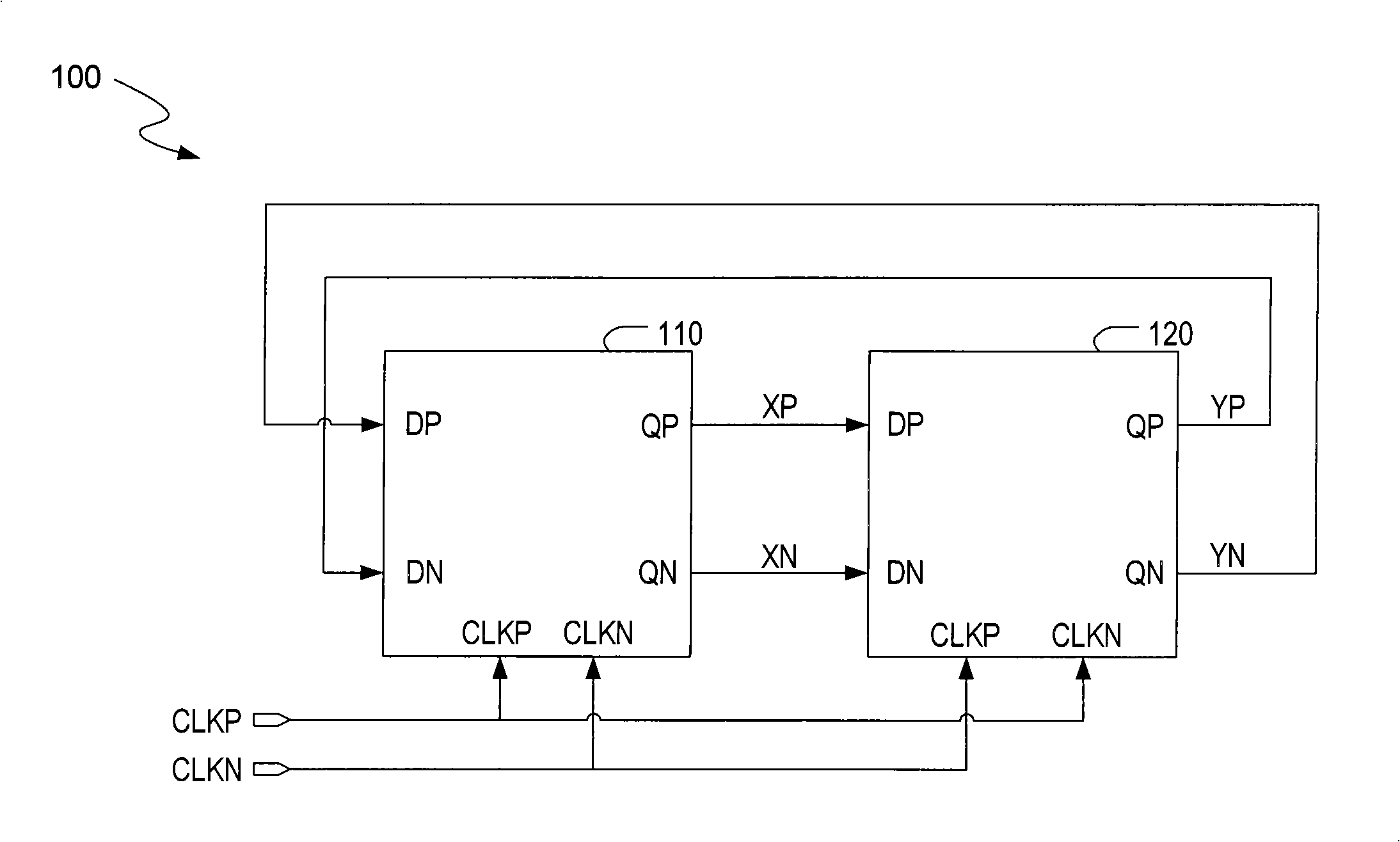

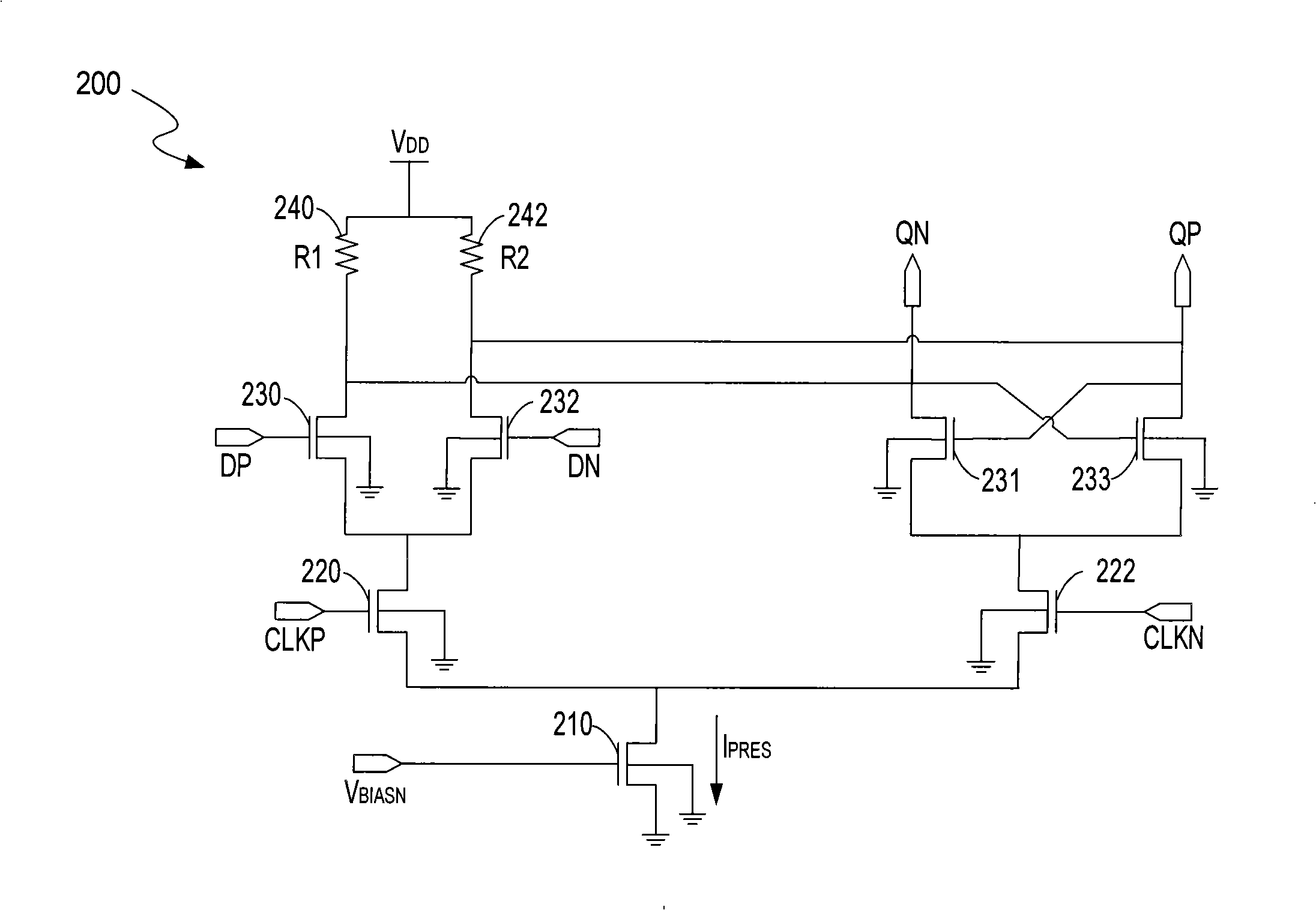

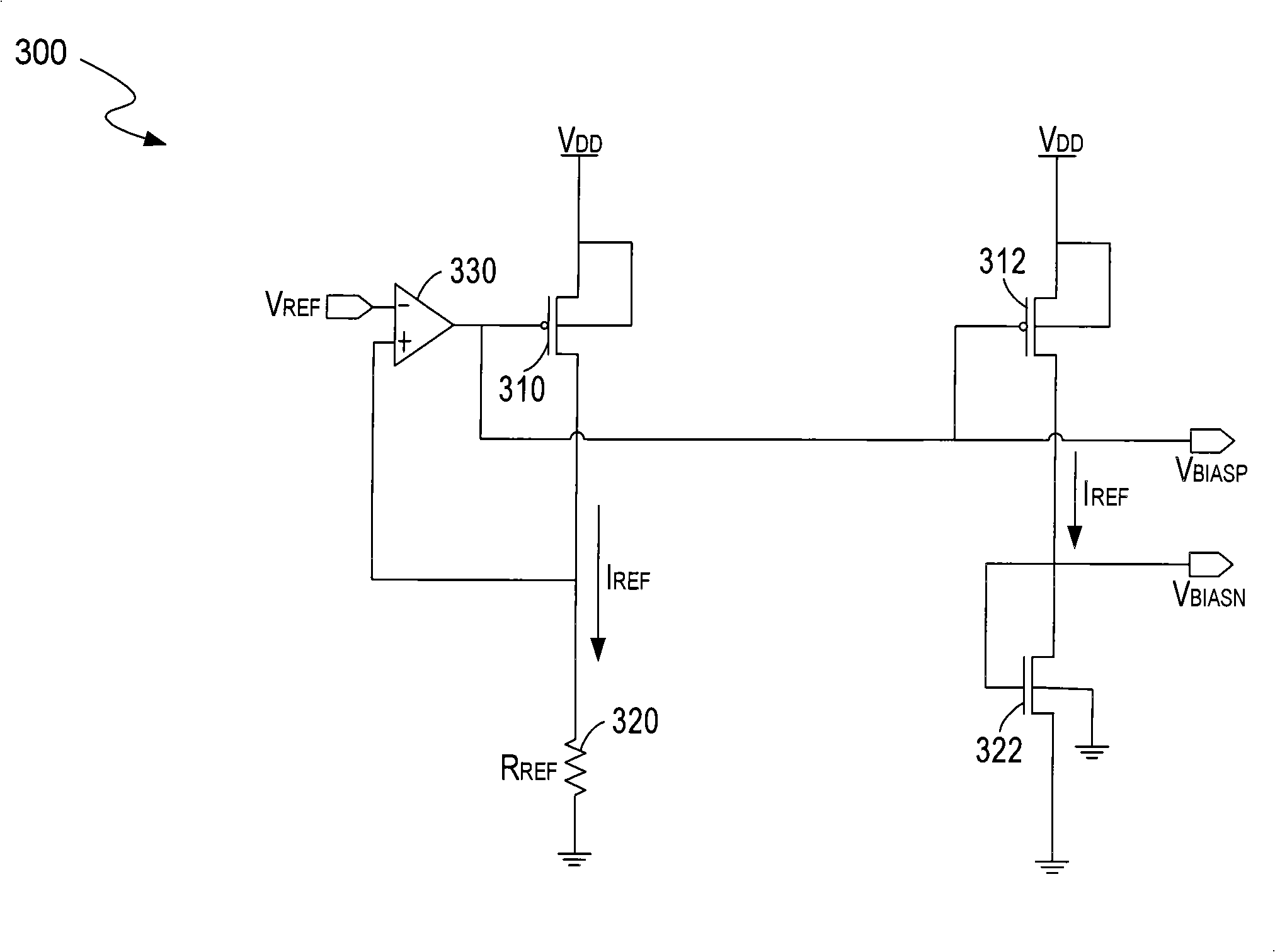

Frequency divider including latch circuits and method

ActiveCN101320971AEliminates Substrate Bias EffectsEliminate parasitic capacitanceCounting chain synchronous pulse countersElectric pulse generatorVoltage amplitudeEngineering

A frequency divider is disclosed herein. The frequency divider includes a first latch circuit and a second latch circuit coupled to the first latch circuit. Each of the first latch circuit and the second latch circuit includes a first level for generating a source current, a second level for receiving a pair of input signals and for generating a pair of output signals, and a third level for receiving the source current and a pair of clock signals. The second level is coupled between the first level and the third level. The first level includes a first transistor having a source terminal and a substrate both coupled to a source voltage. The third level includes a plurality of transistors controlled by the pair of clock signals. Each transistor in the third level has a source terminal and a substrate both coupled to ground. Compared with current technique, the frequency divider provided in the invention removes transistor bias effect and parasitic capacitance, with the input signal having smaller value capable of conducting the input level thereof, which is capable of provided with relatively high output voltage amplitude free of buffer so as to enhance property thereof.

Owner:凹凸科技平潭有限公司

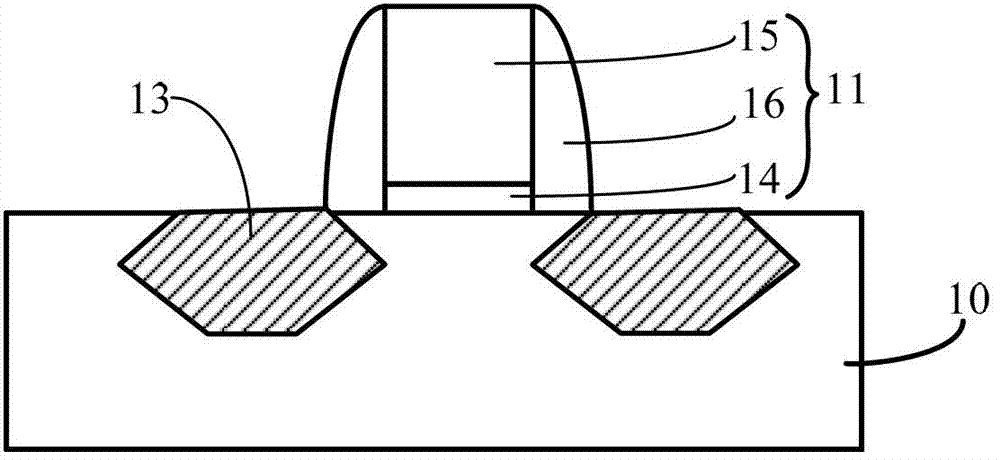

Transistor and forming method thereof

ActiveCN103715088AEliminate parasitic capacitanceEliminate signal delaysTransistorSemiconductor/solid-state device manufacturingGate dielectricParasitic capacitance

The invention relates to a transistor and a forming method thereof. The forming method comprises the following steps that: a semiconductor substrate is provided; gate structures are formed at the semiconductor substrate, wherein the gate structures include gate dielectric layers formed at the semiconductor substrate and gate electrodes arranged at the gate dielectric layers and first side walls are formed at the semiconductor substrate around the gate structures; a sigma-shaped groove is formed in the semiconductor substrate at the two sides of the gate structures; a first stress liner layer is formed in the sigma-shaped groove, wherein the surface of the first stress liner layer is flush with the surface of the substrate; second side walls are formed around the first side walls; a second stress liner layer is formed on the first stress liner layer, wherein the thickness of the second stress liner layer is less than or equal to the height of the second side wall. Because of the second side walls, the distance between the second stress liner layer and the gate structures to be enlarged; the parasitic capacitance between the second stress liner layer and the gate structures is reduced or even eliminated; and the semiconductor device performance is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

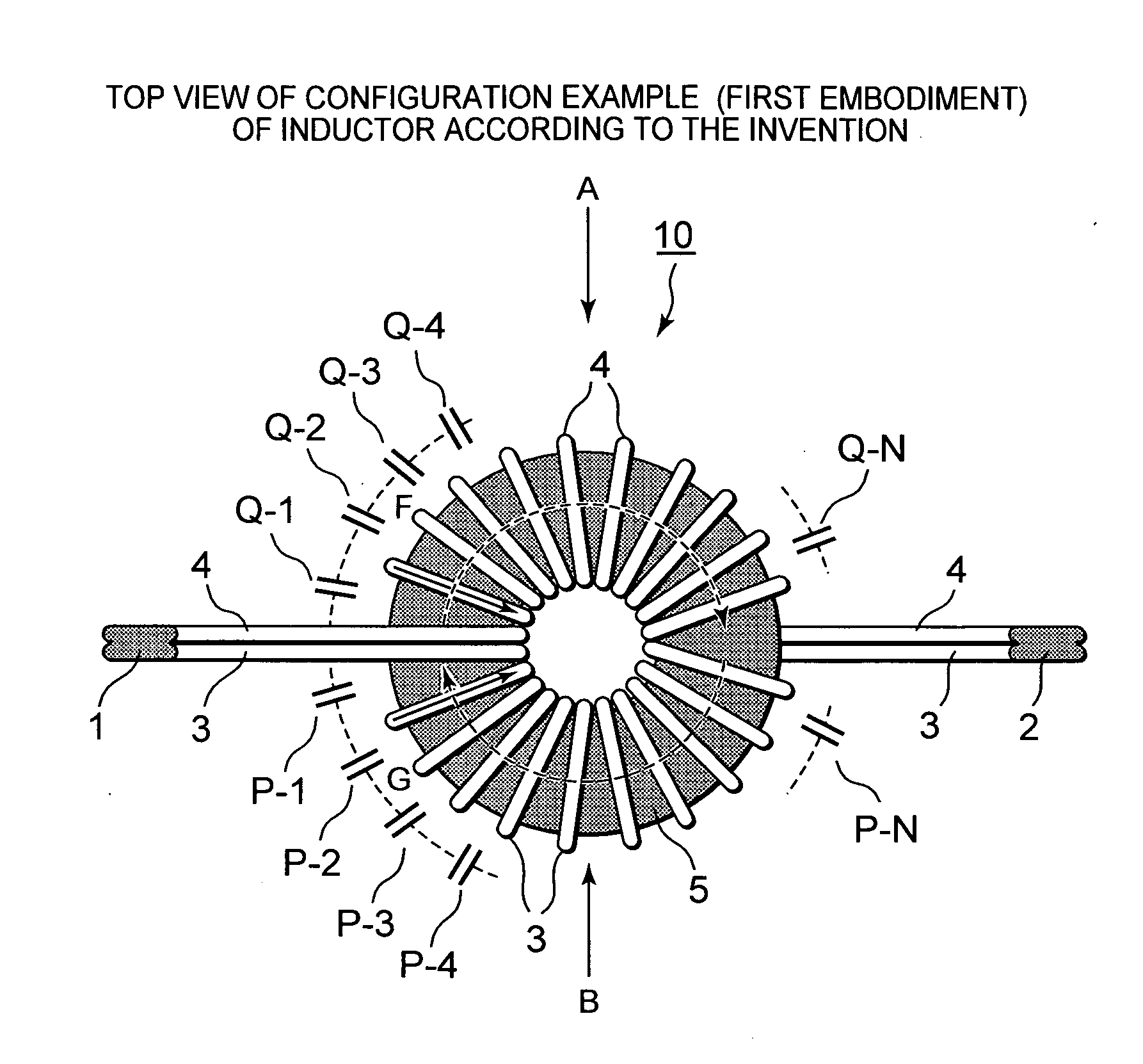

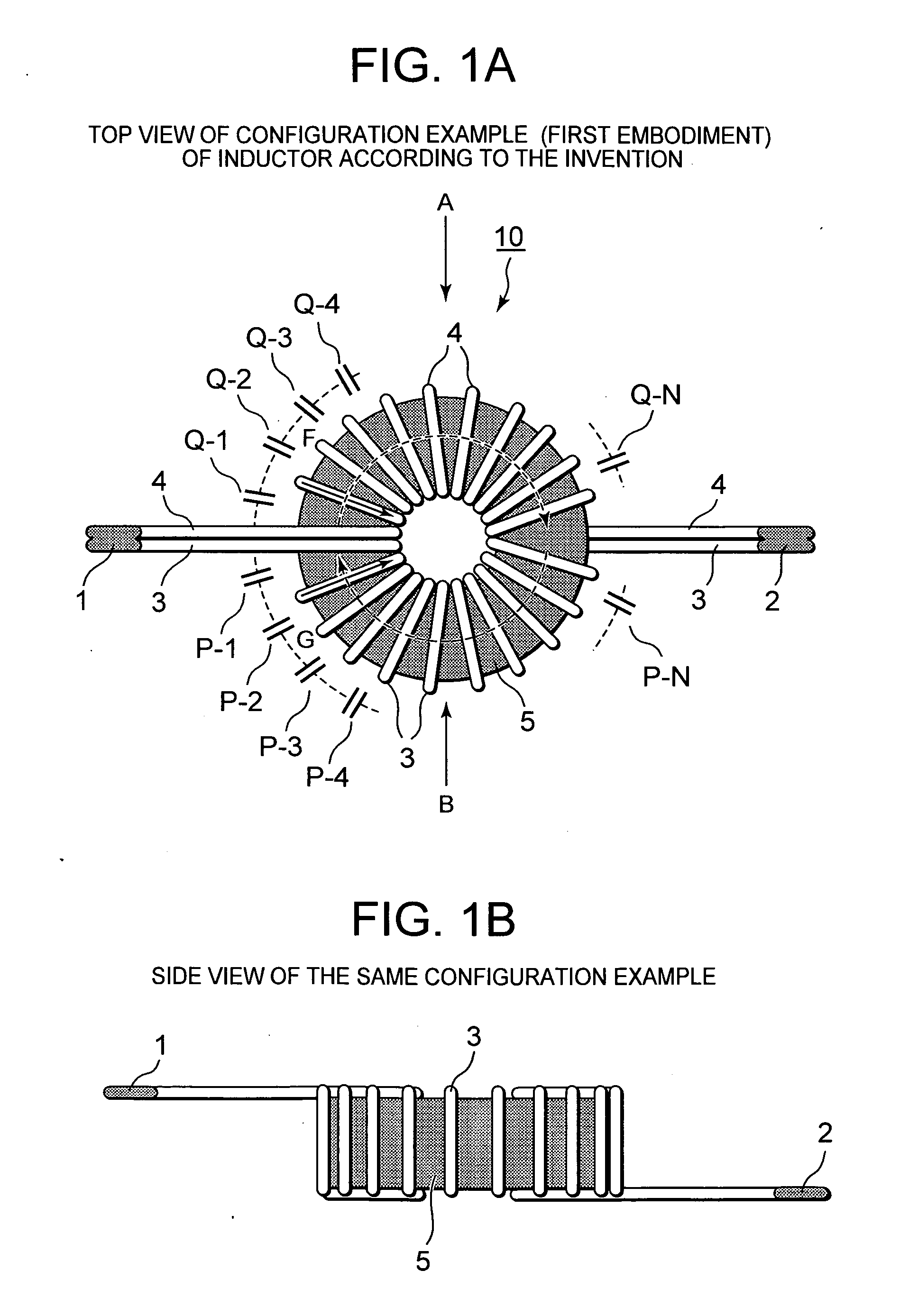

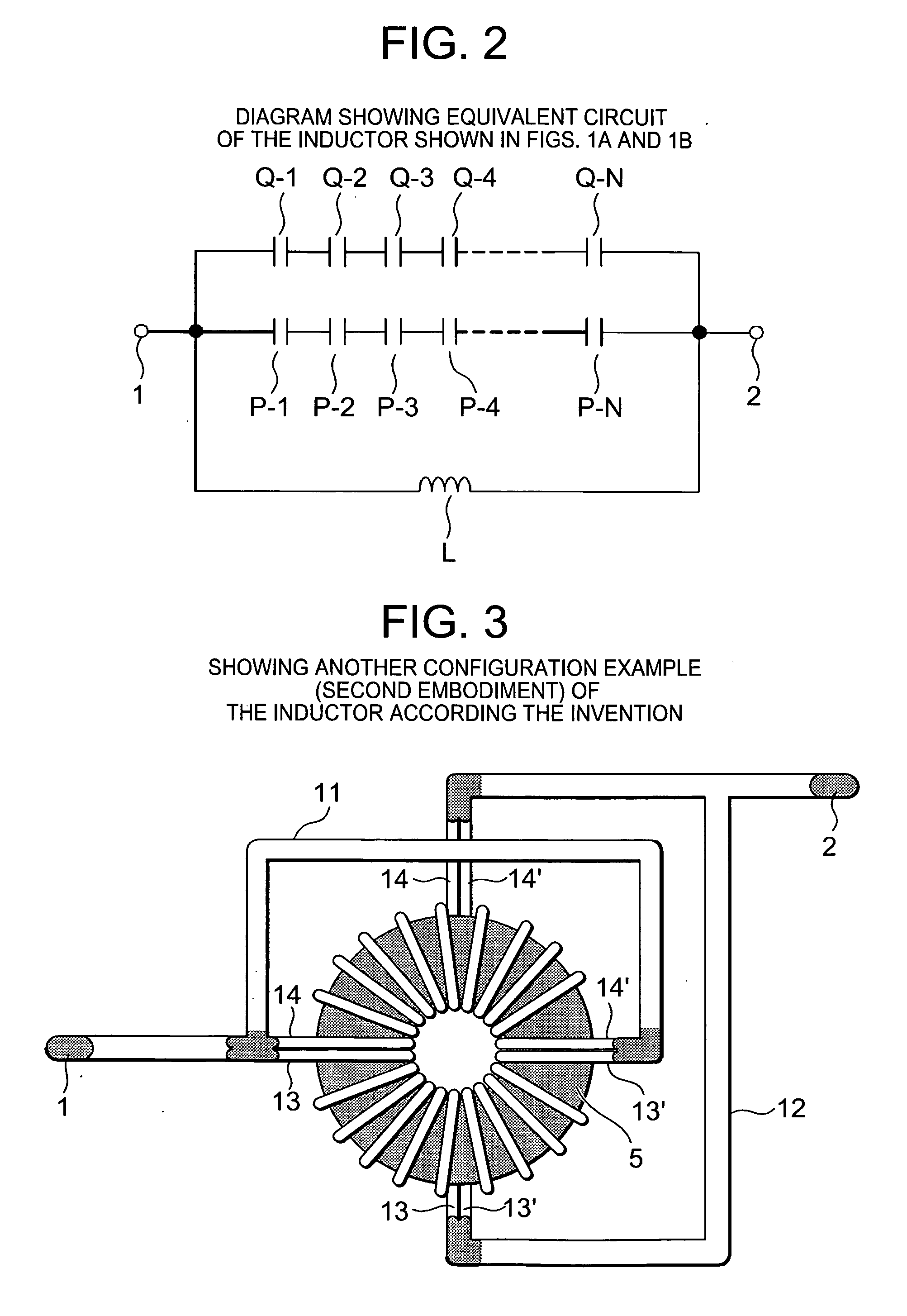

Inductor

ActiveUS20110199175A1Reduce parasitic capacitanceLow costTransformers/inductances coils/windings/connectionsInductance with magnetic coreInductorMagnetic flux

Two conducting wires are used in one embodiment of an inductor. Opposite ends of each of the conducting wires are connected to leader lines (terminals) shared by the conducting wires. Each of the conducting wires is wound to make half a round of an annular or ring-like magnetic substance. One of the conducting wires is wound around a lower half area of the magnetic substance to form one winding while the other conducting wire is wound around an upper half area of the magnetic substance to form another winding. In this manner, the distance between the leader lines can be increased to eliminate parasitic capacitance between the leader lines. The magnetic fluxes generated by current flowing in the two windings are in the same direction. Thus, it is possible to provide an inductor whose total parasitic capacitance is reduced. In other embodiments, additional conducting wires are used.

Owner:FUJI ELECTRIC CO LTD

Semiconductor device and manufacture method thereof

ActiveCN102487085AEliminate parasitic capacitanceReduce parasitic capacitanceSemiconductor/solid-state device detailsSolid-state devicesMOSFETCapacitance

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Touch substrate, display apparatus and driving method of display apparatus

ActiveCN106648191ARealize two-dimensional detection functionReduce capacitanceNon-linear opticsInput/output processes for data processingPressure.driveEngineering

The invention discloses a touch substrate, a display apparatus and a driving method of the display apparatus. Touch pressure driving electrodes and touch pressure induction electrodes, which are arranged between a film layer where touch detection electrodes are located and a substrate, and form a mutual capacitance structure, are added in the touch substrate; and when the touch substrate is pressed, the distance between the touch substrate and a metal layer below is reduced and a capacitance value of the mutual capacitance structure is correspondingly reduced. During a pressure detection time period, the touch pressure driving electrodes are loaded with touch driving signals, and semaphore changes of the touch pressure induction electrodes caused by a pressure of a touch position are detected, so that a capacitance value change of the mutual capacitance structure can be determined and a pressure induction function is realized. During a touch detection time period, the touch detection electrodes, the touch pressure driving electrodes and the touch pressure induction electrodes can be loaded with the same touch detection signals at the same time, and the capacitance value changes of all the touch detection electrodes are detected to judge the touch position, so that a two-dimensional touch detection function is realized.

Owner:BOE TECH GRP CO LTD +1