Transistor and forming method thereof

A technology of transistors and semiconductors, applied in the manufacture of transistors, semiconductor devices, semiconductor/solid-state devices, etc., can solve problems such as poor performance of transistors, and achieve the effects of eliminating signal delay, improving performance, and improving mobility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

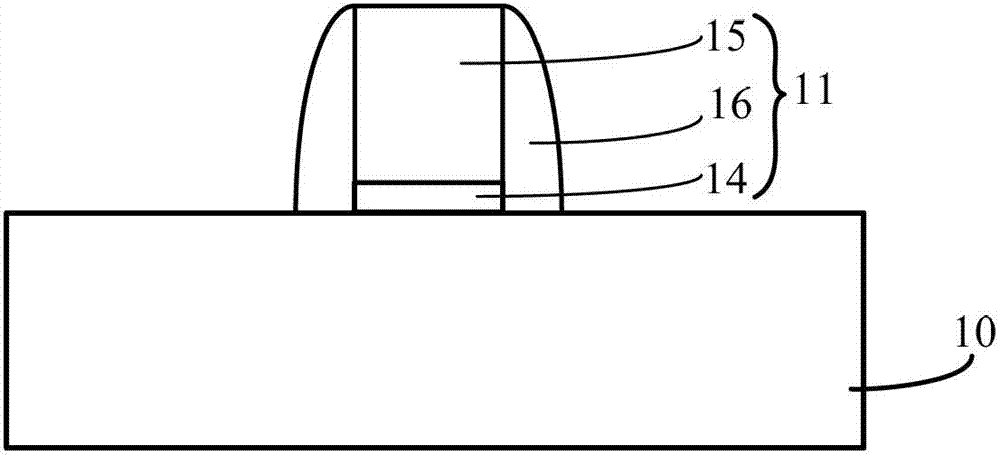

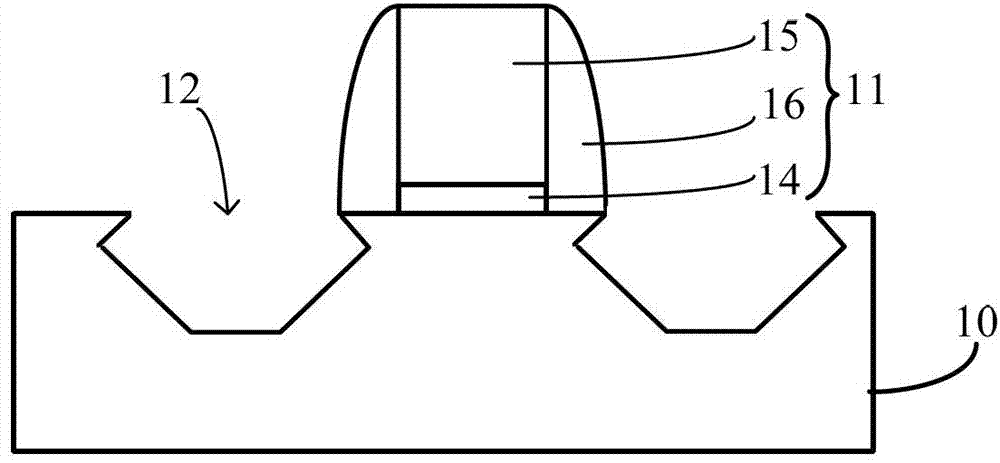

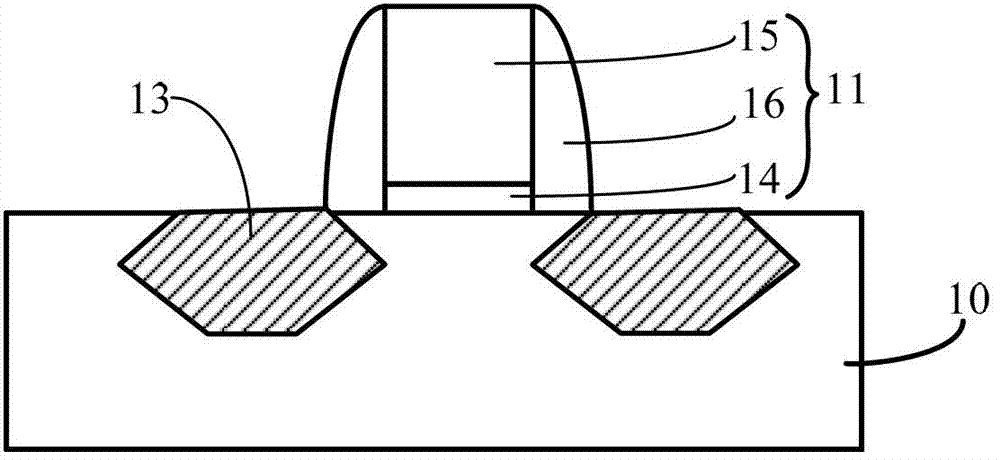

[0050] The inventor analyzed the problems existing in the prior art and found that as the integration of semiconductor devices becomes higher and higher, the distance between the gates gradually decreases, further making the distance between the silicon germanium layer and the gate The smaller and smaller, the parasitic capacitance is generated between the gate and the silicon germanium layer. Moreover, according to the description in the background art, after the stress liner layer is formed in the semiconductor substrate, an additional stress liner layer extending to the outside of the semiconductor substrate is formed on the stress liner layer, so that the gate and the additional stress The relative area between the liner layers increases, resulting in a larger parasitic capacitance between the gate and the entire stressed liner layer including the additional stressed liner layer. Although the additional stress of the liner layer increases the carrier mobility of the transi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More