Patents

Literature

518results about "Counting chain synchronous pulse counters" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

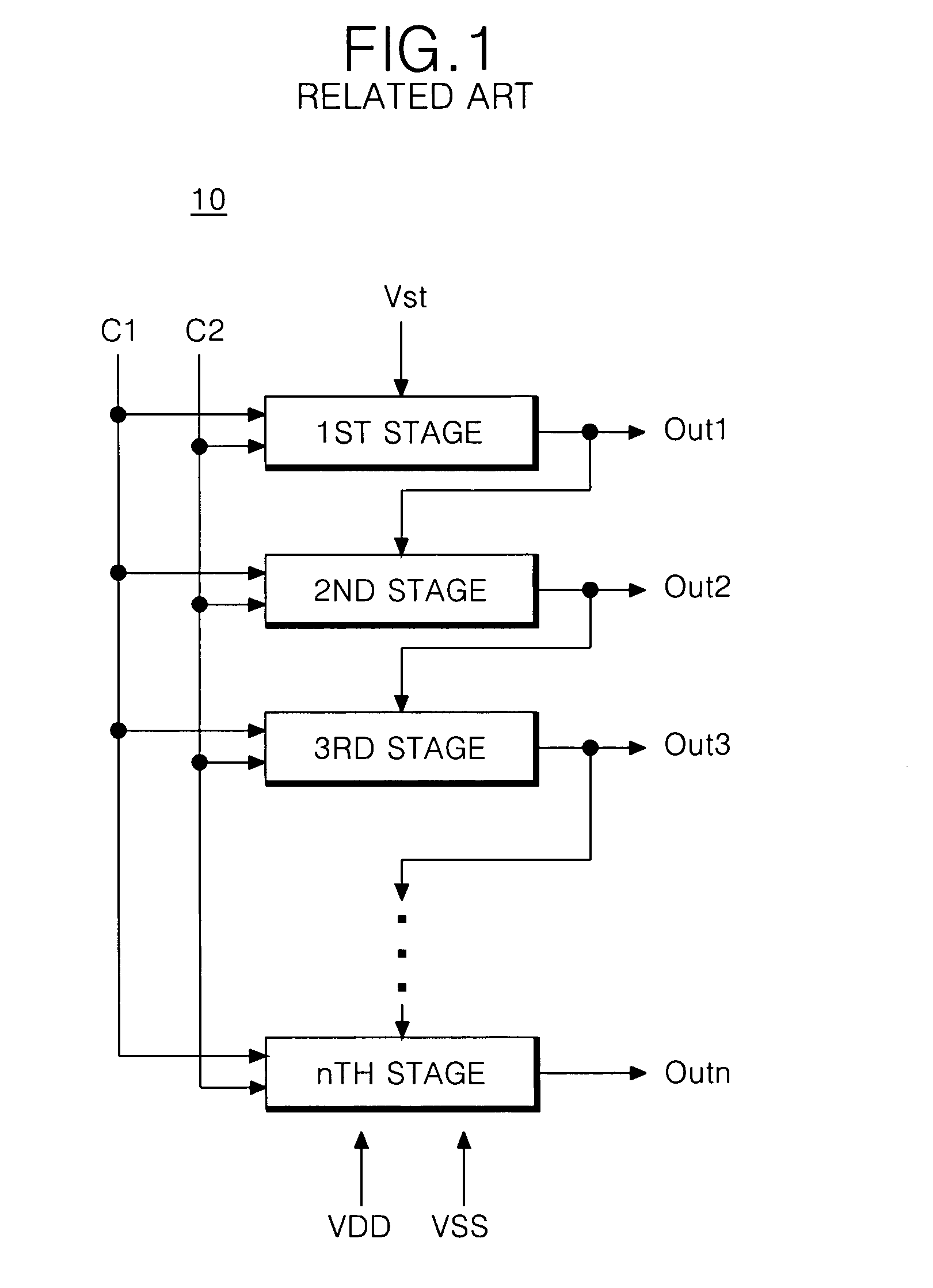

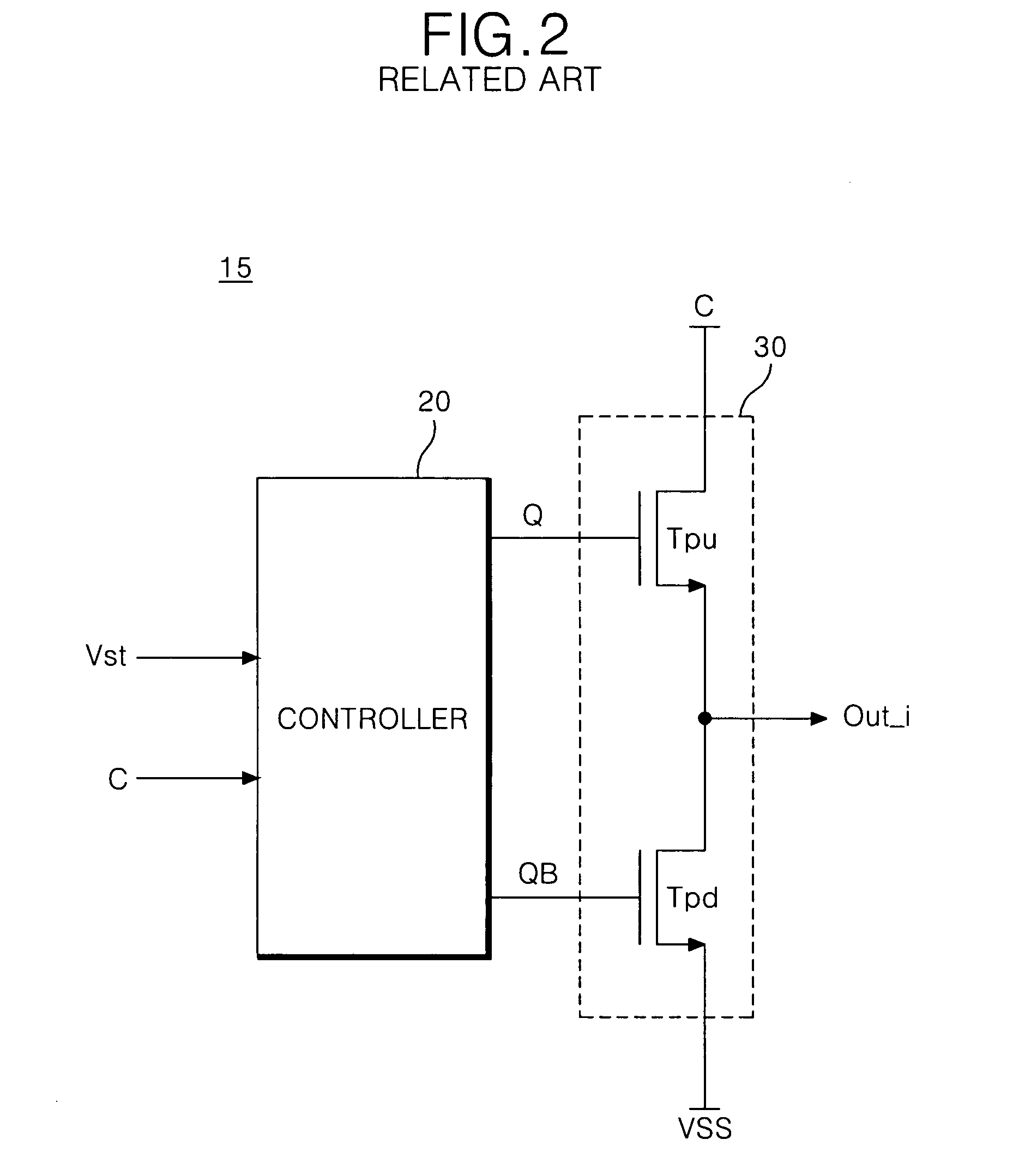

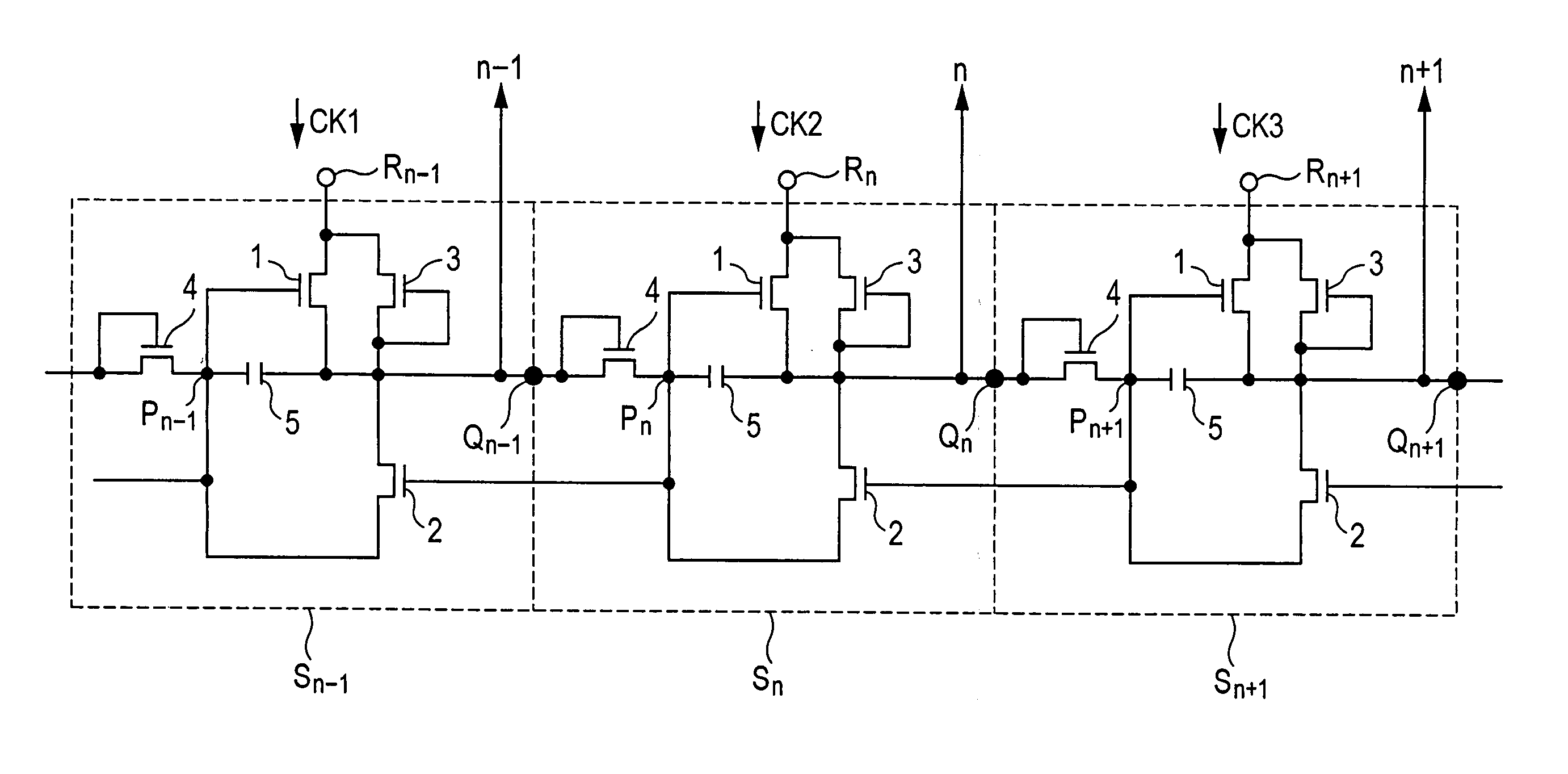

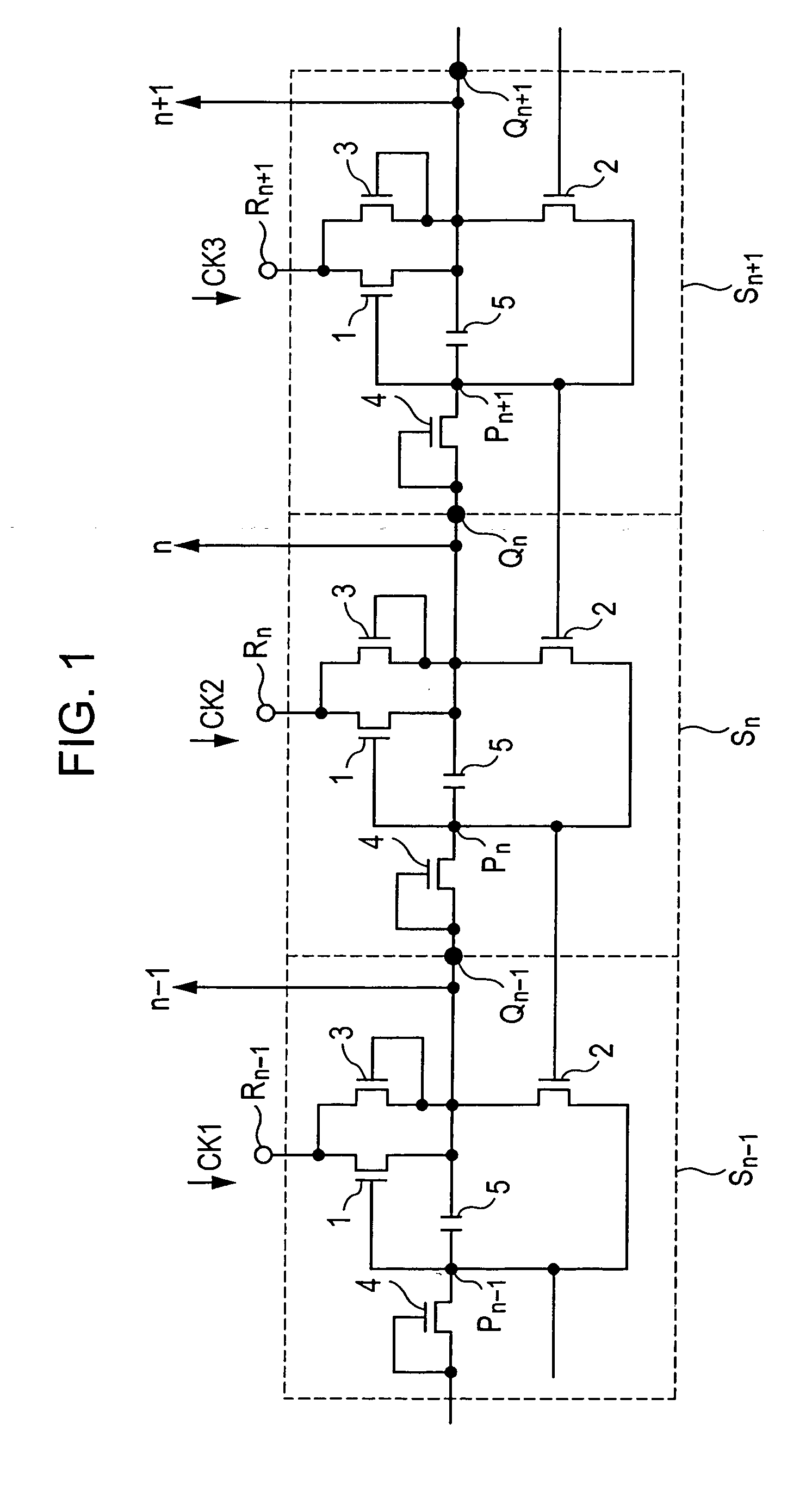

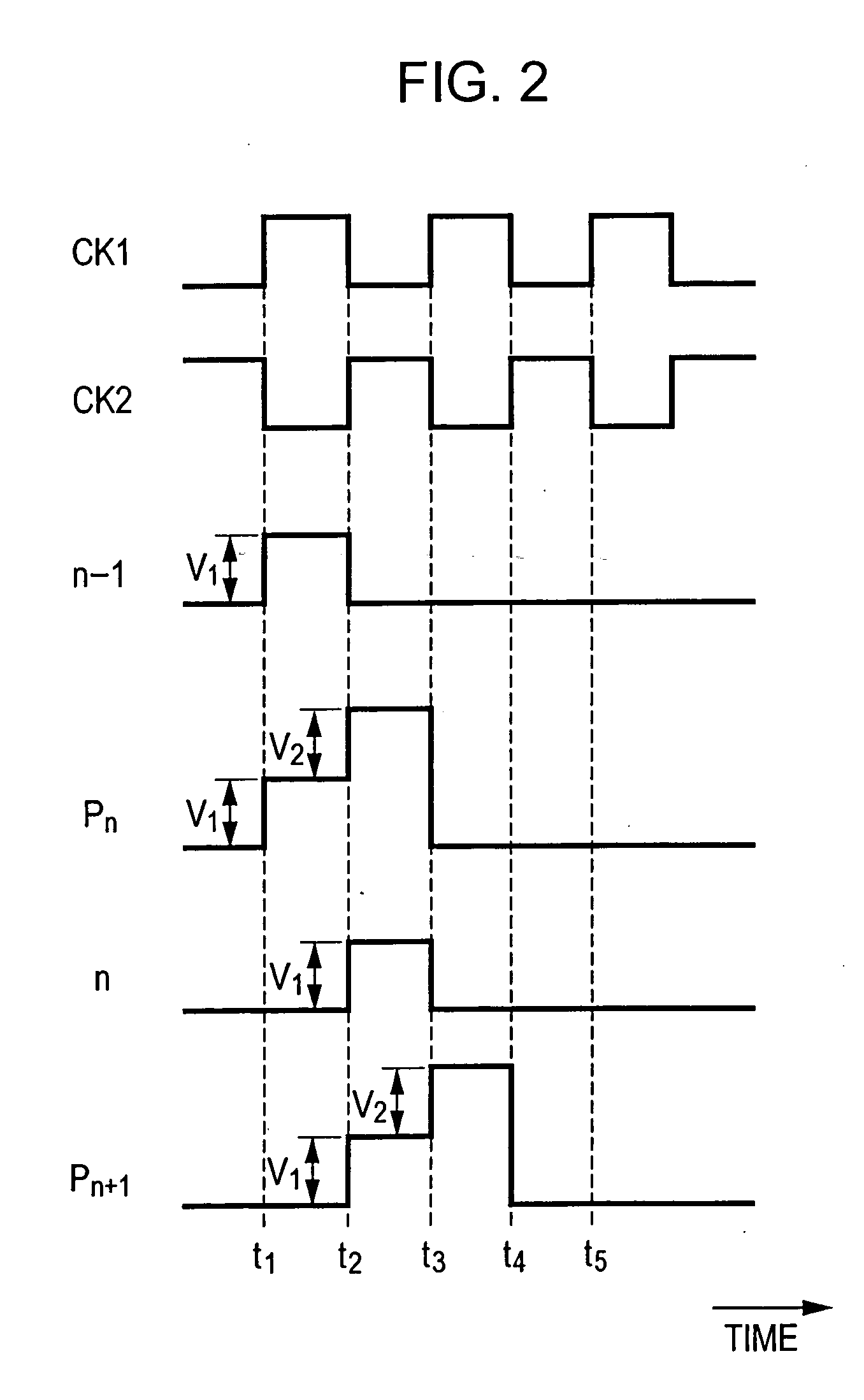

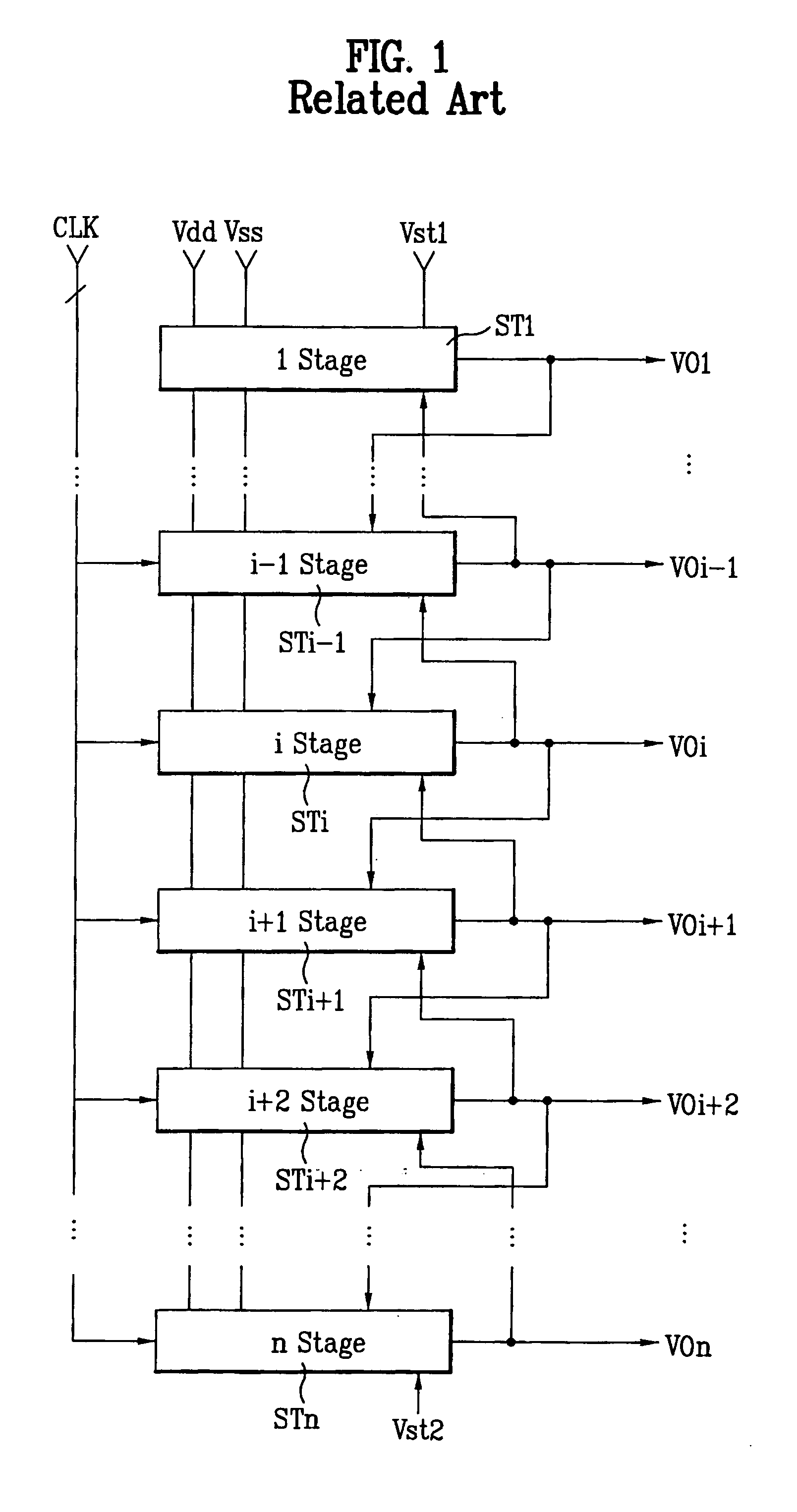

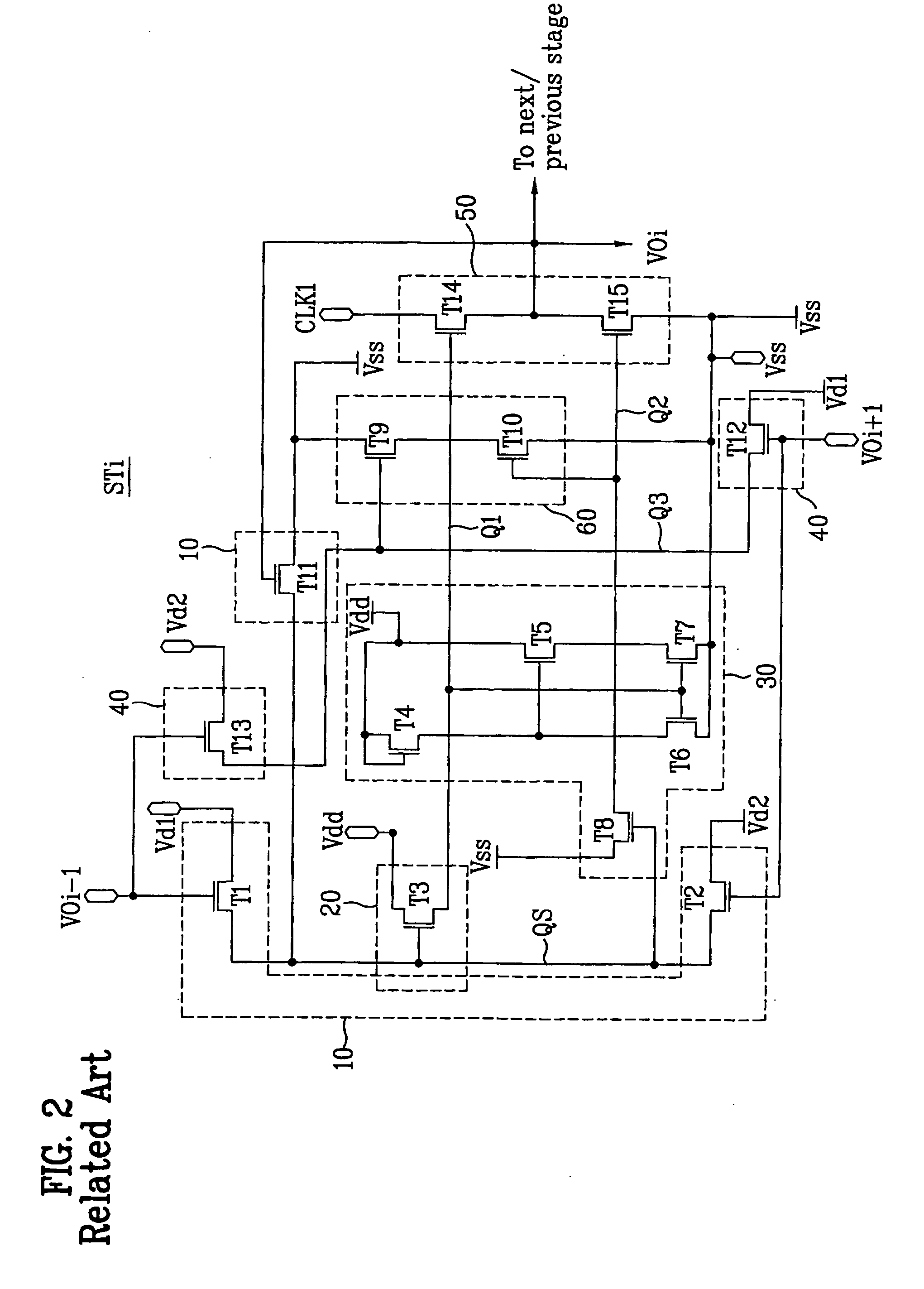

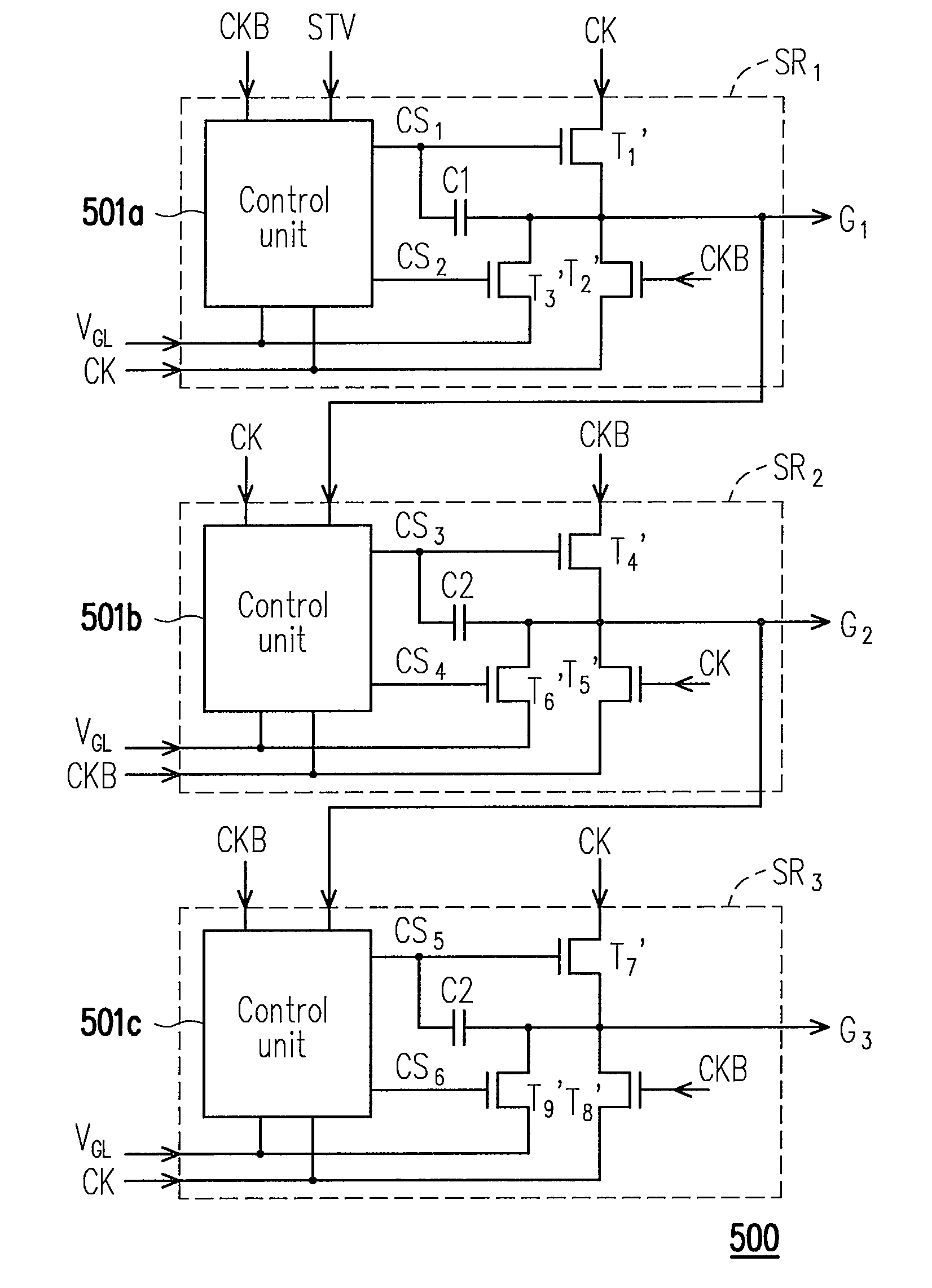

Shift registrer and driving method thereof

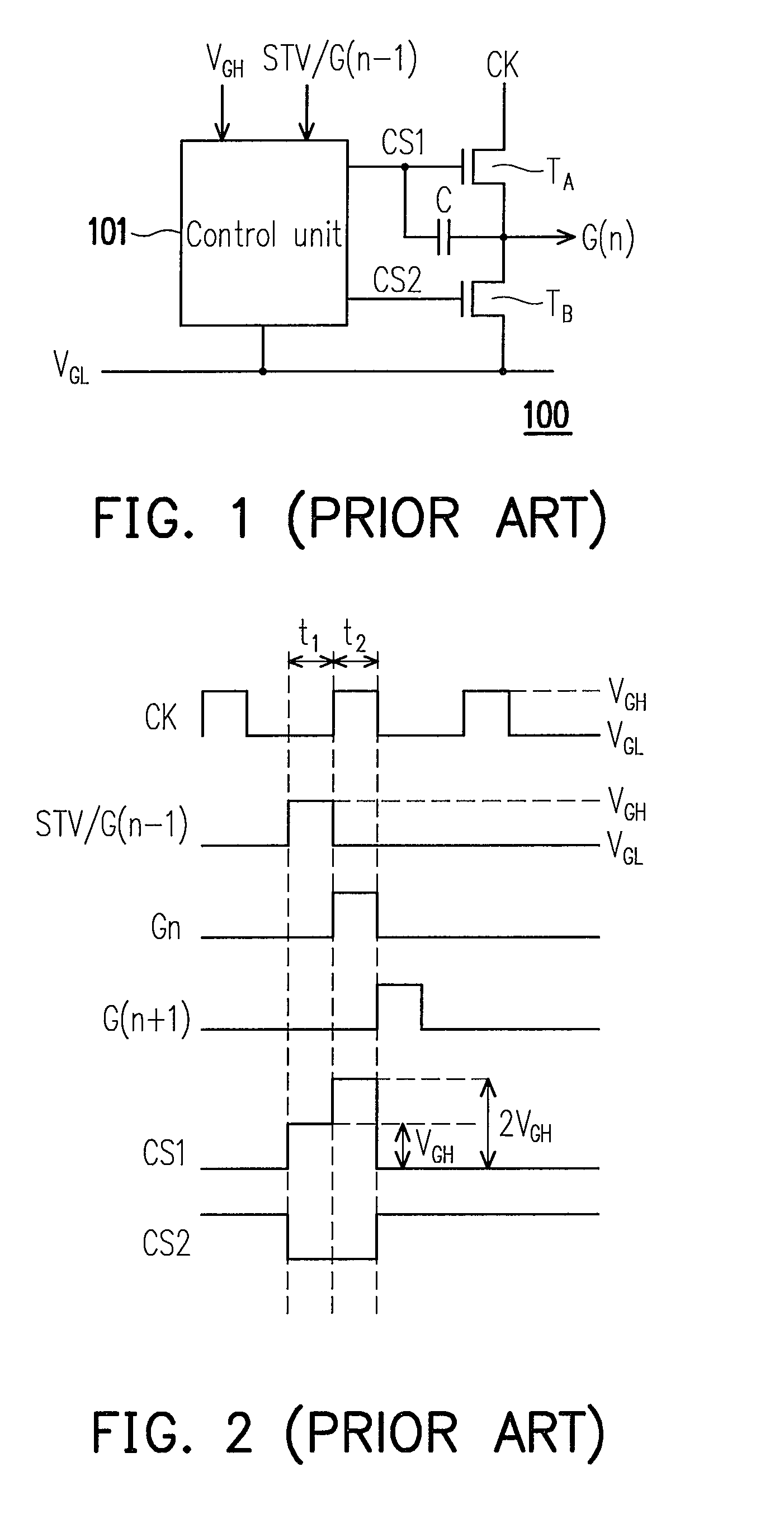

InactiveUS20050220263A1Static indicating devicesCounting chain synchronous pulse countersShift registerCapacitor

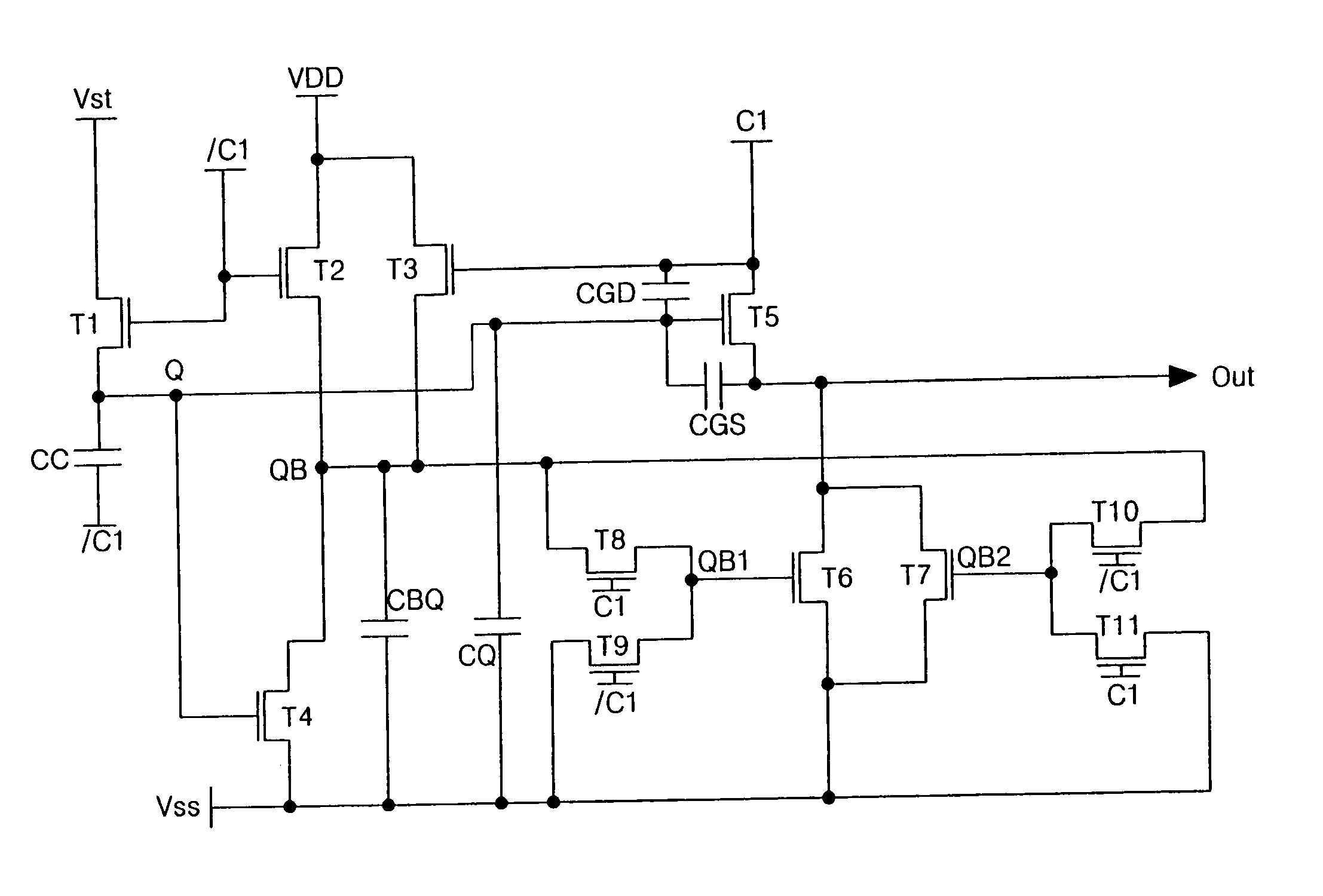

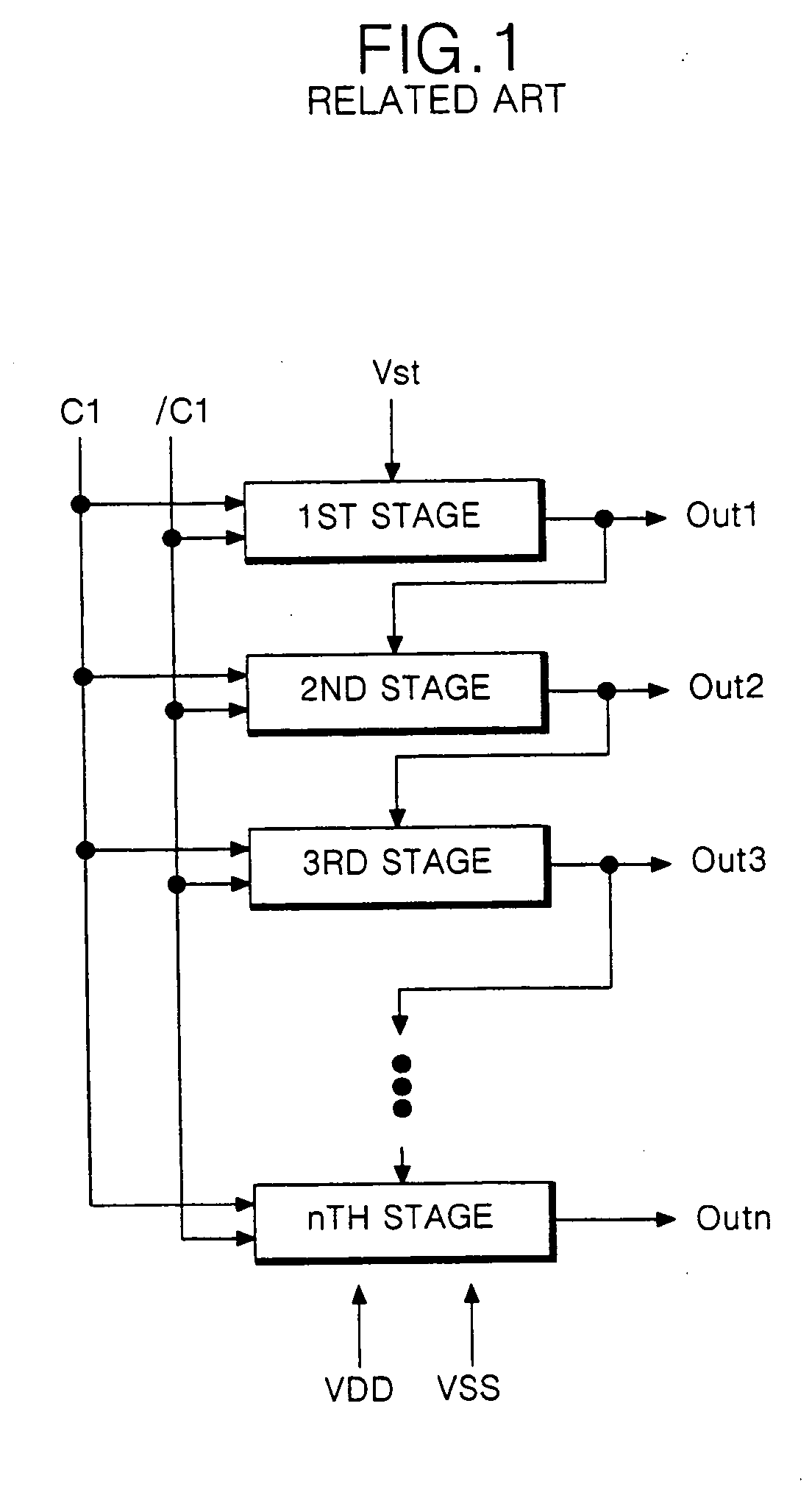

A shift register having a plurality of stages for shifting a start pulse and outputting a shifted start pulse to a next stage, each of the plurality of stages includes a pull-up transistor controlled by a first node to apply a first clock signal to an output line, a first pull-down transistor controlled by a second node to apply a first driving voltage to the output line, a controller for controlling the first and second nodes, and a compensating capacitor connected between the first node and an input line of a second clock signal, the second clock signal being different from the first clock signal.

Owner:LG DISPLAY CO LTD

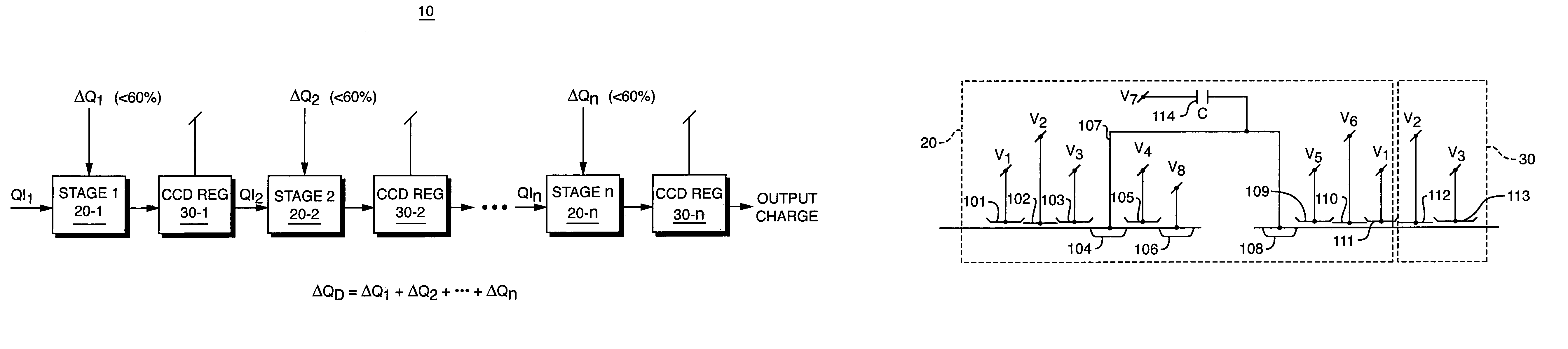

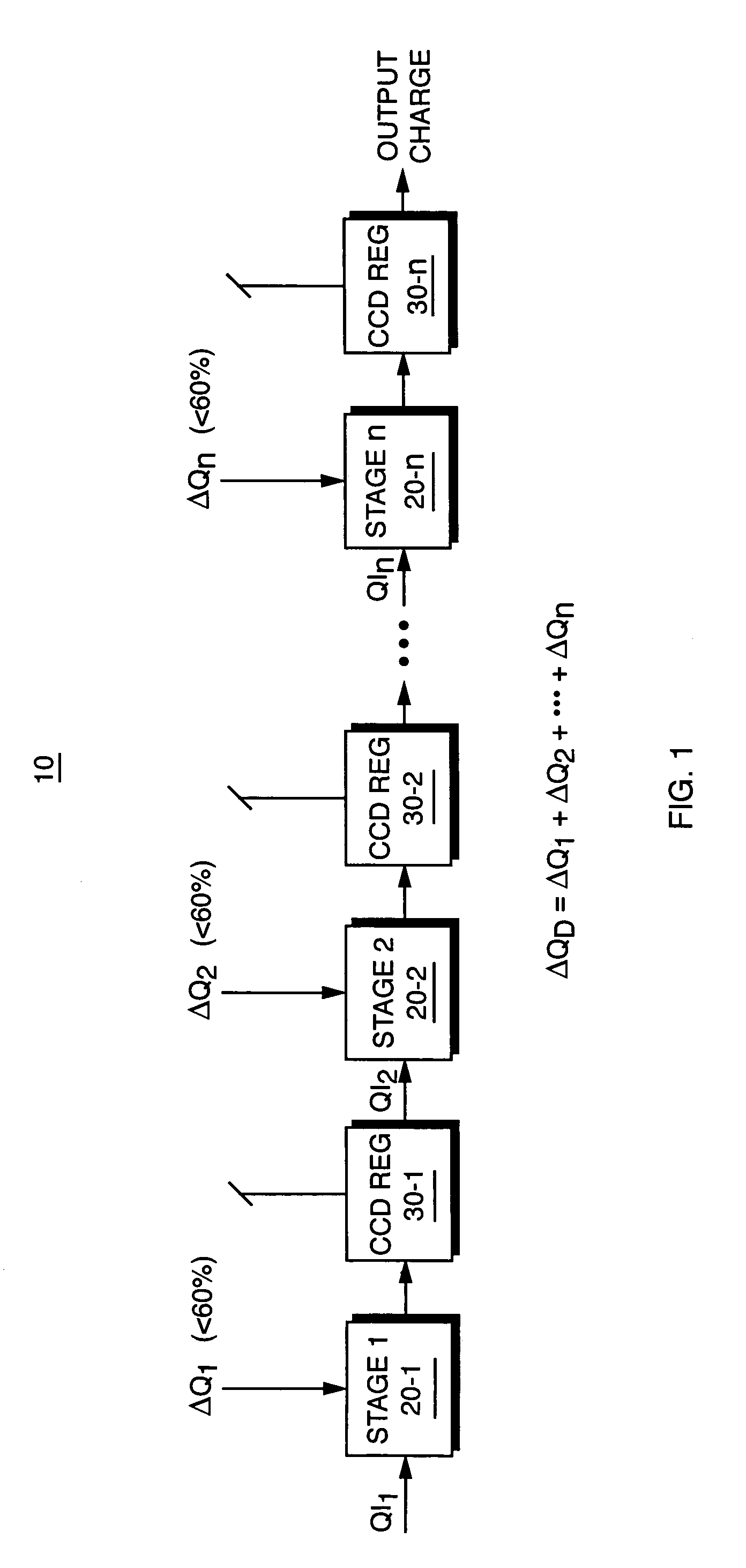

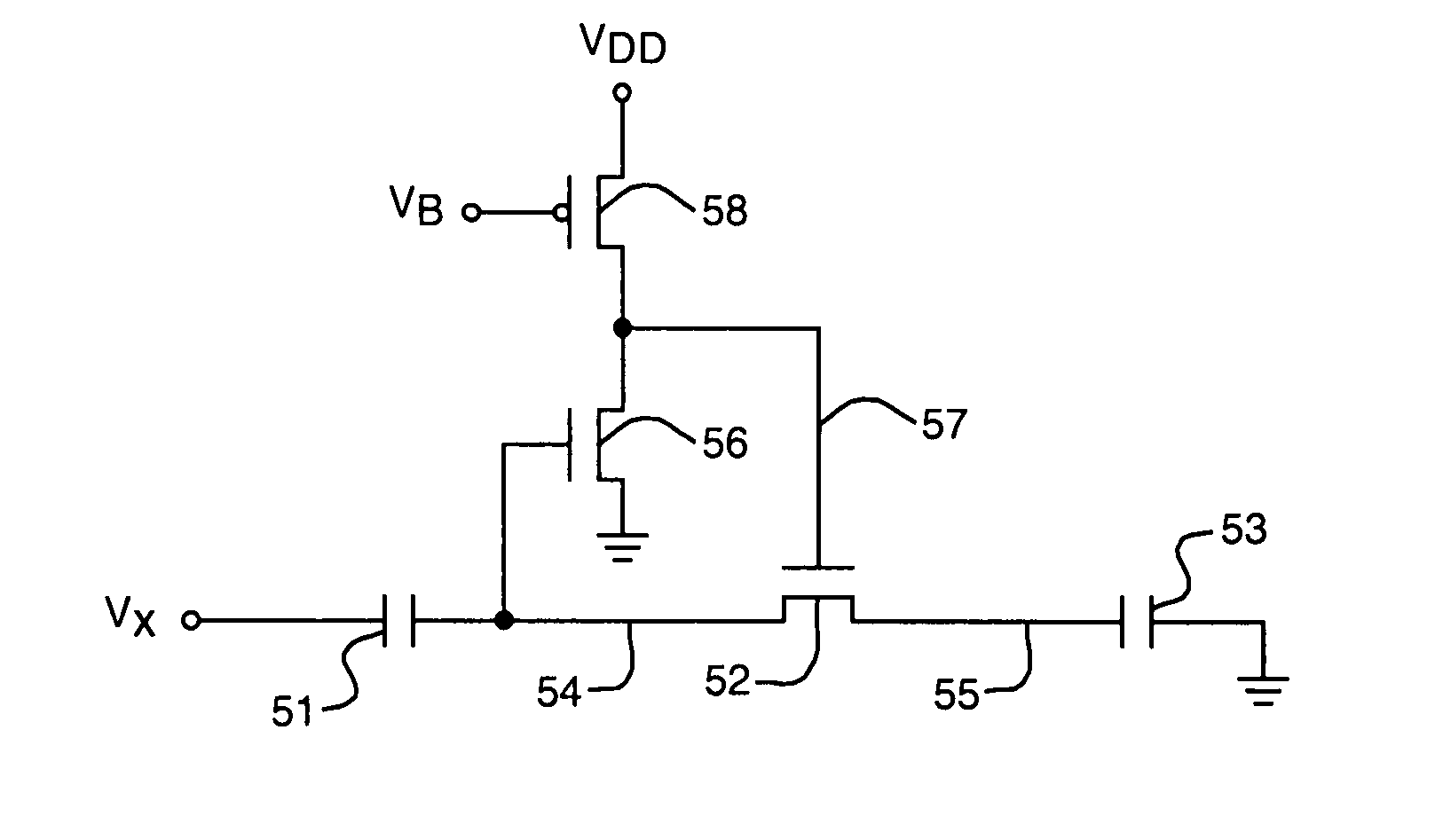

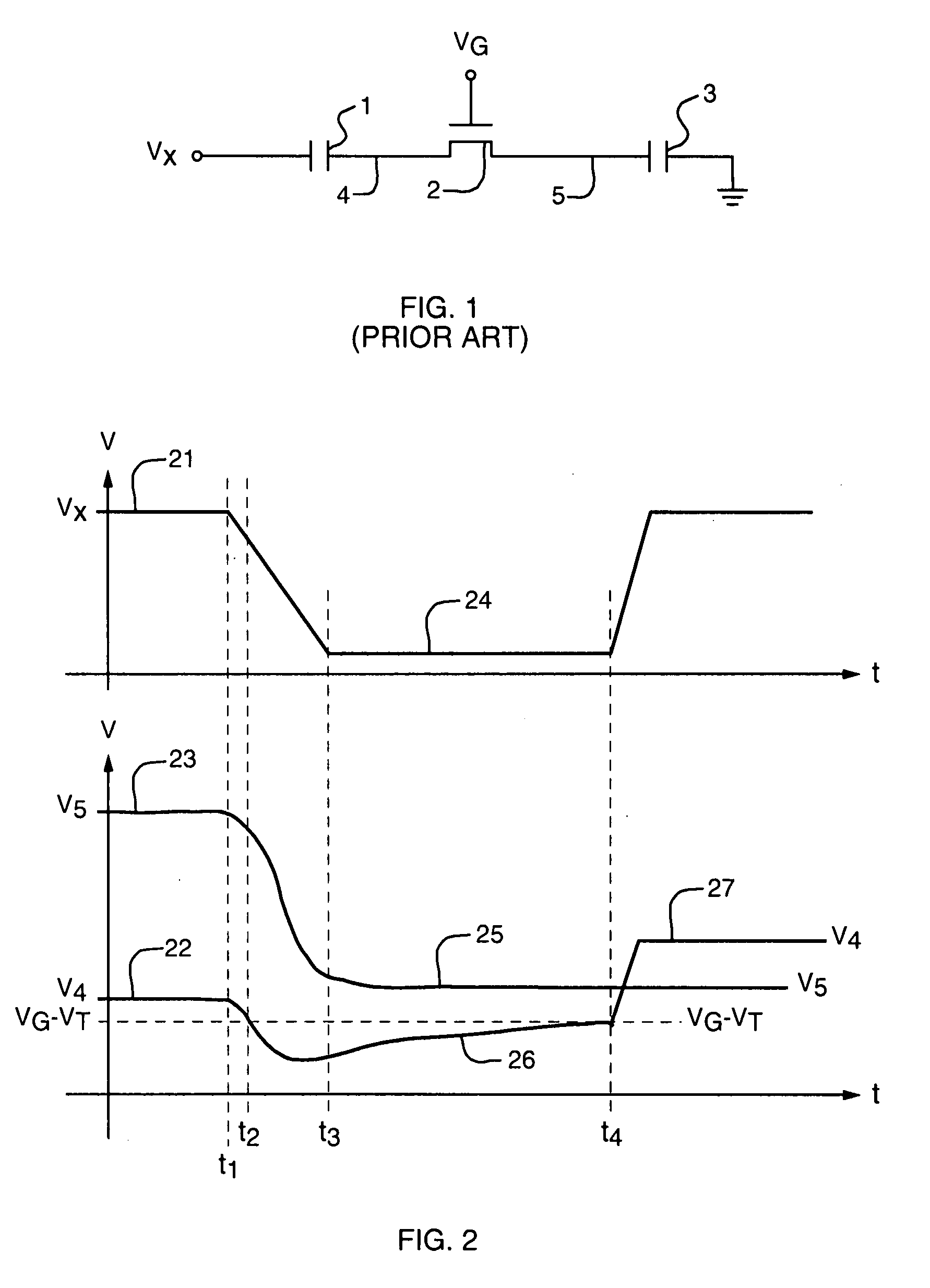

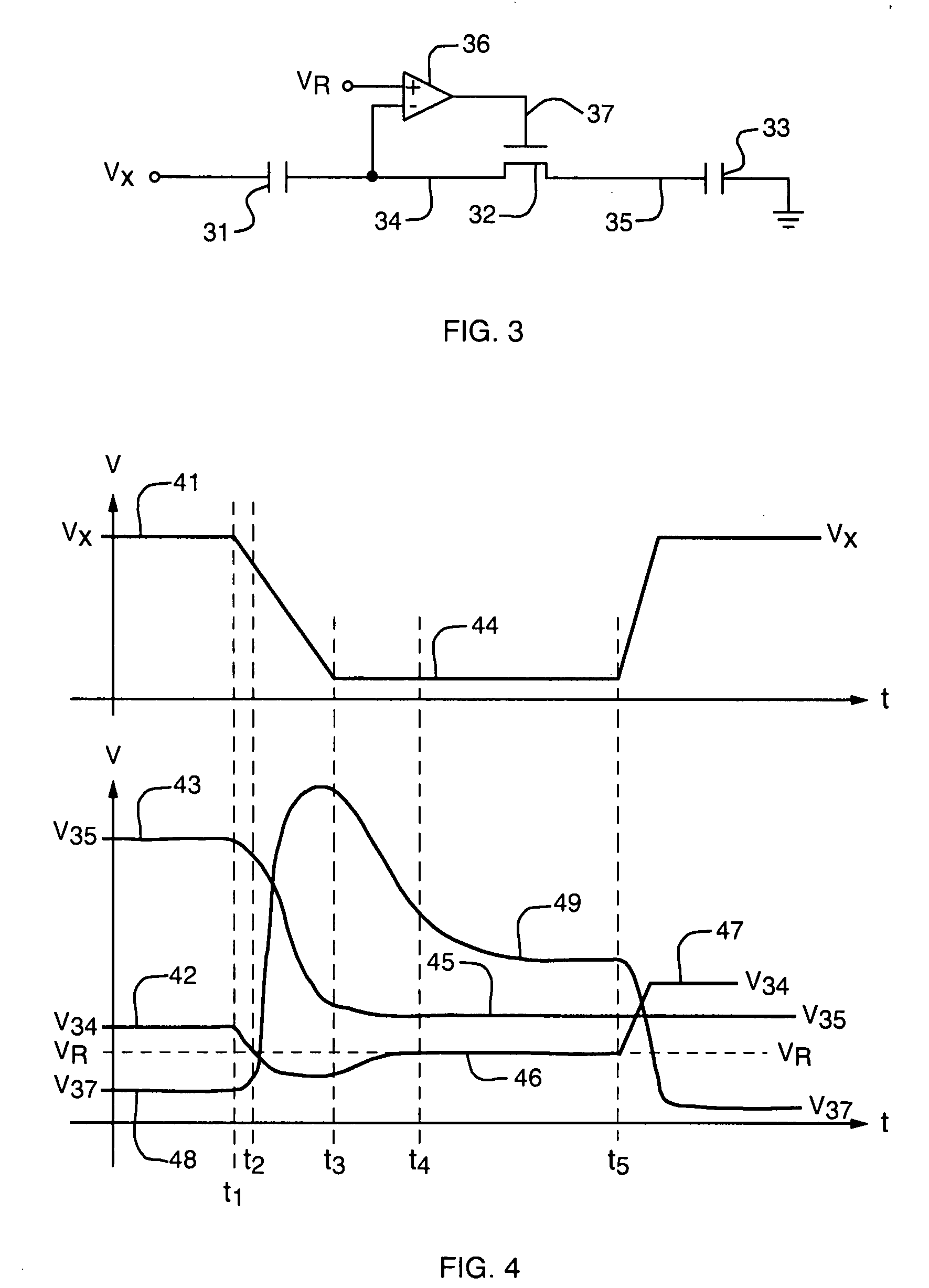

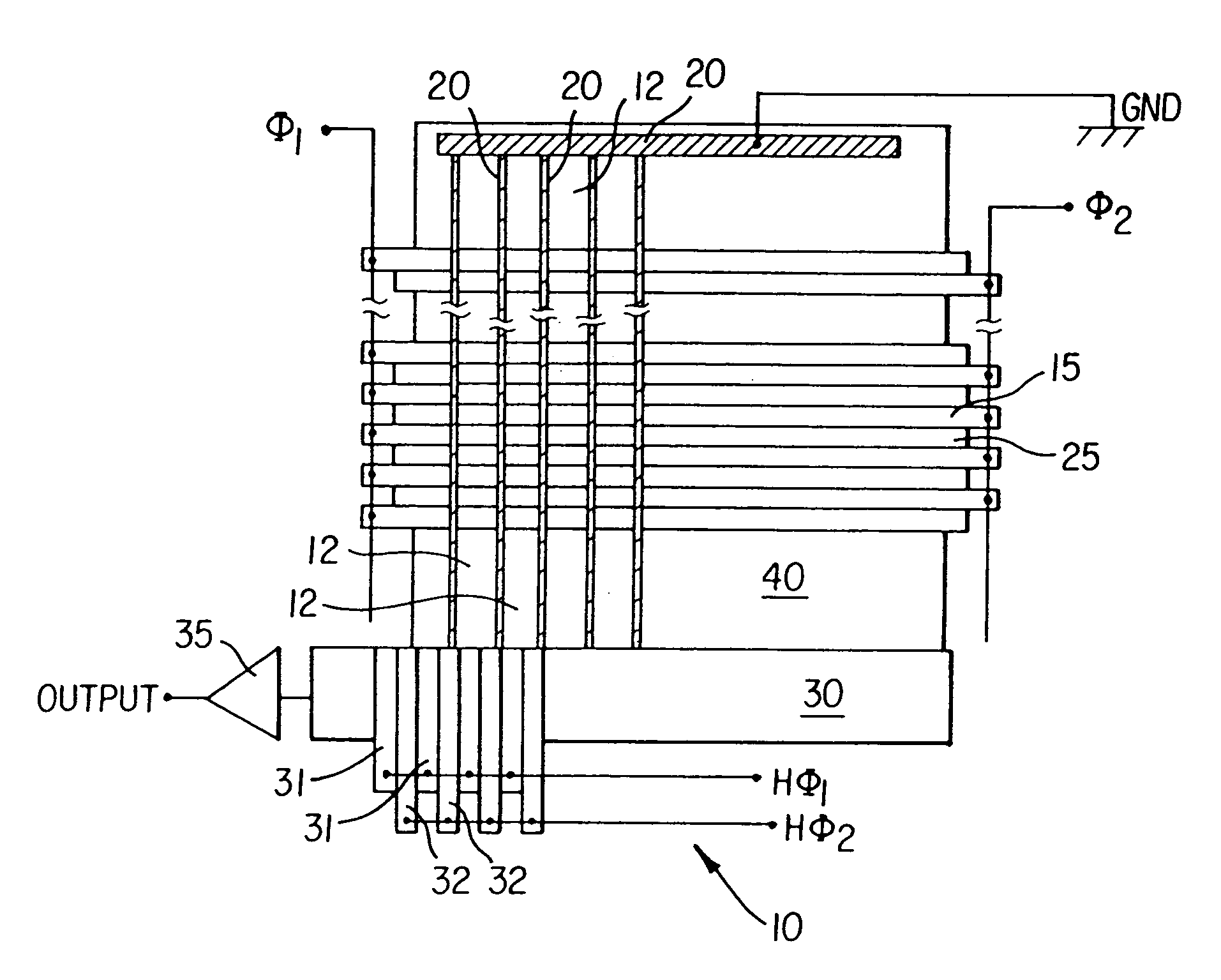

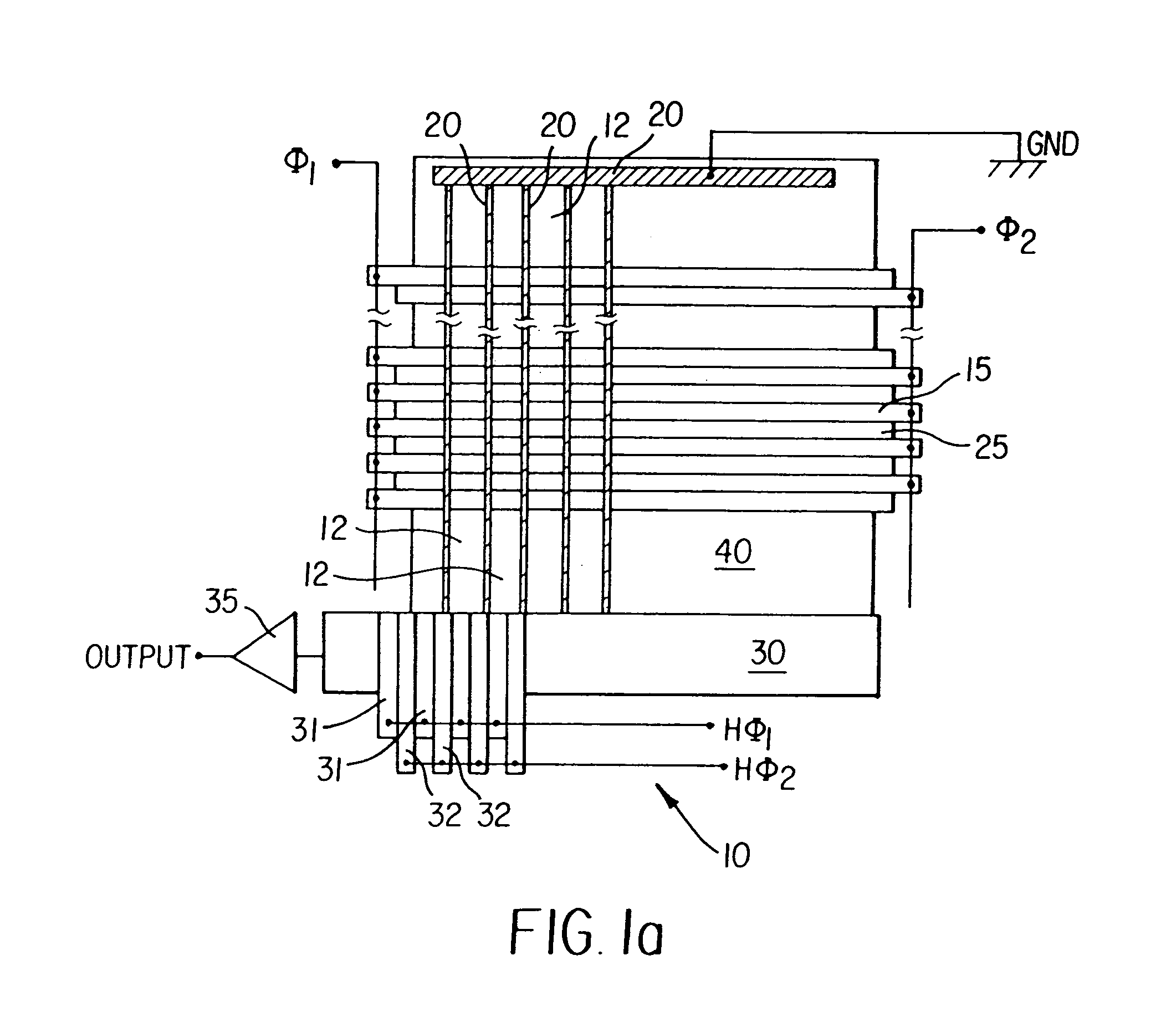

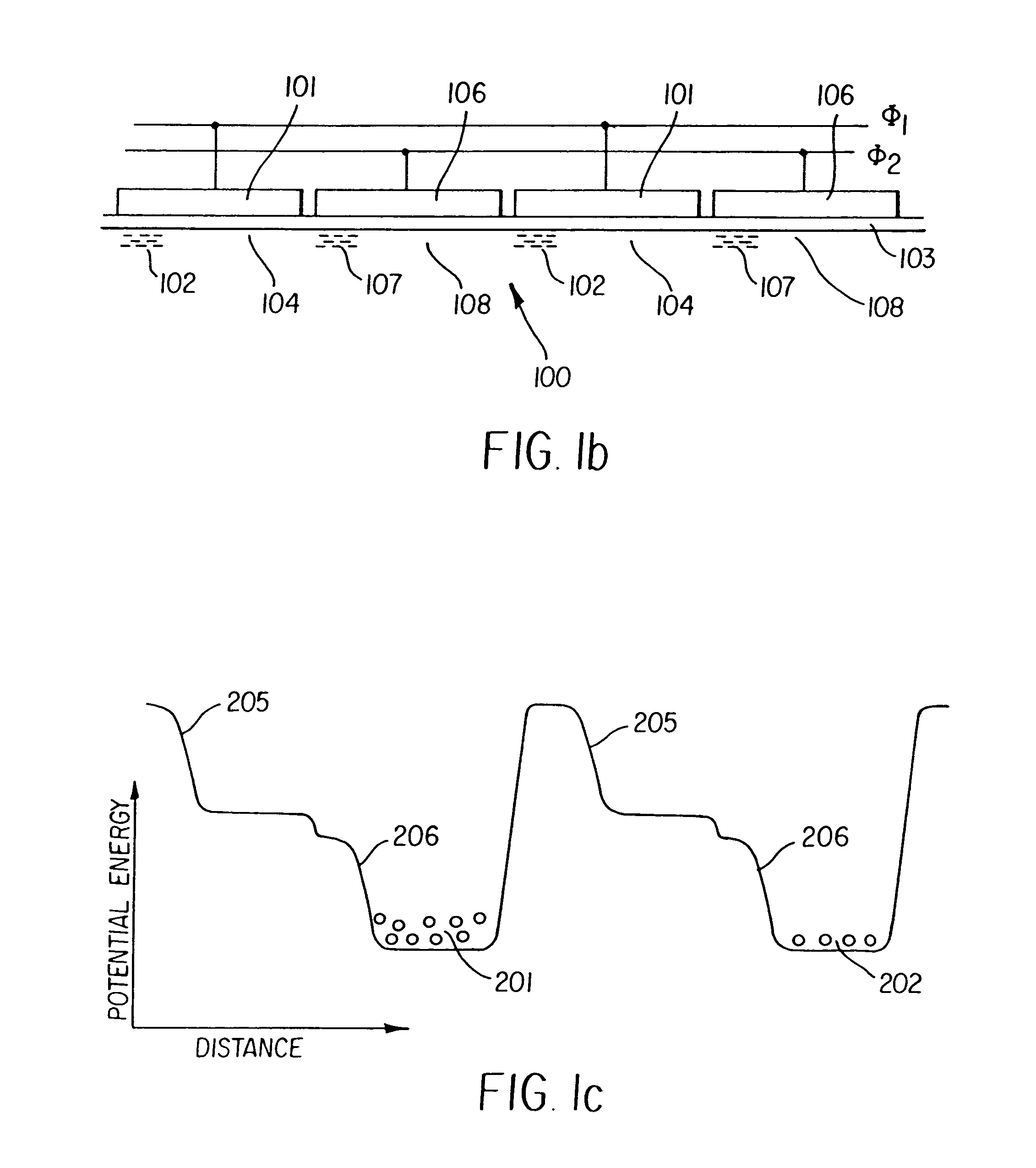

Device for subtracting or adding a constant amount of charge in a charge-coupled device at high operating frequencies

InactiveUS7003068B2Counting chain synchronous pulse countersSolid-state devicesMemory effectEngineering

Owner:KENET

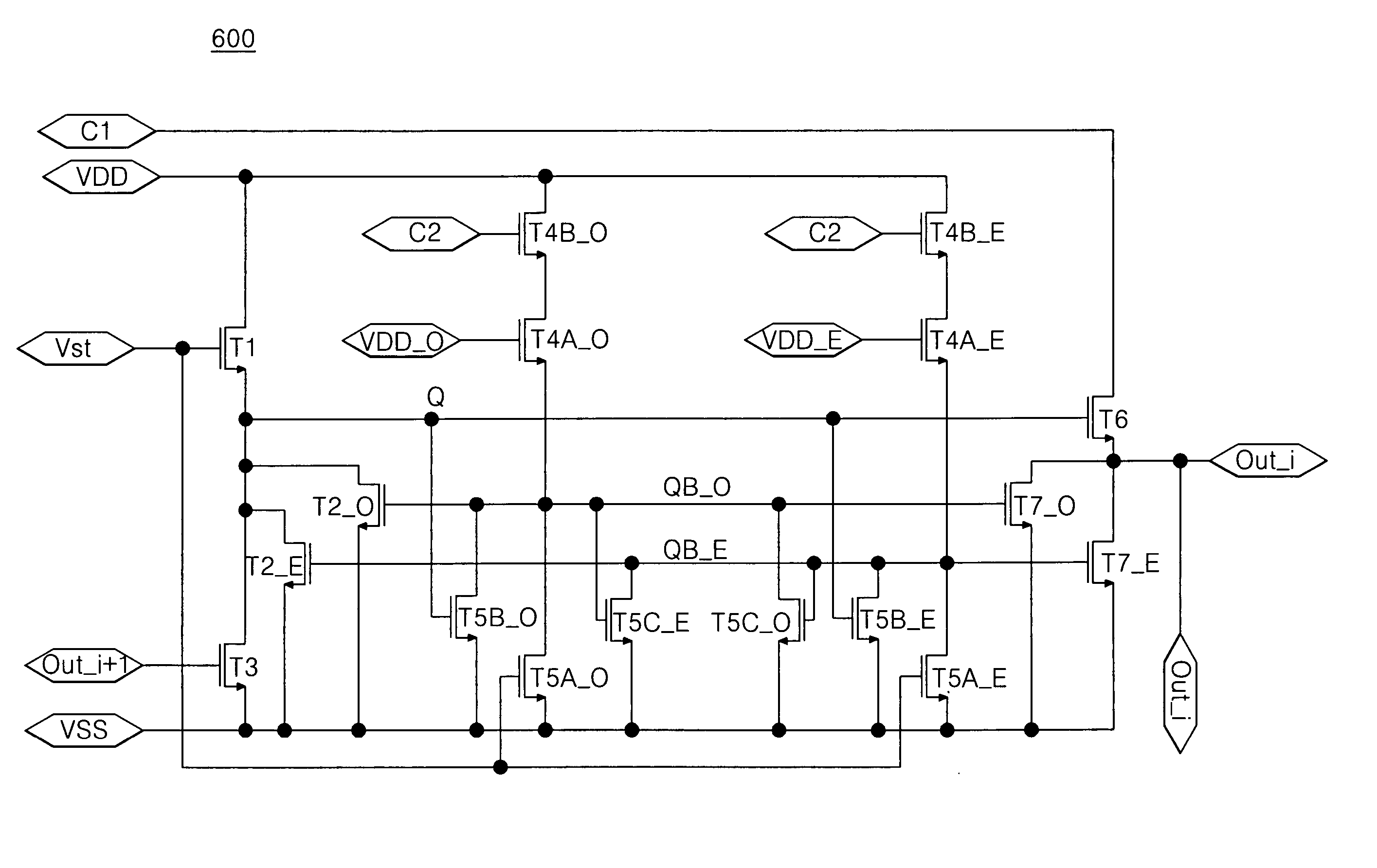

Shift register

ActiveUS20060145999A1Static indicating devicesCounting chain synchronous pulse countersLiquid-crystal displayCharge and discharge

A shift register for use with a liquid crystal display device includes a plurality of stages. A stage of the shift register includes a first controller, a second controller and an output buffer. The first controller charges and discharges a first node. The second controller charges and discharges a second node and a third node. The output buffer outputs a first output signal in response to the state of the first node and a second output signal in response to the state of the second and third nodes. The shift register may be adaptive to avoid a malfunction caused by a gate bias stress.

Owner:LG DISPLAY CO LTD

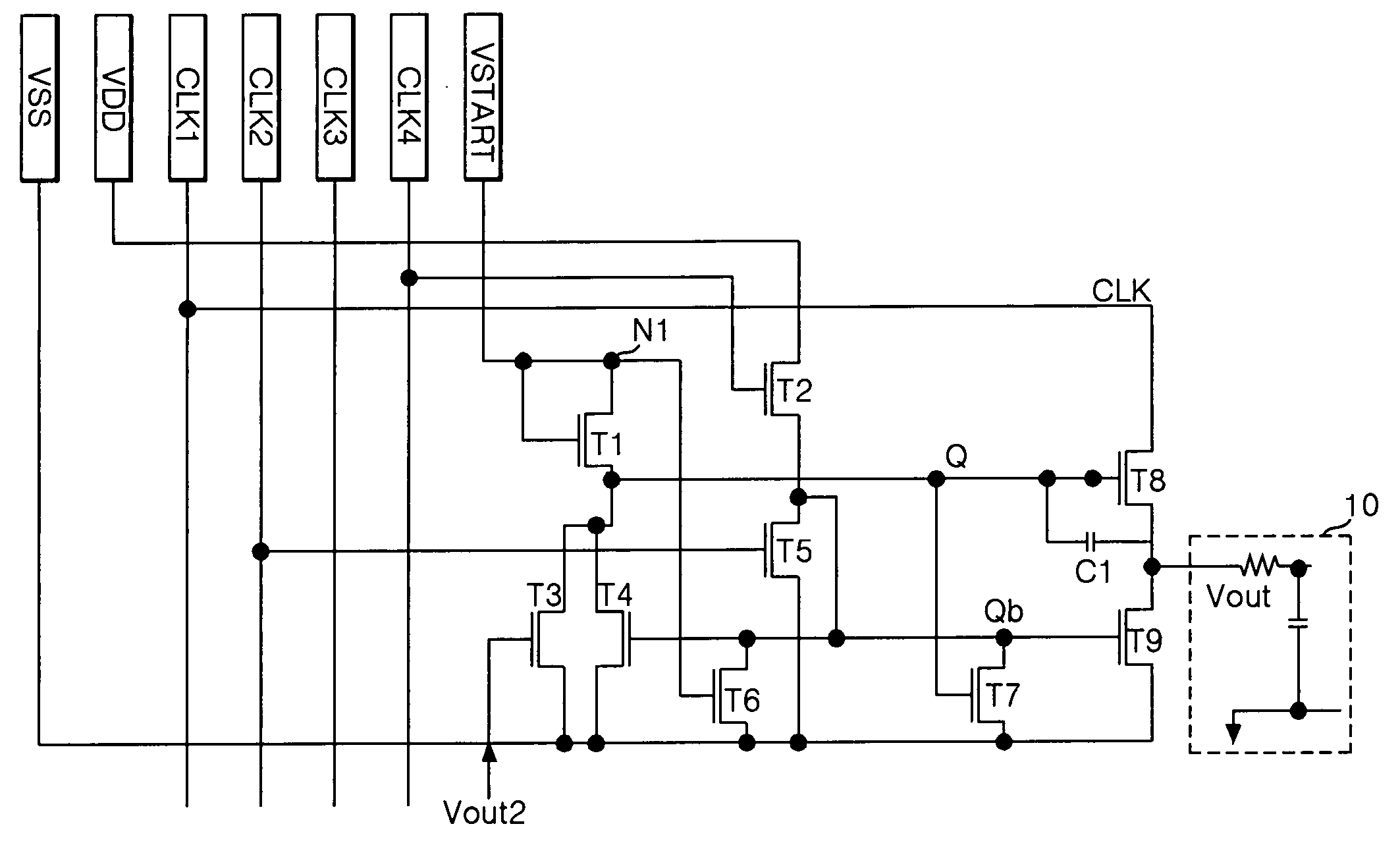

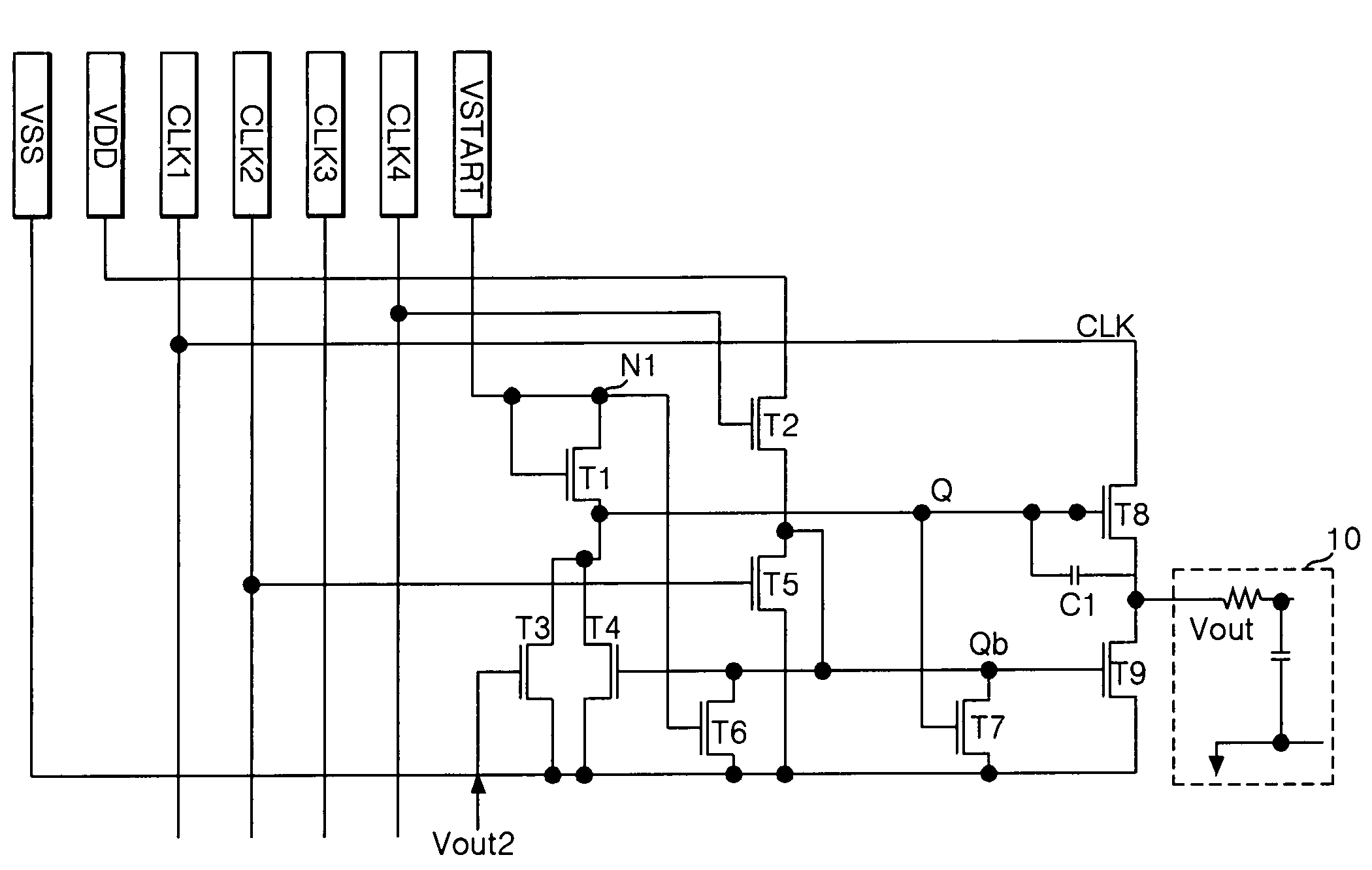

Shift register and method for driving the same

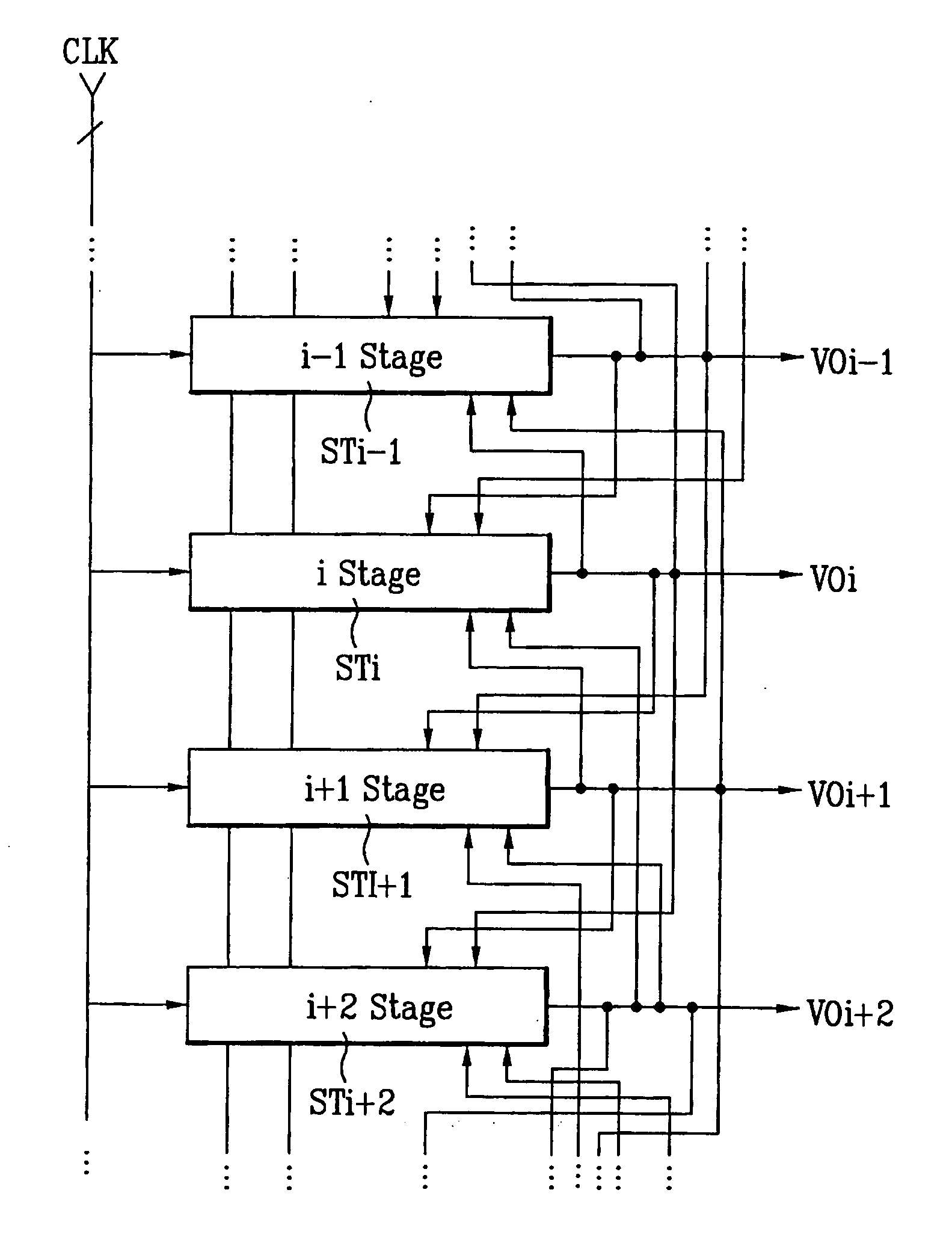

ActiveUS20060146978A1Static indicating devicesCounting chain synchronous pulse countersShift registerVoltage source

This invention relates to a shift register that is adaptive for preventing malfunction and damage, and a driving method thereof. A shift register having a plurality of stages which output an output signal through an output signal line by using any three of a first voltage supply source, a previous stage's output signal, a next stage's output signal, and first to fourth clock signals, includes a pull-up transistor to output the first clock signal through the output signal line in response to a logic value of a Q node; a pull-down transistor to supply a supply voltage from the first voltage supply source to the output signal line in response to a logic value of a Qb node; a Q node controller to control the logic value of the Q node in response to any one of the previous stage's output signal and the next stage's output signal; and a Qb node controller to control the logic value of the Qb node to alternate repeatedly between low and high by use of at least one of the second clock signal, the third clock signal and the logic value of the Q node when the output signal line is in a low state.

Owner:LG DISPLAY CO LTD

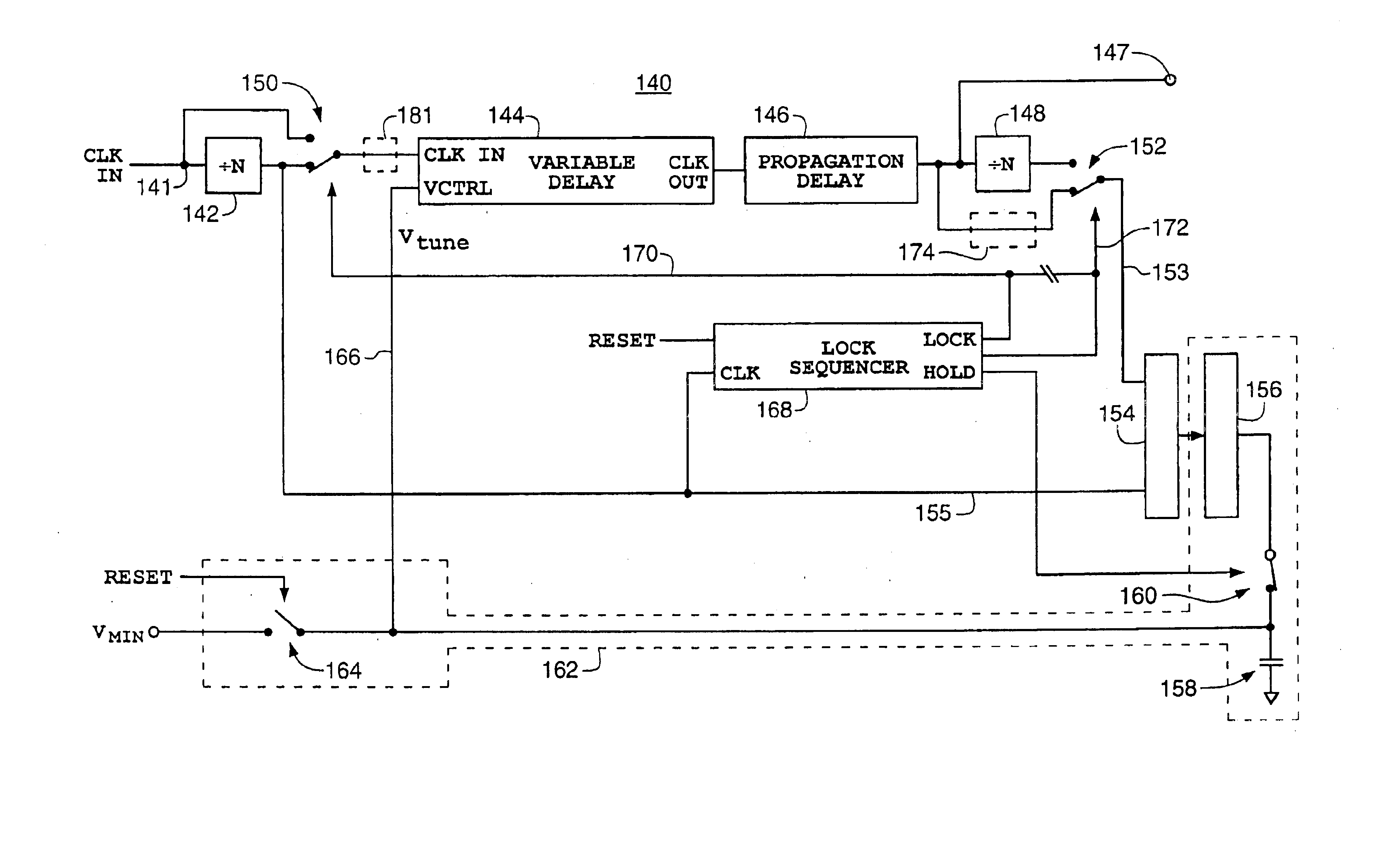

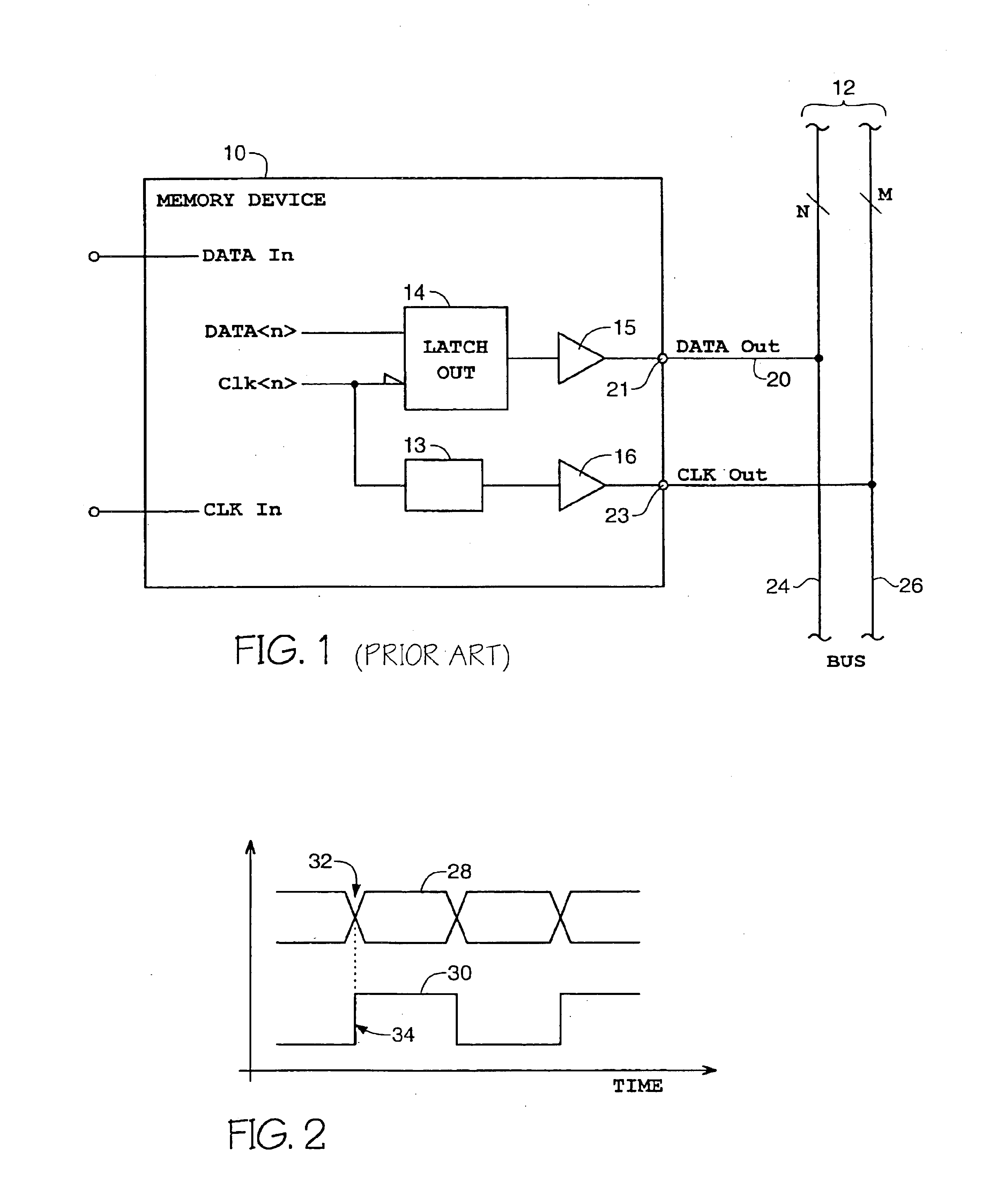

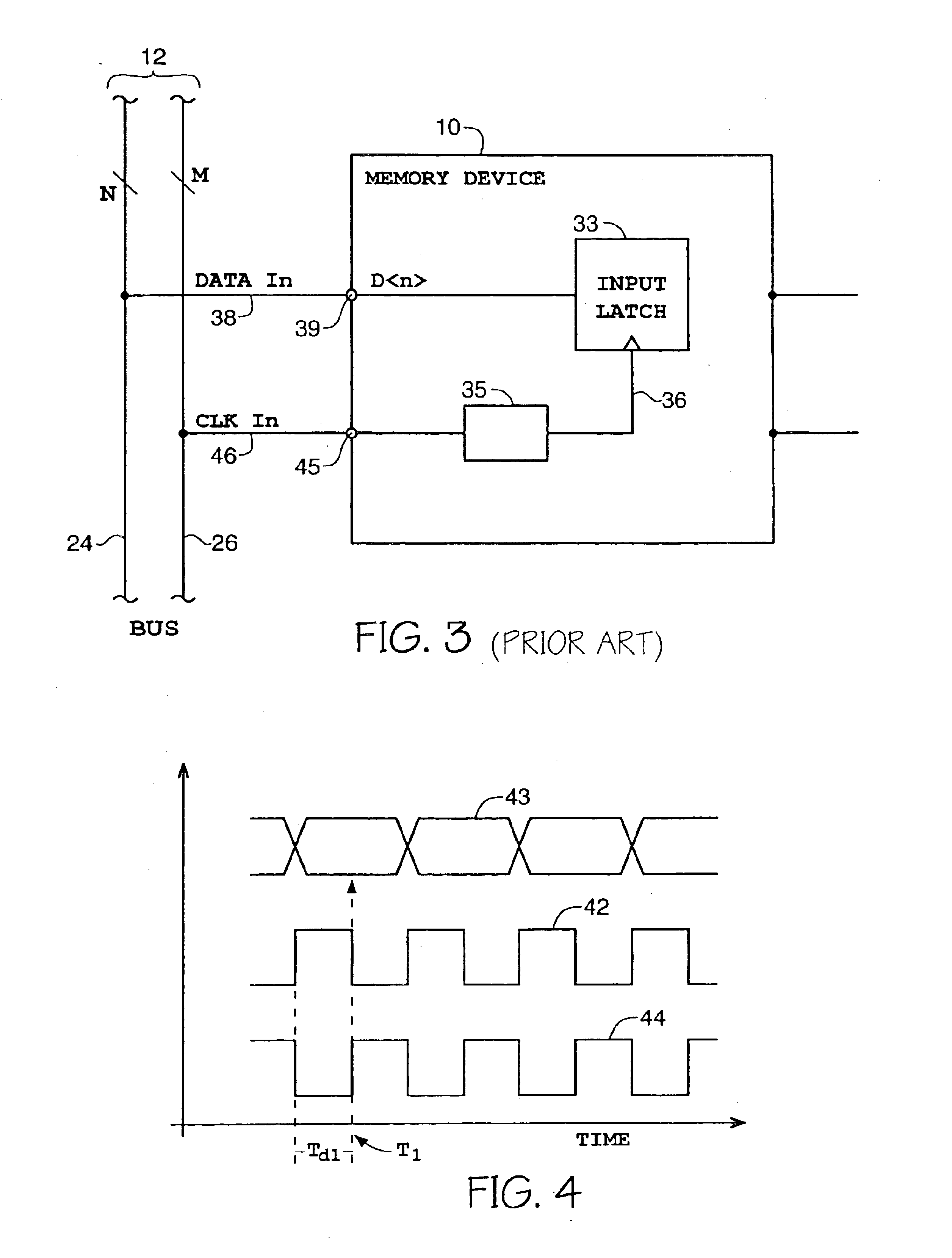

Delay lock loop circuit useful in a synchronous system and associated methods

InactiveUS6842399B2Continuously circulated pulse countersPulse automatic controlPhase detectorControl signal

A method and circuitry for a delay lock loop useful in synchronizing the accessing of a memory array with a system clock is disclosed. In a preferred embodiment, the delay lock loop includes a variable delay element. The delay of the variable delay element is initially set to a minimum delay value. The system clock is then frequency divided and sent to the variable delay element, the output of which will ultimately be used to access the memory array in a synchronized manner with the system clock. The frequency divided clock and the output of the variable delay element are input to a phase detector, which creates a control signal for adjusting the delay of the variable delay element. After the signals are determined to be locked by the phase detector, an undivided clock signal version of the clock signal is sent to the variable delay element, and a frequency divided version of the output of the variable delay element is sent to the phase detector in lieu of the previous output of the variable delay element.

Owner:ROUND ROCK RES LLC

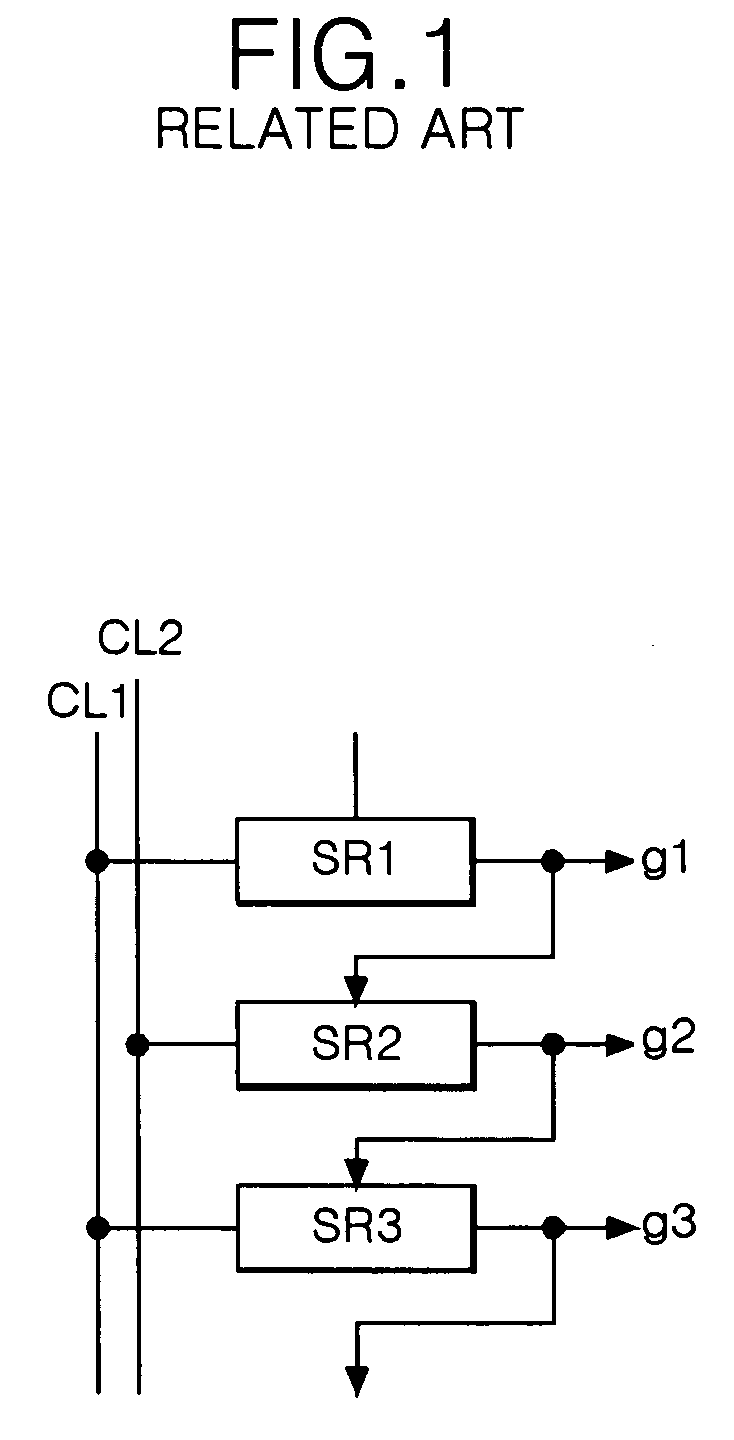

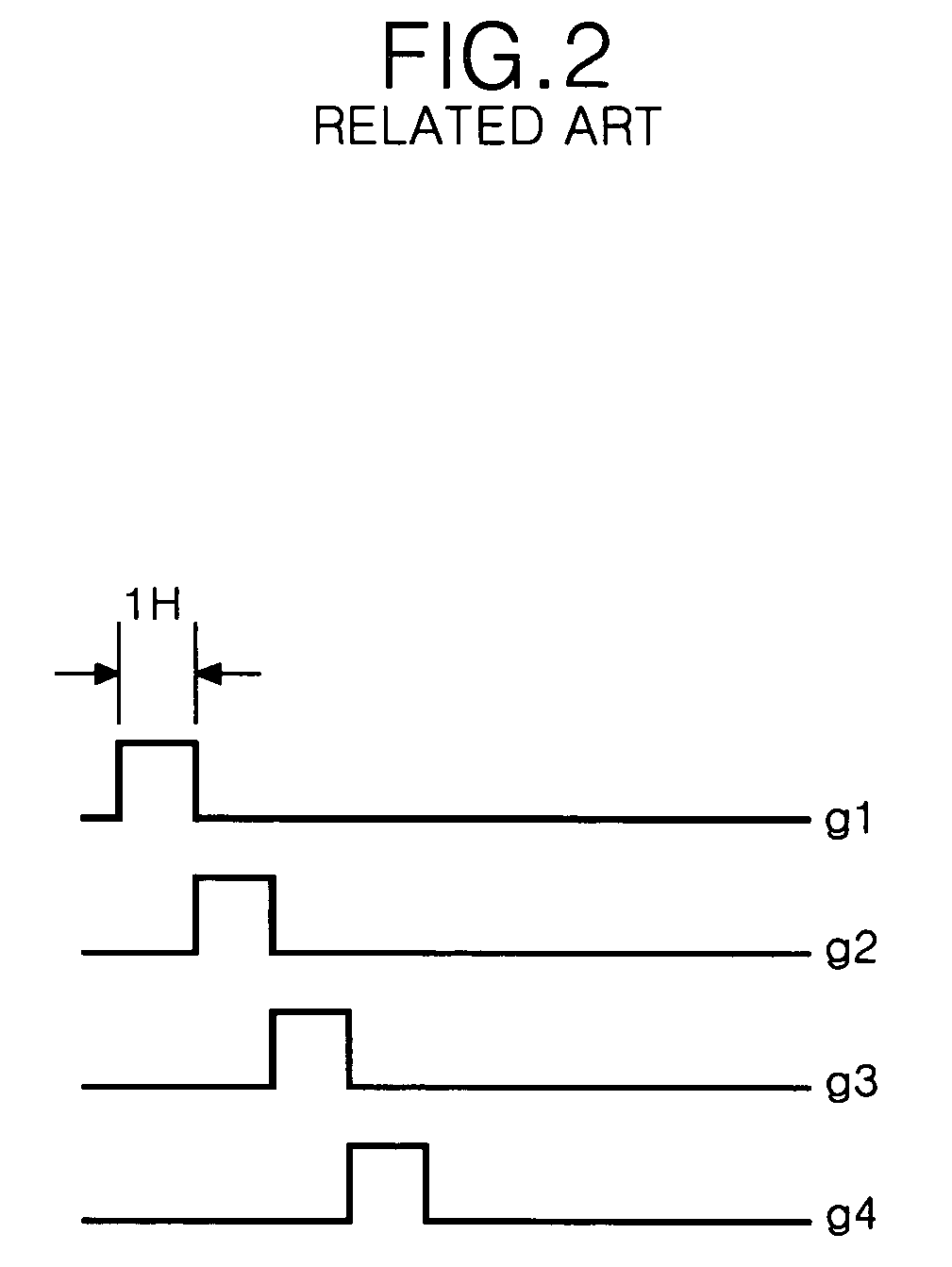

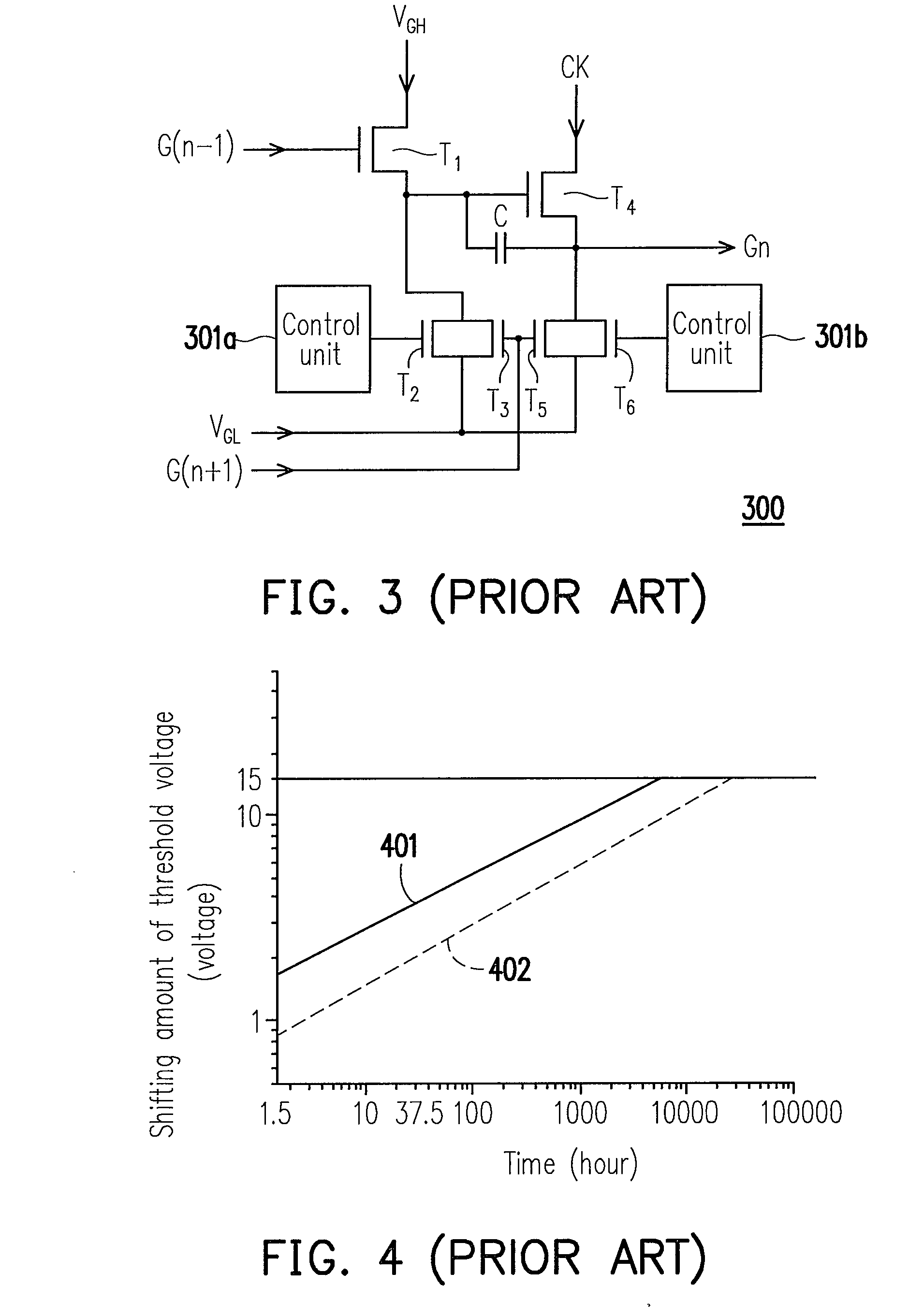

Shift register that suppresses operation failure due to transistor threshold variations, and liquid crystal driving circuit including the shift register

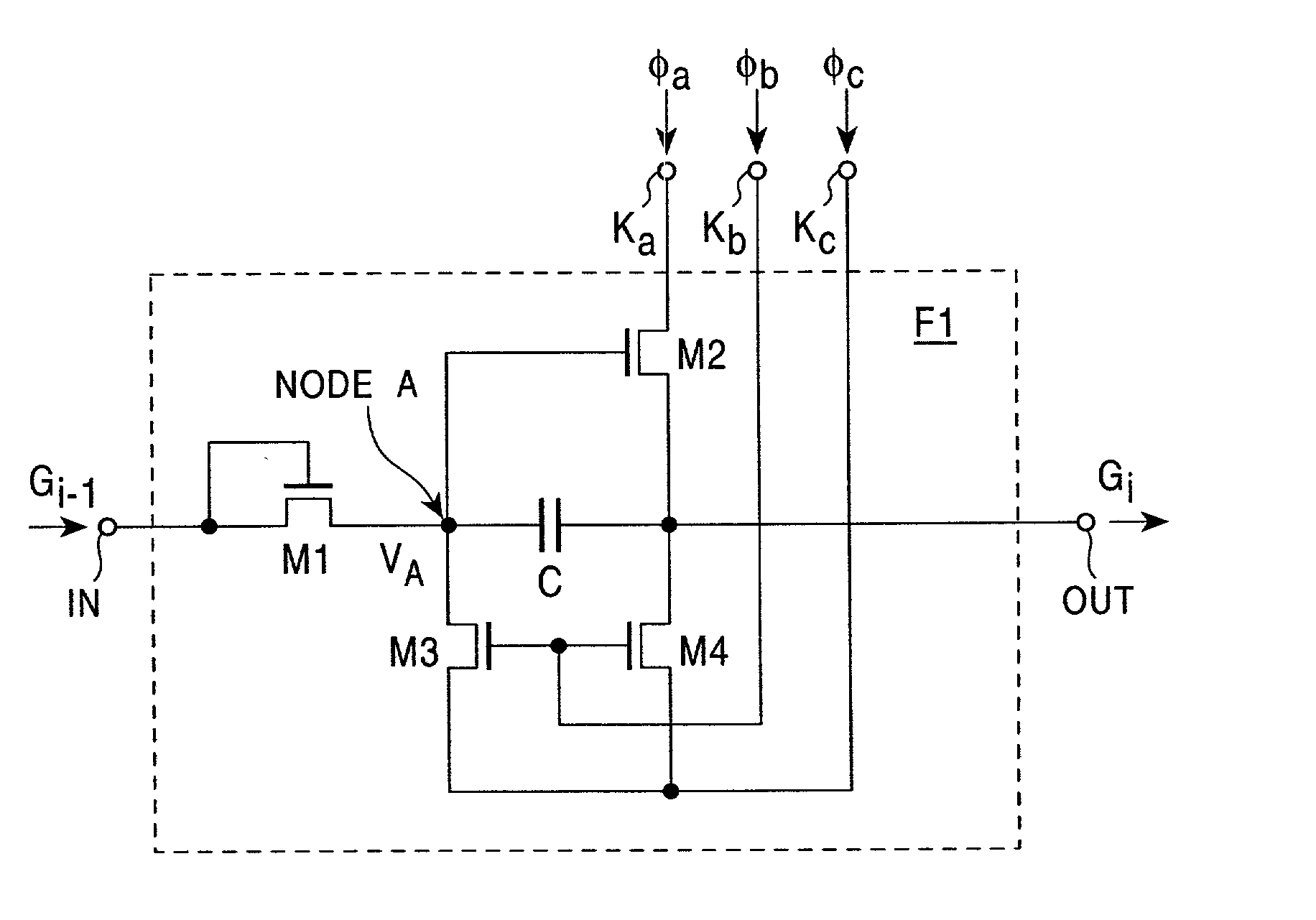

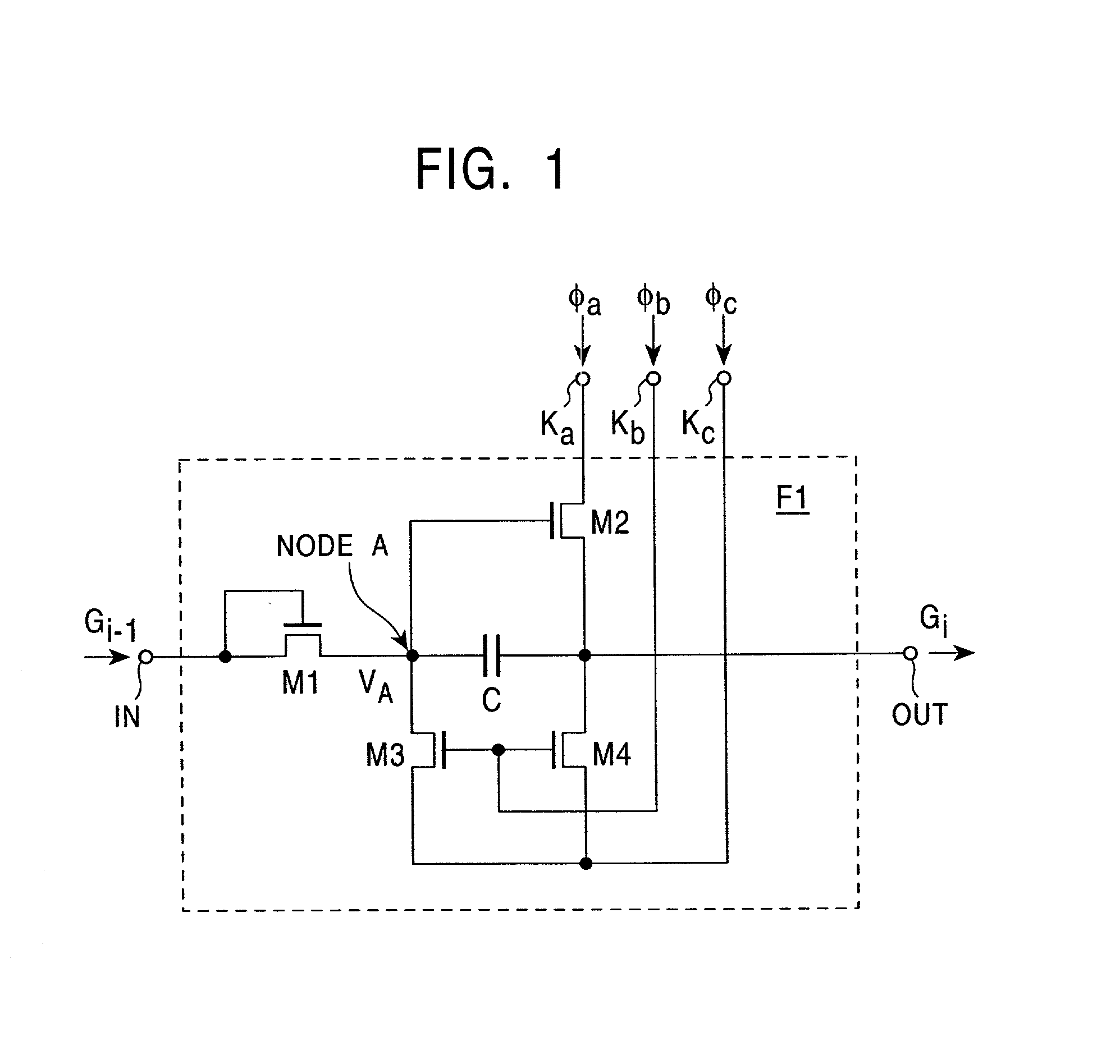

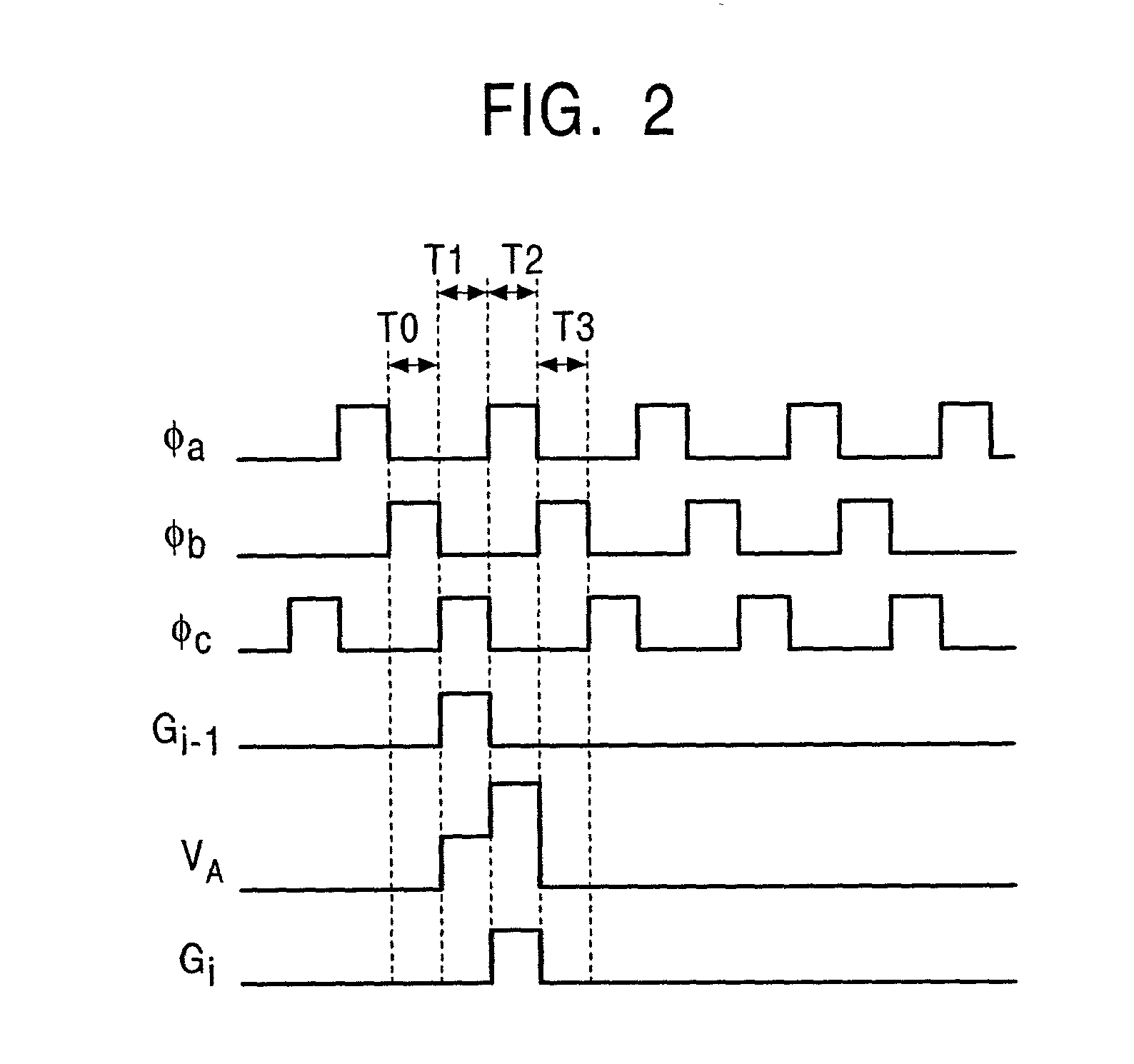

InactiveUS20050212746A1Reduce voltage application timeReduce areaTelevision system detailsCounting chain synchronous pulse countersShift registerPhase shifted

A shift register having a plurality of stages connected in cascade shifts an output signal by a plurality of clocks having different phases. Each of the stage includes an input diode to which a signal is input from a preceding stage, a capacitor for holding charge having a voltage level of the input signal, a first transistor that is turned on or off by the held voltage level to output an output signal to a following stage in synchronization with a clock signal, and a second transistor connected between the input diode and an output terminal. A control electrode of the second transistor is connected to the input diode in the following stage. The second transistor has a clamping function for discharging the accumulated charge and turning off the first transistor when the clock signal is phase-shifted.

Owner:ONANOVICH GROUP

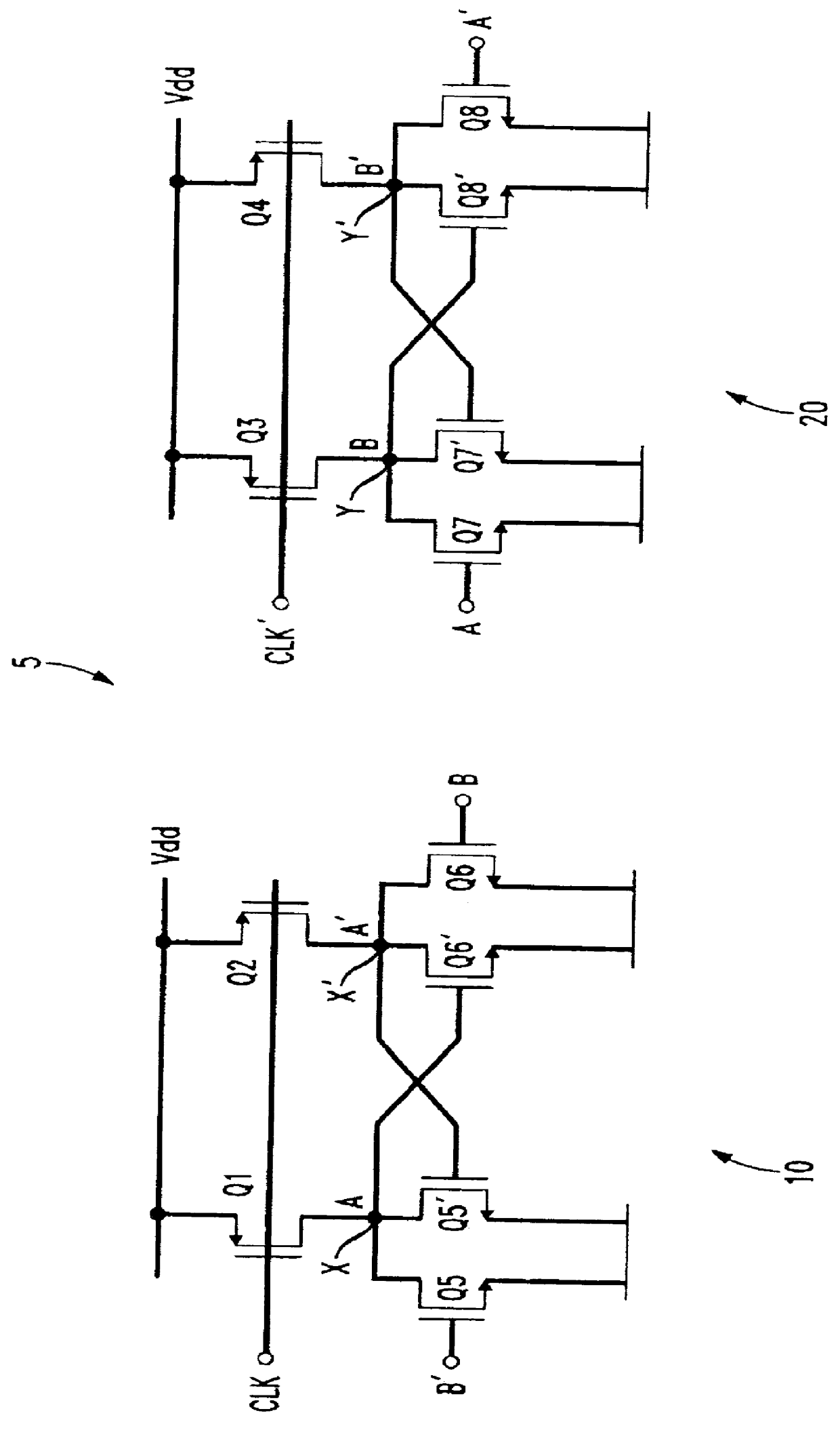

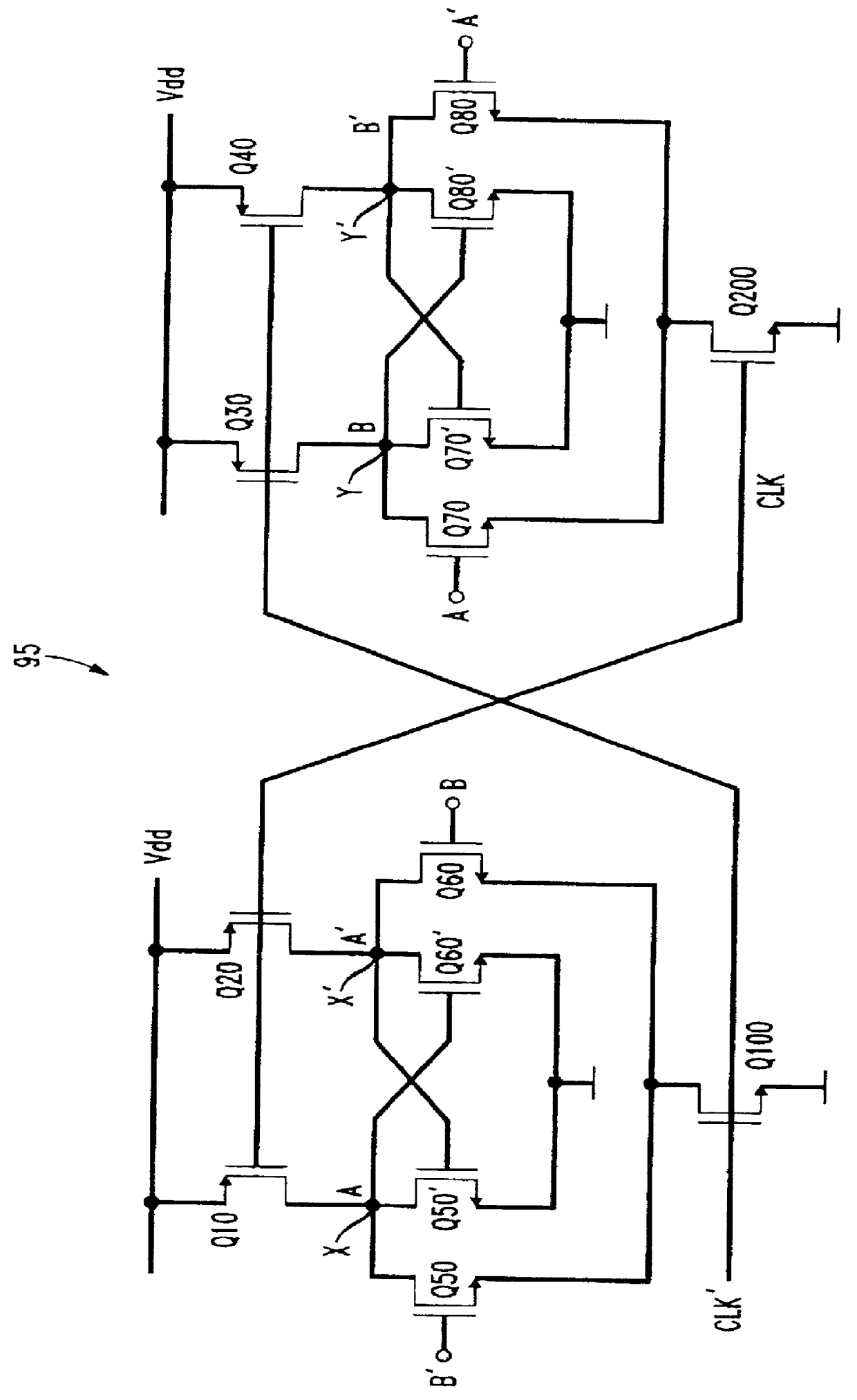

High speed frequency divider circuit

InactiveUS6166571ACounting chain synchronous pulse countersPulse counters with static storageRC time constantEngineering

A high frequency divider circuit for producing output signals of half the frequency of an input clock signal includes two identical circuit sections, each producing an output signal and its complement. The circuit sections are connected to each other so that the output signals of one circuit section serve as input signals to the other circuit section. Each circuit section contains a load transistor which is controlled by one of the clock signal and the clock signal complement, and a switch transistor which is controlled by the other of the clock signal and the clock signal complement. The inventive circuit exhibits a reduced RC time constant for each circuit section and an increased output signal swing between the output signals and their respective complements, as contrasted with prior art frequency dividers, thereby increasing the overall circuit response time and its ability to operate at high frequencies.

Owner:LUCENT TECH INC

Shift register and electronic apparatus

InactiveUSRE40673E1Correct operation of circuitGuaranteed uptimeCounting chain synchronous pulse countersPower supply linesShift registerTelecommunications

Each of stages RS(1), RS(2), . . . of a shift register is constituted by six TFTs. A ratio of a channel width and a channel length (W / L) of each of these TFTs 1 to 6 is set in accordance with a transistor characteristic of each TFT in such a manner that the shift register normally operates for a long time even at a high temperature.

Owner:ORTUS TECH

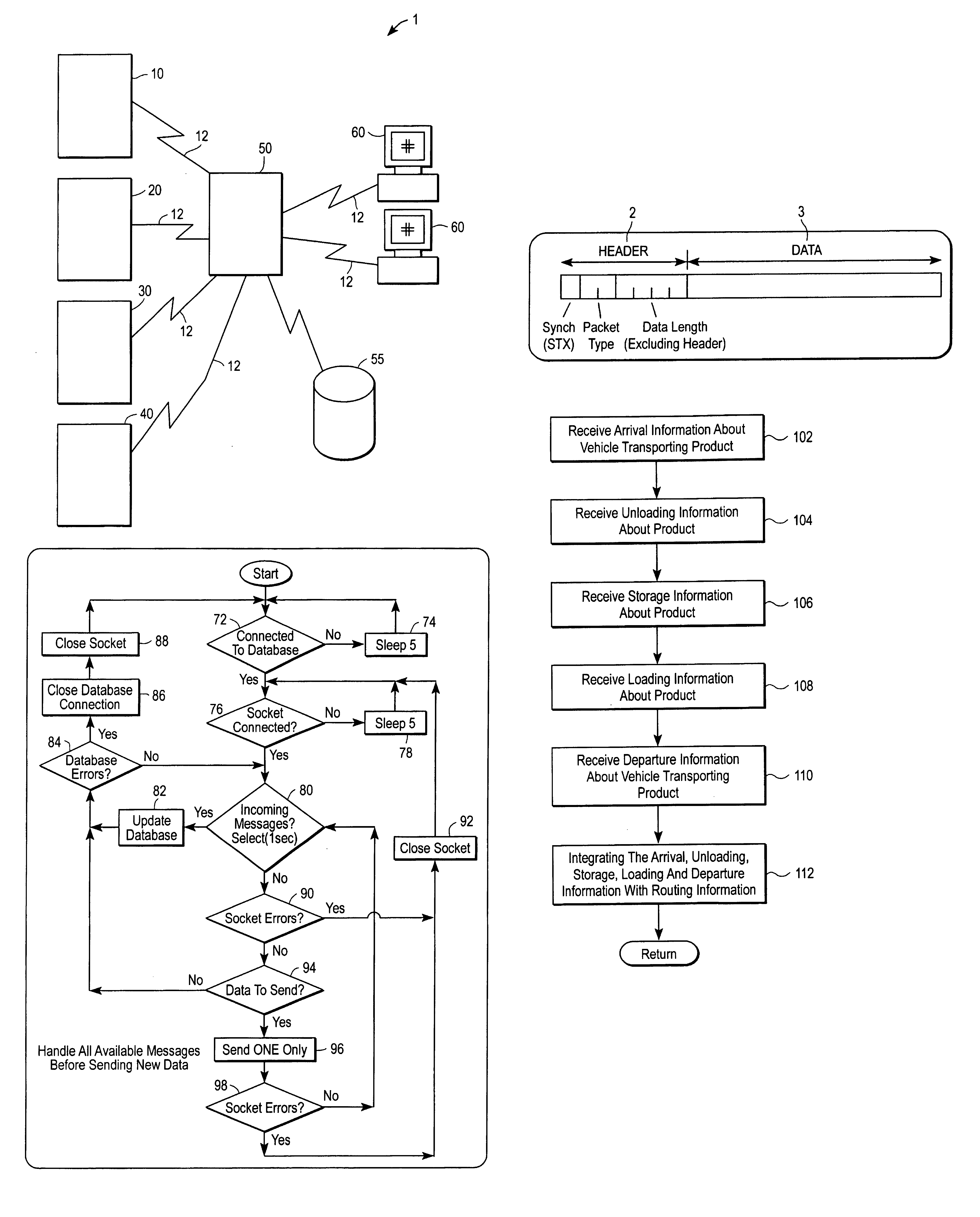

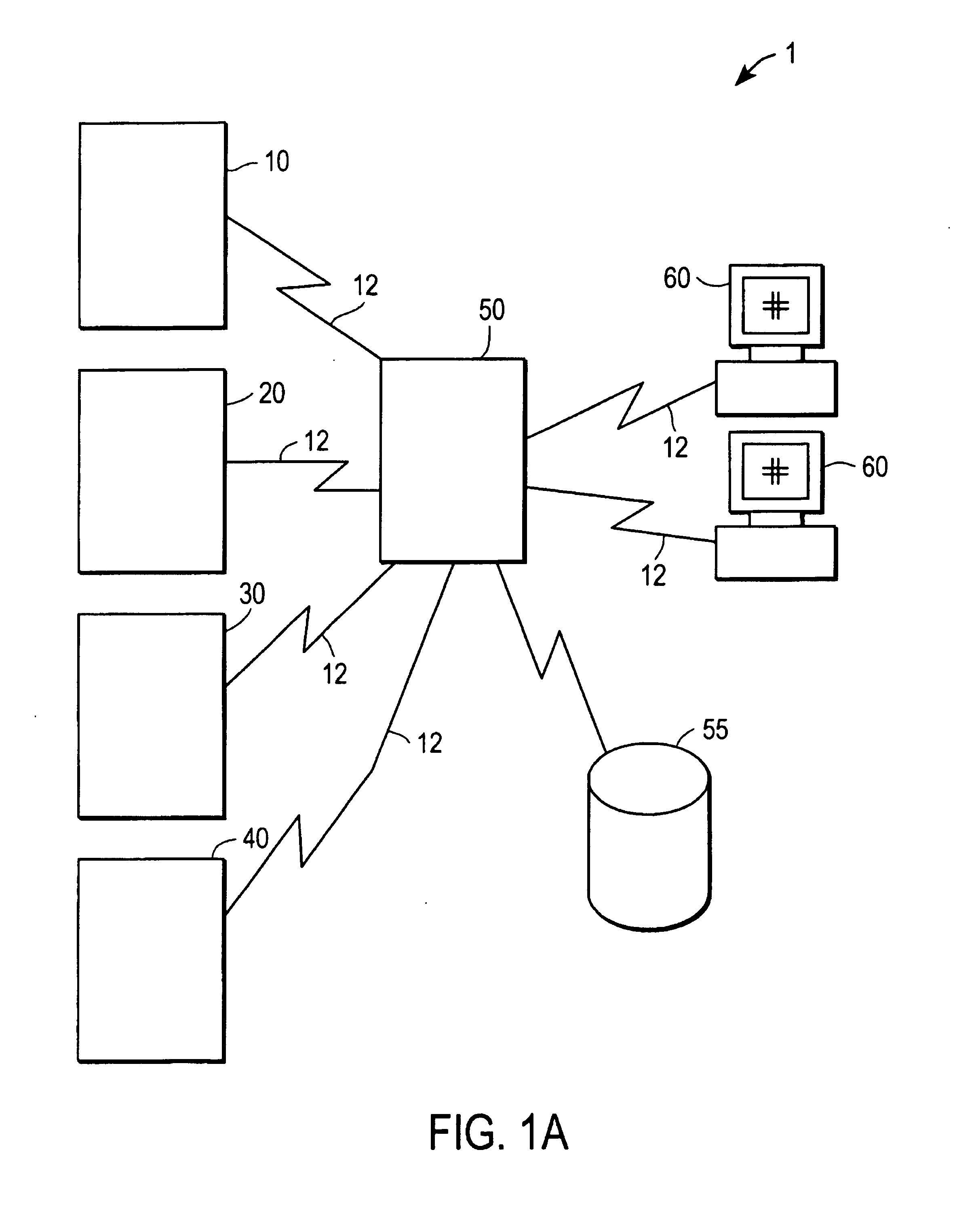

Database method and system for conducting integrated dispatching

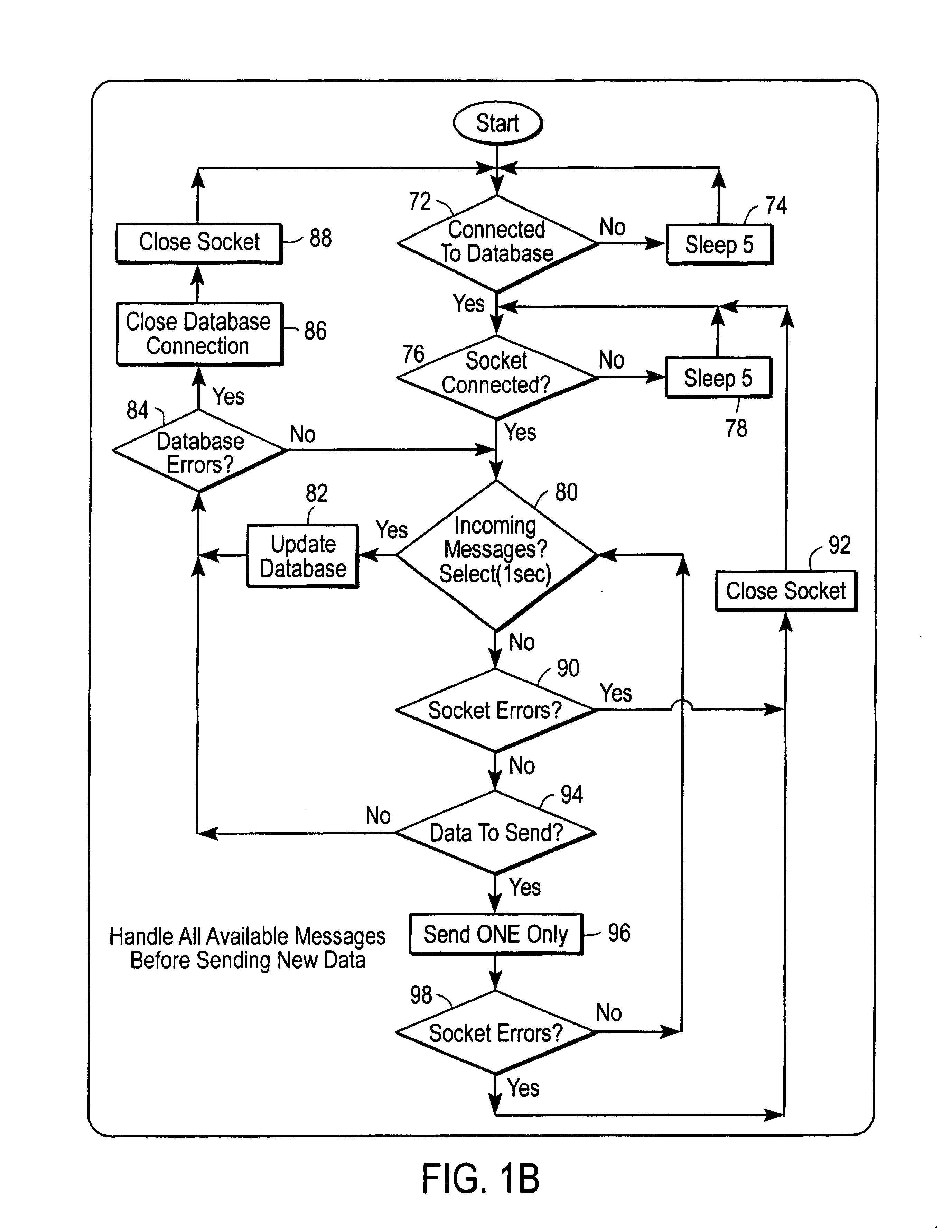

InactiveUS7085775B2Easily interfaceFirmly connectedInstruments for road network navigationDatabase management systemsFleet managementDisplay device

A technique for integrating a pre-existing business system with a fleet management system. The pre-existing business system includes, for example, an accounting system, a warehousing system, a dock management system, a yard management system. These fleet management system uses, for example, a combination of a raster map and vector data to provide an easy-to-read display for managing objects or articles, e.g., vehicle, container. The method uses a host gateway to provide a TCP / IP or like interface between the various systems.

Owner:MOBILE INFORMATION SYST

Shift register

ActiveUS7333586B2Static indicating devicesCounting chain synchronous pulse countersShift registerVoltage source

A shift register has a plurality of stages which output driving signals, each stage including a pull-up transistor to output a first clock signal in response to a logic value of a Q node; a pull-down transistor to supply a voltage from a first voltage supply source to the output in response to a logic value of a Qb node; a Q node controller to control the logic value of the Q node in response to any one of the previous stage's output signal and the next stage's output signal; and a Qb node controller to control the logic value of the Qb node to alternate repeatedly between low and high by use of at least one of a second clock signal, a third clock signal and the logic value of the Q node when the output signal is in a low state.

Owner:LG DISPLAY CO LTD

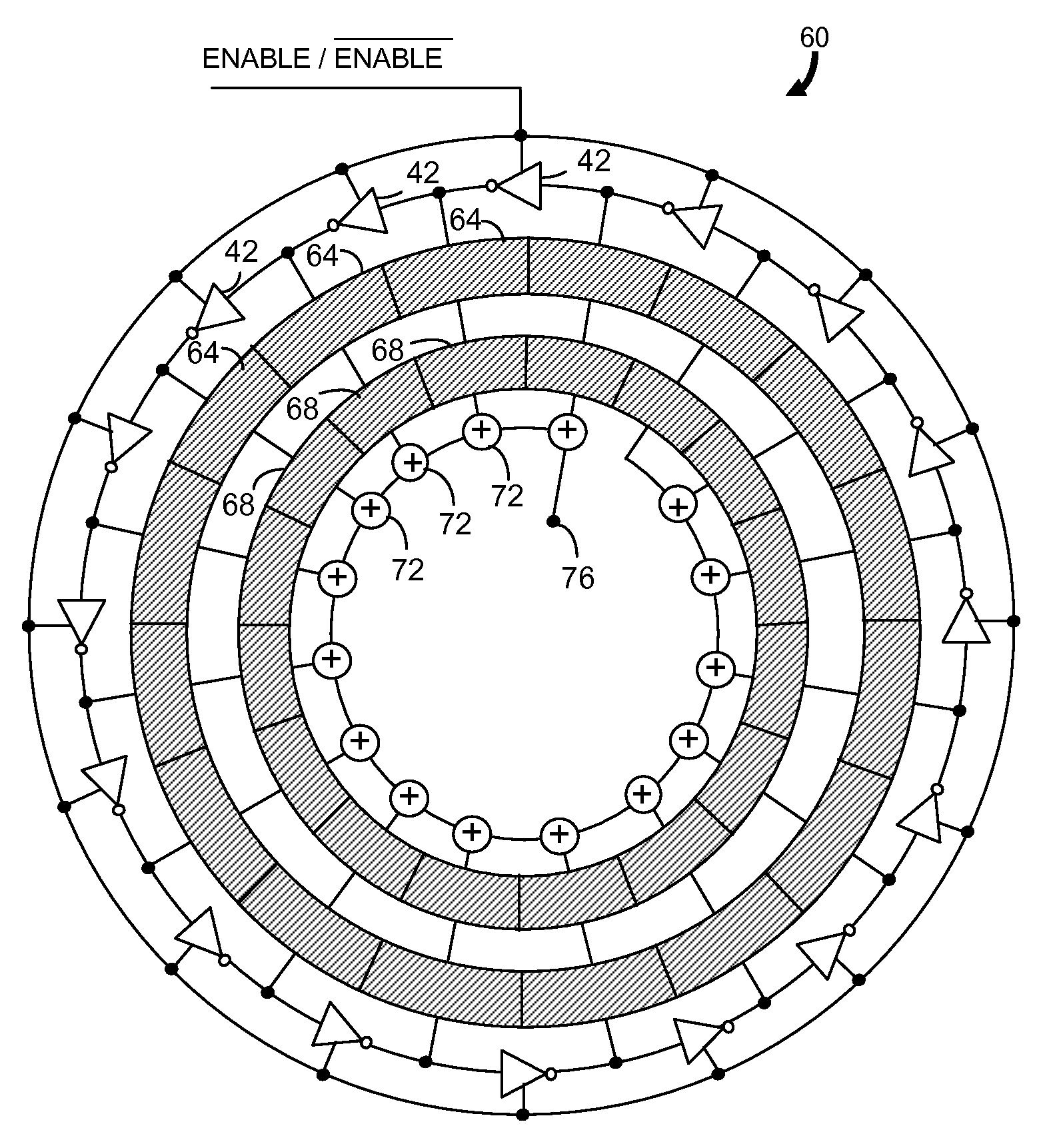

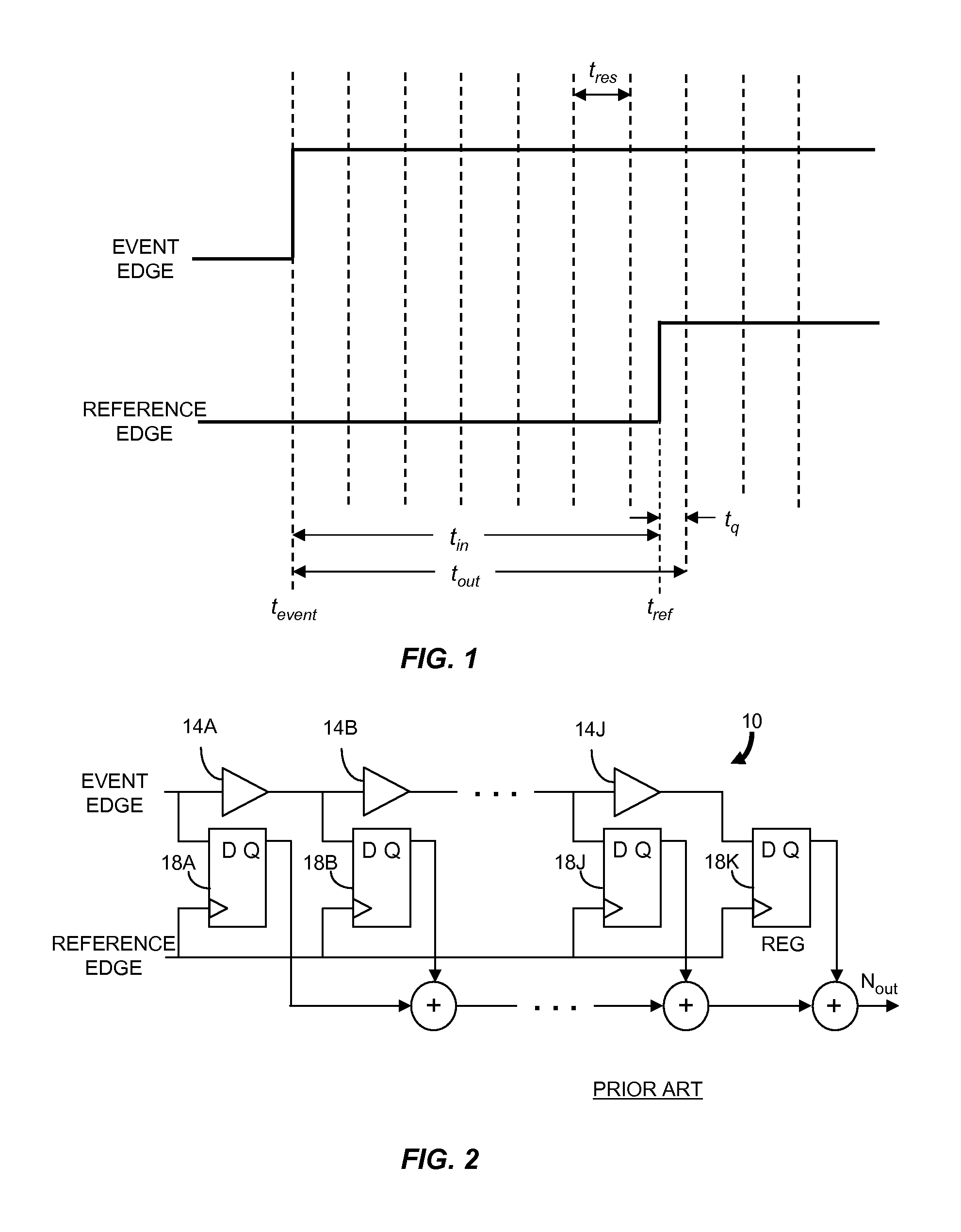

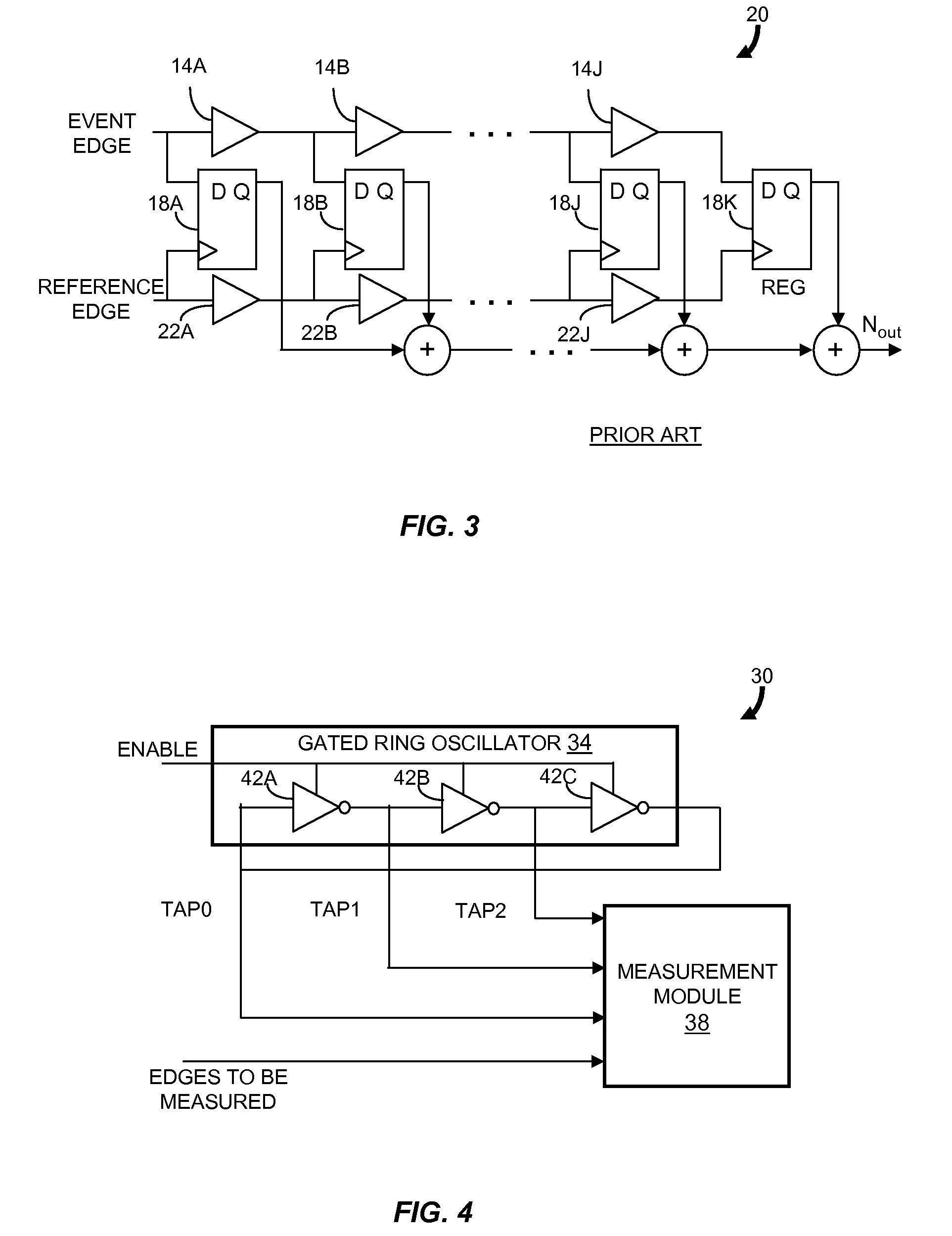

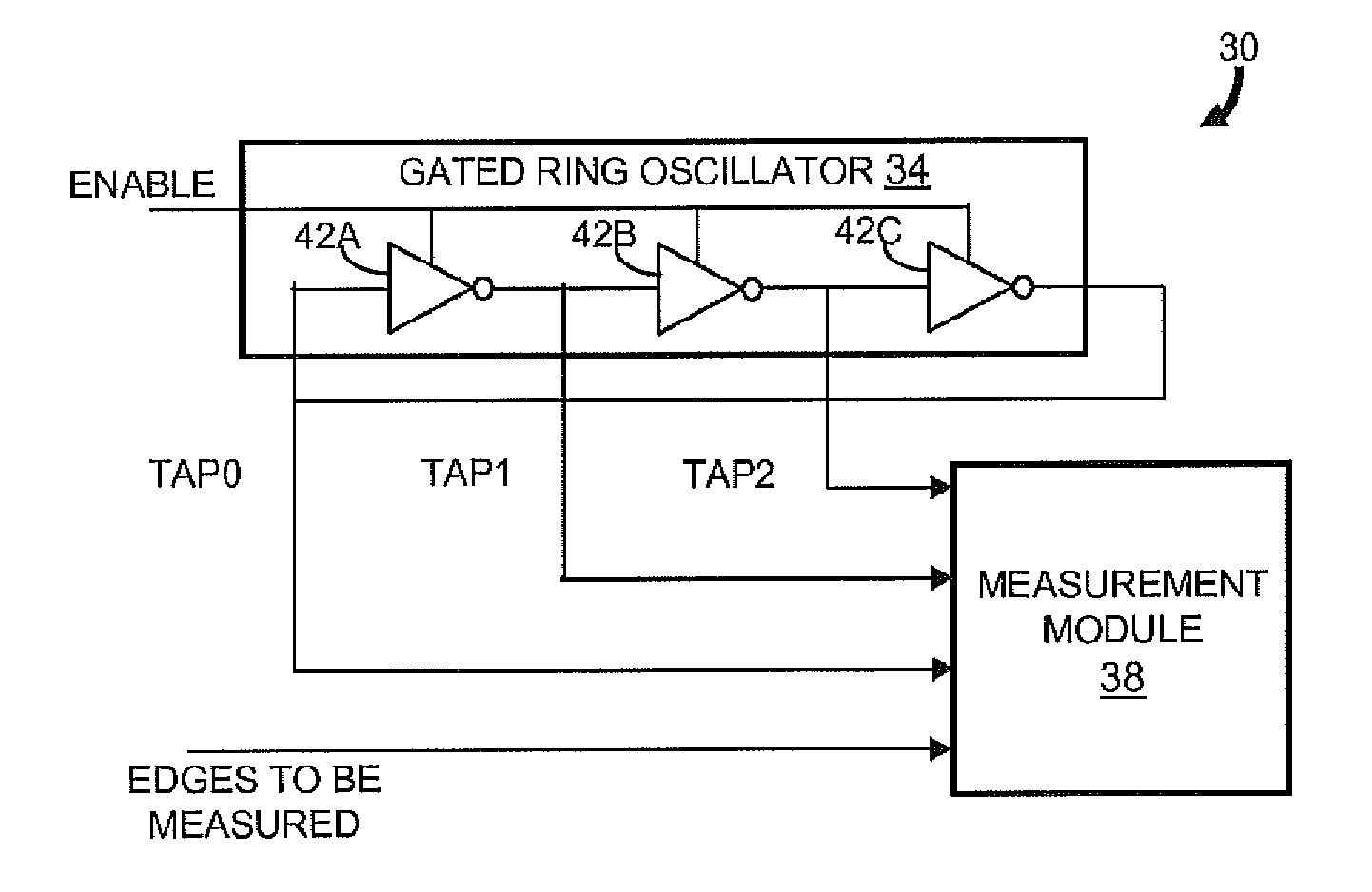

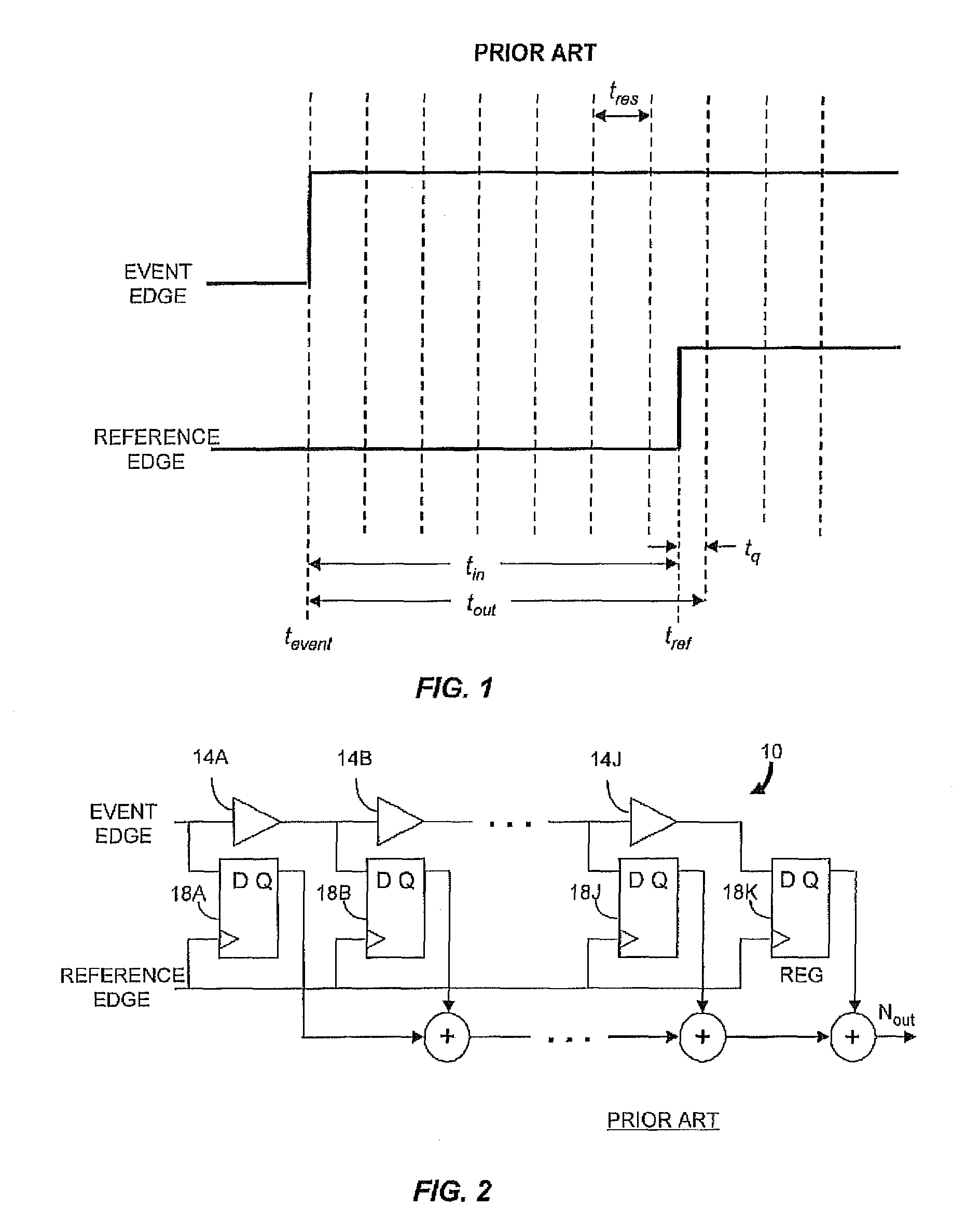

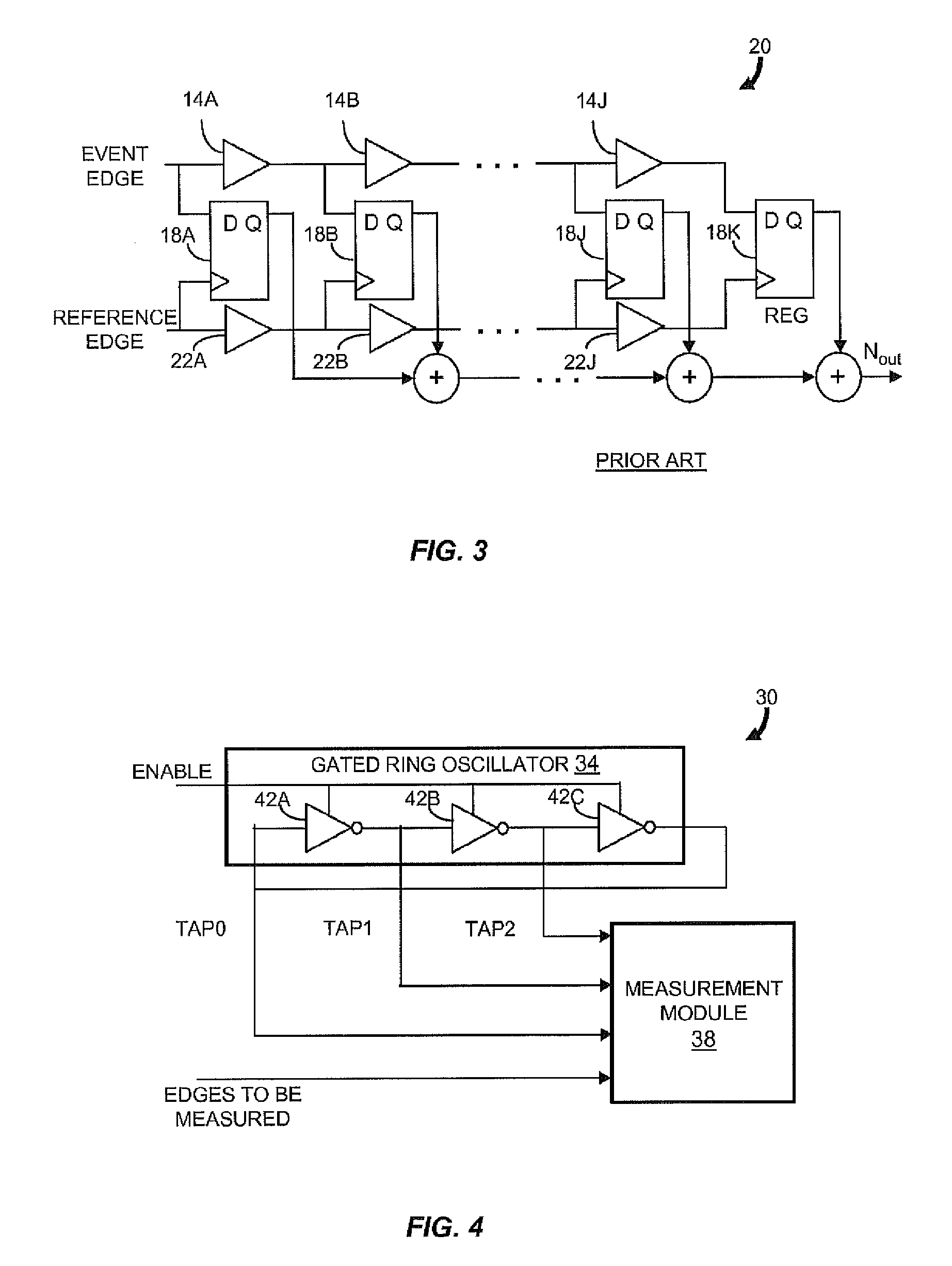

Gated ring oscillator for a time-to-digital converter with shaped quantization noise

ActiveUS20080069292A1Resolution timeContinuously circulated pulse countersCounting chain synchronous pulse countersImage resolutionNoise shaping

Described is a compact, lower power gated ring oscillator time-to-digital converter that achieves first order noise shaping of quantization noise using a digital implementation. The gated ring oscillator time-to-digital converter includes a plurality of delay stages configured to enable propagation of a transitioning signal through the delay stages during an enabled state and configured to inhibit propagation of the transitioning signal through the delay stages during a disabled state. Delay stages are interconnected to allow sustained transitions to propagate through the delay stages during the enabled state and to preserve a state of the gated ring oscillator time-to-digital converter during the disabled state. The state represents a time resolution that is finer than the delay of at least one of the delay stages. A measurement module determines the number of transitions of the delay stages.

Owner:MASSACHUSETTS INST OF TECH

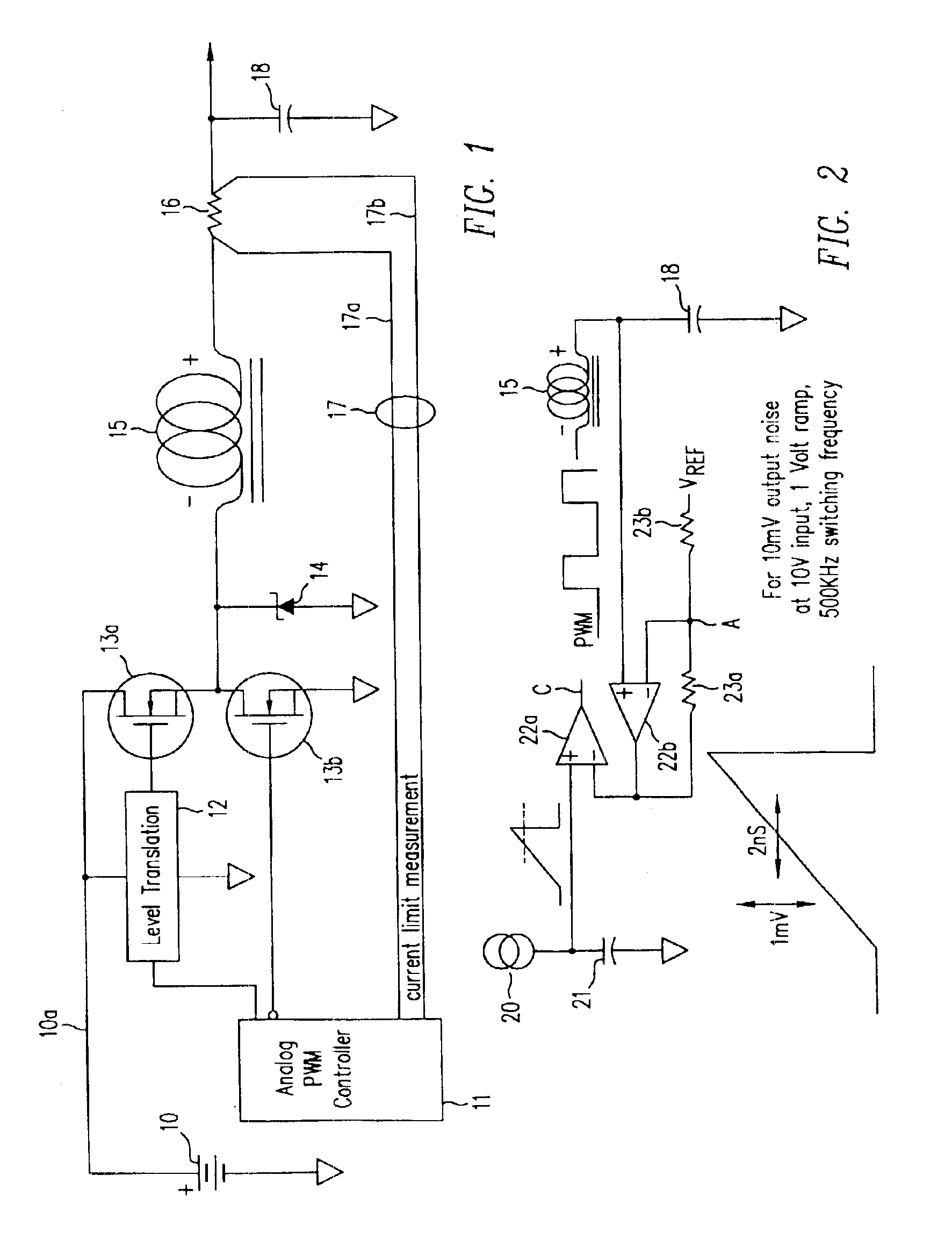

Multi-channel control methods for switched power converters

InactiveUS6912139B2Channel interference is avoided and minimizedExclusive-OR circuitsCounting chain pulse counters with non-natural counting orderVoltage pulseTransverter

Owner:EXAR CORP

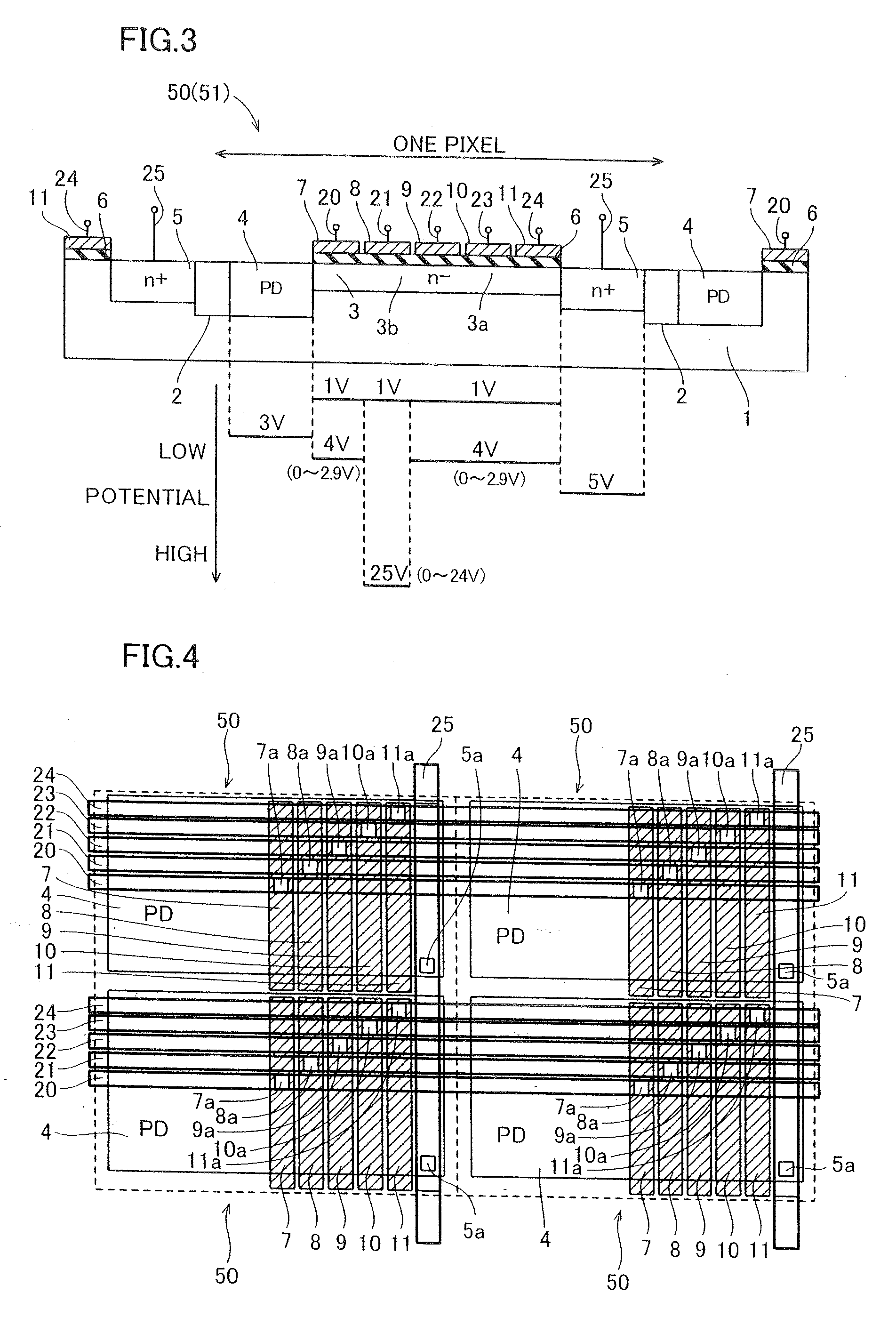

Counter circuit, AD conversion method, AD converter, semiconductor device for detecting distribution of physical quantities, and electronic apparatus

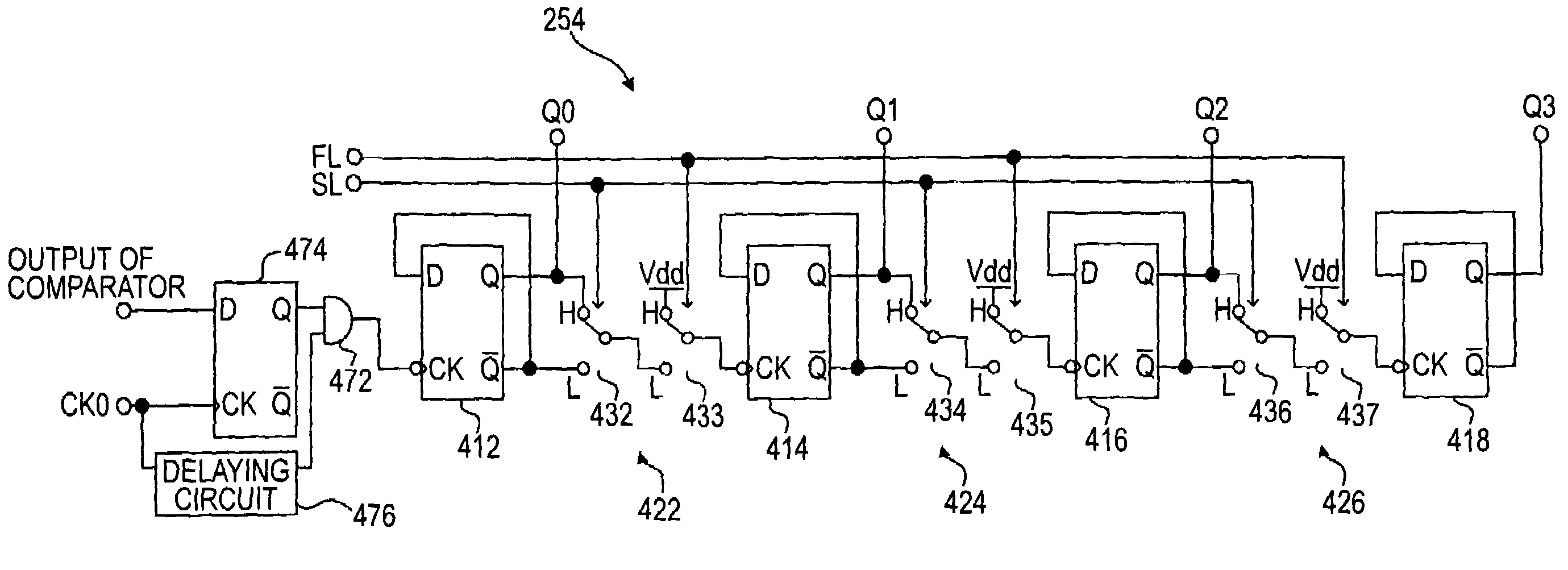

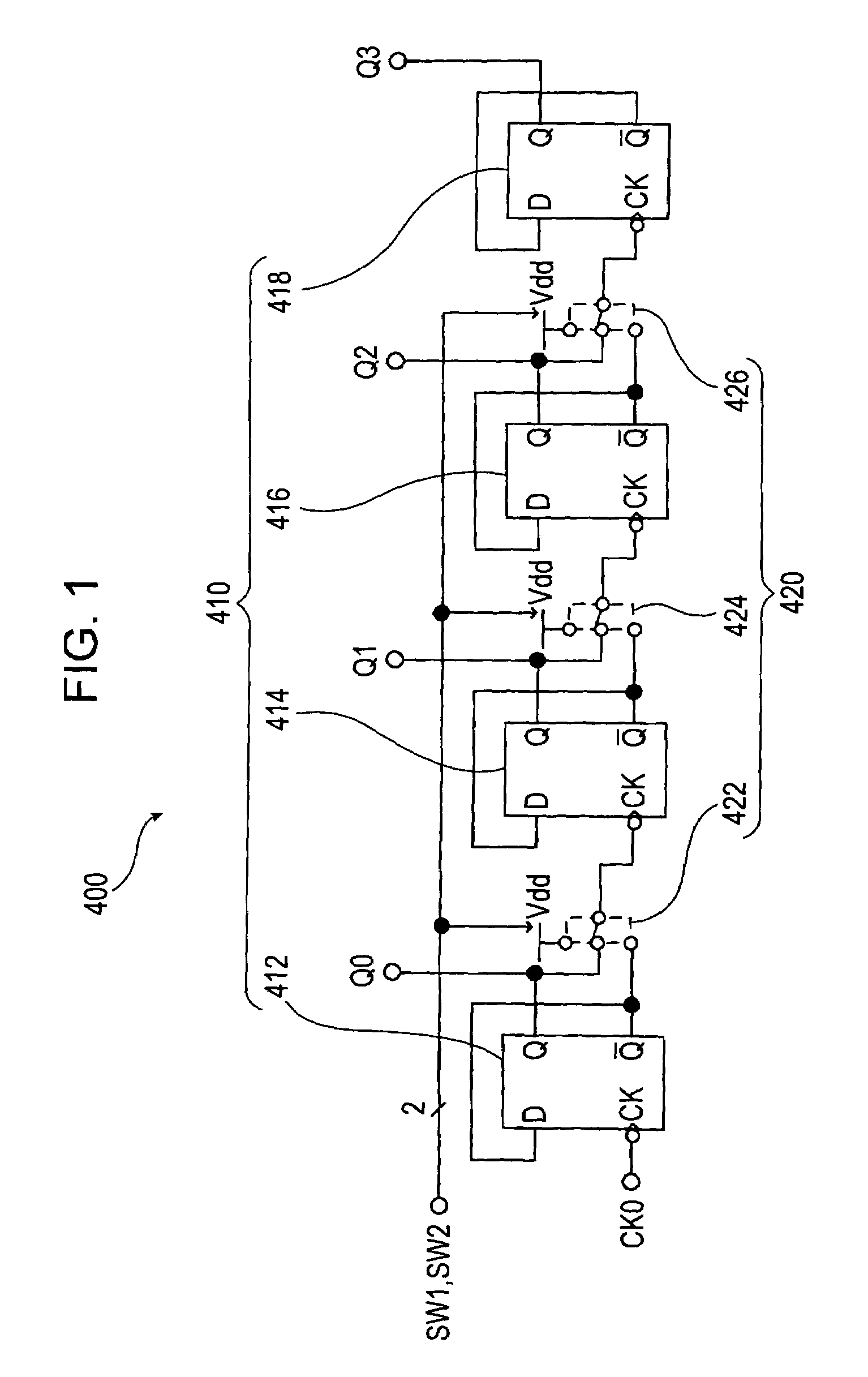

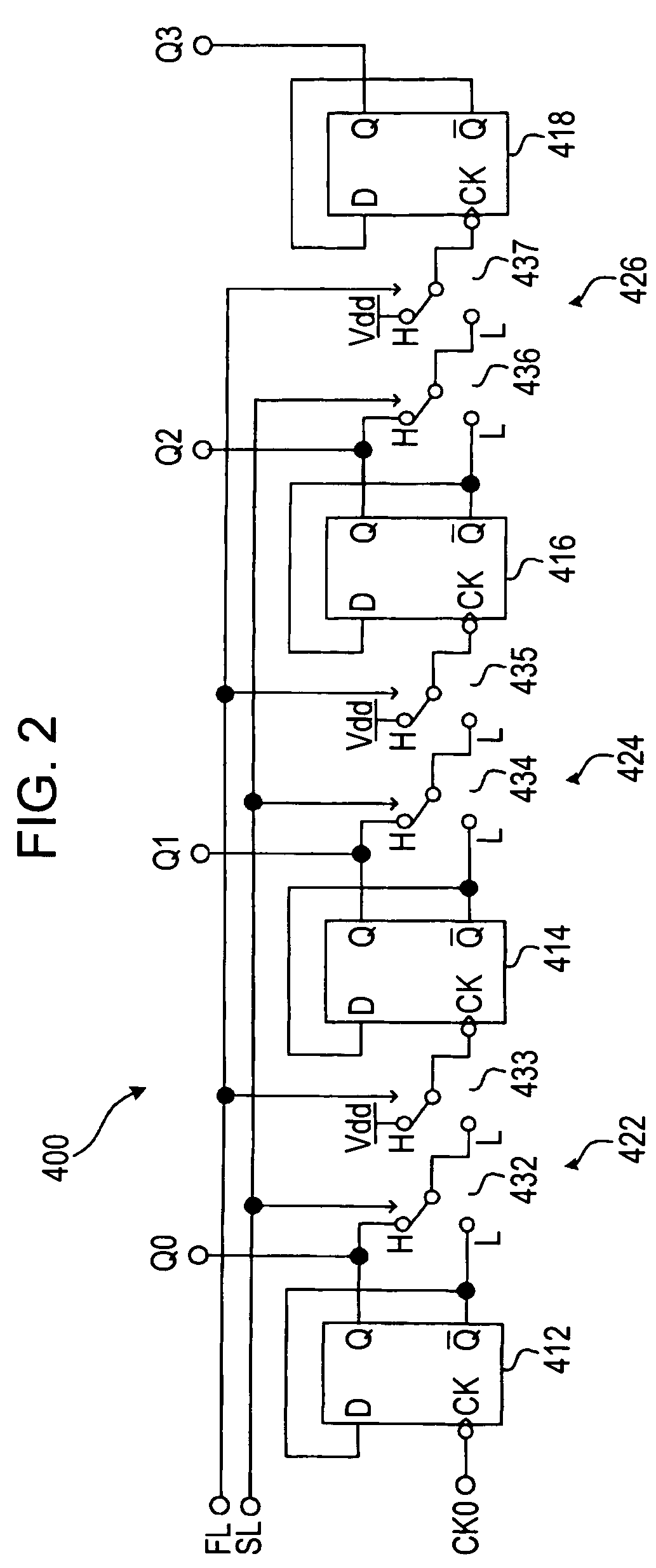

An asynchronous counter that is capable of switching count mode includes flip-flops, and three-input single-output tri-value switches respectively provided between the adjacent pairs of the flip-flops. The tri-value switches switch among three values, namely, non-inverting outputs and inverting outputs of the flip-flops and a power supply level. Each of the tri-value switches switch among the three input signals according to two-bit control signals, and input a selected signal to a clock terminal of a subsequent flip-flop. When count mode is switched according to the control signals, a count value immediately before the mode switching is set as an initial value, and counting after the mode switching is started from the initial value.

Owner:SONY CORP

Counter circuit, AD conversion method, AD converter, semiconductor device for detecting distribution of physical quantities, and electronic apparatus

An asynchronous counter that is capable of switching count mode includes flip-flops, and three-input single-output tri-value switches respectively provided between the adjacent pairs of the flip-flops. The tri-value switches switch among three values, namely, non-inverting outputs and inverting outputs of the flip-flops and a power supply level. Each of the tri-value switches switch among the three input signals according to two-bit control signals, and input a selected signal to a clock terminal of a subsequent flip-flop. When count mode is switched according to the control signals, a count value immediately before the mode switching is set as an initial value, and counting after the mode switching is started from the initial value.

Owner:SONY CORP

Boosted charge transfer circuit

ActiveUS20070279507A1Reduce the impactSufficient performanceTelevision system detailsTelevision system scanning detailsAudio power amplifierEngineering

A charge transfer circuit, such as a charge coupled device or other bucket brigade device, which incorporates an amplifier to assist with charge transfer.

Owner:INTERSIL INC

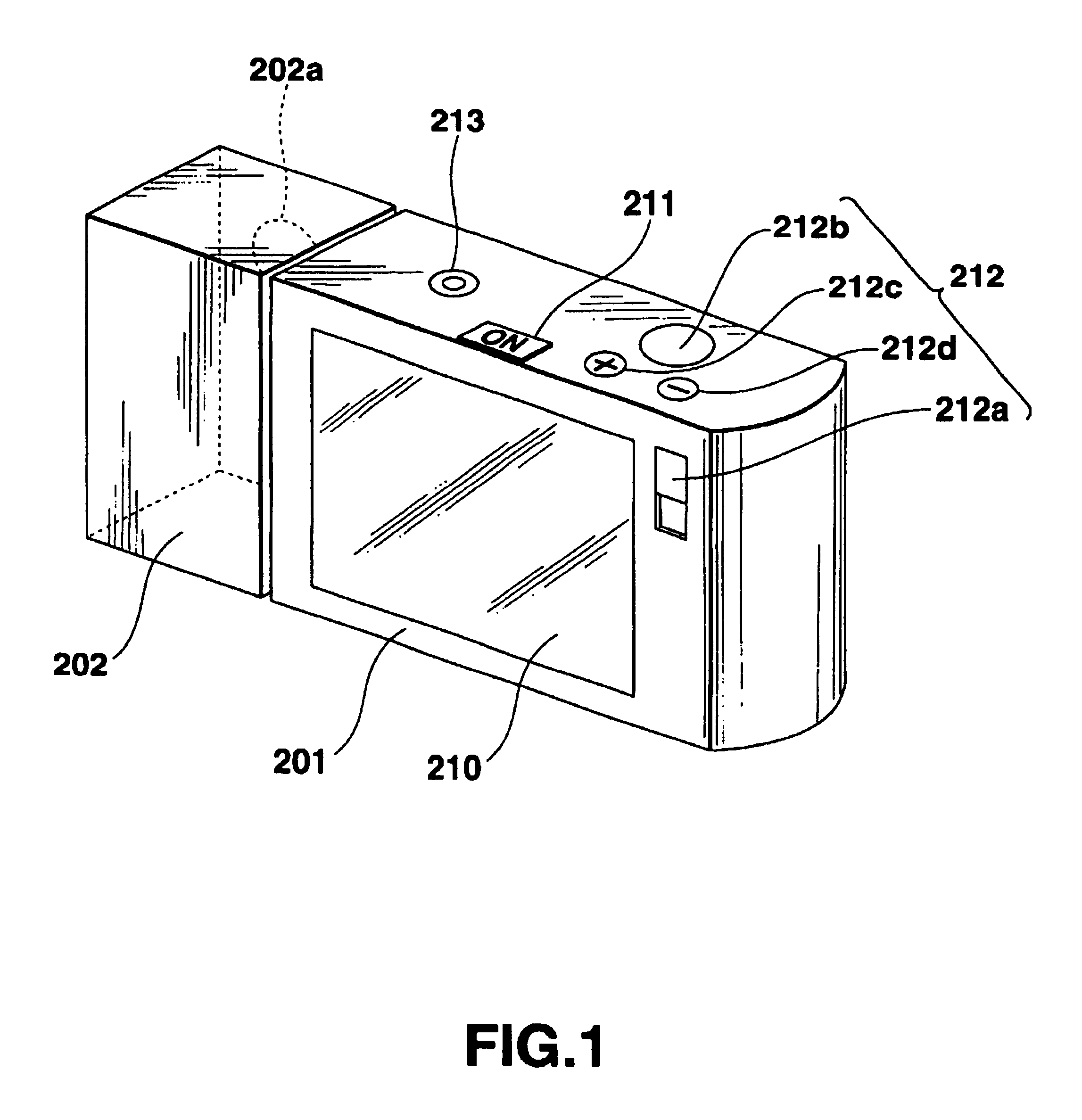

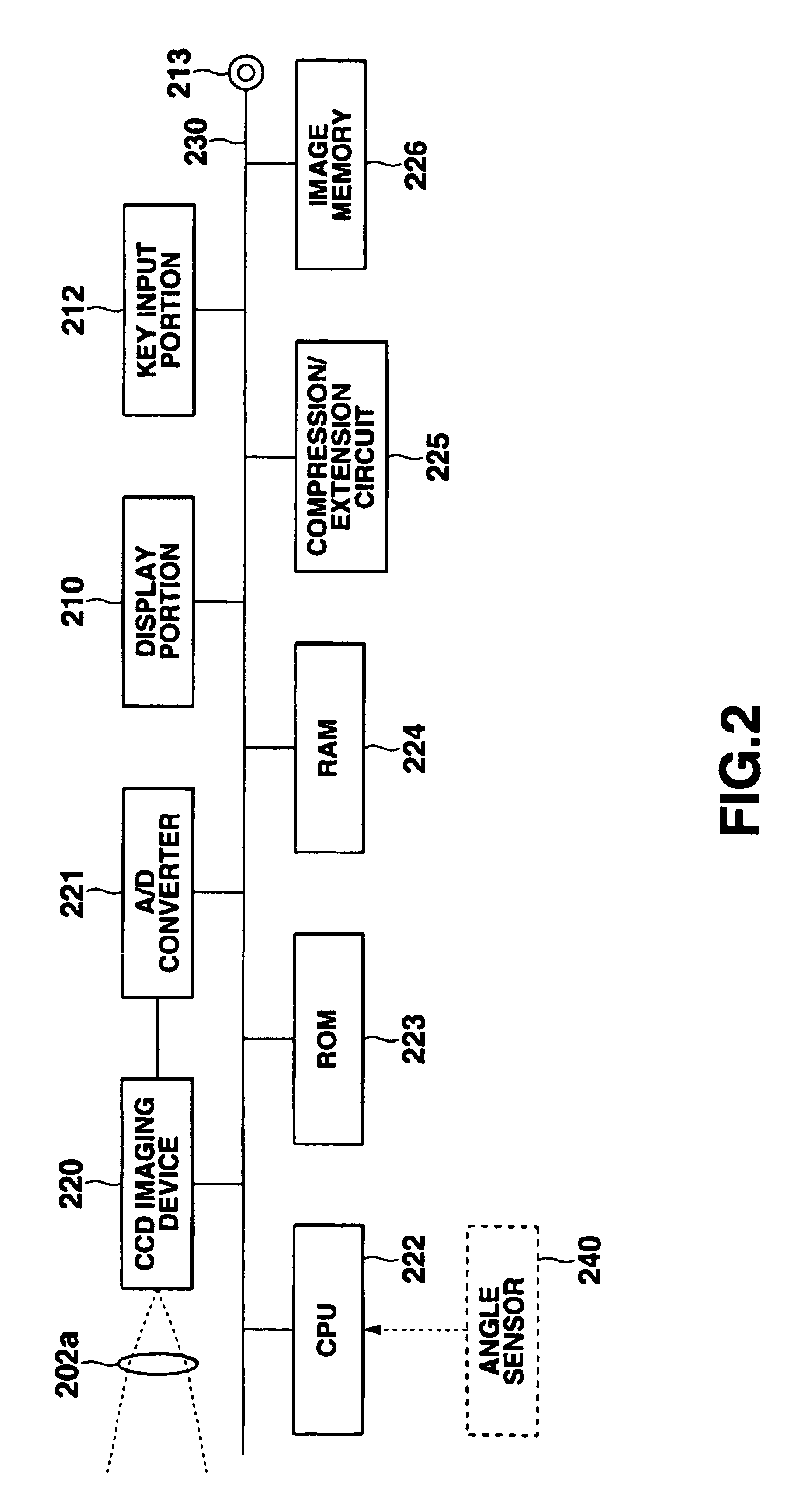

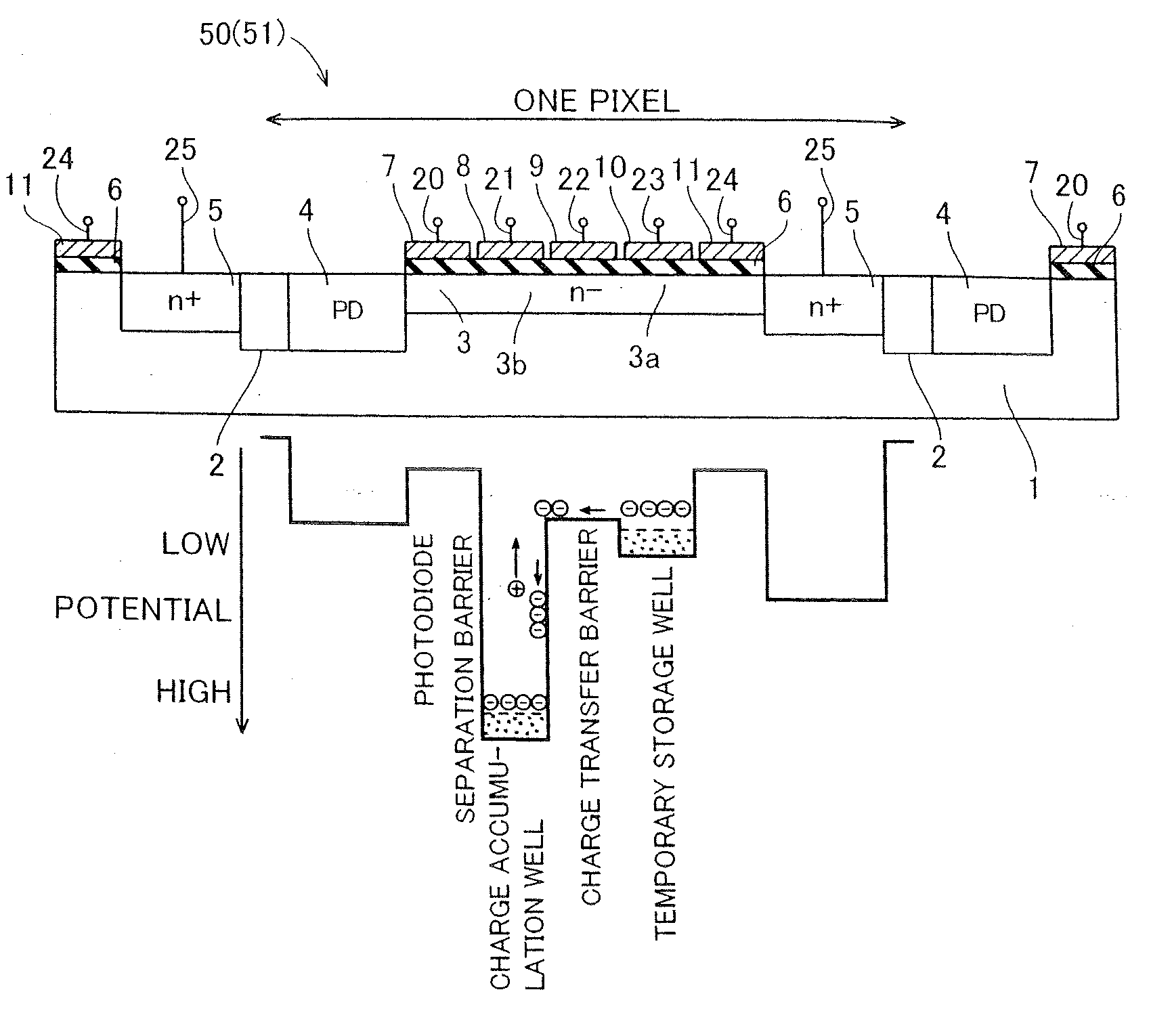

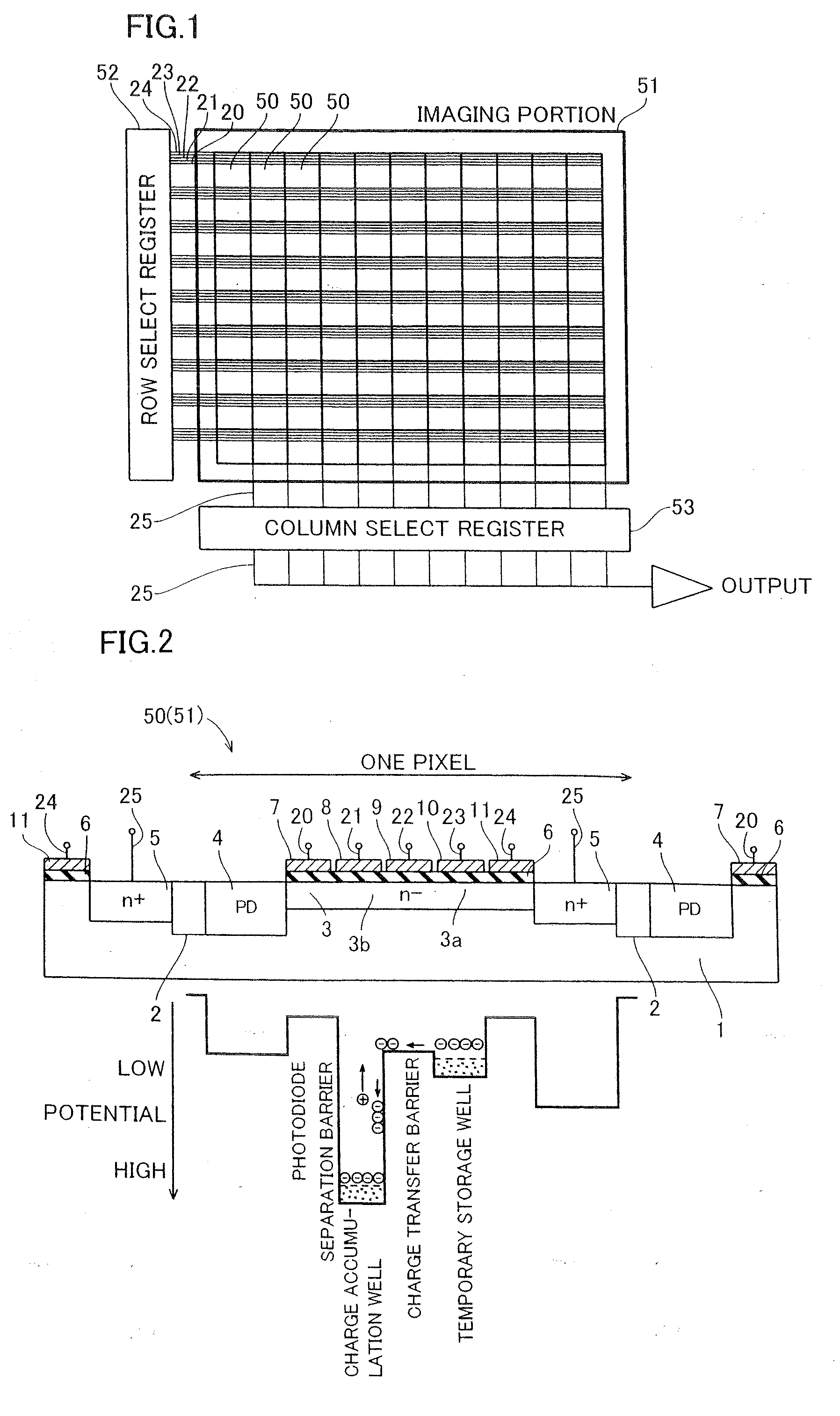

Imaging device

InactiveUS20080048212A1Television system detailsCounting chain synchronous pulse countersEngineeringImaging equipment

An imaging device includes a first electrode for generating an electric field storing signal charges, a charge multiplication section for multiplying the stored signal charges, a second electrode for generating the electric field in the charge multiplication section, a voltage conversion portion for converting the signal charges into a voltage, a third electrode for transferring the signal charges to the voltage conversion portion, provided between the first electrode and the voltage conversion portion, wherein the second electrode is provided on a side opposite to the third electrode and the voltage conversion portion with respect to the first electrode.

Owner:SANYO ELECTRIC CO LTD

Gated ring oscillator for a time-to-digital converter with shaped quantization noise

ActiveUS8138843B2Continuously circulated pulse countersCounting chain synchronous pulse countersDigital down converterImage resolution

Described is a compact, lower power gated ring oscillator time-to-digital converter that achieves first order noise shaping of quantization noise using a digital implementation. The gated ring oscillator time-to-digital converter includes a plurality of delay stages configured to enable propagation of a transitioning signal through the delay stages during an enabled state and configured to inhibit propagation of the transitioning signal through the delay stages during a disabled state. Delay stages are interconnected to allow sustained transitions to propagate through the delay stages during the enabled state and to preserve a state of the gated ring oscillator time-to-digital converter during the disabled state. The state represents a time resolution that is finer than the delay of at least one of the delay stages. A measurement module determines the number of transitions of the delay stages.

Owner:MASSACHUSETTS INST OF TECH

Shift register

ActiveUS20070127620A1Stress minimizationStatic indicating devicesCounting chain synchronous pulse countersShift registerBias stress

A shift register minimizing bias stress applied to transistors is disclosed. A shift register including n stages outputting scan pluses that are sequentially delayed in a forward or reverse direction thereof, where n is positive integer and wherein each stage includes: a scan direction controller that provides a first or second voltage to a scan direction control node according to a first or second enable signal and controlling the forward or reverse direction output; a first node controller that controls a first node according to a voltage on the scan direction control node; a second node controller that controls a second node according to the voltage on the scan direction control node and a voltage on the first node; an output unit that outputs a clock signal as scan pulse according to voltages on the first and second nodes; a third node controller that provides one of the first and second voltages to a third node according to the first and second enable signals; a first discharge circuit unit that discharges the voltage on the first node according to voltages of the second and third nodes; and a second discharge circuit unit that discharges the voltage on the third node according to one of a third enable signal and a fourth enable signal.

Owner:LG DISPLAY CO LTD

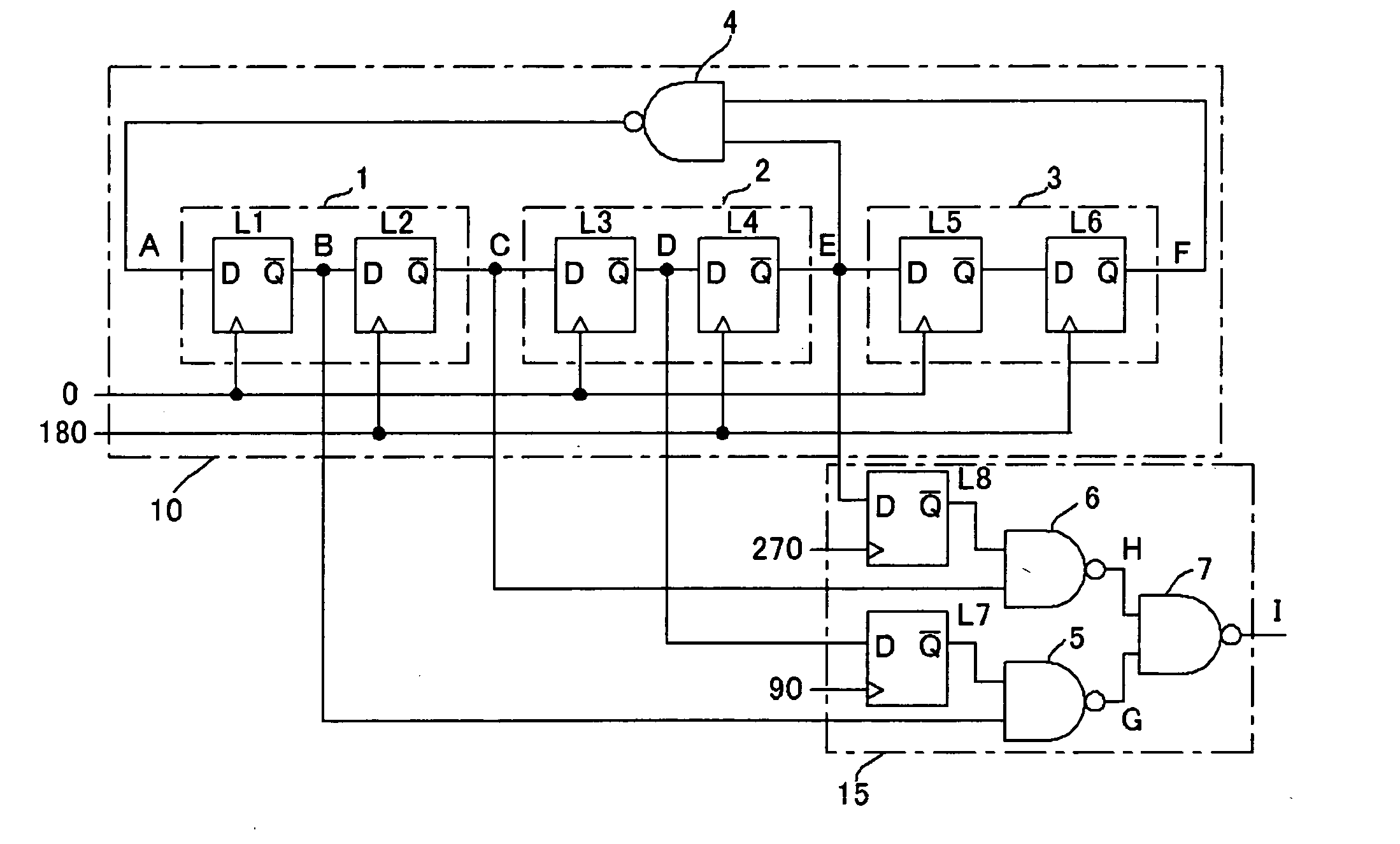

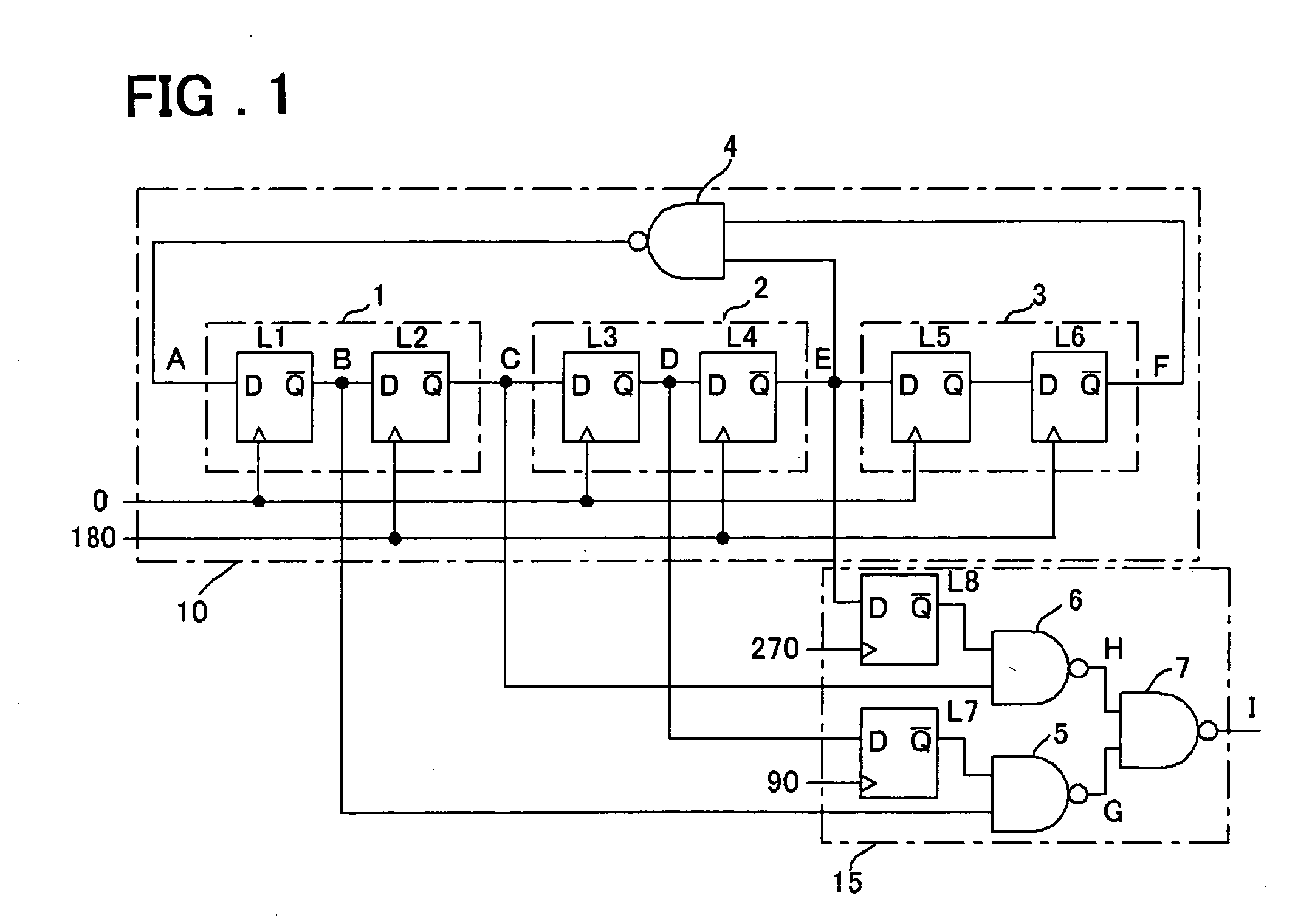

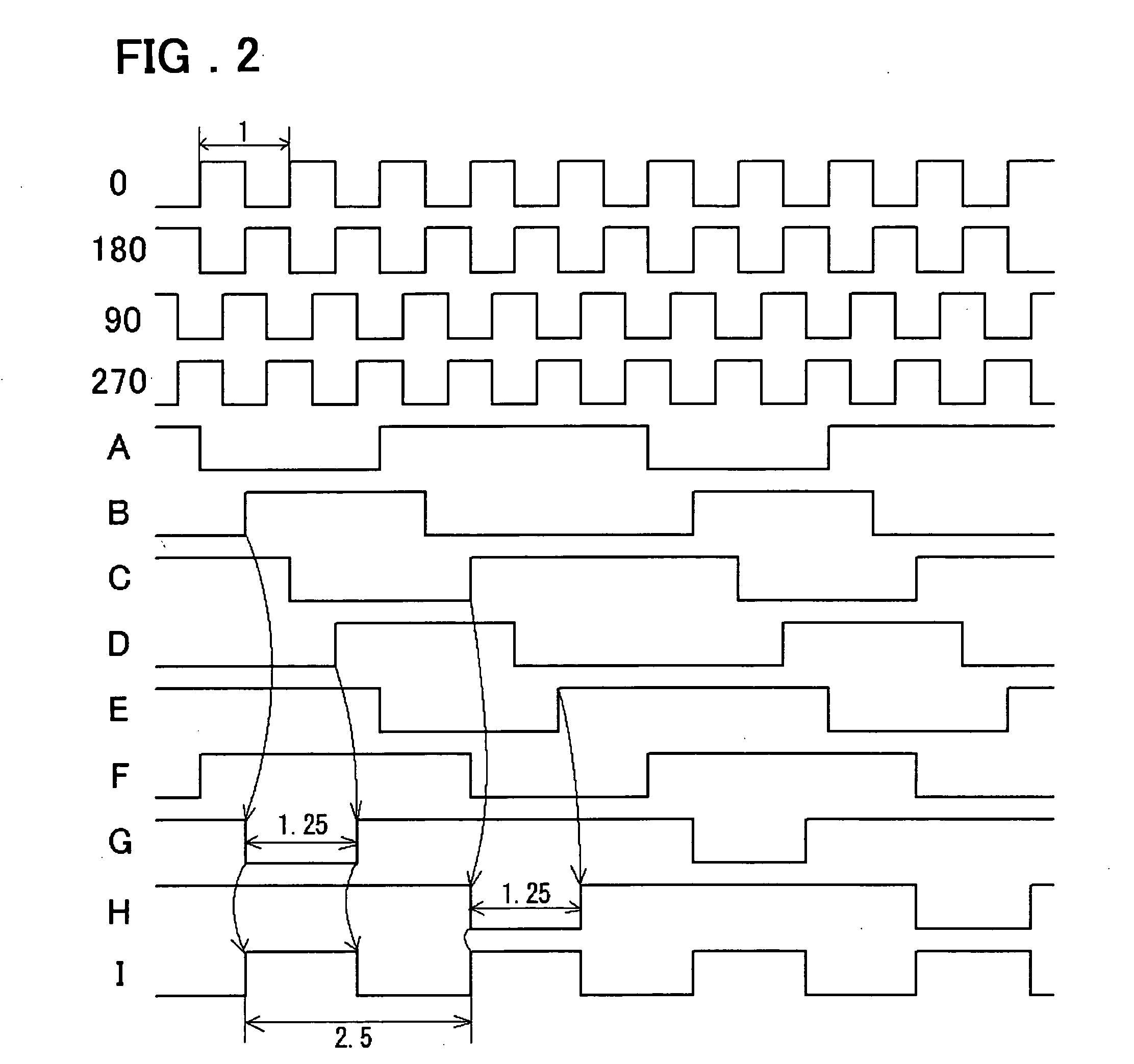

Fractional frequency divider circuit and data transmission apparatus using the same

InactiveUS20050174153A1Small sizeReduce power consumptionContinuously circulated pulse countersPulse automatic controlEngineeringData transmission

A fractional frequency divider circuit with a small circuit scale that outputs a clock with a duty ratio of 50%, and a data transmission apparatus comprising same. The fractional frequency divider circuit is constituted by multiple master-slave flip-flops, and comprises an integer frequency divider circuit that frequency-divides a clock signal with a frequency-division ratio of 1 / N(N is an integer), and a logic circuit into which multiple signals outputted from master stages and slave stages of the master-slave flip-flops are inputted and that outputs a signal with a duty ratio of 50% obtained by frequency-dividing the clock signal with a frequency-division ratio of 2 / N. The data transmission apparatus is constituted such that it is possible to switch over between a frequency-multiplied clock outputted by a PLL and a clock obtained by frequency-dividing the frequency-multiplied clock with the fractional frequency divider circuit for each channel.

Owner:RENESAS ELECTRONICS CORP

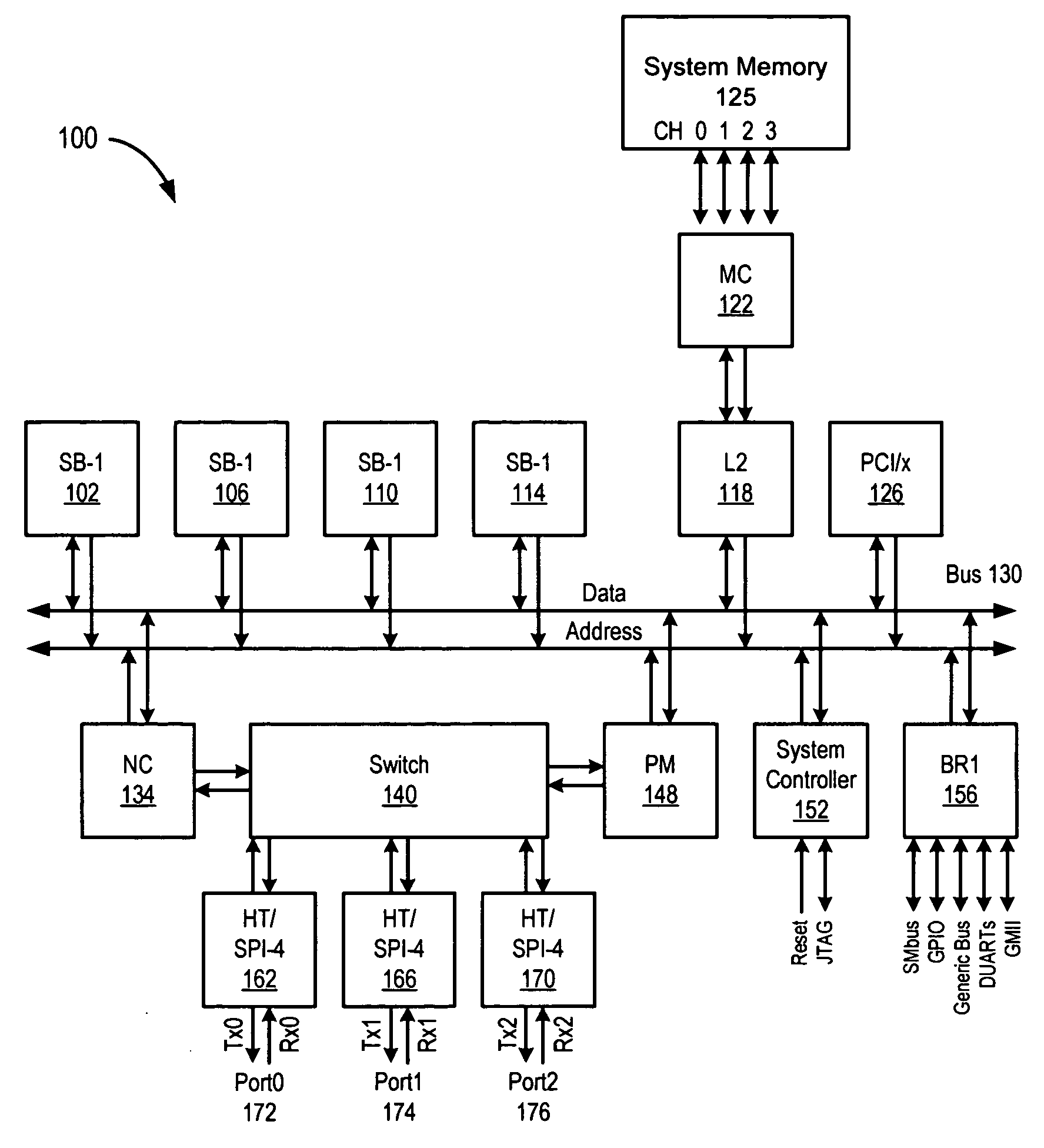

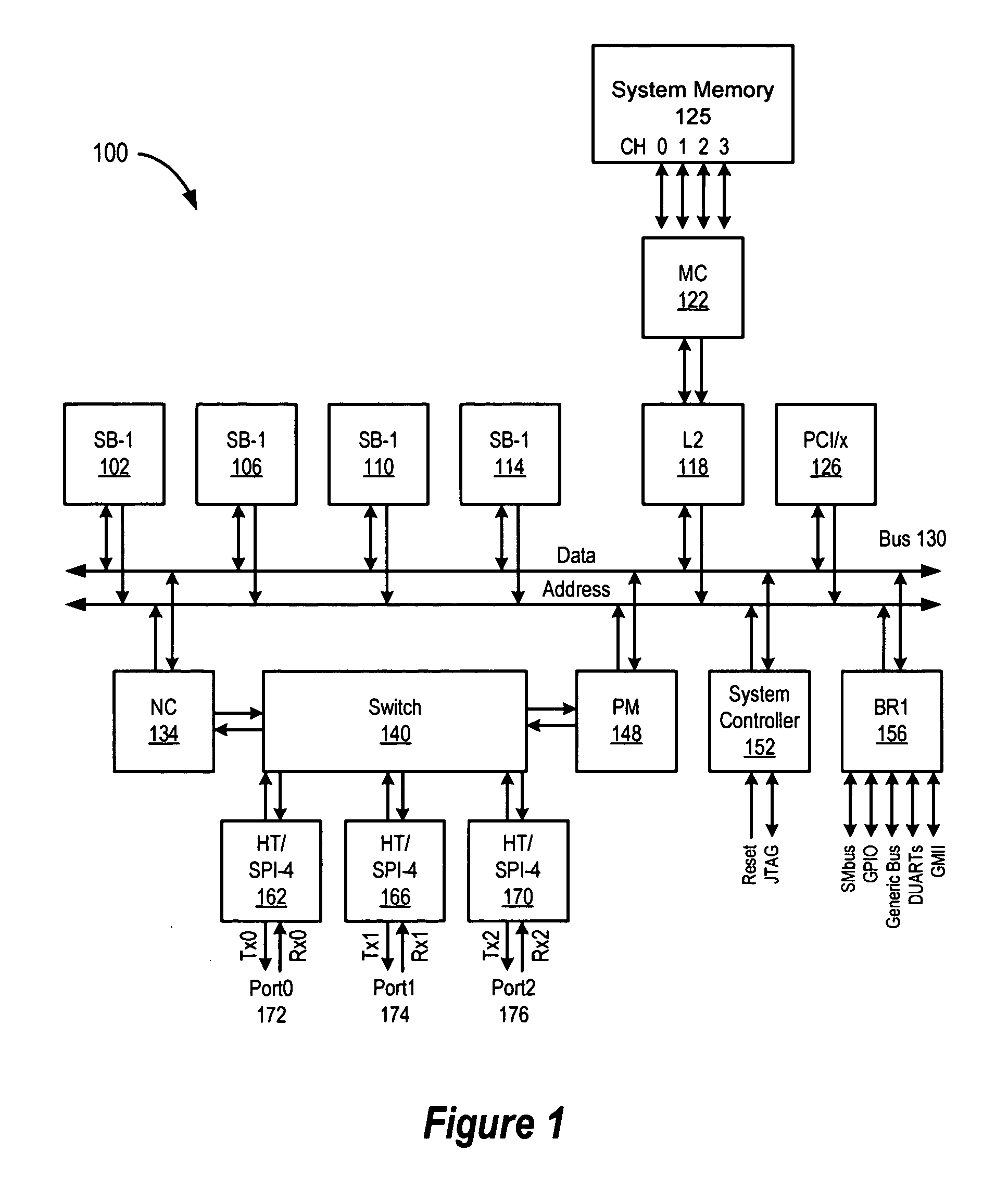

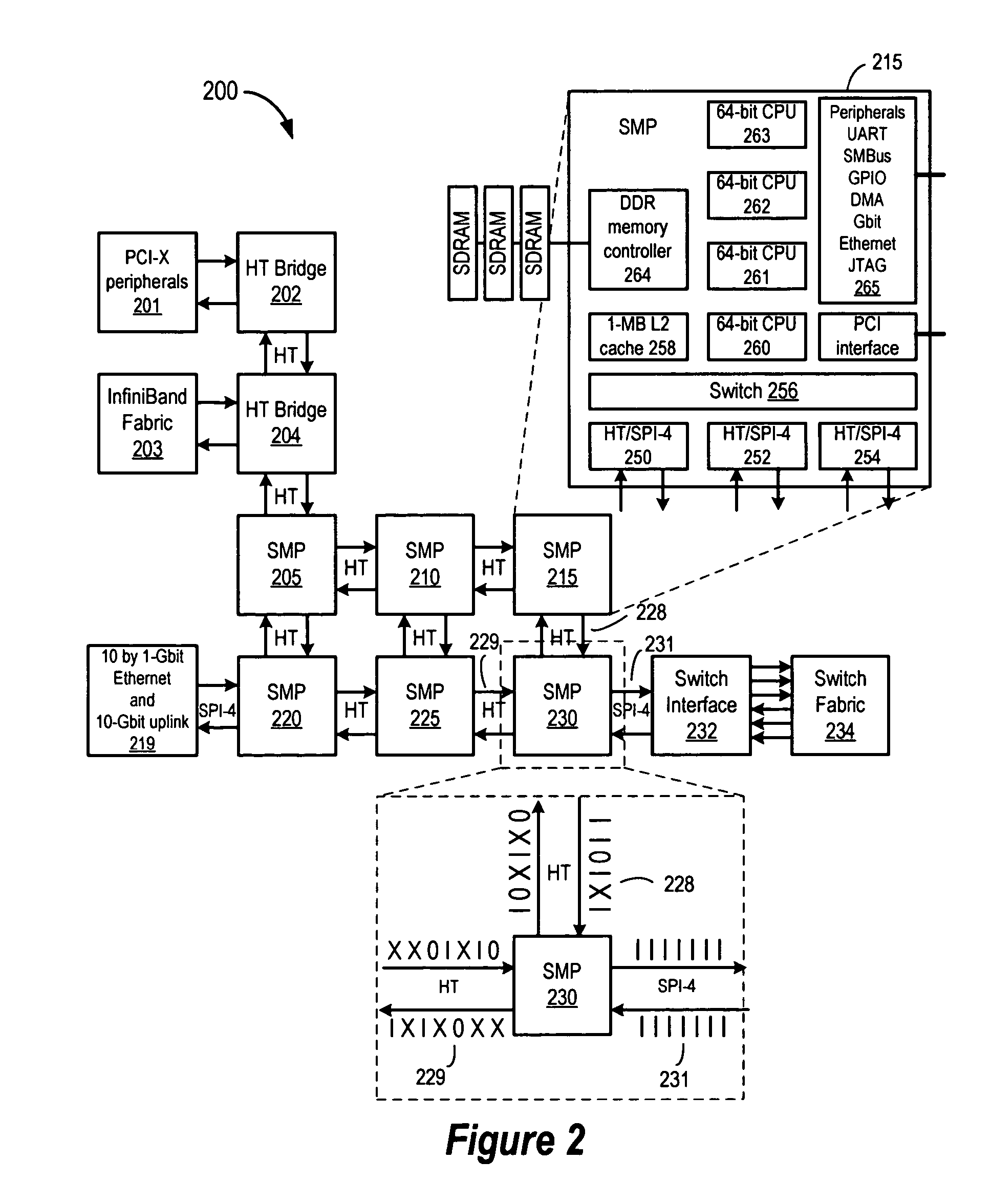

Exponential channelized timer

InactiveUS20050078669A1Generate efficientlyCounting chain synchronous pulse countersTime-division multiplexCMOSControl register

A multiprocessor switching device substantially implemented on a single CMOS integrated circuit is described in connection with a channelized timer for use in controlling the issuance of signals to the processor(s) or control logic (such as interrupts, descriptors, etc.) that that identify system-related functions for a plurality of channels. Using control registers to select an individual bit of a multi-bit counter, a timing interval pulse is provided for prompting signal generation that is otherwise subject to a minimum count requirement.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

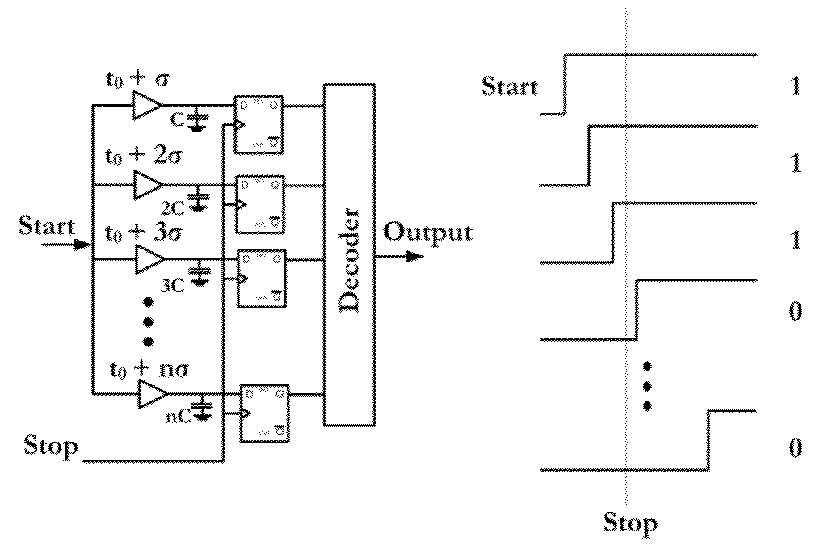

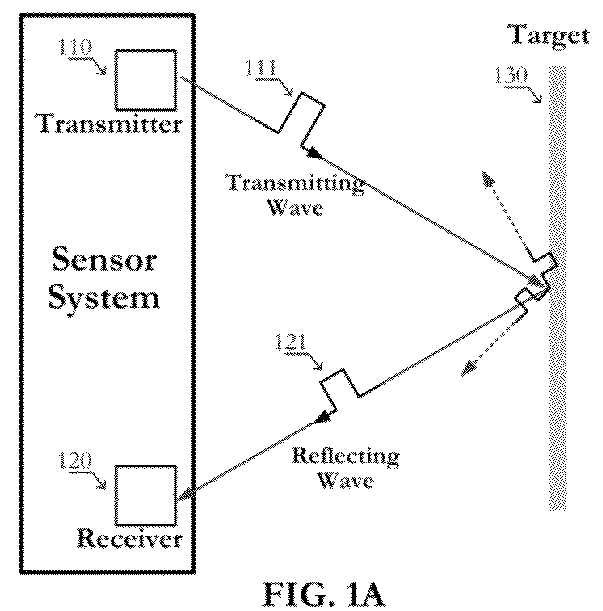

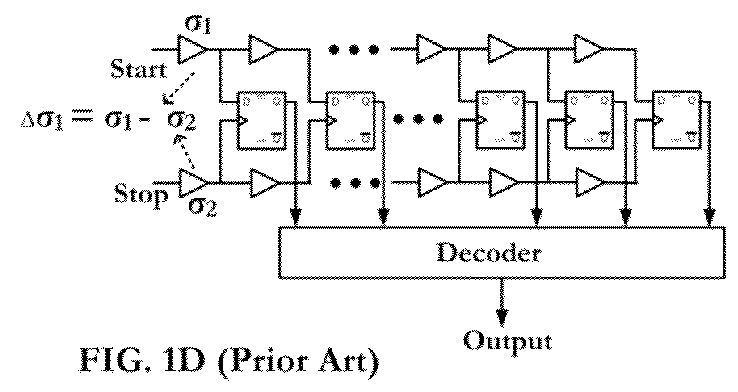

Circuits and methods of TAF-DPS vernier caliper for time-of-flight measurement

ActiveUS9379714B1High resolutionPowerful frequency generation capabilityPulse automatic controlCounting chain synchronous pulse countersPhase detectorFrequency synthesizer

Circuits for measuring TOF between two electrical signals comprises 1) a slow TAF-DPS clock signal generator for generating a slow clock signal, a fast TAF-DPS clock signal generator for generating a fast clock signal, said slow TAF-DPS clock signal generator comprises a gated ring oscillator and a TAF-DPS frequency synthesizer, said fast TAF-DPS clock signal generator comprises a gated ring oscillator and a TAF-DPS frequency synthesizer; 2) a phase detector for receiving said slow and fast clock signals and detecting point-of-coincidence between said slow and fast clock signals; 3) a first digital counter driven by said slow clock signal for storing the number of slow clock cycles and a second digital counter driven by said fast clock signal for storing the number of fast clock cycles; 4) a calibrator for calibrating said gate ring oscillators; 5) a calculation block for calculating TOF measurement result. Methods of using a slow TAF-DPS clock generator and a fast TAF-DPS clock generator for measuring TOF between two electrical signals are also disclosed.

Owner:XIU LIMING

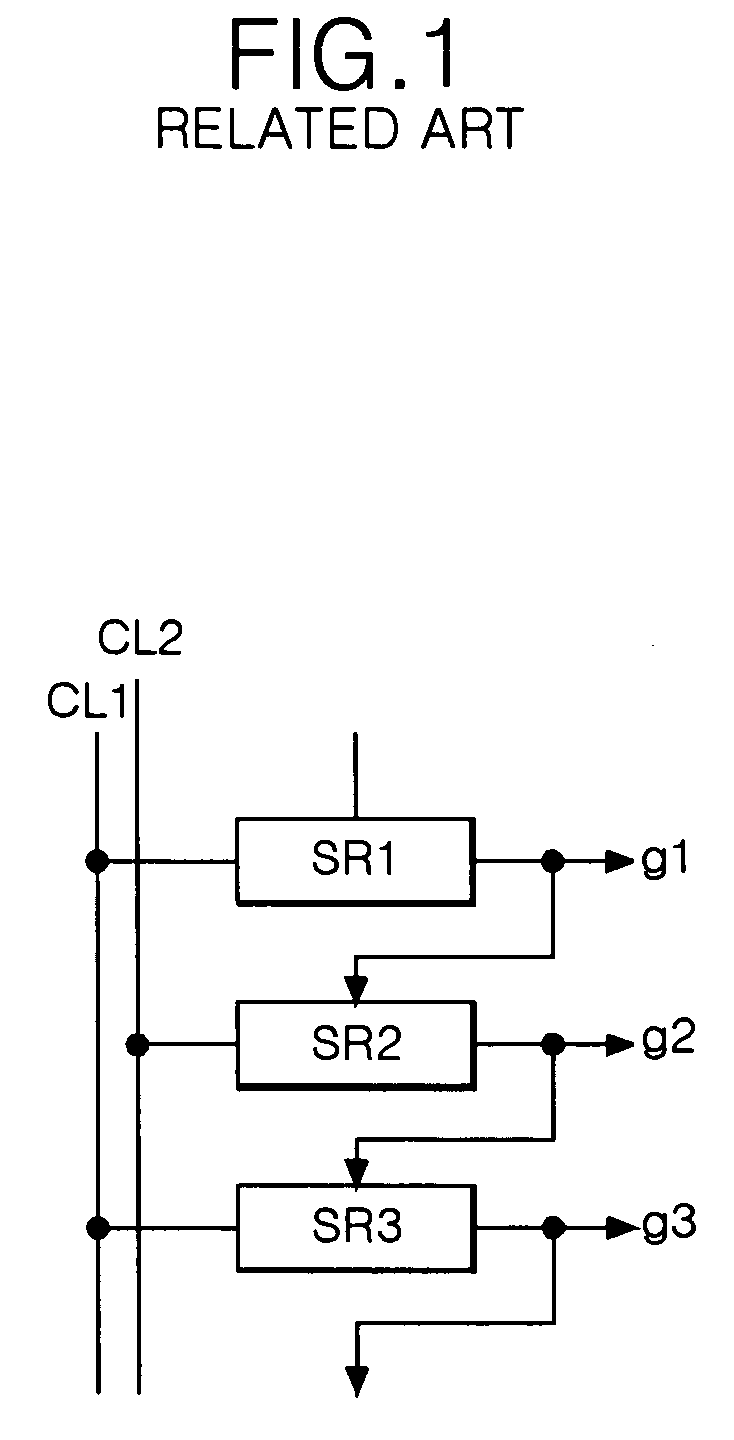

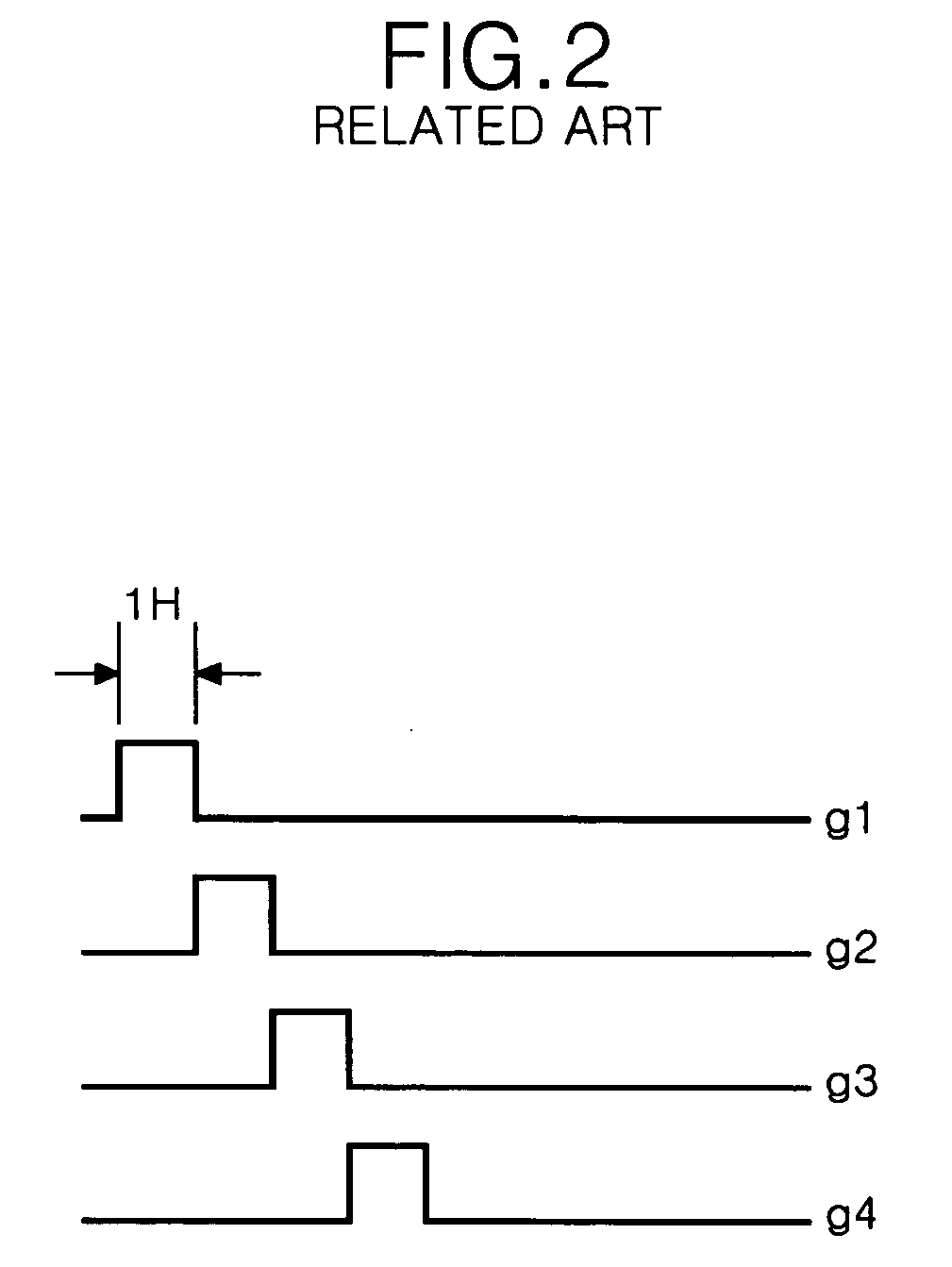

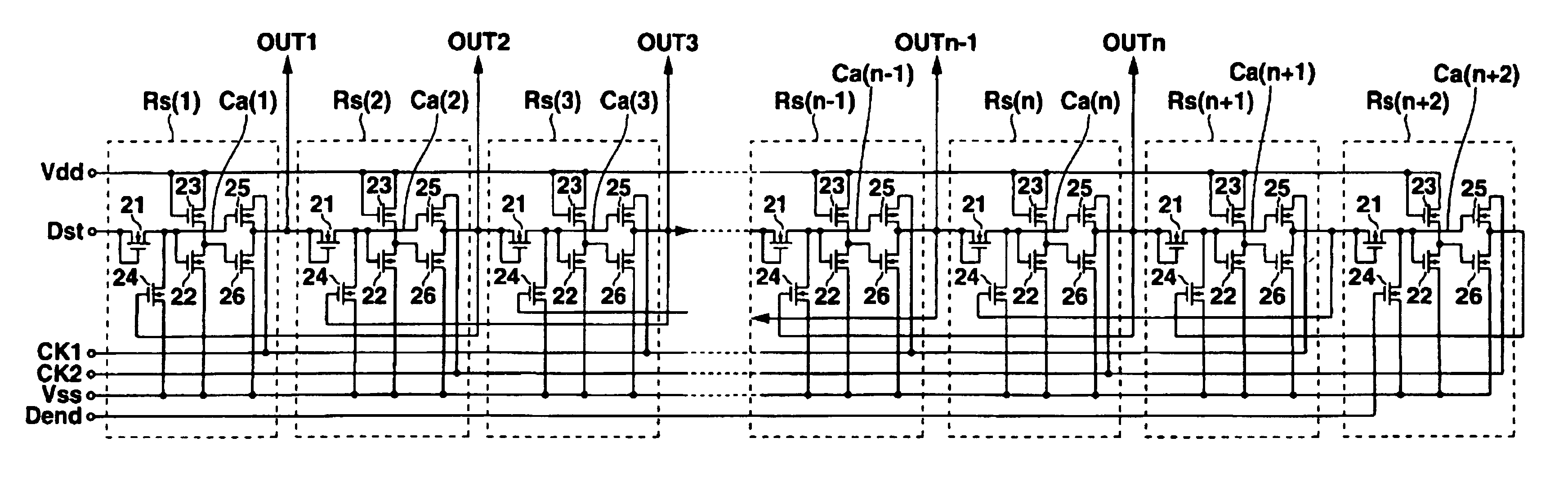

Shift register having fewer lines therein, and liquid crystal display having the same

InactiveUS20020097829A1Small sizeReduced wiring areaTelevision system detailsStatic indicating devicesShift registerLiquid-crystal display

A shift register has m stages which store one of two states, where m is an integer more than 1, each stage including clock input terminals at which n-phase clock signals are input, where n is an integer more than 1, and an input terminal, and an output terminal. The input terminal of one stage receives the signal delivered from an input terminal of the shift register or from the output terminal of the previous stage. The signal output at the output terminal of one stage is passed to the input terminal of the subsequent stage or to an output terminal of the shift register. Each stage receives an initial state level from one of the clock input terminals. The initial state level is used to initialize the state of each stage.

Owner:MIND FUSION LLC

Shift register apparatus and method thereof

InactiveUS20100002827A1Improve use reliabilityIncrease profitStatic indicating devicesCounting chain synchronous pulse countersShift registerProcessor register

A shift register apparatus and a method thereof are provided. The technique manner submitted by the present invention utilizes two NMOS transistors for pulling down the voltage level of the scan signals output by the shift registers within the shift register apparatus to the low level gate voltage, wherein one of the NMOS transistors is controlled by a control unit, and the other NMOS transistor is controlled by a clock signal or the inverted clock signal provided to the shift registers. Therefore, shifting amount of the threshold voltage of those NMOS transistors can trend to be flat, and the reliability of those NMOS transistors can be promoted. In addition, since only one control unit is needed to dispose in each shift register so that the layout area of whole shift register apparatus can be reduced, and the panel with narrow frame size also can be achieved by the present invention.

Owner:CHUNGHWA PICTURE TUBES LTD

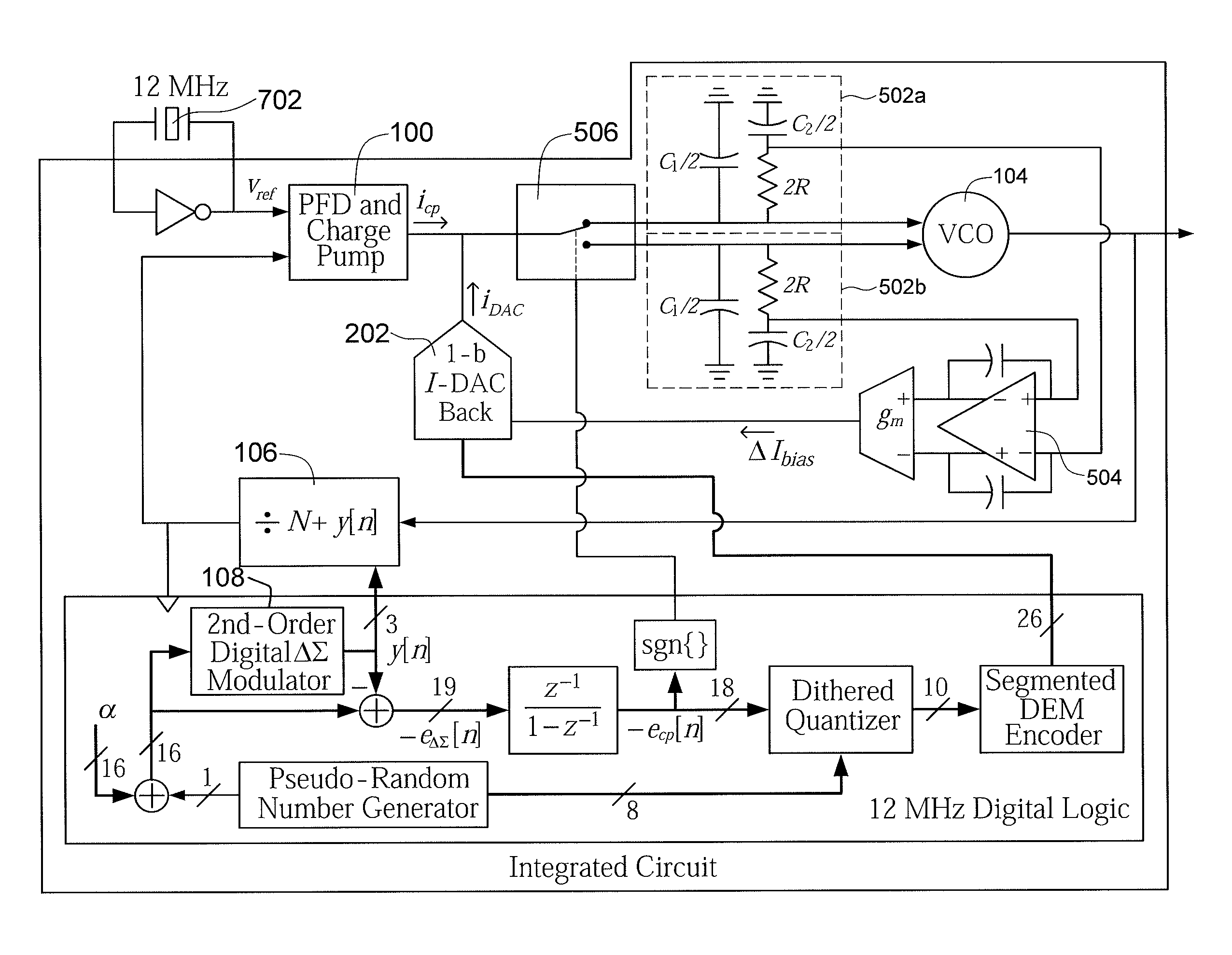

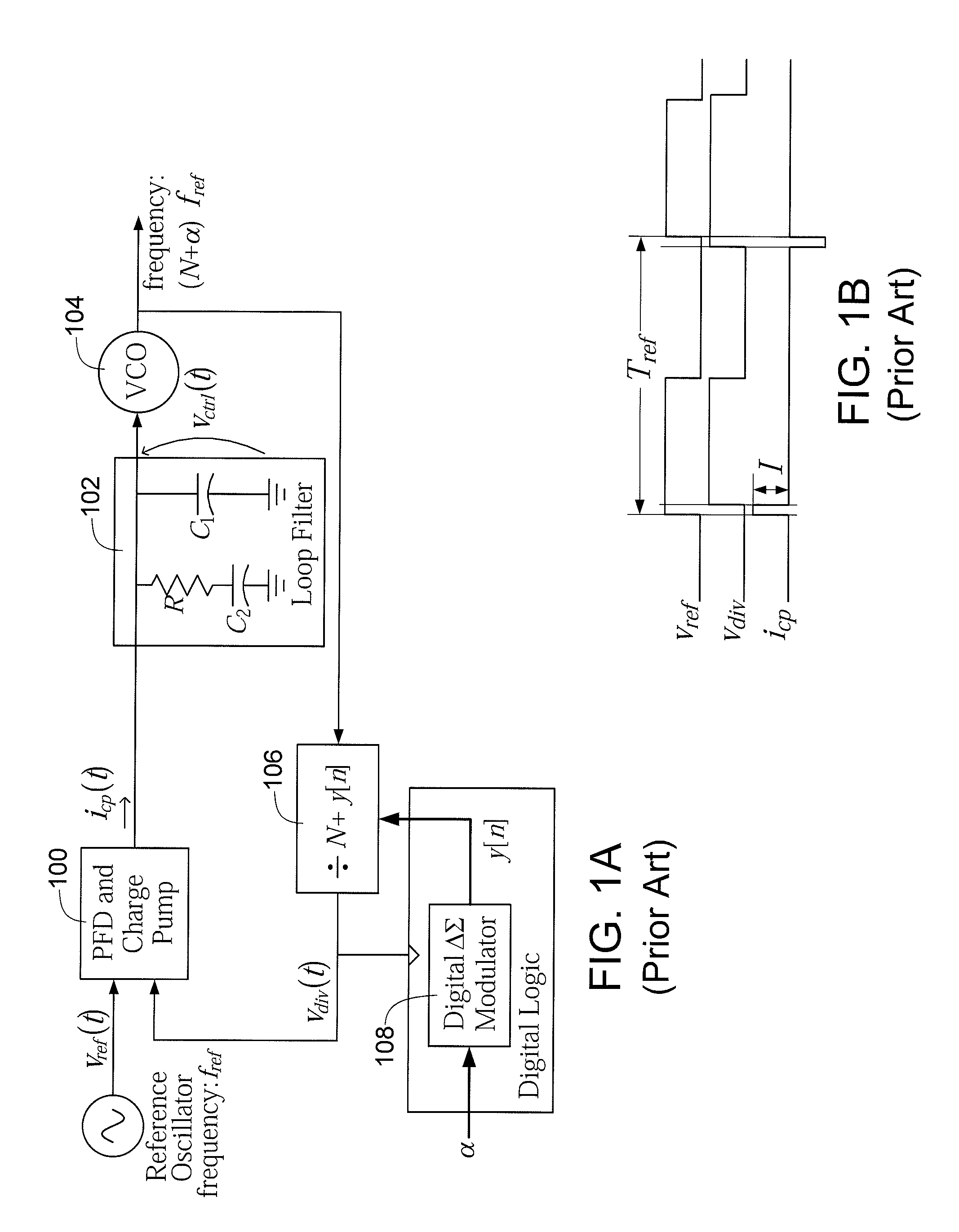

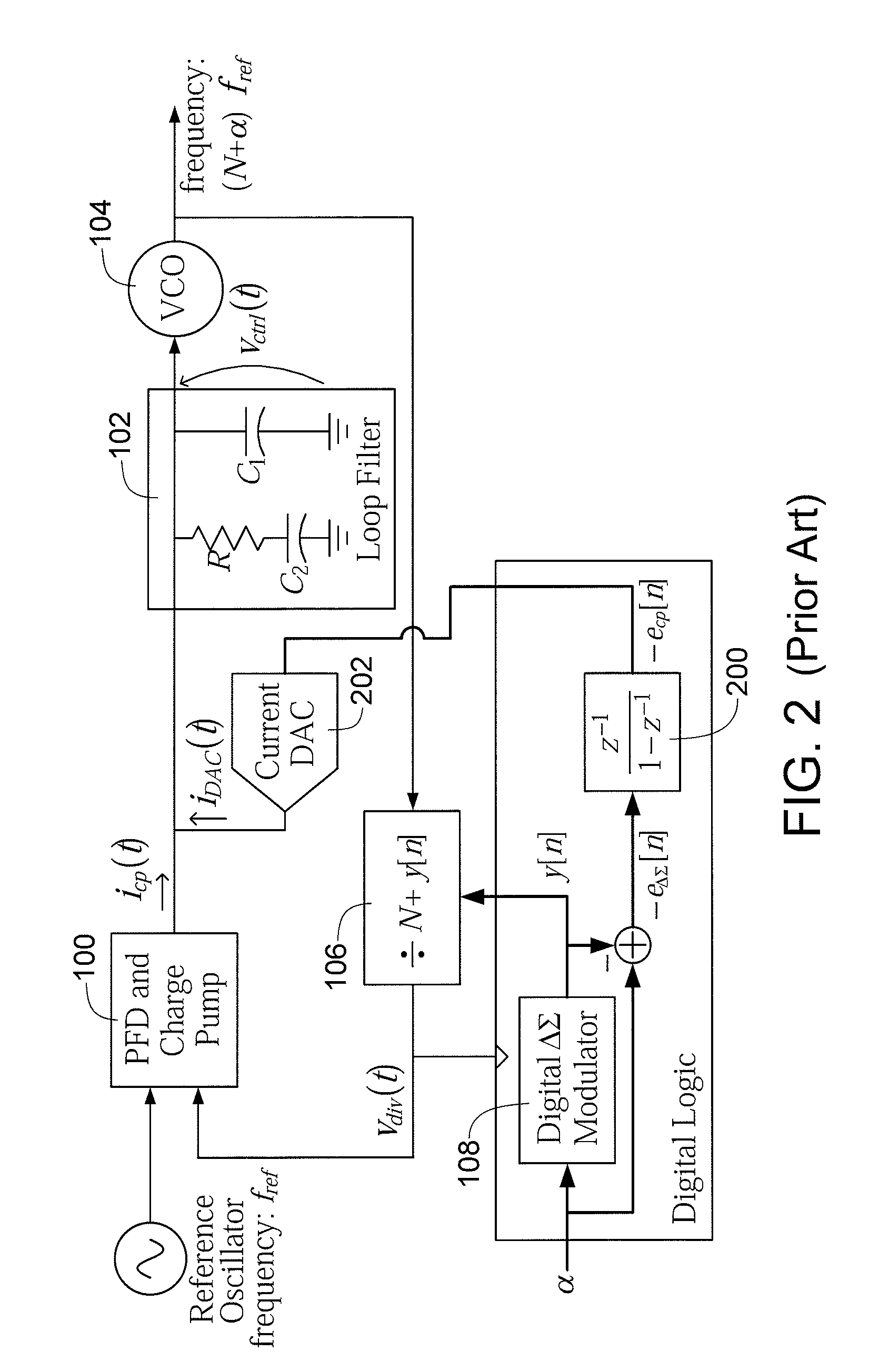

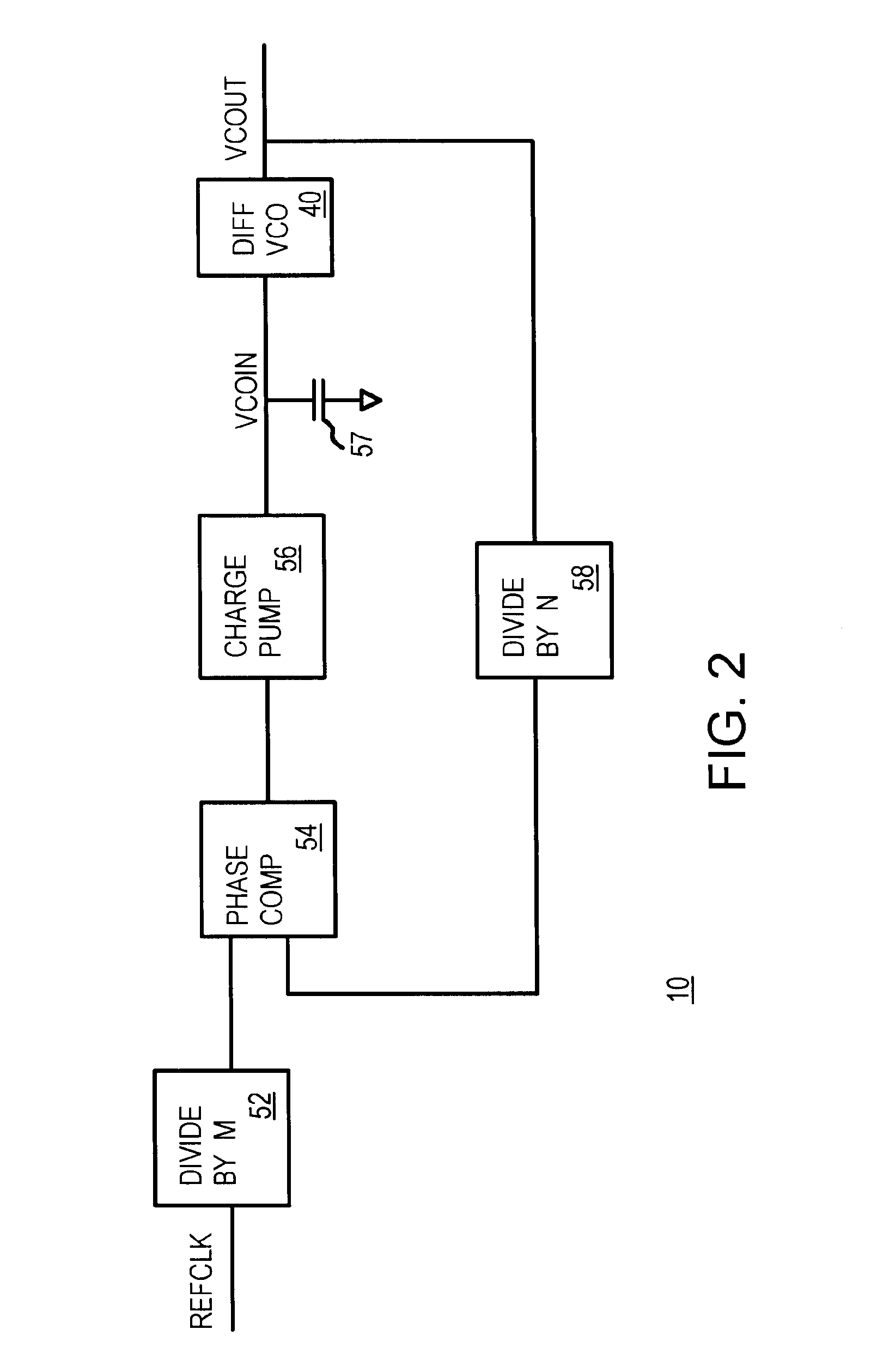

Adaptive phase noise cancellation for fractional-N phase locked loop

InactiveUS7999622B2Angle modulation by variable impedencePulse automatic controlLoop filterPhase noise

An embodiment of the invention is a circuit for adaptive phase noise cancellation for a fractional-N PLL. A preferred embodiment employs a split loop filter architecture. Two loop filter halves separately drive half-sized parallel varactors in a voltage controlled oscillator (VCO) and also drive a differential-input lowpass frequency selective circuit, e.g., a differential-input integrator in a least mean squared (LMS) feedback loop. The output of the differential-input lowpass frequency selective circuit controls the gain matching of a phase noise cancellation path to minimize phase noise arising from quantization error associated with the sequence of divider modulus values in the fractional-N PLL. The two varactor capacitances add together in the VCO tank, so the VCO frequency depends on the common-mode loop filter voltage and is relatively insensitive to differential-mode voltage. In contrast, the differential integrator operates on the differential-mode voltage from the two loop filter halves but attenuates their common-mode voltage.

Owner:RGT UNIV OF CALIFORNIA

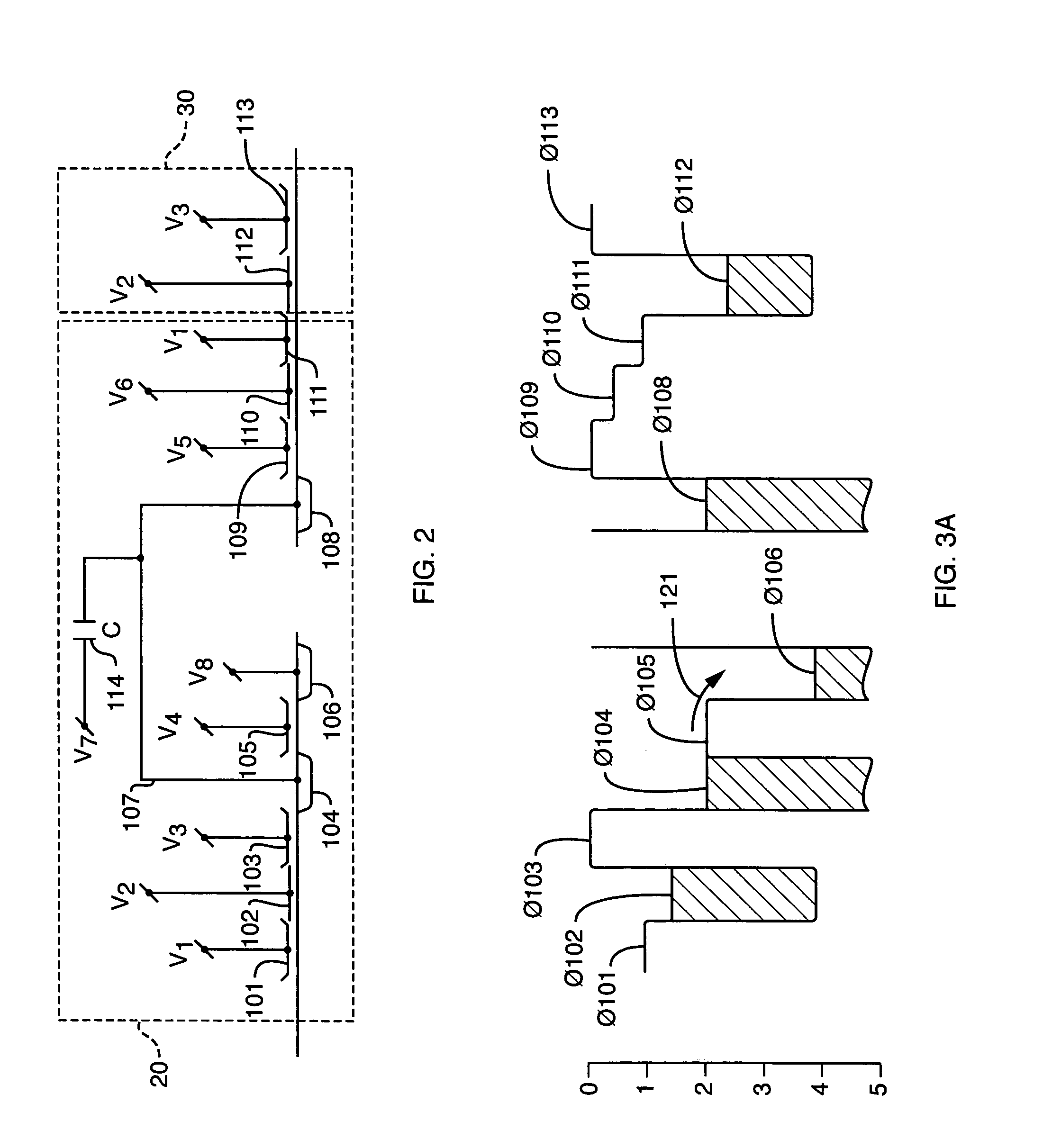

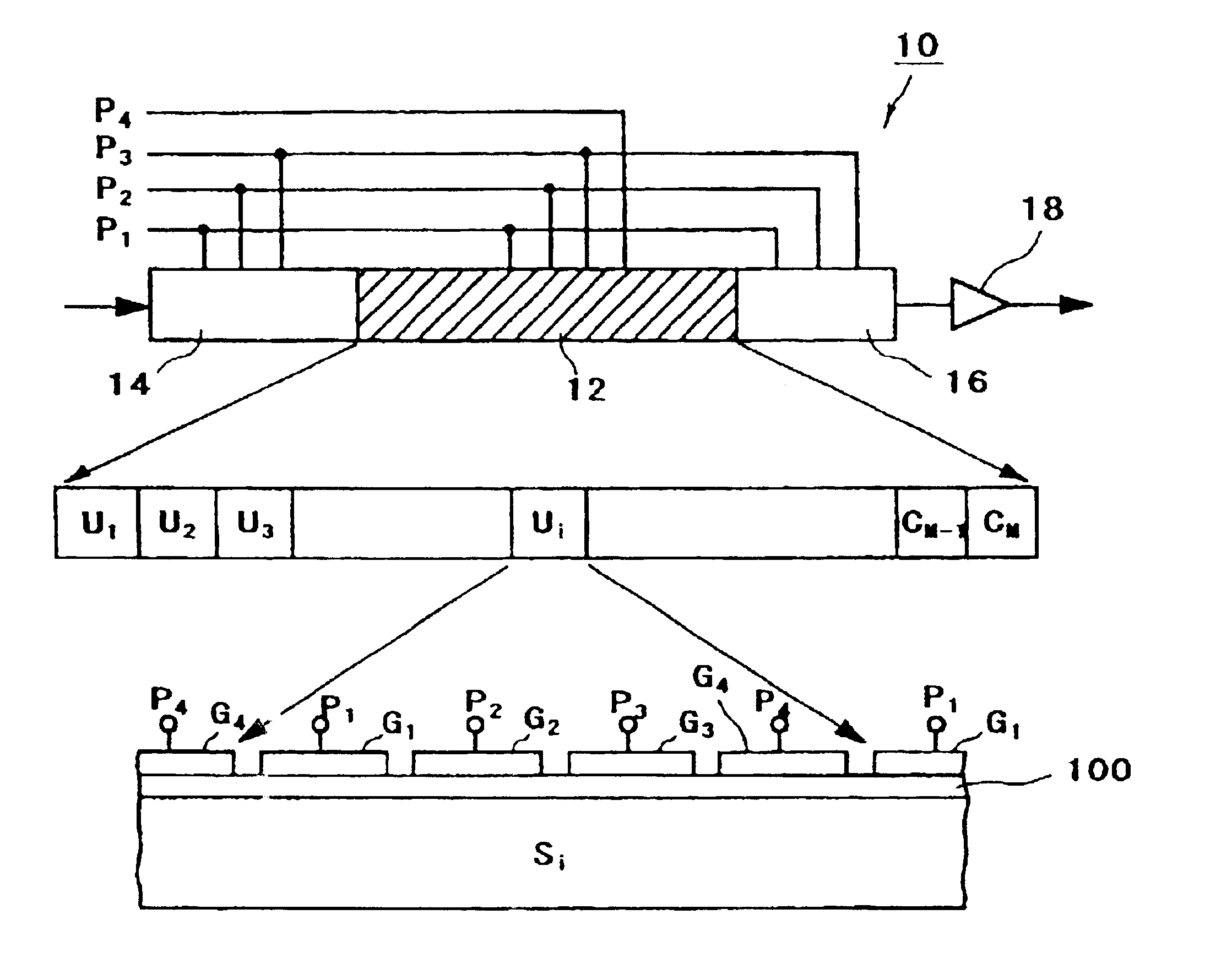

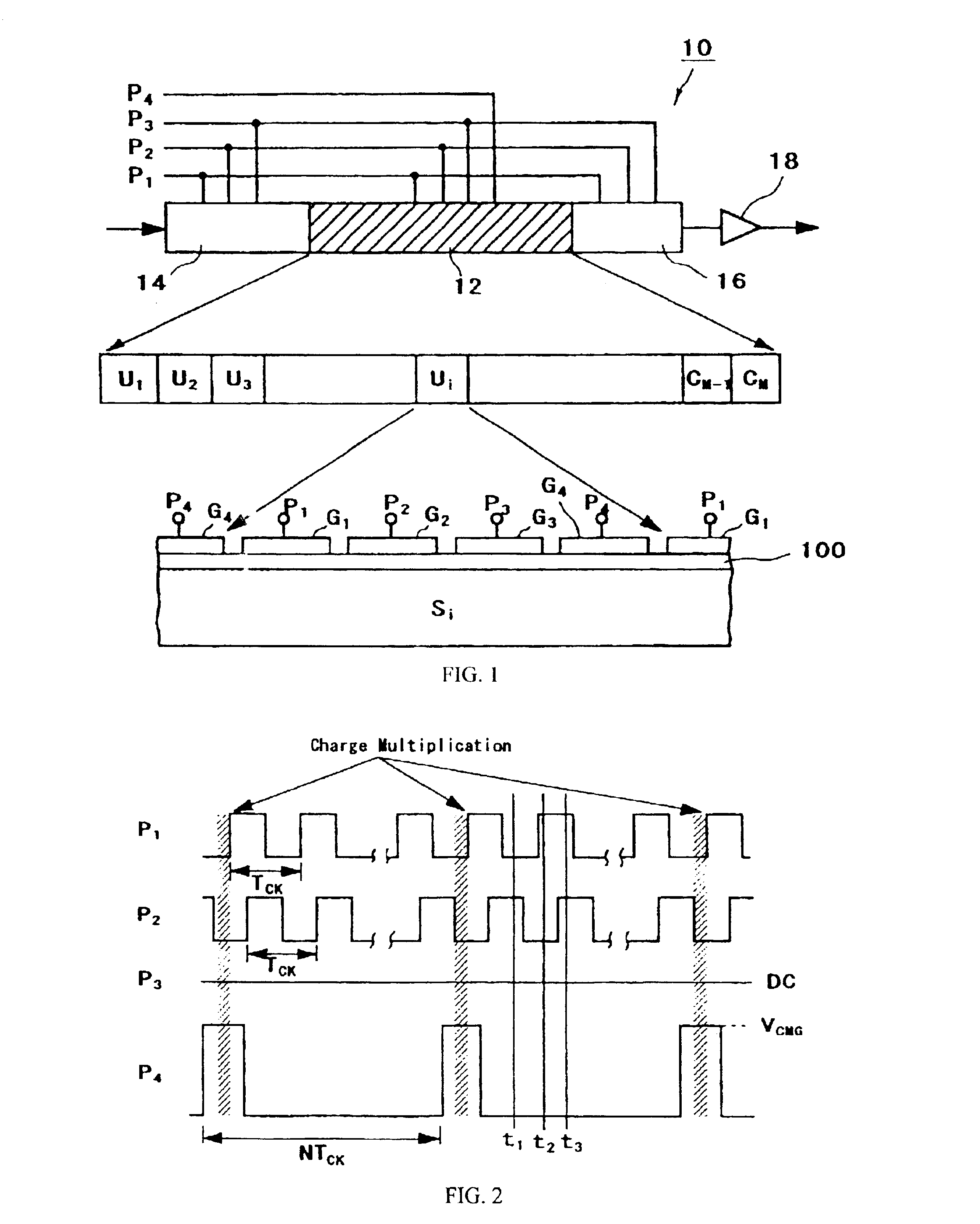

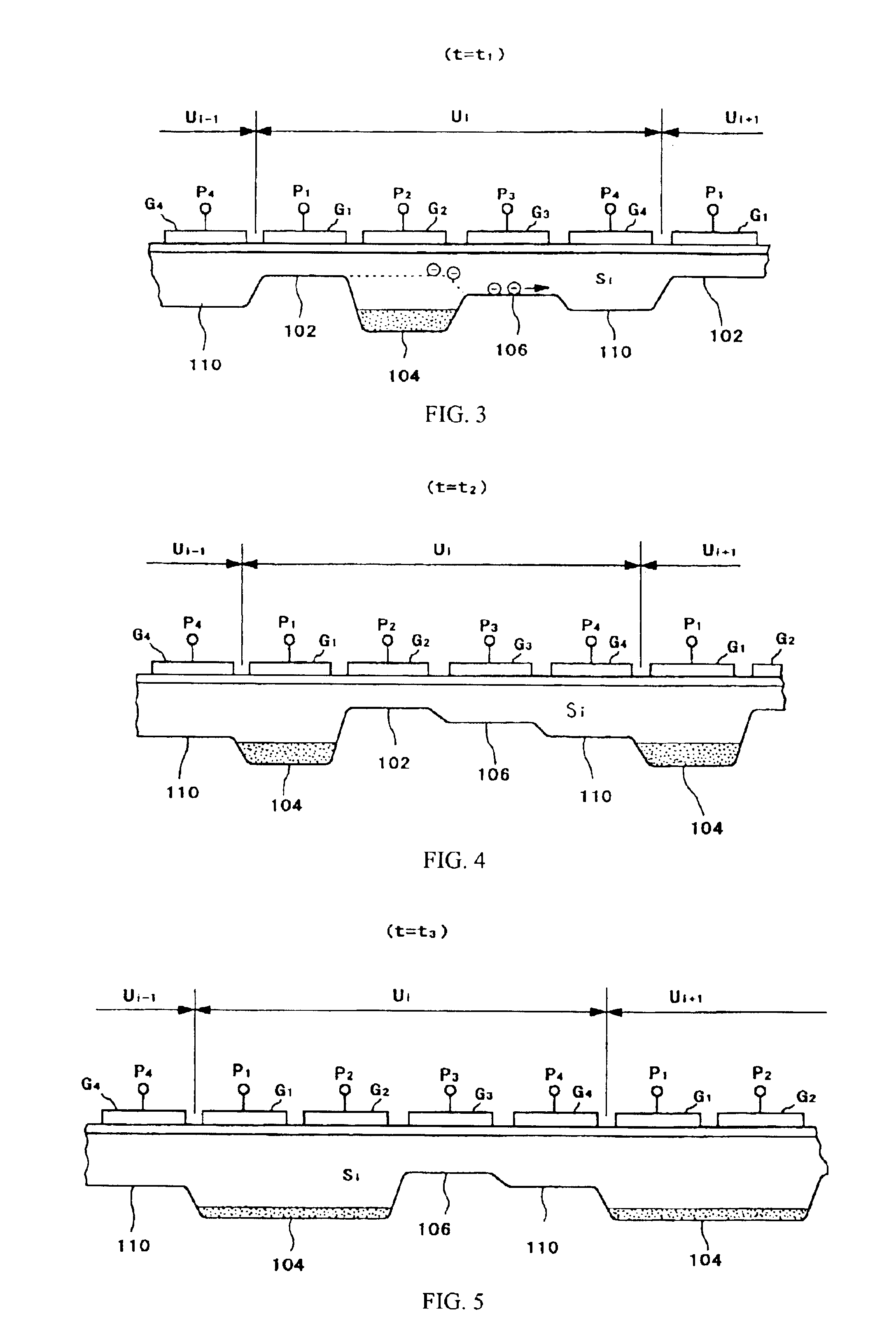

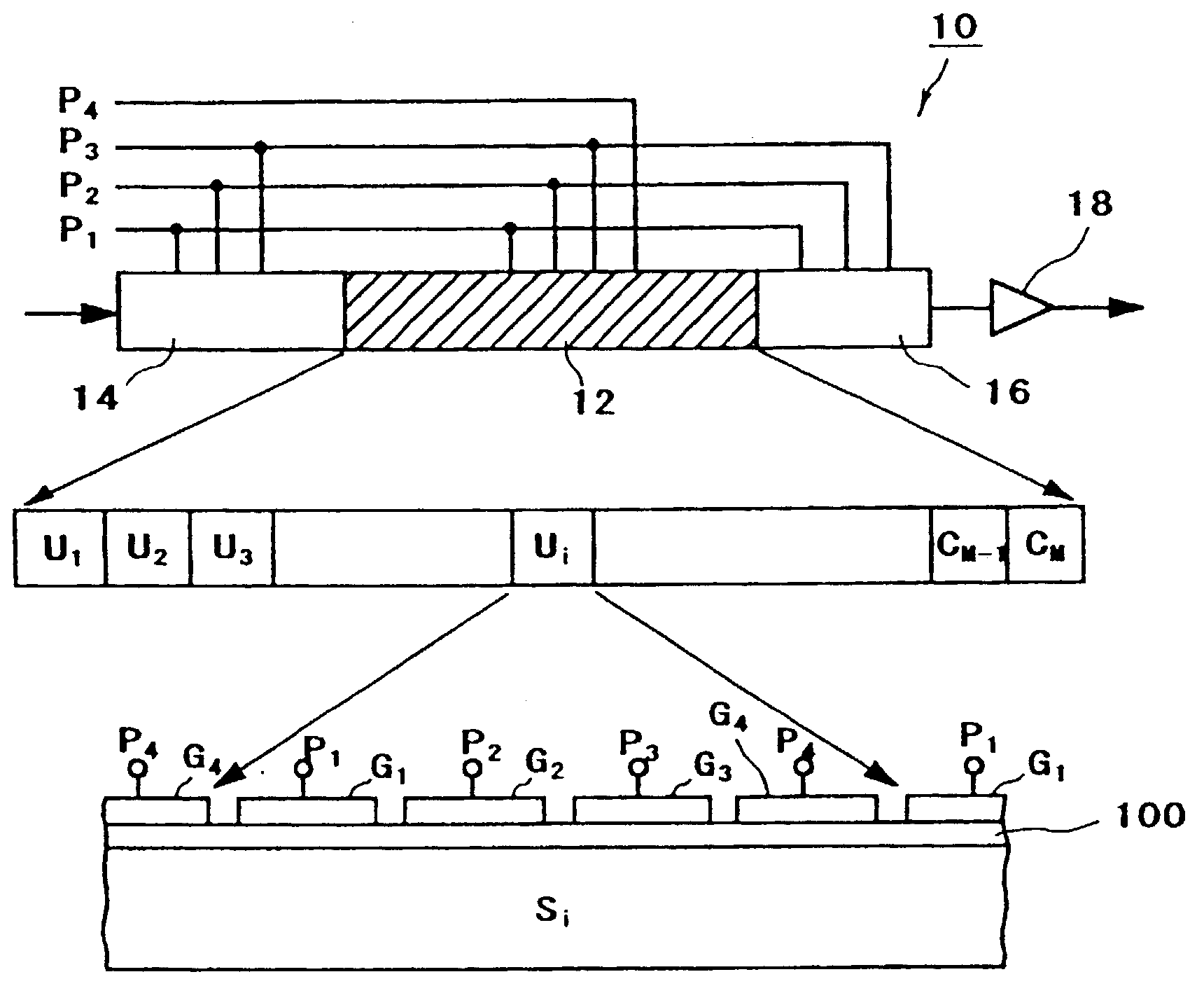

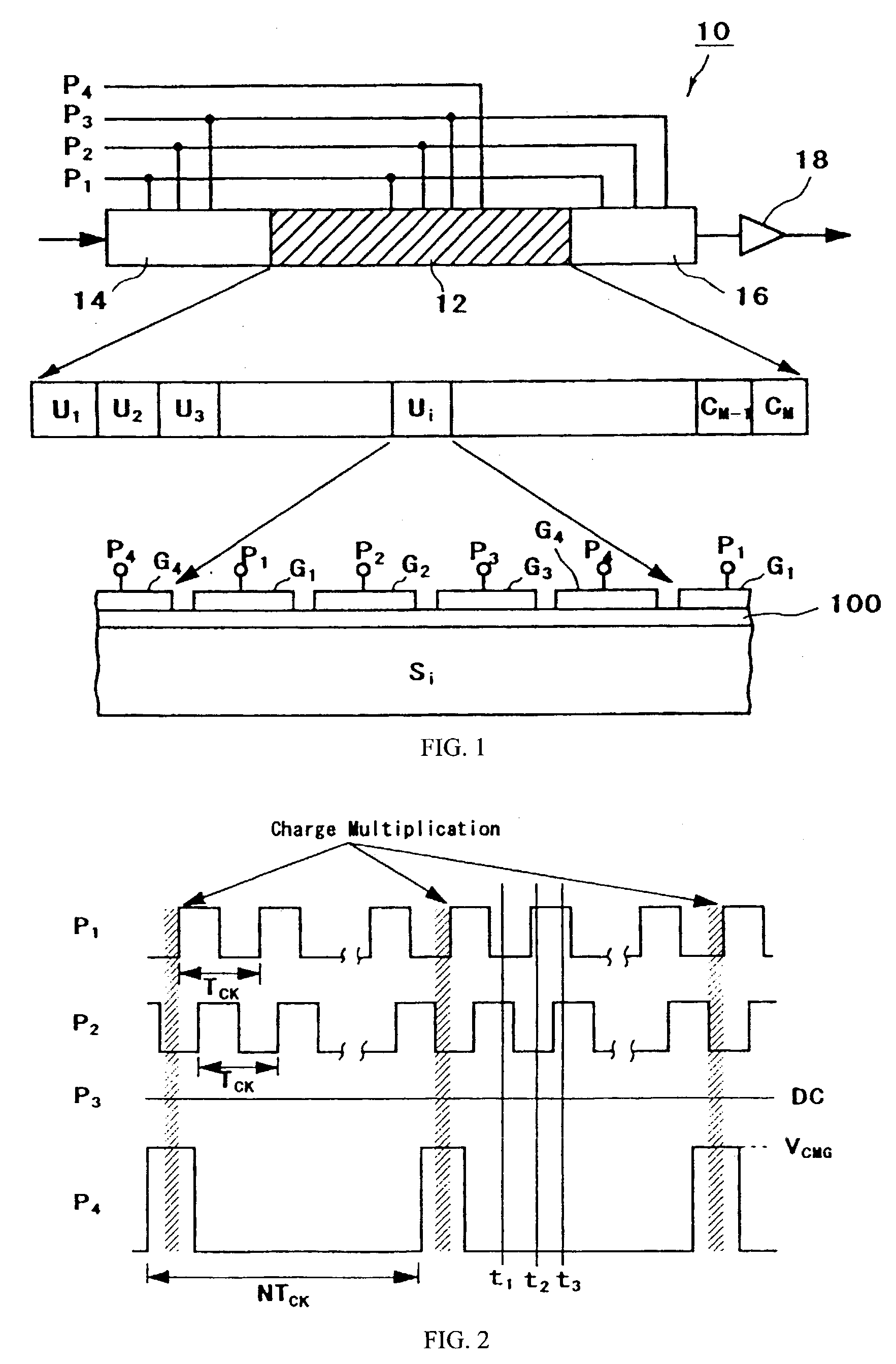

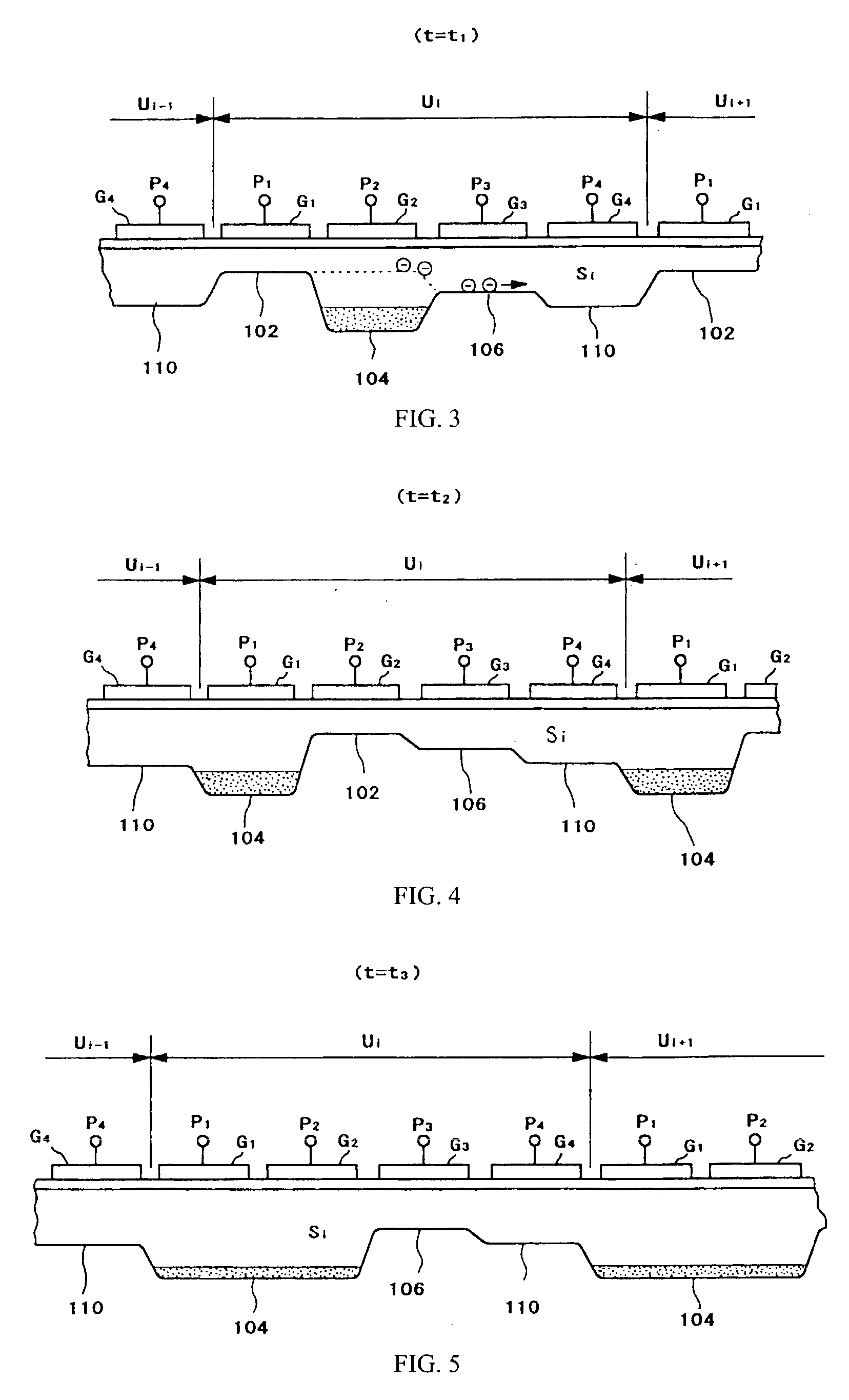

CMD and CMD-carrying CCD device

InactiveUS6862333B2Uniform rateTelevision system detailsCounting chain synchronous pulse countersControl signalSilicon oxide

This invention controls the signal amplification rate in a simple way with high precision in a CMD or CMD-carrying CCD device. CMD 12 has plural sections, such as M sections (U1-UM), each of which is a CMD unit U that can perform a charge multiplication operation, set in series. Each section of CMD unit Ui has plural (such as 4) electrodes G1, G2, G3, G4 set in a row via an insulating film, such as silicon oxide film 100, on a silicon insulating film. Among driving voltages P1, P2, P3, P4 applied on the electrodes G1, G2, G3 and G4, P1 and P2 are applied in the same cycle as the transfer clock, P4 for impact ionization is applied in intermittent cycles with respect to P1 and P2, and P3 is applied as a DC voltage at a prescribed level.

Owner:TEXAS INSTR INC

CMD and CMD-carrying CCD device

InactiveUS20030223531A1Uniform rateTelevision system detailsCounting chain synchronous pulse countersControl signalSilicon oxide

This invention controls the signal amplification rate in a simple way with high precision in a CMD or CMD-carrying CCD device. CMD 12 has plural sections, such as M sections (U1-UM), each of which is a CMD unit U that can perform a charge multiplication operation, set in series. Each section of CMD unit Ui has plural (such as 4) electrodes G1, G2, G3, G4 set in a row via an insulating film, such as silicon oxide film 100, on a silicon insulating film. Among driving voltages P1, P2, P3, P4 applied on the electrodes G1, G2, G3 and G4, P1 and P2 are applied in the same cycle as the transfer clock, P4 for impact ionization is applied in intermittent cycles with respect to P1 and P2, and P3 is applied as a DC voltage at a prescribed level.

Owner:TEXAS INSTR INC

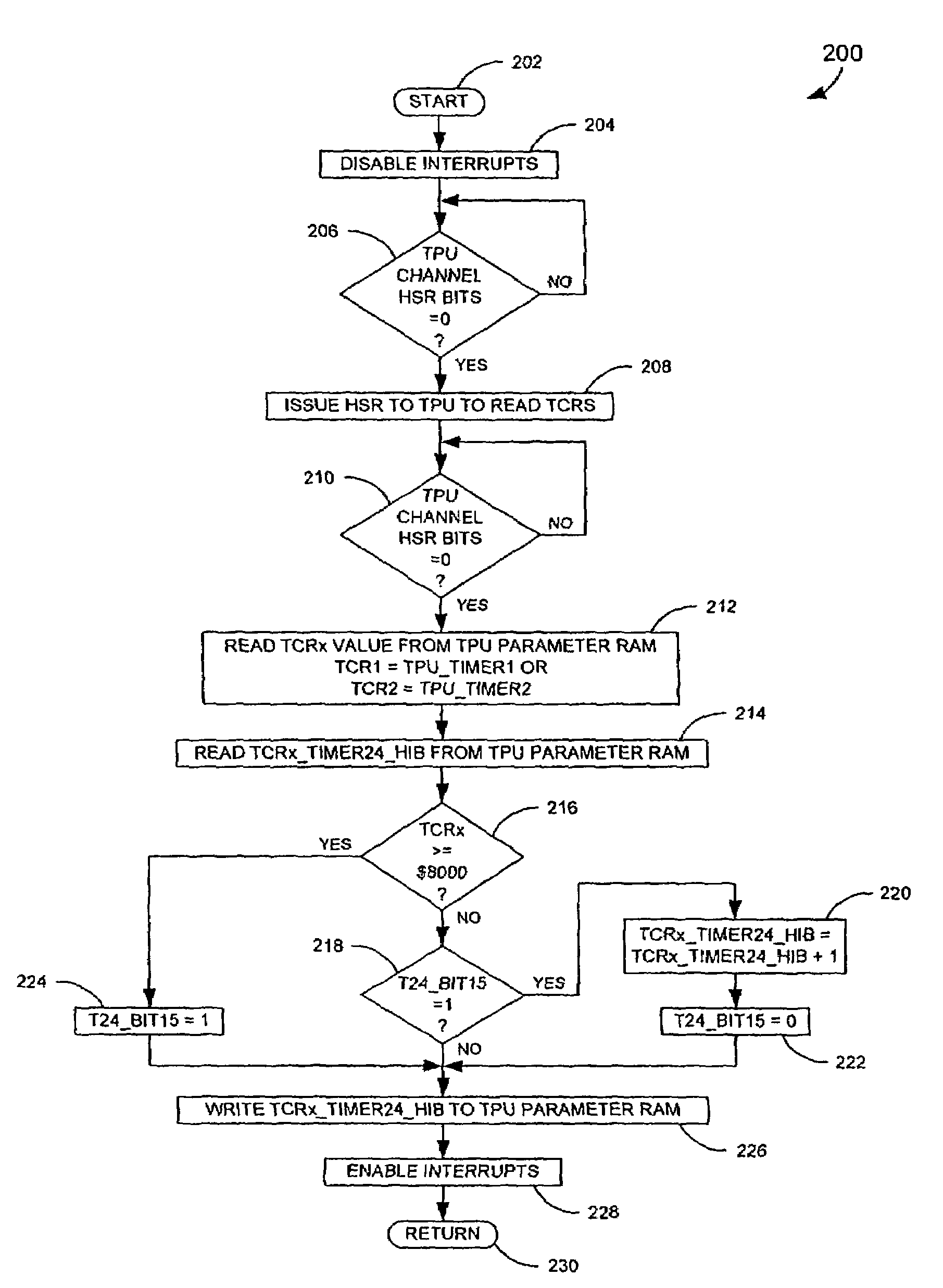

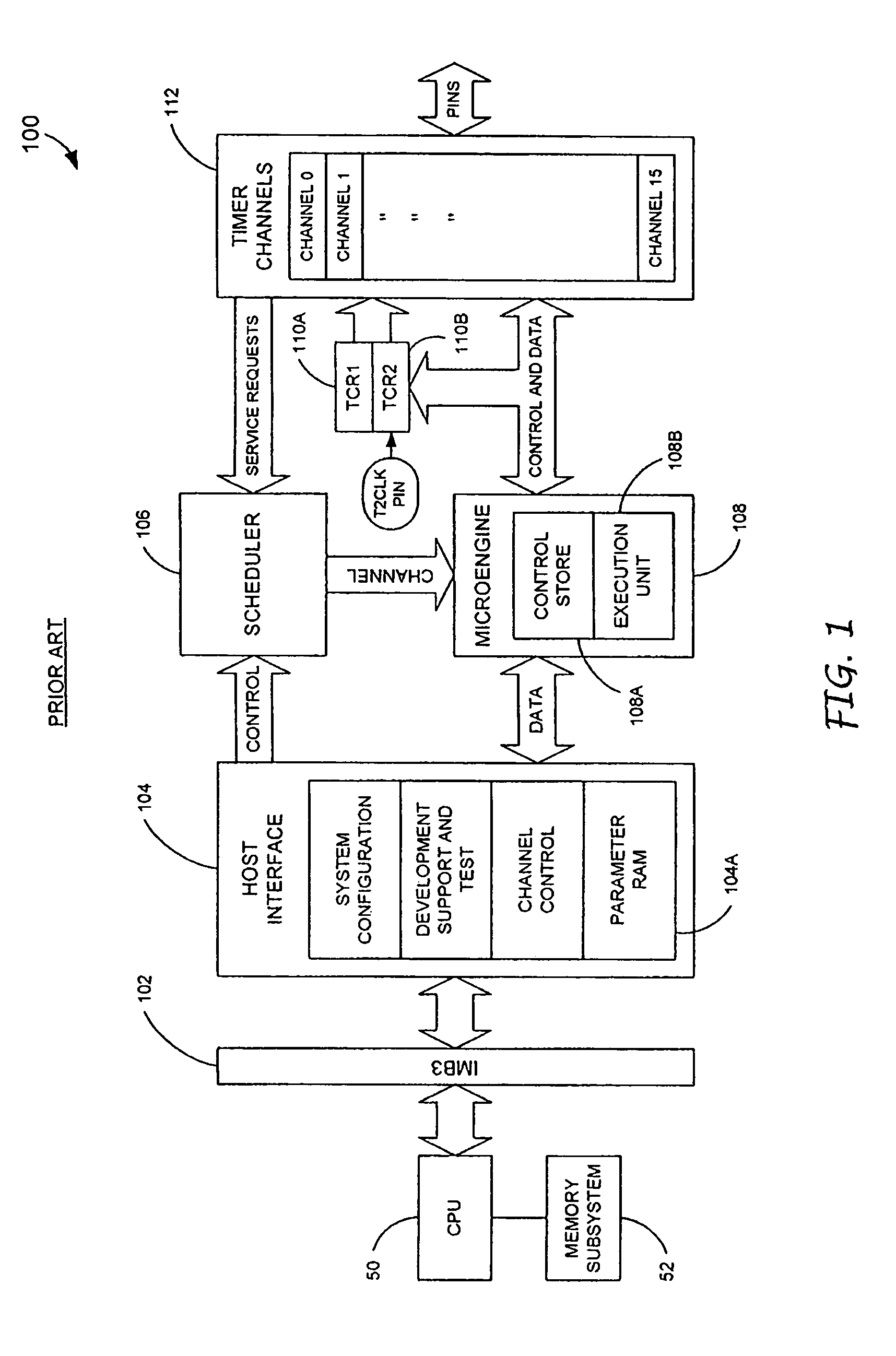

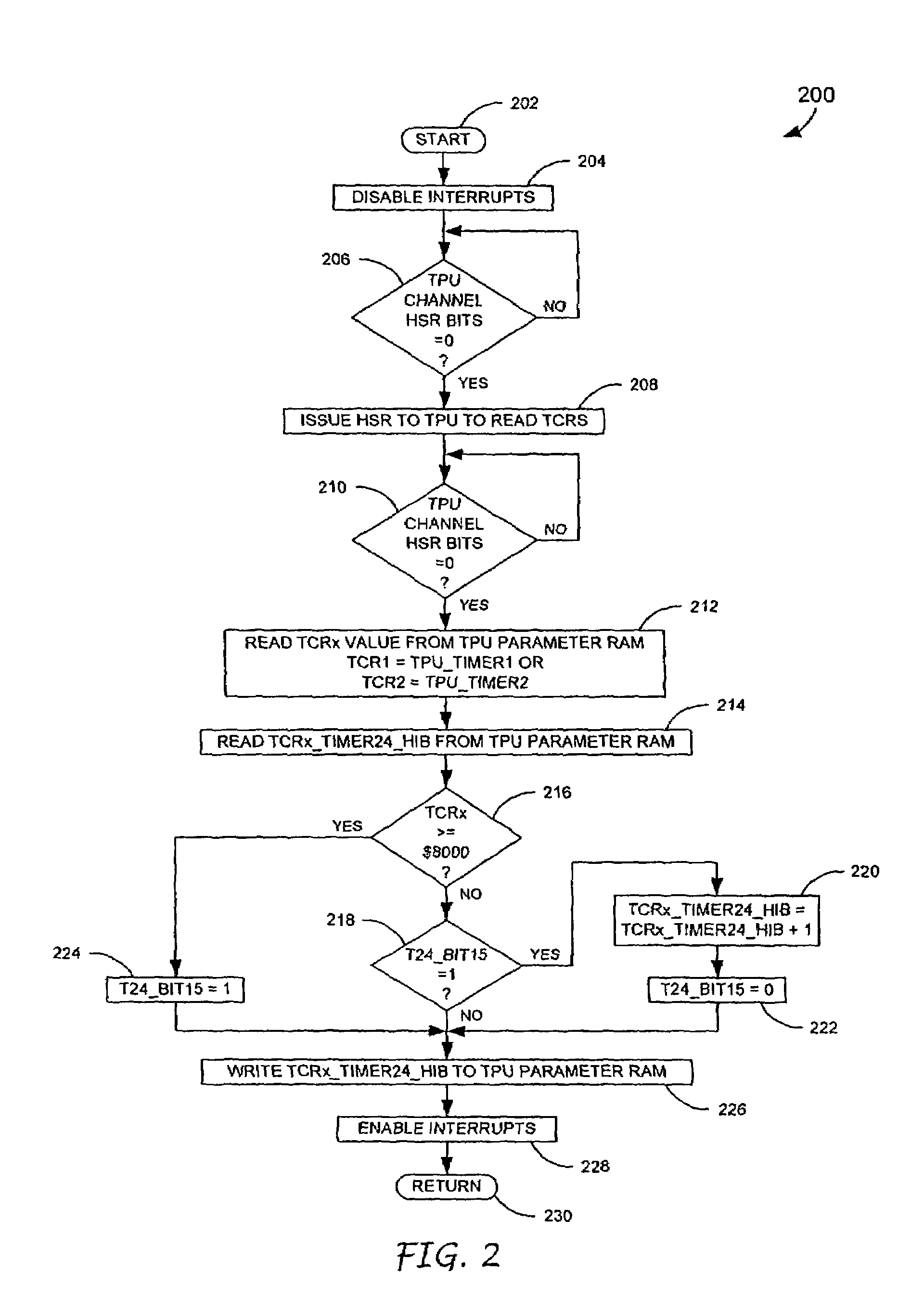

Technique for creating extended bit timer on a time processing unit

A technique for implementing an extended bit timer with a time processing unit (TPU), without using the channel hardware of the TPU includes a number of steps. A timer of the TPU is periodically read to determine the value of the timer. A counter is incremented when rollover of the timer has occurred and a coherency flag is de-asserted after the timer transitions through a first count. The coherency flag is asserted after the value of the timer transitions through a third count and the value of the timer is combined with the value of the counter to provide a current count. When the coherency flag is asserted and the value of the timer is equal to or between the first and second counts, the current count is adjusted.

Owner:DELPHI TECH INC

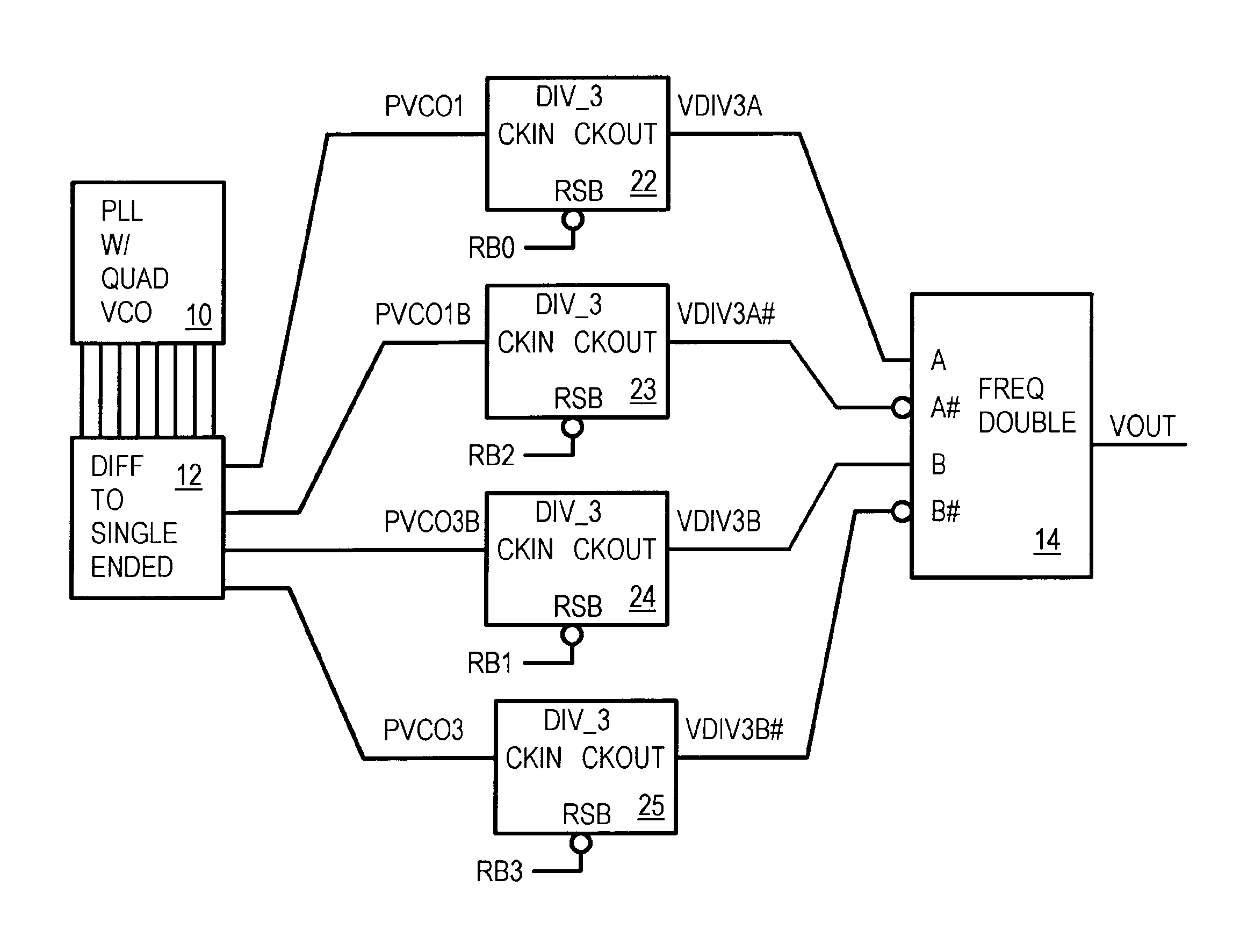

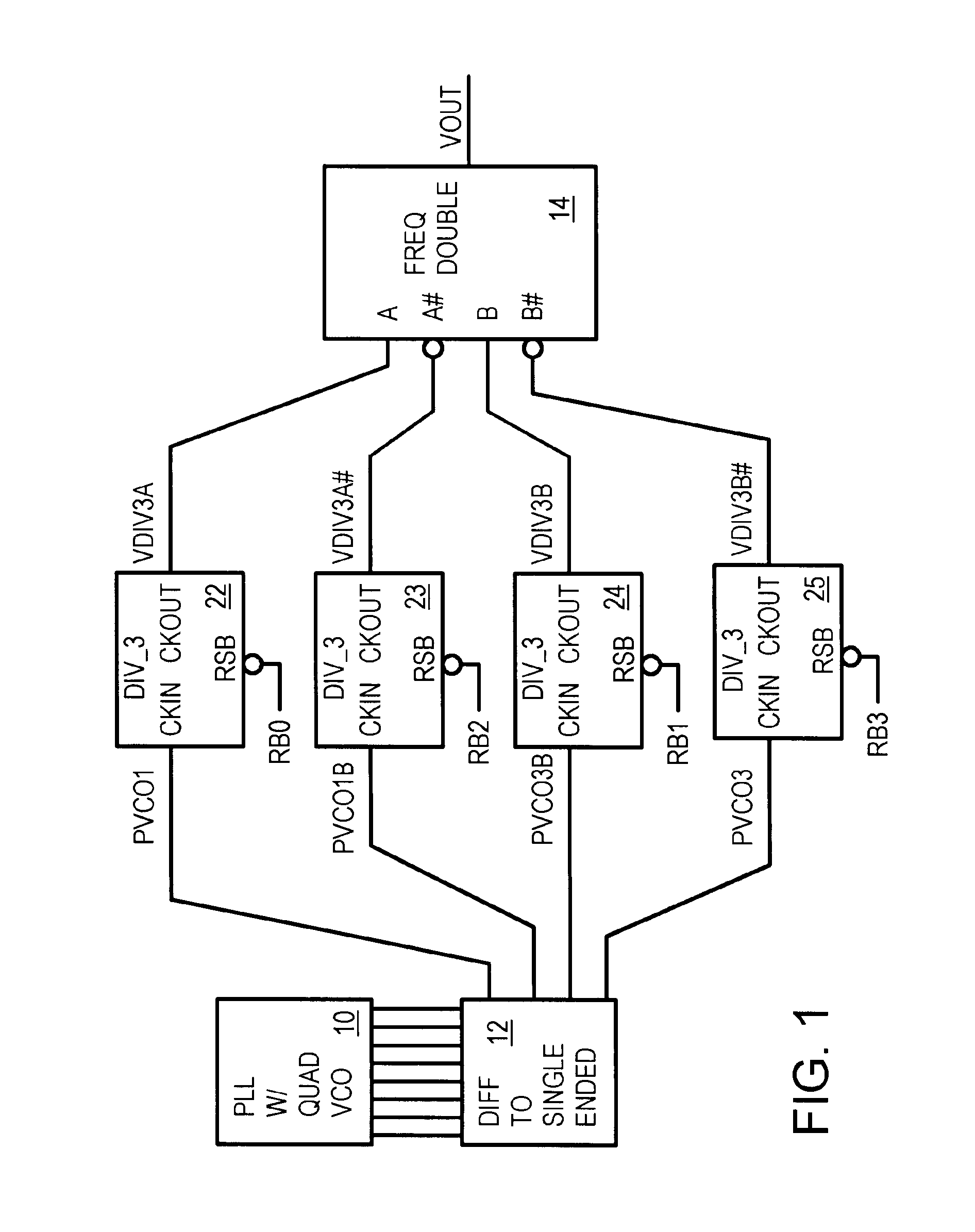

Divide-by-X.5 circuit with frequency doubler and differential oscillator

InactiveUS6882229B1Pulse automatic controlCounting chain synchronous pulse countersFrequency multiplierQuadrature voltage controlled oscillator

A divide by X.5 circuit can be implemented as a divided by 1.5 circuit. A phase-locked loop (PLL) has a quadrature voltage-controlled oscillator (VCO) that generates four phases offset at 0, 90, 180, and 270 degrees. Differential signals from the VCO are converted to single-ended VCO clocks that drive four divide-by-3 circuits, each clocked by one of the four phases of the VCO clocks. Resets to the divide-by-3 circuits are staggered to activate each divide-by-3 circuit synchronously with its phase clock. Outputs from the divide-by-3 circuits are applied to a frequency doubler that generates the final clock that is 1.5 times slower than the VCO clocks. The final clock has a near 50%-50% duty cycle.

Owner:DIODES INC

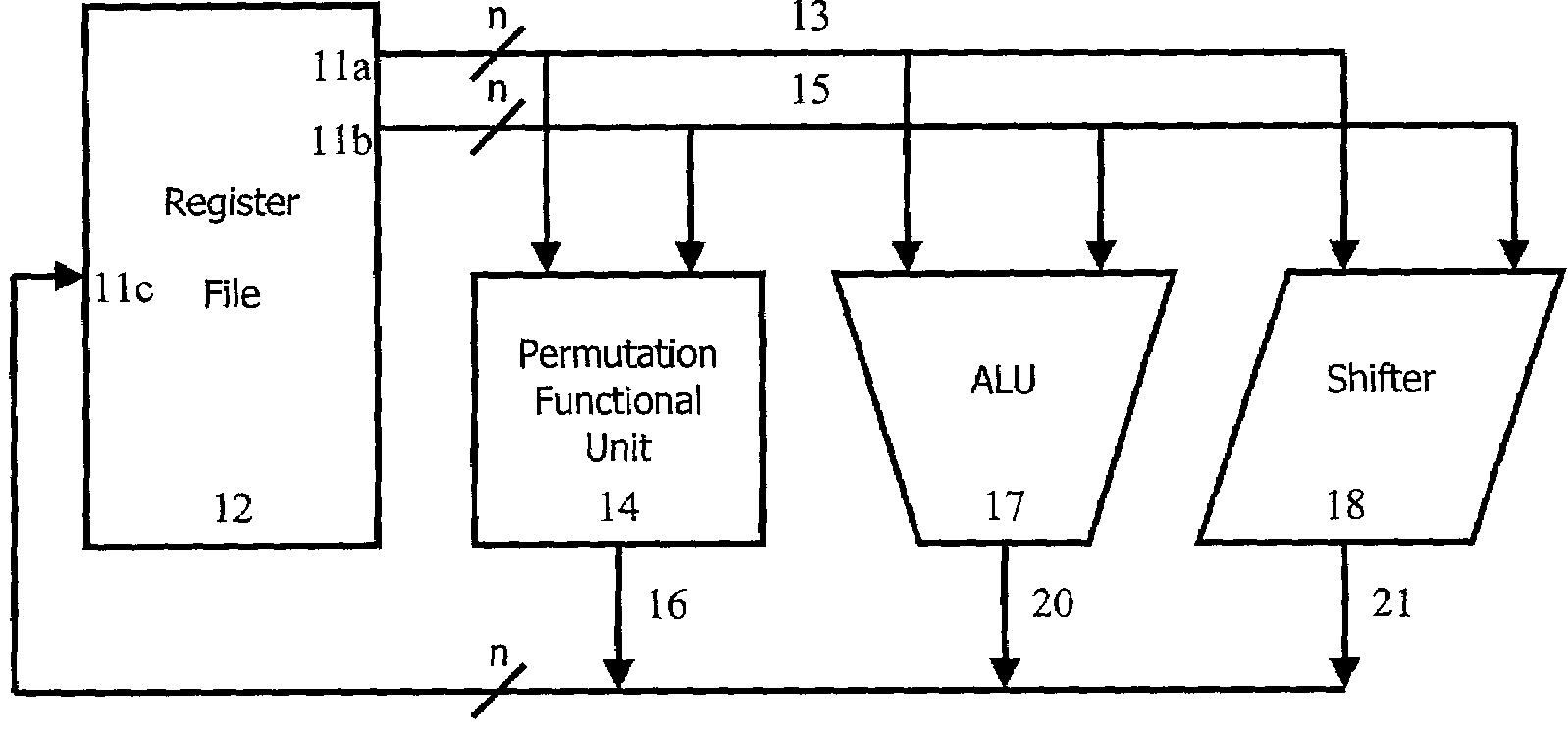

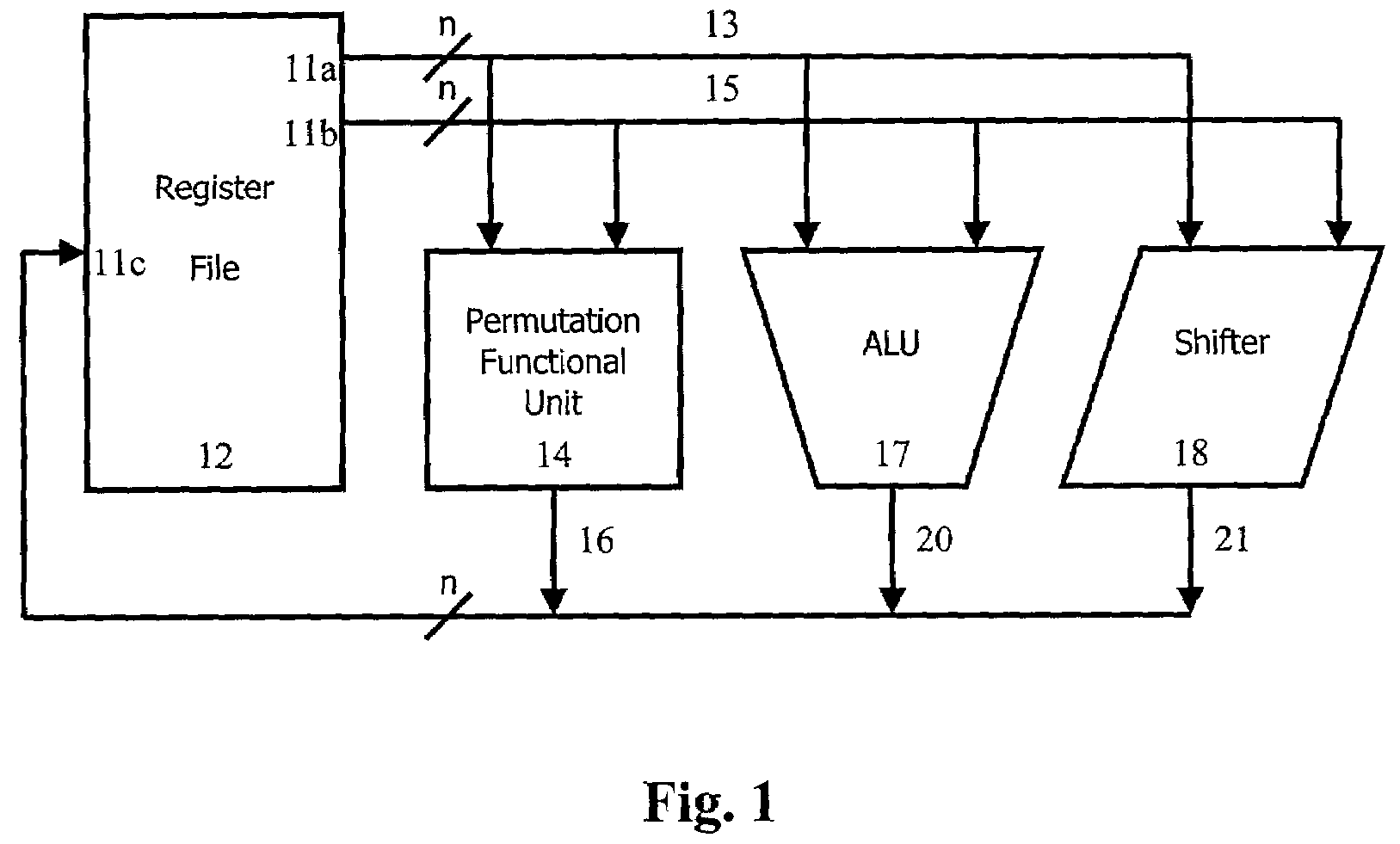

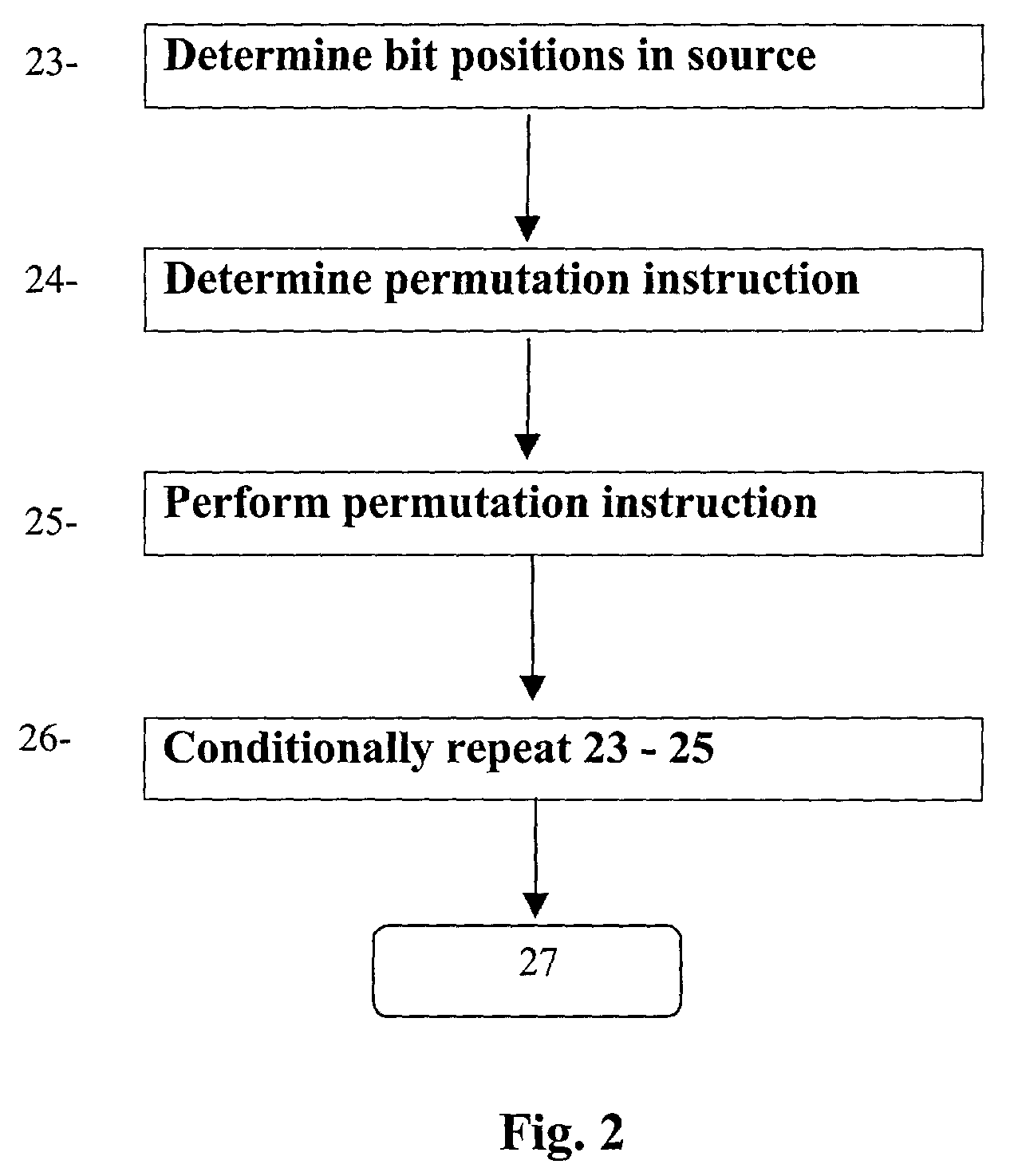

Method and system for performing permutations with bit permutation instructions

InactiveUS7174014B2Counting chain synchronous pulse countersHandling data according to predetermined rulesProcessor registerParallel computing

Owner:TELEPUTERS

Method for reducing dark current

InactiveUS6995795B1Reduce dark currentEliminate needTelevision system detailsColor signal processing circuitsTime segmentEngineering

A method for reducing dark current within an image sensor includes applying, at a first time period, a first set of voltages to the phases of gate electrodes of vertical shift registers sufficient to accumulate holes of the vertical shift register, beneath each gate electrode and applying, at a second time period, a second voltage to a first set of the gate electrodes while simultaneously applying a more positive voltage to a second set of gate electrodes, the second voltage being of sufficient potential so holes that were accumulated beneath the second set of gate electrodes during the first time are collected and stored beneath the first set of gate electrodes during the second time period. Moreover, the method applies, at a third time period, a third voltage to the second set of gate electrodes while simultaneously applying a more positive voltage to the first set of gate electrodes, such that the previously accumulated holes beneath the first set of gate electrodes are transferred beneath the second set of gate electrodes; and returns the first and second sets of gate electrode voltages to their levels at the first time period.

Owner:SEMICON COMPONENTS IND LLC