Patents

Literature

210results about How to "Parasitic capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor device and method for manufacturing the same

ActiveUS20110037068A1Manufacturing cost be reduceEasily breakTransistorSolid-state devicesOxide semiconductorOxide

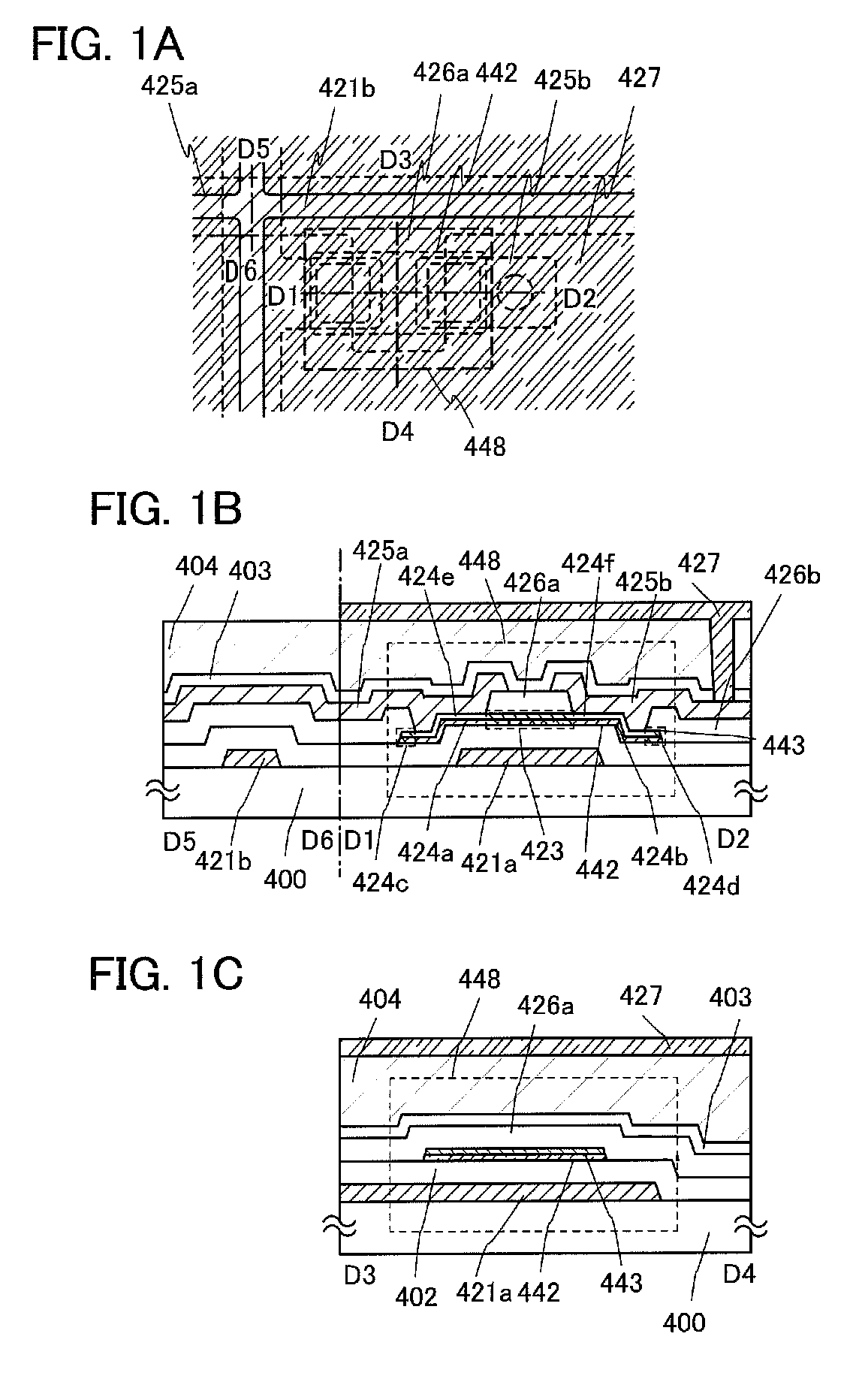

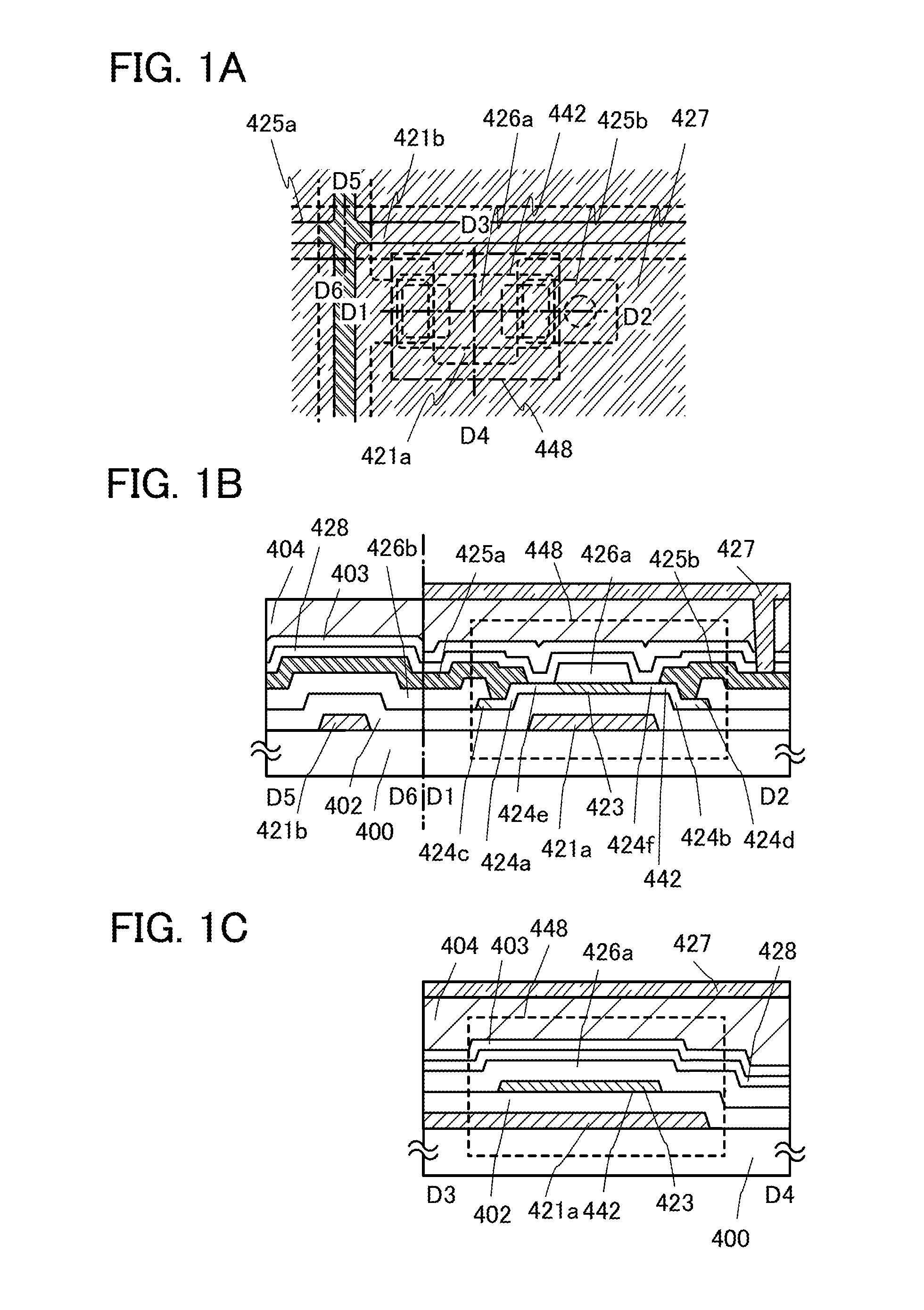

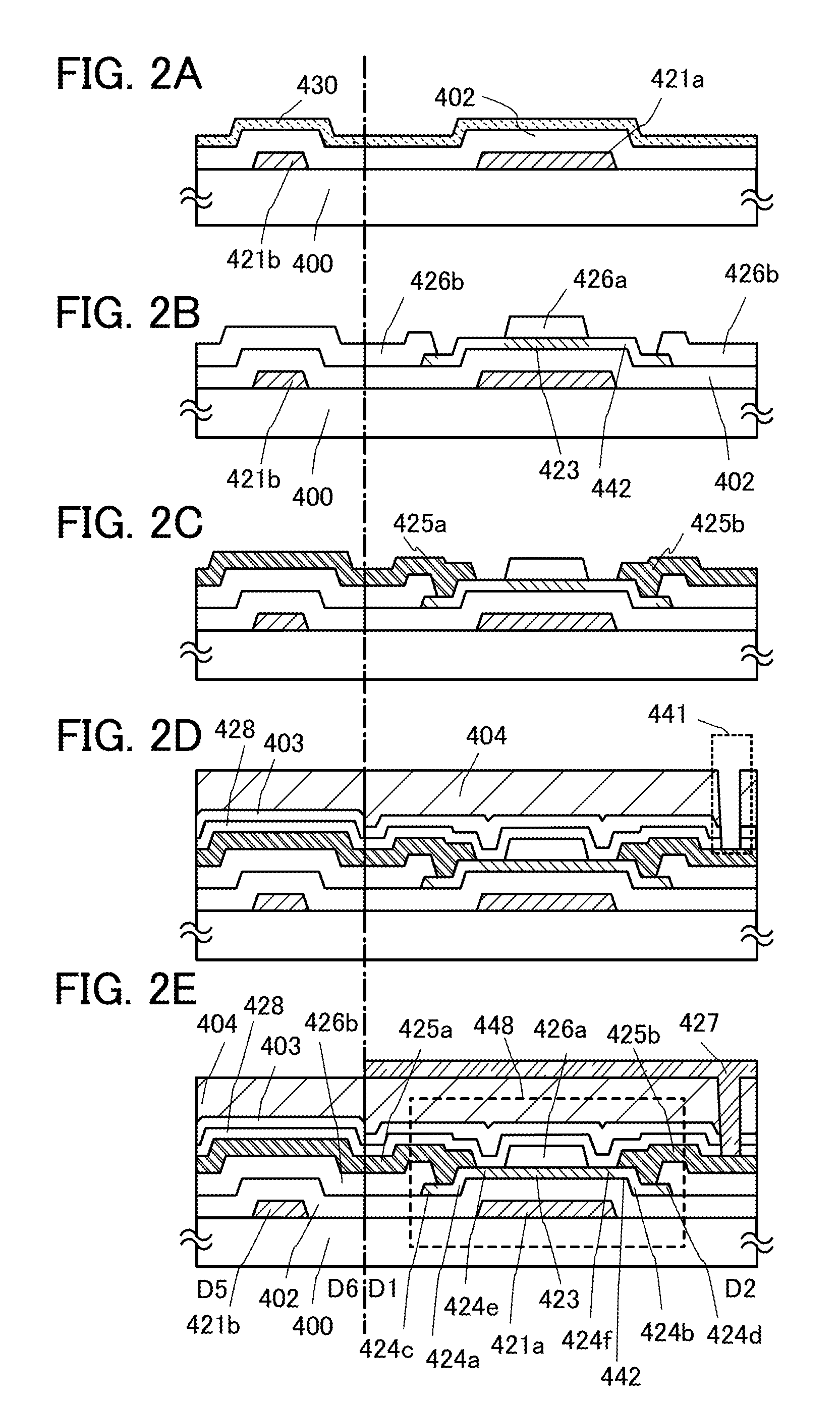

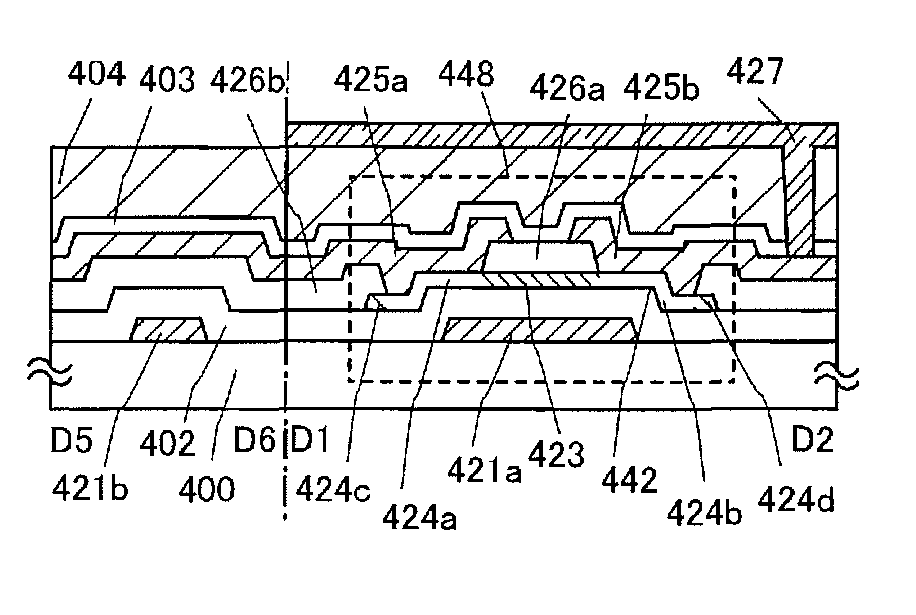

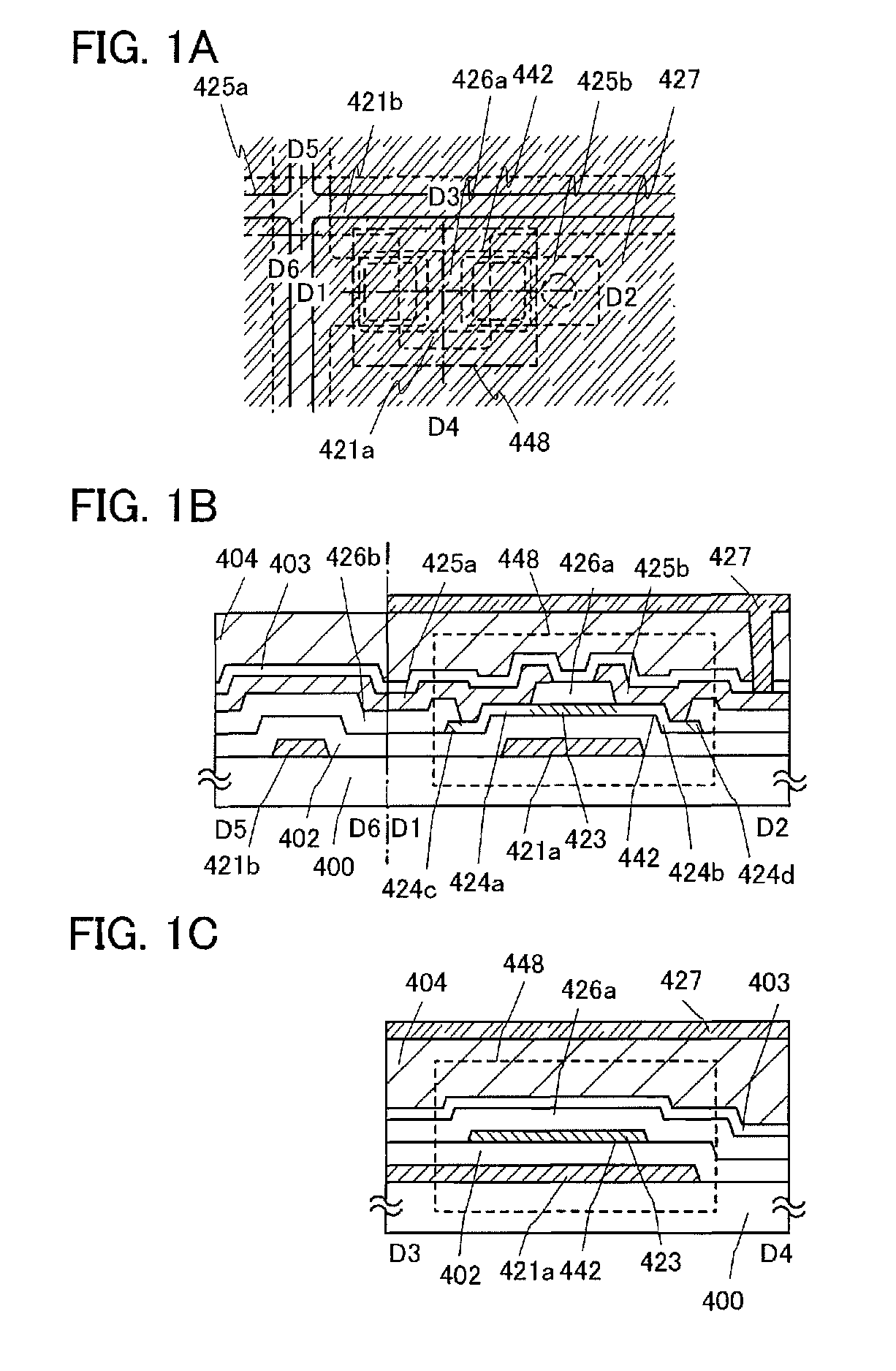

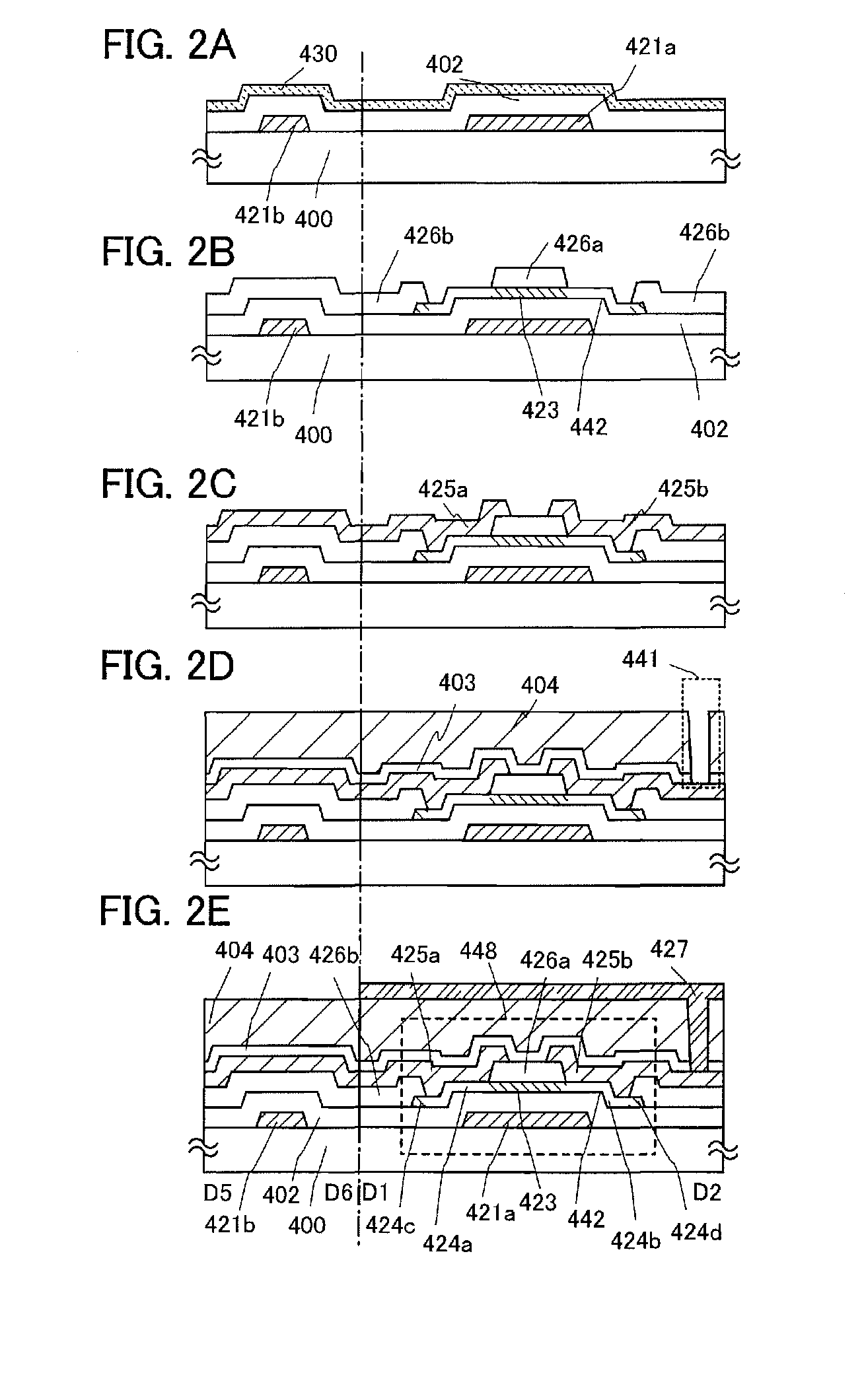

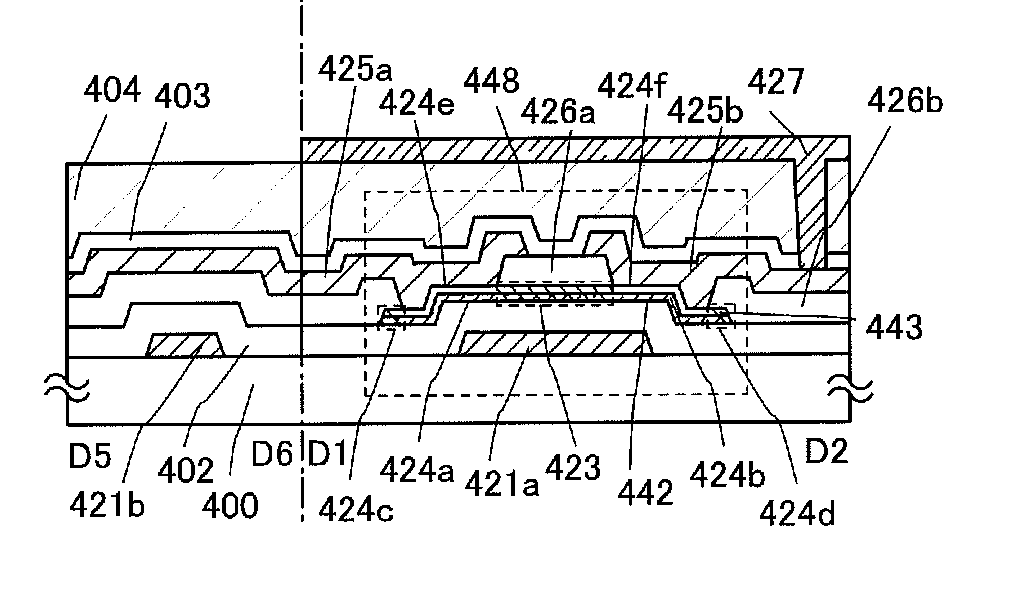

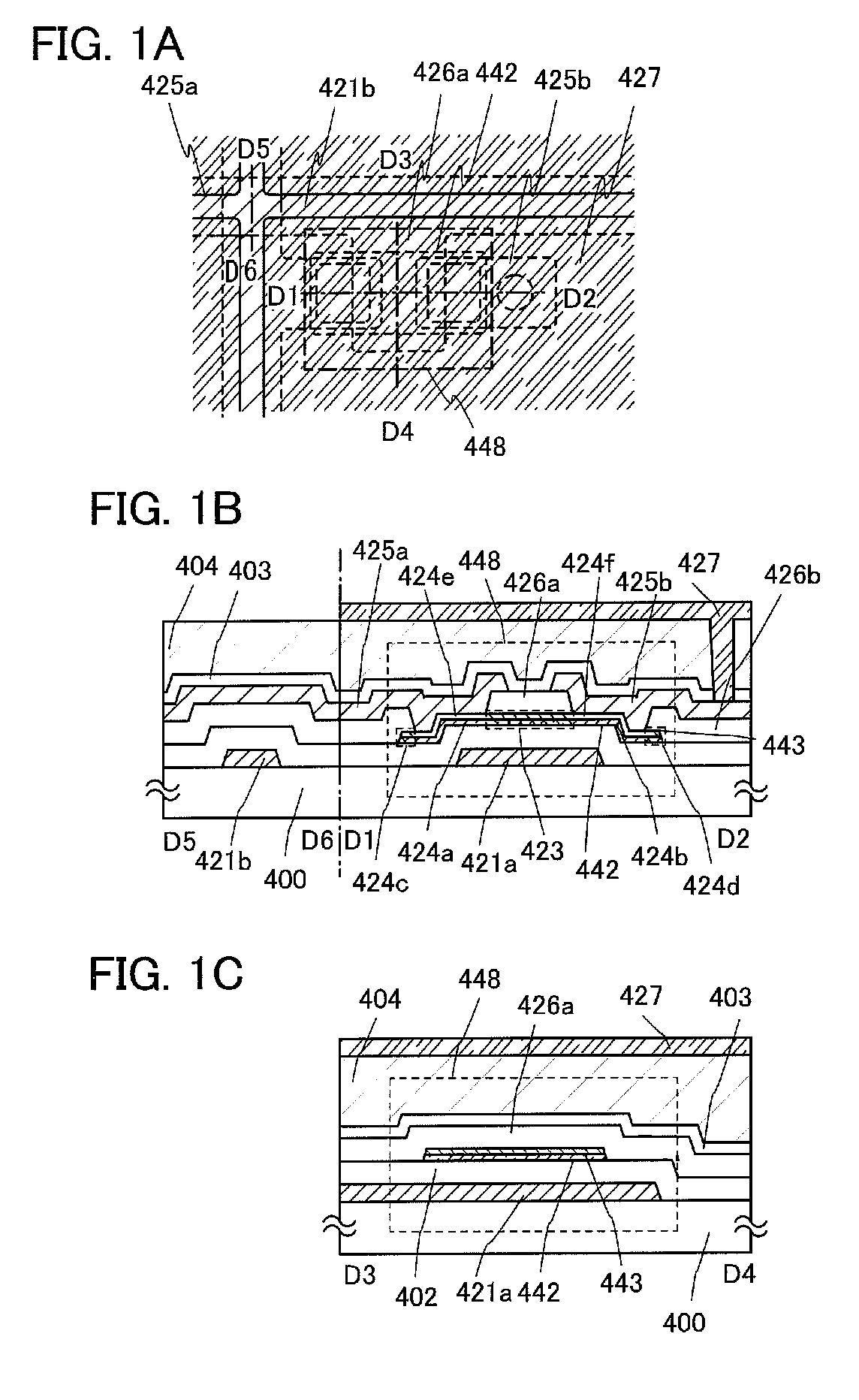

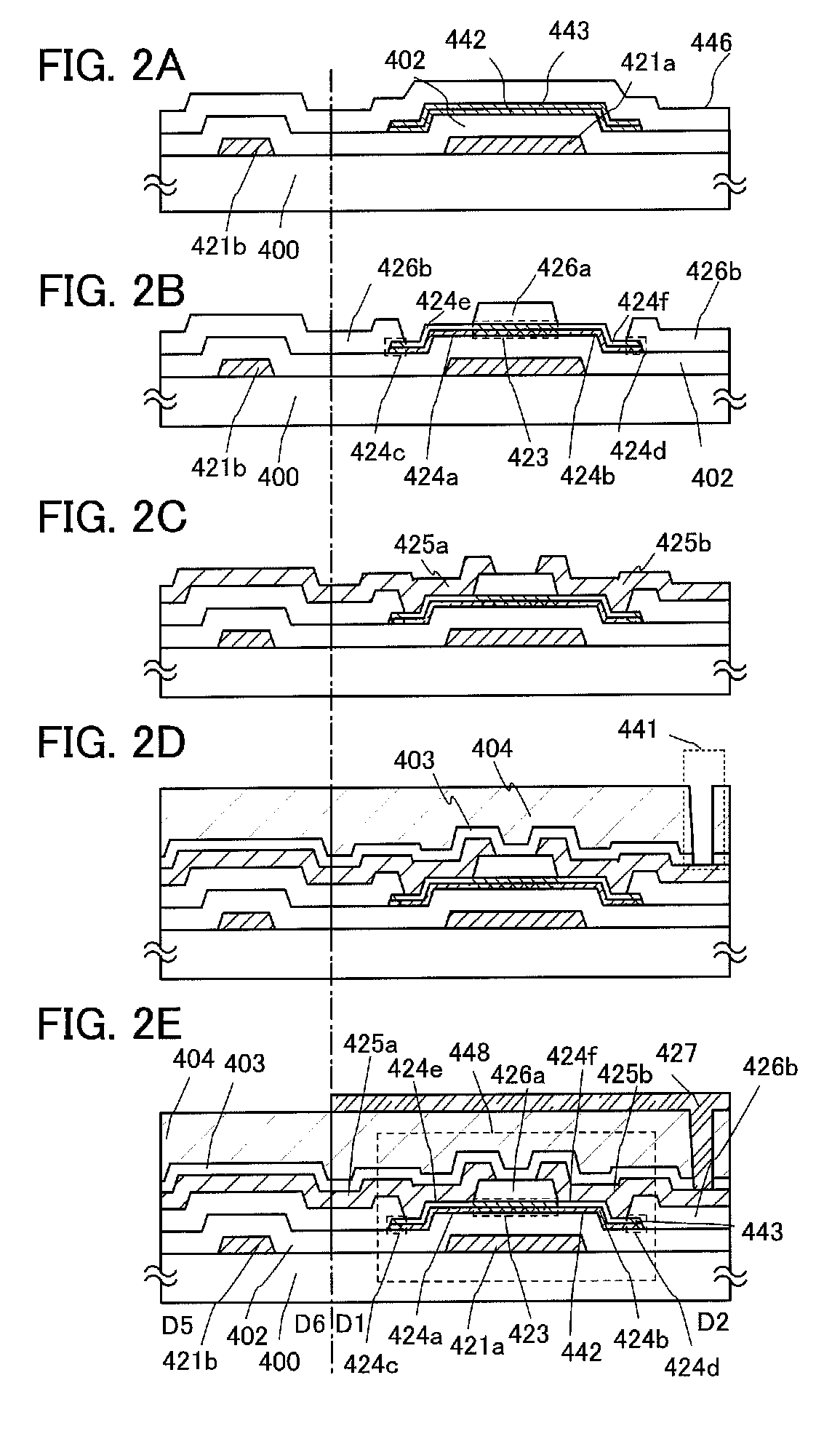

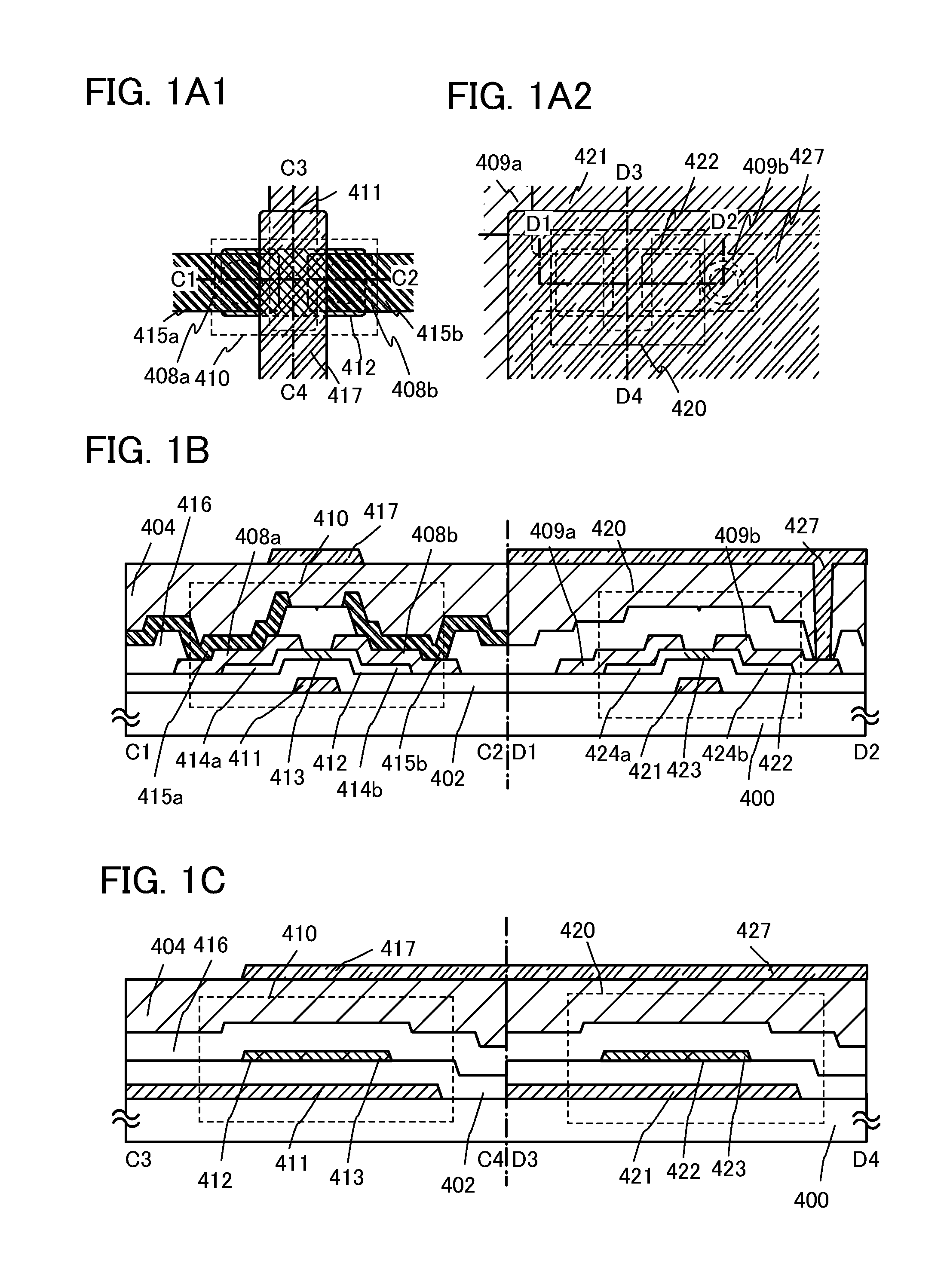

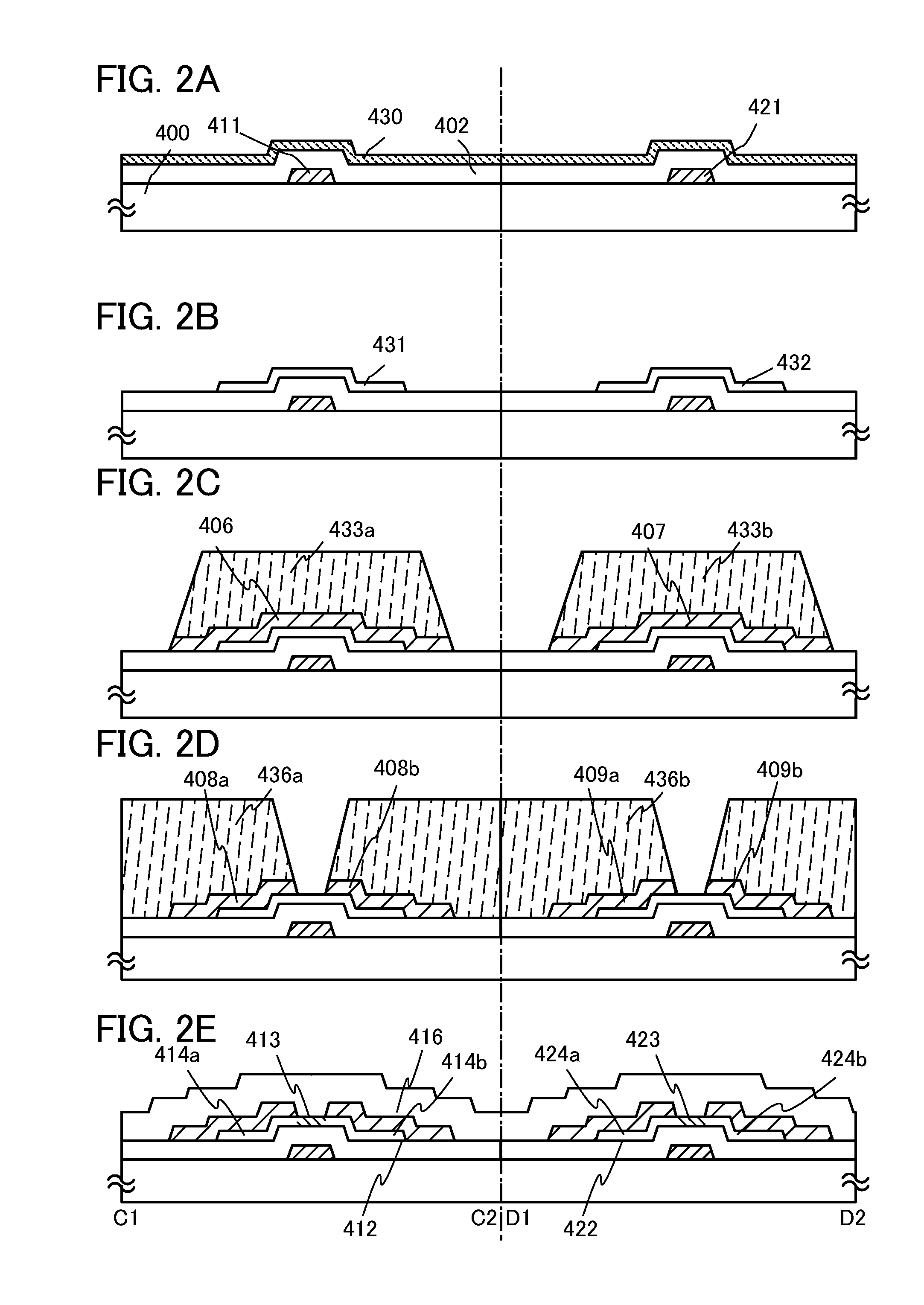

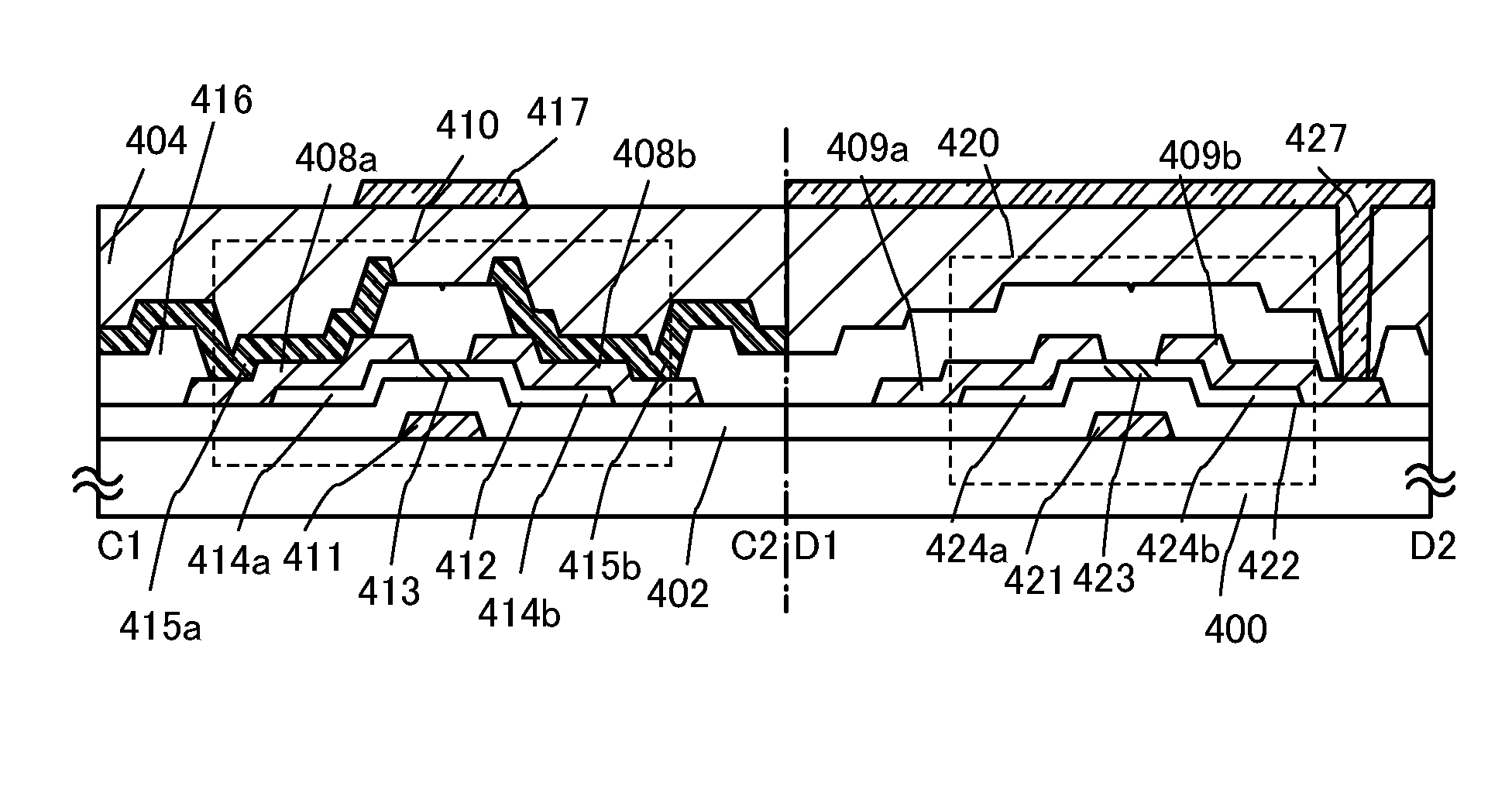

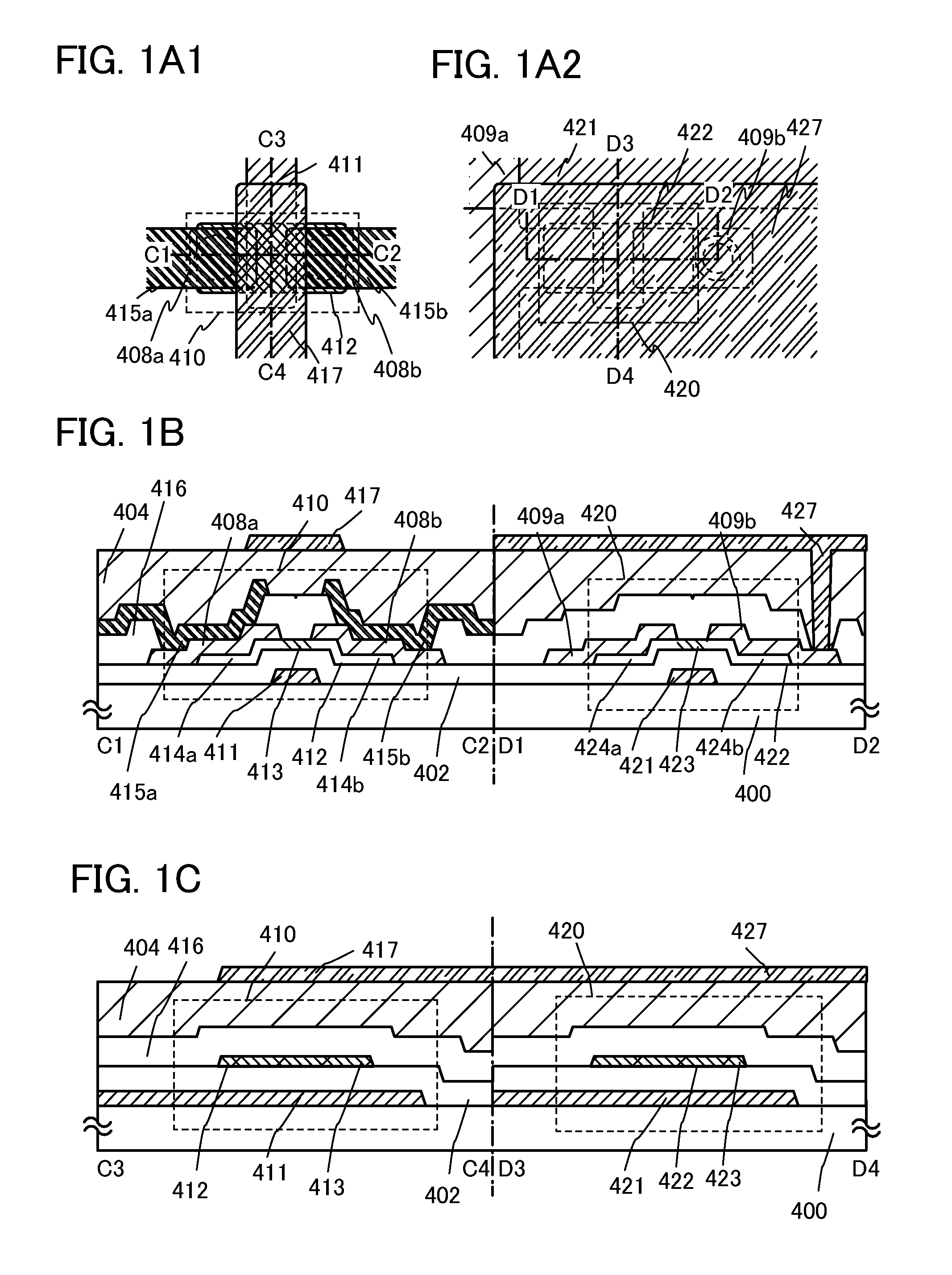

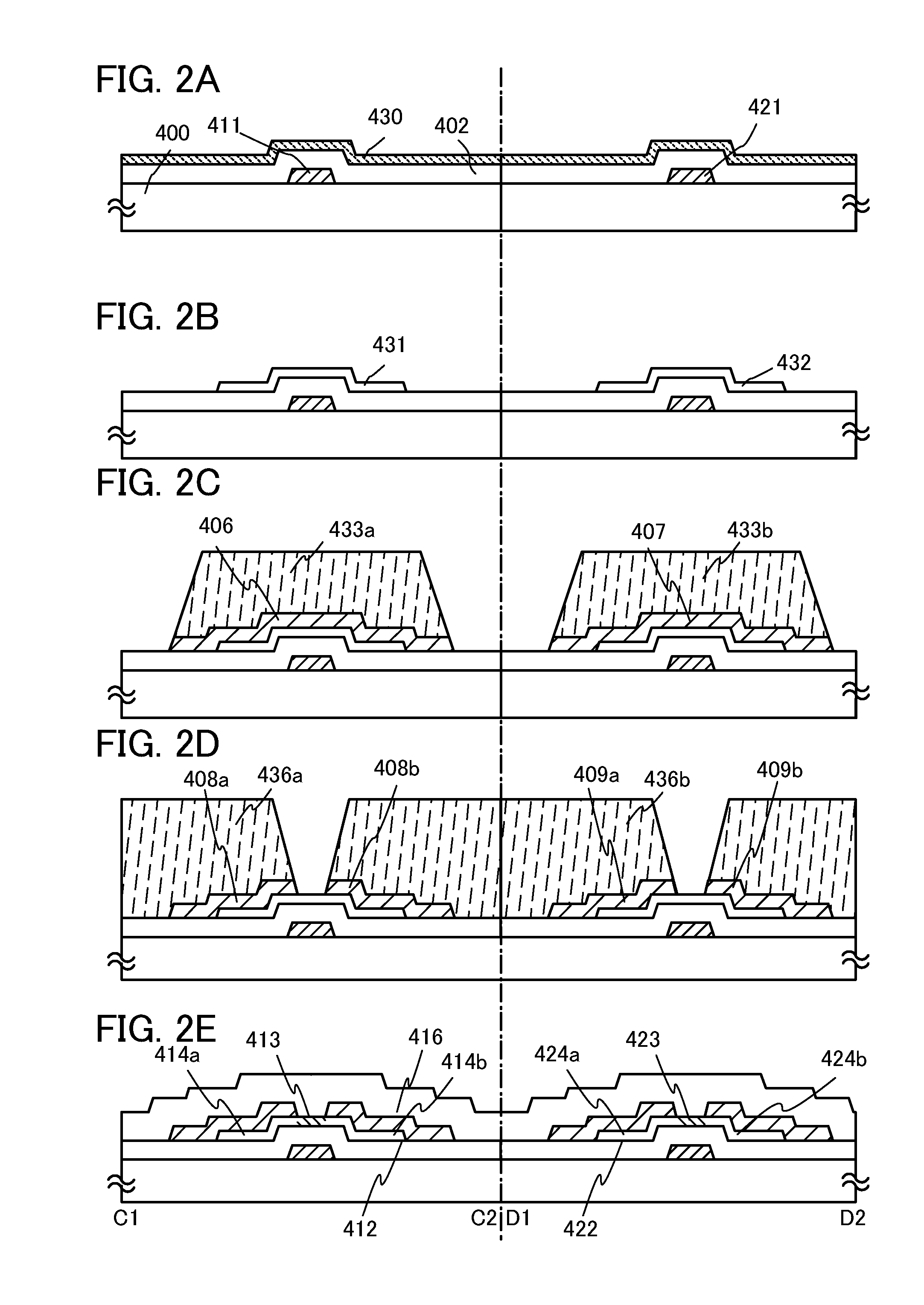

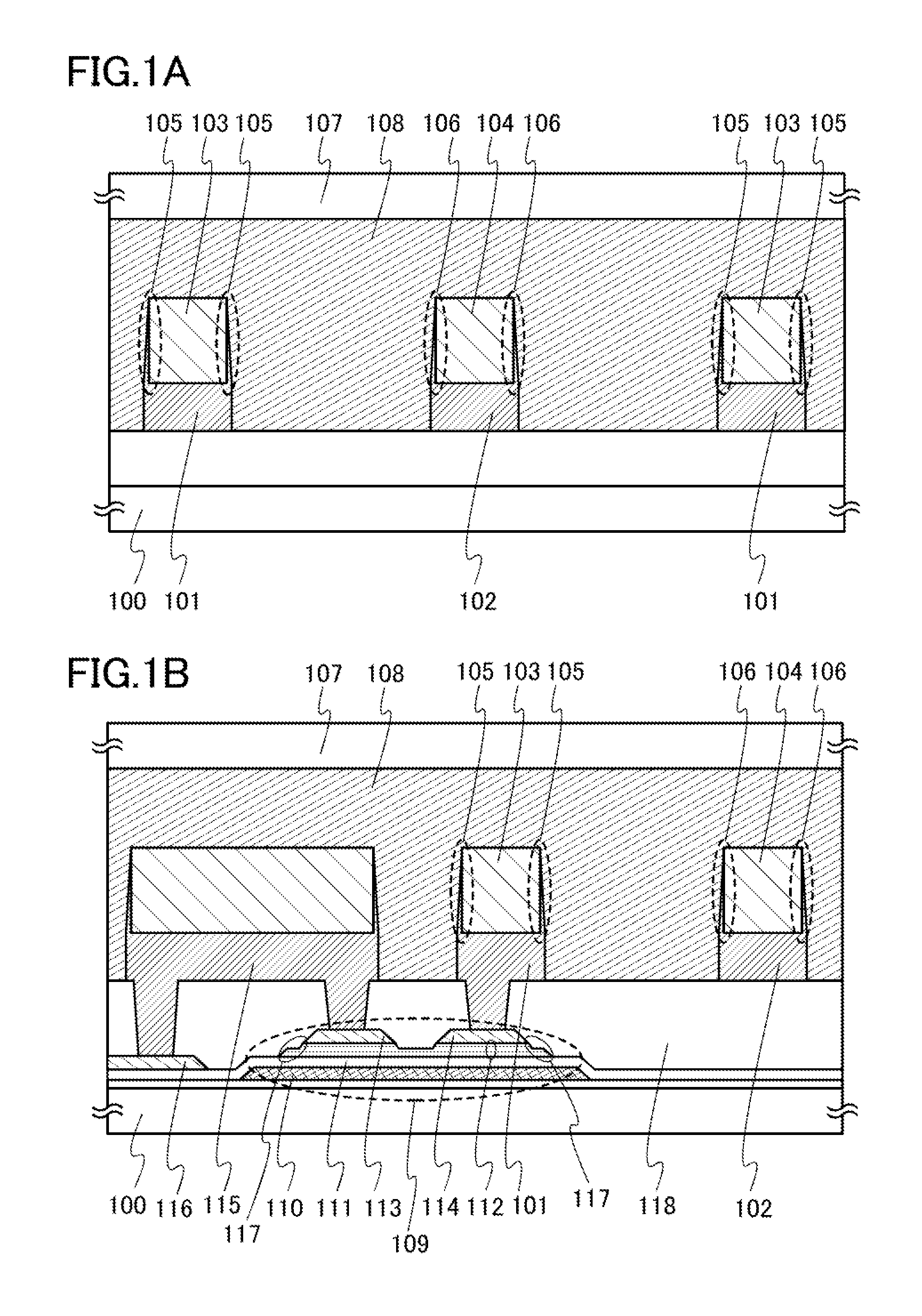

One object is to provide a semiconductor device with a structure which enables reduction in parasitic capacitance sufficiently between wirings. In a bottom-gate type thin film transistor including a stacked layer of a first layer which is a metal thin film oxidized partly or entirely and an oxide semiconductor layer, the following oxide insulating layers are formed together: an oxide insulating layer serving as a channel protective layer which is over and in contact with a part of the oxide semiconductor layer overlapping with a gate electrode layer; and an oxide insulating layer which covers a peripheral portion and a side surface of the stacked oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

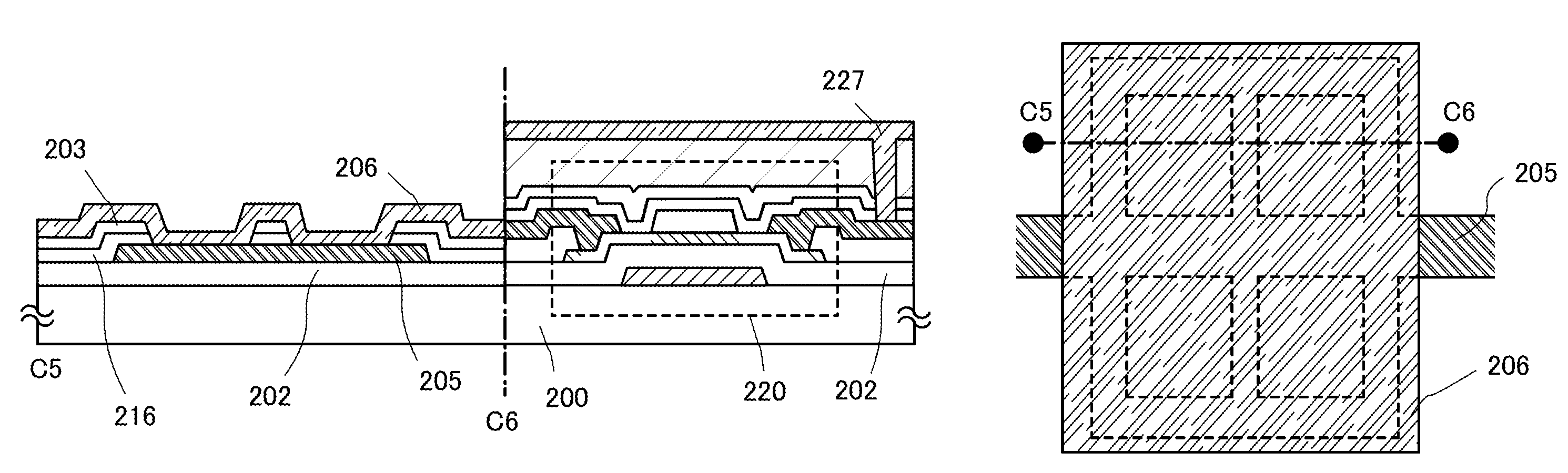

Semiconductor device and manufacturing method thereof

ActiveUS20110024751A1Reduce manufacturing costEasily brokenTransistorSolid-state devicesBottom gateSemiconductor

In a bottom-gate thin film transistor using the stack of the first oxide semiconductor layer and the second oxide semiconductor layer, an oxide insulating layer serving as a channel protective layer is formed over and in contact with part of the oxide semiconductor layer overlapping with a gate electrode layer. In the same step as formation of the insulating layer, an oxide insulating layer covering a peripheral portion (including a side surface) of the stack of the oxide semiconductor layers is formed.

Owner:SEMICON ENERGY LAB CO LTD

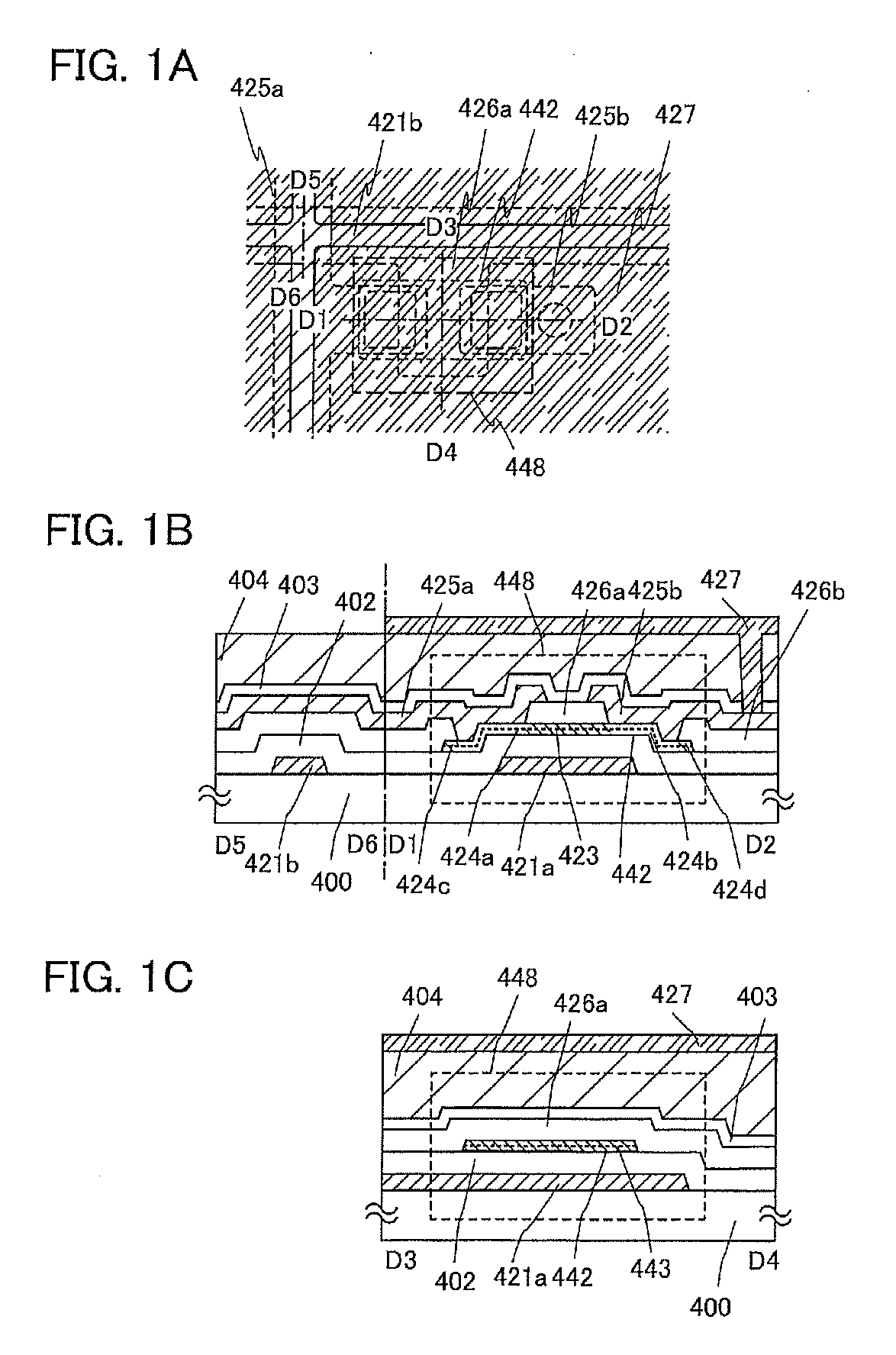

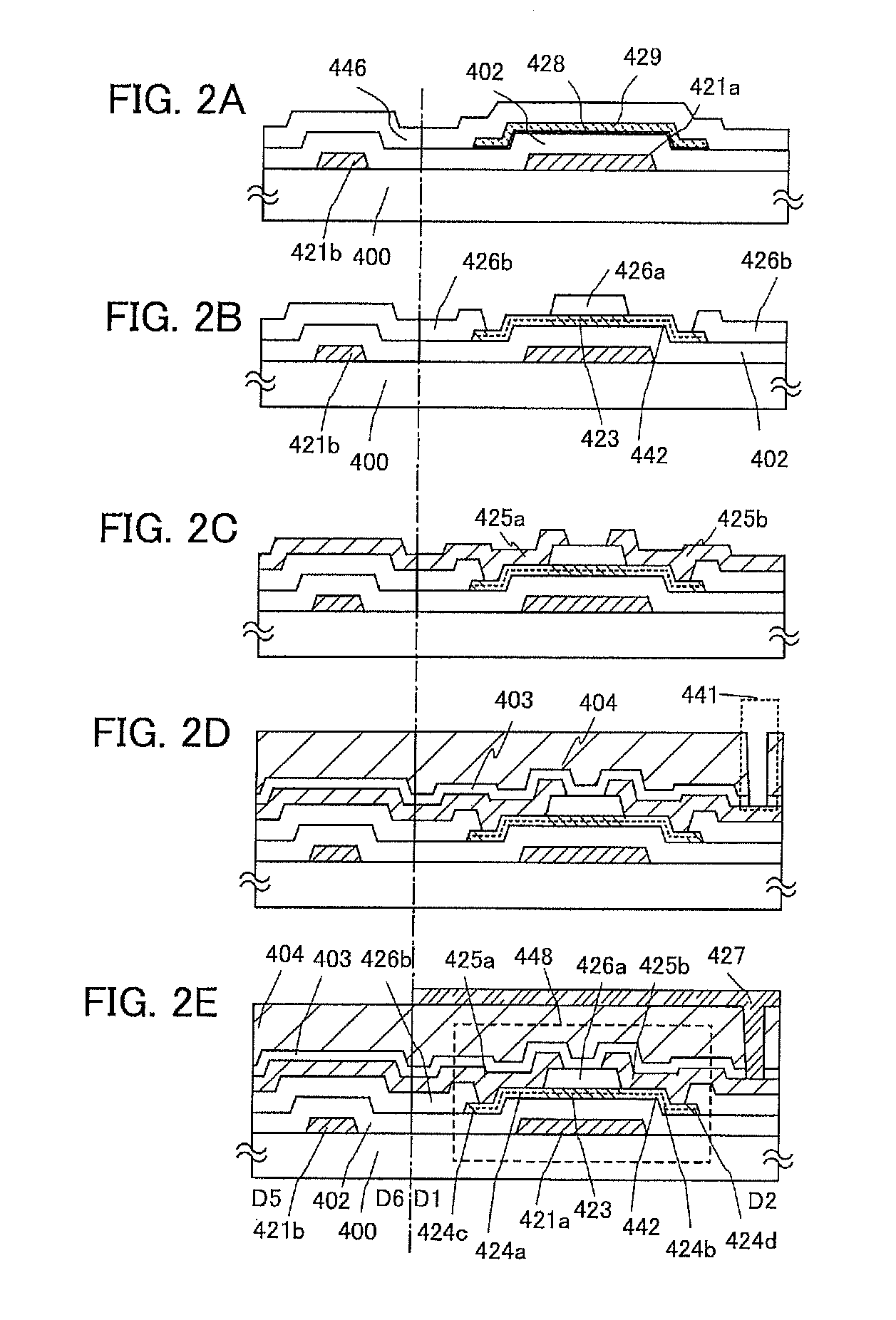

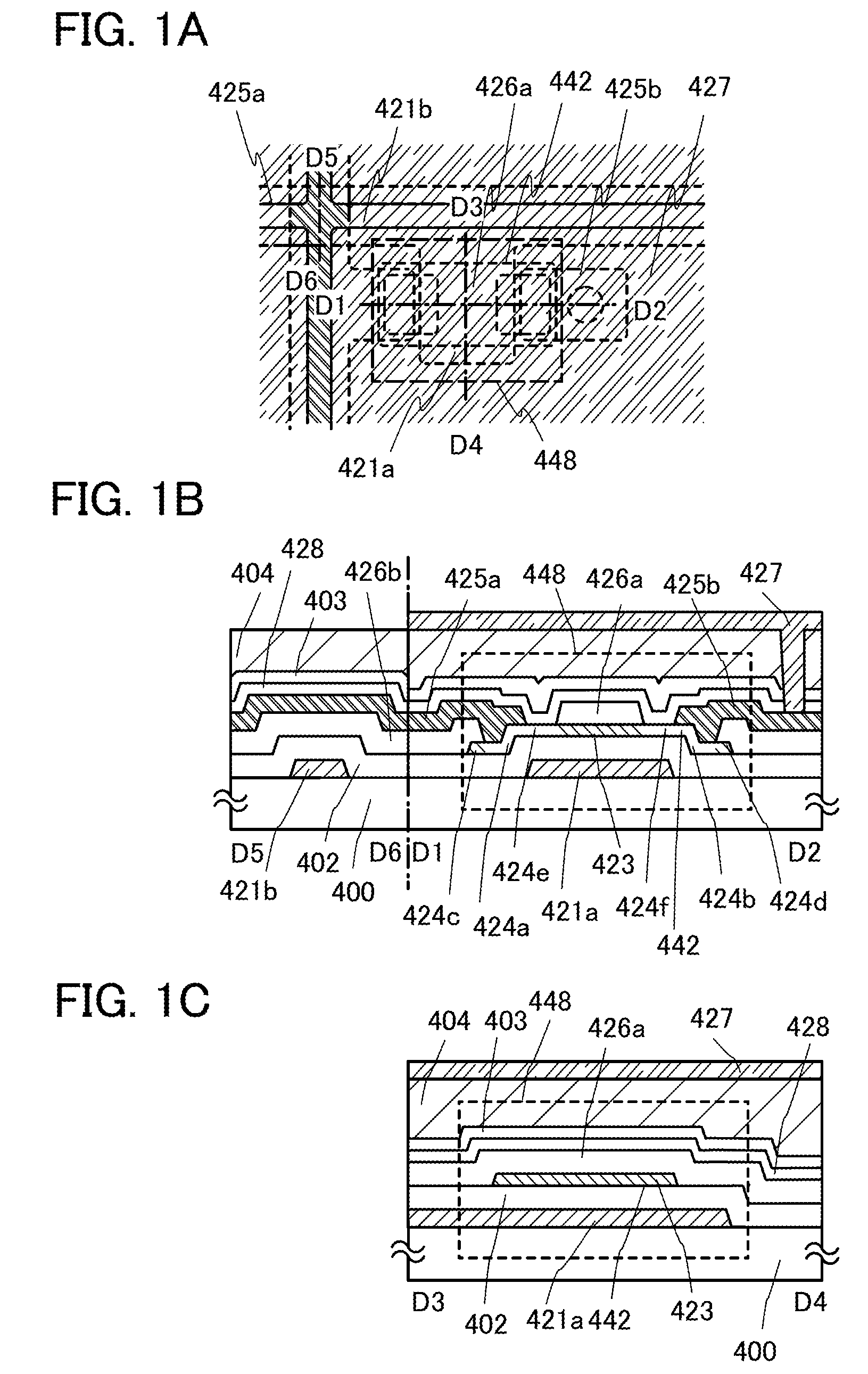

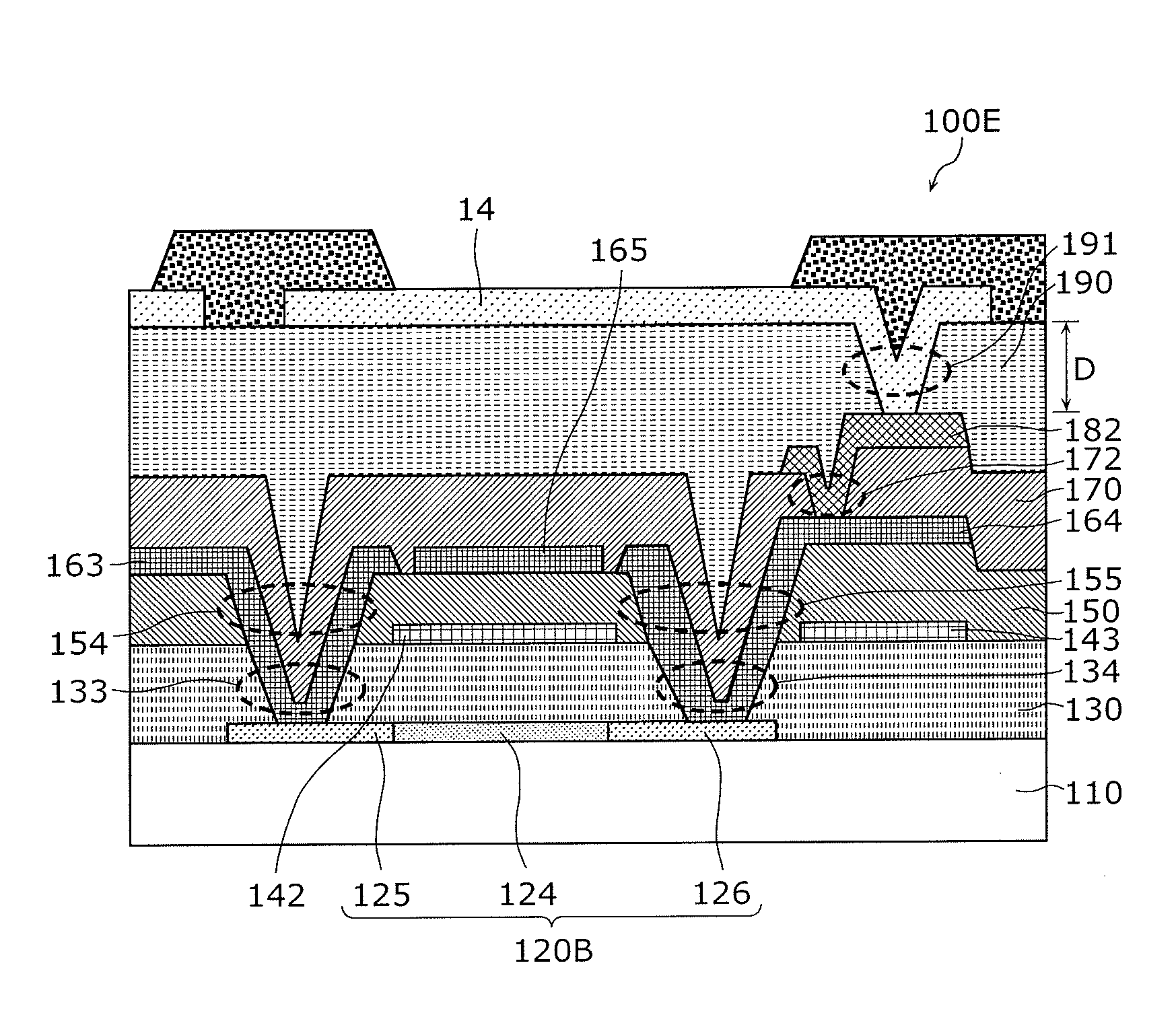

Semiconductor device and manufacturing method thereof

ActiveUS20110031491A1Reduce parasitic capacitanceOff-current can be reducedTransistorStatic indicating devicesBottom gateParasitic capacitance

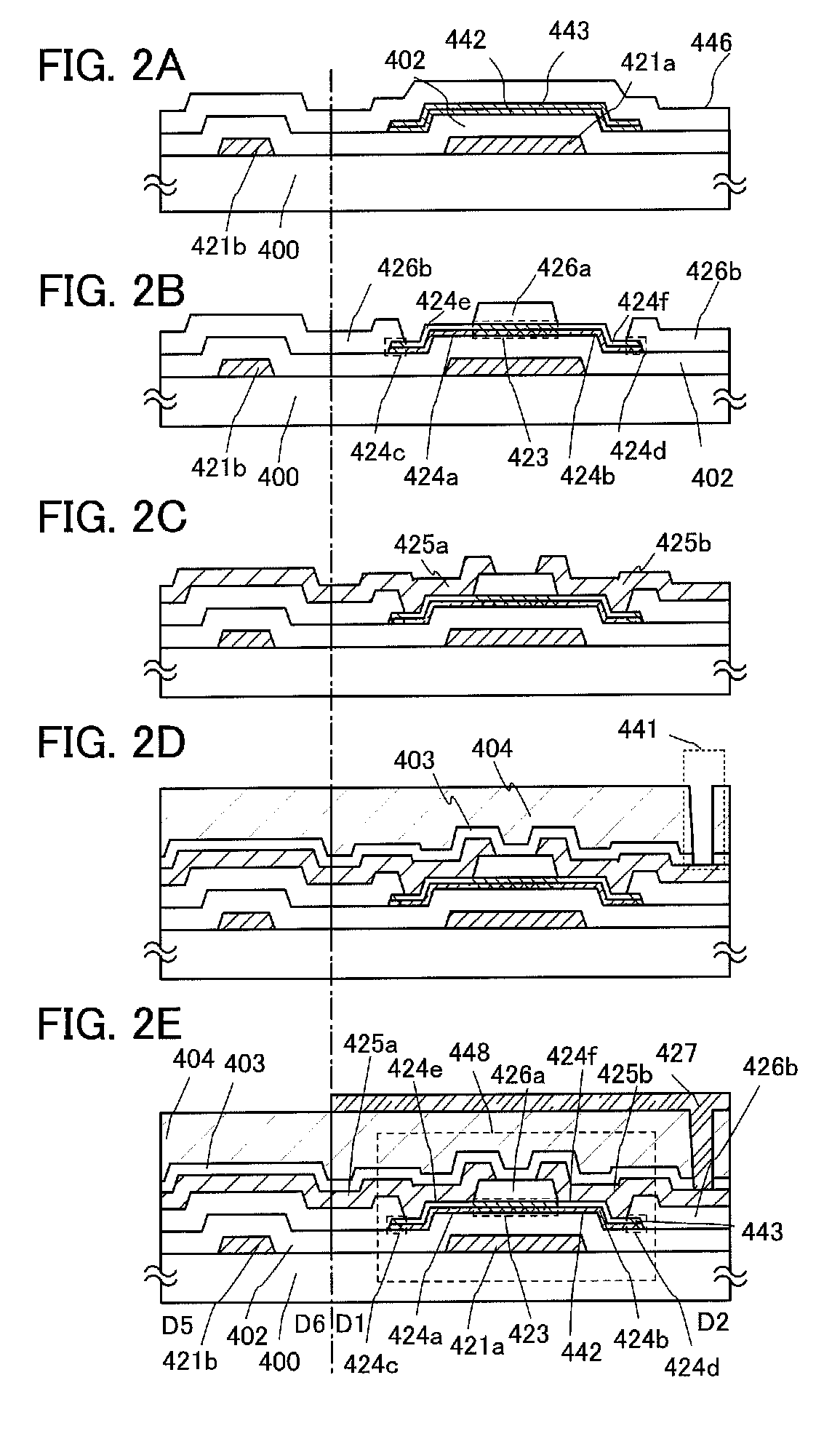

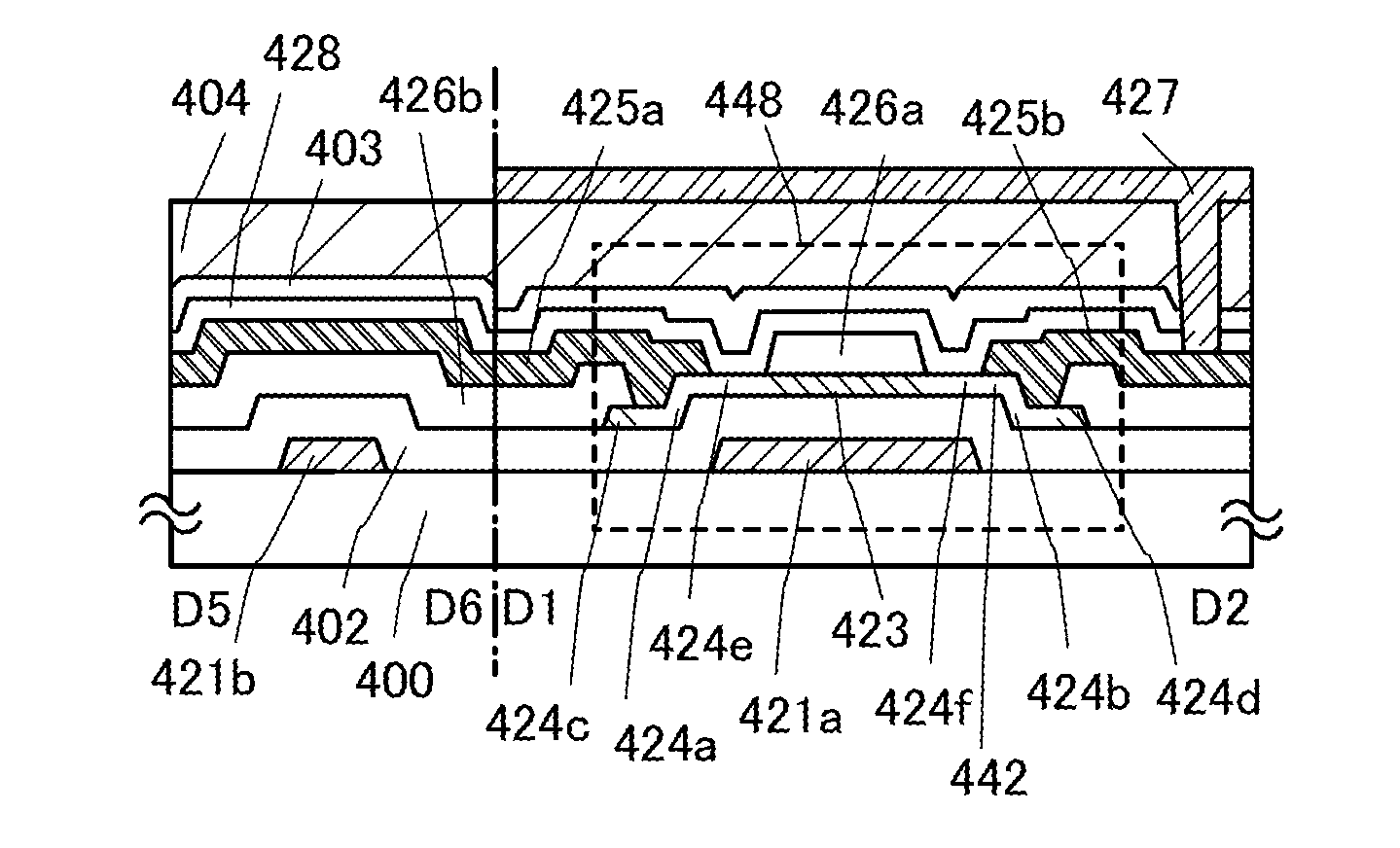

An object is to provide a semiconductor device having a structure in which parasitic capacitance between wirings can be efficiently reduced. In a bottom gate thin film transistor using an oxide semiconductor layer, an oxide insulating layer used as a channel protection layer is formed above and in contact with part of the oxide semiconductor layer overlapping with a gate electrode layer, and at the same time an oxide insulating layer covering a peripheral portion (including a side surface) of the stacked oxide semiconductor layer is formed. Further, a source electrode layer and a drain electrode layer are formed in a manner such that they do not overlap with the channel protection layer. Thus, a structure in which an insulating layer over the source electrode layer and the drain electrode layer is in contact with the oxide semiconductor layer is provided.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and method for manufacturing the same

ActiveUS20110024750A1Excellent electrical propertiesImprove reliabilityTransistorSolid-state devicesDevice materialParasitic capacitance

An object is to provide a semiconductor device having a structure with which parasitic capacitance between wirings can be sufficiently reduced. An oxide insulating layer serving as a channel protective layer is formed over part of an oxide semiconductor layer overlapping with a gate electrode layer. In the same step as formation of the oxide insulating layer, an oxide insulating layer covering a peripheral portion of the oxide semiconductor layer is formed. The oxide insulating layer which covers the peripheral portion of the oxide semiconductor layer is provided to increase the distance between the gate electrode layer and a wiring layer formed above or in the periphery of the gate electrode layer, whereby parasitic capacitance is reduced.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device with two oxide semiconductor layers and manufacturing method thereof

In a bottom-gate thin film transistor using the stack of the first oxide semiconductor layer and the second oxide semiconductor layer, an oxide insulating layer serving as a channel protective layer is formed over and in contact with part of the oxide semiconductor layer overlapping with a gate electrode layer. In the same step as formation of the insulating layer, an oxide insulating layer covering a peripheral portion (including a side surface) of the stack of the oxide semiconductor layers is formed.

Owner:SEMICON ENERGY LAB CO LTD

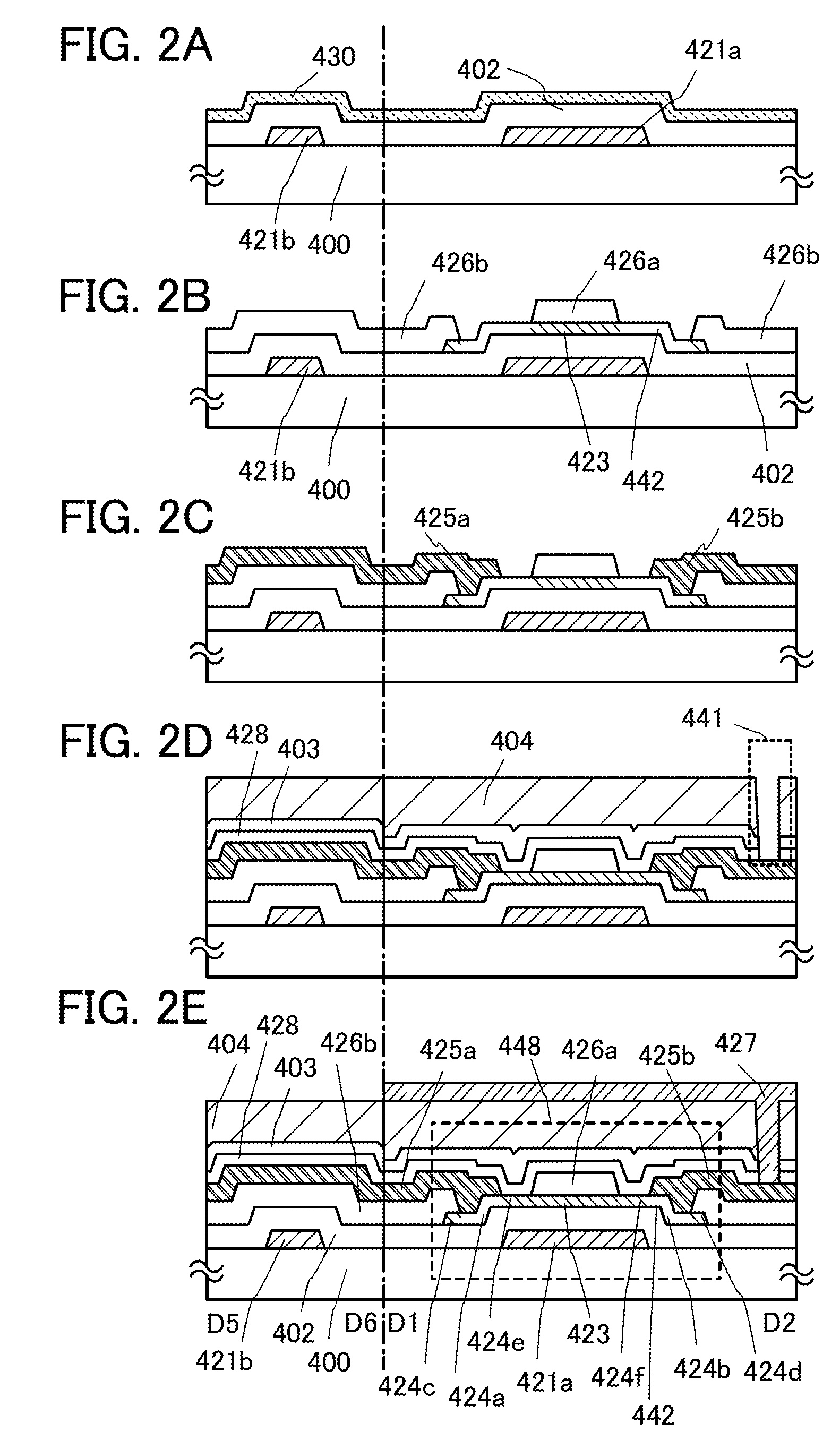

Semiconductor device and method for manufacturing semiconductor device

ActiveUS20110031492A1Stable electrical characteristicsExcellent electrical propertiesTransistorElectroluminescent light sourcesDriver circuitSemiconductor

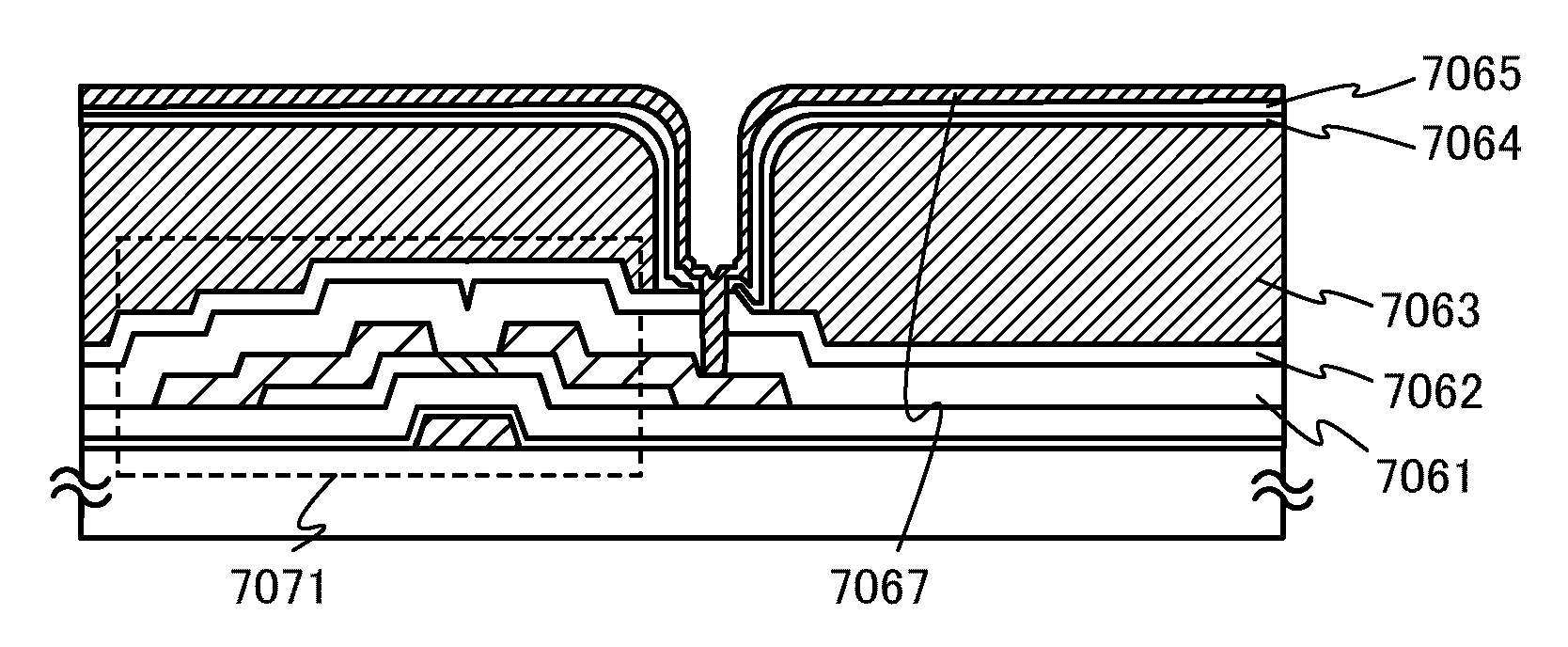

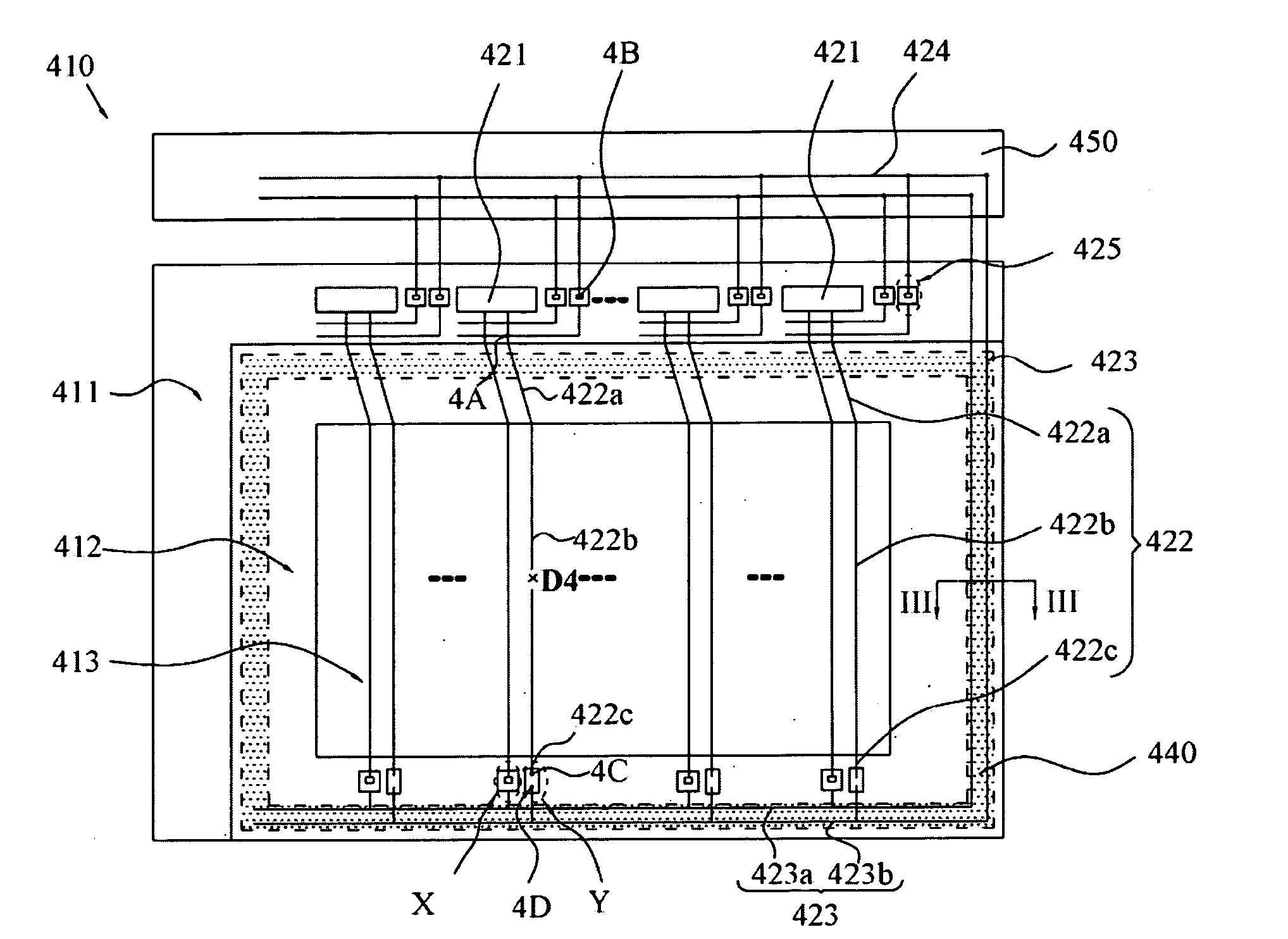

The semiconductor device includes a driver circuit including a first thin film transistor and a pixel including a second thin film transistor over one substrate. The first thin film transistor includes a first gate electrode layer, a gate insulating layer, a first oxide semiconductor layer, a first oxide conductive layer, a second oxide conductive layer, an oxide insulating layer which is in contact with part of the first oxide semiconductor layer and which is in contact with peripheries and side surfaces of the first and second oxide conductive layers, a first source electrode layer, and a first drain electrode layer. The second thin film transistor includes a second gate electrode layer, a second oxide semiconductor layer, and a second source electrode layer and a second drain electrode layer each formed using a light-transmitting material.

Owner:SEMICON ENERGY LAB CO LTD

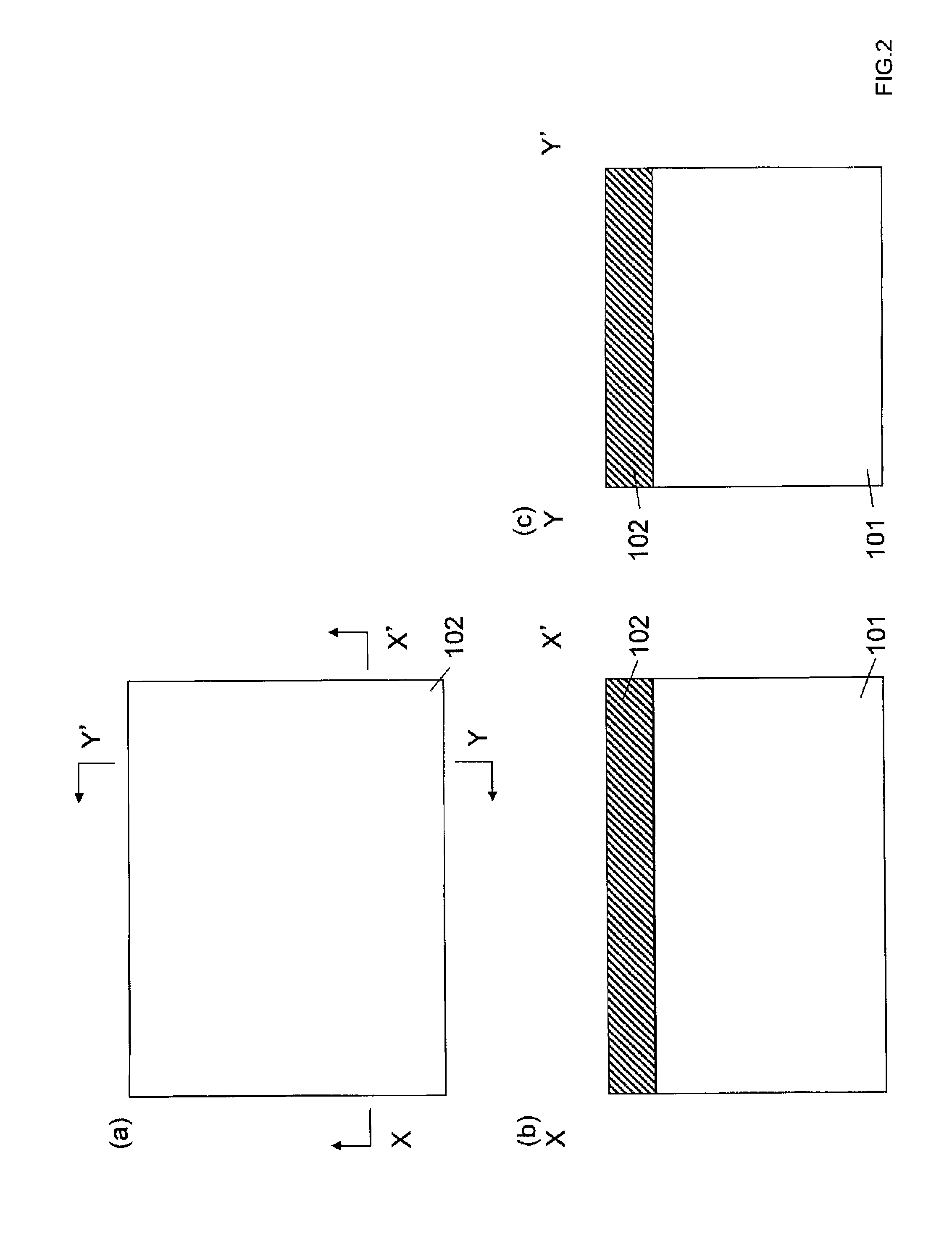

Multigate field effect transistor and process thereof

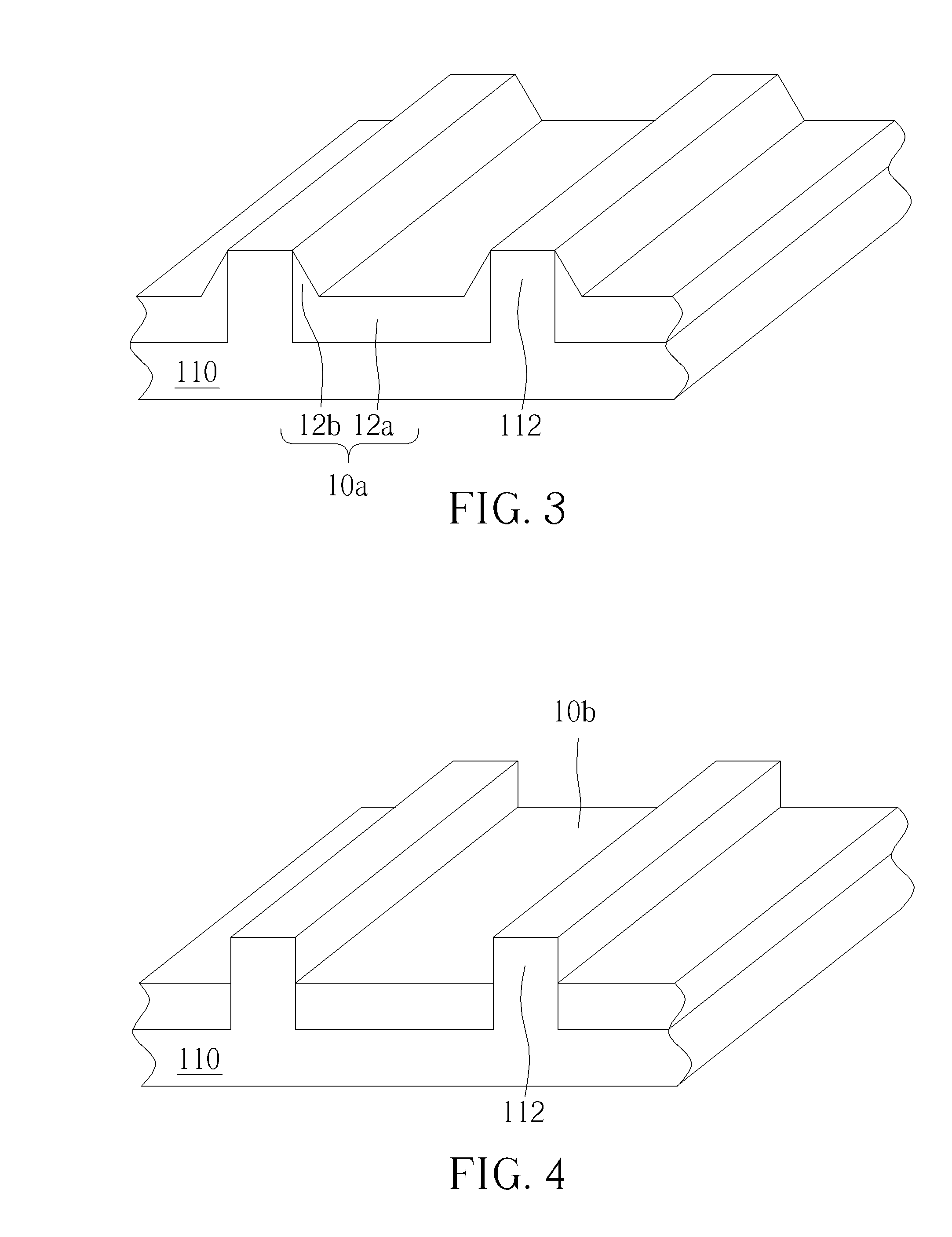

ActiveUS20140117455A1Reduce parasitic capacitanceParasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesField effectField-effect transistor

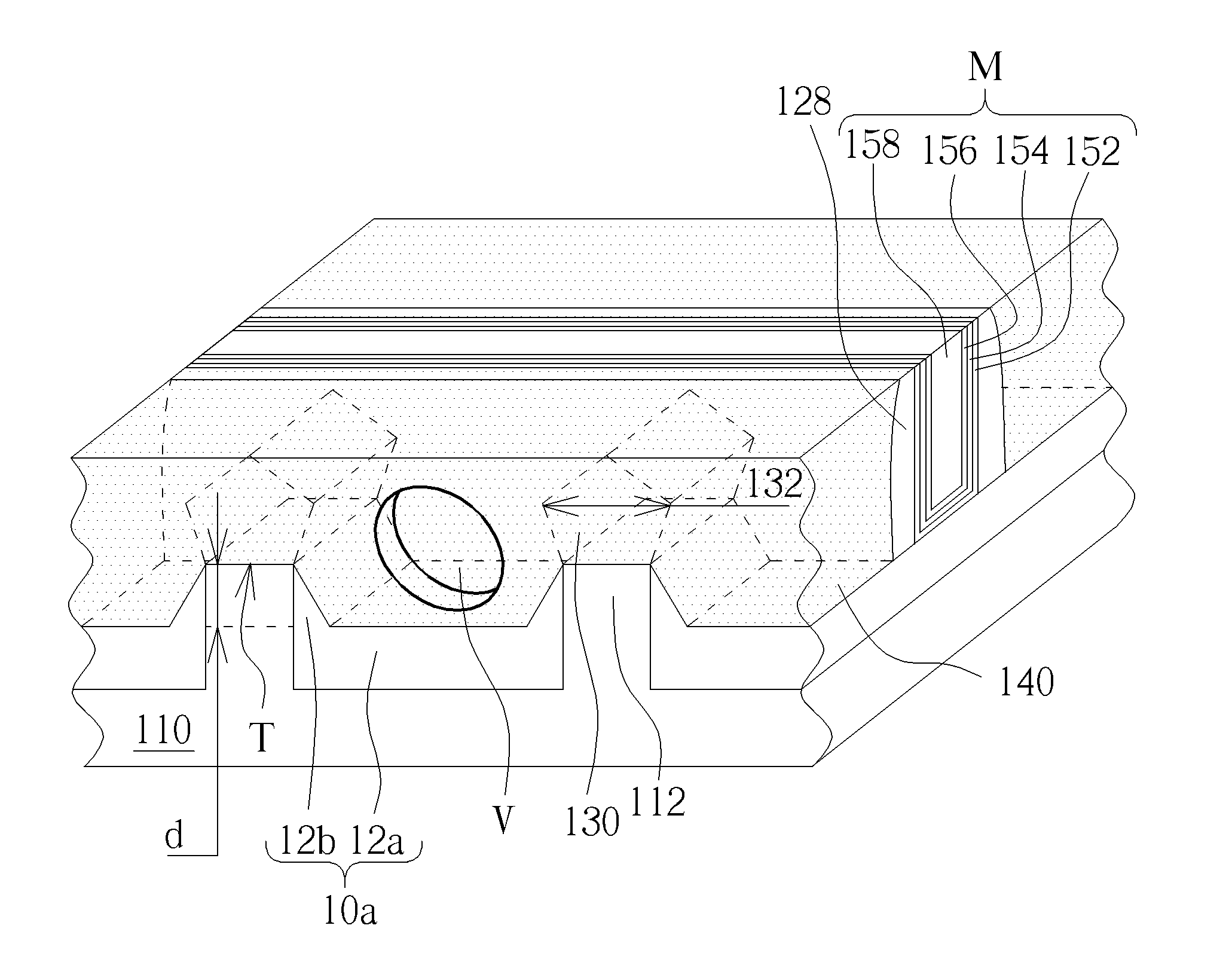

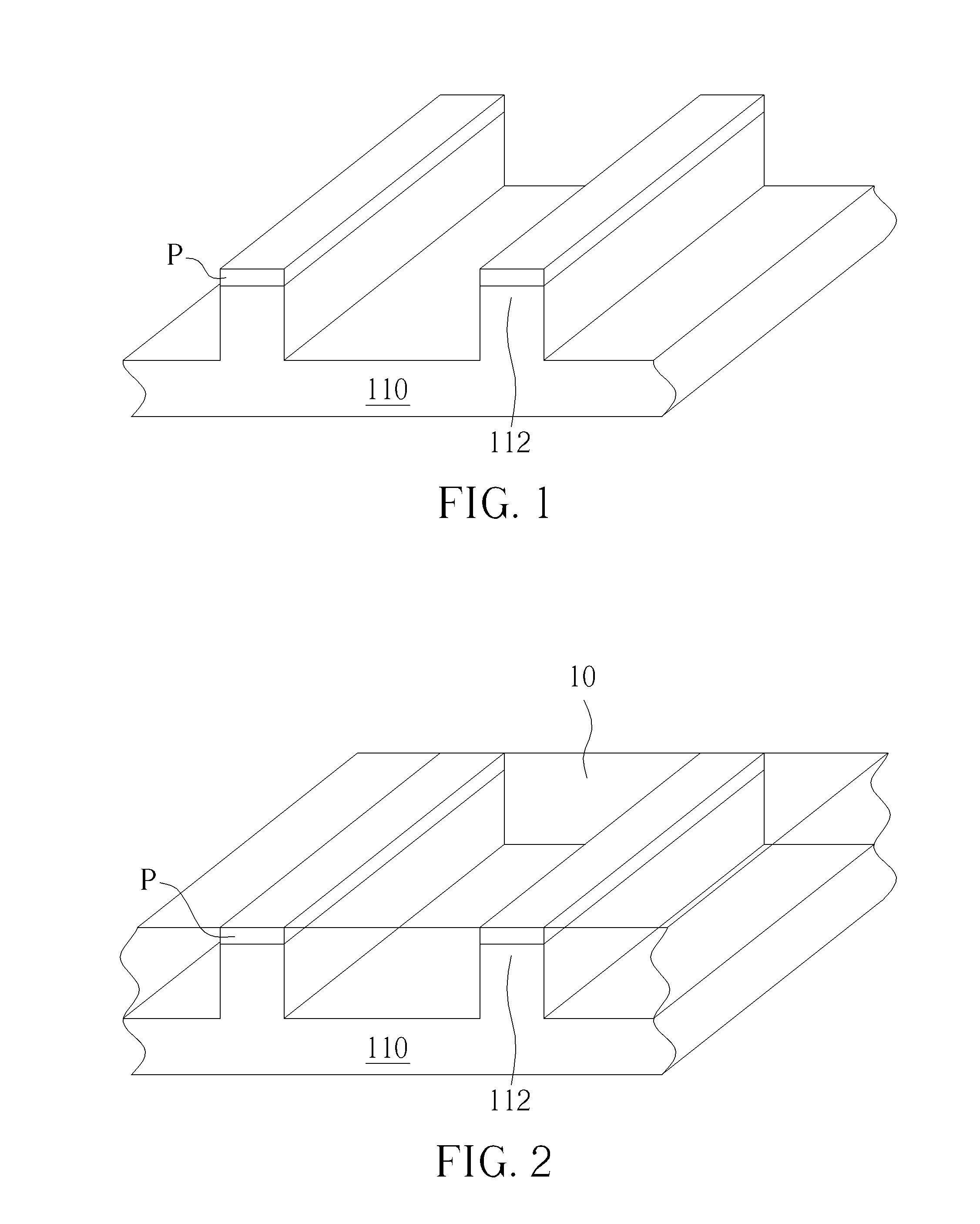

A multigate field effect transistor includes two fin-shaped structures and a dielectric layer. The fin-shaped structures are located on a substrate. The dielectric layer covers the substrate and the fin-shaped structures. At least two voids are located in the dielectric layer between the two fin-shaped structures. Moreover, the present invention also provides a multigate field effect transistor process for forming said multigate field effect transistor including the following steps. Two fin-shaped structures are formed on a substrate. A dielectric layer covers the substrate and the two fin-shaped structures, wherein at least two voids are formed in the dielectric layer between the two fin-shaped structures.

Owner:UNITED MICROELECTRONICS CORP

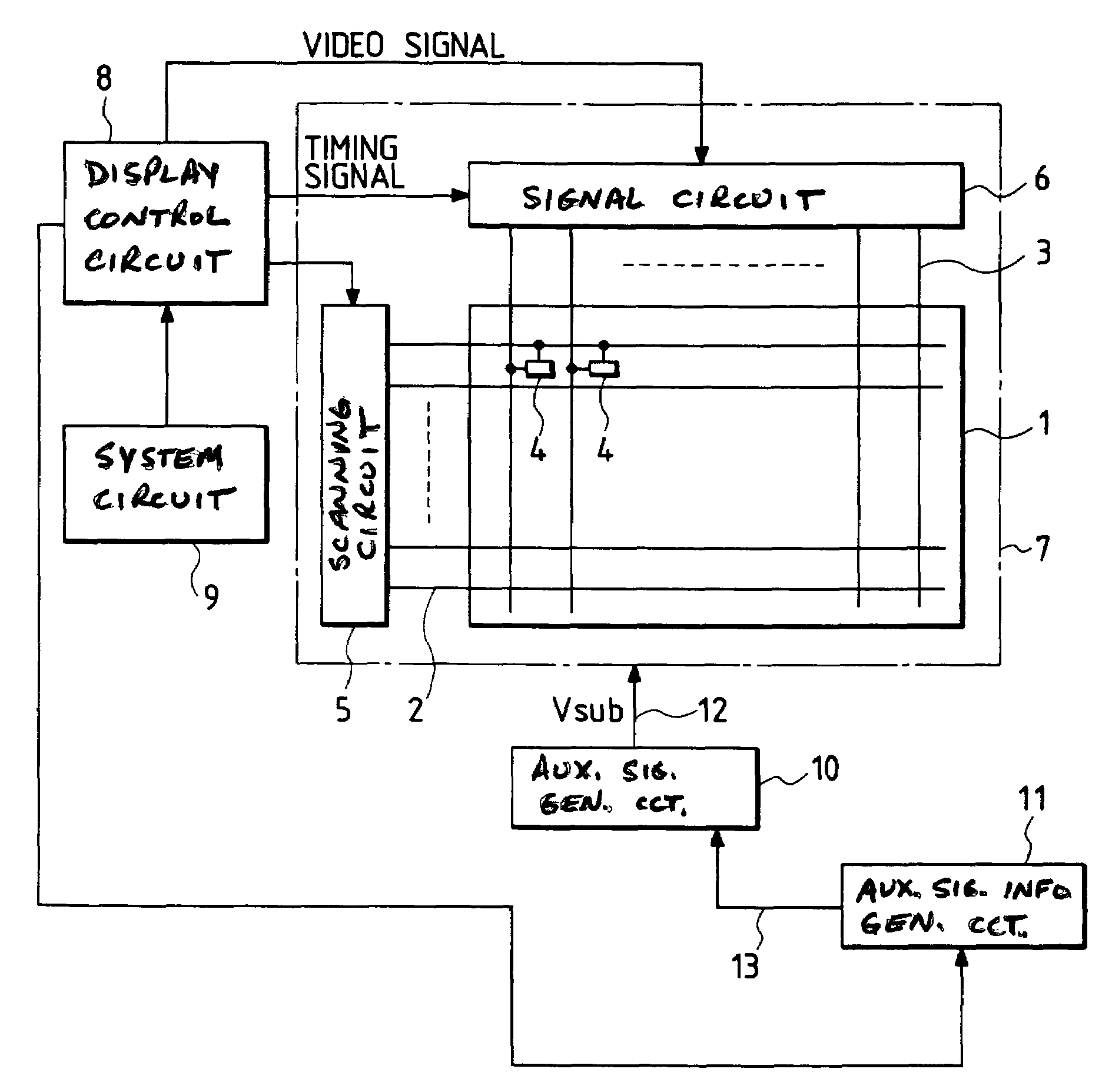

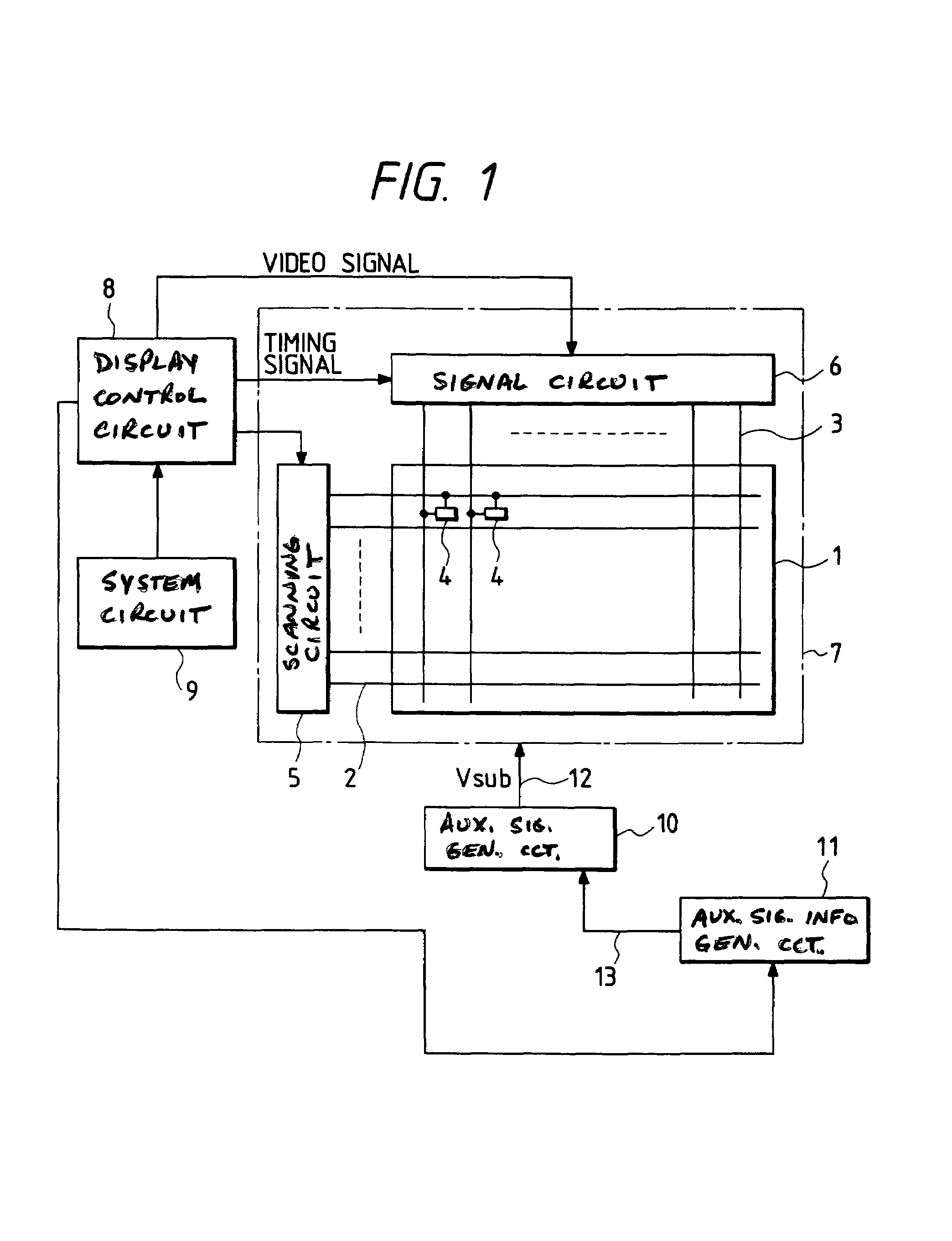

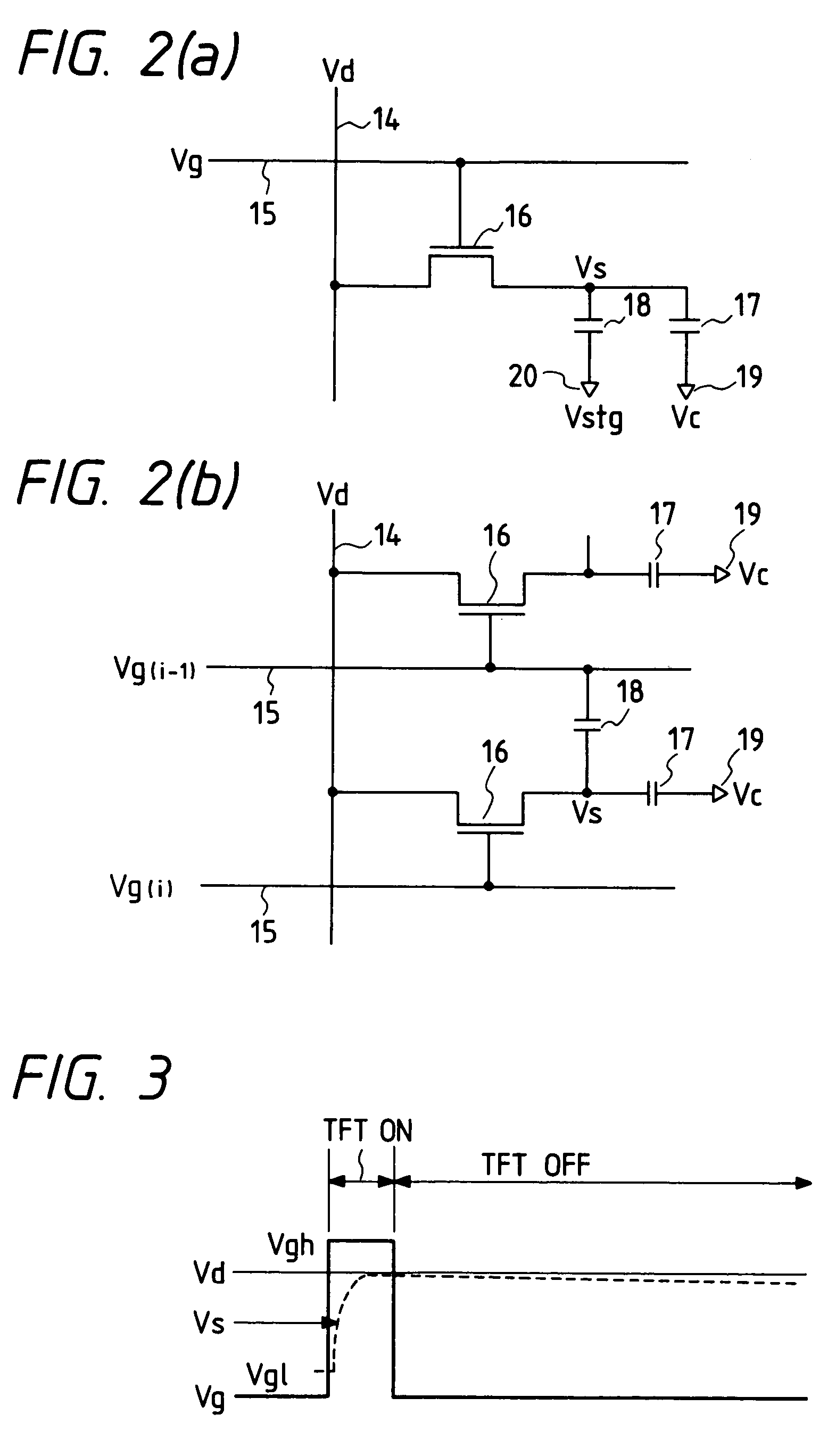

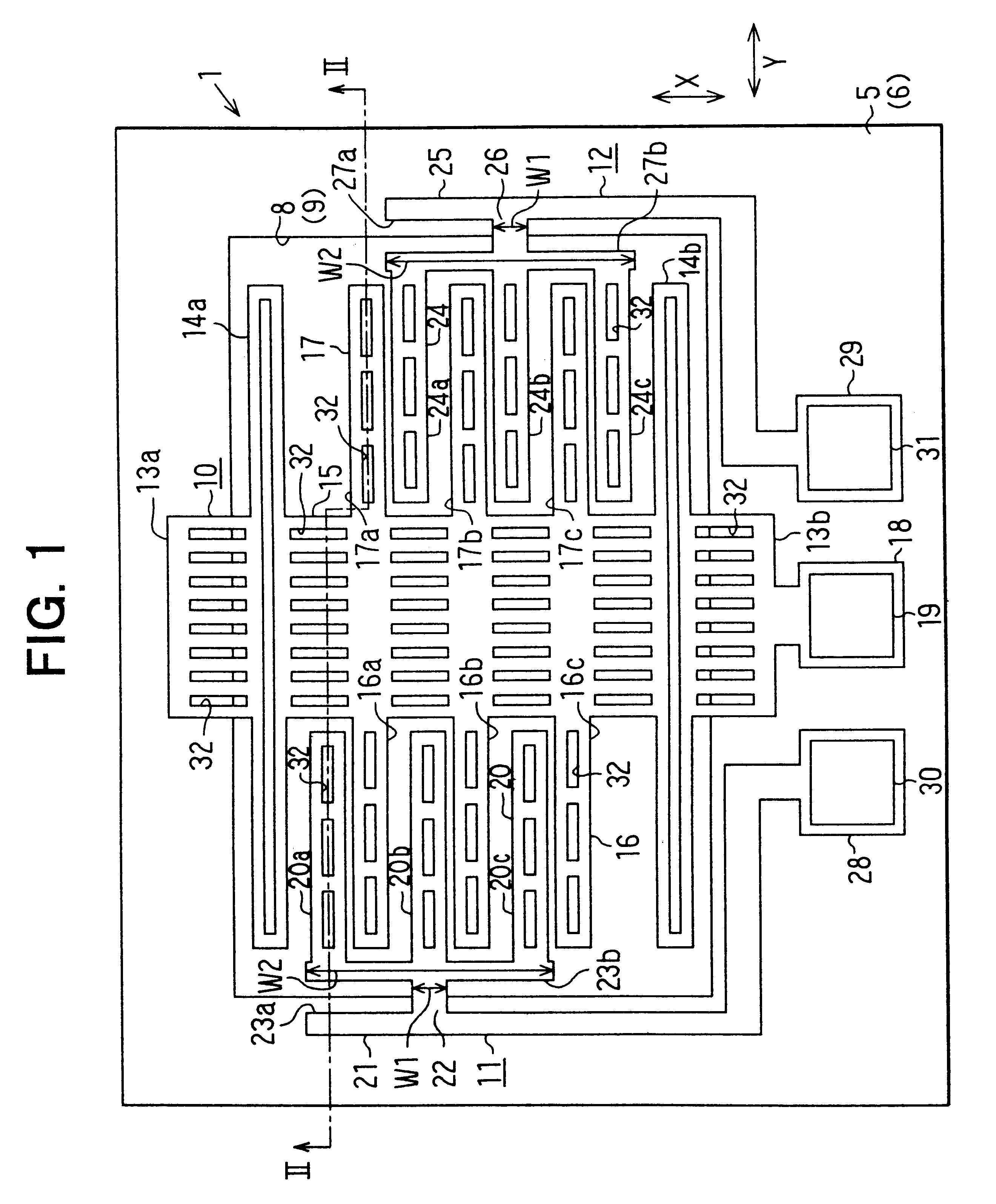

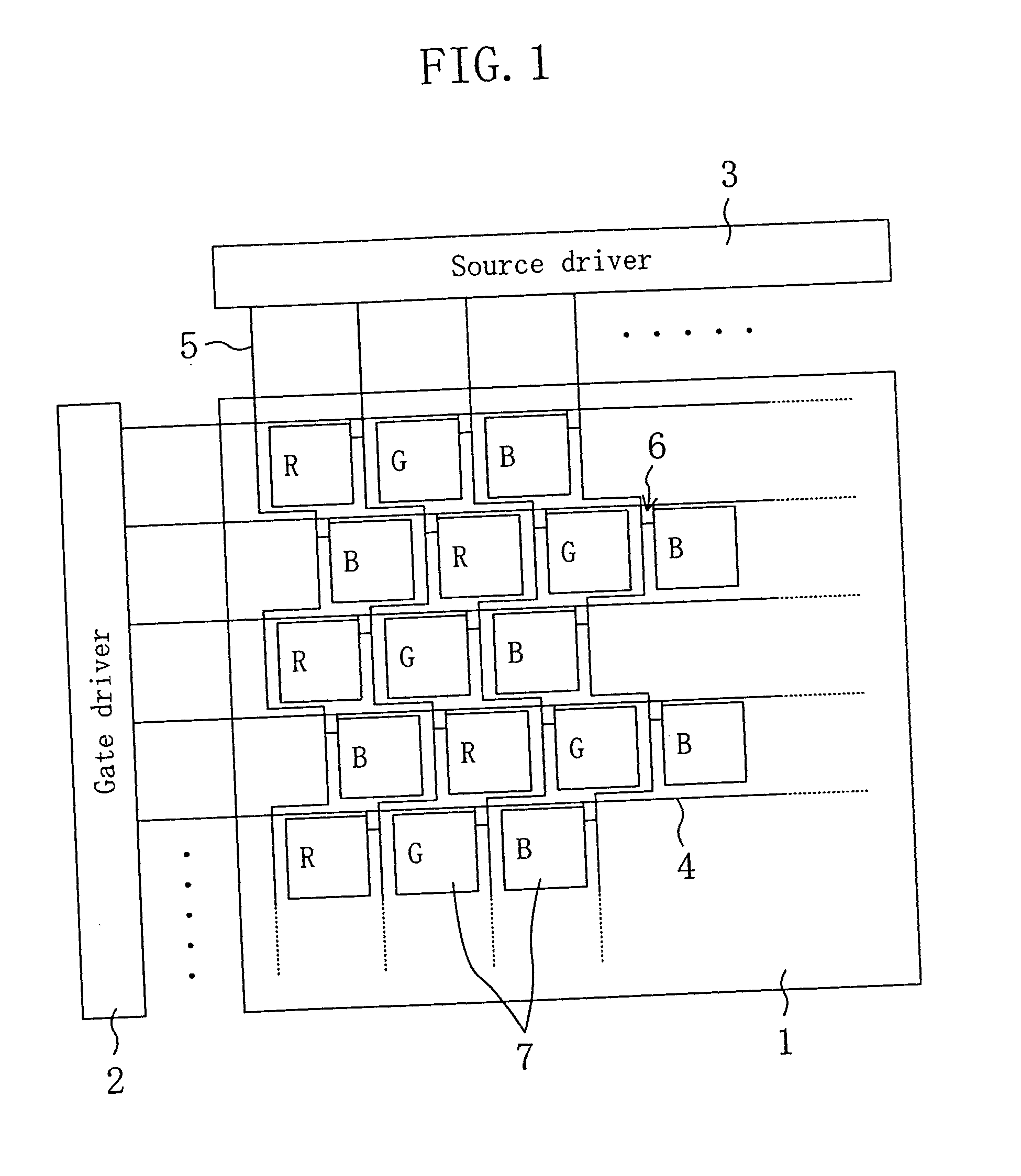

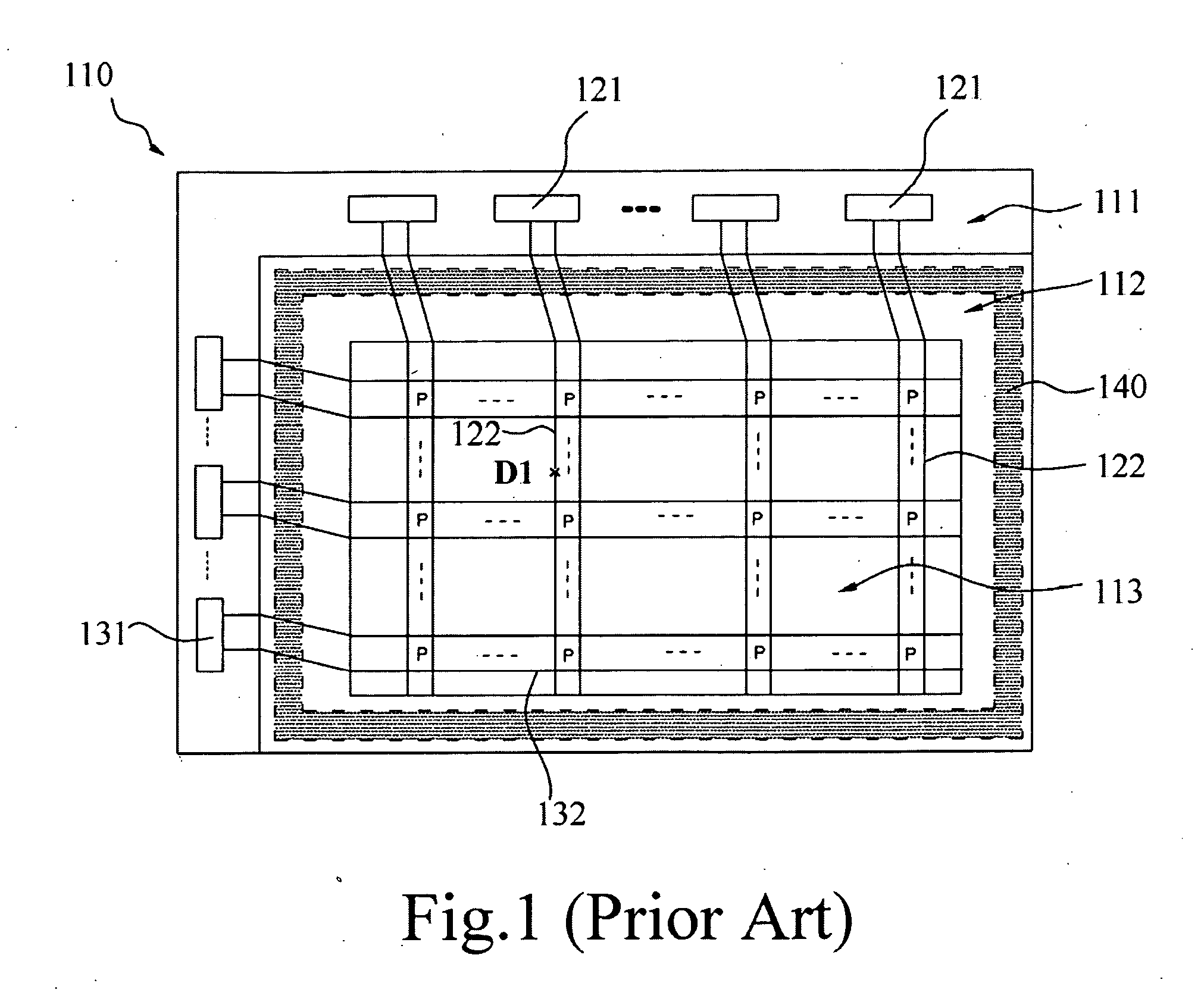

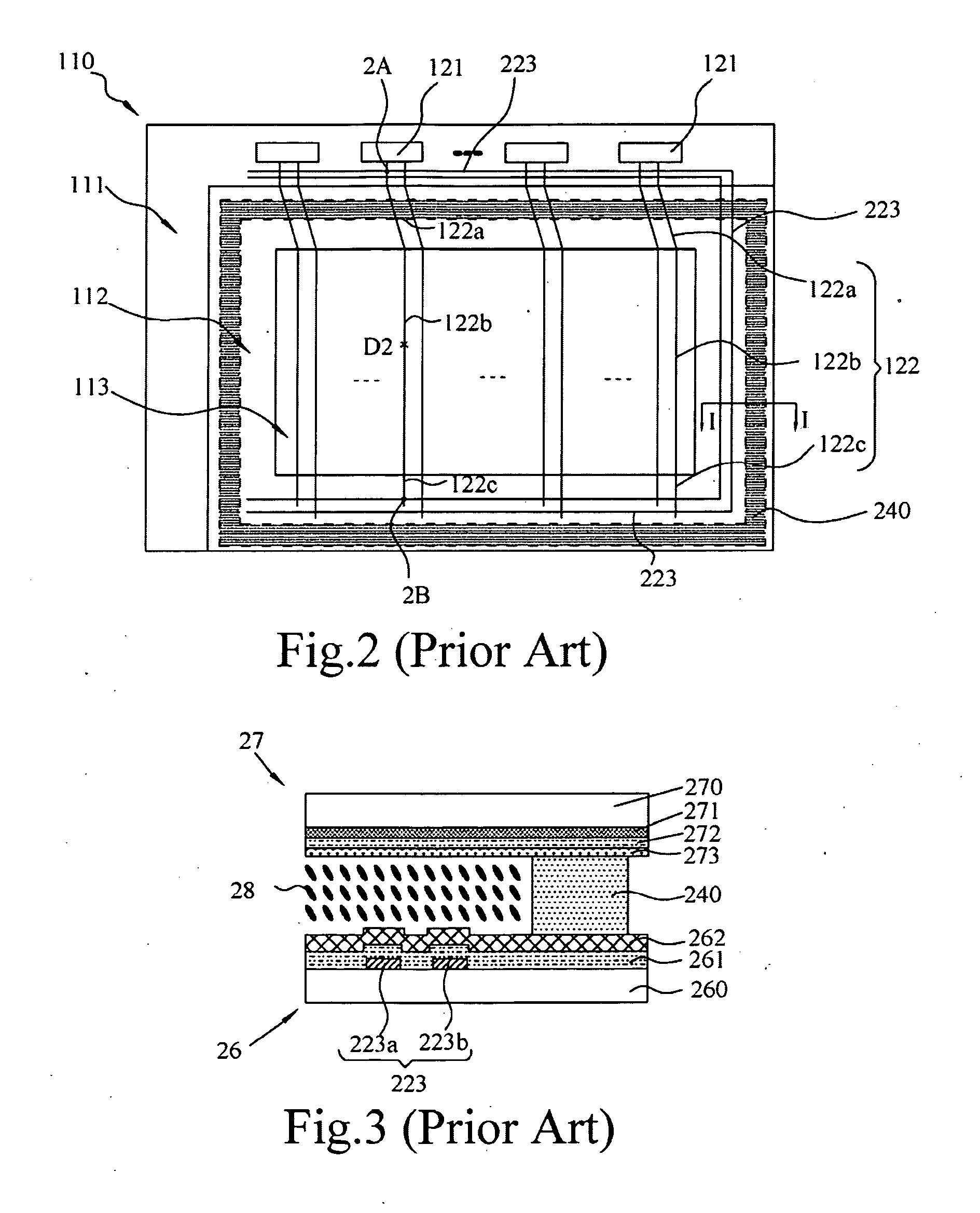

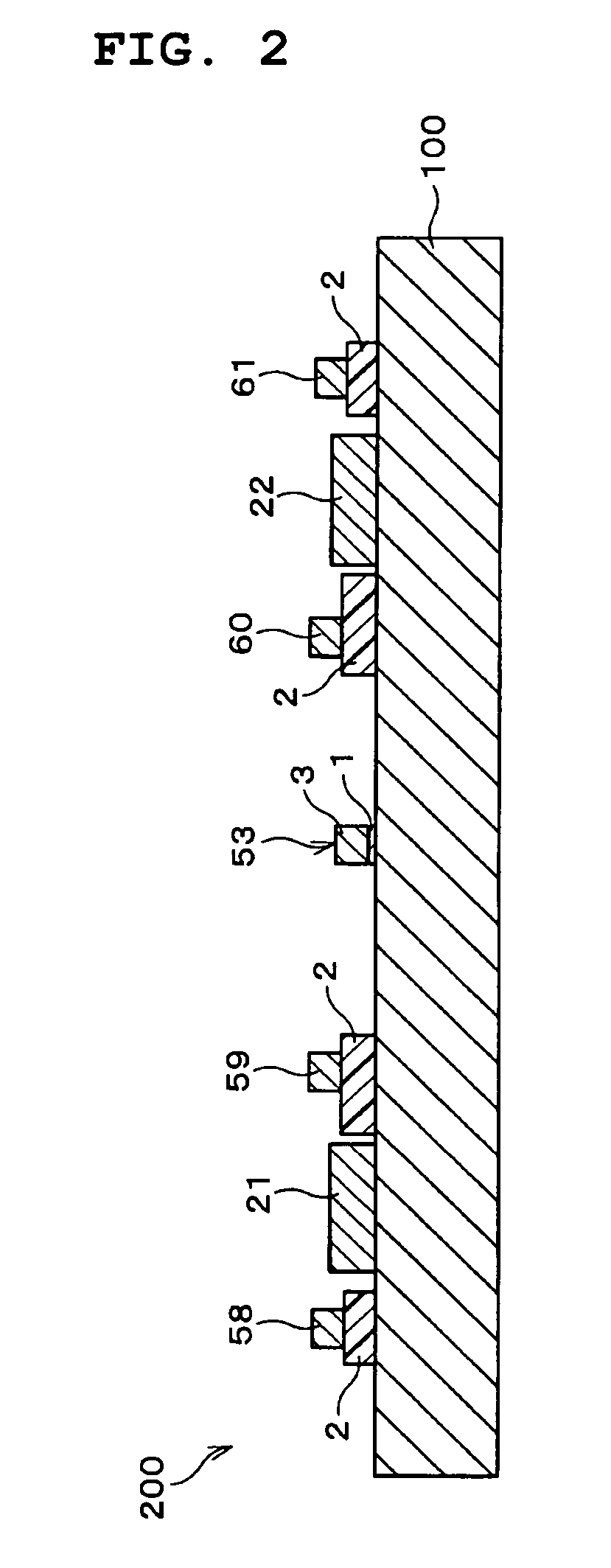

Matrix panel display apparatus and driving method therefor wherein auxiliary signals are applied to non-selected picture elements

InactiveUS7355575B1Without deteriorating picture qualityNon-uniform brightnessStatic indicating devicesImage signalImaging Signal

A matrix panel display apparatus includes plural signal lines and plural scanning lines intersecting each other and, near each intersection point, a picture element including a picture element electrode, a counter electrode, a display medium disposed between the picture element electrode and the counter electrode, and a transistor for applying image signals from the signal line to the picture element electrode. The transistor is controlled in response to scanning signals received on a scanning line. An auxiliary signal generating circuit generates auxiliary signals for increasing effective voltages of the image signals and applies the auxiliary signals to the picture elements while each of the transistors is in a non-conducting state and each of the picture elements is not selected. Preferably, the auxiliary signal generating circuit applies the auxiliary signals to the picture elements during a predetermined period in which all of the transistors are in the non-conducting state and none of the picture elements is selected.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

Oxide semiconductor device

ActiveUS8384079B2DistanceParasitic capacitanceTransistorStatic indicating devicesBottom gateParasitic capacitance

An object is to provide a semiconductor device having a structure in which parasitic capacitance between wirings can be efficiently reduced. In a bottom gate thin film transistor using an oxide semiconductor layer, an oxide insulating layer used as a channel protection layer is formed above and in contact with part of the oxide semiconductor layer overlapping with a gate electrode layer, and at the same time an oxide insulating layer covering a peripheral portion (including a side surface) of the stacked oxide semiconductor layer is formed. Further, a source electrode layer and a drain electrode layer are formed in a manner such that they do not overlap with the channel protection layer. Thus, a structure in which an insulating layer over the source electrode layer and the drain electrode layer is in contact with the oxide semiconductor layer is provided.

Owner:SEMICON ENERGY LAB CO LTD

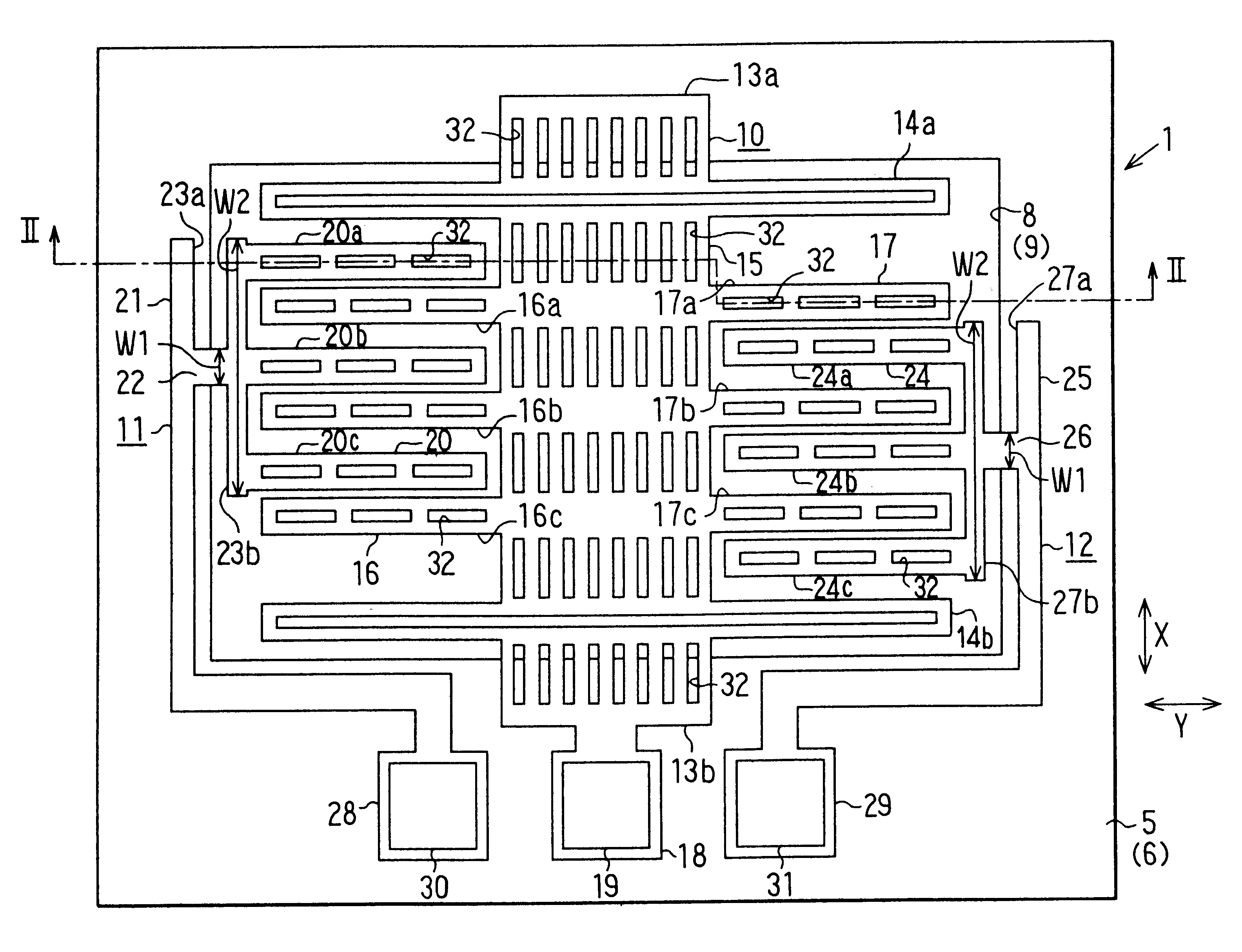

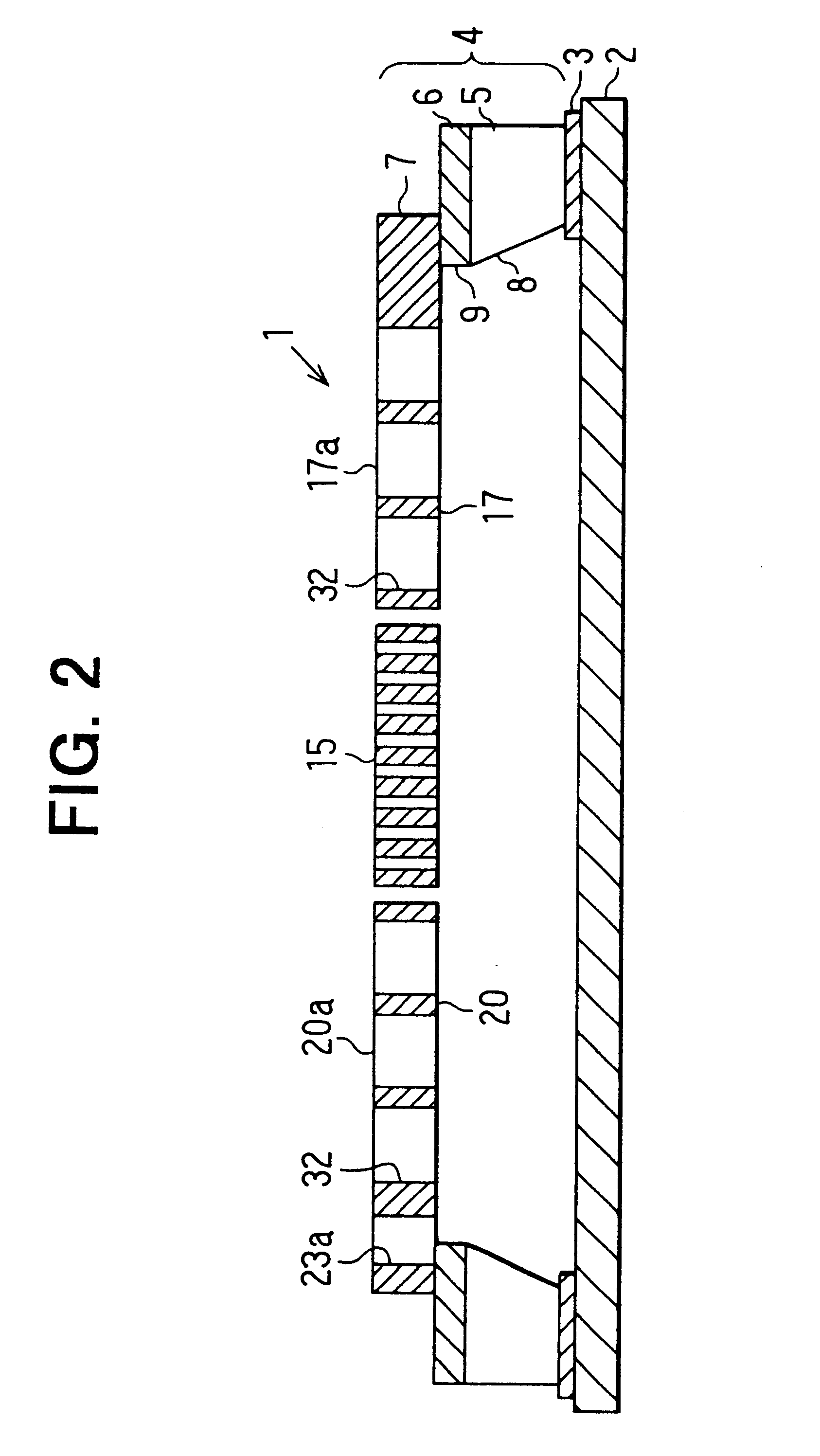

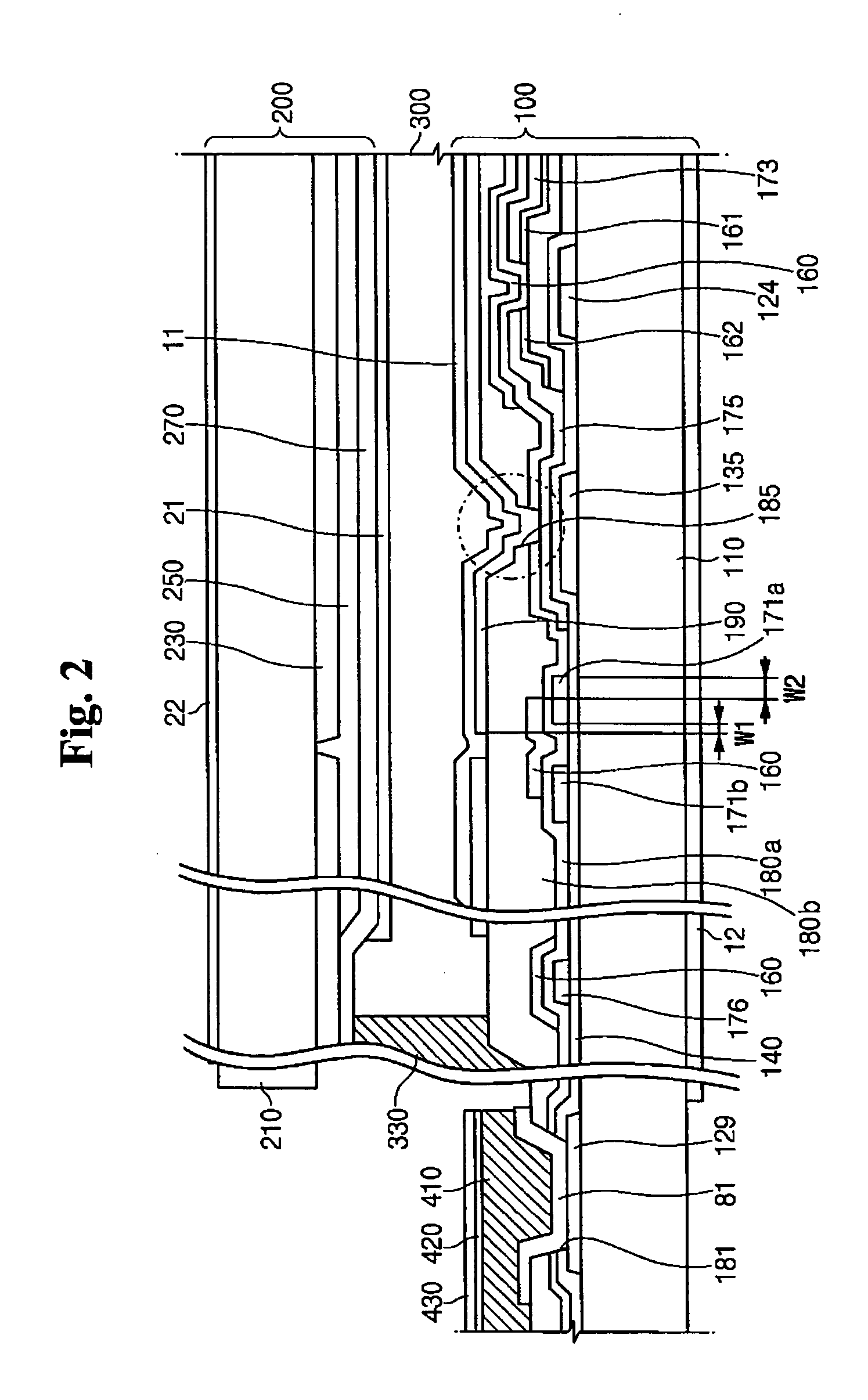

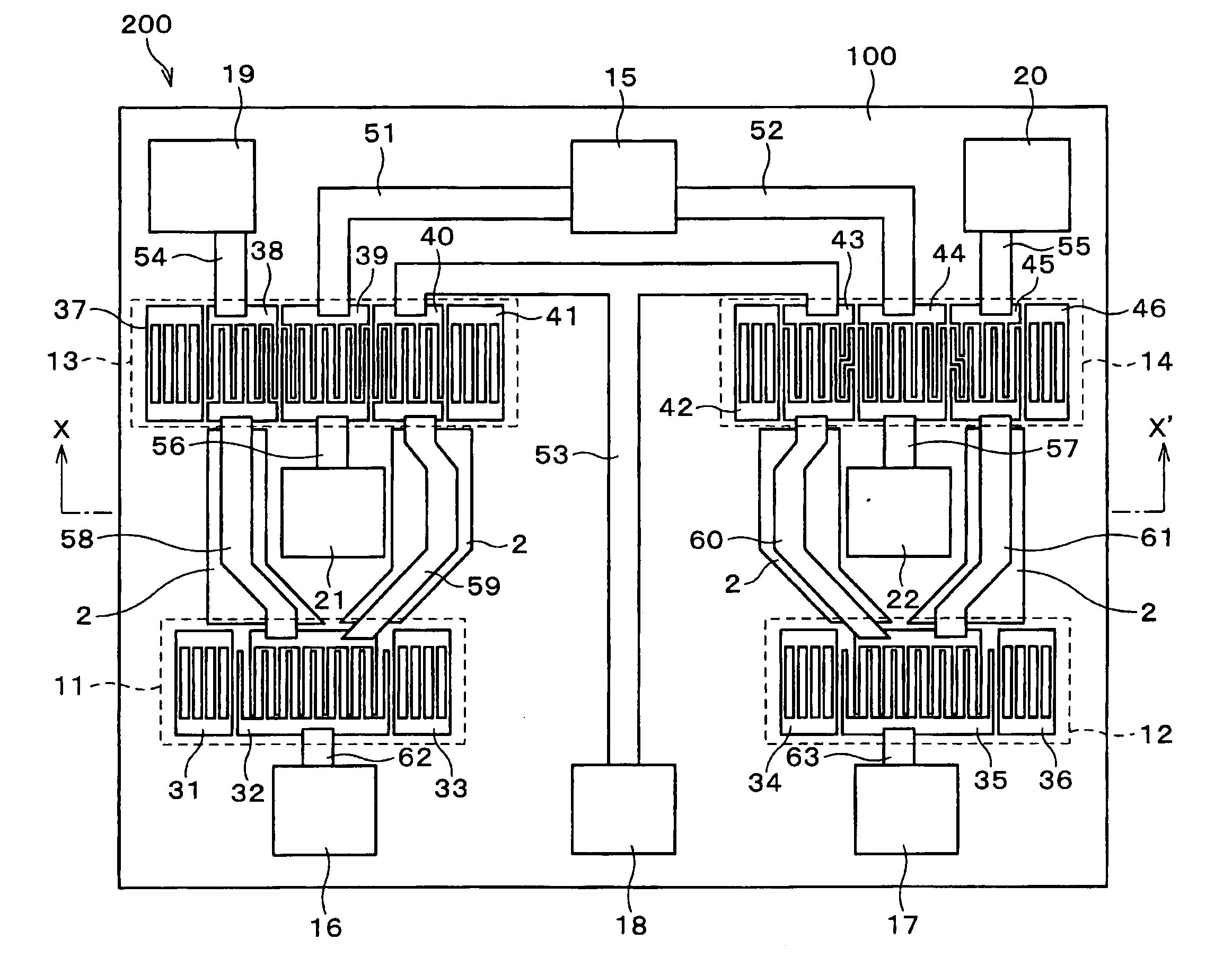

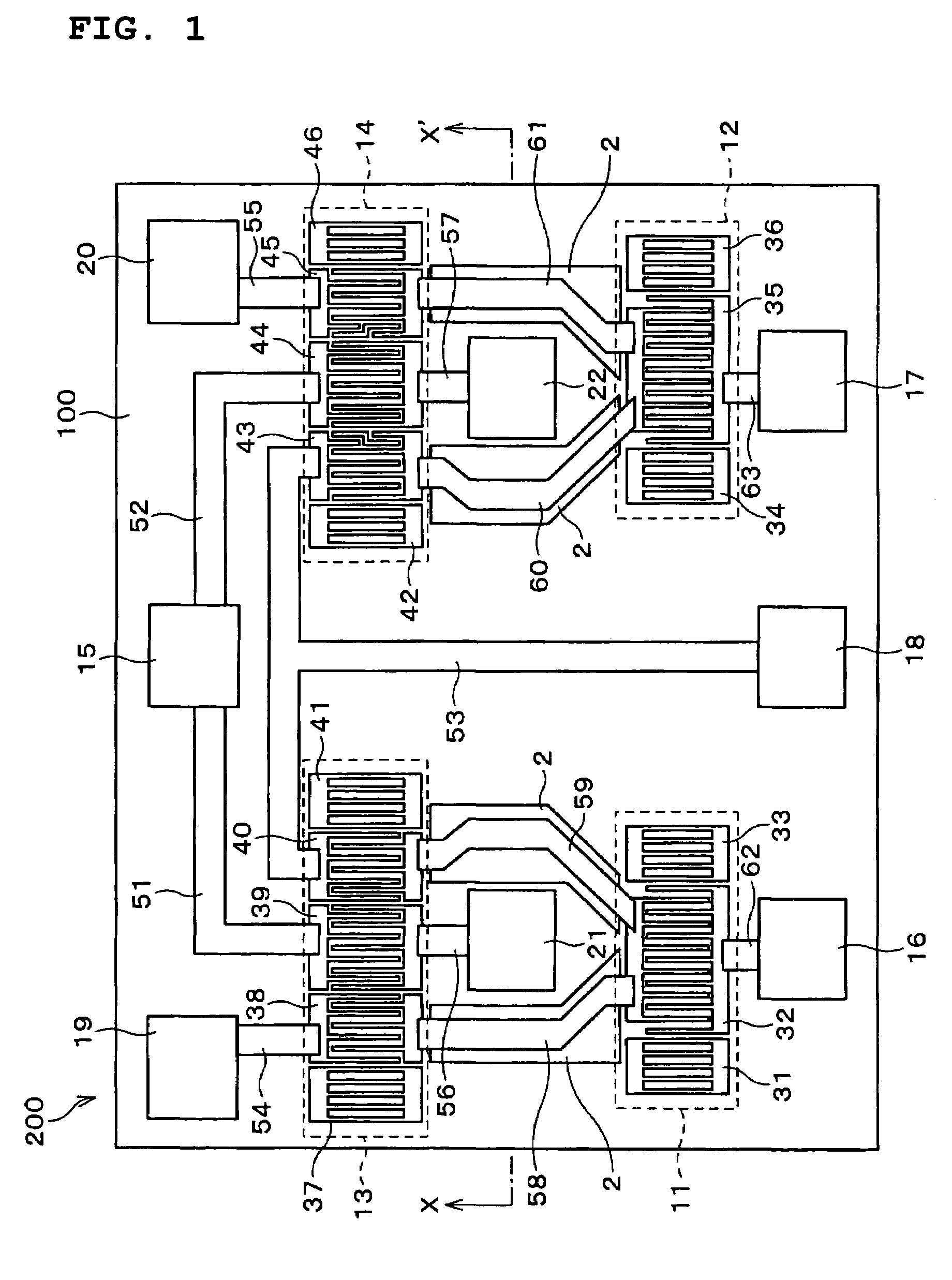

Semiconductor physical quantity sensor

InactiveUS6450031B1Minimize offsetDistanceAcceleration measurement using interia forcesPiezoelectric/electrostrictive devicesSilicon thin filmCantilever

A semiconductor physical quantity sensor from which a stable sensor output can be obtained even when the usage environment changes. A silicon thin film is disposed on an insulating film on a supporting substrate, and a bridge structure having a weight part and moving electrodes and cantilever structures having fixed electrodes are formed as separate sections from this silicon thin film. The moving electrodes provided on the weight part and the cantilevered fixed electrodes are disposed facing each other. Slits are formed at root portions of the cantilevered fixed electrodes at the fixed ends thereof, and the width W1 of the root portions is thereby made narrower than the width W2 of the fixed electrodes proper. As a result, the transmission of warp of the supporting substrate to the cantilevered fixed electrodes is suppressed.

Owner:DENSO CORP

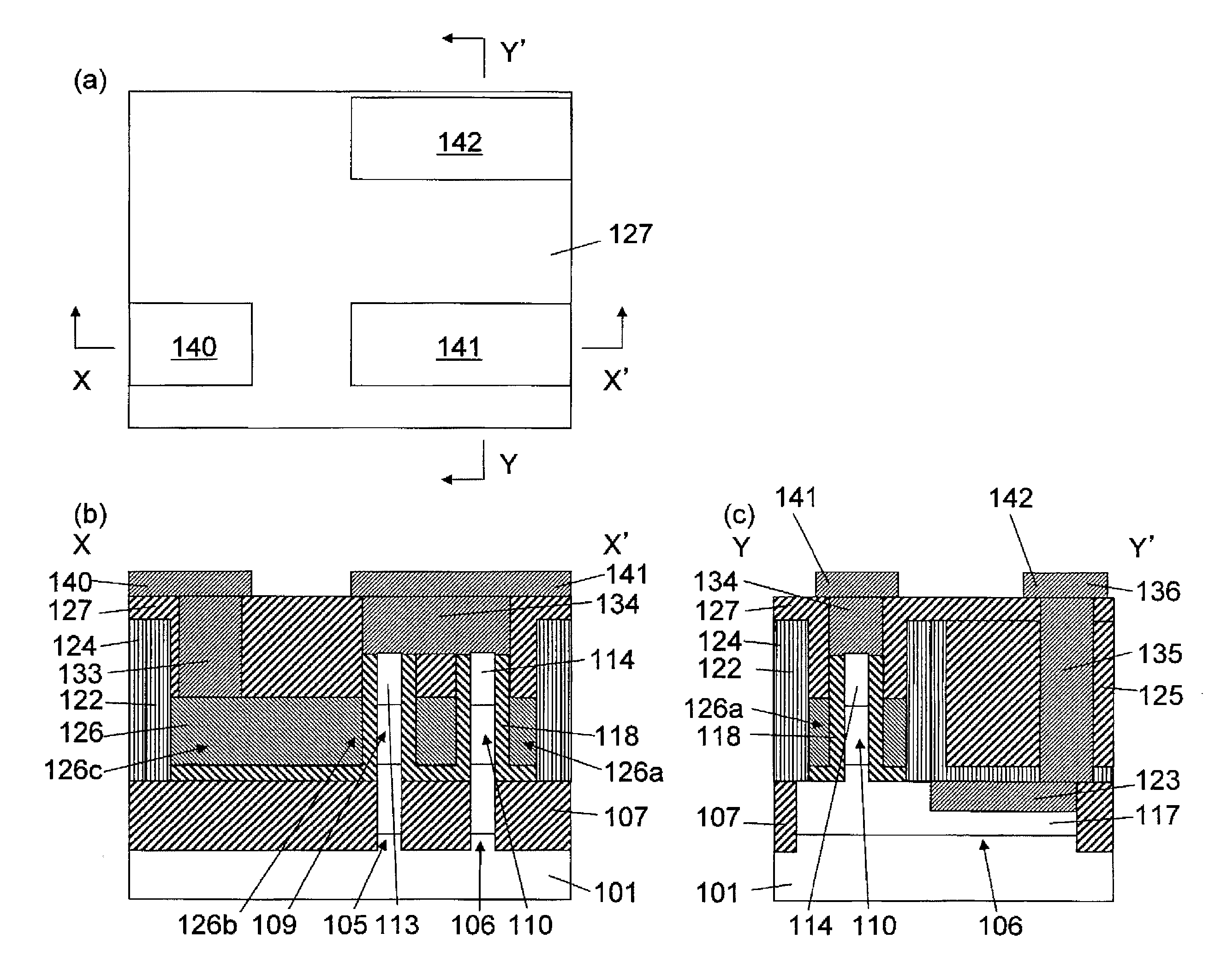

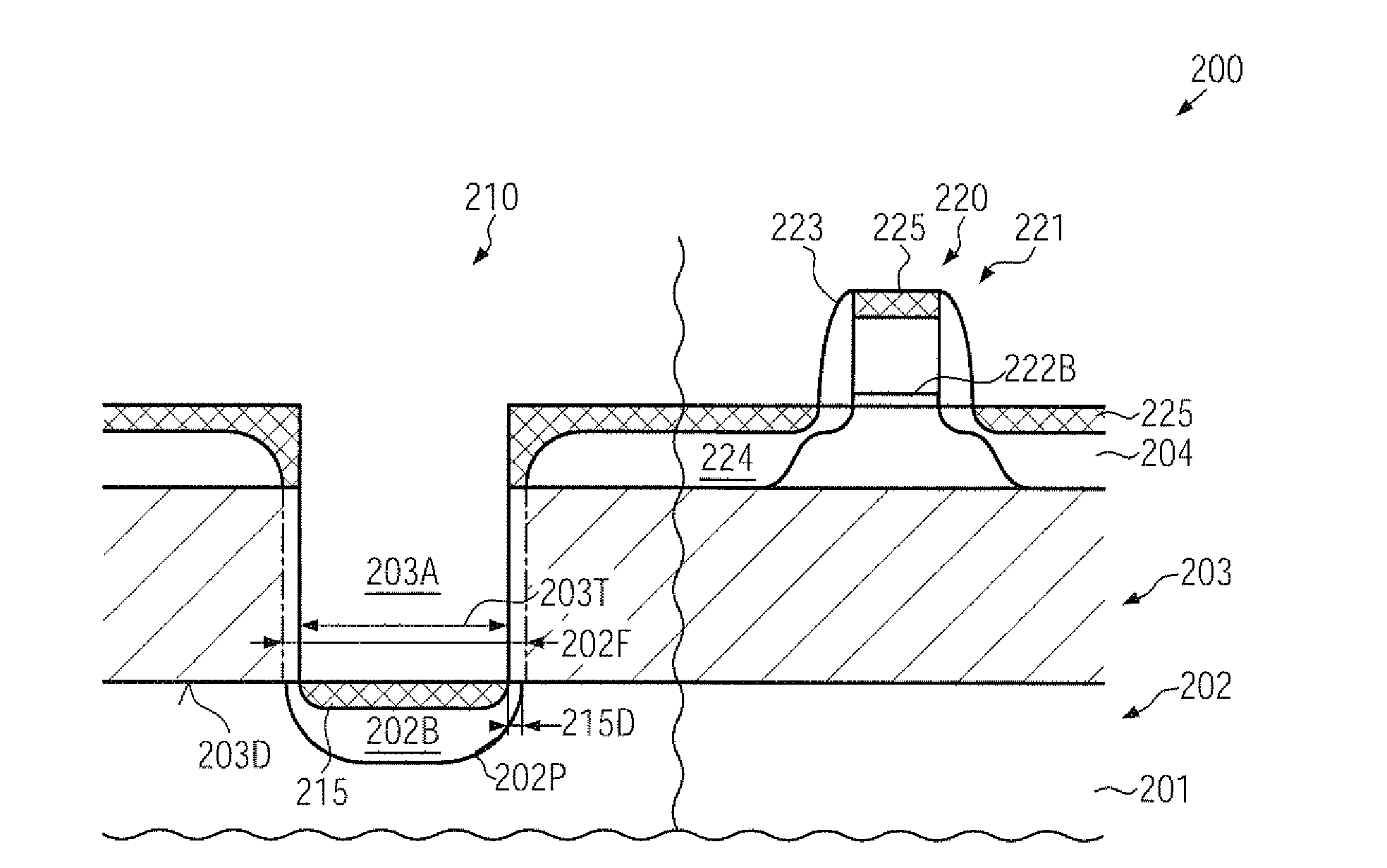

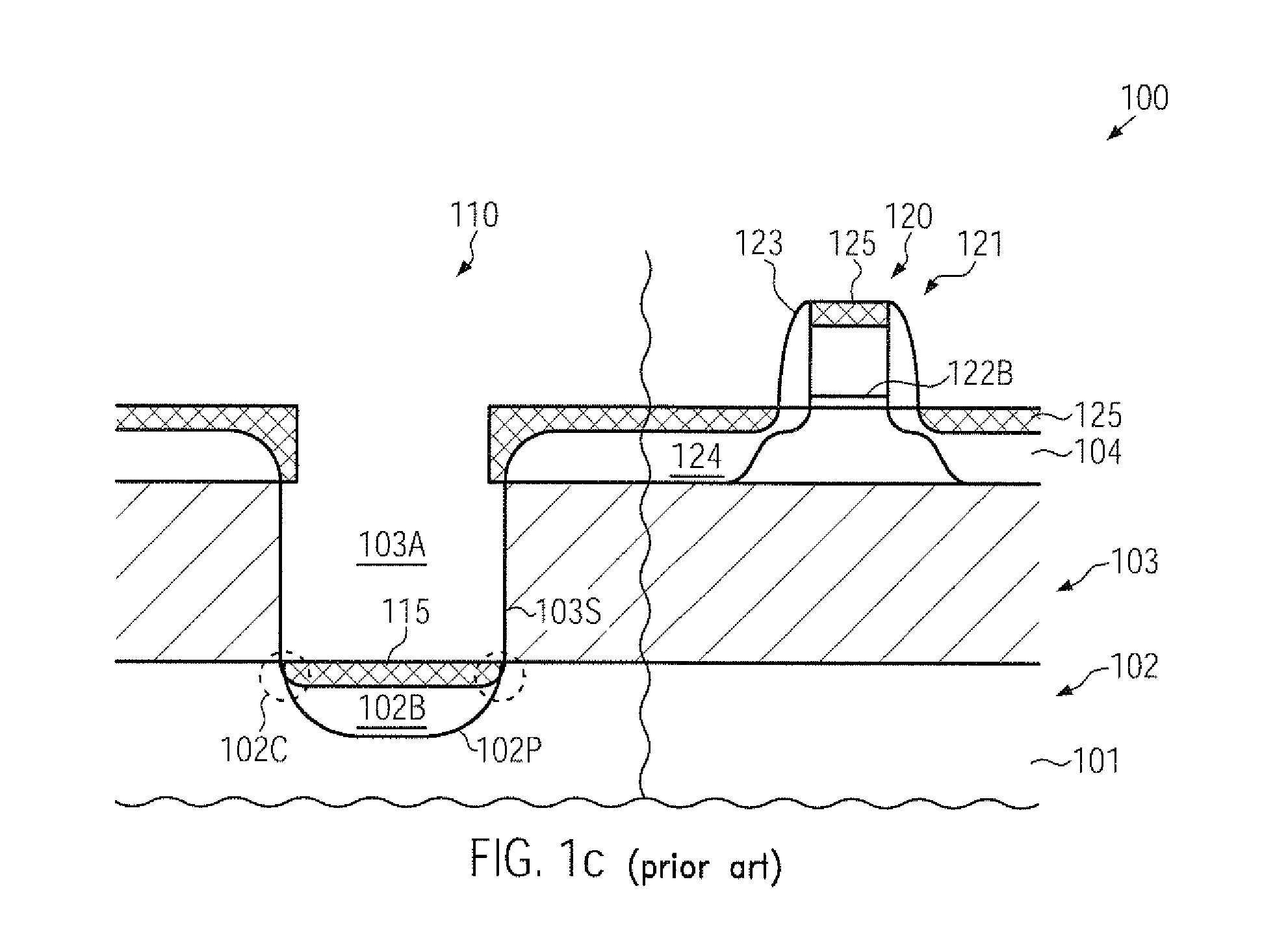

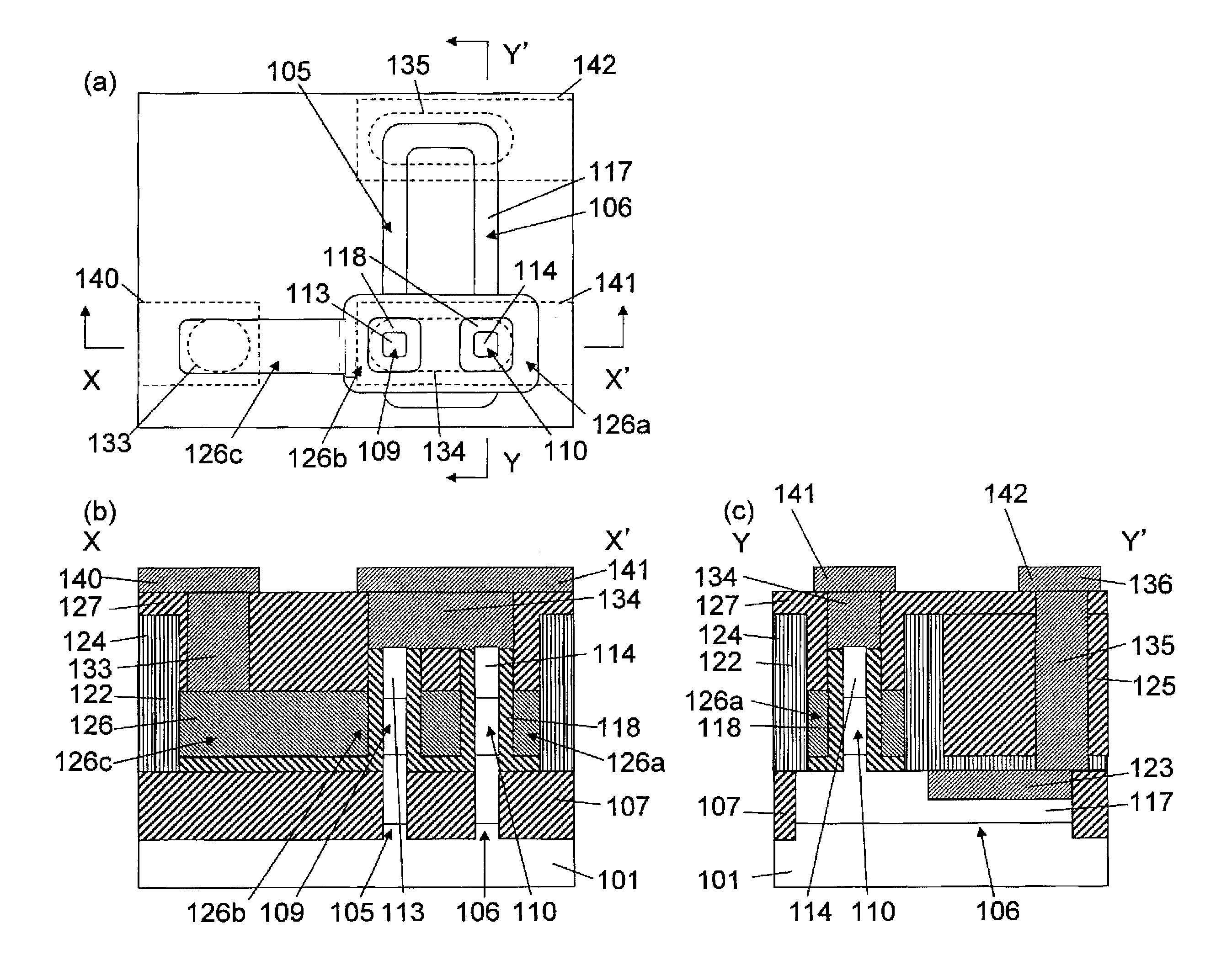

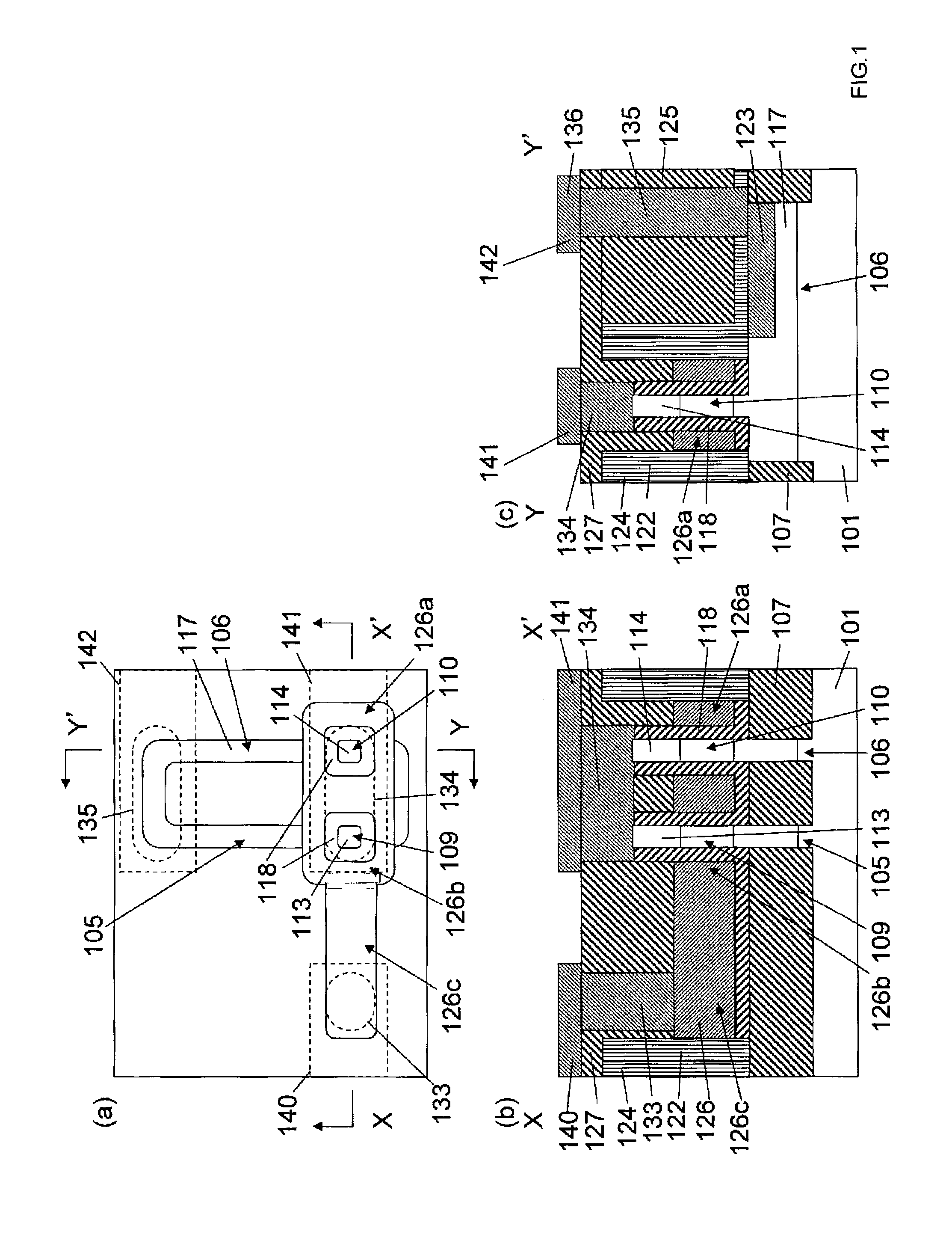

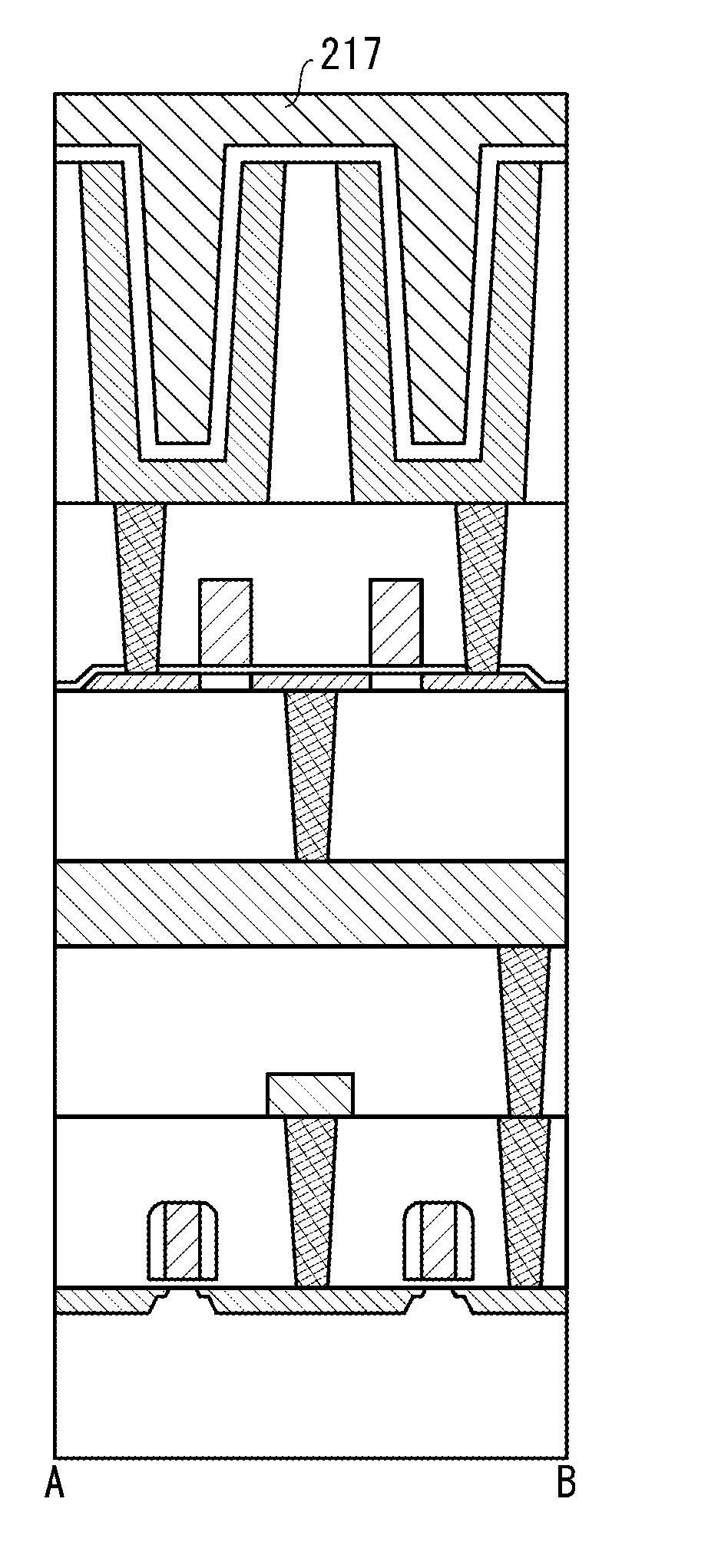

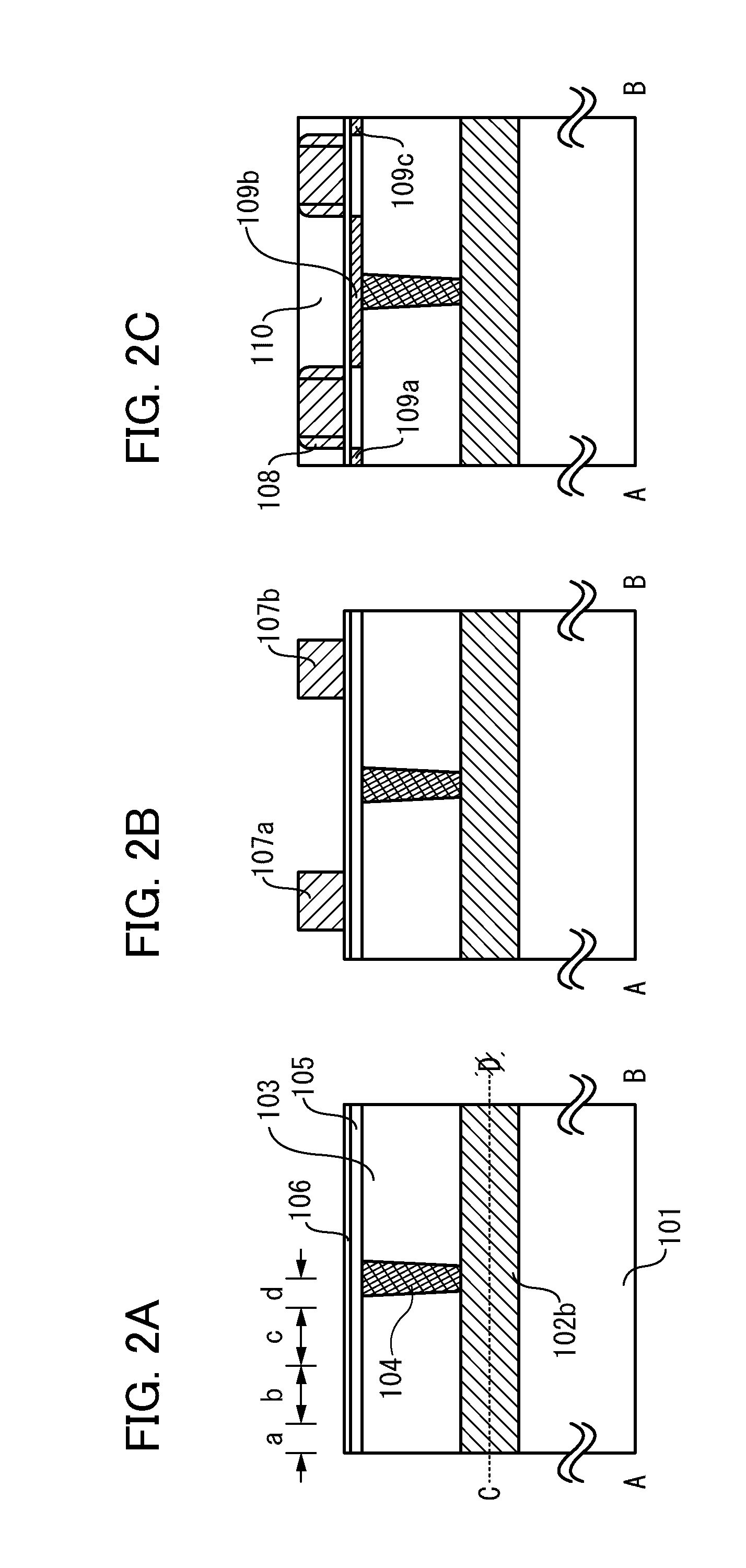

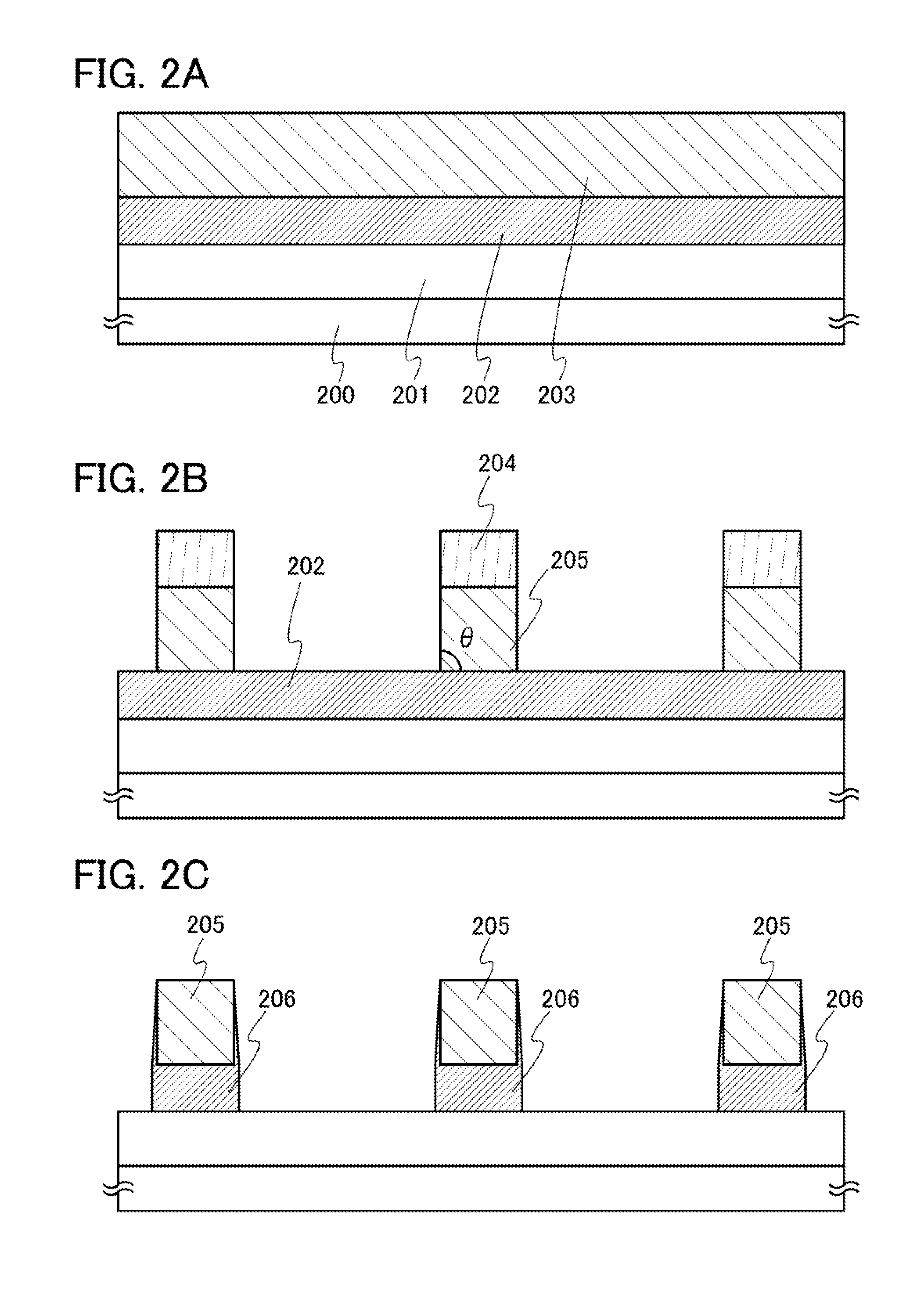

Method for producing semiconductor device and semiconductor device

ActiveUS20130140627A1Parasitic capacitanceReduce parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

A SGT production method includes a step of forming first and second fin-shaped silicon layers, forming a first insulating film, and forming first and second pillar-shaped silicon layers; a step of forming diffusion layers by implanting an impurity into upper portions of the first and second pillar-shaped silicon layers, upper portions of the first and second fin-shaped silicon layers, and lower portions of the first and second pillar-shaped silicon layers; a step of forming a gate insulating film and first and second polysilicon gate electrodes; a step of forming a silicide in upper portions of the diffusion layers formed in the upper portions of the first and second fin-shaped silicon layers; and a step of depositing an interlayer insulating film, exposing and etching the first and second polysilicon gate electrodes, then depositing a metal, and forming first and second metal gate electrodes.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

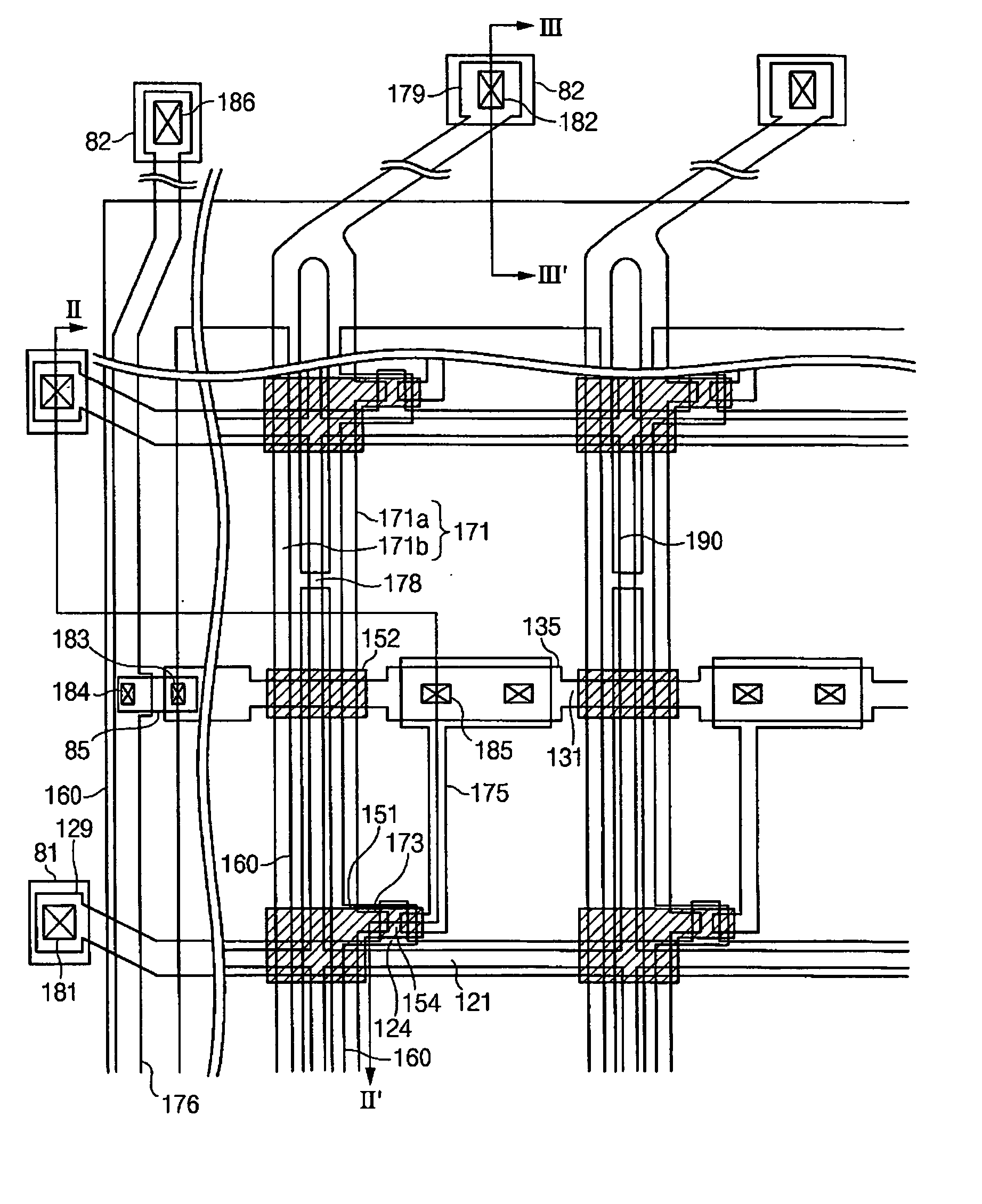

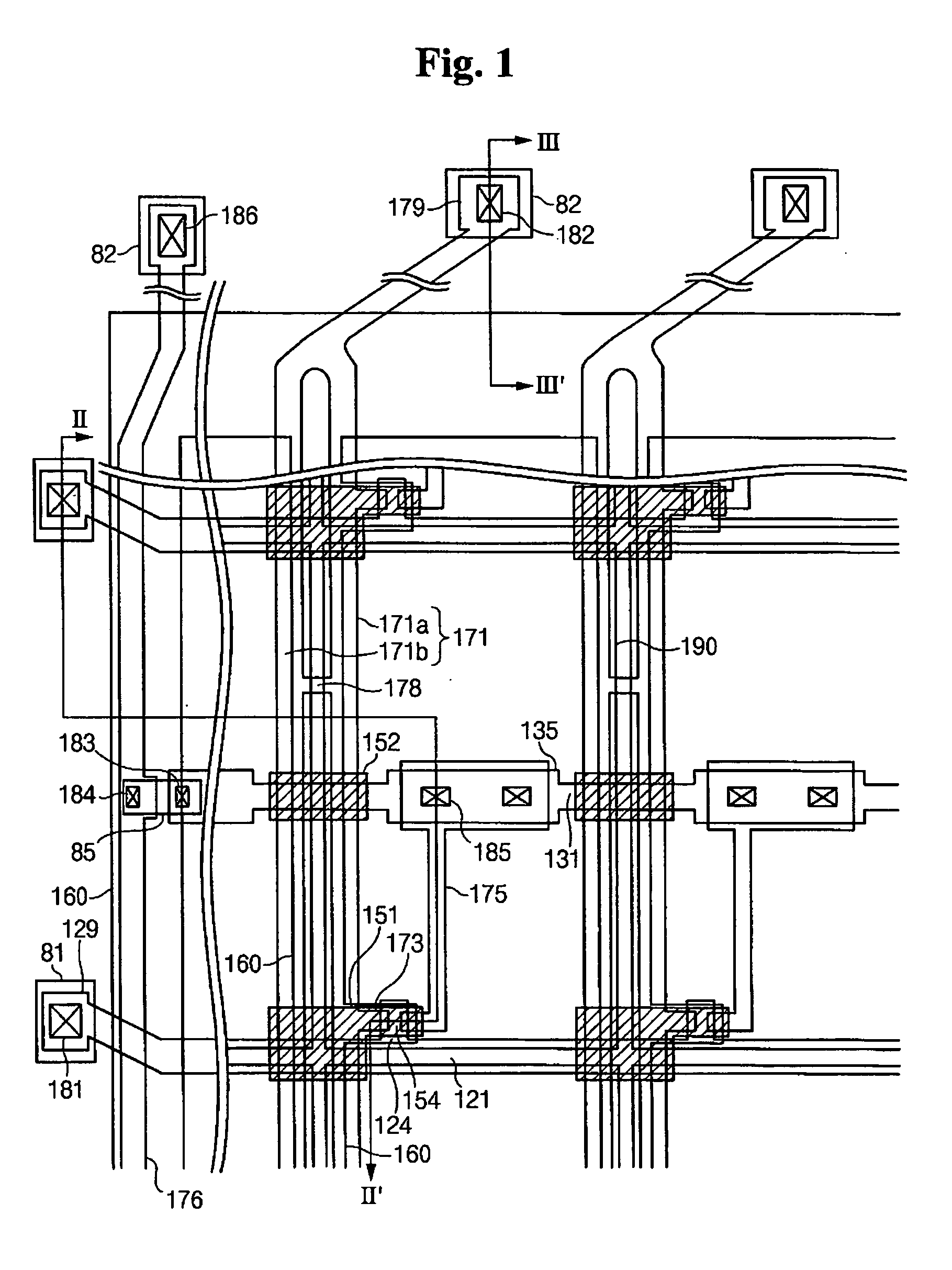

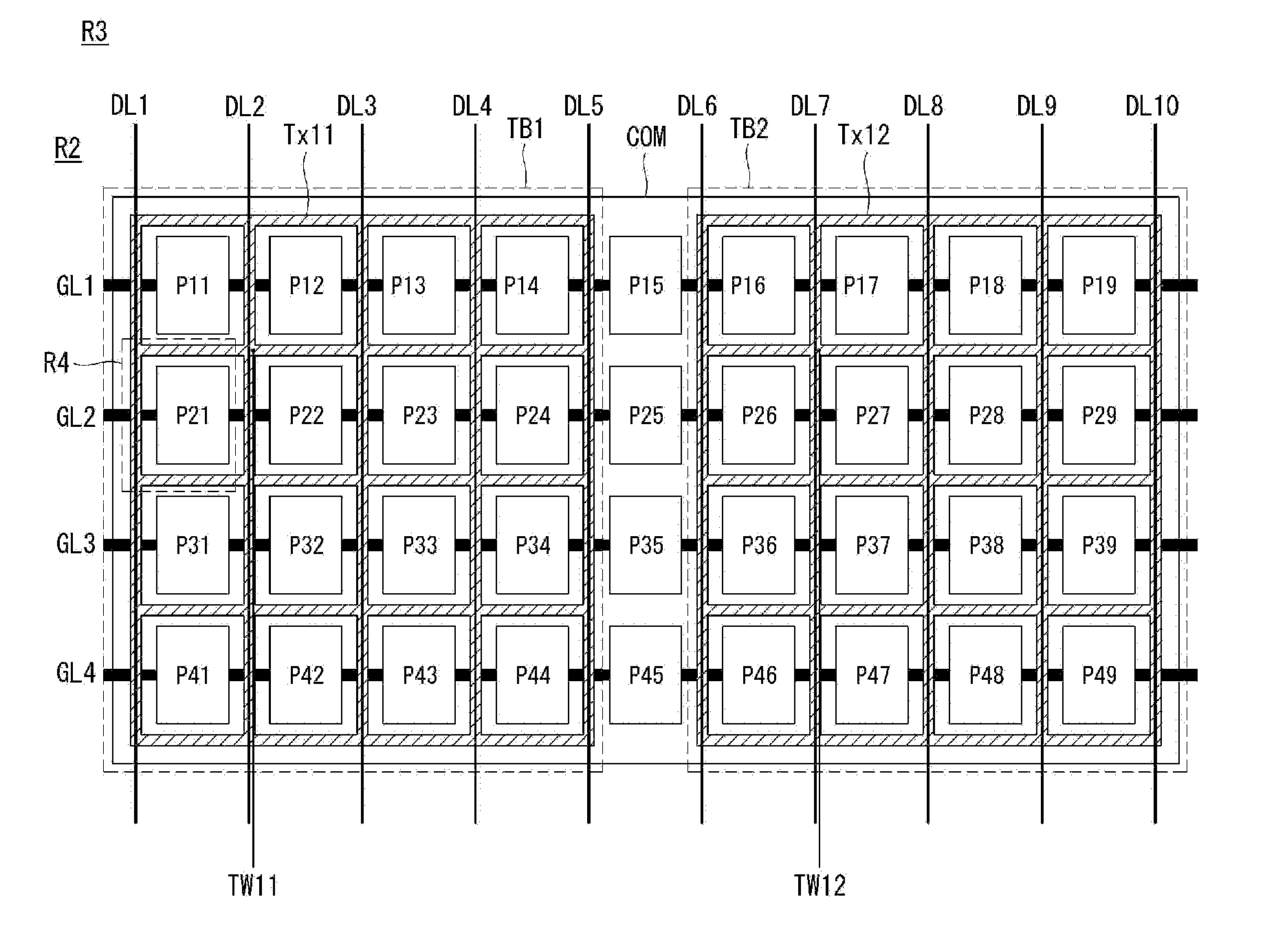

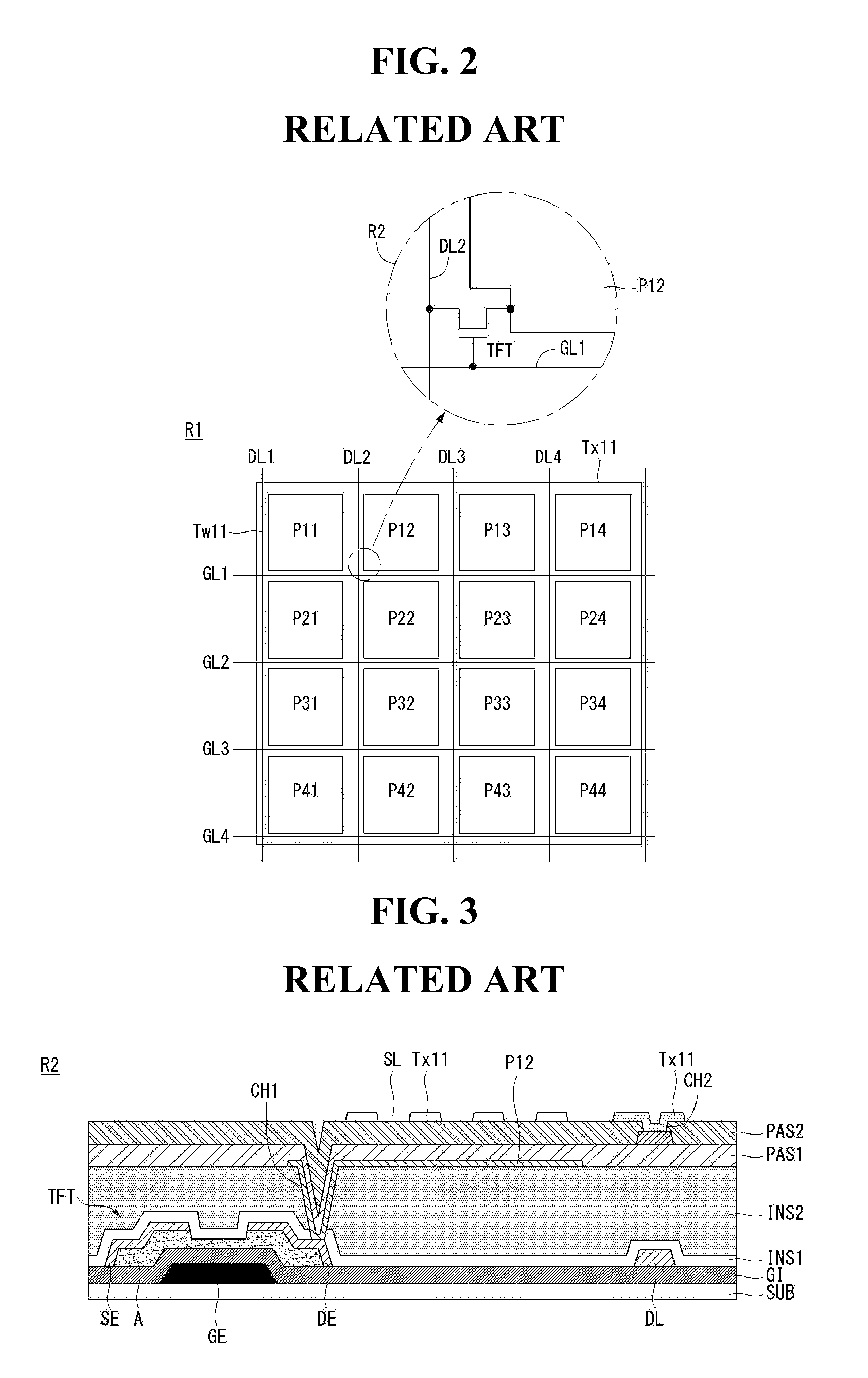

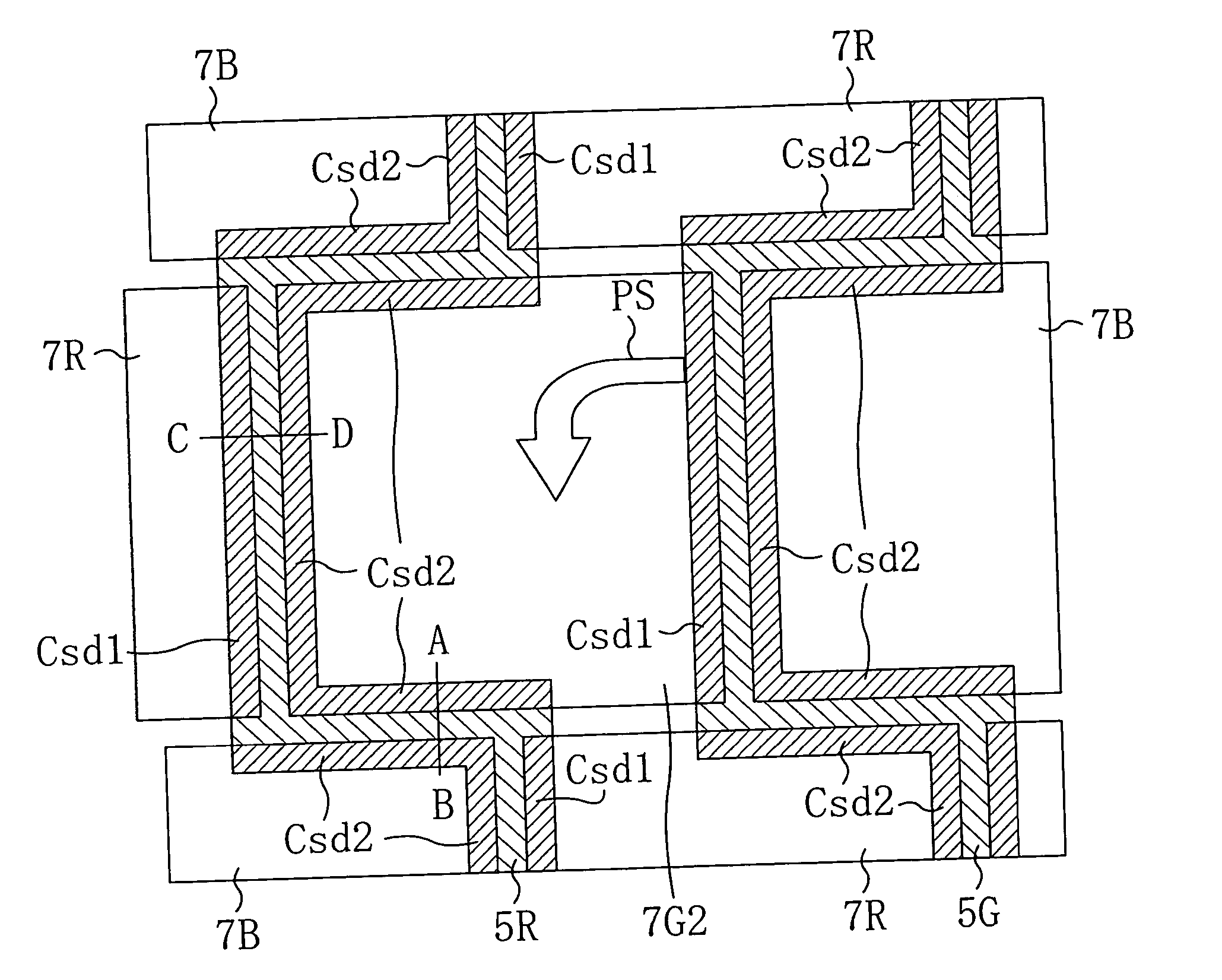

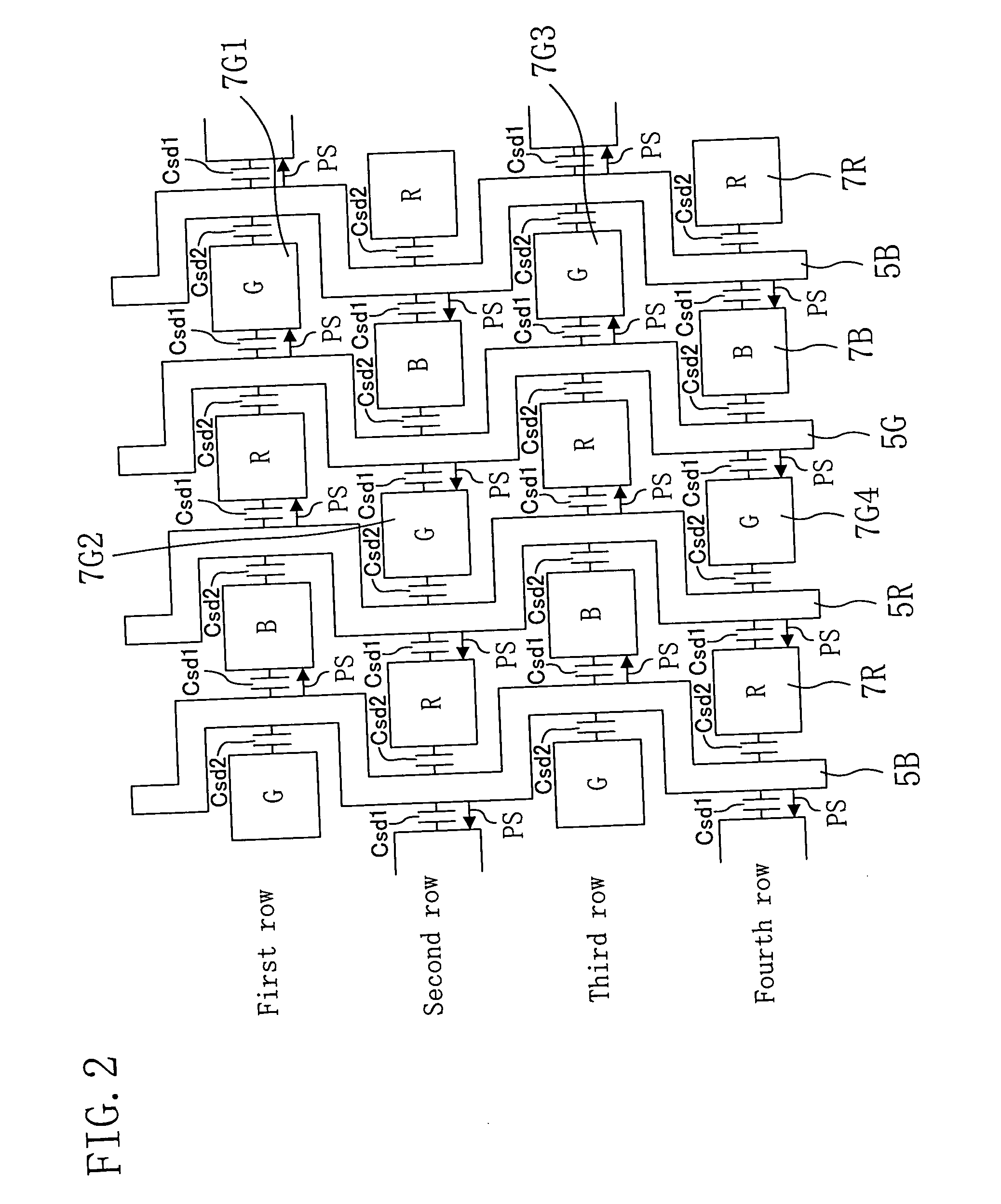

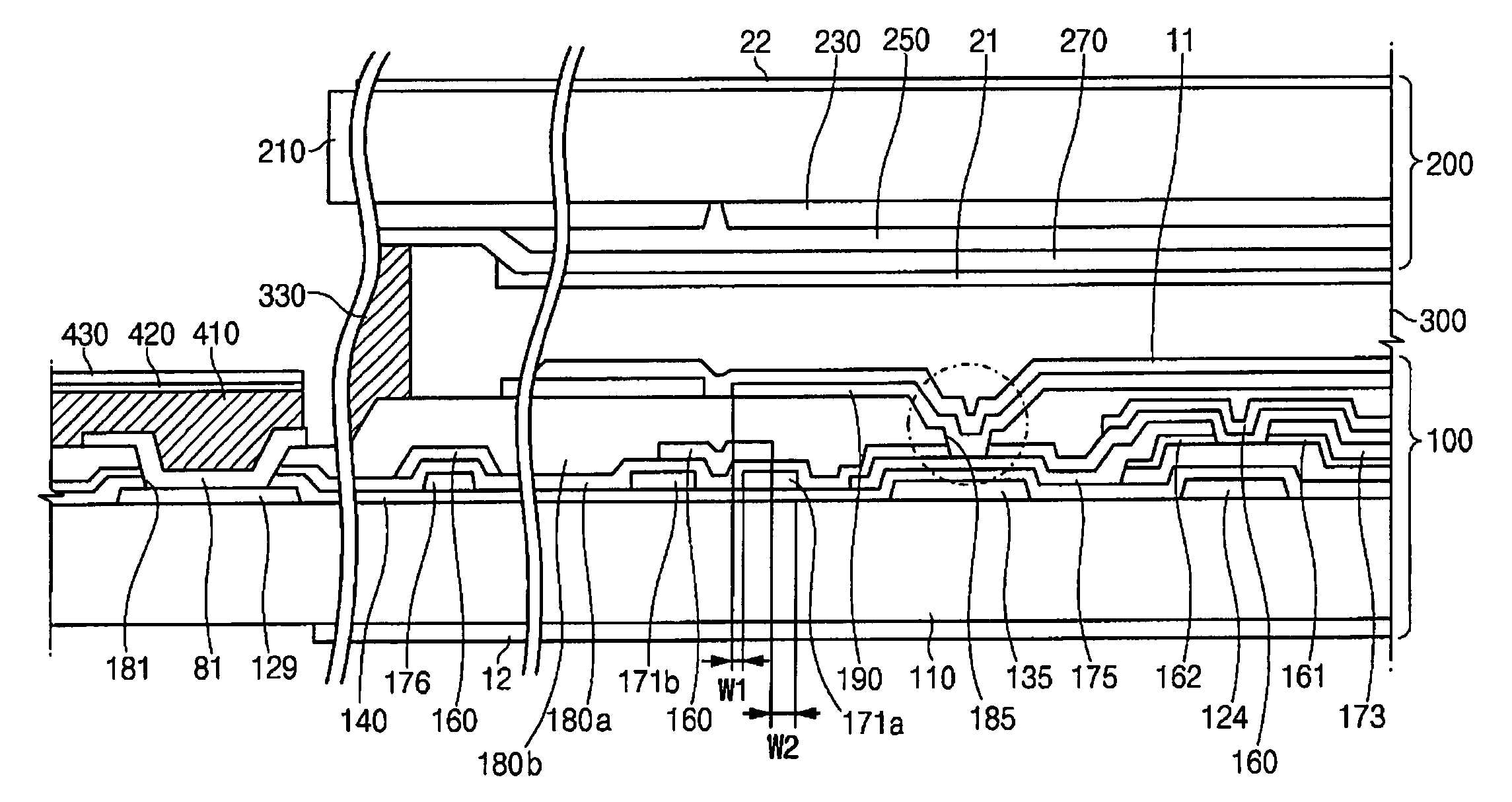

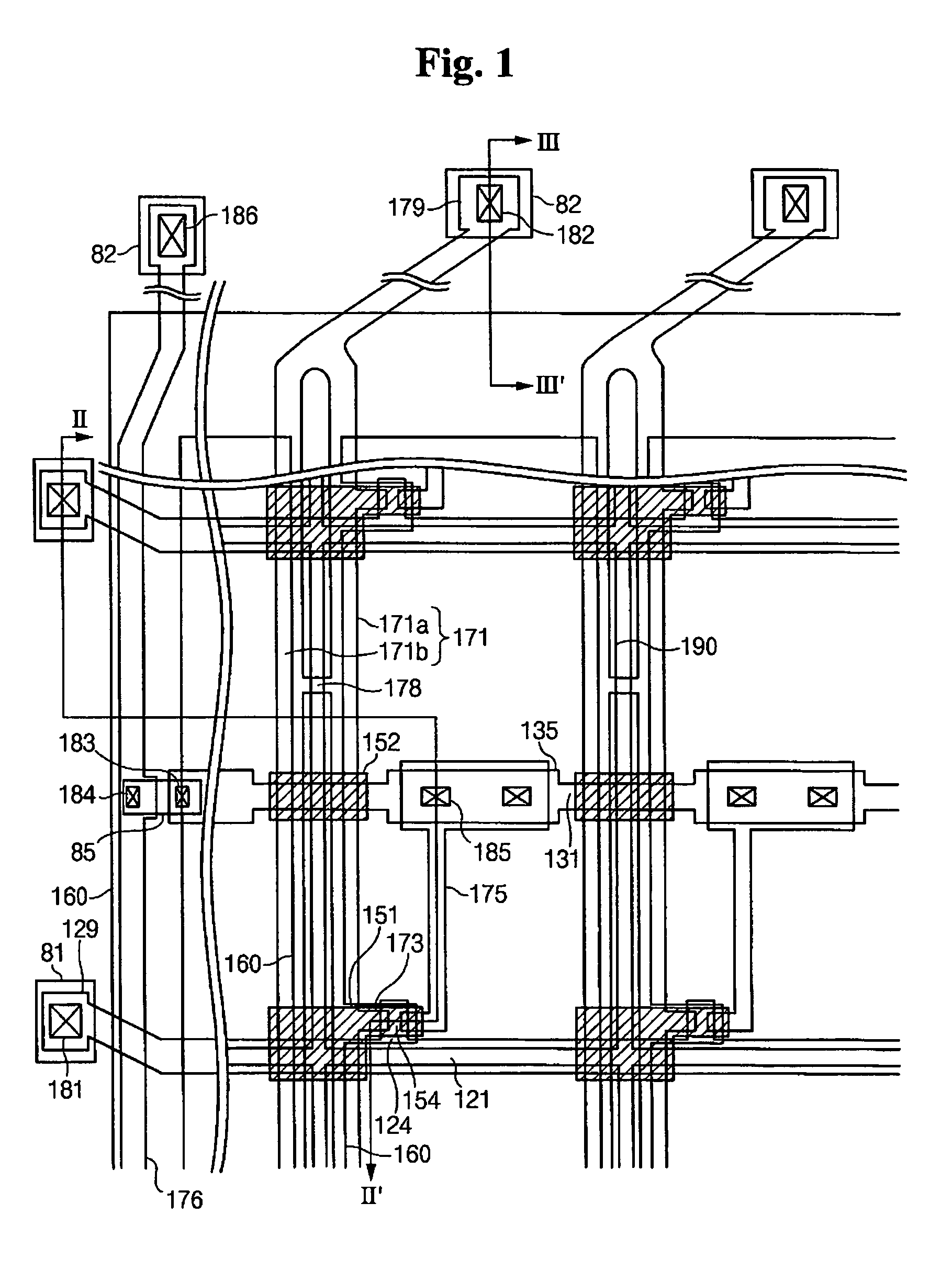

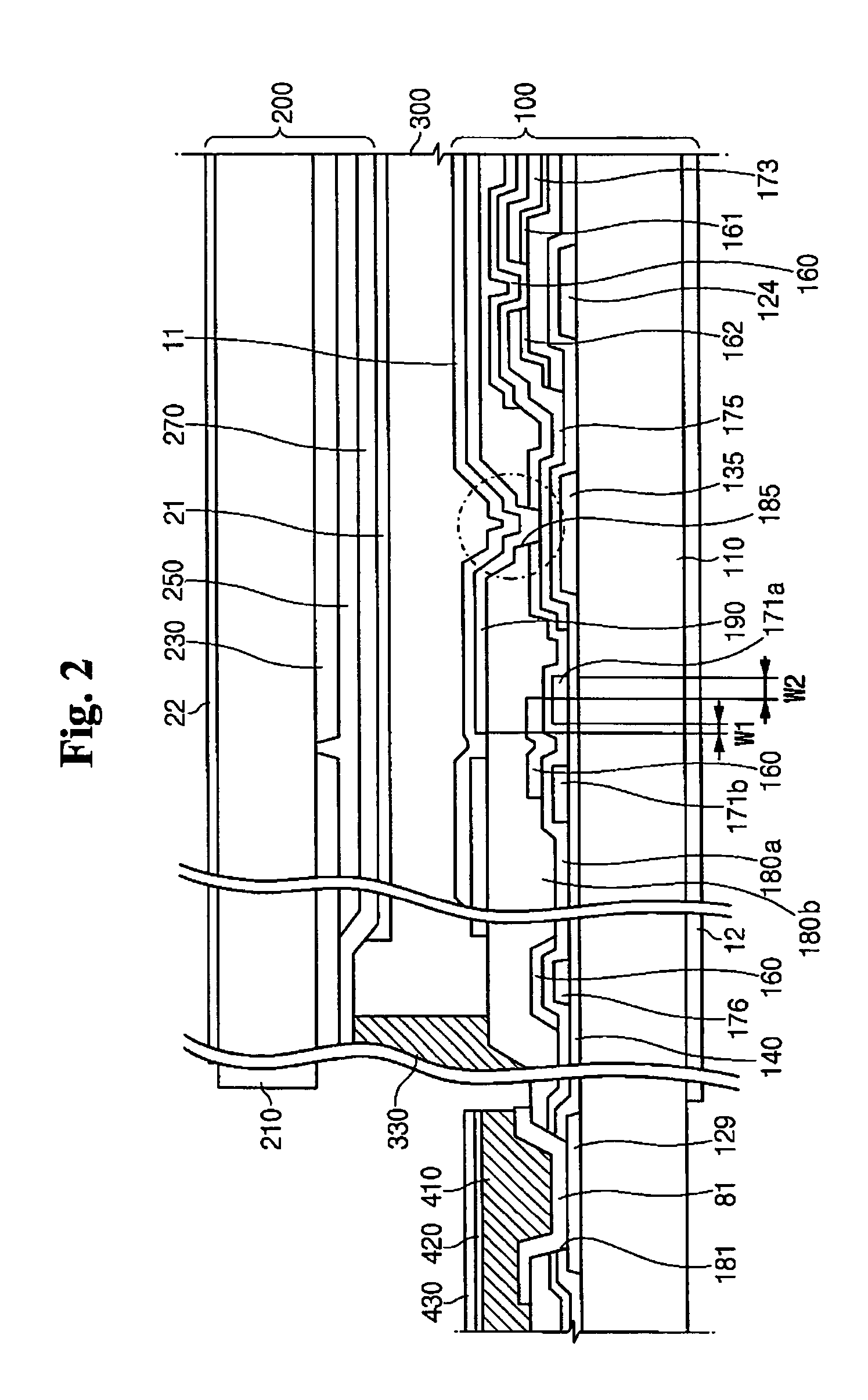

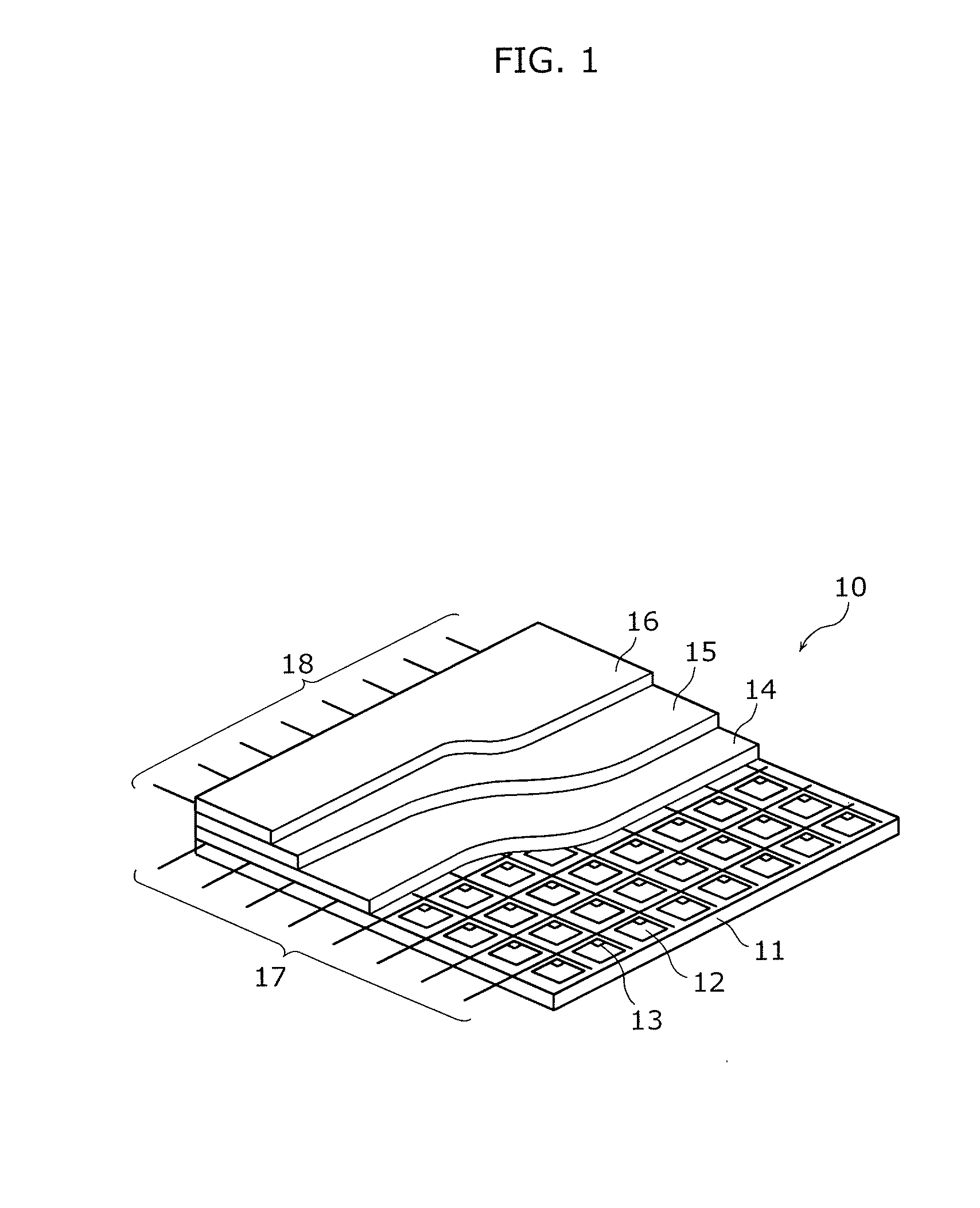

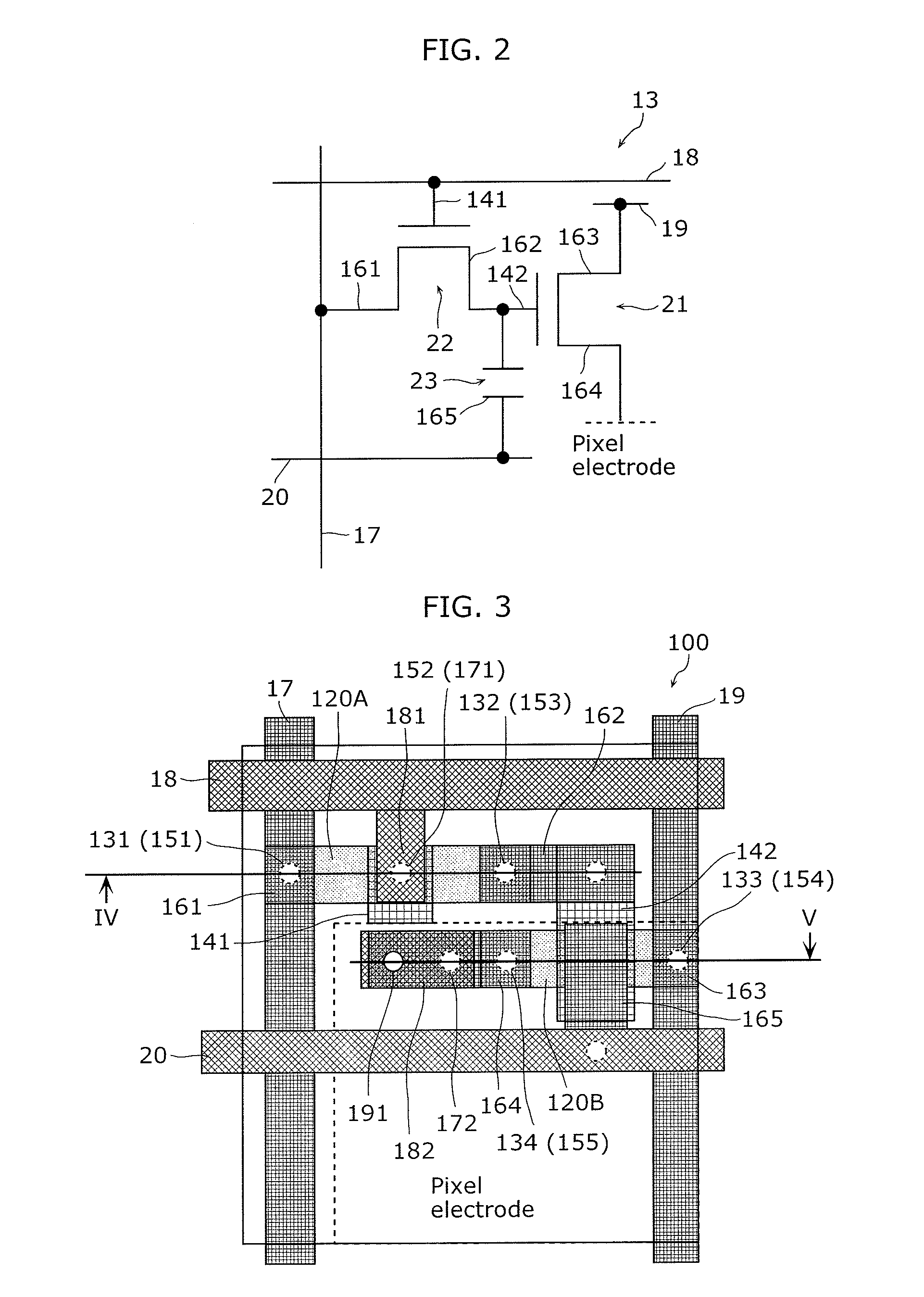

Thin film transistor array panel and liquid crystal display including the panel

ActiveUS20050174503A1Parasitic capacitanceIncrease the aperture ratioTransistorStatic indicating devicesTransistor arrayLiquid-crystal display

A thin film transistor (TFT) array panel is provided, which includes: a plurality of gate lines transmitting gate signals; a plurality of data lines intersecting the gate lines and transmitting data signals, each data line including first and second data line branches electrically connected to each other and spaced apart from each other; a plurality of pixel electrodes electrically connected to the gate lines and the data lines through thin film transistor and covering edges of the first or the second data line branches; a passivation layer disposed between the data lines and the pixel electrodes; and a light blocking member covering gaps between the first data line branches and the second data line branches.

Owner:SAMSUNG DISPLAY CO LTD

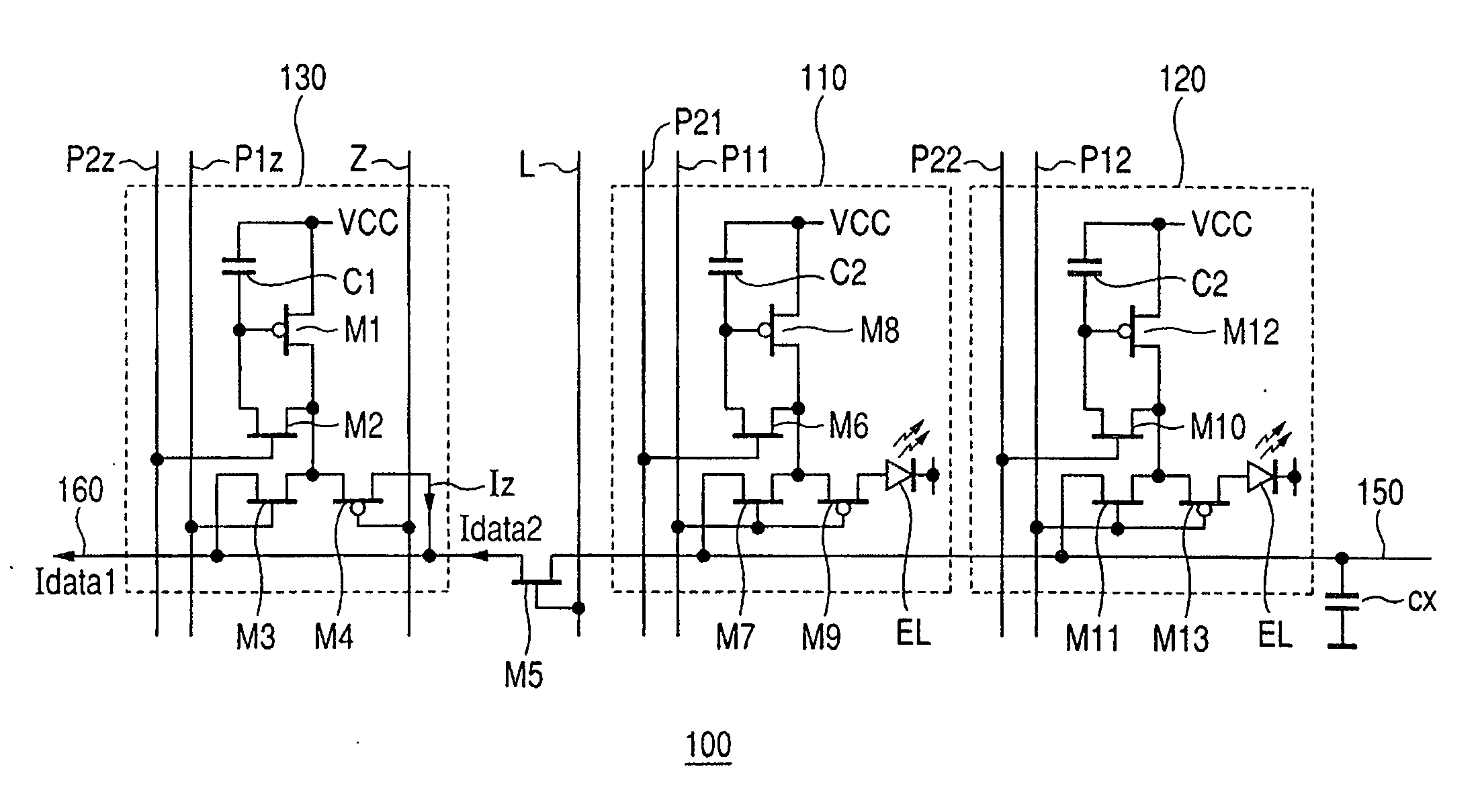

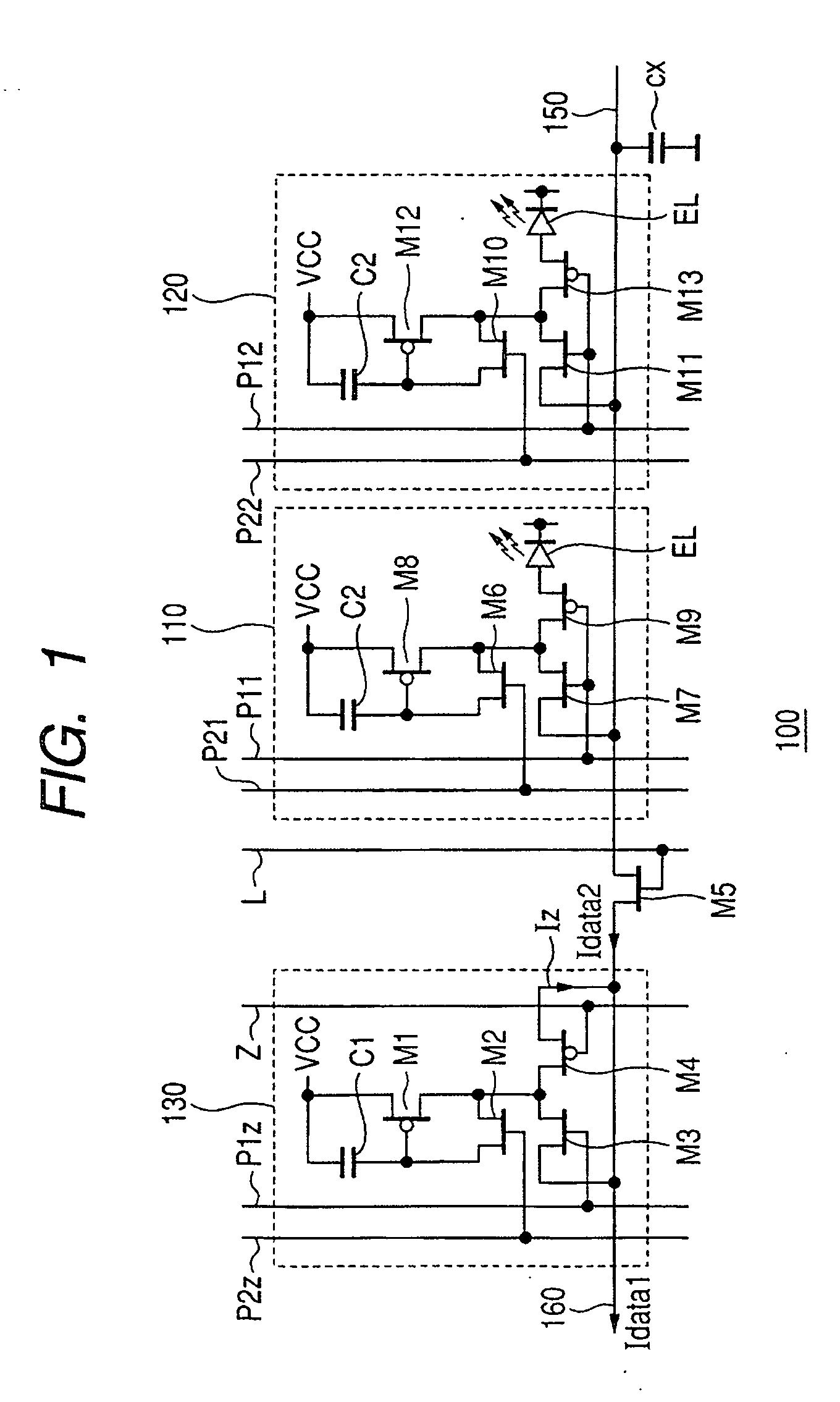

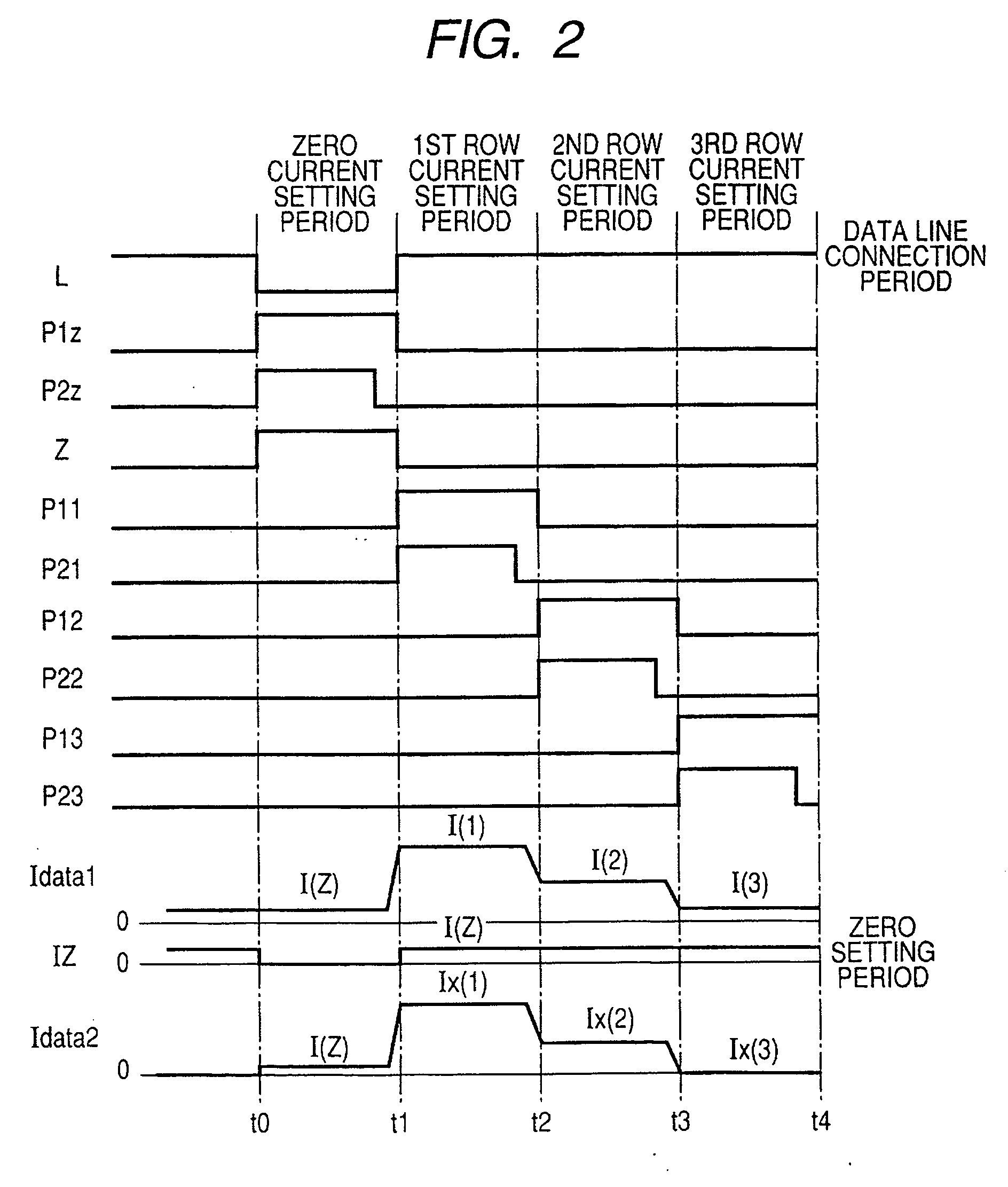

Current programming apparatus and matrix type display apparatus

InactiveUS20060114195A1Parasitic capacitanceGuaranteed uptimeStatic indicating devicesParasitic capacitanceEngineering

A current programming apparatus includes a current source; a plurality of first circuits to which data currents are supplied through a data line, the first circuits commonly connected with the data line; a second circuit having a terminal connected to the current source; a switch connecting or breaking the second circuit with or from the data line, wherein the current source generates a predetermined current to supply the generated current to the second circuit through the terminal while the switch is off, whereby the value of the predetermined current is written in the second circuit, and wherein the current source generates a current based on data, and the second circuit generates a current based on the written value of the predetermined current, and a difference current between the current generated by the current source and the current generated by second circuit is supplied to the first circuits through the data line while the switch is on, whereby the value of the current is written in the first circuits as the value of the data current. The influence of parasitic capacitance of the data line can be suppressed to stabilize the writing operation of the current.

Owner:CANON KK

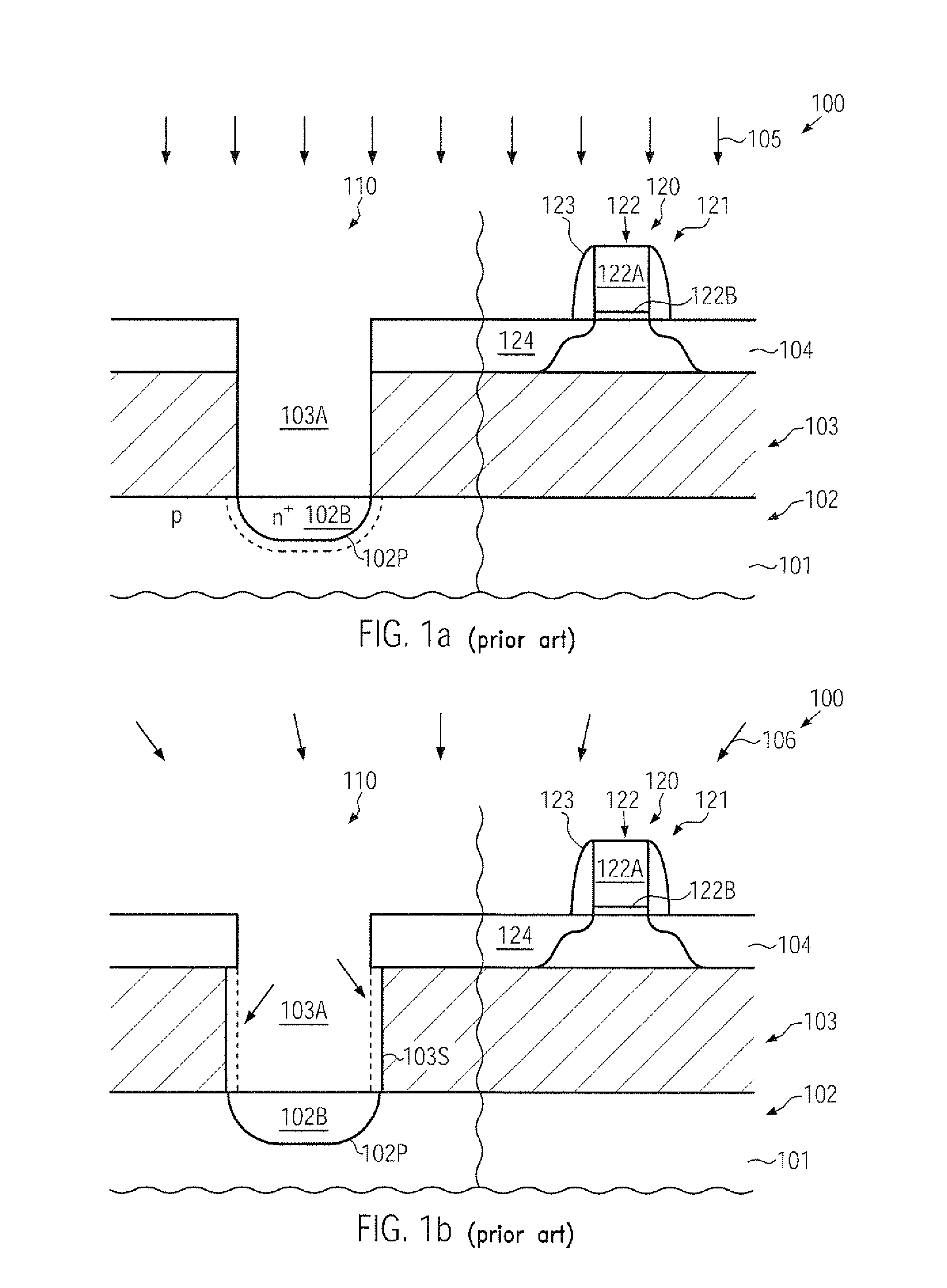

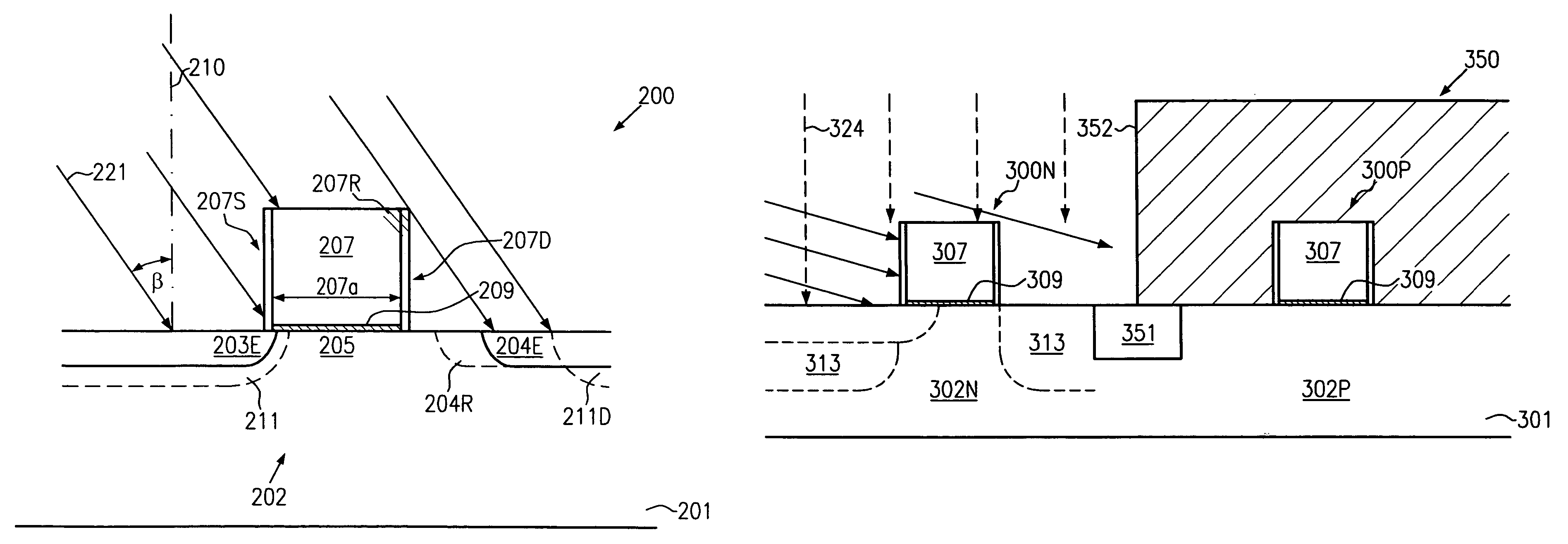

Soi device with a buried insulating material having increased etch resistivity

ActiveUS20100163994A1Improve compatibilityIncreased etch resistivityTransistorSolid-state devicesP–n junctionSilicon dioxide

In SOI devices, the PN junction of circuit elements, such as substrate diodes, is formed in the substrate material on the basis of the buried insulating material that provides increased etch resistivity during wet chemical cleaning and etch processes. Consequently, undue exposure of the PN junction formed in the vicinity of the sidewalls of the buried insulating material may be avoided, which may cause reliability concerns in conventional SOI devices comprising a silicon dioxide material as the buried insulating layer.

Owner:ADVANCED MICRO DEVICES INC

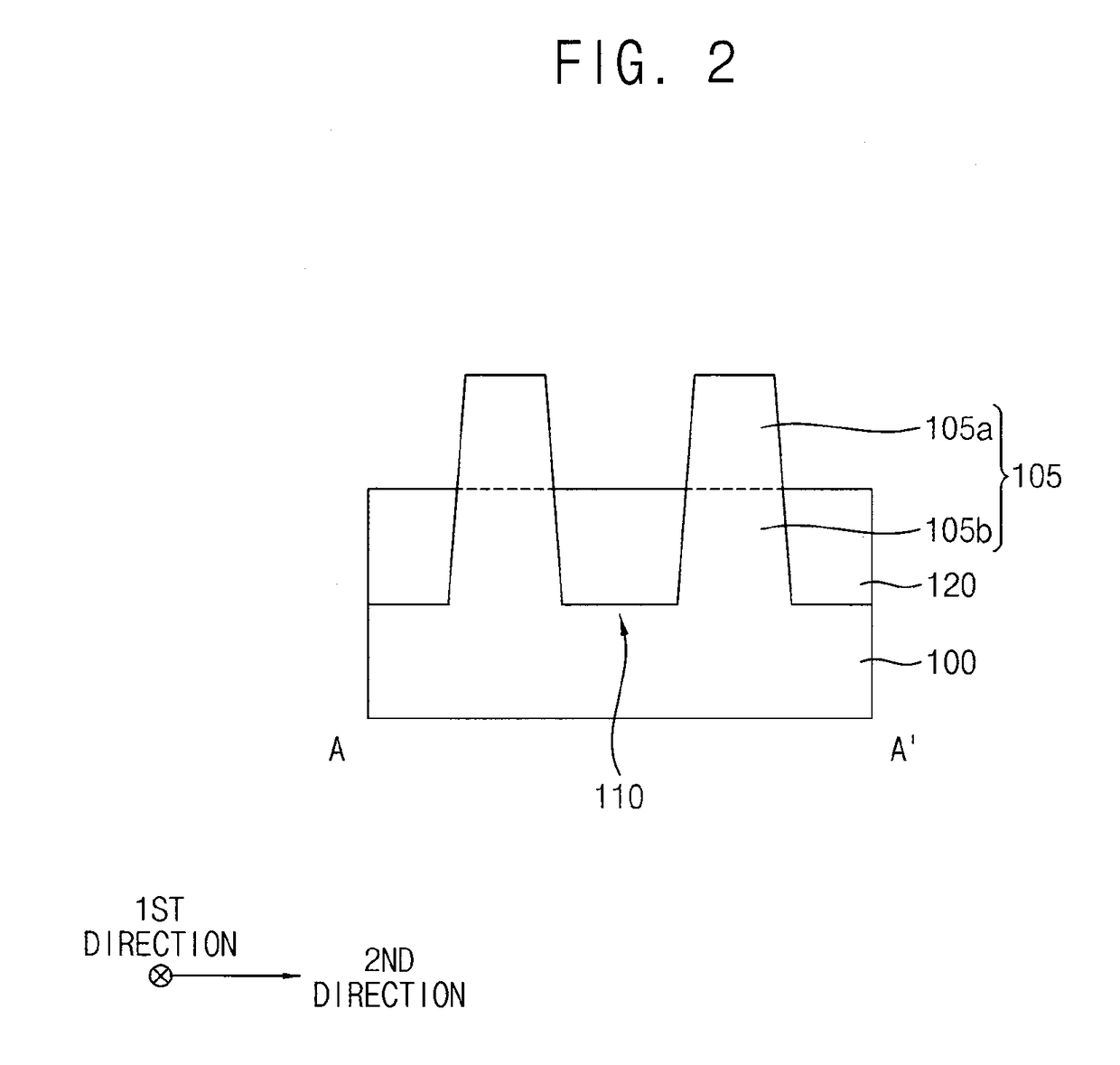

Semiconductor devices

InactiveUS20170317213A1Excellent electrical propertiesReduced structureSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialSilicon dioxide

A semiconductor device includes an active fin on a substrate, a gate structure on the active fin, a gate spacer structure directly on a sidewall of the gate structure, and a source / drain layer on a portion of the active fin adjacent the gate spacer structure. The gate spacer structure includes a silicon oxycarbonitride (SiOCN) pattern and a silicon dioxide (SiO2) pattern sequentially stacked.

Owner:SAMSUNG ELECTRONICS CO LTD

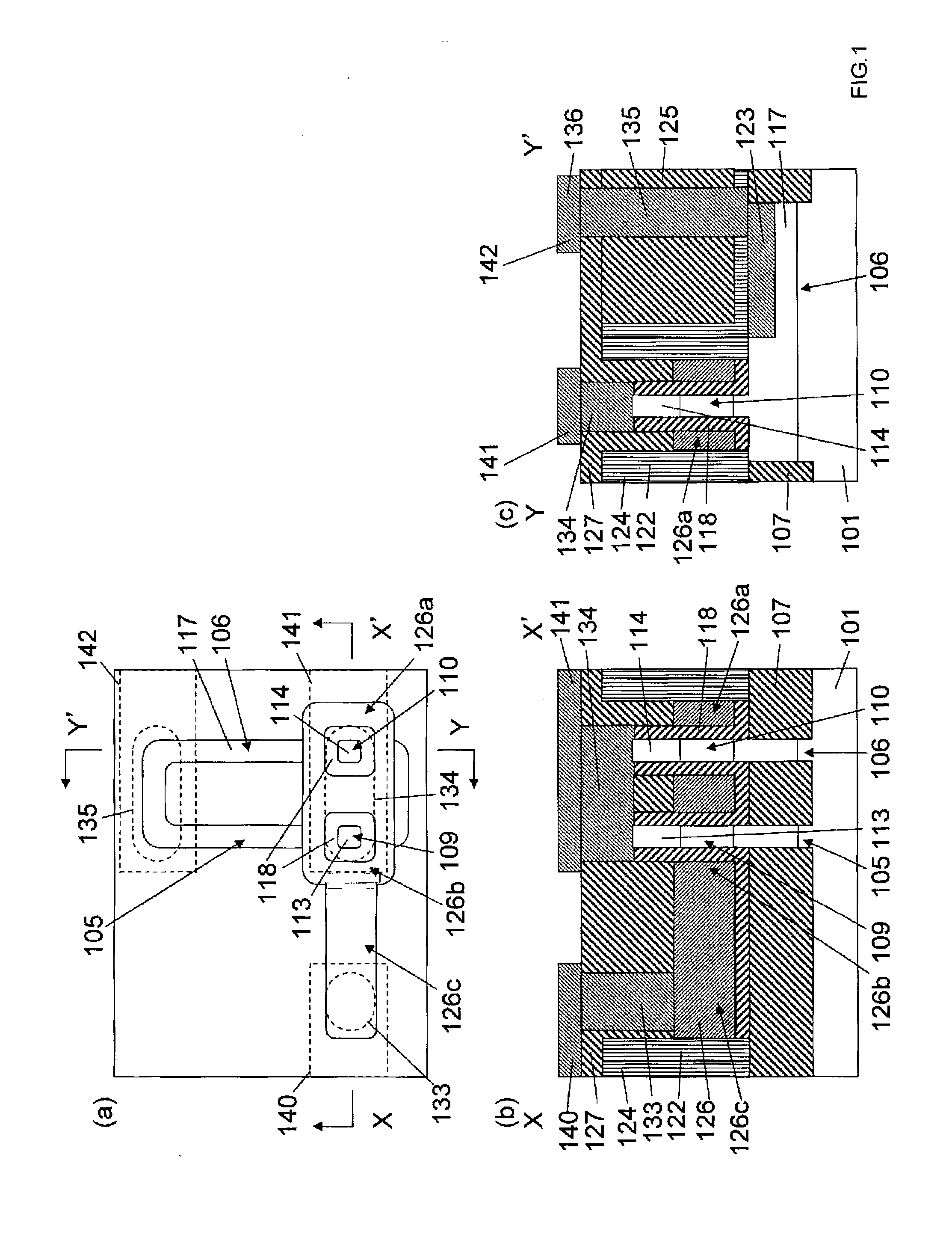

Method for producing semiconductor device and semiconductor device

ActiveUS8735971B2Parasitic capacitanceReduce parasitic capacitanceTransistorSolid-state devicesSalicidePolysilicon gate

A SGT production method includes a step of forming first and second fin-shaped silicon layers, forming a first insulating film, and forming first and second pillar-shaped silicon layers; a step of forming diffusion layers by implanting an impurity into upper portions of the first and second pillar-shaped silicon layers, upper portions of the first and second fin-shaped silicon layers, and lower portions of the first and second pillar-shaped silicon layers; a step of forming a gate insulating film and first and second polysilicon gate electrodes; a step of forming a silicide in upper portions of the diffusion layers formed in the upper portions of the first and second fin-shaped silicon layers; and a step of depositing an interlayer insulating film, exposing and etching the first and second polysilicon gate electrodes, then depositing a metal, and forming first and second metal gate electrodes.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

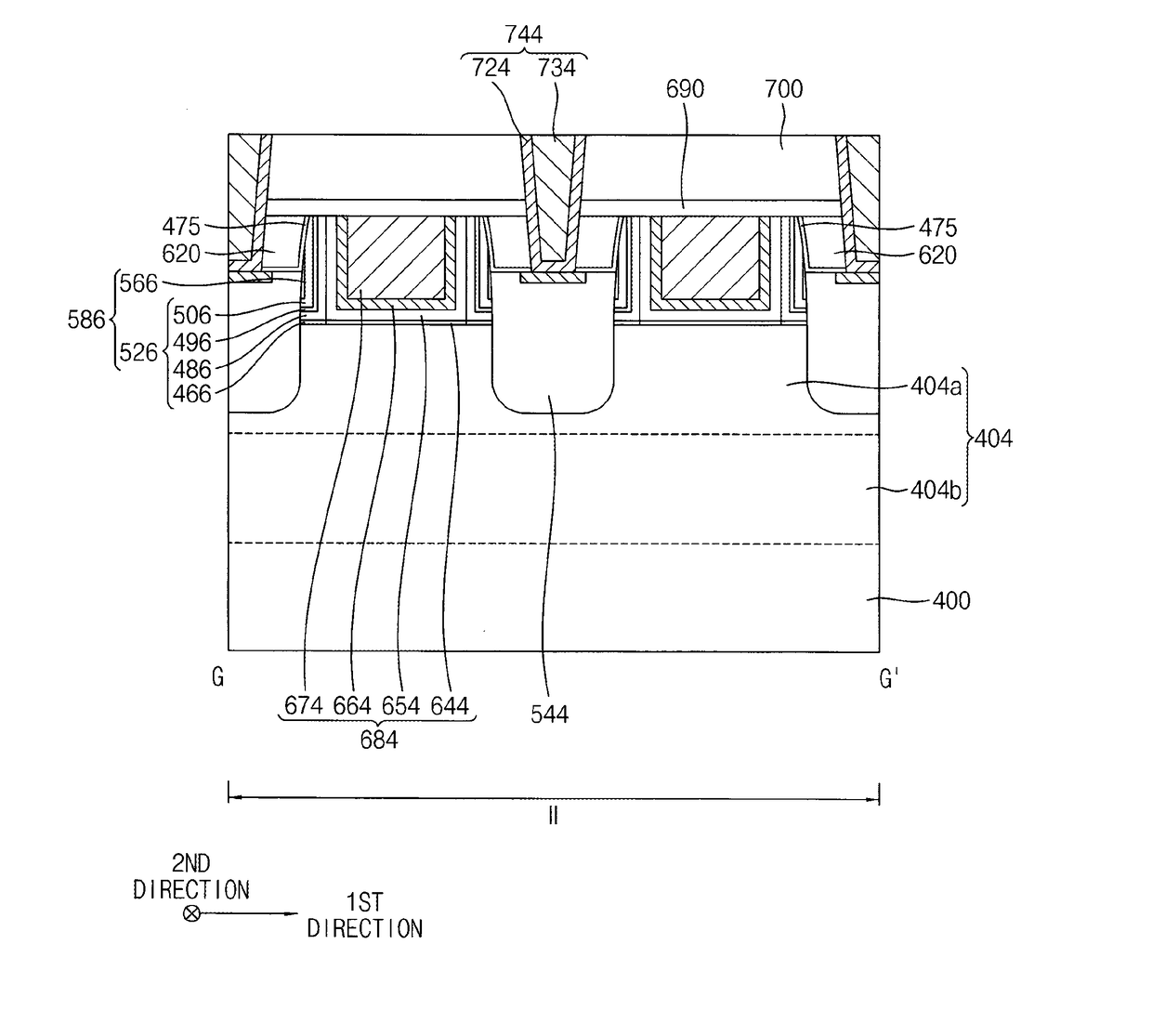

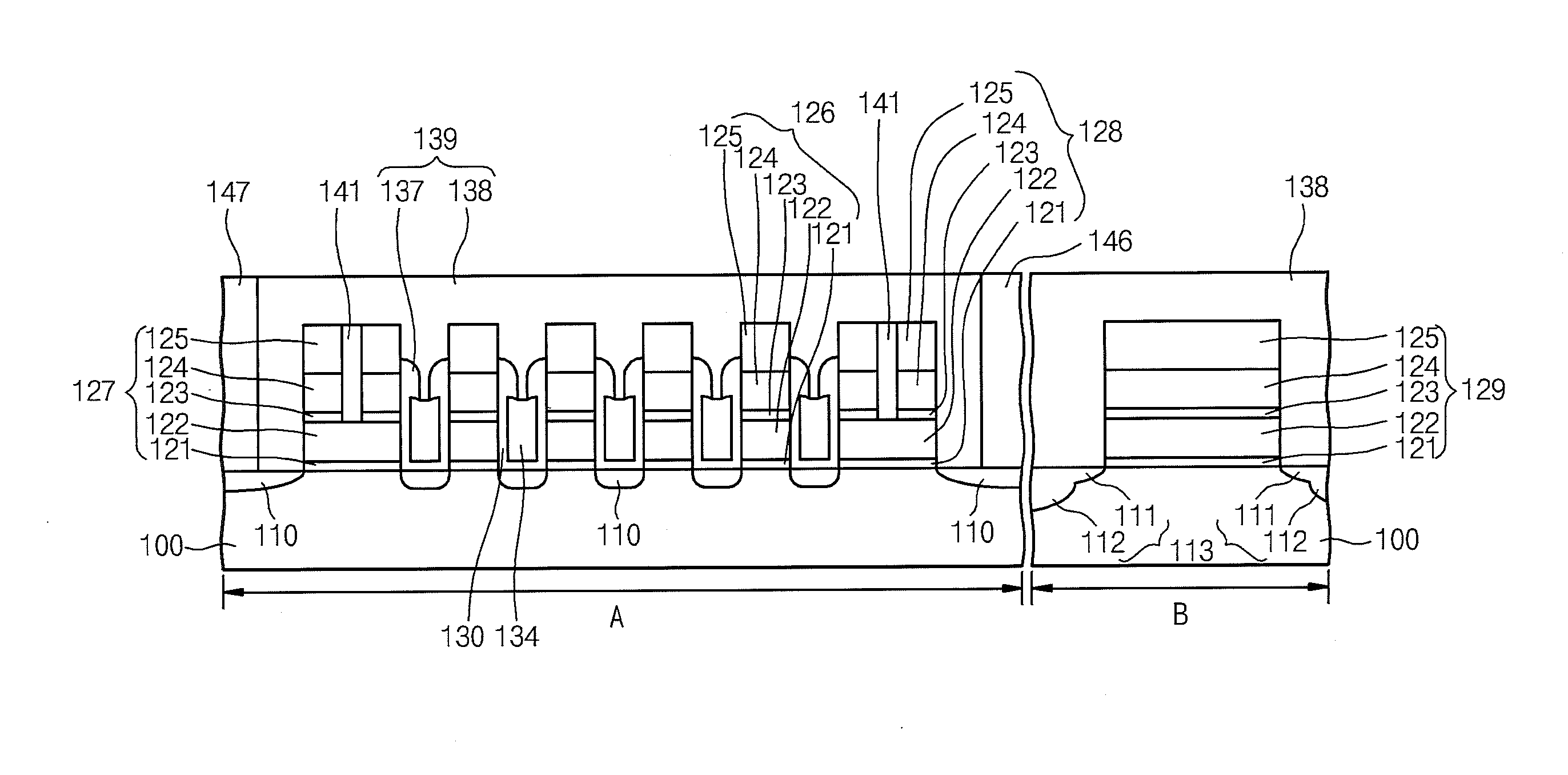

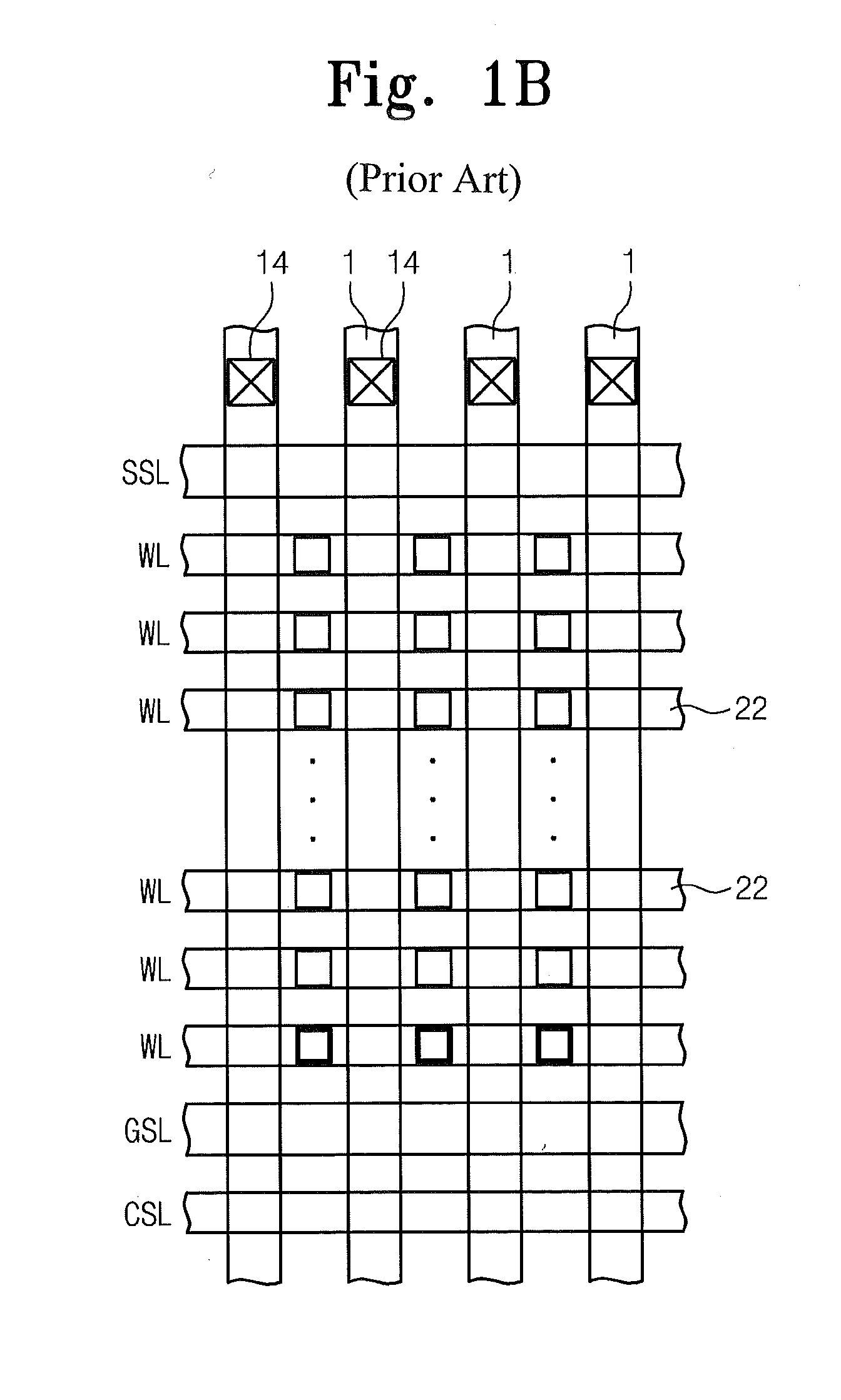

Semiconductor memory device

InactiveUS20120193697A1High degree of integrationChannel length can be largeTransistorSolid-state devicesBit lineMemory cell

A highly integrated DRAM is provided. A circuit for driving a memory cell array is formed over a substrate, a bit line is formed thereover, and a semiconductor region, word lines, and a capacitor are formed over the bit line. Since the bit line is located below the semiconductor region, and the word lines and the capacitor are located above the semiconductor region, the degree of freedom of the arrangement of the bit line is high. When an open-bit-line DRAM is formed, an area per memory cell less than or equal to 6F2, or when a special structure is employed for a cell transistor, an area per memory cell less than or equal to 4F2 can be achieved.

Owner:SEMICON ENERGY LAB CO LTD

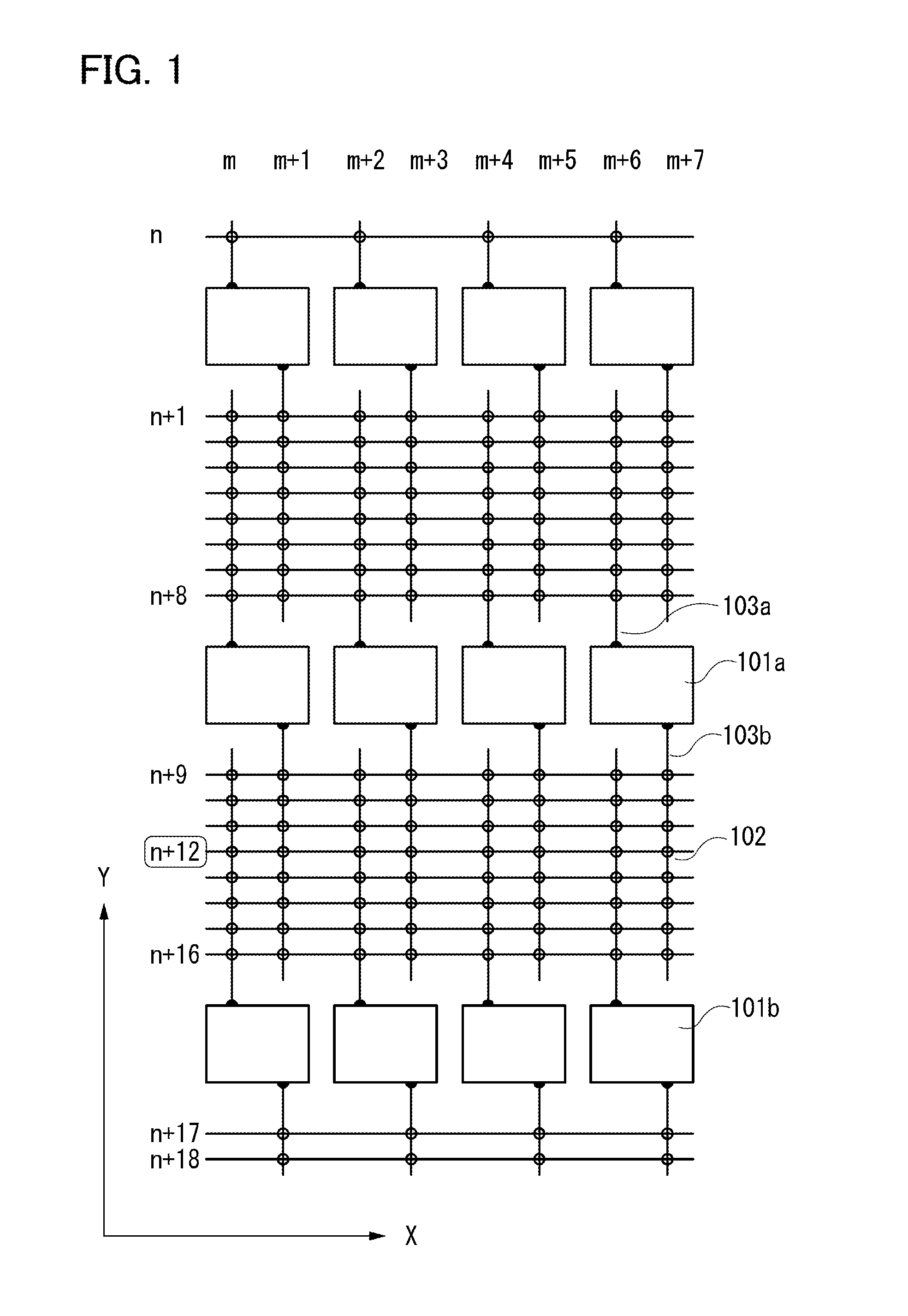

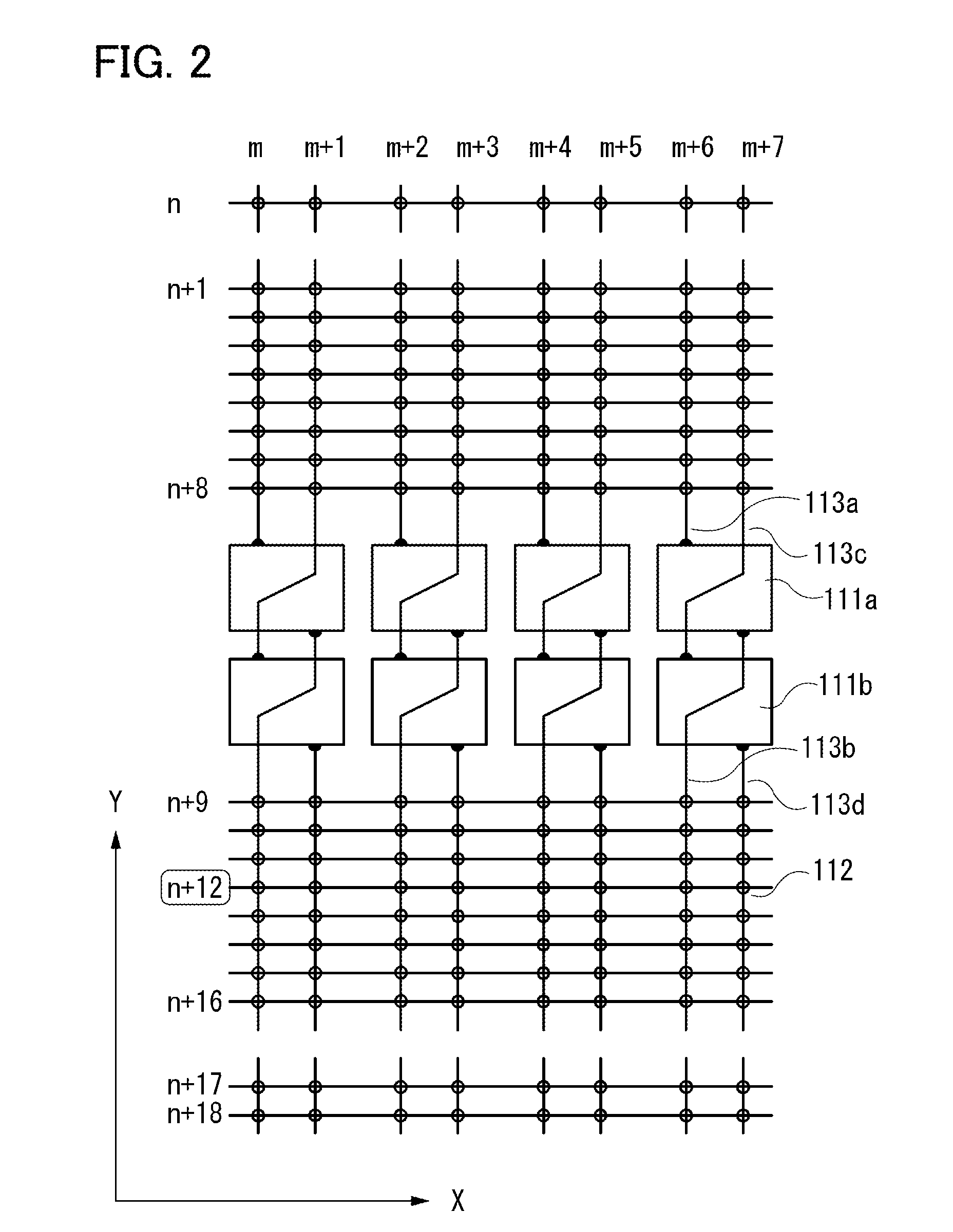

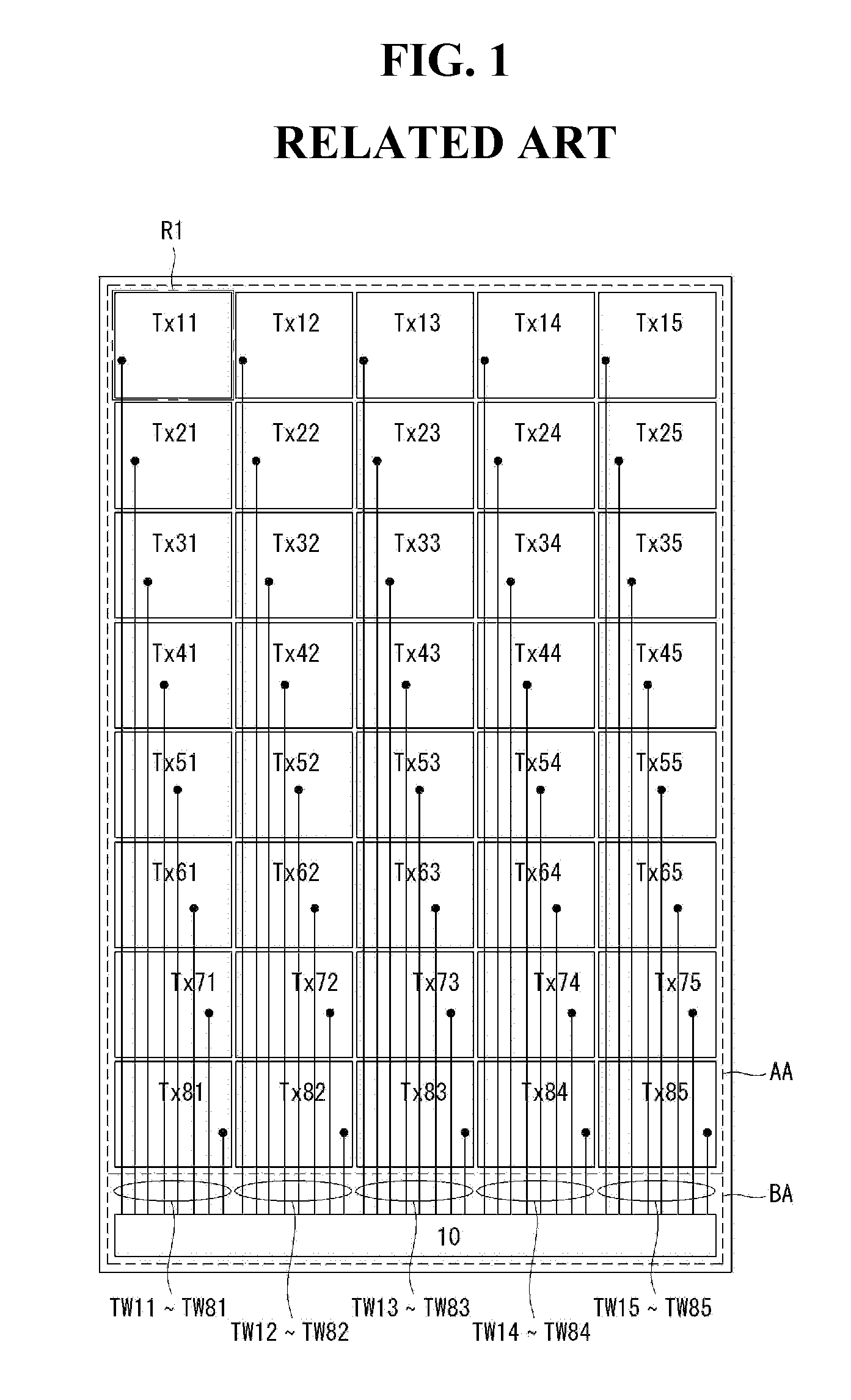

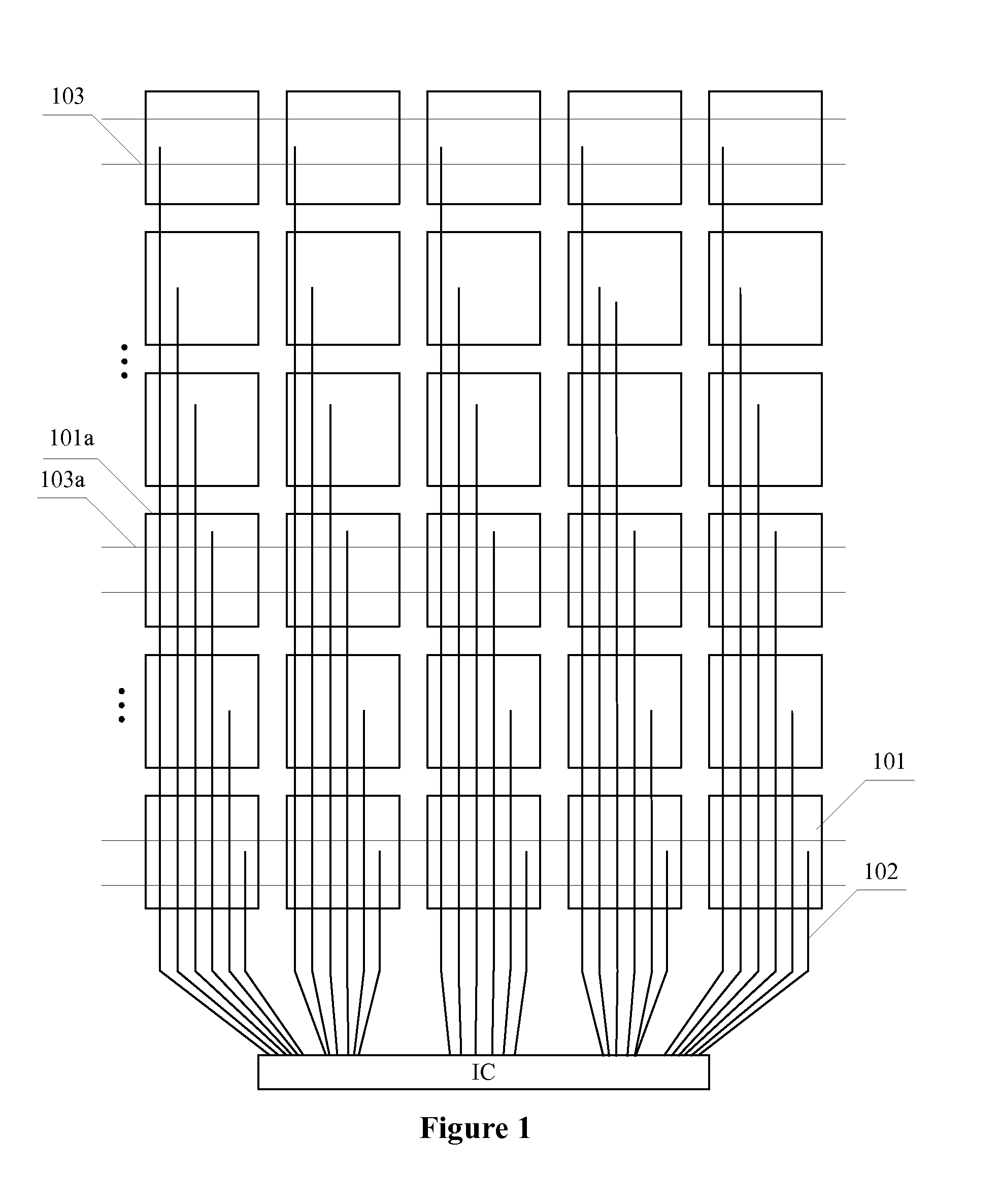

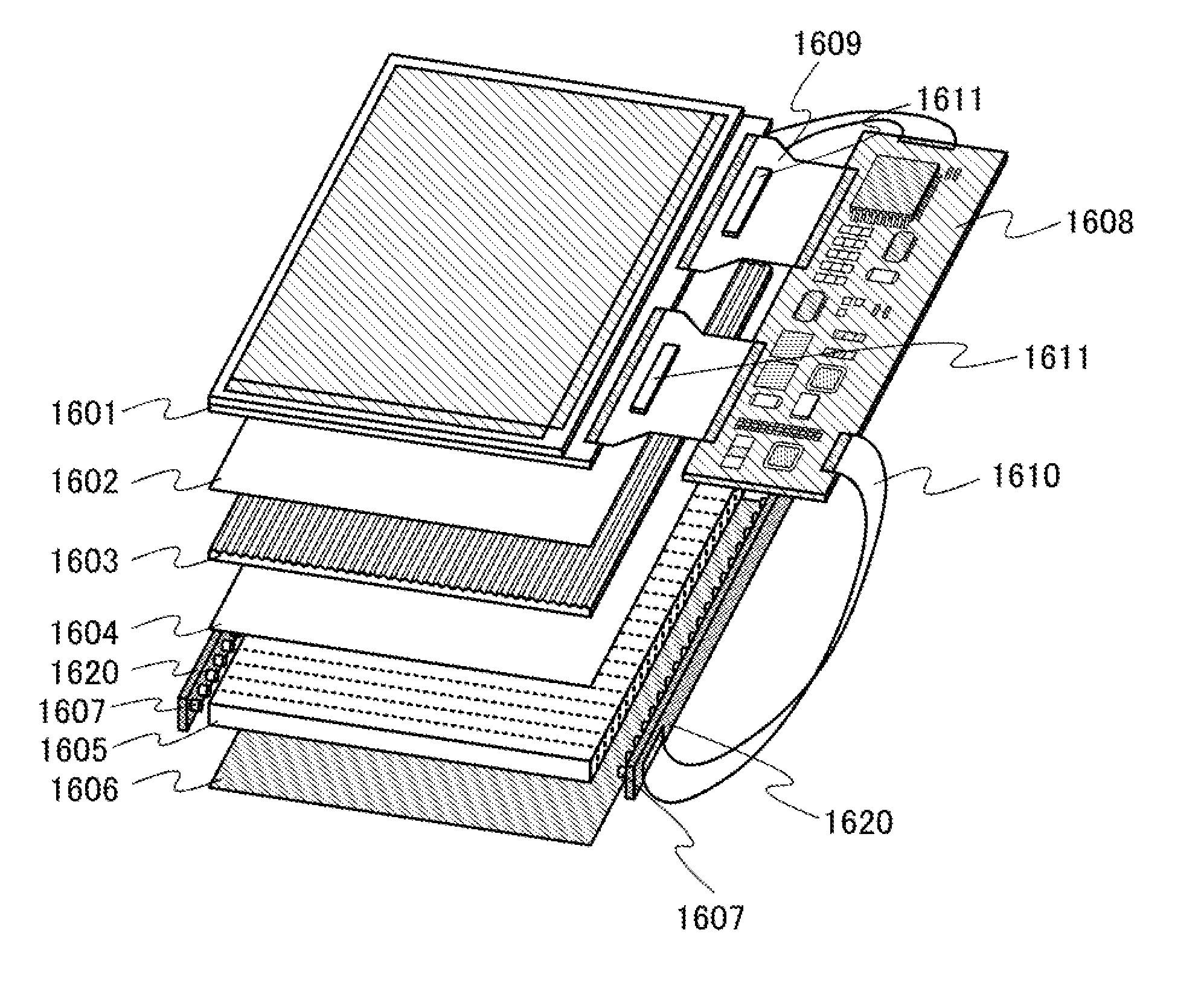

Touch sensor integrated type display device

ActiveUS20160048267A1Improve touch sensitivityParasitic capacitanceNon-linear opticsInput/output processes for data processingDisplay deviceEngineering

Touch sensor integrated type display device improving touch sensibility. The touch sensor integrated type display device includes a plurality of gate lines and data lines configured to cross over each other, a plurality of thin film transistors disposed at crossings of the gate lines and the data lines, a plurality of pixel electrodes configured to be respectively connected to the thin film transistors and disposed between the data lines so that each of the gate lines crosses over pixel electrodes disposed on a same line, a plurality of touch electrodes configured to overlap the gate lines and the data lines without contacting and overlapping the pixel electrodes, a plurality of touch routing wires configured to be respectively connected to the touch electrodes and arranged in parallel with each other, and a common electrode configured to overlap the data lines, the gate lines, the pixel electrodes and the touch electrodes.

Owner:LG DISPLAY CO LTD

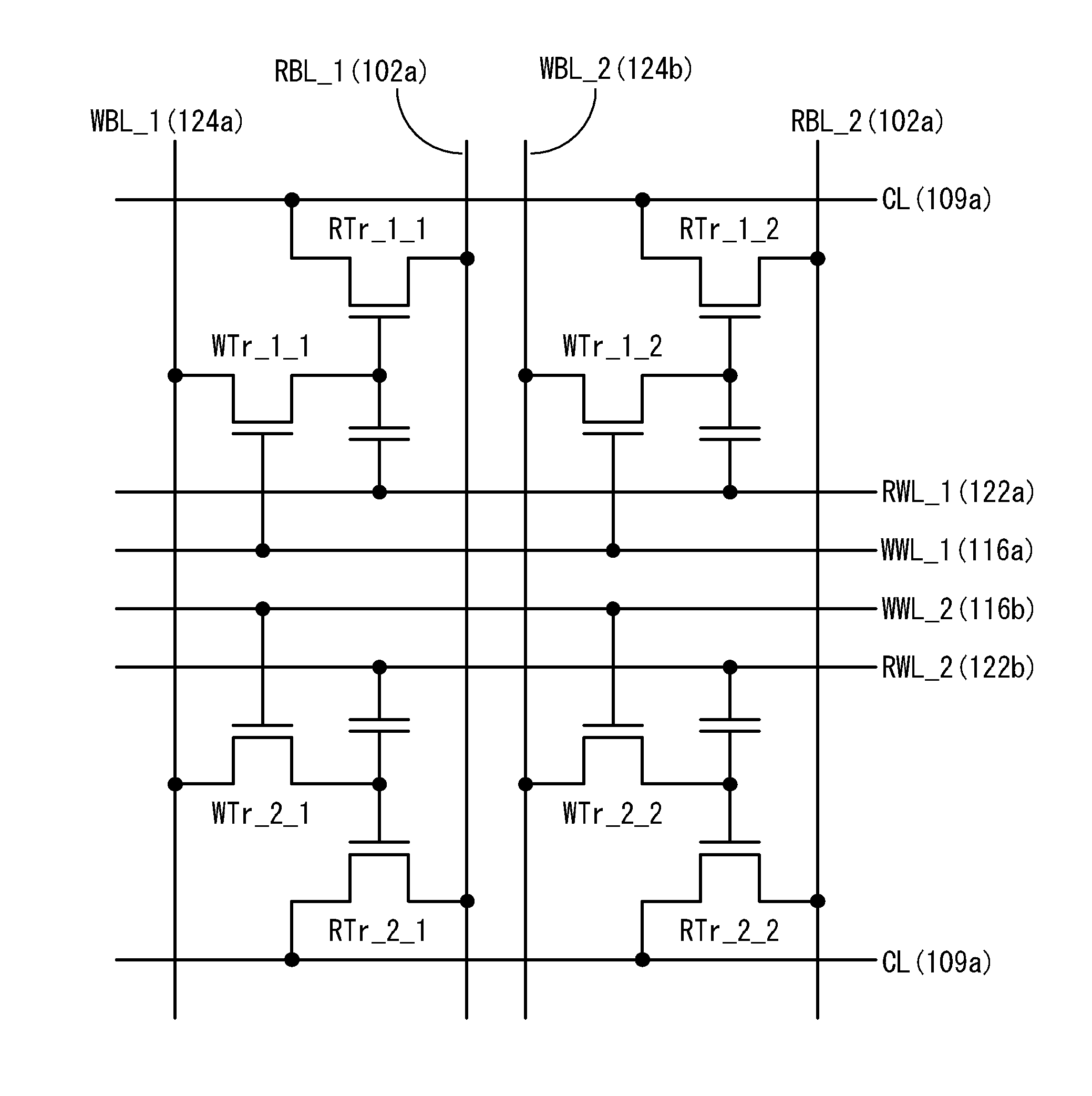

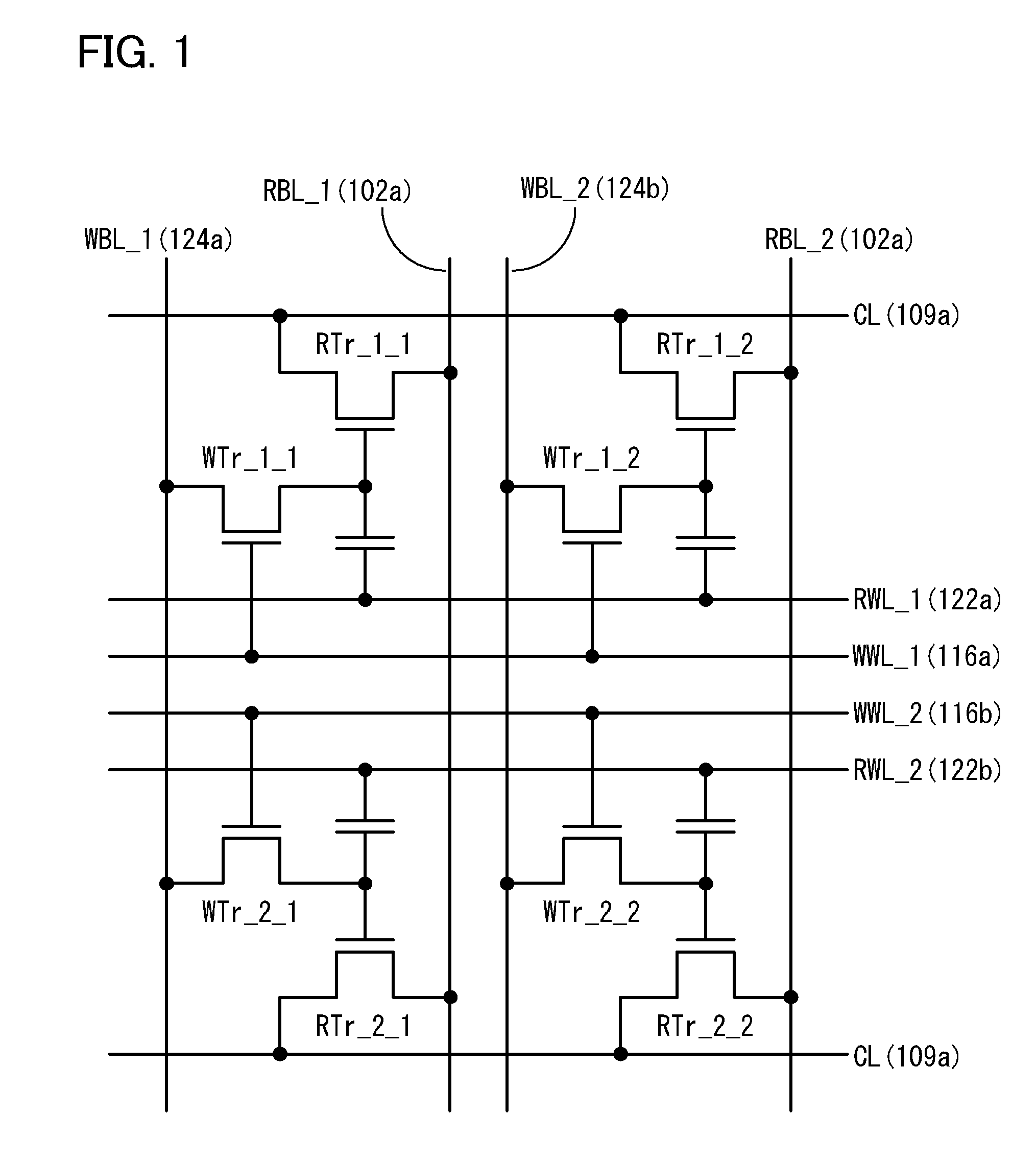

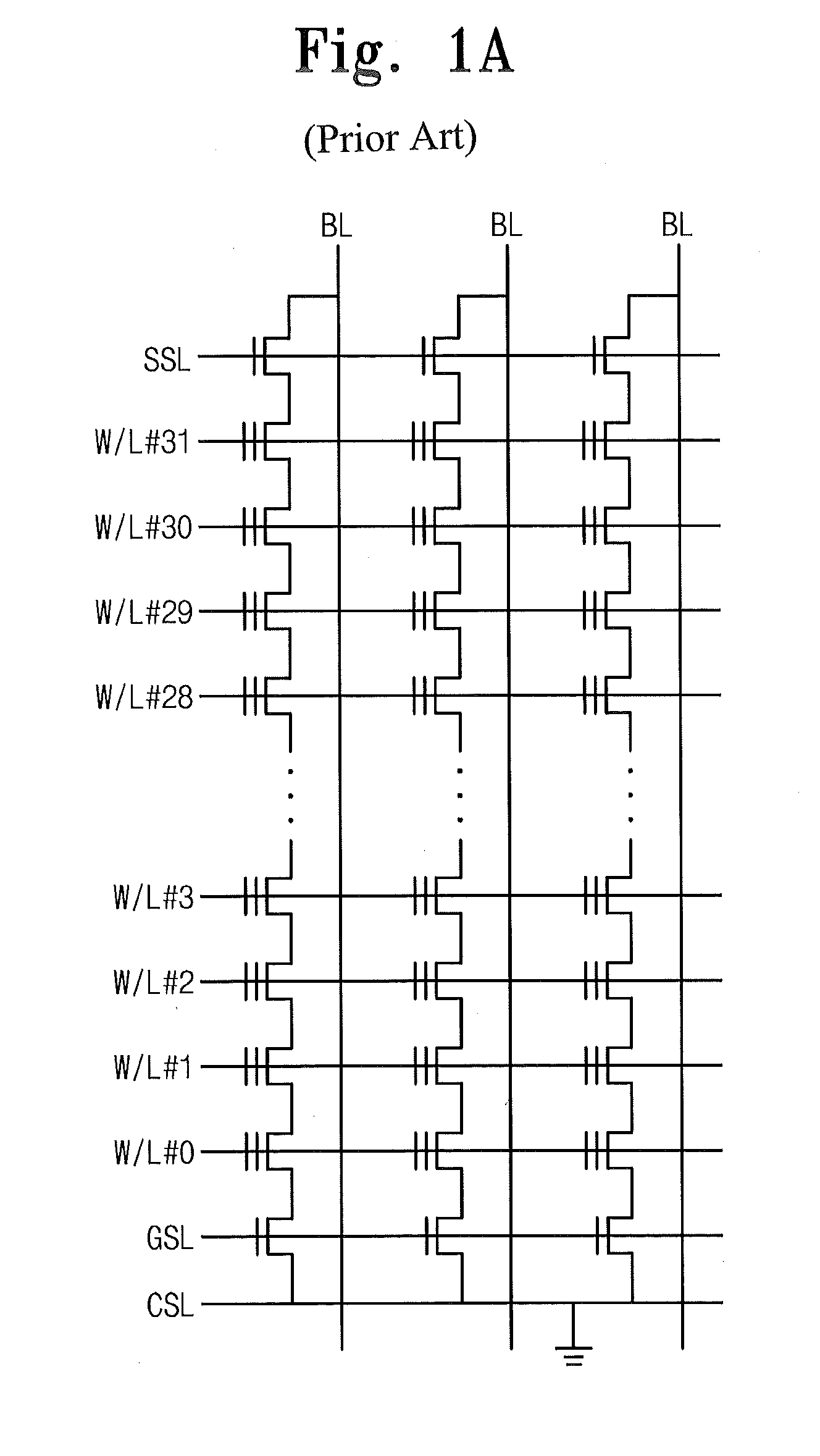

Semiconductor memory device and method of manufacturing semiconductor memory device

InactiveUS20120213000A1Reduce parasitic capacitanceParasitic capacitance is generatedTransistorSolid-state devicesWrite bitMemory cell

A highly integrated gain cell-type semiconductor memory is provided. A first insulator, a read bit line, a second insulator, a third insulator, a first semiconductor film, first conductive layers, and the like are formed. A projecting insulator is formed thereover. Then, second semiconductor films and a second gate insulating film are formed to cover the projecting insulator. After that, a conductive film is formed and subjected to anisotropic etching, so that write word lines are formed on side surfaces of the projecting insulator. A third contact plug for connection to a write bit line is formed over a top of the projecting insulator. With such a structure, the area of the memory cell can be 4 F2 at a minimum.

Owner:SEMICON ENERGY LAB CO LTD

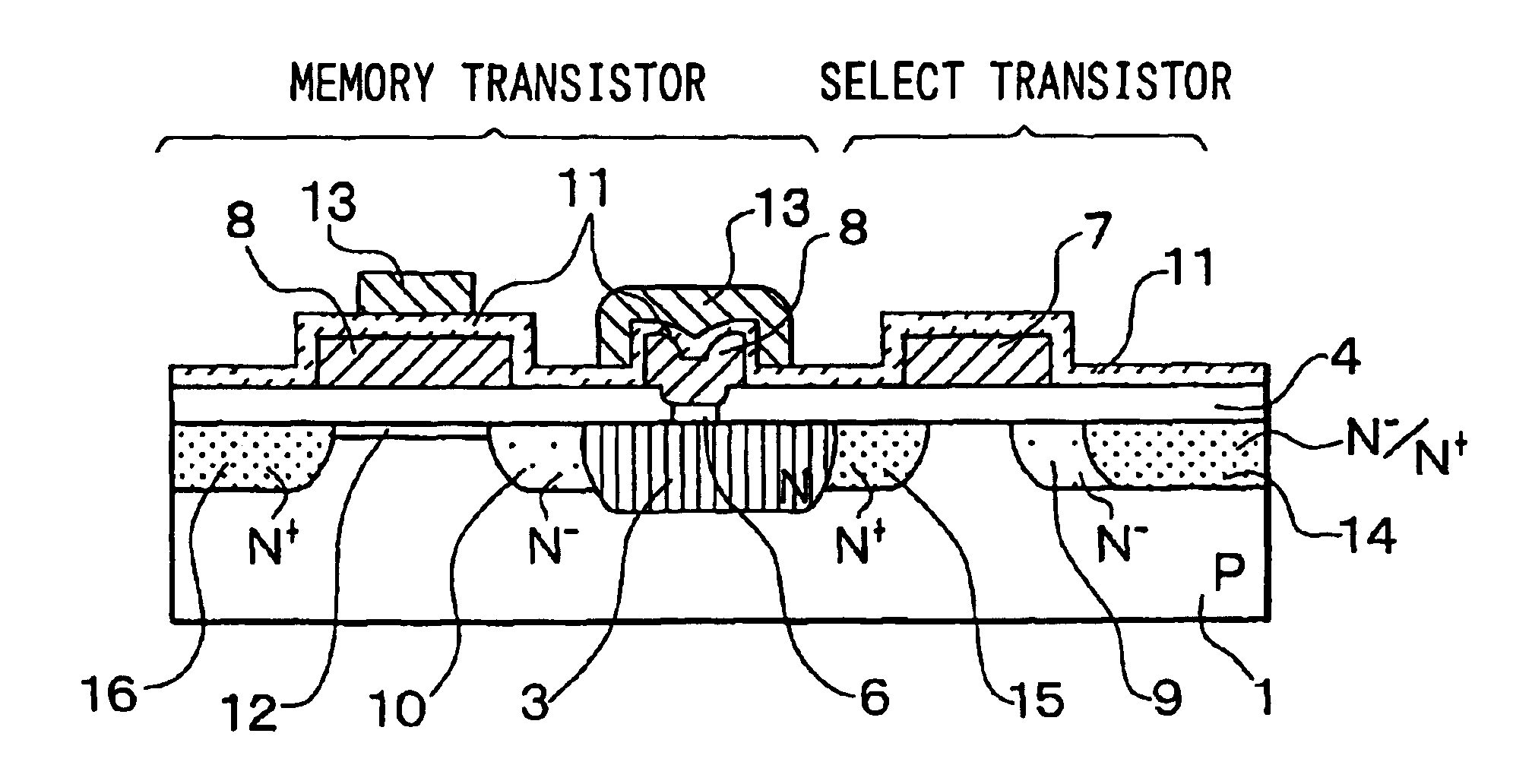

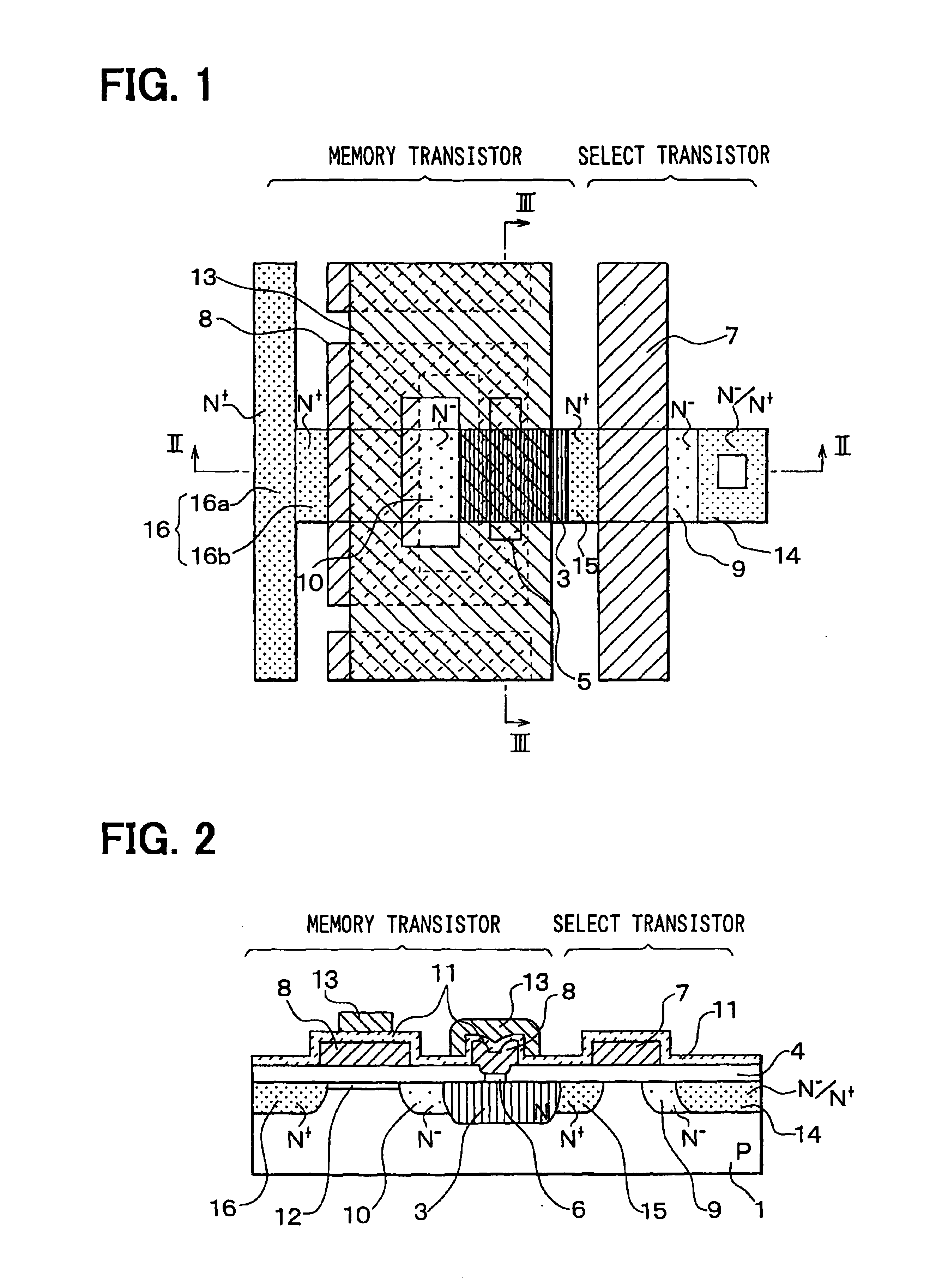

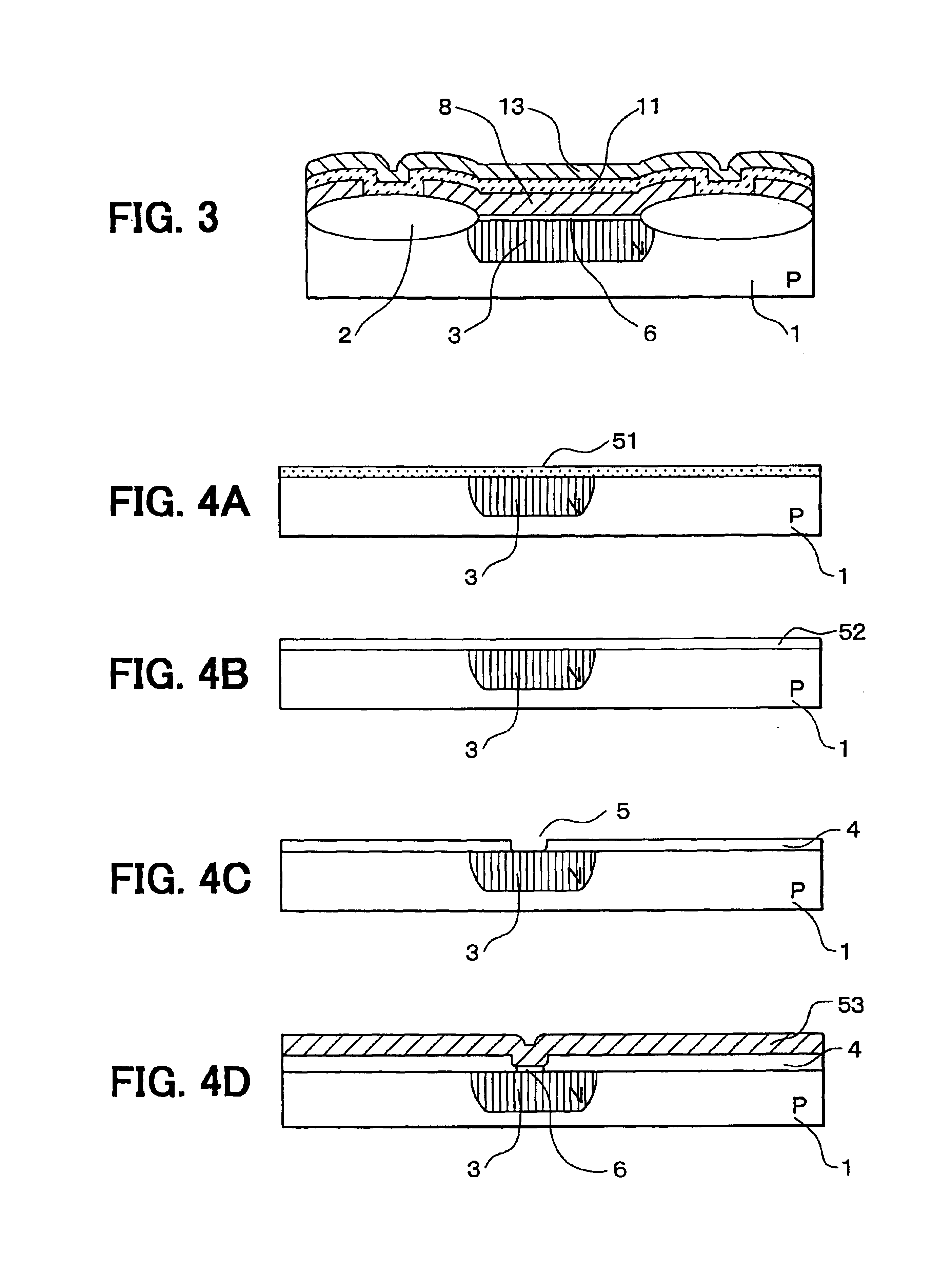

EEPROM and EEPROM manufacturing method

InactiveUS6914288B2Suppress reduction of overwriting life and deterioration of charge holding characteristicSimple methodTransistorSolid-state devicesEngineeringTransistor

A memory transistor of an EEPROM has a floating gate electrode of a shape such that it covers the entirety of a tunnel film and a channel region and does not cover a region between the channel region and an embedded layer. And, a control gate electrode is formed on an interlayer insulating film on the floating gate electrode into a shape such that it is wider than the floating gate electrode above the tunnel film, and is narrower than the floating gate electrode above the channel region.

Owner:DENSO CORP

Display device

InactiveUS20050168678A1Improve display qualityHorizontal stripes can be suppressedElectroluminescent light sourcesSolid-state devicesLine widthDisplay device

A display device includes: a plurality of signal lines which extend in a zigzag manner in a column direction and to which image signals are supplied, respectively; an insulation film which covers the plurality of signal lines; and a plurality of pixel electrodes which are formed on the insulation film and to which the image signals are input from the plurality of signal lines, respectively. A distance between ones of the pixel electrodes located adjacent to each other in the column direction is equal to or larger than a line width of the signal lines.

Owner:SHARP KK

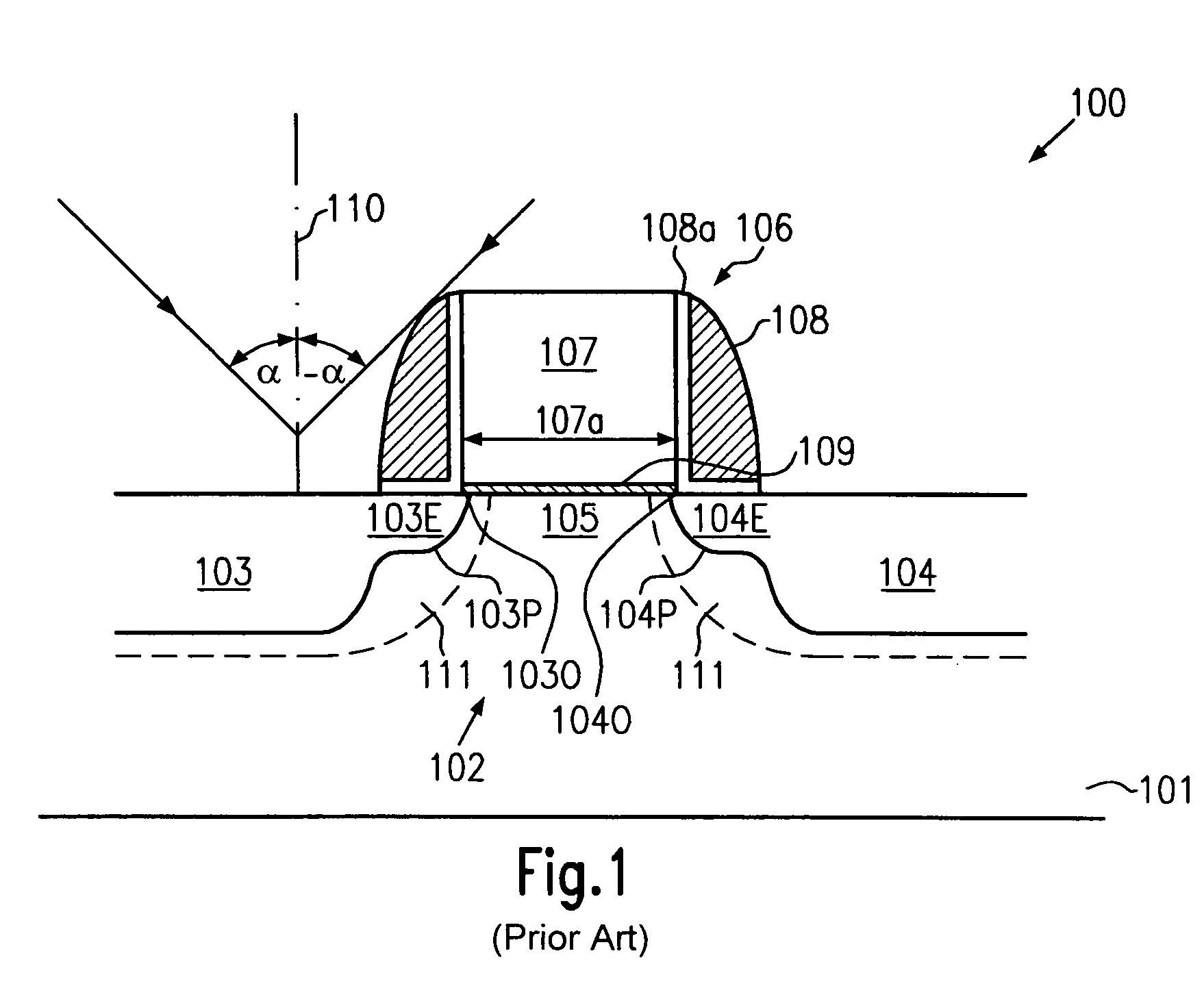

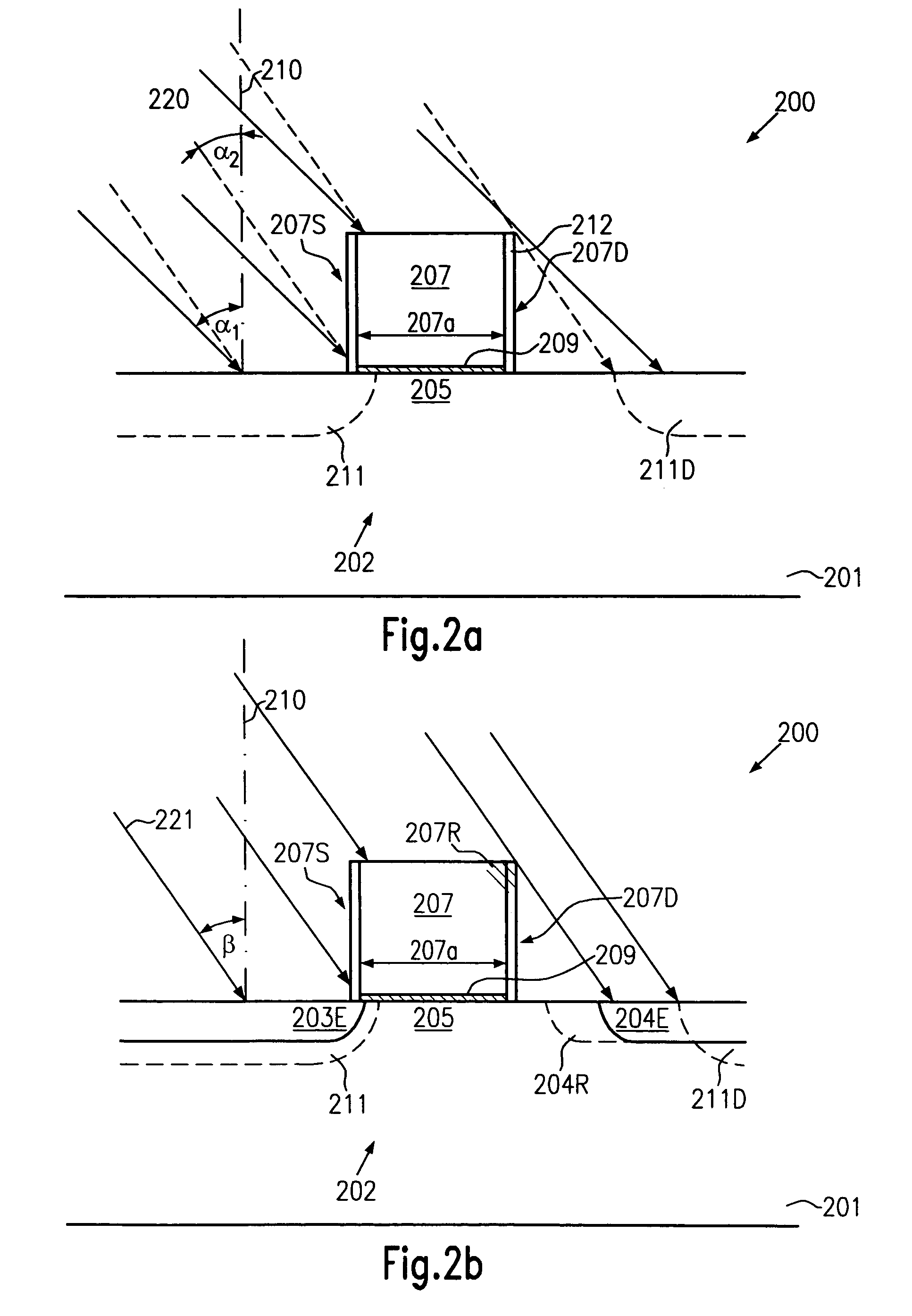

Transistor having an asymmetric source/drain and halo implantation region and a method of forming the same

ActiveUS7208397B2Improving drive current capabilityImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesConcentration gradientField-effect transistor

By providing an asymmetric design of a halo region and extension regions of a field effect transistor, the transistor performance may significantly be enhanced for a given basic transistor architecture. In particular, a large overlap area may be created at the source side with a steep concentration gradient of the PN junction due to the provision of the halo region, whereas the drain overlap may be significantly reduced or may even completely be avoided, wherein a moderately reduced concentration gradient may further enhance the transistor performance.

Owner:ADVANCED MICRO DEVICES INC

Semiconductor Devices Comprising a Plurality of Gate Structures

ActiveUS20110163367A1Volume of the gaps may be increased/maximizedParasitic capacitanceTransistorSolid-state devicesGate dielectricDevice material

Semiconductor devices are provided. The semiconductor devices may include a plurality of gate structures disposed on a semiconductor substrate, each of the gate structures including a floating gate, an inter-gate dielectric layer, and a control gate. The semiconductor devices may also include liners on opposing sidewalls of adjacent ones of the gate structures. The liners may define a gap. A first width of the gap may be less than a second width of the gap.

Owner:SAMSUNG ELECTRONICS CO LTD

Thin film transistor array panel and liquid crystal display including the panel

ActiveUS7417694B2Parasitic capacitanceIncrease the aperture ratioTransistorStatic indicating devicesLiquid-crystal displayEngineering

A thin film transistor (TFT) array panel is provided, which includes: a plurality of gate lines transmitting gate signals; a plurality of data lines intersecting the gate lines and transmitting data signals, each data line including first and second data line branches electrically connected to each other and spaced apart from each other; a plurality of pixel electrodes electrically connected to the gate lines and the data lines through thin film transistor and covering edges of the first or the second data line branches; a passivation layer disposed between the data lines and the pixel electrodes; and a light blocking member covering gaps between the first data line branches and the second data line branches.

Owner:SAMSUNG DISPLAY CO LTD

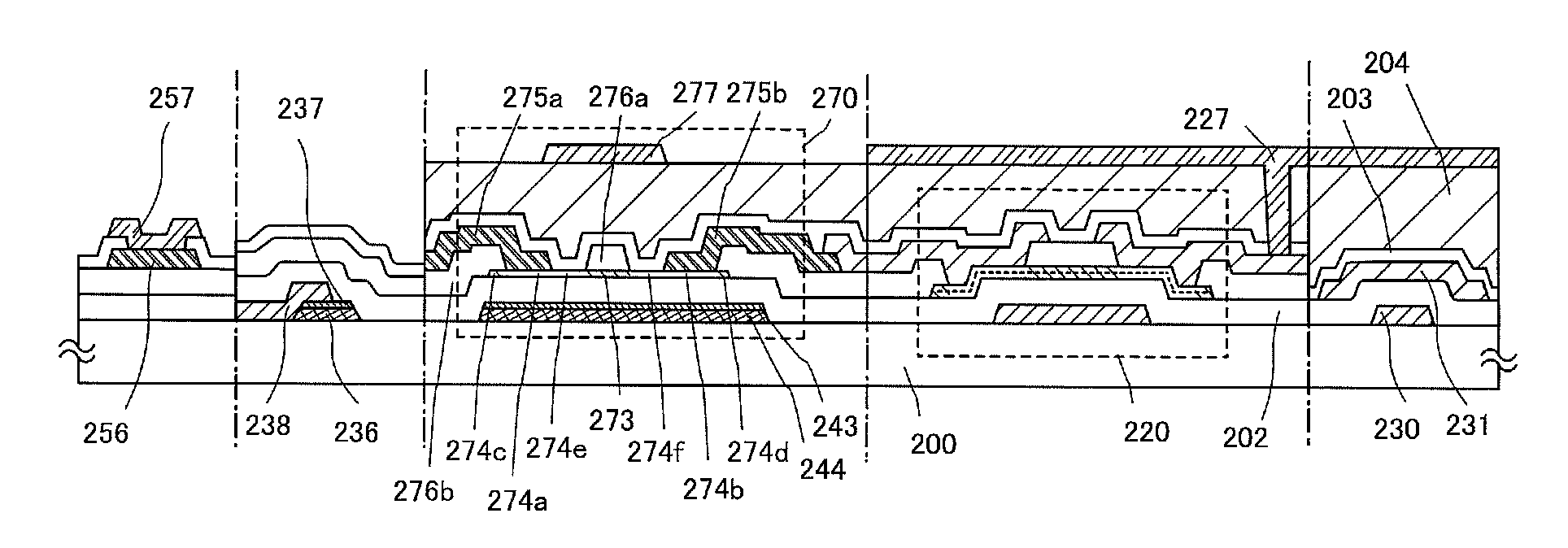

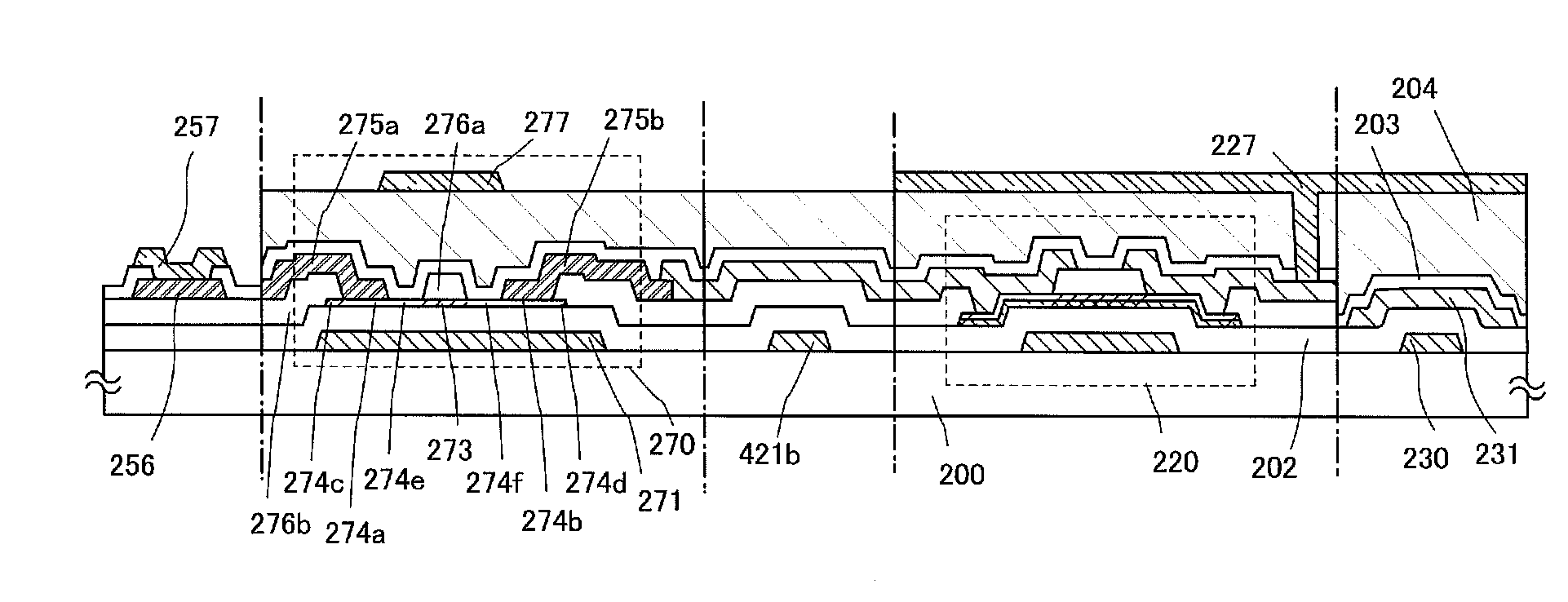

Semiconductor device and method for manufacturing semiconductor device

ActiveUS8629441B2DistanceParasitic capacitanceTransistorElectroluminescent light sourcesDriver circuitDevice material

The semiconductor device includes a driver circuit including a first thin film transistor and a pixel including a second thin film transistor over one substrate. The first thin film transistor includes a first gate electrode layer, a gate insulating layer, a first oxide semiconductor layer, a first oxide conductive layer, a second oxide conductive layer, an oxide insulating layer which is in contact with part of the first oxide semiconductor layer and which is in contact with peripheries and side surfaces of the first and second oxide conductive layers, a first source electrode layer, and a first drain electrode layer. The second thin film transistor includes a second gate electrode layer, a second oxide semiconductor layer, and a second source electrode layer and a second drain electrode layer each formed using a light-transmitting material.

Owner:SEMICON ENERGY LAB CO LTD

Liquid Crystal Display and Substrate Thereof

ActiveUS20090033823A1Reduce parasitic capacitanceImprove signal transmission qualityStatic indicating devicesNon-linear opticsLiquid-crystal displayParasitic capacitance

A liquid crystal display having a repair circuit structure and an array substrate of the liquid crystal display are provided. Each of the repair lines of the repair circuit comprises a front repair line portion arranged to cross with a front data line portion in a substantially perpendicular manner, an end repair line portion arranged to cross with an end data line portion in a substantially perpendicular manner, and an intermediate repair line portion connecting the front and end repair line portions. At least two repair lines in the end repair line portion are positioned in different layers so that a parasitic capacitance between respective repair lines in the repair circuit structure can be reduced and signal transmission quality can be ensured.

Owner:KUSN INFOVISION OPTOELECTRONICS

Surface acoustic wave filter and communication apparatus

InactiveUS7295089B2Improve balanceParasitic capacitanceImpedence networksPiezoelectric/electrostriction/magnetostriction machinesElectrical conductorPermittivity

A surface acoustic wave (SAW) filter includes a piezoelectric substrate. A resin pattern having a permittivity less than that of the piezoelectric substrate and first and second conductor patterns are disposed on the piezoelectric substrate. The first conductor pattern defines two one-terminal-pair SAW resonators and two longitudinally coupled resonator SAW filters. A portion of the second conductor pattern defines wiring traces having different potentials. Portions of the wiring traces facing each other in a plan view are disposed on the resin pattern.

Owner:MURATA MFG CO LTD

Semiconductor device and display apparatus

ActiveUS20140097455A1Parasitic capacitanceReduce parasitic capacitanceTransistorSolid-state devicesSemiconductor packageSemiconductor device

A semiconductor device according to an aspect of the present invention includes: a semiconductor layer including a channel region and a contact region; a pattern of a first conducting layer disposed at a position which overlaps with the channel region; a gate line formed in one of a second conducting layer or a third conducting layer, and connected to the pattern of the first conducting layer; and a source line formed in the other of the second conducting layer and the third conducting layer, and connected to the contact region.

Owner:JOLED INC

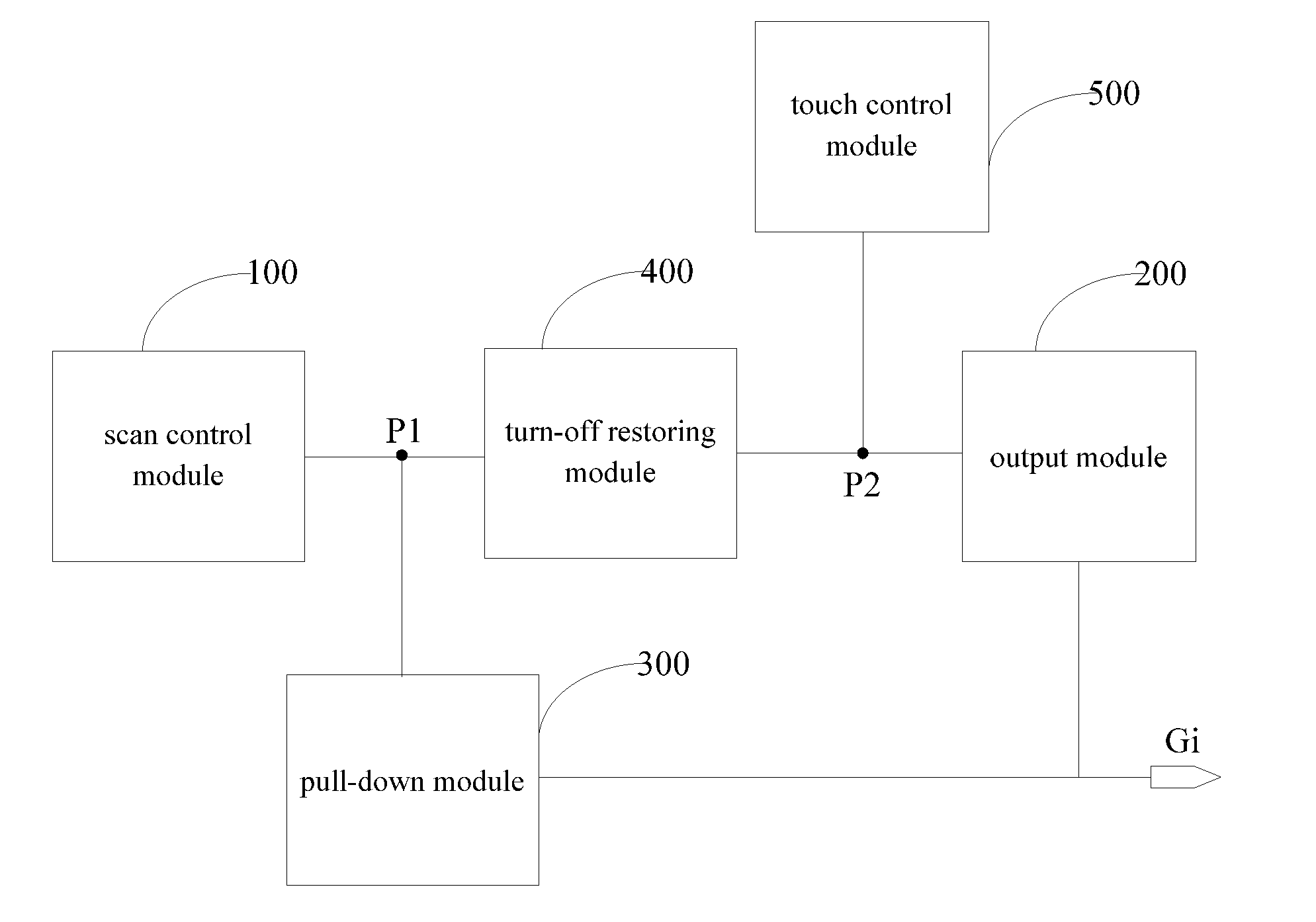

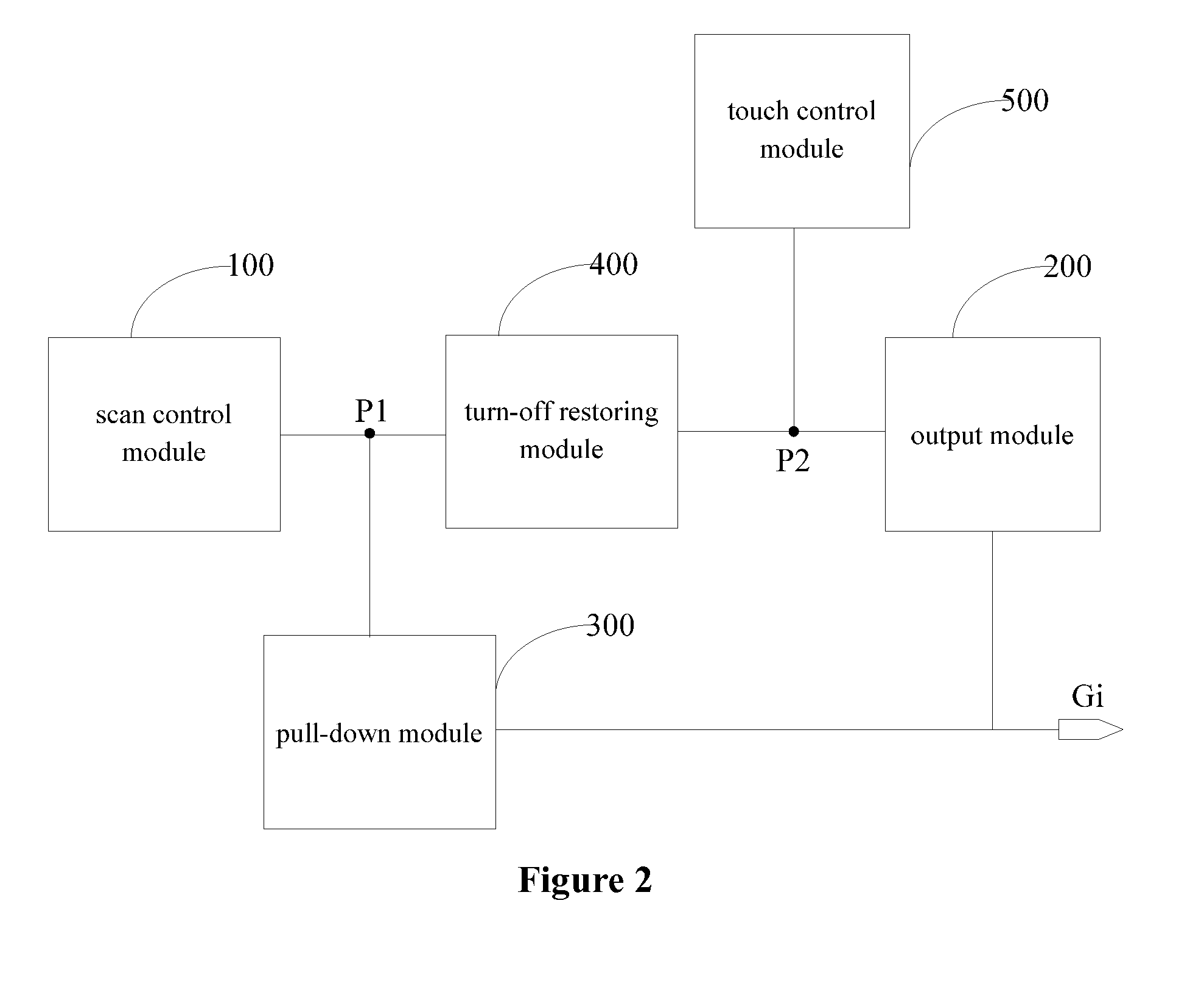

Shift register, driving method, gate driving circuit and display device

ActiveUS20160328045A1Parasitic capacitanceReduce loadStatic indicating devicesInput/output processes for data processingElectricityShift register

A shift register, a driving method, a gate driving circuit and a display device are provided. The shift register includes a scan control module, an output module, a pull-down module, a turn-off restoring module and a touch control module. The turn-off restoring module is electronically connected to the scan control module at a first node and electronically connected to the touch control module and the output module at a second node. The turn-off restoring module controls the first node to be electrically insulated from the second node during a touch scan phase, and restores a potential of the second node to a potential at a time instant before the touch scan phase when the touch scan phase is finished. The touch control module controls the output module to output a touch scan signal to an output terminal of the shift register during the touch scan phase.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD +1

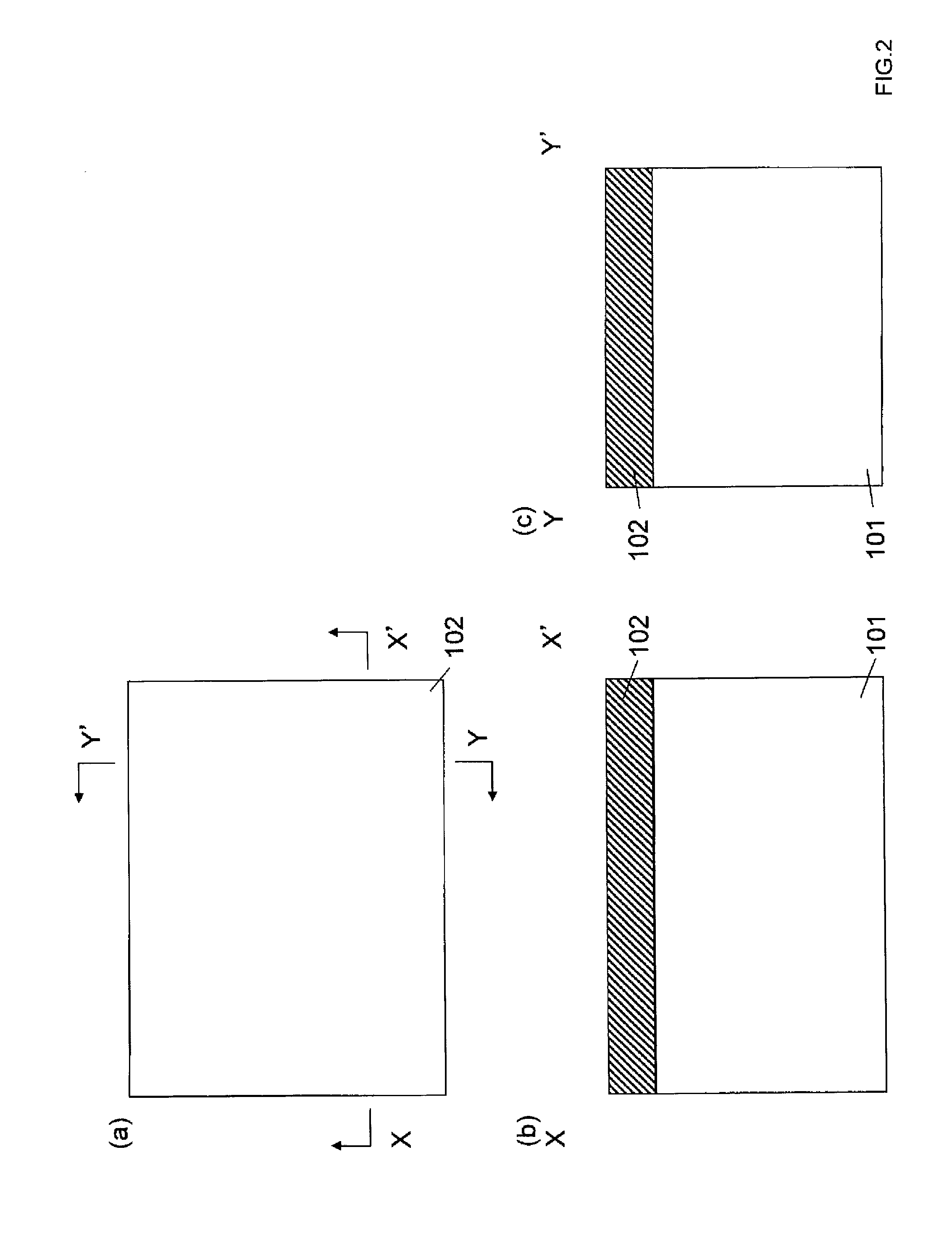

Liquid crystal display device and manufacturing method of liquid crystal display device

ActiveUS20120229724A1Increase contrastIncrease display areaLiquid crystal compositionsPretreated surfacesElectric fieldLiquid-crystal display

A horizontal electric field mode liquid crystal display device having a novel electrode structure, and a manufacturing method thereof are provided. The liquid crystal display device includes a first substrate having an insulating surface; a first conductive film and a second conductive film over the insulating surface; a first insulating film over the first conductive film; a second insulating film over the second conductive film; a second substrate facing the first substrate; and a liquid crystal layer positioned between the first substrate and the second substrate. Part of the first conductive film exists also on a side portion of the first insulating film, and part of the second conductive film exists also on a side portion of the second insulating film. The liquid crystal layer includes liquid crystal exhibiting a blue phase.

Owner:SEMICON ENERGY LAB CO LTD