Patents

Literature

299 results about "Write bit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

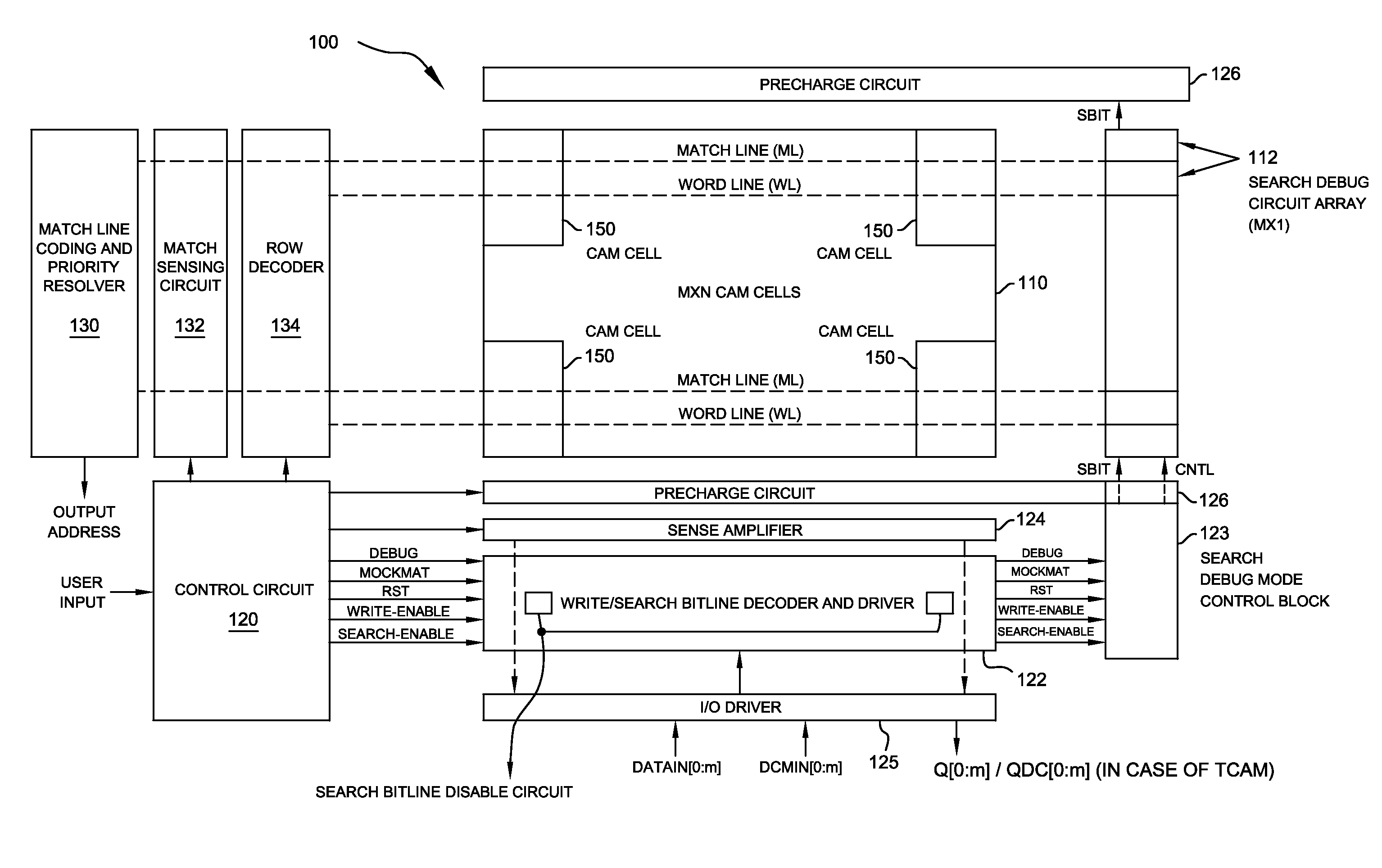

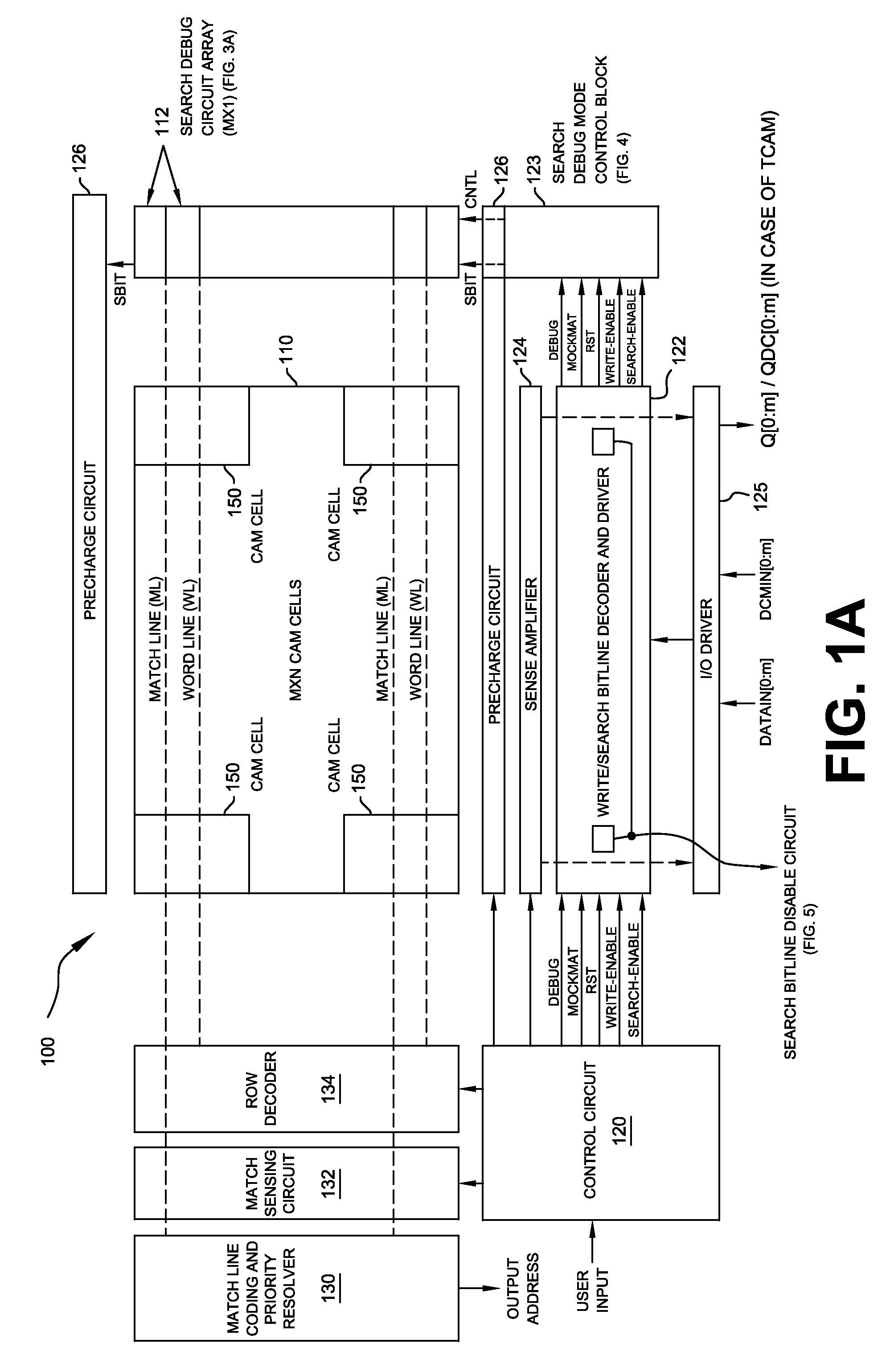

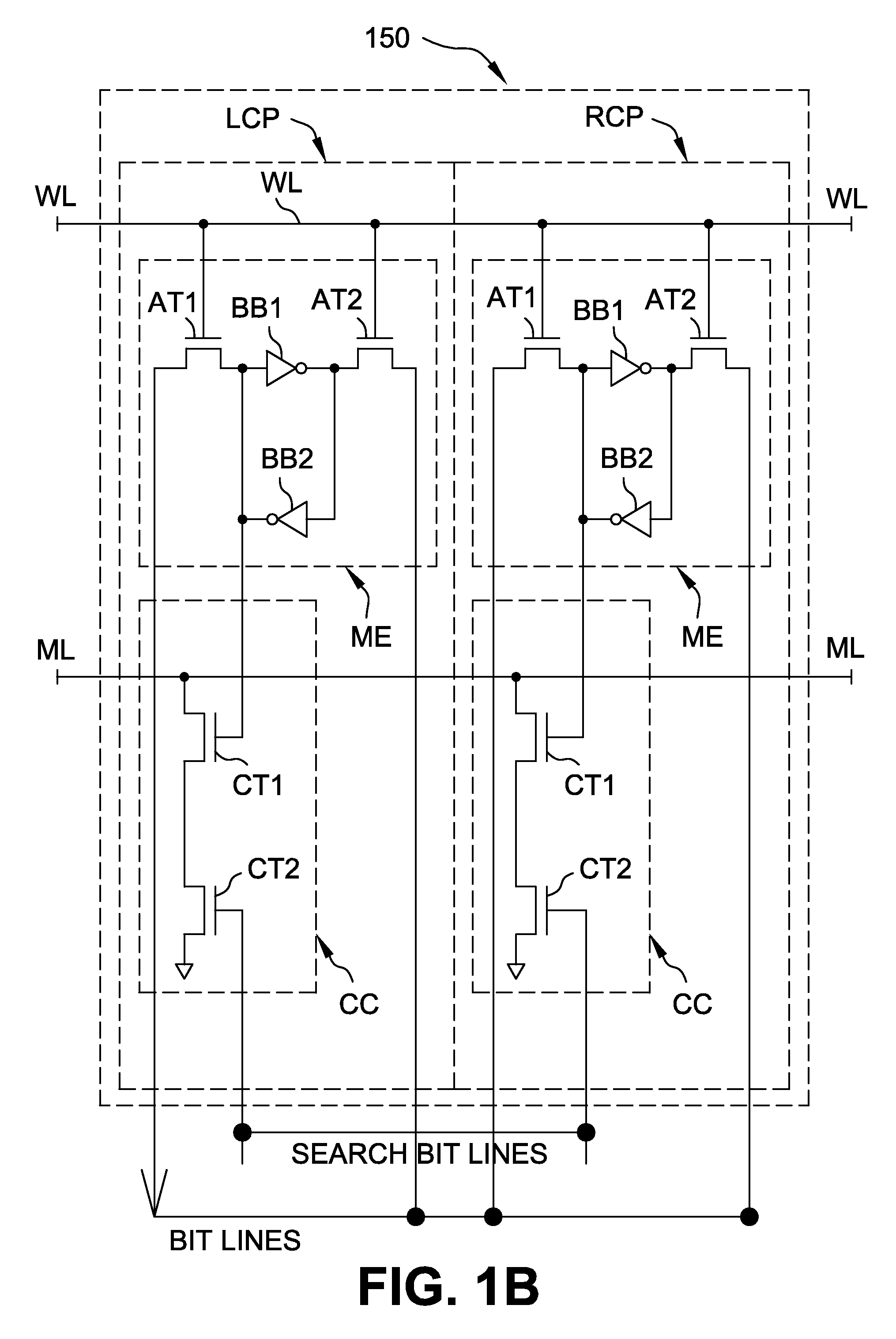

Novel match mismatch emulation scheme for an addressed location in a cam

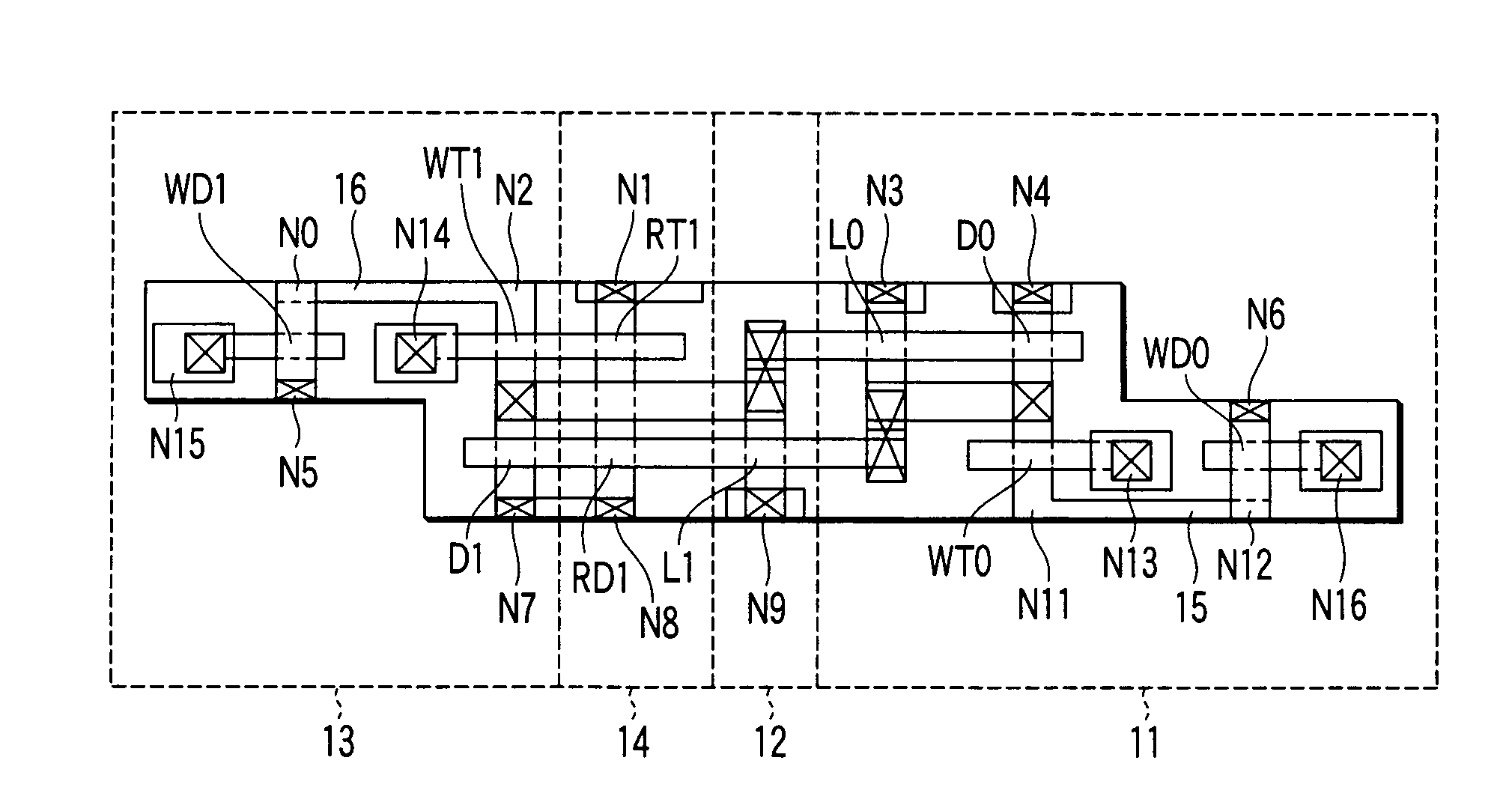

A novel match / mismatch emulation scheme for an addressed location in a CAM system that includes a plurality of CAM blocks. The plurality of CAM blocks are organized into at least one rectangular array having rows each having a plurality of CAM blocks, a group of CAM cells and associated read / write bit lines connecting the group of CAM cells to an addressed search circuit. During debug mode, where the individual array cells do not participate in search, all the cells in the debug column behave the same way to emulate a match / mismatch on all words. The circuit provides a control input to include address evaluation of a debug cell in a row. The circuit also provides simultaneous switching noise analysis on an evaluating row. The resulting CAM cell provides a circuit to test individual rows for defects and noise analysis.

Owner:TEXAS INSTR INC

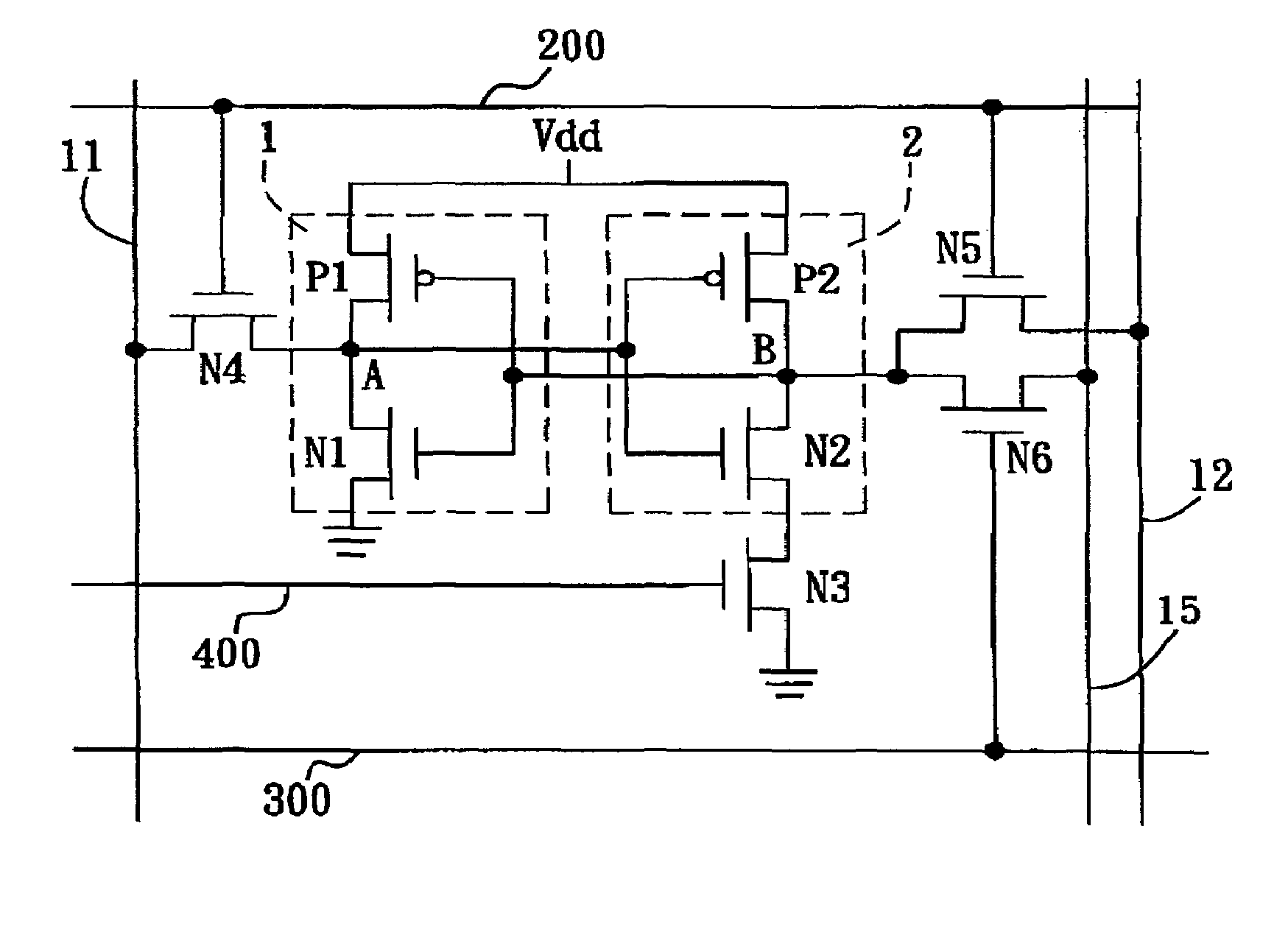

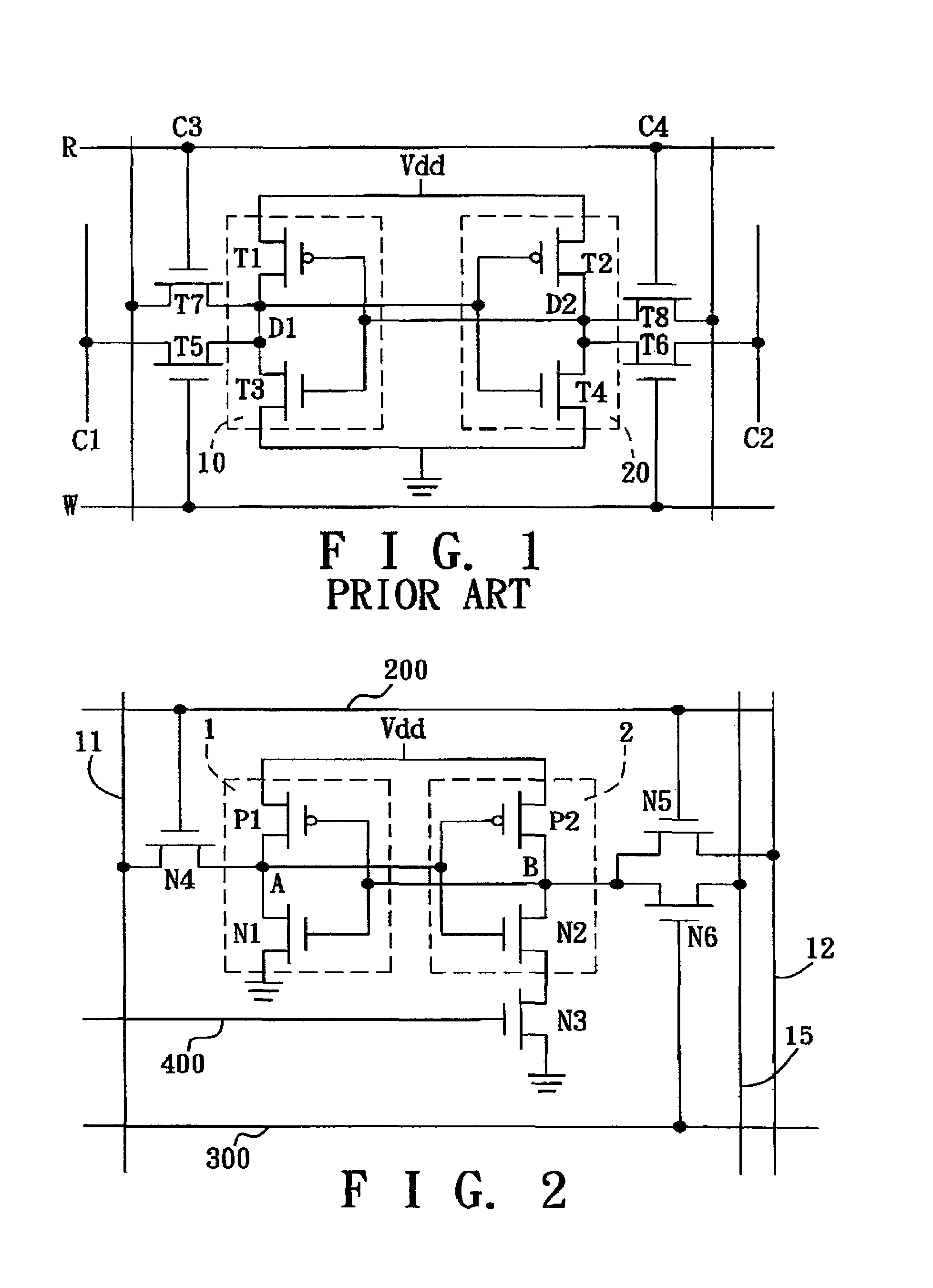

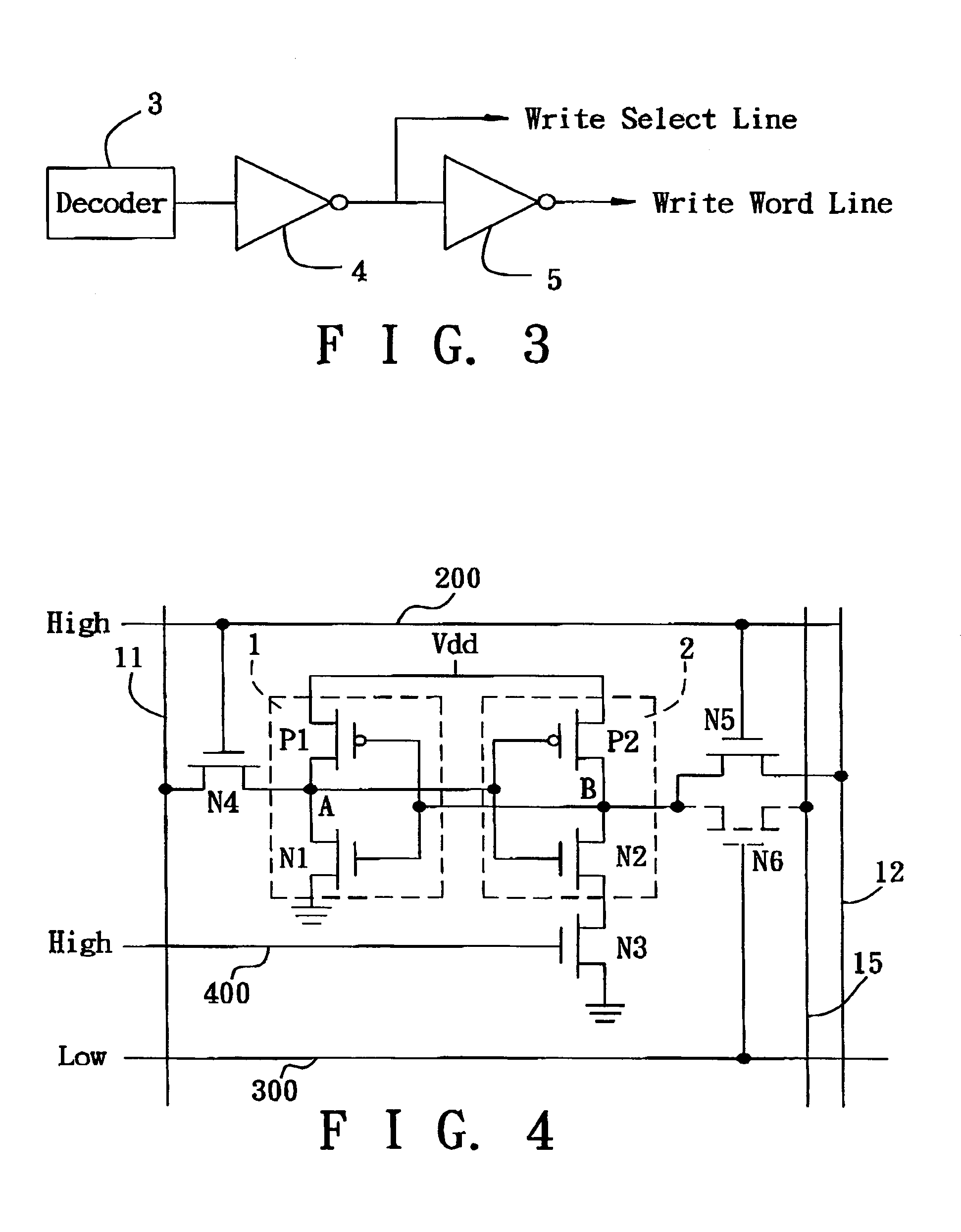

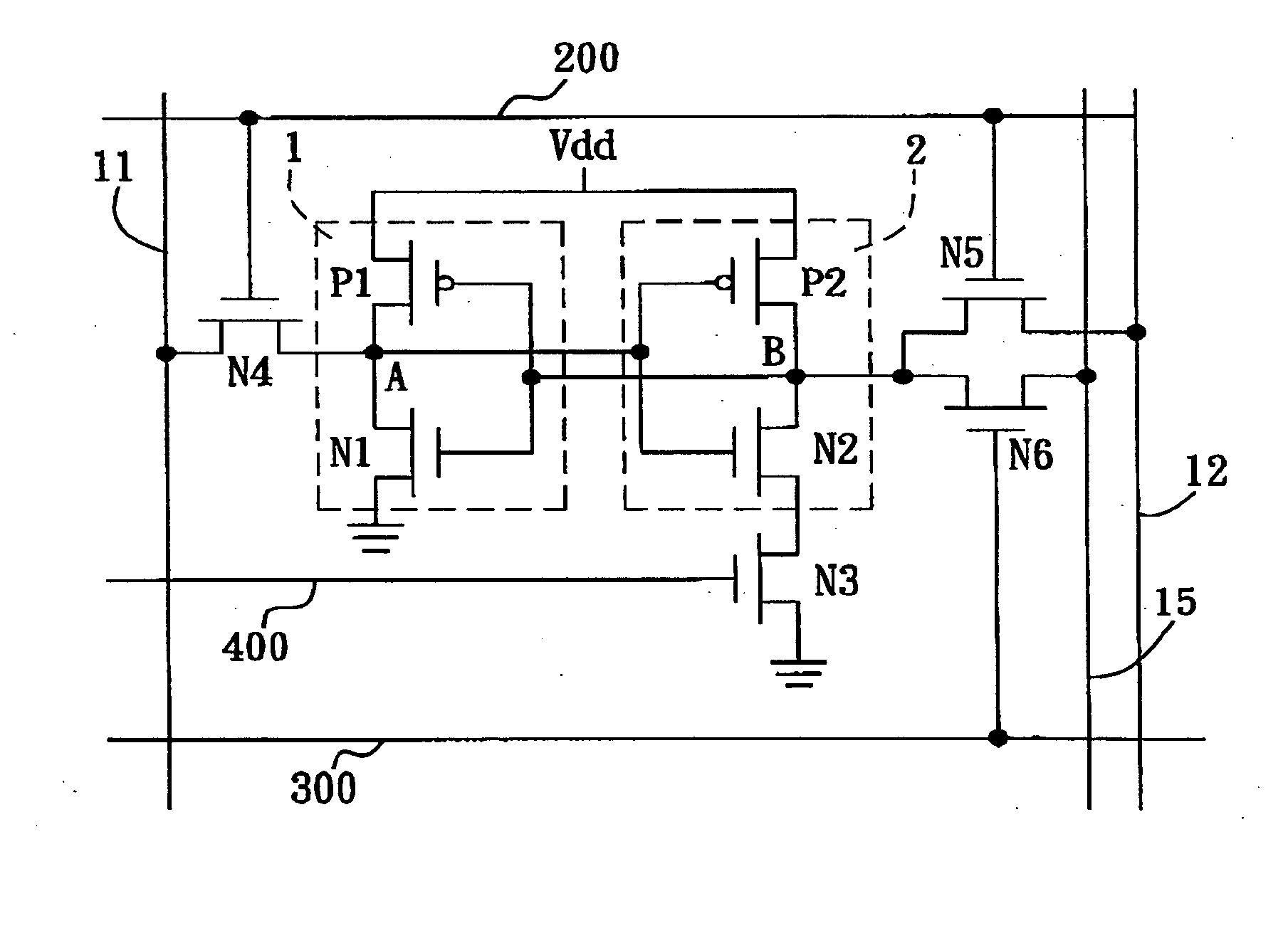

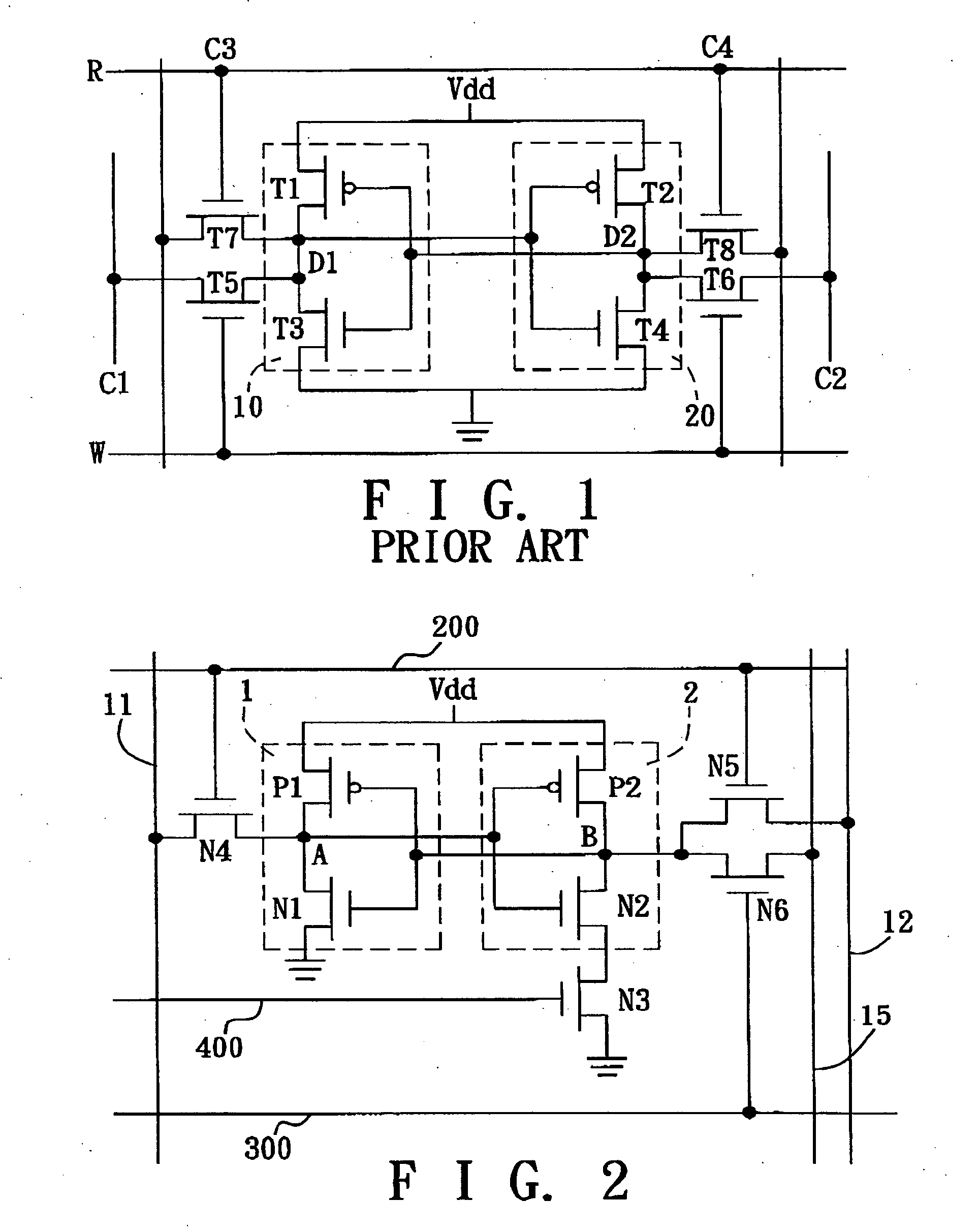

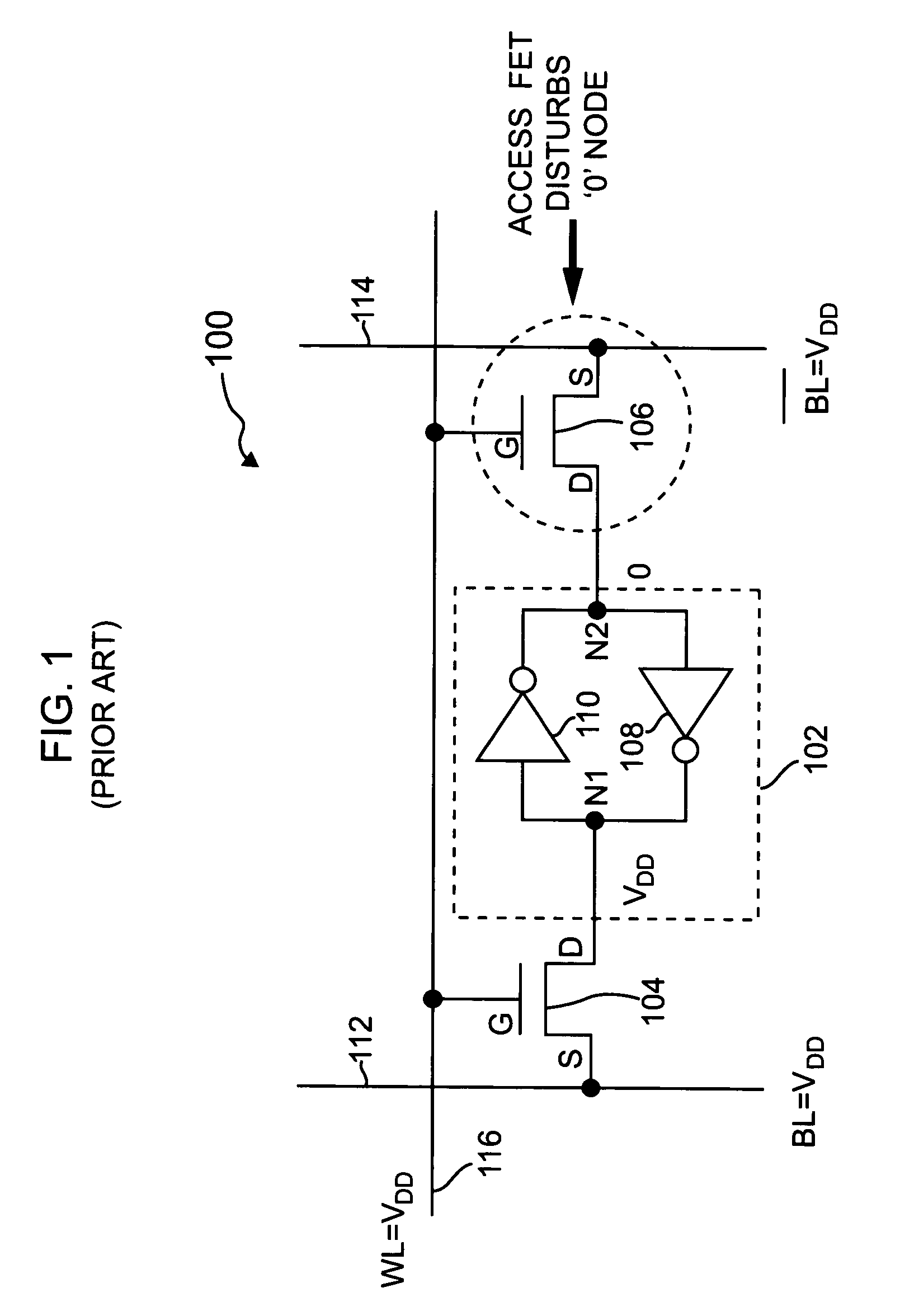

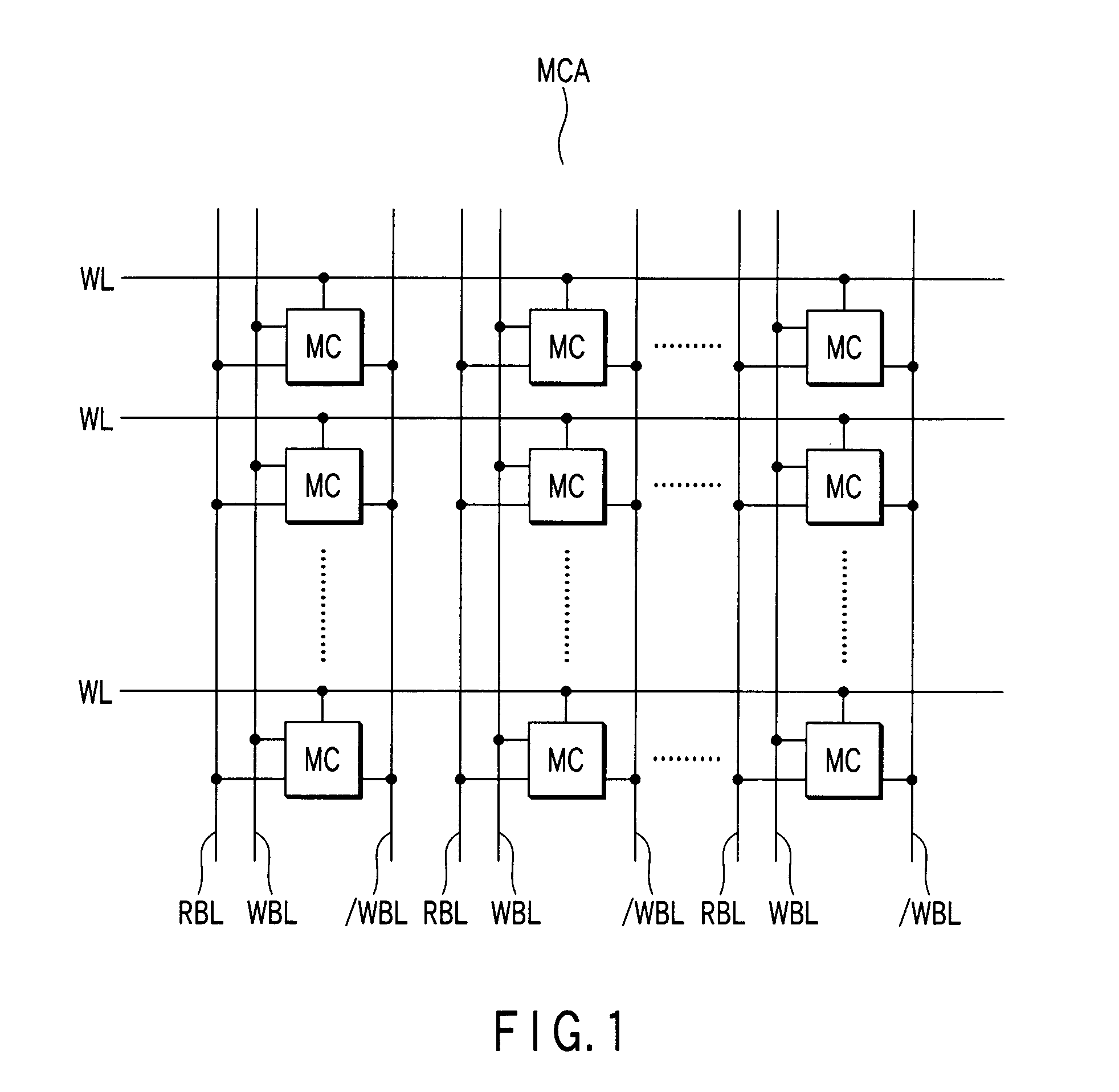

Low-power SRAM memory cell

An SRAM memory cell that has a relatively small power consumption when writing a write value of ‘0’ to the memory cell includes cross-coupled first and second inverters, at least one read access transistor for selectively coupling a respective read bit line to a common connection node of a respective one of the first and second inverters, a switching transistor for selectively coupling the second inverter to a ground terminal, and a write access transistor for selectively coupling the common connection node of the second inverter to a write bit line.

Owner:NAT TAIWAN UNIV

Low-power SRAM memory cell

An SRAM memory cell that has a relatively small power consumption when writing a write value of ‘0’ to the memory cell includes cross-coupled first and second inverters, at least one read access transistor for selectively coupling a respective read bit line to a common connection node of a respective one of the first and second inverters, a switching transistor for selectively coupling the second inverter to a ground terminal, and a write access transistor for selectively coupling the common connection node of the second inverter to a write bit line.

Owner:NAT TAIWAN UNIV

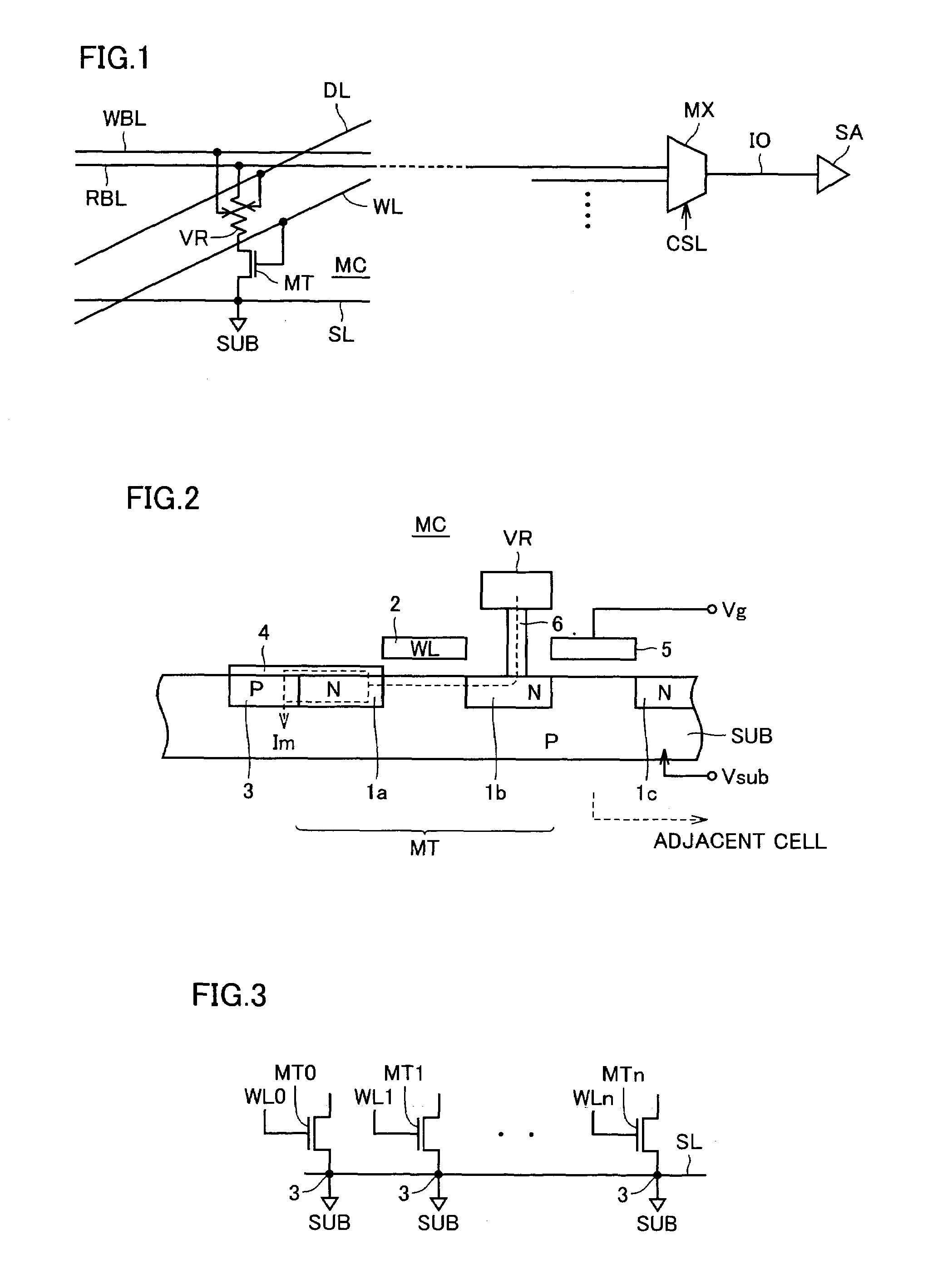

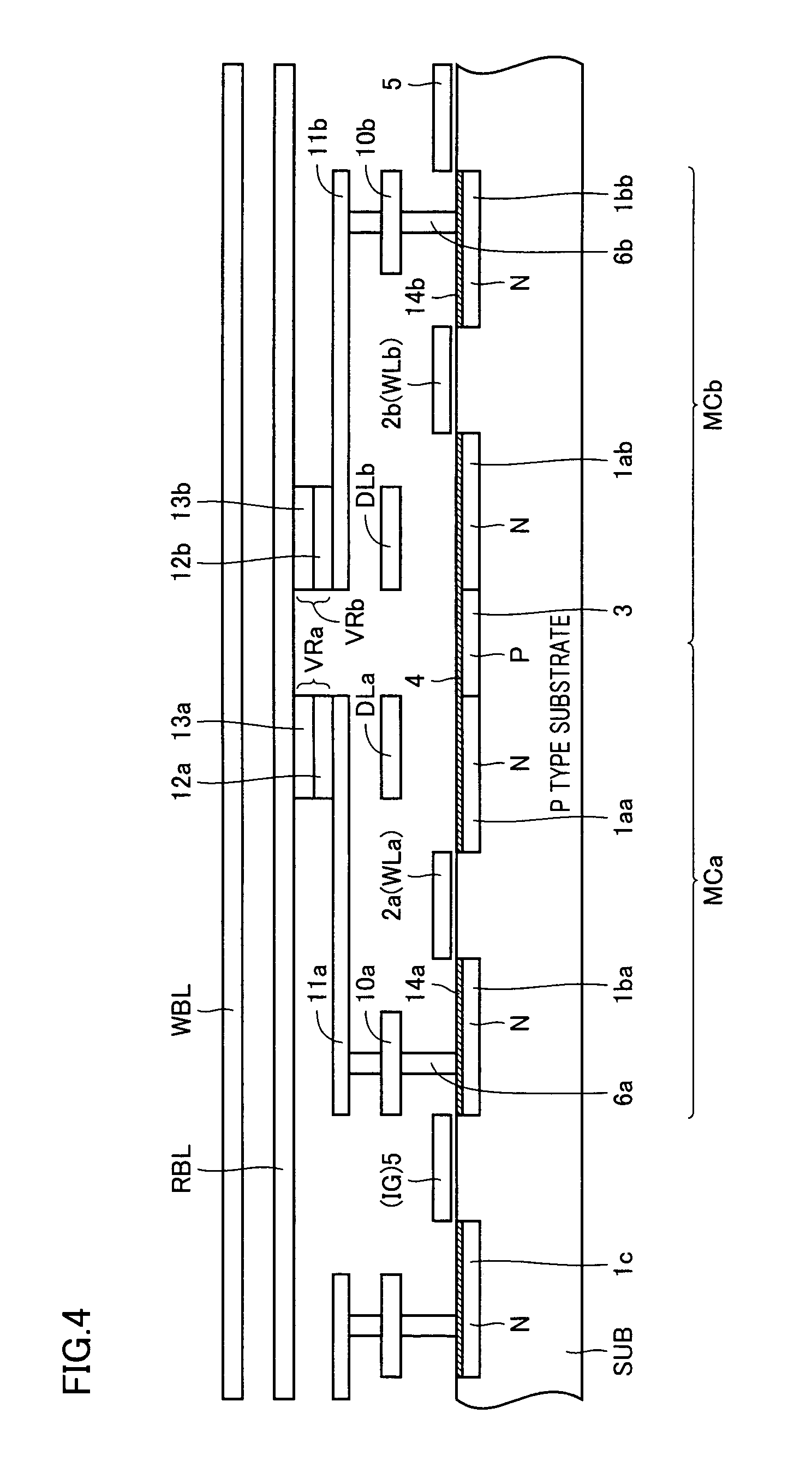

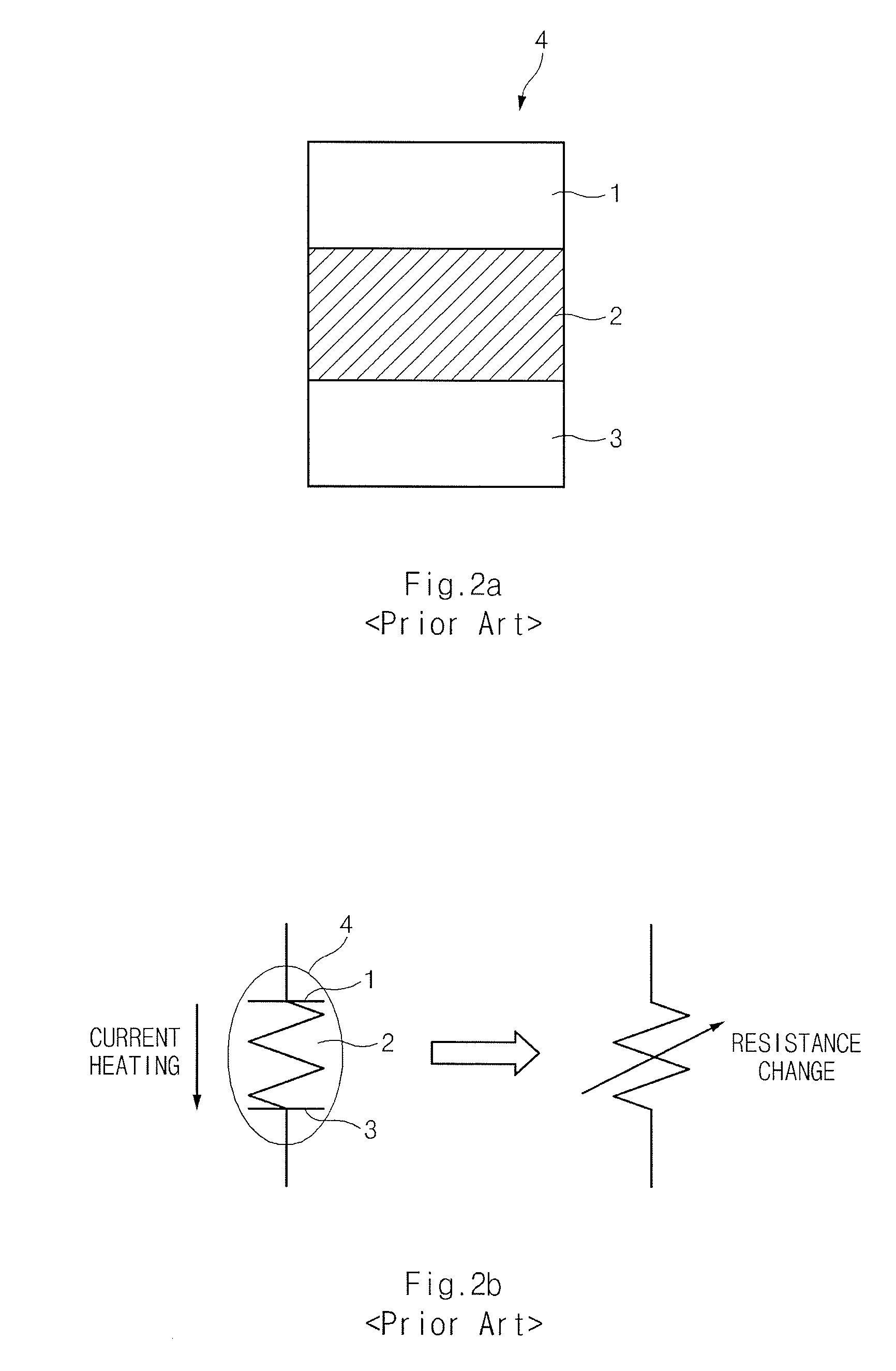

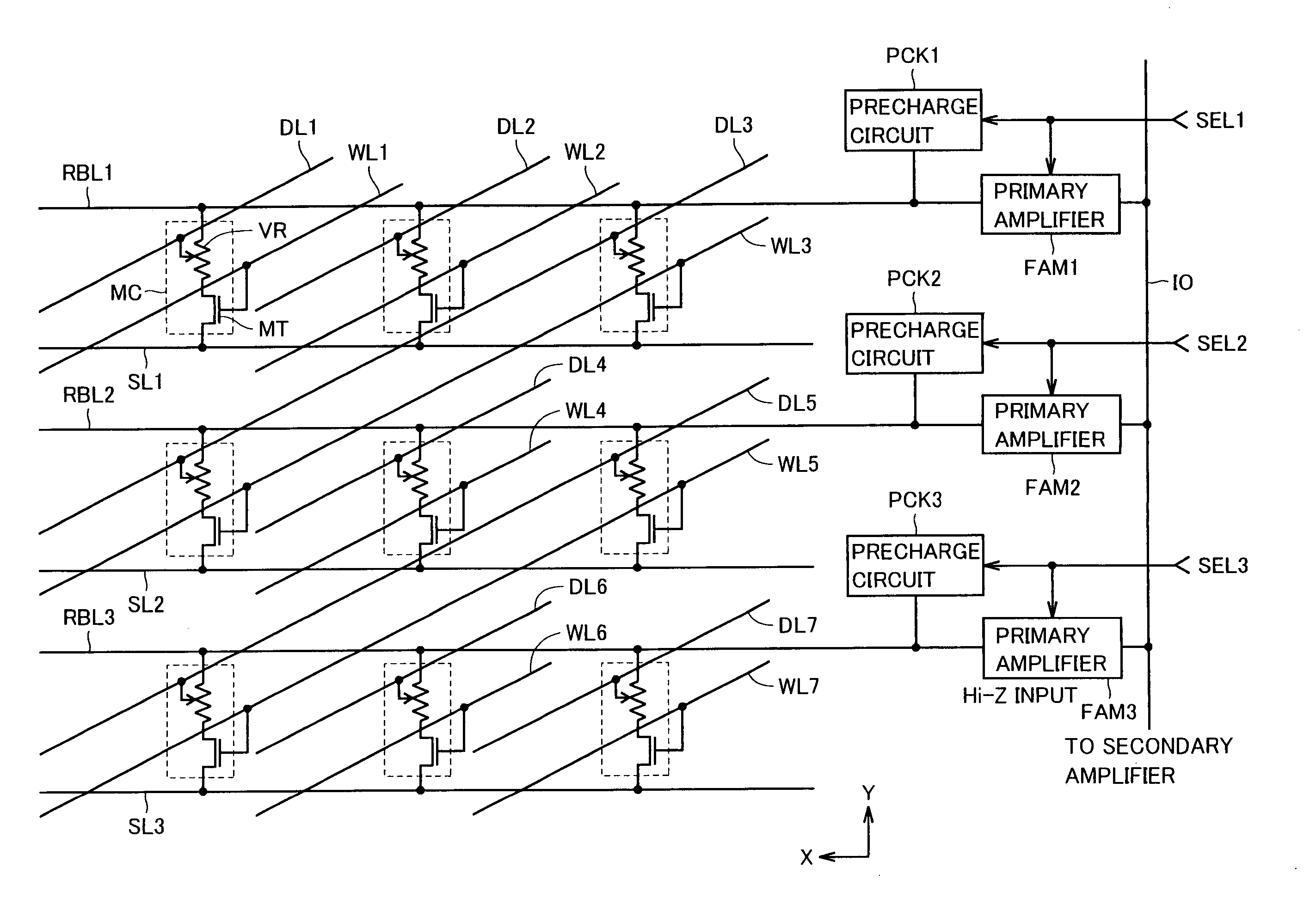

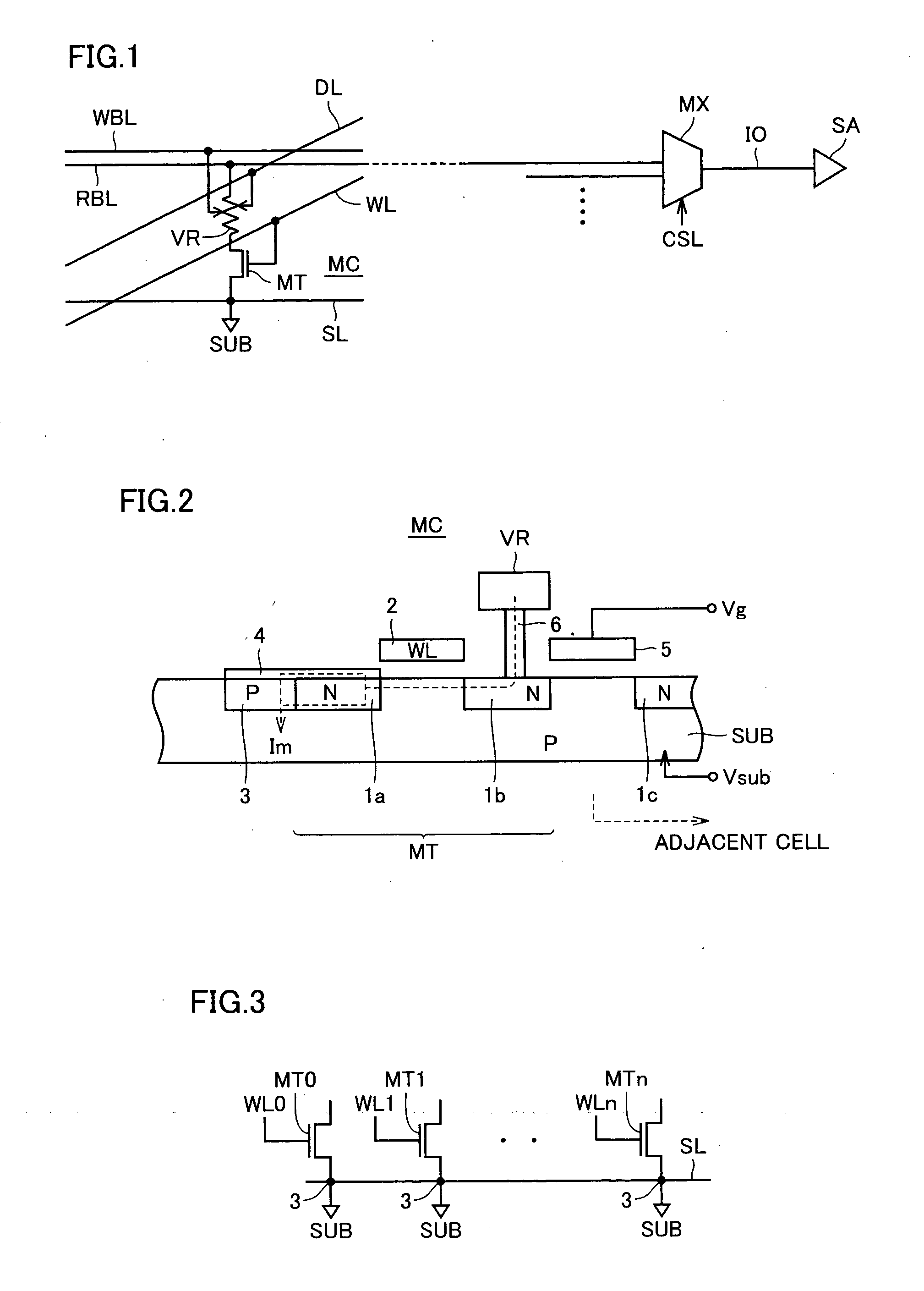

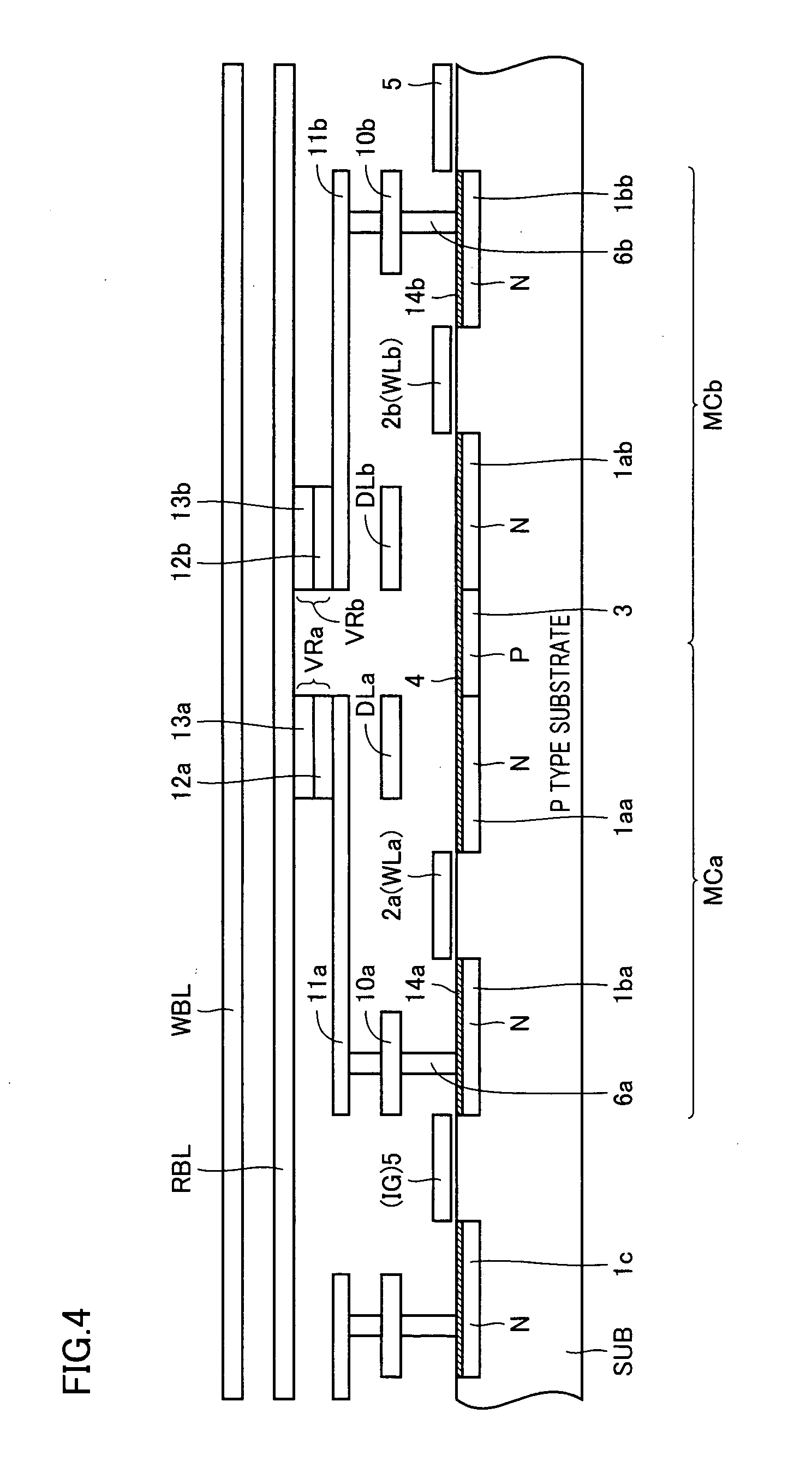

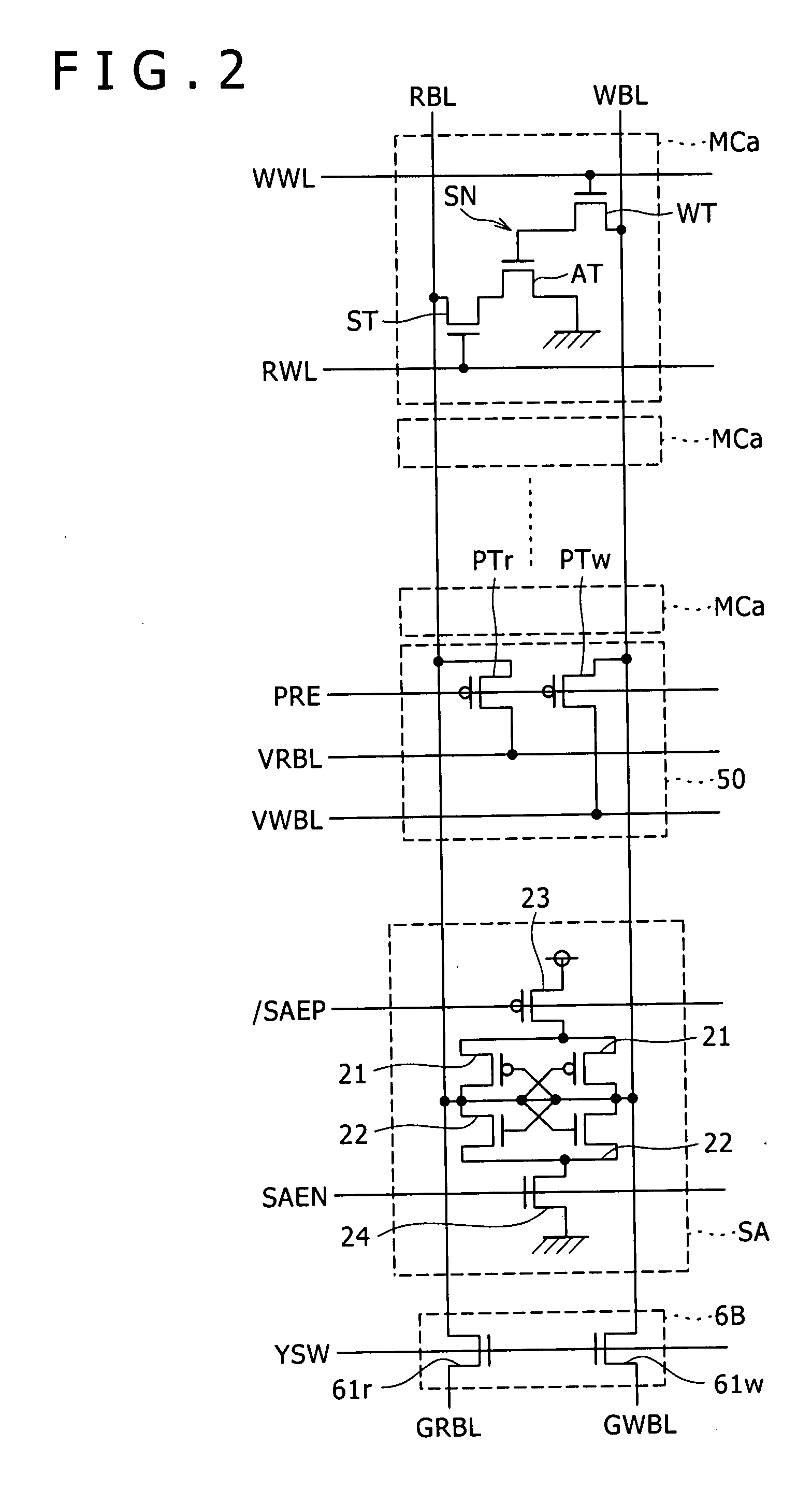

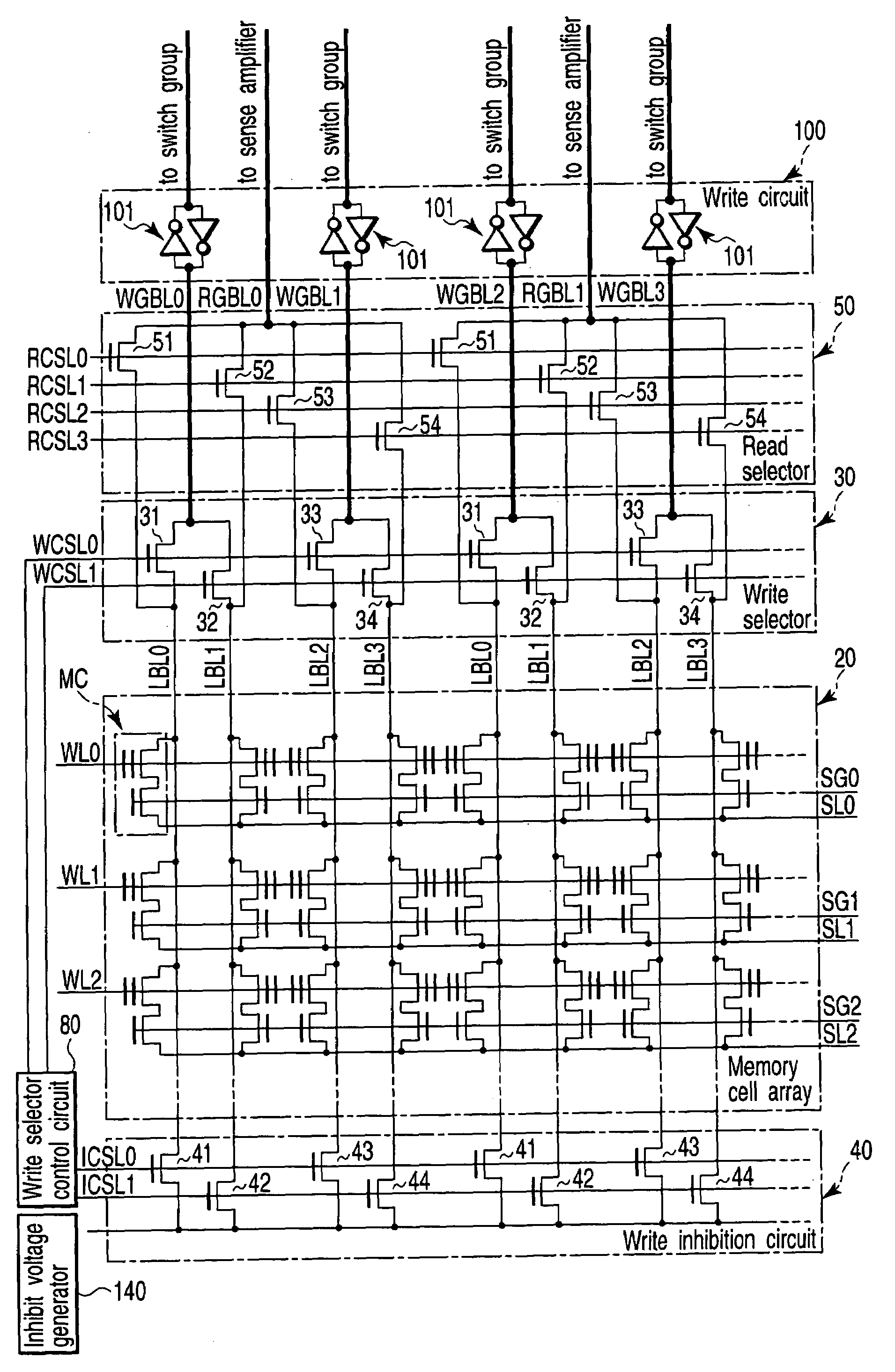

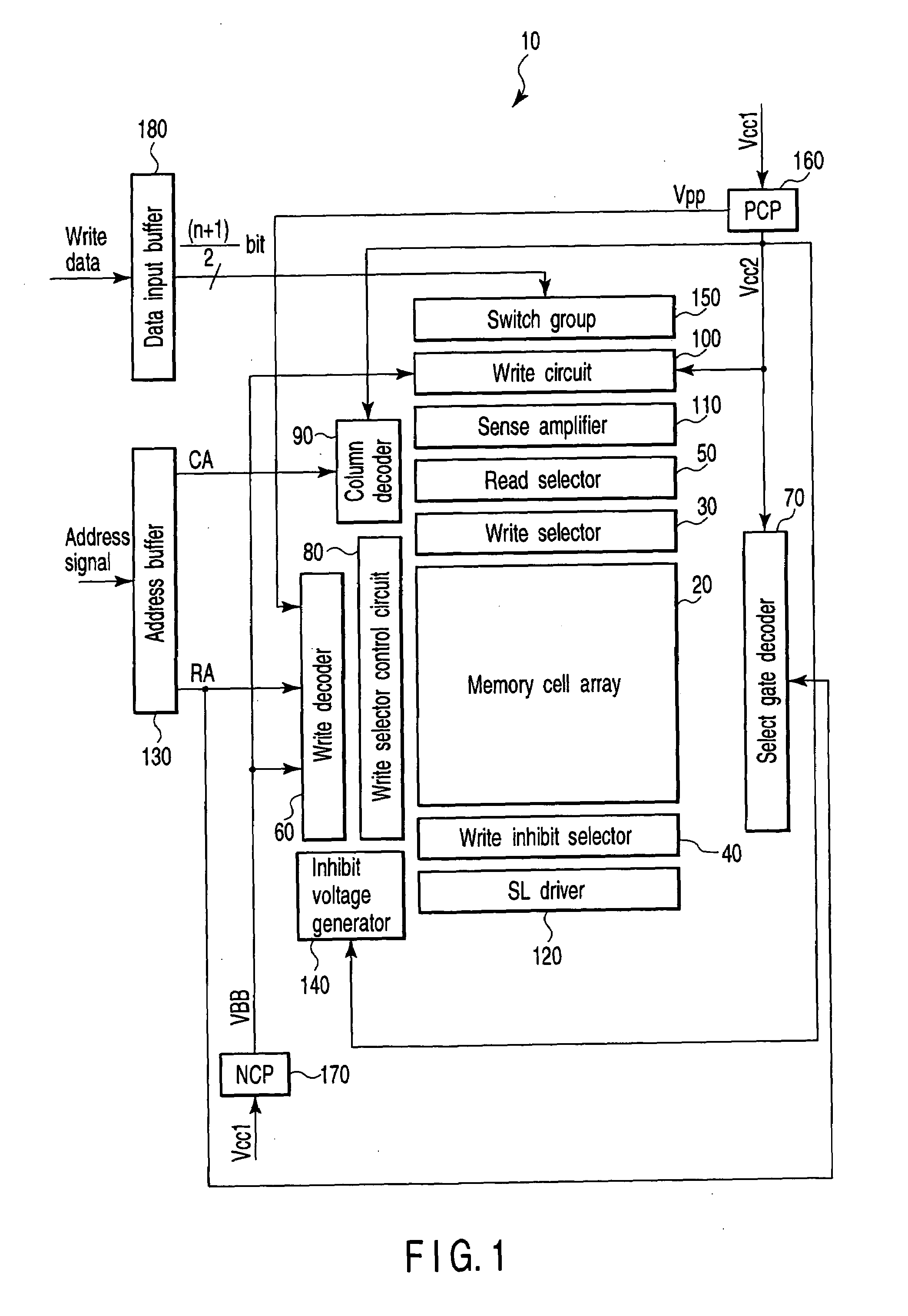

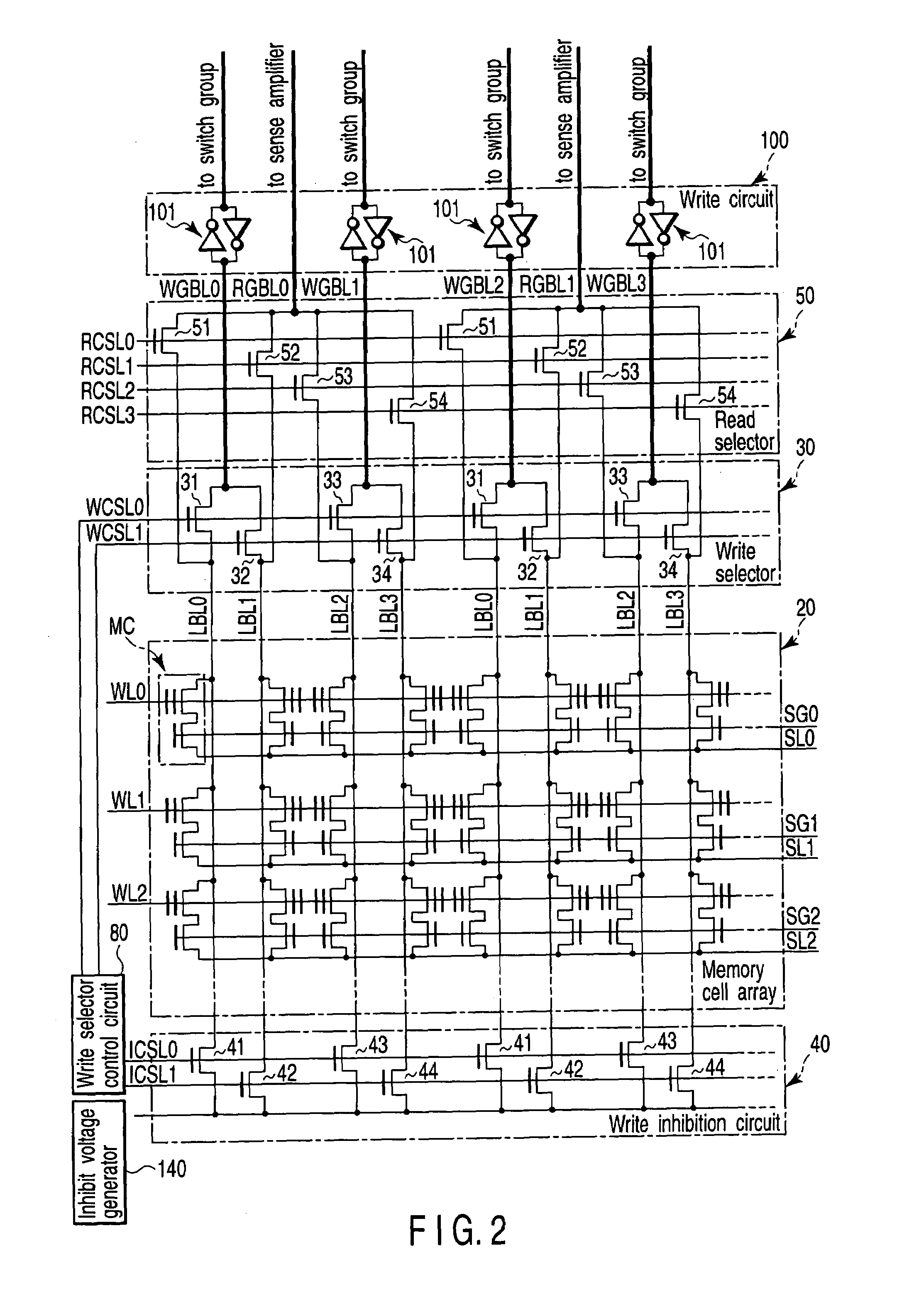

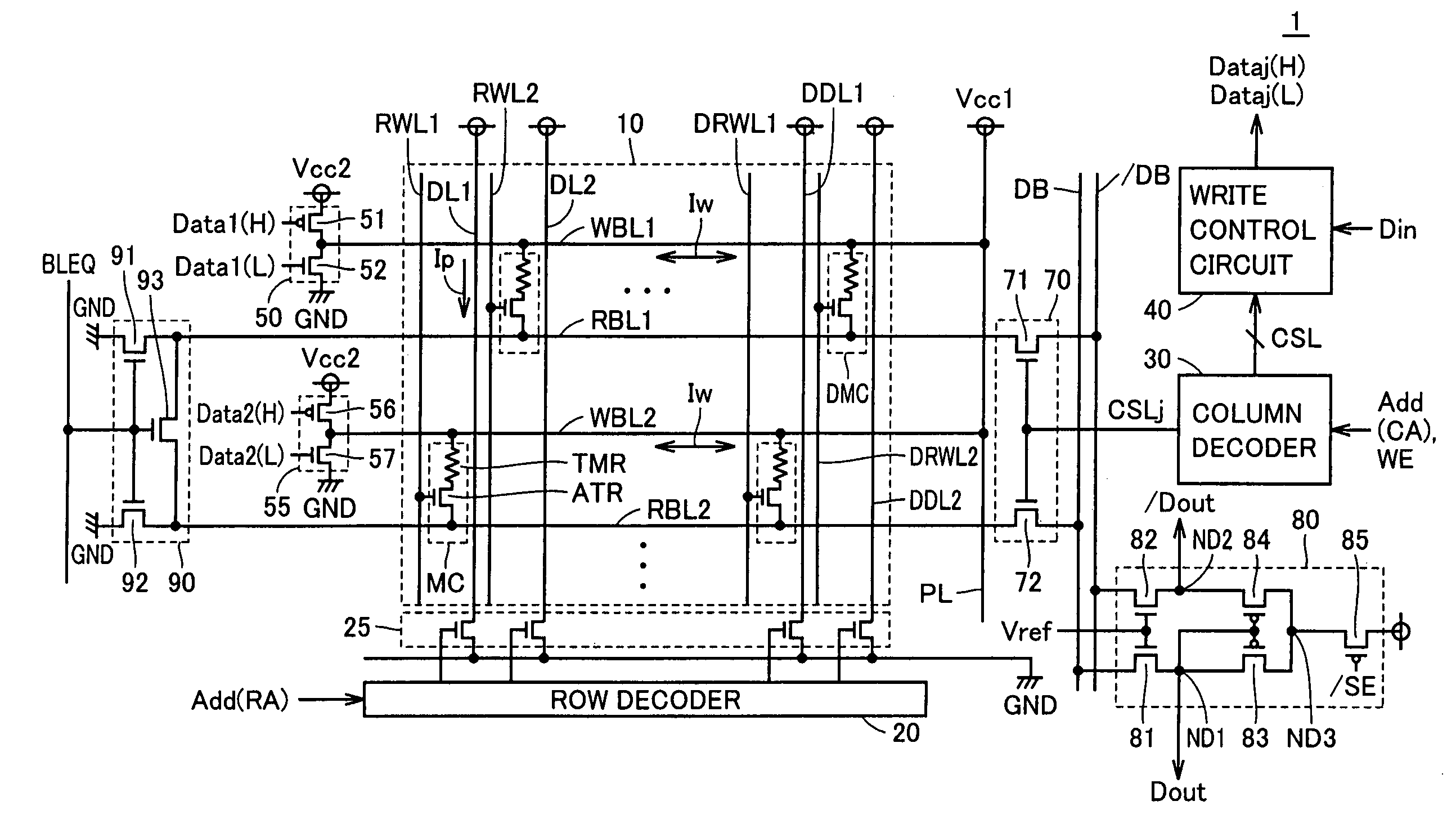

Non-volatile semiconductor memory device allowing concurrent data writing and data reading

A write bit line and a read bit line are provided separately for a memory cell. A source line connecting to the memory cell is formed of a source impurity region the same in conductivity type as a substrate region. A memory cell transistor and the source impurity region are connected by a metal interconnection line of a low resistance. A rise in the source line potential can be prevented, and a memory cell current can reliably be generated according to storage data. Further, fast data reading can be achieved. Additionally, by performing precharging and data amplification in a unit of read bit line, the load of the read bit line can be alleviated to achieve fast reading. An accessing time of a non-volatile semiconductor memory device that uses a variable resistance element as a storage element is reduced without increasing the current consumption.

Owner:RENESAS ELECTRONICS CORP

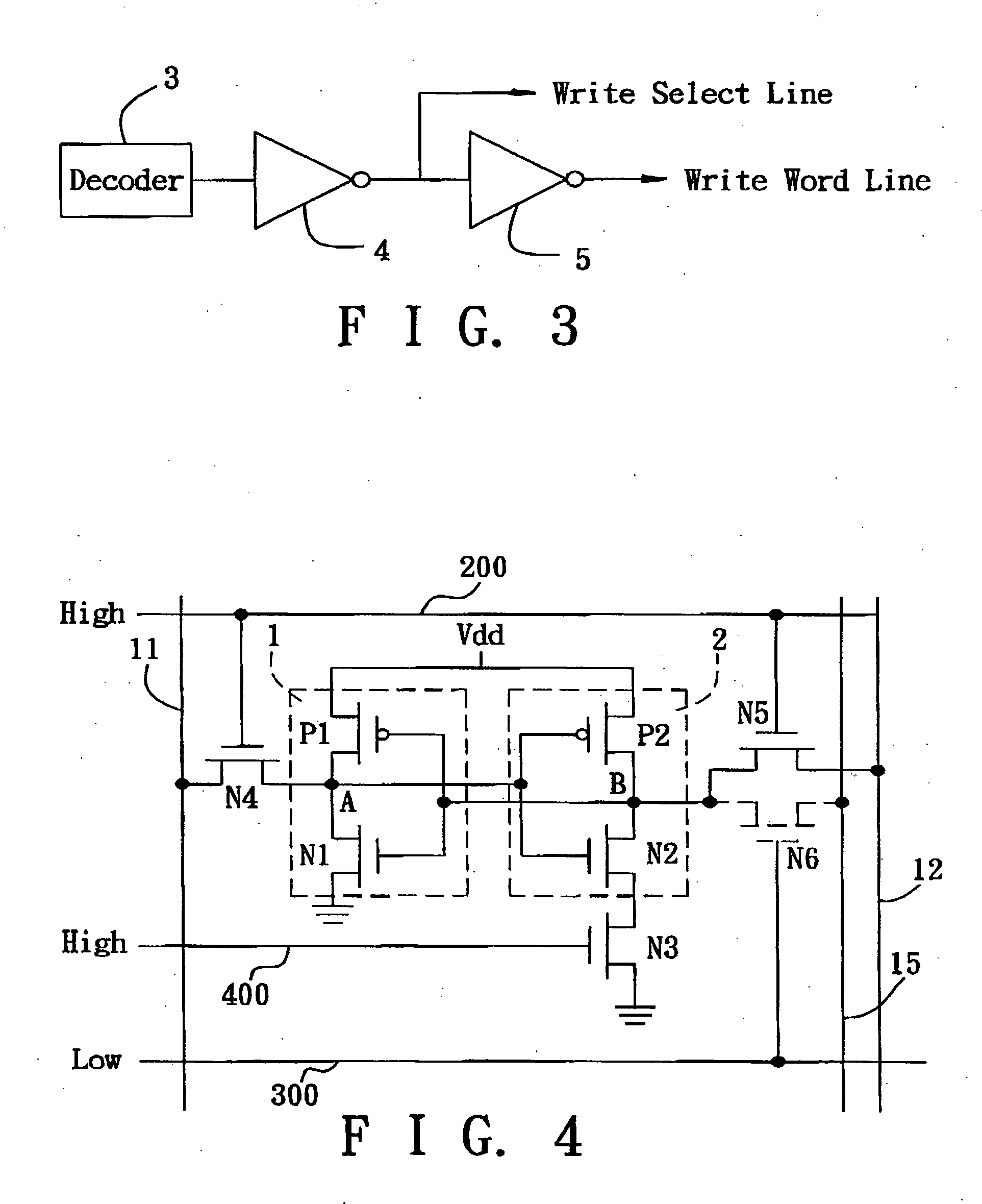

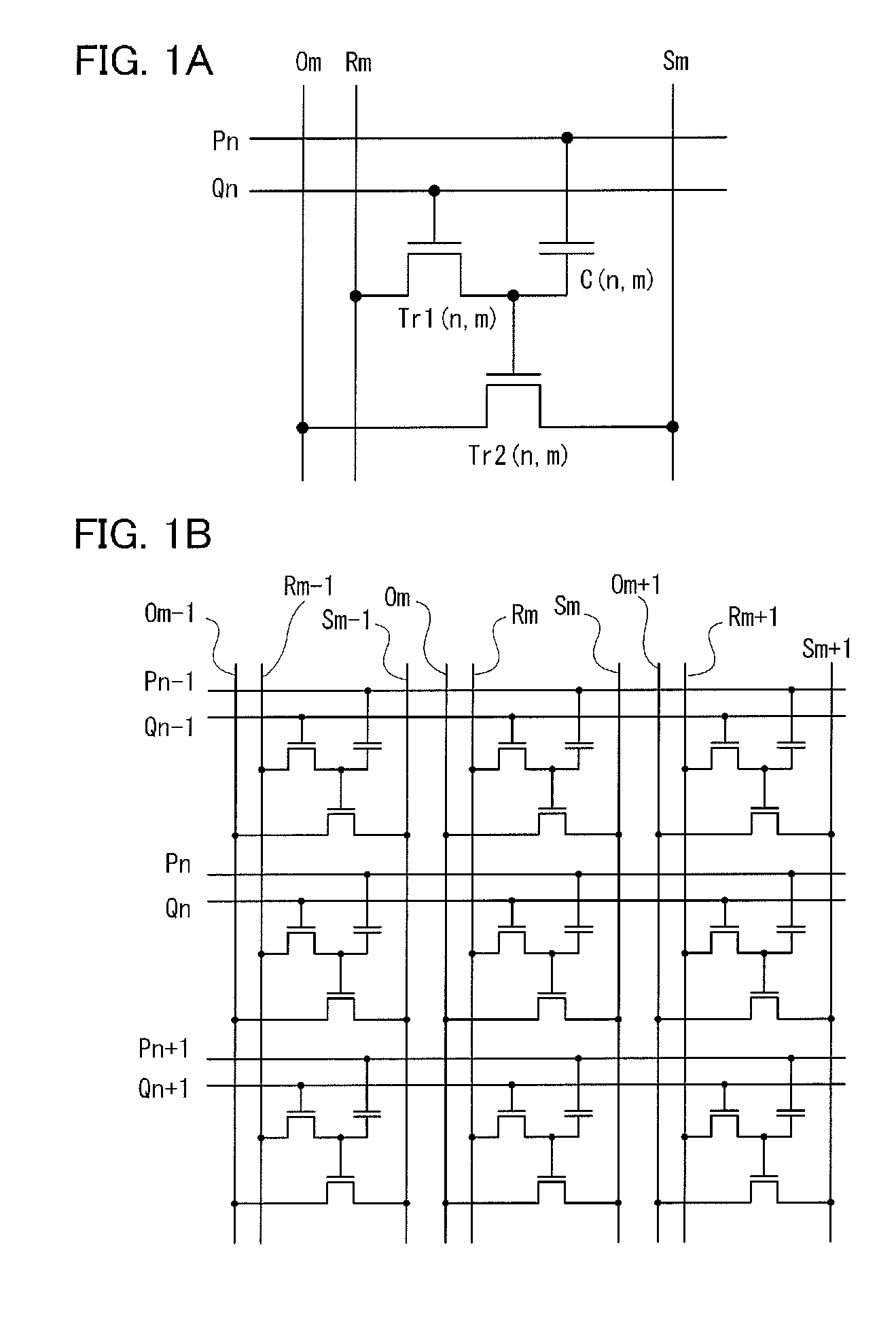

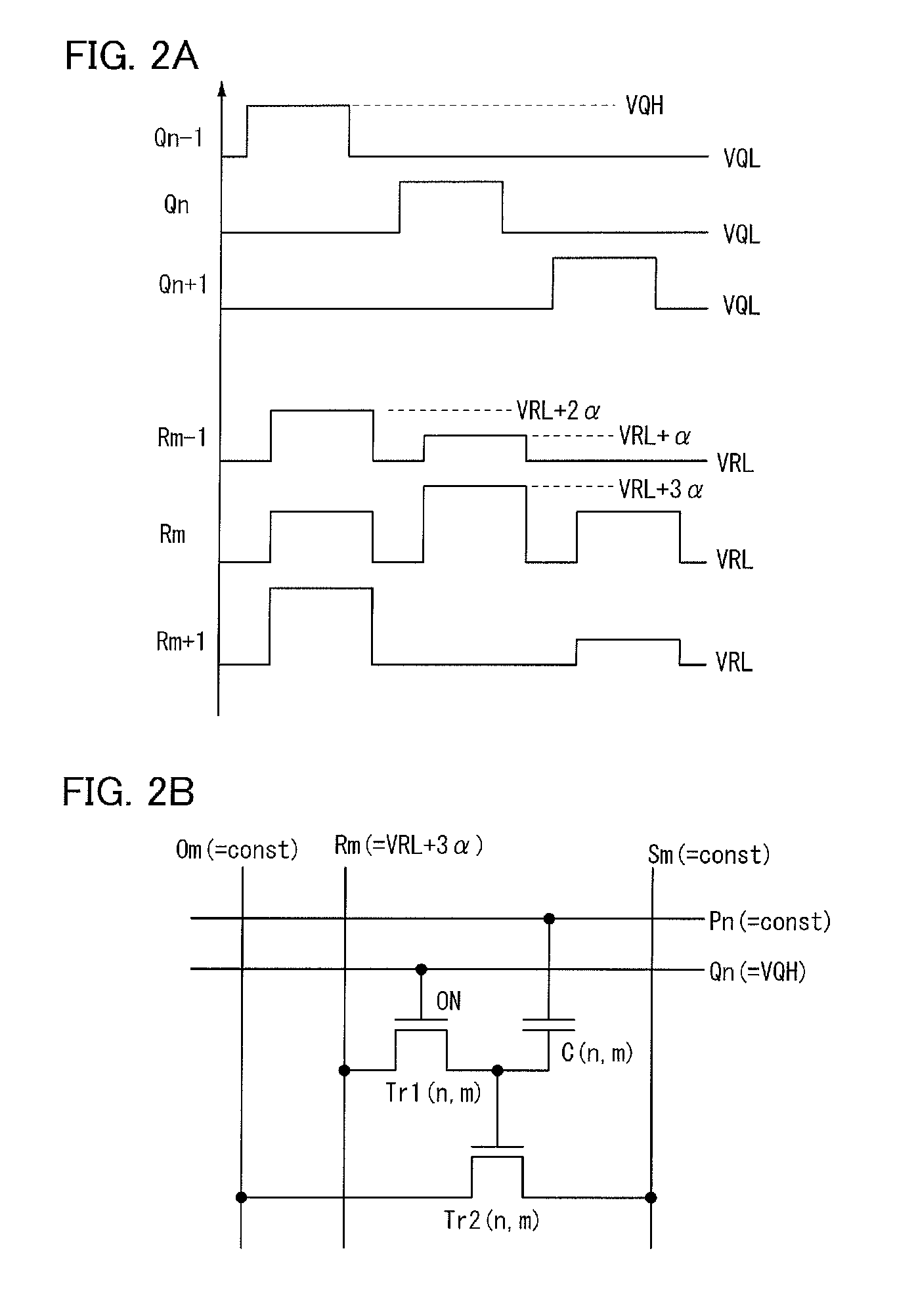

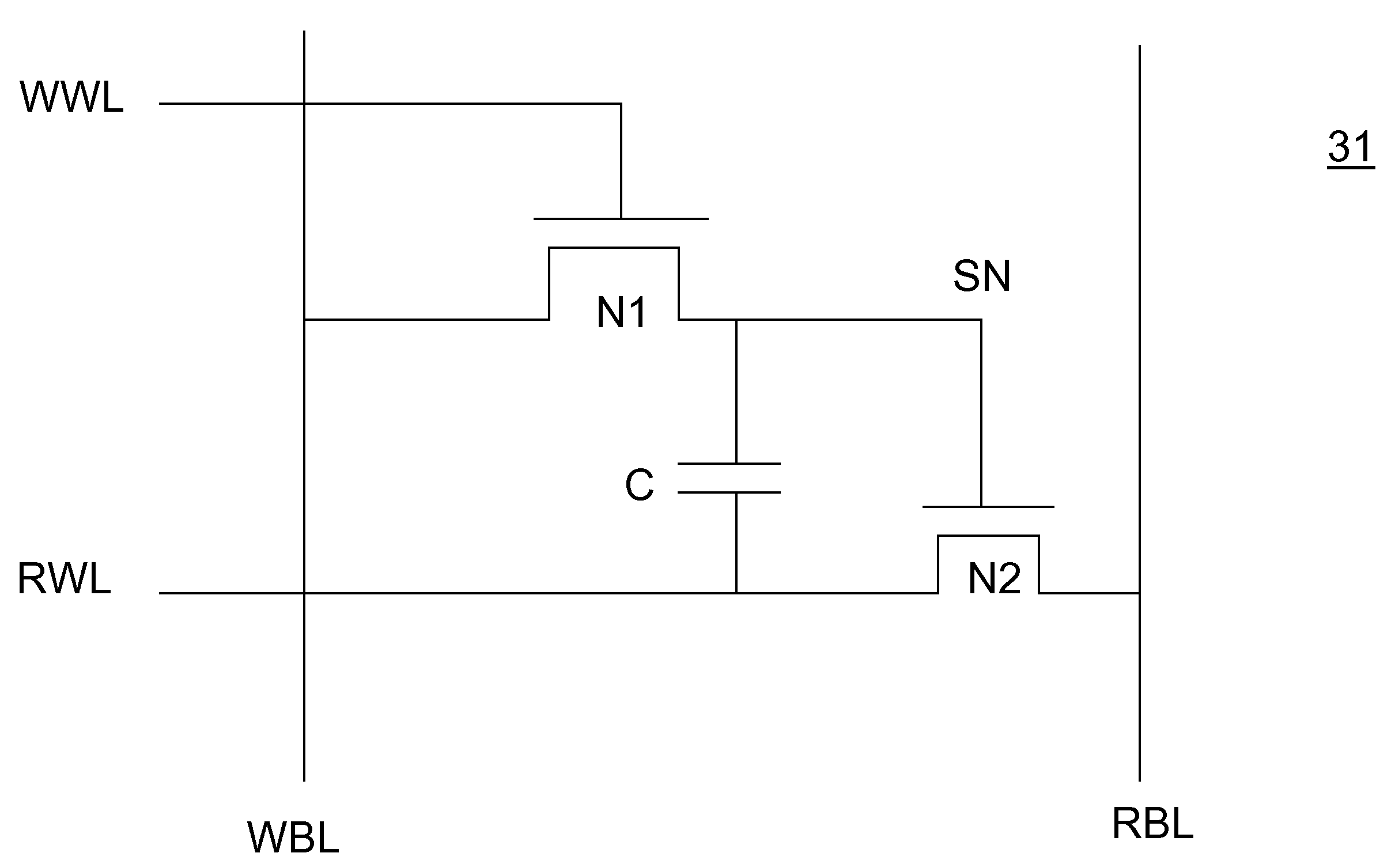

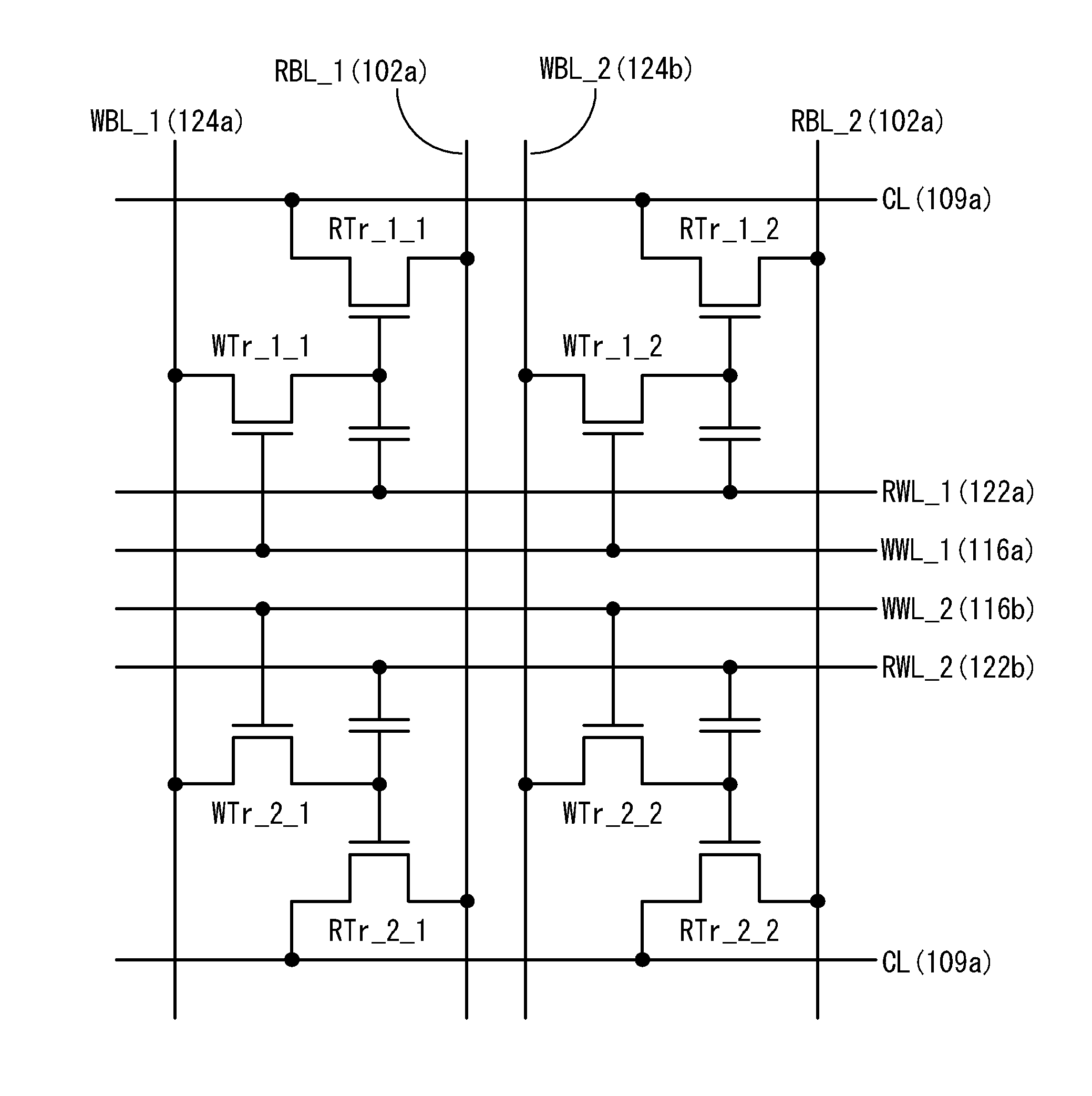

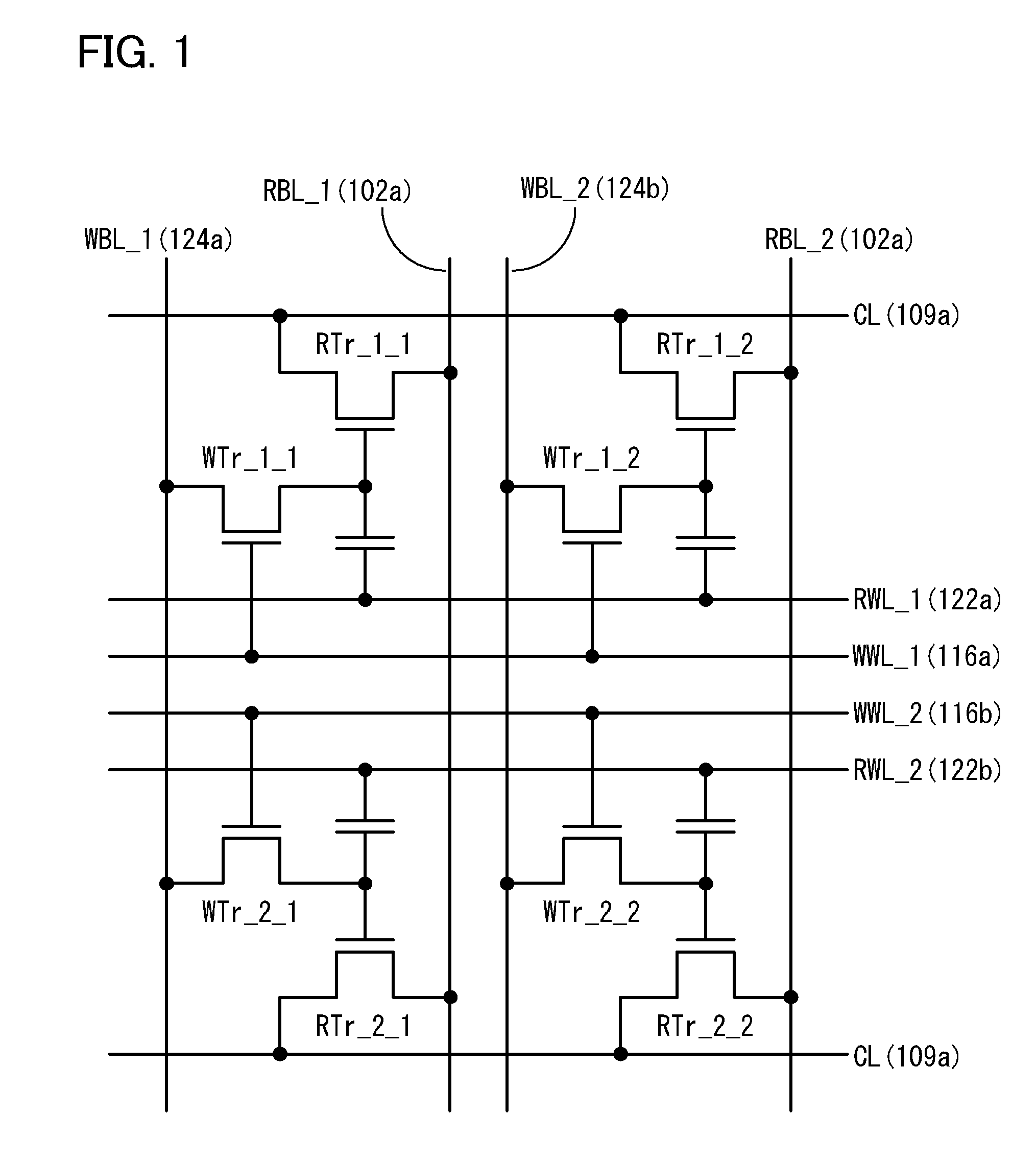

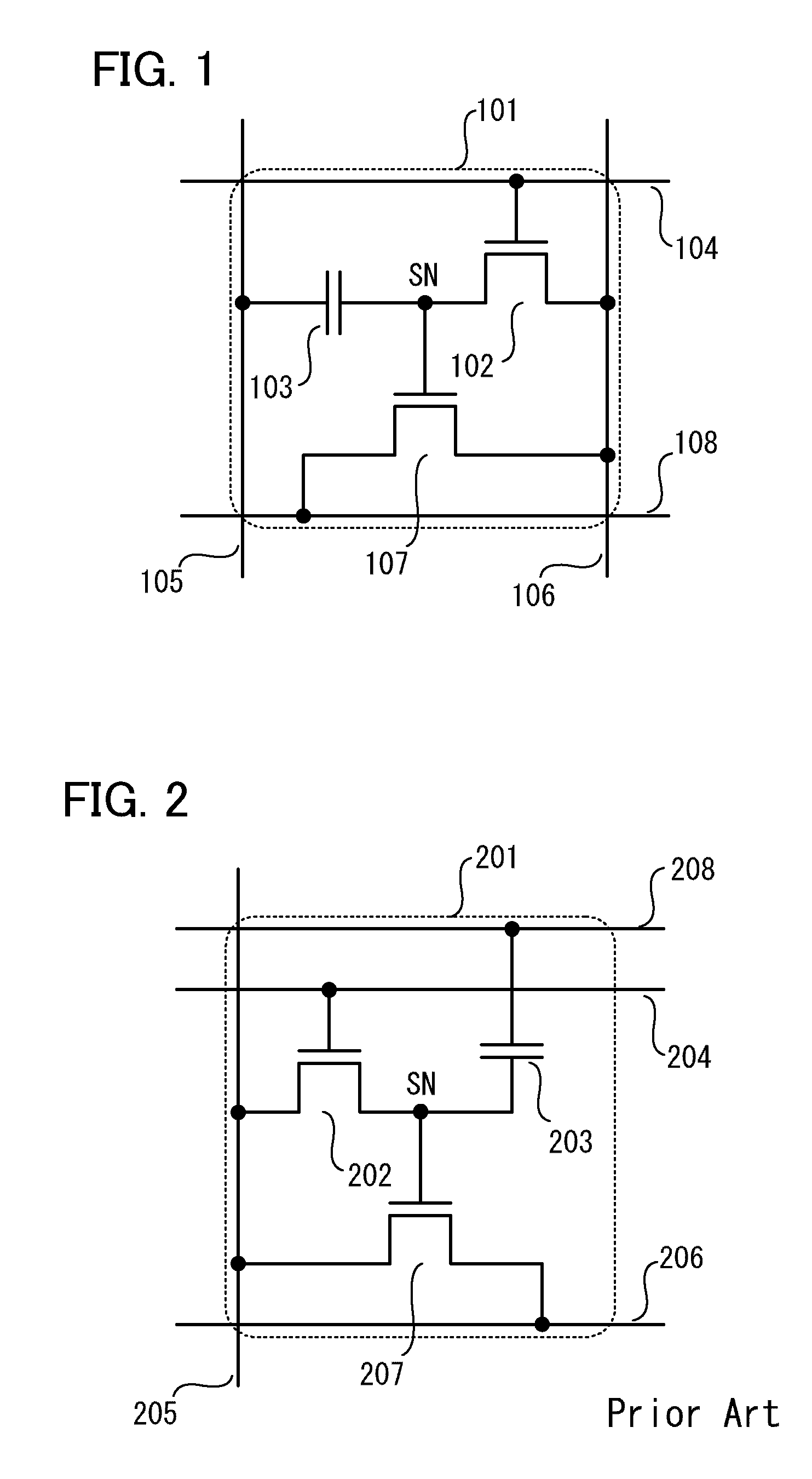

Semiconductor memory device and driving method thereof

ActiveUS20110182110A1Reduce power consumptionNovel structureSolid-state devicesRead-only memoriesWrite bitEngineering

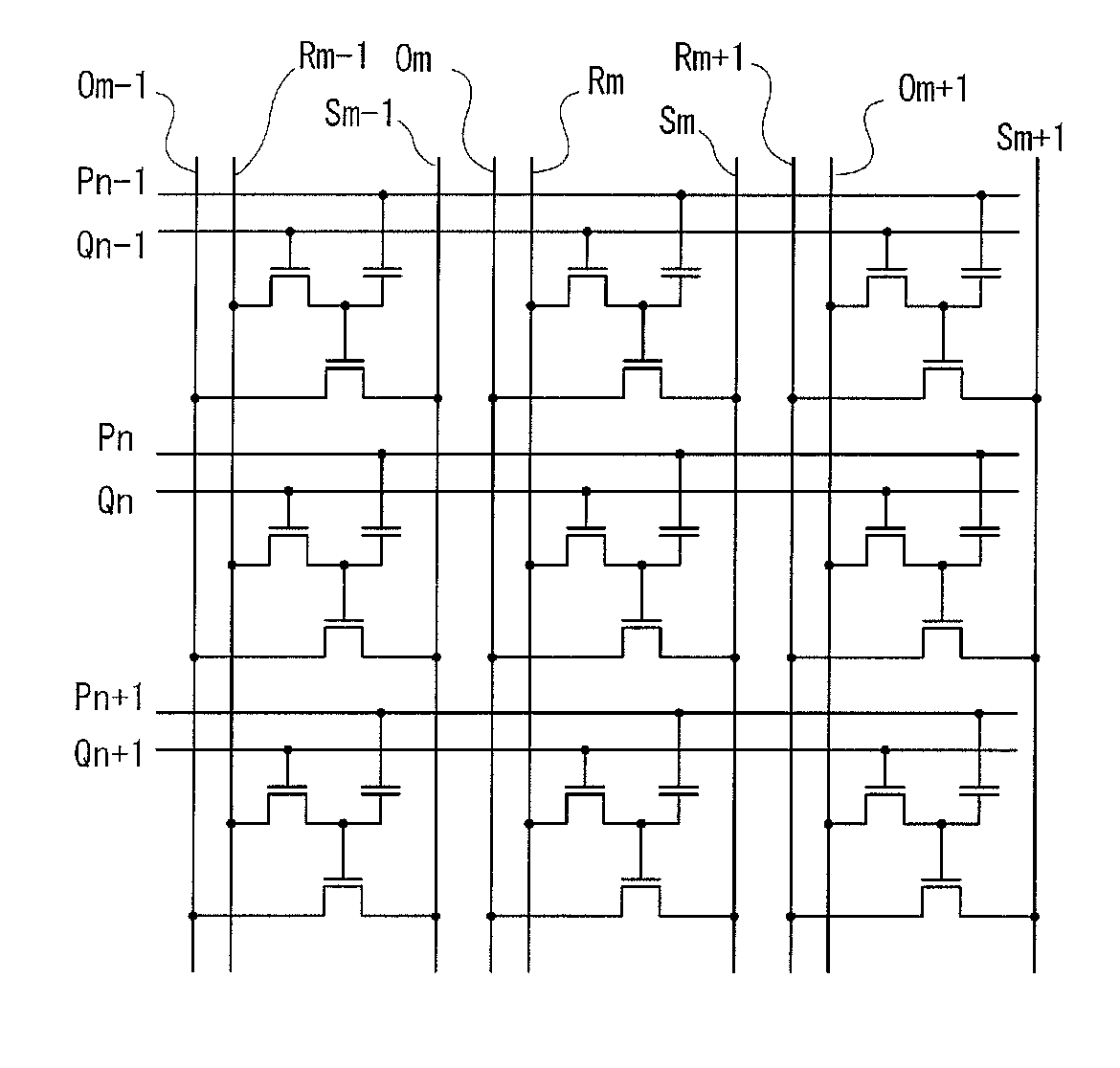

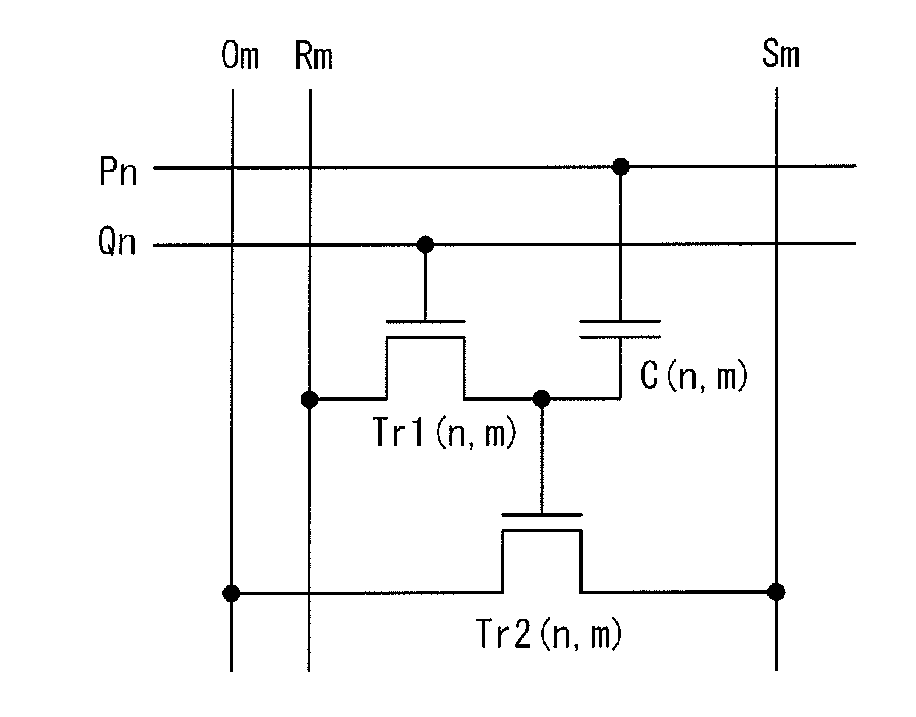

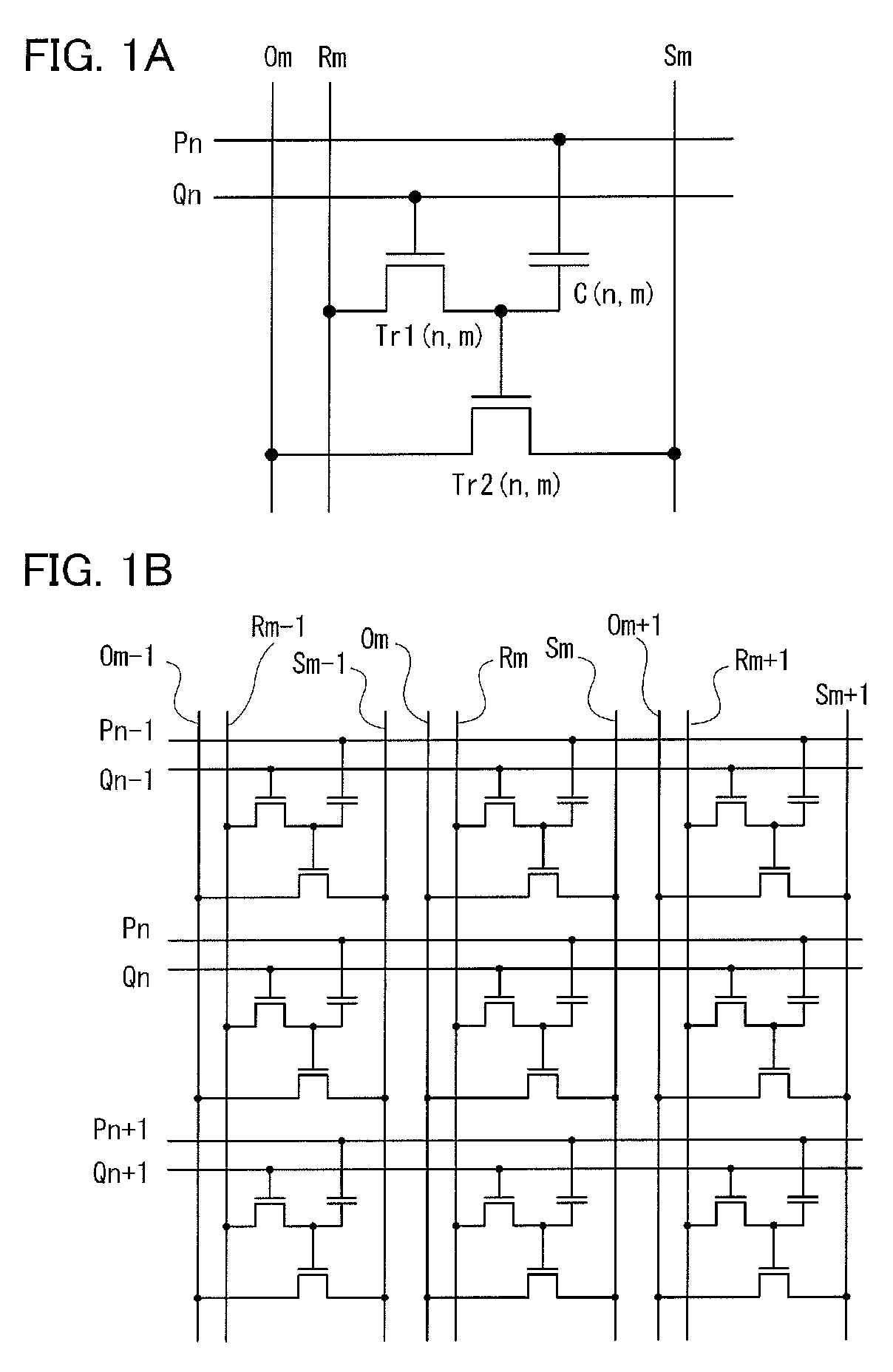

A semiconductor device which stores data by using a transistor whose leakage current between source and drain in an off state is small as a writing transistor. In a matrix including a plurality of memory cells in which a drain of the writing transistor is connected to a gate of a reading transistor and the drain of the writing transistor is connected to one electrode of a capacitor, a gate of the writing transistor is connected to a writing word line; a source of the writing transistor is connected to a writing bit line; and a source and a drain of the reading transistor are connected to a reading bit line and a bias line. In order to reduce the number of wirings, the writing bit line or the bias line is substituted for the reading bit line in another column.

Owner:SEMICON ENERGY LAB CO LTD

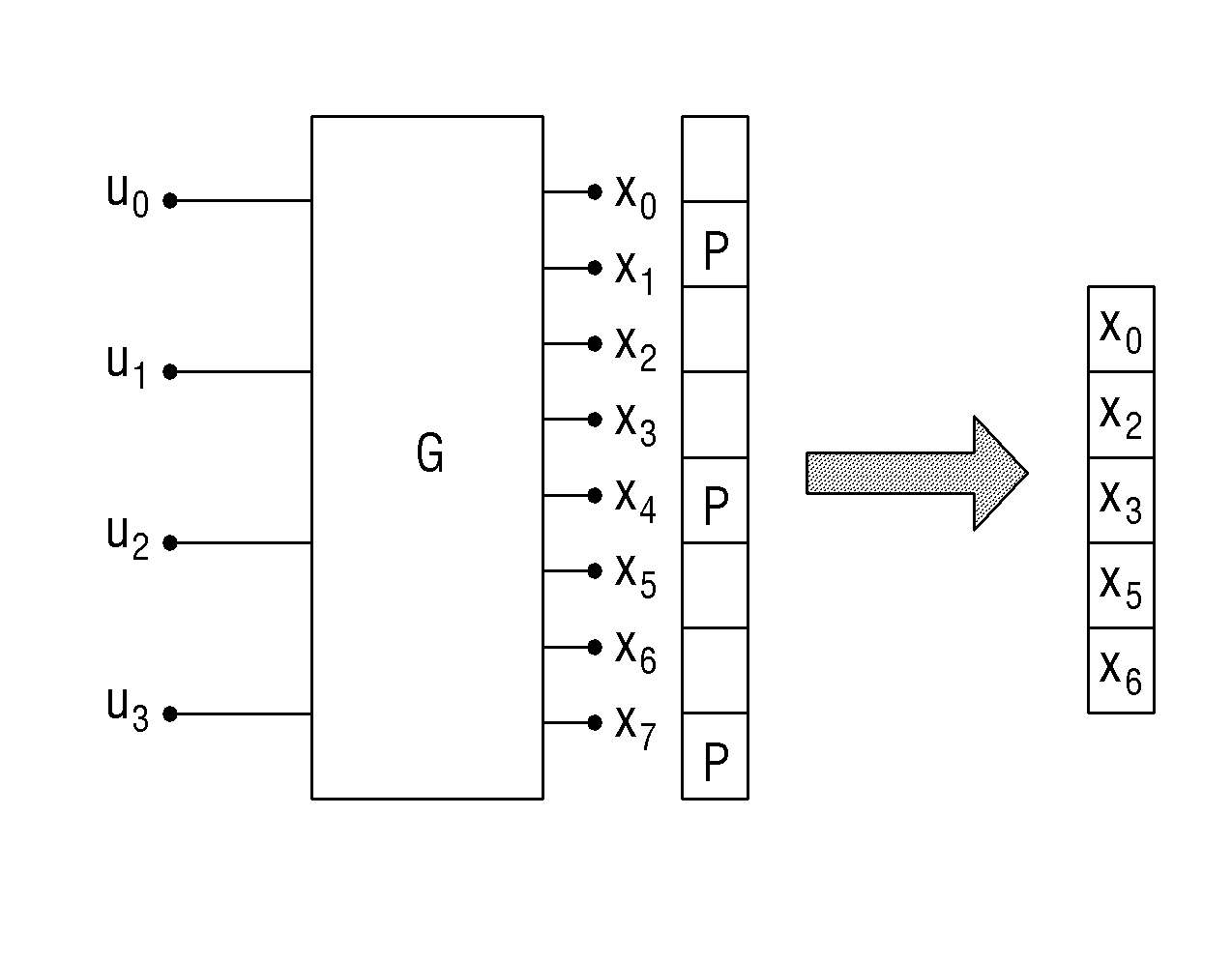

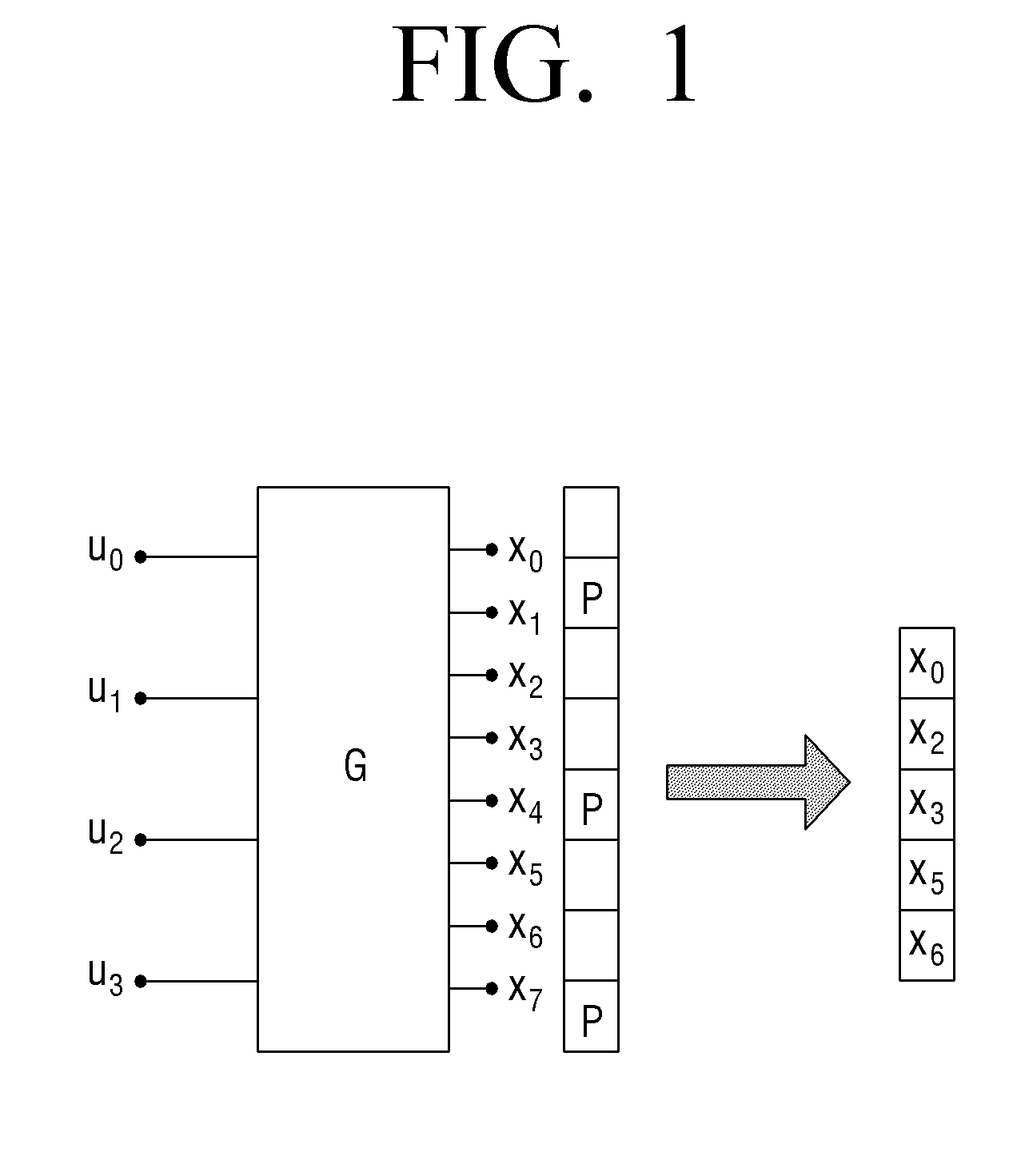

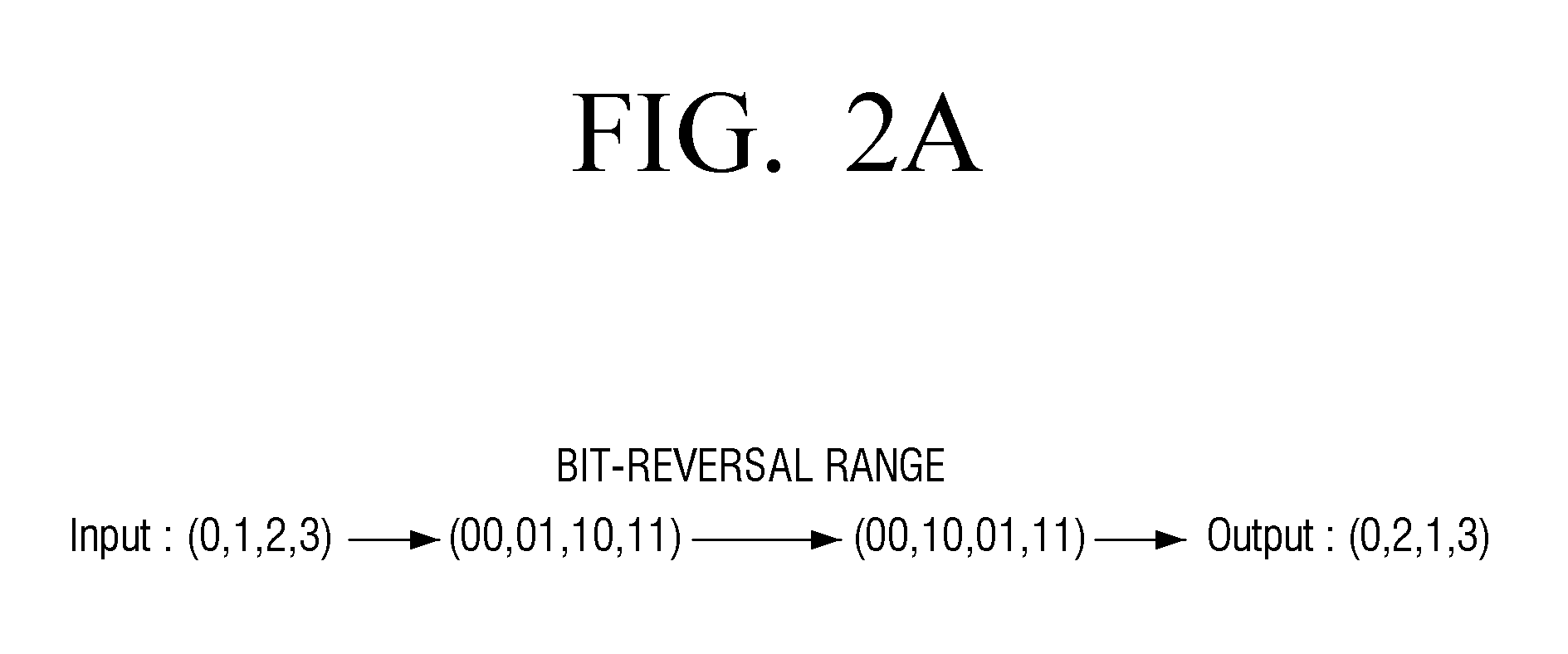

Interleaving and puncturing apparatus and method thereof

ActiveUS20150333769A1Code conversionError correction/detection using interleaving techniquesWrite bitComputer science

An apparatus and method for interleaving and puncturing are provided. The apparatus includes: an interleaver formed of a plurality of columns and rows, configured to perform interleaving by writing bits input to the interleaver in the plurality of columns and reading the bits from each row of the plurality of columns in which the bits are written; and a puncturer configured to puncture a predetermined number of bits among the bits read from the interleaver.

Owner:SAMSUNG ELECTRONICS CO LTD +1

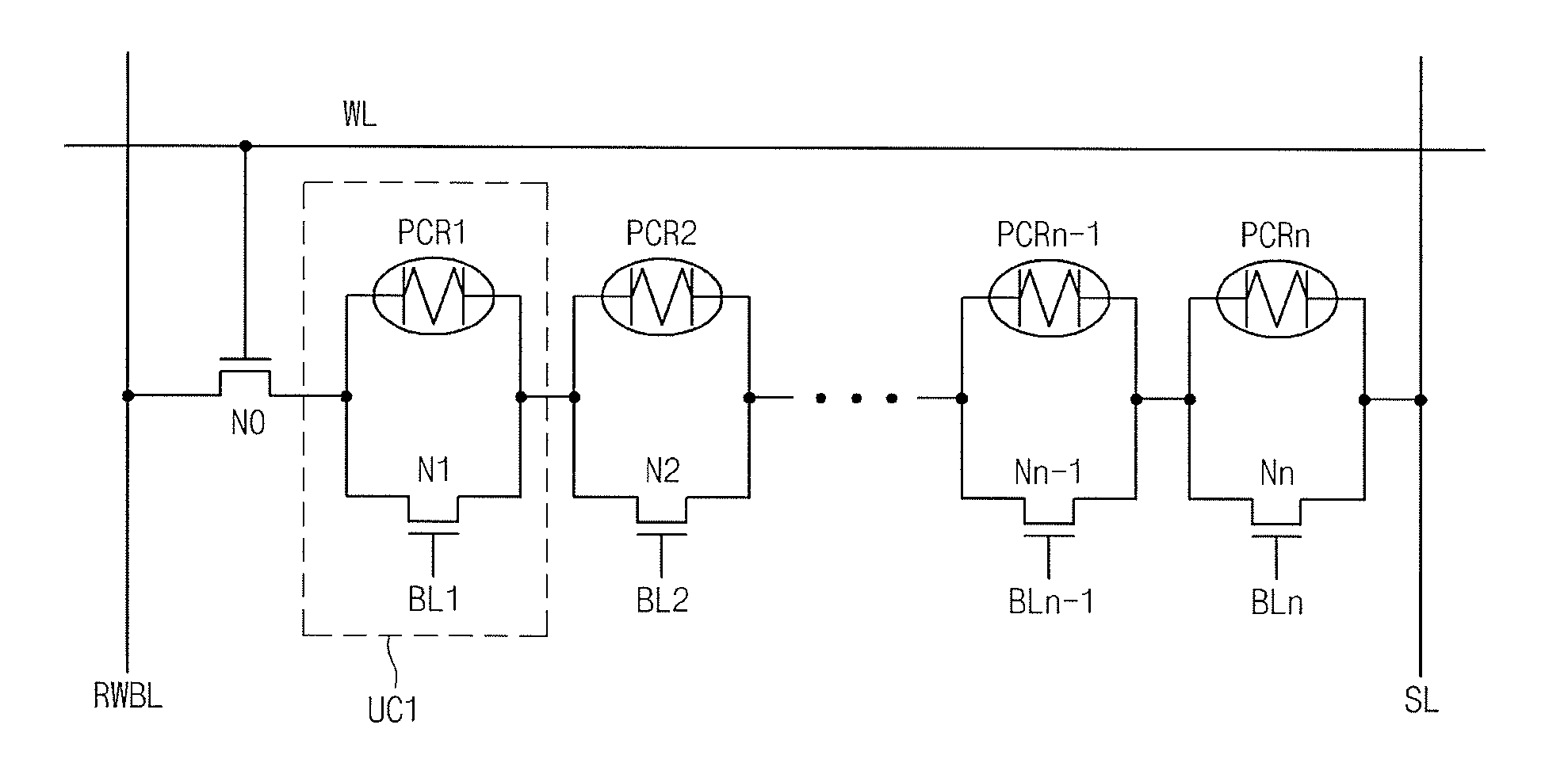

Semiconductor memory device for writing data to multiple cells simultaneously and refresh method thereof

ActiveUS20090067229A1Improve data retentionShorten write timeRead-only memoriesDigital storageWrite bitComputer architecture

A semiconductor memory device includes a read / write bit line configured to supply a cell driving voltage. A selecting unit is connected to the read / write bit line and is controlled by a word line. A plurality of cells are connected between the selecting unit and a source line, and the cells are configured to read and write data according to a cell driving voltage. Each switching element of a plurality of switching elements are connected in parallel with a single cell of the plurality of cells, and the plurality of switching elements are controlled selectively by a plurality of bit lines.

Owner:SK HYNIX INC

Non-volatile semiconductor memory device

A write bit line and a read bit line are provided separately for a memory cell. A source line connecting to the memory cell is formed of a source impurity region the same in conductivity type as a substrate region. A memory cell transistor and the source impurity region are connected by a metal interconnection line of a low resistance. A rise in the source line potential can be prevented, and a memory cell current can reliably be generated according to storage data. Further, fast data reading can be achieved. Additionally, by performing precharging and data amplification in a unit of read bit line, the load of the read bit line can be alleviated to achieve fast reading. An accessing time of a non-volatile semiconductor memory device that uses a variable resistance element as a storage element is reduced without increasing the current consumption.

Owner:RENESAS ELECTRONICS CORP

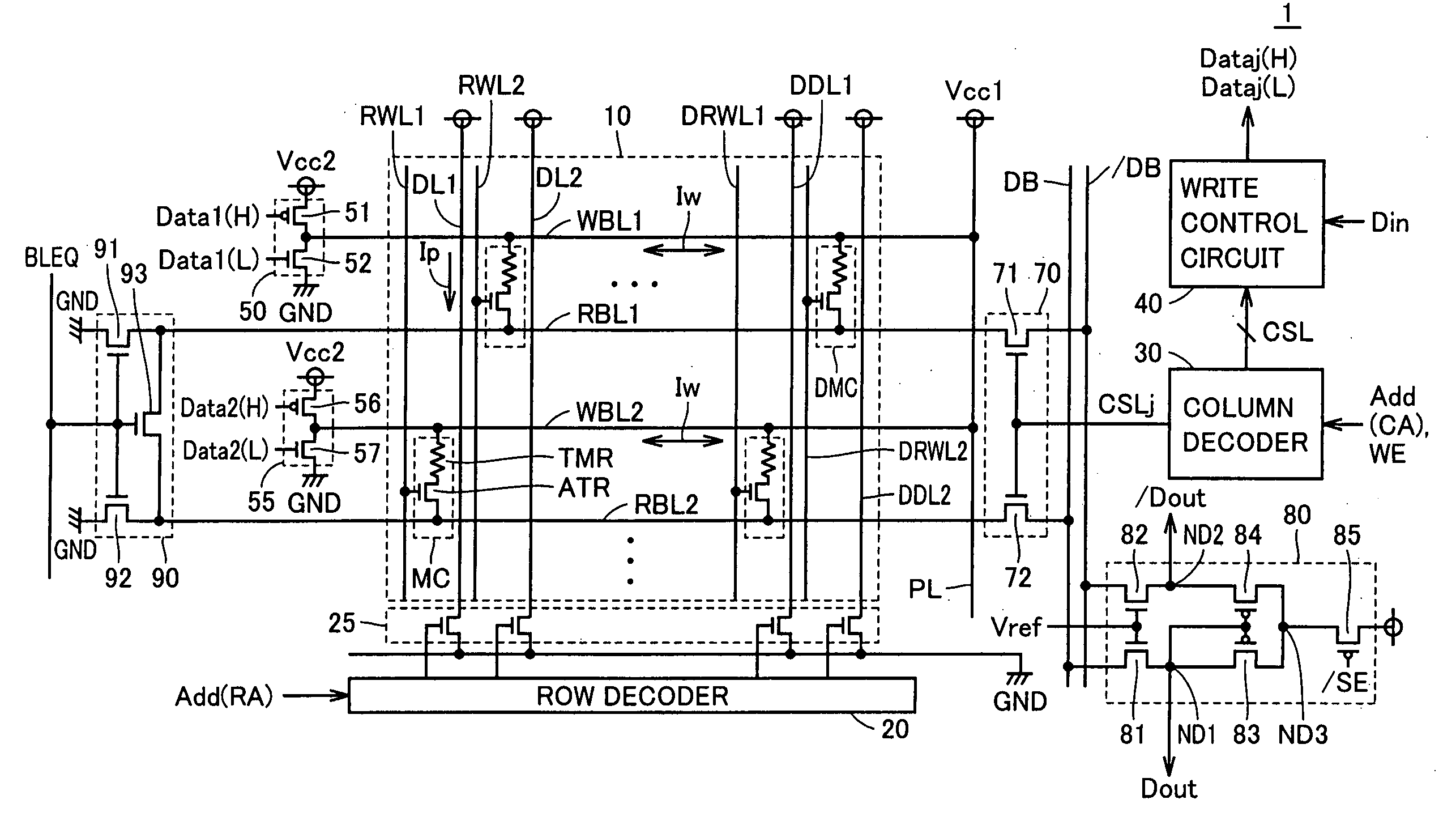

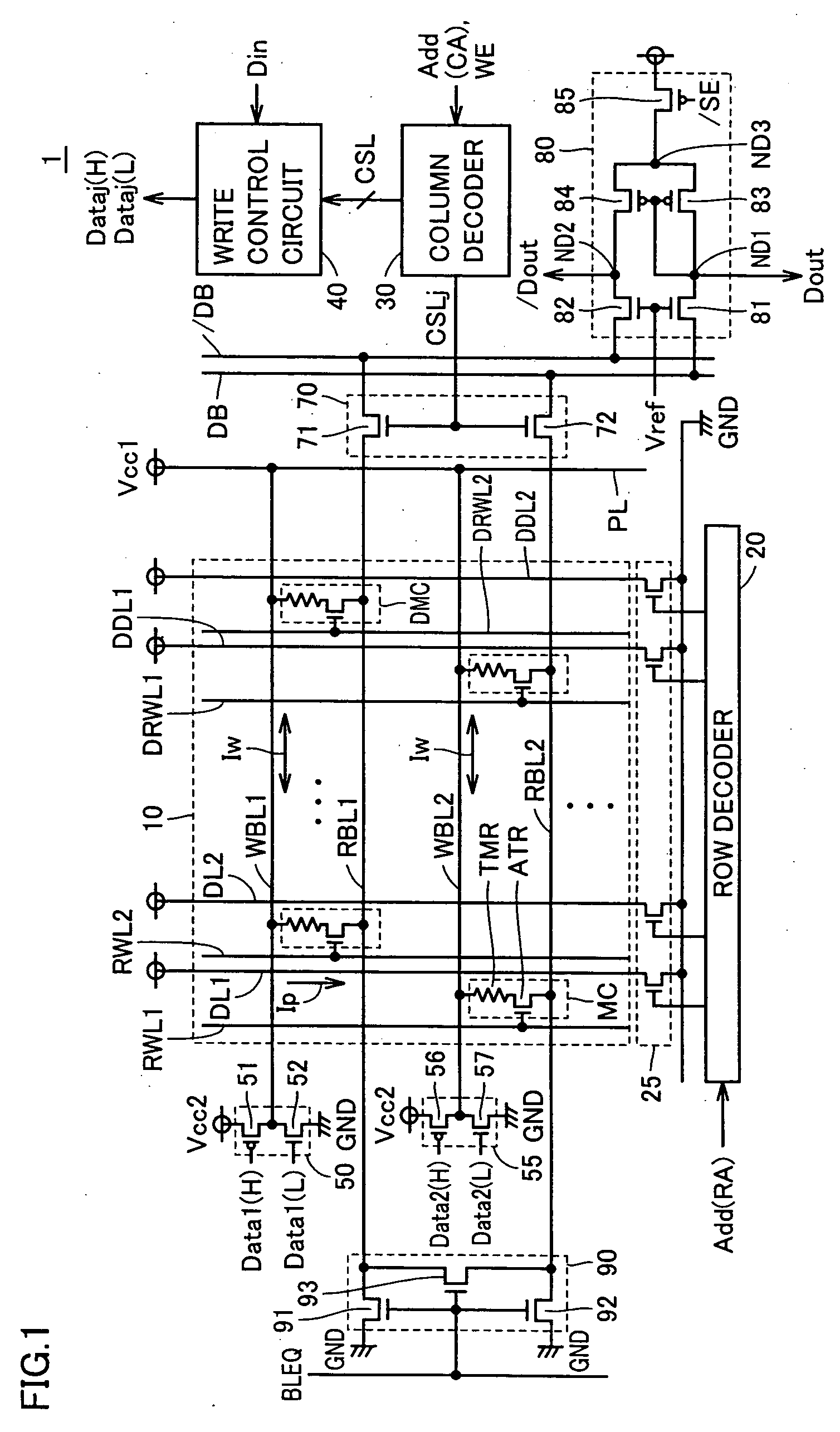

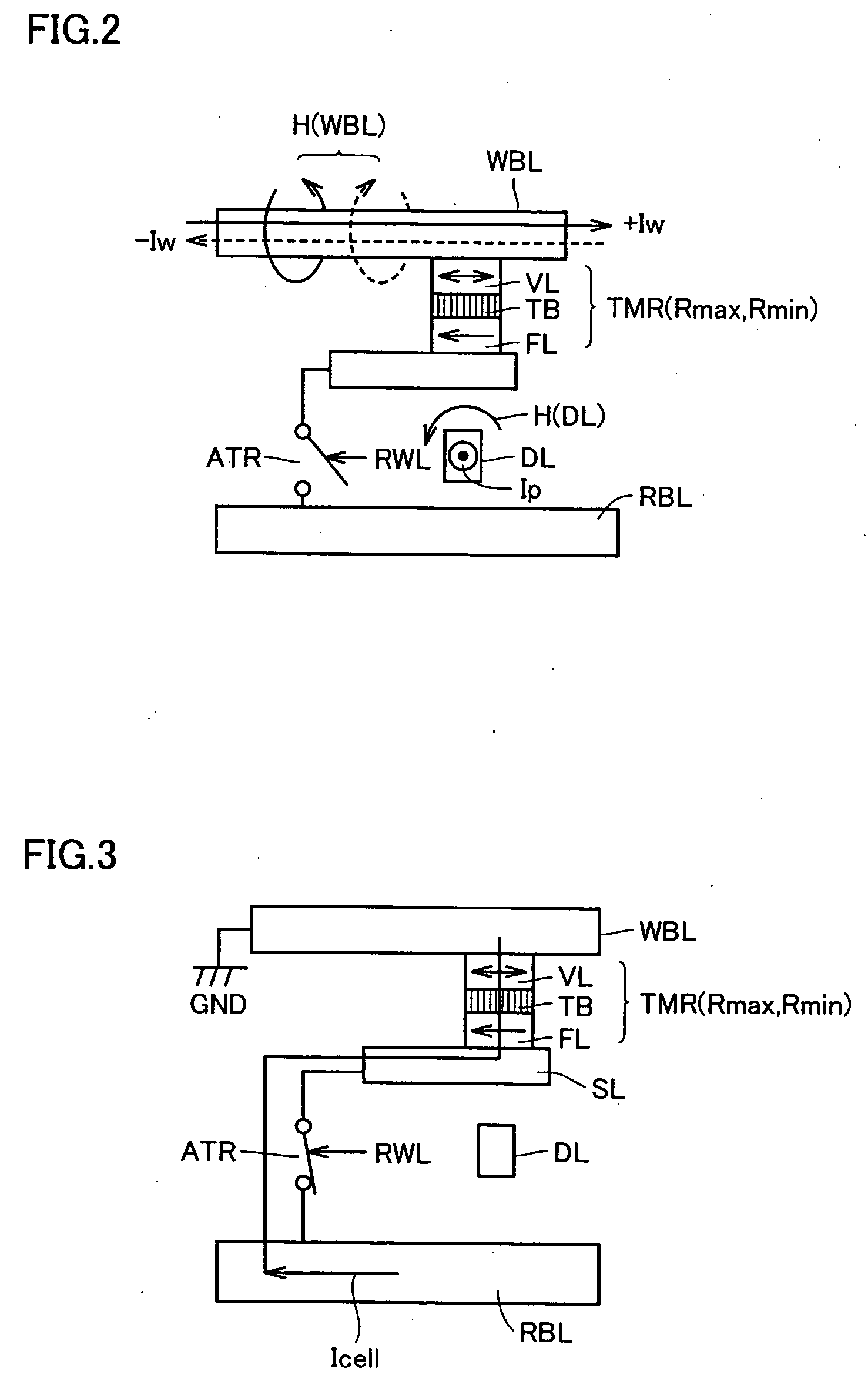

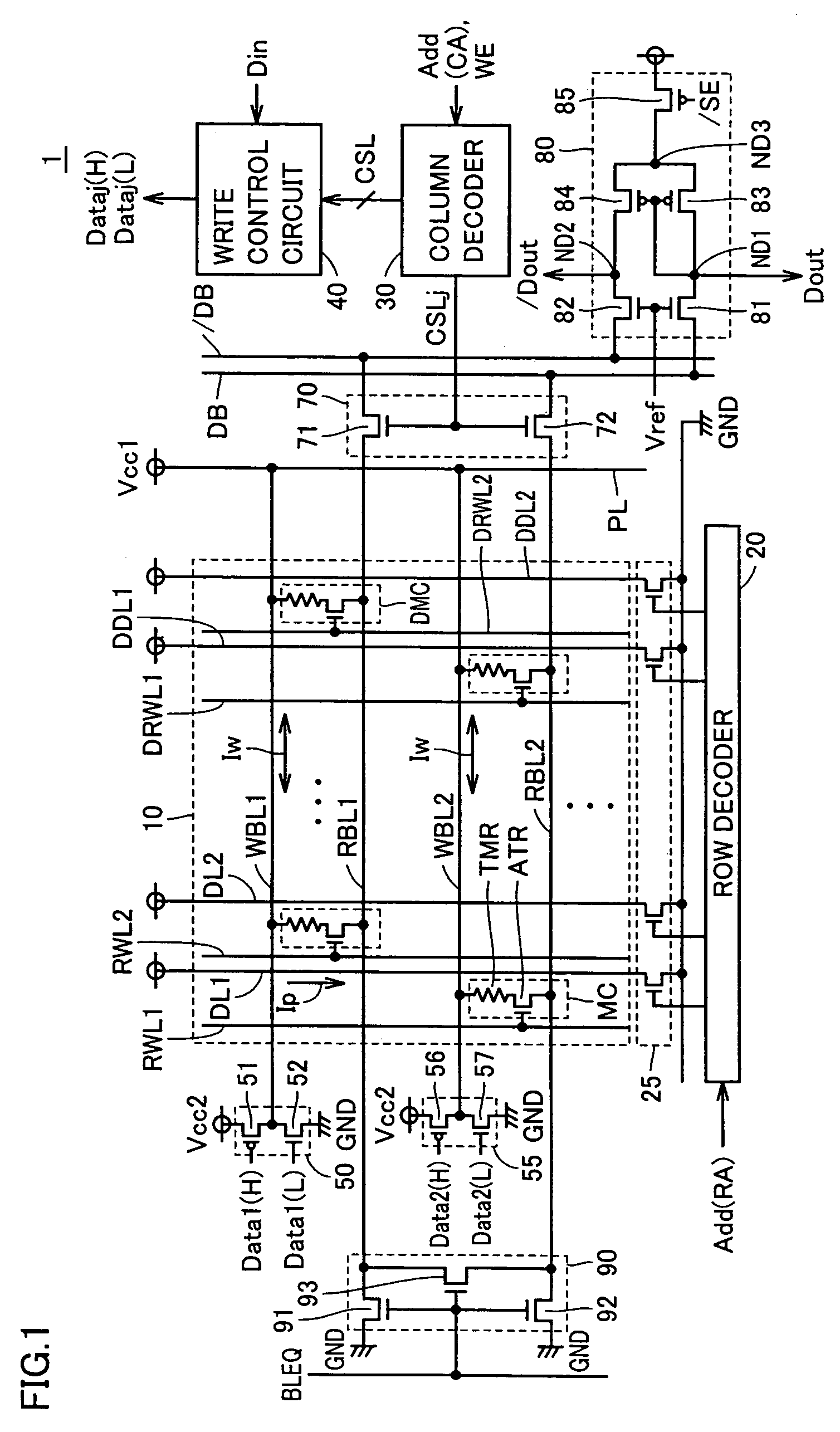

Semiconductor memory device with current driver providing bi-directional current to data write line

First and second current drivers are connected to one end of corresponding first and second write bit lines, respectively, and the first and second write bit lines are directly connected, at the other end, to a common line. The first and second current drivers receive a first power supply voltage and the ground voltage, while the common line receives a second power supply voltage higher than the ground voltage and lower than the first power supply voltage. The first and second current drivers cause a current for data writing to flow in a first direction based on a voltage difference between the first power supply voltage and the second power supply voltage, and cause a current for data writing to flow in a second direction based on a voltage difference between the second power supply voltage and the ground voltage.

Owner:RENESAS ELECTRONICS CORP

Circuit and Method for a High Speed Memory Cell

InactiveUS20100165704A1Easy to operateHigh operating requirementsDigital storageWrite bitHigh speed memory

A memory cell is disclosed, including a write access transistor coupled between a storage node and a write bit line, and active during a write cycle responsive to a voltage on a write word line; a read access transistor coupled between a read word line and a read bit line, and active during a read cycle responsive to a voltage at the storage node; and a storage capacitor coupled between the read word line and the storage node. Methods for operating the memory cell are also disclosed.

Owner:TAIWAN SEMICON MFG CO LTD

Seven transistor SRAM cell

Owner:TEXAS INSTR INC

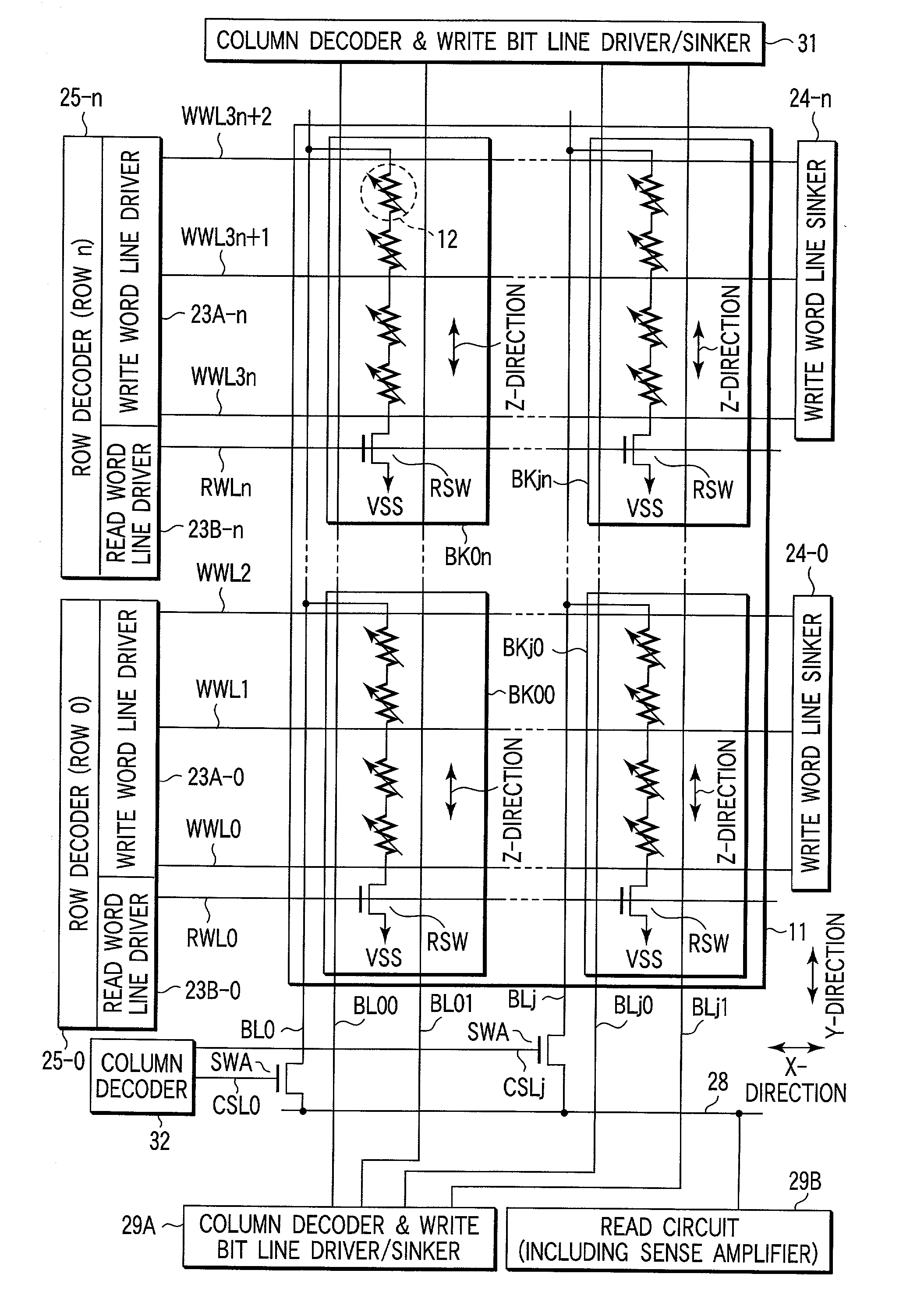

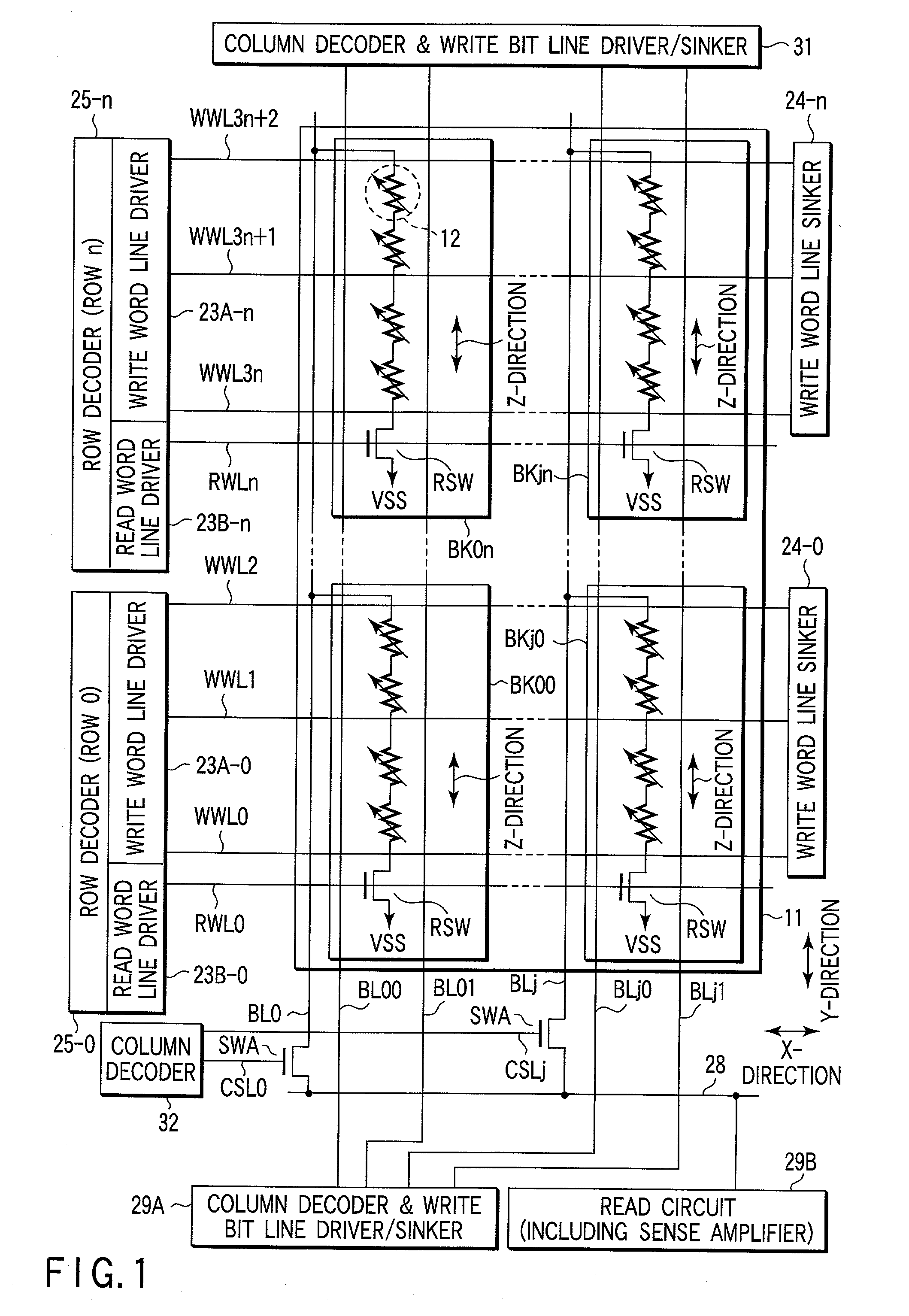

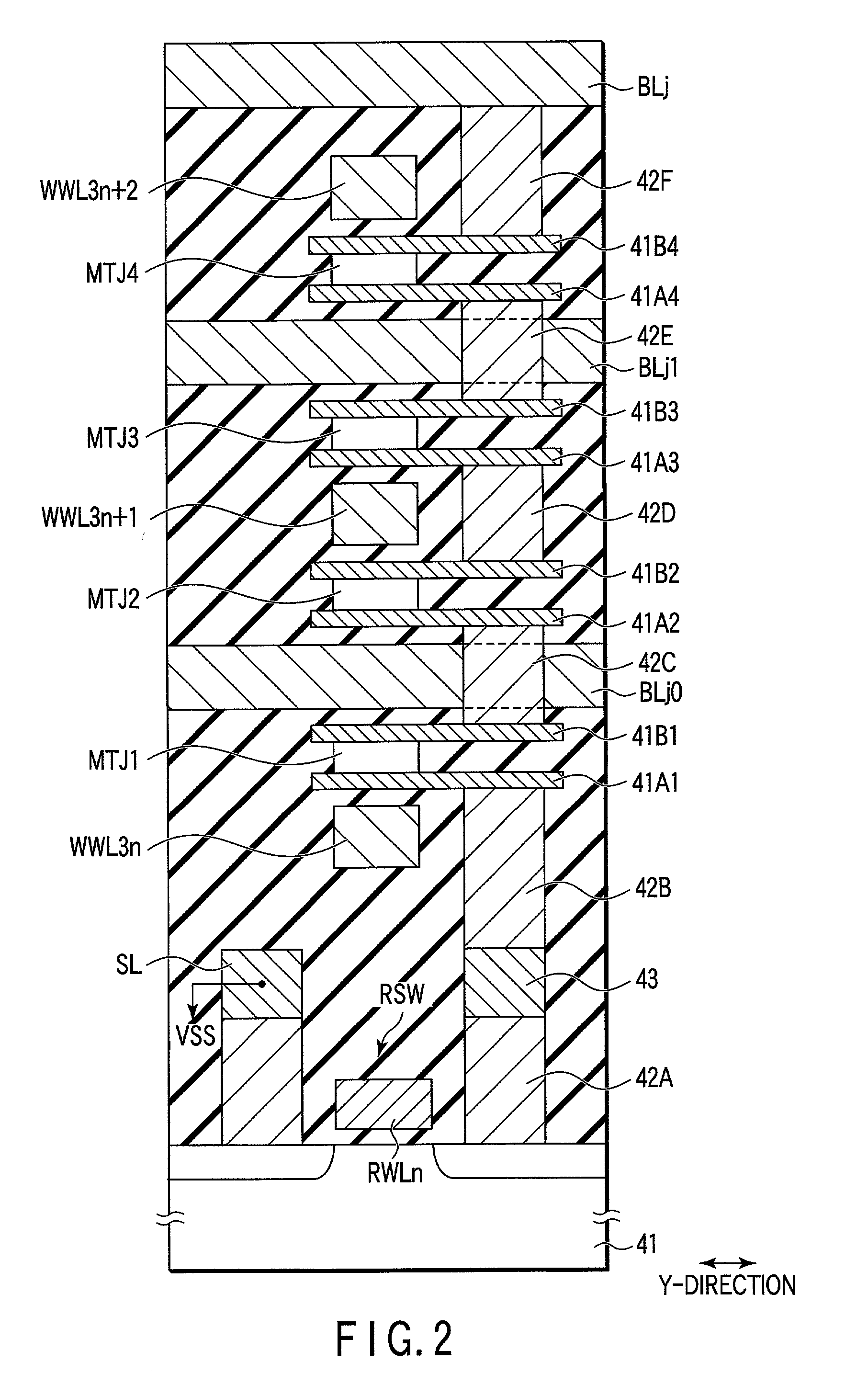

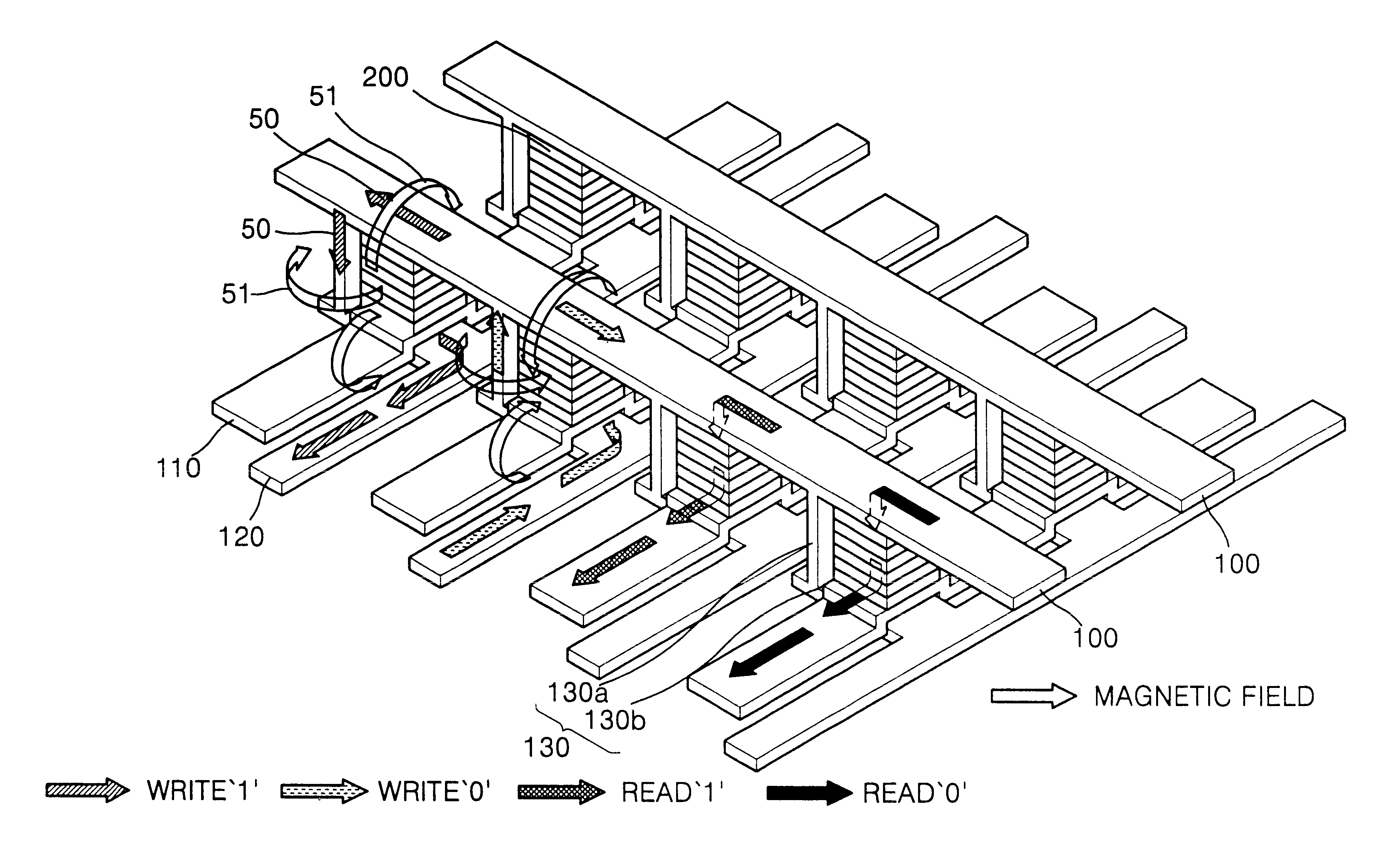

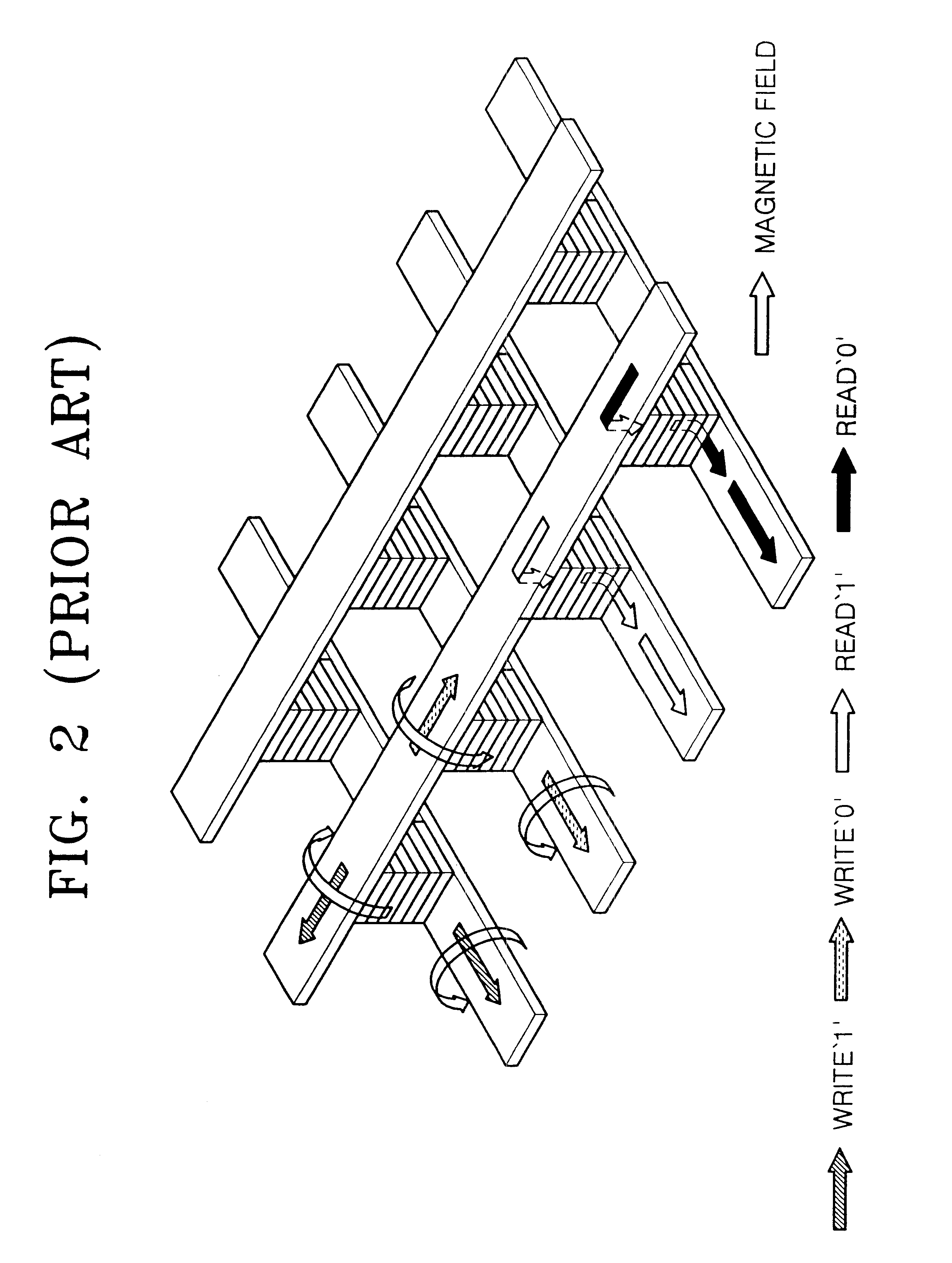

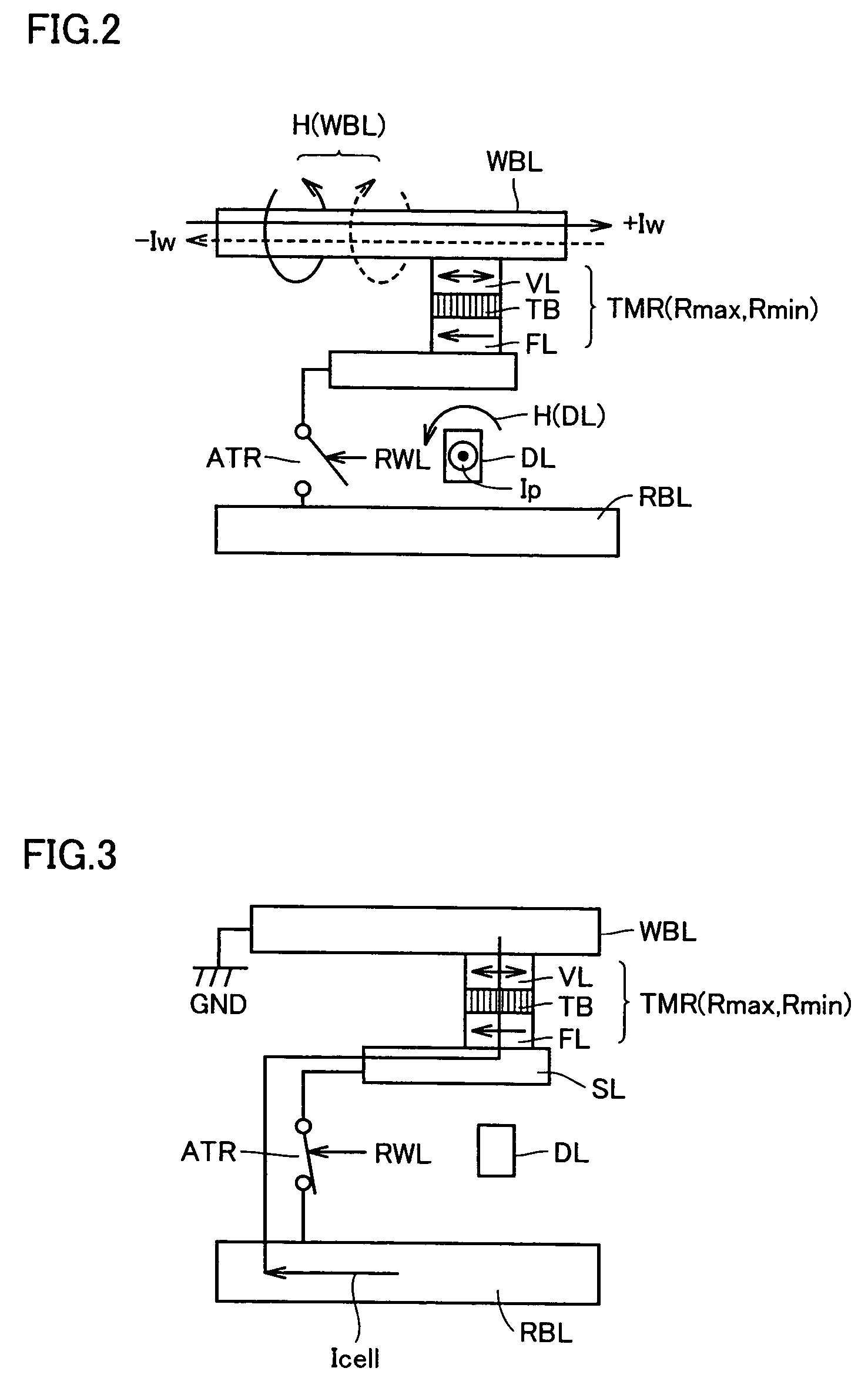

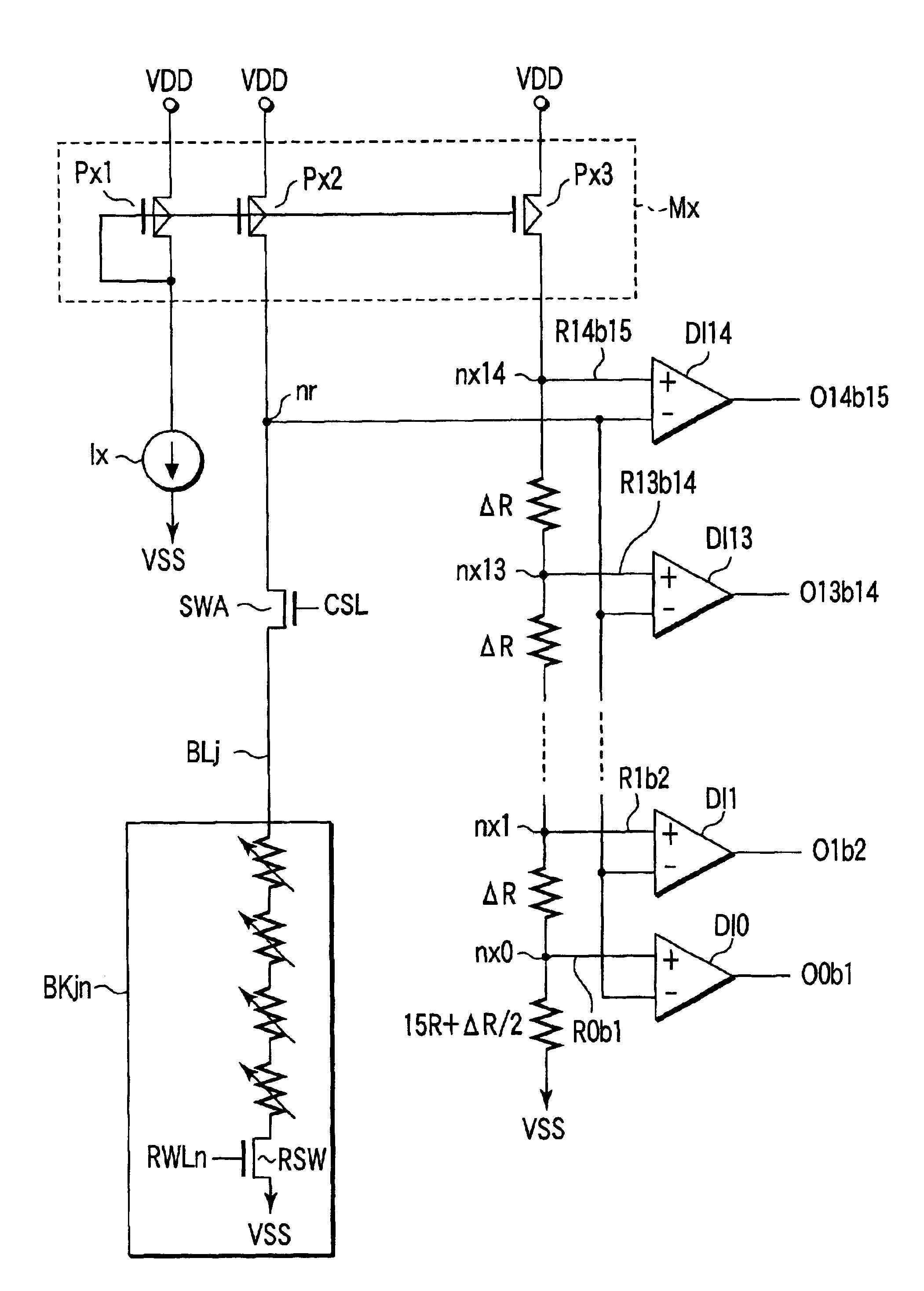

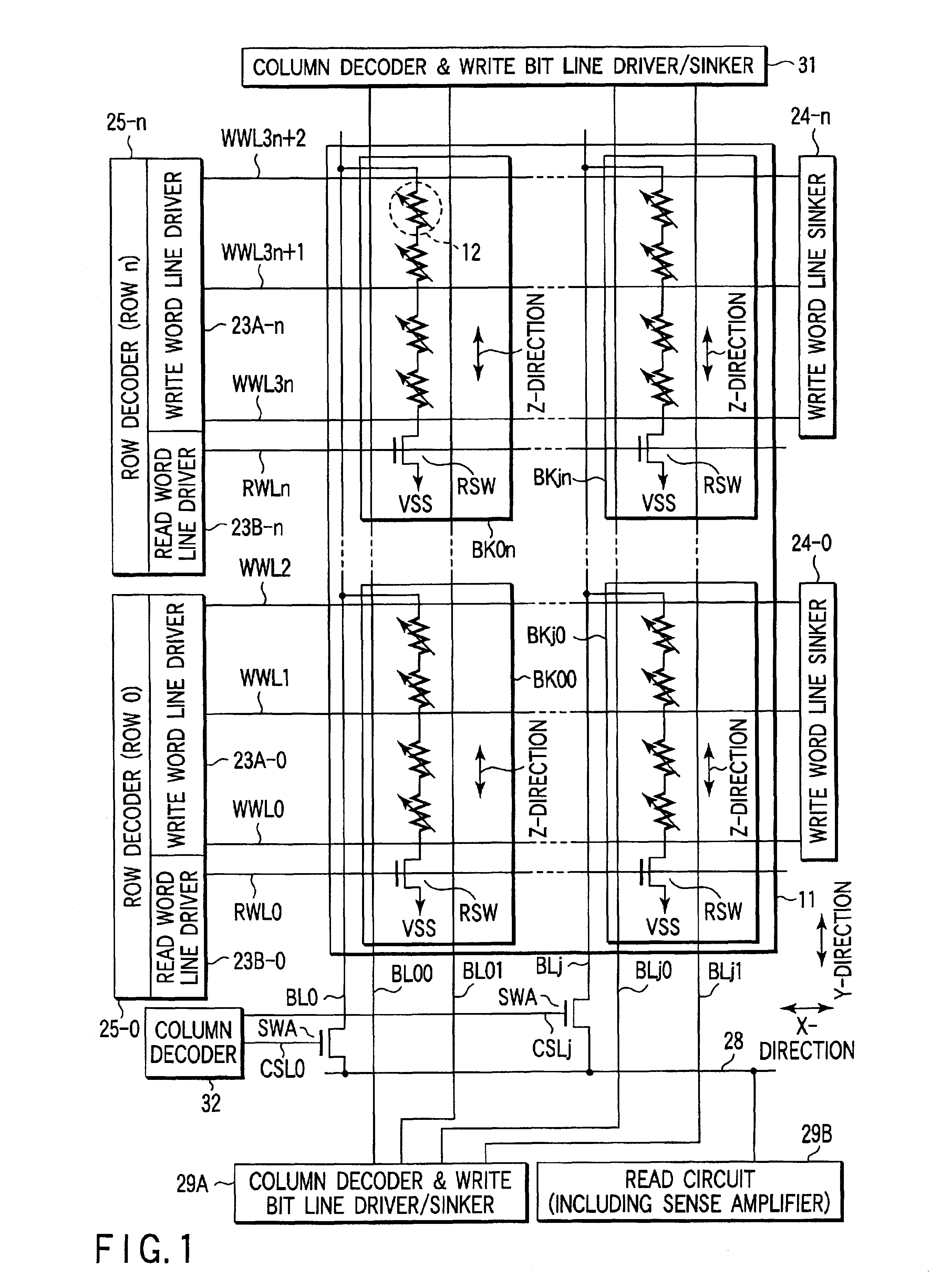

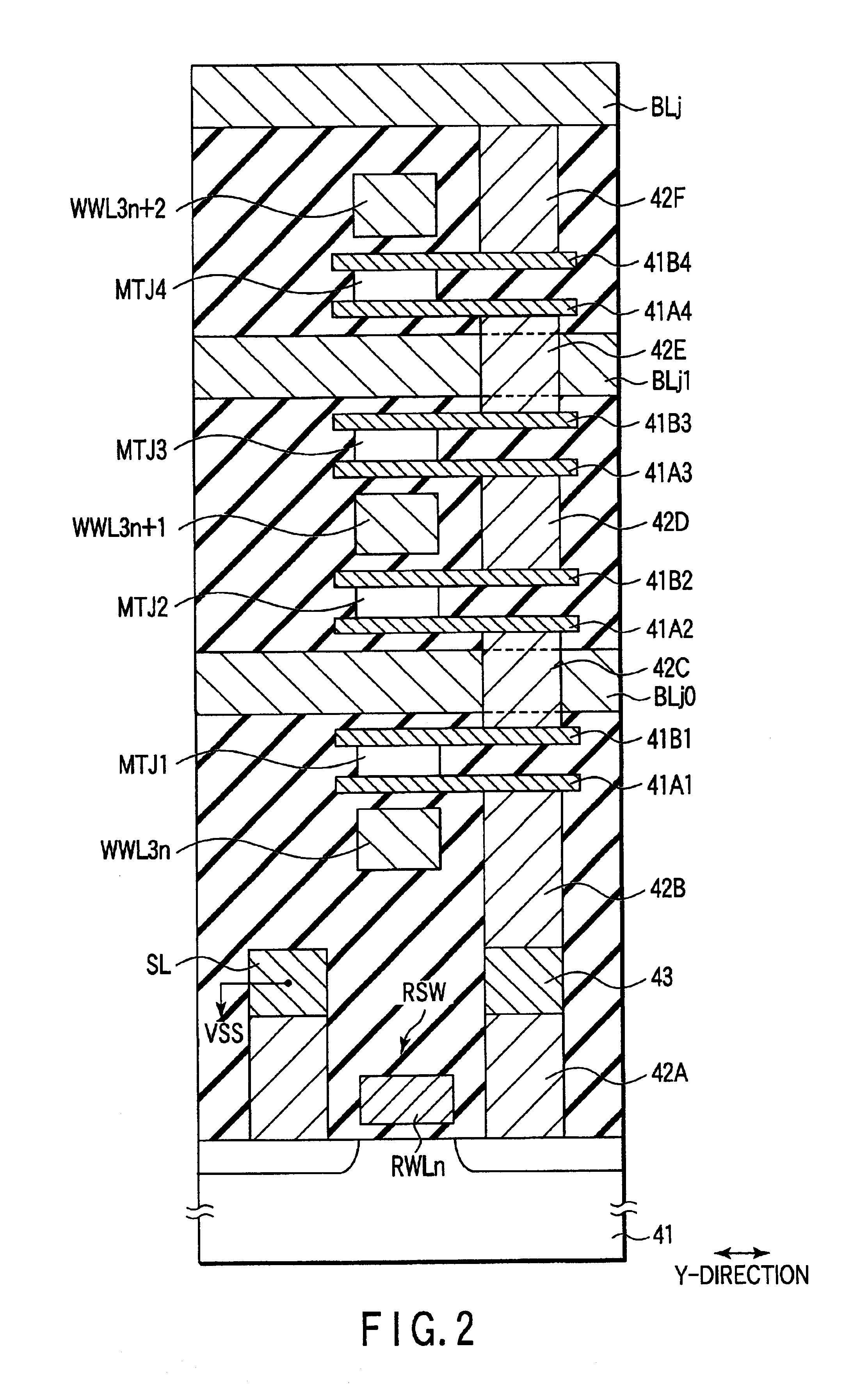

Magnetic random access memory

Blocks are connected to a read bit line. One block has MTJ elements which are connected to each other in series between the read bit line and a ground terminal. A MTJ elements are superposed on, e.g., a semiconductor substrate. A read bit line is arranged on the superposed MTJ elements. A write word line extending in a X-direction and a write bit line extending in a Y-direction are arranged in the vicinity of the MTJ elements in the block.

Owner:KK TOSHIBA

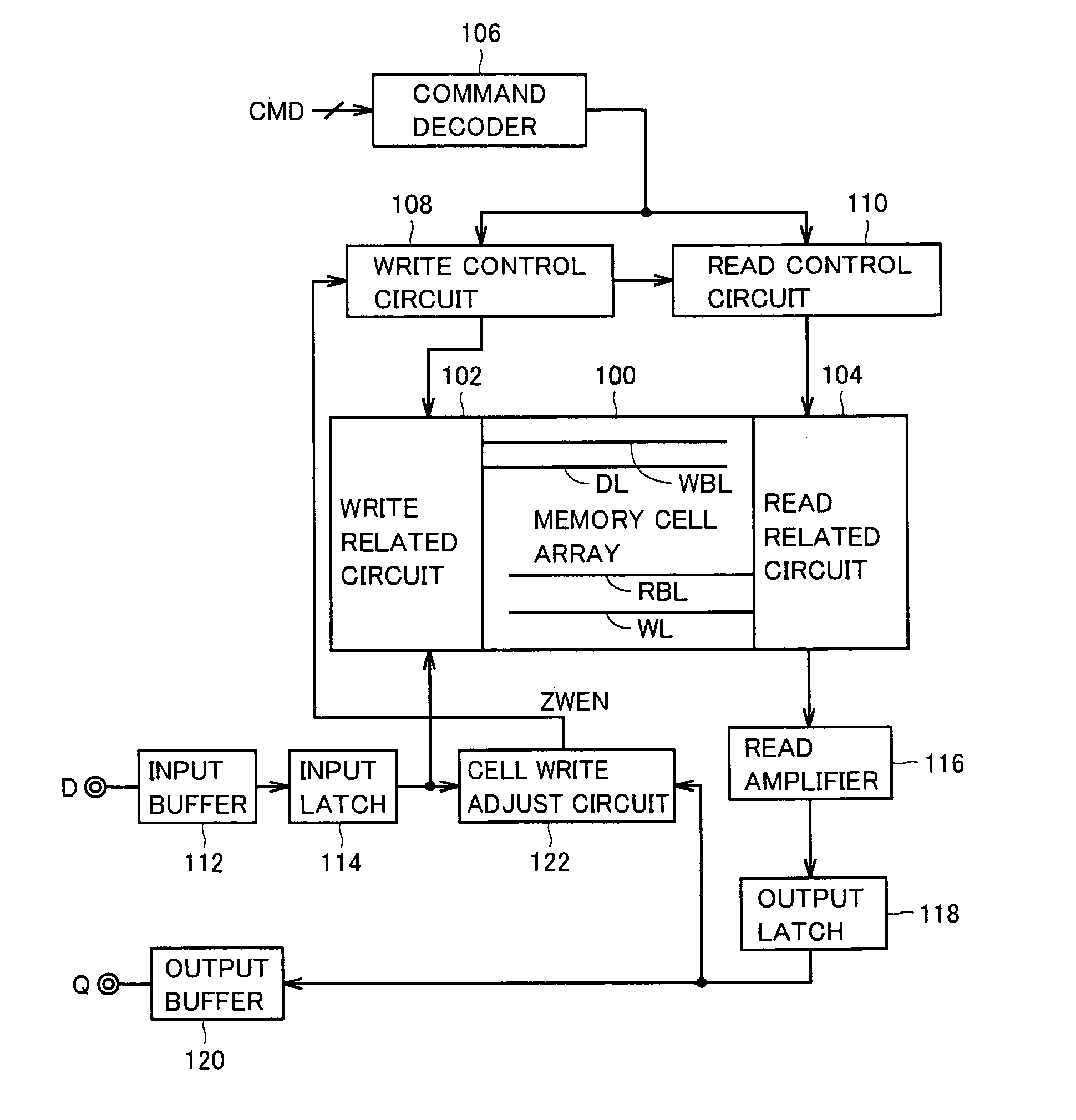

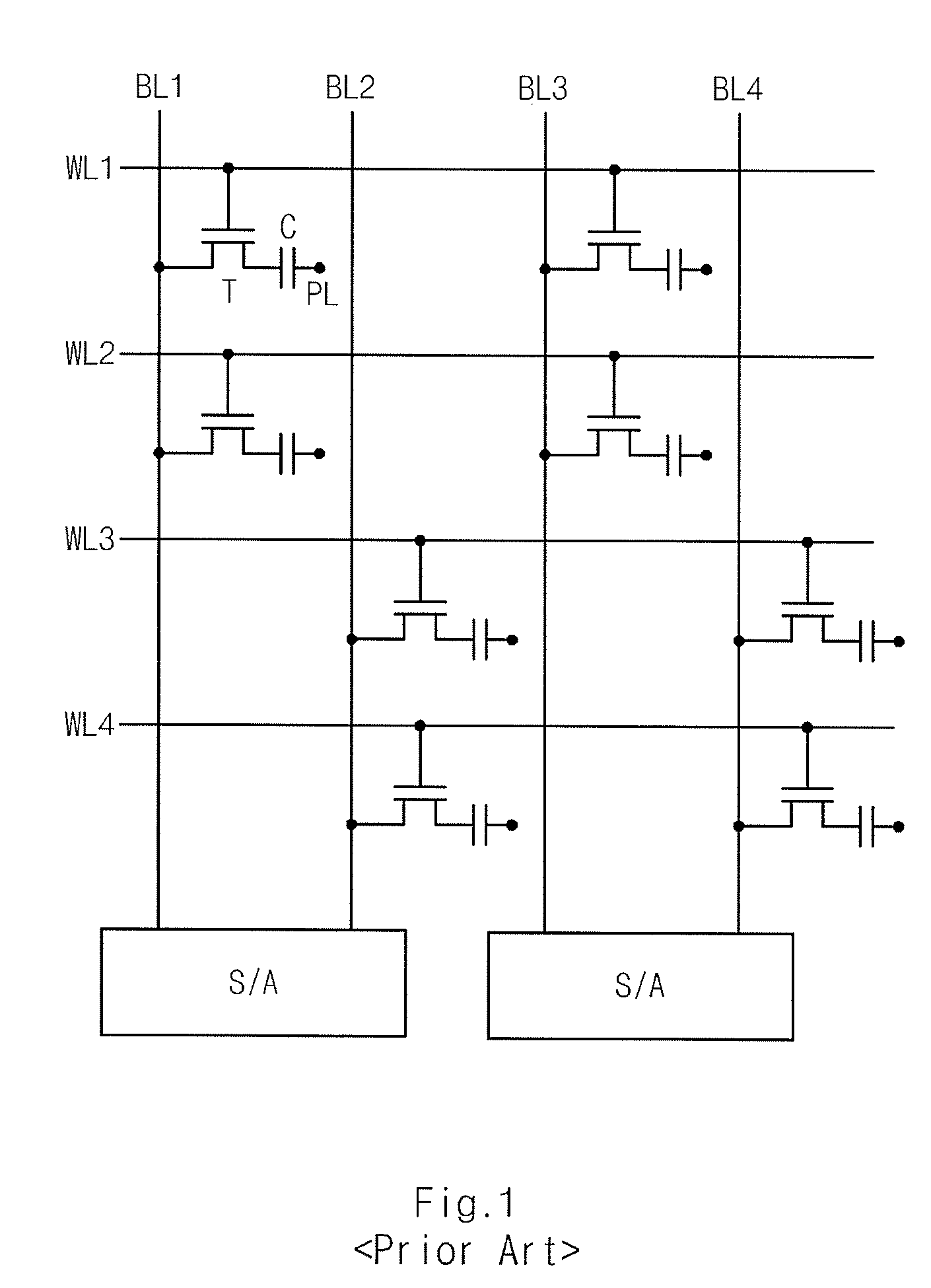

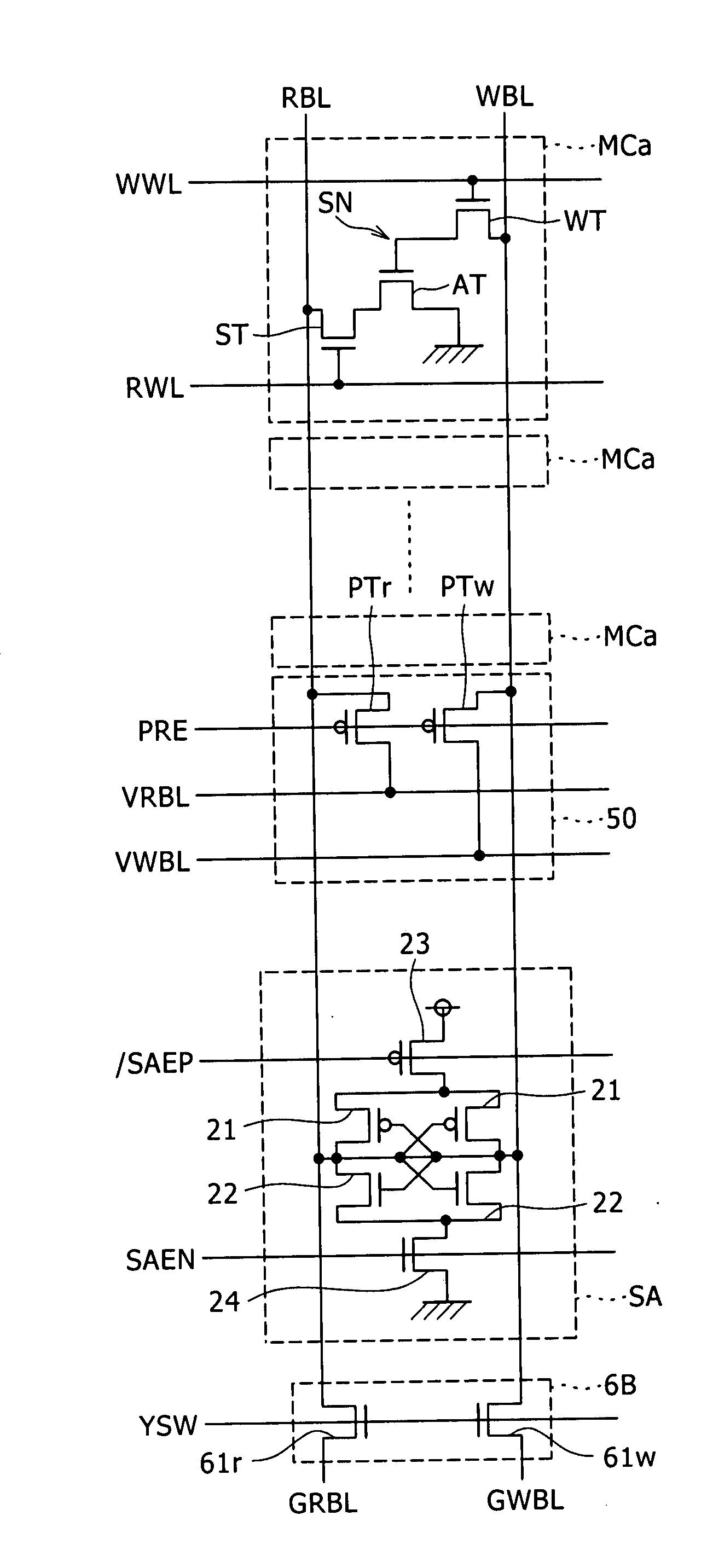

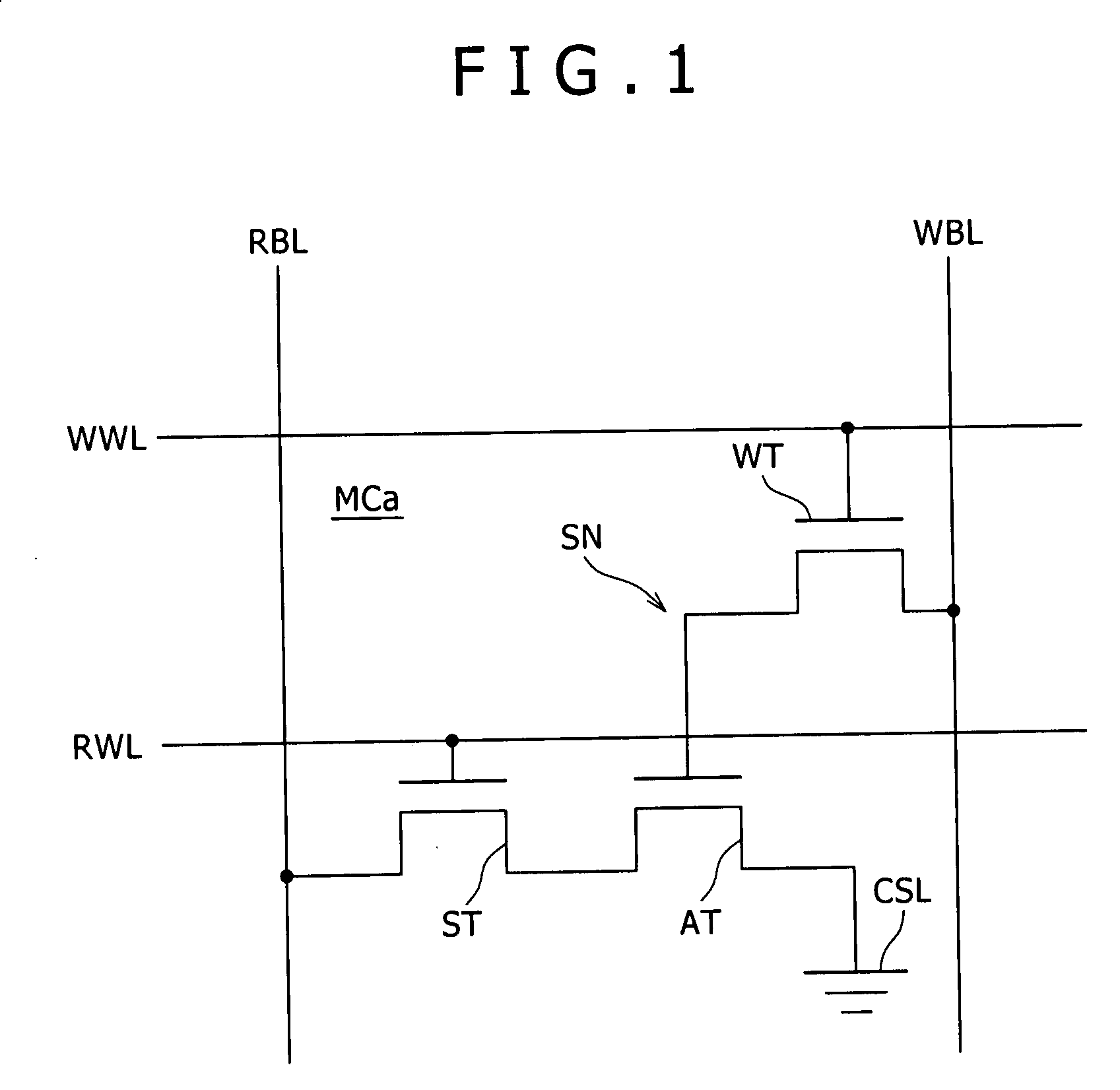

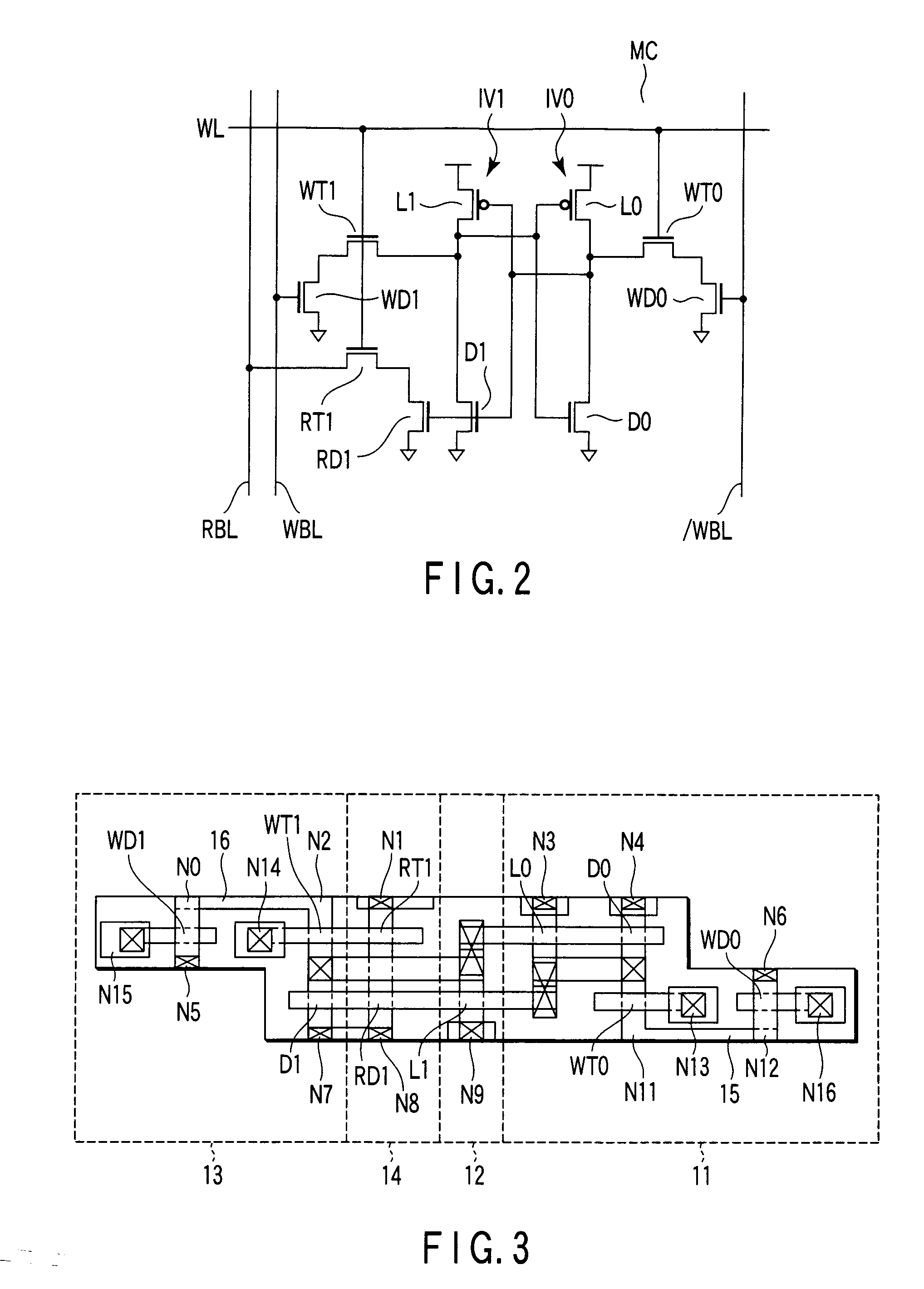

Semiconductor memory device

InactiveUS20060227648A1Increase the number ofArea of memory cell is increasedTransistorSolid-state devicesWrite bitComputer science

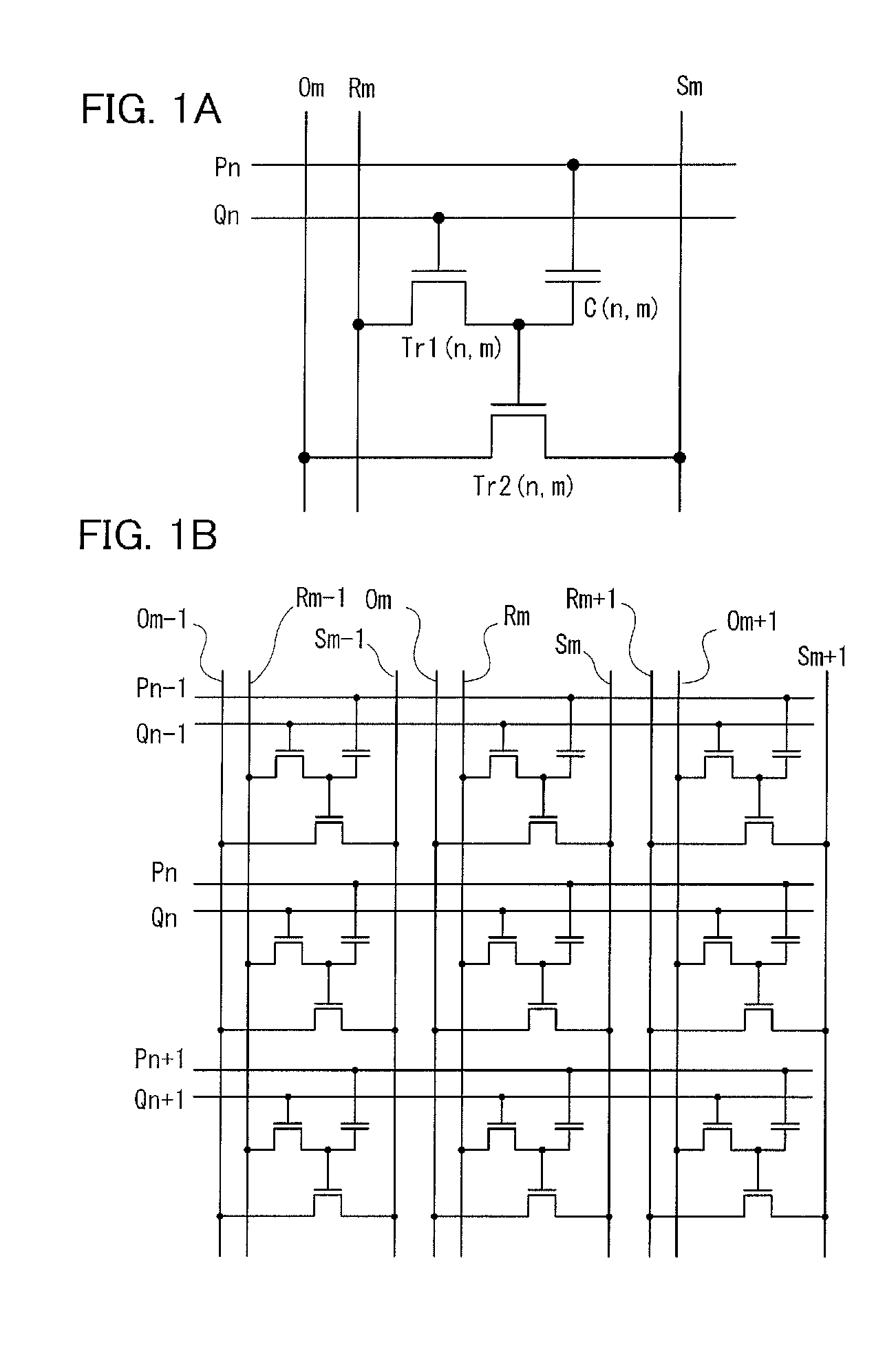

In a two-transistor gain cell structure, a semiconductor memory device capable of stable reading without malfunction and having small-area memory cells is provided. In a two-transistor gain cell memory having a write transistor and a read transistor, a write word line, a read word line, a write bit line, and a read bit line are separately provided, and voltages to be applied are independently set. Furthermore, a memory cell is connected to the same read word line and write bit line as those of an adjacent memory cell.

Owner:RENESAS ELECTRONICS CORP

Semiconductor memory device

InactiveUS20080025113A1Speedup of readSpeedup of write operationDigital storageWrite bitWrite buffer

Disclosed herein is a semiconductor memory device including, a memory array with memory cells array-like arranged, a read bit line connected to a data output node of the memory cells and shared by a plurality of the memory cells arranged in one direction in the memory array, a write bit line connected to a data input node of the memory cells and shared by a plurality of the memory cells, a sense amplifier for sensing a voltage of the reading bit line, a first sense line and a second sense line connected to the sense amplifier, a read bit line switch for controlling electrical connection and disconnection between the first sense line and the read bit line, a write buffer connected between the second sense line and the write bit line, capable of controlling electrical connection and disconnection between the second sense line and the write bit line.

Owner:SONY CORP

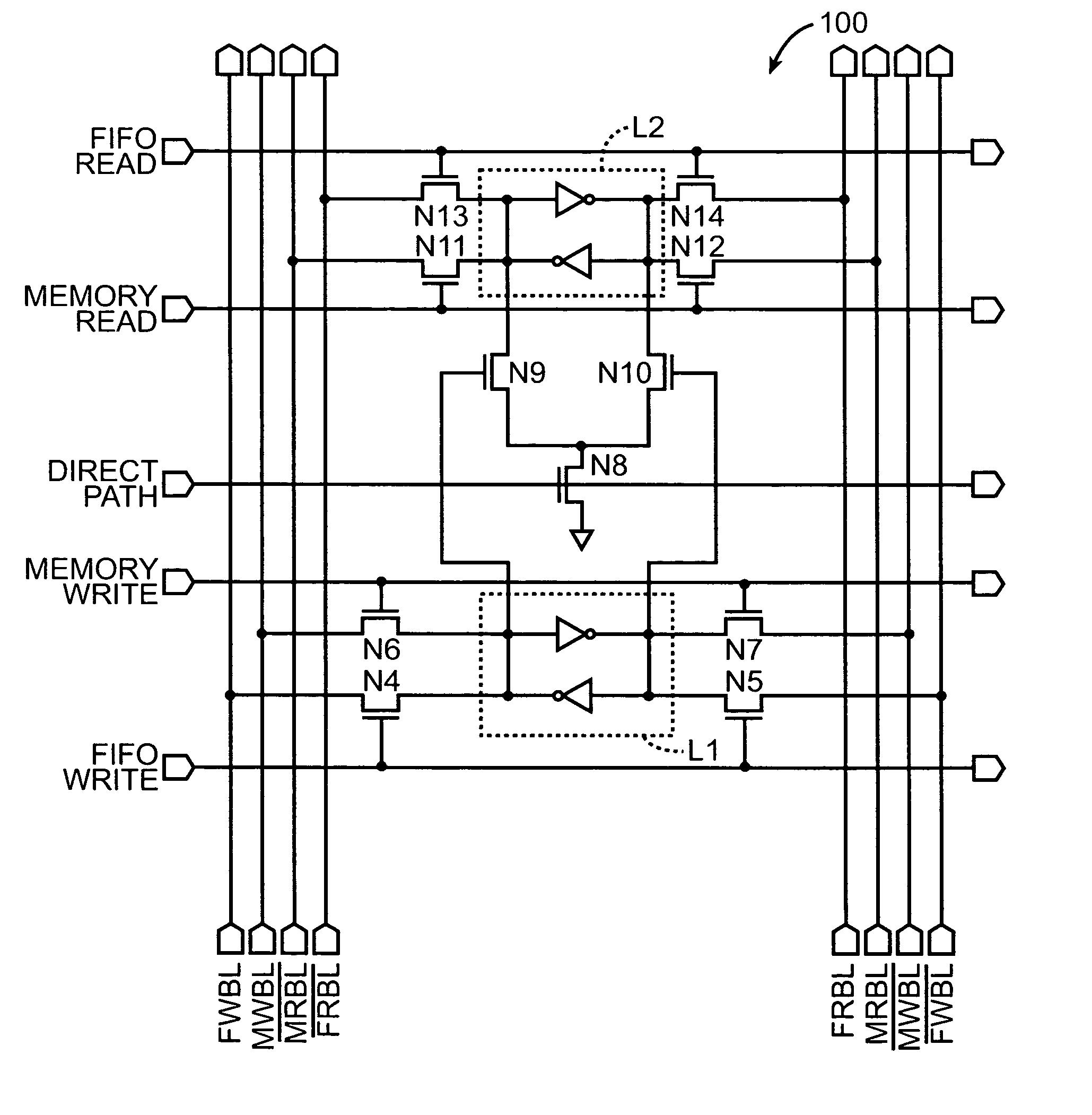

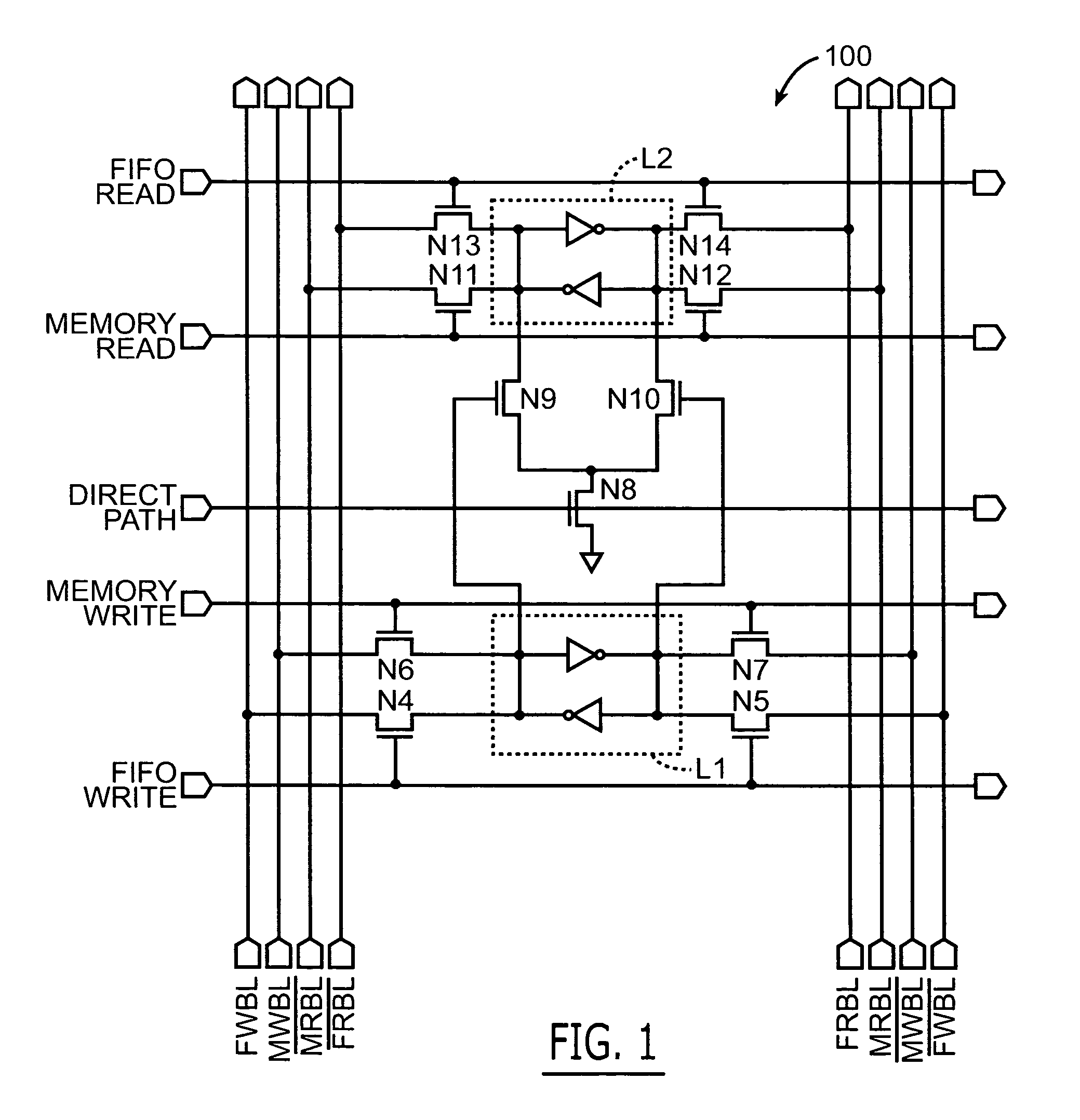

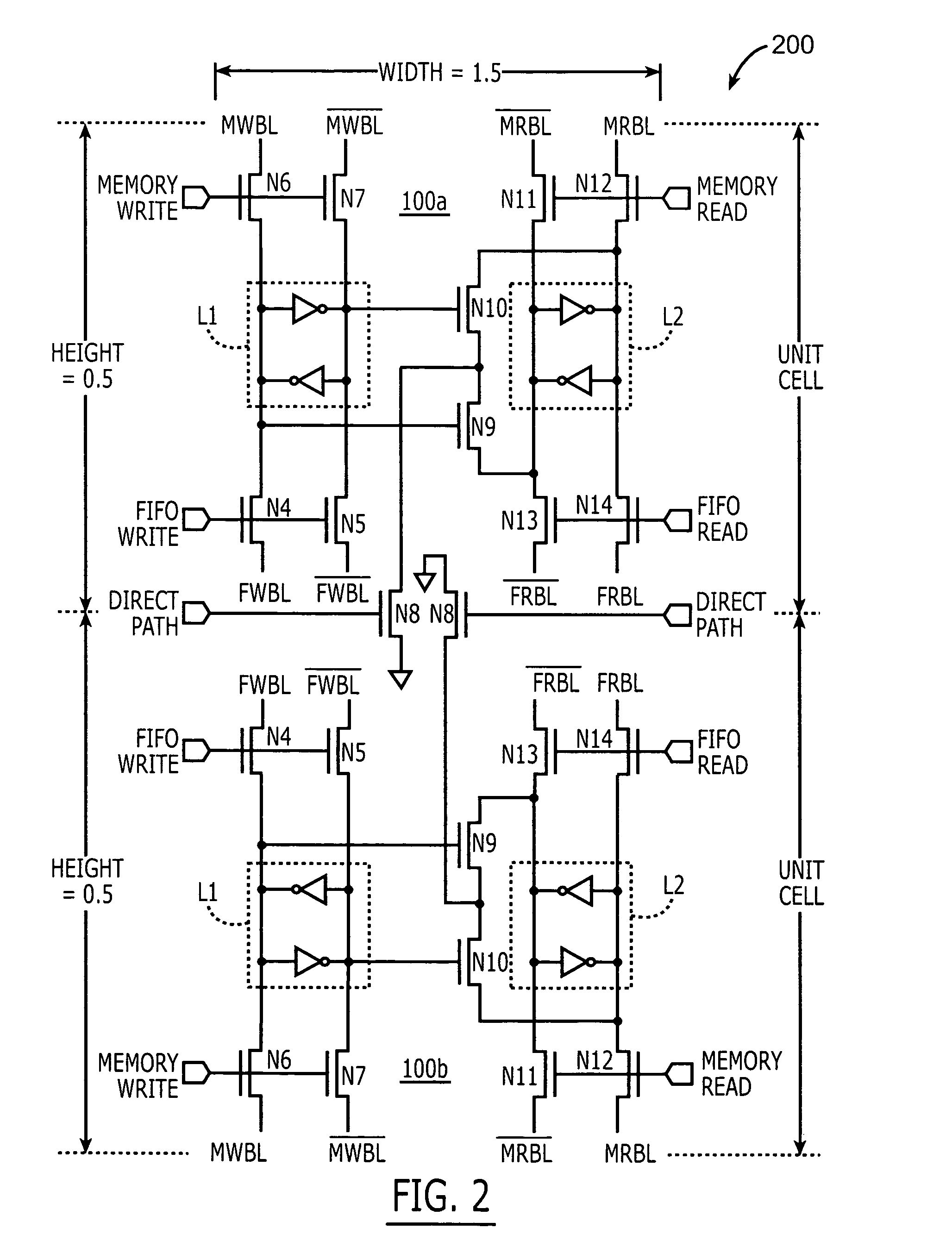

Multi-port memory cells for use in FIFO applications that support data transfers between cache and supplemental memory arrays

A multi-port memory cell includes a first SRAM element having a first pair of access transistors electrically coupled to a pair of FIFO write bit lines. A second dual-port SRAM element is also provided. This second dual-port SRAM element has a second pair of access transistors electrically coupled to a pair of FIFO read bit lines and a third pair of access transistors electrically coupled to a pair of memory read bit lines. A direct path data transfer circuit is provided. This transfer circuit is configured to support a unidirectional data transfer path that extends from first storage nodes within the first SRAM element to second storage nodes within the second dual-port SRAM element. This transfer circuit is also responsive to a direct path word line signal.

Owner:INTEGRATED DEVICE TECH INC

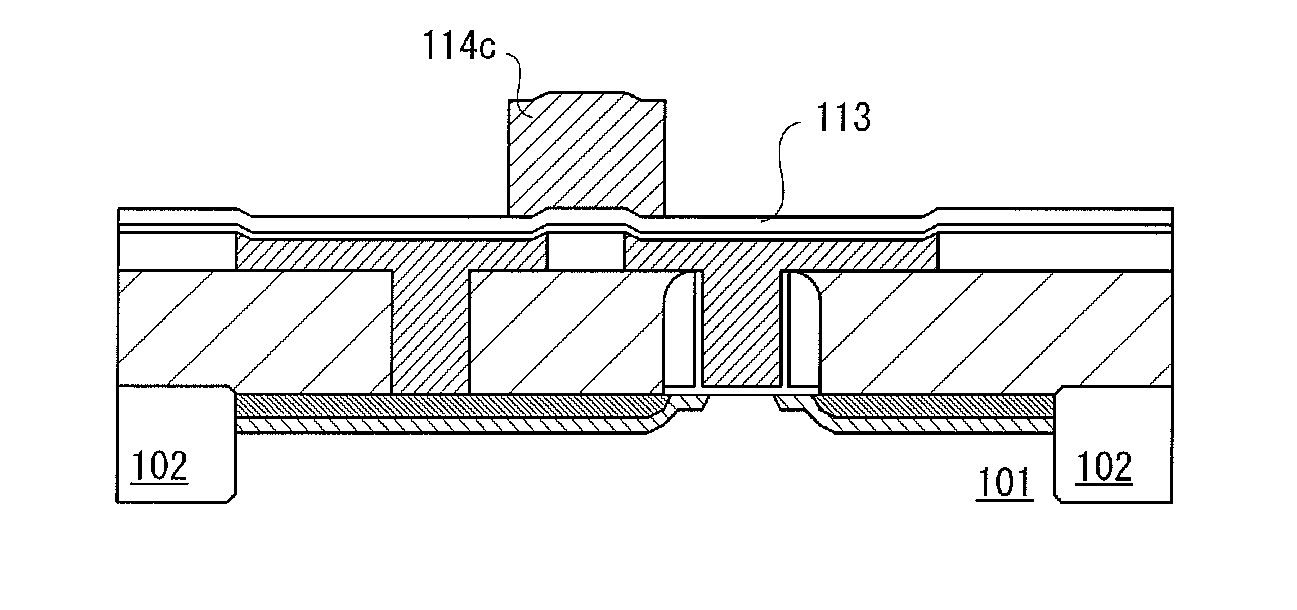

Semiconductor memory device, driving method thereof, and method for manufacturing semiconductor device

InactiveUS20110205774A1Reduce power consumptionHighly integratedTransistorSolid-state devicesWrite bitEngineering

A matrix is formed using a plurality of memory cells in each of which a drain of the writing transistor is connected to a gate of a reading transistor and one electrode of a capacitor. A gate of the writing transistor, a source of the writing transistor, a source of the reading transistor, and a drain of the reading transistor are connected to a writing word line, a writing bit line, a reading bit line, and a bias line, respectively. The other electrode of the capacitor is connected to a reading word line. In order to decrease the number of wirings, the writing bit line is substituted for the reading bit line. The reading bit line is formed so as to be embedded in a groove-like opening formed over a substrate.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor memory device and driving method thereof

ActiveUS8395931B2Reduce power consumptionNovel structureRead-only memoriesDigital storageWrite bitEngineering

Owner:SEMICON ENERGY LAB CO LTD

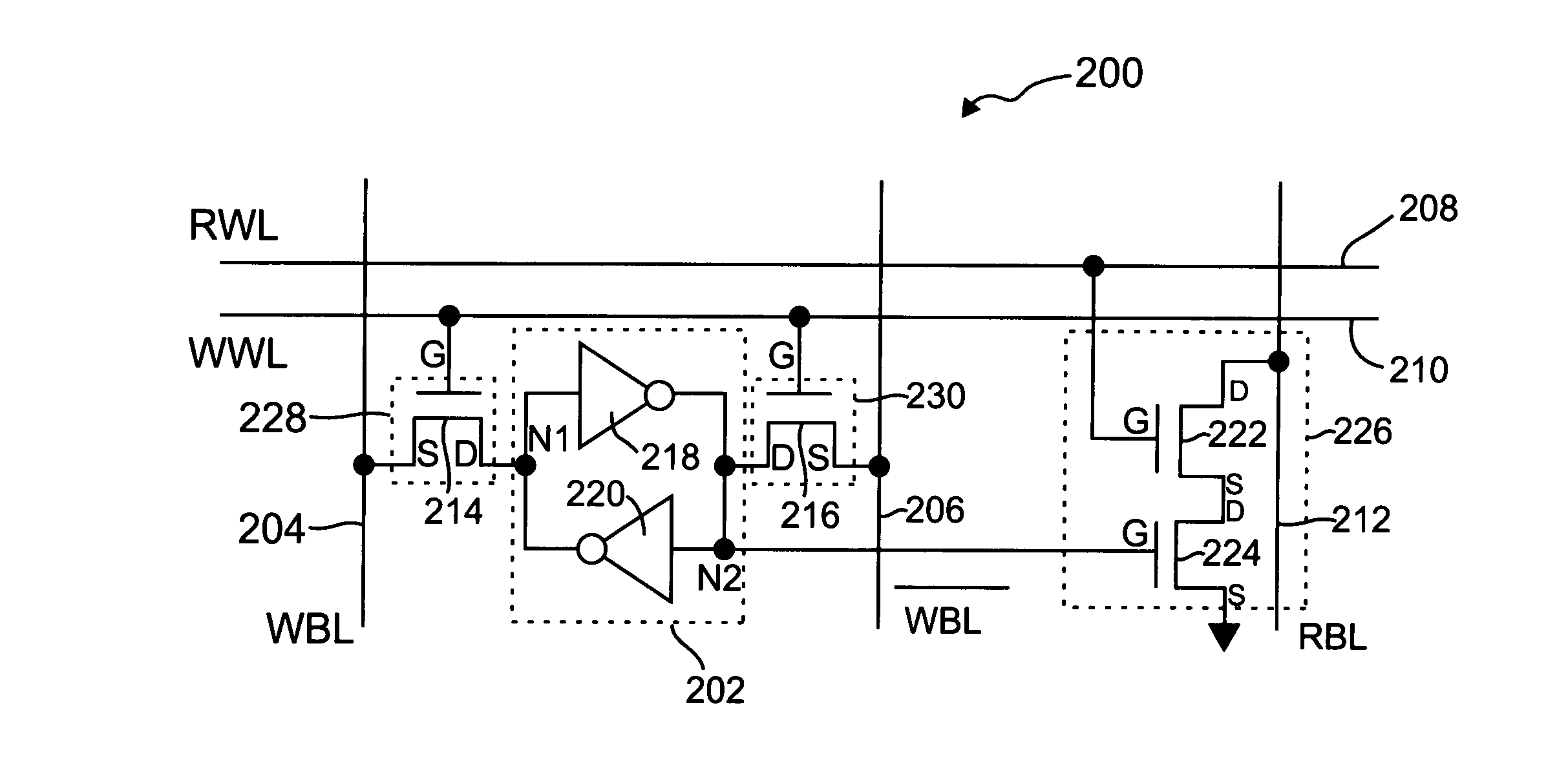

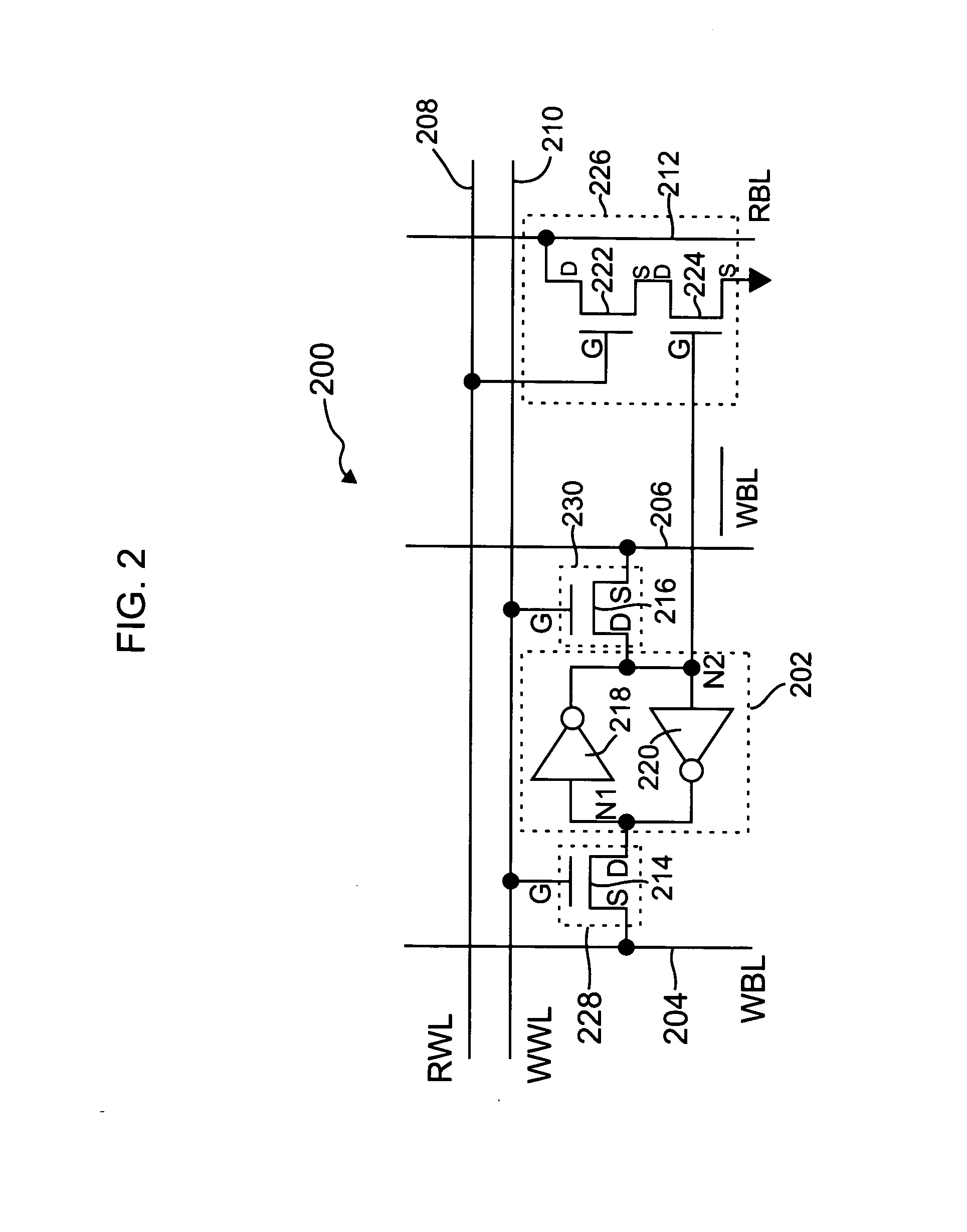

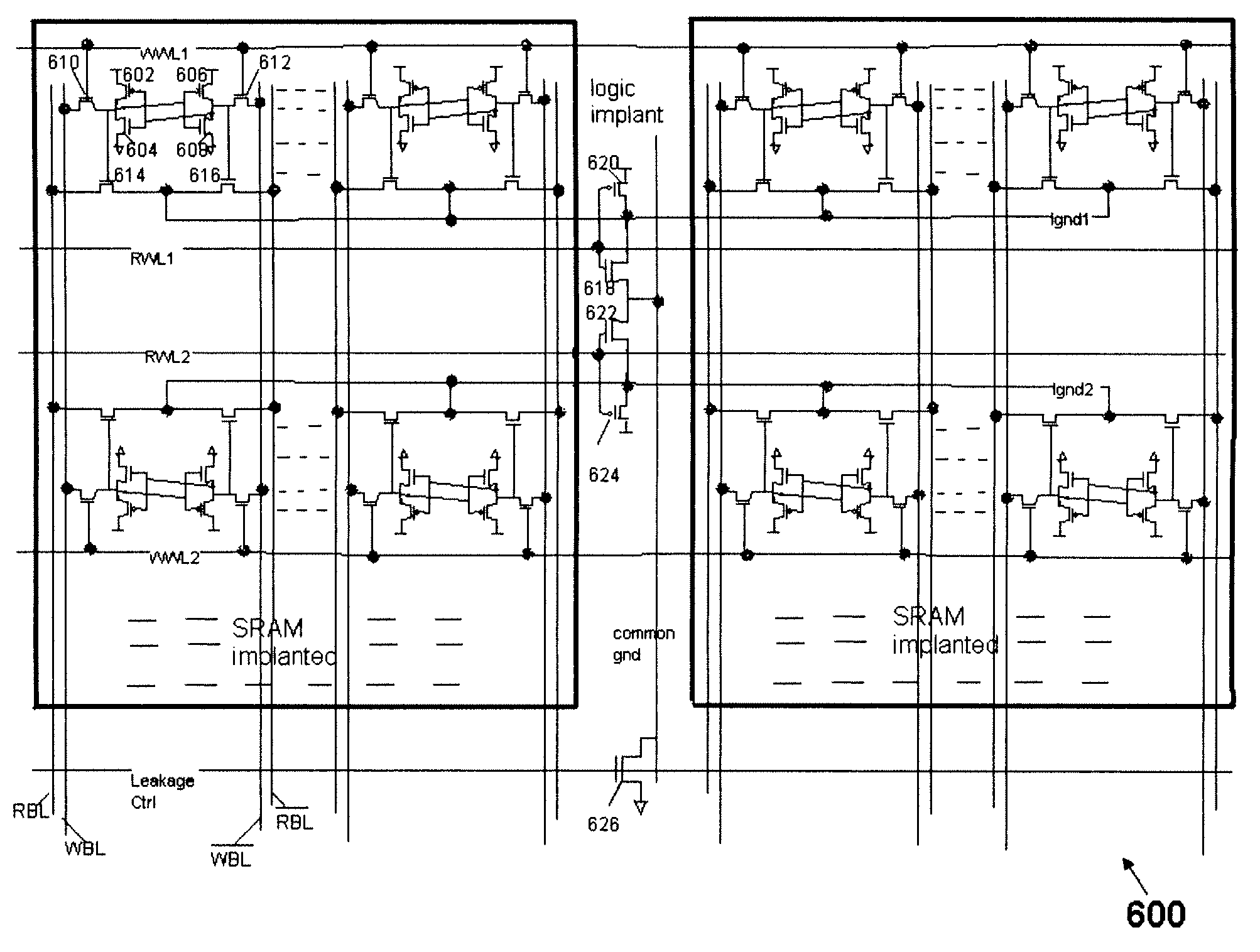

Memory cell having improved read stability

ActiveUS7106620B2Virtually eliminates disturbs of the memory cellTransistorSolid-state devicesWrite bitMemory cell

A memory cell for use in a memory array includes a storage element for storing a logical state of the memory cell, a write circuit and a read circuit. The write circuit is operative to selectively connect a first node of the storage element to at least a first write bit line in the memory array in response to a write signal for selectively writing the logical state of the memory cell. The read circuit includes a substantially high impedance input node connected to the storage element and an output node connectable to a read bit line of the memory array. The read circuit is configured to generate an output signal at the output node which is representative of the logical state of the storage element in response to a read signal applied to the read circuit. The memory cell is configured such that the write circuit is disabled during a read operation of the memory cell so as to substantially isolate the storage element from the first write bit line during the read operation. A strength of at least one transistor device in the storage element is separately optimized relative to a strength of at least one transistor device in the write circuit and / or the read circuit.

Owner:MICROSOFT TECH LICENSING LLC

Non-volatile memory device

InactiveUS7123498B2Improve reliabilityHighly reliable reading of informationMagnetic-field-controlled resistorsElectric analogue storesWrite bitComputer science

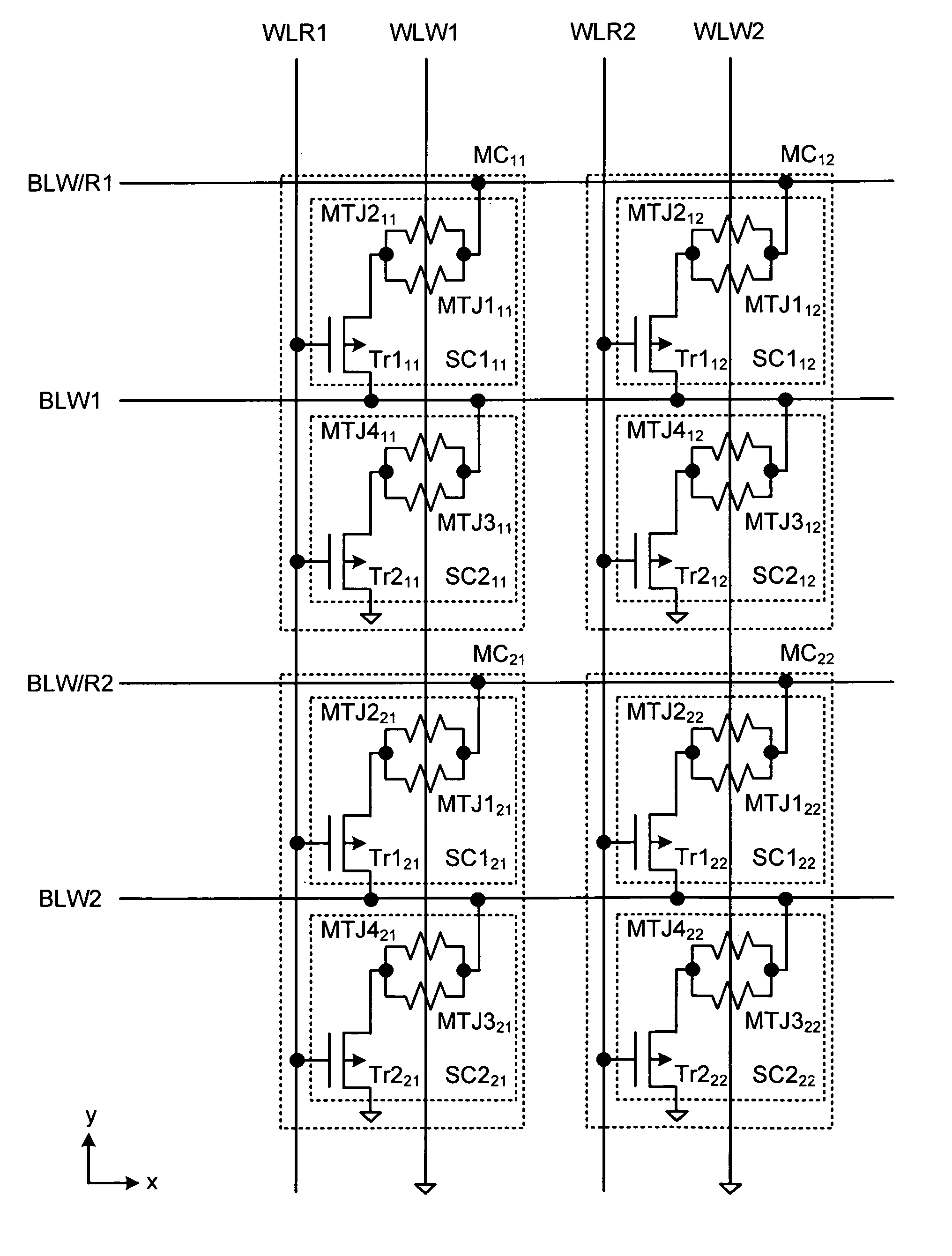

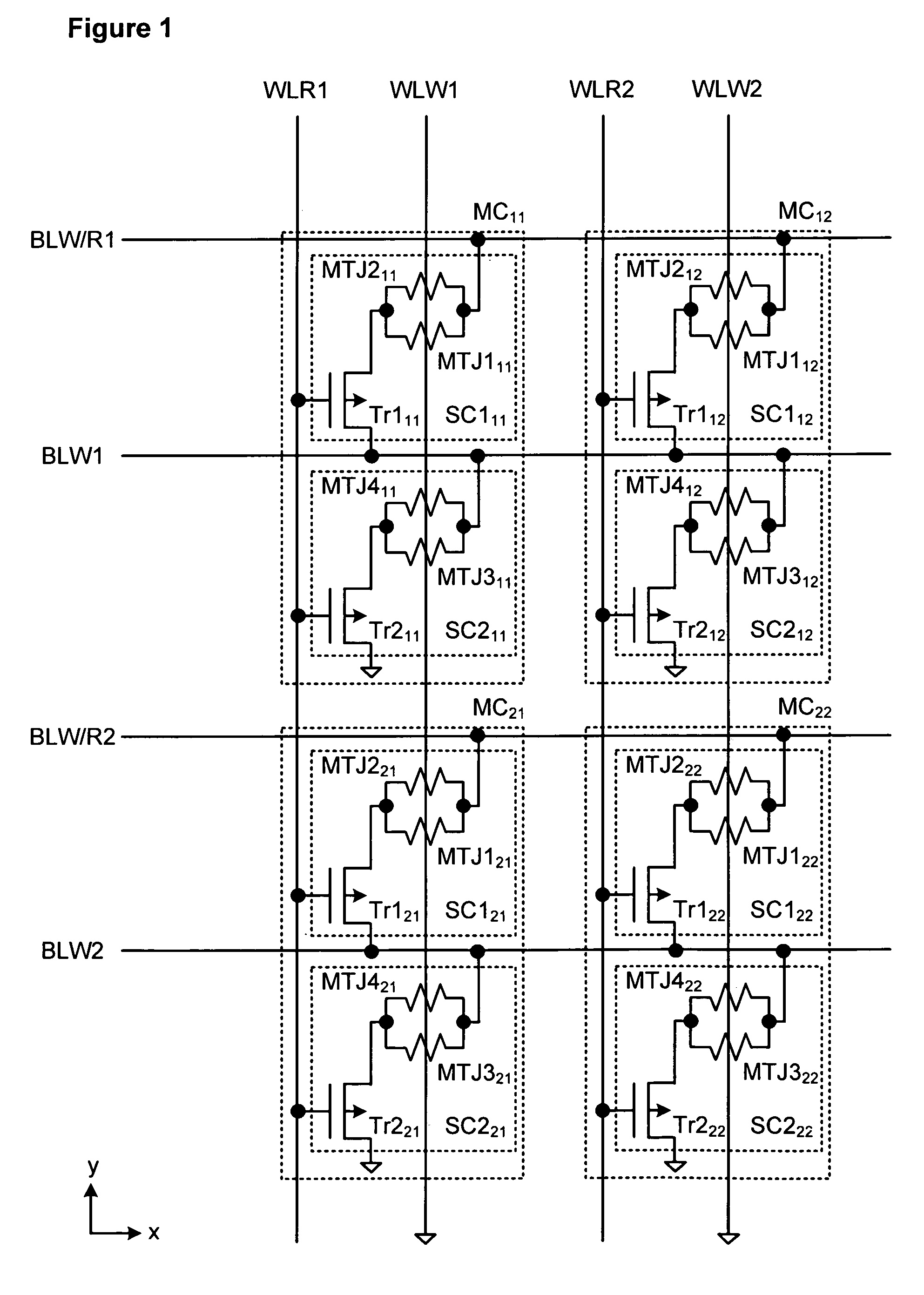

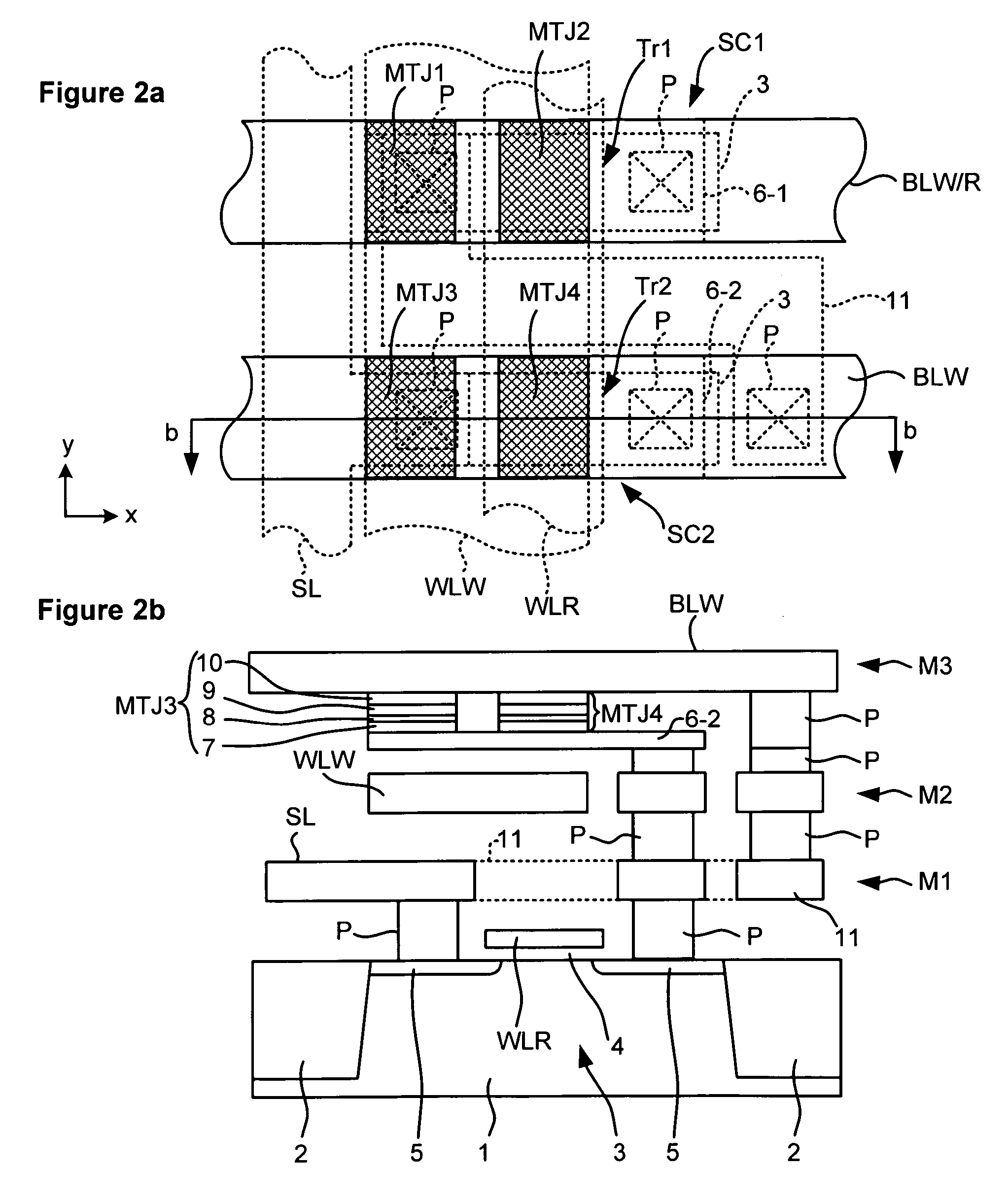

MRAM has read word lines WLR and write word line WLW extending in the y direction, write / read bit line BLW / R and write bit line BLW extending in the x direction, and the memory cells MC disposed at the points of the intersection of these lines. The memory MC includes sub-cells SC1 and SC2. The sub-cell SC1 includes magneto resistive elements MTJ1 and MTJ2 and a selection transistor Tr1, and the sub-cell SC2 includes magneto resistive elements MTJ3 and MTJ4 and a selection transistor Tr2. The magneto resistive elements MTJ1 and MTJ2 are connected in parallel, and the magneto resistive elements MTJ3 and MTJ4 are also connected in parallel. Further, the sub-cells SC1 and SC2 are connected in series between the write / read bit line BLW / R and the ground.

Owner:INT BUSINESS MASCH CORP

Semiconductor memory device where write and read disturbances have been improved

A data write transfer gate and a write driver transistor are connected to a data latch circuit for storing data, thereby producing a write data path. The data path is controlled by a word line and a data write bit line. In addition, a read drive transistor and a read transfer gate are connected to the latch circuit, thereby producing a read data path. The data path is controlled by a word line, a read bit line, and the data in the data latch circuit.

Owner:KK TOSHIBA

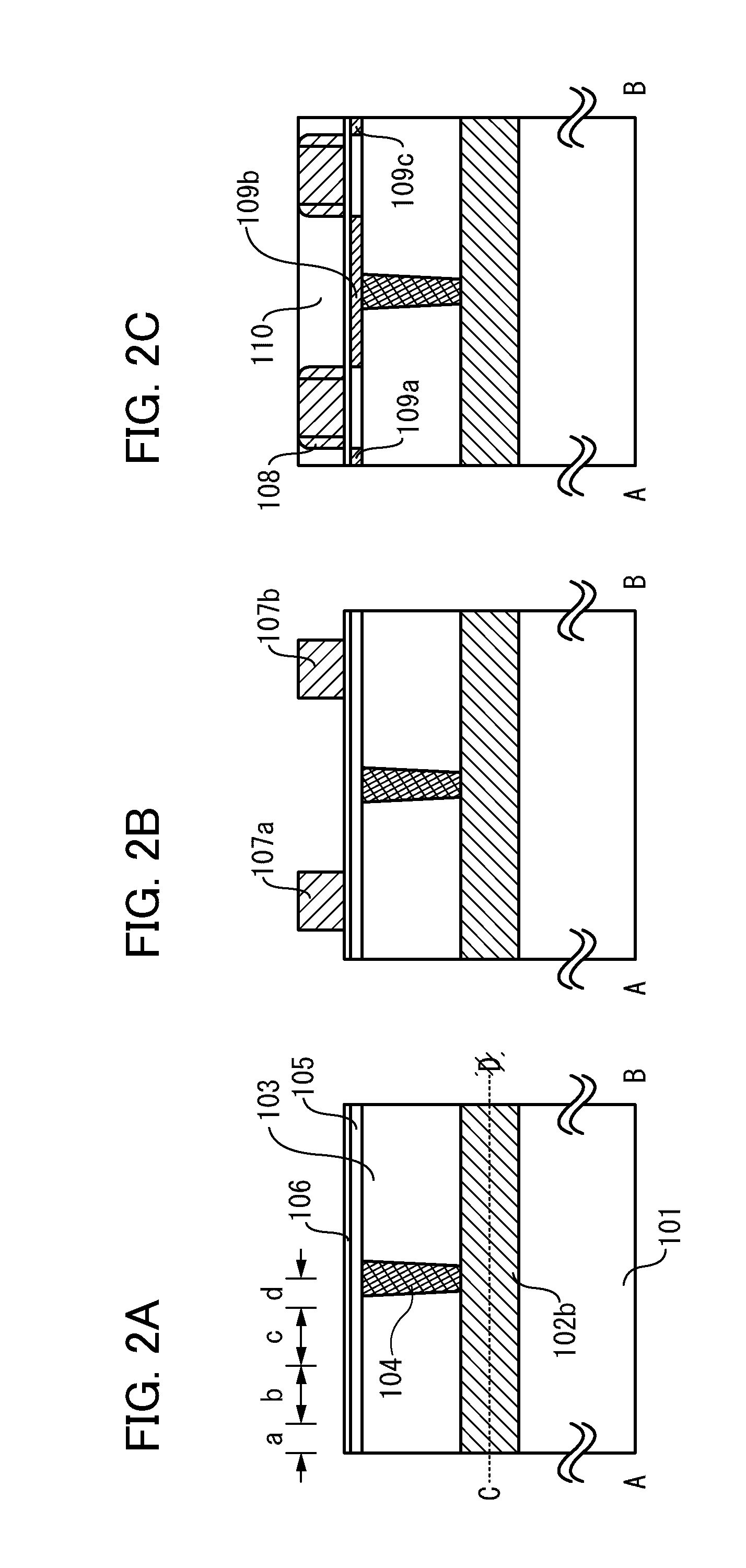

Semiconductor memory device and method of manufacturing semiconductor memory device

InactiveUS20120213000A1Reduce parasitic capacitanceParasitic capacitance is generatedTransistorSolid-state devicesWrite bitMemory cell

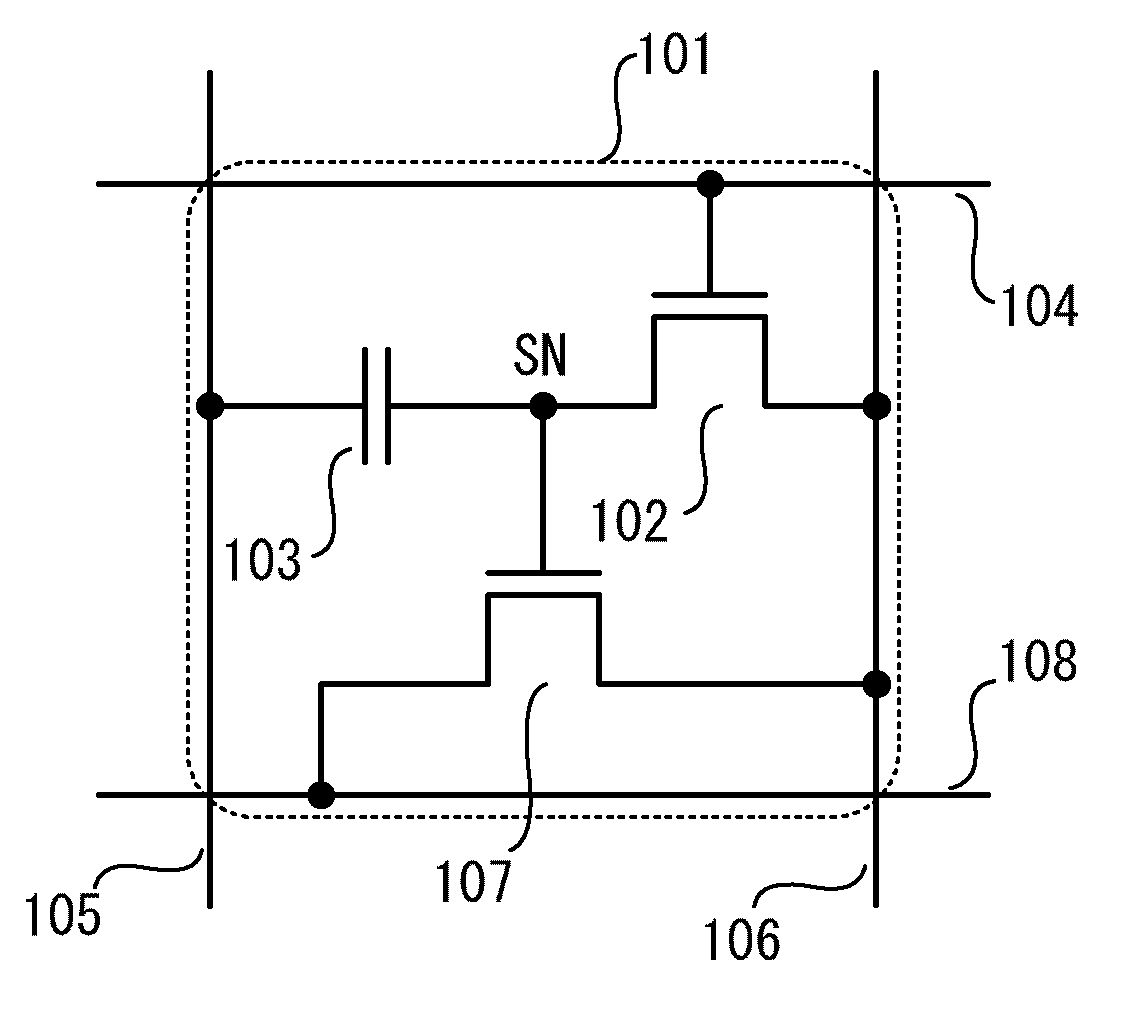

A highly integrated gain cell-type semiconductor memory is provided. A first insulator, a read bit line, a second insulator, a third insulator, a first semiconductor film, first conductive layers, and the like are formed. A projecting insulator is formed thereover. Then, second semiconductor films and a second gate insulating film are formed to cover the projecting insulator. After that, a conductive film is formed and subjected to anisotropic etching, so that write word lines are formed on side surfaces of the projecting insulator. A third contact plug for connection to a write bit line is formed over a top of the projecting insulator. With such a structure, the area of the memory cell can be 4 F2 at a minimum.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor memory device with MOS transistors, each including a floating gate and a control gate, a control method thereof, and a memory card including the same

A semiconductor memory device includes memory cells, write bit lines, read bit lines, latch circuits, a n-channel MOS transistor, and voltage setting circuits. The memory cell includes a first MOS transistor having a charge accumulation layer and a control gate. The first MOS transistors are connected commonly to the write bit lines and read bit lines. The latch circuits are provided for the write bit lines and hold write data for the memory cells. The n-channel MOS transistor transfer “1” data to the latch circuits in a data latch operation. The voltage setting circuits supply a potential corresponding to “0” data to the write bit lines in a read operation. In a data latch operation, the latch circuit corresponding to the write bit line connected to the memory cell into which “0” data is to be written latches the potential supplied to the write bit lines in a read operation.

Owner:KK TOSHIBA

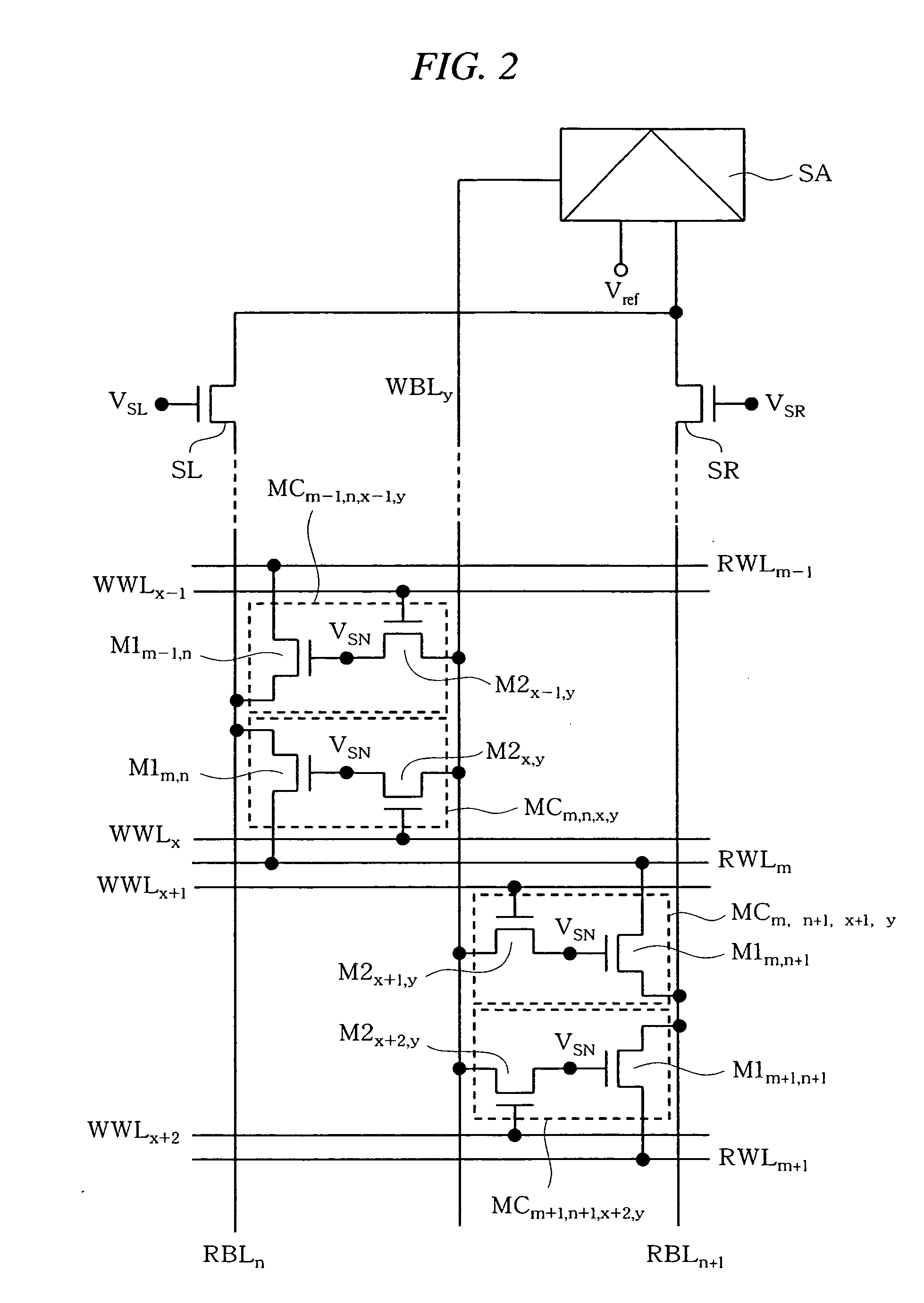

Semiconductor memory device and driving method of semiconductor memory device

InactiveUS20120113707A1Small fluctuationResistance of the wiring connected to the source of the reading transistor does notRead-only memoriesDigital storageWrite bitHemt circuits

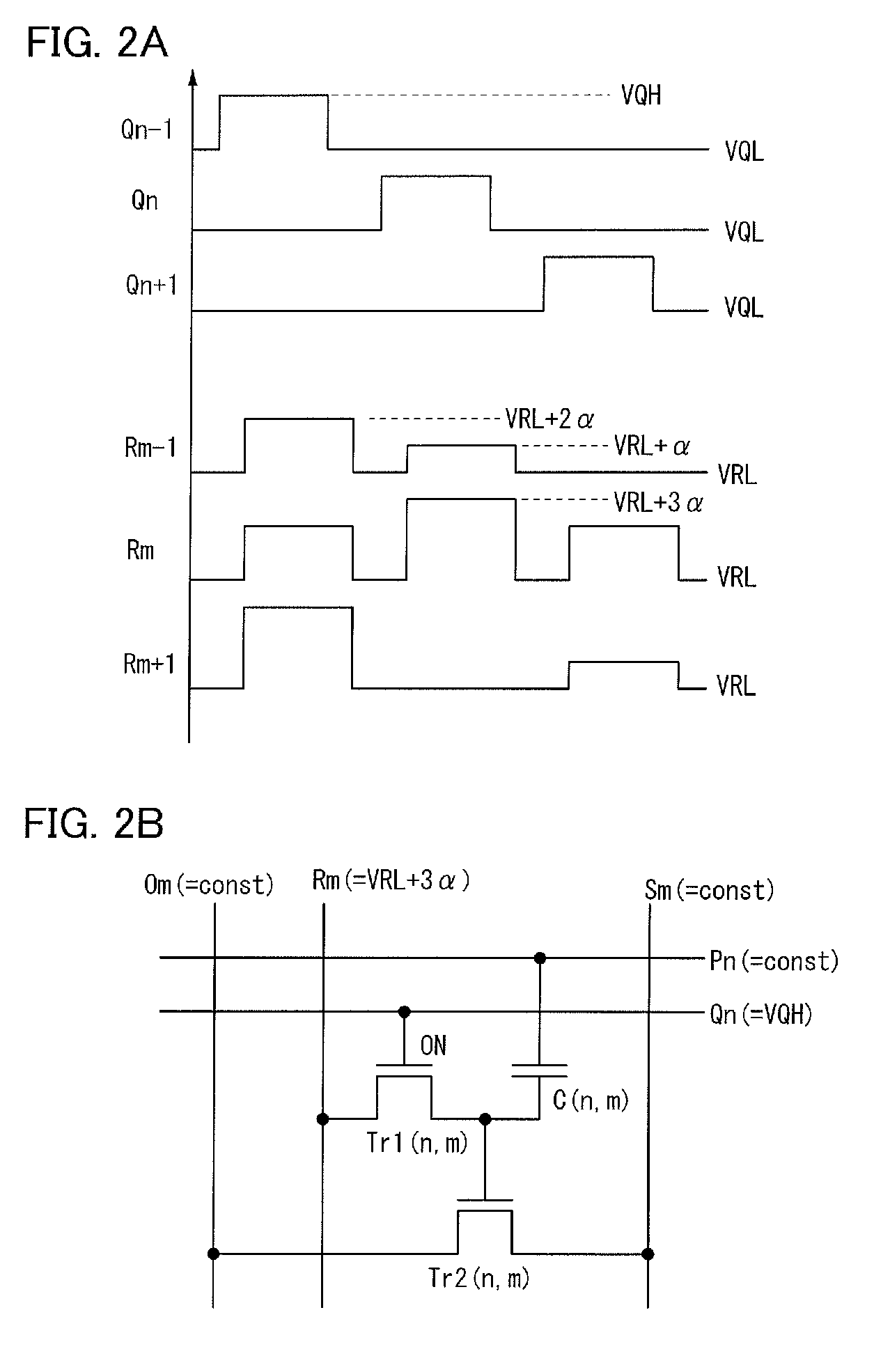

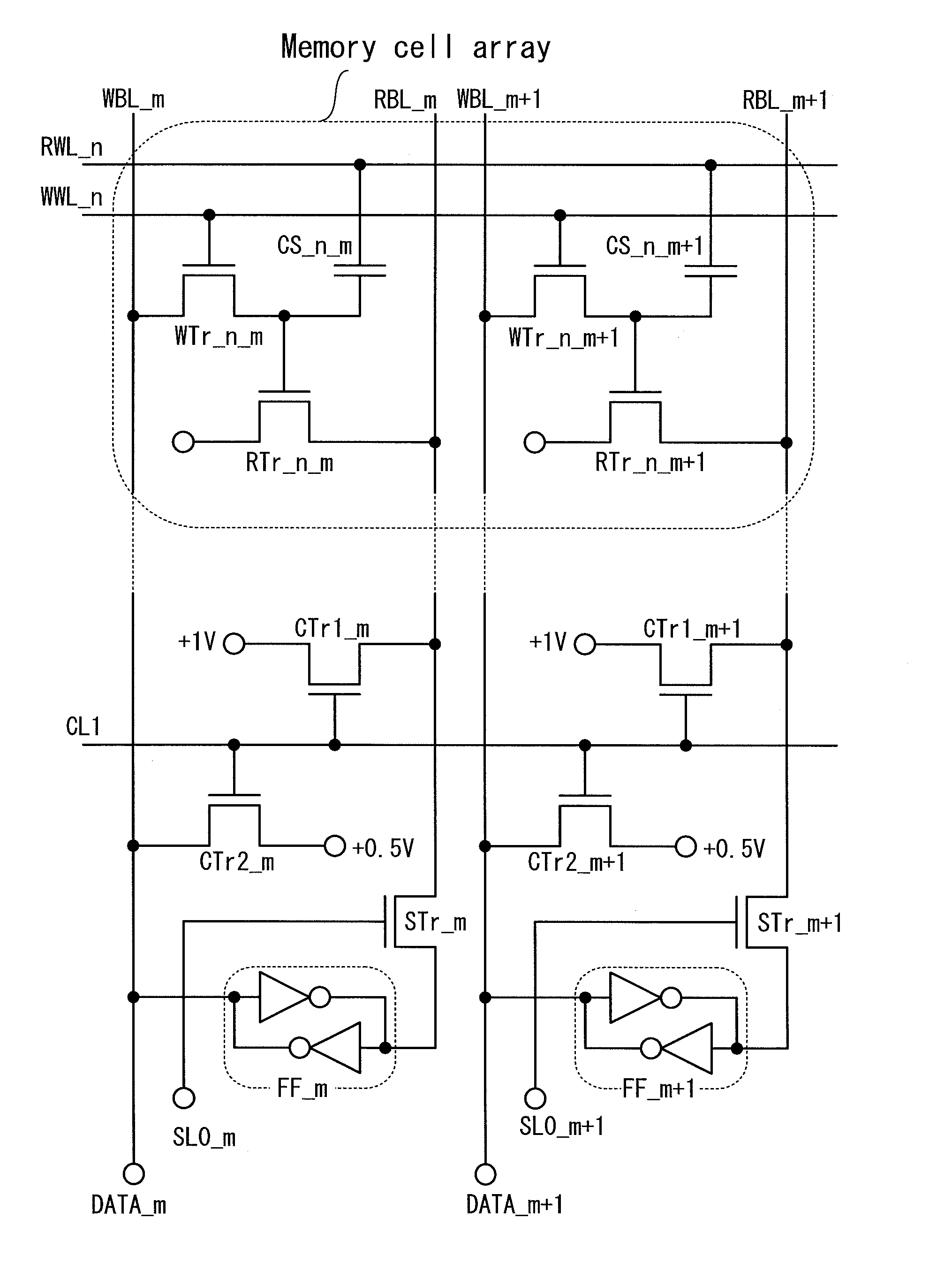

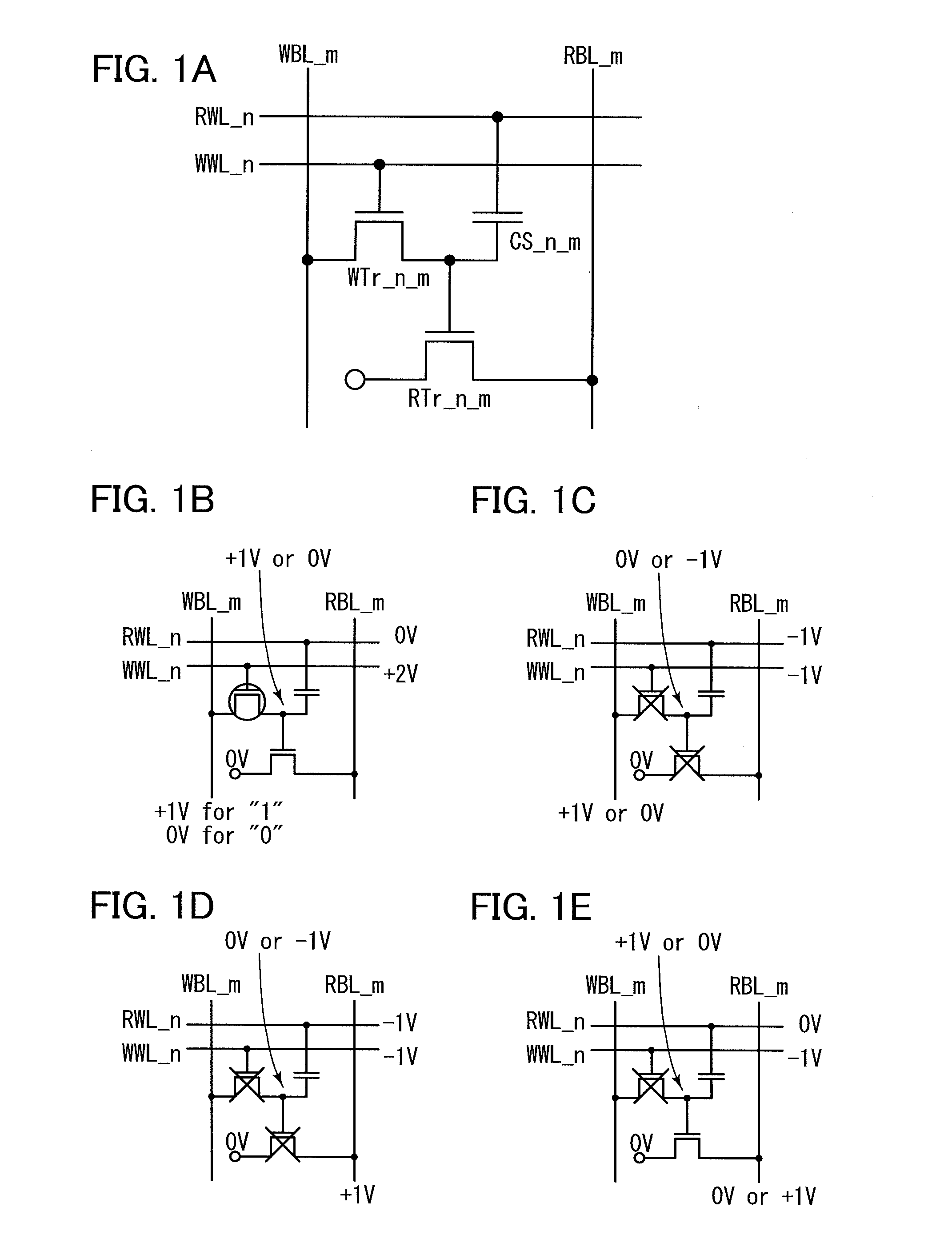

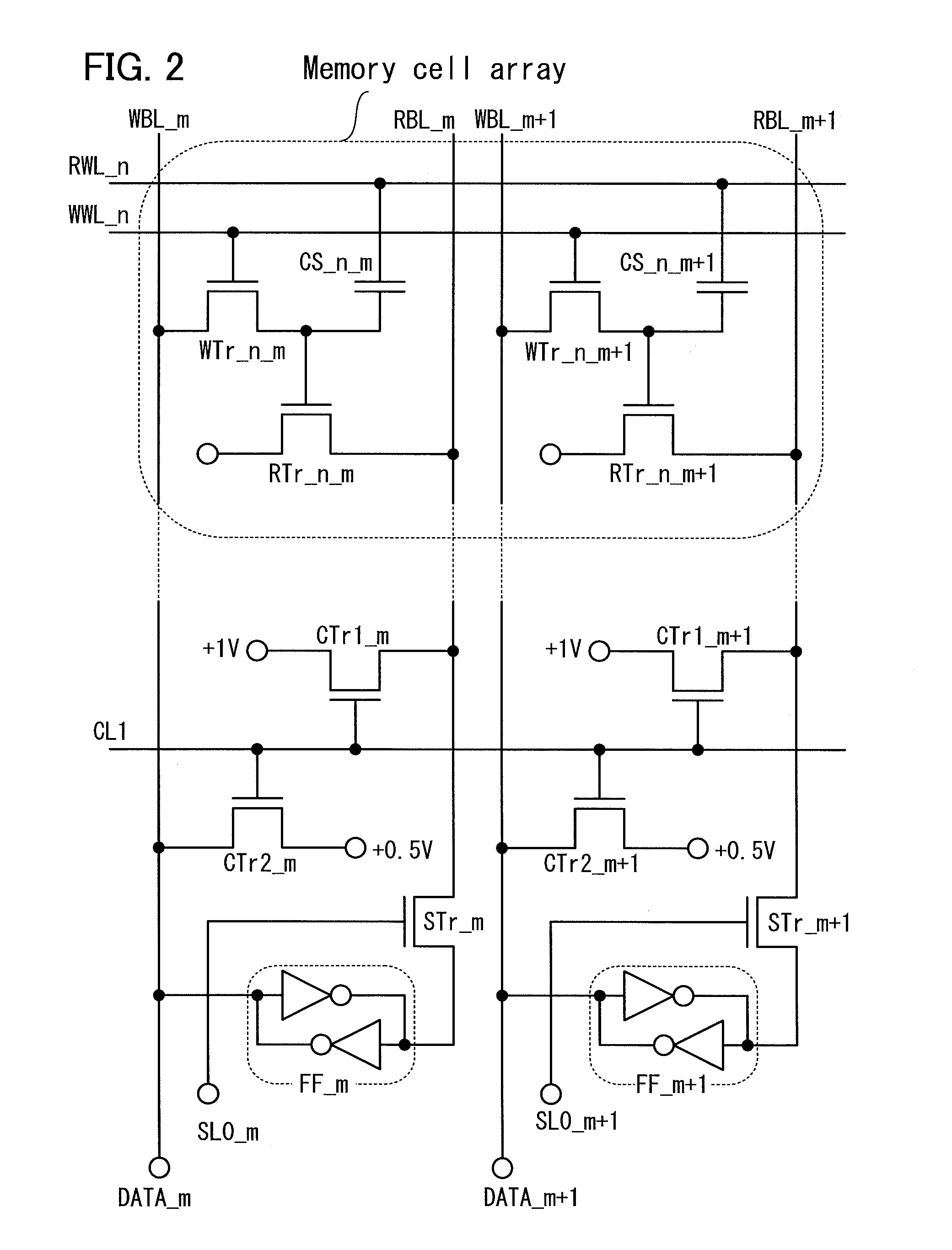

A novel semiconductor memory device whose power consumption is low is provided. A source of a writing transistor WTr_n_m, a gate of a reading transistor RTr_n_m, and one electrode of a capacitor CS_n_m are connected to each other. A gate and a drain of the writing transistor WTr_n_m are connected to a writing word line WWL_n and a writing bit line WBL_m, respectively. The other electrode of the capacitor CS_n_m is connected to a reading word line RWL_n. A drain of the reading transistor RTr_n_m is connected to a reading bit line RBL_m. Here, the potential of the reading bit line RBL_m is input to an inverting amplifier circuit such as a flip-flop circuit FF_m to be inverted by the inverting amplifier circuit. This inverted potential is output to the writing bit line WBL_m.

Owner:SEMICON ENERGY LAB CO LTD

Gain cell semiconductor memory device and driving method thereof

A memory cell including two transistors and one capacitor, which is known as a gain cell, is improved. One electrode of the capacitor is connected to a bit line, and the other electrode thereof is connected to a drain of a write transistor. A source of the write transistor is connected to a source line. As a result, for example, in the case where a stacked capacitor is used, the one electrode of the capacitor can be part of the bit line. Only one specific write transistor is turned on when a potential of the source line and a potential of the write bit line are set; thus, only one memory cell can be rewritten.

Owner:SEMICON ENERGY LAB CO LTD

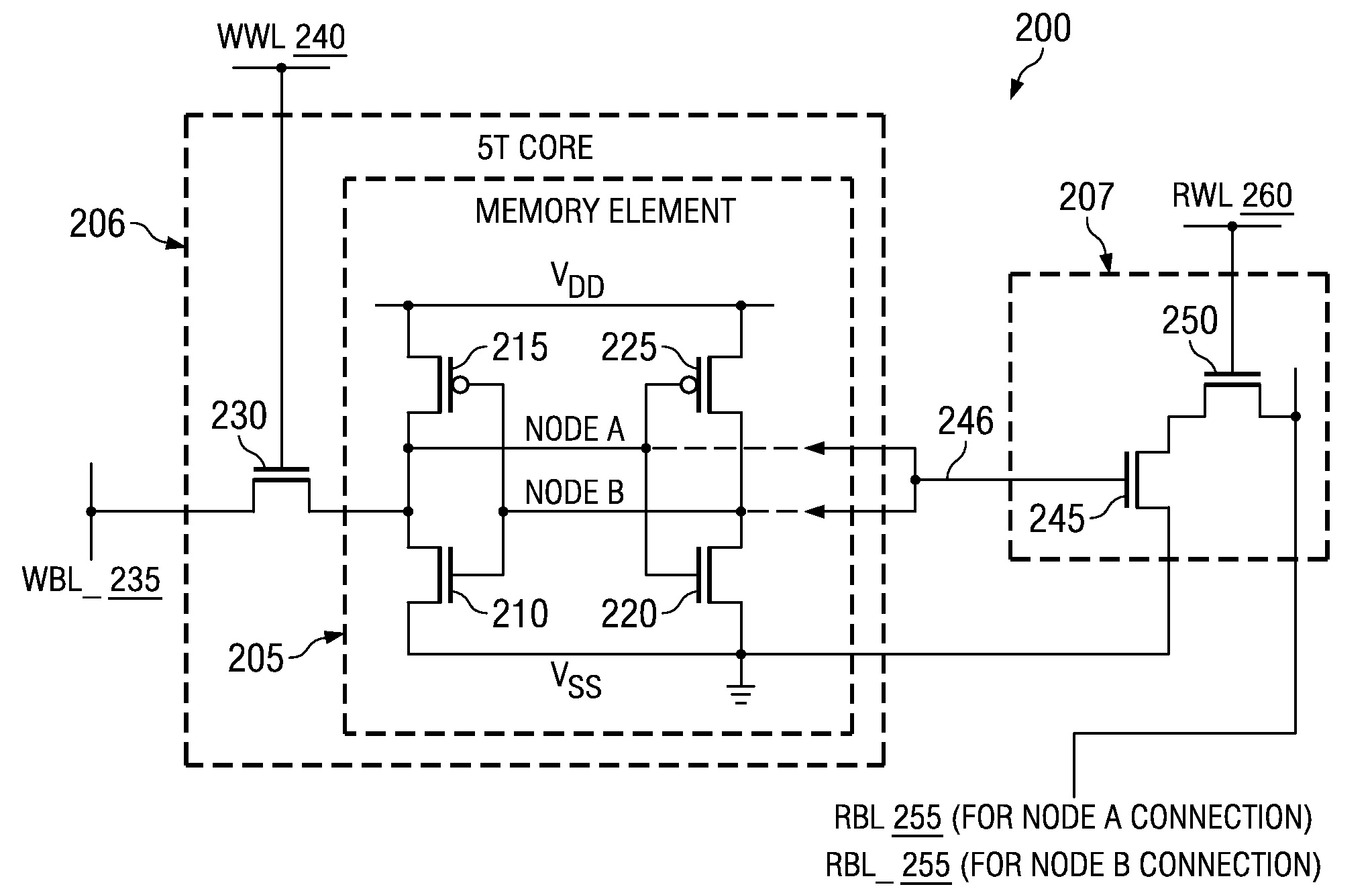

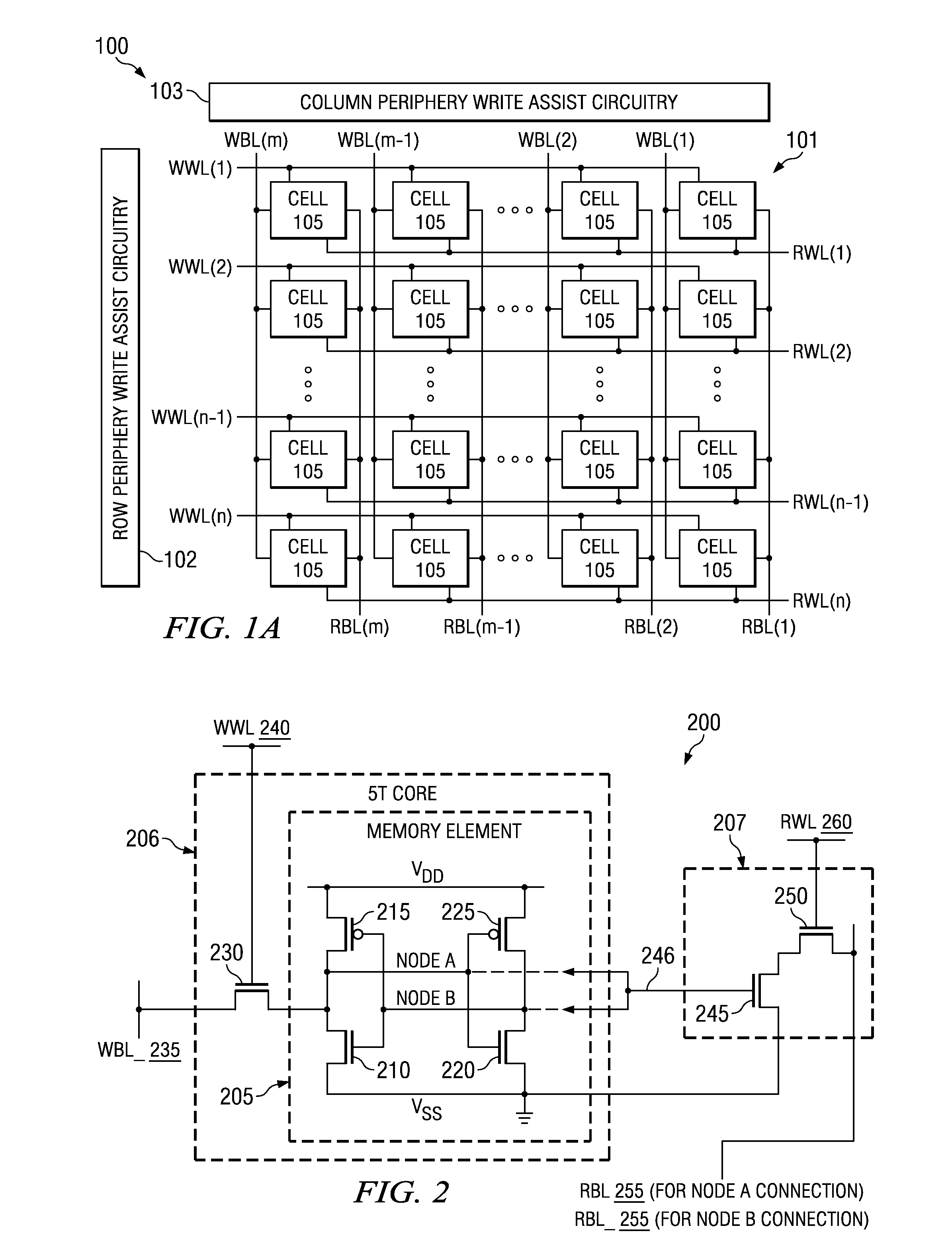

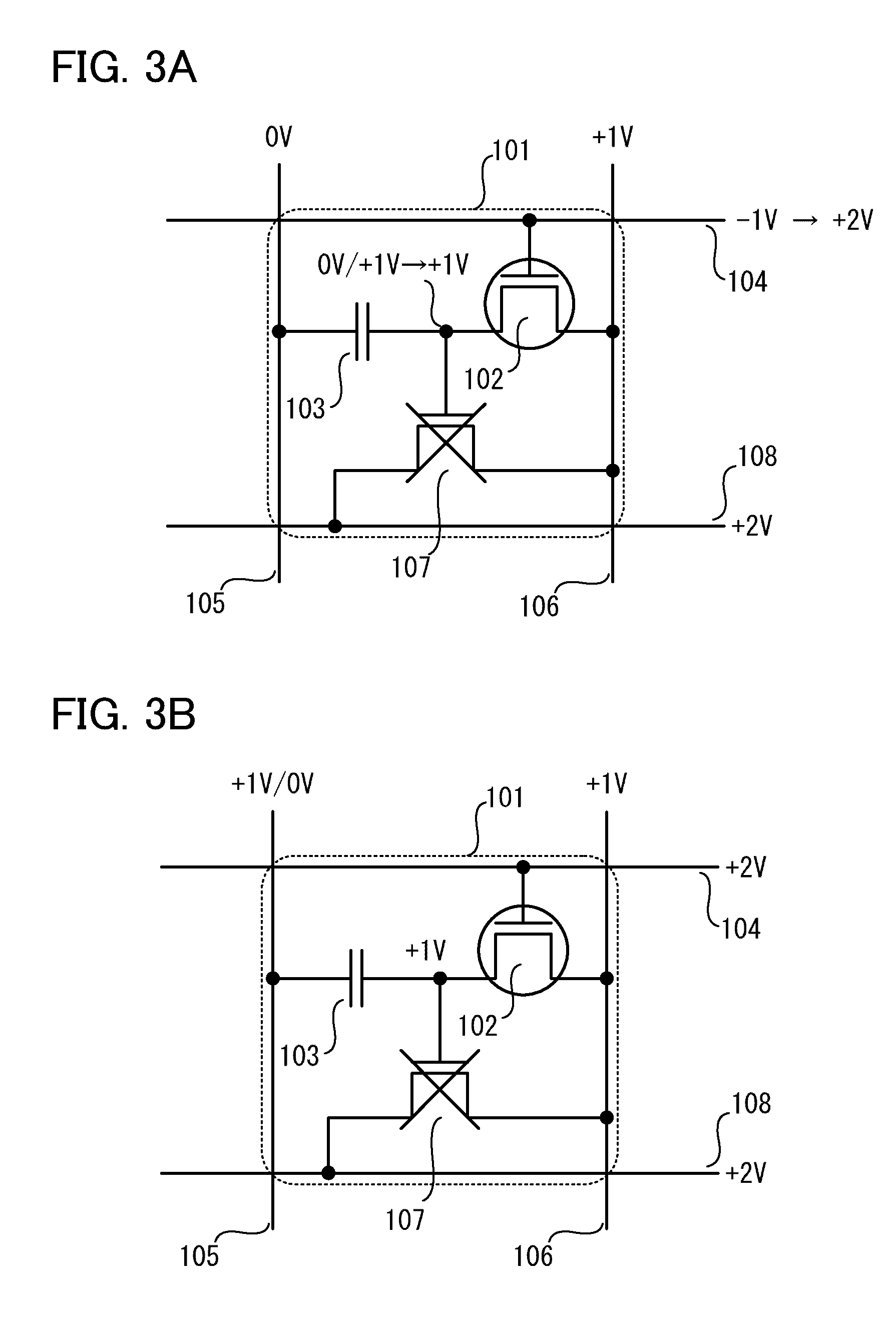

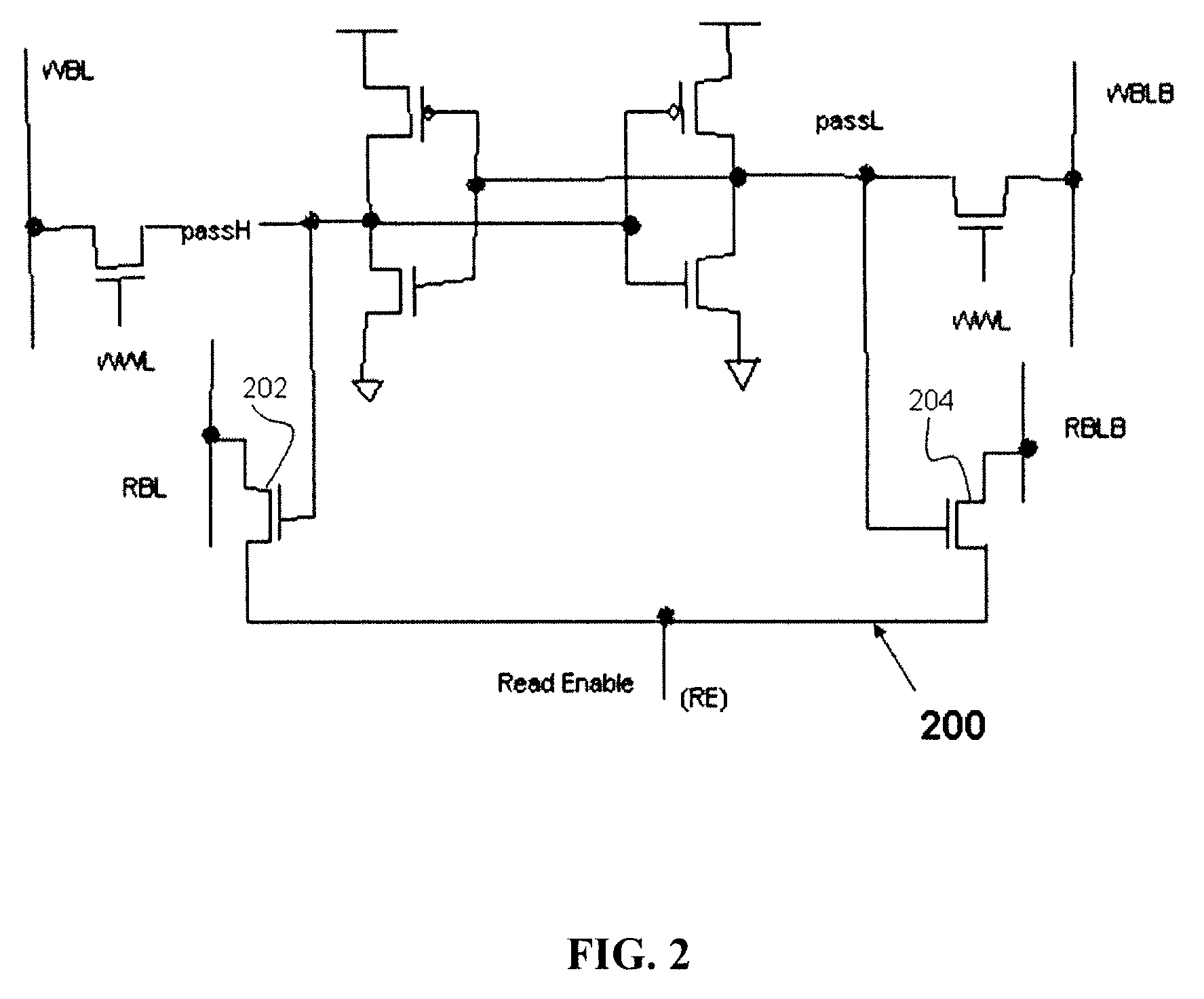

Dual port SRAM with dedicated read and write ports for high speed read operation and low leakage

InactiveUS7813161B2Low static leakageHigh operating requirementsDigital storageWrite bitStatic random-access memory

Owner:STMICROELECTRONICS PVT LTD

Magnetic random access memory with write and read circuits using magnetic tunnel junction (MTJ) devices

InactiveUS6479848B2High strengthTransistorMagnetic-field-controlled resistorsWrite bitRandom access memory

A magnetic random access memory with write and read circuits using magnetic tunnel junction (MTJ) devices wherein MTJs are arranged at cross points of word lines and read bit lines to form memory cells. After write bit lines and read bit lines are arranged parallel to each other, current bypass paths are formed allowing current to bypass the side and bottom of the MTJ. Thus, an electric field having intensity enough to change the magnetization direction of the MTJ, is applied only to each selected cell. In a write operation, the magnetization direction of a free layer in the MTJ is formed to be parallel or antiparallel to the magnetization direction of a pinned ferromagnetic layer by the current passing through the word line and the current bypass path.

Owner:SAMSUNG ELECTRONICS CO LTD

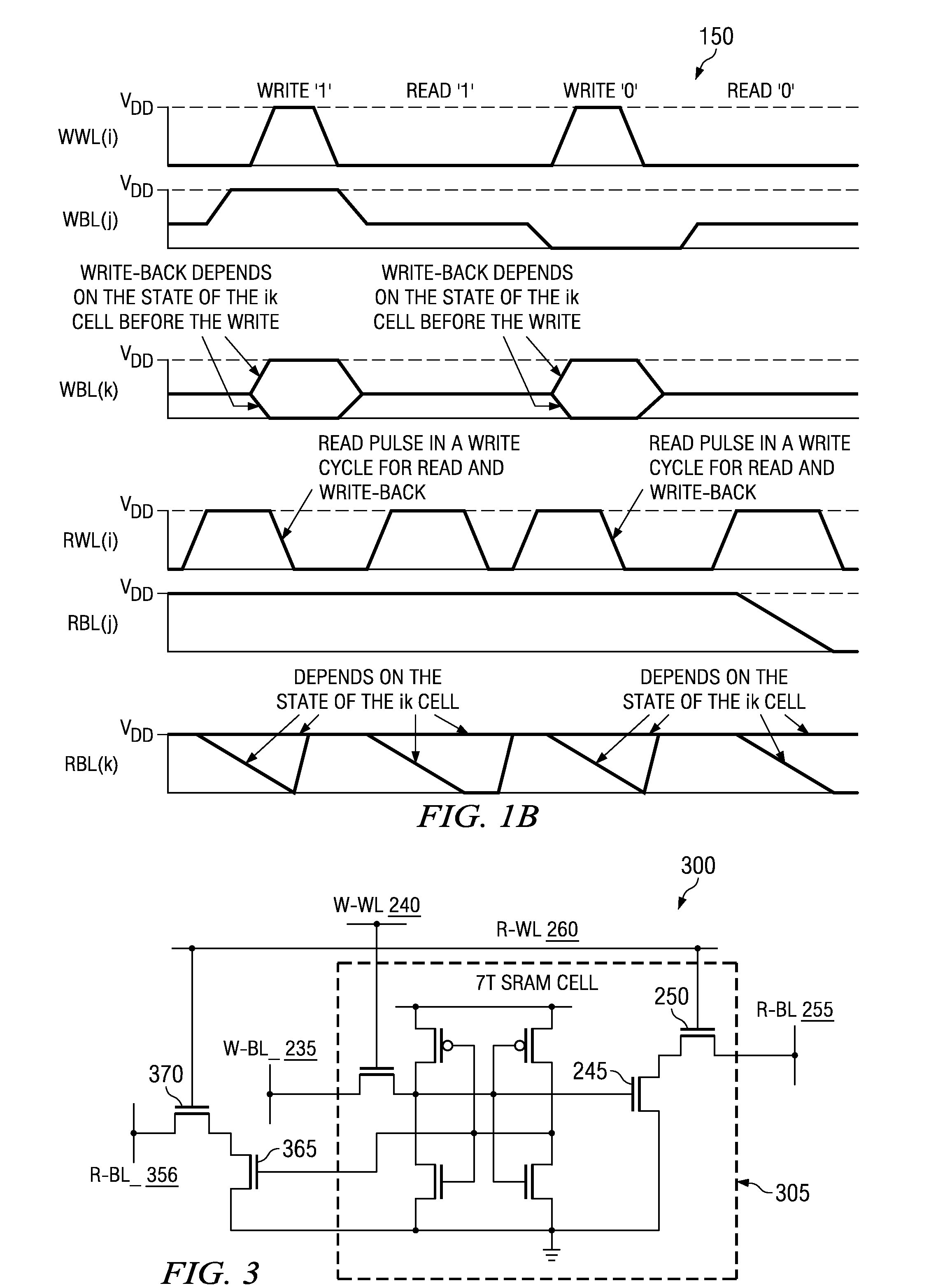

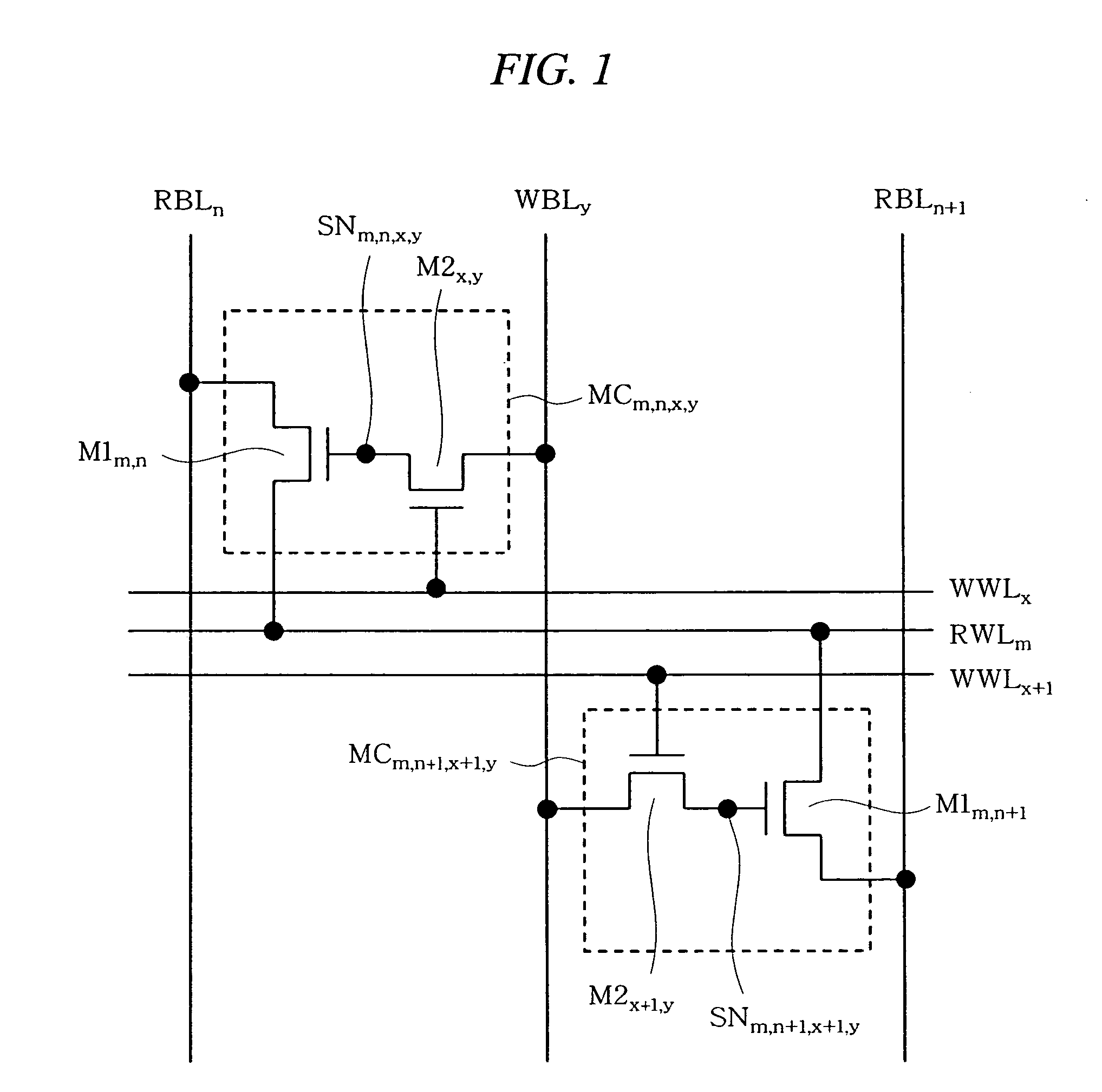

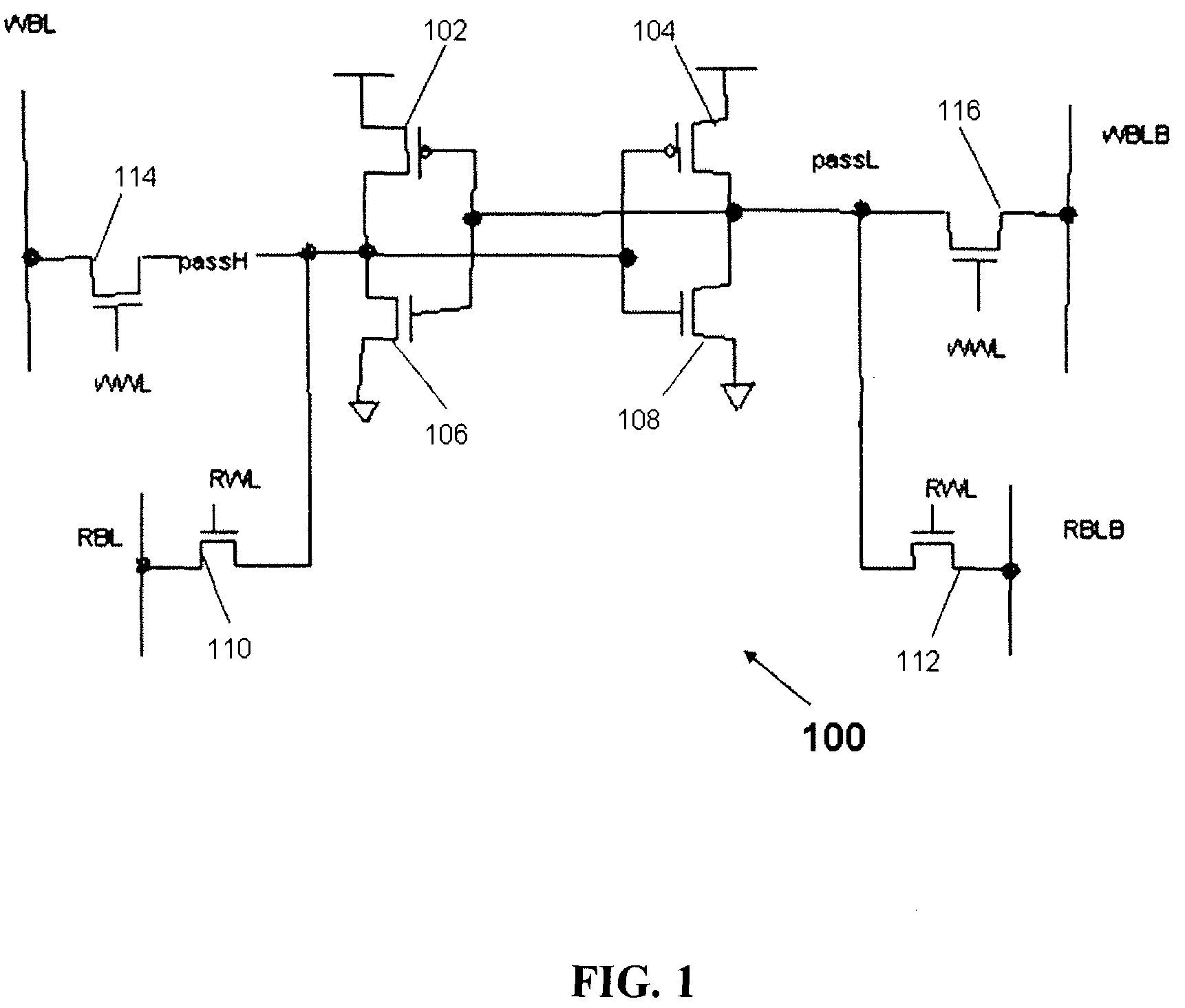

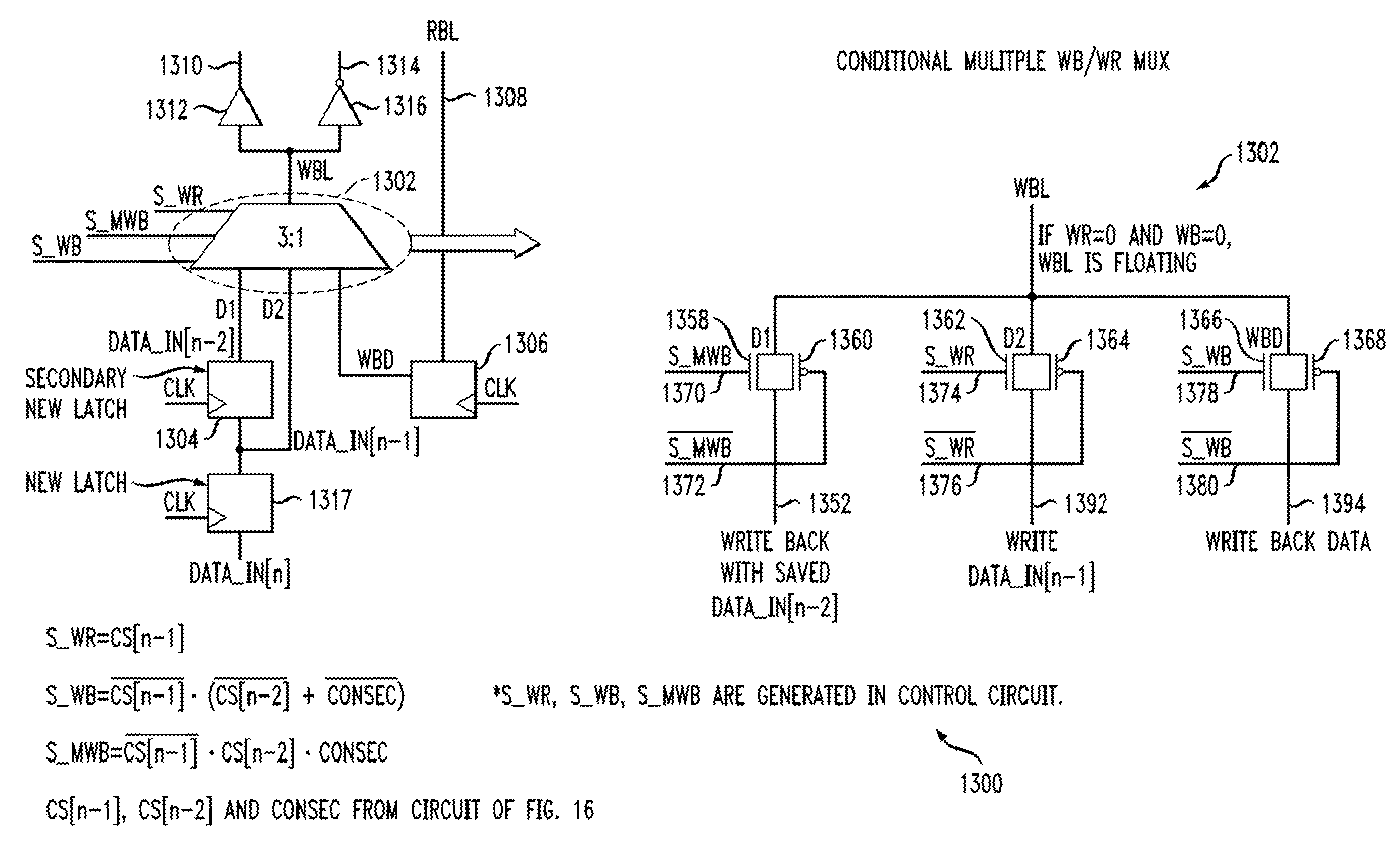

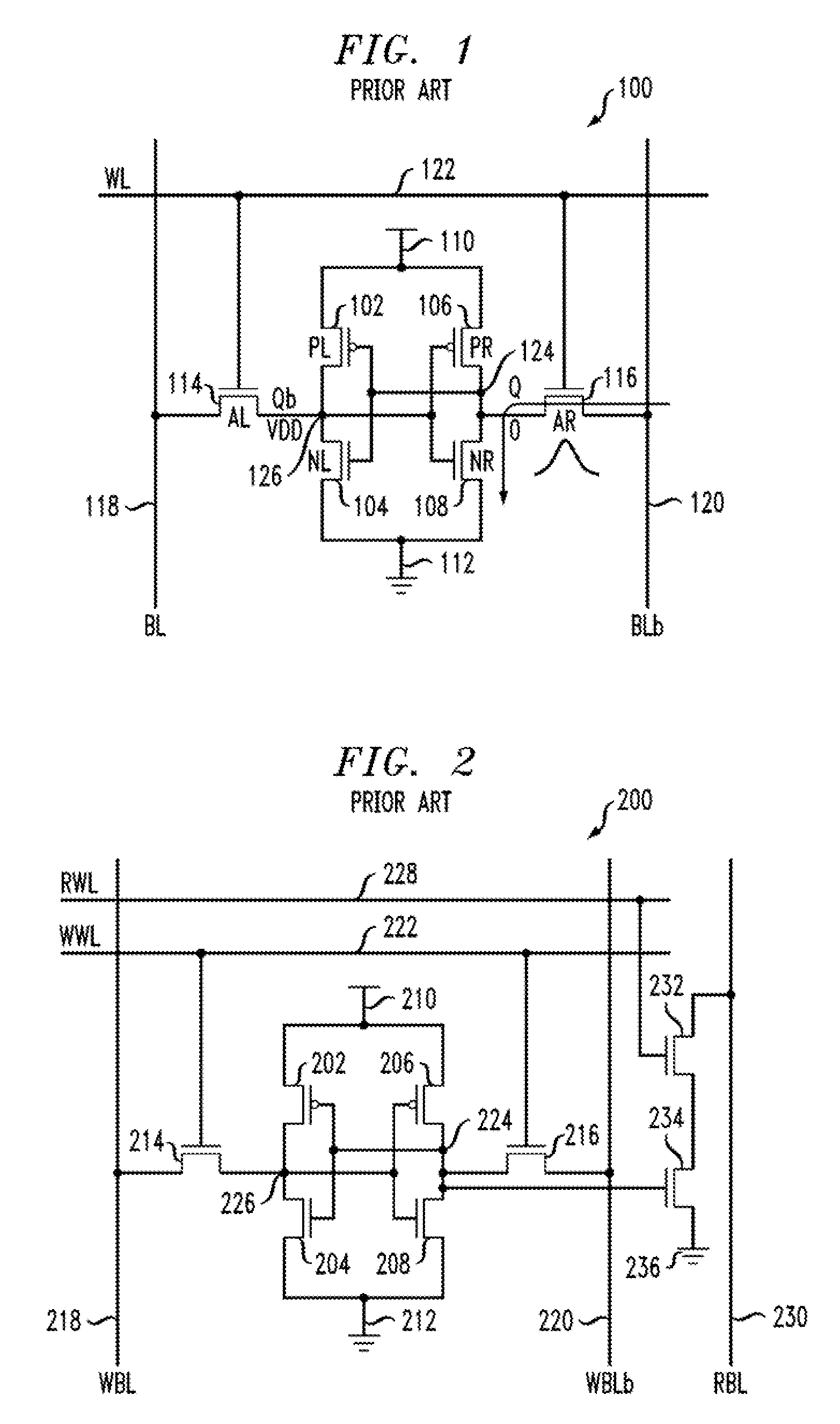

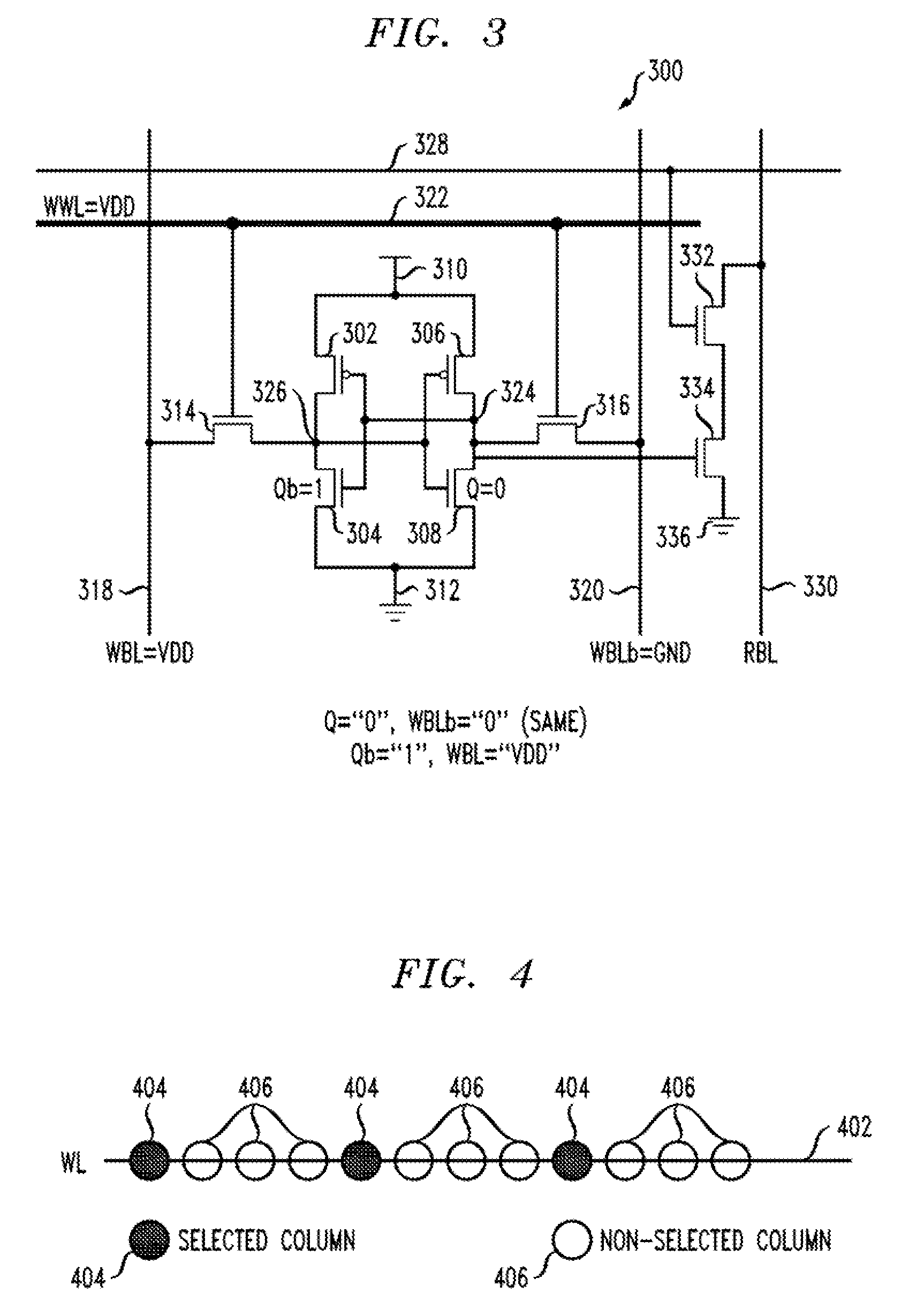

Techniques For Improving Write Stability Of Memory With Decoupled Read And Write Bit Lines

In a memory circuit, data from all cells along a selected word line is read. Then, the read data is written back to half-selected cells and new data is written to the selected cells in the next cycle. In cases where a READ bit line (RBL) and WRITE bit line (WBL) are decoupled, RBL and WBL can be accessed simultaneously. Hence, the WRITE in the n-th cycle can be delayed to the n+1-th cycle as far as there is no data hazard such as reading data from memory before correct data are actually written to memory. As a result, there is no bandwidth loss, although the latency of the WRITE operation increases. WRITE stability issues in previous configurations with decoupled RBL and WBL are thus addressed.

Owner:GLOBALFOUNDRIES INC

Semiconductor memory device with current driver providing bi-directional current to data write line

First and second current drivers are connected to one end of corresponding first and second write bit lines, respectively, and the first and second write bit lines are directly connected, at the other end, to a common line. The first and second current drivers receive a first power supply voltage and the ground voltage, while the common line receives a second power supply voltage higher than the ground voltage and lower than the first power supply voltage. The first and second current drivers cause a current for data writing to flow in a first direction based on a voltage difference between the first power supply voltage and the second power supply voltage, and cause a current for data writing to flow in a second direction based on a voltage difference between the second power supply voltage and the ground voltage.

Owner:RENESAS ELECTRONICS CORP

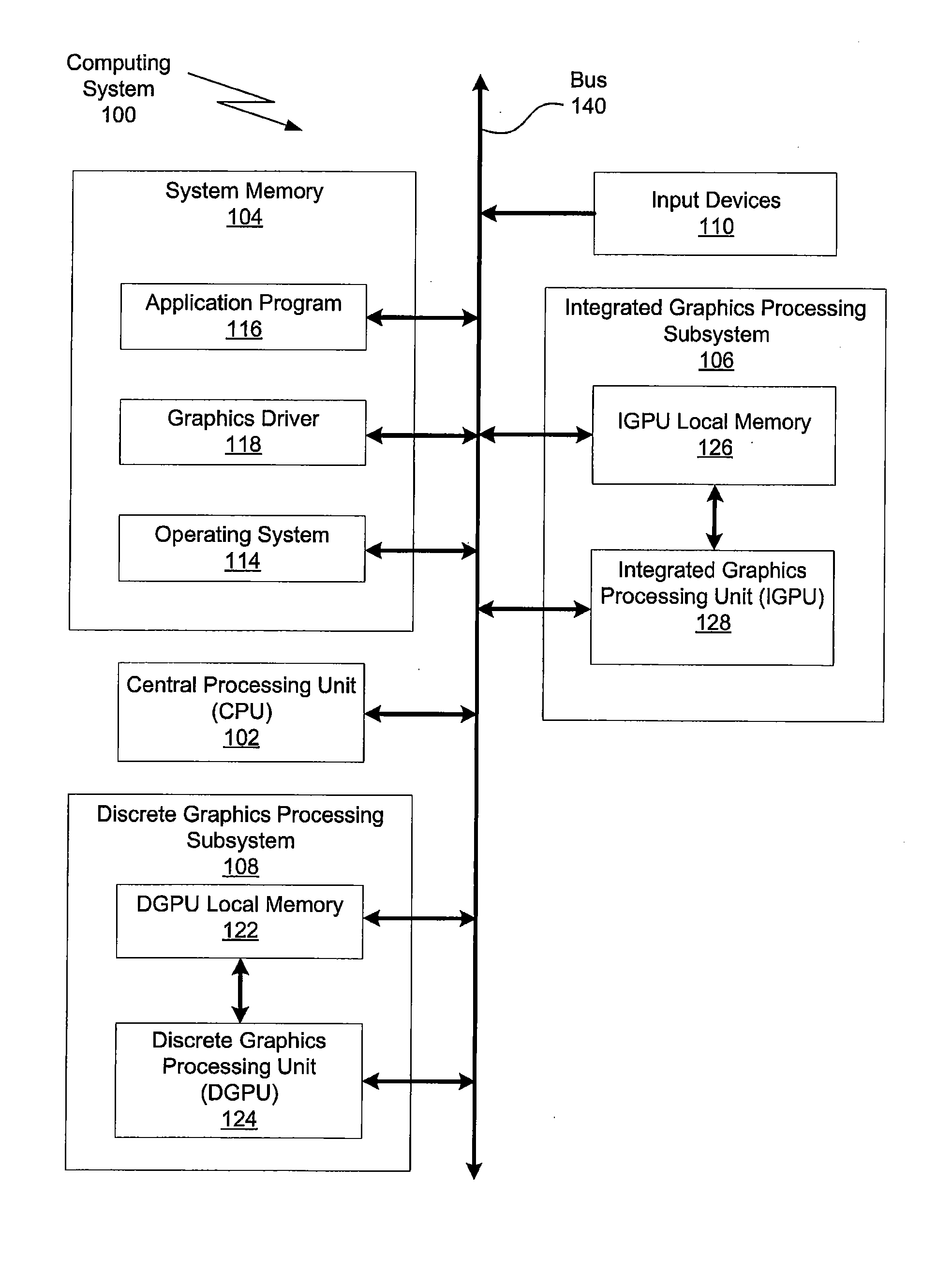

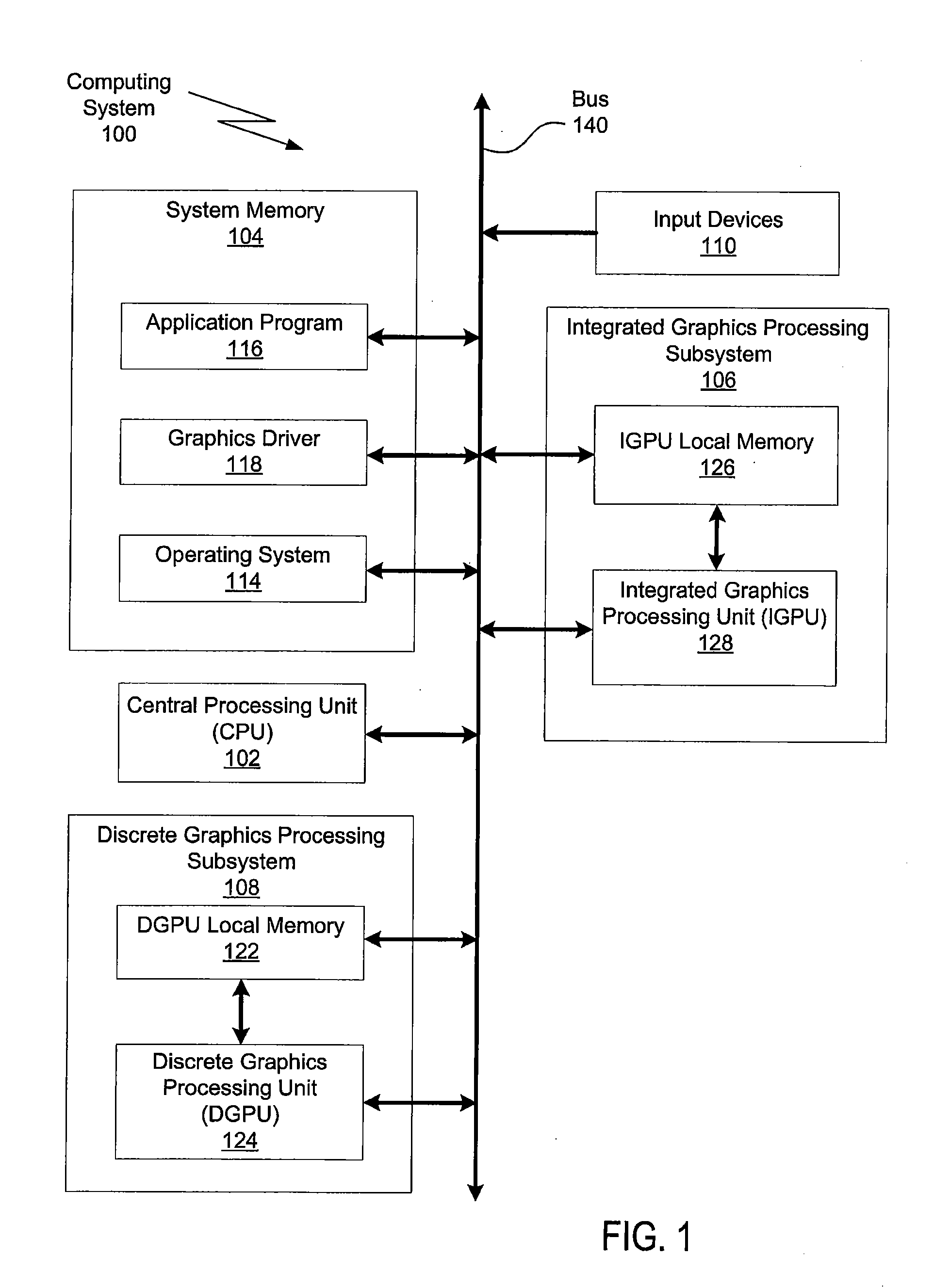

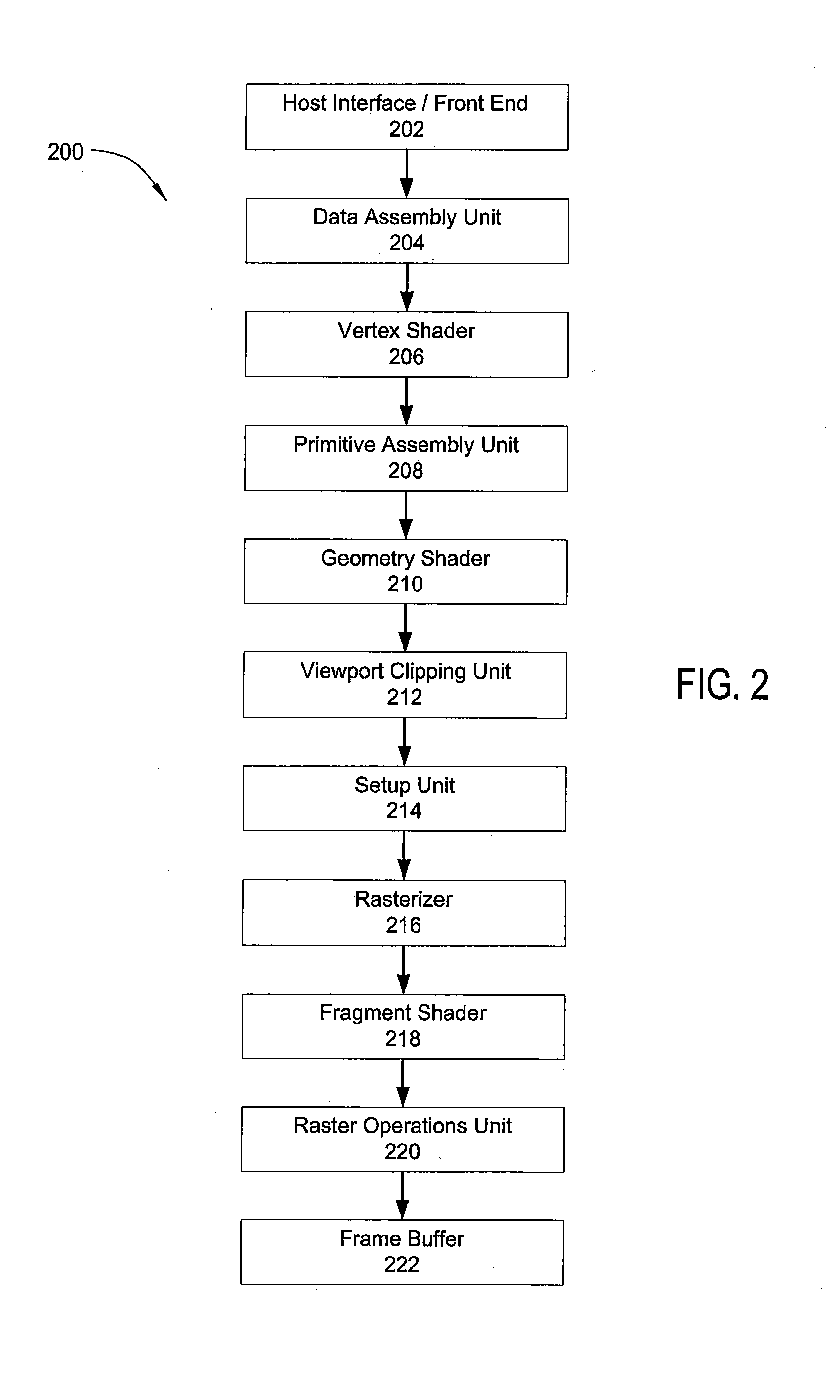

Cull streams for fine-grained rendering predication

One embodiment of the present invention sets forth a technique to perform fine-grained rendering predication using an IGPU. A graphics driver divides a 3D object into batches of triangles. The IGPU processes each batch of triangles through a modified rendering pipeline to determine if the batch is culled. The IGPU writes bits into a bitstream corresponding to the visibility of the batches. Advantageously, this approach to rendering predication provides fine-grained culling without adding unnecessary overhead, thereby optimizing both hardware resources and performance.

Owner:NVIDIA CORP

Magnetic random access memory

Blocks are connected to a read bit line. One block has MTJ elements which are connected to each other in series between the read bit line and a ground terminal. A MTJ elements are superposed on, e.g., a semiconductor substrate. A read bit line is arranged on the superposed MTJ elements. A write word line extending in a X-direction and a write bit line extending in a Y-direction are arranged in the vicinity of the MTJ elements in the block.

Owner:KK TOSHIBA