Patents

Literature

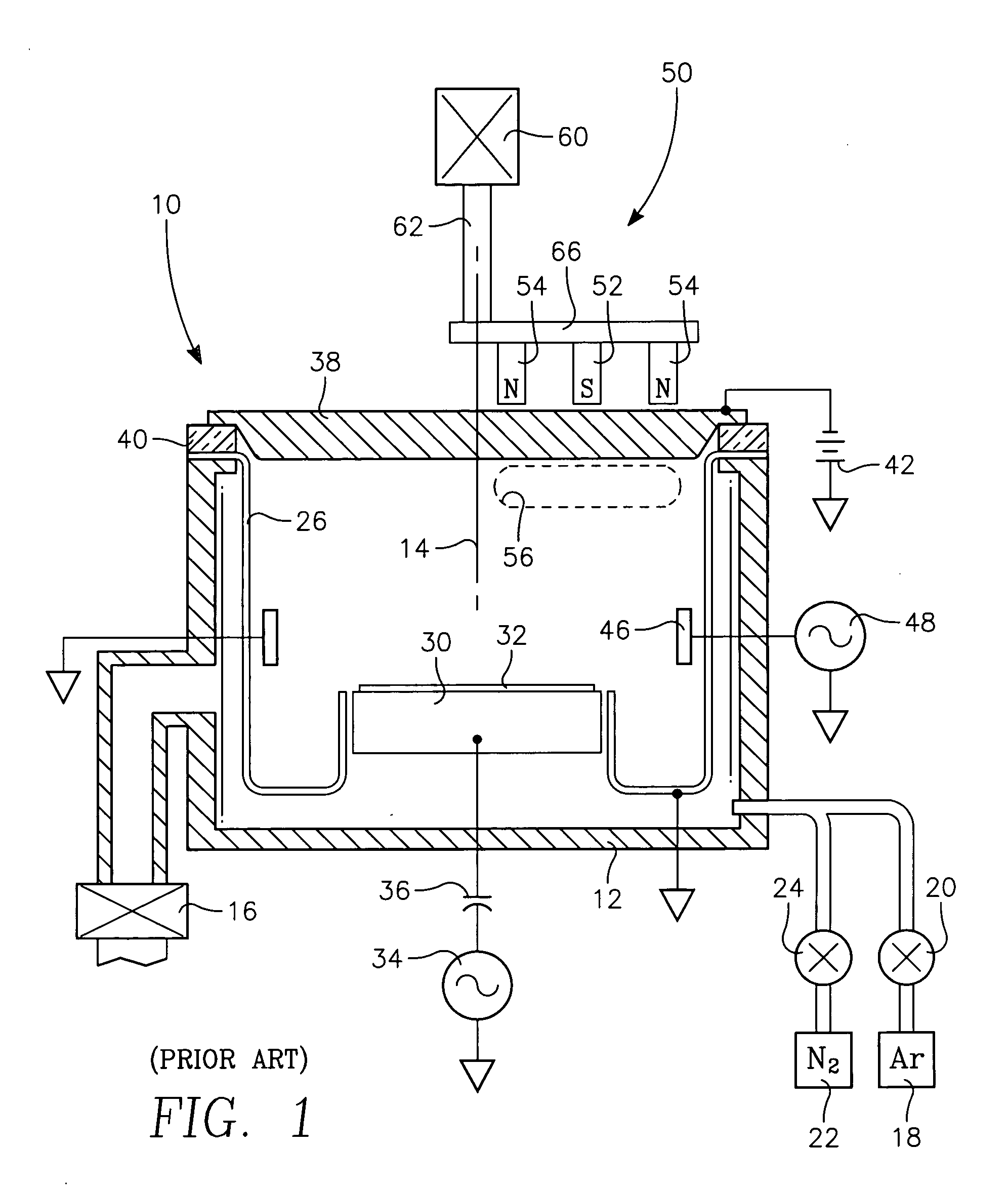

1617 results about "Rectangular array" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A rectangular array is an array of two (or more) dimensions separated by comma. You can think of a rectangular array as a table, where the first dimension is the number of rows and the second dimension is the number of columns keeping in mind that every row is the same length.

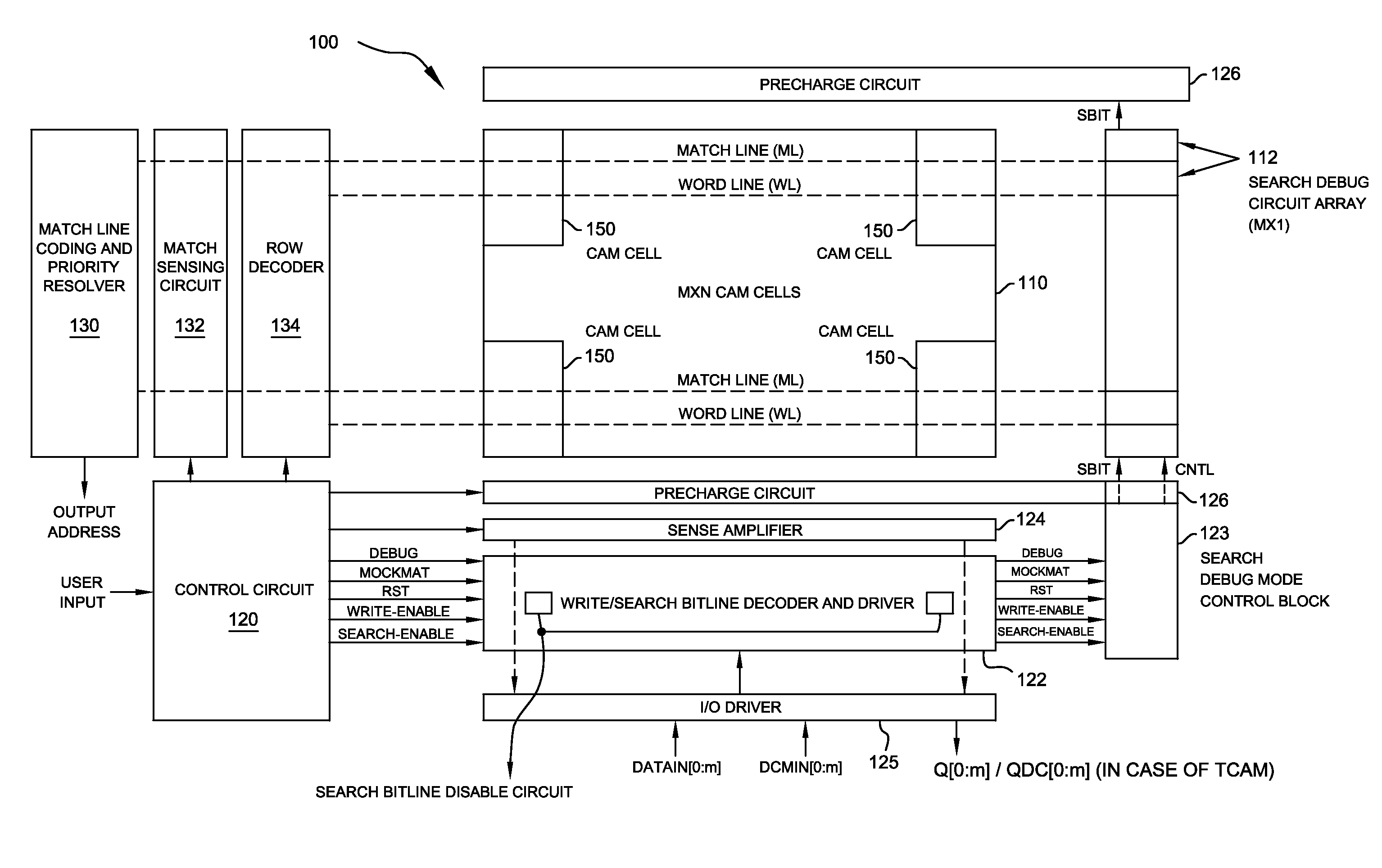

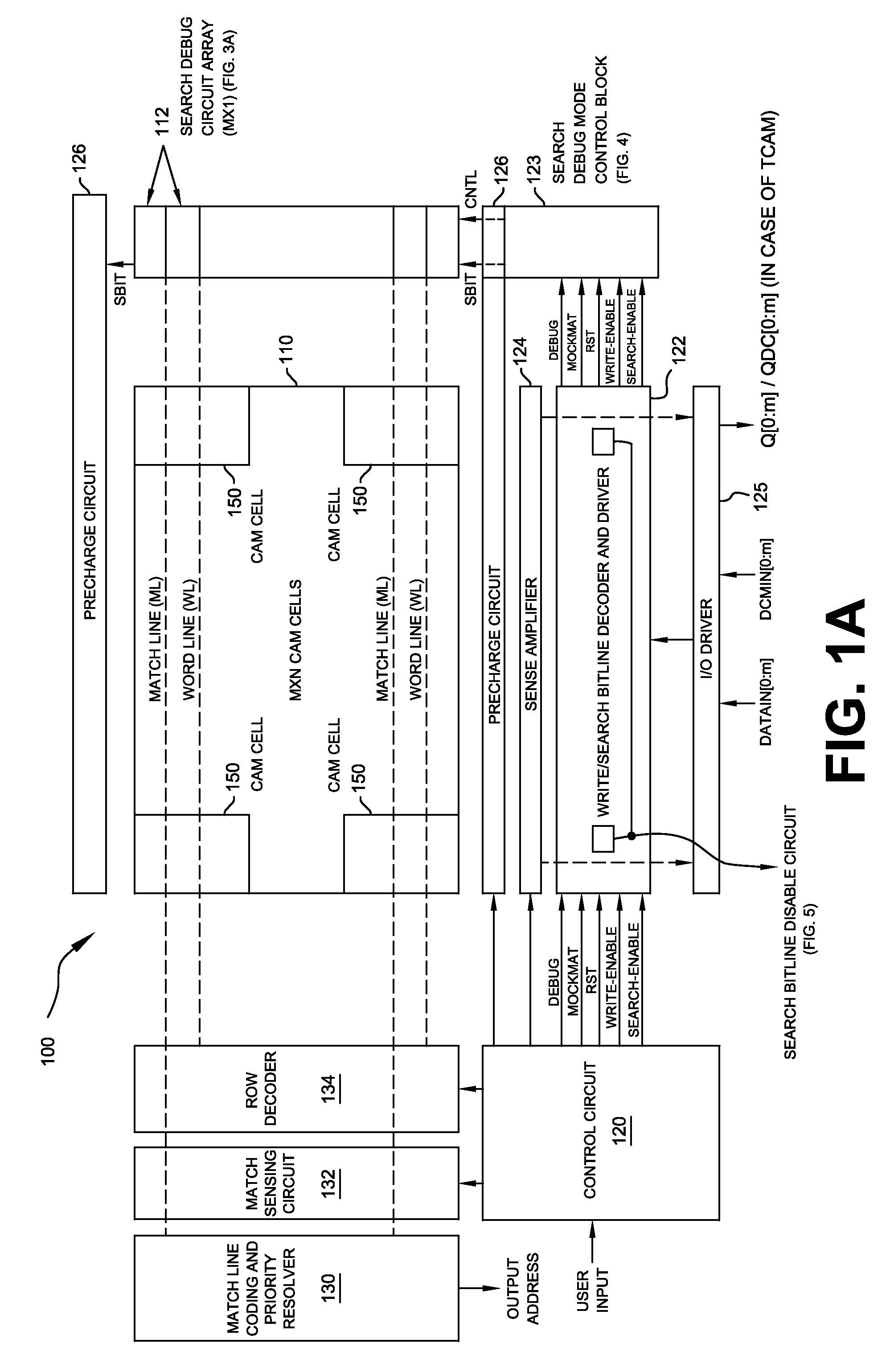

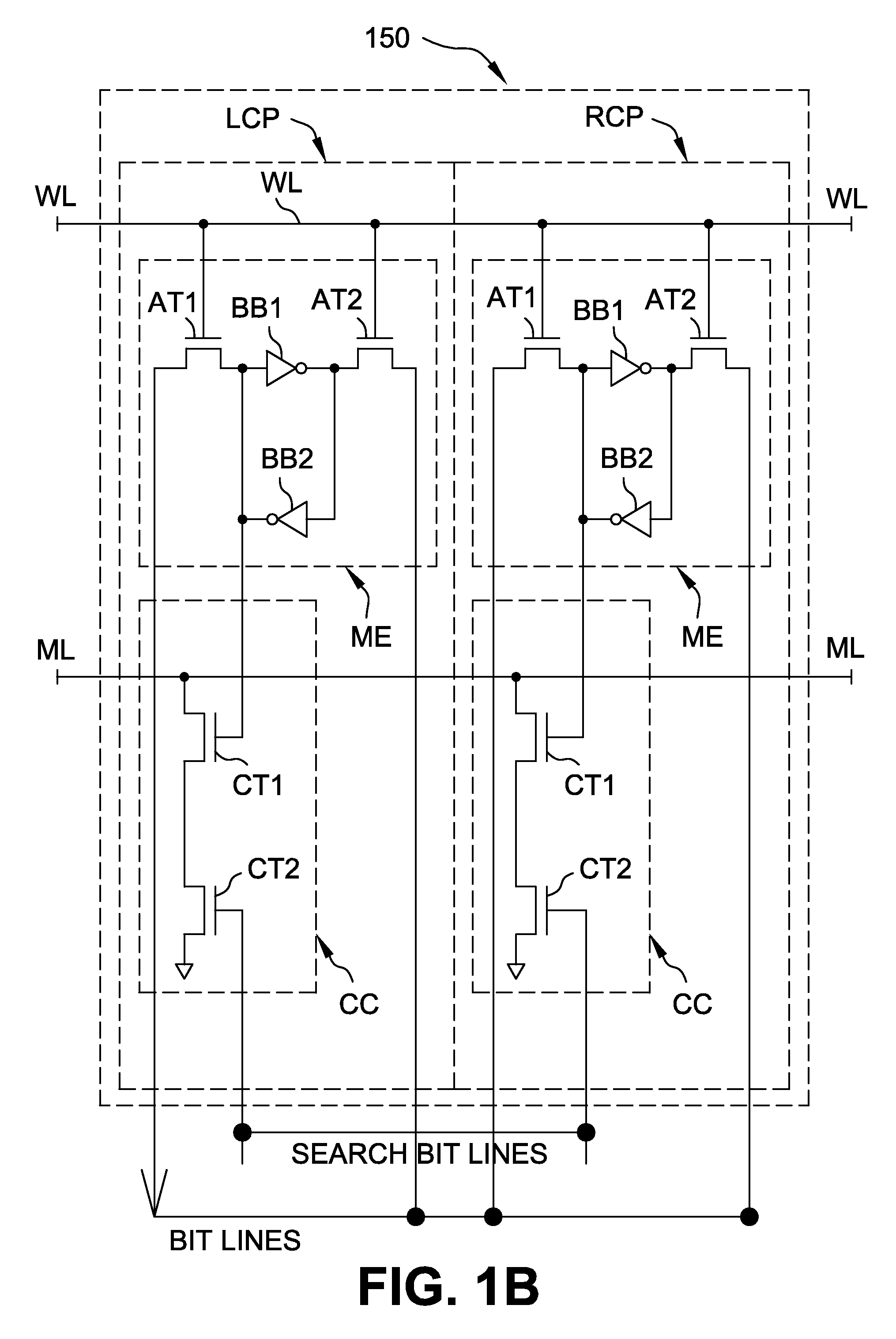

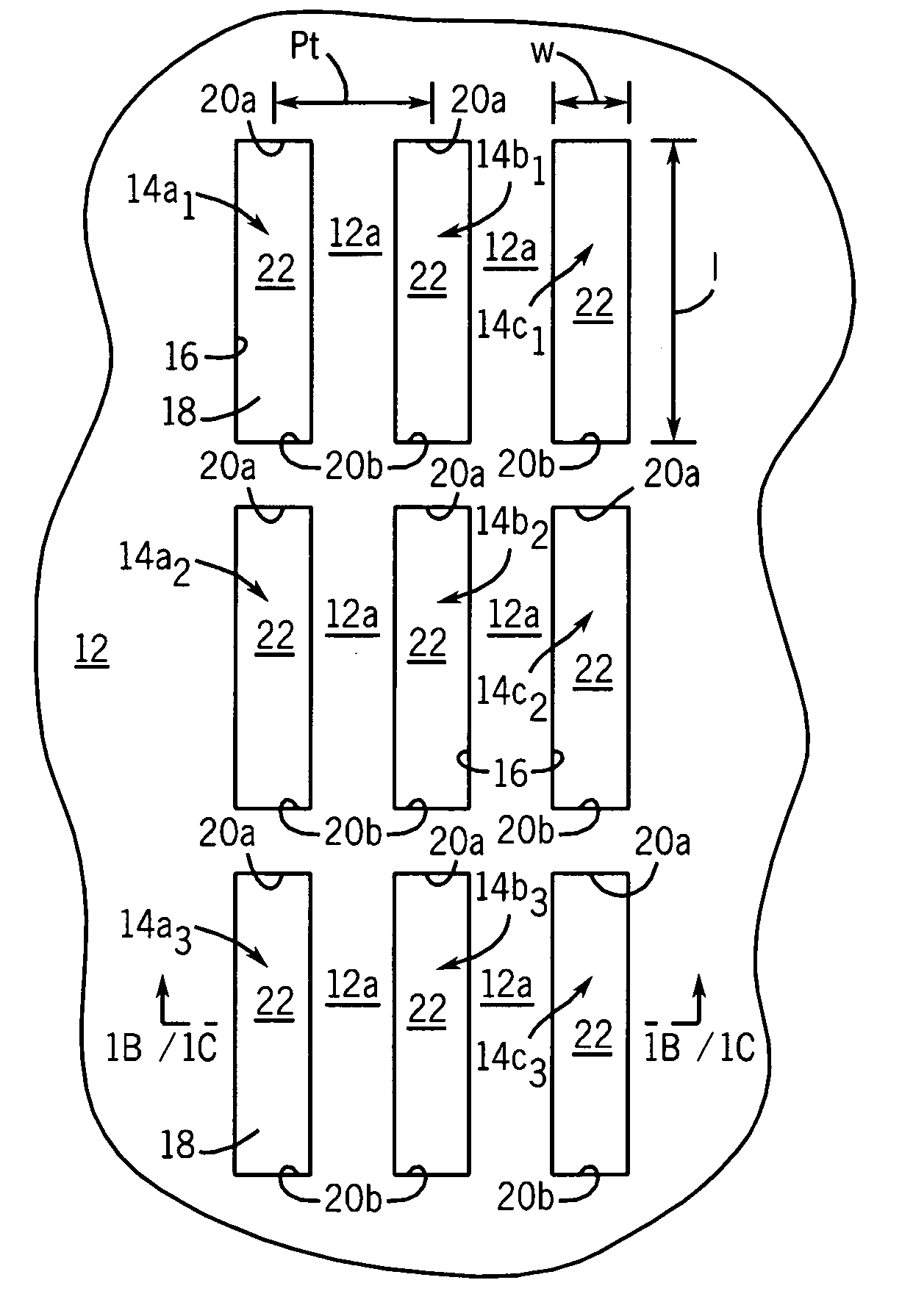

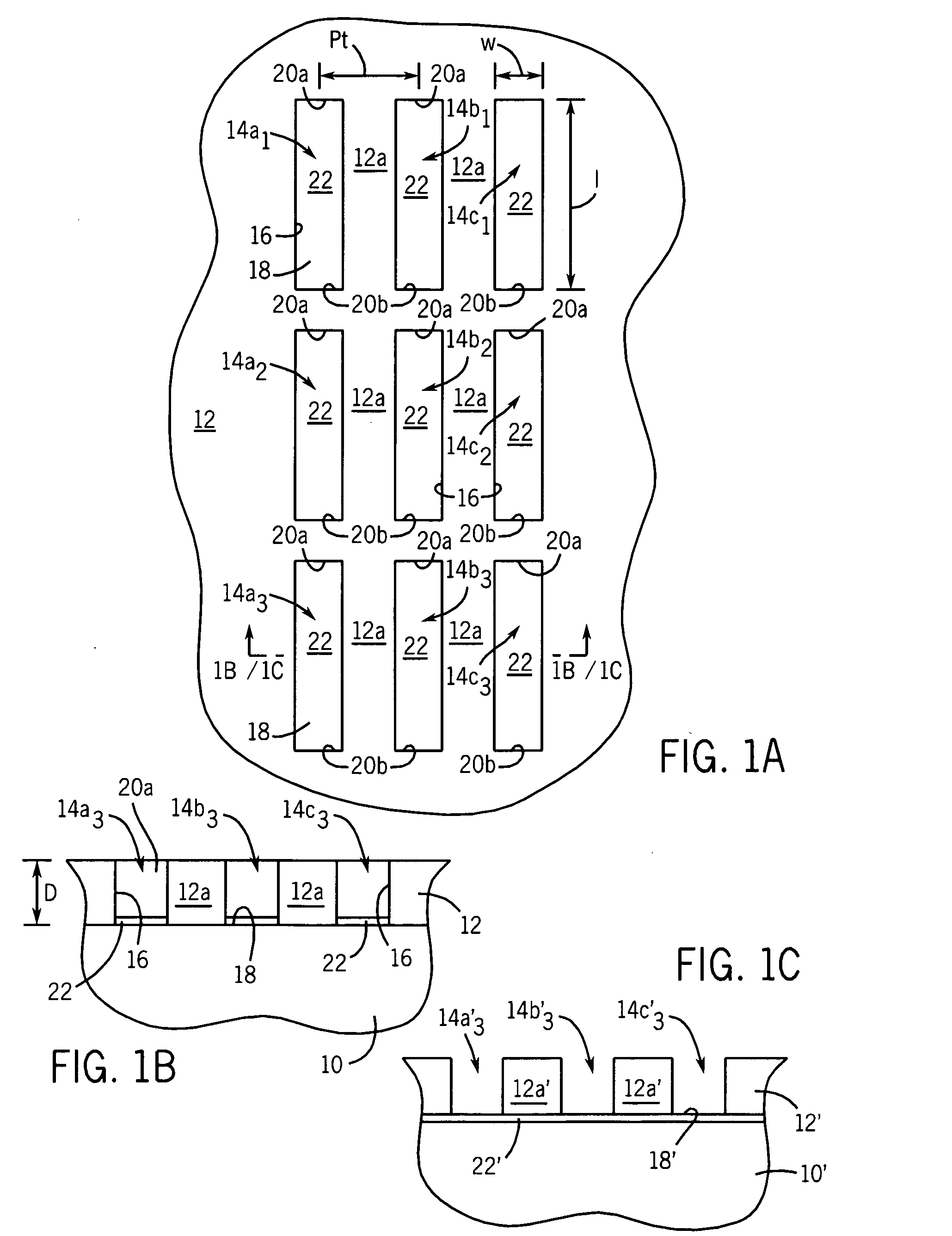

Novel match mismatch emulation scheme for an addressed location in a cam

A novel match / mismatch emulation scheme for an addressed location in a CAM system that includes a plurality of CAM blocks. The plurality of CAM blocks are organized into at least one rectangular array having rows each having a plurality of CAM blocks, a group of CAM cells and associated read / write bit lines connecting the group of CAM cells to an addressed search circuit. During debug mode, where the individual array cells do not participate in search, all the cells in the debug column behave the same way to emulate a match / mismatch on all words. The circuit provides a control input to include address evaluation of a debug cell in a row. The circuit also provides simultaneous switching noise analysis on an evaluating row. The resulting CAM cell provides a circuit to test individual rows for defects and noise analysis.

Owner:TEXAS INSTR INC

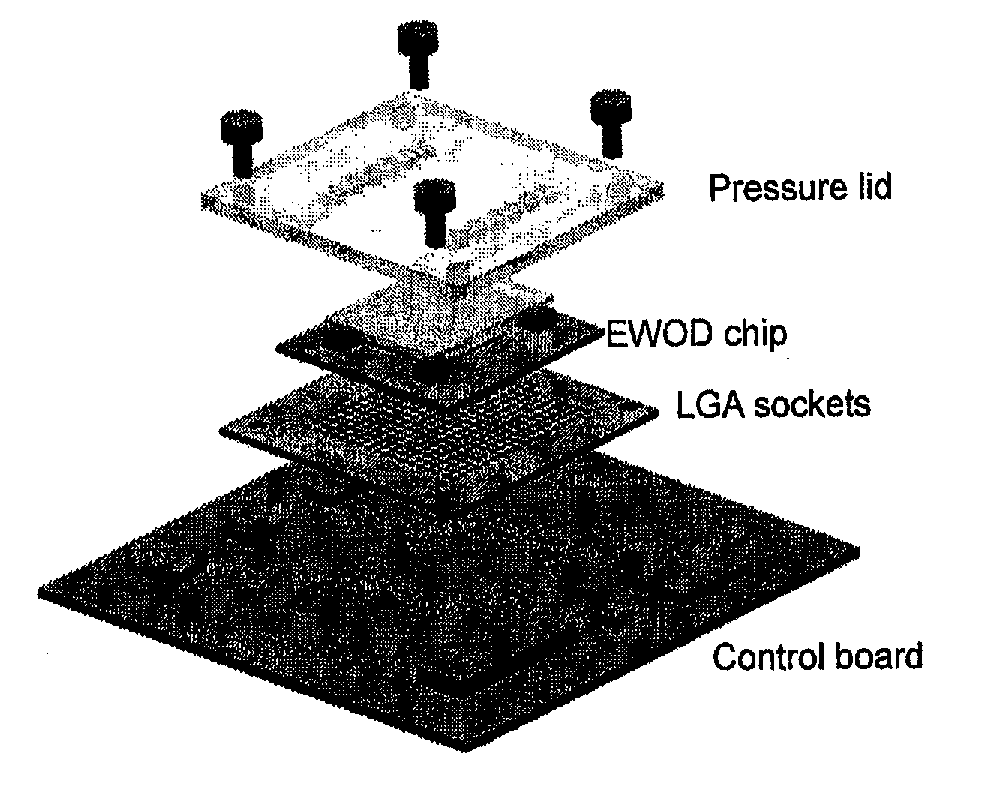

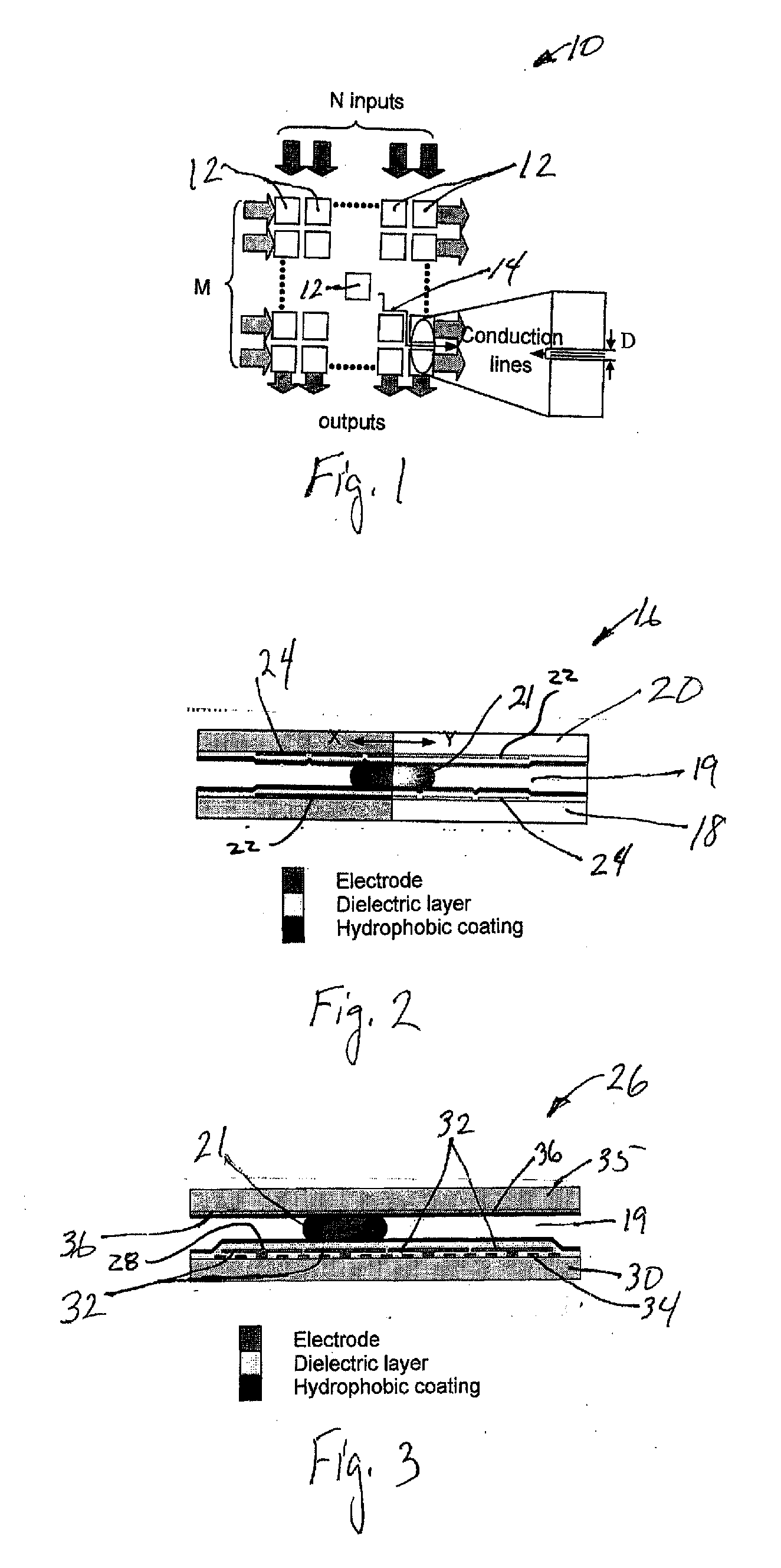

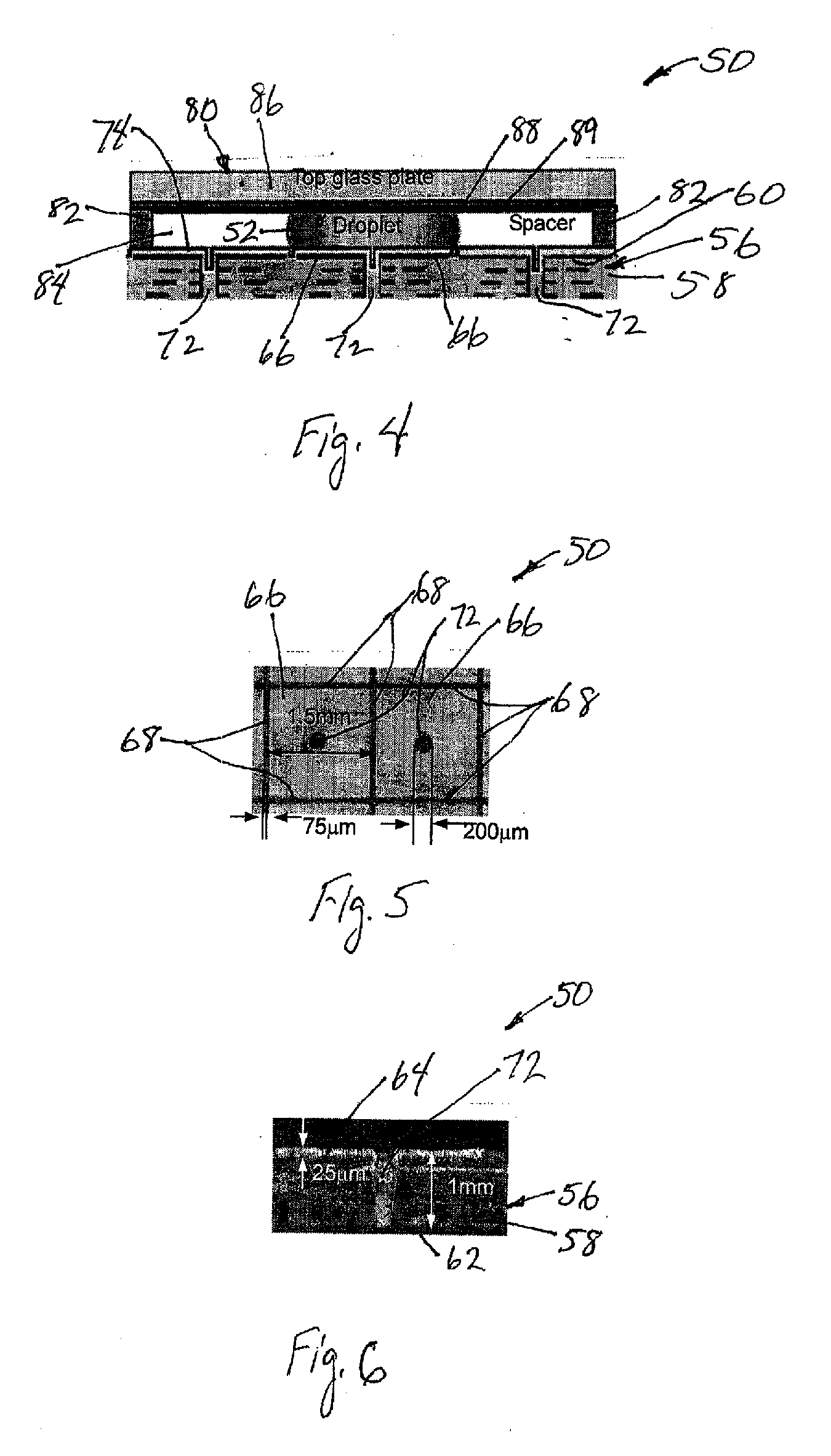

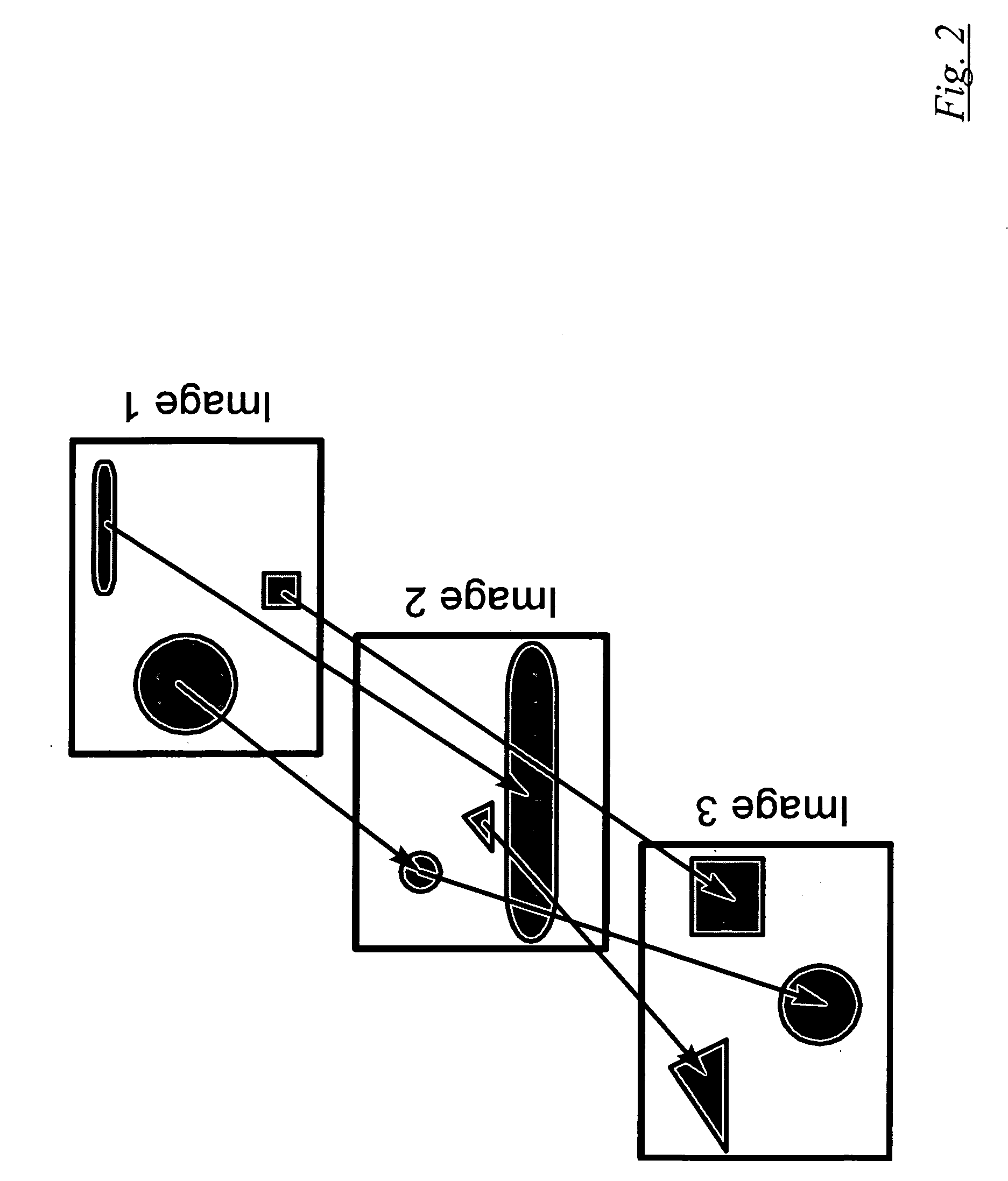

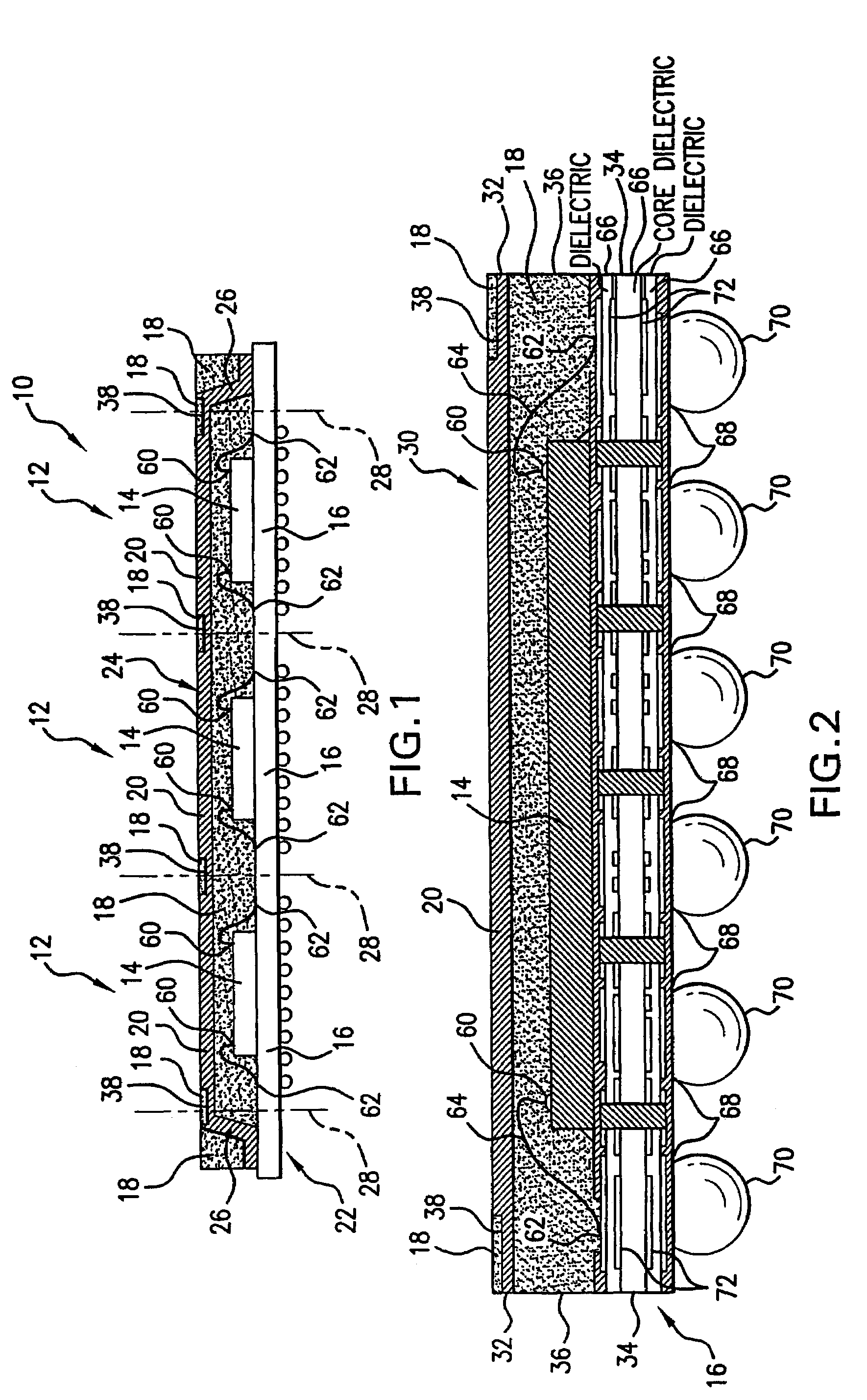

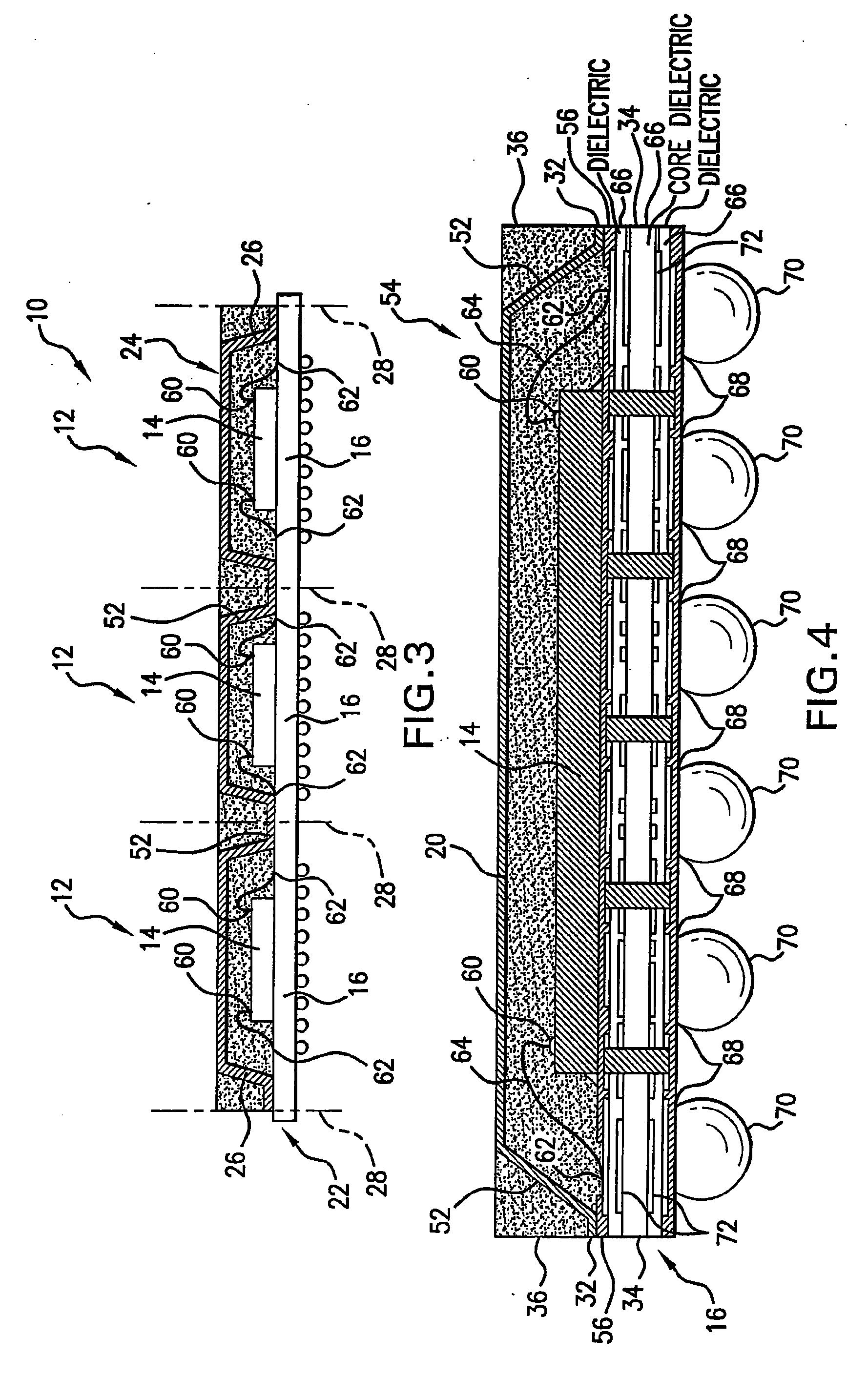

Small object moving on printed circuit board

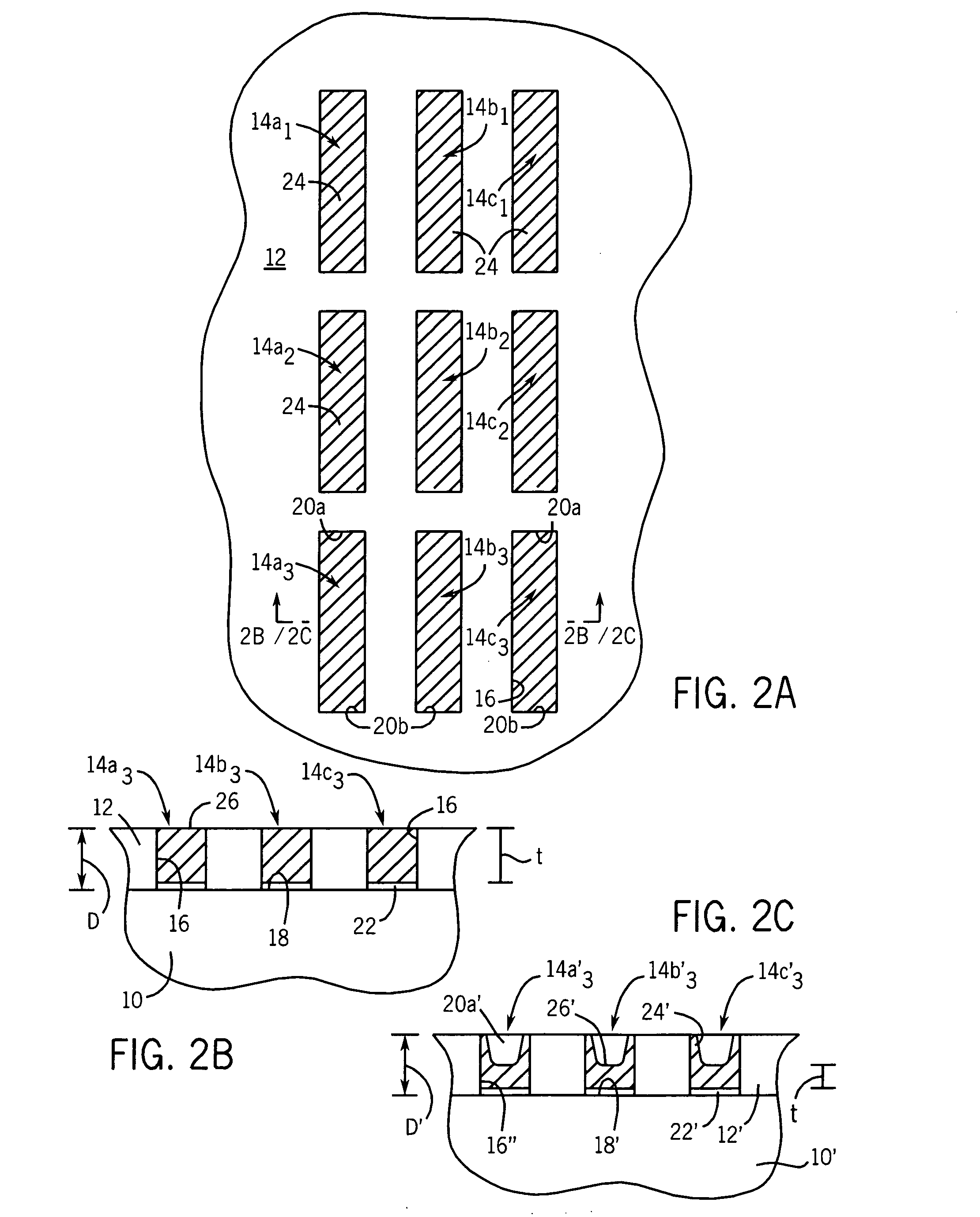

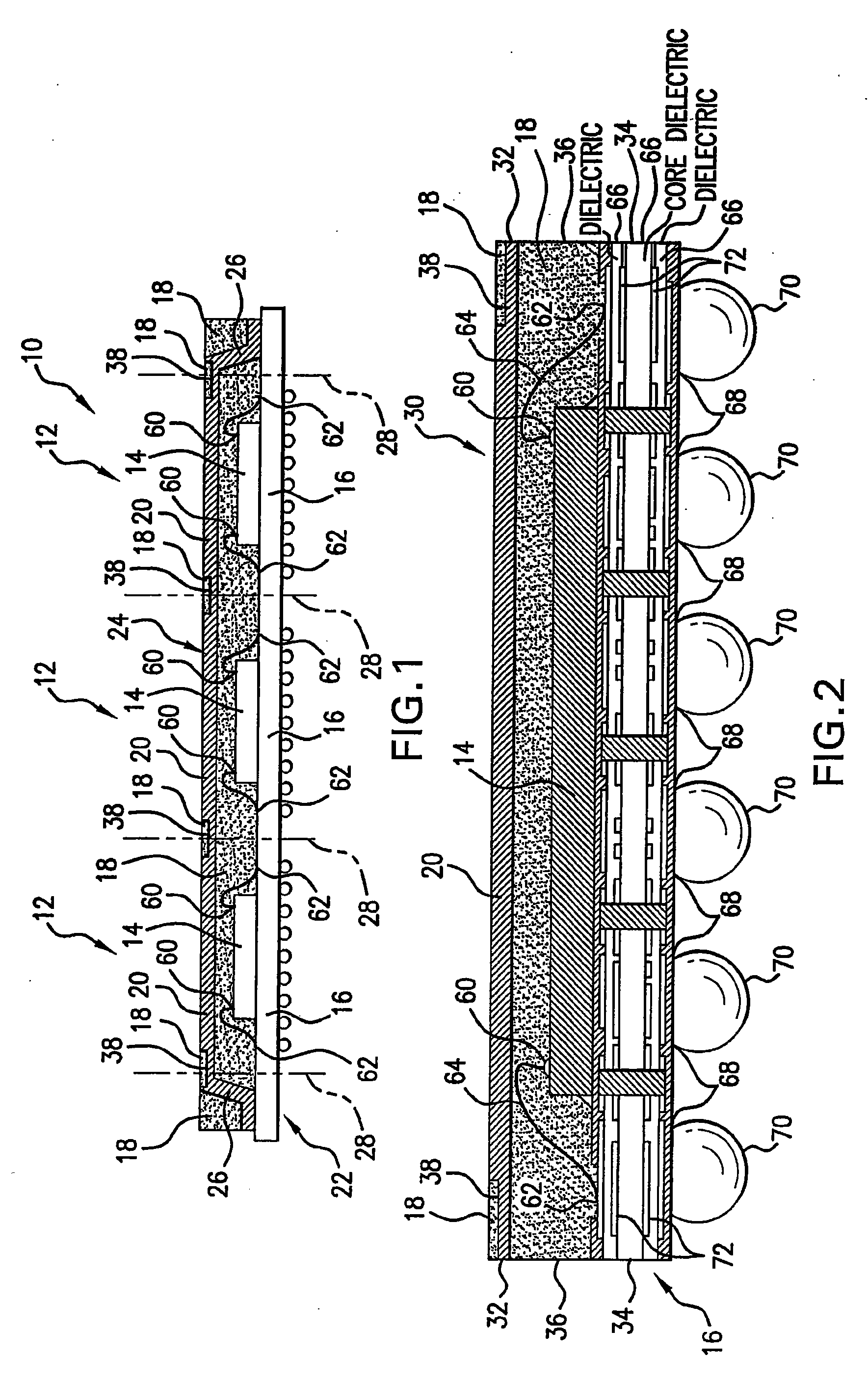

A printed circuit board based digital or droplet microfluidic system and method for producing such microfluidic system are disclosed. The digital microfluidic device comprises a printed circuit board having a substrate and a plurality of electrode pads disposed on the top surface of the substrate in a rectangular array. A via extends from each electrode pad through the substrate to other locations on the substrate . A dielectric layer is disposed on the electrode pads. Droplets may be manipulated using electrowetting principles and others by applying a voltage to the desired electrodes. Each electrode pad can be controlled directly and independently from the other electrode pads to modify the surface wettability of the dielectric layer in the vicinity of the electrode pad by applying a voltage to the desired electrode pad(s). In this way, droplets may be formed, moved, mixed, and / or divided or other small objects manipulated while in air or immersed in a liquid on the dielectric surface.

Owner:RGT UNIV OF CALIFORNIA

Two-dimensional arrays of holes with sub-lithographic diameters formed by block copolymer self-assembly

Owner:MICRON TECH INC

Supporting region-of-interest cropping through constrained compression

InactiveUS20100232504A1Color television with pulse code modulationColor television with bandwidth reductionDigital videoComputer graphics (images)

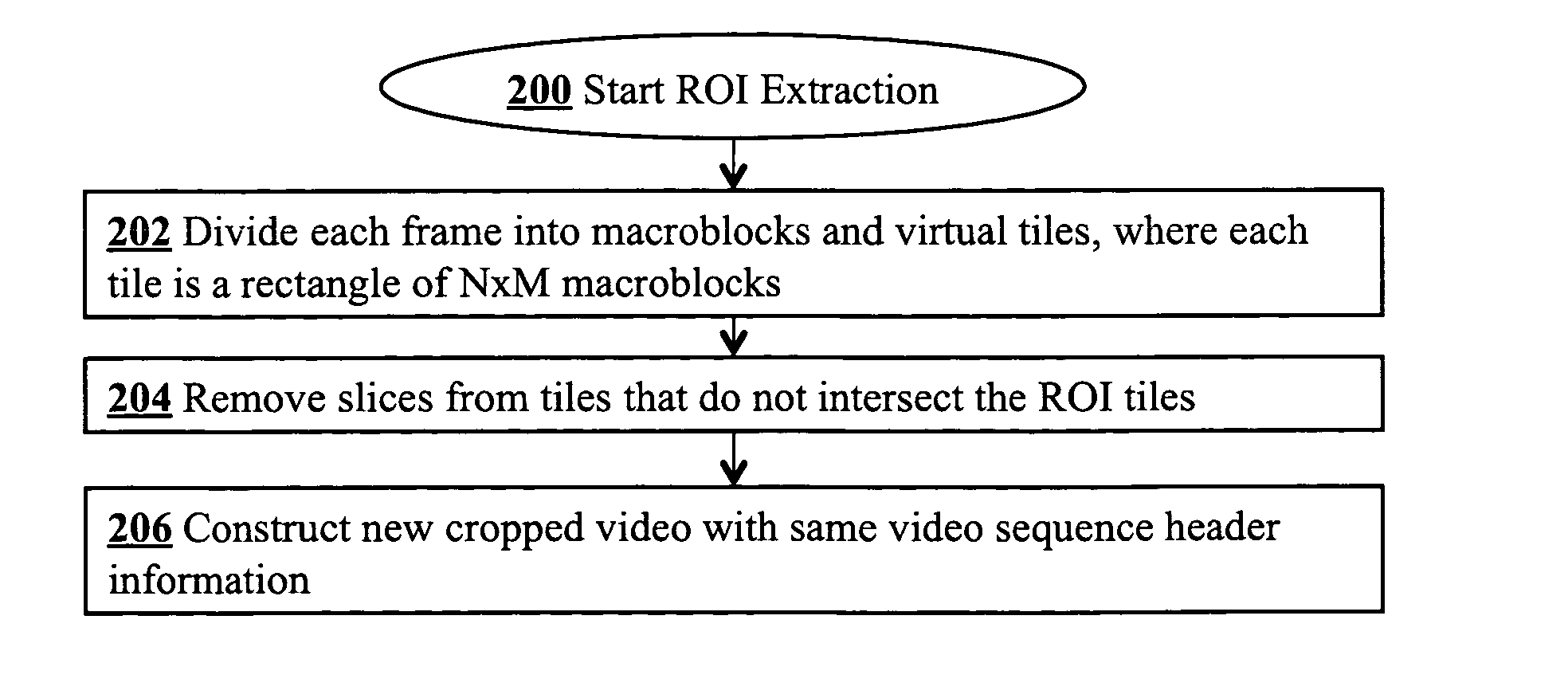

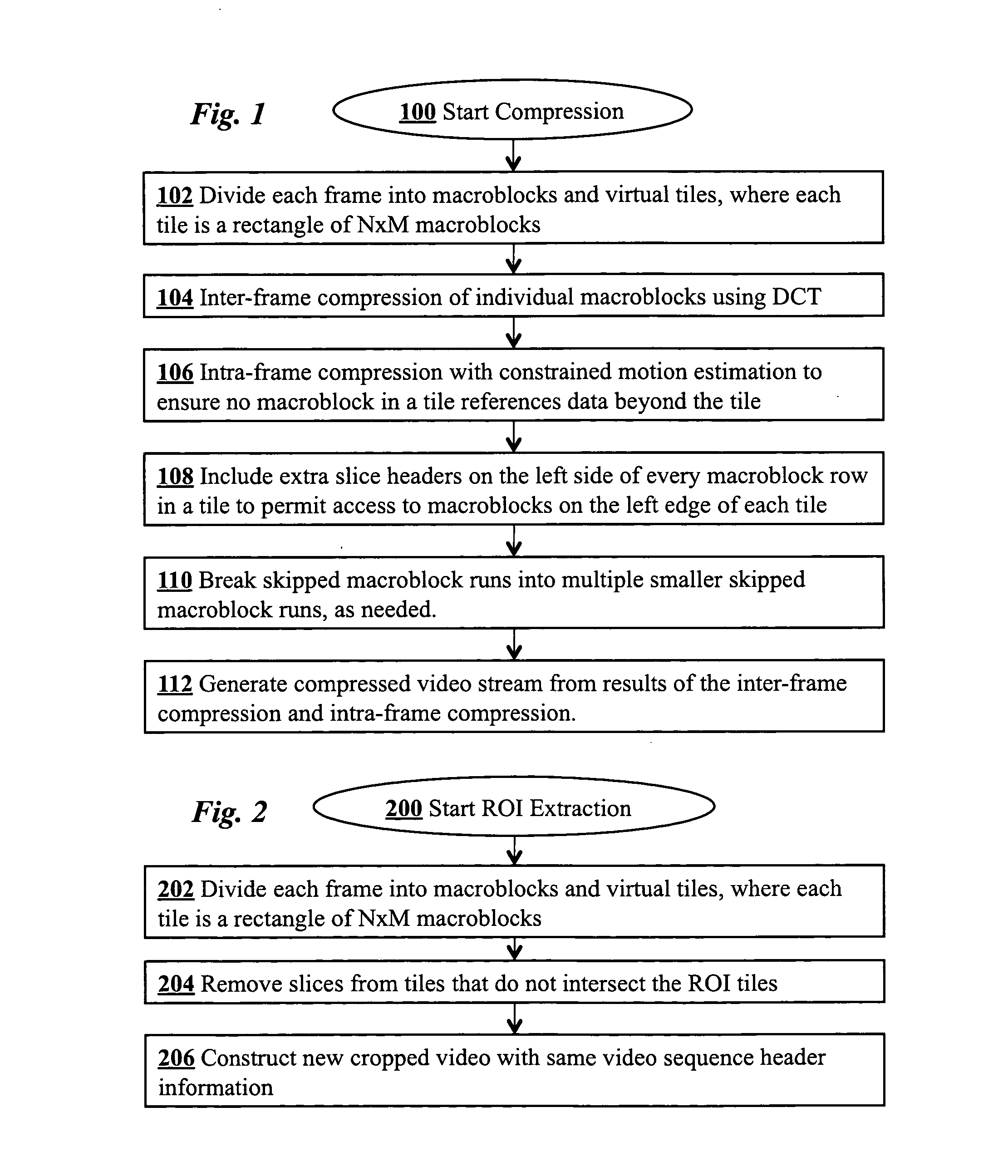

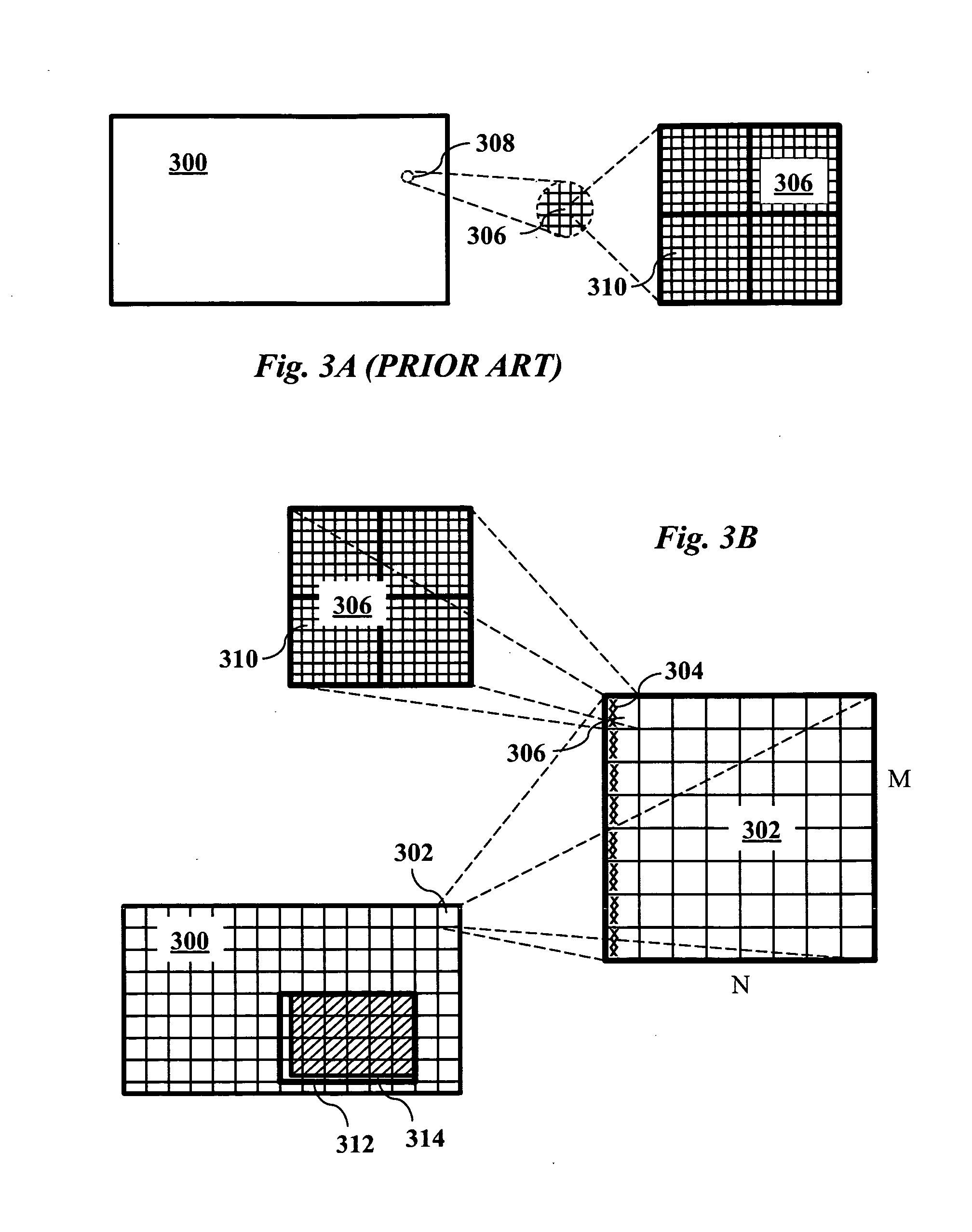

Region-of-interest cropping of high-resolution video is supported video compression and extraction methods. The compression method divides each frame into virtual tiles, each containing a rectangular array of macroblocks. Intra-frame compression uses constrained motion estimation to ensure that no macroblock references data beyond the edge of a tile. Extra slice headers are included on the left side of every macroblock row in the tiles to permit access to macroblocks on the left edge of each tile during extraction. The compression method may also include breaking skipped macroblock runs into multiple smaller skipped macroblock runs. The extraction method removes slices from virtual tiles that intersect the region-of-interest to produce cropped frames. The cropped digital video stream and the compressed digital video stream have the same video sequence header information.

Owner:THE STATE OF OREGON ACTING BY & THROUGH THE STATE BOARD OF HIGHER EDUCATION ON BEHALF OF THE PORTLAND STATE UNIV

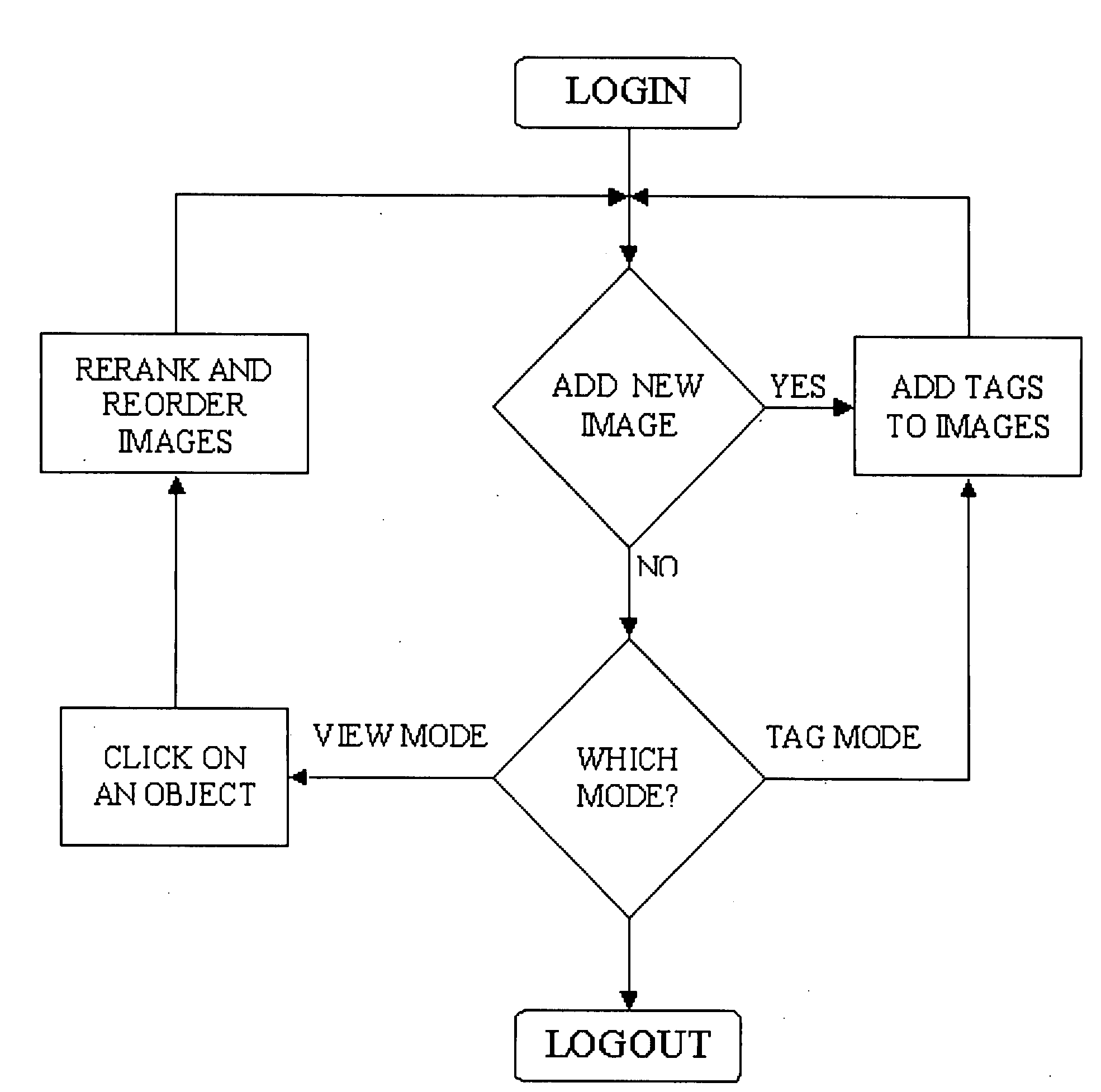

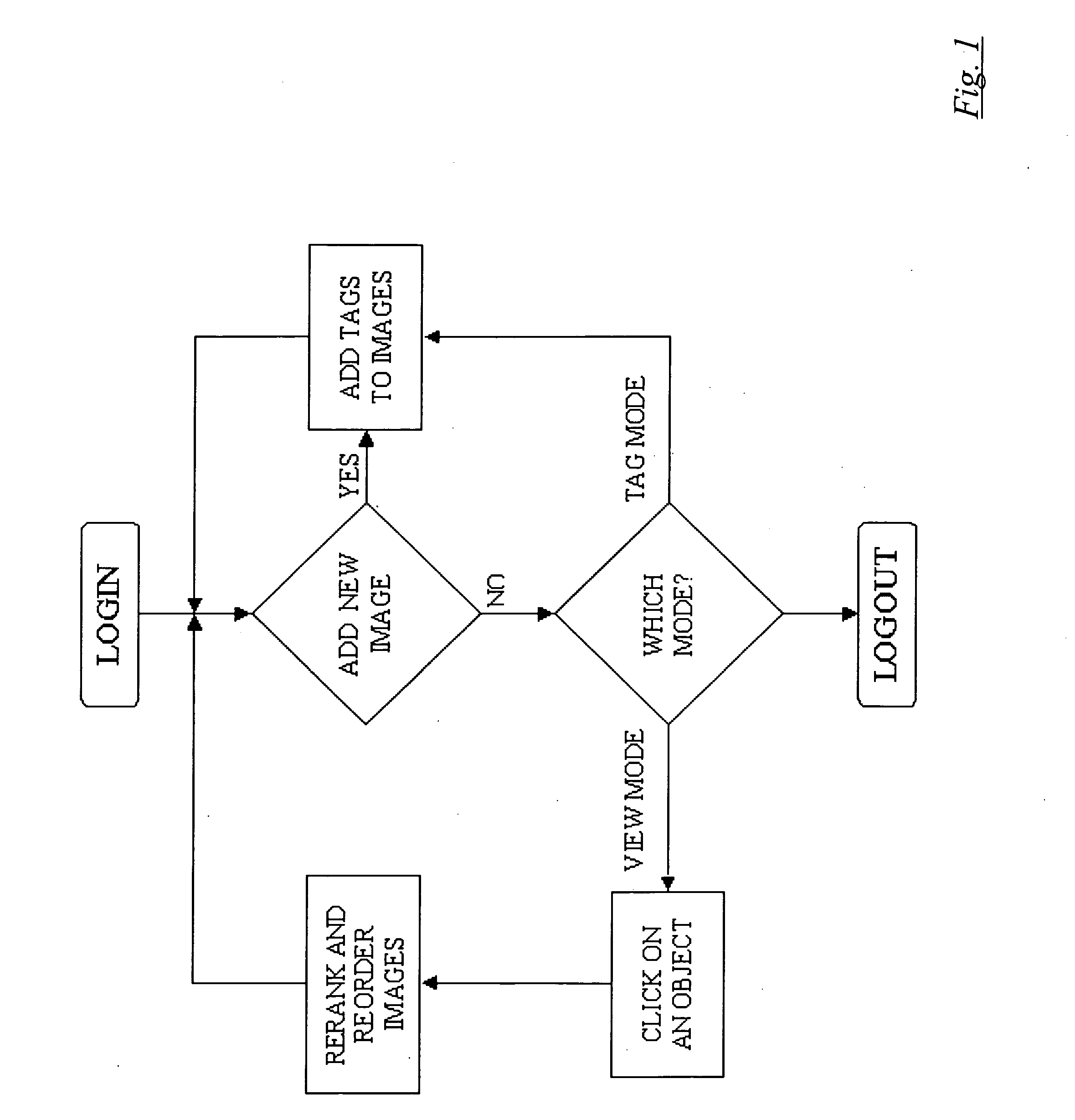

Method, system and computer program for interactive spatial link-based image searching, sorting and/or displaying

ActiveUS20080069480A1Effective registrationEfficient use ofCharacter and pattern recognitionStill image data indexingApplication softwareFast methods

A web-based application provides more accurate and clearer methods of searching, sorting, and displaying a set of images stored in a database. A first aspect of the present invention is the method by which image data is stored. Typical content-based systems use colour information, whereas the present invention uses an image-location tagging method. A second aspect of the present invention is the method by which the set of images are sorted in relevancy. Tag data of the images allows for a new and fast method of searching through an entire set. A third aspect of the present invention is the method by which the sorted images are displayed to the user. Instead of the common method of just displaying the images in a rectangular array, where each image is the same size, the web-based application positions and sizes each image based on how relevant it is.

Owner:AARABI PARHAM +1

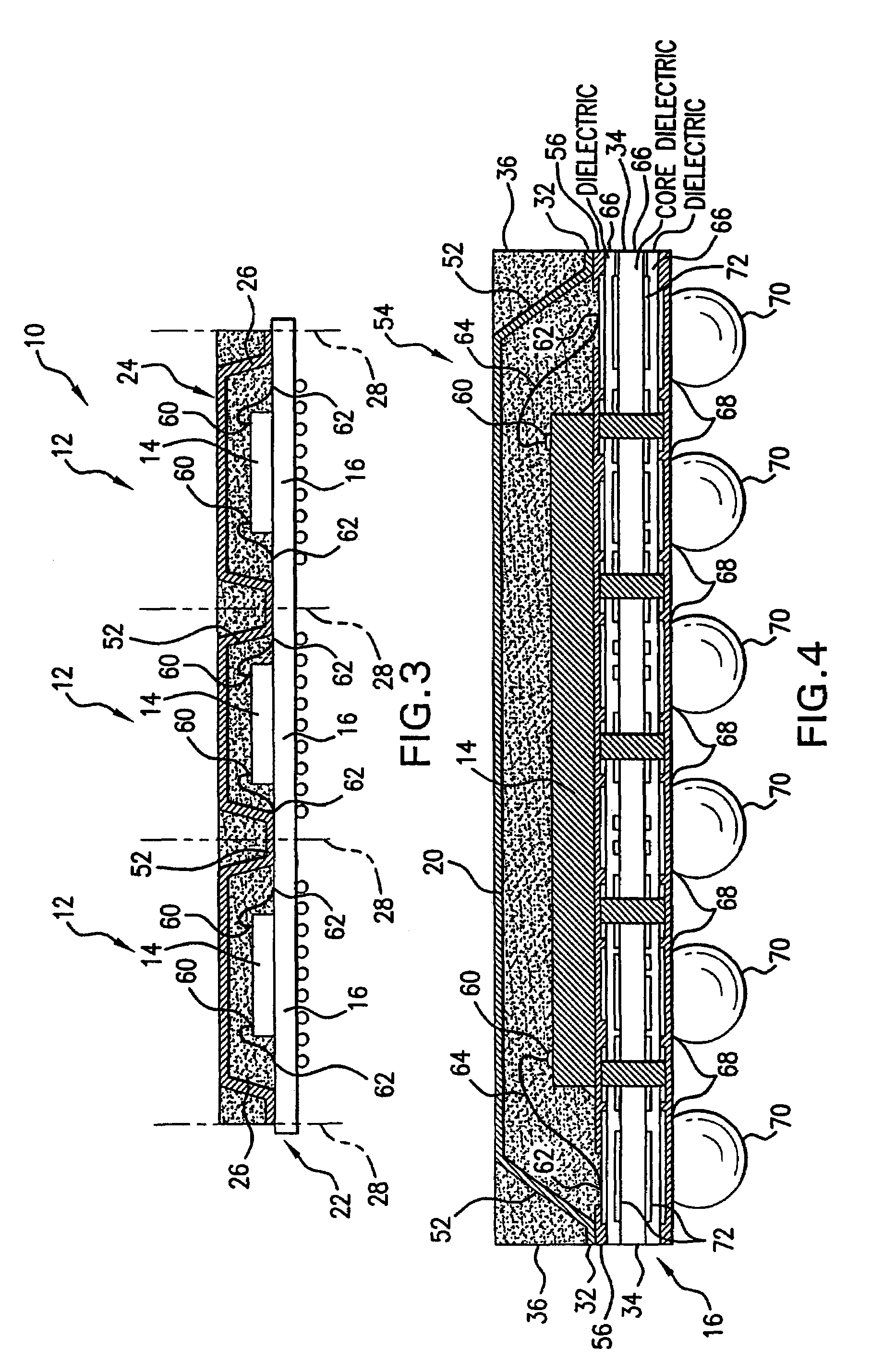

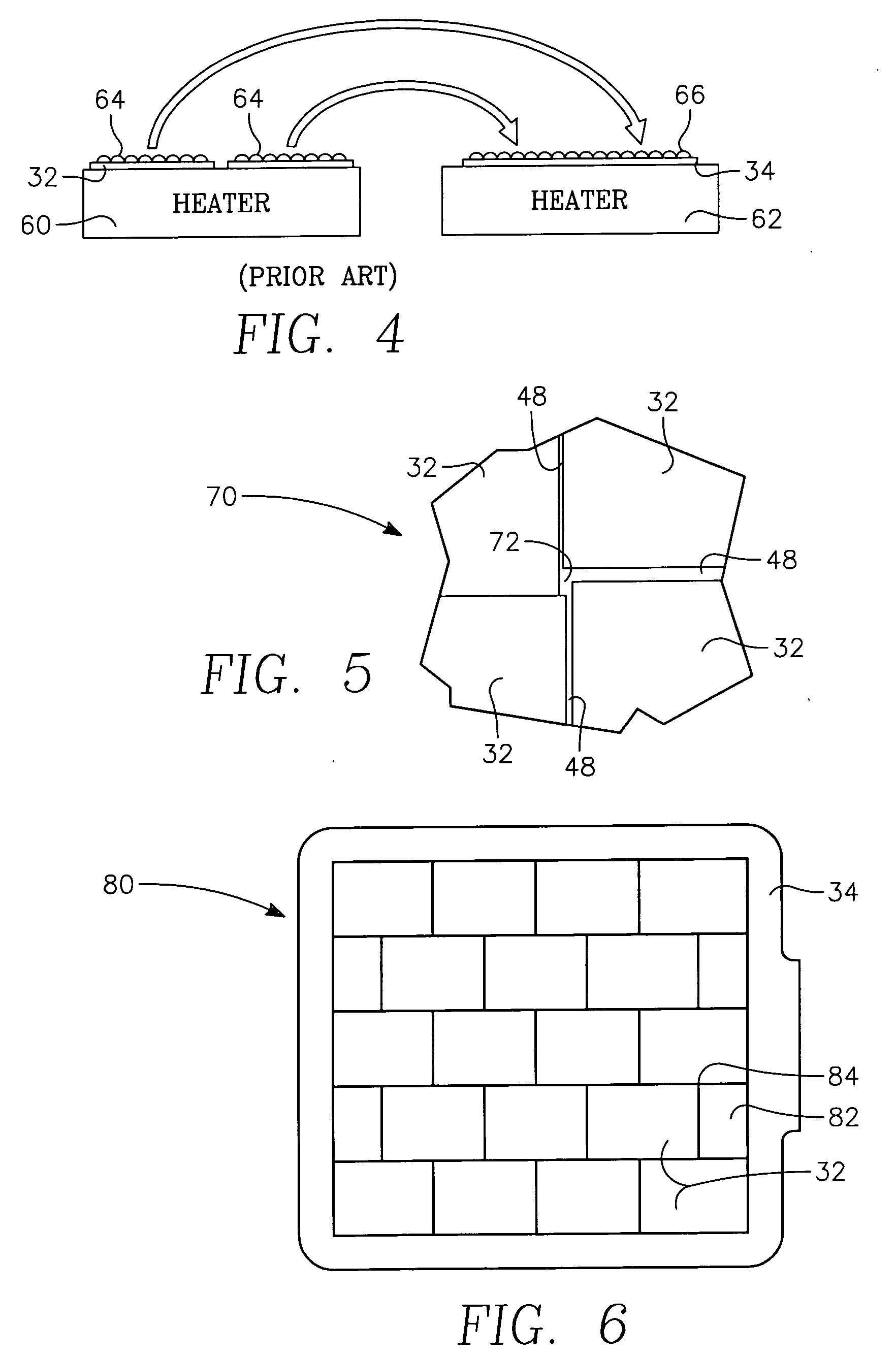

Thermal enhanced package for block mold assembly

InactiveUS7259445B2Semiconductor/solid-state device detailsSolid-state devicesElectrical performanceEngineering

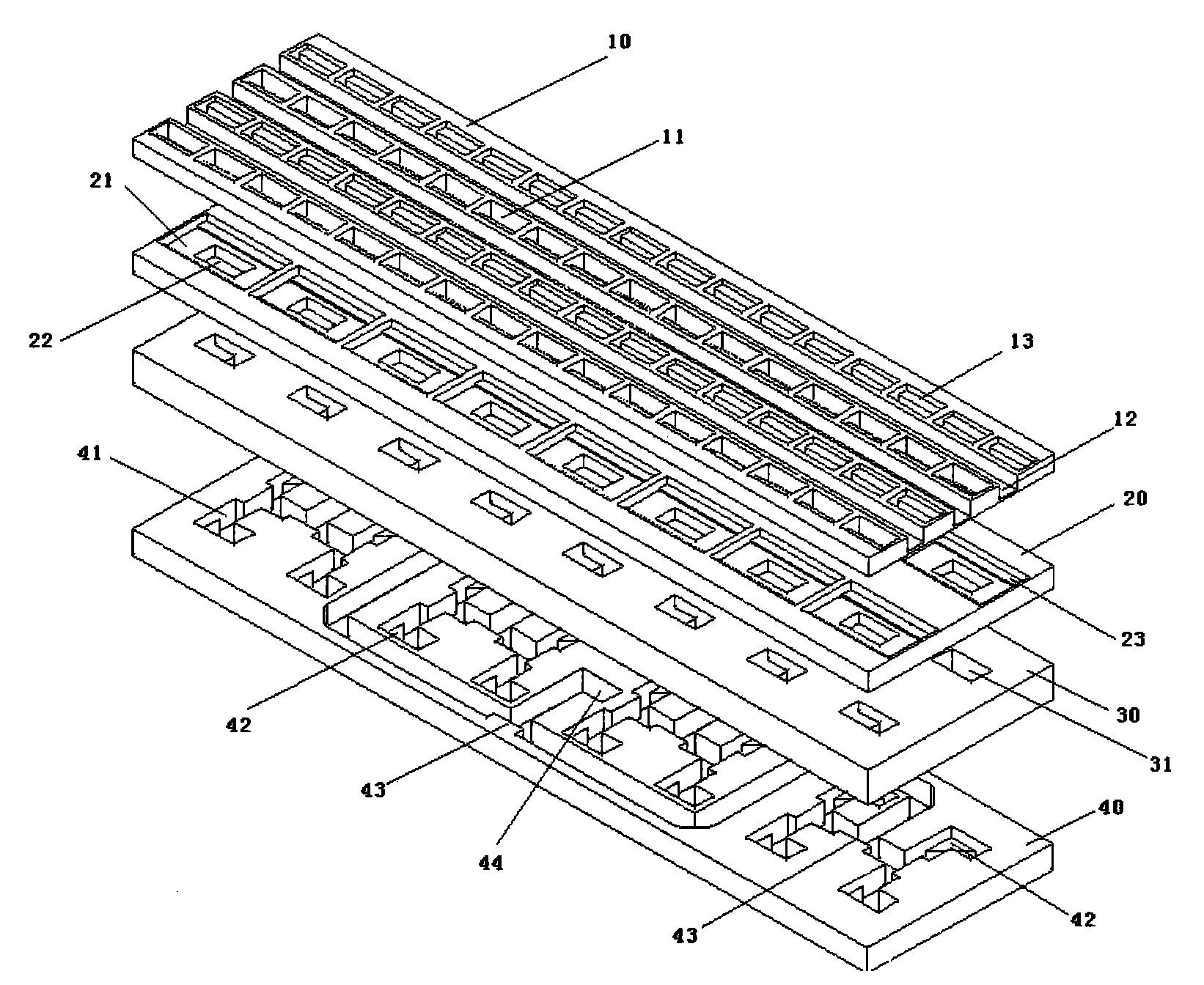

A heat spreader (20) is added to a package to enhance thermal and advantageously electrical performance. In manufacture, a heat spreader precursor (24) is advantageously placed over a group of dies and secured after bonding (e.g., wire or tape bonding or flip-chip bonding) and before matrix / block mold. For example, a package strip (10) may consist of a row (linear array) of groups of die attach areas (e.g. in a rectangular array of four). The heat spreader precursor (20) may accommodate one such group or multiple groups along the package strip (10). The package strip (10) may then be singulated to form the individual packages. Each singulated package includes a die (14), its associated substrate 16 (e.g., either a lead frame or interposer type substrate) and a portion of the heat spreader precursor (24) as a heat spreader (20).

Owner:ADVANCED INTERCONNECT TECH LTD

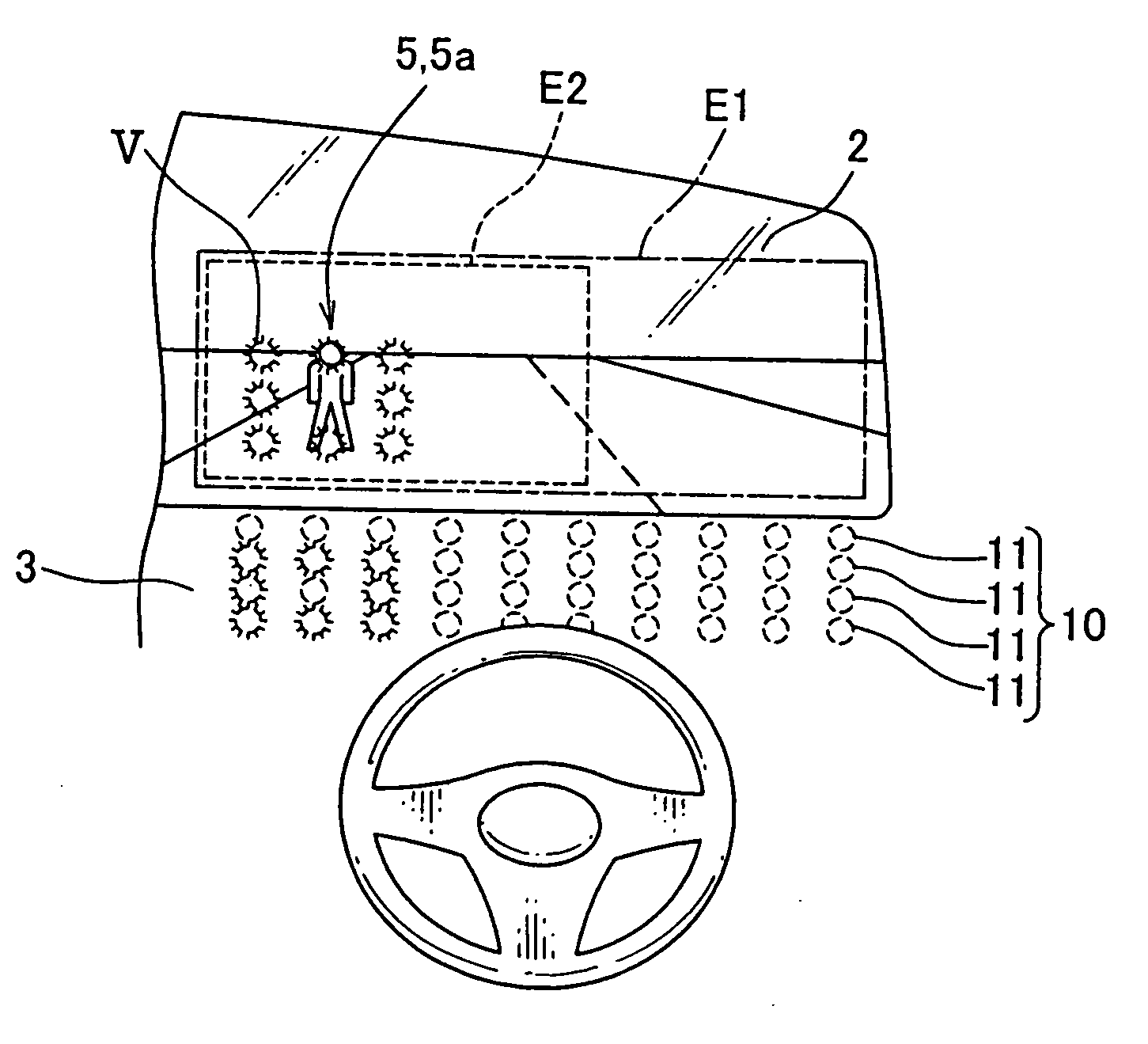

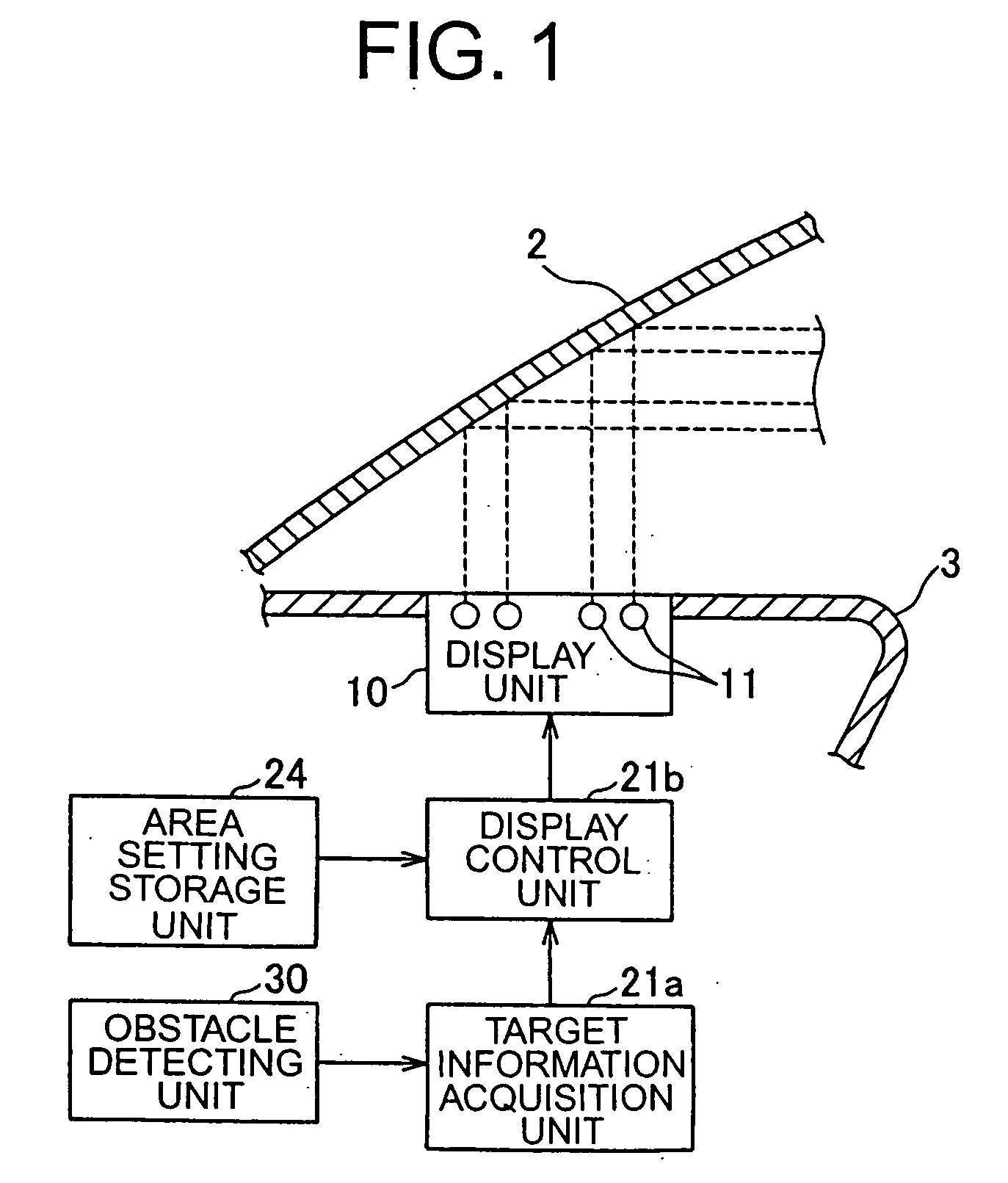

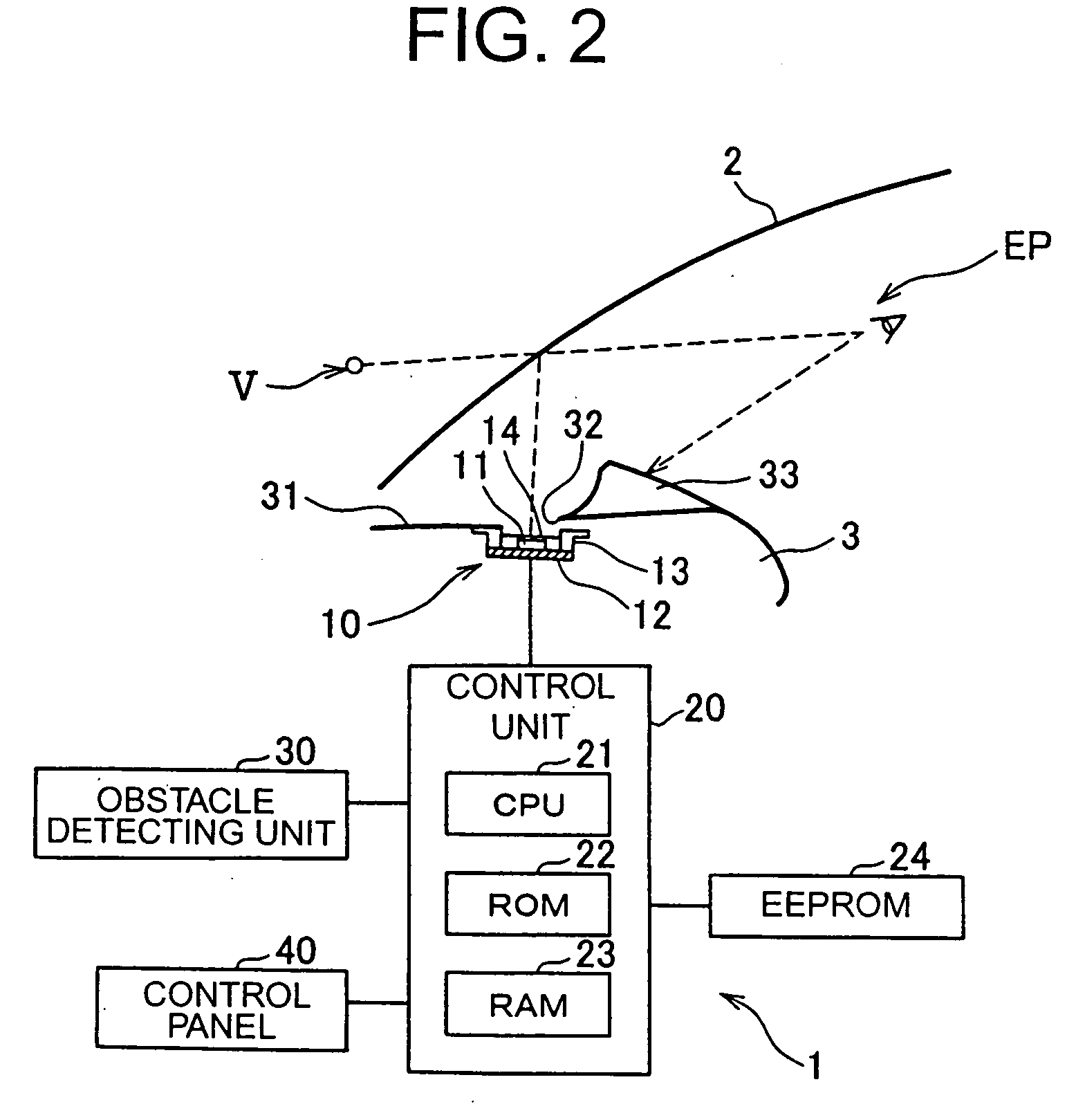

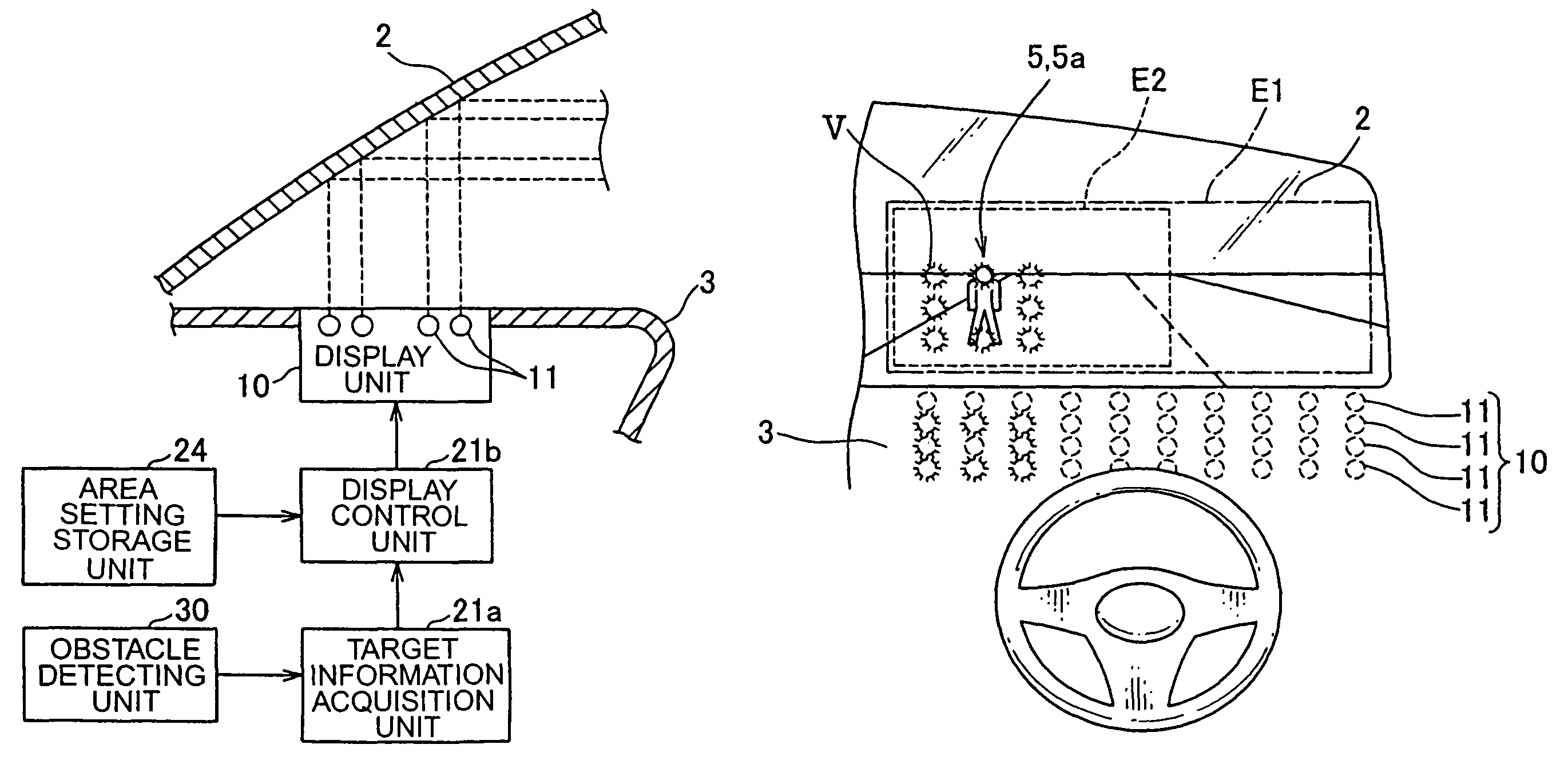

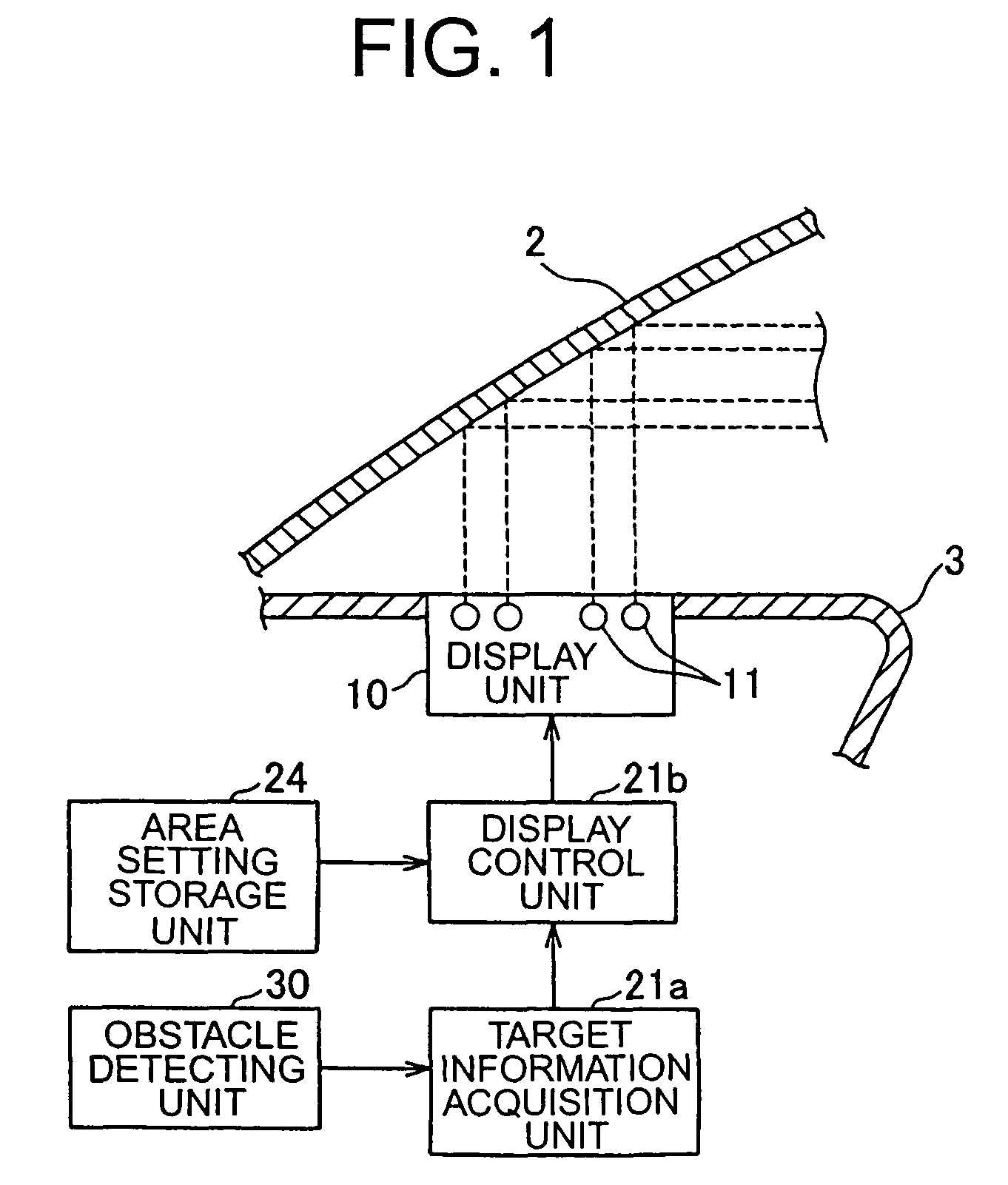

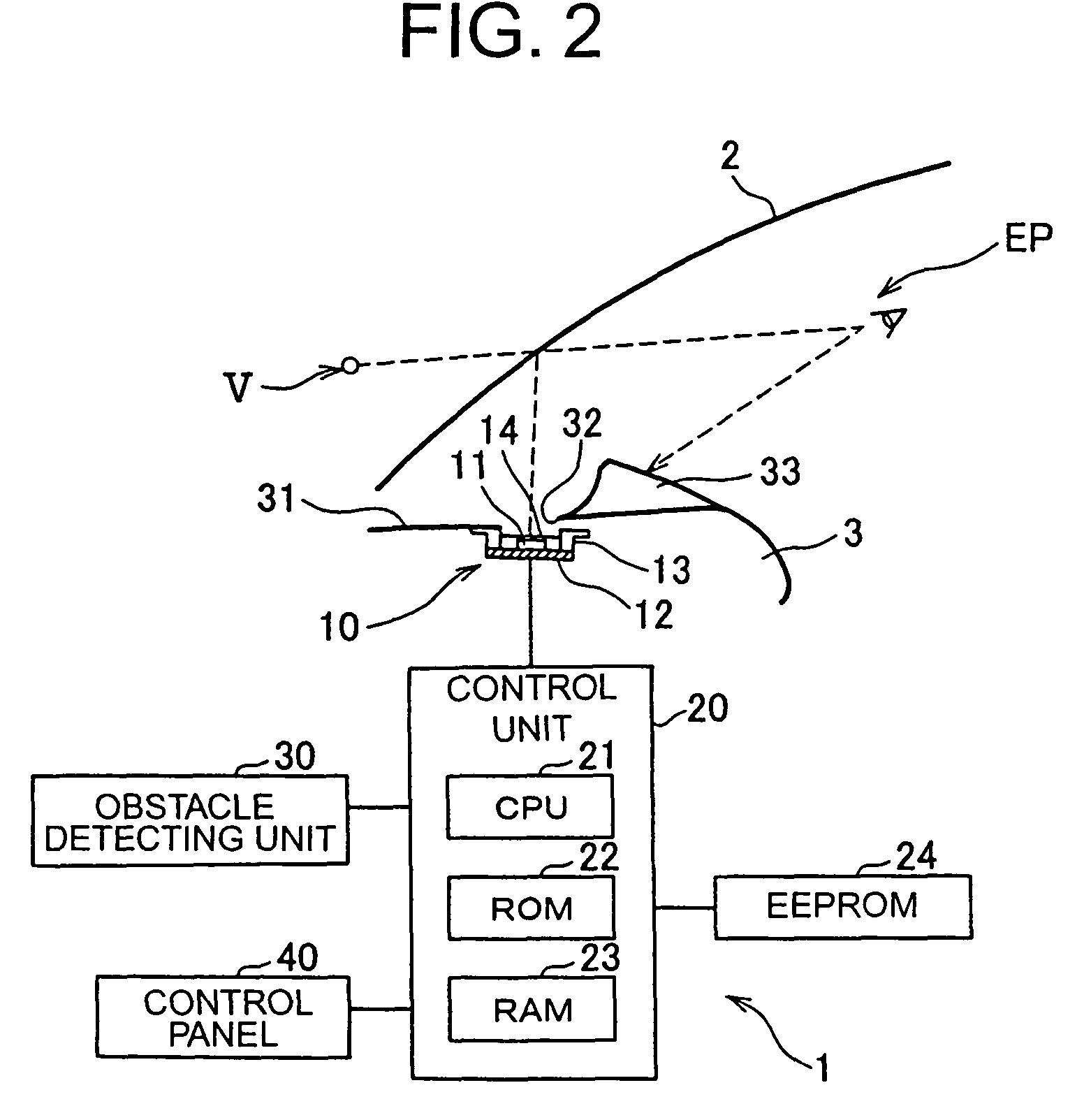

In-vehicle display device

InactiveUS20090231116A1Increase awarenessReduce manufacturing costProjectorsCharacter and pattern recognitionObjective informationIn vehicle

An in-vehicle display device includes (a) a display unit provided on a surface of an instrument panel of a vehicle, opposed to a windshield of the vehicle, and configured to indicate a plurality of information dots V in a row or in a rectangular array on the windshield such that the necessary information dots are selectably displayed from among the plurality of the information dots and superposed upon a real image viewed through the windshield, (b) a target information acquisition unit that obtains target information of which a driver of the vehicle is to be notified, and (c) a display control unit that controls the display unit and makes the display unit indicate the predetermined information dots V that correspond to the target information that has been obtained by the target information acquisition unit.

Owner:YAZAKI CORP

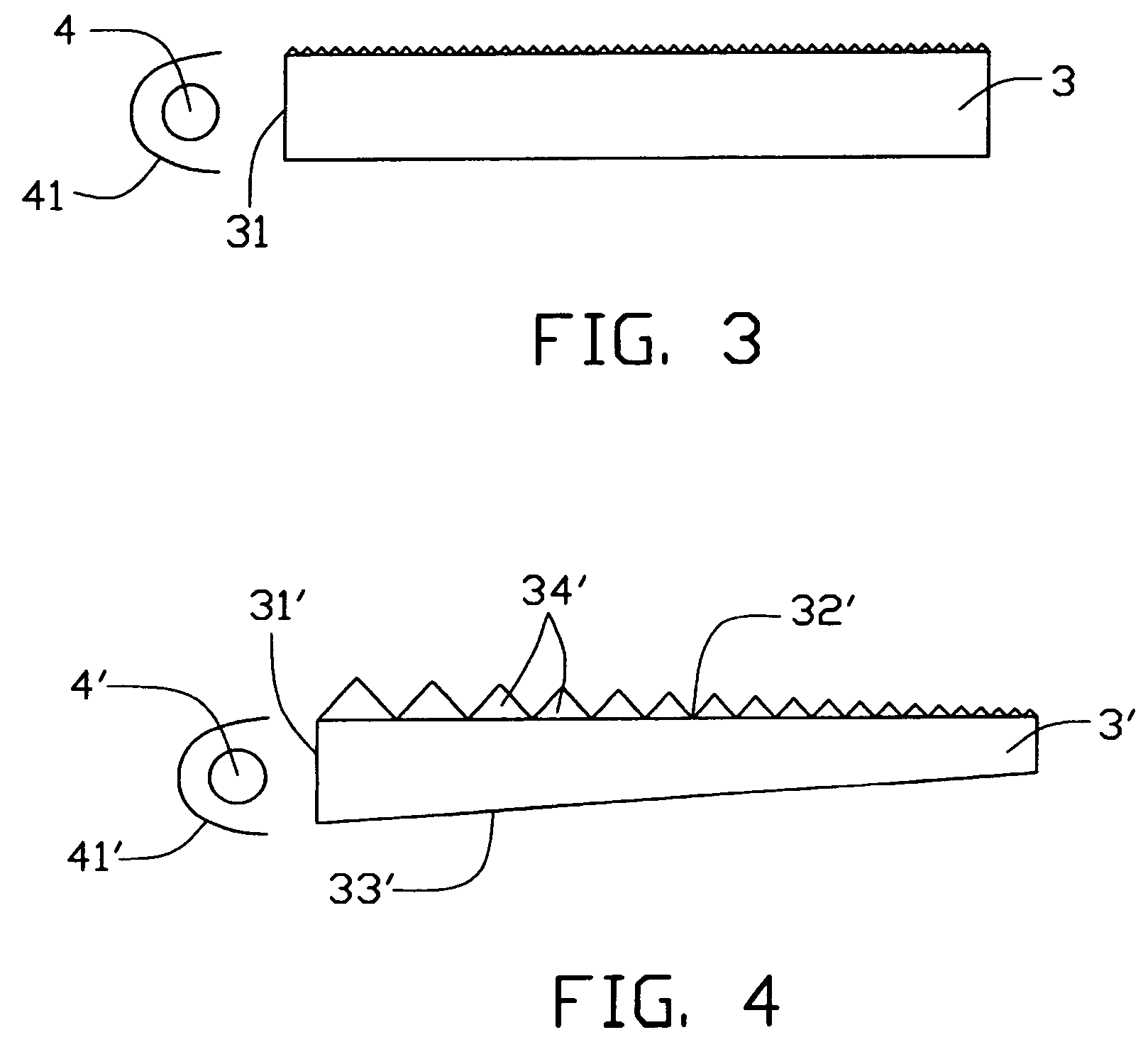

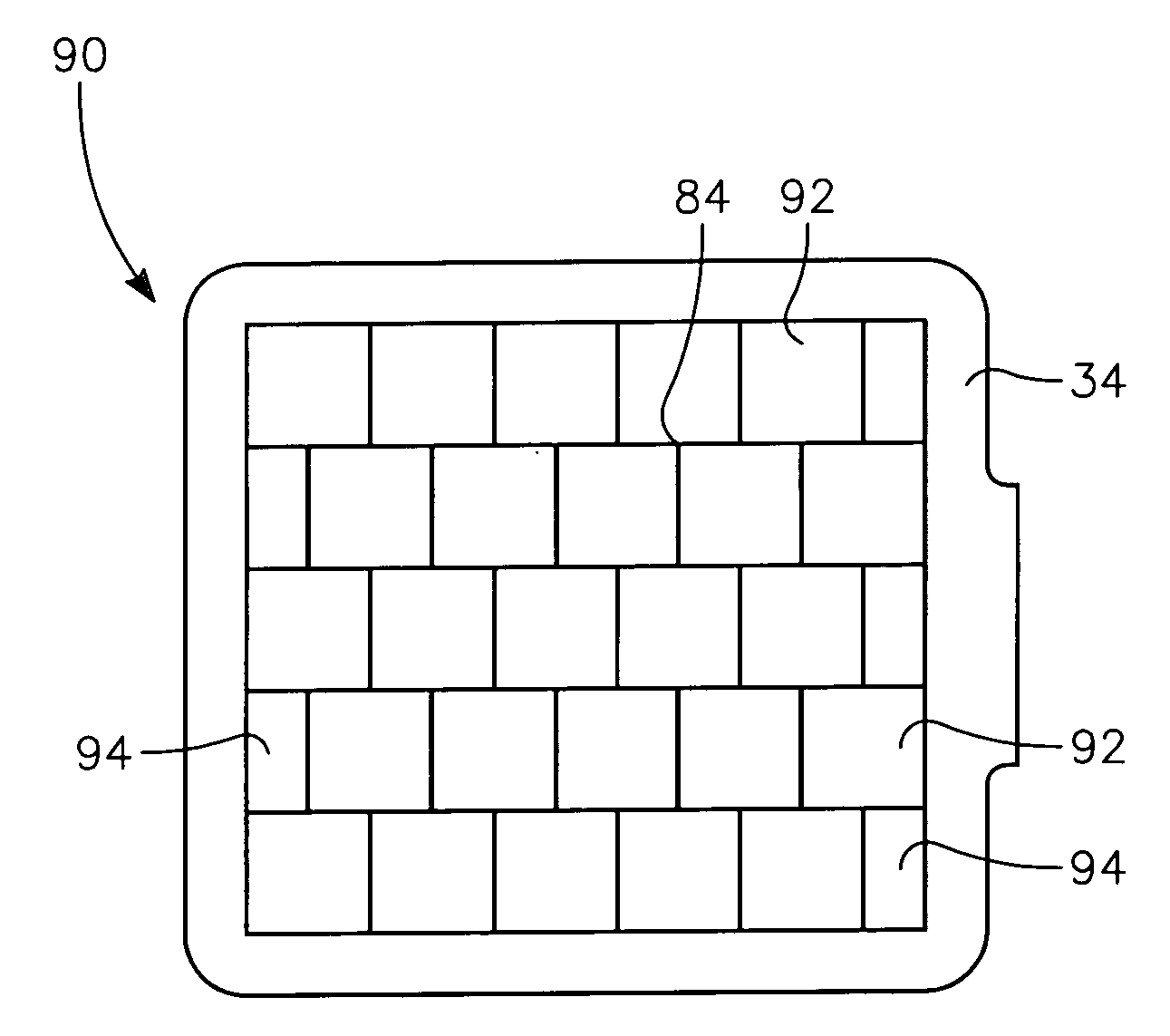

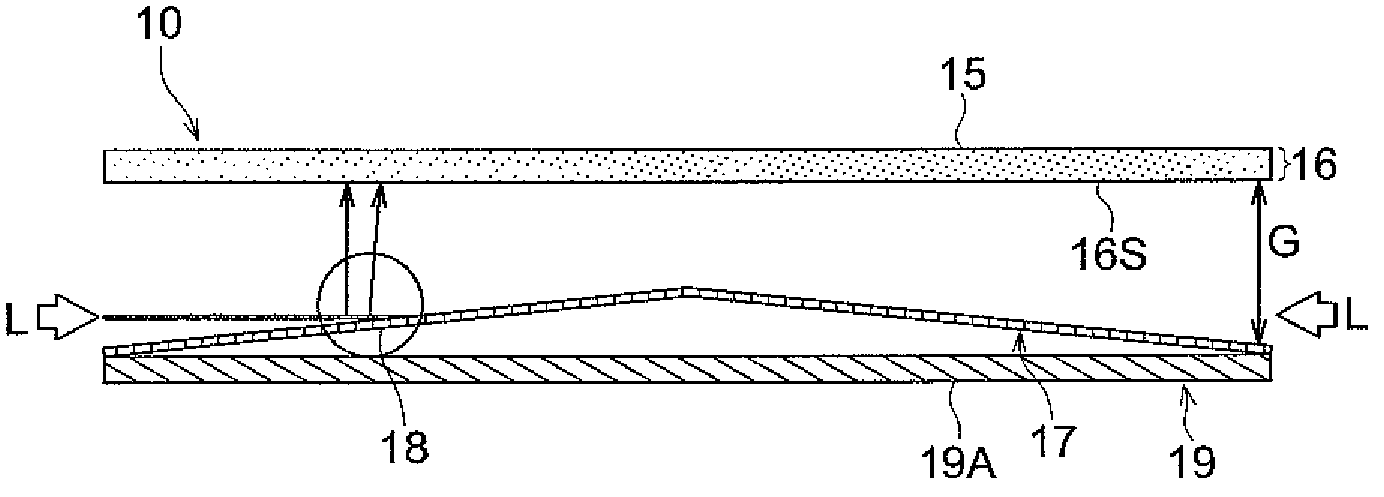

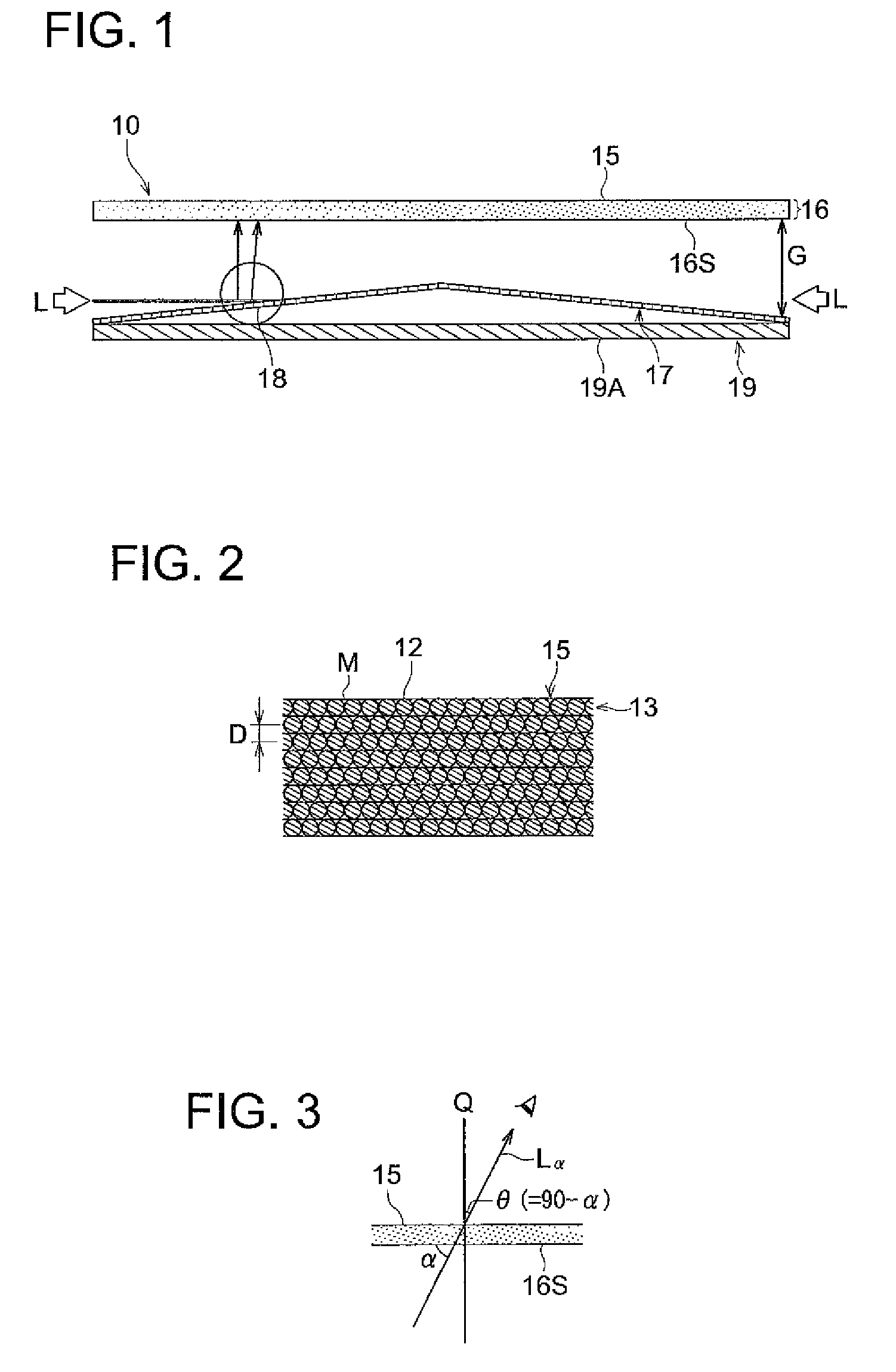

Light guide plate for liquid crystal display

InactiveUS7018088B2Reduce manufacturing costImprove uniformityMechanical apparatusLight guides for lighting systemsLiquid-crystal displayLight guide

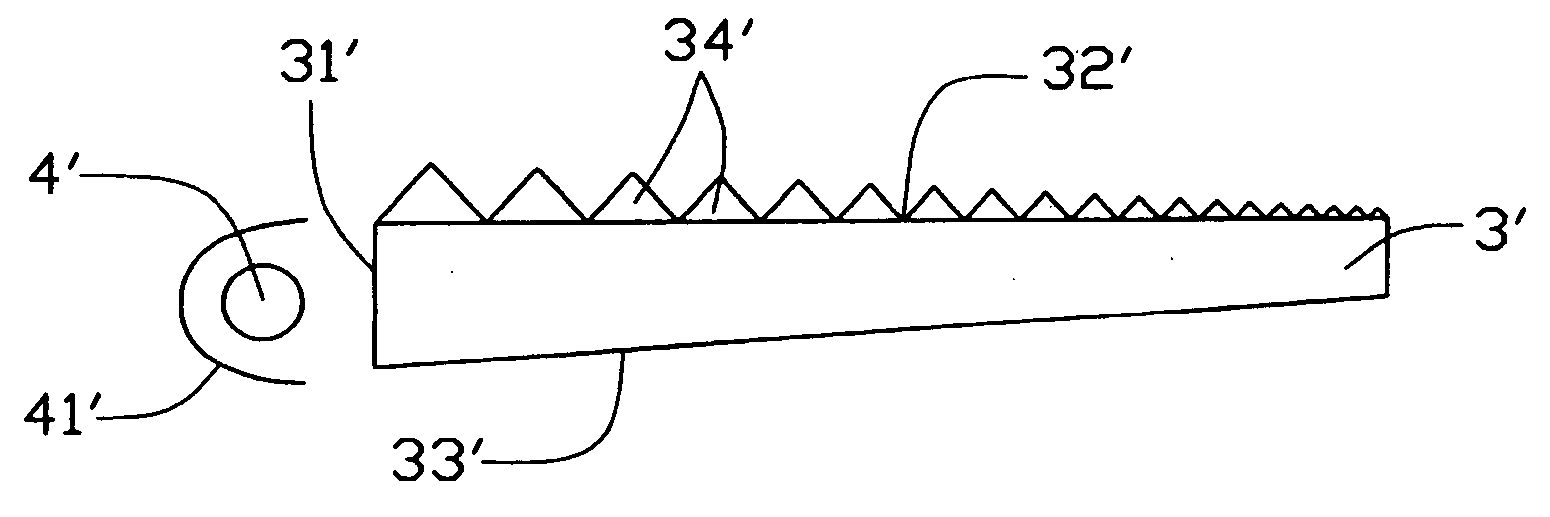

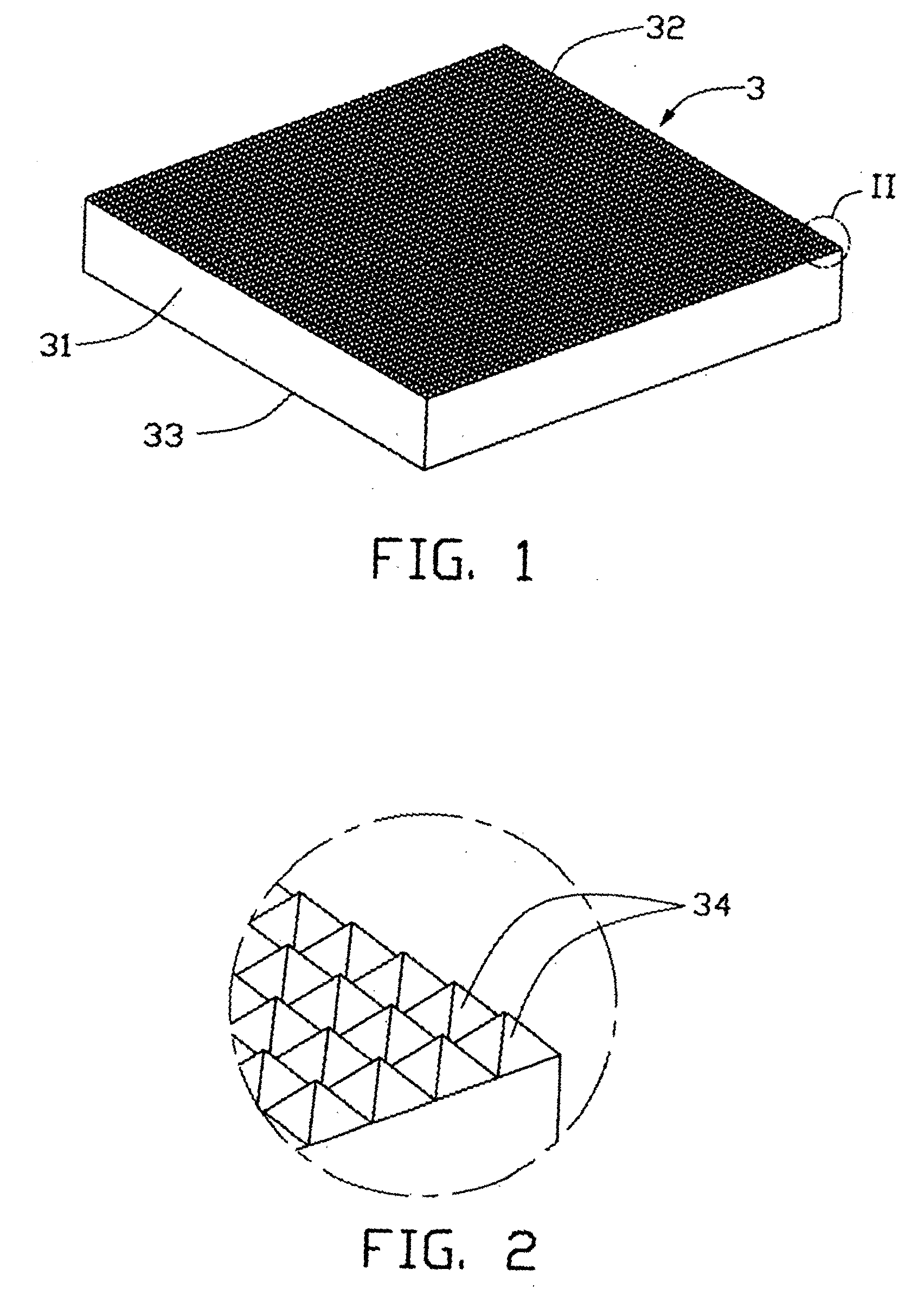

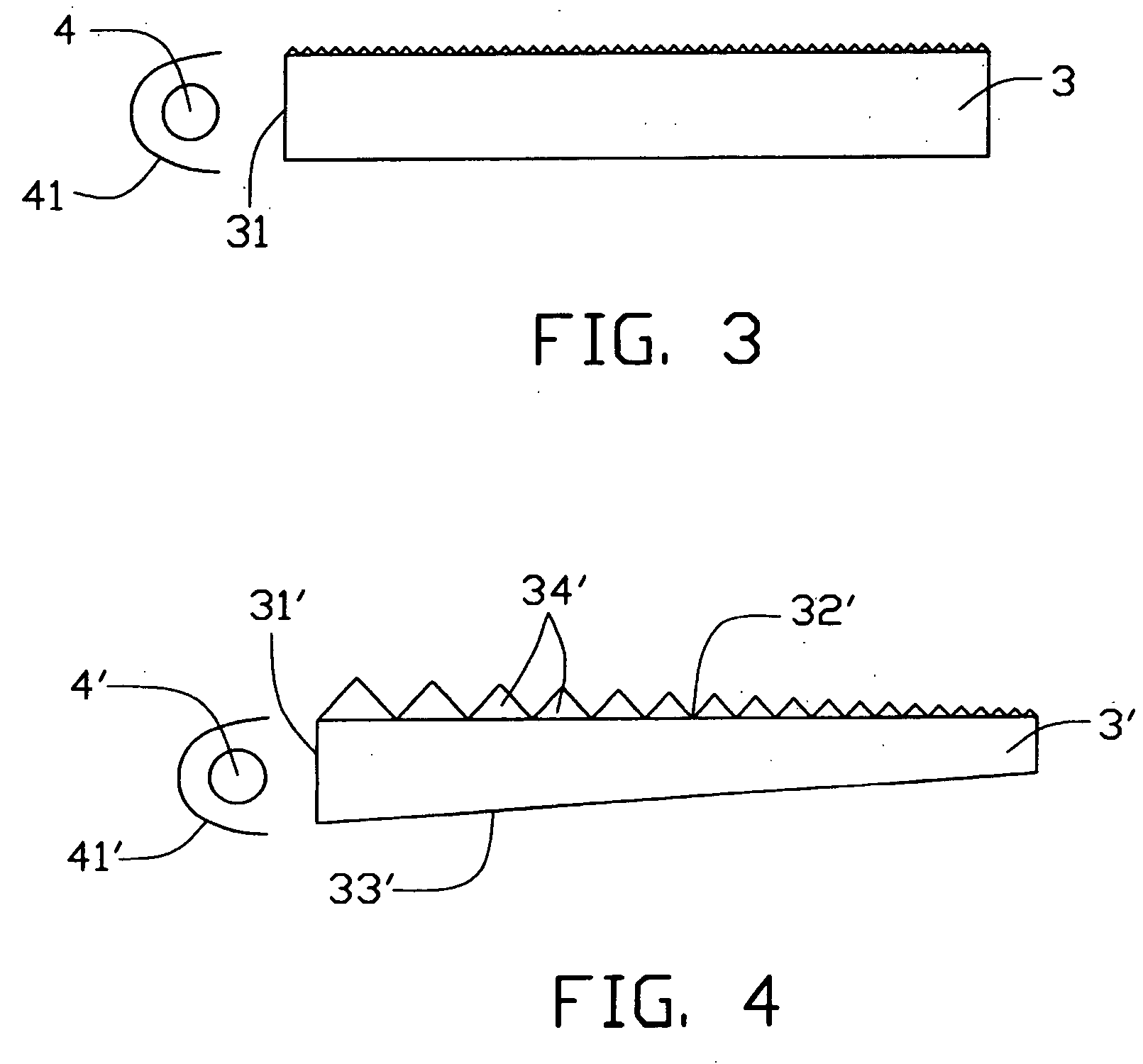

A light guide plate (3) includes a parallelepiped block. The block includes an input surface (31) for receiving light beams irradiated from a light source; two side surfaces perpendicularly adjoining the incident surface; an output surface (32) perpendicularly adjoining the incident surface and the side surfaces; and a bottom surface (33) opposing to the output surface. An array of prisms (34) is integrally formed on the output surface. Each prism is shaped as a square pyramid. All the prisms have a same size and are arranged contiguously with each other. Alternatively, the light guide plate may be a wedge-shaped block (3′). A rectangular array of prisms (34′) is integrally formed on an output surface (32′) thereof. Each prism is shaped as a square pyramid. The prisms are arranged contiguously with each other, and sizes of the prisms gradually decrease from a thick end to a thin end of the block.

Owner:HON HAI PRECISION IND CO LTD

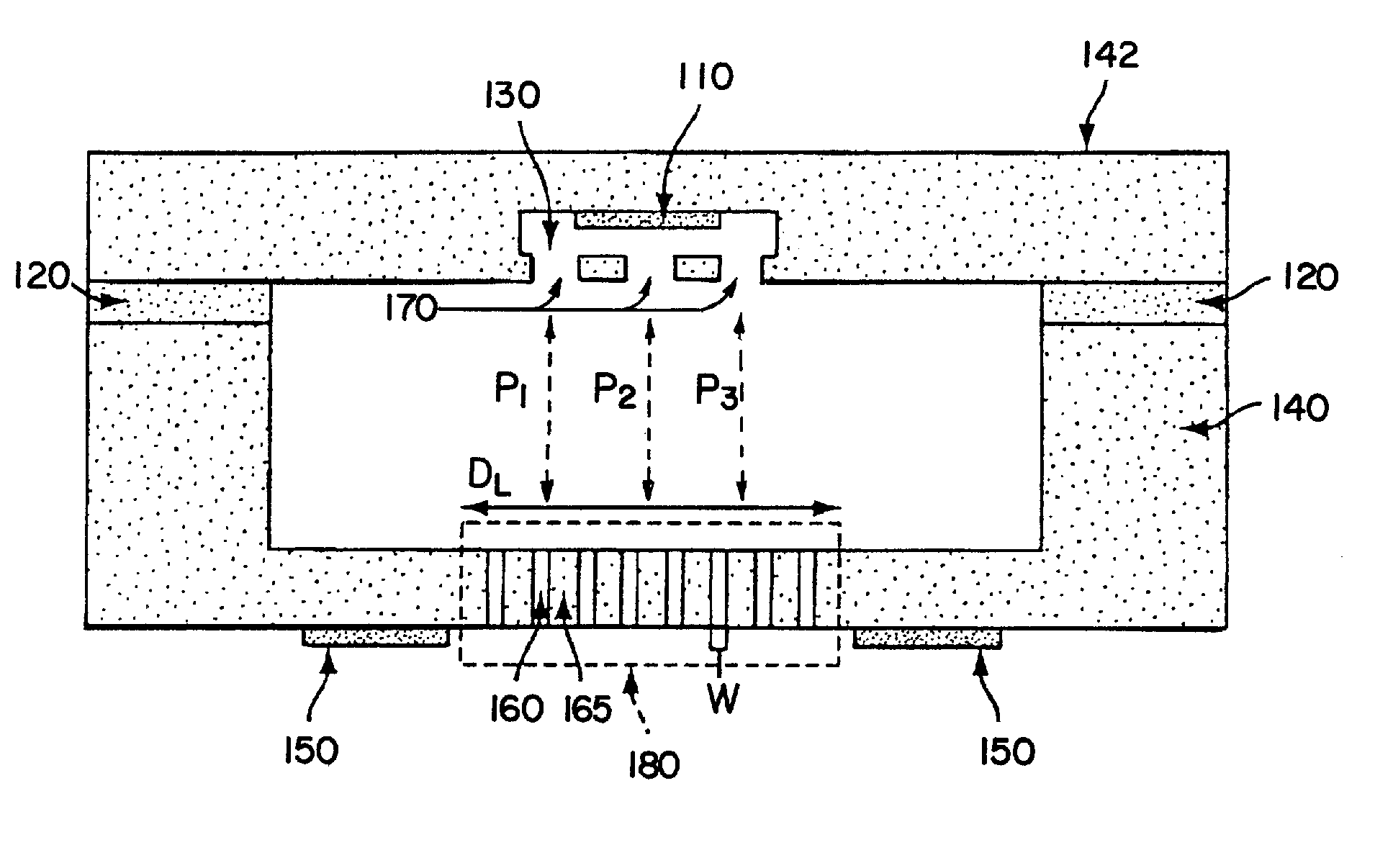

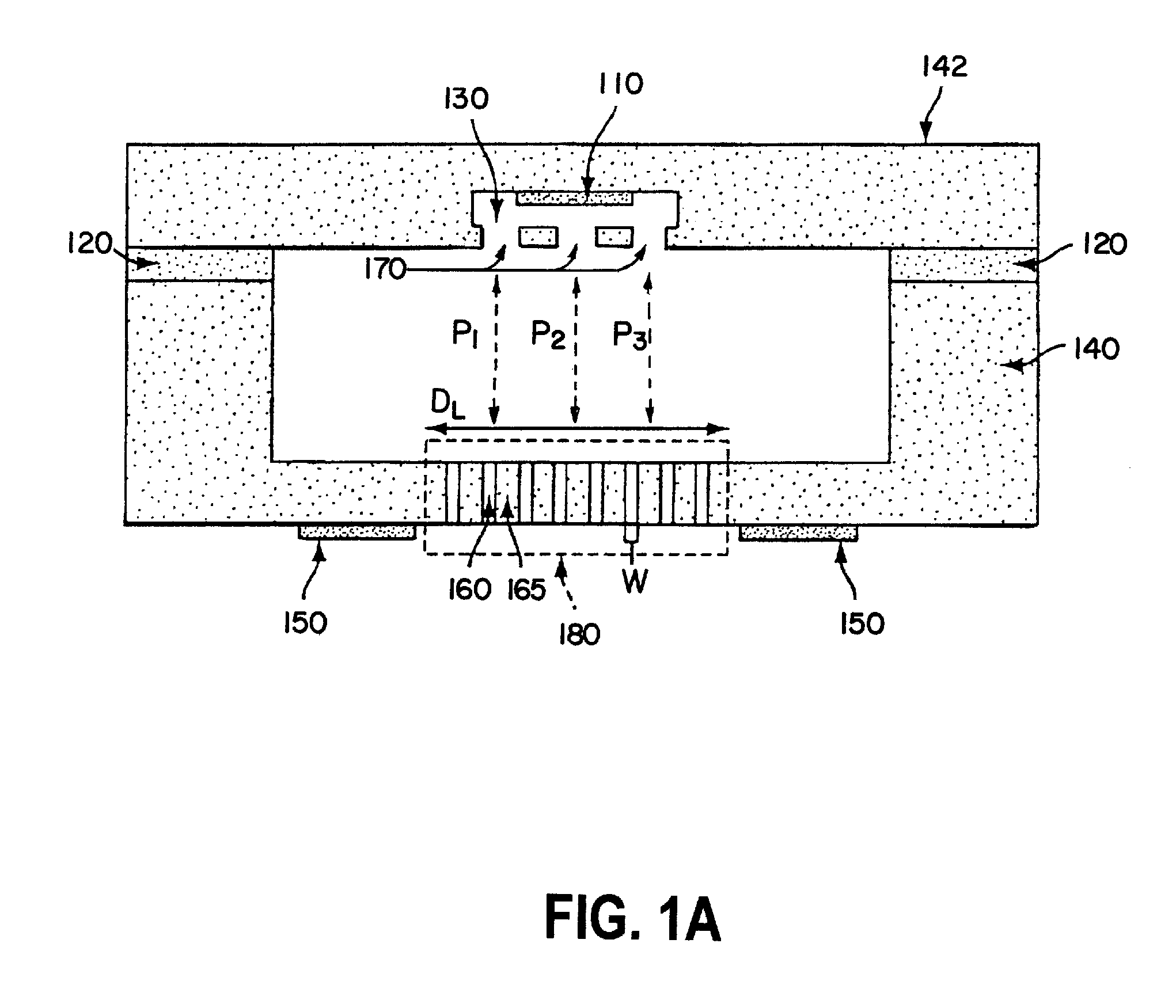

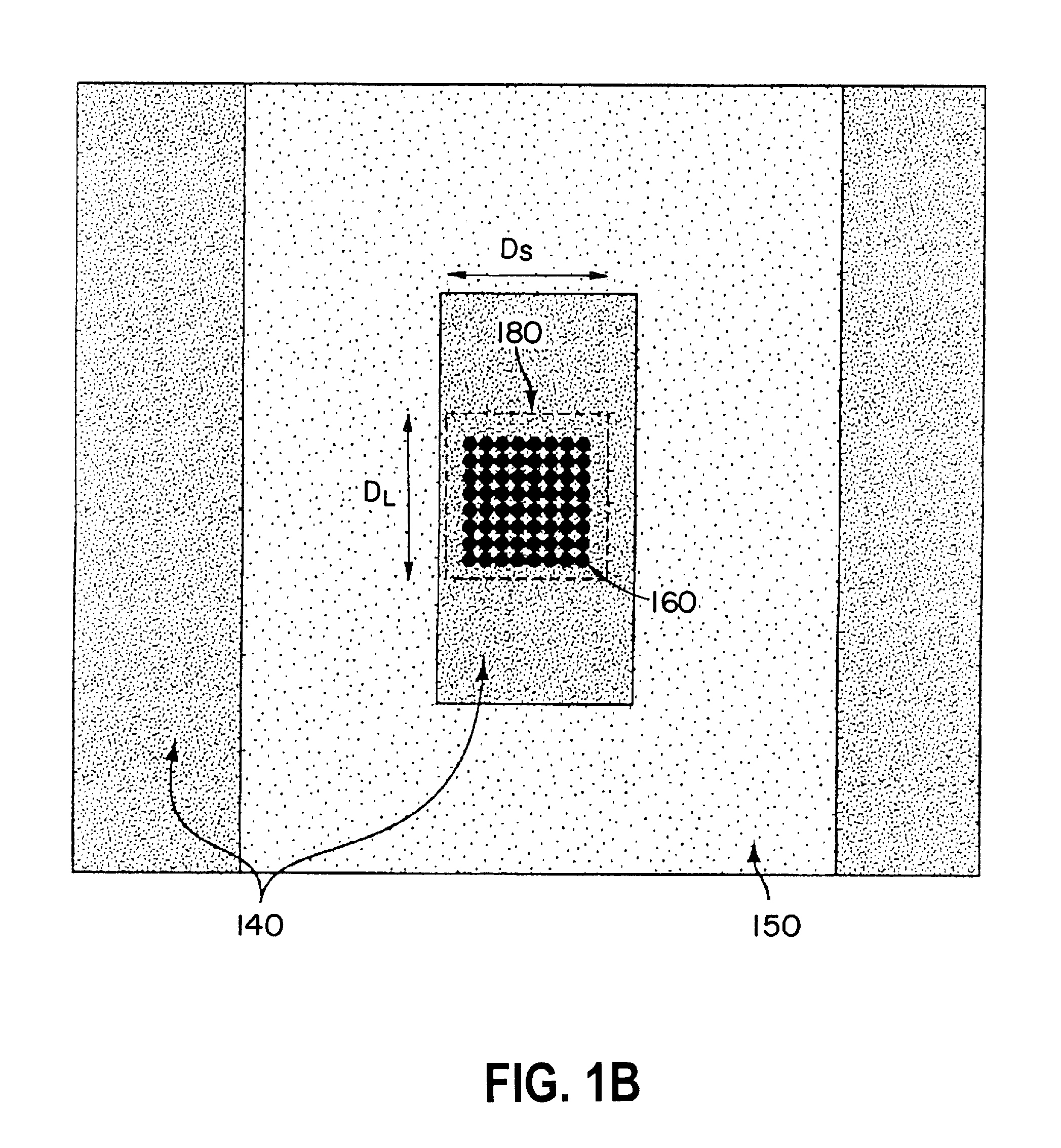

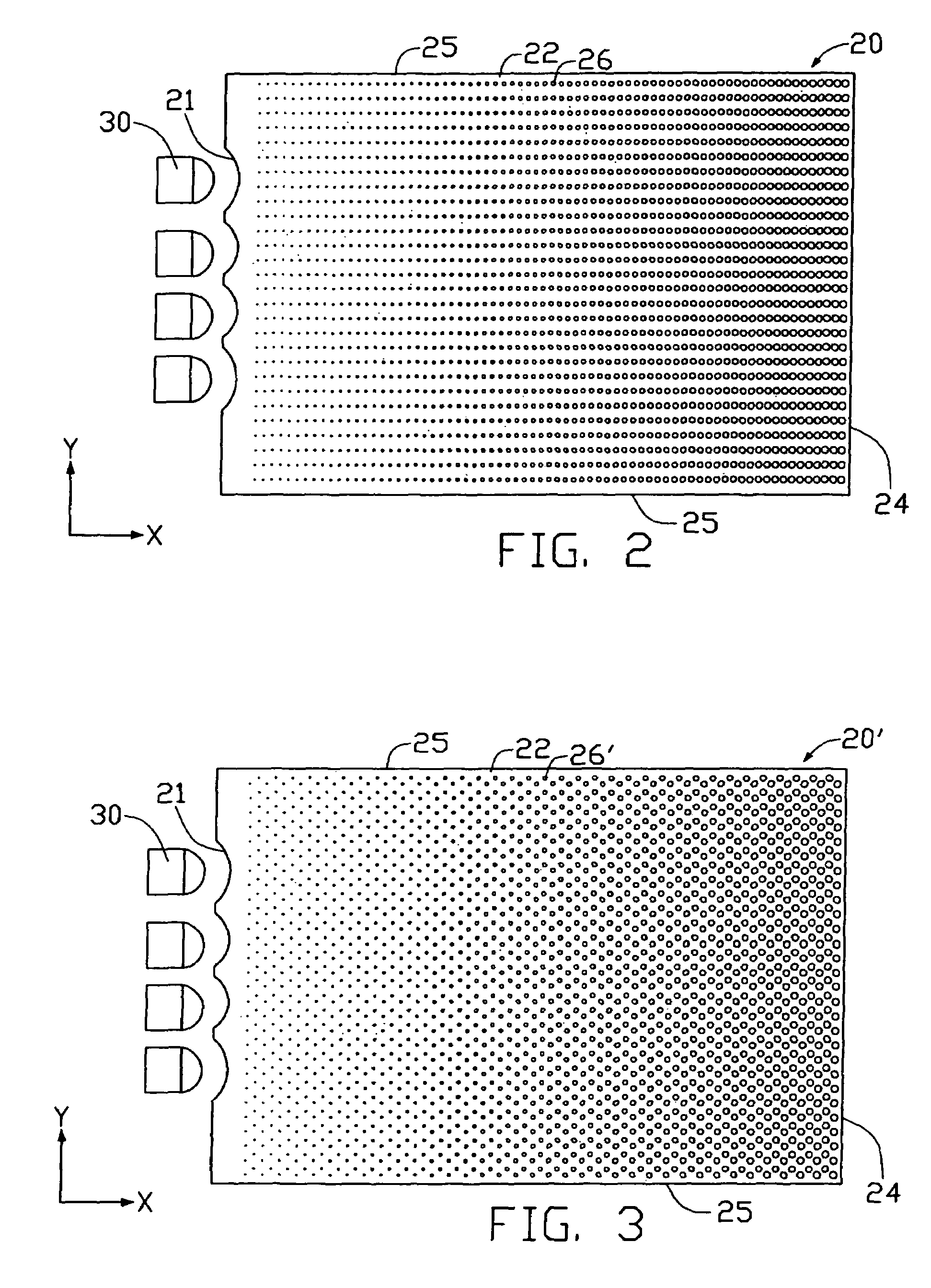

Rapid Ink-Charging Of A Dry Ink Discharge Nozzle

InactiveUS20100171780A1Sufficient materialSolid-state devicesMachines/enginesMulti materialSuspended particles

The present teachings relate to methods and apparatus for depositing one or more materials (e.g., one or more films, such as one or more solids) on one or more substrates, which may form part of an OLED or other type(s) of display. In some embodiments, the disclosure relates to apparatus and methods for depositing ink on one or more substrates. The apparatus can include, for example, one or more chambers for receiving ink, and plural orifices configured in the one or more chambers which are adapted for ejecting droplets of the ink; a discharge nozzle comprising an array of micro-pores (e.g., configured in a rectangular array), with each micro-pore having an inlet port and an outlet port, and the discharge nozzle receiving plural quantities (e.g., droplets) of ink from the chamber(s) via the orifices at the inlet ports and dispensing the ink from the outlet ports. The droplets of ink can be received at unique, spaced-apart locations on the inlet ports of the discharge nozzle. In some embodiments, a single liquid ink-holding chamber, which includes plural orifices (e.g., three), receives ink in liquid form having a plurality of suspended particles, and droplets of the ink are ejected substantially simultaneously from the chamber to respective, spaced-apart locations on the discharge nozzle; and the discharge nozzle evaporates the carrier liquid and deposits the solid particles on one or more substrates.

Owner:KATEEVA

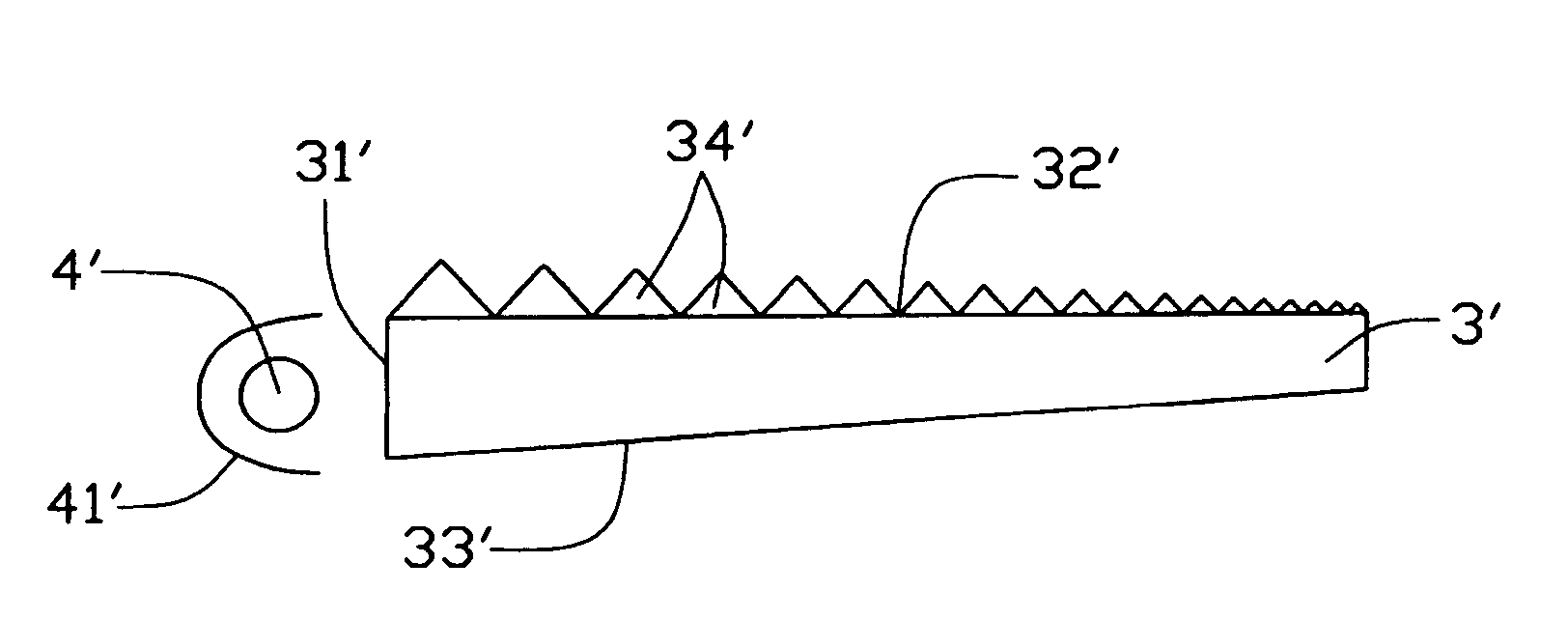

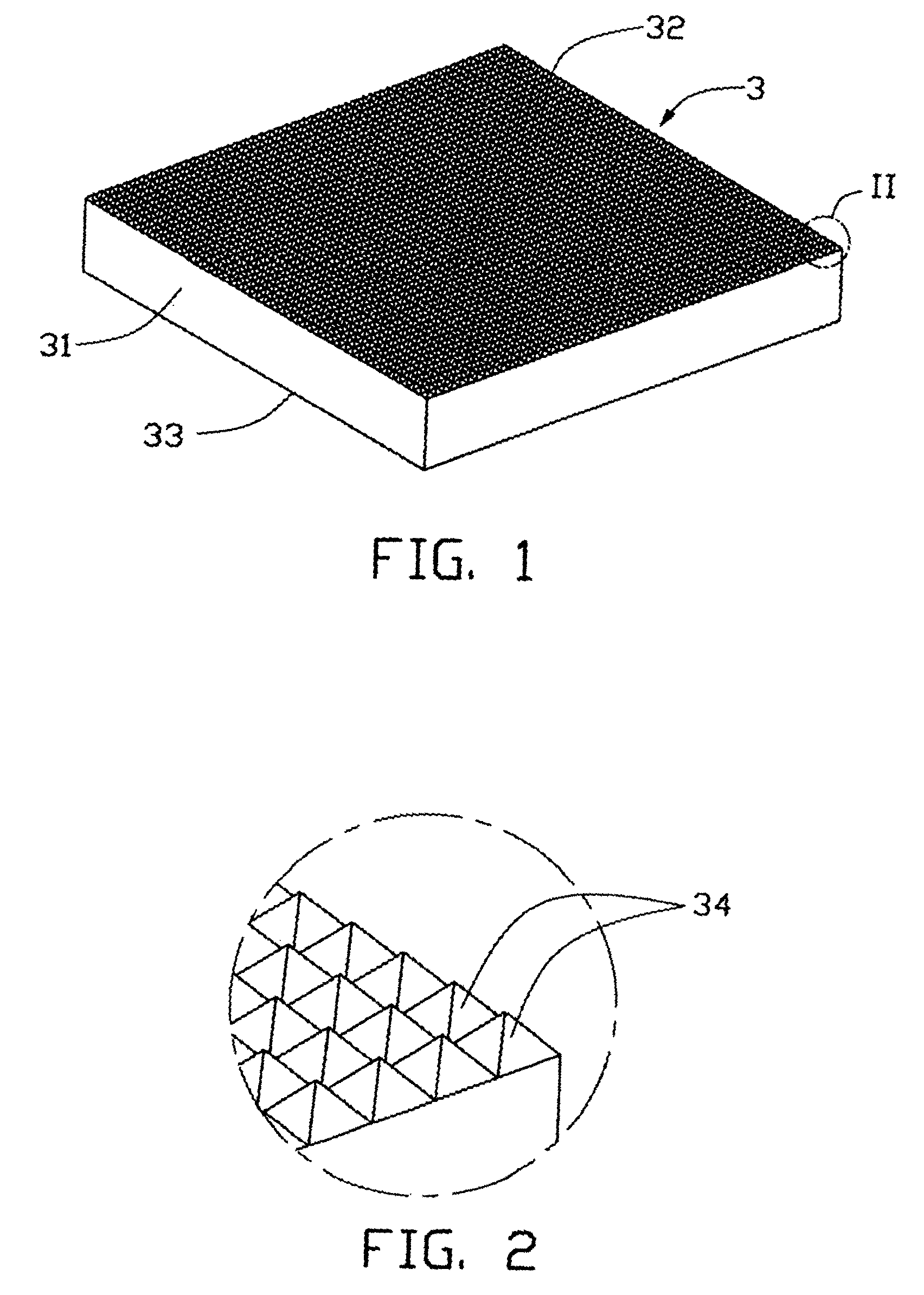

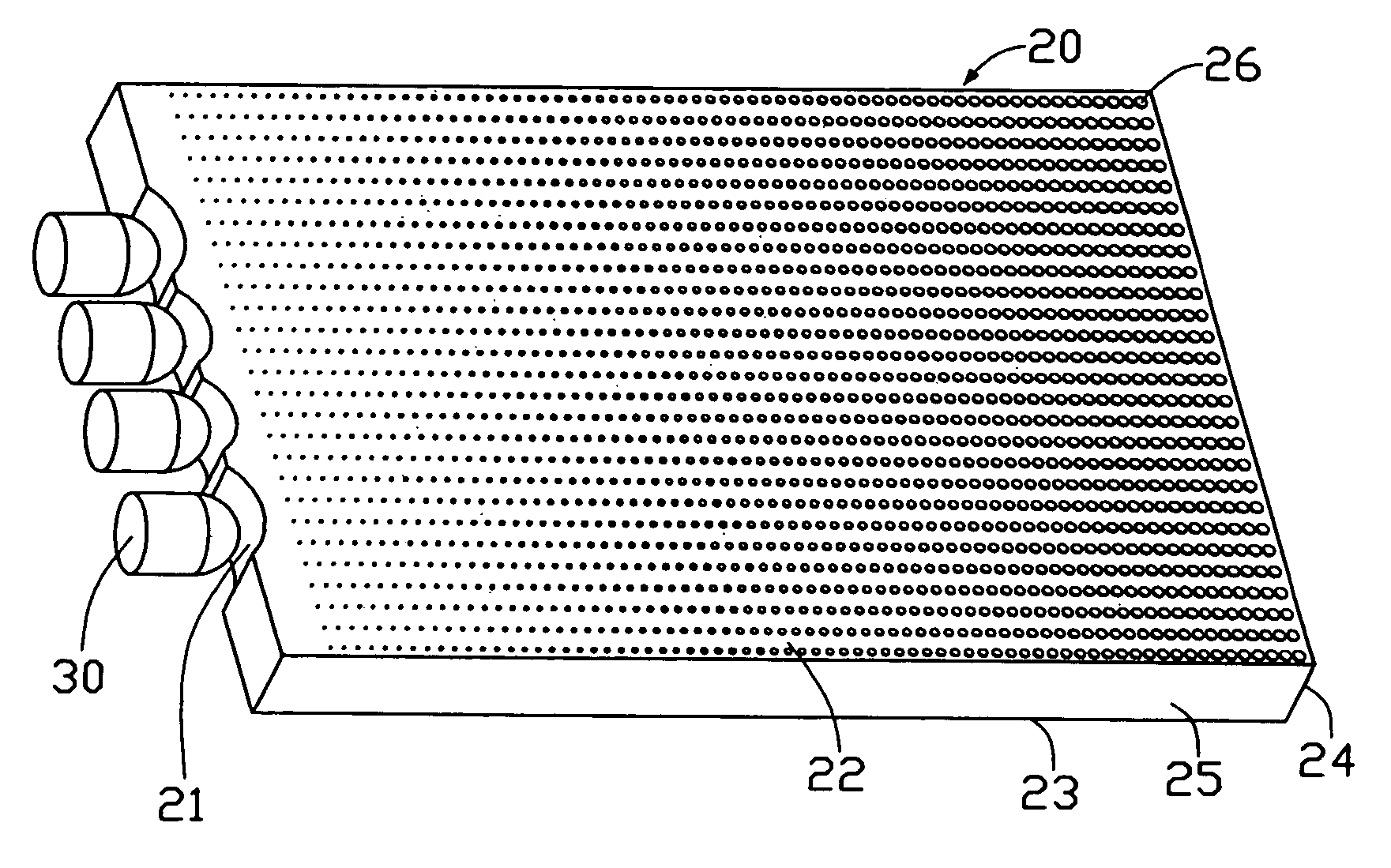

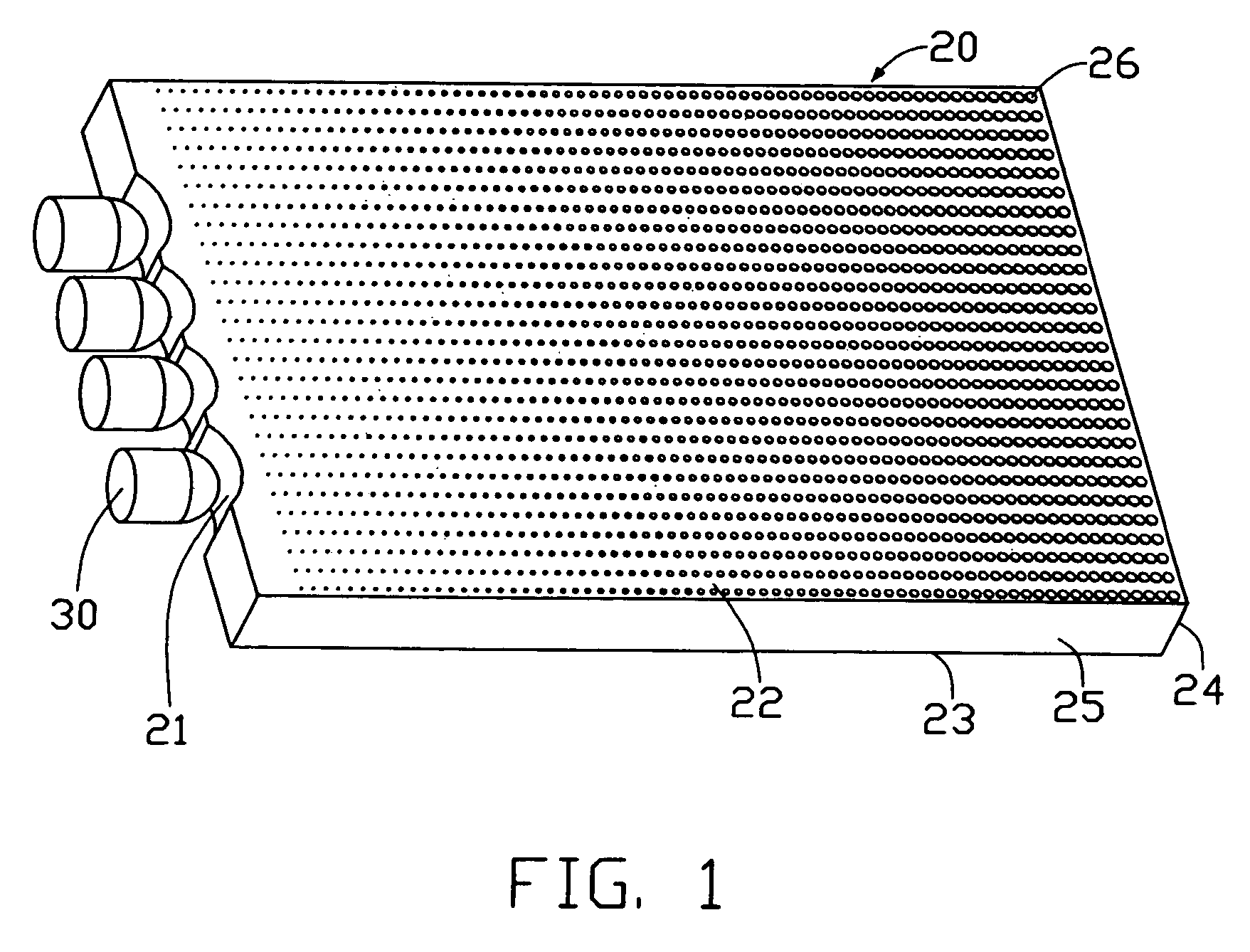

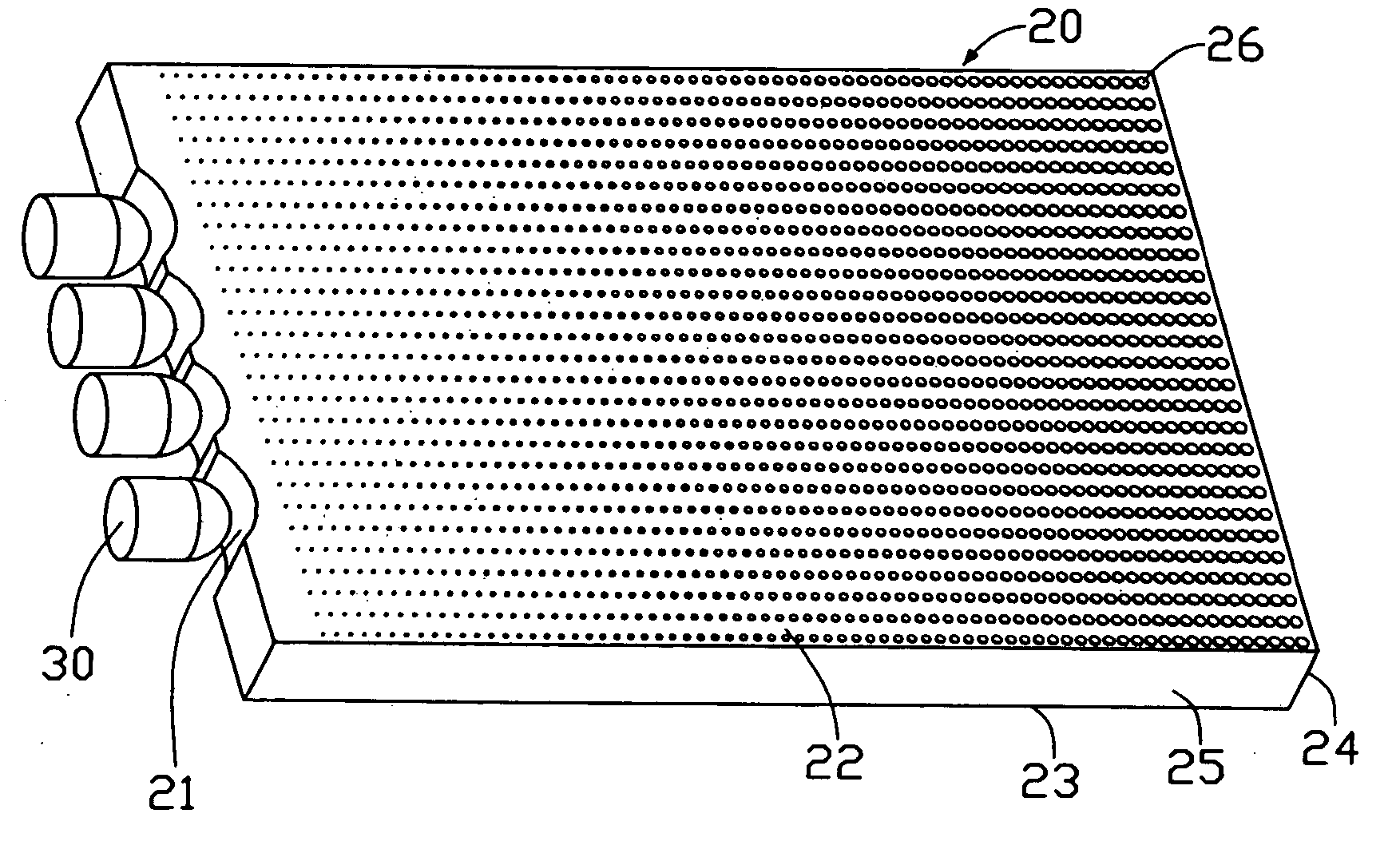

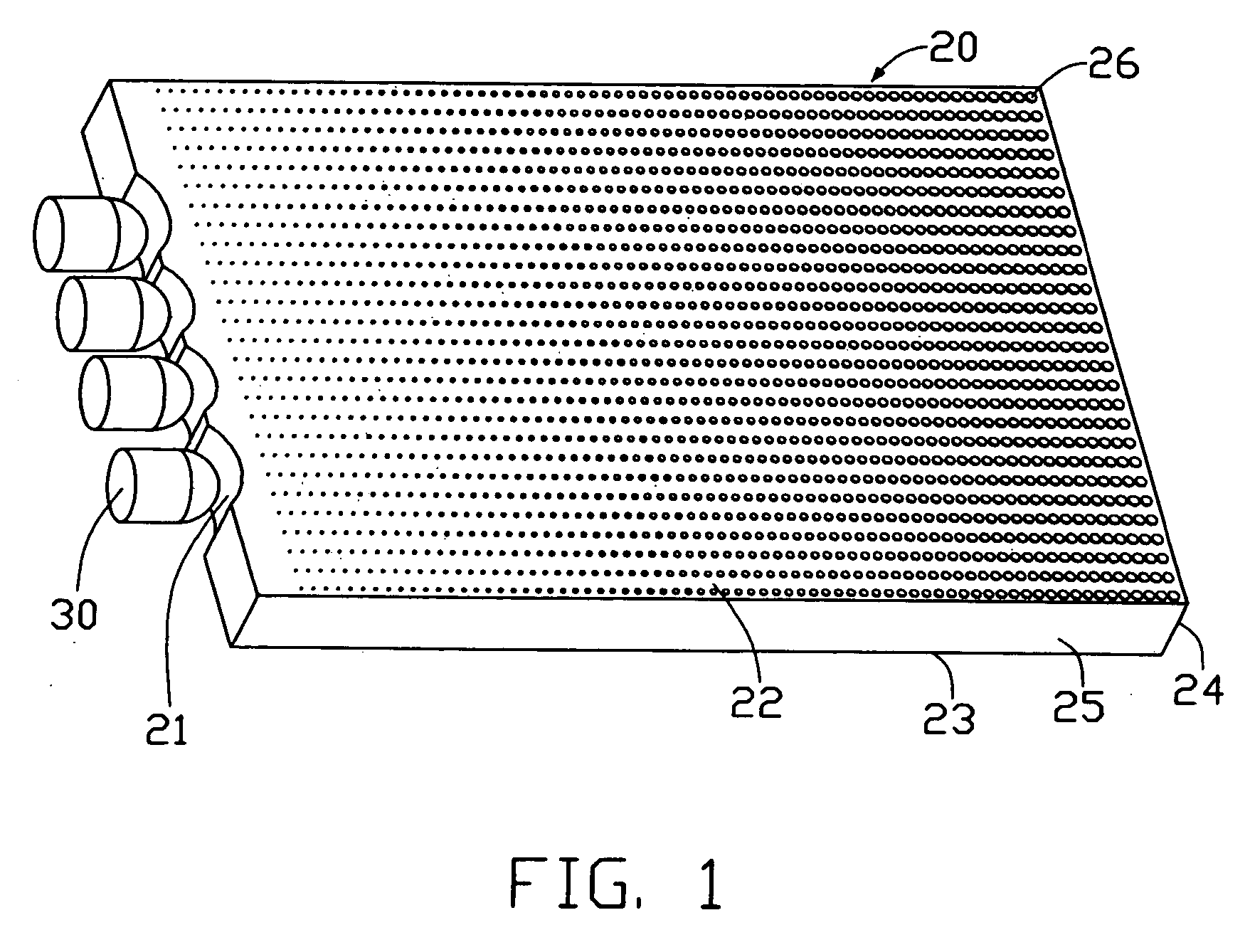

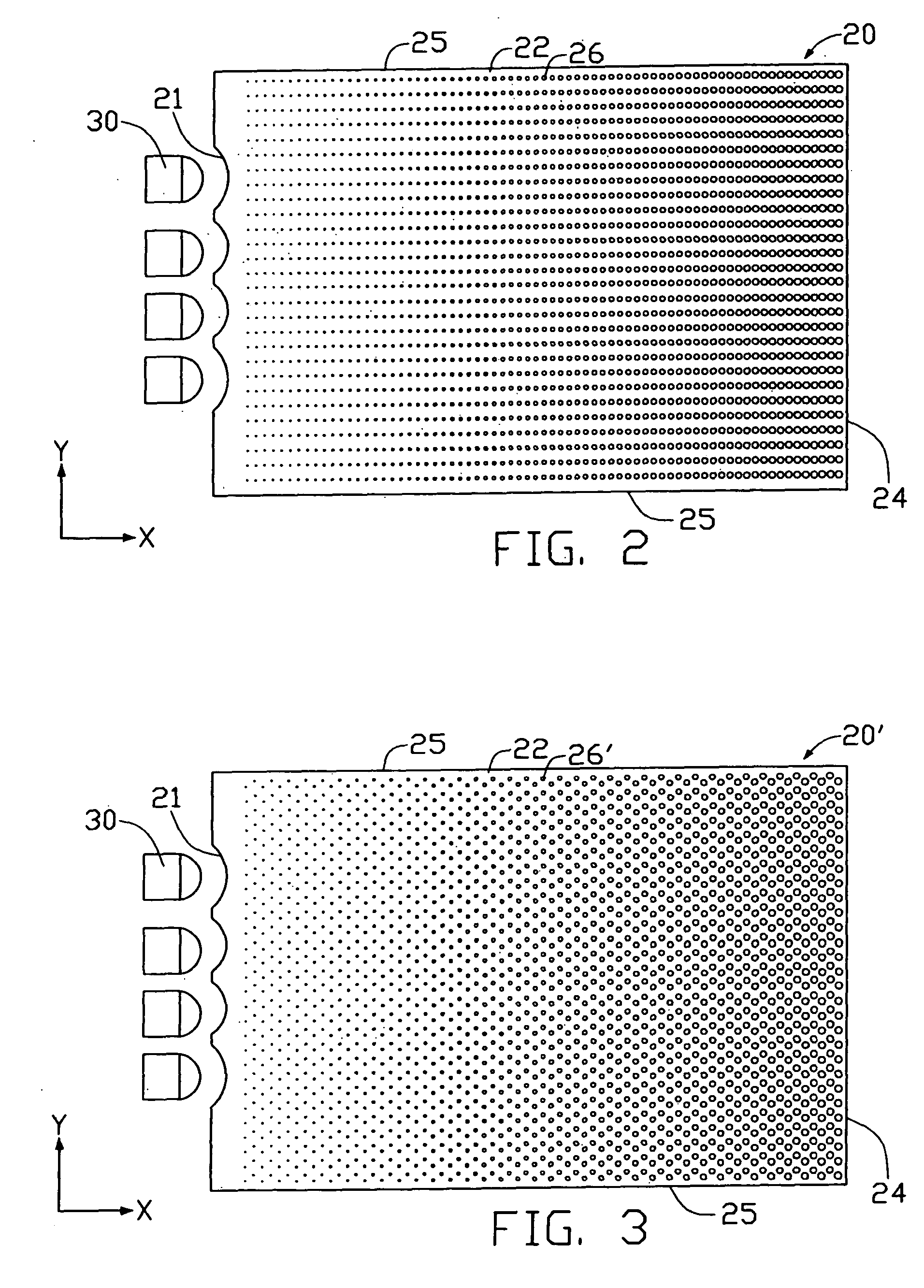

Light guide plate

InactiveUS6979112B2Improve brightness uniformityMeasurement apparatus componentsMachines/enginesLight guideOptics

A light guide plate (20) includes a light input end (21), a light output face (23) adjacent the light input end, and a back face (22) opposite to the light output face. A plurality of fine dots (26) are formed on the back face arranged in a uniform, rectangular array. The dots in a same column have a same size. The dots in a same row increase in size. A radius r of the dots in each row thereof varies as a function of a column number X of a given dot, in accordance with the formula: r=A+BX+CX2+DX3+EX4+FX5, wherein: the column number X varies in consecutive whole numbers from a value of one for the column nearest the light input end to a maximum value for the column most distal from the light input end; and A, B, C, D, E, and F are constants.

Owner:HON HAI PRECISION IND CO LTD

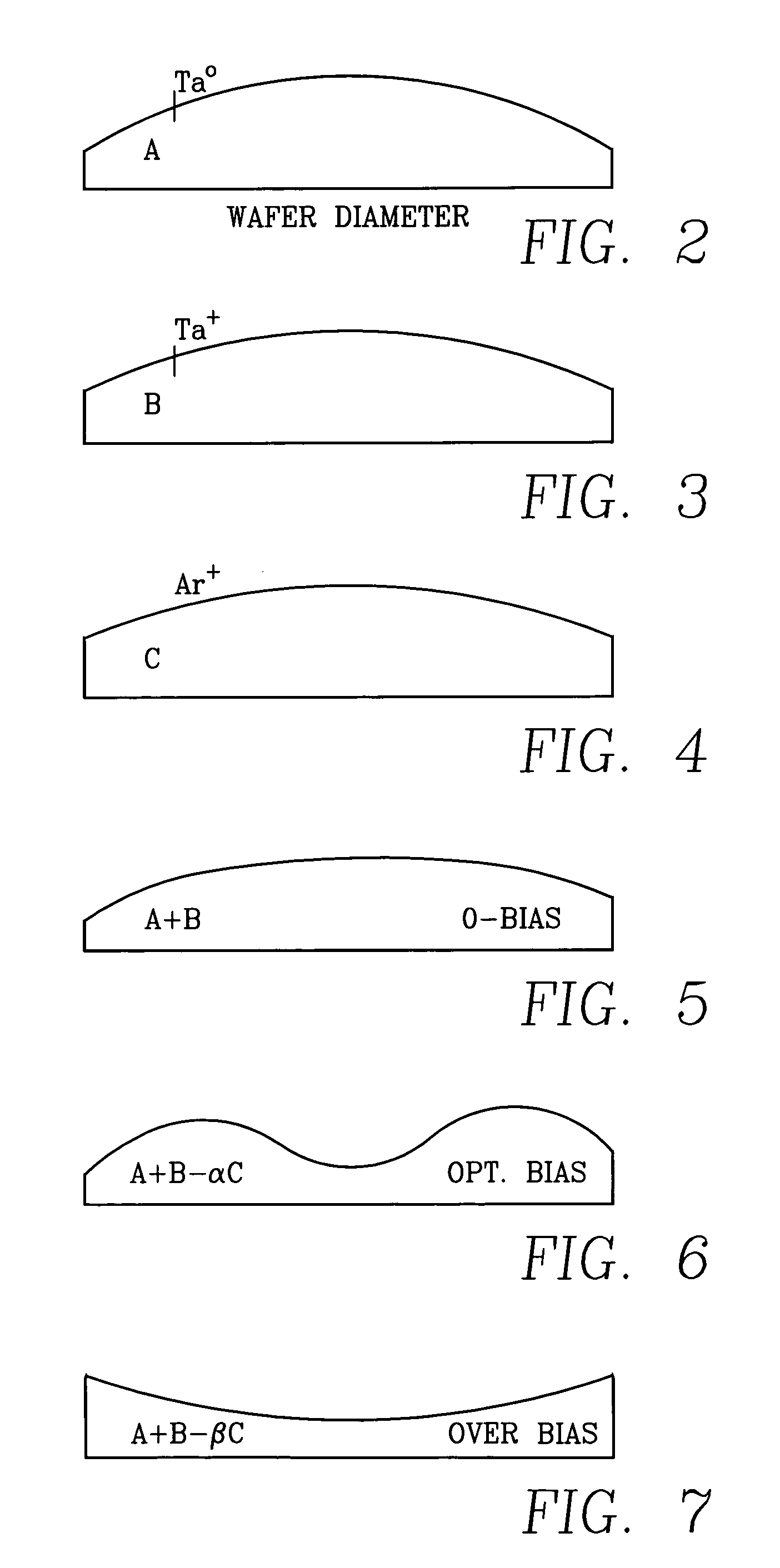

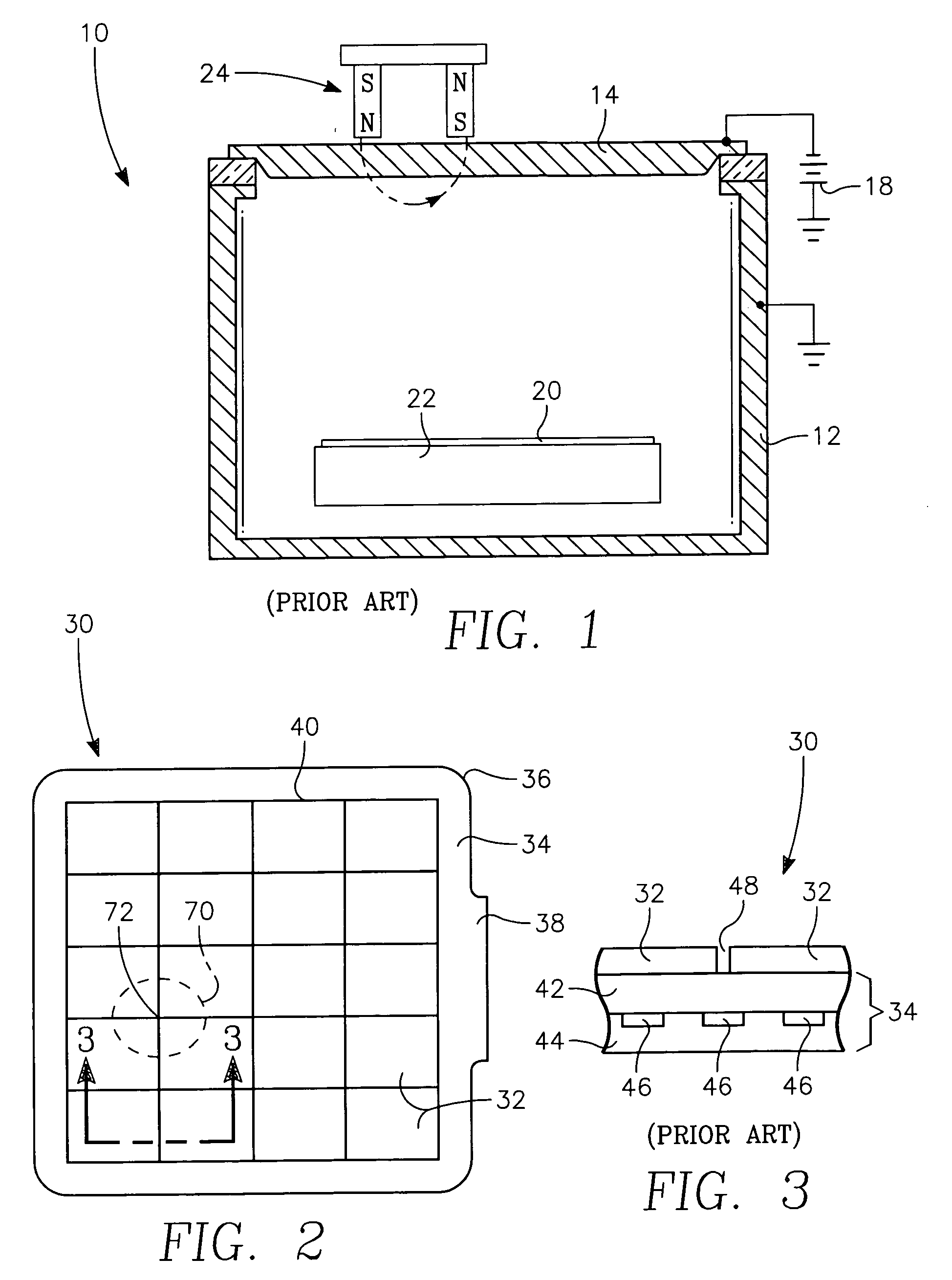

Multi-step process for forming a metal barrier in a sputter reactor

ActiveUS20050263390A1Reducing stray magnetic fieldReduce needCellsElectric discharge tubesEtchingSputter deposition

Owner:APPLIED MATERIALS INC

Porous glass

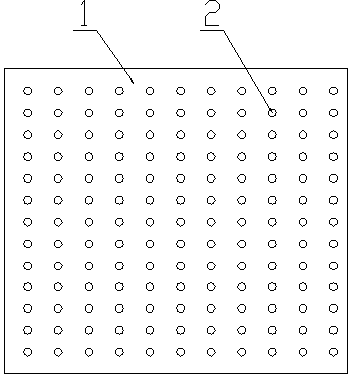

InactiveCN104344202AImprove breathabilityImprove sound absorptionSheets/panelsFlat glassOptoelectronics

The invention relates to porous glass which comprises a glass body (1), wherein a plurality of air holes (2) are formed in the glass body (1), are distributed in a rectangular array manner, penetrate through the whole glass body (1) in the thickness direction and are round, square or hexagonal. According to the porous glass, the plurality of air holes are formed in the plate glass of the porous glass in the rectangular array manner, so that the porous glass has good air permeability and sound absorption performance.

Owner:张玉芬

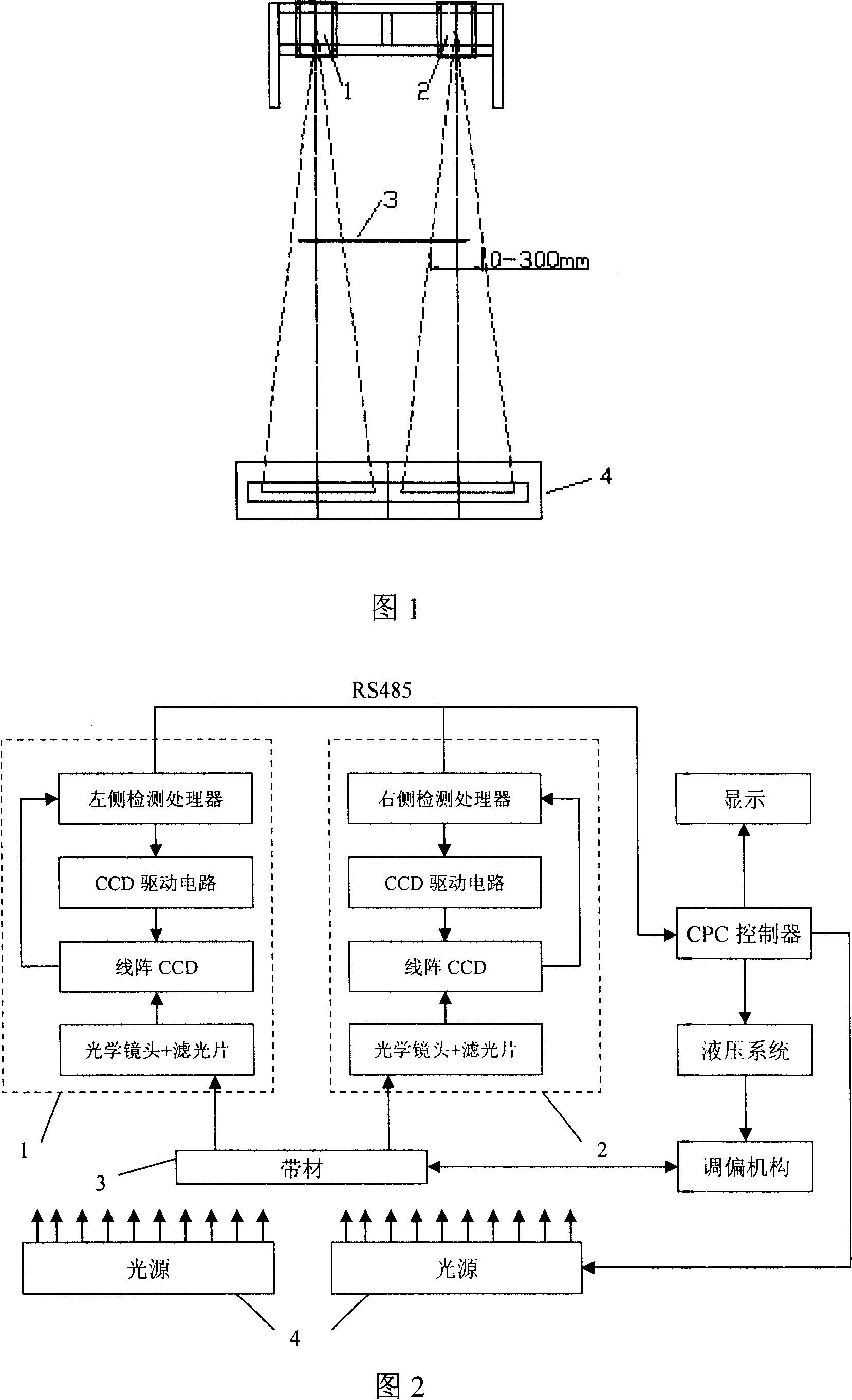

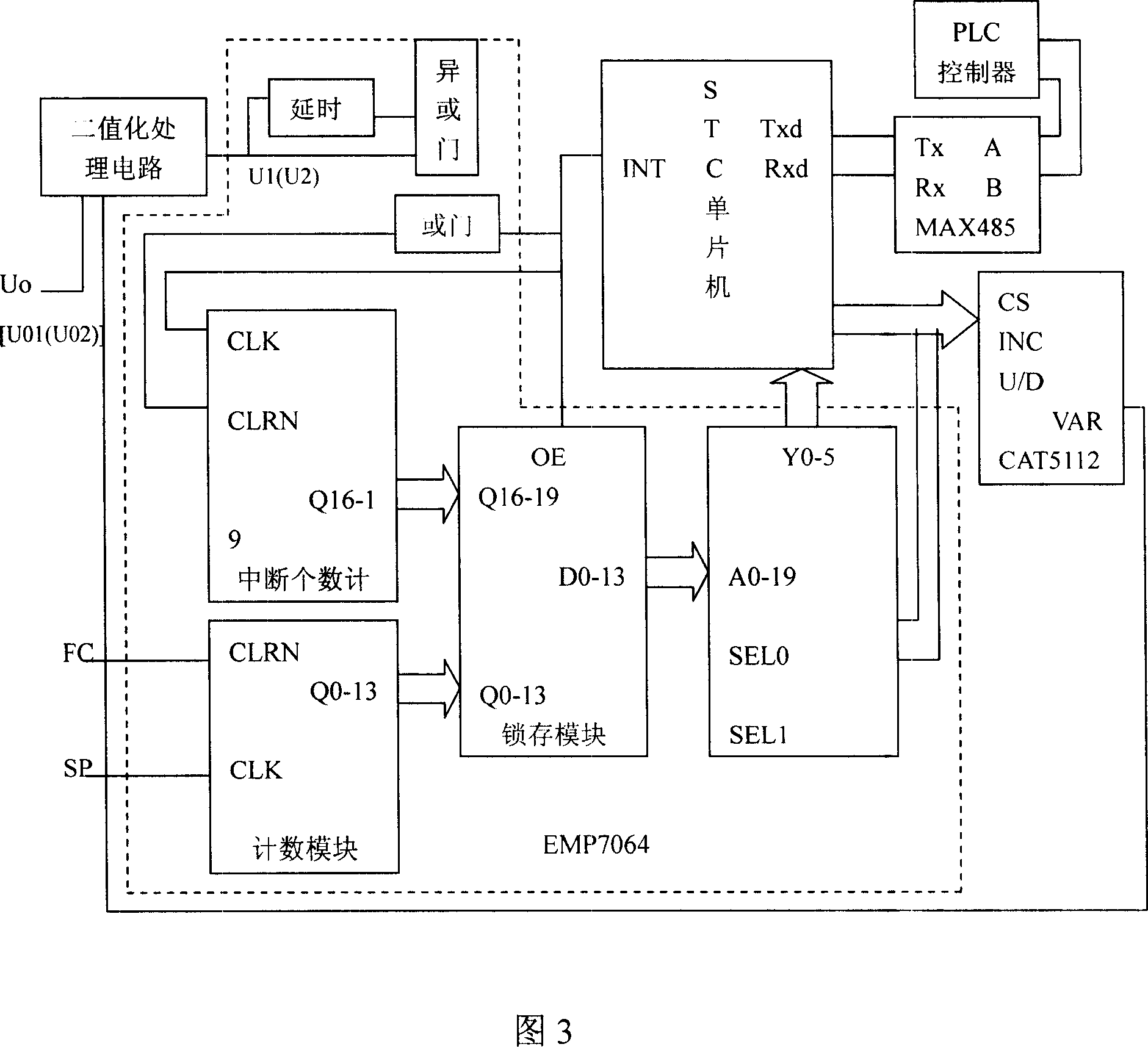

CCD based strip automatic centering CPC detecting system and detecting method

InactiveCN101013023AImprove detection accuracyWide detection rangeGuiding/positioning/aligning arrangementsUsing optical meansDriver circuitLength wave

The invention discloses a CCD-strip-based automatic aiming CPC photoelectric detection system, including the detection sensor and the light source, and the light source using rectangular array of 700~900nm wavelength infrared light-emitting diodes, and the detection sensor including optical lens, narrowband filters, linear array CCD and laser alignment, also including CCD driver circuit and detection processor. The detection method of the system uses the fixed installation positive exposure, and the light of the light source through the both sides of the detected strip, and respectively received by the left and right detection sensors, and when the detected strip moving left and right, the photosensitive pixels of the linear array CCD generates the strip edge location-related changes, and outputs the corresponding strip edge location signal, and respectively sends into the left and right detection processor and CPC controller for subtraction calculation, to determine whether the location of the strip departs from the center line of the machine, and the departure distance. The system has the features of high accuracy detection, board detection range, fast response speed, good stability, and anti-disturbance ability.

Owner:XIAN UNIV OF TECH

Light guide plate

A light guide plate (20) includes a light input end (21), a light output face (23) adjacent the light input end, and a back face (22) opposite to the light output face. A plurality of fine dots (26) are formed on the back face arranged in a uniform, rectangular array. The dots in a same column have a same size. The dots in a same row increase in size. A radius r of the dots in each row thereof varies as a function of a column number X of a given dot, in accordance with the formula: r=A+BX+CX<2>+DX<3>+EX<4>+FX<5>, wherein: the column number X varies in consecutive whole numbers from a value of one for the column nearest the light input end to a maximum value for the column most distal from the light input end; and A, B, C, D, E, and F are constants.

Owner:HON HAI PRECISION IND CO LTD

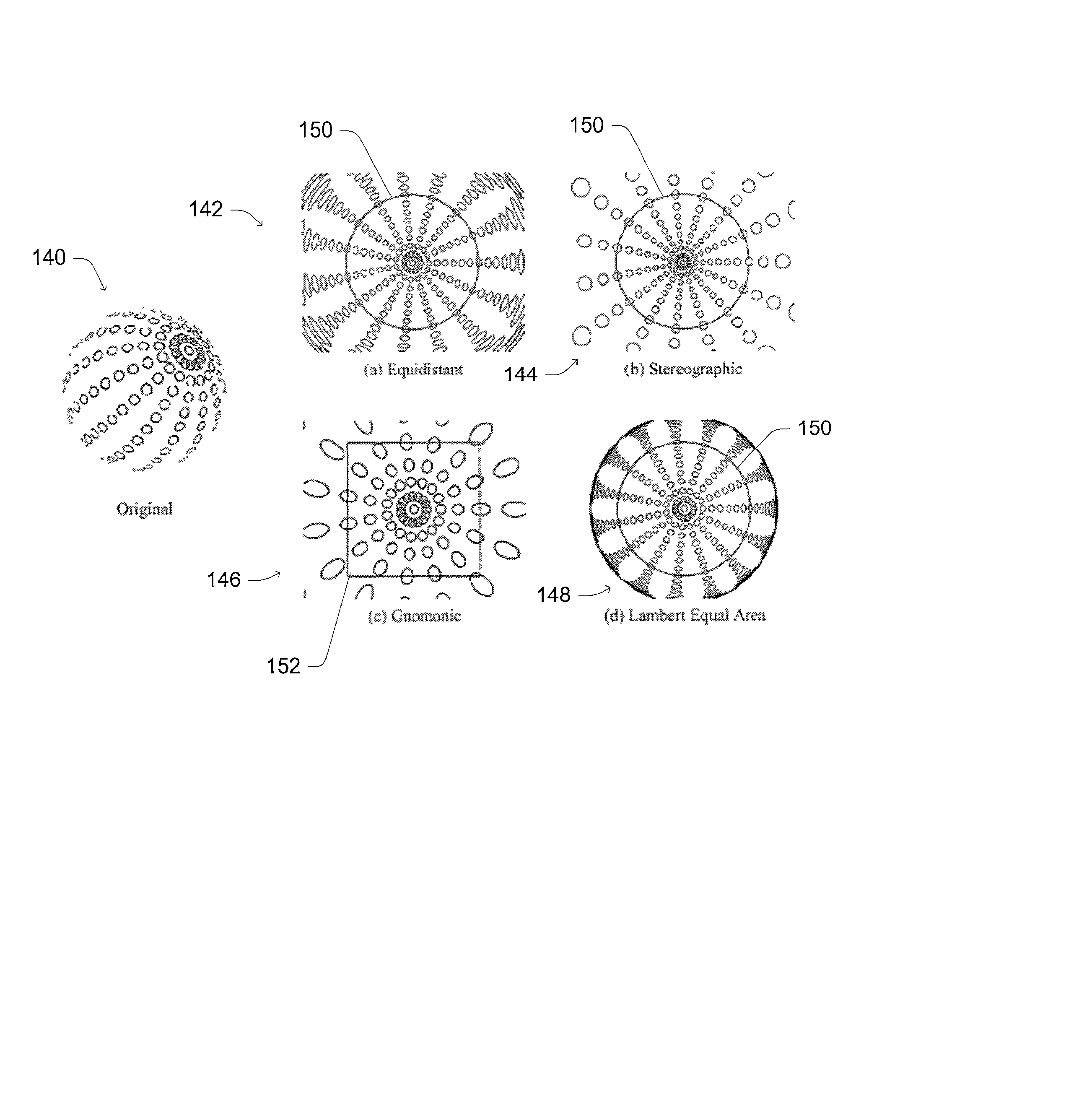

Sampling-efficient mapping of images

InactiveUS20020126129A1Reduce memory/bandwidth requirementDrawing from basic elementsGeometric image transformationGraphicsArray data structure

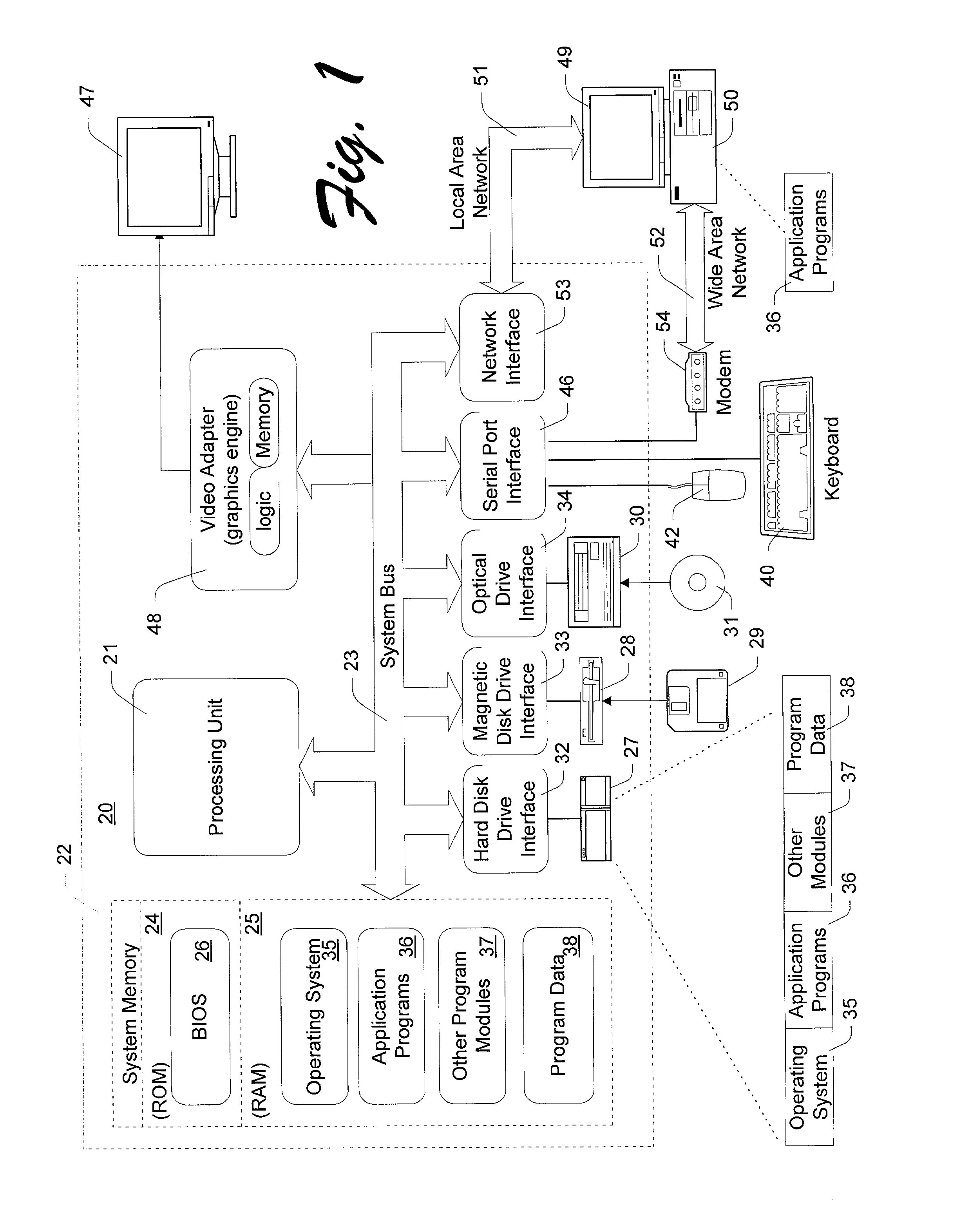

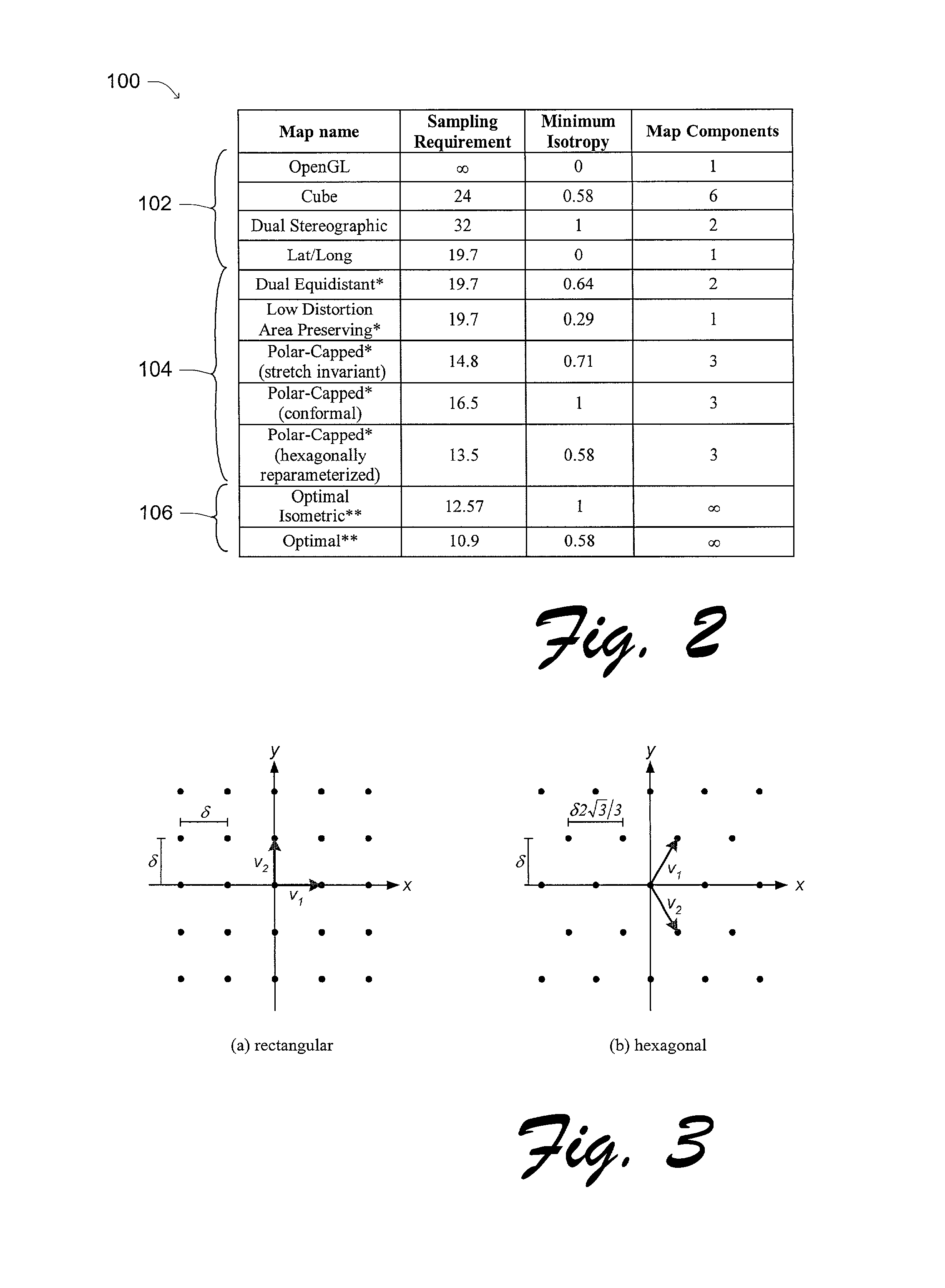

Spherical-like textures are useful to simulate reflections and to generate arbitrary views from a point. For addressing simplicity, graphics systems typically require rectangular arrays of texture samples but an infinite variety of functions can be used to map these samples to a sphere-like object. A new metric is presented for measuring how well various maps use a given number of samples to provide the greatest worst-case frequency content of the image everywhere over the sphere. Using this metric and other important local properties, a comparison is presented of maps used previously in computer graphics as well as other mapping techniques borrowed from cartography. Based on these analysis several novel mapping techniques are presented that are fairly simple to implement and significantly more efficient in terms of the amount of processing and data required, and the quality of the resulting images. The novel metric and mapping techniques can be employed to analyze or otherwise improve the sampling efficiency of mapping textures onto any three-dimensional surface.

Owner:MICROSOFT TECH LICENSING LLC

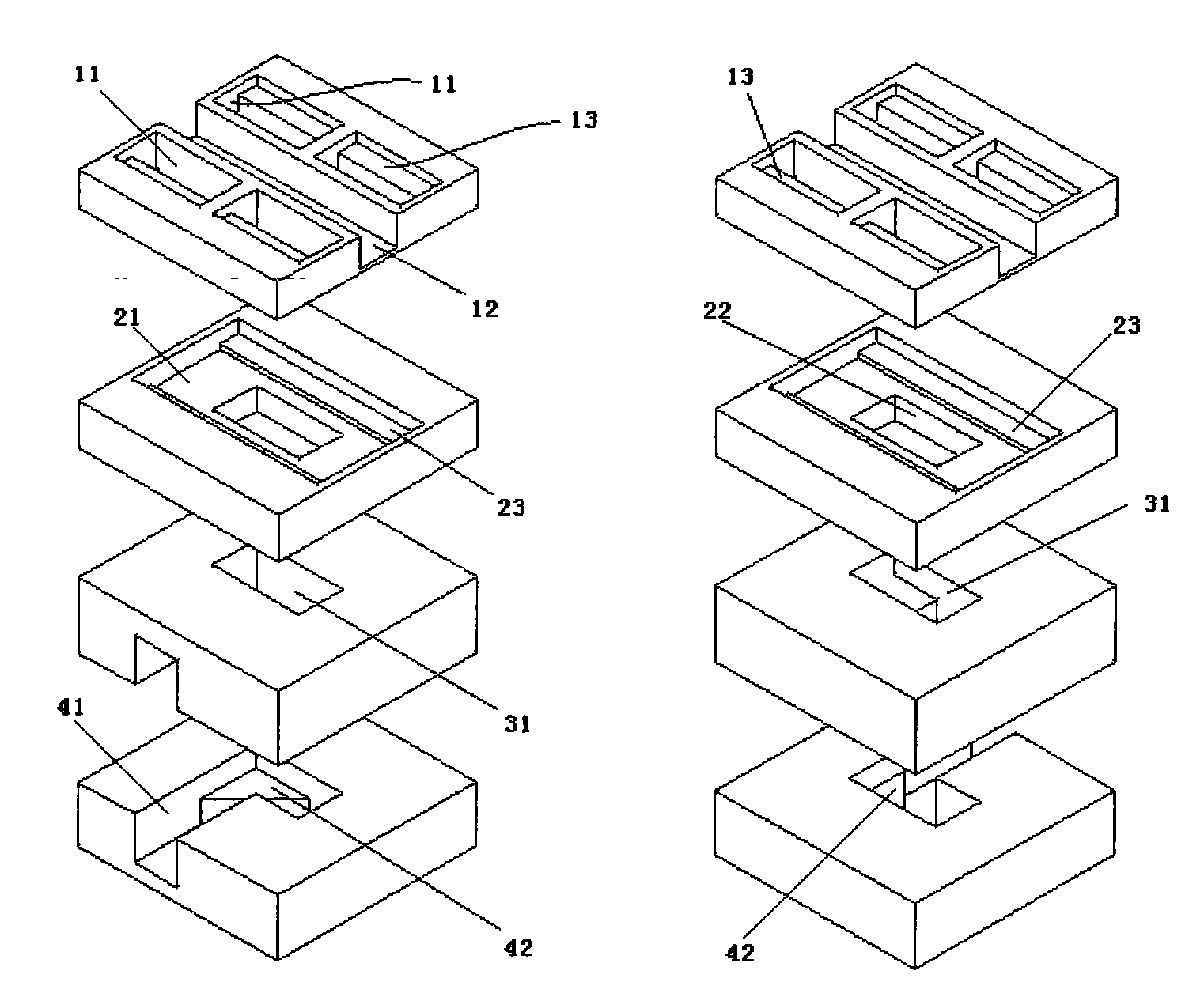

Thermal enhanced package for block mold assembly

InactiveUS20070065984A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical performance

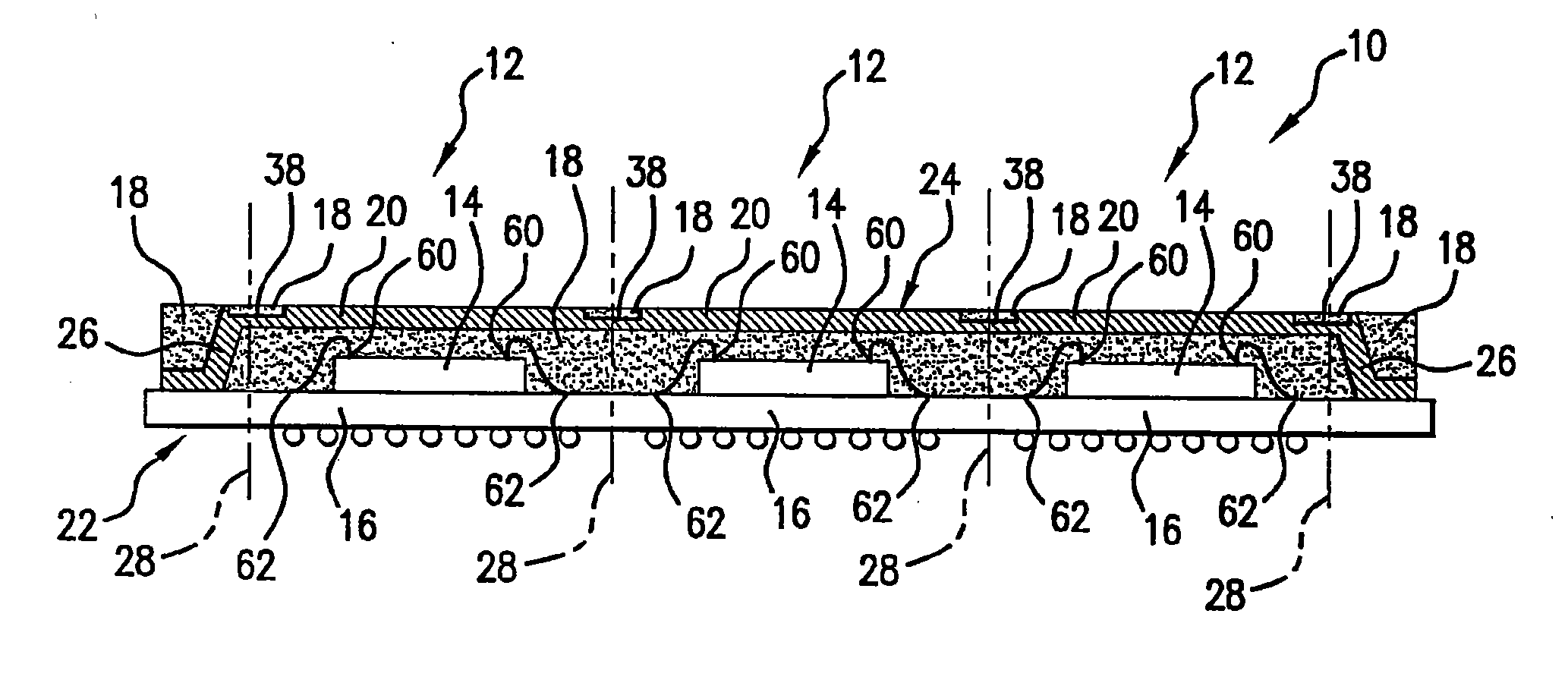

A heat spreader (20) is added to a package to enhance thermal and advantageously electrical performance. In manufacture, a heat spreader precursor (24) is advantageously placed over a group of dies and secured after bonding (e.g., wire or tape bonding or flip-chip bonding) and before matrix / block mold. For example, a package strip (10) may consist of a row (linear array) of groups of die attach areas (e.g. in a rectangular array of four). The heat spreader precursor (20) may accommodate one such group or multiple groups along the package strip (10). The package strip (10) may then be singulated to form the individual packages. Each singulated package includes a die (14), its associated substrate 16 (e.g., either a lead frame or interposer type substrate) and a portion of the heat spreader precursor (24) as a heat spreader (20).

Owner:LAU DANIEL K +1

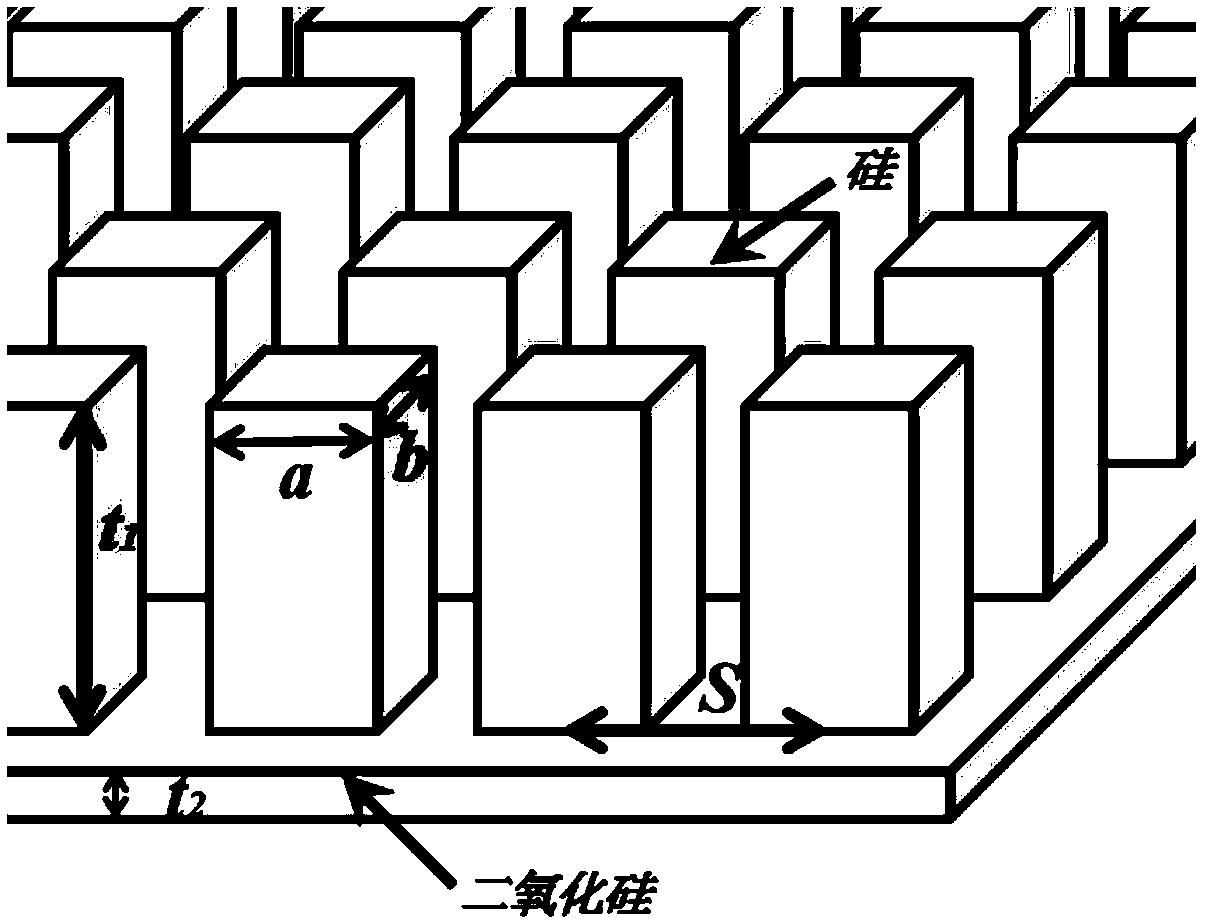

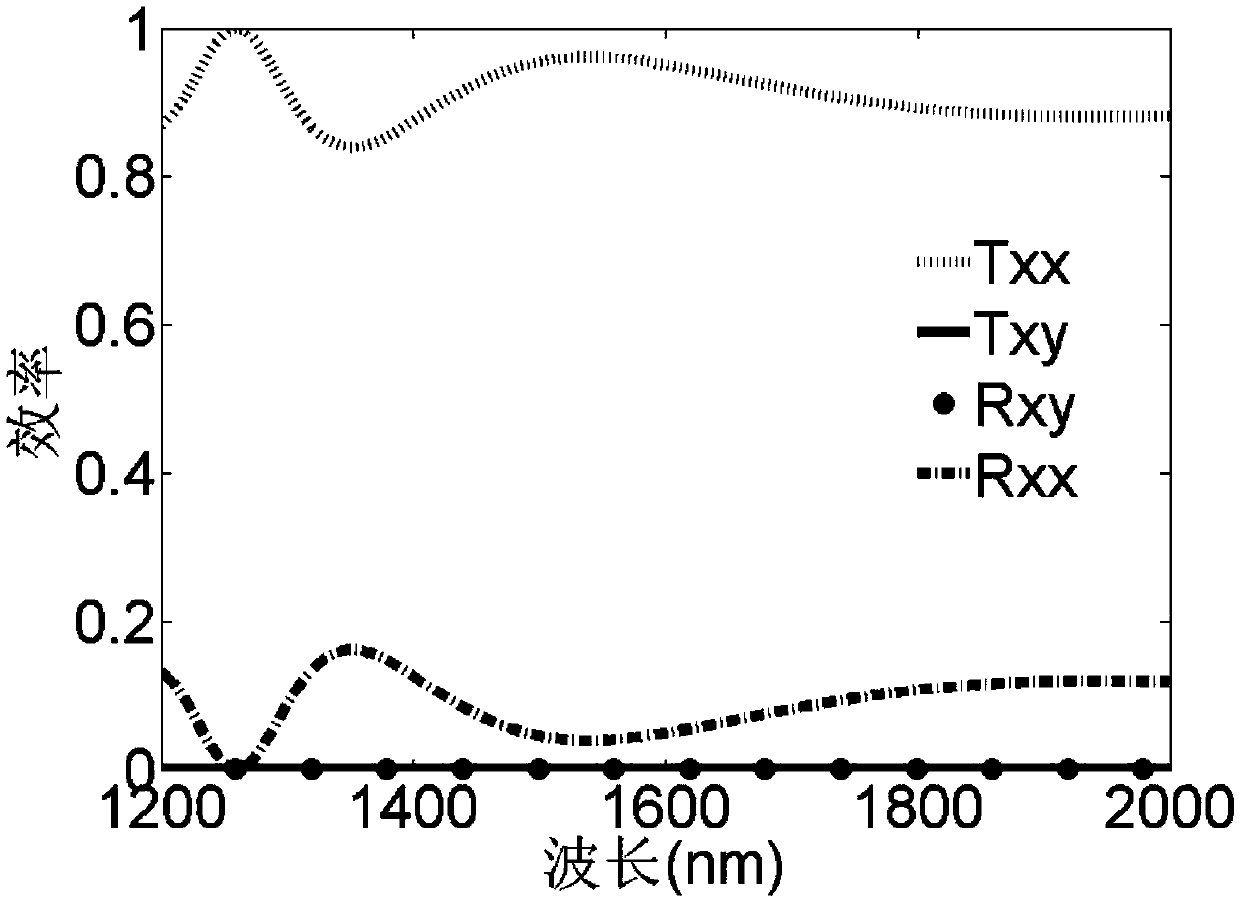

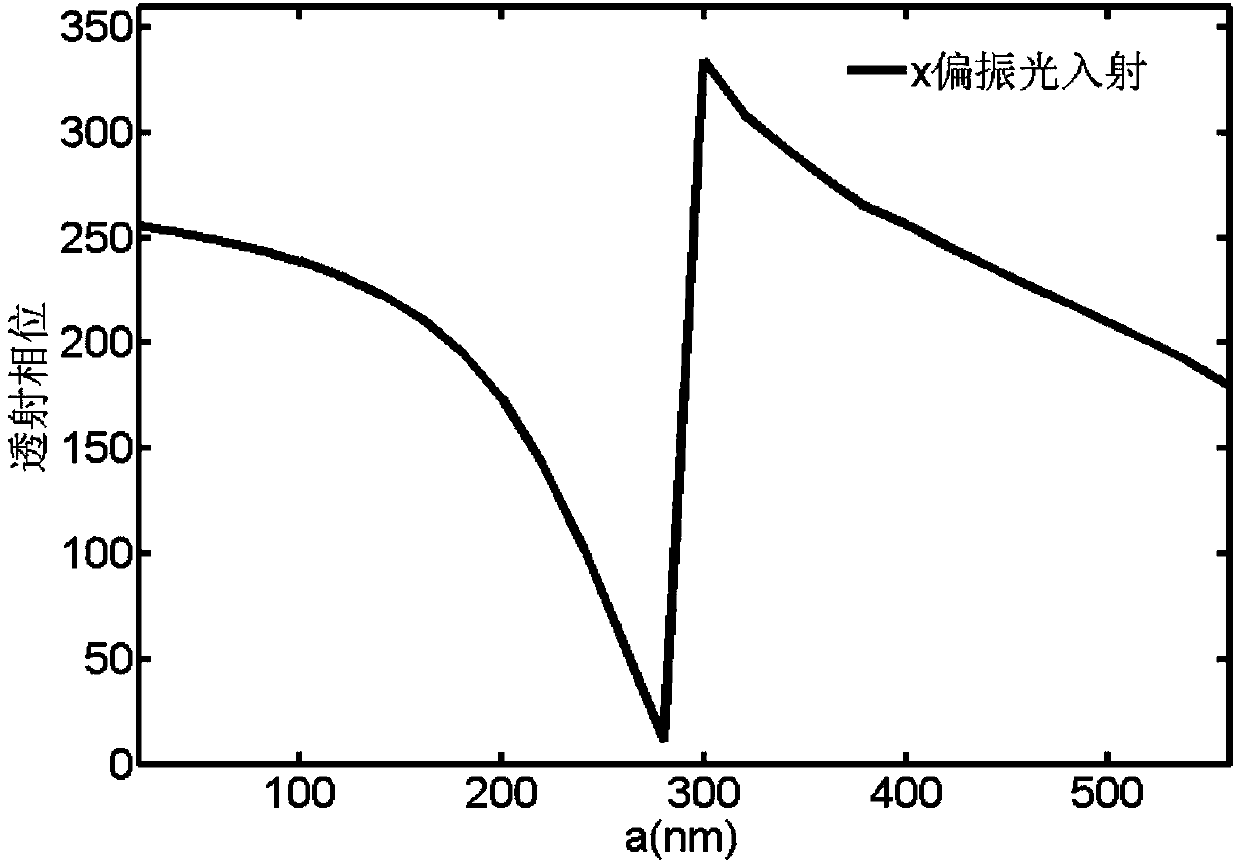

Difunctional device integrating wave plate based on medium meta-surface and optical device

The invention discloses a wave plate based on a medium meta-surface, a beam deflector and a difunctional device integrating the wave plate and a focusing lens. The devices work in a communication waveband, silicon is adopted as a dielectric material, and a substrate is made from silicon dioxide. The devices are characterized in that the brick shape of the silicon material serves as the design ofa unit structure, and a plurality of brick-shaped structures conforming to required phase gradient are arranged according to two-dimensional crystal lattice periodicity to form a rectangular array; the thickness of silicon nano-bricks of the unit structures with medium meta-surfaces is 0.9 microns. The transmitted phase difference of an x-line deflection light component and a y-line deflection light component of incident light is controlled by adjusting the length and width of the unit structures while the deflector or the focusing lens is achieved before phase wave control, and accordingly functions of the wave plate are achieved. Compared with existing devices, the devices are simple in structure, and the deflection efficiency is improved to 80%. Compared with existing wave plates and optical devices which are used in a stacked way, processing and manufacturing inconvenience is overcome, and integration and miniaturization of the optical devices are facilitated.

Owner:DONGGUAN UNIV OF TECH

Light guide plate for liquid crystal display

A light guide plate (3) includes a parallelepiped block. The block includes an input surface (31) for receiving light beams irradiated from a light source; two side surfaces perpendicularly adjoining the incident surface; an output surface (32) perpendicularly adjoining the incident surface and the side surfaces; and a bottom surface (33) opposing to the output surface. An array of prisms (34) is integrally formed on the output surface. Each prism is shaped as a square pyramid. All the prisms have a same size and are arranged contiguously with each other. Alternatively, the light guide plate may be a wedge-shaped block (3'). A rectangular array of prisms (34') is integrally formed on an output surface (32') thereof. Each prism is shaped as a square pyramid. The prisms are arranged contiguously with each other, and sizes of the prisms gradually decrease from a thick end to a thin end of the block.

Owner:HON HAI PRECISION IND CO LTD

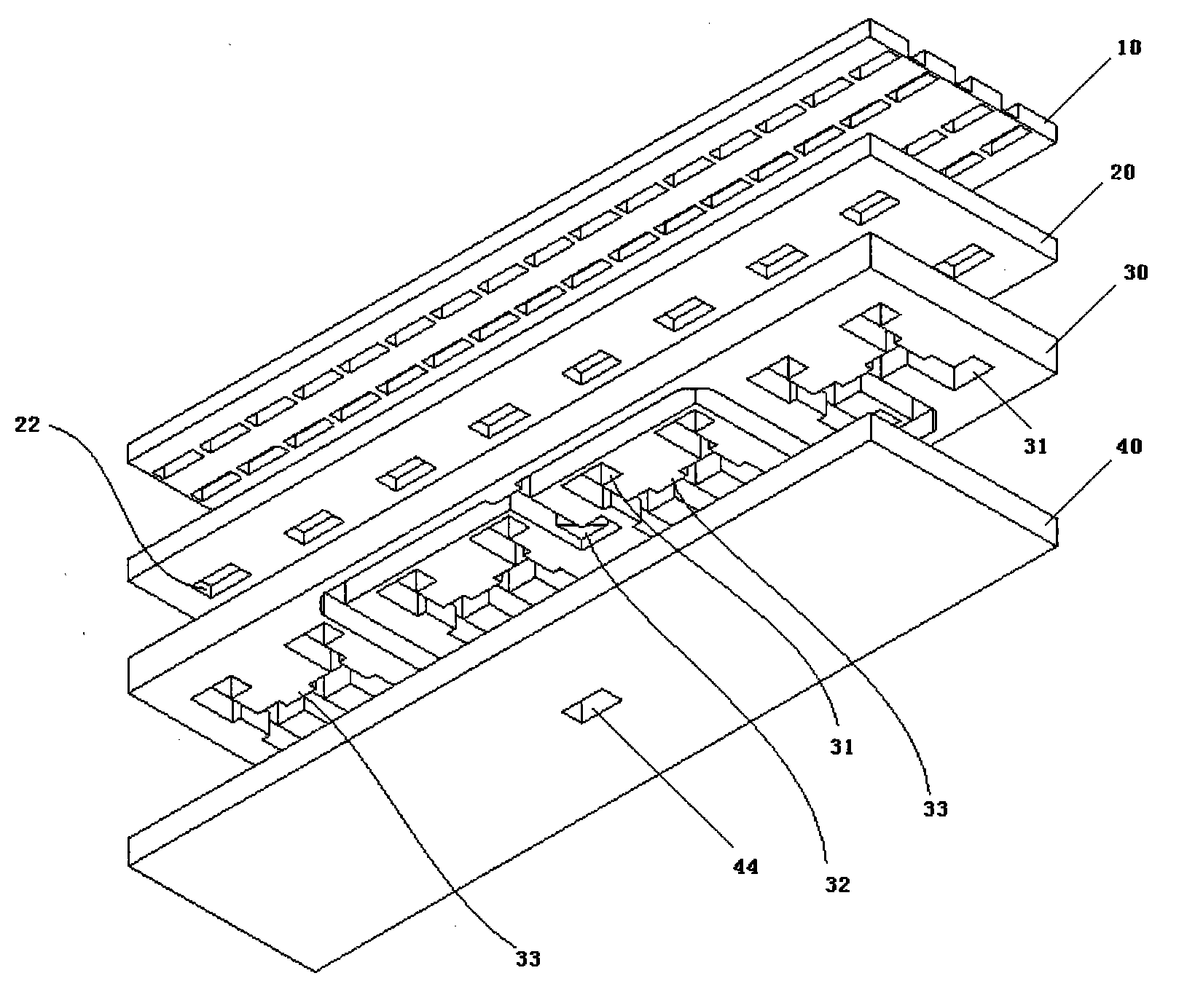

Waveguide flat array antenna

InactiveCN102064380AAvoid complex welding processesExpand standing wave bandwidthWaveguide mouthsAntenna arraysElectricityWaveguide

The invention provides a waveguide flat array antenna, which has the characteristics of broadband and high-efficiency feed. Rectangular open waveguides 11 are used as radiation units; four rectangular open waveguides in one group form a sub array, and are arranged in a 2*2 rectangle and supplied with broadband equal-amplitude in-phase feed by a rectangular cavity 21; and in order to ensure efficient transmission of electromagnetic wave, the joint of each rectangular open waveguide 11 and the rectangular cavity 21 is provided with matched steps 13 and 23. The center of the rectangular cavity 21 is provided with a rectangular window 22 which is connected with a feed network of the next layer. In order to ensure smooth signals, a rectangular matching block 42 is arranged at the feed network corner connected with each rectangular window 22. The feed network consists of multistage parallel E-T so as to ensure that the antenna has enough bandwidth. The transceiving capacity of circularly polarized wave is realized by arranging a circularly polarized cover. Compared with the conventional flat antenna, the waveguide flat array antenna has broader bandwidth and higher feed efficiency.

Owner:李峰

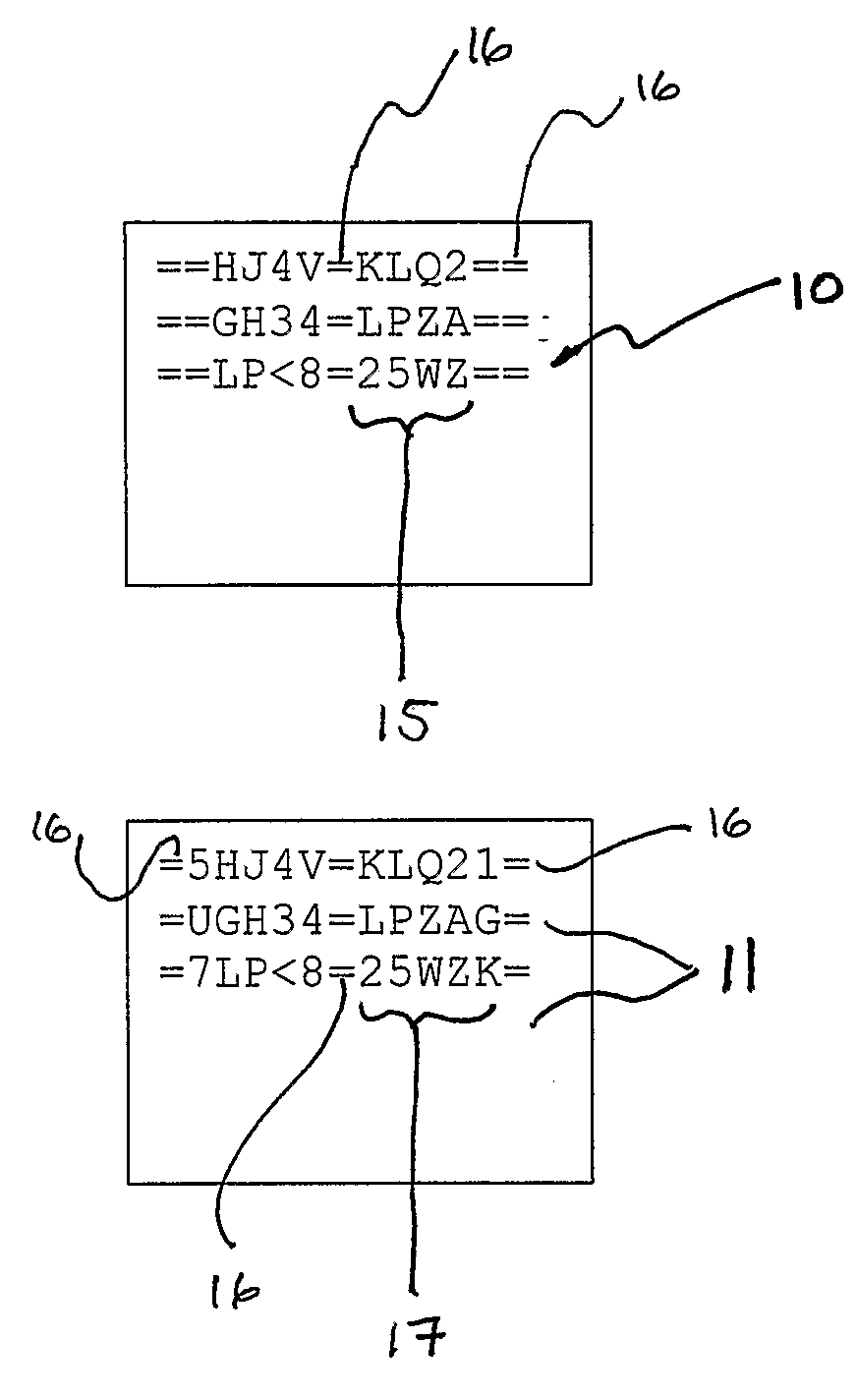

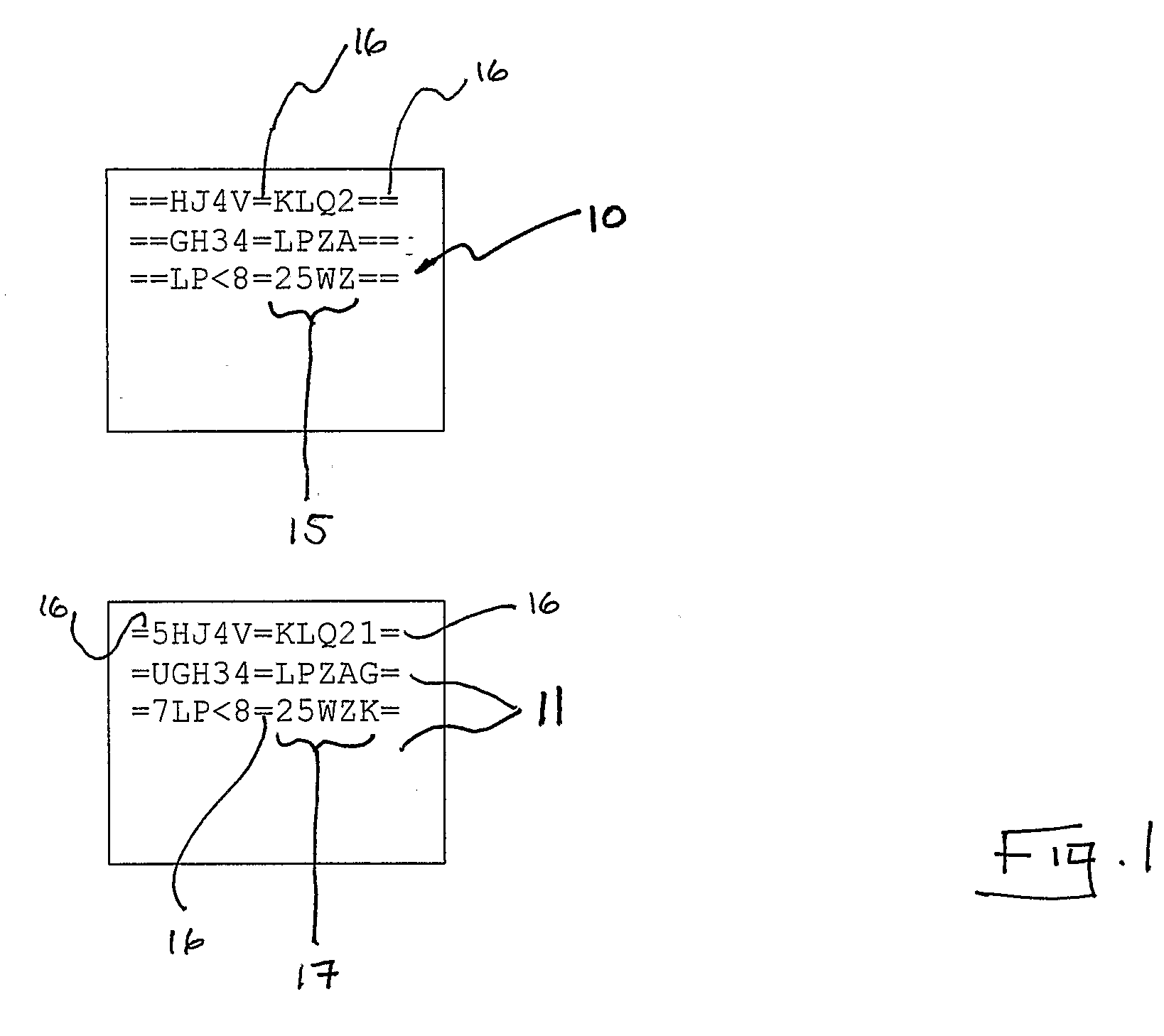

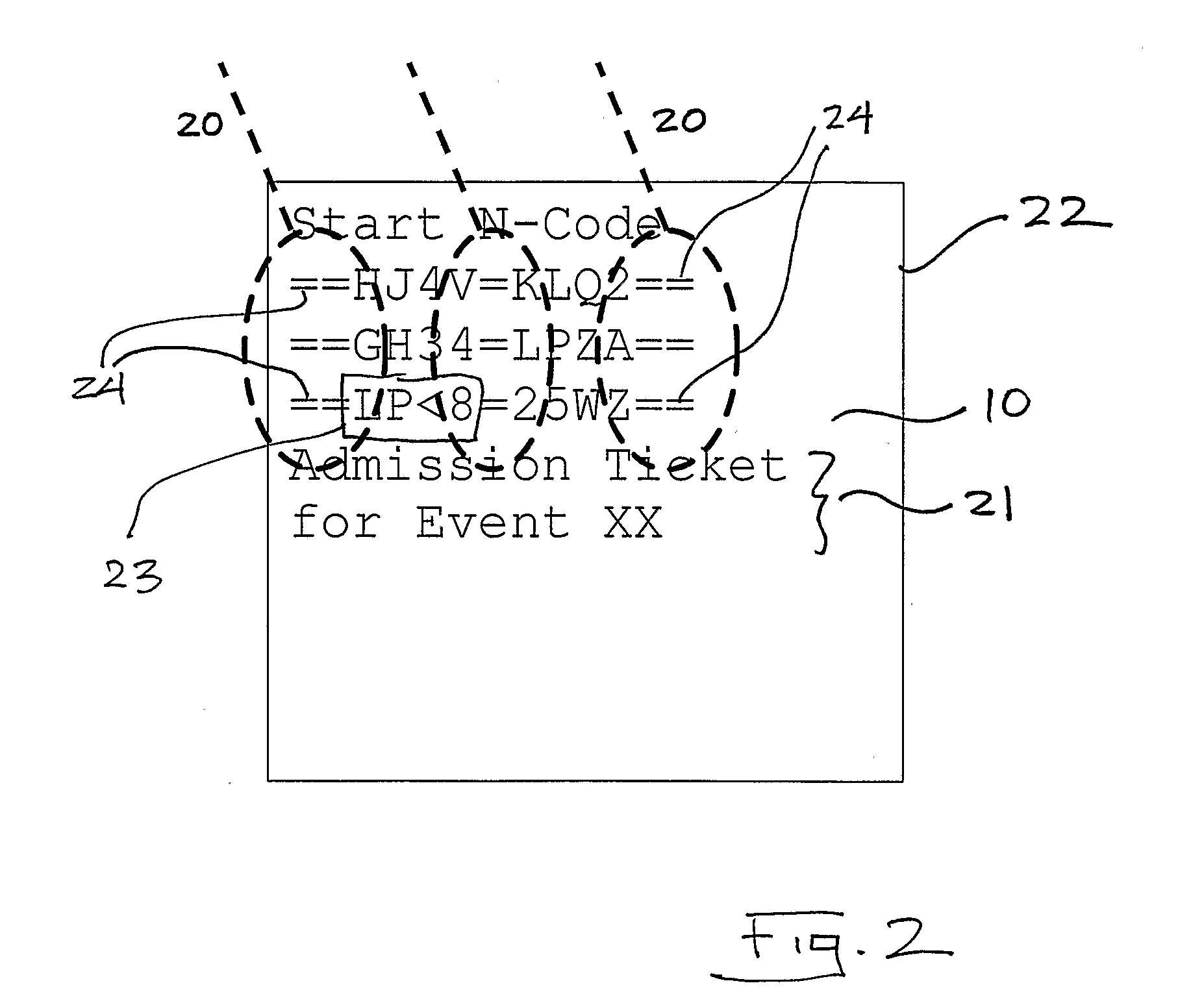

Encoding and Decoding Alphanumeric Data

ActiveUS20080191909A1Accurately arriveTicket-issuing apparatusCharacter printing data arrangement from carrierDigital dataAlgorithm

Information, such as ticket information is encoded, for transmission of the encoded information to a device that can display the encoded information as visible alphanumeric characters. Original information is converted into a binary format then separated into x bit binary words, where x is the same as a maximum number of bits data required by every data character in a pre-determined data character map. The binary words are formed into a sequence of characters using a data character map. Special marker characters are inserted into the sequence. The special characters demarcate the sequence into sets of characters separated by one or more special marker characters. Line feed command characters are also inserted. The encoded information is transmitted to a client device that displays it as a rectangular array of characters bounded by the special marker characters.

Owner:MOBILE TECH HLDG LTD +1

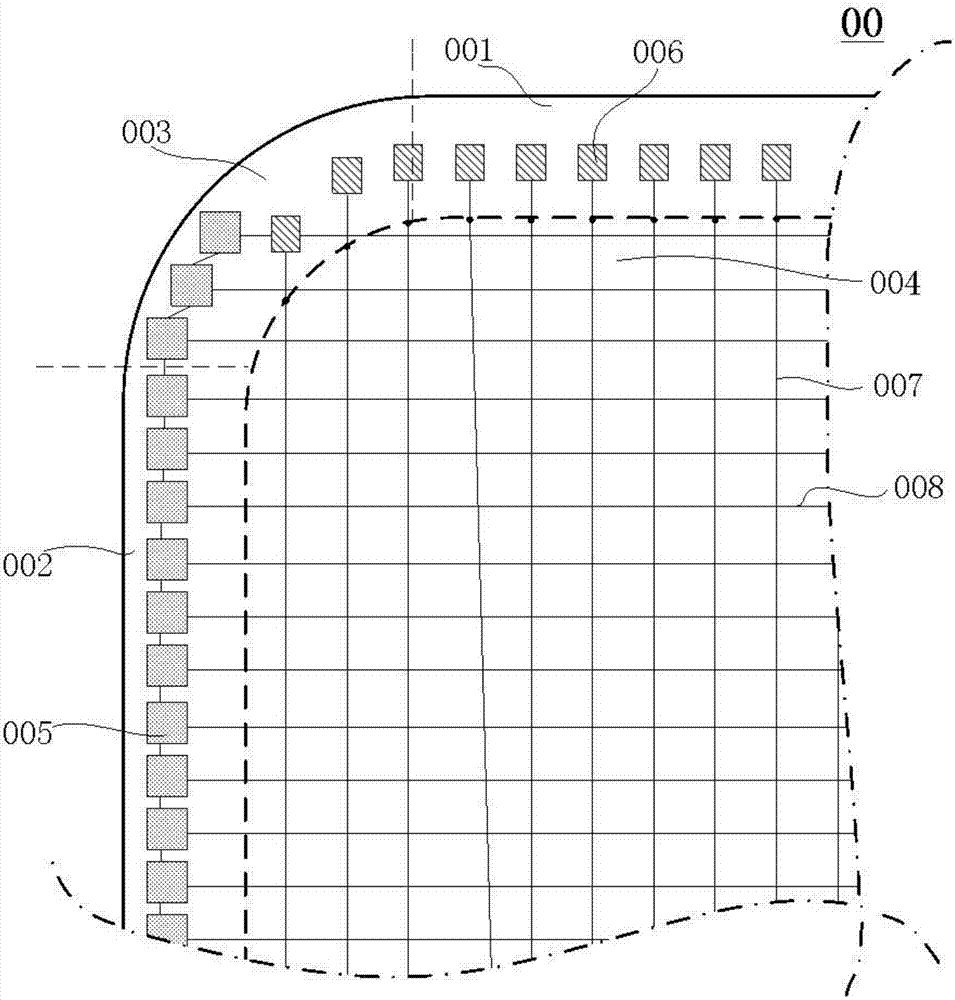

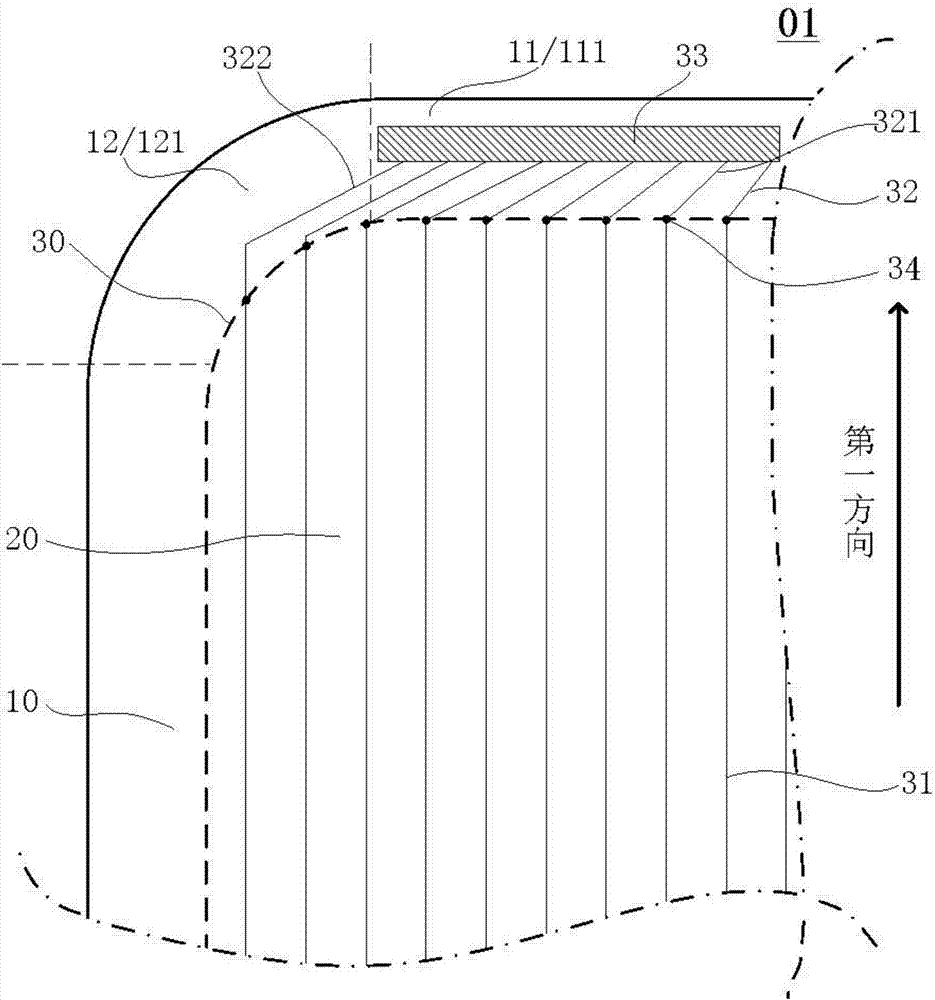

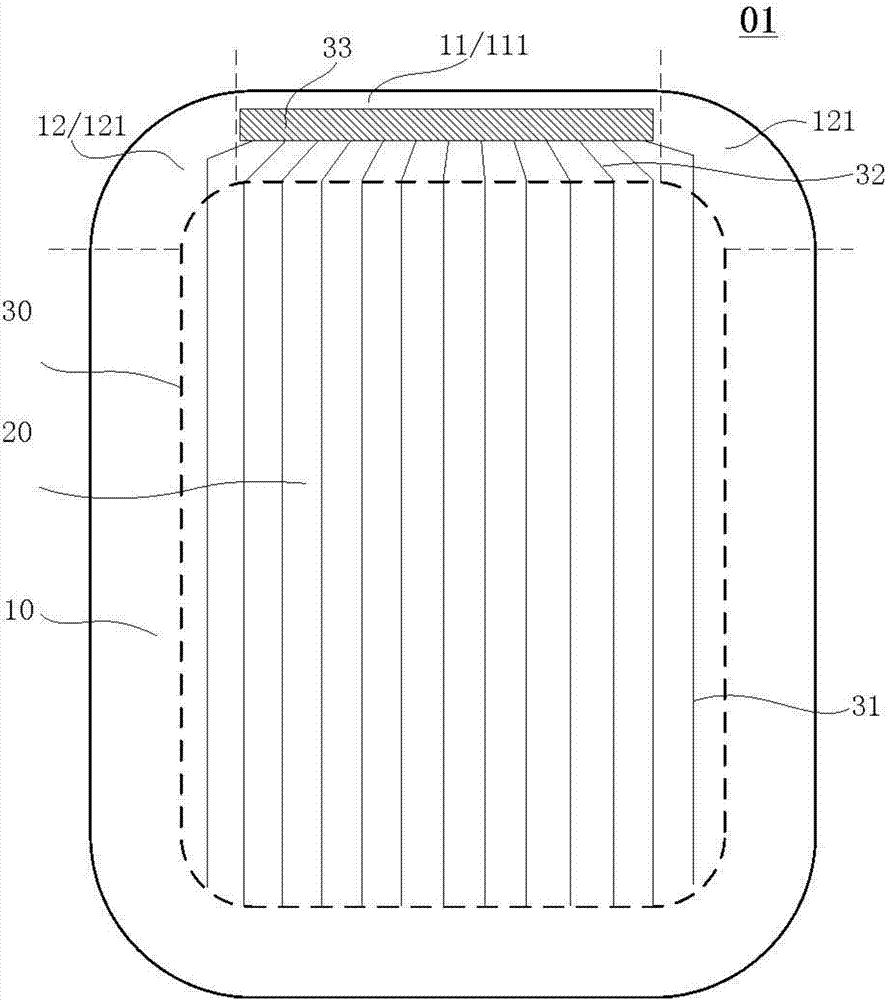

Array substrate and display panel

ActiveCN107203080AReduce border widthReduce widthStatic indicating devicesNon-linear opticsEngineeringControl circuit

The invention provides an array substrate and a display panel comprising the array substrate. The array substrate is a non-rectangular array substrate and comprises a display area and a non-display area surrounding the display area; the non-display area comprises a first linear area and a first non-linear area connected with the first linear area, and the first linear area and the display area are arranged in the first direction; the display area comprises a plurality of signal lines extending in the first direction; the non-display area comprises a plurality of signal connecting lines; the first linear area comprises a signal control circuit; the signal connecting lines are connected with the signal lines and the signal control circuit, wherein the signal connecting lines comprise first signal connecting lines only extending in the first linear area and second signal connecting lines extending from the first linear area to the first non-linear area. According to the array substrate and the display panel, a voltage signal provided by the signal control circuit can be normally received by the signal lines, and the border width of the first non-linear area can be decreased, so that the border width of the linear area is decreased.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

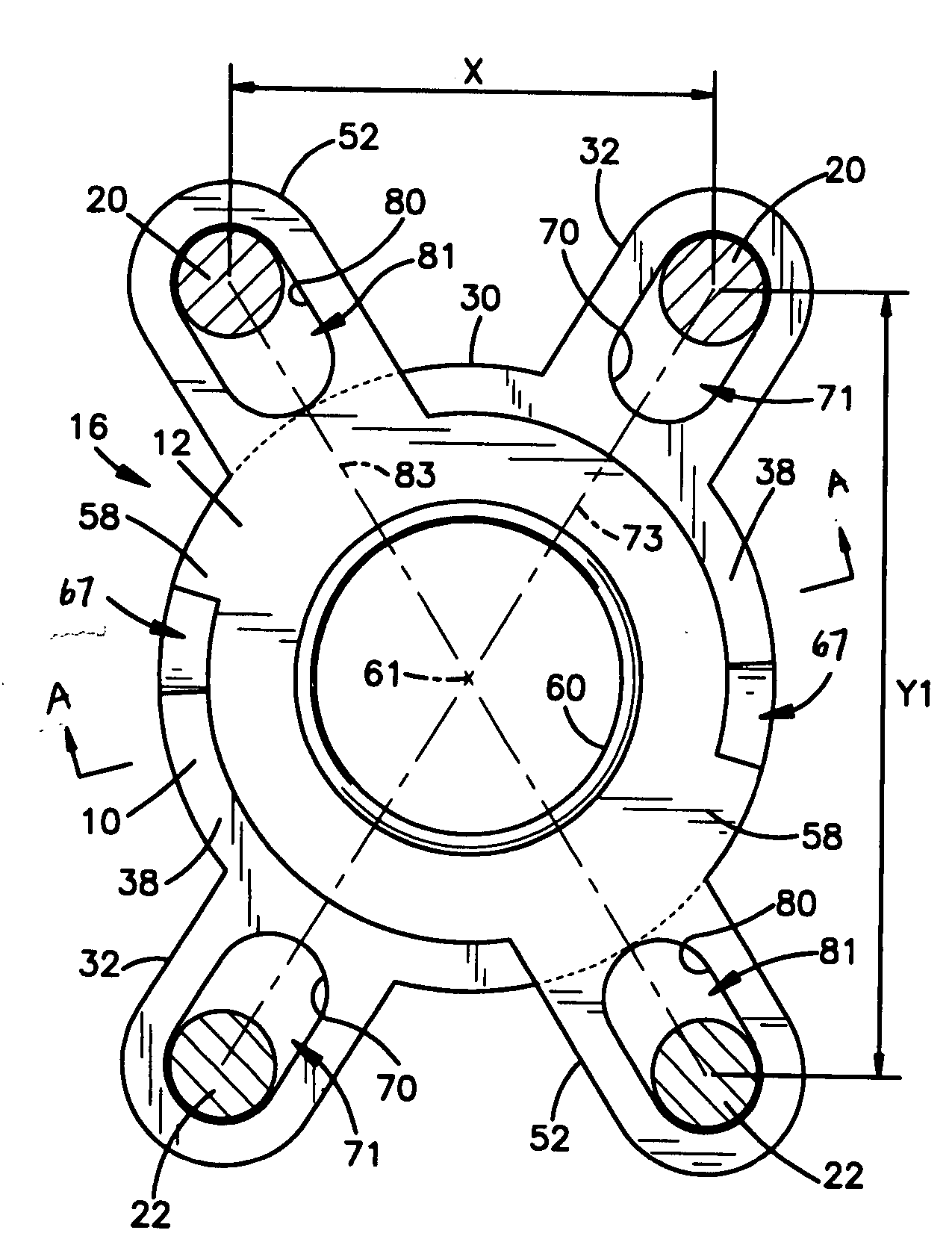

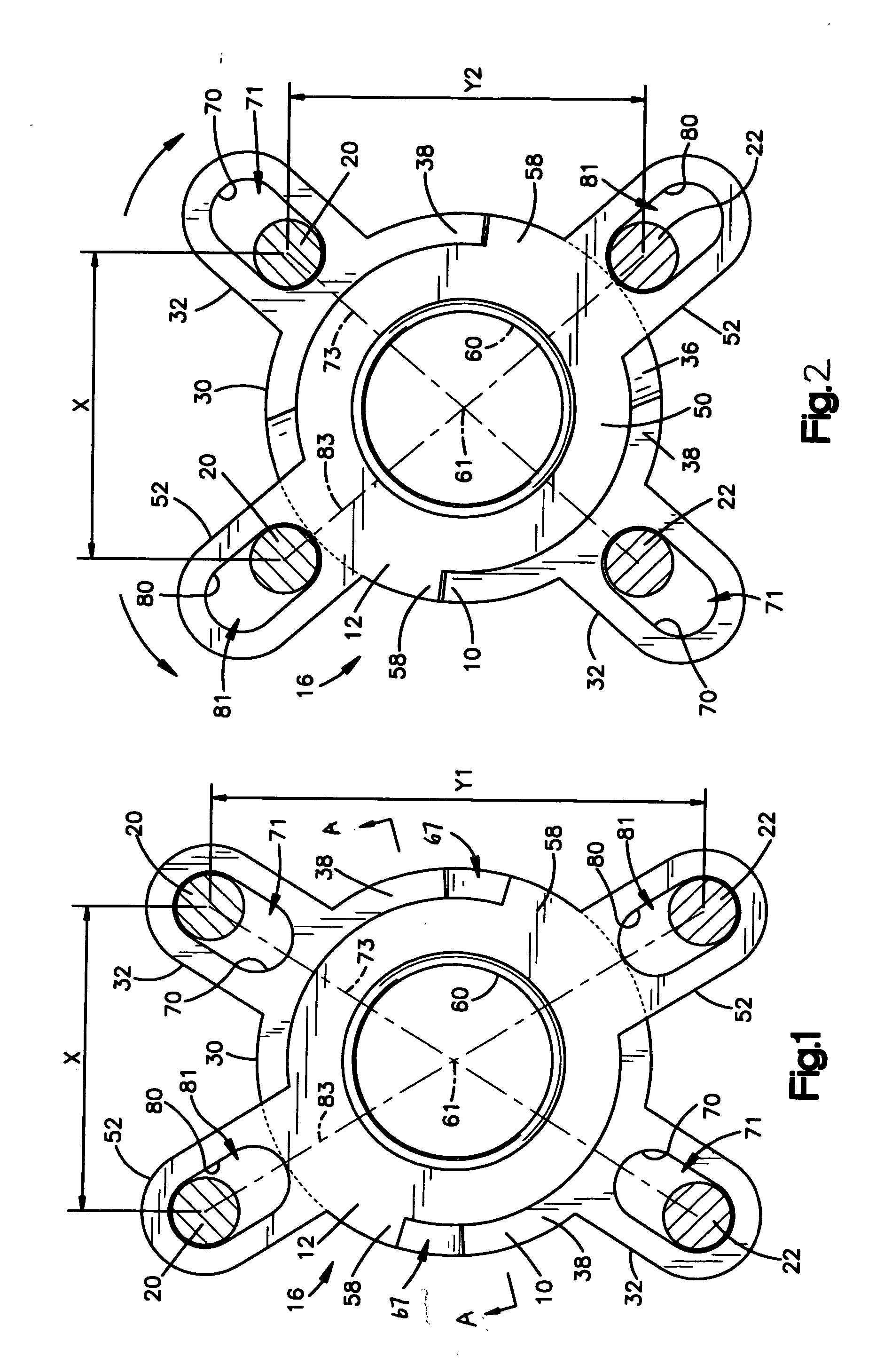

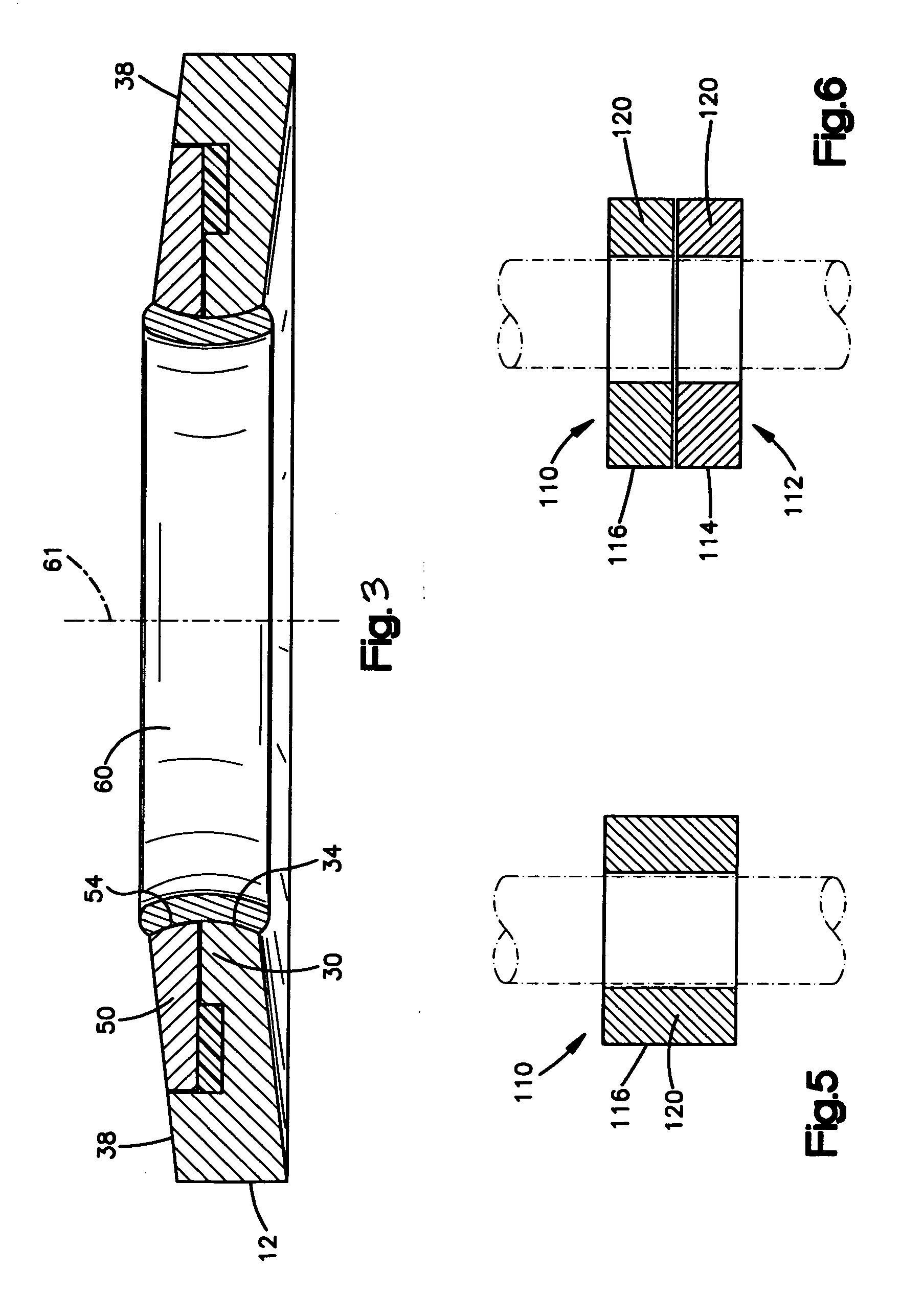

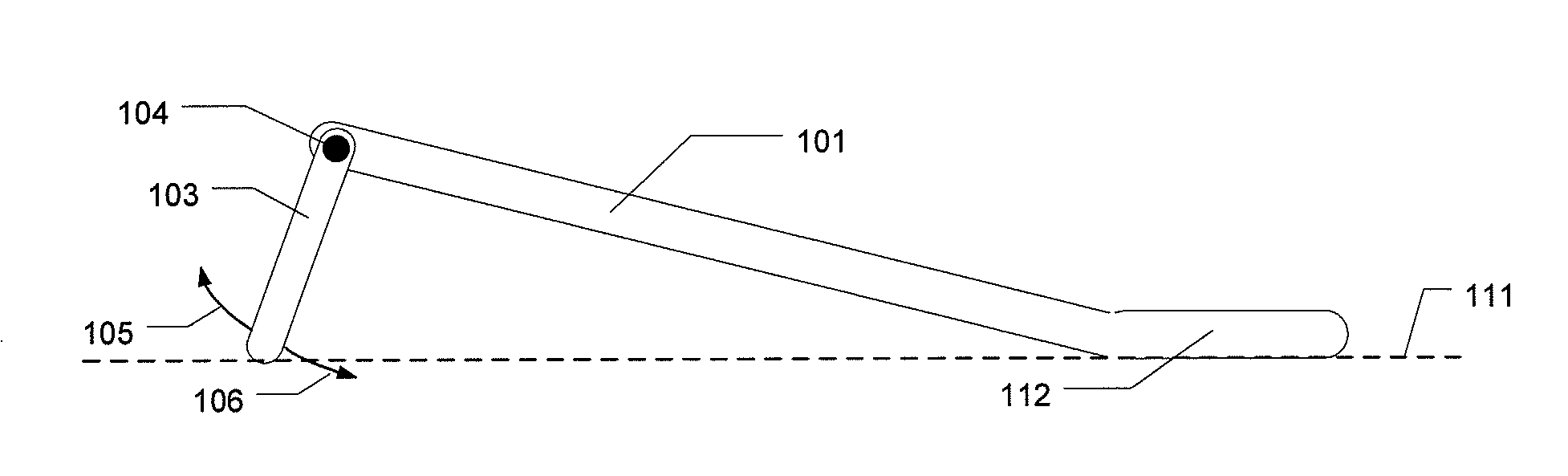

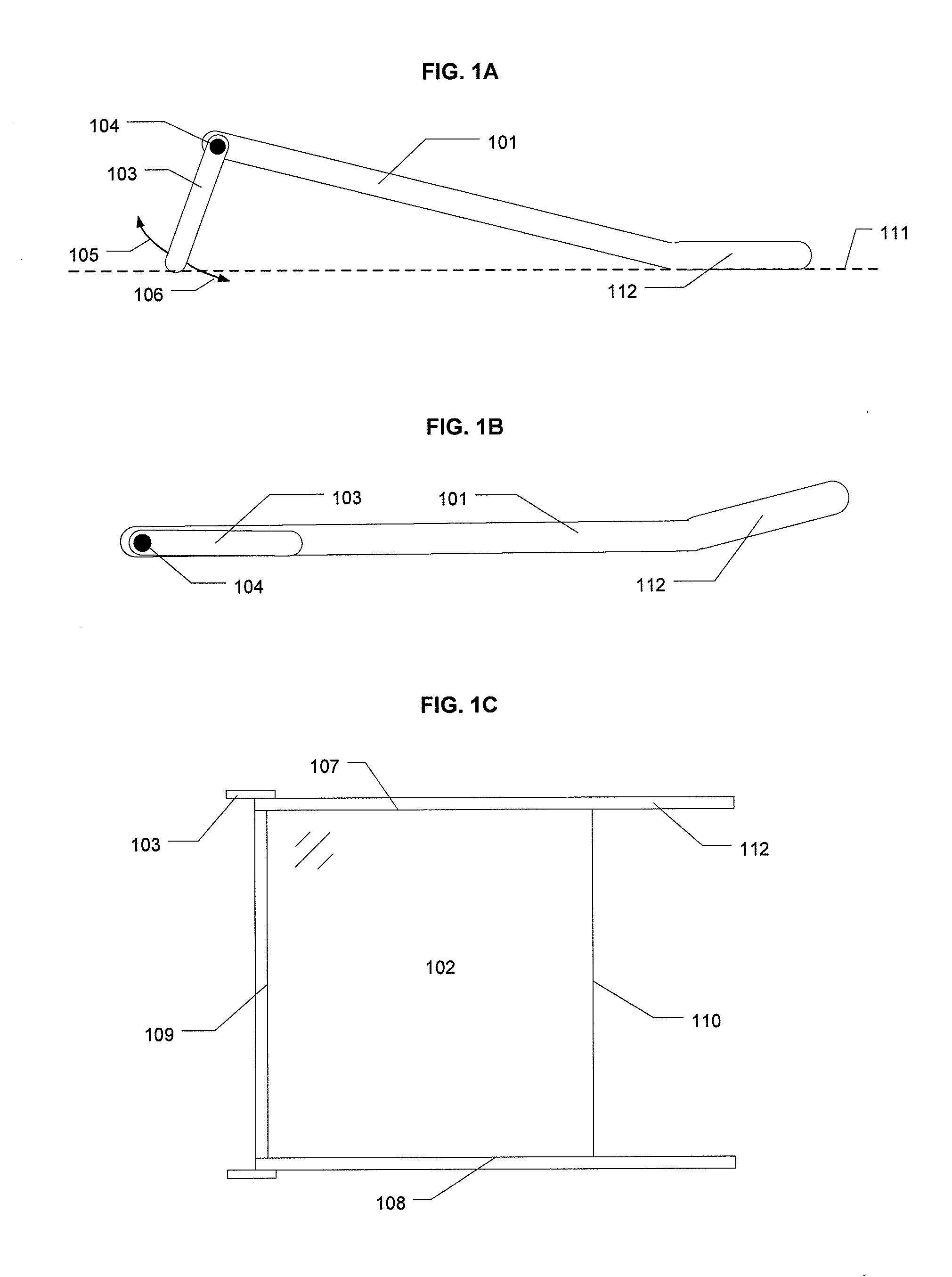

Translational scissor plate fixation system

An apparatus for use with bone fasteners comprises a first fixation device having a slot configured to receive a bone fastener, and a second fixation device having another slot configured to receive another bone fastener. The first and second fixation devices are interconnected for rotation relative to each other when the bone fasteners are in the slots. Summarized differently, an apparatus for use with bone fasteners comprises a first fixation device having a first pair of openings defining bone fastener locations, and a second fixation device having a second pair of openings defining bone fastener locations. The first and second fixation devices are interconnected for movement relative to each other such that the bone fastener locations defined by the first and second pairs of openings are located at four corners of a rectangular array.

Owner:SYNTHES GMBH

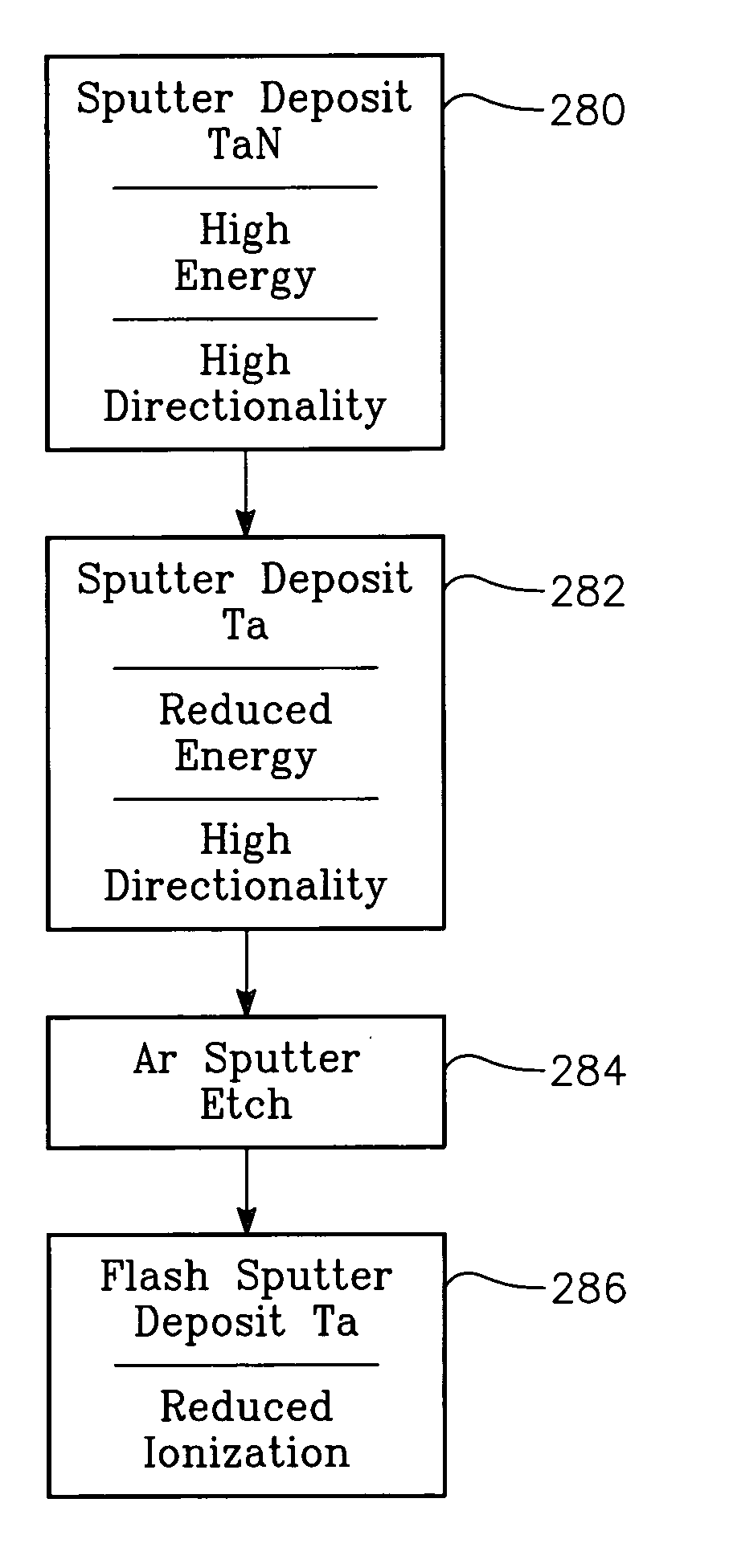

Target tiles in a staggered array

A sputtering target, particularly for sputter depositing a target material onto large rectangular panels, in which a plurality of target tiles are bonded to a backing plate in a two-dimensional non-rectangular array such that the tiles meet at interstices of no more than three tile, thus locking the tiles against excessive misalignment during bonding and repeated thermal cycling. The rectangular tiles may be arranged in staggered rows or in a herringbone or zig-zag pattern. Hexagonal and triangular tiles also provide many of the advantages of the invention. Sector-shaped tiles may be arranged in a circular target with a staggered offset at the center.

Owner:APPLIED MATERIALS INC

Solar panel racking system

InactiveUS20120298201A1Easy to adjustQuick alignmentPhotovoltaic supportsSolar heating energyEngineeringElectrical and Electronics engineering

Photovoltaic modules that are collapsible and angularly adjustable are made by mounting a photovoltaic panel in a frame, with a leg joined to the frame, the leg being manually adjustable to various angles, tilting the frame at various angles relative to the horizontal by simply lifting the frame. Certain embodiments also include interlocking features that join adjacent frames to form a rectangular array of modules.

Owner:PEGASUS SOLAR

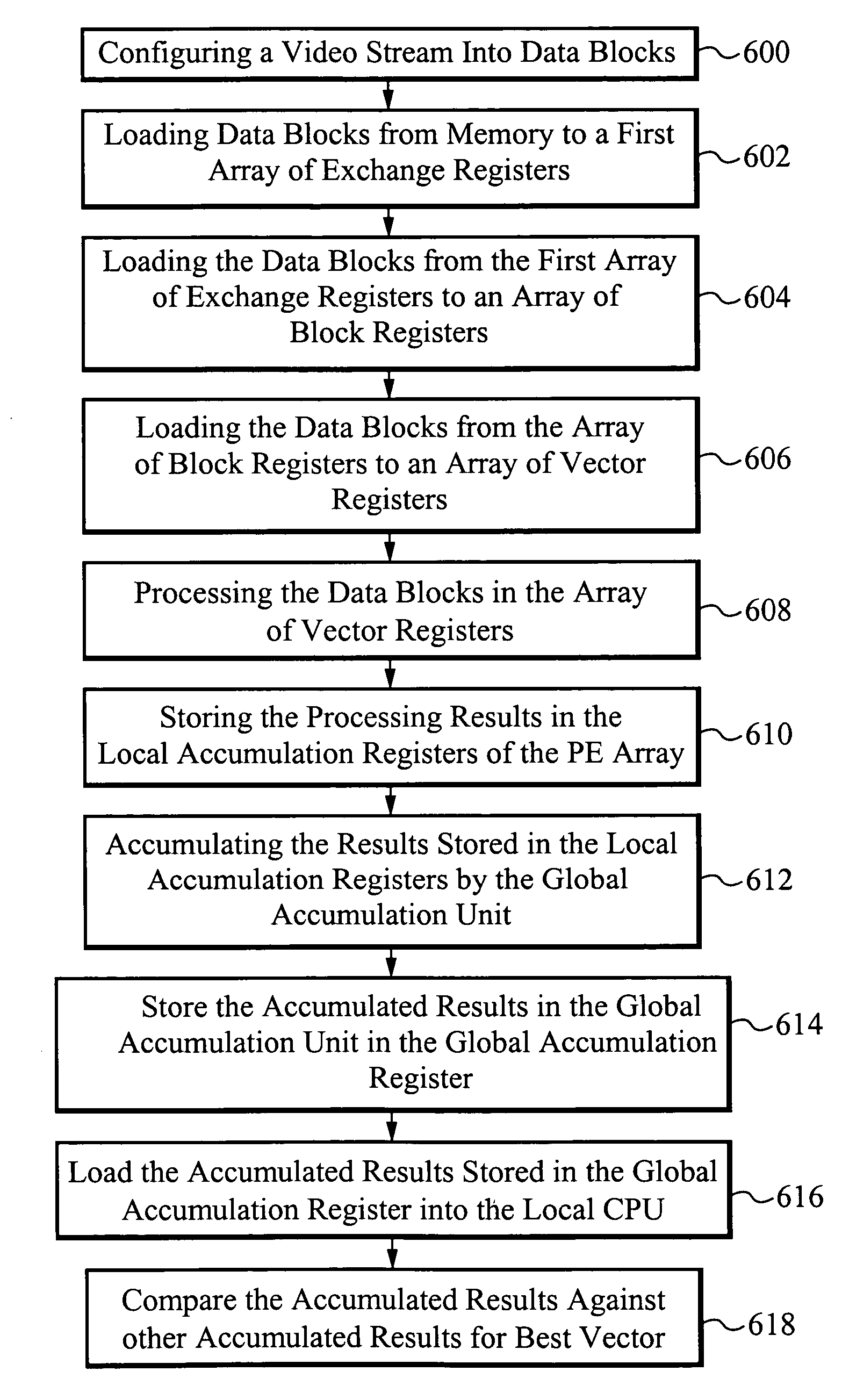

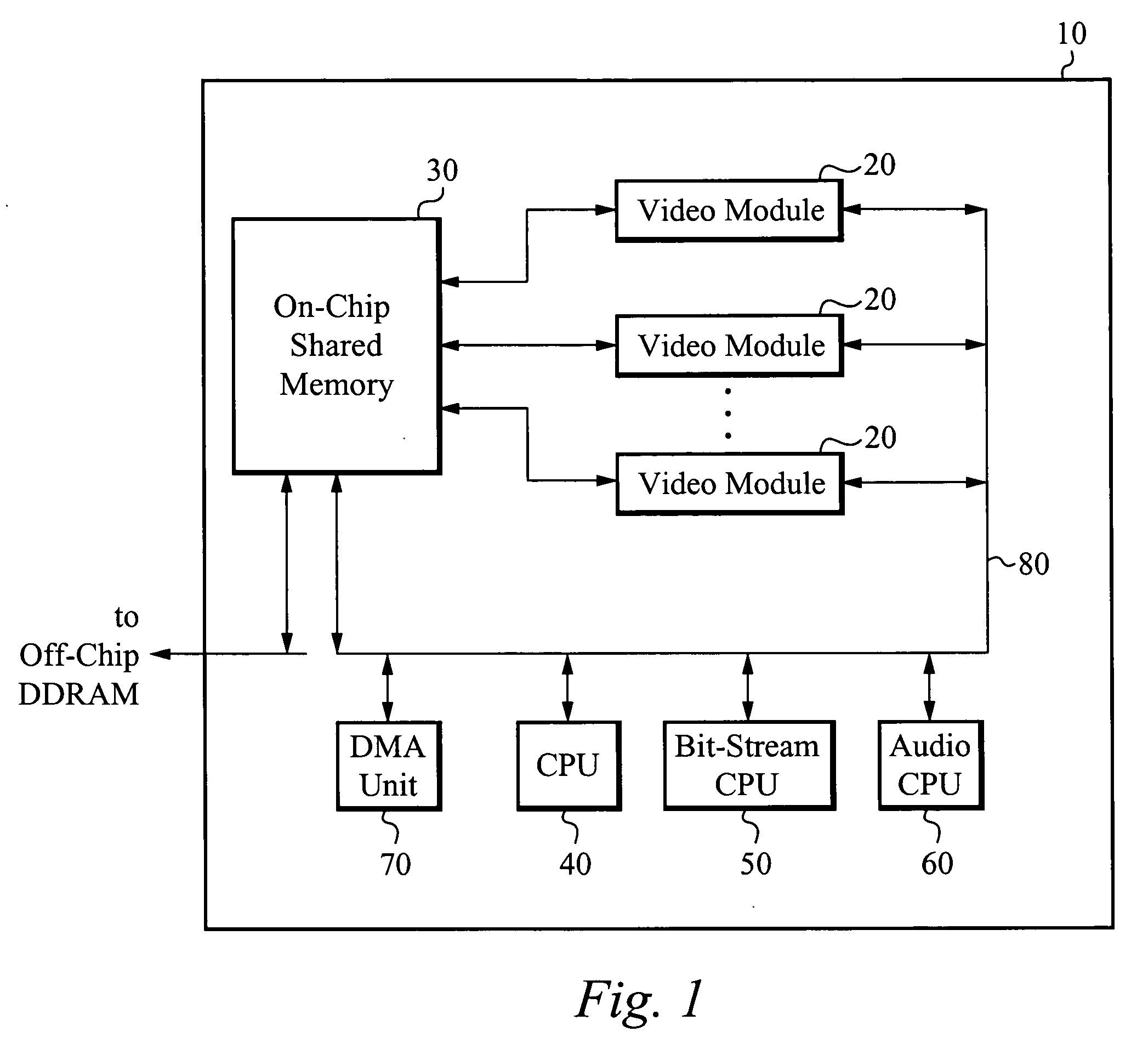

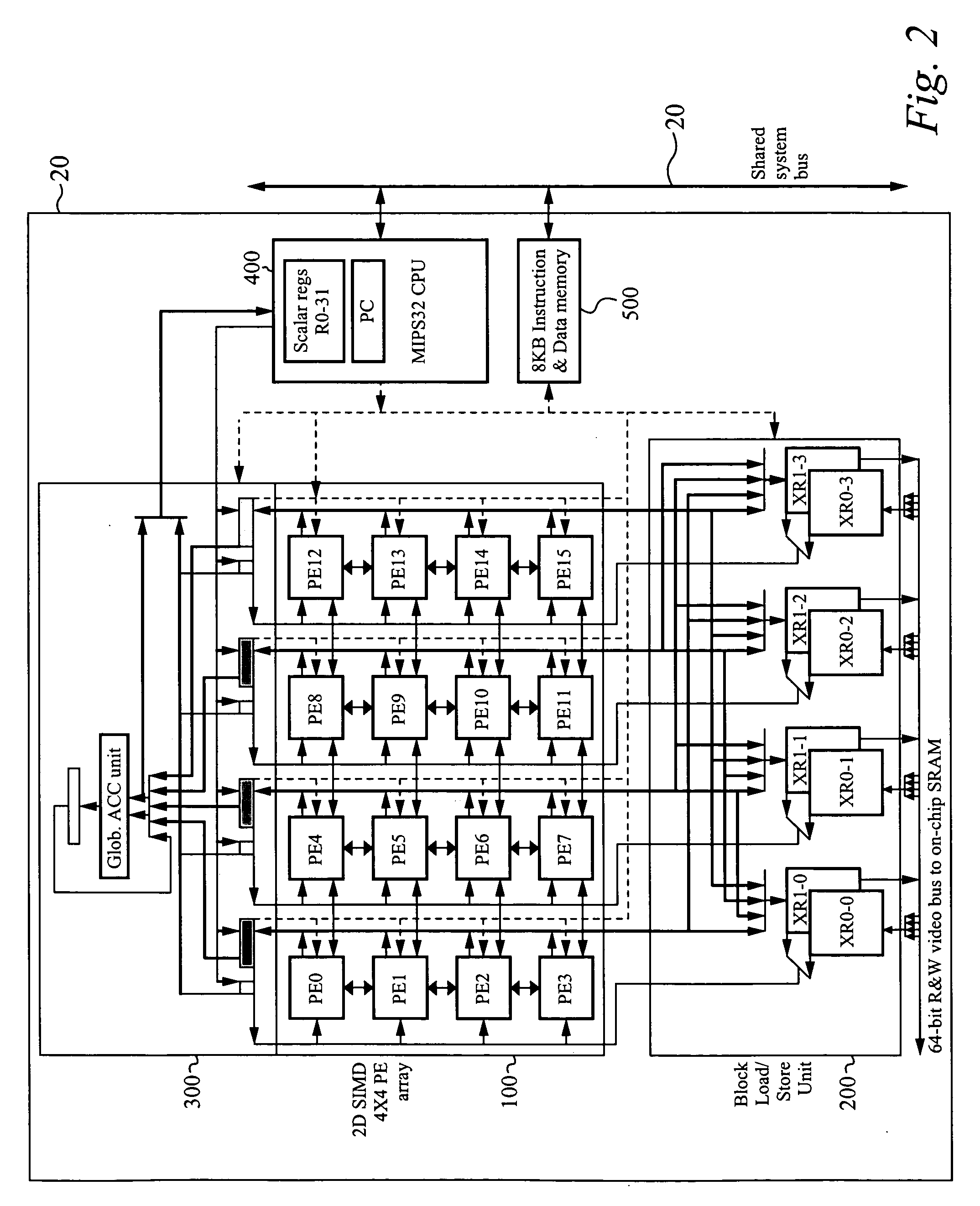

2D block processing architecture

InactiveUS20050226337A1Color television with pulse code modulationColor television with bandwidth reductionGeneral purposeData stream

A video platform architecture for video processing includes complex video compression / decompression algorithms in a computer with a two-dimensional Single-Instruction Multiple-Data (SIMD) array architecture. The video platform architecture includes one or more video processing modules, on-chip shared memory, and a general-purpose RISC central processing unit CPU used as a system controller. Each video processing module includes a rectangular array of processing elements (PEs), a block load / store unit, a global-accumulation unit. Video to be processed is configured into blocks of data, and a general-purpose CPU used as a local controller. A plurality of registers are provided in the processing elements and the block load / store unit to support two-dimensional processing of the data blocks. Types of registers used include block registers, vector registers, scalar registers, and exchange registers. Each of these registers is designed to hold a short ordered one- or two-dimensional set of video data (data blocks). These registers are arranged in a hierarchical configuration along the data flow path between the on-chip memory and processing units within the PE array.

Owner:SONY CORP +1

Structural color display

InactiveUS7848008B2Bright enoughReduce power consumptionProjectorsOptical elementsDisplay deviceComputer science

Disclosed is a structural color display including: (a) a pattern forming member which forms a plurality of cells each lined up in two dimension; and (b) a light transmissive image display sheet comprising a color showing layer which shows a structural color, the light transmissive image display sheet being faced to the pattern forming member, wherein each cell is independently controlled to reflect a light from a light source corresponding to an image pattern to be displayed, provided that the reflected light is made to enter in the image display sheet from a side facing the pattern forming member by a predetermined incident angle corresponding to the cell. The pattern image forming member comprises the element having a plurality of microscopic mirrors arranged in a rectangular array and being individually rotated.

Owner:KONICA MINOLTA BUSINESS TECH INC

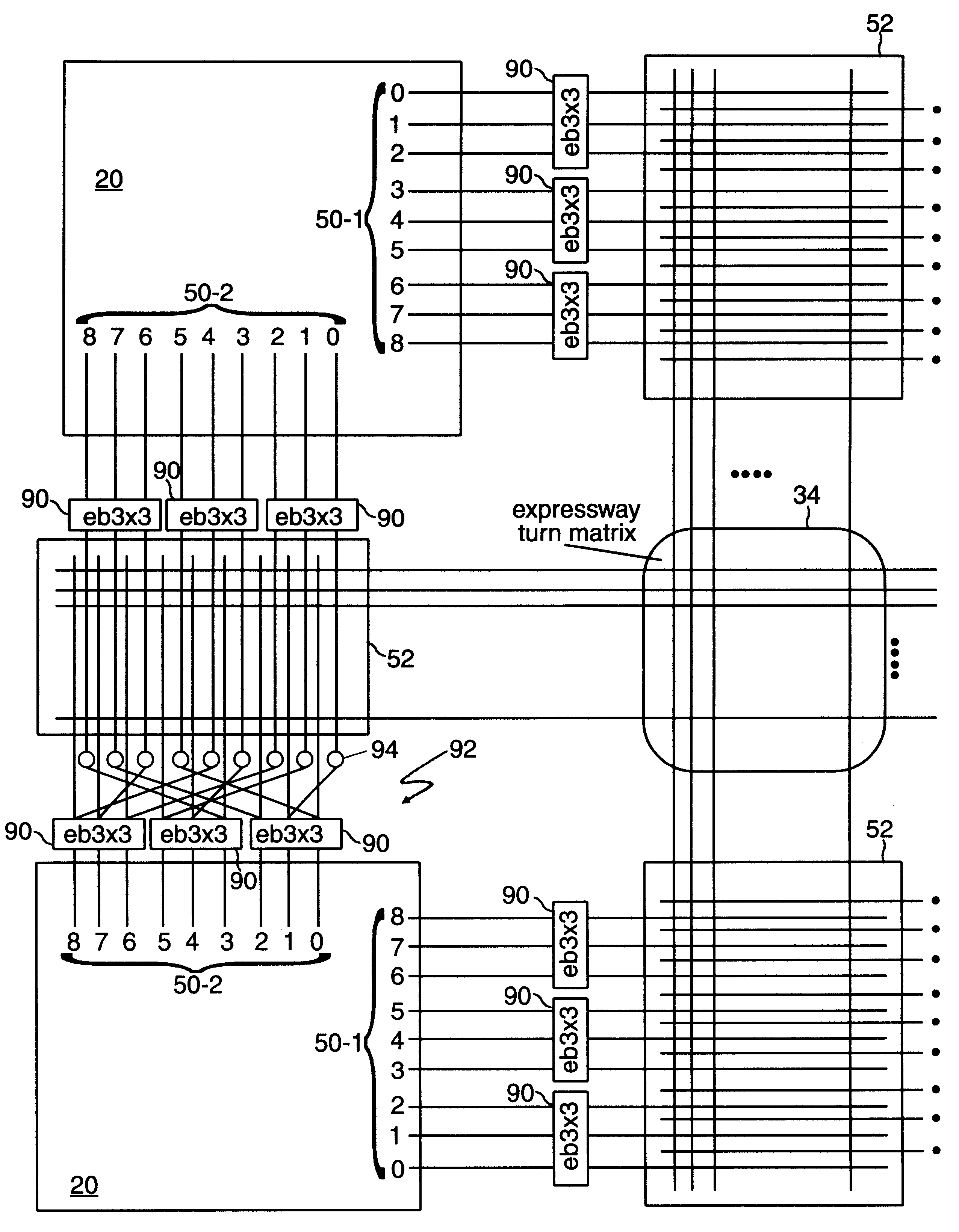

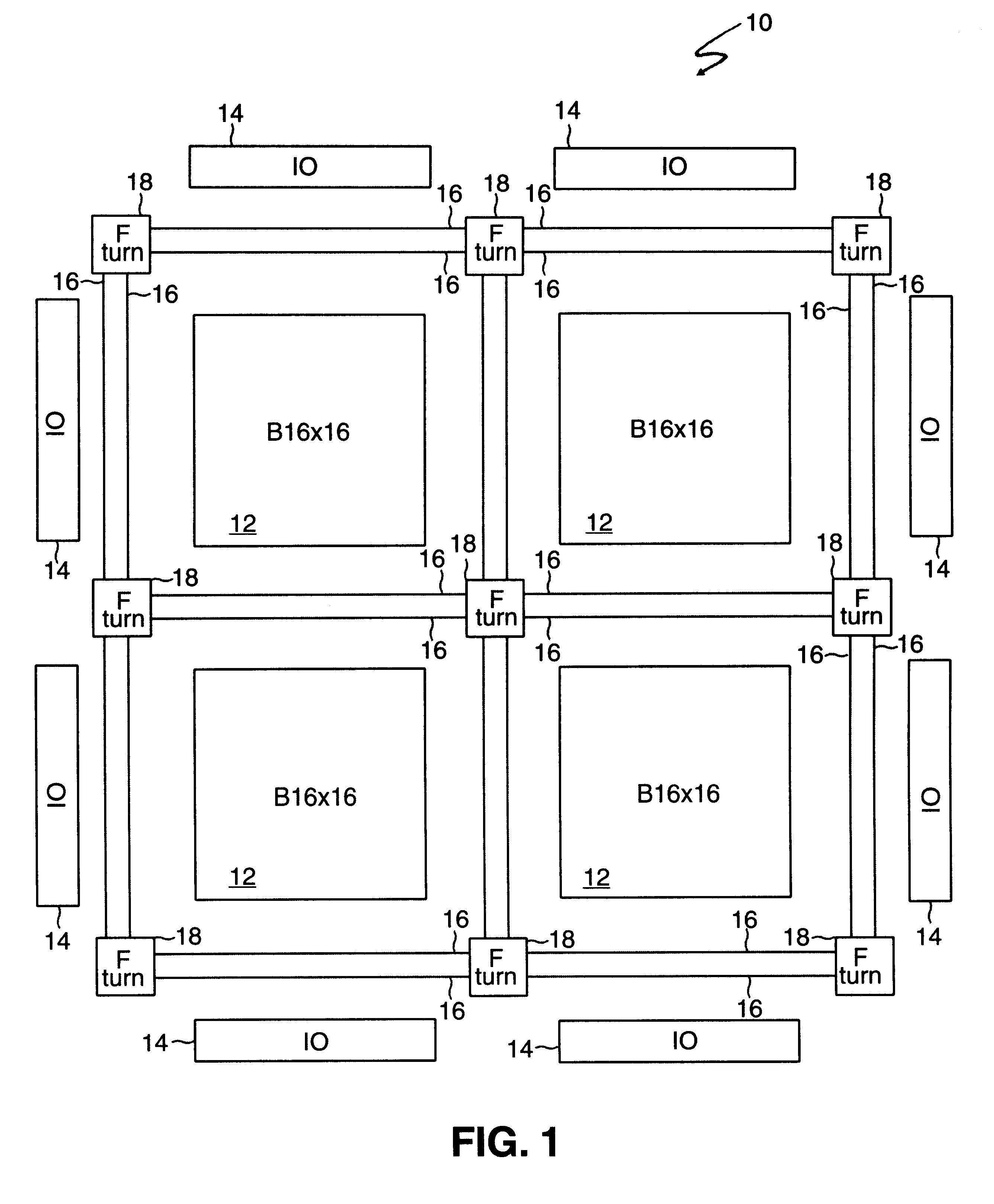

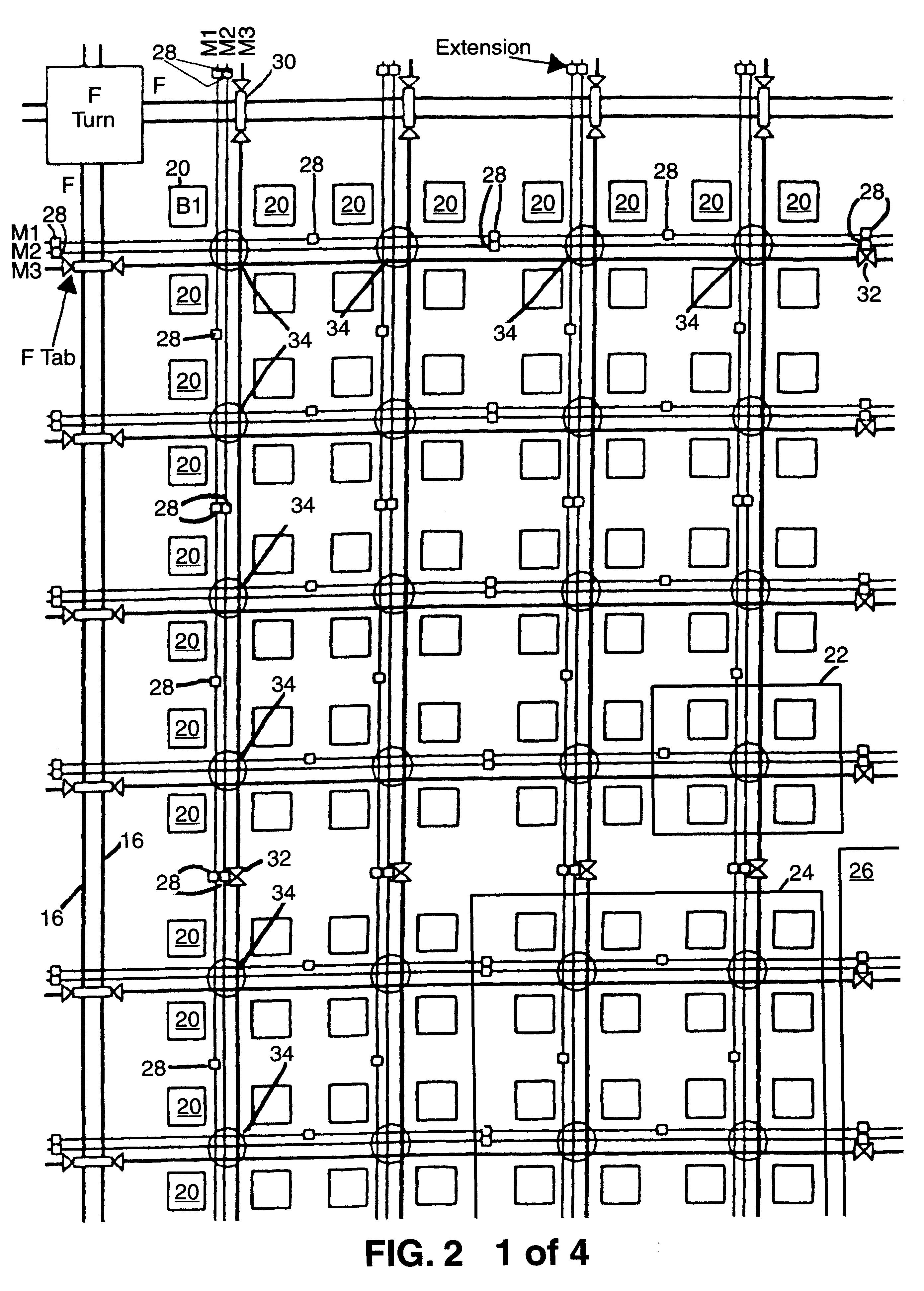

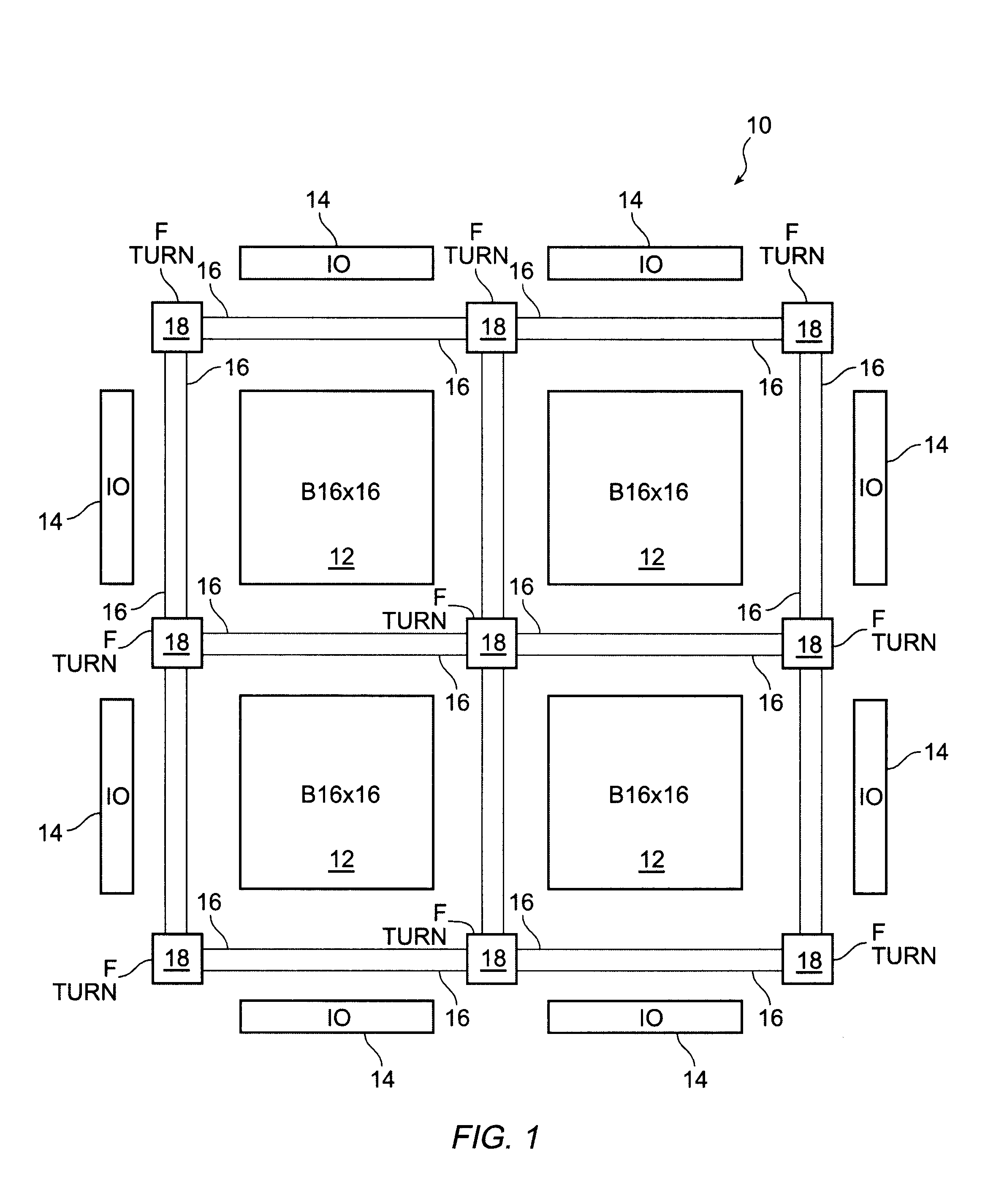

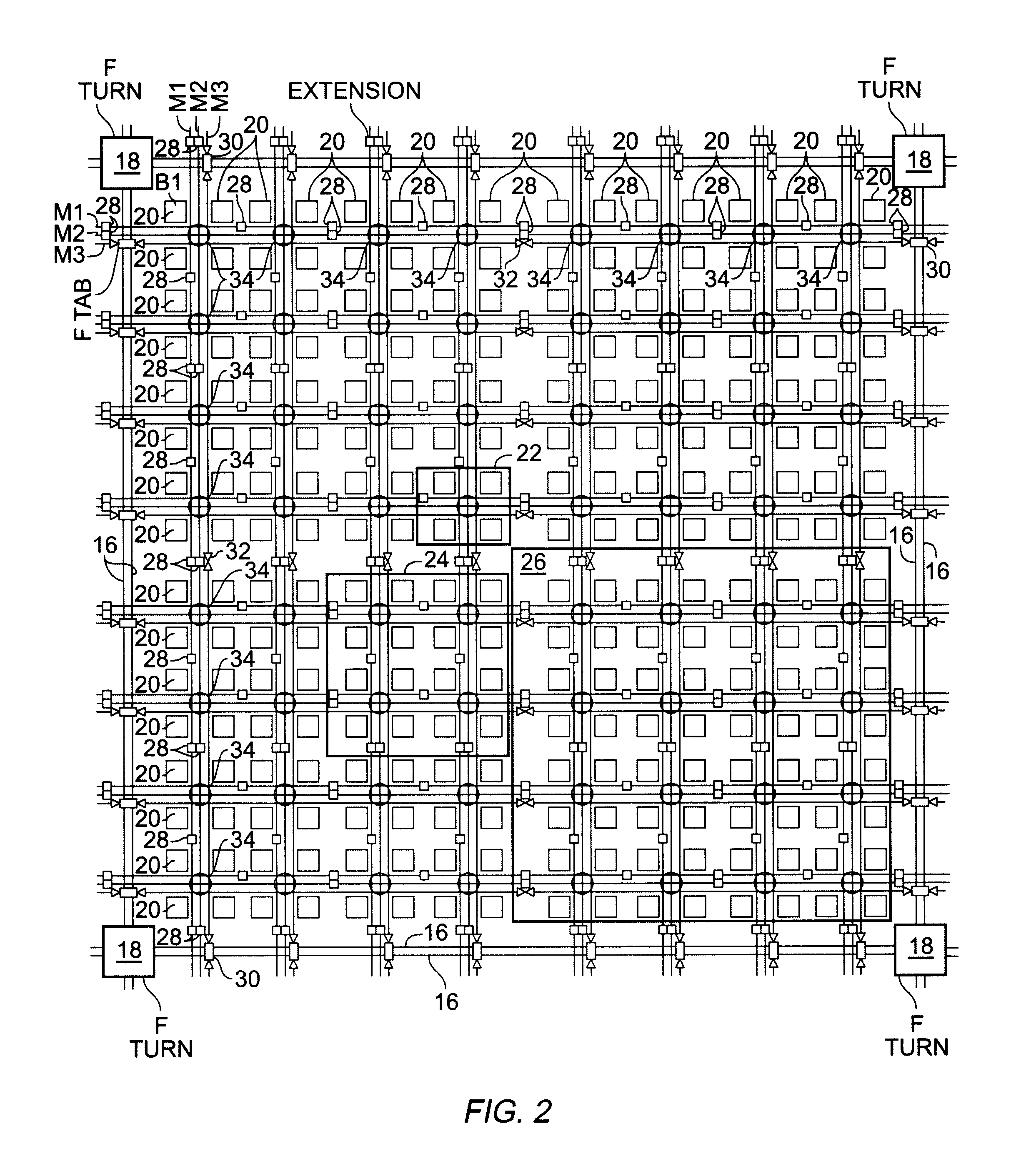

Block level routing architecture in a field programmable gate array

InactiveUS6567968B1Good symmetryEasy to placeSolid-state devicesSpecial data processing applicationsFpga architectureElectrical conductor

An FPGA architecture has top, middle and low levels. The top level of the architecture is an array of the B16x16 tiles arranged in a rectangular array and enclosed by I / O blocks on the periphery. On each of the four sides of a B16x16 tile, and also associated with each of the I / O blocks is a freeway routing channel. A B16x16 tile in the middle level of hierarchy is a sixteen by sixteen array of B1 blocks. The routing resources in the middle level of hierarchy are expressway routing channels M1, M2, and M3 including groups of interconnect conductors. At the lowest level of the semi-hierarchical FPGA architecture, there are block connect (BC) routing channels, local mesh (LM) routing channels, and direct connect (DC) interconnect conductors. Each BC routing channel is coupled to an expressway tab to provide access for each B1 block to the expressway routing channels M1, M2, and M3, respectively. Each BC routing channel has nine interconnect conductors which are grouped into three groups of three interconnect conductors. Each group of three interconnect conductors is connected to a first side of a Extension Block (EB) 3x3 switch matrix. A second side of each EB 3x3 switch matrix is coupled to the E-tab. Between adjacent B1 blocks, in both the horizontal and vertical directions, the leads on the second side of a first EB 3x3 switch matrix may be coupled to the leads on the second side of second EB3x3 switch matrix by BC criss-cross extension.

Owner:ACTEL CORP

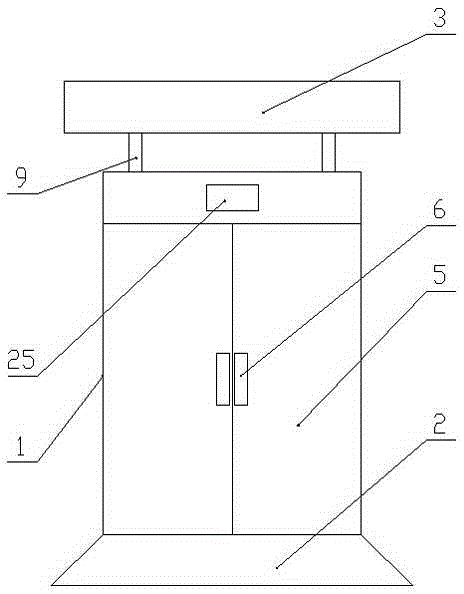

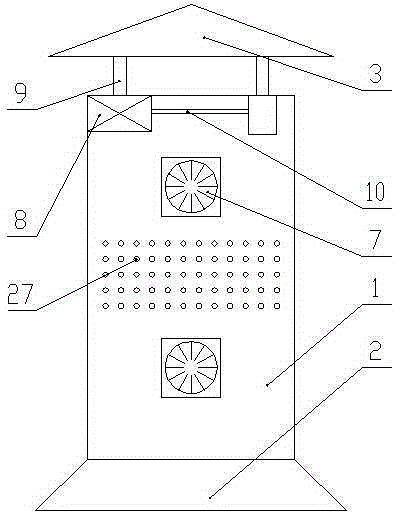

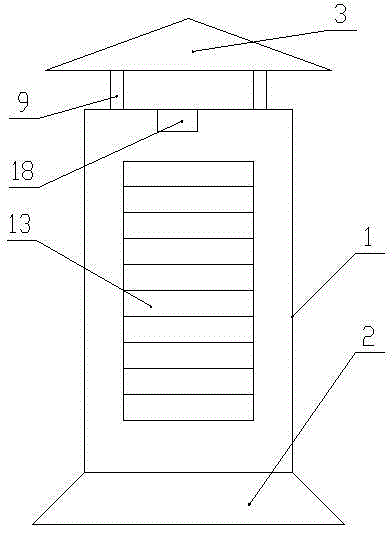

Ventilated moistureproof switch cabinet

ActiveCN105337192AGuaranteed uptimeImprove cooling and dehumidification efficiencySubstation/switching arrangement cooling/ventilationSubstation/switching arrangement casingsControl systemEngineering

The invention provides a ventilated moistureproof switch cabinet comprising a cabinet body, a base and a top cover, wherein the cabinet body is in a cuboid structure; the base is in a quadrangular frustum pyramid; the top cover is in a triangular prism structure; the cabinet body is arranged on the top of the base; the top cover is positioned on the top of the cabinet body; a hydraulic jacking device is arranged between the top cover and the cabinet body; a plurality of ventilation holes are formed in the top of the cabinet body and are distributed along a rectangular array; a double-opening door is formed in the front end of the cabinet body; two cooling fans are arranged on the left side surface of the cabinet body and are distributed in an up-down manner; a ventilation and cooling mechanism is arranged on the right side surface of the cabinet body; a control system is arranged in the cabinet body; a dust prevention filtering net is positioned at the inner side of the ventilation and cooling mechanism on the right side surface of the cabinet body; a plurality of cooling holes are formed between the two cooling fans on the left side surface of the cabinet body. The ventilated moistureproof switch cabinet is good in cooling and moistureproof effects, reliable to work, long in service life and capable of achieving automatic cooling and moistureproof effects.

Owner:STATE GRID CORP OF CHINA +1

In-vehicle display device

InactiveUS8049609B2Reduce manufacturing costImprove accuracyProjectorsCharacter and pattern recognitionIn vehicleDisplay device

Owner:YAZAKI CORP

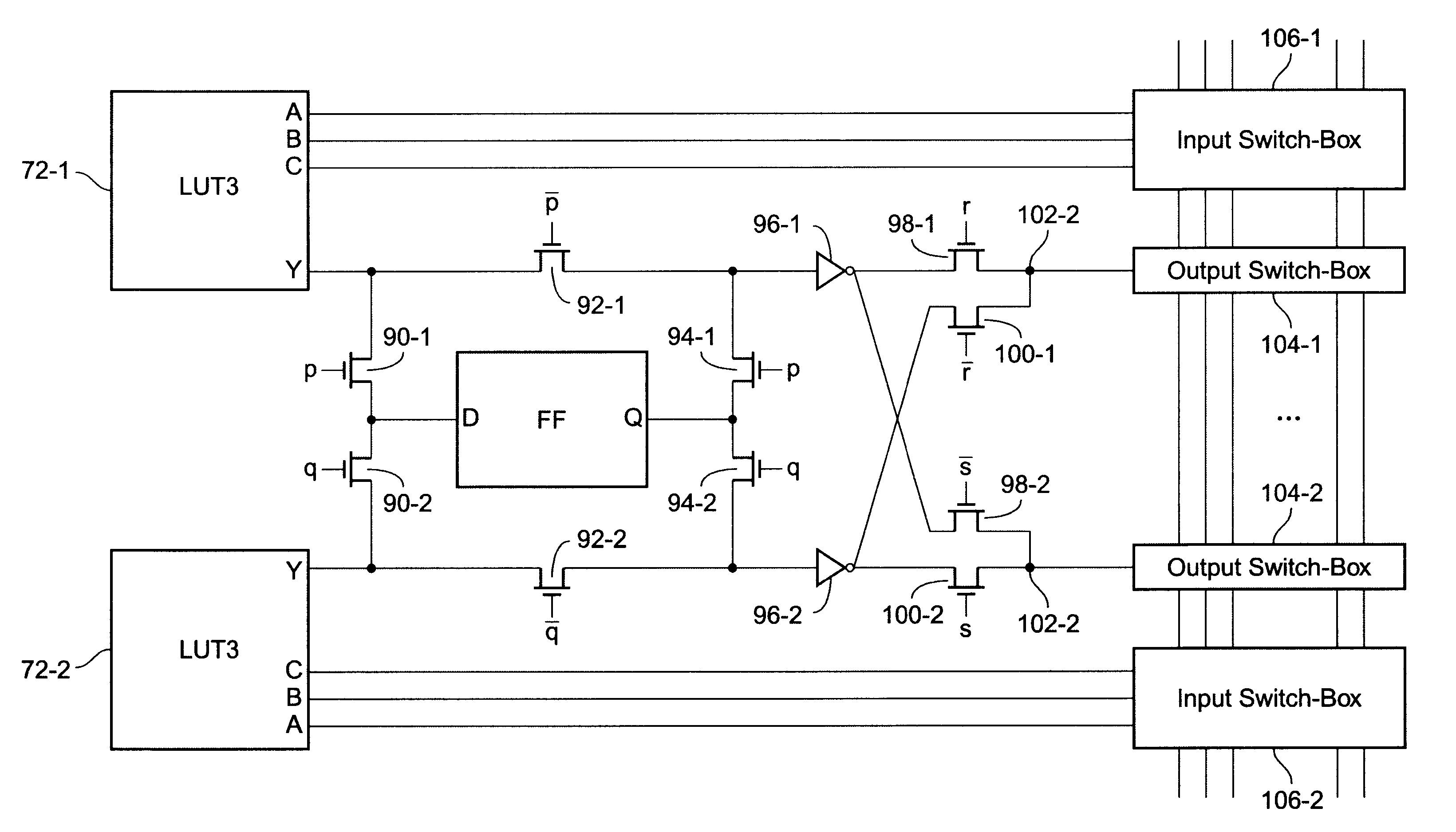

Block symmetrization in a field programmable gate array

InactiveUS6268743B1Good symmetryEasy to placeLogic circuits using elementary logic circuit componentsComputation using denominational number representationFpga architectureMultiplexing

An FPGA architecture has top, middle and low levels. The top level of the architecture is an array of the B16x16 tiles arranged in a rectangular array and enclosed by I / O blocks on the periphery. On each of the four sides of a B16x16 tile, and also associated with each of the I / O blocks is a freeway routing channel. A B16x16 tile in the middle level of hierarchy is a sixteen by sixteen array of B1 blocks. The routing resources in the middle level of hierarchy are expressway routing channels M1, M2, and M3 including groups of interconnect conductors. At the lowest level of the semi-hierarchical FPGA architecture, there are block connect (BC) routing channels, local mesh (LM) routing channels, and direct connect (DC) interconnect conductors to connect the logic elements to further routing resources. Each B1 block includes four clusters of devices. Each of the four clusters includes first and second LUT3s, a LUT2, and a DFF . Each of the LUT3s have first, second, and third inputs and a single output. Each of the LUT2s have first and second inputs and a single output. Each DFF has a data input and a data output. In each of the clusters the outputs of the LUT3s are muliplexed to the input of DFF, and symmetrized with the output of the DFF to form first and second outputs of each of the clusters.

Owner:MICROSEMI SOC