Patents

Literature

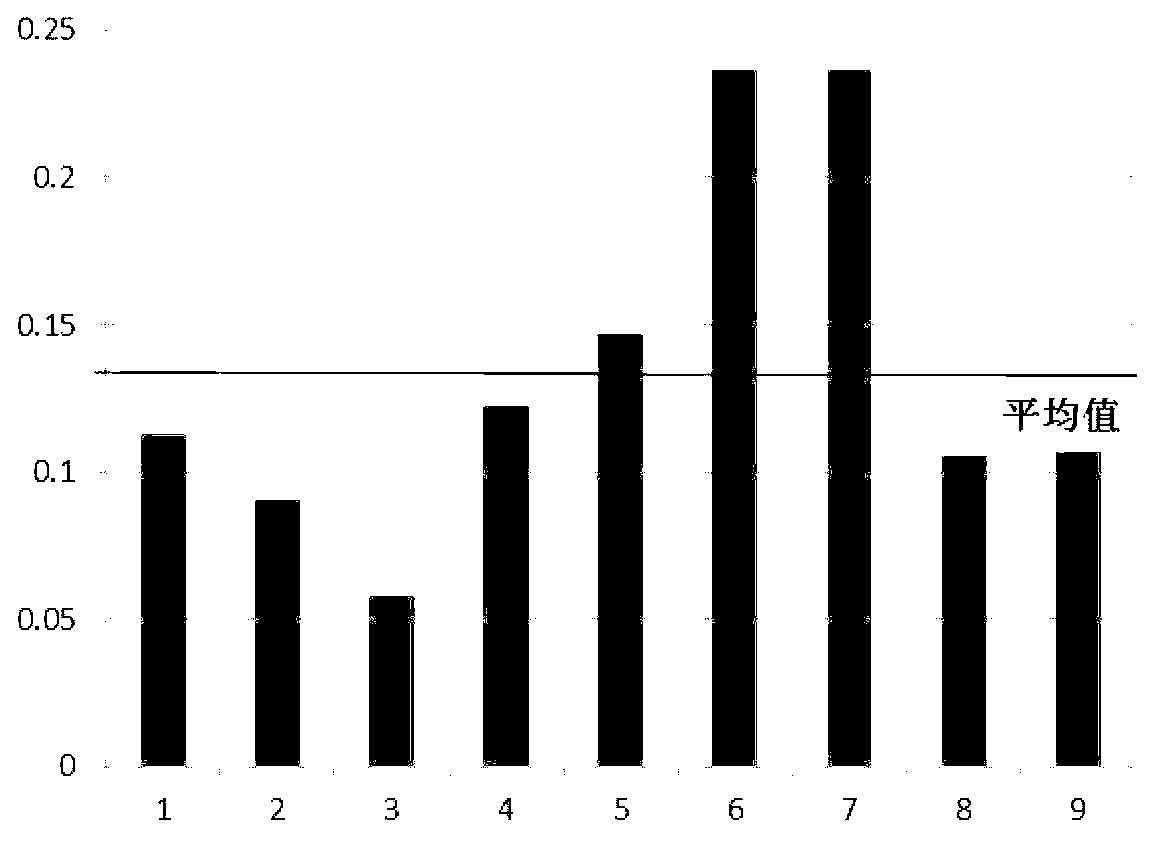

122 results about "Fpga architecture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Field-programmable gate array (FPGA) is a device that has array of Configurable logic gates and can be programmed on-board through dedicated Joint Test Action Group (JTAG) or through any other serial/ Parallel non-volatile Memory. FPGA architecture are based on static random-access memory (SRAM) Volatile memory.

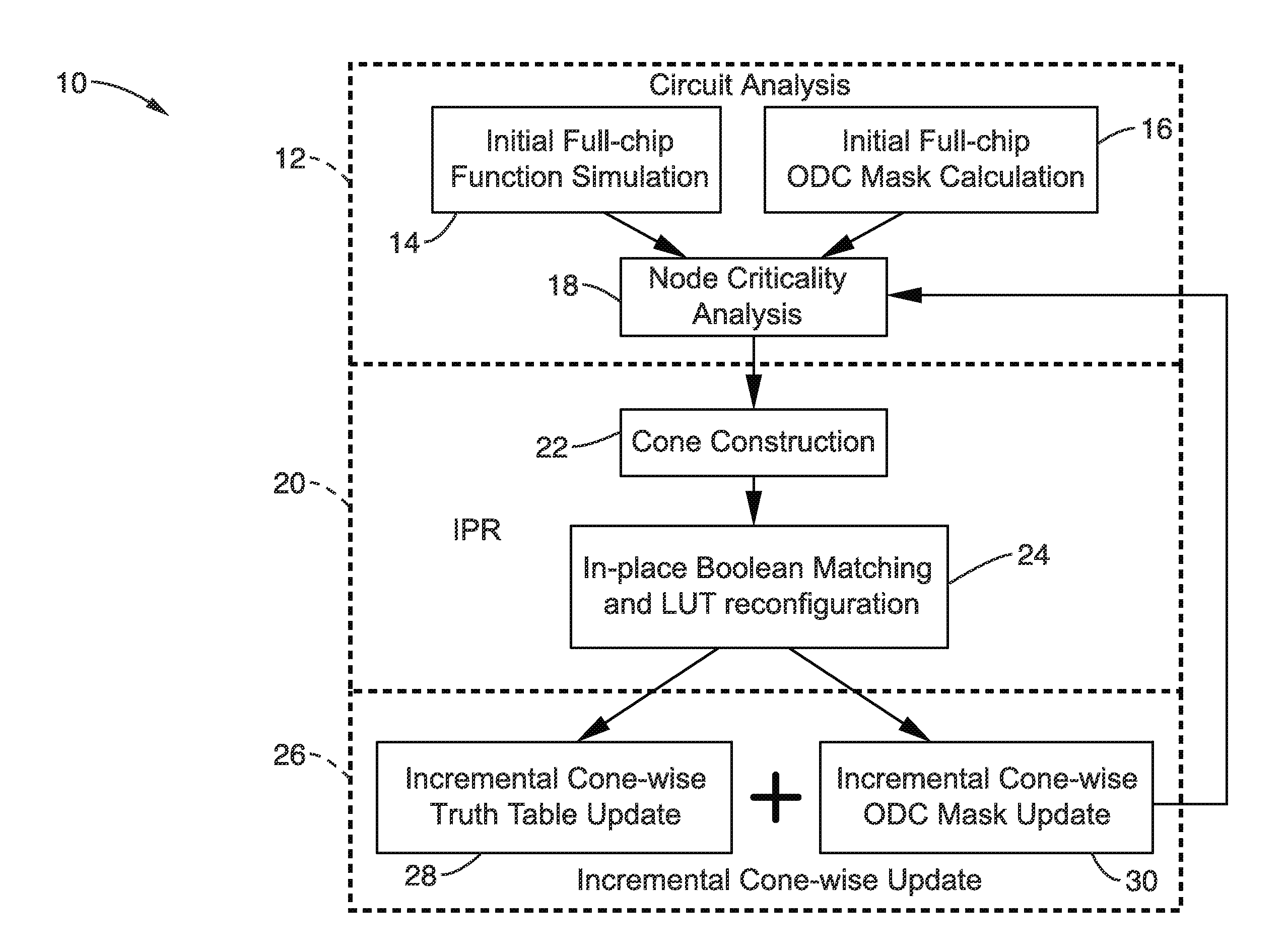

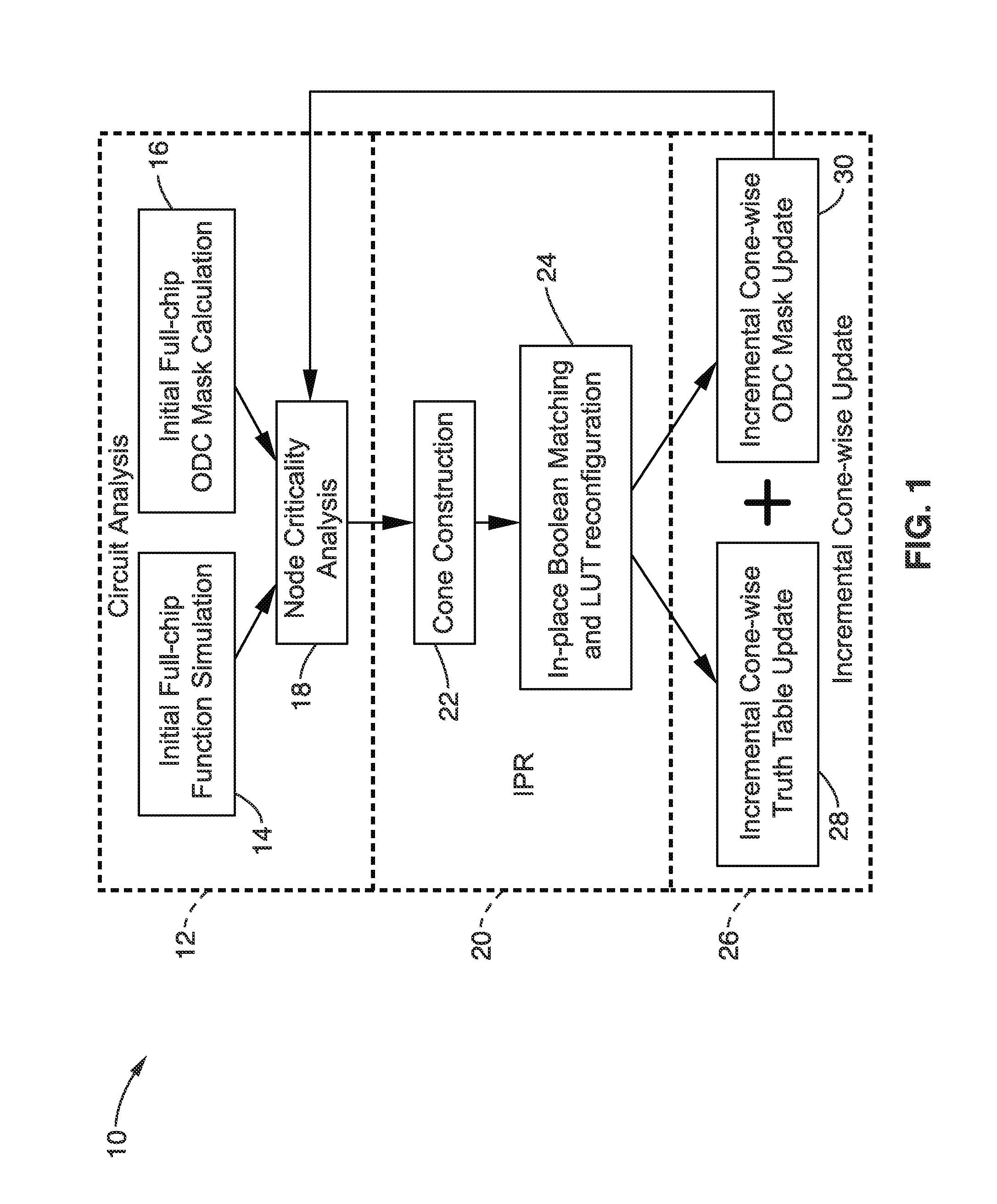

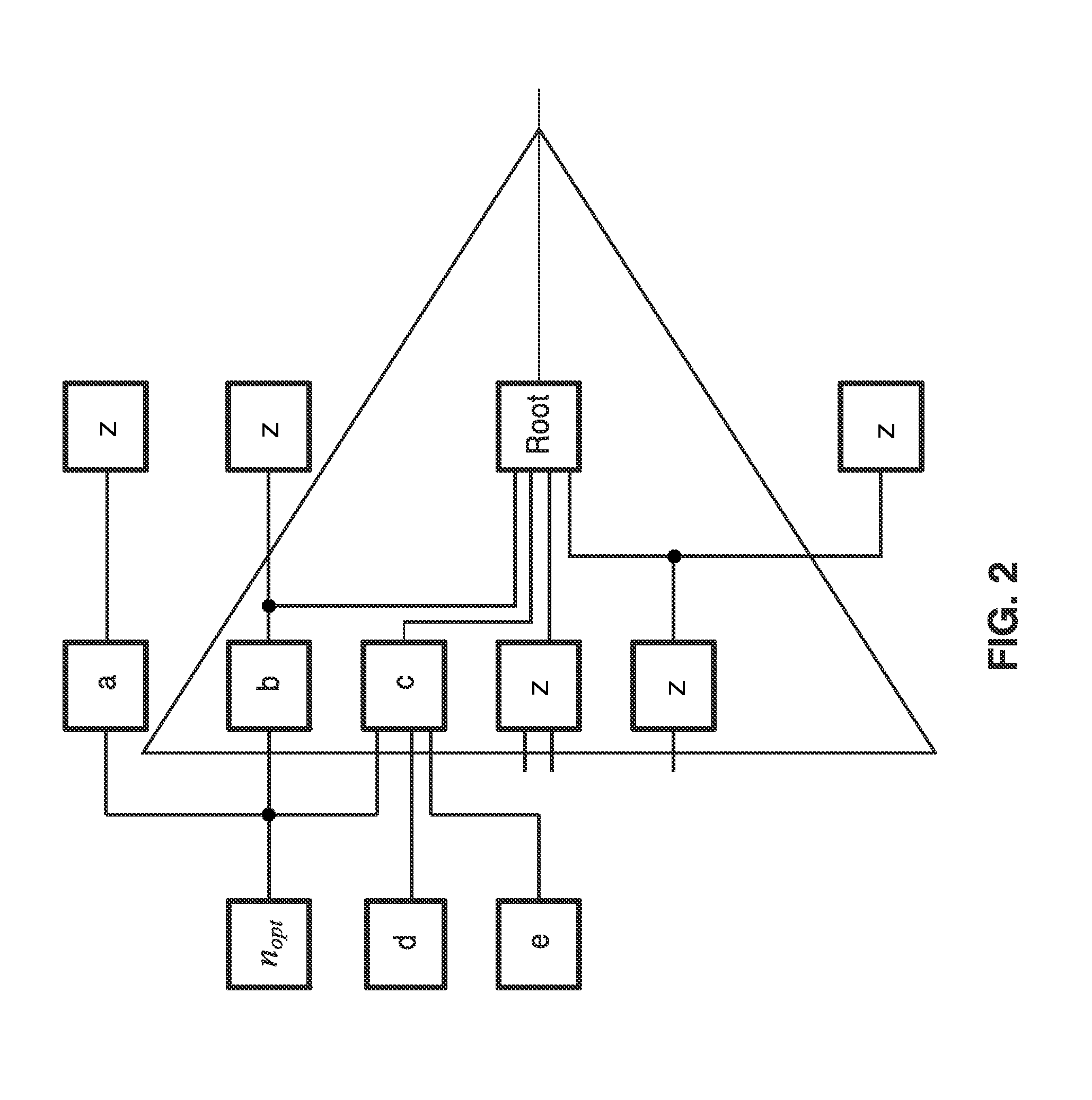

In-place resynthesis and remapping techniques for soft error mitigation in FPGA

InactiveUS20130305199A1Efficient and accurateImprove fault toleranceCAD circuit designRadiation hardeningFpga architectureDecomposition

In-place resynthesis for static memory (SRAM) based Field Programmable Gate Arrays (FPGAs) toward reducing sensitivity to single event upsets (SEUs). Resynthesis and remapping are described which have a low overheard and improve FPGA designs without the need of rerouting LUTs of the FPGA. These methods include in-place reconfiguration (IPR), in-place X-filling (IPF), and in-place inversion (IPV), which reconfigure LUT functions only, and can be applied to any FPGA architecture. In addition, for FPGAs with a decomposable LUT architecture (e.g., dual-output LUTs) an in-place decomposition (IPD) method is described for remapping a LUT function into multiple smaller functions leveraging the unused outputs of the LUT, and making use of built-in hard macros in programmable-logic blocks (PLBs) such as carry chain or adder. Methods are applied in-place to mapped circuits before or after routing without affecting placement, routing, and design closure.

Owner:RGT UNIV OF CALIFORNIA

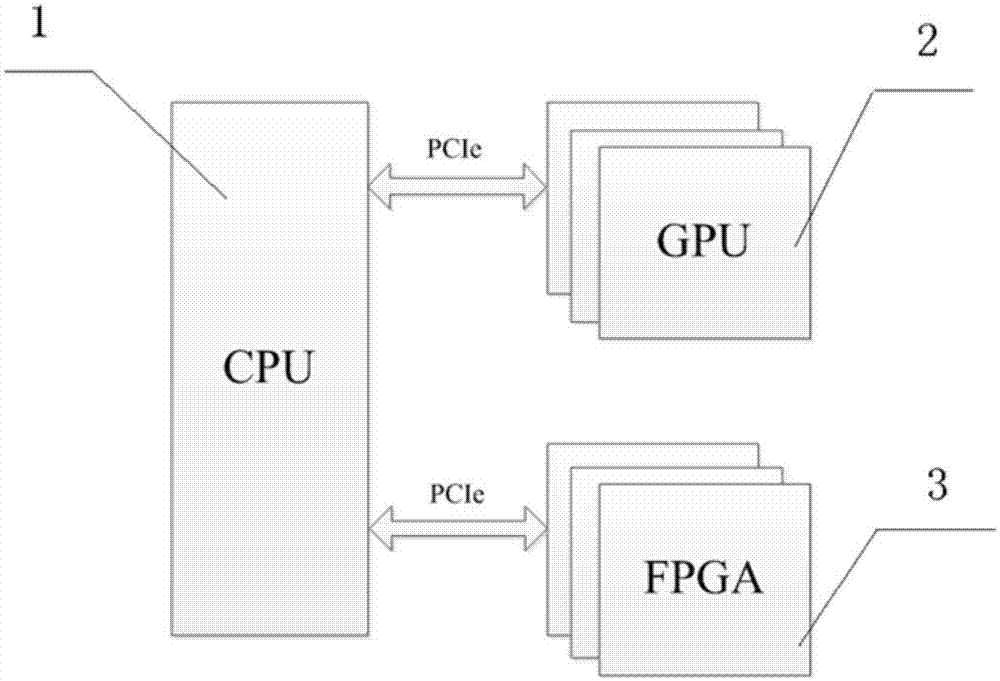

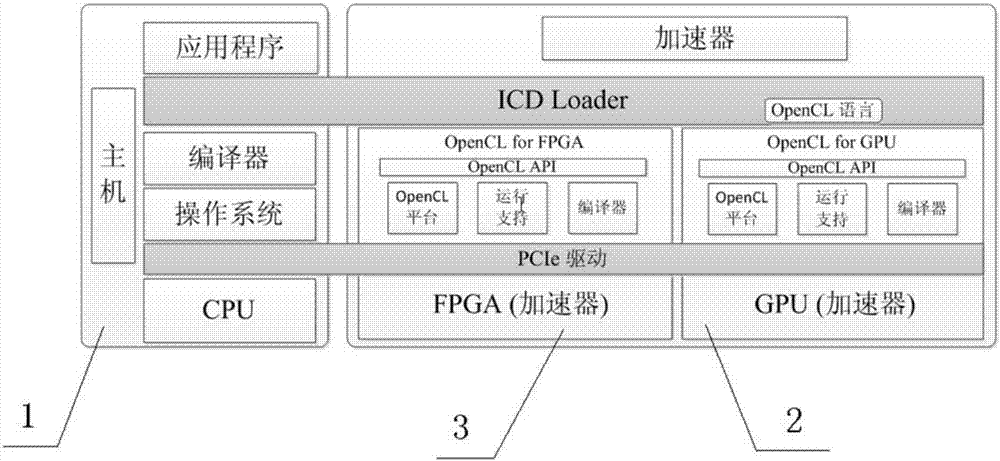

Heterogeneous computing system and method based on CPU+GPU+FPGA architecture

InactiveCN107273331AGive full play to the advantages of management and controlTake full advantage of parallel processingArchitecture with single central processing unitEnergy efficient computingFpga architectureResource management

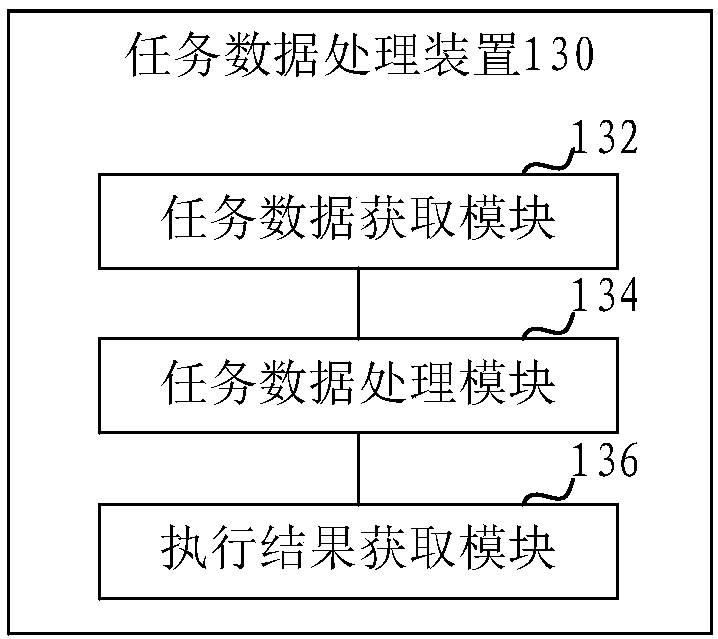

The invention provides a heterogeneous computing system based on CPU+GPU+FPGA architecture. The system comprises a CPU host unit, one or more GPU heterogeneous acceleration units and one or more FPGA heterogeneous acceleration units. The CPU host unit is in communication connection with the GPU heterogeneous acceleration units and the FPGA heterogeneous acceleration units. The CPU host unit is used for managing resources and allocating processing tasks to the GPU heterogeneous acceleration units and / or the FPGA heterogeneous acceleration units. The GPU heterogeneous acceleration units are used for carrying out parallel processing on tasks from the CPU host unit. The FPGA heterogeneous acceleration units are used for carrying out serial or parallel processing on the tasks from the CPU host unit. According to the heterogeneous computing system provided by the invention, the control advantages of the CPU, the parallel processing advantages of the GPU, the performance and power consumption ratio and flexible configuration advantages of the FPGA can be exerted fully, the heterogeneous computing system can adapt to different application scenes and can satisfy different kinds of task demands. The invention also provides a heterogeneous computing method based on the CPU+GPU+FPGA architecture.

Owner:SHANDONG CHAOYUE DATA CONTROL ELECTRONICS CO LTD

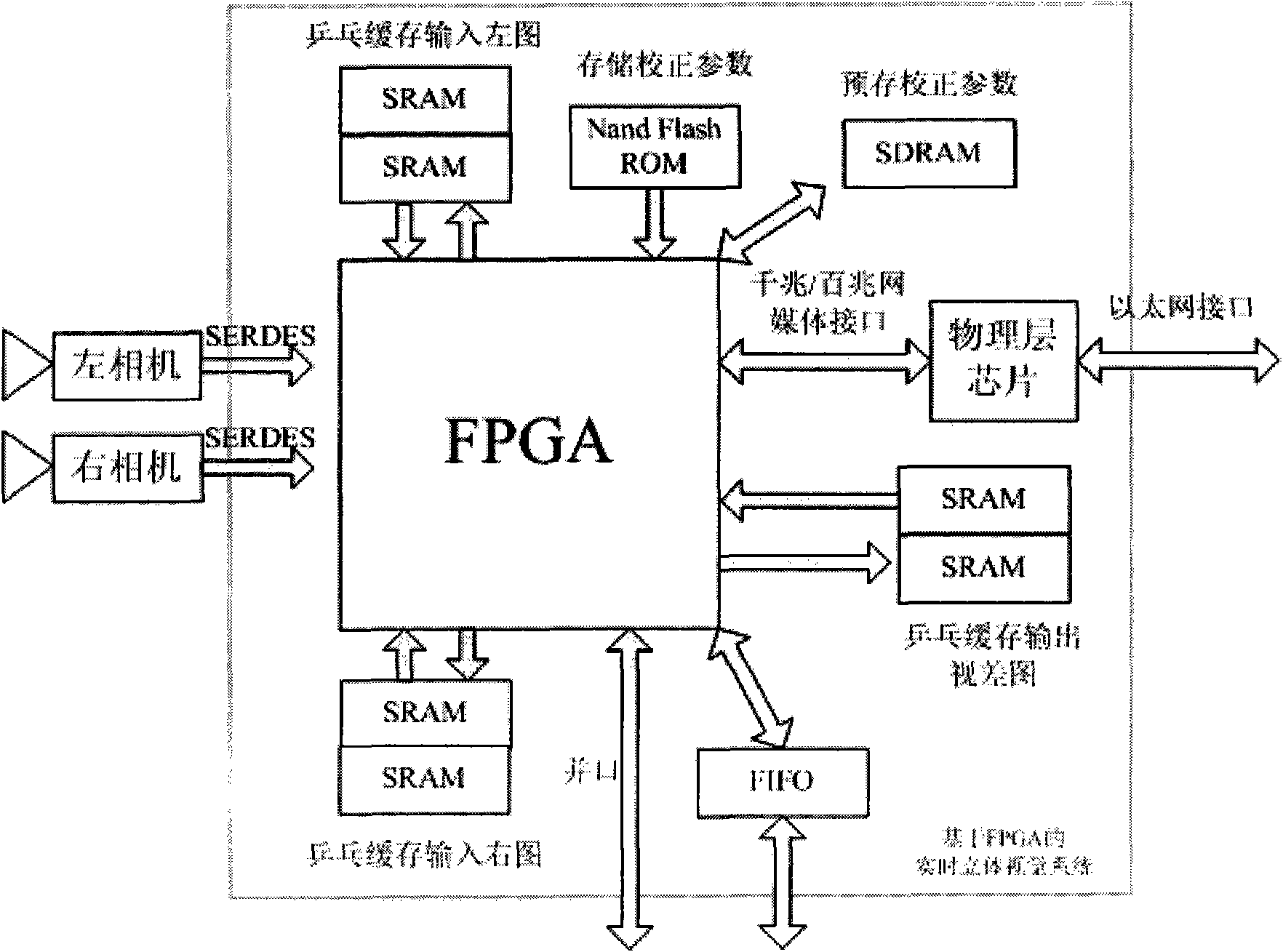

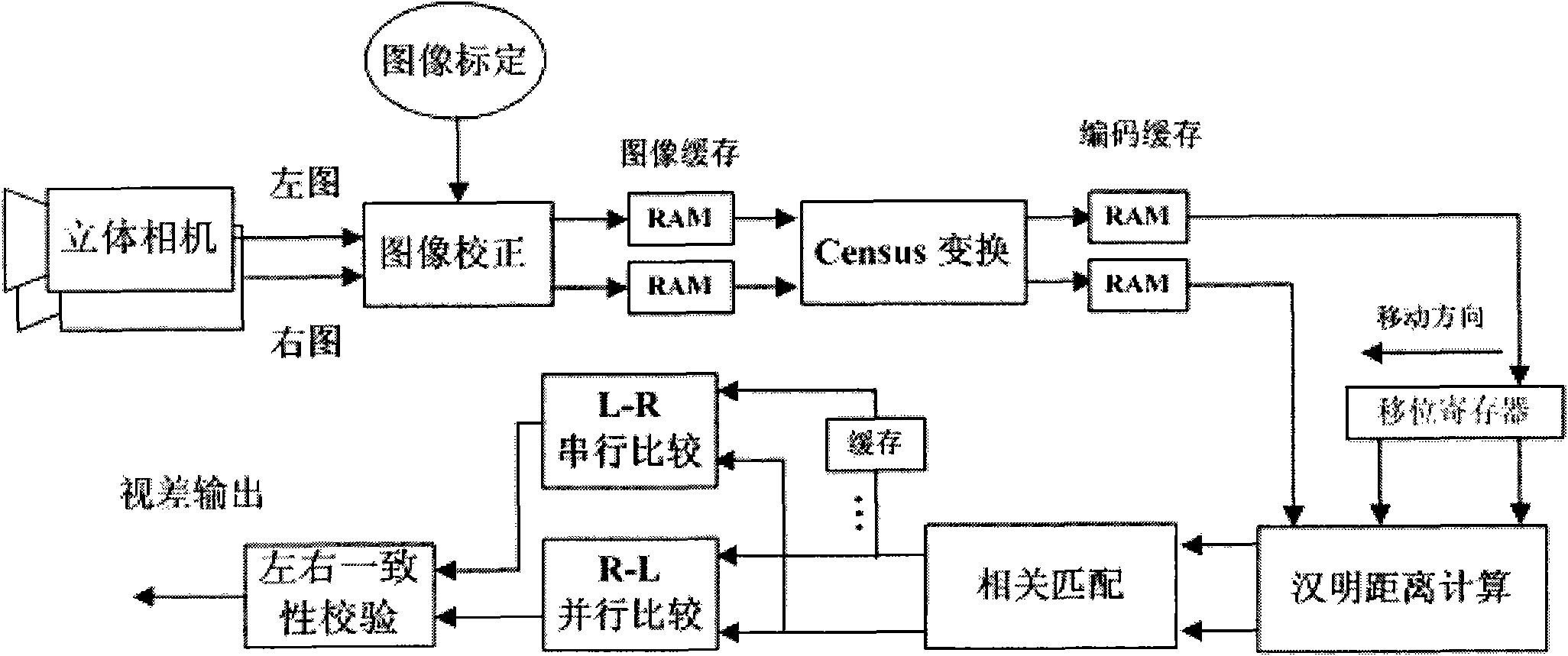

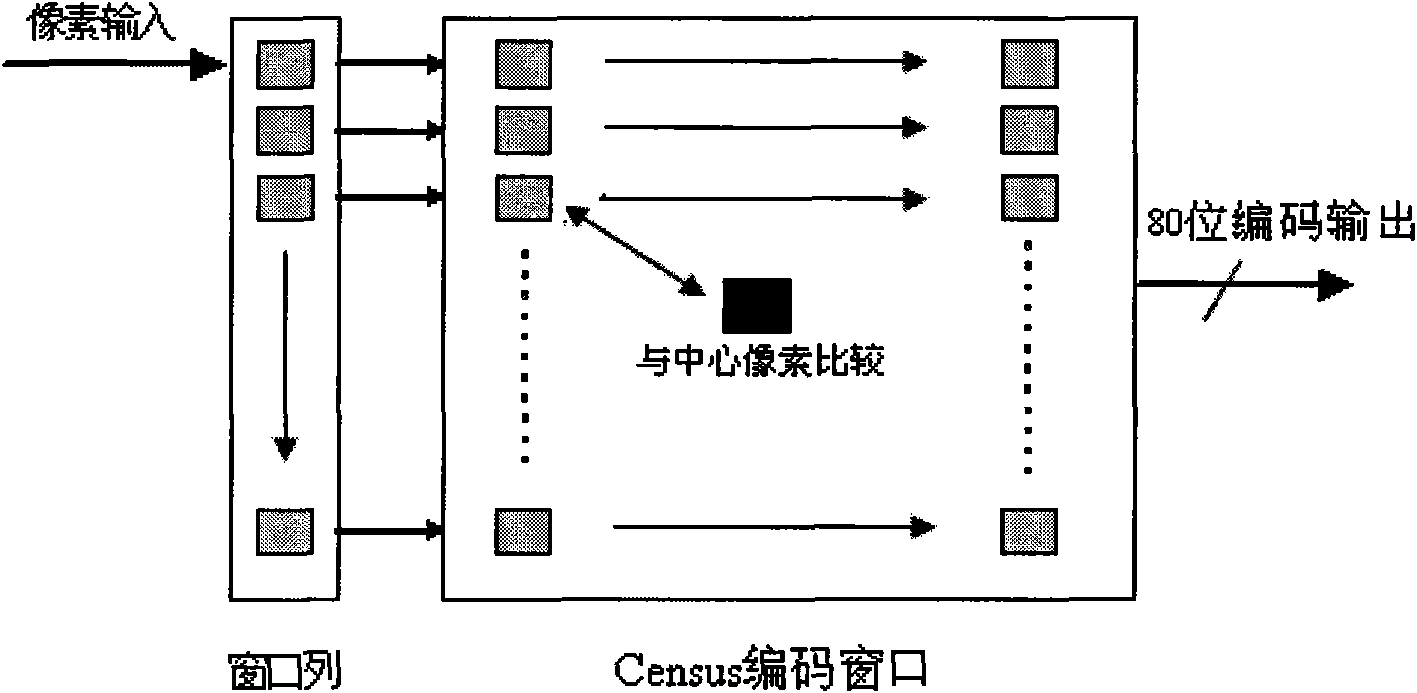

Real-time stereoscopic vision implementation method based on FPGA

InactiveCN101841730AReduce false match rateReasonable hardware architectureImage data processing detailsSteroscopic systemsHardware structureProduction line

The invention discloses a real-time stereoscopic vision implementation method based on FPGA. The implementation method operates in stereoscopic vision system which takes the FPGA as a core processing unit, has reasonable hardware structure, can meet the requirements of high-speed operation and high-seed transmission images, has multiple general interfaces and rich hardware resources, and can be further expanded and strengthened. Simultaneously a stereoscopic matching algorithm based on Census conversion is a non-parameterized matching method, is more robust for the conditions of non-uniform brightness, gain and the like, and improves the accuracy of the system. The invention adopts the reasonable hardware structure on the FPGA architecture, simultaneously implements a Census stereoscopic matching method by an ingenious logic design, and improves the accuracy and speed of stereoscopic vision implementation. Compared with the traditional method based on a general processor, the real-time stereoscopic vision implementation method utilizes parallel calculation and a reasonable production line design fully to map the algorithm on the structure, greatly improves the operating speed of the system, meets the requirements of high resolution, high accuracy and high speed and can be applicable to fields of autonomous vehicle navigation and the like.

Owner:ZHEJIANG UNIV

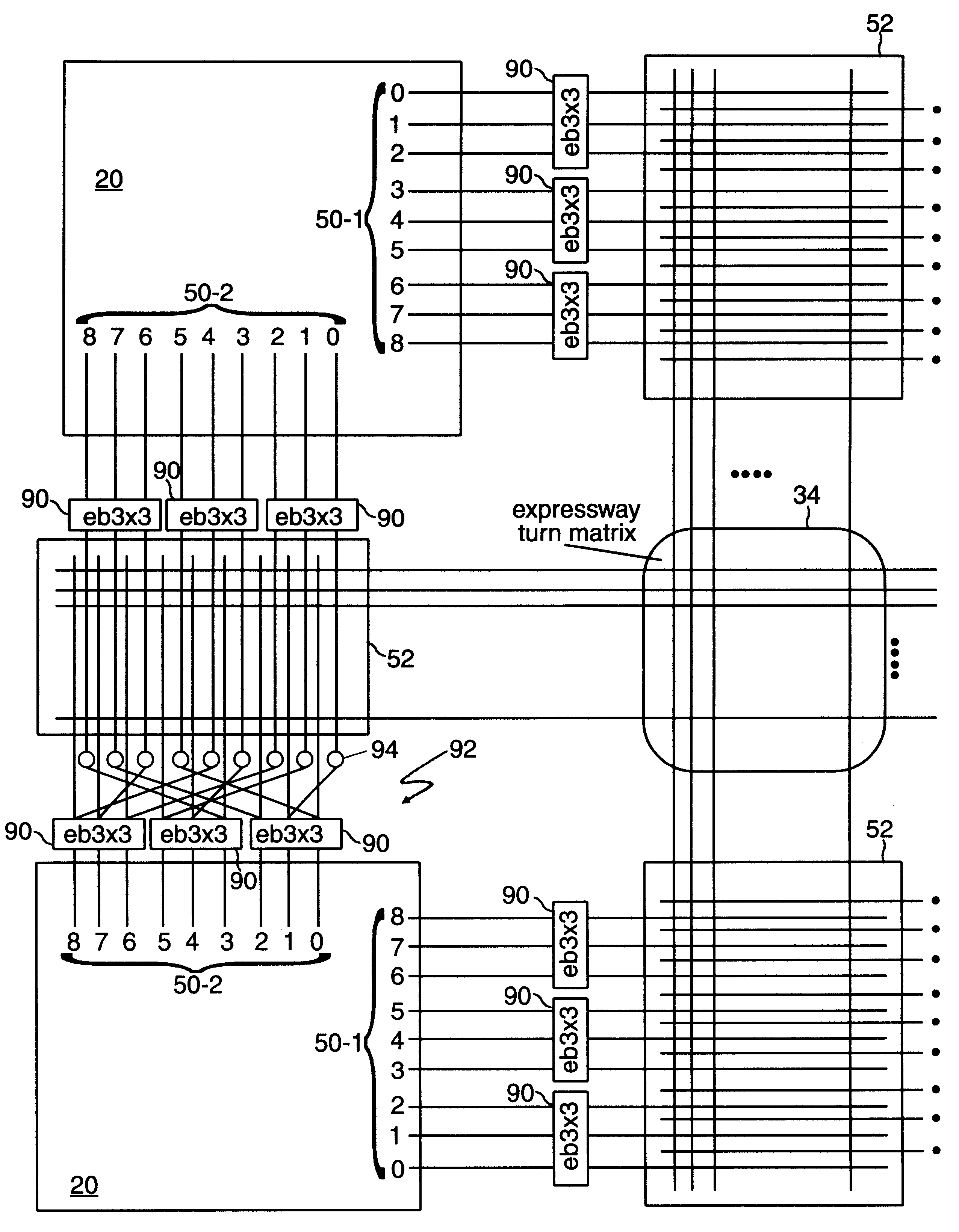

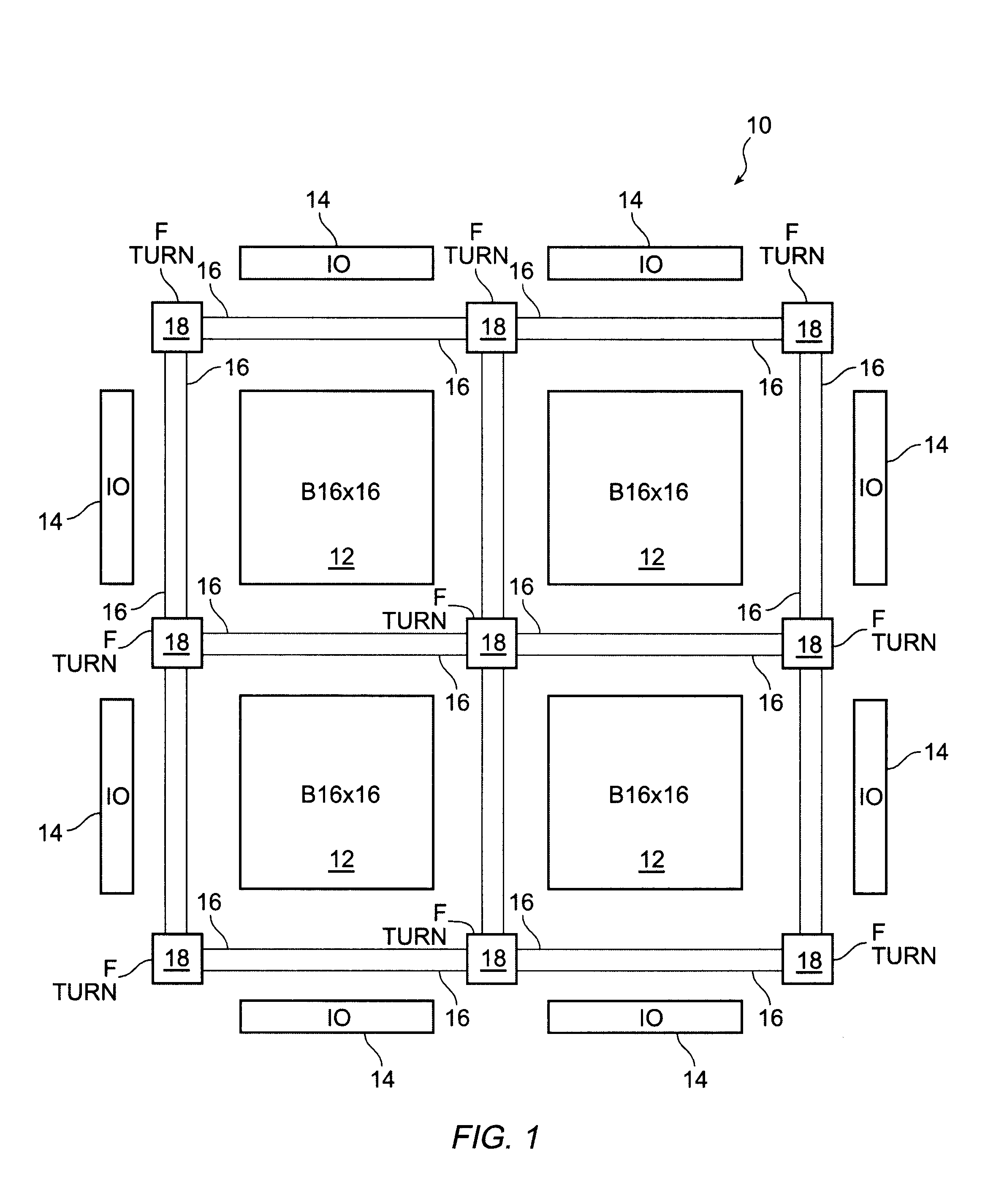

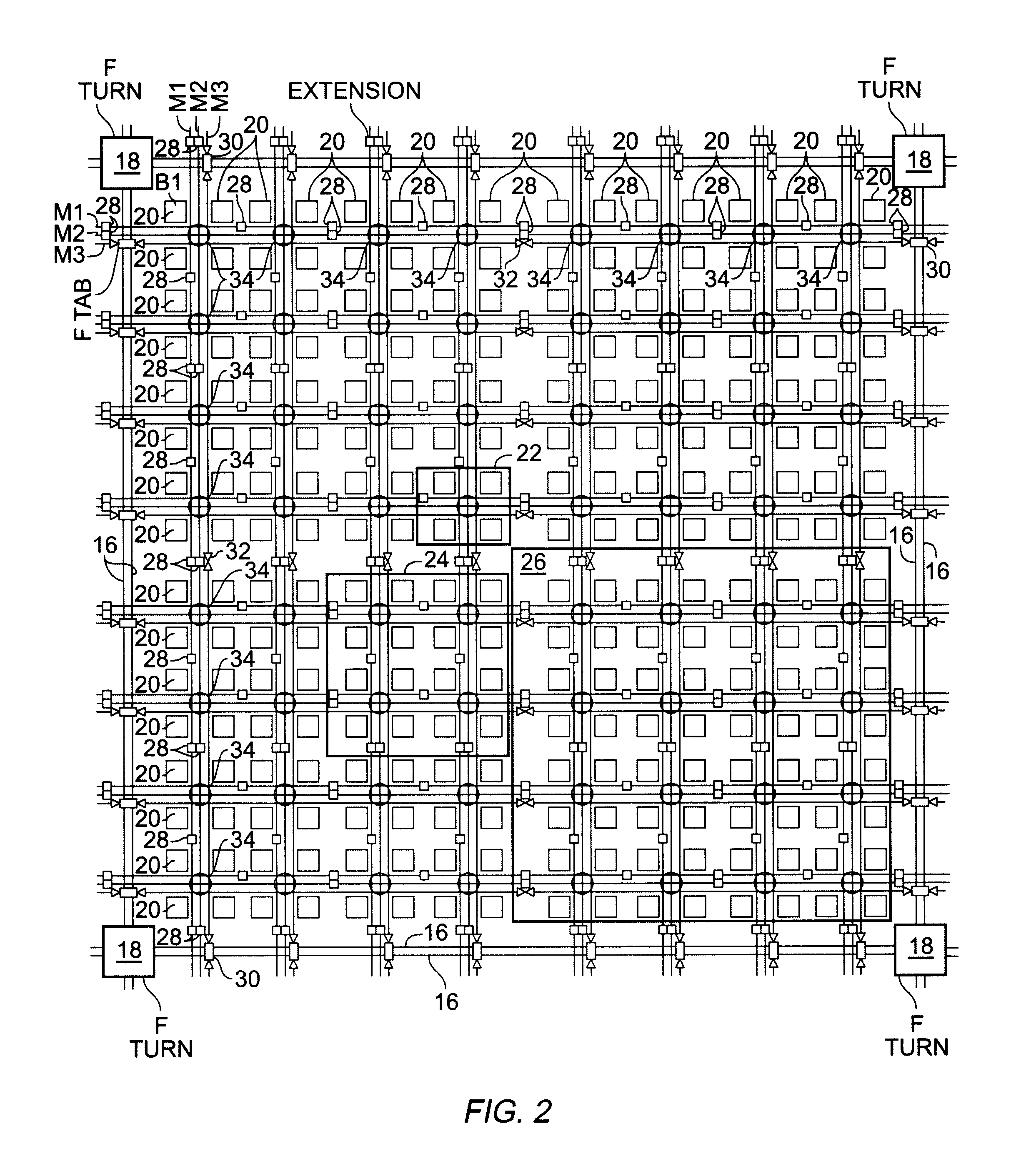

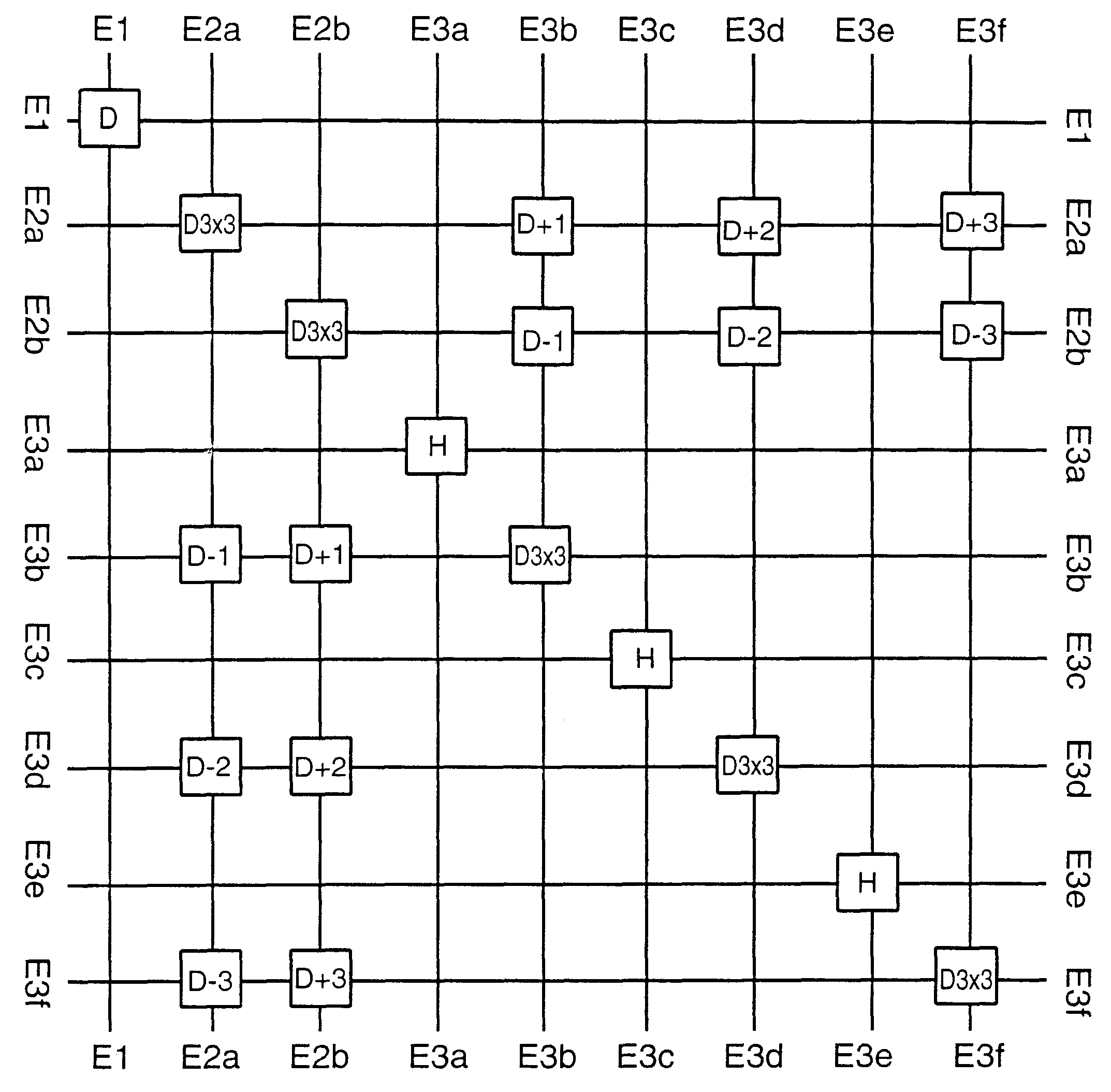

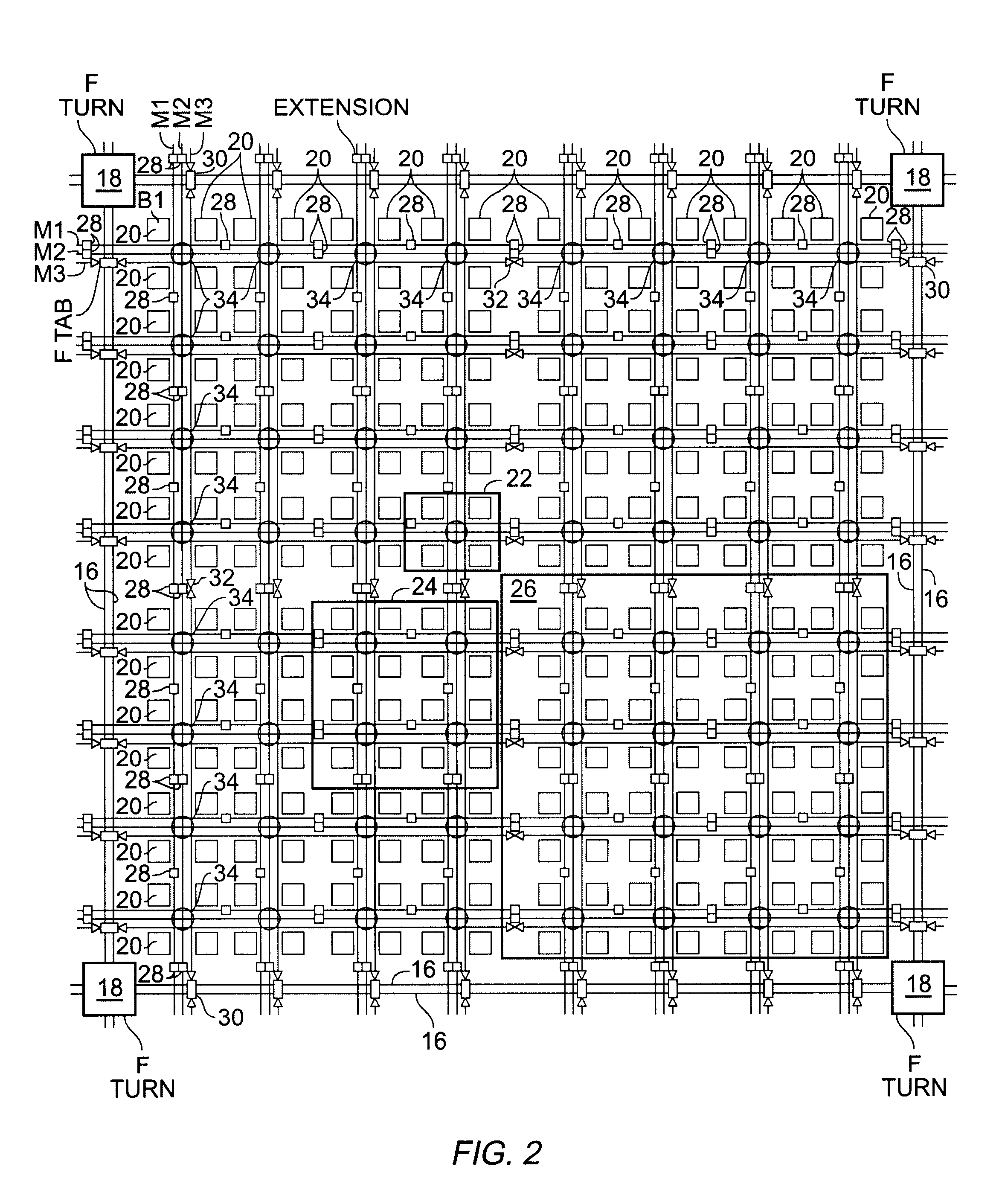

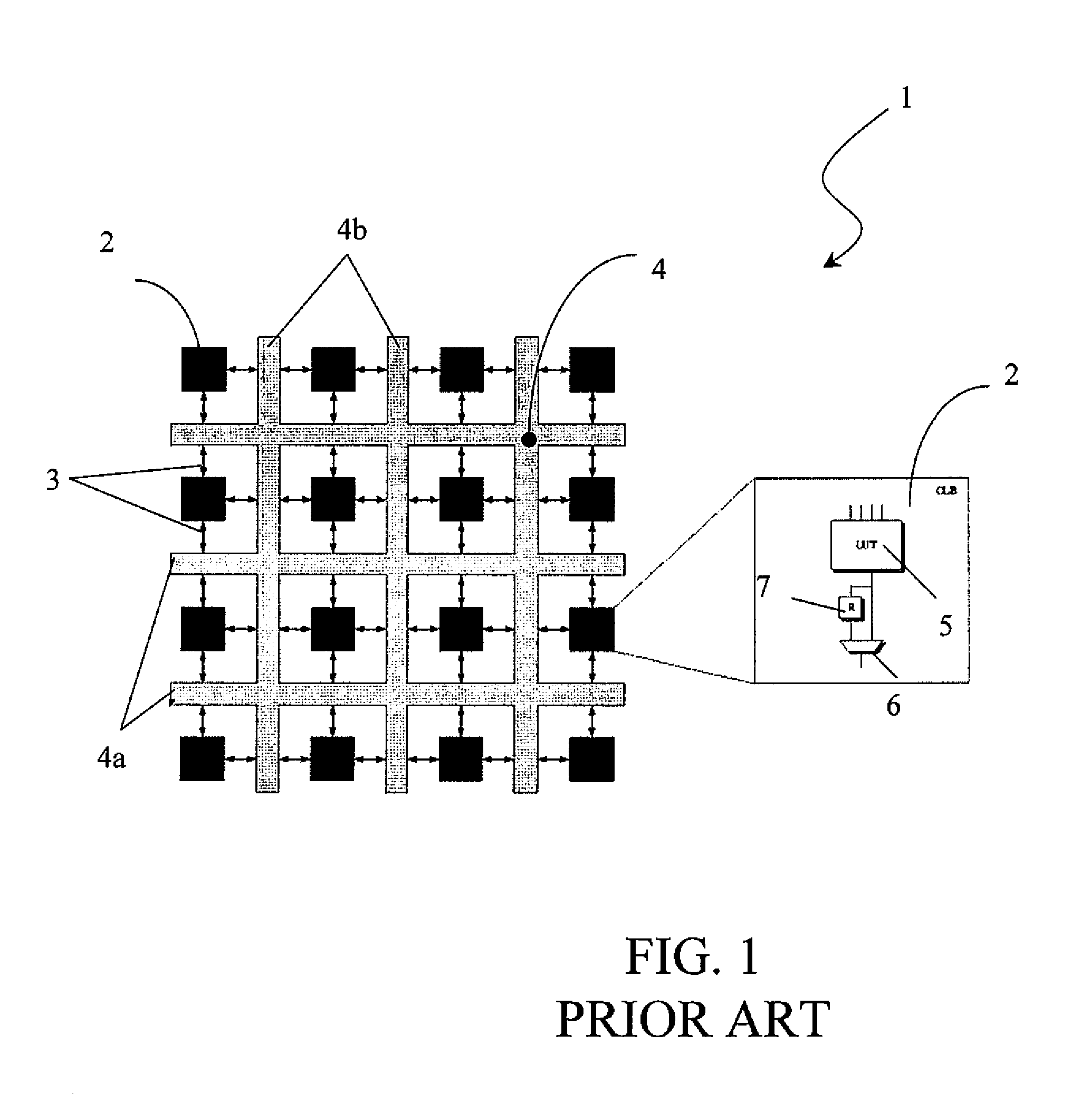

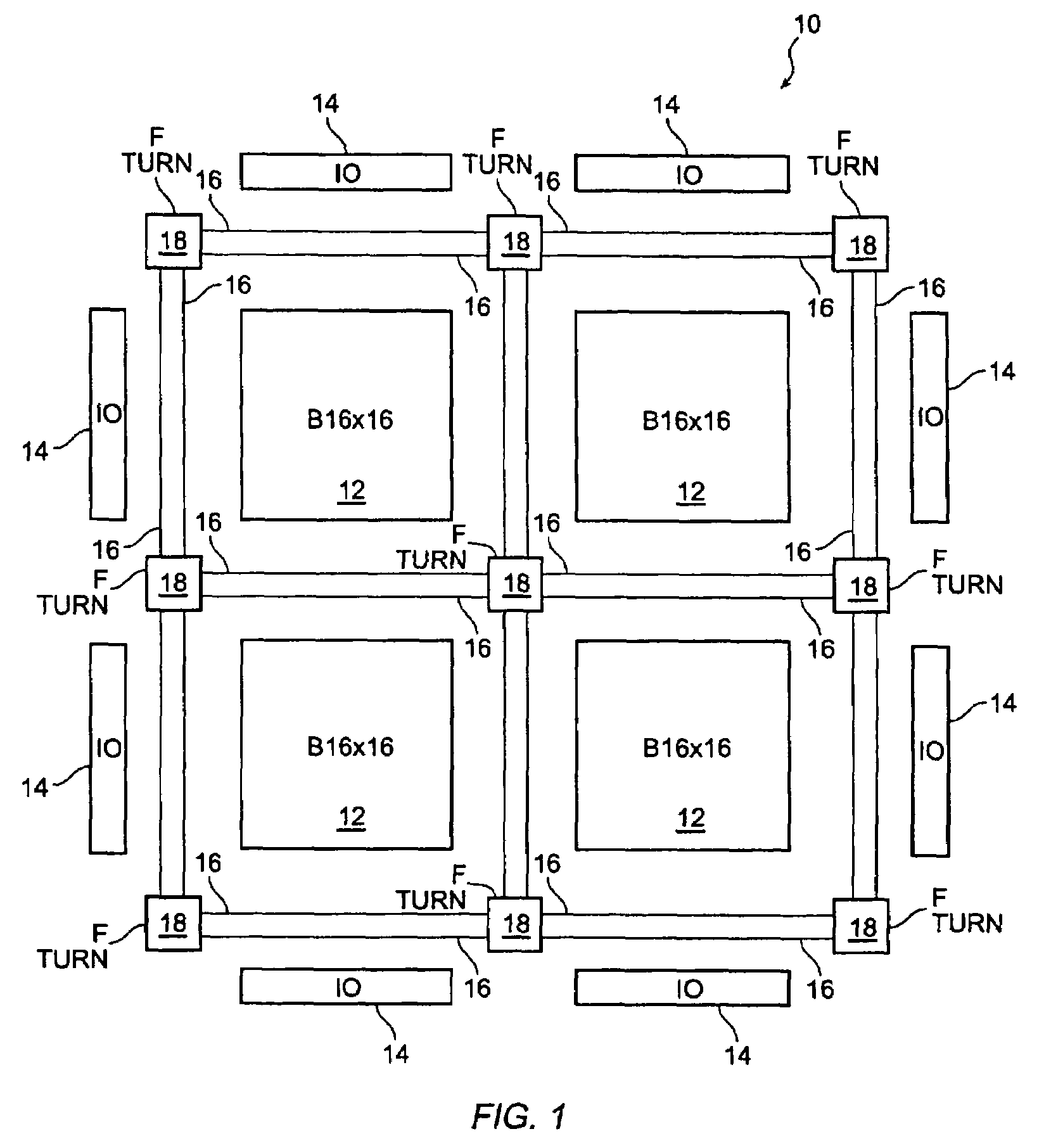

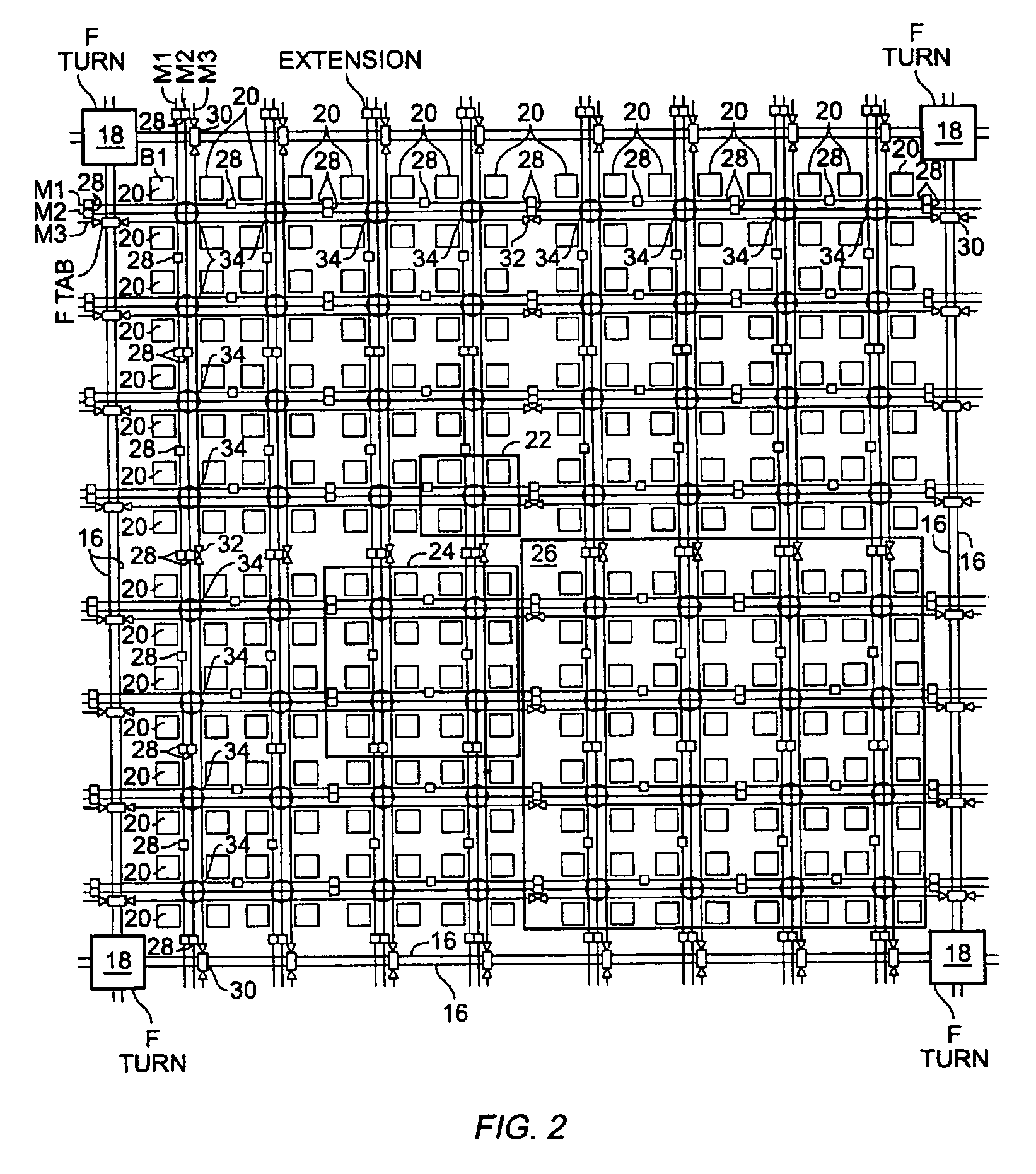

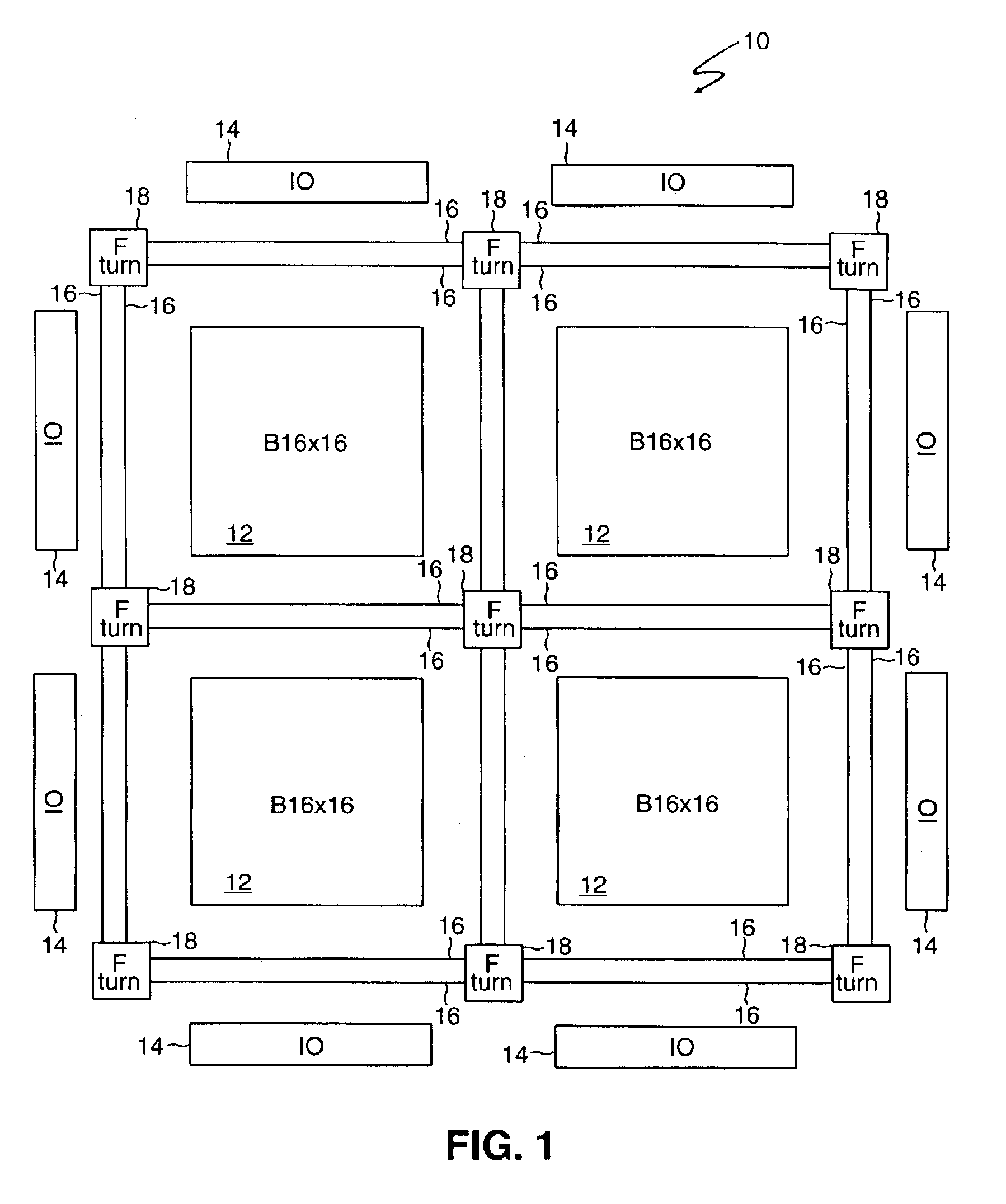

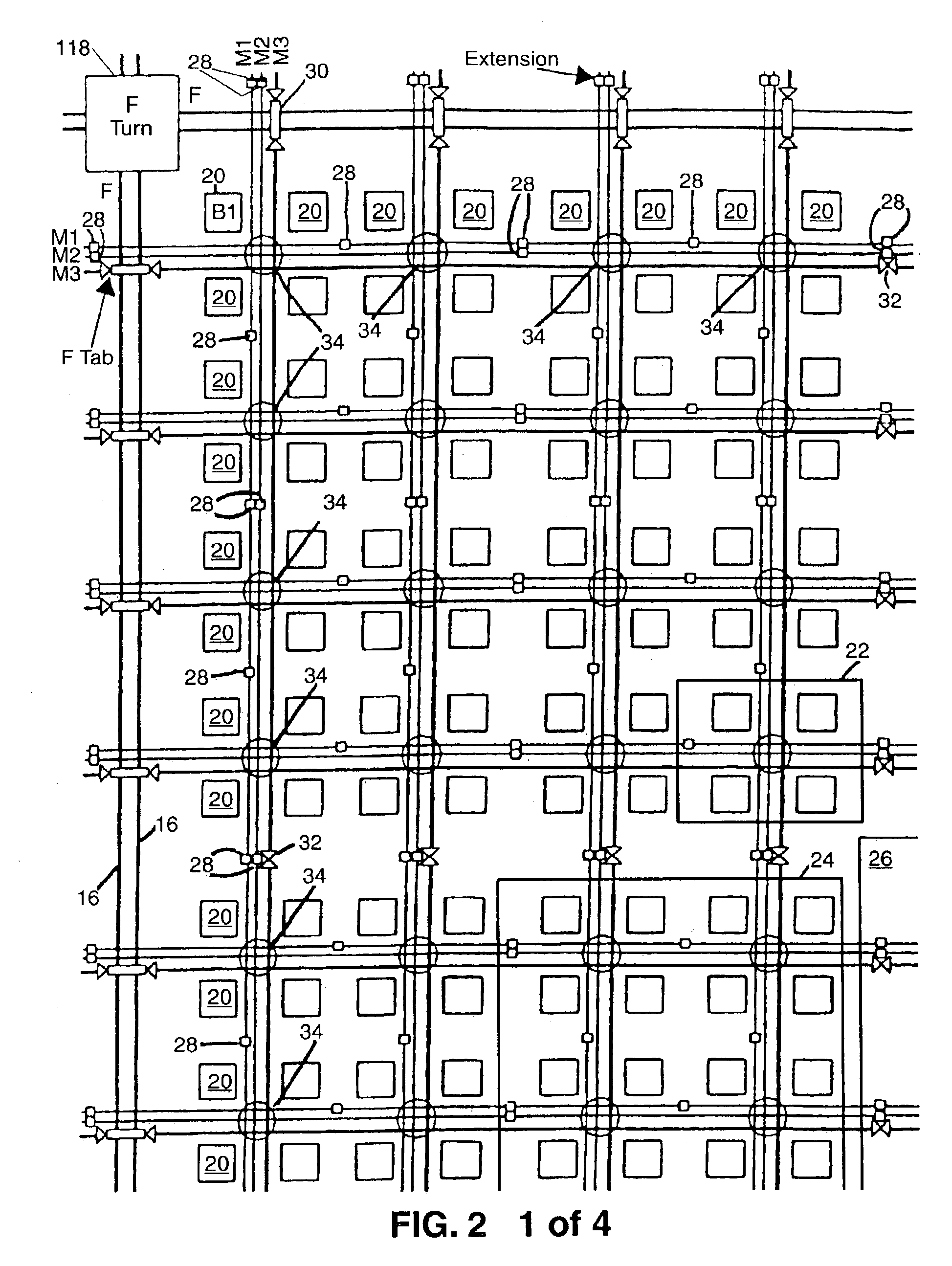

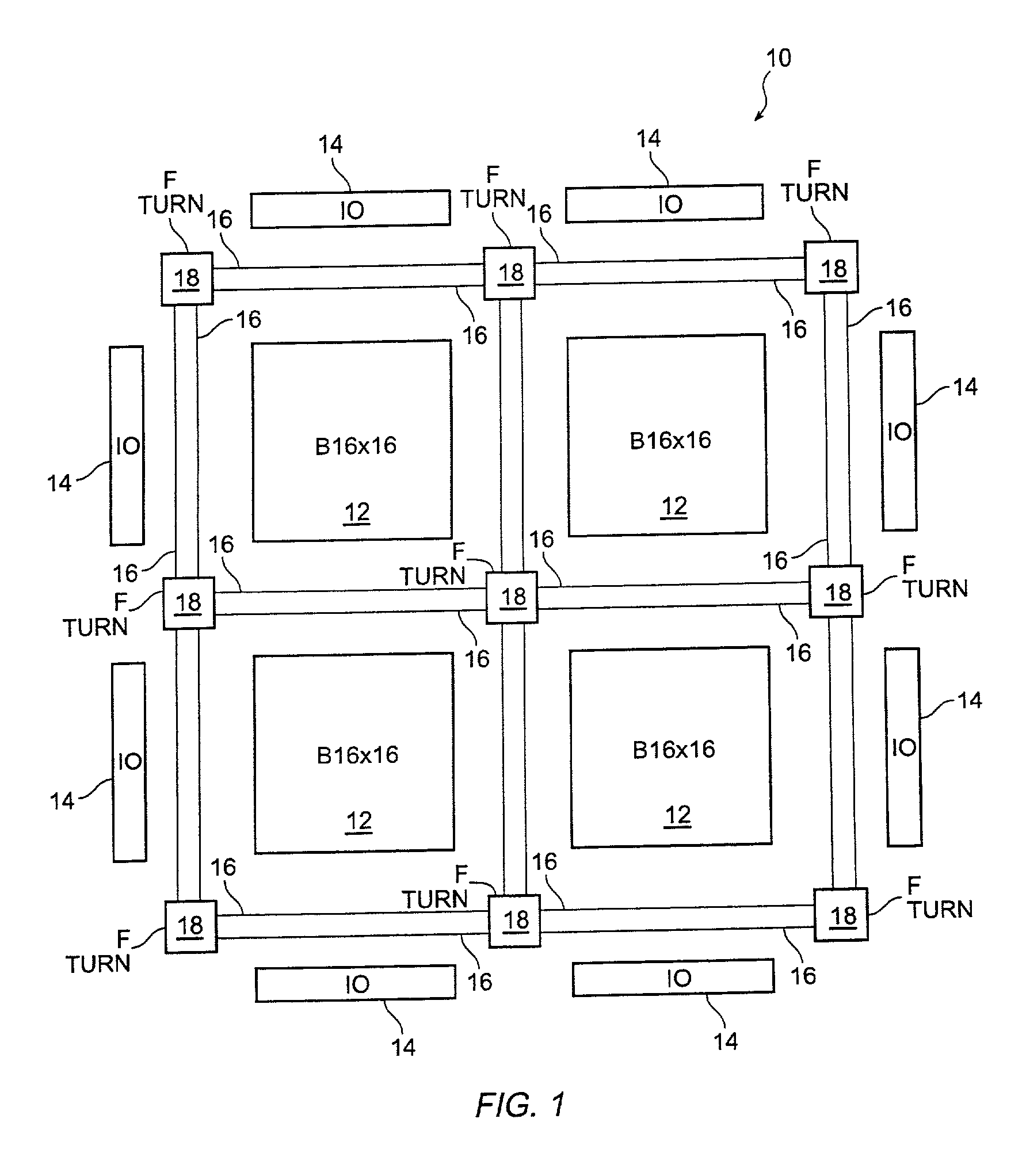

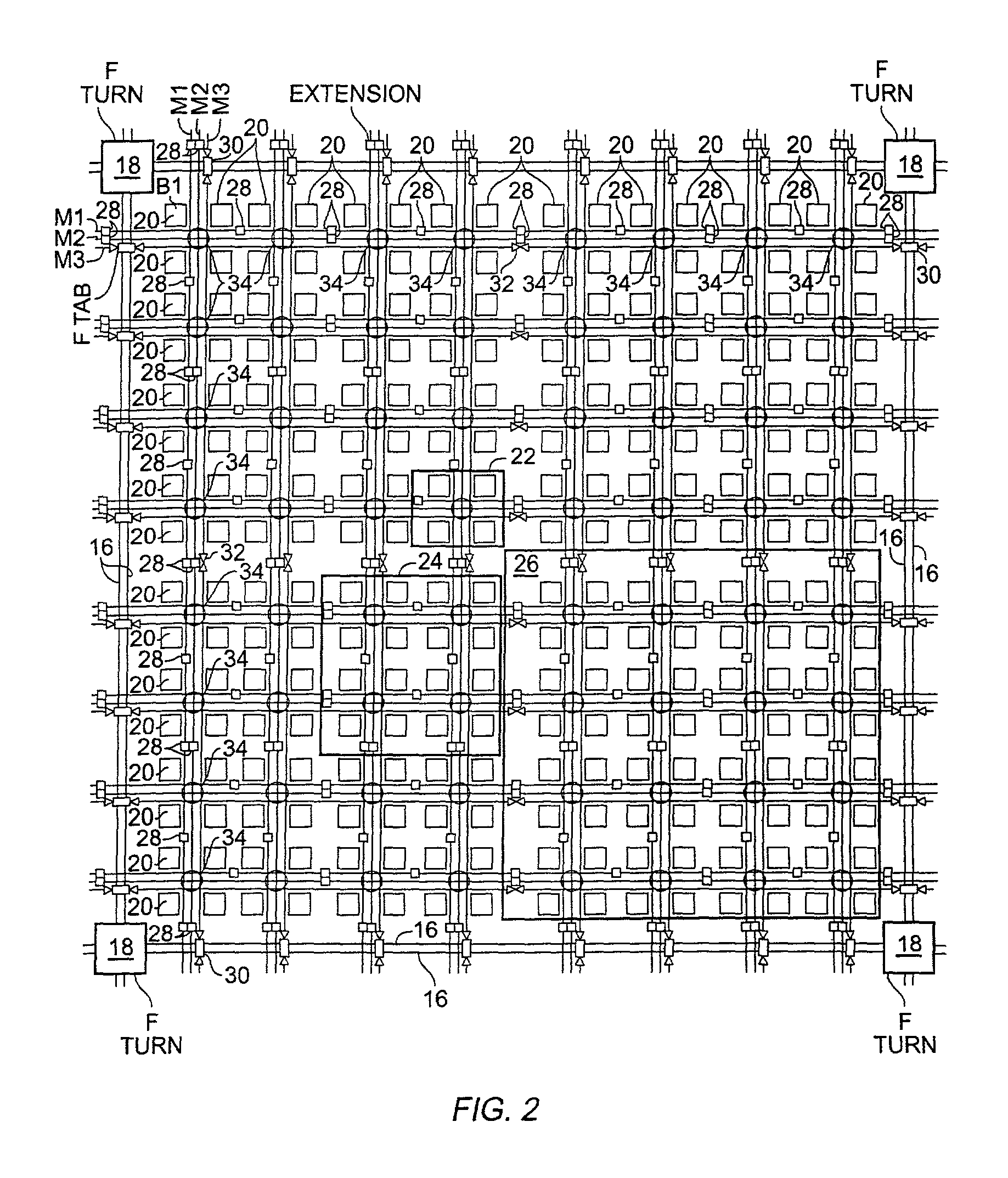

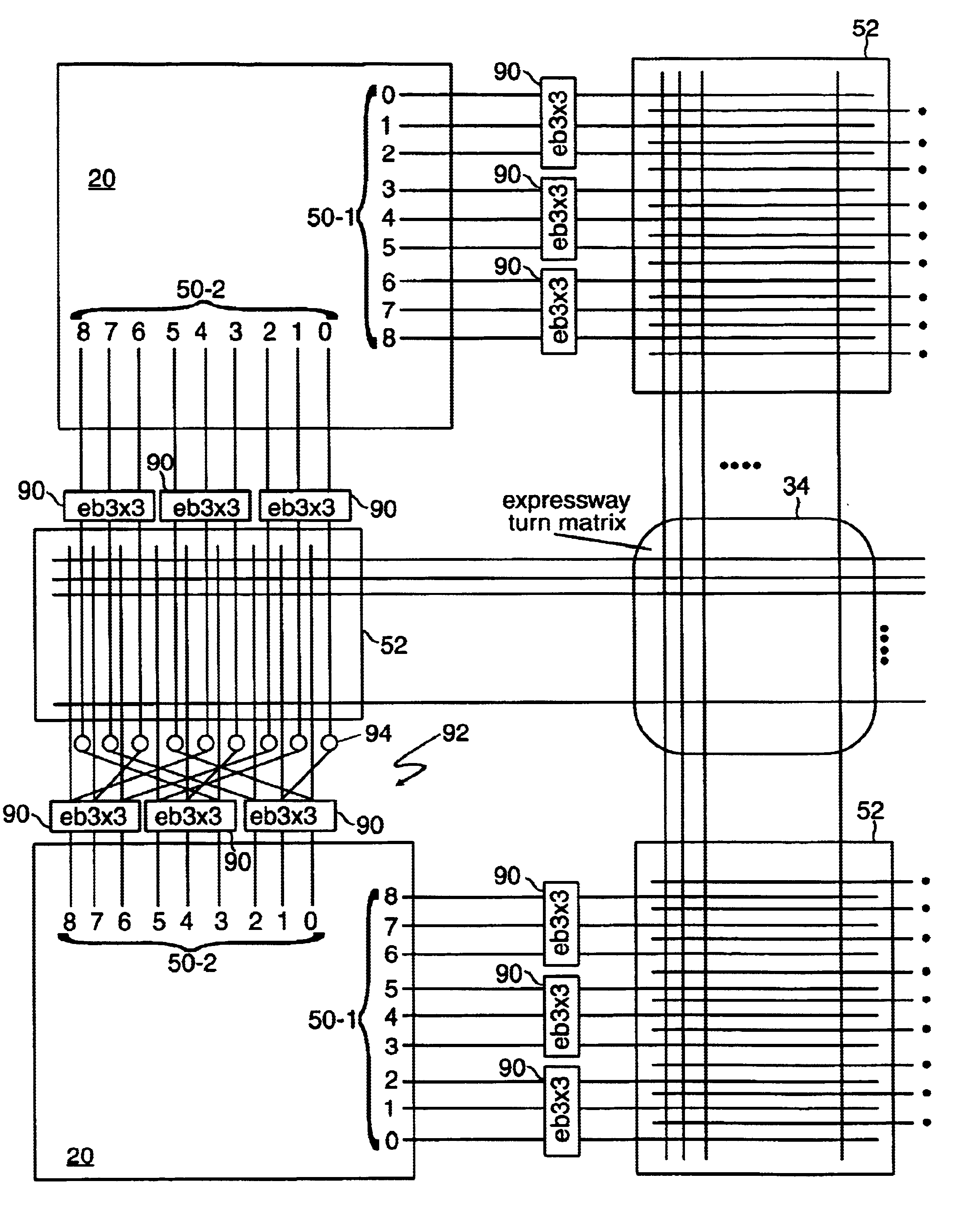

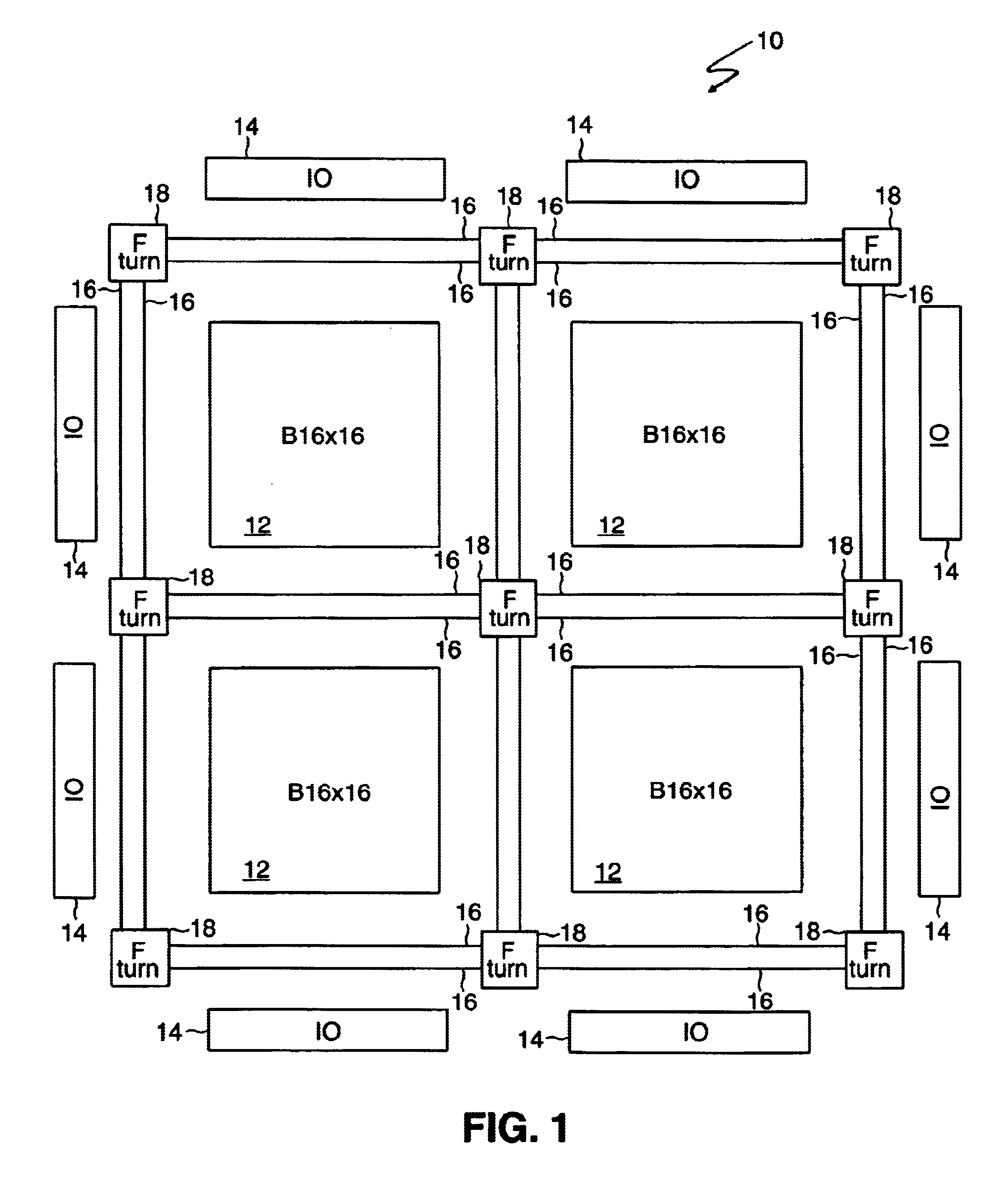

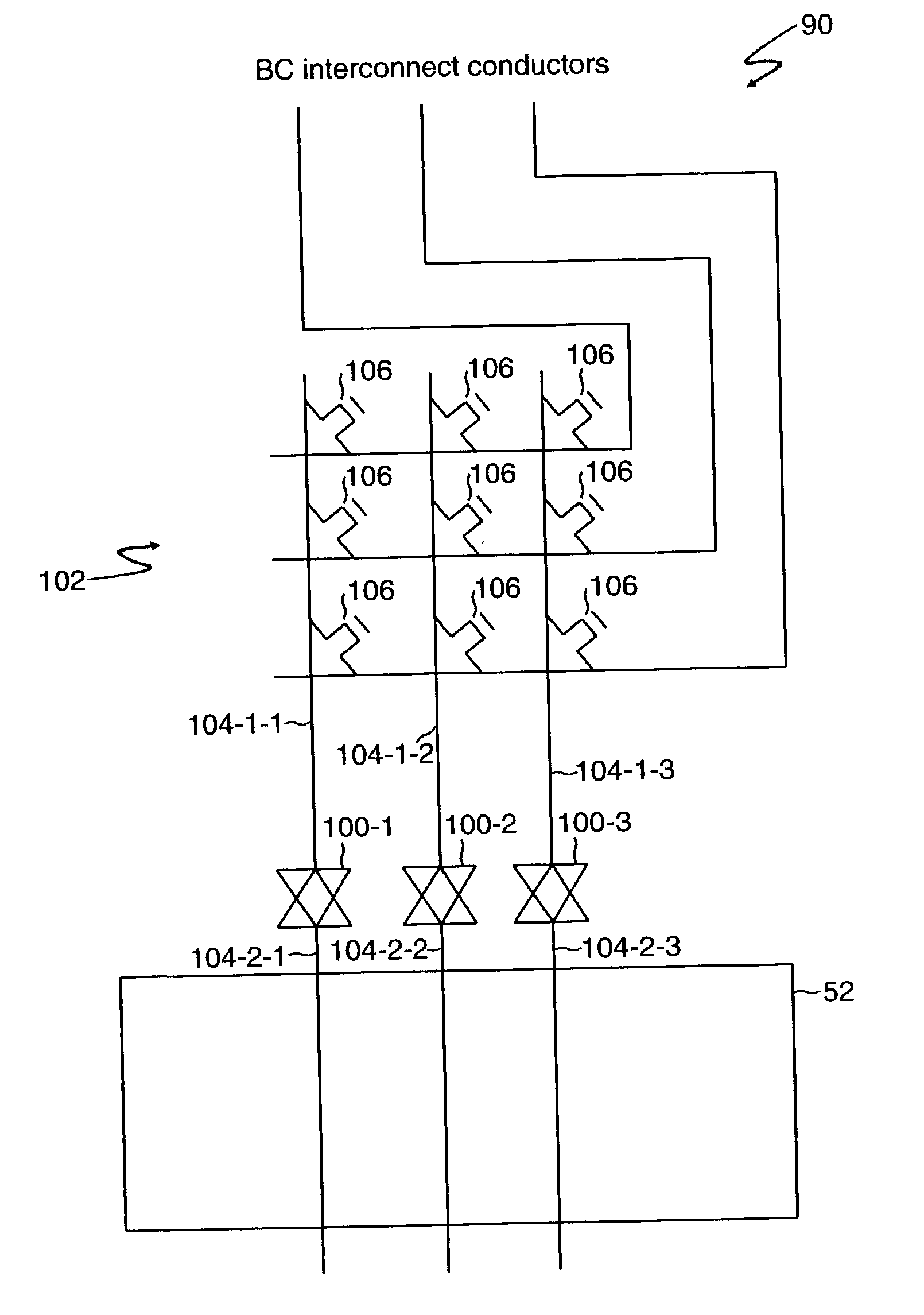

Block level routing architecture in a field programmable gate array

InactiveUS6567968B1Good symmetryEasy to placeSolid-state devicesSpecial data processing applicationsFpga architectureElectrical conductor

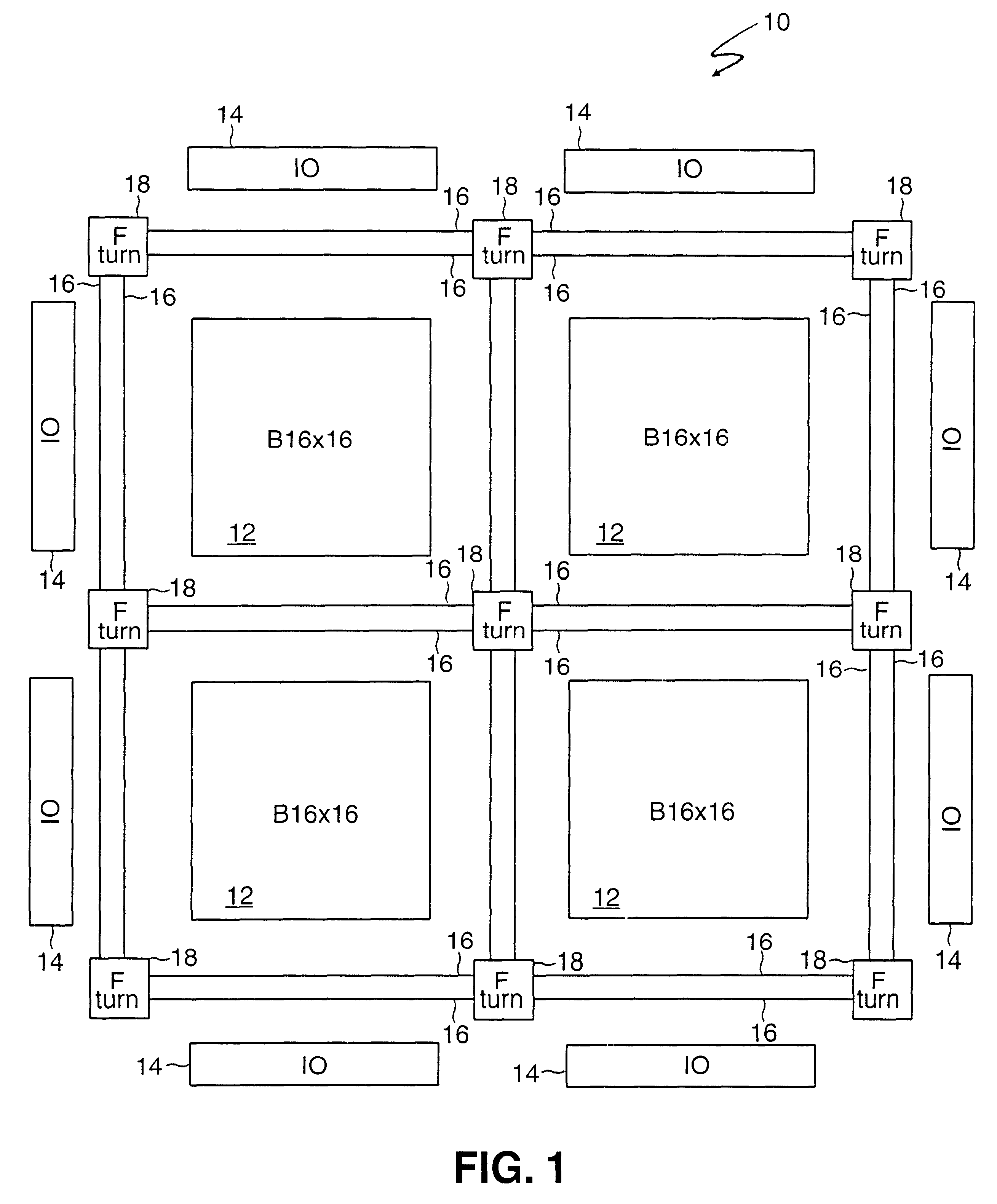

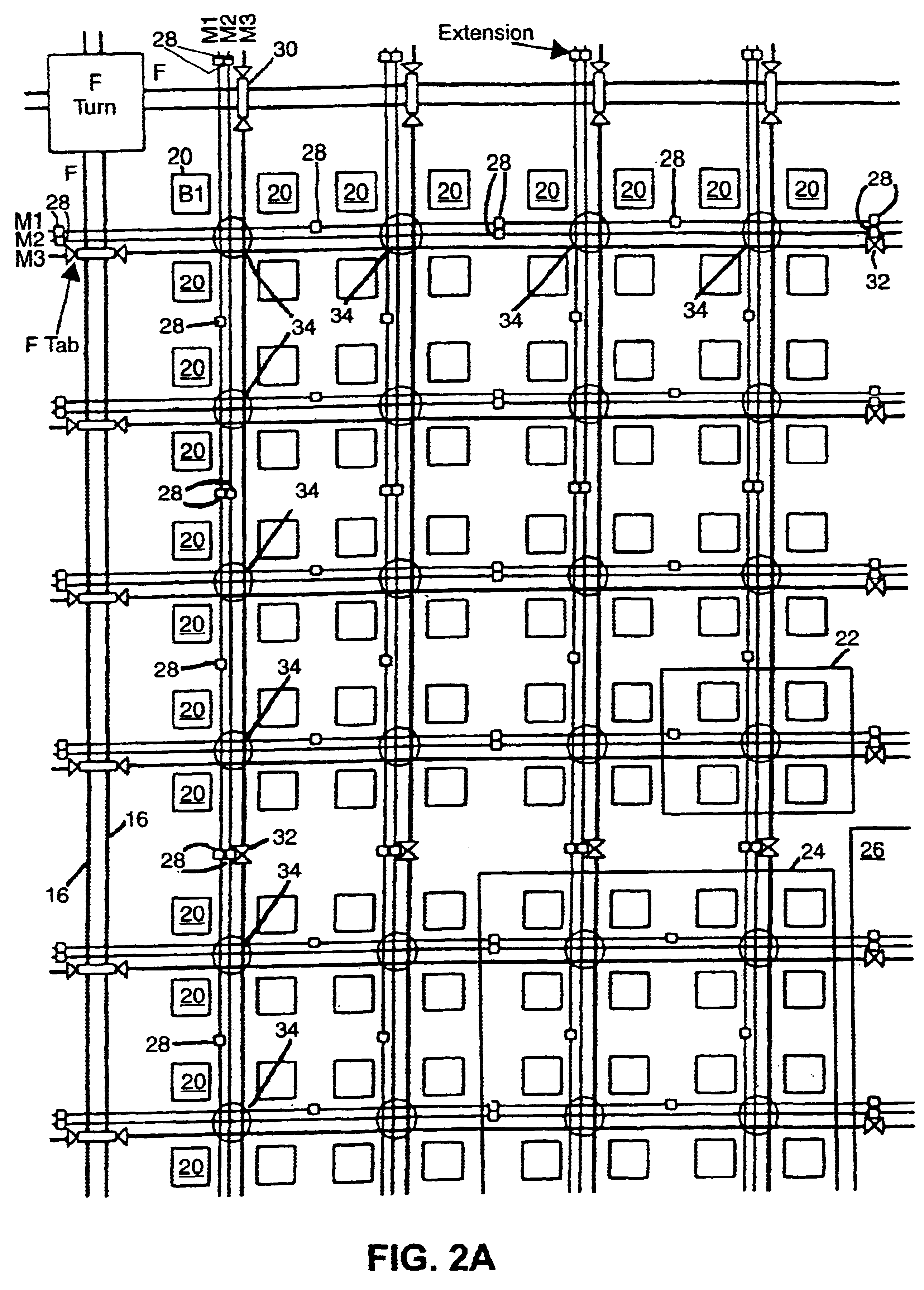

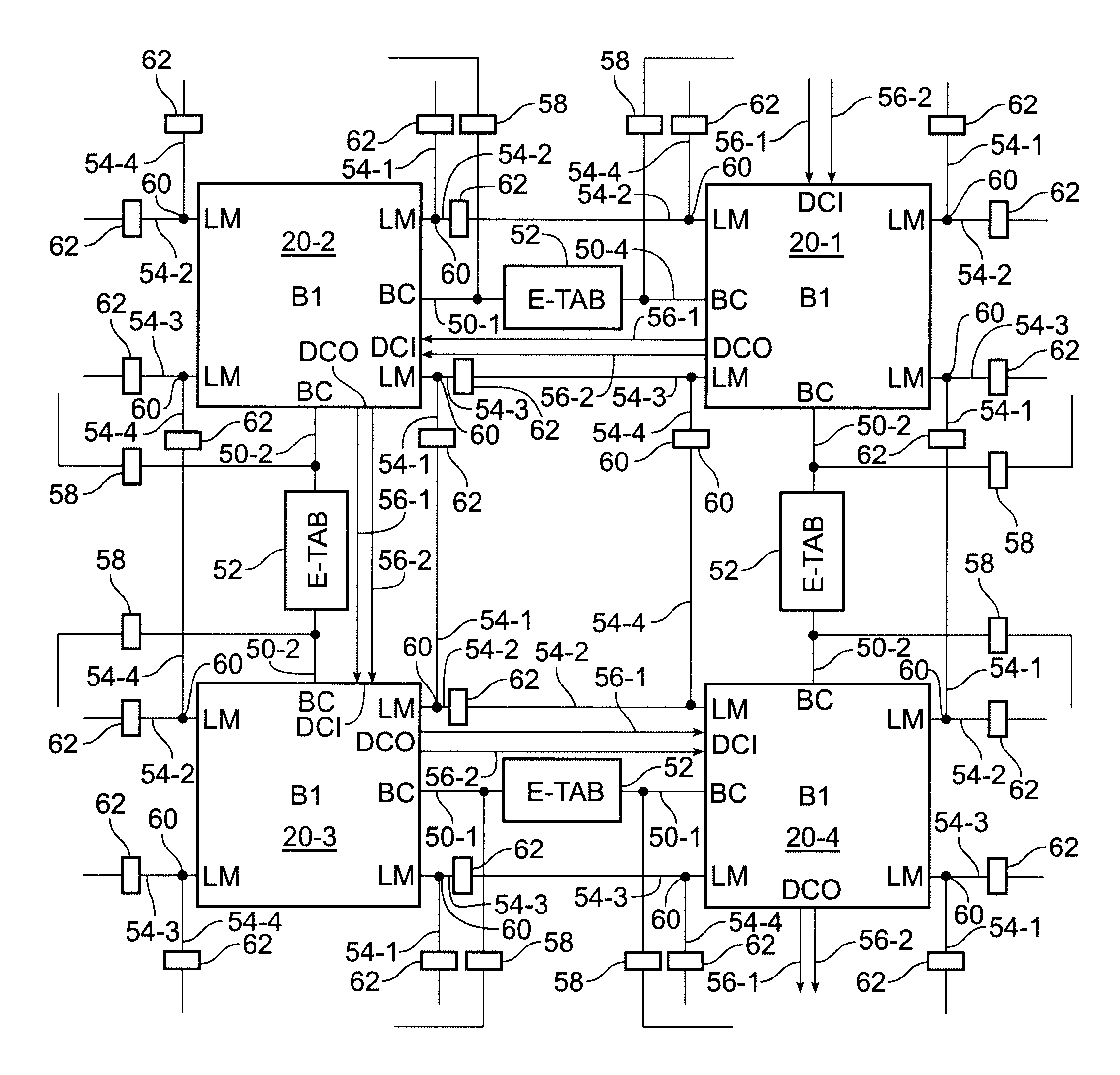

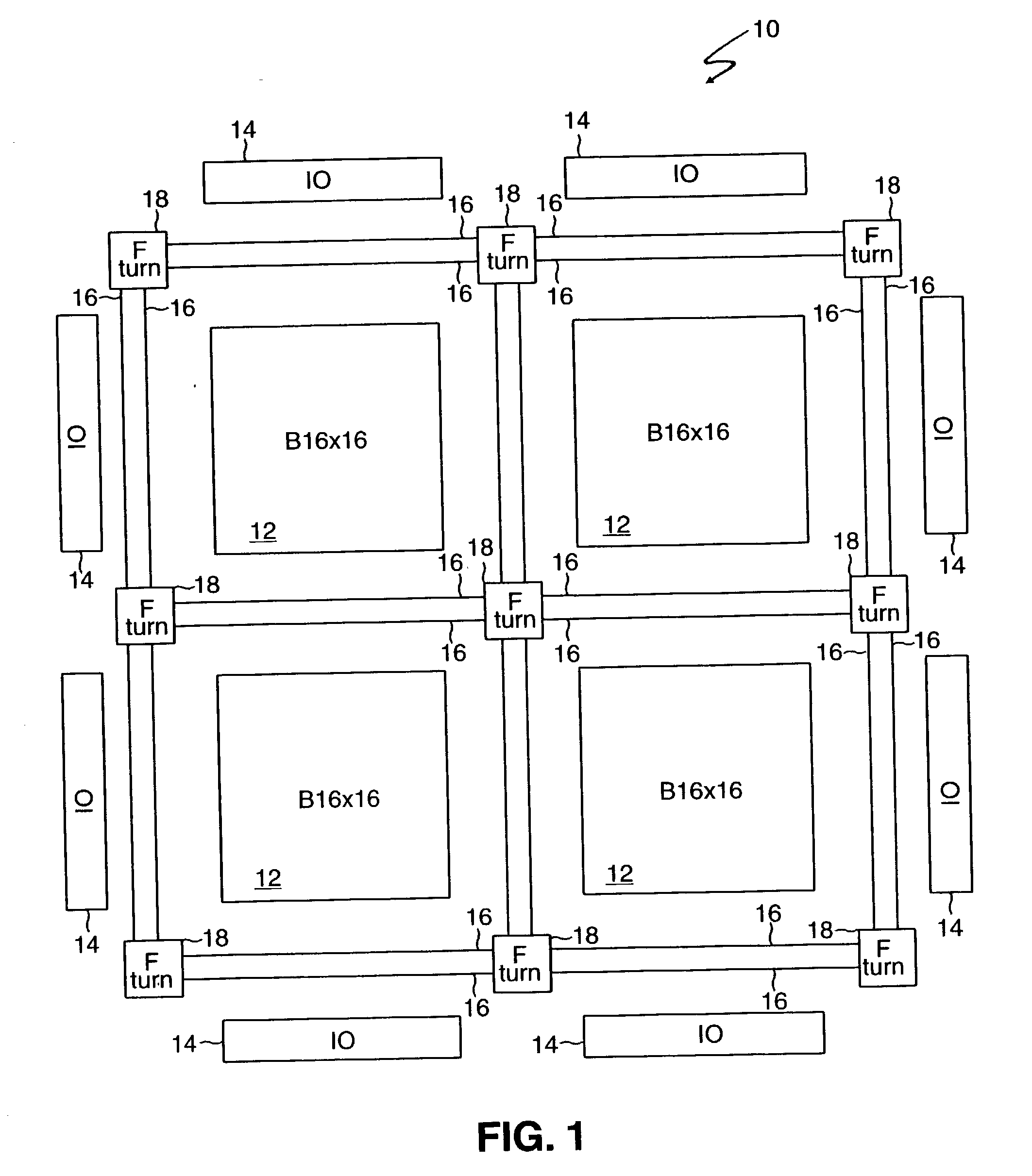

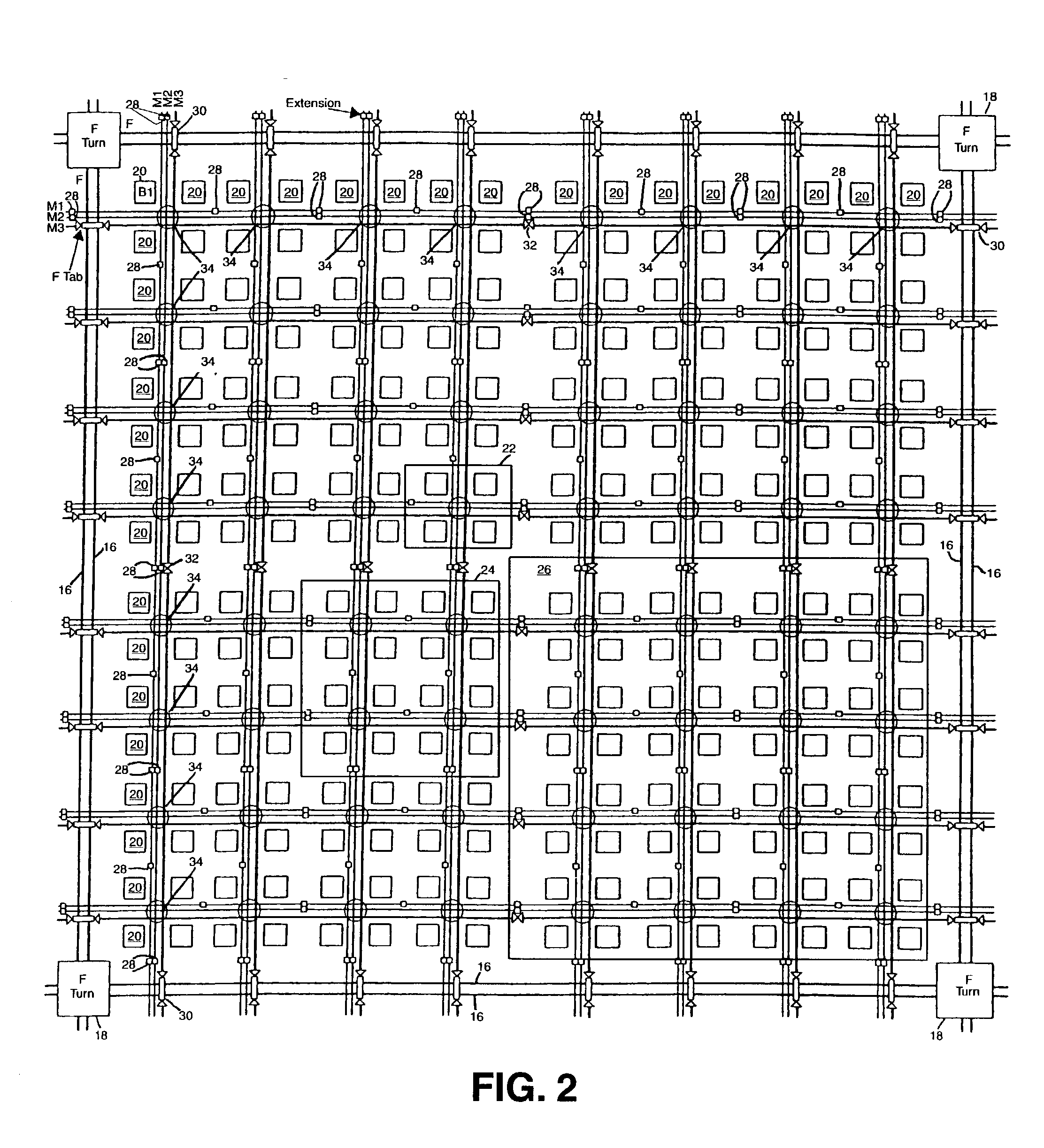

An FPGA architecture has top, middle and low levels. The top level of the architecture is an array of the B16x16 tiles arranged in a rectangular array and enclosed by I / O blocks on the periphery. On each of the four sides of a B16x16 tile, and also associated with each of the I / O blocks is a freeway routing channel. A B16x16 tile in the middle level of hierarchy is a sixteen by sixteen array of B1 blocks. The routing resources in the middle level of hierarchy are expressway routing channels M1, M2, and M3 including groups of interconnect conductors. At the lowest level of the semi-hierarchical FPGA architecture, there are block connect (BC) routing channels, local mesh (LM) routing channels, and direct connect (DC) interconnect conductors. Each BC routing channel is coupled to an expressway tab to provide access for each B1 block to the expressway routing channels M1, M2, and M3, respectively. Each BC routing channel has nine interconnect conductors which are grouped into three groups of three interconnect conductors. Each group of three interconnect conductors is connected to a first side of a Extension Block (EB) 3x3 switch matrix. A second side of each EB 3x3 switch matrix is coupled to the E-tab. Between adjacent B1 blocks, in both the horizontal and vertical directions, the leads on the second side of a first EB 3x3 switch matrix may be coupled to the leads on the second side of second EB3x3 switch matrix by BC criss-cross extension.

Owner:ACTEL CORP

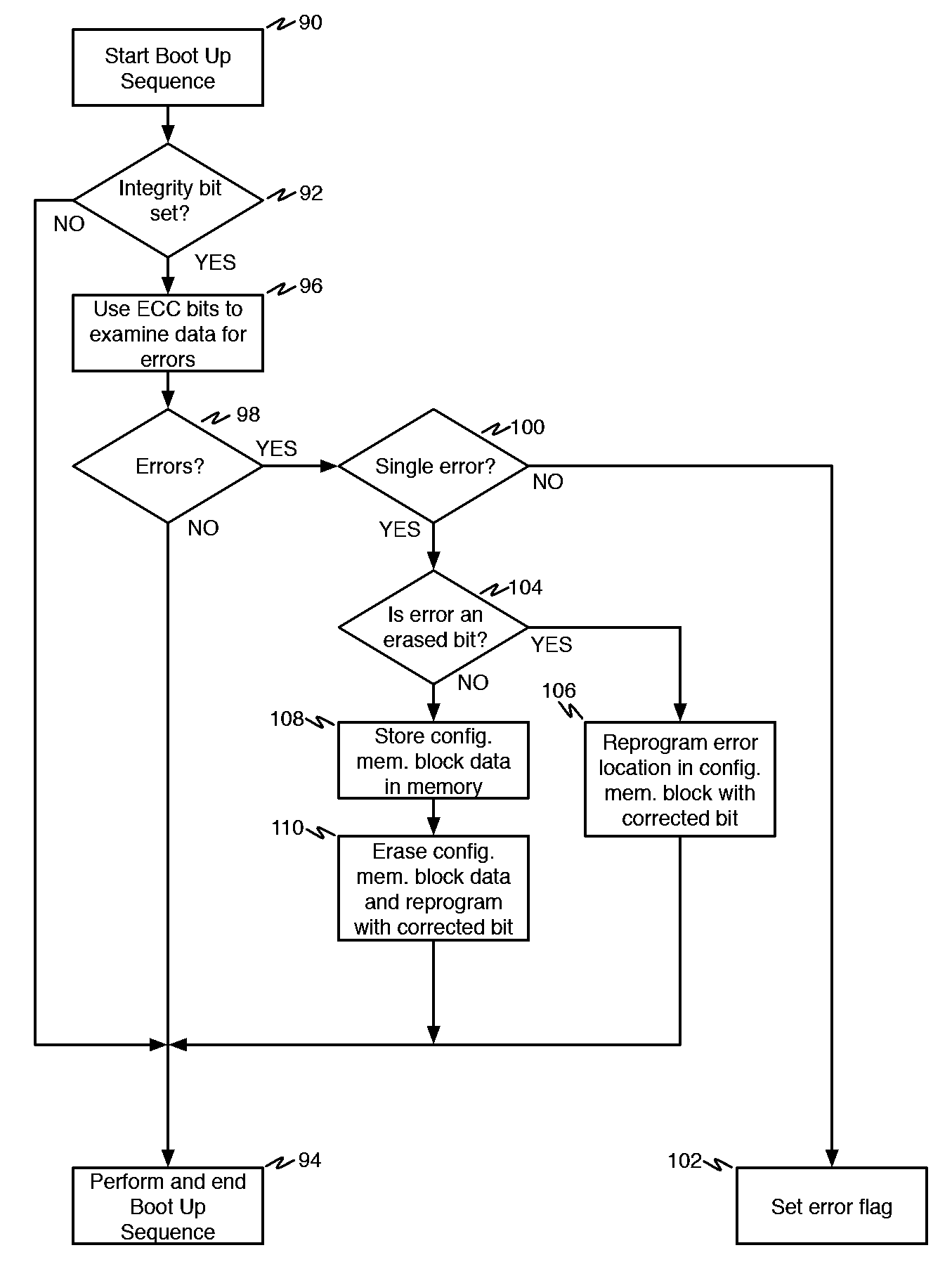

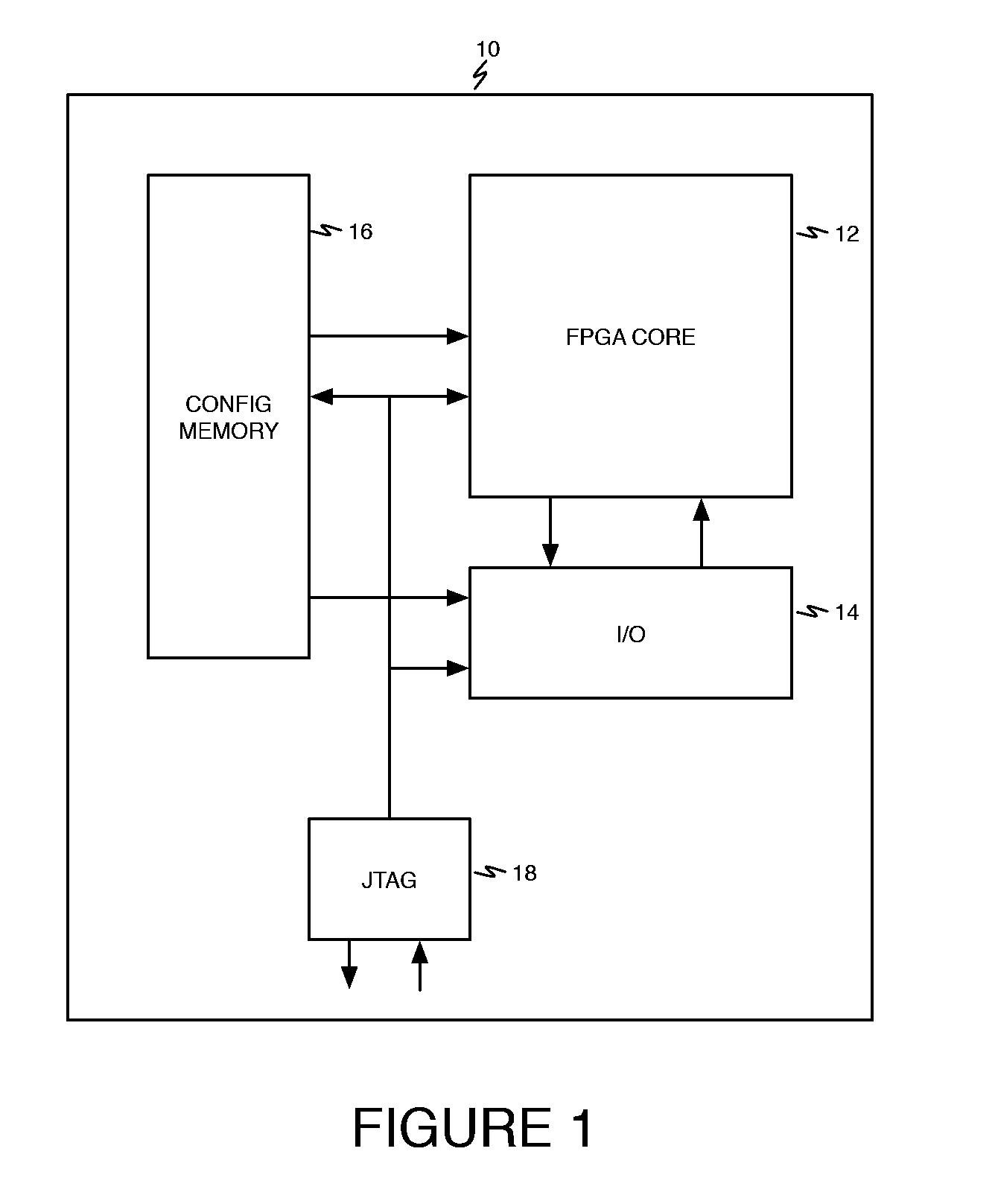

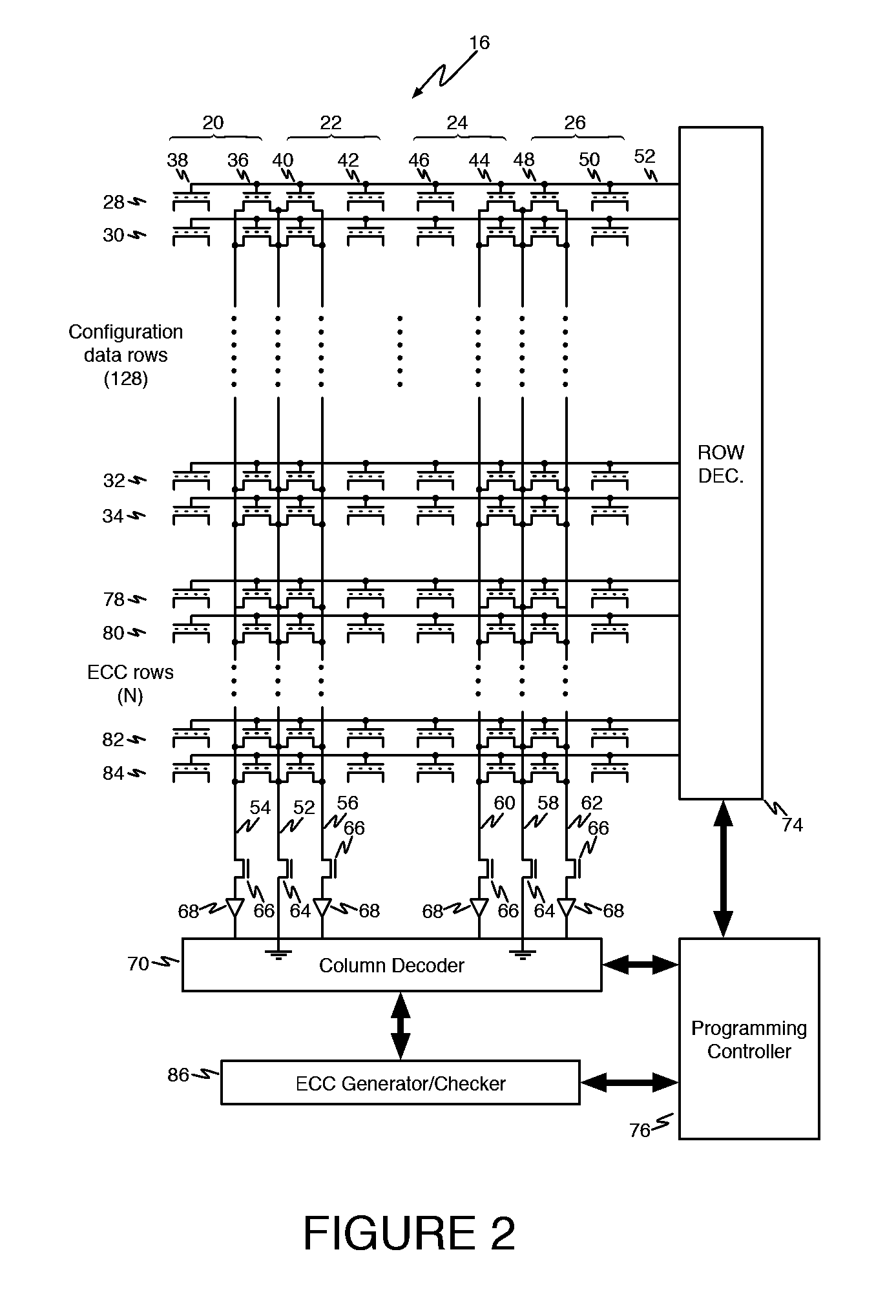

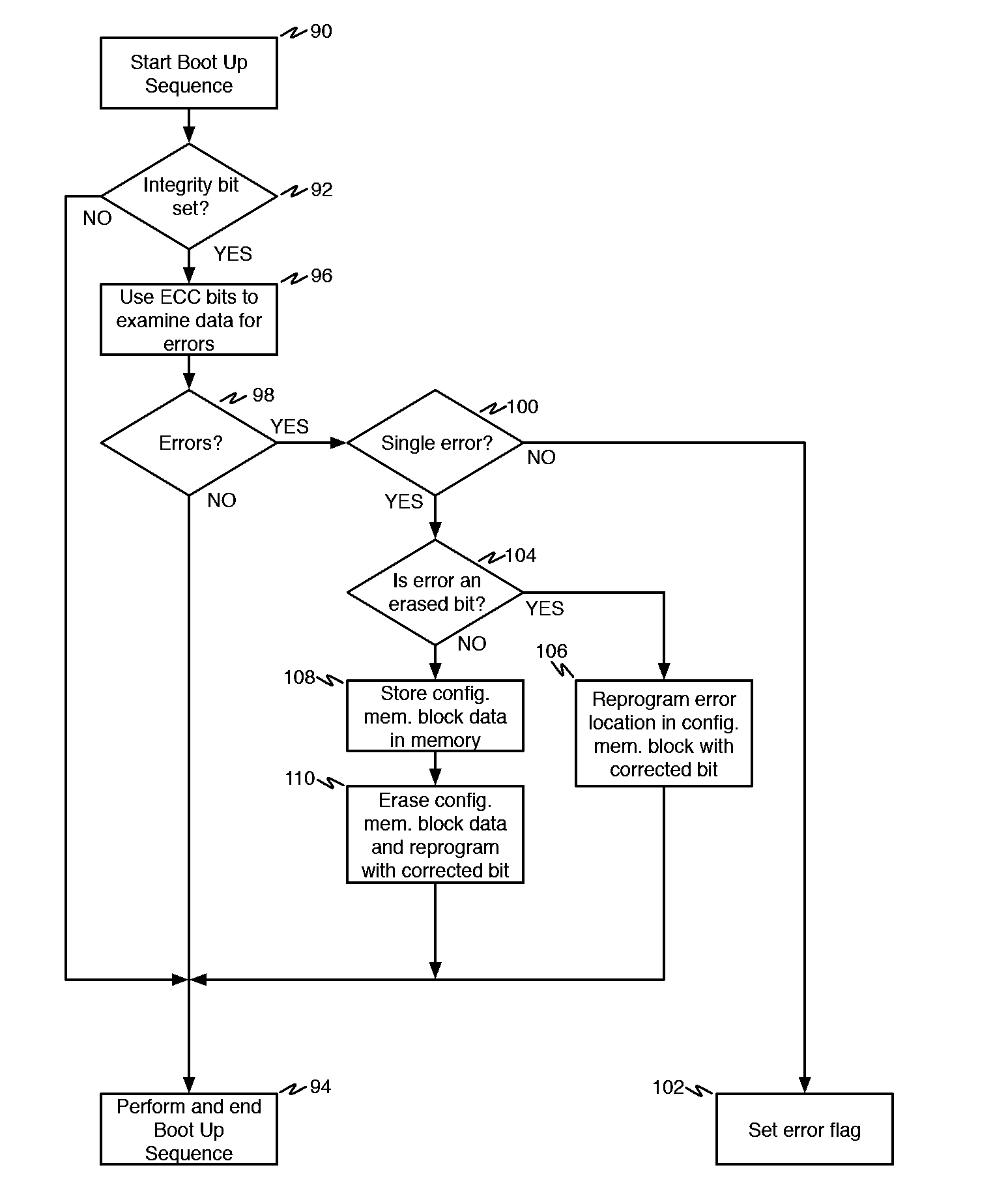

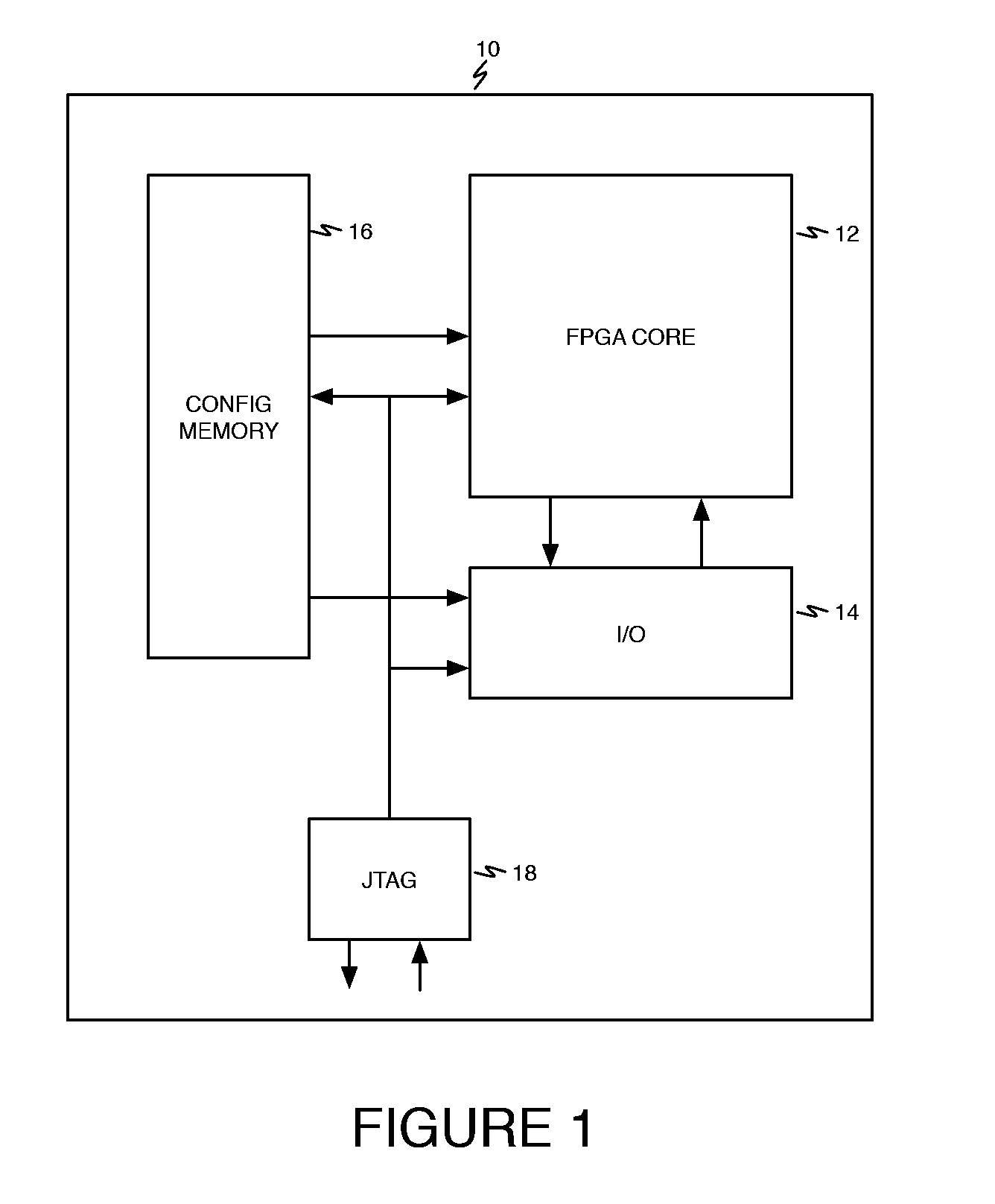

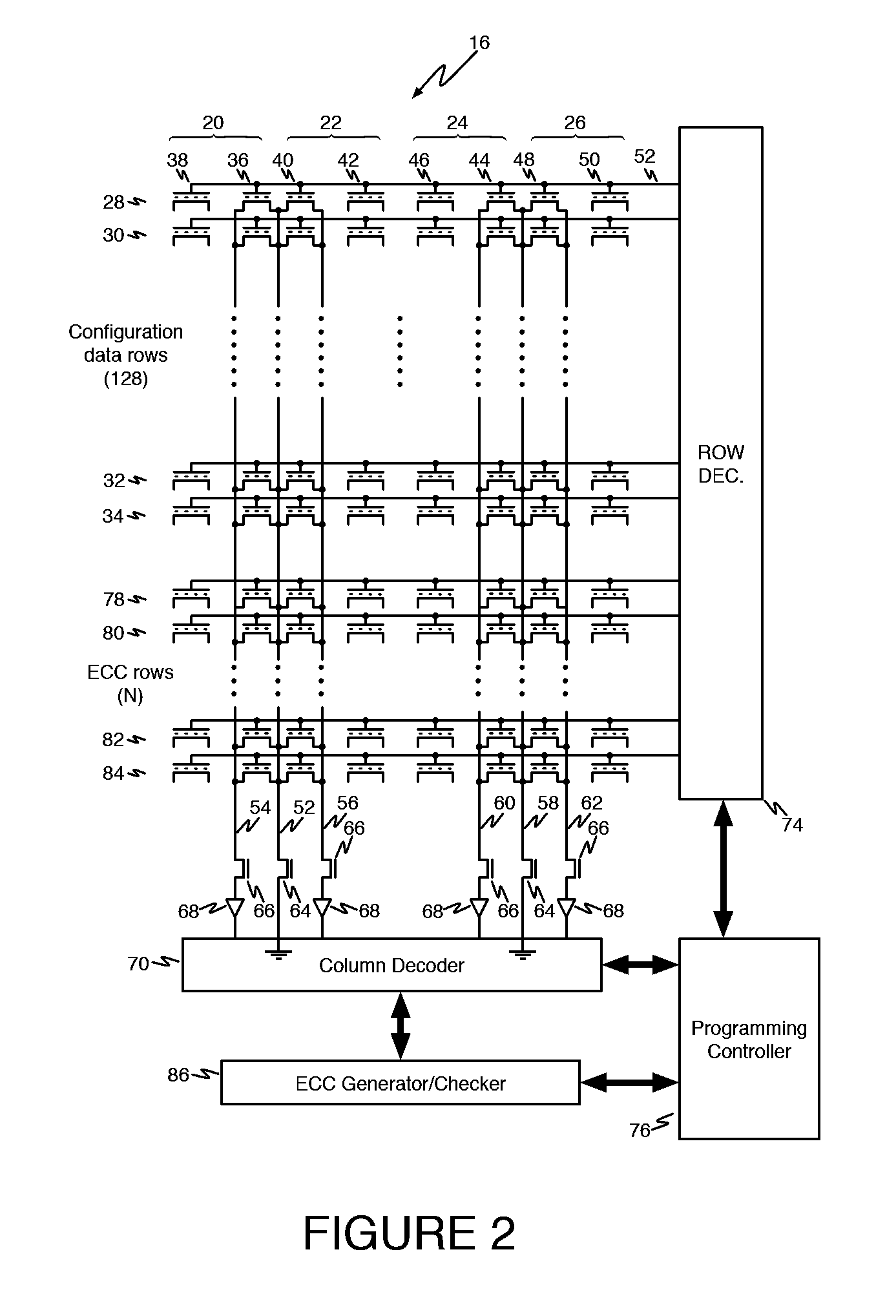

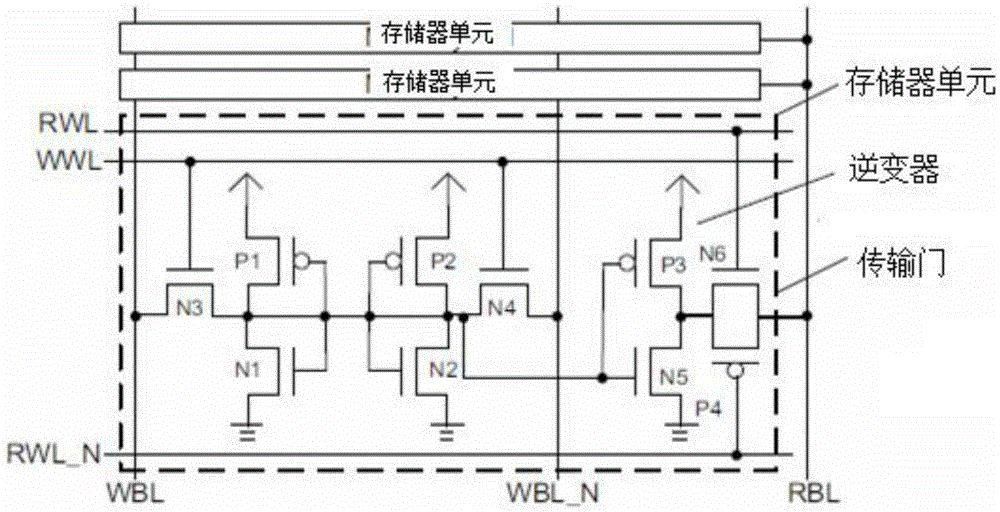

Error-detecting and correcting FPGA architecture

ActiveUS20090031194A1Error detection/correctionCode conversionFpga architectureJoint Test Action Group

A method and apparatus are provided for an error-correcting FPGA. ECC data for configuration is generated and programmed into the ECC rows in the configuration memory. While booting, it is determined whether an integrity-check bit is set. If so, an integrity check is performed. If a single-bit error is detected, if the bit error is an erroneous “0” value, the memory location containing the erroneous “0” value is reprogrammed to a “1” value. If the bit error is an erroneous “1,” value, the memory block data is saved in a non-volatile memory block, the configuration memory block containing the error is erased and reprogrammed using the corrected bit. If there is more than one error, an error flag is set. The user reads the status of the error flag through the JTAG port. If the error flag is set then a full reprogramming cycle is initiated.

Owner:MICROSEMI SOC

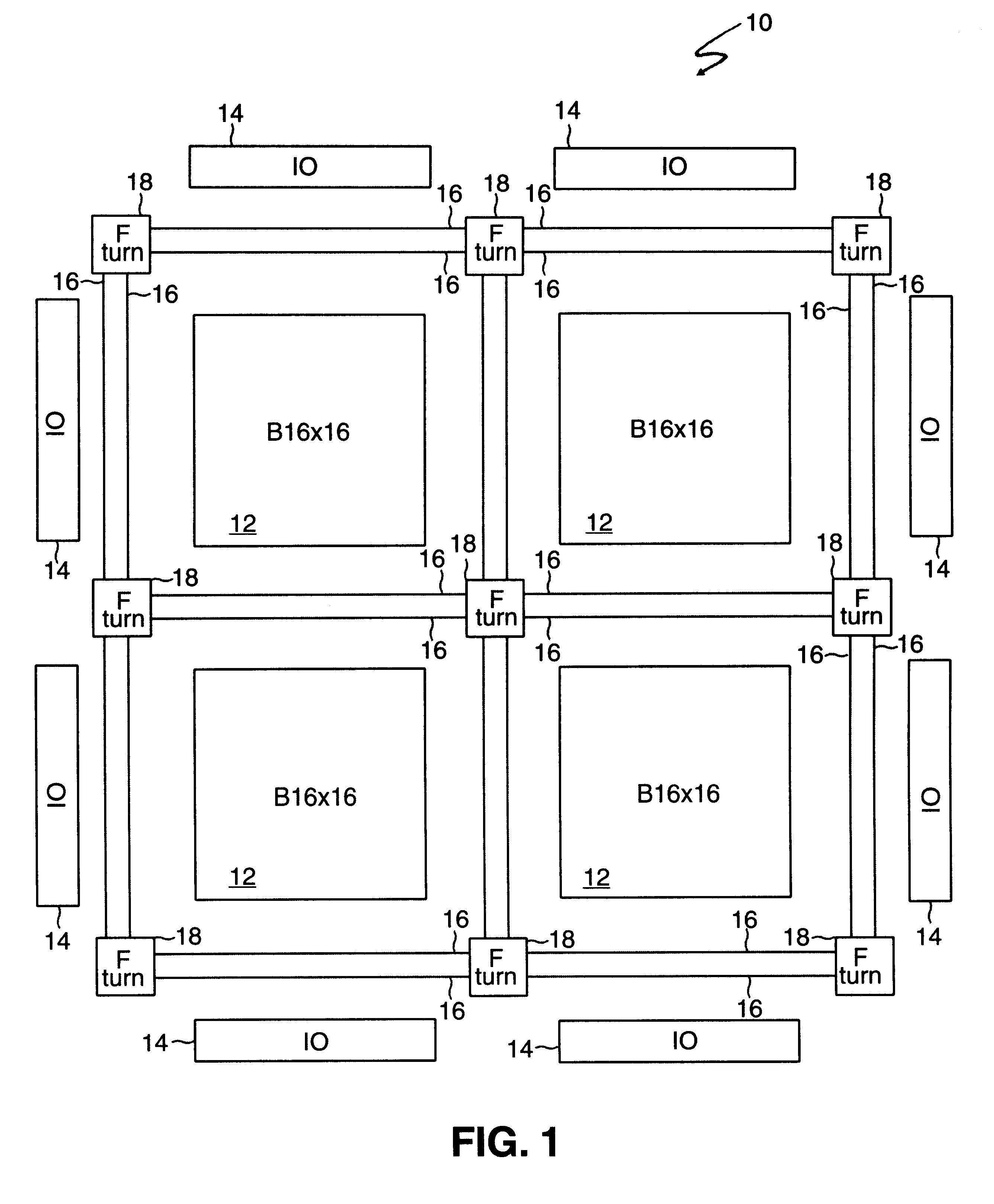

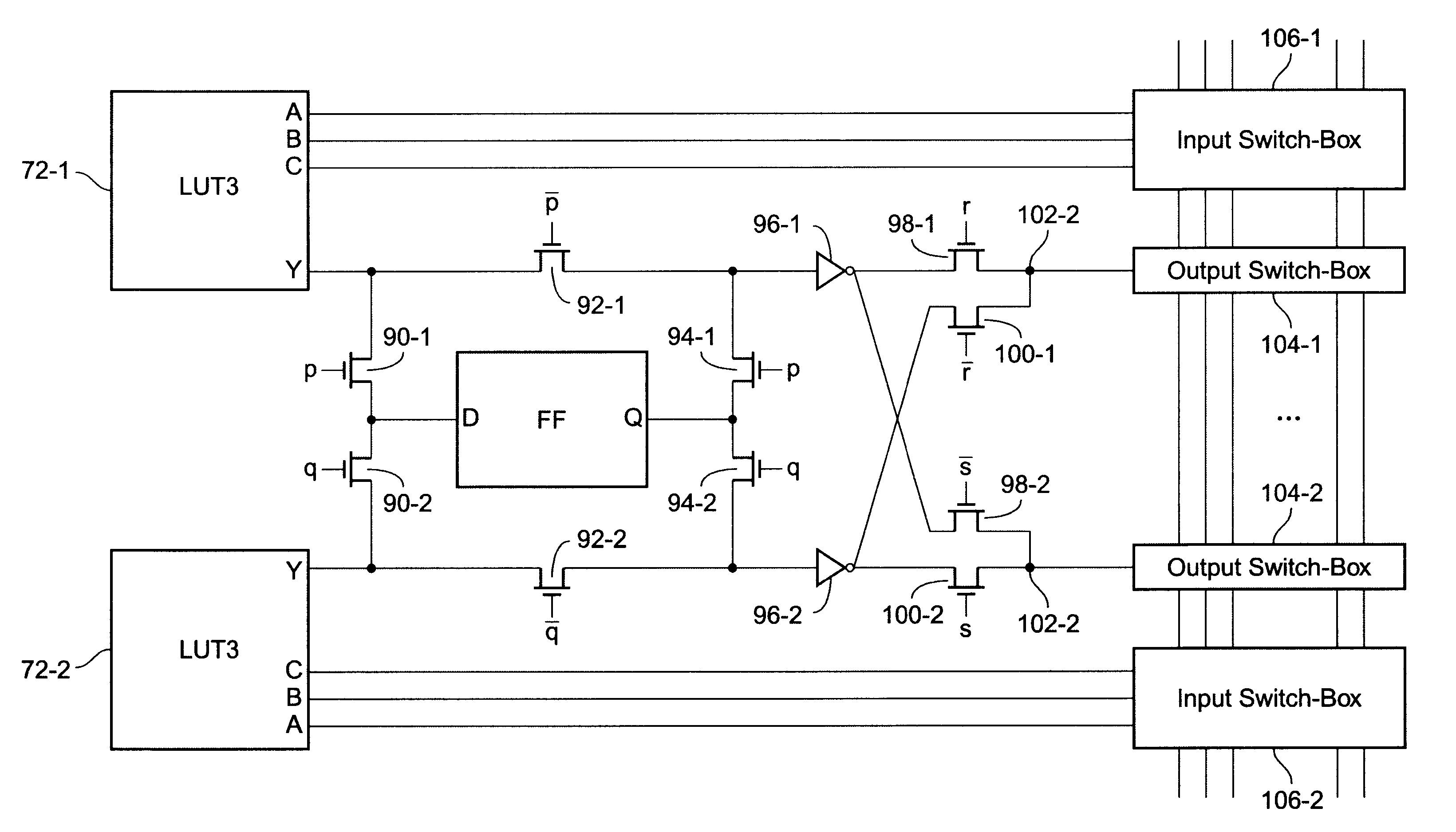

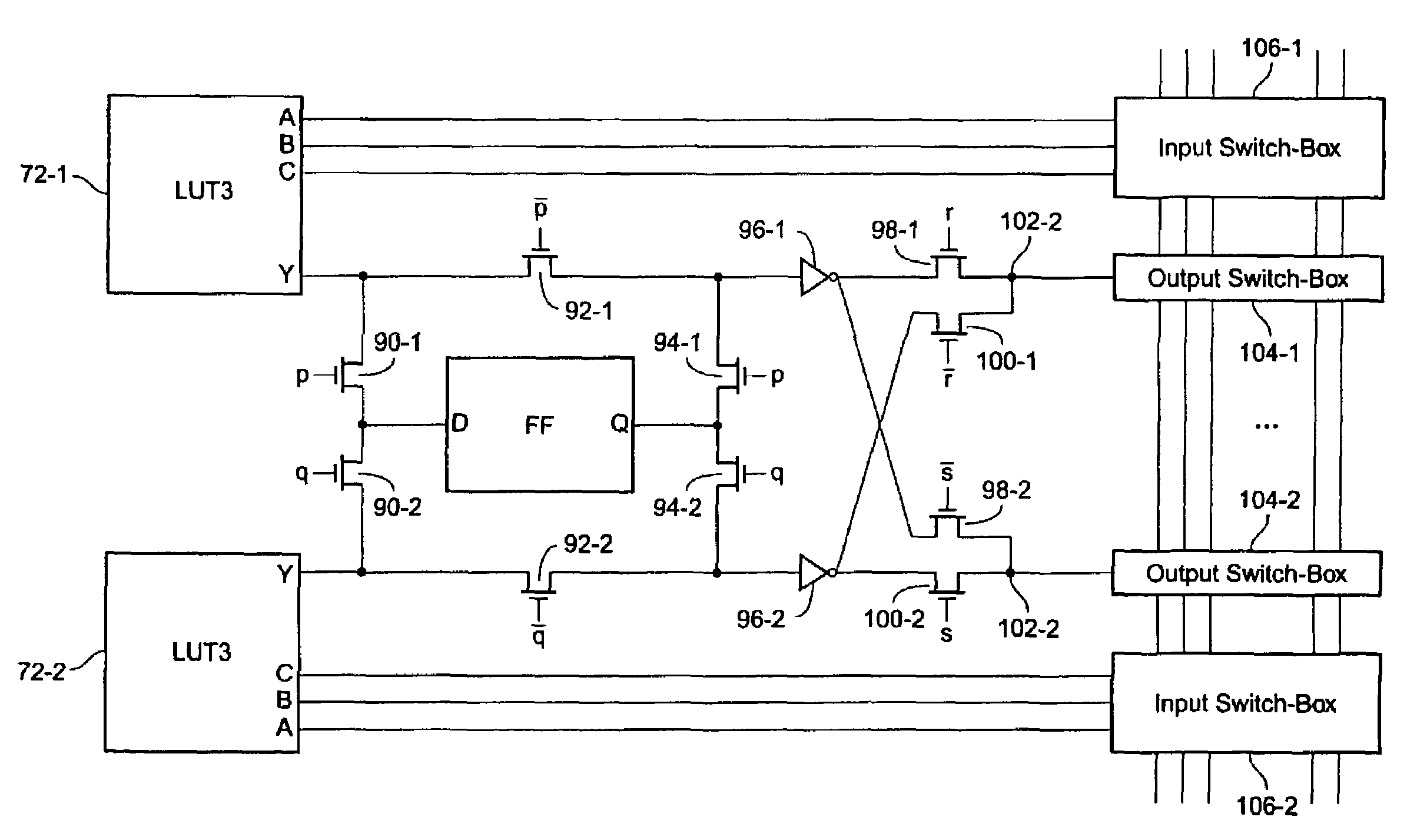

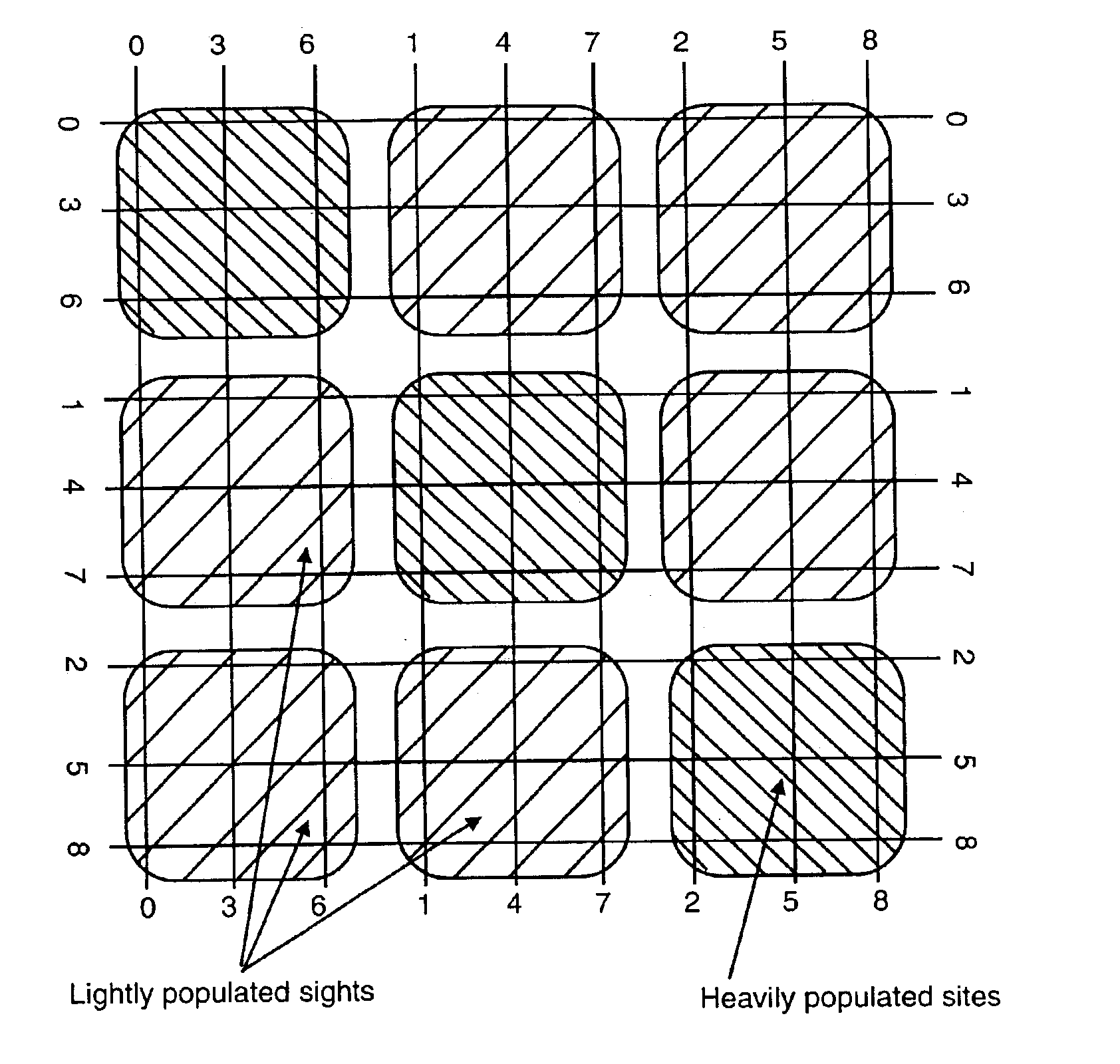

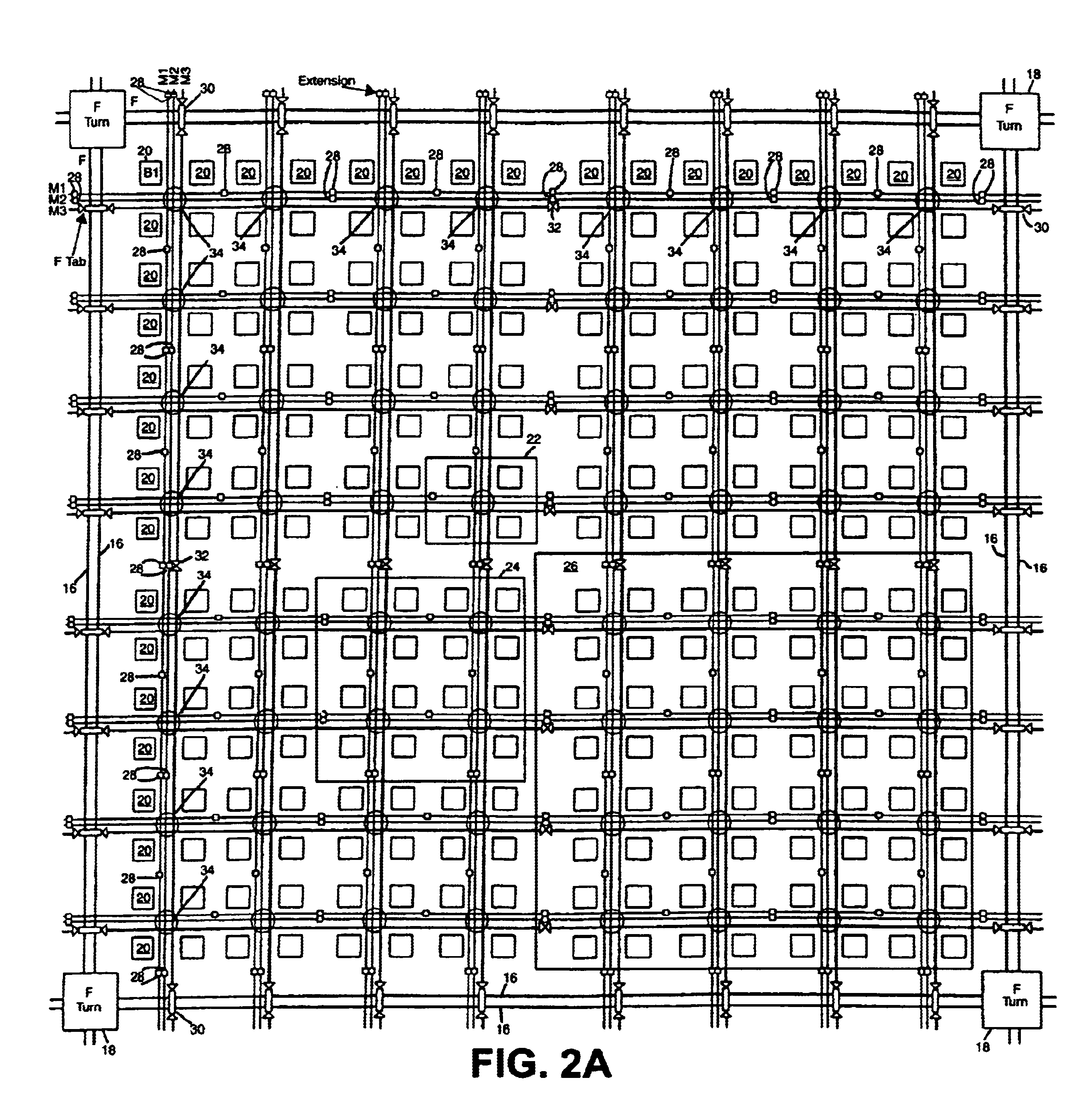

Block symmetrization in a field programmable gate array

InactiveUS6268743B1Good symmetryEasy to placeLogic circuits using elementary logic circuit componentsComputation using denominational number representationFpga architectureMultiplexing

An FPGA architecture has top, middle and low levels. The top level of the architecture is an array of the B16x16 tiles arranged in a rectangular array and enclosed by I / O blocks on the periphery. On each of the four sides of a B16x16 tile, and also associated with each of the I / O blocks is a freeway routing channel. A B16x16 tile in the middle level of hierarchy is a sixteen by sixteen array of B1 blocks. The routing resources in the middle level of hierarchy are expressway routing channels M1, M2, and M3 including groups of interconnect conductors. At the lowest level of the semi-hierarchical FPGA architecture, there are block connect (BC) routing channels, local mesh (LM) routing channels, and direct connect (DC) interconnect conductors to connect the logic elements to further routing resources. Each B1 block includes four clusters of devices. Each of the four clusters includes first and second LUT3s, a LUT2, and a DFF . Each of the LUT3s have first, second, and third inputs and a single output. Each of the LUT2s have first and second inputs and a single output. Each DFF has a data input and a data output. In each of the clusters the outputs of the LUT3s are muliplexed to the input of DFF, and symmetrized with the output of the DFF to form first and second outputs of each of the clusters.

Owner:MICROSEMI SOC

FPGA (field programmable gate array) architecture of HOG (histogram of oriented gradient) and SVM (support vector machine) based pedestrian detection system and implementing method of FPGA architecture

InactiveCN103177262ATroubleshoot Migration Optimization IssuesAvoid detection accuracyCharacter and pattern recognitionFpga architectureComputer architecture

The invention discloses an implementing method of FPGA (field programmable gate array) architecture of an HOG (histogram of oriented gradient) and SVM (support vector machine) based pedestrian detection system. The implementing method includes steps of inputting, gradient and direction computation, histogram generation, binaryzation, SVM classification and outputting. The invention further provides the FPGA (field programmable gate array) architecture of the HOG and SVM based pedestrian detection system. By the FPGA architecture and the implementing method thereof, the problem that an HOG and SVM based pedestrian detection algorithm is slow in computation on a PC(personal computer) is solved, transplant optimization of hardware is realized, the FPGA architecture of an embedded pedestrian detection system is implemented in the scheme with low power consumption, high detection efficiency and low resource consumption in real time, and thus, pedestrian detection is popularized and developed in the embedded field according to the scheme.

Owner:SHANDONG UNIV

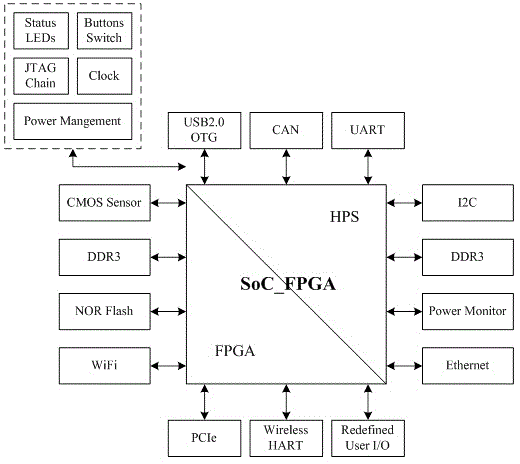

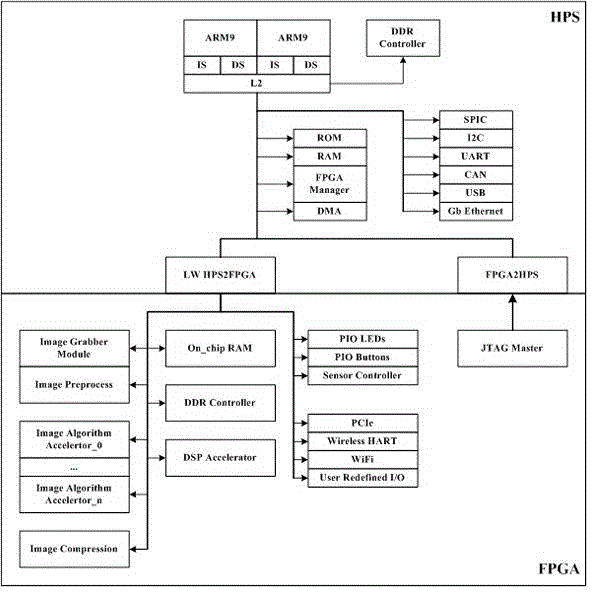

SoC_FPGA-based flexible intelligent machine vision detection system

InactiveCN104835162AHighly integratedReduce volumeImage analysisCharacter and pattern recognitionComputer hardwareImage manipulation

Owner:李鹏飞

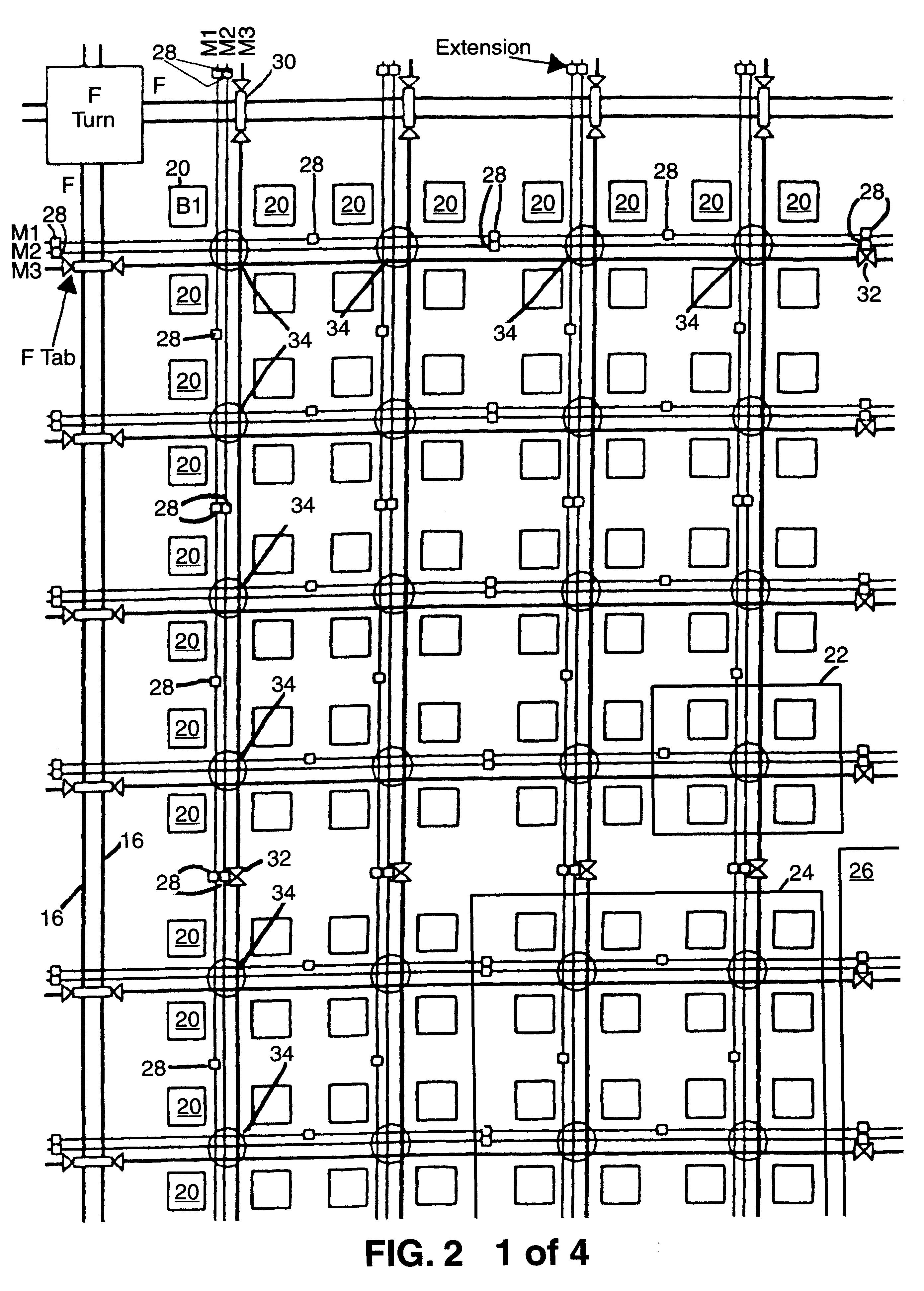

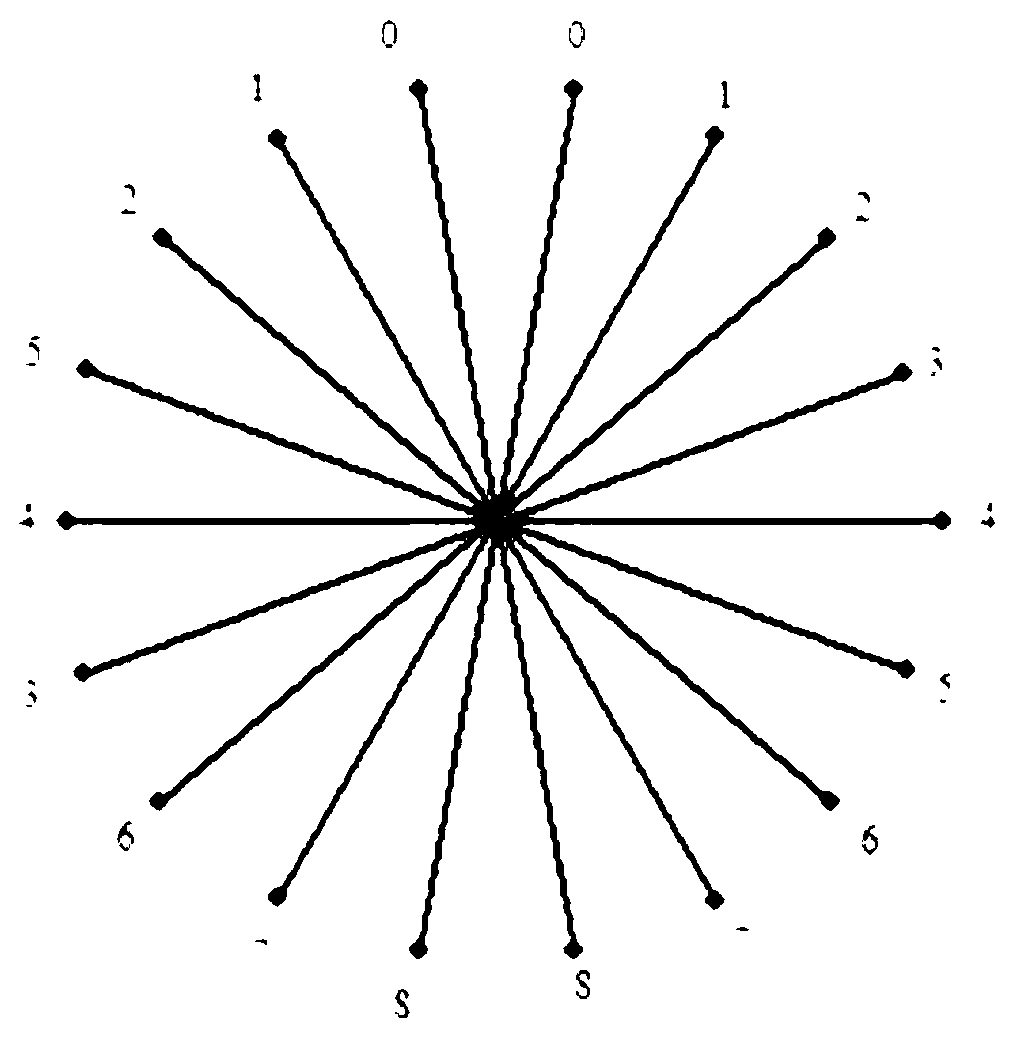

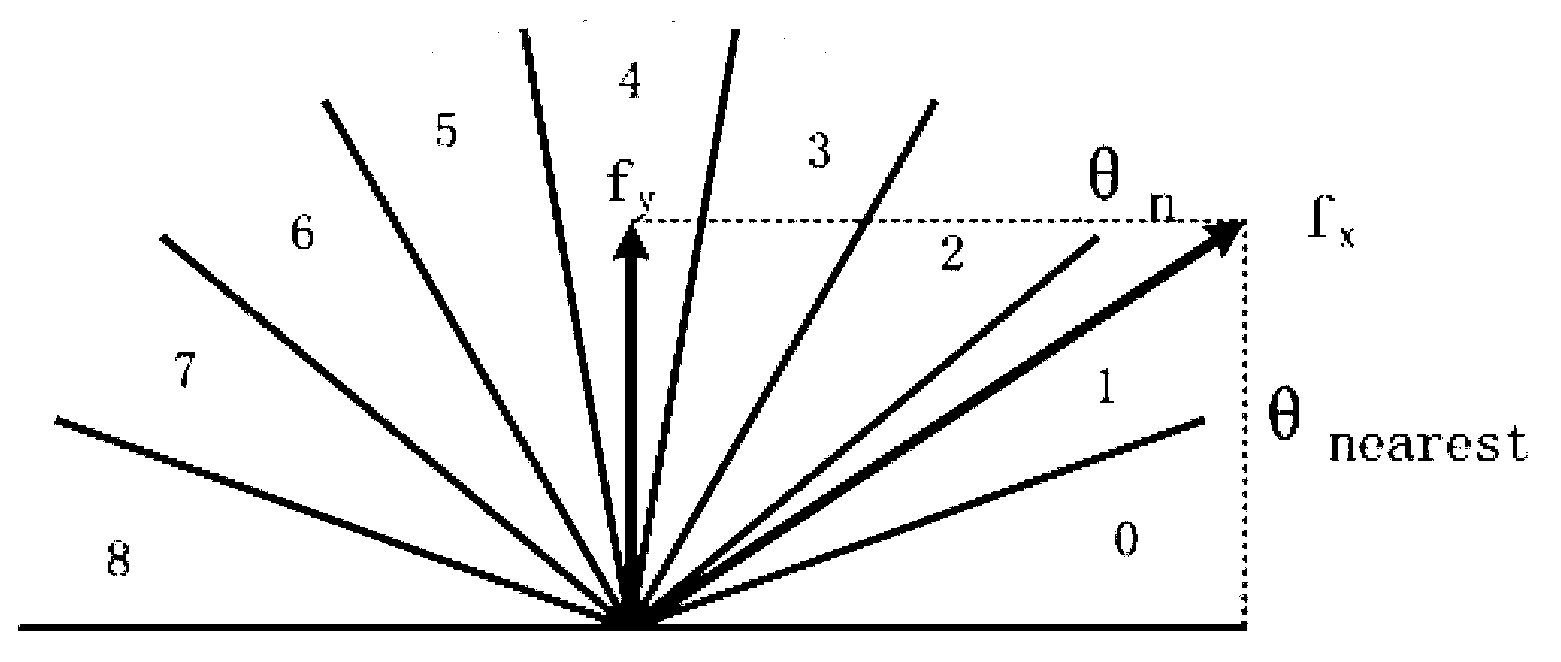

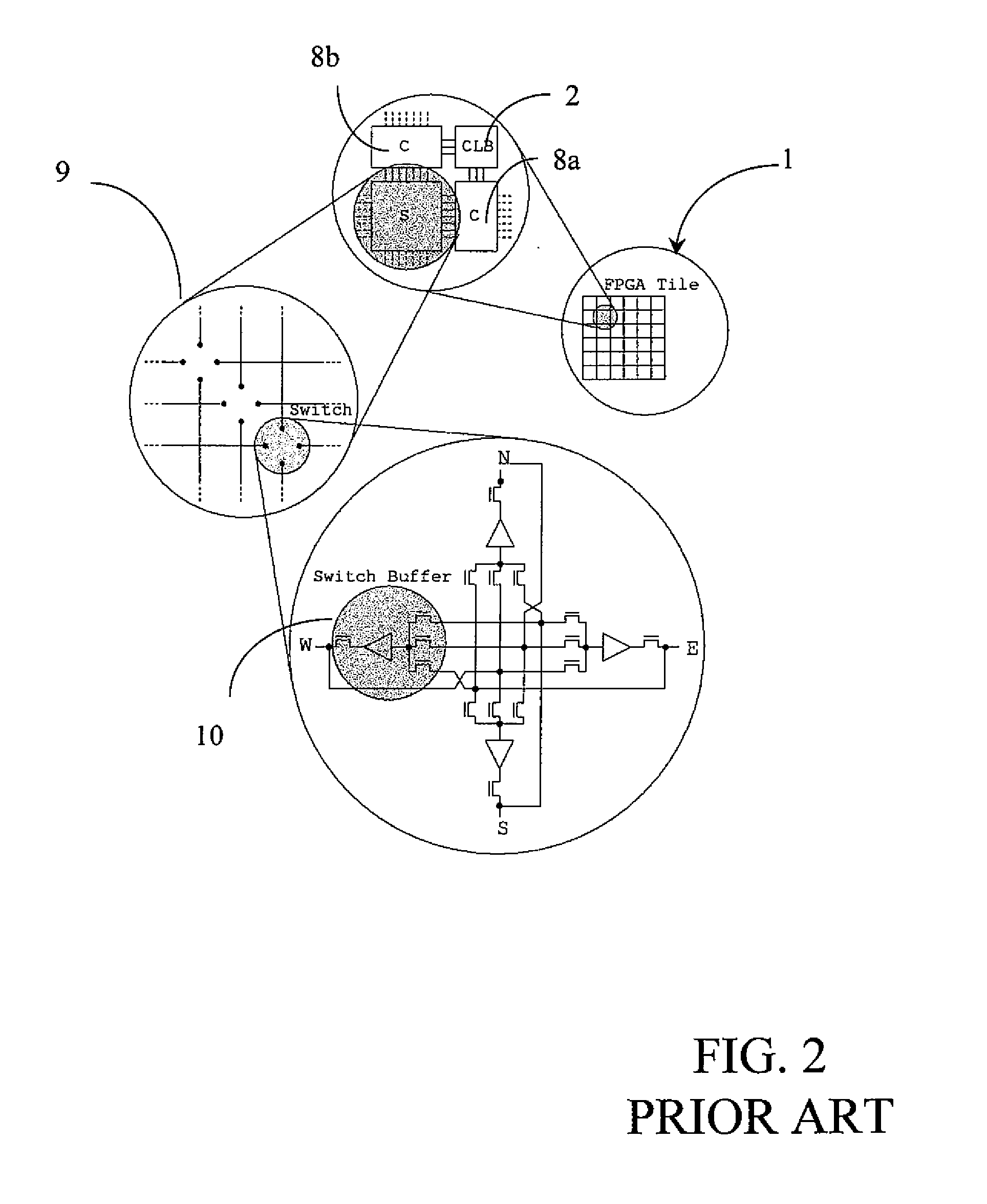

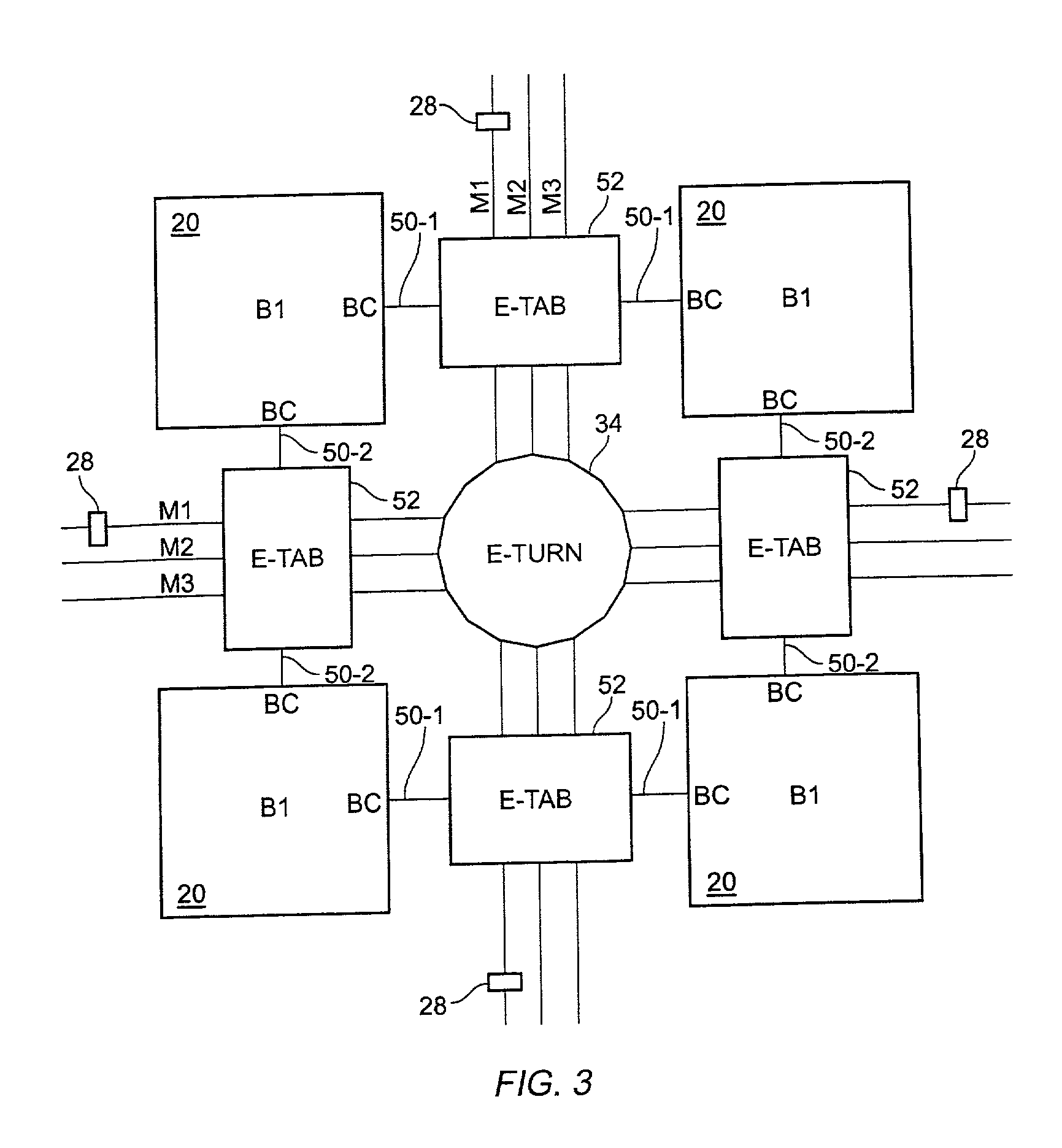

Turn architecture for routing resources in a field programmable gate array

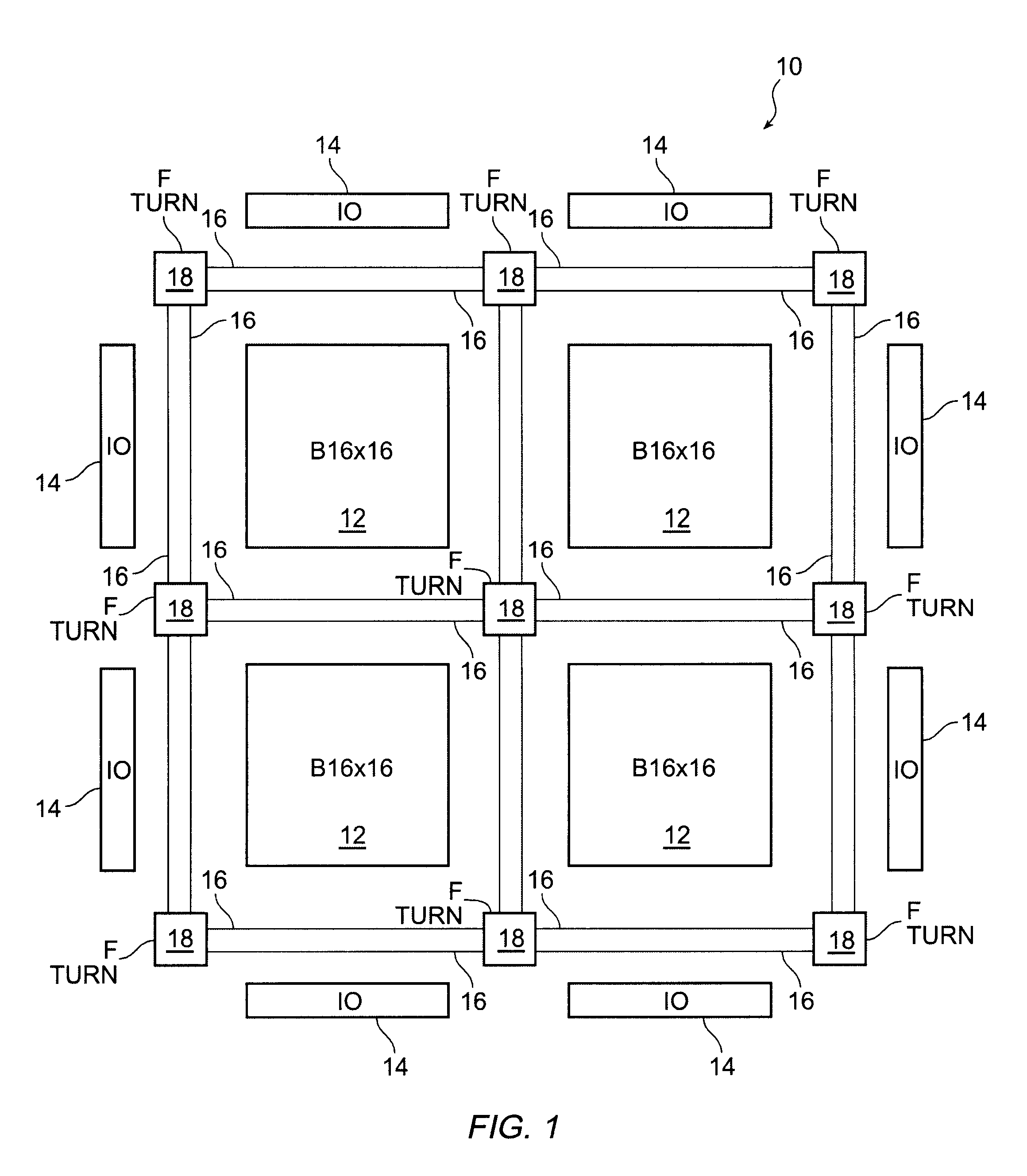

InactiveUS6636930B1Good symmetryEasy to placeSolid-state devicesGeneral purpose stored program computerFpga architectureElectrical conductor

An FPGA architecture has top, middle and low levels. The top level of the architecture is an array of the B16x16 tiles arranged in a rectangular array and enclosed by I / O blocks on the periphery. A B16x16 tile in the middle level of hierarchy is a sixteen by sixteen array of B1 blocks. The B16x16 tile is a nesting of a B2x2 tile that includes a two by two array of four B1 blocks. The routing resources in the middle level of hierarchy are expressway routing channels M1, M2, and M3 including groups of interconnect conductors. The expressway routing channels M1, M2, and M3 are segmented, and between each of the segments in the expressway routing channels M1, M2, and M3 are disposed extensions that can extend the expressway routing channel M1, M2, or M3 an identical distance along the same direction. The expressway routing channels M1, M2, and M3 run both vertically through every column and horizontally through every row of B2x2 tiles. At the intersections of each of the expressway routing channels M1, M2, and M3 in the horizontal direction with the expressway routing channels M1, M2 and M3 in the vertical direction is an expressway turn (E-turn) disposed at the center of each B2x2 tile. An E-turn is a passive device that includes a matrix of reprogrammable switches. The reprogrammable switches are preferably a pass device controlled by an SRAM bit. The interconnect conductors in the expressway routing channels M1, M2 and M3 that are fed into an E-turn may be coupled to many of the other interconnect conductors in the expressway routing channels M1, M2 and M3 that come into the E-turn by the programmable switches. Further, the interconnect conductors in the expressway routing channels M1, M2 and M3 that are fed into an E-turn continue in the same direction through the E-turn, even though the interconnect conductors are coupled to other interconnect conductors by the reprogrammable switches.

Owner:MICROSEMI SOC

Block connector splitting in logic block of a field programmable gate array

InactiveUS6285212B1Good symmetryEasy to placeSolid-state devicesLogic circuits using elementary logic circuit componentsFpga architectureElectrical conductor

An FPGA architecture has top, middle and low levels. The top level of the architecture is an array of the B16x16 tiles arranged in a rectangular array and enclosed by I / O blocks on the periphery. On each of the four sides of a B16x16 tile, and also associated with each of the I / O blocks is a freeway routing channel. A B16x16 tile in the middle level of hierarchy is a sixteen by sixteen array of B1 blocks. The routing resources in the middle level of hierarchy are expressway routing channels M1, M2, and M3 including groups of interconnect conductors. At the lowest level of the semi-hierarchical FPGA architecture, there are block connect (BC) routing channels, local mesh (LM) routing channels, and direct connect (DC) interconnect conductors to connect the logic elements to further routing resources. Within the B1 block, a horizontal BC routing channel is disposed between two upper and two lower clusters of devices, and a vertical BC routing channel is disposed between two clusters of devices on the left side of the B1 block and two clusters of devices on the right side of the B1 block. The BC routing channel forms intersections with the inputs and outputs of the devices in the clusters. The horizontal BC routing channel forms a first diagonally hardwired connection with a routing channel that effectively sends the horizontal BC routing channel in a vertical direction. A second diagonally hardwired connection pairwise shorts the horizontal and vertical BC routing channels to provide dual accessibility to the logic resources in the B1 block from more than one side. Disposed between the first diagonally hardwired connection and the second diagonally hardwired connection is a BC splitting extension which provides a programmable one-to-one coupling between the interconnect conductors of the horizontal BC routing channel on either side of the BC splitting extension.

Owner:MICROSEMI SOC

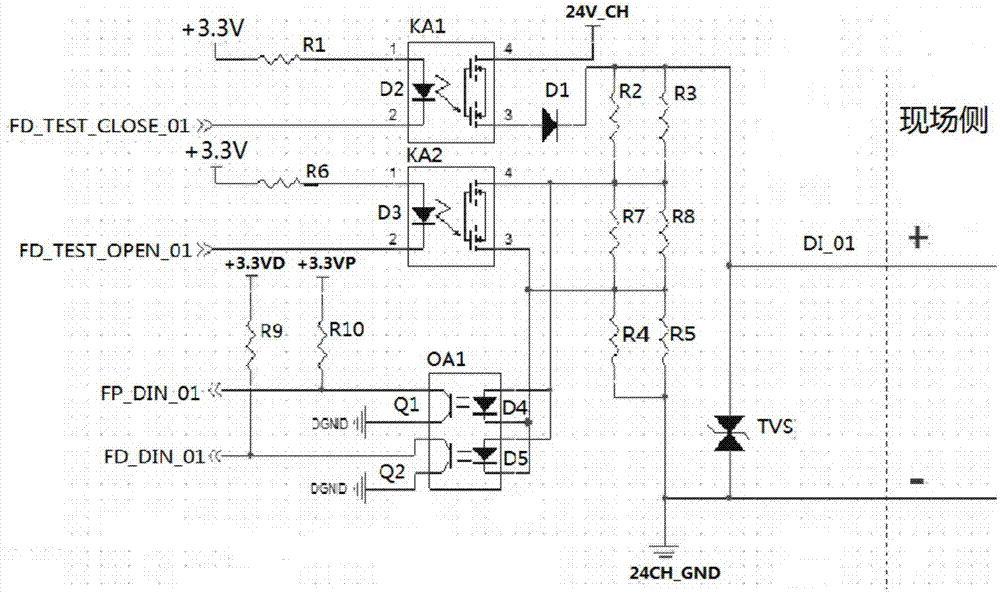

Digital volume acquisition circuit with dynamic fault diagnosis ability

ActiveCN107065716ACoverage failure rateReal-time uploadProgramme controlElectric signal transmission systemsNuclear gradeElectricity

The present invention provides a digital volume acquisition circuit with dynamic fault diagnosis ability. A dynamic read-back signal is used to achieve more complete channel self diagnosis. The circuit is applied to a nuclear grade DCS system and comprises an opto-coupler signal acquisition circuit and an optical relay dynamic diagnosis circuit. The opto-coupler signal acquisition circuit is applied to a dual FPGA architecture system, one channel is connected to a processing FPGA, and the other channel is connected to a diagnosis FPGA. According to the fault diagnosis of the invention, the judgment is carried out according to a condition whether a read square wave can be received, after the FPGA reads a condition that a channel is in a power or loss of power state from an optocoupler output end, a dynamic diagnosis test is carried out, corresponding high and low level pulses can be read, and passed diagnosis is judged. According to the circuit of the invention, whether the digital volume acquisition circuit collects a fault can be judged, and state information can be uploaded in real time.

Owner:CHINA NUCLEAR CONTROL SYST ENG

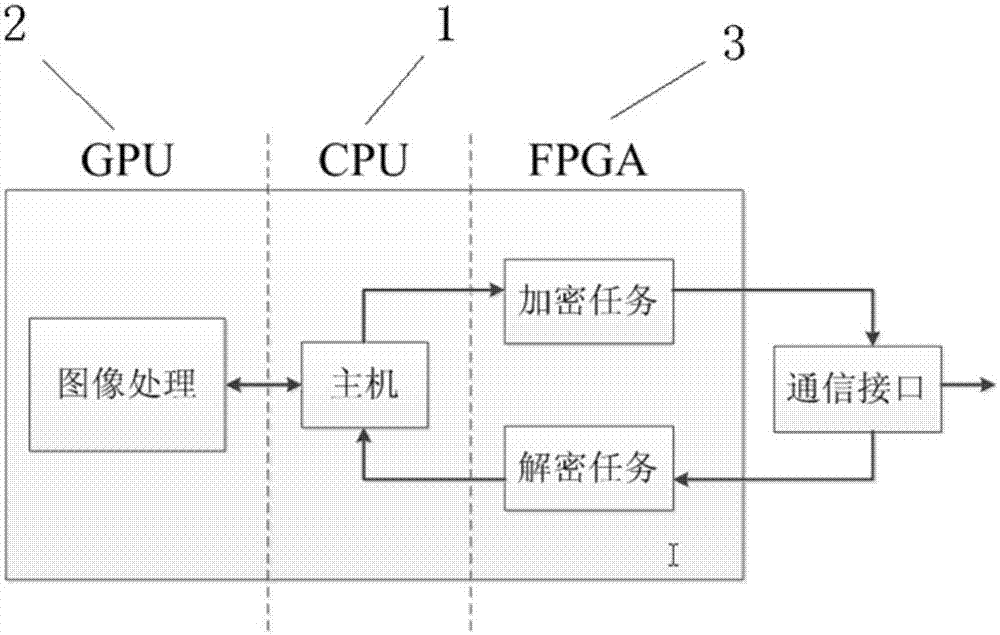

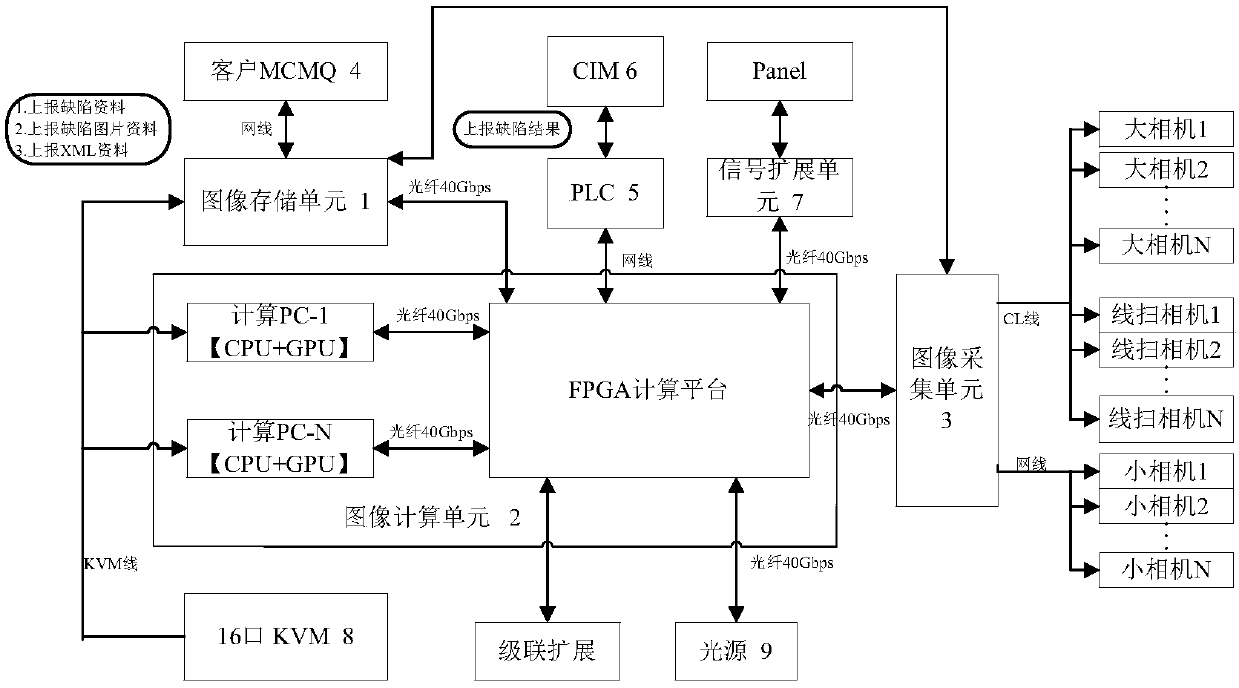

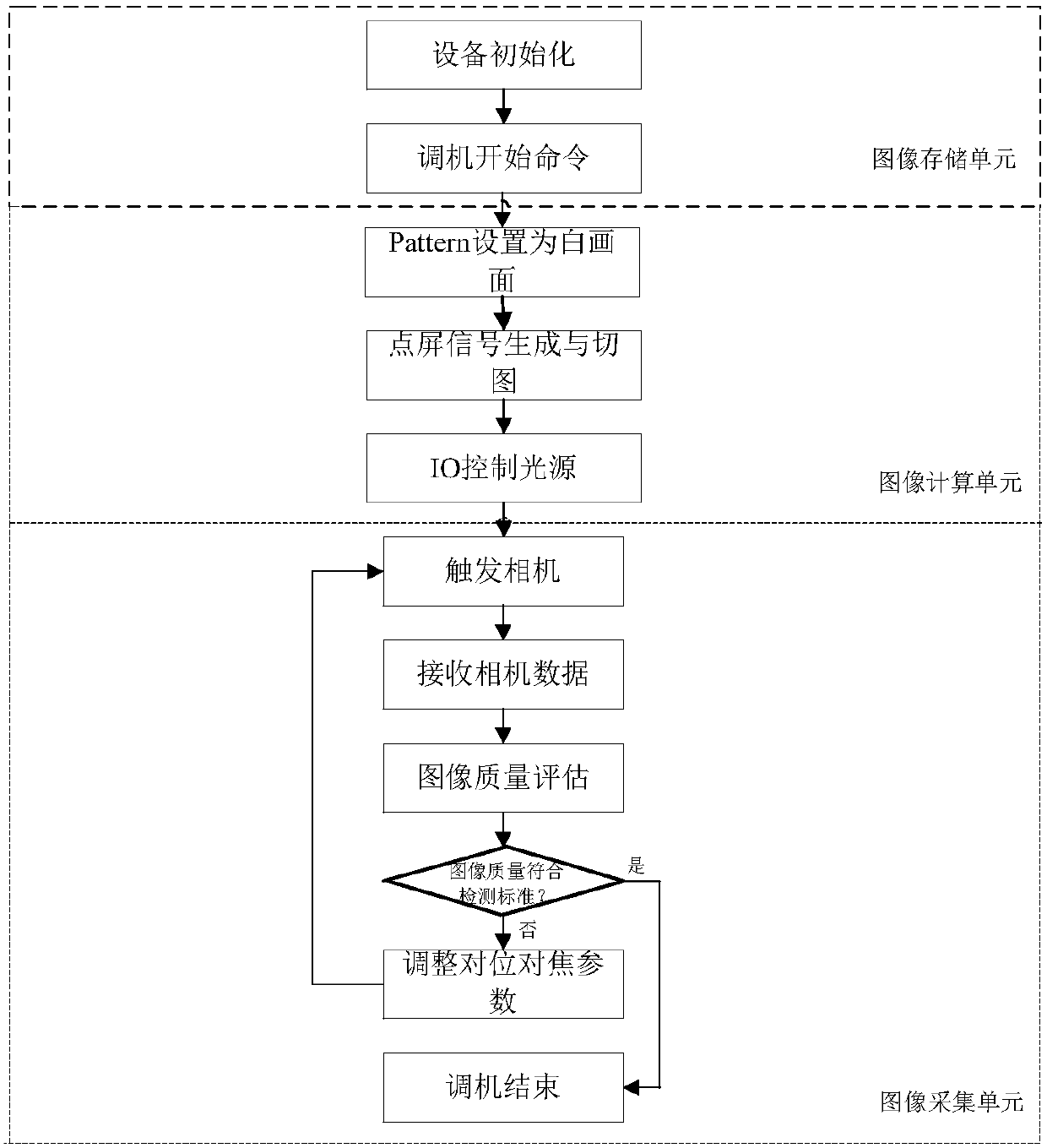

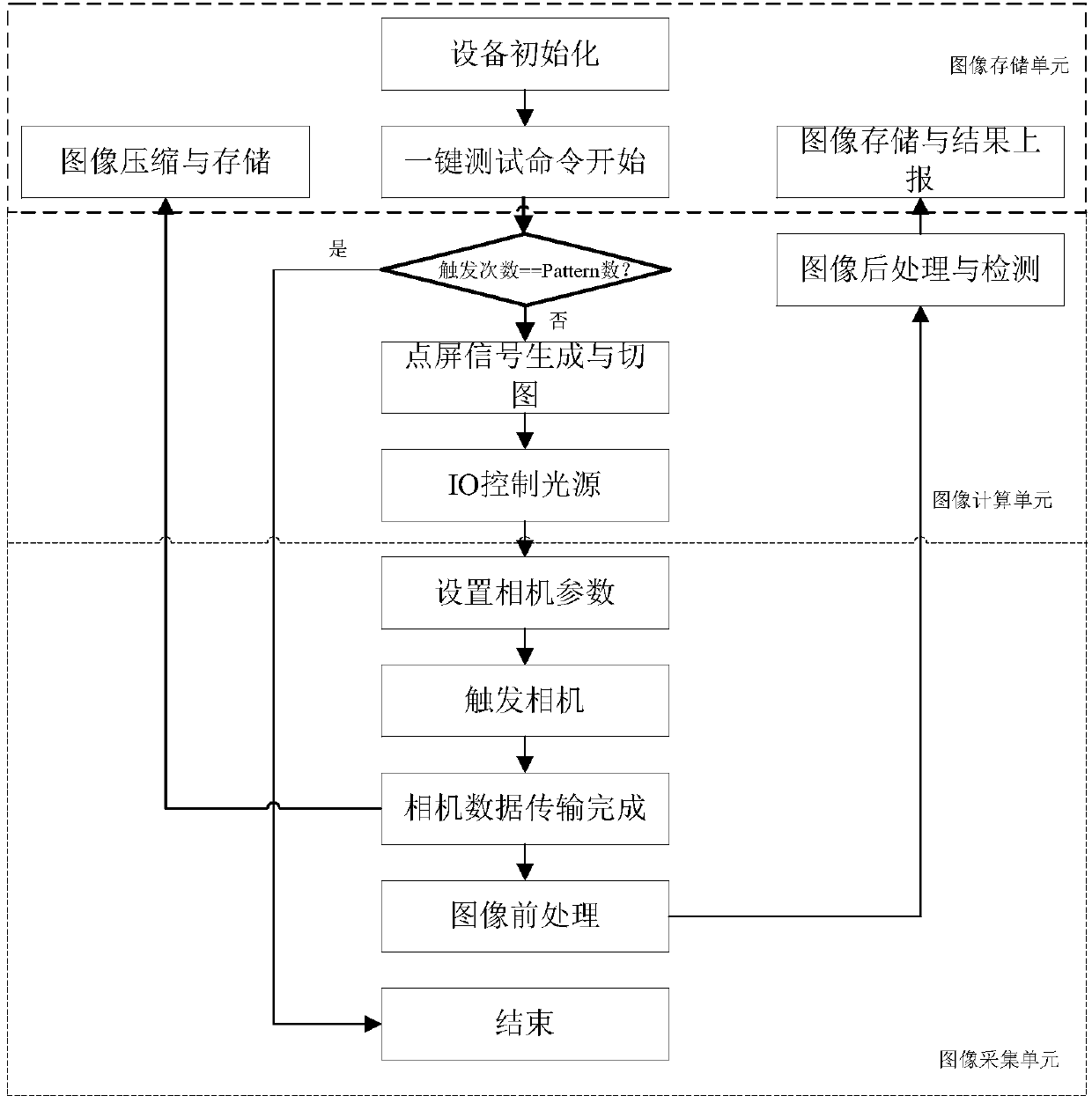

Automatic optical detection system based on CPU+GPU+FPGA architecture

ActiveCN107817216ARealize integrated control functionShort cycle timeProgramme controlImage enhancementFpga architectureCommunication interface

The invention discloses an automatic optical detection system based on a CPU+GPU+FPGA architecture. The automatic optical detection system comprises an image storage unit, an image calculation unit and an image acquisition unit, wherein the image storage unit is provided with a first communication interface and a second communication interface, the image calculation unit is provided with a first optical-fiber interface, a second optical-fiber interface, a third optical-fiber interface and a fourth optical-fiber interface, and the image acquisition unit is provided with a third communication interface and a camera interface; and the image calculation unit receives configuration parameters and test orders transmitted by the image storage unit and transmits a test result to the image storageunit by virtue of the first optical-fiber interface, receives data of the image acquisition unit and transmits the configuration parameters and the test orders to the image acquisition unit by virtueof the second optical-fiber interface, controls the generation of a point-screen signal by virtue of the third optical-fiber interface, and controls an IO light source by virtue of the fourth optical-fiber interface. The automatic optical detection system based on the CPU+GPU+FPGA architecture has the advantages of simple structure, low cost, good stability, good coordination capacity, high calculation processing capacity and the like.

Owner:WUHAN JINGCE ELECTRONICS GRP CO LTD

Error-detecting and correcting FPGA architecture

A method and apparatus are provided for an error-correcting FPGA. ECC data for configuration is generated and programmed into the ECC rows in the configuration memory. While booting, it is determined whether an integrity-check bit is set. If so, an integrity check is performed. If a single-bit error is detected, if the bit error is an erroneous “0” value, the memory location containing the erroneous “0” value is reprogrammed to a “1” value. If the bit error is an erroneous “1,” value, the memory block data is saved in a non-volatile memory block, the configuration memory block containing the error is erased and reprogrammed using the corrected bit. If there is more than one error, an error flag is set. The user reads the status of the error flag through the JTAG port. If the error flag is set then a full reprogramming cycle is initiated.

Owner:MICROSEMI SOC

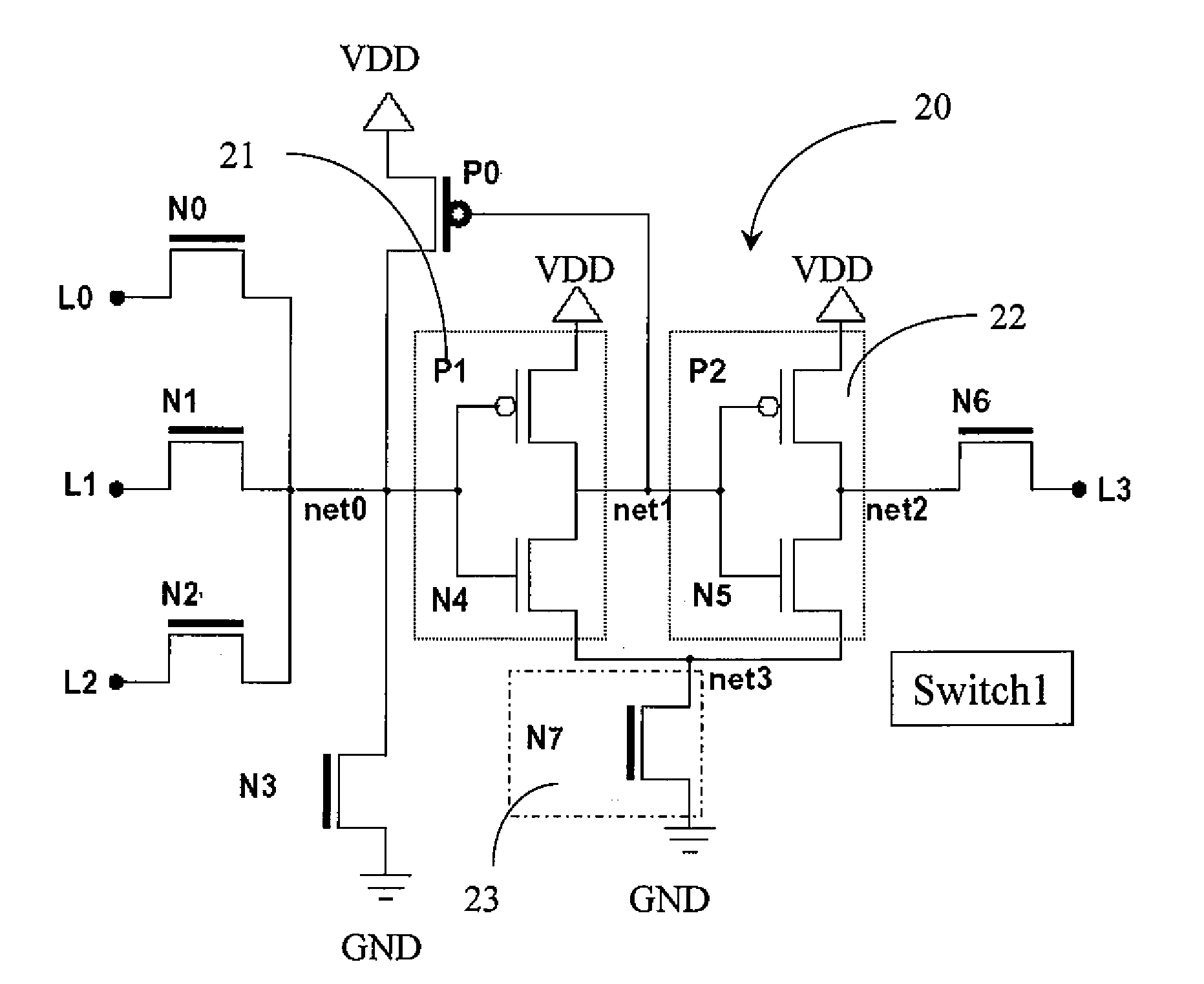

Switch block for FPGA architectures

ActiveUS20070085563A1Reduced static consumptionReduce consumptionLogic circuits characterised by logic functionSolid-state devicesComputer hardwareFpga architecture

A switch block for FPGA architectures combining hardware and software techniques in order to reduce both active and standby leakage power.

Owner:STMICROELECTRONICS SRL

Block symmetrization in a field programmable gate array

InactiveUS7233167B1Improve routabilityGood symmetryLogic circuits using elementary logic circuit componentsComputation using denominational number representationMultiplexingFpga architecture

An FPGA architecture has top, middle and low levels. The top level is an array of B16×16 tiles enclosed by I / O blocks. The routing resources in the middle level are expressway routing channels including interconnect conductors. At the lowest level, there are block connect routing channels, local mesh routing channels, and direct connect interconnect conductors to connect the logic elements to further routing resources. Each B1 block includes four clusters of devices. Each of the clusters includes first and second LUT3s, a LUT2, and a DFF. Each of the LUT3s have three inputs and one output. Each of the LUT2s have two inputs and one output. Each DFF has a data input and a data output. In each of the clusters the outputs of the LUT3s are multiplexed to the input of DFF, and symmetrized with the output of the DFF to form two outputs of each of the clusters.

Owner:ACTEL CORP

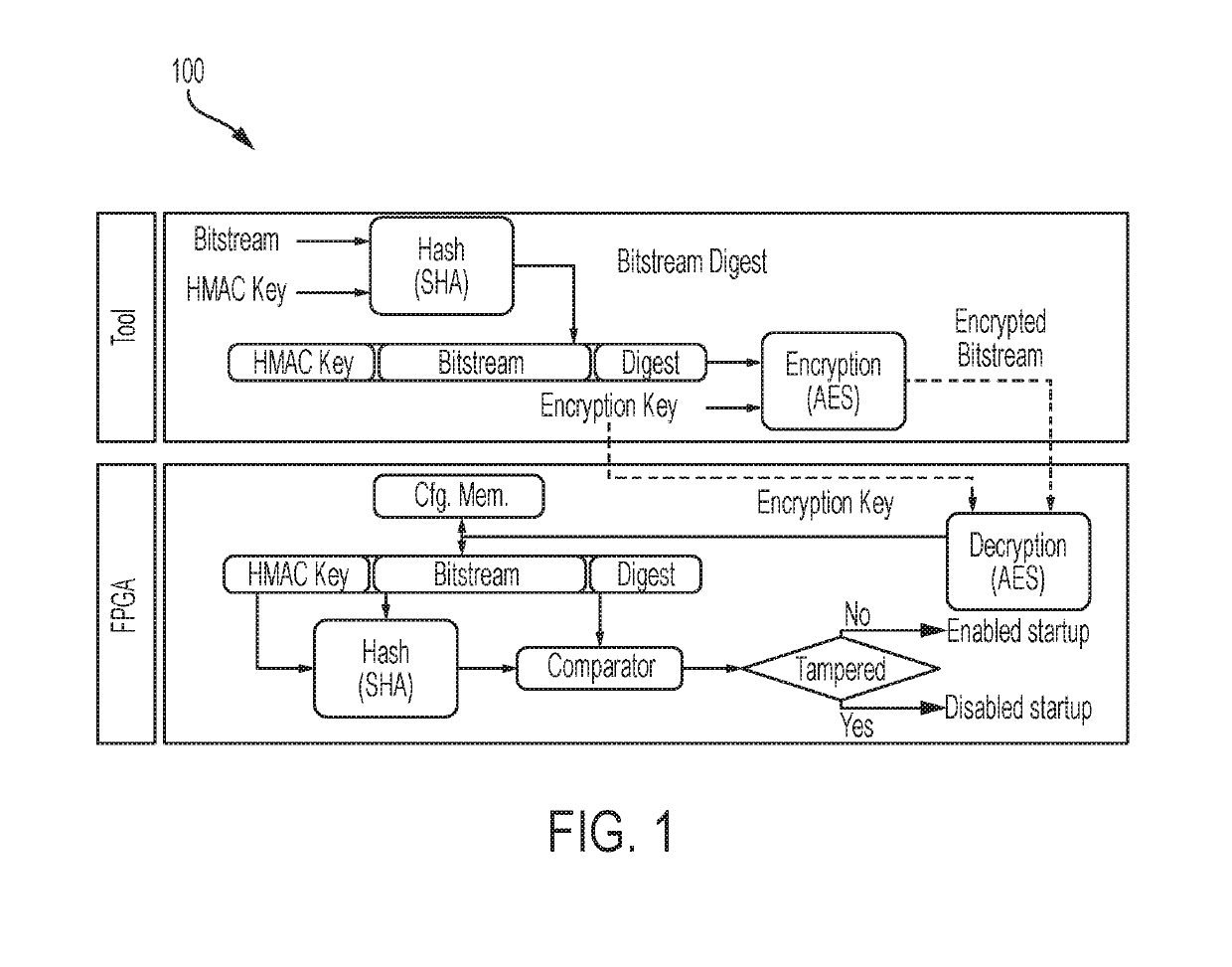

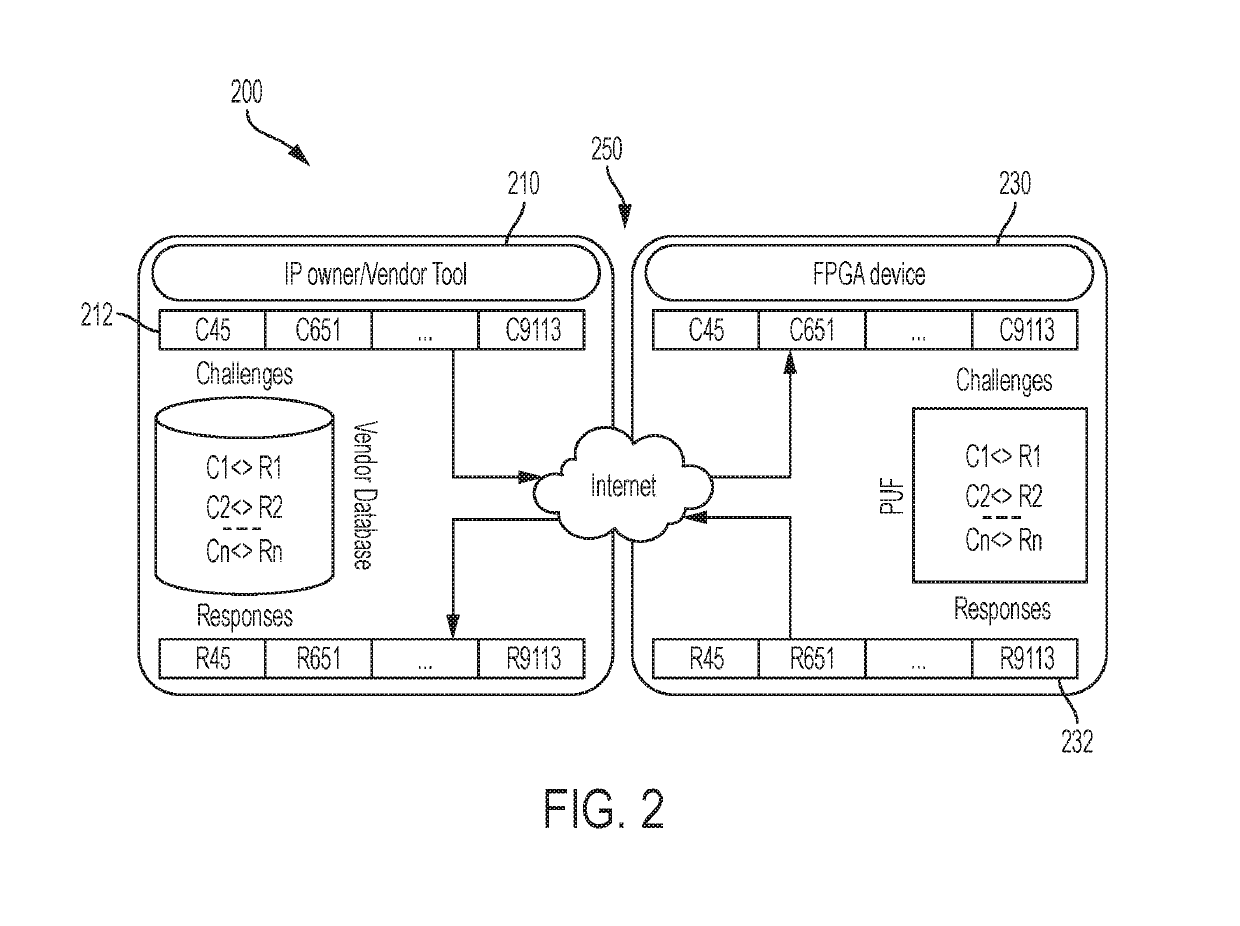

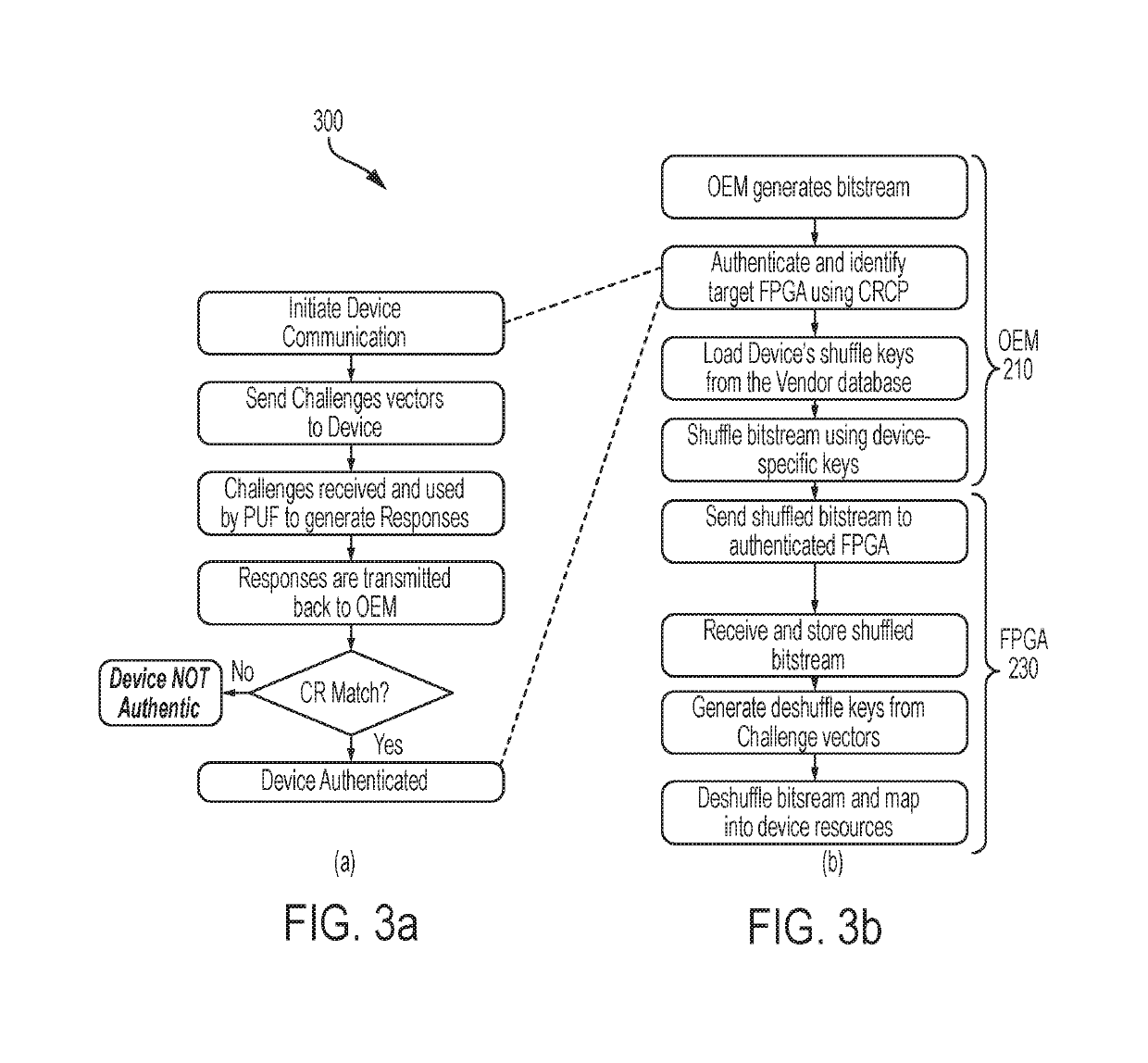

Bitstream security based on node locking

InactiveUS20190305927A1Key distribution for secure communicationInternal/peripheral component protectionFpga architectureIndex locking

A technique to generate node locked bitstreams for FPGAs to simultaneously protect against malicious reconfiguration as well as FPGA IP piracy is provided. According to some aspects, modifications in FPGA architecture along with an associated mapping flow enable authenticating and programming a device in a way that maintains FPGA security while requiring low overhead. The technique is more robust against side channel and destructive reverse-engineering attacks in comparison with key-based encryption methods, and has less area, power, and latency overhead. The node locked bitstream approach is attractive in many existing and emerging applications including IoTs, which may require field upgrade of FPGA.

Owner:UNIV OF FLORIDA RES FOUNDATION INC

Turn architecture for routing resources in a field programmable gate array

InactiveUS6934927B2Good symmetryEasy to placeSolid-state devicesElectronic switchingFpga architectureElectrical conductor

An FPGA architecture has top, middle and low levels. The top level of the architecture is an array of the B16×16 tiles arranged in a rectangular array and enclosed by I / O blocks on the periphery. A B16×16 tile in the middle level of hierarchy is a sixteen by sixteen array of B1 blocks. The B16×16 tile is a nesting of a B2×2 tile that includes a two by two array of four B1 blocks. The routing resources in the middle level of hierarchy are expressway routing channels M1, M2, and M3 including groups of interconnect conductors. The expressway routing channels M1, M2, and M3 are segmented, and between each of the segments in the expressway routing channels M1, M2, and M3 are disposed extensions that can extend the expressway routing channel M1, M2, or M3 an identical distance along the same direction. The expressway routing channels M1, M2, and M3 run both vertically through every column and horizontally through every row of B2×2 tiles. At the intersections of each of the expressway routing channels M1, M2, and M3 in the horizontal direction with the expressway routing channels M1, M2 and M3 in the vertical direction is an expressway turn (E-turn) disposed at the center of each B2×2 tile. An E-turn is a passive device that includes a matrix of reprogrammable switches. The reprogrammable switches are preferably a pass device controlled by an SRAM bit. The interconnect conductors in the expressway routing channels M1, M2 and M3 that are fed into an E-turn may be coupled to many of the other interconnect conductors in the expressway routing channels M1, M2 and M3 that come into the E-turn by the programmable switches. Further, the interconnect conductors in the expressway routing channels M1, M2 and M3 that are fed into an E-turn continue in the same direction through the E-turn, even though the interconnect conductors are coupled to other interconnect conductors by the reprogrammable switches.

Owner:MICROSEMI SOC

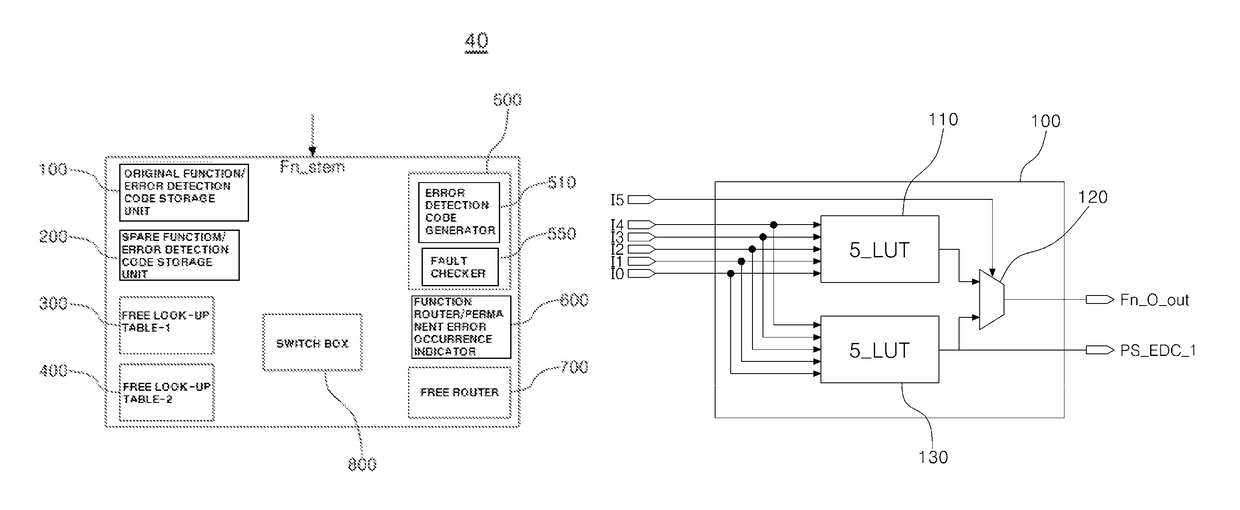

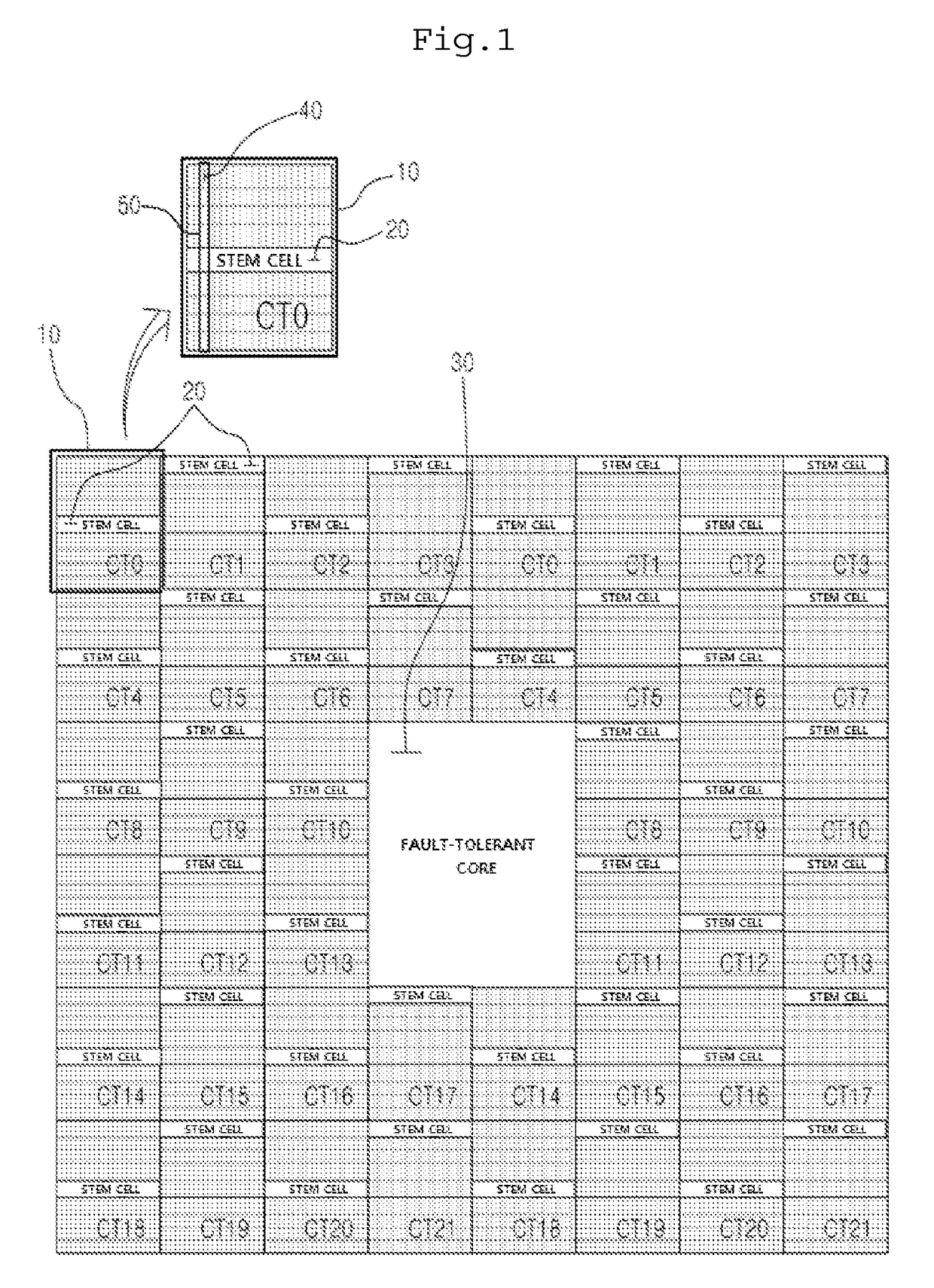

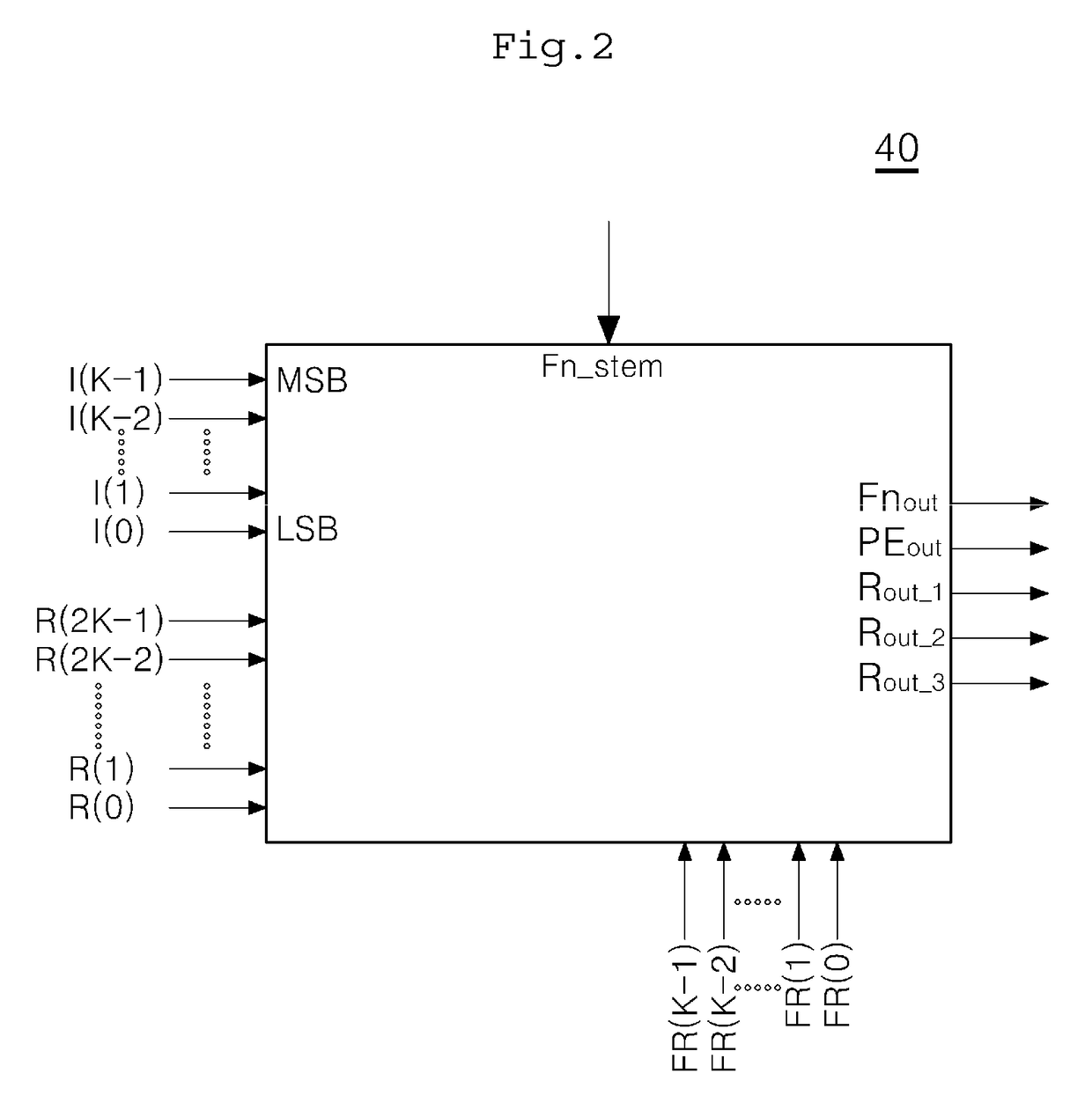

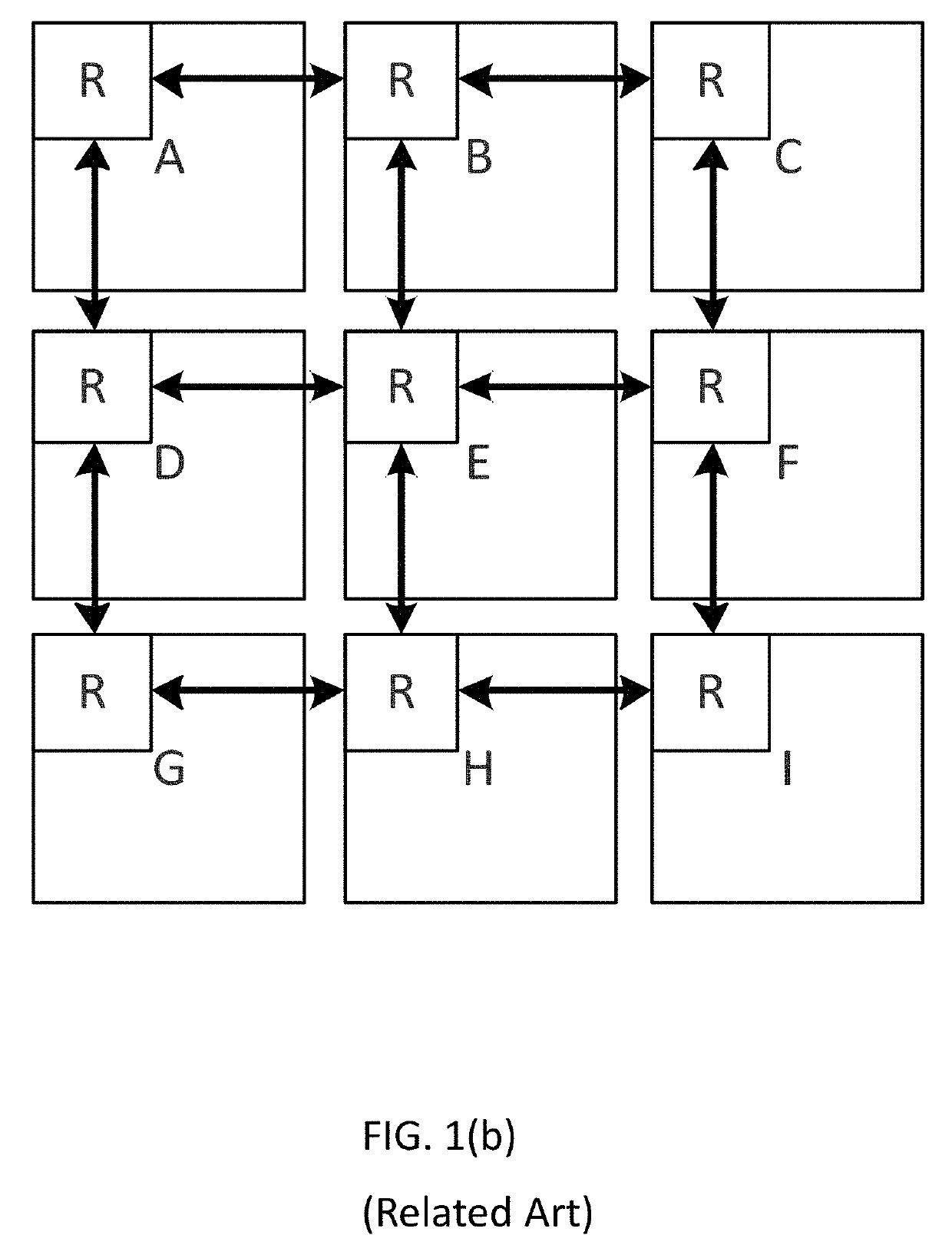

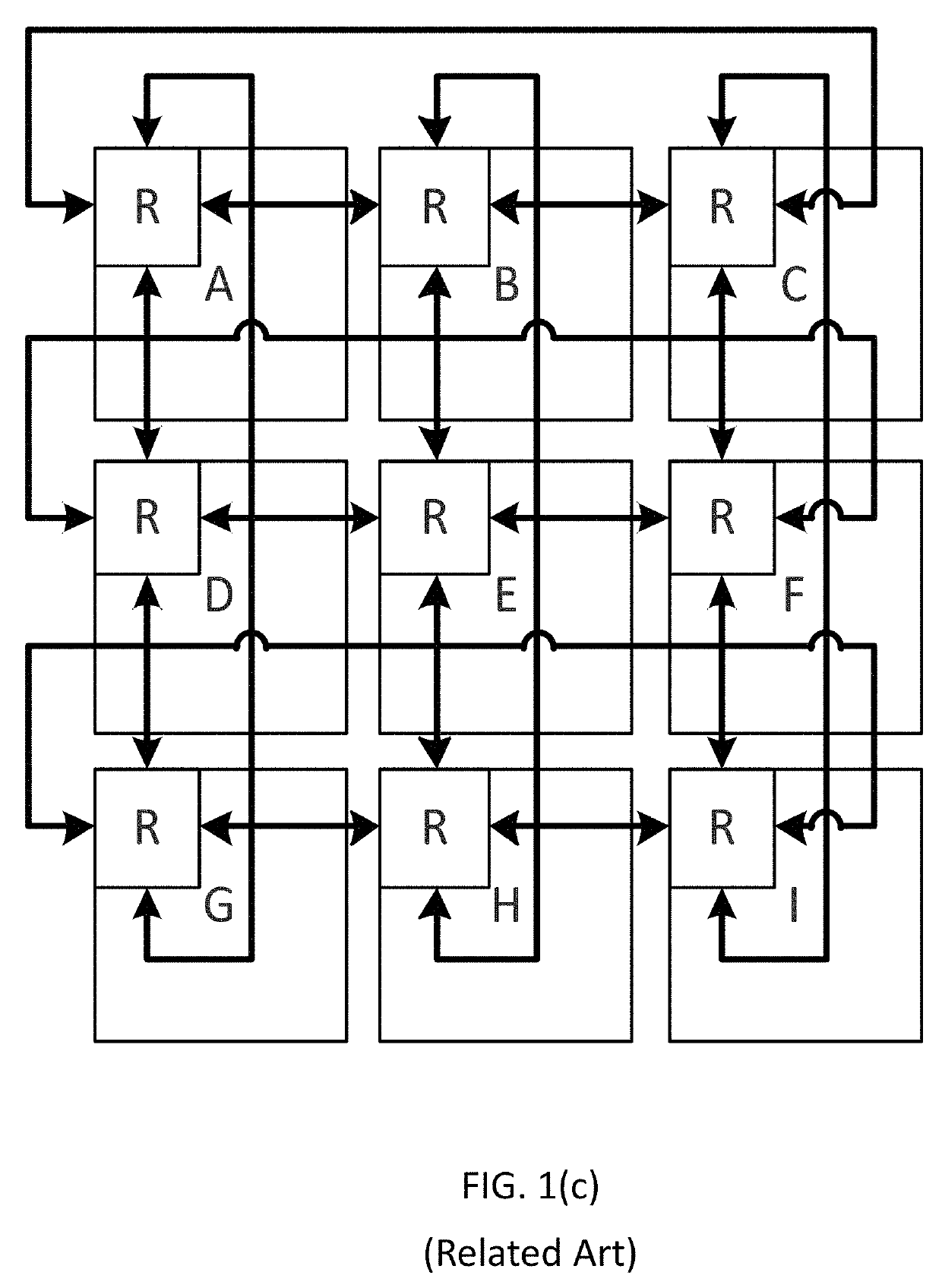

Self-healing, fault-tolerant FPGA computation and architecture

InactiveUS9720766B2Guaranteed uptimeRedundant data error correctionLogic circuits using elementary logic circuit componentsComputer hardwareFpga architecture

The present invention relates to a computation cell and a self-healing, fault-tolerant FPGA architecture and, more particularly, to a computation cell and an FPGA including the same, which can detect a transient internal error or permanent internal error by inputting an original function and a spare function and comparing a prestored error detection code with a generated error detection code signal. The computation cell and the self-healing, fault-tolerant FPGA architecture of the present invention can reconfigure stem cells and look-up tables included in the computation cell and can output a normal output signal even if a transient error or a permanent error is generated in an computation cell such that the corresponding computation cell and an computation tile can be normally operated.

Owner:IND ACADEMIC CORP FOUND YONSEI UNIV

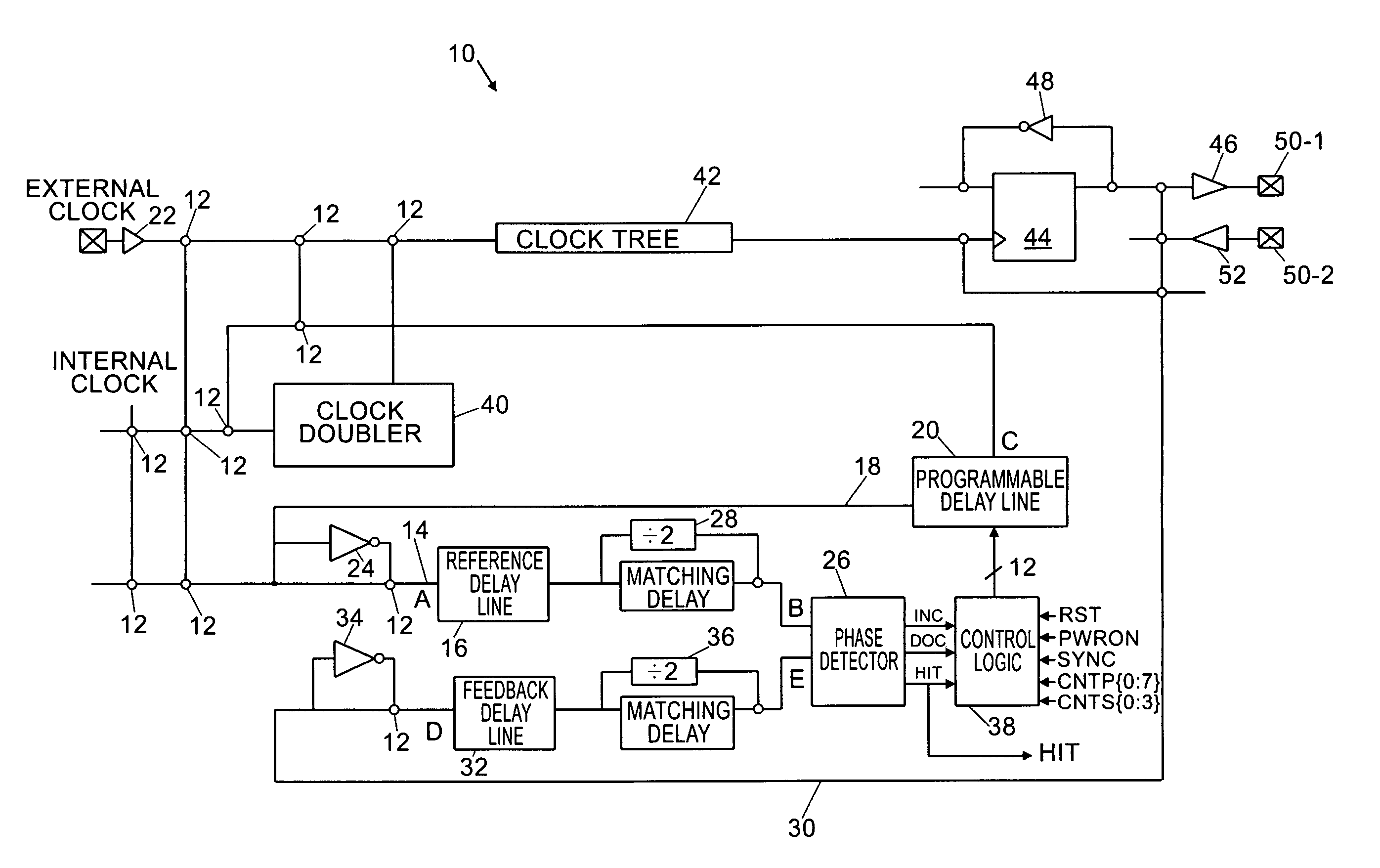

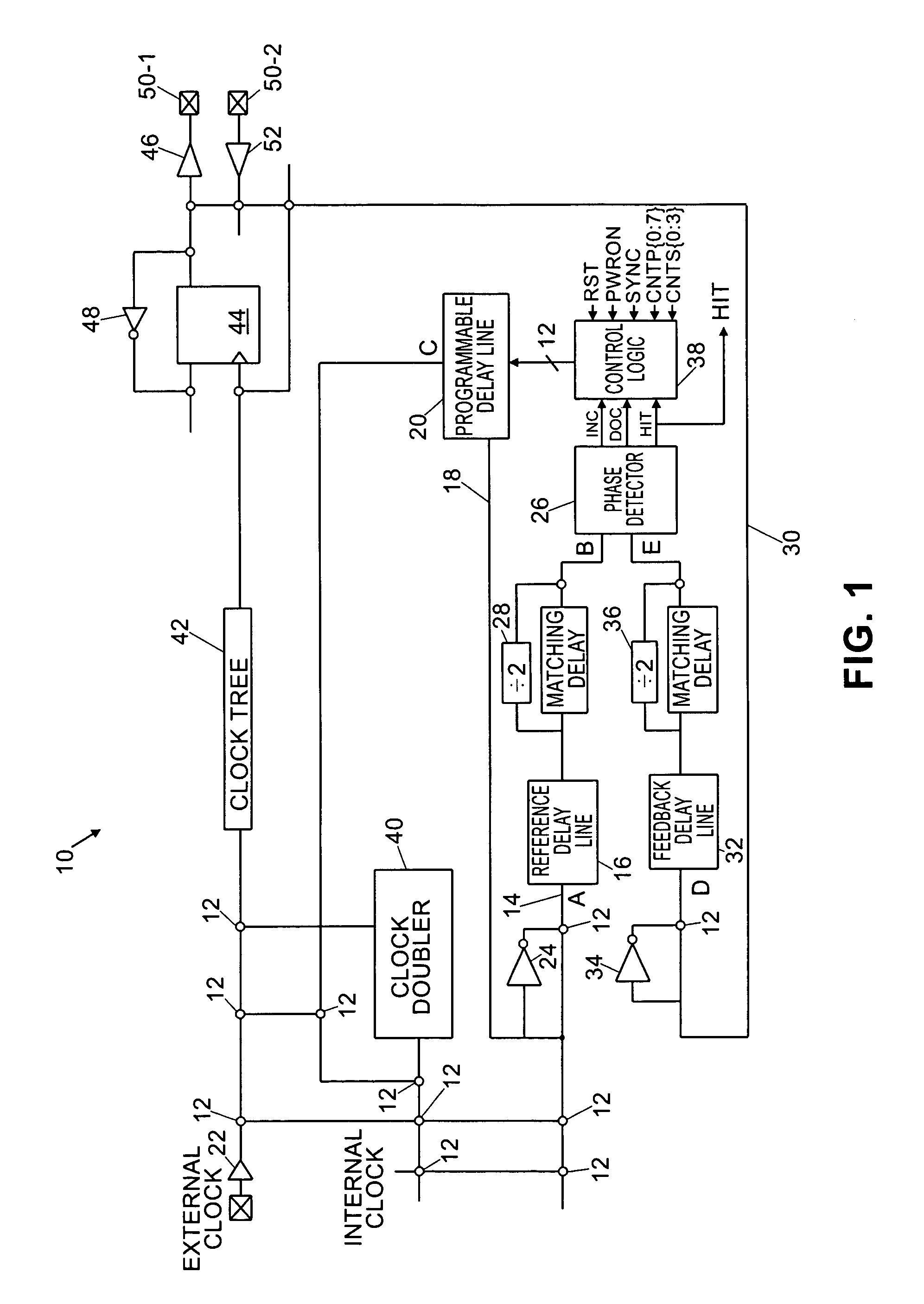

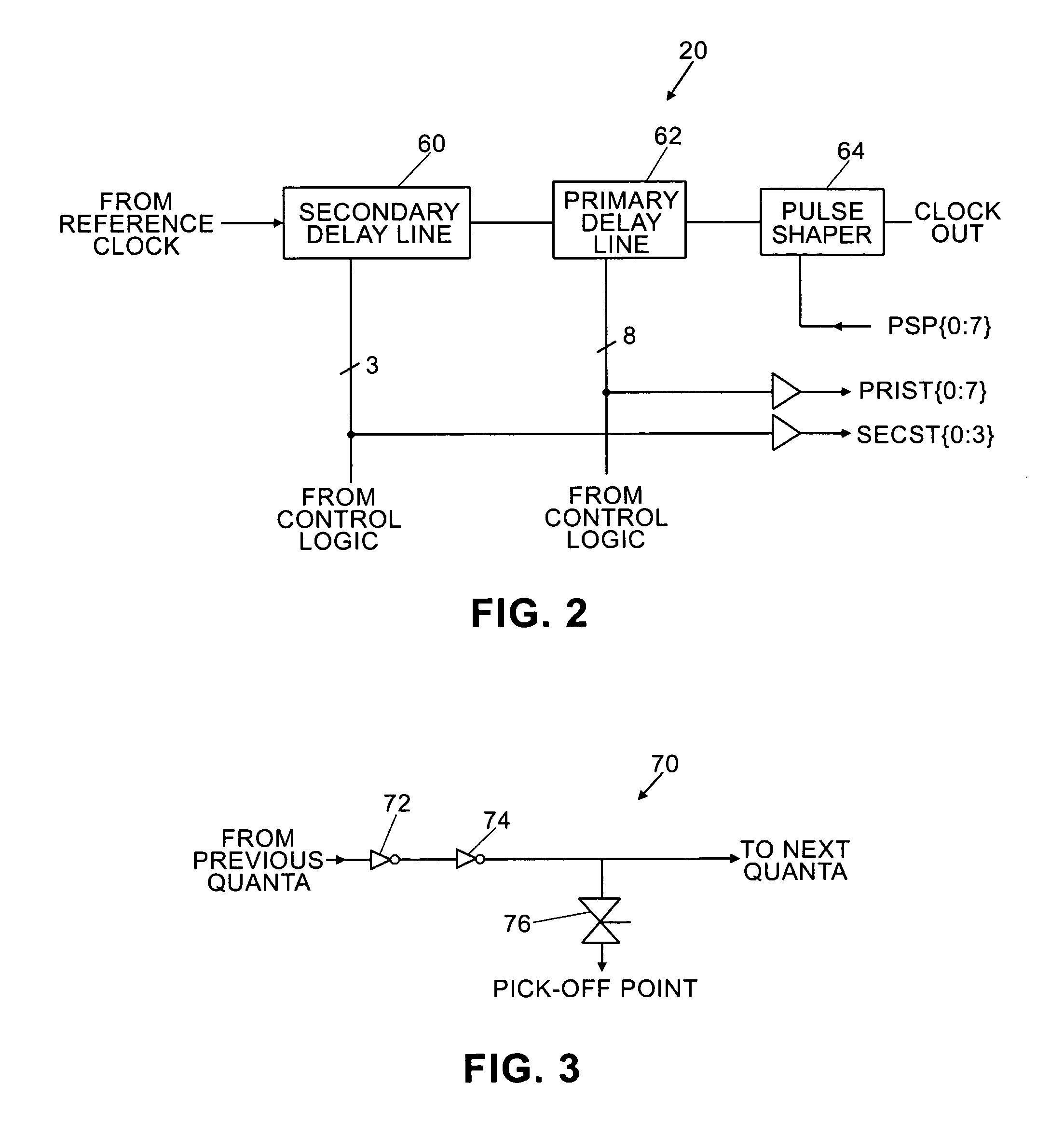

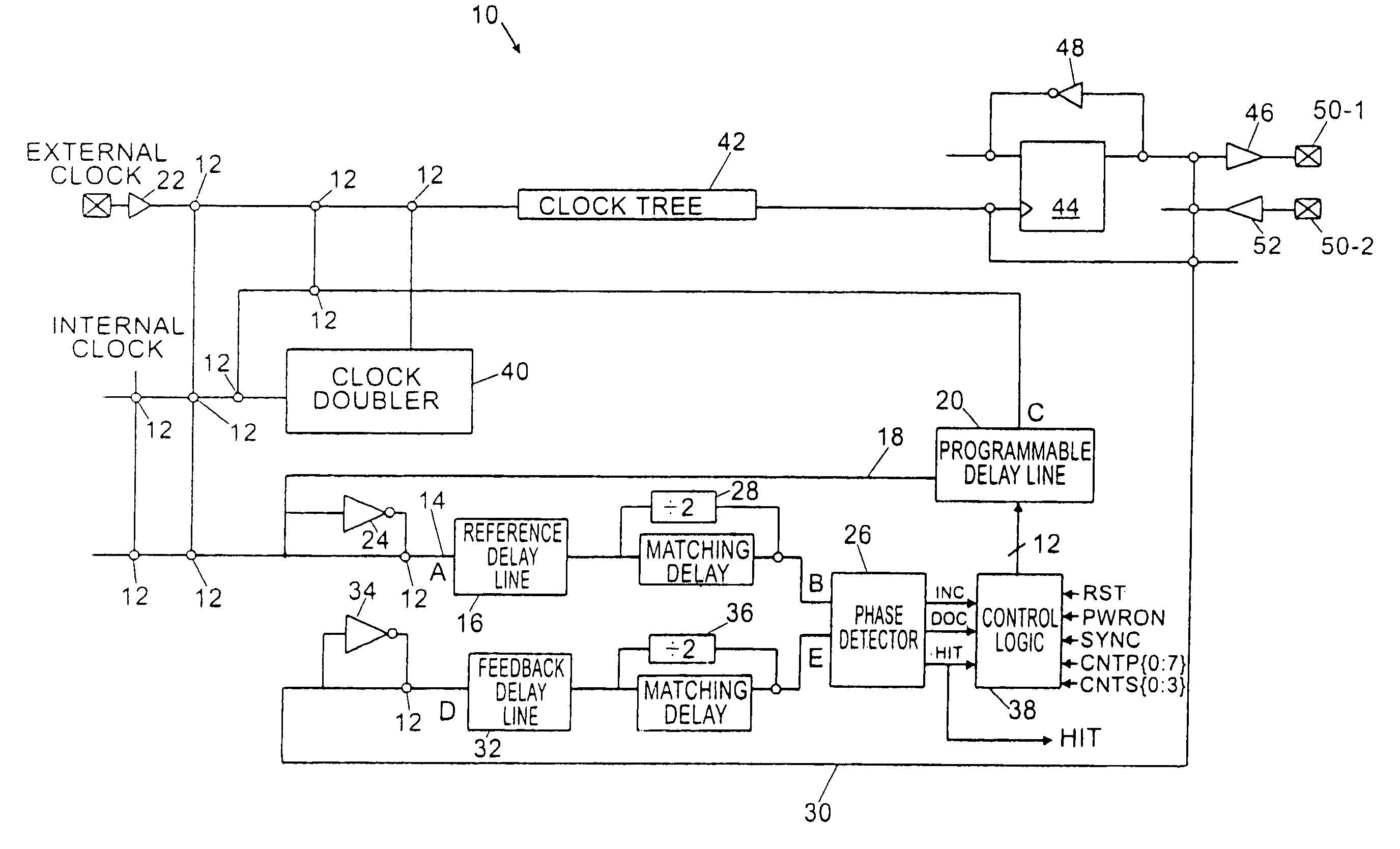

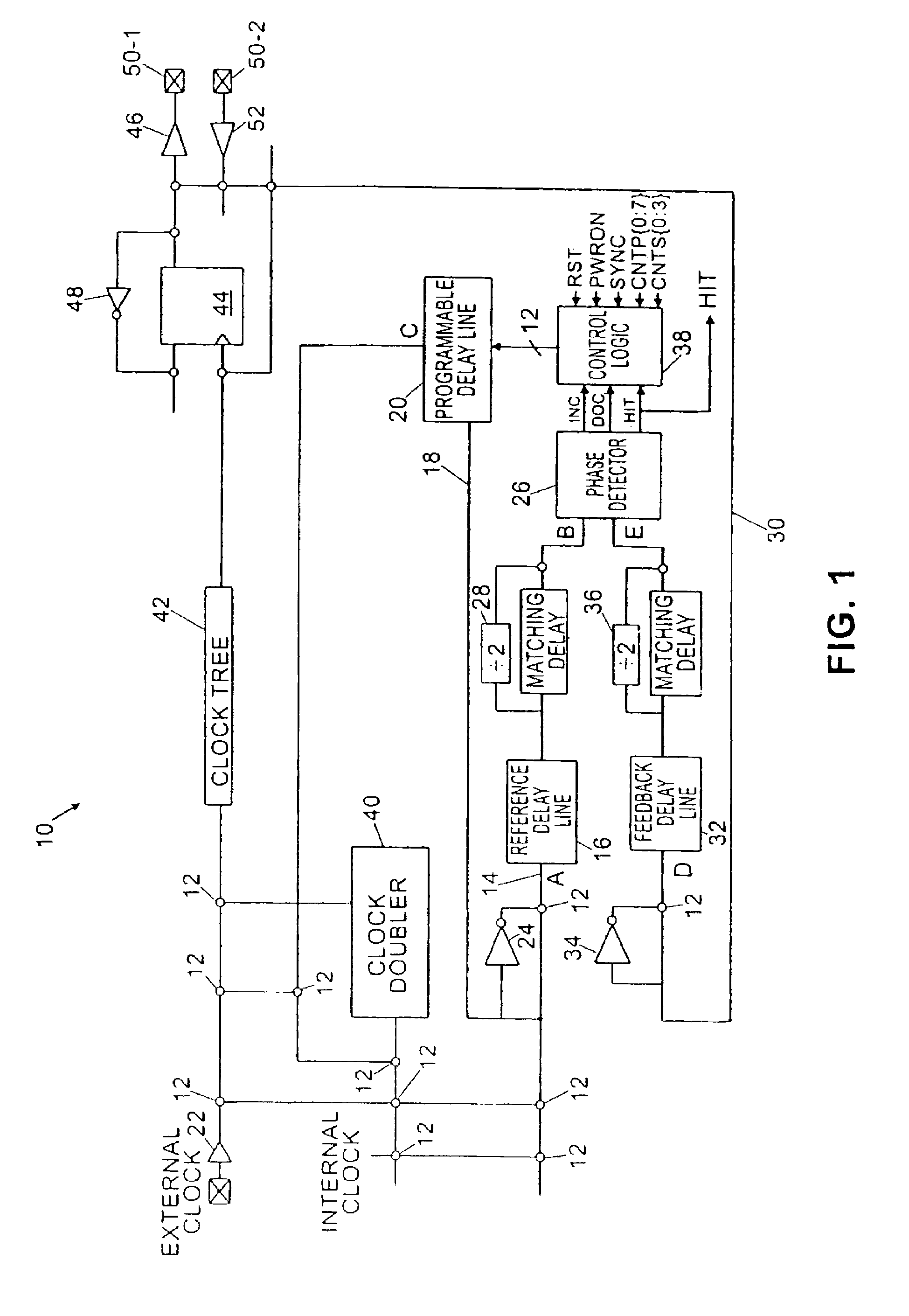

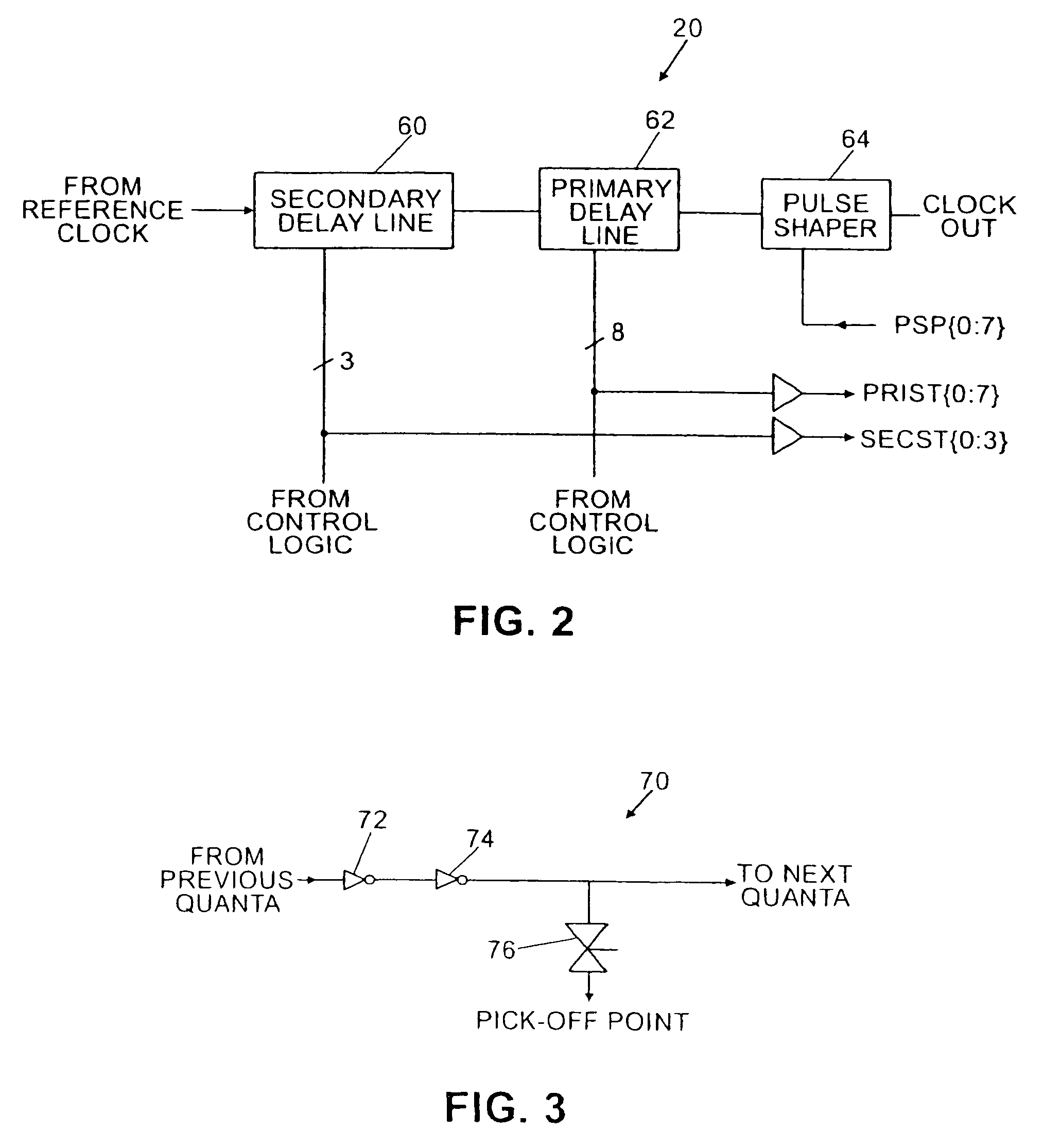

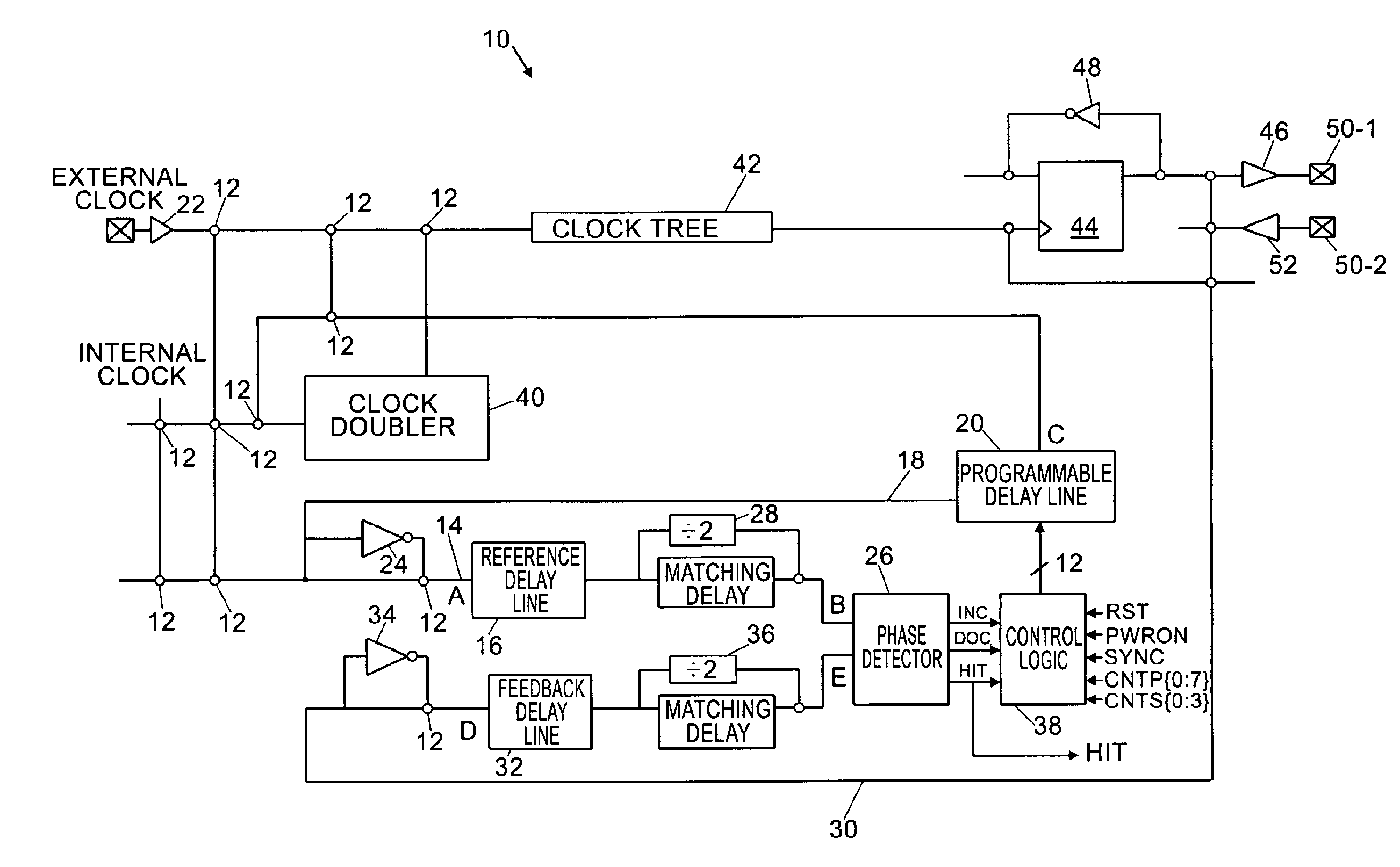

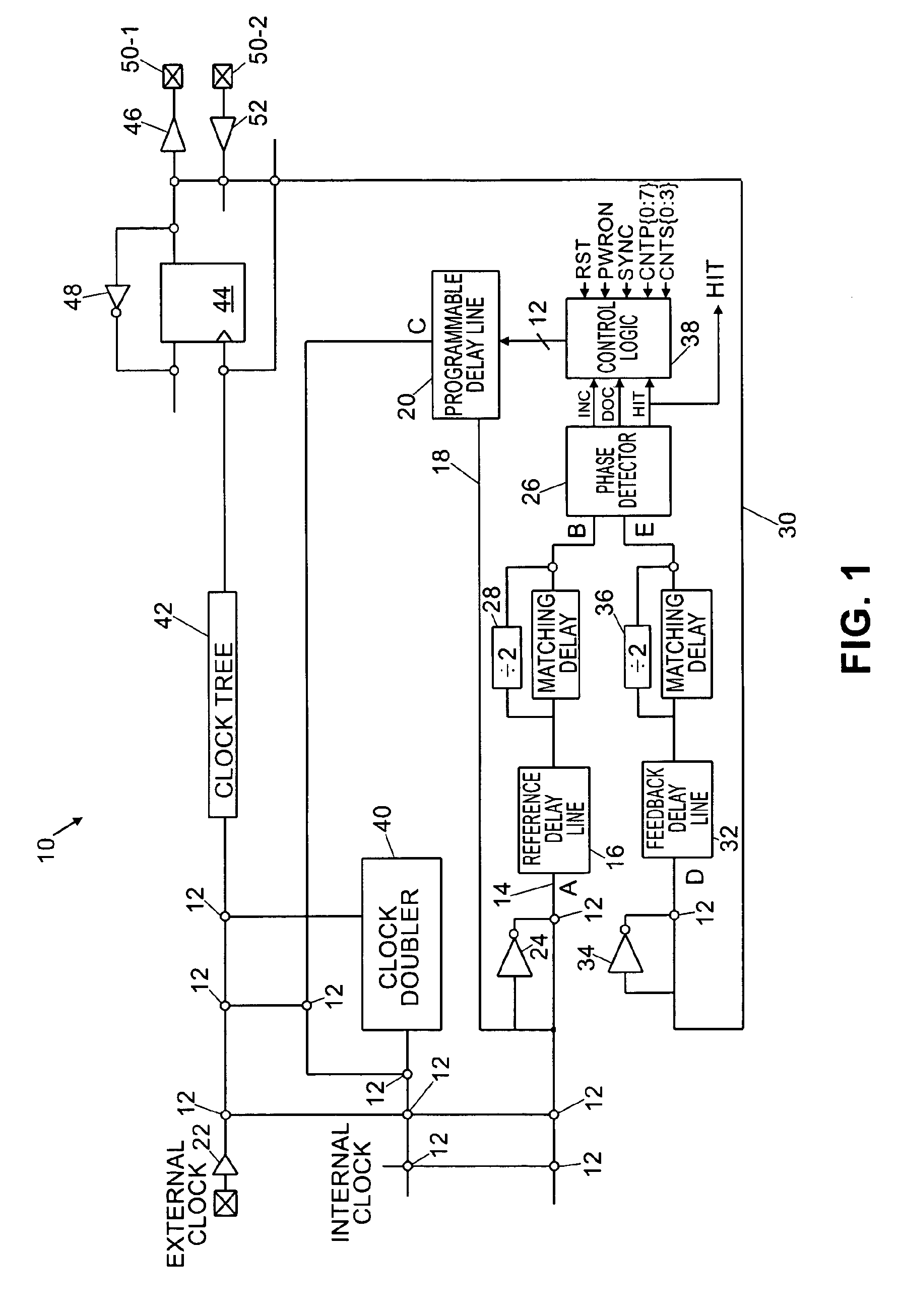

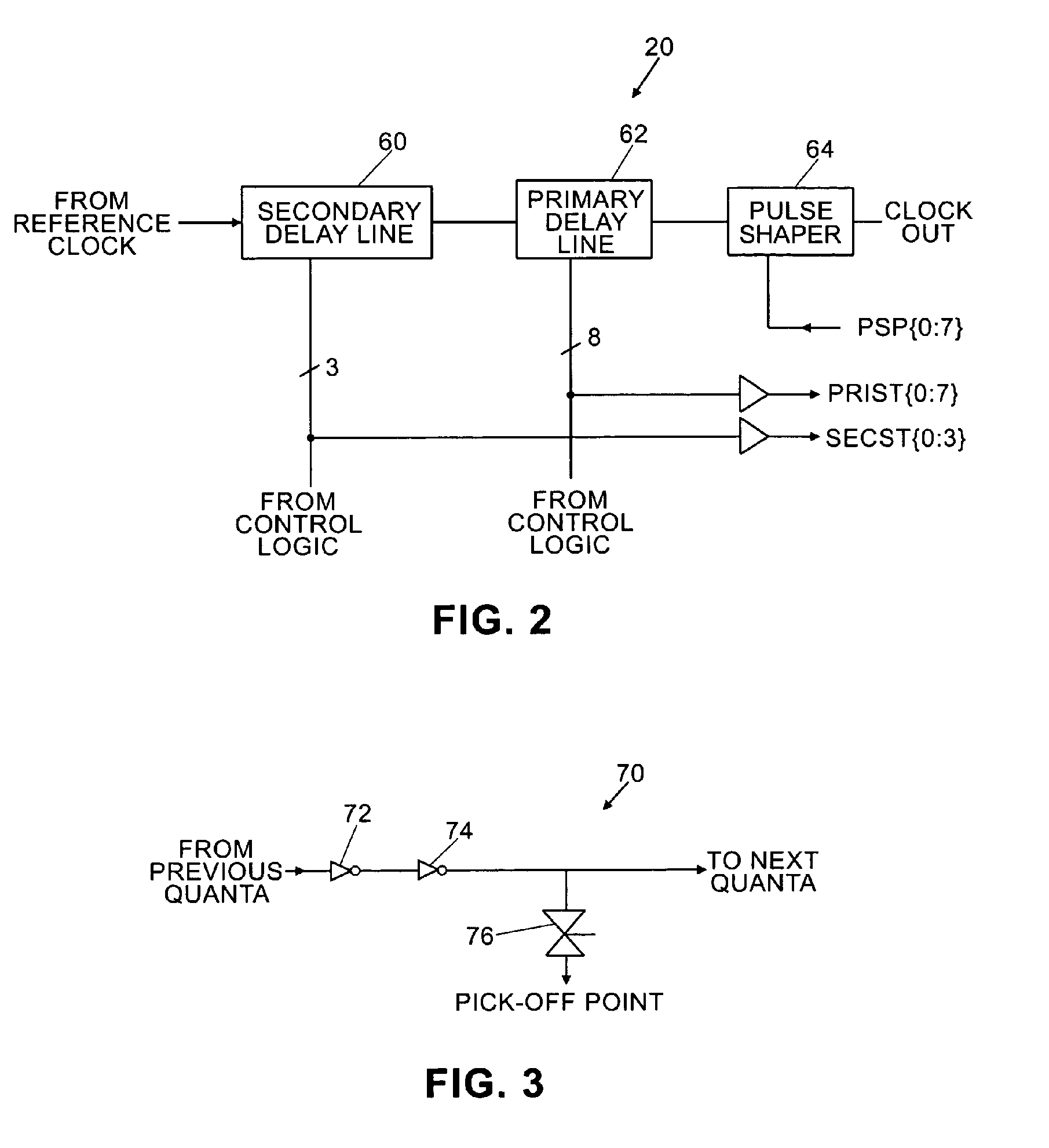

Delay locked loop for an FPGA architecture

A DLL provides a deskew mode for aligning a reference clock that passes through a clock distribution tree to a feedback by adding additional delay to the feedback clock to align the feedback clock with reference clock at one cycle later. A 0 ns clock-to-out mode is provided by adding additional delay to account for an input buffer into a feedback path. The feedback clock can be doubled by a clock doubler with 50% duty cycle adjustment disposed in the feedback path. Flexible timing is aligning the reference clock to the feedback clock is obtained with additional delay elements disposed in the feedback and reference clock paths.

Owner:MICROSEMI SOC

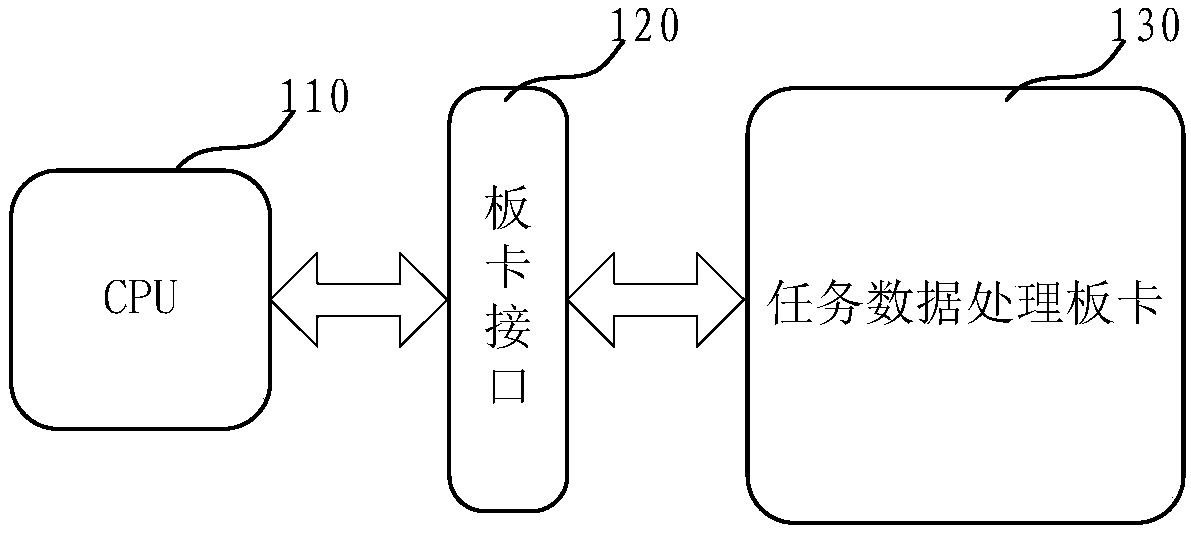

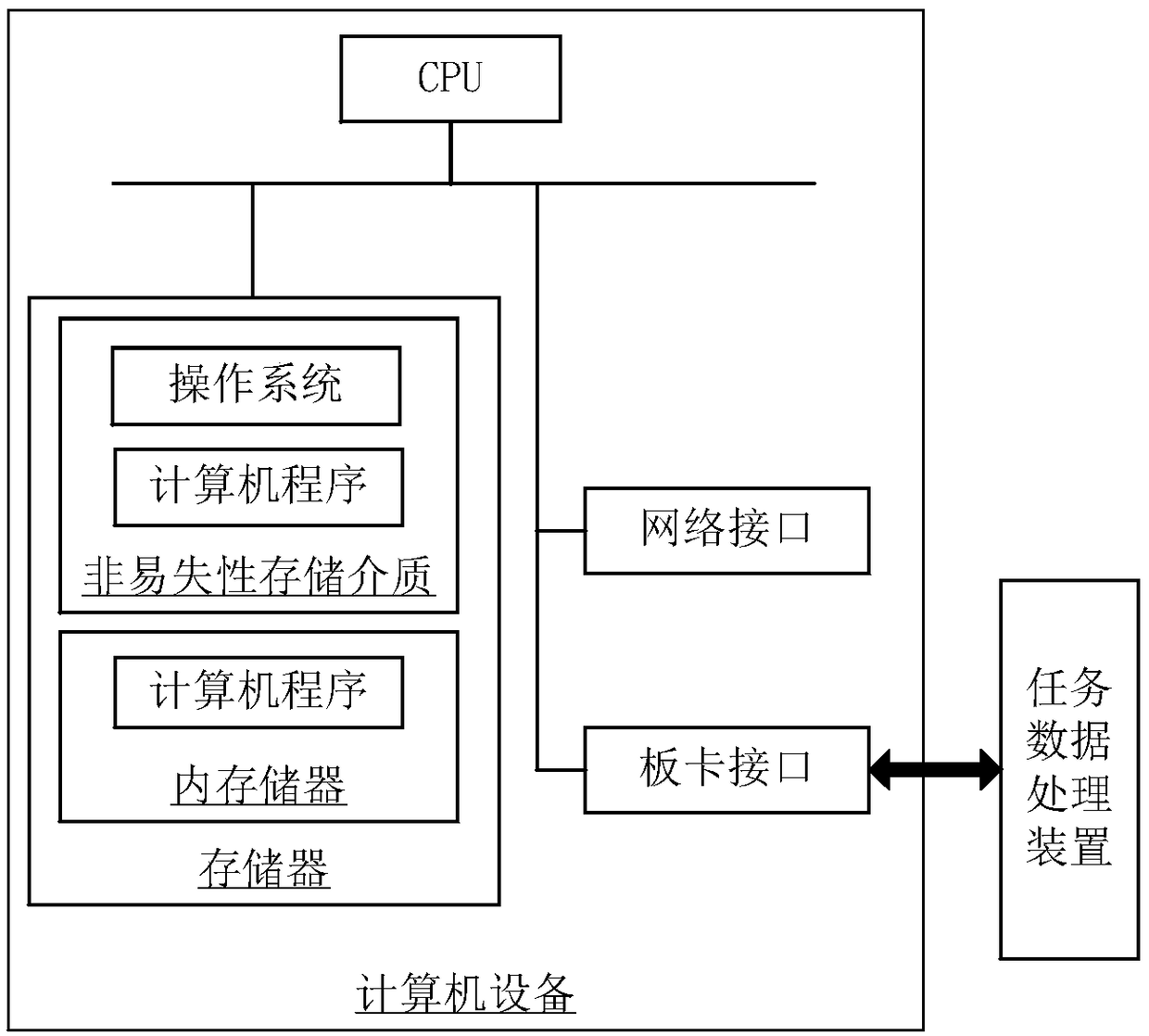

Picture processing method, task data processing method and device

ActiveCN109325494AImprove processing efficiencyCharacter and pattern recognitionConcurrent instruction executionFpga architectureText recognition

Owner:TENCENT TECH (SHENZHEN) CO LTD

Block symmetrization in a field programmable gate array

InactiveUS20010028257A1Good symmetryEasy to placeSolid-state devicesLogic circuits using elementary logic circuit componentsFpga architectureMultiplexing

An FPGA architecture has top, middle and low levels. The top level of the architecture is an array of the B16x16 tiles arranged in a rectangular array and enclosed by I / O blocks on the periphery. On each of the four sides of a B16x16 tile, and also associated with each of the I / O blocks is a freeway routing channel. A B16x16 tile in the middle level of hierarchy is a sixteen by sixteen array of B1 blocks. The routing resources in the middle level of hierarchy are expressway routing channels M1, M2, and M3 including groups of interconnect conductors. At the lowest level of the semi-hierarchical FPGA architecture, there are block connect (BC) routing channels, local mesh (LM) routing channels, and direct connect (DC) interconnect conductors to connect the logic elements to further routing resources. Each B1 block includes four clusters of devices. Each of the four clusters includes first and second LUT3s, a LUT2, and a DFF. Each of the LUT3s have first, second, and third inputs and a single output. Each of the LUT2s have first and second inputs and a single output. Each DFF has a data input and a data output. In each of the clusters the outputs of the LUT3s are muliplexed to the input of DFF, and symmetrized with the output of the DFF to form first and second outputs of each of the clusters.

Owner:MICROSEMI SOC

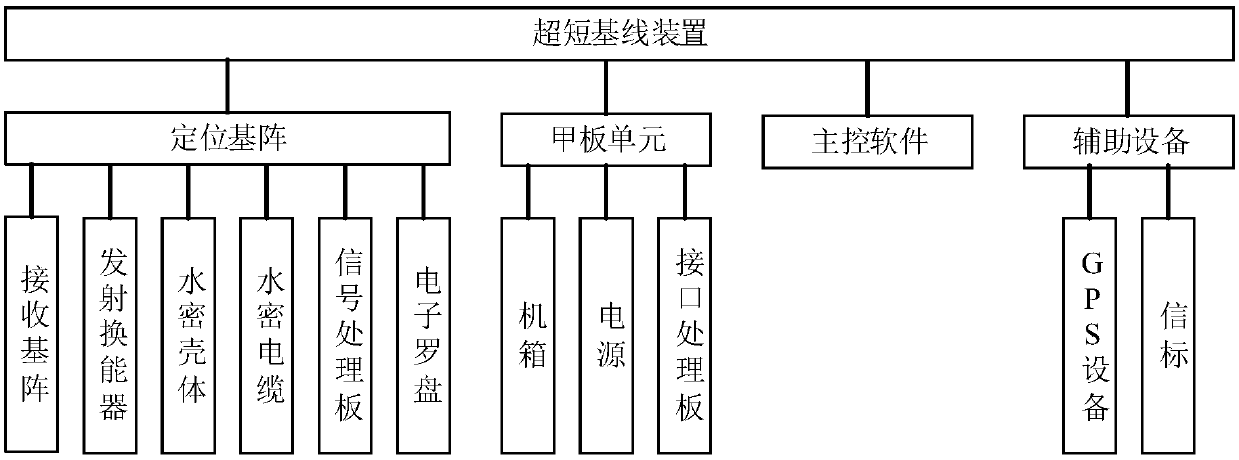

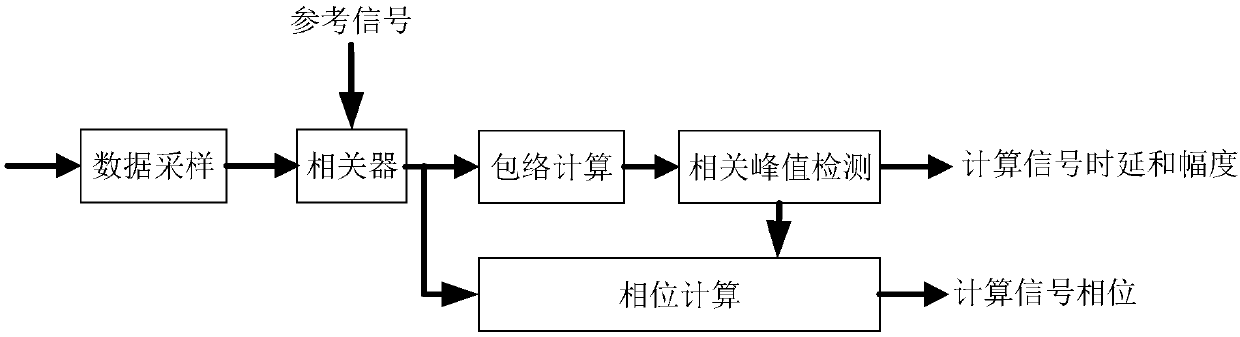

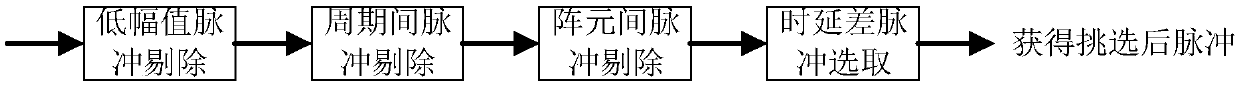

Ultra-short baseline device suitable for shallow water positioning and positioning method

PendingCN107748352ALess wildHigh positioning accuracyPosition fixationSatellite radio beaconingPhase correctionFpga architecture

The invention discloses an ultra-short baseline device suitable for shallow water positioning and a positioning method. The ultra-short baseline device suitable for shallow water positioning includesa positioning array, a deck unit, and an auxiliary device, and is controlled by main control software. A receiving array has a plurality of array elements, the array elements are in the same plane, and the array elements receive acoustic signals at the same time. A transmitting transducer is used to transmit an interrogation signal in an answer mode, and is arranged in the middle of the array elements of the receiving array. A signal processing board is provided with a processor, and the processor adopts a combined architecture of the FPGA and DSP. The ultra-short baseline device suitable forshallow water positioning and the positioning method disclosed in the invention adopt the pulse selection technology and time-delay difference phase correction technology to precisely track and position the target trajectory, and the positioning trajectory is smooth and stable, with few outliers and high positioning accuracy.

Owner:嘉兴易声电子科技有限公司

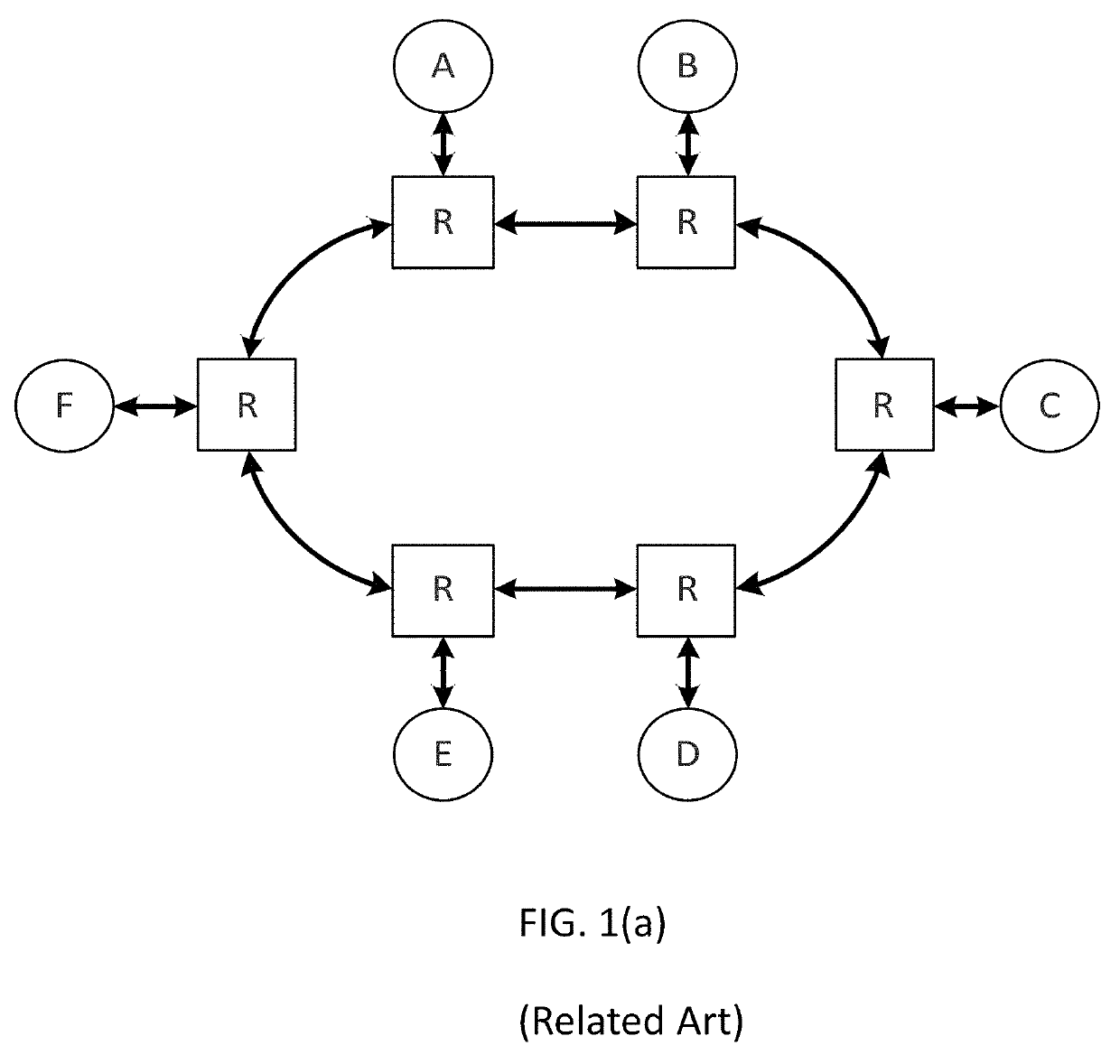

Backbone network-on-chip (NOC) for field-programmable gate array (FPGA)

InactiveUS20190266088A1Improve system efficiencyCreate efficientlyDigital computer detailsConcurrent instruction executionFpga architectureProgrammable logic device

Methods and example implementations described herein are generally directed to Field-Programmable Gate-Arrays (FPGAs) or other programmable logic devices (PLDs) or other devices based thereon, and more specifically, to the addition of networks-on-chip (NoC) to FPGAs. This includes both modifications to the FPGA architecture and design flow. An aspect of the present disclosure relates to a Field-Programmable Gate-Array (FPGA) system. The FPGA system can include an FPGA having one or more lookup tables (LUTs) and wires, and a Network-on-Chip (NoC) having a hardened network topology configured to provide connectivity at a higher frequency that the FPGA. The NoC is coupled to the FPGA to provide a connectivity at a higher frequency that the FPGA.

Owner:INTEL CORP

Delay locked loop for and FPGA architecture

A DLL provides a deskew mode for aligning a reference clock that passes through a clock distribution tree to a feedback by adding additional delay to the feedback clock to align the feedback clock with reference clock at one cycle later. A 0 ns clock-to-out mode is provided by adding additional delay to account for an input buffer into a feedback path. The feedback clock can be doubled by a clock doubler with 50% duty cycle adjustment disposed in the feedback path. Flexible timing is aligning the reference clock to the feedback clock is obtained with additional delay elements disposed in the feedback and reference clock paths.

Owner:ACTEL CORP

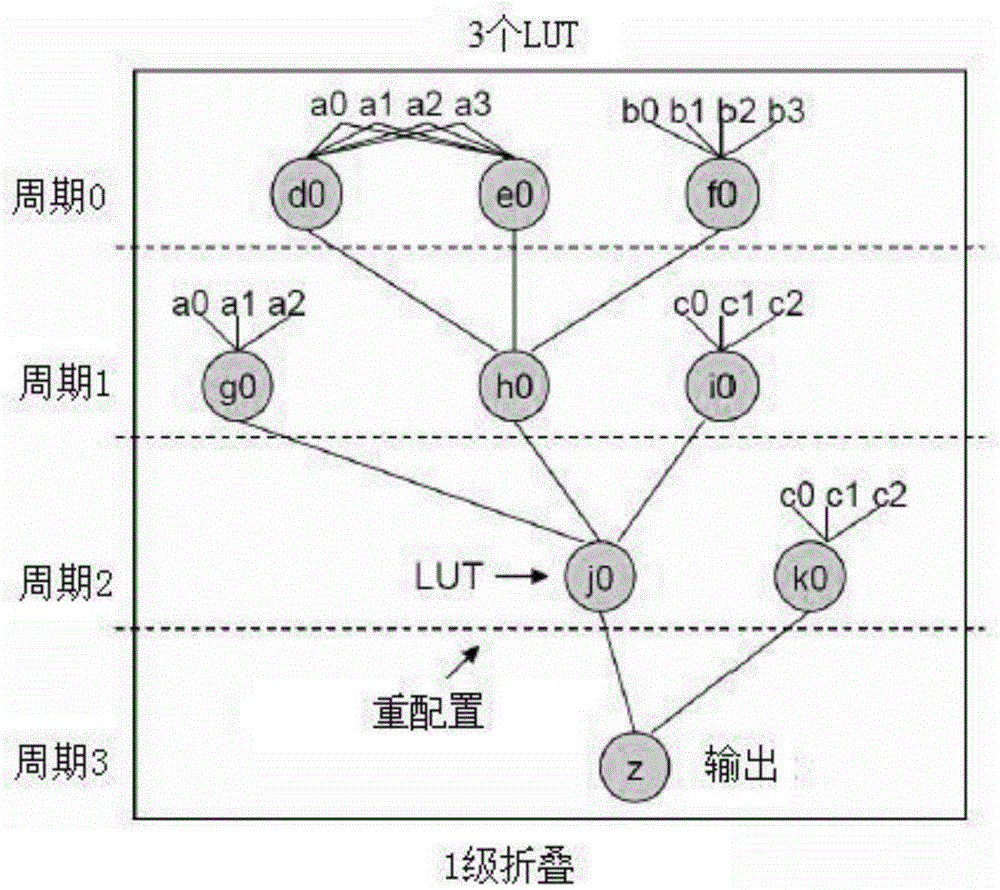

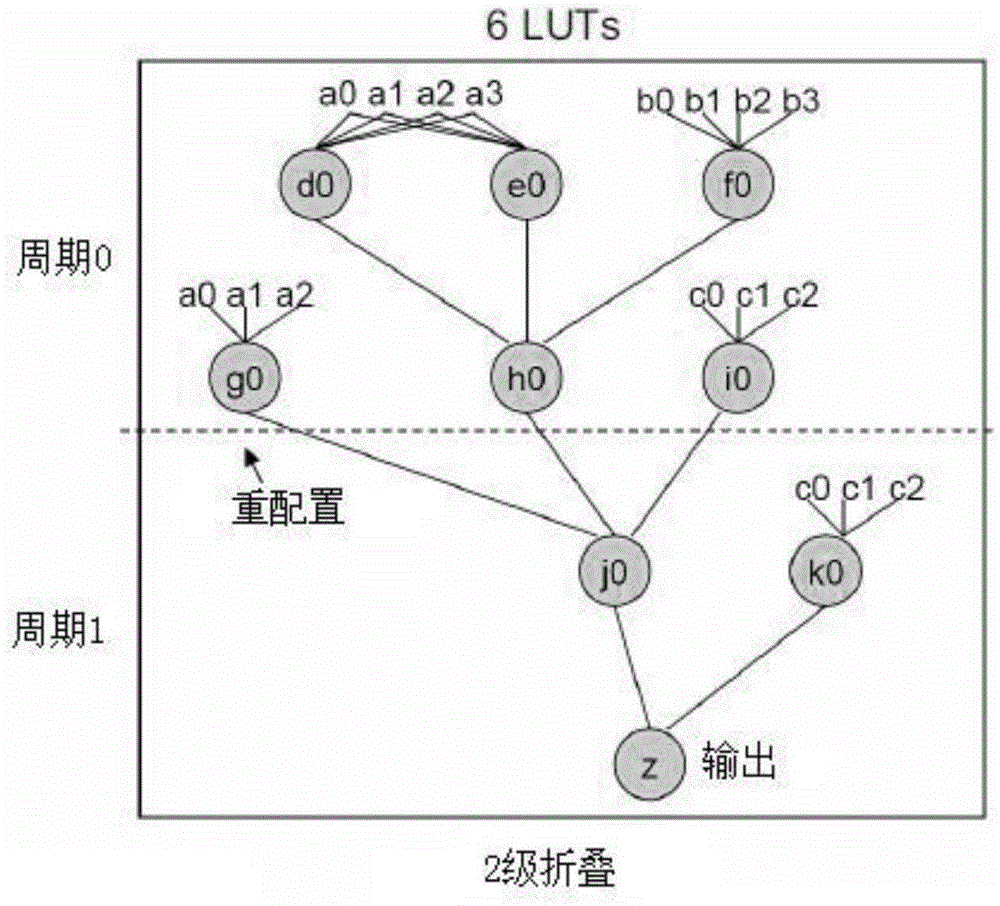

Fine-grain dynamically reconfigurable FPGA architecture

InactiveCN105340181APower consumption reductionLogic circuits using elementary logic circuit componentsFpga architectureRandom access memory

Owner:PRINCETON UNIV TRUSTEESHIPS

Block level routing architecture in a field programmable gate array

InactiveUS6898777B2Good symmetryEasy to placeSolid-state devicesSpecial data processing applicationsFpga architectureElectrical conductor

An FPGA architecture has top, middle and low levels. The top level of the architecture is an array of the B16×16 tiles arranged in a rectangular array and enclosed by I / O blocks on the periphery. On each of the four sides of a B16×16 tile, and also associated with each of the I / O blocks is a freeway routing channel. A B16×16 tile in the middle level of hierarchy is a sixteen by sixteen array of B1 blocks. The routing resources in the middle level of hierarchy are expressway routing channels M1, M2, and M3 including groups of interconnect conductors. At the lowest level of the semi-hierarchical FPGA architecture, there are block connect (BC) routing channels, local mesh (LM) routing channels, and direct connect (DC) interconnect conductors. Each BC routing channel is coupled to an expressway tab to provide access for each B1 block to the expressway routing channels M1, M2, and M3, respectively. Each BC routing channel has nine interconnect conductors which are grouped into three groups of three interconnect conductors. Each group of three interconnect conductors is connected to a first side of a Extension Block (EB) 3×3 switch matrix. A second side of each EB 3×3 switch matrix is coupled to the E-tab. Between adjacent B1 blocks, in both the horizontal and vertical directions, the leads on the second side of a first EB 3×3 switch matrix may be coupled to the leads on the second side of second EB3×3 switch matrix by BC criss-cross extension.

Owner:MICROSEMI SOC

Delay locked loop for an FPGA architecture

Owner:MICROSEMI SOC

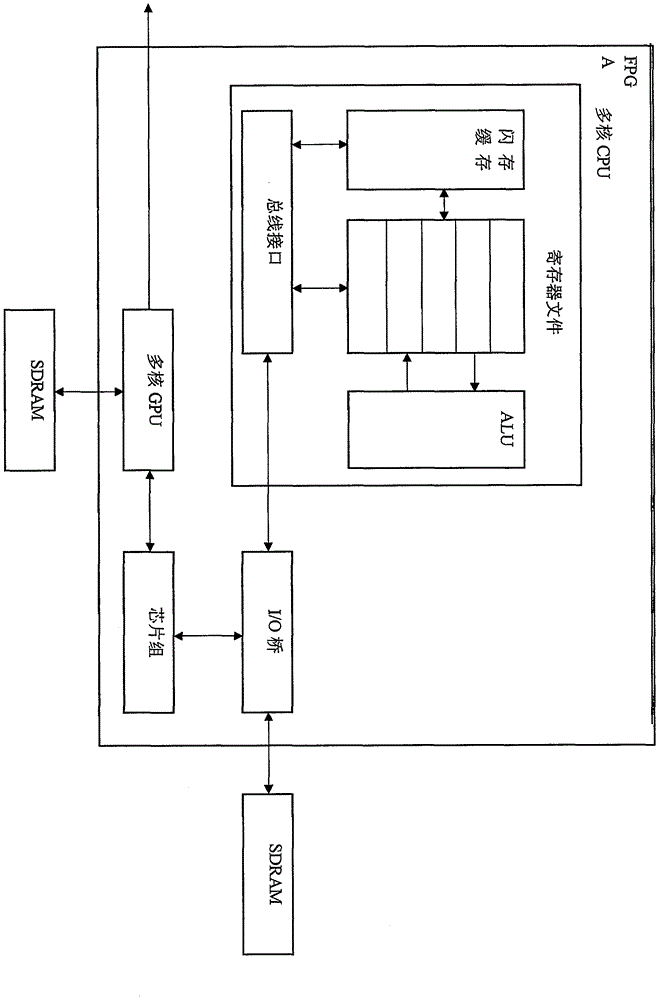

Multi-core heterogeneous CPU - CPU - FPGA architecture

The invention discloses a multi-core heterogeneous CPU - CPU - FPGA architecture. An architecture is characterized of having a separate parallel CPU and parallel GPU, having their own SDRAM, being capable of accessing each other's SDRAM, and they are in the outside of the FPGA structure; a GPU is connected to a chip set via an I / O bus and then connected to the CPU via an I / O bridge. The CPU consists of an ALU, a register file, a flash cache, and a bus interface.

Owner:SHANGHAI DATACENT SCI CO LTD

Block level routing architecture in a field programmable gate array

InactiveUS20030121020A1Good symmetryEasy to placeSolid-state devicesSpecial data processing applicationsFpga architectureElectrical conductor

An FPGA architecture has top, middle and low levels. The top level of the architecture is an array of the B16x16 tiles arranged in a rectangular array and enclosed by I / O blocks on the periphery. On each of the four sides of a B16x16 tile, and also associated with each of the I / O blocks is a freeway routing channel. A B16x16 tile in the middle level of hierarchy is a sixteen by sixteen array of B1 blocks. The routing resources in the middle level of hierarchy are expressway routing channels M1, M2, and M3 including groups of interconnect conductors. At the lowest level of the semi-hierarchical FPGA architecture, there are block connect (BC) routing channels, local mesh (LM) routing channels, and direct connect (DC) interconnect conductors. Each BC routing channel is coupled to an expressway tab to provide access for each B1 block to the expressway routing channels M1, M2, and M3, respectively. Each BC routing channel has nine interconnect conductors which are grouped into three groups of three interconnect conductors. Each group of three interconnect conductors is connected to a first side of a Extension Block (EB) 3x3 switch matrix. A second side of each EB 3x3 switch matrix is coupled to the E-tab. Between adjacent B1 blocks, in both the horizontal and vertical directions, the leads on the second side of a first EB 3x3 switch matrix may be coupled to the leads on the second side of second EB3x3 switch matrix by BC criss-cross extension.

Owner:MICROSEMI SOC

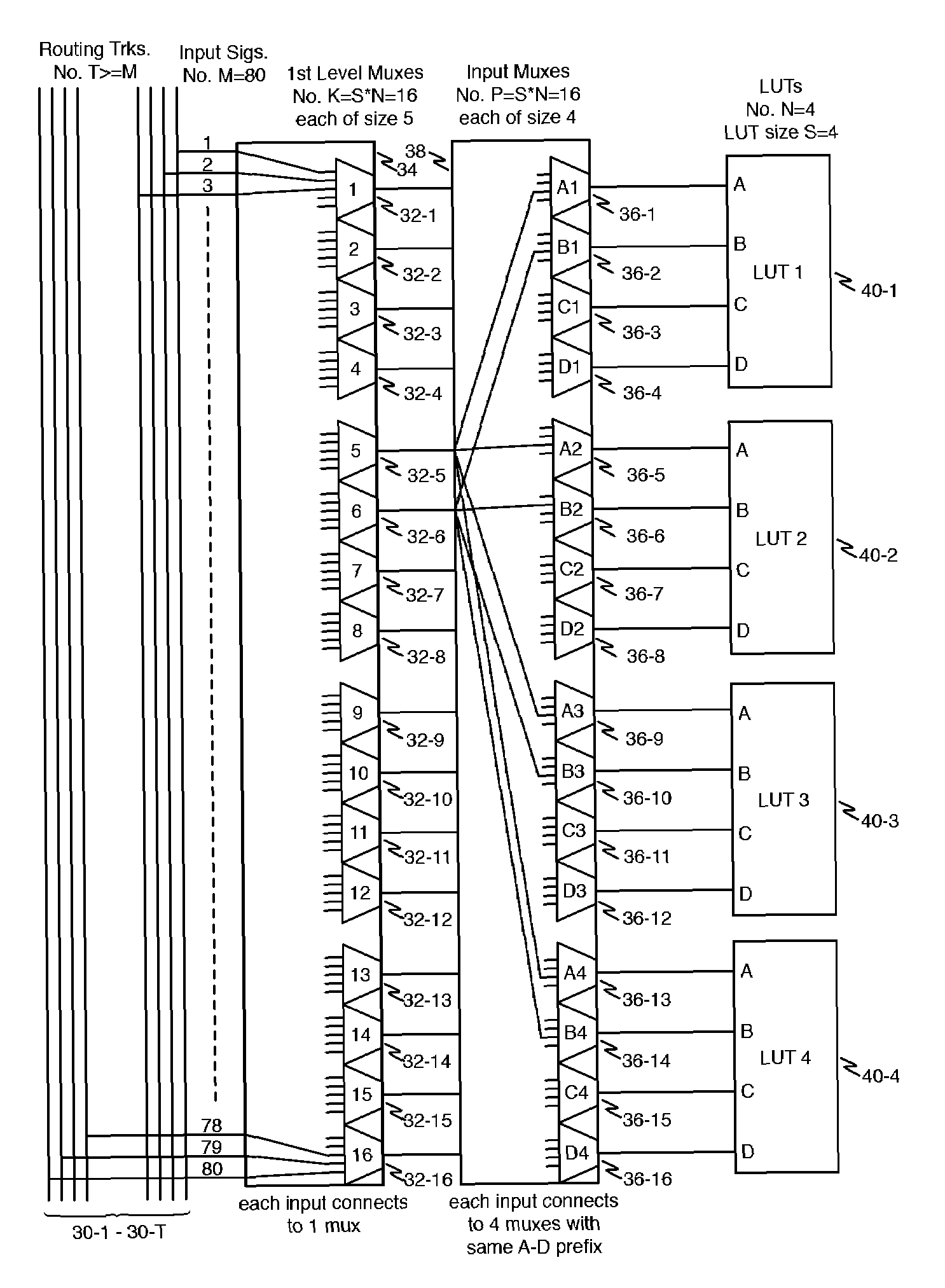

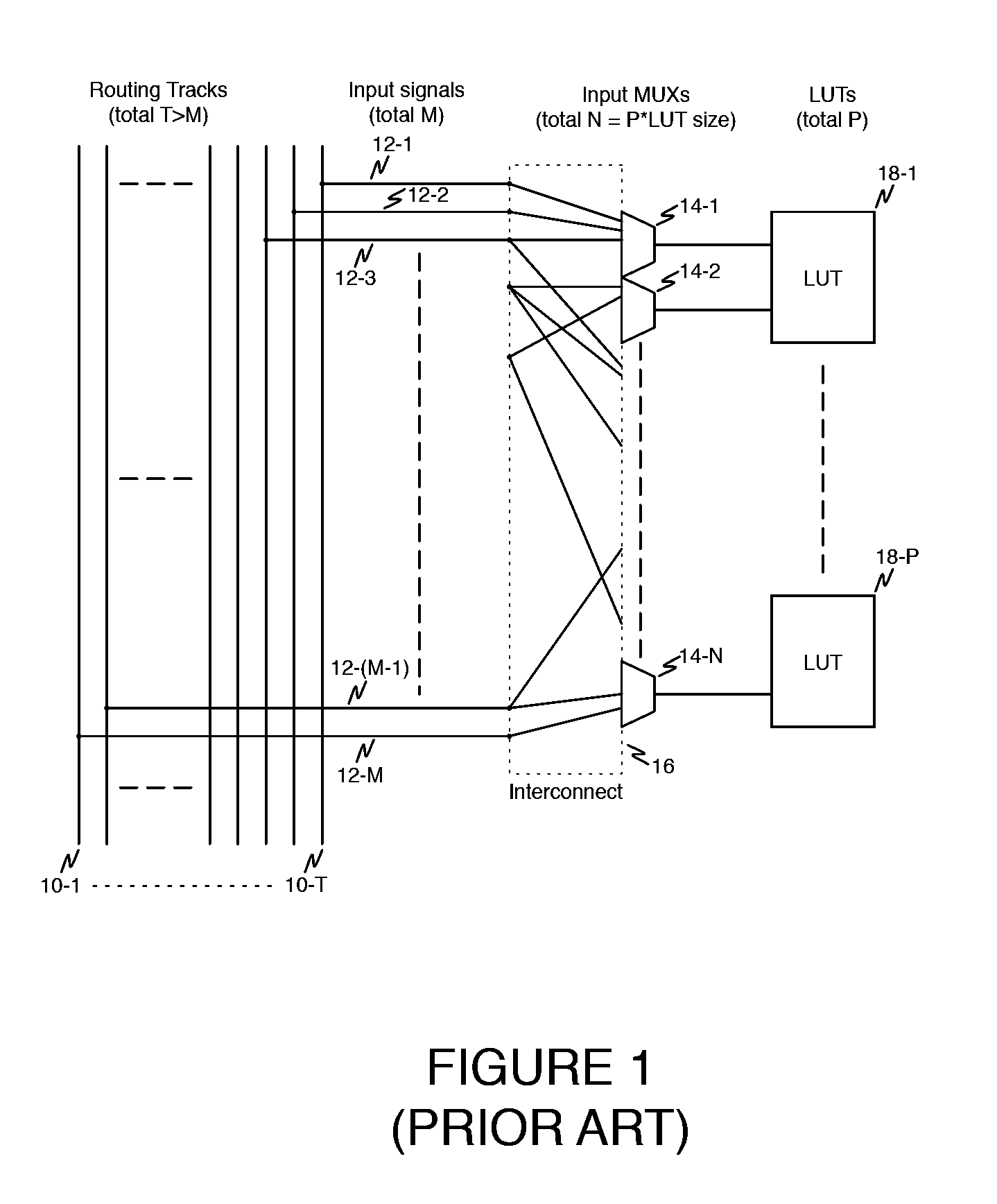

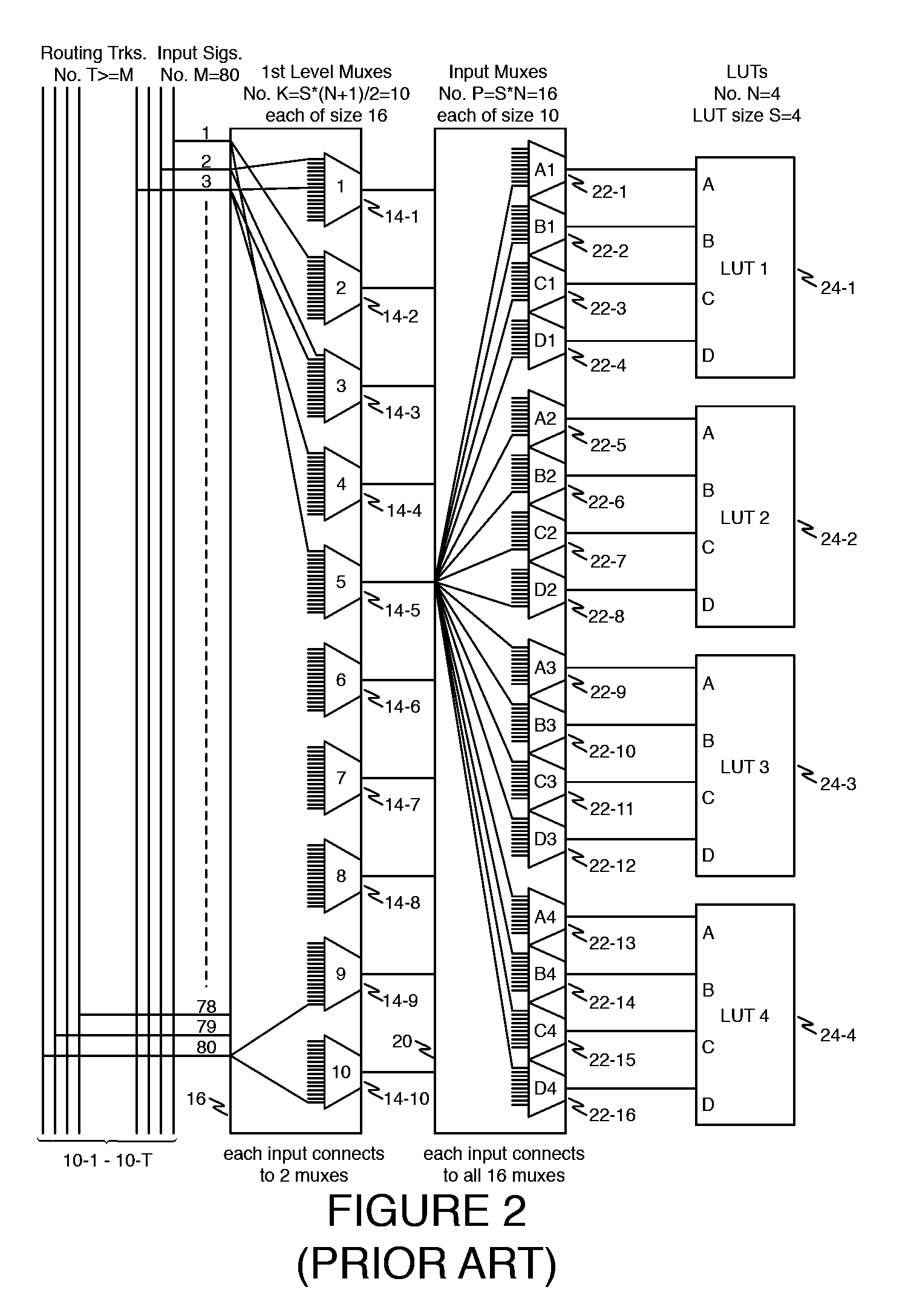

FPGA architecture having two-level cluster input interconnect scheme without bandwidth limitation

ActiveUS7408383B1RoutabilityImprove connectivitySolid-state devicesLogic circuits using elementary logic circuit componentsFpga architectureMultiplexer

An interconnect architecture for a programmable logic device comprises a plurality of interconnect routing lines. The data inputs of a plurality of first-level multiplexers are connected to the plurality of interconnect routing lines such that each interconnect routing line is connected to only one multiplexer. A plurality of second-level multiplexers are organized into multiplexer groups. Each of a plurality of lookup tables is associated with one of the multiplexer groups and has a plurality of lookup table inputs. Each lookup table input is coupled to the output of a different one of the second-level multiplexers in the one of the multiplexer groups with which it is associated. The data inputs of the second-level multiplexers are connected to the outputs of the first-level multiplexers such that each output of each first-level multiplexer is connected to an input of only one second-level multiplexer in each multiplexer group.

Owner:MICROSEMI SOC