Fine-grain dynamically reconfigurable FPGA architecture

一种门阵列、存储器的技术,应用在逻辑电路、脉冲技术、降低功耗等方向,能够解决未取得ASIC、类似面积等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be described in detail below in conjunction with the accompanying drawings.

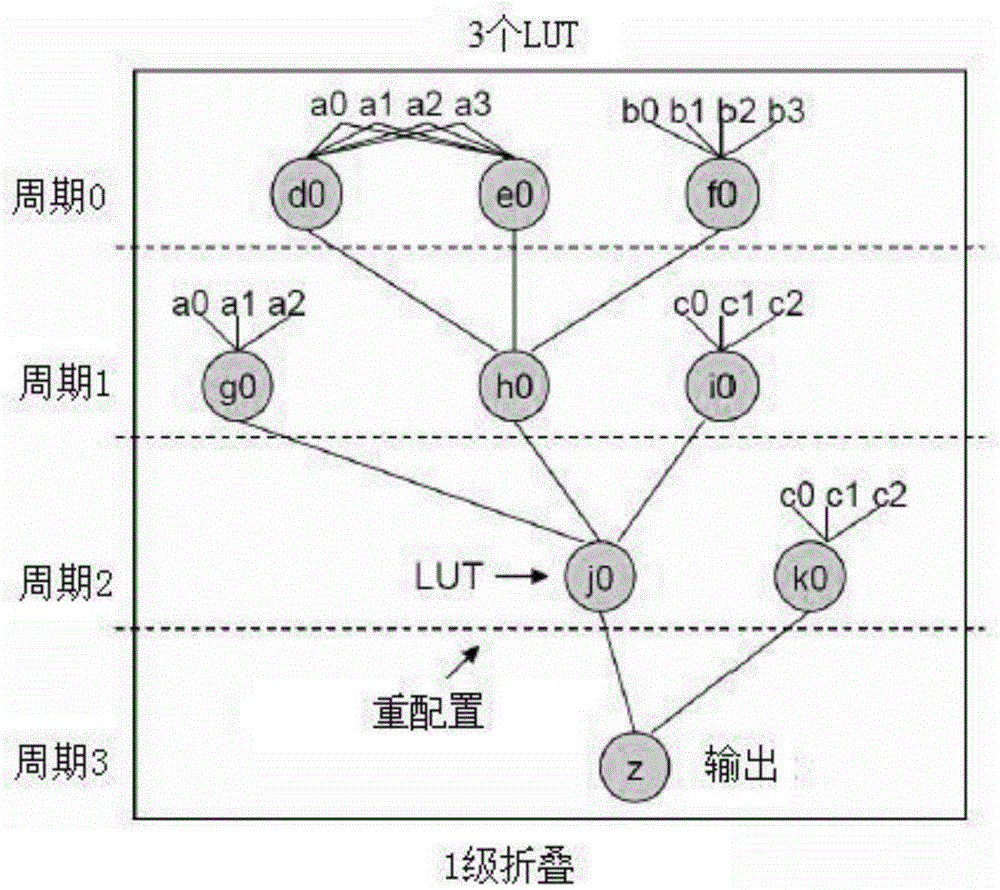

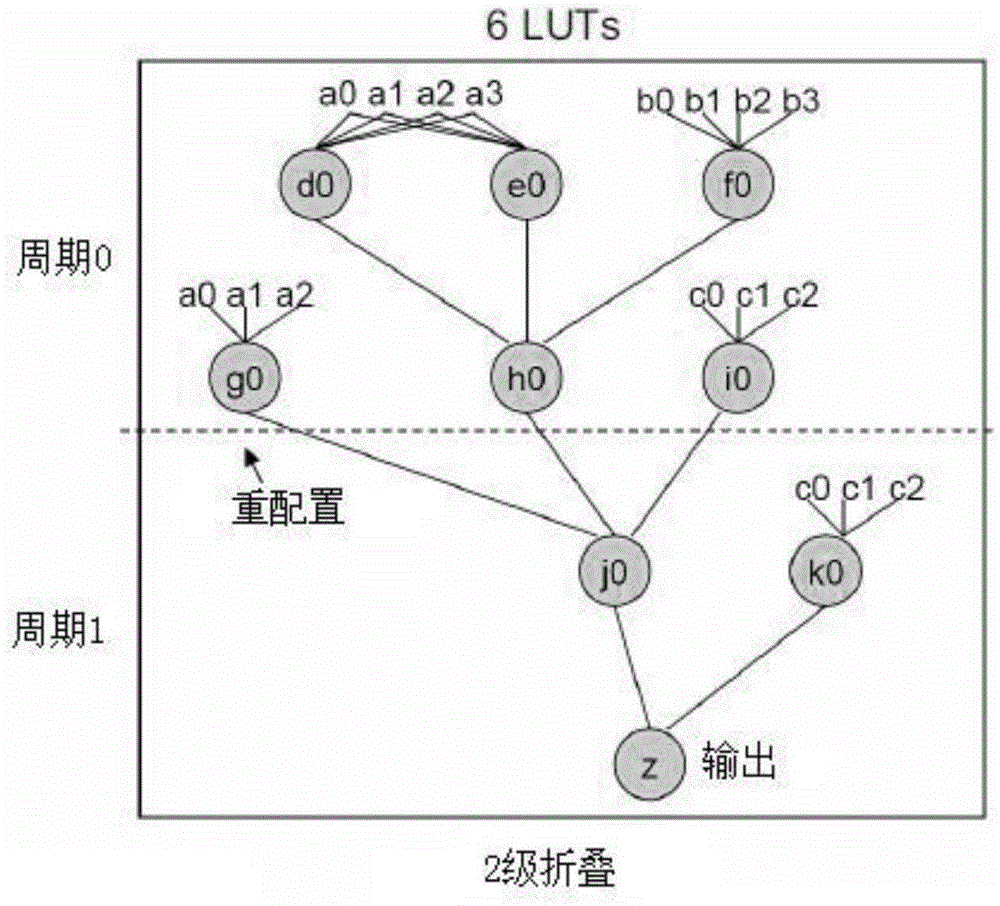

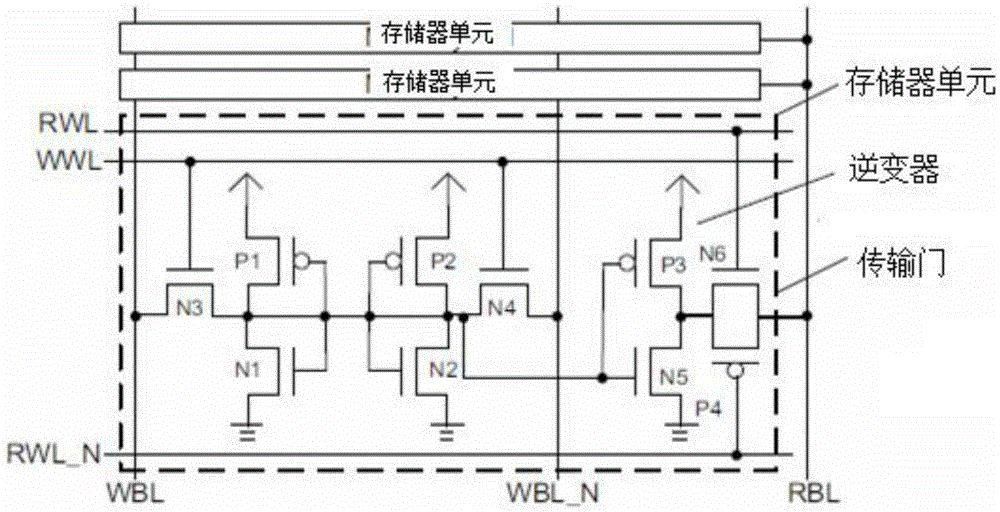

[0029] This paper discloses a hybrid CMOS nanotechnology reconfigurable architecture, called NATURE, which can solve some existing FPGA problems: logic density and run-time reconfiguration efficiency. The architecture utilizes the concept of sequential logic folding, which divides the circuit into multiple cascaded stages, and utilizes the same logic element (LE, logicmement) to implement each stage through very fast dynamic reconfiguration. Since logic folding greatly limits on-chip communication, the number of global interconnects can be greatly reduced by deep logic folding, i.e., when reconfiguration occurs after only one or two look-uptable (LUT) levels in the circuit , because most local or short-distance interconnects are required. Due to its reliance on traditional siled architectures, NATURE was unable to take full advantage of this phenomenon. In order to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More