Patents

Literature

128 results about "Interconnect architecture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

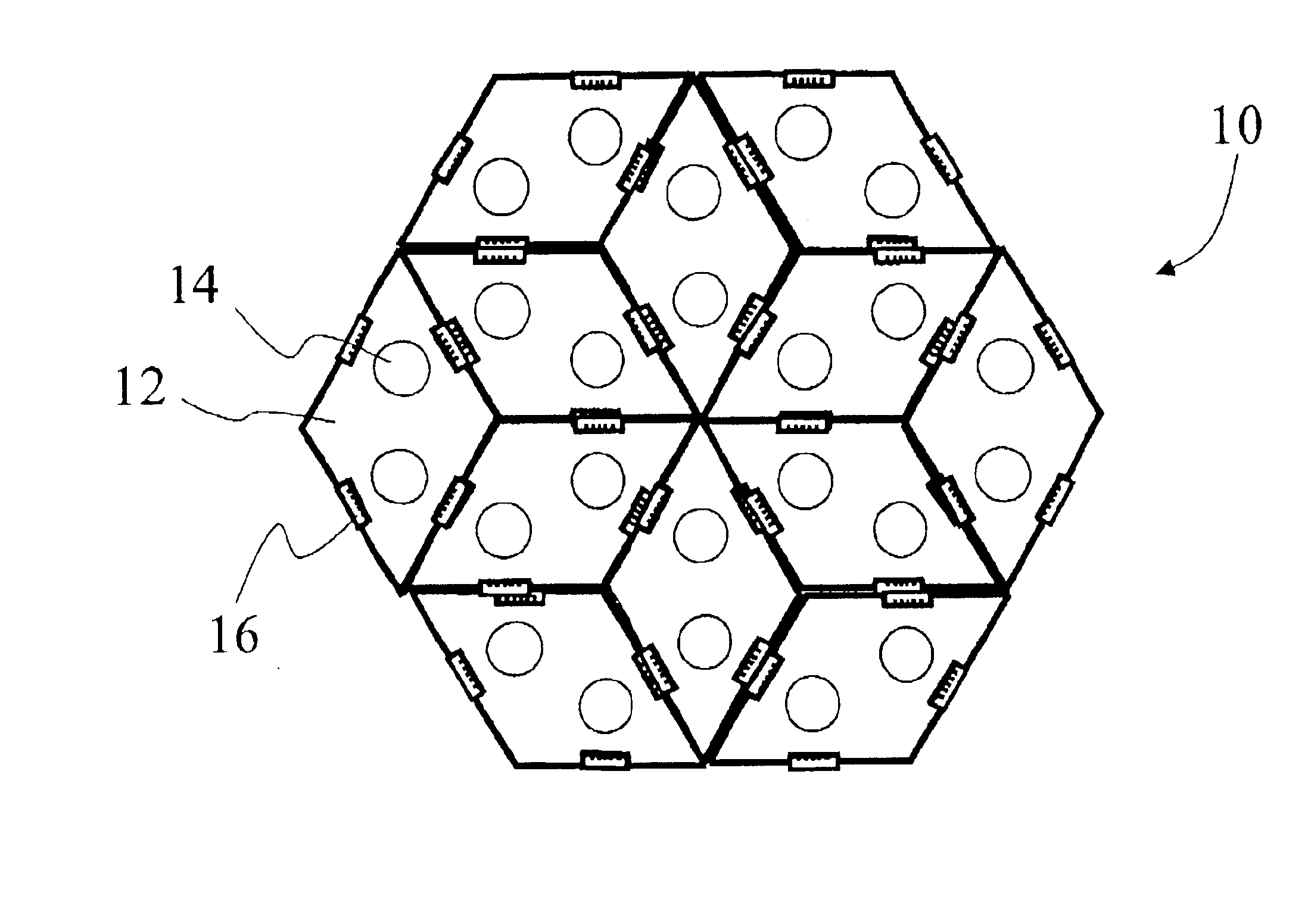

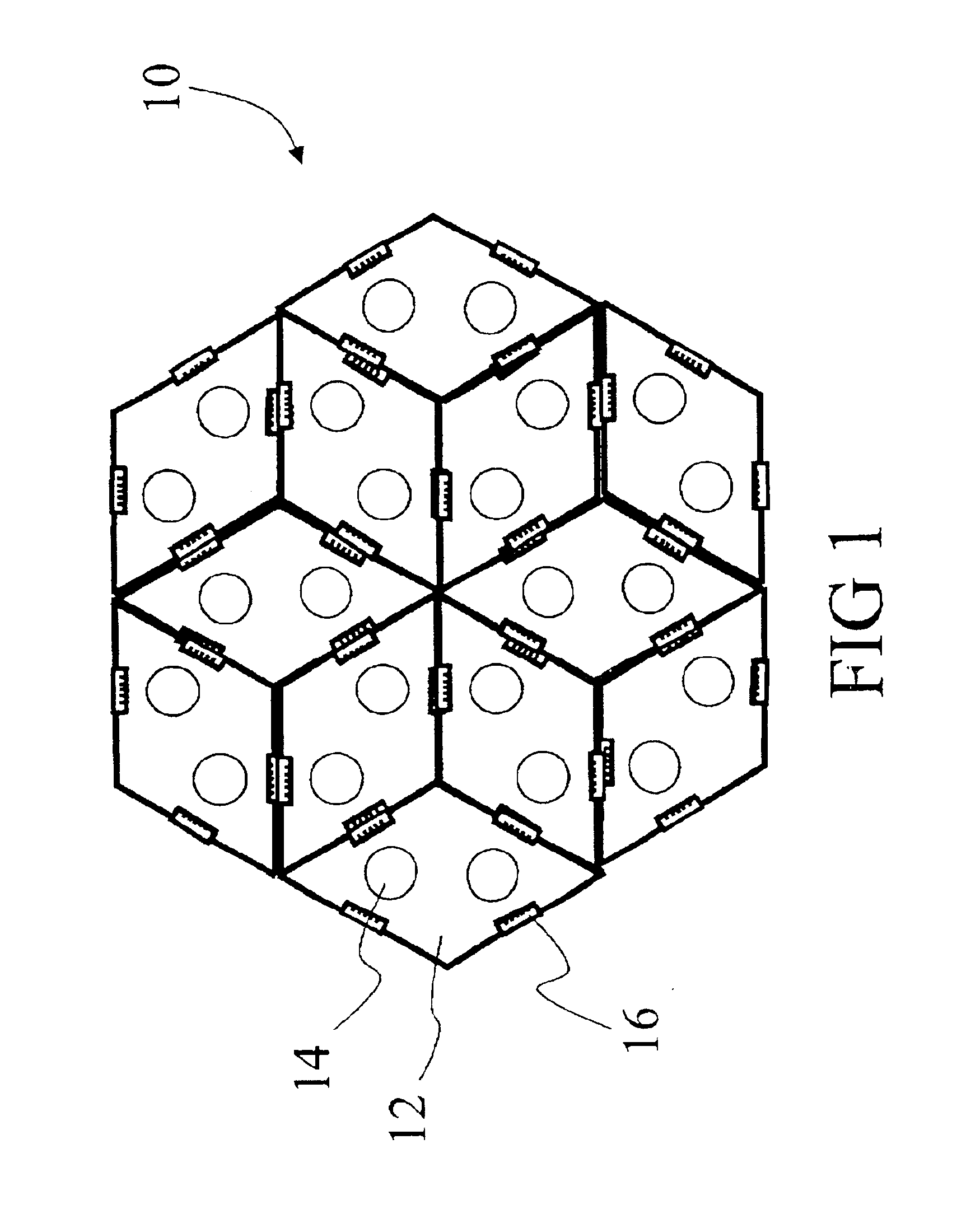

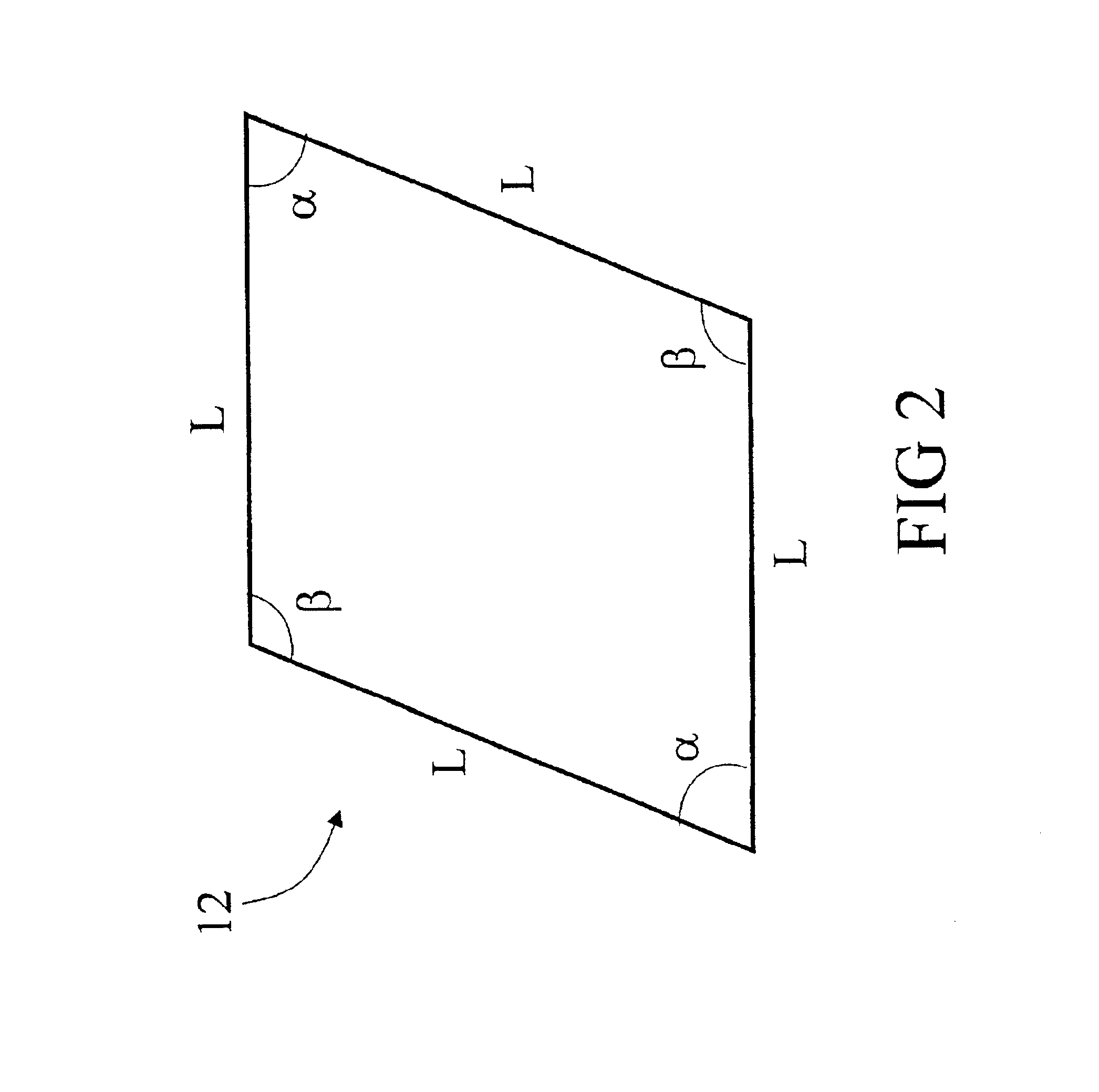

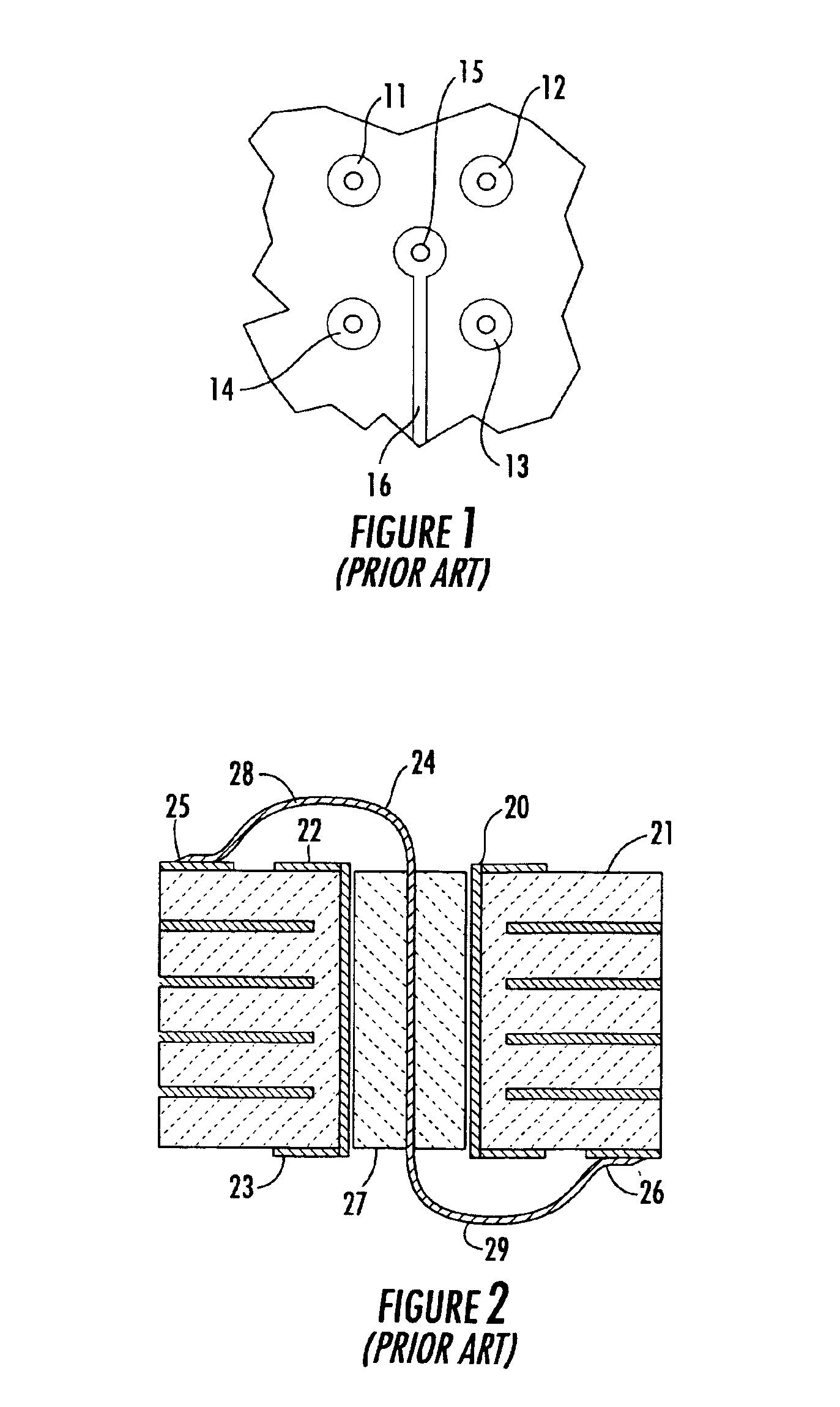

Close packing LED assembly with versatile interconnect architecture

InactiveUS6851831B2Coupling device connectionsLight source combinationsElectrical conductorModularity

A modular mounting assembly (10) for connecting a plurality of LEDs in a selectable electrical and spatial arrangement includes a plurality of substrates (12) each having at least one LED (14a, 14b) fixedly arranged thereon, and a plurality of connectors (16) arranged thereon that are in operative communication with the at least one LED (14a, 14b) fixedly arranged thereon. The plurality of substrates (12) are arranged in a selected spatial arrangement having selected pairs of connectors (16) in operative communication with each other to effectuate electrical connection therebetween, whereby an electrical arrangement of the plurality of LEDs is effectuated. A plurality of interconnecting elements (50A, 50D, 50S, 50P) electrically and structurally interconnect selected spatially adjacent substrates (12) in cooperation with the selected pairs of connectors. A connector (16) has a plurality of electrical conductor members (1, 2, 3, 4, 5), and an interconnecting element (50) has a selected electrical configuration that effectuates a selected interconnection of conductor members (1, 2, 3, 4, 5).

Owner:GELCORE LLC (US)

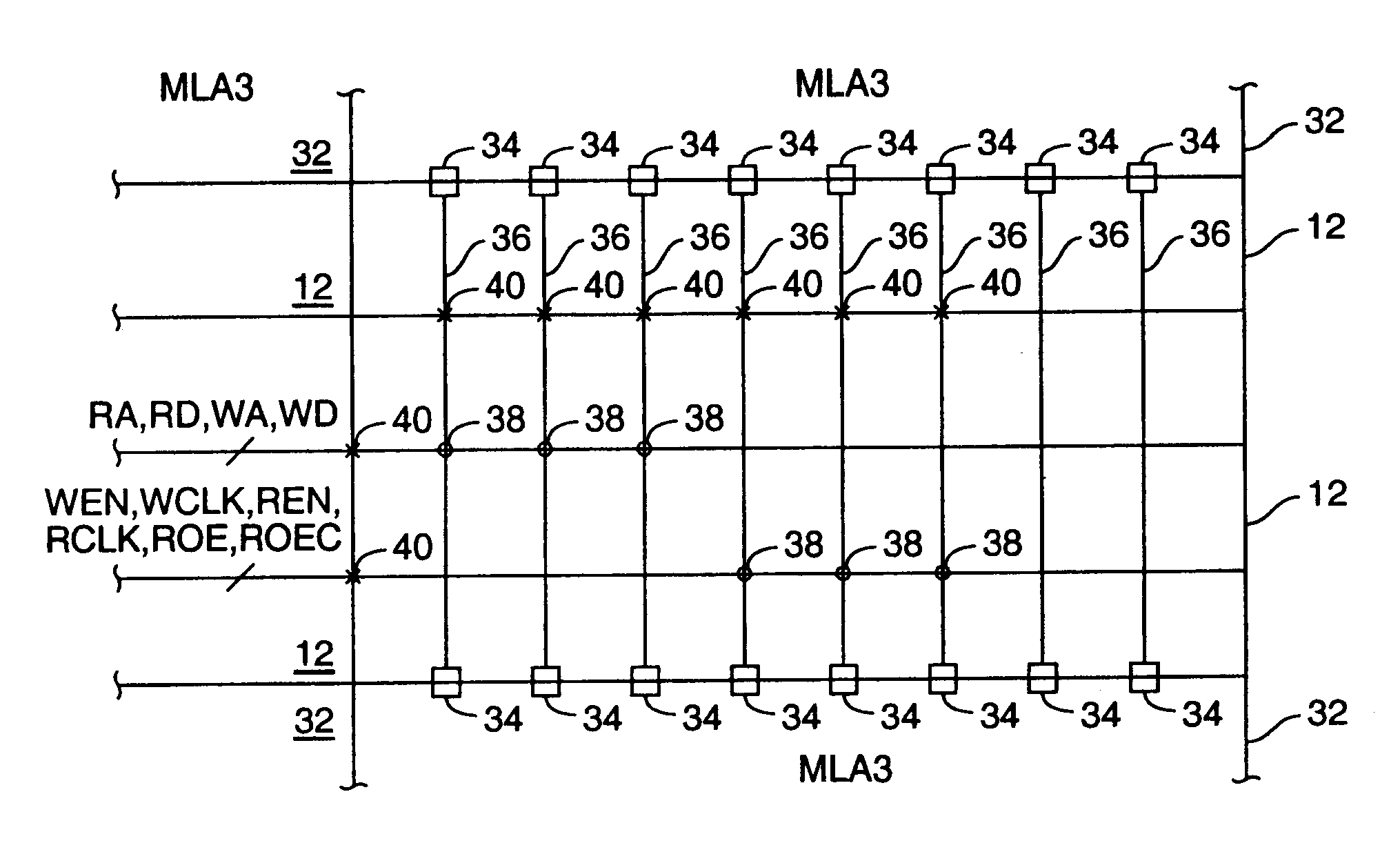

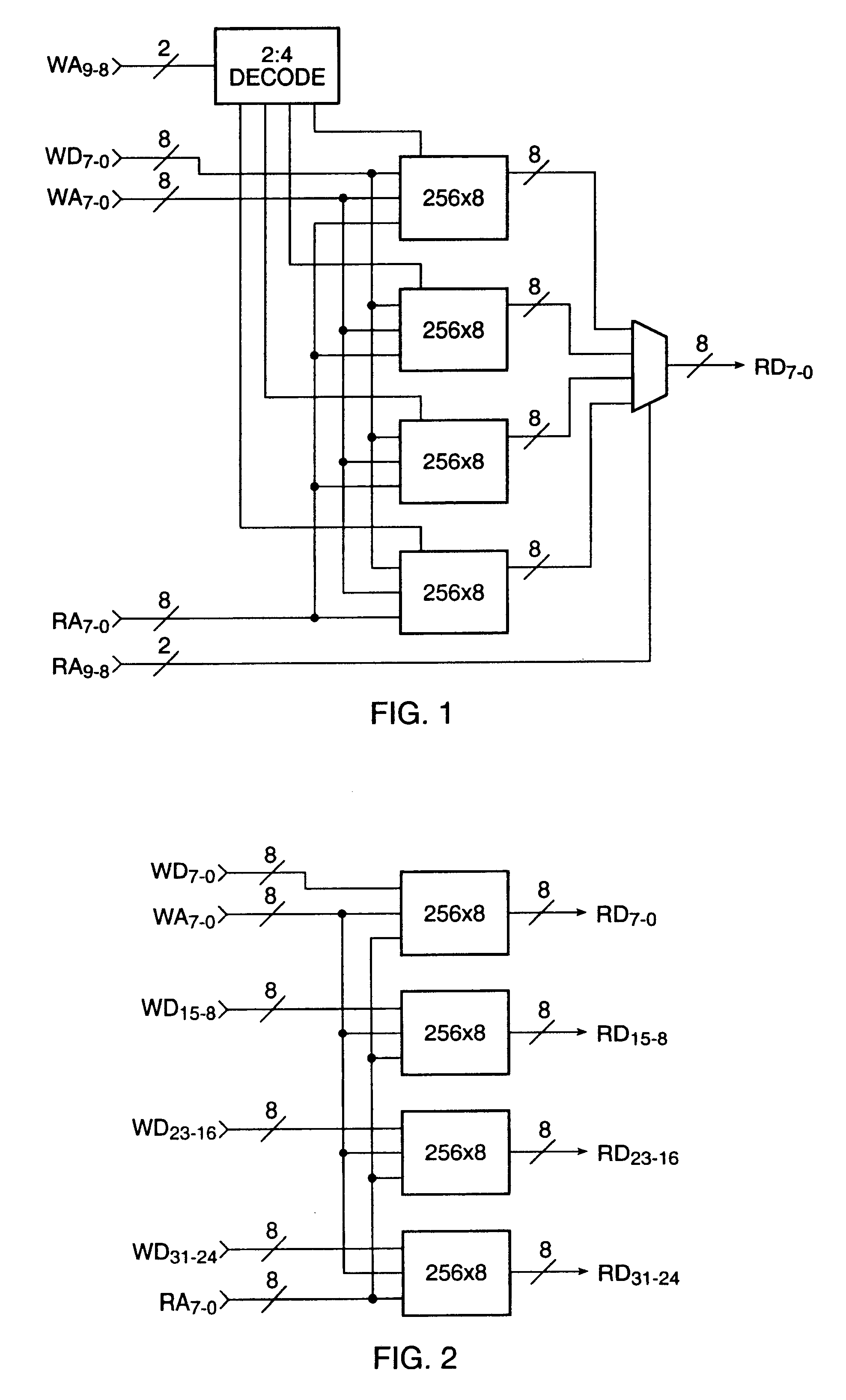

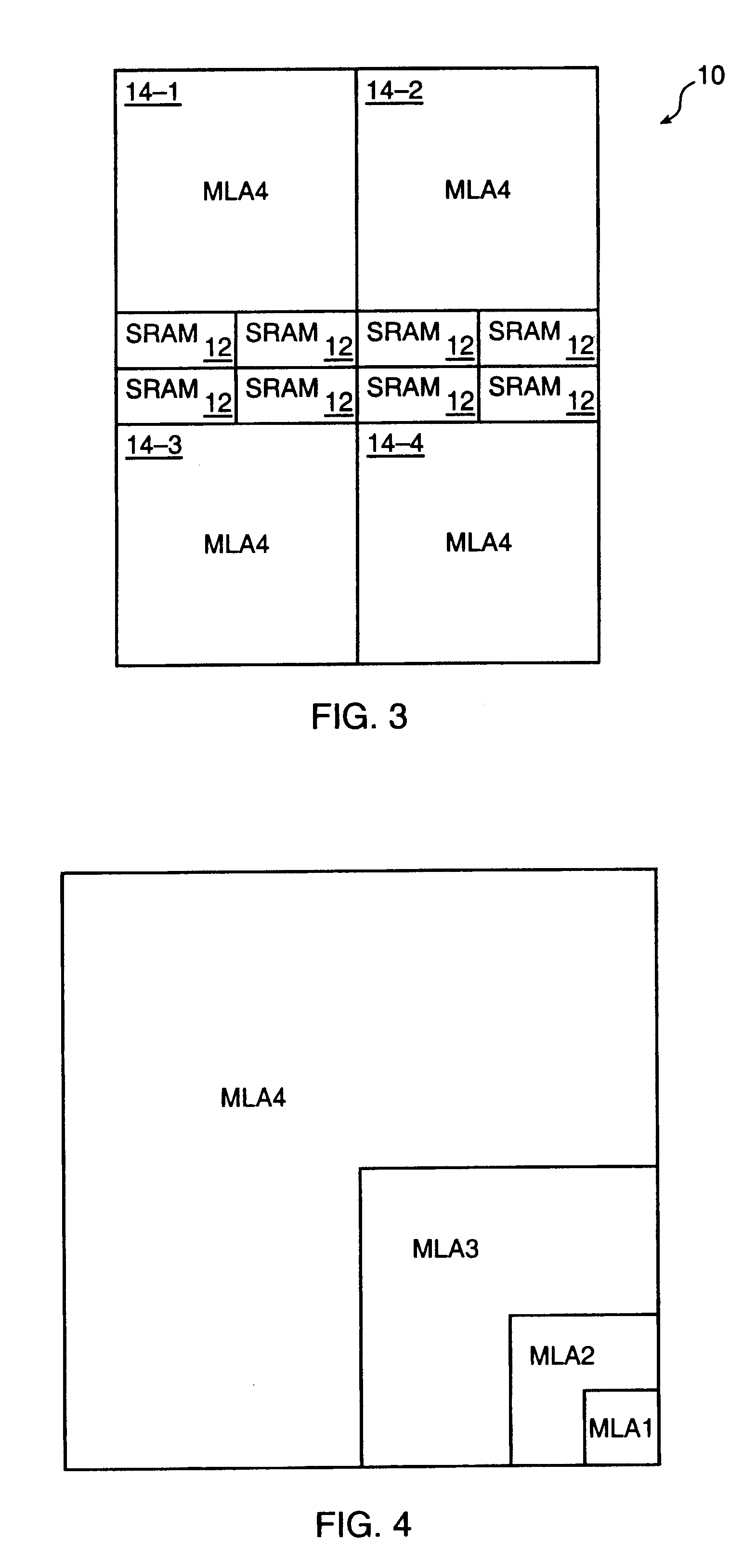

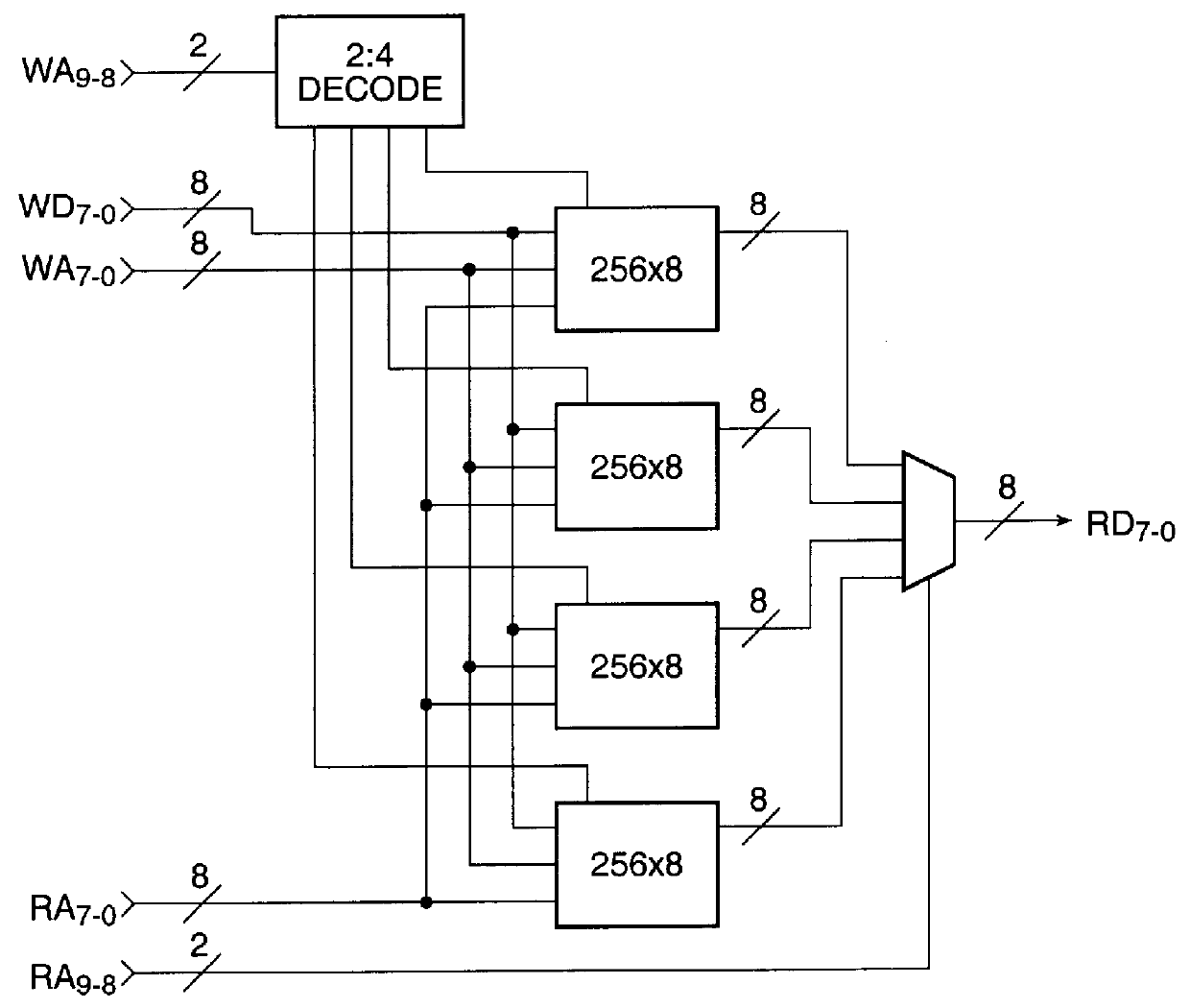

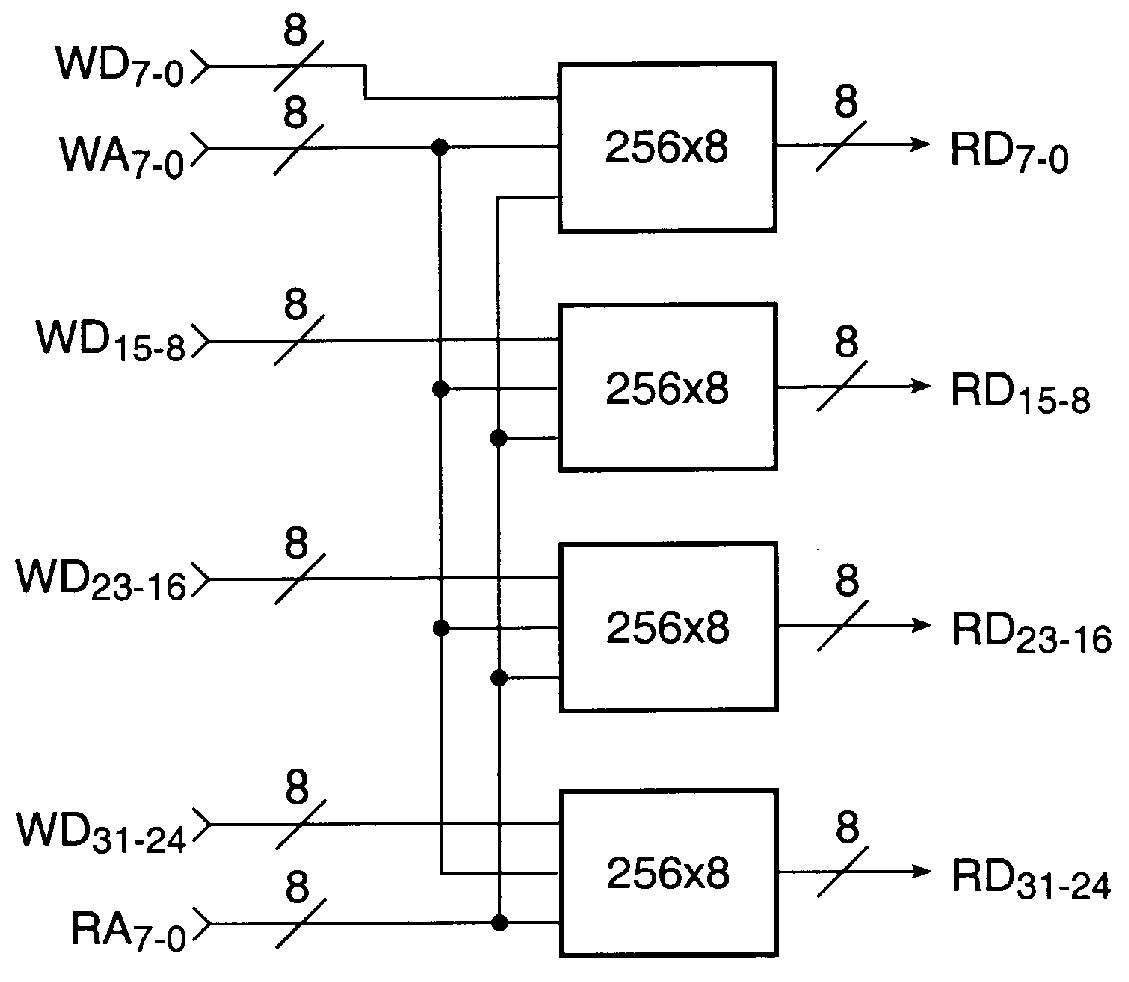

SRAM bus architecture and interconnect to an FPGA

Owner:ACTEL CORP

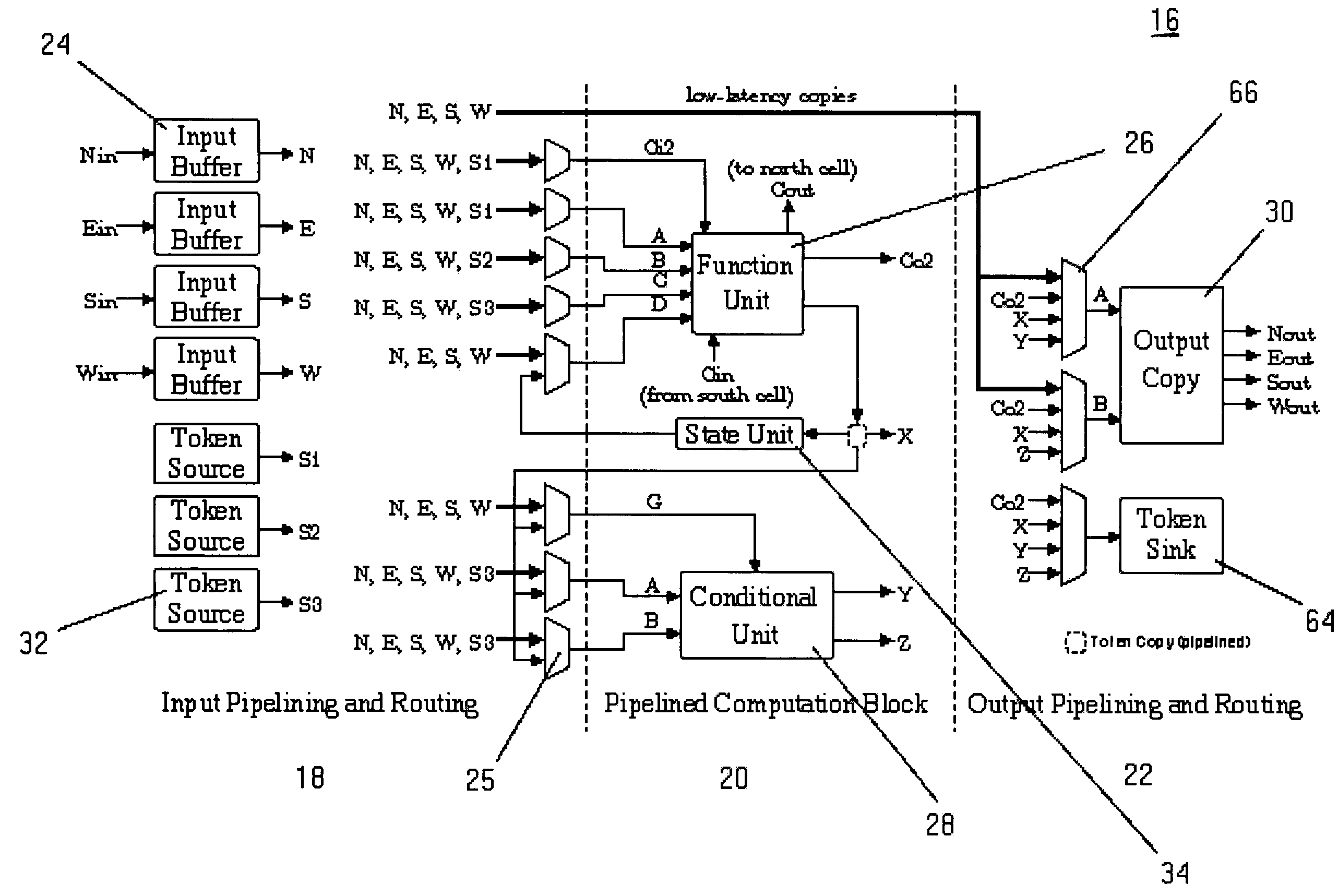

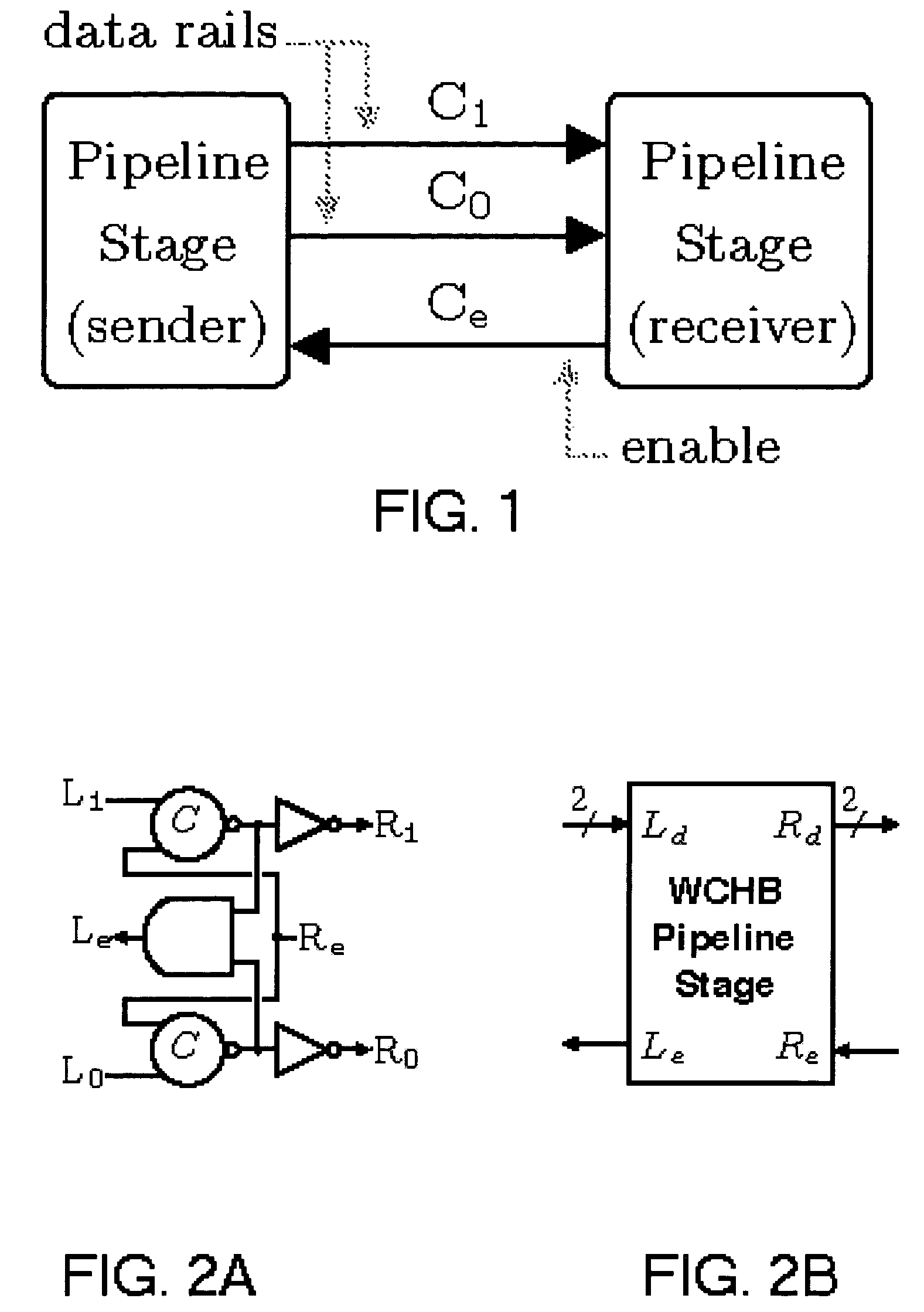

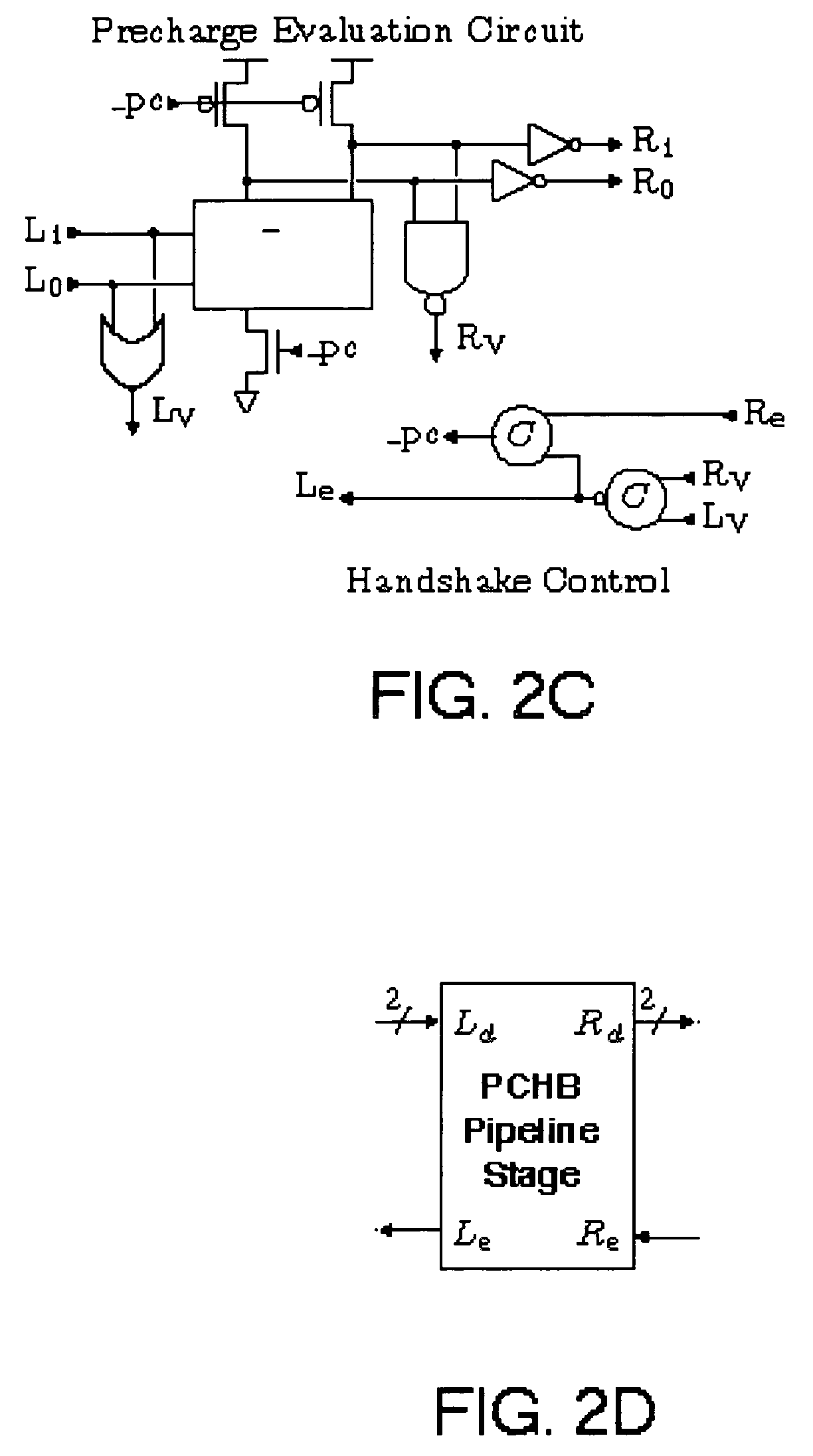

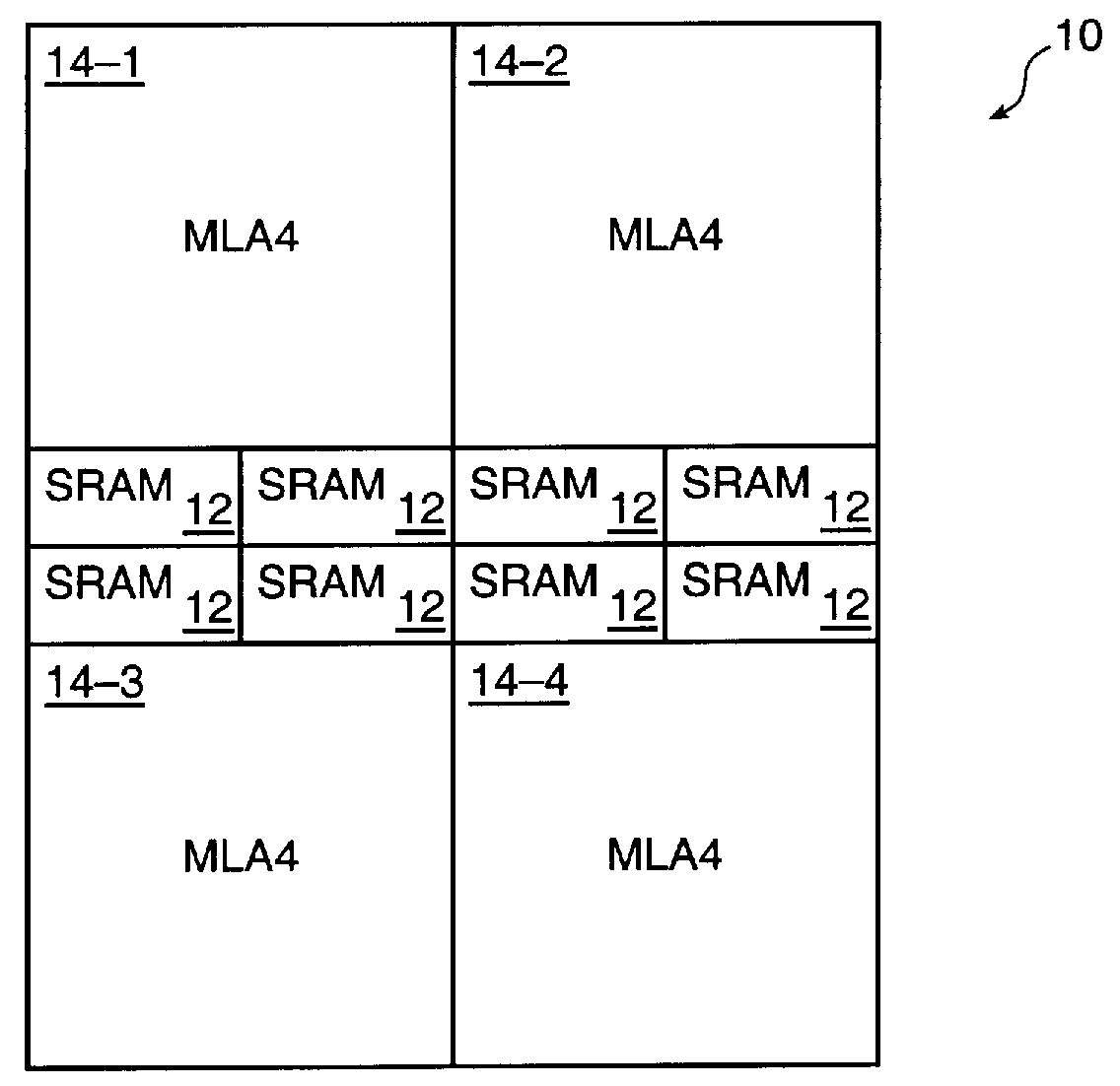

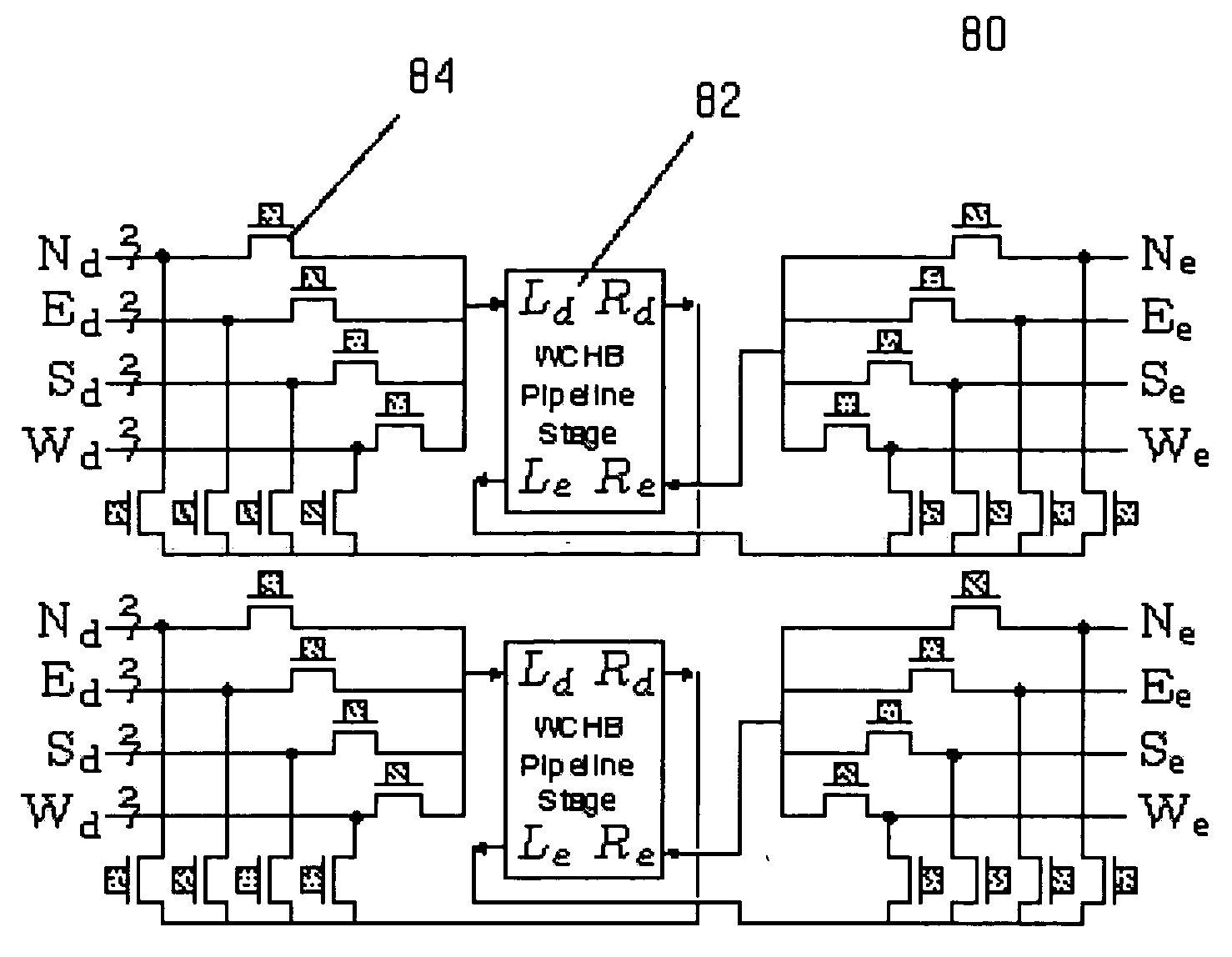

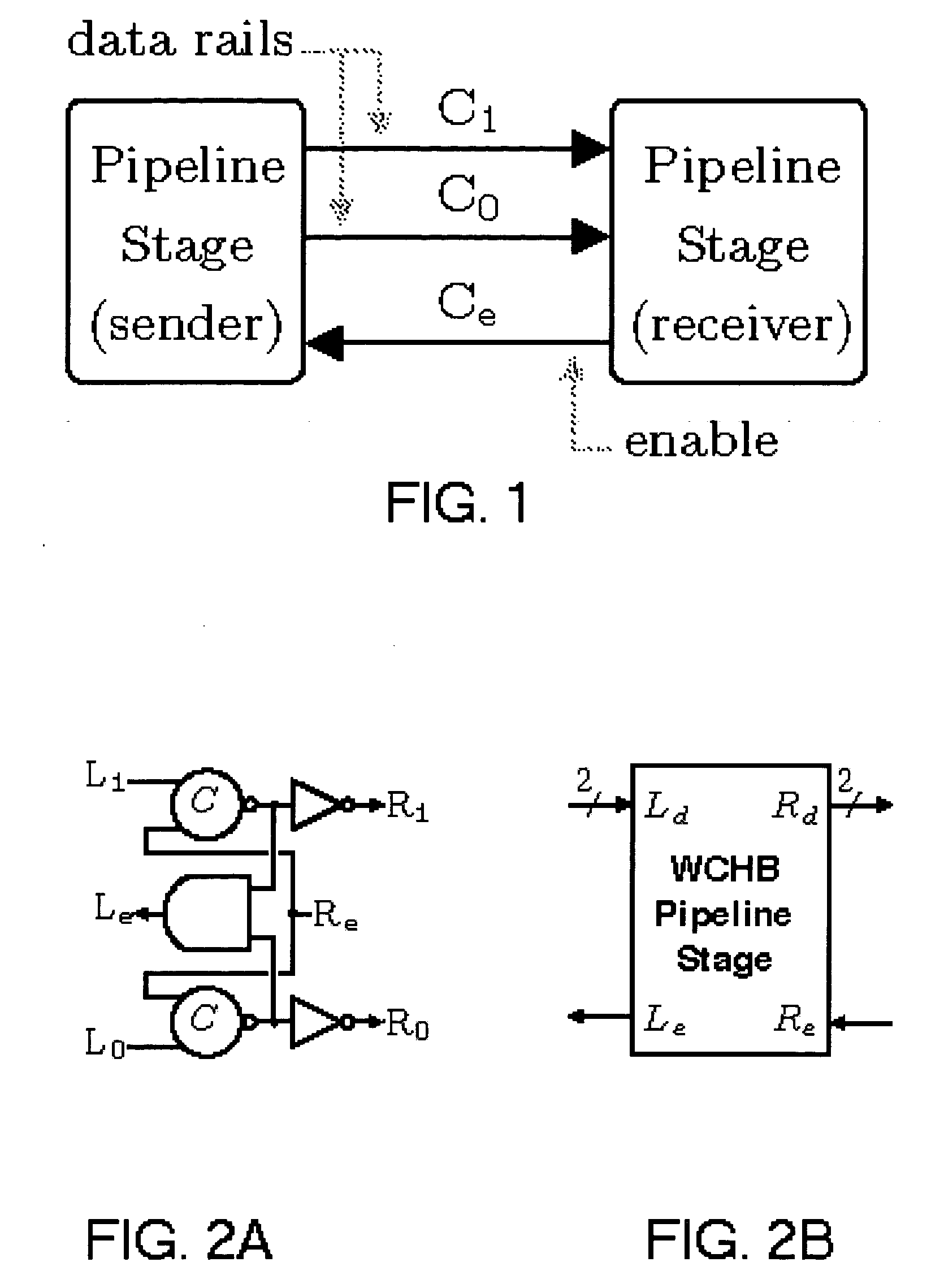

Programmable asynchronous pipeline arrays

ActiveUS7157934B2Improve data throughputEfficient implementationSolid-state devicesLogic circuits using elementary logic circuit componentsComputer scienceInterconnect architecture

Owner:CORNELL RES FOUNDATION INC +1

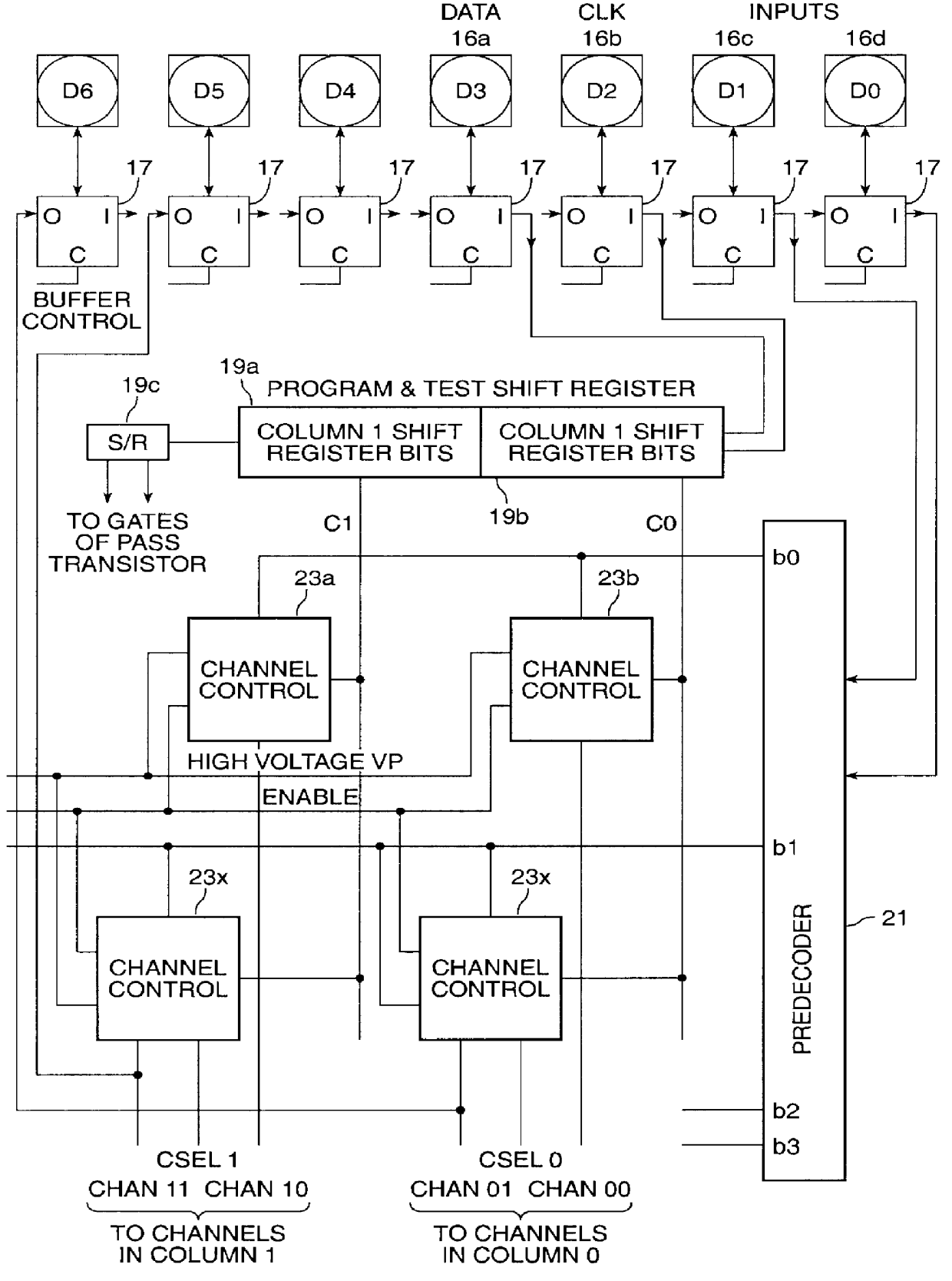

SRAM bus architecture and interconnect to an FPGA

An SRAM bus architecture includes pass-through interconnect conductors. Each of the pass-through interconnect conductors is connected to routing channels of the general interconnect architecture of the FPGA through an element which includes a pass transistor connected in parallel with a tri-state buffer. The pass transistors and tri-state buffers are controlled by configuration SRAM bits. Some of the pass-through interconnect conductors are connected by programmable elements to the address, data and control signal lines of the SRAM blocks, while other pass through the SRAM blocks without being further connected to the SRAM bussing architecture.

Owner:MICROSEMI SOC

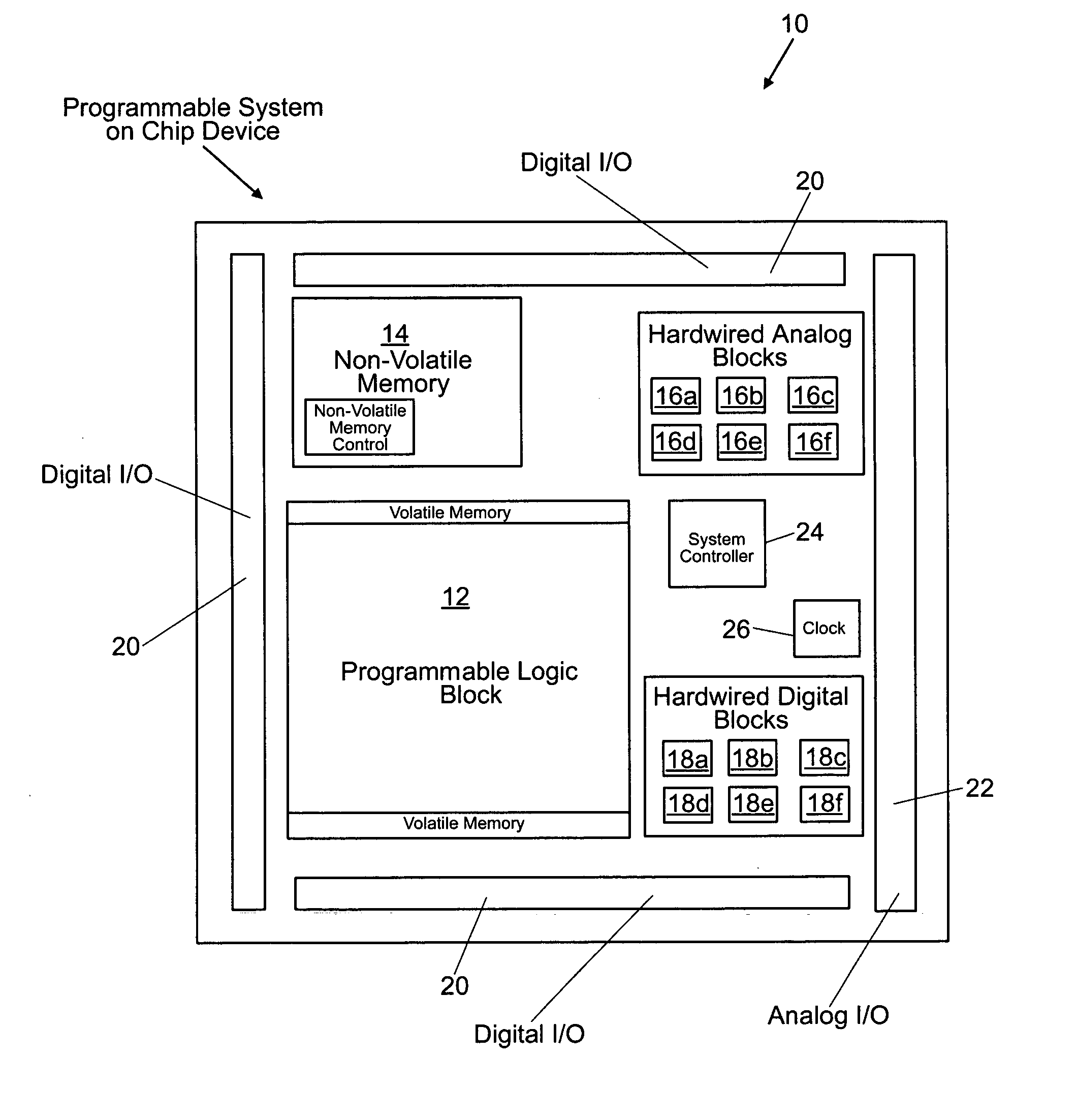

Programmable system on a chip

ActiveUS20050237083A1Thermometers using electric/magnetic elementsSolid-state devicesElectrical conductorEngineering

A programmable system-on-a-chip integrated circuit device comprises a programmable logic block, a non-volatile memory block, an analog sub-system, an analog input / output circuit block, and a digital input / output circuit block. A programmable interconnect architecture includes programmable elements and interconnect conductors. Ones of the programmable elements are coupled to the programmable logic block, the non-volatile memory block, the analog sub-system, the analog input / output circuit block, the digital input / output circuit block, and to the interconnect conductors, such that inputs and outputs of the programmable logic block, the non-volatile memory block, the analog sub-system, the analog input / output circuit block, and the digital input / output circuit block can be programmably coupled to one another.

Owner:MICROSEMI SOC

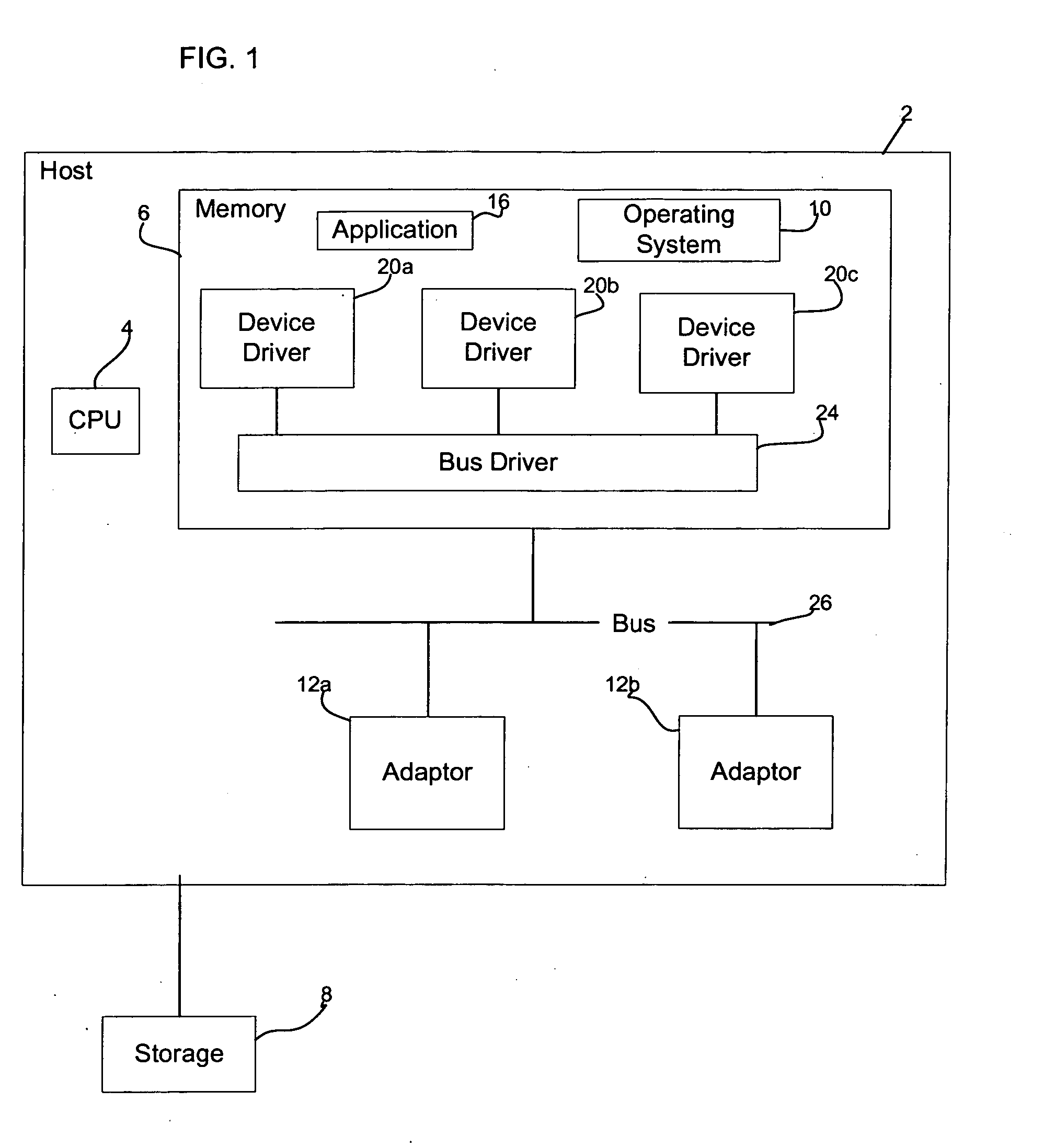

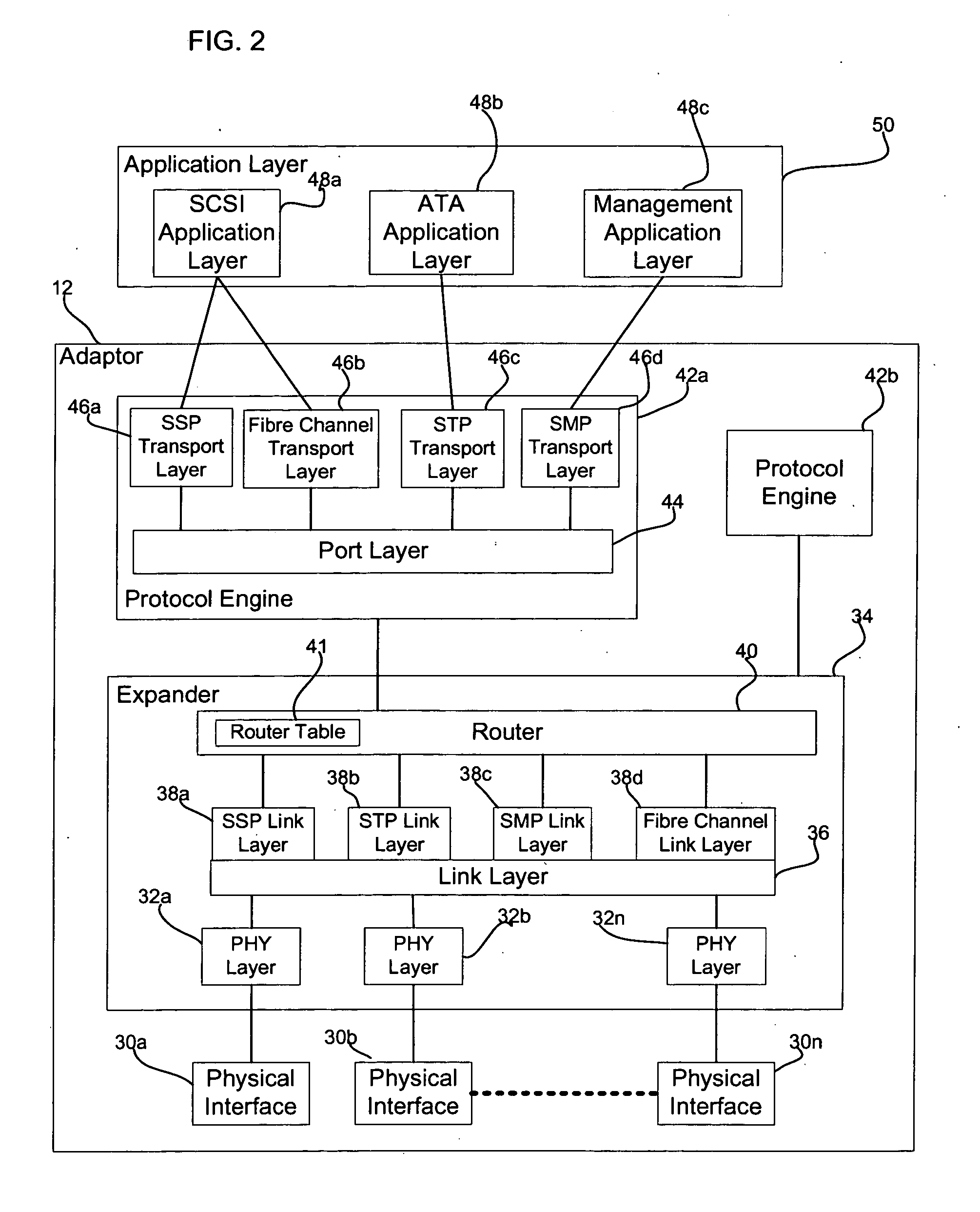

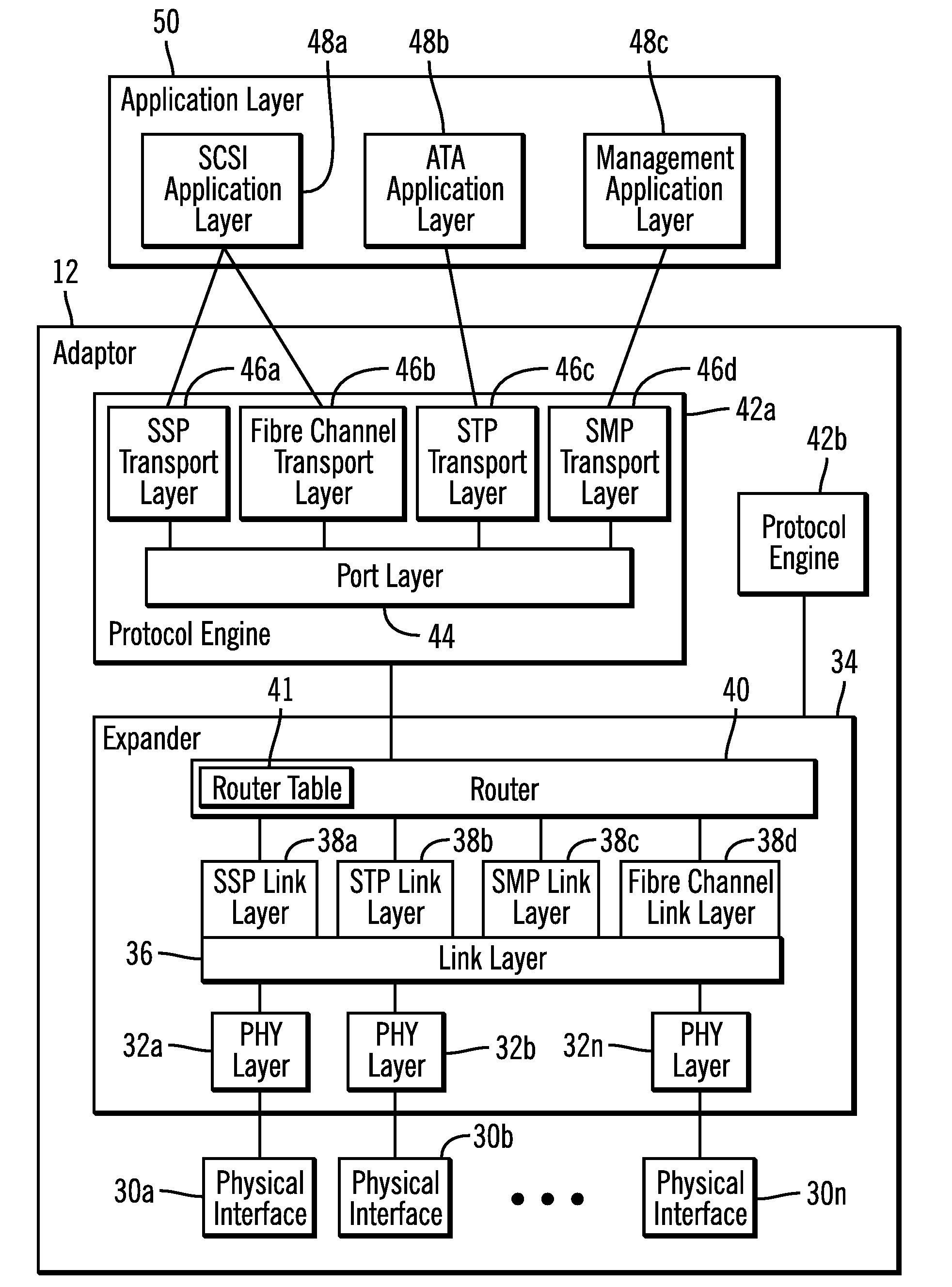

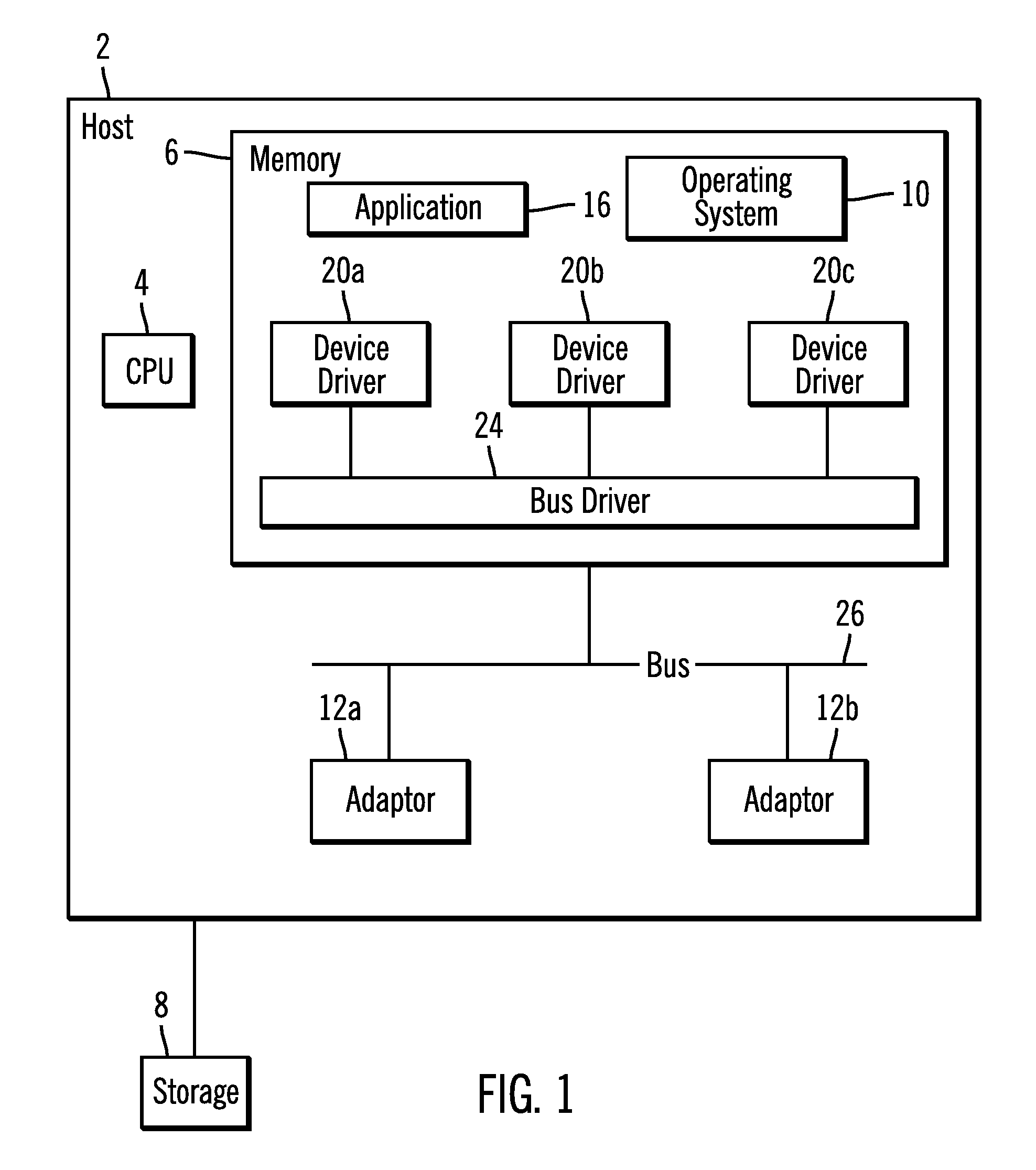

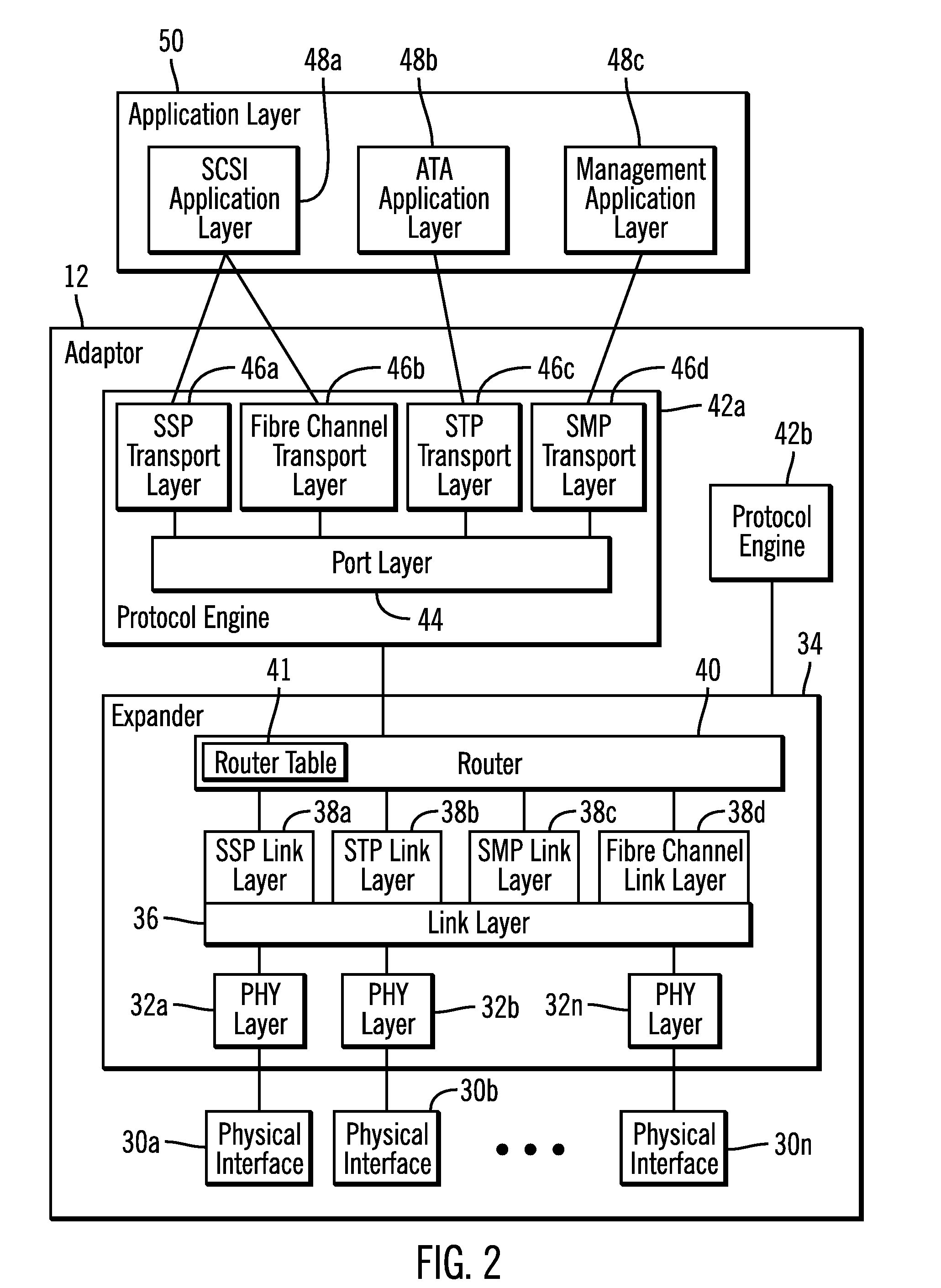

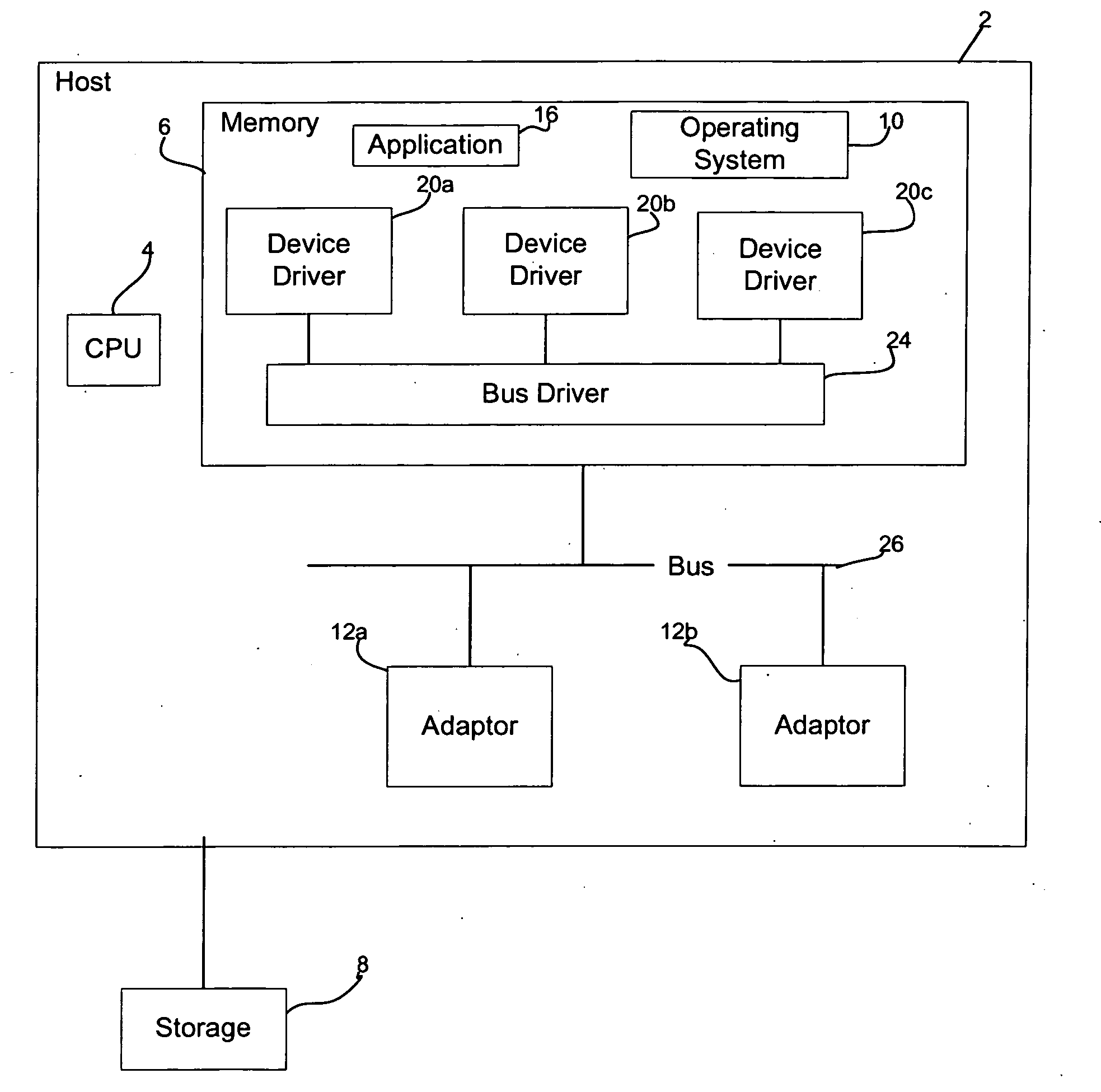

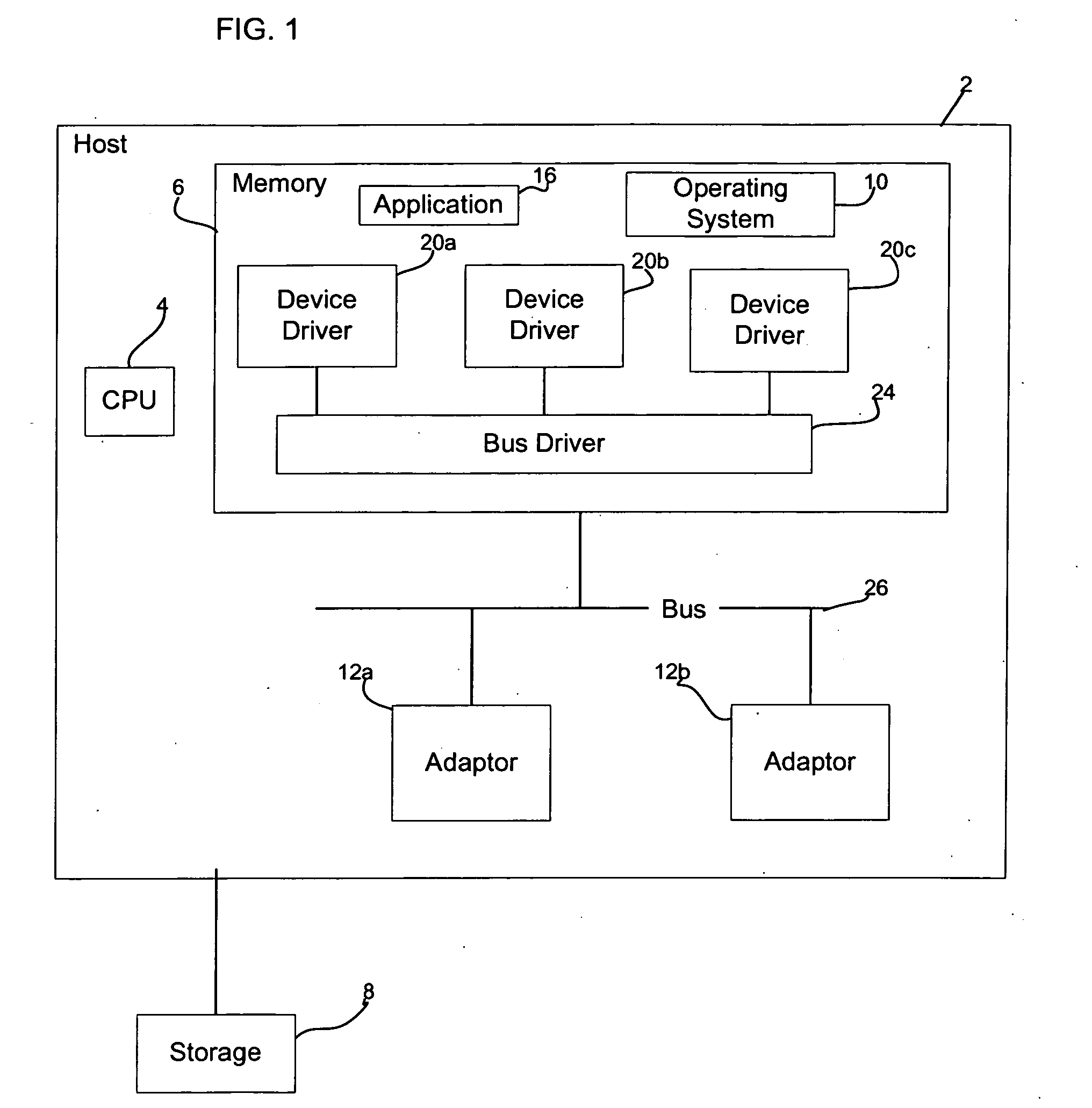

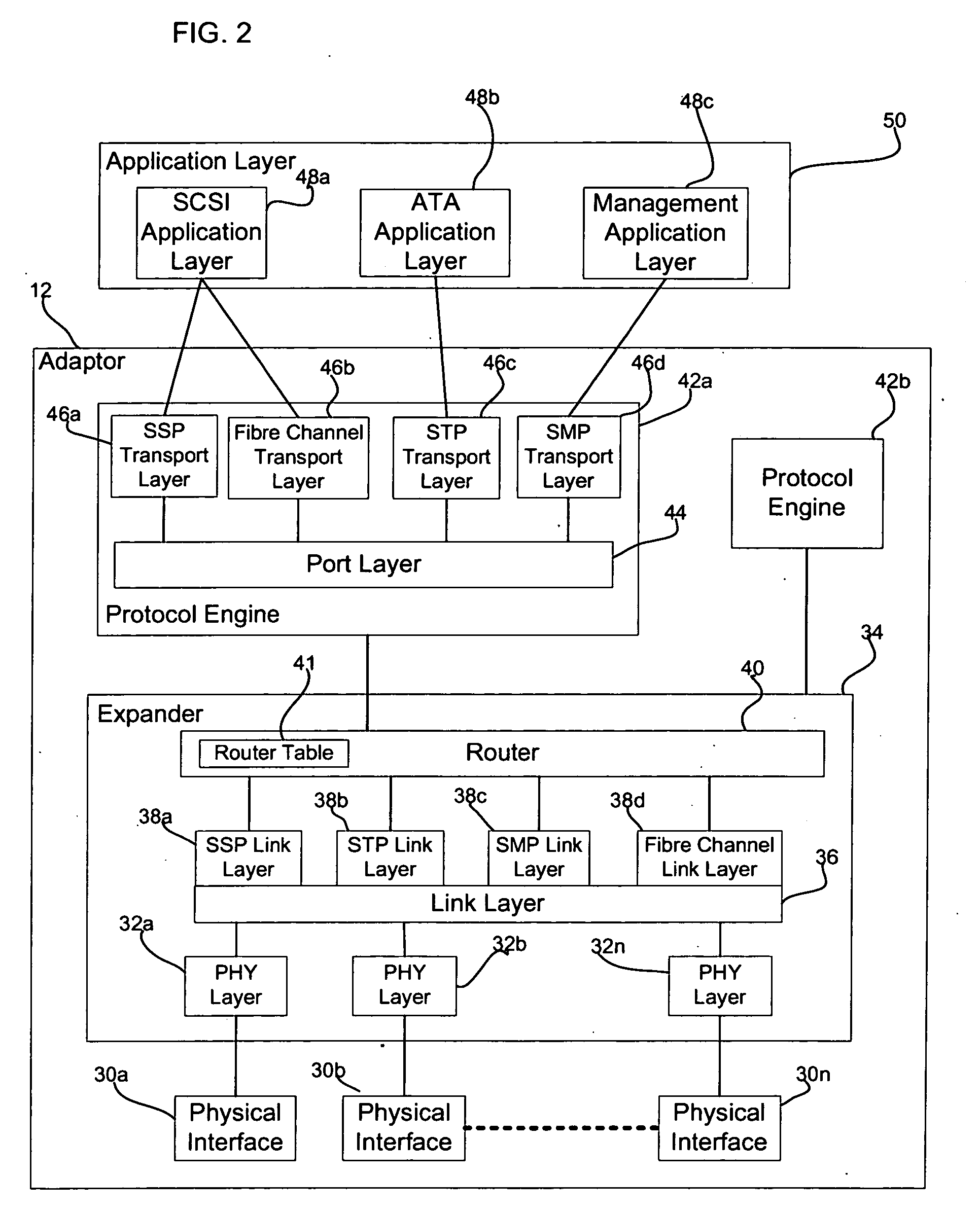

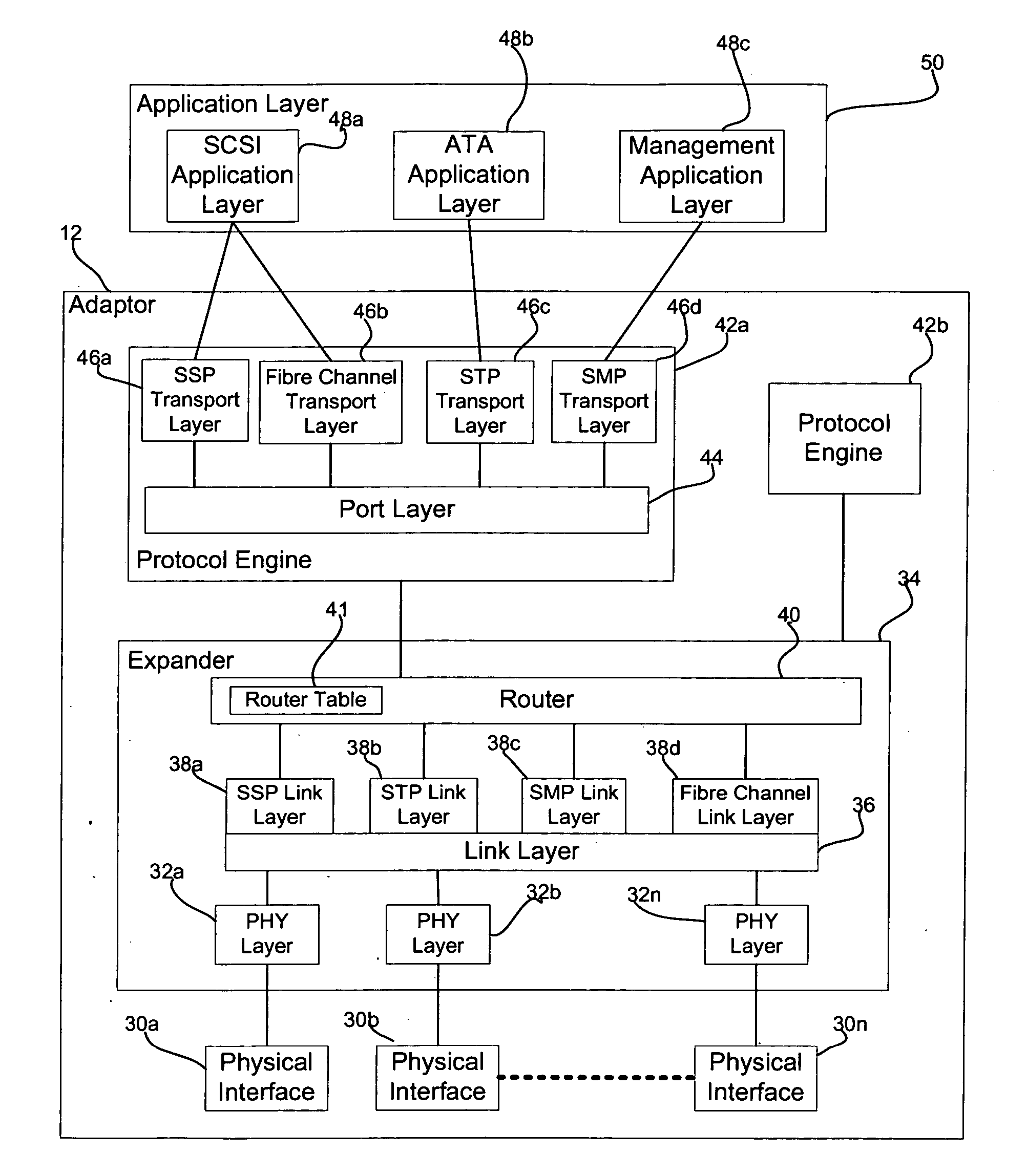

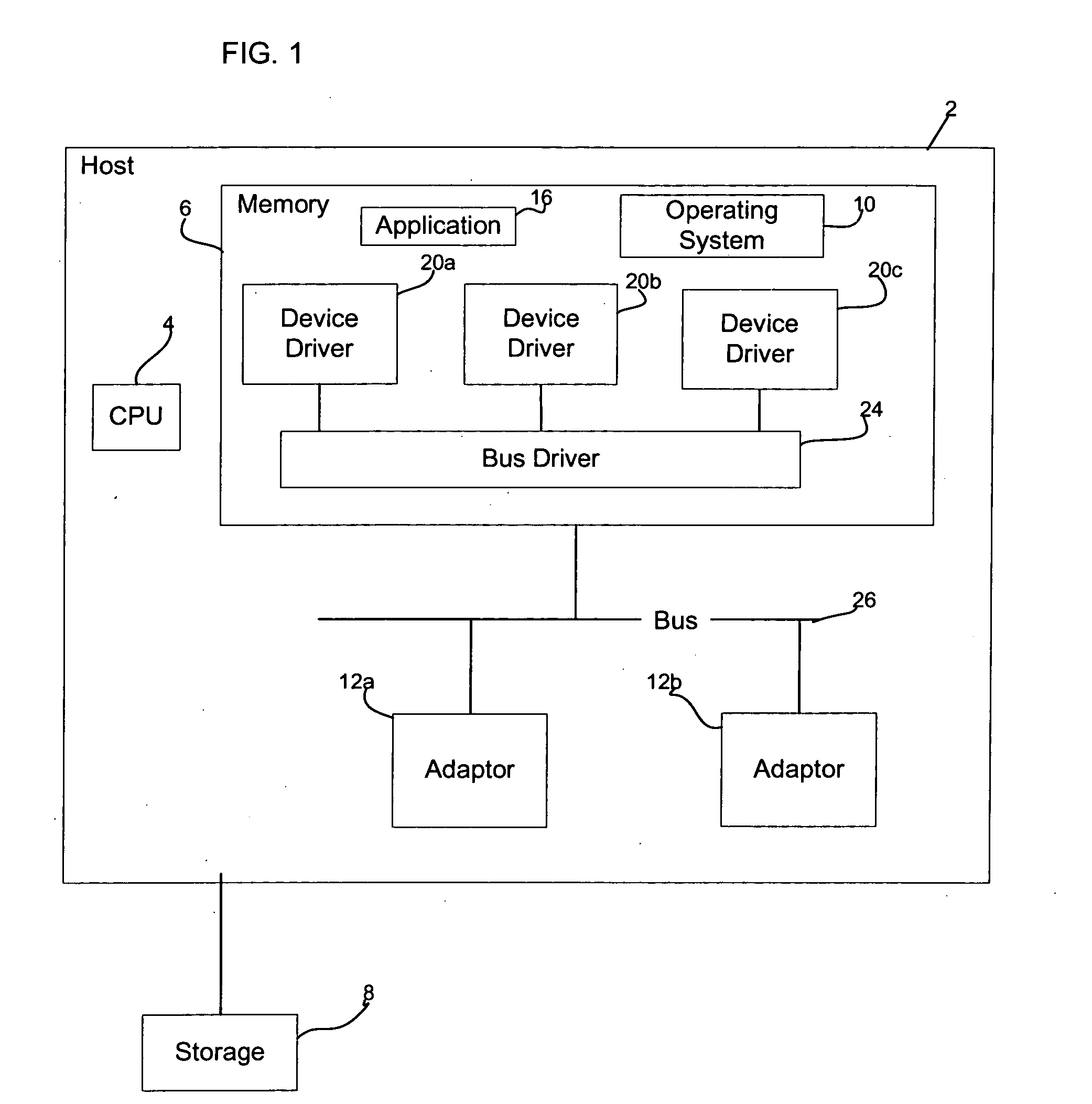

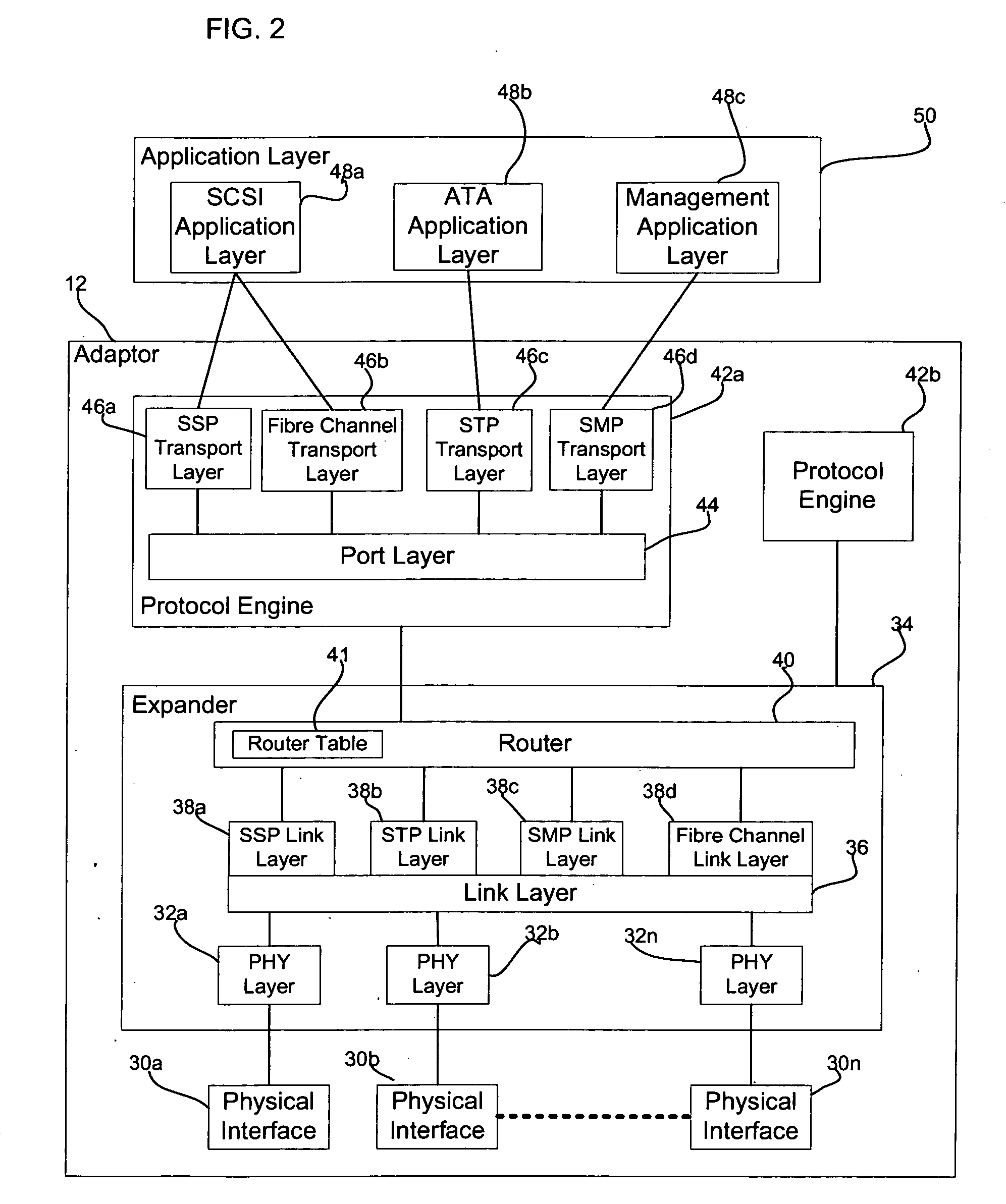

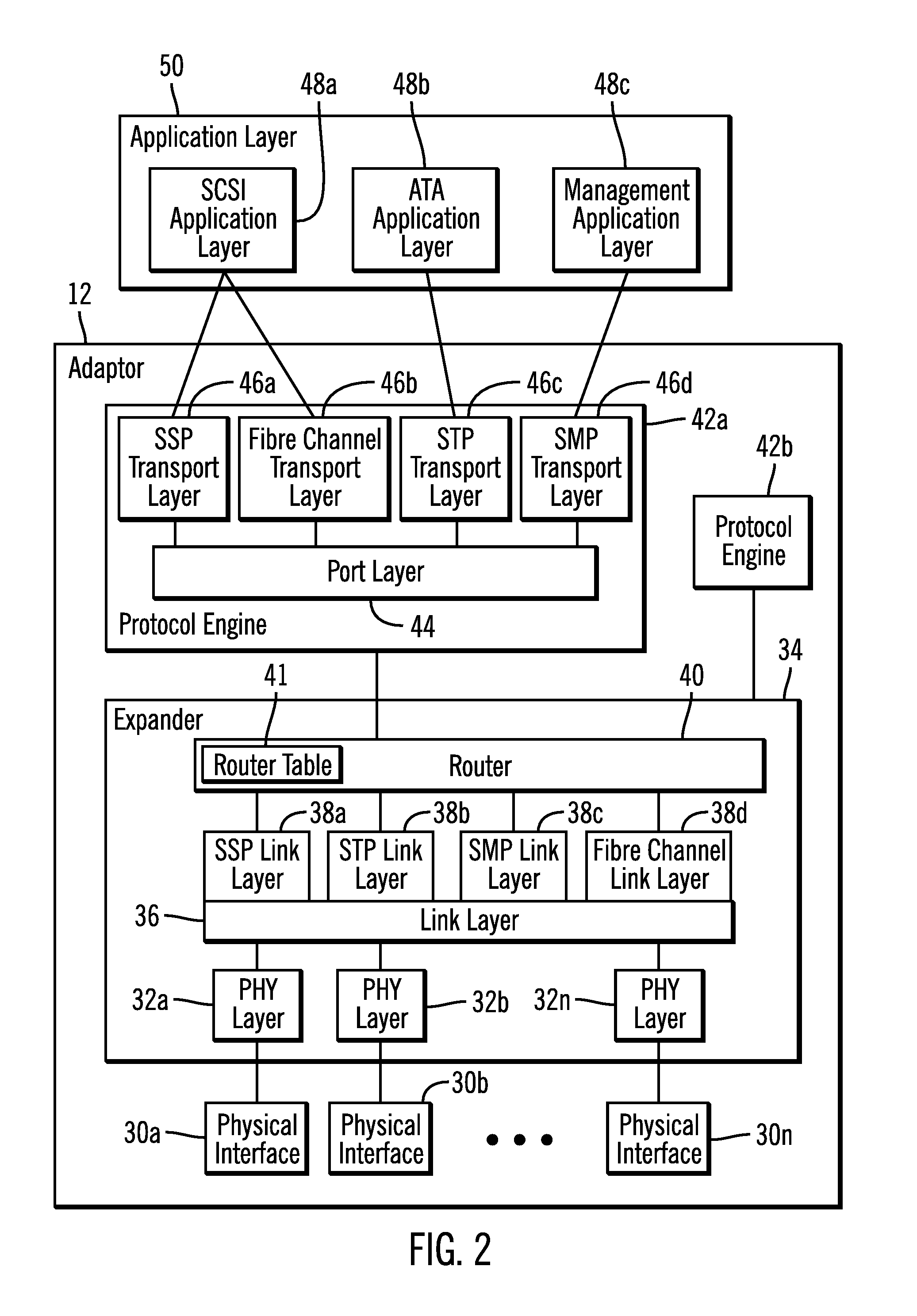

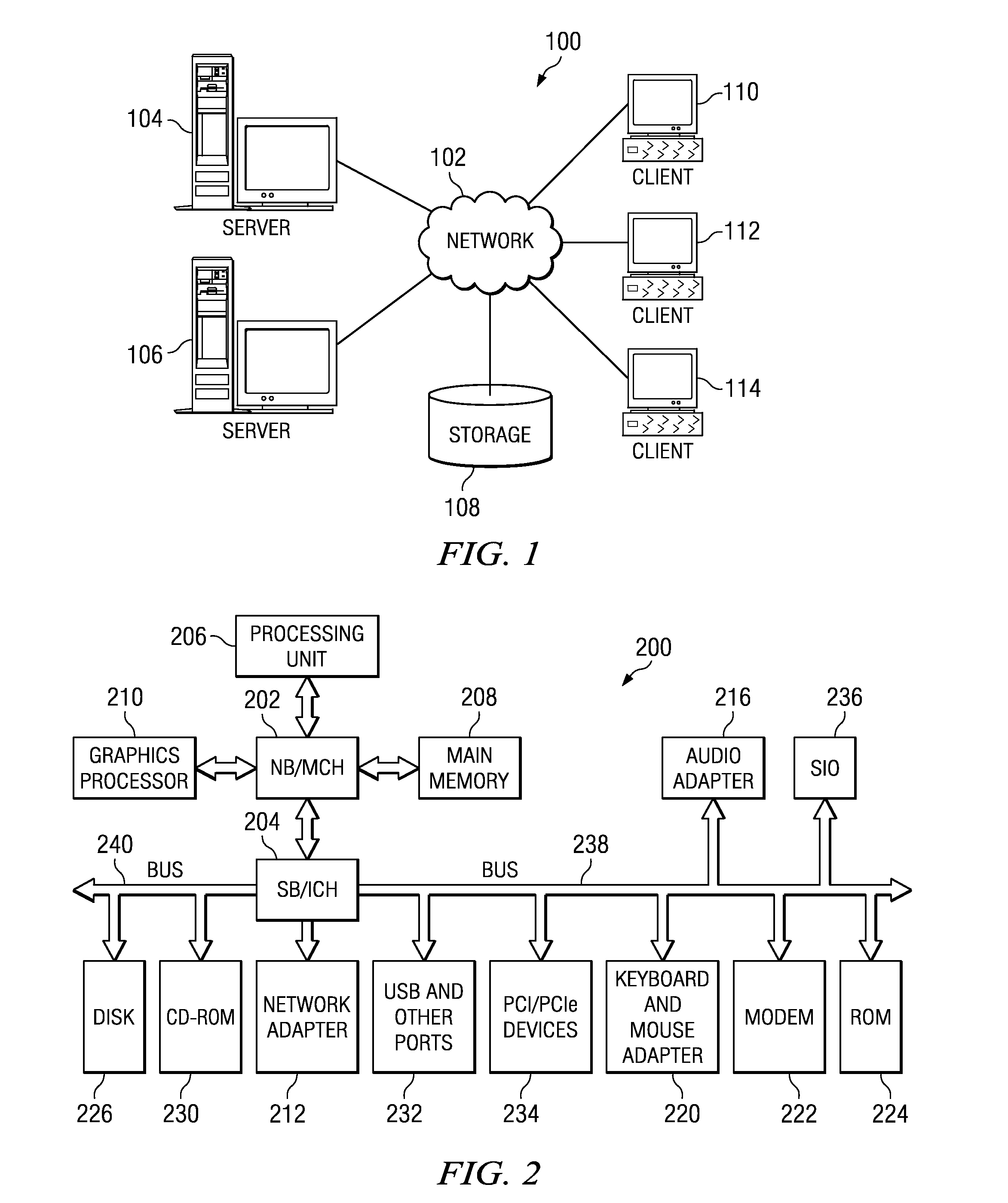

Enclosure management device

Provided are a method, expander, system, and program for receiving a transmission at an interface supporting multiple storage interconnect architectures having different transmission characteristics, and wherein the transmission uses one of the supported storage interconnect architectures. The interface forwards the transmission to the enclosure management device. The enclosure management device processes the transmission using one of a plurality of transport layers supported at the enclosure management device, wherein the enclosure management device includes at least one transport layer used with each supported storage interconnect architecture.

Owner:INTEL CORP

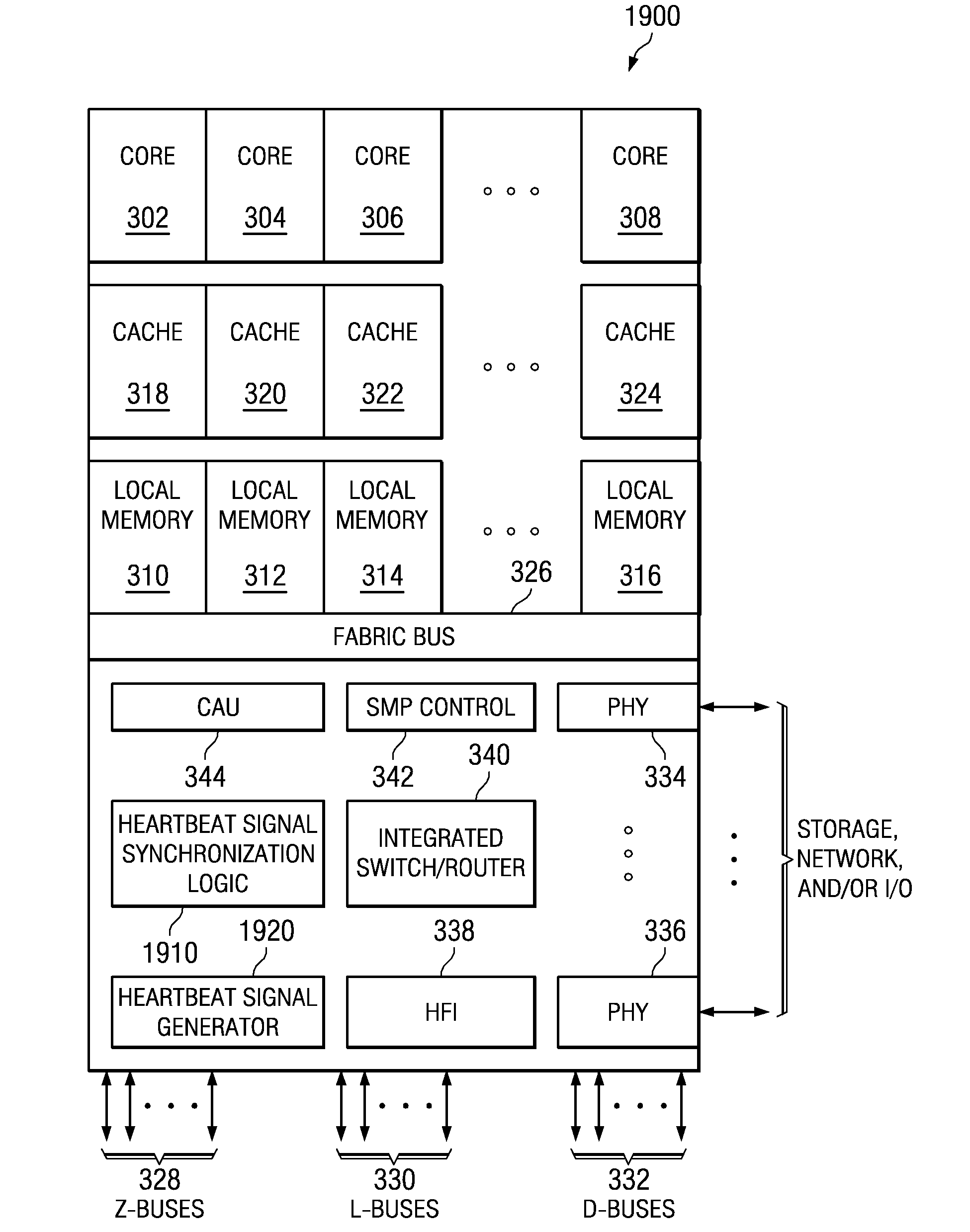

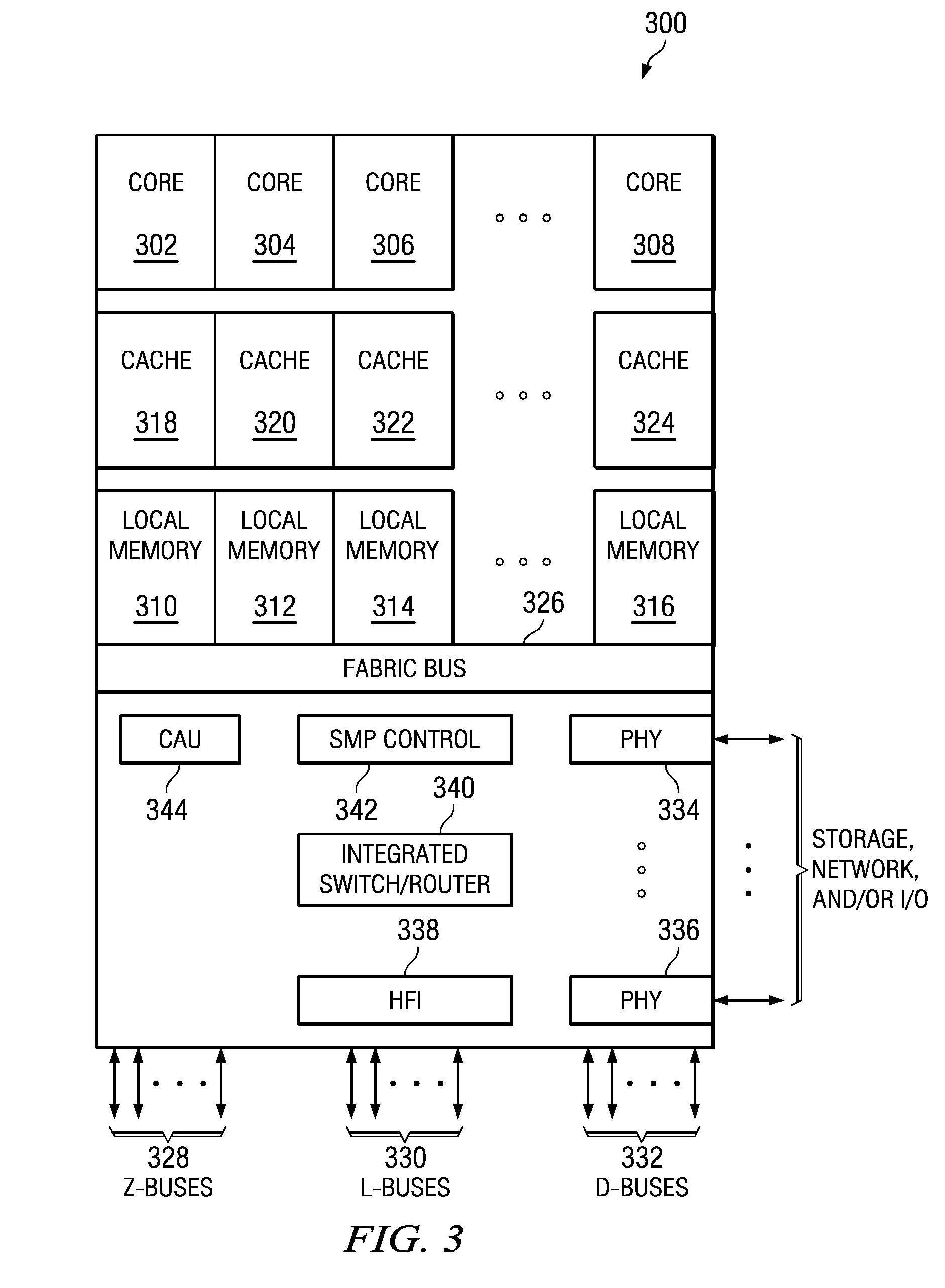

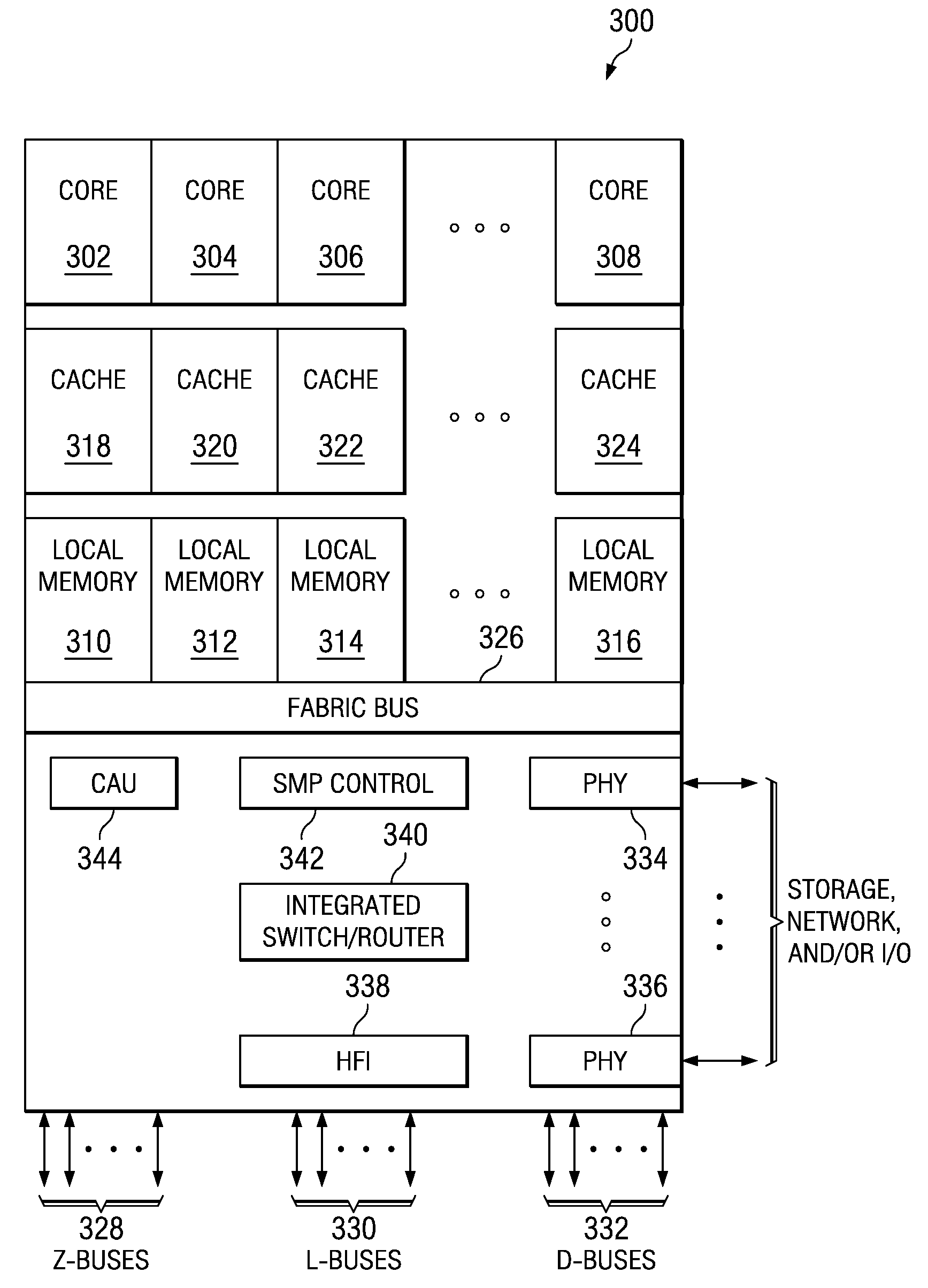

Method for Providing a Cluster-Wide System Clock in a Multi-Tiered Full-Graph Interconnect Architecture

InactiveUS20090070617A1Lower latencyReduce wasteMultiple digital computer combinationsGenerating/distributing signalsDirect couplingComputer science

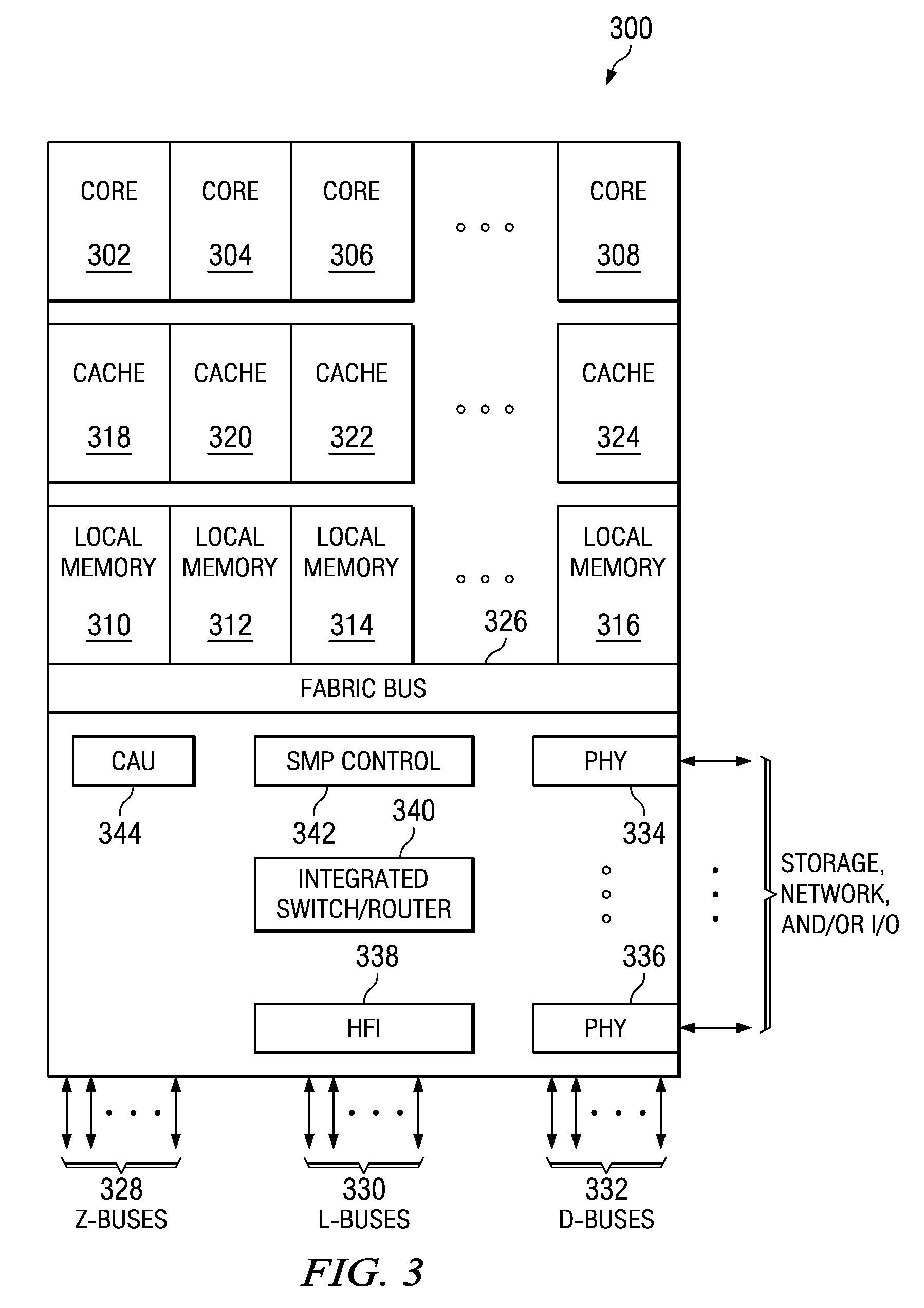

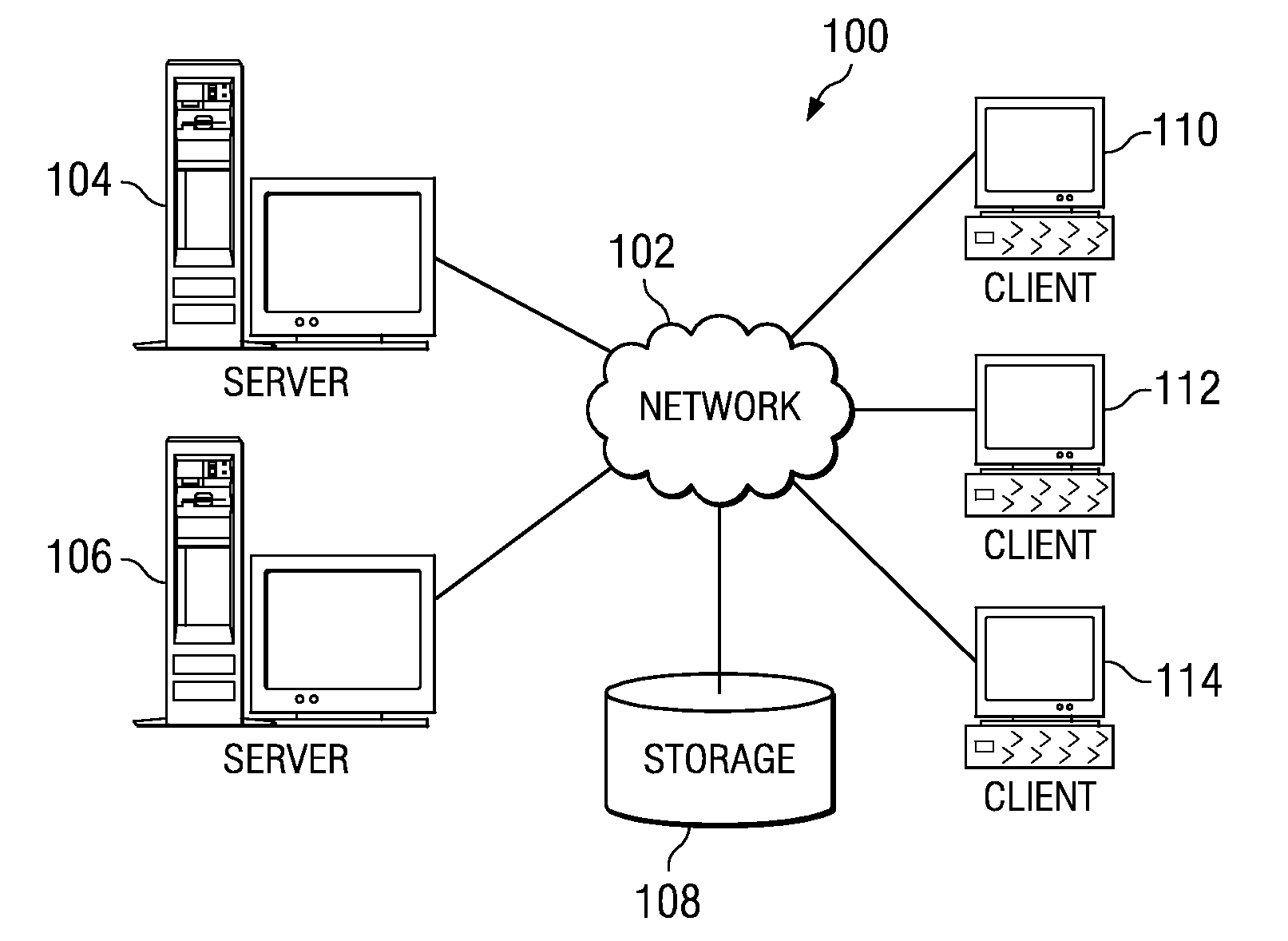

A method for providing a cluster-wide system clock in a multi-tiered full graph (MTFG) interconnect architecture are provided. Heartbeat signals transmitted by each of the processor chips in the computing cluster are synchronized. Internal system clock signals are generated in each of the processor chips based on the synchronized heartbeat signals. As a result, the internal system clock signals of each of the processor chips are synchronized since the heartbeat signals, that are the basis for the internal system clock signals, are synchronized. Mechanisms are provided for performing such synchronization using direct couplings of processor chips within the same processor book, different processor books in the same supernode, and different processor books in different supernodes of the MTFG interconnect architecture.

Owner:IBM CORP

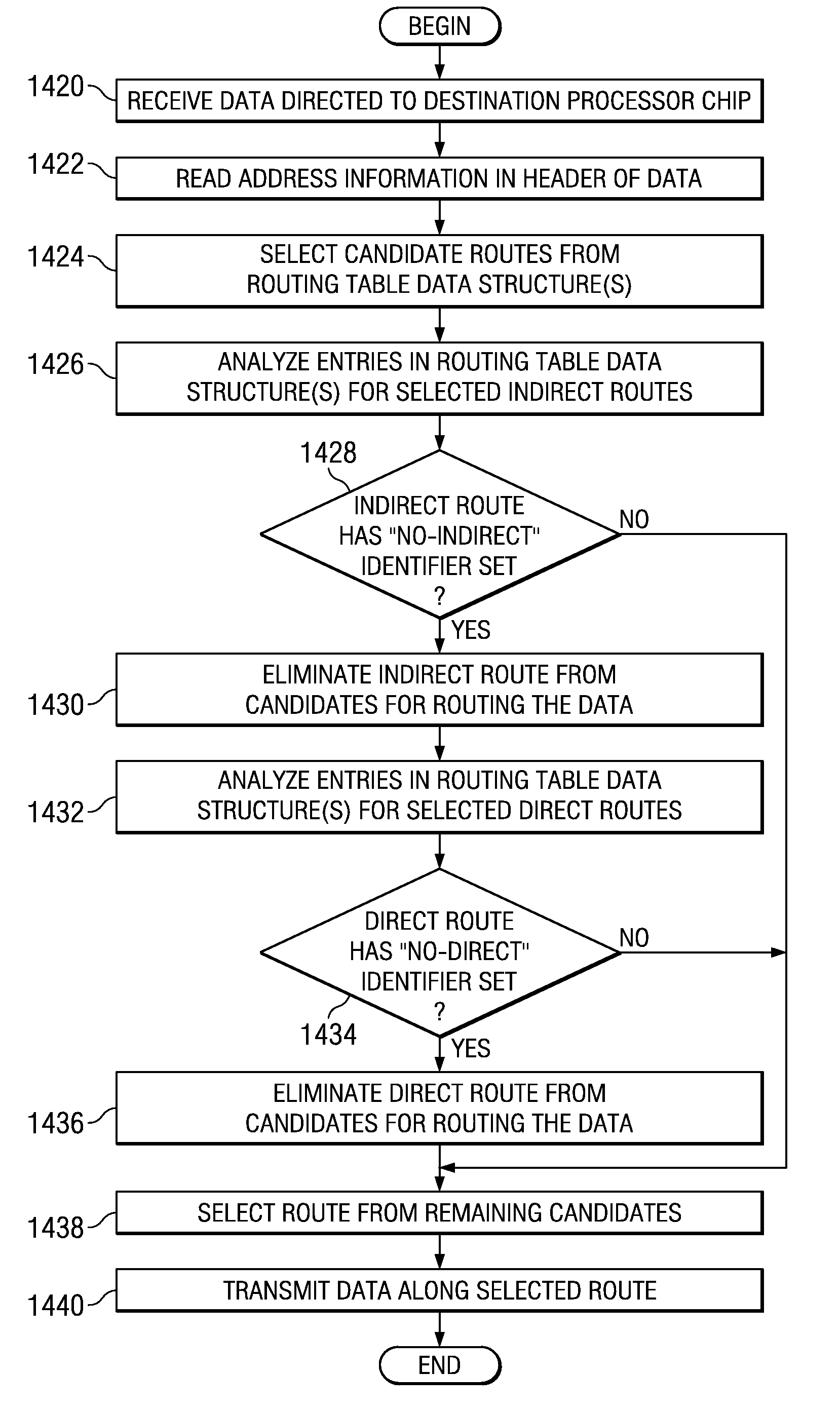

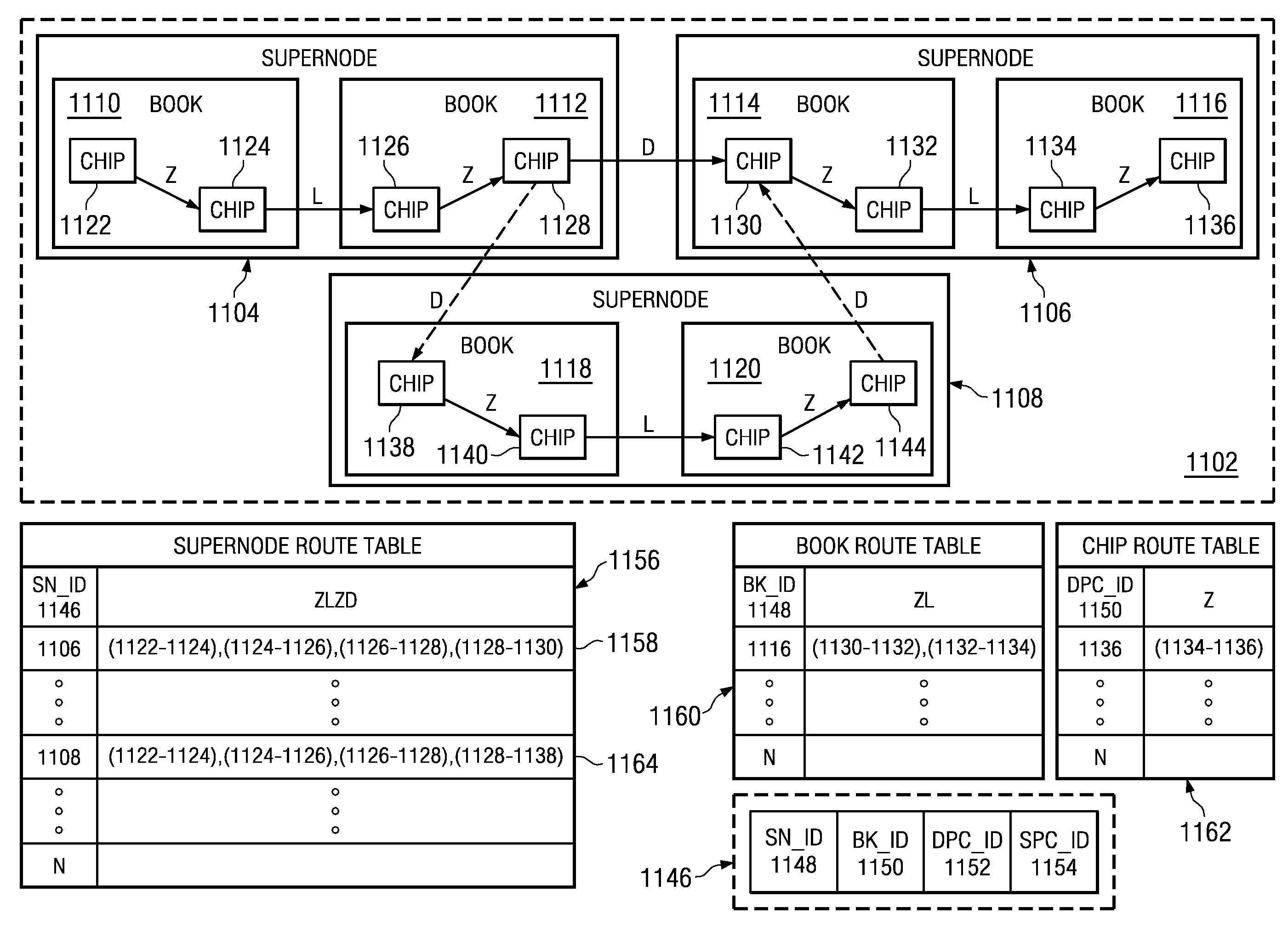

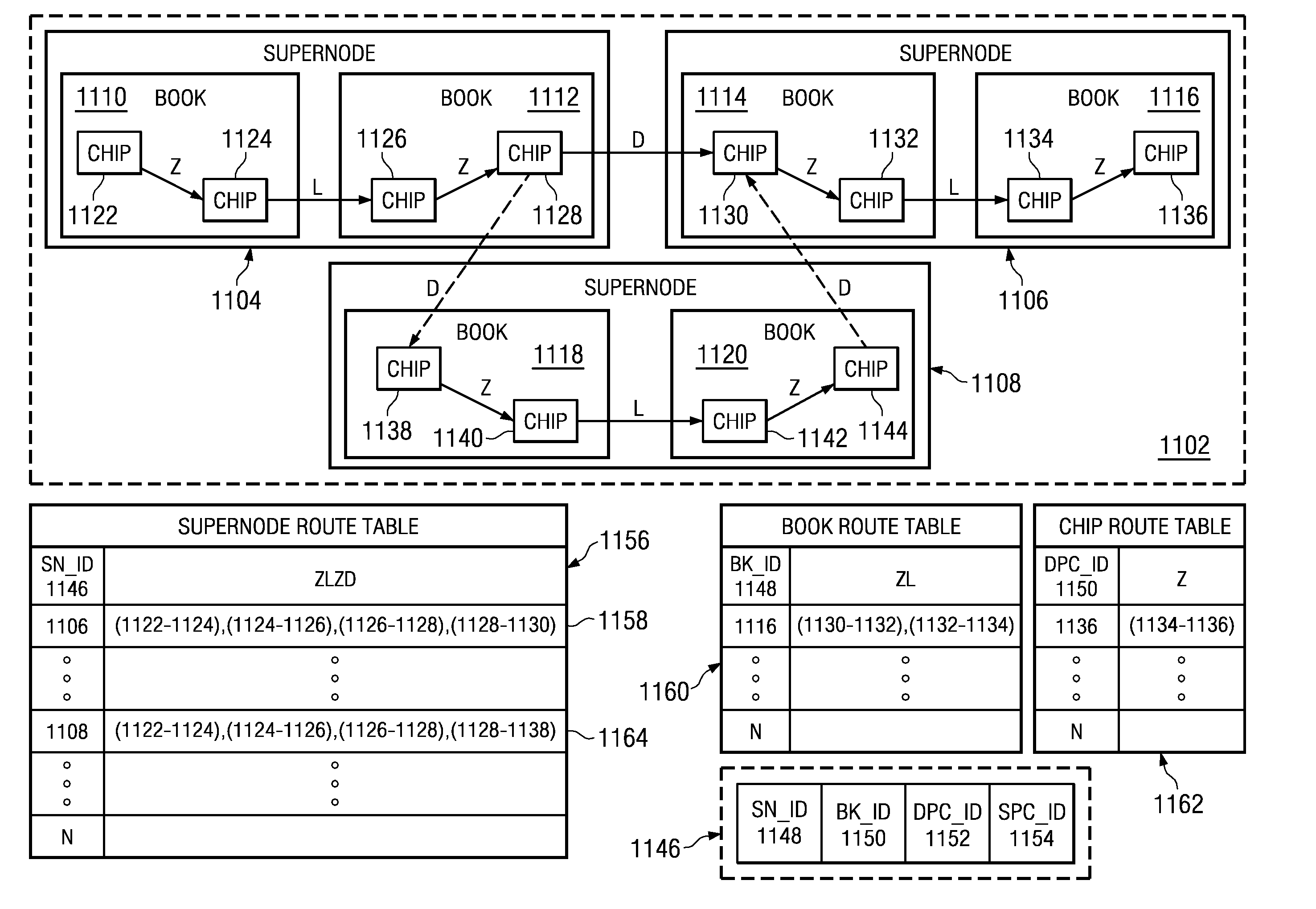

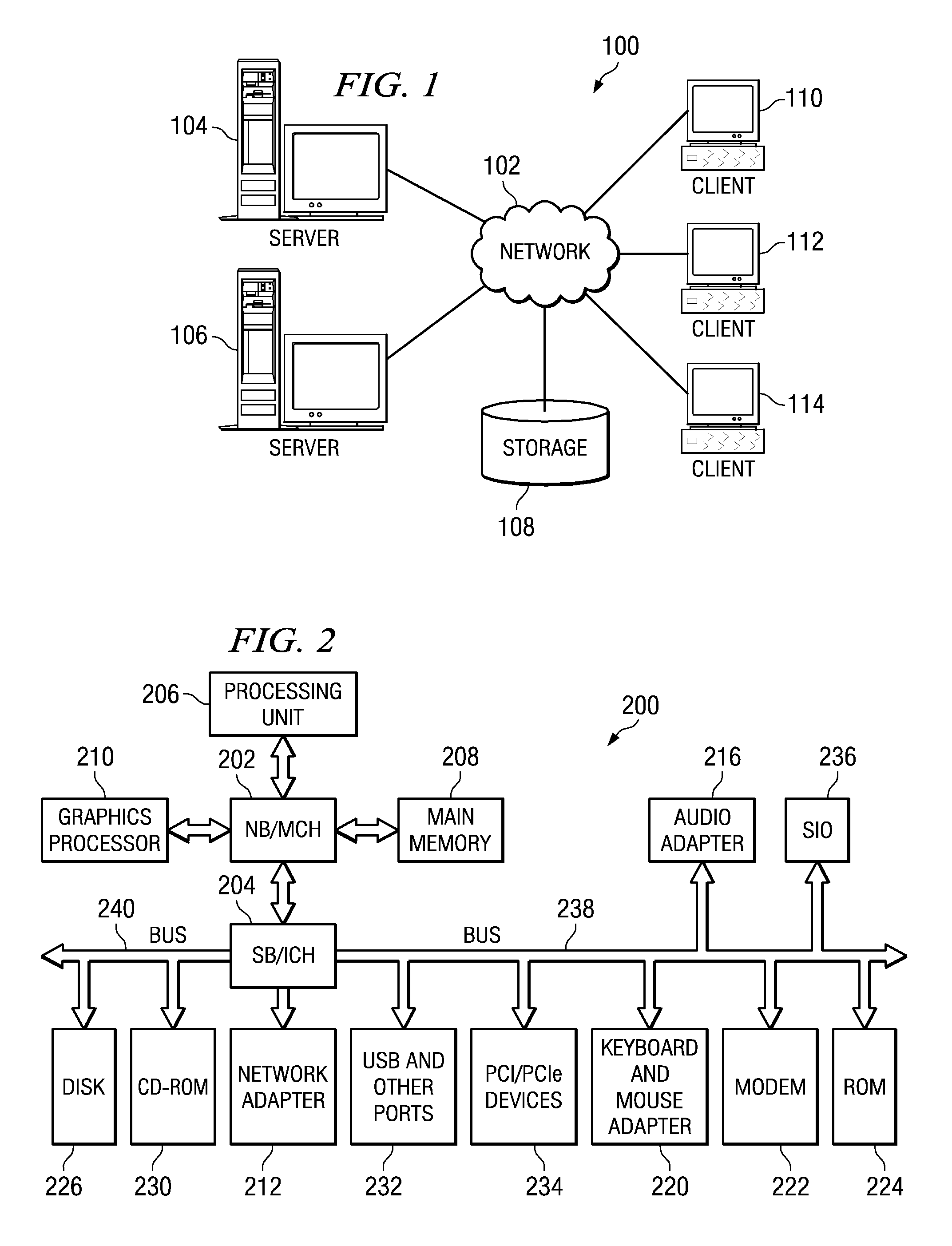

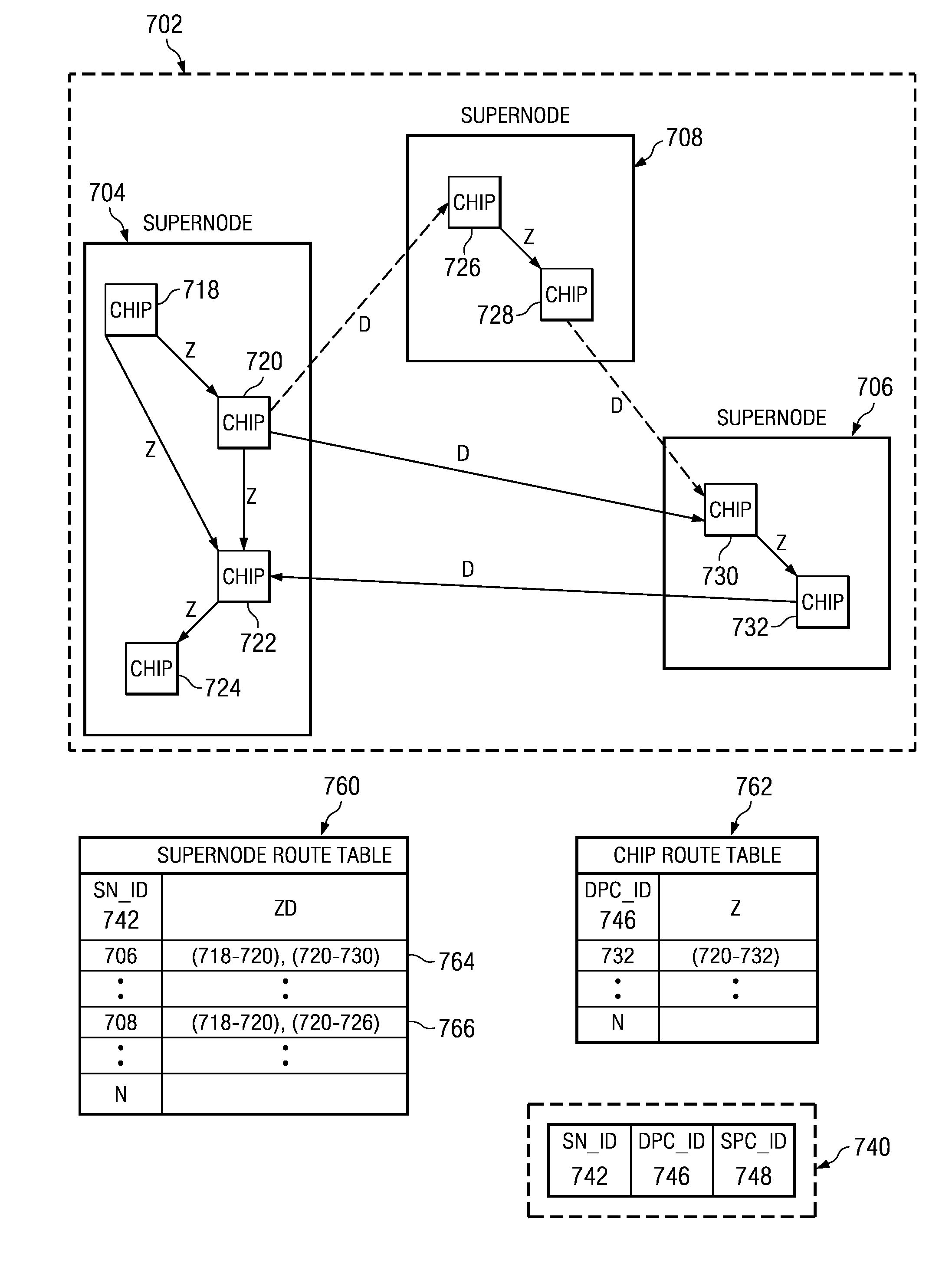

System and Method for Dynamically Supporting Indirect Routing Within a Multi-Tiered Full-Graph Interconnect Architecture

InactiveUS20090063443A1Improve communication performanceHighly-configurableDigital data processing detailsDigital computer detailsData processing systemRouting table

A method, computer program product, and system are provided for dynamically routing data through the data processing system. Data is received at a first processor that is to be transmitted to a destination processor. The data that is received includes address information. A lookup is performed in routing table data structures based on the address information to identify candidate paths through which the data is routed to the destination processor. A determination is made as to whether any of the candidate paths are not able to be used to route the data to the destination processor based on a setting of at least one identifier. A path is selected from the identified candidate paths for routing of the data based on a setting of the at least one identifier. Then, the data is transmitted from the first processor along the selected path toward the destination processor.

Owner:IBM CORP

System and Method for Providing a Fully Non-Blocking Switch in a Supernode of a Multi-Tiered Full-Graph Interconnect Architecture

InactiveUS20090064140A1Improve communication performanceImprove productivityMultiplex system selection arrangementsDigital computer detailsData processing systemParallel computing

A method, computer program product, and system are provided for transmitting data from a first processor of a data processing system to a second processor of the data processing system. In one or more switches, a set of virtual channels is created, the one or more switches comprising, for each processor, a corresponding switch in the one or more switches. The data is transmitted from the first processor to the second processor through a path comprising a subset of processors of a set of processors in the data processing system. In each processor of the subset of processors, the data is stored in a virtual channel of a corresponding switch before transmitting the data to a next processor. The virtual channel of the corresponding switch in which the data is stored corresponds to a position of the processor in the path through which the data is transmitted.

Owner:IBM CORP

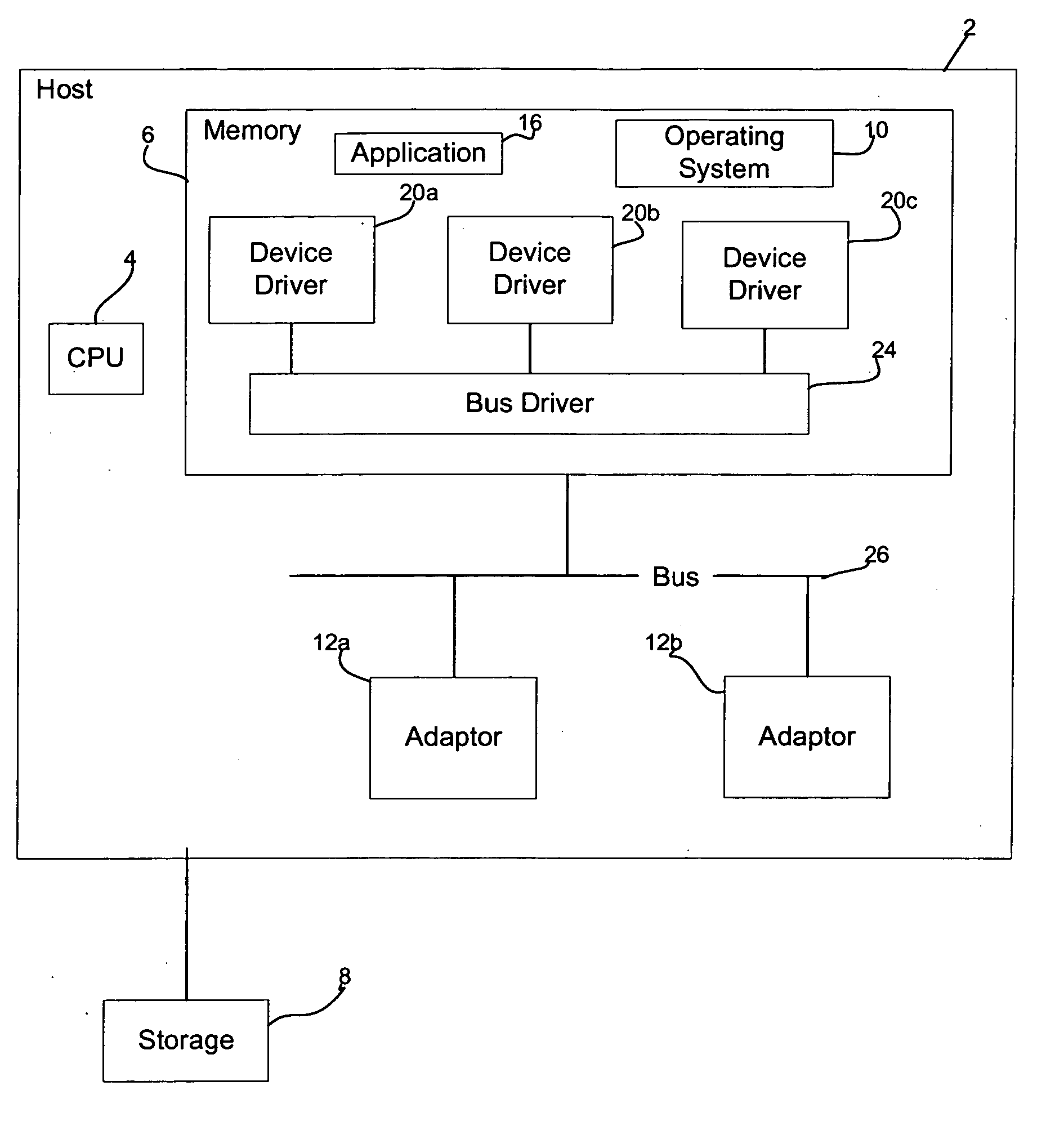

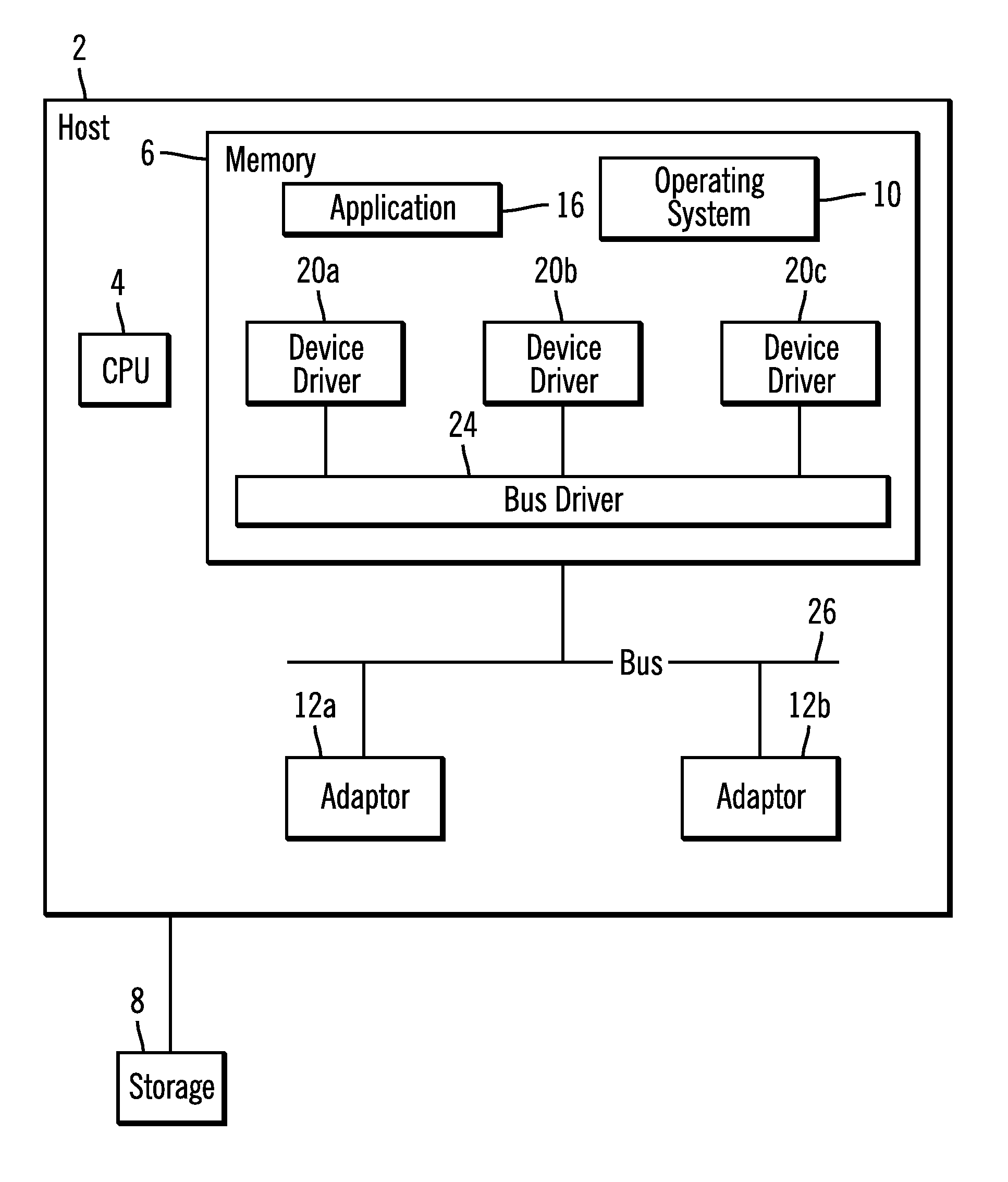

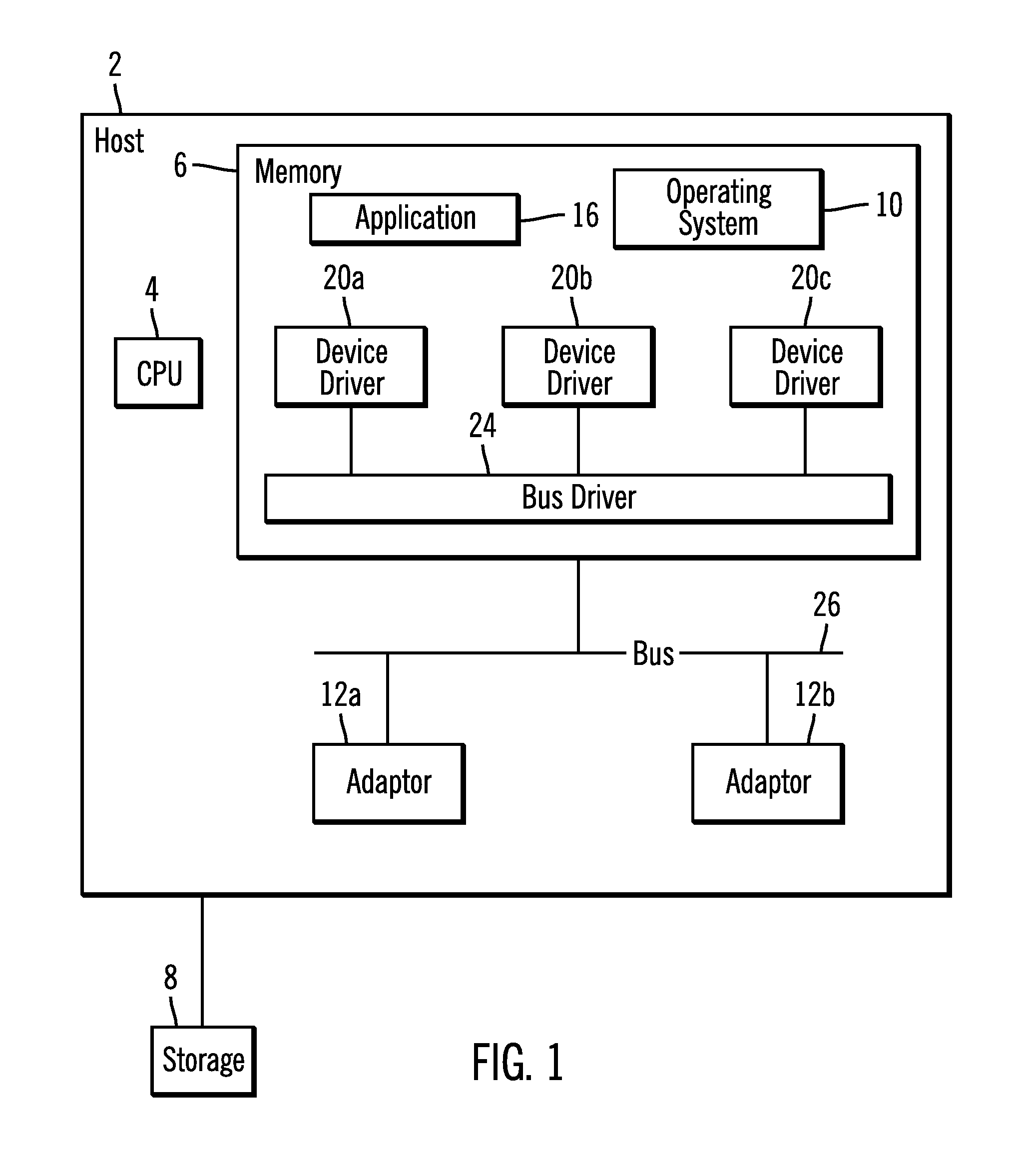

Adaptor supporting different protocols

InactiveUS7376147B2Time-division multiplexMultiple digital computer combinationsComputer hardwareTransport layer

Provided are a method, adaptor, system, and program for receiving a transmission at one of multiple connections. Information is maintained on storage interconnect architectures and transmission characteristics, wherein the storage interconnect architectures have different transmission characteristics. At least one transmission characteristic of the received transmission is determined and a determination is made from the information of the storage interconnect architecture associated with the determined transmission characteristic. The information on the determined storage interconnect architecture is used to process the transmission and determine a transport layer for the received transmission, wherein there is one transport layer for each supported transport protocol. The transmission is forwarded to the determined transport layer.

Owner:INTEL CORP

Adaptor supporting different protocols

InactiveUS20050138191A1Multiple digital computer combinationsElectric digital data processingComputer hardwareTransport layer

Provided are a method, adaptor, system, and program for receiving a transmission at one of multiple connections. Information is maintained on storage interconnect architectures and transmission characteristics, wherein the storage interconnect architectures have different transmission characteristics. At least one transmission characteristic of the received transmission is determined and a determination is made from the information of the storage interconnect architecture associated with the determined transmission characteristic. The information on the determined storage interconnect architecture is used to process the transmission and determine a transport layer for the received transmission, wherein there is one transport layer for each supported transport protocol. The transmission is forwarded to the determined transport layer.

Owner:INTEL CORP

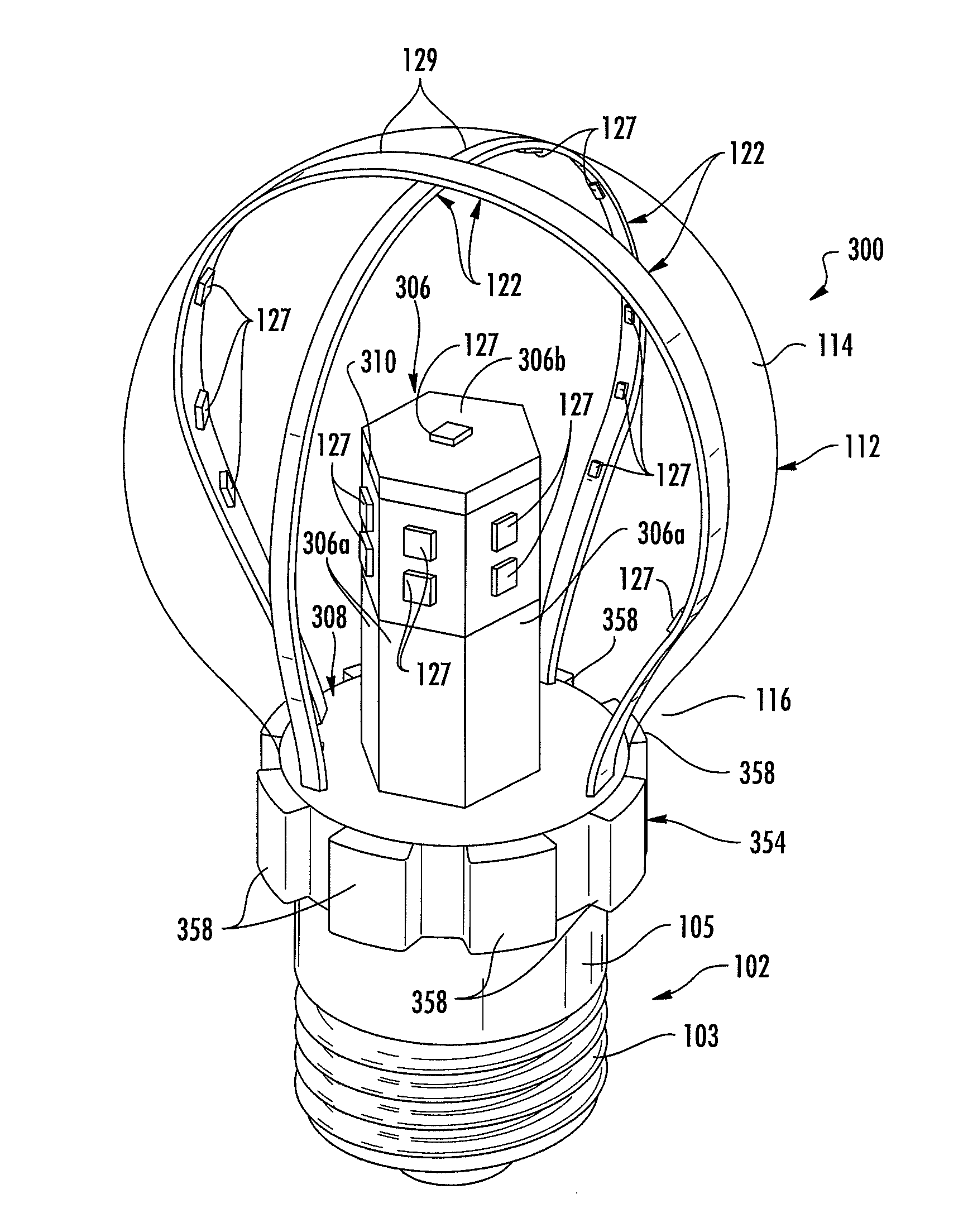

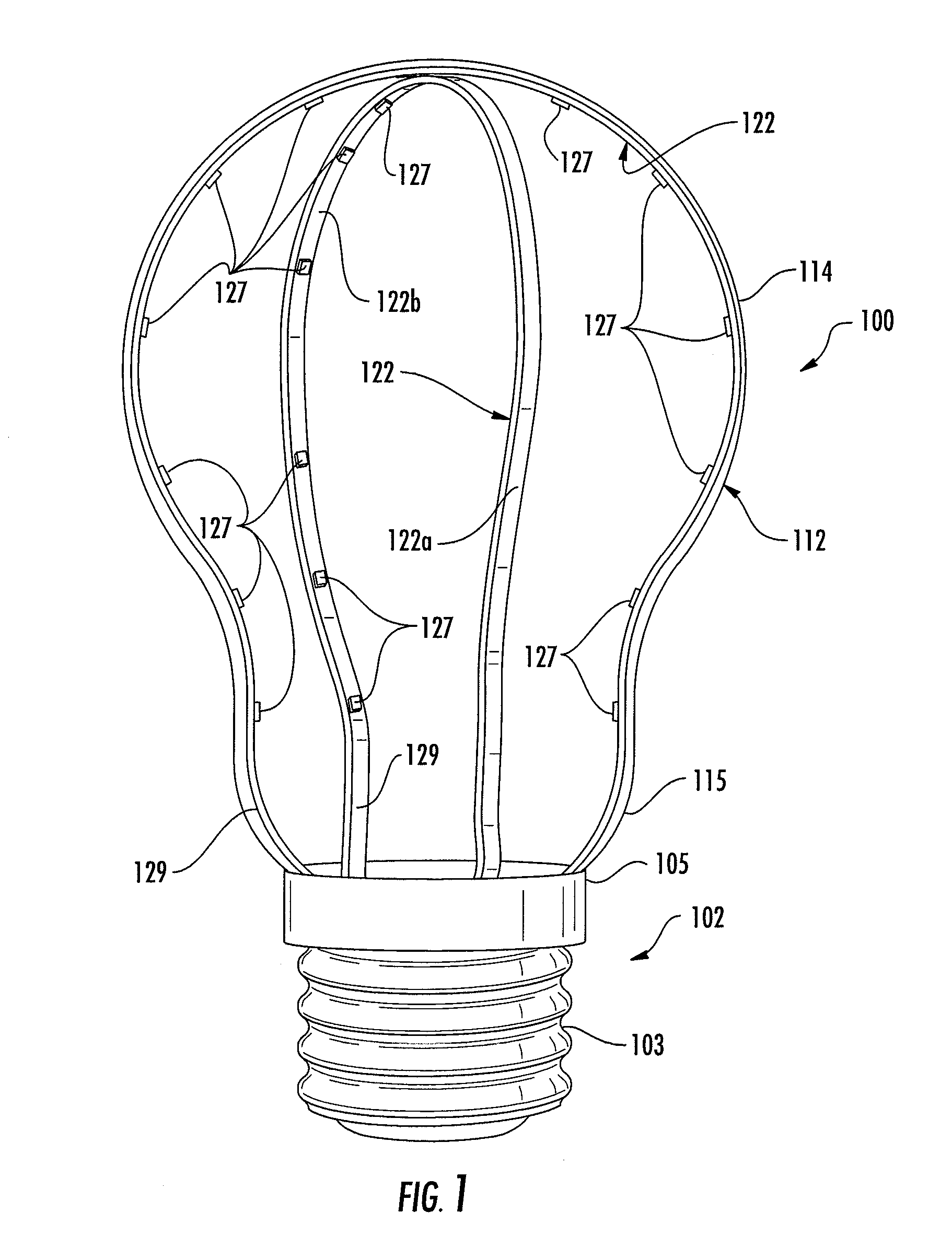

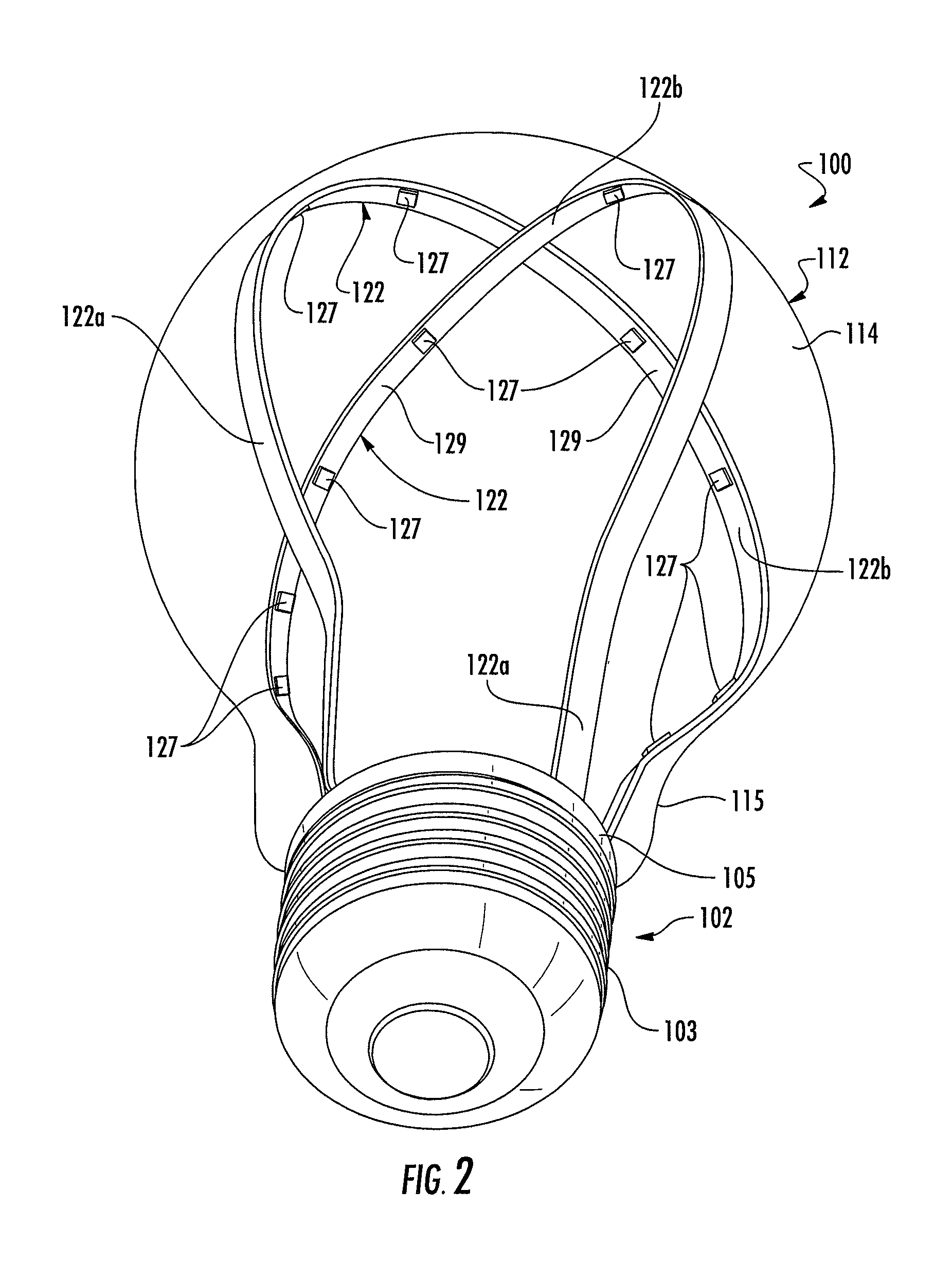

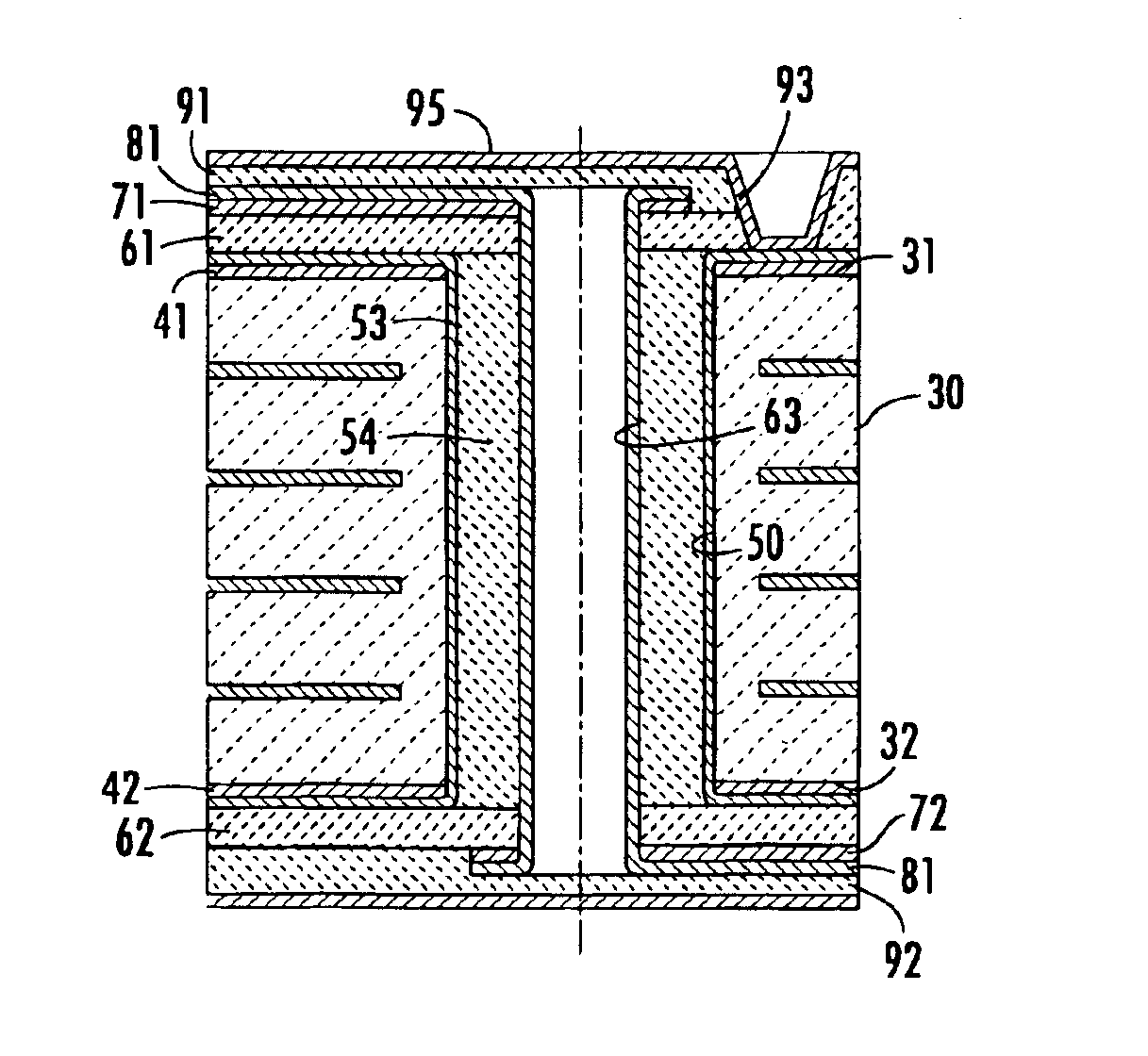

LED luminaire with improved thermal management and novel LED interconnecting architecture

A LED lamp includes an optically transmissive enclosure and a base connected to the enclosure. LEDs are mounted on a ribbon for emitting light when energized though an electrical path from the base. The mounting ribbon for the LEDs has a surface that is positioned adjacent an interior surface of the enclosure for transmitting heat from the plurality of LEDs to the enclosure.

Owner:IDEAL IND LIGHTING LLC

System and method for dynamically supporting indirect routing within a multi-tiered full-graph interconnect architecture

InactiveUS7840703B2Improve communication performanceHighly-configurableError preventionTransmission systemsData processing systemRouting table

A method, computer program product, and system are provided for dynamically routing data through the data processing system. Data is received at a first processor that is to be transmitted to a destination processor. The data that is received includes address information. A lookup is performed in routing table data structures based on the address information to identify candidate paths through which the data is routed to the destination processor. A determination is made as to whether any of the candidate paths are not able to be used to route the data to the destination processor based on a setting of at least one identifier. A path is selected from the identified candidate paths for routing of the data based on a setting of the at least one identifier. Then, the data is transmitted from the first processor along the selected path toward the destination processor.

Owner:INT BUSINESS MASCH CORP

Multiple interfaces in a storage enclosure

InactiveUS20050138258A1Facilitate communicationIncrease connection distanceComponent plug-in assemblagesMemory systemsPhysical interfaceStorage cell

Provided is a system for interfacing with storage units, including a backplane, at least one slot in the storage enclosure for receiving one storage unit, and two physical interfaces on the backplane for at least one slot. The storage unit is capable of being positioned in the slot to mate with one of the two physical interfaces for the slot, wherein each physical interface supports different storage interconnect architectures.

Owner:INTEL CORP

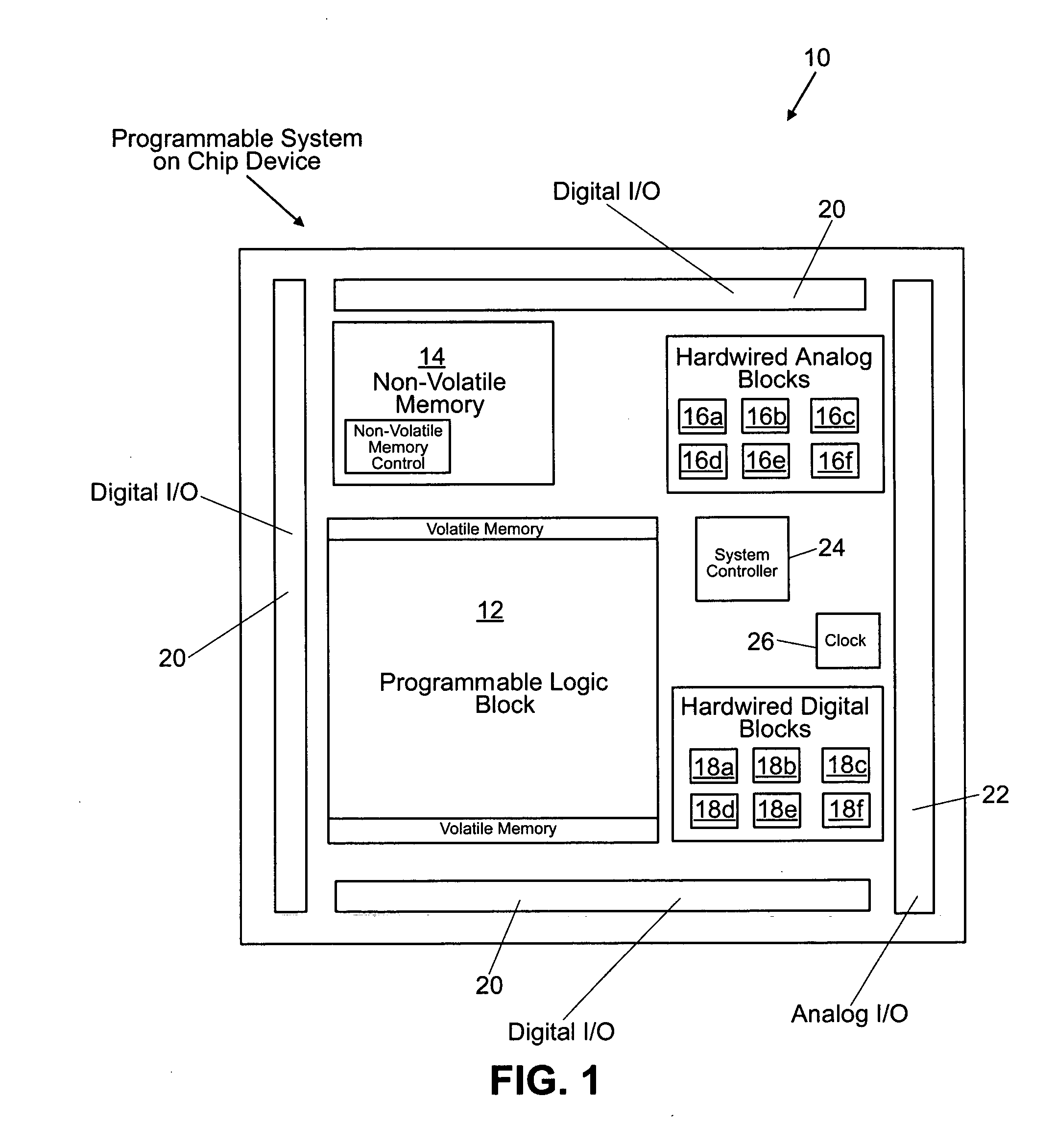

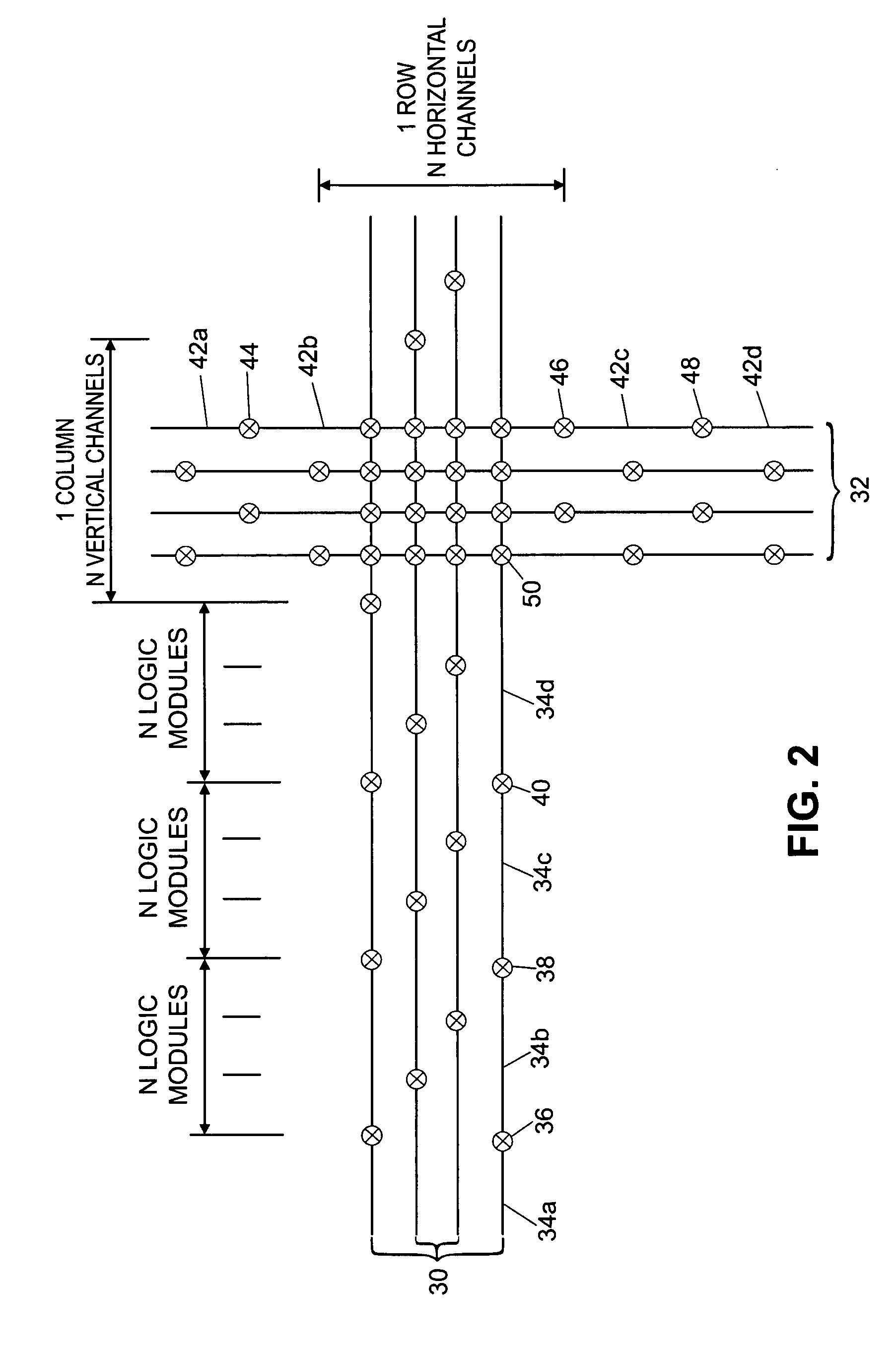

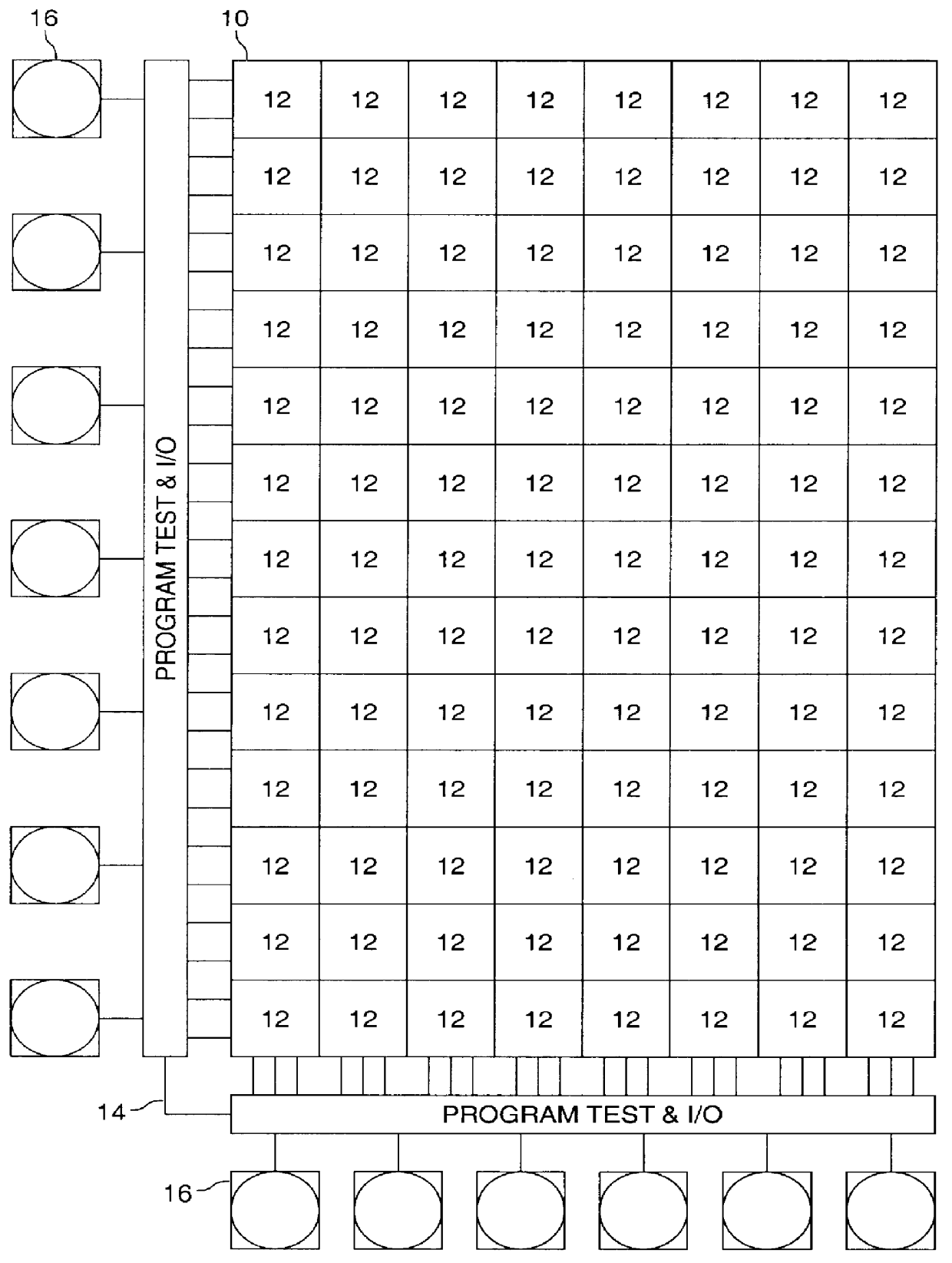

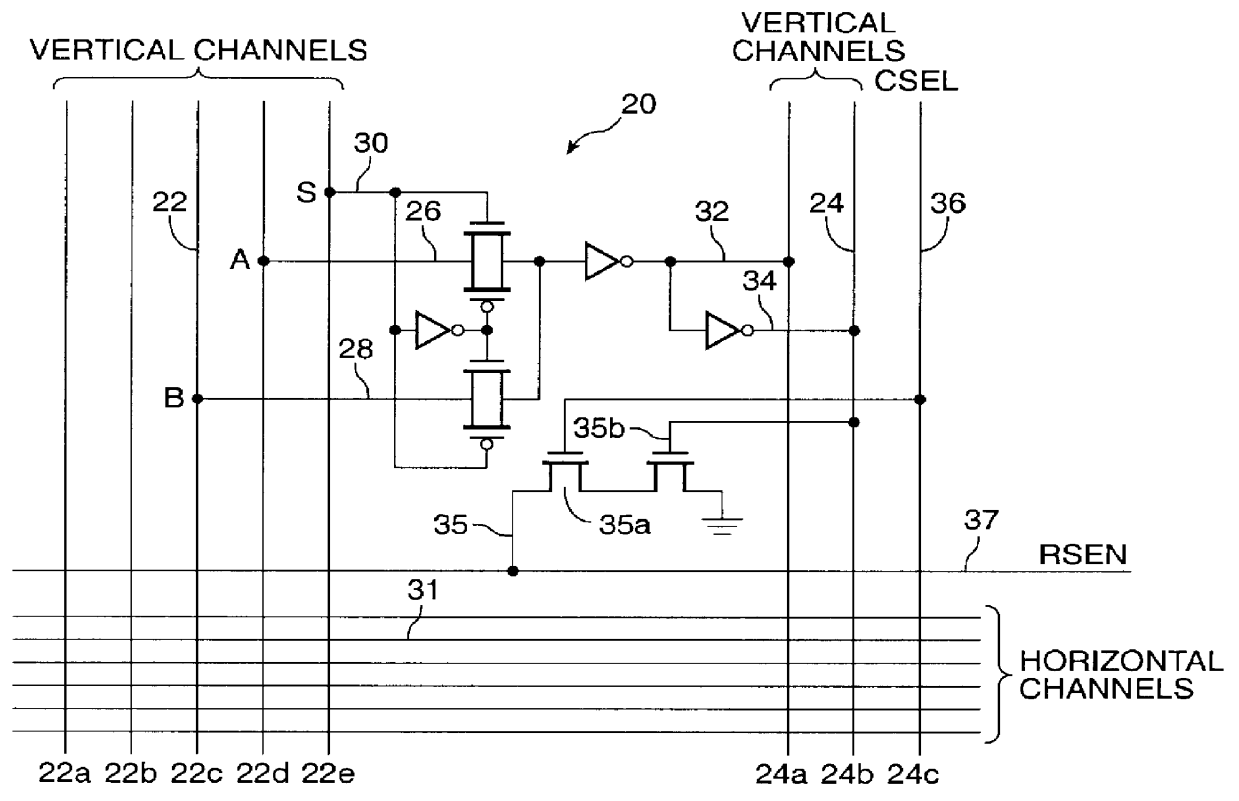

Programmable interconnect architecture

InactiveUS6160420AHigh complexity and performanceLower impedanceElectronic circuit testingSolid-state devicesSystems designLogic cell

A user-programmable interconnect architecture, which may be used for logic arrays for digital and analog system design, is disclosed. In one embodiment, a plurality of logic cells or modules in a matrix are connected by vertical and horizontal wiring channels. The wiring channels may in turn be programmed by the user to interconnect the various logic cells to implement the required logic function. The wiring channels comprise wiring segments connected by normally open programmable. Elements situated at the intersection of any two segments to be connected.

Owner:ACTEL CORP

Multiple physical interfaces in a slot of a storage enclosure to support different storage interconnect architectures

InactiveUS7155546B2Facilitate communicationIncrease connection distanceComponent plug-in assemblagesSpecific program execution arrangementsComputer scienceStorage cell

Provided is a system for interfacing with storage units, including a backplane, at least one slot in the storage enclosure for receiving one storage unit, and two physical interfaces on the backplane for at least one slot. The storage unit is capable of being positioned in the slot to mate with one of the two physical interfaces for the slot, wherein each physical interface supports different storage interconnect architectures.

Owner:INTEL CORP

System and Method for Providing Full Hardware Support of Collective Operations in a Multi-Tiered Full-Graph Interconnect Architecture

InactiveUS20090063815A1Improve communication performanceImprove productivityProgram control using wired connectionsGeneral purpose stored program computerData processing systemCollective operation

A method, computer program product, and system are provided for performing collective operations. In hardware of a parent processor in a first processor book, a number of other processors are determined in a same or different processor book of the data processing system that is needed to execute the collective operation, thereby establishing a plurality of processors comprising the parent processor and the other processors. In hardware of the parent processor, the plurality of processors are logically arranged as a plurality of nodes in a hierarchical structure. The collective operation is transmitted to the plurality of processors based on the hierarchical structure. In hardware of the parent processor, results are received from the execution of the collective operation from the other processors, a final result is generated of the collective operation based on the received results, and the final result is output.

Owner:IBM CORP

System and Method for Providing a High-Speed Message Passing Interface for Barrier Operations in a Multi-Tiered Full-Graph Interconnect Architecture

InactiveUS20090063880A1Improve communication performanceImprove productivityVolume/mass flow measurementMultiprogramming arrangementsData processing systemMessage Passing Interface

A method, computer program product, and system are provided performing a Message Passing Interface (MPI) job. A first processor chip receives a set of arrival signals from a set of processor chips executing tasks of the MPI job in the data processing system. The arrival signals identify when a processor chip executes a synchronization operation for synchronizing the tasks for the MPI job. Responsive to receiving the set of arrival signals from the set of processor chips, the first processor chip identifies a fastest processor chip of the set of processor chips whose arrival signal arrived first. An operation of the fastest processor chip is modified based on the identification of the fastest processor chip. The set of processor chips comprises processor chips that are in one of a same processor book or a different processor book of the data processing system.

Owner:IBM CORP

System and Method for Performing Collective Operations Using Software Setup and Partial Software Execution at Leaf Nodes in a Multi-Tiered Full-Graph Interconnect Architecture

InactiveUS20090063816A1Improve communication performanceImprove productivityProgram control using wired connectionsGeneral purpose stored program computerData processing systemCollective operation

A method, computer program product, and system are provided for performing collective operations. In software executing on a parent processor in a first processor book, a number of other processors are determined in a same or different processor book of the data processing system that is needed to execute the collective operation, thereby establishing a plurality of processors comprising the parent processor and the other processors. In software executing on the parent processor, the plurality of processors are logically arranged as a plurality of nodes in a hierarchical structure. The collective operation is transmitted to the plurality of processors based on the hierarchical structure. In hardware of the parent processor, results are received from the execution of the collective operation from the other processors, a final result is generated of the collective operation based on the received results, and the final result is output.

Owner:IBM CORP

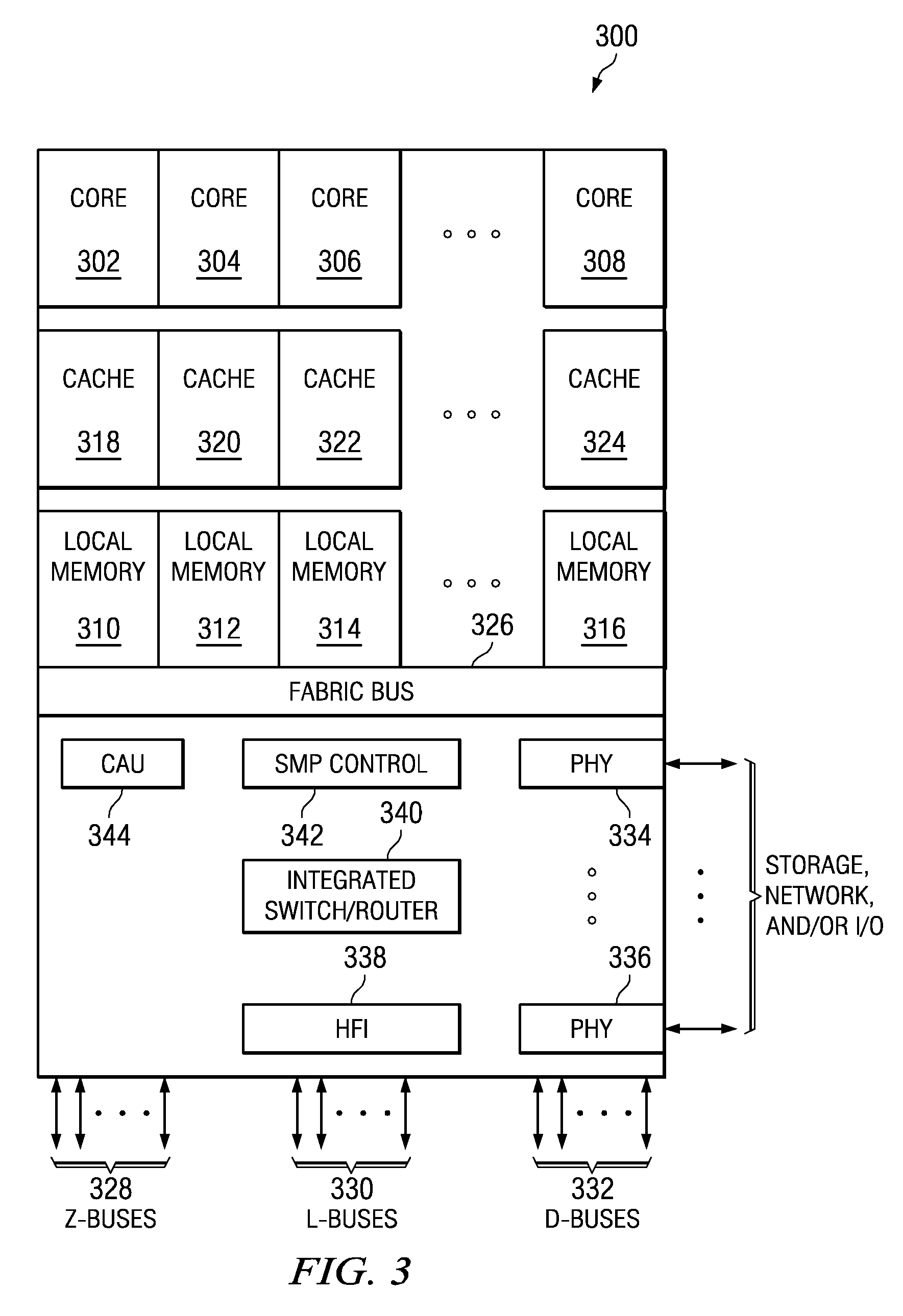

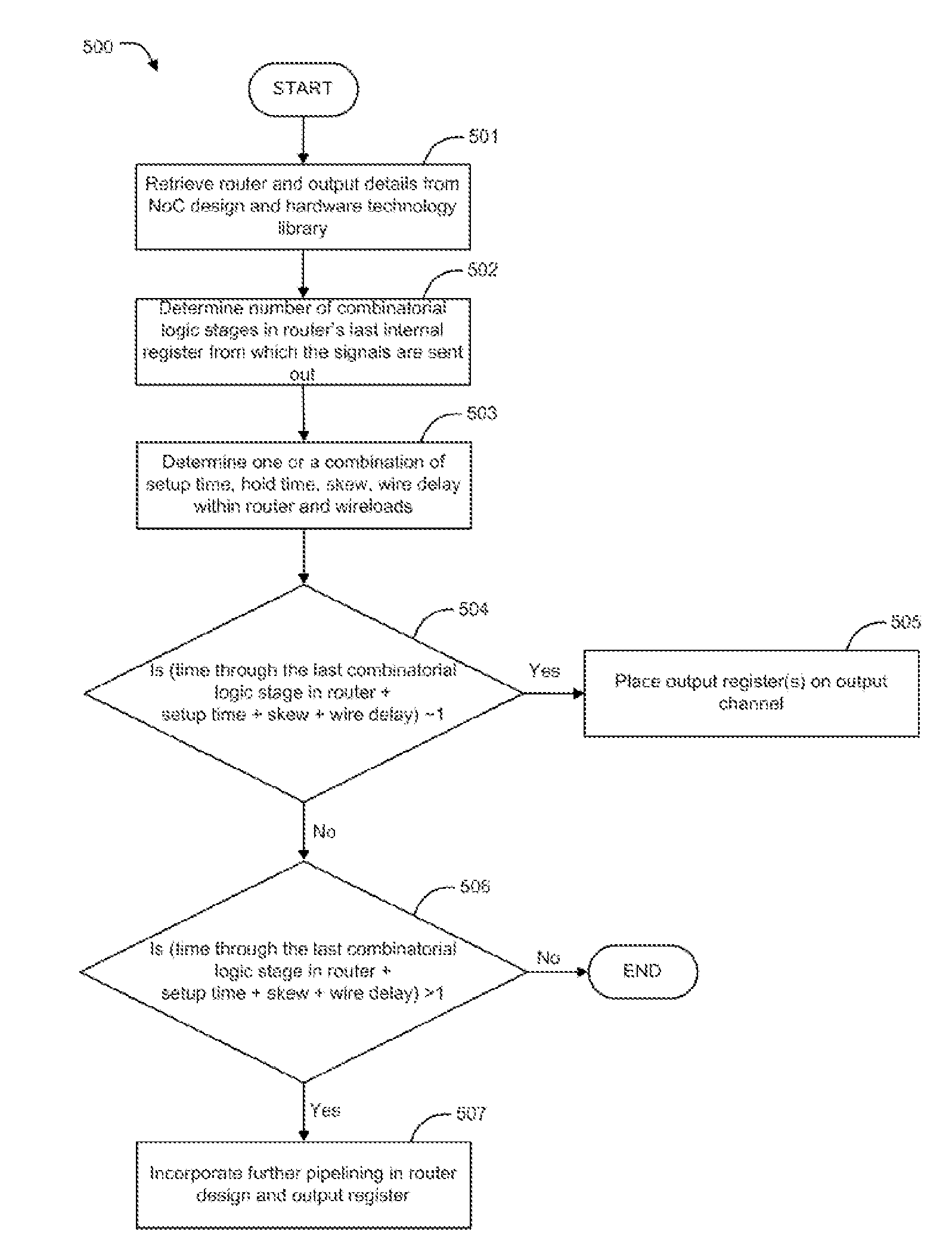

Automatic pipelining of noc channels to meet timing and/or performance

Systems and methods for automatically generating a Network on Chip (NoC) interconnect architecture with pipeline stages are described. The present disclosure includes example implementations directed to automatically determining the number and placement of pipeline stages for each channel in the NoC. Example implementations may also adjust the buffer at one or more routers based on the pipeline stages and configure throughput for virtual channels.

Owner:INTEL CORP

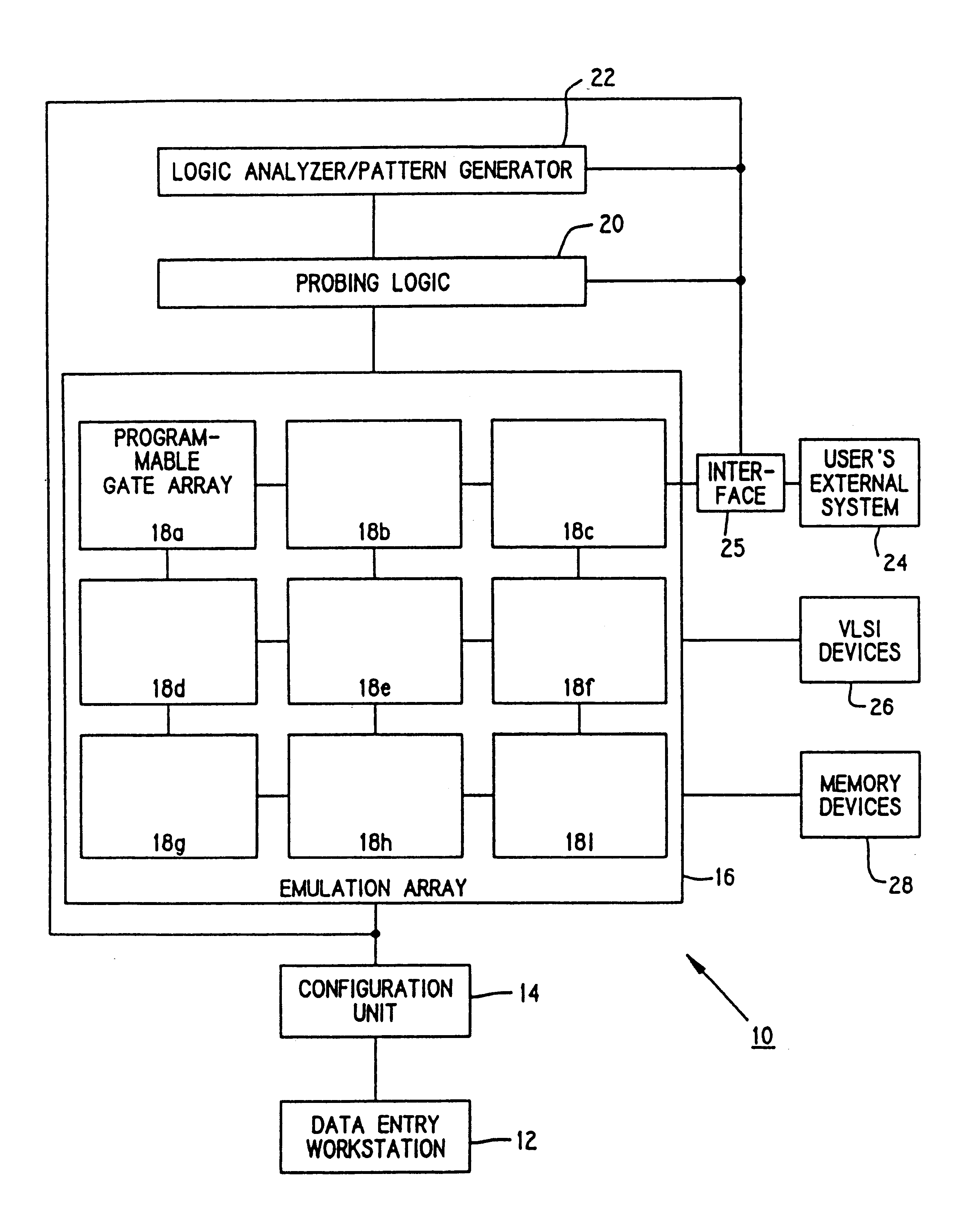

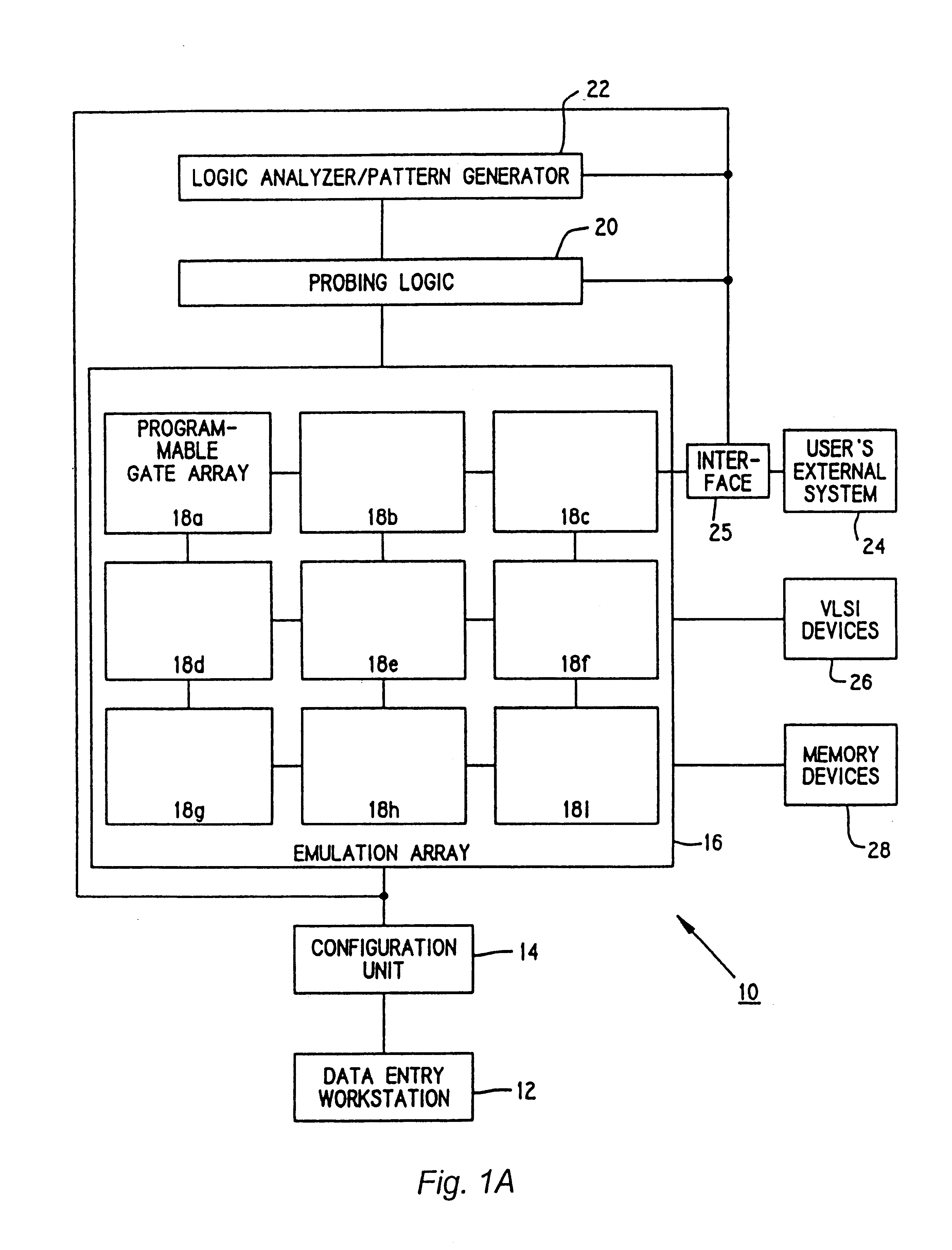

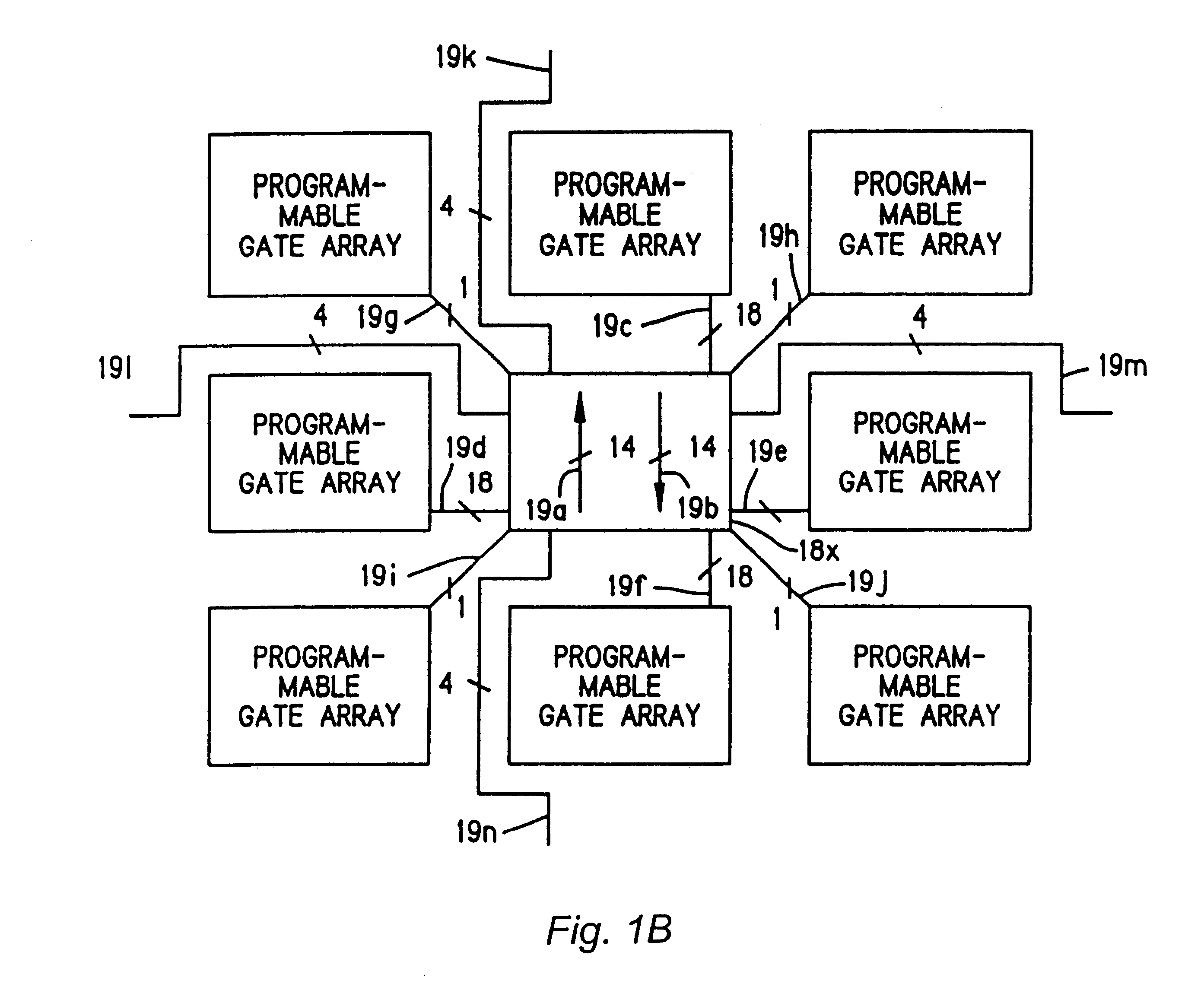

Apparatus for emulation of electronic hardware system

InactiveUS6377911B1Resistance/reactance/impedenceElectronic circuit testingSystem configurationWorkstation

A system for physical emulation of electronic circuits or systems includes a data entry workstation where a user may input data representing the circuit or system configuration. This data is converted to a form suitable for programming an array of programmable gate elements provided with a richly interconnected architecture. Provision is made for externally connecting VLSI devices or other portions of a user's circuit or system. A network of internal probing interconnections is made available by utilization of unused circuit paths in the programmable gate arrays.

Owner:QUICKTURN DESIGN SYST

System and Method for Packet Coalescing in Virtual Channels of a Data Processing System in a Multi-Tiered Full-Graph Interconnect Architecture

InactiveUS20090063817A1Improve communication performanceHighly-configurableError prevention/detection by using return channelGeneral purpose stored program computerData processing systemOriginal data

A method, computer program product, and system are provided for packet coalescing in virtual channels of a data processing system. A first processor bundles original data to be transmitted to a destination processor, the original data provided by a first source processor. The first processor transmits the bundle of data to a second processor along a path to the destination processor. The second processor determines if the second processor has additional data destined for the same destination processor, the additional data being provided by a second source processor that is different from the first source processor. Responsive to the second processor having additional data, the second processor unbundles the original data, adds the additional data to the original data, and rebundles the data along with the additional data. Then the second processor transmits the rebundled data to at least one other processor along the path to the destination processor.

Owner:IBM CORP

System and Method for Direct/Indirect Transmission of Information Using a Multi-Tiered Full-Graph Interconnect Architecture

InactiveUS20090063728A1Improve communication performanceImprove productivityGeneral purpose stored program computerData switching by path configurationTelecommunications linkCommunication link

A method, computer program product, and system are provided for transmitting data in a data network. A first processor of the data network receives data to be transmitted to a second processor within the data network. A determination is made if the data has previously been routed through an indirect communication link from a source processor, the indirect communication link being a communication link that does not directly couple the source processor to a final destination processor which is to receive the data. A communication link is selected over which to transmit the data from the first processor to the second processor based on results of determining if the data has previously been routed through an indirect communication link. Finally, the data is transmitted from the first processor to the second processor using the selected communication link.

Owner:IBM CORP

Programmable asynchronous pipeline arrays

ActiveUS20050077918A1Improve data throughputEfficient implementationSolid-state devicesLogic circuits using elementary logic circuit componentsComputer scienceInterconnect architecture

High-performance, highly pipelined asynchronous FPGAs employ a very fine-grain pipelined logic block and routing interconnect architecture. These FPGAs, which do not use a clock to sequence computations, automatically “self-pipeline” their logic without the designer needing to be explicitly aware of all pipelining details. The FPGAs include arrays of logic blocks or cells that include function units, conditional units and other elements, each of which is constructed using basic asynchronous pipeline stages, such as a weak condition half buffer and a precharge half buffer.

Owner:CORNELL RES FOUNDATION INC +1

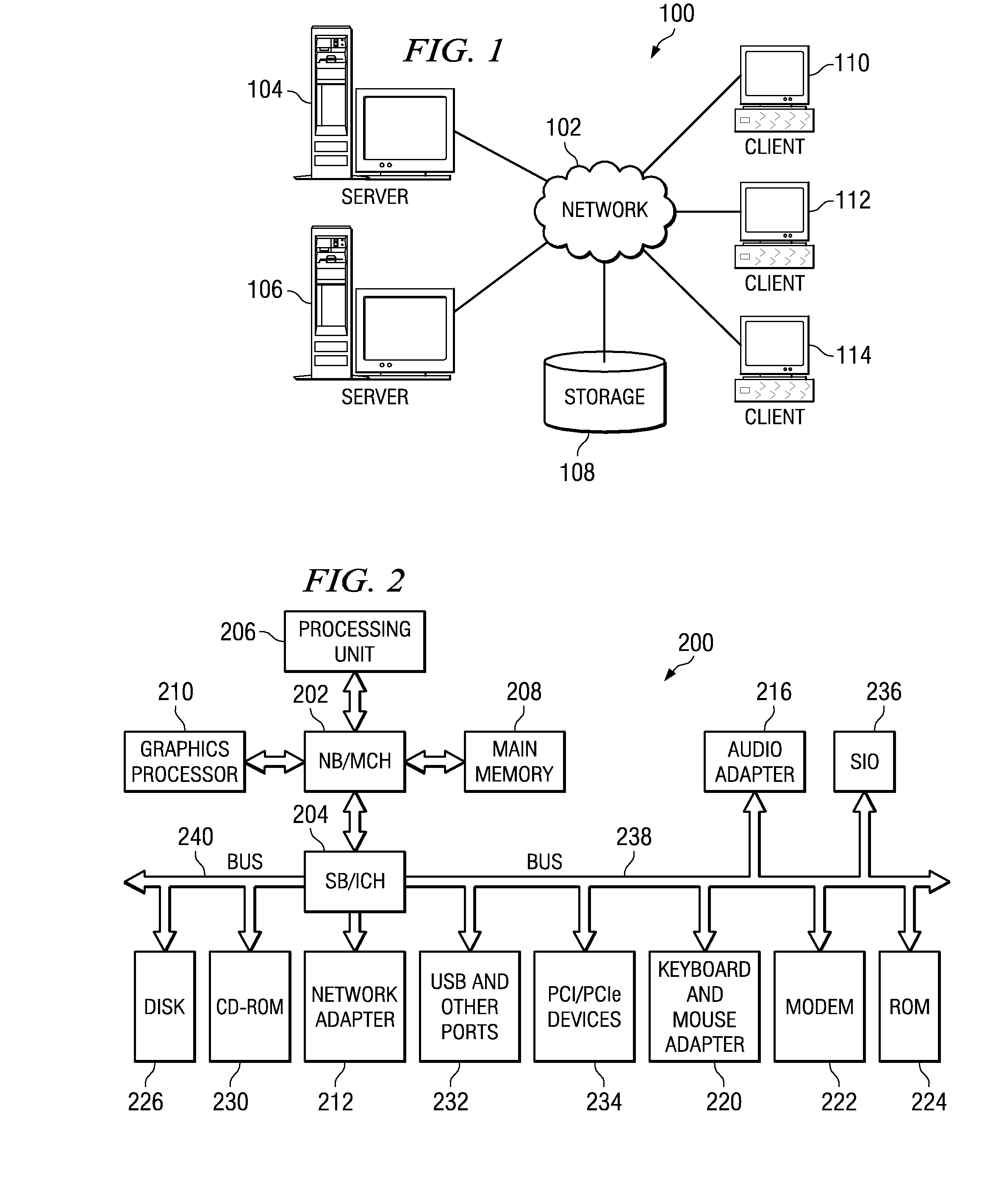

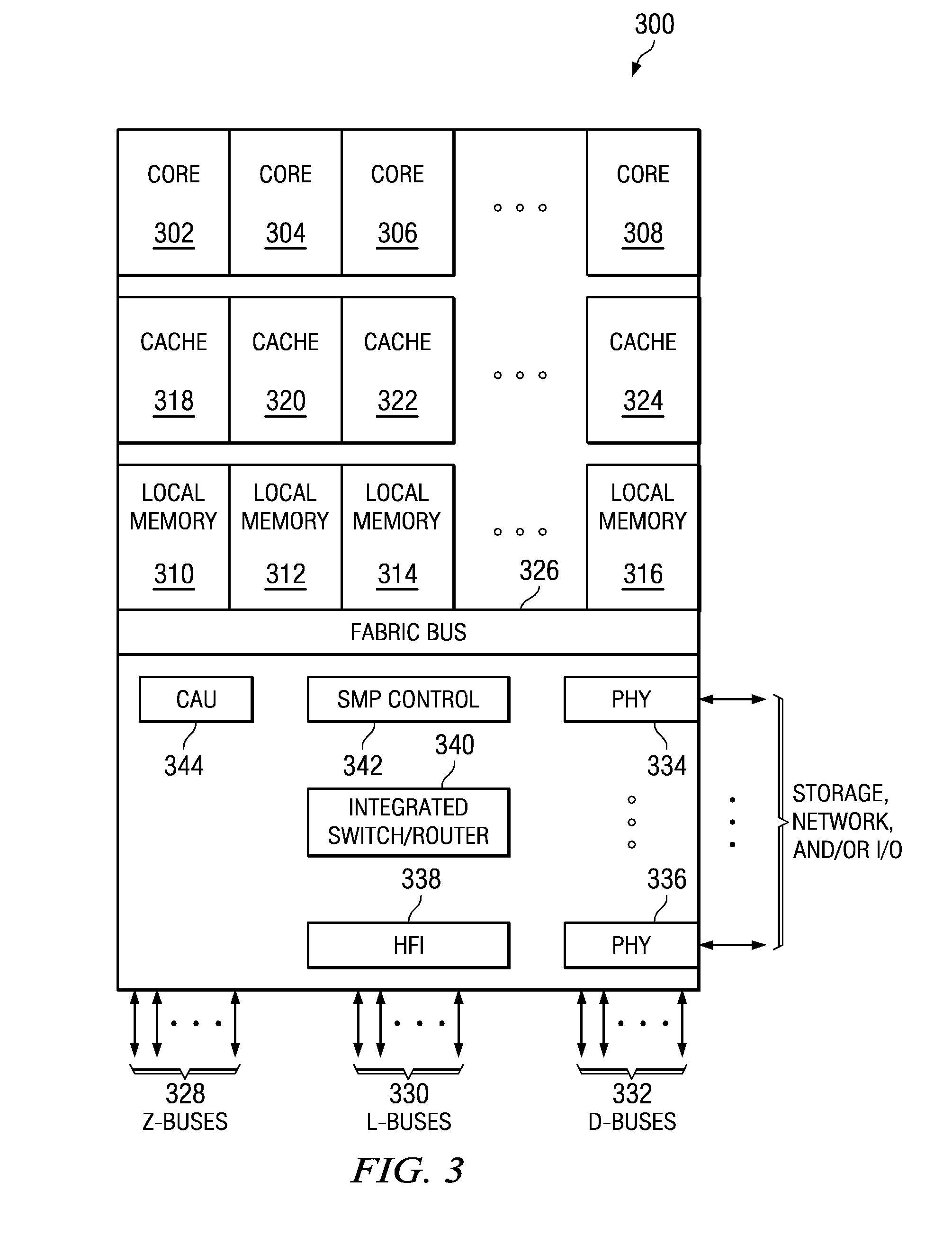

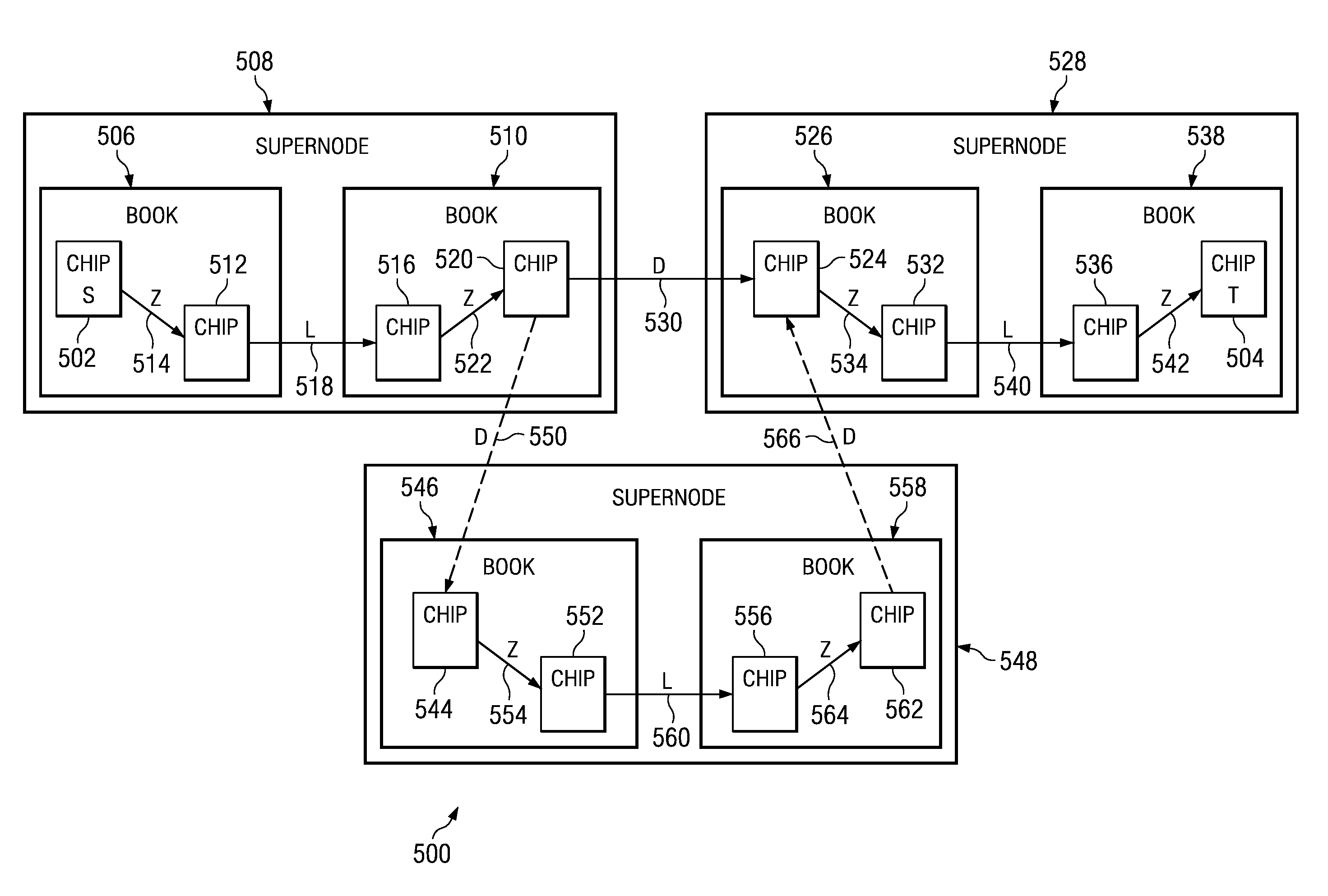

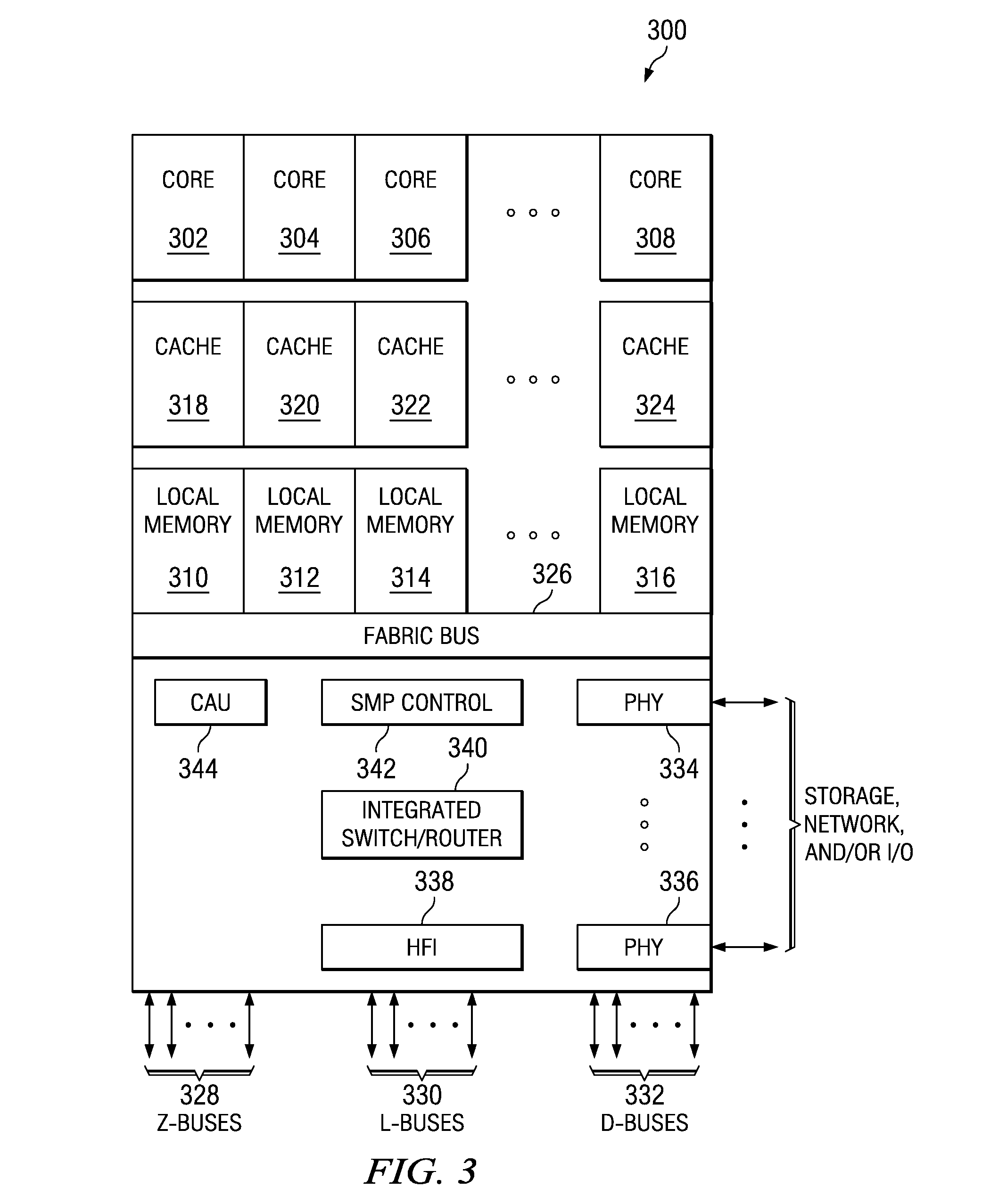

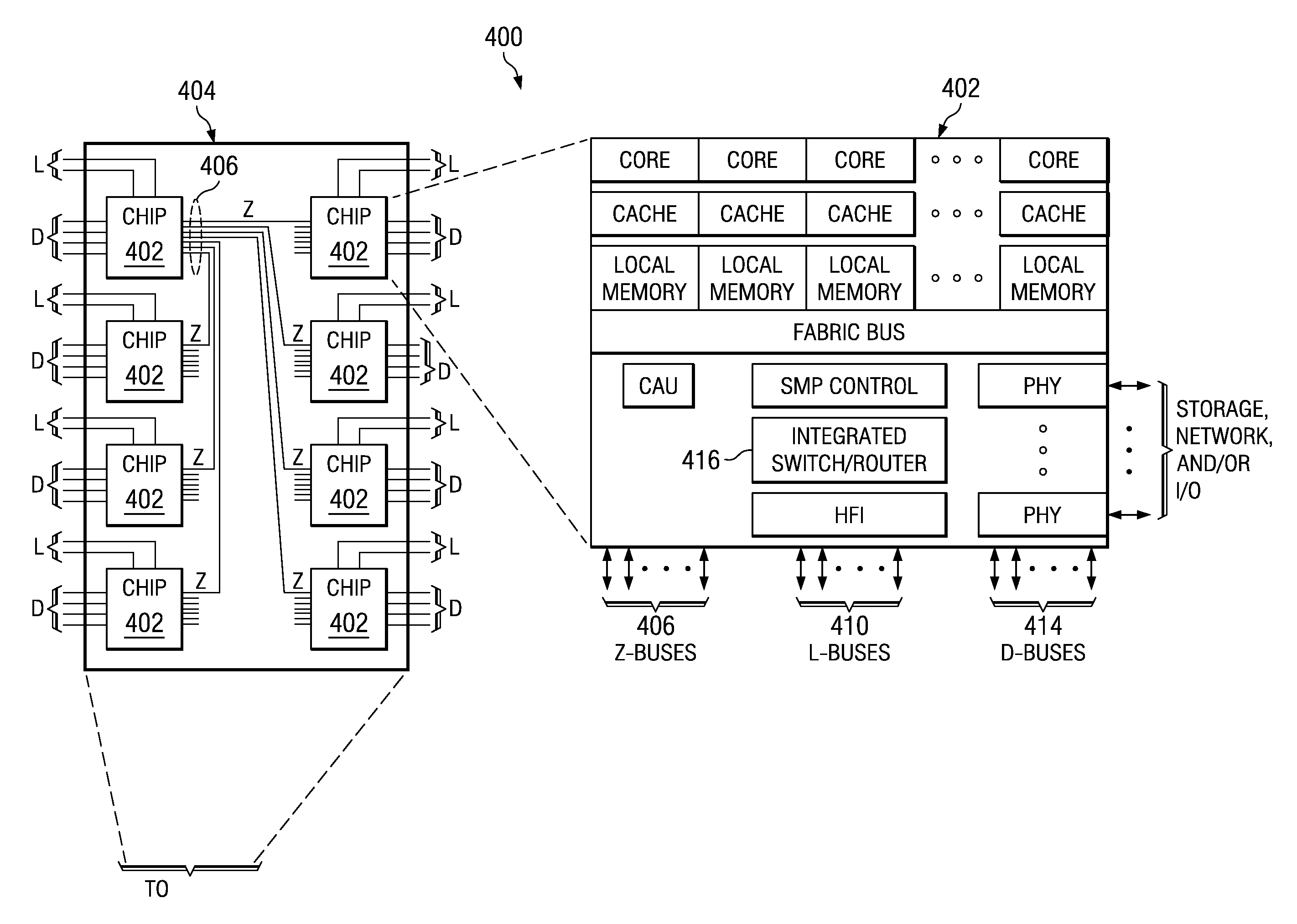

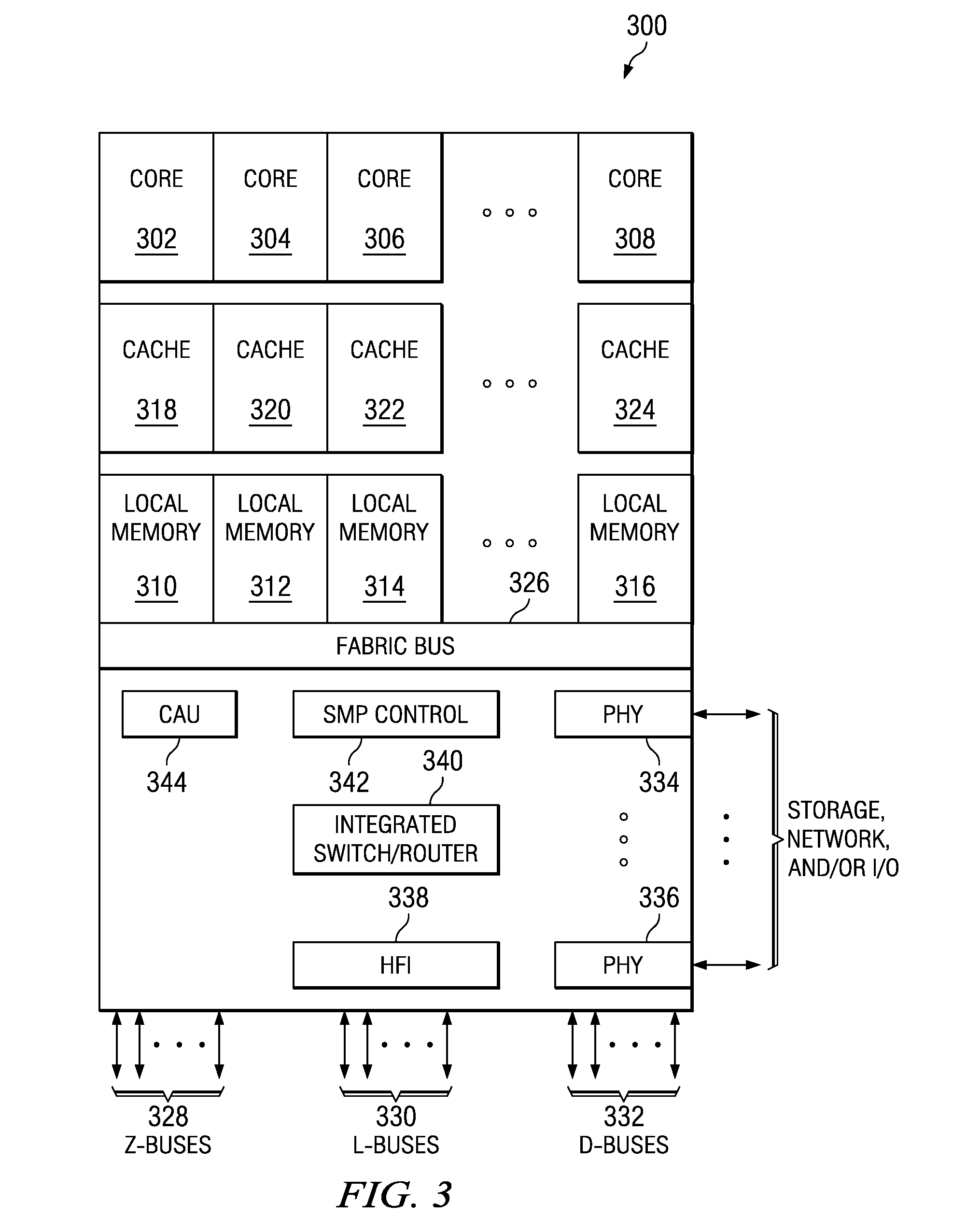

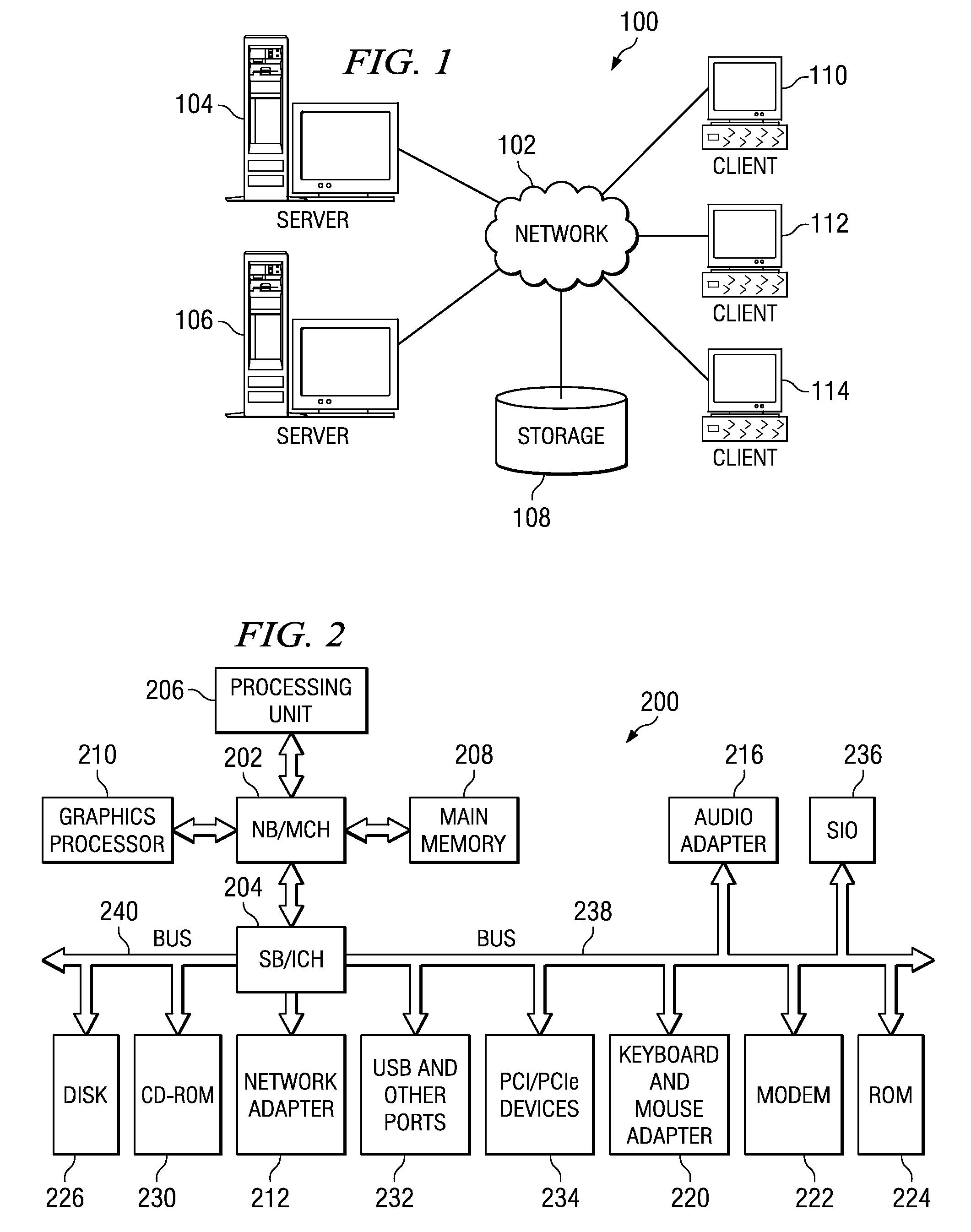

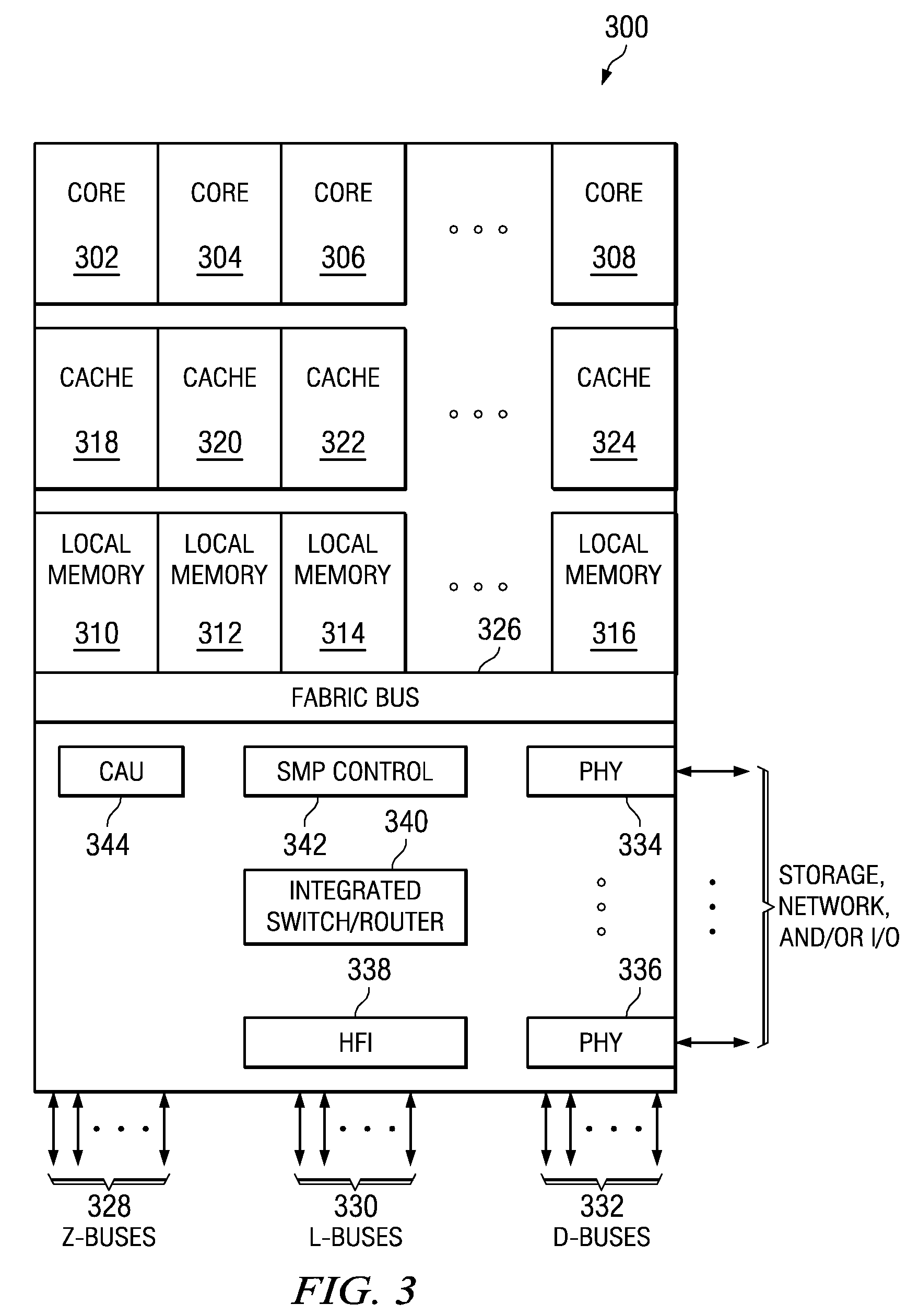

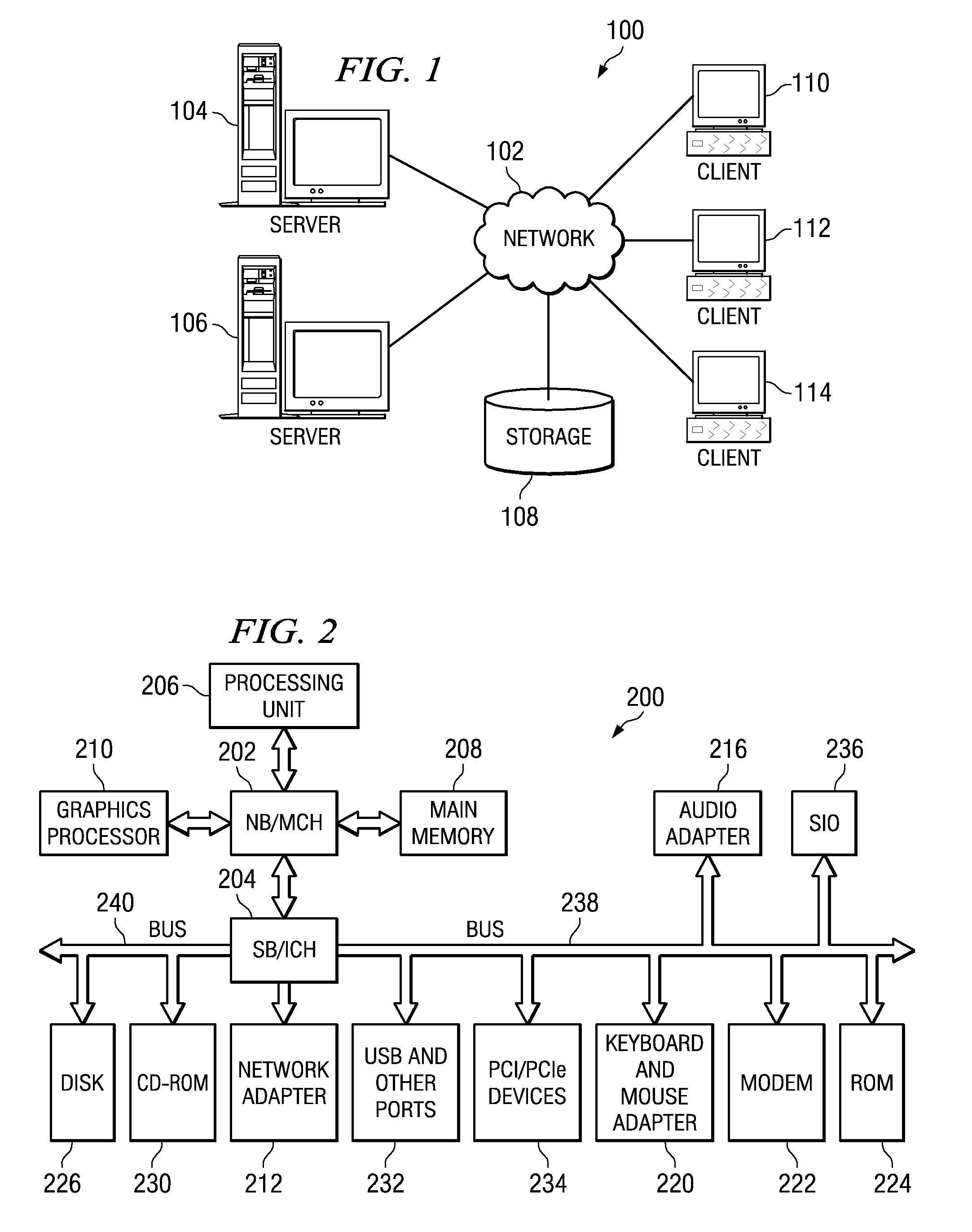

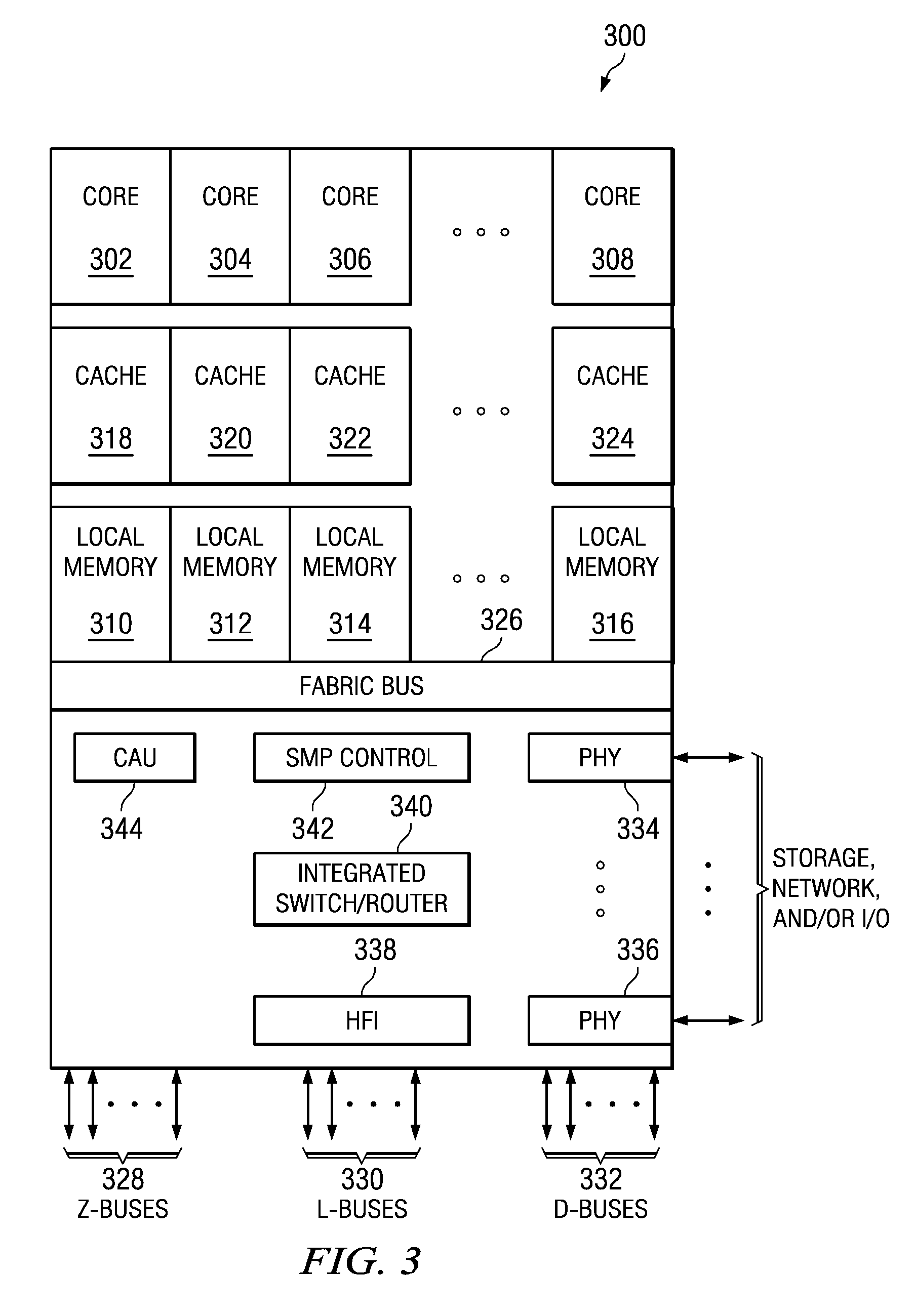

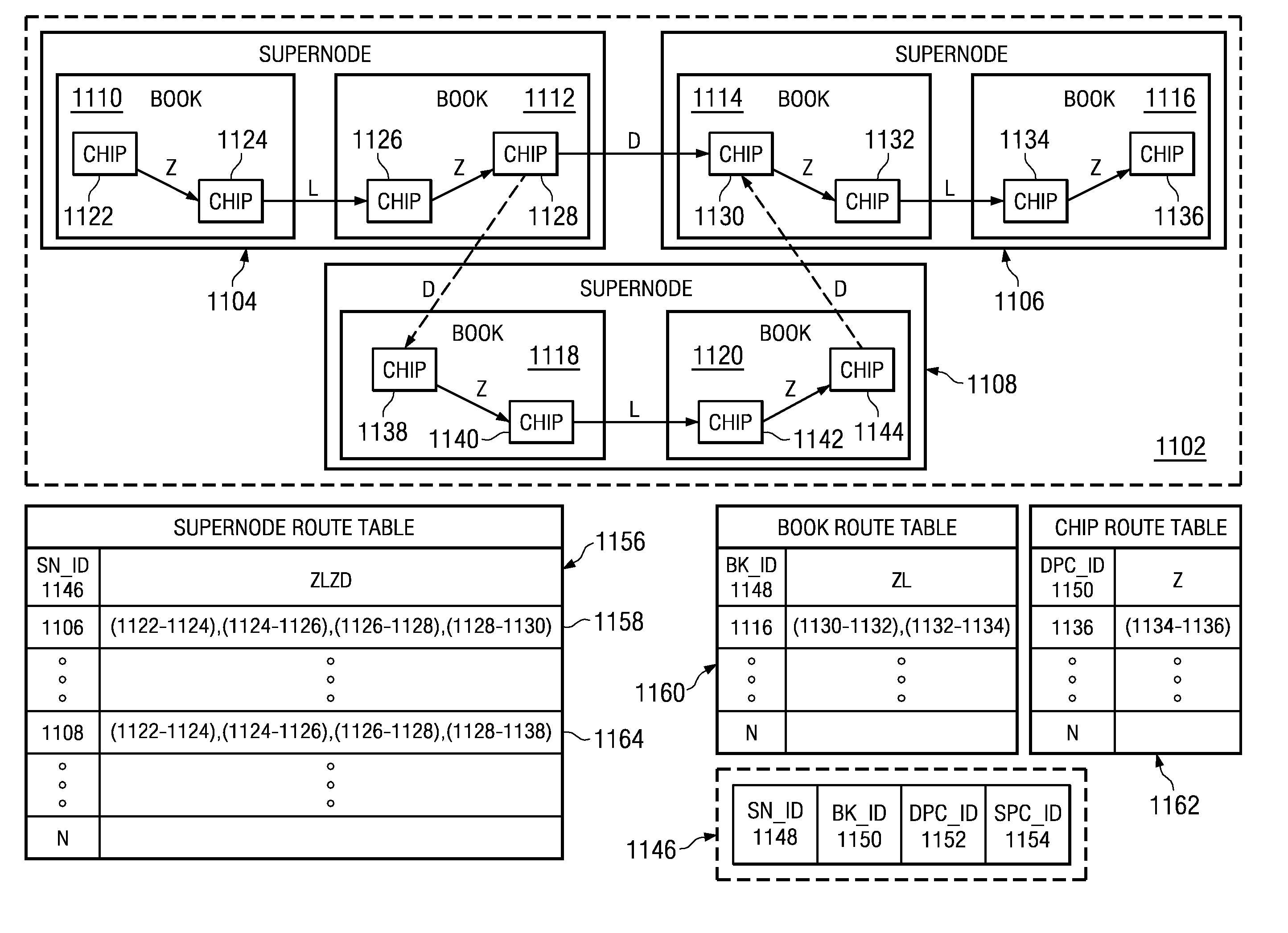

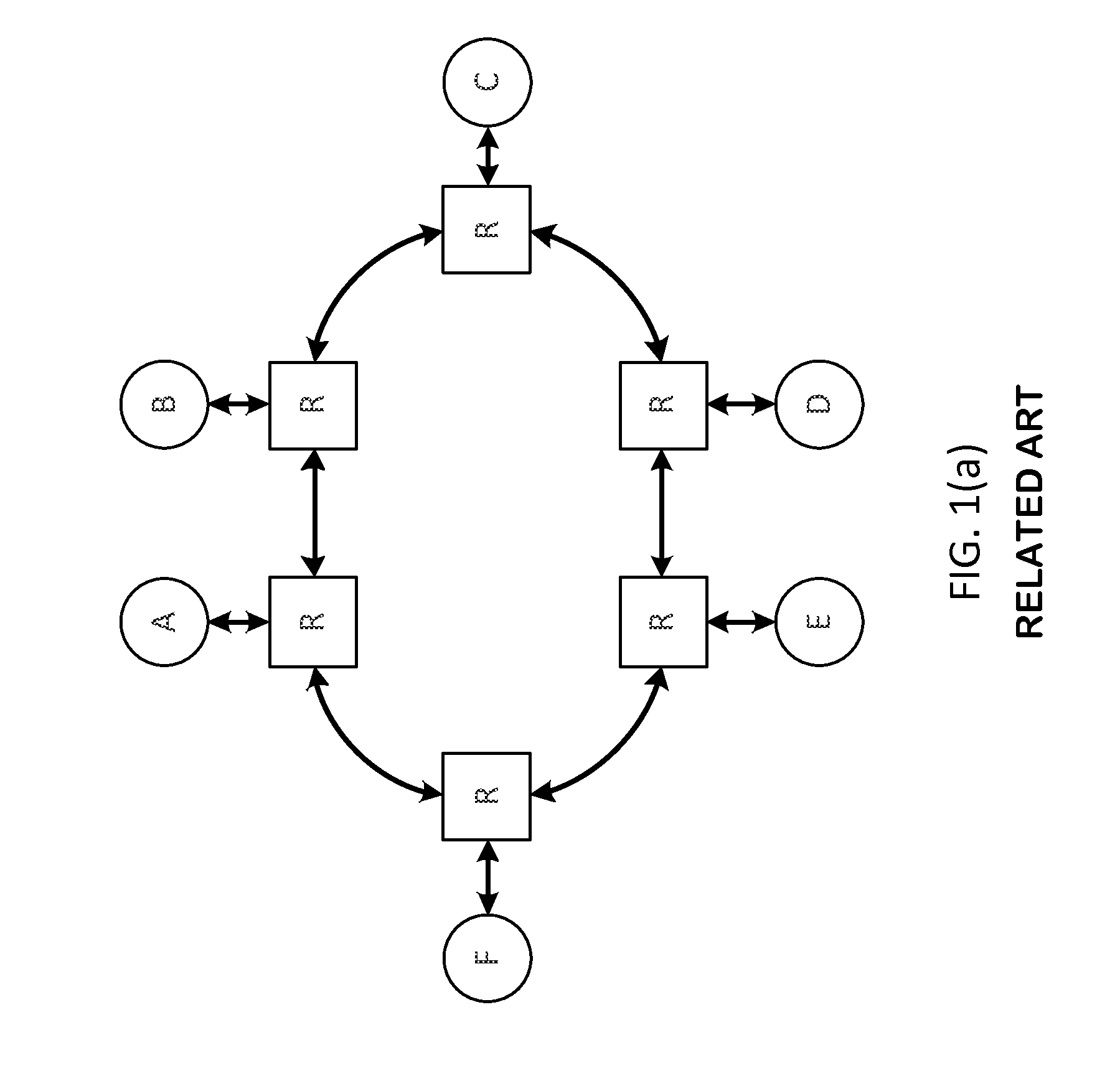

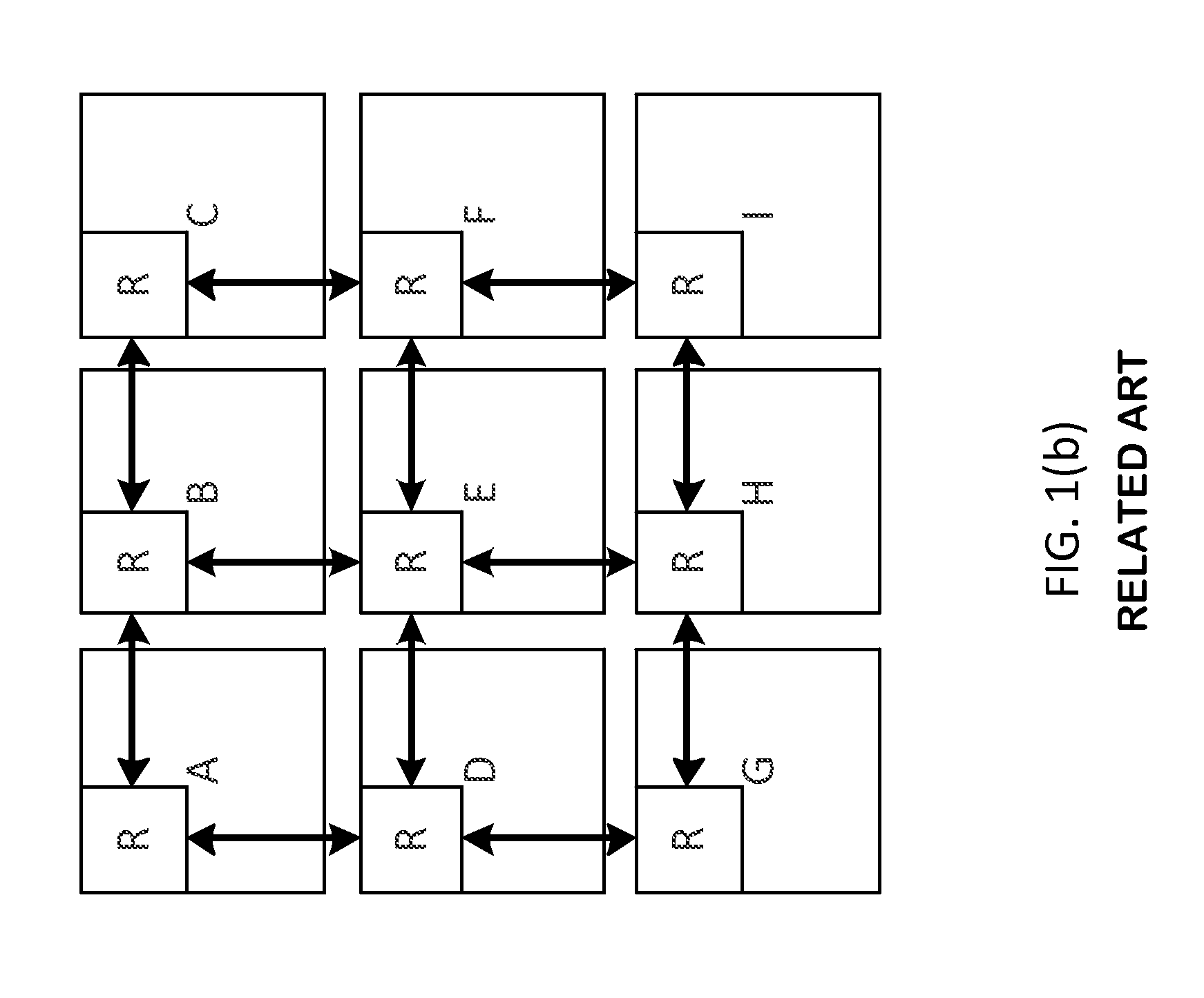

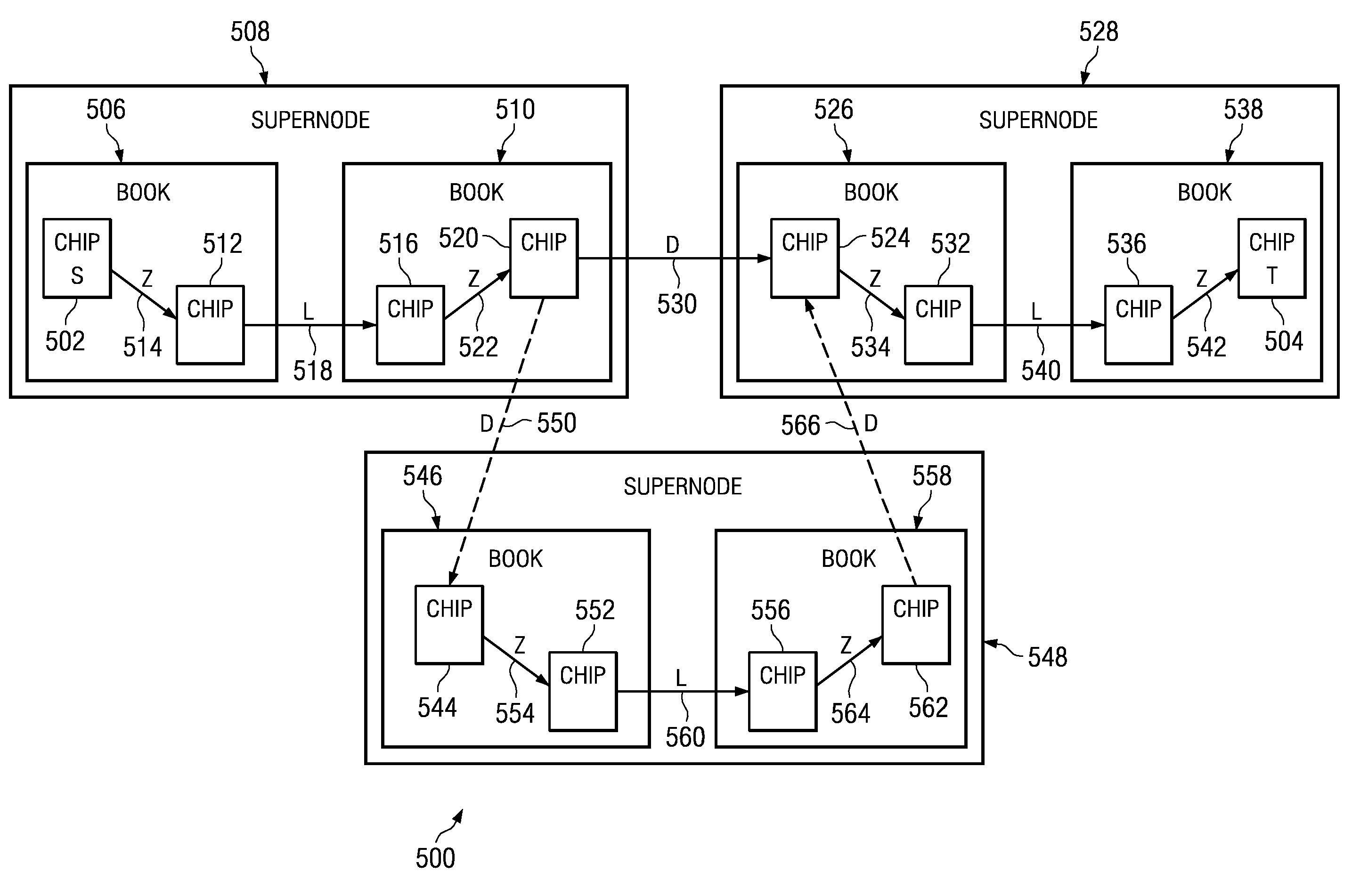

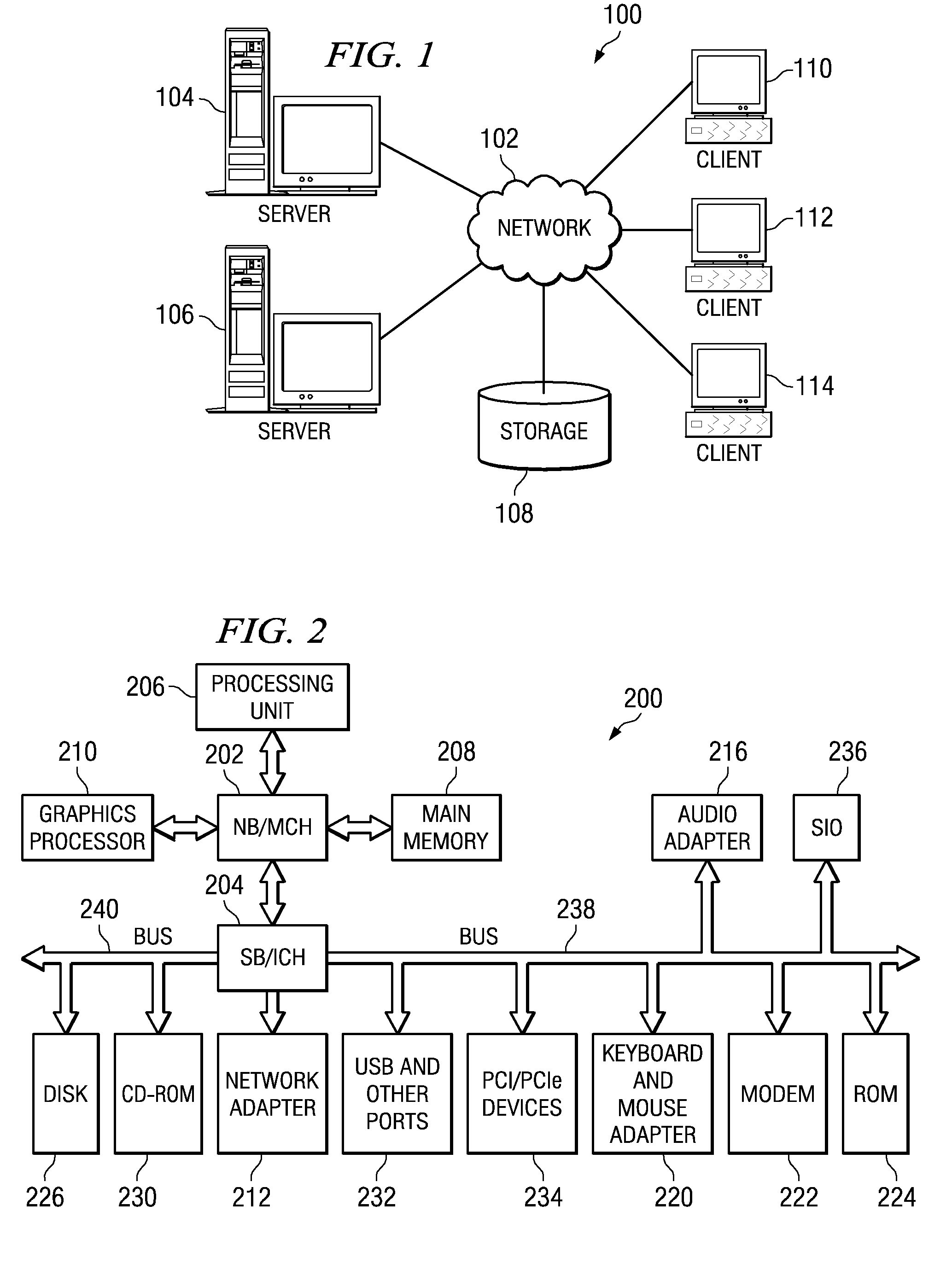

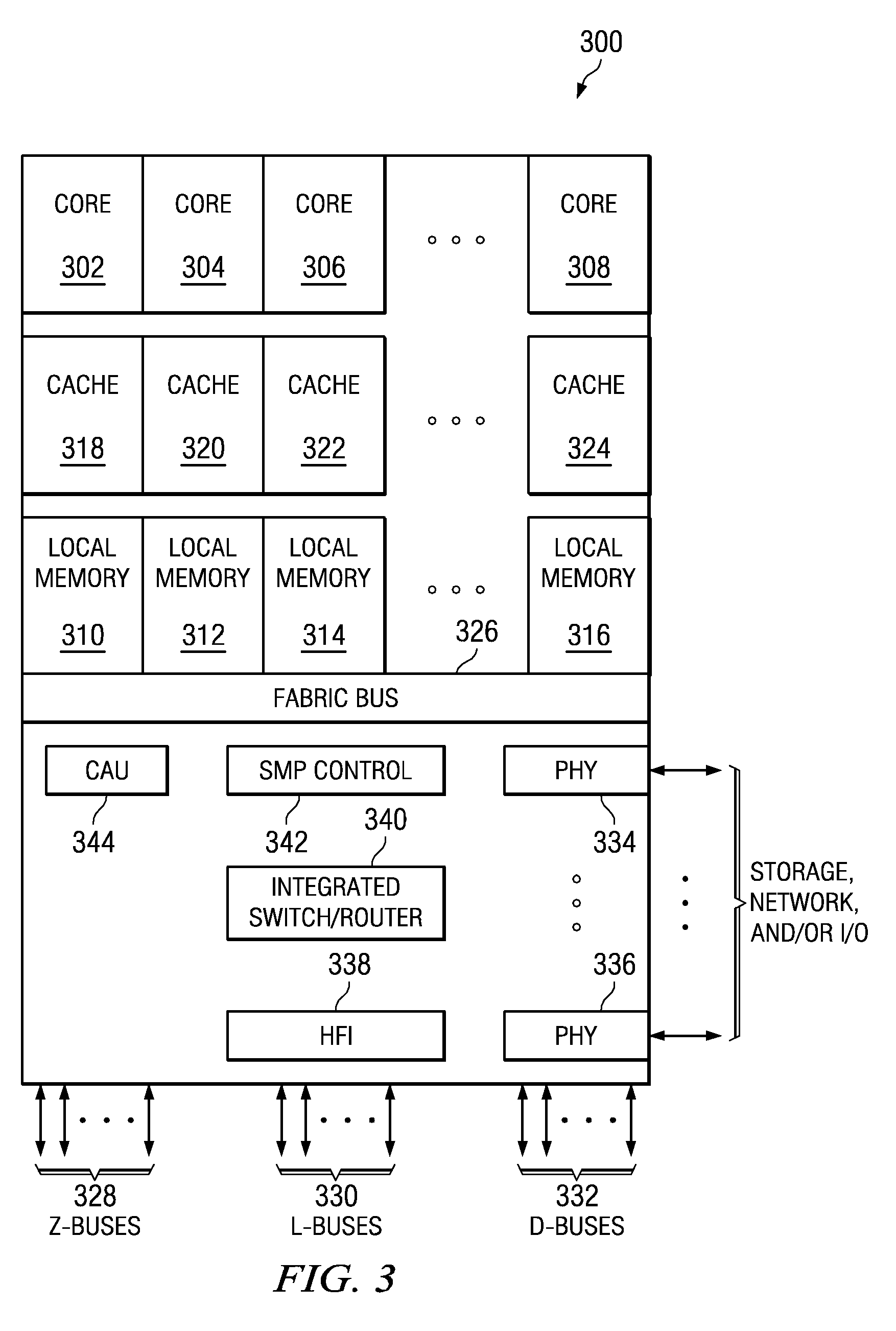

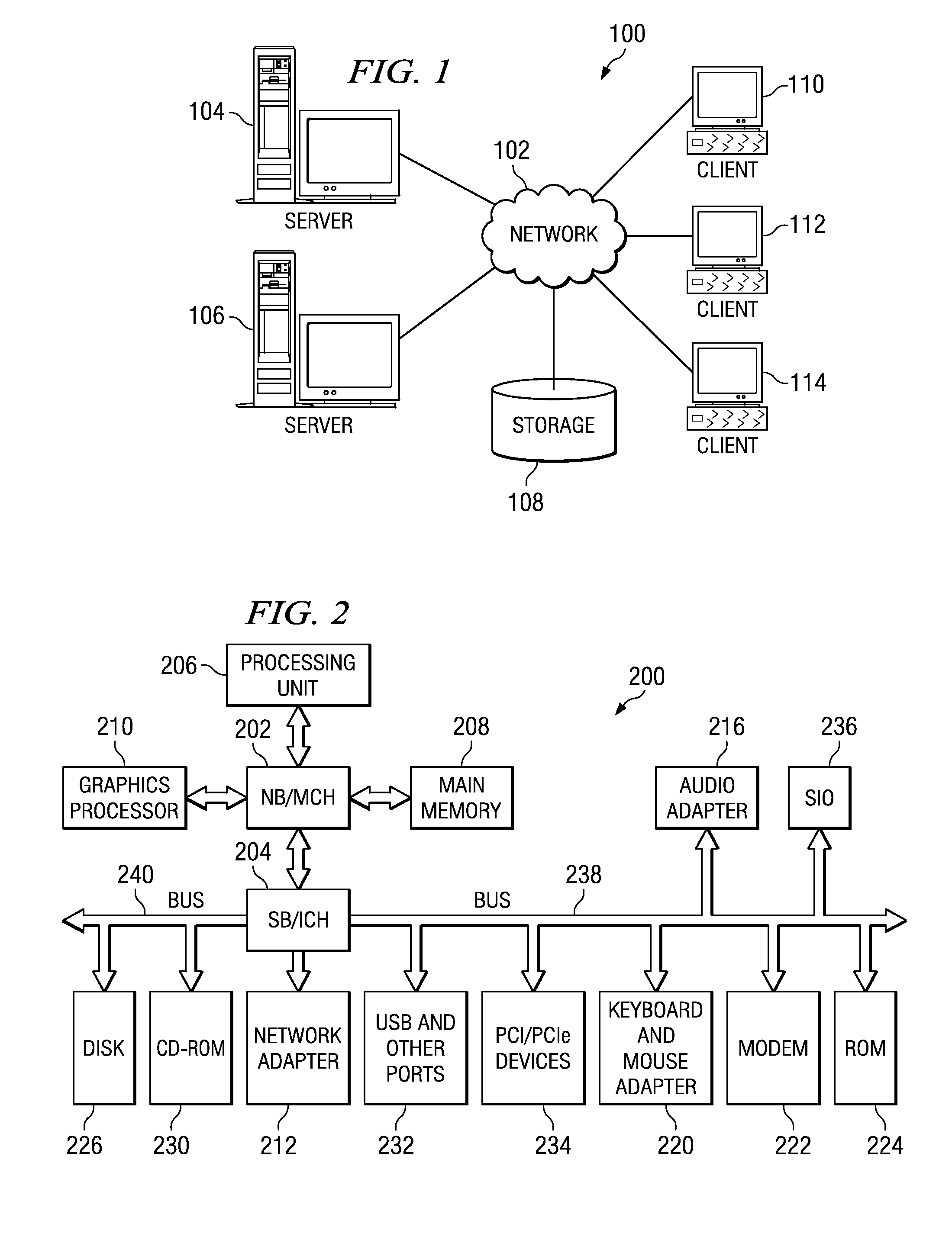

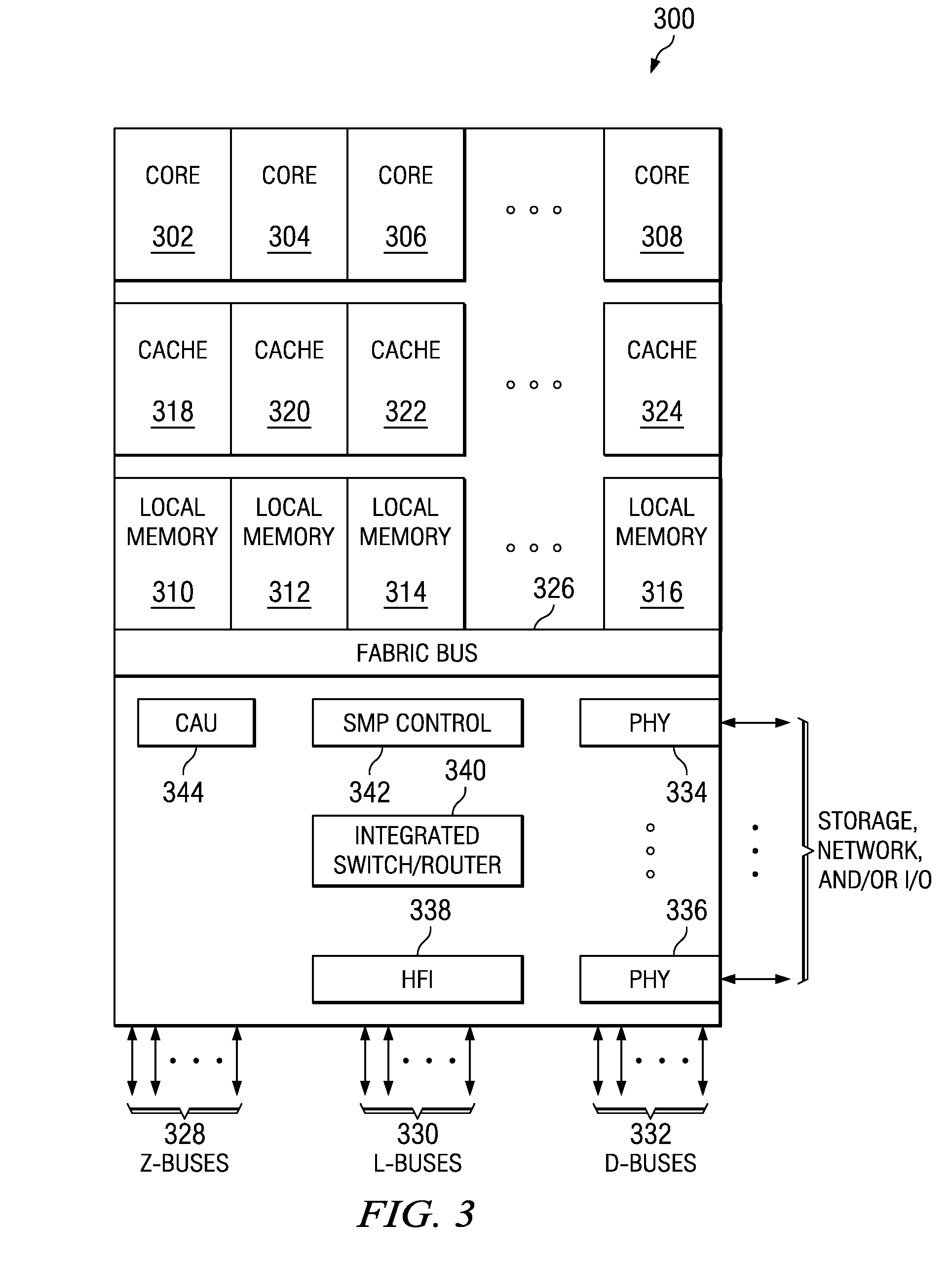

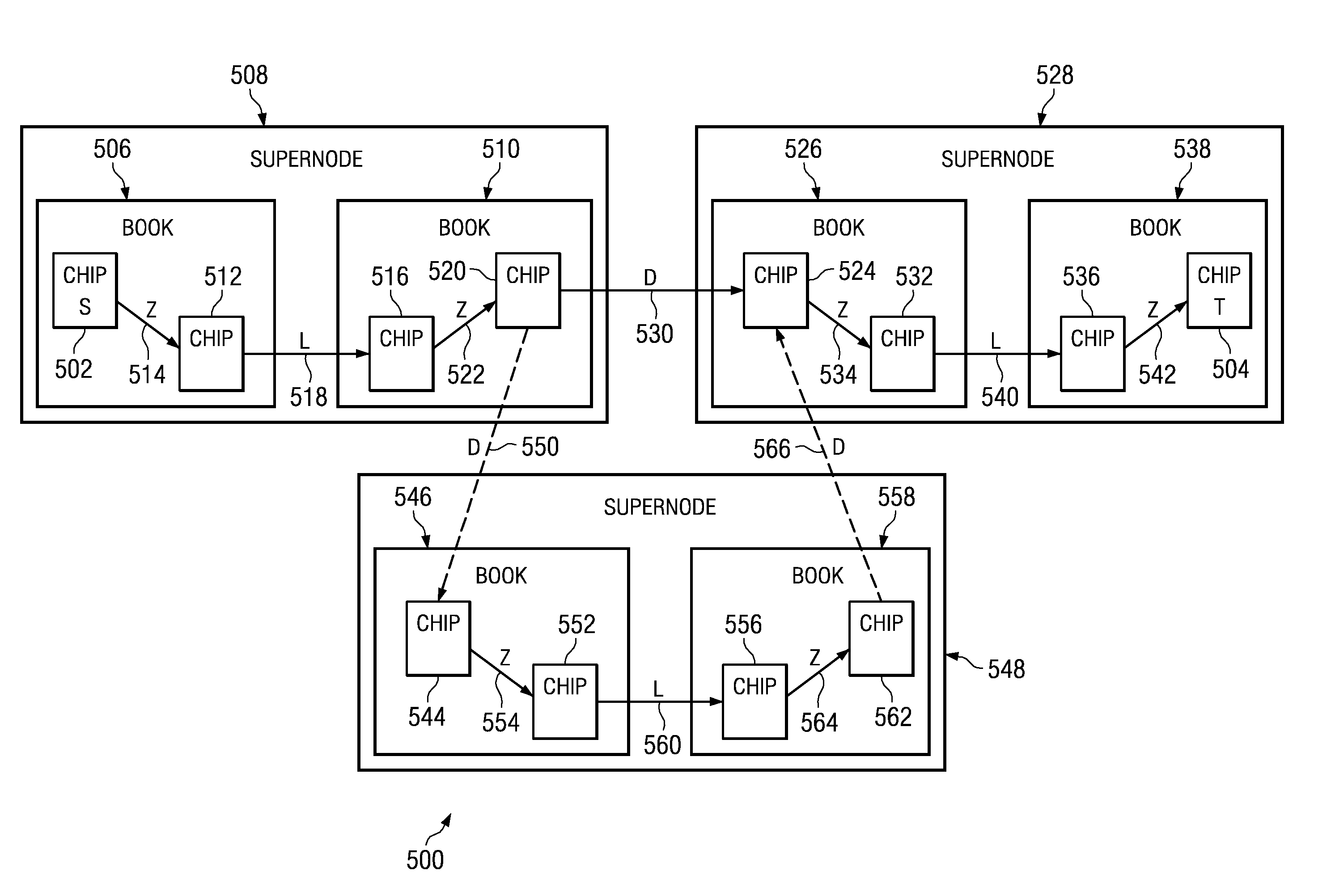

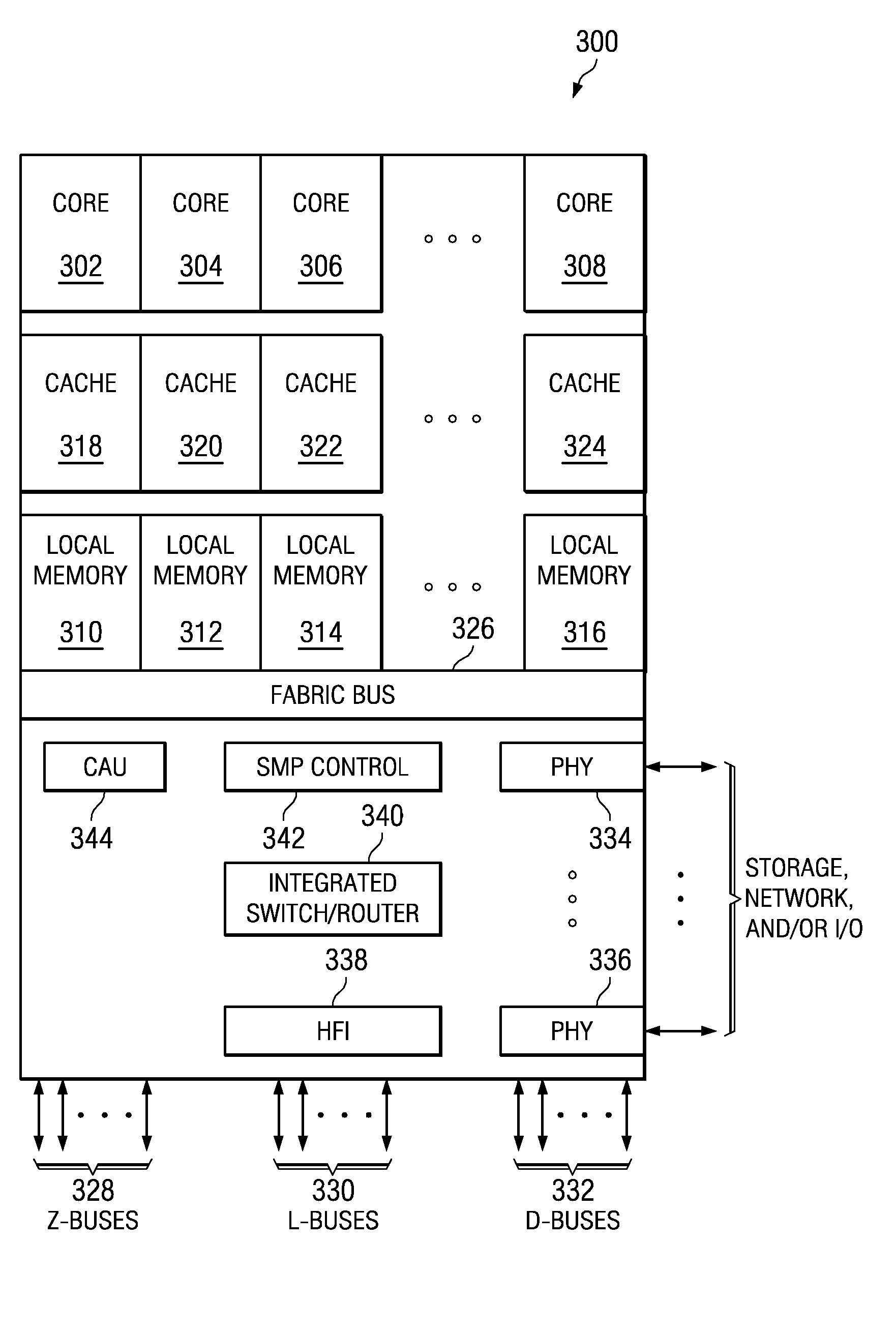

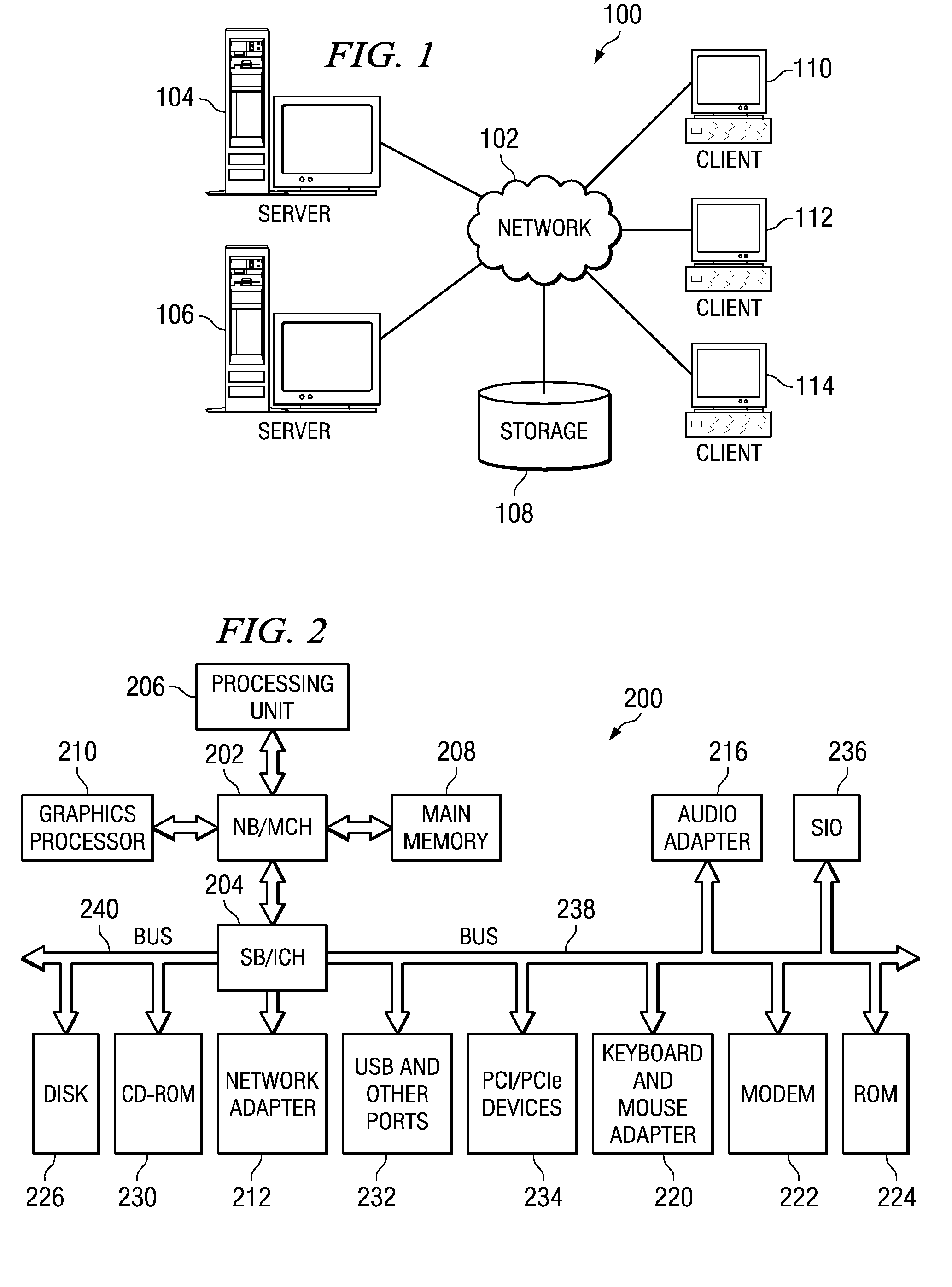

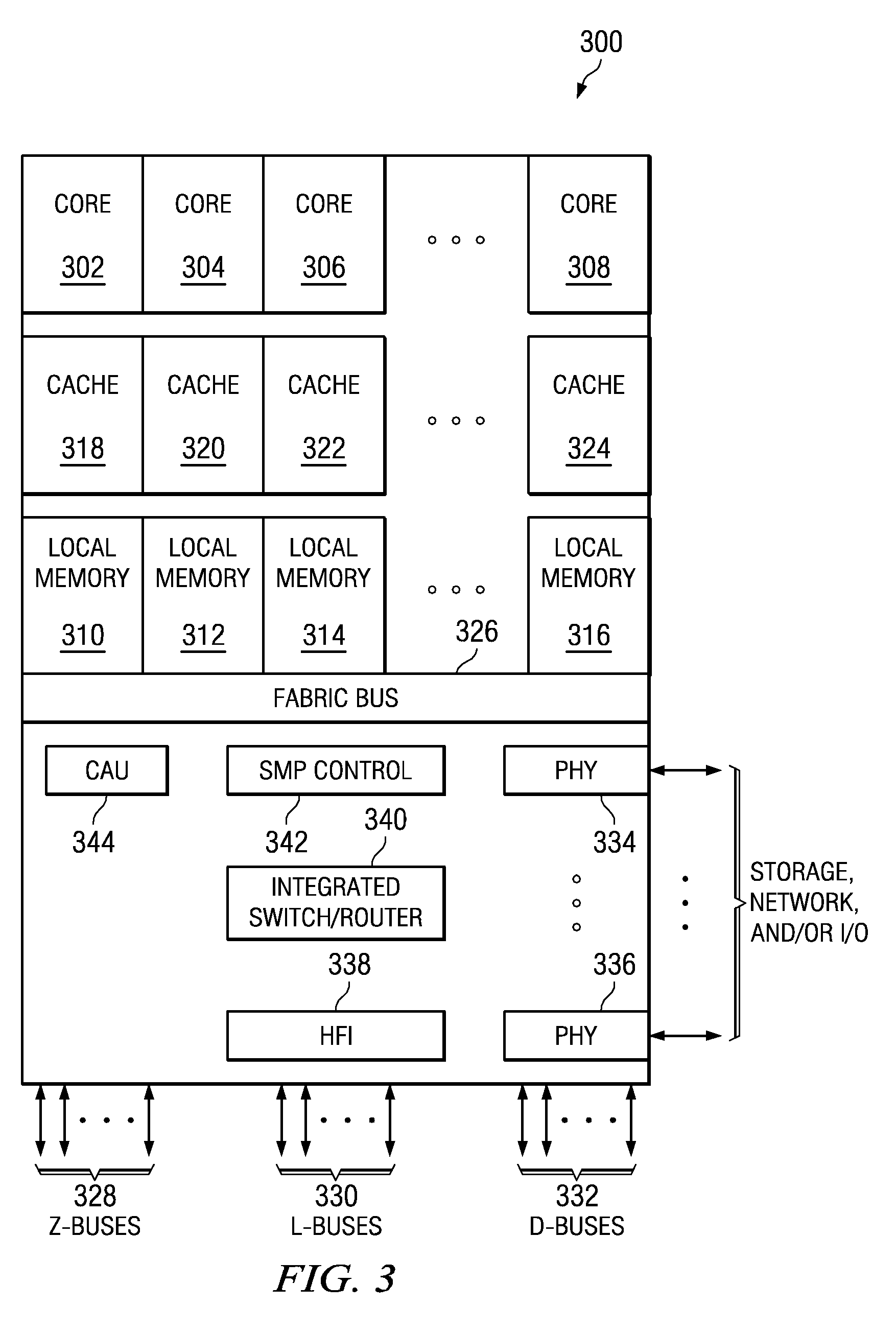

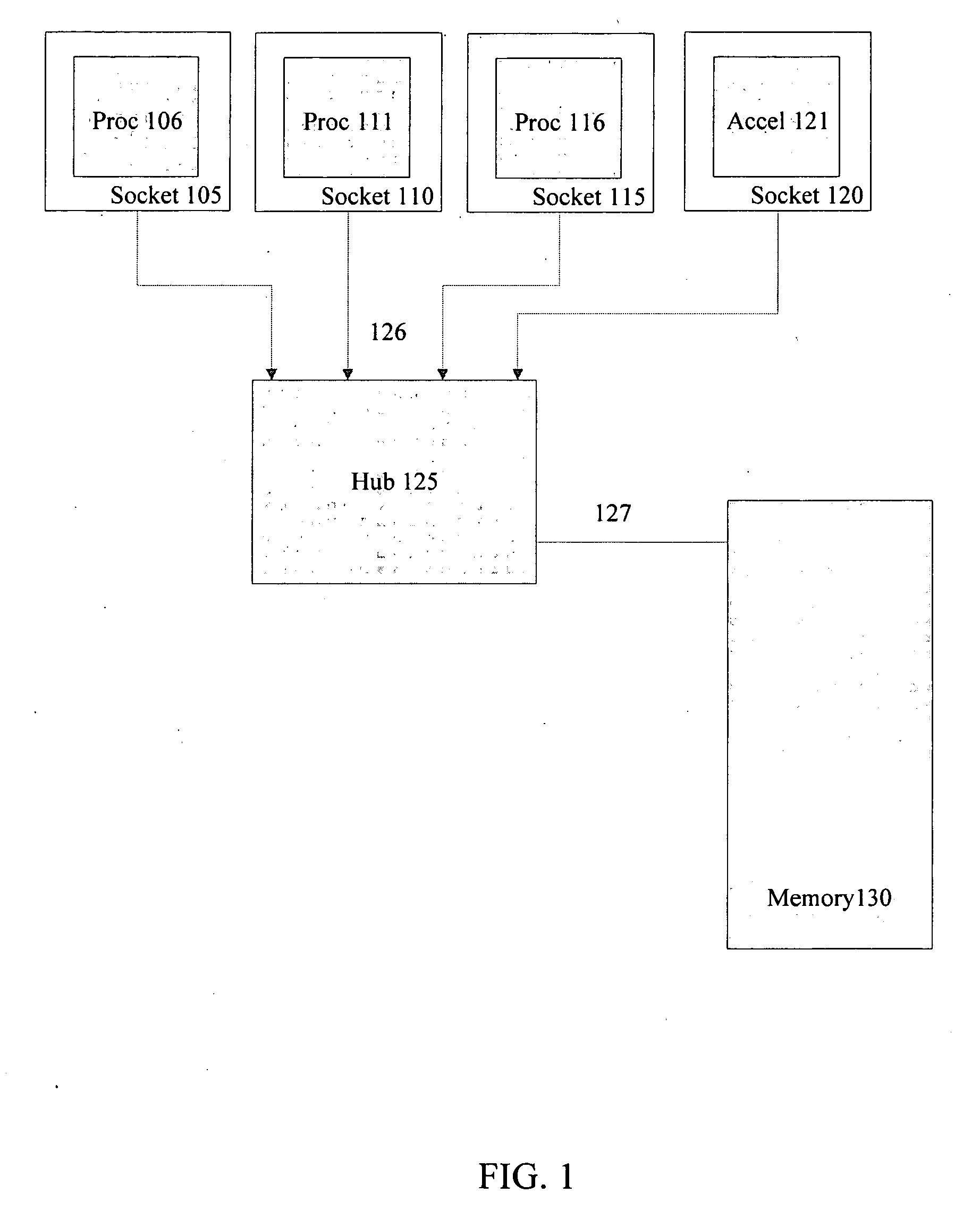

System for Data Processing Using a Multi-Tiered Full-Graph Interconnect Architecture

InactiveUS20090063811A1Improve communication performanceHighly-configurableMultiple digital computer combinationsArchitecture with multiple processing unitsParallel computingInterconnect architecture

A system is provided for implementing a multi-tiered full-graph interconnect architecture. In order to implement a multi-tiered full-graph interconnect architecture, a plurality of processors are coupled to one another to create a plurality of processor books. The plurality of processor books are coupled together to create a plurality of supernodes. Then, the plurality of supernodes are coupled together to create the multi-tiered full-graph interconnect architecture. Data is then transmitted from one processor to another within the multi-tiered full-graph interconnect architecture based on an addressing scheme that specifies at least a supernode and a processor book associated with a target processor to which the data is to be transmitted.

Owner:IBM CORP

Method for Data Processing Using a Multi-Tiered Full-Graph Interconnect Architecture

InactiveUS20090064139A1Improve communication performanceImprove productivityGeneral purpose stored program computerMultiprogramming arrangementsComputer architectureInterconnect architecture

A method is provided for implementing a multi-tiered full-graph interconnect architecture. In order to implement a multi-tiered full-graph interconnect architecture, a plurality of processors are coupled to one another to create a plurality of processor books. The plurality of processor books are coupled together to create a plurality of supernodes. Then, the plurality of supernodes are coupled together to create the multi-tiered full-graph interconnect architecture. Data is then transmitted from one processor to another within the multi-tiered full-graph interconnect architecture based on an addressing scheme that specifies at least a supernode and a processor book associated with a target processor to which the data is to be transmitted.

Owner:IBM CORP

Packet coalescing in virtual channels of a data processing system in a multi-tiered full-graph interconnect architecture

InactiveUS8108545B2Improve communication performanceHighly-configurableError prevention/detection by using return channelGeneral purpose stored program computerData processing systemNetwork packet

Owner:INT BUSINESS MASCH CORP

Conductor-within-a-via microwave launch

InactiveUS6937120B2Efficiency problemEffective expansionPrinted circuit aspectsHigh frequency circuit adaptationsElectrical conductorBand shape

A concentric ‘conductor within a via’ RF interconnect architecture, has an inner via through which at least one RF signal conductor passes. The inner conductive via is coaxially formed within and stably coaxially aligned within an outer conductive via, which serves as a coaxial ground plane that completely surrounds the inner conductive via. The outer conductive via passes through dielectric layers of microstrip or stripline structures on opposite sides of a multi printed circuit laminate.

Owner:NORTH SOUTH HLDG

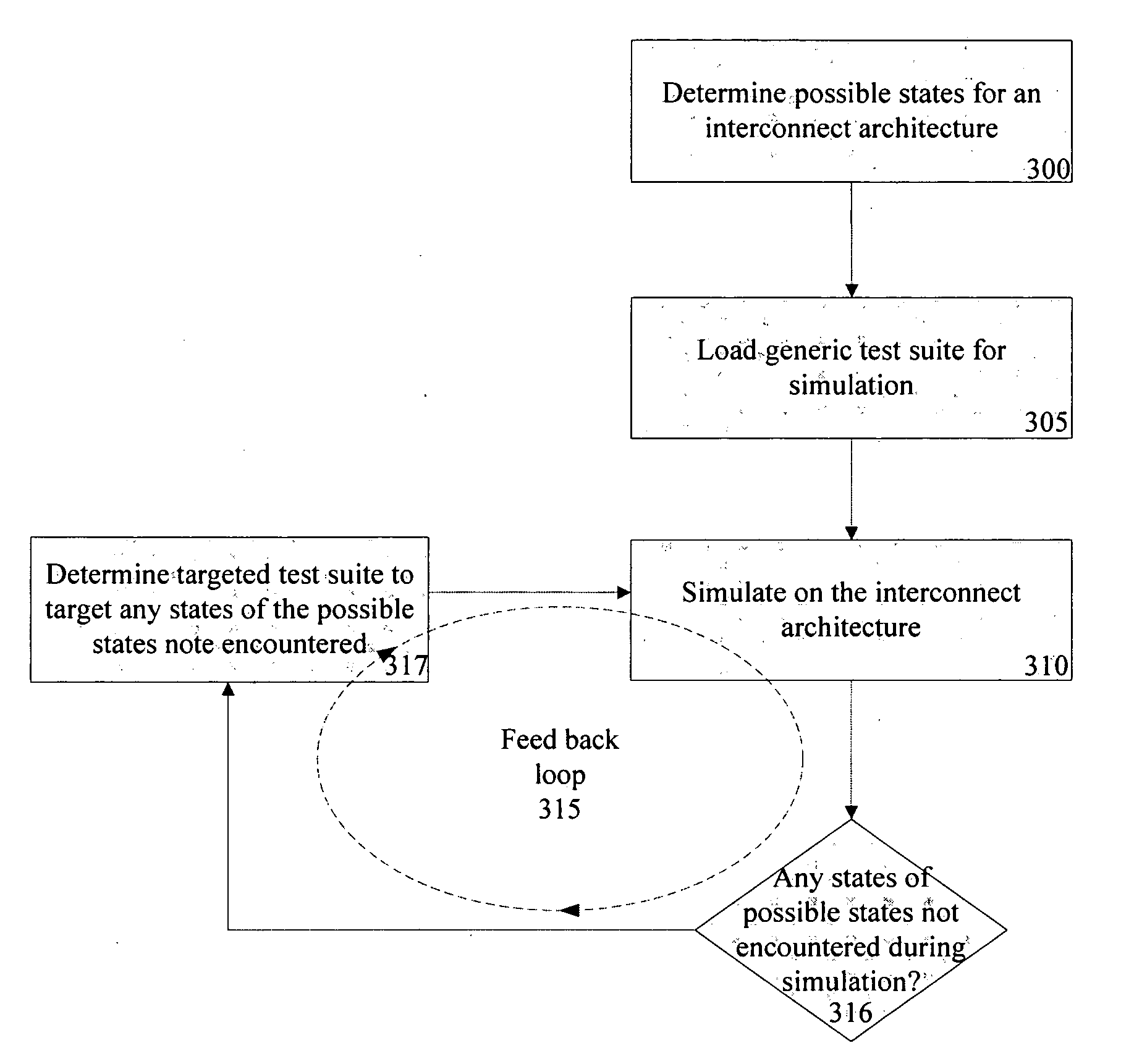

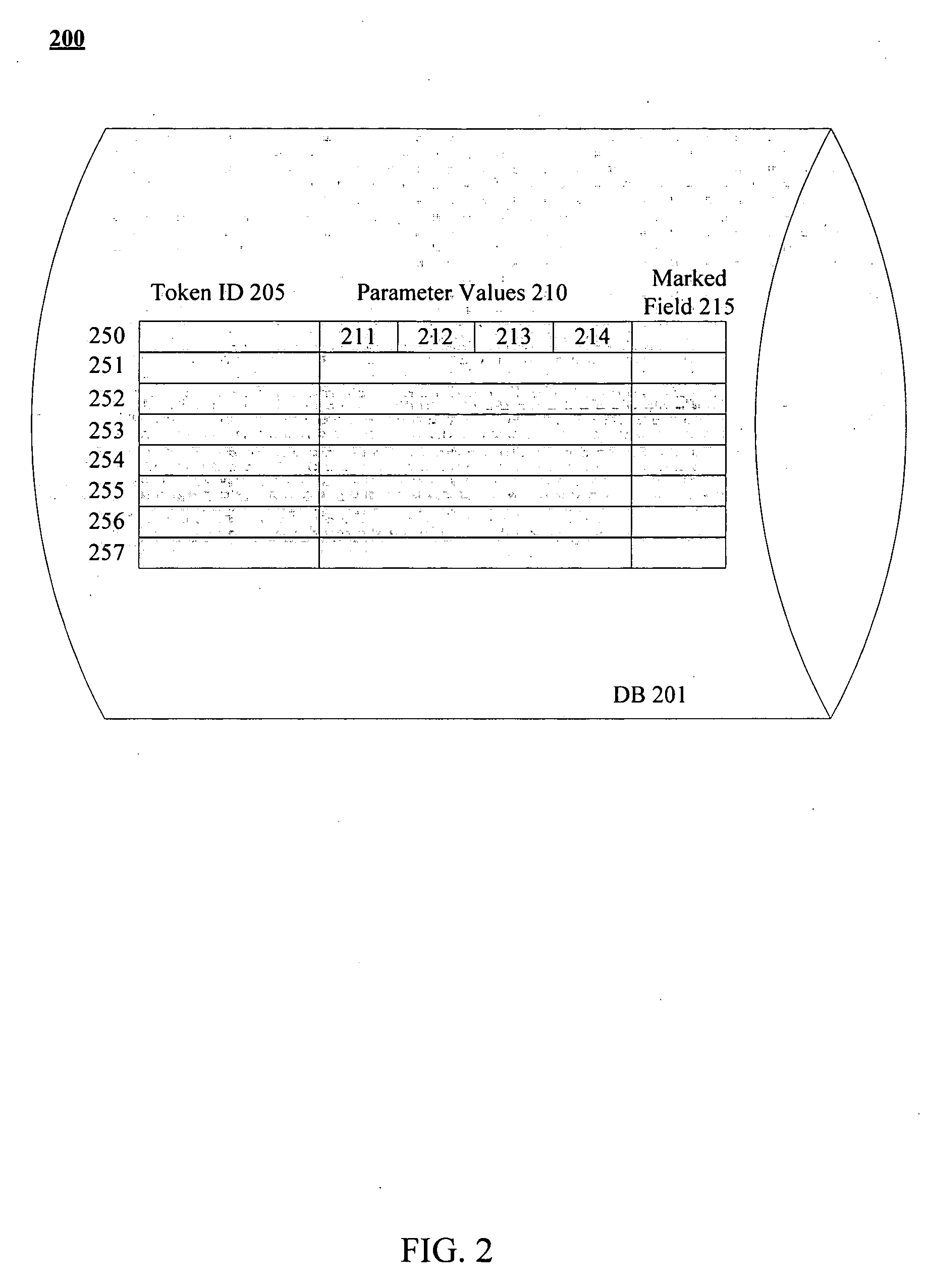

Interconnect architectural state coverage measurement methodology

InactiveUS20090171647A1CAD circuit designSpecial data processing applicationsTest suiteSimulation based

A method and apparatus for ensuring efficient validation coverage of an architecture, such as protocol or interconnect architecture, is herein described. A coverage space of states for an architecture is generated and stored in a database. During simulation, states of the coverage space encountered are marked. From this, the states encountered and not encountered may be determined. Based on the states not encountered, a targeted test suite is developed to target at least some of the states not encountered during previous simulation. This feedback loop from simulation to refining of a test suite based on states of a coverage space not encountered during simulation may be recursively repeated until adequate validation, i.e. an adequate confidence level of validation, of the coverage space is achieved.

Owner:INTEL CORP

System and Method for Data Processing Using a Low-Cost Two-Tier Full-Graph Interconnect Architecture

InactiveUS20090198956A1Improve communication performanceHighly-configurableProgram controlTransmissionComputer architectureInterconnect architecture

A system and method are provided for implementing a two-tier full-graph interconnect architecture. In order to implement a two-tier full-graph interconnect architecture, a plurality of processors are coupled to one another to create a plurality of supernodes. Then, the plurality of supernodes are coupled together to create the two-tier full-graph interconnect architecture. Data is then transmitted from one processor to another within the two-tier full-graph interconnect architecture based on an addressing scheme that specifies at least a supernode and a processor chip identifier associated with a target processor to which the data is to be transmitted.

Owner:IBM CORP