Method for Providing a Cluster-Wide System Clock in a Multi-Tiered Full-Graph Interconnect Architecture

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

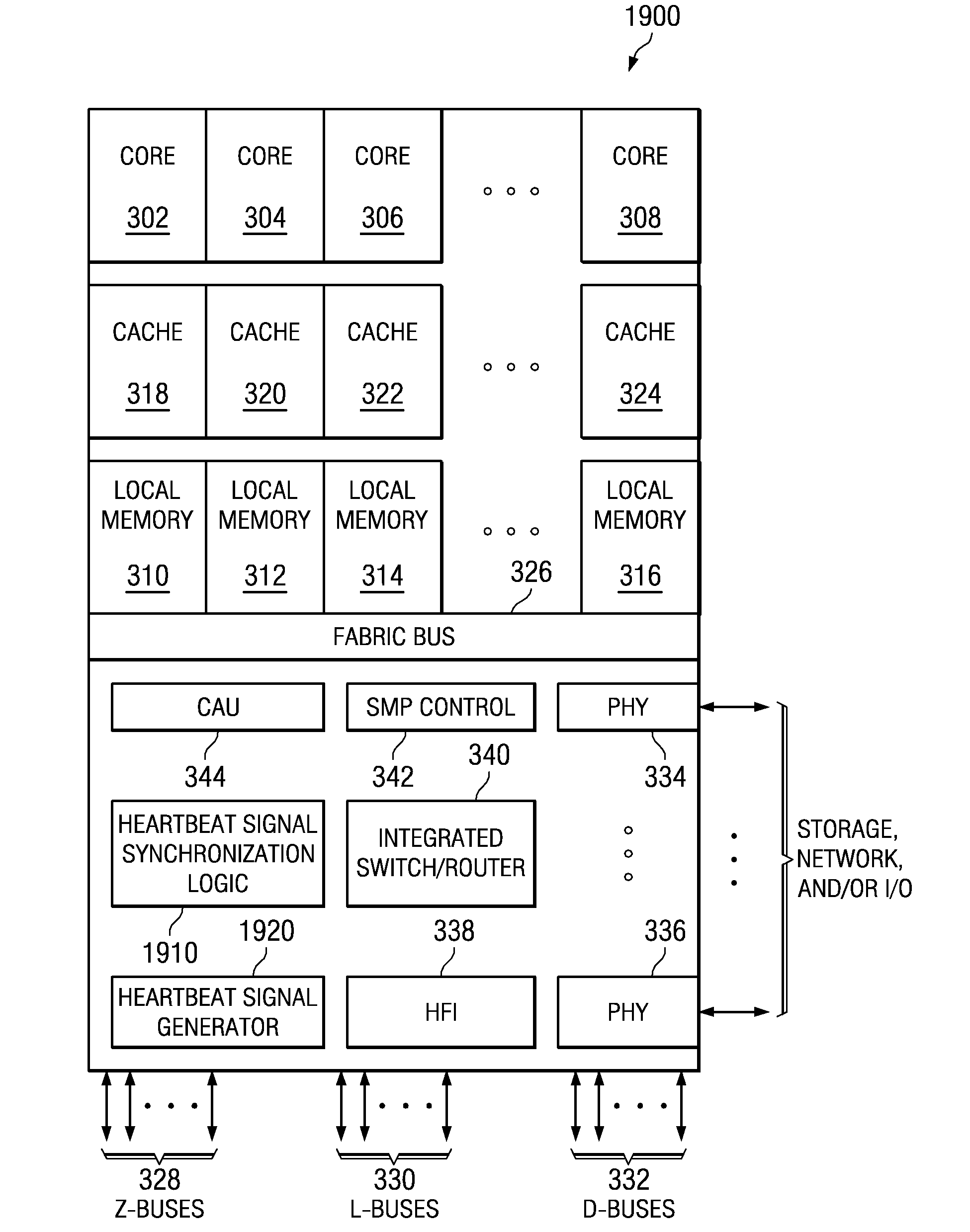

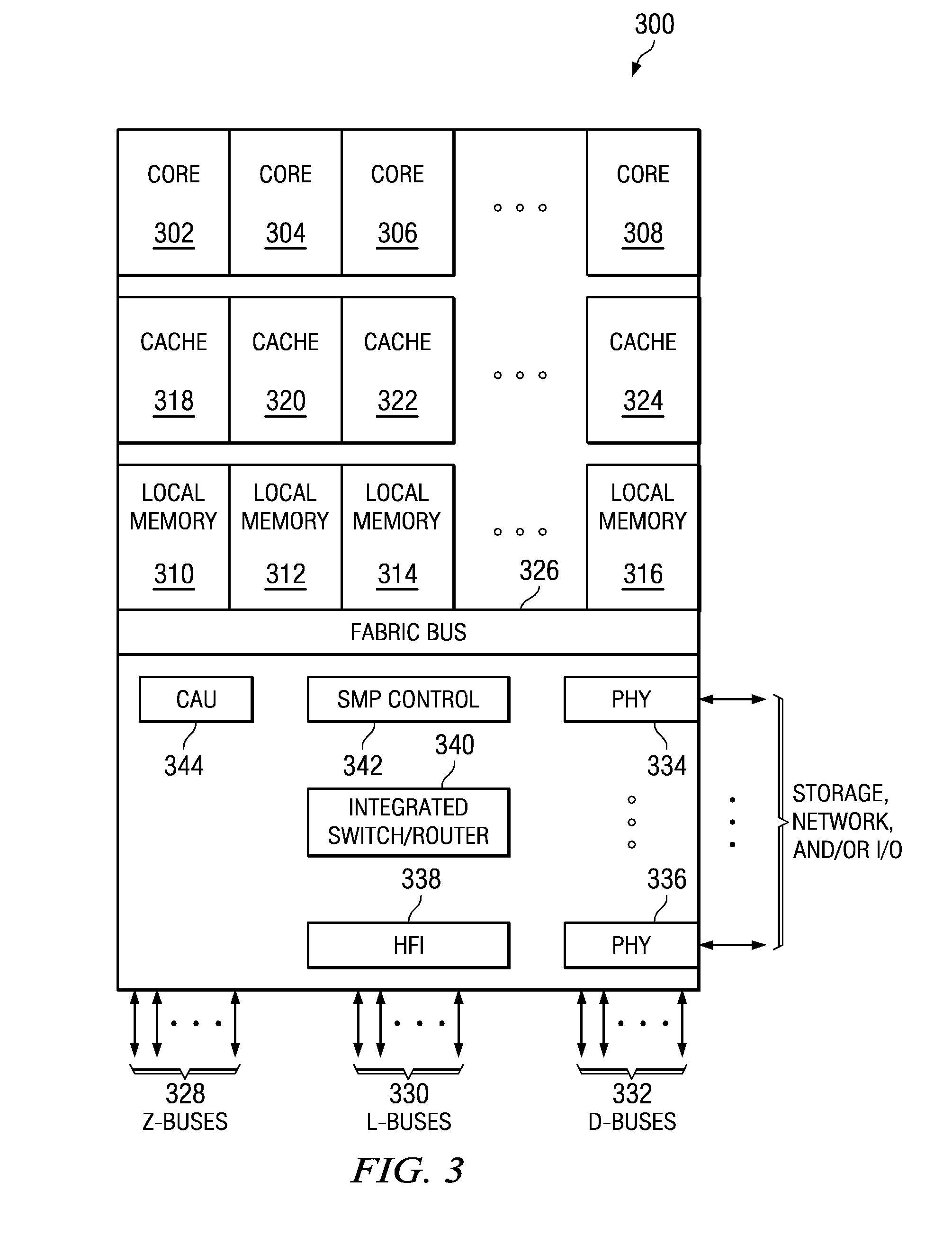

[0048]The illustrative embodiments provide an architecture and mechanisms for facilitating communication between processors, or nodes, collections of nodes, and supernodes. Furthermore, the illustrative embodiments provide routing mechanisms for routing communications directly or indirectly through the architecture and mechanisms for dynamic selection of indirect and / or direct routes through the architecture. Moreover, the illustrative embodiments provide mechanisms for providing a cluster-wide system clock for a plurality of processor chips in the same or different collections of processors on the same or different supernodes of the architecture.

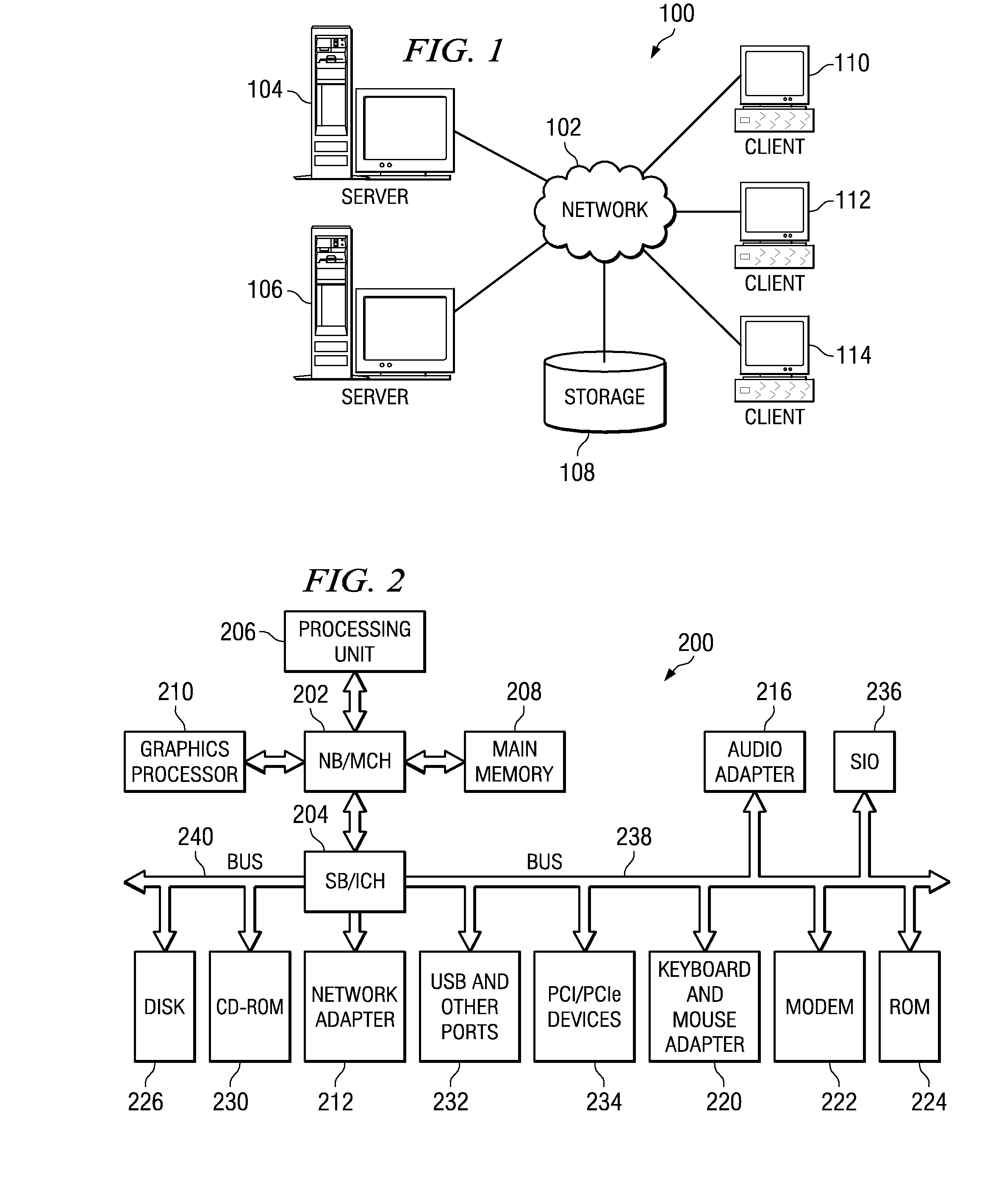

[0049]As such, the mechanisms of the illustrative embodiments are especially well suited for implementation within a distributed data processing environment and within, or in association with, data processing devices, such as servers, client devices, and the like. In order to provide a context for the description of the mechanisms of the il...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More