FPGA (field programmable gate array) architecture of HOG (histogram of oriented gradient) and SVM (support vector machine) based pedestrian detection system and implementing method of FPGA architecture

An implementation method and pedestrian detection technology, applied in character and pattern recognition, instruments, calculations, etc., can solve problems such as high algorithm complexity, performance degradation, and poor detection speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

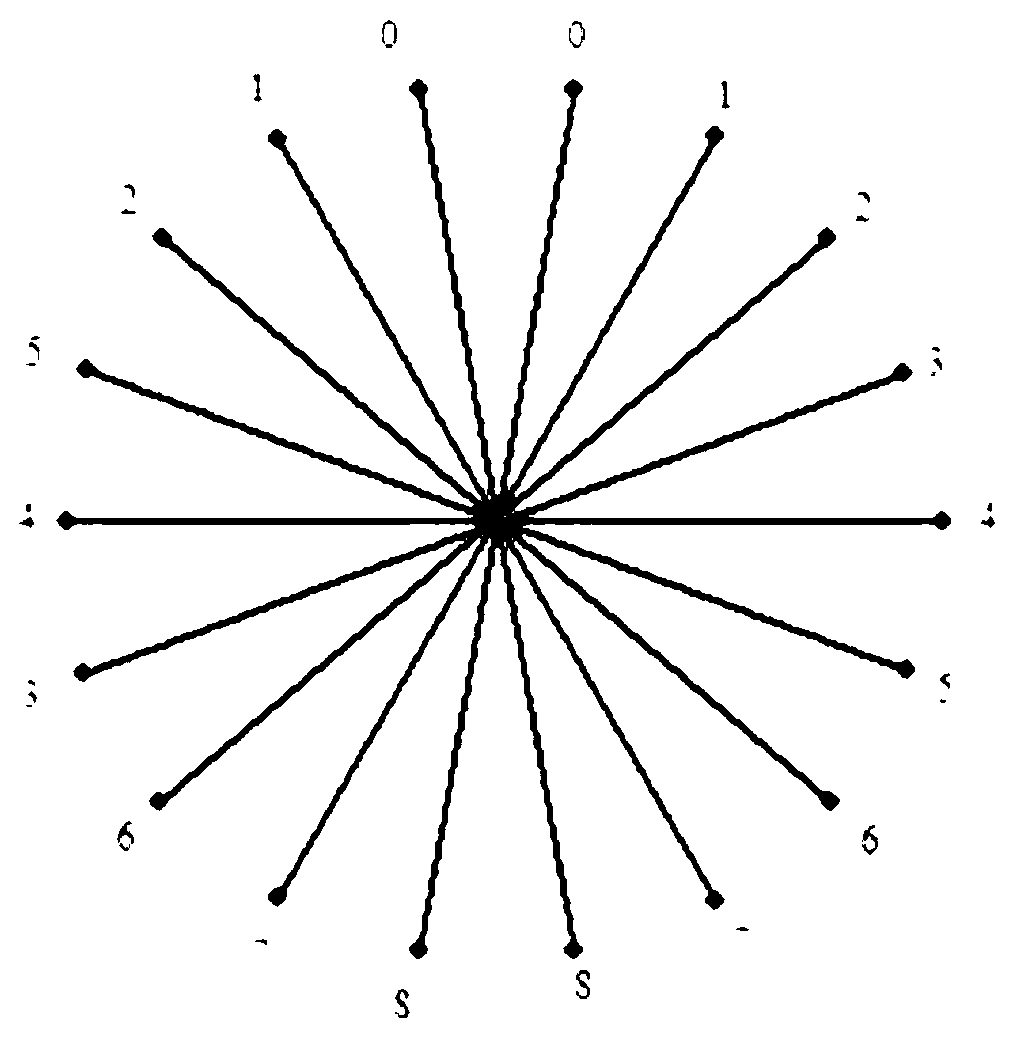

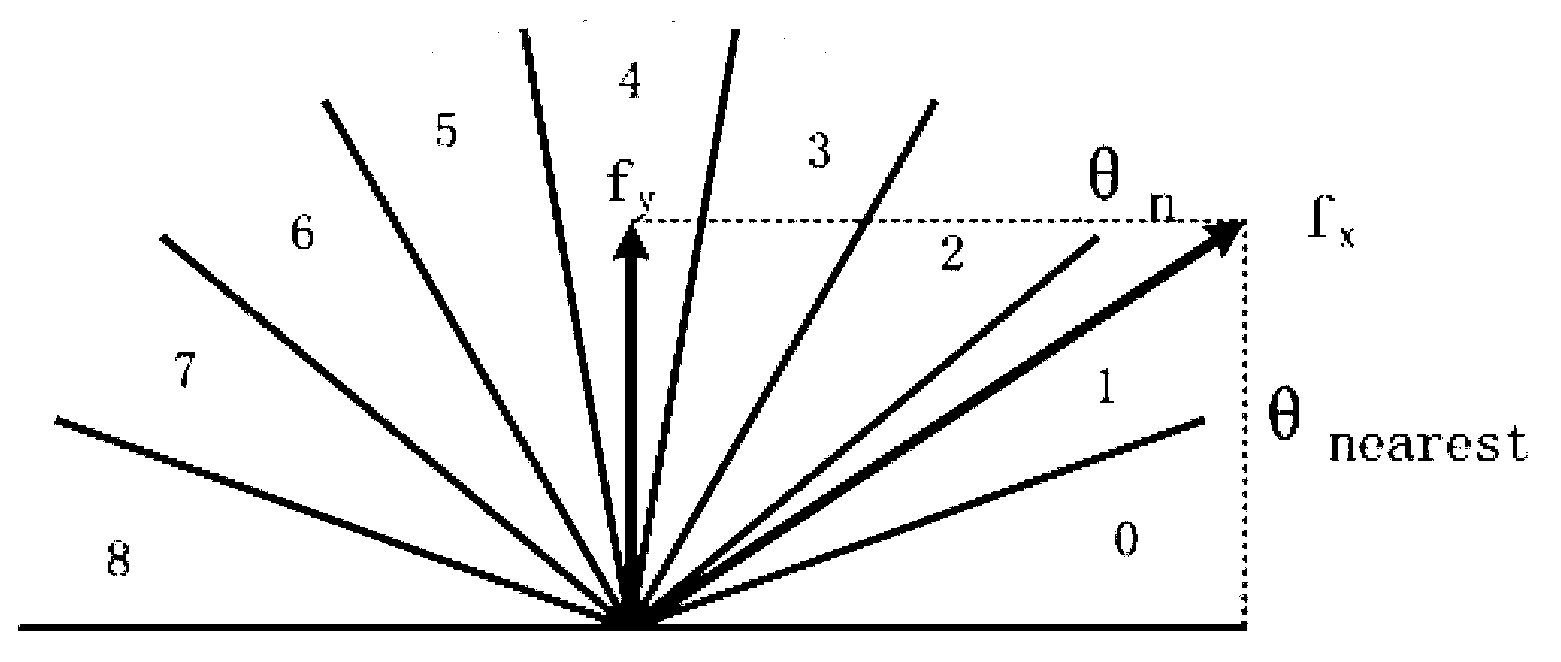

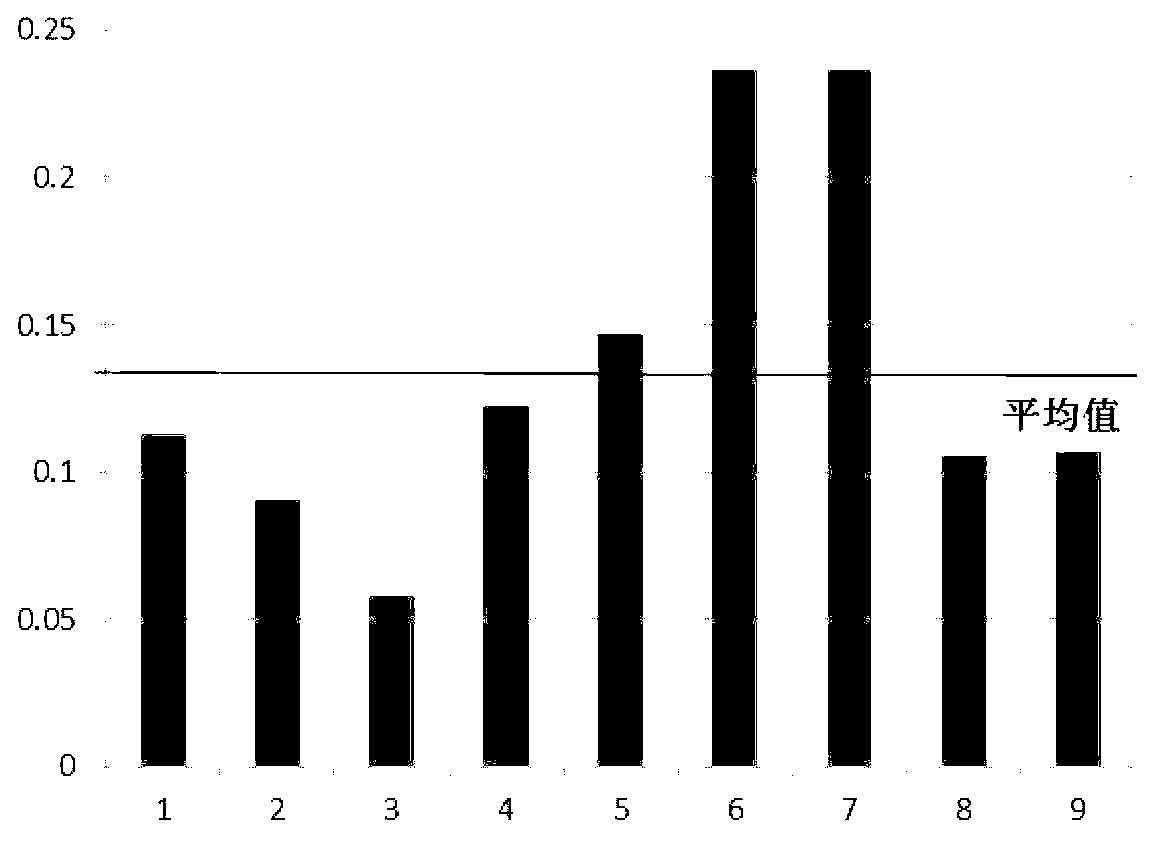

Method used

Image

Examples

Embodiment Construction

[0065] The present invention will be further described below in conjunction with the accompanying drawings and embodiments. It should be noted that the following description is only for explaining the present invention and not limiting its content.

[0066] FPGA implementation method of pedestrian detection system based on HOG and SVM, including:

[0067] In the input step, an embedded camera collects the image to be inspected, and transmits it to the FPGA chip via the ARM microcontroller. The image to be inspected is a standard RGB565 image with a size of 320×240 pixels;

[0068] In the output step, the detection result after processing and judging the image data by the FPGA is returned to the ARM microcontroller, and finally the ARM microcontroller transmits the portion of the image to be detected with pedestrians to the host computer through the wireless transmission module according to the detection result returned by the FPGA;

[0069] The FPGA implementation method also ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More