Patents

Literature

2259results about "Error correction/detection using interleaving techniques" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

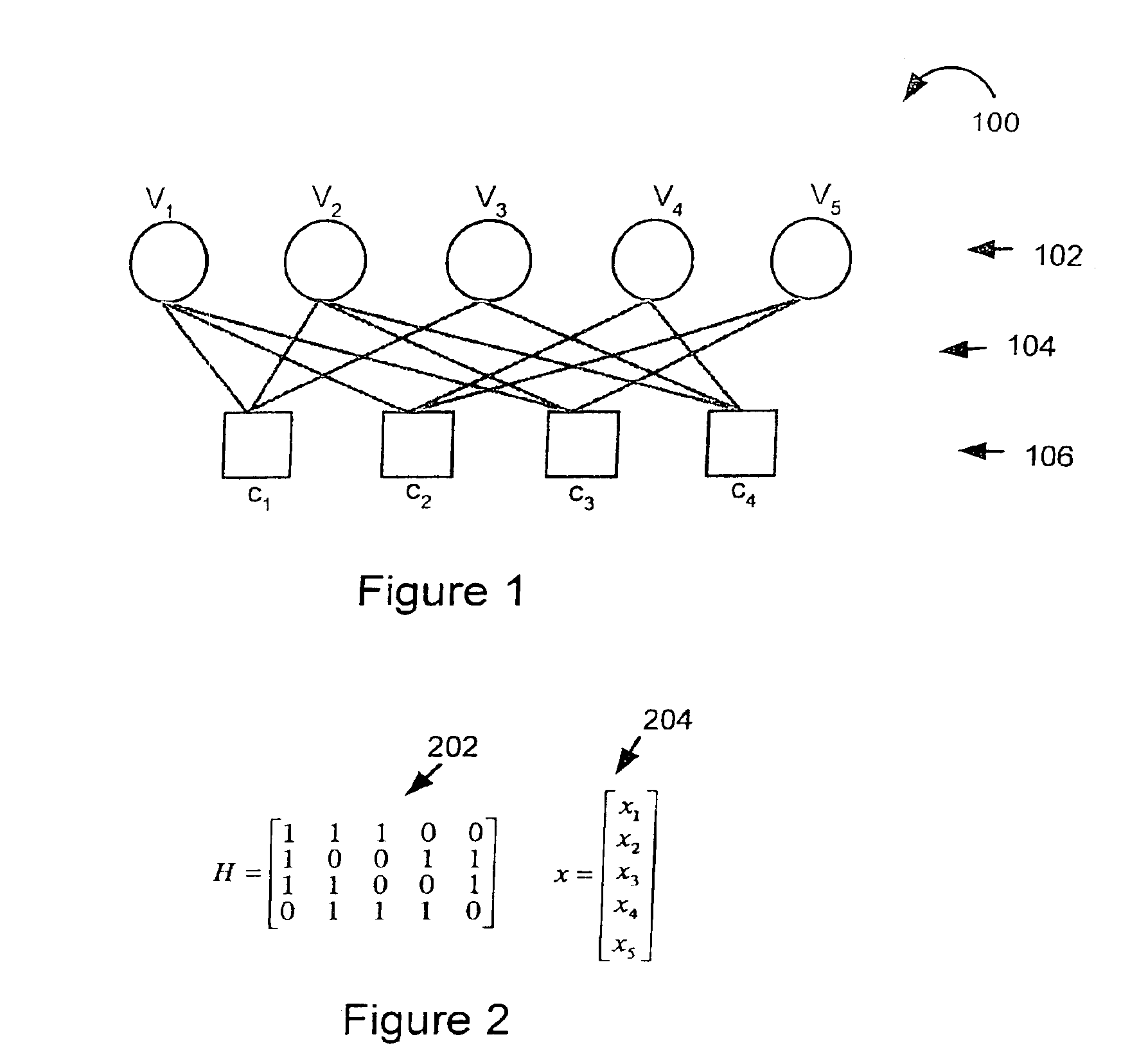

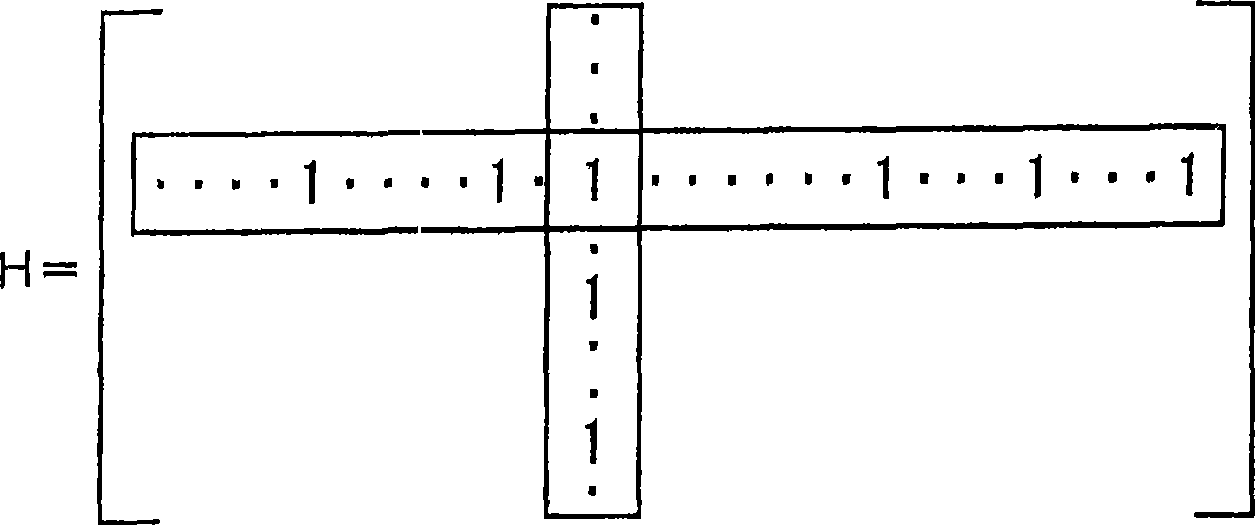

Method and system for providing low density parity check (LDPC) encoding

ActiveUS7191378B2Readily apparentInterconnection arrangementsError correction/detection using LDPC codesAlgorithmParity-check matrix

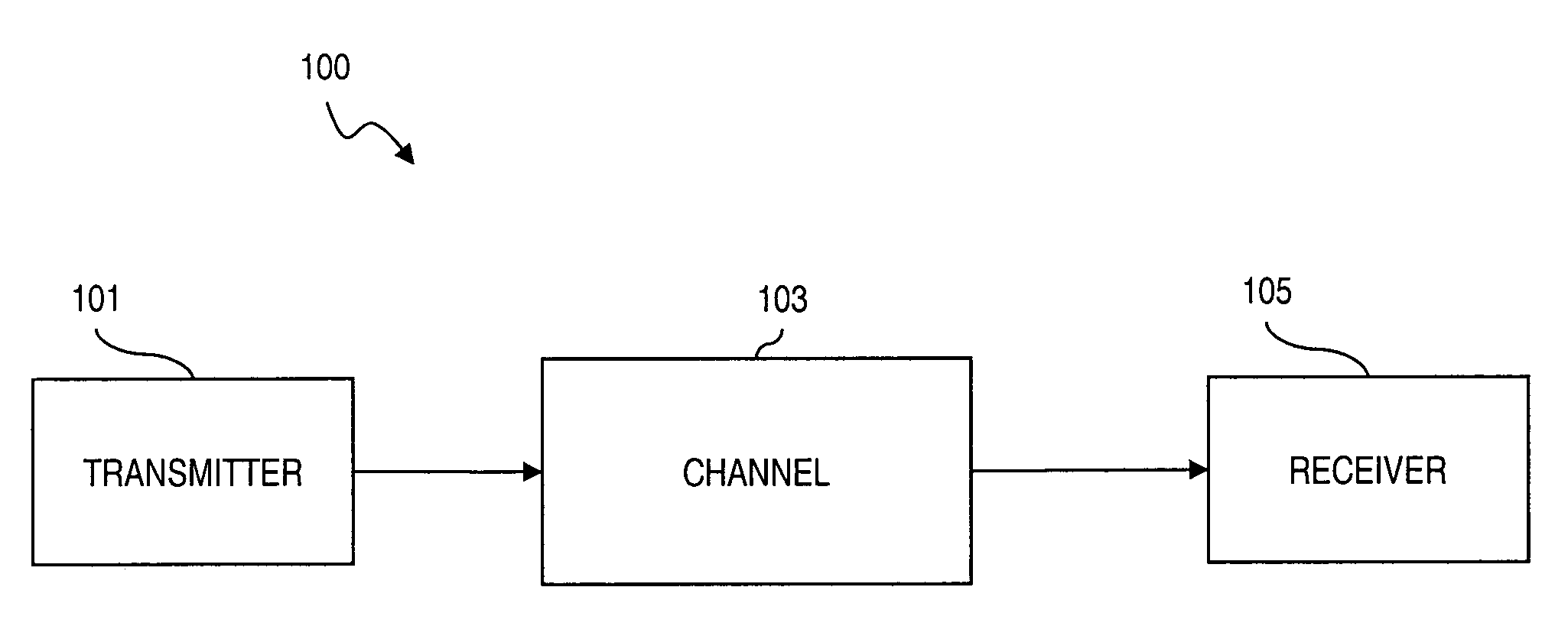

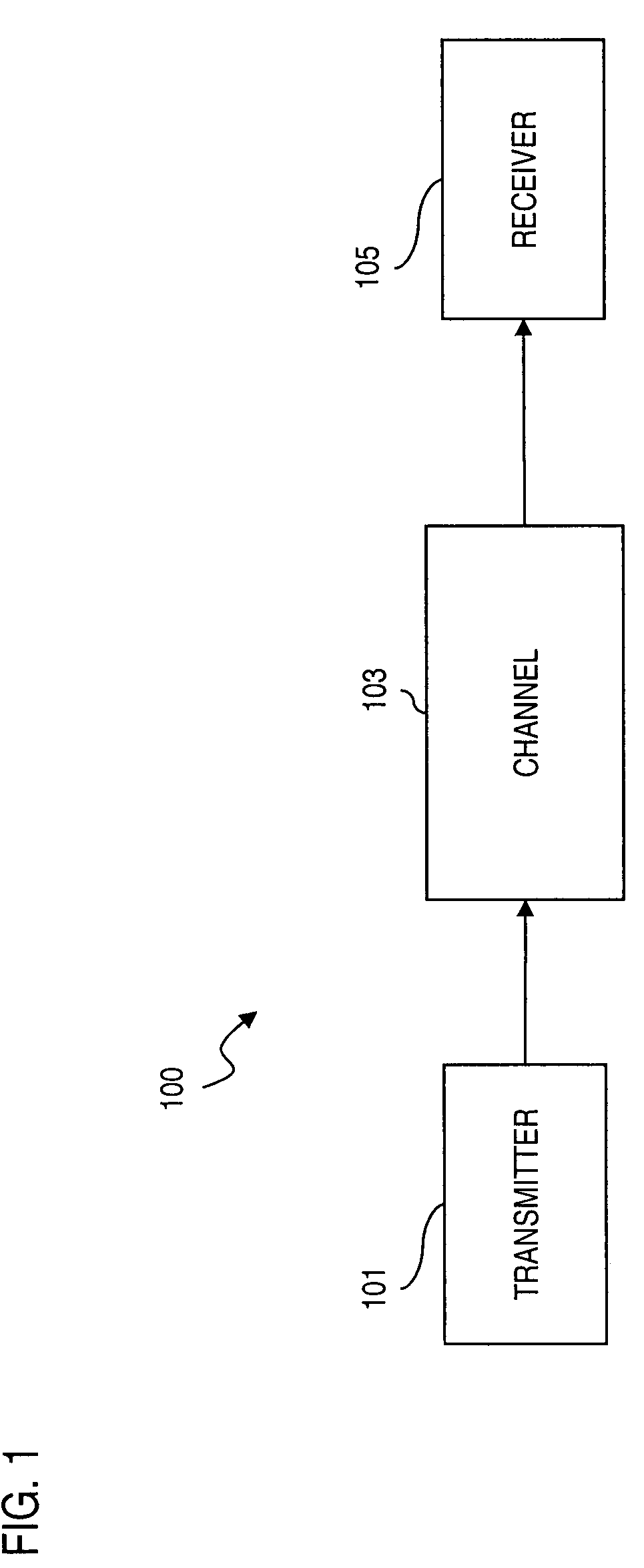

An approach is provided for a method of encoding structure Low Density Parity Check (LDPC) codes. Memory storing information representing a structured parity check matrix of Low Density Parity Check (LDPC) codes is accessed during the encoding process. The information is organized in tabular form, wherein each row represents occurrences of one values within a first column of a group of columns of the parity check matrix. The rows correspond to groups of columns of the parity check matrix, wherein subsequent columns within each of the groups are derived according to a predetermined operation. An LDPC coded signal is output based on the stored information representing the parity check matrix.

Owner:DTVG LICENSING INC

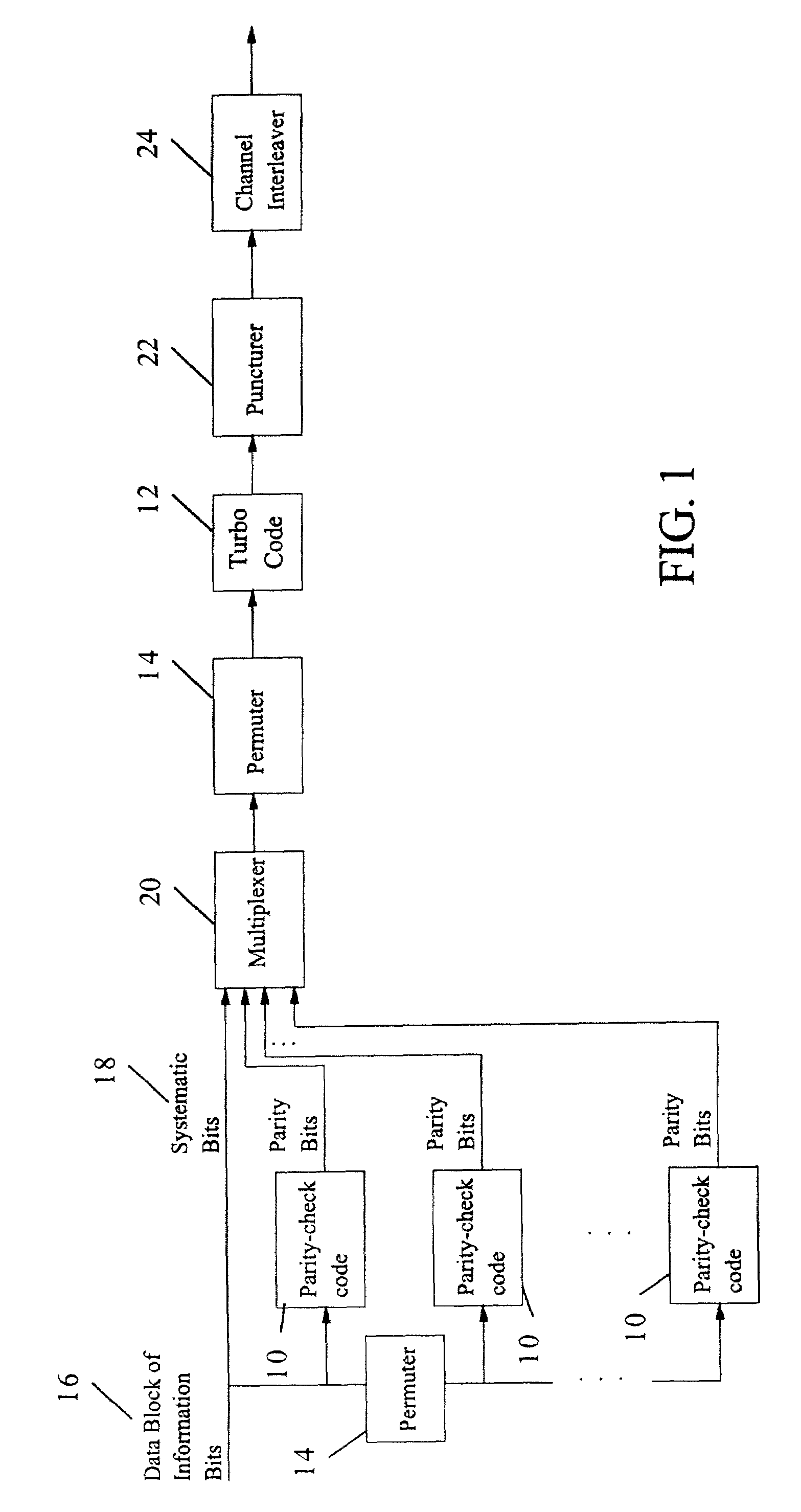

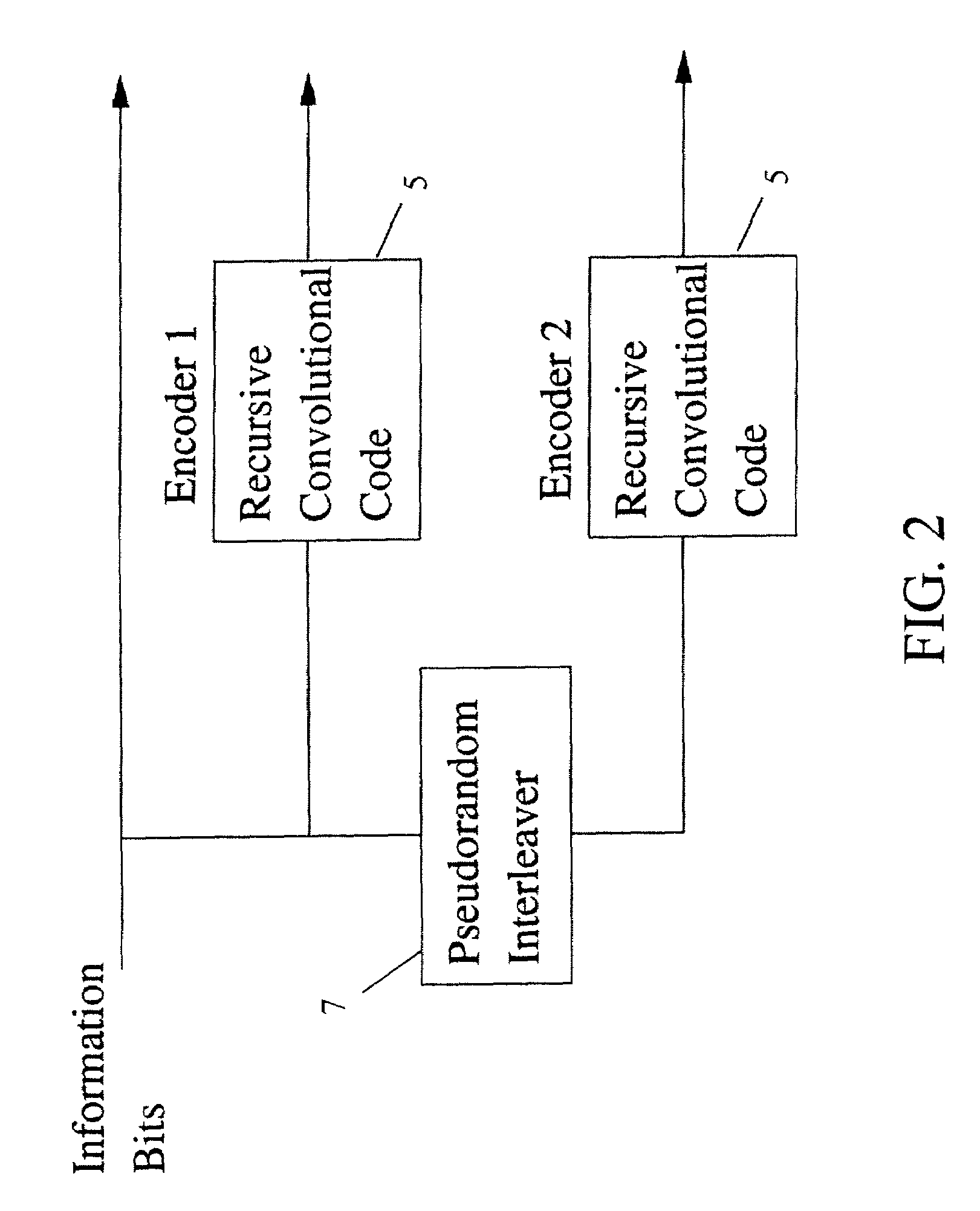

Method and coding means for error-correction utilizing concatenated parity and turbo codes

InactiveUS7093179B2Reduction in rateImprove overall utilizationError preventionError detection/correctionParallel computingTurbo coded

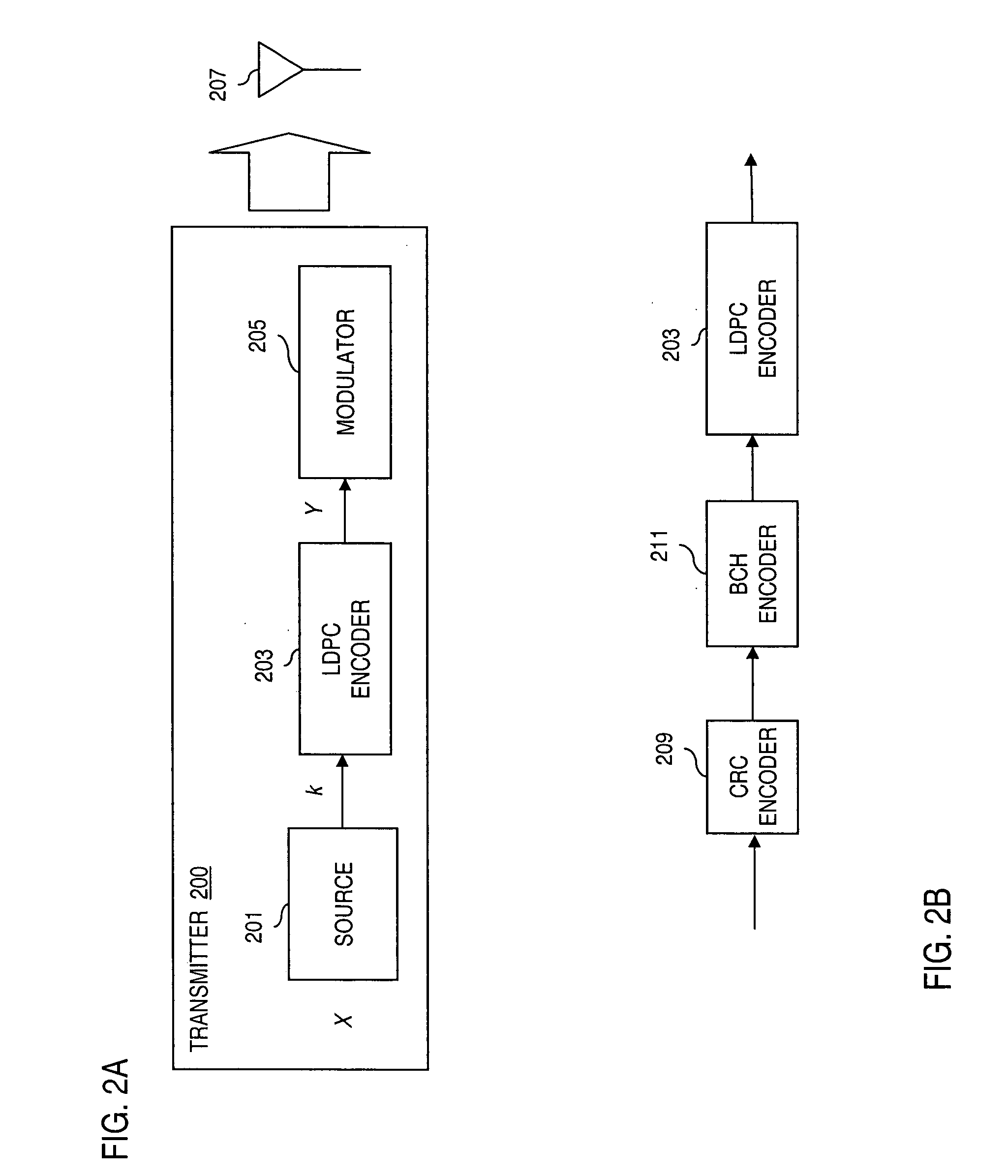

A method and apparatus for encoding and decoding data using an overall code comprising an outer parity-check and an inner parallel concatenated convolutional, or turbo code. The overall code provides error probabilities that are significantly lower than can be achieved by using turbo codes alone. The output of the inner code can be punctured to maintain the same turbo code rate as the turbo code encoding without the outer code. Multiple parity-check codes can be concatanated either serially or in parallel as outer codes. Decoding can be performed with iterative a posteriori probability (APP) decoders or with other decoders, depending on the requirements of the system. The parity-check code can be applied to a subset of the bits to achieve unequal error protection. Moreover, the techniques presented can be mapped to higher order modulation schemes to achieve improved power and bandwidth efficiency.

Owner:FLORIDA UNIV OF A FLORIDA +1

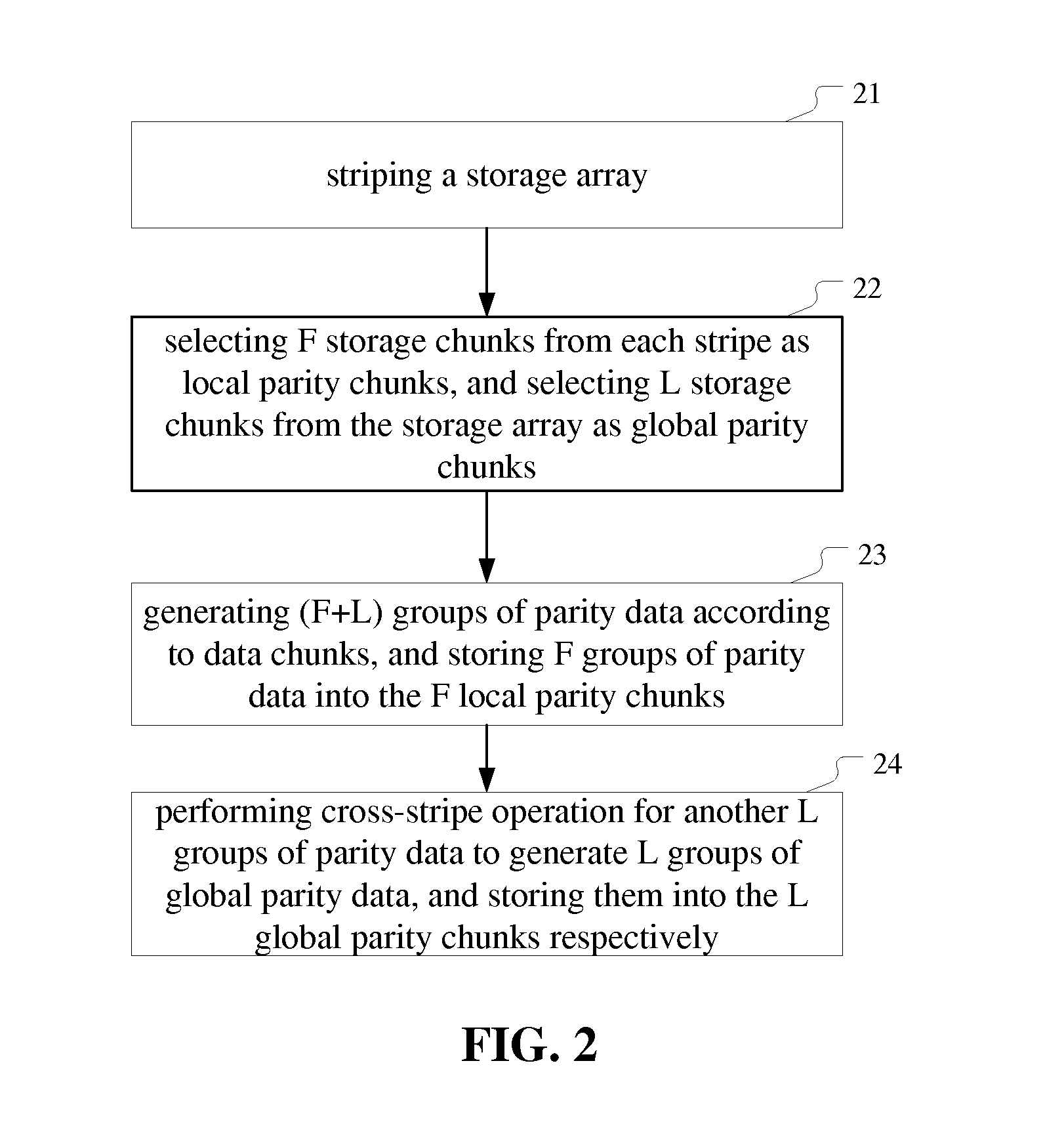

Managing a storage array

ActiveUS20140040702A1Easy to manageError capabilityCode conversionError correction/detection using interleaving techniquesFault toleranceErasure code

The present invention provides a method and apparatus of managing a storage array. The method comprises: striping the storage array to form a plurality of stripes; selecting F storage chunks from each stripe as local parity chunks, and selecting another L storage chunks from the storage array as global parity chunks; performing (F+L) fault tolerant erasure coding on all data chunks in a stripe to generate (F+L) groups of parity data, and storing F groups of parity data therein into the F local parity chunks; performing cross-stripe operation on another L groups of parity data to generate L groups of global parity data, and storing them into the L global parity chunks, respectively. The apparatus corresponds to the method. With the invention, a plurality of errors in the storage array can be detected and / or recovered to improve fault tolerance and space utilization of the storage array.

Owner:IBM CORP

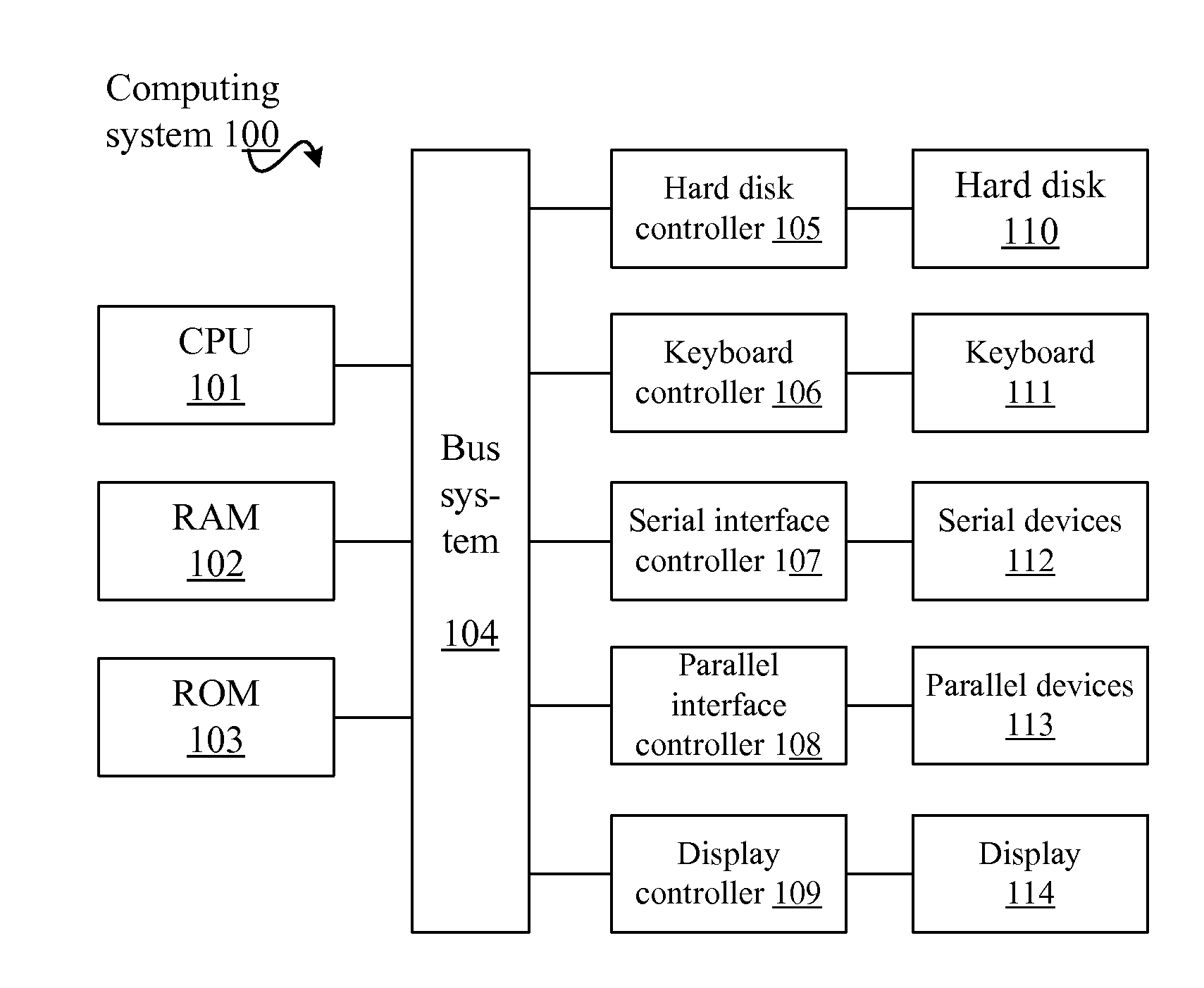

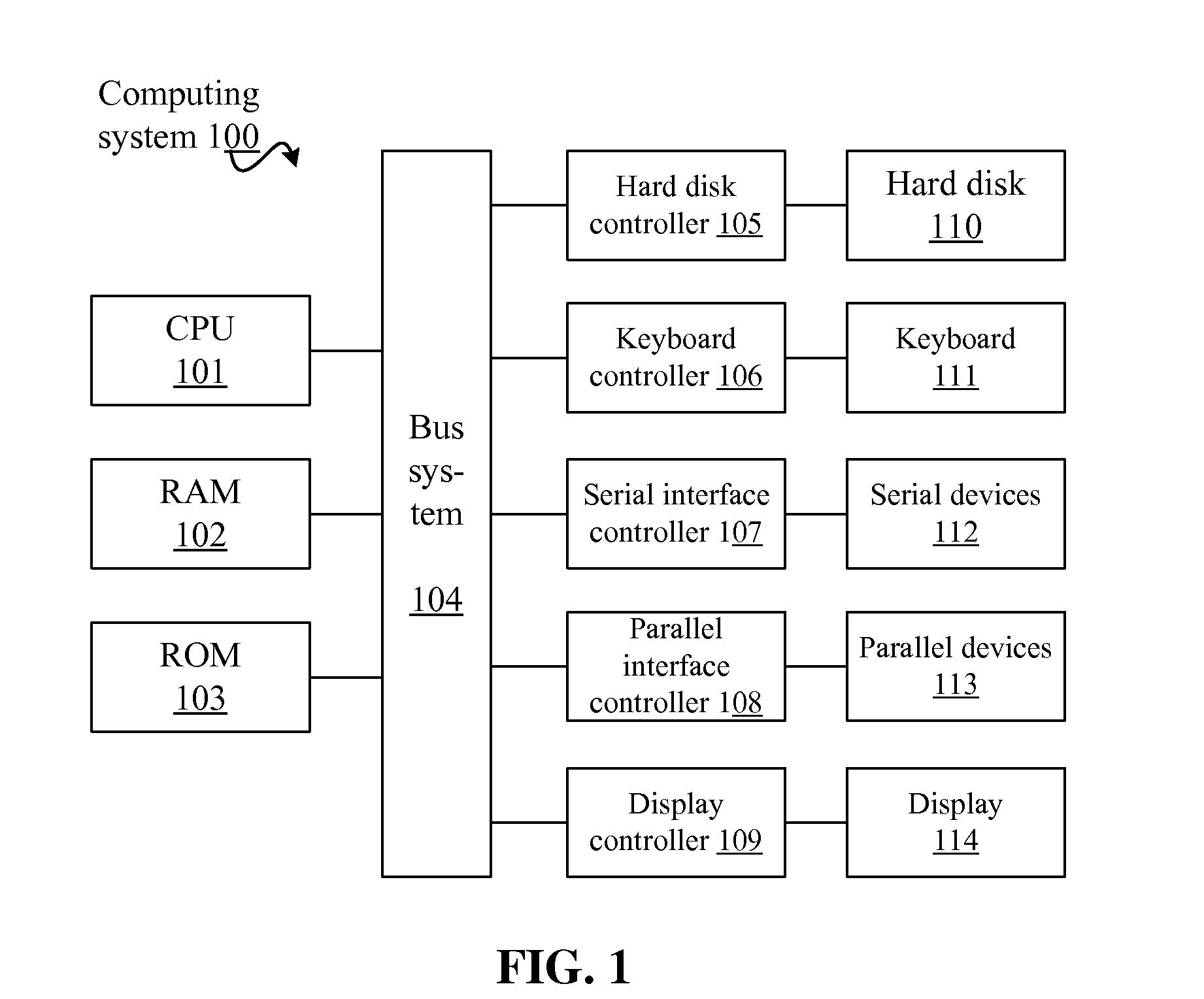

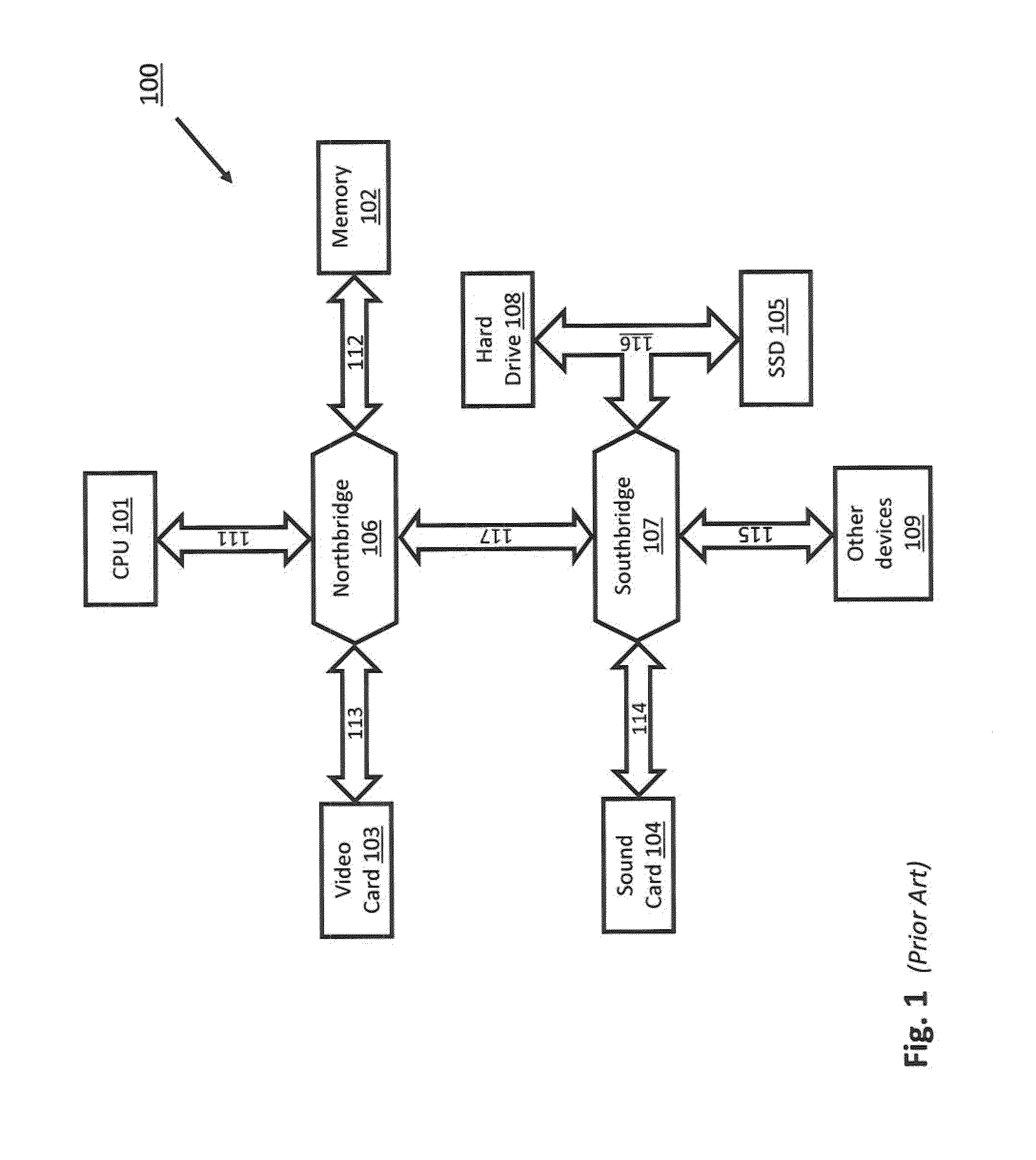

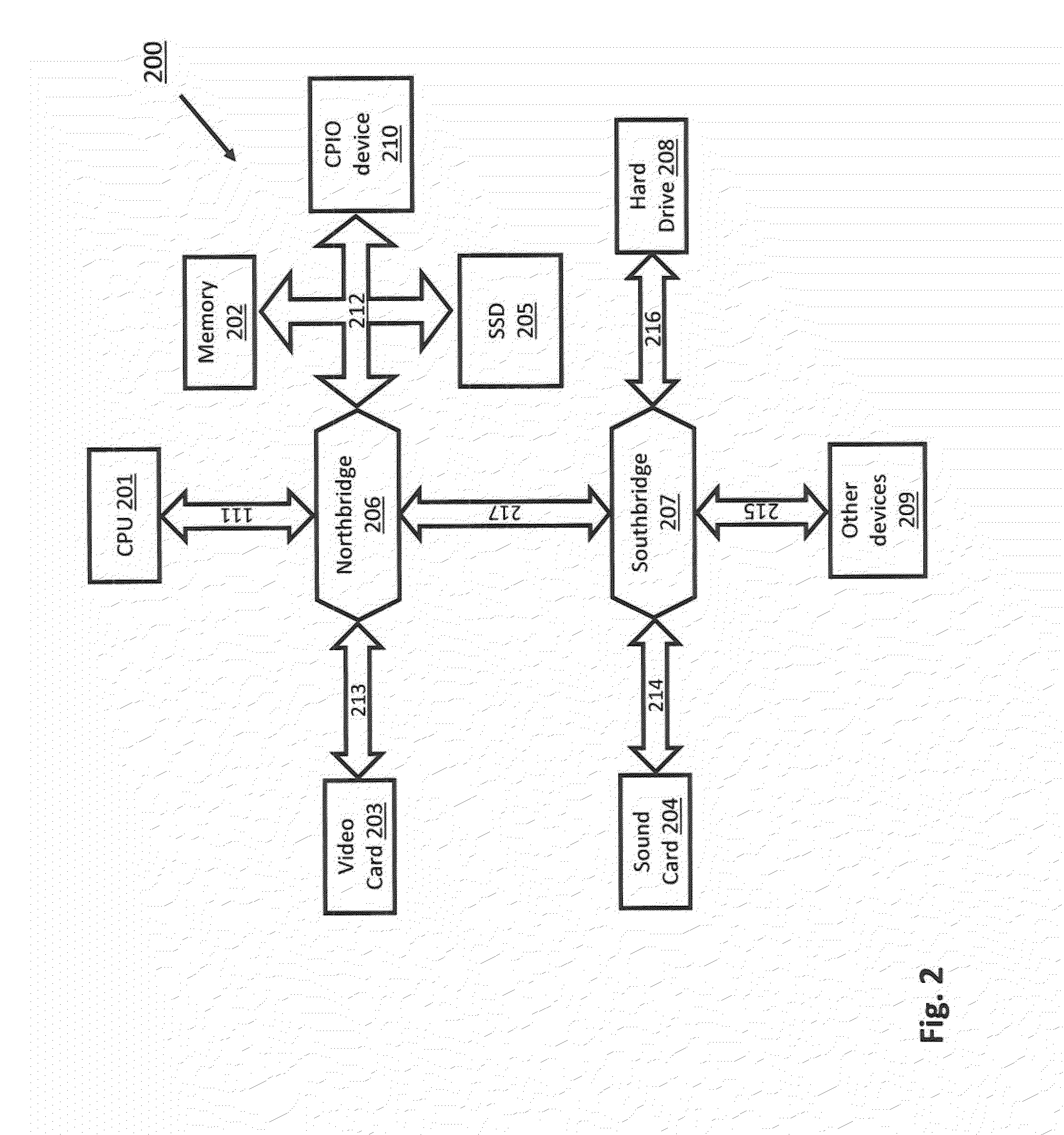

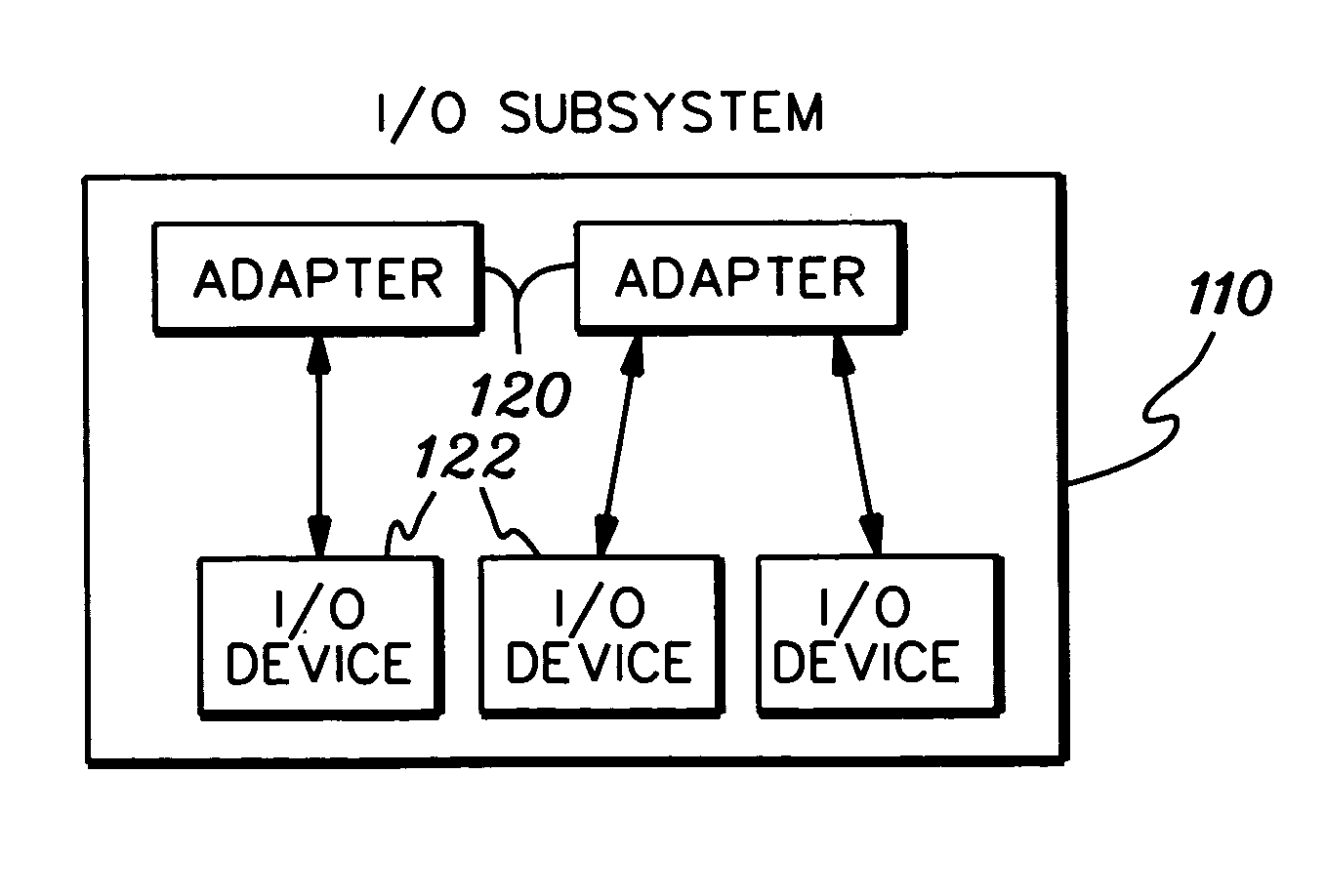

System and method of interfacing co-processors and input/output devices via a main memory system

ActiveUS20120204079A1Memory architecture accessing/allocationError detection/correctionComputer moduleMemory bus

A system for interfacing with a co-processor or input / output device is disclosed. According to one embodiment, the system includes a computer processing unit, a memory module, a memory bus that connects the computer processing unit and the memory module, and a co-processing unit or input / output device, wherein the memory bus also connects the co-processing unit or input / output device to the computer processing unit.

Owner:RAMBUS INC

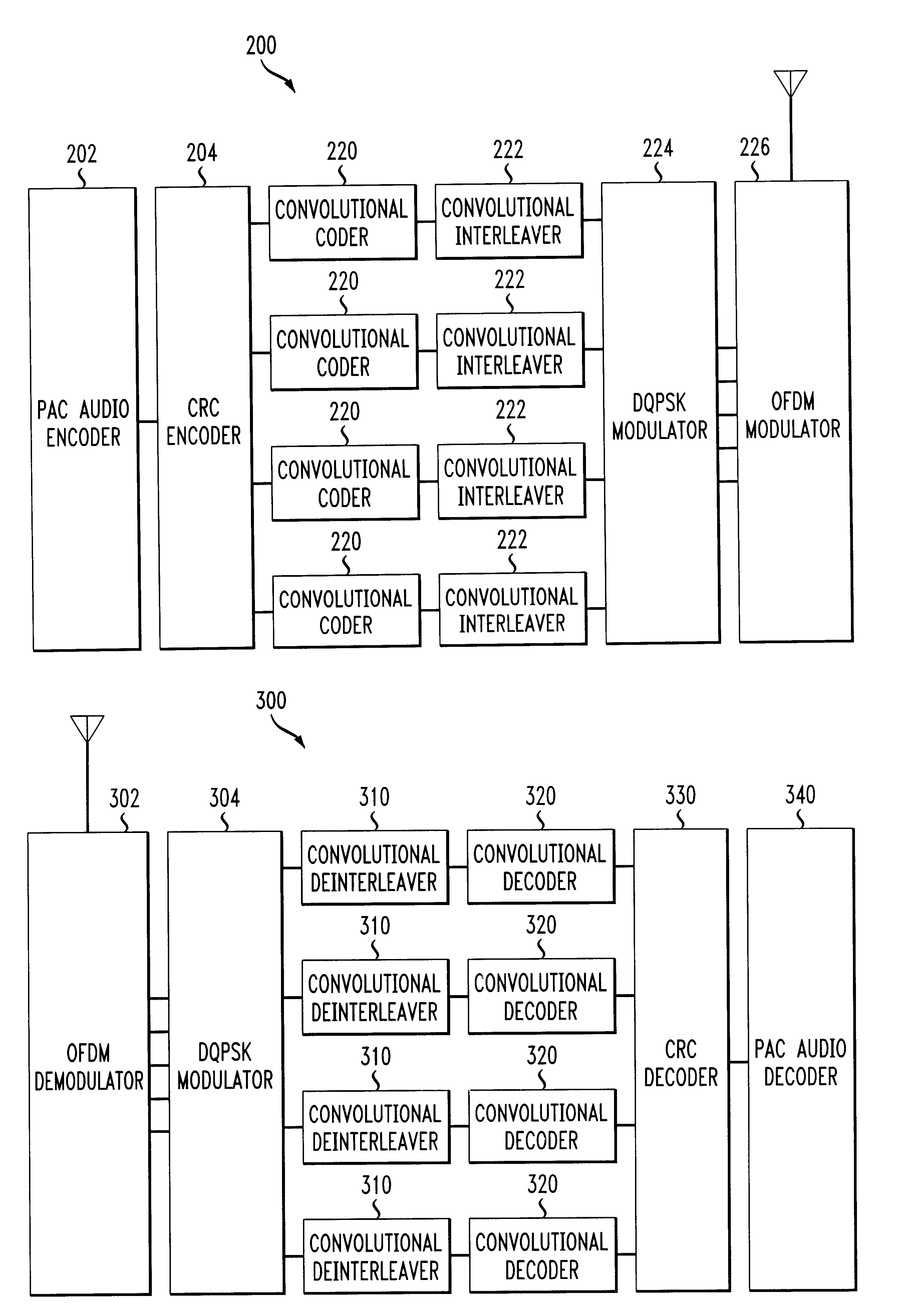

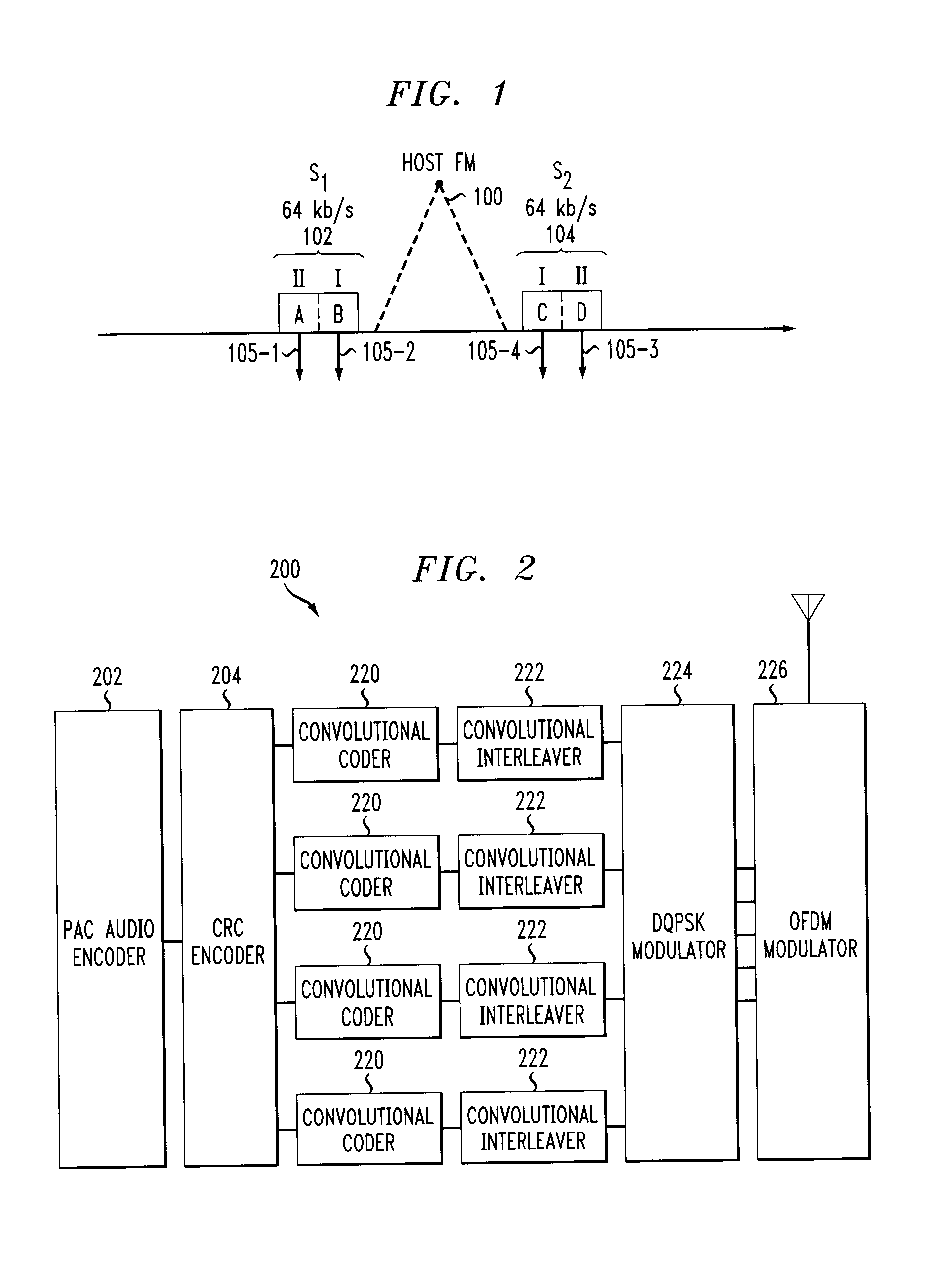

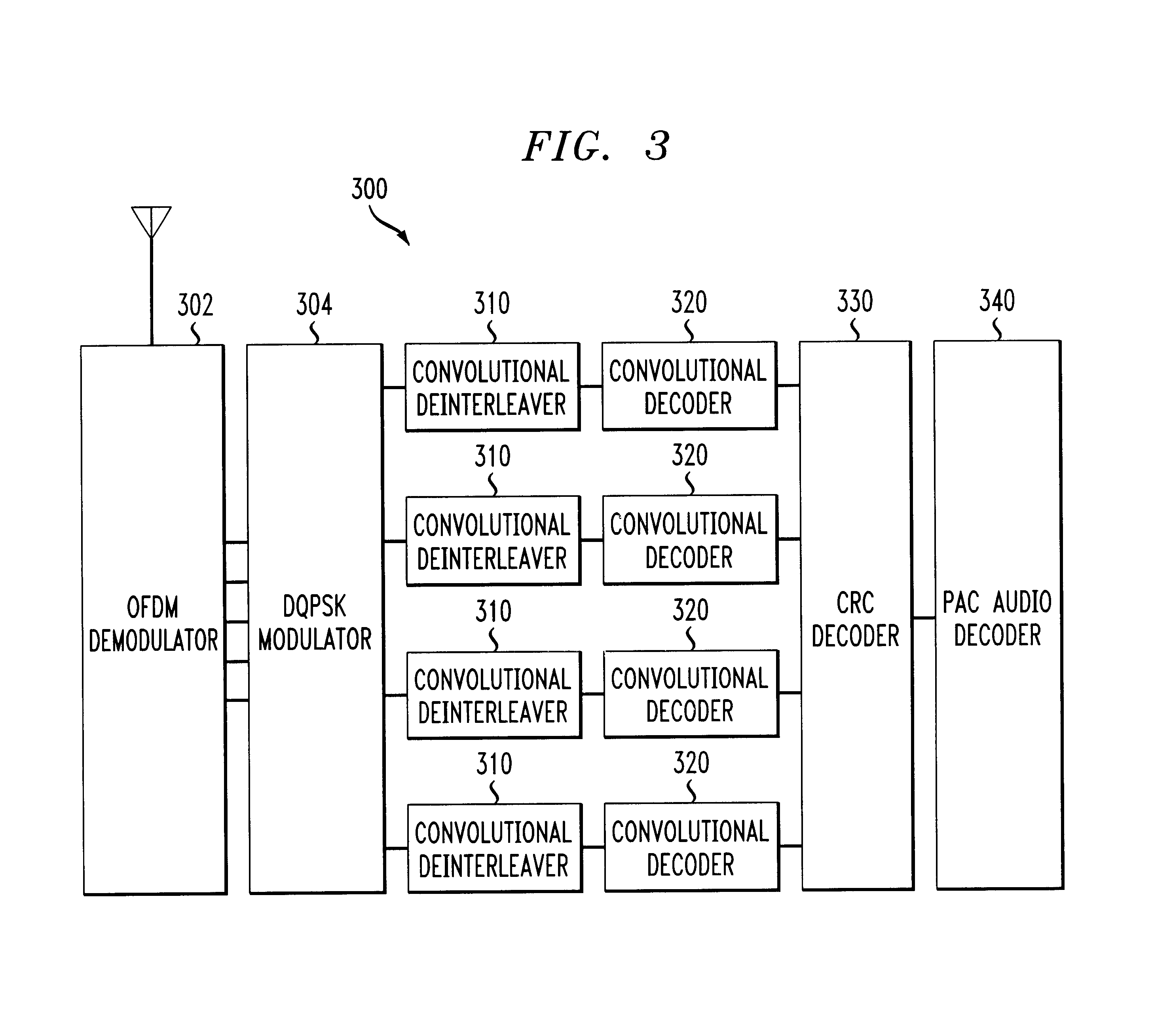

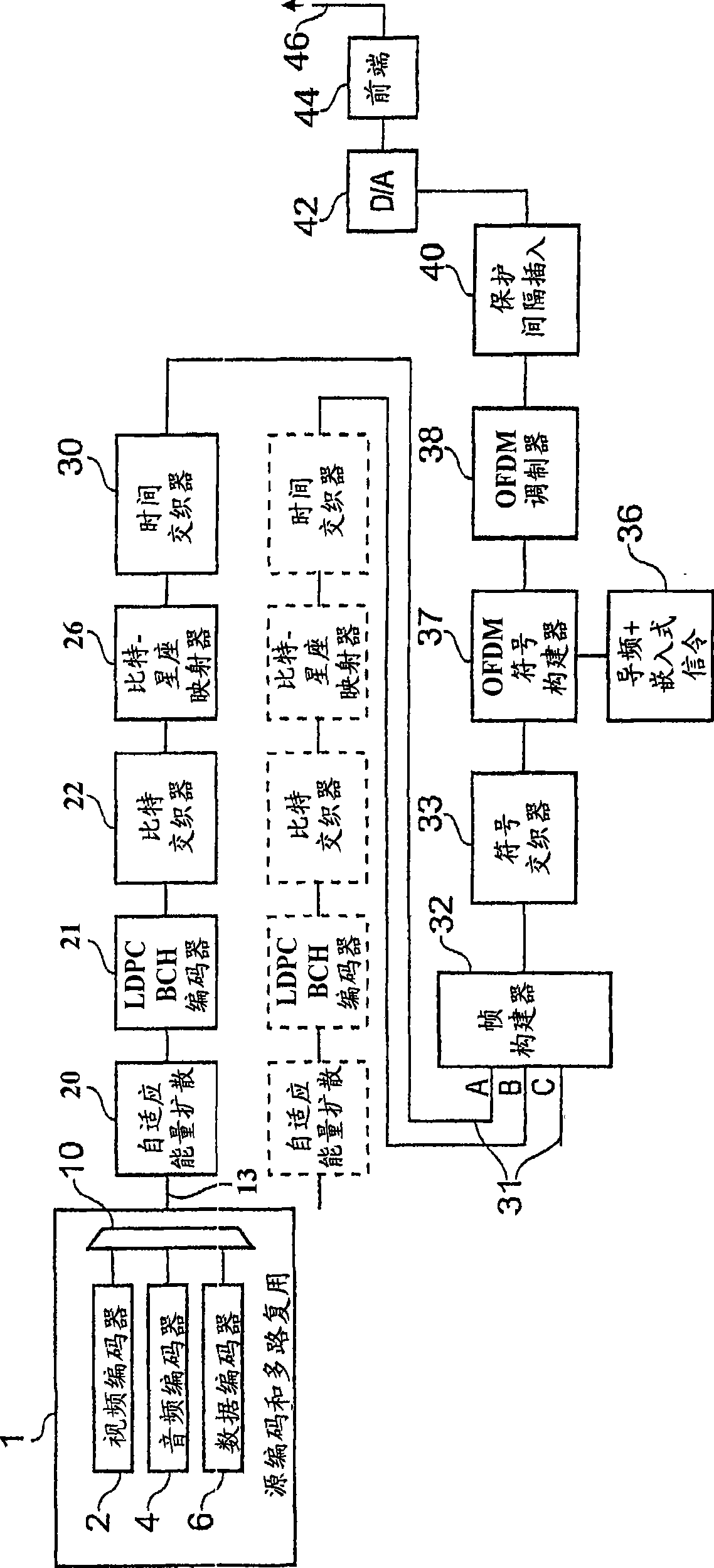

Symbol self synchronous interleaving method and apparatus for OFDM-based communication system

InactiveUS6985537B1Reduce delaysBroadcast with distributionRadio transmissionIn-band on-channelCommunications system

An interleaving method and apparatus is disclosed for an in-band on-channel (IBOC) digital audio broadcasting (DAB) system. The disclosed interleaver method and apparatus utilize a convolutional interleaver having a row size equal to one OFDM symbol and a time span of arbitrary size. A structured memory block is utilized in the de-interleaver at the receiver having a row size of one OFDM symbol (the number of active sub-carriers in the applicable sub-band of the IBOC system). The self-synchronizing nature of the present invention permits a receiver in an OFDM-based IBOC system to sort the scrambled blocks and descramble the received symbols according to its own frame count, without regard to the frame count of the transmitter. The disclosed interleaver method and apparatus does not require interleaver synchronization between the transmitter and receiver. In one implementation, separate convolutional encoders and convolutional interleavers are applied to each sub-band in a multi-stream structure to provide independent error spreading for each sub-band.

Owner:LUCENT TECH INC

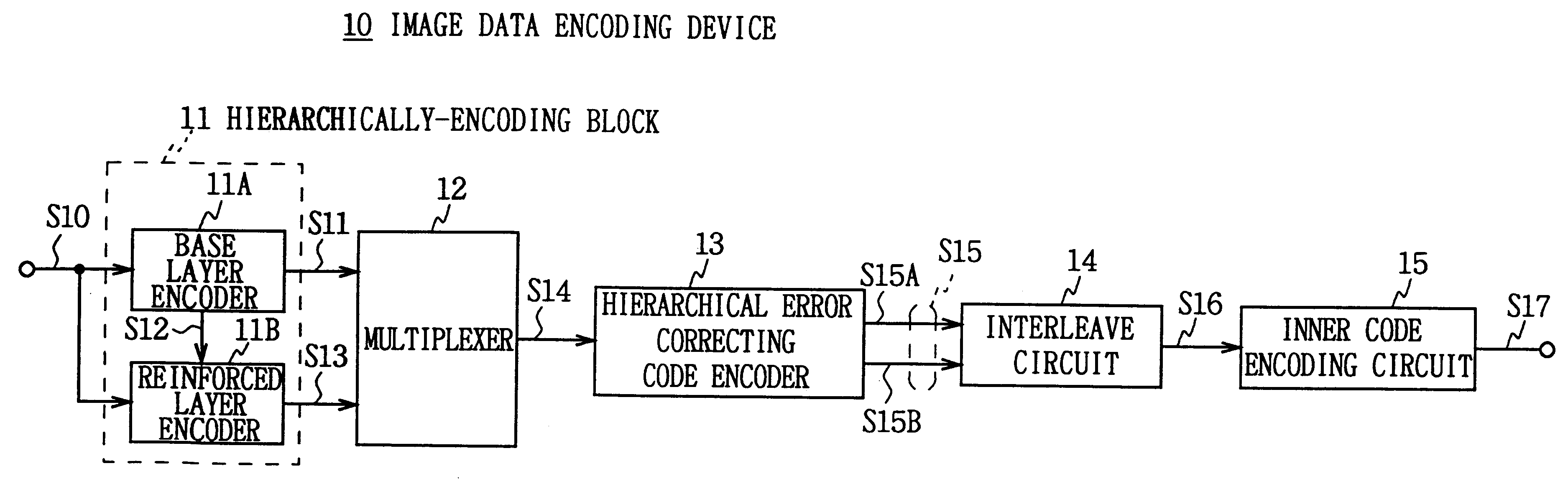

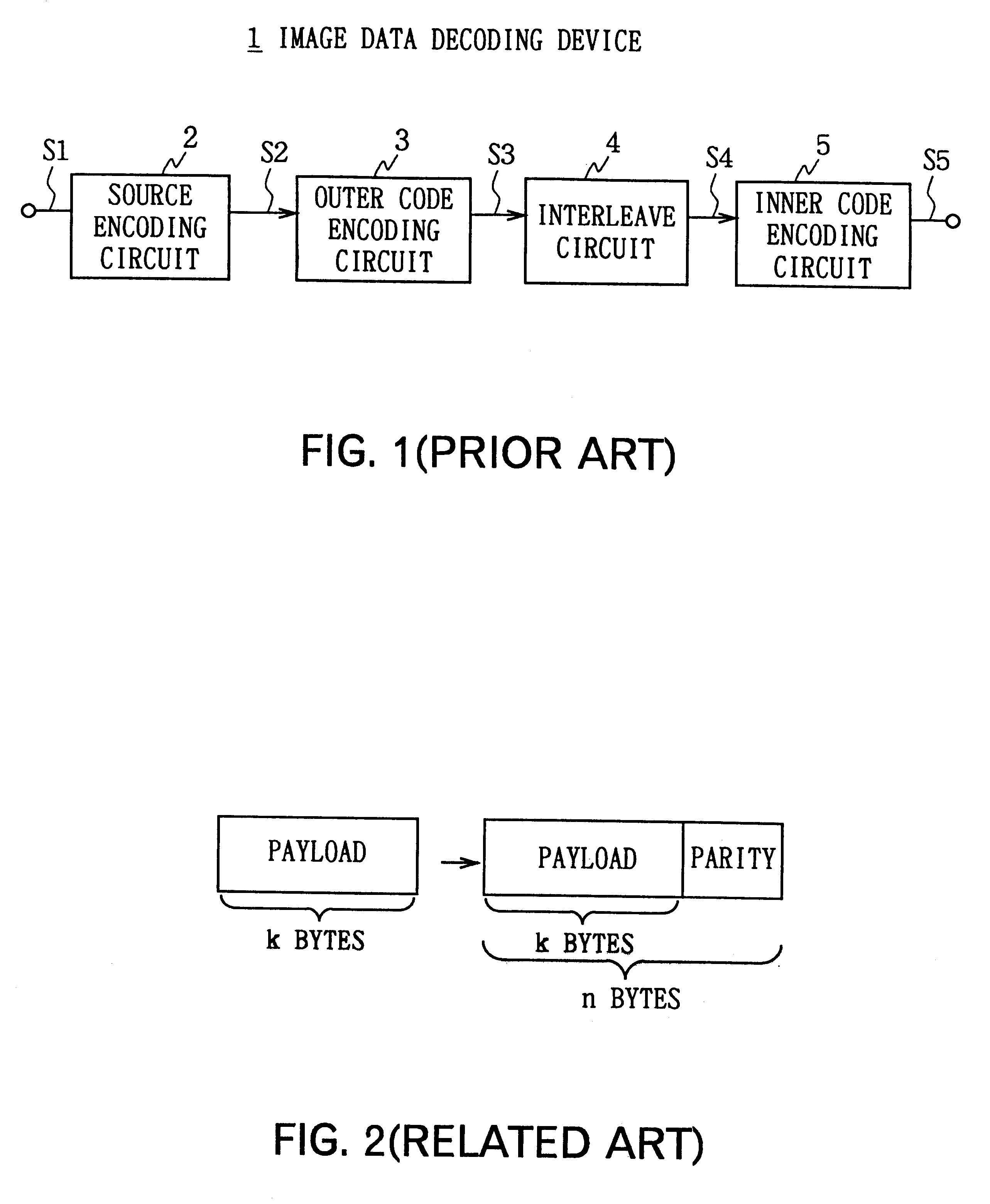

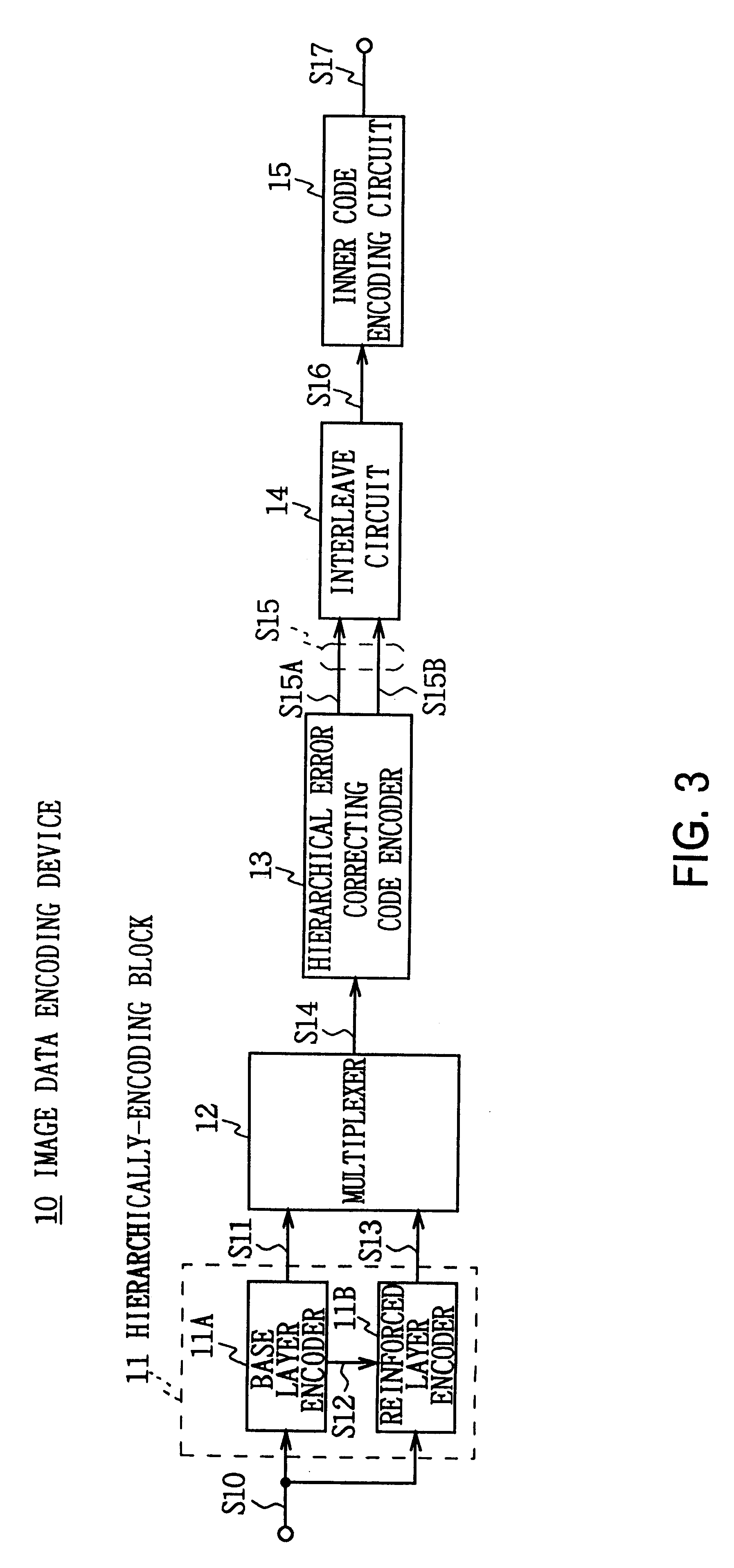

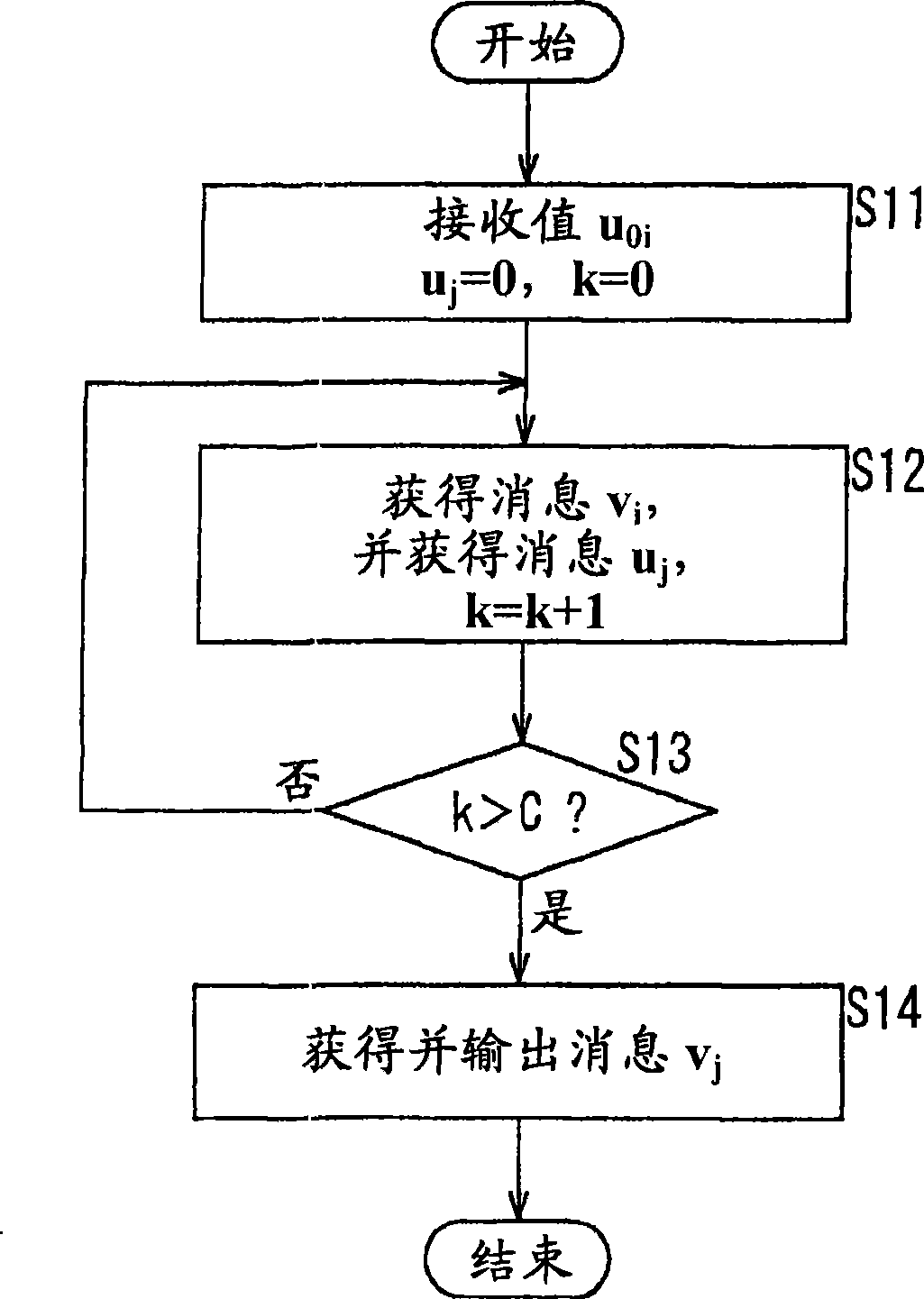

Method for adding and encoding error correcting codes and its device and method for transmitting data having error correcting codes added

A method for encoding error correcting codes to generate plural coded data having different error correction ability according to significance. An error correcting code having different code length is added to a fixed length of input data according to the significance of the input data (S14). The error correcting codes added which have different error correction ability corresponding to its code length are encoded to generate coded data having different packet length according to the code length of the error correcting code. Thus, plural coded data (S15A and S15B) which have different error correction ability according to significance can be generated. Thereby, even if a quality of transmission system deteriorates when the above coded data is transmitted, the coded data having high error correction ability can be surely decoded.

Owner:SONY CORP

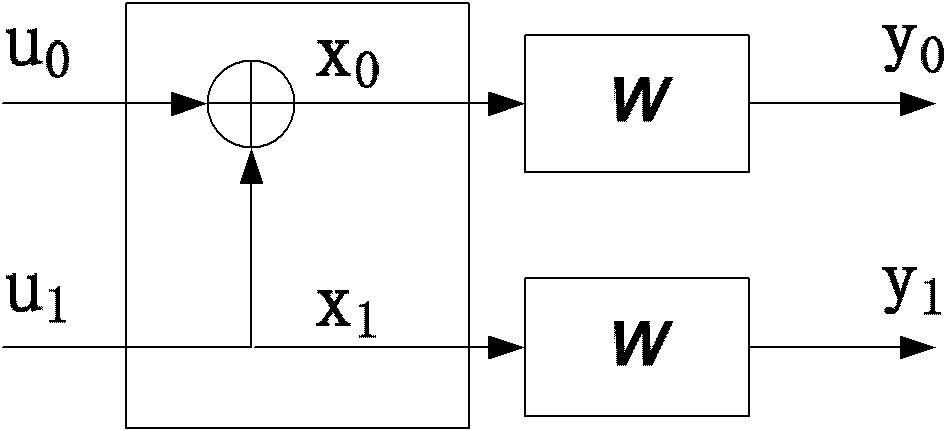

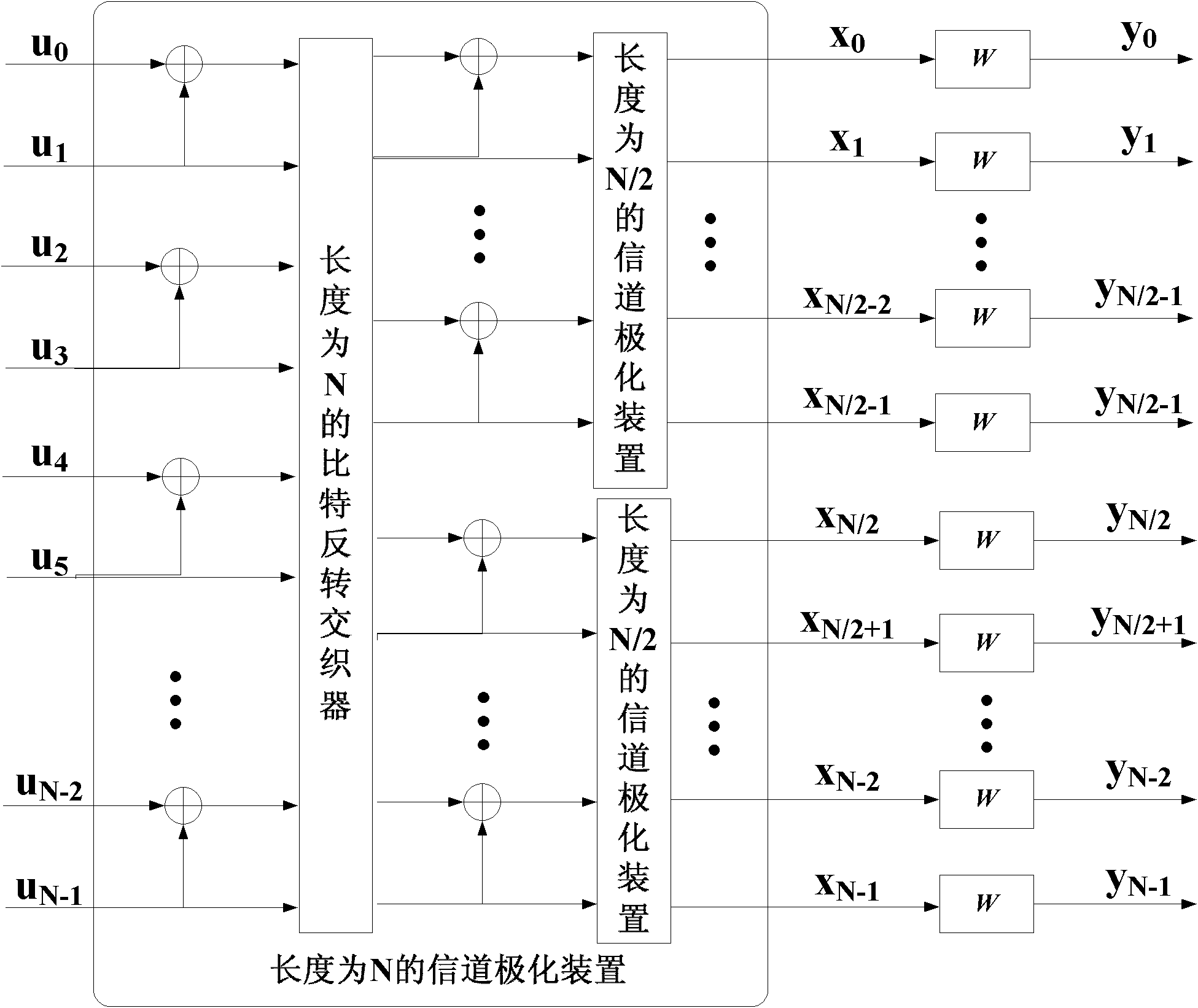

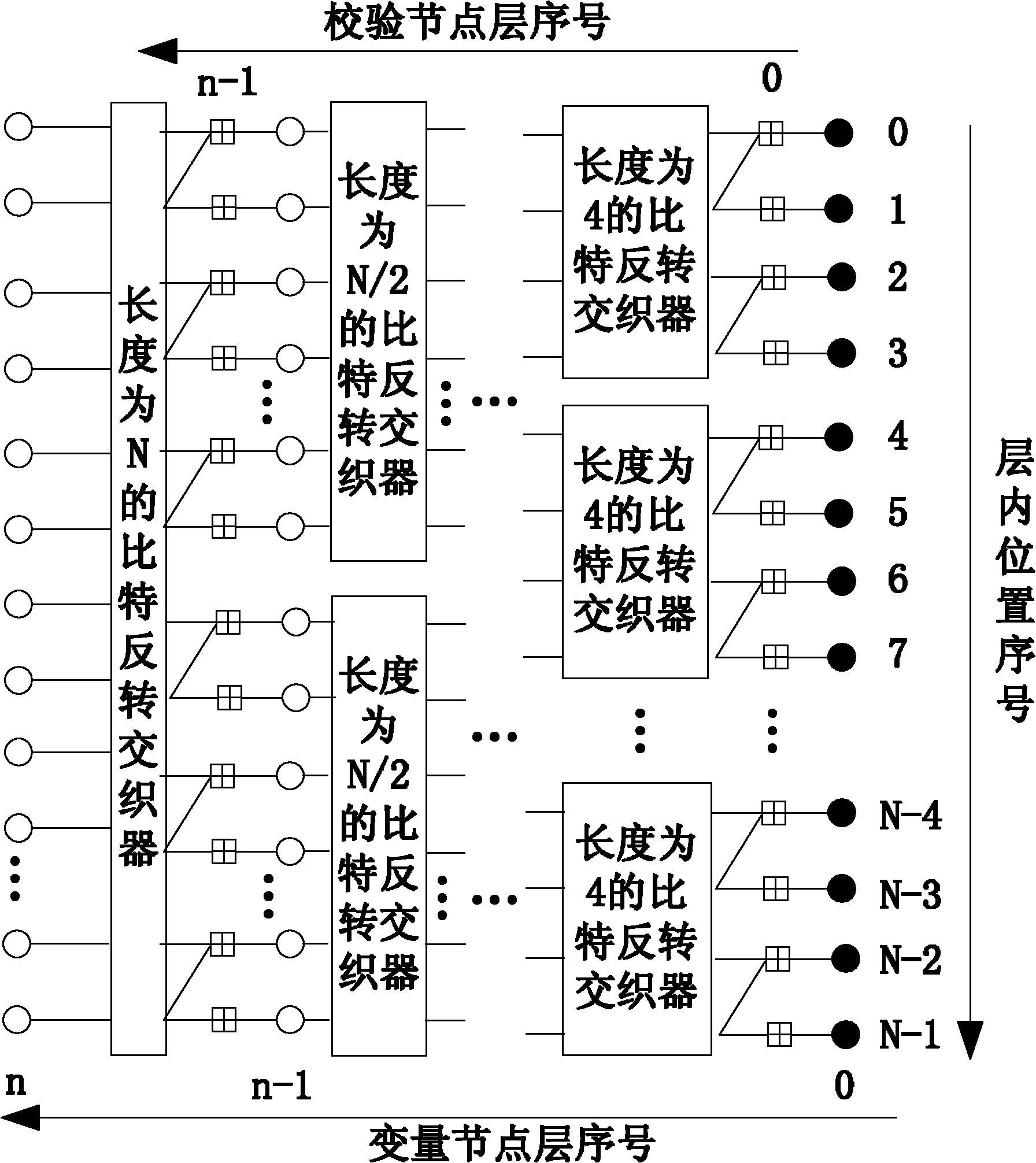

Channel-polarization-based encoder for staggered structure duplication code, and encoding and decoding methods thereof

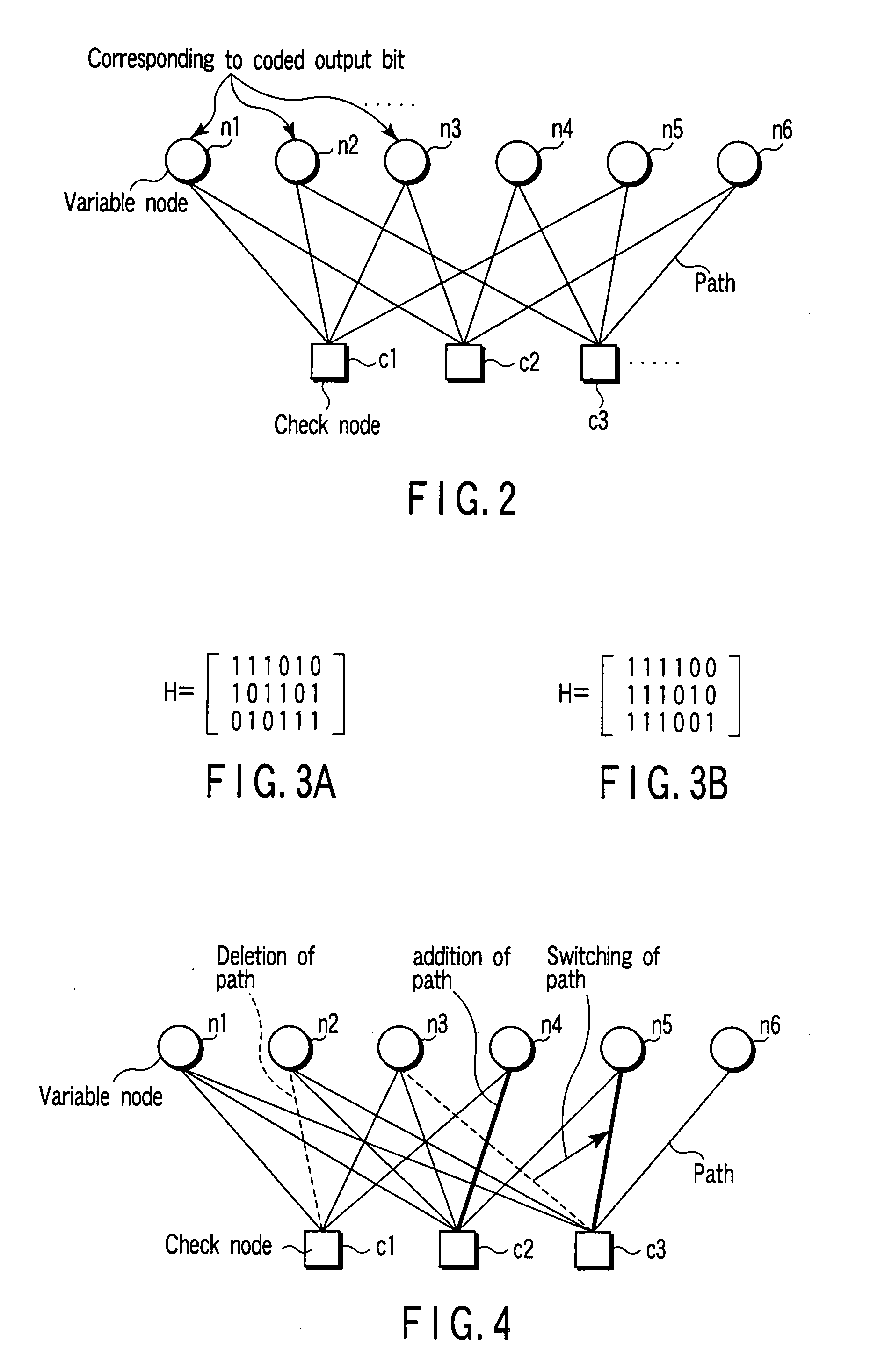

InactiveCN102122966ASimple structureStrong error correction abilityCode conversionError correction/detection using interleaving techniquesTanner graphCoding block

The invention discloses a channel-polarization-based encoder for a staggered structure duplication code, and an encoding method and decoding methods thereof. The encoder consists of a duplication bit buffer with a storage capacity of L bits, a bit position mapper with a length N and a channel polarization device with the length N which are connected in sequence. The encoding method based on the encoder comprises the following steps of: embedding duplicated encoding into a channel polarization process, and introducing a duplicated relationship between parts of the bits of code blocks transmitted in sequence during the channel polarization for encoding. In addition, the invention further provides two decoding methods, which comprise the following steps of: decoding by using a simple and rapid successive cancellation (SC) algorithm, and performing iterative decoding by using a Tanner-graph-based belief propagation algorithm with excellent performance. On the basis of the innovative structure encoder, the encoding and decoding methods provided by the invention are stronger in error correction capability under the condition of not increasing the decoding complexity, and the transmission performance is obviously improved. The encoding and decoding methods are particularly applicable to an actual communication engineering system and have a good popularization and application prospect.

Owner:BEIJING UNIV OF POSTS & TELECOMM

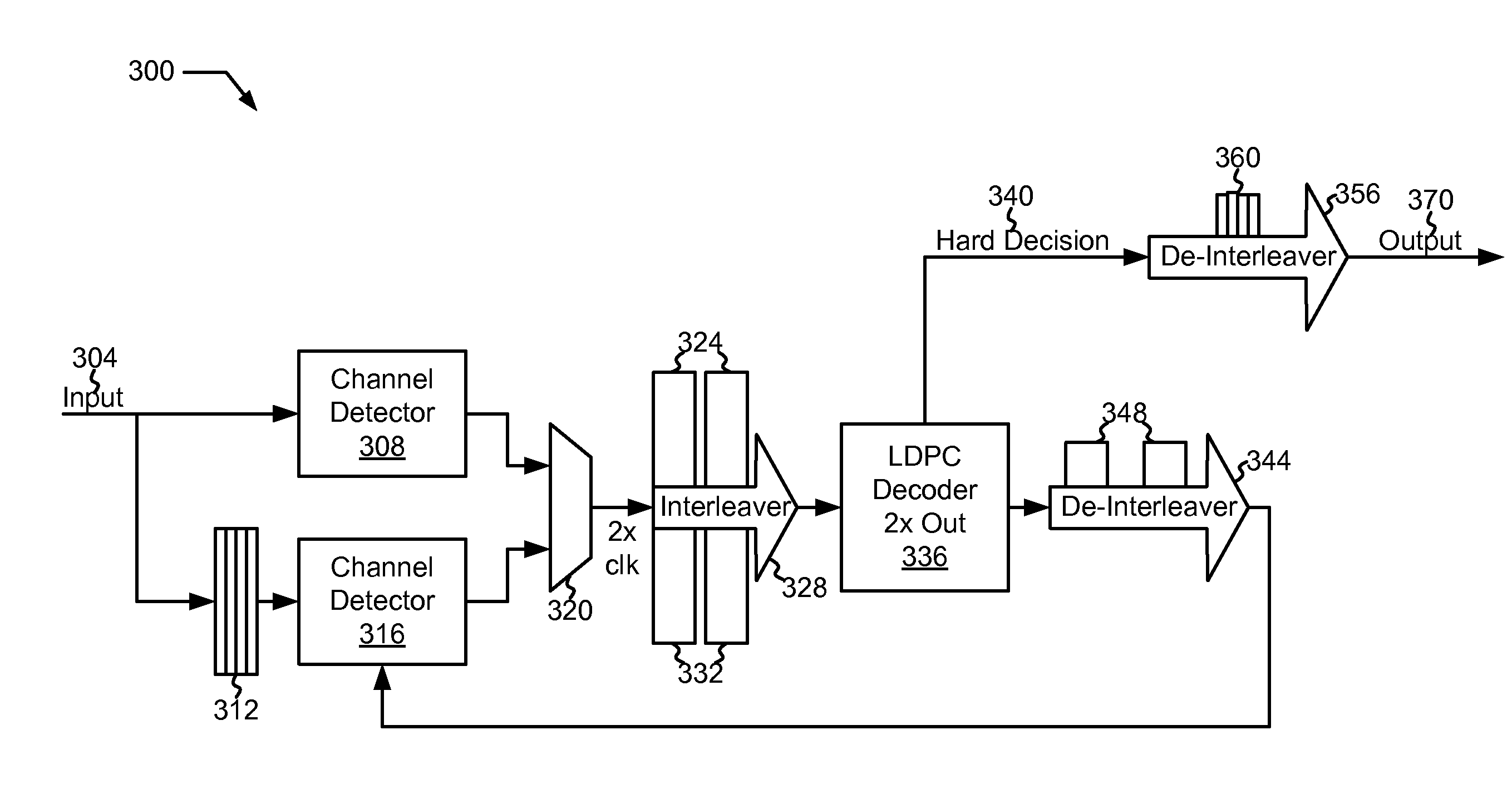

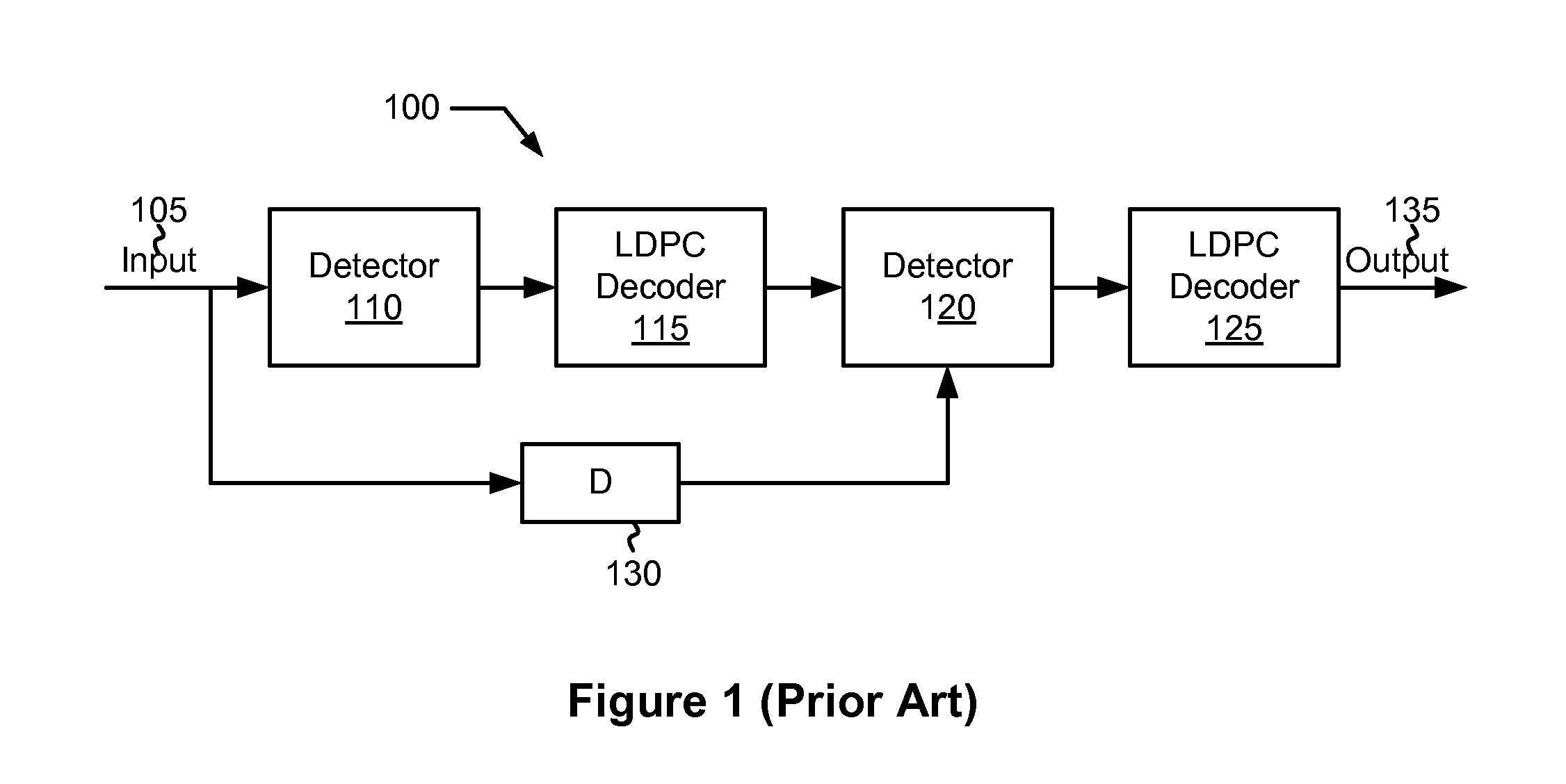

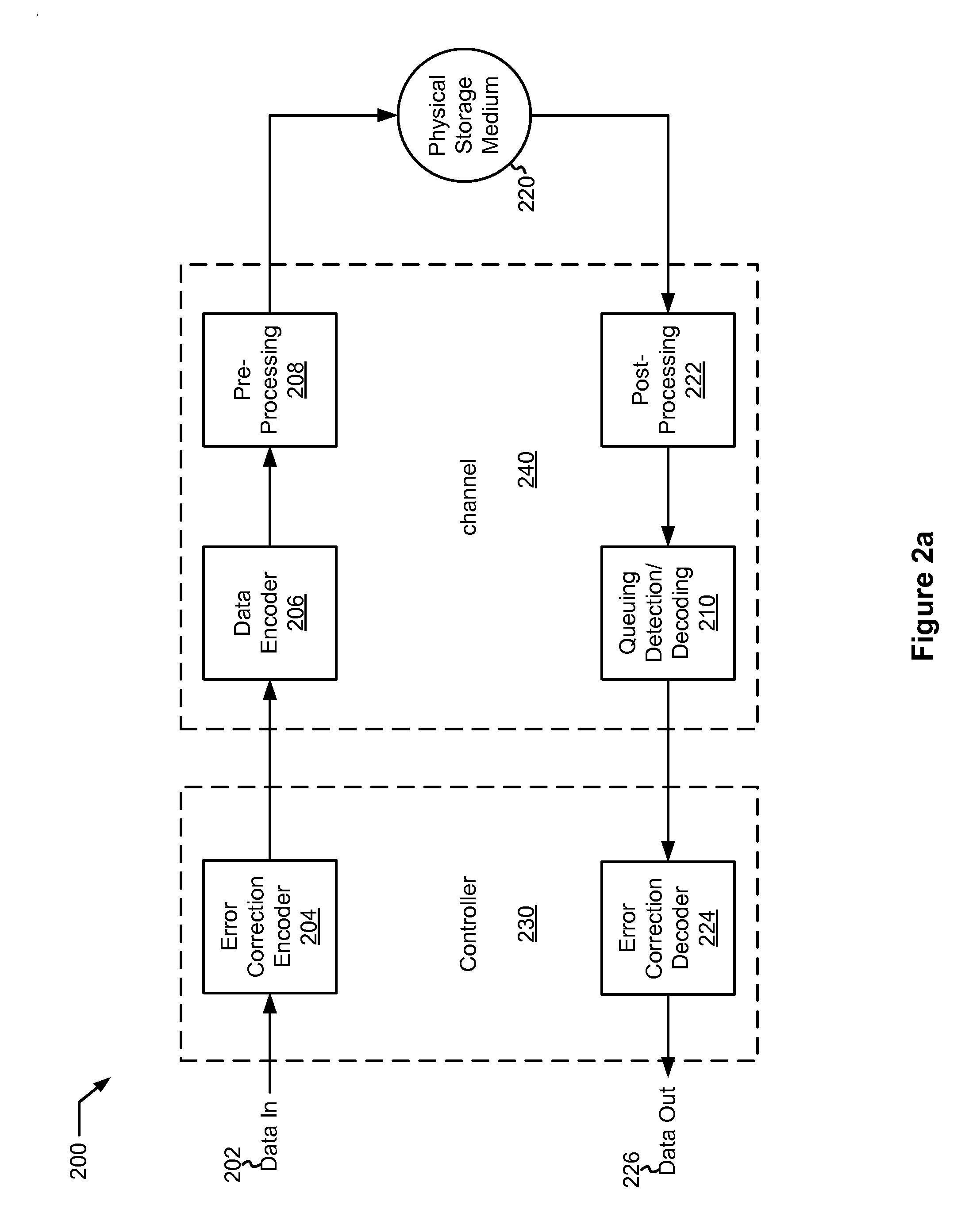

Systems and Methods for Queue Based Data Detection and Decoding

Various embodiments of the present invention provide systems and methods for data processing. For example, a variable iteration data processing system is disclosed that includes at least a first detector, a second detector, a decoder, and a queuing buffer. The first detector is operable to perform a data detection on an input data set at a first time. The decoder receives a derivation of an output from the first detector and performs a decoding process. Where the decoding process fails to converge, the decoder output is passed to the second detector for a subsequent detection and decoding process at a second time.

Owner:AVAGO TECH INT SALES PTE LTD

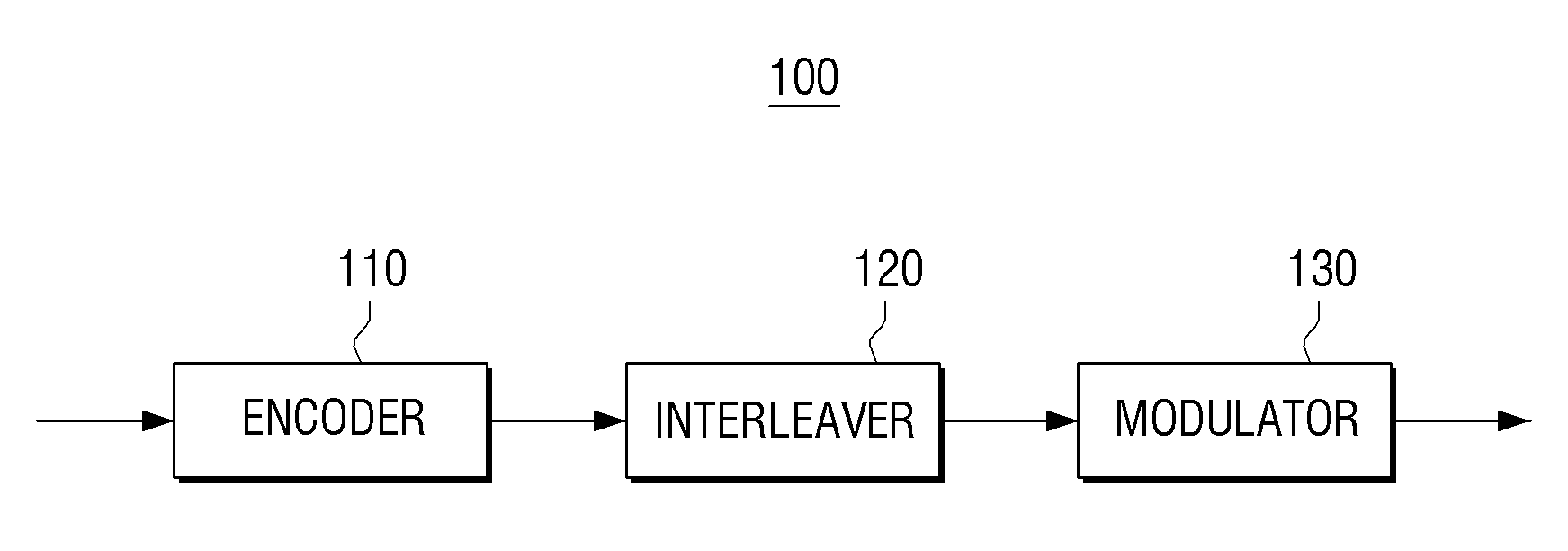

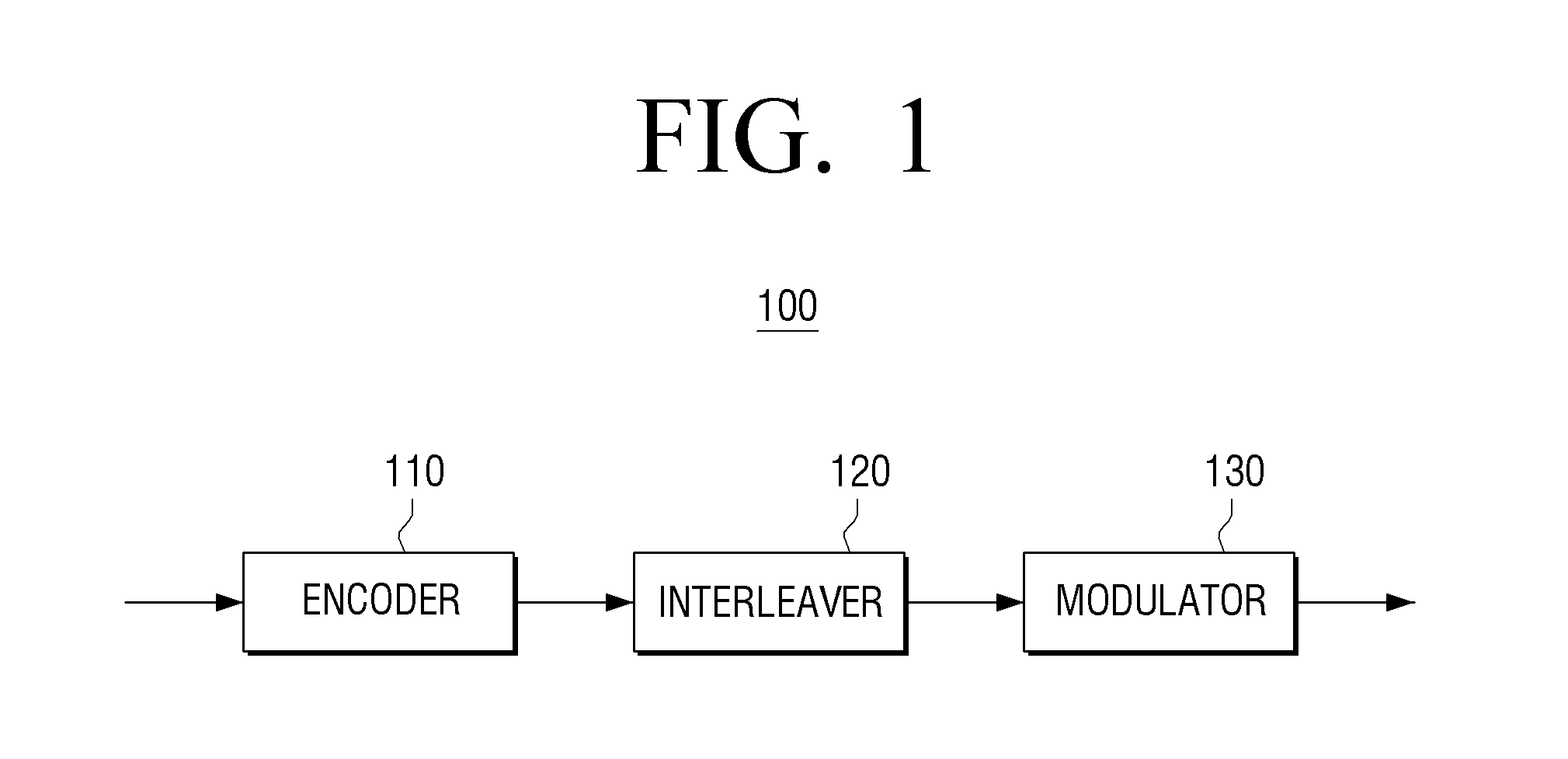

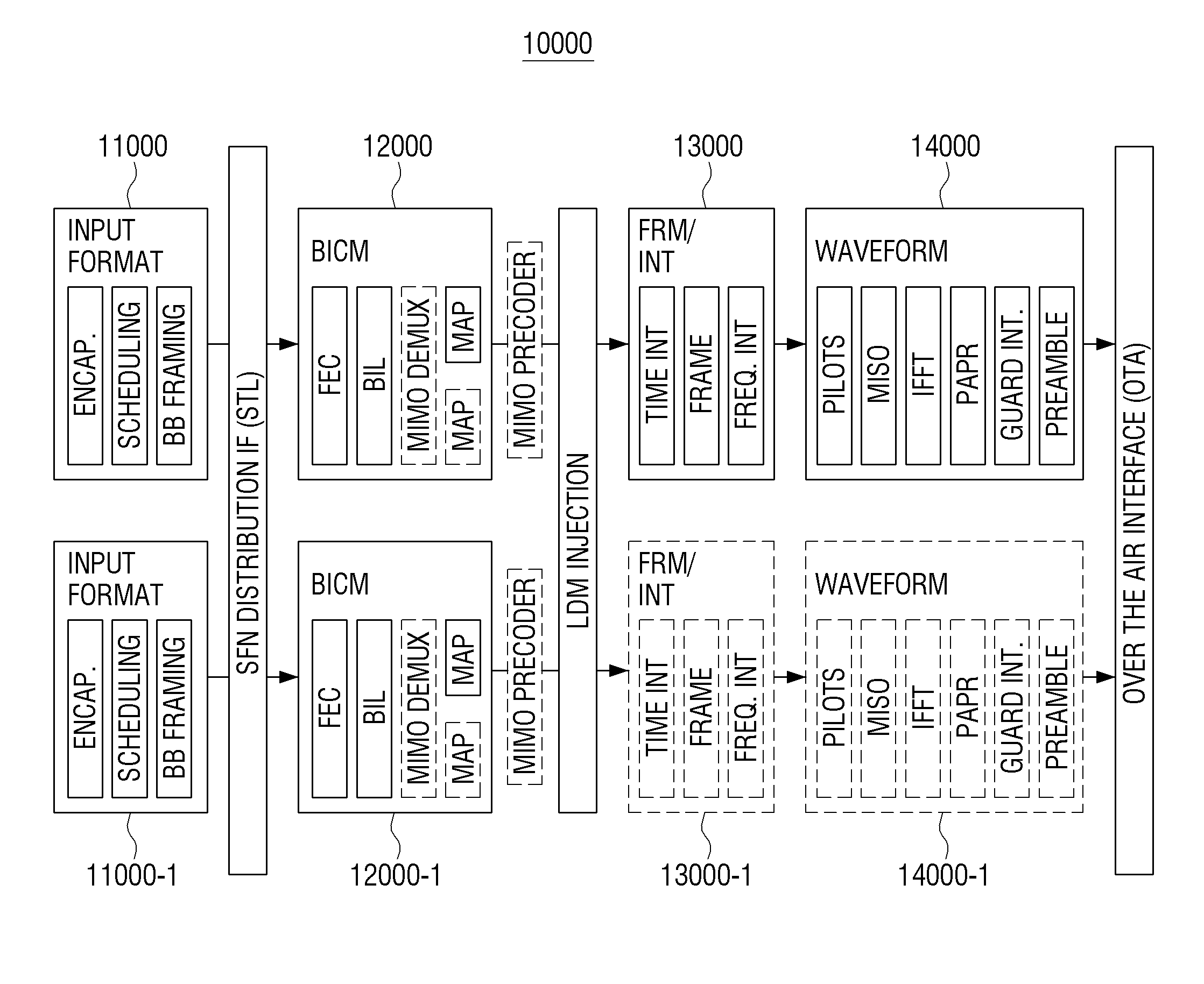

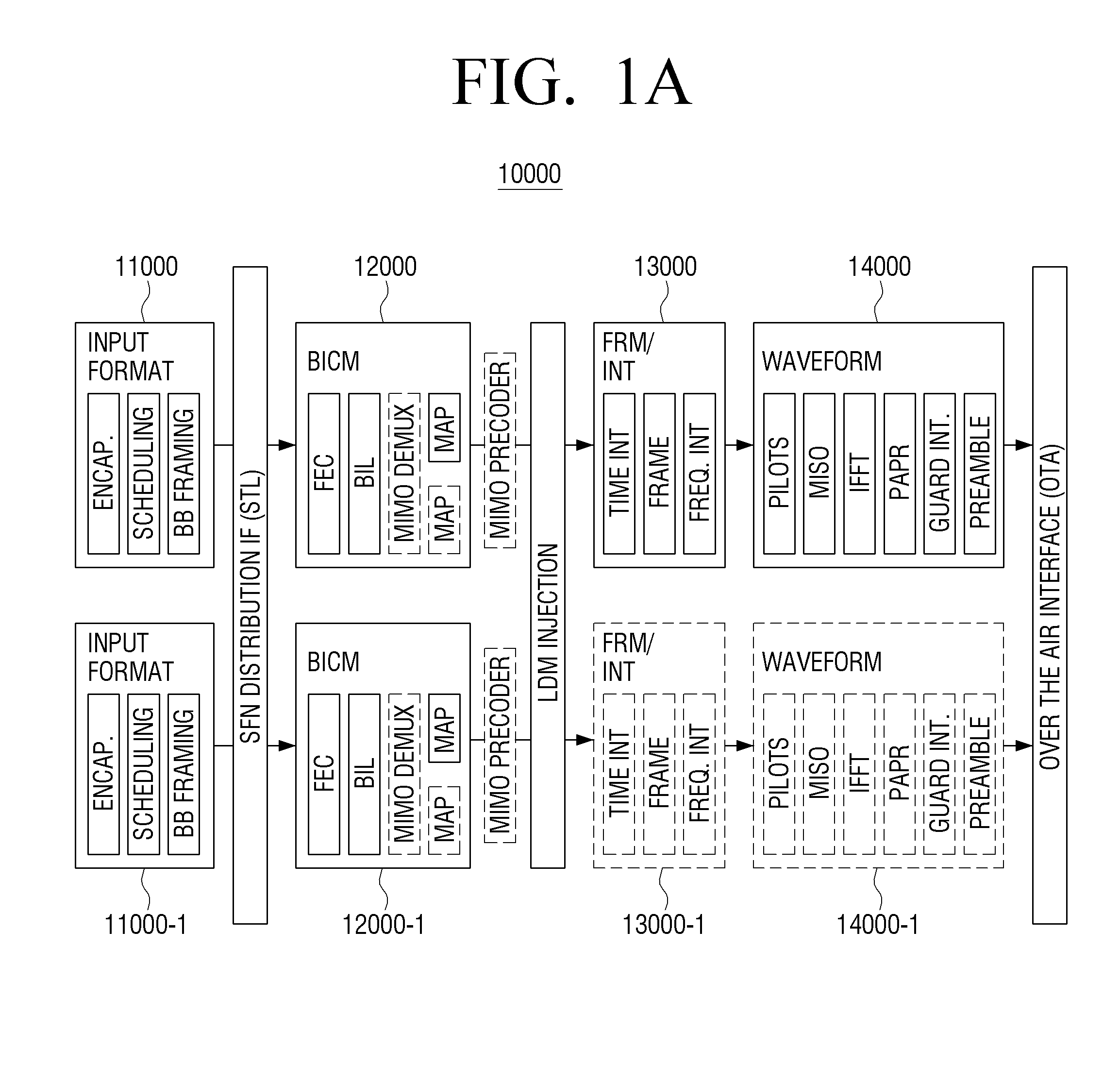

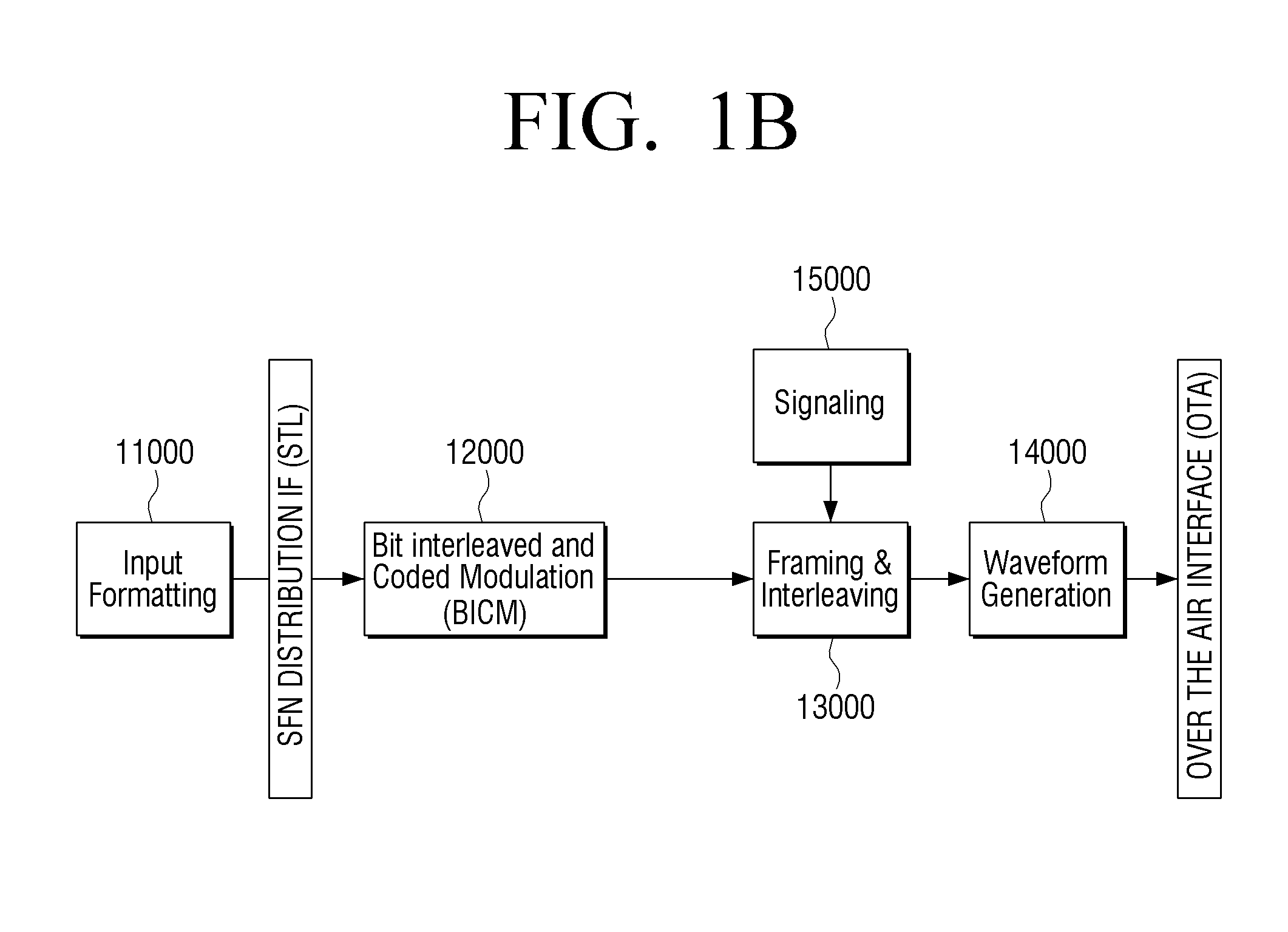

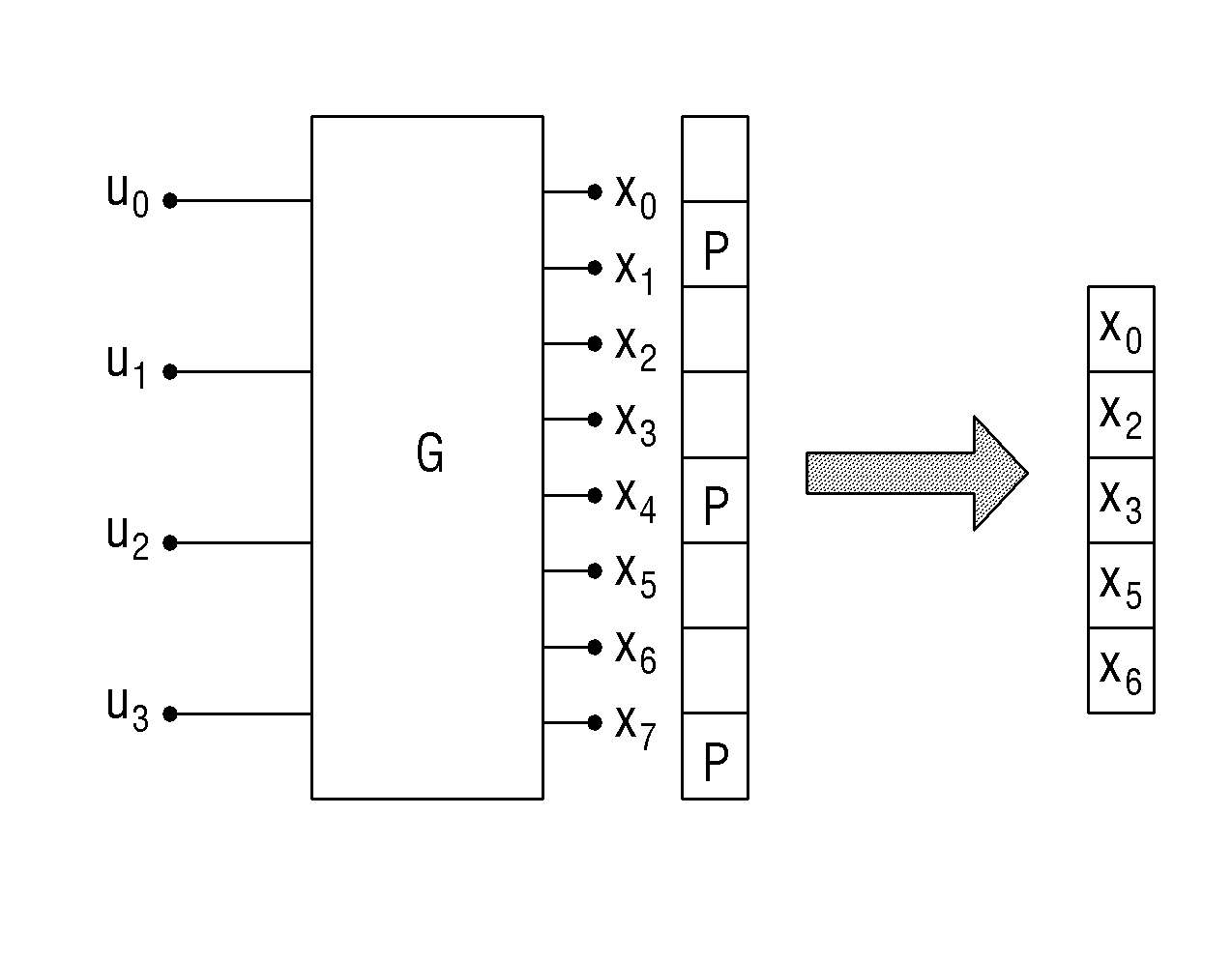

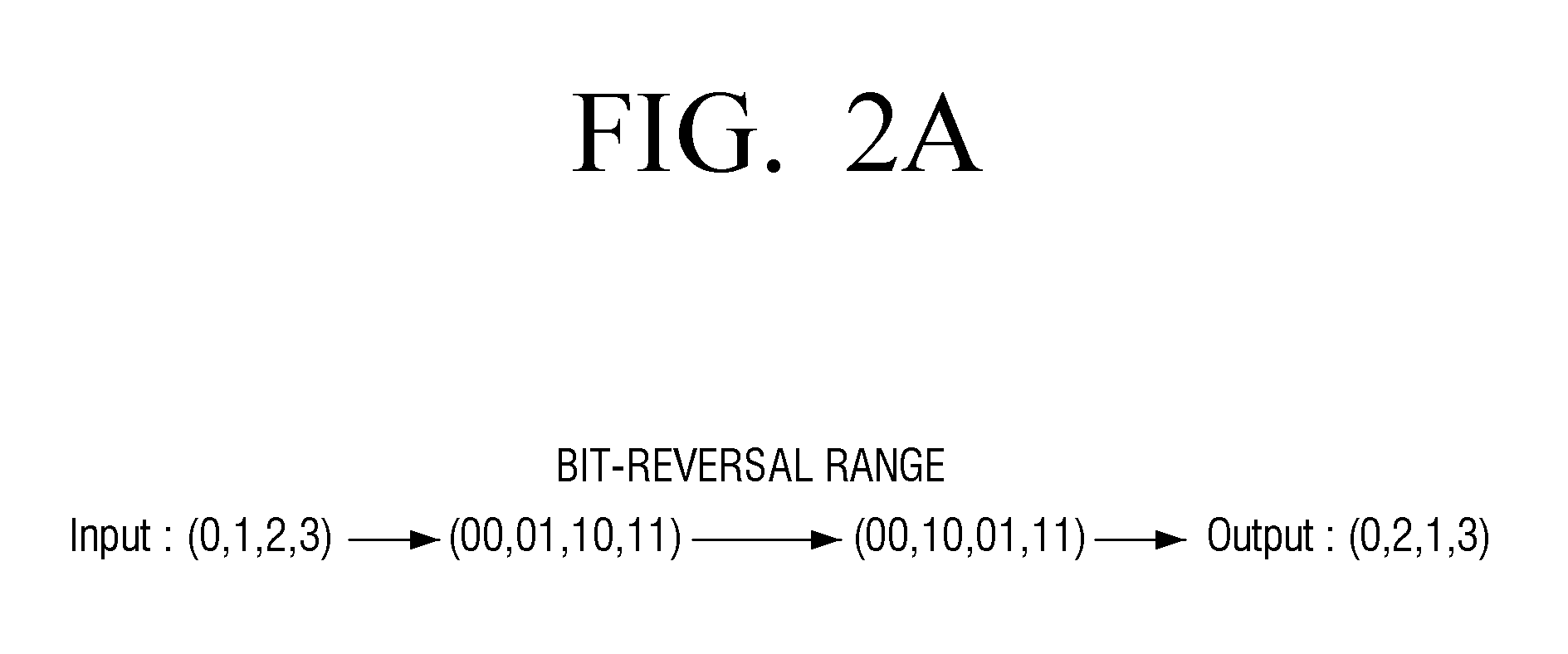

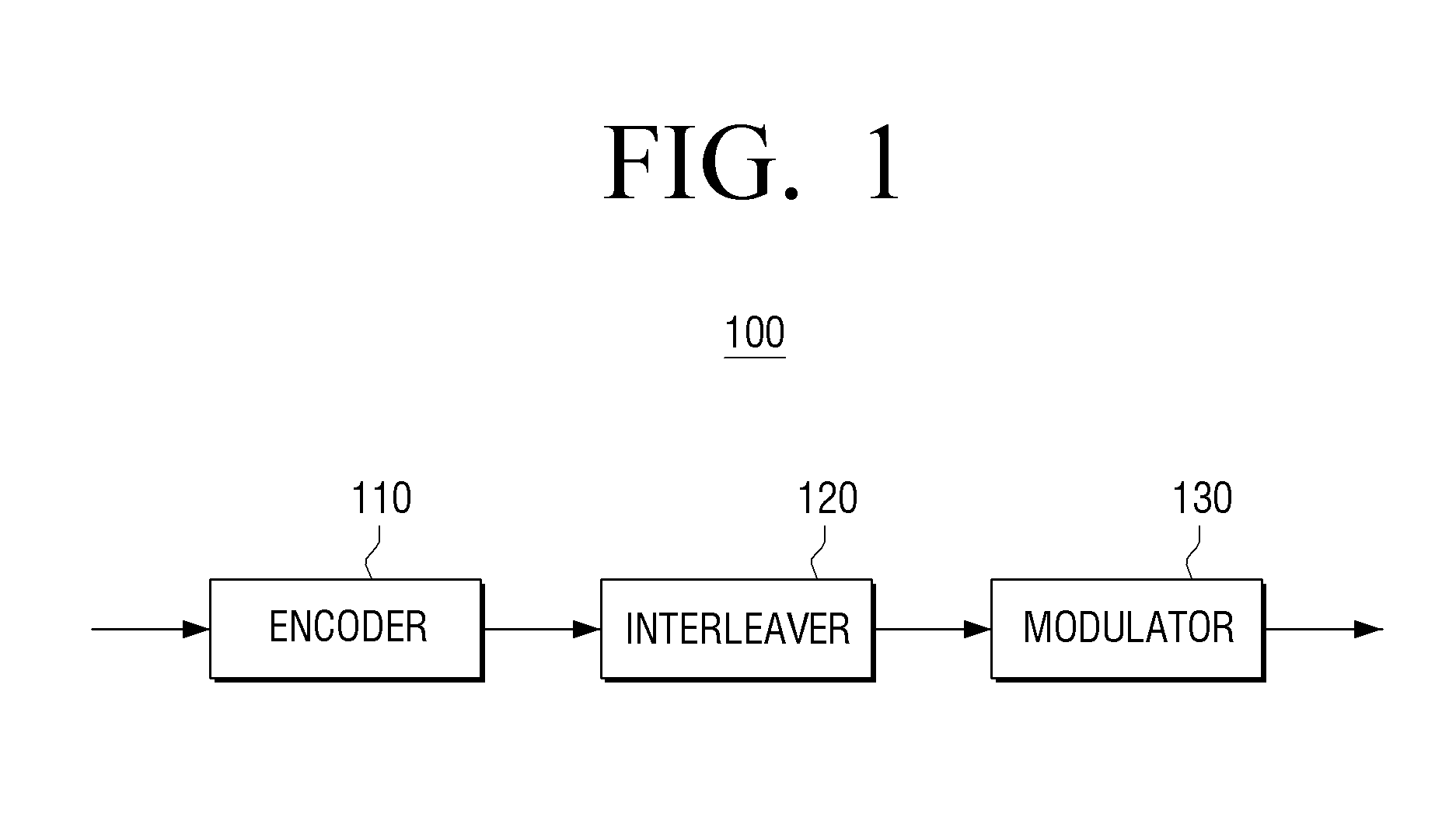

Transmitter apparatus and signal processing method thereof

ActiveUS20150039973A1Improve decoding performanceImprove reception performanceError correction/detection using LDPC codesError correction/detection using multiple parity bitsLow densityComputer science

A transmitter apparatus and a receiver apparatus are provided. The transmitter apparatus includes: an encoder configured to generate a low density parity check (LDPC) by performing LDPC encoding; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol. The modulator maps a bit included in a predetermined group from among a plurality of groups constituting the LDPC codeword onto a predetermined bit in the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

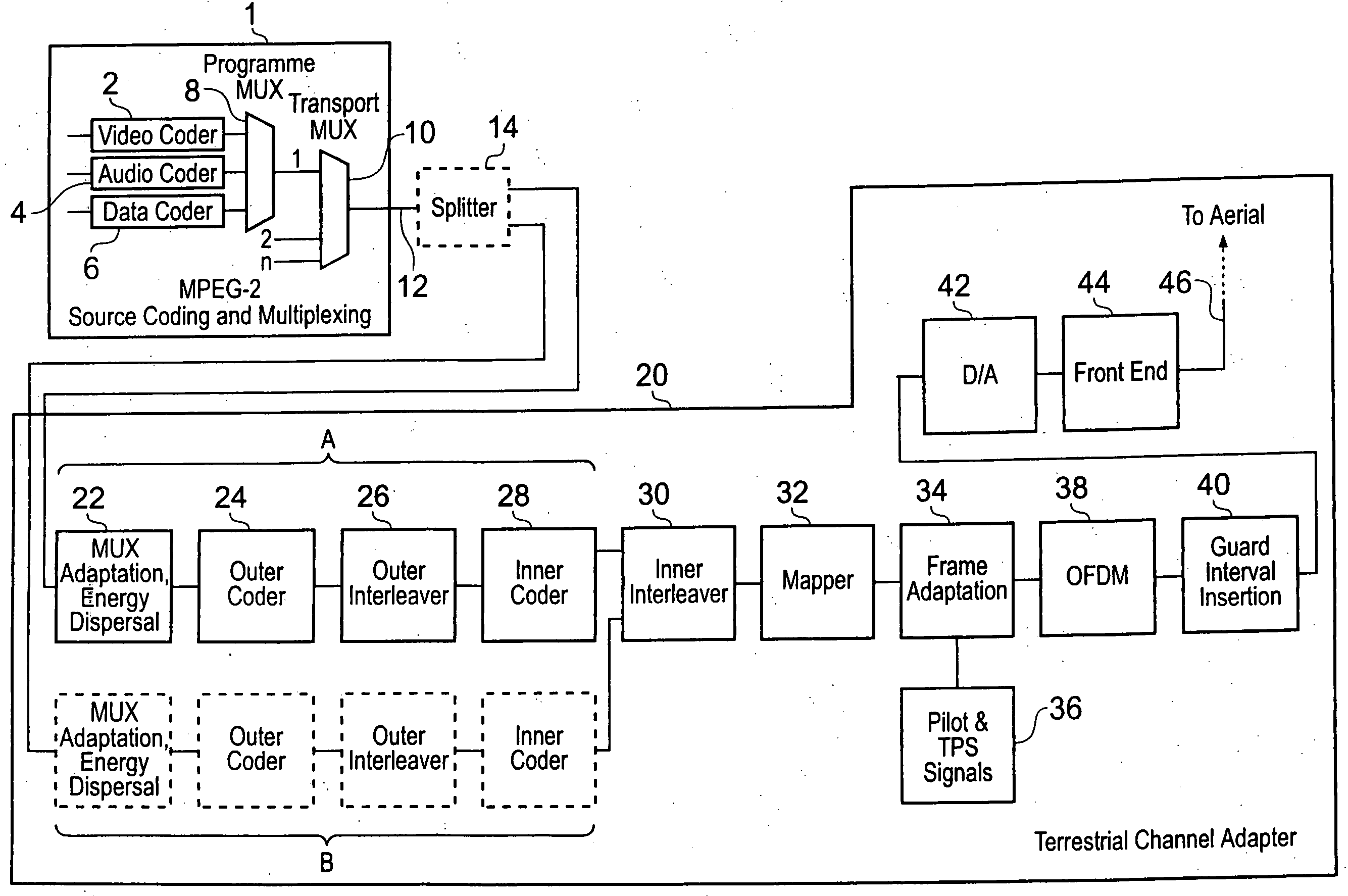

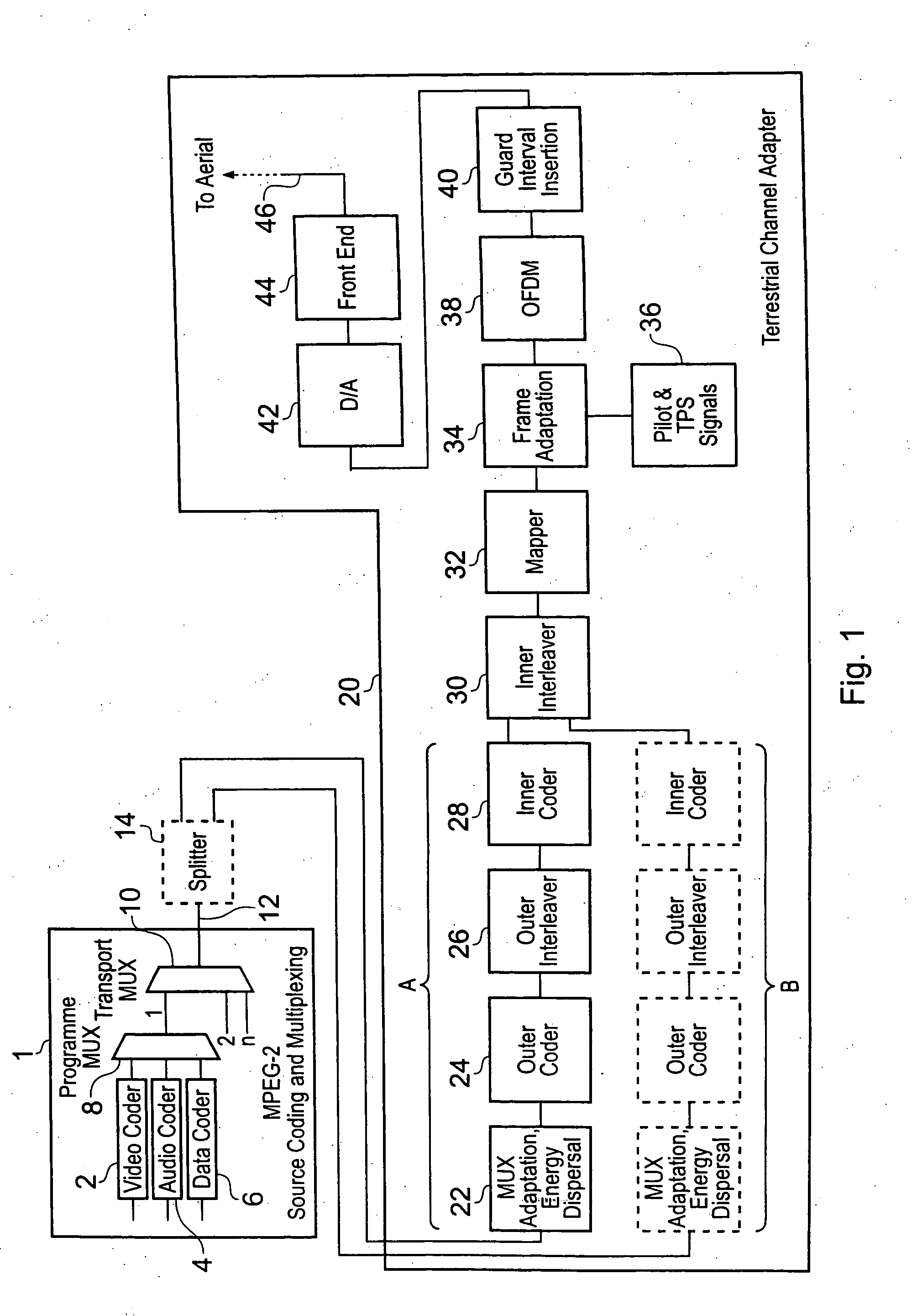

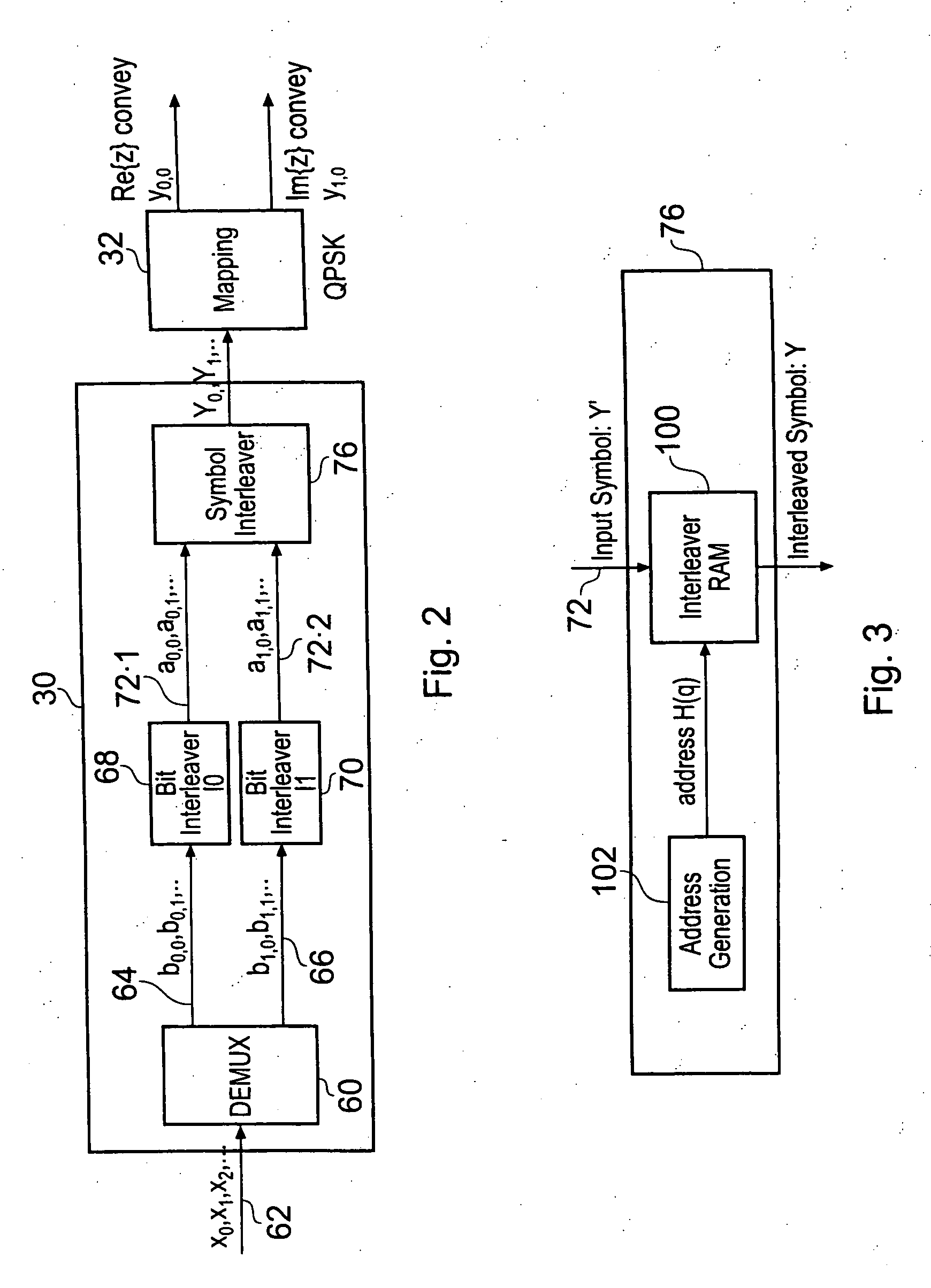

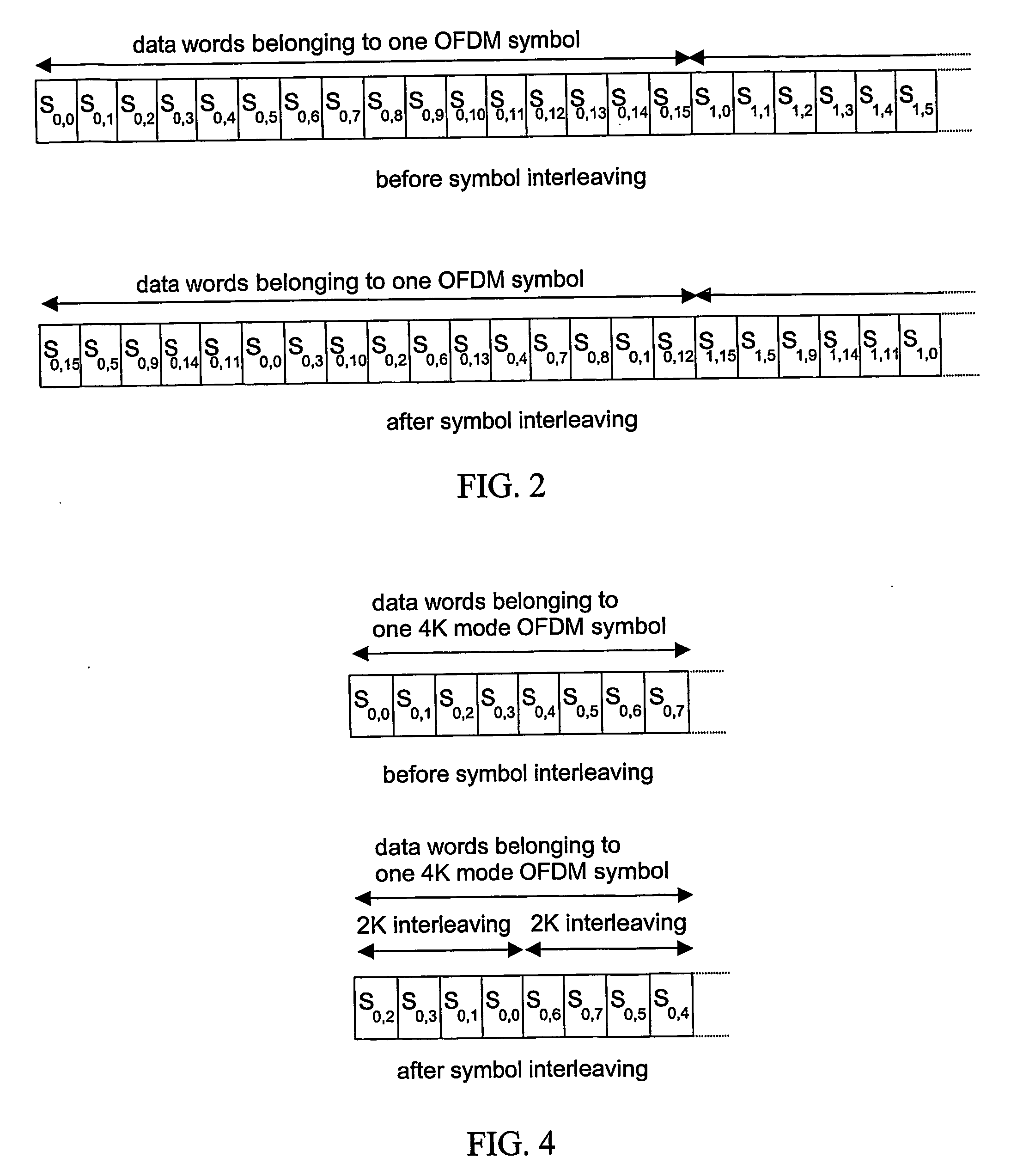

Data processing apparatus and method

ActiveUS20040246888A1Easy to receiveTrack time variationTelevision system detailsCode conversionCarrier signalAddress generator

A data processing apparatus maps input symbols to be communicated onto a predetermined number of carrier signals of an Orthogonal Frequency Division Multiplexed (OFDM) symbol. The data processor includes an interleaver memory which reads-in the predetermined number of data symbols for mapping onto the OFDM carrier signals. The interleaver memory reads-out the data symbols on to the OFDM carriers to effect the mapping, the read-out being in a different order than the read-in, the order being determined from a set of addresses, with the effect that the data symbols are interleaved on to the carrier signals. The set of addresses are generated from an address generator which comprises a linear feedback shift register and a permutation circuit. In order to provide a 4 k mode for an OFDM modulated system such as a Digital Video Broadcasting (DVB) standard such as DVB-Terrestrial (DVB-T) or DVB-Handheld (DVB-H) standards, a generator polynomial for the linear feedback shift register of Ri'[10]=Ri-1'[0]⊕Ri-1'[2] is provided with a permutation order which has been established by simulation analysis to optimise communication performance via typical radio channels.

Owner:SONY EUROPE BV

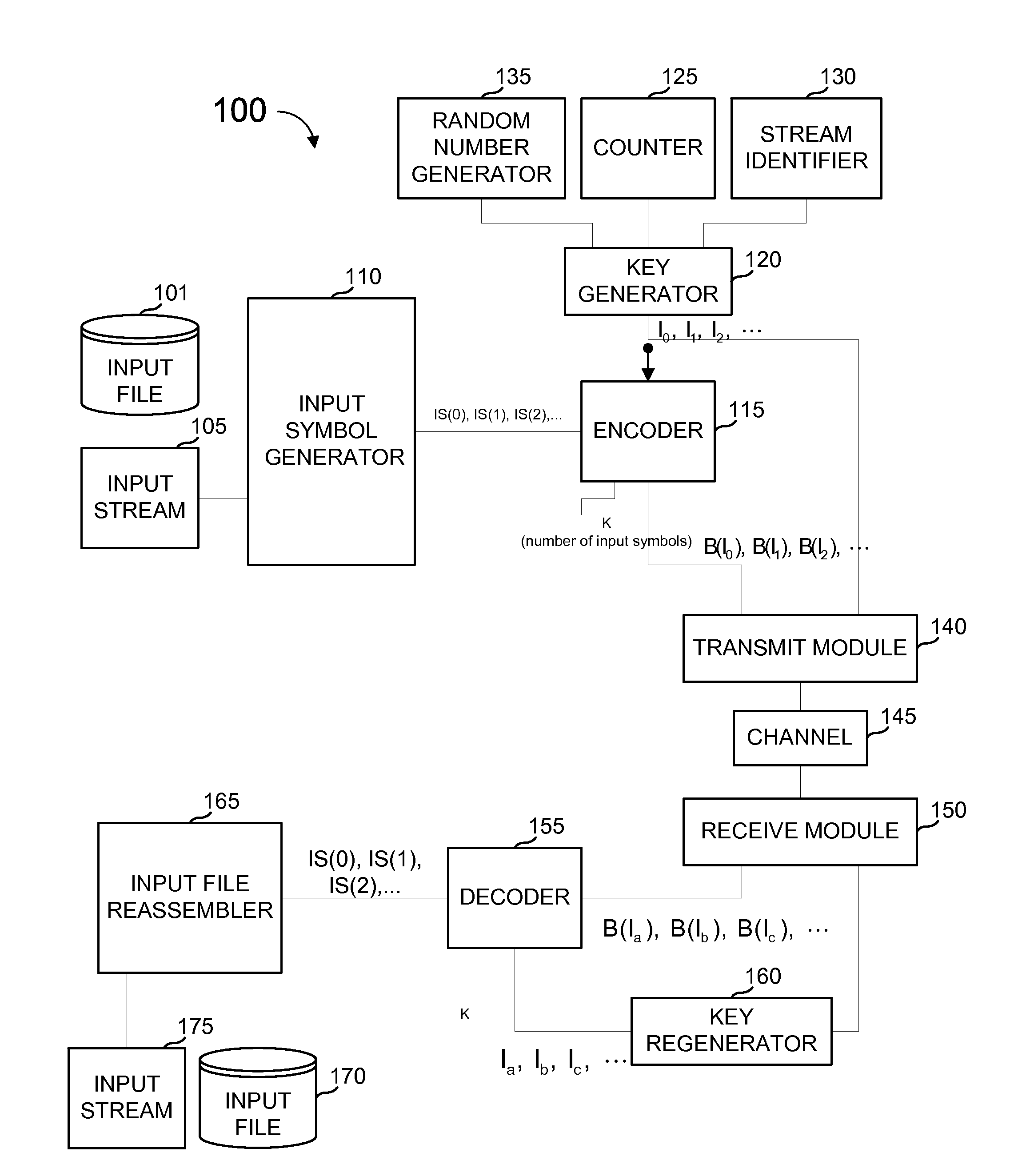

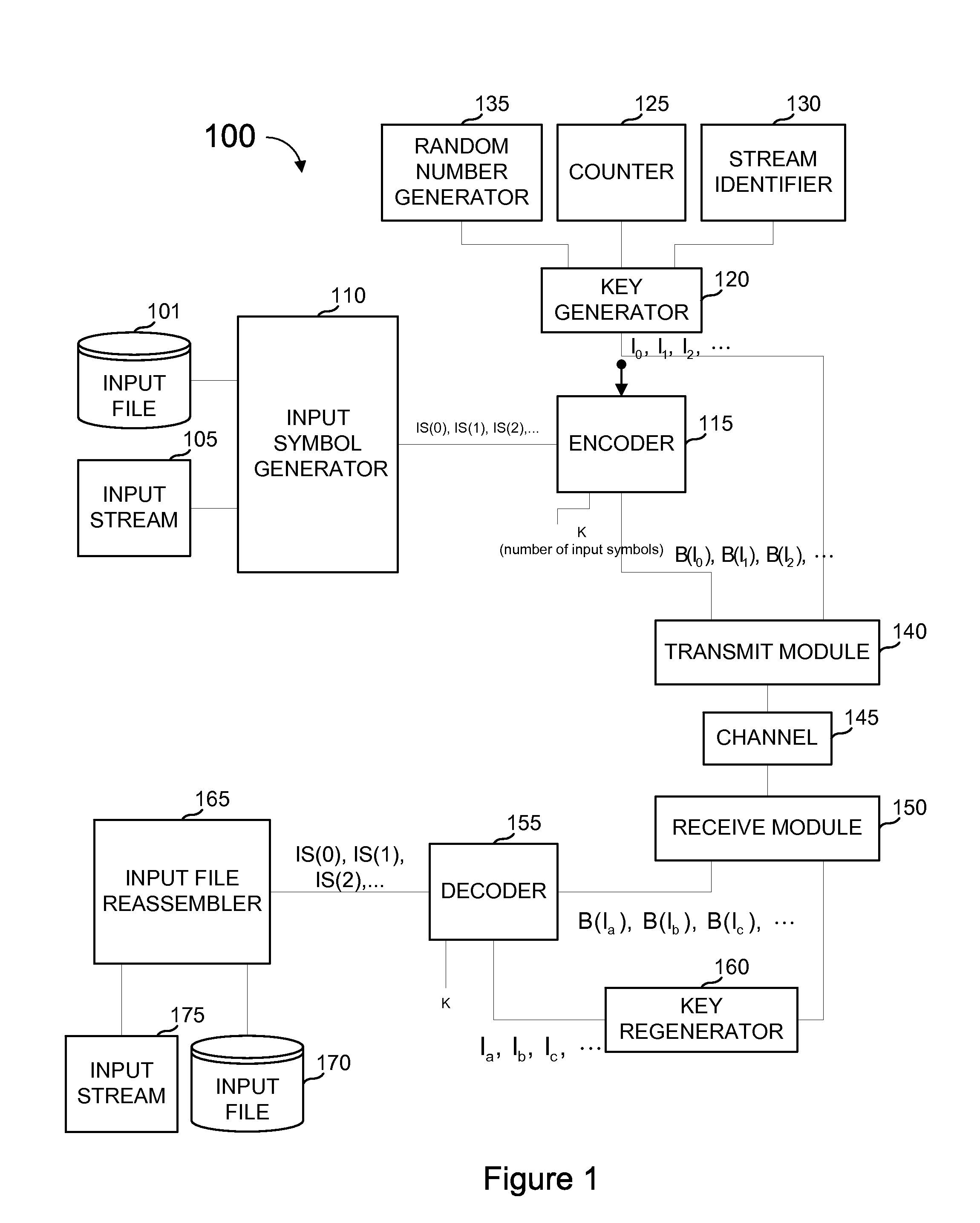

Dynamic stream interleaving and sub-stream based delivery

ActiveUS20080256418A1Convenient amountLoss of protectionFault responseCode conversionPacket lossCommunications system

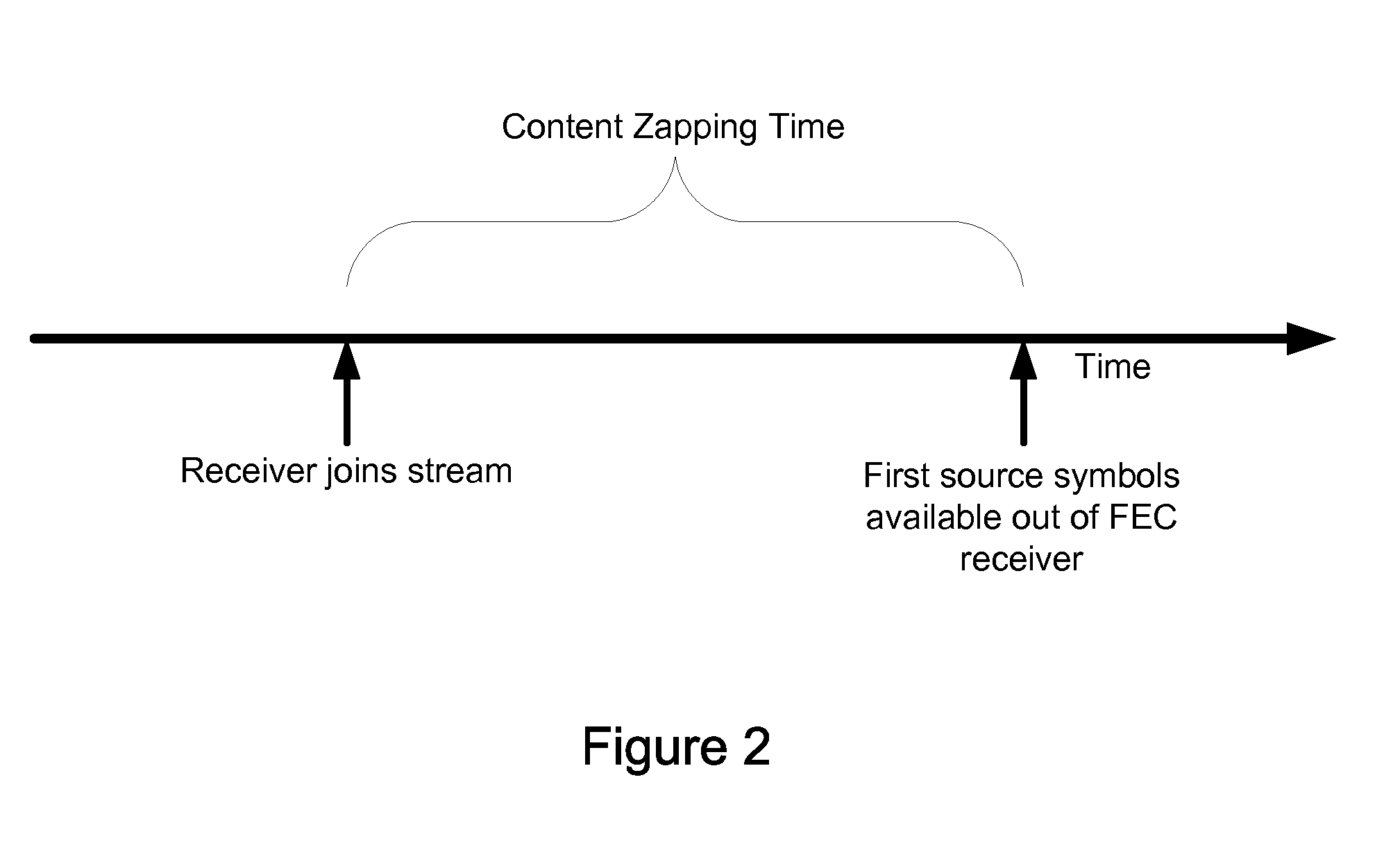

A communications system can provide methods of dynamically interleaving streams, including methods for dynamically introducing greater amounts of interleaving as a stream is transmitted independently of any source block structure to spread out losses or errors in the channel over a much larger period of time within the original stream than if interleaving were not introduced, provide superior protection against packet loss or packet corruption when used with FEC coding, provide superior protection against network jitter, and allow content zapping time and the content transition time to be reduced to a minimum and minimal content transition times. Streams may be partitioned into sub-streams, delivering the sub-streams to receivers along different paths through a network and receiving concurrently different sub-streams at a receiver sent from potentially different servers. When used in conjunction with FEC encoding, the methods include delivering portions of an encoding of each source block from potentially different servers.

Owner:QUALCOMM INC

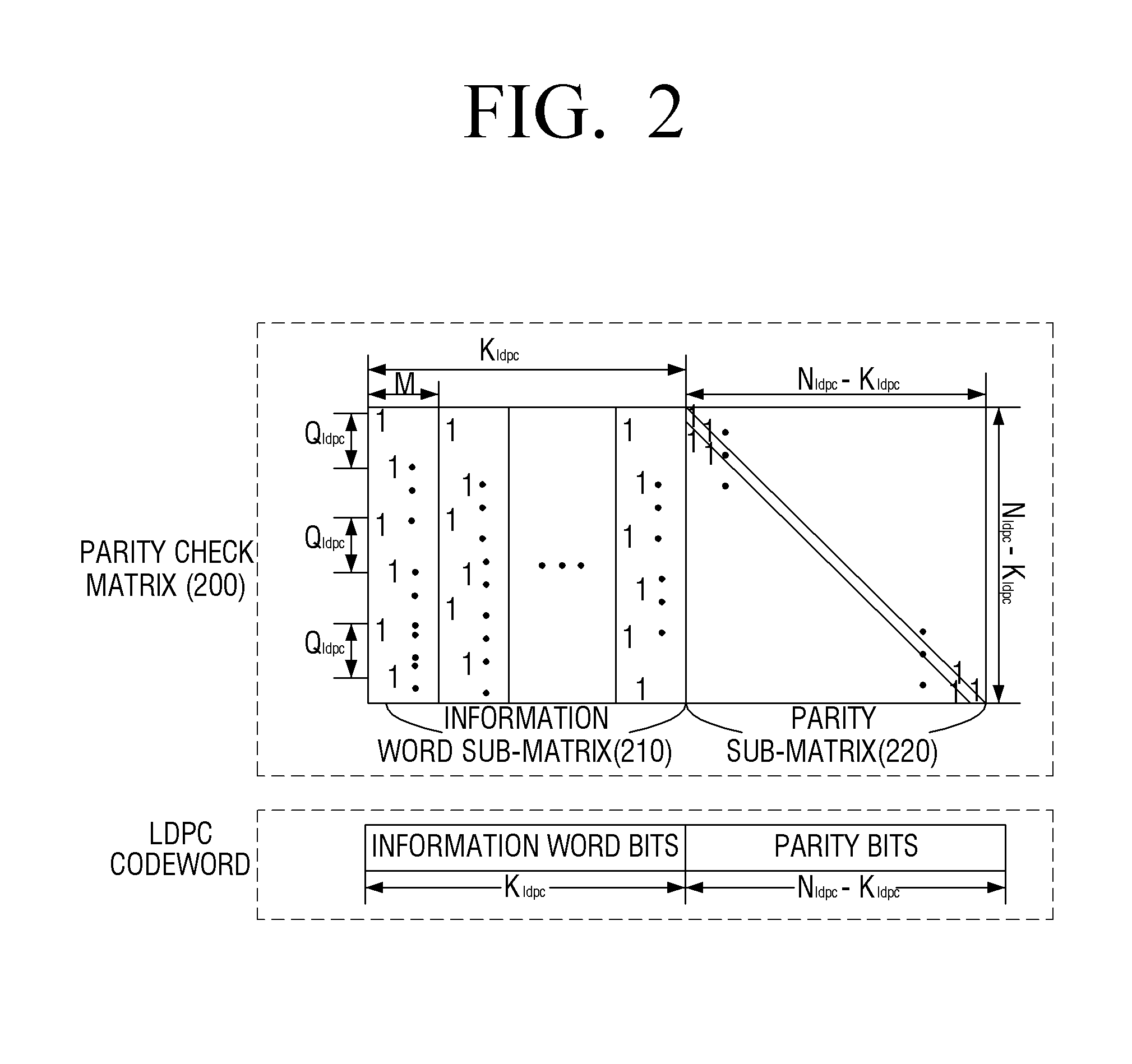

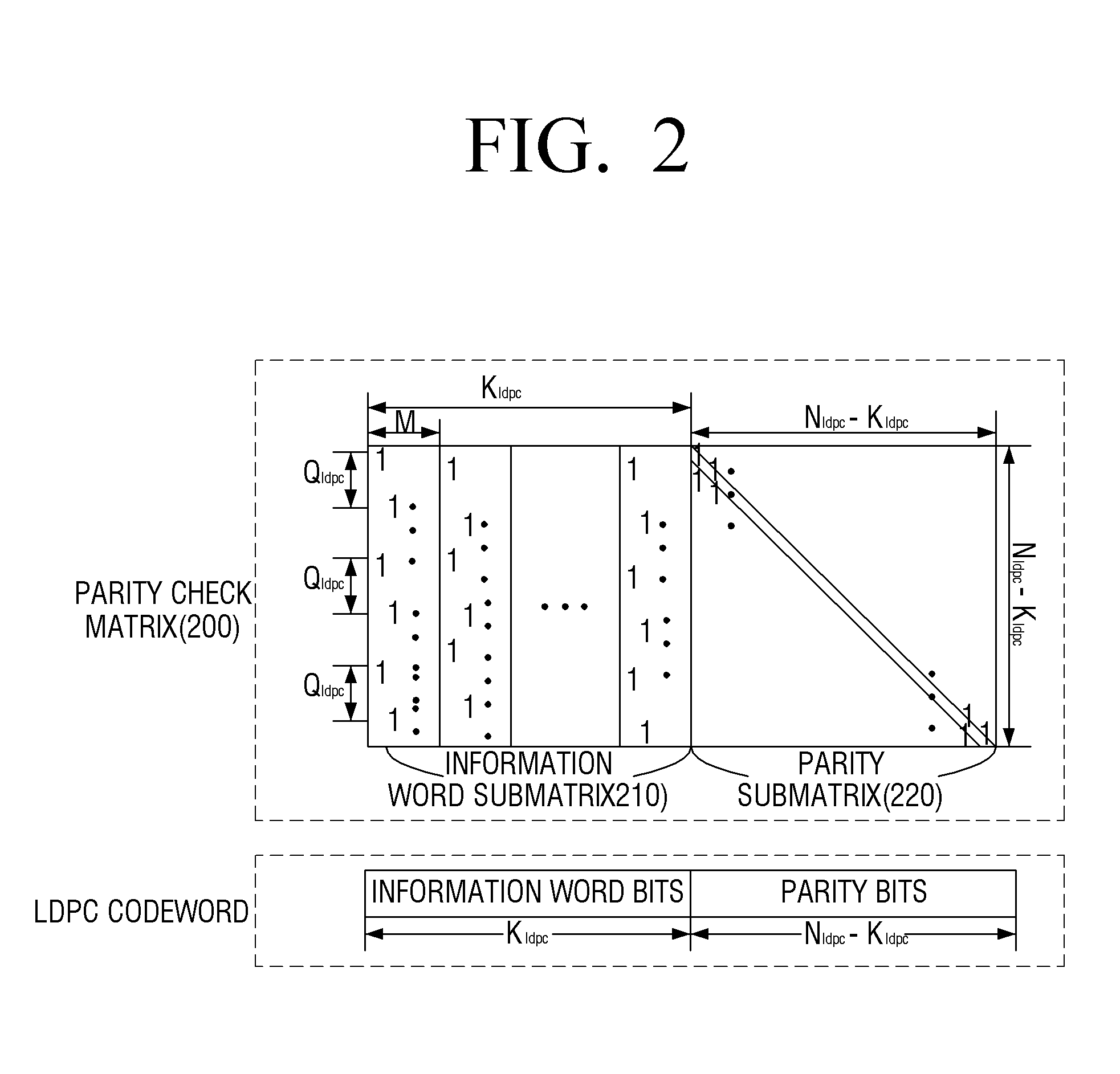

Transmitter apparatus and interleaving method thereof

ActiveUS20150236816A1Improve decoding performanceImprove reception performanceModulated-carrier systemsError correction/detection using LDPC codesComputer hardwareParity-check matrix

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to generate a low-density parity check (LDPC) codeword by LDPC encoding based on a parity check matrix; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the modulator is further configured to map a bit included in a predetermined bit group from among a plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

Bit labeling for amplitude phase shift constellation used with low density parity check (LDPC) codes

InactiveUS6963622B2Improve performanceError correction/detection using LDPC codesCode conversionParity-check matrixEngineering

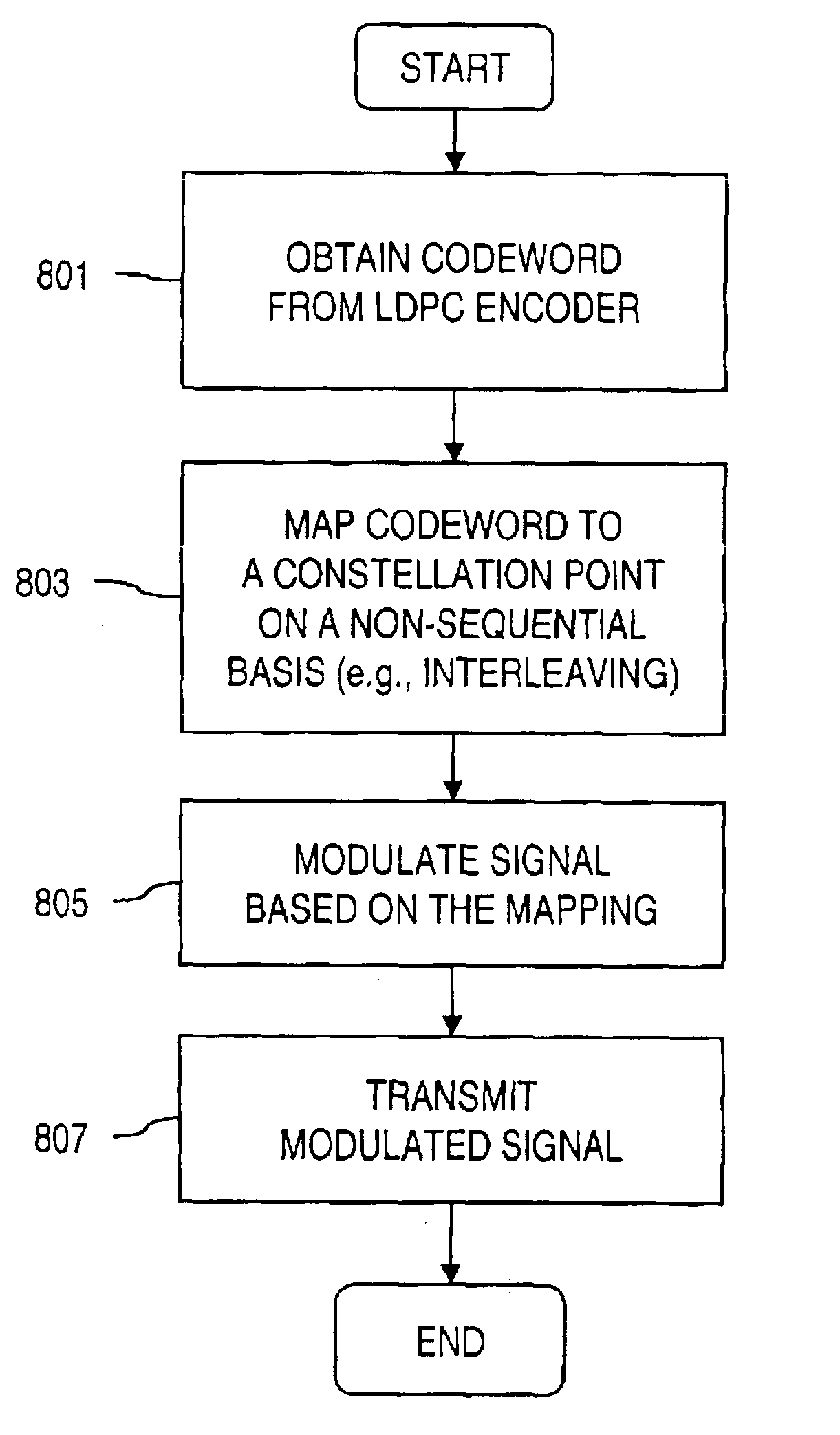

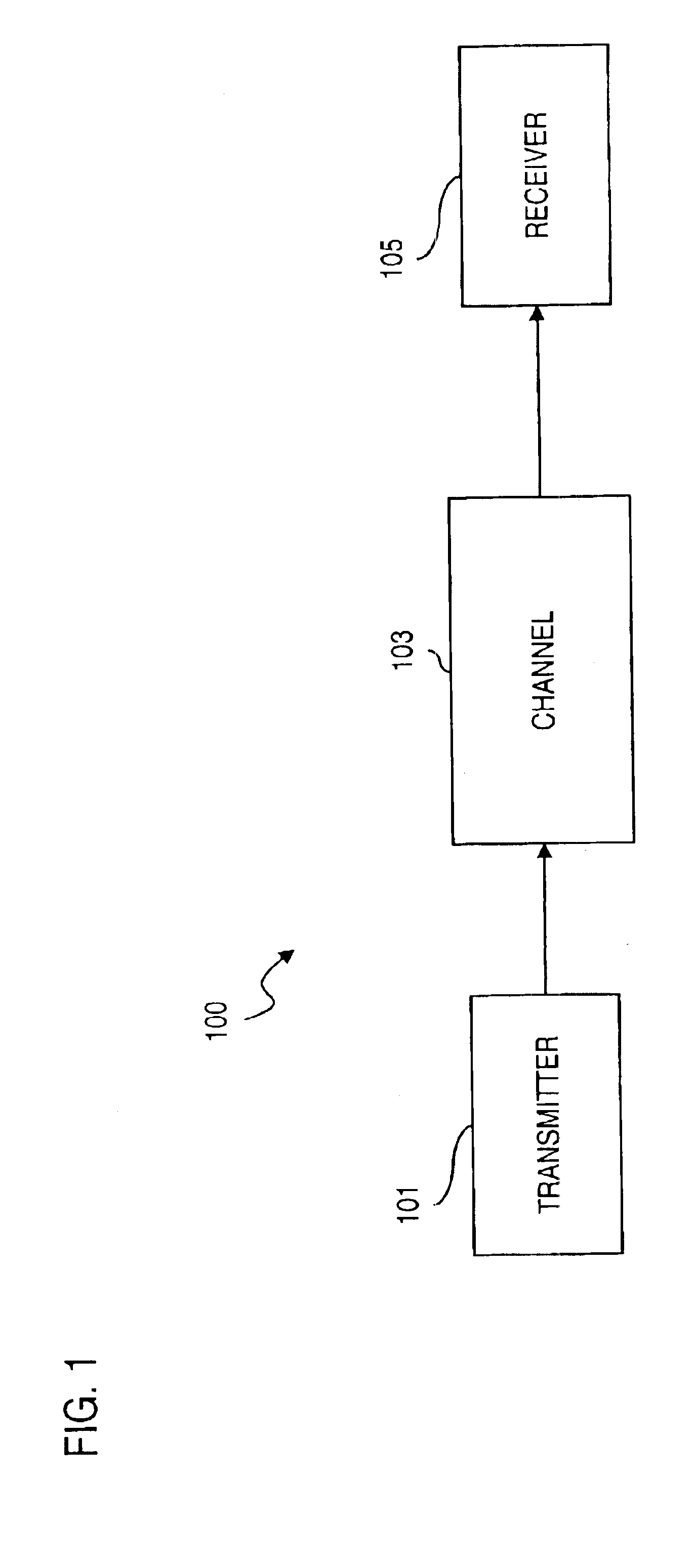

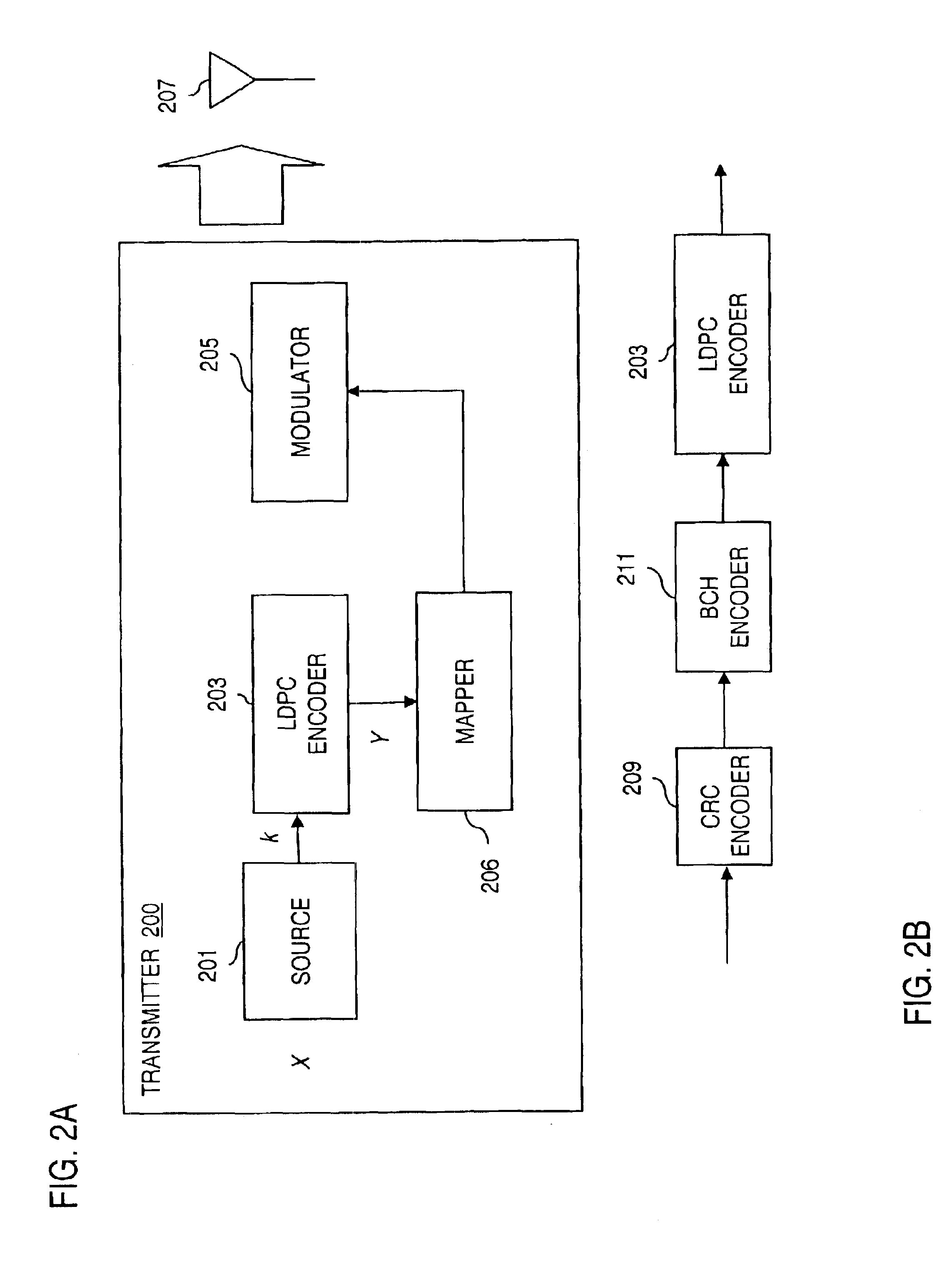

An approach is provided for bit labeling of a signal constellation. A transmitter generates encoded signals using, according to one embodiment, a structured parity check matrix of a Low Density Parity Check (LDPC) code. The transmitter includes an encoder for transforming an input message into a codeword represented by a plurality of set of bits. The transmitter includes logic for mapping non-sequentially (e.g., interleaving) one set of bits into a higher order constellation (Quadrature Phase Shift Keying (QPSK), 8-PSK, 16-APSK (Amplitude Phase Shift Keying), 32-APSK, etc.), wherein a symbol of the higher order constellation corresponding to the one set of bits is output based on the mapping.

Owner:DTVG LICENSING INC

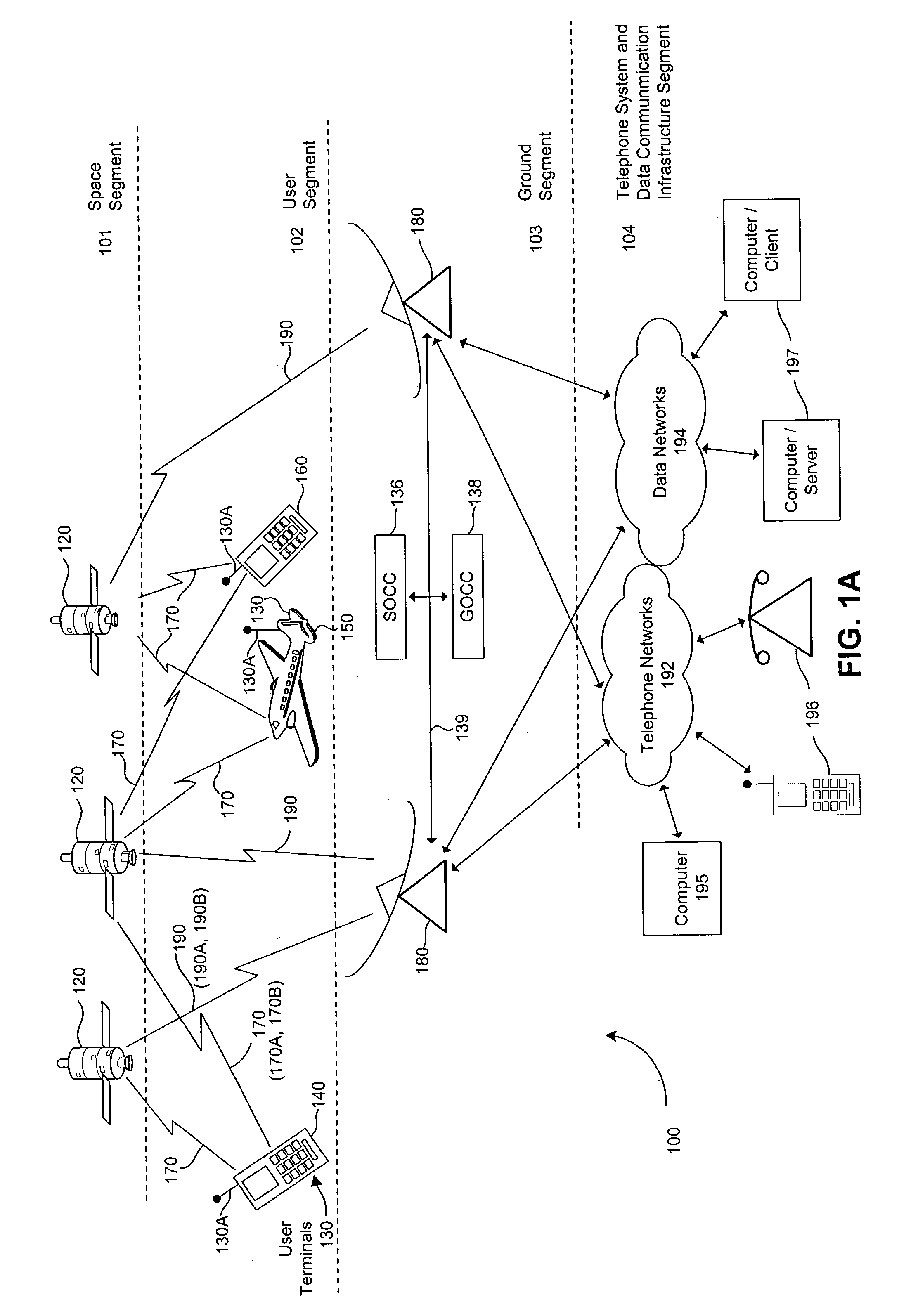

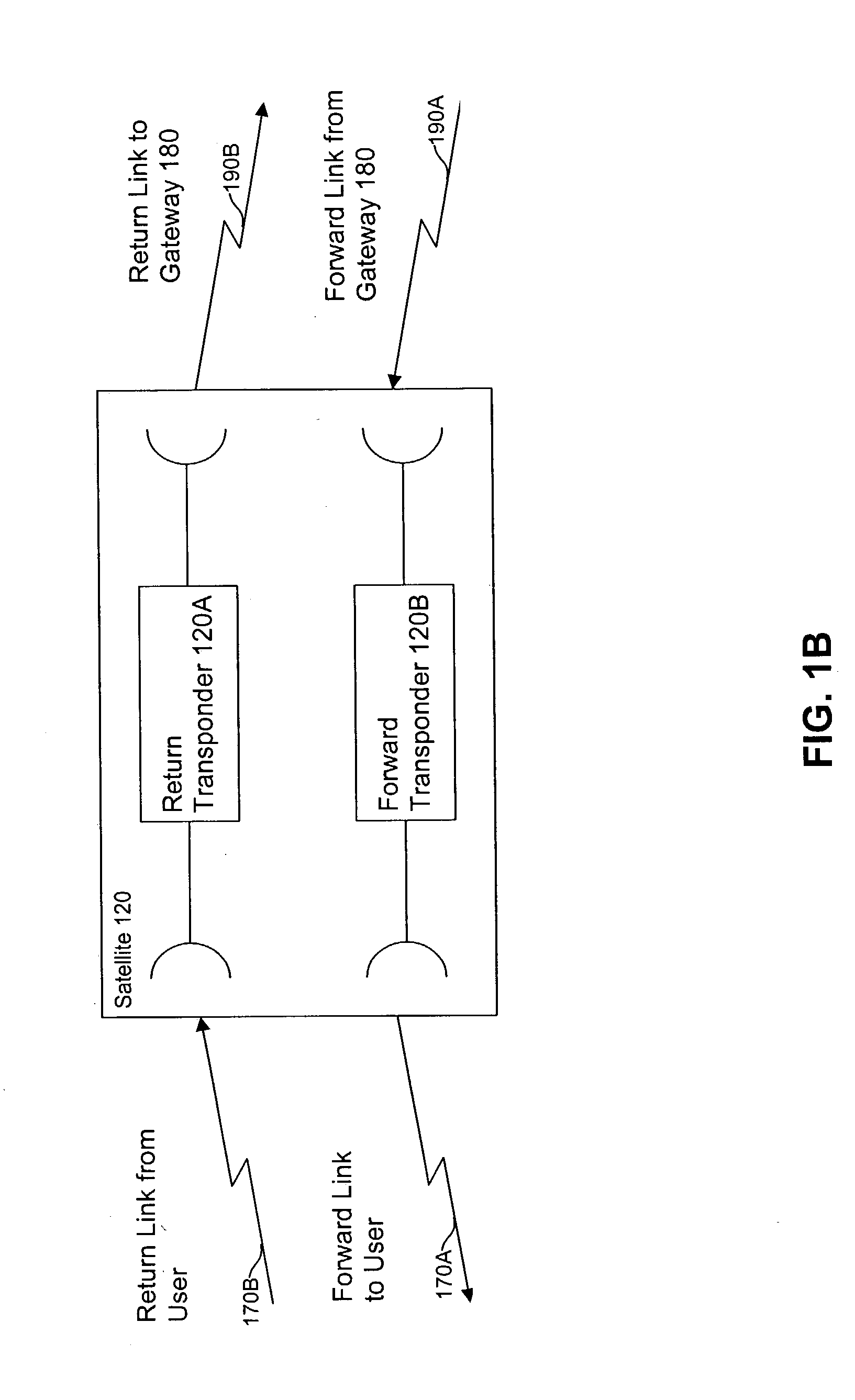

Aggregating multiple wireless communication channels for high data rate transfers

InactiveUS20030081582A1Appropriate performancePulse modulation television signal transmissionTelevision system scanning detailsNetwork connectionComputer terminal

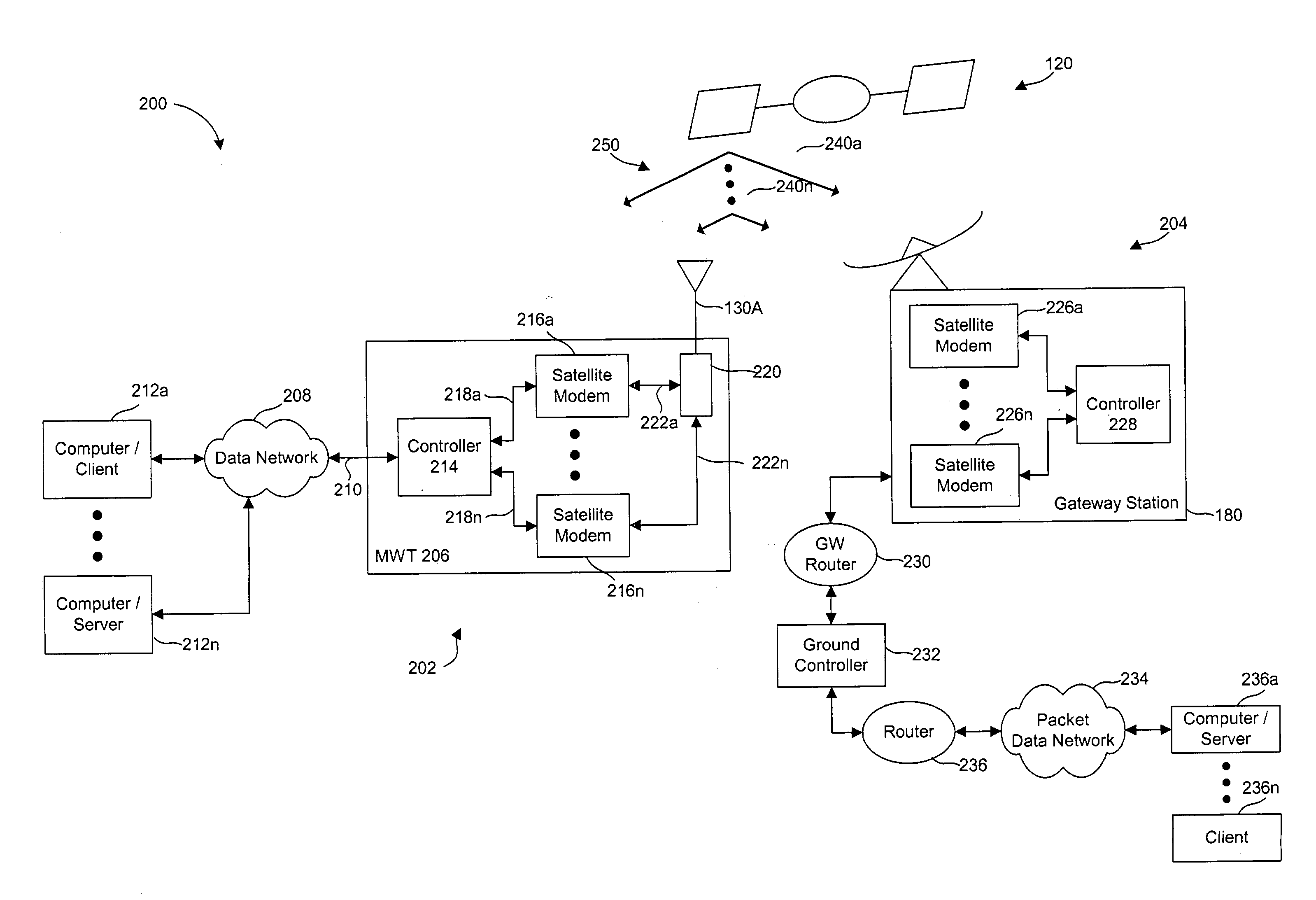

A mobile wireless terminal (MWT) receives IP packets destined for a ground network in a predetermined sequence order. The MWT fragments each of the IP packets into many smaller packet fragments, appends identifying information to each of the packet fragments, and transmits the packet fragments in parallel with one another over concurrently operating satellite channels. A receiving station receives the packet fragments transmitted by the MWT. The receiving station forwards the received packet fragments to a ground controller over a network connection, based on the identifying information appended to the packet fragments. The ground controller combines the packet fragments into reconstructed IP packets based on the identifying information appended to the fragments. The ground controller also sequences the reconstructed IP packets in the predetermined sequence order based on the identifying information. The ground controller forwards the reconstructed IP packets in the correct sequence order to the destination ground network. The same sequence of events occur in the opposite direction as well i.e., from the ground controller to the MWT.

Owner:QUALCOMM INC

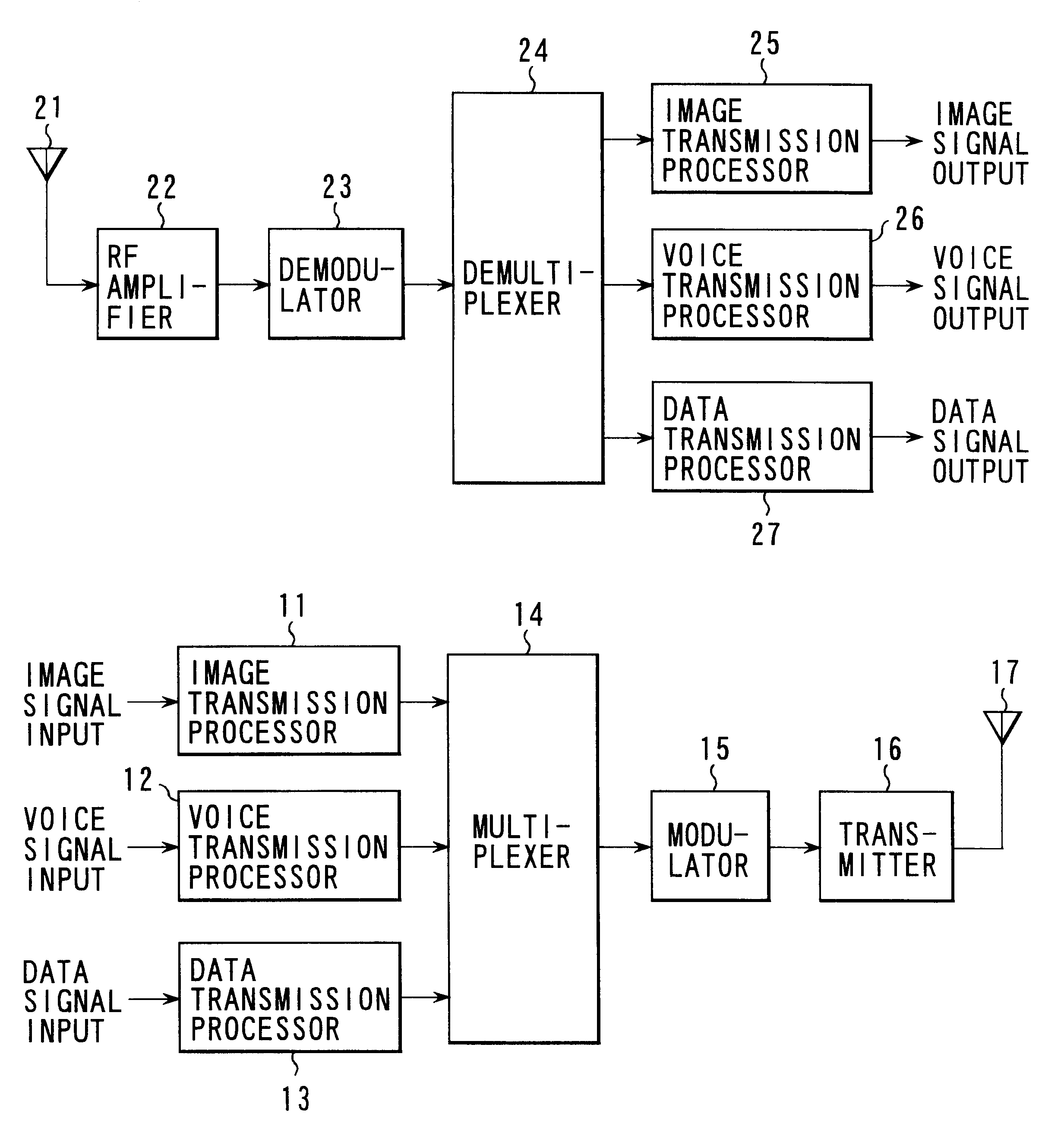

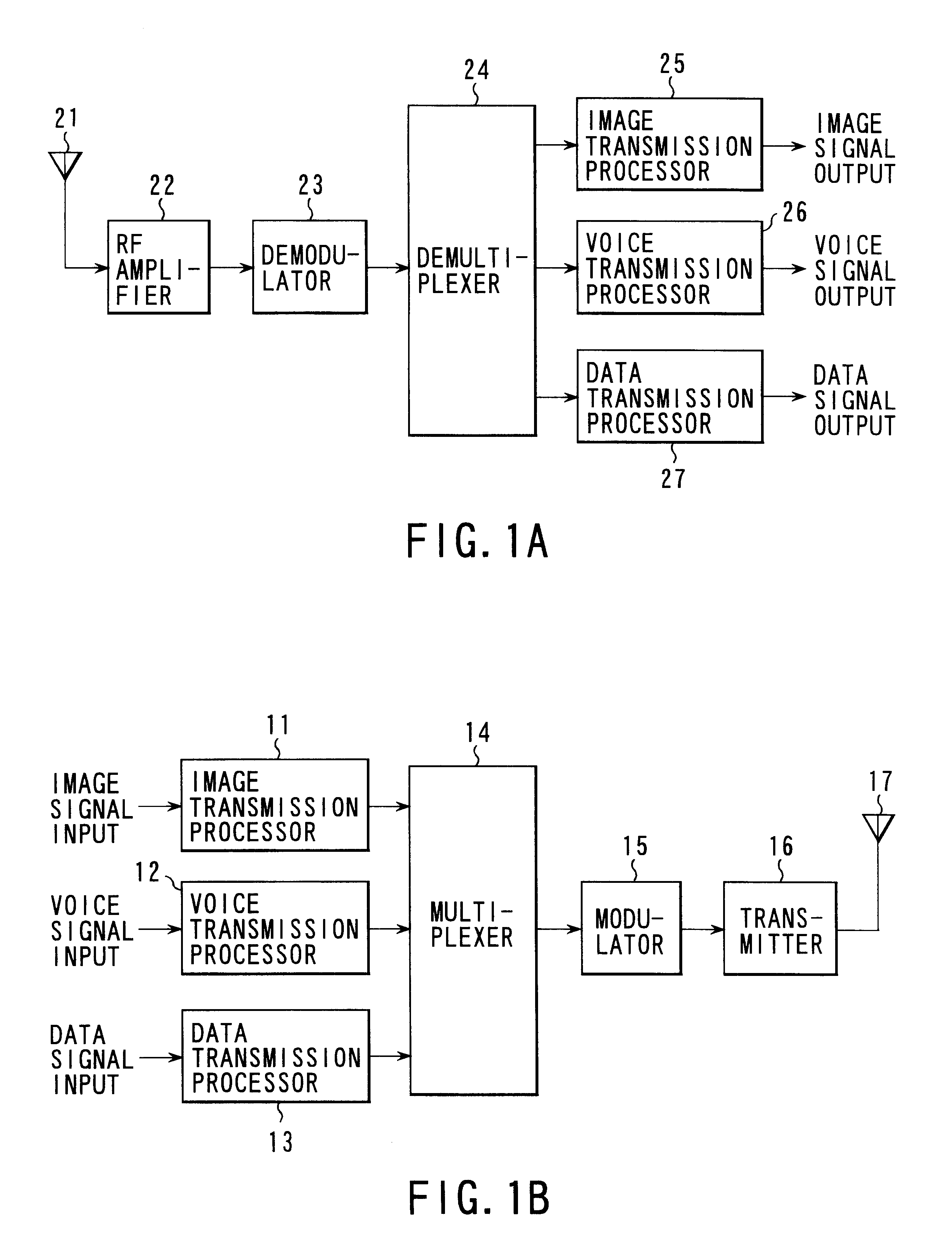

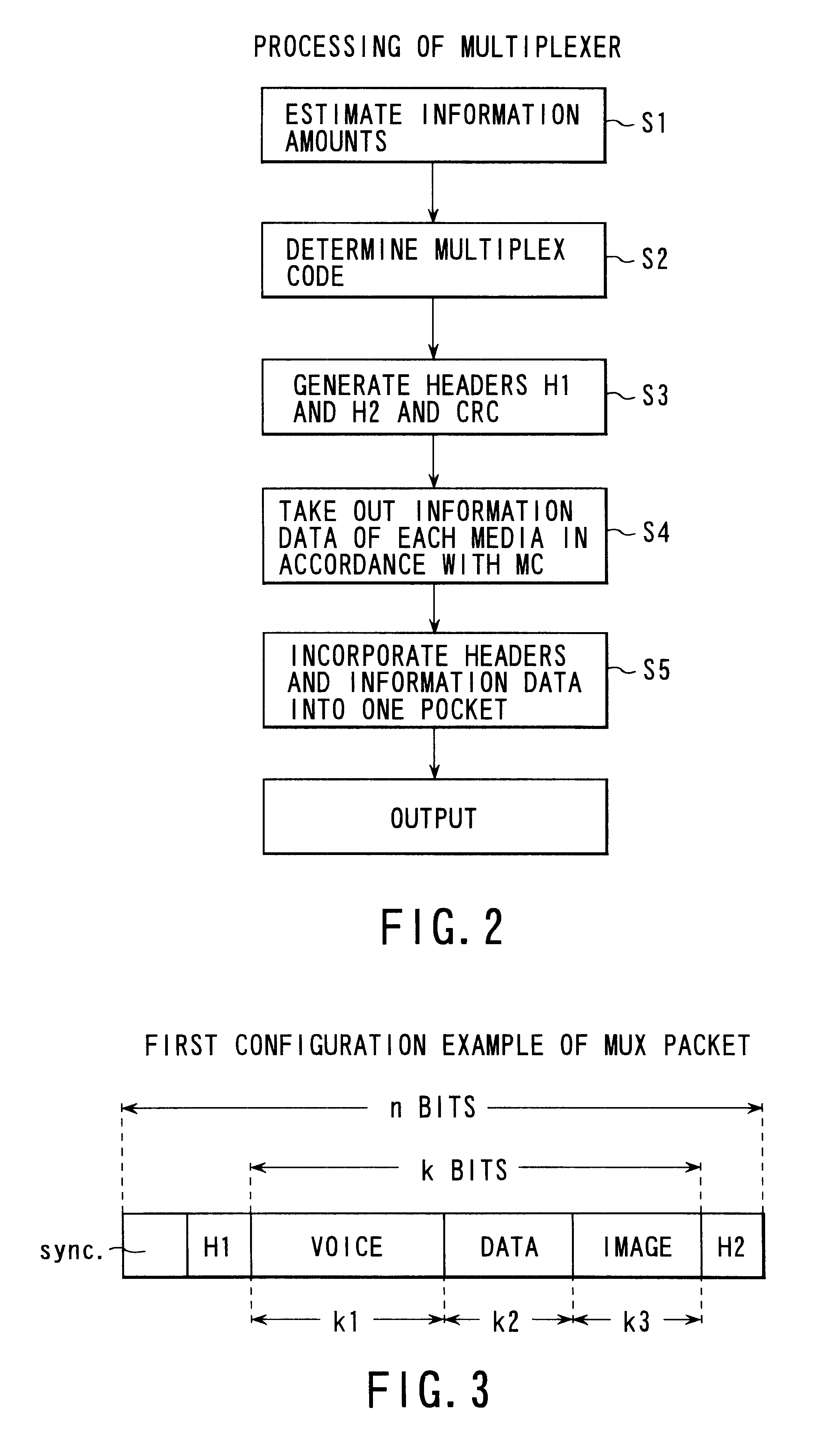

Information data multiplex transmission system, its multiplexer and demultiplexer and error correction encoder and decoder

InactiveUS6490243B1Reduce the probability of packet lossAccurate readingData representation error detection/correctionPulse modulation television signal transmissionMultiplexingMultiplexer

A multiplexing unit on the transmitting side estimates information amounts supplied from respective signal processing units, determines a multiplex code on the basis of respective information amounts, derives a parity of the first determined multiplex code to form a second multiplex code, adds a CRC to each of the multiplex codes to generate two headers H1 and H2, takes out information data of respective media according to the multiplex codes, incorporates the information data into a packet together with the two headers H1 and H2, and outputs the packet. If error correction of H1 is impossible on the receiving side, error correction decoding is conducted by using the header H2. If error correction of H2 is also impossible, error correction decoding is conducted collectively for H1 and H2.

Owner:KK TOSHIBA

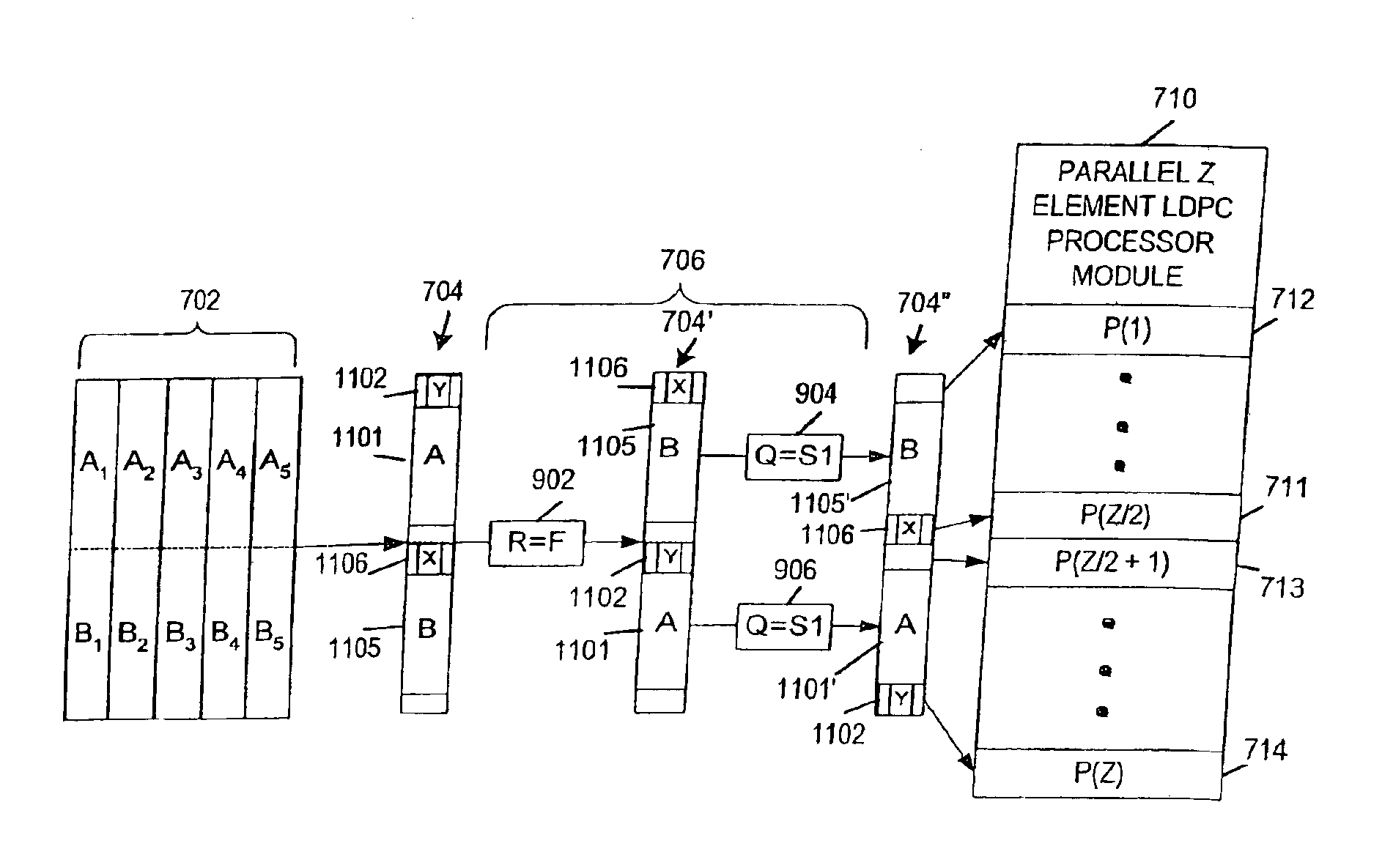

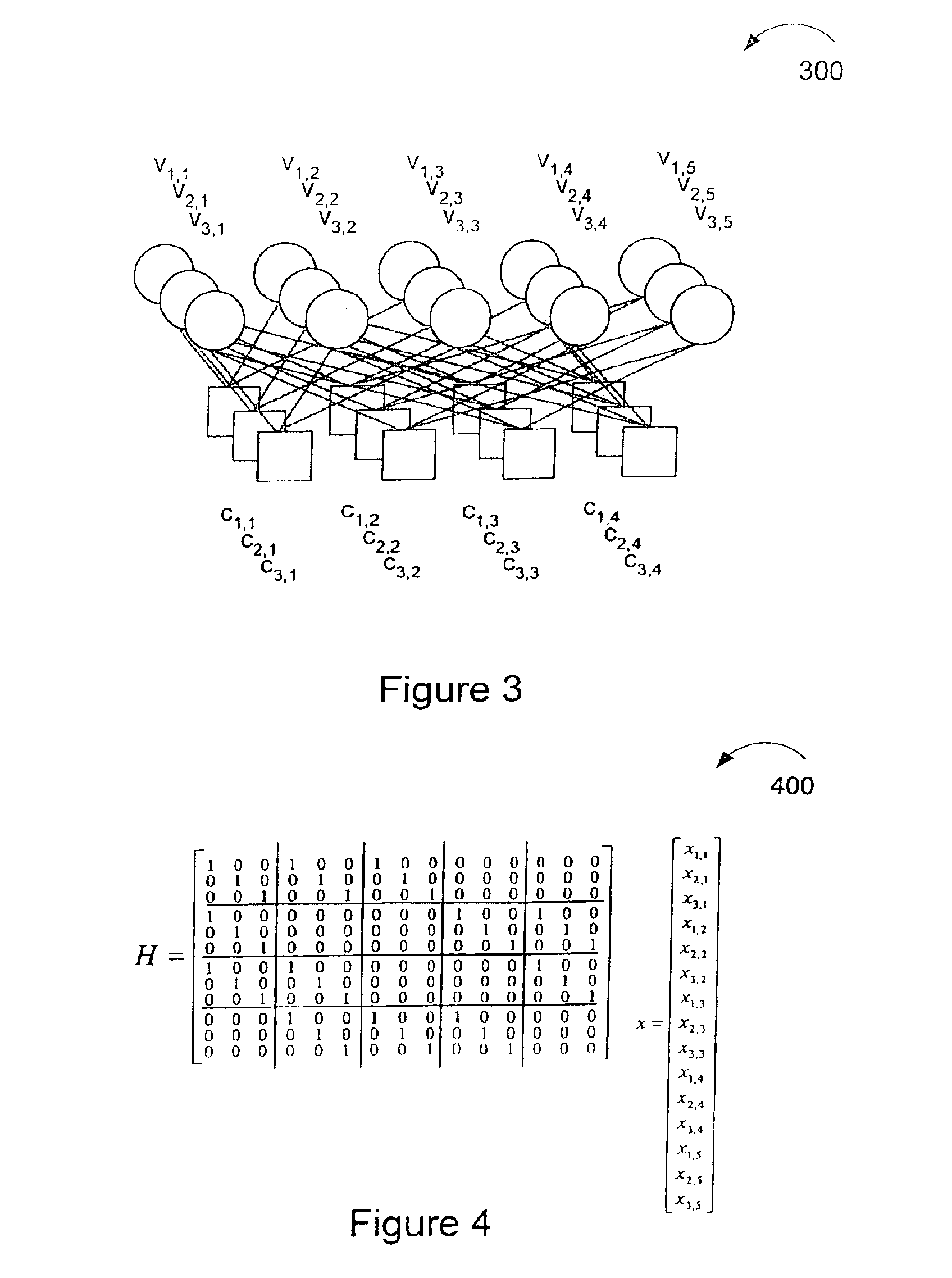

Method and apparatus for performing low-density parity-check (LDPC) code operations using a multi-level permutation

ActiveUS6957375B2Easy to implementError correction/detection using multiple parity bitsCode conversionGraphicsCommunications system

Methods and apparatus of the present invention can be used to implement a communications system wherein different devices using the same LDPC code can be implemented using different levels of parallelism. The use of a novel class of LDPC codes makes such differences in parallelism possible. Use of a factorable permuter in various embodiments of the invention make LDPC devices with different levels of parallelism in the encoder and decoder relatively easy to implement when using the codes in the class of LDPC codes discussed herein. The factorable permuter may be implemented as a controllable multi-stage switching devices which performs none, one, or multiple sequential reordering operations on a Z element vector passed between memory and a Z element vector processor, with the switching one individual vectors being controlled in accordance with the graph structure of the code being implemented.

Owner:QUALCOMM INC

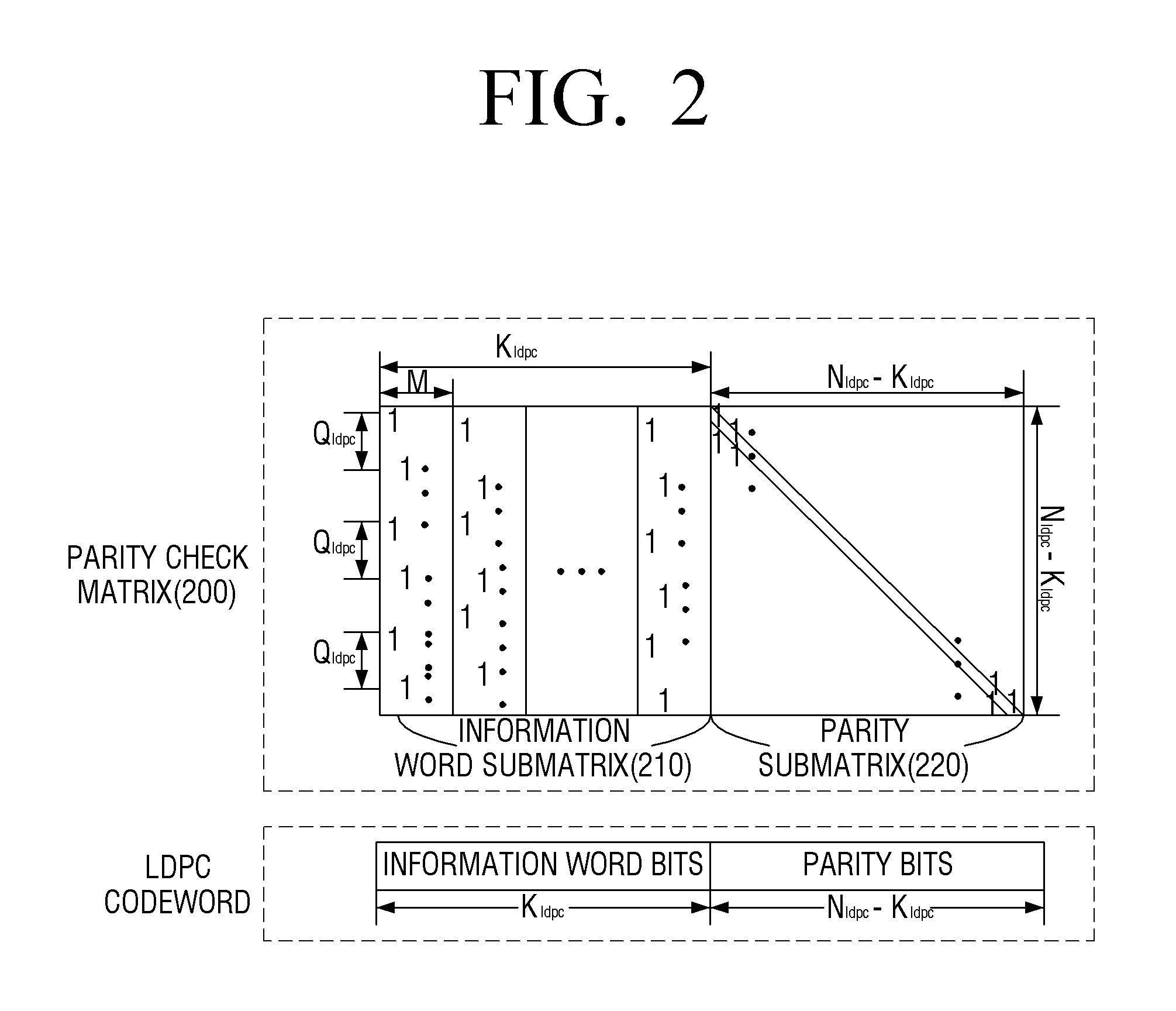

Transmitter apparatus and bit interleaving method thereof

ActiveUS20150341054A1Improve decoding performanceImprove reception performanceError correction/detection using concatenated codesError correction/detection using LDPC codesParity-check matrixCheck digit

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to generate a low-density parity check (LDPC) codeword by LDPC encoding of input bits based on a parity check matrix including information word bits and parity bits, the LDPC codeword including a plurality of bit groups each including a plurality of bits; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the interleaver is further configured to interleave the LDPC codeword such that a bit included in a predetermined bit group from among the plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

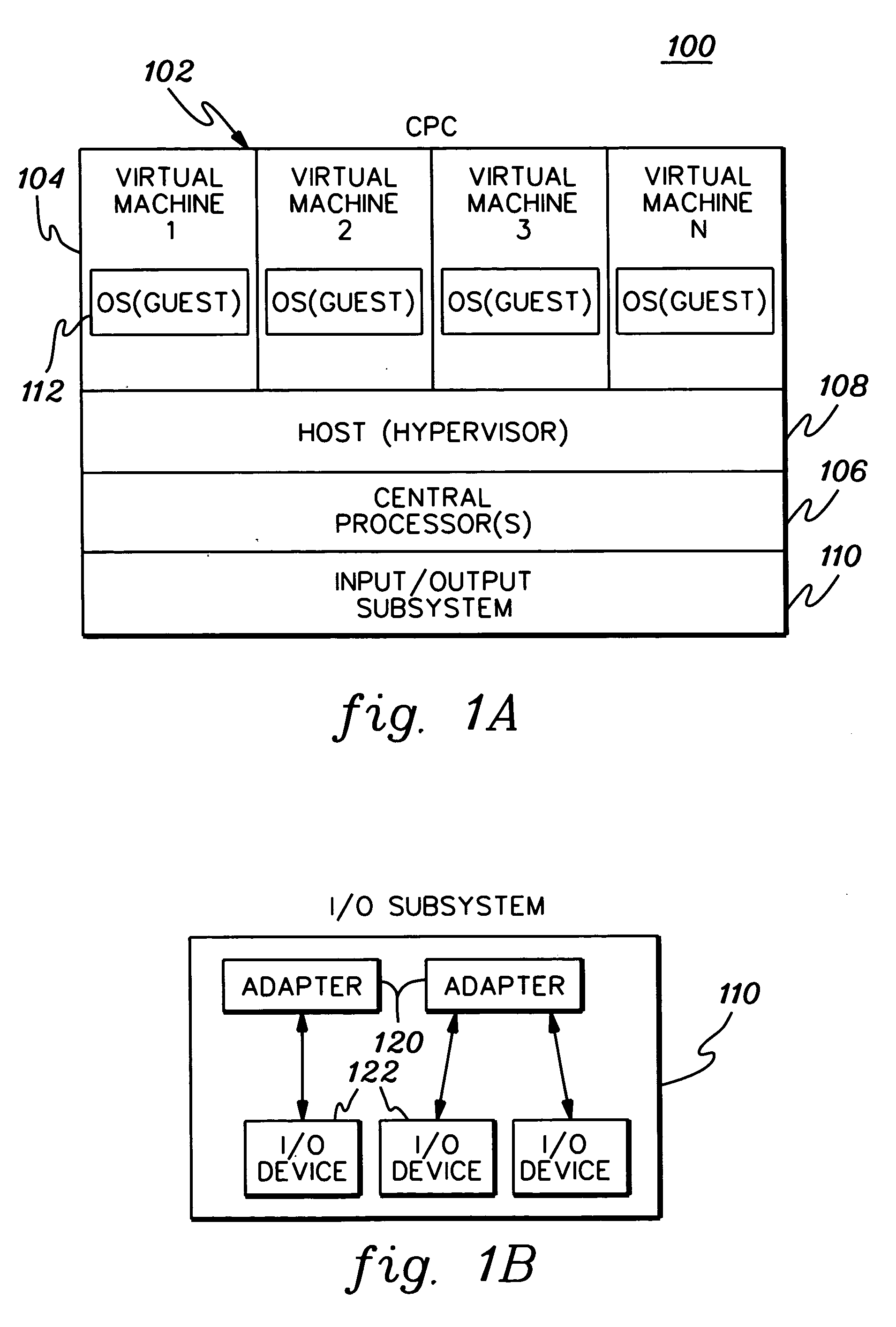

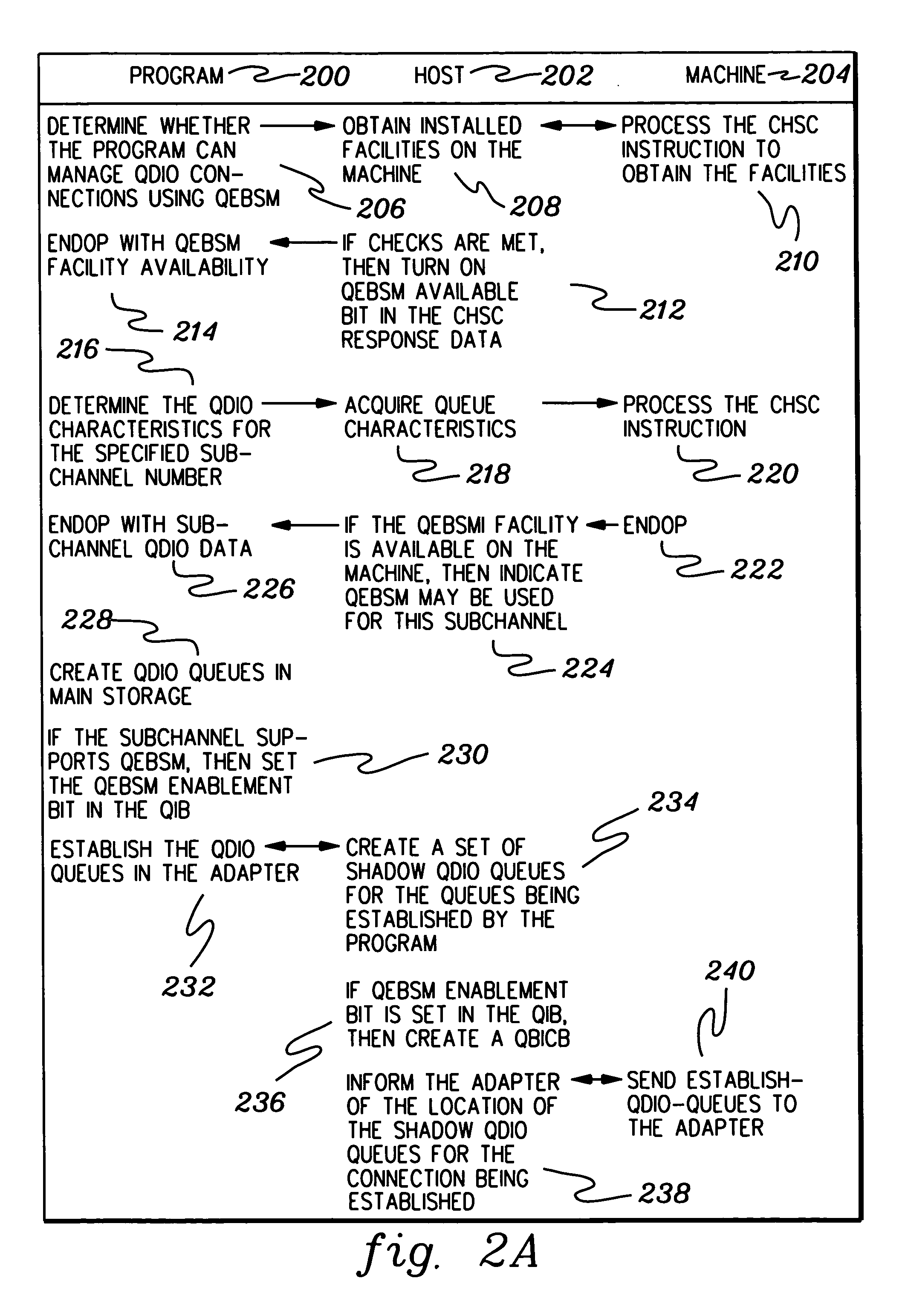

Interpreting I/O operation requests from pageable guests without host intervention

ActiveUS20050289246A1Easy to processPulse modulation television signal transmissionTelevision system scanning detailsPagingInformation storage

Input / output (I / O) operation requests from pageable storage mode guests are interpreted without host intervention. In a pageable mode virtual environment, requests issued by pageable storage mode guests are processed by one or more processors of the environment absent intervention from one or more hosts of the environment. Processing of the requests includes manipulating, by at least one processor on behalf of the guests, buffer state information stored in host storage. The manipulating is performed via instructions initiated by the guests and processed by one or more of the processors.

Owner:IBM CORP

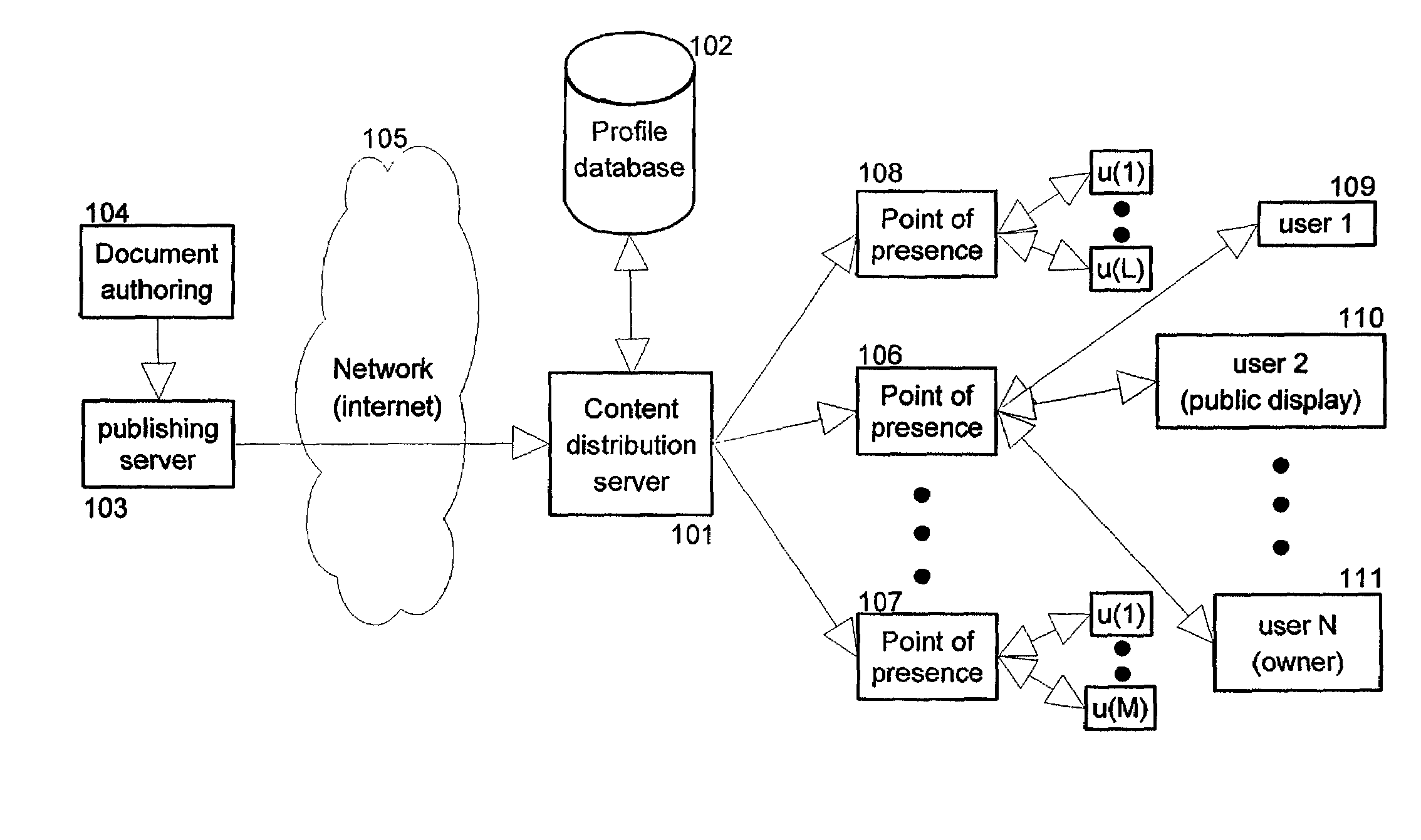

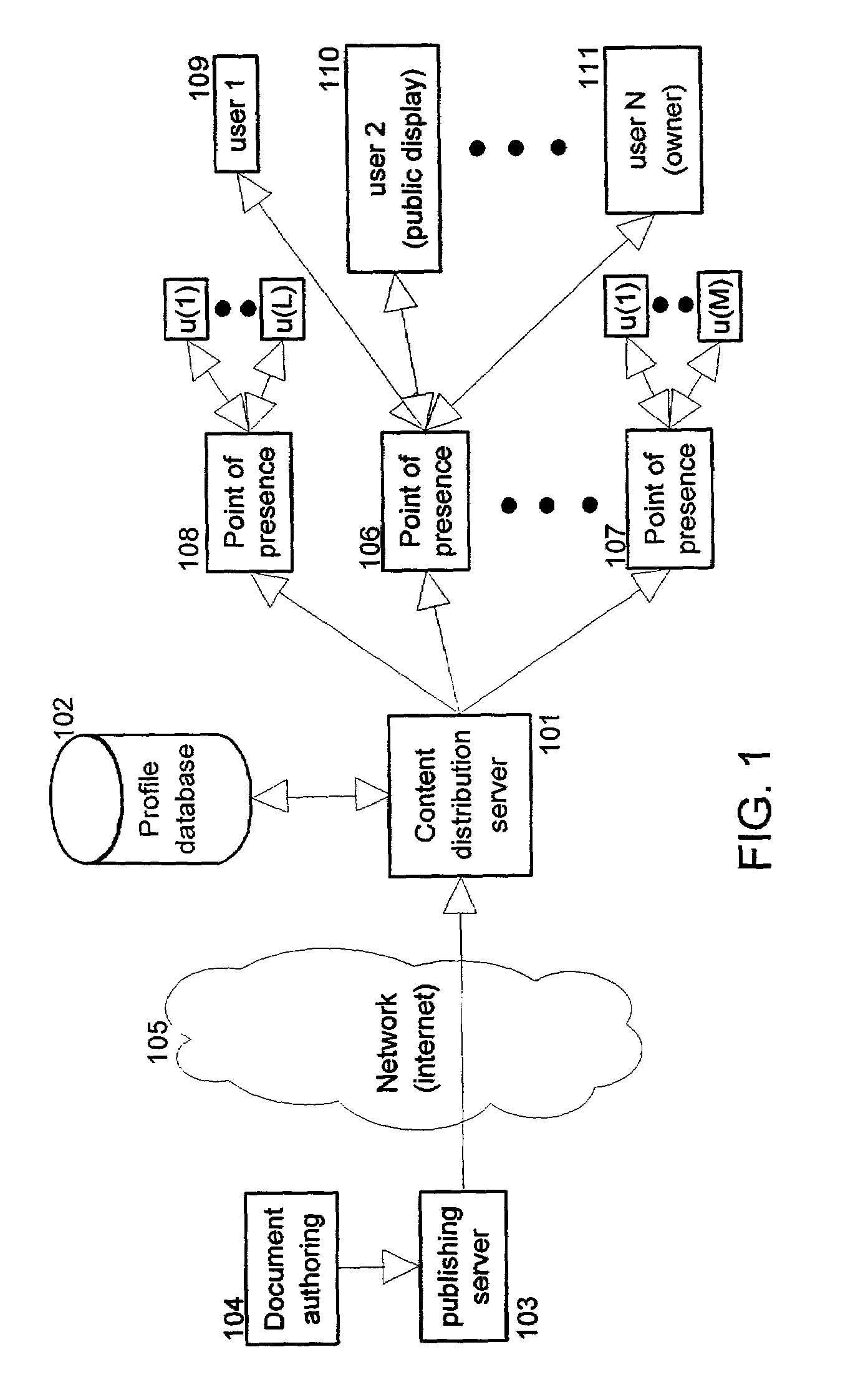

Information content distribution based on privacy and/or personal information

InactiveUS7162451B2Protect user privacyData representation error detection/correctionError preventionContent distributionPublic place

The present invention provides methods and apparatus to protect user privacy while accessing information in public places, using both public and personal devices. This is achieved by employing a mechanism that prevents private information from being displayed on public devices. Instead, this type of information is made available only to a user's personal device(s) that the user carries and / or trusts. An example embodiment of the invention shows relevant parts of the information content, referred to also as information documents or simply documents, to multiple devices based on privacy level and user preferences. Embodiments of the present invention also provide personalized services based on privacy levels defined by users. These users can for example be customers of a retail store. The service provided is sometimes also based on user history of accessing information documents. It permits personalized information to be sent to a customer's personal device.

Owner:IBM CORP

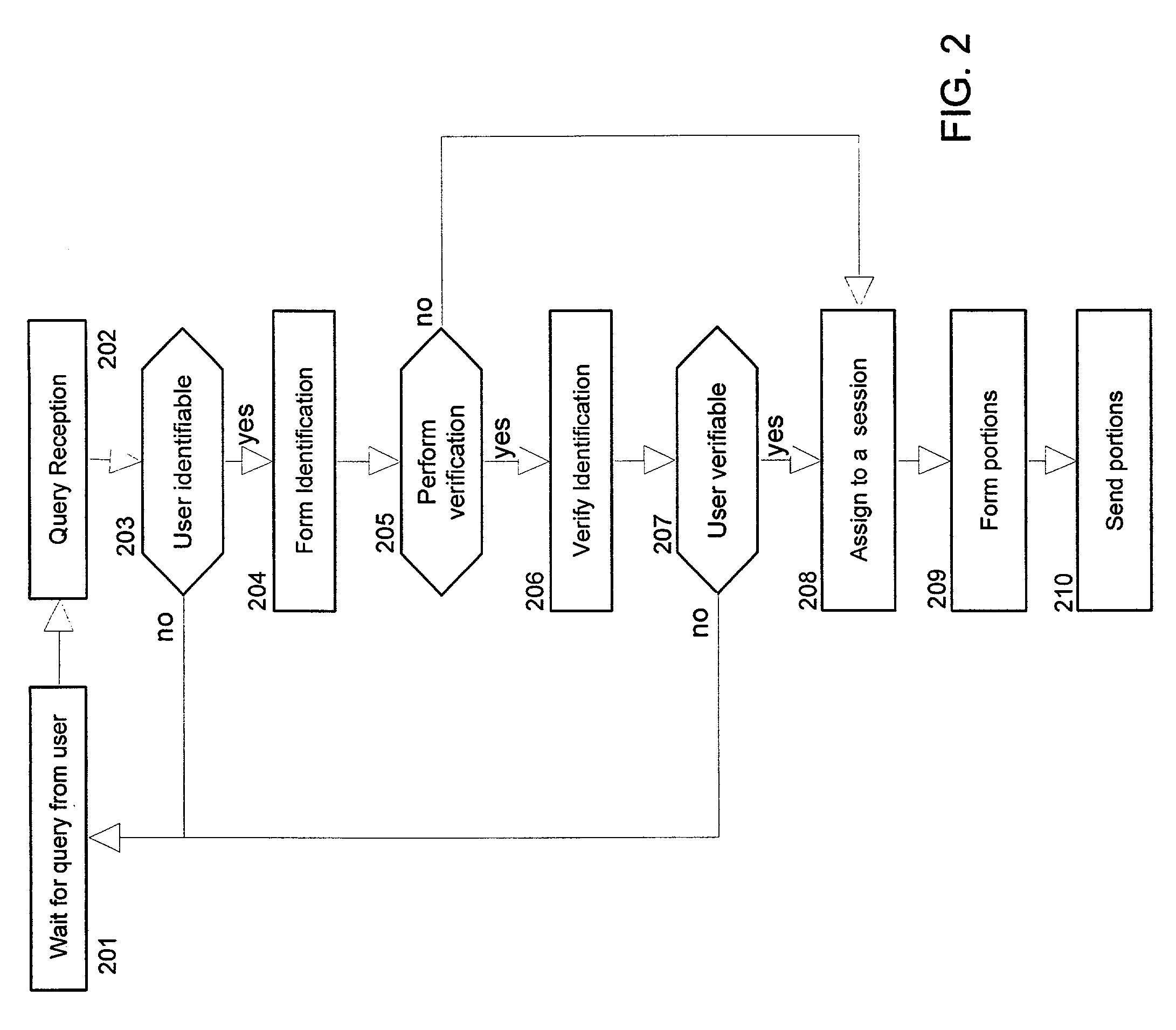

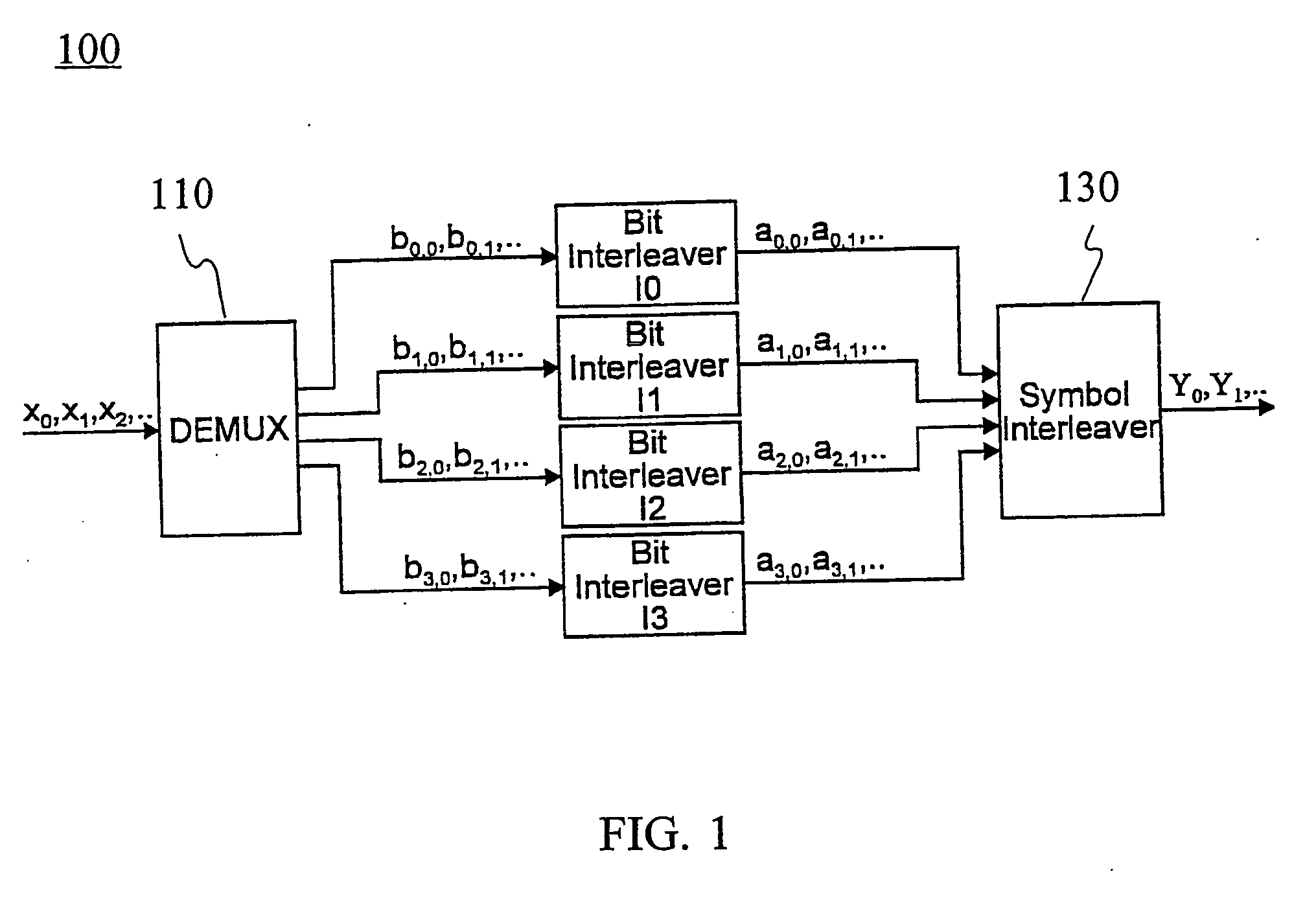

Symbol interleaving

ActiveUS20060062314A1Receiver specific arrangementsSecret communicationDigital dataSymbol interleaving

The invention relates to a method for communicating digital data using an orthogonal frequency division multiplexing (OFDM) transmission system (10) including at least one transmitter (600, 601) and receivers (700, 701). The method comprises selecting a mode of operation in a transmitter among at least one mode, each mode of operation being associated with a number of active carriers for payload data transmission, selecting a symbol interleaver in the transmitter from a set of symbol interleavers for symbol interleaving in said selected mode of operation, applying symbol interleaving in the transmitter on blocks of data units, mapping the interleaved data units onto the active carriers of said selected mode of operation, receiving the interleaved data units in the receiver, recognizing in the receiver the symbol interleaver used in the data transmission, selecting a de-interleaver in the receiver to correspond to the recognized symbol interleaver, and de-interleaving in the receiver the received data units using the selectedde-interleaver.

Owner:NOKIA TECHNOLOGLES OY

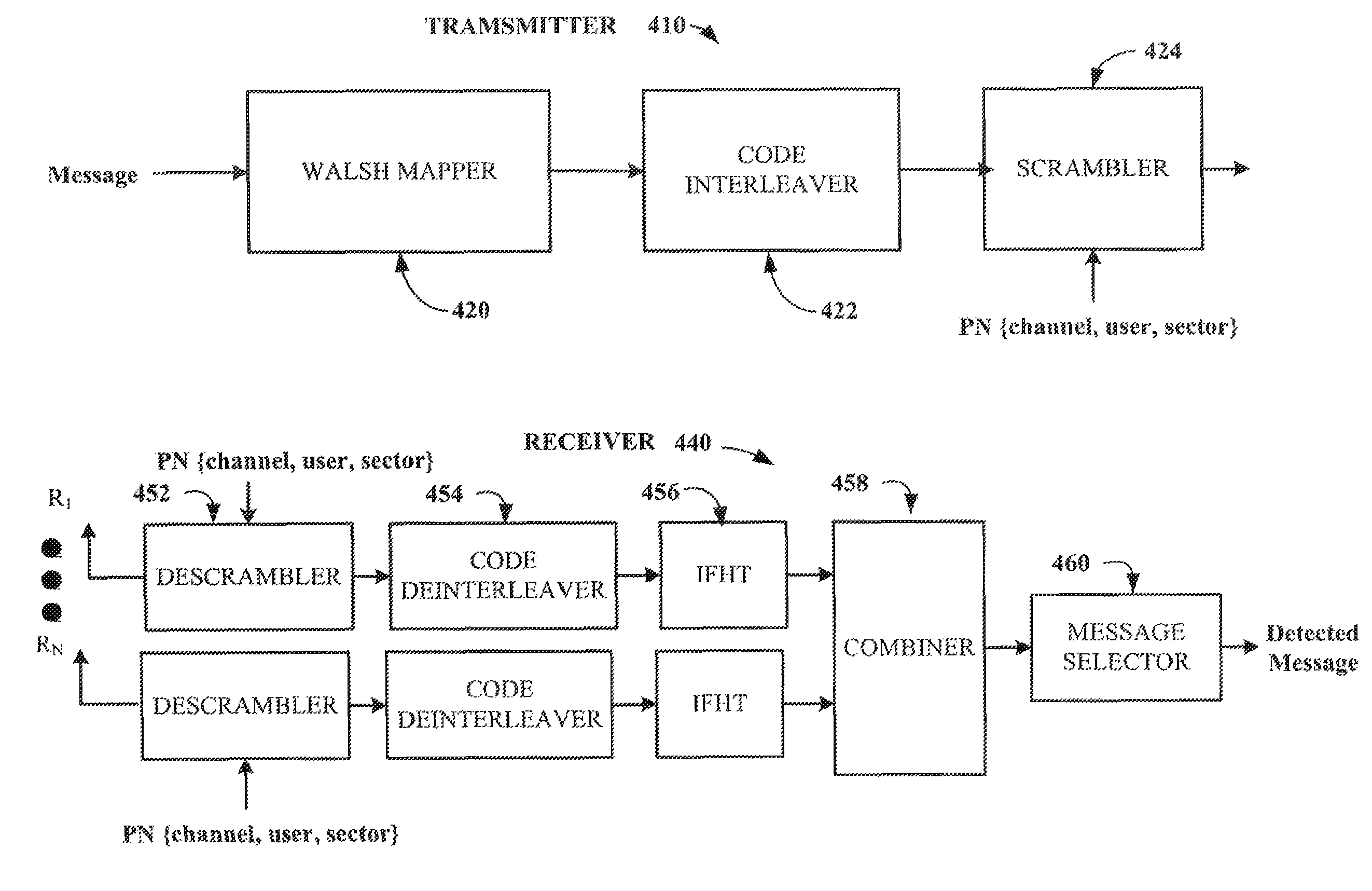

Code interleaving for a structured code

ActiveUS8295250B2Higher false alarmsRadio transmissionError correction/detection using interleaving techniquesComputer hardwareCommunications system

Communication systems and methods that mitigate false alarms due to Doppler shift are disclosed. Received message data is mapped to orthogonal Walsh codes, interleaved and scrambled with appropriate PN sequence prior to transmission. The transmitted message data is descrambled and deinterleaved upon reception. The energies associated with each of the Walsh code from various antennas and / or signal paths are combined to obtain a total energy for each Walsh code. If the total energy of the Walsh code exceeds a certain threshold it is declared as the received message else an erasure is indicated. As the data is interleaved prior to transmission, any phase ramp introduced due to Doppler is transformed into random phase errors upon deinterleaving at the receiver thereby mitigating false alarms.

Owner:QUALCOMM INC

Transmitting apparatus and interleaving method thereof

ActiveUS20150341052A1Improve decoding performanceImprove reception performanceError correction/detection using concatenated codesError detection/correctionParity-check matrixComputer engineering

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to perform a low-density parity check (LDPC) encoding on input bits using a parity check matrix to generate an LDPC codeword comprising information word bits and parity bits; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the modulator is further configured to map a bit included in a predetermined bit group from among a plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

Data processing device and method

ActiveCN101510865APulse modulation television signal transmissionError preventionAddress generatorCarrier signal

A data processing device transmits the data bits on the predetermined quantity carrying wave signal of the OFDM sign. The data processing device comprises a parity interweaver for operating the pairs of LDPC coding data. The data bits are obtained by the parity matrix LDPC detecting with the LDPC code. The parity matrix has a ladder-type structure interweaving the LDPC code data to the different parity bit position. The mapping unit maps the parity interweaving bit to the data signs corresponding to the modulating signs of the solution. The sign interweaver reads the quantity signs to the sign interweaving store, carrying out the data sig of the sign interweaving store reading the order with different reading; the order address set is confirmed. The address set is generated by the address generator.

Owner:SONY CORP

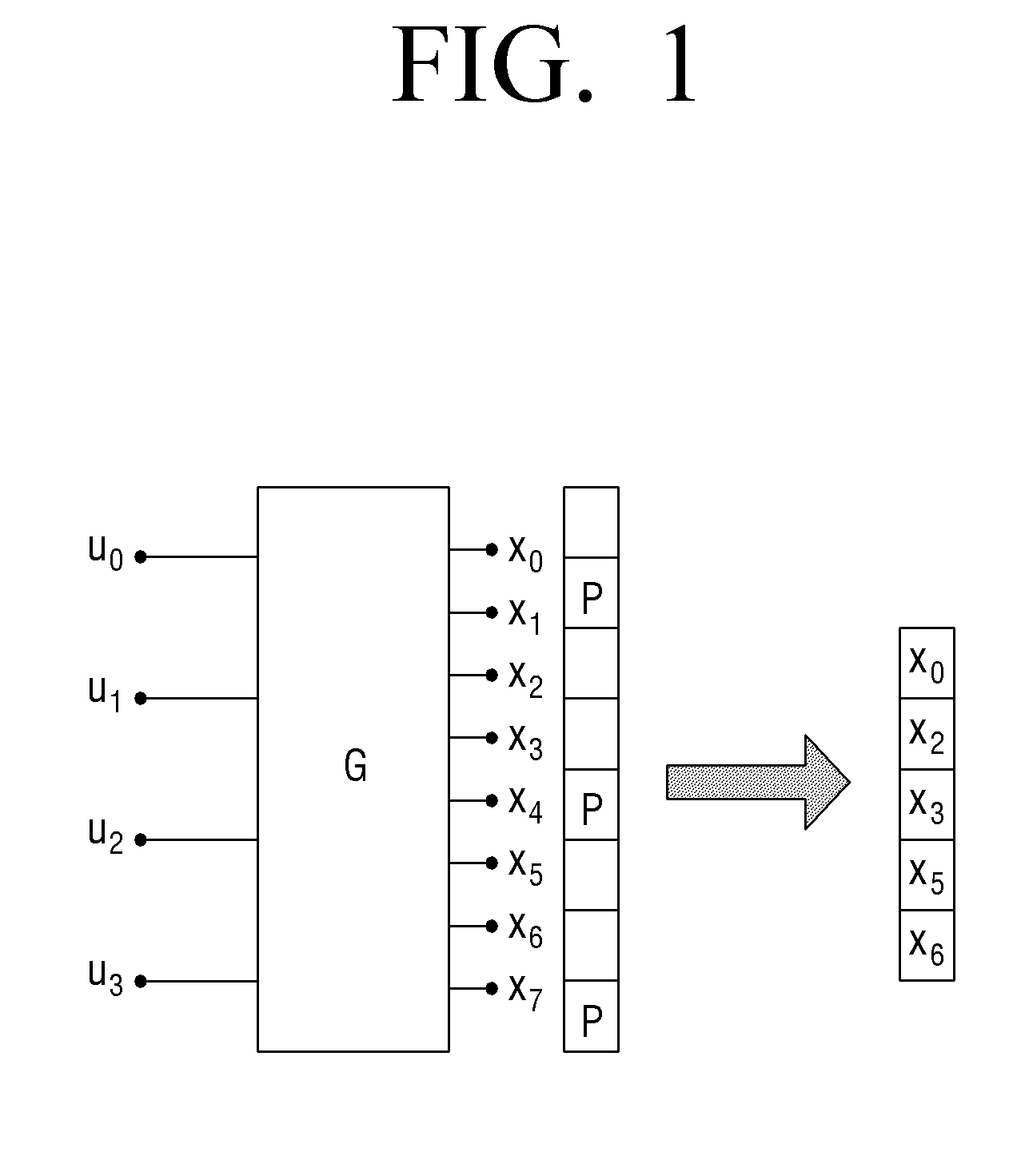

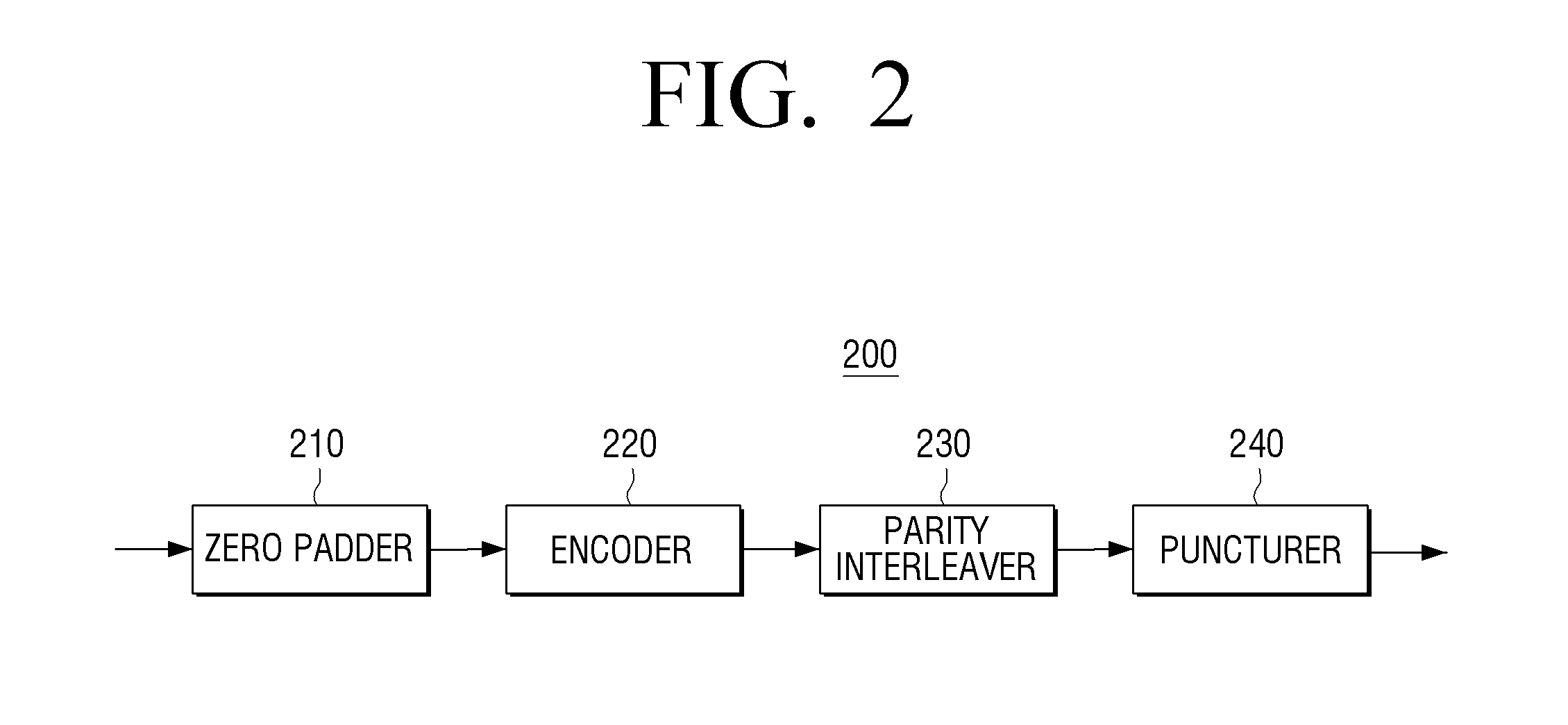

Interleaving and puncturing apparatus and method thereof

ActiveUS20150333769A1Code conversionError correction/detection using interleaving techniquesWrite bitComputer science

An apparatus and method for interleaving and puncturing are provided. The apparatus includes: an interleaver formed of a plurality of columns and rows, configured to perform interleaving by writing bits input to the interleaver in the plurality of columns and reading the bits from each row of the plurality of columns in which the bits are written; and a puncturer configured to puncture a predetermined number of bits among the bits read from the interleaver.

Owner:SAMSUNG ELECTRONICS CO LTD +1

Transmitting apparatus and puncturing method thereof

InactiveUS20150082118A1Improve decoding performanceError correction/detection using multiple parity bitsCode conversionLow-density parity-check codeLow density

Provided are a transmitting apparatus, a receiving apparatus and methods of puncturing and depuncturing of parity bits. The transmitting apparatus includes: a zero padder configured to pad at least one zero bit to input bits; an encoder configured to generate a Low Density Parity Check (LDPC) codeword by performing LDPC encoding with respect to the bits to which the at least one zero bit is padded; a parity interleaver configured to interleave LDPC parity bits constituting the LDPC codeword; and a puncturer configured to puncture at least a part of the interleaved LDPC parity bits based on a pre-set puncturing pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

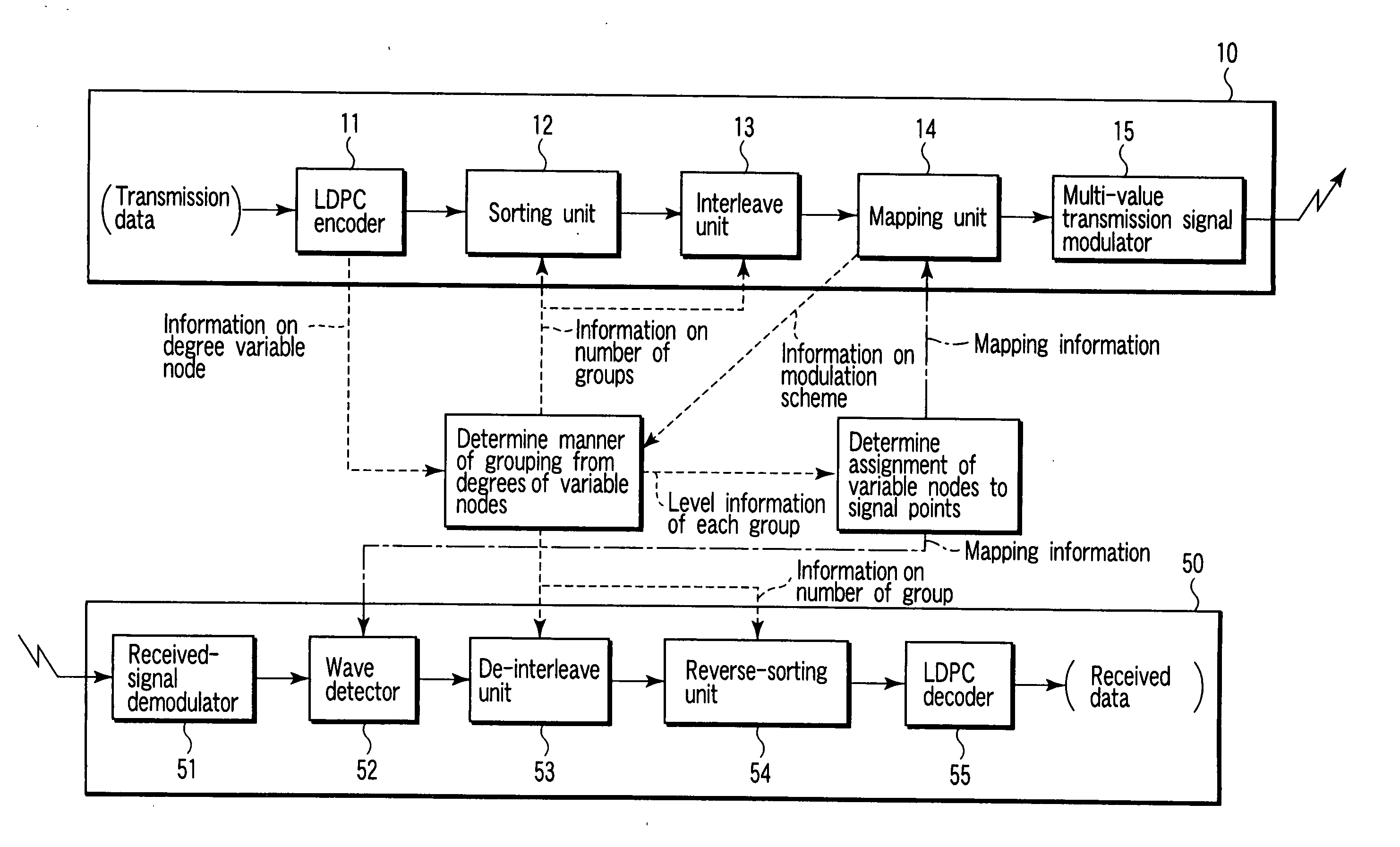

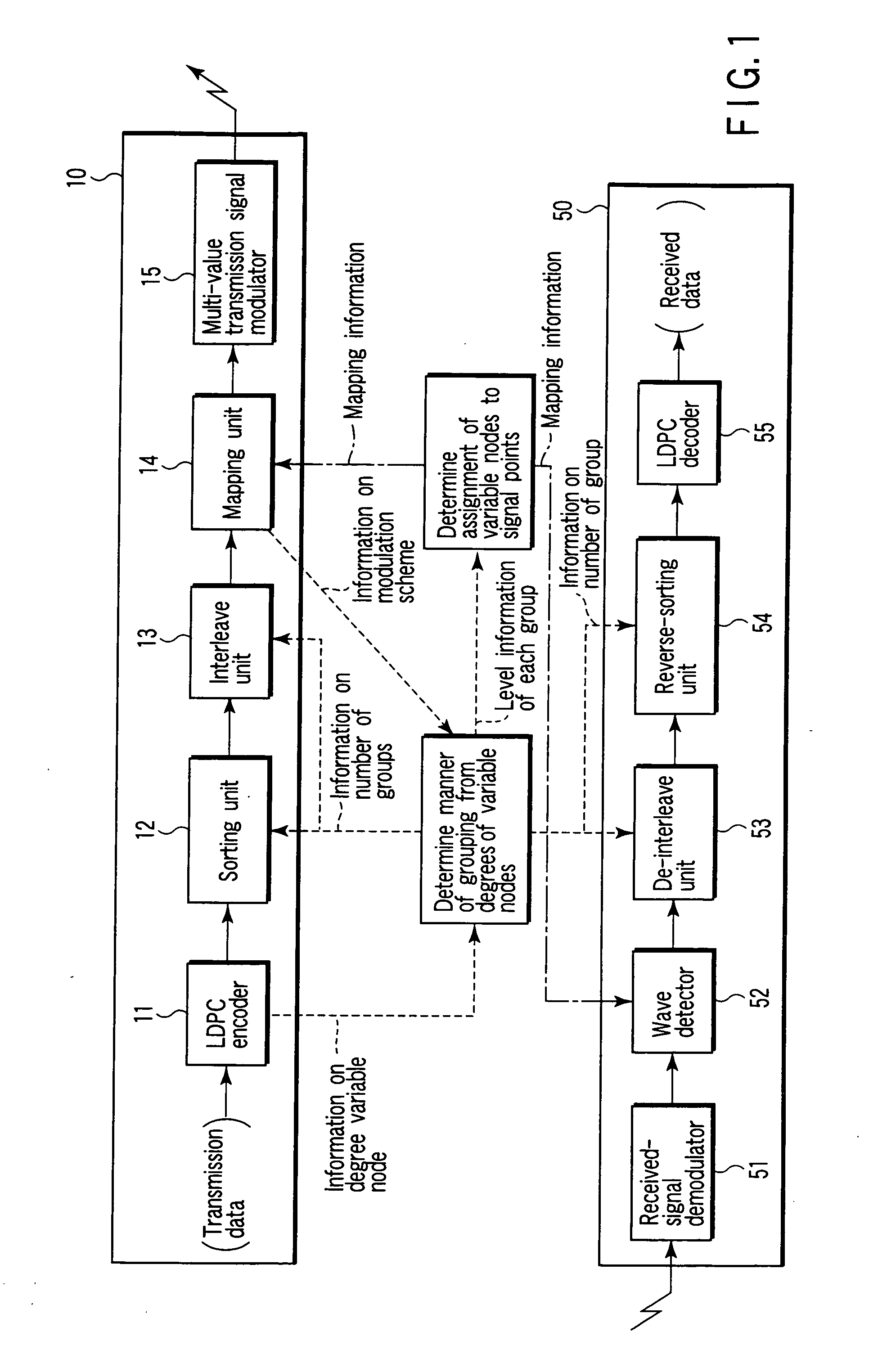

Mapping method for encoded bits using LDPC code, transmitting and receiving apparatuses employing this method, and program for executing this method

InactiveUS20050216821A1Transmission path divisionError correction/detection using LDPC codesTheoretical computer scienceParity-check matrix

A method for mapping of coded bits using a low density parity check (LDPC) code, comprises encoding information bits by using the LDPC code to generate coded bits, sorting the coded bits in accordance with degrees of variable nodes represented by a parity check matrix of the LDPC code, dividing the sorted coded bits into a plurality of groups in accordance with a using modulation scheme, and mapping the coded bits to respective modulation signal points by considering an error resistance of each of the groups and an error resistance of a corresponding one of the modulation signal points.

Owner:KK TOSHIBA

Transmitting apparatus and interleaving method thereof

ActiveUS20150236721A1Improve decoding performanceImprove reception performanceError correction/detection using LDPC codesError correction/detection using multiple parity bitsParity-check matrixLow density

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to generate a low density parity check (LDPC) codeword by LDPC encoding based on a parity check matrix; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the modulator is further configured to map a bit included in a predetermined bit group from among a plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

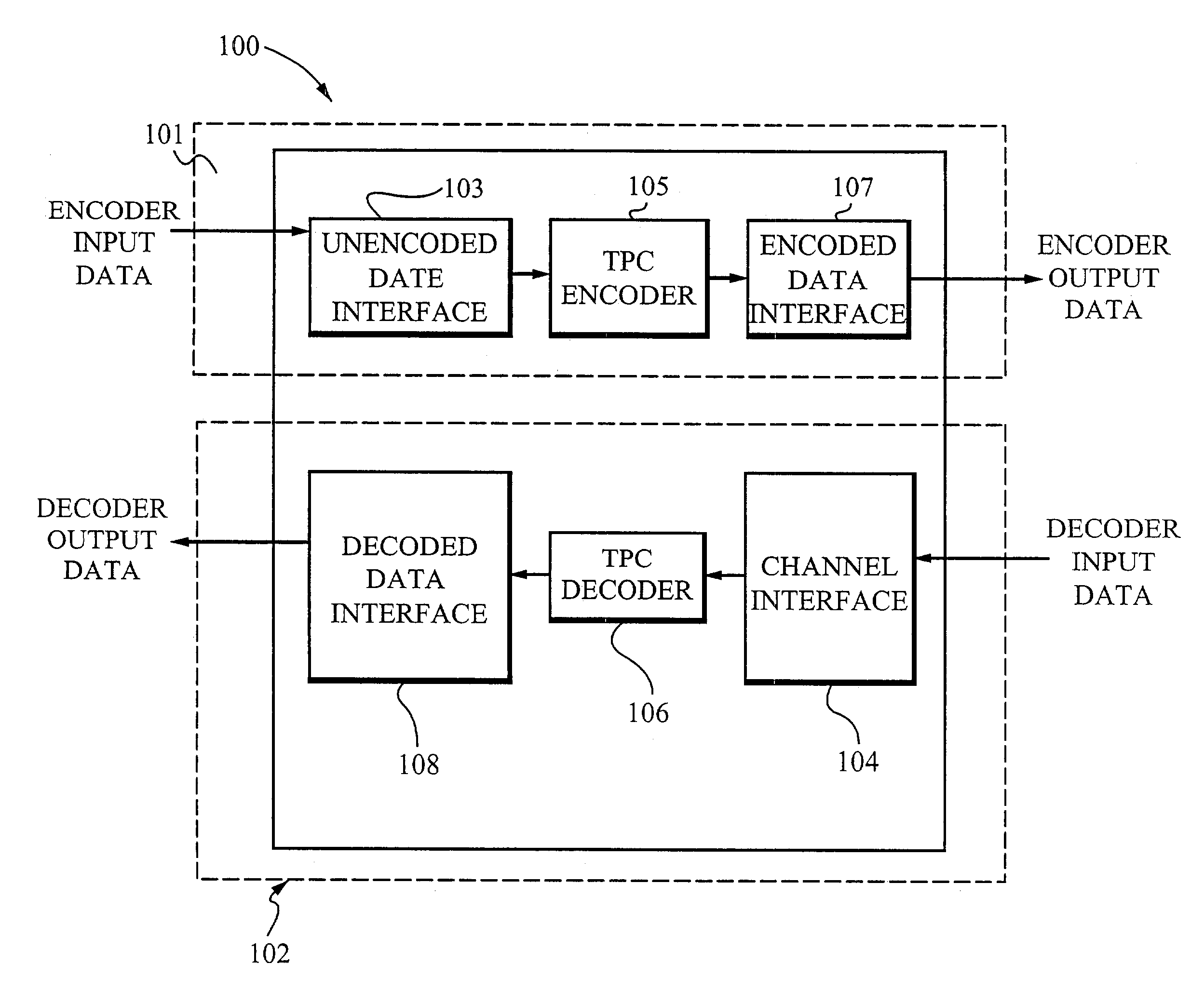

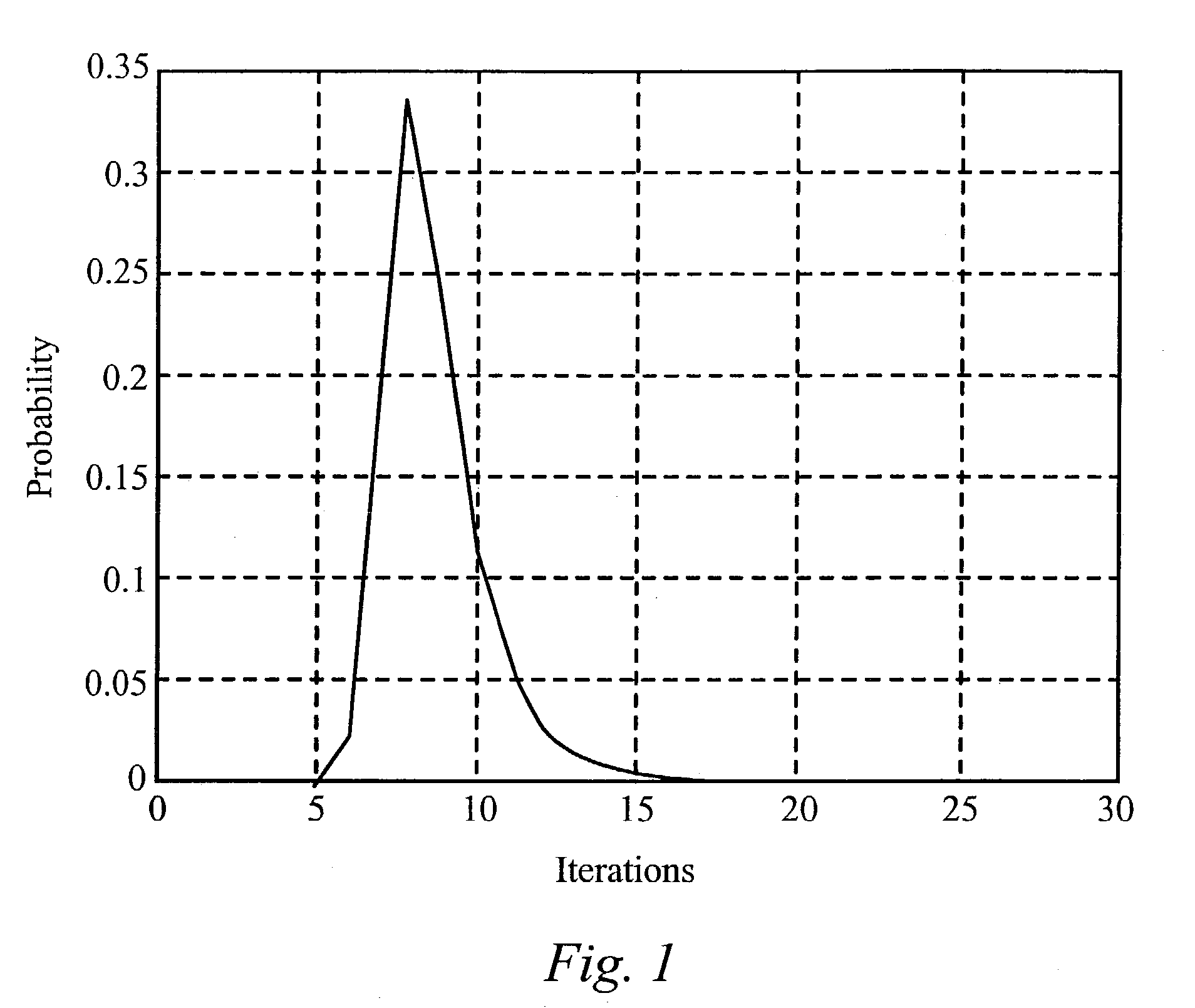

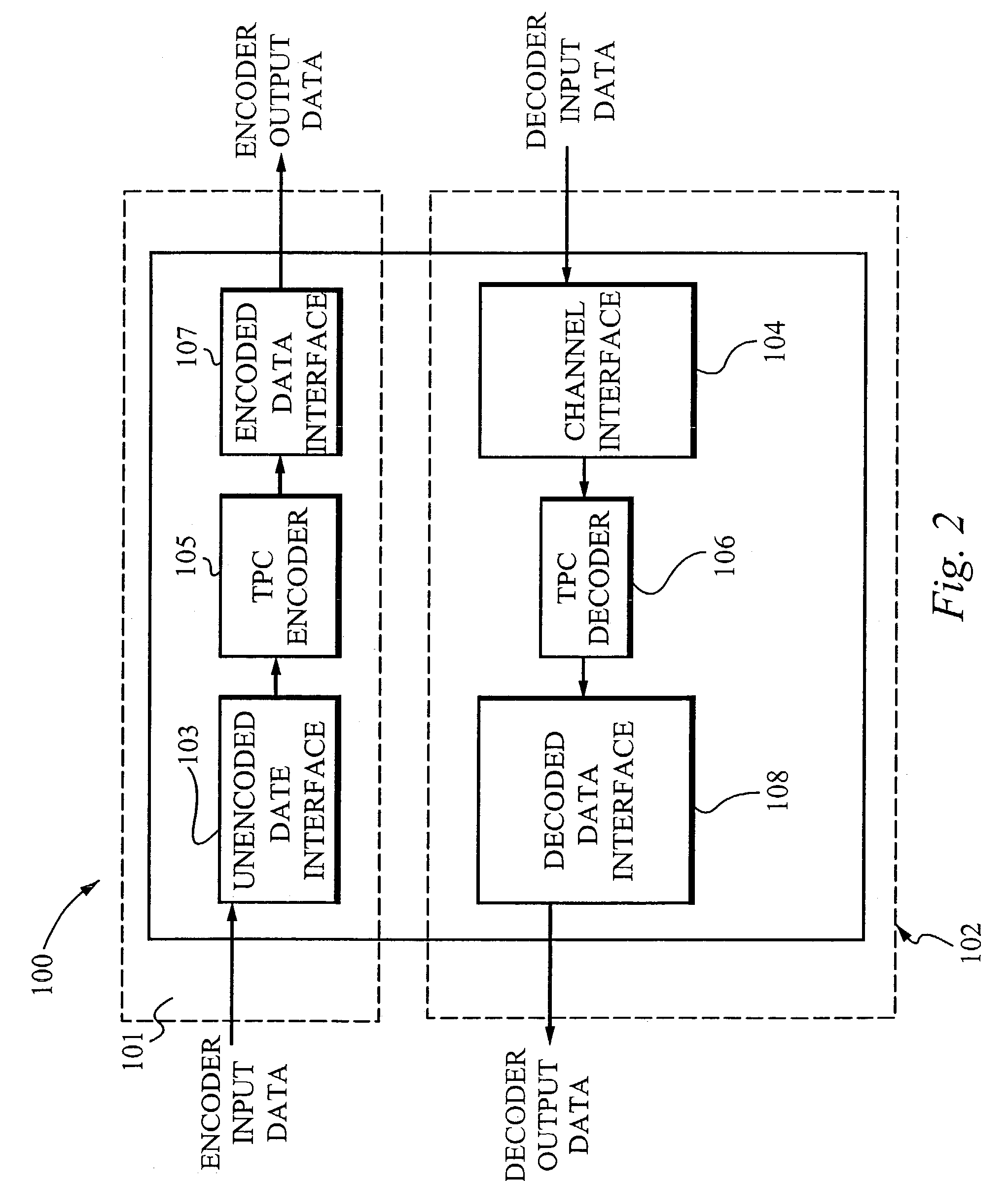

Enhanced turbo product code decoder system utilizing a codeword organization method

InactiveUS7039846B2Error preventionOther decoding techniquesMemory addressTheoretical computer science

A method and apparatus for decoding a linear block encoded string of information bits comprising: converting the string into a plurality of codewords. Performing hard and soft decisions on each codeword to generate a hard and soft decision vector. Computing the syndrome and finding the location of the two minimum values by Galois Field Arithmetic. Designating these values LOW1 and LOW2 and xoring with a Nc1, thus generating Nc2. Swapping Nc1 with Nc2 and determining the lowest soft decision value, Min1 and a next lowest value, Min2. The two bit locations creating Min1 are designated as MinA and MinB. MinA being replaced with Min2 minus the value MinA. MinB being replaced with Min2 minus the value at MinB. Generating an output codeword by subtracting Min1 from all other bit locations values and 2's complementing all soft values with 0 in their location. Creating the new soft value vector. Some embodiments include a system and method that organizes an encoded codeword. The encoded codeword has several codeword bits. The method receives the encoded codeword, assigns multiple codeword bits to at least one memory address in a plurality of memory addresses, and iteratively decodes the received codeword by utilizing the plurality of memory addresses in a predetermined order. The predetermined order is based on a dimension of the received codeword.

Owner:COMTECH TELECOMM CORP

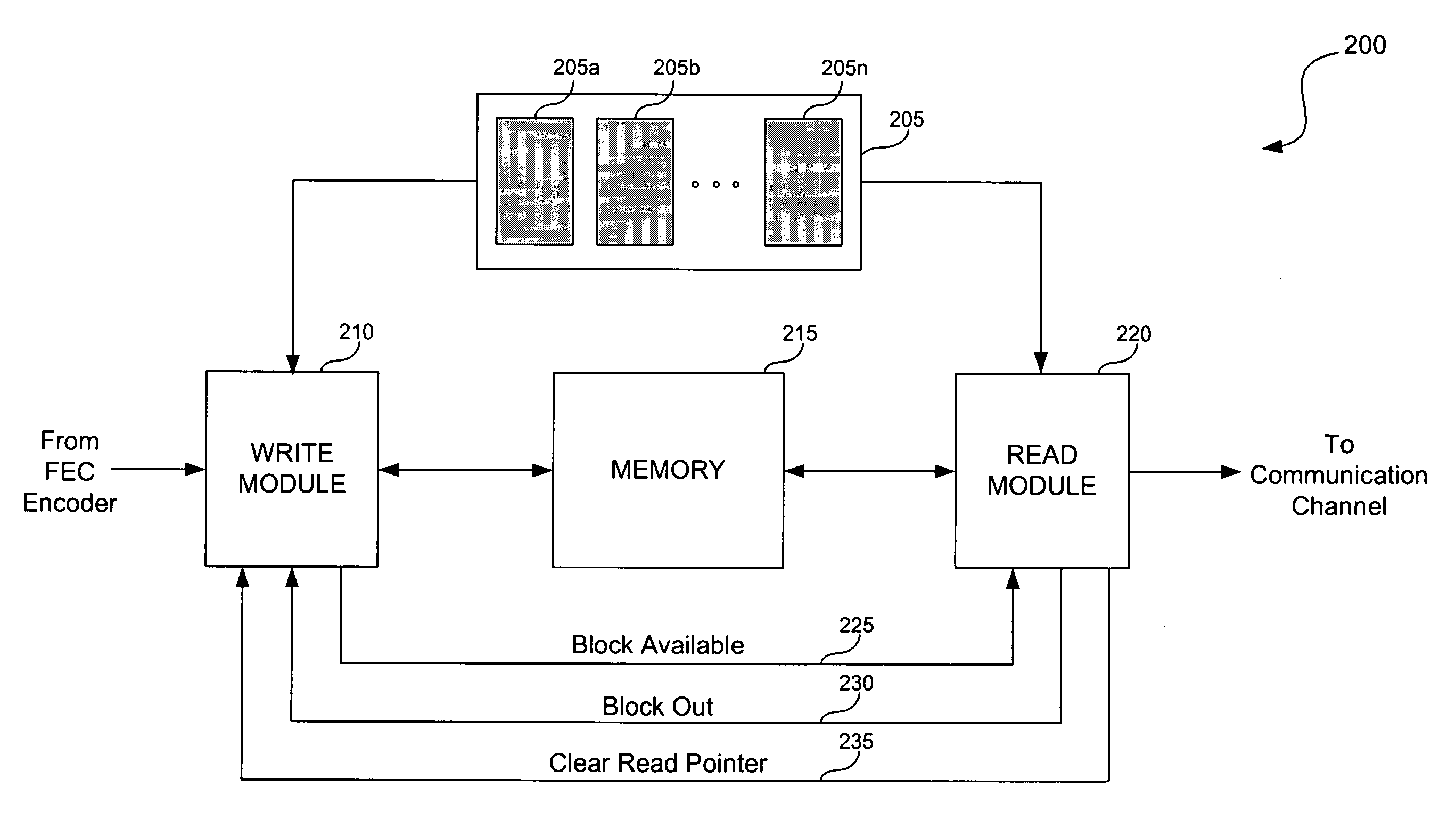

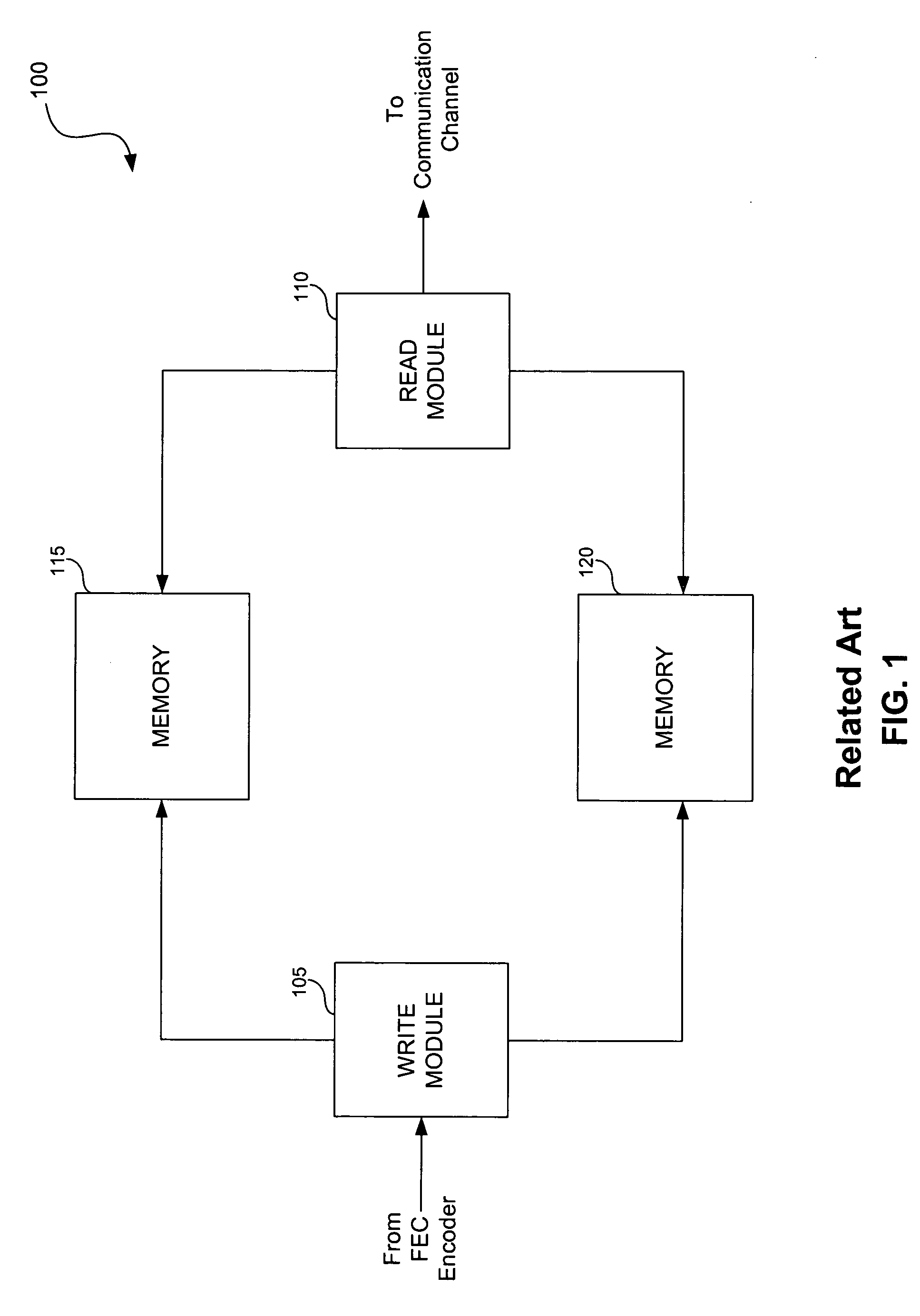

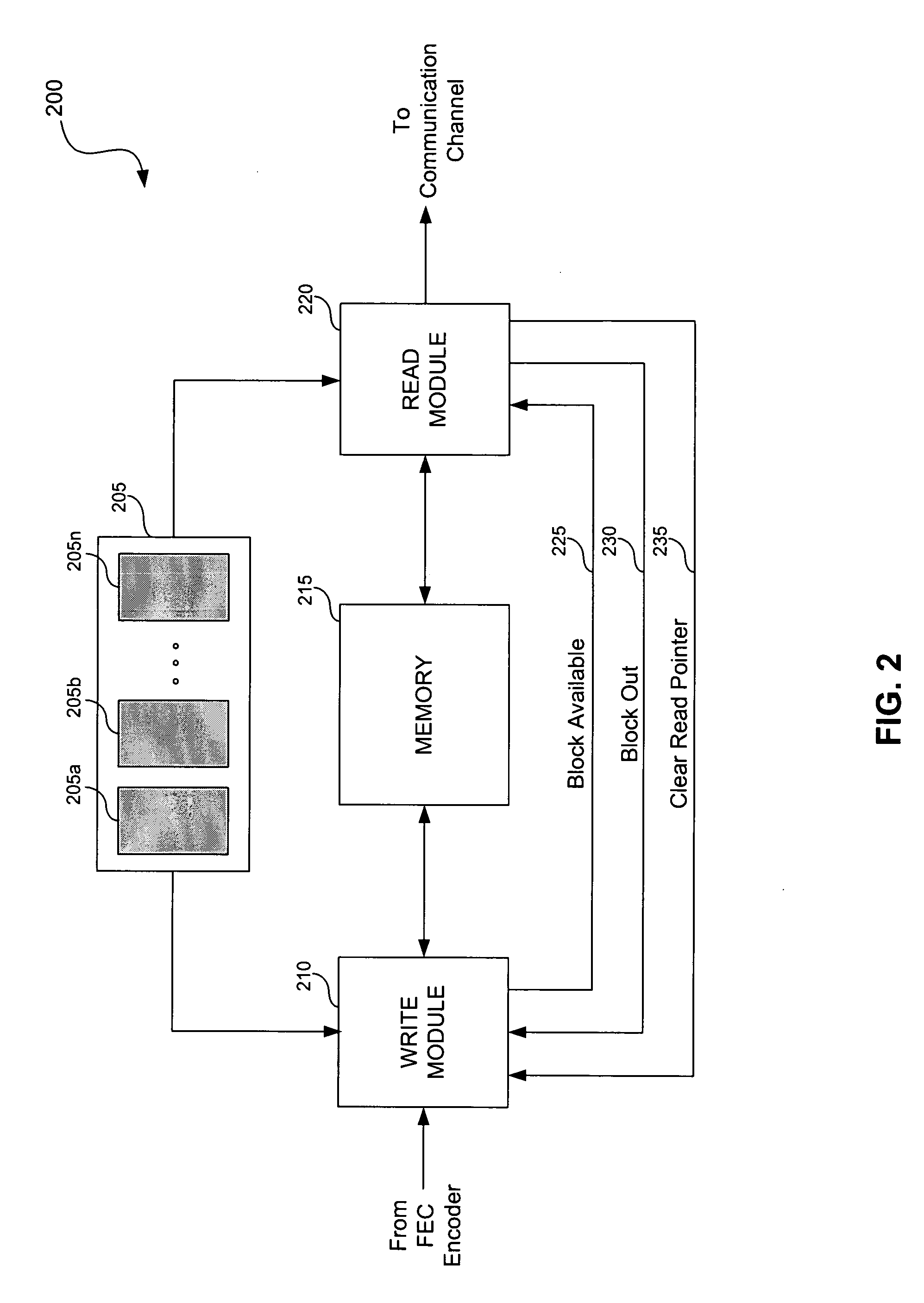

System and method for interleaving data in a communication device

InactiveUS20060026484A1Optimal throughput and efficiencyMinimize delayTransmission systemsCode conversionByteCommunication device

A system and method is provided for interleaving data in a communication device. The system includes a memory that stores blocks of data to be interleaved. In addition to the memory, the system includes a write module and a read module, each of which is coupled to the memory. The write module is configured to receive a burst of data and write blocks of data from the burst into the memory. The write module is also configured to provide control information to the read logic. The control information includes a rolling burst counter and a burst profile bank identifier for each block. If interleaving is activated, the control information also includes information pertaining to how the read module should interleave the block. If interleaving is not activated, the control information also includes the byte length size of the burst. The read module reads blocks of data from memory in either an interleaved fashion or a non-interleaved fashion in accordance with the control information. A block available signal and a block out signal is also provided to determine when a block of data is available to be read from the memory.

Owner:AVAGO TECH INT SALES PTE LTD

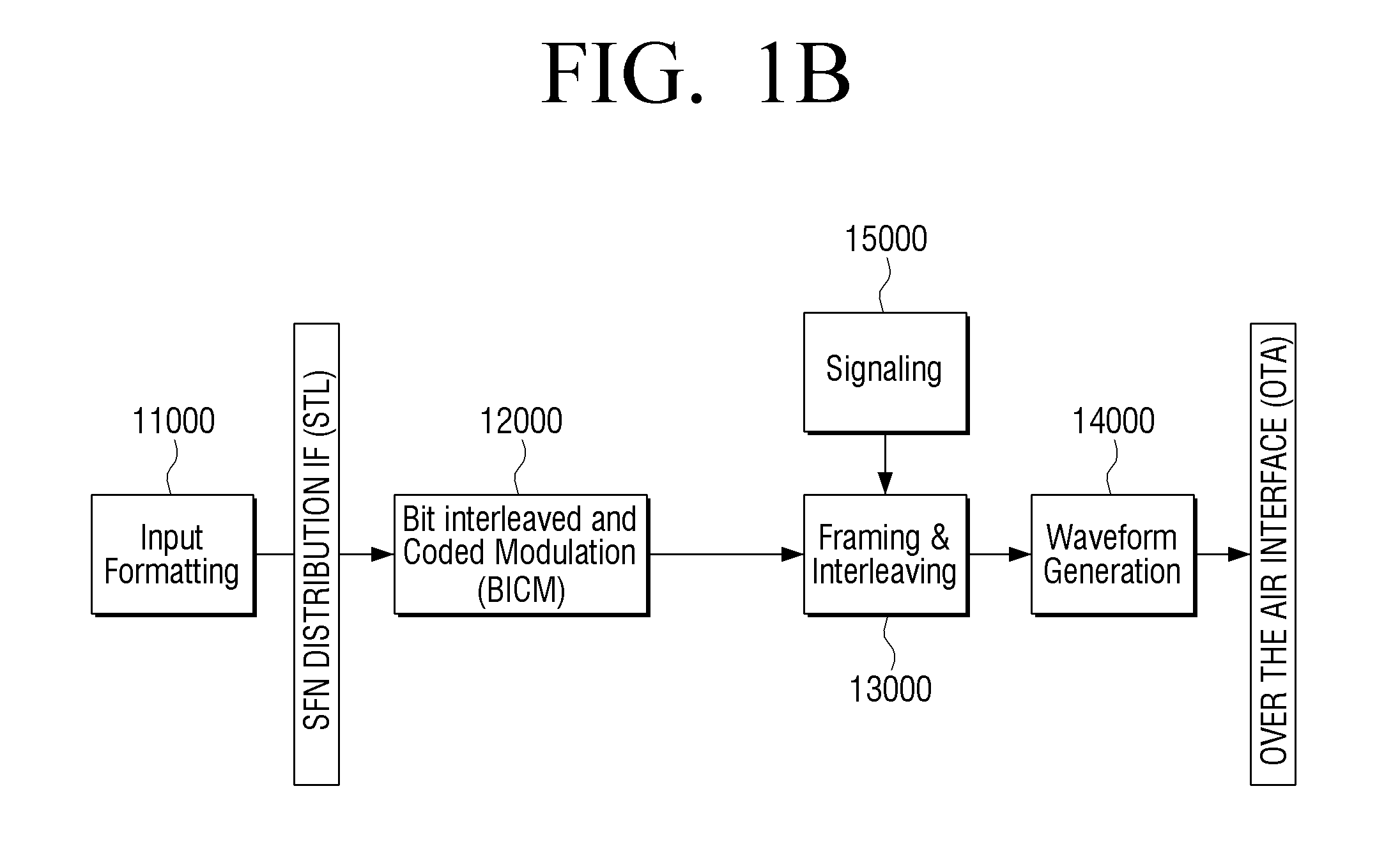

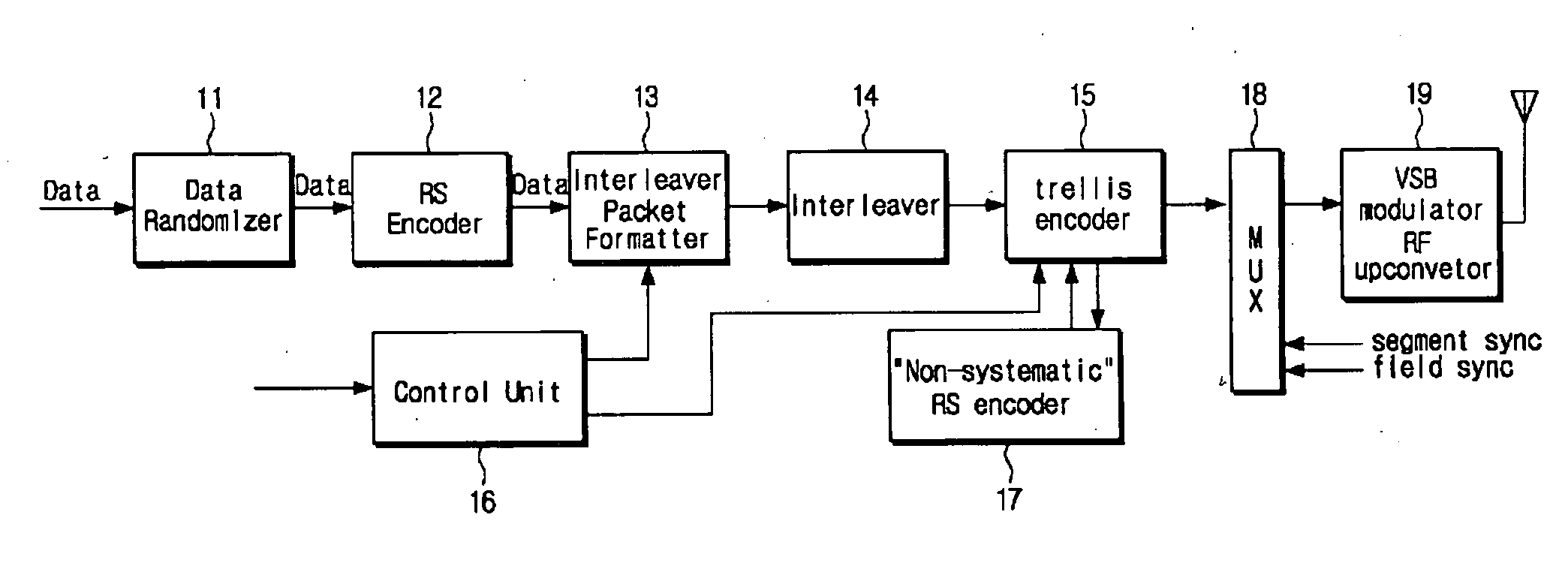

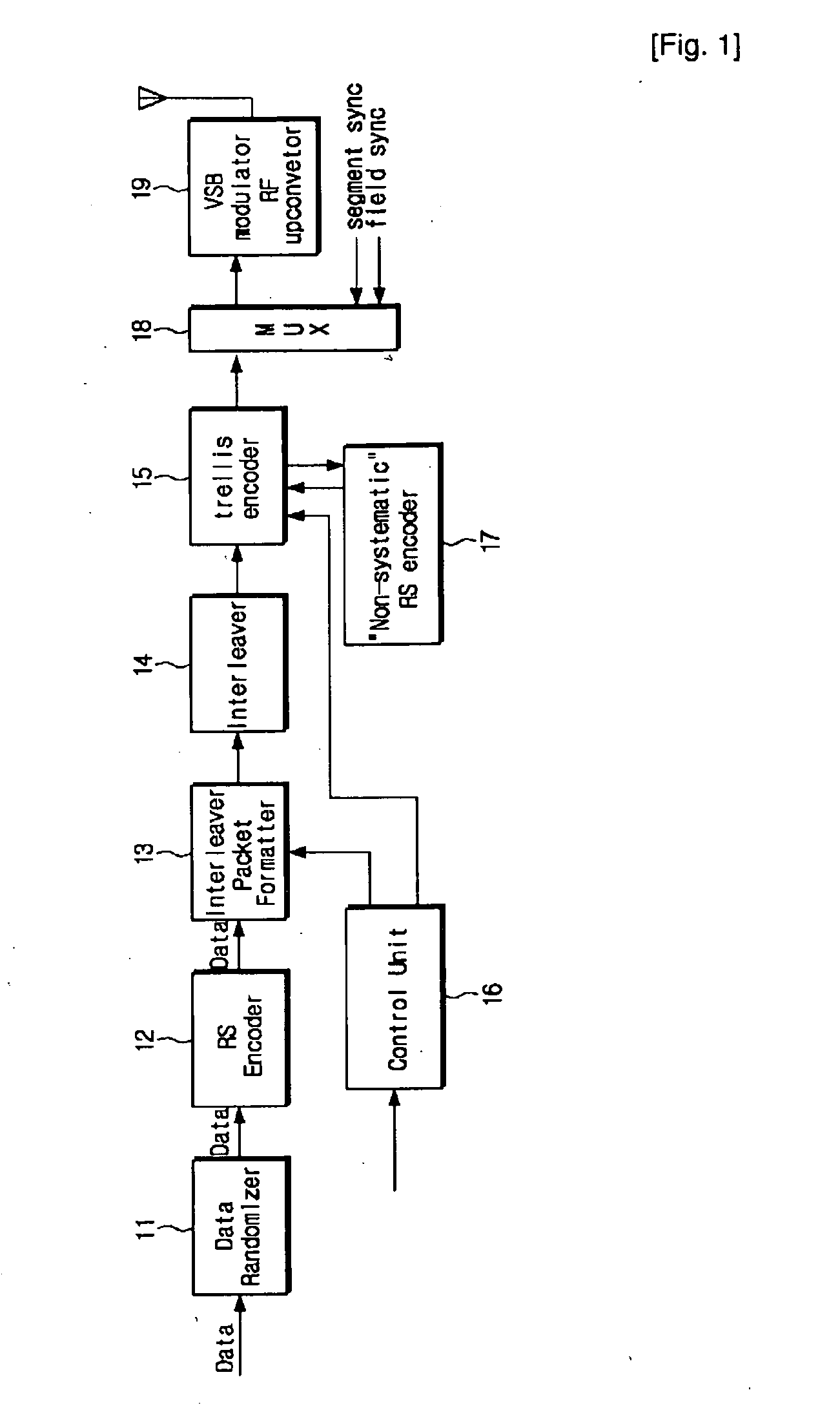

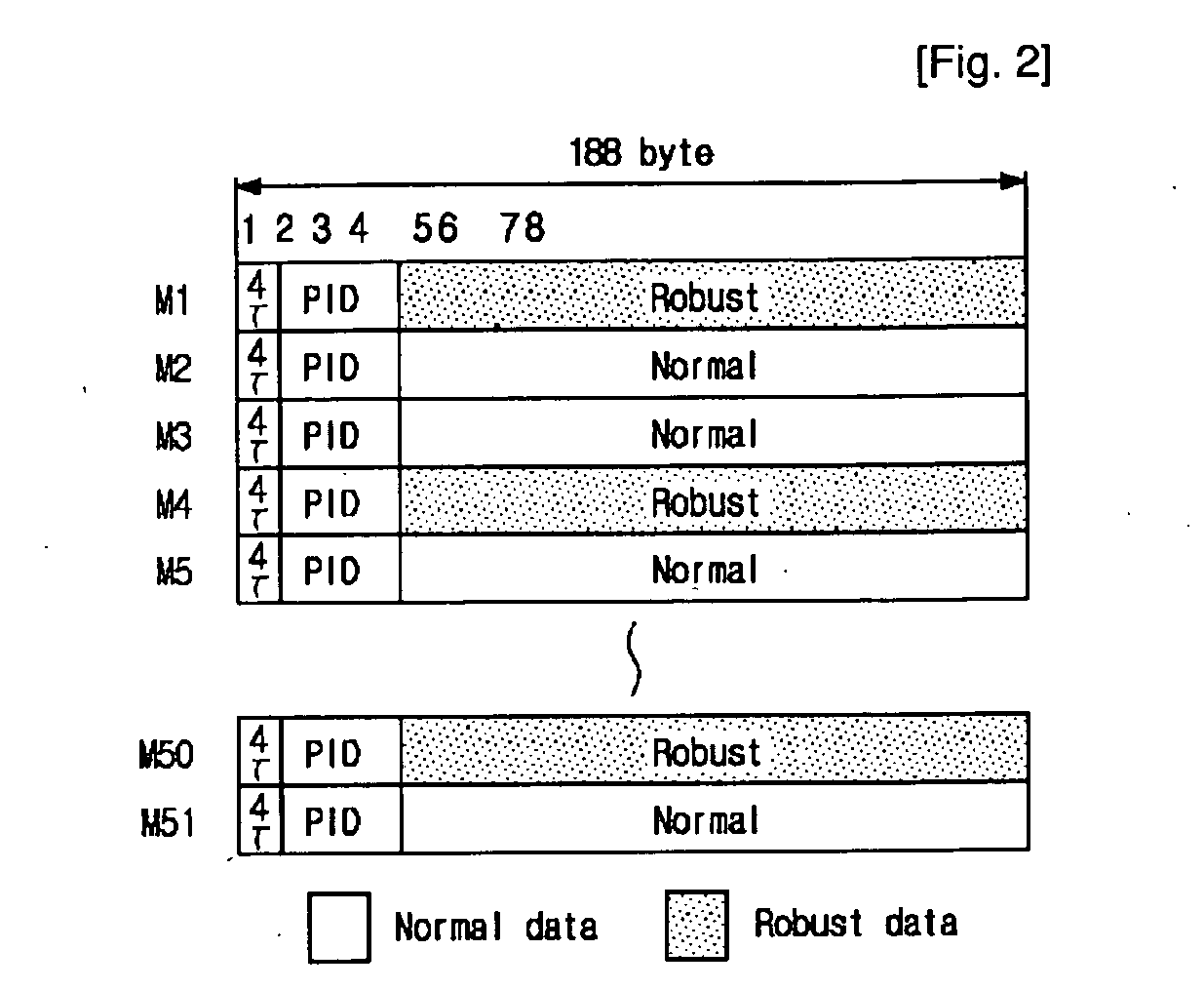

Digital Broadcasting Transmission/Reception Devices Capable Of Improving A Receiving Performance And Signal Processing Method Thereof

InactiveUS20080267307A1Low hardware complexityEnhanced digital broadcasting reception performanceMultiple-port networksError correction/detection by combining multiple code structuresData streamMultipath channels

Disclosed is a digital broadcasting transmission / reception system having an improved reception performance and a signal-processing method thereof. A digital broadcasting transmitter comprises a randomizer for inputting dual TS stream consists of robust and normal packets having stuff bytes inserted in predetermined positions and randomizing the dual TS stream; a stuff byte exchanger for replacing the stuff byte of a randomized data stream from the randomizer to a predetermined known data; and an encoder for encoding a data streams to which the known data is inserted. Accordingly, the present invention detects the known data from a signal received from a reception side and uses the detected known data for synchronization and equalization, so that the digital broadcasting reception performance can be improved at poor multipath channels.

Owner:SAMSUNG ELECTRONICS CO LTD