Patents

Literature

73 results about "Symbol interleaving" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Symbol interleaving

ActiveUS20060062314A1Receiver specific arrangementsSecret communicationDigital dataSymbol interleaving

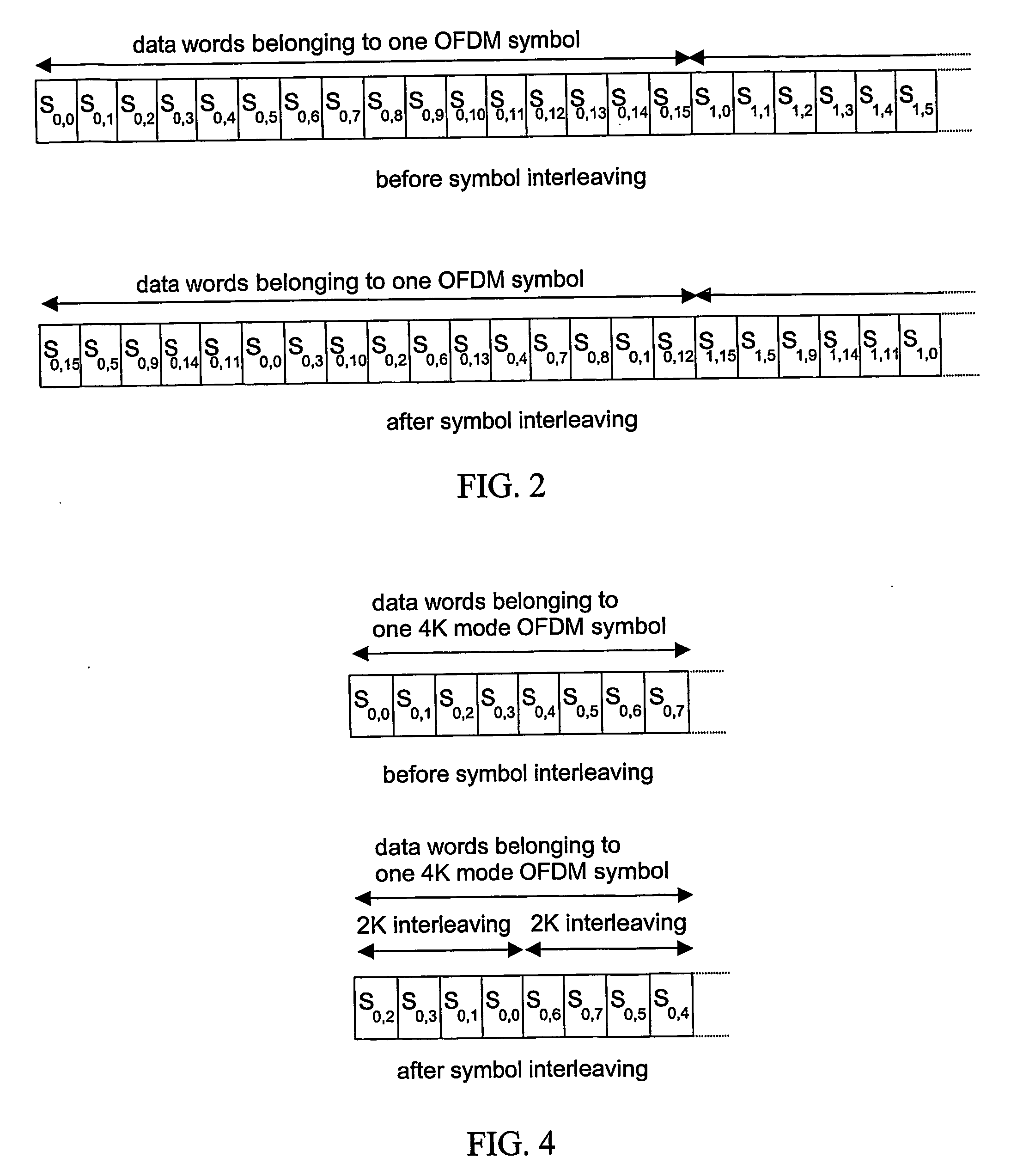

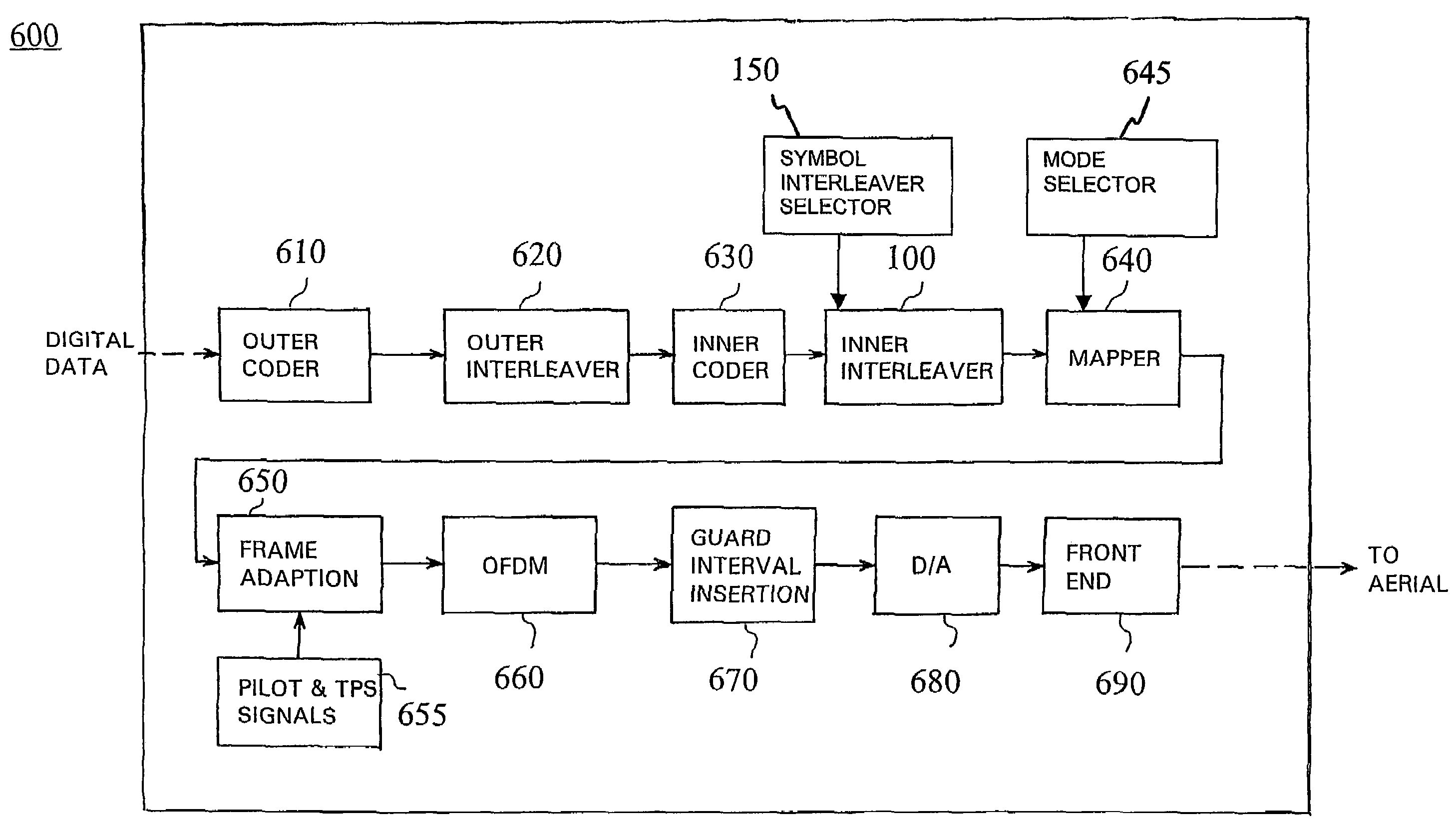

The invention relates to a method for communicating digital data using an orthogonal frequency division multiplexing (OFDM) transmission system (10) including at least one transmitter (600, 601) and receivers (700, 701). The method comprises selecting a mode of operation in a transmitter among at least one mode, each mode of operation being associated with a number of active carriers for payload data transmission, selecting a symbol interleaver in the transmitter from a set of symbol interleavers for symbol interleaving in said selected mode of operation, applying symbol interleaving in the transmitter on blocks of data units, mapping the interleaved data units onto the active carriers of said selected mode of operation, receiving the interleaved data units in the receiver, recognizing in the receiver the symbol interleaver used in the data transmission, selecting a de-interleaver in the receiver to correspond to the recognized symbol interleaver, and de-interleaving in the receiver the received data units using the selectedde-interleaver.

Owner:NOKIA TECHNOLOGLES OY

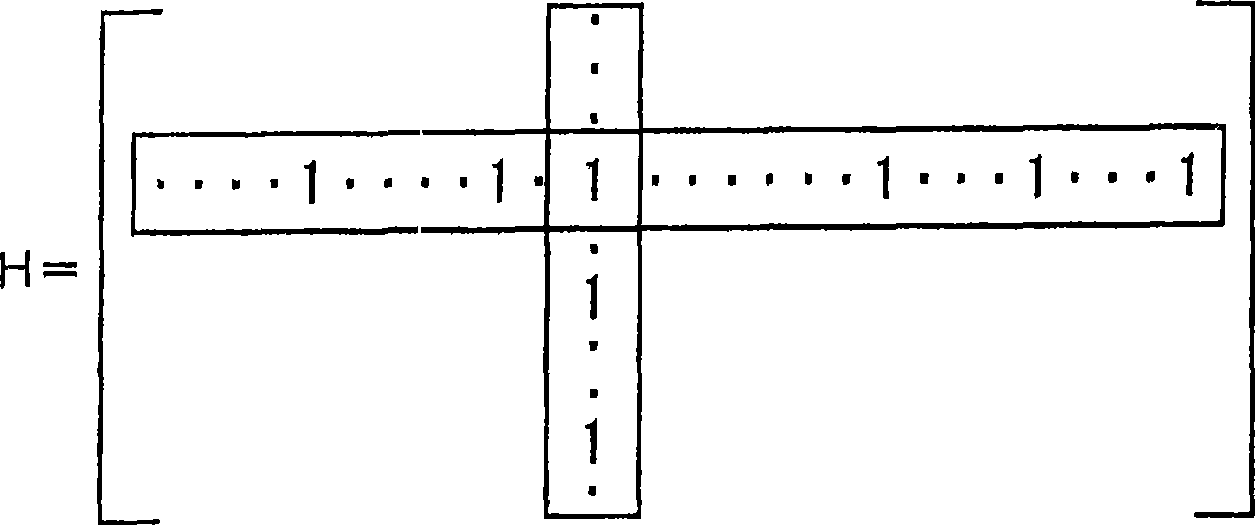

Data processing device and method

ActiveCN101510865APulse modulation television signal transmissionError preventionAddress generatorCarrier signal

A data processing device transmits the data bits on the predetermined quantity carrying wave signal of the OFDM sign. The data processing device comprises a parity interweaver for operating the pairs of LDPC coding data. The data bits are obtained by the parity matrix LDPC detecting with the LDPC code. The parity matrix has a ladder-type structure interweaving the LDPC code data to the different parity bit position. The mapping unit maps the parity interweaving bit to the data signs corresponding to the modulating signs of the solution. The sign interweaver reads the quantity signs to the sign interweaving store, carrying out the data sig of the sign interweaving store reading the order with different reading; the order address set is confirmed. The address set is generated by the address generator.

Owner:SONY CORP

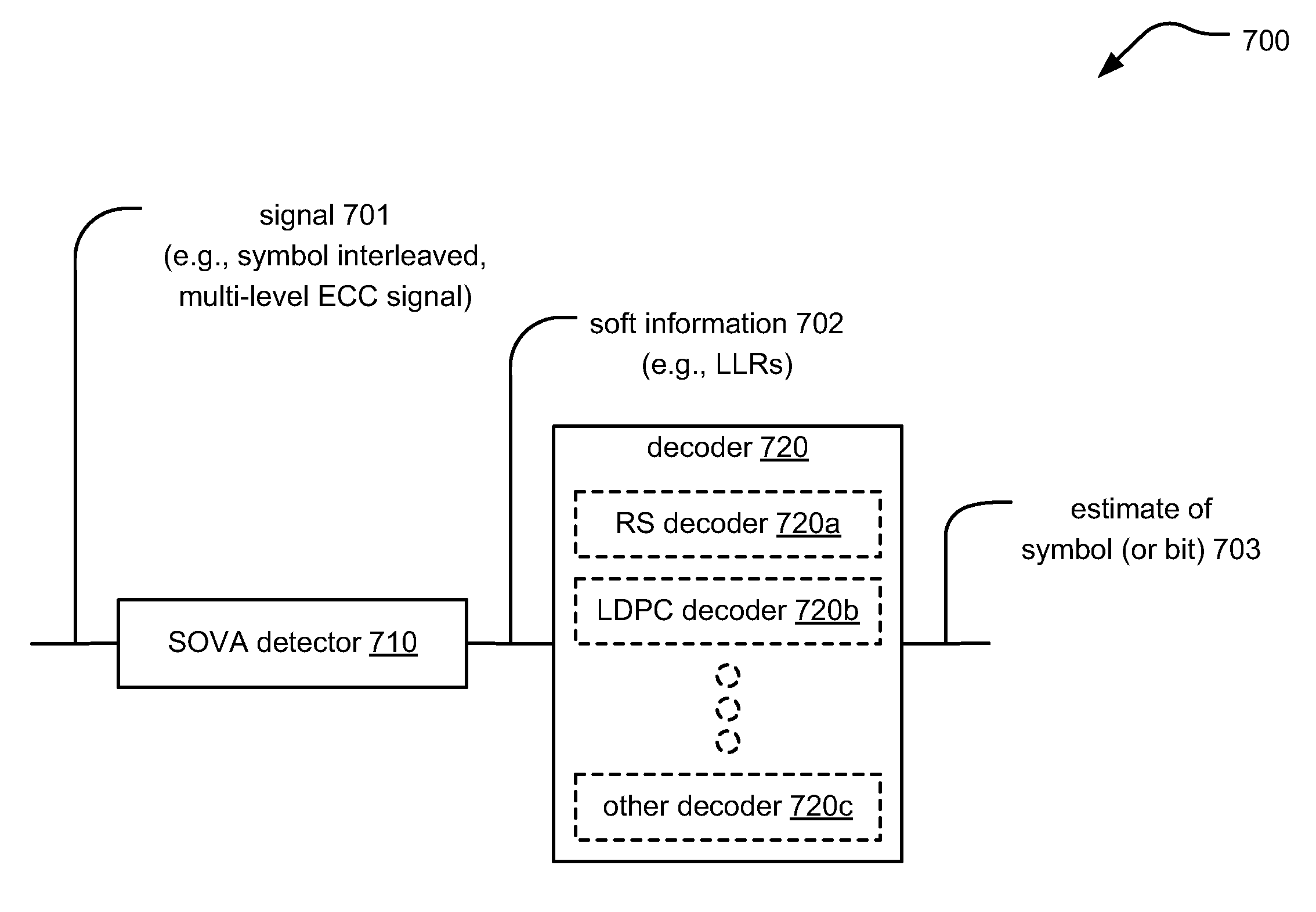

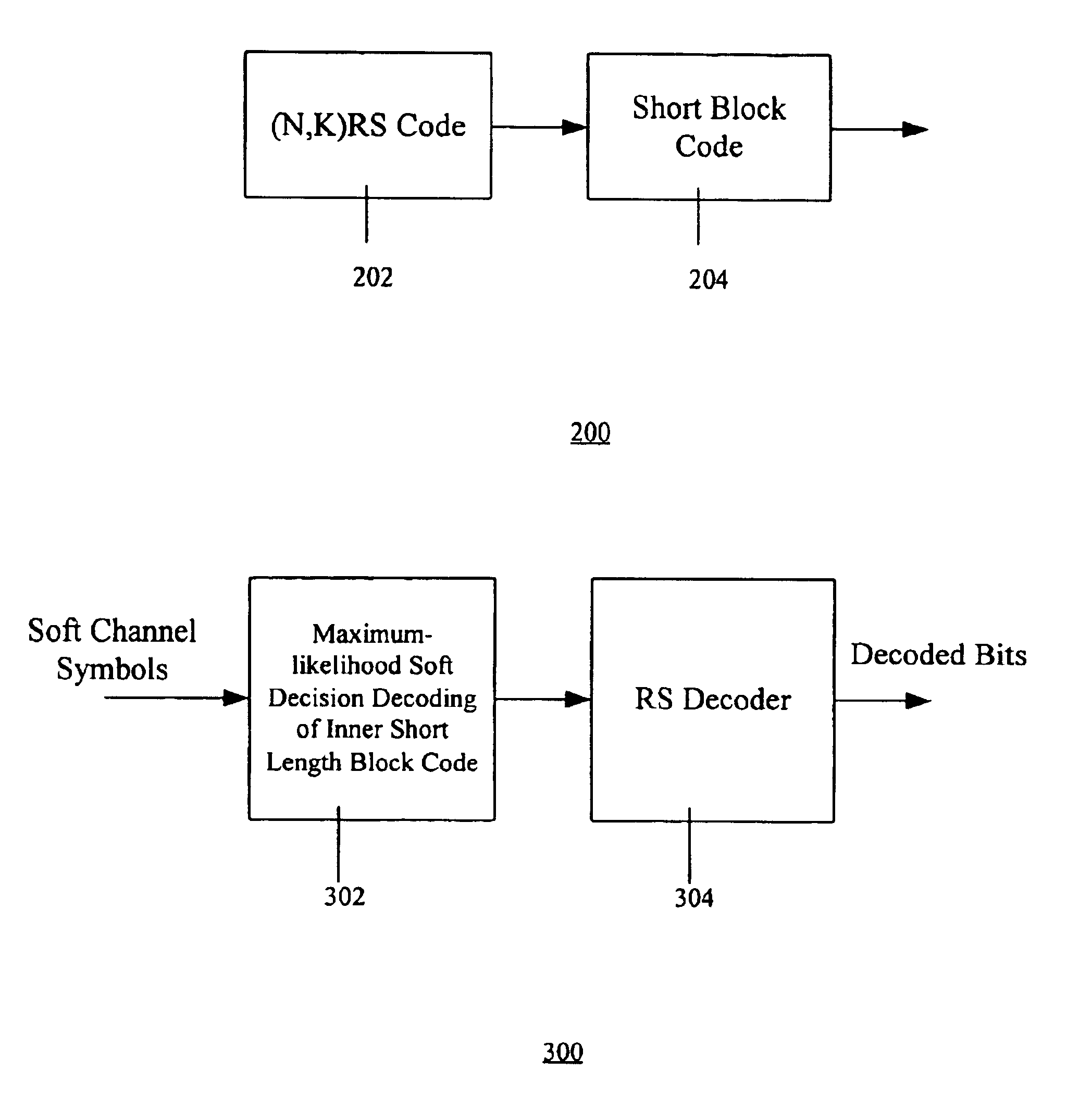

Error correction coding using soft information and interleaving

Error correction coding using soft information and interleaving. A symbol interleaved ECC signal (which can be a symbol interleaved multi-level ECC signal) initially undergoes detection (e.g., such as using SOVA detection) to generate soft information. A decoder uses the soft information to generate estimates of at least one symbol (or at least one bit) of the symbol interleaved multi-level ECC signal. Initially, each of the interleaves of the symbol interleaved multi-level ECC signal undergo decoding to determine whether or not any of the interleaves has correctable errors. If not, then a receiving device can request re-transmission of the symbol interleaved multi-level ECC signal from a transmitting device (or a re-read from media of a hard disk drive (HDD)). Interleaves having uncorrectable errors are associated with interleaves having correctable errors. Uncorrectable errors can be corrected via the use of erasure pointers or bit-flipping, among other means.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

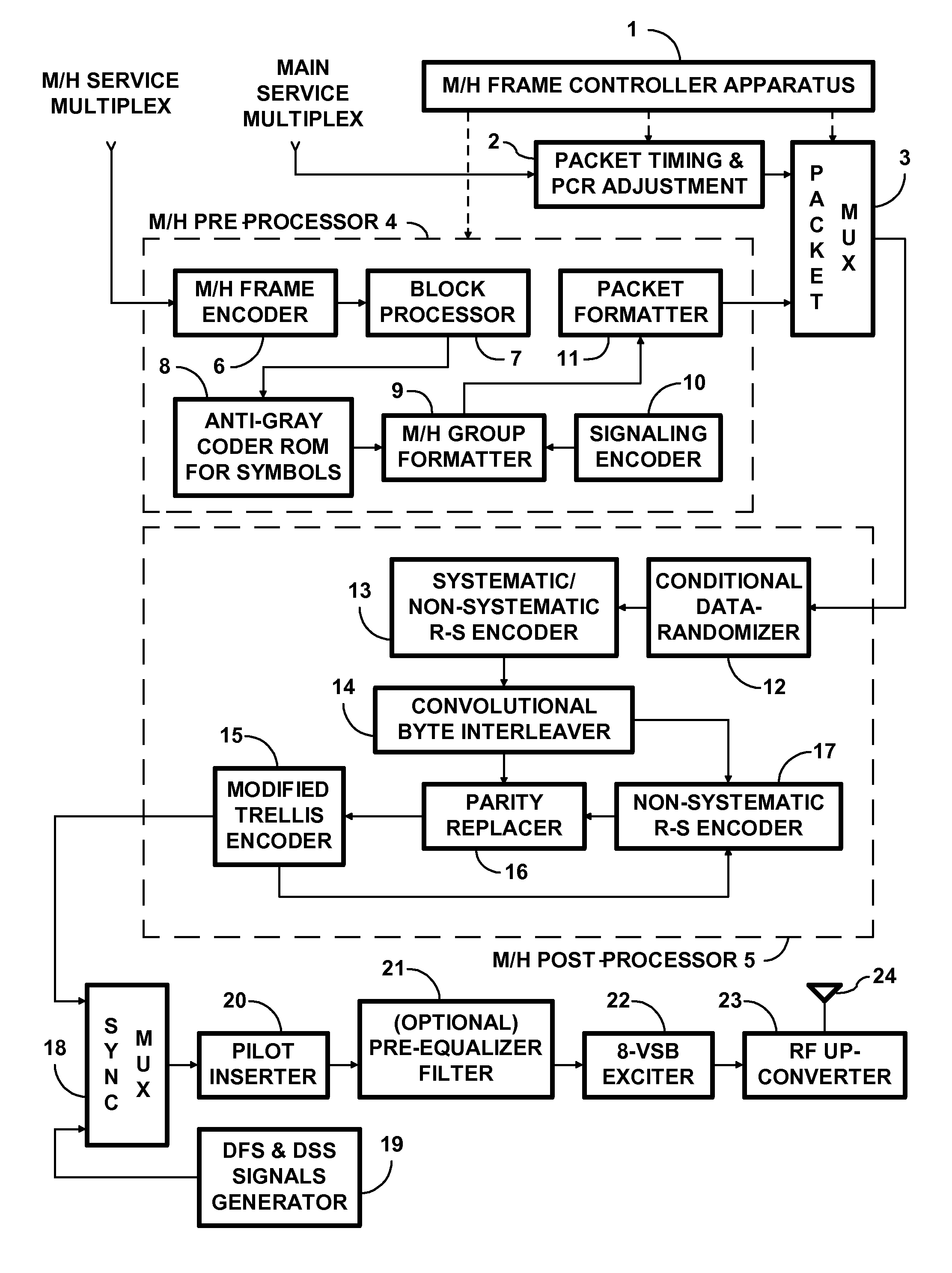

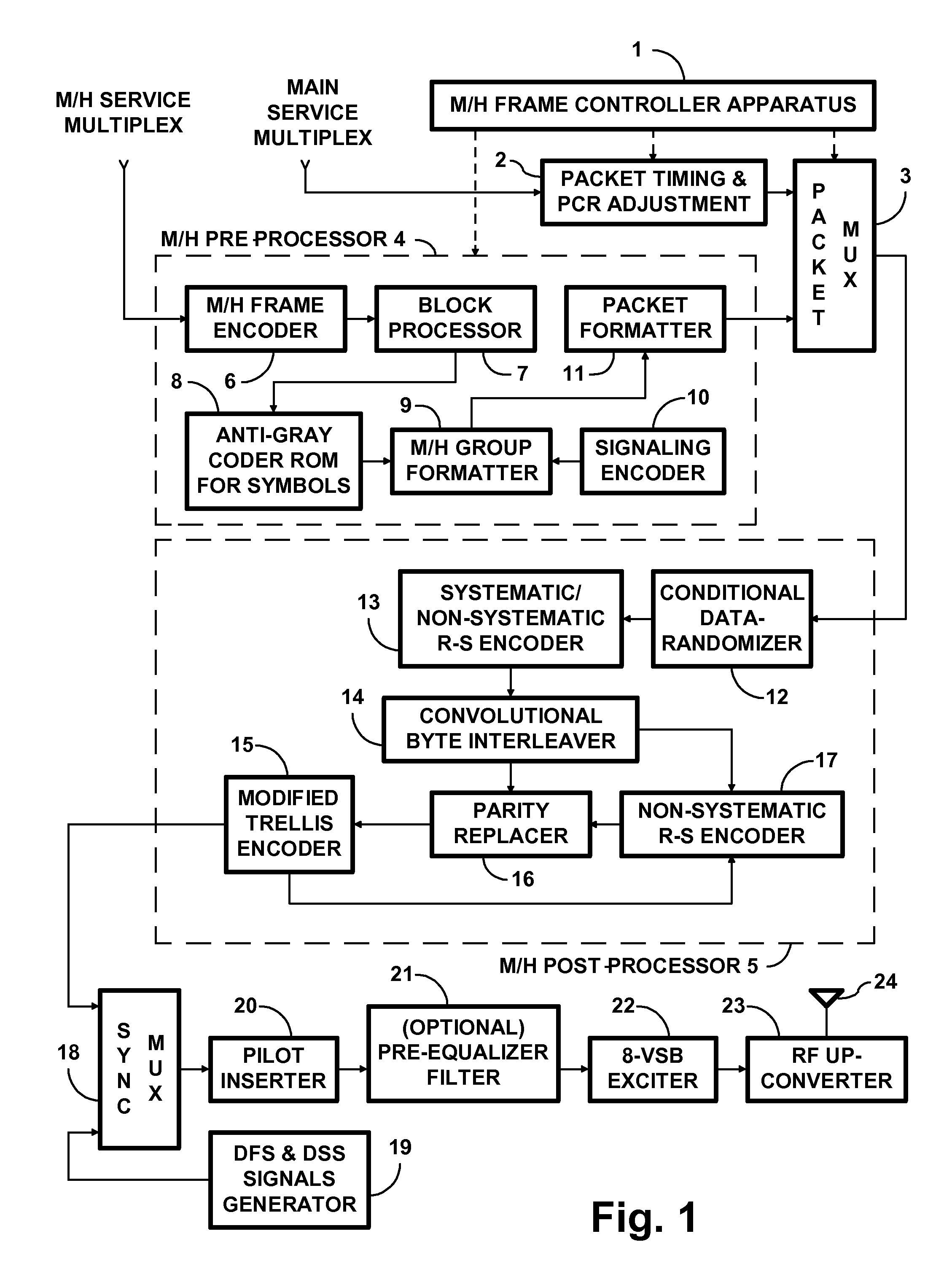

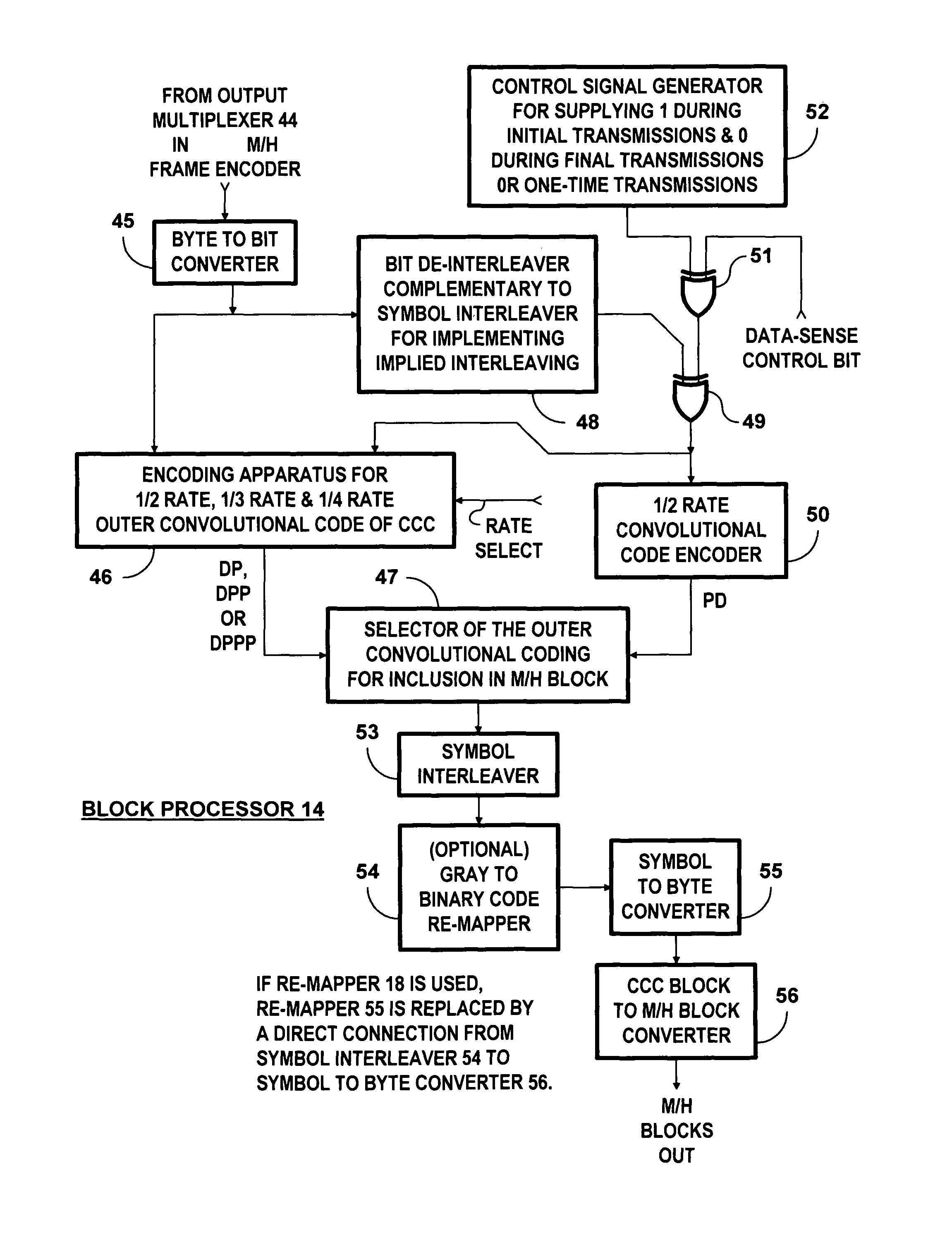

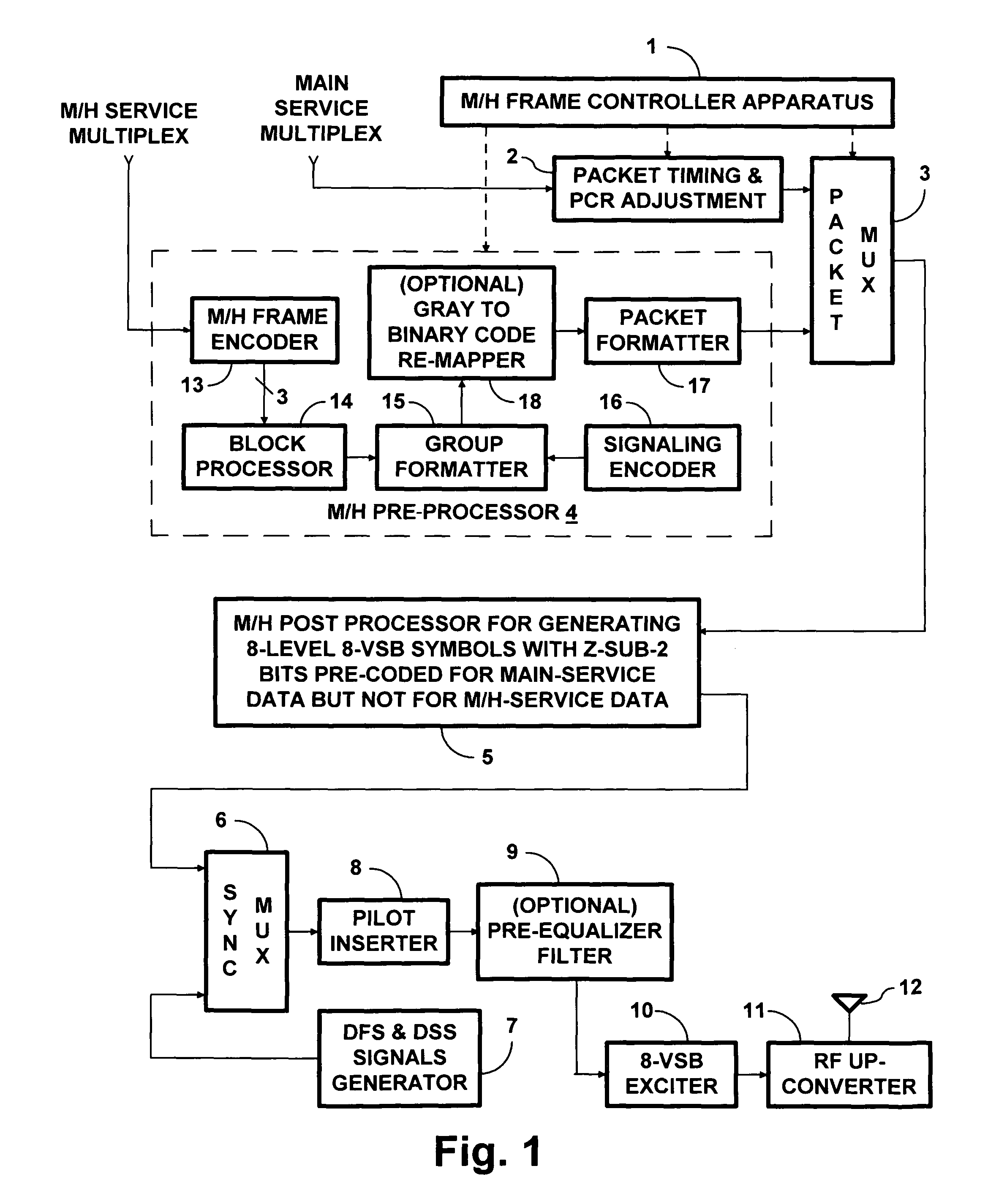

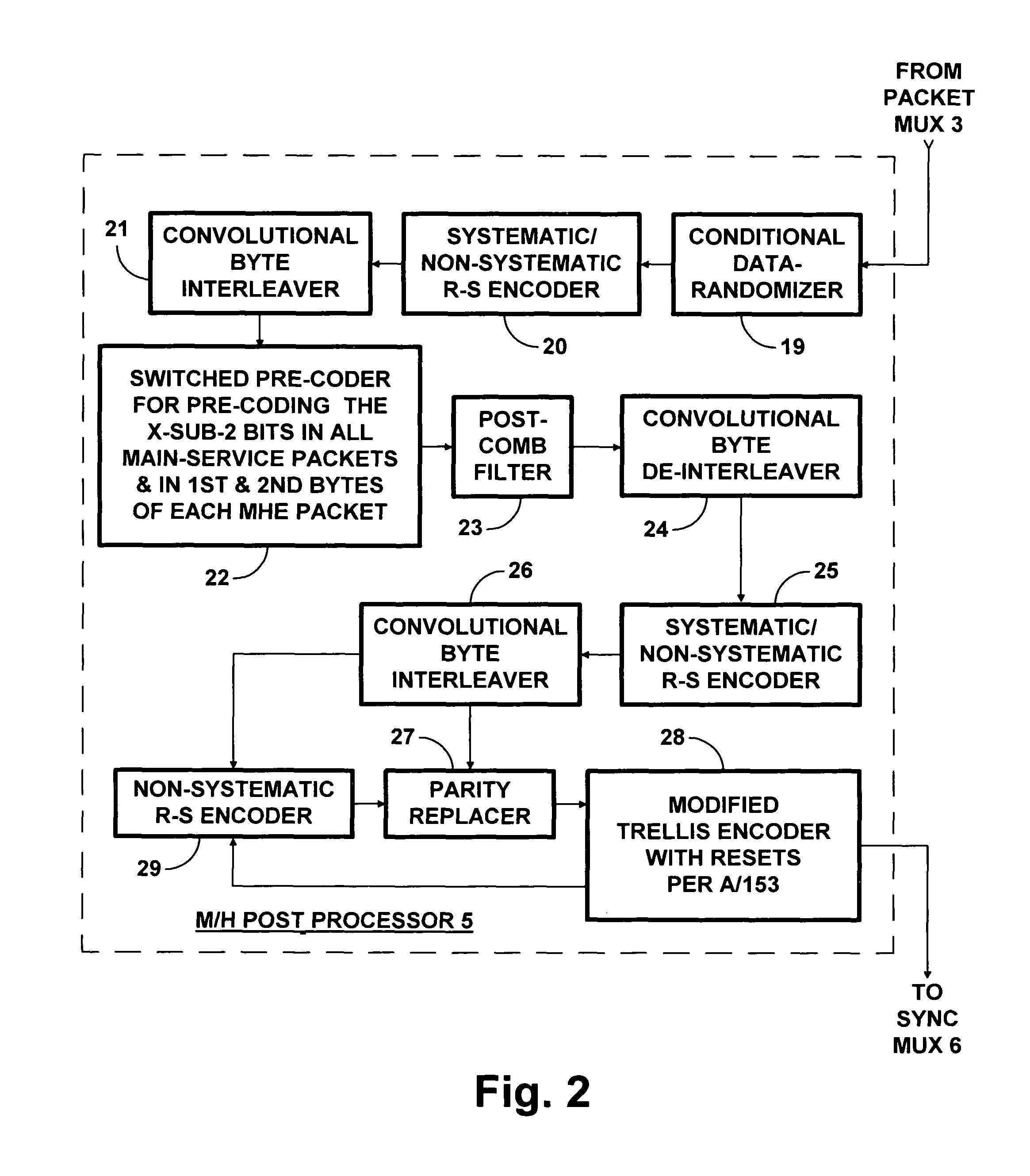

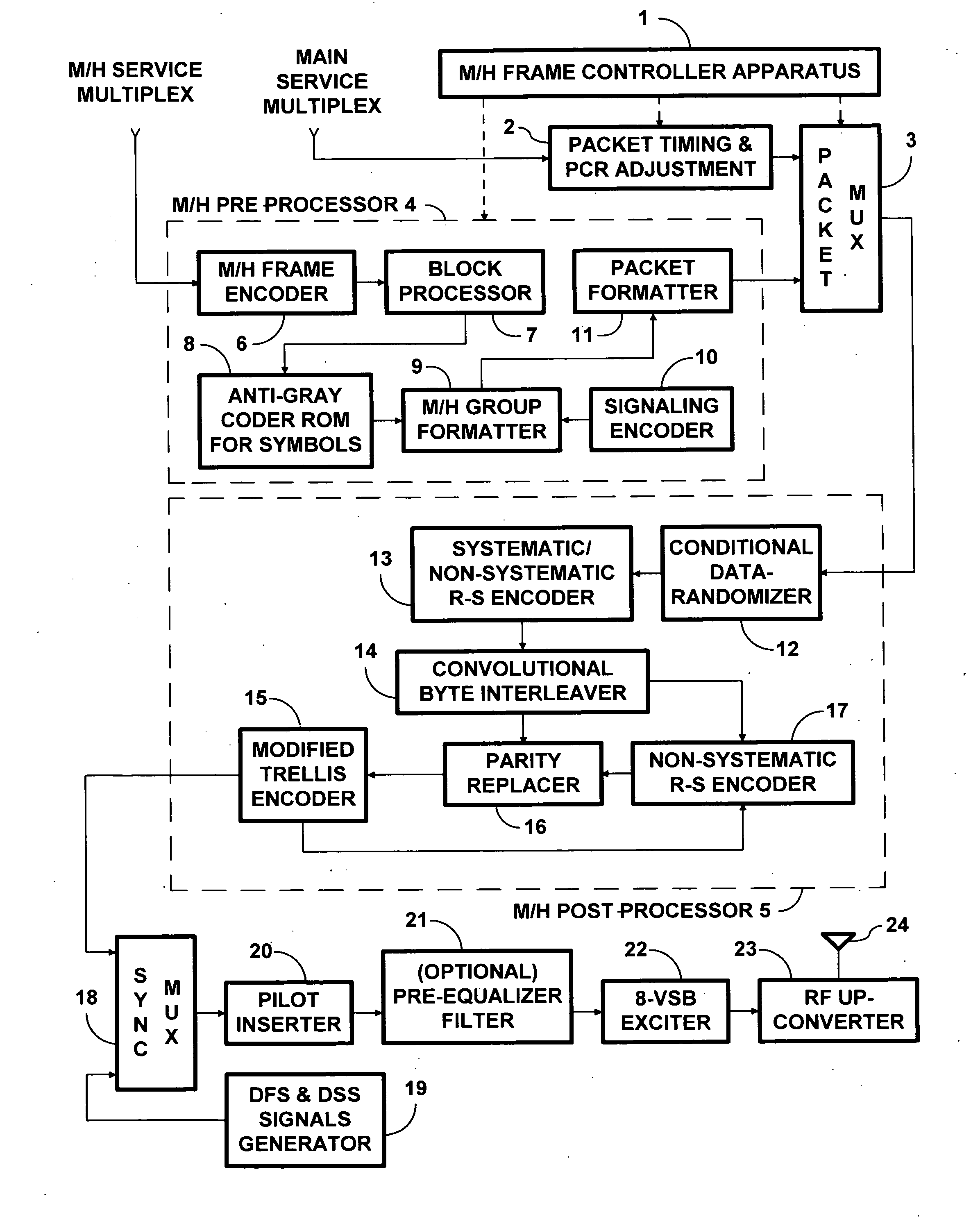

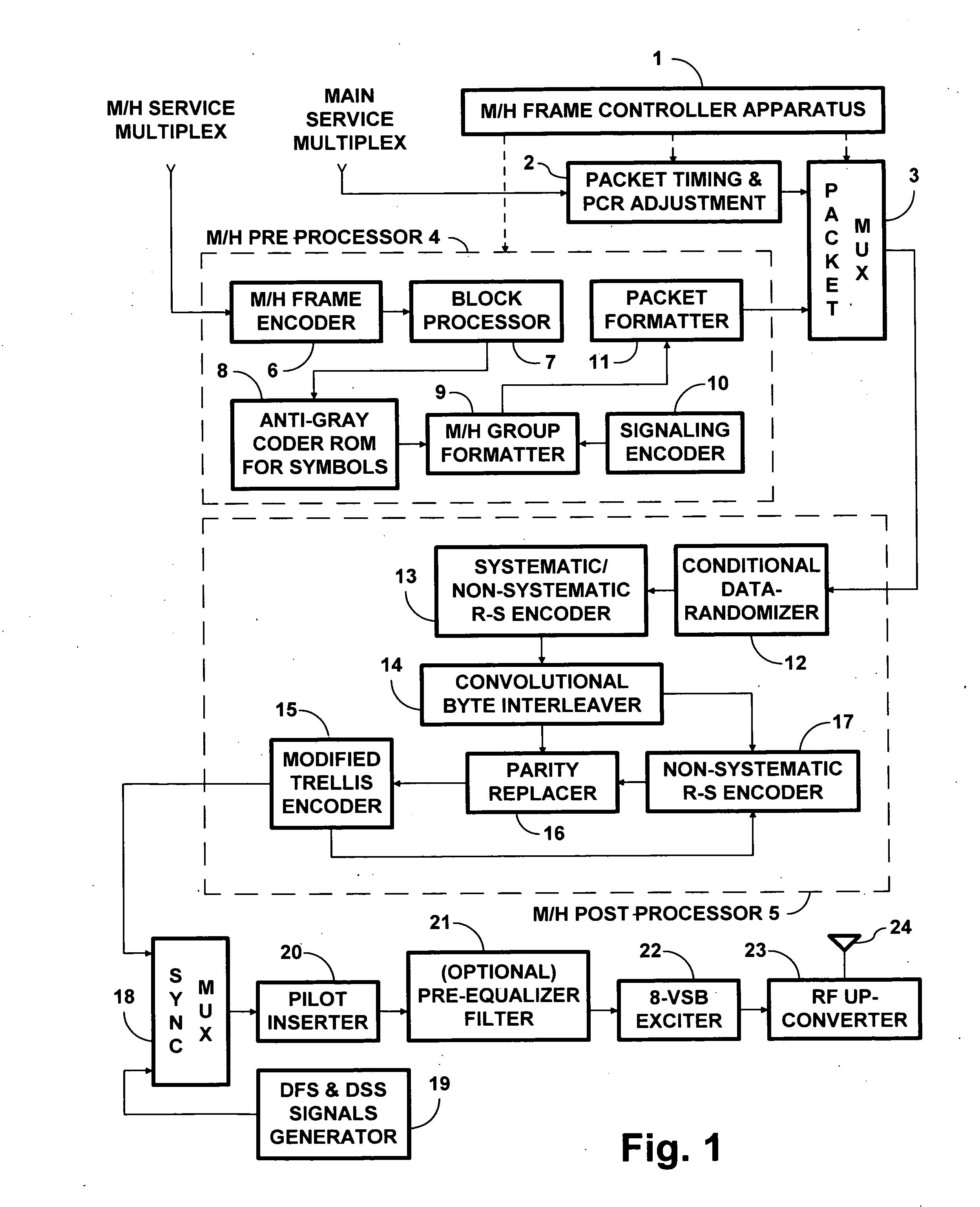

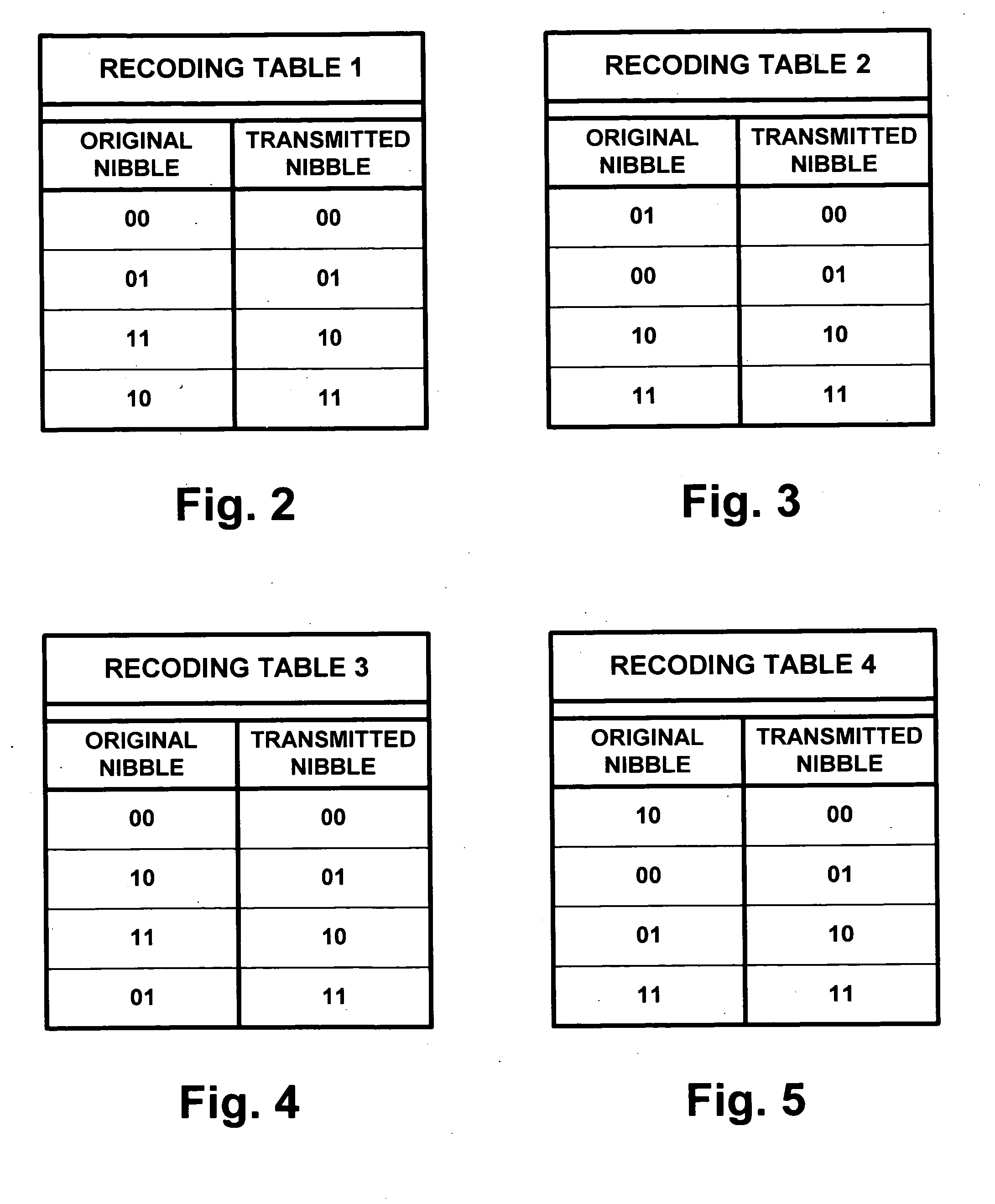

System for digital television broadcasting using modified 2/3 trellis coding

ActiveUS20090323823A1Television system detailsPicture reproducers using cathode ray tubesSymbol interleavingComputer science

The outer convolutional coding of the signals used to transmit mobile-handheld (M / H) service data within digital-television (DTV) signals is subjected to anti-Gray coding, either before or after its interleaving, but before its inner convolutional coding. In a receiver for such M / H-service data, portions of the trellis decoded DTV signal containing soft decisions concerning symbol-interleaved convolutionally coded M / H-service data are recoded for a Gray-code mapping of symbols to modulation levels. This is done either before or after symbol de-interleaving, but before decoding the outer convolutional coding. Soft decisions concerning extrinsic information to be fed back to the ⅔ trellis decoder to close a turbo decoding loop are derived from soft decisions as to the M / H-service data, which derivation includes re-coding for a binary-code mapping of symbols to modulation levels. Each re-coding procedure can be performed using ROM, but preferably is performed using simple digital logic.

Owner:SAMSUNG ELECTRONICS CO LTD

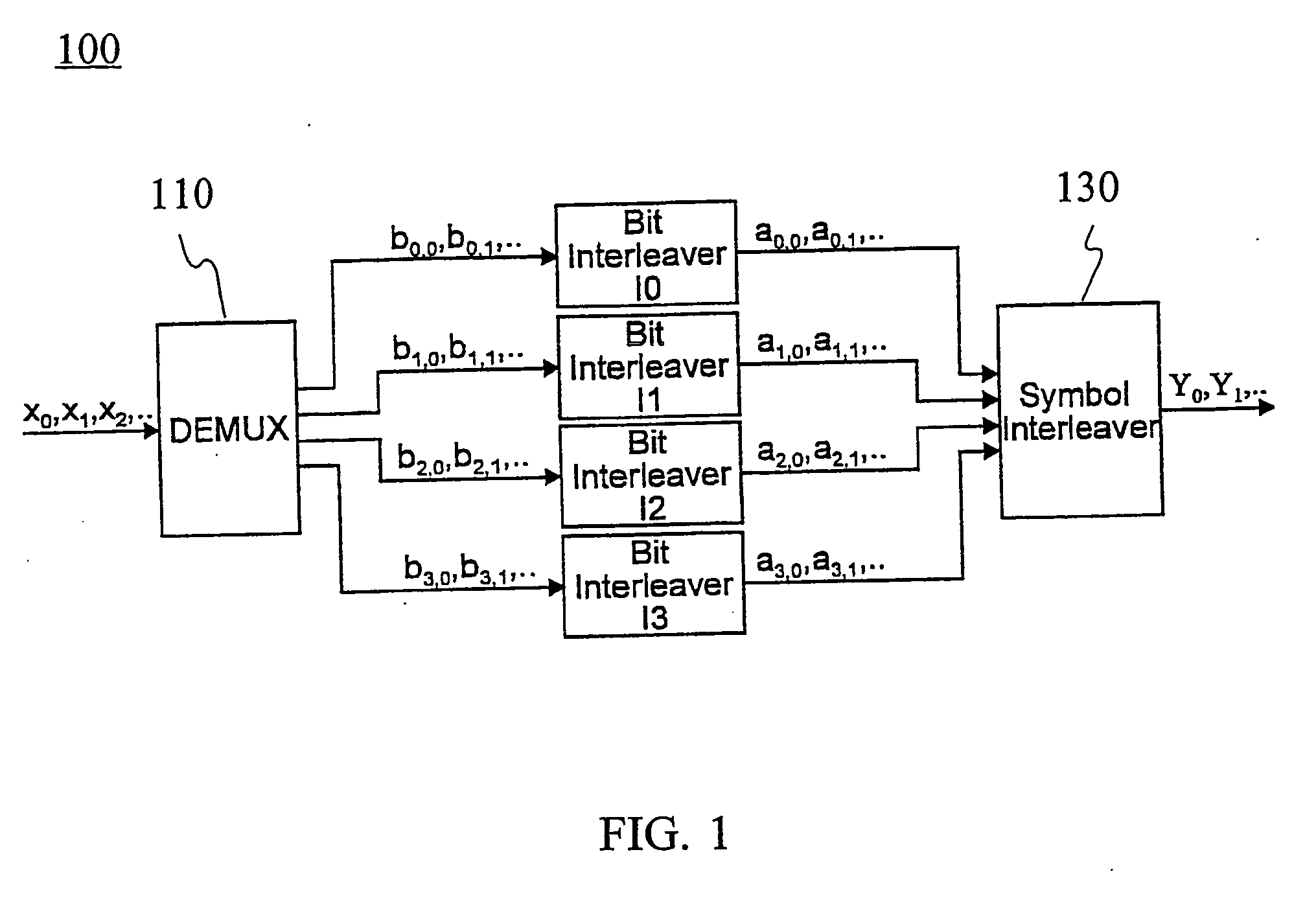

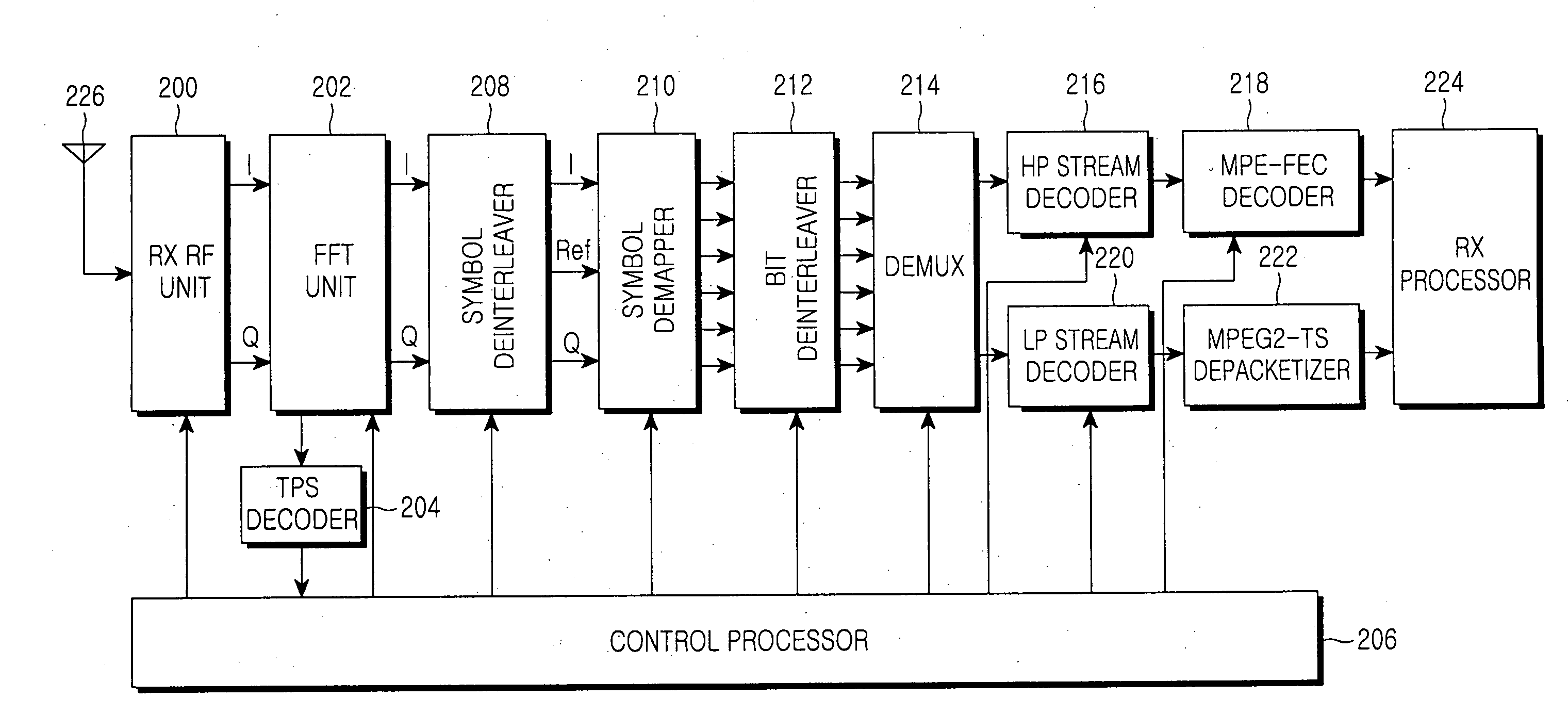

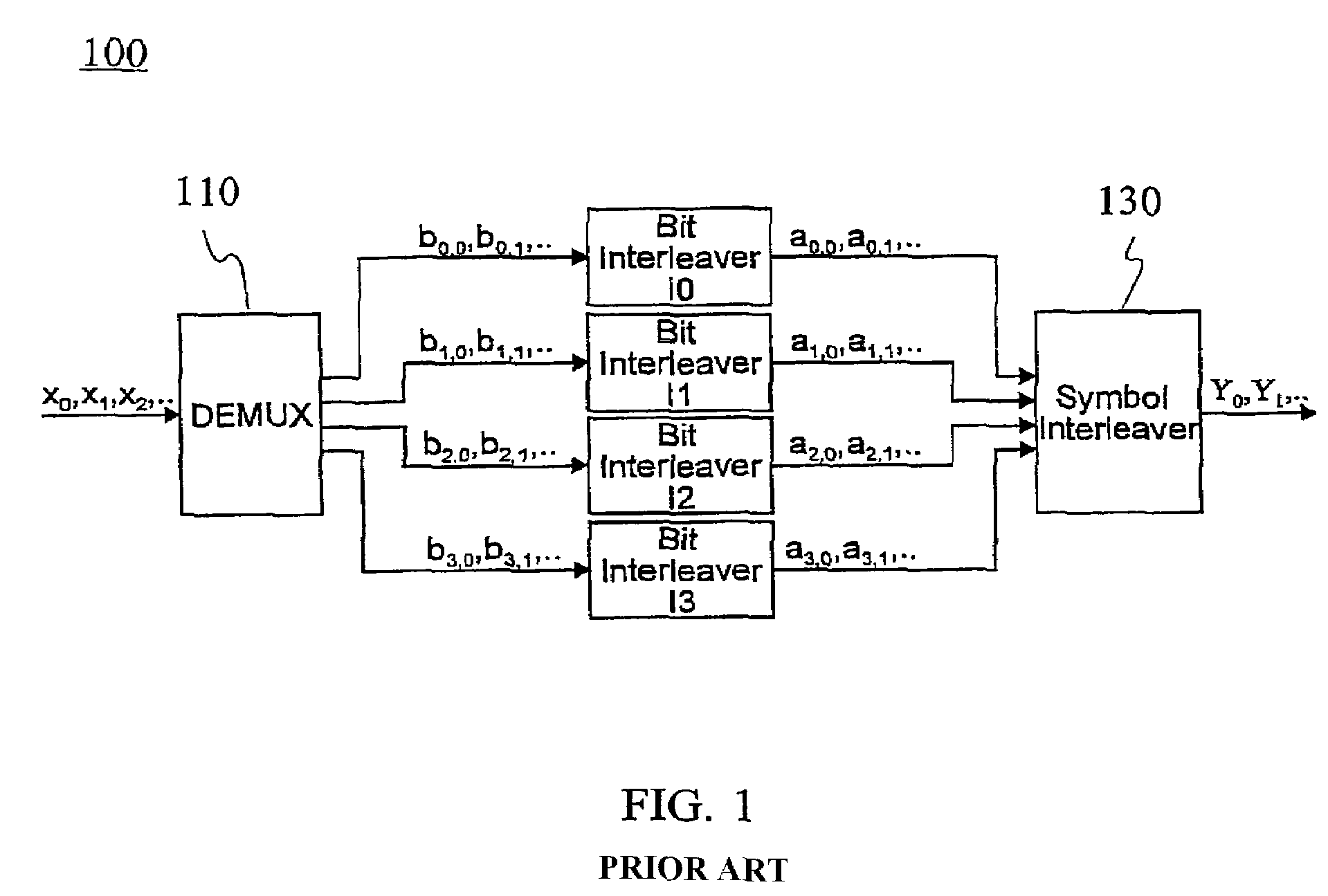

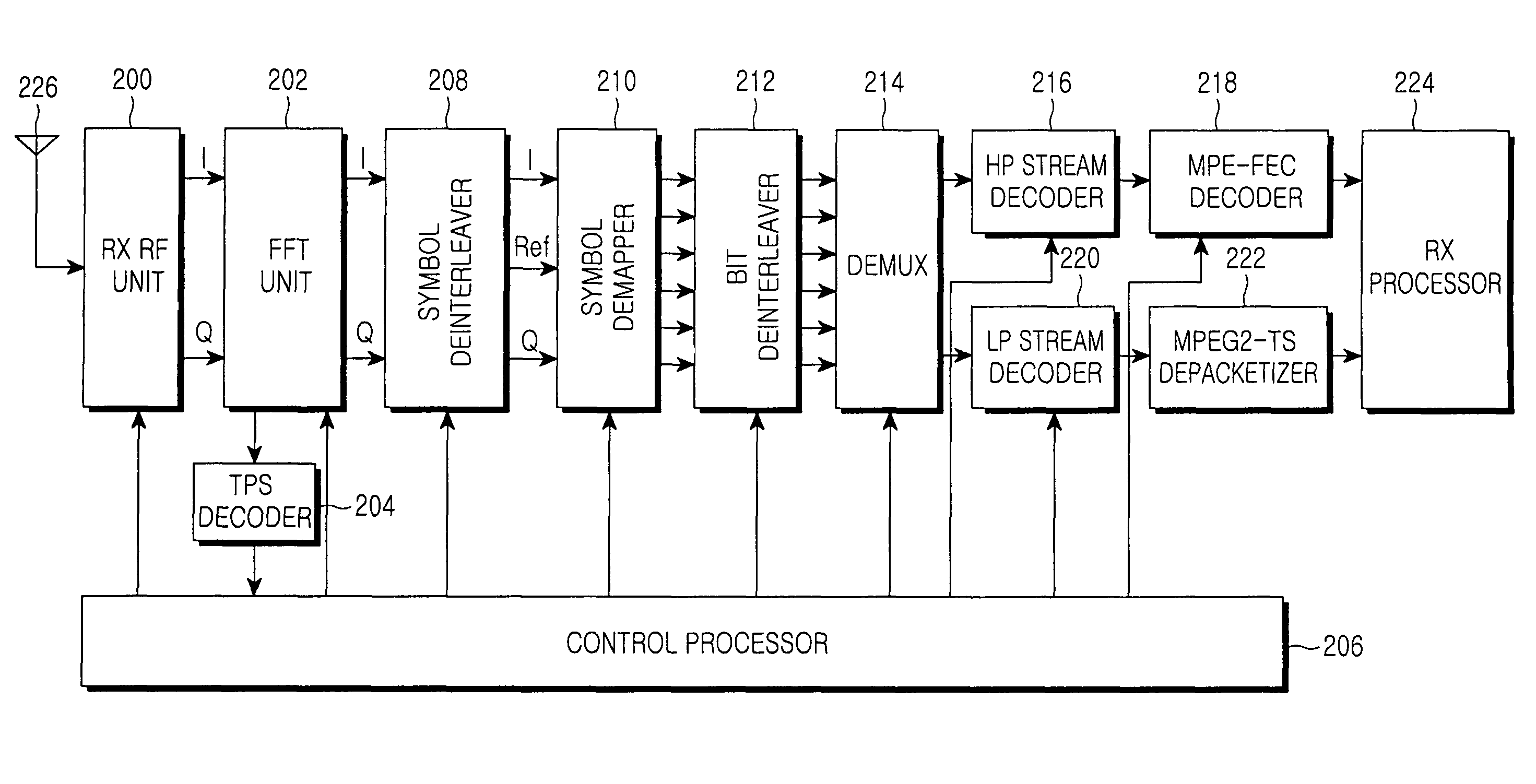

Apparatus and method for receiving data in a wireless communication system using bit interleaving, symbol interleaving and symbol mapping

InactiveUS20070165729A1Increase in hardware complexityIncrease power consumptionTime-division multiplexAmplitude-modulated carrier systemsFast Fourier transformCommunications system

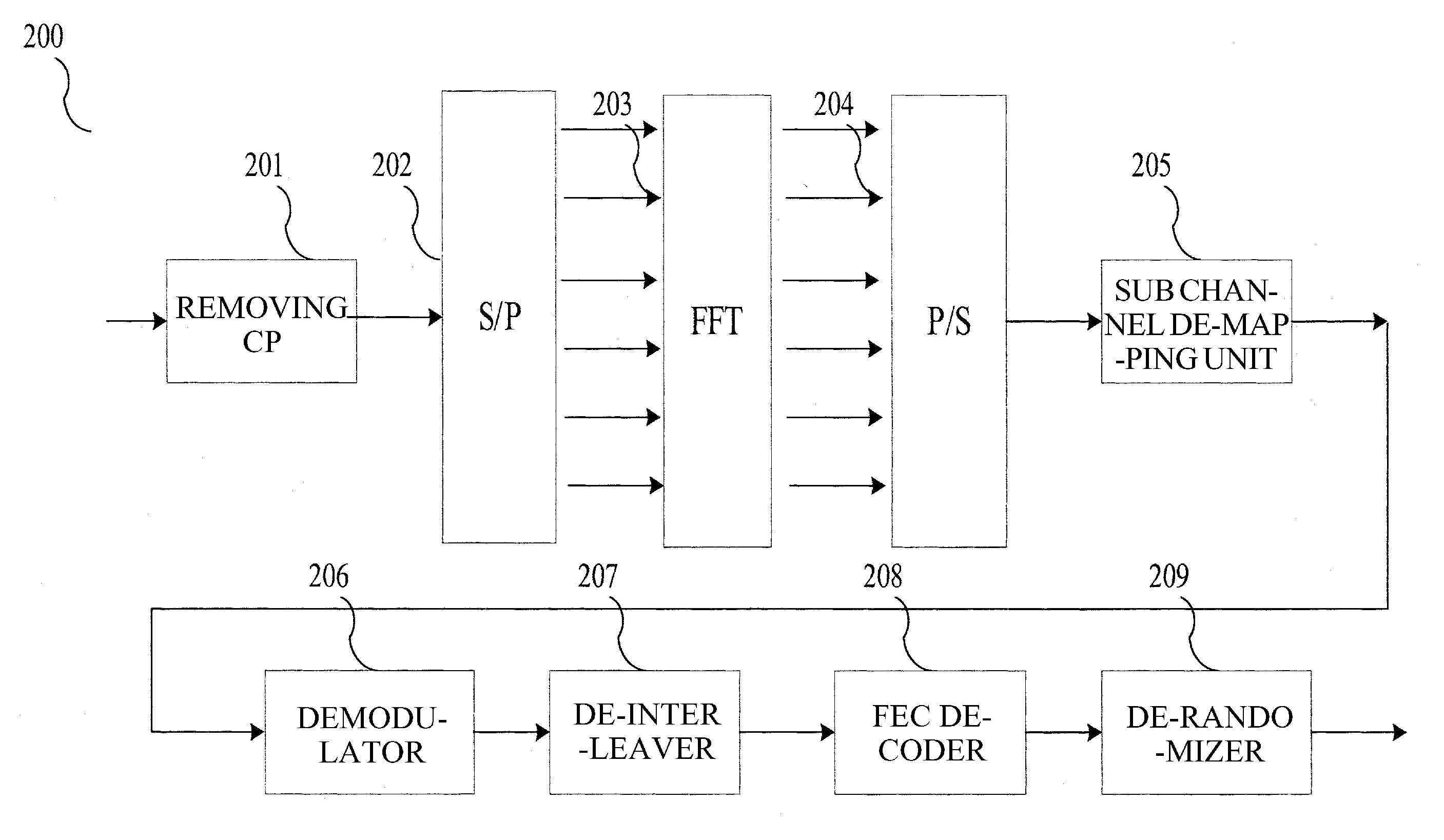

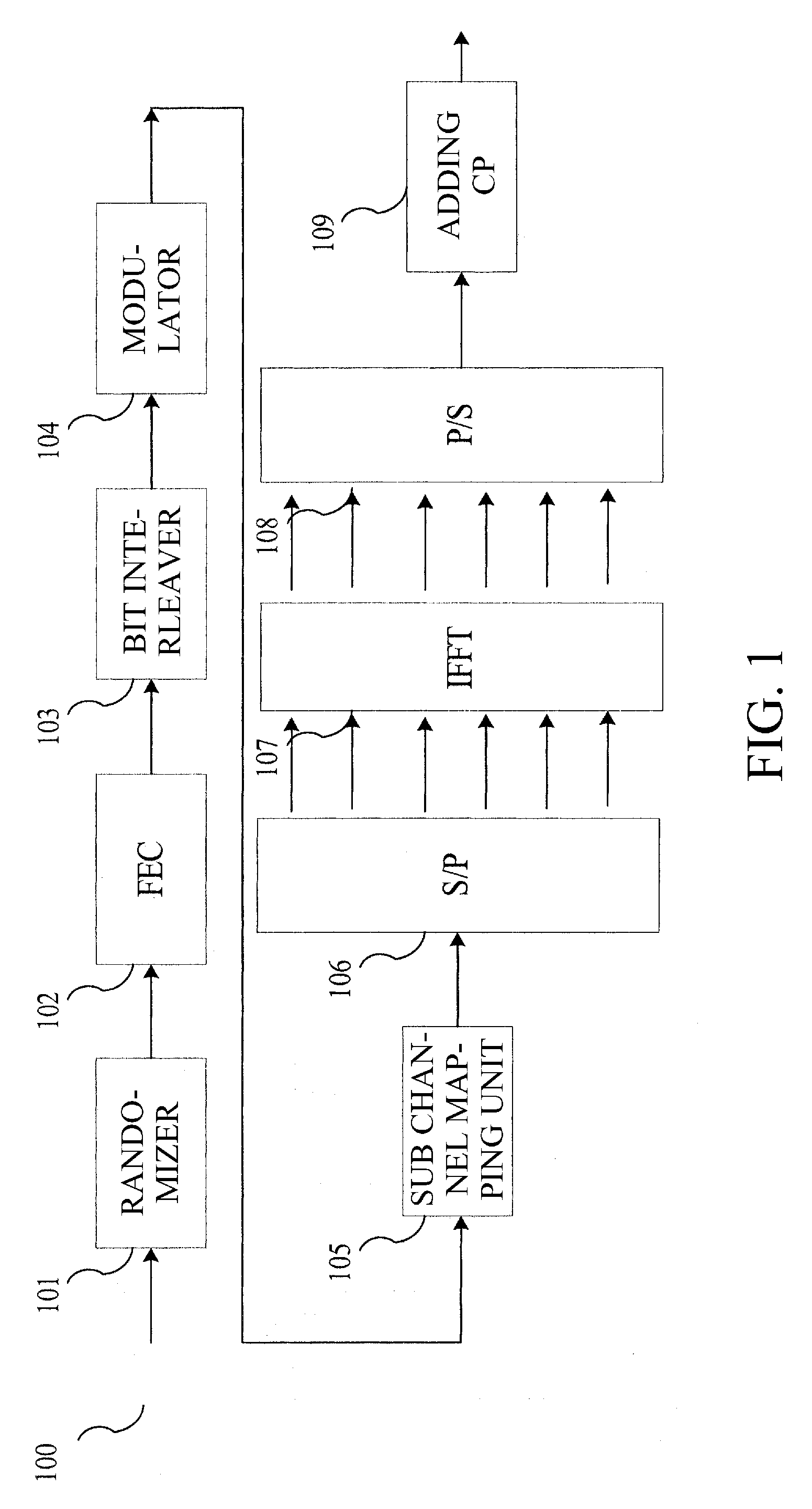

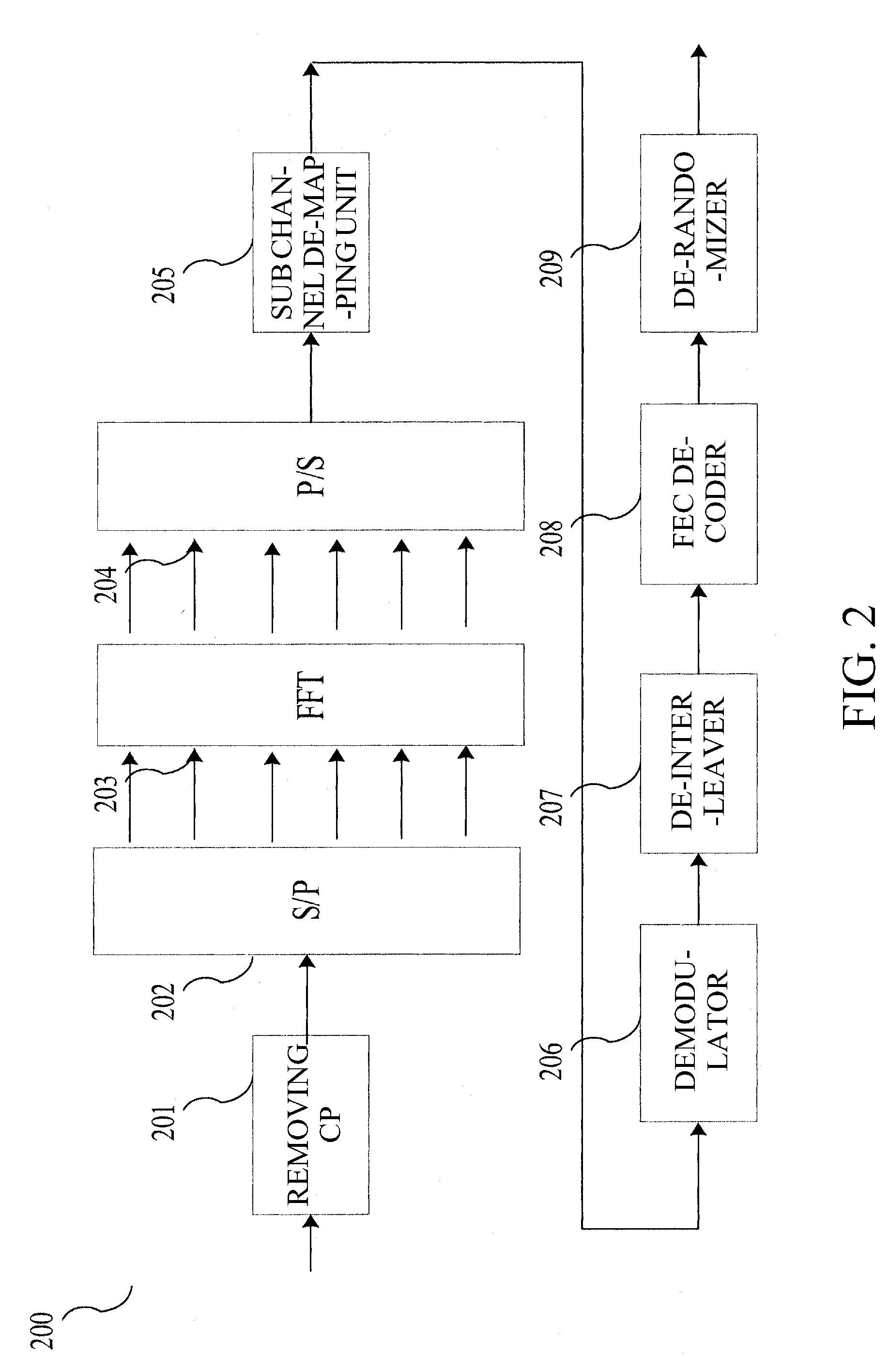

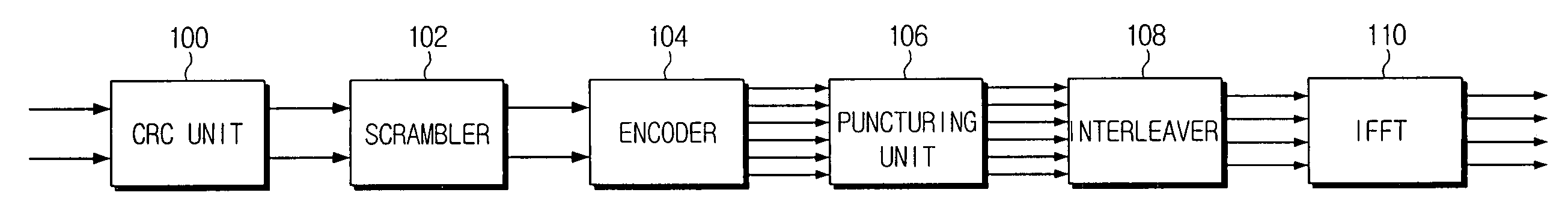

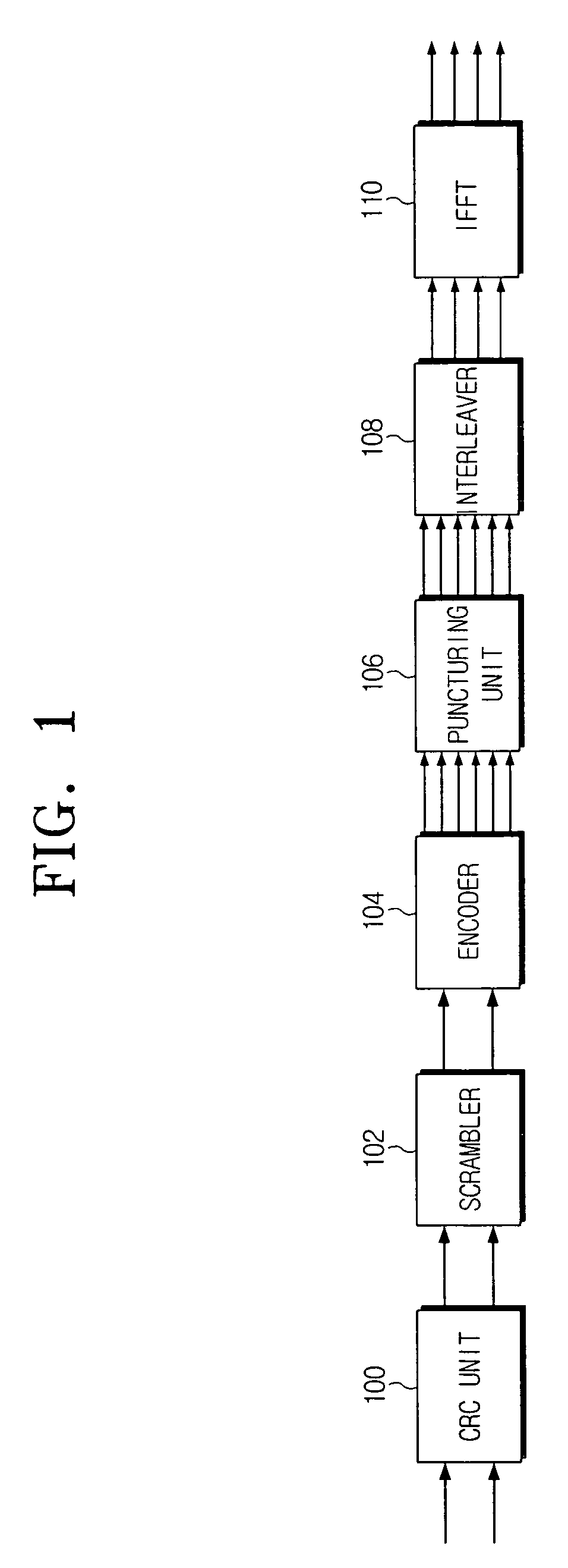

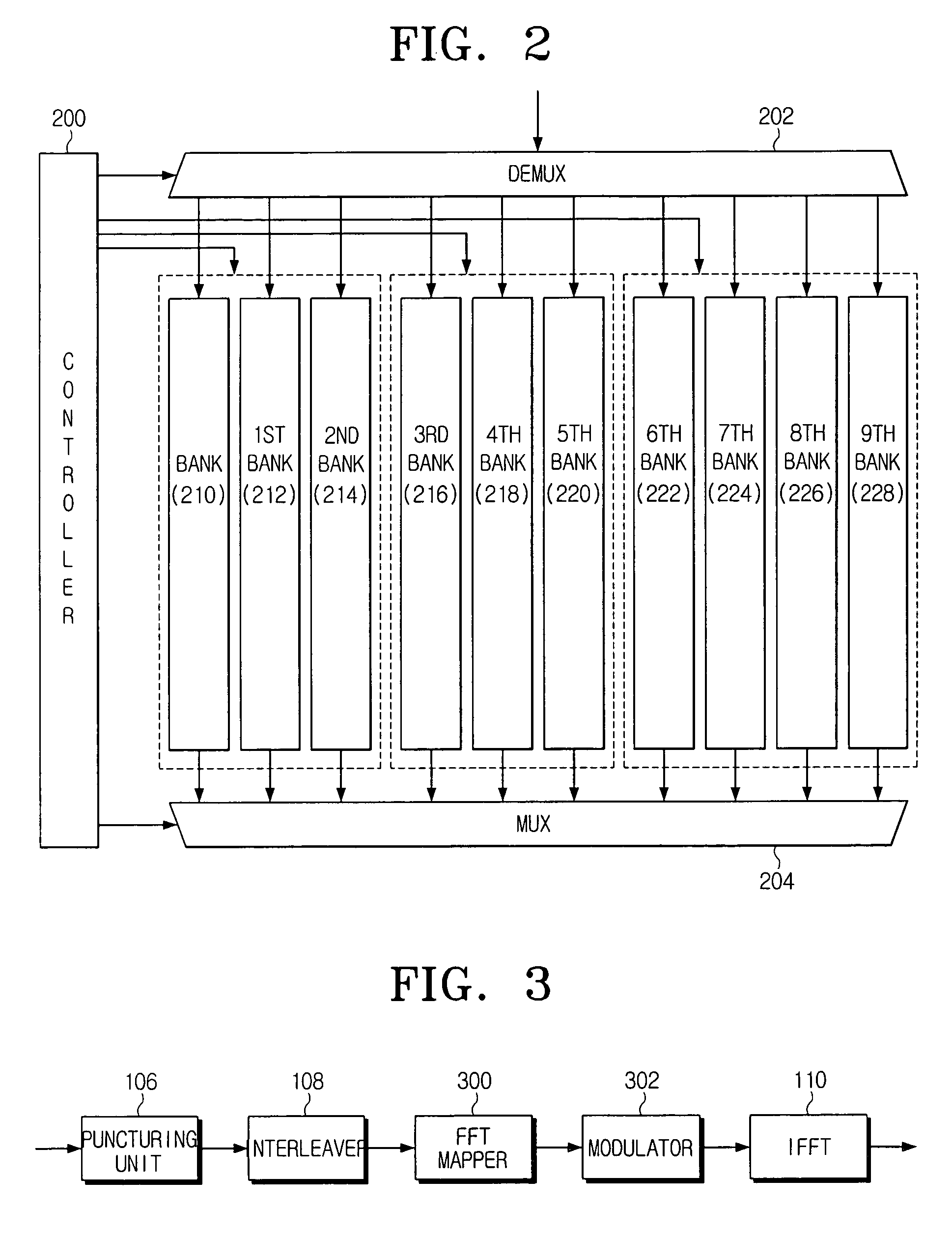

An apparatus and method are provided for receiving data generated by sequentially performing bit interleaving, symbol interleaving and symbol mapping in a wireless communication system. A fast Fourier transform (FFT) processor receives in-phase / quadrature phase (I / Q) data of a radio channel generated by sequentially performing bit interleaving, symbol interleaving and symbol mapping, and performs an FFT process for the I / Q data. A symbol deinterleaver performs a process for symbol deinterleaving the FFT I / Q data and reference values to be used for symbol demapping of the I / Q data and outputs the symbol-deinterleaved I / Q data and reference values. A symbol demapper performs a process for symbol demapping the symbol-deinterleaved I / Q data according to the reference values. A bit deinterleaver performs a process for bit deinterleaving the symbol-demapped data. A demultiplexer demultiplexes the bit-deinterleaved data.

Owner:SAMSUNG ELECTRONICS CO LTD

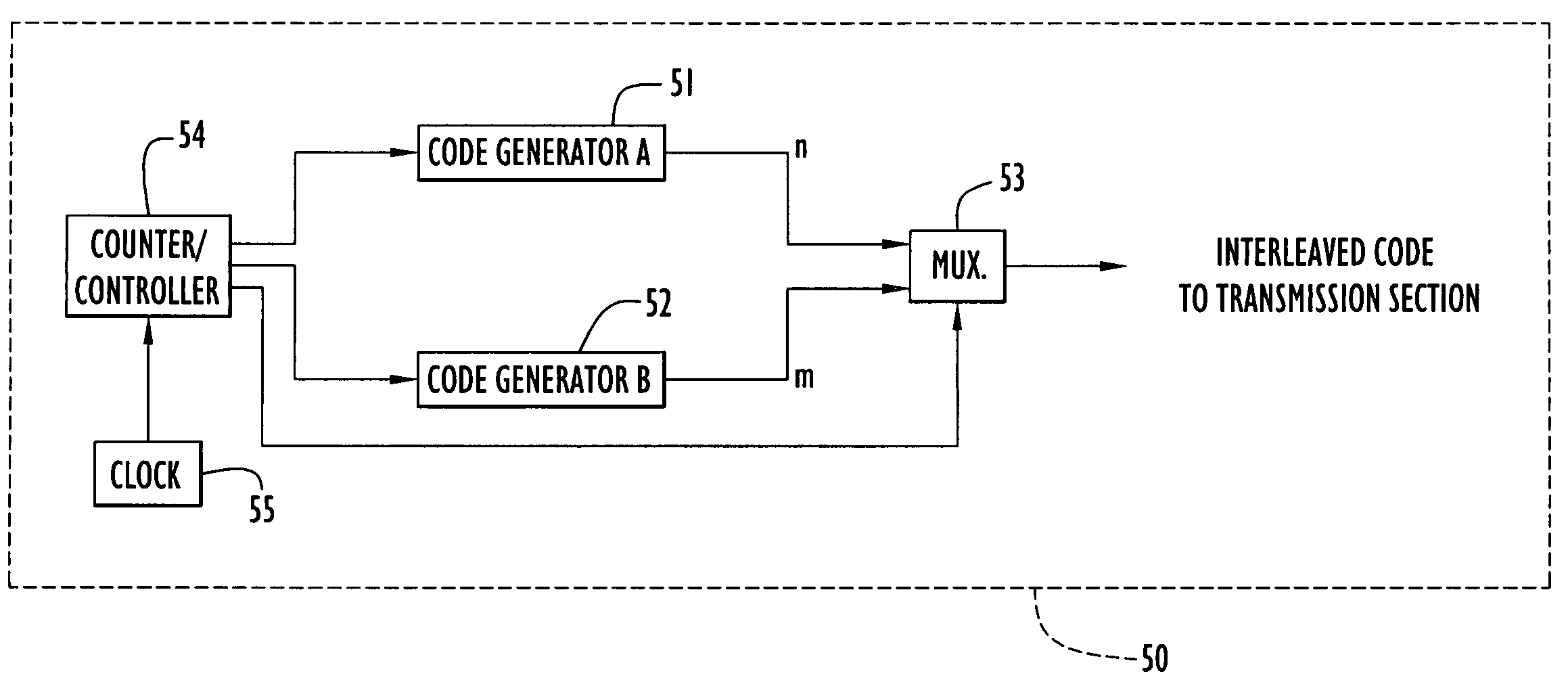

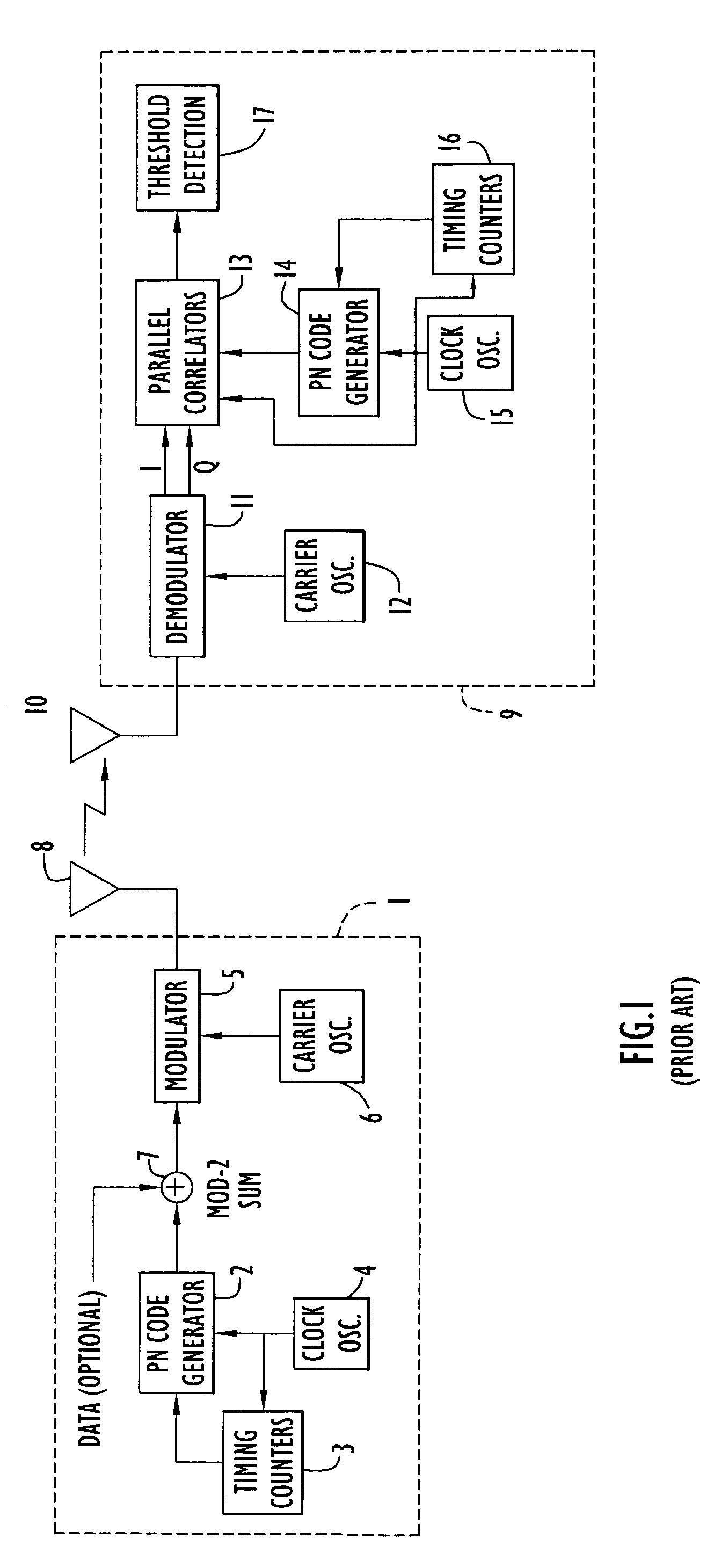

Method and apparatus for generating an interleaved code

InactiveUS6959030B1Improve toleranceQuick checkError detection/correctionCode division multiplexCode generationSymbol interleaving

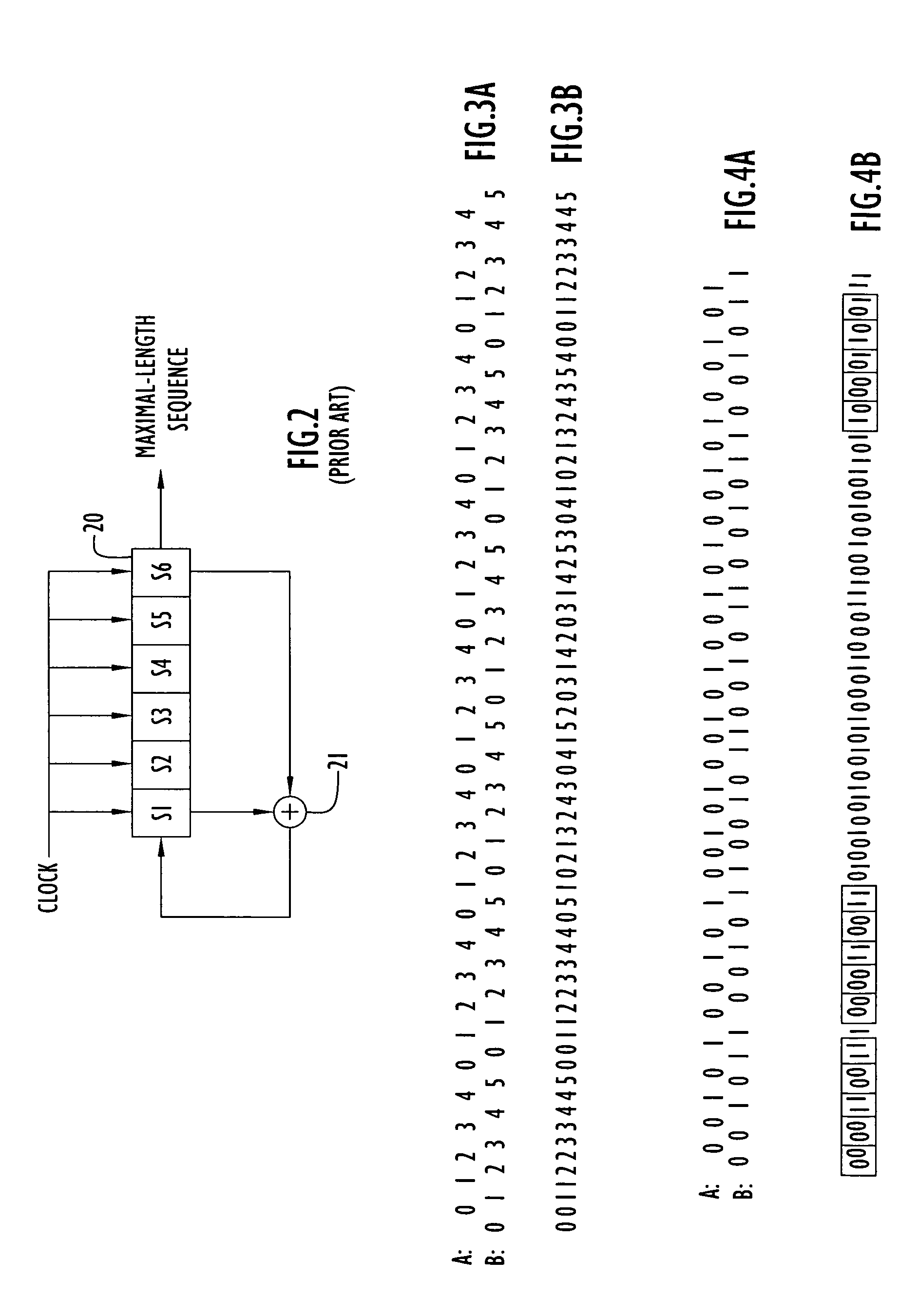

An interleaved coding method can be used in a transmitter, in which the two or more pseudonoise (PN) codes are interleaved to form a longer interleaved code. The method can be used in a transmitter that includes a first code generator generating a first code of n symbols, and a second code generator generating a second code of m symbols, where n and m can be mutually prime, such as m=n+1. An interleave unit is coupled to the first and second code generators, and interleaves the symbols of the first code with the symbols of the second code to output an interleaved code. The interleaved code has a period longer than either of the constituent PN codes, providing for much increased noise tolerance over using the short codes alone, and can be detected at a much lower hardware and time cost than if using a single PN code of equal length.

Owner:HARRIS CORP

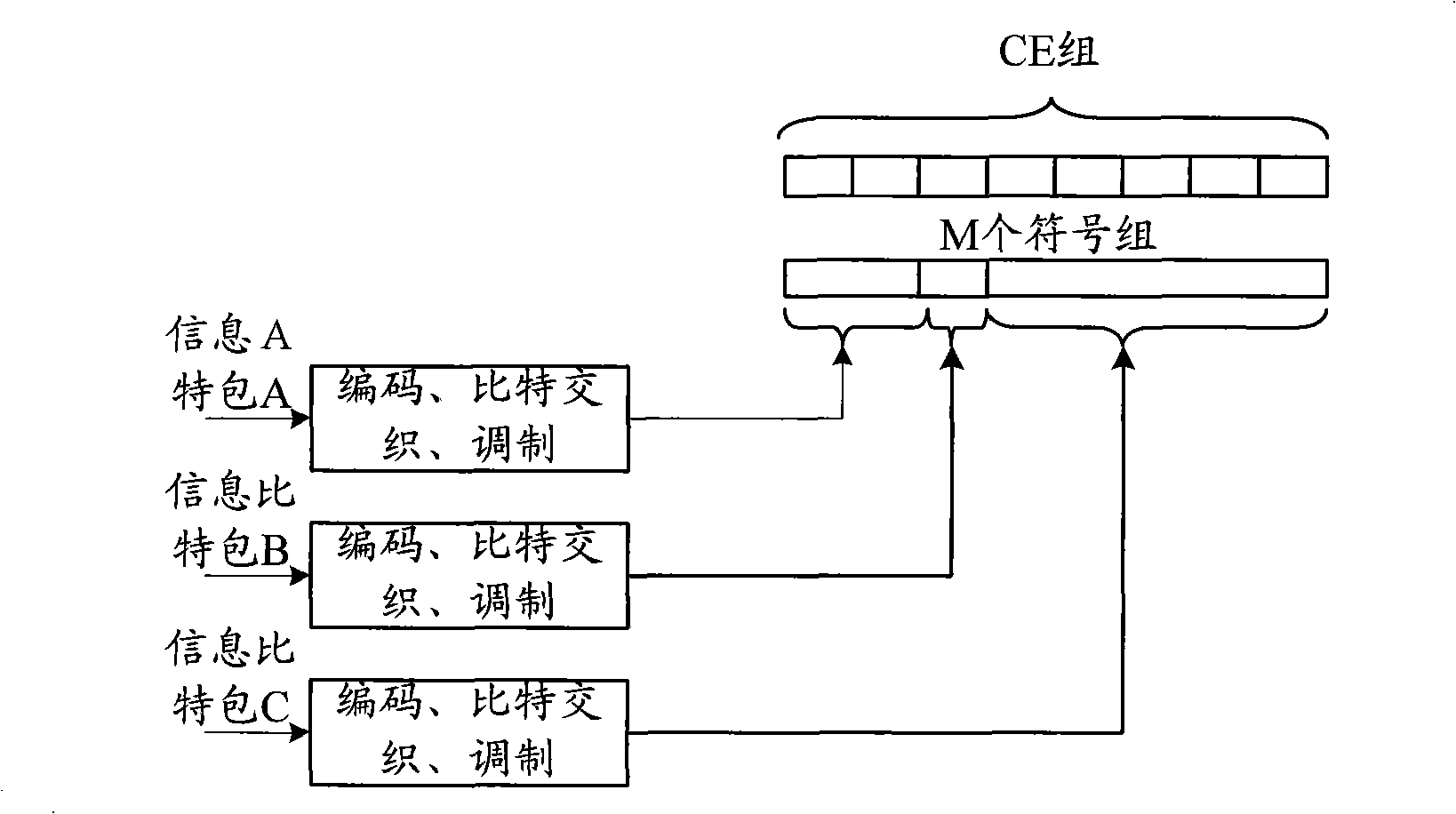

Symbol interleaving and channel mapping device and method and mobile communication system

InactiveUS20090022237A1Minimizes valueImprove system performanceFrequency-division multiplexDiversity/multi-antenna systemsChannel state informationCarrier signal

The present invention discloses a symbol interleaving and channel mapping device and method as well as a mobile communication system. The symbol interleaving and channel mapping device is used in a transmitter of a mobile communication system, said transmitter receiving the channel state information fed back from a receiver of the mobile communication system; the symbol interleaving and channel mapping device comprises a symbol classification unit for classifying symbols according to their importance; a symbol sub-carrier mapping unit for performing a sub-carrier mapping according to the classification result of said symbol classification unit and the channel state information such that the important symbols correspond to the non deep fading sub-carrier as much as possible.

Owner:FUJITSU LTD

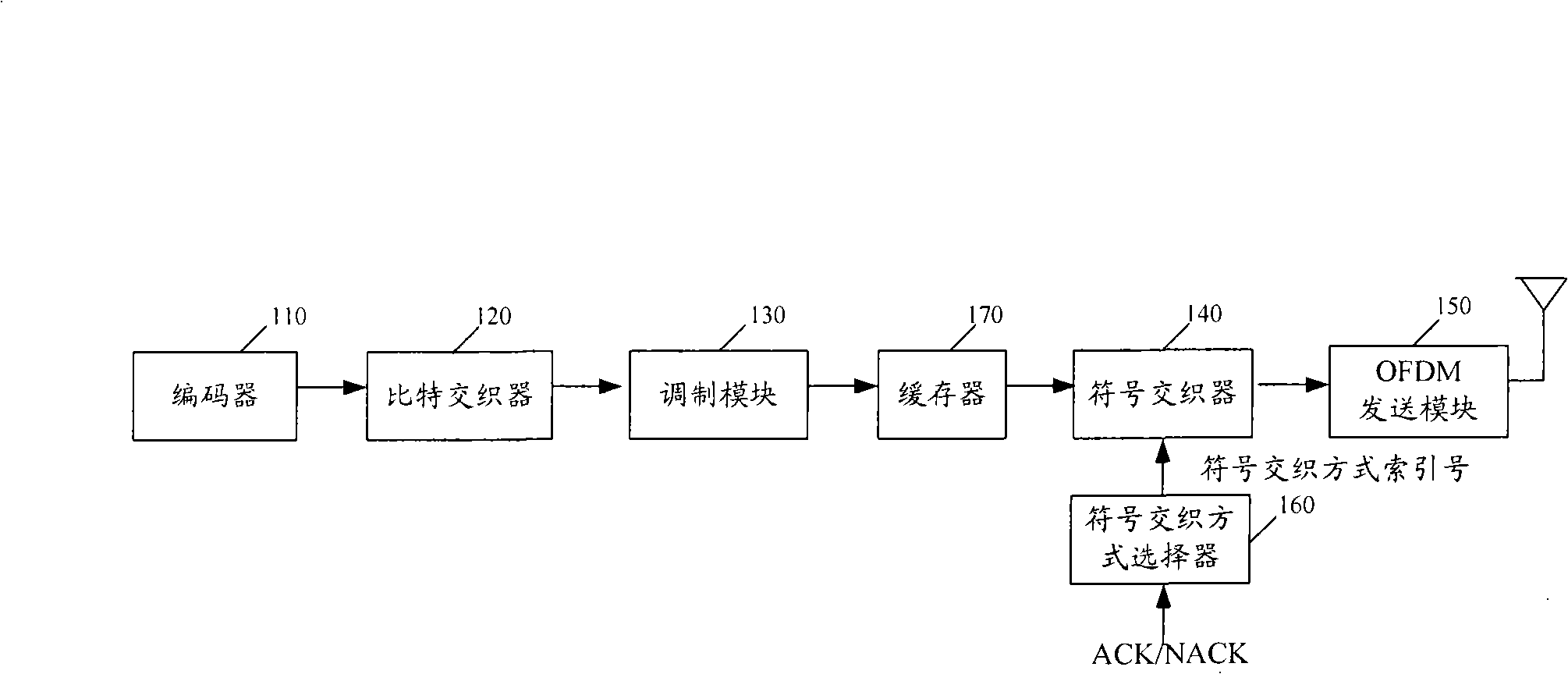

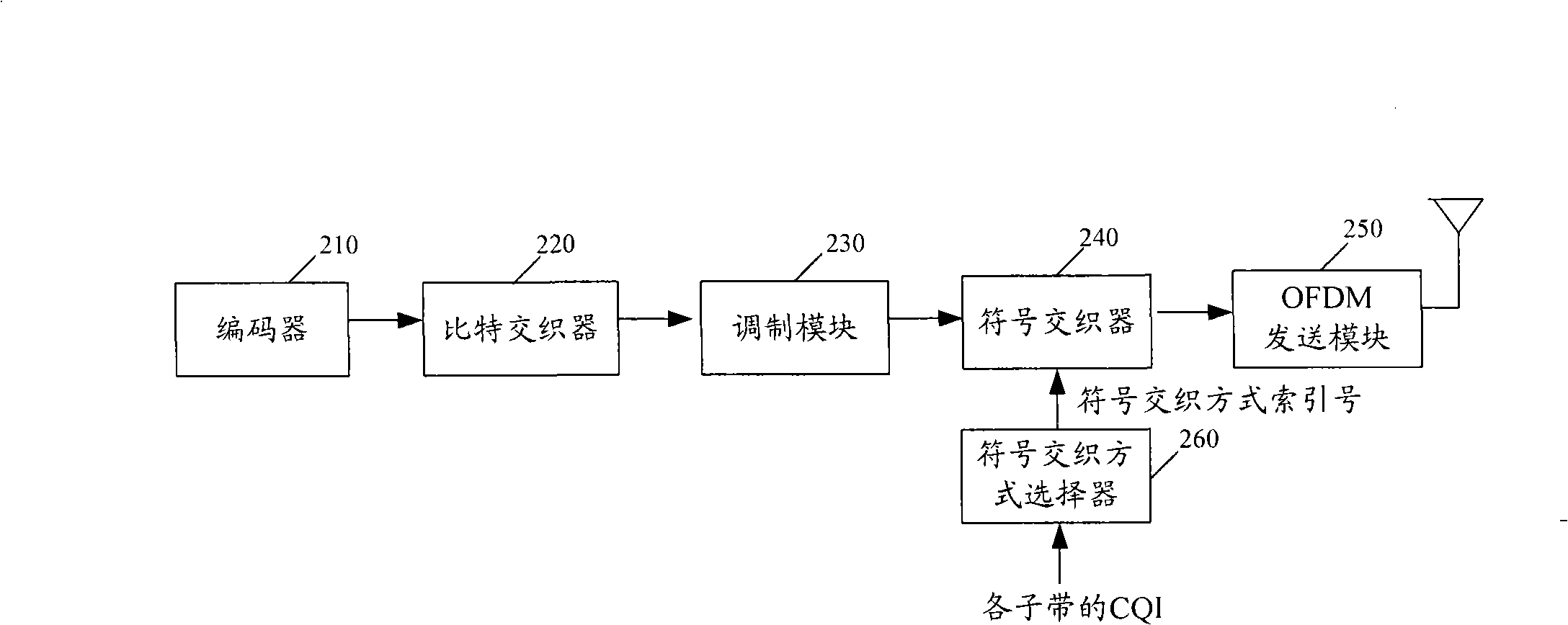

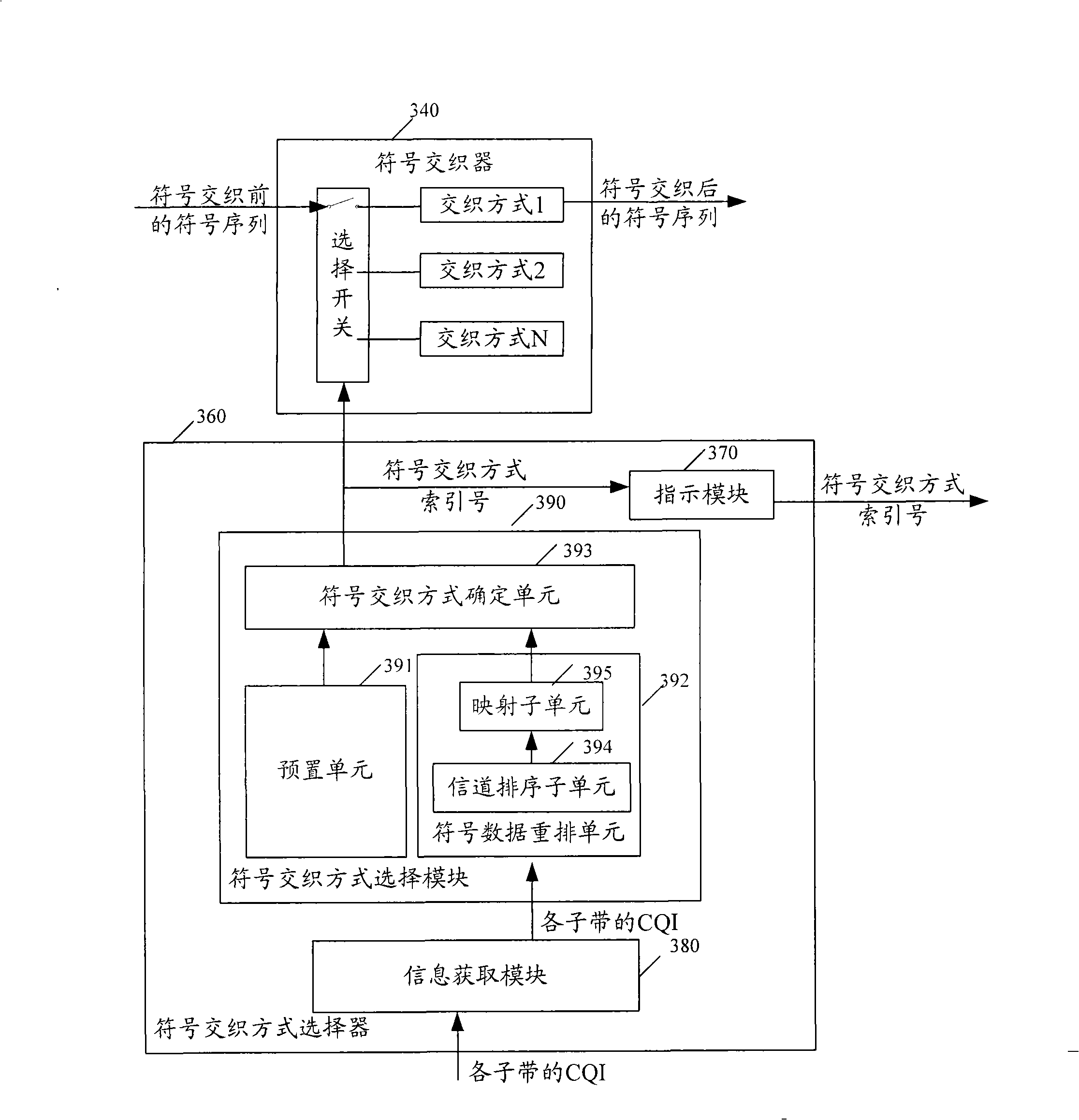

Symbol interleaving mode selection method, apparatus and transmitter implementing symbol interleaving

ActiveCN101335732ASymbol interleaving method is excellentReduce transmission errorsMulti-frequency code systemsForward error control useSymbol interleavingMode selection

The invention discloses a method for selecting symbol interleaving modes. The method comprises the steps that: a transmission end acquires channel quality information and selects a symbol interleaving mode by utilizing the channel quality information. The invention also discloses a device for realizing symbol interleaving mode selection, which comprises an information acquiring module and a symbol interleaving mode selecting module. The invention can improve the throughput.

Owner:HUAWEI TECH CO LTD

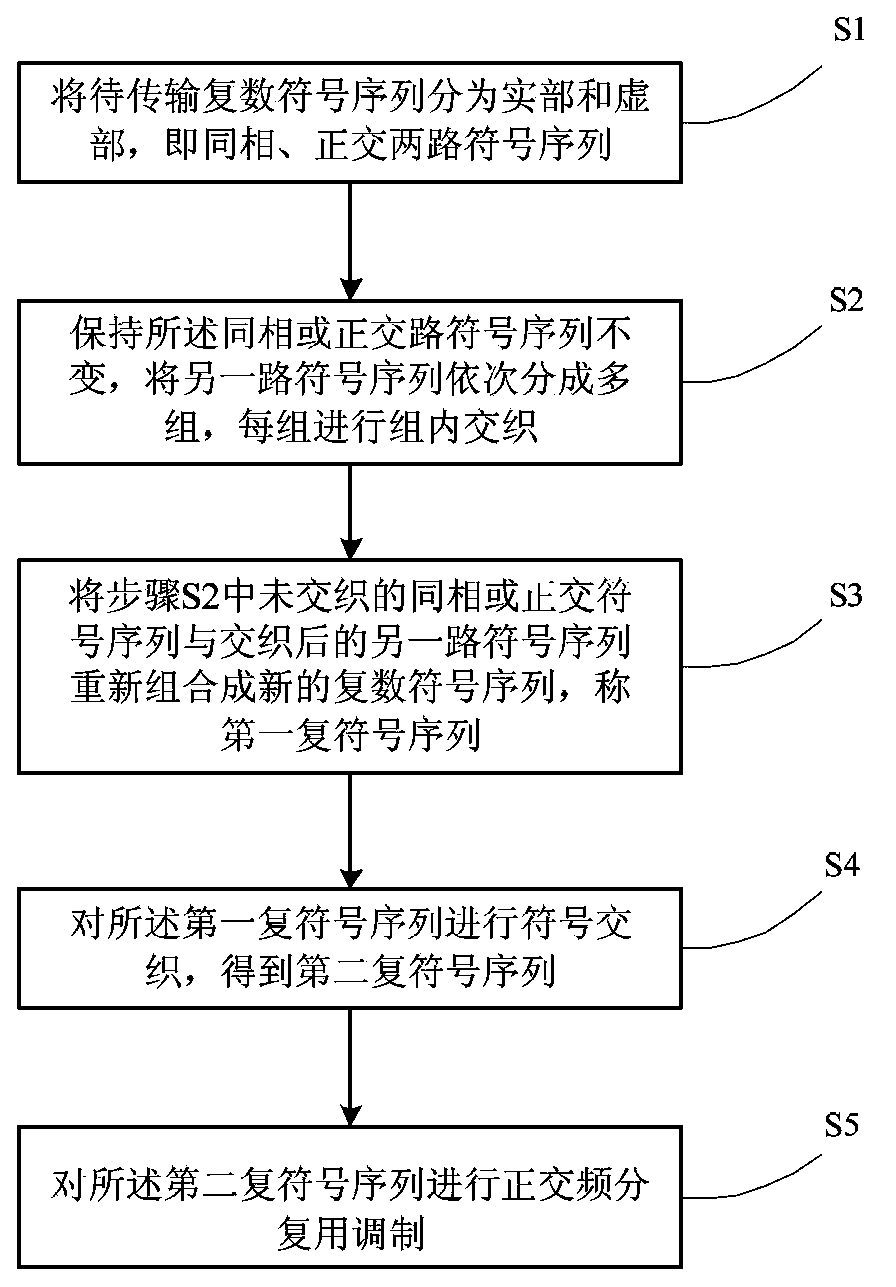

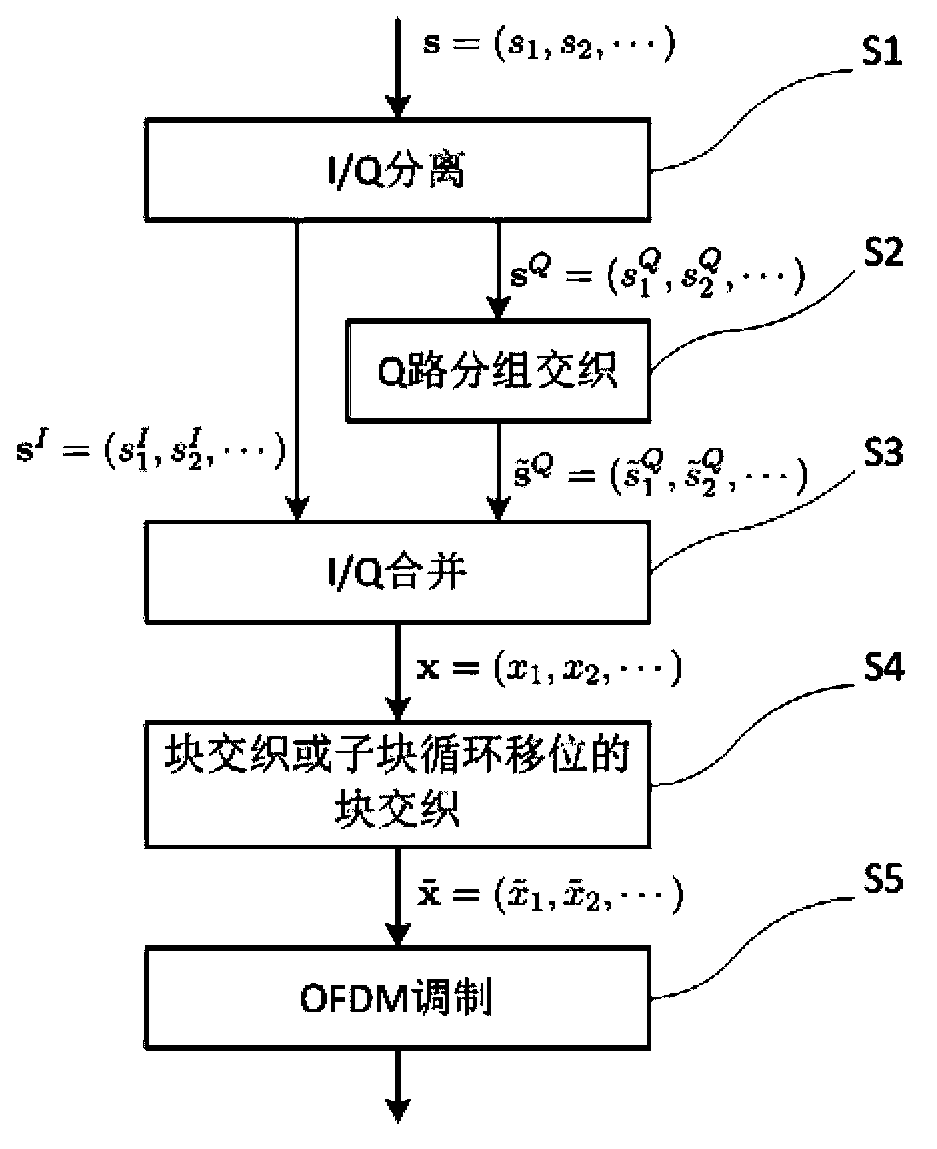

Interleaving method in orthogonal frequency division multiplexing system and device thereof

ActiveCN103873187AExtension of timeHigh frequencyError preventionMulti-frequency code systemsSymbol interleavingComputer science

The invention discloses an interleaving method in an orthogonal frequency division multiplexing system and a device thereof. The method comprises that: S1. plural symbol sequences to be transmitted are divided into a real part and an imaginary part, i.e. two paths of same-phase and orthogonal symbol sequences; S2. the same-phase or the orthogonal paths of symbol sequences are maintained to be unchanged, another path of symbol sequences are divided into multiple groups in turn, and intra-group interleaving is performed in each group; S3. the same-phase or the orthogonal paths of symbol sequences which are not interleaved in the step S2 are recombined with the another path of symbols after interleaving so that new plural symbol sequences are formed and are called first plural symbol sequences; S4. symbol interleaving is performed on the first plural symbol sequences so that second plural symbol sequences are obtained; S5. and orthogonal frequency division multiplexing modulation is performed on the second plural symbol sequences. Time, frequency and signal space diversity gain of the orthogonal frequency division multiplexing system are enhanced. Meanwhile, higher throughput and lower realization complexity are maintained.

Owner:TSINGHUA UNIV +1

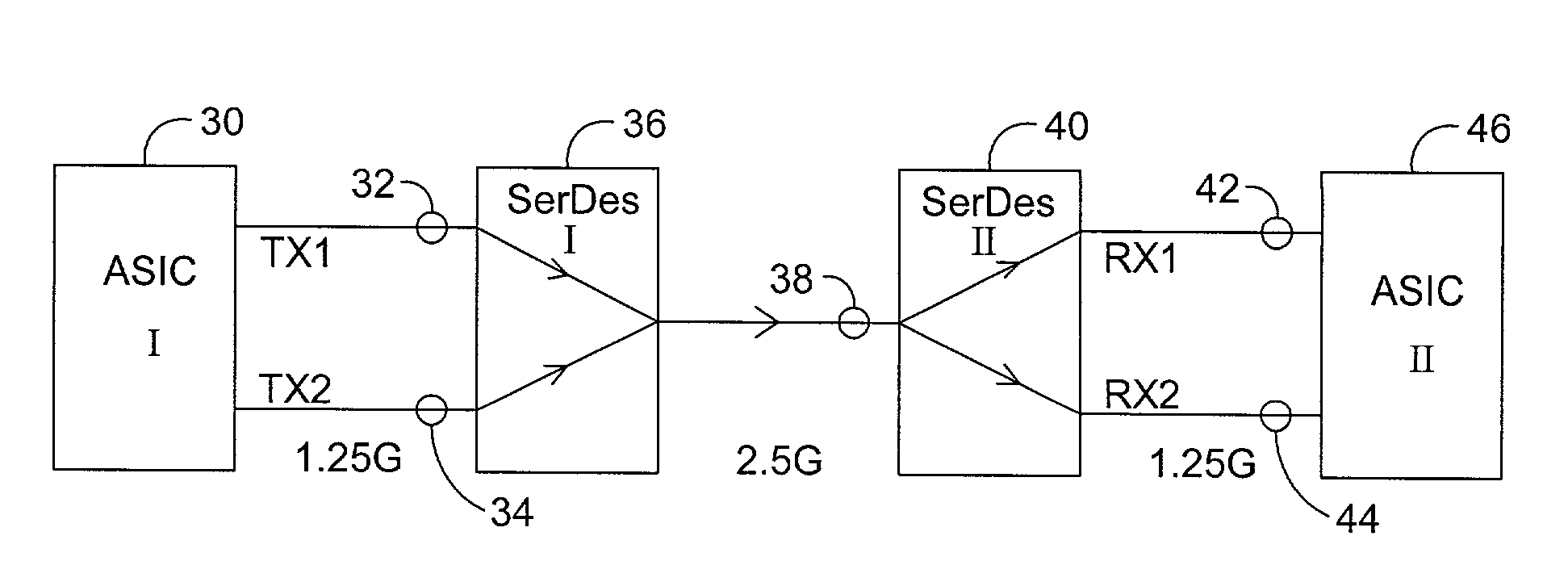

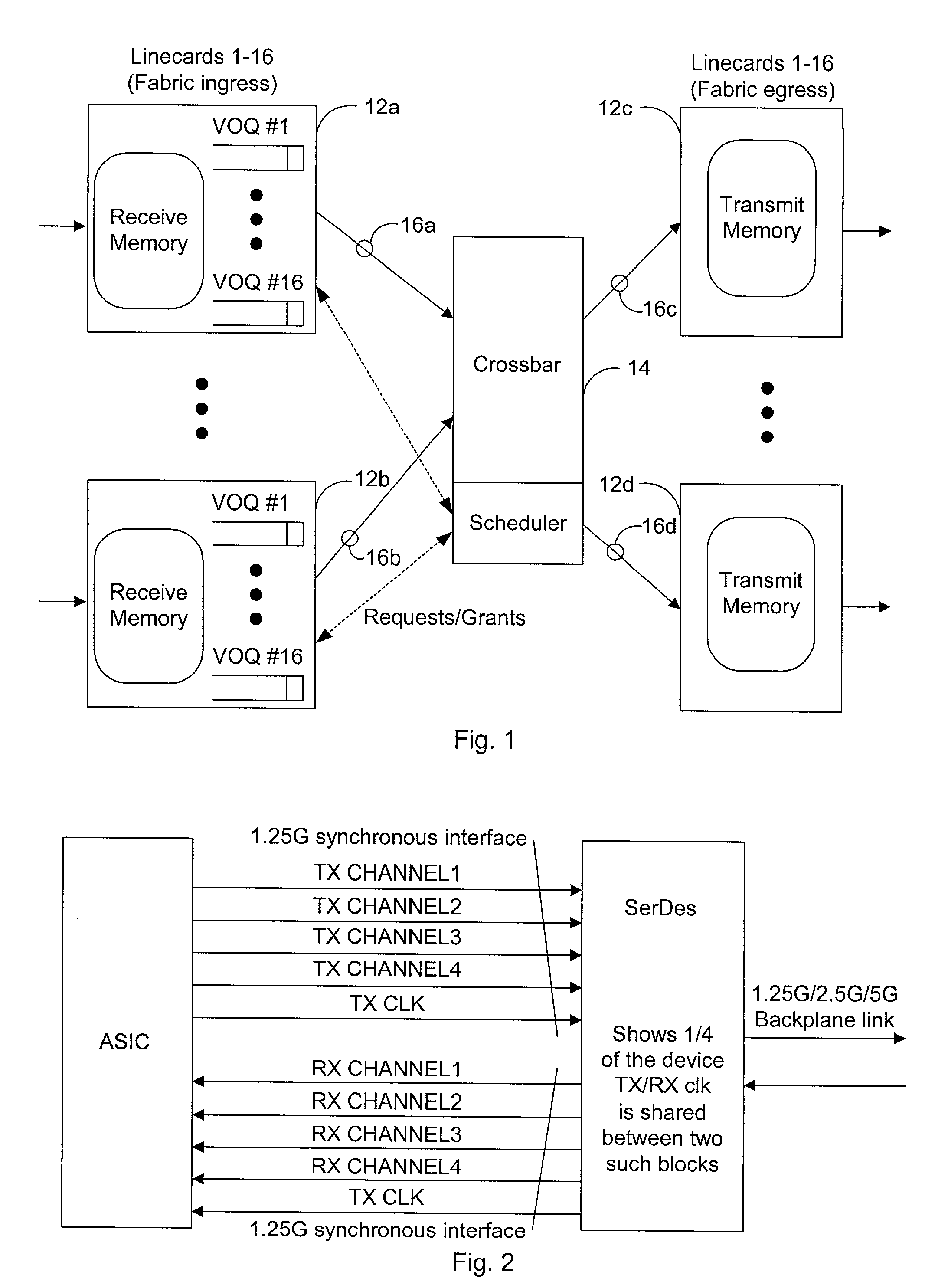

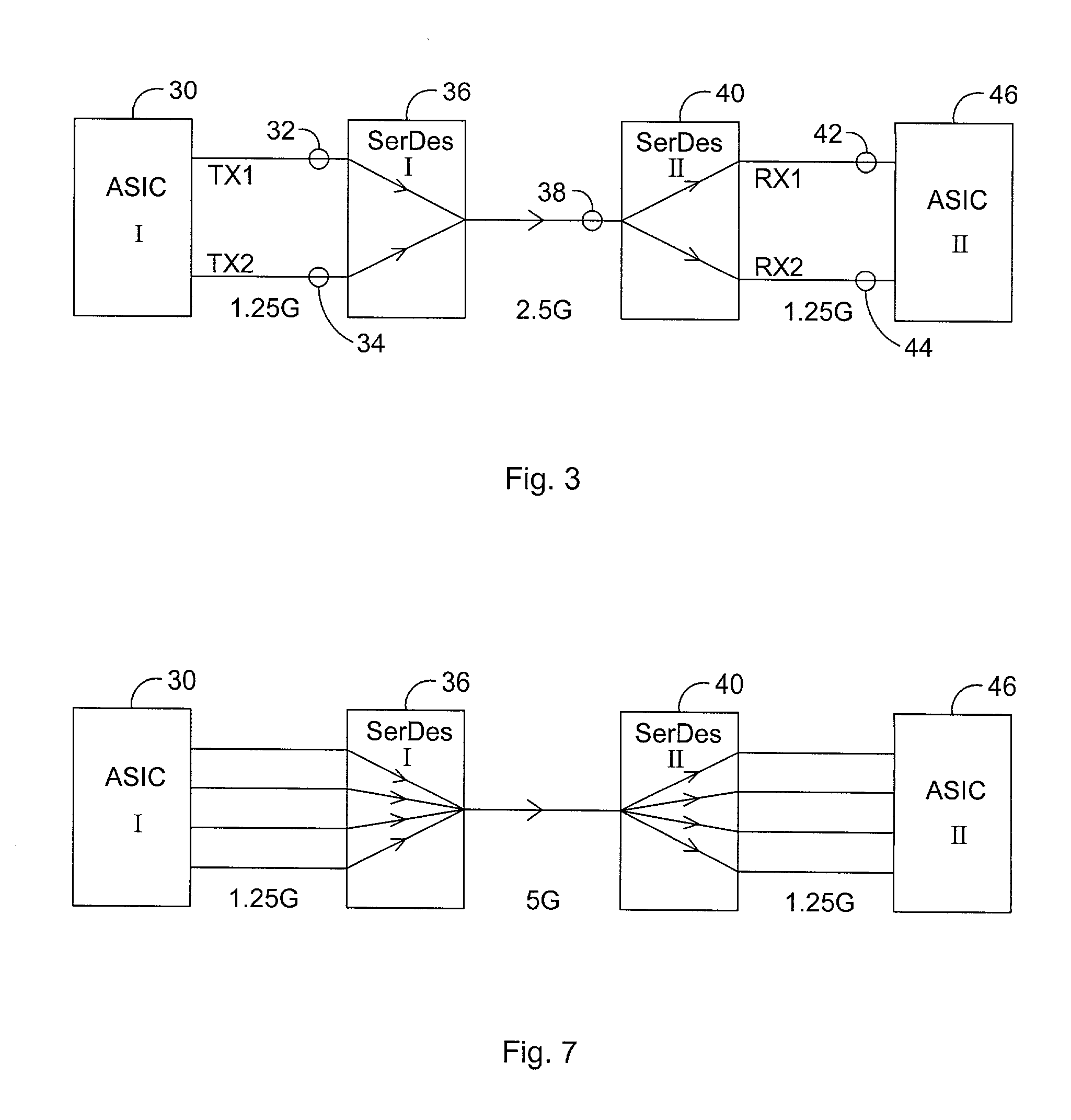

Apparatus and method for SerDes rate matching using symbol interleaving

ActiveUS7068650B1Improve interoperabilityMultiplex system selection arrangementsTime-division multiplexData streamData rate

A system and method for interleaving symbols to facilitate compatibility between serializer / deserializer (SerDes) units operating at different data rates multiplexes duplicates of a parallel data stream into a fast data rate serial data stream to form a serial data steam at a psuedo-slow data rate which can be received by a SerDes unit operating at the slow data rate. The psuedo-slow data rate serial data stream can also be received by a SerDes operating at the fast data rate by sampling each bit multiple times and demultiplexing the samples into duplicates of the parallel data stream.

Owner:CISCO TECH INC

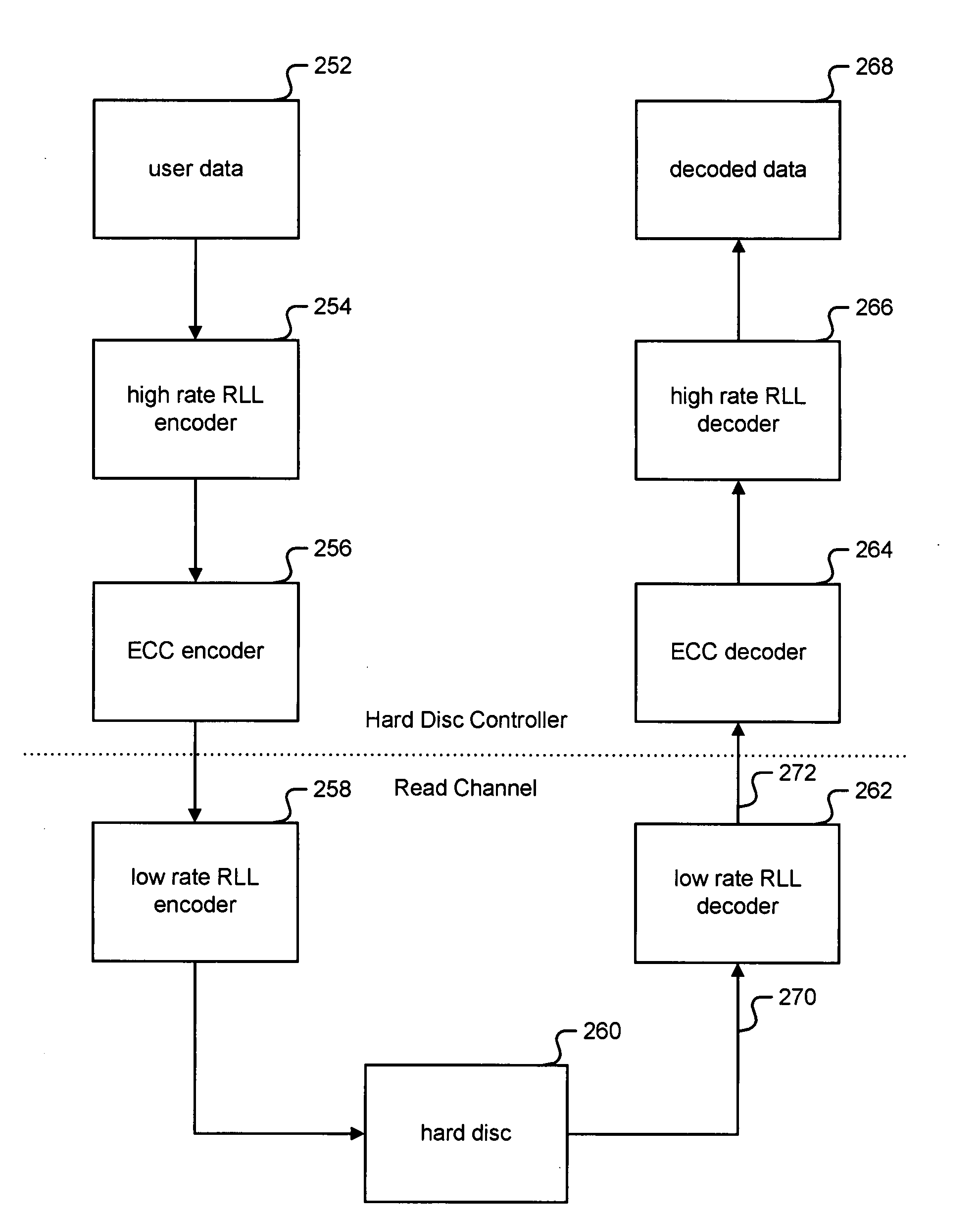

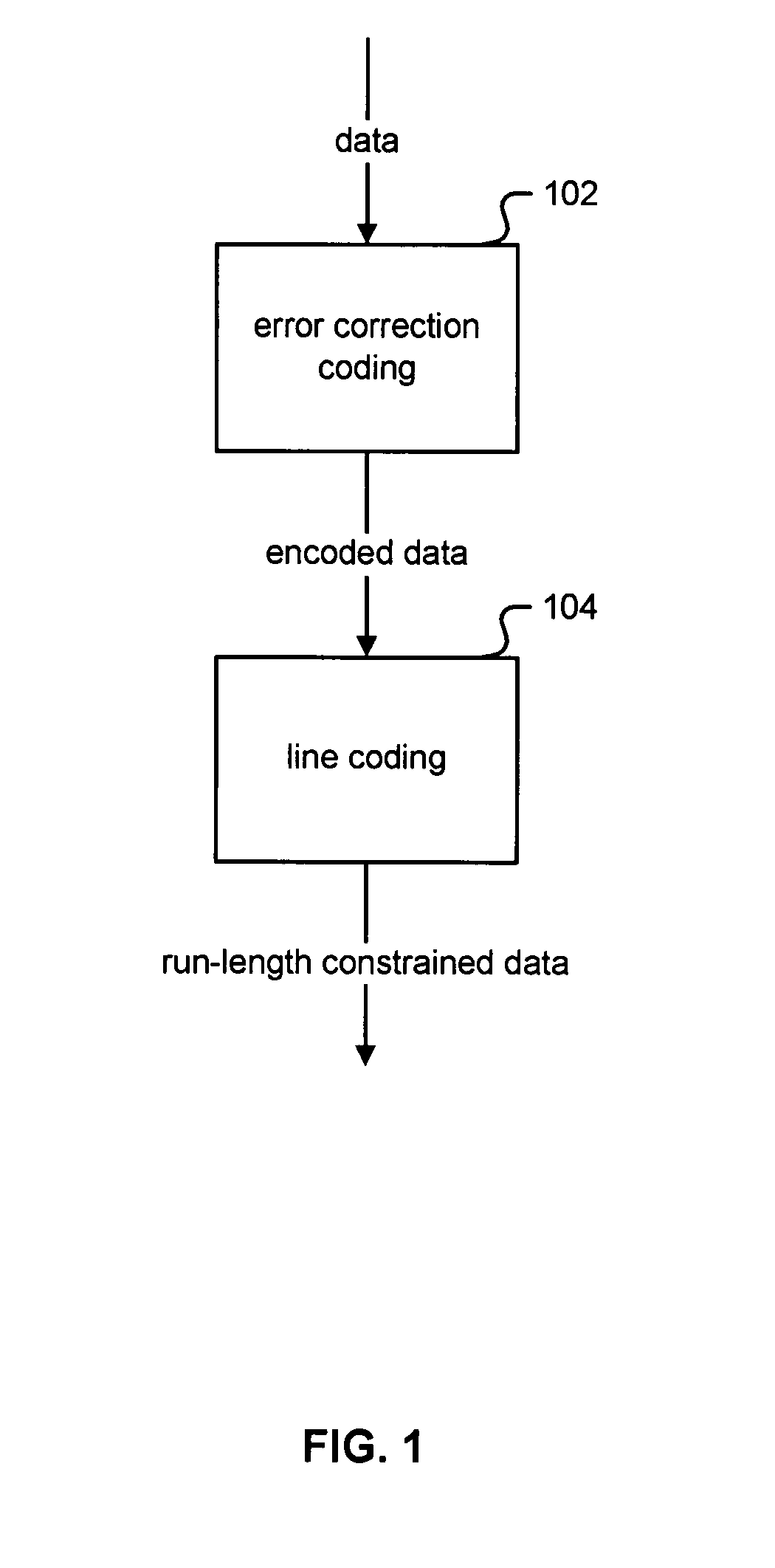

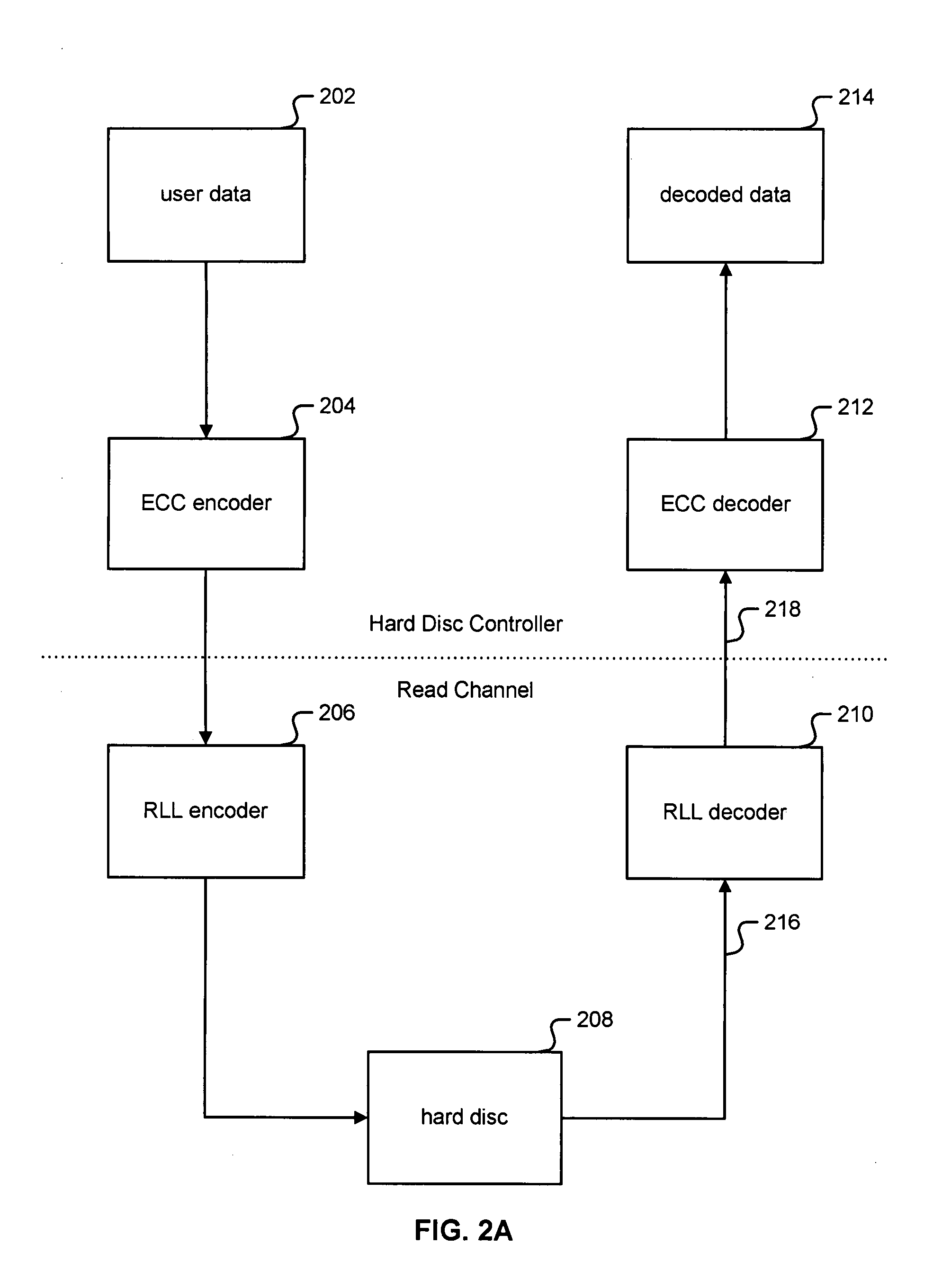

Interleaving parity bits into user bits to guarantee run-length constraint

ActiveUS8161347B1Error correction/detection by combining multiple code structuresRecord information storageSymbol interleavingParity bit

Owner:SK HYNIX MEMORY SOLUTIONS

Interleaving method and system

Owner:SAMSUNG ELECTRONICS CO LTD

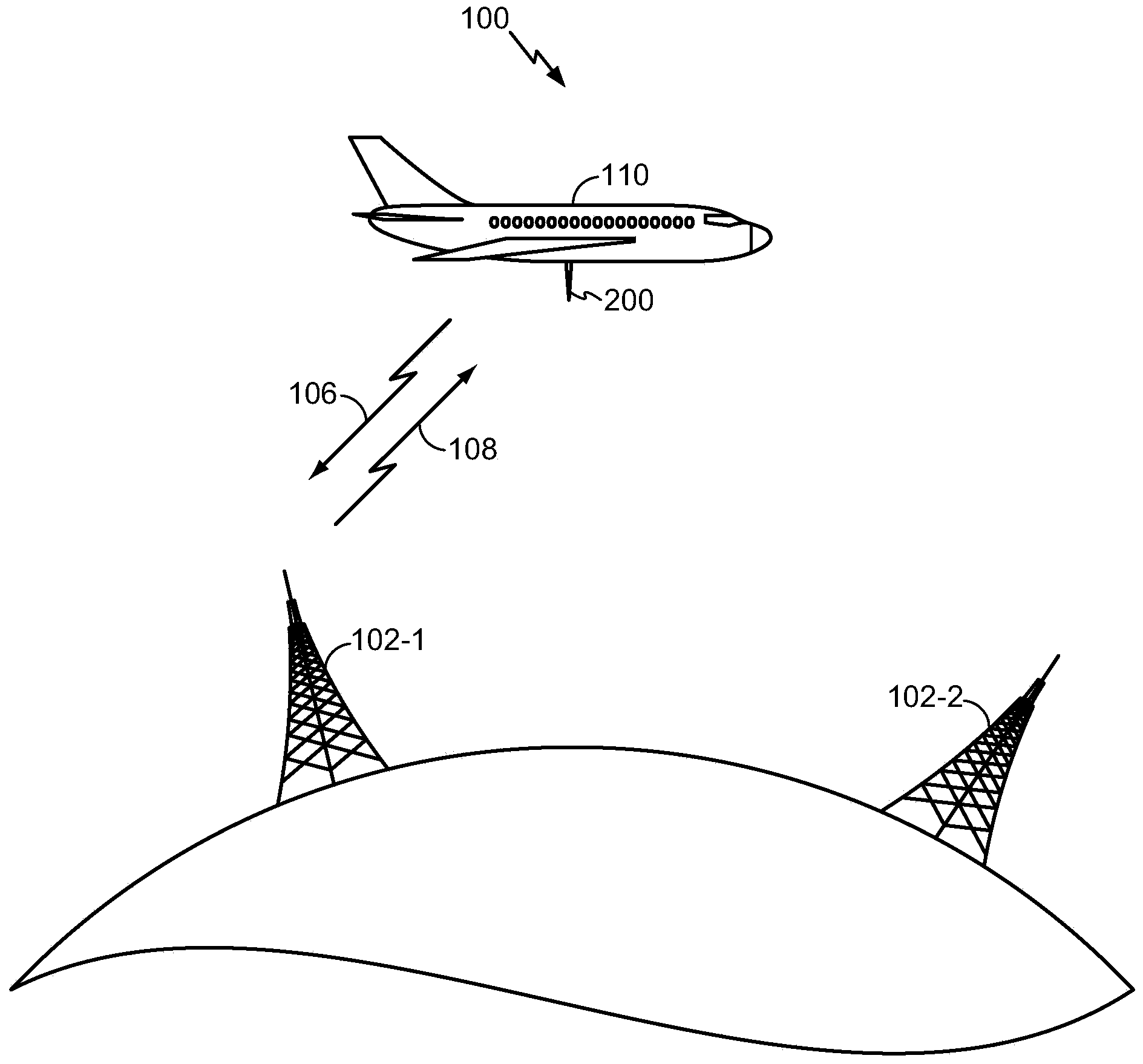

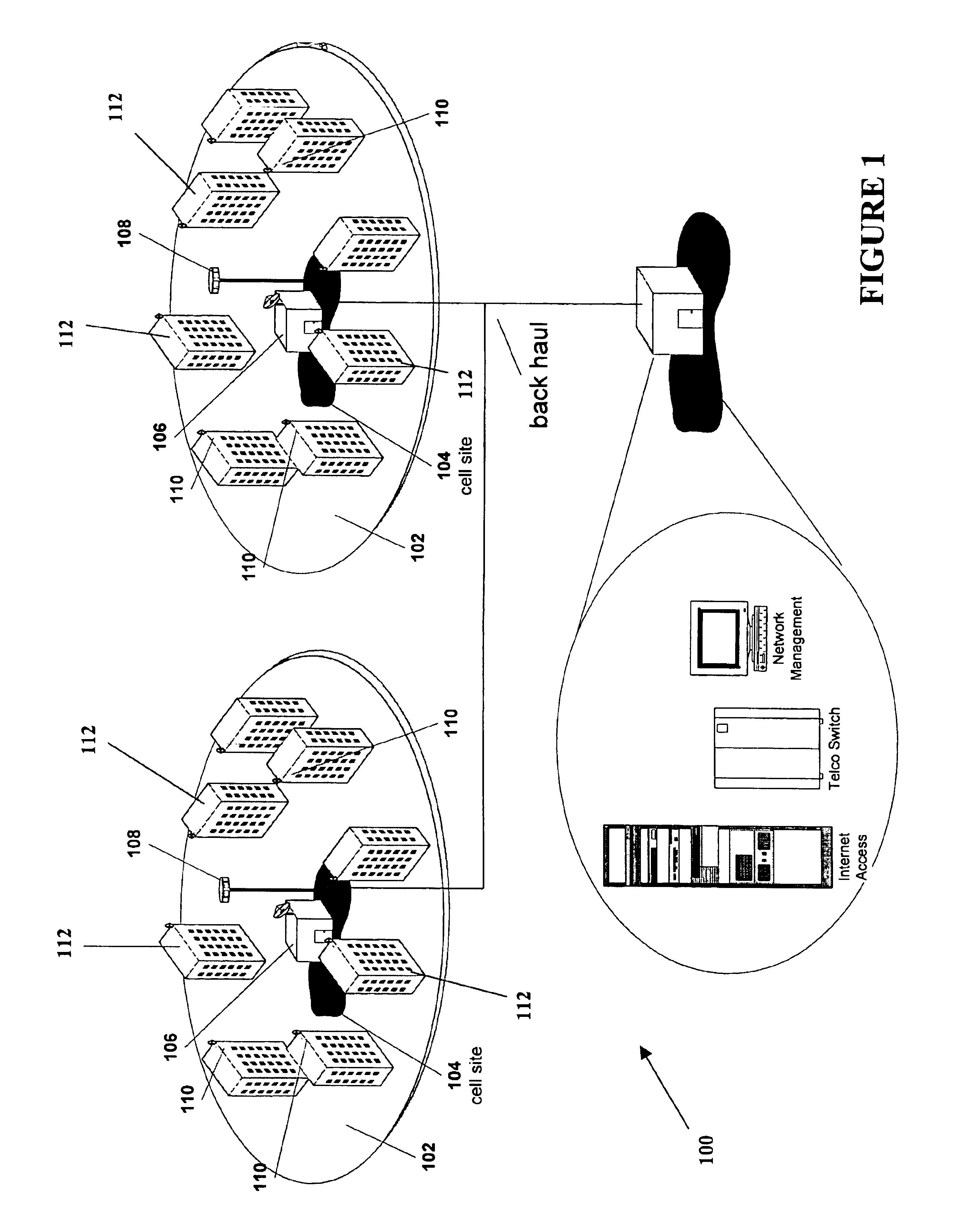

Interference mitigation techniques for air to ground systems

A method for air to ground communication interference mitigation within an aircraft equipped with a multi-beam array antenna includes adjusting a modulation symbol interleaving and / or forward error correction of an aircraft receiver interface in response to detected interference from an interferer. The method further includes reducing a data rate of the aircraft receiver interface when the adjusting of the modulation symbol interleaving and / or forward error correction does not mitigate the detected interference. Another method for interference mitigation may include performing antenna beam-steering away from a geographic (GEO) arc during an aircraft turn. This method further includes reducing an aircraft transmitter transmit power when a signal quality of a forward link is within a predetermined range of a signal quality threshold.

Owner:QUALCOMM INC

Interleaving method in OFDM system

ActiveUS20060164973A1Reduce errorsSimple structureModulated-carrier systemsError correction/detection using interleaving techniquesFast Fourier transformSymbol interleaving

Provided is an interleaving method that can reduce error occurring during transmission at a receiving end in an Orthogonal Frequency Division Multiplexing (OFDM) system. According to the interleaving method, transmitted data bits are recorded in an interleaving memory; and the stored data bits are read based on a predetermined sequence to perform symbol interleaving, tone interleaving and cyclic shift simultaneously. Also, to simplify the logic of the OFDM system, the data bits transmitted from an interleaver go through Fast Fourier Transform (FFT) mapping, and the FFT mapped data bits are modulated. In short, the logic can be simplified by performing FFT mapping followed by modulation.

Owner:SAMSUNG ELECTRONICS CO LTD

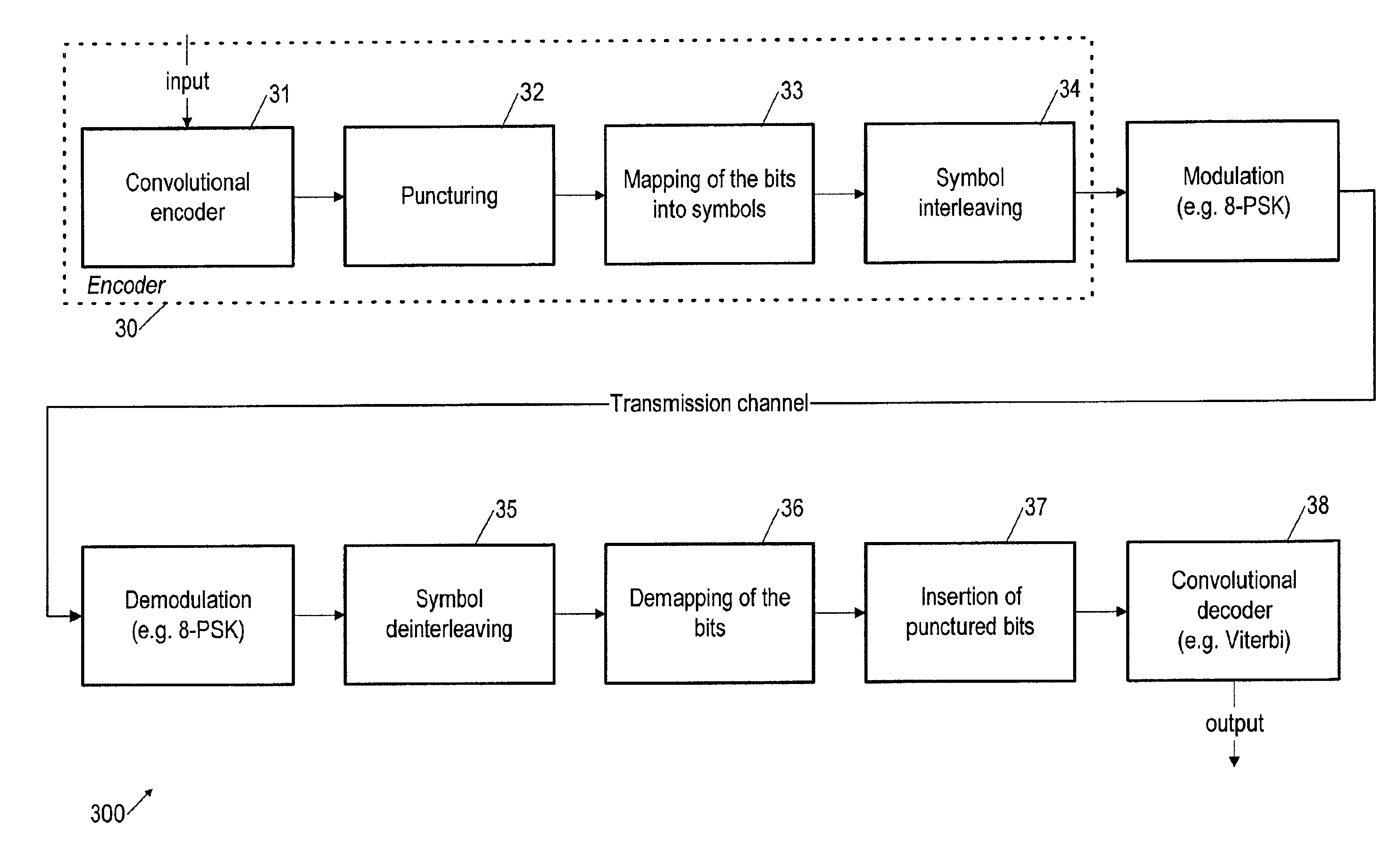

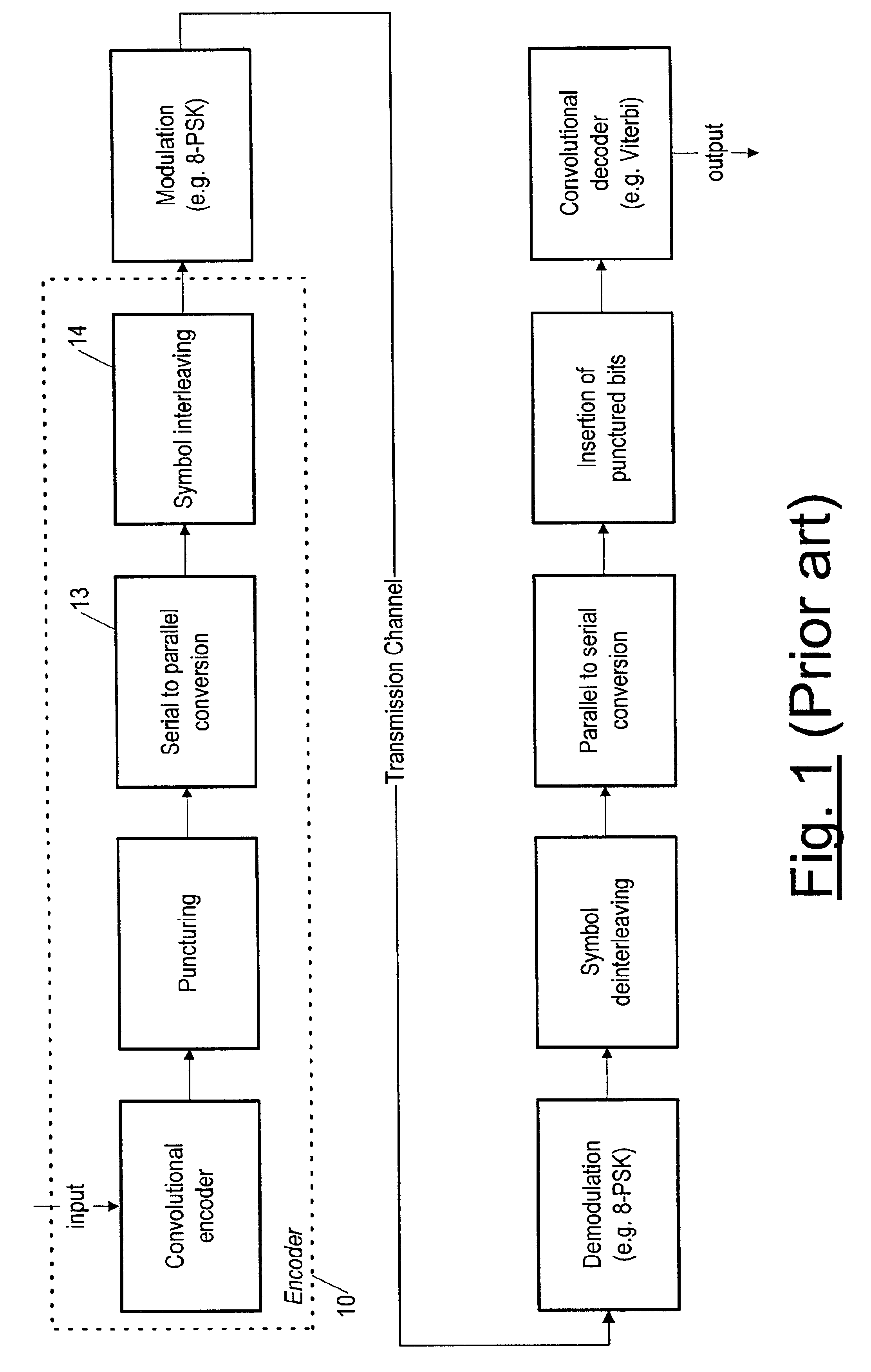

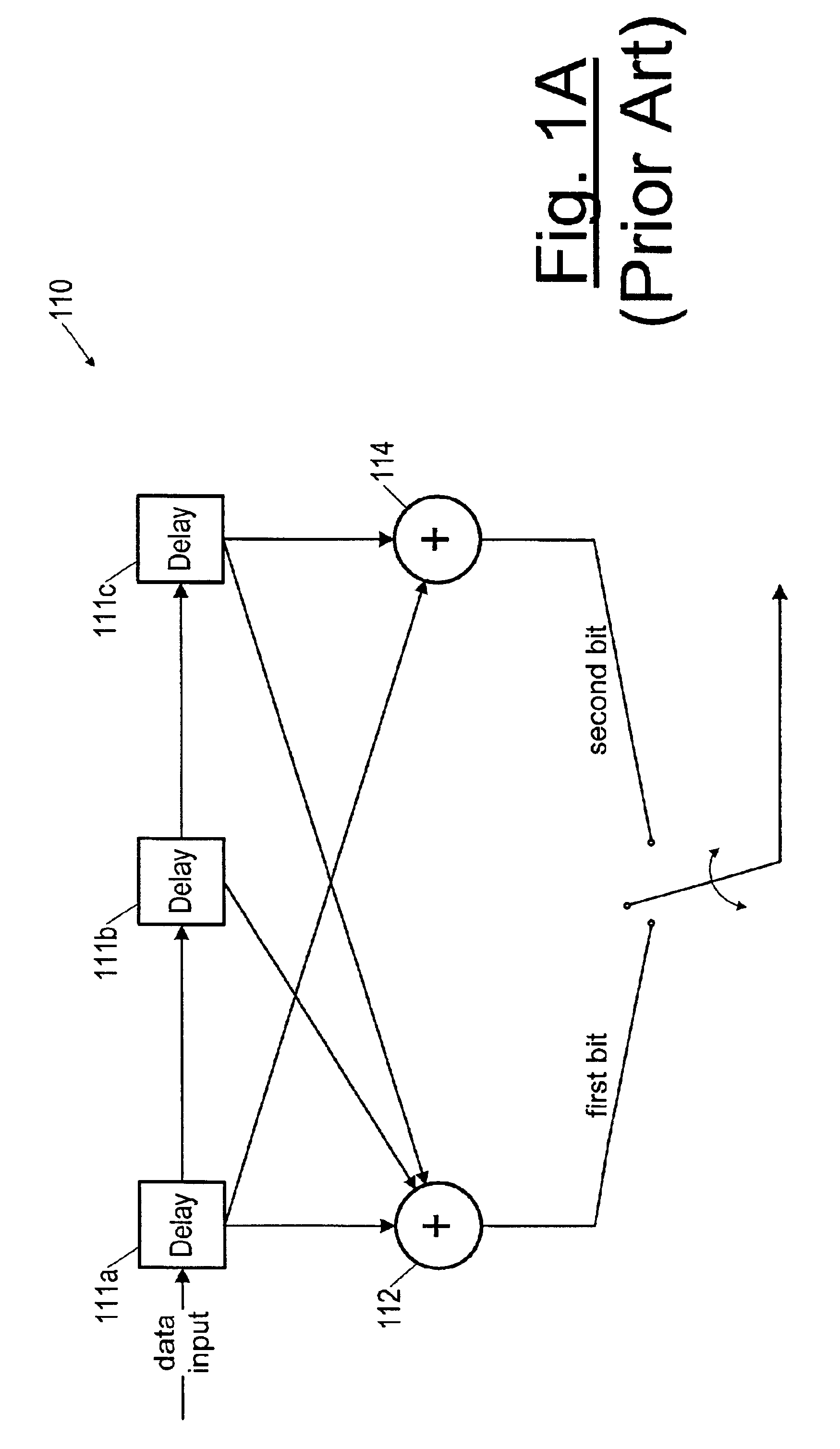

Method and apparatus for concatenated channel coding with variable code rate and coding gain in a data transmission system

InactiveUS6883133B1Valid encodingReduce complexityError correction/detection using convolutional codesOther decoding techniquesComputer hardwareBlock code

A novel method and apparatus for efficiently coding and decoding data in a data transmission system is described. A concatenated coding scheme is presented that is easily implemented, and that provides acceptable coding performance characteristics for use in data transmission systems. The inventive concatenated channel coding technique is well suited for small or variable size packet data transmission systems. The technique may also be adapted for use in a continuous mode data transmission system. The method and apparatus reduces the complexity, cost, size and power consumption typically associated with the prior art channel coding methods and apparatuses, while still achieving acceptable coding performance. The present invention advantageously performs concatenated channel coding without the necessity of a symbol interleaver. In addition, the present invention is simple to implement and thereby consumes much less space and power that do the prior art approaches. The present invention not only eliminates the need for a symbol interleaver between the outer and inner codes, but it also enjoys a drastically reduced implementation complexity of the inner code Viterbi decoder. The preferred embodiment of the present invention comprises an inner code having short length block codes derived from short constraint length convolutional codes utilizing trellis tailbiting and a decoder comprising four four-state Viterbi decoders having a short corresponding maximum length. The inner code preferably comprises short block codes derived from four-state (i.e., constraint length 3), nonsystematic, punctured and unpunctured convolutional code. One significant advantage of the preferred embodiment of the present concatenated coding technique is that packet data transmission systems can be designed to have variable coding gains and coding rates.

Owner:TUMBLEWEED HLDG LLC +1

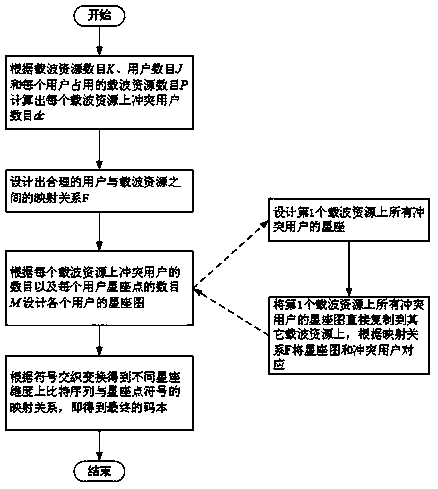

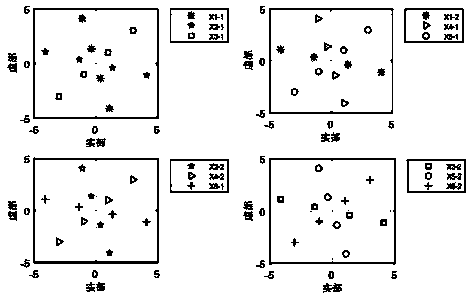

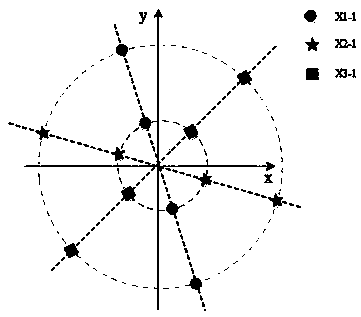

Modulation codebook design method for sparse code multiple access system

ActiveCN108366036AImprove performanceEasy to implementForward error control useMultiple carrier systemsMultiplexingHigh dimensionality

The invention provides a modulation codebook design method for a sparse code multiple access system. The method comprises the following steps: firstly, calculating the number of resource multiplexingusers on each carrier according to current system parameters, comprising the number of carrier resources, the number of users and the number of carrier resources occupied by each user, and designing amapping relationship between the users and the carrier resources; then, designing a modulation constellation graph of each user according to the number of the resource multiplexing users on each carrier and the number of constellation points of each user on each dimension; and finally, obtaining the modulation constellation graphs of the resource multiplexing users on all carriers according to the mapping relationship between the users and the carrier resources, obtaining the mapping relationship between bit sequences and modulation constellation point symbols on different constellation dimensions according to symbol interleaving transformation, and obtaining a final modulation codebook constellation graph. The high-dimensional codebook design method provided by the invention has the advantages of being simple in operation steps, being advantageous for implementation, and being able to bring better transmission performance to the system.

Owner:SOUTHEAST UNIV

Burst-error correction methods and apparatuses for wireless digital communications systems

Frames of data that have transverse Reed-Solomon (TRS) coding and subsequent cyclical-redundancy-check (CRC) coding are subjected to de-interleaving before concatenated convolutional coding (CCC). The de-interleaving is related to the symbol interleaving of the outer convolutional coding prior to the inner convolutional coding so as to result in implied interleaving of data bits in the CCC on which wireless digital transmissions are based. The CCC is turbo decoded in a receiver for the wireless digital transmissions and re-interleaved to reproduce soft data, hard data bits of which data are TRS coded. CRC coding is decoded during the turbo decoding procedures and used to influence the confidence levels of the soft data. The confidence levels of the soft data are used for locating byte errors when the TRS coded hard data bits of the soft data are decoded.

Owner:LIMBERG ALLEN LEROY

Method and system for allocating convolutional encoded bits into symbols before modulation for wireless communication

InactiveUS6981202B2Easy to implementLess memoryError correction/detection using convolutional codesElectronic circuit testingSymbol interleavingComputer science

A method and corresponding apparatus for encoding a sequence of bits for transmission as symbols, some of the bit positions of the symbols having a higher bit error rate than other bit positions. A plurality of sequences of bits is provided using a convolutional encoder, in response to a sequence of input bits, each sequence of bits being defined by a predetermined generator polynomial having a predetermined level of sensitivity to puncturing. Then the bits of each sequence of bits are mapped to symbol positions based on the level of sensitivity of the generator polynomial defining the sequence of bits. With interleaving, the mapping of bits of each sequence of bits to symbol positions can precede a symbol interleaving step, or it can follow a bit interleaving step.

Owner:CONVERSANT WIRELESS LICENSING LTD

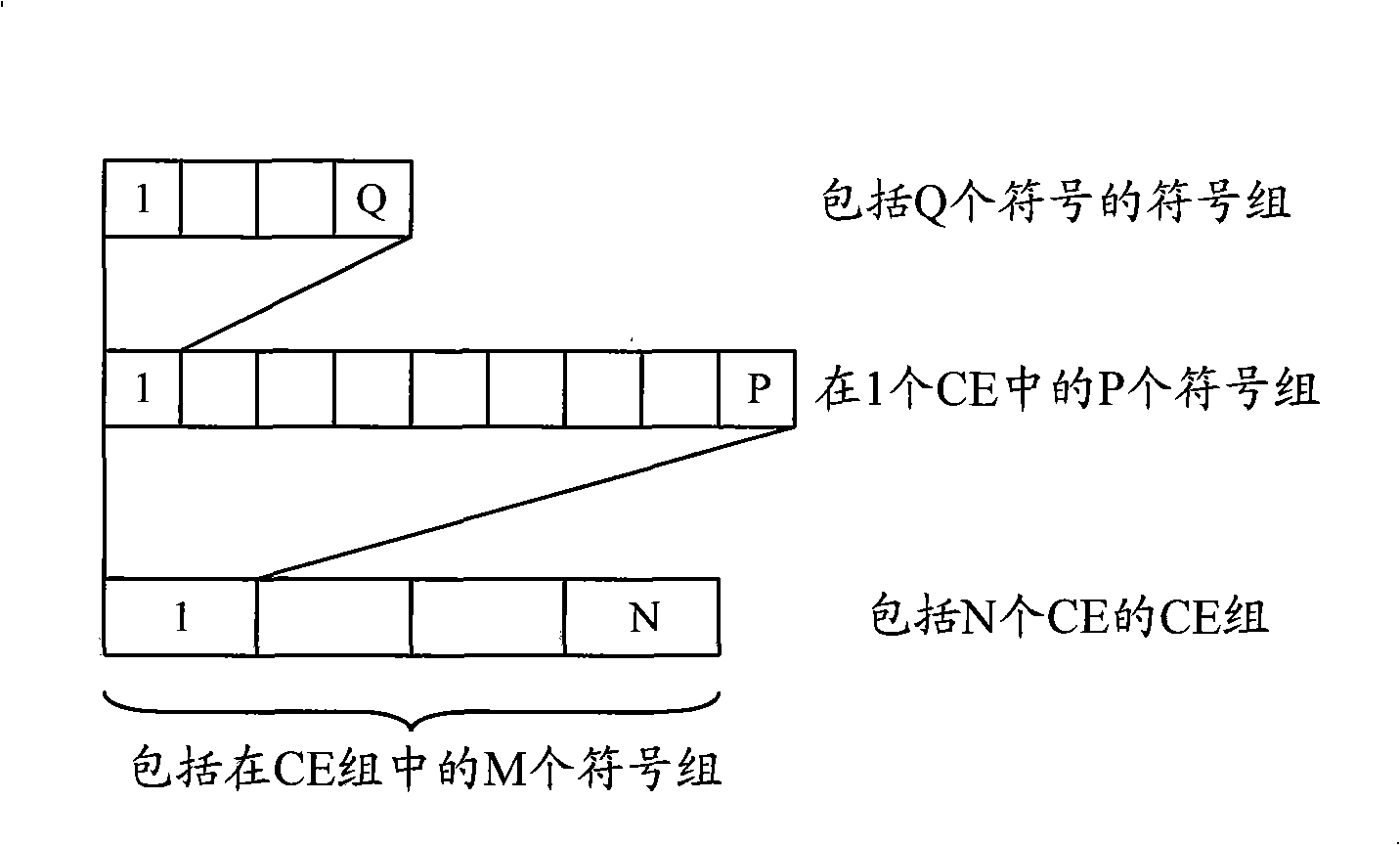

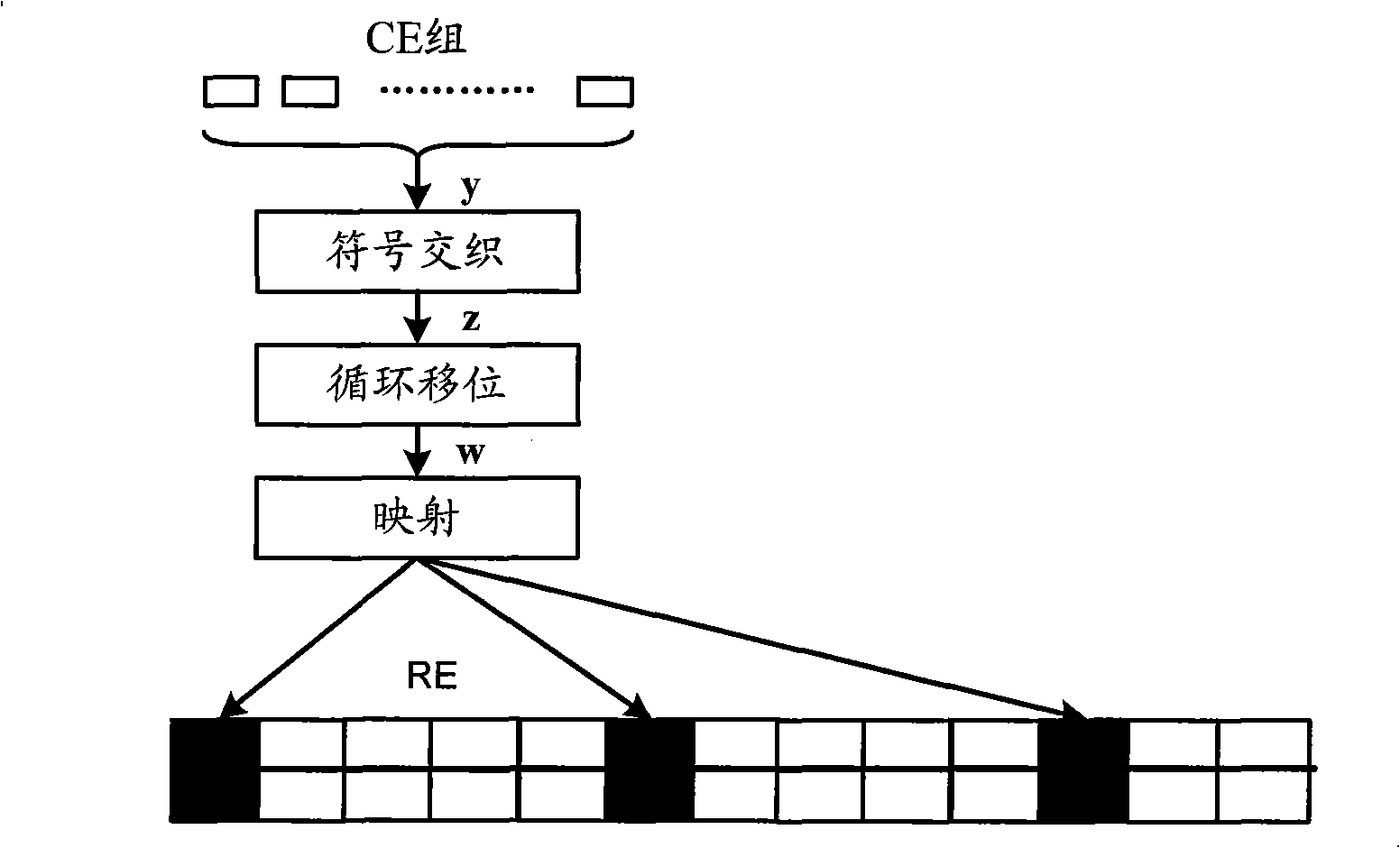

Symbol interlacing method, apparatus and terminal equipment

ActiveCN101330487AImprove the effect of disturbance randomizationReduce the impactTransmission path divisionMulti-frequency code systemsSymbol interleavingTerminal equipment

The invention discloses a symbol interleaving method and a symbol interleaving device. A symbol interleaving sequence is generated through the transformation of a sequence S(i). Because the numerical value in the sequence S(i) is corresponding to the serial number of a CE, the symbol interleaving sequence generated through the sequence S(i) can effectively ensure that different cells enable less amount of symbol set in one CE to be mapped to an identical physical resource position, the effect of the interference randomization between the cells can be improved, and the influence of the interference between the cells to the system performance can be reduced. The symbol interleaving sequence can be also obtained by using a Costas sequence, and similarly, the symbol interleaving sequence can ensure that the different cells enable less amount of the symbol set in one CE to be mapped to the identical physical resource position more effectively, so that the effect of the interference randomization between the cells can be improved, the influence of the interference between the cells to the system performance can be reduced, and the generation of the symbol interleaving sequence is also simplified.

Owner:HUAWEI TECH CO LTD

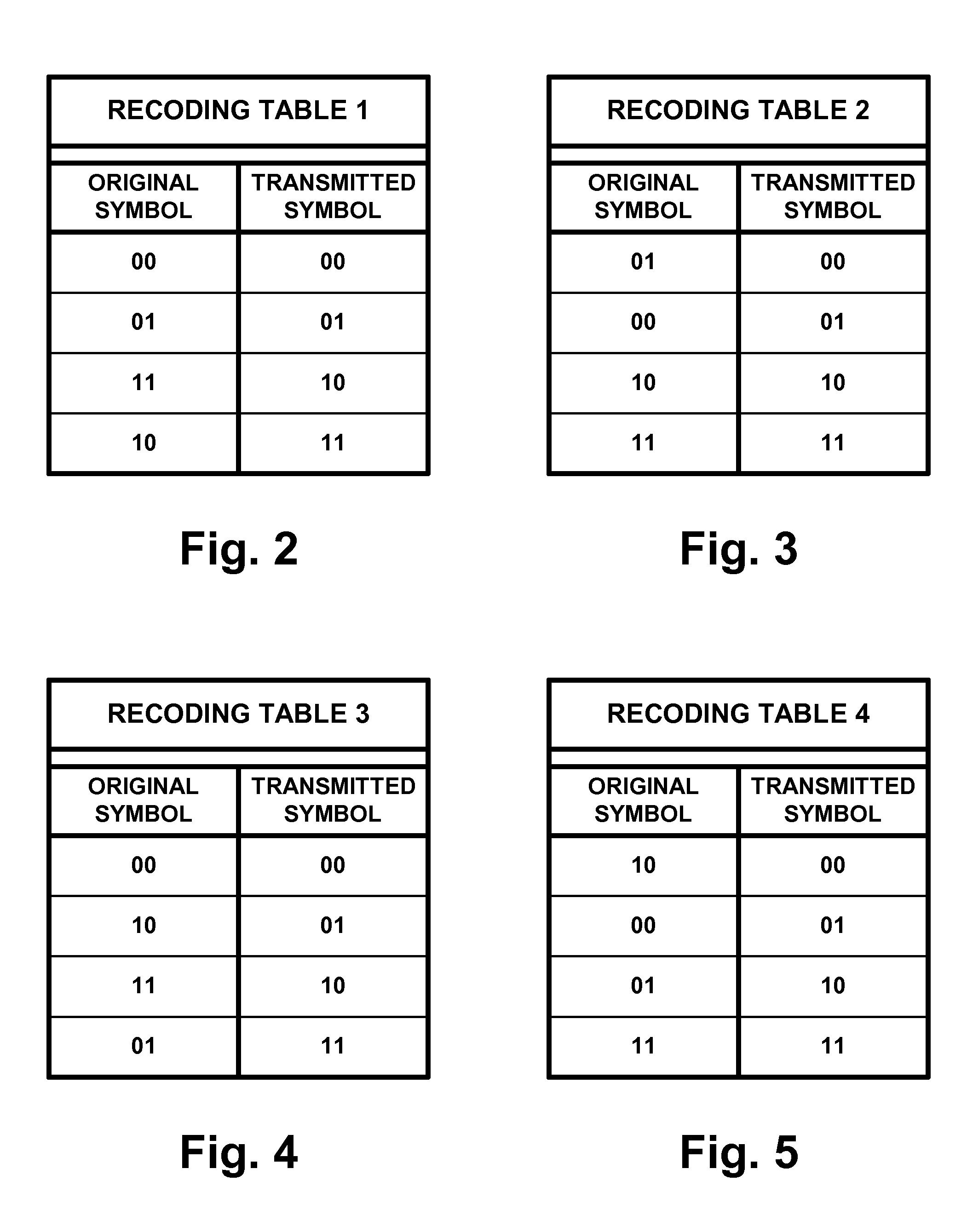

System for digital television broadcasting using modified 2/3 trellis coding

InactiveUS20090322961A1Television system detailsAmplitude demodulation by homodyne/synchrodyne circuitsSymbol interleavingGray code

Serially concatenated convolutional coding (SCCC) transmitting ancillary data within DTV signals incorporates the ⅔ trellis coding used for all DTV signals as its inner convolutional coding. The outer convolutional coding of the SCCC is subjected to _“anti-Gray”_ coding, either before or after its interleaving, but before its inner convolutional coding. In a receiver for ancillary data as so transmitted, simple logic circuitry recodes portions of the trellis decoded DTV signal containing soft decisions as to the symbol-interleaved convolutionally coded ancillary data to provide a Gray-code mapping of symbols to modulation levels. This recoding is done either before or after symbol de-interleaving, but before decoding the outer convolutional coding to recover ancillary data. Soft decisions concerning extrinsic information to be fed back to the ⅔ trellis decoder to close a turbo decoding loop are derived from soft decisions as to the ancillary data, and this derivation includes recoding for a binary-code mapping of symbols to modulation levels.

Owner:LIMBERG ALLEN LEROY

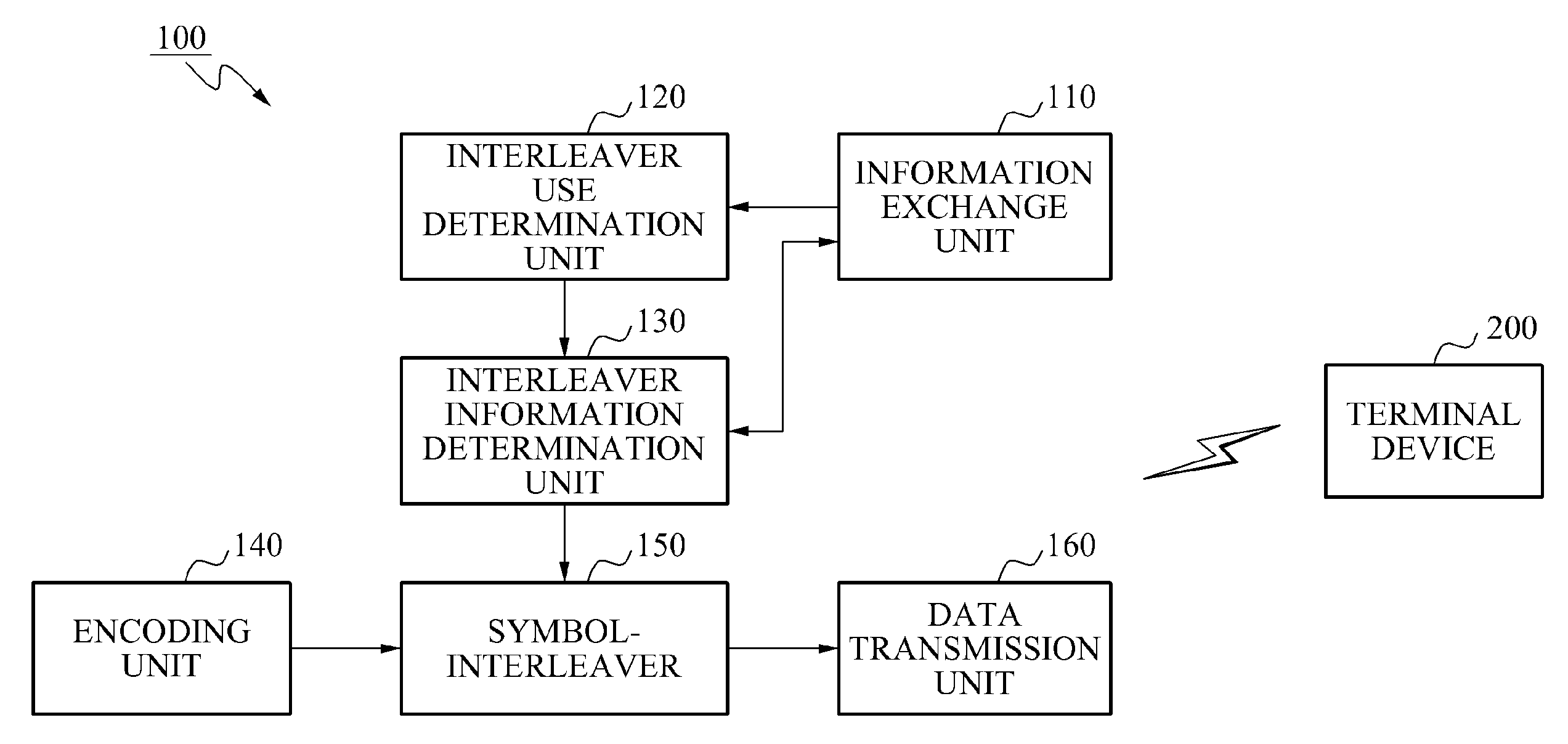

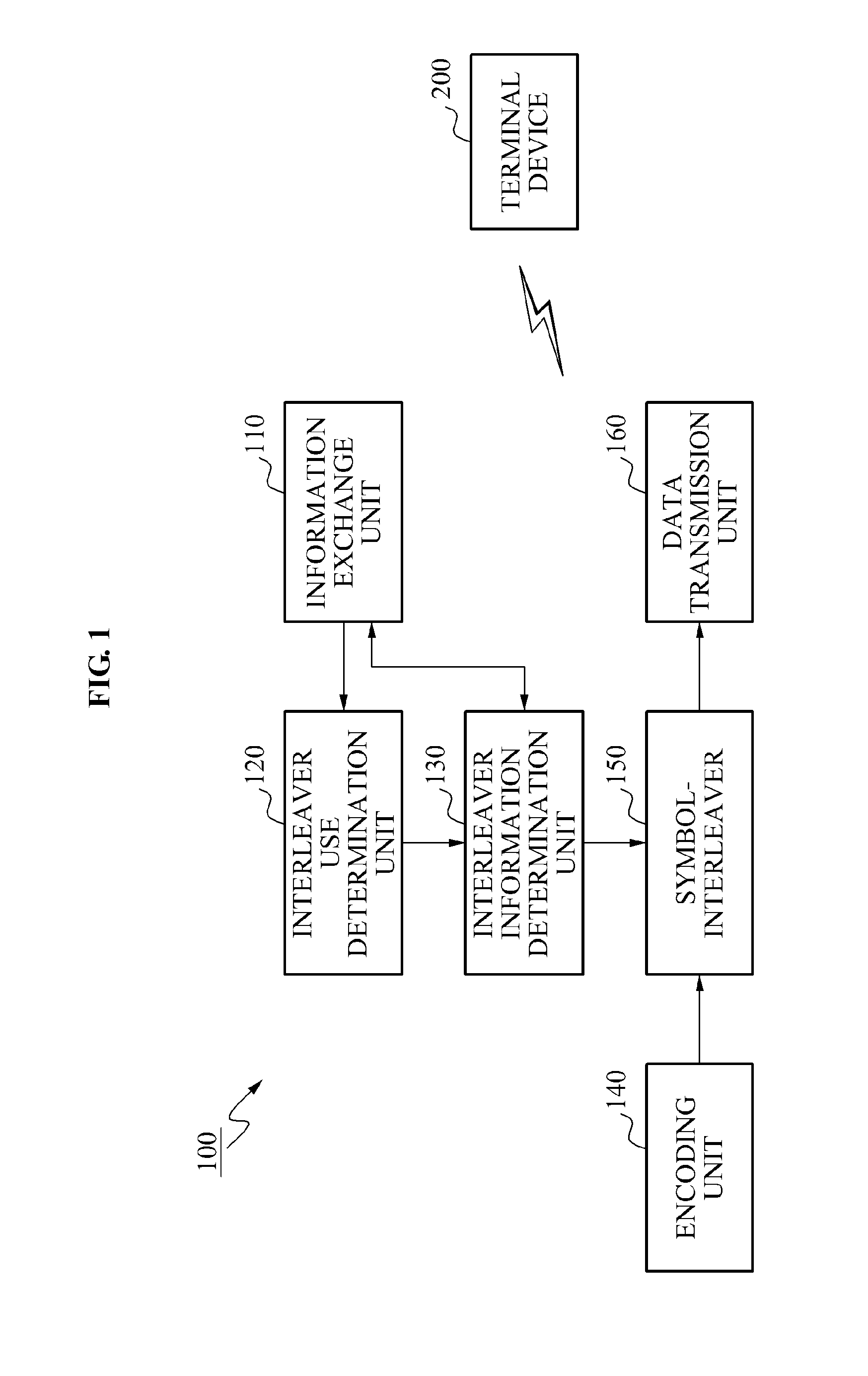

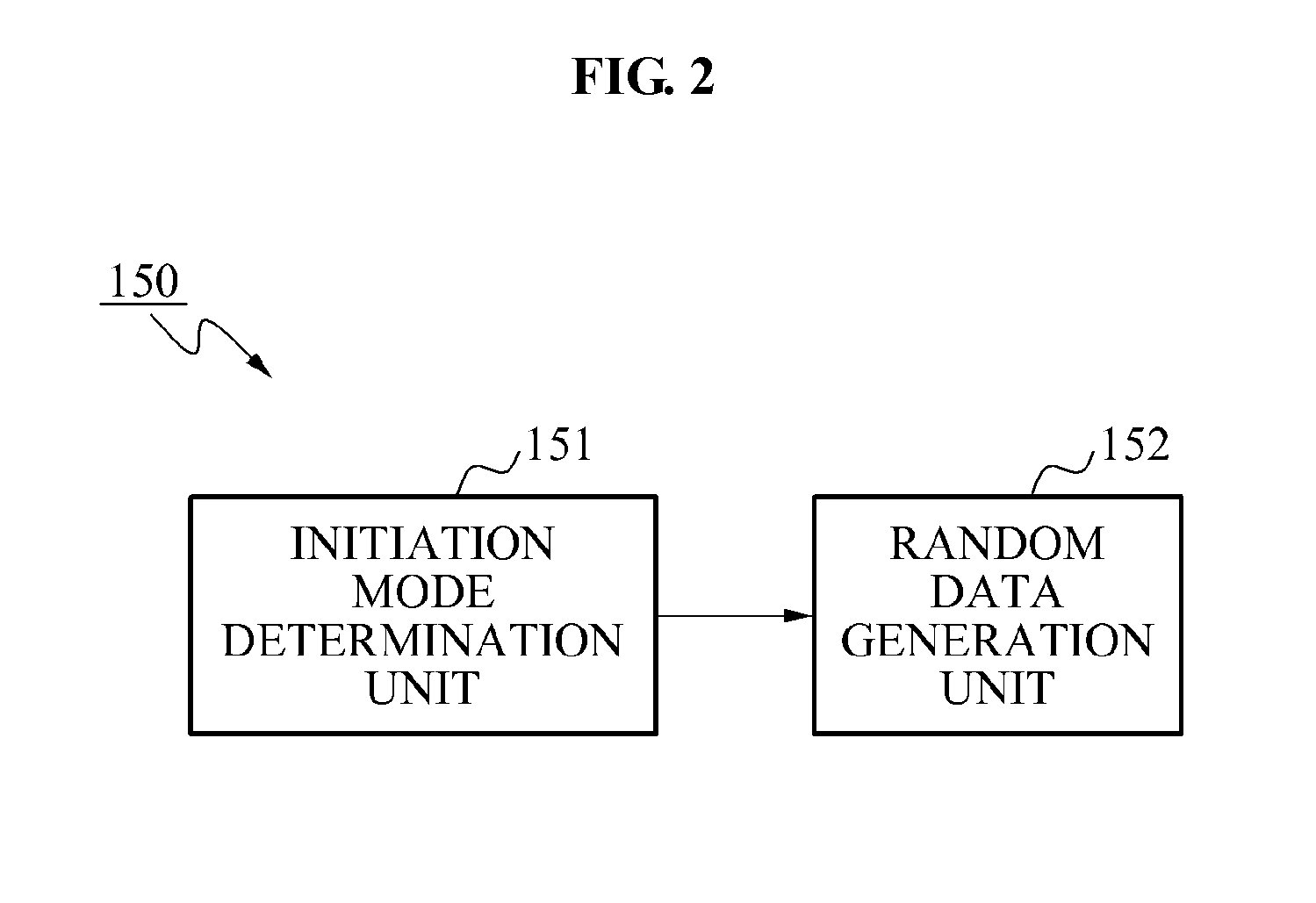

Communicaiton method and apparatus using symbol interleaving

InactiveUS20120093014A1Reduce data transferTransmission systemsFrequency-division multiplex detailsComputer hardwareSymbol interleaving

A communication method and apparatus using a symbol interleaver in a long term evolution (LTE)-based satellite communication system are provided. The communication method may include determining whether to use an interleaver based on service information, and interleaving the data using the symbol interleaver designed based on interleaver information. Also, the communication method may include generating random data using a timer and interleaving the random data.

Owner:ELECTRONICS & TELECOMM RES INST

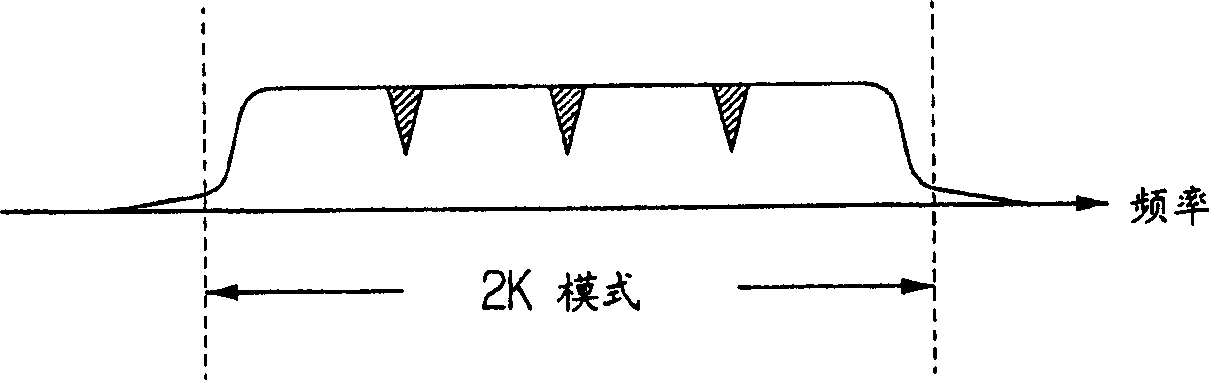

Symbol interleaving

InactiveUS7620111B2Receiver specific arrangementsSecret communicationDigital dataSymbol interleaving

The invention relates to a method for communicating digital data using an orthogonal frequency division multiplexing (OFDM) transmission system (10) including at least one transmitter (600, 601) and receivers (700, 701). The method comprises selecting a mode of operation in a transmitter among at least one mode, each mode of operation being associated with a number of active carriers for payload data transmission, selecting a symbol interleaver in the transmitter from a set of symbol interleavers for symbol interleaving in said selected mode of operation, applying symbol interleaving in the transmitter on blocks of data units, mapping the interleaved data units onto the active carriers of said selected mode of operation, receiving the interleaved data units in the receiver, recognizing in the receiver the symbol interleaver used in the data transmission, selecting a de-interleaver in the receiver to correspond to the recognized symbol interleaver, and de-interleaving in the receiver the received data units using the selected de-interleaver.

Owner:NOKIA TECH OY

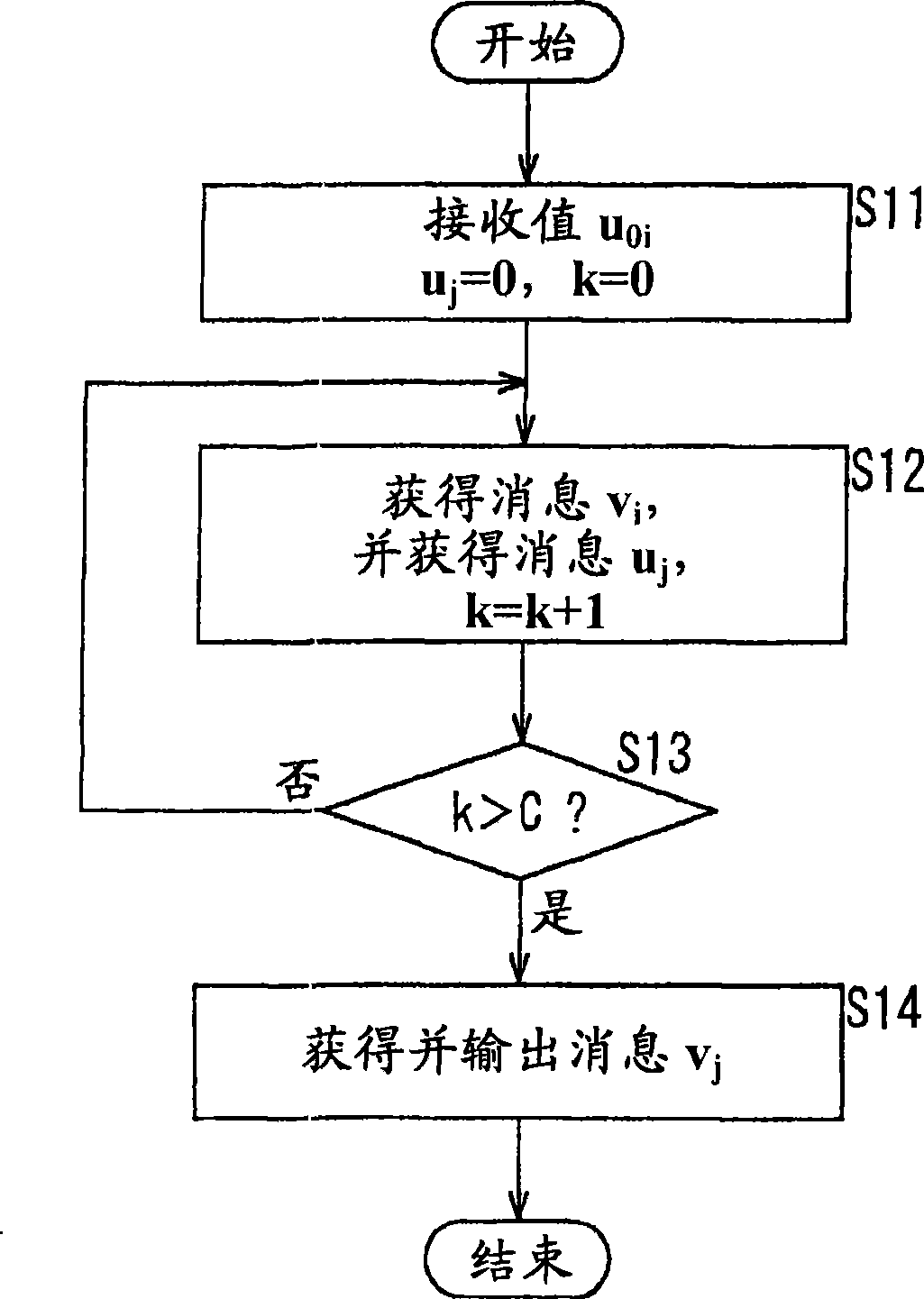

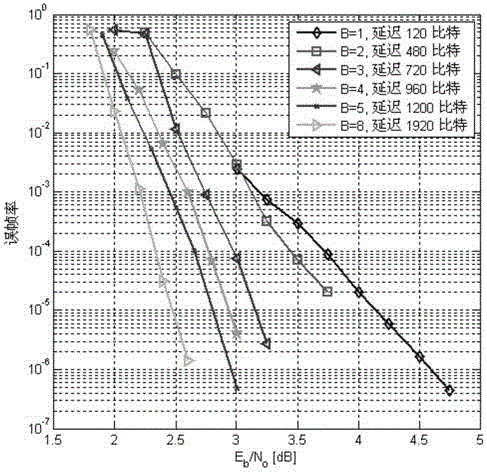

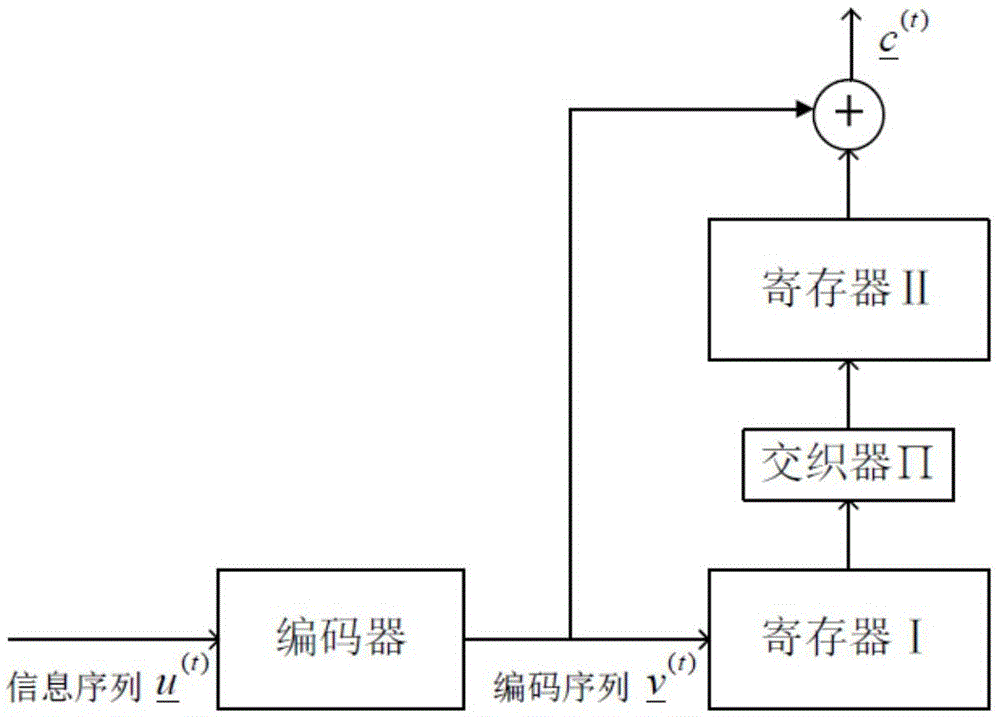

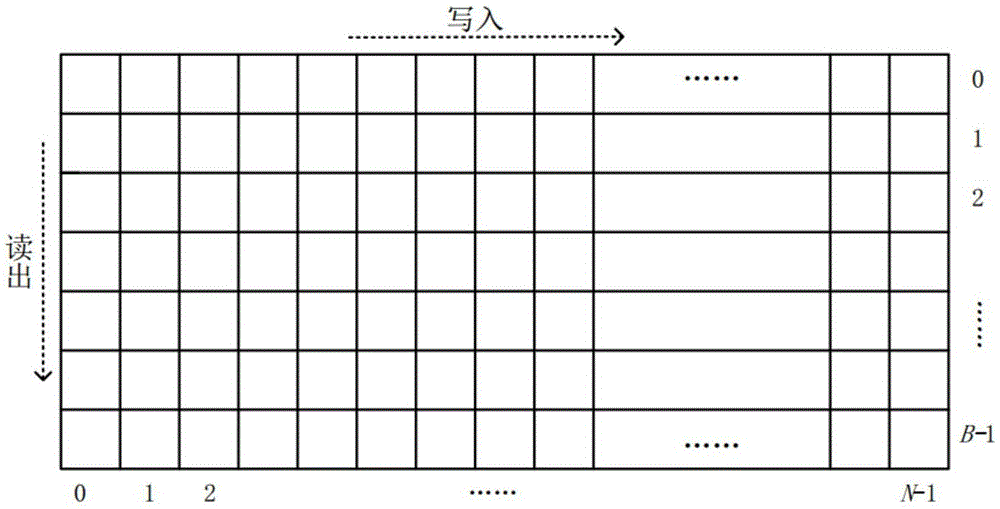

Delay-adjustable encoding method

ActiveCN105680988AMeet fixedGuaranteed fixed effectForward error control useAdaptation strategy characterisationBlock codeProcessor register

The invention belongs to the field of digital communications and digital storage, and discloses a delay-adjustable encoding method. The method comprises the following steps: I, configuring a delay parameter B, wherein B is a positive integer; II, taking an information sequence underlined-u<(t)> of which a length is BK, and blocking the sequence into underlined-u<(t)>=(underlined-u<0><(t)>, underlined-u<1><(t)>, . . ., underlined-u<B-1><(t)>), wherein a length of underlined-u<(t)> (0<=i>=(B-1)) is a positive integer K; III, encoding the information sequence underlined-u<(t)> into a code word underlined-v<(t)> through a linear block code encoder to obtain a symbol sequence underlined-v<(t)>=(underlined-v<0><(t)>, underlined-v<1><(t)>, . . ., underlined-v<B-1><(t)>) of which a total length is BN, and storing the symbol sequence in a register I, wherein a length of underlined-v<(t)> (0<=i>=(B-1)) is a positive integer N; and IV, setting underlined-c<(t)>=underlined-v<(t)> xor pi(underlined-v<(t-1)>), wherein pi(underlined-v<(t-1)>) is a code word obtained after symbol interleaving through an interleaver pi, storing the pi(underlined-v<(t-1)> in a register II, inputting the underlined-v<(t)>=(underlined-v<0><(t)>, underlined-v<1><(t)>, . . ., underlined-v<B-1><(t)>) into the interleaver pi to perform interleaving, and writing an interleaved sequence into the register II. The method is simple in steps, convenient to implement, and low in complexity. Different delays can be met under the situation of ensuring a fixed code rate through simple configuration without changing a basic encoding and decoding hardware module for linear block codes, so that a compromise between delay and performance can be realized.

Owner:SUN YAT SEN UNIV

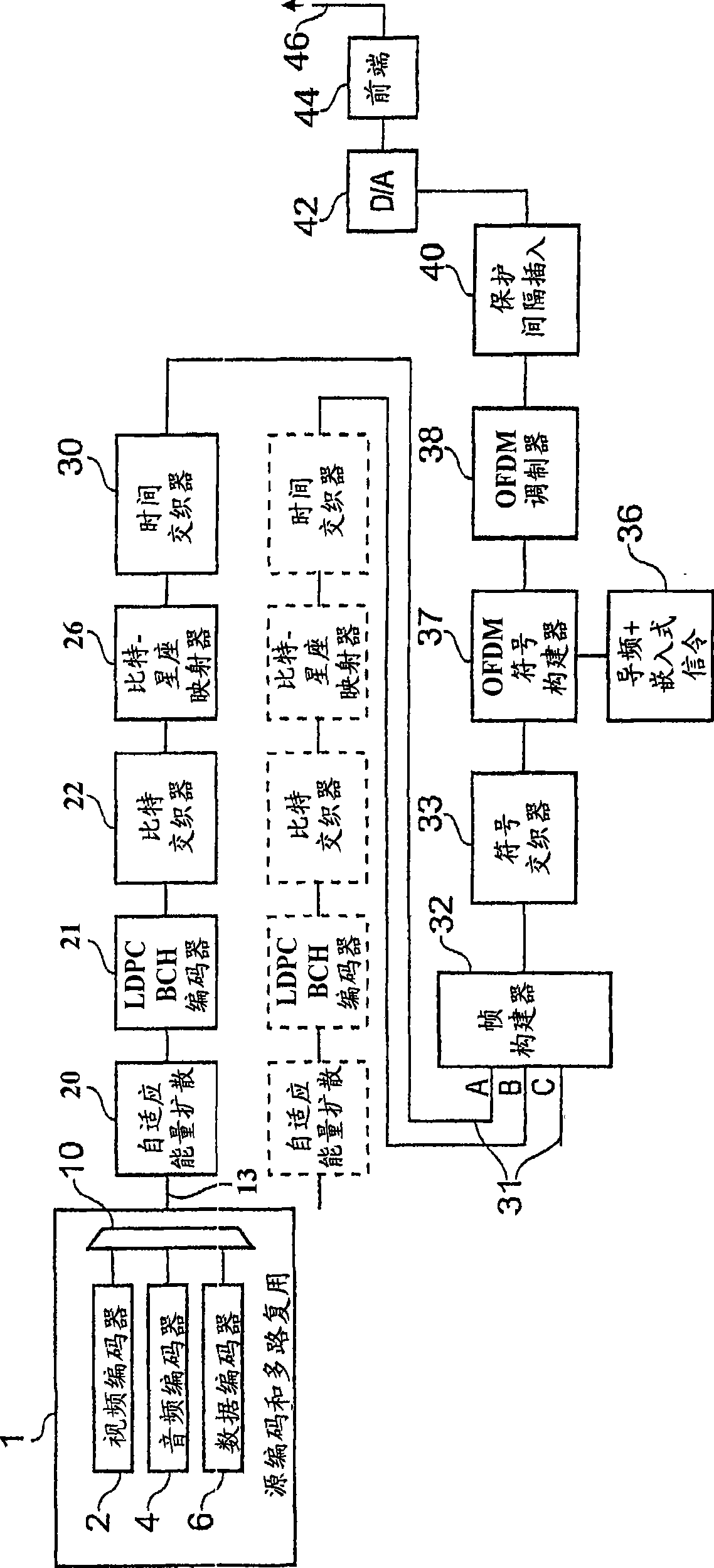

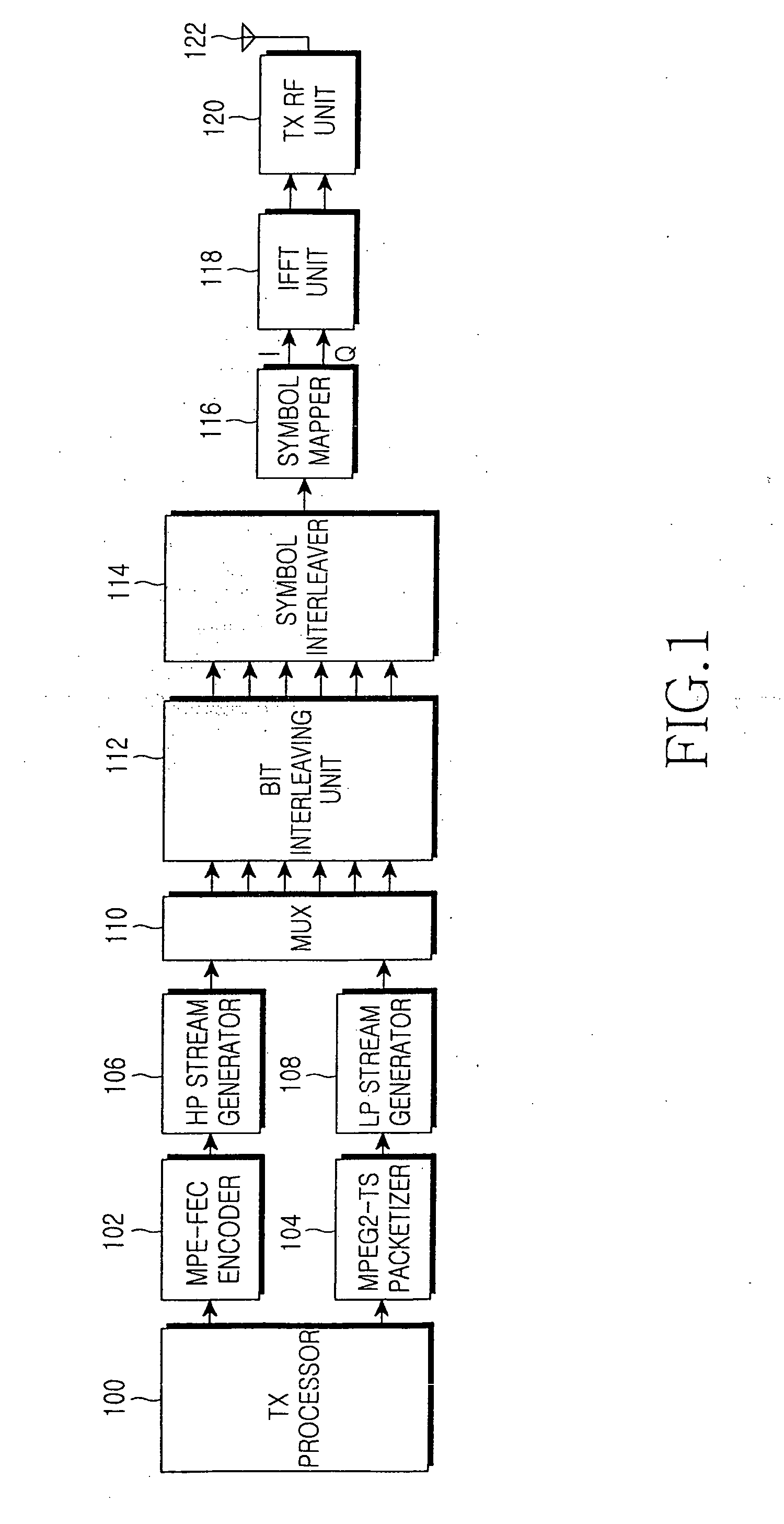

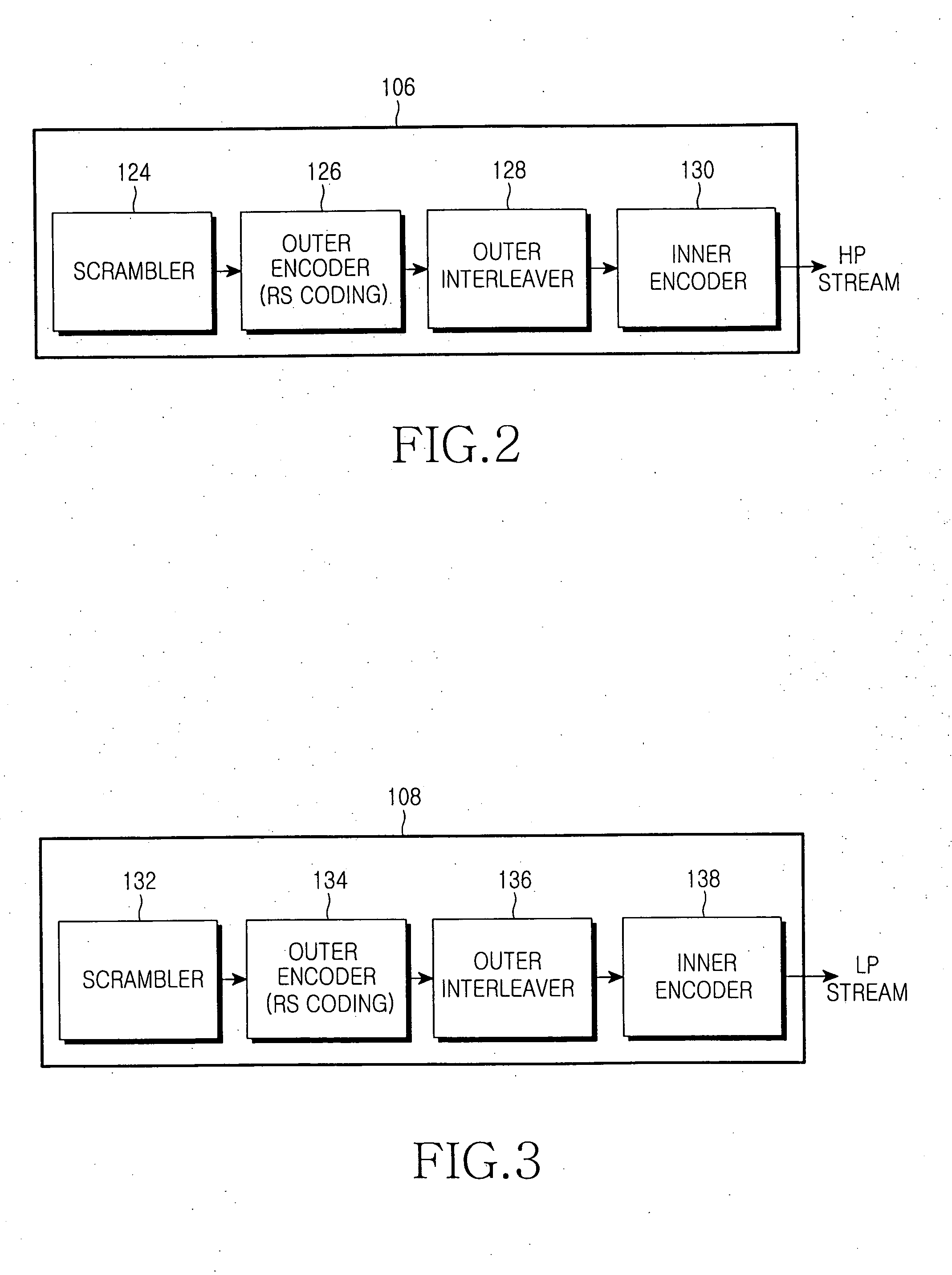

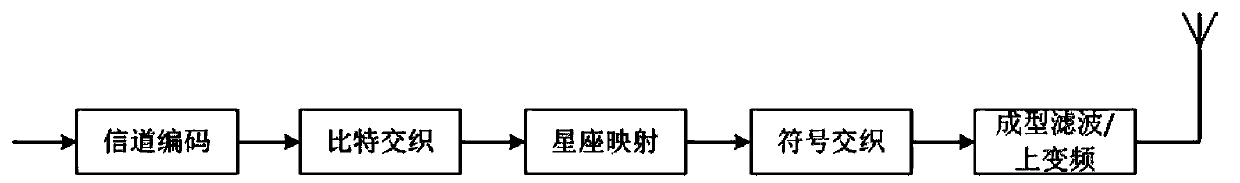

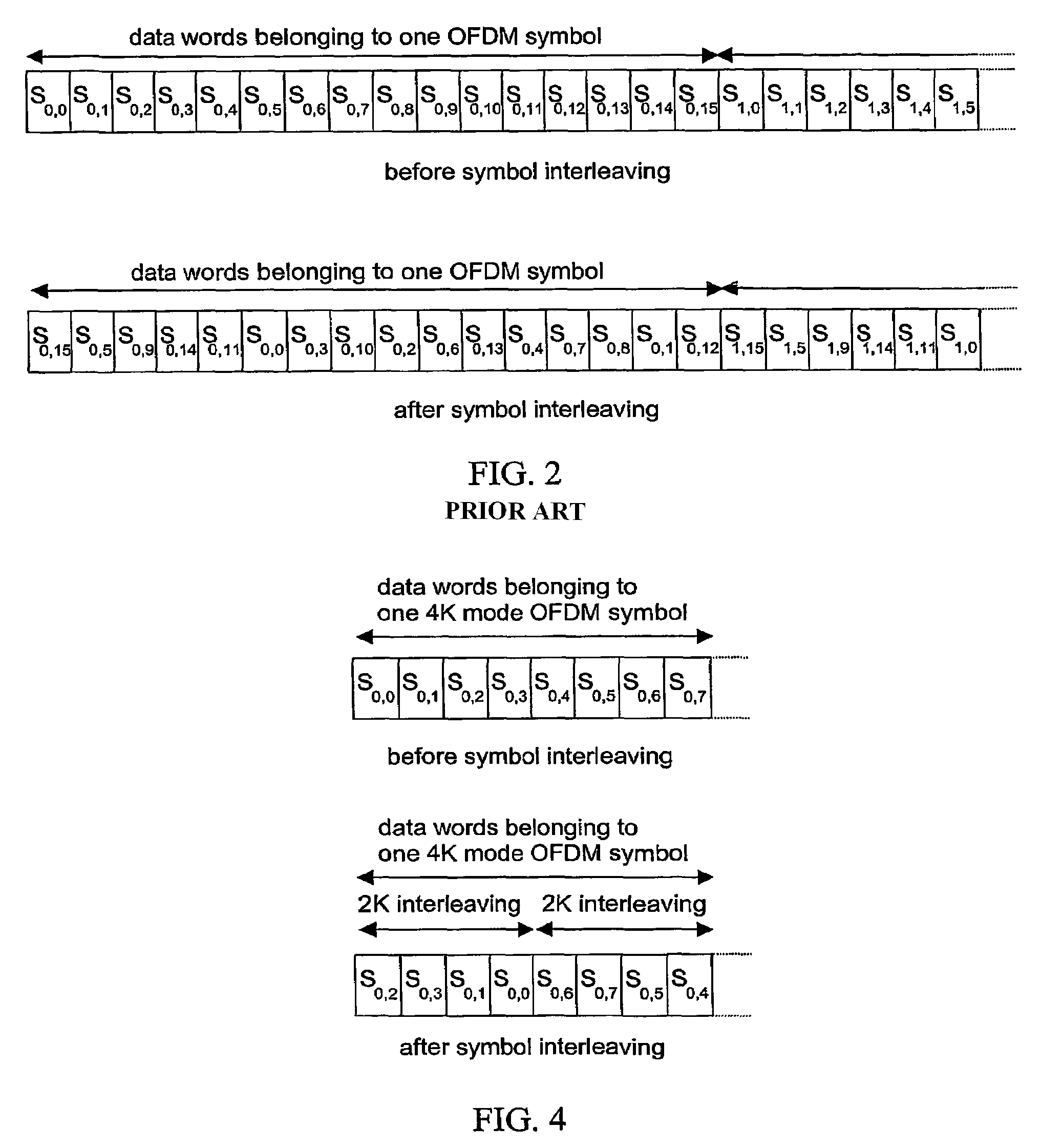

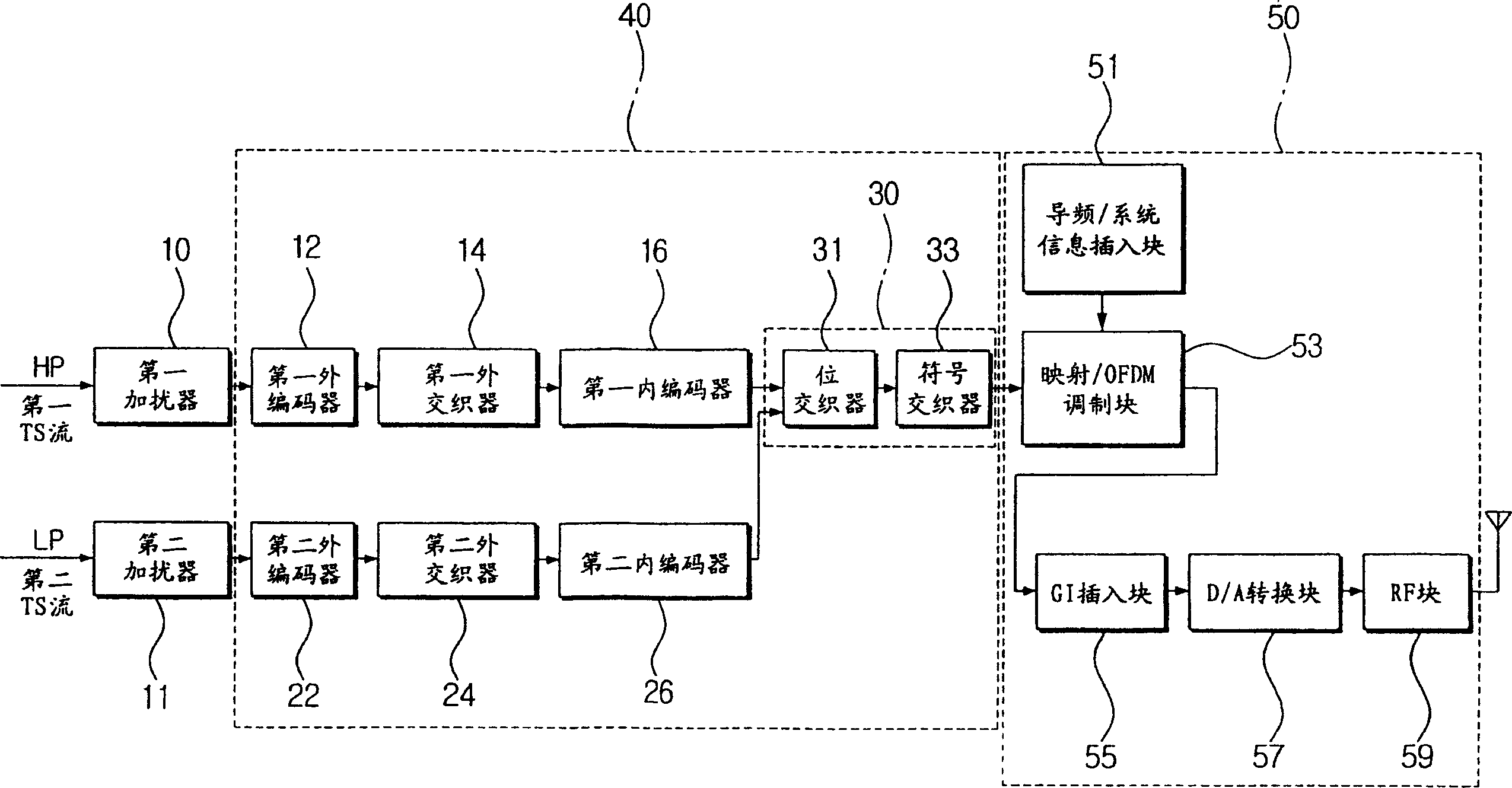

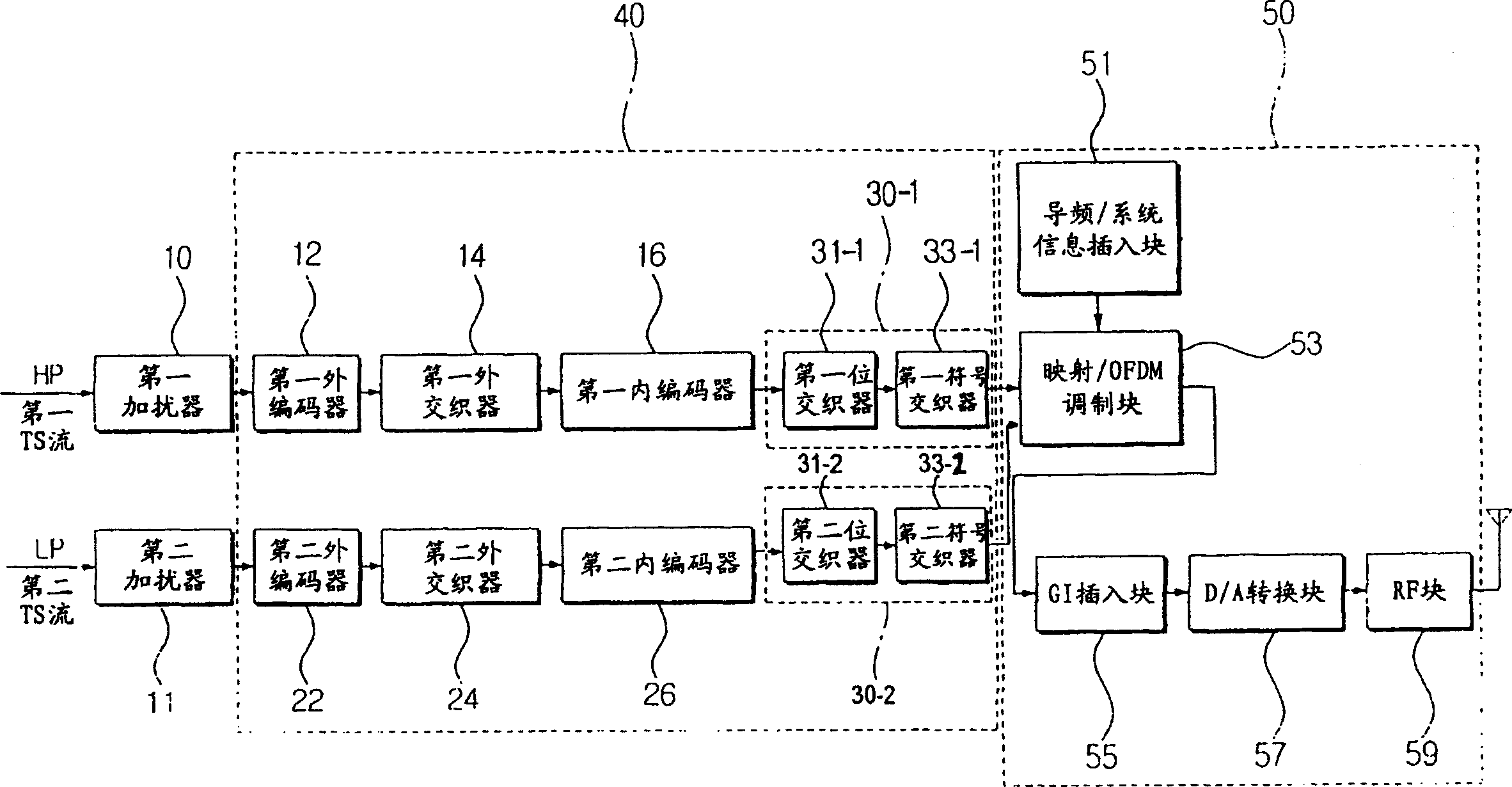

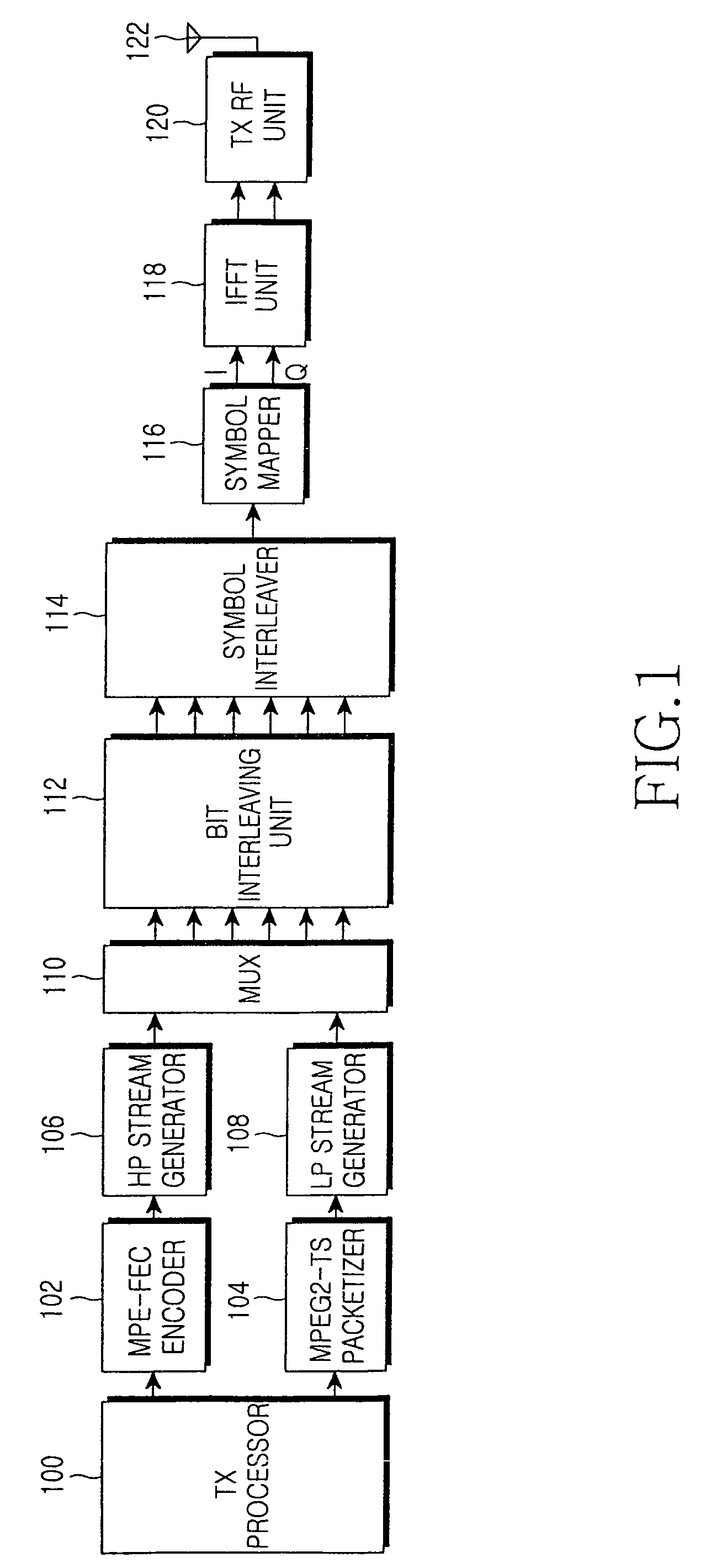

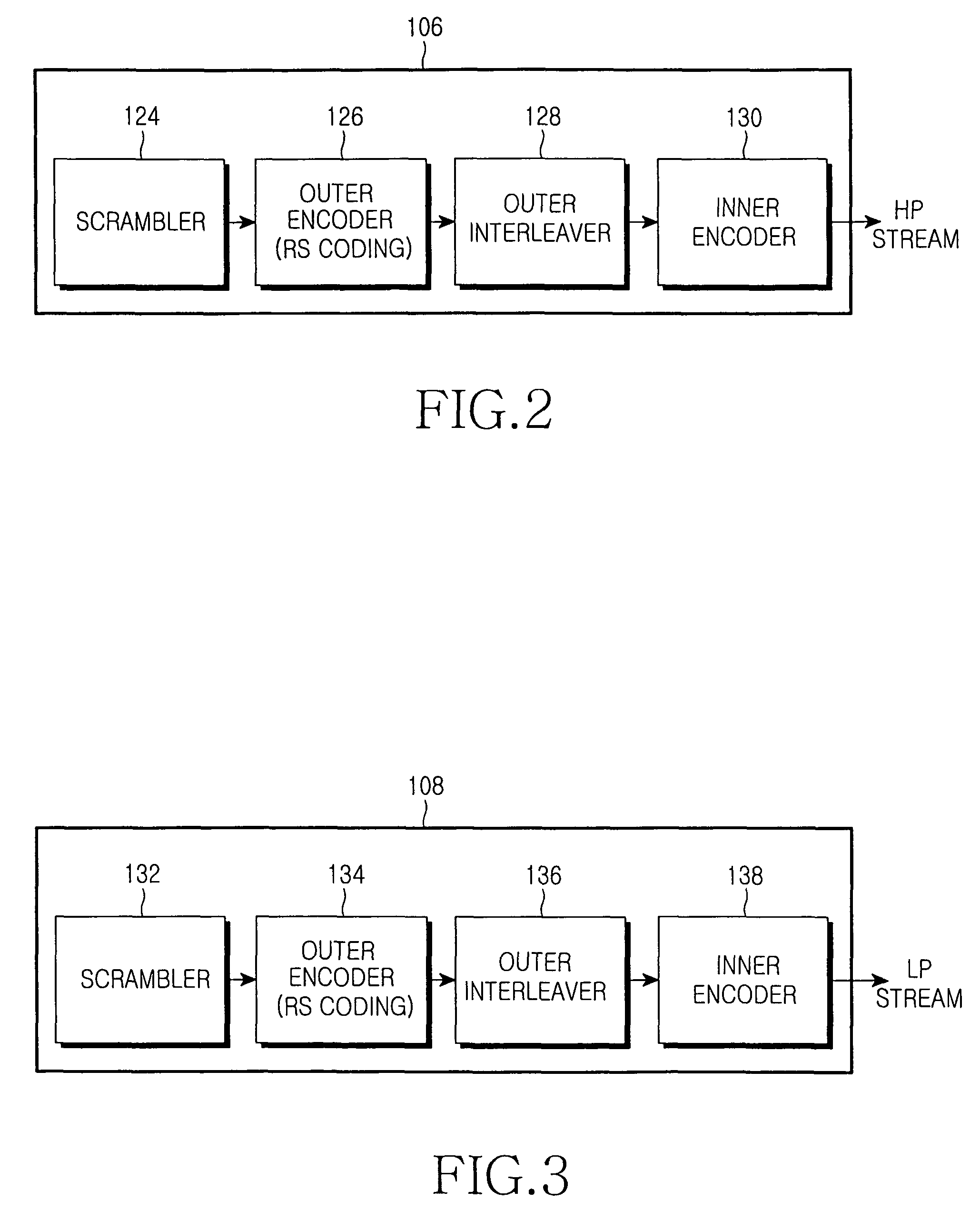

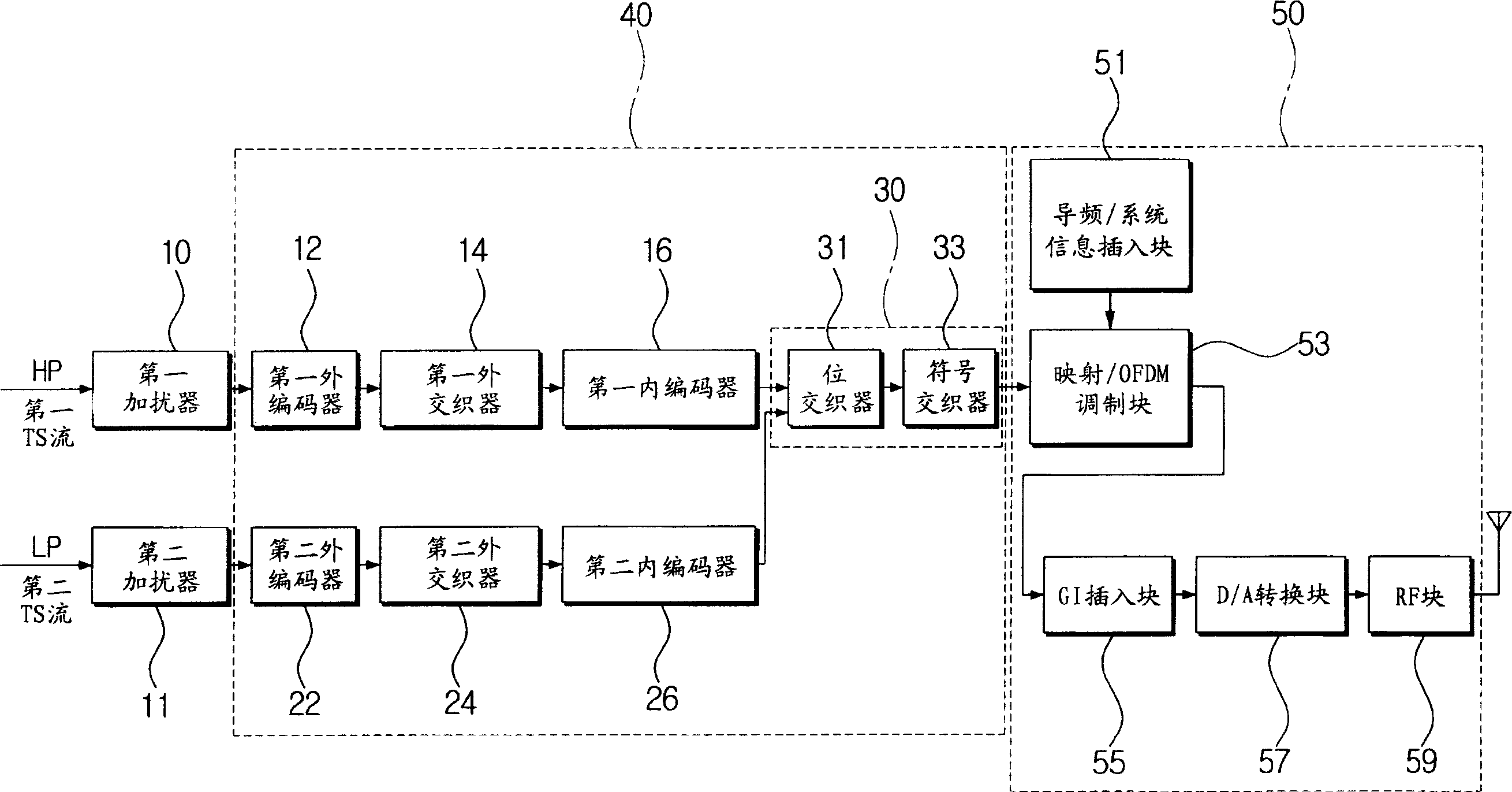

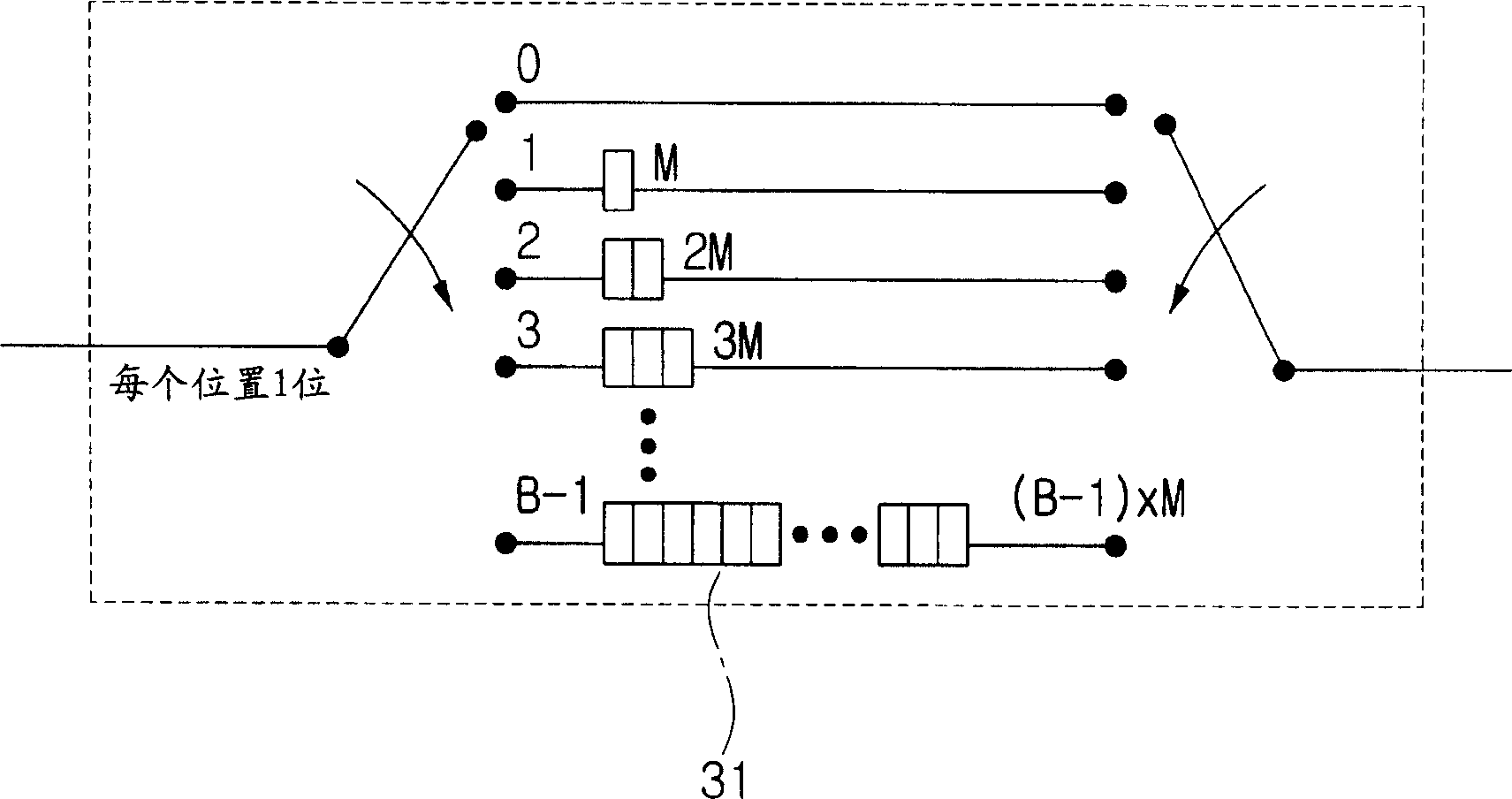

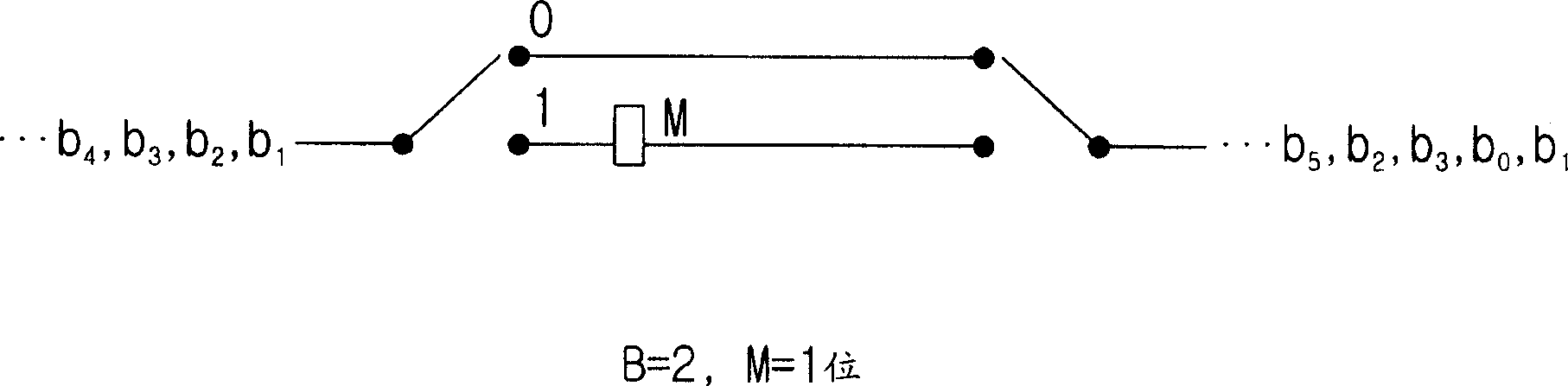

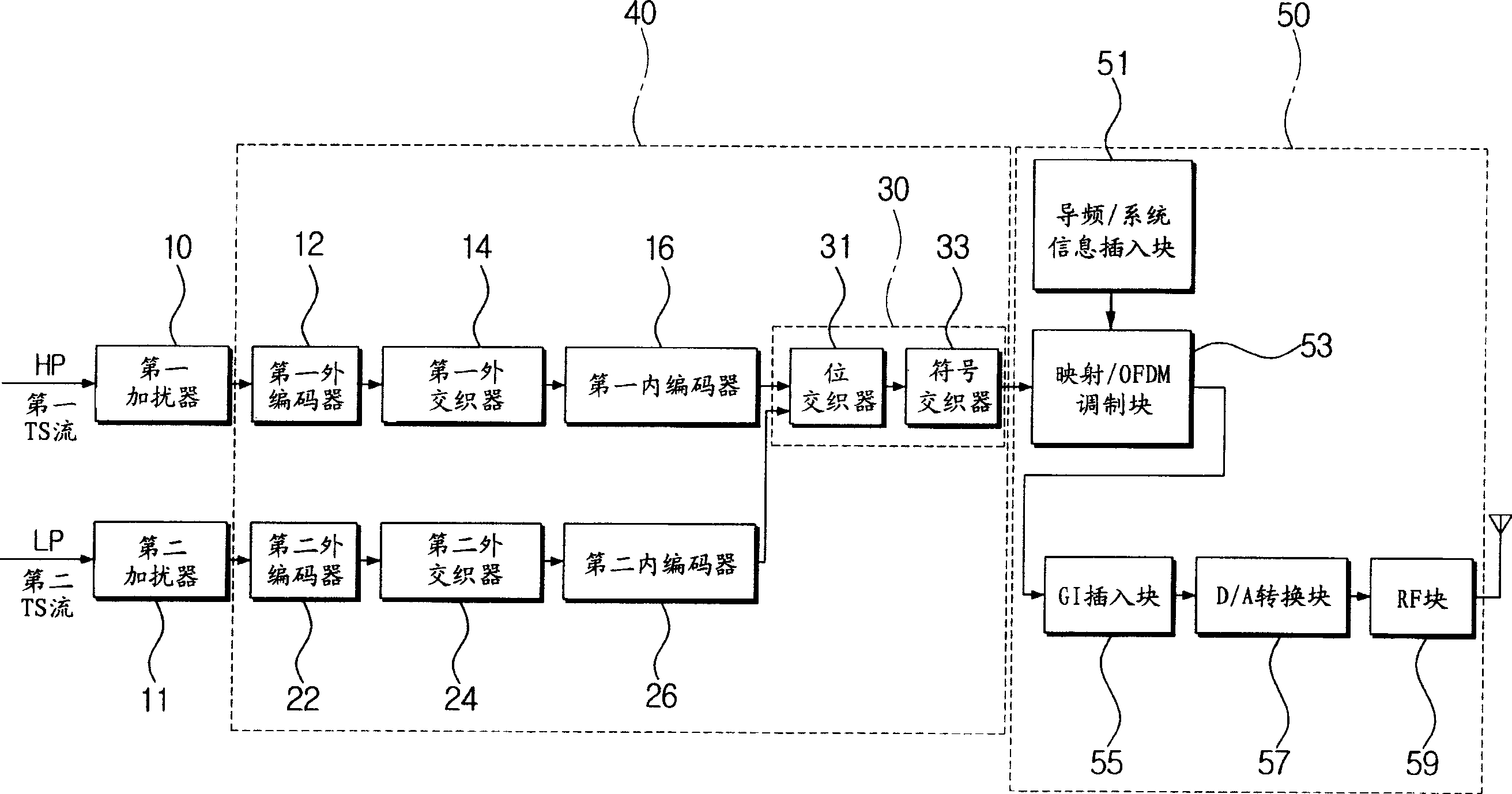

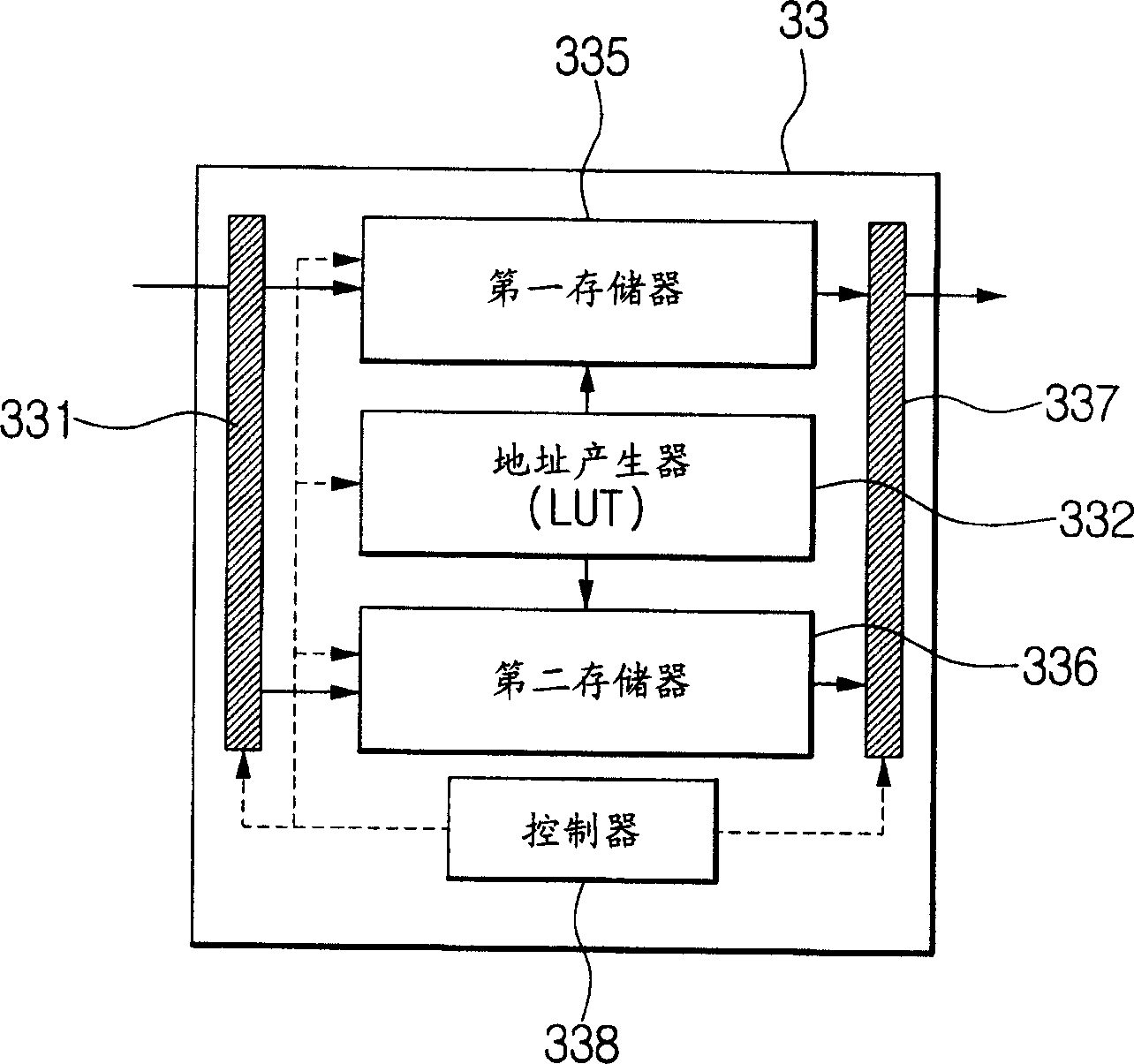

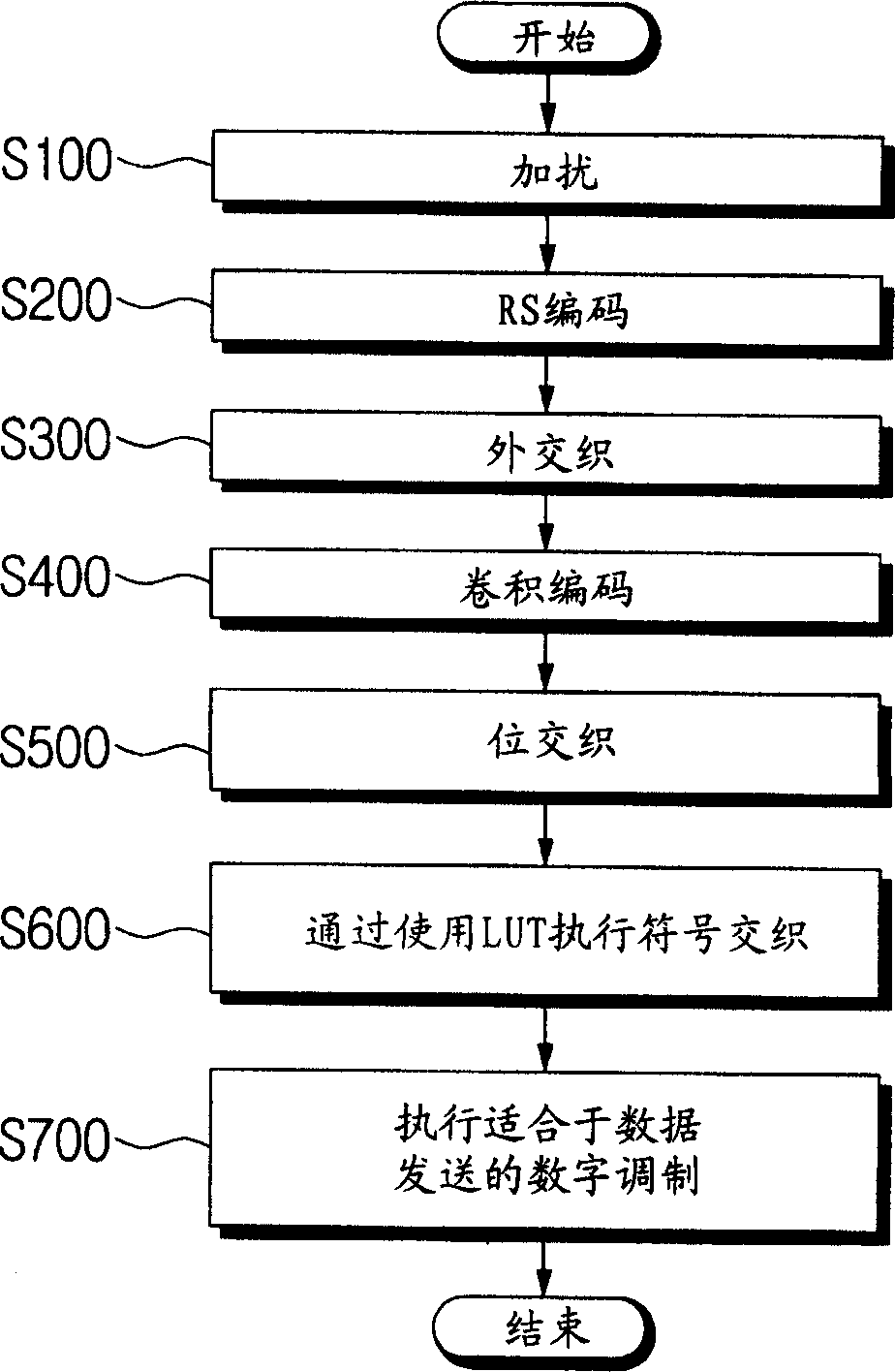

Sending apparatus and method of digital broadcasting system

InactiveCN1738373AIncrease randomnessECC performance is effectiveTelevision system detailsBroadcast with distributionComputer hardwareDigital audio broadcasting

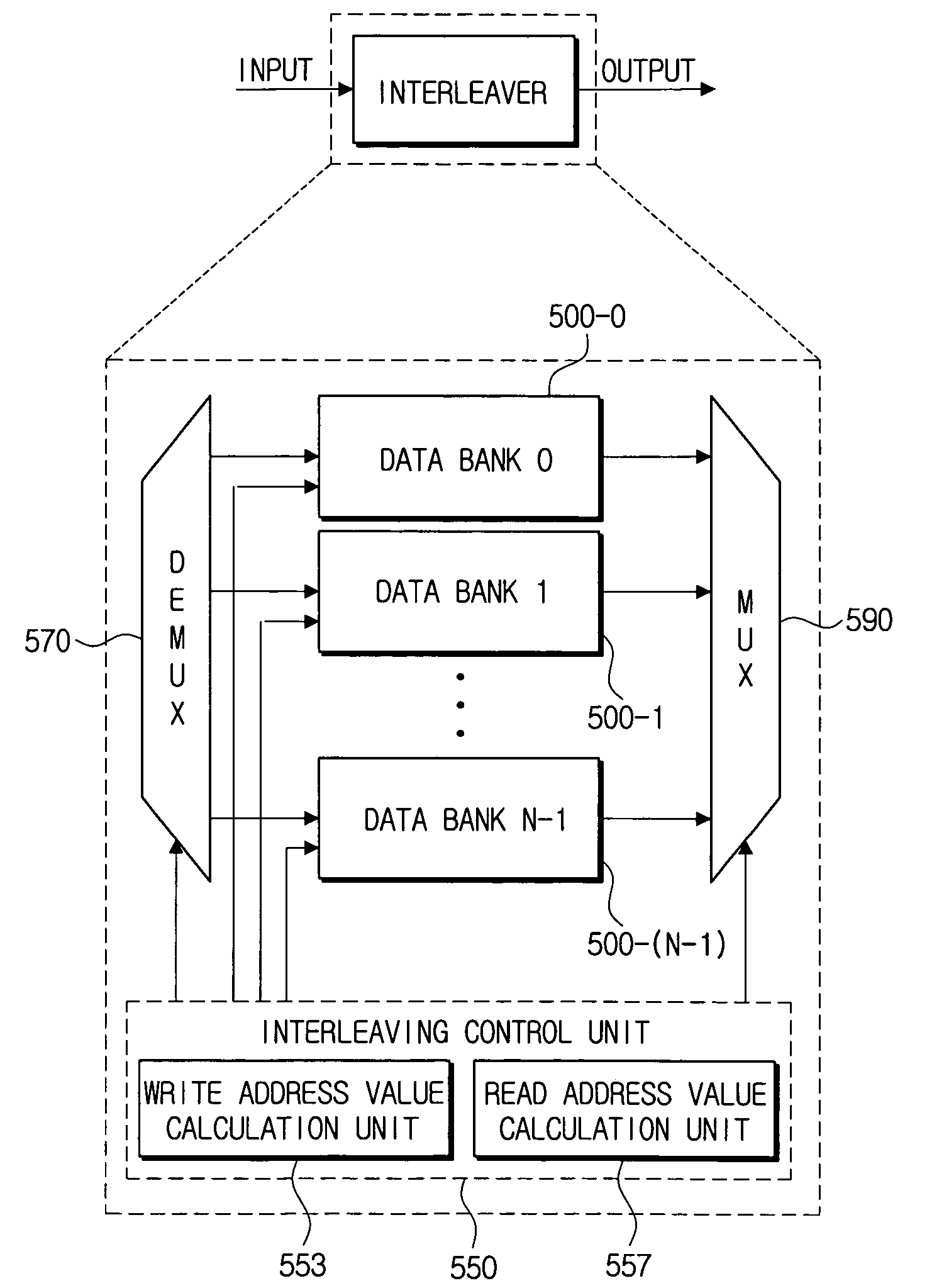

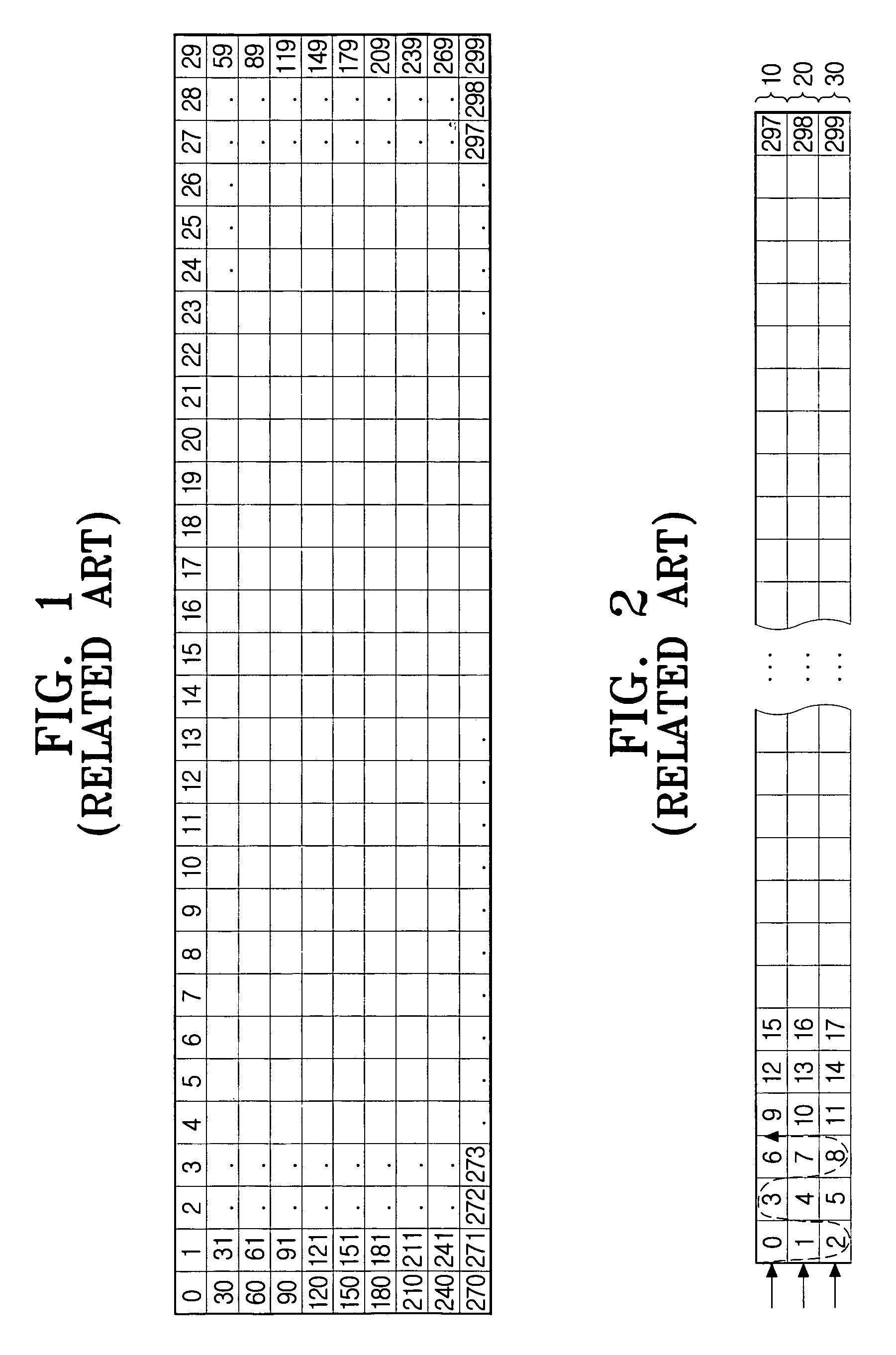

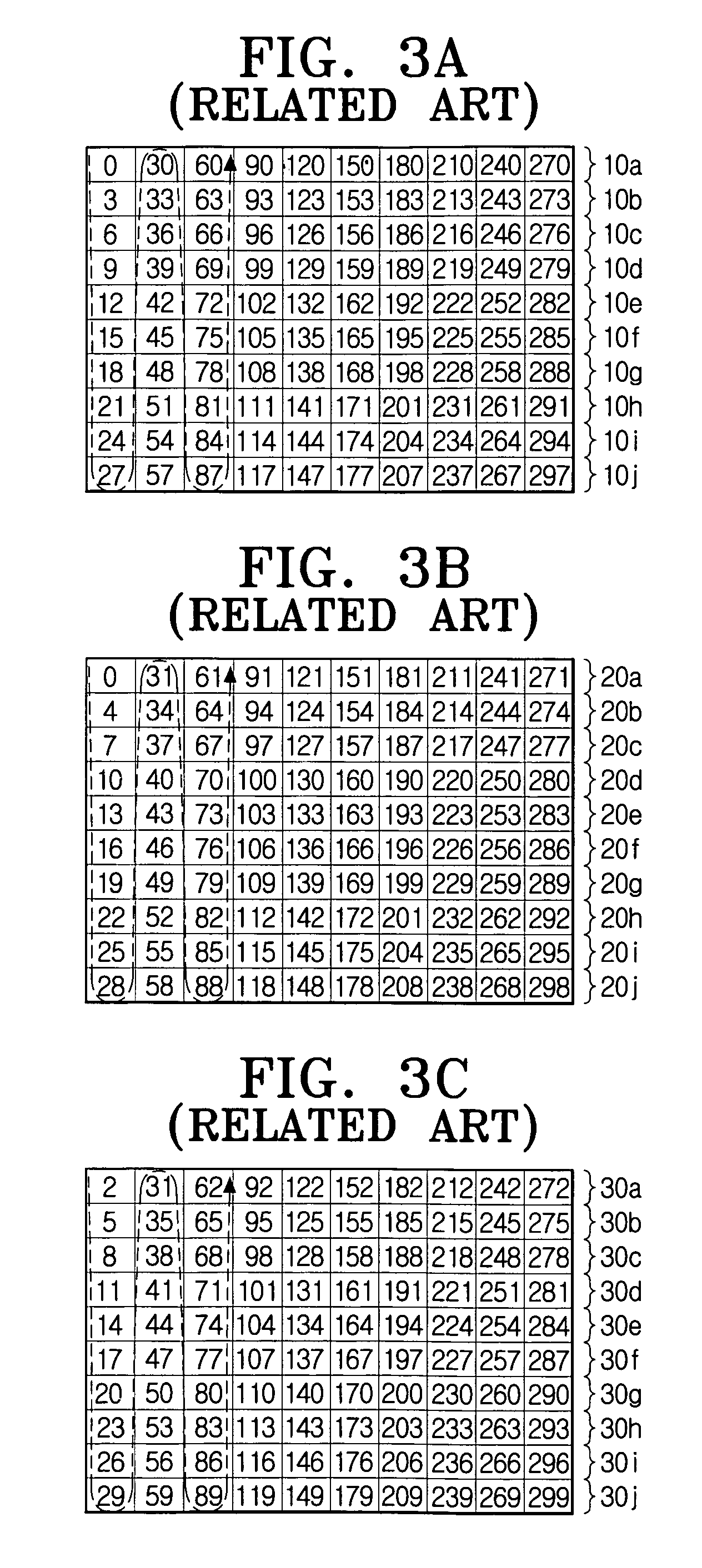

The invention discloses a digital broadcast system transmission device and a sending method thereof, wherein, the transmission device comprises: a first outer encoder and a second outer encoder, executing coding on a first input TS stream and a second input TS stream respectively; a first outer interleaver and a second outer interleaver, executing interleaving on the coded data of the first outer encoder and the second encoder respectively; a first inner encoder and a second inner encoder, executing coding on the interleaved data of the first outer interleaver and the second outer interleaver respectively; an inner interleaver comprising a bit-interleaver, used for executing bit interleaving on the coded data of the first inner encoder and the second inner encoder by a convolution interleaver; a symbol interleaver, used for applying N sets of interleaving addresses to carry out symbol interleaving on the bit-interleaved data of the bit-interleaver; a modulation unit, used for carrying out digital modulation to the interleaved data of the inner interleaver and sending the data. Therefore, by means of improving the randomicity of the symbol interleaver, more effective error correction coding performance is acquired.

Owner:SAMSUNG ELECTRONICS CO LTD

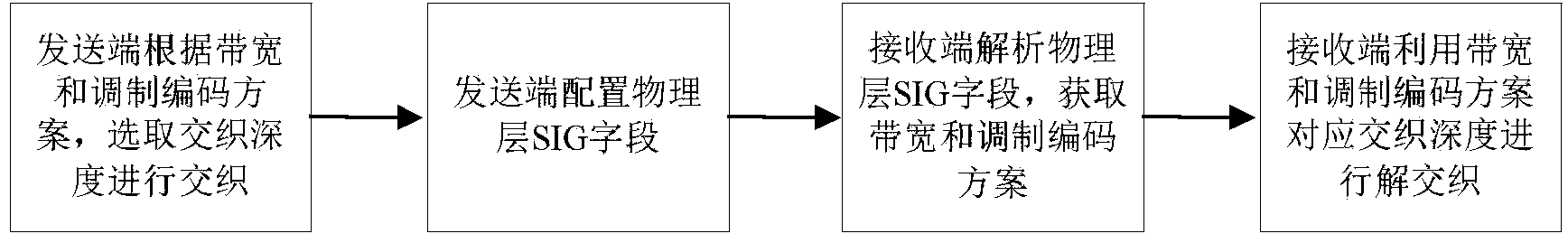

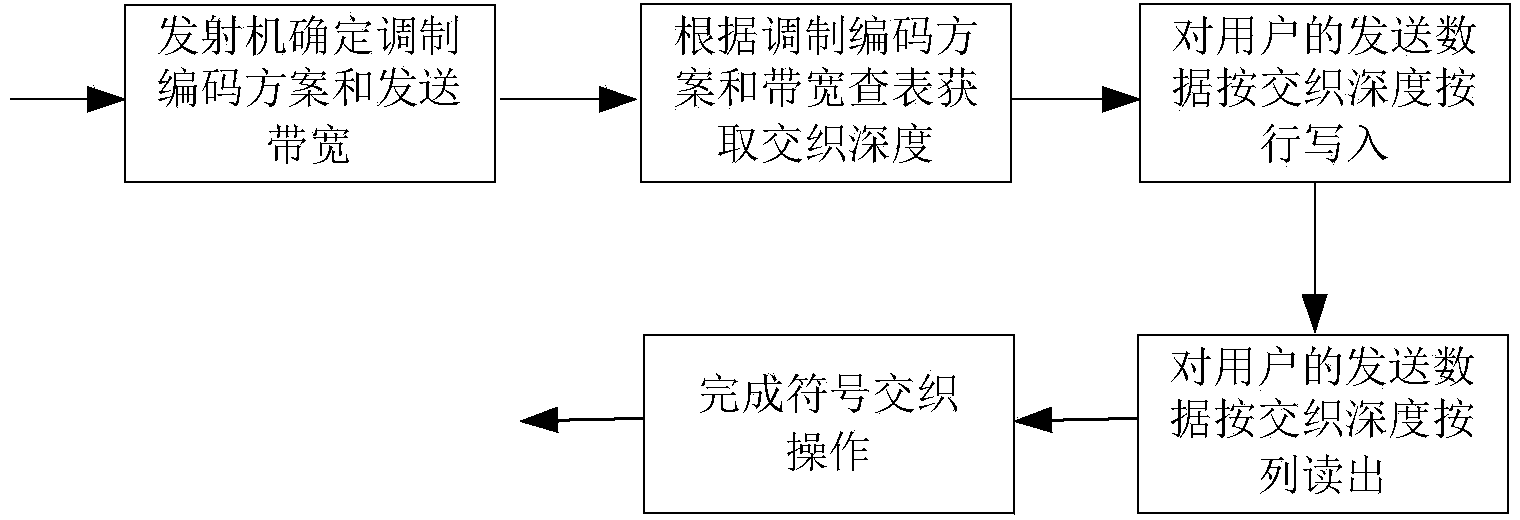

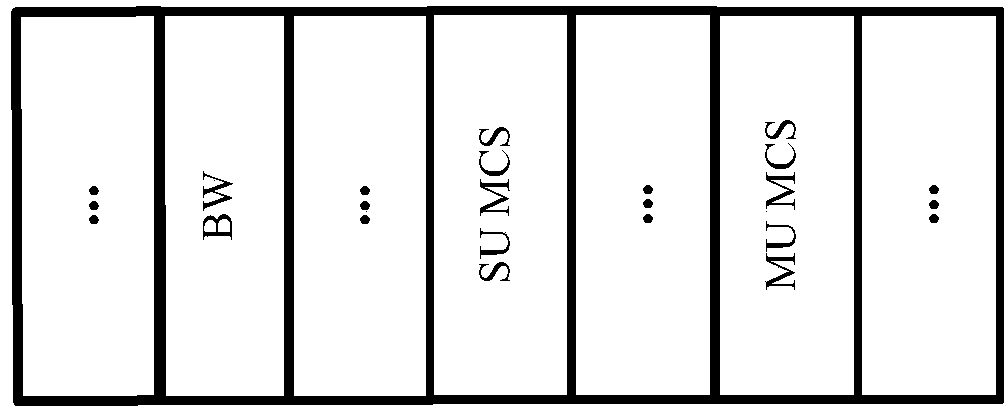

Symbol interleaving and de-interleaving method and device adaptive to modulation coding scheme

ActiveCN104168084AImprove performanceSolve the problem that interleaving cannot be performed according to the optimal interleaving depth of the modulation and coding schemeError preventionMulti-frequency code systemsCommunications systemSymbol interleaving

The invention discloses a symbol interleaving and de-interleaving method and device adaptive to a modulation coding scheme and belongs to the technical field of wireless communication. The method is as follows: a transmitter adopts different optimal interleaving depths to carry out symbol interleaving processing on sending data for combination values of different channel bandwidths and different modulation coding schemes; and a receiver carries out de-interleaving processing through obtaining of the bandwidth of a physical-layer signaling field and information of the modulation coding scheme and selection of an optimal interleaving depth and restores data before the interleaving. The invention also provides an interleaving and de-interleaving device adopting the method so as to realize symbol interleaving and de-interleaving functions adaptive to the modulation coding scheme. Compared with the prior art, the symbol interleaving and de-interleaving method and device are capable of improving significantly error-packet-rate performance of a wireless communication system under a condition that no extra signaling communication service volume is introduced.

Owner:南京易太可通信技术有限公司

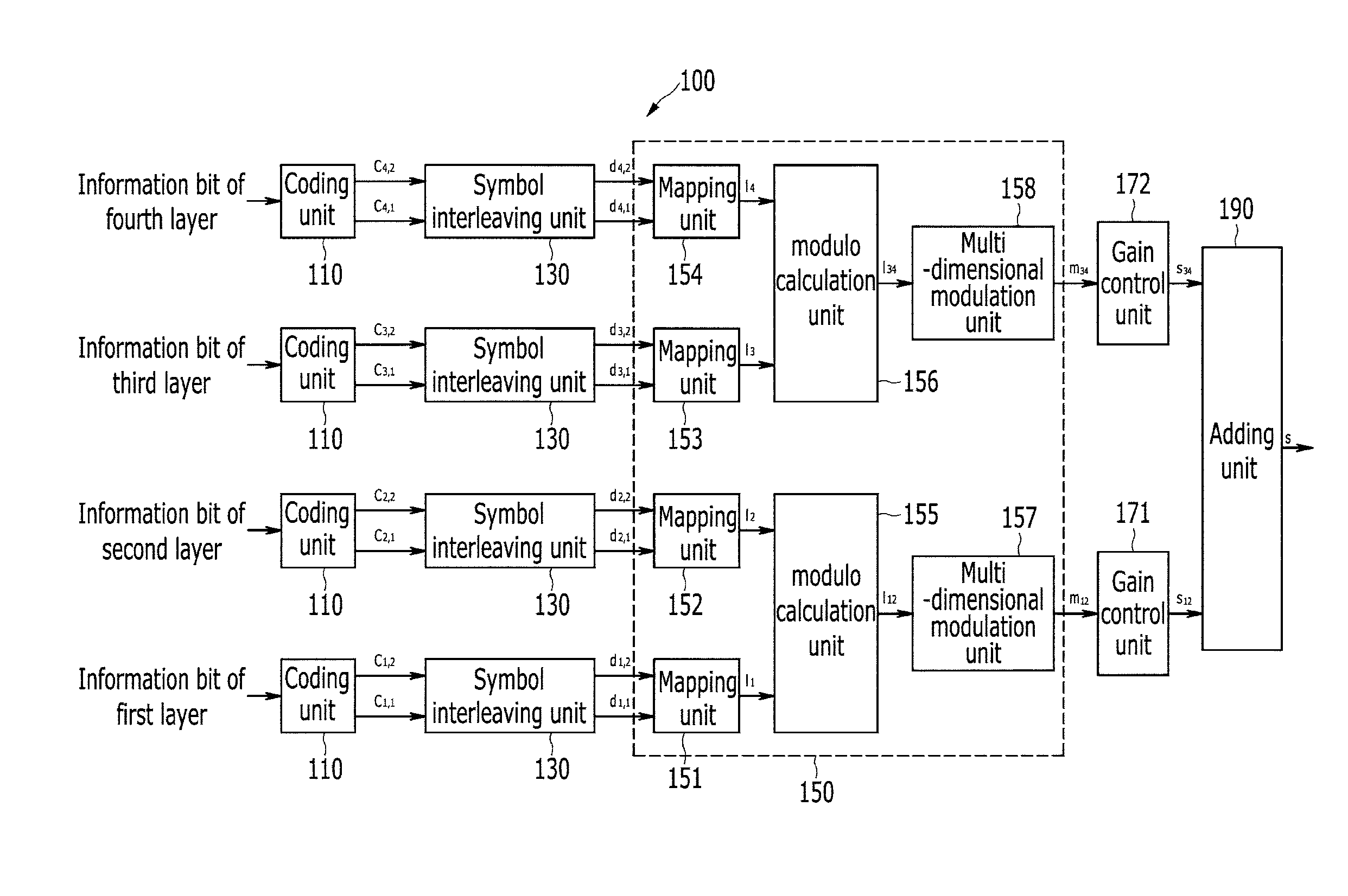

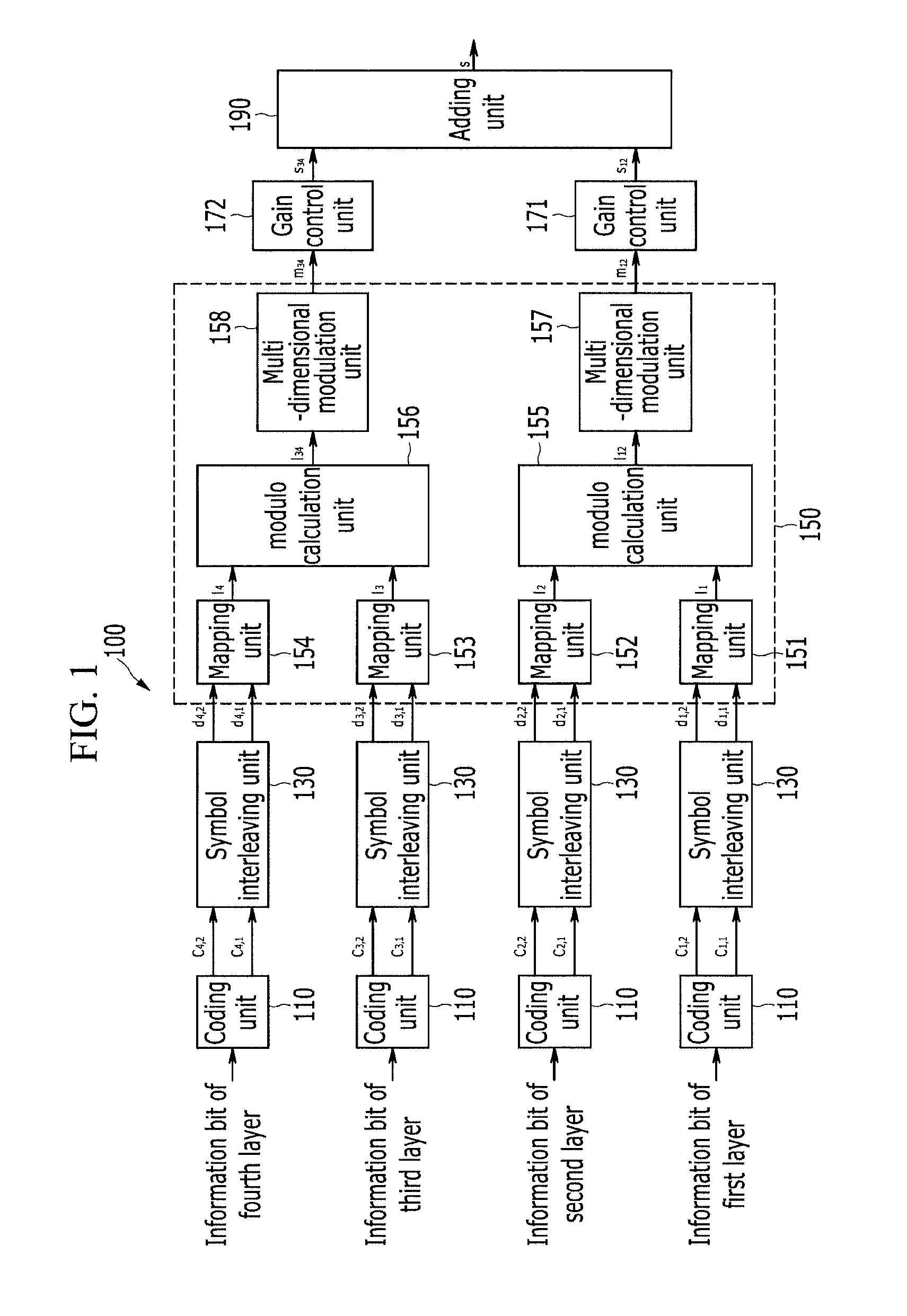

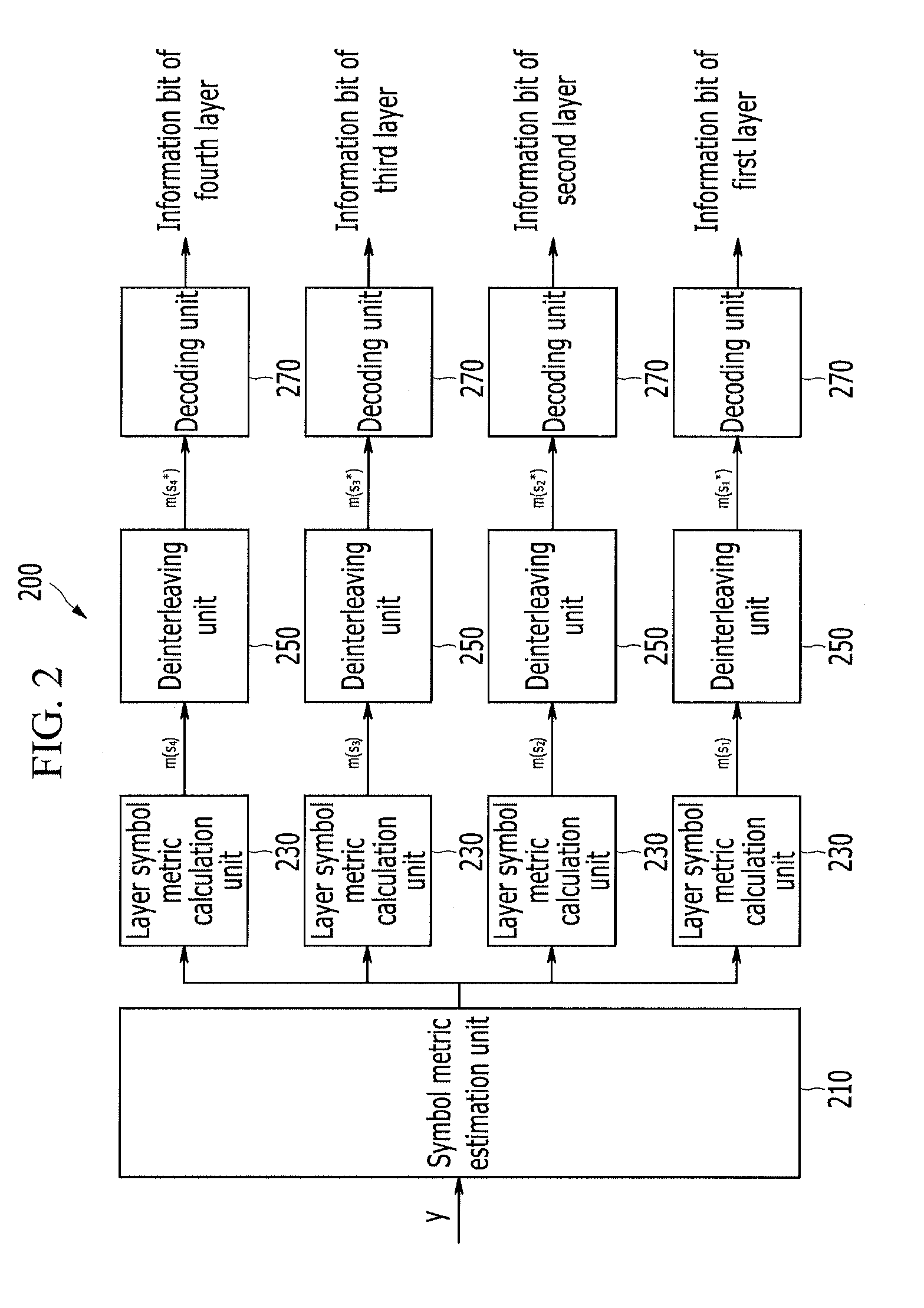

Layered transmission apparatus and method, reception apparatus, and reception method

InactiveUS20110194645A1Increase the number of layersReduce Interlayer InterferenceModulated-carrier systemsPulse demodulatorComputer architectureSymbol interleaving

A layered transmission apparatus for transmitting information regarding a plurality of layers includes: a plurality of coding units, which correspond to each of the plurality of layers, configured to code an information bit of a corresponding layer to generate code bits; a plurality of symbol interleaving units, which correspond to each of the plurality of coding units, configured to symbol-interleave the code bit of a corresponding coding unit to generate an interleaved symbol; a modulation unit configured to classify the plurality of layers into a plurality of layer groups, and modulate the interleaved symbol corresponding to each of the layer groups to generate a modulation symbol of each of the layer groups; a gain control unit configured to control the gain of the modulation symbol of each of the layer groups; and an adding unit configured to add the gain-controlled modulation symbols of the plurality of layer groups to generate a transmission symbol.

Owner:ELECTRONICS & TELECOMM RES INST

Apparatus and method for receiving data in a wireless communication system using bit interleaving, symbol interleaving and symbol mapping

InactiveUS7945001B2Increased complexityIncrease power consumptionTime-division multiplexAmplitude-modulated carrier systemsFast Fourier transformCommunications system

An apparatus and method are provided for receiving data generated by sequentially performing bit interleaving, symbol interleaving and symbol mapping in a wireless communication system. A fast Fourier transform (FFT) processor receives in-phase / quadrature phase (I / Q) data of a radio channel generated by sequentially performing bit interleaving, symbol interleaving and symbol mapping, and performs an FFT process for the I / Q data. A symbol deinterleaver performs a process for symbol deinterleaving the FFT I / Q data and reference values to be used for symbol demapping of the I / Q data and outputs the symbol-deinterleaved I / Q data and reference values. A symbol demapper performs a process for symbol demapping the symbol-deinterleaved I / Q data according to the reference values. A bit deinterleaver performs a process for bit deinterleaving the symbol-demapped data. A demultiplexer demultiplexes the bit-deinterleaved data.

Owner:SAMSUNG ELECTRONICS CO LTD

Transmitting device and method of digital broadcasting system with improved internal rondam mechanism

InactiveCN1491035AIncrease randomnessImprove error correction coding performanceCode conversionCyclic codesDigital audio broadcastingSymbol interleaving

A transmission device of a digital broadcasting system having an inner interleaver with an improved structure is provided to perform a bit interleaving process by a convolution interleaving method, and to carry out a symbol interleaving process by using an optional random lookup table, thereby improving randomized properties of an inner interleaver. The first and second RS encoders(12,22) RS(Read-Solomon)-encode the first and second TSs(Transport Streams). The first and second outer interleavers(14,24) re-array data encoded in the first and second RS encoders(12,22), respectively. The first and second convolution encoders(16,26) convolution-encode the re-arrayed data, respectively. An inner interleaver(30) consists of a bit interleaver(31) and a symbol interleaver(33). The bit interleaver(31) re-arrays the encoded data in bit unit by the convolution encoders(16,26). The symbol interleaver(33) re-arrays the data in symbol unit by a predetermined interleaving address of a lookup table. A modulator portion(50) digitally modulates the re-arrayed data, and transmits the modulated data.

Owner:SAMSUNG ELECTRONICS CO LTD

Digital broadcasting system transmitter and method

InactiveCN1491038AIncrease randomnessImprove error correction coding performanceTelevision system detailsCode conversionSymbol interleavingLookup table

A transmission device of a digital broadcasting system having an inner interleaver with an improved structure is provided to perform a bit interleaving process by a convolution interleaving method, and to carry out a symbol interleaving process by using an optional random lookup table, thereby improving randomized properties of an inner interleaver. The first and second RS encoders(12,22) RS(Read-Solomon)-encode the first and second TSs(Transport Streams). The first and second outer interleavers(14,24) re-array data encoded in the first and second RS encoders(12,22), respectively. The first and second convolution encoders(16,26) convolution-encode the re-arrayed data, respectively. An inner interleaver(30) consists of a bit interleaver(31) and a symbol interleaver(33). The bit interleaver(31) re-arrays the encoded data in bit unit by the convolution encoders(16,26). The symbol interleaver(33) re-arrays the data in symbol unit by a predetermined interleaving address of a lookup table. A modulator portion(50) digitally modulates the re-arrayed data, and transmits the modulated data.

Owner:SAMSUNG ELECTRONICS CO LTD

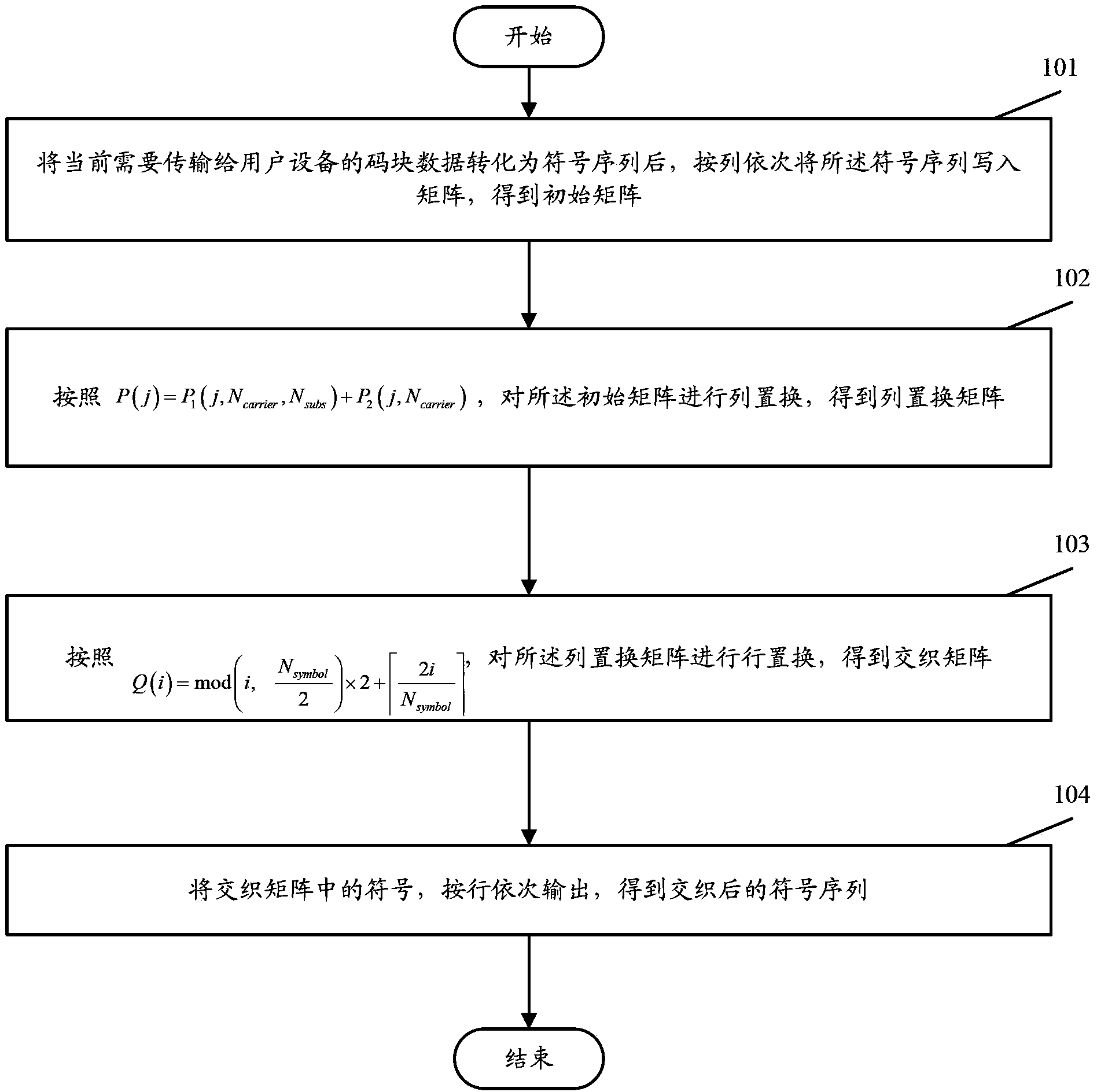

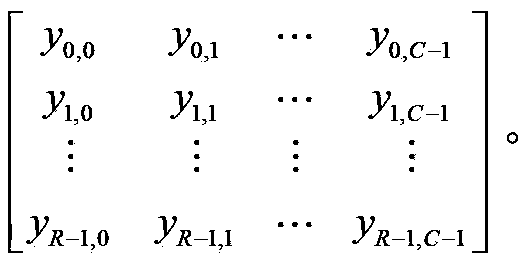

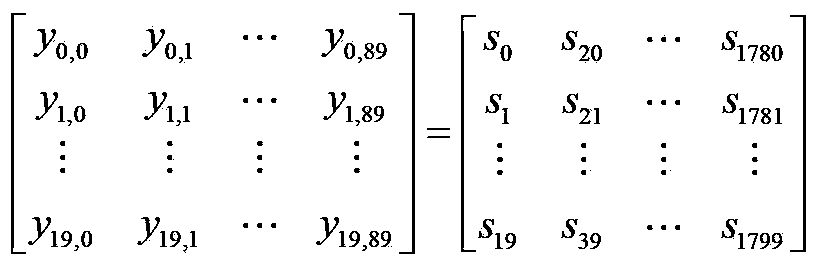

Symbol interleaving method

InactiveCN104243382AAnti-interferenceImprove decoding accuracyMulti-frequency code systemsTransmission path multiple useAlgorithmSymbol interleaving

The invention discloses a symbol interleaving method. The symbol interleaving method includes the steps that after current data needing to be transmitted to user equipment are converted into symbol sequences, the symbol sequences are sequentially written into a matrix by columns to obtain an initial matrix, wherein the row number R of the initial matrix is an OFDM symbolic number Nsymbol corresponding to the symbol sequences, and the column number C of the initial matrix is the product of the number Ncarrier of subcarriers occupied by OFDM symbols and the number Nsubs of sub-bands occupied by the symbol sequences; according to the formula: P(j)=P1(j, Ncarrier, Nsubs)+P2(j, Ncarrier), column permutation is carried out on the initial matrix to obtain a column permutation matrix, wherein P(j) is the column number of the j column, in the initial matrix, of the column permutation matrix, P1(j, Ncarrier, Nsubs)=pi (mod (j, Ncarrier)) * Nsubs, pi() is a preset permutation function, P2(j, Ncarrier) meets a formula (please see the formula in the specification), and according to a formula (please see the formula in the specification), permutation is carried out on the column permutation matrix to obtain an interleaved matrix, wherein Q(i) is the row number of the i row, in the column permutation matrix, of the interleaved matrix; symbols in the interleaved matrix are sequentially output by rows to obtain interleaved symbol sequences. The symbol interleaving method is suitable for the LTE 230 system.

Owner:POTEVIO INFORMATION TECH