Patents

Literature

7604results about "Printed element electric connection formation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

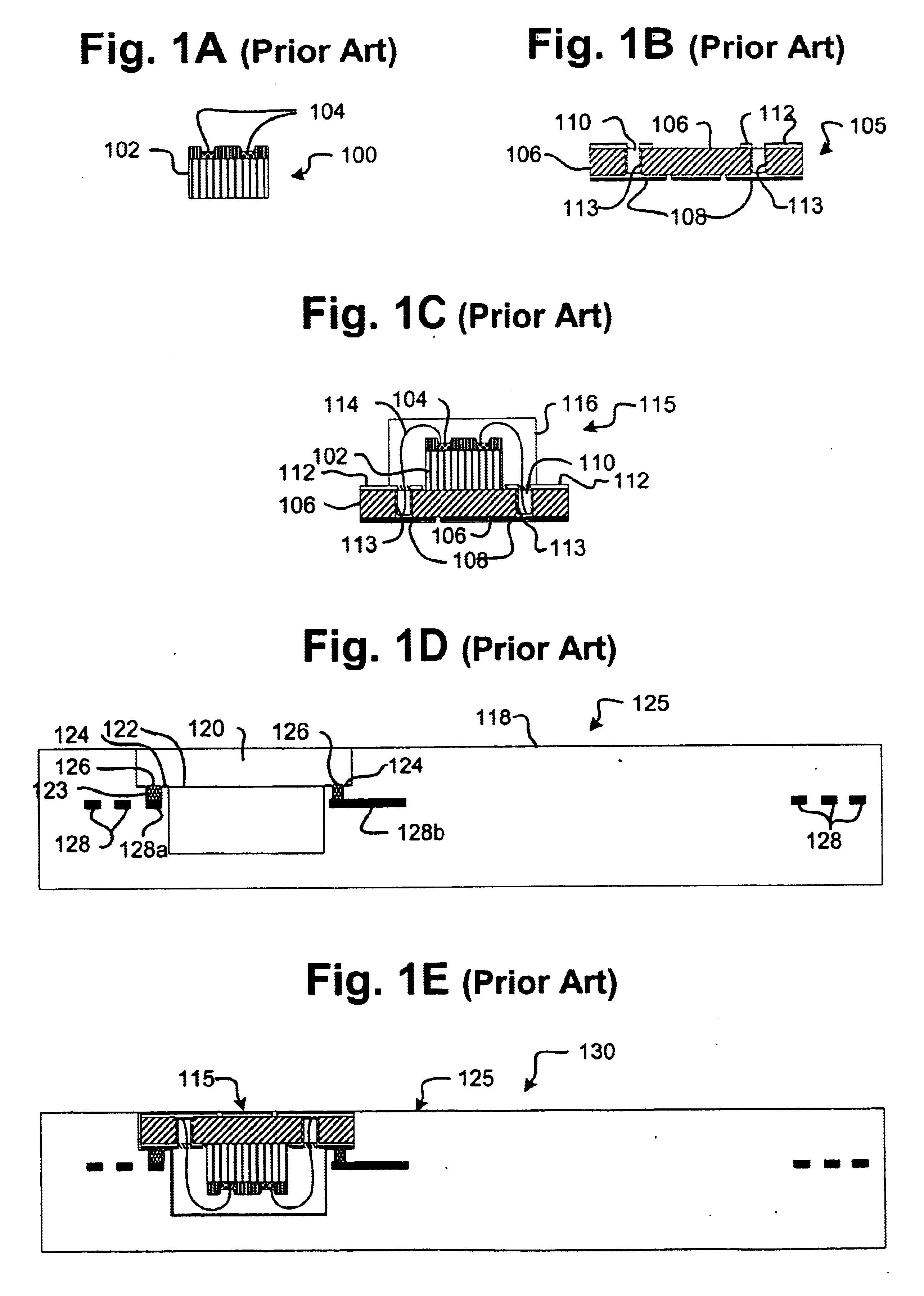

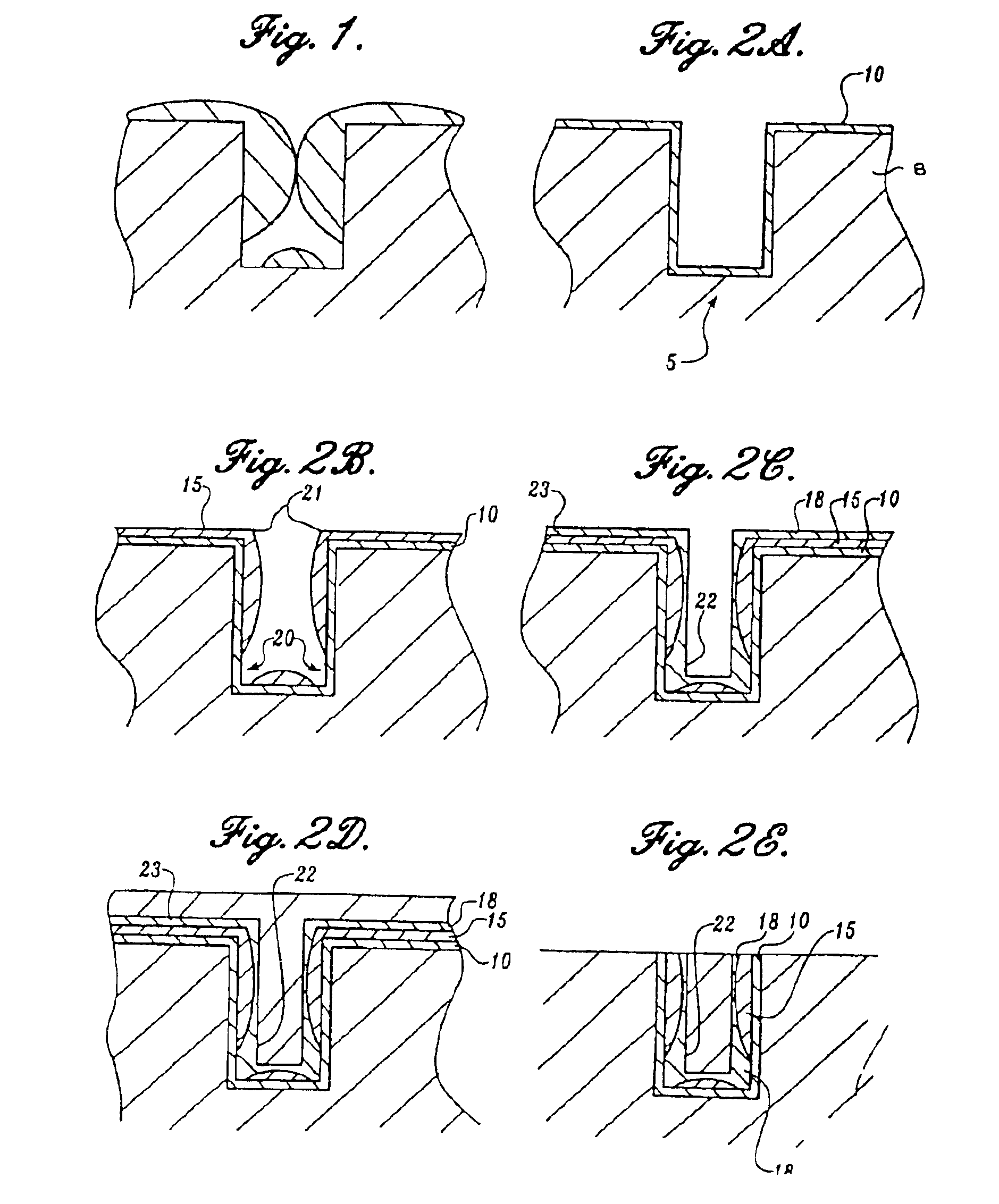

Method of manufacturing a semiconductor package

InactiveUS7185426B1Printed circuit assemblingSemiconductor/solid-state device detailsElectrical conductorSemiconductor package

A semiconductor package including top-surface terminals for mounting another semiconductor package provides a three-dimensional circuit configuration that can provide removable connection of existing grid-array packages having a standard design. A semiconductor die is mounted on an electrically connected to a circuit substrate having terminals disposed on a bottom side for connection to an external system. The die and substrate are encapsulated and vias are laser-ablated or otherwise formed through the encapsulation to terminals on the top surface of the substrate that provide a grid array mounting lands to which another grid array semiconductor package may be mounted. The bottom side of the vias may terminate and electrically connect to terminals on the substrate, terminals on the bottom of the semiconductor package (through terminals) or terminals on the top of the semiconductor die. The vias may be plated, paste-filled, filled with a low melting point alloy and may have a conical profile for improved plating performance.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

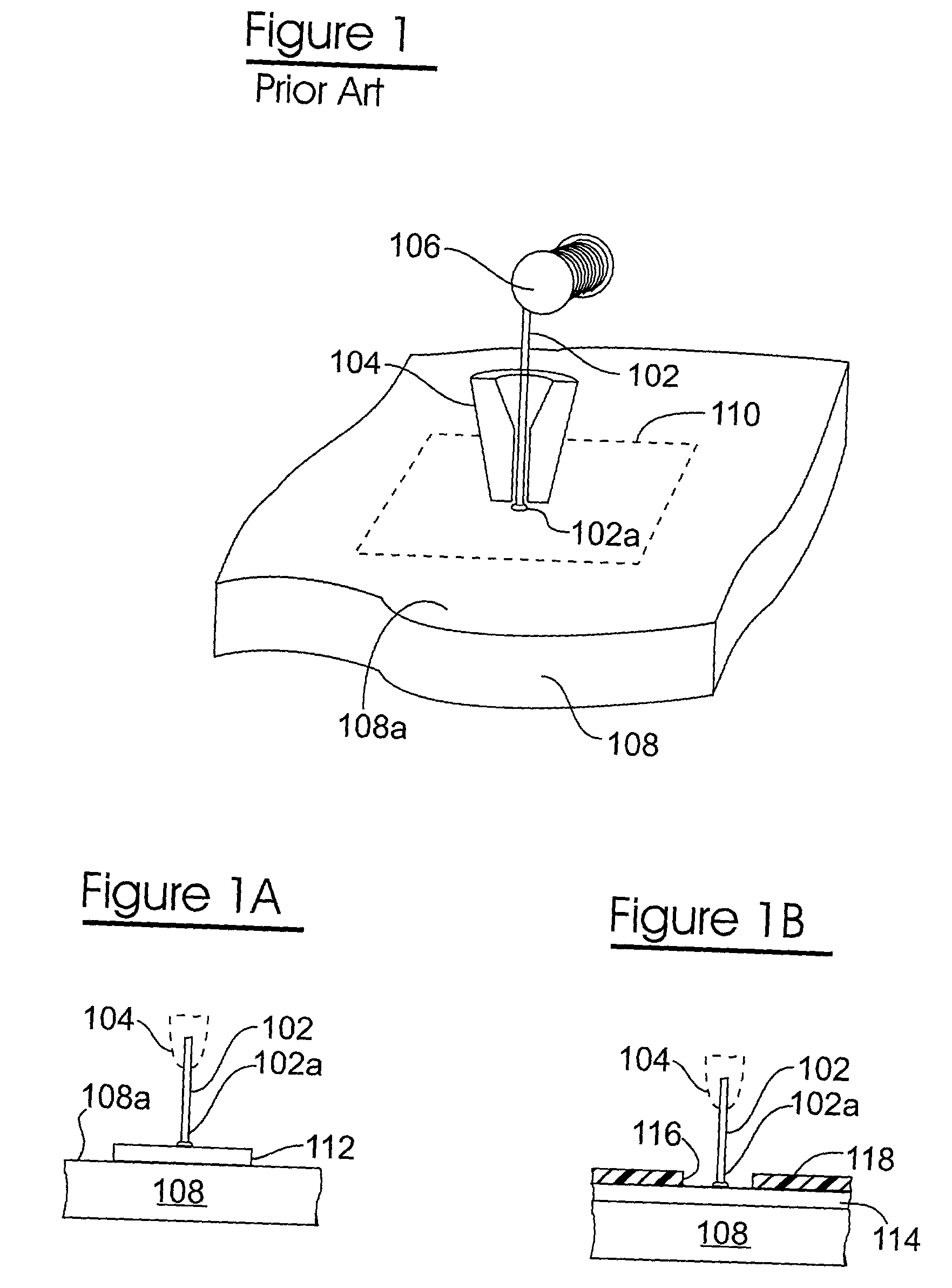

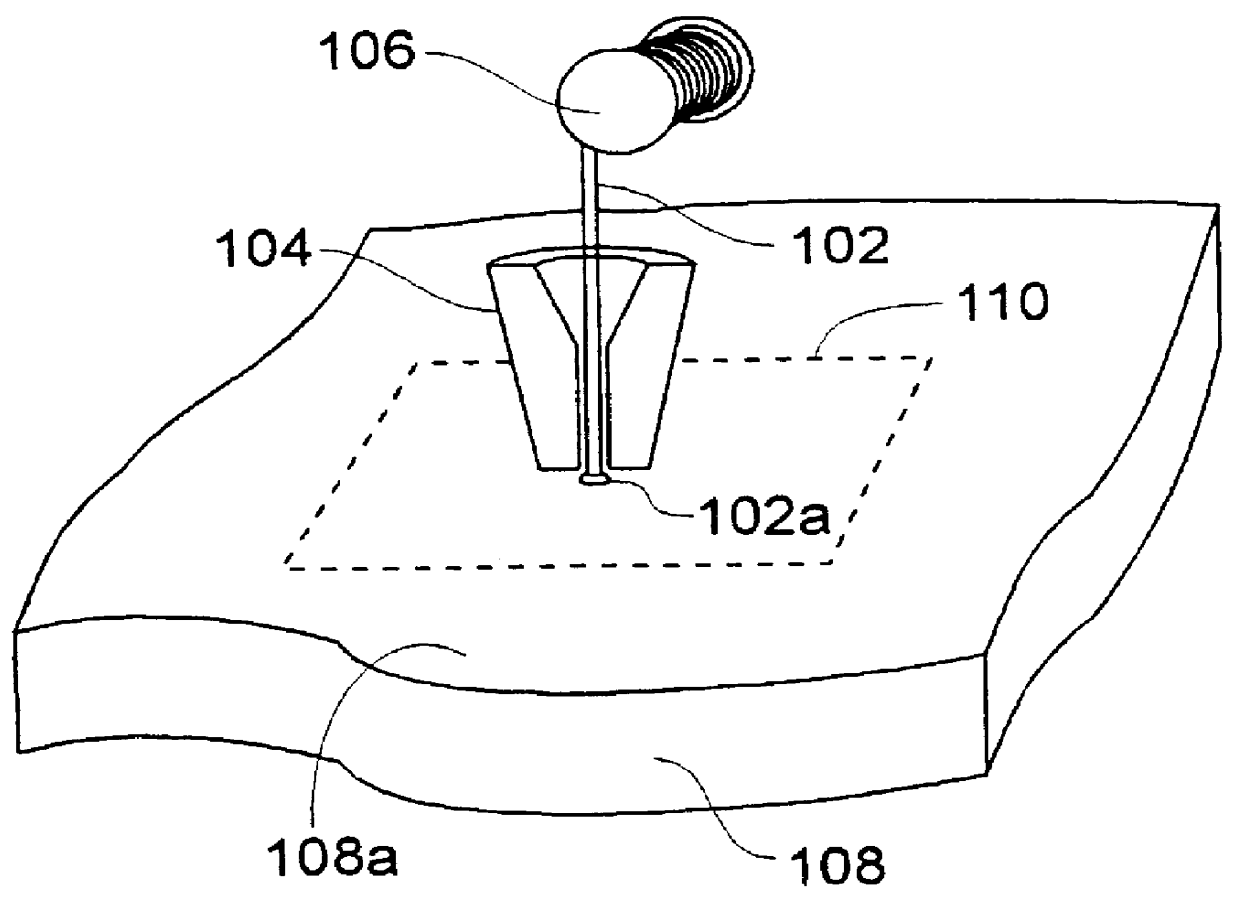

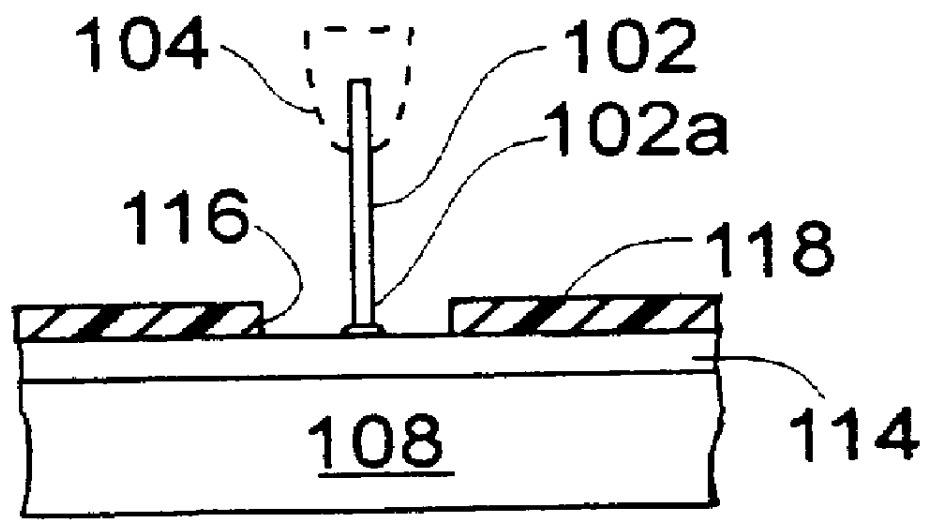

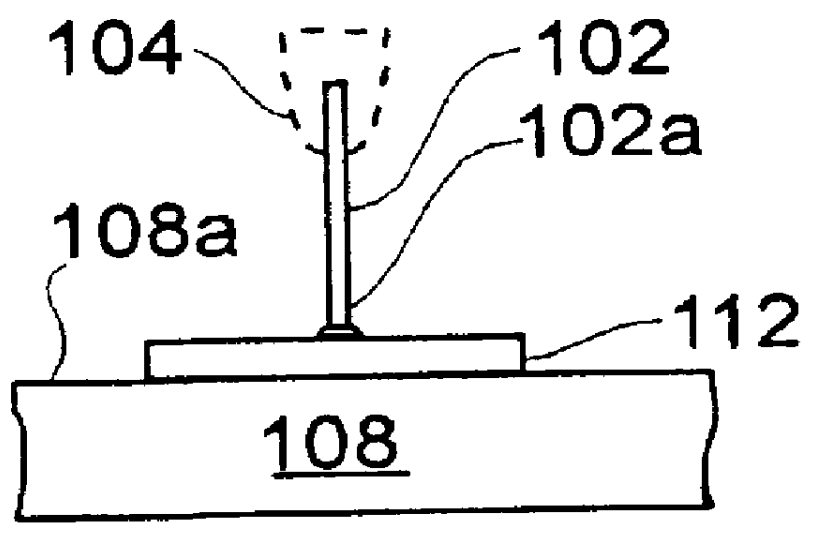

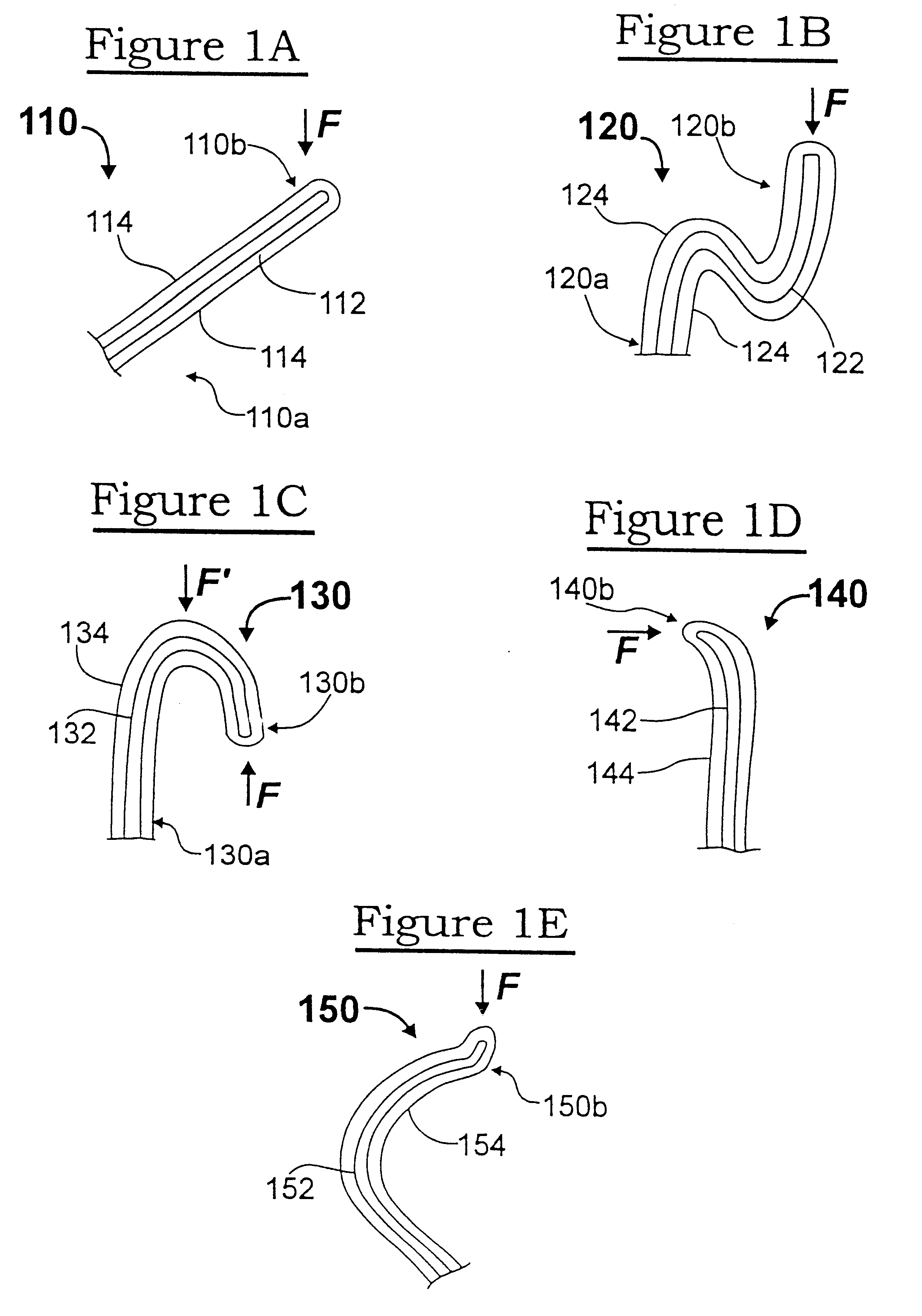

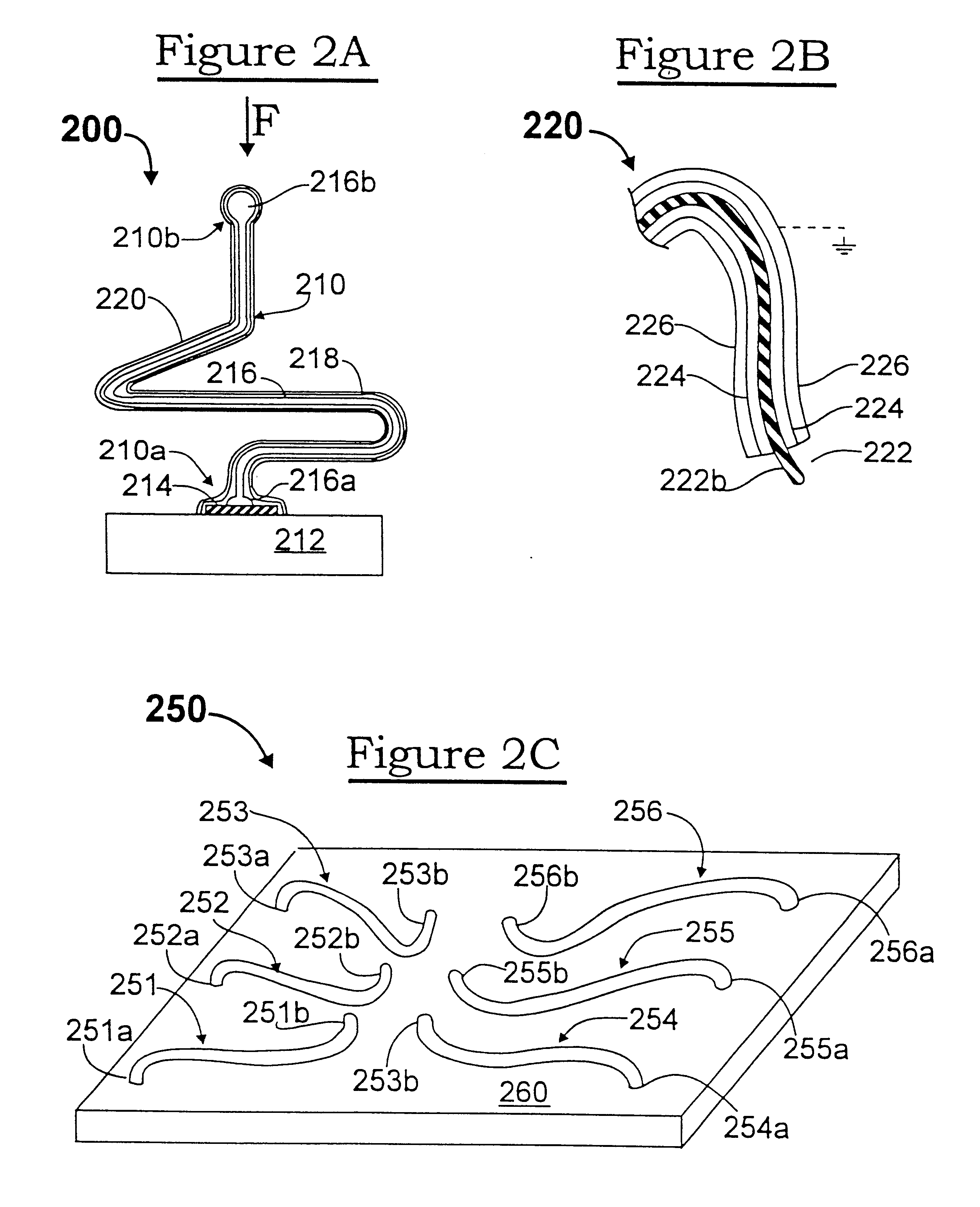

Resilient contact structures formed and then attached to a substrate

InactiveUS20020117330A1Simple technologyCoupling device connectionsSemiconductor/solid-state device testing/measurementEngineeringTopography

Owner:FORMFACTOR INC

High reliability multlayer circuit substrates and methods for their formation

InactiveUS20040061234A1Semiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorOptoelectronics

A multilayer circuit substrate for multi-chip modules or hybrid circuits includes a dielectric base substrate, conductors formed on the base substrate and a vacuum deposited dielectric thin film formed over the conductors and the base substrate. The vacuum deposited dielectric thin film is patterned using sacrificial structures formed by shadow mask techniques. Substrates formed in this manner enable significant increases in interconnect density and significant reduction of over-all substrate thickness.

Owner:MEDTRONIC MIMIMED INC

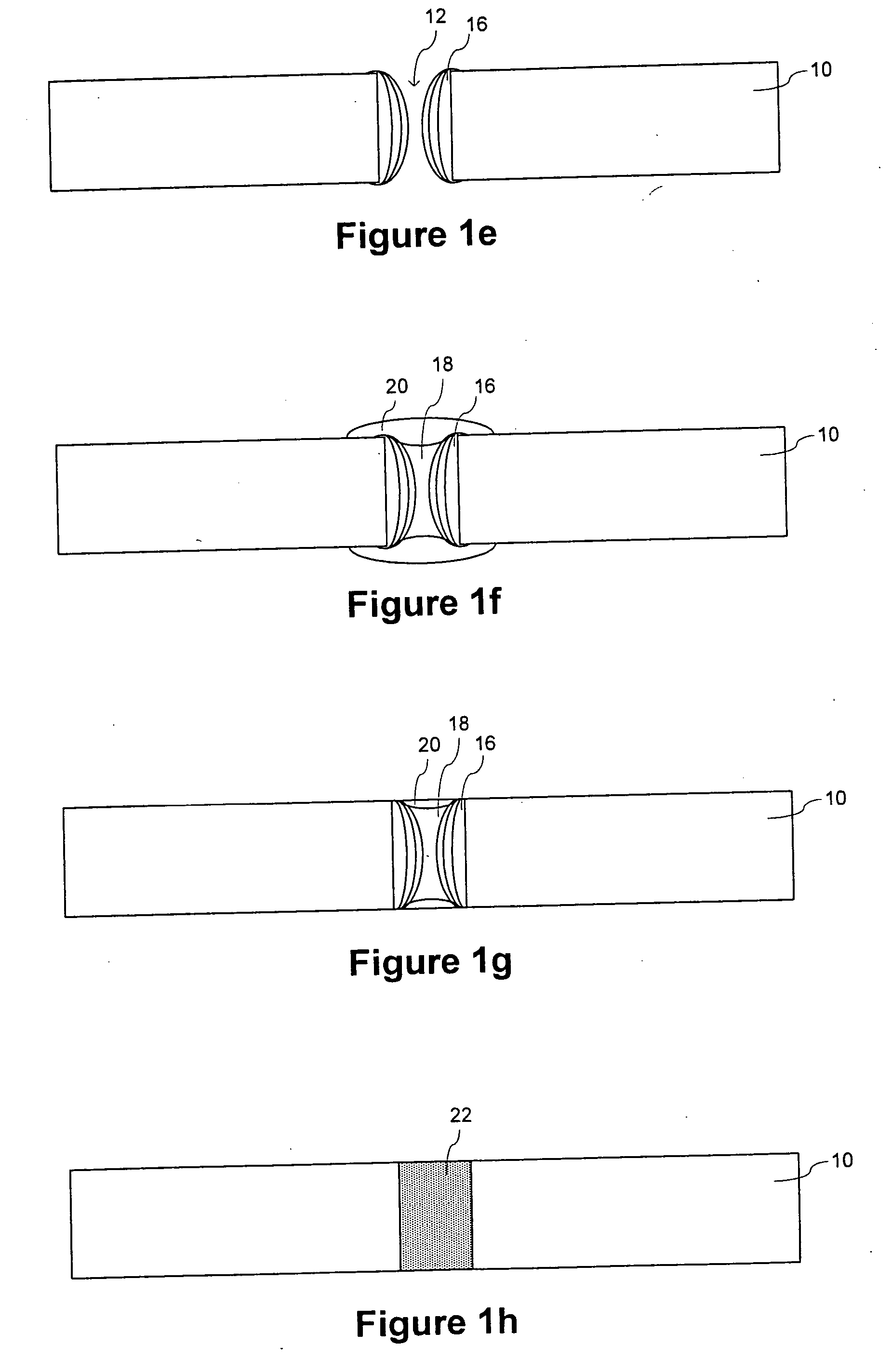

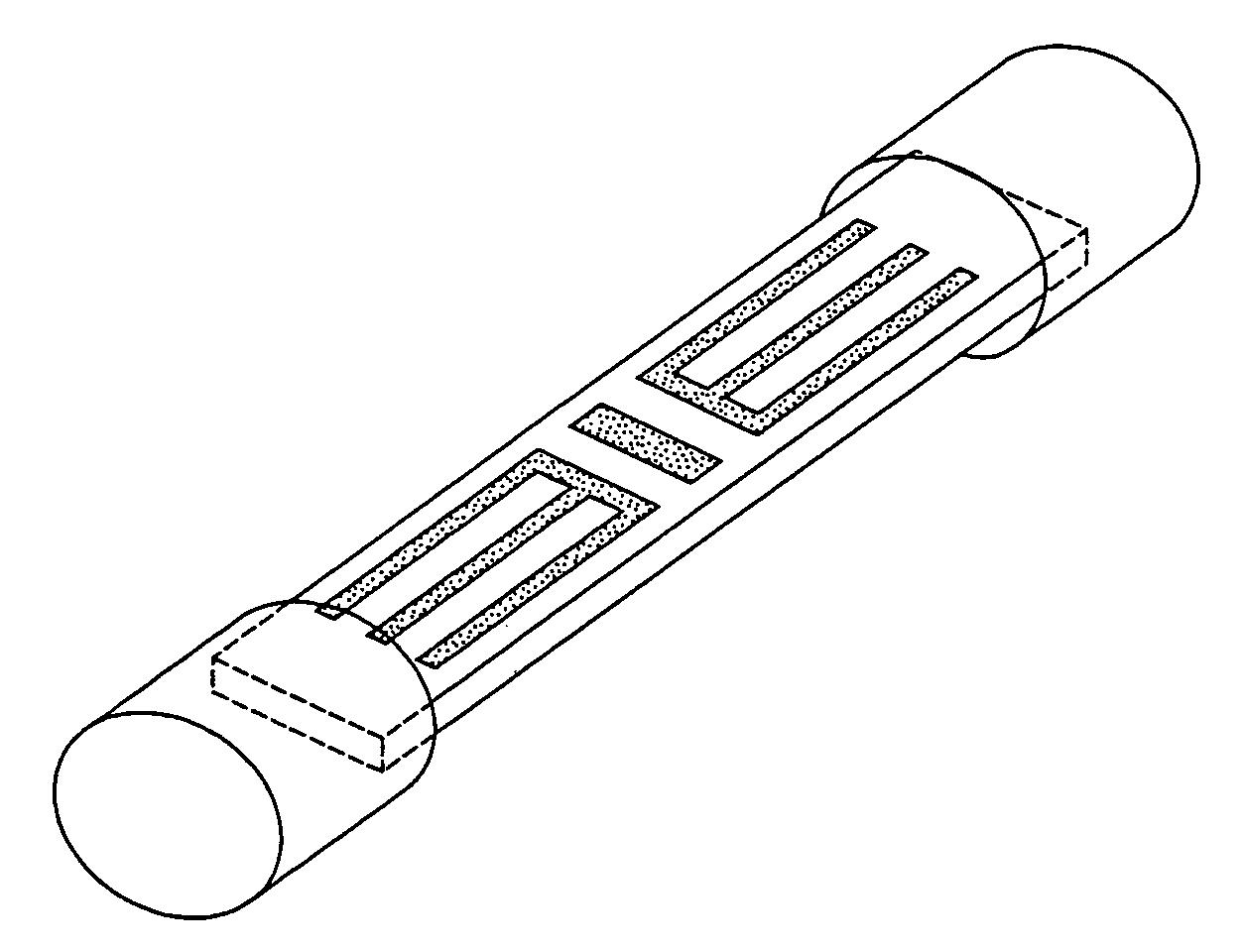

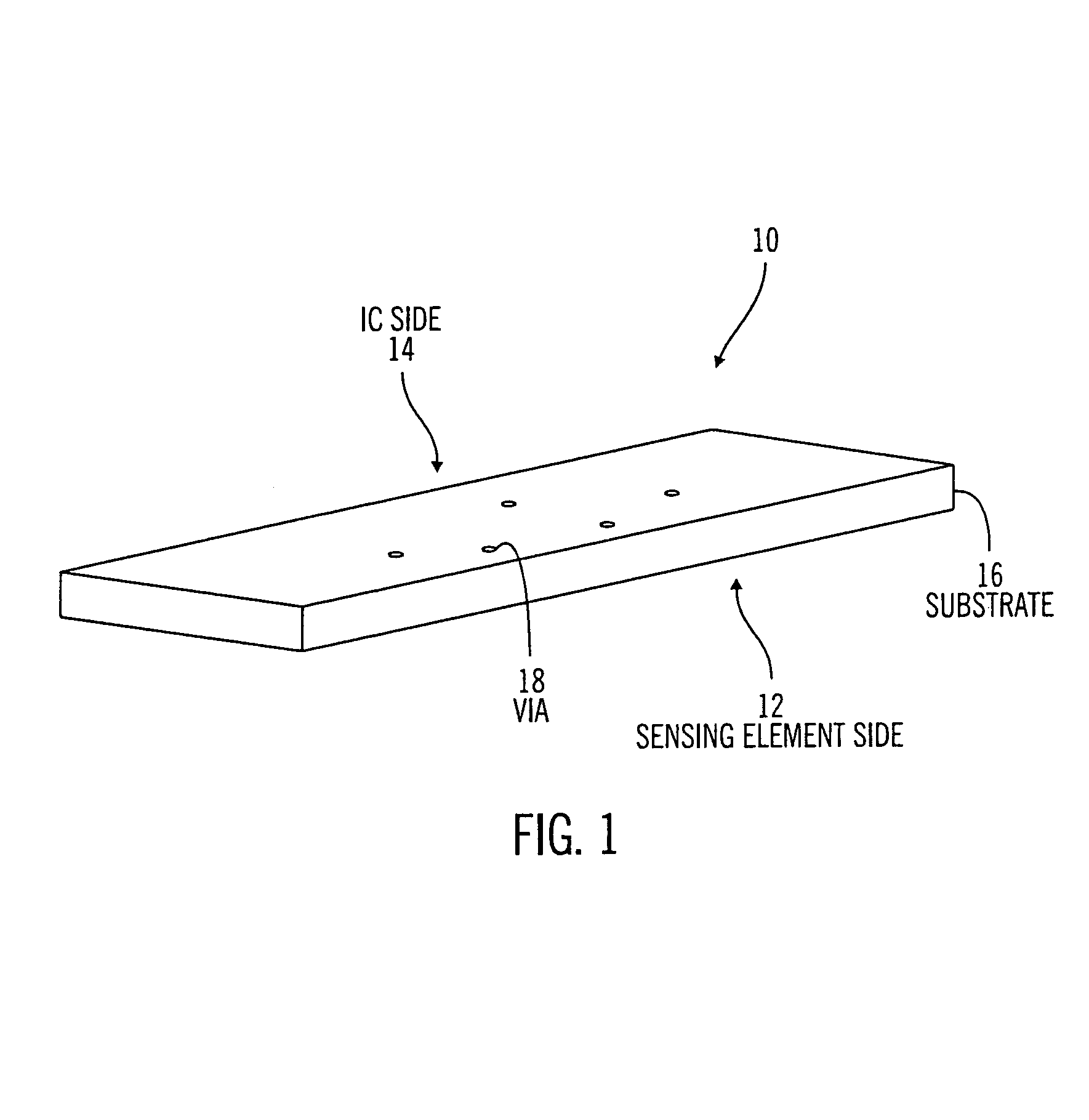

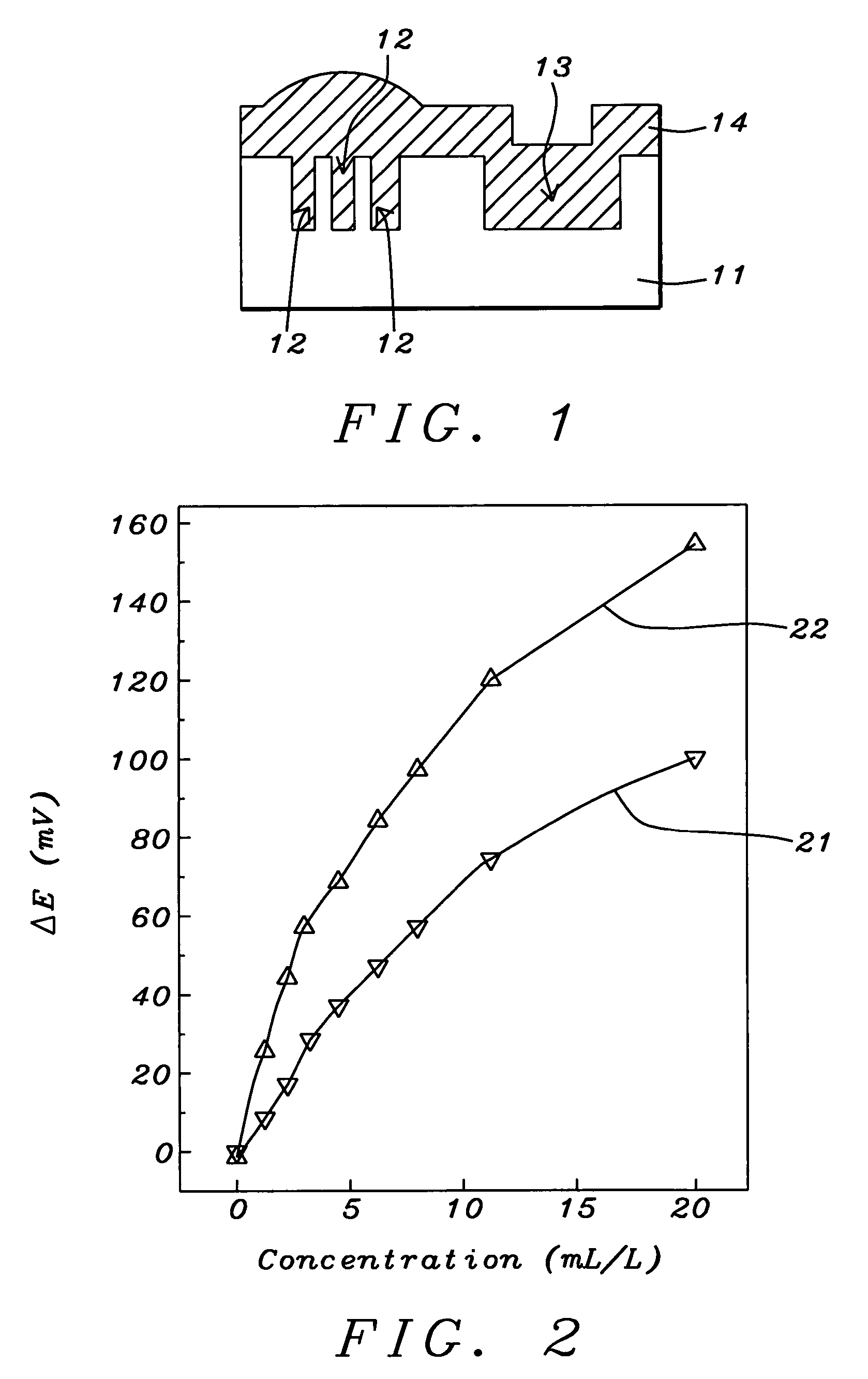

Sensor substrate and method of fabricating same

A substrate with hermetically sealed vias extending from one side of the substrate to another and a method for fabricating same. The vias may be filled with a conductive material such as, for example, a fritless ink. The conductive path formed by the conductive material aids in sealing one side of the substrate from another. One side of the substrate may include a sensing element and another side of the substrate may include sensing electronics.

Owner:MEDTRONIC MIMIMED INC

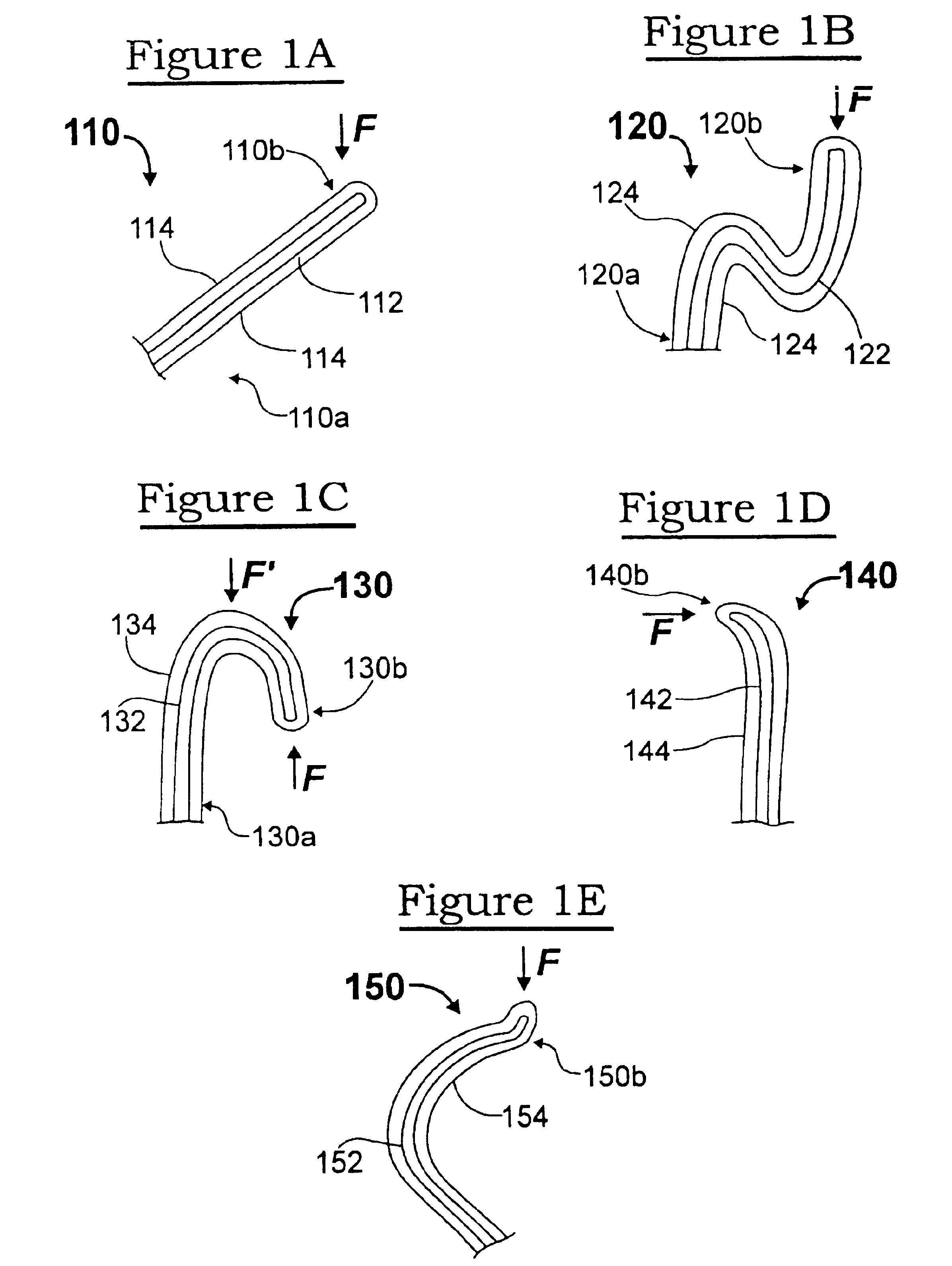

Method of modifying the thickness of a plating on a member by creating a temperature gradient on the member, applications for employing such a method, and structures resulting from such a method

InactiveUS6110823ASimple technologyTrend downSemiconductor/solid-state device testing/measurementFinal product manufactureEngineeringElectronic component

Contact structures exhibiting resilience or compliance for a variety of electronic components are formed by bonding a free end of a wire to a substrate, configuring thw wire into a wire stem having a springable shape, serving thw wire stem, and overcoating the wire stem with at least one layer of a material chosen primarily for its structural (resiliency, compliance) characteristics. A variety of techniques for configuring, serving, and overcoating the wire stem are disclosed. In an exemplary embodiment, a free end of a wire stem is bonded to a contact area on a substrate, the wire stem is configured to ahve a springable shape, the wire stem is served to be free-standing by an electrical discharge, and the free-standing wire stem is overcoating by plating.

Owner:FORMFACTOR INC

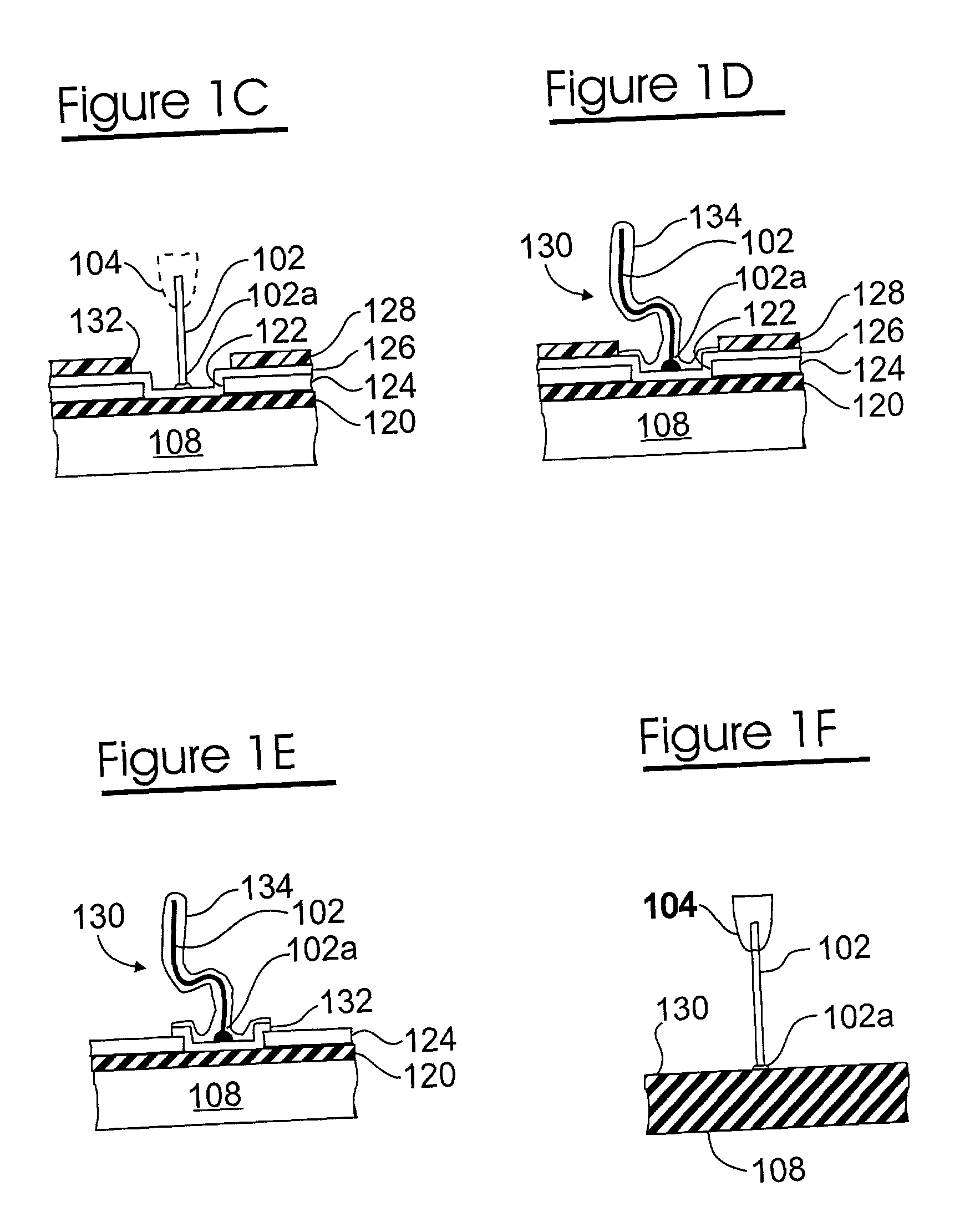

Component and antennae assembly in radio frequency identification devices

InactiveUS6853087B2Easy to produceAdditional componentPrinted circuit assemblingSemiconductor/solid-state device detailsAdhesiveSmart card

Permanent physical and electrical attachment of electrically conductive contacts of a first component in a RFID device, such as a smart card or smart inlay, is made to the electrically conductive contacts of a second component of the device, for example, a conductive area, such as an antenna. Attachment is achieved by co-depositing metal and electrically conductive hard particles upon the conductive contacts of either the first or second components and then using a non-conductive adhesive to provide permanent bond between the components and their conductive contacts.

Owner:NANOPIERCE TECH

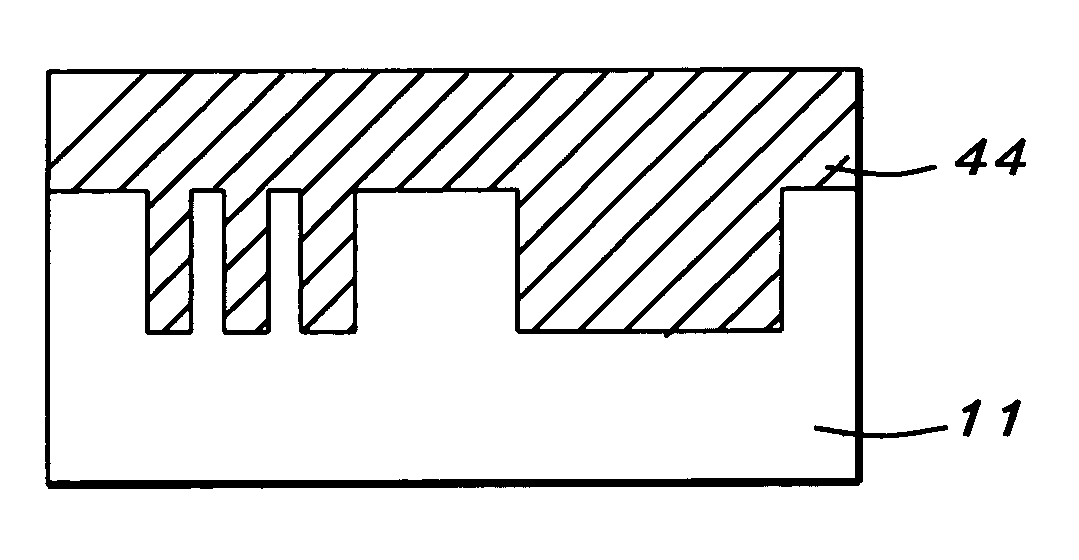

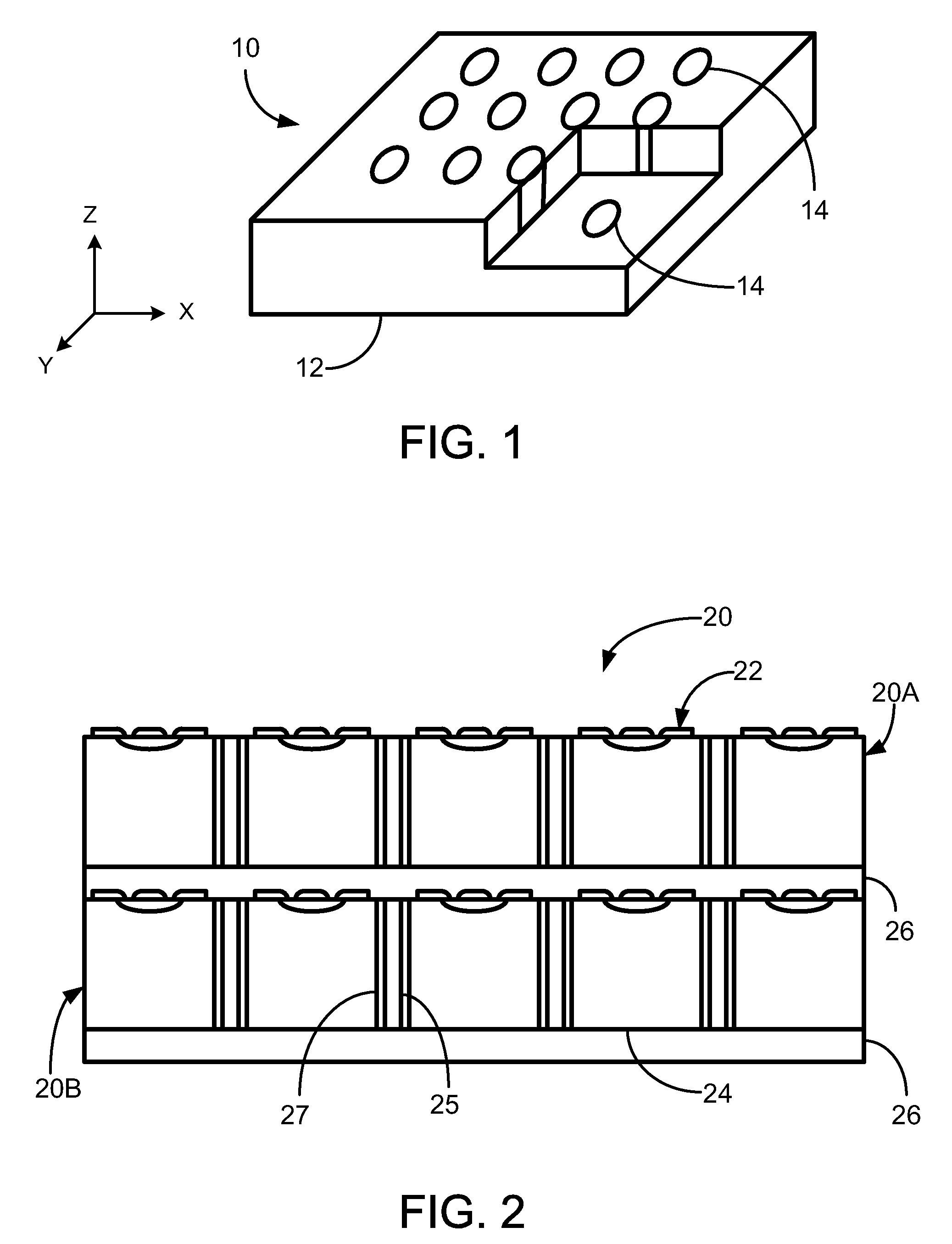

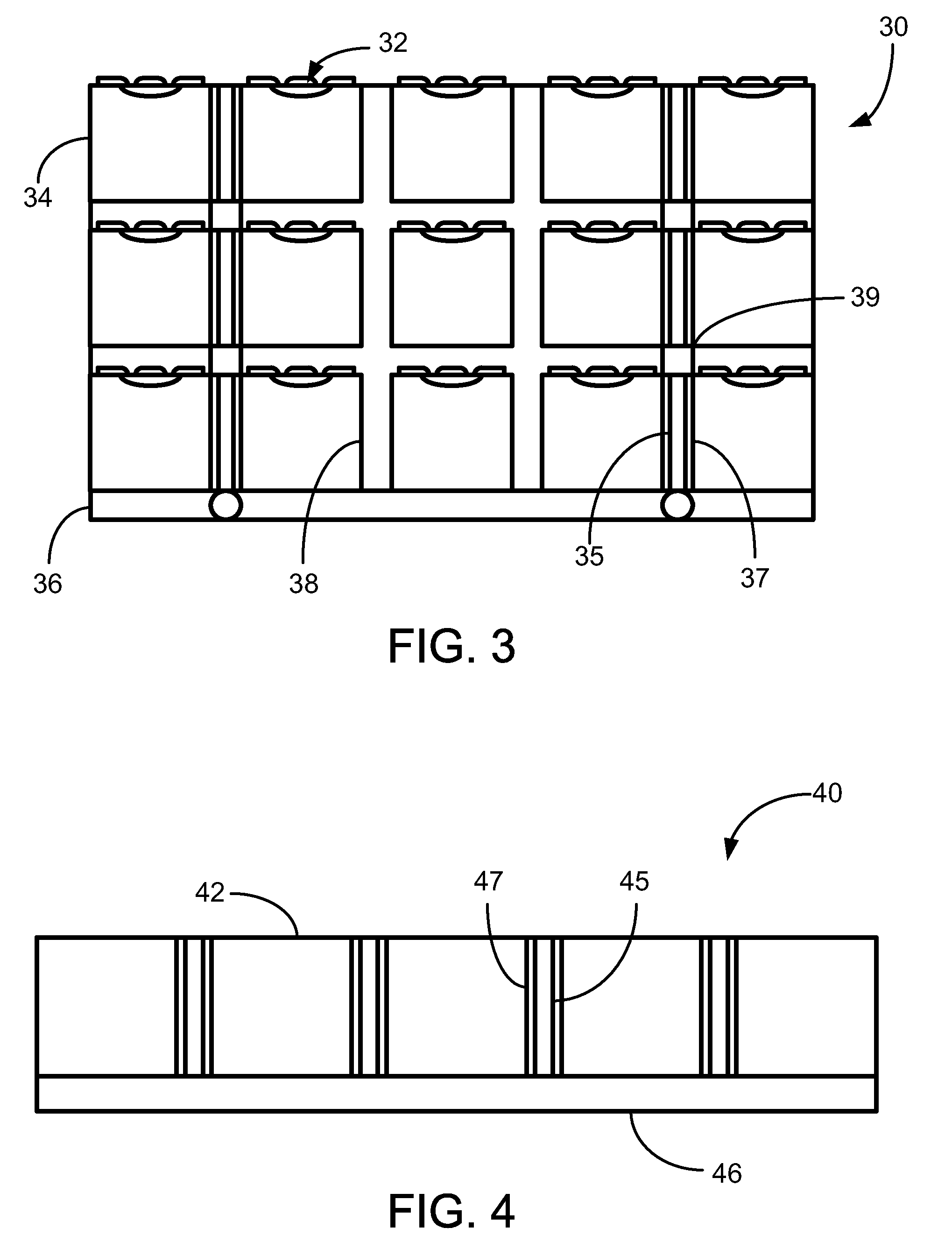

Integrated circuit substrate having laser-embedded conductive patterns and method therefor

InactiveUS6930256B1Printed electric component incorporationSemiconductor/solid-state device detailsScreen printingHigh density

An integrated circuit substrate having laser-embedded conductive patterns provides a high-density mounting and interconnect structure for integrated circuits. Conductive patterns within channels on the substrate provide interconnects that are isolated by the channel sides. A dielectric material is injection-molded or laminated over a metal layer that is punched or etched. The metal layer can provide one or more power planes within the substrate. A laser is used to ablate channels on the surfaces of the outer dielectric layer for the conductive patterns. The conductive patterns are electroplated or paste screen-printed and an etchant-resistive material is applied. Finally, a plating material can be added to exposed surfaces of the conductive patterns. An integrated circuit die and external terminals can then be attached to the substrate, providing an integrated circuit having a high-density interconnect.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

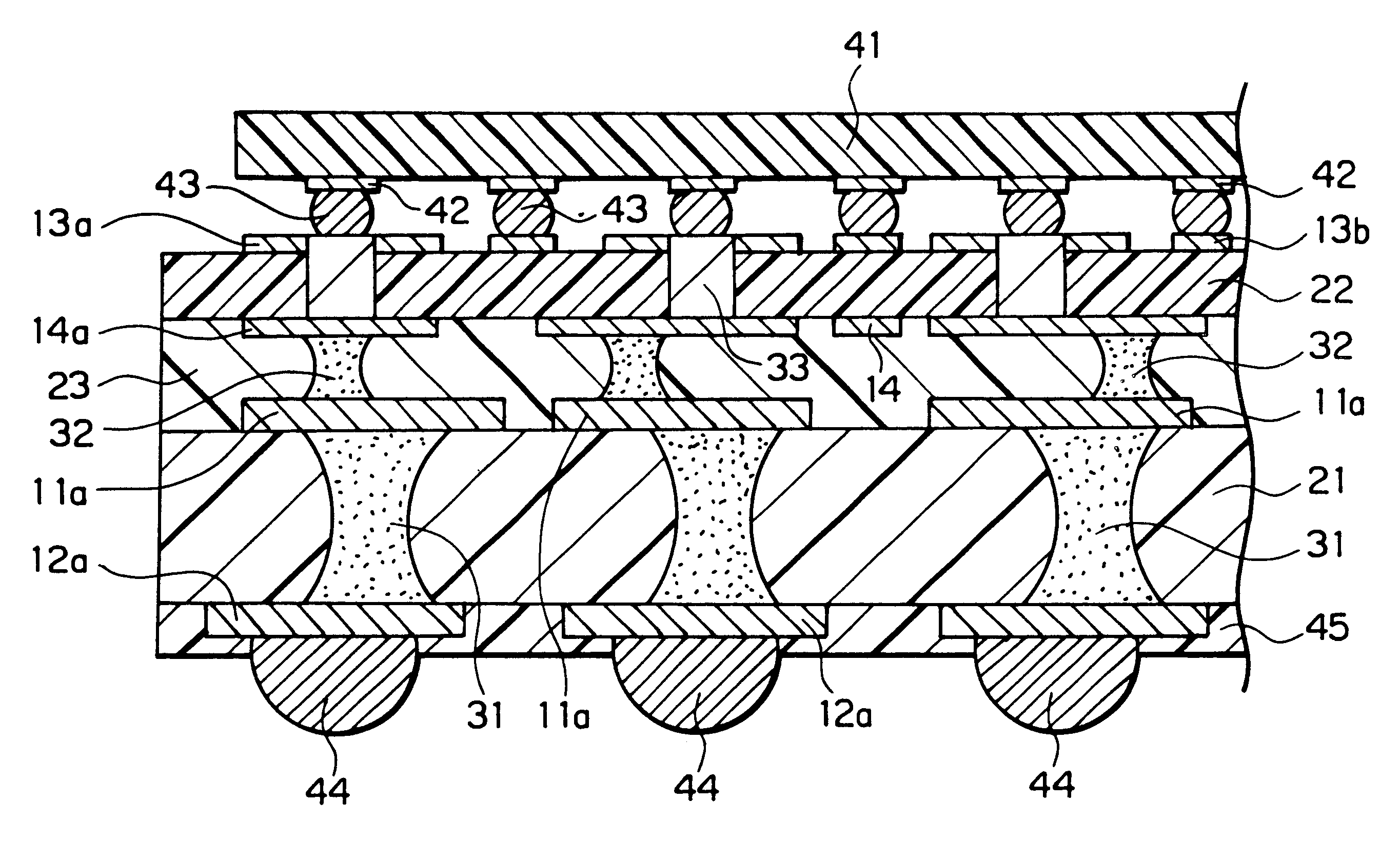

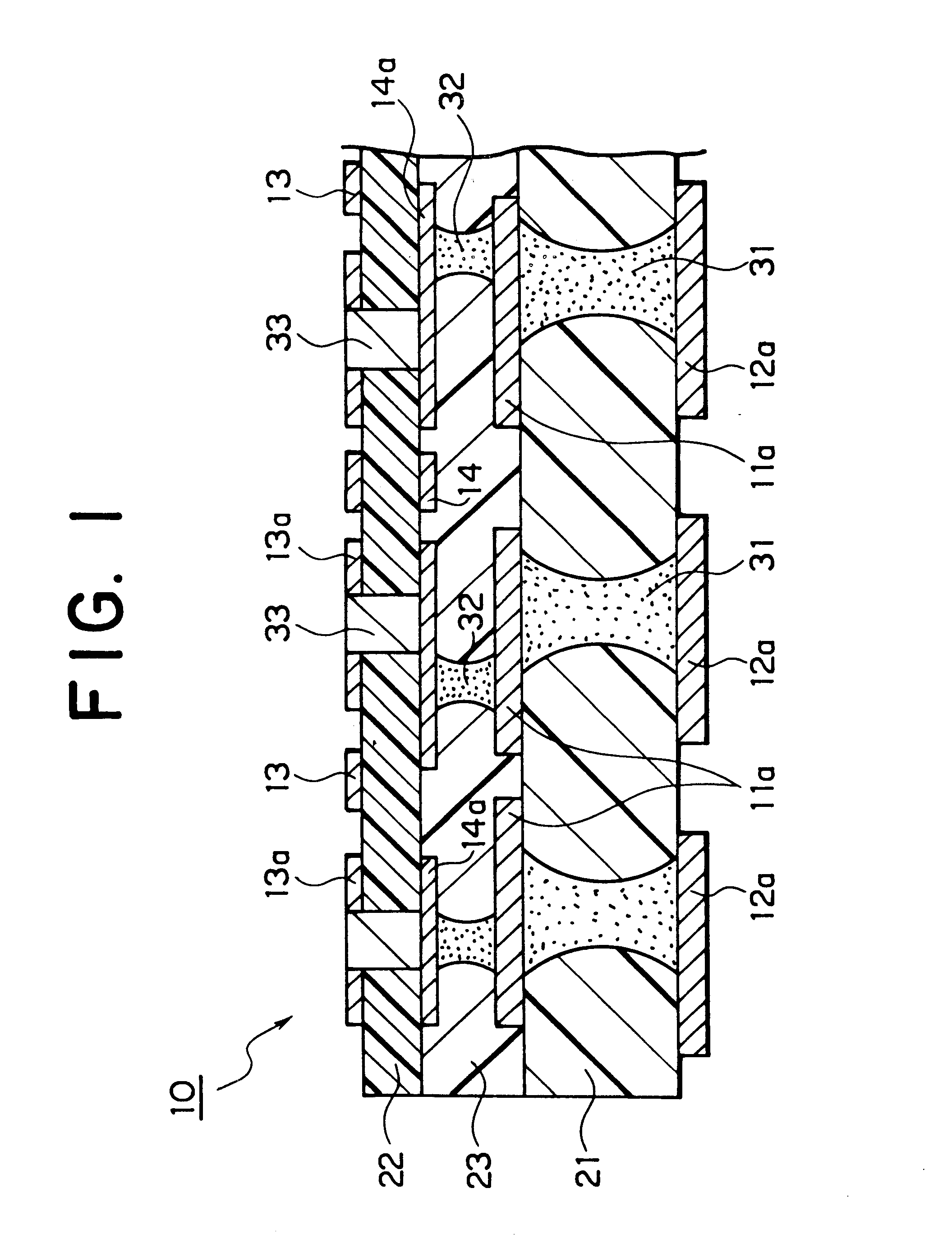

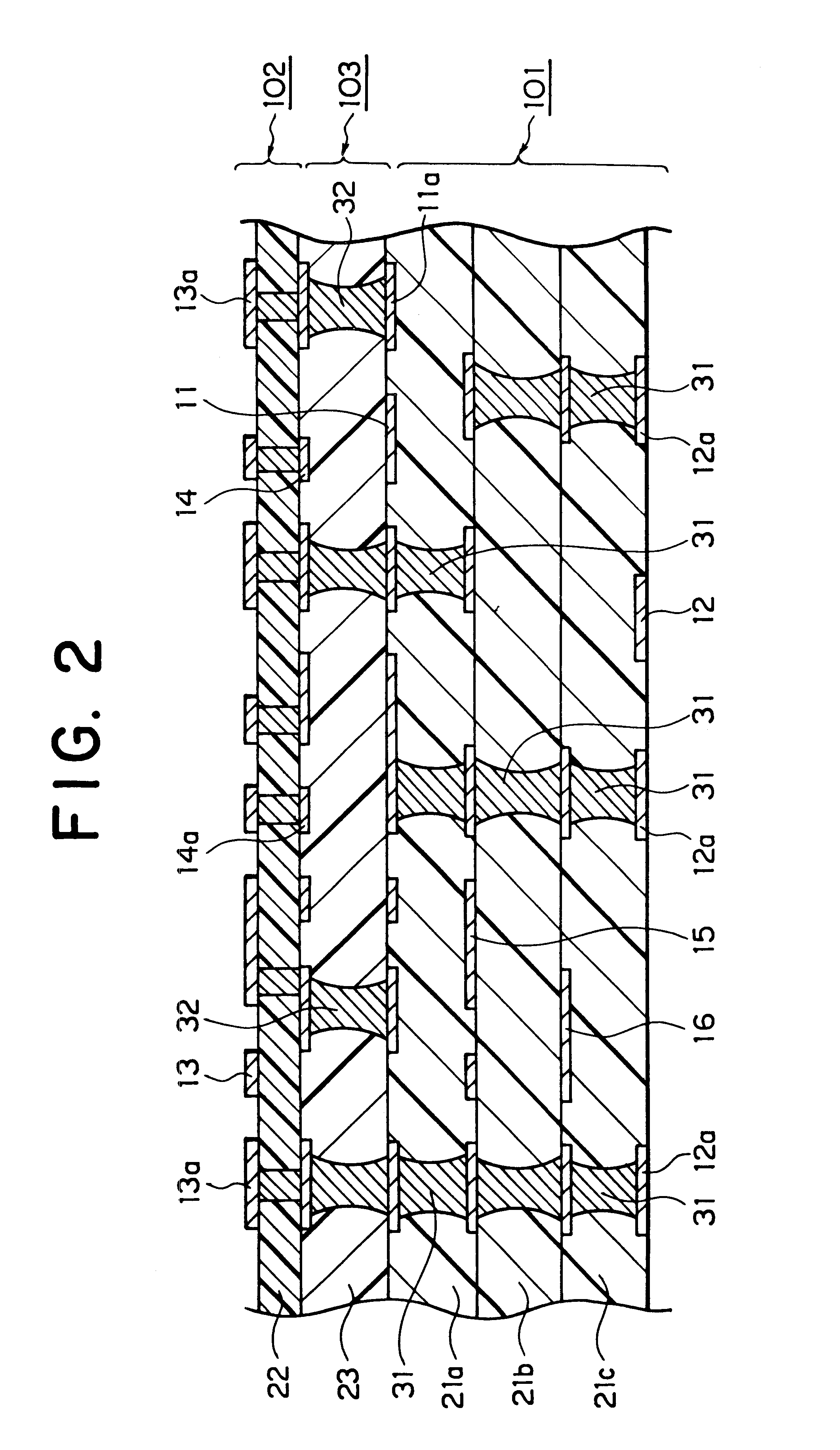

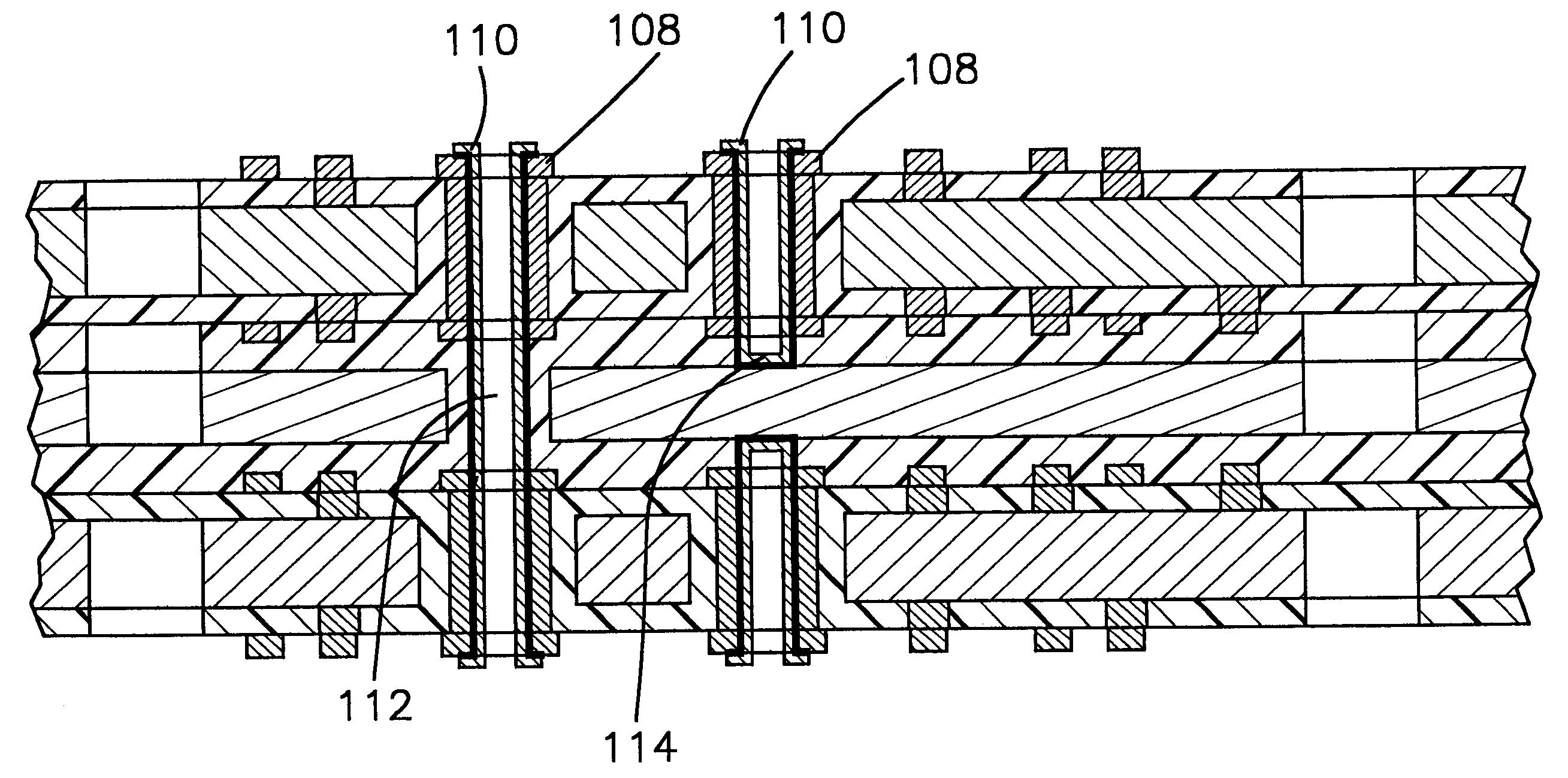

Hybrid wiring board, semiconductor apparatus, flexible substrate, and fabrication method of hybrid wiring board

InactiveUS6329610B1Semiconductor/solid-state device detailsPrinted electric component incorporationInsulation layerEngineering

A first via land of a wiring layer on a first surface of a first insulation layer that is a rigid layer and a second via land of a wiring layer on a second surface of a second insulation layer that is a flexible layer are electrically and mechanically connected with a conductive pillar pierced through a third insulation layer disposed between the first insulation layer and the second insulation layer. In such a structure, a wiring board that can mount a highly integrated semiconductor device, that is small and thin, and that has high reliability can be accomplished.

Owner:KK TOSHIBA

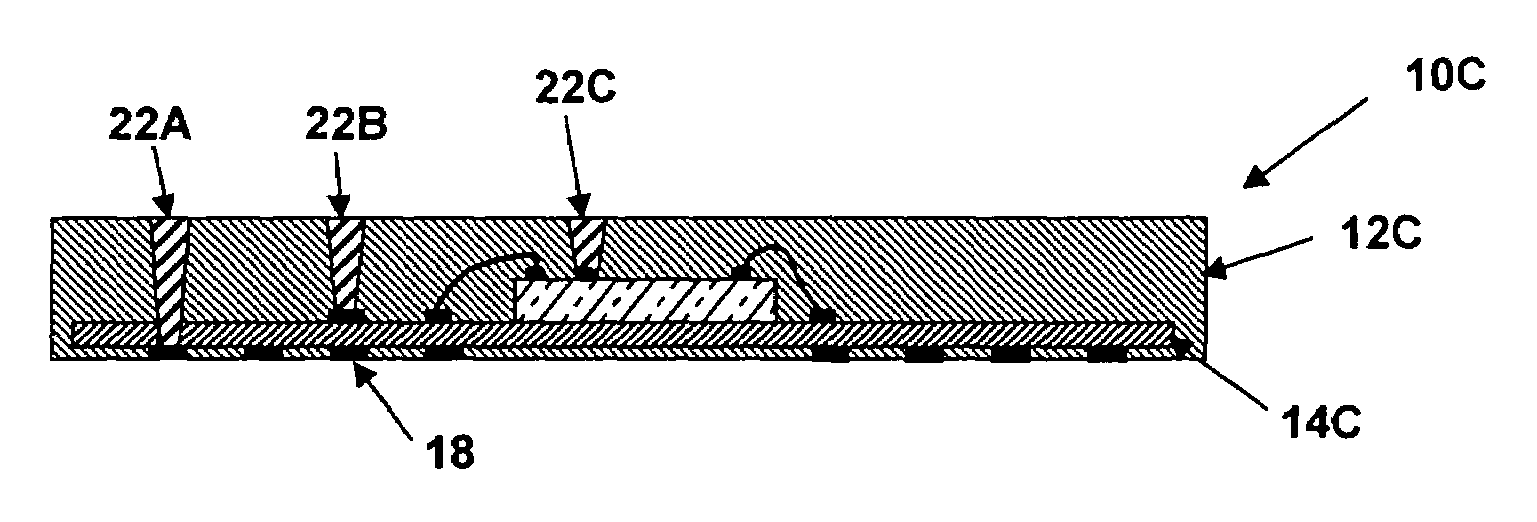

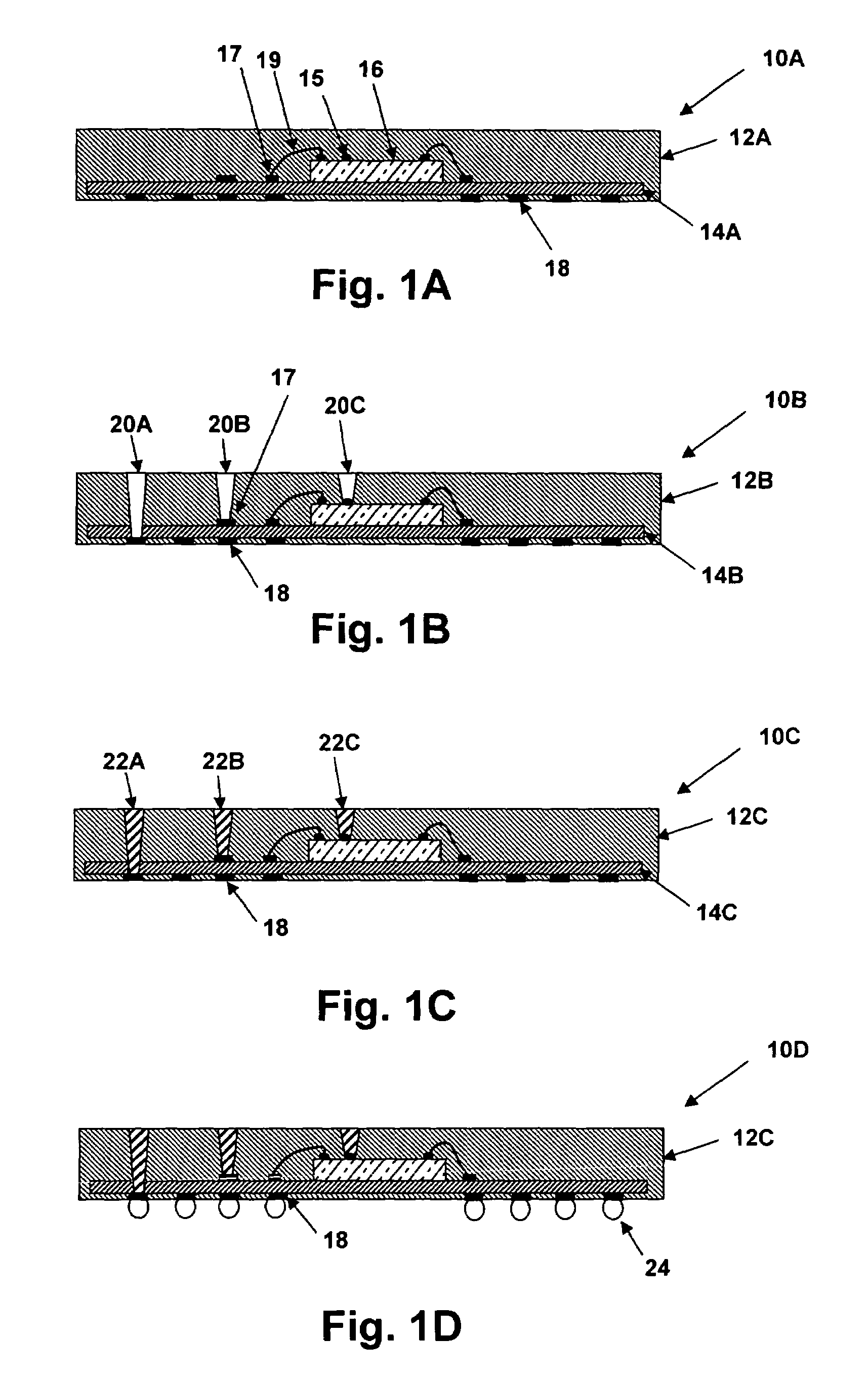

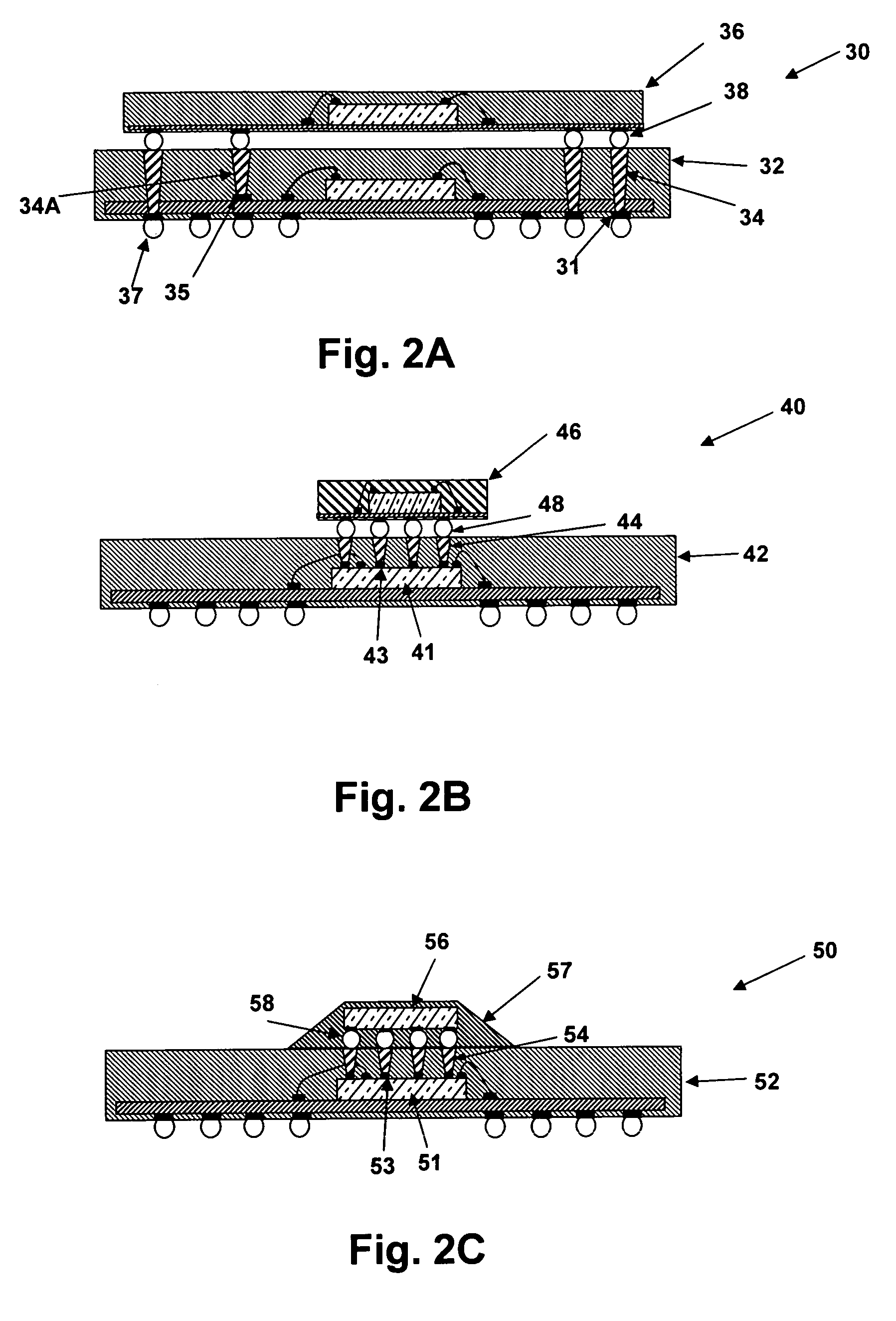

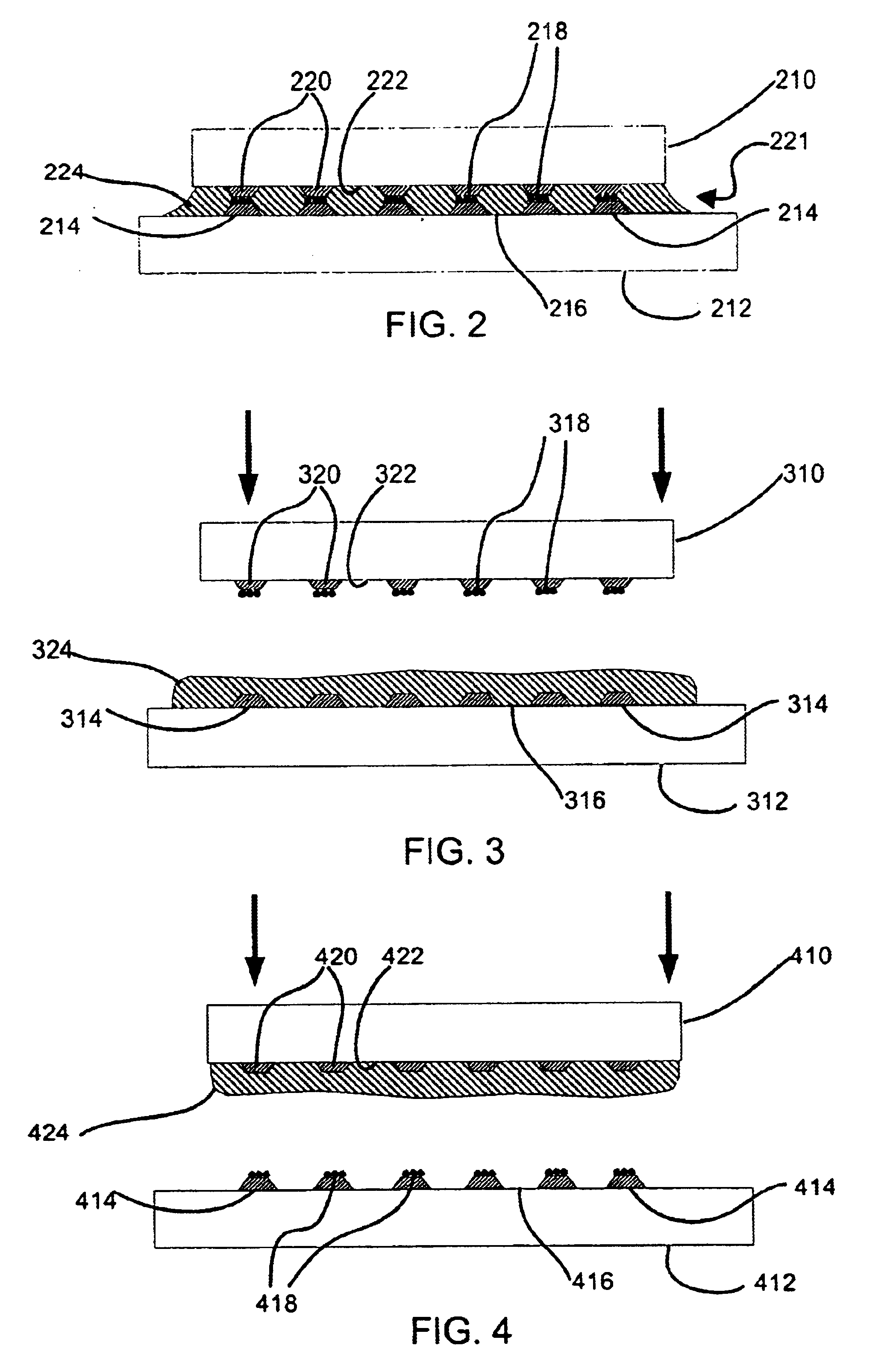

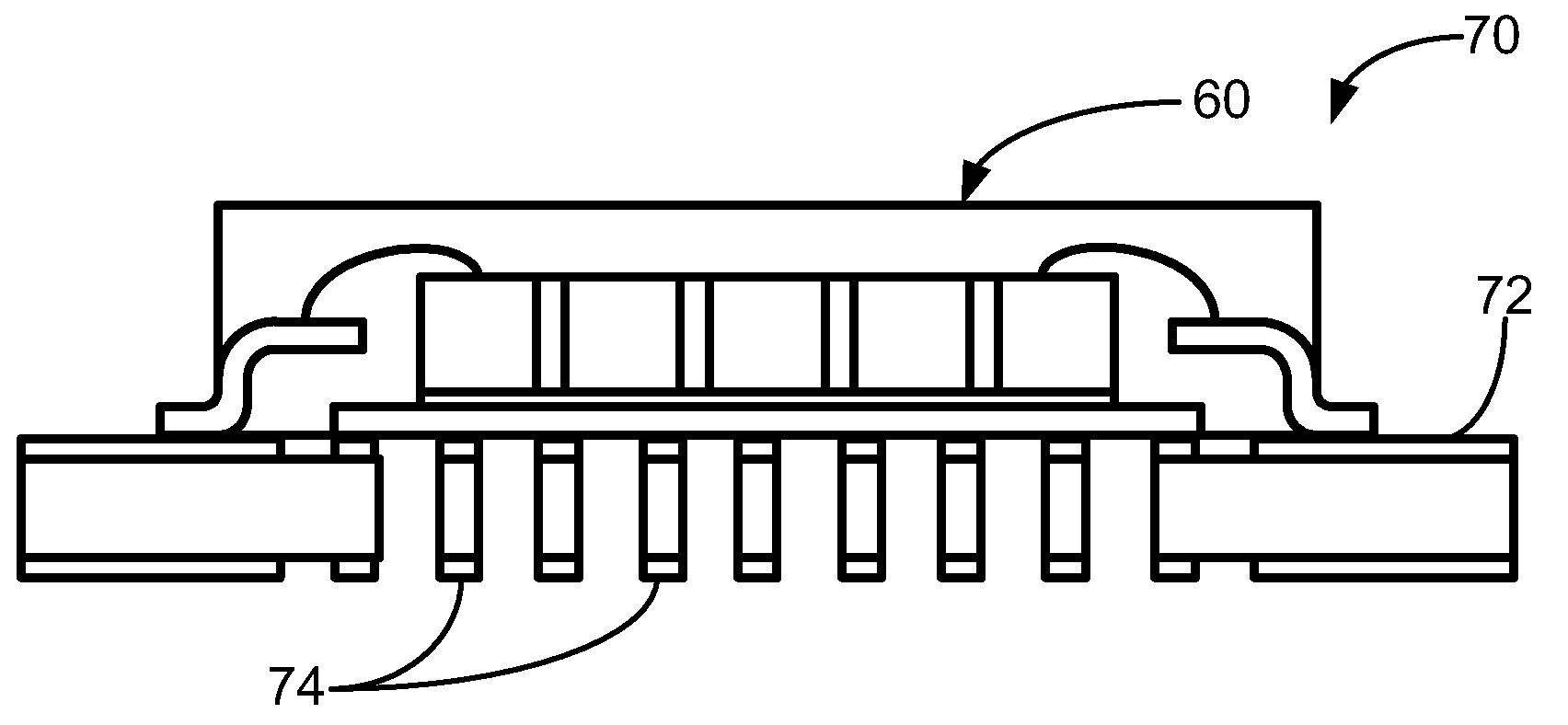

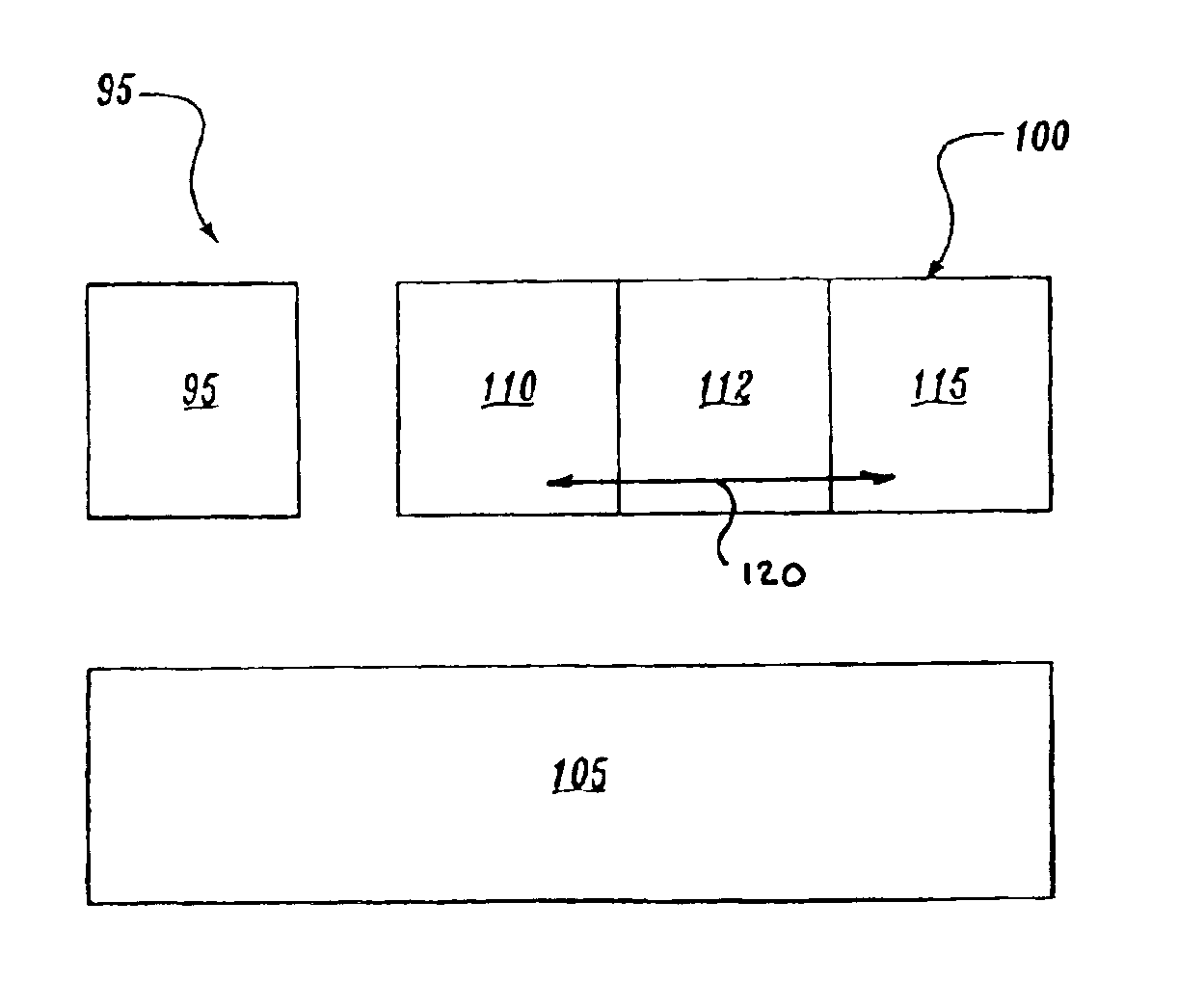

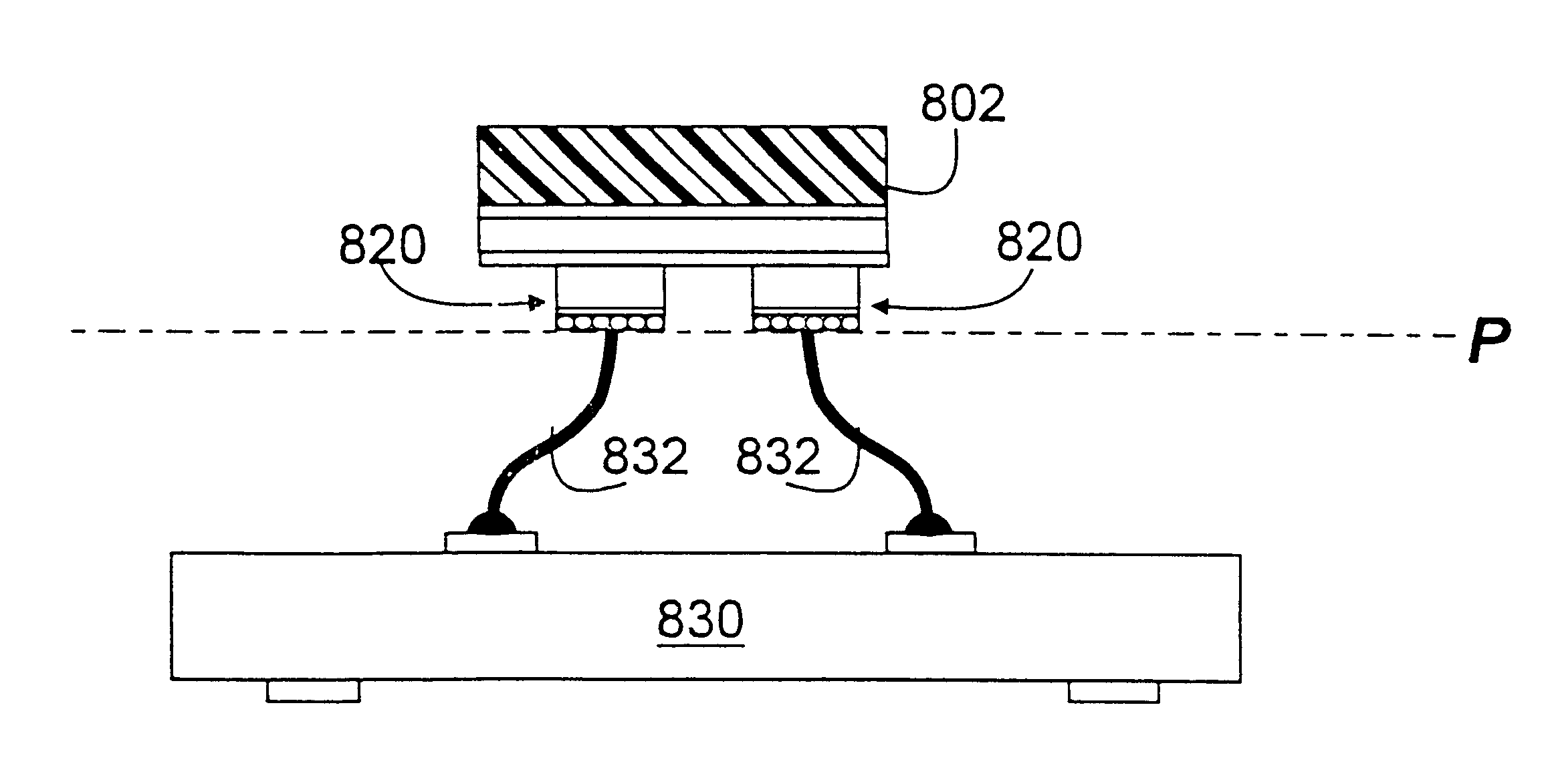

Methods for assembling multiple semiconductor devices

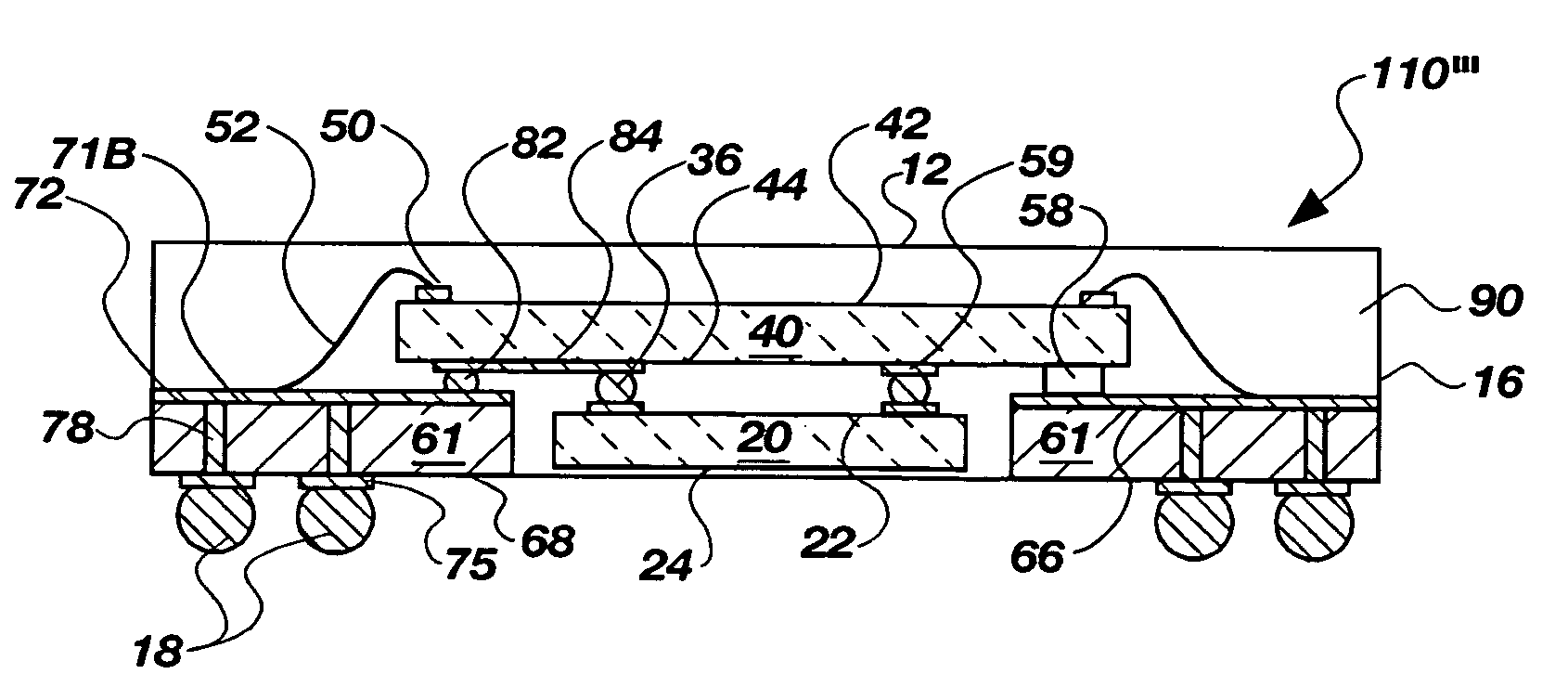

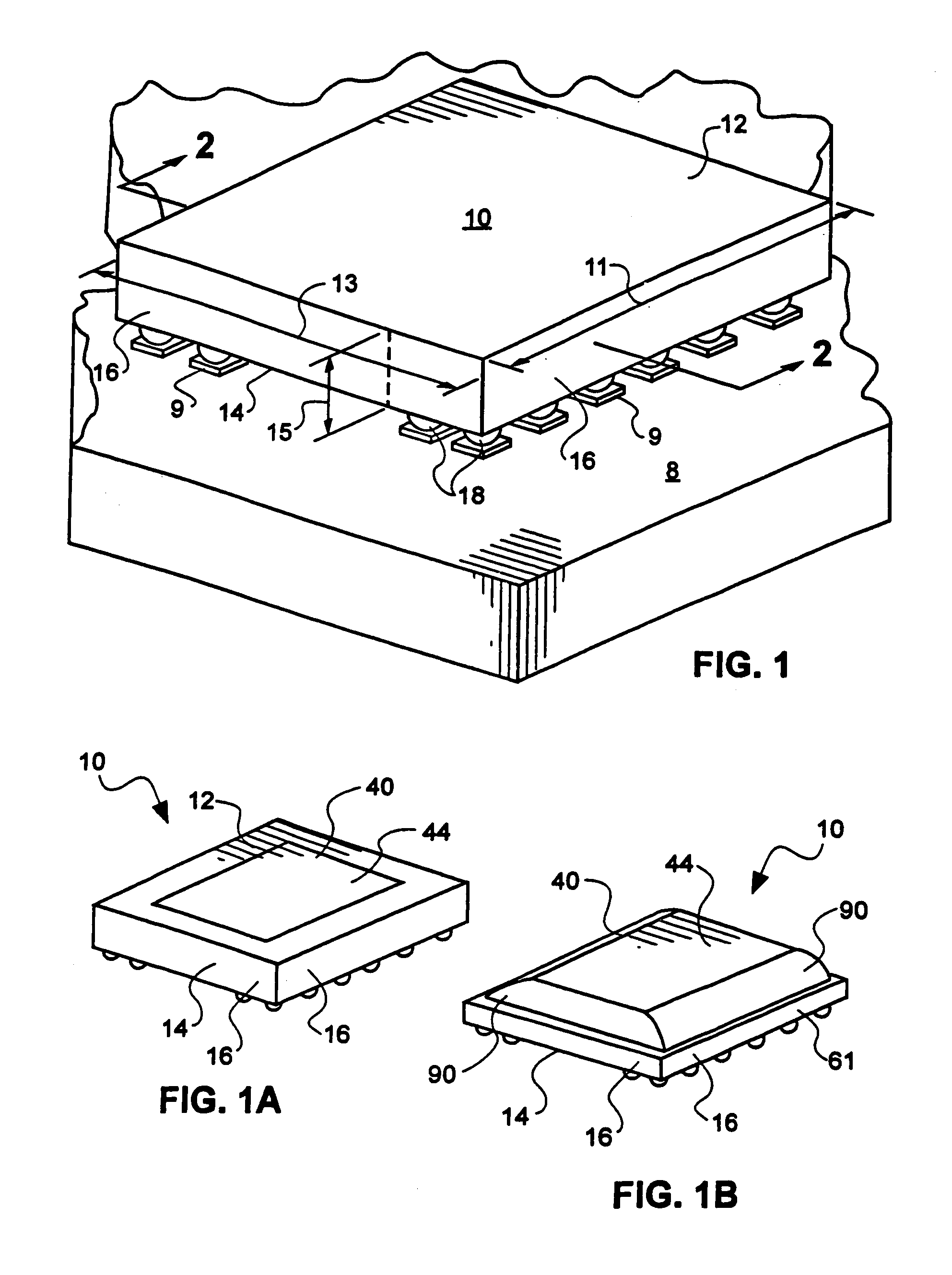

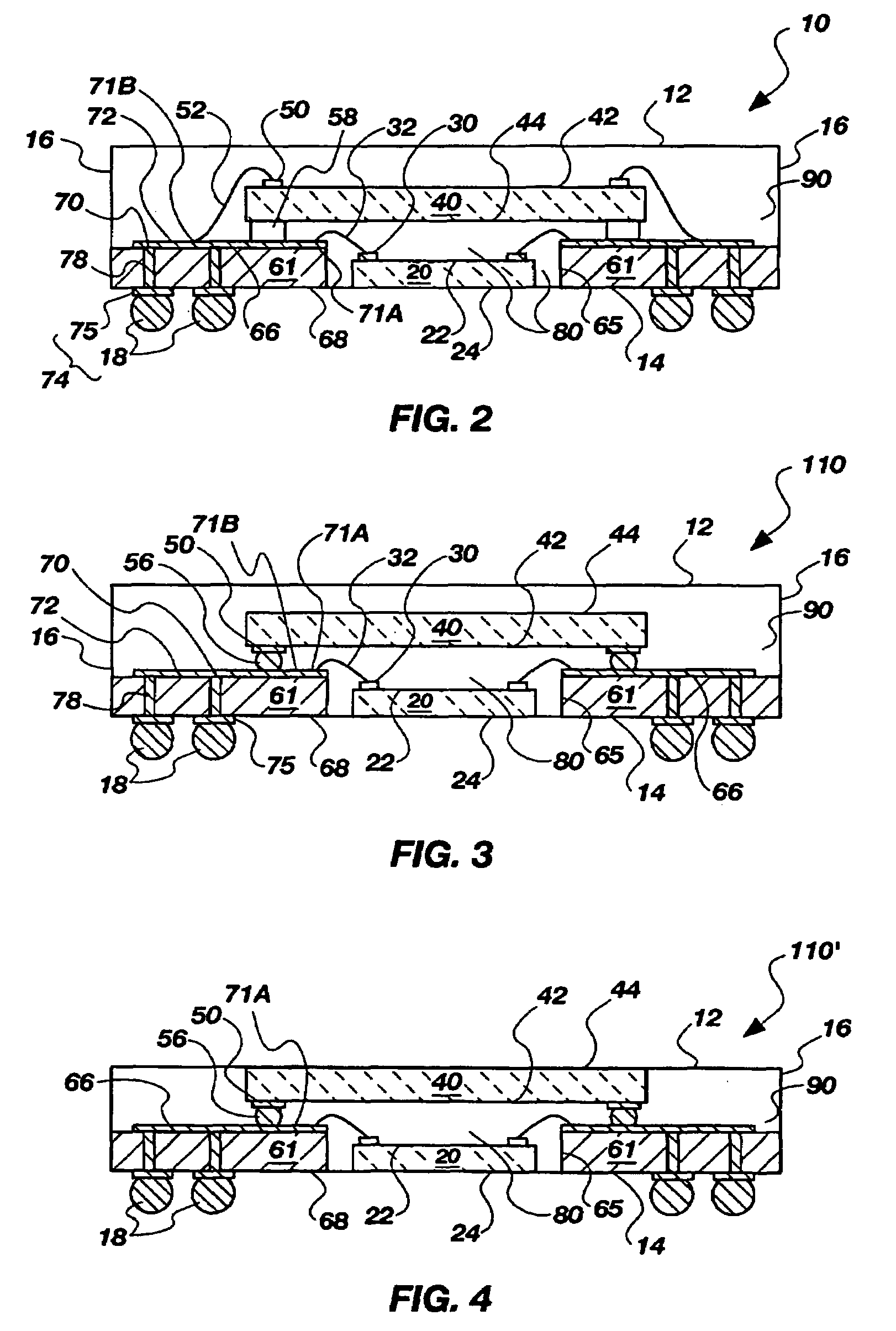

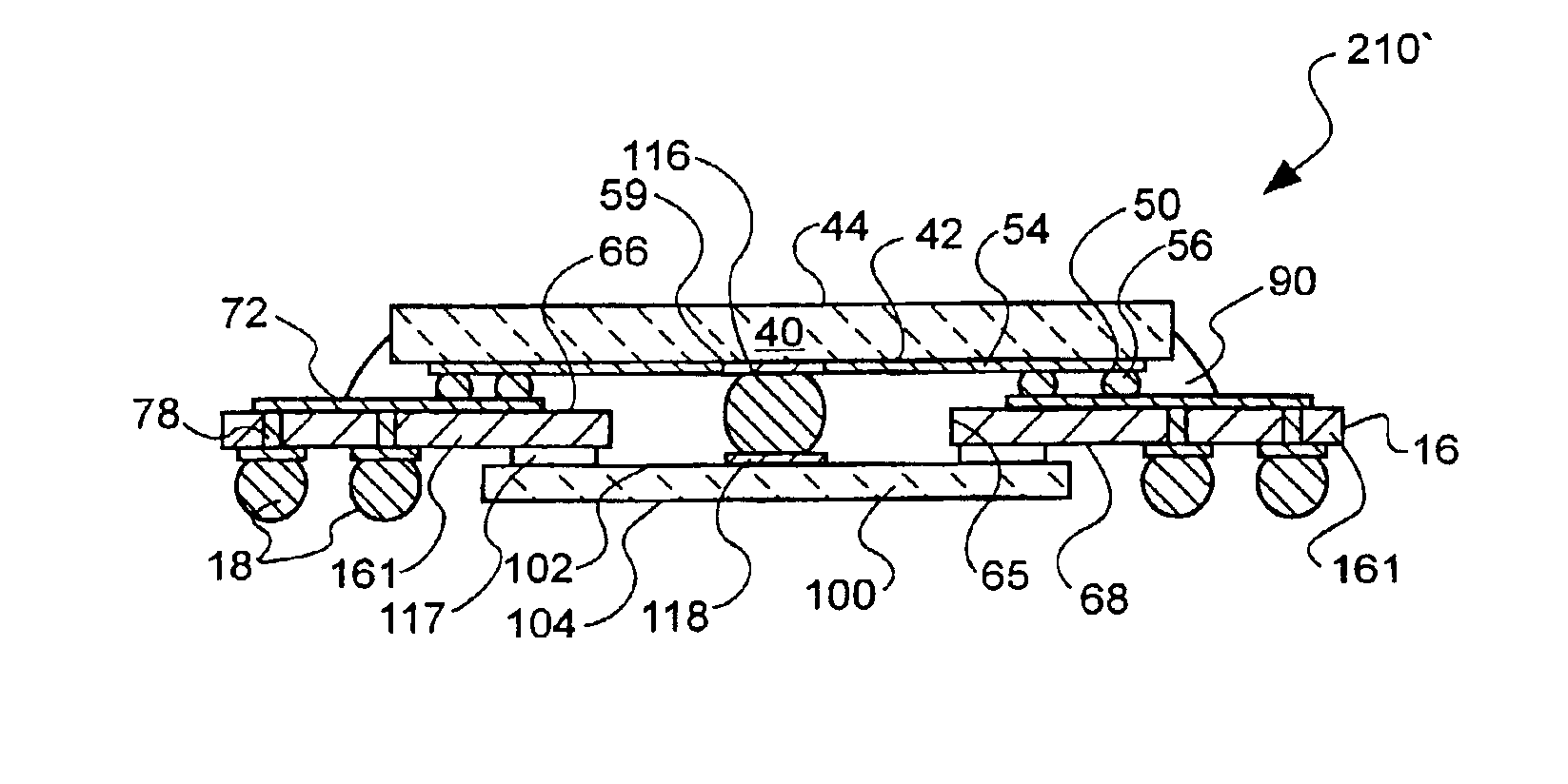

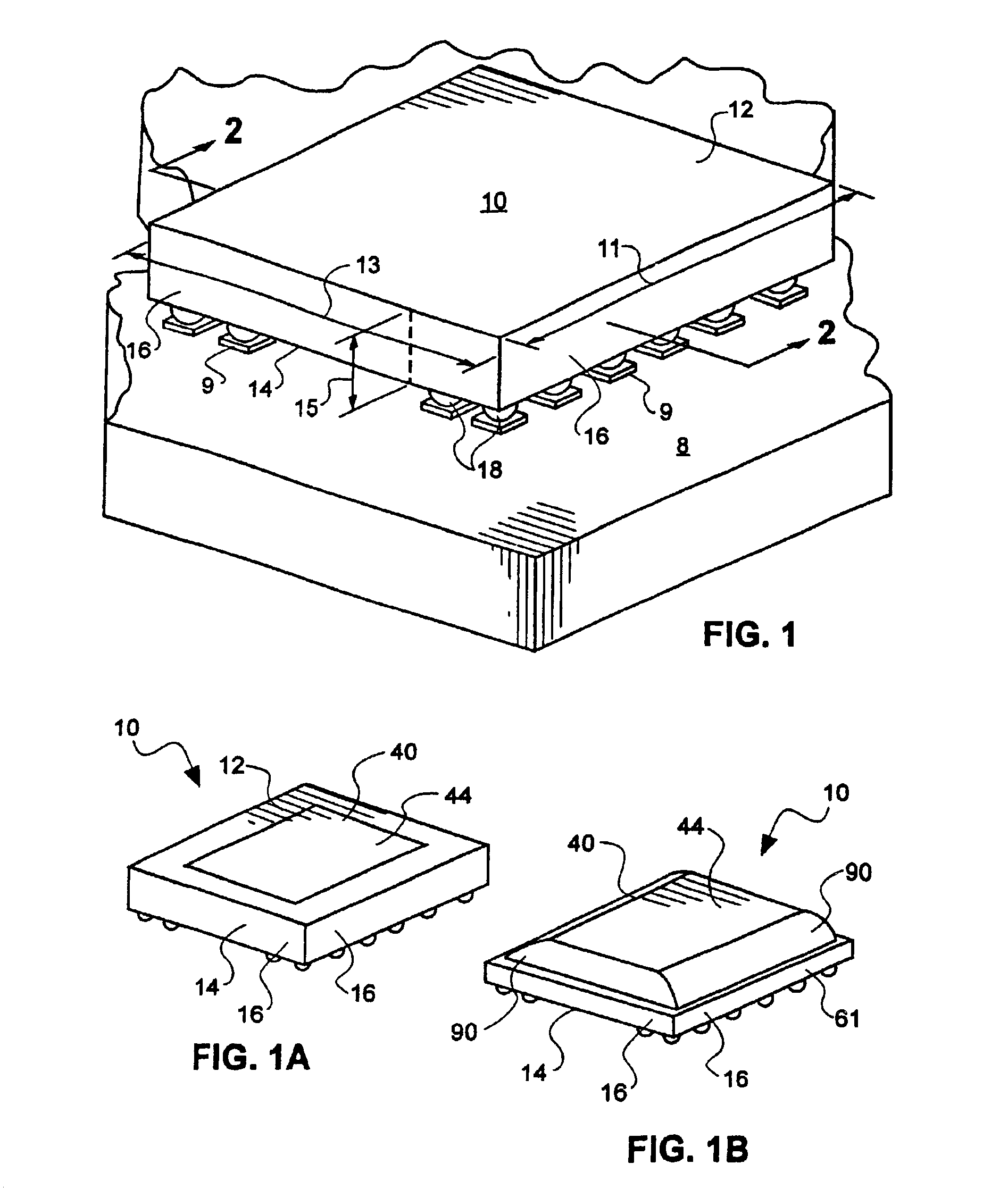

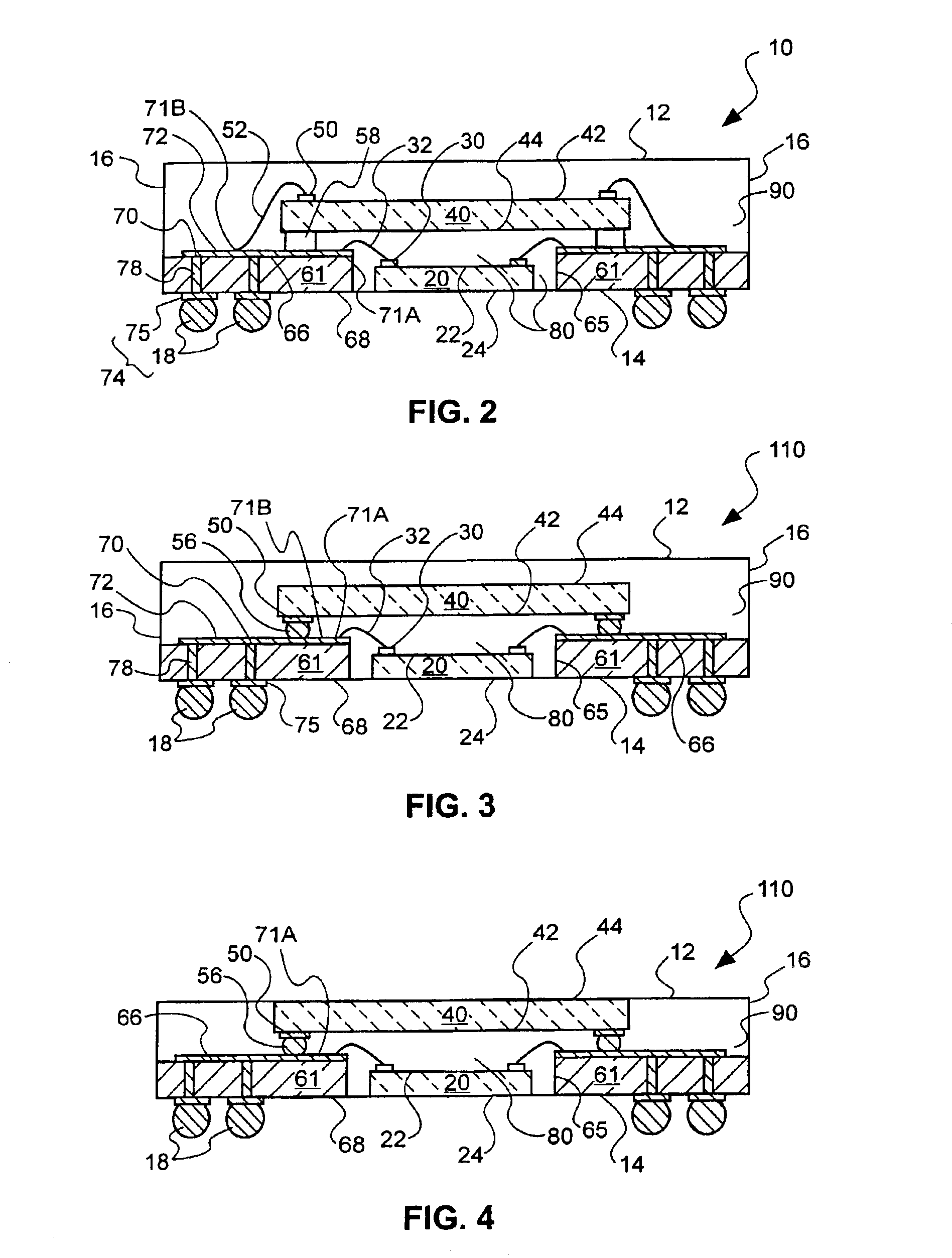

InactiveUS7198980B2Reduce area requirementsHelp positioningPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorElectrical connection

A multidie semiconductor device (MDSCD) package includes a generally planar interposer comprising a substrate with a central receptacle, upper surface conductors, and outer connectors on the lower surface of the interposer. Conductive vias connect upper surface conductors with outer connectors. One or more semiconductor devices may be mounted in the receptacle and one or more other semiconductor devices mounted above and / or below the interposer and attached thereto. The package may be configured to have a footprint not significantly larger than the footprint of the largest device and / or a thickness not significantly greater than the combined thickness of included devices. Methods for assembling and encapsulating packages from multidie wafers and multi-interposer sheets or strips are disclosed. Methods for combining a plurality of packages into a single stacked package are disclosed. The methods may include use of somewhat laterally extending intermediate conductive elements, flip-chip style electrical connection, or both within the same package.

Owner:MICRON TECH INC

Semiconductor device assemblies and packages including multiple semiconductor devices and methods

InactiveUS6906415B2Reduce area requirementsHelp positioningPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorElectrical connection

A multidie semiconductor device (MDSCD) package includes a generally planar interposer comprising a substrate with a central receptacle, upper surface conductors, and outer connectors on the lower surface of the interposer. Conductive vias connect upper surface conductors with outer connectors. One or more semiconductor devices may be mounted in the receptacle and one or more other semiconductor devices mounted above and / or below the interposer and attached thereto. The package may be configured to have a footprint not significantly larger than the footprint of the largest device and / or a thickness not significantly greater than the combined thickness of included devices. Methods for assembling and encapsulating packages from multidie wafers and multi-interposer sheets or strips are disclosed. Methods for combining a plurality of packages into a single stacked package are disclosed. The methods may include use of somewhat laterally extending intermediate conductive elements, flip-chip style electrical connection, or both within the same package.

Owner:MICRON TECH INC

Method to improve planarity of electroplated copper

InactiveUS7064068B2Semiconductor/solid-state device manufacturingPrinted element electric connection formationEngineeringCopper

Owner:TAIWAN SEMICON MFG CO LTD

Chip having thermal vias and spreaders of CVD diamond

InactiveUS20100140790A1Minimize and preferably eliminate localized hot spotHeat dissipationSemiconductor/solid-state device detailsPrinted circuit aspects3d integrated circuitHeat spreader

An integrated circuit chip having a heat spreader comprising CVD diamond extending along the chip support body and thermal vias extending through the support body in regions free of active devices or functional elements. The thermal vias may thermally conductive and electrically conductive or may be thermally conductive and electrically resistive. The integrated circuit chips may be 3D integrated circuit chips.

Owner:SEAGATE TECH LLC

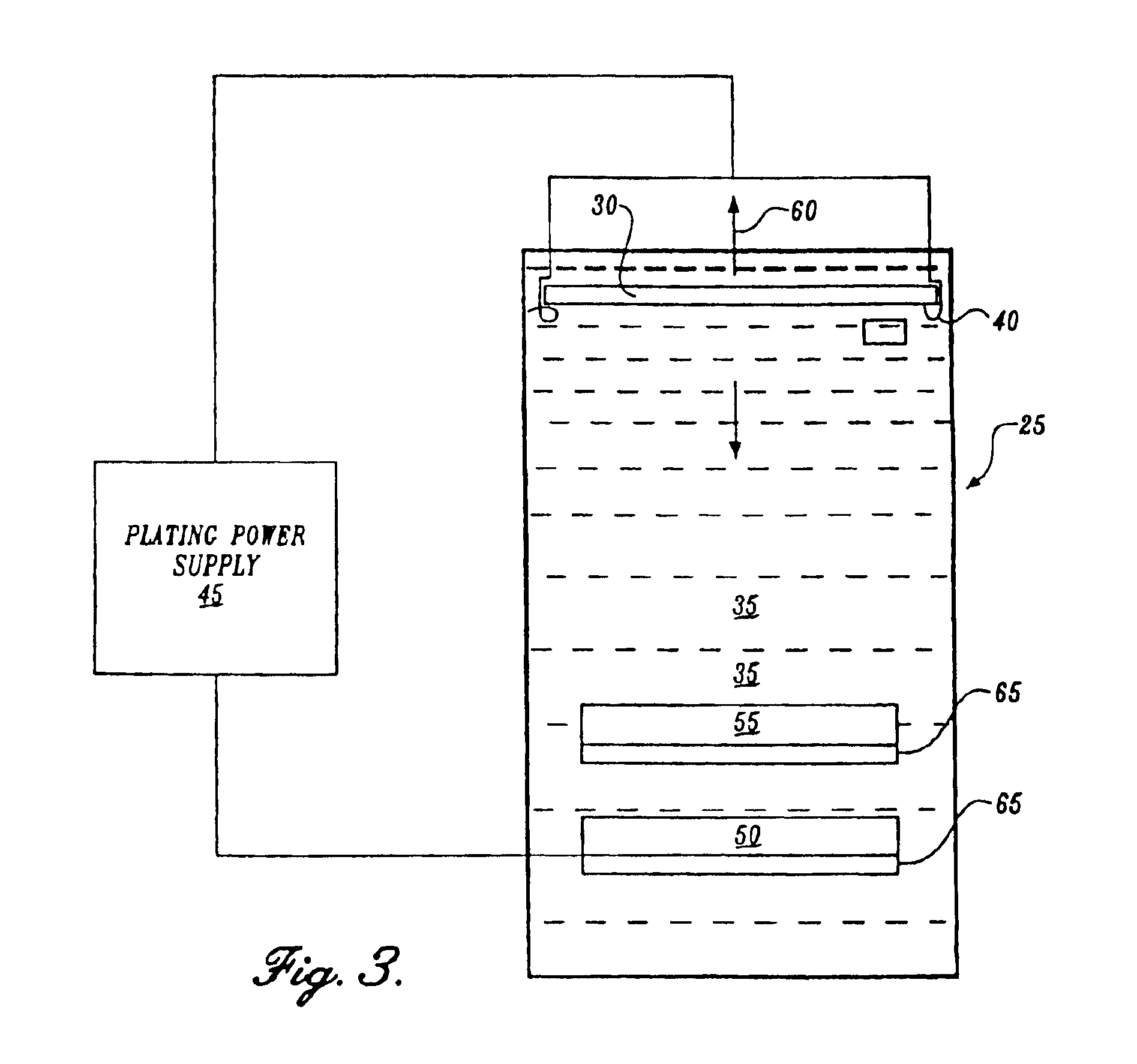

Apparatus and method for electrolytically depositing copper on a semiconductor workpiece

A process for applying a metallization interconnect as to a semiconductor workpiece having a barrier layer deposited on a surface thereof is set forth. The process includes the forming of an ultra-thin metal seed layer on the barrier layer. The ultra-thin seed layer having a thickness of less than or equal to about 500 Angstroms. The ultra-thin seed layer is then enhanced by depositing additional metal thereon to provide an enhanced sed layer. The enhanced seed layer has a thickness at all points on sidewalls of substantially all recessed features distributed within the workpiece that is equal to or greater than about 10% of the nominal seed layer thickness over an exteriorly disposed surface of the workpiece.

Owner:SEMITOOL INC

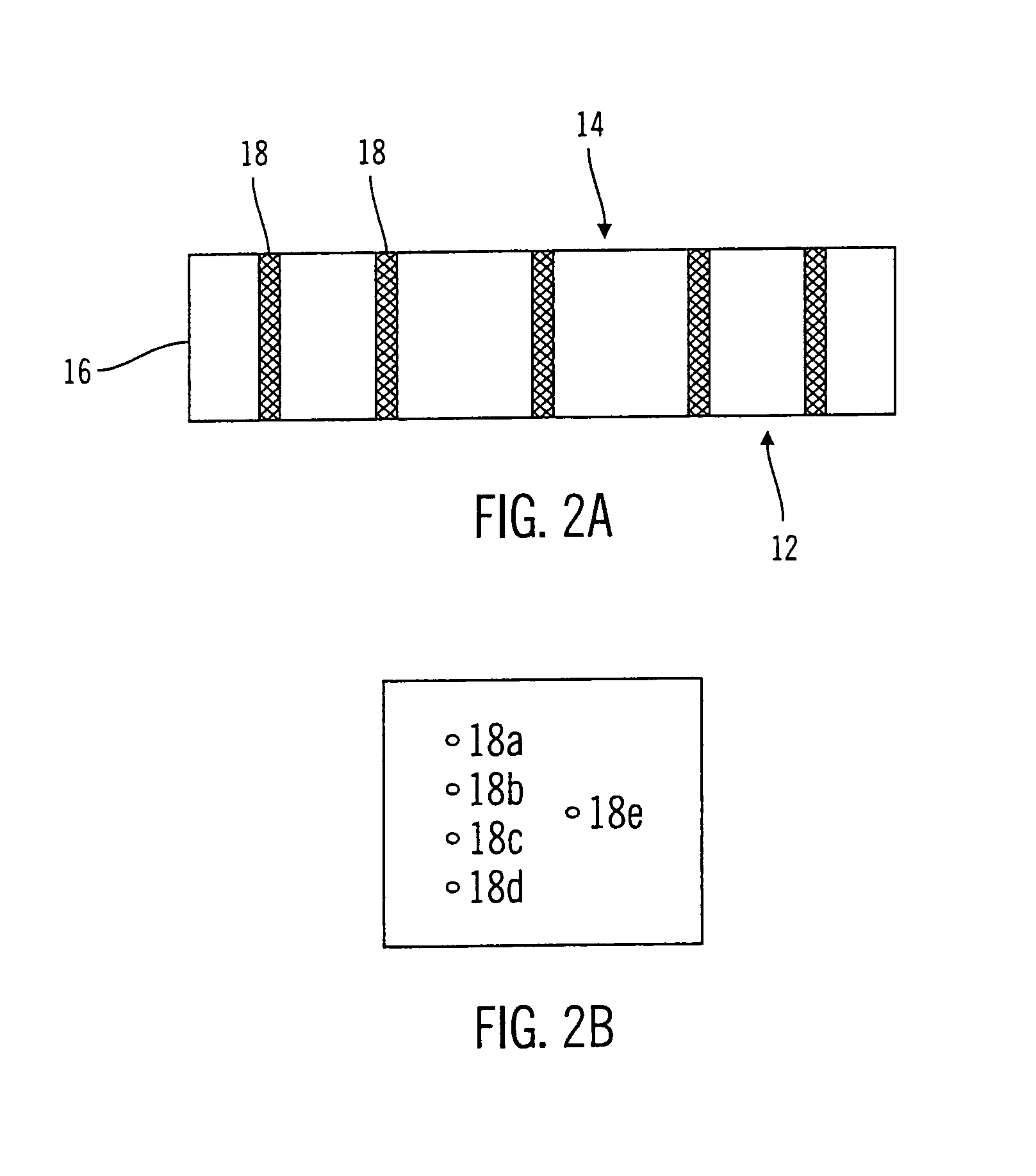

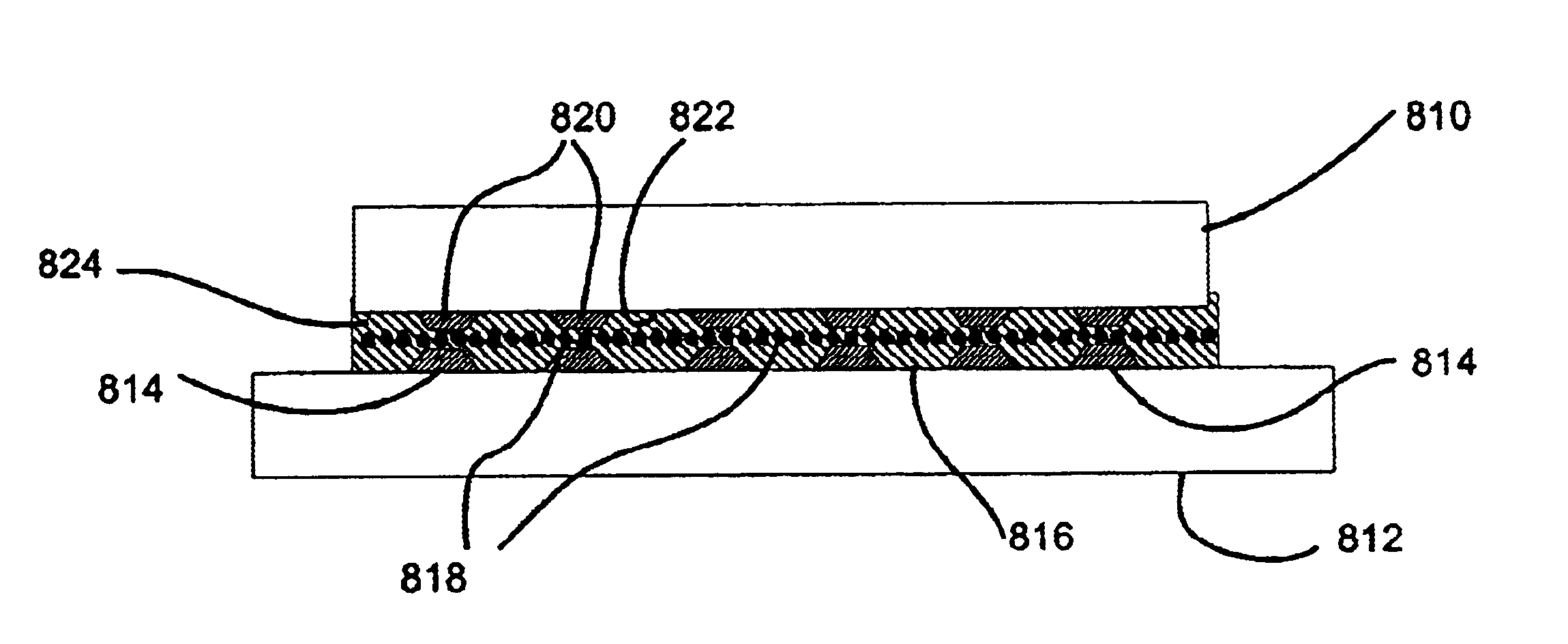

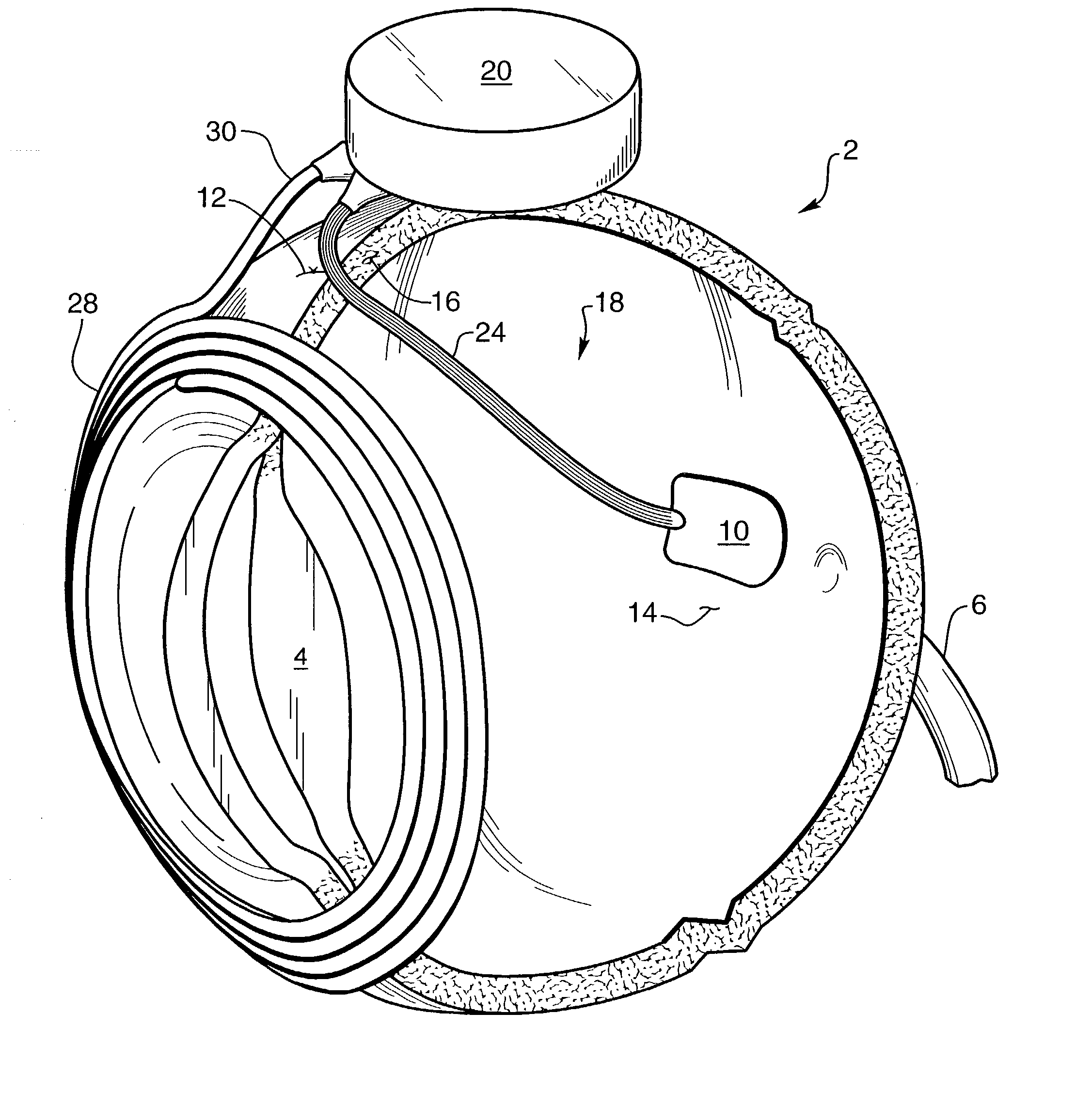

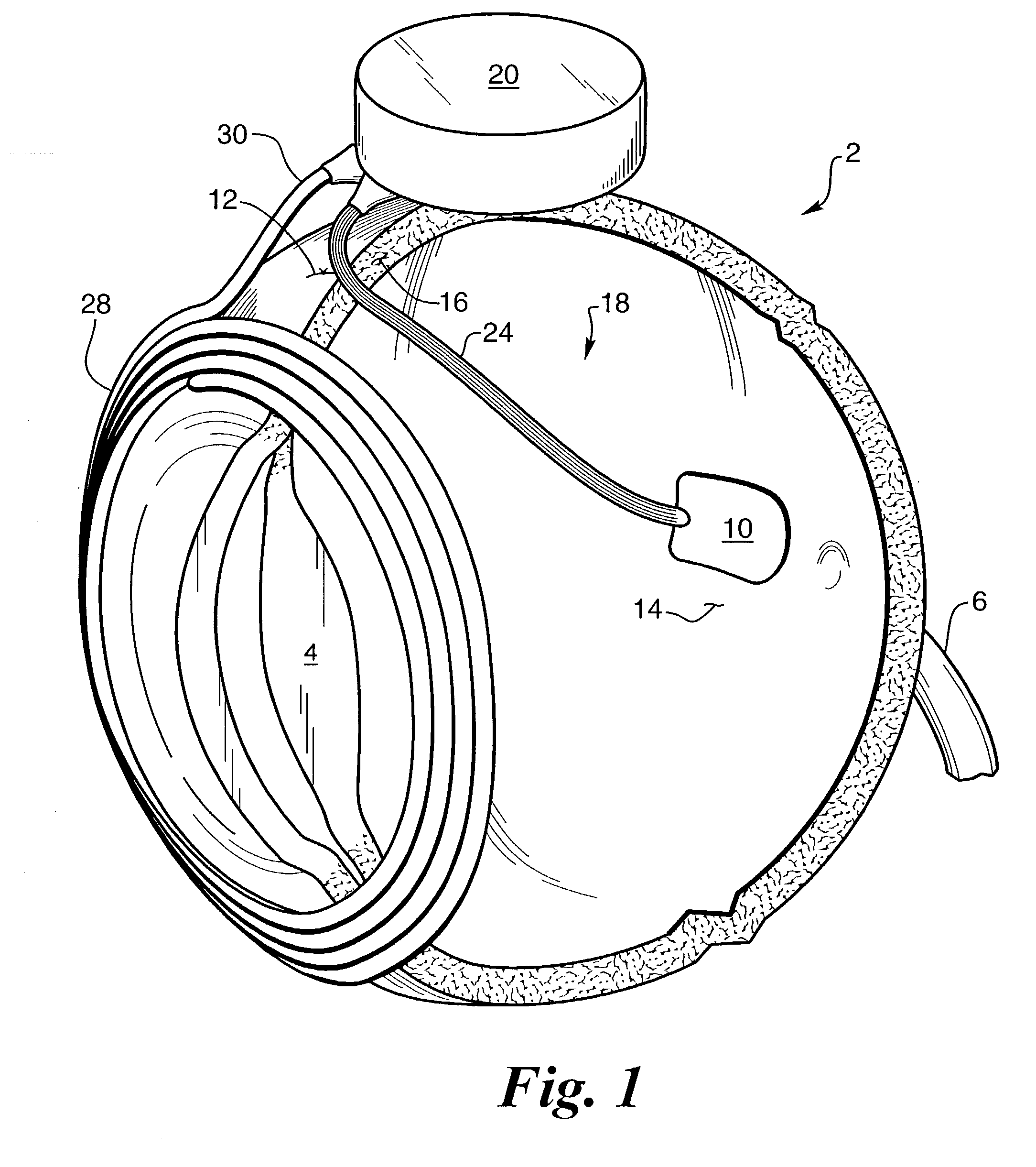

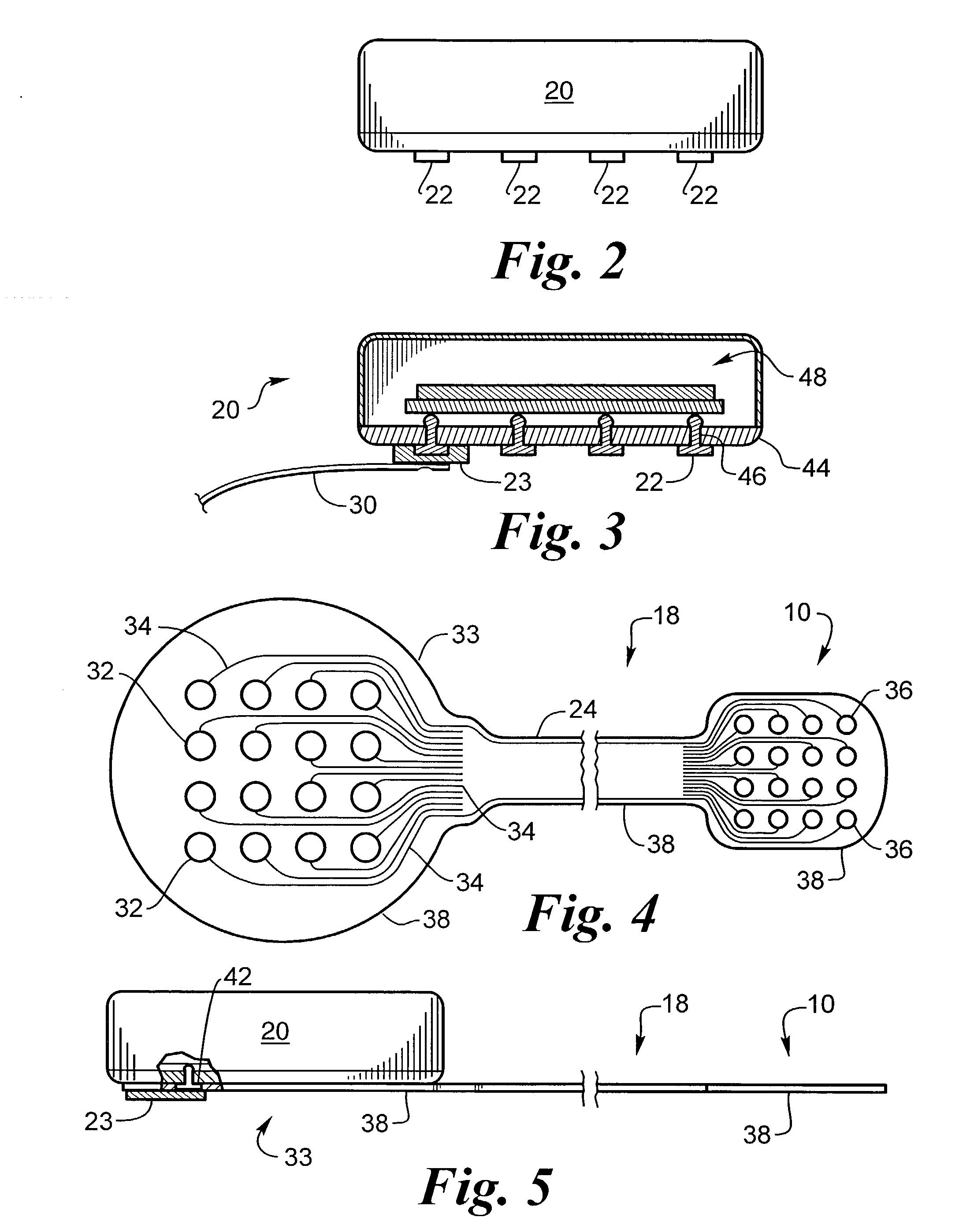

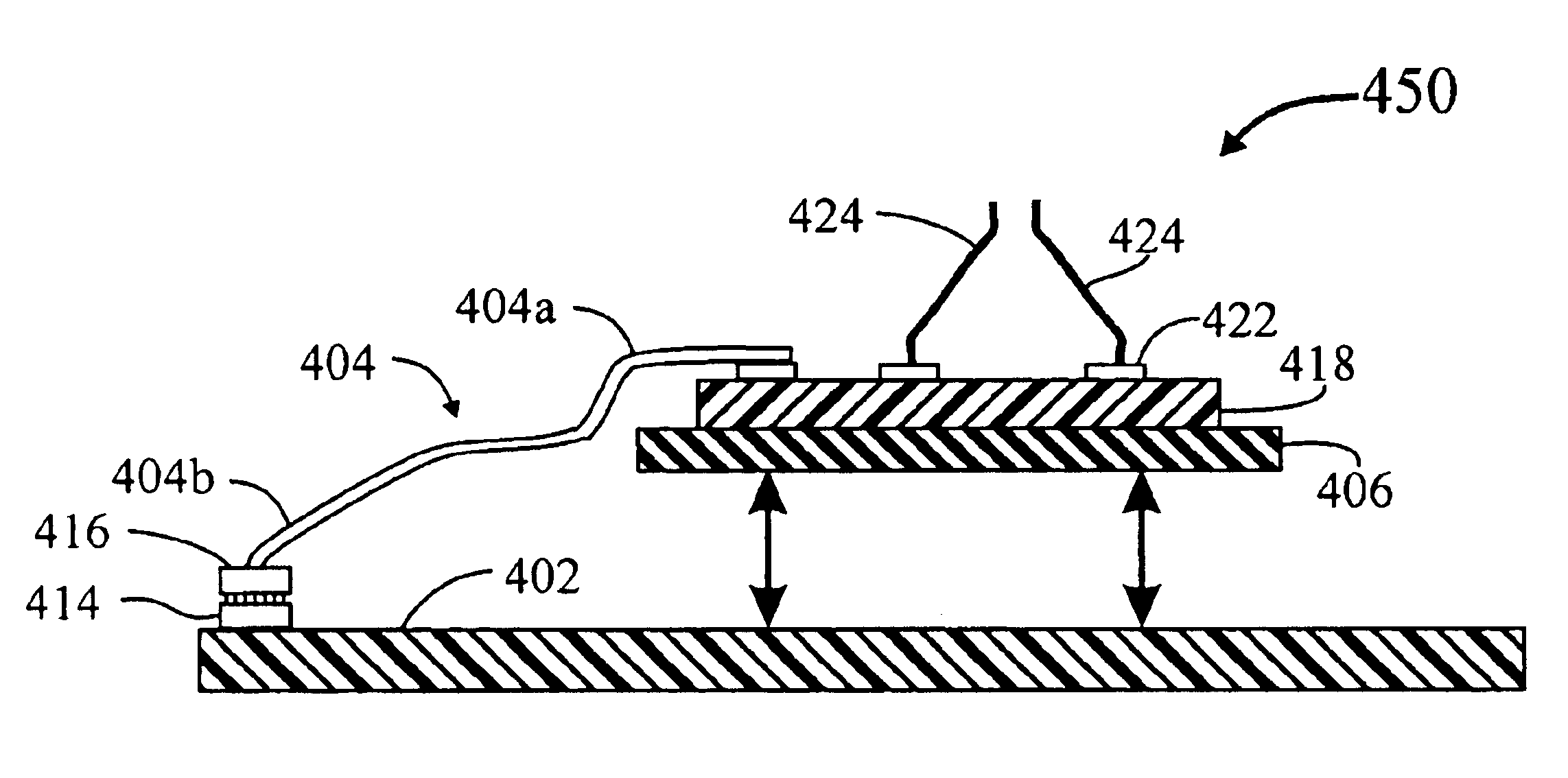

Biocompatible bonding method and electronics package suitable for implantation

ActiveUS20030233134A1Uniform propertySemiconductor/solid-state device detailsSolid-state devicesFlexible circuitsHermetic seal

The invention is directed to a method of bonding a hermetically sealed electronics package to an electrode or a flexible circuit and the resulting electronics package, that is suitable for implantation in living tissue, such as for a retinal or cortical electrode array to enable restoration of sight to certain non-sighted individuals. The hermetically sealed electronics package is directly bonded to the flex circuit or electrode by electroplating a biocompatible material, such as platinum or gold, effectively forming a plated rivet-shaped connection, which bonds the flex circuit to the electronics package. The resulting electronic device is biocompatible and is suitable for long-term implantation in living tissue.

Owner:CORTIGENT INC +1

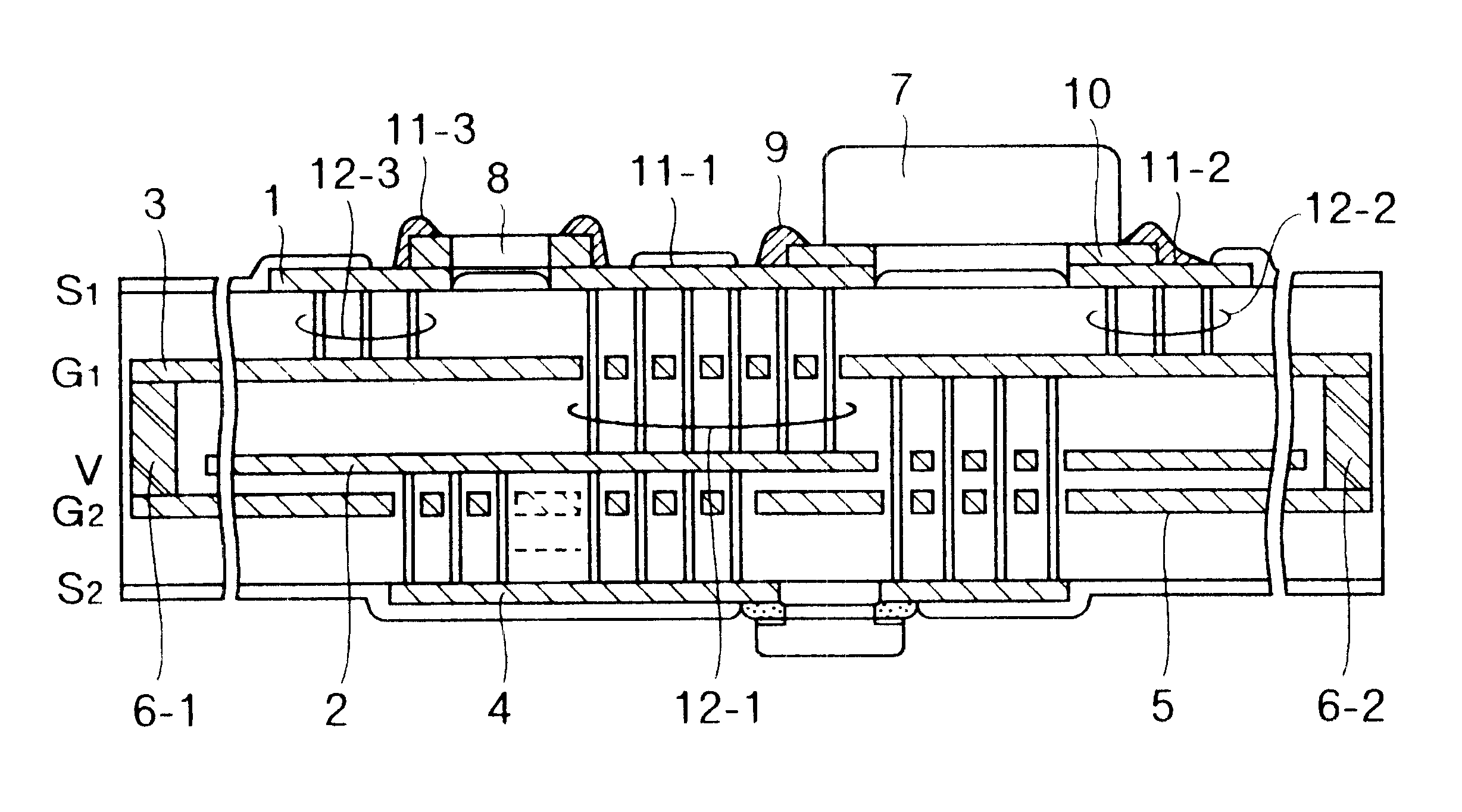

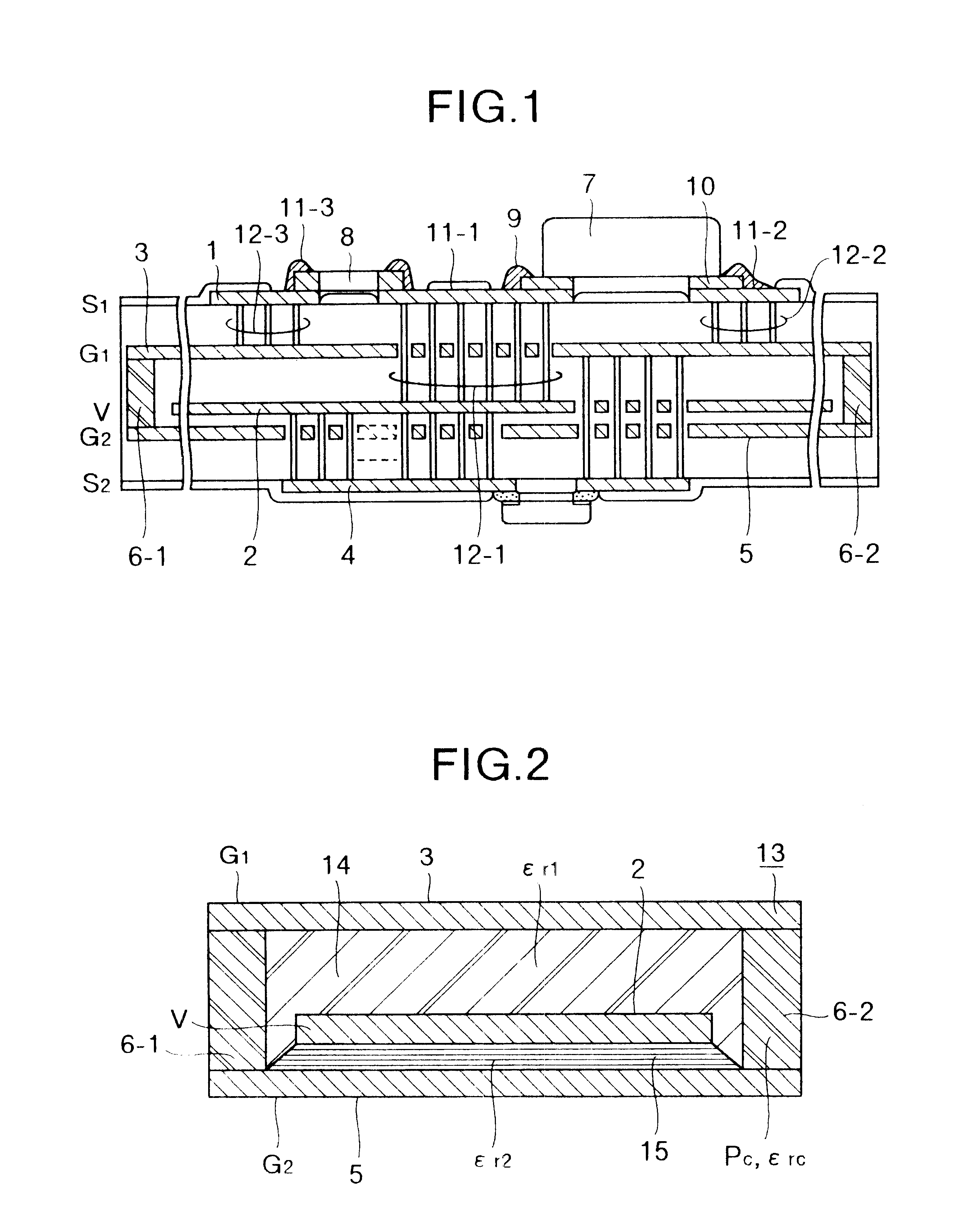

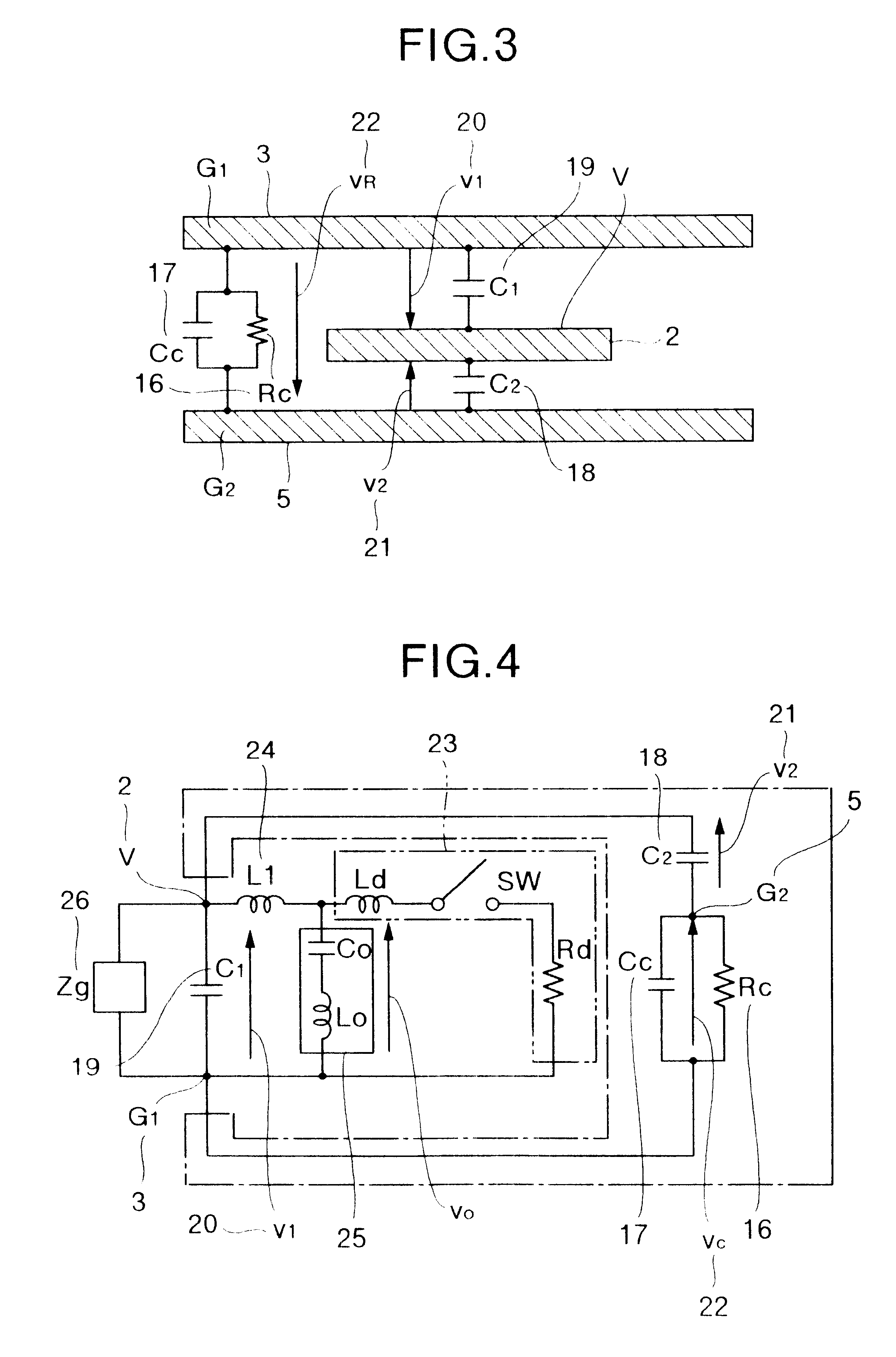

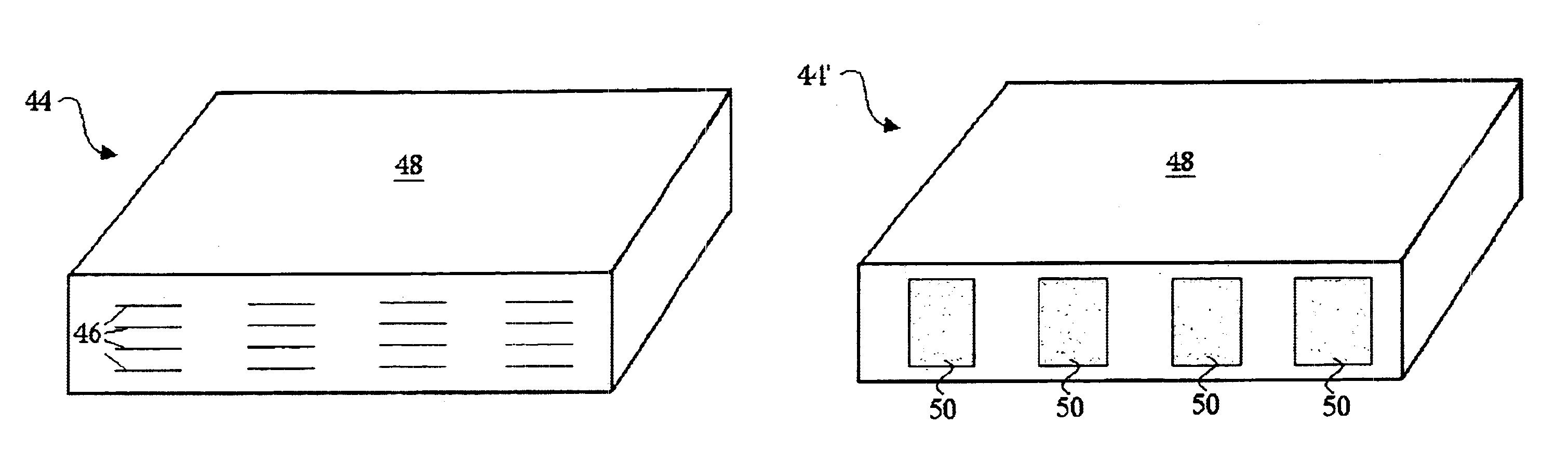

Low-EMI electronic apparatus, low-EMI circuit board, and method of manufacturing the low-EMI circuit board.

InactiveUS6353540B1Radiation suppressionHigh packageMagnetic/electric field screeningFinal product manufactureCapacitanceCountermeasure

Owner:HITACHI LTD

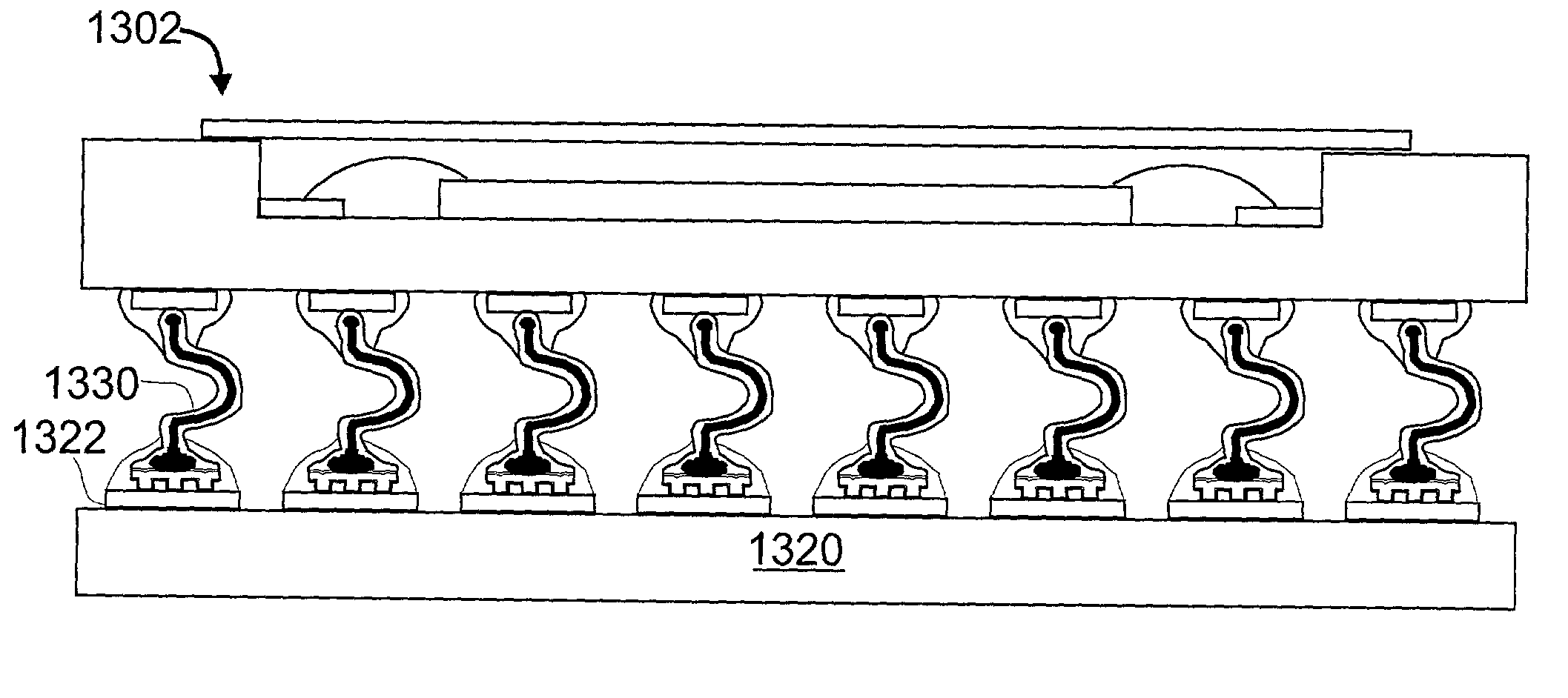

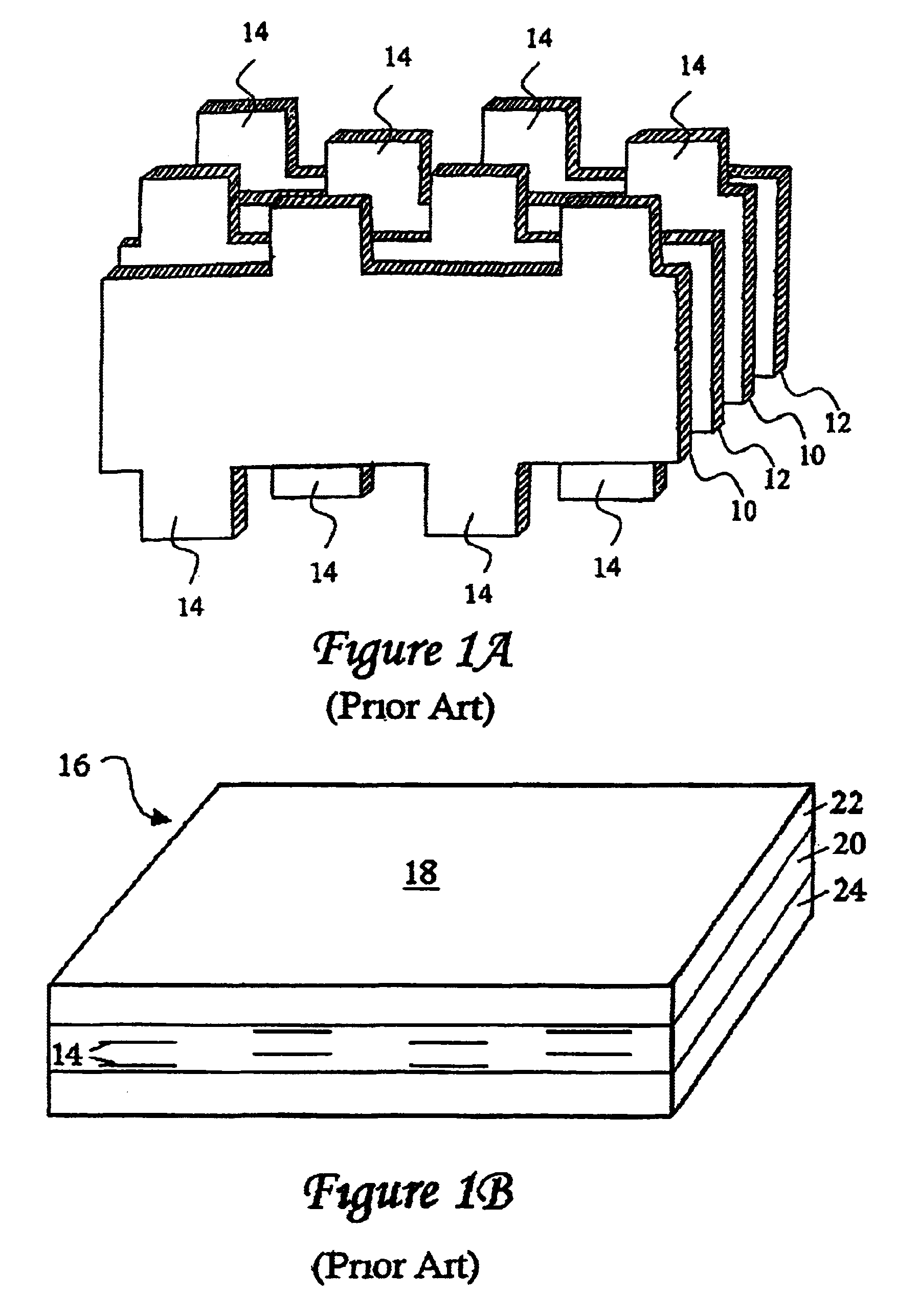

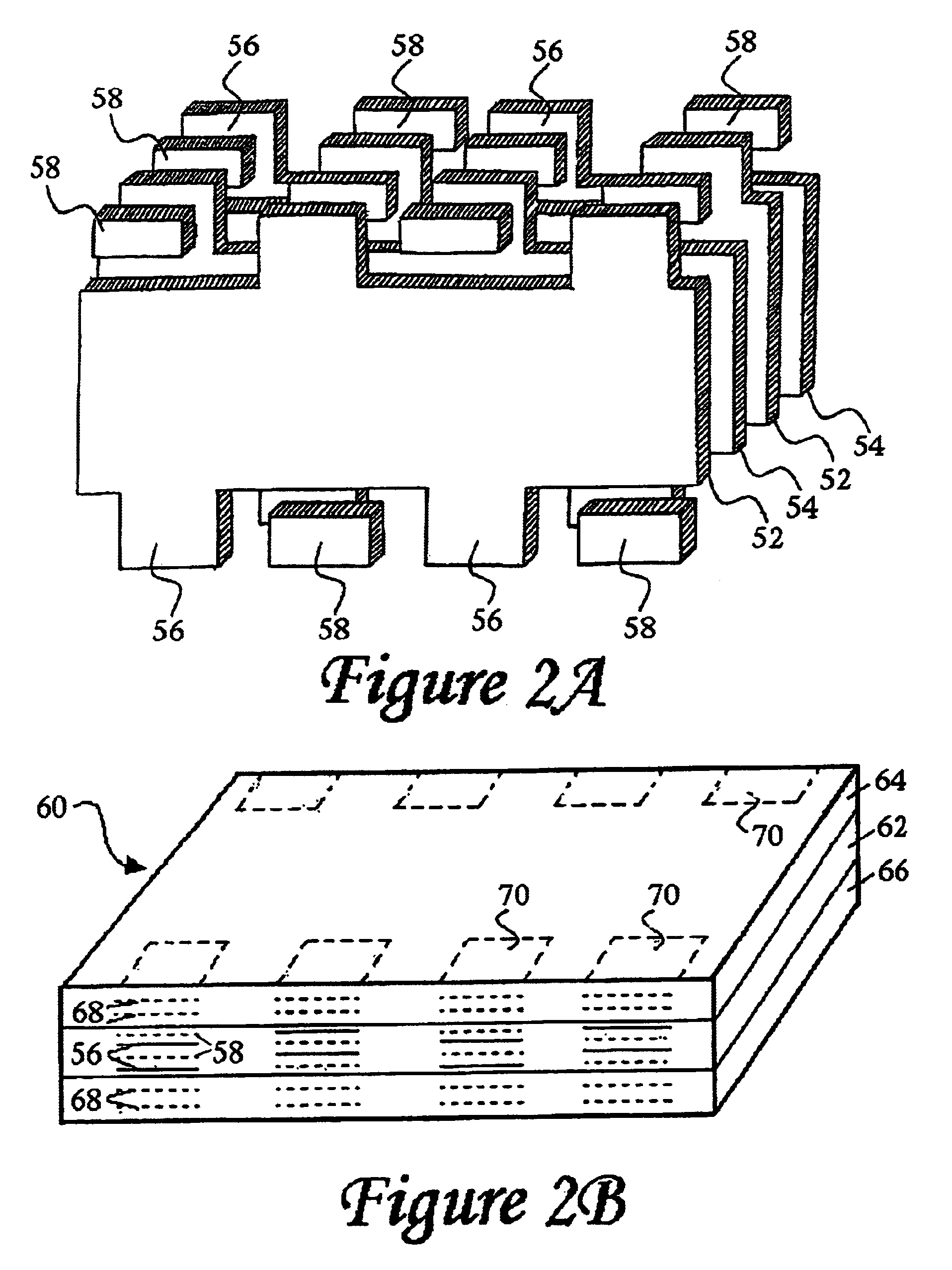

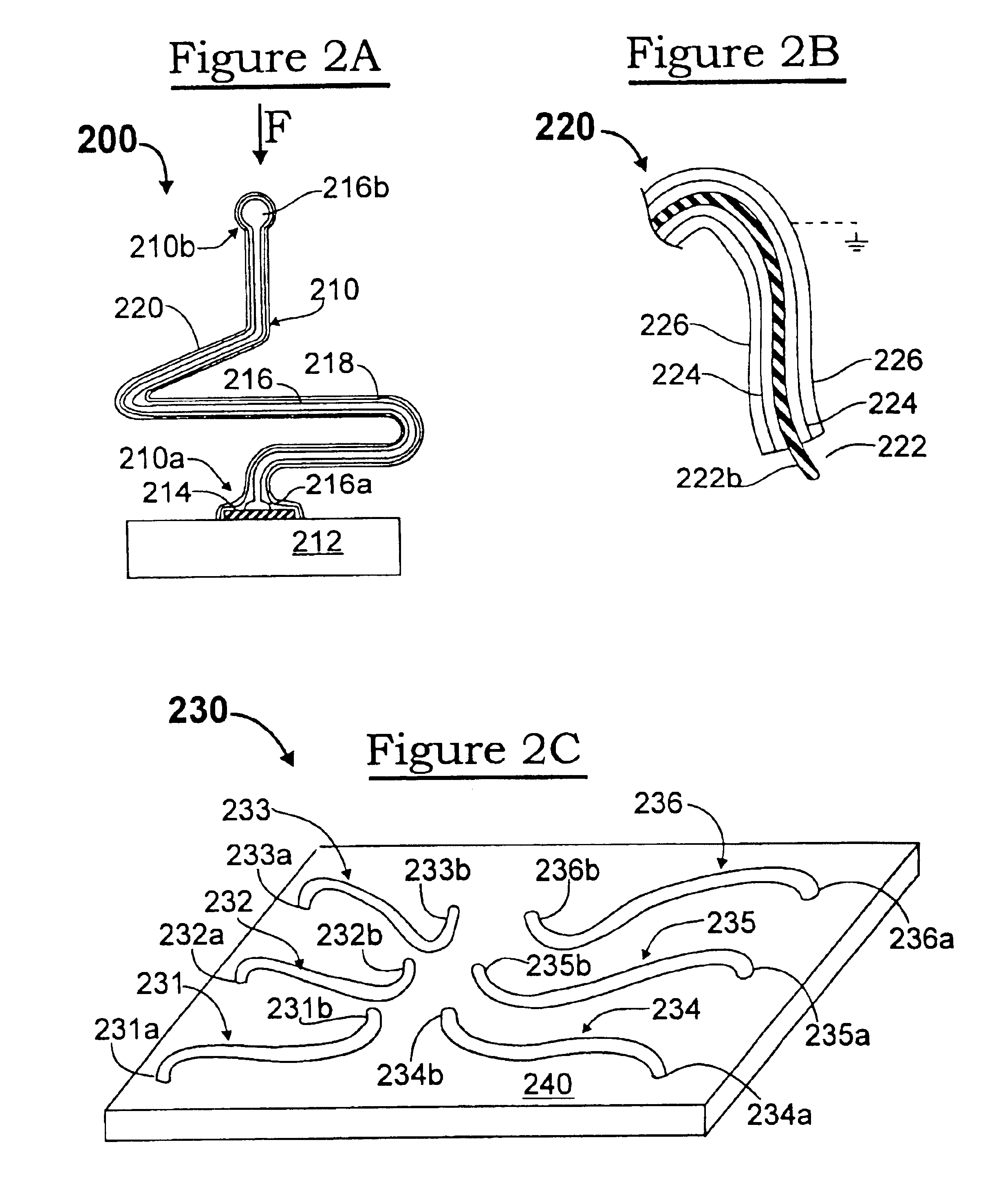

Probe card assembly and kit, and methods of using same

InactiveUS6246247B1Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureElectricityProbe card

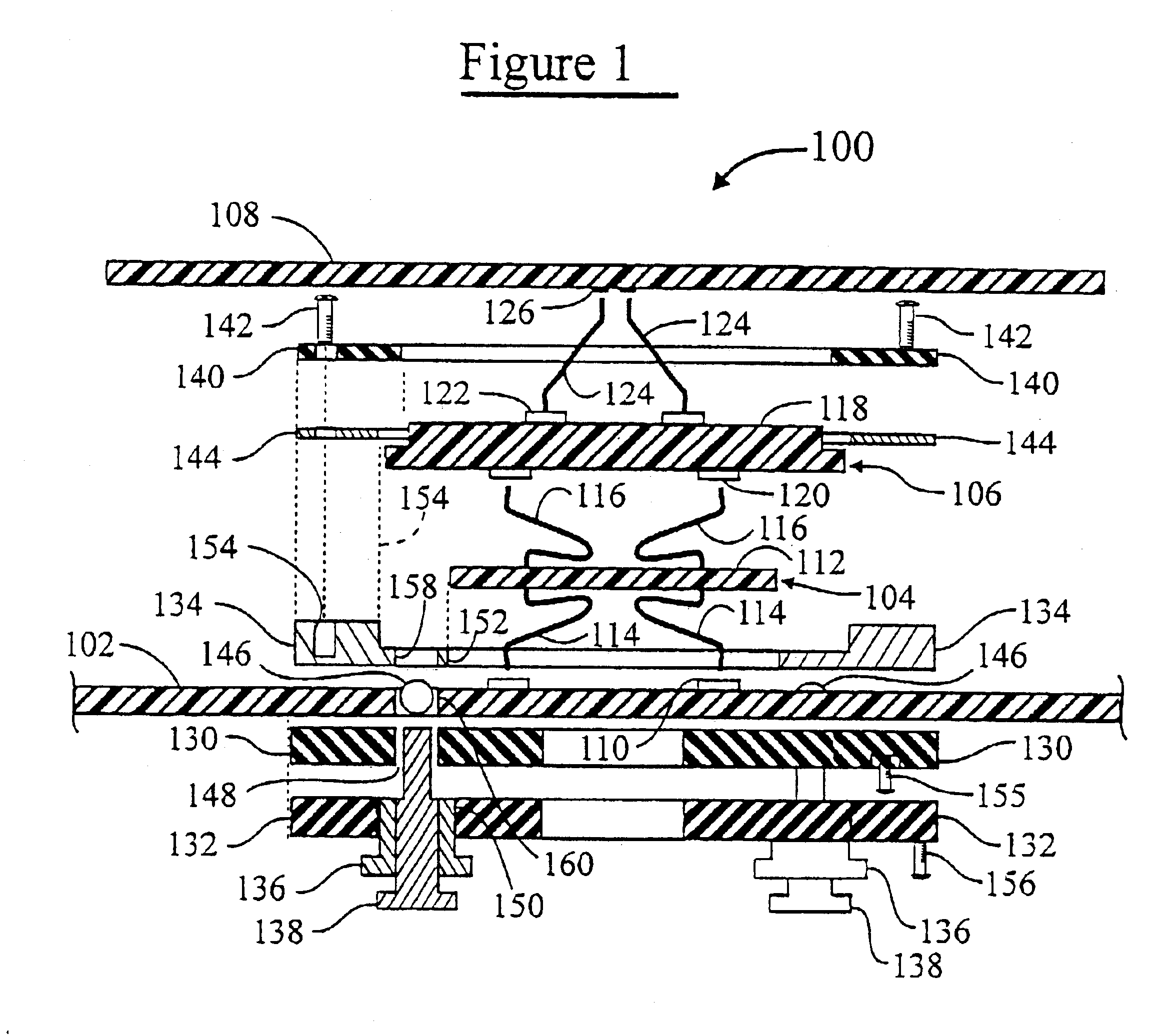

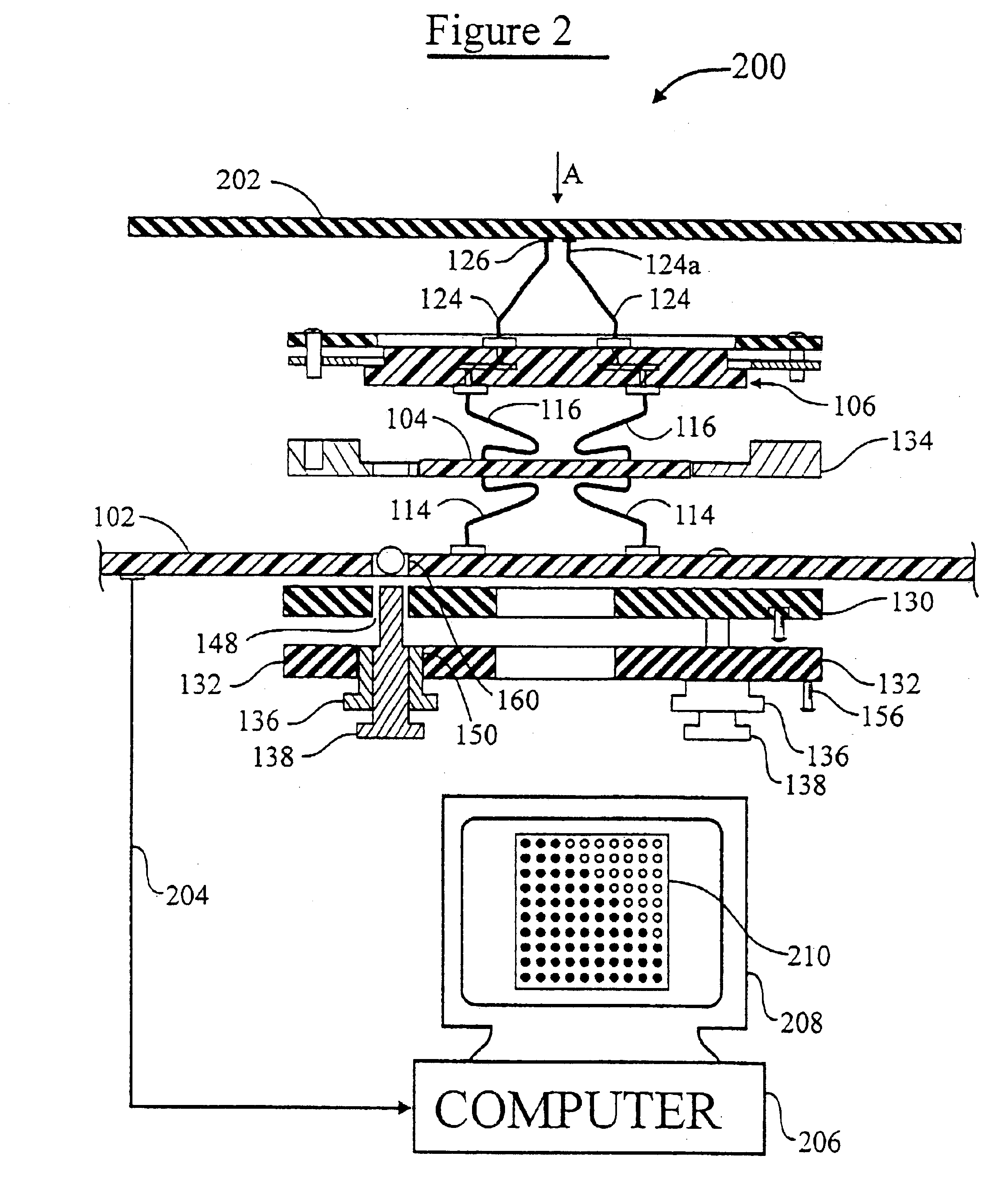

A probe card assembly includes a probe card, a space transformer having resilient contact structures (probe elements) mounted directly thereto (i.e., without the need for additional connecting wires or the like) and extending from terminals on a surface thereof, and an interposer disposed between the space transformer and the probe card. The space transformer and interposer are "stacked up" so that the orientation of the space transformer, hence the orientation of the tips of the probe elements, can be adjusted without changing the orientation of the probe card. Suitable mechanisms for adjusting the orientation of the space transformer, and for determining what adjustments to make, are disclosed. The interposer has resilient contact structures extending from both the top and bottom surfaces thereof, and ensures that electrical connections are maintained between the space transformer and the probe card throughout the space transformer's range of adjustment, by virtue of the interposer's inherent compliance. Multiple die sites on a semiconductor wafer are readily probed using the disclosed techniques, and the probe elements can be arranged to optimize probing of an entire wafer. Composite interconnection elements having a relatively soft core overcoated by a relatively hard shell, as the resilient contact structures are described.

Owner:FORMFACTOR INC

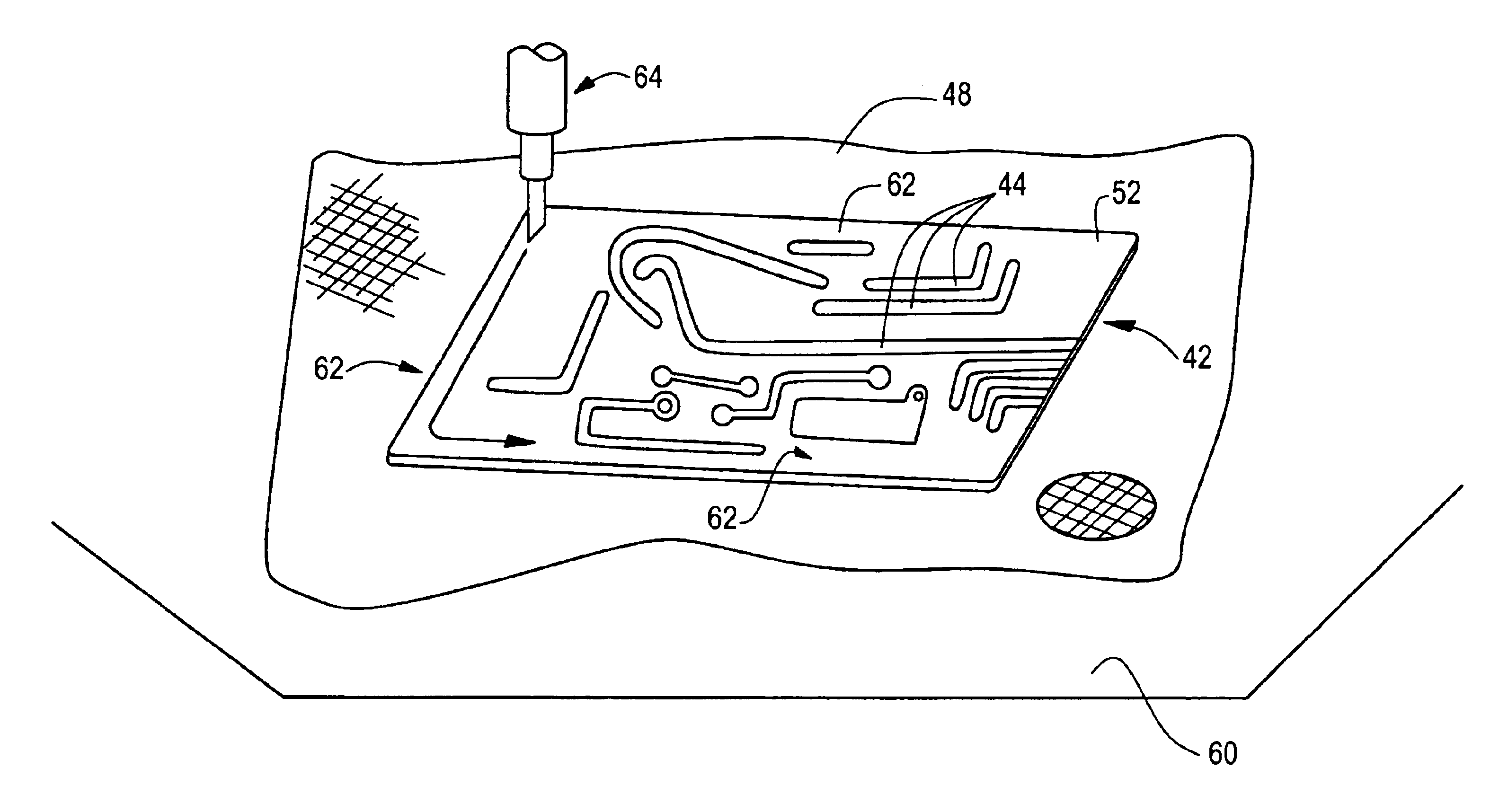

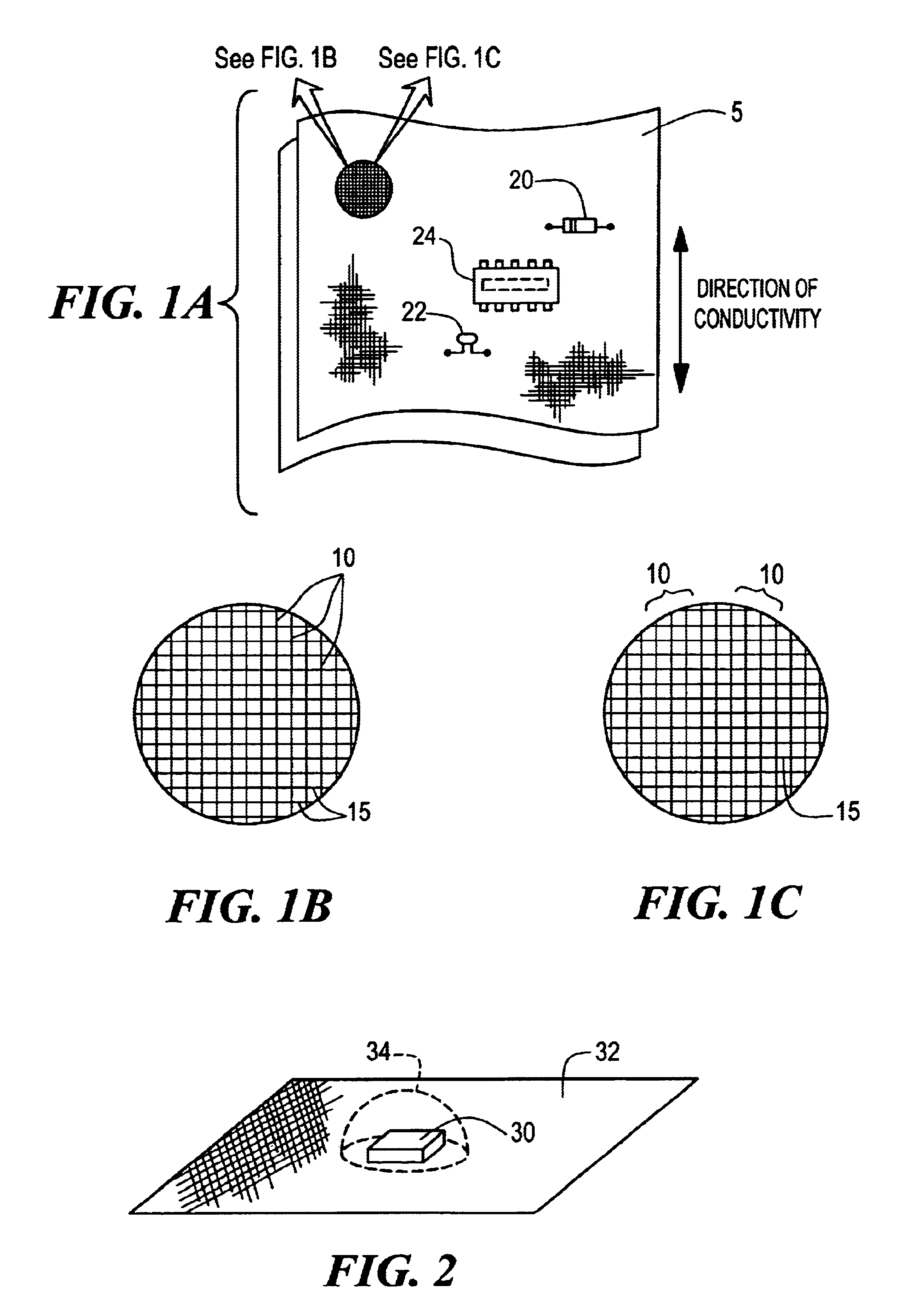

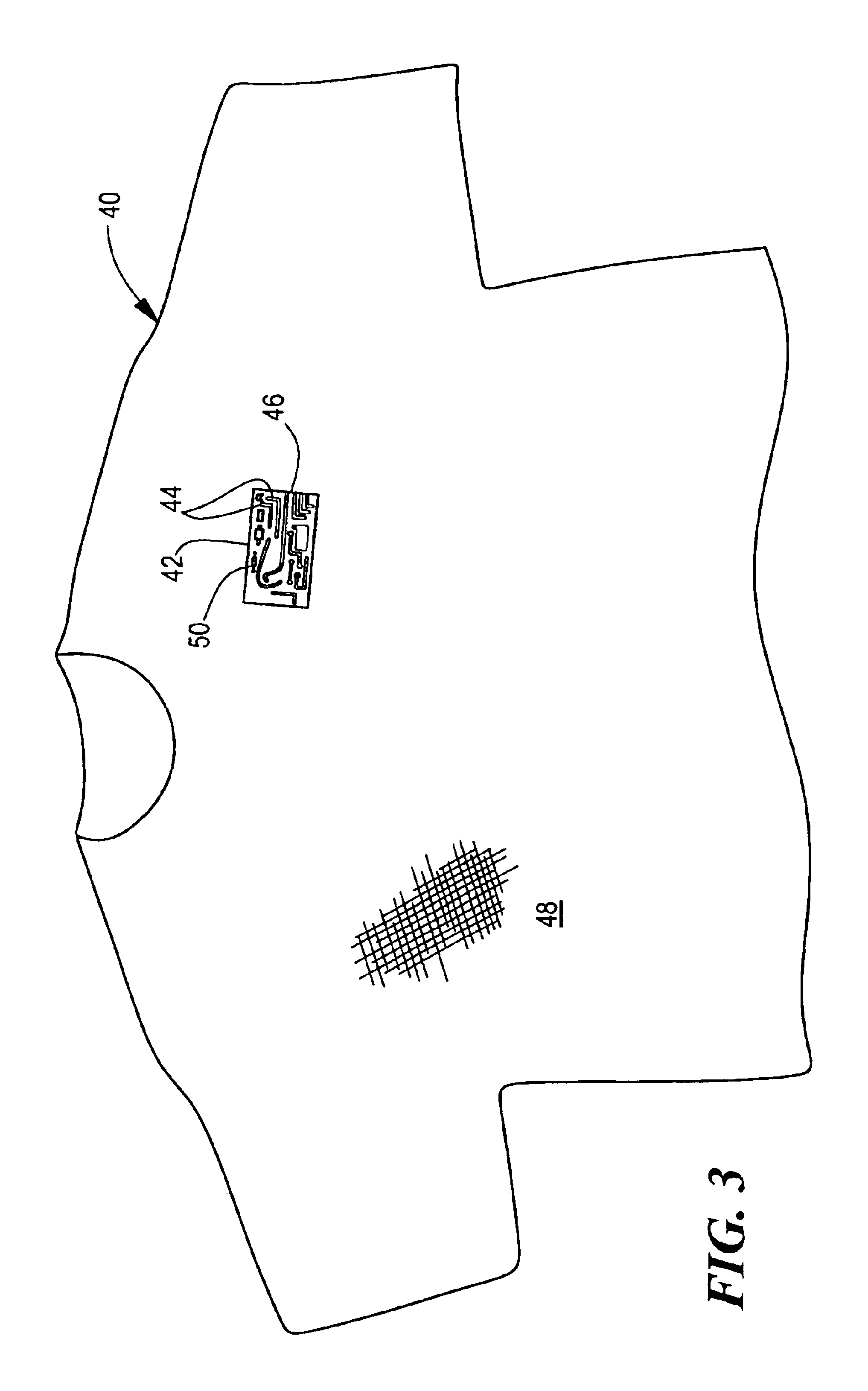

Method of manufacturing a fabric article to include electronic circuitry and an electrically active textile article

InactiveUS6729025B2Low-profileEliminate needLayered productsSemiconductor/solid-state device detailsEngineeringElectron

A method of manufacturing a fabric article to include electronic circuitry in which a flex circuit is assembled to include conductive traces and pads on a flexible substrate, a fabric article is placed on a rigid surface, and the substrate of the flex circuit is secured to the fabric article. Also disclosed is a fabric article which includes electronic circuitry and an electrically active textile article.

Owner:FOSTER-MILLER

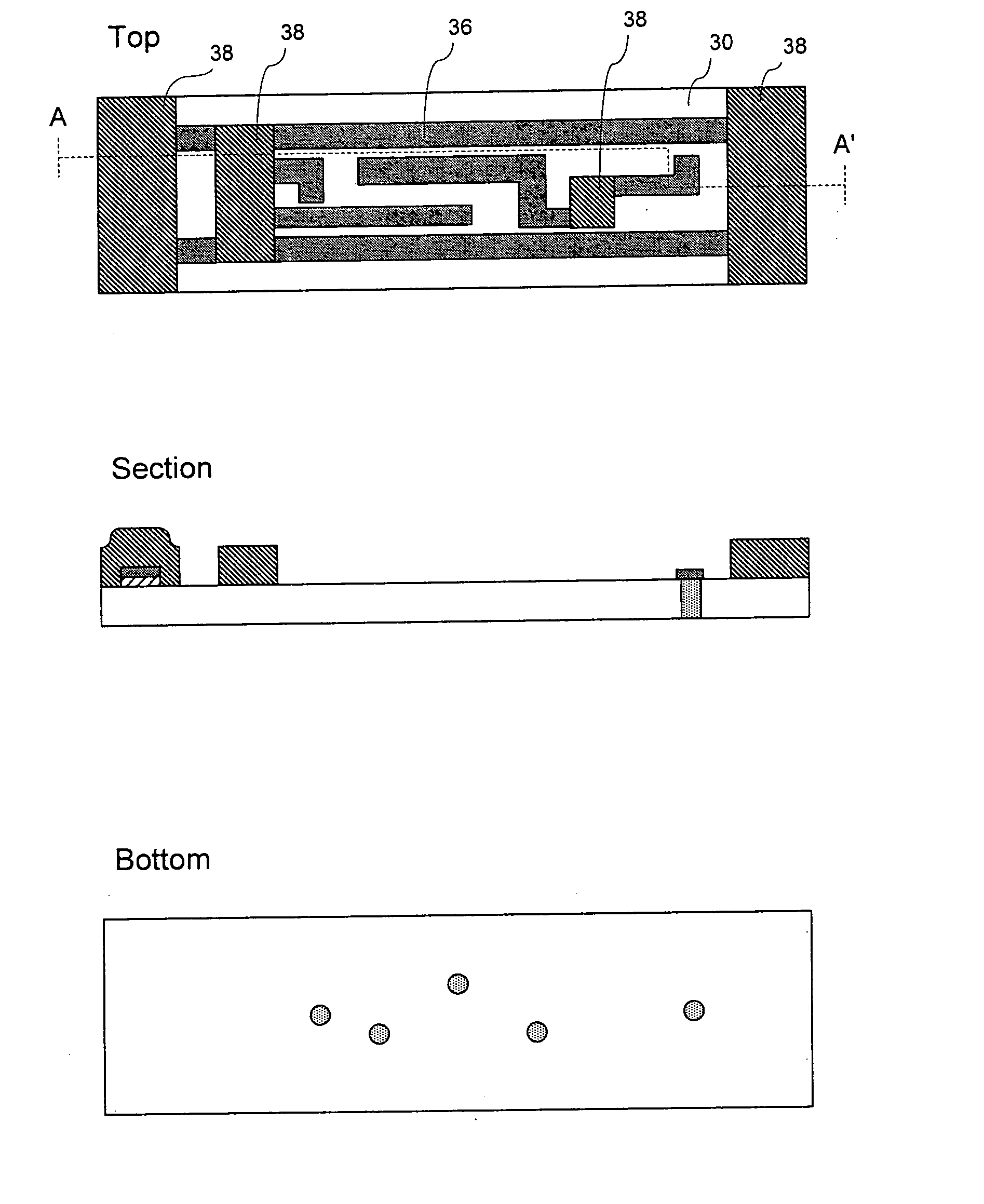

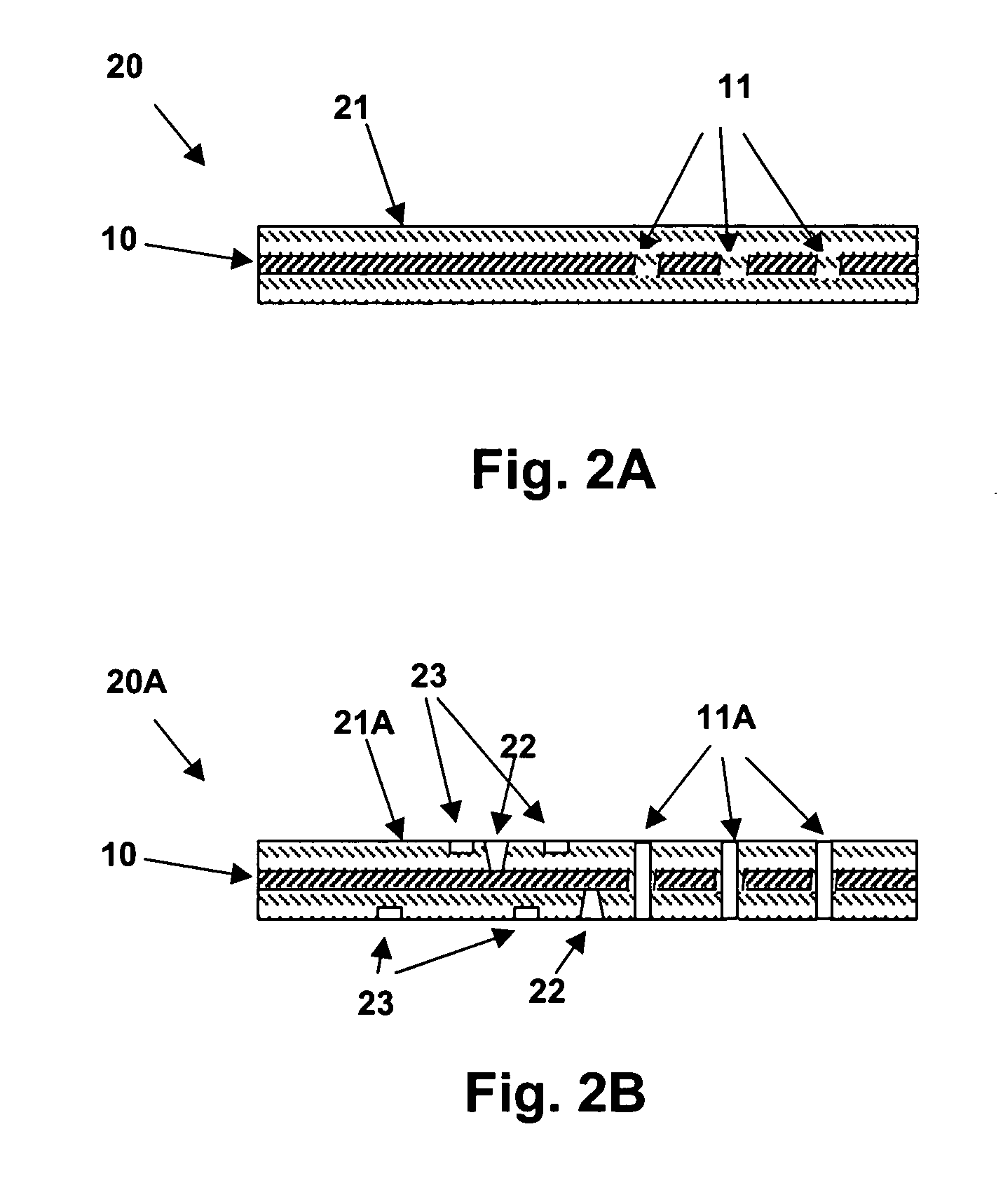

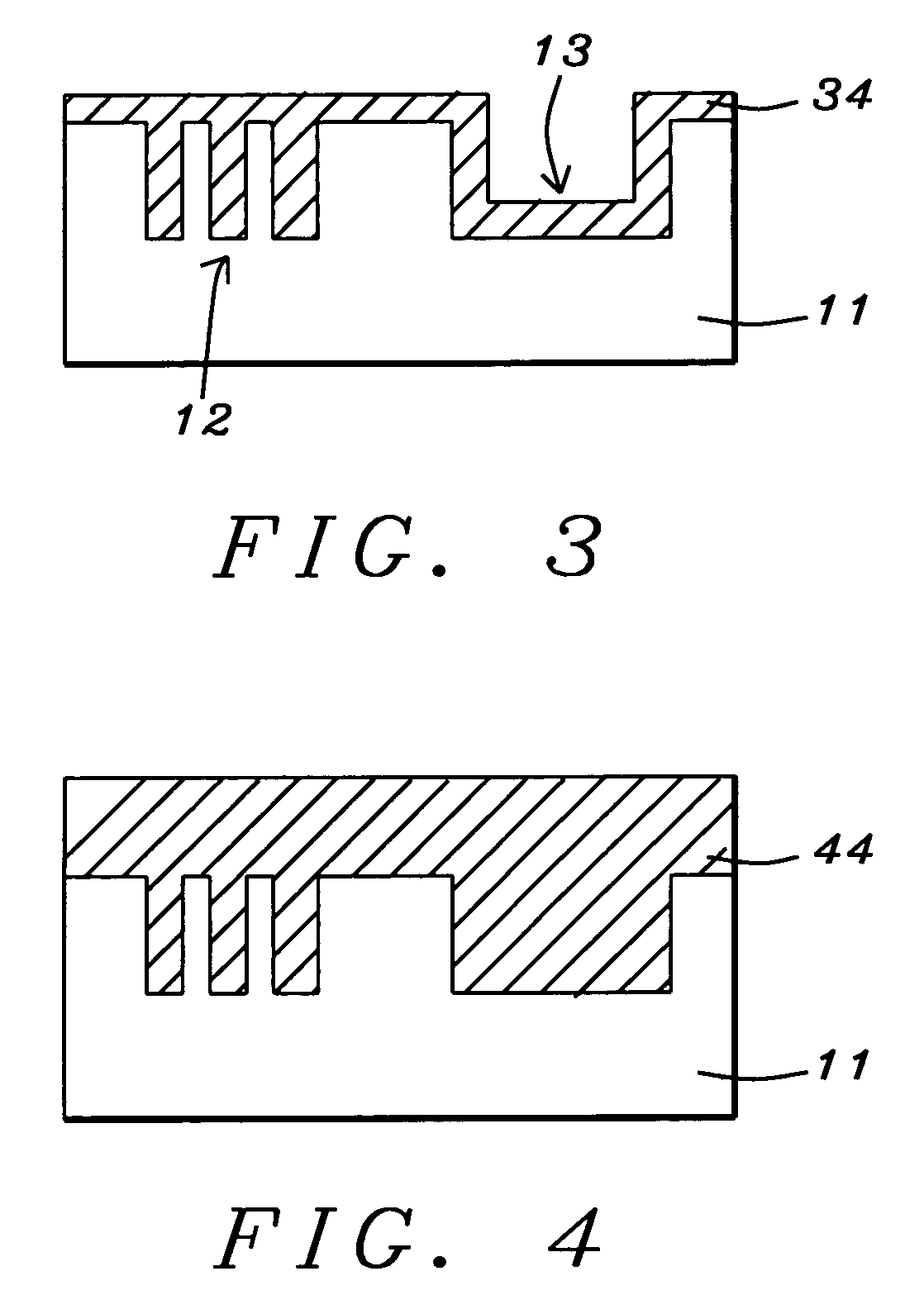

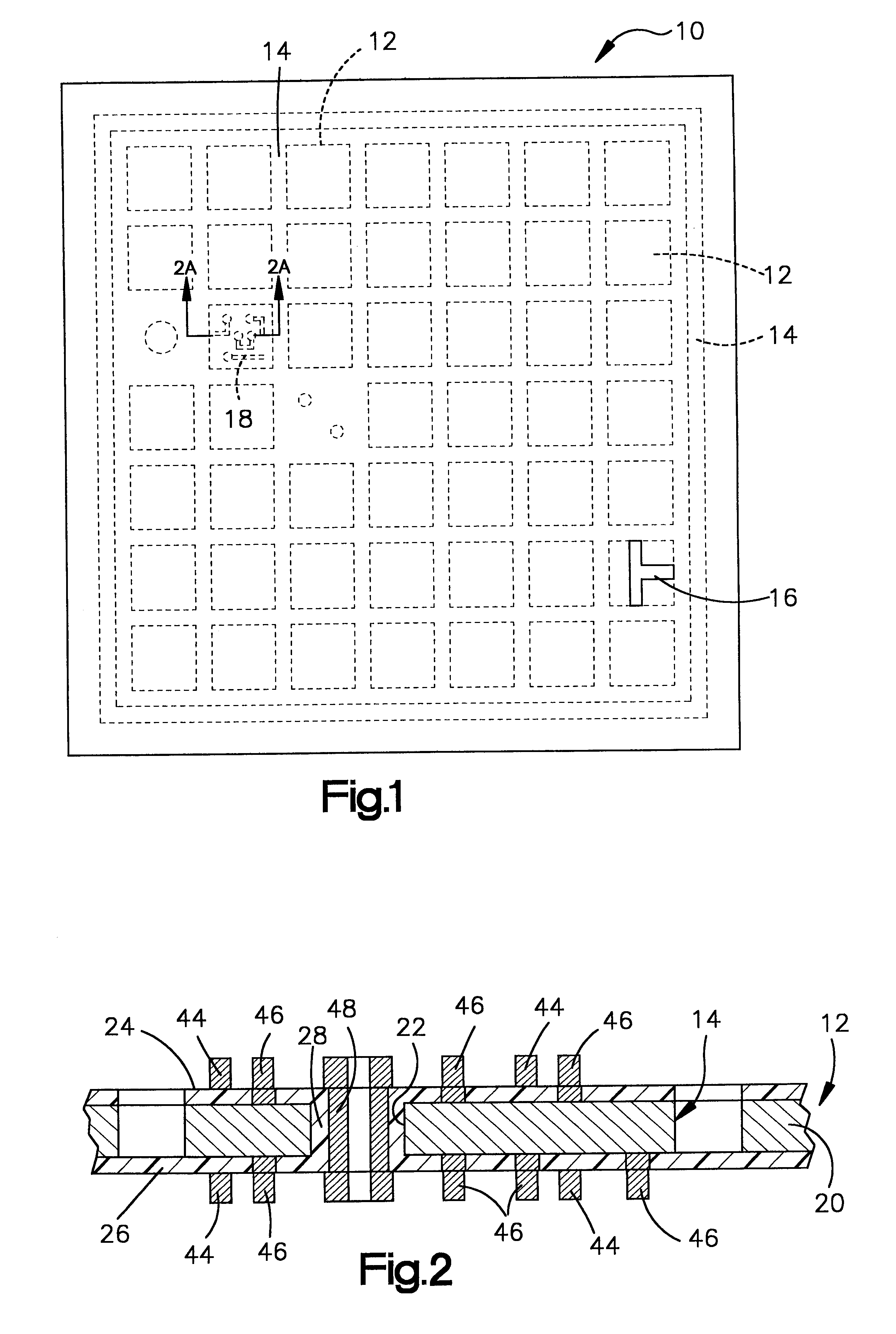

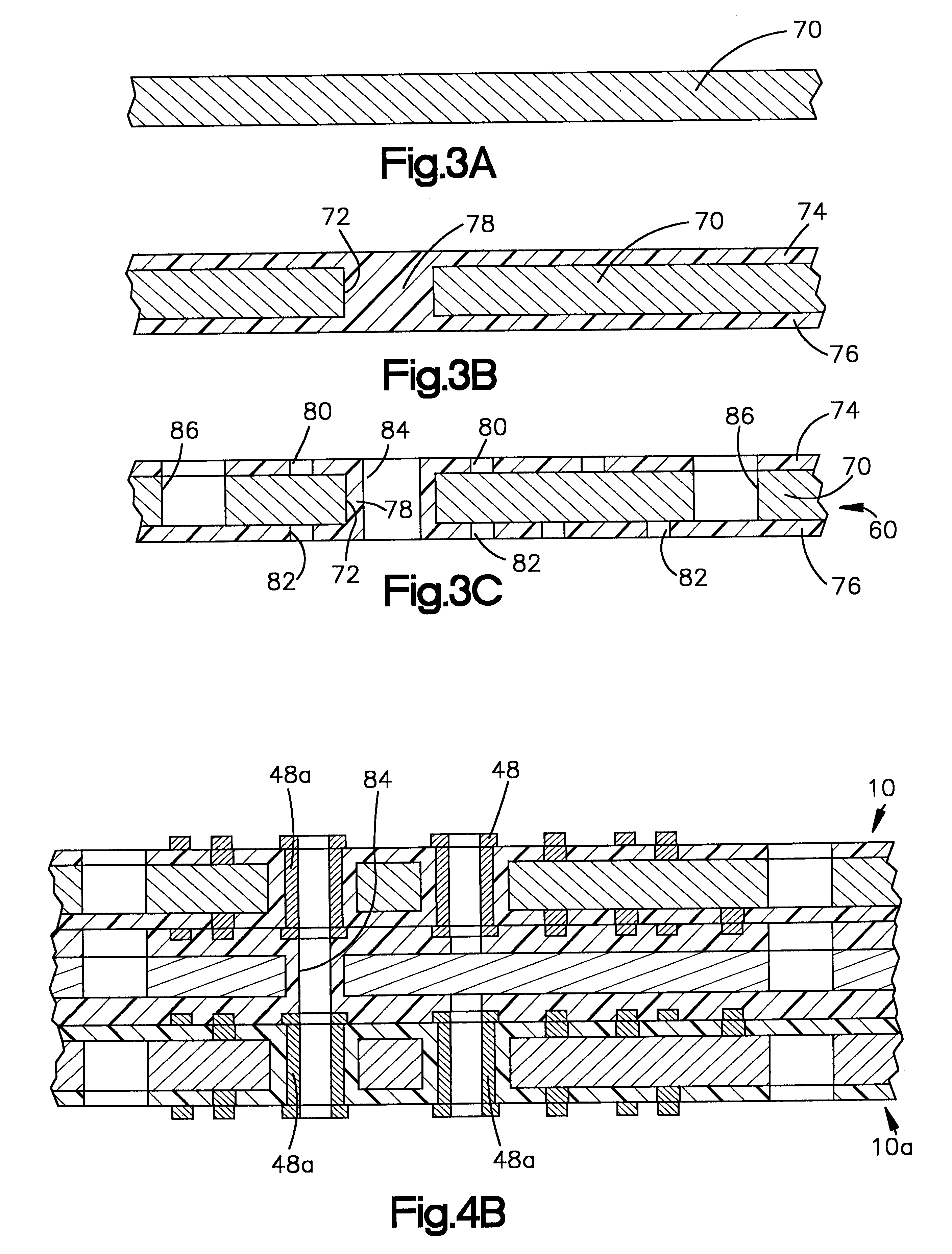

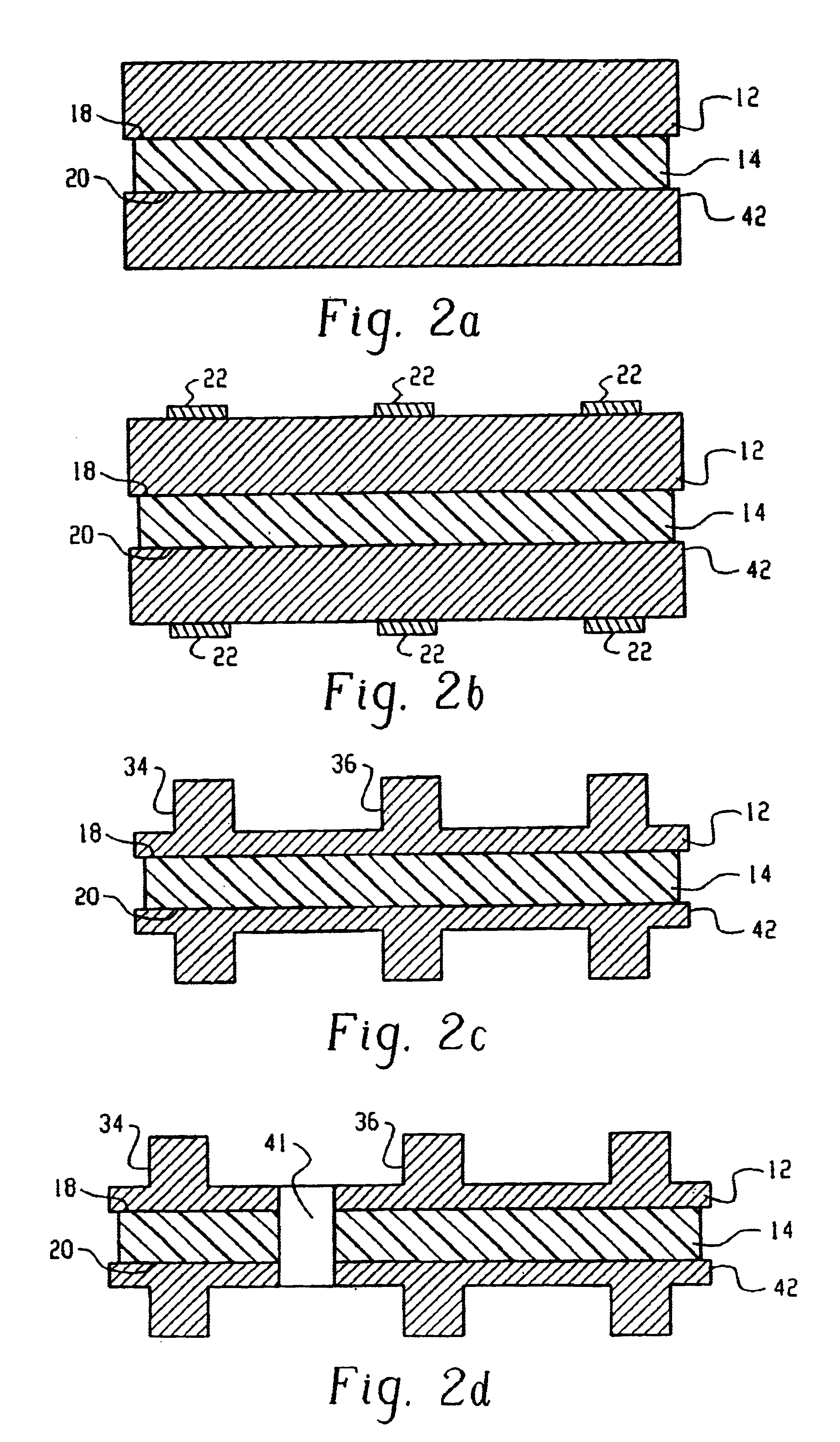

Composite laminate circuit structure and method of forming the same

InactiveUS6175087B1Printed circuit aspectsElectrical connection printed elementsComposite laminatesConductive materials

A method forming a composite laminate structure includes providing first and second circuit board element each having circuitry on at least one face thereof and plated through holes. A voltage plane element is provided having at least one voltage plane having opposite faces with layers of partially cured photodielectric material on each face. At least one hole is photopatterned and etched through the voltage plane element but completely isolated from the voltage plane. Each through hole in the voltage plane element is aligned with a plated through hole in each of the circuit board elements to provide a surface on the voltage plane element communicating with the plated through holes. The voltage plane is laminated between the circuit board elements and the photoimageable material on the voltage plane is fully cured. The surfaces of the voltage plane element communicating with the plated through holes in the circuit board elements are plated with a conducting material to establish a connection between the circuitry on the first and second circuit board elements.

Owner:GLOBALFOUNDRIES INC

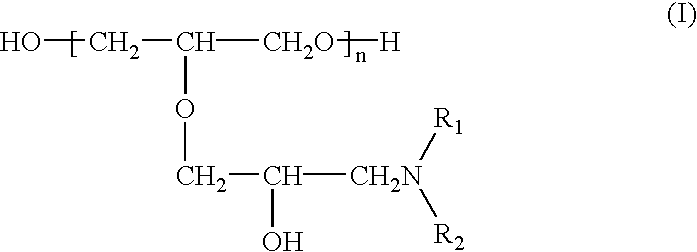

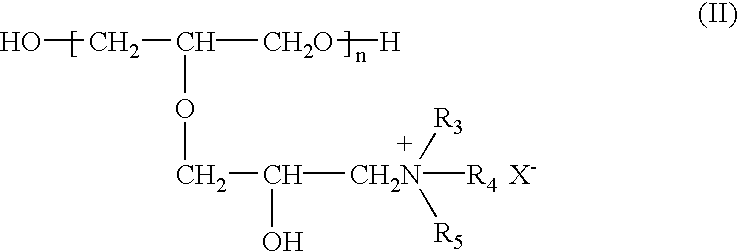

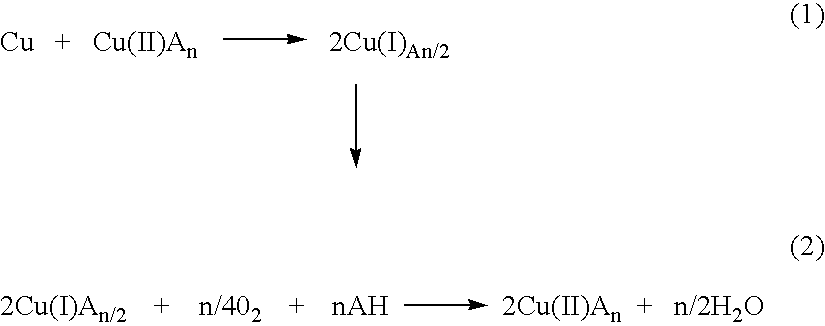

Copper plating bath and plating method for substrate using the copper plating bath

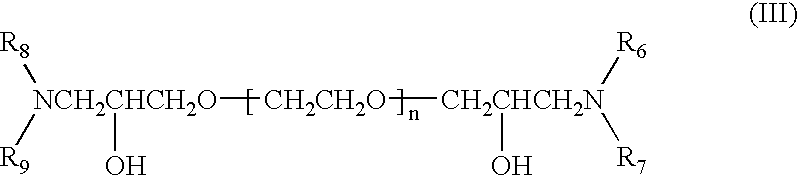

InactiveUS6800188B2Excellent characteristic and uniformityImprove reliabilityAnti-corrosive paintsLiquid/solution decomposition chemical coatingCopper platingGlycidyl ethers

A copper plating bath comprising a reaction condensate of an amine compound and glycidyl ether and / or a quaternary ammonium derivative of this reaction condensate, and a plating method using this copper plating bath are disclosed. A copper plating bath capable of providing highly reliable copper plating on a substrate such as a silicone wafer semiconductor substrate or printed board having minute circuit patterns and small holes such as blind via-holes, through-holes, and the like, and a method of copper plating using the copper plating bath can be provided.

Owner:EBARA-UDYLITE CO LTD

Plated terminations

InactiveUS6960366B2Improved termination featureEliminate and greatly simplifyResistor terminals/electrodesFinal product manufactureTermination problemEngineering

Improved termination features for multilayer electronic components are disclosed. Monolithic components are provided with plated terminations whereby the need for typical thick-film termination stripes is eliminated or greatly simplified. Such termination technology eliminates many typical termination problems and enables a higher number of terminations with finer pitch, which may be especially beneficial on smaller electronic components. The subject plated terminations are guided and anchored by exposed internal electrode tabs and additional anchor tab portions which may optionally extend to the cover layers of a multilayer component. Such anchor tabs may be positioned internally or externally relative to a chip structure to nucleate additional metallized plating material. External anchor tabs positioned on one or both of top and bottom surfaces of a monolithic structure can facilitate the formation of selective wrap-around plated terminations. The disclosed technology may be utilized with a plurality of monolithic multilayer components, including interdigitated capacitors, multilayer capacitor arrays, and integrated passive components. A variety of different plating techniques and termination materials may be employed in the formation of the subject self-determining plated terminations.

Owner:KYOCERA AVX COMPONENTS CORP

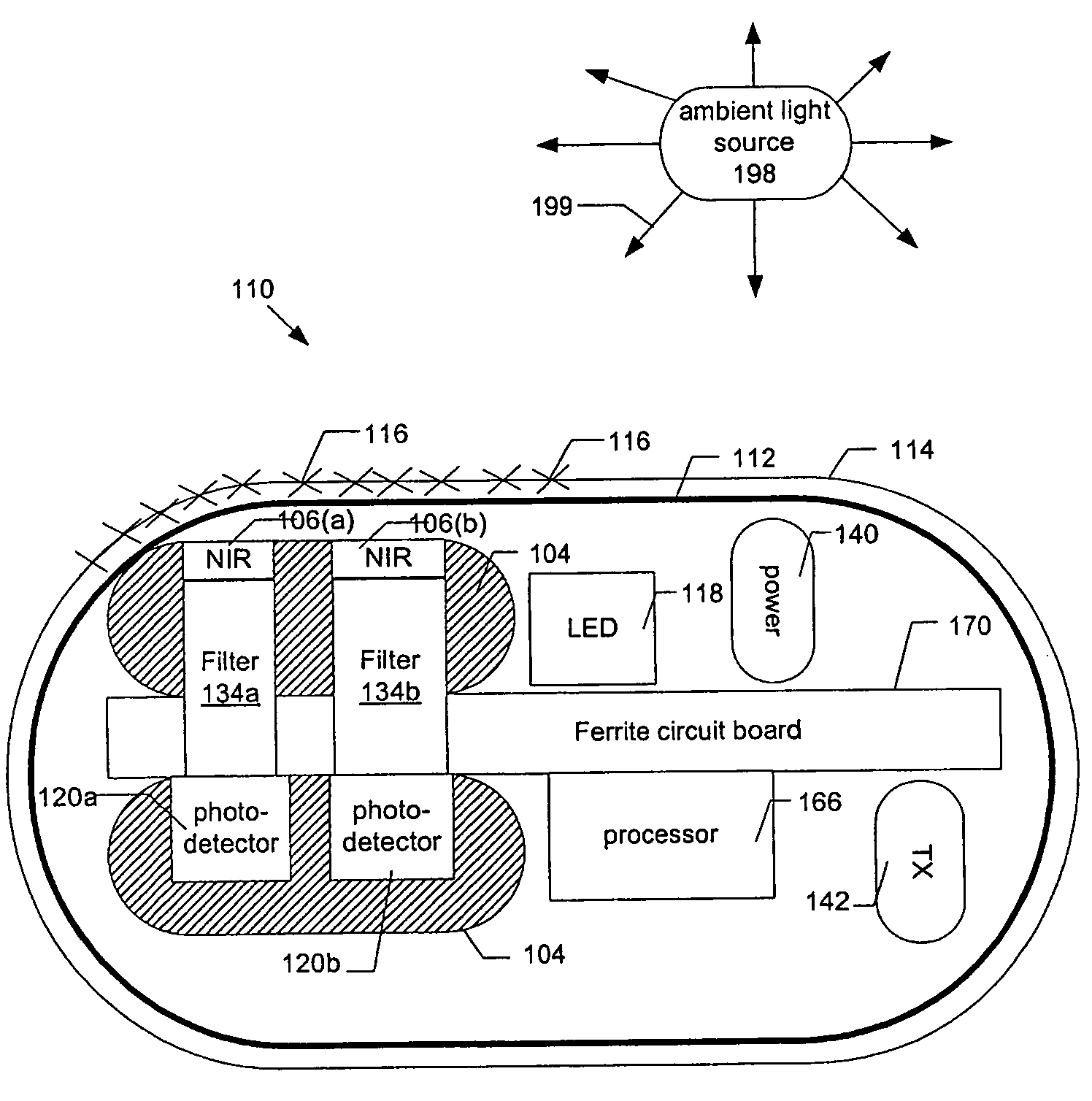

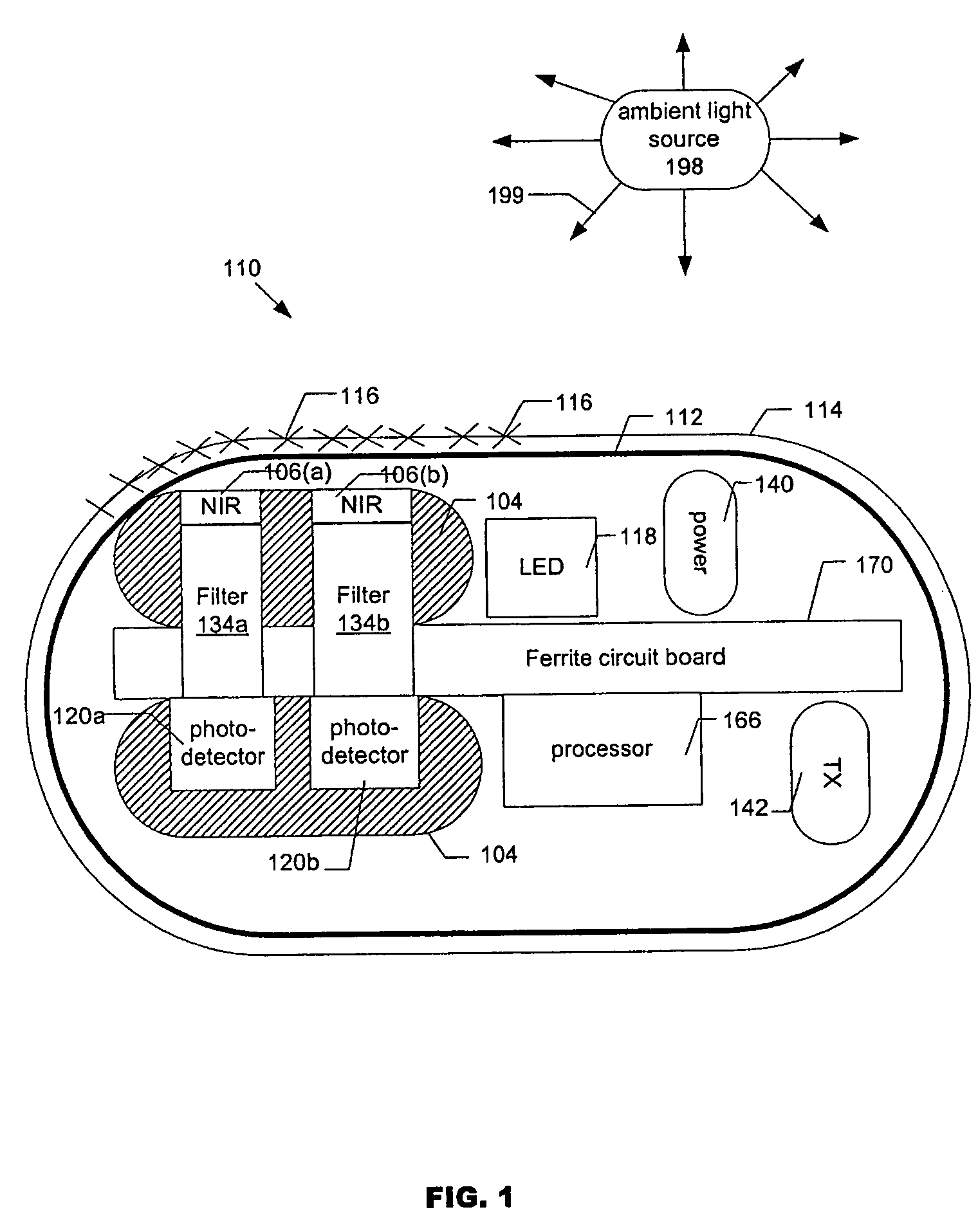

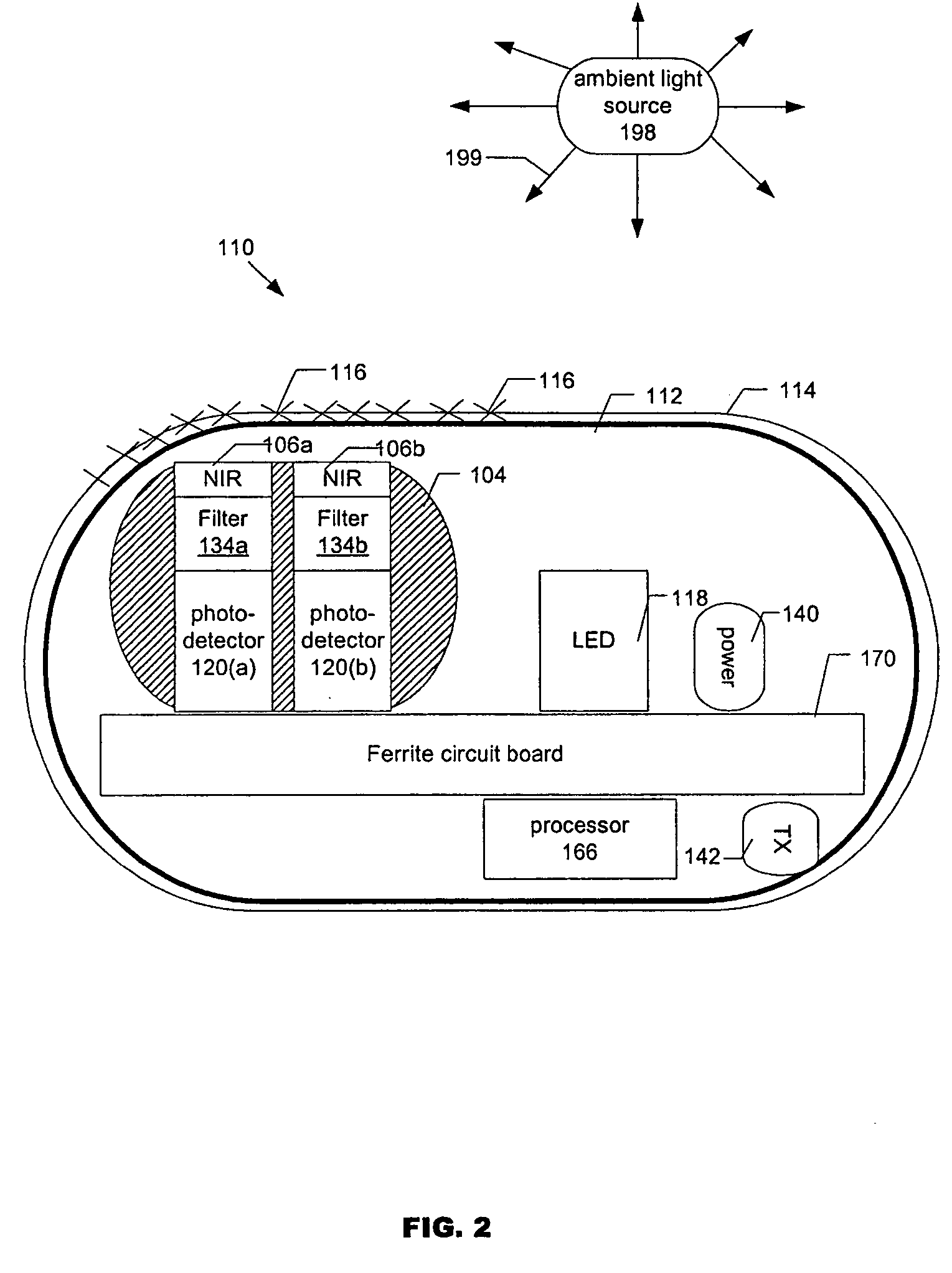

System and method for attenuating the effect of ambient light on an optical sensor

Owner:SENSEONICS INC

Method of making a product with improved material properties by moderate heat-treatment of a metal incorporating a dilute additive

InactiveUS6150186AStable mechanical propertiesImprove conductivitySemiconductor/solid-state device testing/measurementFinal product manufactureUltimate tensile strengthMechanical property

Deposition of metal in a preferred shape, including coatings on parts, or stand-alone materials, and subsequent heat treatment to provide improved mechanical properties. In particular, the method gives products with relatively high yield strength. The products often have relatively high elastic modulus, and are thermally stable, maintaining the high yield strength at temperatures considerably above 25 DEG C. This technique involves depositing a material in the presence of a selected additive, and then subjecting the deposited material to a moderate heat treatment. This moderate heat treatment differs from other commonly employed "stress relief" heat treatments in using lower temperatures and / or shorter times, preferably just enough to reorganize the material to the new, desired form. Coating a shape and heat treating provides a shaped deposit with improved material properties. Coating a shape with a portion connected to a base and a portion detached therefrom can provide a resilient, conductive contact useful for electronic applications.

Owner:FORMFACTOR INC

Probe card assembly

InactiveUS6838893B2Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureProbe cardTransformer

In a probe card assembly, a series of probe elements can be arrayed on a silicon space transformer. The silicon space transformer can be fabricated with an array of primary contacts in a very tight pitch, comparable to the pitch of a semiconductor device. One preferred primary contact is a resilient spring contact. Conductive elements in the space transformer are routed to second contacts at a more relaxed pitch. In one preferred embodiment, the second contacts are suitable for directly attaching a ribbon cable, which in turn can be connected to provide selective connection to each primary contact. The silicon space transformer is mounted in a fixture that provides for resilient connection to a wafer or device to be tested. This fixture can be adjusted to planarize the primary contacts with the plane of a support probe card board.

Owner:FORMFACTOR INC

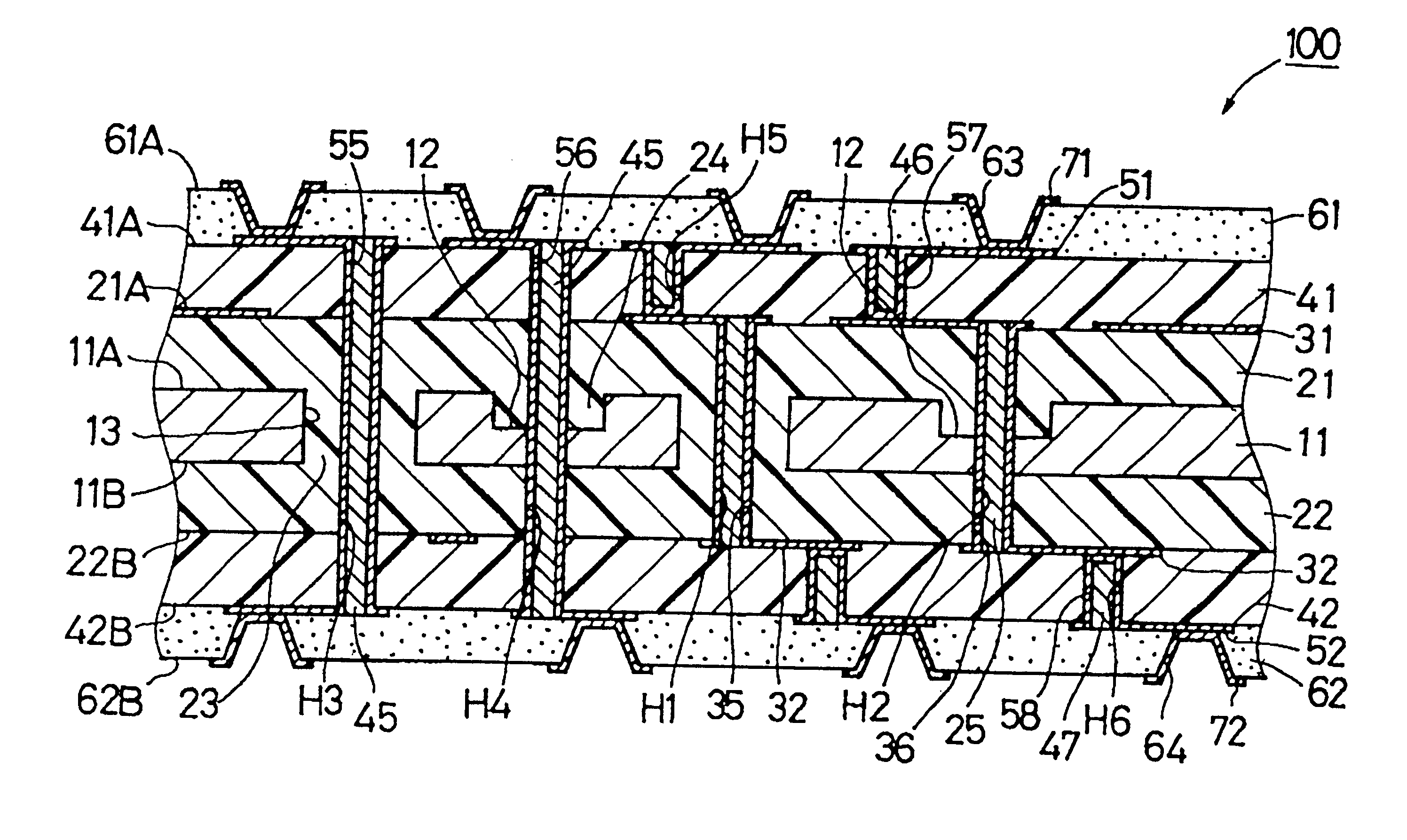

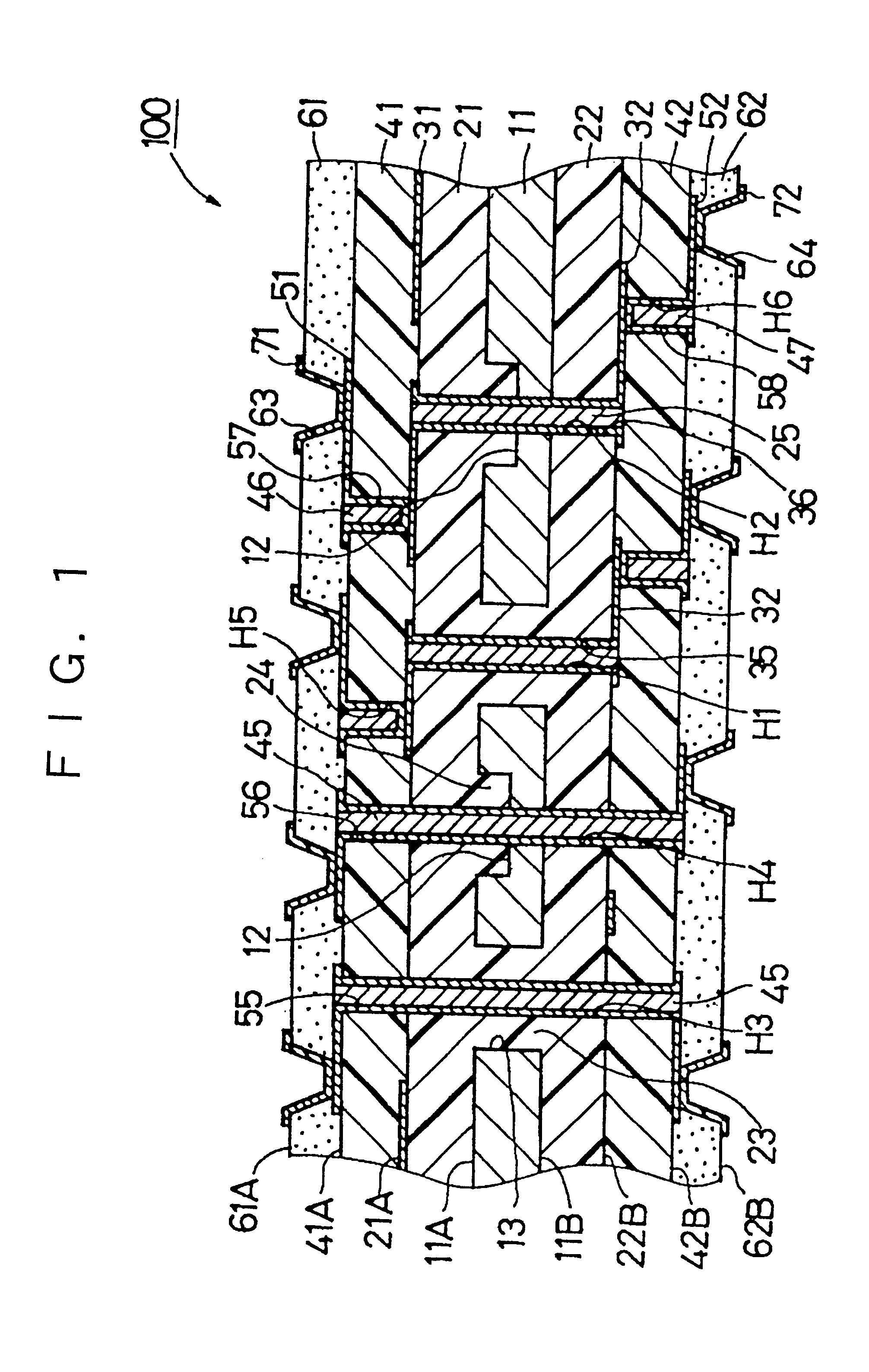

Metal core multilayer resin wiring board with thin portion and method for manufacturing the same

InactiveUS6323439B1Improve rigidityFirmly connectedElectrically conductive connectionsPrinted circuit aspectsEngineeringMachining

A multilayer resin wiring board includes a metal core substrate having a first main surface and a second main surface; a plurality of wiring layers located on the first and second main surfaces of the metal core substrate; a plurality of insulating resin layers, each intervening between the metal core substrate and the wiring layers and between the metal core substrate and the wiring layers and between the wiring layers; and a via formed on the wall of a through hole for connection to the metal core substrate extending through the insulating resin layers and the metal core substrate so as to establish electrical conductivity to the metal core substrate. The metal core substrate has a thin portion which is thinner than the remaining portion of the metal core substrate. The through hole for connection to the metal core substrate is formed through the thin portion by laser machining.

Owner:NGK SPARK PLUG CO LTD

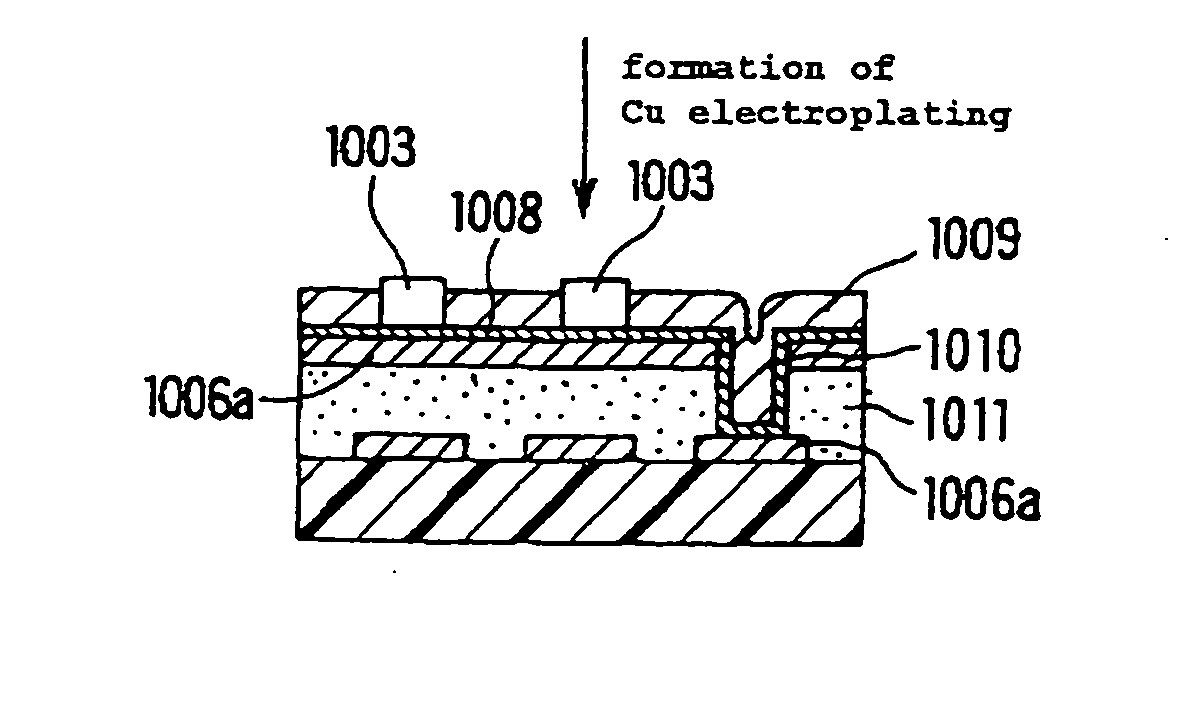

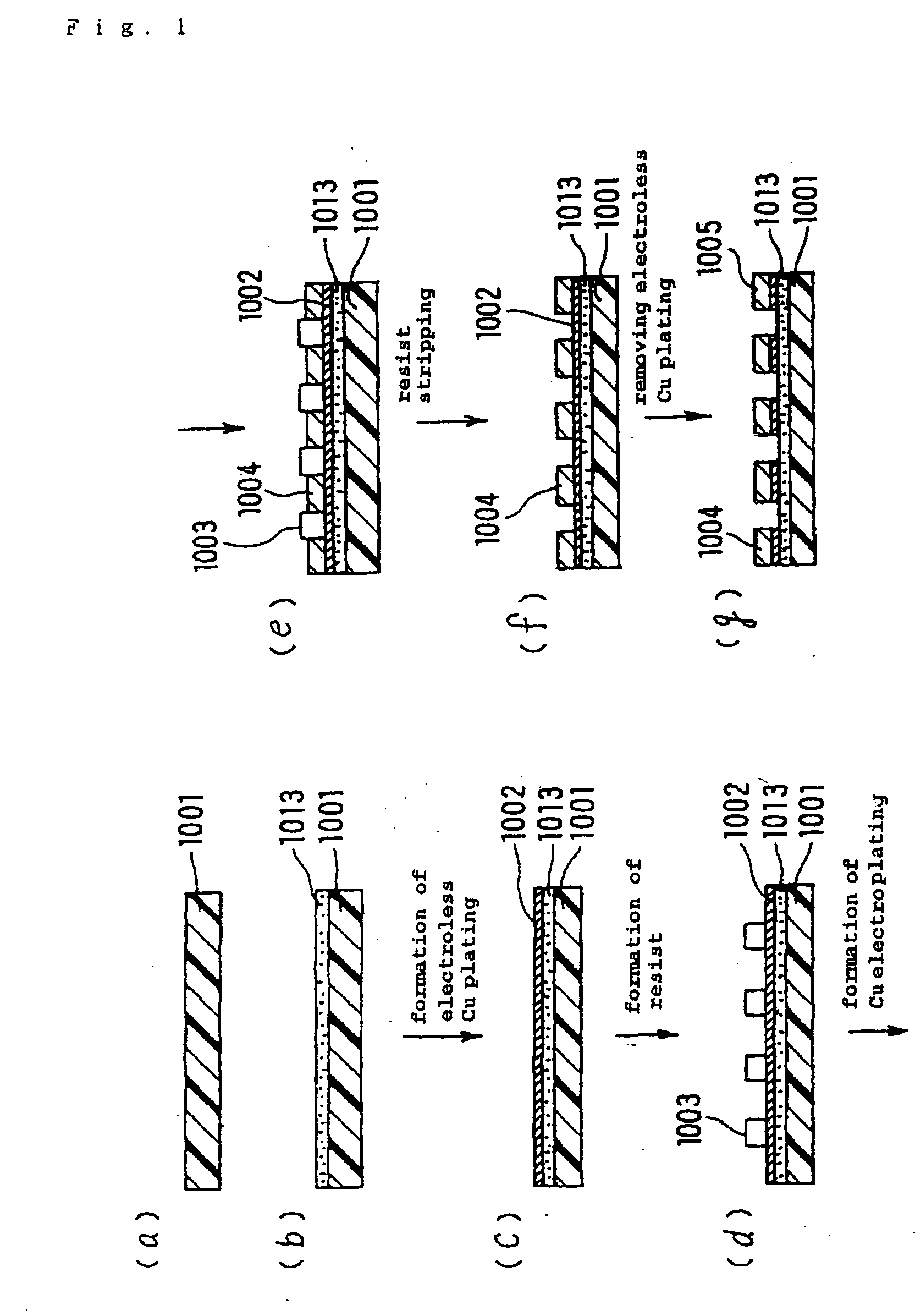

Printed wiring board and its manufacturing method

The present invention has for its object to provide a process for manufacturing multilayer printed circuit boards which is capable of simultaneous via hole filling and formation of conductor circuit and via holes of good crystallinity and uniform deposition can be constructed on a substrate and high-density wiring and highly reliable conductor connections can be realized without annealing. The present invention is related to a process for manufacturing multilayer printed circuit boards which comprises disposing an interlayer resin insulating layer on a substrate formed with a conductor circuit, creating openings for formation of via holes in said interlayer resin insulating layer, forming an electroless plated metal layer on said interlayer resin insulating layer, disposing a resist thereon, performing electroplating, stripping the resist off and etching the electroless plated metal layer to provide a conductor circuit and via holes, wherein the electroplating is performed intermittently using said electroless plated metal layer as cathode and a plating metal as anode at a constant voltage between said anode and said cathode.

Owner:IBIDEN CO LTD

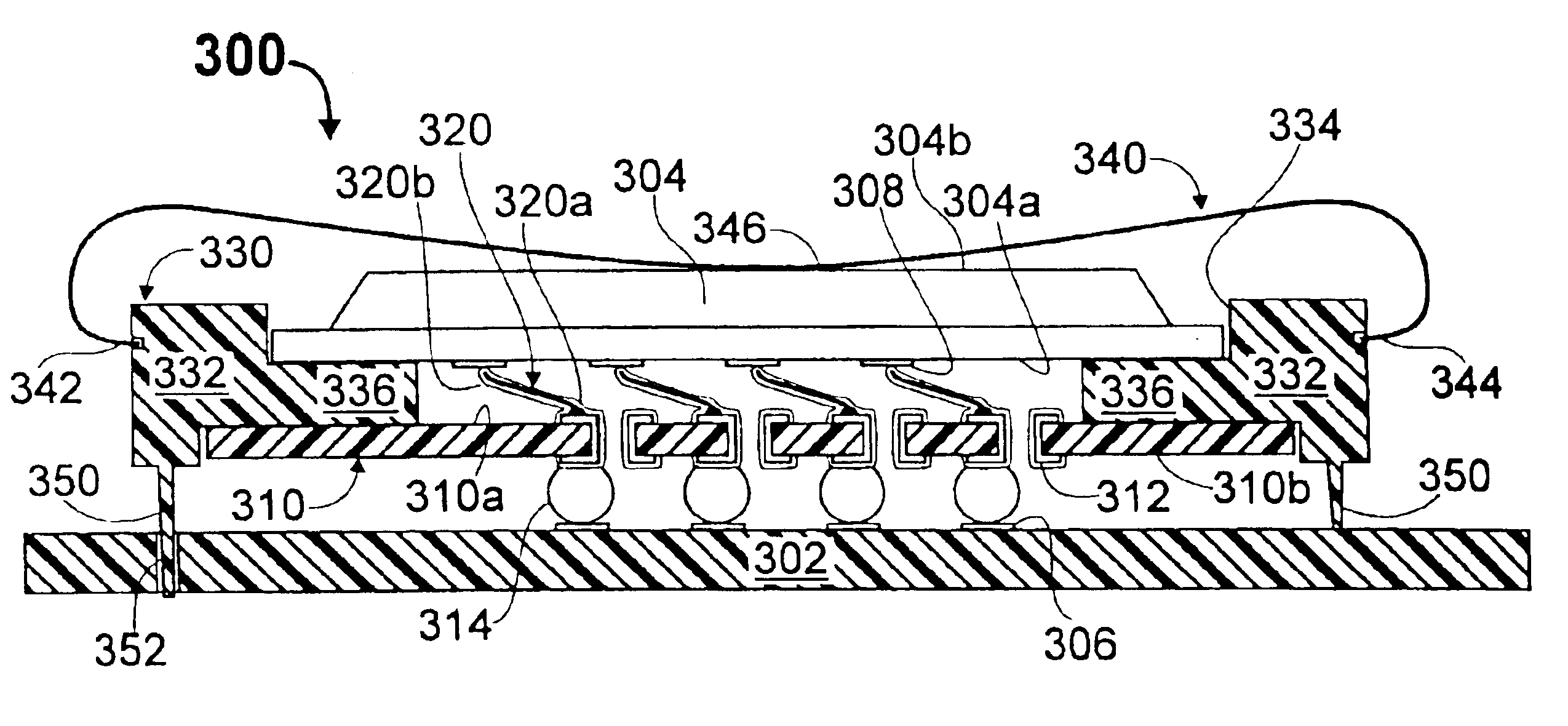

Methods of removably mounting electronic components to a circuit board, and sockets formed by the methods

InactiveUS6913468B2Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureSurface mountingSolder ball

Surface-mount, solder-down sockets are described which permit electronic components such as semiconductor packages to be releasably mounted to a circuit board. Generally, the socket includes resilient contact structures extending from a top surface of a support substrate, and solder-ball (or other suitable) contact structures disposed on a bottom surface of the support substrate. Composite interconnection elements are described for use as the resilient contact structures disposed atop the support substrate. In use, the support substrate is soldered down onto the circuit board, the contact structures on the bottom surface of the support substrate contacting corresponding contact areas on the circuit board. In any suitable manner, selected ones of the resilient contact structures atop the support substrate are connected, via the support substrate, to corresponding ones of the contact structures on the bottom surface of the support substrate.

Owner:FORMFACTOR INC

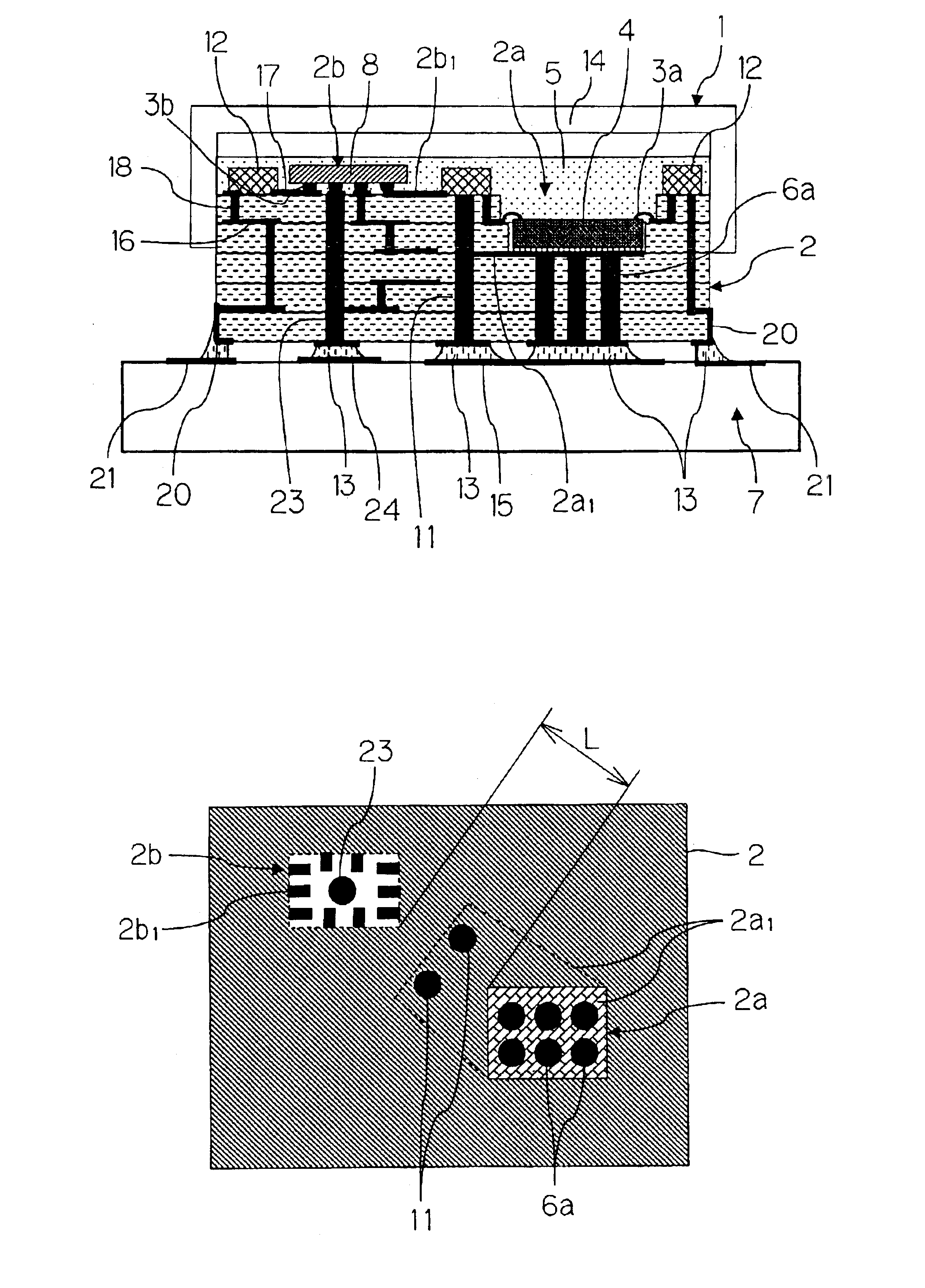

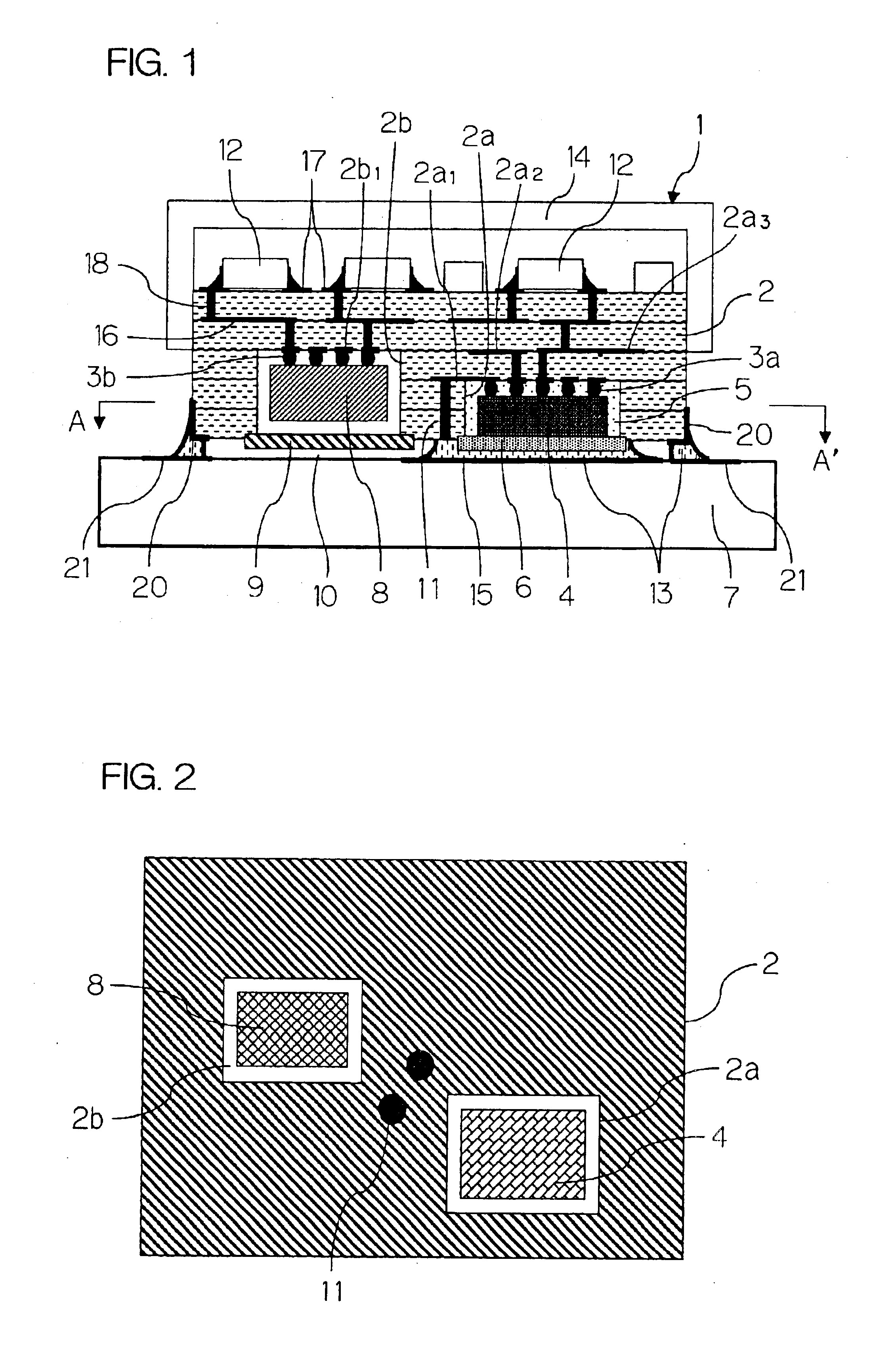

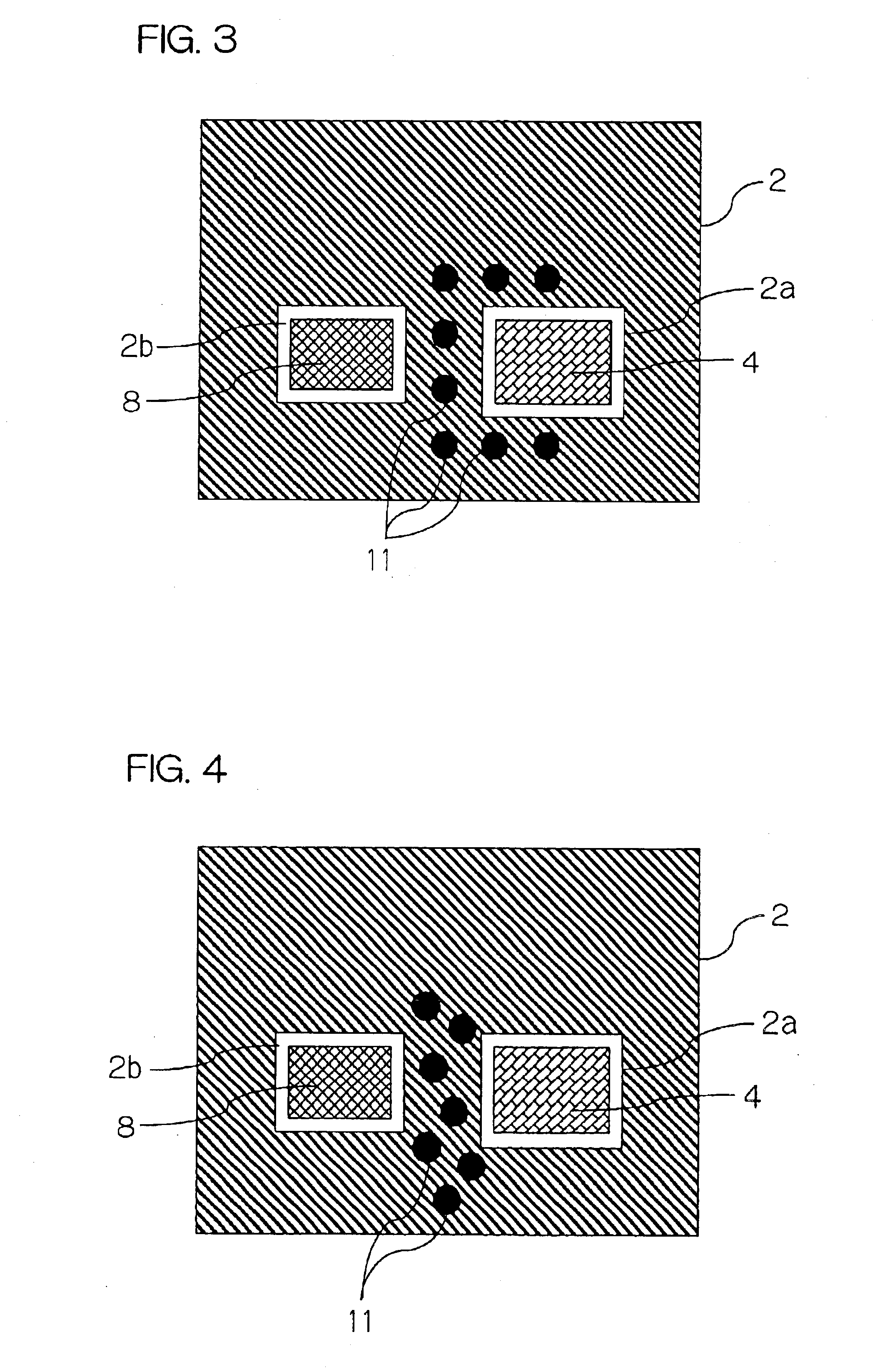

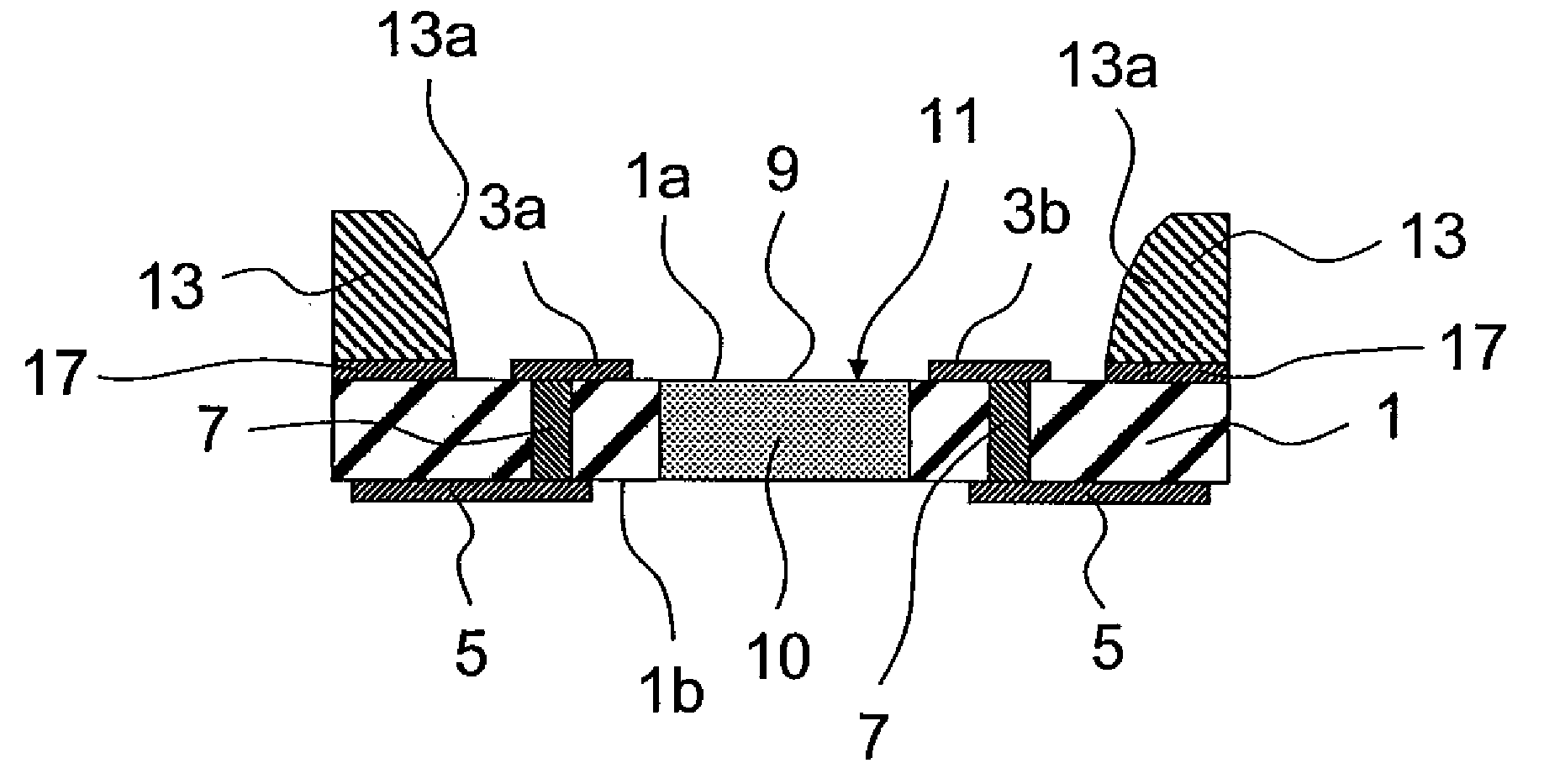

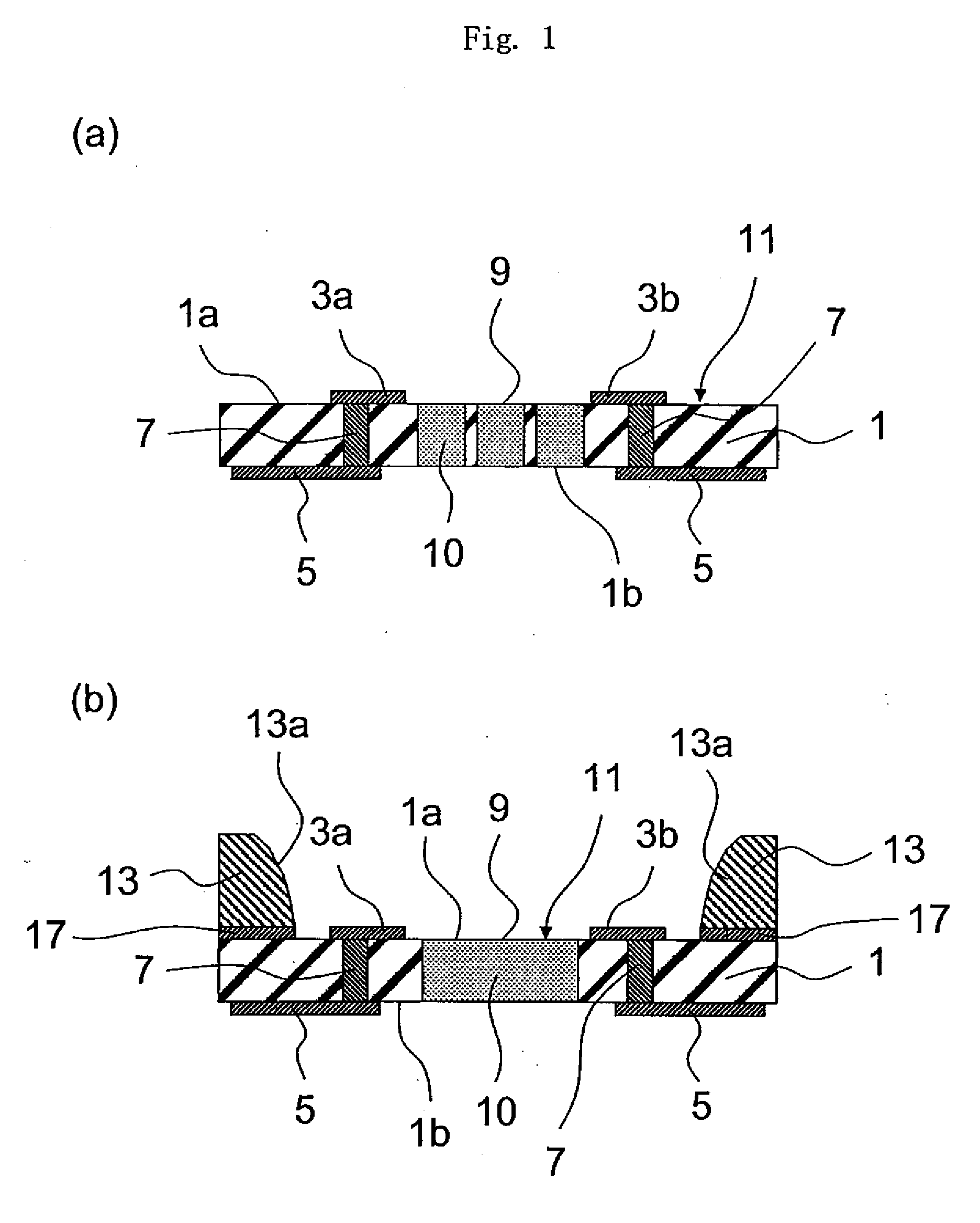

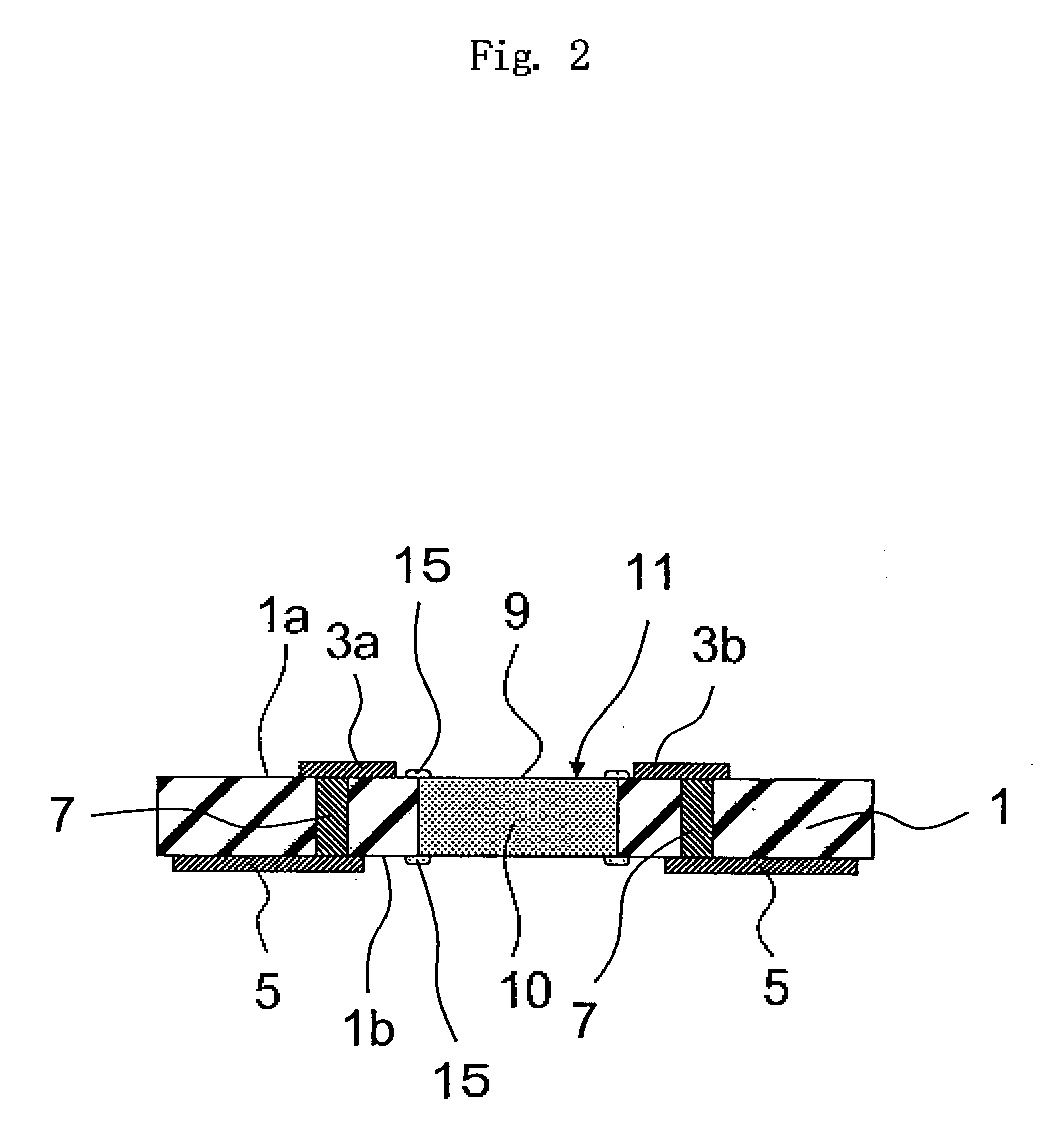

High frequency module

InactiveUS6873529B2Low costImprove performanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringSurface acoustic wave

There is presented a high frequency module, in which a recess 2a for mounting power amplifier device is formed on a lower surface of a dielectric substrate 2, and a recess 2b for mounting surface acoustic wave filter is formed on an upper surface of the dielectric substrate 2, and a power amplifier device 4 and a surface acoustic wave filter 8 are mounted through conductive bumps 3a and 3b on the recesses 2a and 2b, respectively. In addition, a through-hole conductor 11 whose one end is exposed at the lower surface of the dielectric substrate 2 is provided between the recesses 2a and 2b. The exposed end of the through-hole conductor 11 is attached to a thermal dissipation conductor 15 on an upper surface of an external electric circuit board 7 through a brazing material 13.

Owner:KYOCERA CORP

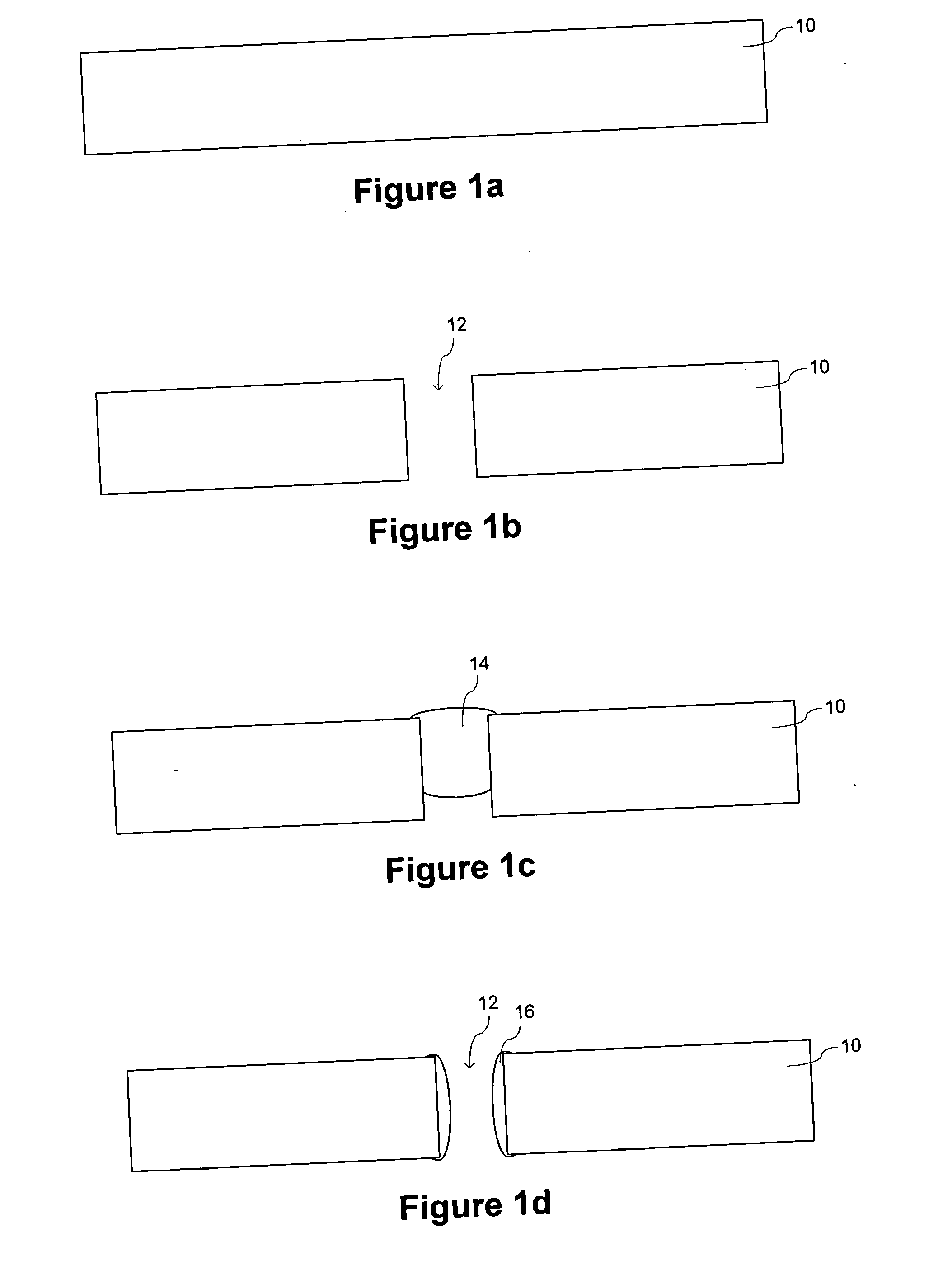

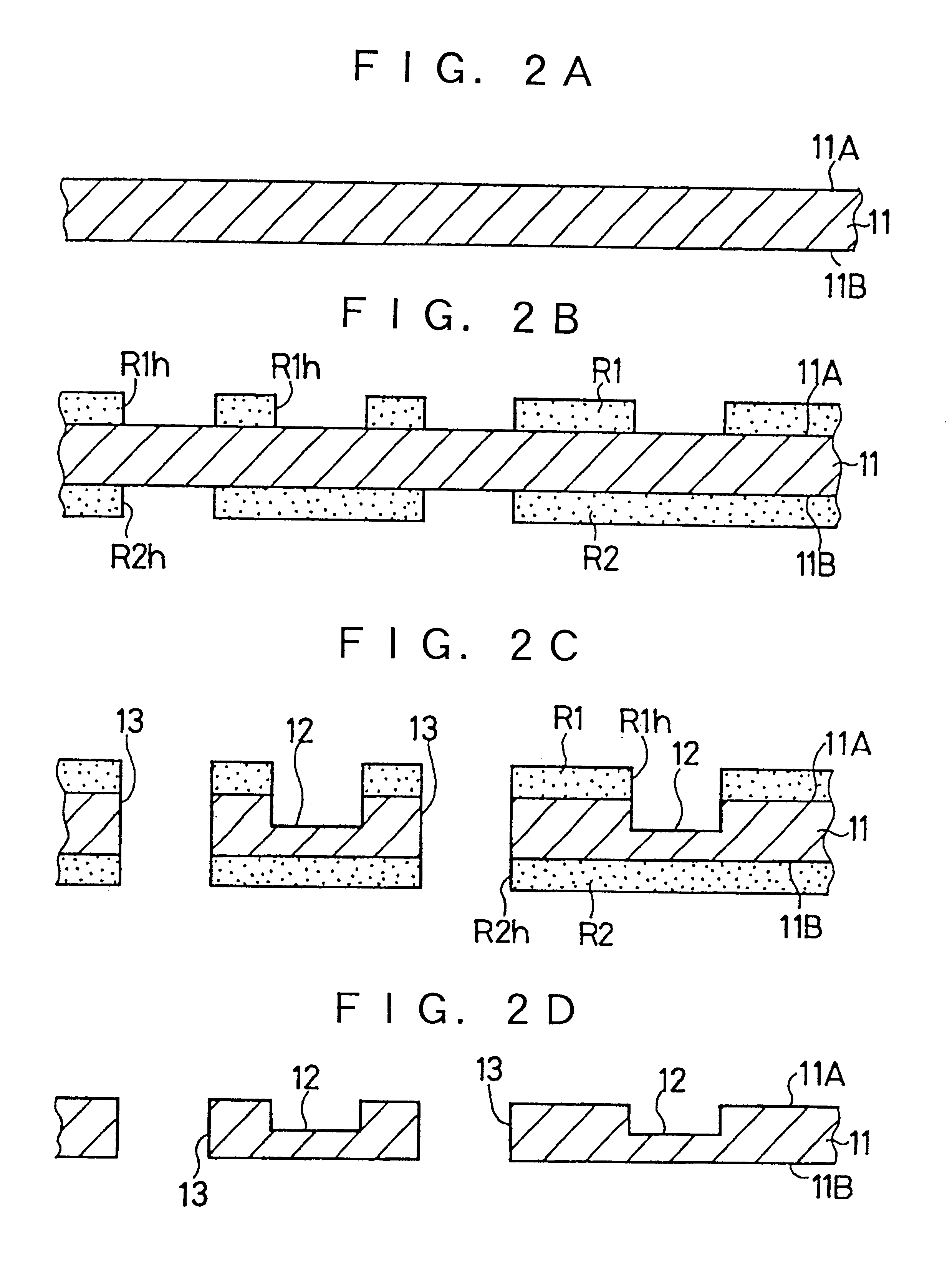

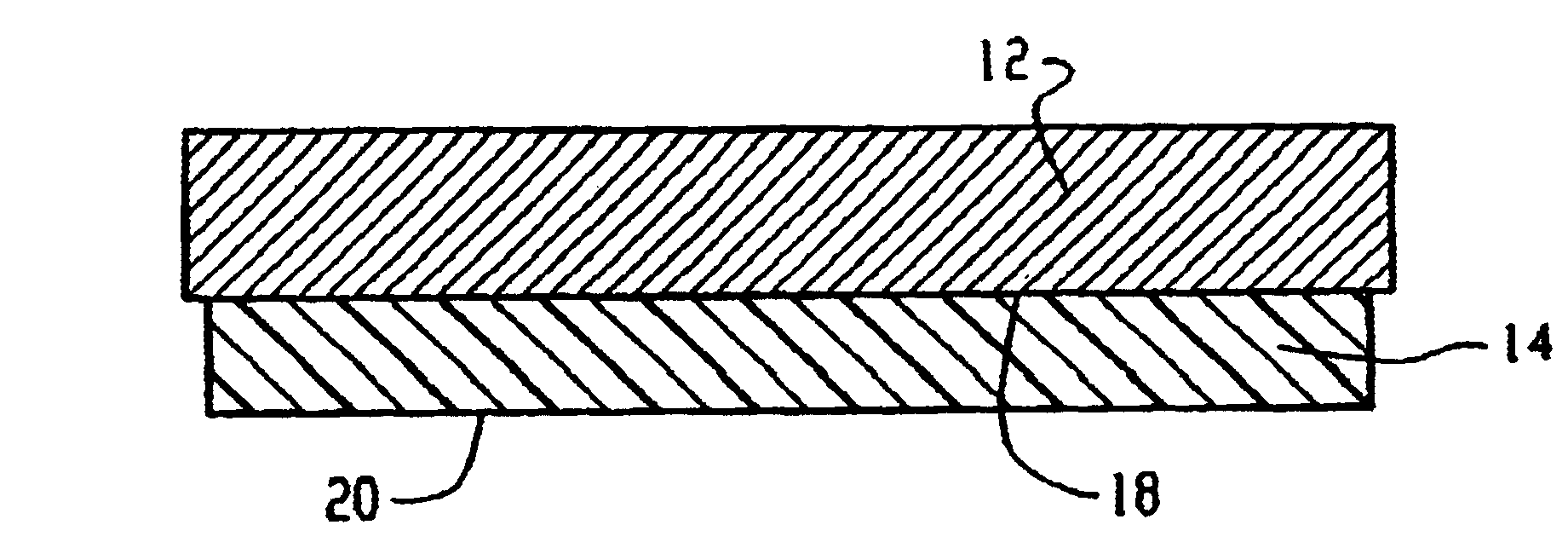

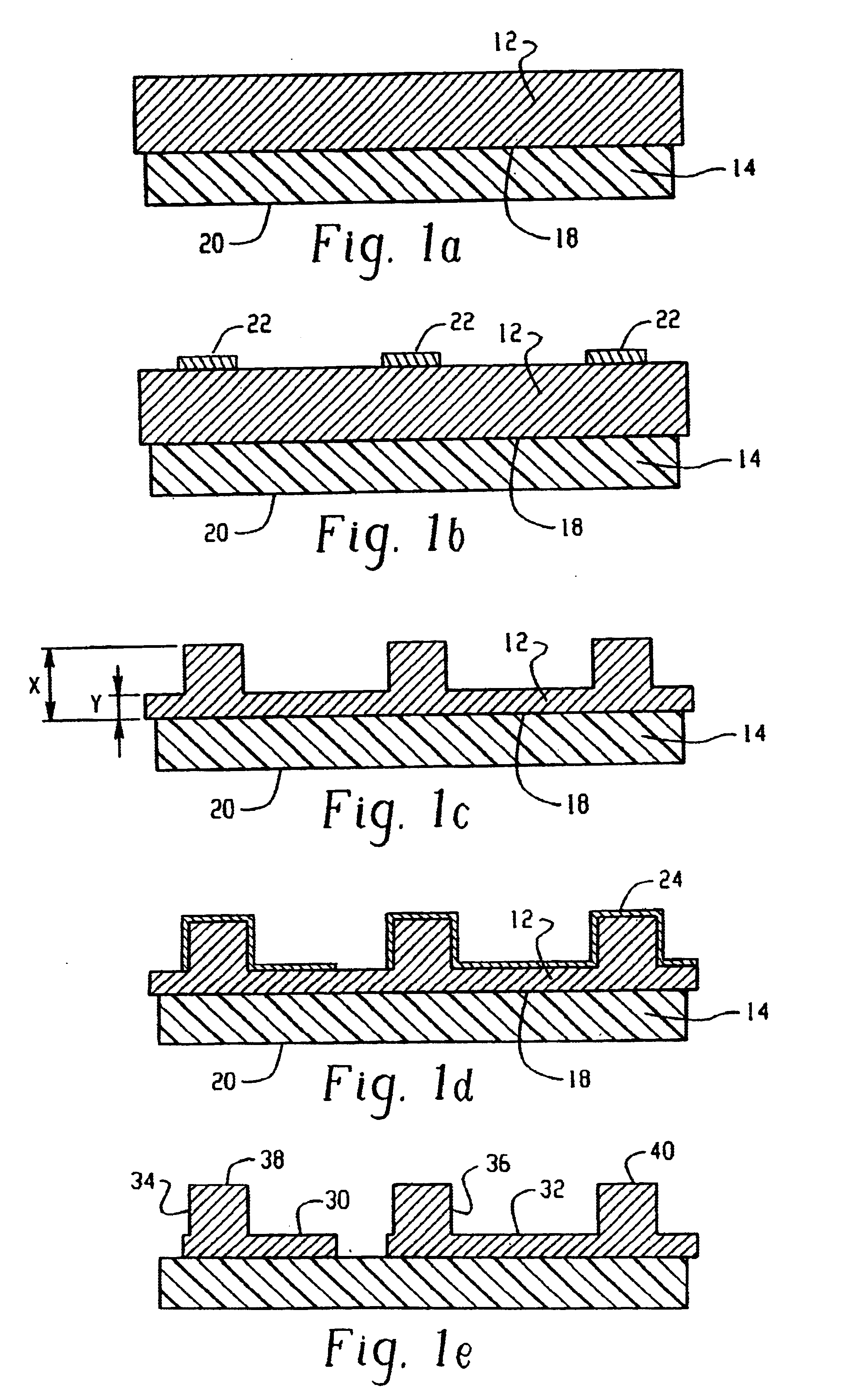

Manufacturing methods for printed circuit boards

InactiveUS6902869B2Improve rigidityEasy to handleLine/current collector detailsWave amplification devicesDielectric substratePhotoresist

A method of forming a plurality of solid conductive bumps for interconnecting two conductive layers of a circuit board with substantially coplanar upper surfaces. The method comprises the steps of applying a continuous homogenous metal layer onto a dielectric substrate, applying a first photoresist and exposing and developing said first photoresist to define a pattern of conductive bumps; etching the metal layer exposed by said development to form said plurality of conductive bumps; removing said first photoresist; applying a second photoresist onto the metal layer; exposing and developing said second photoresist to define a pattern of conductive bumps and circuit lines; etching the metal layer exposed by said development to form a pattern of circuit lines in said metal layer; and removing said second photoresist. The methods of the present invention also provides for fabricating a multilayer circuit board and a metallic border for providing rigidity to a panel.

Owner:GLOBALFOUNDRIES INC

Wiring Board for Light-Emitting Element

InactiveUS20080043444A1InhibitionHigh bonding strengthPrinted circuit aspectsSolid-state devicesElectrical conductorHeat conducting

A wiring board for light-emitting element, comprising a ceramic insulating substrate, and a conductor layer formed on the surface or in the inside of the insulating substrate, and having a mounting region mounting a light-emitting element on one surface of the insulating substrate; wherein the insulating substrate is provided with a heat-conducting pole-like conductor having a thermal conductivity higher than that of said insulating substrate; and the heat-conducting pole-like conductor is extending through the insulating substrate in the direction of thickness thereof from the light-emitting element mounting region of the insulating substrate, and is formed by the co-firing with the insulating substrate. The wiring board is produced inexpensively by co-firing, features excellent heat-radiating performance, is capable of quickly radiating the heat from the light-emitting element when the light-emitting element is mounted, and effectively prevents a decrease in the brightness of the light-emitting element caused by the heat.

Owner:KYOCERA CORP

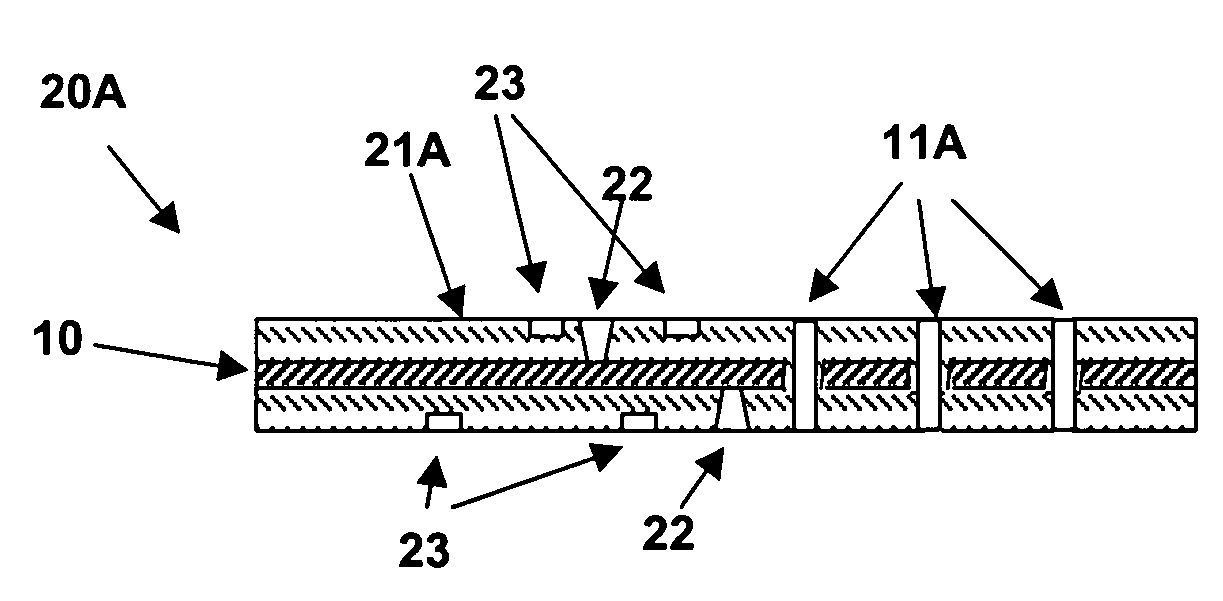

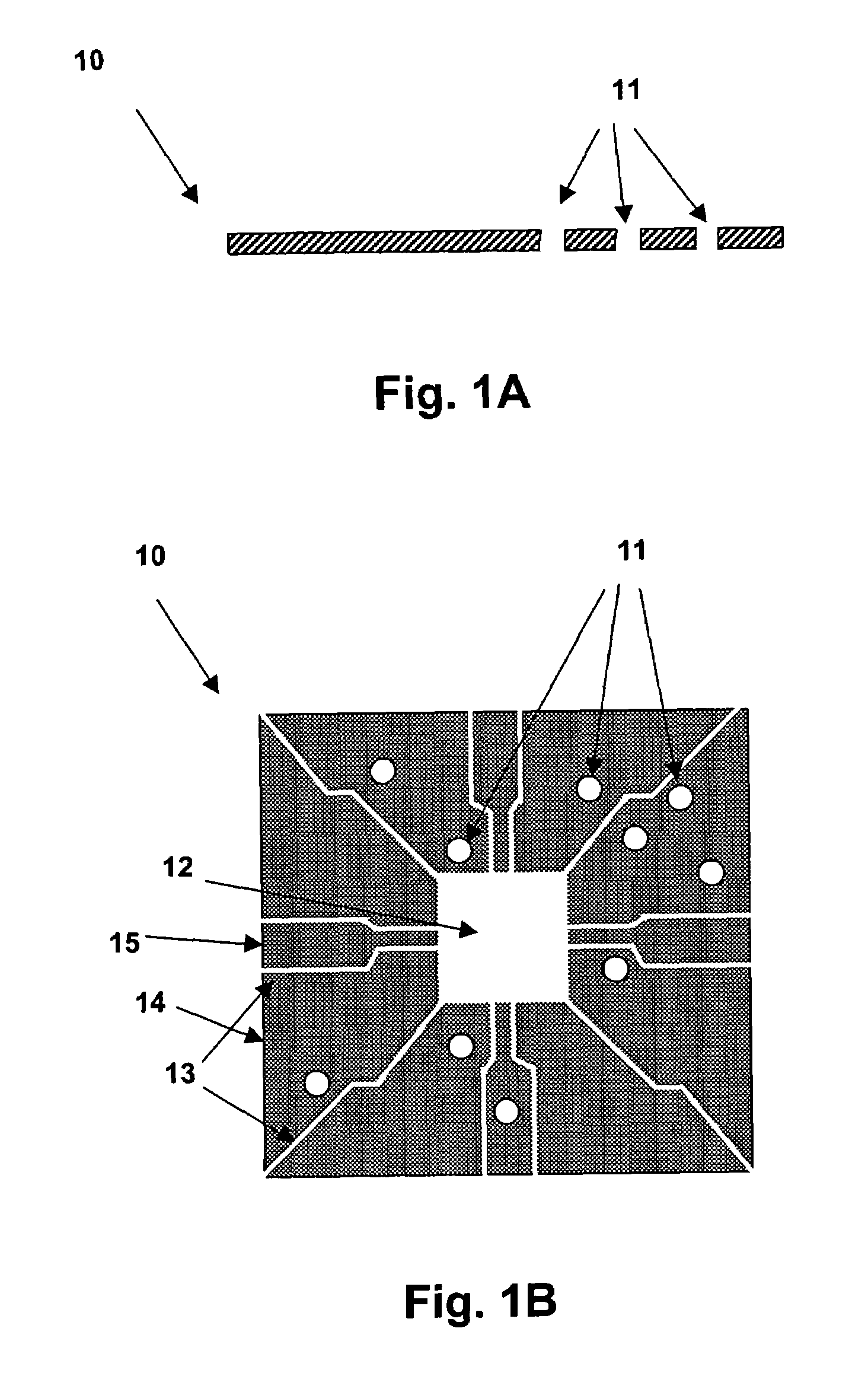

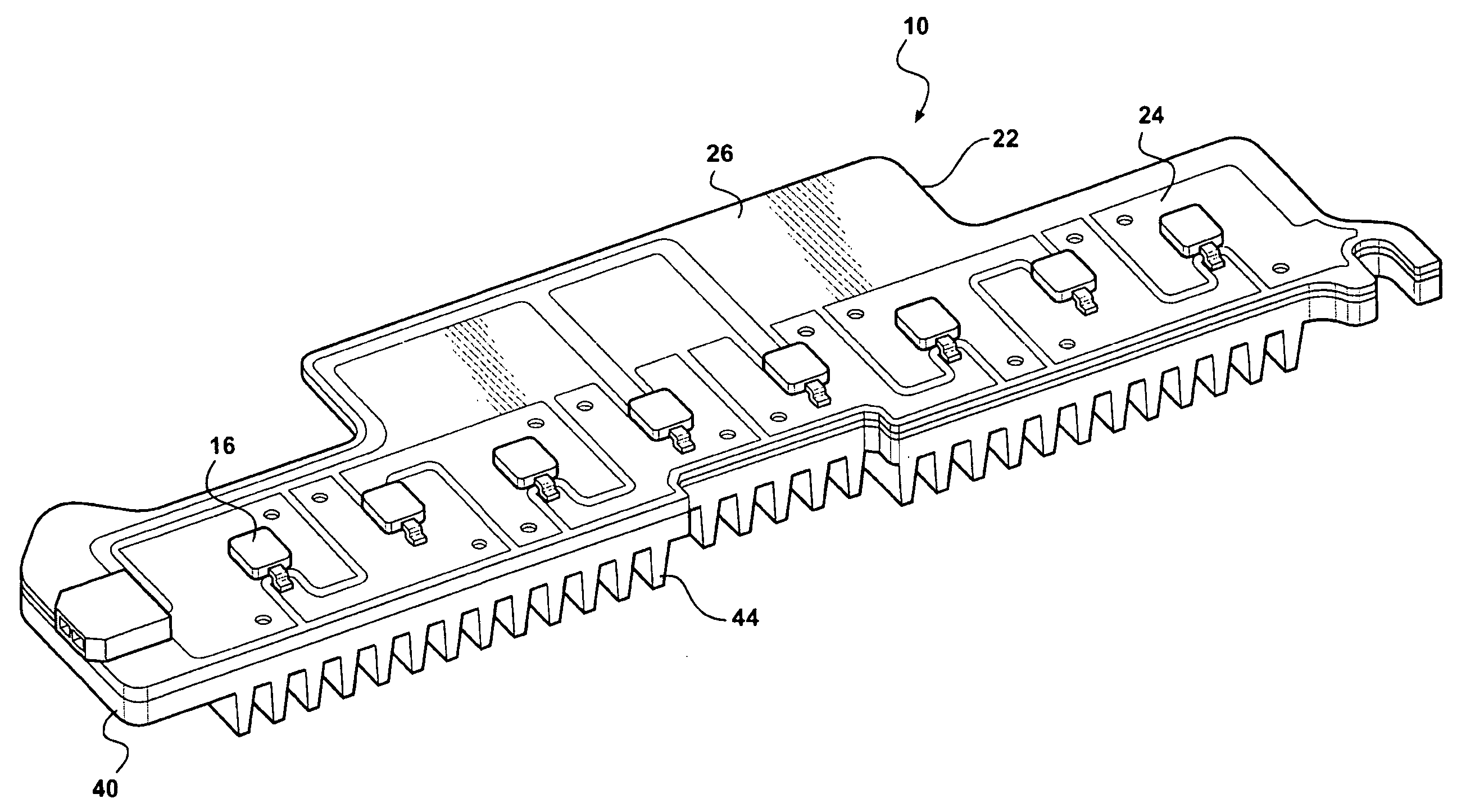

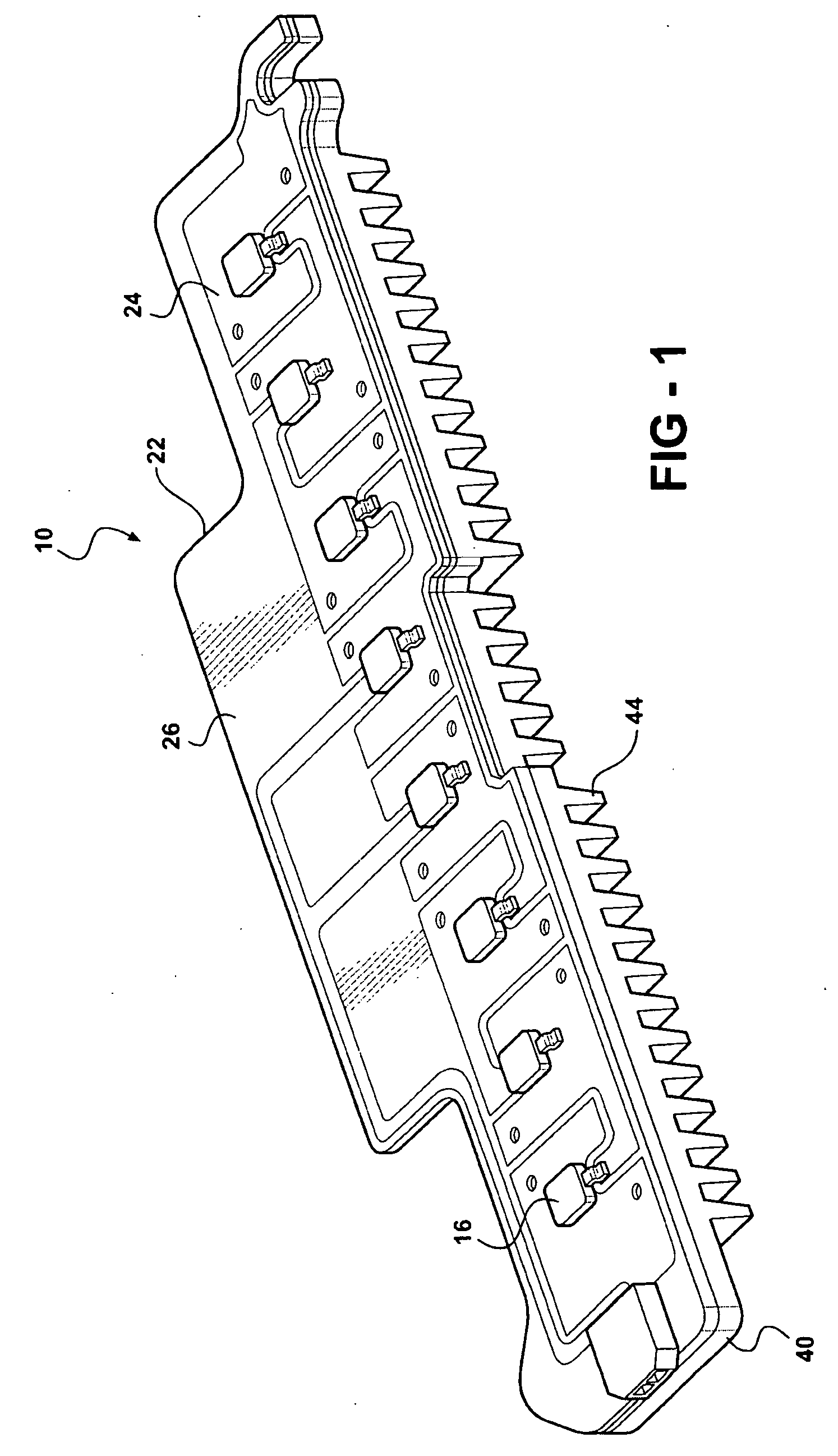

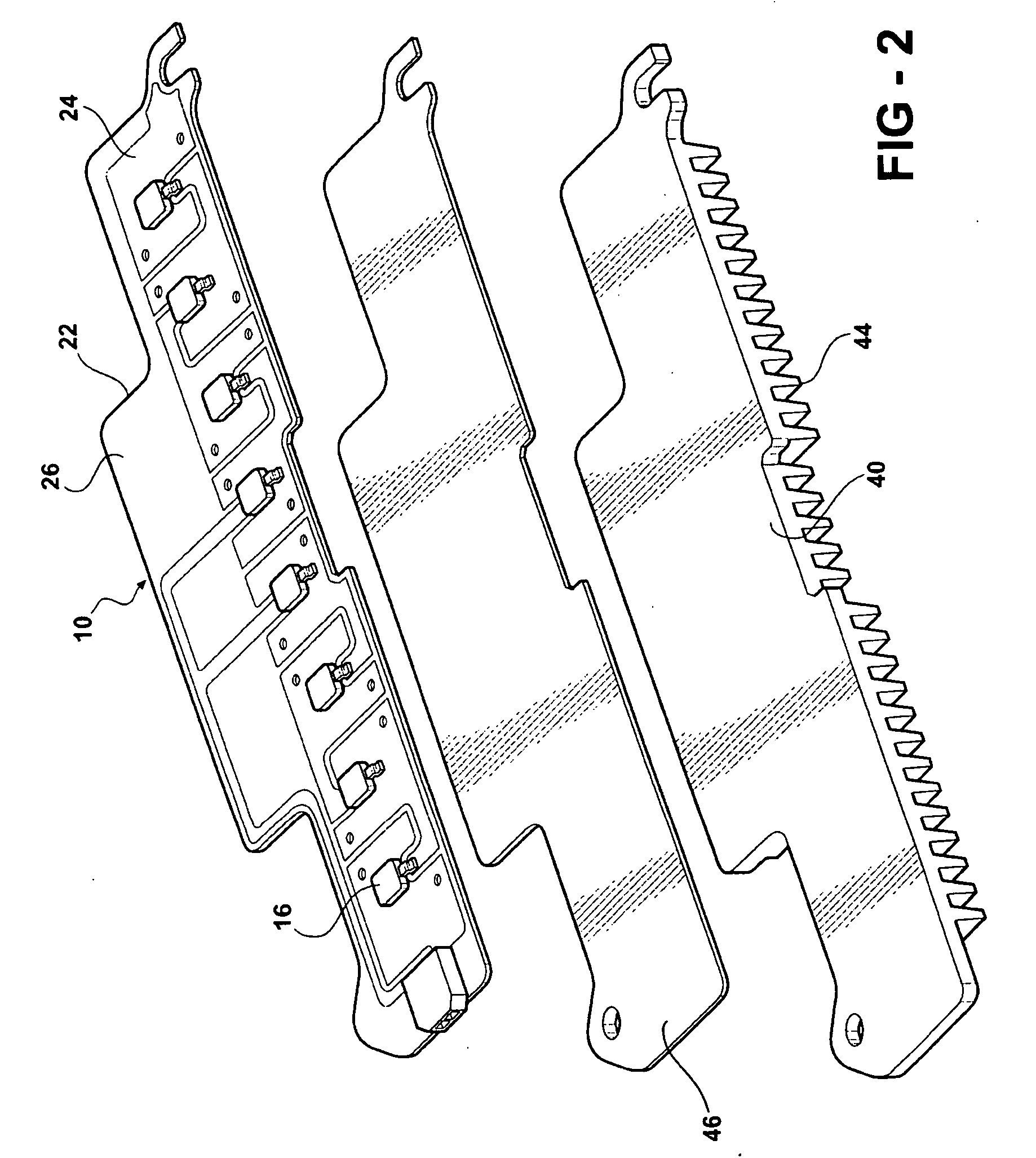

LED light module assembly

ActiveUS20060181878A1Point-like light sourceLighting heating/cooling arrangementsSurface mountingFlexible circuits

An LED light module assembly for use with high power, high light output LED's includes a thin flexible circuit board with surface mounted LED's and other electronic components which is attached to a metal heat sink using a layer of a thermally conductive adhesive, such as a thermally conductive epoxy adhesive. A conduction path is provided from the LED carrier through the flexible circuit board by the incorporation of one or more thermally conductive vias in the region of the attachment pad used to bond the LED to the flexible circuit board. These vias provide a conduction path from the back side of the LED carrier through the circuit board to the thermally conductive adhesive and heat sink. The LED light module assembly has the capacity to dissipate between about 10-14 W of power without exceeding a maximum LED junction temperature of about 125° C.

Owner:FEDERAL MOGUL WORLD WIDE LLC