3D NAND storage device and manufacturing method thereof

A technology for storage devices and manufacturing methods, applied in the direction of electric solid-state devices, semiconductor devices, electrical components, etc., can solve problems that affect device performance and device failure, and achieve the effects of improving device performance, eliminating parasitic capacitance, and avoiding breakdown

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

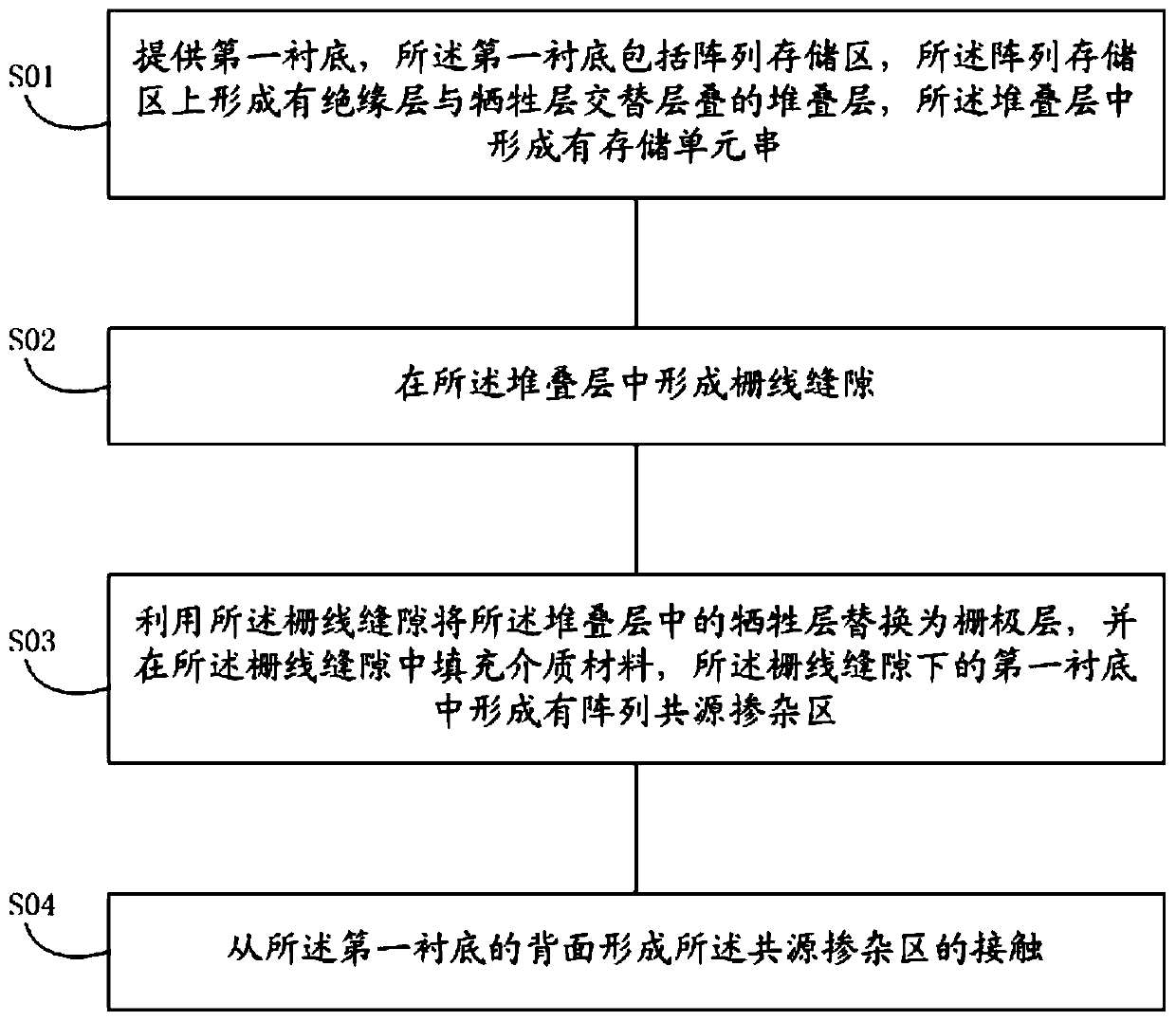

[0052] In this embodiment, before forming the stacked layers, an array of common source doping regions is formed in the substrate, and then the contact of the array common source doping regions is formed from the back of the substrate. This method has more advantages than the existing process. Good compatibility and high integration.

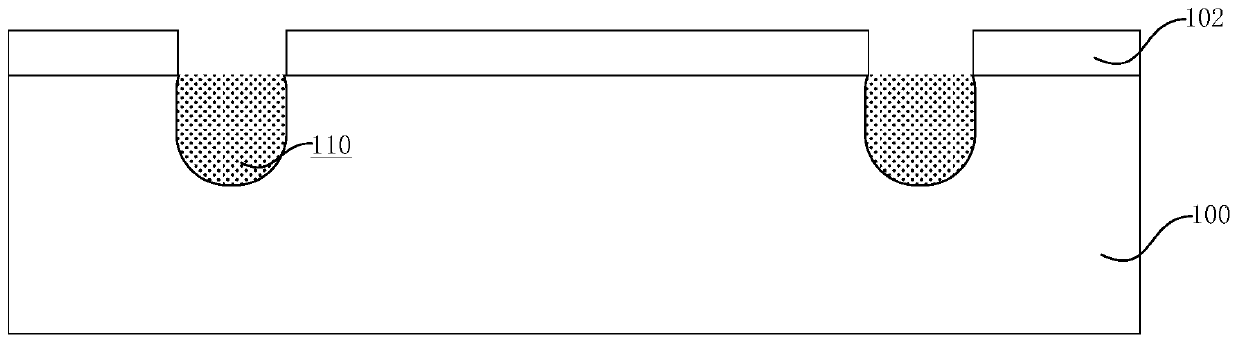

[0053] In step S01, a first substrate 100 is provided, the first substrate 100 includes an array storage area, an array common source doping area 110 is formed in the first substrate 100, and an insulating layer 110 is formed on the array storage area. A stacked layer 120 in which layers 122 and sacrificial layers 124 are alternately stacked, and memory cell strings 130 are formed in the stacked layer 120, refer to Figure 4 shown.

[0054] In the embodiment of the present application, the first substrate 100 is a semiconductor substrate, such as Si substrate, Ge substrate, SiGe substrate, SOI (Silicon On Insulator, Silicon On Insulator) or GOI...

Embodiment 2

[0083] In this embodiment, after the formation of stacked layers and the replacement of the gate layer, the array common source doping region is formed in the back process, and then the contact of the array common source doping region is formed from the back of the substrate, which is more conducive to the array common source doping region. Alignment of source doped regions and their contacts. The parts that are different from those in the first embodiment will be mainly described below, and the same parts will not be described again.

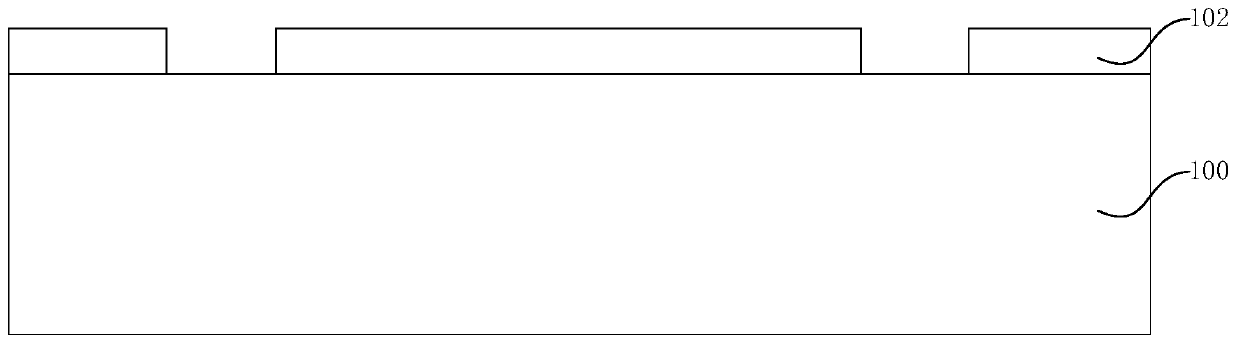

[0084] In step S201, a first substrate 100 is provided, and the first substrate 100 includes an array storage area, and stacked layers 120 in which insulating layers 122 and sacrificial layers 124 are alternately stacked are formed on the array storage area, and the stacked layers 120 is formed with memory cell string 130, refer to Figure 8 shown.

[0085] Different from step S101 in the first embodiment, in this embodiment, the array common...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More