Patents

Literature

33 results about "Soi ldmos" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

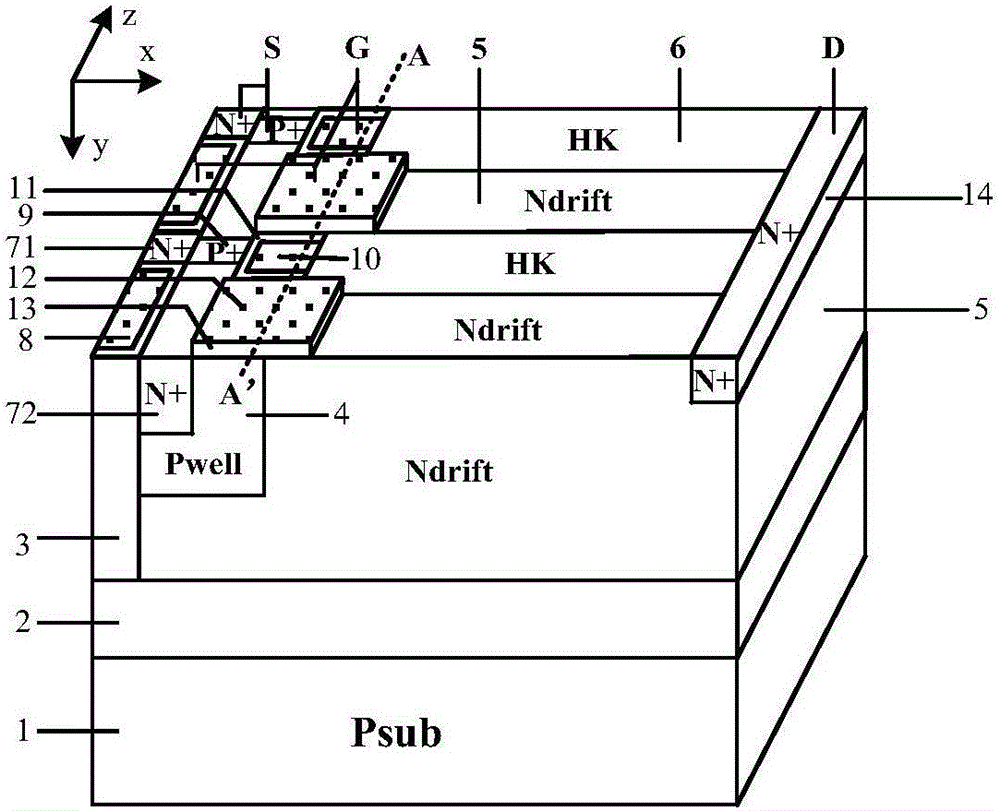

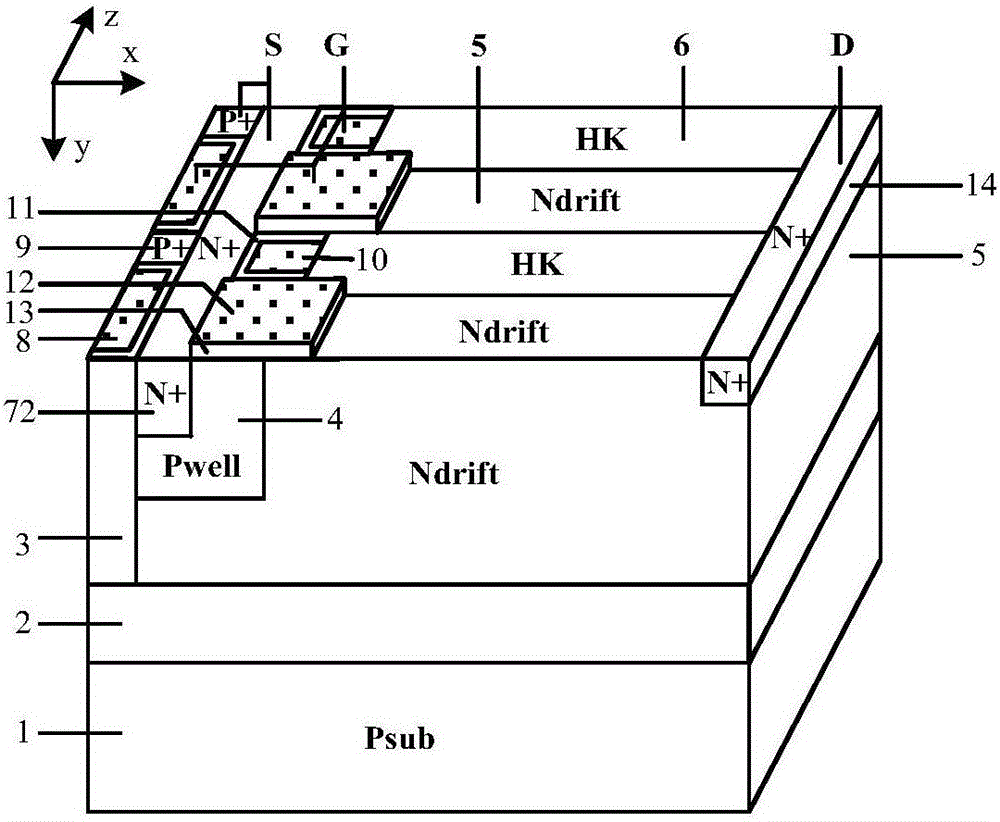

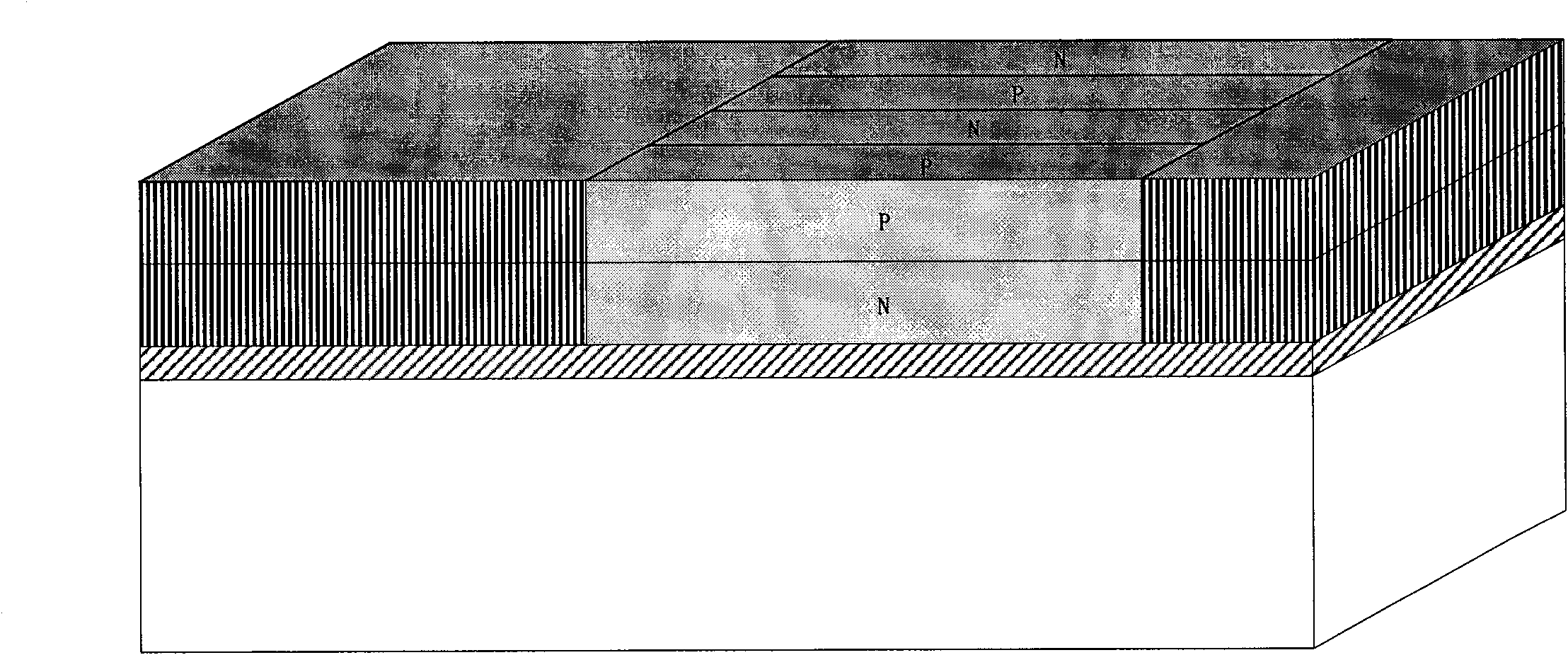

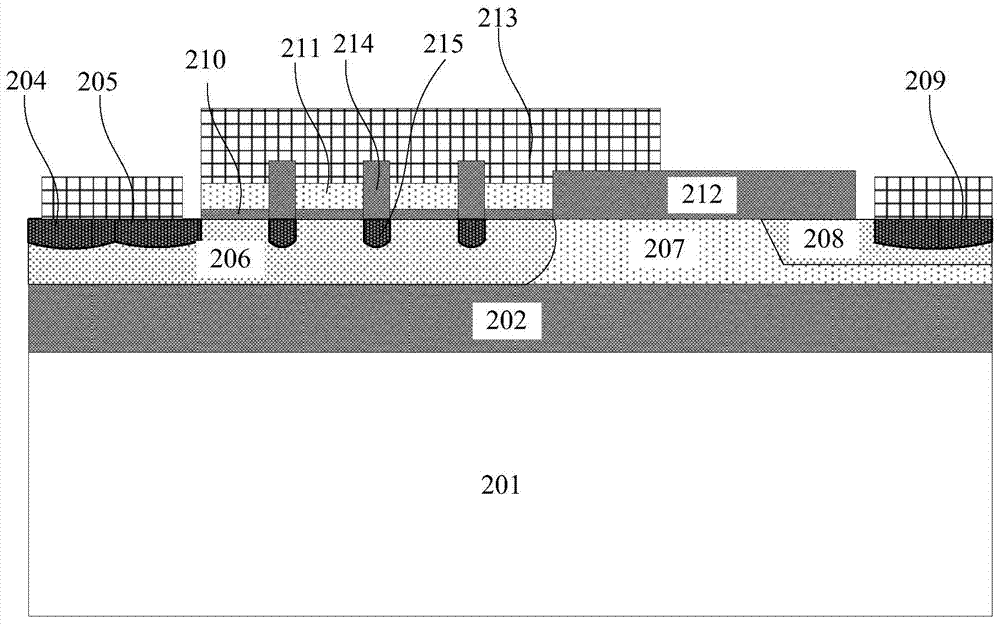

HK SOI LDMOSdevice having three-grating structure

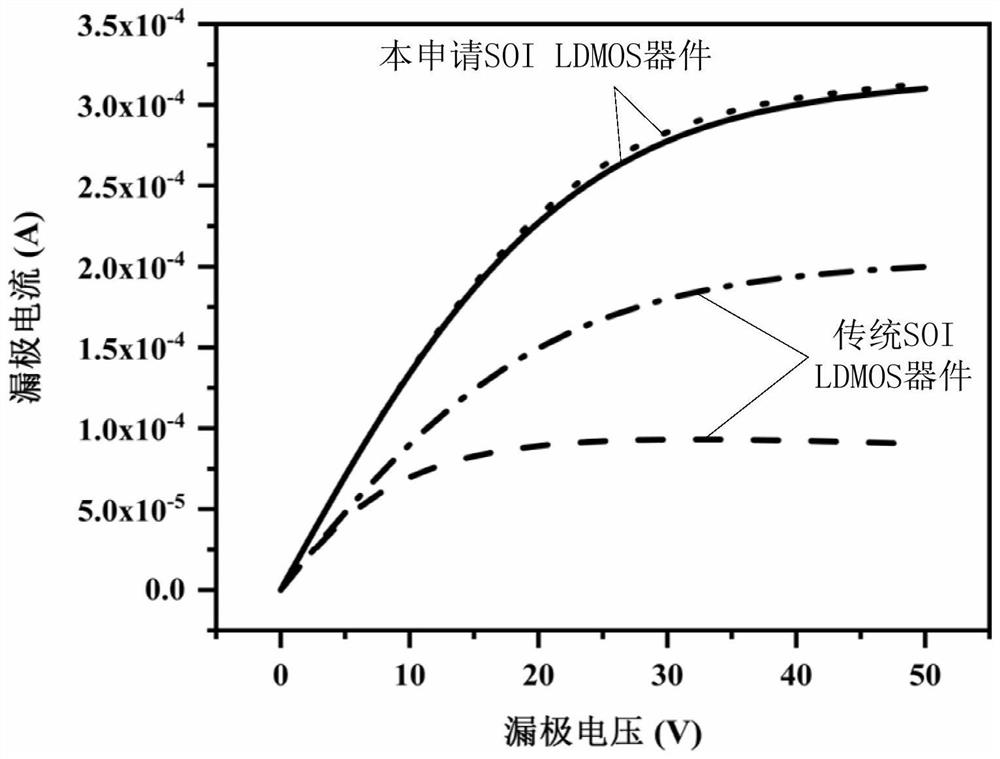

The invention belongs to a field of semiconductor technology and specifically relates to an HK SOI LDMOS (Lateral Double-Diffusion Metal Oxide Semiconductor) device. The device has the following characteristics. First, the device has three separated grating structures including a plane grate and two channel grates. In an open state, the three-grating structure an form a plurality of crosswise and longitudinal channels, thus increasing channel density, increasing current and reducing specific on-resistance. Second, high K mediums are embedded into drifting zones adjacent to a semiconductor zone and are arranged in alternation with the drifting zones. In the open state, electron accumulation layers are formed on side walls of the drifting zones adjacent to the high K mediums, so that low resistance channels are provided and the specific on-resistance is reduced. In a closed state, the high K mediums assist to drain the drifting zones, so that the drifting zone doping is improved, the electric field is improved and the specific on-resistance is reduced and the voltage holding performance is improved further. Third, an SOI structure is adopted, so that longitudinal voltage holding performance is improved, leakage current is reduced and a latch-up effect is eliminated.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

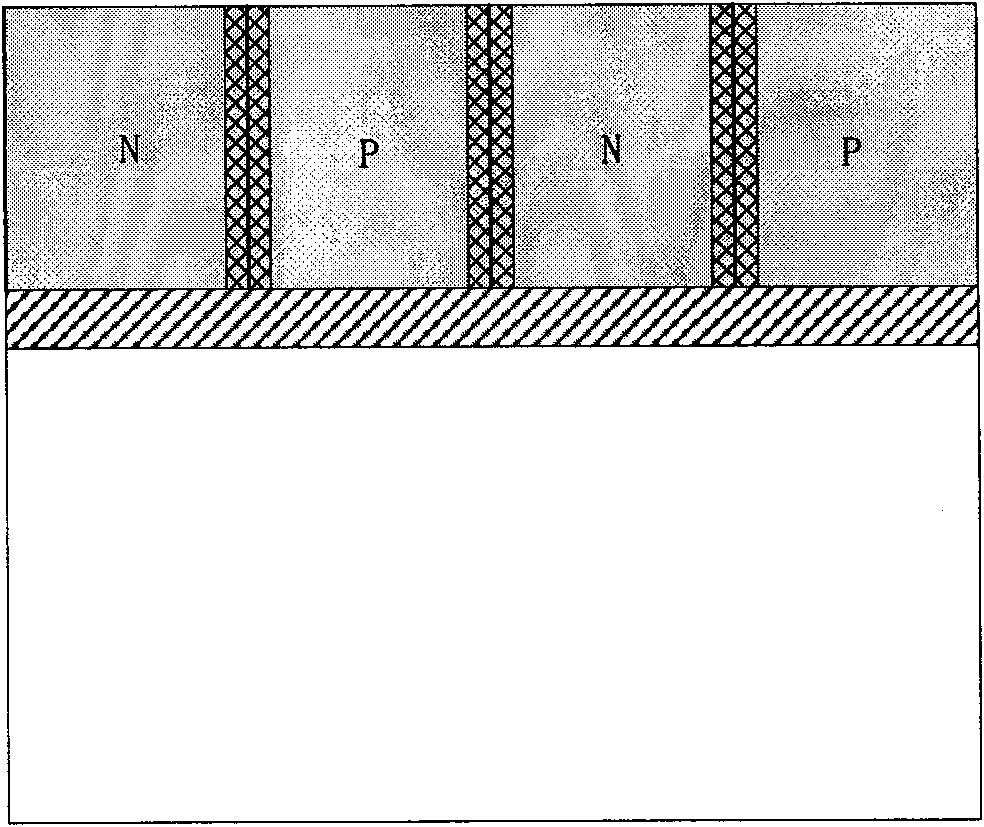

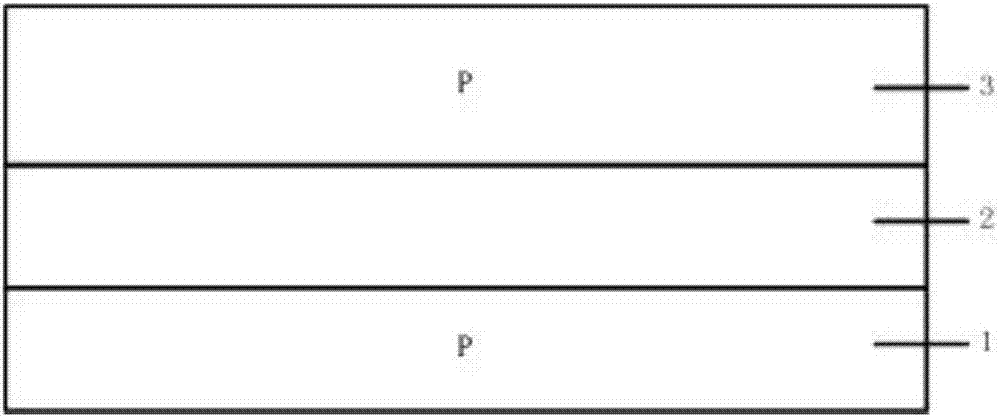

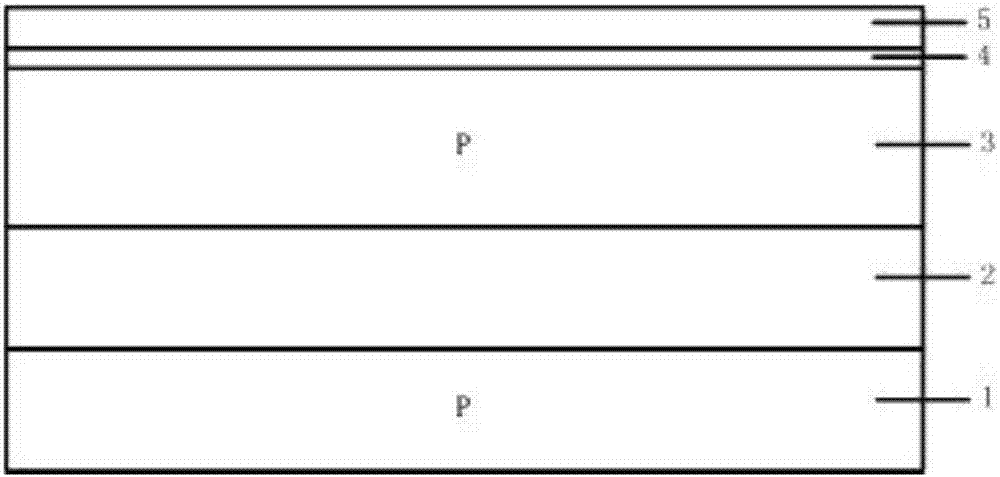

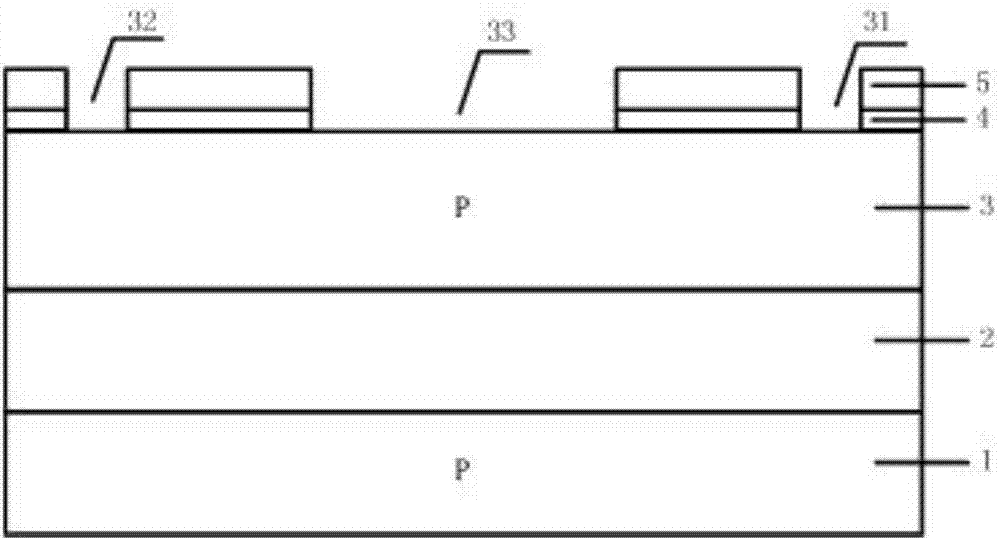

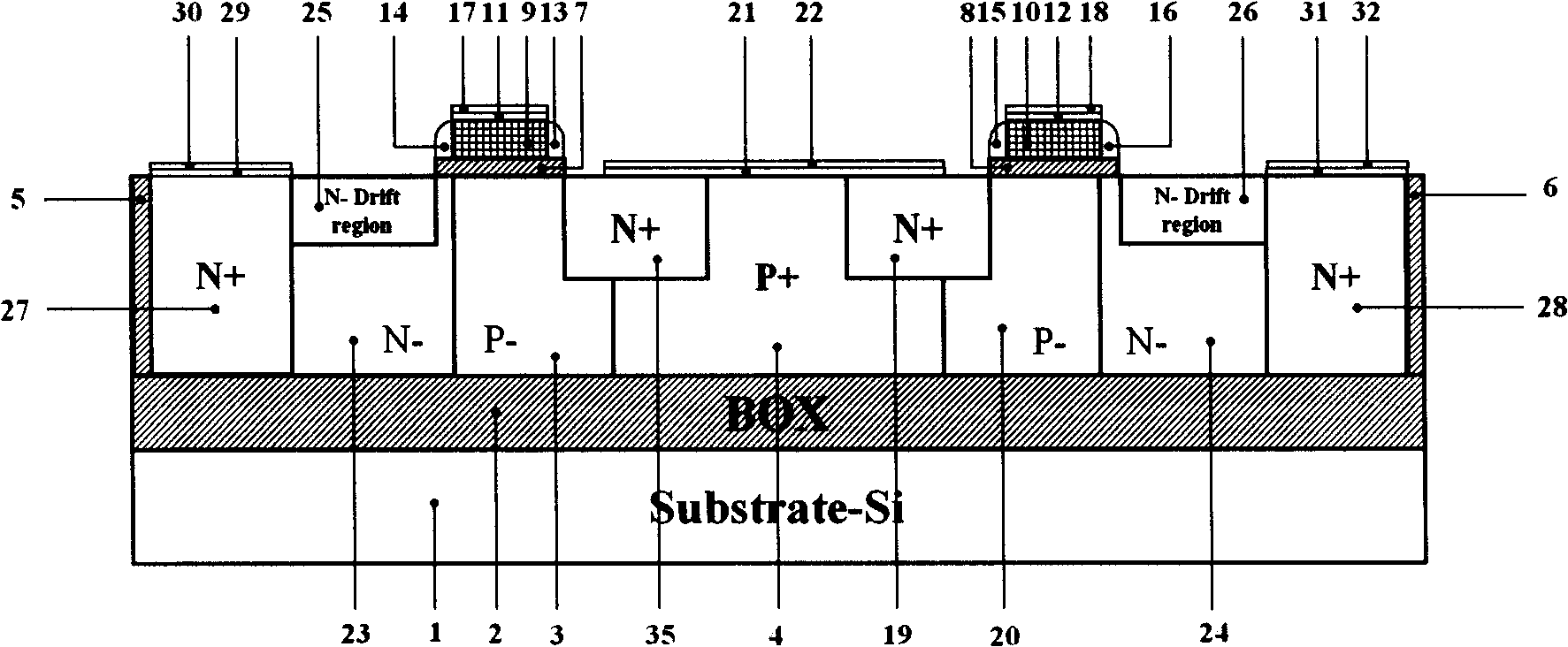

Method for producing SOI (Silicon on Insulator) LDMOS (Laterally Diffused Metal Oxide Semiconductor) device provided with multi-layer super-junction structure

InactiveCN101916729AIncrease contact areaImprove breakdown resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesBody contactSoi substrate

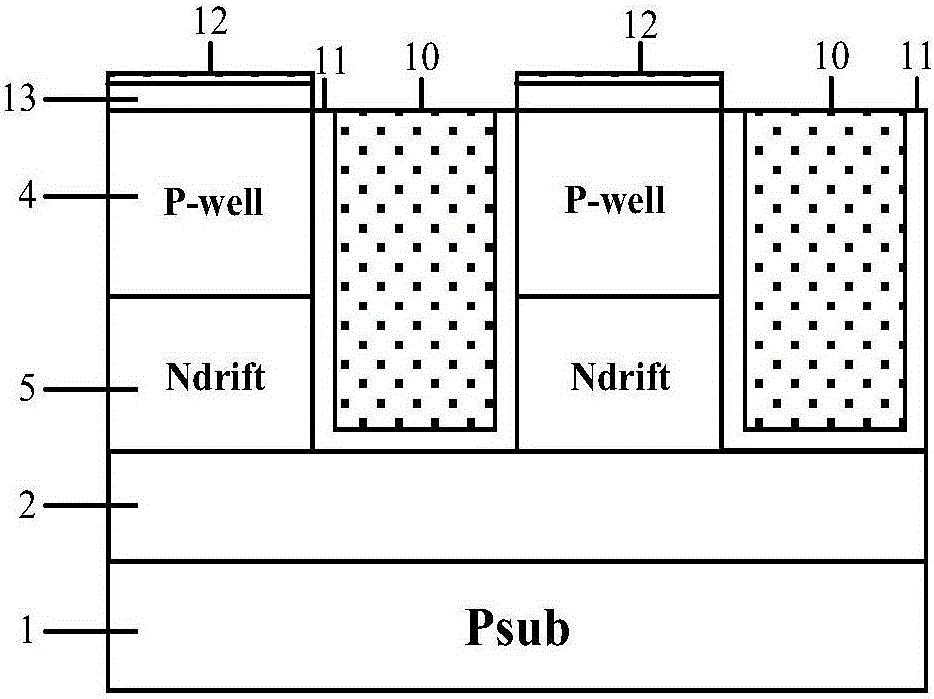

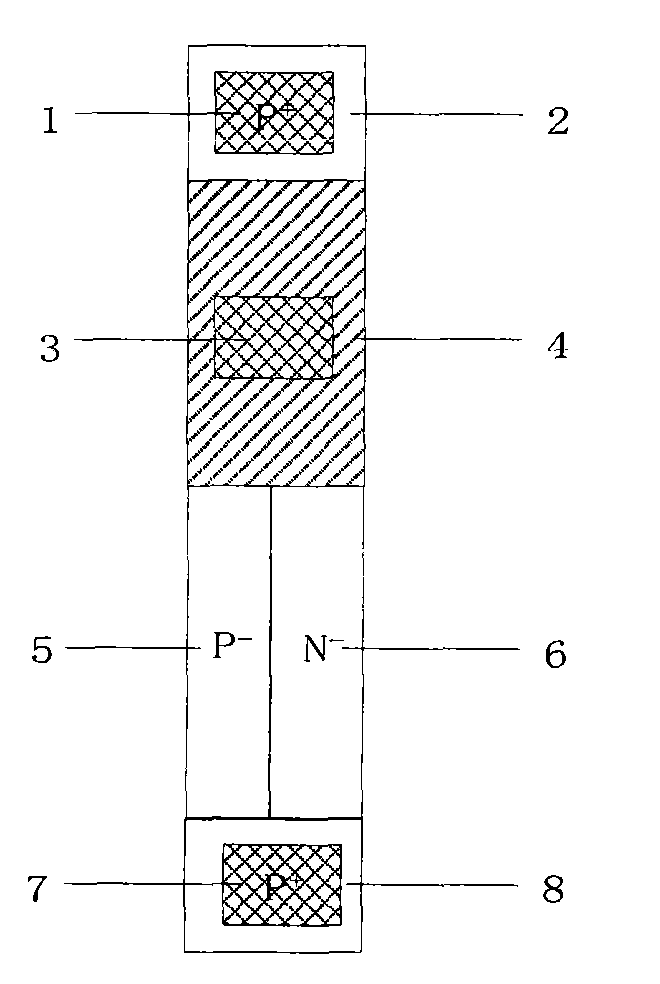

The invention discloses a method for producing an SOI LDMOS device provided with a multi-layer super-junction structure, which comprises the steps of: carrying out ion implantation on top layer silicon by adopting SOI substrate to form a first layer of super-junction structure; then preparing an extensionality layer on the SOI substrate provided with at least one layer of super-junction structure, manufacturing the other layer of super-junction structure by utilizing the same technological conditions for manufacturing the first layer of super-junction structure, and ensuring that the n-type pillar regions and the p-type pillar regions of the upper layer and the lower layer are alternately arranged to form a multi-layer super-junction structure comprising at least two layers of super-junction structure; and manufacturing body regions, grid regions, source regions, drain regions and body contact regions to finish the device. The multi-layer super-junction structure is formed by adopting the extensionality and ion implantation technology, the p-type pillar regions and the n-type pillar regions of the upper and the lower layer super-junction structures are alternately arranged to further increase the contact area among the p-type pillar regions and the n-type pillar regions without bringing remarkable side effects; and the anti-breakdown capacity of the device produced by the invention is higher than that of the traditional super-junction LDMOS.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI +1

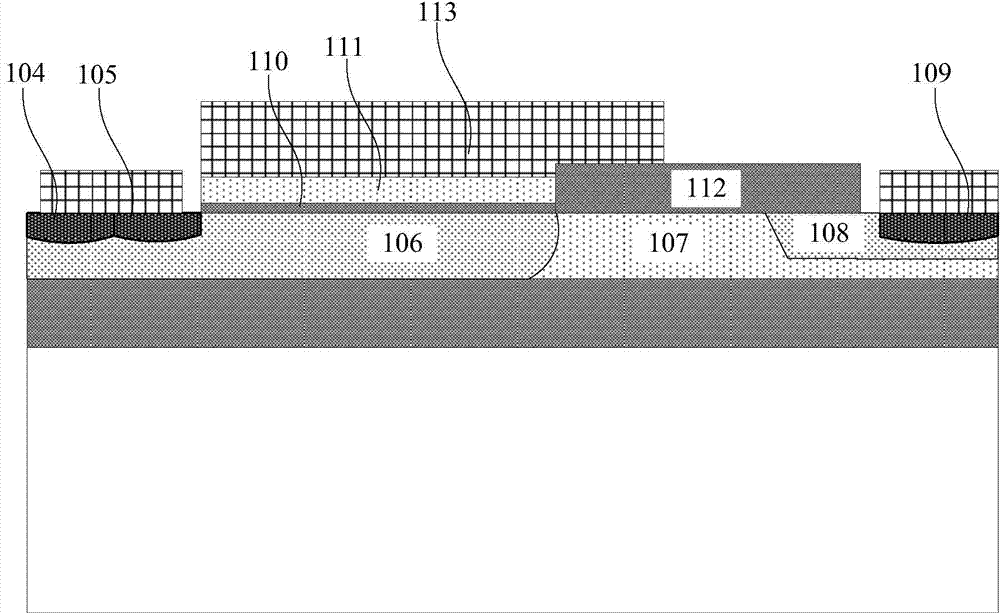

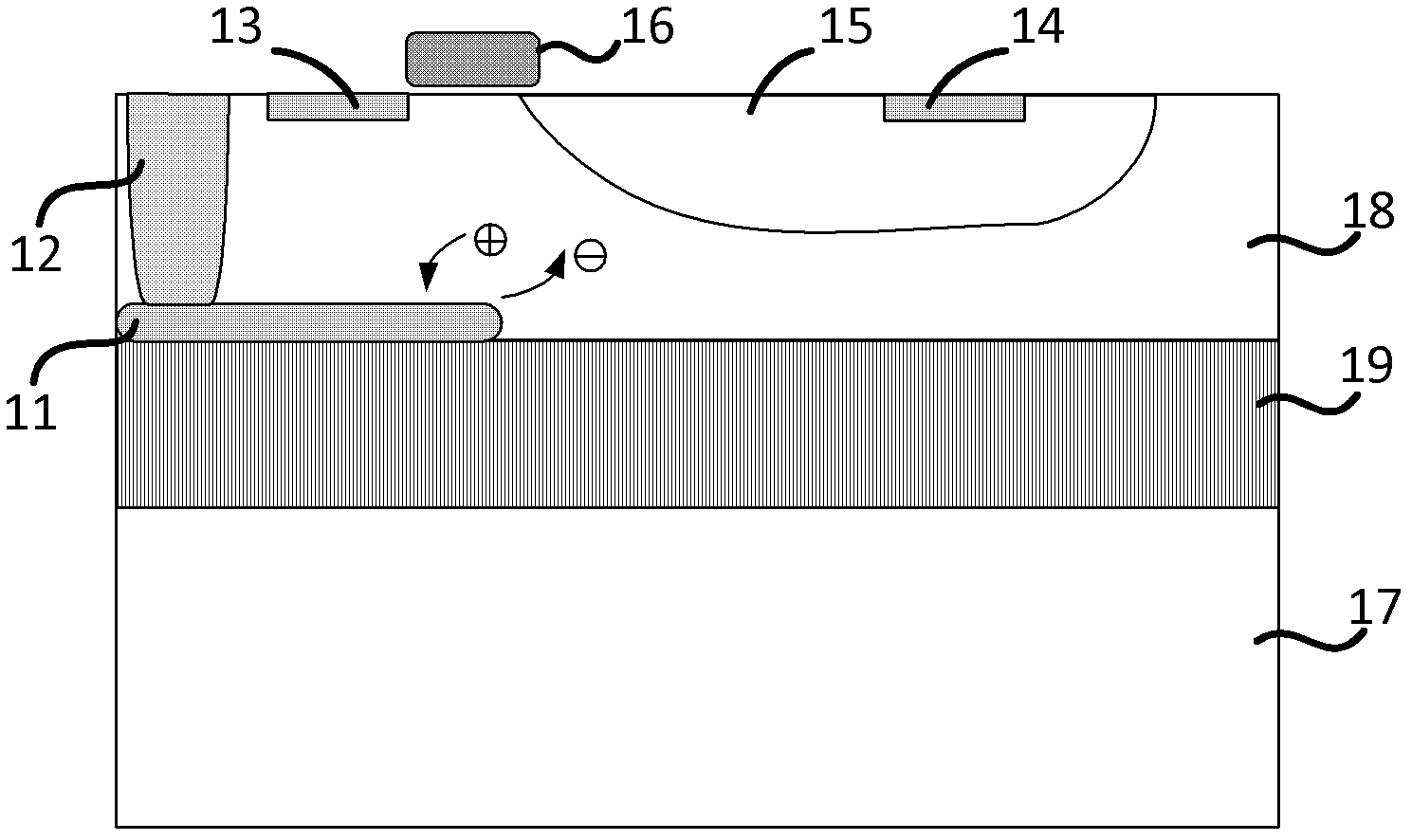

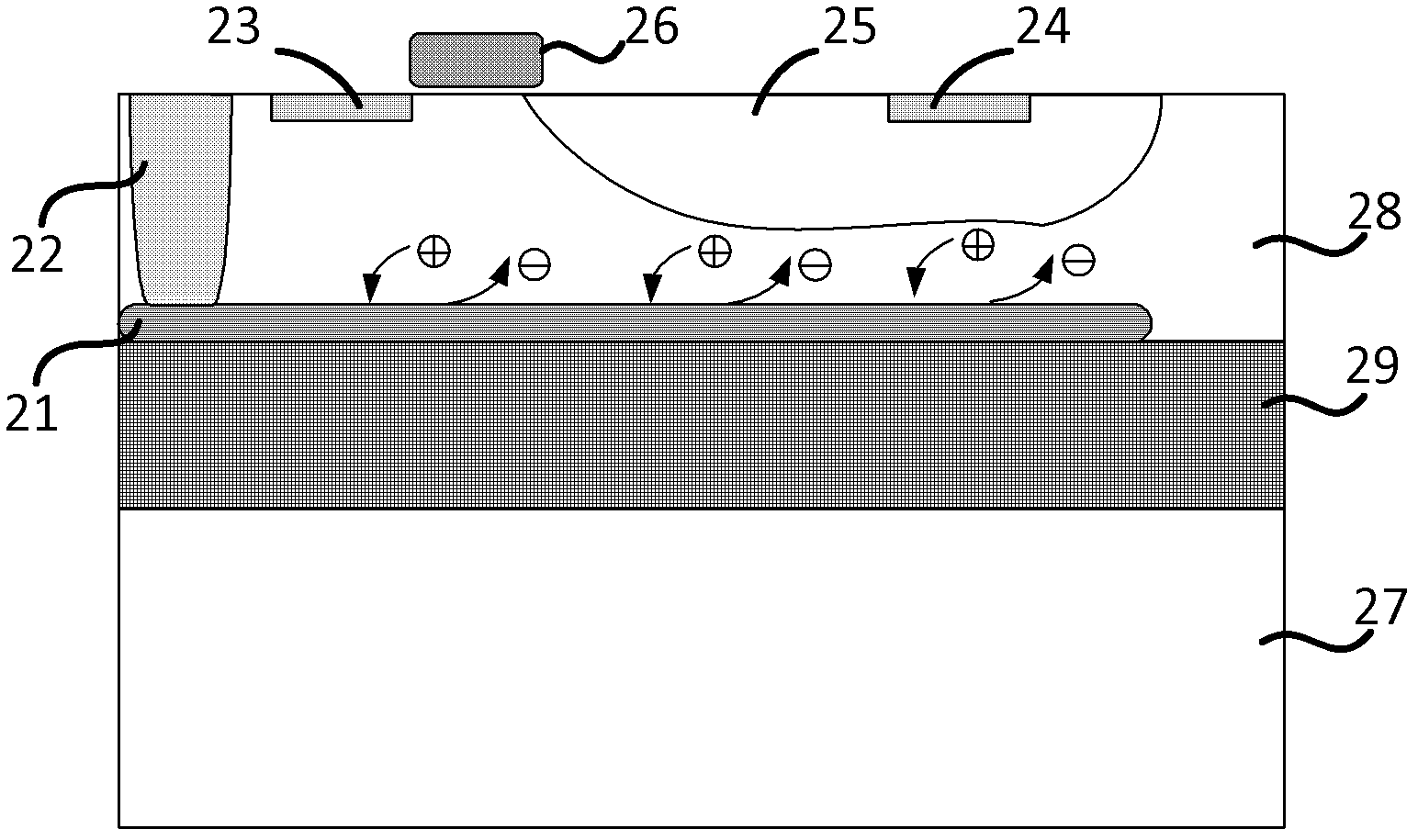

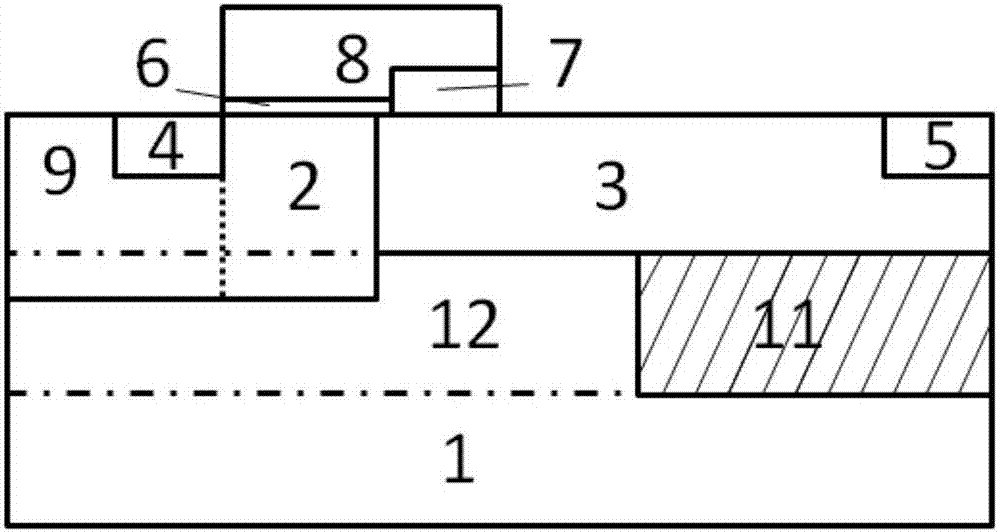

Multi-gate SOI-LDMOS device structure

InactiveCN103594517AImprove breakdown voltageGood transconductance characteristicsSemiconductor devicesElectron holeSoi substrate

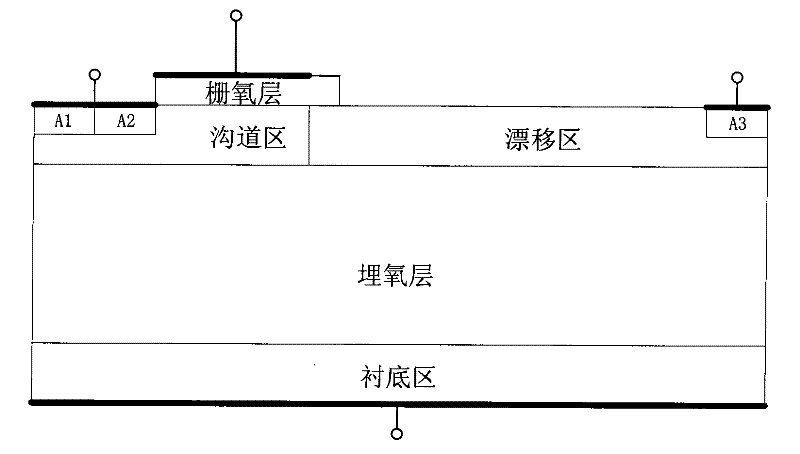

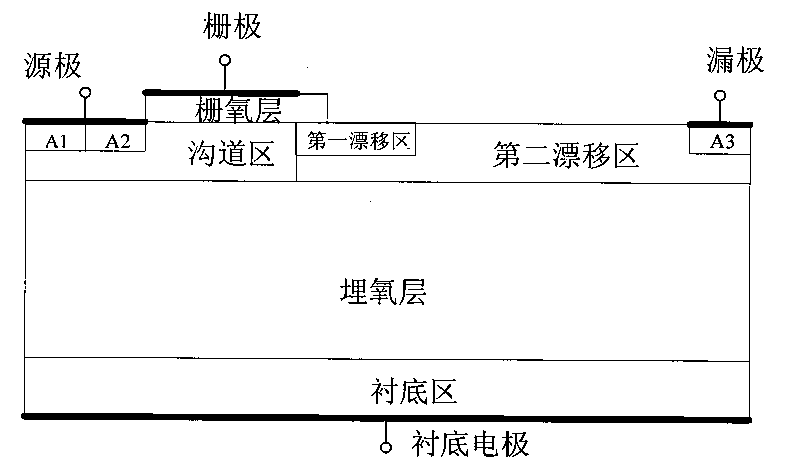

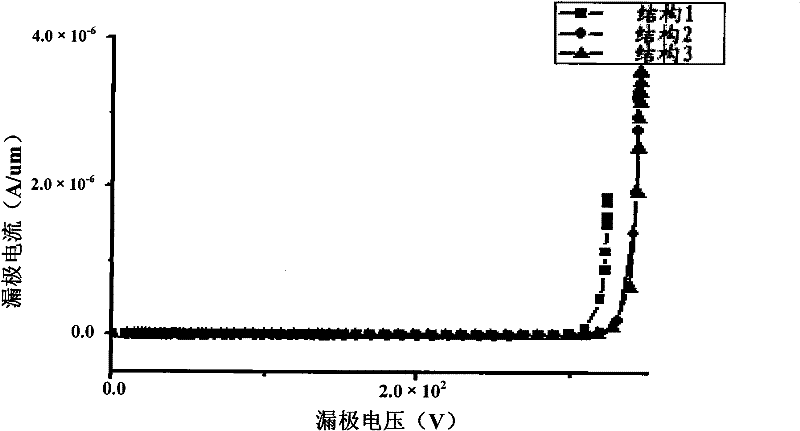

The invention provides a multi-gate SOI-LDMOS device structure which comprises an SOI substrate, an active region and a polysilicon gate. The SOI substrate comprises a silicon substrate body, an oxygen buried layer and a top silicon layer, the active region is formed in the top silicon layer and comprises a source region, a channel region, a drift region, a shallow doping drain region and a drain region, the source region, the channel region, the drift region, the shallow doping drain region and the drain region are sequentially connected, the polysilicon gate comprises a gate-oxide layer and a polysilicon layer, the gate-oxide layer is combined to the surface of the channel region, the polysilicon gate is separated by at least one dielectric layer into two short gate structures, and heavy doping regions inversed with the channel region in doping type are formed corresponding to the position, below the dielectric layer, in the channel region. The multi-gate SOI-LDMOS device structure has the advantages of being high in breakdown voltage, good in transconductance characteristic, small in positive break-over resistance, low in self-heating effect and the like. As the heavy doping regions inversed with the channel region in doping type are formed between short gates, when a device is irradiated, the heavy doping regions serve as recombination centers, the large number of recombination centers are provided for electron hole pairs generated by irradiation, and the whole radiation resisting performance of the device is accordingly improved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI +1

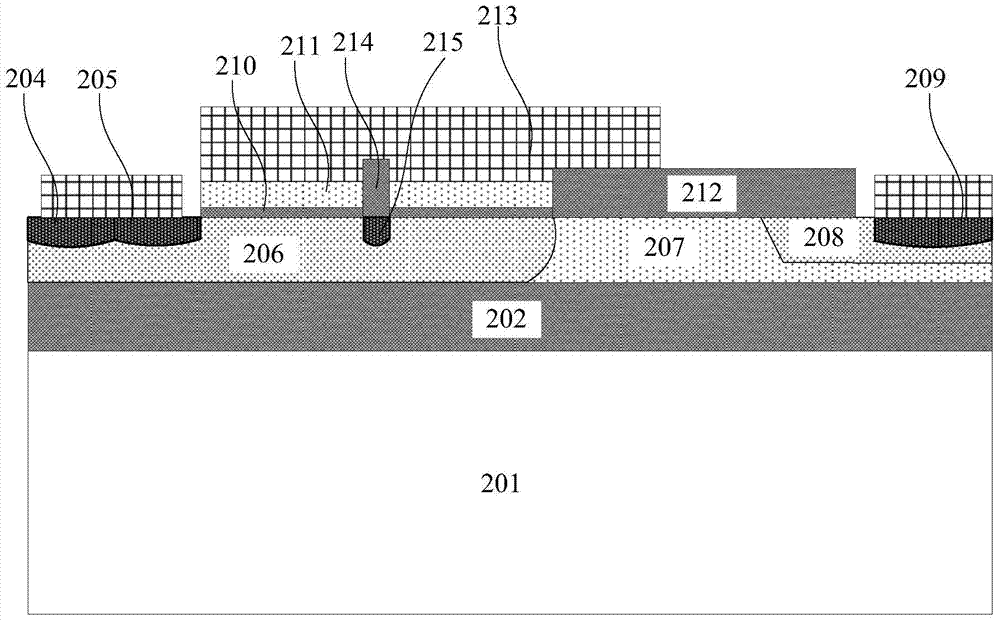

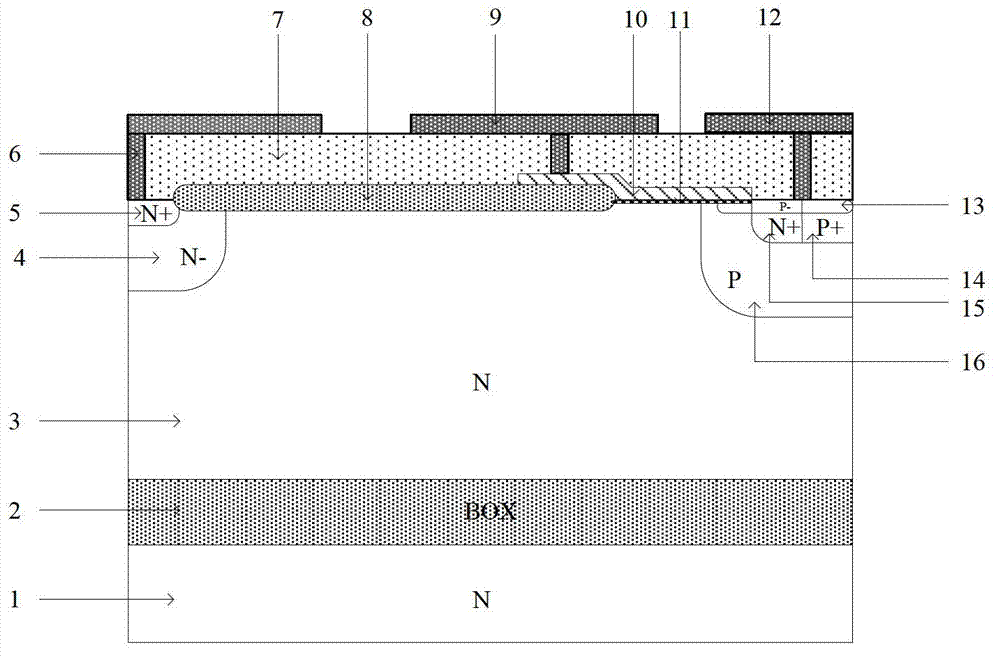

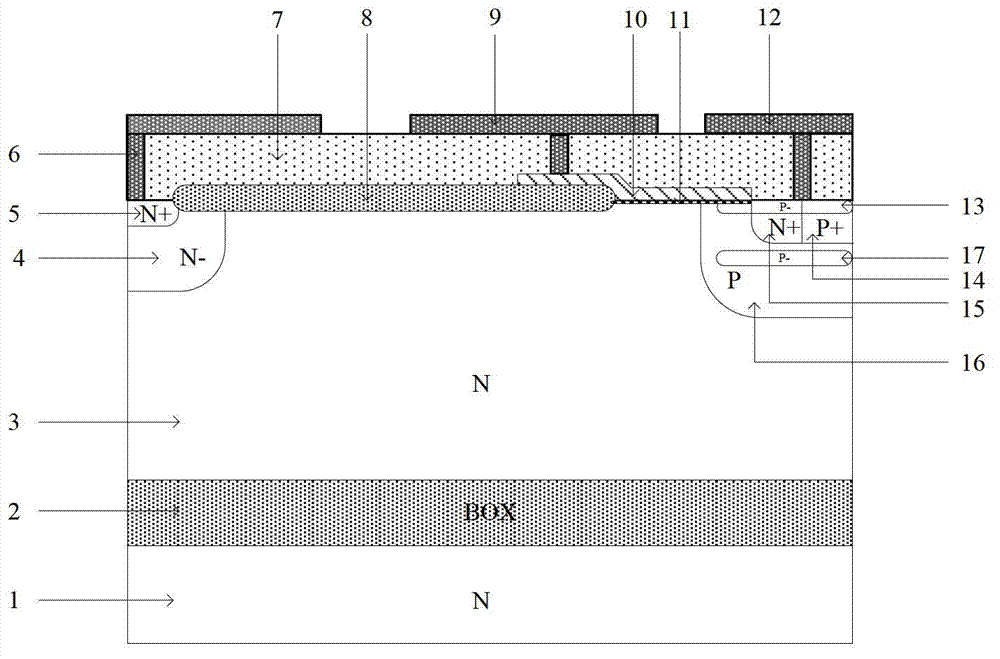

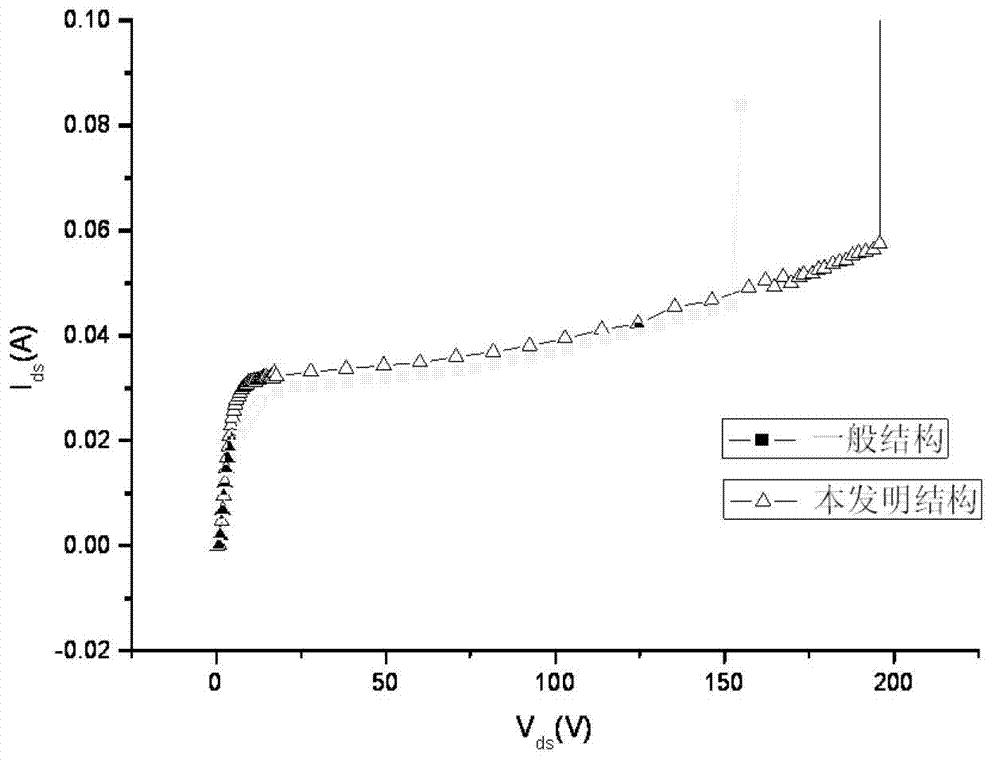

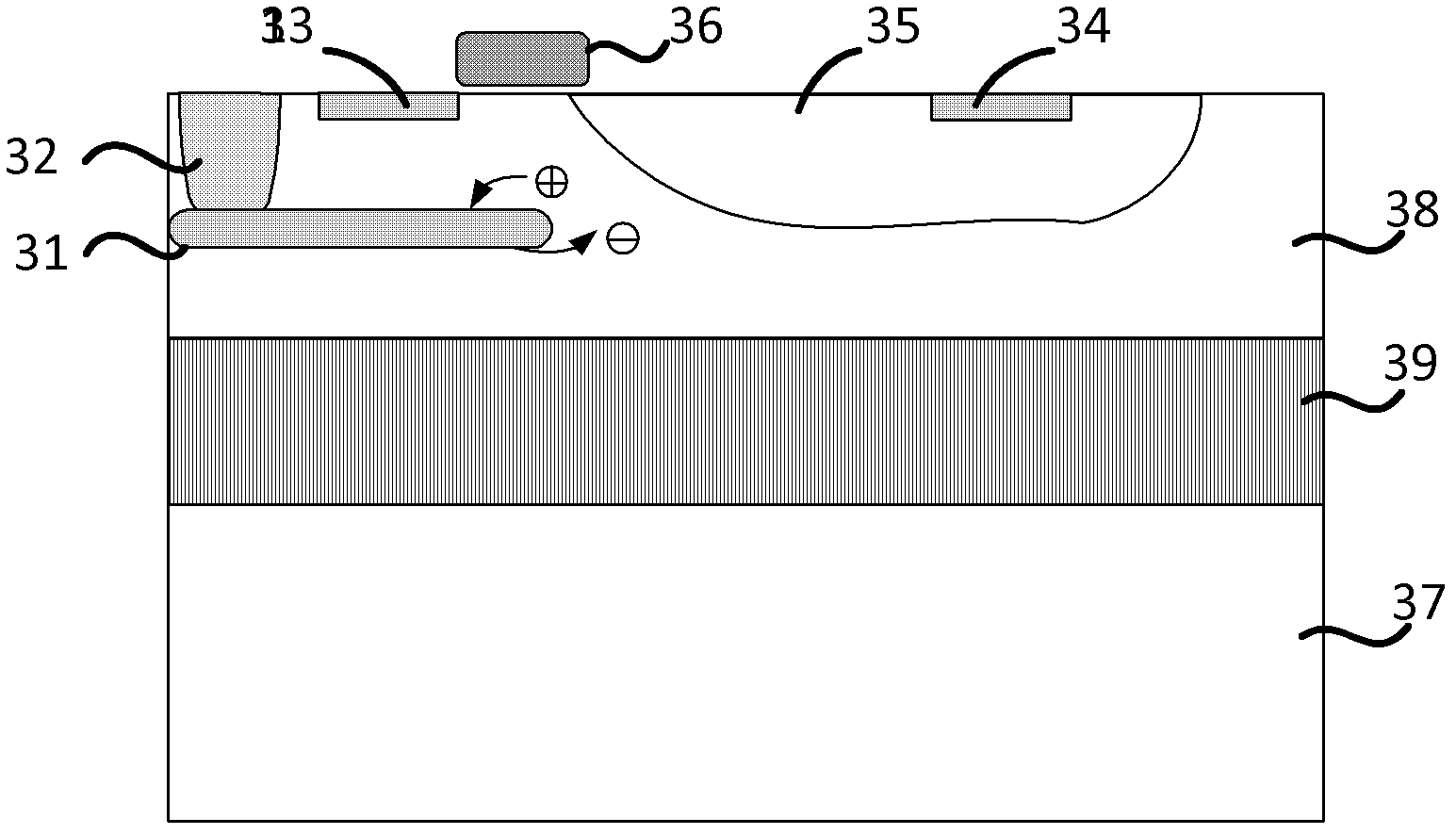

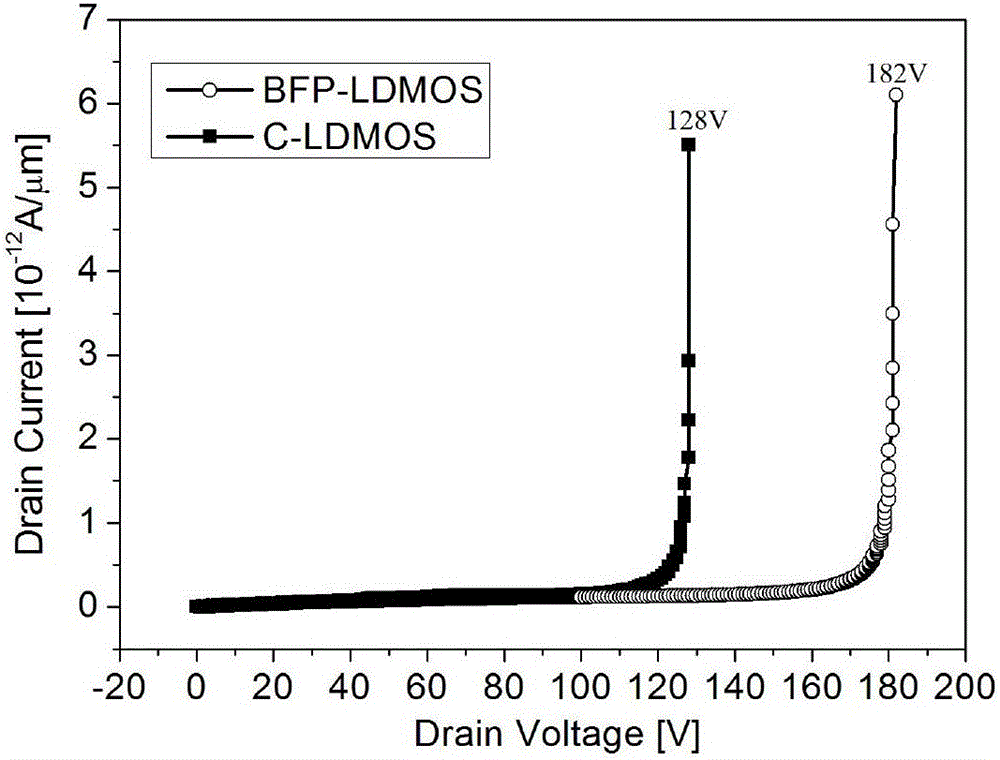

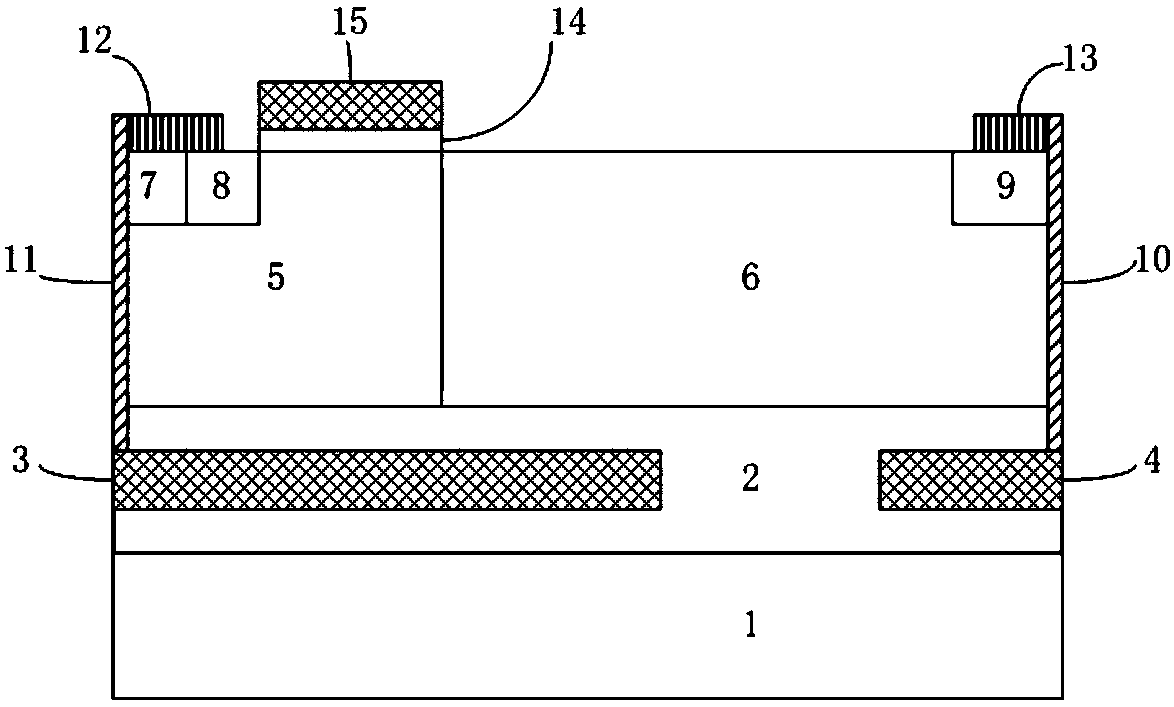

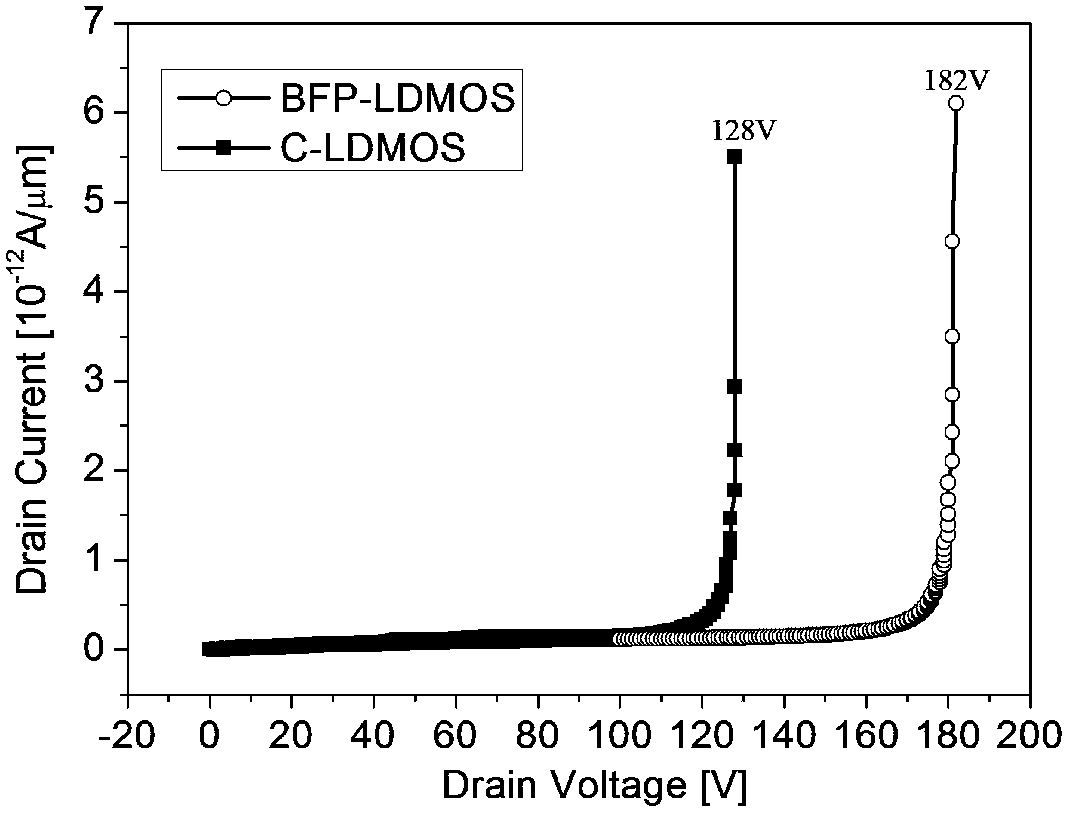

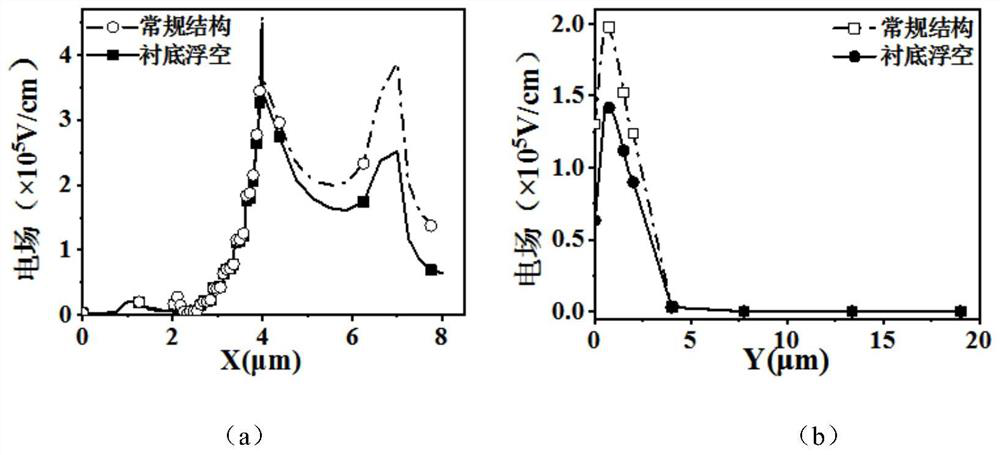

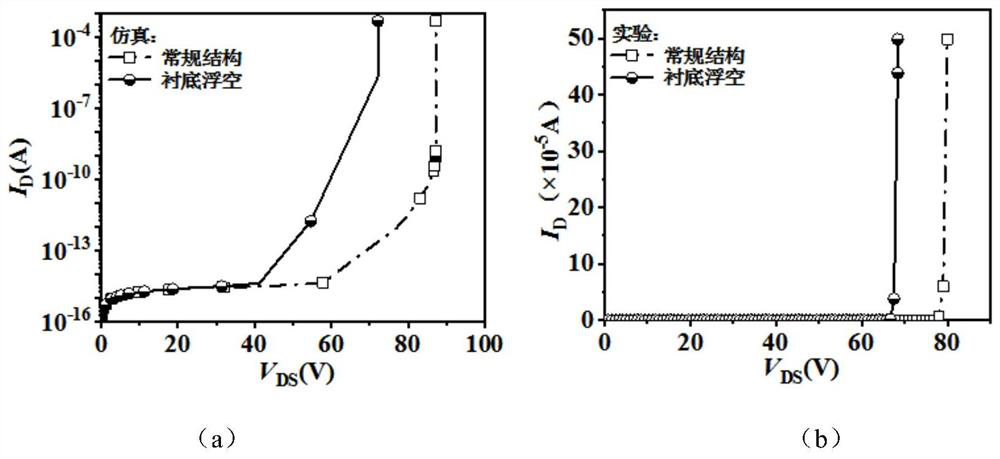

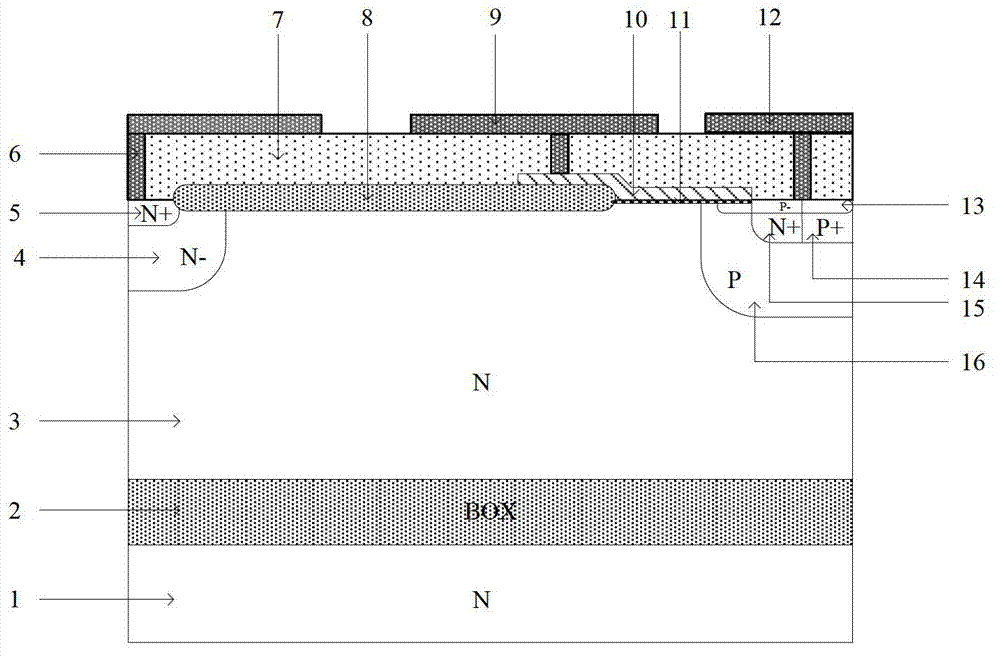

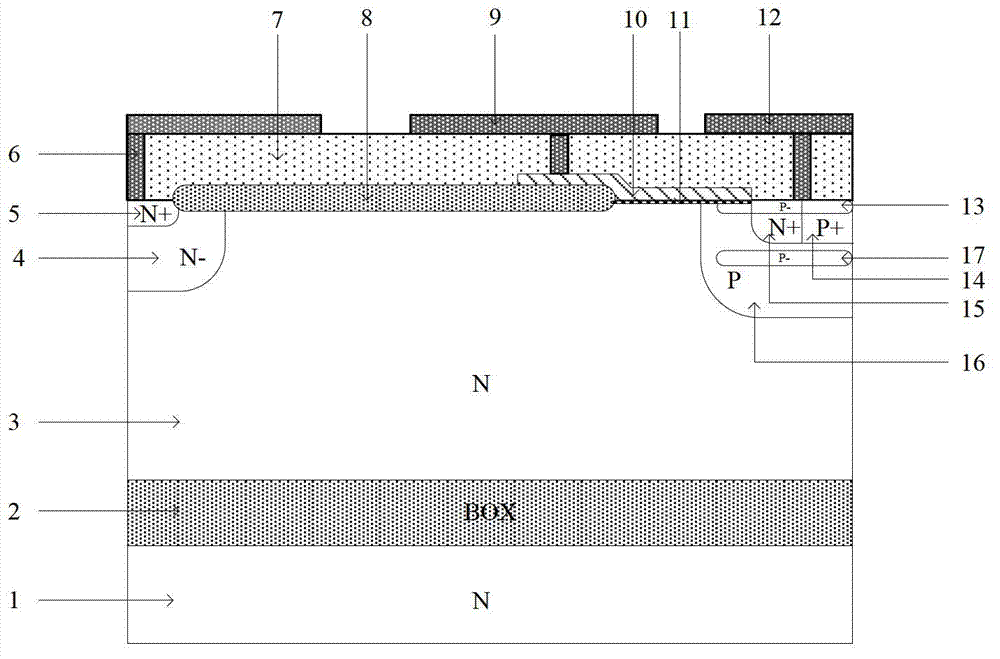

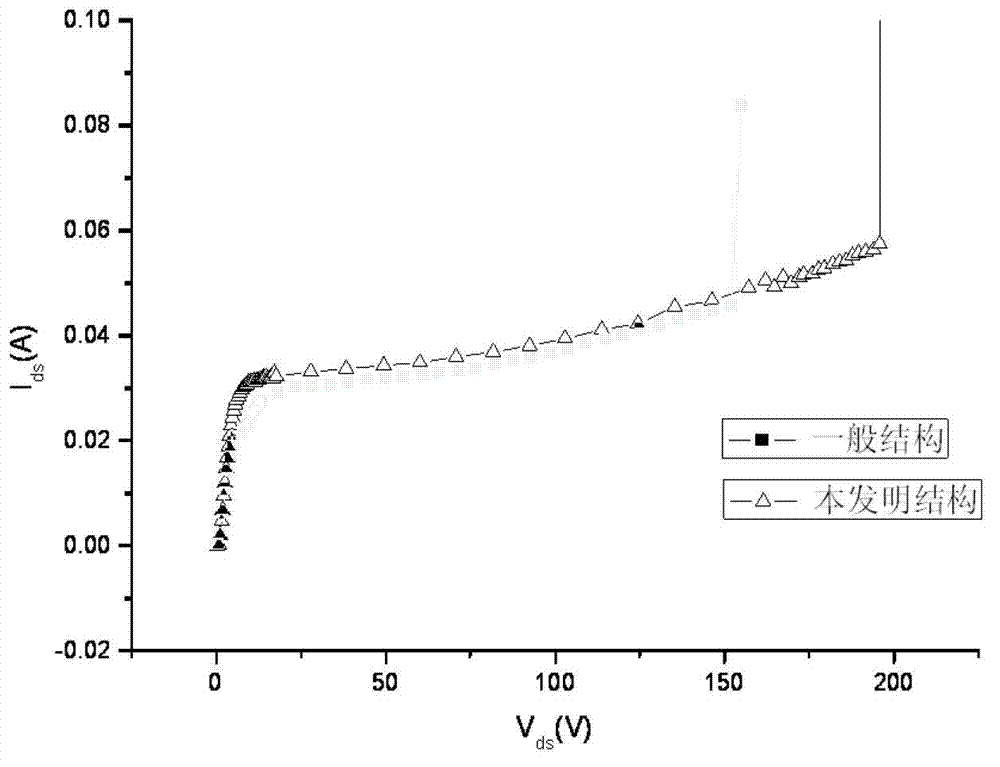

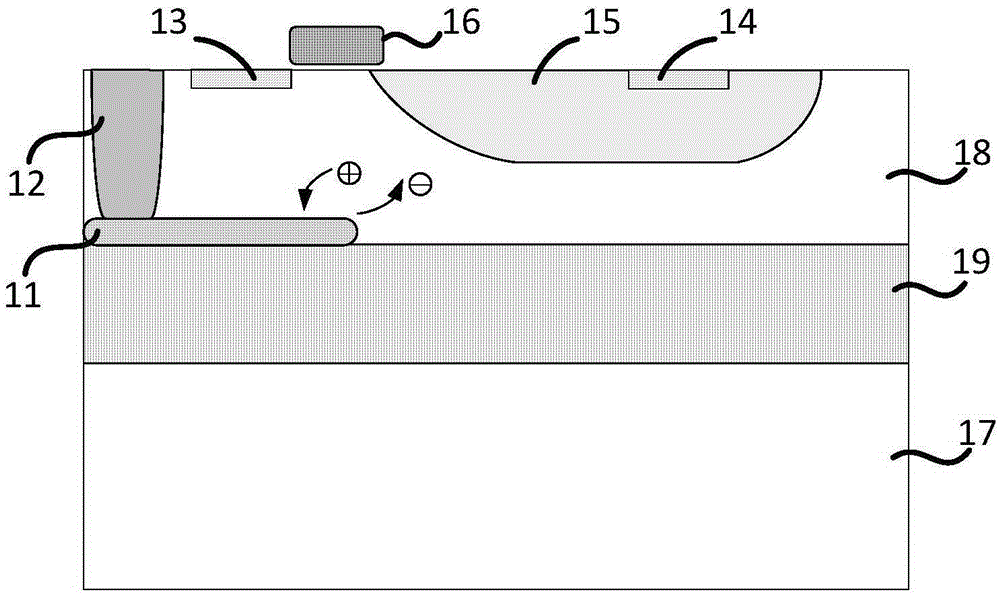

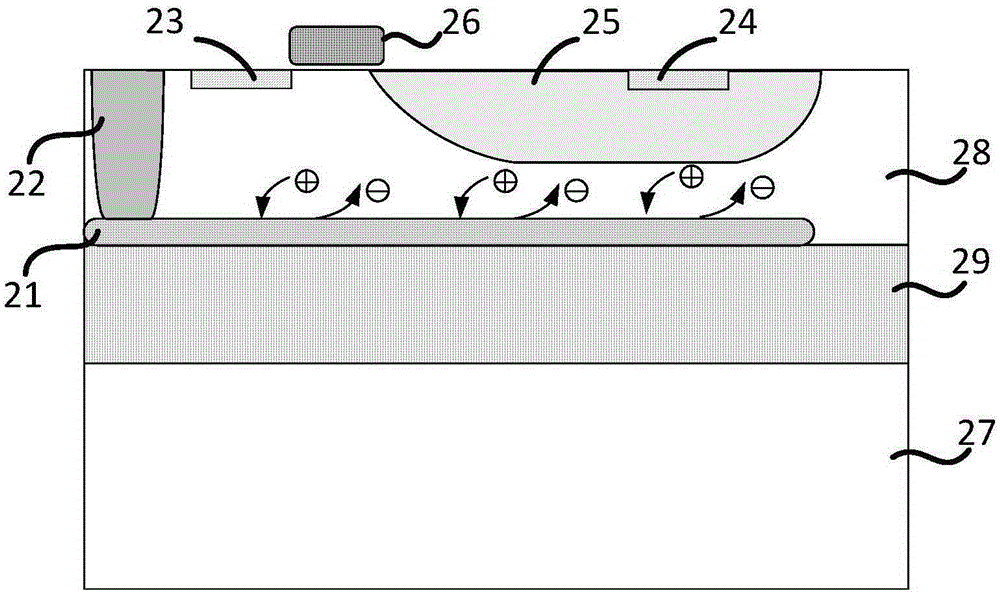

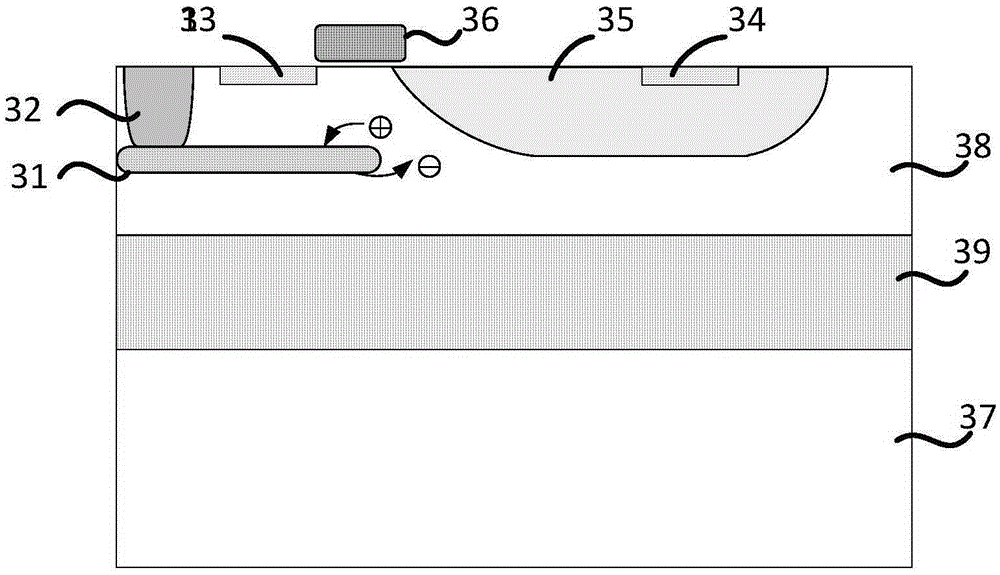

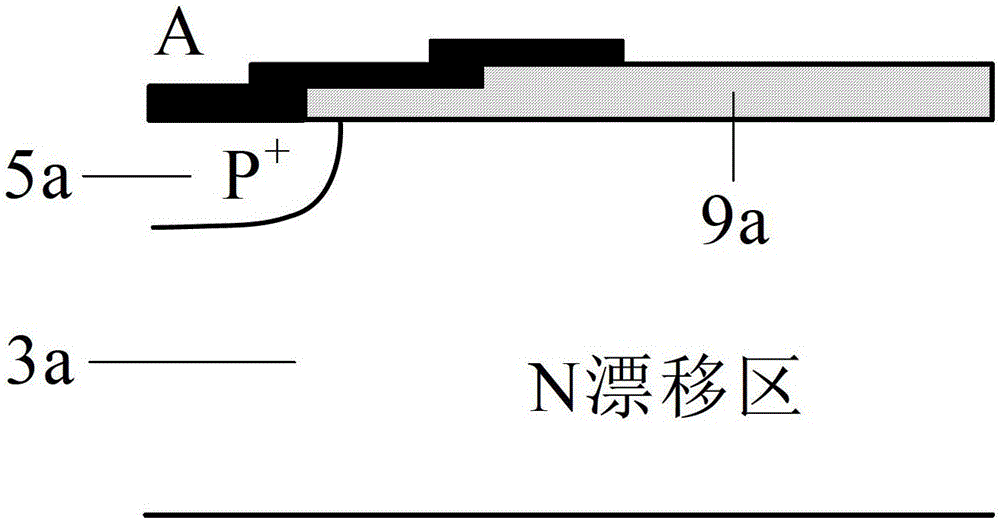

SOI power LDMOS device provided with junction type field plate

InactiveCN103325835AGood static electrical propertiesIncrease the on-resistanceDiodeSoi cmosPower semiconductor device

The invention discloses an SOI power LDMOS device provided with a junction type field plate structure, and belongs to the technical field of power semiconductor devices. According to the JFP SOI LDMOS device, a PN junction is adopted as a field plate, and a high-K medium is used as a field plate medium. On one hand, a PN junction electric field of the junction type field plate modulates the electric field on the surface of the device to improve the electric field distribution of the device and enhance the pressure resistance of the device; on the other hand, in a reverse blocking state, the junction type field plate assists in exhausting a drift region of the device to enable the doping density of the drift region of the device to be increased substantially, so that on-resistance is lowered; the high-K medium is used as a field dielectric layer so that the on-resistance and static power consumption can be lowered more beneficially. Compared with a conventional metal field plate, the junction type field plate technology also effectively avoids the defect that an electric field peak exists at the tail end of the field plate; compared with a polycrystalline resistance field plate, the junction type field plate has a PN junction potential barrier so that a high leakage current can be avoided. In addition, the SOI power LDMOS device provided with the junction type field plate structure also has good compatibility with SOI CMOS circuits.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA +1

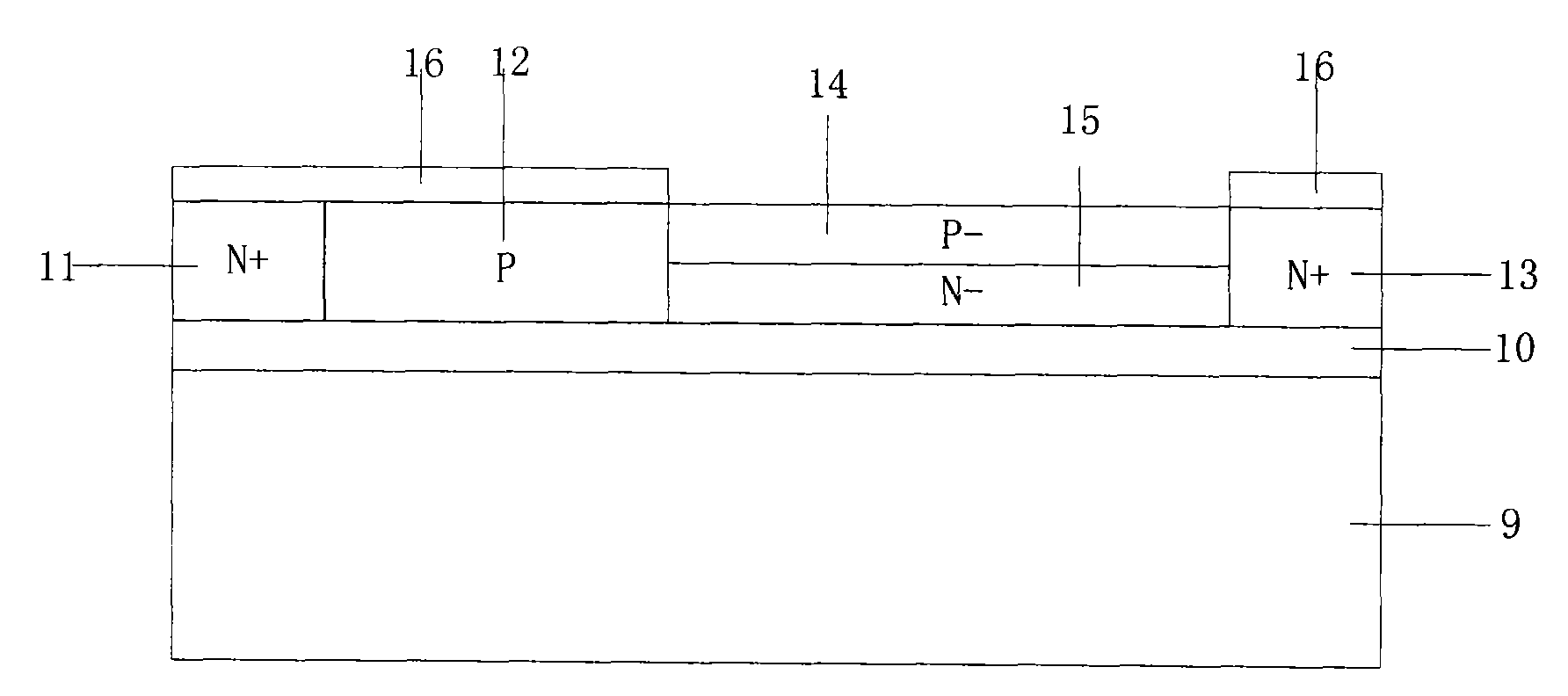

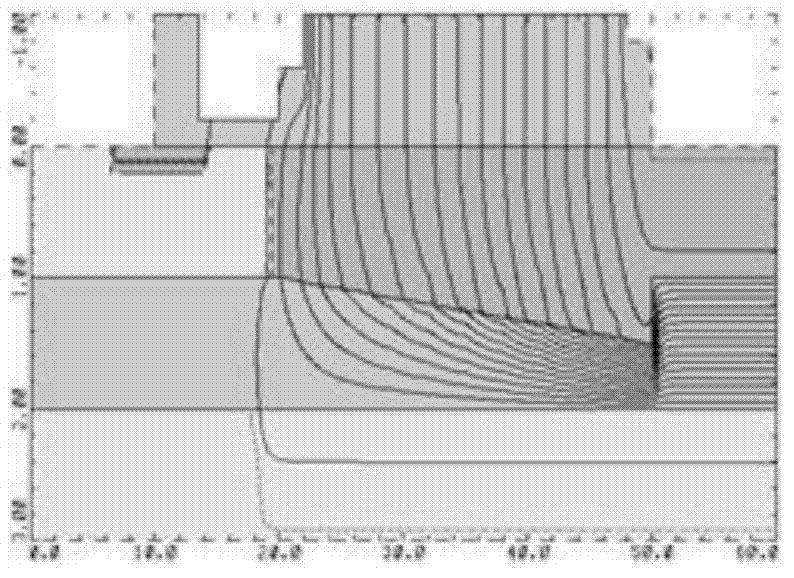

Silicon-on-insulator laterally diffused metal oxide semiconductor (SOI LDMOS) device containing composite drift region

InactiveCN102446967AIncrease the breakdown voltage valueSmall on-state resistanceSemiconductor devicesAdditional valuesSoi ldmos

The invention discloses a silicon-on-insulator laterally diffused metal oxide semiconductor (SOI LDMOS) device containing a composite drift region. The device sequentially comprises a grid oxide layer, a top silicon layer, a buried oxide layer and a bottom silicon layer from top to bottom, wherein the top silicon layer contains the composite drift region; and the composite drift region contains a first drift region and a second drift region, wherein the first drift region is adjacent to a channel region and is encircled by the second drift region. By adopting the composite drift region in the device, the maximum electric field value of the drift region close to one end of the channel, and the breakdown voltage value is improved; and because the first drift region is thinner than the top silicon layer, the additional value of the on resistance caused by the first drift region is reduced, and the on conduction property is improved.

Owner:PEKING UNIV

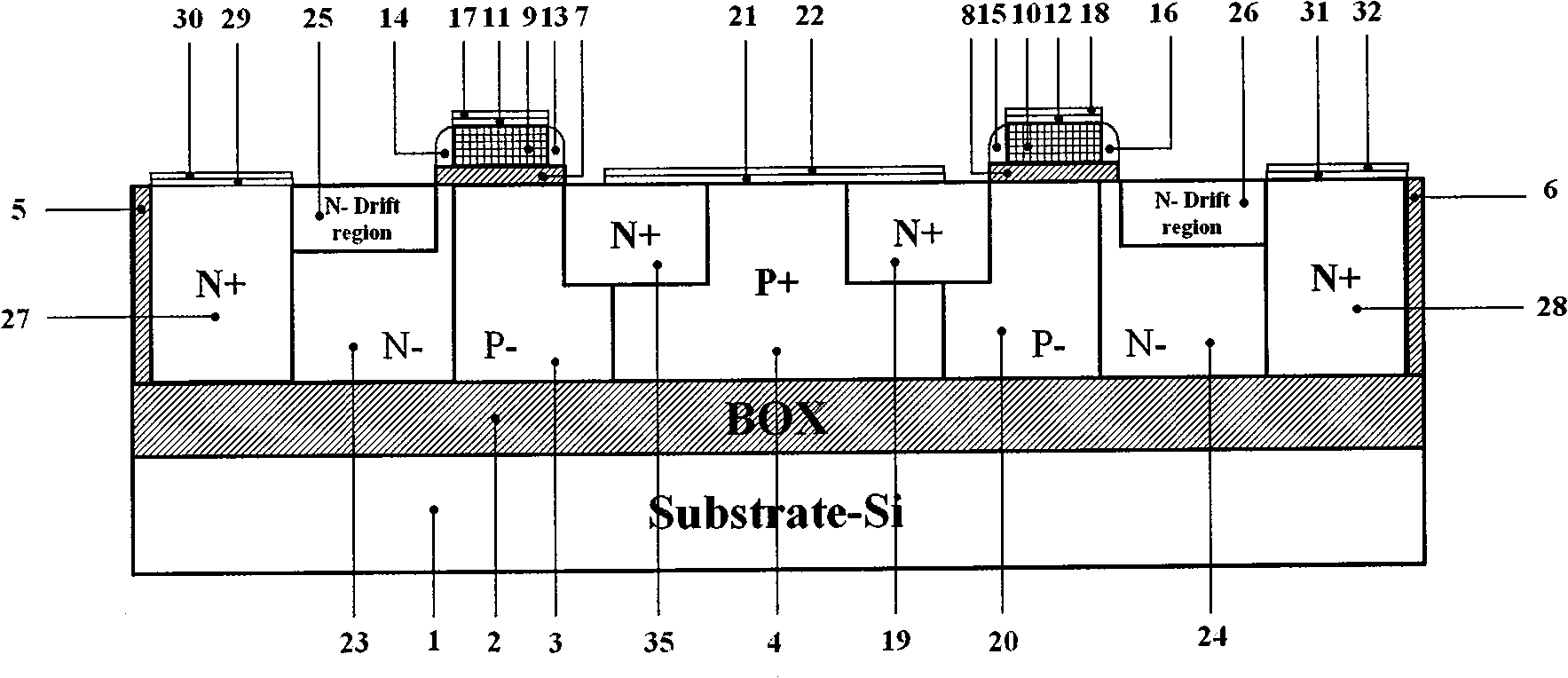

Super structure based on vertical gate SOI CMOS device and manufacturing method thereof

InactiveCN101789435AImprove breakdown voltageImprove electric field distributionSolid-state devicesSemiconductor/solid-state device manufacturingSoi cmosFloating body effect

The invention discloses a super structure based on a vertical gate SOI CMOS device and a manufacturing method thereof. The structure comprises an SOI substrate, a gate region, a source region, a channel region, a drift region and a drain region, wherein the gate region, the source region, the channel region, the drift region and the drain region grow on the SOI substrate; the gate region is vertical to and in direct contact with a buried oxide layer; the drift region in which pn column regions are arranged up and down is arranged between the channel region and the drain region; and the doping type of the lower column region in the drift region is consistent with the doping type of the drain region. On the basis of the vertical gate SOI CMOS device, the invention transforms the single doping type drift region into the drift region in which the pn column regions are arranged alternately, enables the drift region to be fully exhausted as much as possible when the breakdown voltage is achieved, optimizes the distribution of each electric field, reduces and levels the peak values of electric fields at the drift region, the junction of the drift region and the channel region and the junction of the drift region and the drain region, keeps the function of the vertical gate SOI CMOS device for eliminating the floating-body effect, and simultaneously greatly improves the high-voltage breakdown resistance of the SOI LDMOS.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI +1

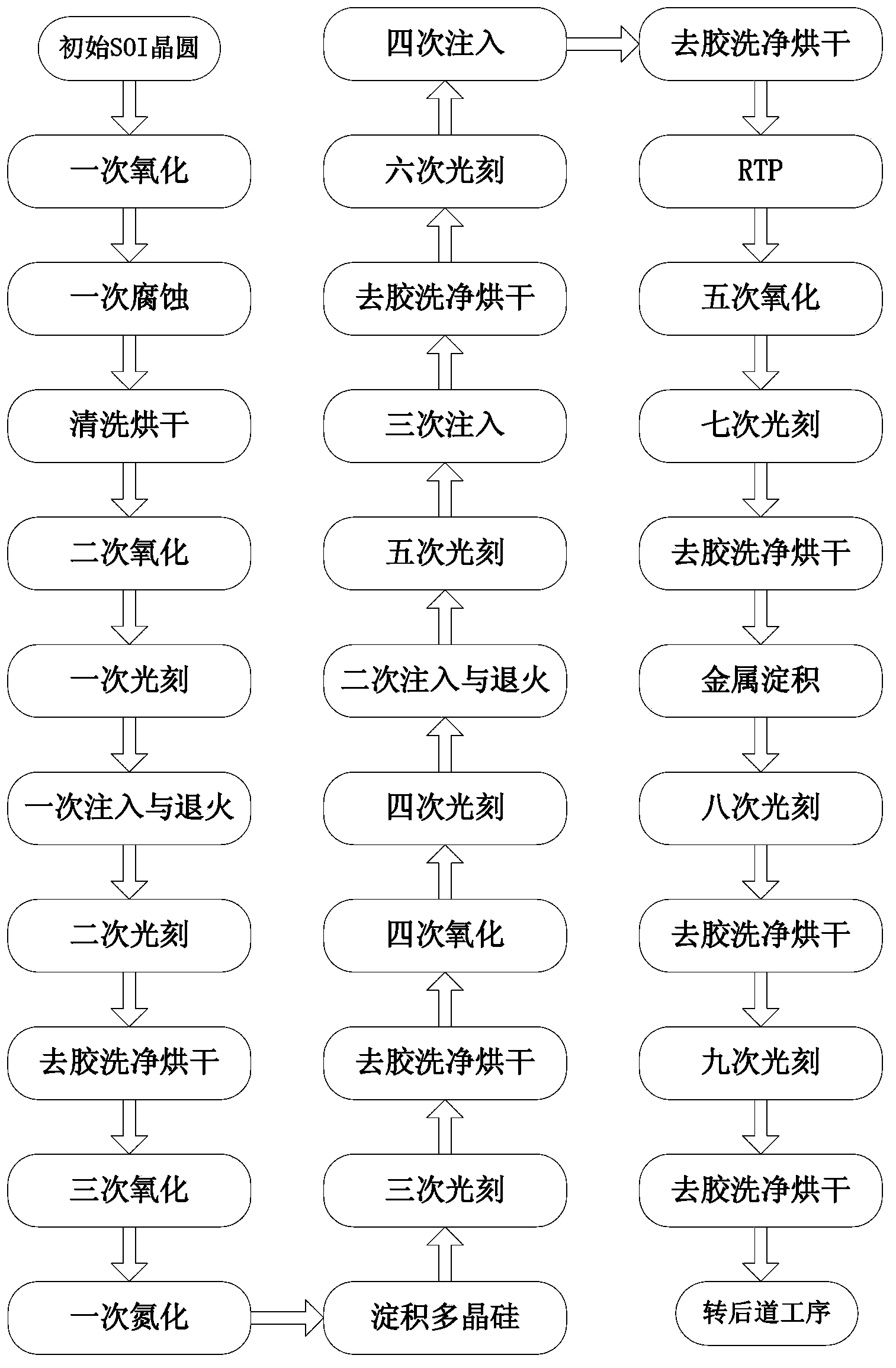

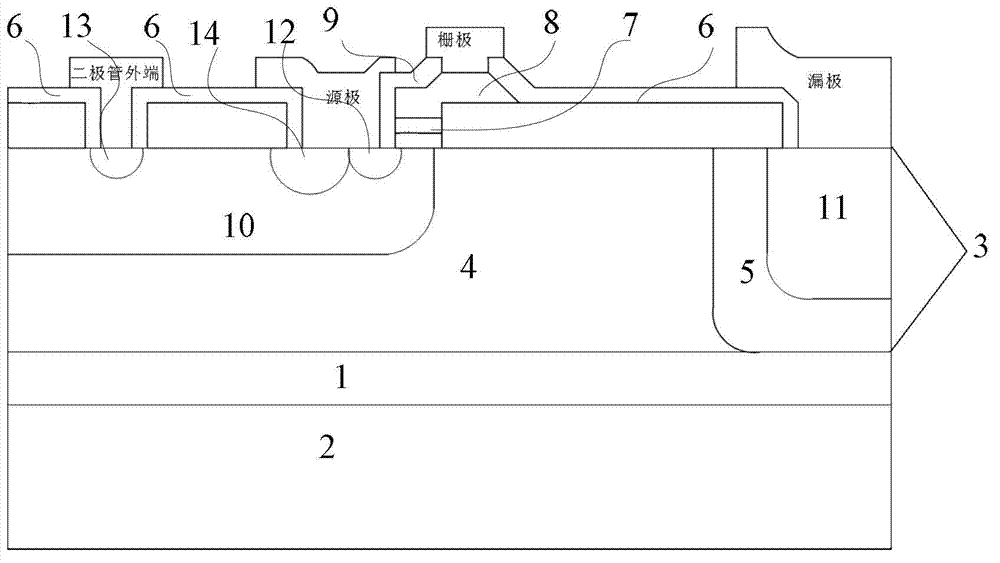

Manufacturing method of anti-ESD integration SOI LDMOS device unit

ActiveCN103354207AExcellent ElectricalGood thermal propertiesSemiconductor/solid-state device manufacturingElectronic systemsRadio frequency

The invention relates to a manufacturing method of an anti-ESD integration SOI LDMOS device unit. By using the SOI LDMOS device manufactured through using the prior art, system weight is heavy; cost is high and reliability is low. According to the invention, through using five-time oxidation and nine-time photoetching, the SOI LDMOS device unit which integrates an anti-ESD structure and a function is manufactured. By using the method of the invention, under the condition that chip area cost is increased slightly, the integrated power and radio frequency SOI LDMOS device possesses an excellent integrated anti-ESD self-protection function; anti-ESD self-protection performance of the SOI LDMOS device is significantly improved; sizes, weight and cost of various kinds of power electronics systems using the device are reduced; and system reliability is increased.

Owner:HANGZHOU DIANZI UNIV

Latch-up resisting N-type SOI laterally diffused metal oxide semiconductor

ActiveCN102769038AImprove latching abilityLower on-resistanceSemiconductor devicesHigh energyBody contact

A latch-up resisting N-type SOI (Silicon On Insulator) laterally diffused metal oxide semiconductor (LDMOS) comprises an N-type substrate, wherein a buried oxide is arranged on the N-type substrate; an N-type epilayer is arranged on the buried oxide; an N-type buffering well and a P-type body region are arranged in the N-type epilayer; an N-type drain region is arranged in the N-type buffering well; an N-type source region and a P-type body contact region are arranged in the P-type body region; a gate oxide and a field oxide are arranged on the surface of the N-type epilayer; a shallow P-type well region is arranged on the surfaces of both the N-type source region and the P-type body contact region; a polysilicon gate is arranged on the surface of the gate oxide; and a passivation layer is arranged on the surfaces of the field oxide, the P-type body contact region, the N-type source region, the polysilicon gate and the N-type drain region. The latch-up resisting N-type SOI-LDMOS is characterized in that a deep P-type well region sharing the same photoetching board together with the shallow P-type well region and formed by high-energy ion implantation is arranged right below the shallow P-type well region, and the deep P-type well region effectively reduces the conducting resistance of the body region and lowers the latch-up risk in the working process while improving the current capacity of devices.

Owner:SOUTHEAST UNIV

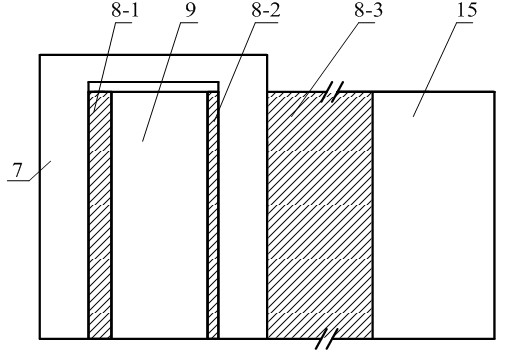

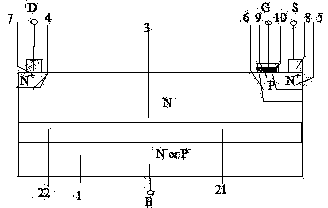

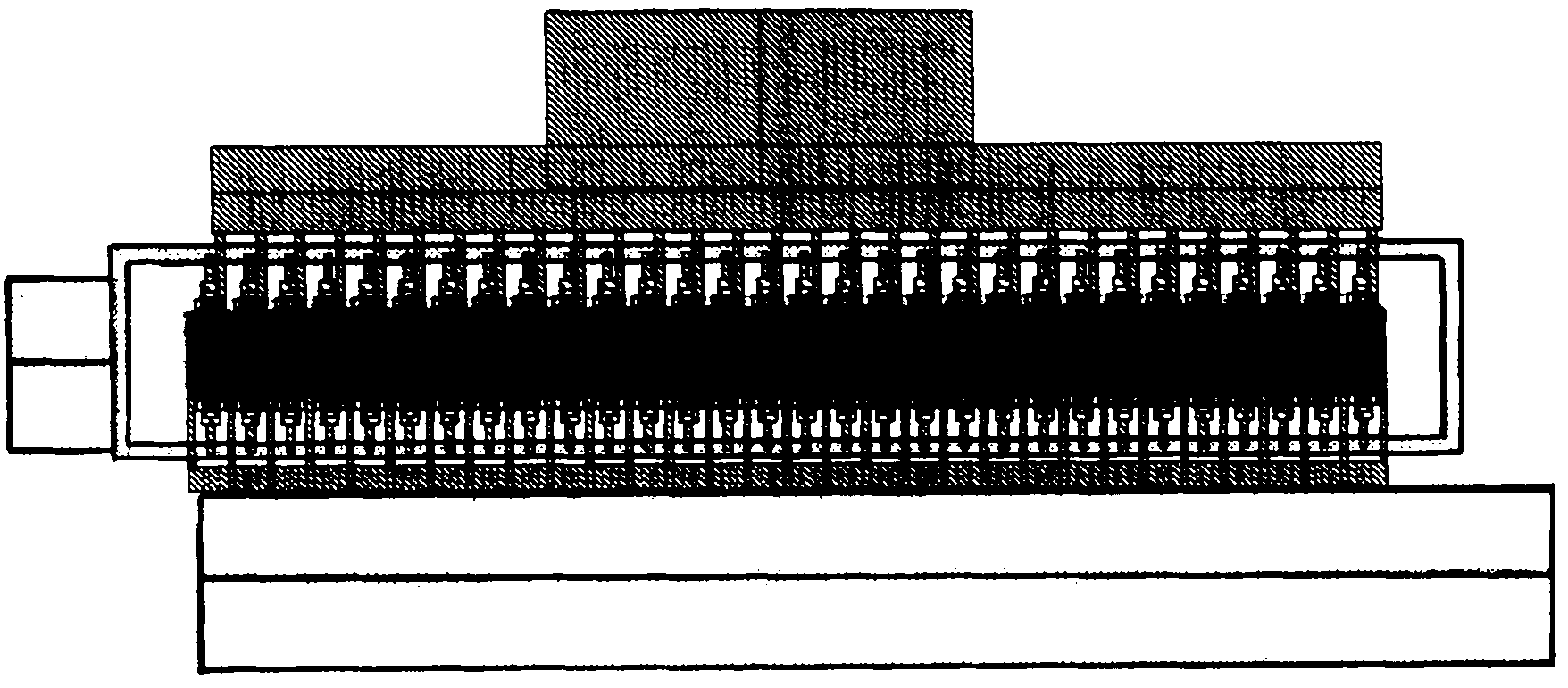

Radio frequency SOI LDMOS device with H-shaped gate

InactiveCN101515588AIncrease working frequencyImprove breakdown voltageTransistorSemiconductor/solid-state device detailsRadio frequencyPolysilicon gate

The invention relates to the field of radio frequency power devices, and discloses a radio frequency SOI LDMOS device with H-shaped gate. The device comprises bottom layer silicon, an embedding oxide layer, top layer silicon, a P region, an N region, an H-shaped gate oxide layer, an H-shaped polysilicon gate layer, an H-shaped gate poly-silicide layer, a gate electrode, a silicon nitride side wall, an N drift region, a drain region, a drain region silicide layer, a drain electrode, a source region, a body lead-out region, a source region silicide layer and a source electrode. The radio frequency LDMOS device is manufactured on an SOI substrate, and forms the body lead-out which is in short circuit with the source region by utilizing a heavily doped region in the same form as the P region; the source / body, a drain / body and the gate and the corresponding electrodes are interconnected by the silicide; and a plurality of gate bars are connected in parallel in the forked mode so as to improve the driving capability of the device. Simultaneously, the invention discloses a method for adjustment, back-gate injection, N region injection and N drift region injection, which is compatible with the CMOS process and a method for hiding the silicide in the N drift region, which is compatible with the CMOS process.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

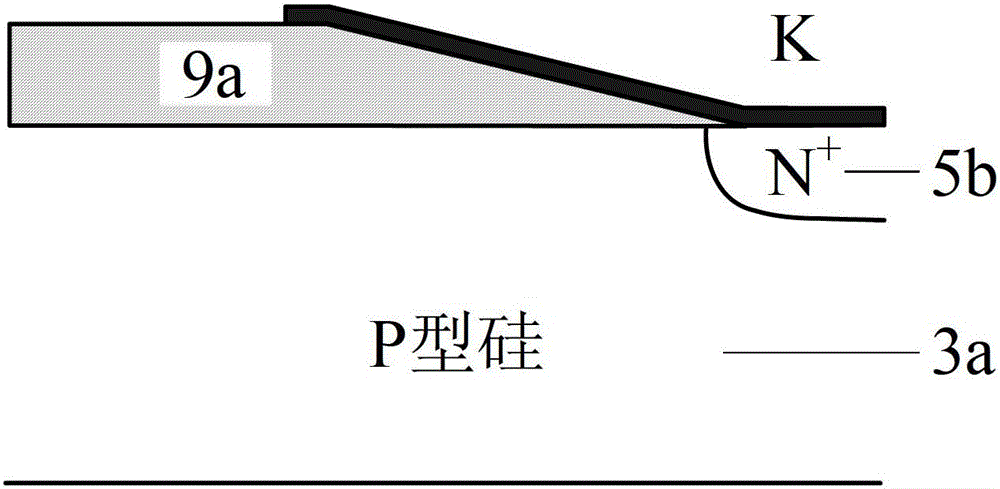

SOI LDMOS device with interface N<+> layer

ActiveCN102760753AAvoid premature breakdownImprove vertical pressure resistanceSemiconductor devicesHigh concentrationP type silicon

The invention discloses an SOI (Semiconductor ON Insulator) LDMOS (Laterally Diffused Metal Oxide Semiconductor) device with an interface N<+> layer, and relates to a semiconductor power device. The SOI LDMOS device comprises a substrate silicon layer, a medium buried layer and active top layer silicon, wherein the medium buried layer is arranged between the substrate silicon layer and the active top layer silicon; and the active top layer silicon is divided into an N-type silicon layer, a P-type silicon layer and an N<+> silicon layer from the surface of a semiconductor to the medium buried layer. According to the invention, as the N<+> silicon layer is arranged between the medium buried layer and the active top layer silicon, when the device is in a reverse blocking state, exhausted high-concentration ionized donor at the interface part enhances the electric field of the medium buried layer, the distribution of the electric field in the active top layer silicon is effectively modulated, and accordingly, the longitudinal voltage resistance and the transverse voltage resistance of the device are effectively improved. Meanwhile, the P-type silicon layer in the active top layer silicon can adjust the RESURF (Reduced SURface Field) condition of the device and relieve the contradiction between the breakdown voltage and the on resistance of the device.

Owner:NO 24 RES INST OF CETC

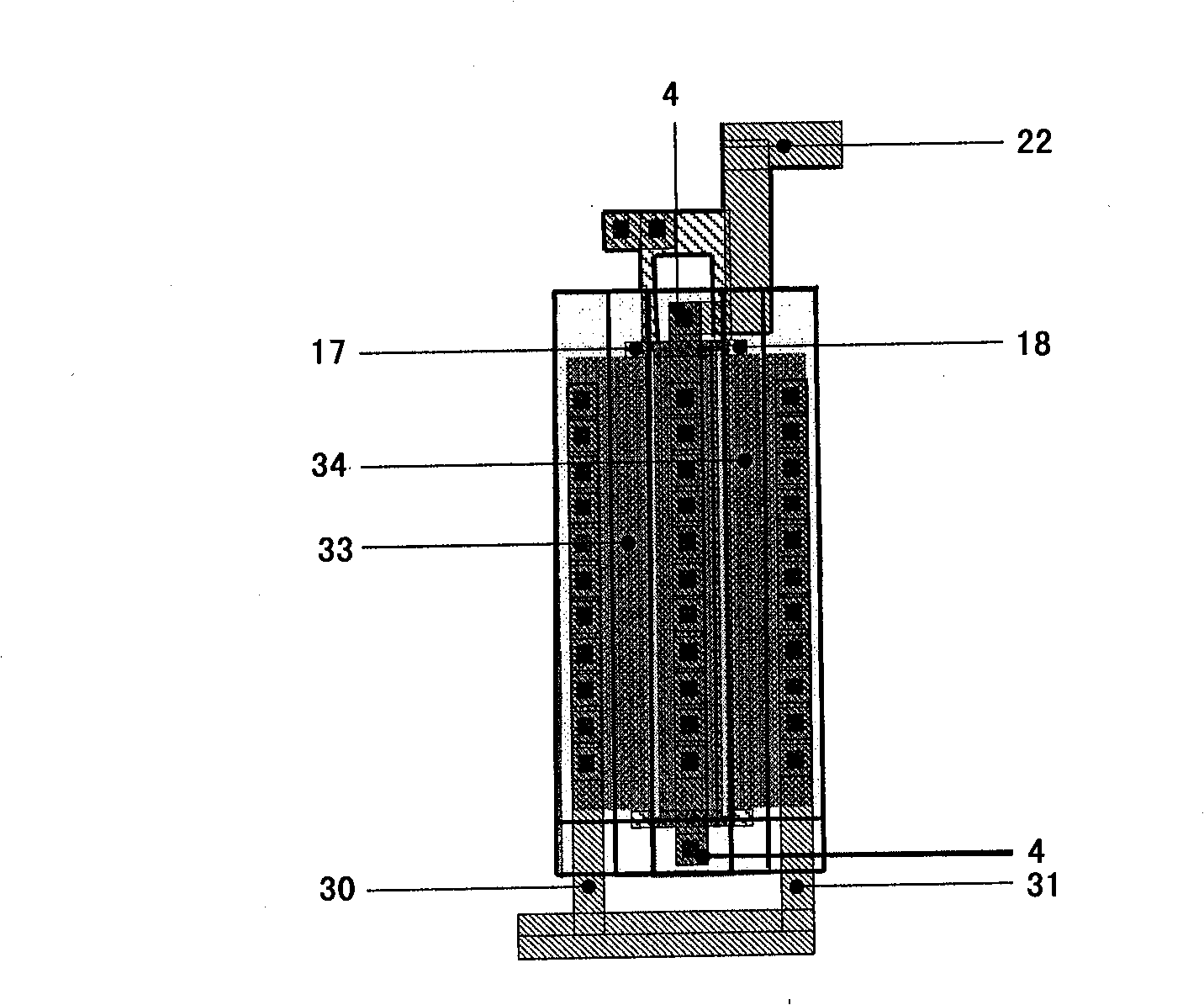

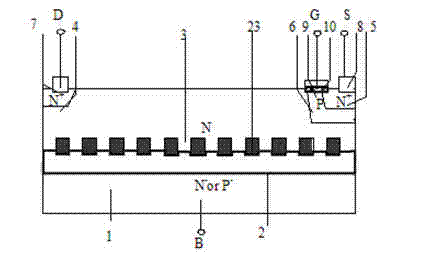

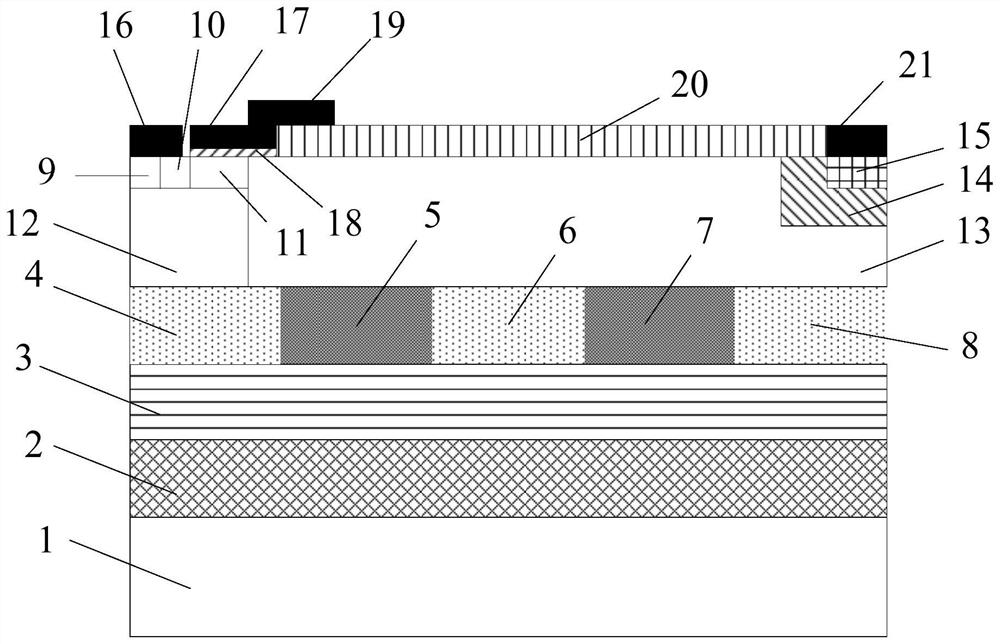

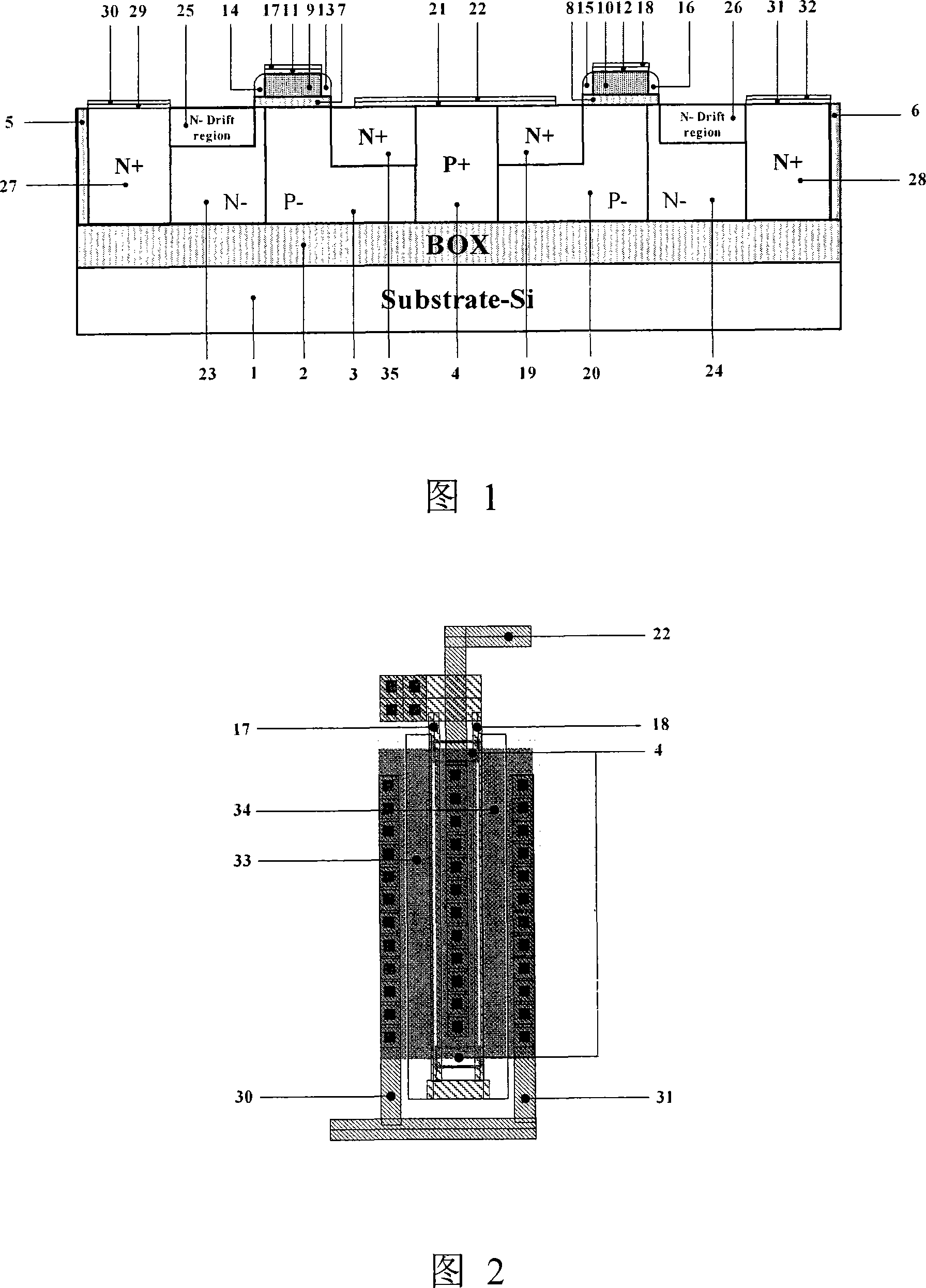

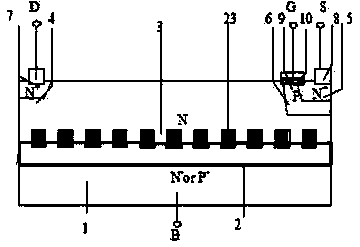

Integrated double longitudinal channel SOI LDMOS (silicon on insulator laterally double diffusion metal oxide semiconductor) device unit

InactiveCN102097482AExtended conduction current pathImprove high temperature resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDouble diffusionEngineering

The invention relates to an integrated double longitudinal channel SOI LDMOS (silicon on insulator laterally double diffusion metal oxide semiconductor) device unit. Improvement on the device structure and electrical properties of the traditional product is restricted. In the invention, a hidden buried oxidation layer divides a semiconductor substrate into a semiconductor substrate and a lightly doped drift region, wherein the two sides of the lightly doped drift region are respectively provided with a buffer zone of the LDMOS and a first low resistance polycrystalline silicon gate, and a longitudinal gate oxidation layer is arranged between the first low resistance polycrystalline silicon gate and the lightly doped drift region. The top of the lightly doped drift region is provided with a well region and a slot oxygen region, the well region is internally provided with two source electrodes and an ohm contact region, and the slot oxygen region is internally embedded with a second polycrystalline silicon gate. The upper part of the device is provided with three field oxidation layers and a metal layer. In the invention, a shallow slot gate is added between the well region and the drift region, a longitudinal conducting channel is added, the transconductance and on state current of the device are improved, and the on state resistance and on state voltage drop of the device are reduced, thus the on state power consumption is reduced, the thermostability and resistance to voltage of the device are improved, and the reliability of the device is improved.

Owner:SERVICE CENT OF COMMLIZATION OF RES FINDINGS HAIAN COUNTY

High-reliability silicon on insulator (SOI) laterally diffused metal oxide semiconductor (LDMOS) power element

Disclosed is a high-reliability silicon-on-insulator (SOI) laterally diffused metal oxide semiconductor (LDMOS) power element, which comprises a buried layer with high concentration and a contact injection region, wherein the buried layer with high concentration and the contact injection region are injected in top layer silicon of the SOI LDMOS power element, and the buried layer is connected with the contact injection region; current carriers which are located near a SOI LDMOS gate in the SOI LDMOS power element can be extracted through the buried layer and educed through the contact injection region, and electric potentials which are near the SOI LDMOS gate can be controlled. According to the high-reliability SOI LDMOS power element, in the top layer silicon of the SOI LDMOS, the buried layer with high concentration is produced and educed through the contact injection region, the current carriers which are located near the SOI LDMOS gate in the SOI LDMOS power element can be extracted through the buried layer, the electric potentials which are near the gate can be controlled, so that damages or burning of LDMOS elements caused by the fact that parasitic transistors open due to noise current or colliding current, maintaining voltage of the LDMOS elements under static shock is raised simultaneously, electrical safety working areas of the LDMOS power elements are expanded, and reliability of the elements is strengthened.

Owner:BEIJING YANDONG MICROELECTRONICS

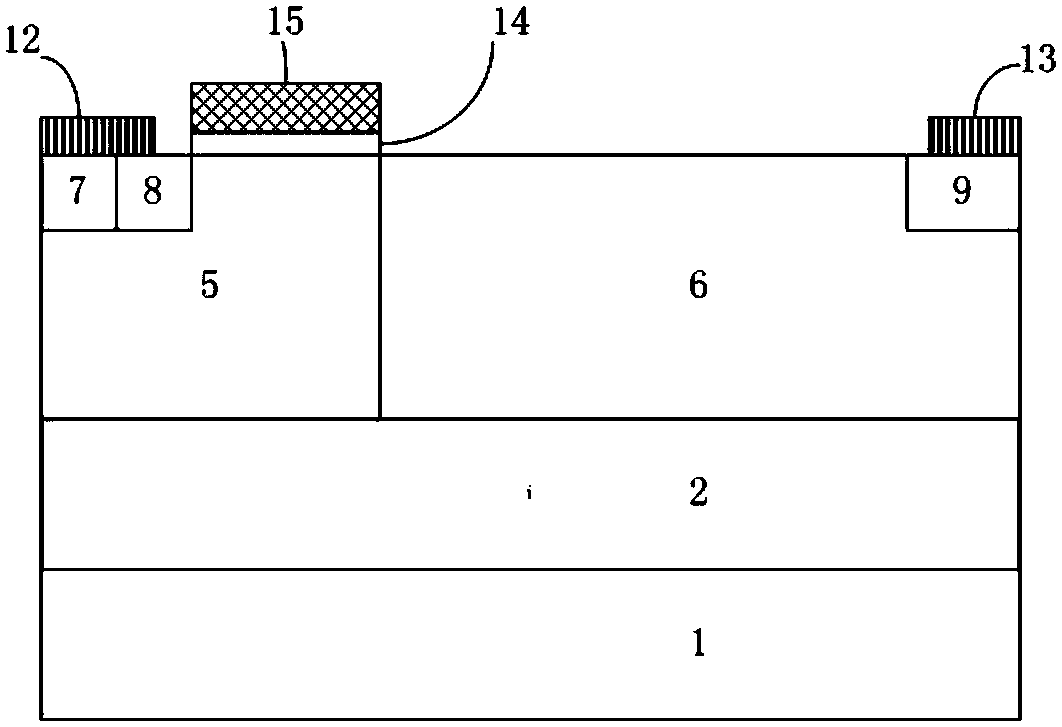

SOI LDMOS device with buried field plates

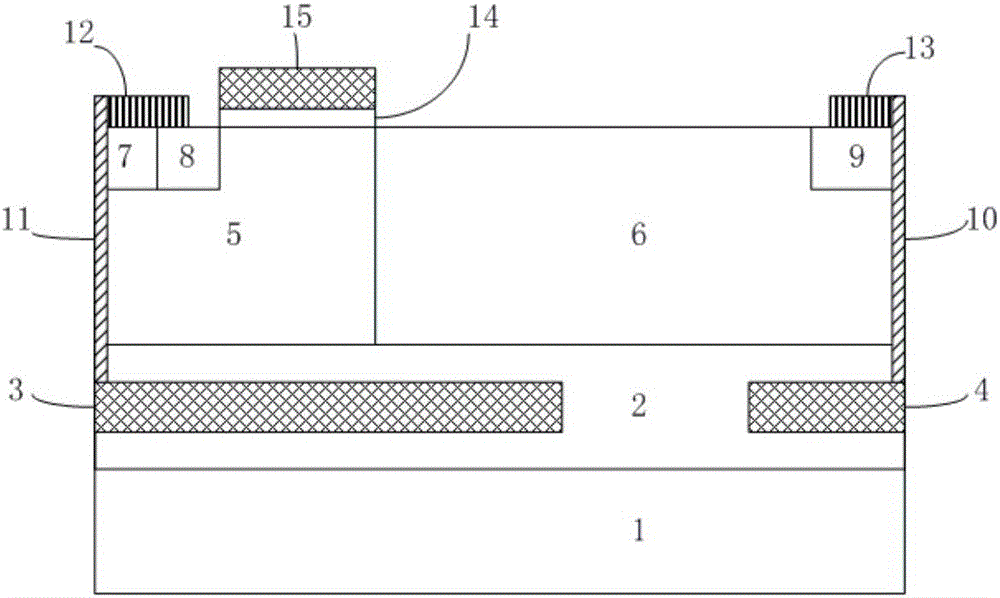

ActiveCN105932062AImproved self-heating effectImprove breakdown voltageSemiconductor devicesMOSFETSilicon dioxide

The invention discloses an SOI LDMOS (Silicon On Insulator Laterally Double-Diffused MOSFET) device with buried field plates, and relates to a semiconductor power device. The SOI LDMOS device comprises a P-type substrate, buried oxide layers, the buried field plates, top silicon, transverse polysilicon gate, a source electrode, a drain electrode, a metal electrode and a gate oxide layer. The SOI LDMOS device is provided with the source and drain buried oxide plates; due to the introduction of the drain buried oxide plate, a drift region in an N<+> drain region is shielded, so that a longitudinal voltage of the device is applied to the buried oxide layer in the drain buried field plate; due to the introduction of the source buried field plate, body exhaustion of the device is enhanced and transverse electric field distribution of the device is modulated, so that a breakdown voltage of the device is increased and on-resistance is reduced; and in addition, the buried field plates replace part of buried oxide layers and the heat conductivity of polysilicon is greater than that of silicon dioxide, so that a self-heating effect of the device can be effectively improved.

Owner:HANGZHOU DIANZI UNIV

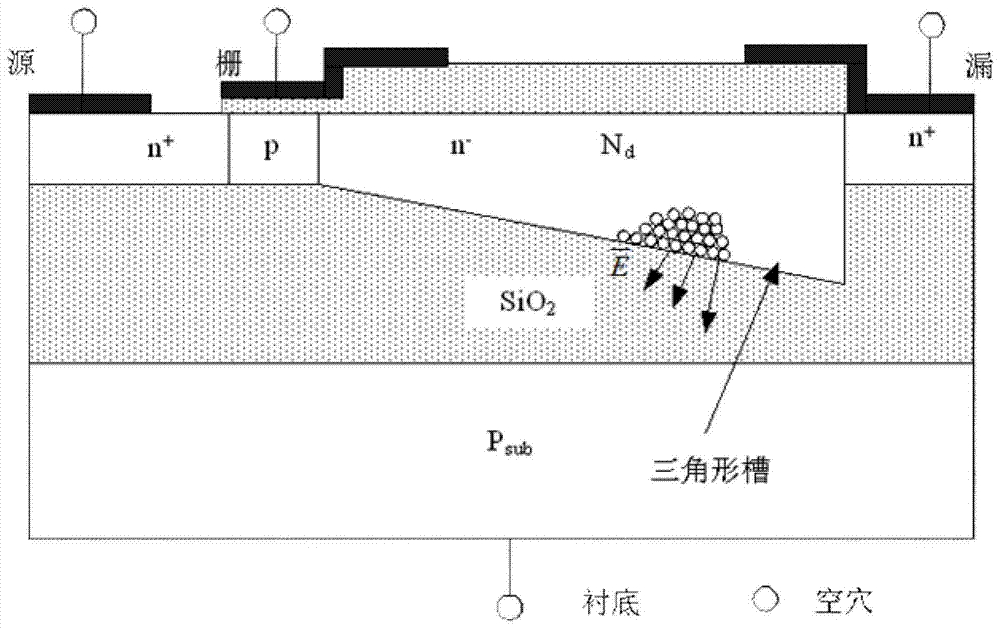

SOI-LDMOS (silicon-on-insulator laterally diffused metal oxide semiconductor) high-tension power device with triangular trench

InactiveCN104241388AImprove vertical pressure resistanceRealize the process is simpleSemiconductor devicesHigh densityEngineering

The invention discloses an SOI-LDMOS (silicon-on-insulator laterally diffused metal oxide semiconductor) high-tension power device with a triangular trench and aims to solve the problems that voltage of a drain of the prior SOI-LDMOS device is induced out of an electronic inversion layer from beneath a buried oxide layer, an equipotential line is prevented from penetrating the buried oxide layer, and early breakdown occurs to a silicon layer, and breakdown voltage withstanding is difficult to increase. The SOI-LDMOS high-tension power device is mainly characterized in that the triangular trench is etched in a buried oxide layer under a drift area; a buried oxide slope exists under the drift area and is capable of constraining positively charged holes, high-density positive charge is produced, and breakdown voltage withstanding of the device is greatly increased through the high-density positive charge; thickness of the drift area linearly increases from a source to a drain, according to the principle of RESURF (reduced surface field), a transverse electric field is uniformized owing to modulation, lateral voltage withstanding can be improved, and rejection ratio on resistance can be increased fast.

Owner:XIHUA UNIV

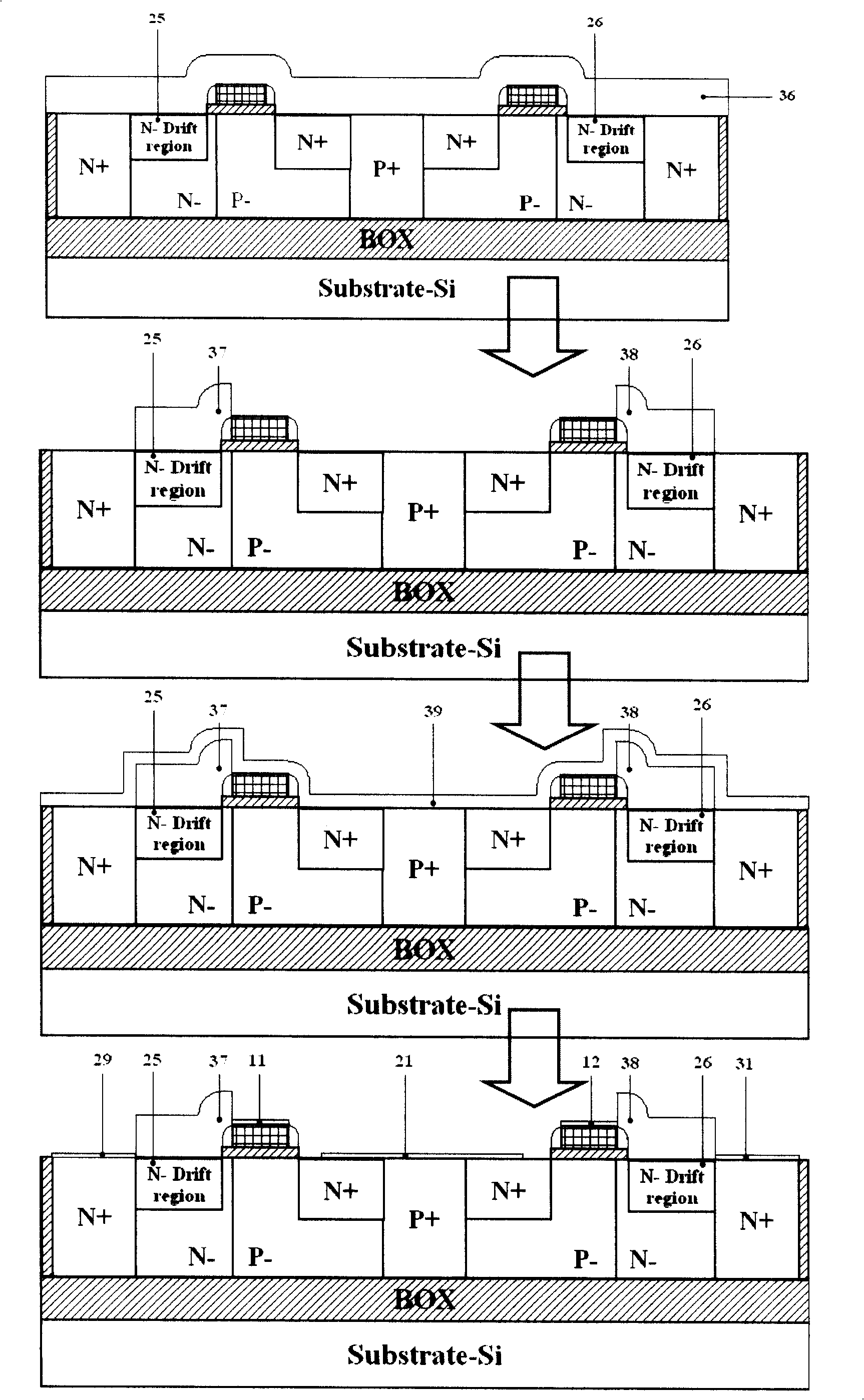

Method for making integrated silicon on insulator (SOI) laterally diffused metal oxide semiconductor (LDMOS) device with double vertical channels

InactiveCN102130061AExcellent ElectricalGood thermal propertiesSemiconductor/solid-state device manufacturingSource areaSilicon on insulator

The invention relates to a method for making an integrated silicon on insulator (SOI) laterally diffused metal oxide semiconductor (LDMOS) device with double vertical channels. The SOI LDMOS device made by the traditional method does not have a double-vertical-channel structure and an excellent performance corresponding to the double-vertical-channel structure. In the method, a channel etching technology is adopted to realize a double-vertical-groove grid electrode structure and a stepped-groove drain electrode structure, pit doping is replaced by a reverse doping distributed ion implantationpit ohmic contact doping technology, and a grid electrode and a drain electrode are simultaneously doped when an n+ source area is doped. By adopting the traditional SOI complementary metal-oxide-semiconductor transistor (CMOS) very large scale integrated circuits (VLSI) process technology under the condition of slightly increasing the process complexity and the cost, the integrated power and the electric and thermal performance of the SOI LDMOS device can be obviously improved so as to be beneficial to saving of resources and energy sources and protection on the environment.

Owner:SERVICE CENT OF COMMLIZATION OF RES FINDINGS HAIAN COUNTY

A soi LDMOS device with buried oxygen field plate

ActiveCN105932062BImproved self-heating effectImprove breakdown voltageSemiconductor devicesMOSFETMetal electrodes

The invention discloses an SOI LDMOS (Silicon On Insulator Laterally Double-Diffused MOSFET) device with buried field plates, and relates to a semiconductor power device. The SOI LDMOS device comprises a P-type substrate, buried oxide layers, the buried field plates, top silicon, transverse polysilicon gate, a source electrode, a drain electrode, a metal electrode and a gate oxide layer. The SOI LDMOS device is provided with the source and drain buried oxide plates; due to the introduction of the drain buried oxide plate, a drift region in an N<+> drain region is shielded, so that a longitudinal voltage of the device is applied to the buried oxide layer in the drain buried field plate; due to the introduction of the source buried field plate, body exhaustion of the device is enhanced and transverse electric field distribution of the device is modulated, so that a breakdown voltage of the device is increased and on-resistance is reduced; and in addition, the buried field plates replace part of buried oxide layers and the heat conductivity of polysilicon is greater than that of silicon dioxide, so that a self-heating effect of the device can be effectively improved.

Owner:HANGZHOU DIANZI UNIV

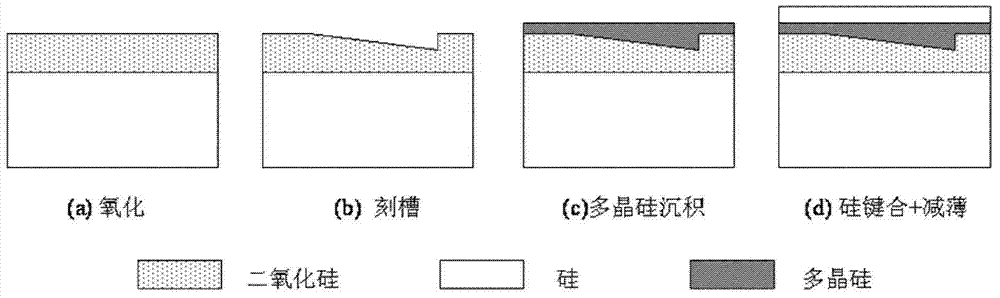

Process method of soi LDMOS device preparation

ActiveCN104392924BGuaranteed isolationGuaranteed withstand voltageSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSSource area

The invention relates to a technical method for preparing an SOI LDMOS device. The method comprises the following steps: (1), performing P-type trap injection in a top-layer silicon film; (2), applying an oxidation backflow technology on the top-layer silicon film; (3), using a photoetching technology; (4), employing the photoetching technology and a corrosion technology; (5), utilizing the oxidation backflow technology;(6), employing the corrosion technology; (7), performing N-type trap injection to form an N-type doped area; (8), performing the P-type trap injection to form a first P-type doped area; (9), performing the P-type trap injection to form a second P-type doped area; (10), performing P-type source-drain injection to form a P-type source area and a P-type drain area; (11), performing deposition to form an insulation medium layer; (12), carrying out photoetching corrosion; (13), performing deposition to form a metal layer; (14), and carrying out the photoetching corrosion. The technical method is compatible with a CMOS technical process, the technology is concise and controllable, voltage withstanding performance of the high-voltage SOI LDMOS device can be ensured, and at the same time, isolation between devices can also be ensured.

Owner:58TH RES INST OF CETC

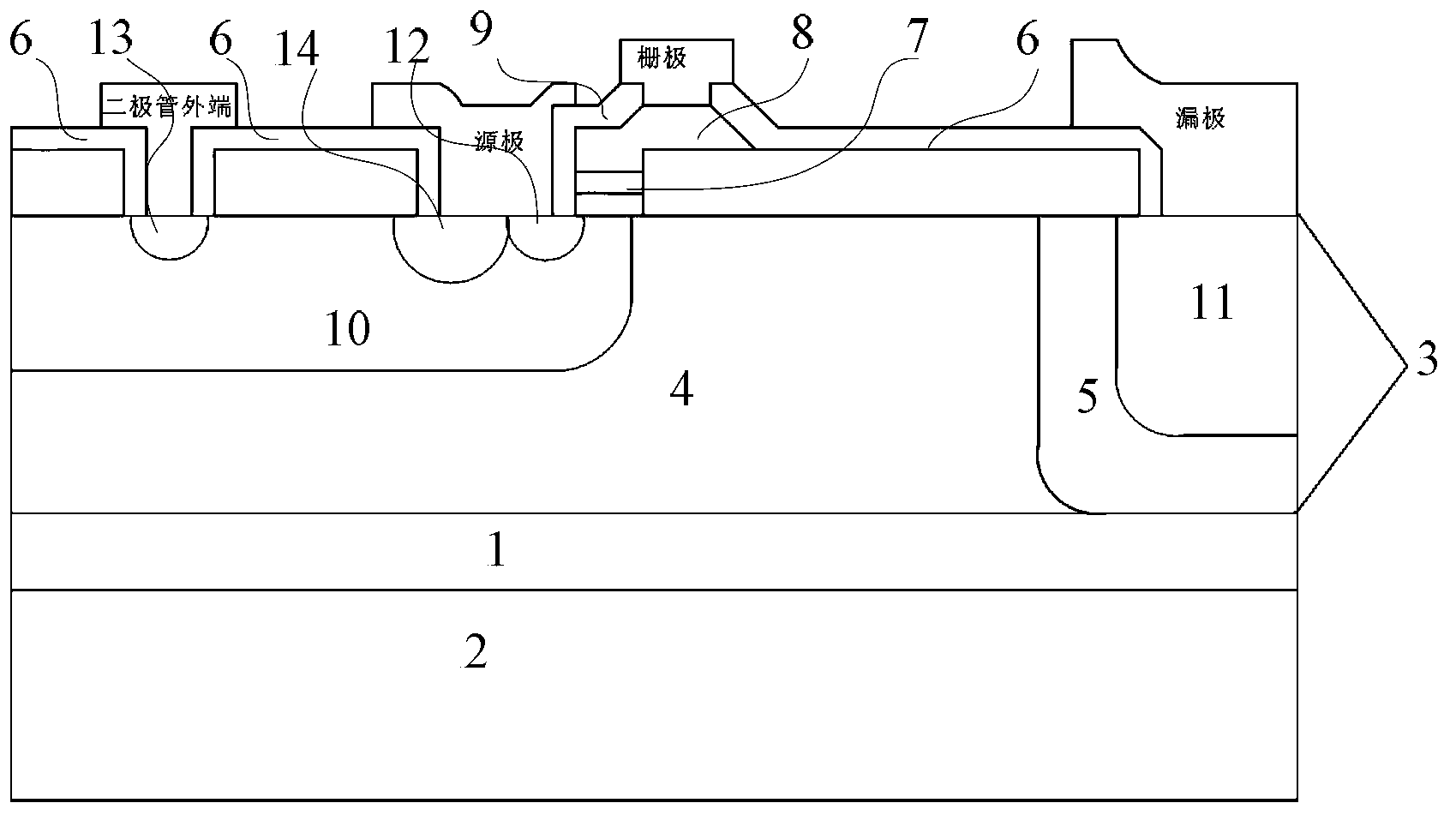

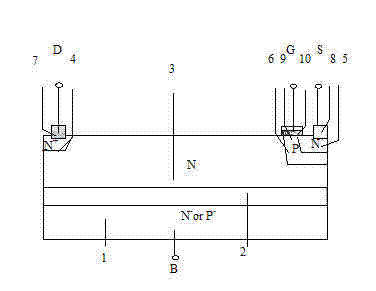

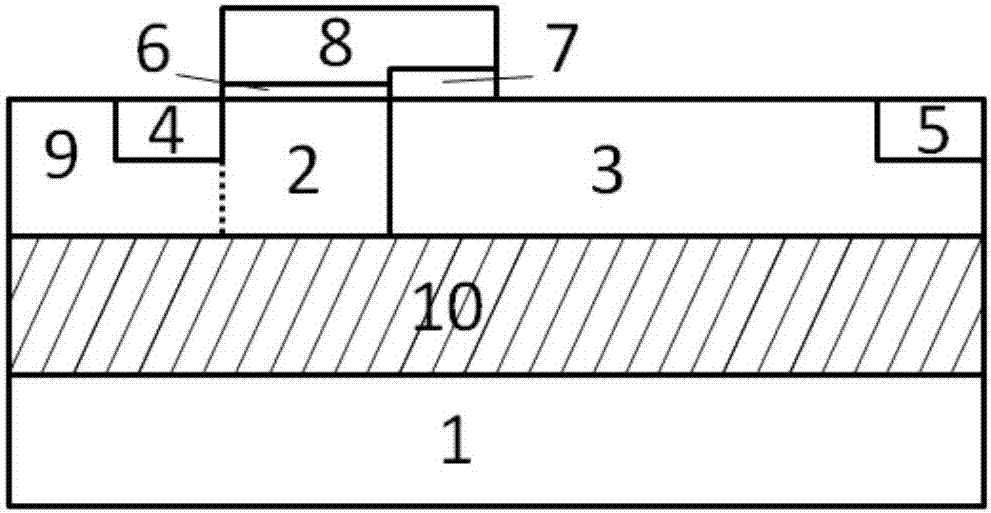

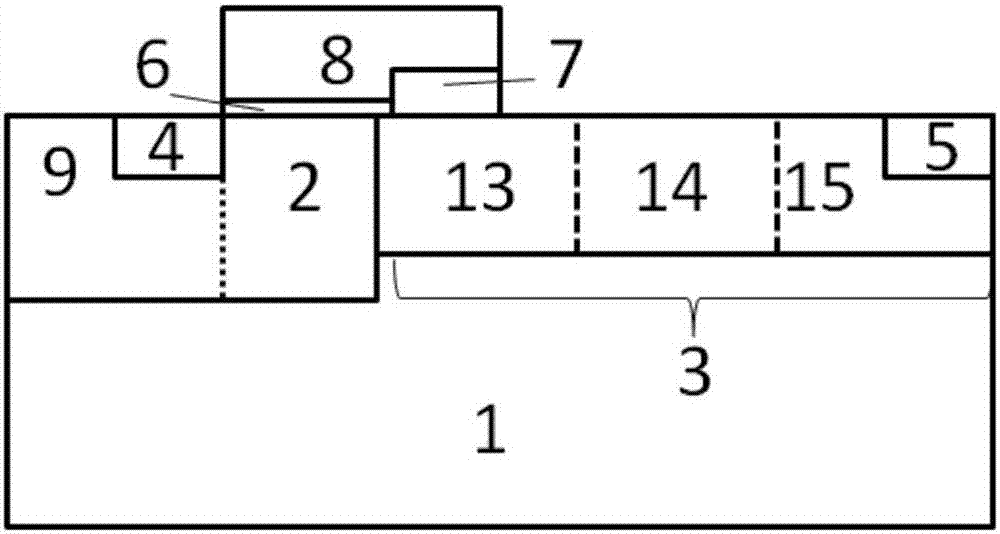

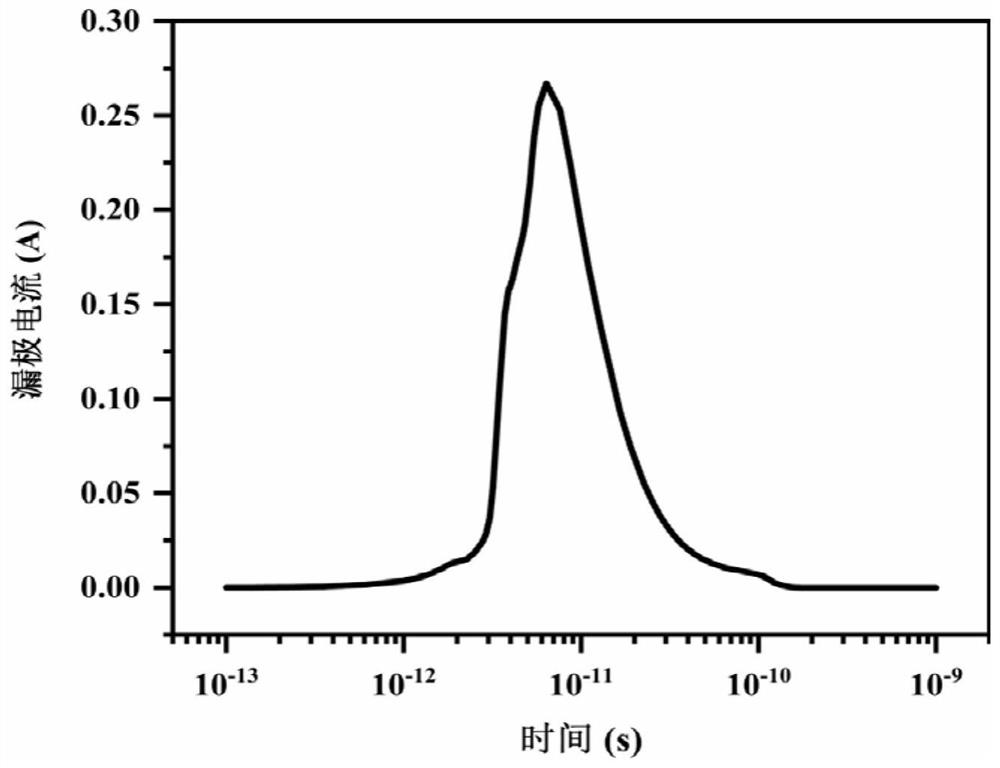

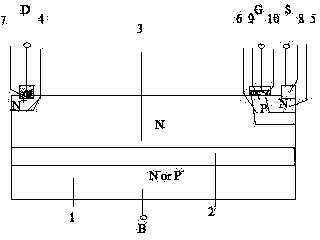

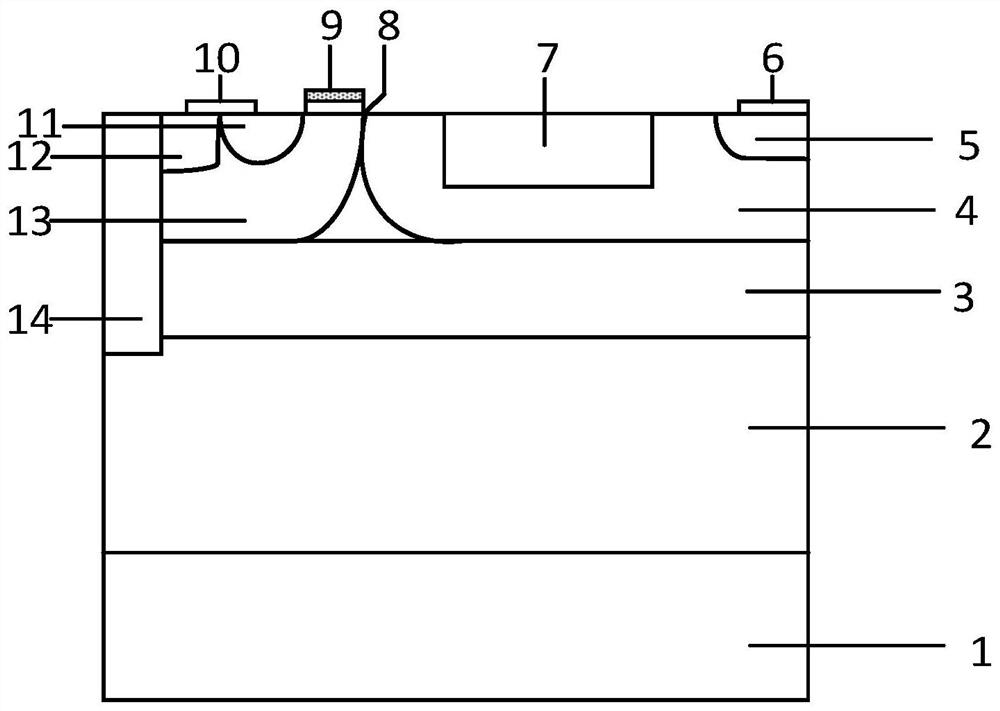

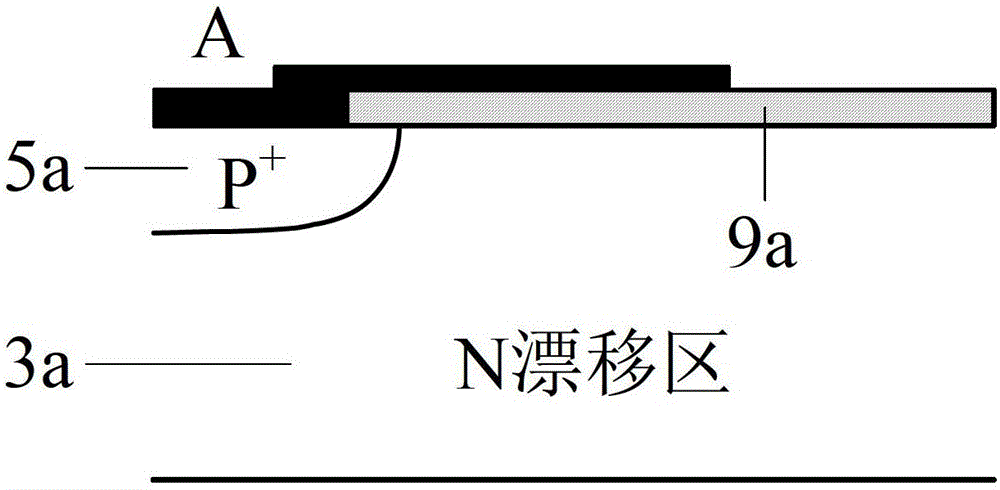

Local soi LDMOS device for frequency boosting overcoming short channel effect

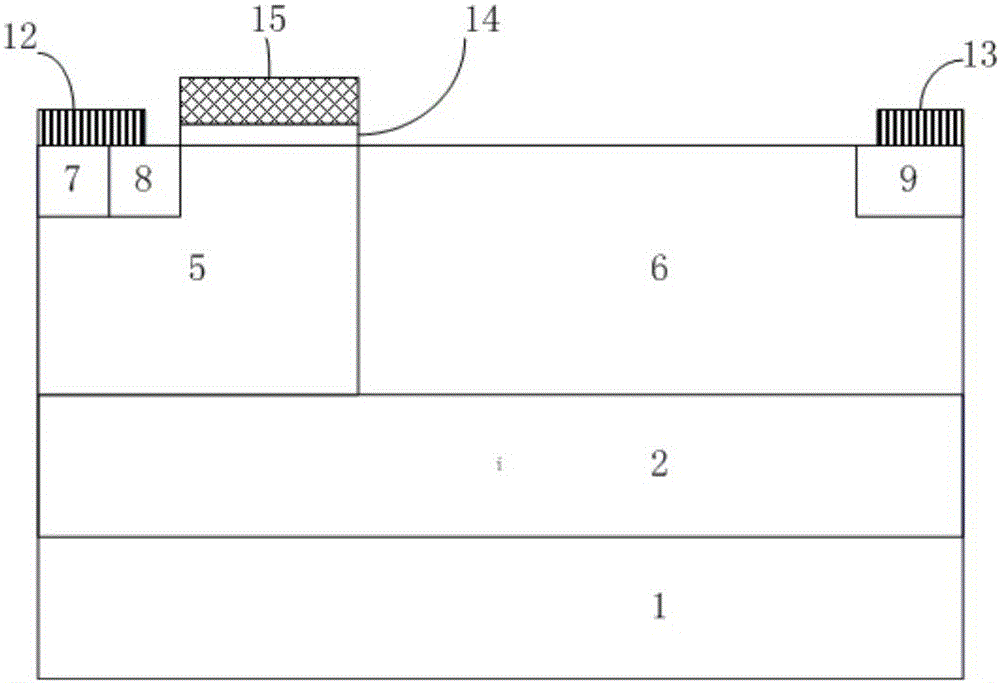

ActiveCN104157692BIncrease working frequencyGood short channel characteristicsSemiconductor devicesOxygenGate oxide

The invention discloses a local ultra-thin SOI LDMOS device which overcomes the short channel effect and increases the frequency, and belongs to the field of semiconductor devices. Including semiconductor substrate 1, channel region 2, drift region 3, source region 4, drain region 5, gate oxide 6, field oxygen 7, gate 8, channel substrate heavily doped region 9, BOX layer 18, sidewall 19. The source extension region 20, wherein the drift region 3 is a lateral variable doping structure, characterized in that a through groove is opened along the width direction of the drift region at one end of the BOX layer close to the drift region, and the BOX layer 18 is located at the side of the channel Directly below, or directly below the channel and part of the source region, or directly below the channel and the source region, to ensure the breakdown voltage while improving the frequency characteristics and drive capability of the device. The invention effectively suppresses the short-channel effect, and improves the frequency characteristic and driving ability while ensuring the breakdown voltage.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

SOI LDMOS device capable of improving self-heating effect

The invention discloses an SOI LDMOS device for improving a self-heating effect, which relates to the field of SOI devices, and adopts a P-type heavily doped silicon layer and an N-type lightly doped semiconductor layer which are stacked to replace a conventional buried oxide layer, so that the dielectric isolation effect of the buried oxide layer can also be realized; and the thermal conductivity of the silicon layer and the semiconductor layer is much higher than that of the conventional buried oxide layer, so that the self-heating effect can be improved on the basis that the SOI LDMOS device has the advantages of high speed and low power consumption.

Owner:江苏芯唐微电子有限公司

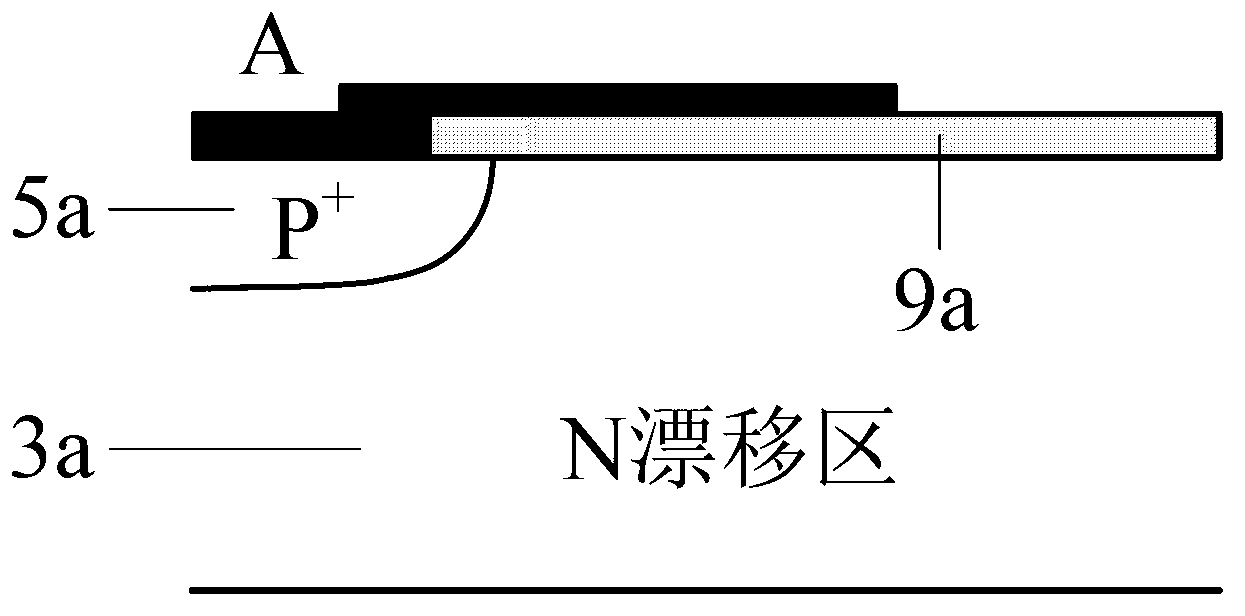

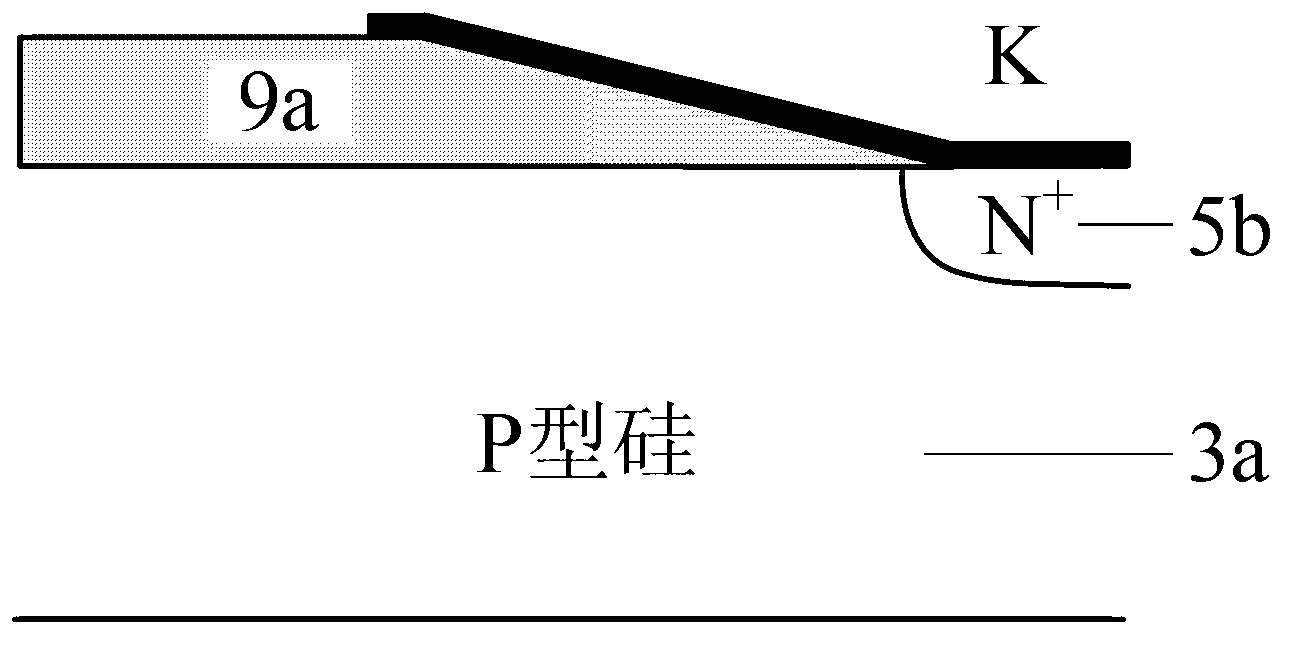

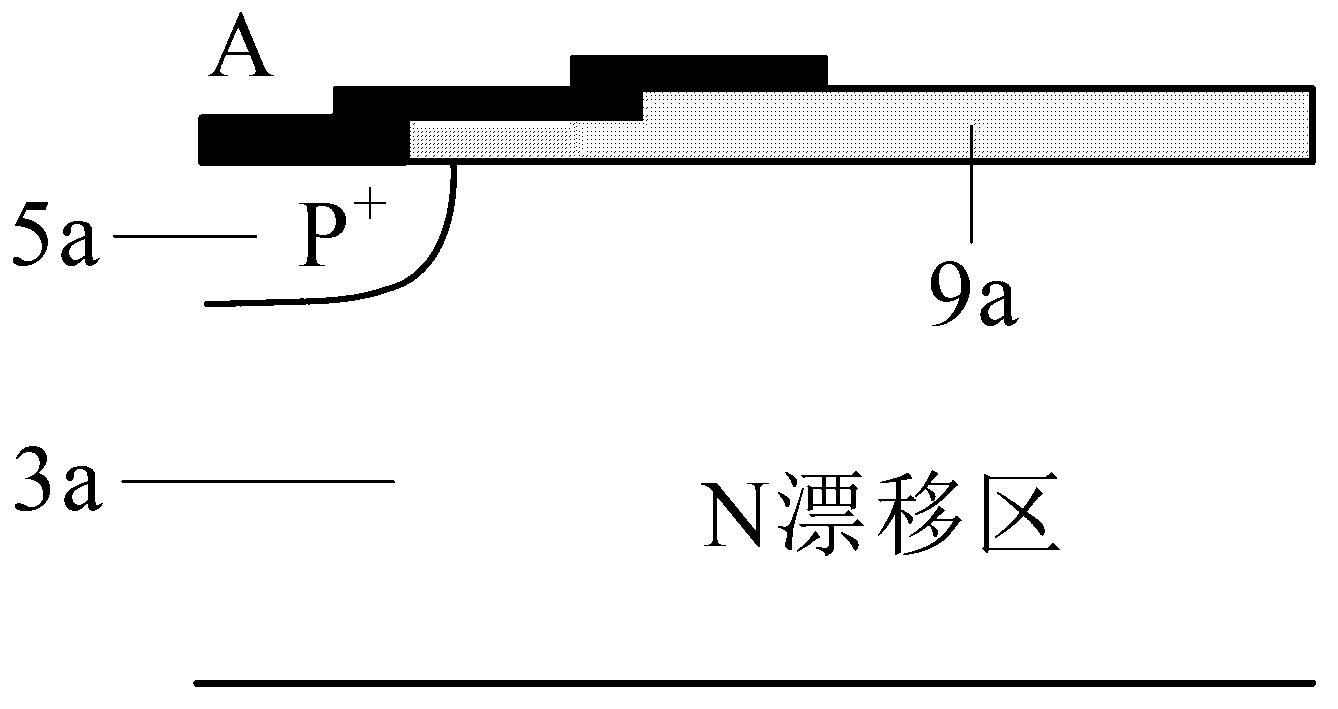

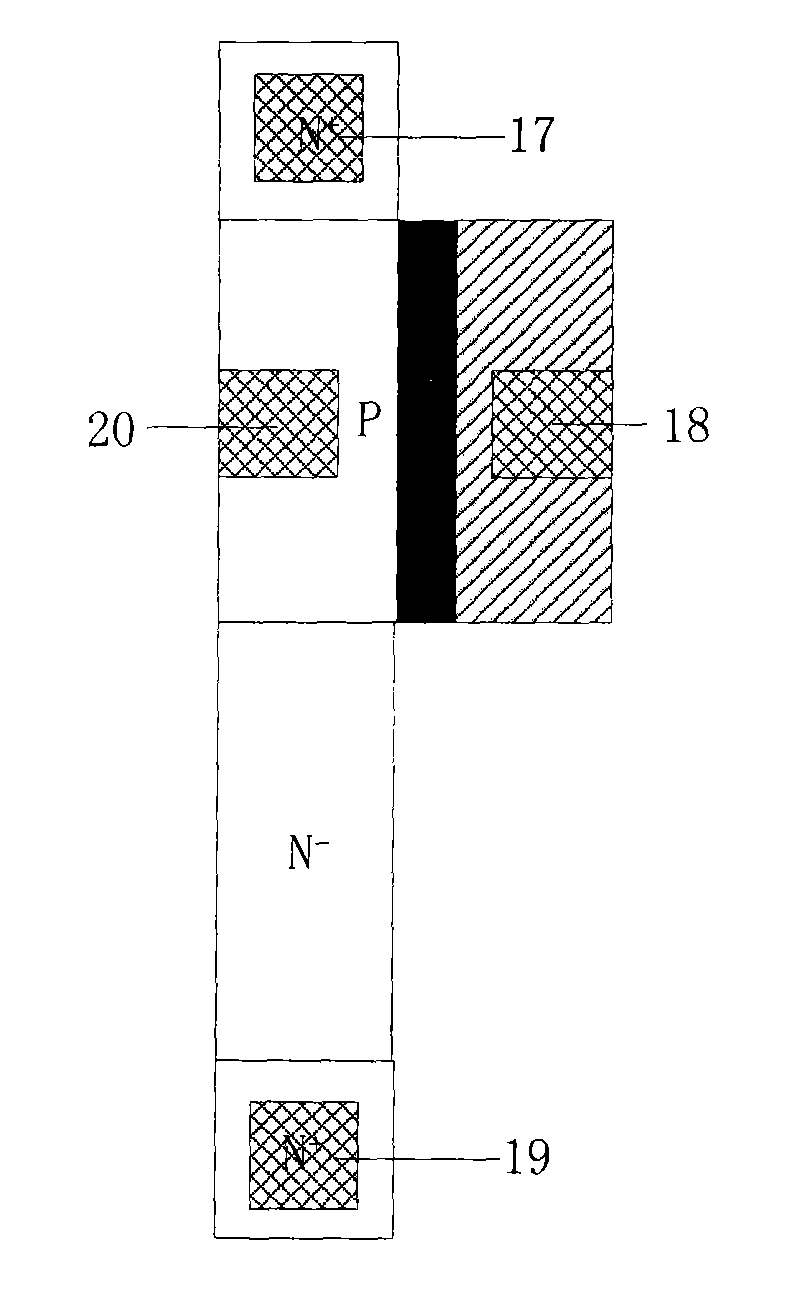

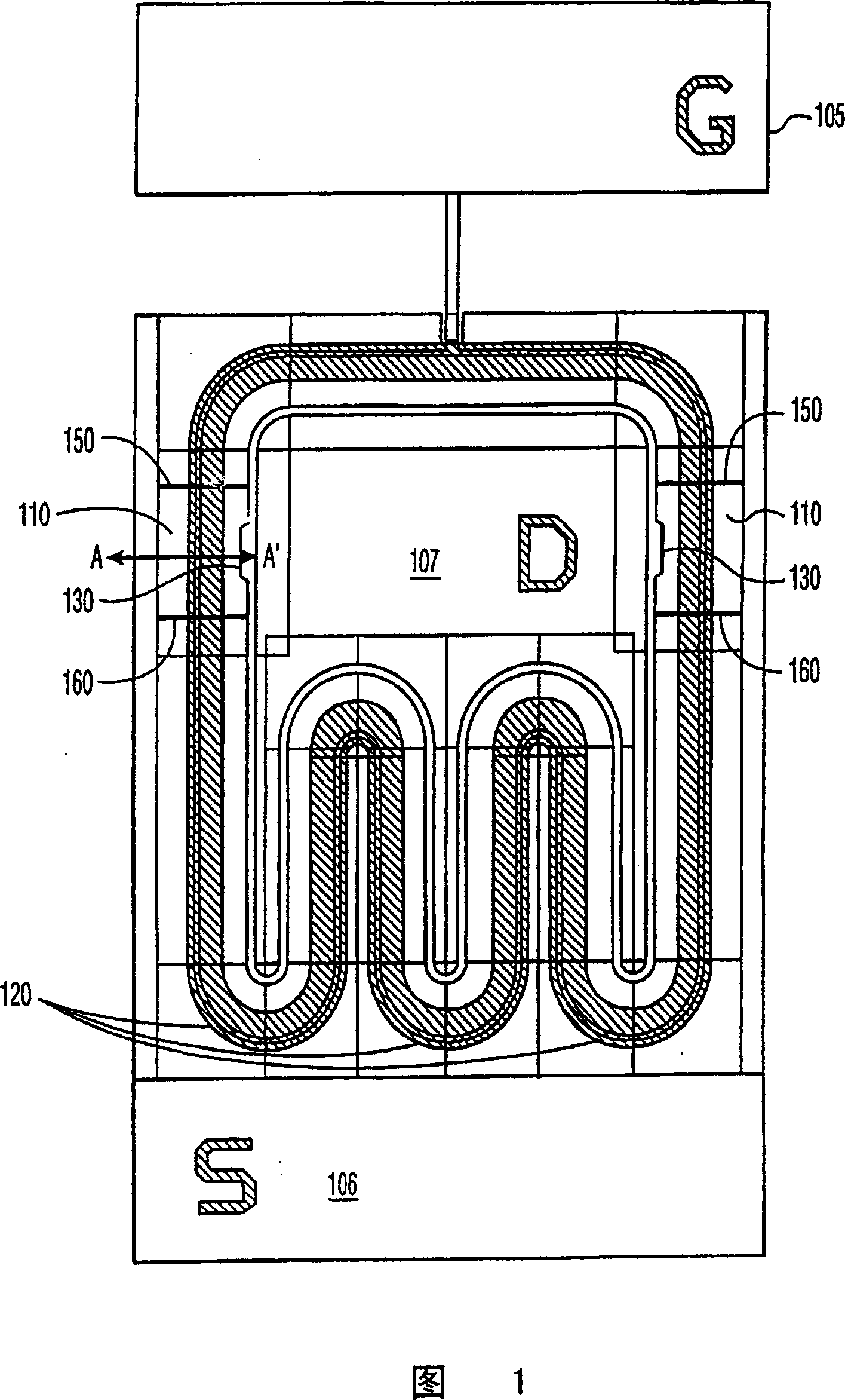

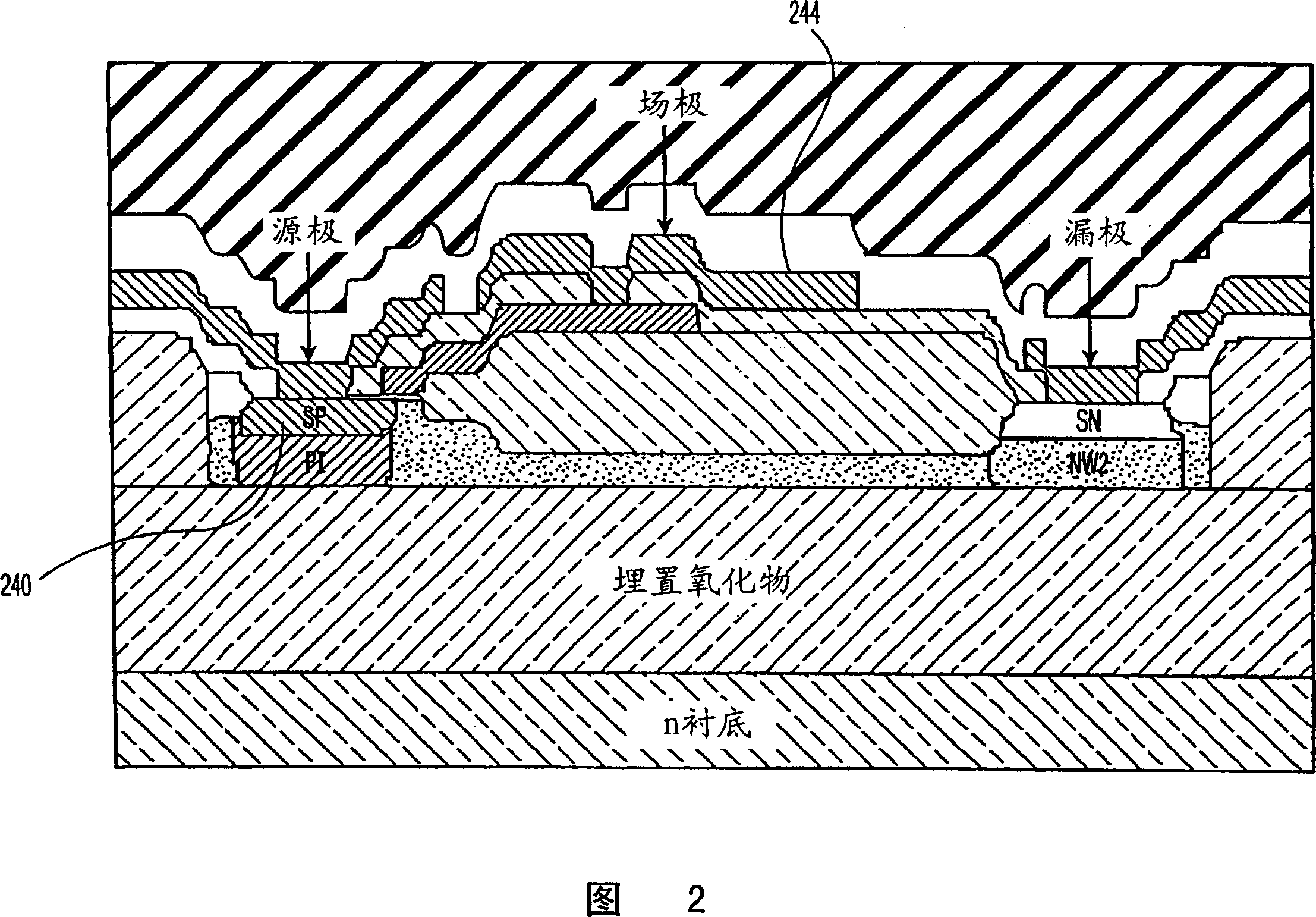

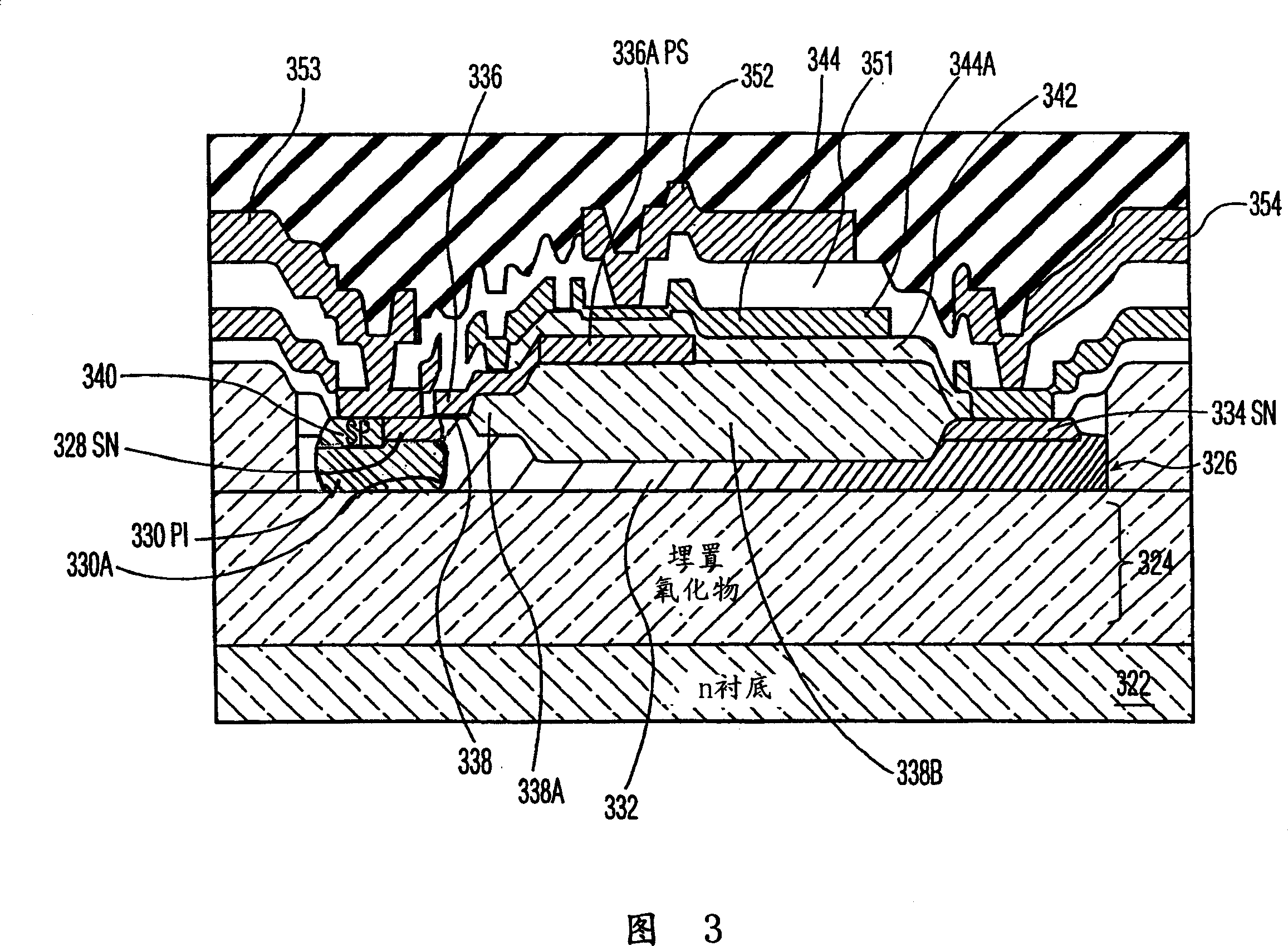

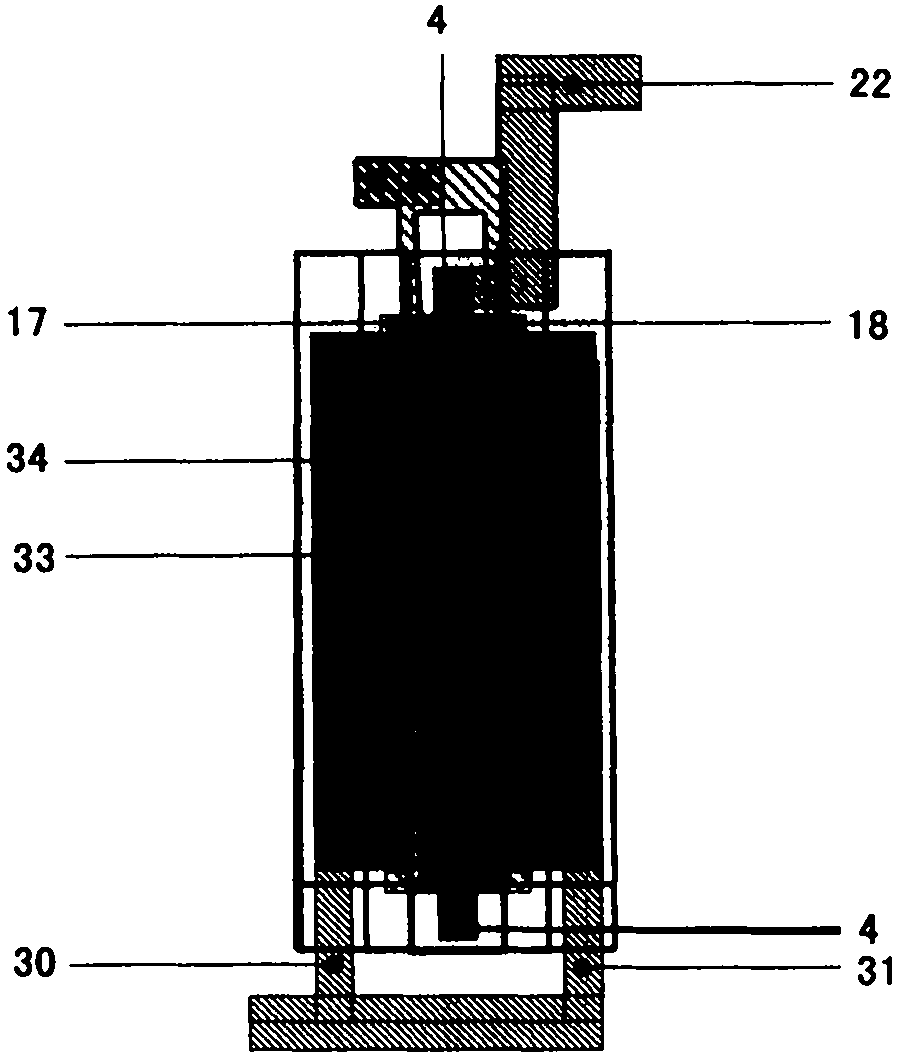

Hv-SOI LDMOS device with integrated diode to improve reliability and avalanche ruggedness

A hybrid semiconductor device is presented in which one or more diode regions are integrated into a transistor region. In a preferred embodiment the transistor region is a continuous (self-terminating) SOI LDMOS device in which are integrated one or more diode portions. Within the diode portions, since there is only one PN junction, the mechanism for breakdown failure due to bipolar turn-on is nonexistent. The diode regions are formed such that they have a lower breakdown voltage than the transistor region, and thus any transient voltage (or current) induced breakdown is necessarily contained in the diode regions. In a preferred embodiment, the breakdown voltage of the diode portions is lowered by narrowing their field plate length relative to the transistor portion of the device. This allows the device to survive any such breakdown without being destroyed, resulting in a more rugged and more reliable device.

Owner:NXP BV

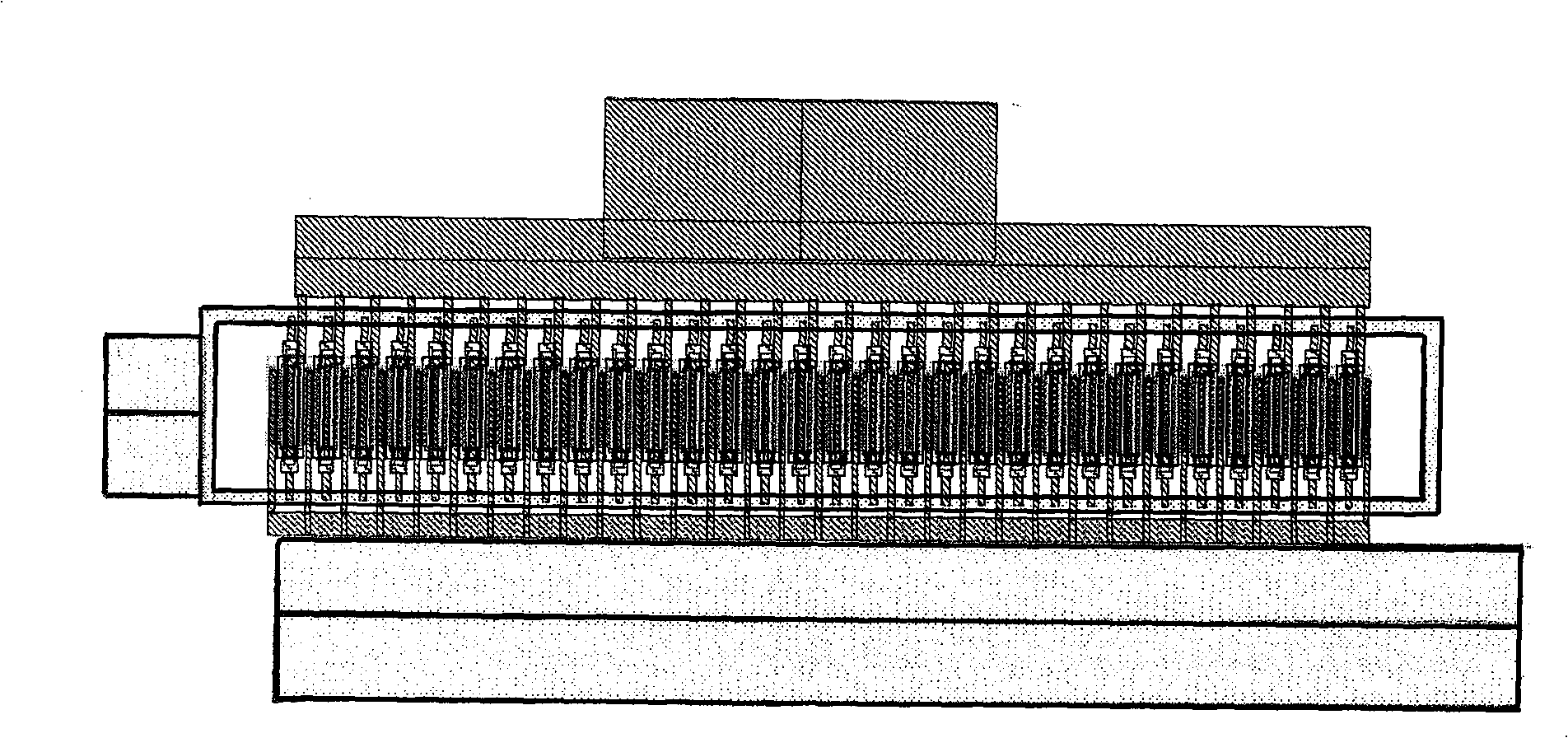

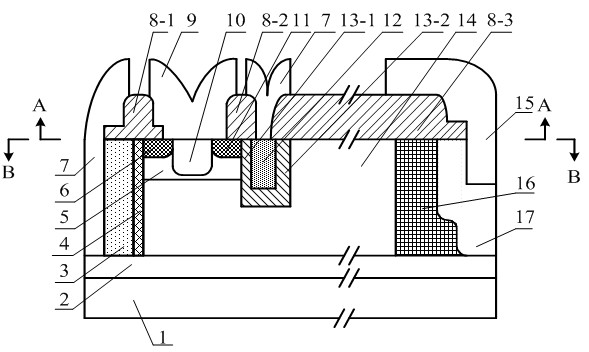

CMOS VLSI Integrated Fabrication Method of Vertical Trench soi LDMOS

InactiveCN101819948BExcellent ElectricalGood thermal propertiesSemiconductor/solid-state device manufacturingSoi cmosOhmic contact

The invention relates to a CMOS VLSI integrated manufacturing method of vertical channel SOI LDMOS. The SOI LDMOS device manufactured by the existing method has no vertical channel structure and corresponding excellent performance. The present invention realizes vertical grid and grid field plate structure, stepped trench drain structure by adopting trench etching technology, well doping is adjusted to reverse doping distribution ion implantation well and well ohmic contact doping process, in the source region It is realized by doping the gate and drain at the same time. The invention adopts the existing SOI CMOS VLSI process technology, under the condition of slightly increasing process complexity and process cost, the electrical and thermal properties of integrated power and radio frequency SOILDMOS devices are significantly improved.

Owner:SERVICE CENT OF COMMLIZATION OF RES FINDINGS HAIAN COUNTY

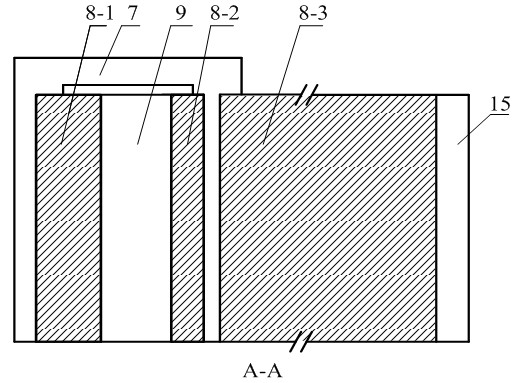

Radio frequency SOI LDMOS device with close body contact

InactiveCN101515586BIncrease working frequencyImprove breakdown voltageTransistorSemiconductor/solid-state device detailsBody contactRadio frequency

The invention relates to the field of a radio frequency power device, and discloses a radio frequency SOI LDMOS device with close body contact. The device comprises bottom layer silicon, an embedding oxidation layer, top layer silicon, a P<-> region an N<-> region, a gate oxidation layer, a polysilicon gate layer, a gate poly-silicide layer, a gate electrode, a silicon nitride side wall, an N<-> drift region, a drain region, a drain region silicide layer, a drain electrode, a source region, a body contact region, a body region, a source region silicide layer and a source electrode. The radio frequency LDMOS device is manufactured on an SOI substrate, and forms the close body contact which is in short circuit with the source region by utilizing a heavily doped region in the same form as the P<-> region; the source / body, a drain / body and the gate and the electrodes are interconnected by the silicide; a plurality of gate bars are connected in parallel in the forked mode so as to improve the driving capability of the device; a method for adjustment, back-gate injection, N<-> region injection and N<-> drift region injection, which is compatible with the CMOS process, is designed; and amethod for hiding the silicide in the N<-> drift region, which is compatible with the CMOS process, is designed.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

SOI LDMOS device with interface N<+> layer

ActiveCN102760753BAvoid premature breakdownImprove vertical pressure resistanceSemiconductor devicesHigh concentrationP type silicon

The invention discloses an SOI (Semiconductor ON Insulator) LDMOS (Laterally Diffused Metal Oxide Semiconductor) device with an interface N<+> layer, and relates to a semiconductor power device. The SOI LDMOS device comprises a substrate silicon layer, a medium buried layer and active top layer silicon, wherein the medium buried layer is arranged between the substrate silicon layer and the active top layer silicon; and the active top layer silicon is divided into an N-type silicon layer, a P-type silicon layer and an N<+> silicon layer from the surface of a semiconductor to the medium buried layer. According to the invention, as the N<+> silicon layer is arranged between the medium buried layer and the active top layer silicon, when the device is in a reverse blocking state, exhausted high-concentration ionized donor at the interface part enhances the electric field of the medium buried layer, the distribution of the electric field in the active top layer silicon is effectively modulated, and accordingly, the longitudinal voltage resistance and the transverse voltage resistance of the device are effectively improved. Meanwhile, the P-type silicon layer in the active top layer silicon can adjust the RESURF (Reduced SURface Field) condition of the device and relieve the contradiction between the breakdown voltage and the on resistance of the device.

Owner:NO 24 RES INST OF CETC

Radio frequency SOI LDMOS device with H-shaped gate

InactiveCN101515588BIncrease working frequencyImprove breakdown voltageTransistorSemiconductor/solid-state device detailsRadio frequencyPolysilicon gate

The invention relates to the field of radio frequency power devices, and discloses a radio frequency SOI LDMOS device with H-shaped gate. The device comprises bottom layer silicon, an embedding oxide layer, top layer silicon, a P<-> region, an N<-> region, an H-shaped gate oxide layer, an H-shaped polysilicon gate layer, an H-shaped gate poly-silicide layer, a gate electrode, a silicon nitride side wall, an N<-> drift region, a drain region, a drain region silicide layer, a drain electrode, a source region, a body lead-out region, a source region silicide layer and a source electrode. The radio frequency LDMOS device is manufactured on an SOI substrate, and forms the body lead-out which is in short circuit with the source region by utilizing a heavily doped region in the same form as the P<-> region; the source / body, a drain / body and the gate and the corresponding electrodes are interconnected by the silicide; and a plurality of gate bars are connected in parallel in the forked mode so as to improve the driving capability of the device. Simultaneously, the invention discloses a method for adjustment, back-gate injection, N<-> region injection and N<-> drift region injection, whichis compatible with the CMOS process and a method for hiding the silicide in the N<-> drift region, which is compatible with the CMOS process.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

SOI-based LDMOS device based on flexible substrate and manufacturing method thereof

InactiveCN112635564AReduced electric field distributionImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceElectronic systems

The invention discloses an SOI-based LDMOS device based on a flexible substrate and a manufacturing method thereof, aims to further optimize the contradictory relation between breakdown voltage and specific on-resistance so as to optimize the performance of the device, and can be applied to a flexible electronic system. According to the device, a power device SOI LDMOS with excellent performance is combined with a flexible substrate, a P-type silicon substrate material with an SOI base is adopted, and a drift region and a base region are formed on an epitaxial layer on the SOI base through doping; a surface electrode is etched and deposited at the left end of the base region, wherein the surface electrode sequentially penetrates through the base region and the SOI base from the surface of the device along the longitudinal direction and goes deep into the upper part of the P-type silicon layer; and an oxidation groove filled with a dielectric material is formed in the surface of the middle region of the drift region. According to the invention, the power device SOI LDMOS is combined with the flexible substrate, so that new breakthrough and innovation in the fields of traditional inorganic semiconductor power devices and flexible electronics are realized, and the defect of poor electronic performance of flexible organic materials can be overcome.

Owner:XIDIAN UNIV +1

Latch-up resisting N-type SOI laterally diffused metal oxide semiconductor

ActiveCN102769038BImprove latching abilityLower on-resistanceSemiconductor devicesPower flowHigh energy

A latch-up resisting N-type SOI (Silicon On Insulator) laterally diffused metal oxide semiconductor (LDMOS) comprises an N-type substrate, wherein a buried oxide is arranged on the N-type substrate; an N-type epilayer is arranged on the buried oxide; an N-type buffering well and a P-type body region are arranged in the N-type epilayer; an N-type drain region is arranged in the N-type buffering well; an N-type source region and a P-type body contact region are arranged in the P-type body region; a gate oxide and a field oxide are arranged on the surface of the N-type epilayer; a shallow P-type well region is arranged on the surfaces of both the N-type source region and the P-type body contact region; a polysilicon gate is arranged on the surface of the gate oxide; and a passivation layer is arranged on the surfaces of the field oxide, the P-type body contact region, the N-type source region, the polysilicon gate and the N-type drain region. The latch-up resisting N-type SOI-LDMOS is characterized in that a deep P-type well region sharing the same photoetching board together with the shallow P-type well region and formed by high-energy ion implantation is arranged right below the shallow P-type well region, and the deep P-type well region effectively reduces the conducting resistance of the body region and lowers the latch-up risk in the working process while improving the current capacity of devices.

Owner:SOUTHEAST UNIV

Fabrication method of anti-esd integrated soi LDMOS device unit

ActiveCN103354207BExcellent ElectricalGood thermal propertiesSemiconductor/solid-state device manufacturingElectronic systemsRadio frequency

The invention relates to a manufacturing method of an anti-ESD integration SOI LDMOS device unit. By using the SOI LDMOS device manufactured through using the prior art, system weight is heavy; cost is high and reliability is low. According to the invention, through using five-time oxidation and nine-time photoetching, the SOI LDMOS device unit which integrates an anti-ESD structure and a function is manufactured. By using the method of the invention, under the condition that chip area cost is increased slightly, the integrated power and radio frequency SOI LDMOS device possesses an excellent integrated anti-ESD self-protection function; anti-ESD self-protection performance of the SOI LDMOS device is significantly improved; sizes, weight and cost of various kinds of power electronics systems using the device are reduced; and system reliability is increased.

Owner:HANGZHOU DIANZI UNIV

High reliability soi LDMOS power device

Disclosed is a high-reliability silicon-on-insulator (SOI) laterally diffused metal oxide semiconductor (LDMOS) power element, which comprises a buried layer with high concentration and a contact injection region, wherein the buried layer with high concentration and the contact injection region are injected in top layer silicon of the SOI LDMOS power element, and the buried layer is connected with the contact injection region; current carriers which are located near a SOI LDMOS gate in the SOI LDMOS power element can be extracted through the buried layer and educed through the contact injection region, and electric potentials which are near the SOI LDMOS gate can be controlled. According to the high-reliability SOI LDMOS power element, in the top layer silicon of the SOI LDMOS, the buried layer with high concentration is produced and educed through the contact injection region, the current carriers which are located near the SOI LDMOS gate in the SOI LDMOS power element can be extracted through the buried layer, the electric potentials which are near the gate can be controlled, so that damages or burning of LDMOS elements caused by the fact that parasitic transistors open due to noise current or colliding current, maintaining voltage of the LDMOS elements under static shock is raised simultaneously, electrical safety working areas of the LDMOS power elements are expanded, and reliability of the elements is strengthened.

Owner:BEIJING YANDONG MICROELECTRONICS

A soi power ldmos device with junction field plate

InactiveCN103325835BImprove static electrical performanceImprove pressure resistanceDiodeSoi cmosPower semiconductor device

The invention discloses an SOI power LDMOS device provided with a junction type field plate structure, and belongs to the technical field of power semiconductor devices. According to the JFP SOI LDMOS device, a PN junction is adopted as a field plate, and a high-K medium is used as a field plate medium. On one hand, a PN junction electric field of the junction type field plate modulates the electric field on the surface of the device to improve the electric field distribution of the device and enhance the pressure resistance of the device; on the other hand, in a reverse blocking state, the junction type field plate assists in exhausting a drift region of the device to enable the doping density of the drift region of the device to be increased substantially, so that on-resistance is lowered; the high-K medium is used as a field dielectric layer so that the on-resistance and static power consumption can be lowered more beneficially. Compared with a conventional metal field plate, the junction type field plate technology also effectively avoids the defect that an electric field peak exists at the tail end of the field plate; compared with a polycrystalline resistance field plate, the junction type field plate has a PN junction potential barrier so that a high leakage current can be avoided. In addition, the SOI power LDMOS device provided with the junction type field plate structure also has good compatibility with SOI CMOS circuits.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

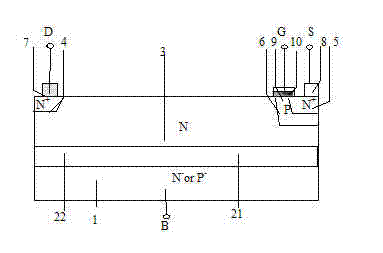

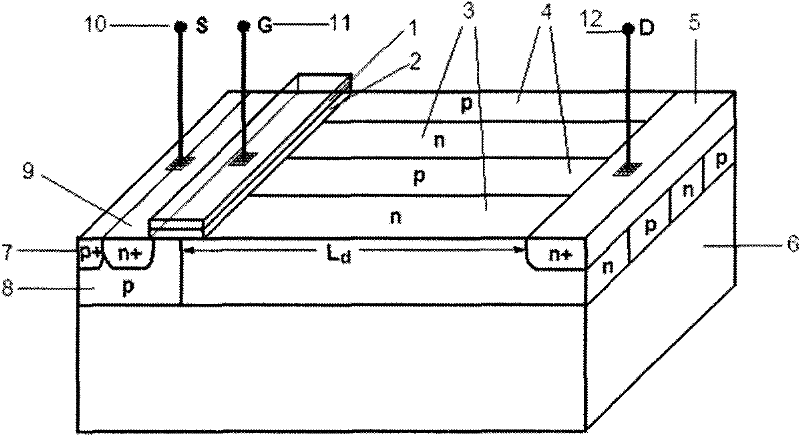

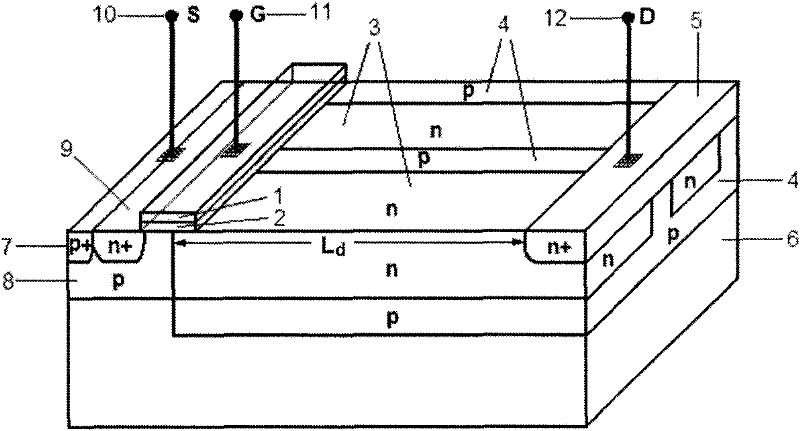

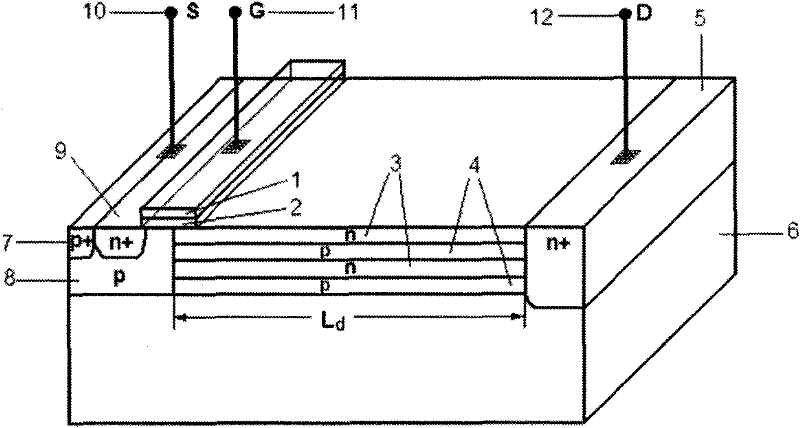

High voltage low power consumption SOI LDMOS transistor having strained silicon structure

InactiveCN101819998BImprove mobilityReduce the on-resistance valueSemiconductor devicesSingle crystalHigh pressure

The invention provides a high voltage low power consumption SOI LDMOS transistor having strained silicon structure, which comprises a source region (9), a body region (8), a drain region (5), a super-junction structure middle n column (3), a super-junction structure middle p column (4), a source electrode (10), a drain electrode (12), a grid electrode (11) and an embedded dielectric layer (6), wherein the super-junction structure middle p column (4) is silicon material lattice-unmatched monocrystal material, which is a material capable of leading silicon to generate strain, like Ge or SiGe, and the super-junction structure middle n column (3) is n-type transverse tensile strain silicon which is parallel to the source electrode and the drain electrode and generated on the basis of the super-junction structure middle p column (4). According to the invention, the requirement of reducing drain-source on-resistance is taken into consideration on the premise of maintaining the pressure resistance of devices. The transistor according to the invention is compatible with conventional SOI LDMOS transistor technology, has quite strong practicability and is easier for meeting the application requirement of power electronic system.

Owner:HARBIN ENG UNIV