Latch-up resisting N-type SOI laterally diffused metal oxide semiconductor

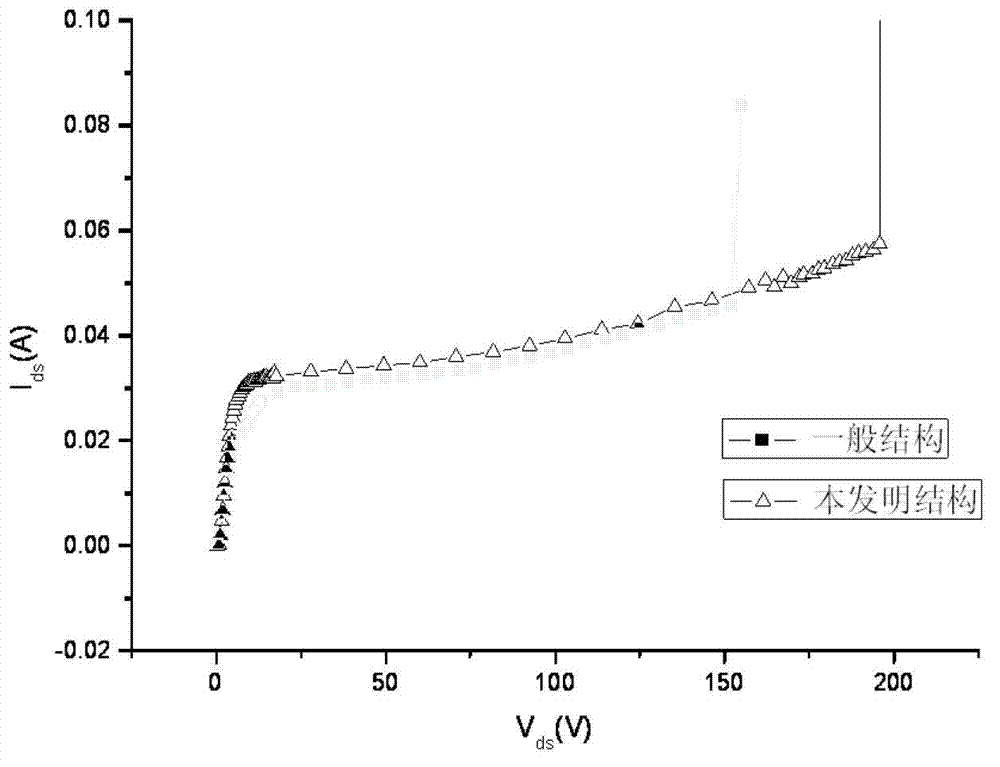

A field effect transistor, lateral double diffusion technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of decreased current capability, increased device area, and increased process version complexity, reducing power consumption, latching The effect of reducing the risk of lock failure and improving the current conduction capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

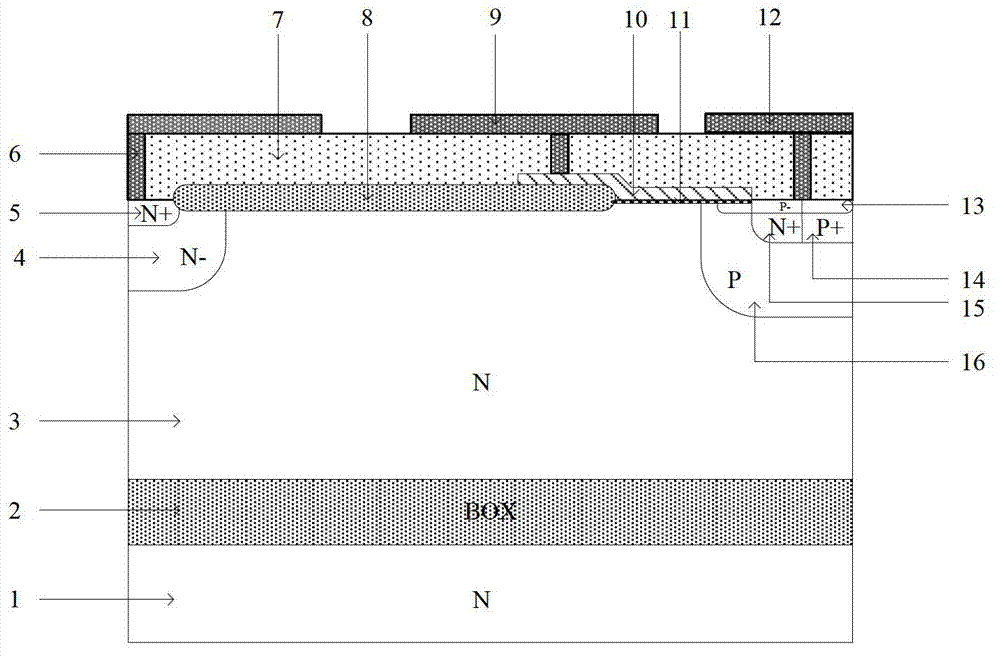

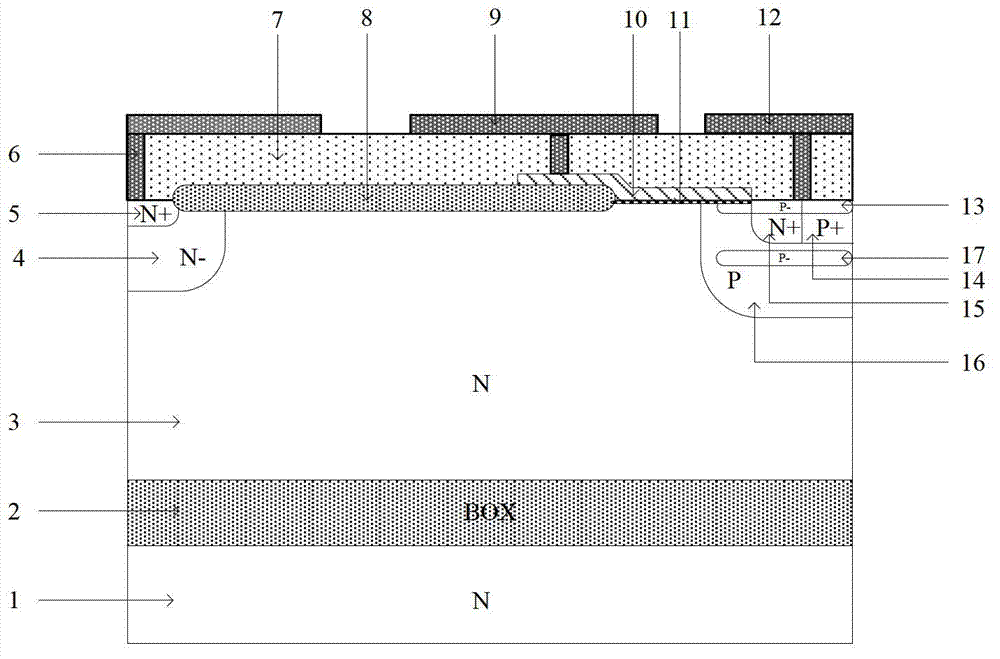

[0017] Attached below figure 2 , the present invention is described in detail, a kind of anti-latch-up N-type silicon-on-insulator lateral double-diffused field effect transistor, comprising: N-type substrate 1, buried oxygen 2 is arranged on N-type substrate 1, buried oxygen 2 An N-type epitaxial layer 3 is provided, an N-type buffer well 4 and a P-type body region 16 are arranged inside the N-type epitaxial layer 3, an N-type drain region 5 is arranged in the N-type buffer well 4, and an N-type drain region 5 is arranged in the P-type body region 16 is provided with an N-type source region 15 and a P-type body contact region 14, and a gate oxide layer 11 and a field oxide layer 8 are provided on the surface of the N-type epitaxial layer 3, and one end of the gate oxide layer 11 and one end of the field oxide layer 8 In contrast, the other end of the gate oxide layer 11 extends to the N-type source region 15 and ends at the N-type source region 15, and the other end of the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More