Patents

Literature

59results about How to "Improve current conduction ability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Winding lithium paste battery

ActiveCN109671987ACompact structureHigh specific powerCell seperators/membranes/diaphragms/spacersFinal product manufactureCurrent distributionConductive materials

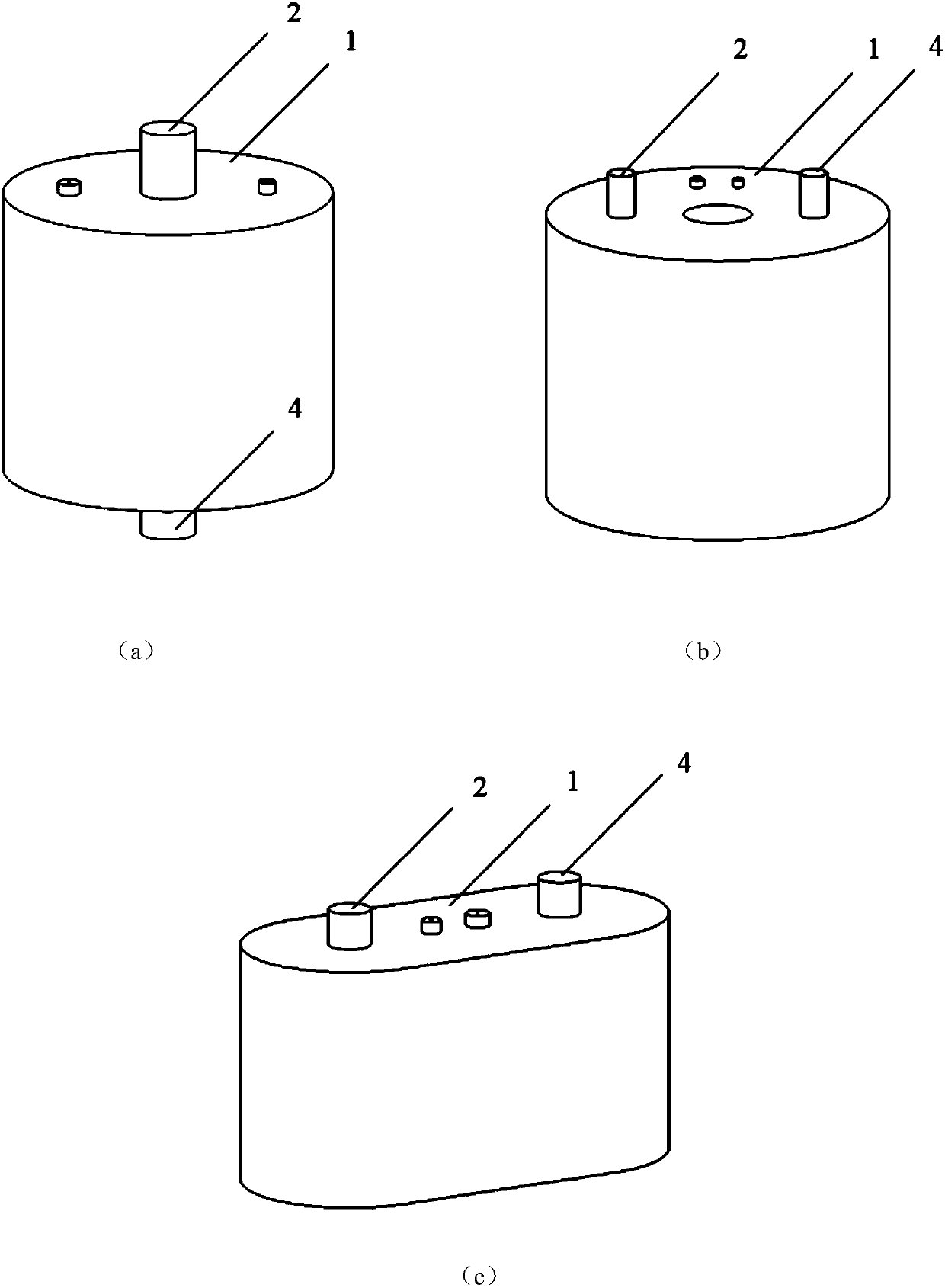

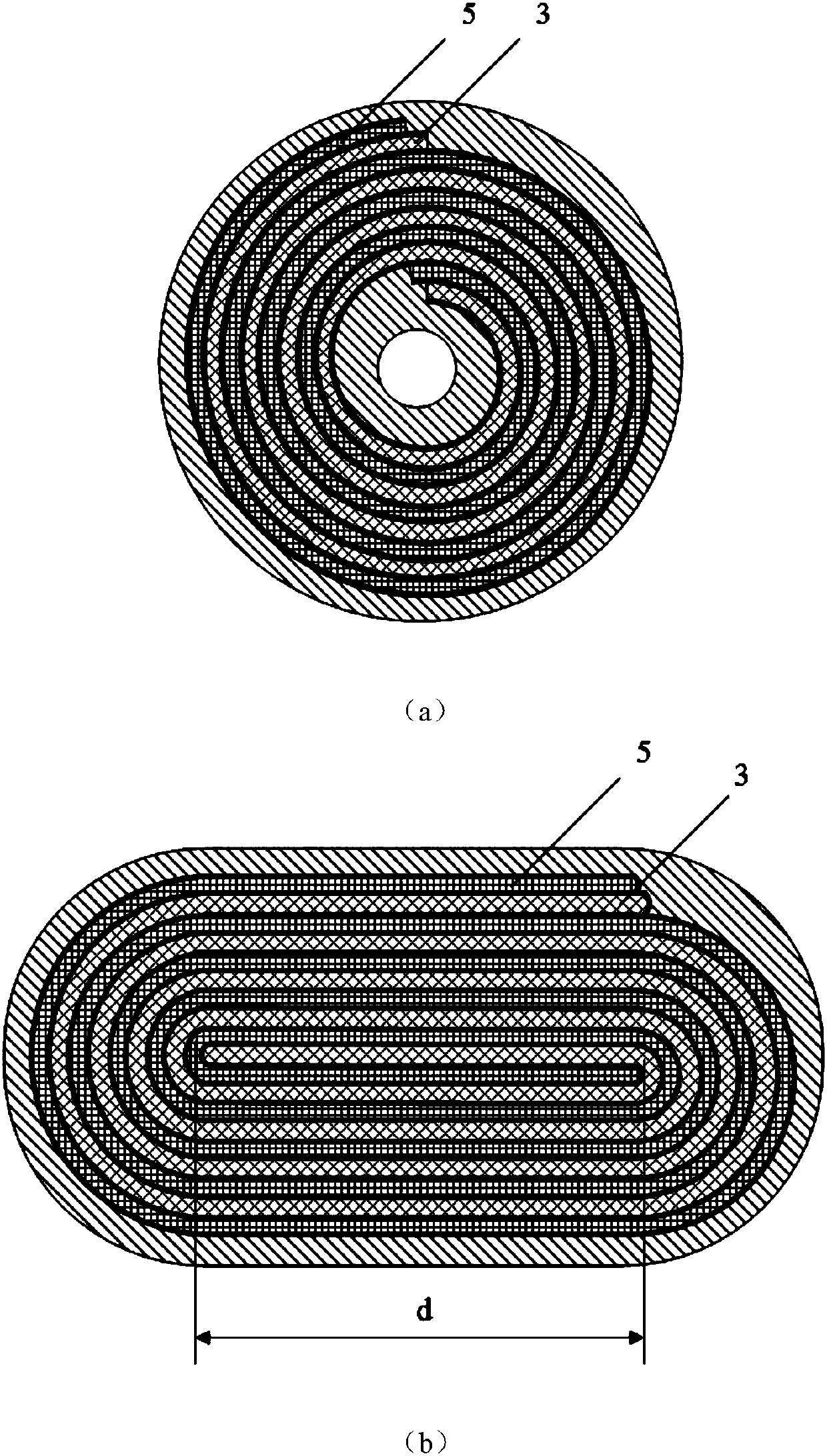

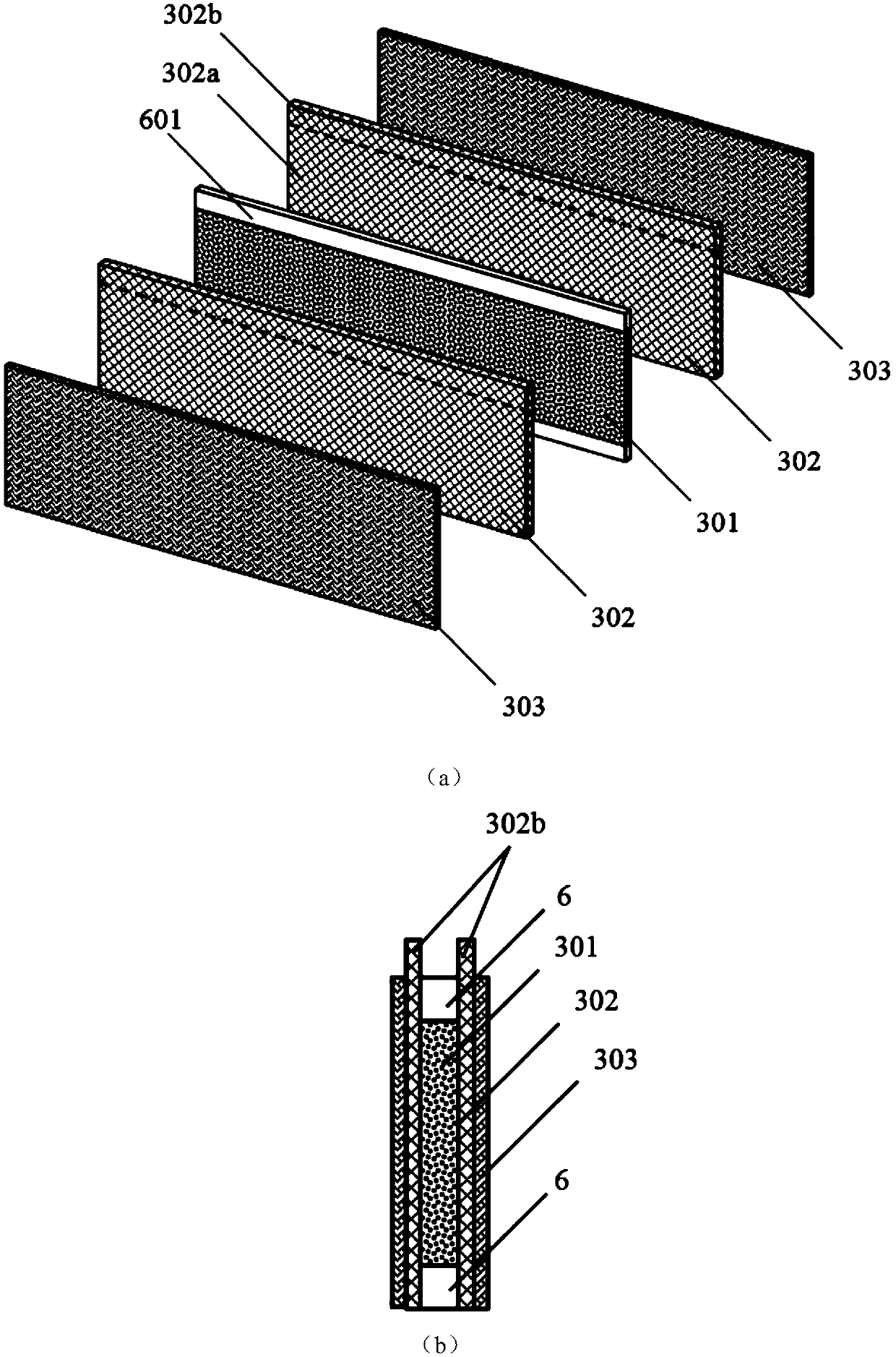

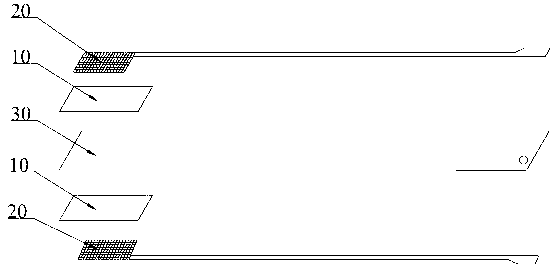

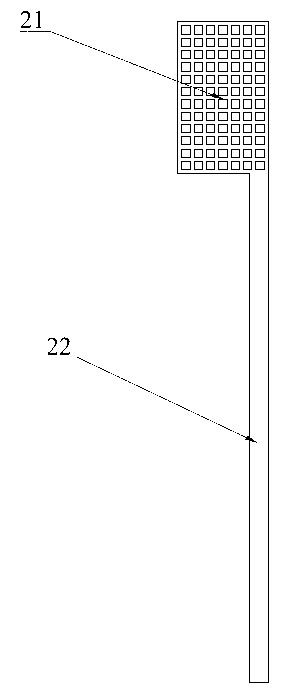

The present invention provides a winding lithium paste battery. The winding lithium paste battery has a battery cell formed by winding of a positive plate and a negative plate, the electrode active conductive material layer of the electrode piece comprises non-bonded and fixed electrode active conductive particles. The winding lithium paste battery further comprises a leakage preventing portion, the leakage preventing portion is arranged at the edge of the positive plate and / or the negative plate or arranged on a housing to prevent the positive pole active conductive particles in the positivepole active conductive material layer from being leaked from the positive plate and / or prevent the negative pole active conductive particles in the negative pole active conductive material layer frombeing leaked from the negative plate. The winding lithium paste battery is more compact in structure, can regulate the shape for the application occasions, and is convenient and flexible in application. Besides, the winding lithium paste battery employs the uniformly distributed multi-tab group or full-tab design to effectively improve the current conduction capacity, improve the current distribution and improve the utilization rate of the electrode active conductive materials.

Owner:BEIJING HAWAGA POWER STORAGE TECH +1

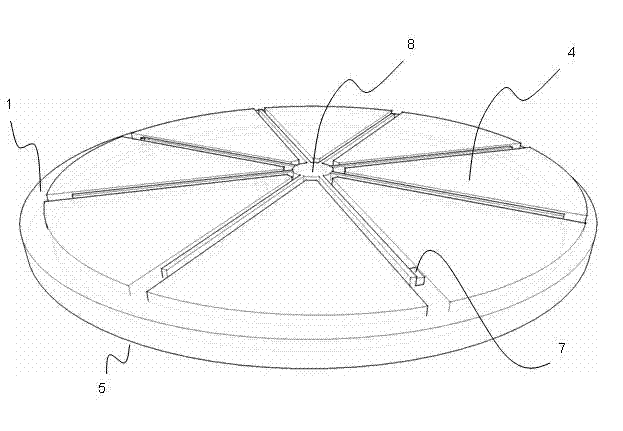

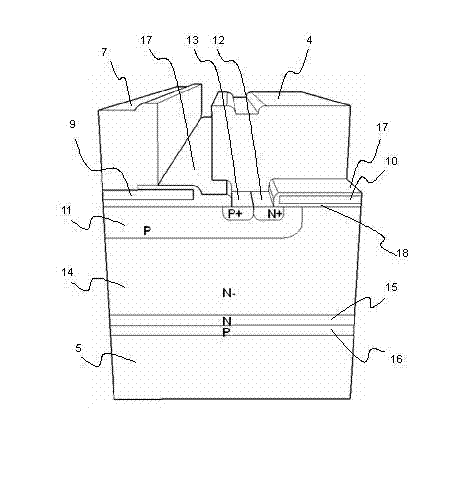

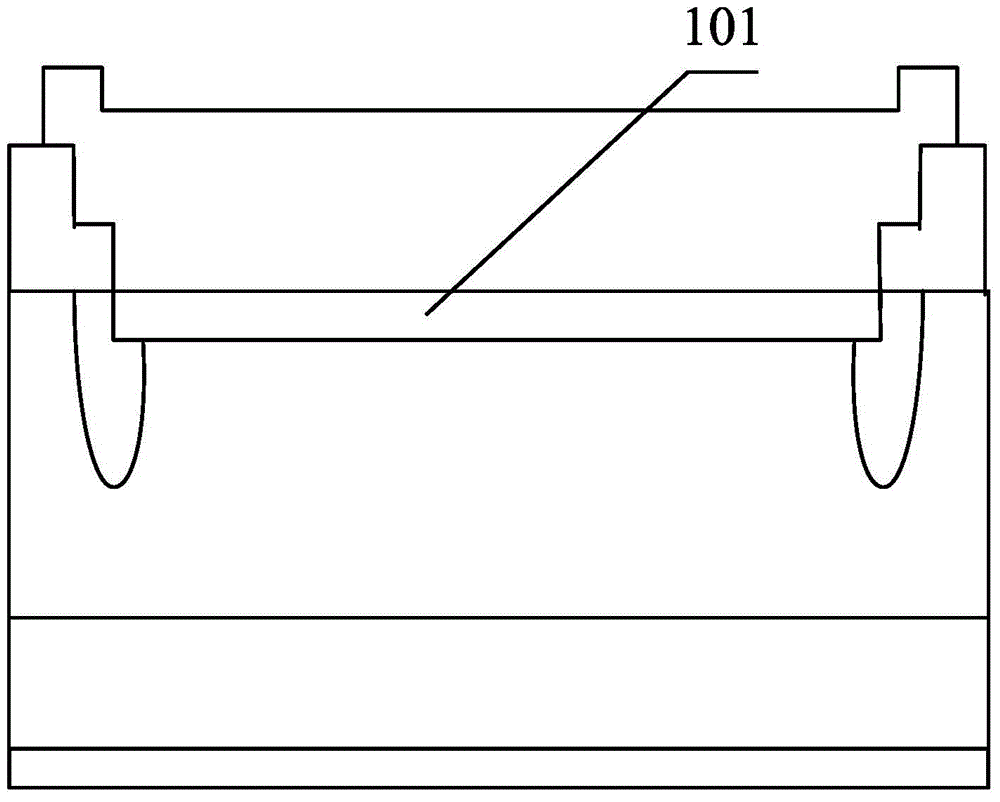

High-current full-wafer full-crimp flat-pack IGBT and manufacturing method thereof

ActiveCN102270640AIncrease working voltageReduce Switching Power ConsumptionTransistorSemiconductor/solid-state device manufacturingEngineeringMetal electrodes

The invention discloses a heavy-current whole-wafer total-pressure-contact flat-plate encapsulated IGBT (Insulated Gate Bipolar Transistor) and a manufacturing method thereof. The heavy-current whole-wafer total-pressure-contact flat-plate encapsulated IGBT comprises an IGBT whole wafer and a total-pressure-contact flat-plate encapsulation, the whole wafer comprises multiple independent IGBT device regions, each IGBT device region is composed of multiple IGBT units which are connected in parallel, collectors of all the IGBT device regions are connected in parallel to form a total collector, atransmitter is led from each IGBT device region independently, gate poles of all the IGBT device regions in a normal operating state are connected to a total gate pole arranged in the center of the wafer by using an interconnecting line, and the transmitter of each IGBT device region is connected with a metal electrode plate of a total transmitter in parallel by virtue of a metal gasket of the transmitter. According to the invention, a heavy-current IGBT whole wafer device is realized, the advantages of high working voltage, low switching power consumption and simple voltage control of the gate pole are maintained, current carrying capacity, heat-conducting property, heat shock resistance and long-term reliability of the device are improved, and the problem of property matching between IGBT units is solved.

Owner:HUNAN UNIV

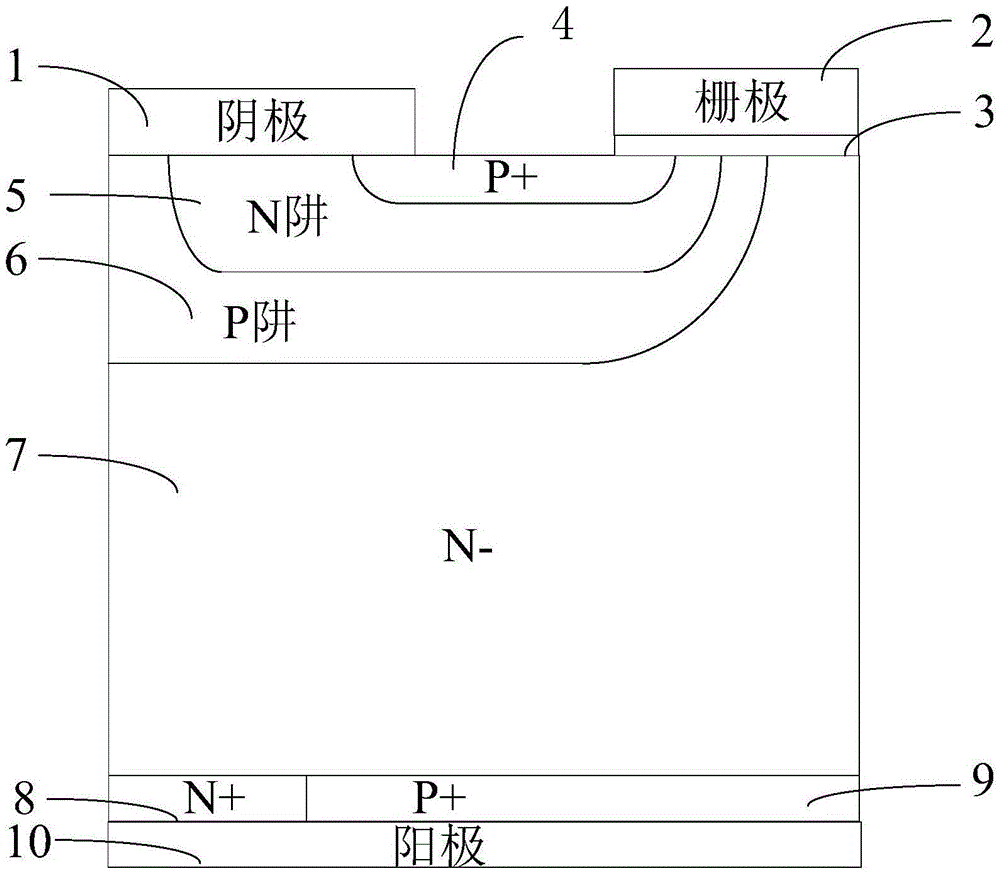

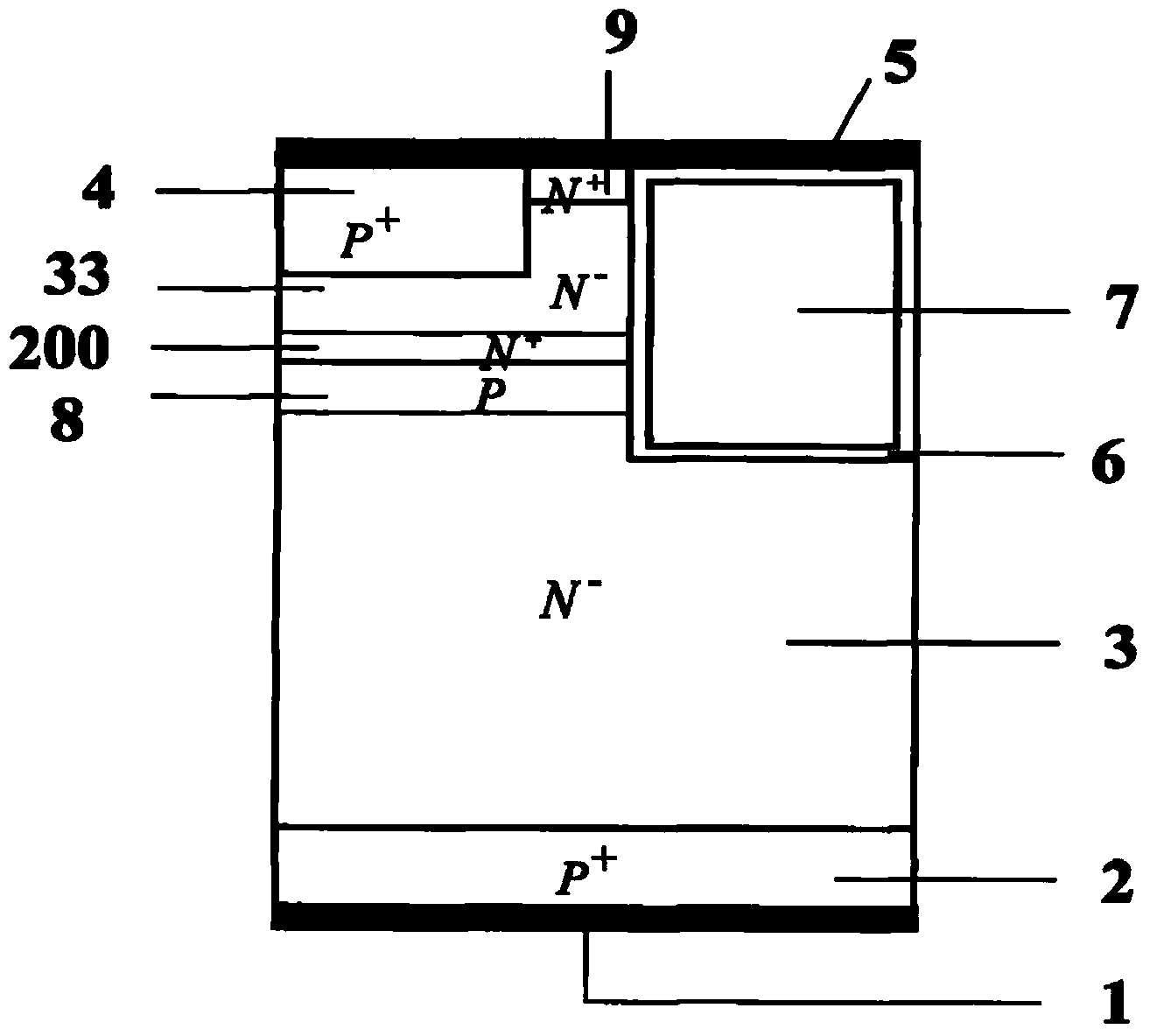

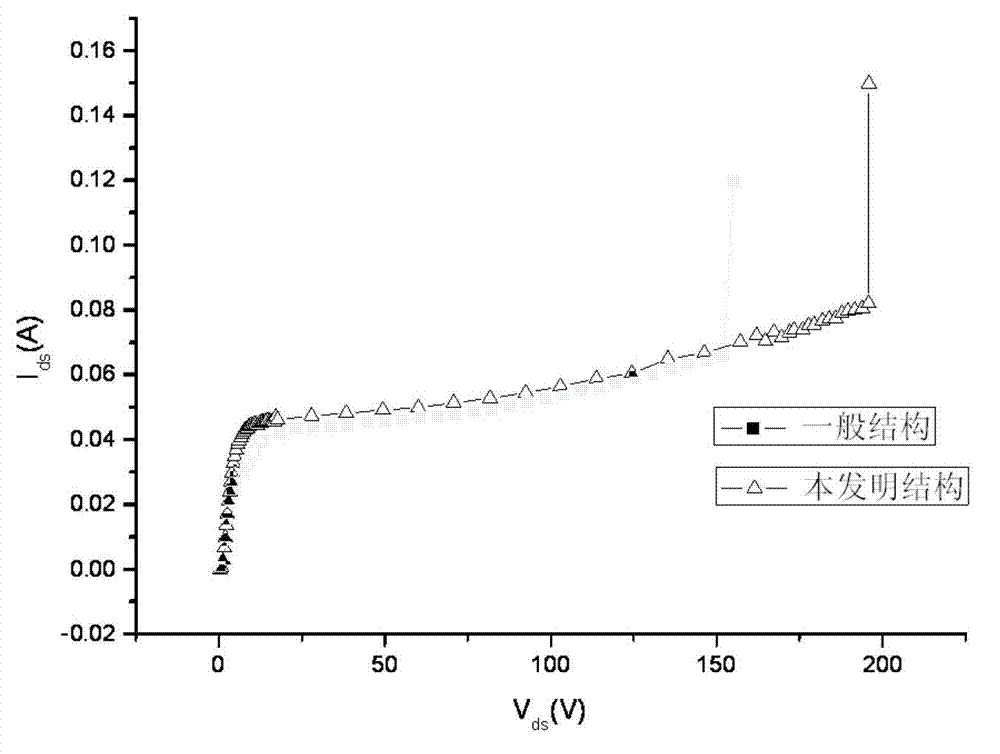

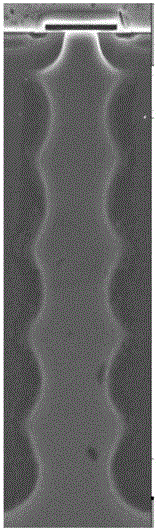

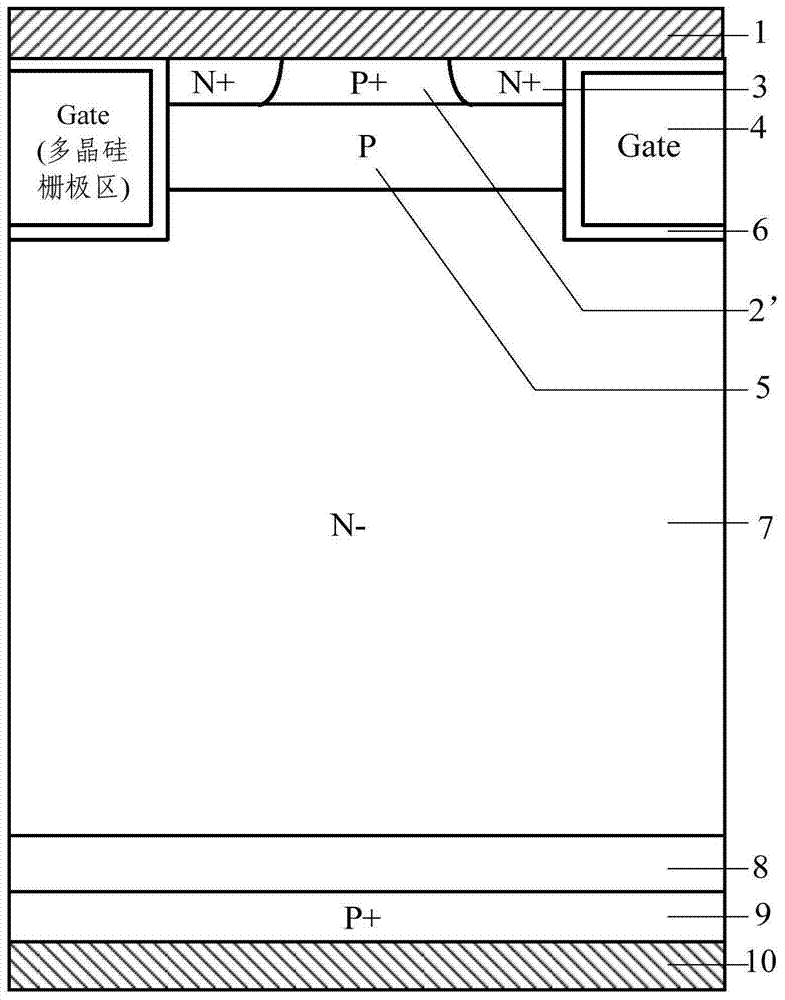

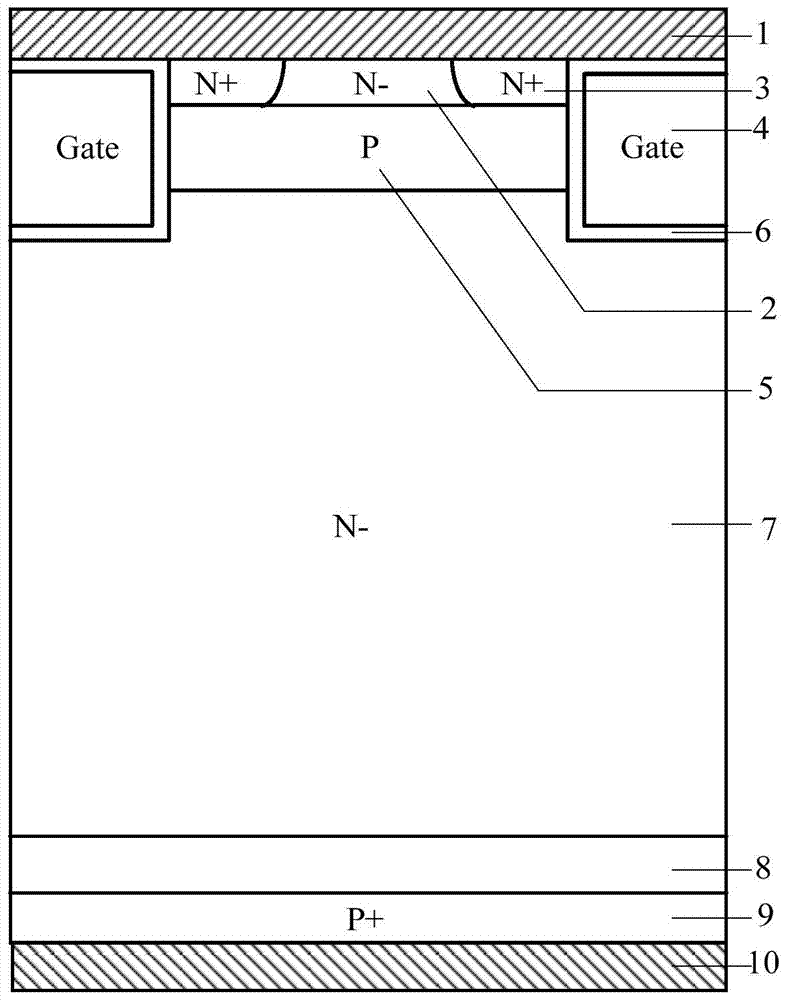

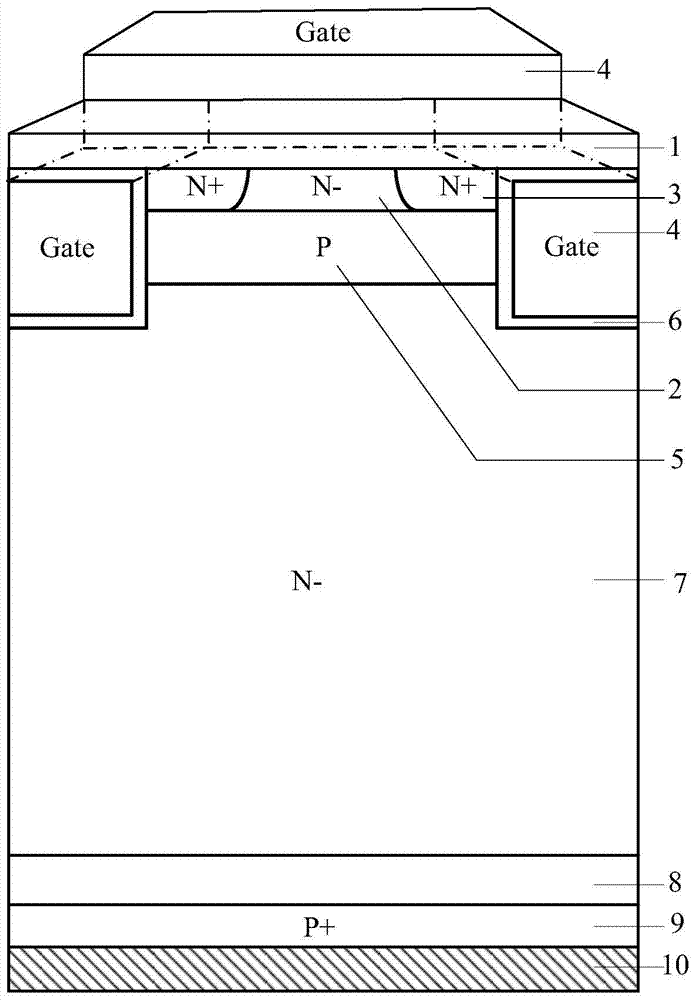

Reverse conducting MOS gate-controlled thyristor and fabrication method thereof

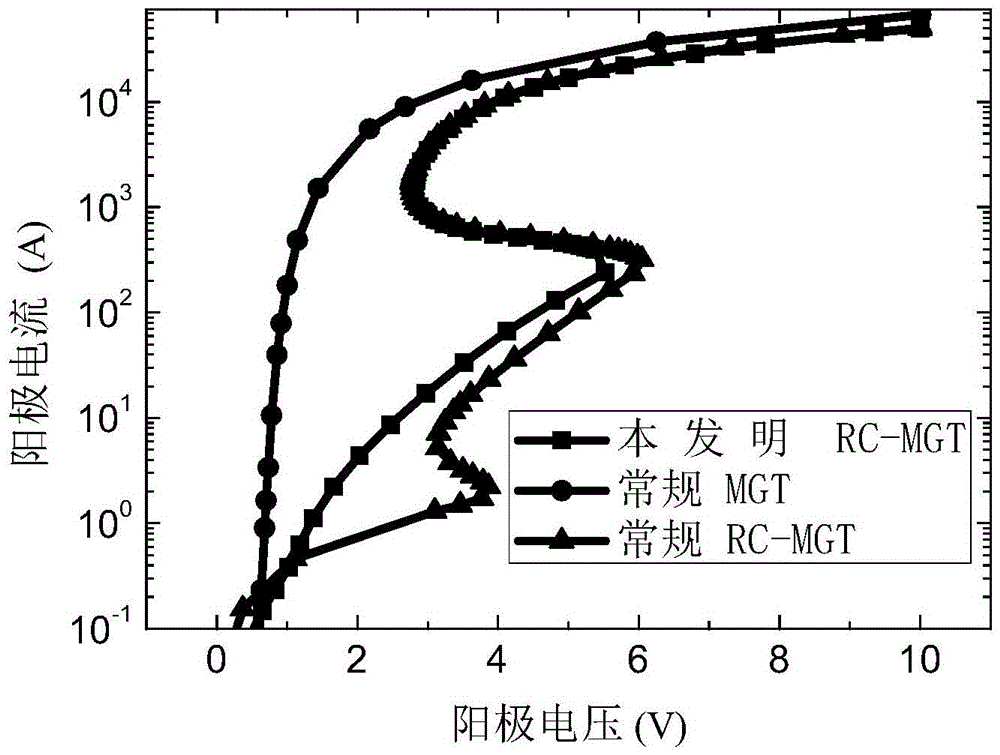

ActiveCN105679819AReduce cell lengthActs as an electron barrierThyristorSemiconductor/solid-state device manufacturingPower semiconductor deviceElectrical resistance and conductance

The invention belongs to the field of power semiconductor devices, and particularly relates to a reverse conducting MOS gate-controlled thyristor and a fabrication method thereof. The novel reverse conducting MOS gate-controlled thyristor provided by the invention can play a role of an electronic potential barrier when the current density is relatively low, so that the cell length of an N anode region is reduced; the effective area is reduced; the snapback effect is inhibited by greatly improving an anode short-circuit resistance; a P floating region also carries out hole emission towards an N drift region along with a voltage increase, so that conductivity modulation is carried out and the snapback effect is inhibited. Meanwhile, due to additionally introduced P floating region in reverse conduction, a parasitic PNPN structure is passed in conduction; the thyristor is conducted when a current reaches a certain magnitude; and the novel reverse conducting MOS gate-controlled thyristor also has high current conduction capability in the reverse direction.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

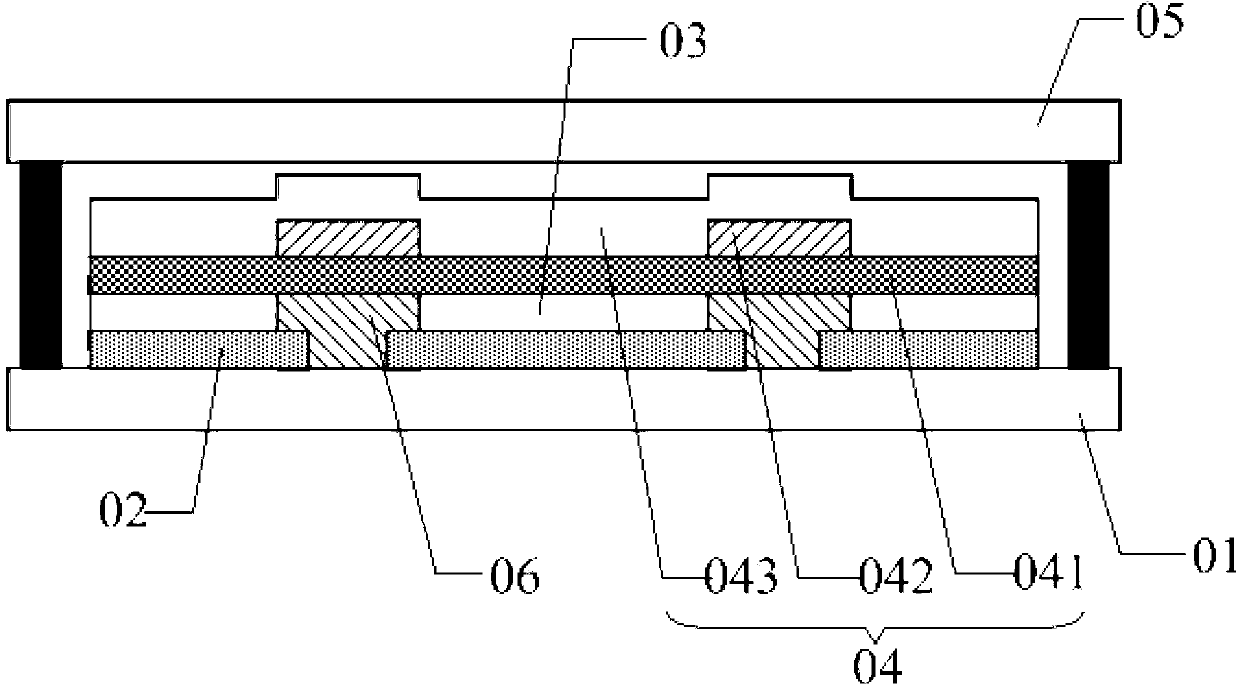

Organic electroluminescence component and manufacturing method thereof

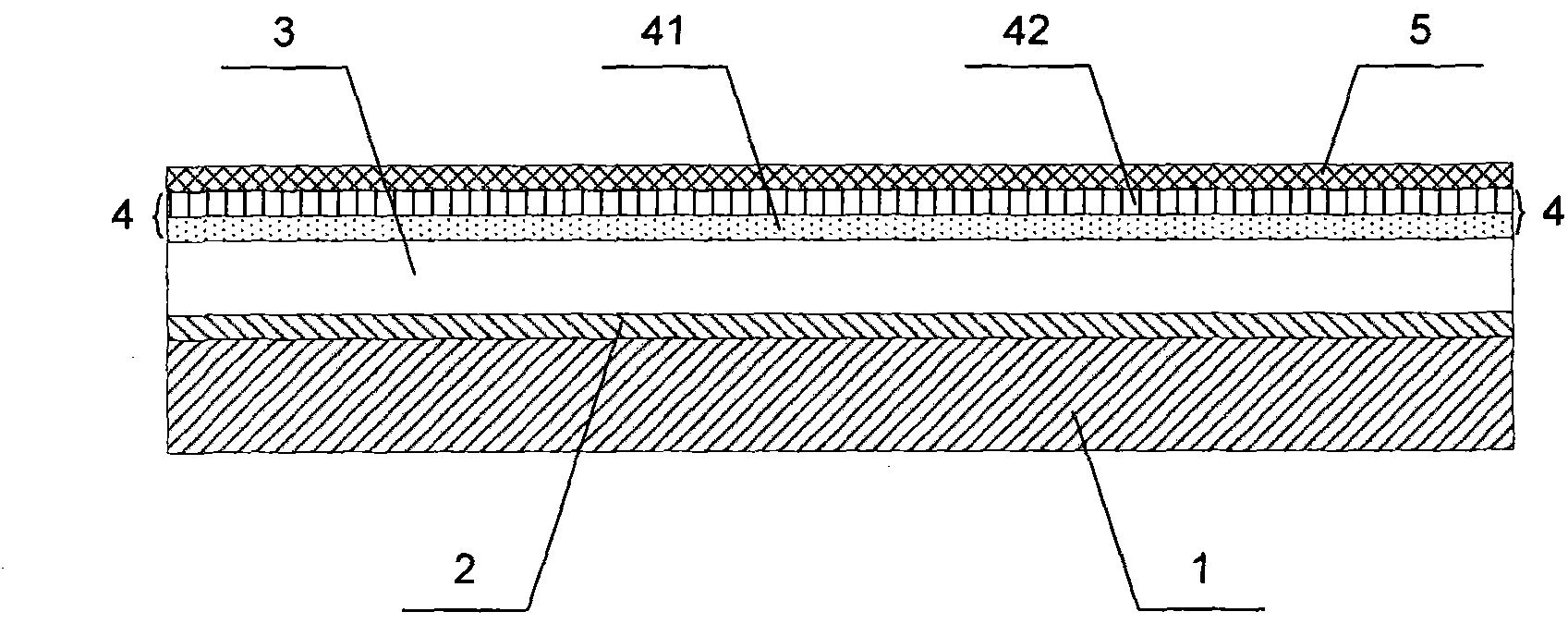

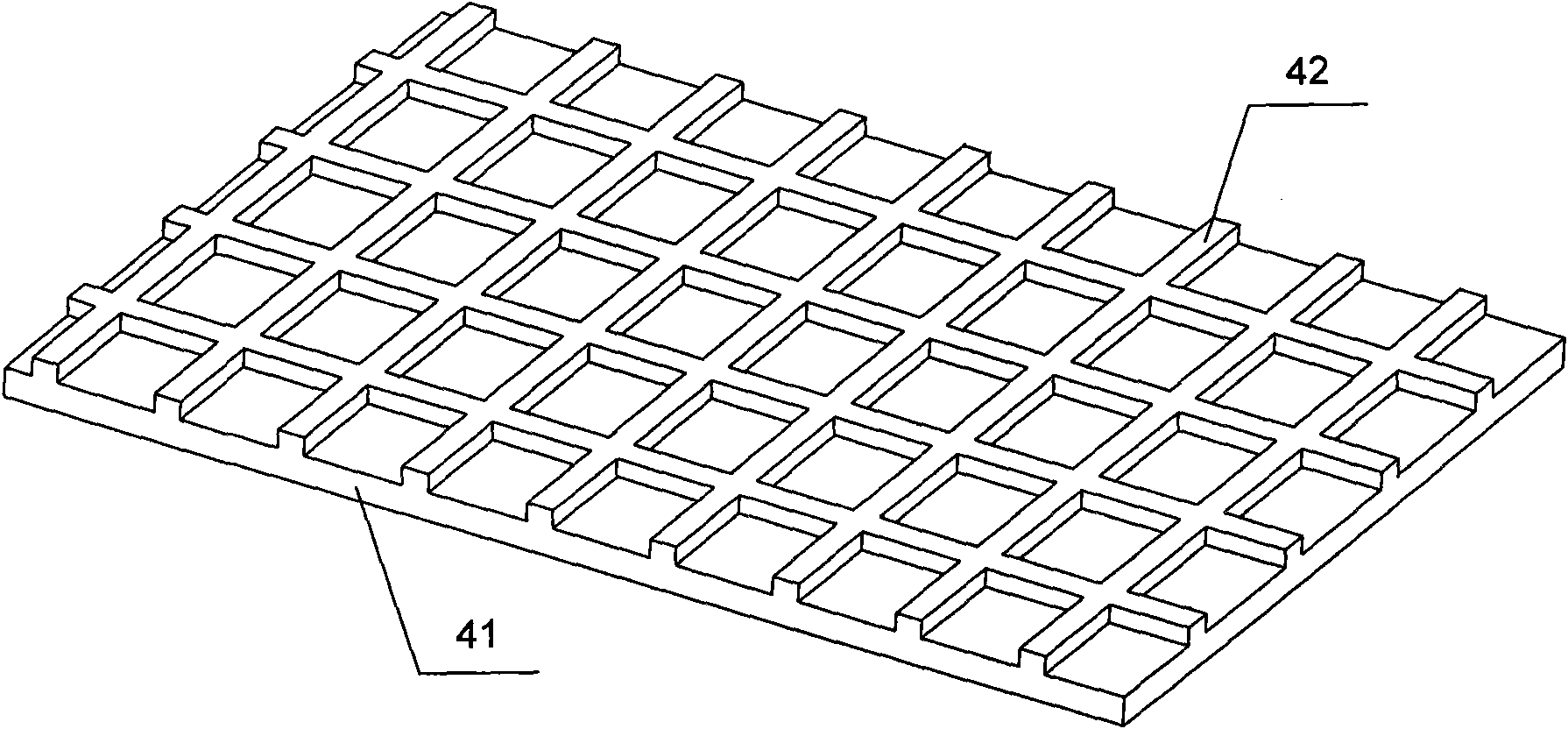

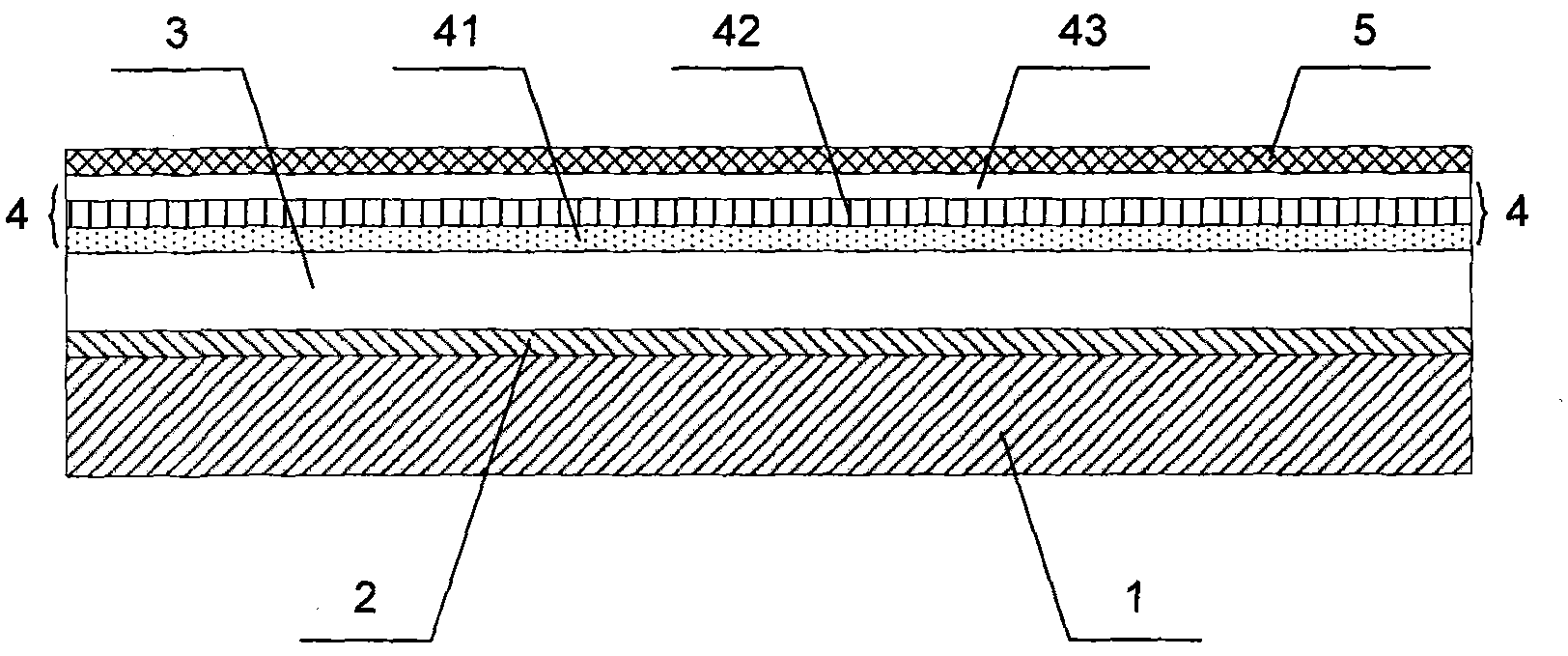

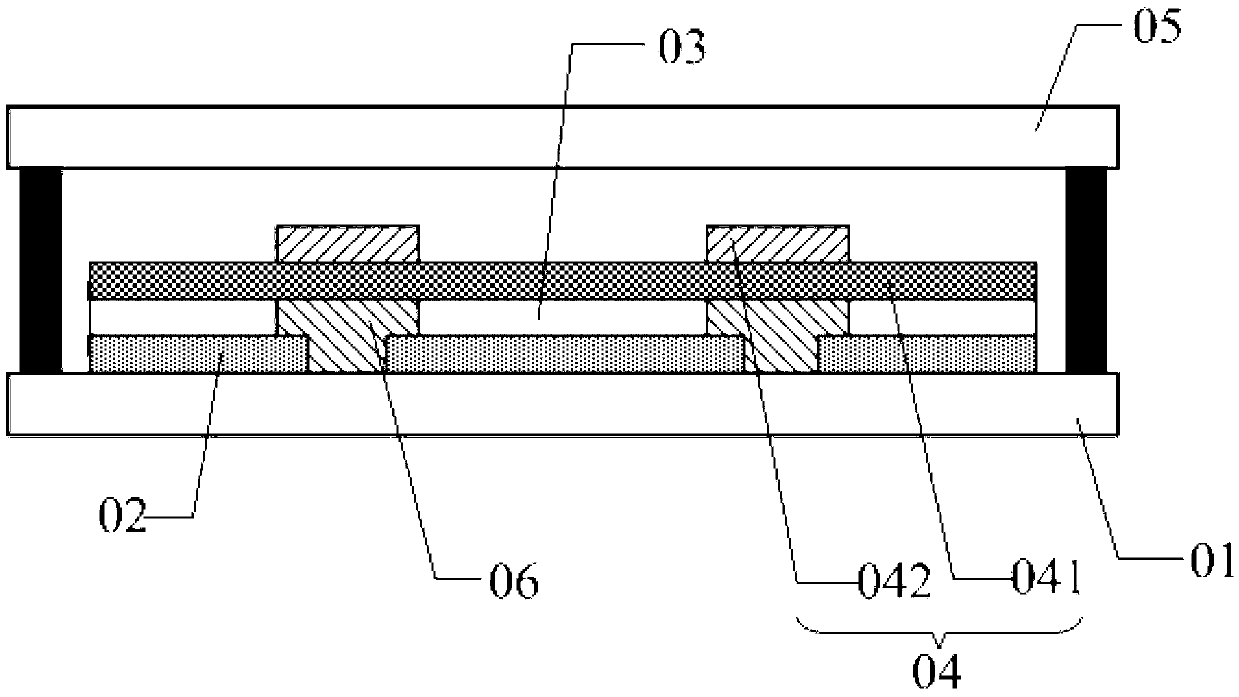

InactiveCN101783395ASolve defects such as low aperture ratioIncrease opening ratioSolid-state devicesSemiconductor/solid-state device manufacturingHigh resistanceDisplay device

The invention relates to an organic electroluminescence component and a manufacturing method thereof. The organic electroluminescence component comprises a basal plate, wherein a first electrode, an organic material layer, a second electrode and a sealing layer are sequentially formed on the basal plate, the first electrode is used as an anode, and the second electrode is used as a cathode and is a composite transparent structure layer for realizing the light emitting at the top. By forming the composite transparent cathode emitting light at the top, the invention enables the organic electroluminescence component to emit the light from the top and enhances the light-emitting utilization rate and the light transmission rate effectively, which not only enhances the aperture opening ratio of a display screen but also can obtain better display effect. Meanwhile, by adding a netty confluence layer on a semitransparent metal layer with high resistance, the invention ensures high transmissivity, also enhances the conducting power of current, meets the requirement of a top transmission type organic electroluminescence component effectively and can be applied to a display device with double-face display. The invention has simple and reliable structure and preparation process and extensive application prospect.

Owner:BOE TECH GRP CO LTD

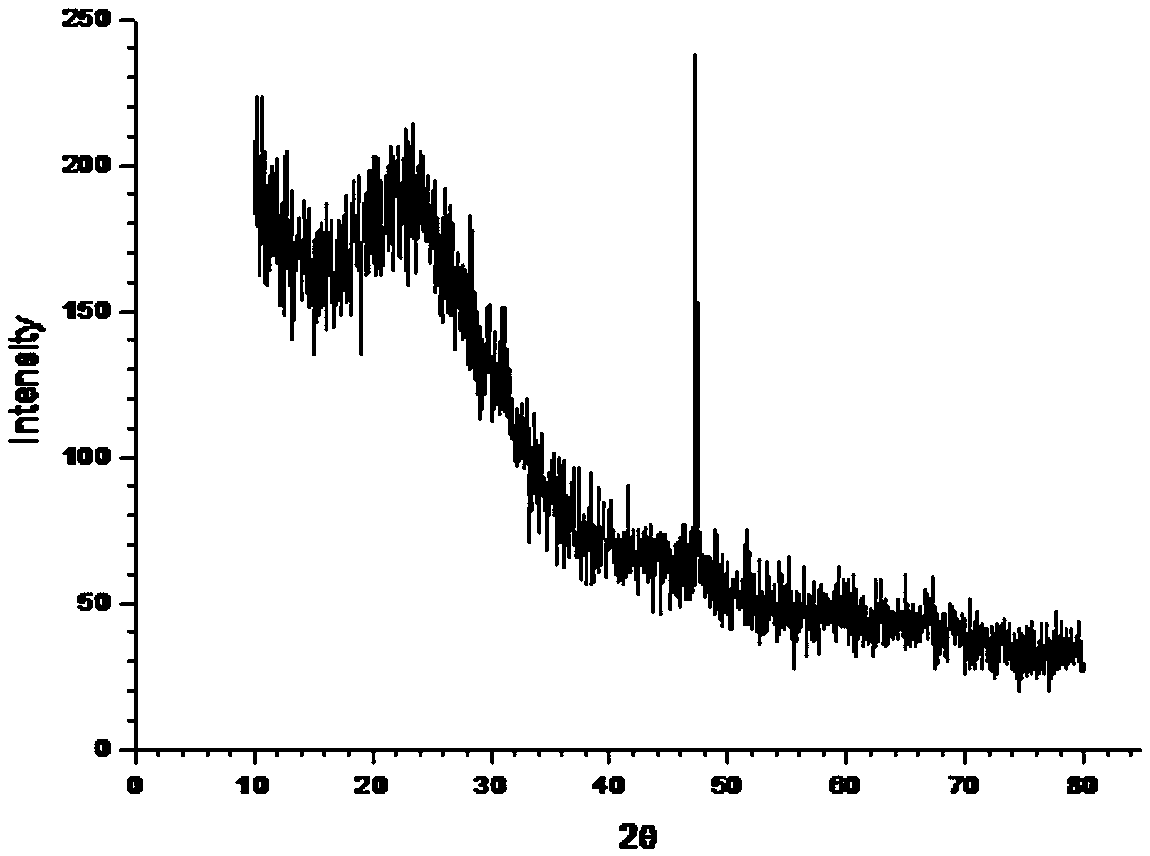

Oxygen sensor electrode, concentration-difference type oxygen sensor with oxygen sensor electrode, and preparation method for same

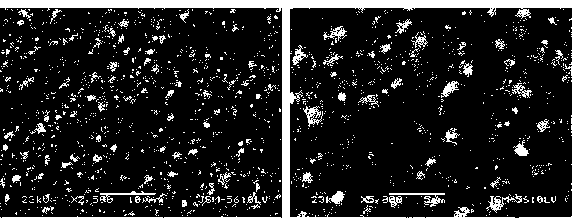

ActiveCN103185738AHigh platinum contentImprove catalytic performanceMaterial electrochemical variablesReaction layerPlatinum

The invention provides an oxygen sensor electrode. The electrode is of a double-layer structure, and comprises a catalytic reaction layer and a flow-collecting layer, wherein the catalytic reaction layer has a high ceramic proportioning ratio, platinum powder is uniformly distributed in ceramic powder, so that a three-phase boundary among zirconium oxide, the platinum powder and oxygen is maximized; and the flow-collecting layer has a high metal platinum proportioning ratio and a good conducting capacity. A forming process of co-sintering the electrode and a solid electrolyte can be adopted for the oxygen sensor with the electrode provided by the invention, thus saving production cost; and moreover, the catalytic reaction layer of the electrode is closely combined with the solid electrolyte and free from the phenomena of layering and cracking, and the reduction of the catalytic performance due to the reduction of the three-phase boundary caused by the overburning of the platinum powder in the catalytic reaction layer is avoided.

Owner:BYD CO LTD

Top-luminescence organic light-emitting diode (OLED) and preparation method and display apparatus thereof

ActiveCN103000814AReduce square resistanceImprove current conduction abilitySolid-state devicesSemiconductor/solid-state device manufacturingOrganic electroluminescencePower flow

The invention discloses a top-luminescence OLED and a preparation method and a display apparatus thereof. A second electrode serving as a cathode in the OLED is composed of a semitransparent electrode layer and at least one non-transparent electrode layer electrically connected with the semitransparent electrode layer. Patterns arranged on the at least one non-transparent electrode layer right face gaps among determined pixel units of an organic material layer, so that the aperture opening ratio of the OLED is not affected; and the at least one non-transparent electrode layer electrically connected with the semitransparent electrode layer can reduce the square resistance of the semitransparent electrode layer, so that the current conduction capacity of the cathode of the OLED is improved. Further, the display perspective of the OLED can be controlled effectively by designing the patterns of the at least one non-transparent electrode layer, so that pictures can be viewed at specific angles, and the display security is guaranteed.

Owner:BOE TECH GRP CO LTD

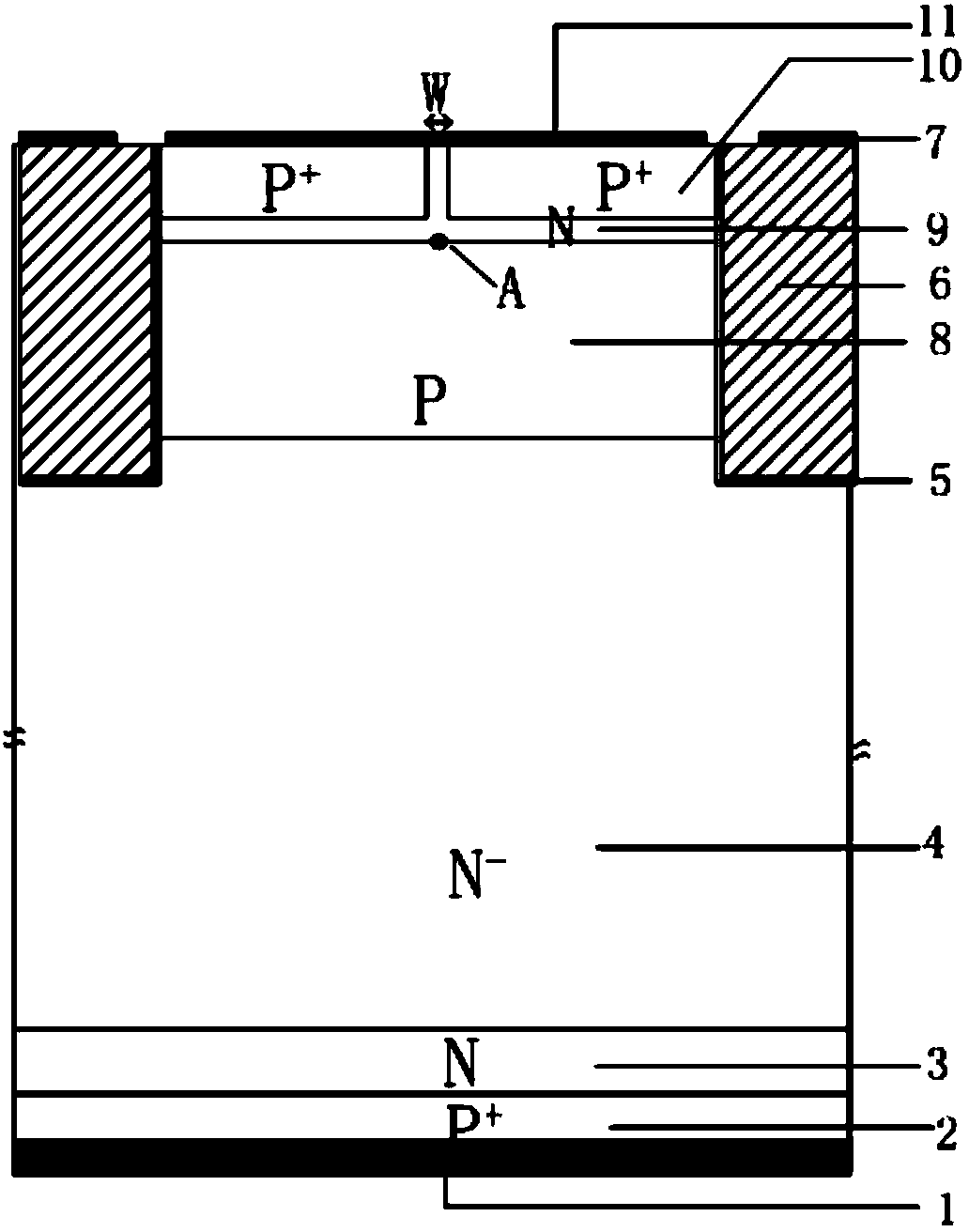

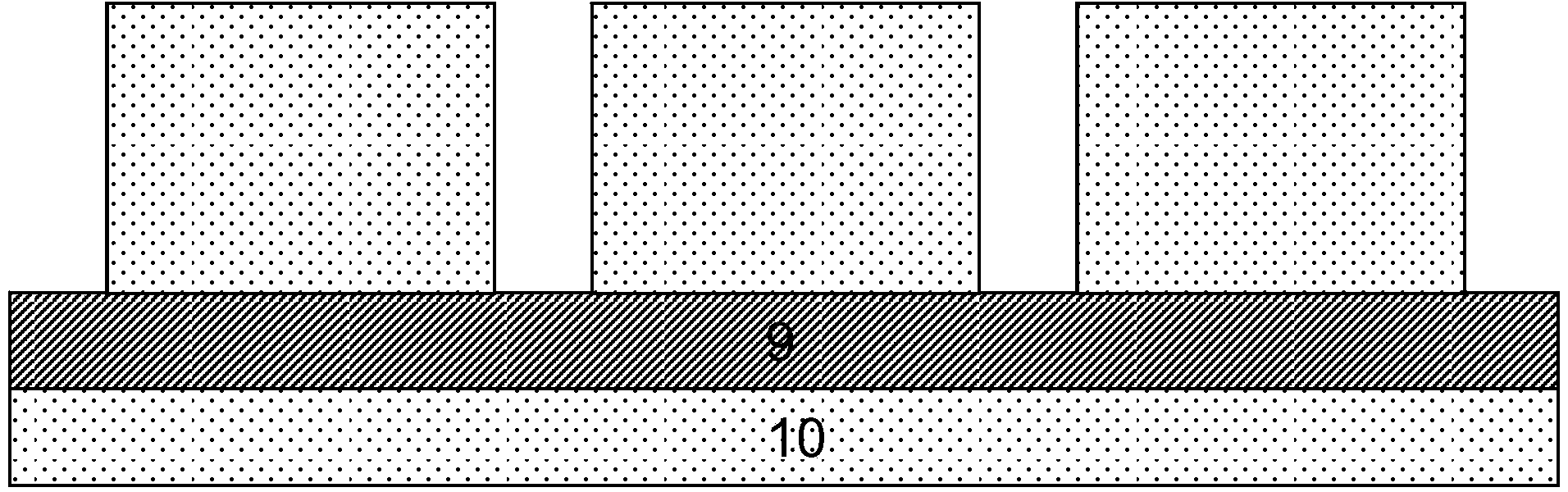

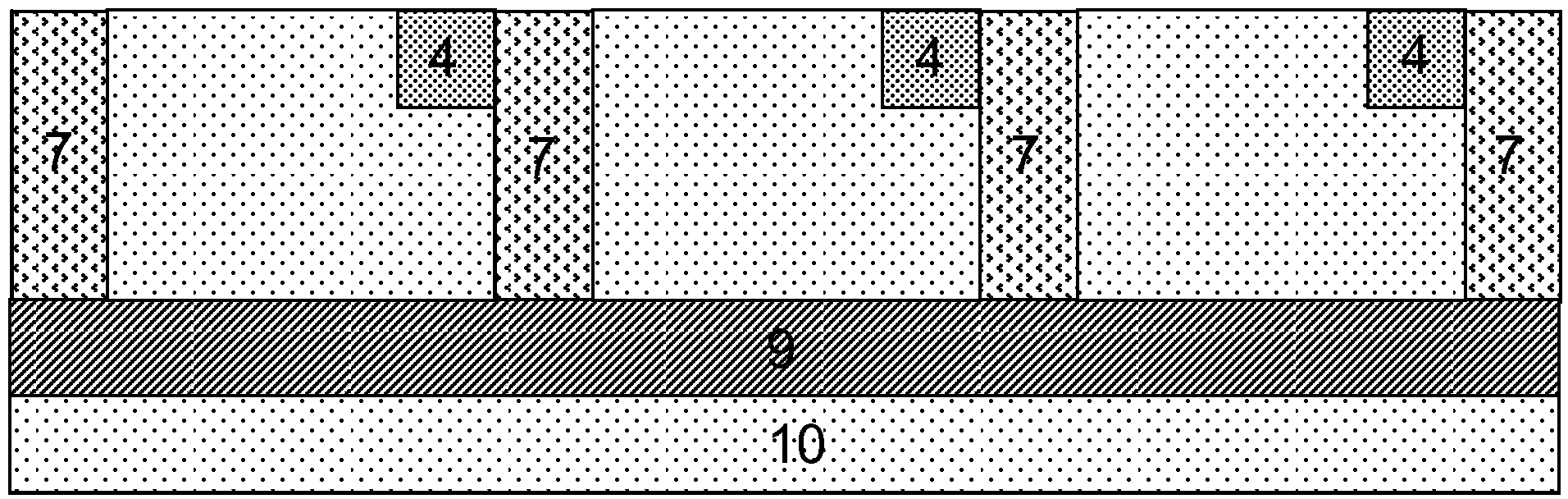

MOS grid-control thyristor

InactiveCN103956381AImprove short-circuit safe working abilityShorten off timeThyristorAnode voltageElectron flow

The invention relates to the semiconductor technology, in particular to an MOS grid-control thyristor. A P+ cathode contact area 10 is modified, the width of the P+ cathode contact area 10 is increased, the metallurgical junction form is changed, and the conveying passage of electrons flowing from cathode metal 11 is shortened. The forward direction work characteristic of a device is controlled by a JFET composed of the P+ cathode contact area 10 and an N-trap 9, a channel pinch-off effect can occur under a relatively small anode voltage, the intensity of saturation current of the device can be controlled, and optimization valuing can be carried on the junction depth and width of the P+ cathode contact area 10 according to the design requirements of the device. The MOS grid-control thyristor is particularly suitable for the MOS grid-control thyristor.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

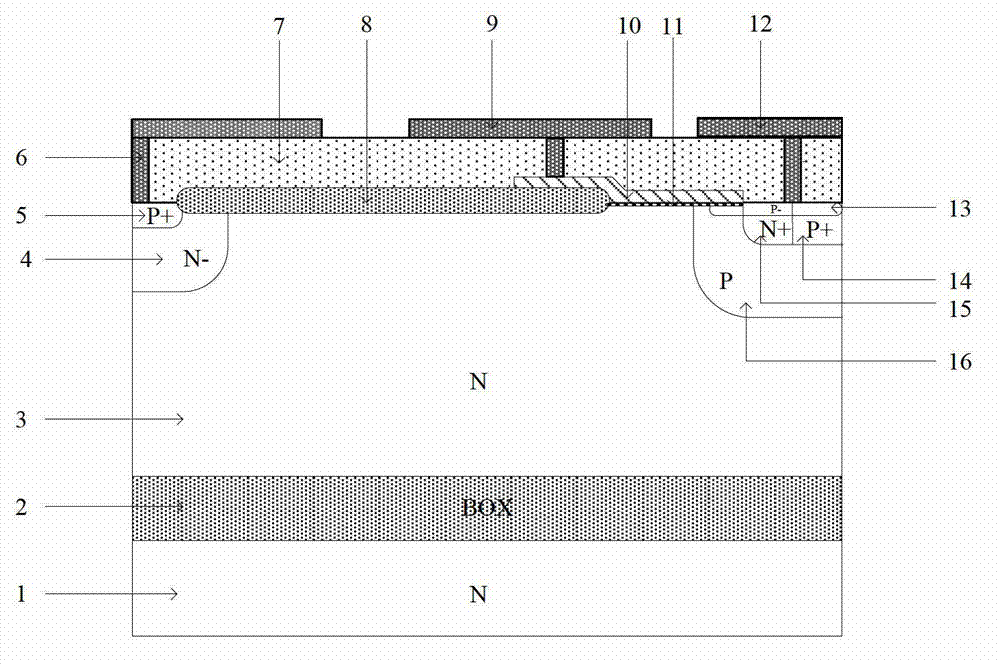

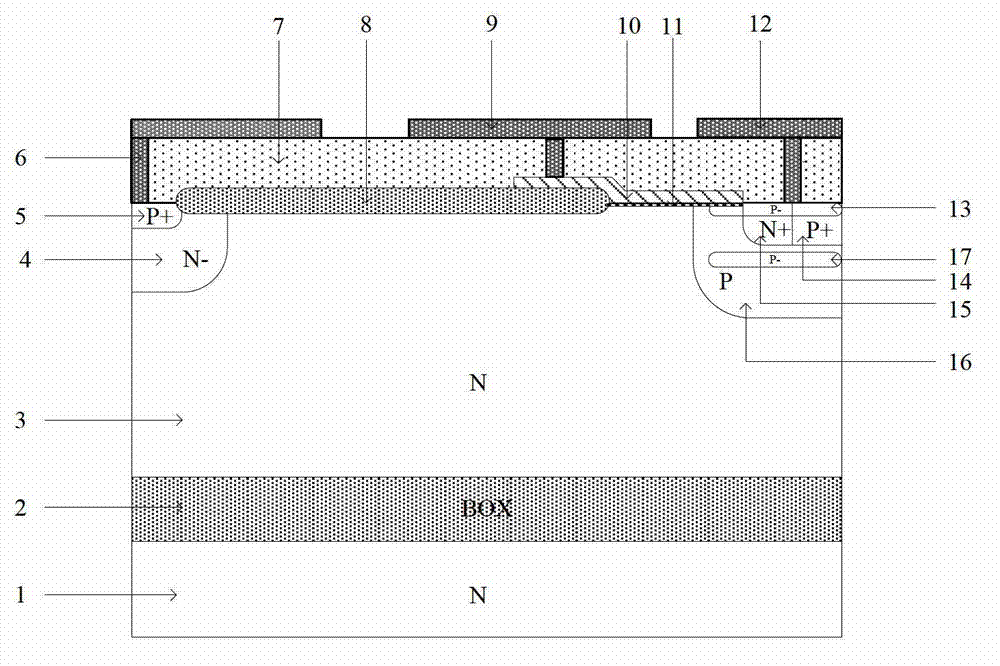

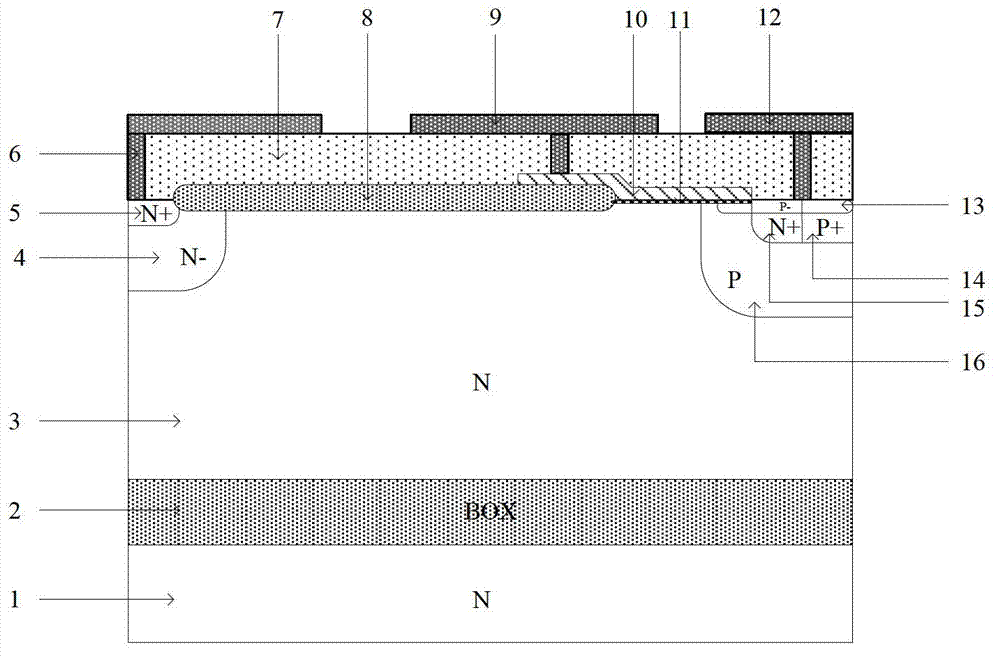

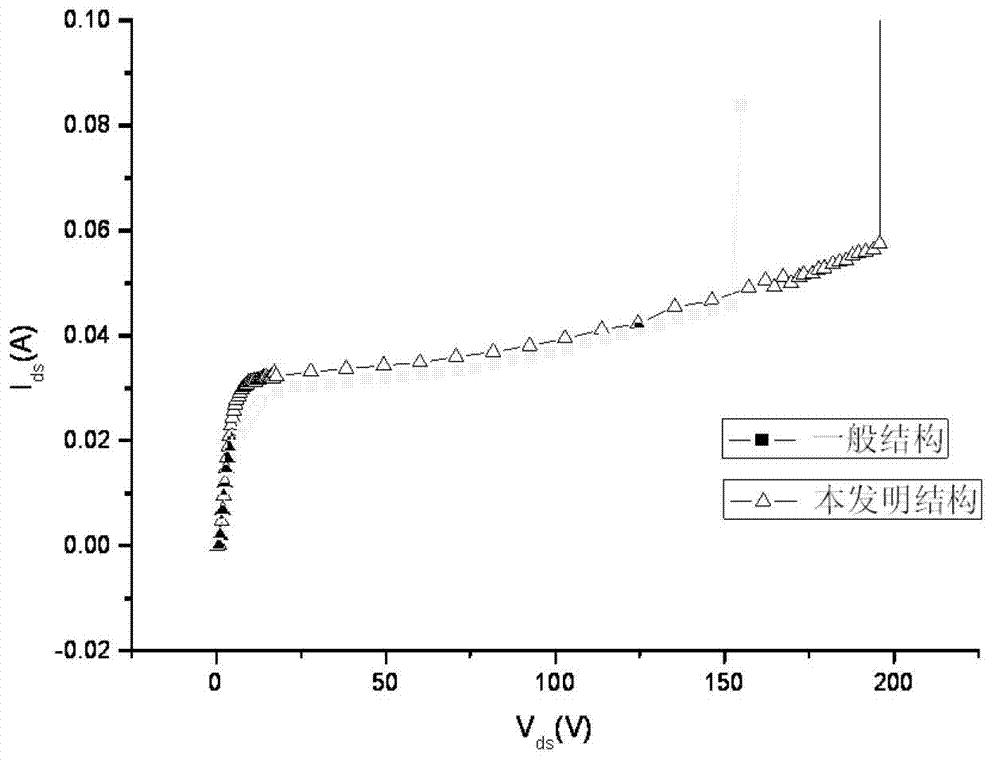

Latch-preventing N type silicon on insulator transverse isolated gate bipolar transistor

ActiveCN102760761AImprove latching abilityLower on-resistanceSemiconductor devicesPower flowBody contact

The invention discloses a latch-preventing N type silicon on insulator transverse isolated gate bipolar transistor which comprises an N type substrate, wherein the N type substrate is provided with buried oxide, the buried oxide is provided with an N type epitaxial layer, and the N type epitaxial layer is internally provided with an N type buffering trap and a P type body region; the N type buffering trap is internally provided with a P type positive region, the P type positive region is provided with an N type negative region and a P type body contact region, and the surface of the N type epitaxial layer is provided with a gate oxide layer and a field oxide layer; and the surfaces of the N type negative region and the P type body contact region are provided with shallow P type trap regions, the surface of the gate oxide layer is provided with a polysilicon gate, and the surfaces of the field oxide layer, the P type body contact region, the N type negative region, the polysilicon gate and the P type positive region are provided with a passivation layer respectively. The transverse isolated gate bipolar transistor is characterized in that the positive inferior of the shallow P type trap region is also provided with a deep P type trap region is arranged under the shallow P type trap region, which shares one photoetching plate together with the shallow P type trap region and is formed by injection of high energy ions; and the deep P type trap region effectively reduces the conduction resistor of a body region, the current capacity of a device is improved, and meanwhile, and the risk of the latch generated in a working process is reduced.

Owner:SOUTHEAST UNIV

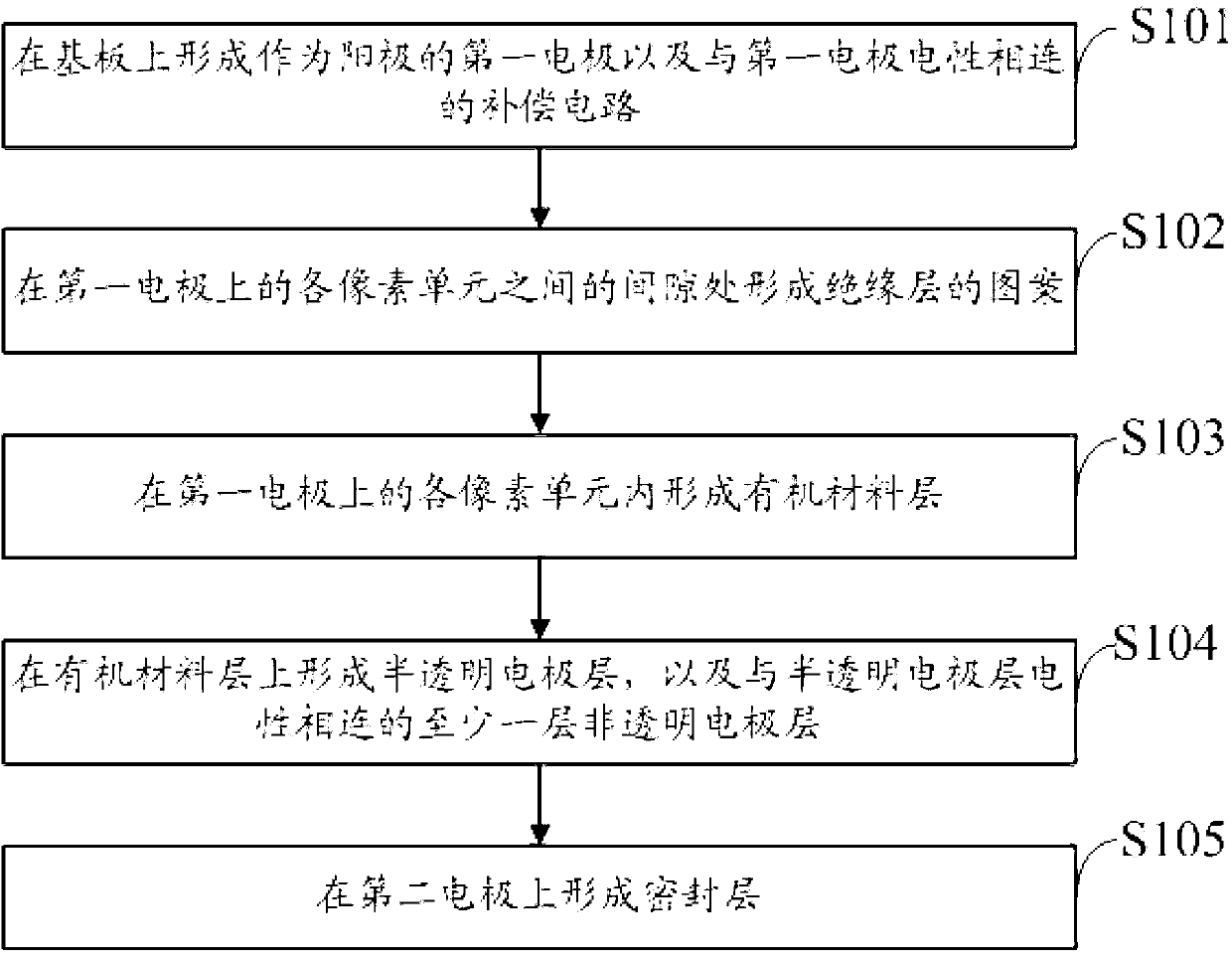

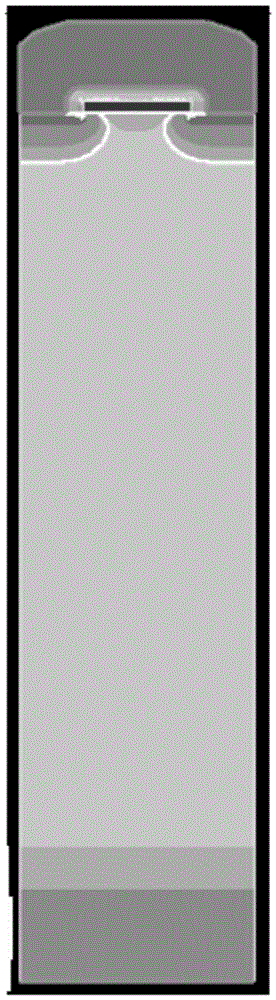

Manufacturing method of OLED display panel and OLED display panel

ActiveCN110137365AImprove current conduction abilityEliminate conduction barriersSolid-state devicesSemiconductor/solid-state device manufacturingVoltage dropEngineering

The invention provides a manufacturing method of an OLED display panel and the OLED display panel. The method comprises the steps: providing an underlying substrate and forming multiple anodes arranged in an array on the substrate and auxiliary electrodes arranged in spaced regions of multipl anodes; forming a pixel definition layer on the underlying substrate, multiple anodes and auxiliary electrodes and forming multiple first openings corresponding to multiple anodes and second openings corresponding to the auxiliary electrodes on the pixel definition layer; forming an OLED light emitting layer covering the whole surface on the auxiliary electrodes, the pixel defining layer and multiple anodes; performing UV illumination on the OLED light emitting layer; and forming a cathode distributedon the whole surface on the OLED light emitting layer. The current conductivity of the electron transmission material in the OLED light emitting layer can be improved by the UV illumination treatment, the conduction obstacle between the auxiliary electrodes and the cathode can be eliminated and the improvement effect of the voltage drop can be improved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

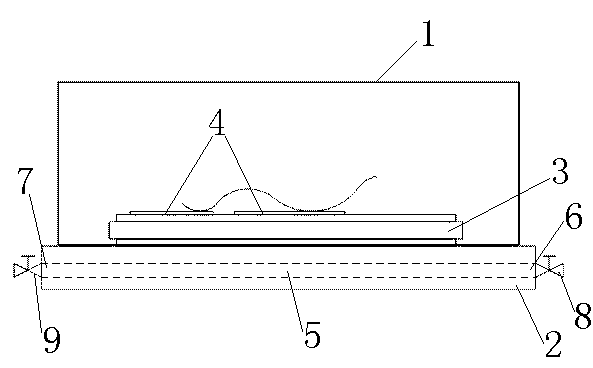

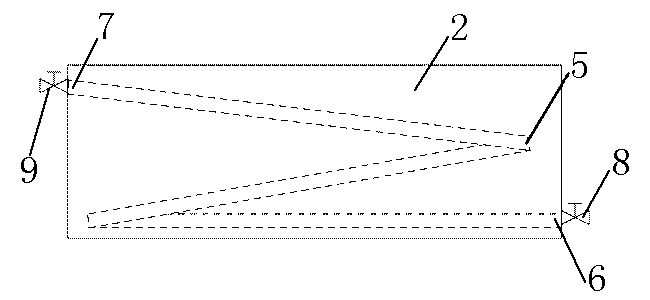

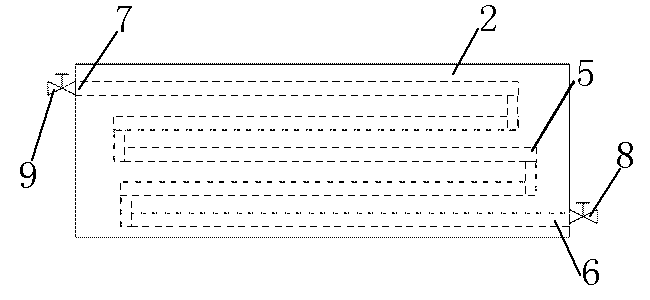

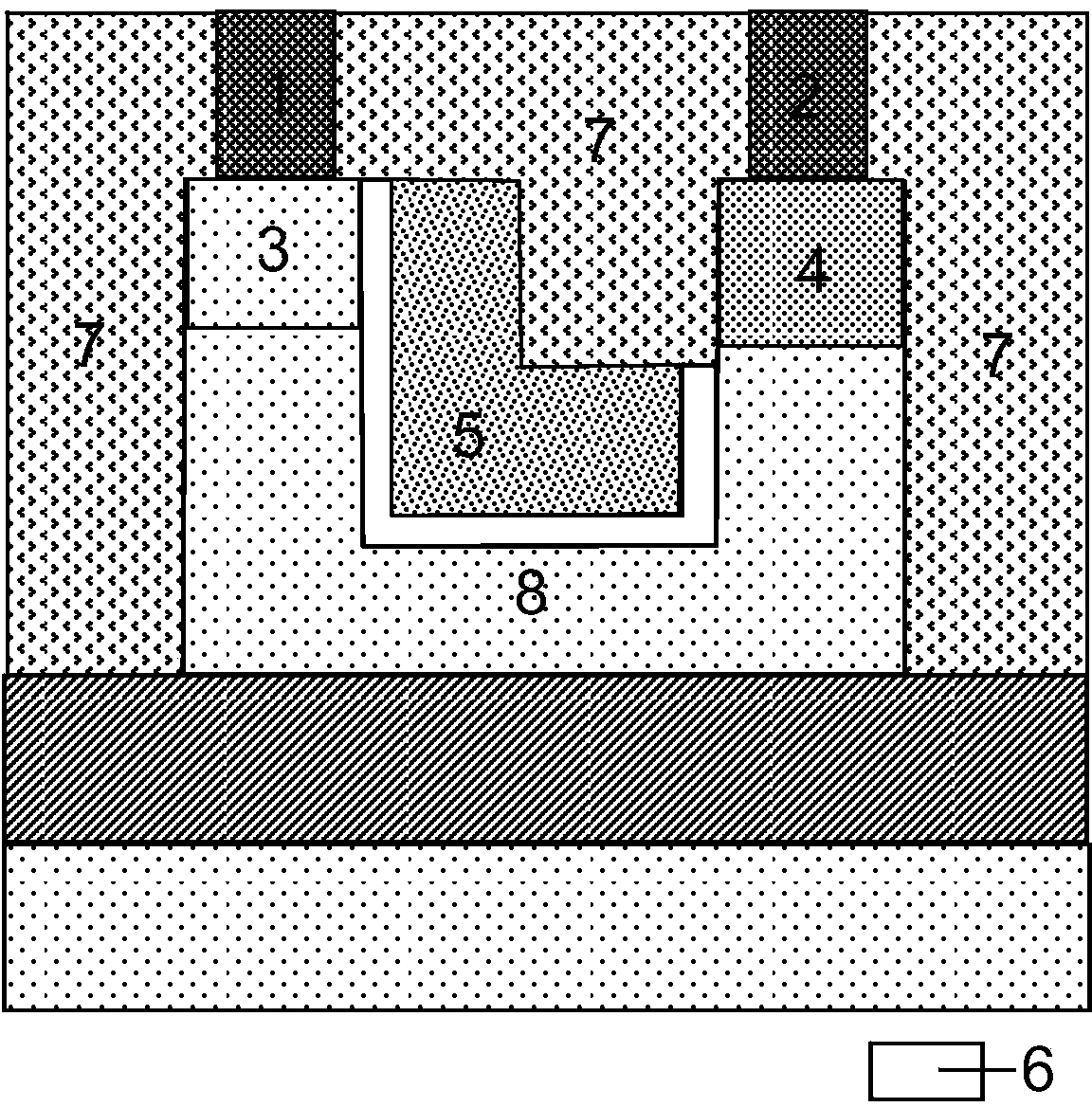

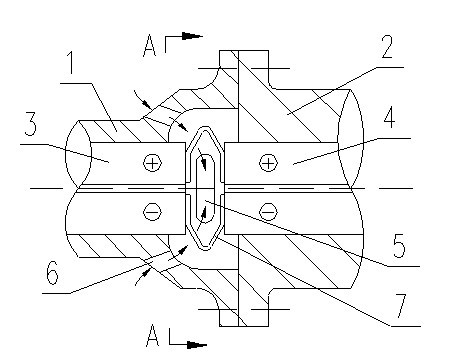

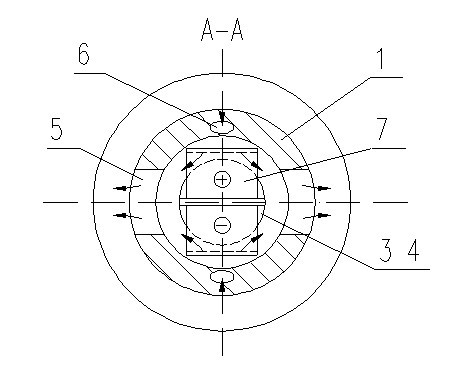

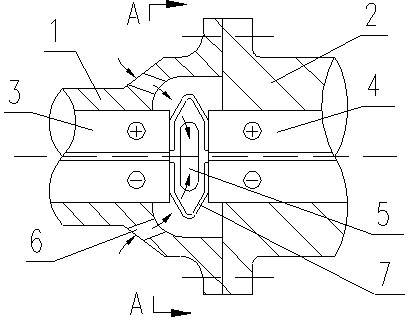

Motor controller

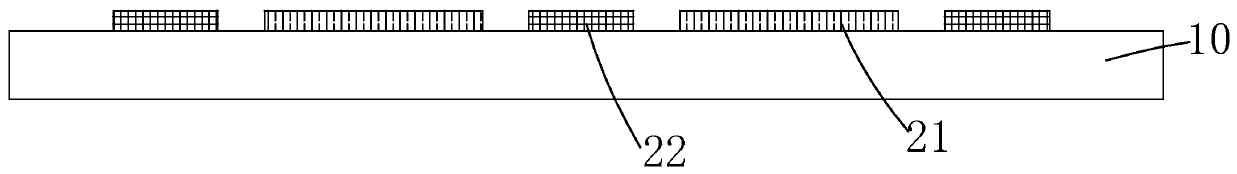

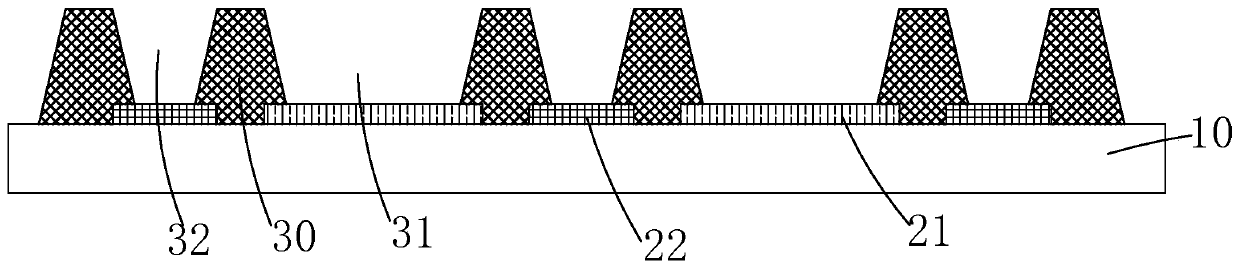

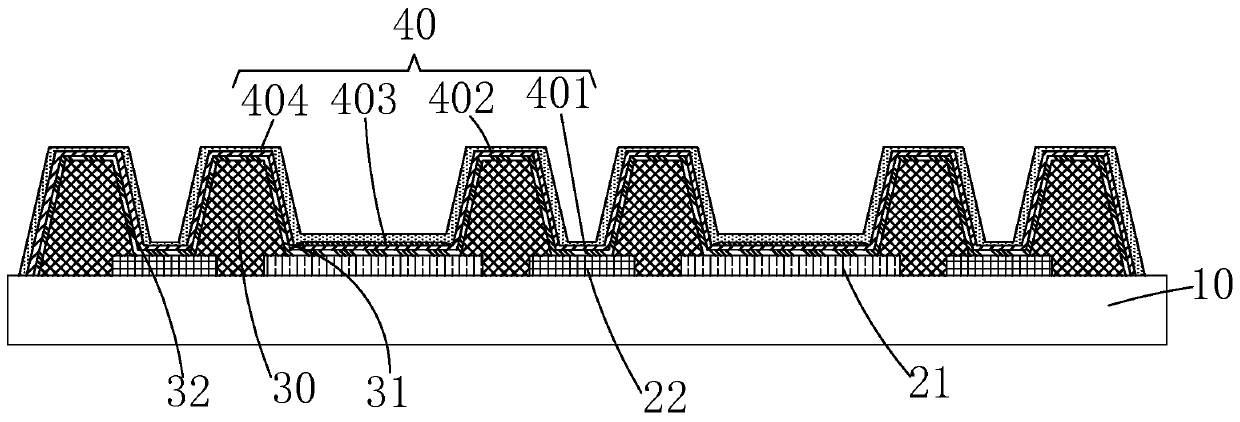

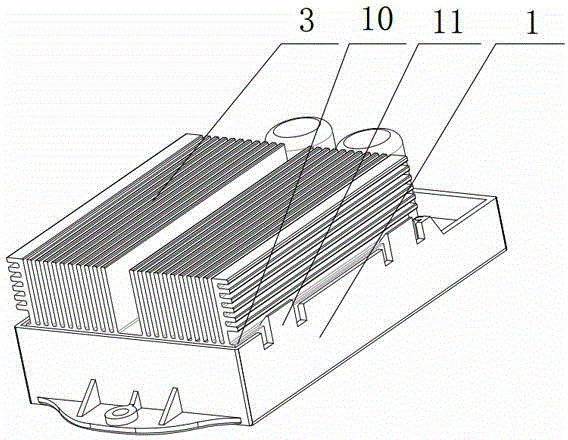

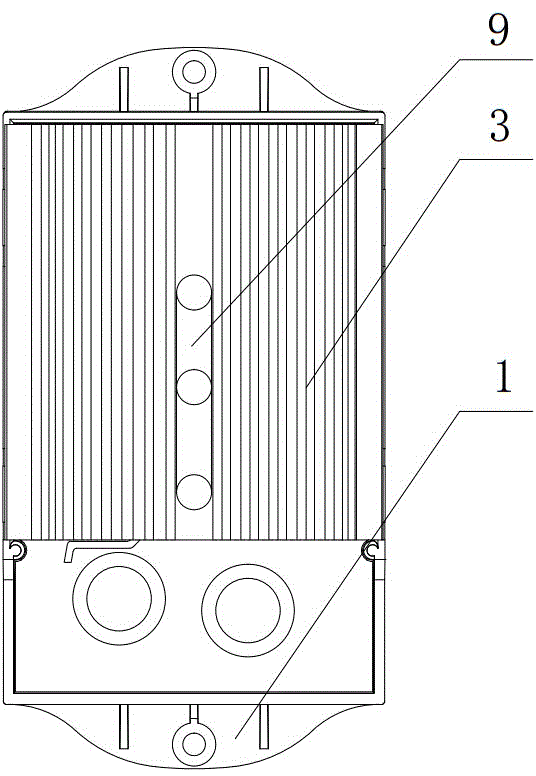

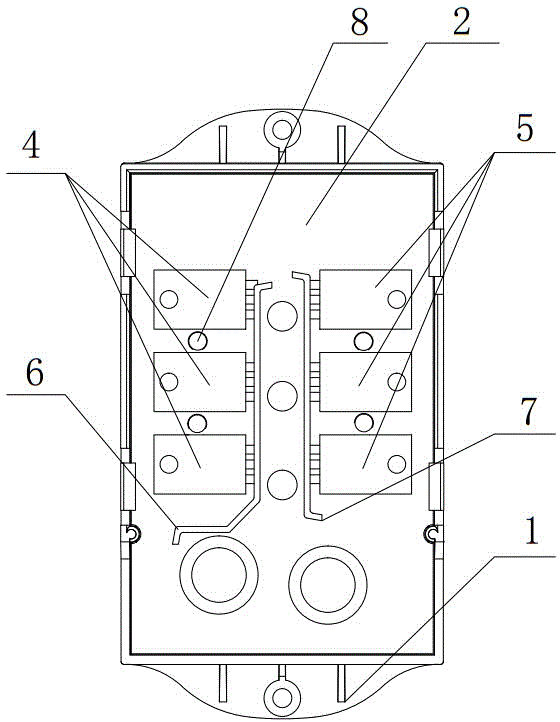

ActiveCN104812164AImprove current conduction abilityReduce feverPrinted circuit detailsCooling/ventilation/heating modificationsElectrical connectionMotor controller

The invention relates to the technical field of controllers, and in particular relates to a motor controller. The motor controller comprises a support (1), a PCB (2) arranged on the support (1) and a cooling fin (3) arranged on the support (1), wherein a plurality of MOS tubes, which are divided into an upper bridge MOS tube set (4) and a lower bride MOS tube set (5), are arranged on the PCB (2), the upper bridge MOS tube set (4) is electrically connected with the input anode of the PCB (2) by a first copper strip (6), and the lower bride MOS tube set (5) is electrically connected with the input cathode of the PCB (2) by a second copper strip (7); the motor controller is good in electrical connection capacity, small in heating, convenient to machine and high in installing efficiency.

Owner:NINGBO JINHONGSHENG ELECTROMECHANICAL TECH CO LTD

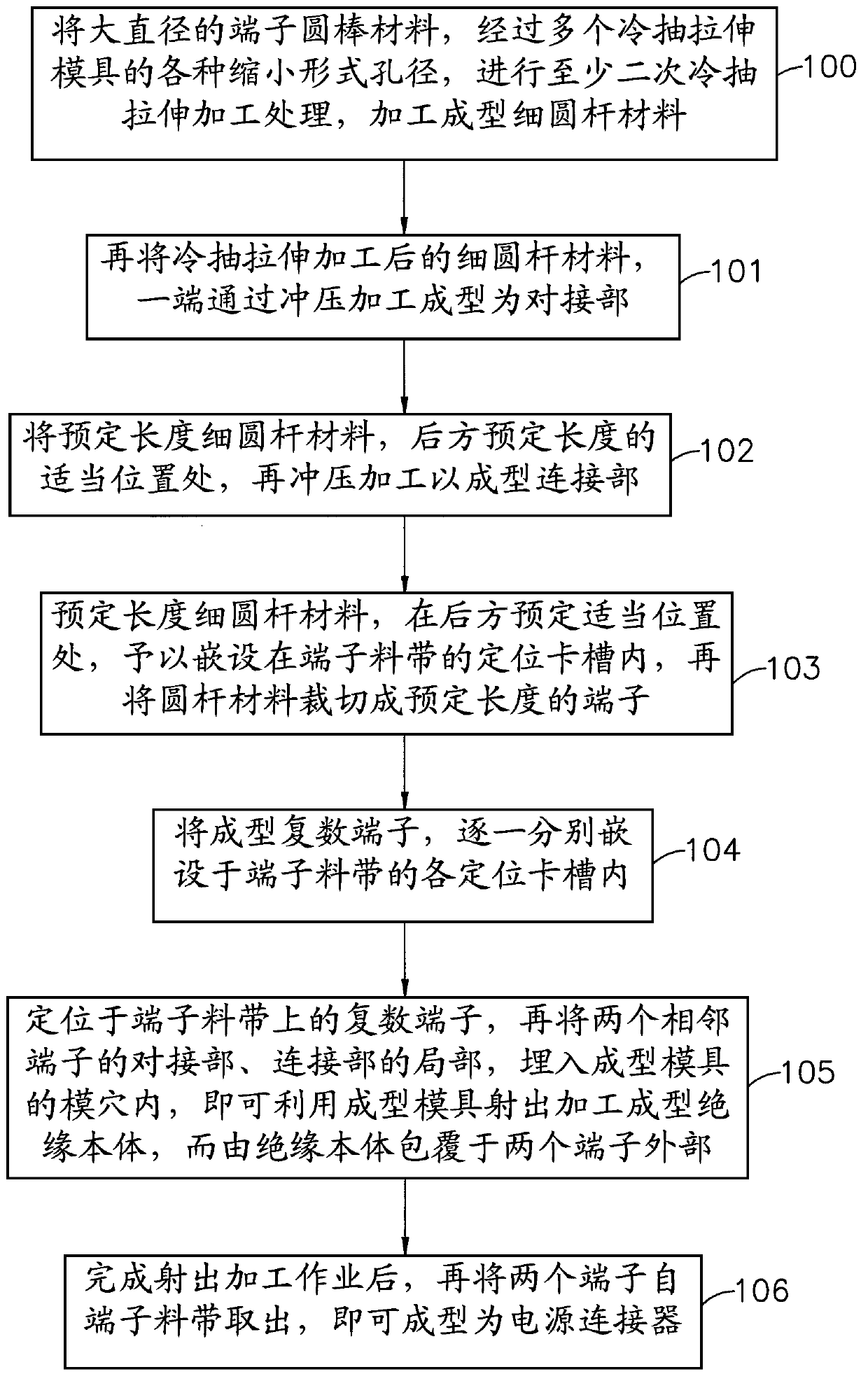

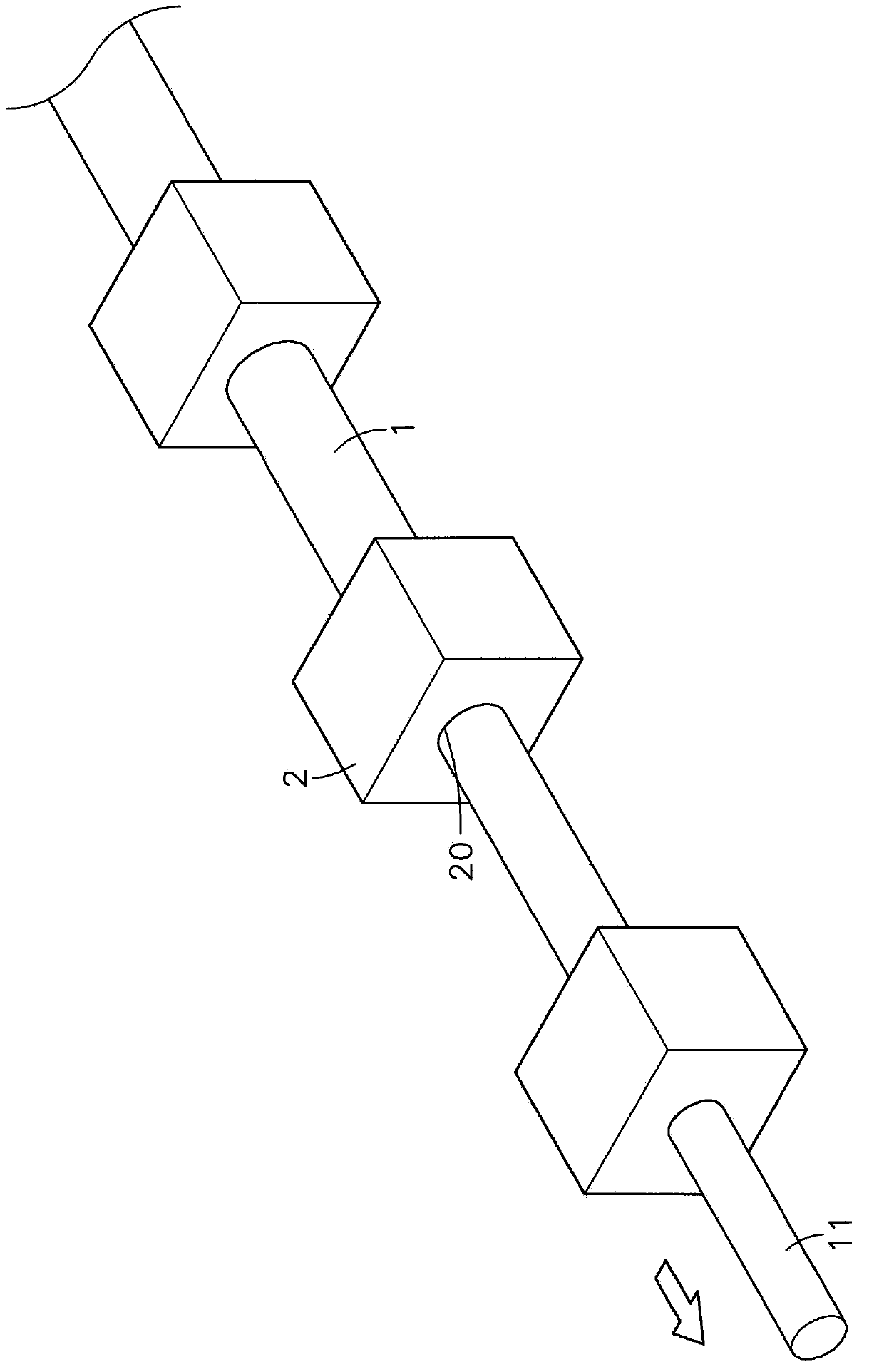

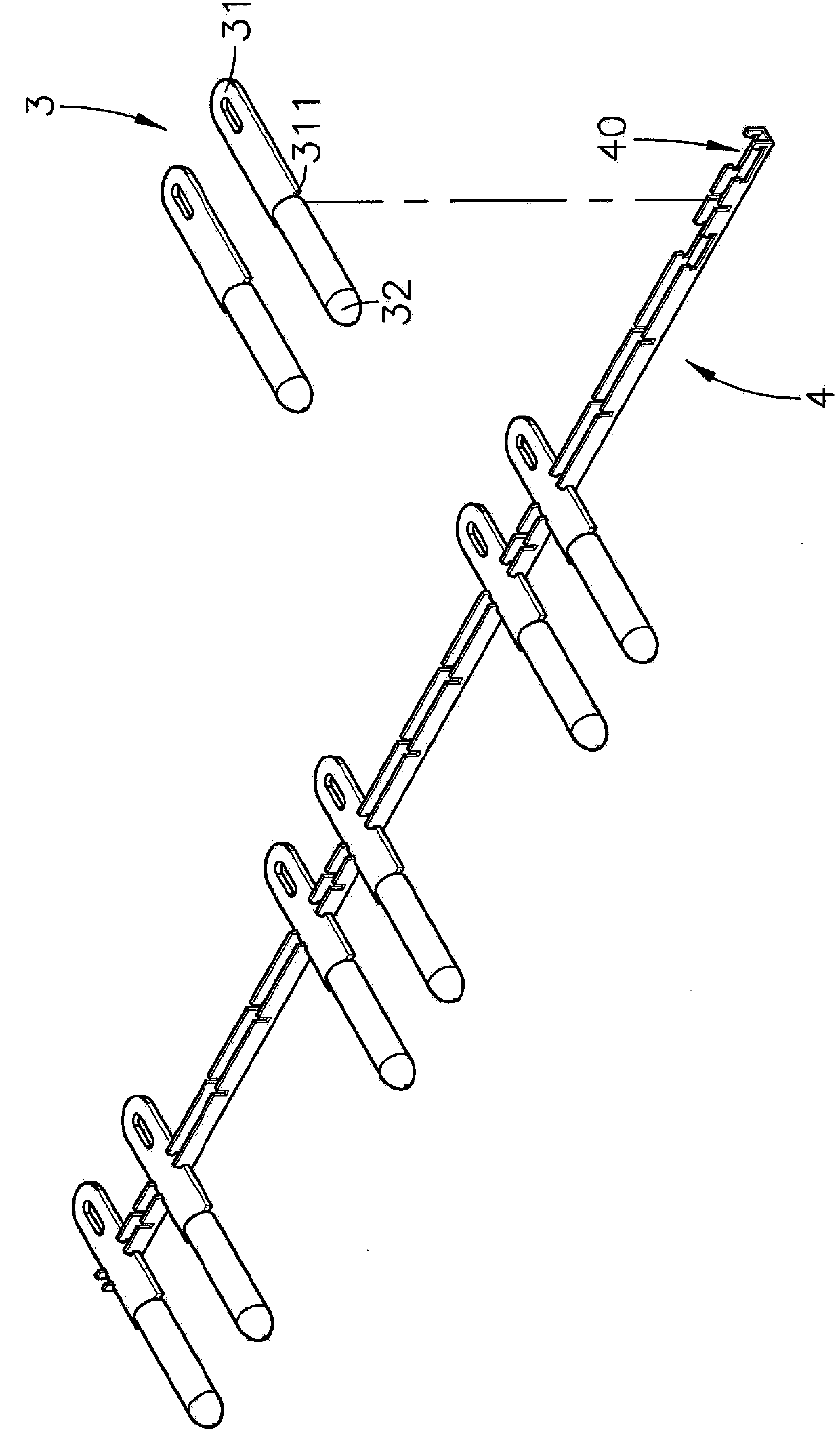

Forming method of power supply connector

InactiveCN103872548AImprove work efficiencyReduce manufacturing costContact member manufacturingContact member assembly/disassemblyManufacturing cost reductionPunching

The invention discloses a forming method of a power supply connector. The forming method comprises the forming steps of processing and forming slender round bar materials by carrying out at least twice cold drawing and stretching processing treatments on terminal round bar materials; punching and forming one ends of the slender round bar materials into terminal butt-joint parts; punching, processing and forming appropriate positions at the rear parts of the slender round bar materials into connecting parts; respectively embedding the slender round bar materials in each locating clamping groove of a terminal material strap one by one, and cutting the slender round bar materials into terminals in preset lengths; respectively locating a plurality of terminals in each locating clamping groove of the terminal material strap after the terminals are formed by repeating the processing mode; embedding the local parts of the butt-joint parts and the connecting parts of two adjacent terminals on the terminal material strap in a die cavity of a forming die, ejecting, processing and forming insulation bodies at the outer parts of the two terminals by utilizing plastics, and separating the two terminals from the terminal material strap; forming the power supply connector after the forming die is removed. According to the forming method disclosed by the invention, the purposes of increasing the working efficiency and reducing the manufacturing cost can be achieved.

Owner:RIIDEA

Novel power module

InactiveCN103021977AGuaranteed stabilityAvoid heat dissipation intermediate mediumSemiconductor/solid-state device detailsSolid-state devicesCoolant flowEngineering

The invention provides a novel power module which comprises a shell, a substrate, a base plate, and a chip. The substrate is connected with a radiator. The chip is fixedly connected with the base plate. The base plate is fixedly connected with the substrate. The power module is provided with a coolant flow loop inside. The coolant flow loop comprises a radiating passage, a coolant inlet, and a coolant outlet. The radiating passage, the coolant inlet and the coolant outlet are arranged inside the substrate and are integrated with the substrate. The radiator of the power module is integrated to the bottom, radiating is achieved by water cooling, the inside of the power module is directly cooled, various radiating intermediate media are avoided, property difference caused by the use of different radiators can be avoided, radiating efficiency is improved, and stable operation of the power module is guaranteed.

Owner:ZHEJIANG UNIV

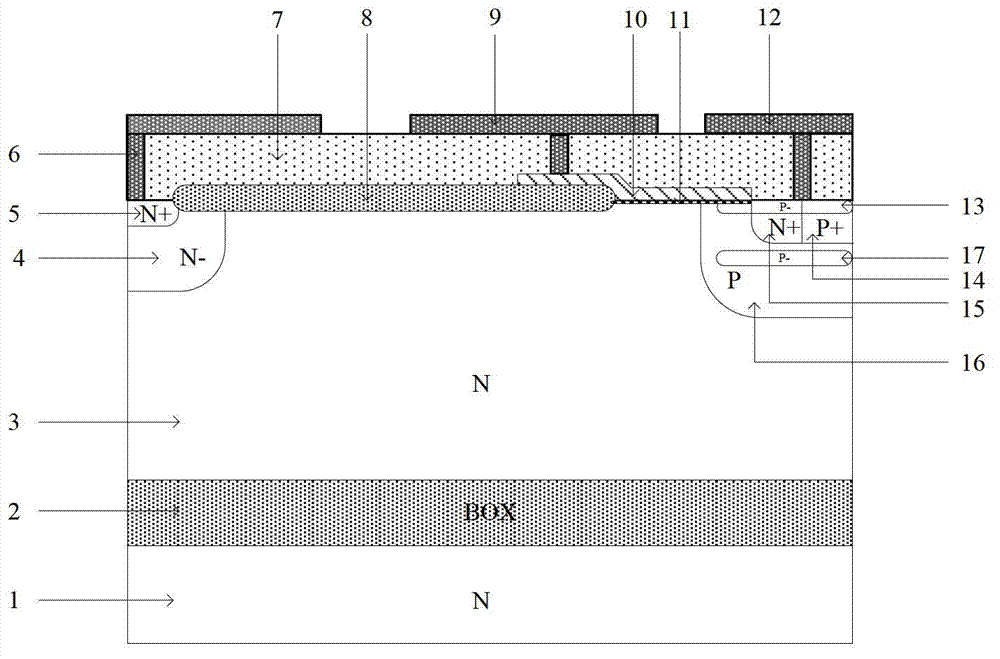

Latch-up resisting N-type SOI laterally diffused metal oxide semiconductor

ActiveCN102769038AImprove latching abilityLower on-resistanceSemiconductor devicesHigh energyBody contact

A latch-up resisting N-type SOI (Silicon On Insulator) laterally diffused metal oxide semiconductor (LDMOS) comprises an N-type substrate, wherein a buried oxide is arranged on the N-type substrate; an N-type epilayer is arranged on the buried oxide; an N-type buffering well and a P-type body region are arranged in the N-type epilayer; an N-type drain region is arranged in the N-type buffering well; an N-type source region and a P-type body contact region are arranged in the P-type body region; a gate oxide and a field oxide are arranged on the surface of the N-type epilayer; a shallow P-type well region is arranged on the surfaces of both the N-type source region and the P-type body contact region; a polysilicon gate is arranged on the surface of the gate oxide; and a passivation layer is arranged on the surfaces of the field oxide, the P-type body contact region, the N-type source region, the polysilicon gate and the N-type drain region. The latch-up resisting N-type SOI-LDMOS is characterized in that a deep P-type well region sharing the same photoetching board together with the shallow P-type well region and formed by high-energy ion implantation is arranged right below the shallow P-type well region, and the deep P-type well region effectively reduces the conducting resistance of the body region and lowers the latch-up risk in the working process while improving the current capacity of devices.

Owner:SOUTHEAST UNIV

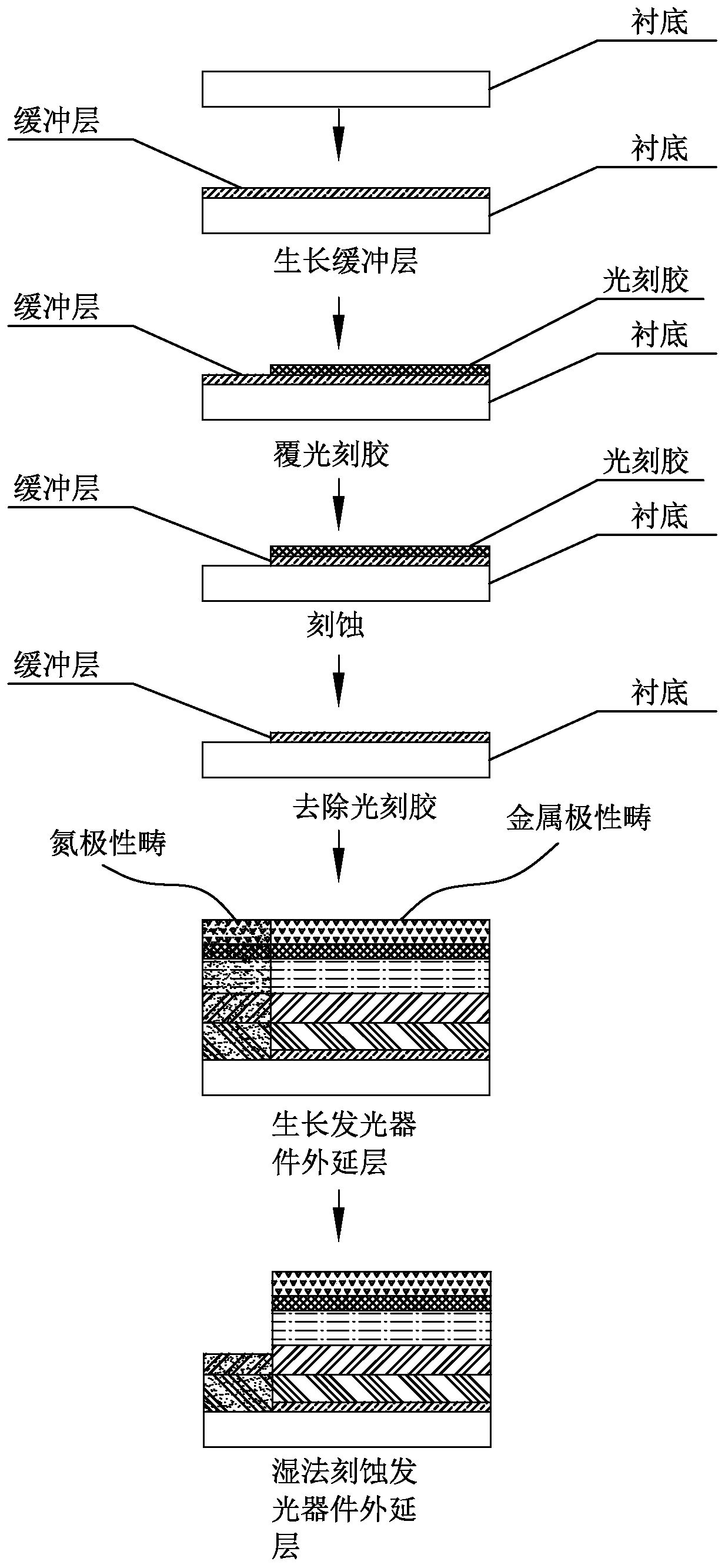

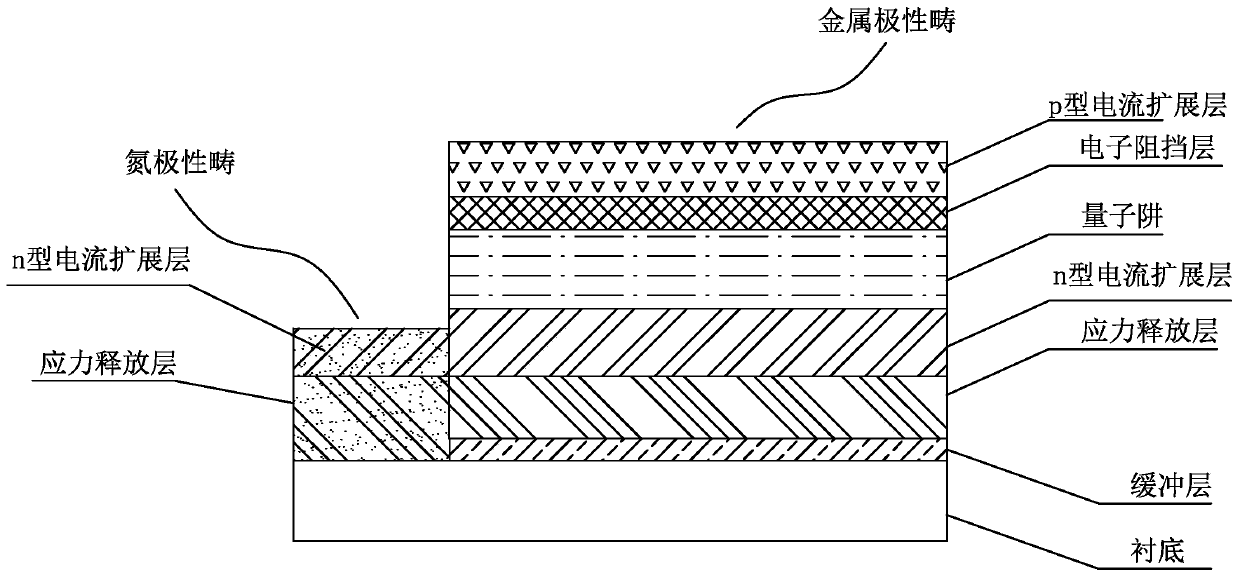

Mesa etching method for III-nitride semiconductor light-emitting device

ActiveCN111326611AImprove crystal qualityFlat surfaceSemiconductor laser structural detailsSemiconductor devicesPhysicsPolar structure

The invention discloses a mesa etching method for an III-nitride semiconductor light-emitting device. The method comprises the steps of firstly, epitaxially growing a buffer layer on a substrate, etching the buffer layer to obtain a patterned buffer layer substrate, and epitaxially growing a light-emitting device epitaxial layer with a transverse polarity structure on the patterned buffer layer substrate, wherein the transverse polarity structure comprises a nitrogen polarity domain and a metal polarity domain; and then etching the non-inert polarity domain by adopting a wet etching process according to the inert difference of the nitrogen polarity domain and the metal polarity domain in the etching liquid. According to the invention, a device mesa without plasma damage can be obtained; and the conversion efficiency of the III-nitride light-emitting device is improved, and the manufacturing cost is reduced.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

Self-locking chuck and electrode slice connecting device

PendingCN108310624AEnsure structural stabilityAvoid sudden changes in therapeutic currentExternal electrodesAgricultural engineeringSelf locking

The invention provides a self-locking chuck and an electrode slice connecting device, and the self-locking chuck does not get loose, and is safe in treatment, good in electrical conductivity, low in cost and good in universality. The self-locking chuck comprises an upper cover, a lower cover and a turning plate; the upper cover and the lower cover are buckled and connected, a clamping channel is formed between the upper cover and the lower cover, a connecting shaft is fixedly arranged at the front end of the upper cover, a half open shaft sleeve is arranged in the eccentric position of the turning plate, a front protruding part and a rear protruding part are arranged at the lower part of the turning plate, the shaft sleeve is correspondingly arranged at the upper end of the rear protrudingpart, the connecting shaft is sleeved with the turning plate through the shaft sleeve, a metal elastic sheet is arranged in the clamping channel, the lower end face of the metal elastic sheet is abutted against the lower cover, the upper end face of the metal elastic sheet is abutted against the rear protruding part and the upper cover respectively, and a wire extending outwards is arranged on the rear part of the metal elastic sheet. The electrode slice connecting device comprises an electrode slice and the self-locking chuck; the electrode slice comprises an electric conduction main body, atransition section and an extending end; the extending end is connected with the electric conduction main body through the transition section, and the front end of the transition section and the extending end are arranged in the clamping channel.

Owner:JIANGSU ZONP TECH

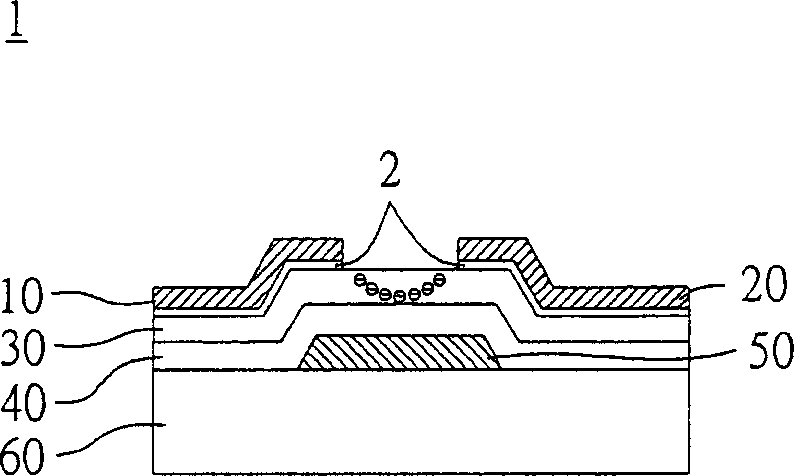

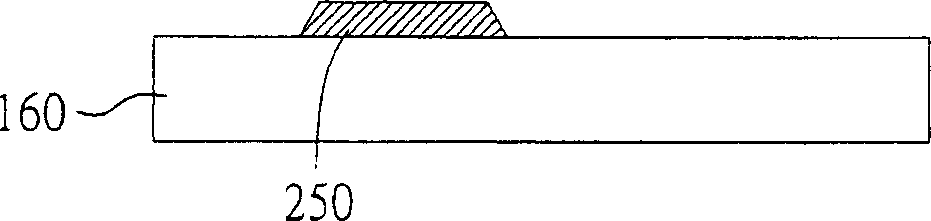

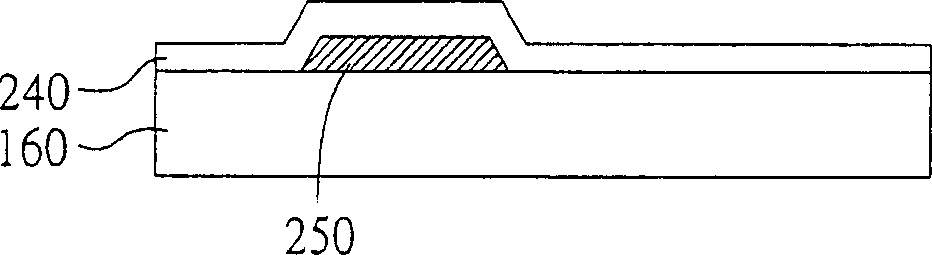

Amorphous silicon film transistor with double grid structure and mfg. method thereof

ActiveCN1719616AReduce operating voltageImprove reliabilityTransistorSemiconductor/solid-state device manufacturingAmorphous siliconEngineering

A non-crystalline silicon film transistor with double-grid structure includes a base plate, a first grid, a non-crystalline channel layer, a source a drain and a second grid. The first grid is formed on the base plate, the non-crystalline channel layer is formed on the first grid, the source and drain are formed on the channel layer corresponding to both ends of the first grid and contacted with both ends of the channel layer, the second grid is formed on the source and drain corresponding to the first grid and electrically connected with the first grid, edges of the second grid is overlapped with part of that of the source and drain and the non-crystalline channel is in the first grid.

Owner:AU OPTRONICS CORP

High-performance and high-integration-level L-shaped gate-control schottky barrier tunneling transistor

InactiveCN104282754AImprove current conduction abilityIncrease chance of tunnelingSemiconductor devicesSchottky barrierField effect

The invention relates to a high-performance and high-integration-level L-shaped gate-control schottky barrier tunneling transistor. A schottky barrier formed between a source electrode and an intrinsic silicon source section is used as a tunneling barrier of a device, the characteristic that the barrier height of the schottky barrier is smaller than the silicon band gap is adopted, on the premise that materials narrower than the silicon band gap do not need to be introduced, the tunneling probability higher than that of a common silicon-material-based PIN type tunneling field effect transistor is achieved, and therefore the subthreshold slope and the electric current conduction capacity of the device are accordingly improved. An L-shaped gate electrode is adopted for controlling an intrinsic silicon channel region with the groove structure characteristics; on one hand, the good control effect on the width of the schottky barrier is achieved; on the other hand, the control effect of the gate electrode on a heavy doping drain electrode region is weakened, and the high-performance and high-integration-level L-shaped gate-control schottky barrier tunneling transistor which has the steep subthreshold slope, the good switching characteristic, the high conduction current, the reversed low leakage current and the quiescent dissipation and is suitable for serving as a deep nanoscale integrated circuit design basic unit is achieved.

Owner:SHENYANG POLYTECHNIC UNIV

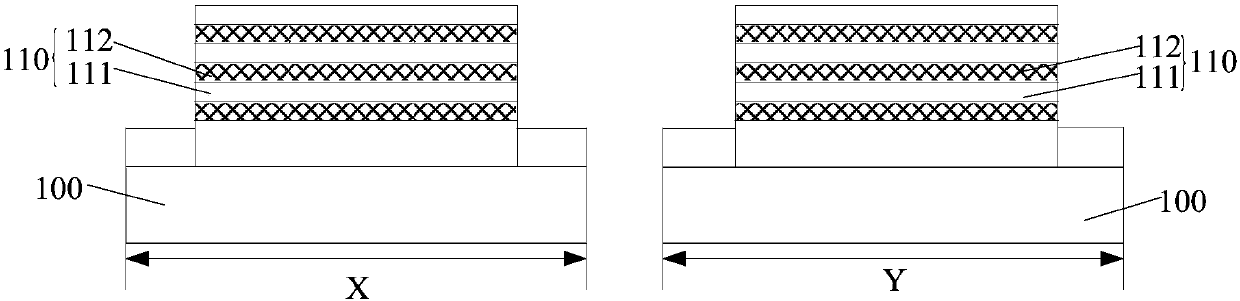

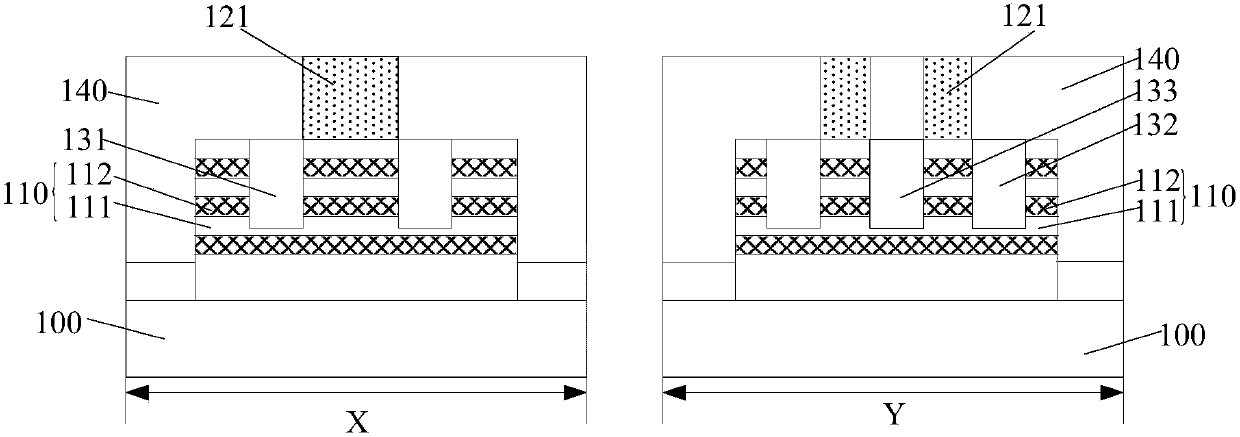

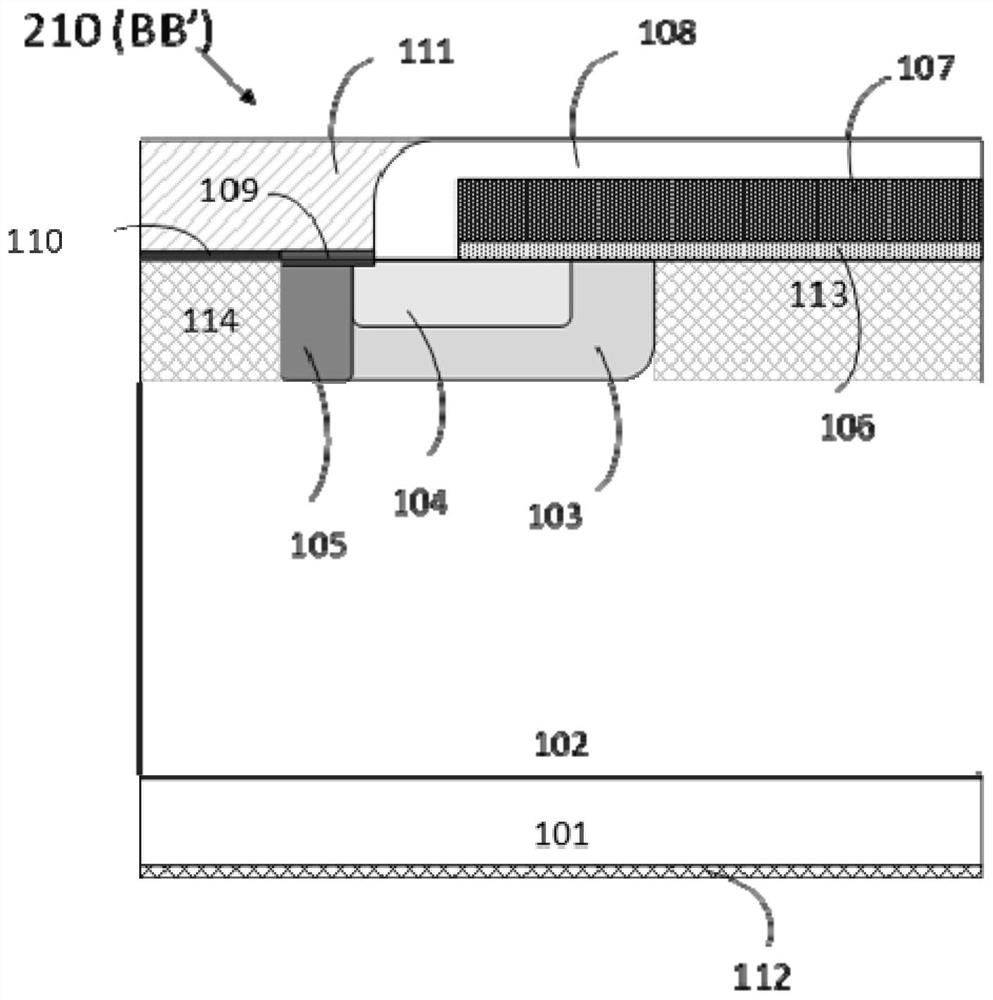

Semiconductor device and forming method thereof

InactiveCN109585379AImprove performanceAvoid problemsTransistorSolid-state devicesEngineeringDielectric layer

The invention provides a semiconductor device and a forming method thereof. The method comprises the following steps that a semiconductor substrate is provided, wherein the semiconductor substrate comprises a first region and a second region; fin parts are arranged on the first region and the second region of the semiconductor substrate respectively; the fin parts comprise a plurality of first finpart layers and second fin part layers which are stacked in a staggered mode in the normal direction of the surface of the semiconductor substrate, and the second fin part layers are located betweenthe adjacent first fin part layers; a pseudo gate structure which only spans the fin parts of the first region is formed; a dielectric layer is formed on the first region and the second region of thesemiconductor substrate, and the fin parts in the first region and the fin parts in the second region, wherein the dielectric layer covers the side wall of the pseudo gate structure and exposes the top surface of the pseudo gate structure; then the pseudo gate structure and the second fin part layers covered by the pseudo gate structure are removed; then a first through hole and a second through hole which penetrate through the dielectric layer are formed in the dielectric layer in the second region; a first doping layer is formed in the fin parts at the bottom of the first through hole; and asecond doping layer is formed in the fin parts at the bottom of the second through hole. According to the method, the performance of the semiconductor device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

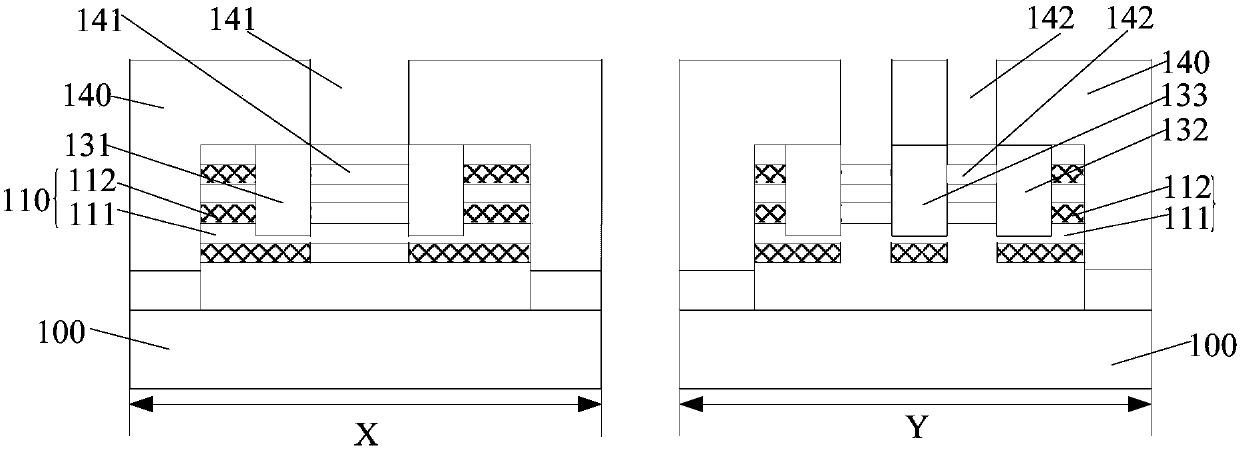

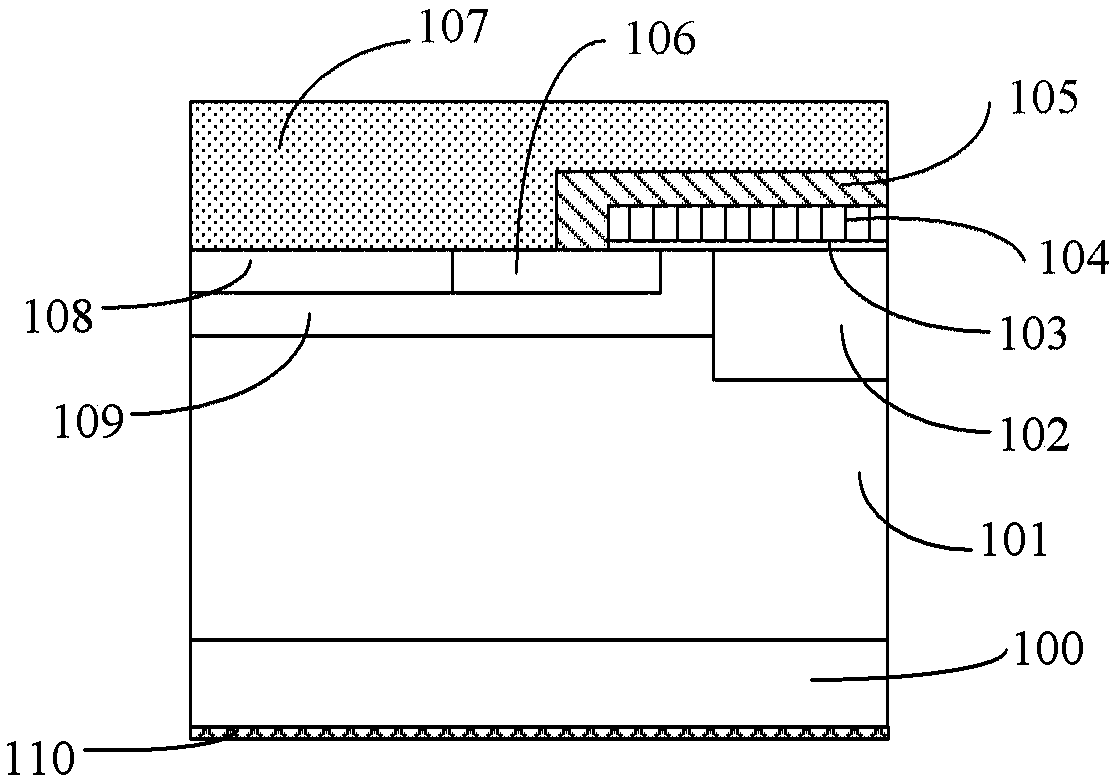

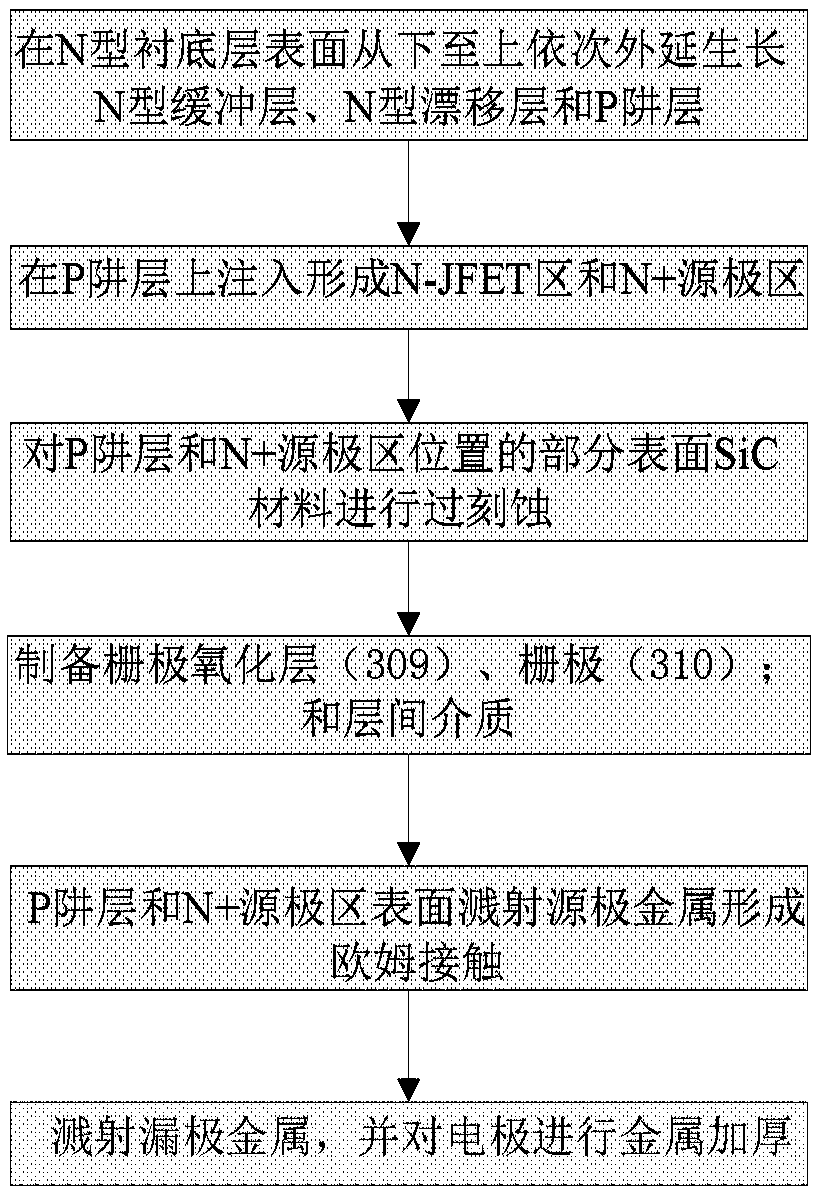

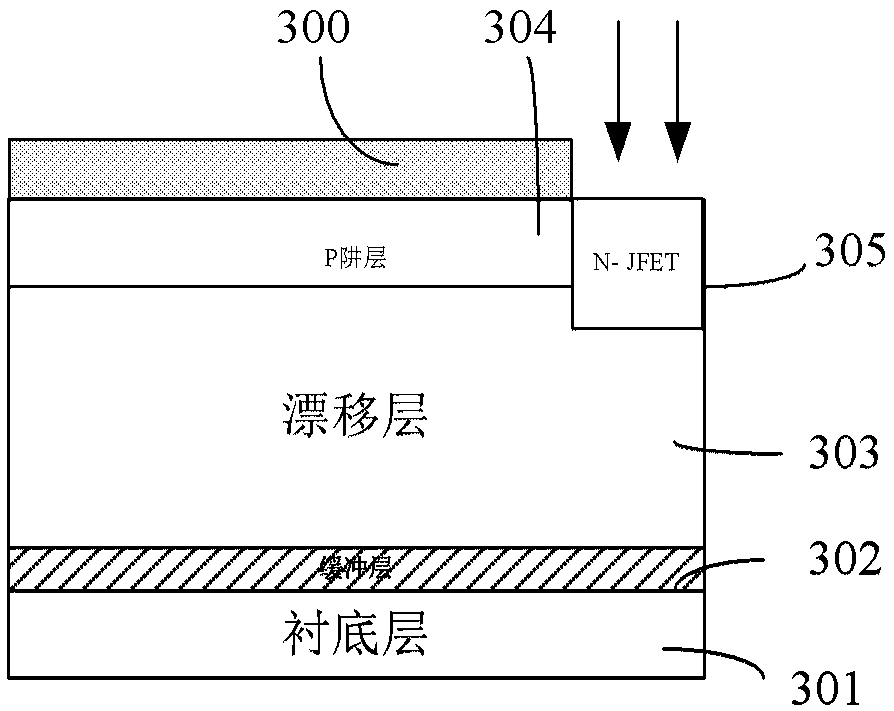

Silicon carbide MOSFET device and preparation method thereof

InactiveCN109461659AOptimize the transmission pathReduced injection damageSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationMOSFET

The invention provides a silicon carbide MOSFET device and a preparation method thereof, and relates to the field of semiconductor manufacturing. The preparation method comprises: over-etching SiC material on a partial surface at a P-well layer and an N+ source region; and etching a source contact window, and sputtering the source metal on the surface of the P-well layer and the N+ source region to form an ohmic contact. In the invention, by etching the surface of the P-well layer, the high-concentration P-well region can be directly in ohmic contact with the source metal, which optimizes thecurrent transmission path, and does not require high-dose P+ injection, reduces injection damage, and reduces preparation cost.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

Static discharge ESD protective circuit

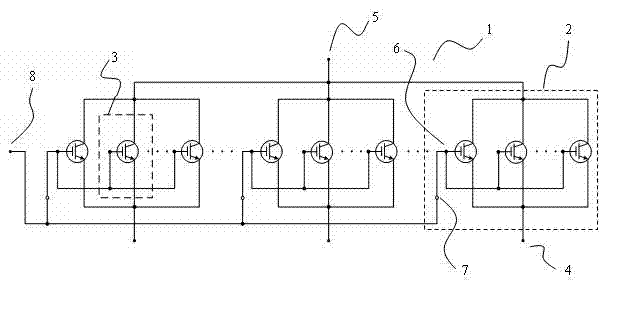

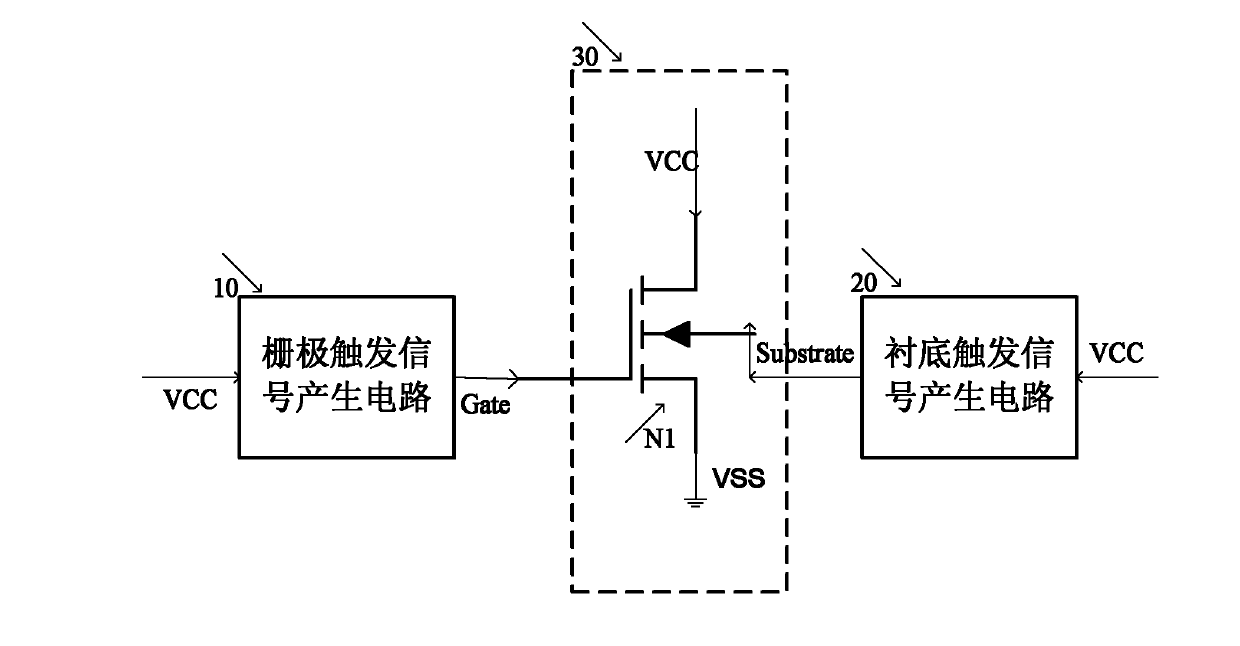

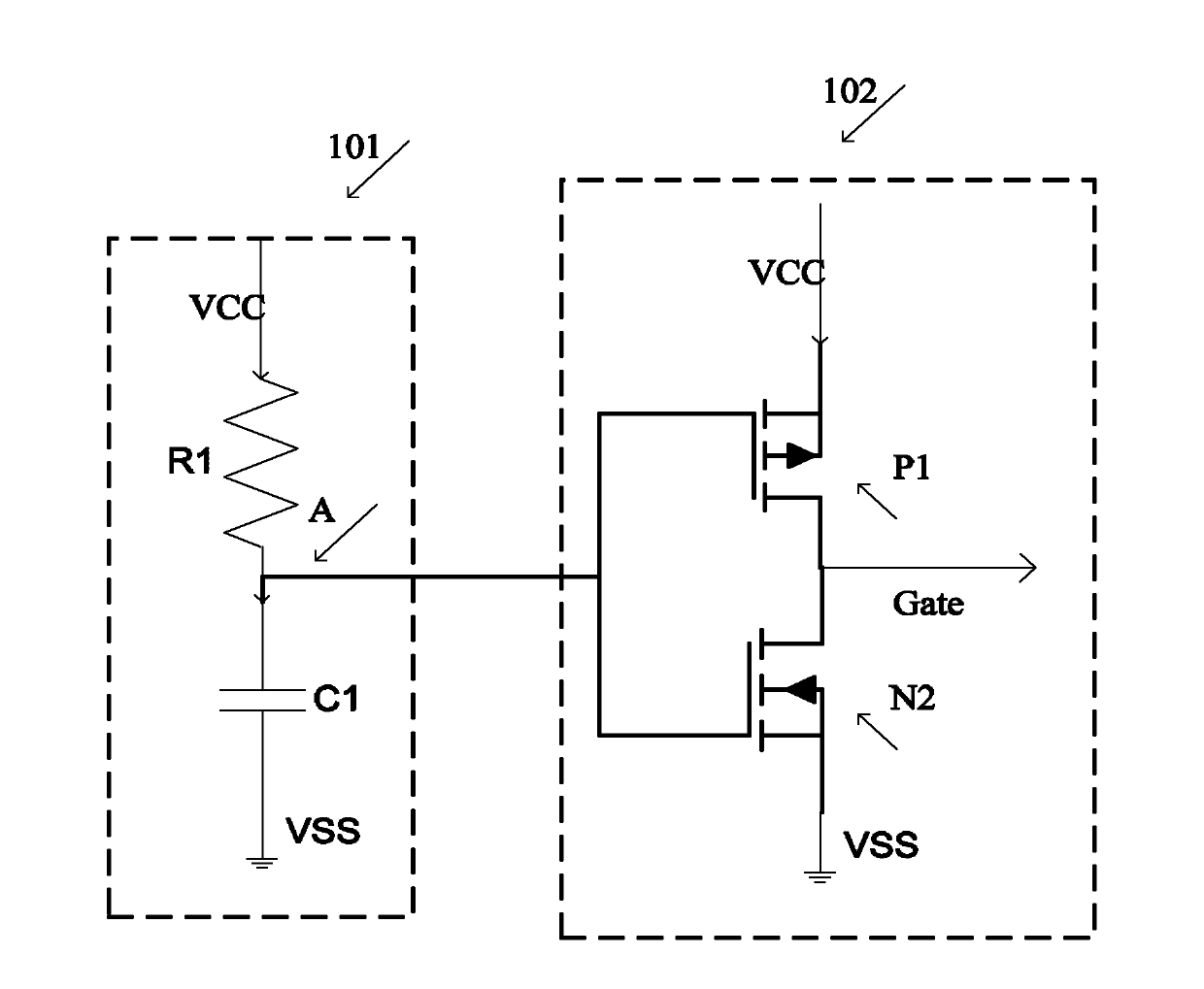

ActiveCN102185301AImprove discharge performanceIn line with design thinkingEmergency protective arrangements for limiting excess voltage/currentEngineeringDrain current

The invention discloses a static discharge ESD protective circuit comprising a static discharge branch with one or more MOS tubes, a grid trigger signal generating circuit and an underlay trigger signal generating circuit, wherein the grid trigger signal generating circuit is used for generating a grid trigger signal; the grid trigger signal is connected to a grid of at least one MOS tube; the underlay trigger signal generating circuit is used for generating underlay trigger signals that are connected to an underlay of at least one MOS tube; and the reaction time of the underlay trigger signal is not less than the rising time of the static discharge voltage or 20ns. The static discharge ESD protective circuit has the advantages of improving the protective capability of the static discharge protective circuit and reducing the possibility of current leakage caused by error trigger.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

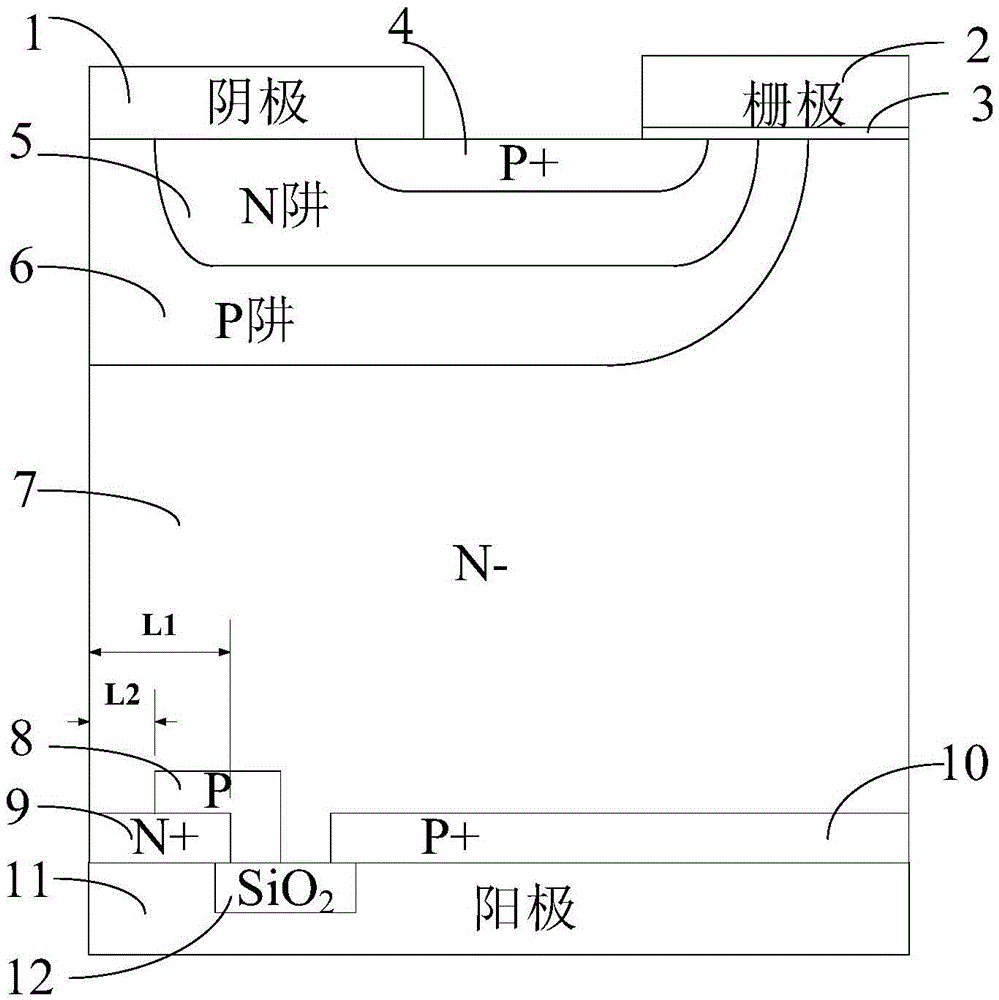

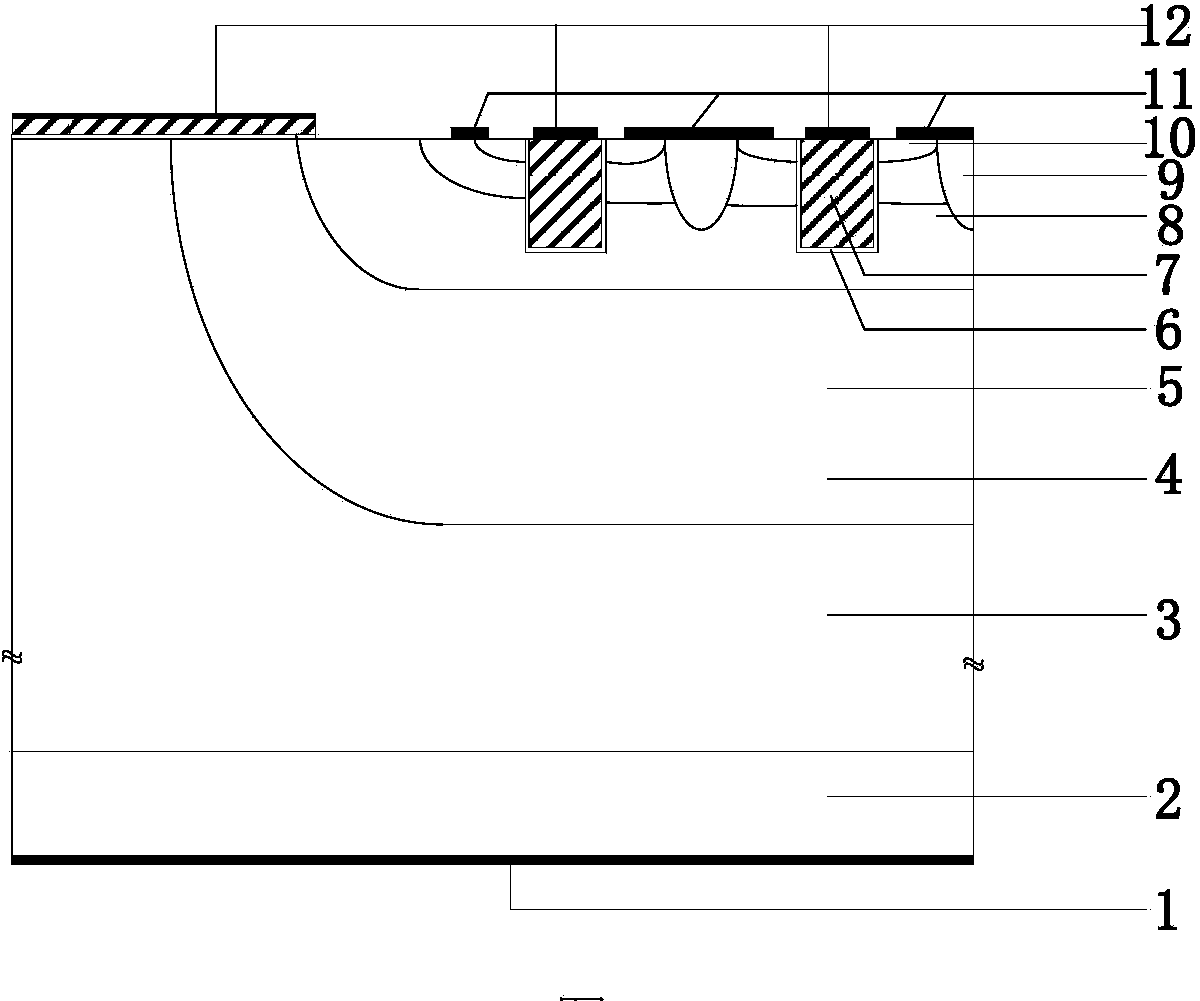

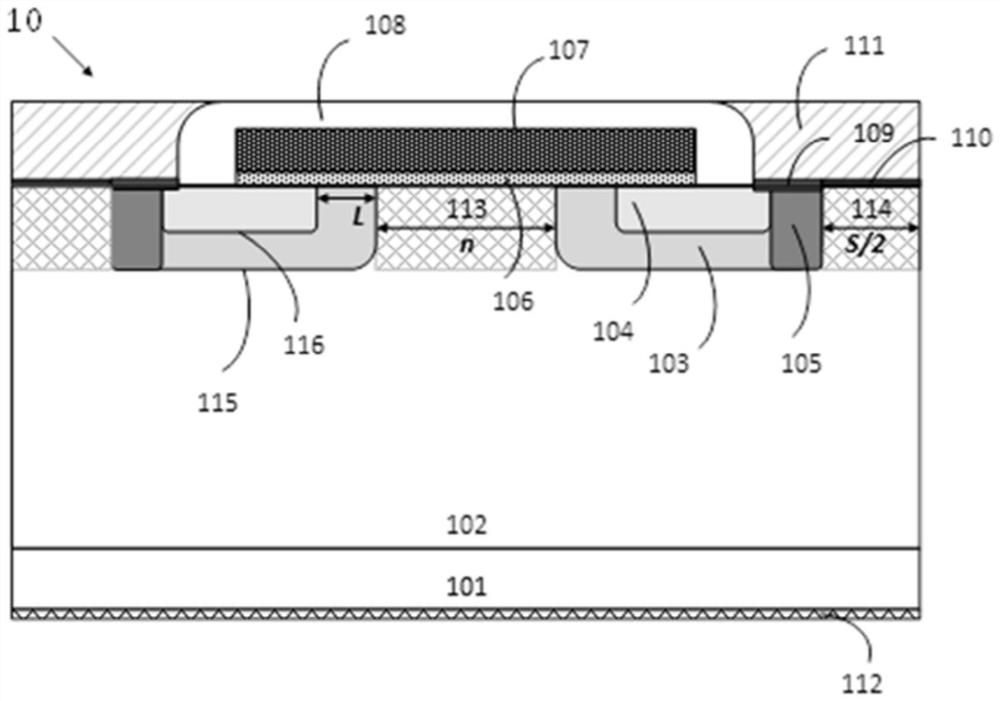

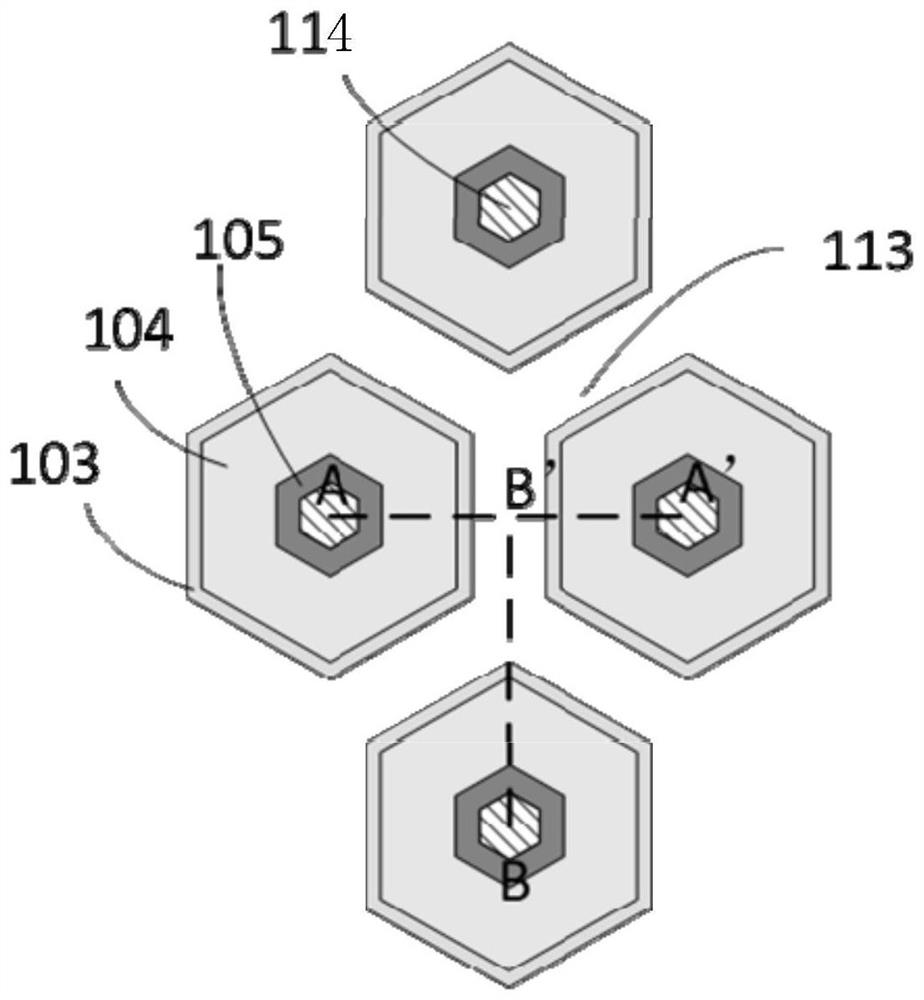

Planar power MOSFET device integrated with junction barrier Schottky diode

PendingCN114400255AResolving Conflicting Technical IssuesImprove current conduction abilityDiodePower MOSFETJFET

The invention discloses a planar power MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) device integrated with a junction barrier Schottky diode, which is used for solving the technical problem that conflicts exist when existing junction barrier Schottky cells and MOSFET cells jointly occupy an active region part of the device. The device comprises an epitaxial layer; a plurality of cells with the same shape and structure are distributed on the first side surface of the epitaxial layer; each cell at least comprises a well region, a source region, a highly doped P-type region and a Schottky region; the well region is in contact with the highly-doped P-type region, and the highly-doped P-type region surrounds the Schottky region; junction field effect transistor (JFET) regions are formed between adjacent well regions. A first PN junction is formed between the well region and the epitaxial layer; a second PN junction is formed between the well region and the source region; the value range of the width of the JFET region and the value range of the spacing of the highly doped P-type region are in the same preset interval. Through the device, the problem that conflicts exist when junction barrier Schottky cells and MOSFET cells jointly occupy the active region part of the device is solved.

Owner:海科(嘉兴)电力科技有限公司

Flexible connecting device for generator rotor conducting rod

ActiveCN102611253AReduce assembly position accuracy requirementsReduce the difficulty of operationStructural associationCooling/ventillation arrangementElectricityForeign matter

The invention discloses a flexible connecting device for generator rotor conducting rods. The flexible connecting device comprises connecting copper bars. The connecting copper bars are V-shaped flexible connecting copper bars. The number of the V-shaped flexible connecting copper bars is two. The two V-shaped flexible connecting copper bars are symmetrically arranged in an exciter shaft or a collector ring shaft. One ends of the connecting copper bars are fit with the conducting rods in the exciter shaft or the collector ring shaft, and the other ends of the connecting copper bars are fit with the conducting rods in a generator shaft. Operating holes and ventilating holes at different radial positions are arranged on the exciter shaft or the collector ring shaft. The flexible connecting device for generator rotor conducting rods has the advantages that the assembling process is simple and the assembling accuracy and the operating difficulty are reduced; the flexible structures of the connecting copper bars can absorb deformation caused by the heating of the conducting rods at the two ends and harmful thermal stress is eliminated; the air friction loss and the noise are reduced, the device is not apt to be polluted by foreign matters and the operation reliability is improved; and the ventilating holes and the operating holes can jointly form a cooling air duct to ventilate and cool the V-shaped connecting copper bars and the conducting rods and take the effects of reducing temperature and improving current conducting performance.

Owner:DONGFANG ELECTRIC MACHINERY

Manufacturing method of semiconductor device and semiconductor device manufactured by method

InactiveCN105529272ALower forward conduction resistanceLow Epitaxial ResistivitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

The invention provides a manufacturing method of a semiconductor device and the semiconductor device manufactured by the method. The method comprises the following steps: (1) growing an N-type epitaxial layer on an N-type substrate; (2) growing an intrinsic epitaxial layer on the N-type epitaxial layer; (3) injecting N-type impurities into the intrinsic epitaxial layer; (4) injecting P-type impurities into the preset position of the intrinsic epitaxial layer; (5) repeating the steps (2) to (4); (6) carrying out thermal annealing; and (7) injecting a P-type well into the preset position. According to the manufacturing method, the process difficulty and the cost are reduced; meanwhile, the performance is not obviously weakened; and the cost performance is relatively high.

Owner:FUJIAN FUXIN ELECTRONICS TECH CO LTD

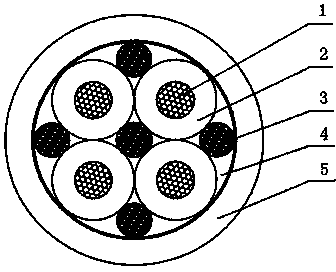

Deicing cable

InactiveCN103426540AReduce weightHigh power transmission efficiencyClimate change adaptationFlexible cablesWeather resistanceFrost

The invention belongs to the technical field of cable manufacturing, and provides a deicing cable. The deicing cable is composed of inner cable cores, an insulation protective layer, outer cable cores, fillers and a frost-proof layer. The peripheries of the inner cable cores are covered with the insulation protective layer, the outer cable cores are distributed in gaps among the inner cable cores, heat generated after the outer cable cores are charged with electricity can deice effectively, and the frost-proof layer can effectively prevent the outer portion of the cables from being frozen. The deicing cable is reasonable in structural design, weight of the cable is reduced, and the deicing cable can deice and keep warm in normal electricity transmission, is good in frost-proof effect, can fast and effectively remove ice layers on the outer portion of the cable, is good in electric current transmission effect, good in weather ability and high in electric energy transmission efficiency, has certain rigidity, is good in torsional property, improves flexibility, can meet various requirements for electrical property and mechanical property, is simple in structure and good in practicability, and has good popularization and application value.

Owner:HENAN KOSEN CABLE

Schottky barrier high current density igbt device

ActiveCN104966730BIncrease working voltageIncrease current densityTransistorSemiconductor/solid-state device manufacturingHigh current densitySchottky barrier

Owner:HUNAN UNIV

Schottky diode manufacturing method

InactiveCN105590850AReduce forward voltage dropIncrease the areaSemiconductor/solid-state device manufacturingConvex structureVoltage drop

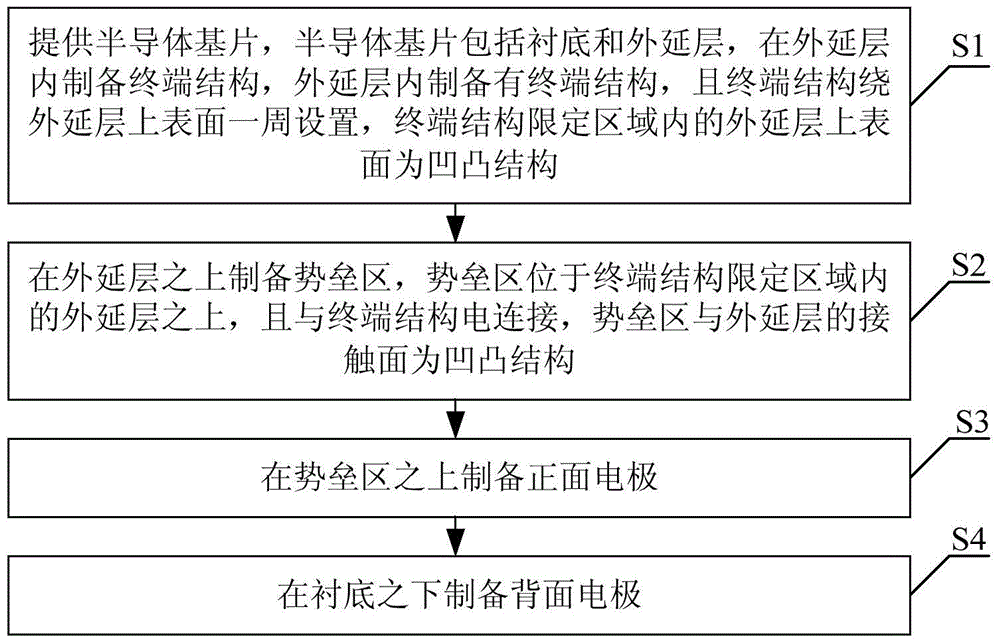

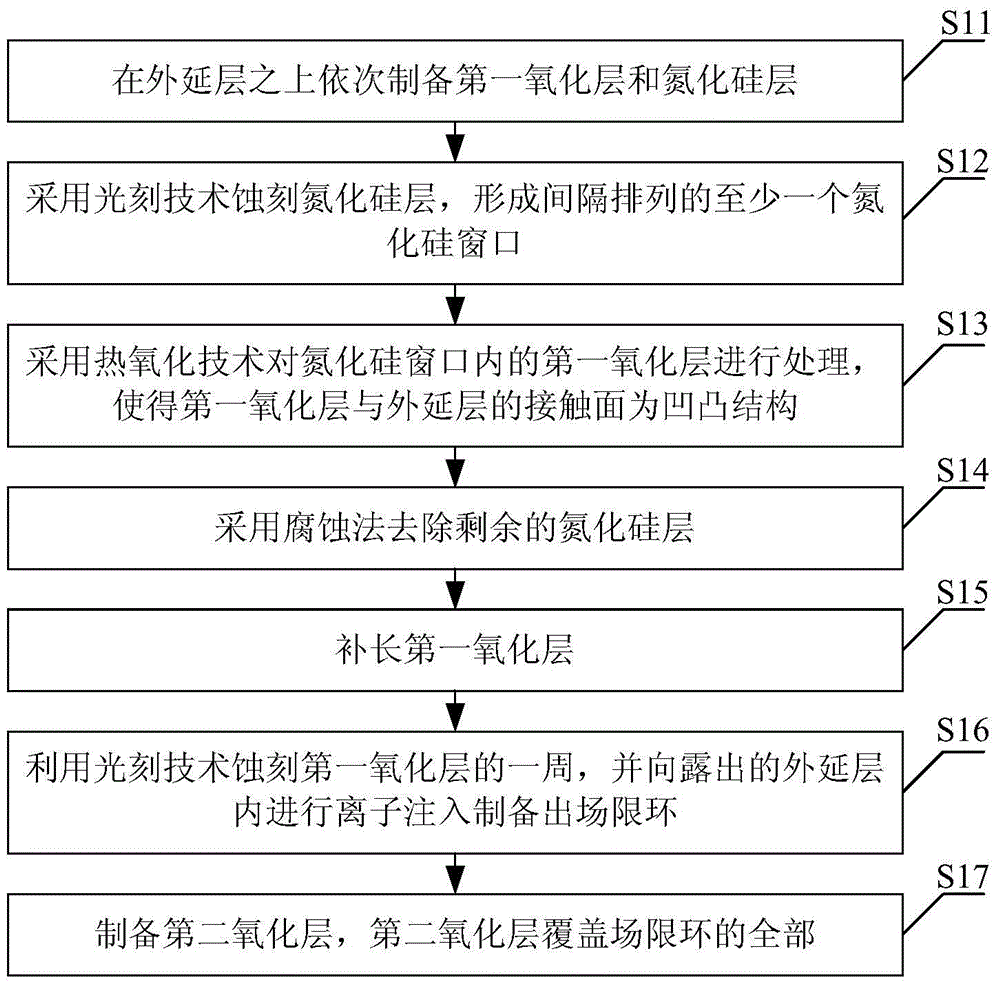

The invention discloses a Schottky diode manufacturing method, which belongs to the technical field of semiconductors. The method comprises the following steps: a semiconductor substrate is provided, wherein the semiconductor substrate comprises a substrate and an epitaxial layer, a terminal structure is manufactured in the epitaxial layer, the terminal structure surrounds the upper surface of the epitaxial layer, and the upper surface of the epitaxial layer in a region limited by the terminal structure has a concave-convex structure; a barrier region is manufactured on the epitaxial layer, wherein the barrier region is located on the epitaxial layer in the region limited by the terminal structure and is electrically connected with the terminal structure, and the contact surface between the barrier region and the epitaxial layer has a concave-convex structure; a positive electrode is manufactured above the barrier region; and a back electrode is manufactured below the substrate. According to the Schottky diode manufacturing method, the surface of the barrier region is manufactured to have a concave-convex structure, forward conduction voltage drop of the Schottky diode is reduced, the manufacturing process is simple, and the cost is low.

Owner:WUXI CHINA RESOURCES HUAJING MICROELECTRONICS

Device for detecting insulating property of vacuum coating nano-film layer of mobile phone rear cover

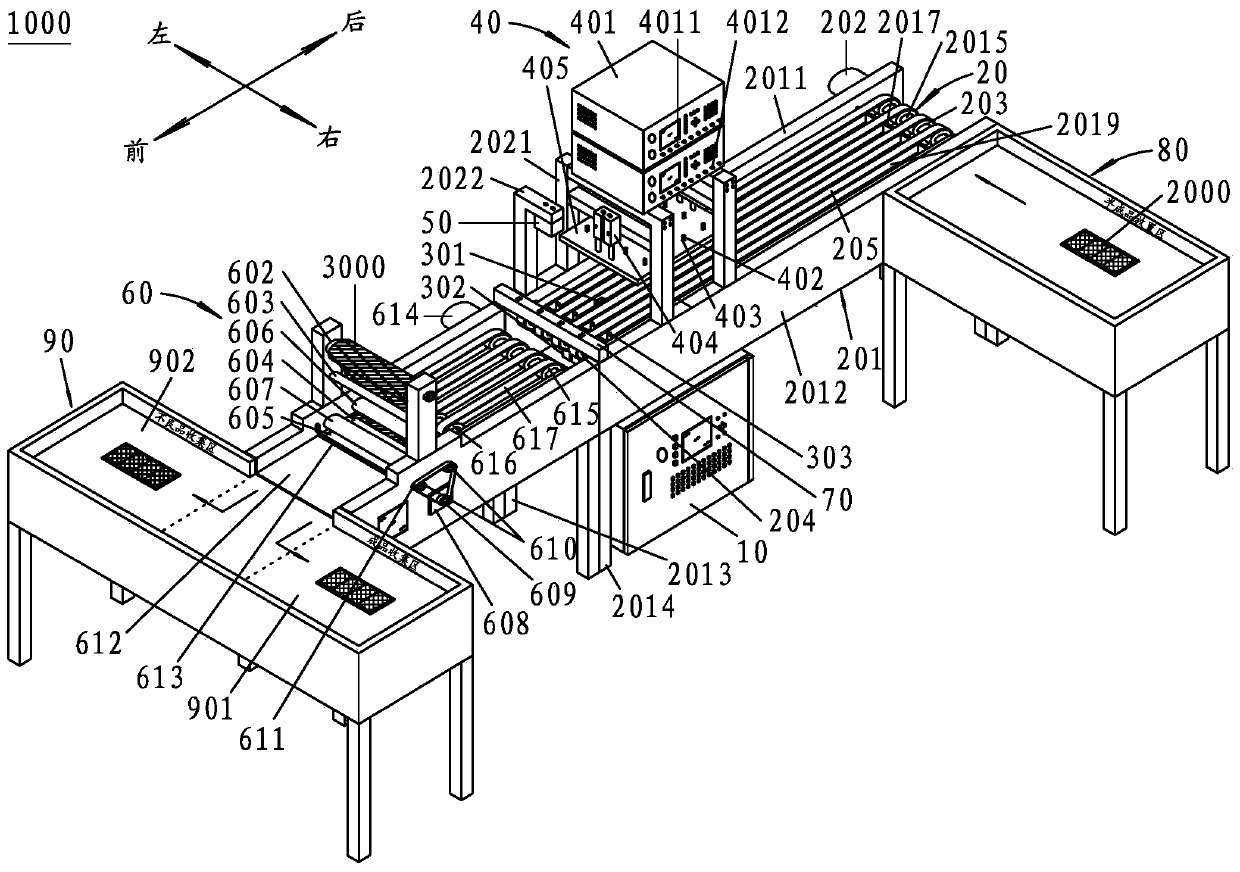

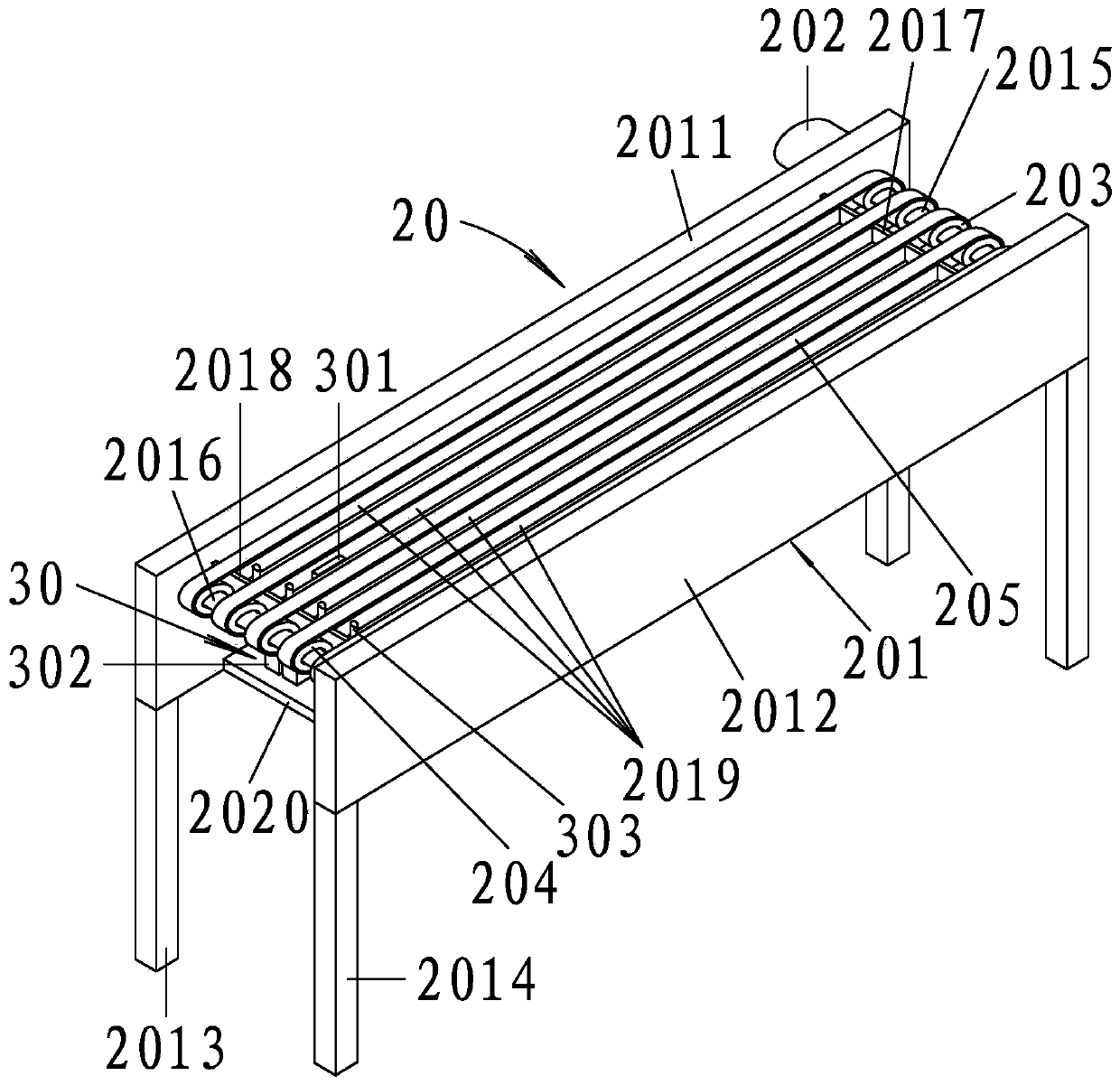

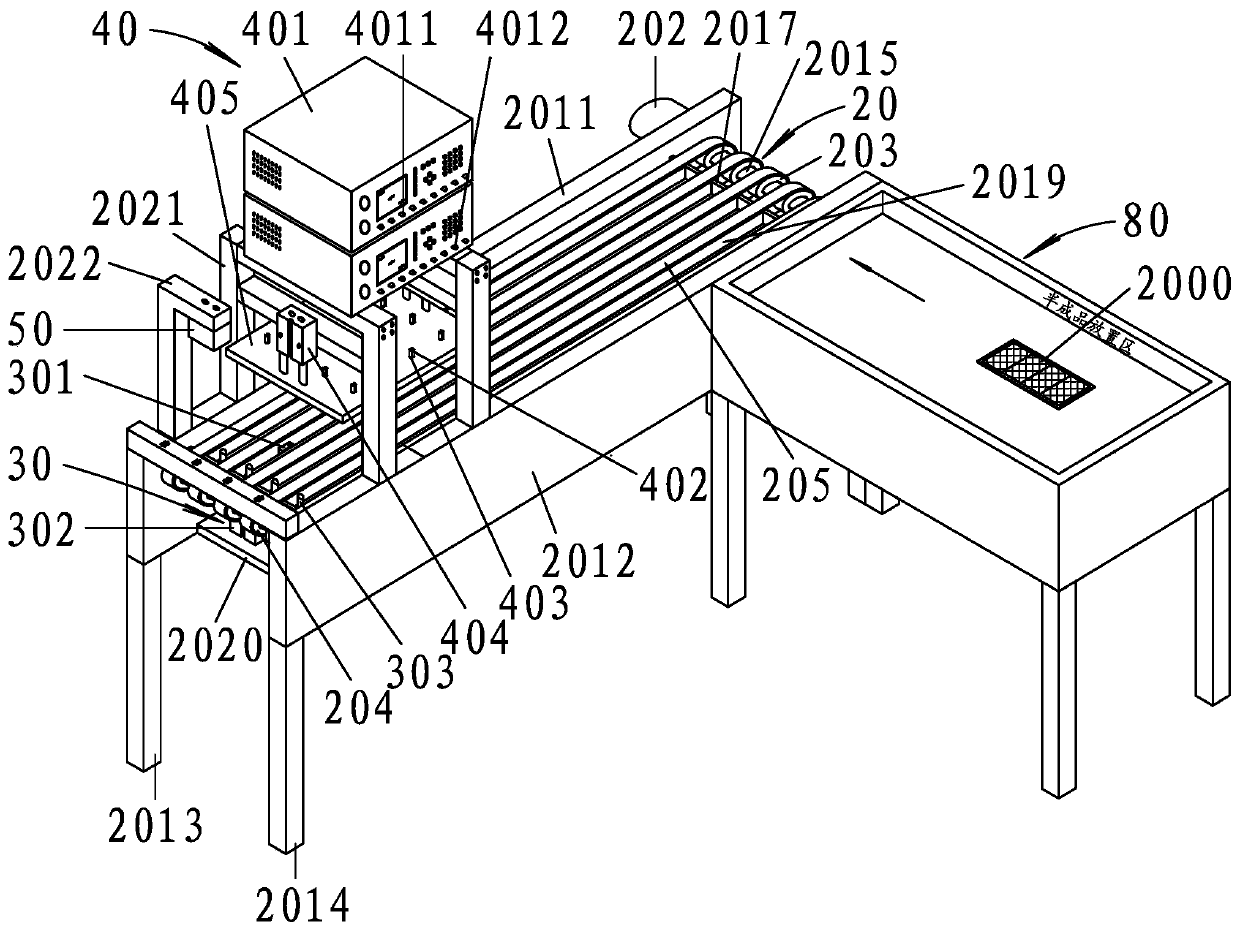

PendingCN111398754ASave human effortReduce labor costsTesting dielectric strengthConveyorsMechanical engineeringMobile phone

The invention discloses a device for detecting the insulating property of a vacuum coating nano film layer of a mobile phone rear cover. The device includes a main controller, a supplied material conveying device which is used for conveying supplied materials of the vacuum coating mobile phone rear cover, a supplied material sensing and positioning device is used for sensing supplied materials ofthe rear cover of the vacuum coating mobile phone and positioning the supplied materials of the rear cover of the vacuum coating mobile phone, an automatic resistance measuring device which is used for measuring the resistance value of the positioned supplied material nano-film layer of the rear cover of the vacuum coating mobile phone; a laser coding device which is used for coding product identification codes on the edge of the vacuum coating mobile phone rear cover incoming material with qualified insulation performance; and a supplied material rear surface film coating device which performs film coating on the back surface of the rear cover supplied material of the vacuum coating mobile phone of which the insulating property is detected as qualified and comprises a printed product identification code and the rear cover supplied material of the vacuum coating mobile phone of which the insulating performance is detected as qualified; the device has the advantages that the vacuum coating mobile phone rear cover incoming material resistance value can be automatically measured so as to evaluate the insulation performance, manpower is saved, and the labor cost is reduced.

Owner:深圳市嘉德真空光电有限公司

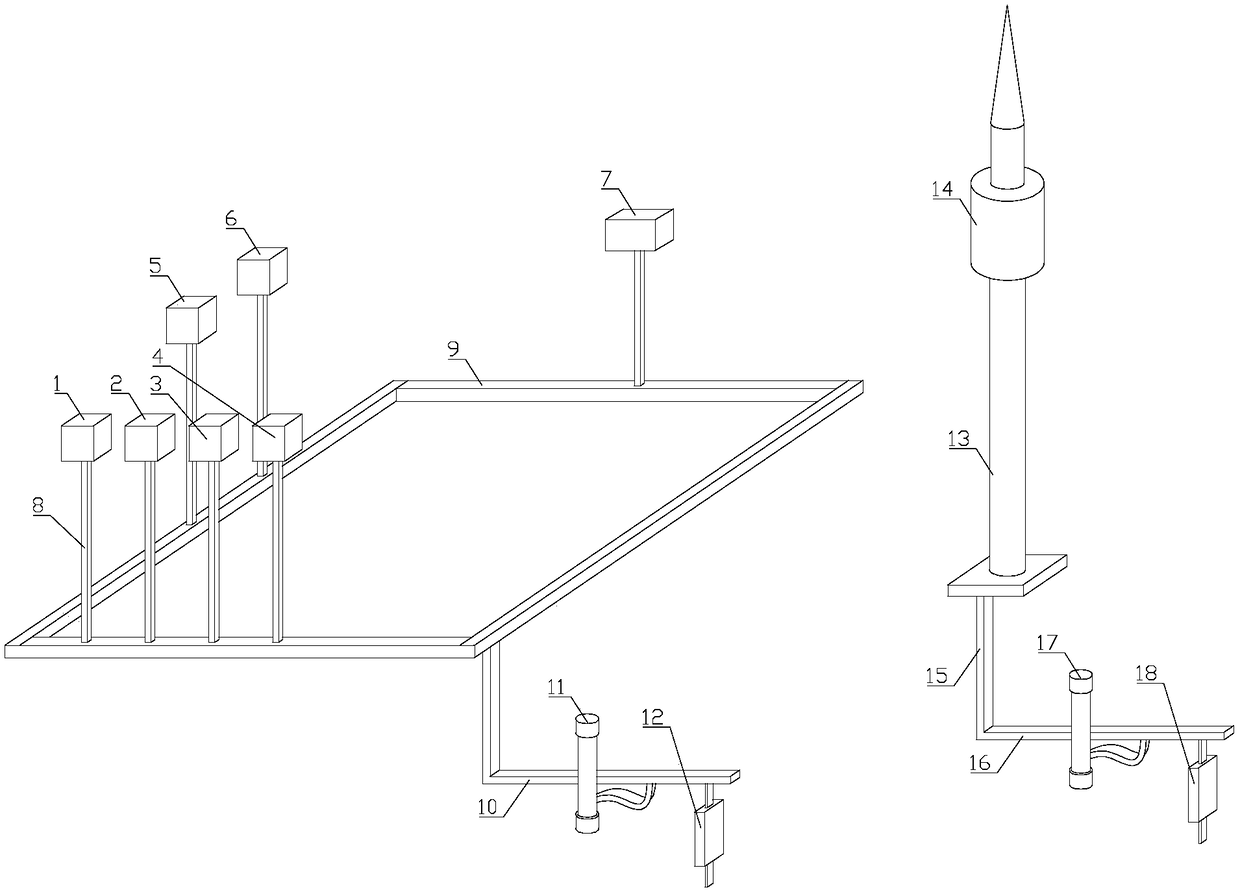

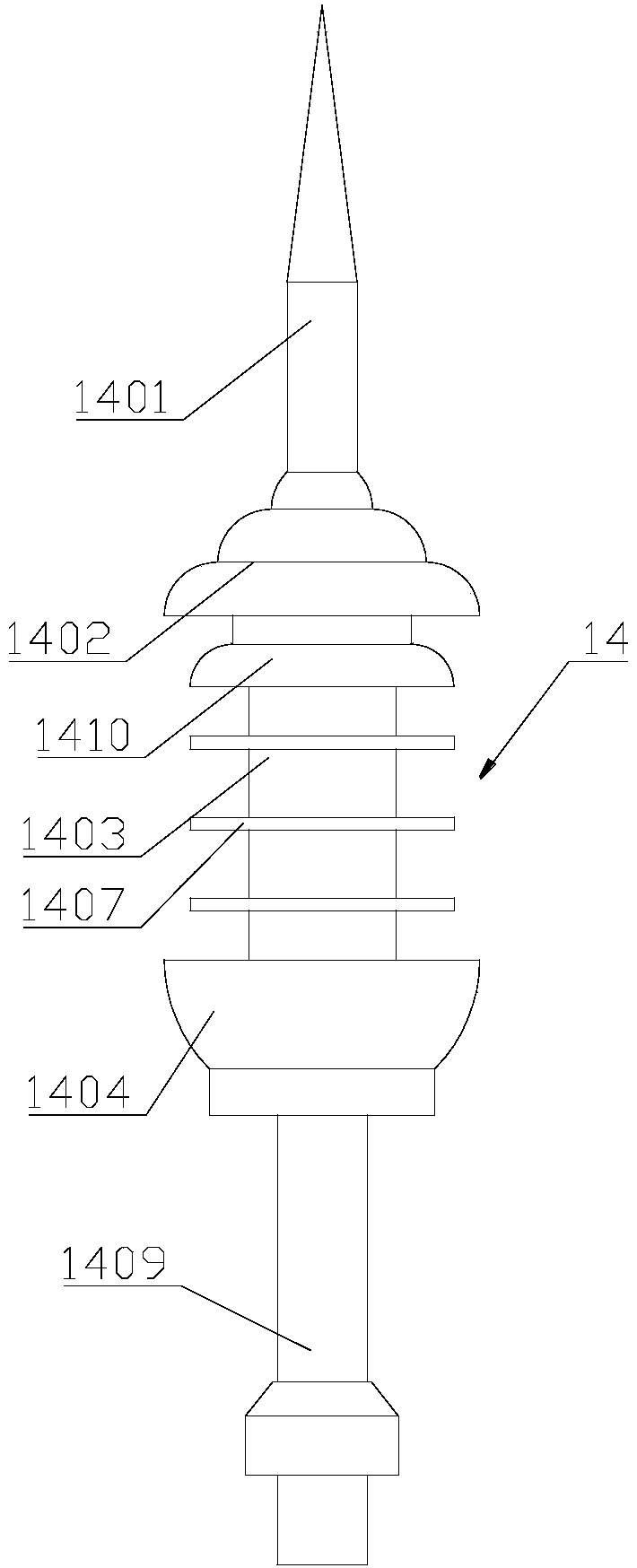

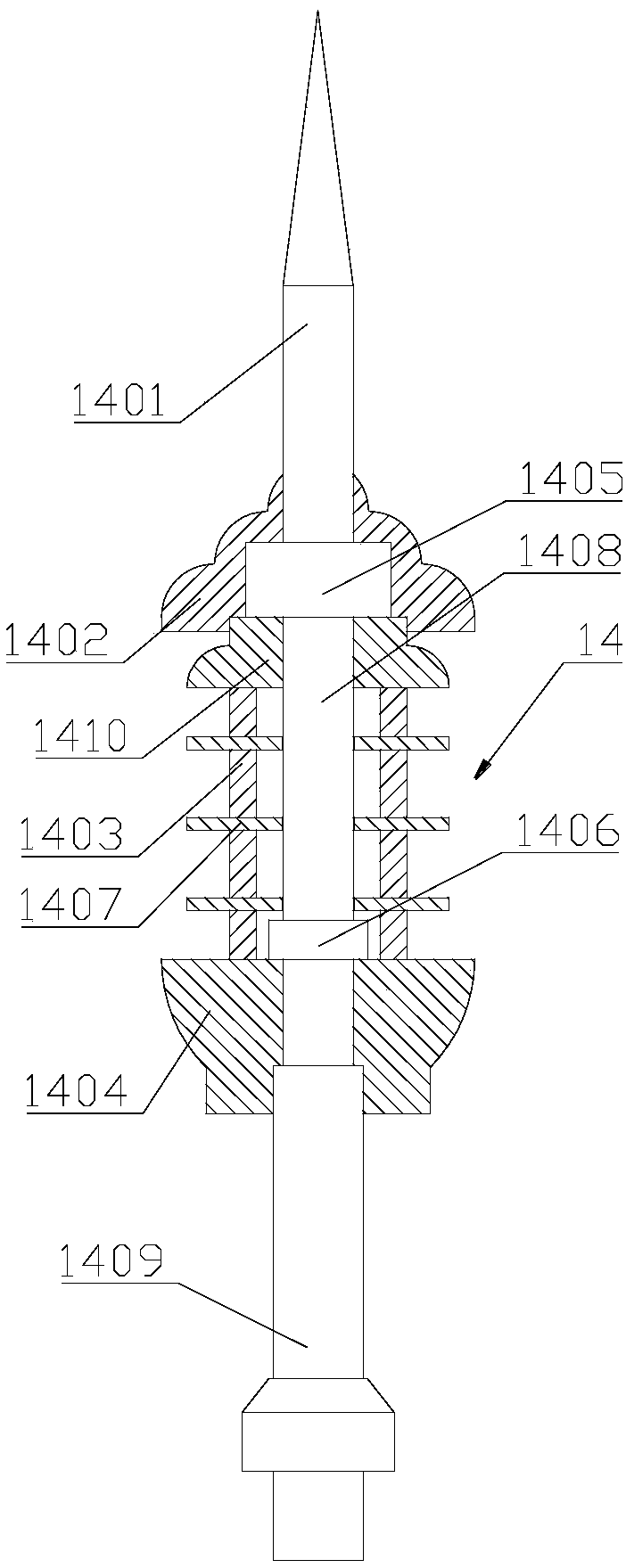

Lightning prevention system used for environment monitoring station and use method of lightening prevention system

ActiveCN108471048AGood protectionLow resistivitySpark gap detailsOvervoltage arrestors using spark gapsThree levelSurge protector

The invention relates to a lightening prevention system used for an environment monitoring station. The system comprises an indoor lightning prevention protection unit and an outdoor lightning protection unit. The indoor lightning protection unit comprises a power supply primary lightning preventer, a power supply secondary lightning preventer, a power supply three-level lightning preventer, a power supply four-level lightning preventer, a network signal lightning preventer, a signal surge protection device, a current collection box and a first grounding unit. The first grounding unit comprises a first copper bar connected to a secondary downlead, a first plasma grounding pole and a first non-metal grounding body. The outdoor lightning protection unit comprises a lightning avoiding device.The lightning avoiding device comprises a support rod. An attenuation lightning arrester is installed on the top of the support rod. A second grounding unit is connected to the bottom of the support.The contact parts between the plasma grounding pole and the non-metal grounding body and the soil are filled with resistance reducing agent. According to the invention, the system is advantaged by high lightning protection grade, good protection effects on devices and wires, reduction of guiding in of earth current and quick conduction speed.

Owner:HENAN YANGBO LIGHTNING PROTECTION TECH

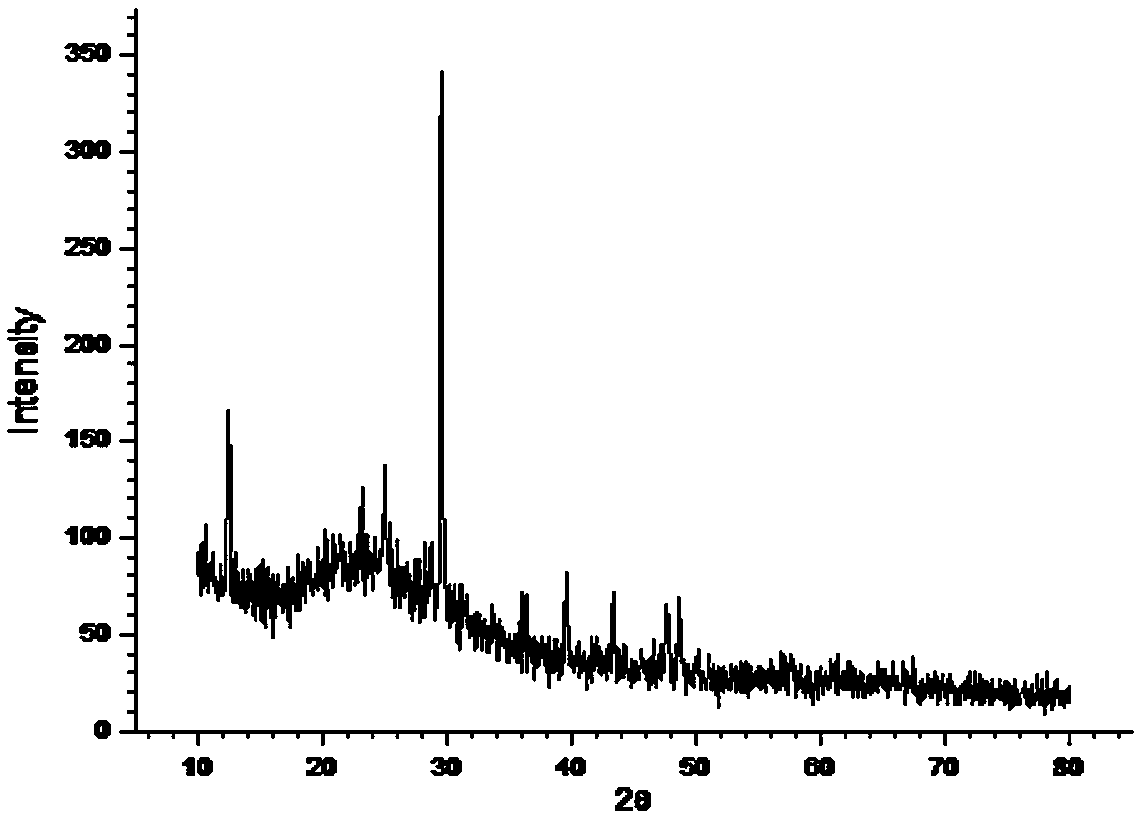

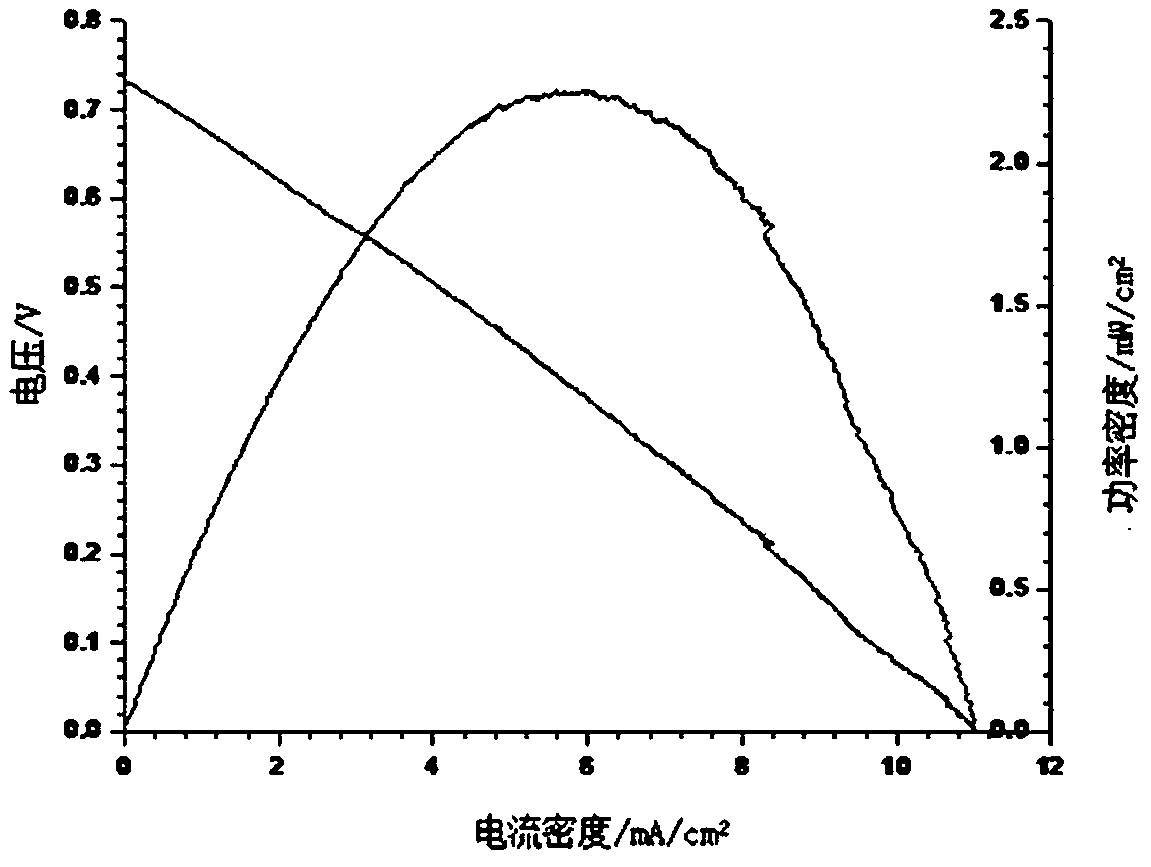

Preparation method for carbon fuel of high-activity direct carbon fuel cell

InactiveCN108736050ALarge specific surface areaAvoid damageCarbon preparation/purificationFuel cellsOxygenHigh activity

The invention relates to a preparation method for a carbon fuel of a high-activity direct carbon fuel cell. The preparation method comprises the following steps of smashing and mixing carbon-rich regenerative biomass or / and solid waste, and throwing the mixture into a high-temperature coking device to obtain the carbon fuel under a condition of no oxygen or oxygen insufficiency after drying. The preparation method for the carbon fuel of the high-activity direct carbon fuel cell is simple in step, and the fuel cell belongs to an amorphous structure, has relatively large specific surface area and is more easily immersed in molten carbonate bath under a working condition of the direct carbon fuel cell; meanwhile, the carbon fuel particle contains many active constituents, an effect of activating and catalyzing carbon oxidization reaction is achieved, and an effect of improving current conduction is also achieved; the preparation method is easy to operate, and amplification engineering iseasy to implement; and more importantly, the utilized carbon source comes from the solid waste and the regenerative biomass, which is very beneficial for reducing environmental damage and reducing consumption of non-renewable resources.

Owner:惠州大亚湾艾利荣化工科技有限公司

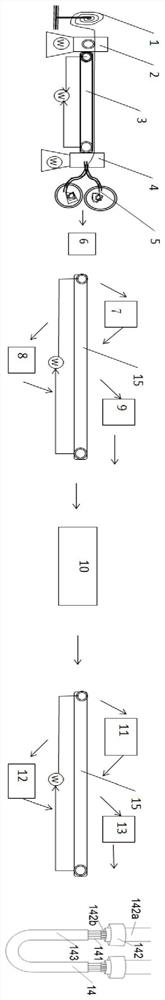

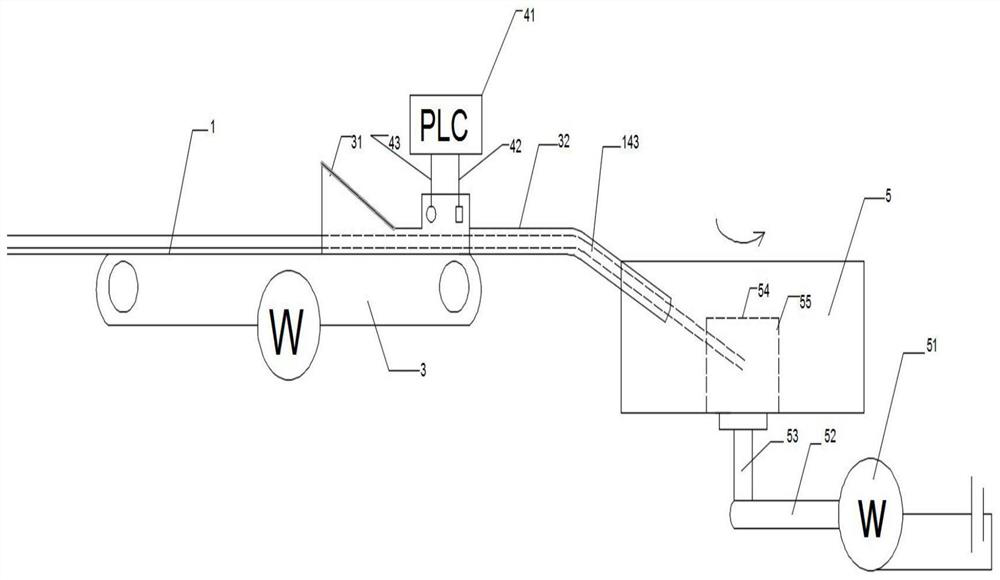

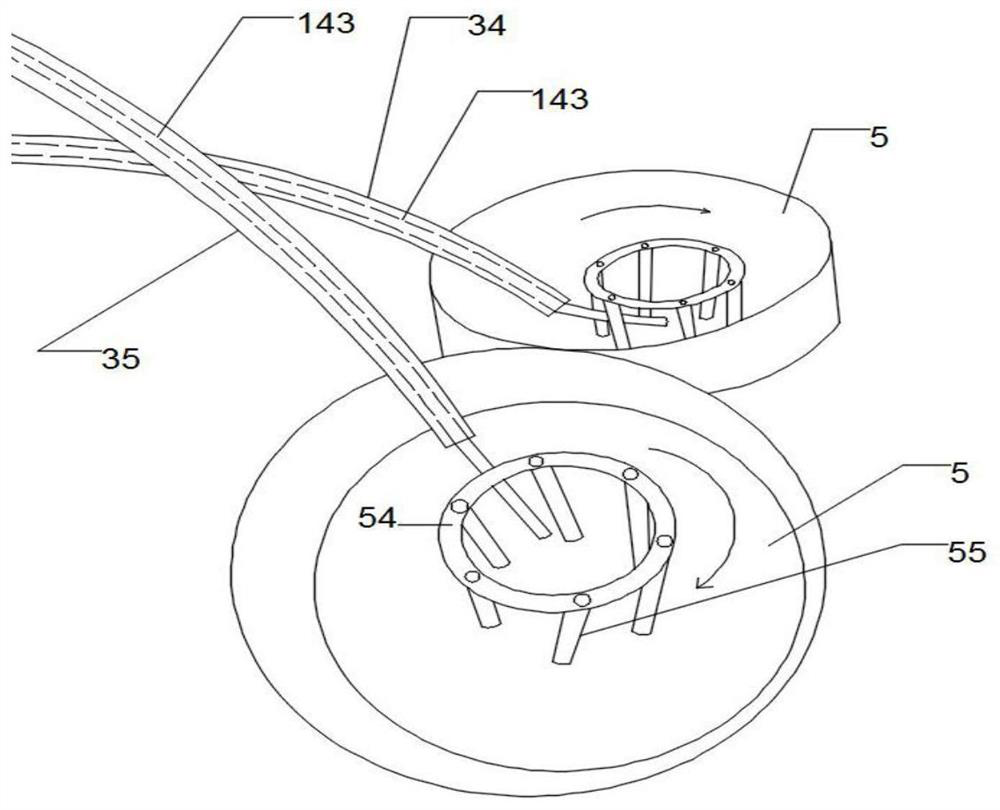

Connector process assembly line and production method thereof

PendingCN112909682AIncrease productivityImprove current conduction performanceContact member assembly/disassemblyDustproof/splashproof/drip-proof/waterproof/flameproof connectionWire cuttingWinding function

The invention discloses a connector assembly process assembly line and a production method thereof. The assembly line comprises a double-line cutting and winding system, a rotary double-face tin soldering system, a double-line protection type injection molding system, an on-off high-voltage testing device, a labeling device and a packaging device. After a cable passes through the double-wire cutting winding system, the cable is conveyed to the rotary double-face tin soldering system through a conveying belt and conveyed to the double-wire protection type injection molding system through the conveying belt, injection molding is carried out on a cable section and a plug tin soldering part, a finished product obtained after injection molding is a connector, and the automatic winding function is completed through cooperation of a channel and a cylinder in an inclined column disc. Tin at the tin dipping part of a wire head inserted into a plug is simultaneously melted by utilizing heat of a welding gun, double-sided tin soldering is realized, a preheating area and a high-temperature area are arranged in a double-wire protection type injection molding system, TPU (thermoplastic polyurethane) fluid is uniformly injected into a double-wire cooling protection mold, and meanwhile, a cooling loop is designed in the double-wire cooling protection mold, so the TPU raw material is quickly cured and formed in the mold cavity.

Owner:图尔克(天津)科技有限公司