Patents

Literature

112results about How to "Increase chance of tunneling" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

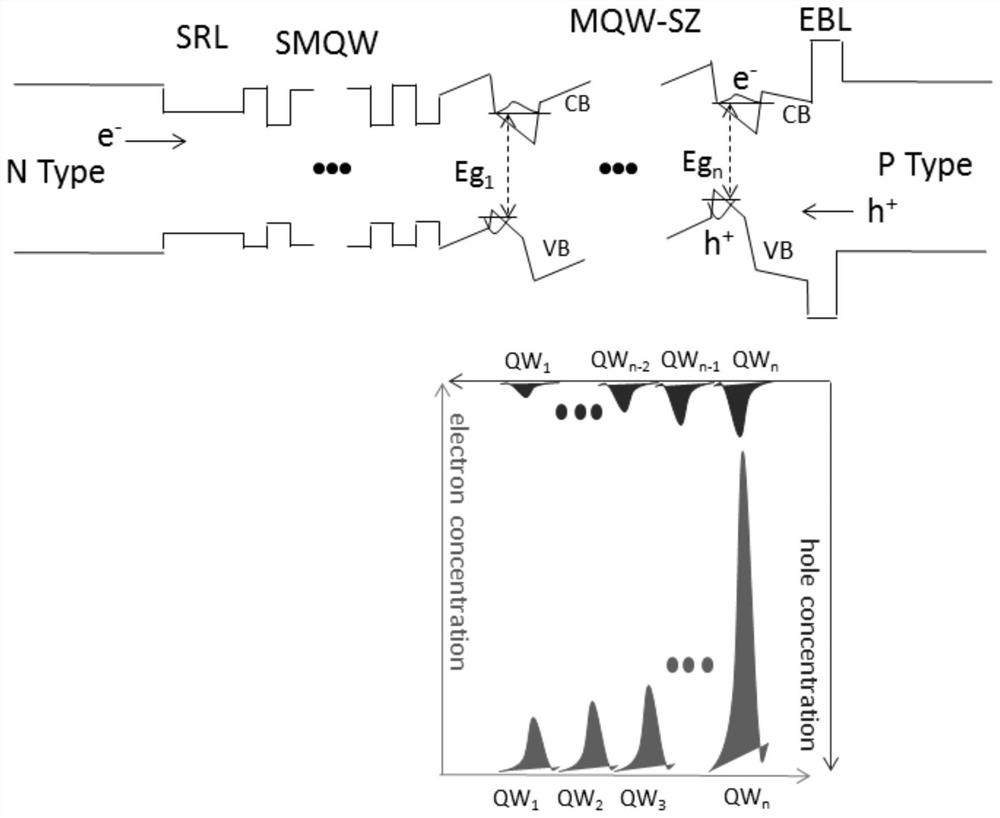

Nitride luminescent device and production method thereof

InactiveCN101540364AIncrease chance of tunnelingEasy to transportLaser active region structureSemiconductor devicesElectron holeHole injection layer

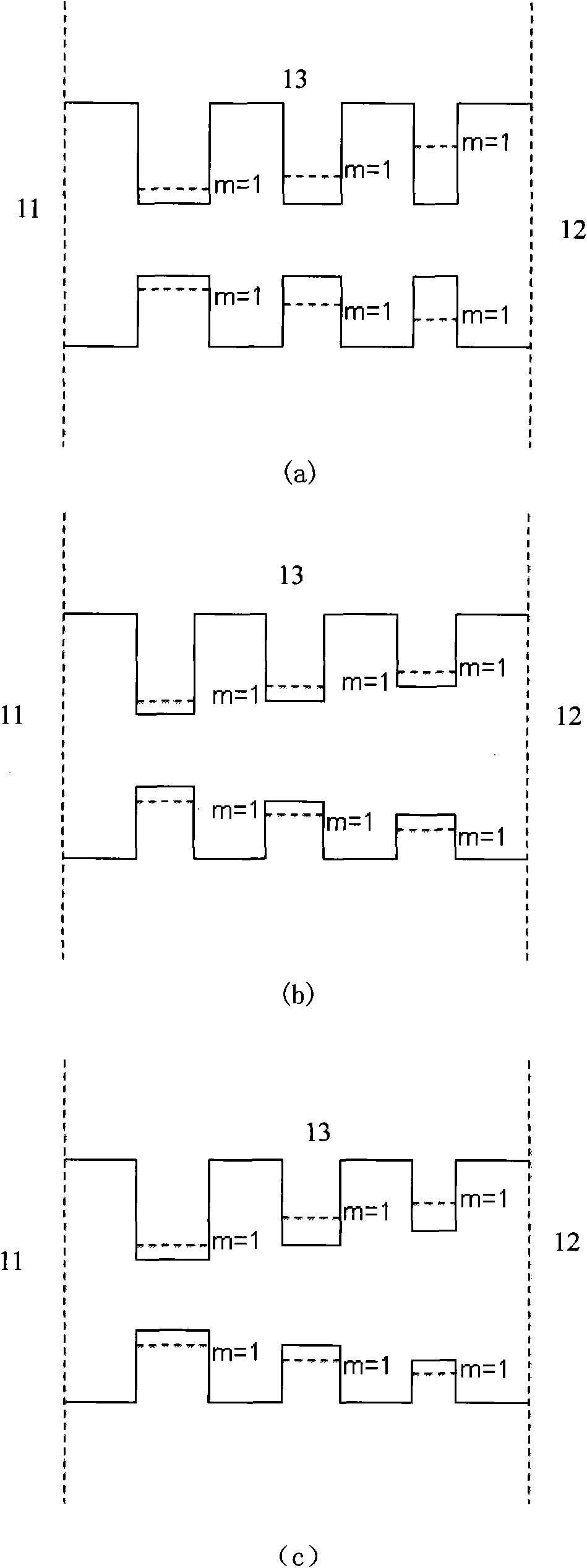

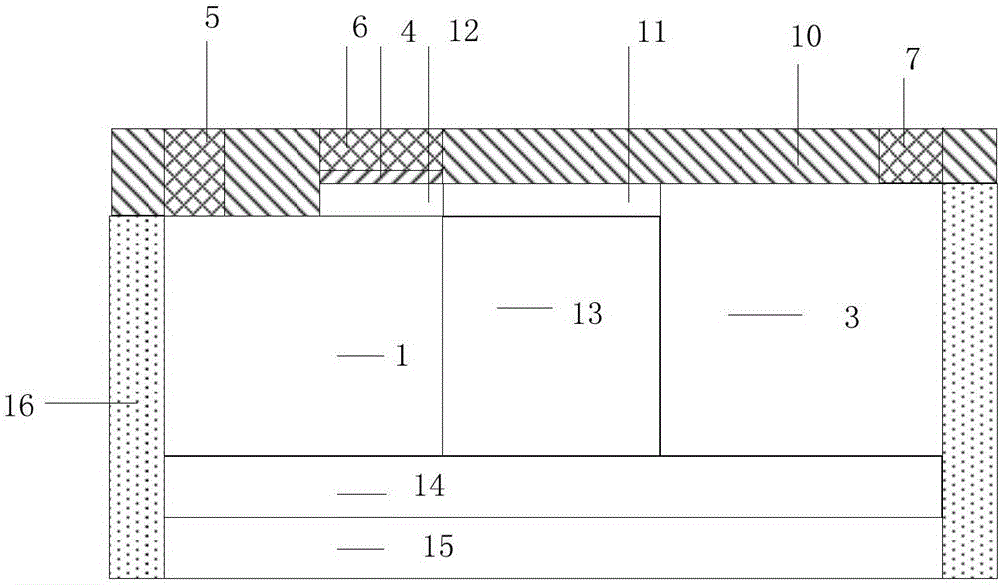

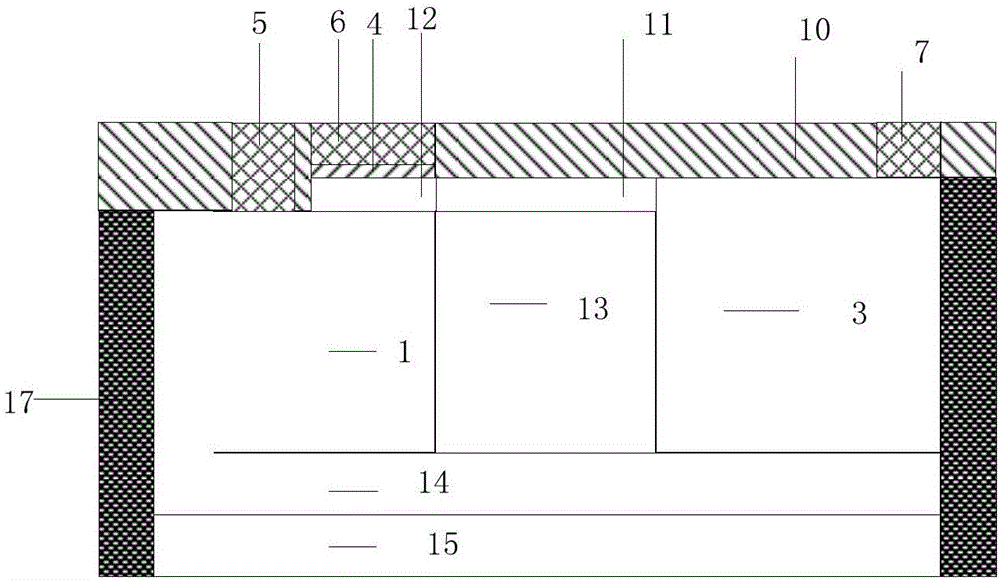

The invention discloses a nitride luminescent device and a production method thereof, which relate to a semiconductor luminescent device and provide a nitride luminescent device with an asymmetric coupled multi-quantum well structure being the active area. The device at least comprises an n-type electron injection layer, a p-type hole injection layer and a multi-quantum well active layer which is sandwiched between the n-type electron injection layer and the p-type hole injection layer, and the active layer is composed of asymmetric coupled quantum well structures. The barrier layer of the quantum well is thinner, thus being easy to realize the tunneling of current carriers; transition energy between ground-state energy level in the quantum wells is gradually changed; the quantum wells with high transition energy are close to the p-type hole injection layer; and the quantum wells with low transition energy are close to the n-type electron injection layer. The active area structure can enhance the tunneling transportation of the holes in the quantum well active area, simultaneously block the tunneling transportation of electrons in the quantum well active area, improve the uneven distribution of current carriers in the active area of the nitride luminescent device, reduce electron leakage and energy band filling effect, and realize high-efficiency luminescence.

Owner:XIAMEN UNIV

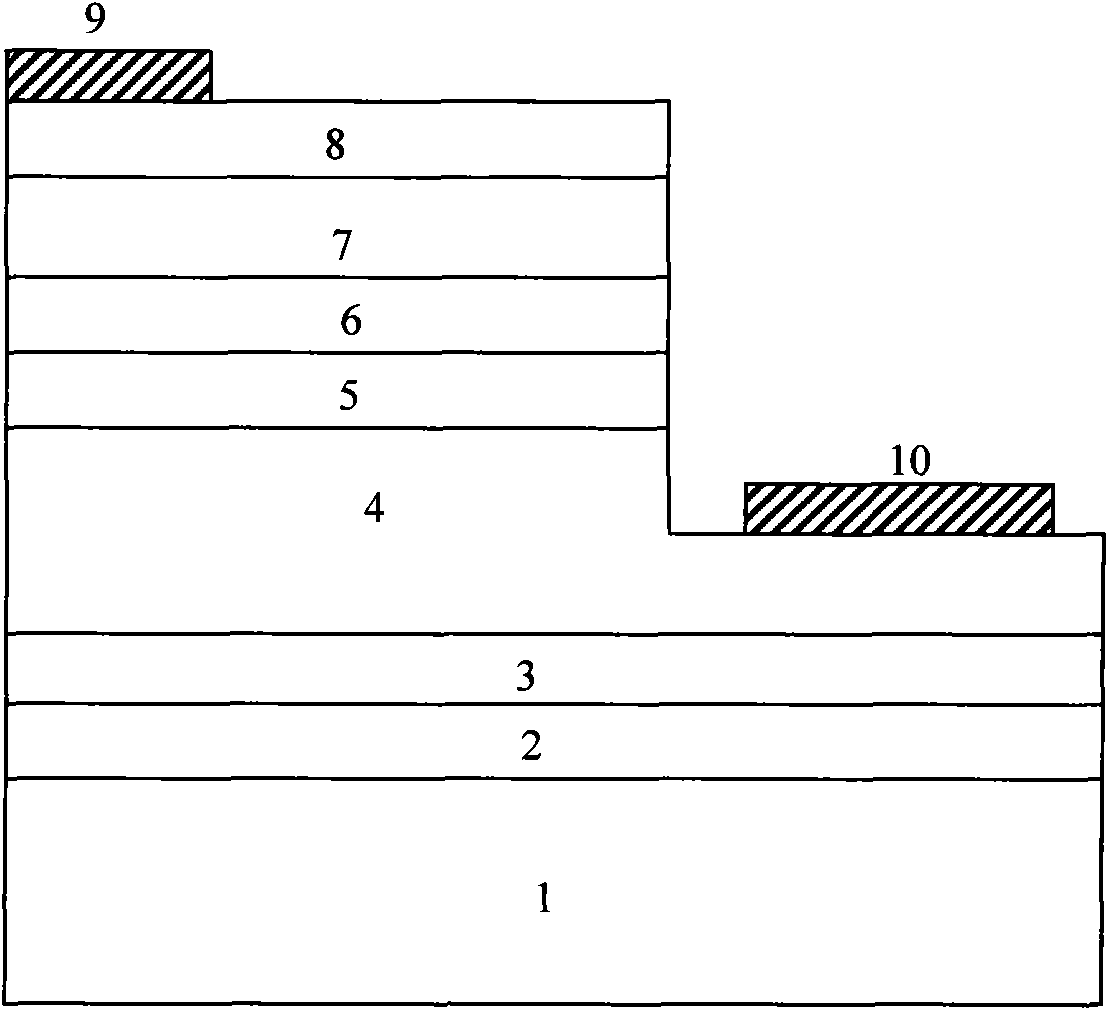

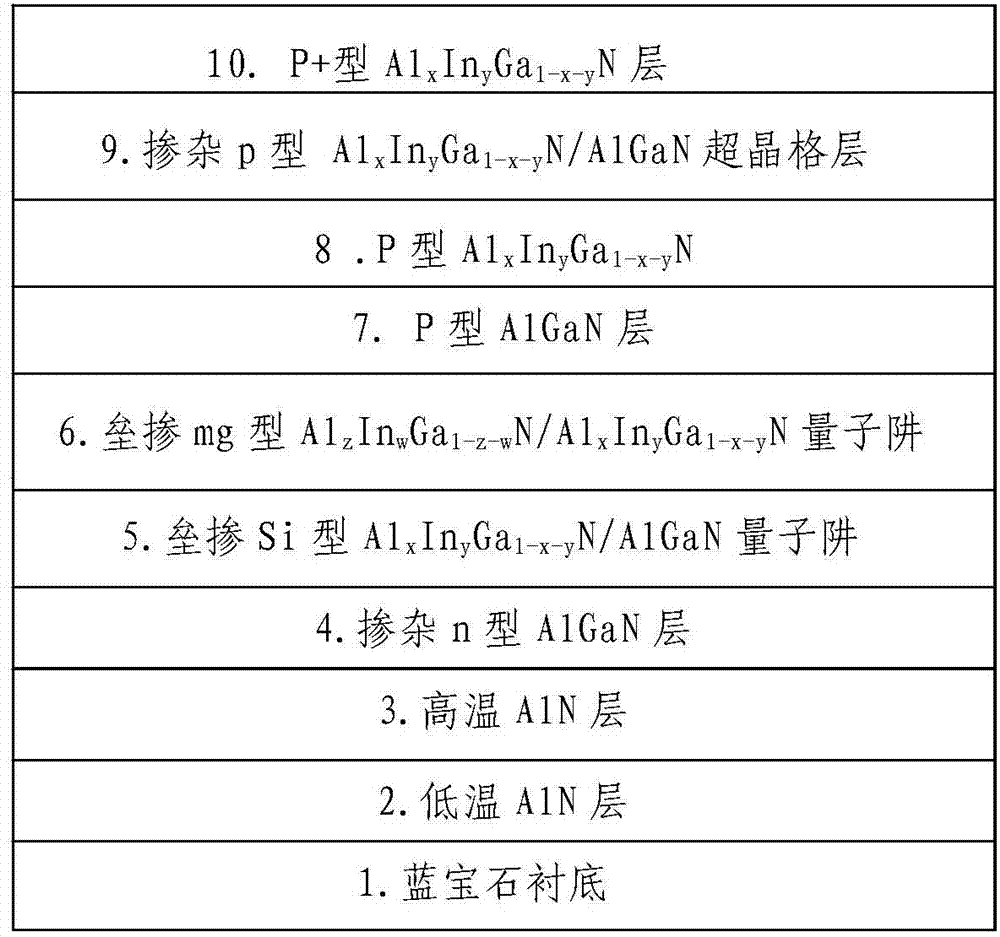

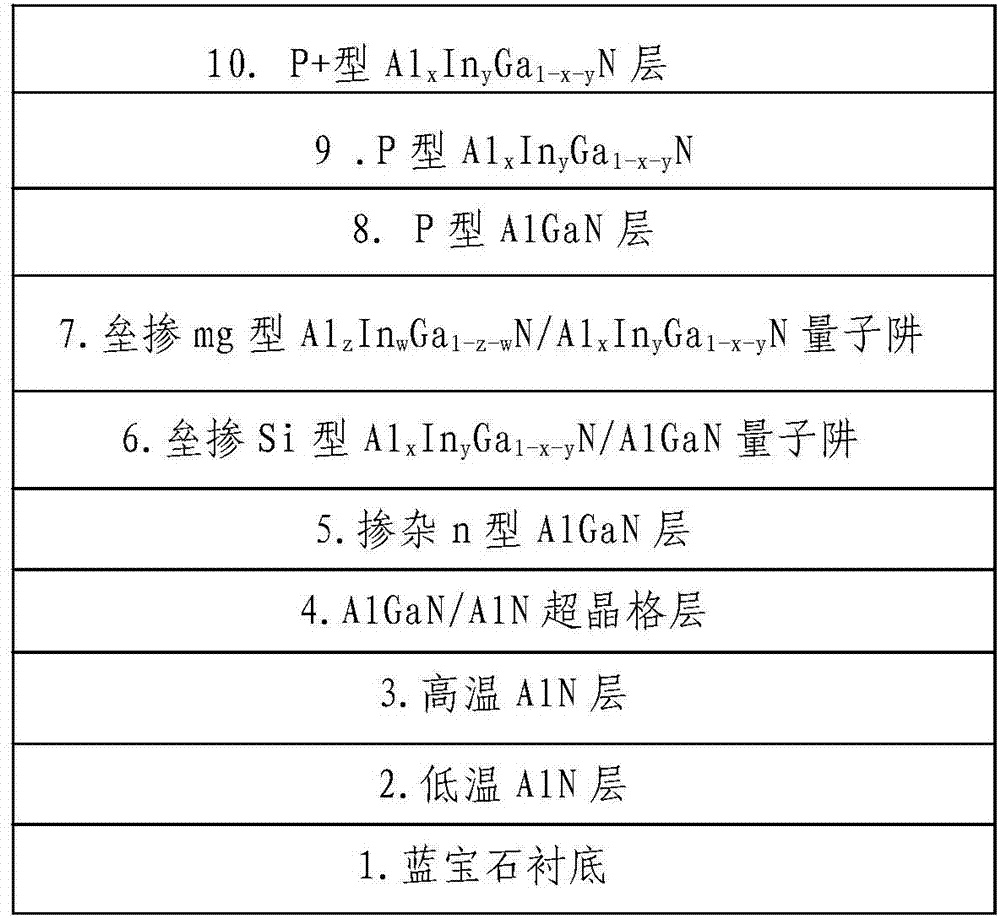

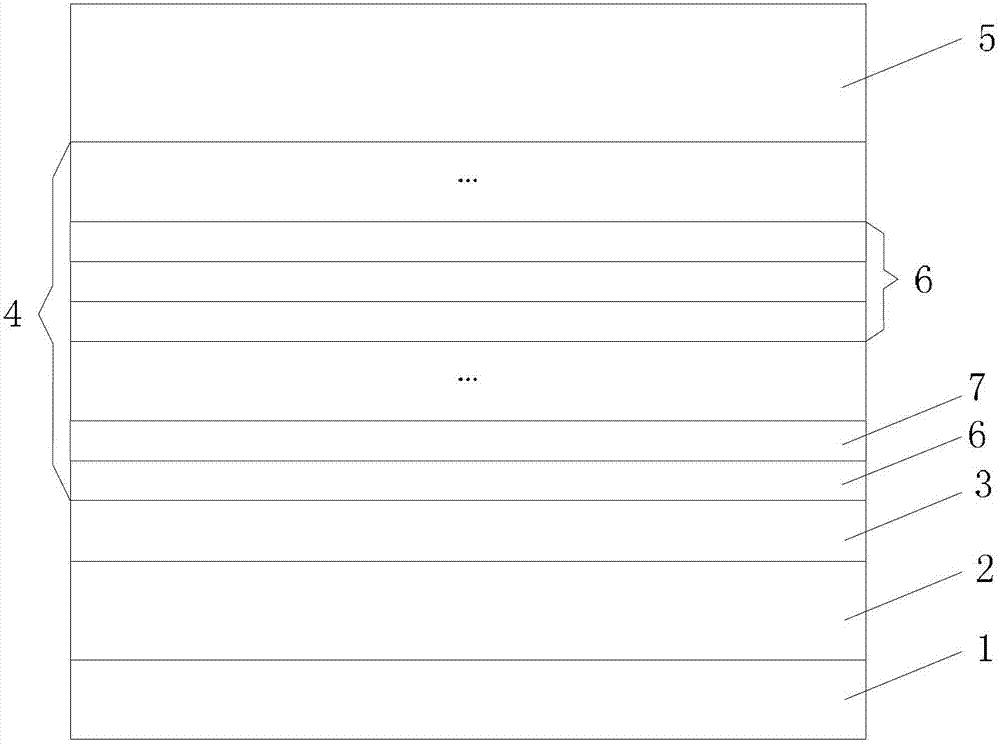

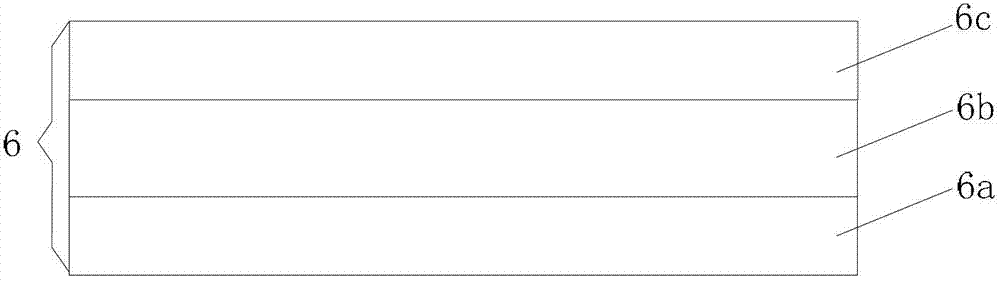

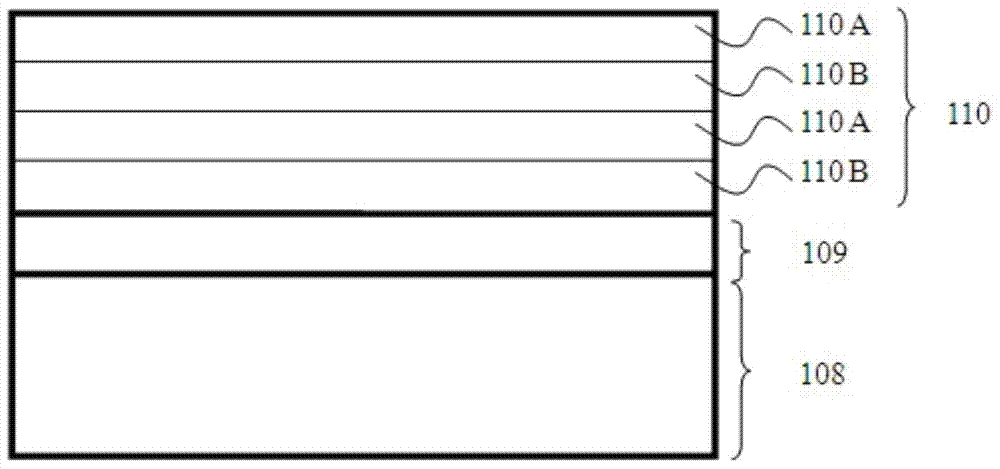

Method for epitaxial growth of ultraviolet LED with high luminous efficacy

The invention provides a new method for epitaxial growth of an ultraviolet LED. By the adoption of the method for epitaxial growth of the ultraviolet LED, the growth difficulty can be greatly lowered, and the radiant power of the ultraviolet LED is greatly increased. An AlGaN / AlxInyGa1-x-y layer is grown for a plurality of periods, wherein x, y, z and w meet the following requirements for x

Owner:西安利科光电科技有限公司

Epitaxial wafer of light-emitting diode (LED) and making method of epitaxial wafer

ActiveCN102760808ASlow down electronsReduced polarizationSemiconductor devicesMultiple quantumQuantum

The invention discloses an epitaxial wafer of a light-emitting diode (LED) and the manufacturing method of the epitaxial wafer and belongs to the technical field of diodes. The epitaxial wafer comprises a substrate layer, a buffer layer, an N-type layer, a multiple quantum well (MQW) layer and a P-type layer, wherein the substrate layer, the buffer layer, the N-type layer, the MQW layer and the P-type layer are sequentially covered on the substrate layer; the N-type layer is made of n-type doped GaN; the MQW layer comprises a plurality of quantum barrier layers and a plurality of quantum well layers which alternately grow with the quantum barrier layers; at least one of the quantum barrier layers comprises three sub-quantum barrier layers; a sub-quantum barrier layer positioned in the middle of the three sub-quantum barrier layers is made of n-type doped AlxInyGa[1-x-y]N, and the n-type doping concentration of the sub-quantum barrier layer is not greater than that of the N-type layer; and the other two sub-quantum barrier layers are made of non-doped GaN, wherein x is more than 0 and less than 1, and y is more than 0 and less than 1. According to the technical scheme, the electrostatic resistance of the LED can be improved.

Owner:HC SEMITEK ZHEJIANG CO LTD

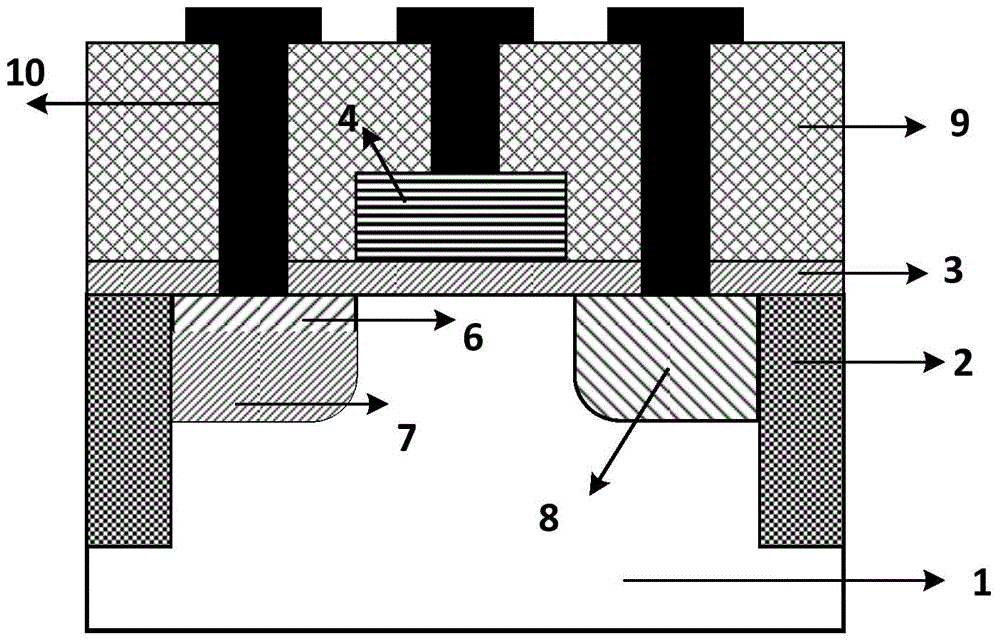

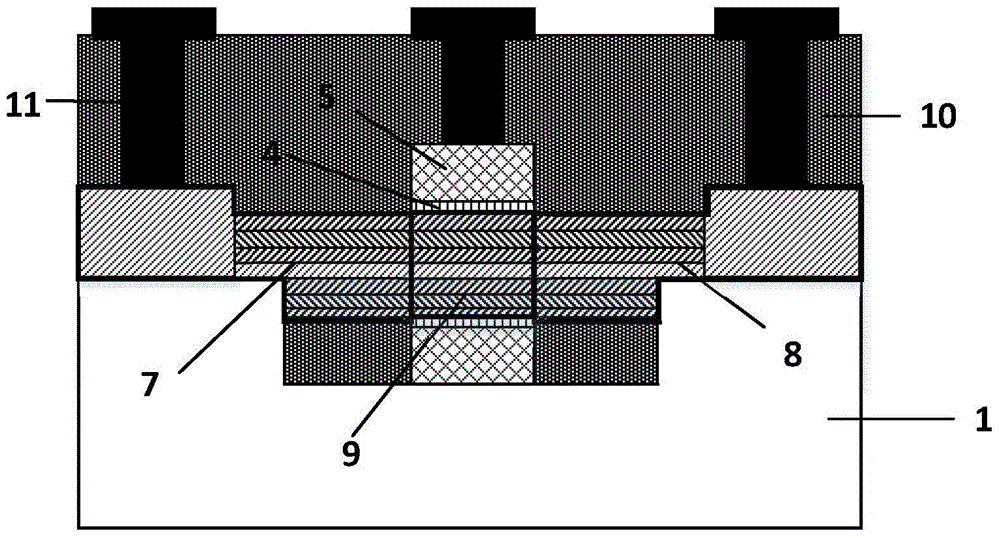

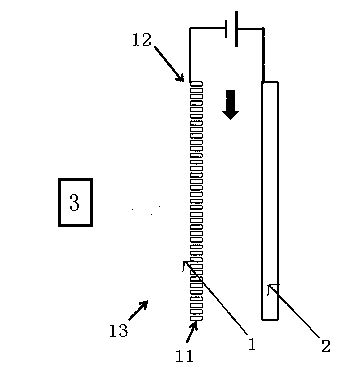

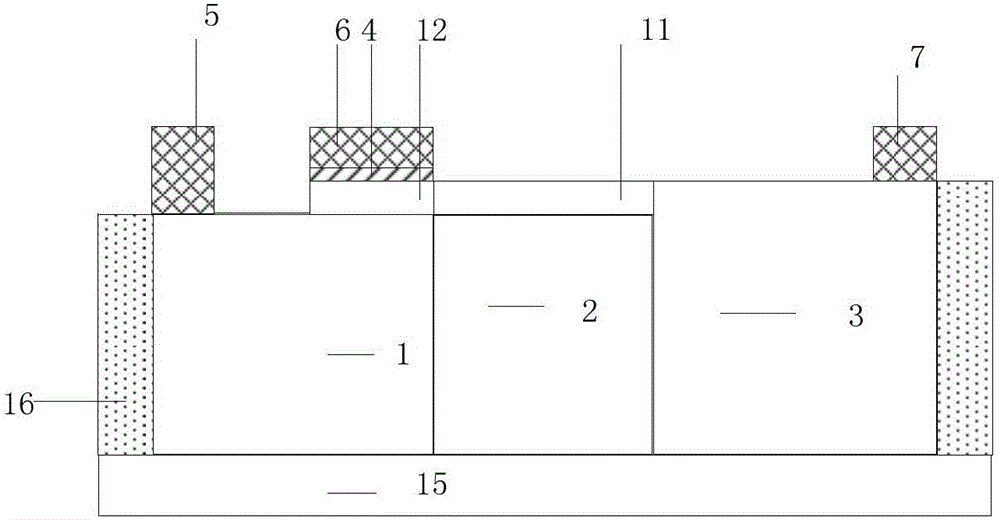

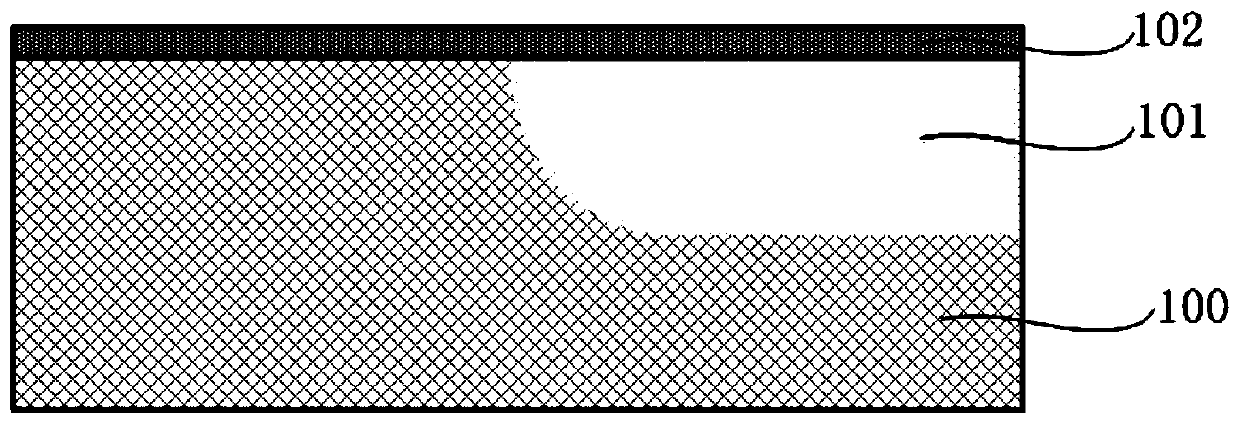

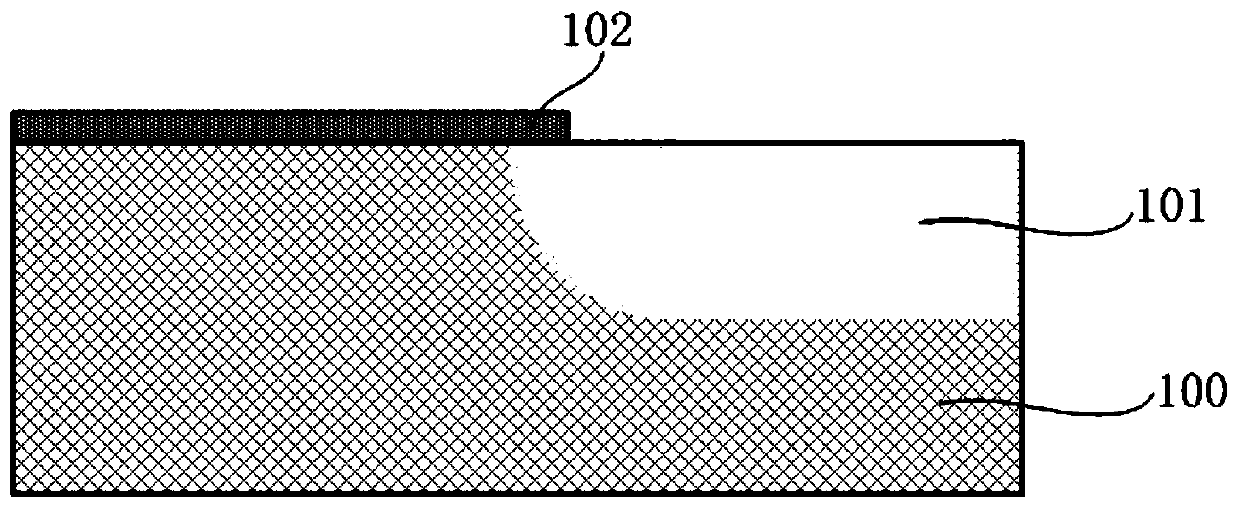

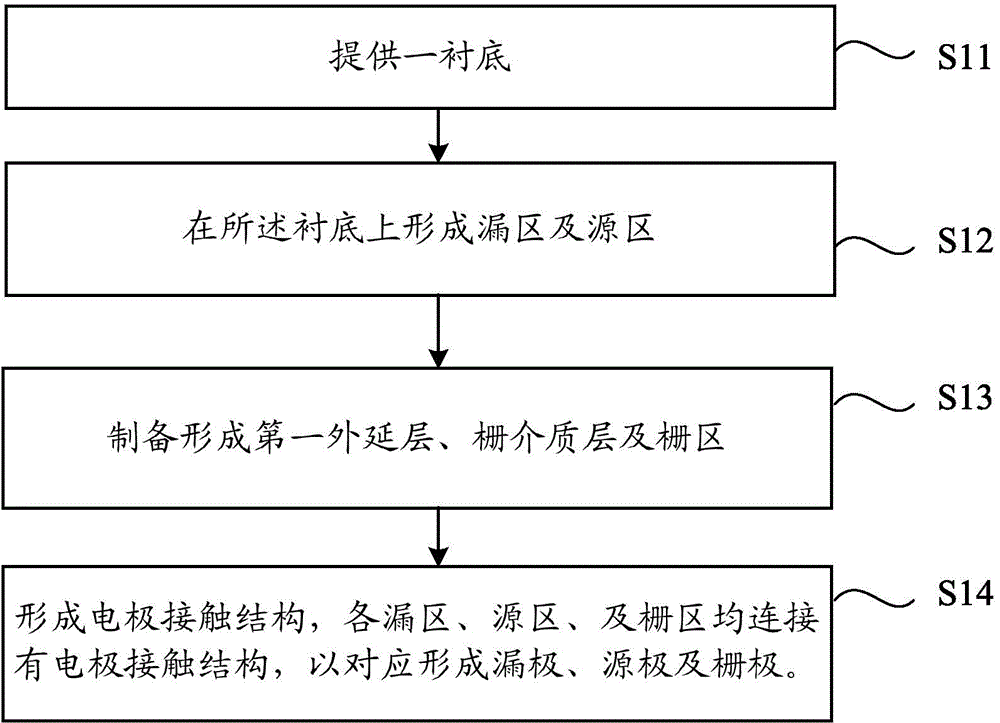

Tunneling effect transistor and production method thereof

ActiveCN102751325AImprove driving abilityExcellent electrical propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesGate stackField-effect transistor

The invention discloses a tunneling effect transistor and production method thereof. The tunneling effect transistor comprises a semiconductor substrate, a strained layer, a channel region, a gate stack, a source region, a leakage region and a bag region. The strained layer is positioned on the semiconductor substrate, and the channel region is arranged in the semiconductor substrate and the trained layer. The gate stack is arranged on the channel region and comprises a gate medium layer and a gate electrode layer, the gate medium layer is arranged on the channel region, and the gate electrode layer is arranged on the gate medium layer. The source region and the leakage region are arranged on two sides of the channel region and embedded into the semiconductor substrate, wherein parts of the source region extend below the gate stack. The bag region is arranged in the source region under the gate stack and wrapped by the source region, and the edges of the bag region and edges of the source region are coincided are connected with the channel region on the side close to the channel region.

Owner:SOI MICRO CO LTD

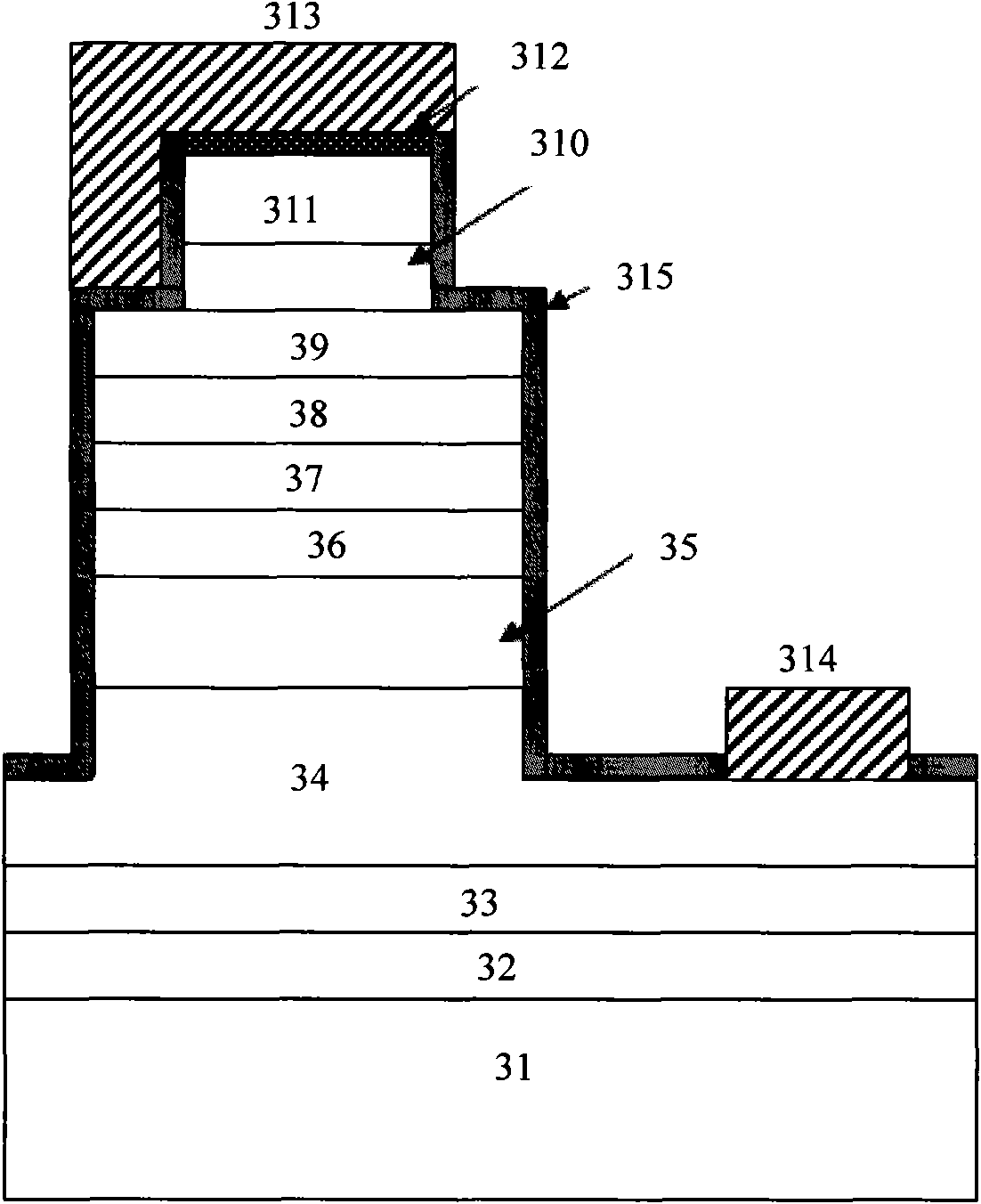

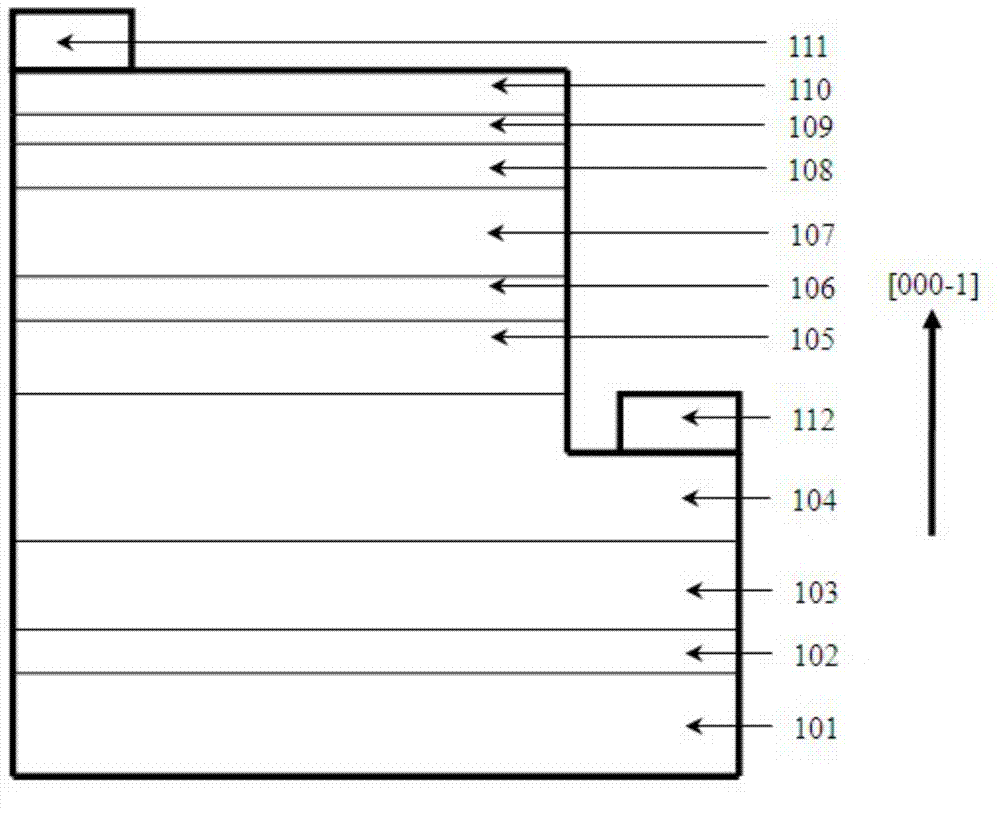

Nitrogen polar surface light emitting diode with tunnel junction structure

ActiveCN103489975AGood ohmic contactImprove acceleration performanceSemiconductor devicesOhmic contactNitrogen

The invention discloses a nitrogen polar surface light emitting diode with a tunnel junction structure. The nitrogen polar surface light emitting diode with the tunnel junction structure comprises a sapphire substrate, a low temperature nucleating layer, a non-doped semiconductor layer, an n-type semiconductor layer, a multiple quantum well active layer, a p-AlGaN electronic barrier layer, a p-type semiconductor layer, a p+-GaN layer, a non-doped InxAlyGal-x-yN layer, an n-type superlattice layer and a metal electrode, wherein the sapphire substrate, the low temperature nucleating layer, the non-doped semiconductor layer, the n-type semiconductor layer, the multiple quantum well active layer, the p-AlGaN electronic barrier layer, the p-type semiconductor layer, the p+-GaN layer, the non-doped InxAlyGal-x-yN layer, the n-type superlattice layer and the metal electrode are arranged from bottom to top in sequence. The p+-GaN layer, the non-doped InxAlyGal-x-yN layer and the n-type superlattice layer form the p-i-n tunnel junction structure together. According to the nitrogen polar surface light emitting diode with the tunnel junction structure, the p-i-n tunnel junction structure is used as an ohmic contact layer on the top of an LED chip so that the current expanding capacity of an LED device can be improved, therefore, the turn-on voltage of the whole chip is reduced, and the light output power of the chip can be effectively improved.

Owner:SOUTHEAST UNIV

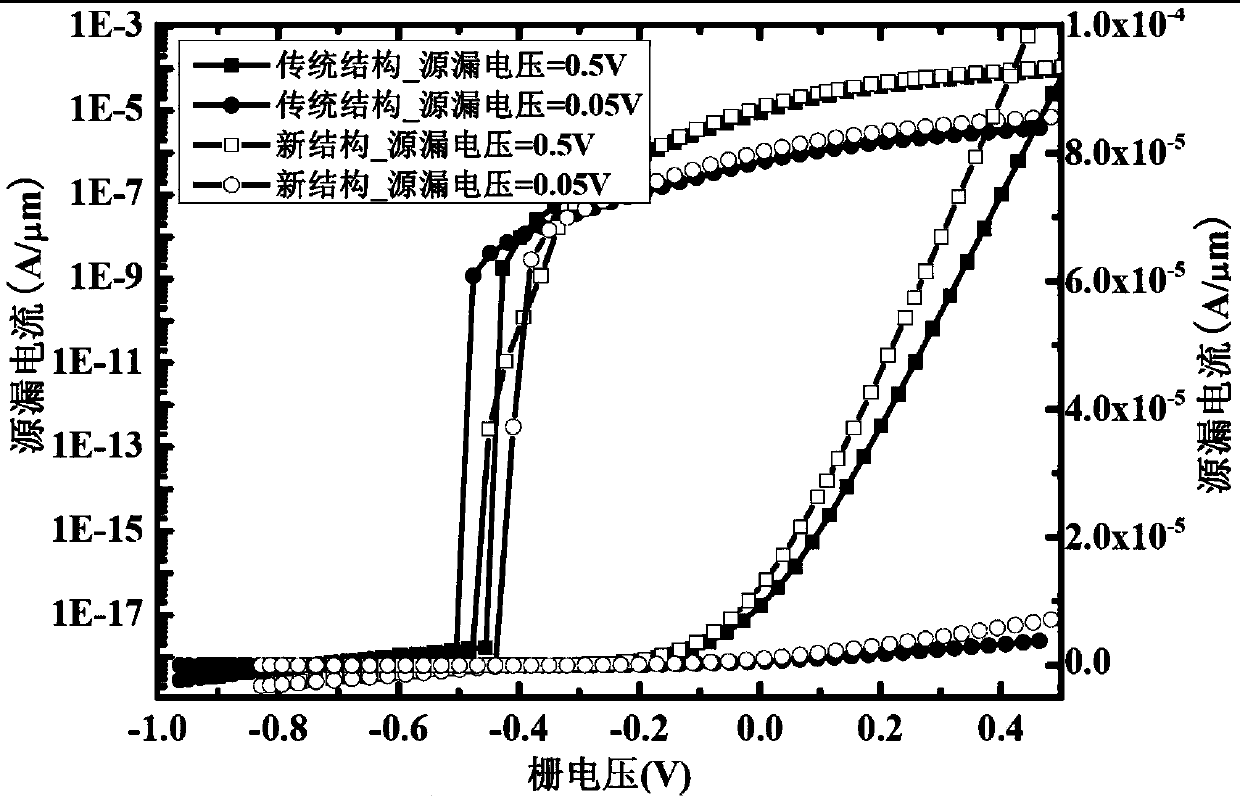

Tunneling field-effect transistor capable of restraining nolinear opening of output and preparation method thereof

ActiveCN103985745ASteep Subthreshold SwingAvoid e-exponential relationshipsSemiconductor/solid-state device manufacturingDiodeHeterojunctionCMOS

A tunneling field-effect transistor capable of restraining nolinear opening of output comprises a tunneling source region, a channel region, a drain region and a control grid positioned above a channel. The tunneling source region is III-V compound semiconductor mixed crystals, and a mixed crystal ratio of the mixed crystals gradually changes in the direction of the surface of a perpendicular device. An energy band structure of a heterogenous tunneling junction on the interface of the tunneling source region and the channel region gradually changes in the direction of the surface of the perpendicular device. A staggered-gap heterojunction tunneling source region is arranged on the surface of the device, and a tunneling junction on the surface of the device is a staggered-gap heterojunction. A broken-gap heterojunction tunneling source region is arranged at the position with a certain distance away from the surface of the device, and a tunneling junction at the position is a broken-gap heterojunction. The staggered-gap heterojunction tunneling source region and the broken-gap heterojunction tunneling source region have the same doping type. The tunneling field-effect transistor is simple in preparation process, a preparation method of the tunneling field-effect transistor is completely based on a standard CMOS IC process, the TFET device can be integrated in a CMOS integrated circuit effectively, a low-power-consumption integrated circuit composed of the TFET can be prepared through a standard process, therefore, production cost is reduced greatly, and the technological process is simplified.

Owner:PEKING UNIV

Tunneling field effect transistor

ActiveCN103474459AIncrease contact areaIncrease chance of tunnelingSemiconductor devicesGate dielectricField effect

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

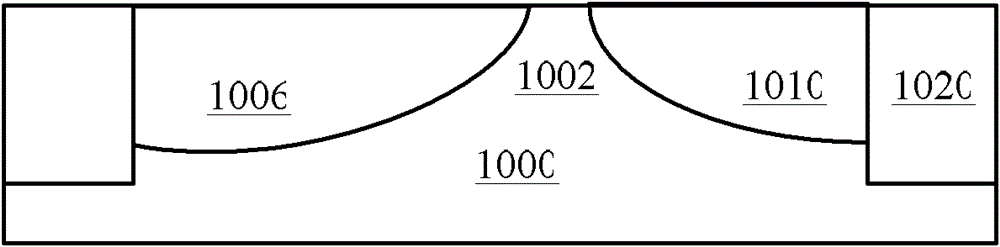

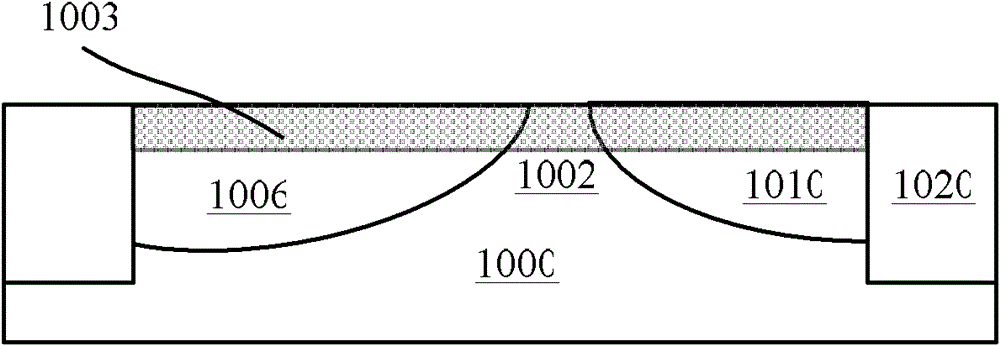

GaN-based heterojunction schottky diode device and preparing method thereof

InactiveCN104332504AAchieve separationLower turn-on voltageSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionReverse current

The invention relates to a GaN-based heterojunction schottky diode device and a preparing method thereof. The GaN-based heterojunction schottky diode device comprises a substrate and an epitaxial layer which grows on the substrate, wherein the epitaxial layer comprises a stress buffer layer, a GaN layer and a heterostructure barrier layer which are arranged from bottom to top. The anode area of the epitaxial layer is etched for forming a recessed trough. A low work function metal layer is plated on the recessed trough and partial surface of the heterostructure barrier layer through vapor plating. A high work function metal layer is plated above the low work function metal layer and the planar area of the heterostructure barrier layer through vapor plating. The high work function metal layer and the low work function metal layer form a mixed anode. Ohmic metal is plated on the cathode area through vapor plating for forming a cathode. The epitaxial layer is integrally covered by a passivation insulating layer. The insulating layer is etched for forming an electrode window. According to the GaN-based heterojunction schottky diode device, combination of mixed anode metal and anode recessed trough technique is realized; current under forward bias is activated in advance through the side wall of the anode recessed trough; reverse leakage current is cut off through the high work function metal layer on the surface of the heterostructure barrier layer under reverse bias, thereby realizing separation of forward and reverse current channels, and achieving a technical object of the GaN-based heterojunction schottky diode device with low turn-on voltage and low reverse leakage current.

Owner:SUN YAT SEN UNIV

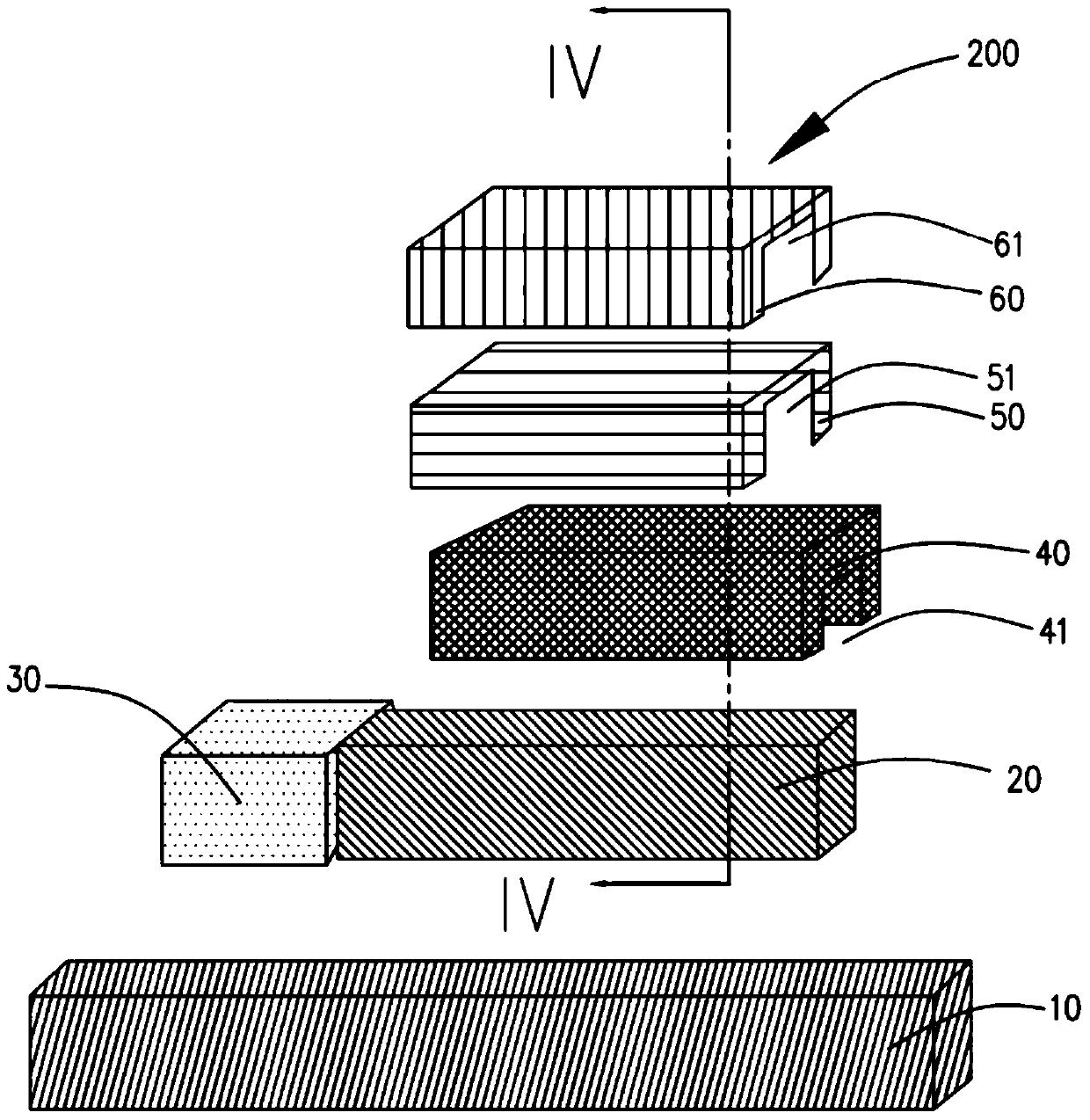

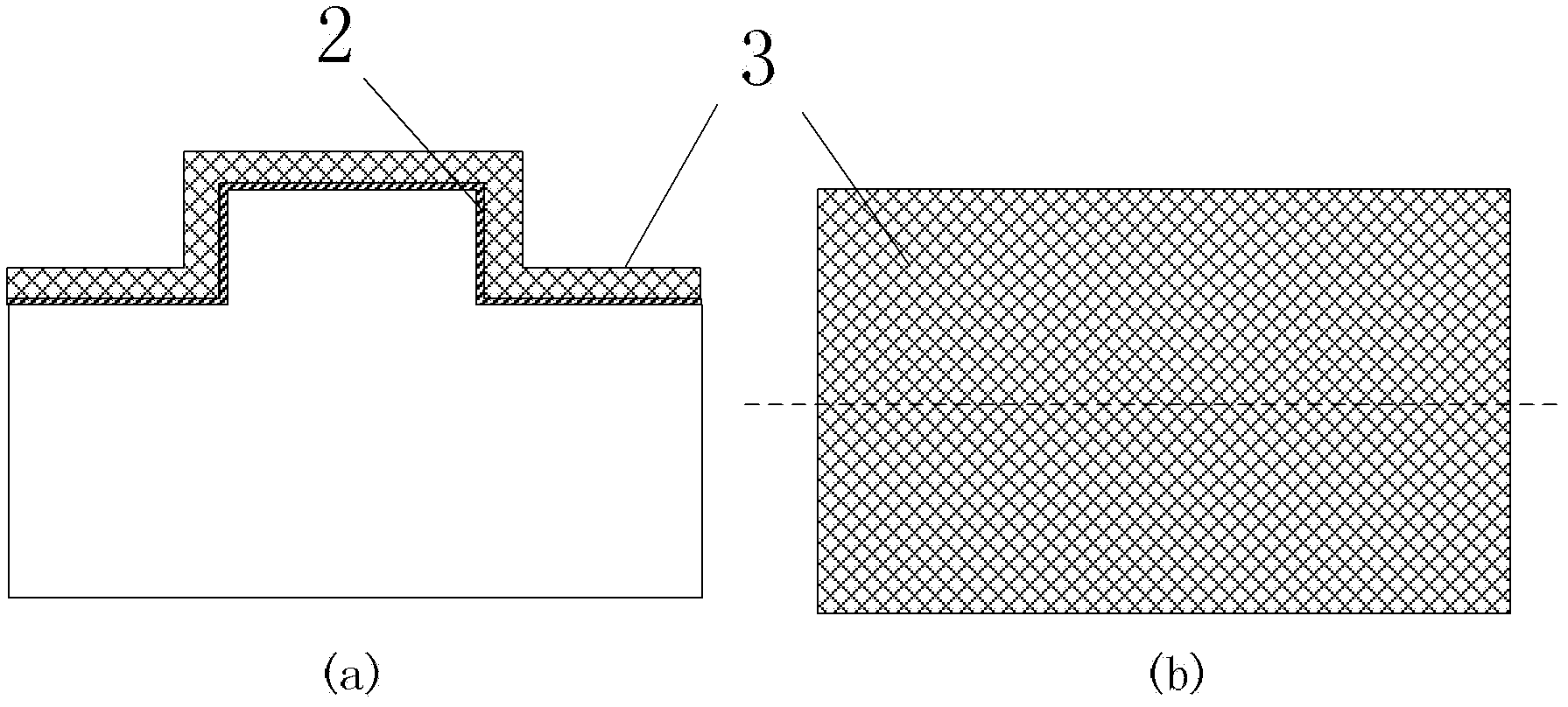

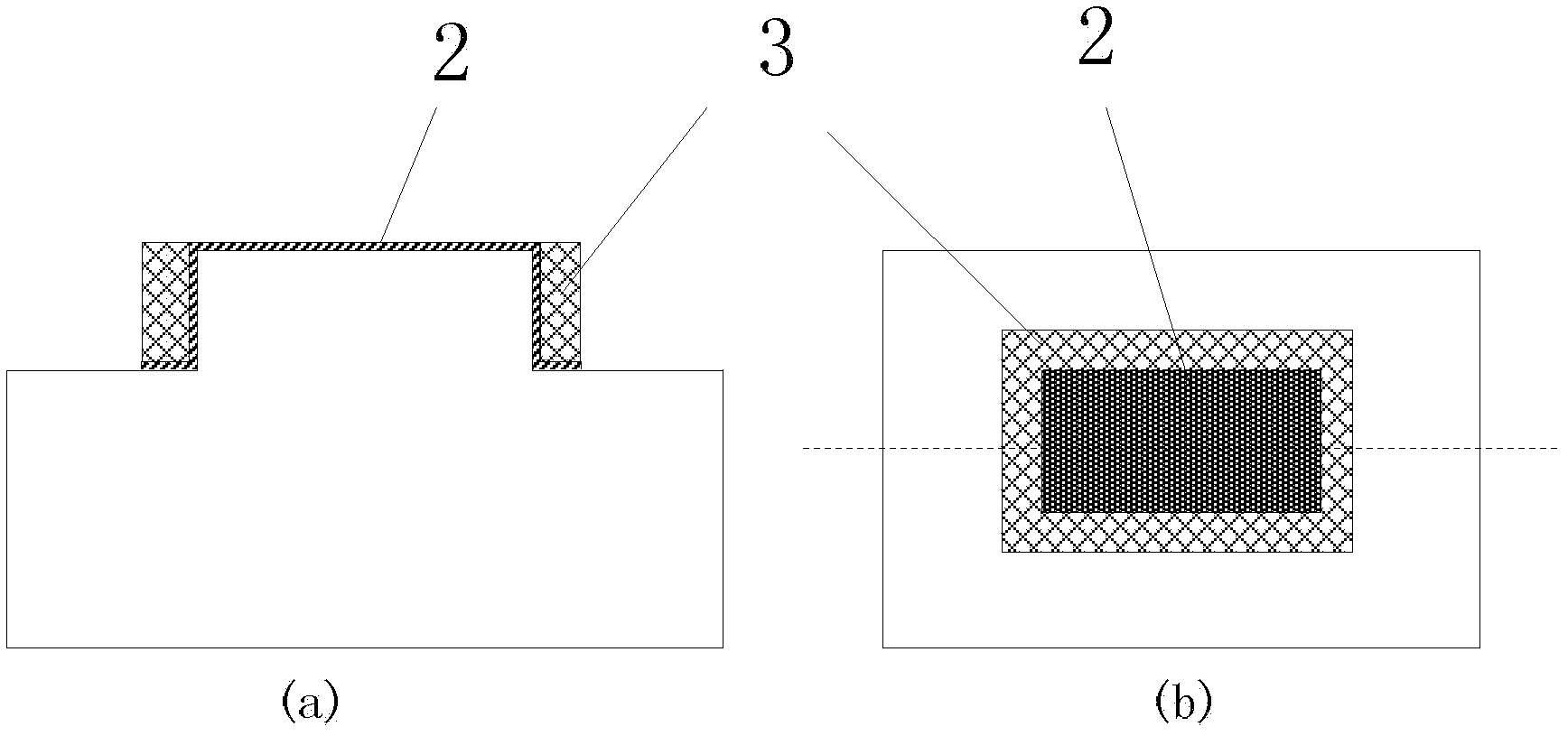

Tunneling transistor structure and manufacturing method thereof

ActiveCN104201198AIncrease the on-state currentLarge tunneling areaSemiconductor/solid-state device manufacturingDiodeGate dielectricDielectric layer

The invention provides a tunneling transistor structure. The tunneling transistor structure comprises a substrate, a silicon strip, a drain electrode area, a source electrode area, a gate dielectric layer and a grid electrode, wherein the silicone strip is formed on the substrate; the drain electrode area is formed at one side of the silicon strip; the source electrode area is equipped with a first groove in which the silicon strip is contained; the grate dielectric layer is formed on the source electrode area and partially covers the source electrode area; the grid electrode is equipped with a second groove in which the gate dielectric layer is contained; the cross section of the second groove is the same as that of the first groove; when in tunneling, the first groove tunnels under the effect of the second groove to form a tunneling current. The invention also provides a manufacturing method of the tunneling transistor structure. According to the tunneling transistor structure, the structures of the source electrode area and the grid electrode are changed; when in tunneling, the tunneling area of the source electrode area is expanded under the effect of the grid electrode, and point tunneling and line tunneling occur in the first groove; therefore, both the tunneling area and the tunneling portability are raised through the structure, and as a result, the on-state current of the whole device can be improved.

Owner:HUAWEI TECH CO LTD

Ultra steep average subthreshold swing nano wire tunneling field effect transistor and method for preparing same

ActiveCN104835840ASteep Minimum Subthreshold SwingIncrease chance of tunnelingSemiconductor/solid-state device manufacturingDiodeCMOSSubthreshold swing

The present invention provides an ultra steep average subthreshold swing nano wire tunneling field effect transistor and a method for preparing the same which belong to the field effect transistor logic device field of the CMOS ultra large scale integration (ULSI). The tunneling field effect transistor adopts a nano wire structure of core-multilayered shell, and the material band gap of a multilayered shell part is increased continuously along the radius direction of the nano wire. According to the present invention, a subthreshold slope degradation phenomenon in a device transfer characteristic can be restrained effectively, at the same time, an average subthreshold slope of the tunneling field effect transistor is reduced remarkably, and a more steep minimum subthreshold slope is kept.

Owner:PEKING UNIV

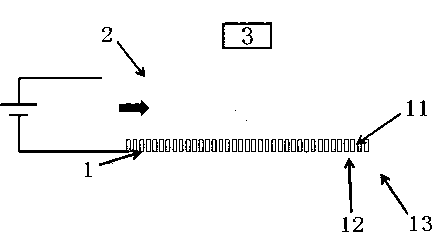

Photoelectric-effect ion source based on carbon nano-tubes

ActiveCN103311089AImprove light absorption efficiencyIncrease the local electric field at the tipIon sources/gunsNanotubeMaterials science

The invention relates to a photoelectric-effect ion source based on carbon nano-tubes. The ion source comprises an ultraviolet ray emitting device and a power source, wherein the anode of the power source is connected with a counter electrode; the cathode of the power source is connected with a carbon nano-tube electrode, the carbon nano-tube electrode comprises a carbon nano-tube layer and a substrate, the carbon nano-tube layer is opposite to the counter electrode, and a passage which is used for a sample to pass through is reserved between the carbon nano-tube layer and the counter electrode; and the ultraviolet ray emitting device irradiates the carbon nano-tube electrode. According to the ion source, ions are generated through the photoelectric effect on the carbon nano-tubes, the carbon nano-tubes are very low in light reflection coefficient and very high in light absorption efficiency, the electron emission is easier due to the unique one-dimensional structure of the carbon nano-tubes, and the carbon nano-tubes can be used in an atmospheric state, so that the problem in the prior art that the vacuum is required when the field-effect ion emission is carried out by using the carbon nano-tubes is solved, the range of use is expanded, and the use is more convenient.

Owner:SUZHOU WEIMU INTELLIGENT SYST CO LTD

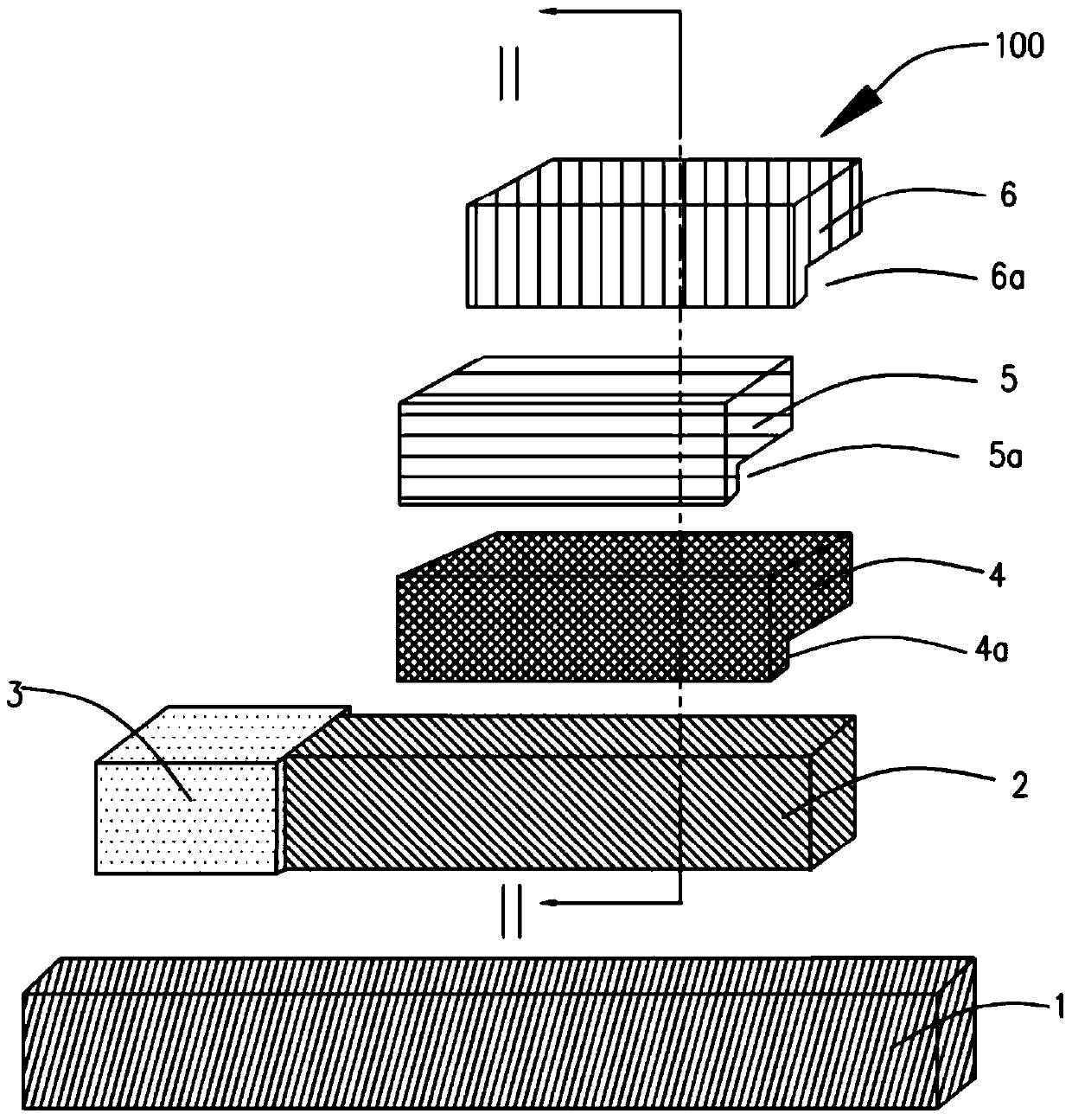

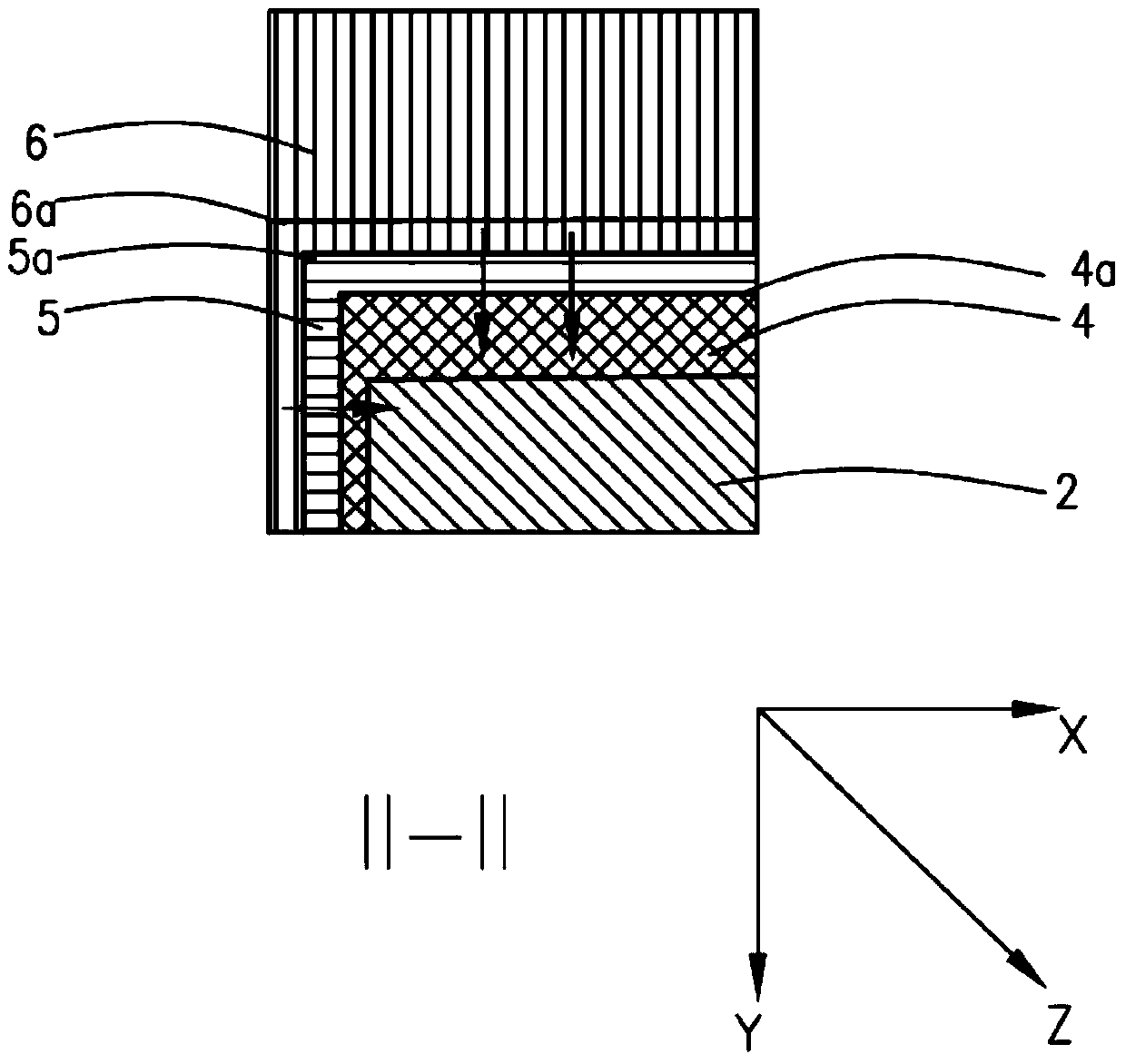

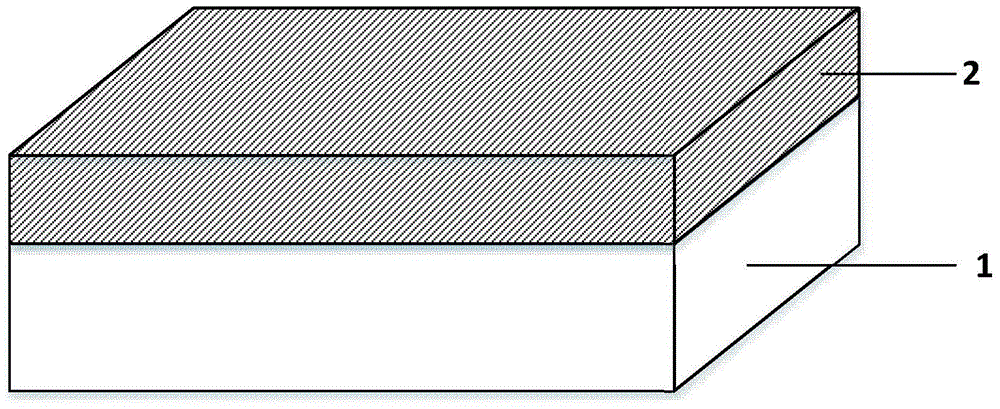

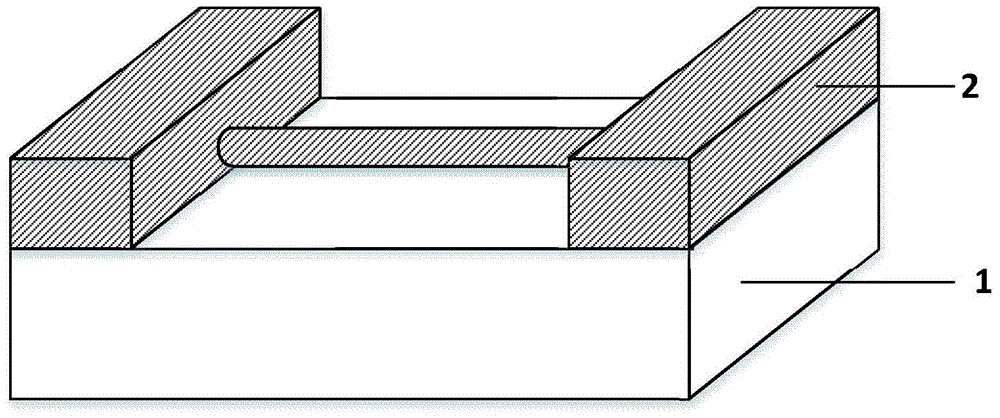

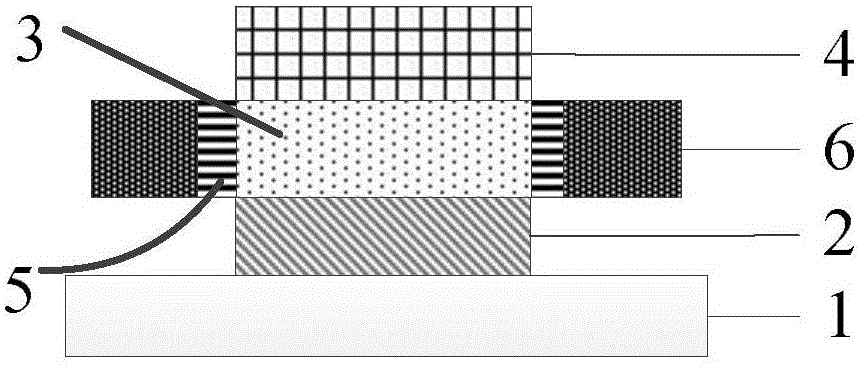

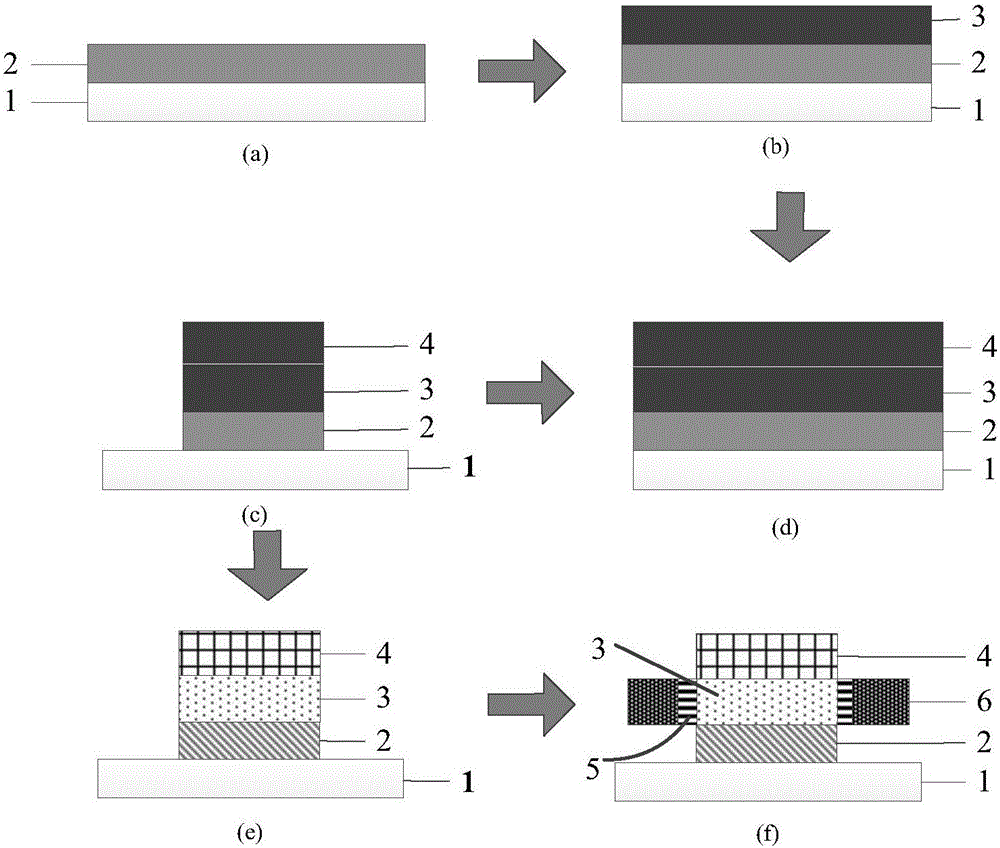

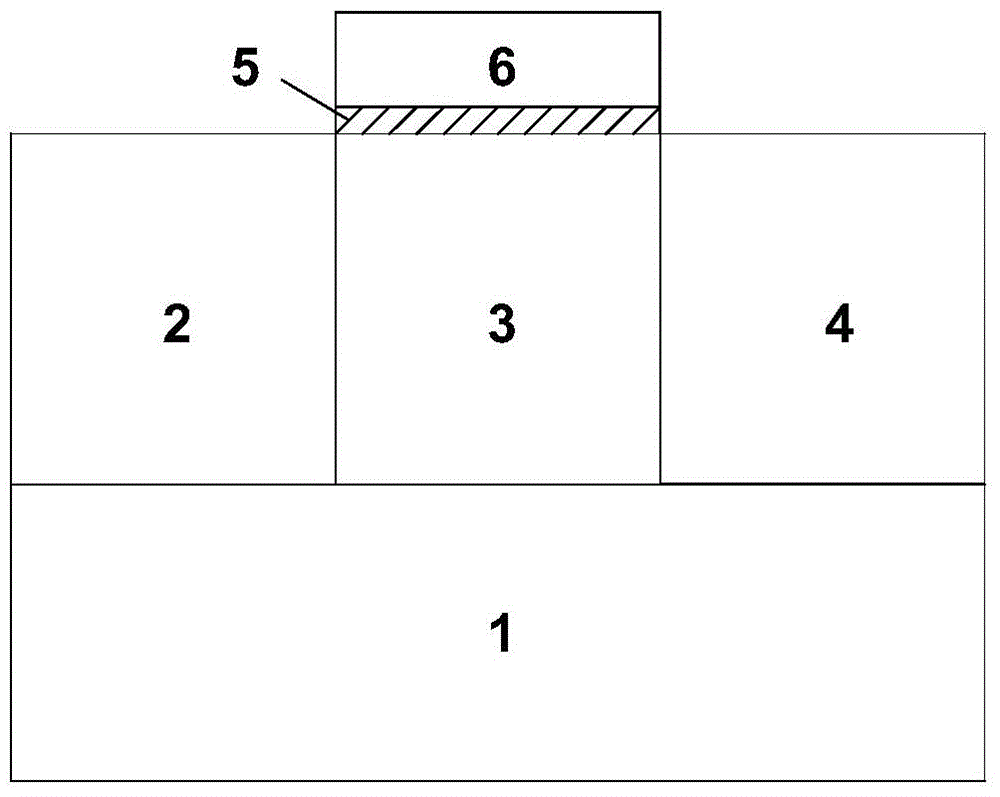

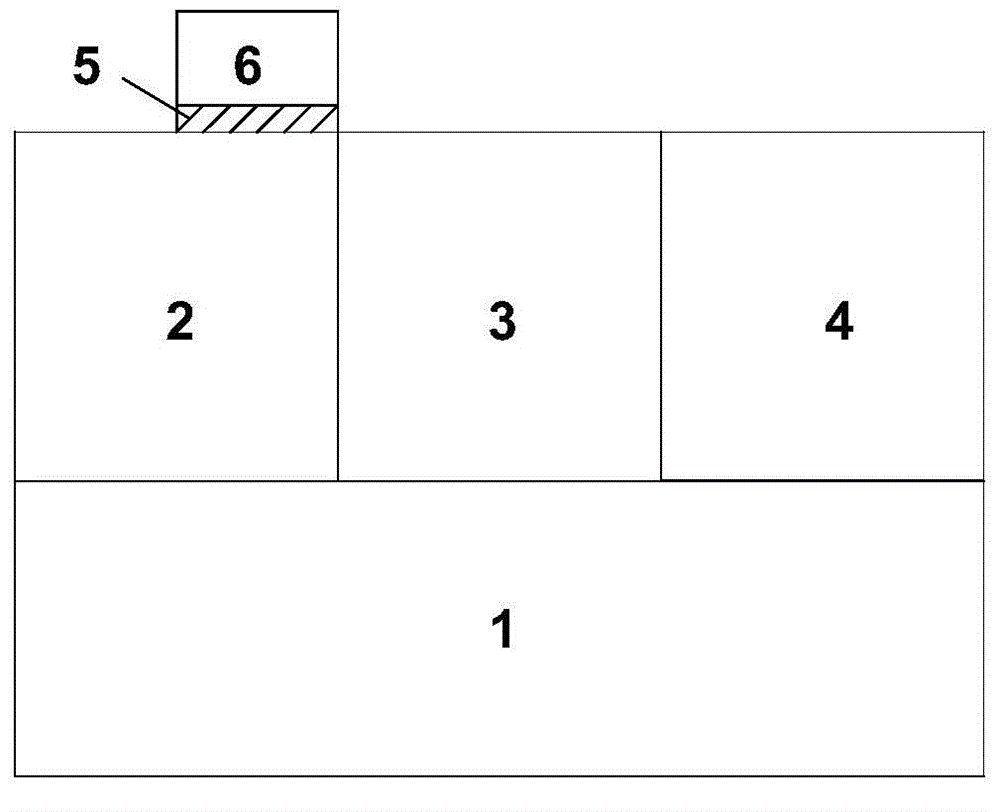

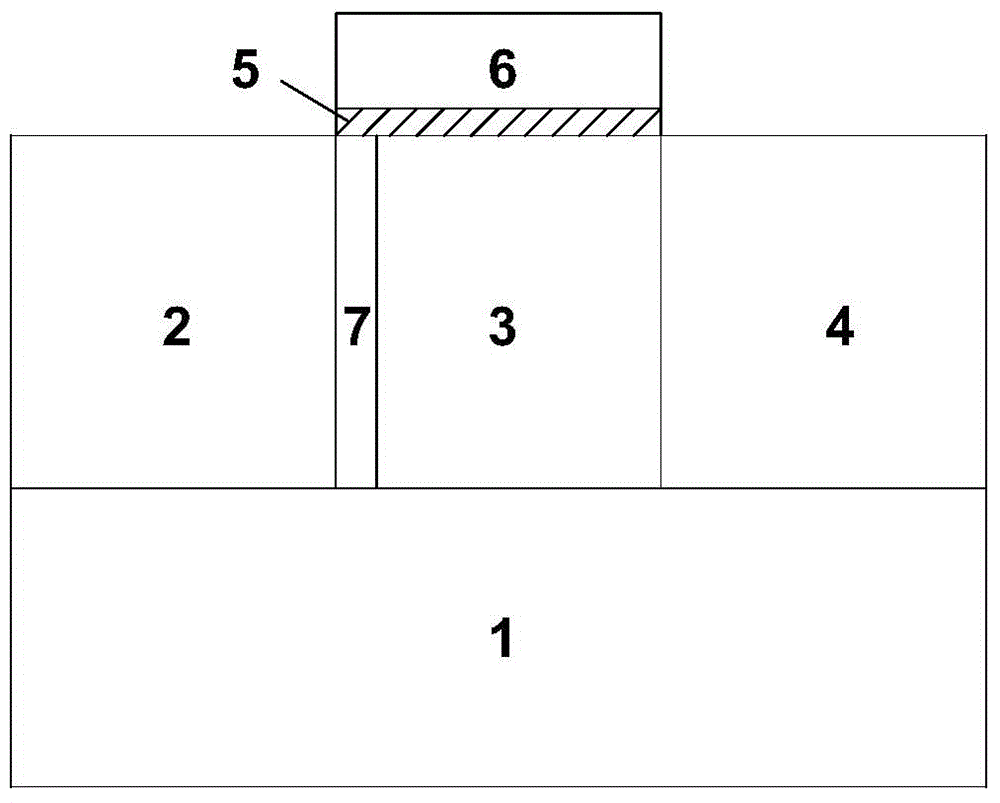

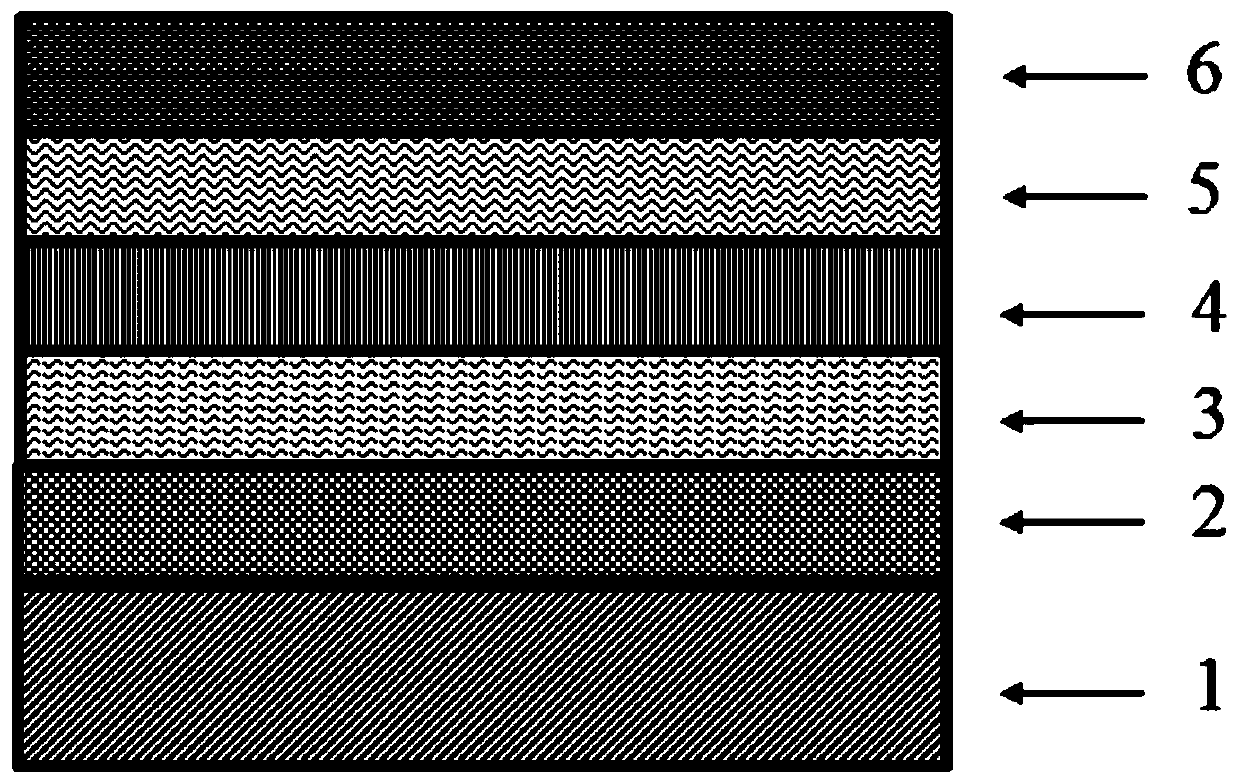

Staggered heterojunction tunneling field effect transistor based on InAsN-GaAsSb material

ActiveCN105047719AChange energy band propertiesLow junction tunneling barrierSemiconductor devicesHeterojunctionPower flow

The invention discloses a staggered heterojunction tunneling field effect transistor based on an InAsN-GaAsSb material, and mainly aims at solving the problem that an existing field effect transistor prepared from the III-V material is relatively low in on-state current. The staggered heterojunction tunneling field effect transistor comprises a substrate (1), a source (2), a channel (3), a drain (4), an insulating dielectric film (5) and a gate electrode (6); an InAsN composite material in which an N component is 0-0.05 is adopted by the source; a GaAsSb composite material in which an Sb component is 0.35-0.65 is adopted by the channel and the drain; and the source, the channel and the drain are vertically distributed on the substrate from bottom to top. The source InAsN material and the channel GaAsSb material contact with each other to form a staggered tunneling heterojunction, so that the low-tunneling barrier height is effectively reduced; the tunneling probability and the tunneling current are increased; the whole performance of the device is improved; and the staggered heterojunction tunneling field effect transistor can be applied to fabrication of large-scale integrated circuits.

Owner:XIDIAN UNIV

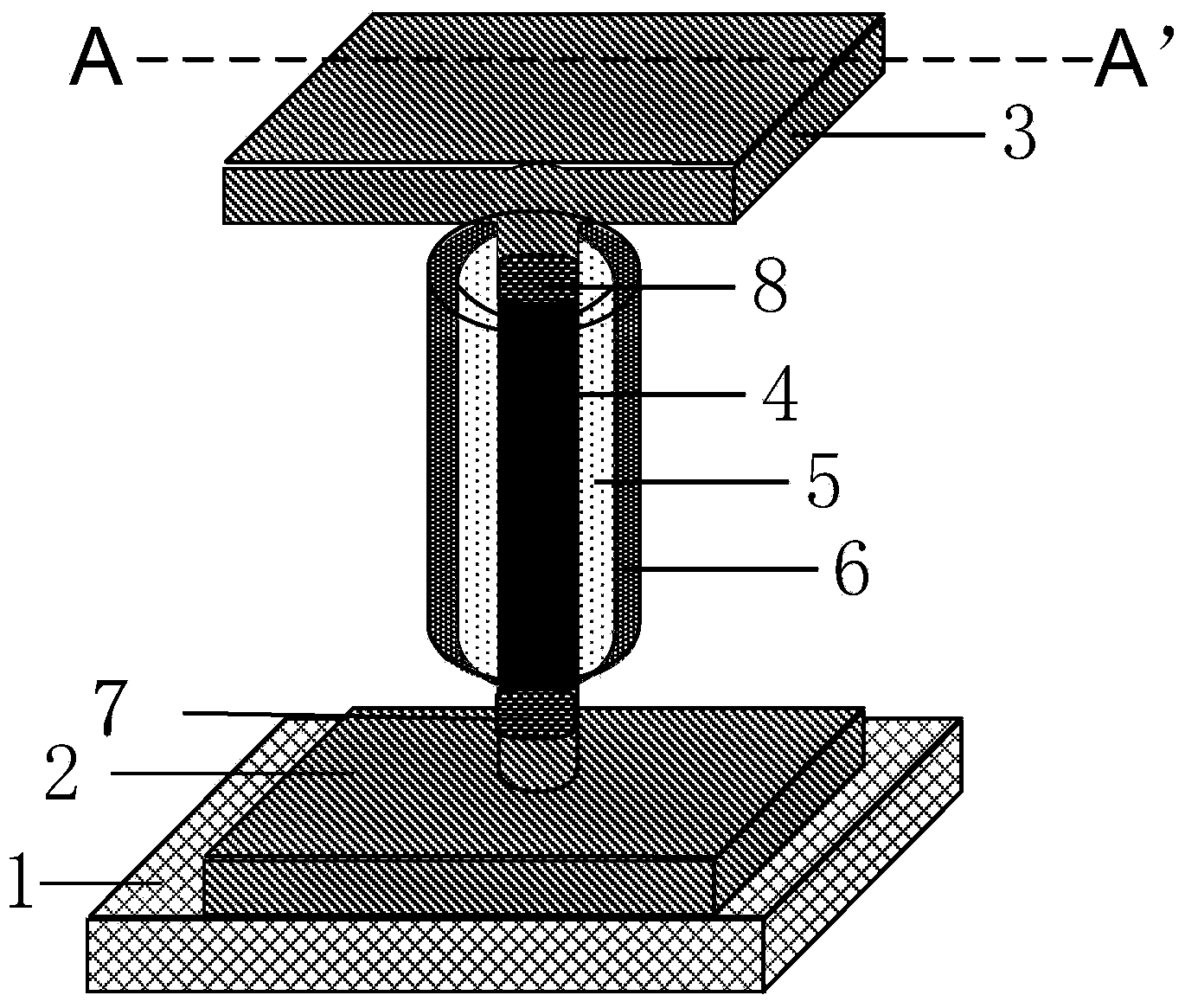

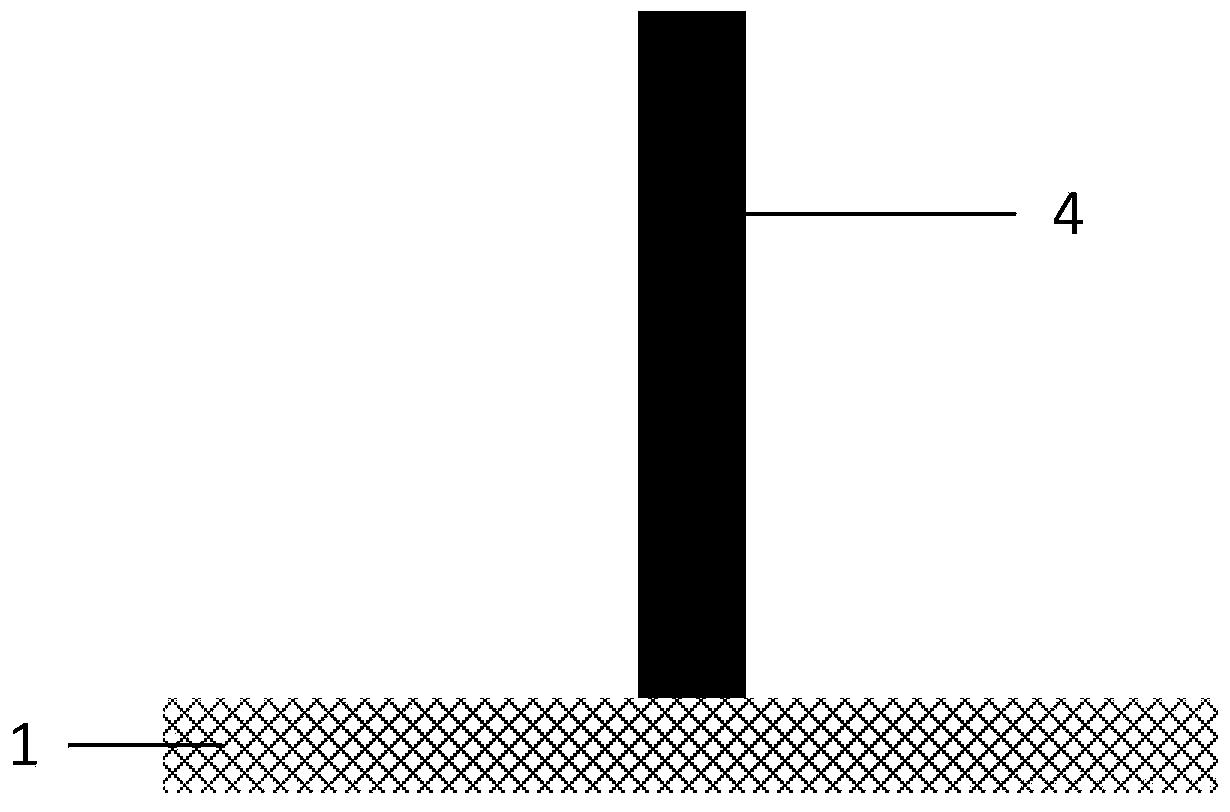

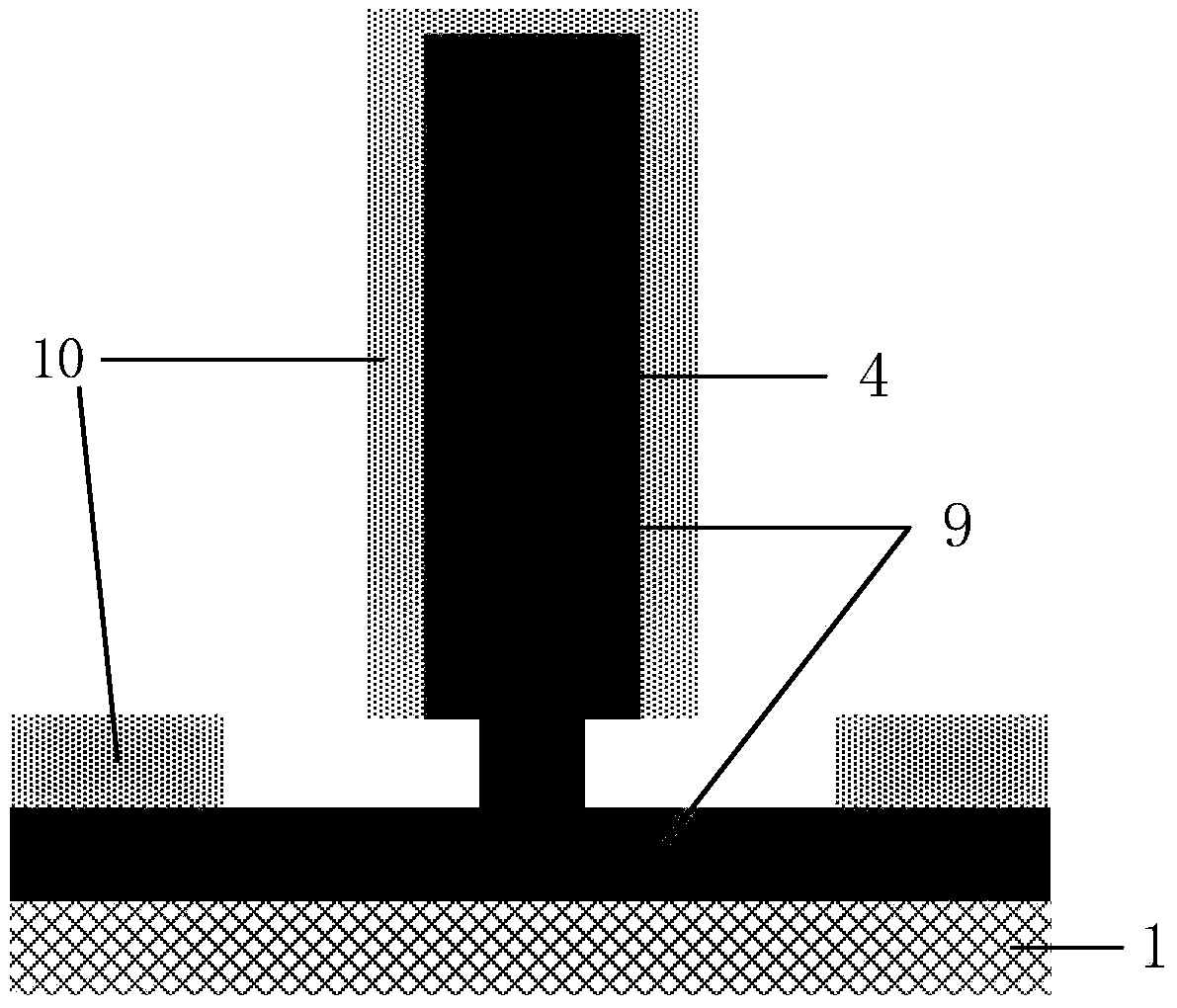

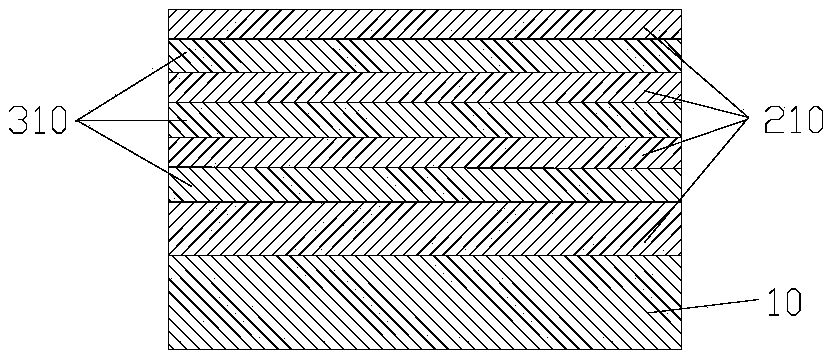

Tunneling field effect transistor with electric field concentration effect to enhance on state current

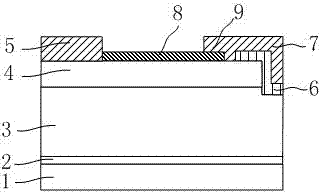

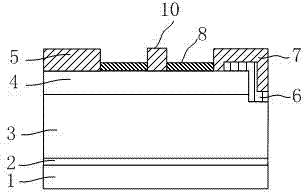

ActiveCN104576721ASteep bendIncrease the on-state currentSemiconductor devicesINCREASED EFFECTTunnel junction

The invention provides a tunneling field effect transistor with an electric field concentration effect to enhance the on state current and belongs to the field of semiconductor apparatuses. The tunneling field effect transistor provided by the invention comprises a semiconductor substrate 1, a source region 2, an intrinsic region 3, a drain region 4, a grid oxide layer 5, a metal grid 6 and a side wall 9 and further comprises a medium block 10 which is arranged in the intrinsic region, wherein the medium block 10 is arranged on an interface of the intrinsic region and the source region, and the medium block can be used for changing electric field distribution in a tunnel junction position, so that the electric field line at the tunnel junction is concentrated so as to enhance the on state current.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Tunneling field effect transistor and manufacturing method thereof

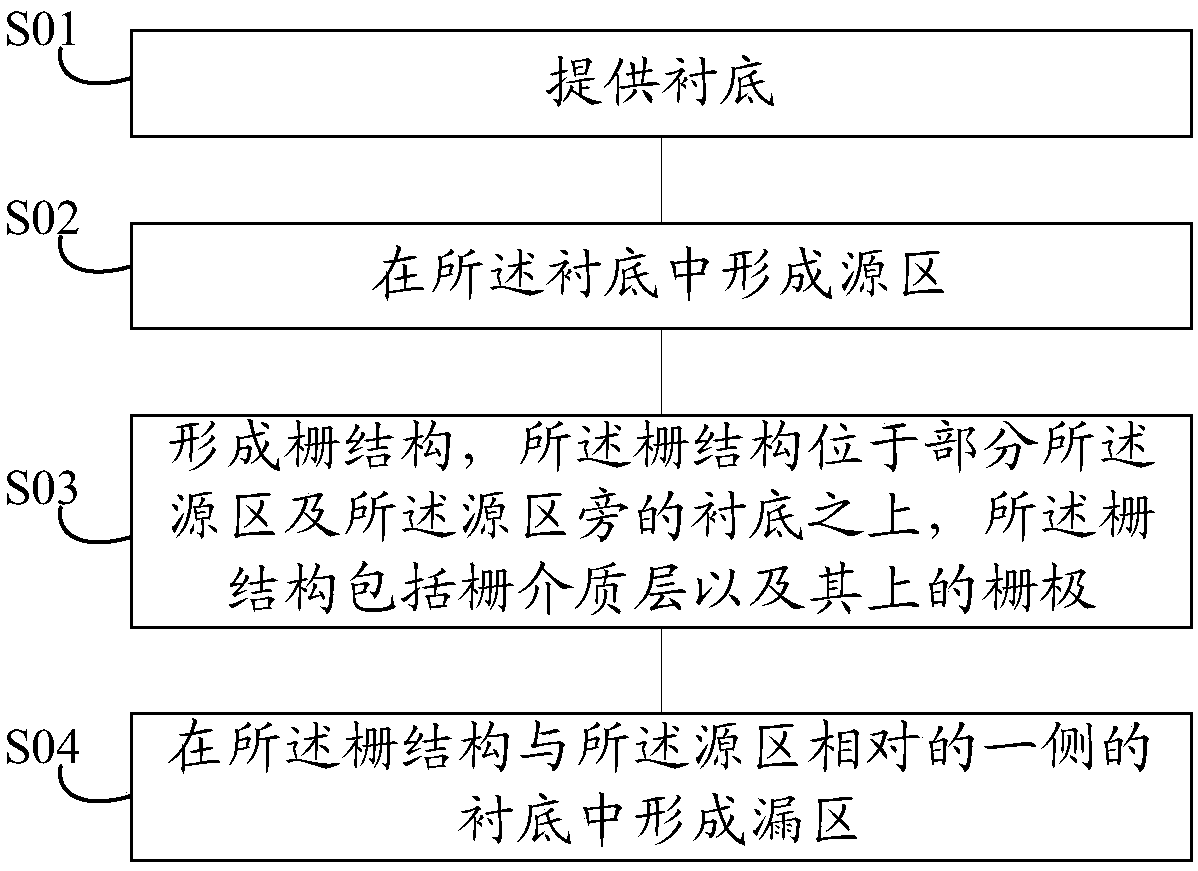

InactiveCN108321197AImproved Potential Control CapabilityIncrease the on-state currentSemiconductor/solid-state device manufacturingDiodeCapacitancePower flow

The present invention provides a tunneling field effect transistor and a manufacturing method thereof. A formed source region is located below part of a gate structure and in a substrate of the side of the gate structure, that is to say, the gate structure alternately covers part of the source region, so that the potential control capacity of a gate voltage on a device source region / channel regionis improved, further, the area of the source region is larger than the area of a drain region, the dosage concentration of the source region is higher than the dosage concentration of the drain region to allow the carrier concentration of the source region to be higher than the carrier concentration of the drain region as a whole, the finally formed gate electrode with a ferroelectric gate layerhas a negative capacitance effect to amplify the gate electrode surface potential, and therefore, the tunneling probability of a device can be increased, and an ON state current of the device can be integrally improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

Tunneling field effect transistor capable of increasing current switching ratio

ActiveCN106098765AGood offMitigate bipolar effectsSemiconductor devicesVery large scale integrated circuitsCMOS

The invention belongs to the logic device and circuit field in the super-large scale integrated circuit field and relates to a tunneling field effect transistor capable of increasing a current switching ratio. According to the tunneling field effect transistor, a low-K dielectric region is arranged between a source region and a drain region, so that an electric field between the source region and an intrinsic region can be increased, and therefore, on-state current can be improved, and off-state current can be suppressed; a doped layer is adopted, so that a reversely biased PN junction can be formed based on the substrate, and therefore, the contact of a source region-low-K dielectric region-drain region structure with the substrate can be isolated, and the off-state current of the tunneling field effect transistor (TFET) can be decreased. An on-state current increasing mode and an off-state current suppressing mode can be combined and overlapped with each other. Thus, the tunneling field effect transistor of the invention can improve the on-state current, is compatible with conventional CMOS technologies, is low in cost and can achieve a high current switching ratio.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Tunneling field effect transistor and manufacturing method thereof

InactiveCN105633147ASmall sizeMeet the ever-reducing size requirementsSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricInsulation layer

The present invention provides a tunneling field effect transistor. The tunneling field effect transistor comprises: a substrate; a drain region with a first doped type disposed on the substrate; a channel region arranged above the drain region; a source region with a second doped type arranged above the channel region; a drain region connection region, arranged on the substrate, connected with the side wall of the drain region; a gate dielectric layer arranged at the side walls of the source region, the drain region and channel region; a gate electrode arranged at the side wall of the gate dielectric layer; and an insulation layer between the gate electrode and the drain region connection region. According to the invention, a source region and a drain region are formed in the vertical direction of the substrate, and a tunneling field effect transistor with a vertical structure is formed; and moreover, the tunneling field effect transistor has smaller size of a device to satisfy the requirement of continuously decreased size of the device, so that the integration level is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

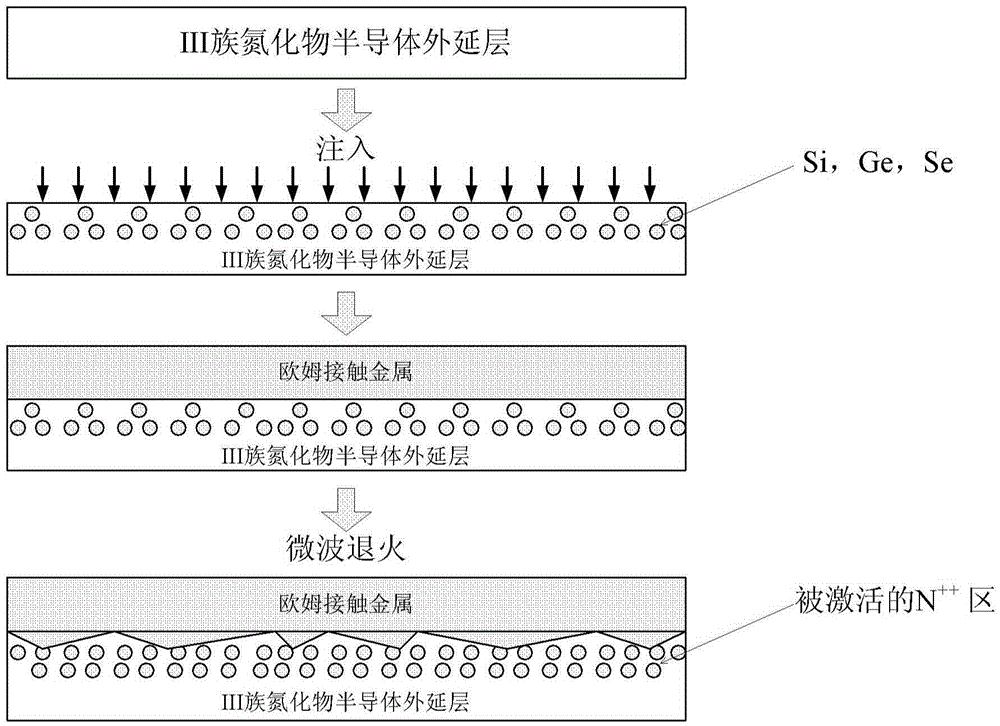

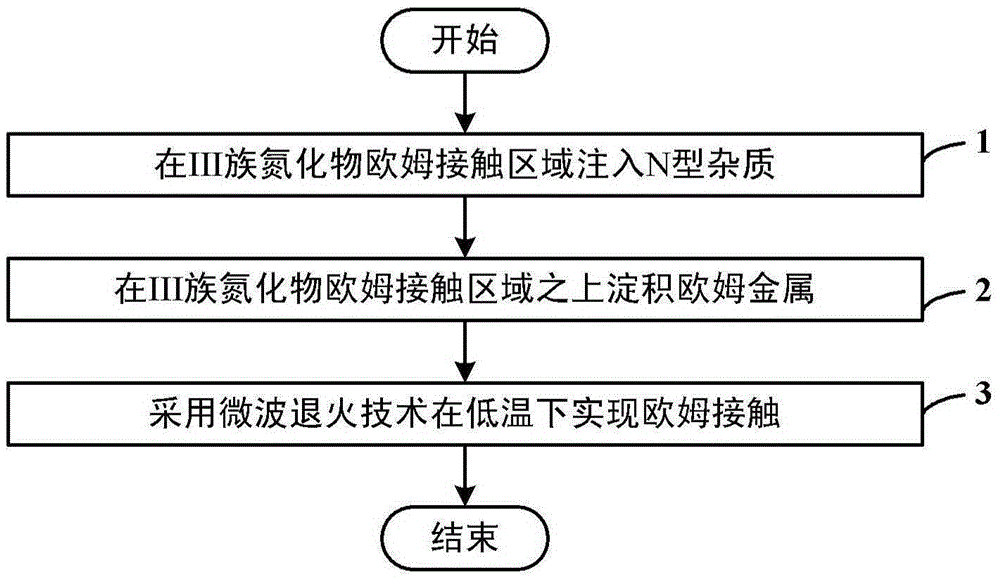

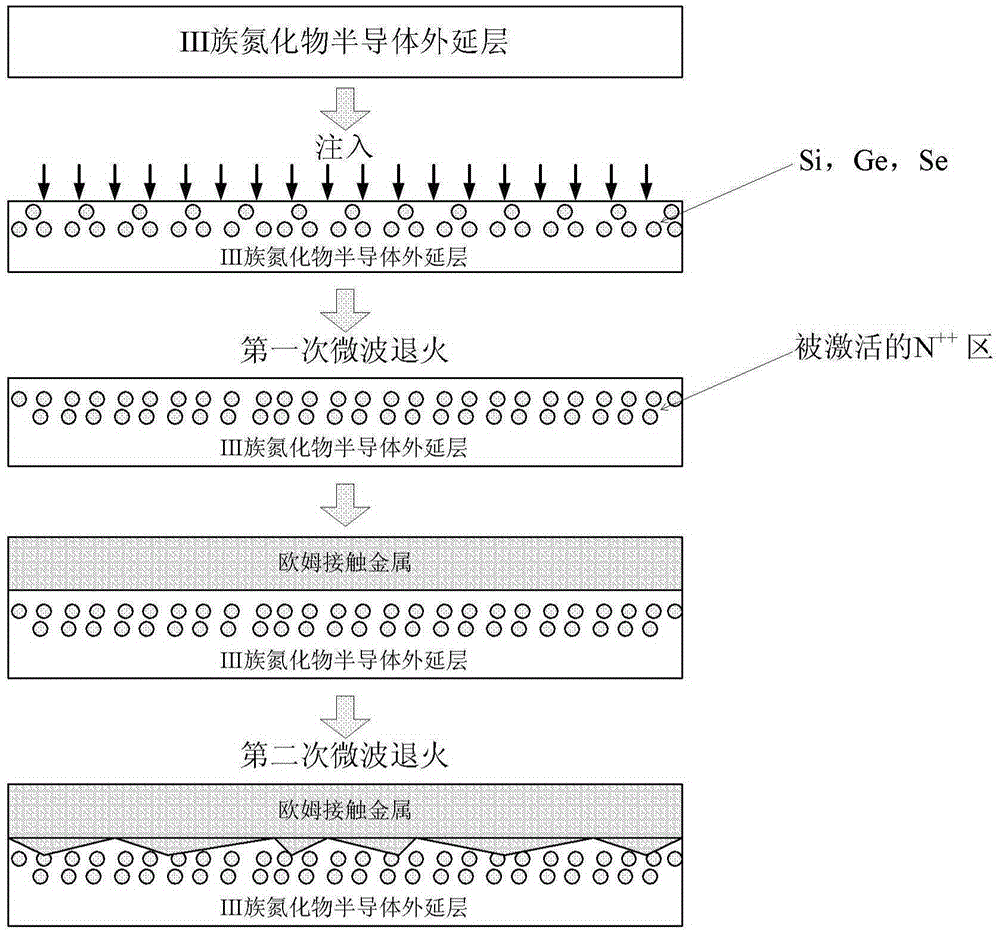

Manufacturing method of low-temperature ohmic contact of III group nitride electronic device

InactiveCN105390382AIncreased chance of electron tunnelingReduced ohmic contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactMetal

The invention discloses a manufacturing method of low-temperature ohmic contact of a III group nitride electronic device. The manufacturing method comprises the steps of: injecting N type impurities in a III group nitride ohmic contact region; depositing ohmic metal on the III group nitride ohmic contact region injected with the N type impurities; and adopting a microwave annealing technology to achieve ohmic contact at low temperature. After the N type impurities are injected to the III group nitride ohmic contact region, the manufacturing method further comprises the step of adopting the microwave annealing technology to activate the injected N type impurities. The microwave annealing technology utilizes the microwave annealing technology to achieve the low-temperature activation of the injected N type impurities in III group nitrides, so as to form an N type heavily-doped layer, increase electronic tunnelling probability, and reduce ohmic contact resistance; furthermore, the manufacturing method can enhance the interface reaction between the ohmic metal and the III group nitride semiconductor, reduce contact-potential barrier, improve ohmic contact area, and further reduce the contact resistance.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

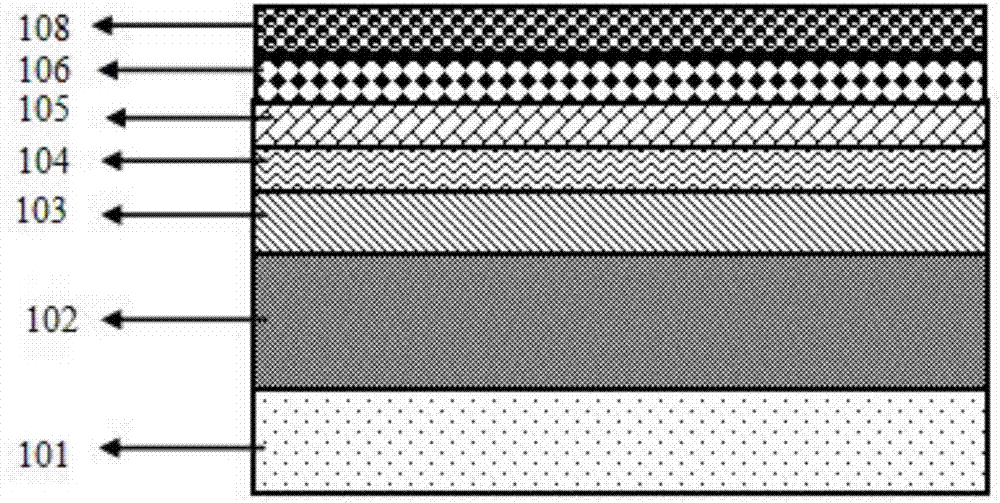

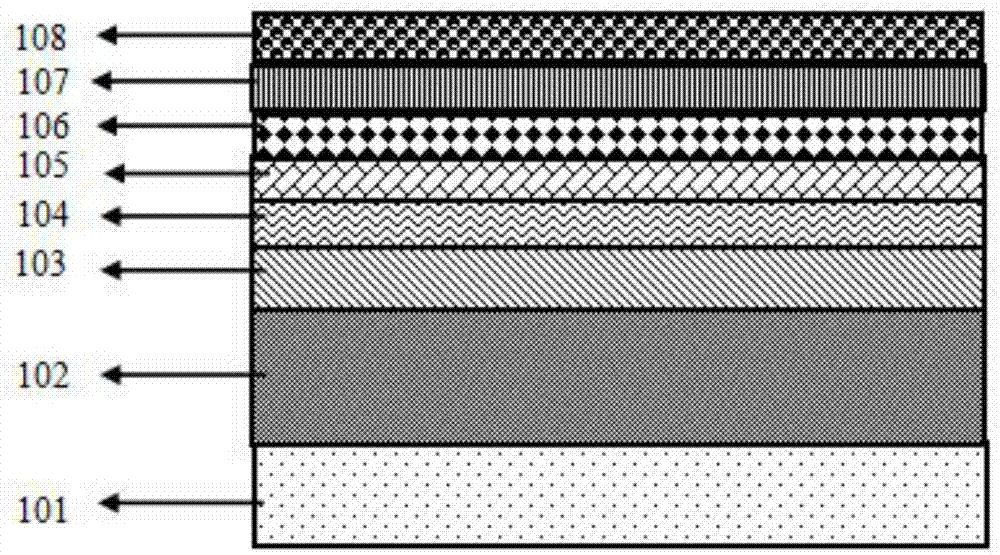

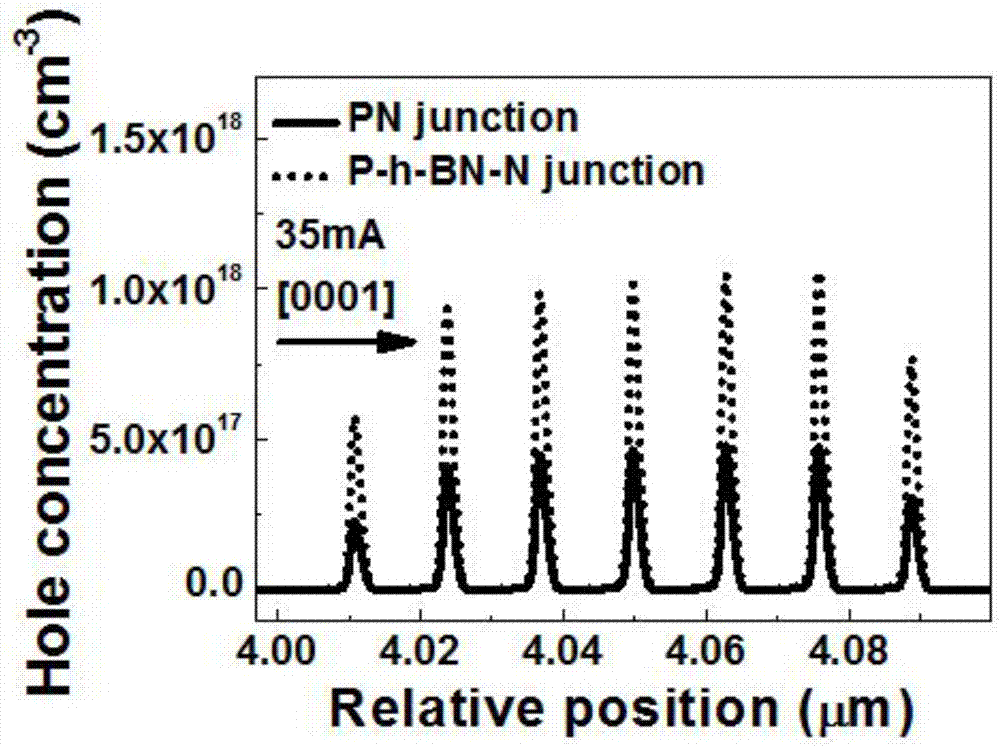

LED epitaxial structure based on h-BN tunnel junction as hole injection layer

ActiveCN107293624AIncrease chance of tunnelingEnhanced electric fieldSemiconductor devicesDielectricSemiconductor materials

The invention relates to an LED epitaxial structure based on an h-BN tunnel junction as a hole injection layer. The invention is characterized in that the epitaxial structure comprises a substrate, an n-type semiconductor material layer, a multi-quantum well layer, a p-type electronic blocking layer, a p-type semiconductor material layer, a p-type heavily doped semiconductor material layer, an h-BN layer and an n-type heavily doped semiconductor material layer, the relative dielectric constant of the n-BN layer is 3-5.1, the relative dielectric constant is less than the relative dielectric constant of the p-type heavily doped semiconductor material layer and the n-type heavily doped semiconductor material layer, the thickness of the h-BN layer is 1nm-5nm; and the p-type heavily doped semiconductor material layer, the h-BN layer and the n-type heavily doped semiconductor material layer constitute a tunnel junction together. The LED epitaxial structure has a tunnel junction structure capable of improving the hole injection efficiency of an LED device, thereby increasing the tunneling probability of carriers, improving the current expansion effect, and significantly improving the quantum efficiency and light output power in the LED.

Owner:HEBEI UNIV OF TECH

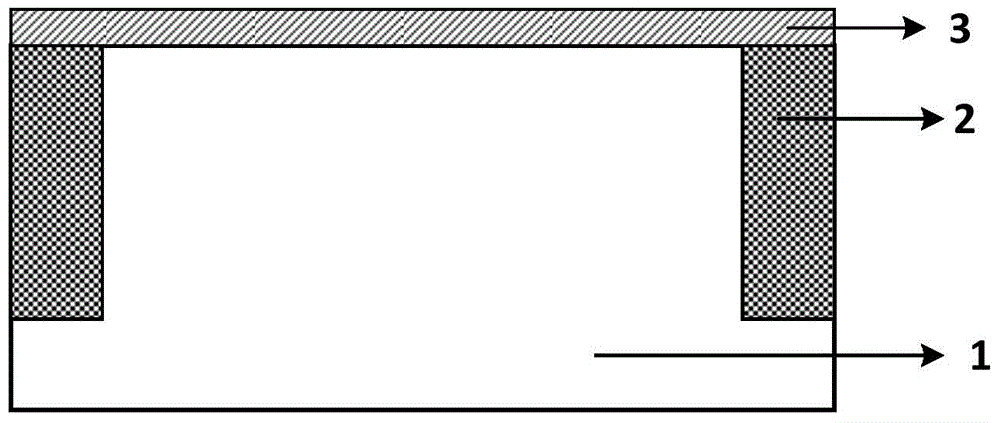

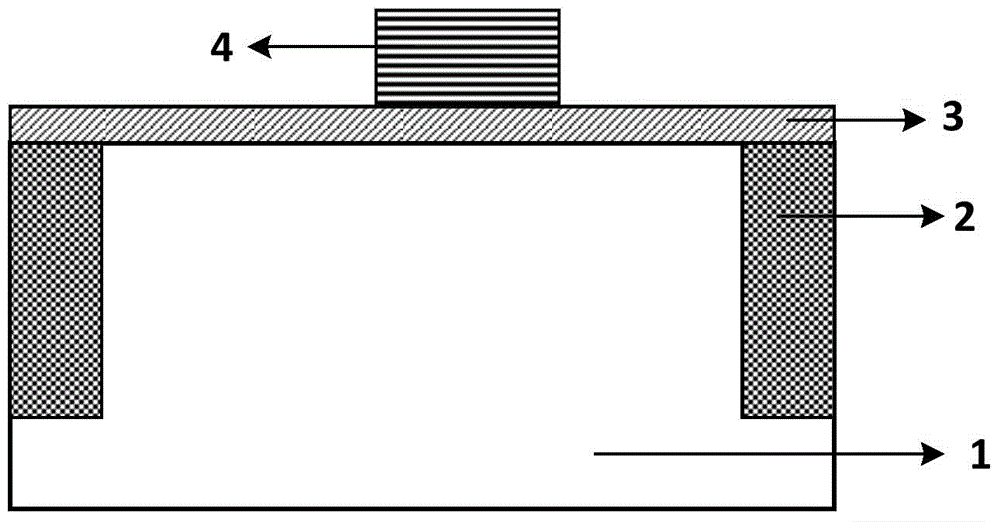

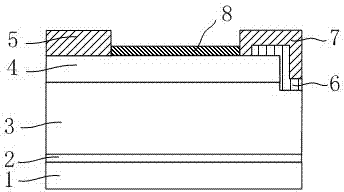

Schottky barrier metal oxide semiconductor (MOS) transistor and preparation method thereof

ActiveCN102324434AReduce parasitic resistanceEliminate uncovered areasSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate dielectric

The invention discloses a Schottky barrier metal oxide semiconductor (MOS) transistor, which comprises a ring-shaped gate electrode (3), a ring-shaped gate dielectric layer (2), a ring-shaped gate electrode side wall (4), a semiconductor substrate, a source region (5) and a ring-shaped drain region (6). The Schottky barrier MOS transistor is characterized in that: the semiconductor substrate is provided with a convex step structure; the source region is positioned on a high plane of a convex step; the ring-shaped drain region surrounds the convex step and is positioned on a low plane; the gate dielectric layer and the gate electrode are positioned at a corner of the convex step, surrounds the step and is raised into a ring shape; and the gate electrode side wall is ring-shaped, surrounds on the outer side of the gate electrode and has a certain thickness to serve as a shelter to form an underlap structure of a drain terminal. The Schottky barrier MOS transistor adopts a step structurecombining a ring-shaped gate structure and an asymmetric source / drain structure, so on the basis of inheriting advantages of traditional SB-MOSFET, the on-state conduction current is improved, a dipolar effect is inhibited, and the process is simplified.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

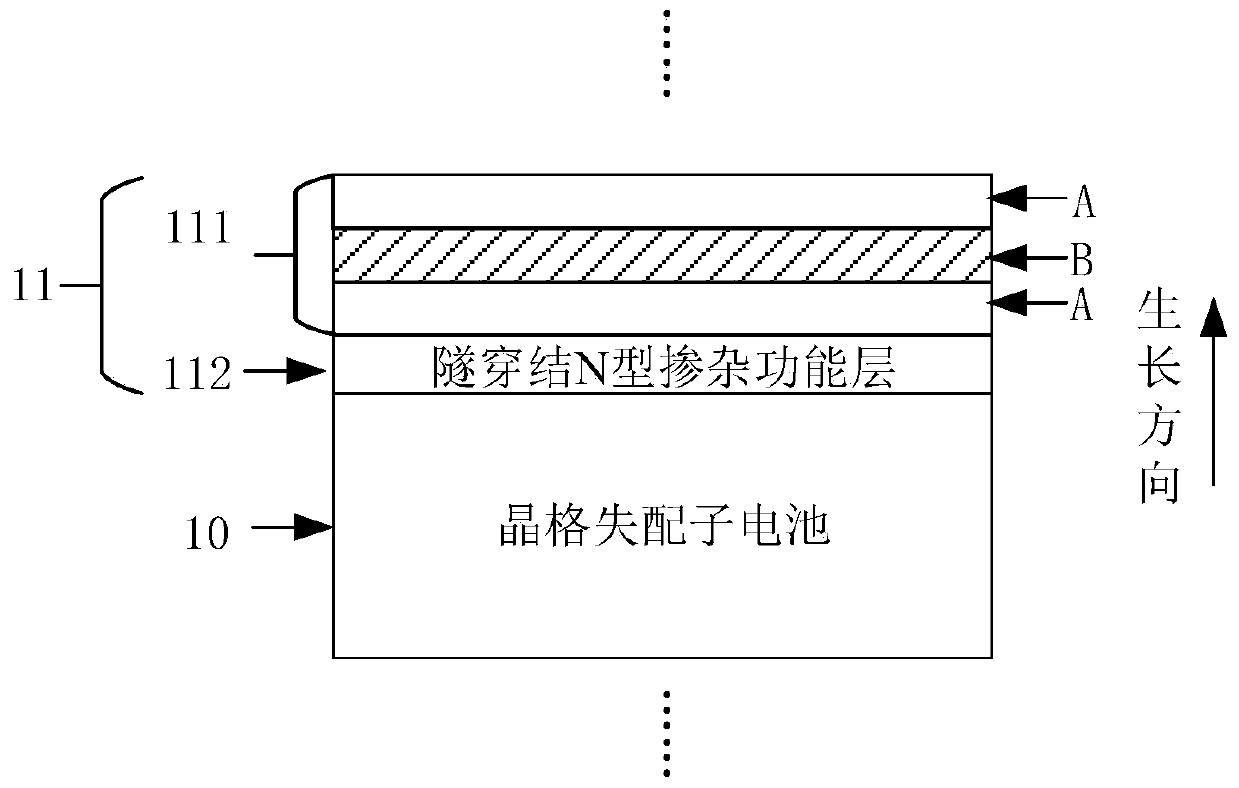

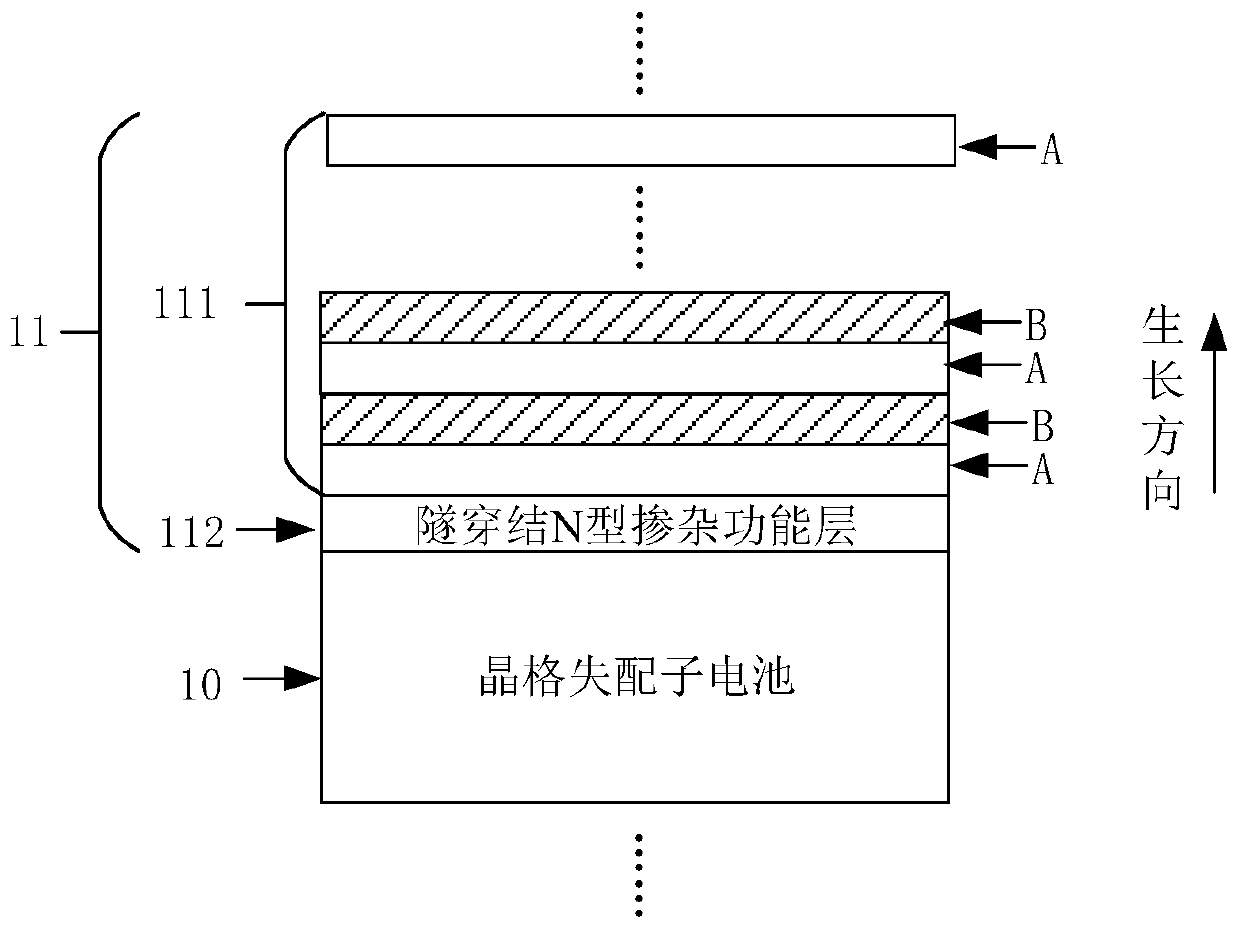

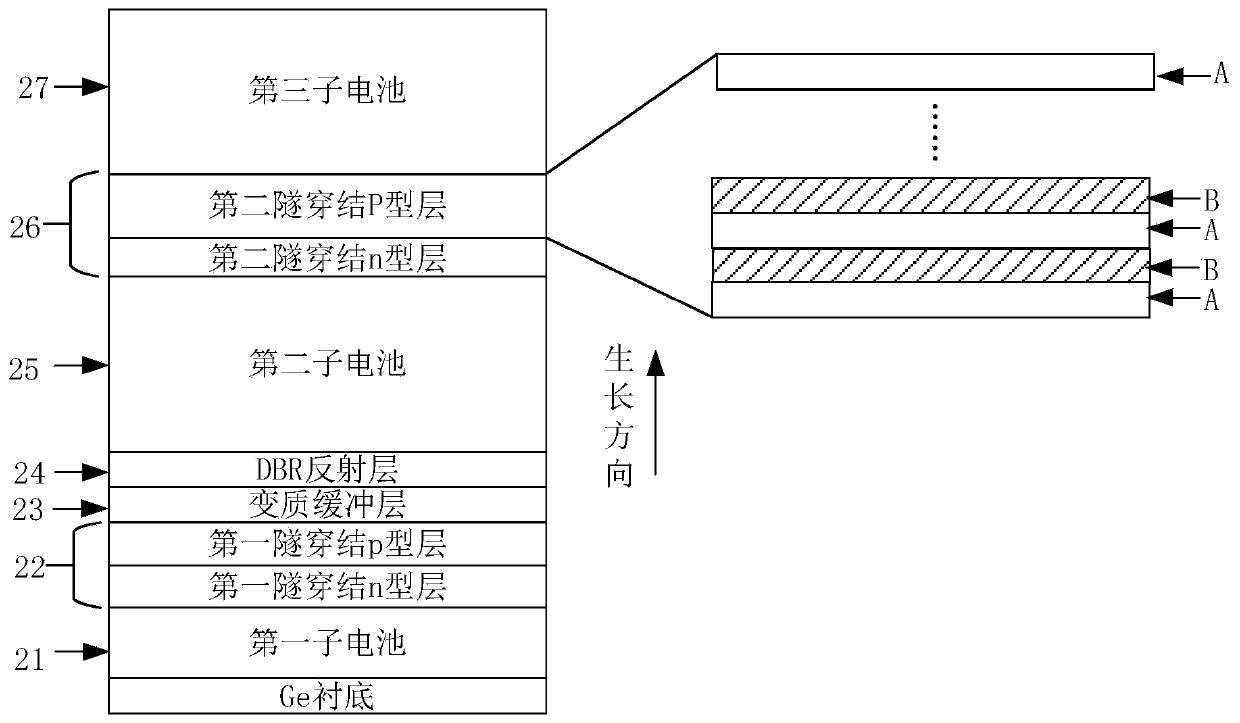

Lattice mismatch multi-junction solar cell

ActiveCN110224036AAvoid mismatchInhibited DiffusionNanotechnologyPhotovoltaic energy generationP type dopingLattice mismatch

The invention provides a lattice mismatch multi-junction solar cell. The lattice mismatch multi-junction solar cell comprises at least one crystal lattice mismatch sub cell and a tunneling junction grown on the crystal lattice mismatch sub cell; the P-type doping functional layer of the tunneling junction is a C-doped p-type AlxGaAs layer / Zn-doped p type AlyInGaAs layer / C-doped p-type AlxGaAs layer, or after the C-doped p-type AlxGaAs layer / Zn-doped p type AlyInGaAs layer alternately grow for N periods, and then the superlattice structure of the C-doped p-type AlxGaAs is grown. A new structureis adopted to replace the C-doped p type (Al) InGaAs layer in the prior art, so that the problem of InGaAs lattice mismatch with the body material in the solar cell caused by suppression of In component access due to the doped reaction source halogen in the p type AlyInGaAs, so that the photoelectric conversion efficiency of the solar cell is improved.

Owner:YANGZHOU CHANGELIGHT

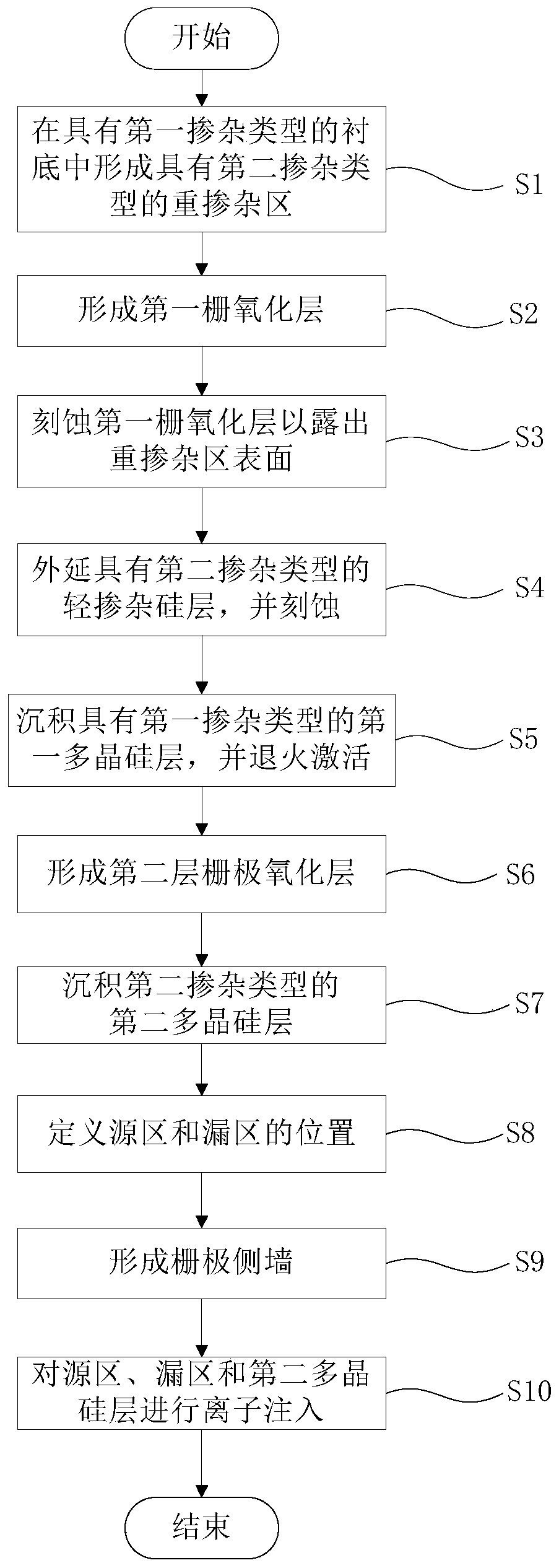

Semi-floating gate transistor of epitaxial TFET channel and preparation method thereof

ActiveCN110416287AIncrease chance of tunnelingAccelerateTransistorSemiconductor/solid-state device manufacturingPhysicsElectric field

The invention belongs to the technical field of semiconductors, and particularly relates to a semi-floating gate transistor of an epitaxial TFET channel and a preparation method of the semi-floating gate transistor. The semi-floating gate transistor provided by the invention comprises a substrate having a heavily-doped region of a first doping type and a heavily-doped region of a second doping type; a first gate oxide layer which partially covers the heavily-doped regions; a lightly-doped silicon layer which is arranged on the surfaces of the heavily-doped regions and extends to cover a part of the first gate oxide layer; a first polycrystalline silicon layer which is of a first doping type, is arranged on the first gate oxide layer and covers a part of the lightly-doped silicon layer; a second gate oxide layer which is arranged on the first polycrystalline silicon layer and the lightly-doped silicon layer; a second polycrystalline silicon layer which is of a second doping type and isarranged on the second gate oxide layer; a gate sidewall; a source region and a drain region which are arranged in the substrate and on two sides of the grid side wall. According to the invention, theslope of the electric fields of the channel and the drain terminal along with the position change is increased, so that the tunneling of the TFET is changed from point tunneling to surface tunneling,the tunneling probability of the semi-floating gate transistor is greatly improved, and the speed of the device is improved.

Owner:FUDAN UNIV +1

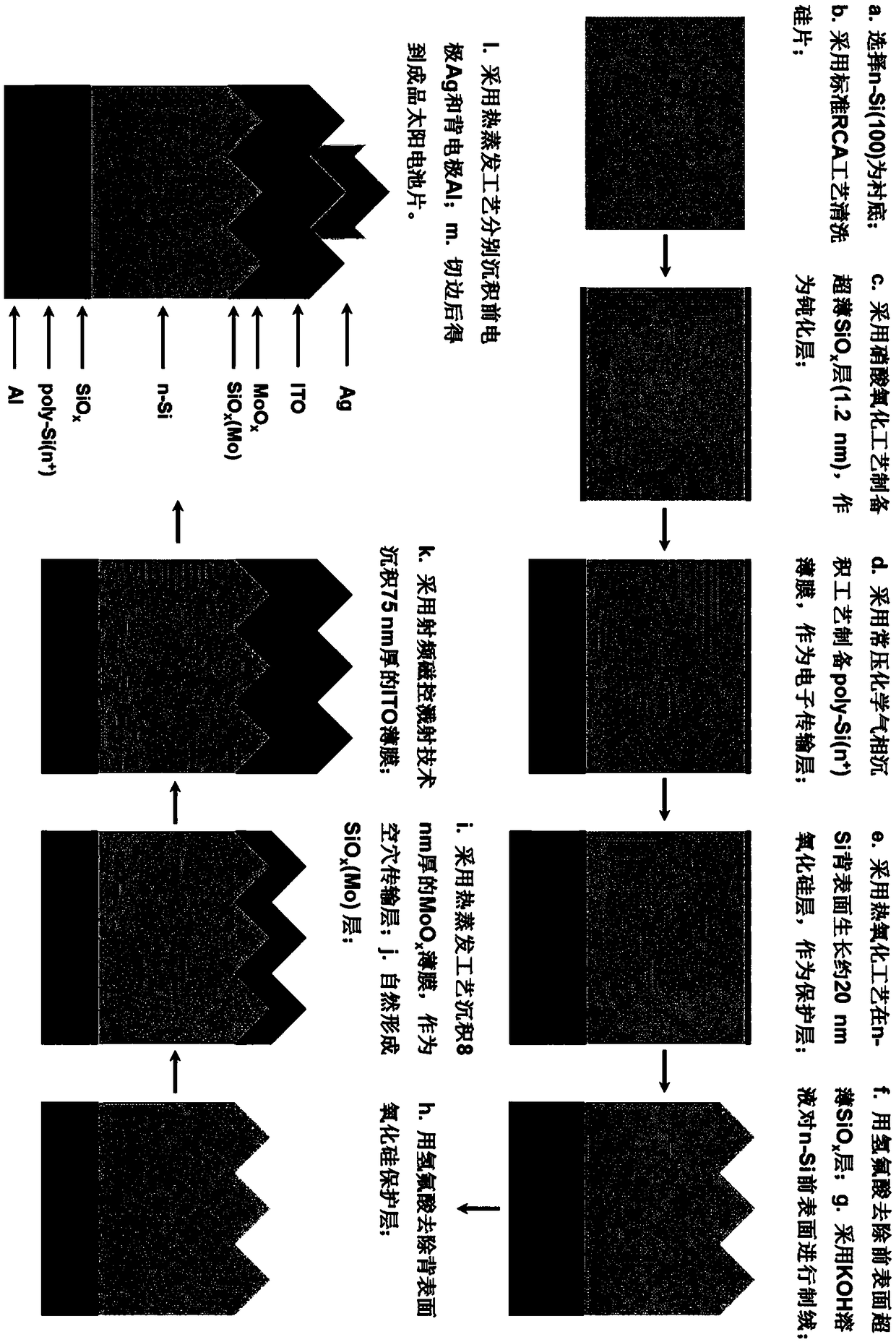

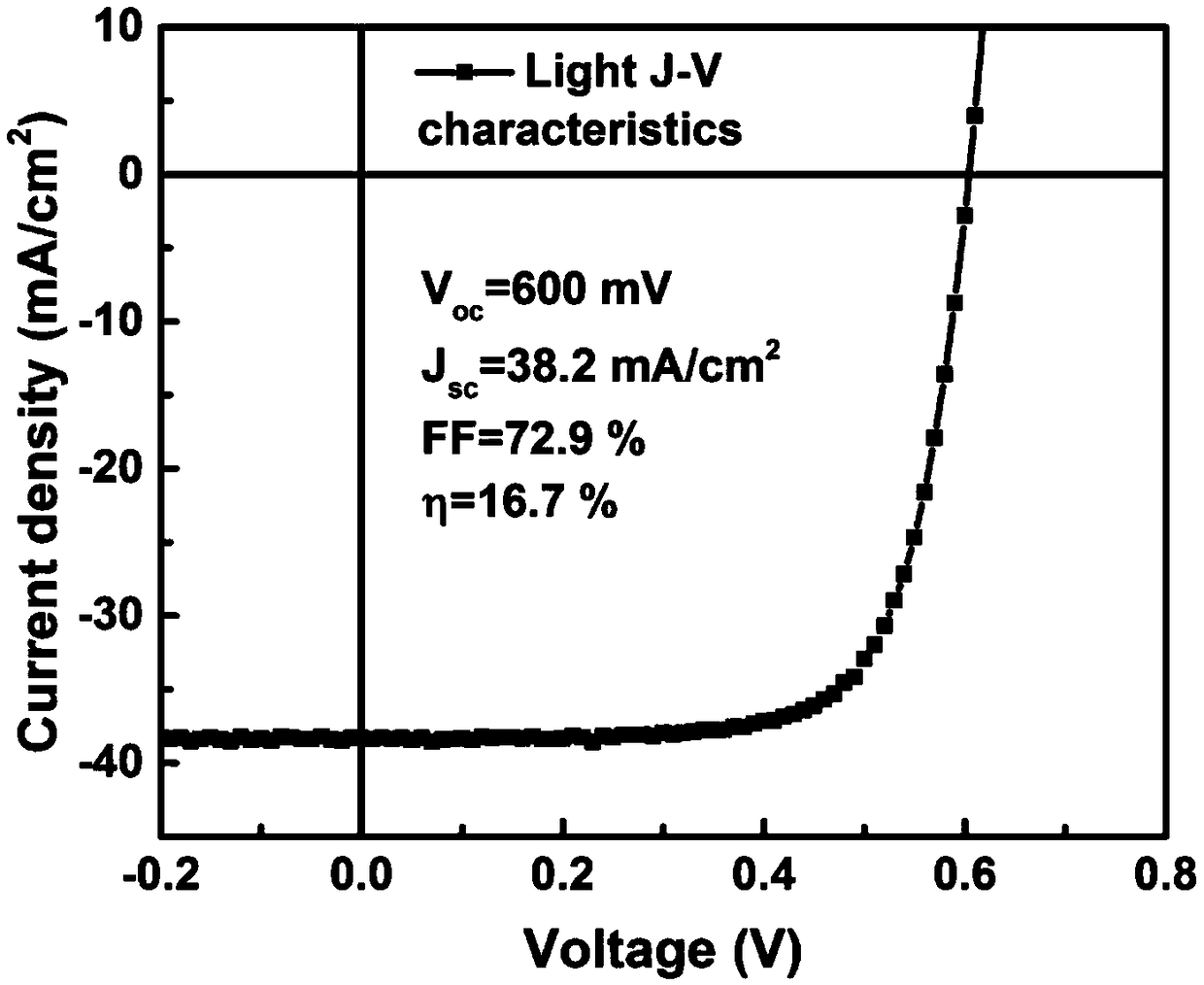

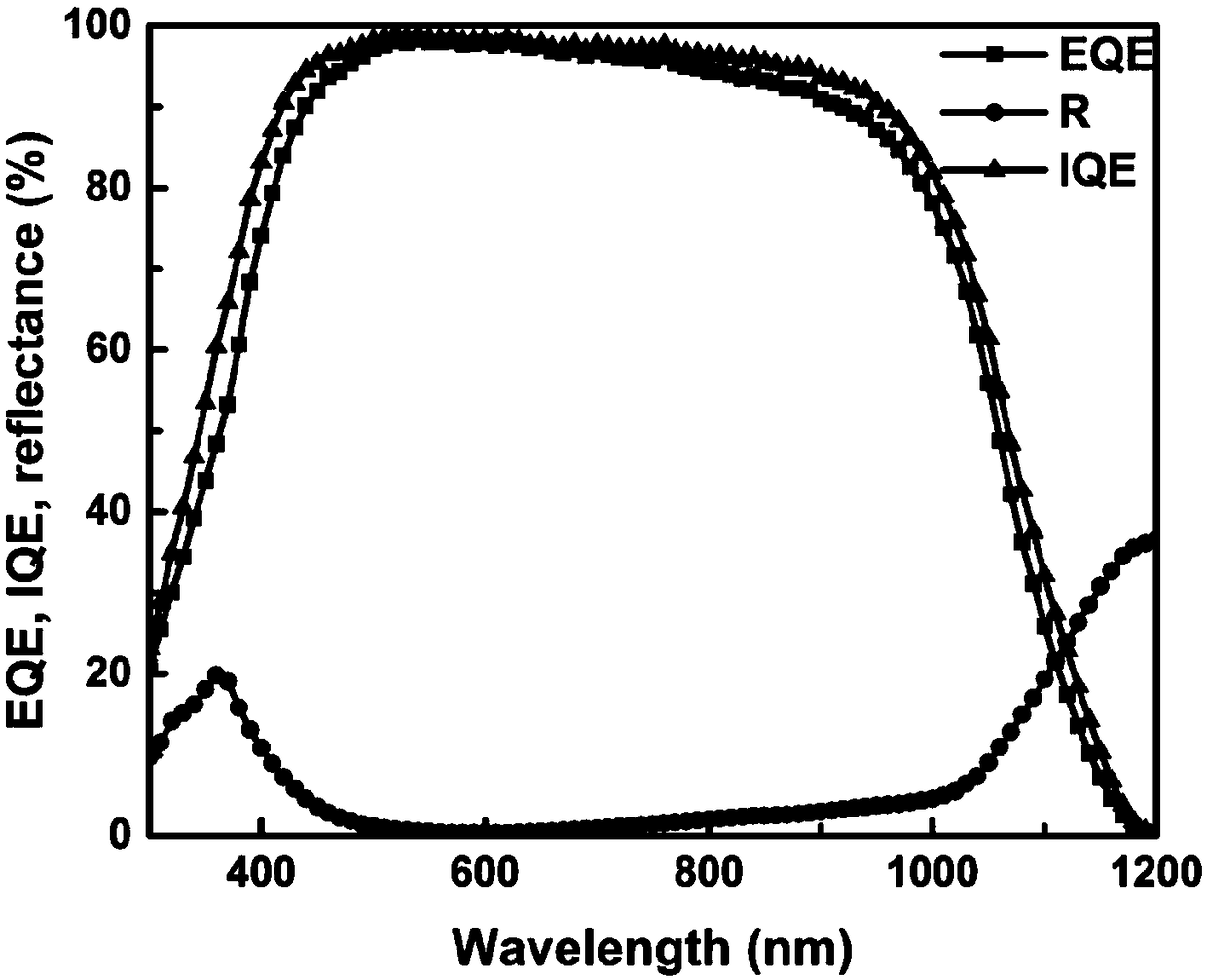

Hole selective MoO<x>/SiO<x>(Mo)/n-Si heterojunction, solar cell device and fabrication method of solar cell device

ActiveCN108878570AImprove stabilityImprove photovoltaic conversion efficiencyFinal product manufacturePhotovoltaic energy generationHeterojunctionSurface cleaning

The invention discloses a hole selective MoO<x> / SiO<x>(Mo) / n-Si heterojunction, a solar cell device and a fabrication method of the solar cell device. The fabrication method comprises the steps of depositing a MoO<x> thin film by taking a single-crystal silicon wafer as a substrate, and enabling MoO3 molecular groups in vapor steam, Mo, O atoms and silicon atoms in a shallow layer of the single-crystal silicon wafer to generate solid-phase reaction to form an ultrathin SiO<x>(Mo) layer by hot evaporation; and forming a functional layer structure body of an interface composite solar cell device, and fabricating an IOT thin film and an electrode to obtain a solar cell piece. The MoO<x> / SiO<x>(Mo) / n-Si heterojunction solar cell is fabricated by combining a crystal silicon surface cleaning process, a MnO<x> thin film deposition process by hot evaporation, a low-energy vapor steam solid-phase reaction method, a ITO thin film deposition process by radio-frequency magnetron sputtering, a nitric acid oxidization process, a normal-pressure chemical vapor deposition thin film process and a hot evaporation metal electrode process, and has relatively good stability and relatively high photoelectric conversion efficiency.

Owner:SHANGHAI UNIV

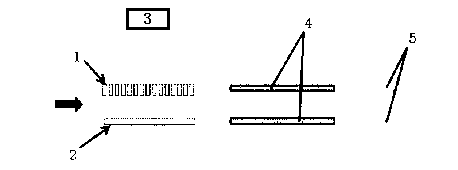

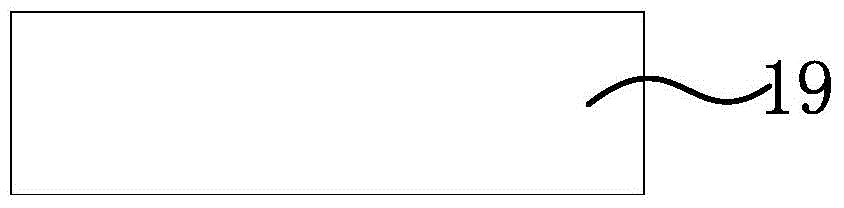

Tunneling field effect transistor and preparation method thereof

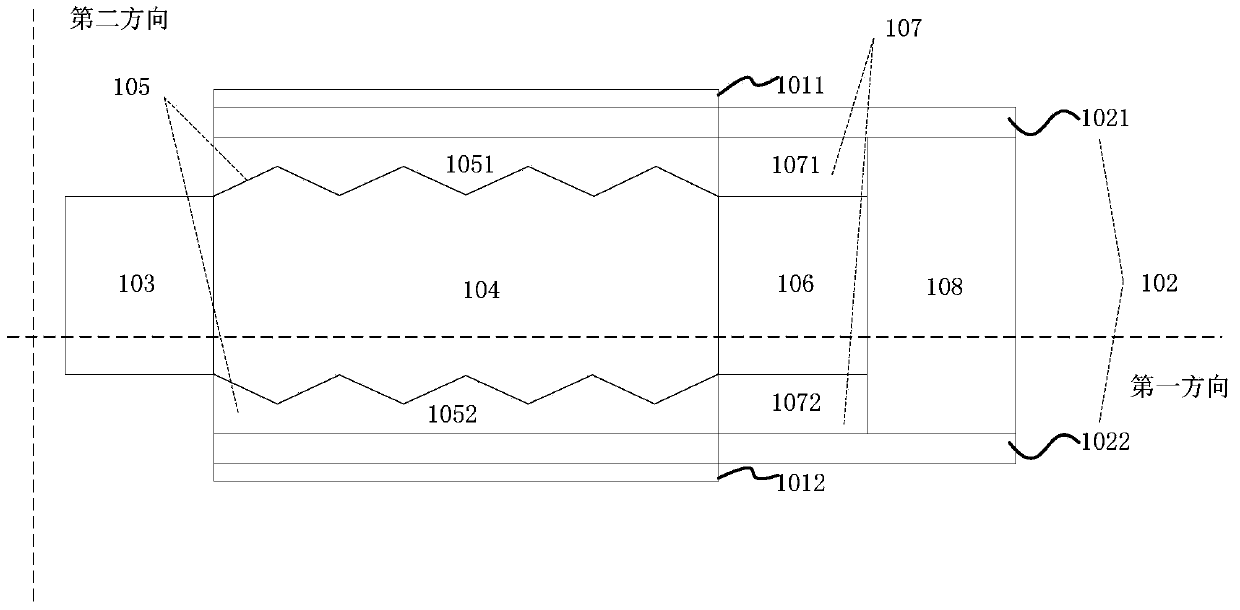

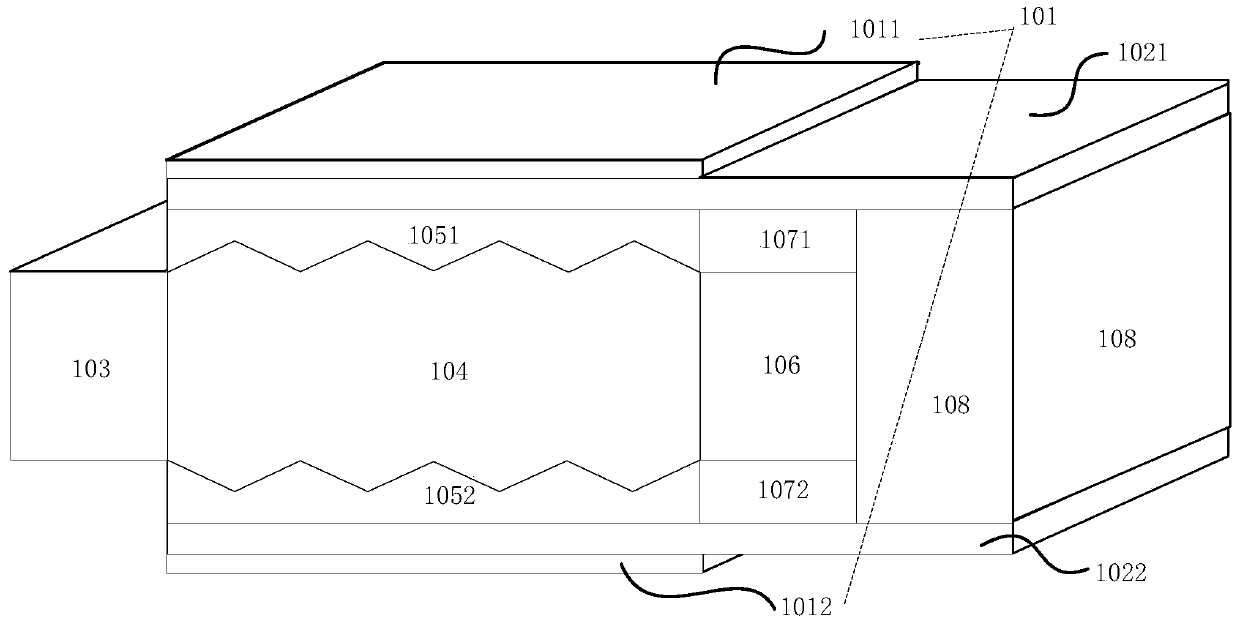

ActiveCN104617138ALarge tunneling areaIncrease chance of tunnelingSemiconductor/solid-state device manufacturingDiodeMedia layerElectron

Disclosed is a tunneling field effect transistor. The tunneling field effect transistor comprises a source region, two drain regions and two grid regions. The two drain regions are arranged on opposite two sides of the source region in a first direction; the two grid regions are arranged on opposite two sides of the source region; first extension layers and grid medium layers are arranged between the source region and the two grid regions, wherein the first extension layers are arranged between the source region and the grid medium layers and form tunneling junction with the source region; the two drain regions and the two grid regions are arranged around the source region, so that the source region can be completely under the control of the two grid regions, and current carrying electrons in the overlapped regions of the source region and the grid regions can tunnel under the action of the electric field of the grid regions; the first extension layers are arranged between the source region and the grid medium layers and is of a linear tunneling mode, thereby being large in tunneling area; the direction of the electric field of the grid regions and the tunneling direction of the electrons of the source region are on the same line, so that high tunneling probability can be achieved, and tunneling current can be increased. Besides, the invention also provides a preparation method of the tunneling field effect transistor.

Owner:HUAWEI TECH CO LTD

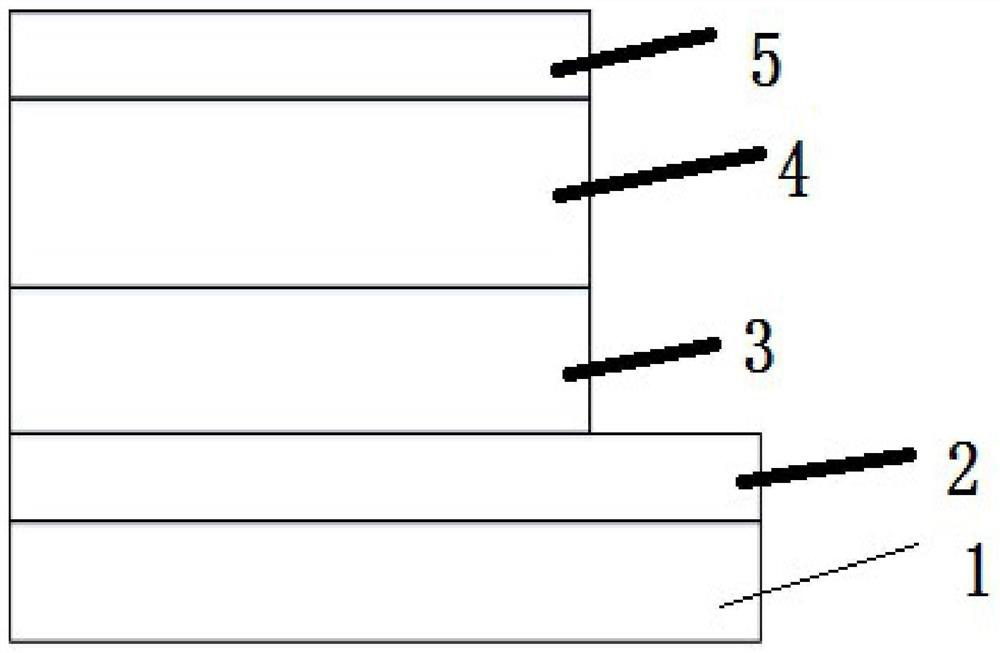

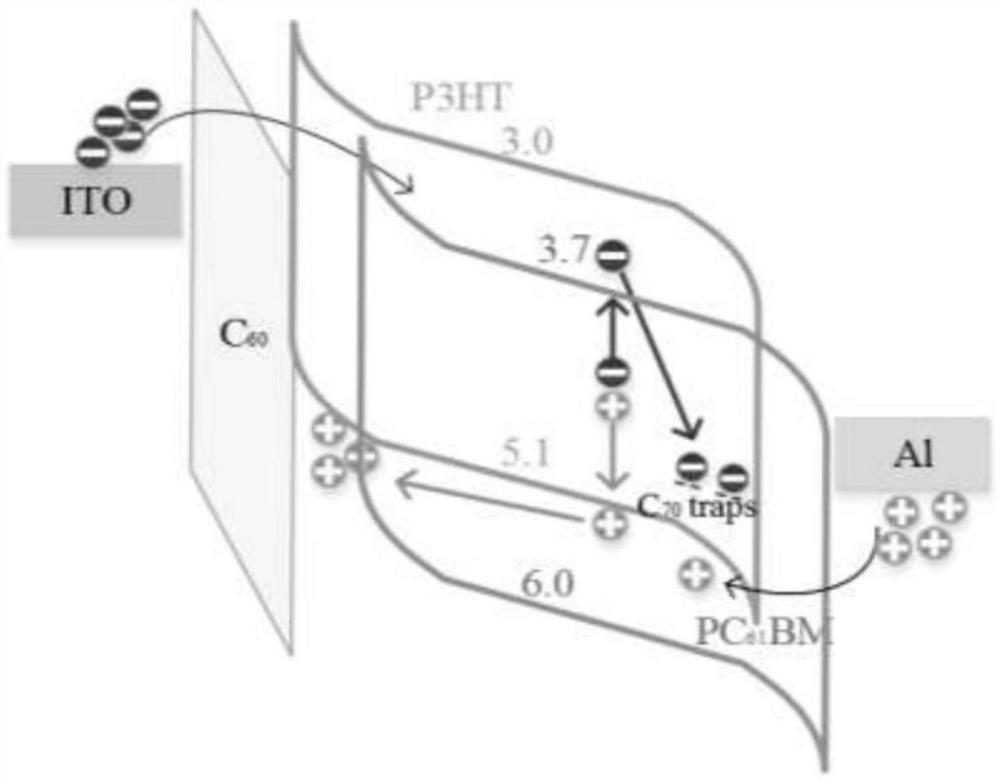

Double-injection multiplication type organic photoelectric detector and preparation method thereof

ActiveCN111883664AImprove photoelectric performanceIncrease chance of tunnelingFinal product manufactureSolid-state devicesHeterojunctionPhotocurrent

The invention discloses a double-injection multiplication type organic photoelectric detector and a preparation method thereof, and the double-injection multiplication type organic photoelectric detector comprises a glass substrate, wherein the surface of the glass substrate is plated with an ITO electrode layer, and the ITO electrode layer is sequentially coated with an anode buffer layer, an active layer and an Al electrode layer from bottom to top; the anode buffer layer is made of C60, the active layer is made of a mixture of P3HT, PC61BM and C70, and the P3HT, the PC61BM and the C70 forma bulk heterojunction. C60 is added into the device to serve as a hole blocking layer, and meanwhile, a small amount of C70 material is doped into an active layer to serve as an electron trap, so tunneling injection of holes is increased, external quantum efficiency is improved, photocurrent is reduced, and photoelectric performance of the detector is improved; the working voltage is small, and the circuit can work under a small bias voltage of 1V; the preparation method of the double-injection multiplication type organic photoelectric detector is simple to operate and easy to implement.

Owner:XIAN UNIV OF TECH

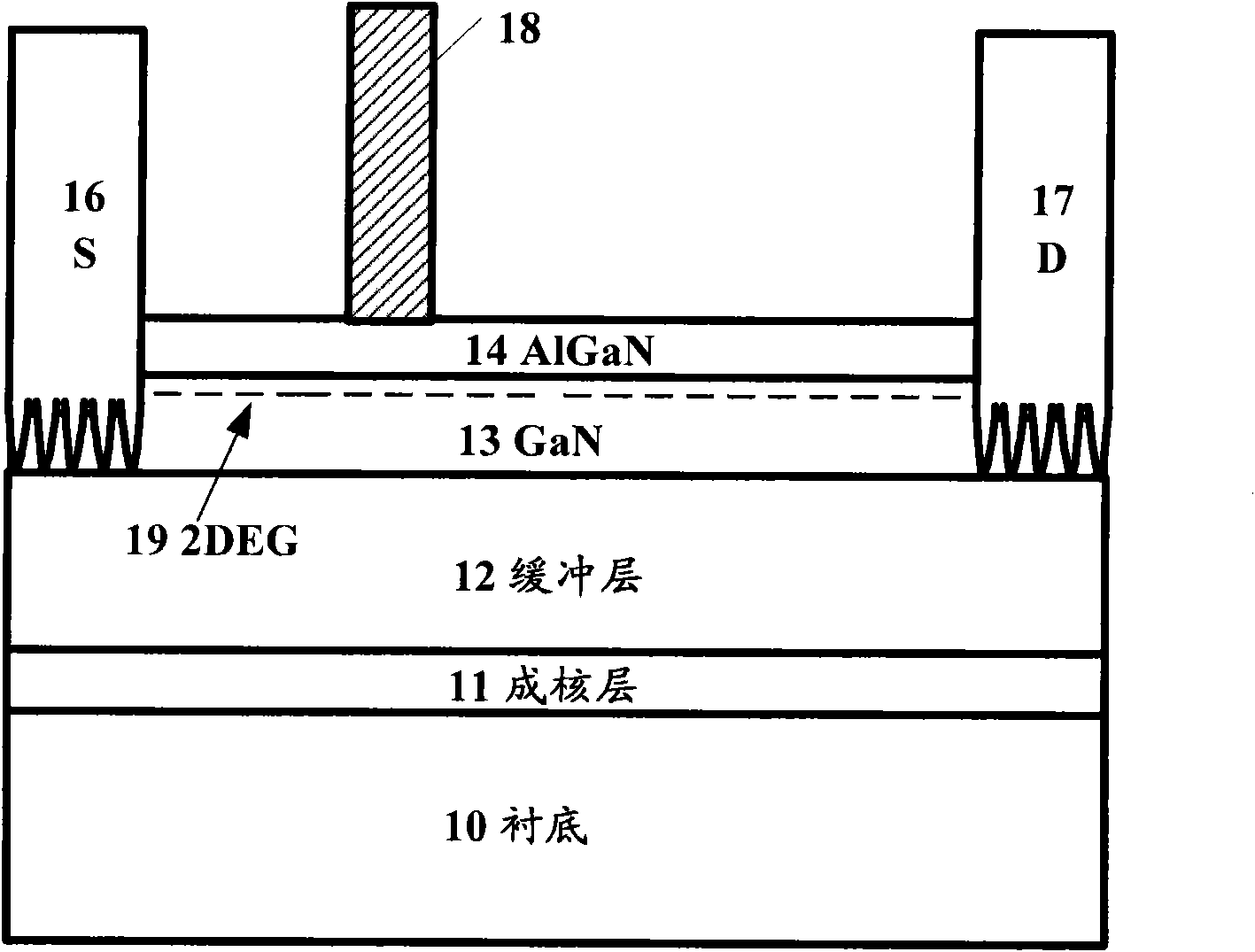

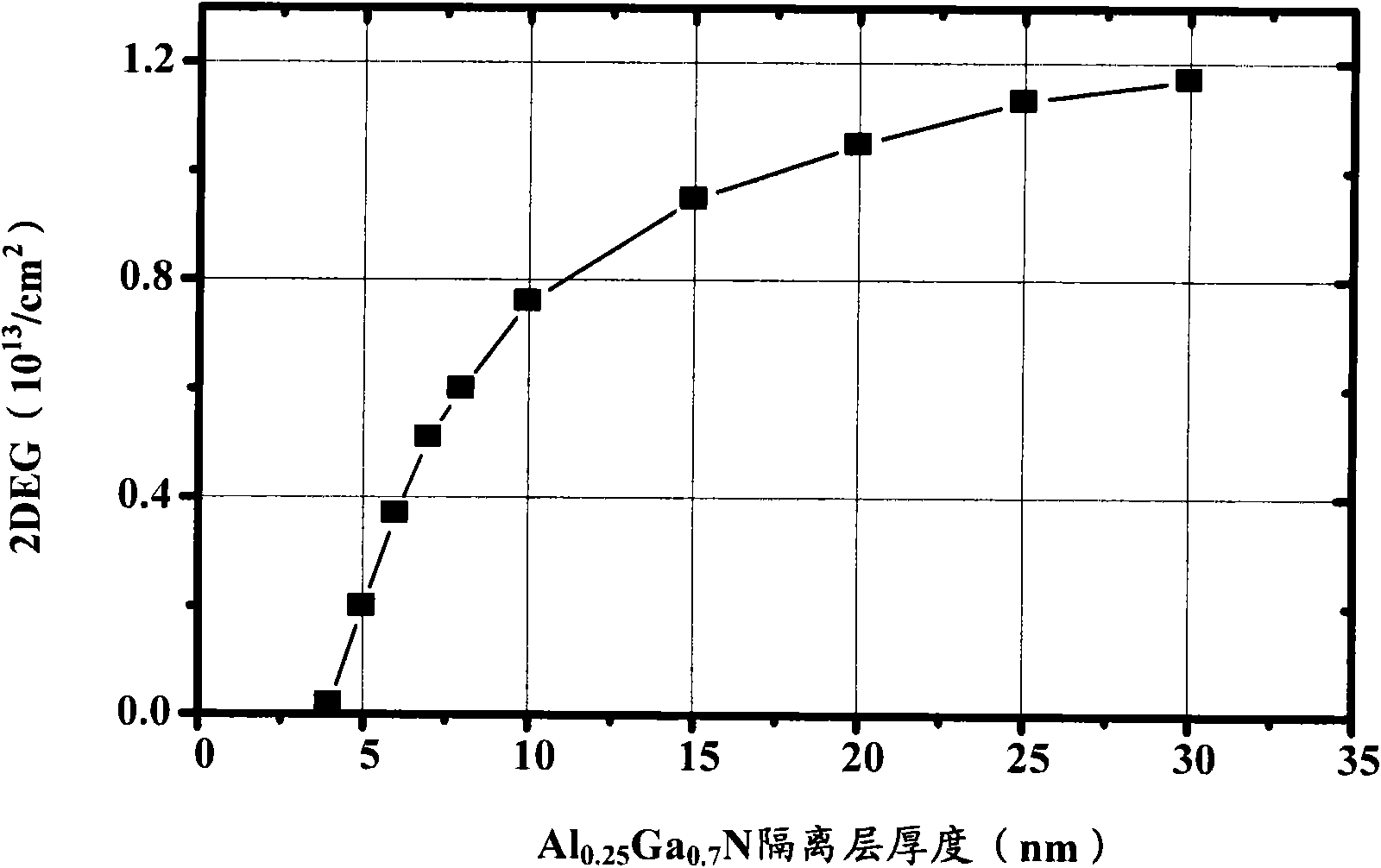

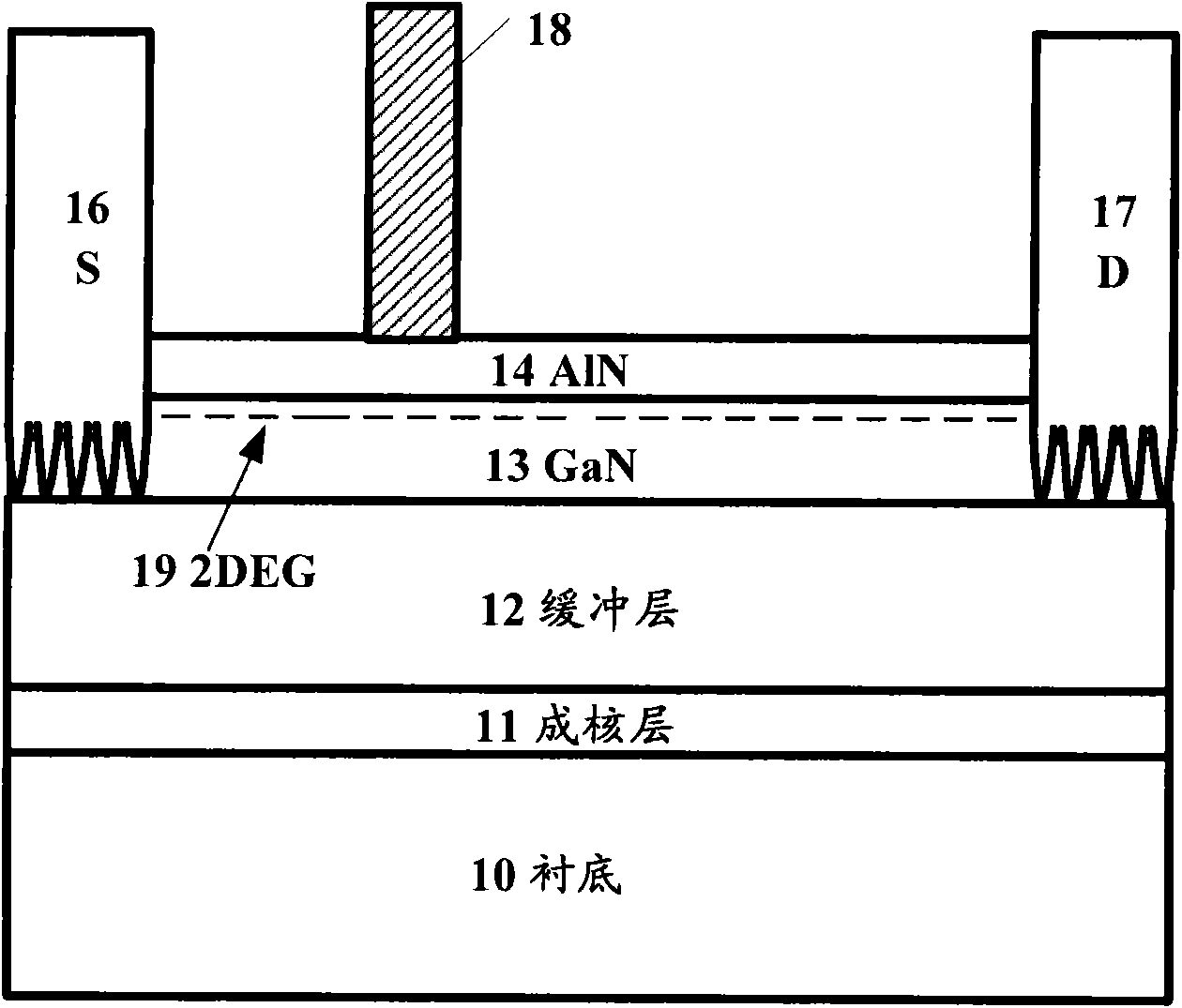

Semiconductor device and making method thereof

ActiveCN102315261AIncrease chance of tunnelingReduce contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceIsolation layer

The invention relates to a semiconductor device and a making method thereof. The semiconductor device comprises a semiconductor layer on a substrate, an isolation layer on the semiconductor layer, an n-type doped layer on the isolation layer, and a source and a drain which are electrically communicated with the semiconductor layer, and a gate which is arranged on the isolation layer and isolated with the n-type doped layer.

Owner:DYNAX SEMICON

Impurity segregation and Schottky source drain component and manufacturing method thereof

ActiveCN104134701AHighly integratedGood gating abilitySemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentSchottky barrier

An impurity segregation and Schottky source drain component comprises an annular semiconductor channel in the perpendicular direction, an annular gate electrode, an annular gate medium layer, a source area, an impurity segregation area, a drain area, an impurity segregation area and a semiconductor substrate. The source area is located at the bottom of the channel in the perpendicular direction and connected with the substrate. The impurity segregation area is located between the source area and the channel in the perpendicular direction. The drain area is located at the top of the channel in the perpendicular direction. The impurity segregation area is located between the drain area and the channel in the perpendicular direction. The gate medium layer and the gate electrode surround the channel in the perpendicular direction in an annular mode. The source area and the drain area respectively make contact with Schottky which are the same as the channel in barrier height. The source end and drain end impurity segregation areas are highly doped areas with the same kind of impurities. According to the structure, the Schottky barrier source drain structure is used for lowering the thermal budget, decreasing leak currents and simplifying technology requirements, impurity segregation is used for thinning barriers and increasing driving currents, and the channel in the perpendicular direction and the annular gate structure are used for breaking through the photo-etching limitation in the integration machining process and increasing the integration level.

Owner:PEKING UNIV

Vertically stacked gate-all-around silicon nanowire tunneling field-field transistor and preparation method thereof

ActiveCN108133960AIncrease chance of tunnelingImprove gate control abilityMaterial nanotechnologySemiconductor/solid-state device manufacturingPhysicsGate stack

The invention provides a vertically stacked gate-all-around silicon nanowire tunneling field-field transistor and a preparation method thereof. The preparation method comprises: a nanowire array and agate stacking structure surrounding the nanowire array are formed, wherein a first notch and a second notch that correspond to each other are formed at the two ends of the gate stacking structure; ahigh-k medium side wall and a low-k medium side wall are formed in the first notch and the second notch respectively; and a heavily-doped layer is formed between the high-k medium side wall and a channel layer. Because the heavily-doped layer having the type opposite to the doping type of a source region is inserted between the source region and the channel layer, the tunneling probability is increased; on the basis of the gate-all-around structure, the gate control capability is enhanced; the local electrical field is increased by introducing the high-k medium side wall into one side of the source region; with the gate-all-around nanowires stacked in a vertical direction, the effective tunneling area is extended and thus the opening current of the tunneling field-field transistor is improved obviously; and because of the low-k medium side wall at one side of the drain region, the bidirectional conduction characteristics of the tunneling field effect transistor are suppressed effectively.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

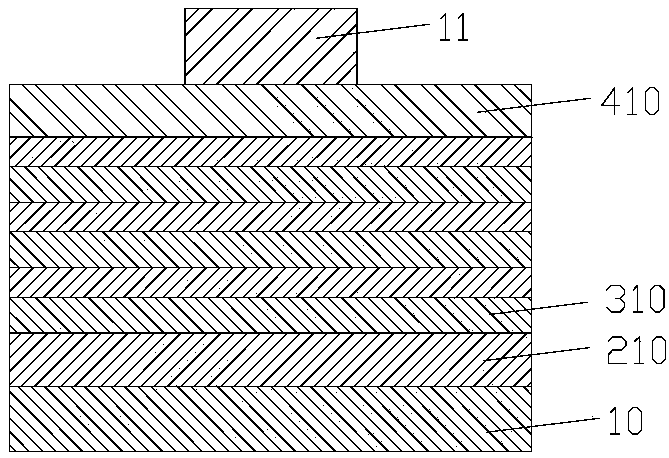

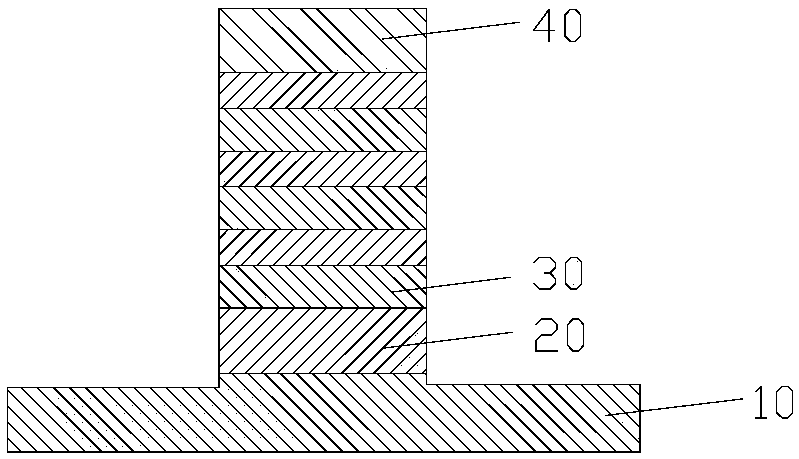

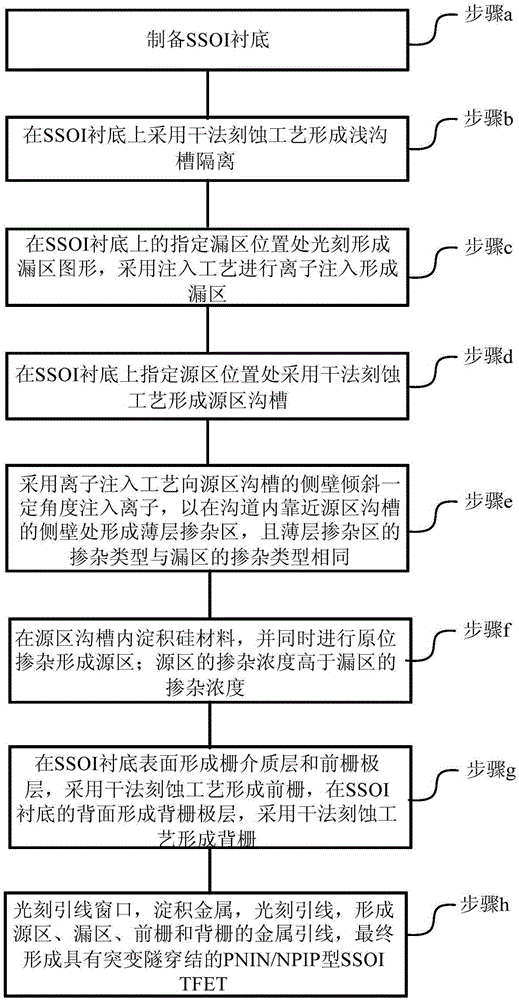

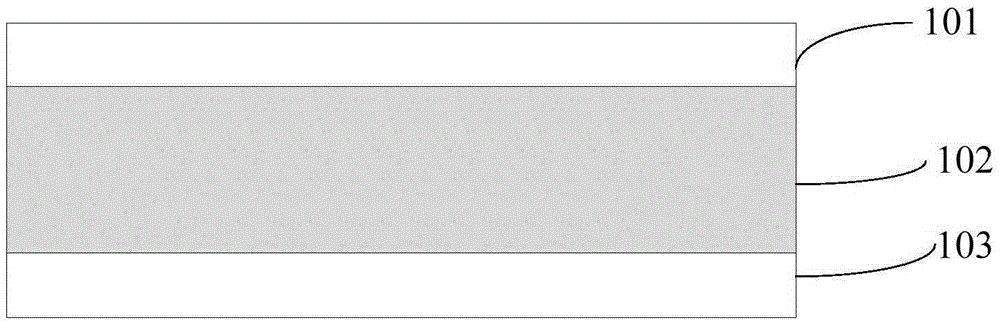

PNIN/NPIP type SSOI TFET with abrupt tunneling junctions and preparation method thereof

InactiveCN105244375APrevent proliferationImprove performanceSemiconductor/solid-state device manufacturingDiodeDriving currentGate dielectric

The invention relates to a PNIN / NPIP type SSOI TFET with abrupt tunneling junctions and a preparation method thereof. The preparation method comprises the steps that an SSOI substrate is prepared; shallow trench isolation is formed; a drain region pattern is formed through photoetching, and adhesive ions are injected so that a drain region is formed; a source region trench is formed through dry etching; the ions are injected in the side wall of the source region trench at a certain inclined angle by adopting an ion injection technology, Si material is deposited in the source region trench, and in-situ doping is performed so that a source region is formed; a gate dielectric layer and a front gate layer are formed on the upper surface of the substrate, a front gate is formed through etching, a back gate layer is formed on the lower surface of the substrate, and a back gate is formed through etching; and a lead-wire window is photoetched, metal is deposited and a lead-wire is photoetched so that source / drain and front / back gate lead-wires are formed. Drive current of the TFET can be effectively enhanced and subthreshold slope of the TFET can be reduced.

Owner:XIAN UNIV OF SCI & TECH

Micro-LED epitaxial structure and manufacturing method thereof

PendingCN111864017ARealize distributionReduce overflowSemiconductor devicesSemiconductorMaterials science

The invention provides a micro-LED epitaxial structure and a manufacturing method thereof, the micro-LED epitaxial structure comprises a substrate and also comprises an n-type semiconductor layer, a light-emitting layer and a p-type semiconductor layer which are arranged on the surface of the substrate, and the light-emitting layer comprises an electron deceleration layer, a superlattice active region and a hole aggregation layer. According to the structure, the epitaxial growth structure can be simplified, the light emitting efficiency of a micro-LED is improved, and the application of the micro-LED in the display field is promoted.

Owner:JIANGSU INST OF ADVANCED SEMICON CO LTD

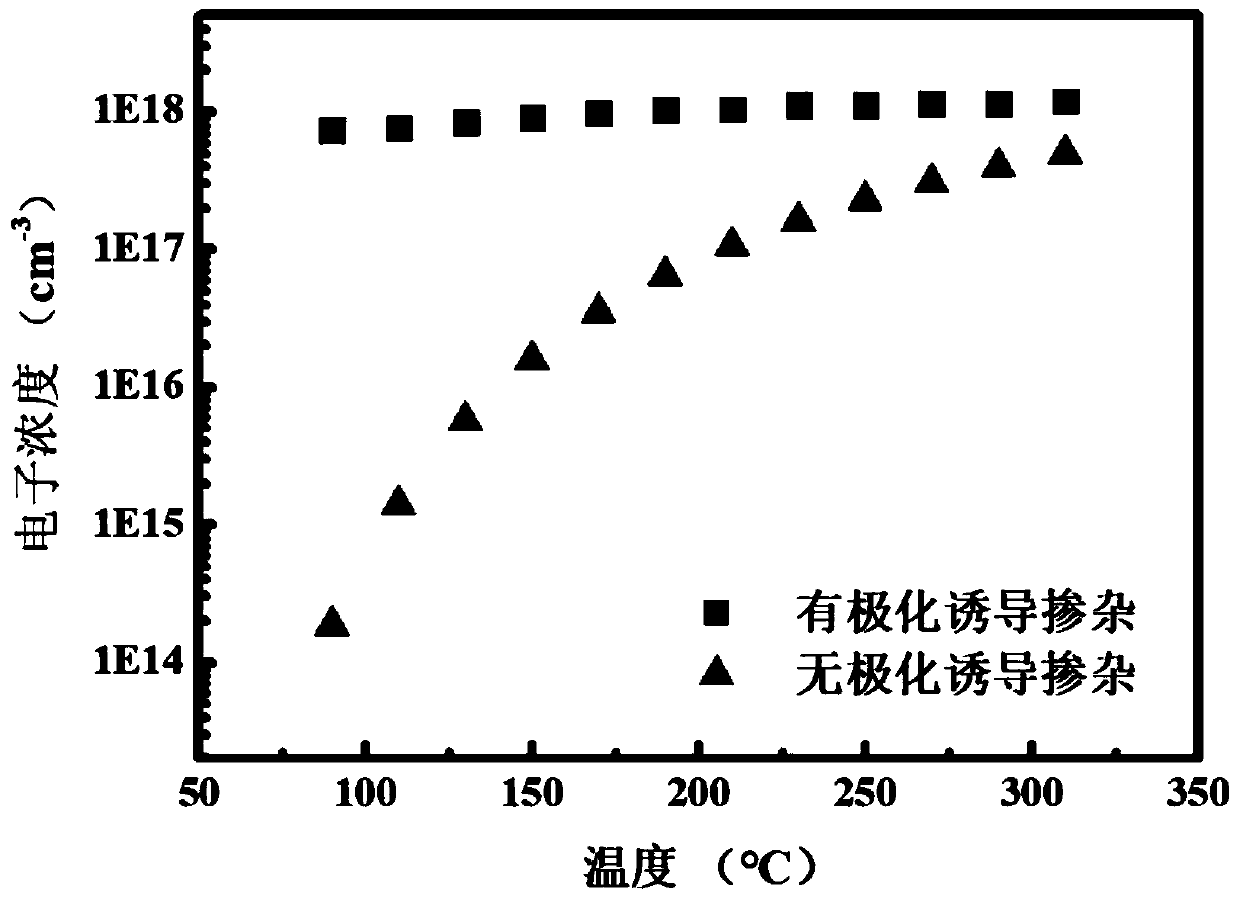

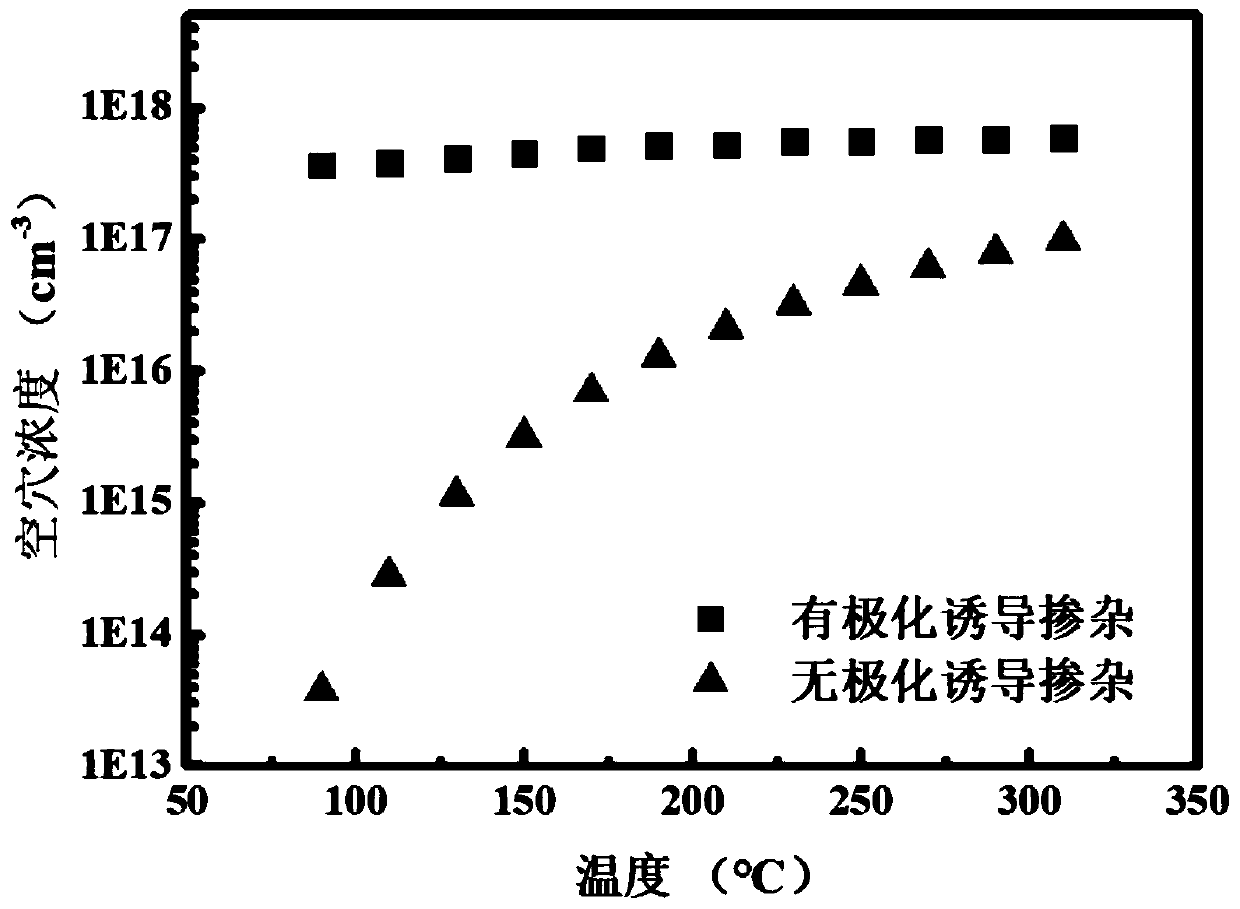

AlGaN-based tunneling junction structure based on polarization induced principle and preparation method thereof

ActiveCN109786531AIncrease chance of tunnelingExcellent performanceSemiconductor/solid-state device manufacturingSemiconductor devicesStructure basedSemiconductor

The invention relates to an AlGaN-based tunneling junction structure based on a polarization induced principle and a preparation method thereof, belonging to the technical field of semiconductor electronic devices. The AlGaN-based tunneling junction structure sequentially consists of a substrate, an Alx0Ga1-x0N template layer, an n-Alx1Ga1-x1N polarization induced doping layer, an Alx2Ga1-x2N insert layer, a p-Alx3Ga1-x3N polarization induced doping layer and a p-Alx4Ga1-x4N heavily doping layer from bottom to top, wherein the n-Alx1Ga1-x1N polarization induced doping layer, the Alx2Ga1-x2N insert layer and the p-Alx3Ga1-x3N polarization induced doping layer jointly form a polarization induced tunneling junction. The tunneling junction structure proposed by the invention is entirely composed of an AlGaN material, improves the problem of difficulty in high-Al component AlGaN doping by using a polarization induced doping method, also takes the high-Al component Alx2Ga1-x2N as the insertlayer, further improves the tunneling probability of the device, and obtains a tunneling junction device with good performance.

Owner:上海镓旦电子信息有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com