Schottky barrier metal oxide semiconductor (MOS) transistor and preparation method thereof

A technology of MOS transistor and Schottky potential, which is applied in the field of Schottky barrier MOS transistor and its preparation, can solve the problems of large conduction current and large conduction current of devices, and achieve the improvement of conduction current and open state Effect of current and low parasitic resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0044] Adopt the following method to prepare the MOS transistor of the present invention:

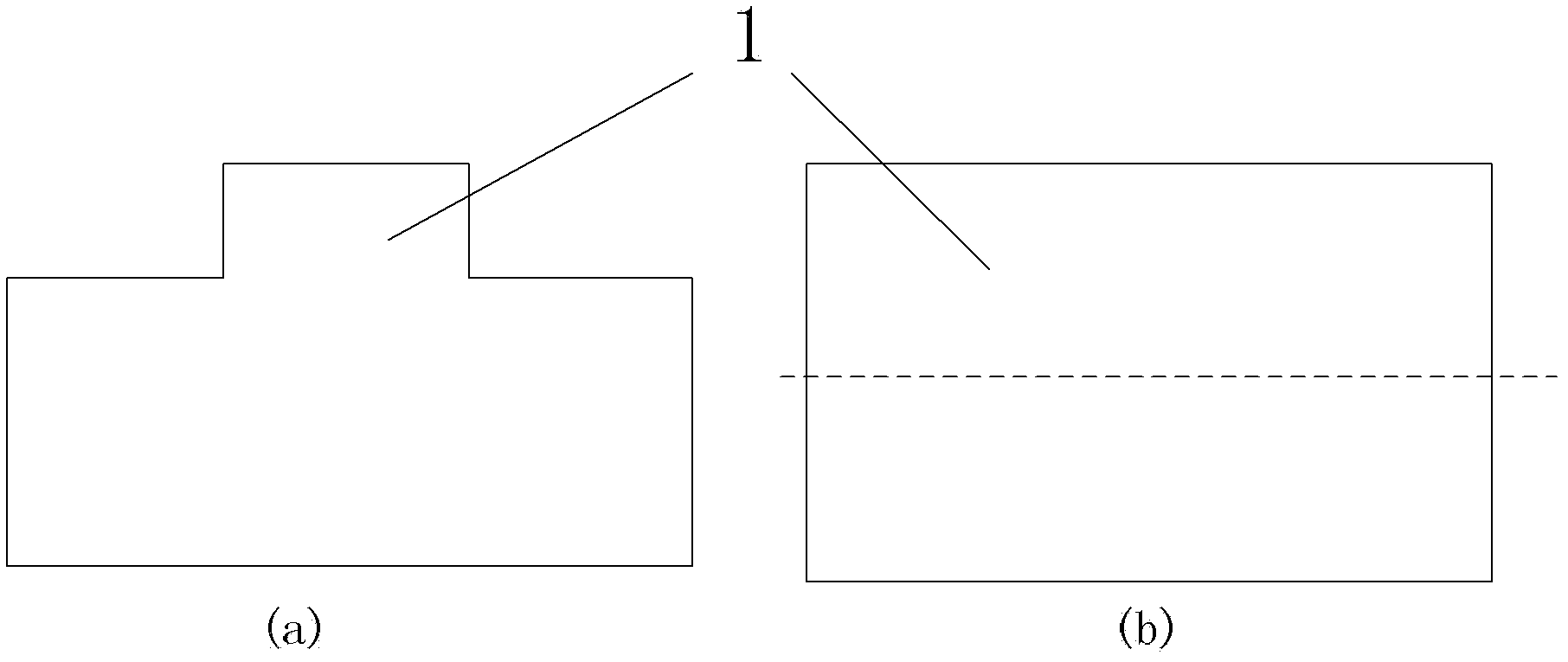

[0045] (1) On the bulk silicon wafer silicon substrate 1 with the crystal orientation of (100), the shallow trench isolation technology is used to fabricate the active region isolation layer, and the doping concentration of the substrate is N-type lightly doped; then, a step pattern is formed by photolithography , etch a step structure, the step height is about 500nm, such as figure 1 (a), 1(b);

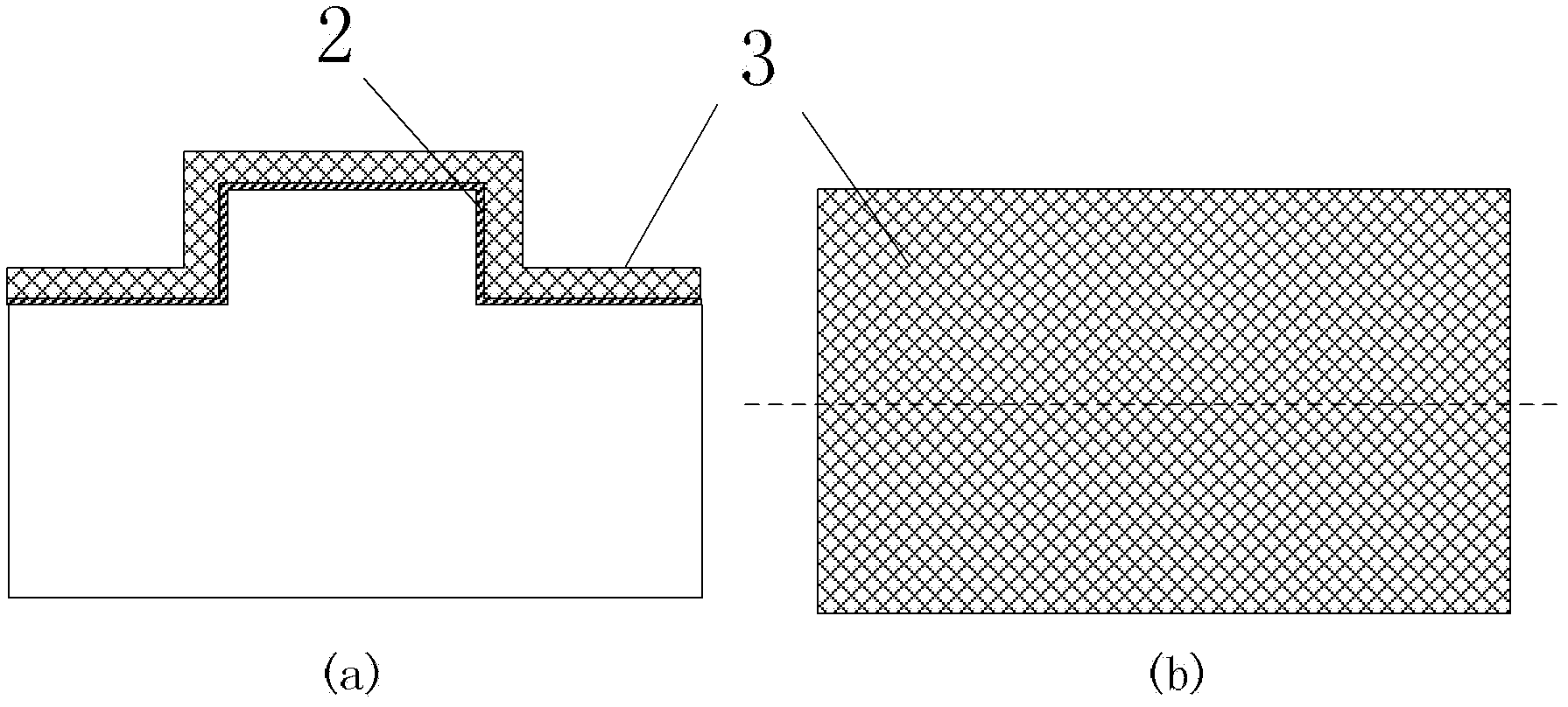

[0046] (2) thermally grow the gate dielectric layer, and then deposit the gate electrode layer, the gate dielectric layer is SiO 2 , the thickness is 1-5nm, the gate electrode layer is a highly doped polysilicon layer, the thickness is about 200nm, such as figure 2 (a), as shown in 2(b);

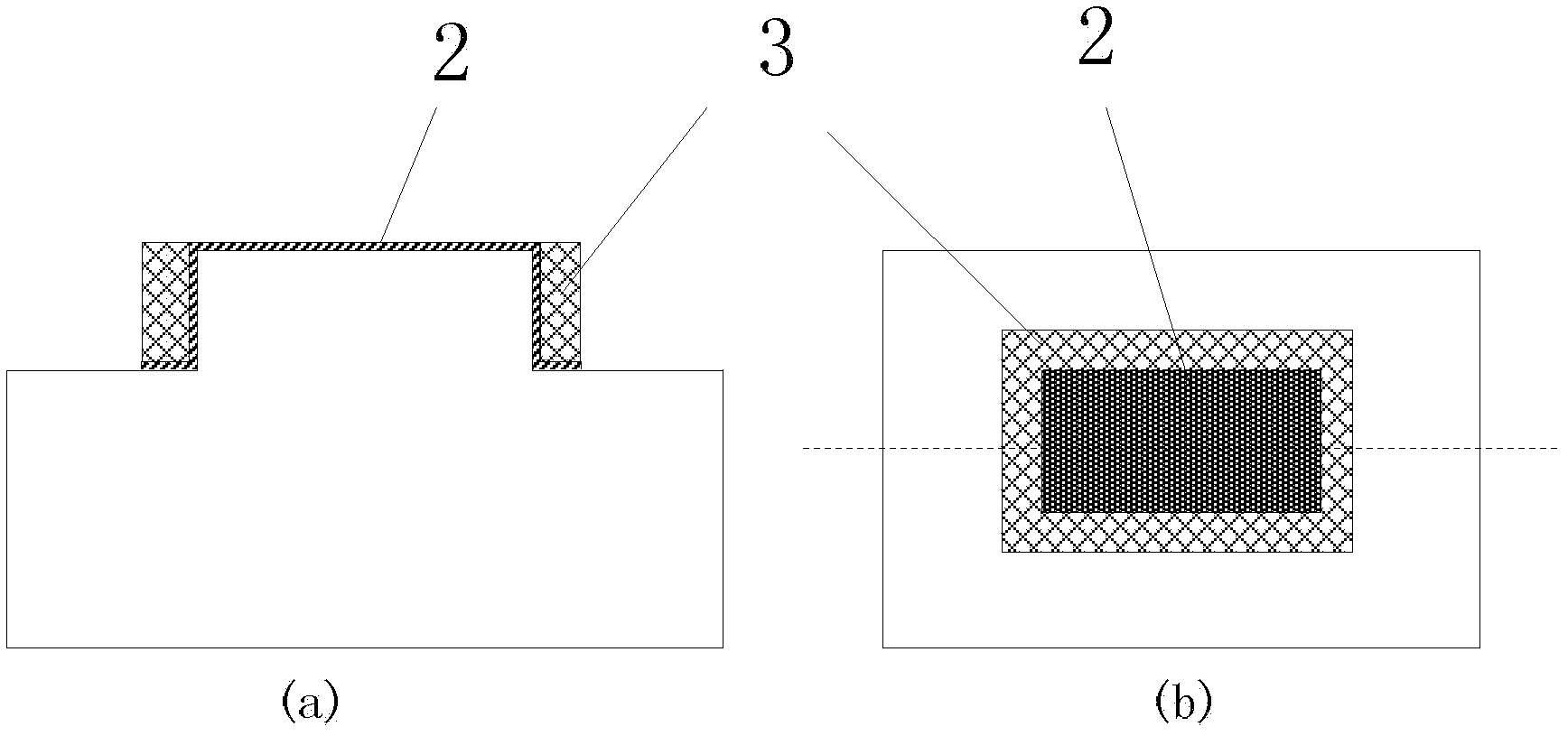

[0047] (3) The ring-shaped gate electrode 3 is formed by using the sidewall process, and the thickness of the gate electrode is about 200nm, such as image 3 (a), 3(b);

[0048] (4) Deposit the side wa...

Embodiment 2

[0053] As in Example 1, the difference is:

[0054] The step height in step (1) is about 200nm;

[0055] The thickness of the gate electrode in steps (2) and (3) is about 100nm;

[0056] The thickness of the sidewall in steps (4) and (5) is about 50nm;

[0057] ●The sputtered metal in step (6) is a metal with a smaller hole Schottky barrier, such as Pt.

Embodiment 3

[0059] As in Example 1, the difference is:

[0060] The substrate doping in step (1) is P-type lightly doped;

[0061] ●The sputtered metal in step (6) is a metal with a small electronic Schottky barrier, such as rare earth metal Er or Yb.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More