Patents

Literature

31results about How to "Suppression of bipolar effects" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Tunneling field effect transistor and preparation method thereof

ActiveCN103560153ALarge tunneling areaIncrease drive currentSemiconductor/solid-state device manufacturingDiodeDriving currentPower flow

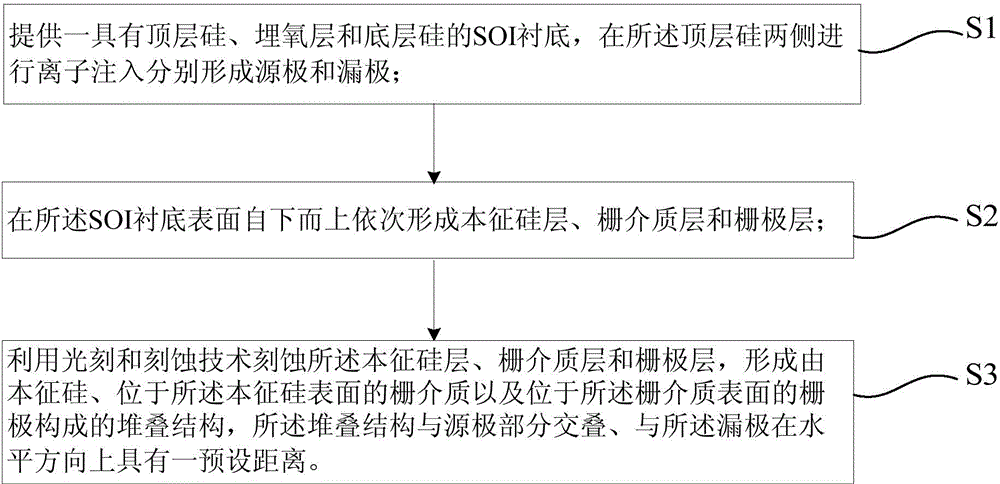

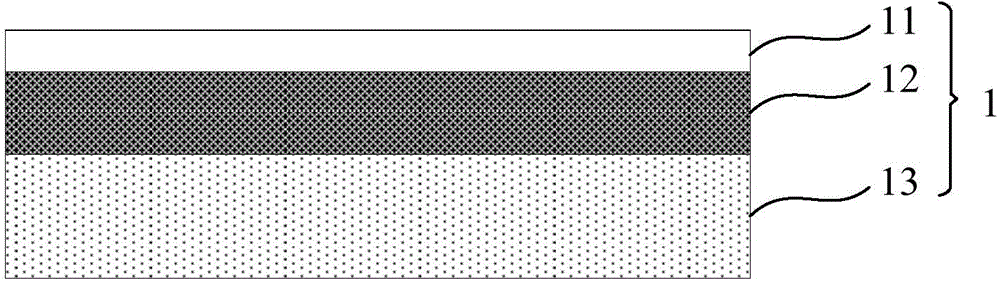

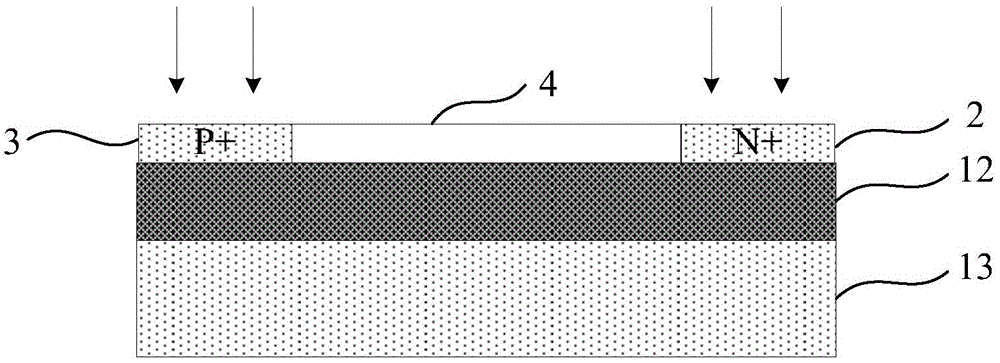

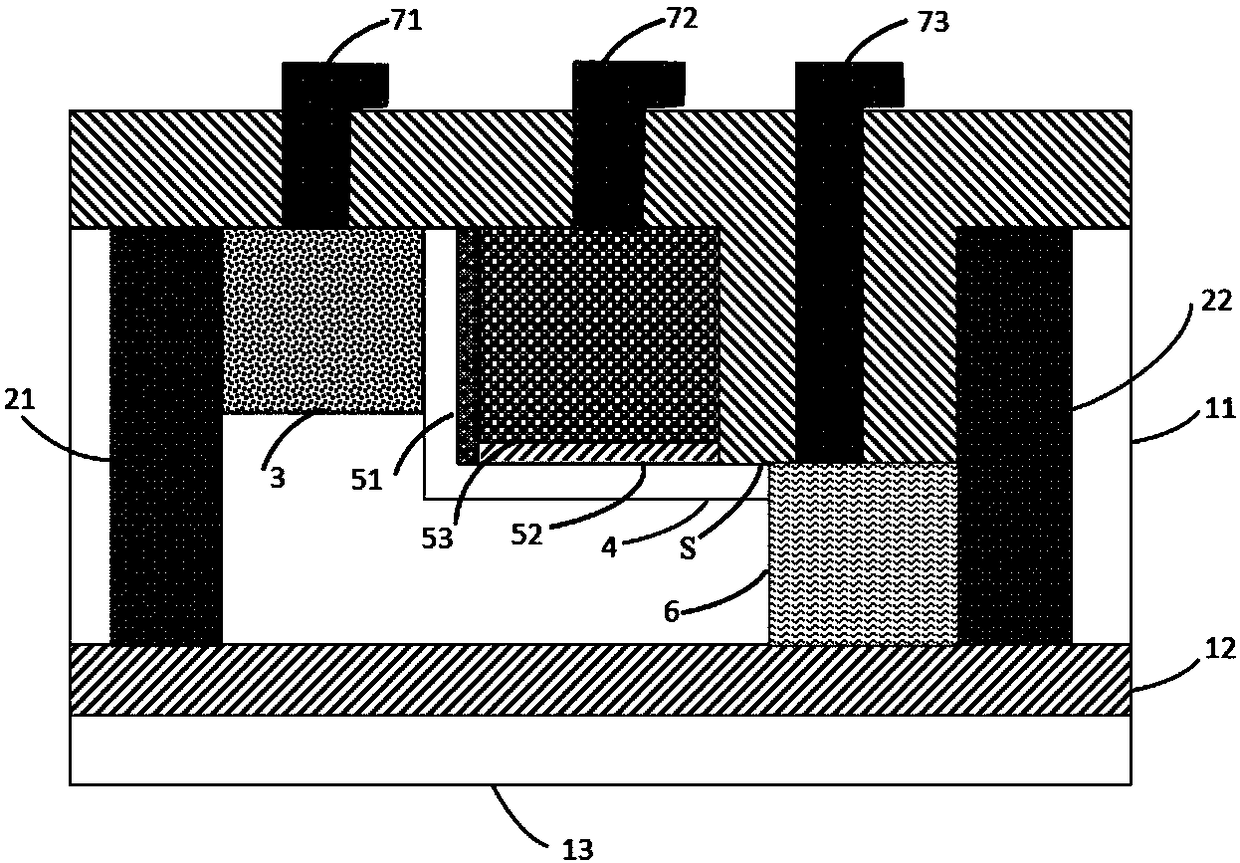

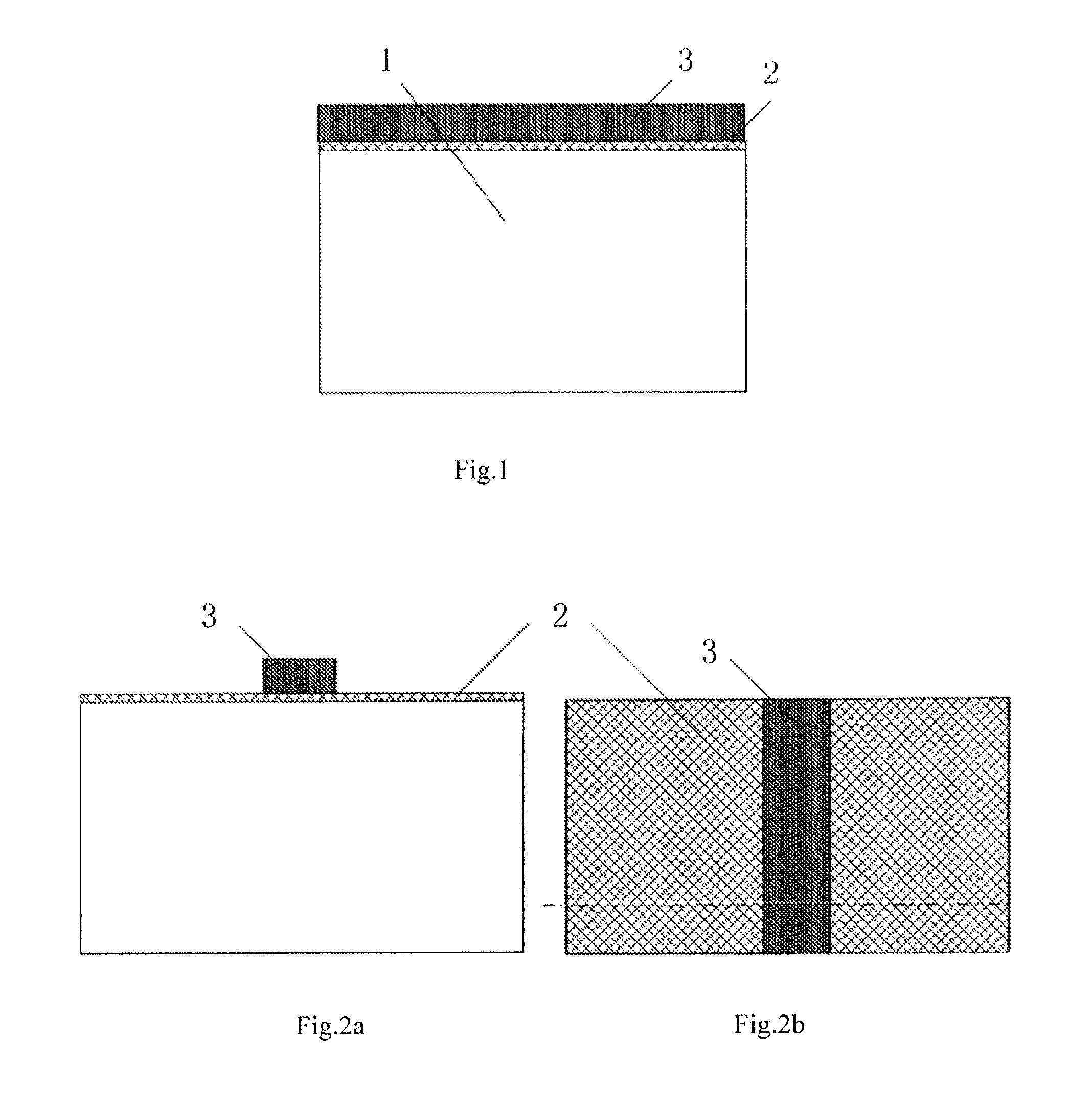

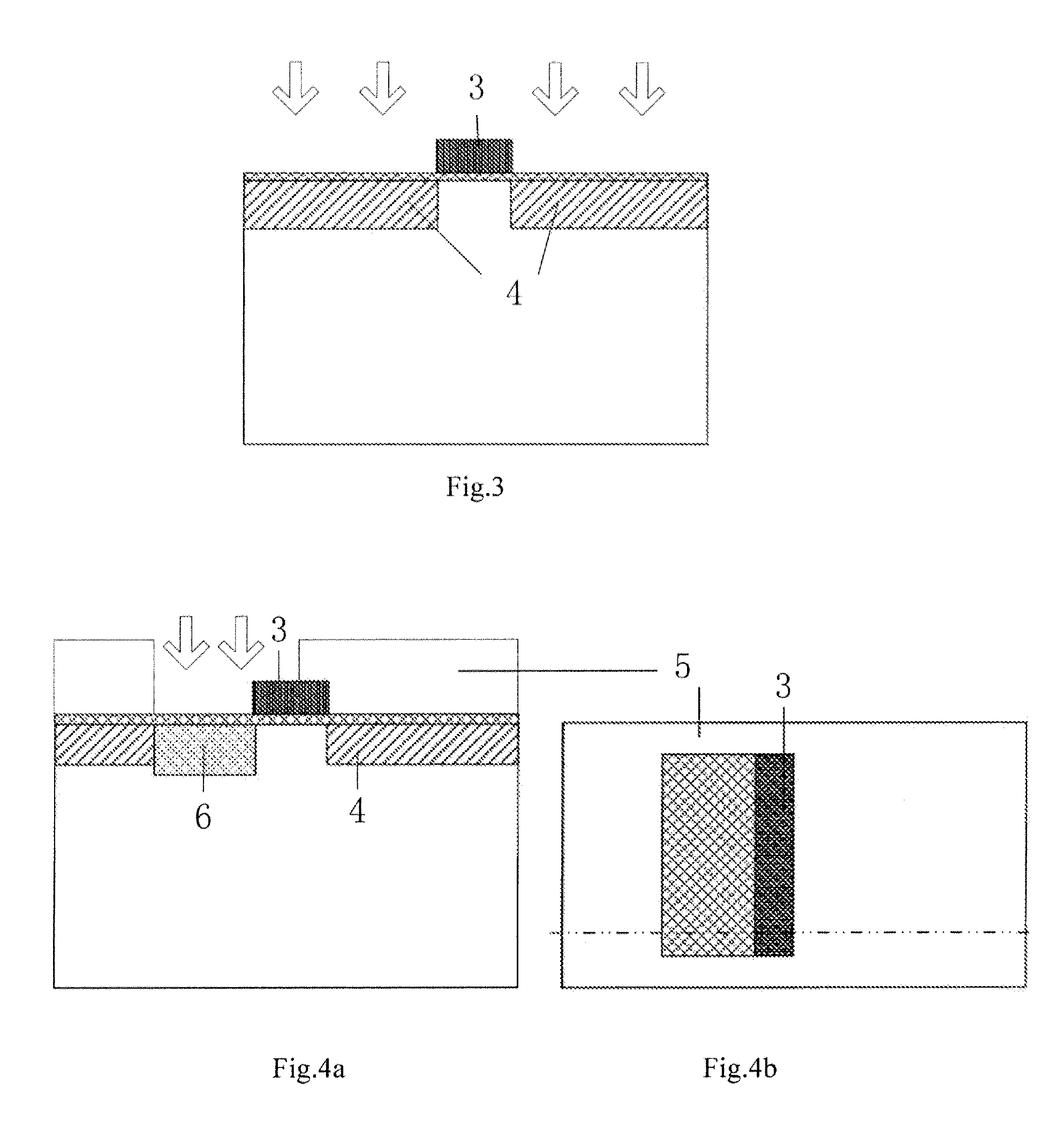

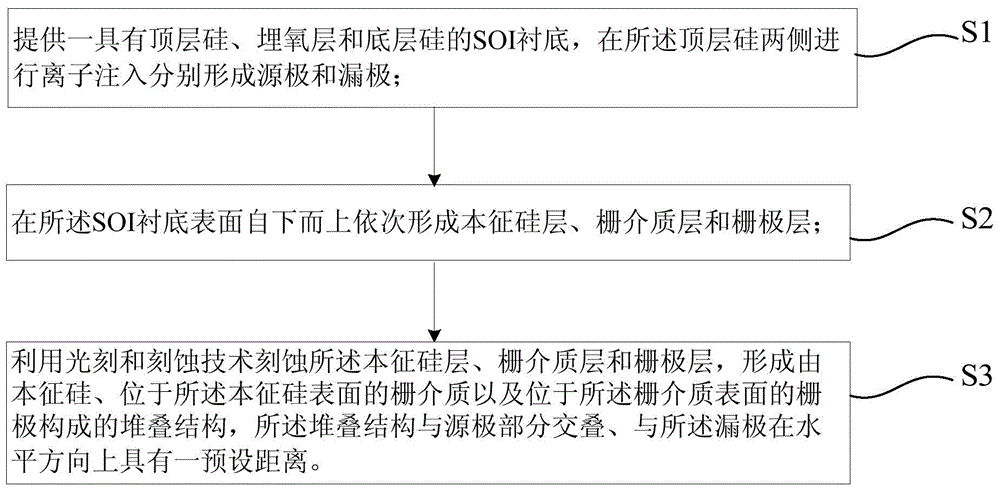

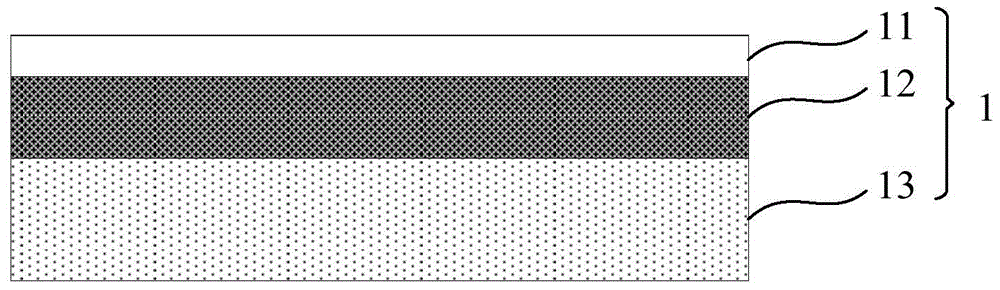

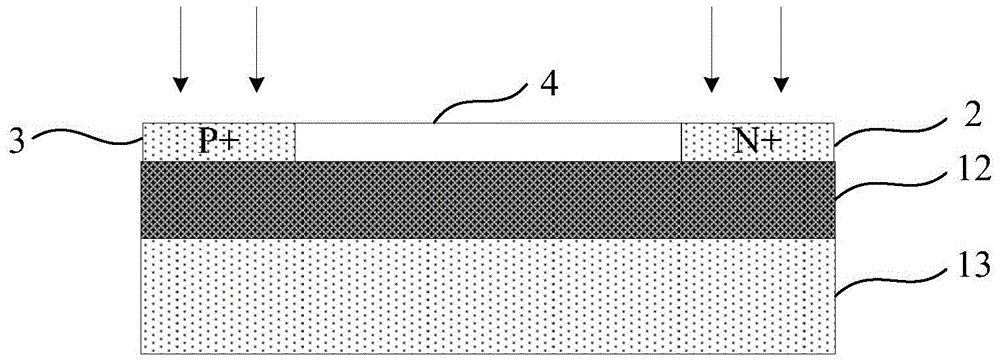

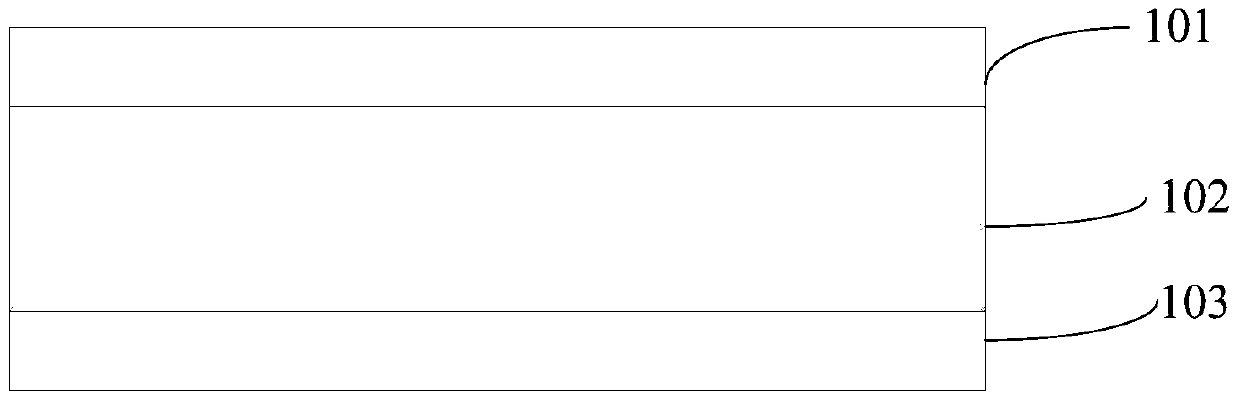

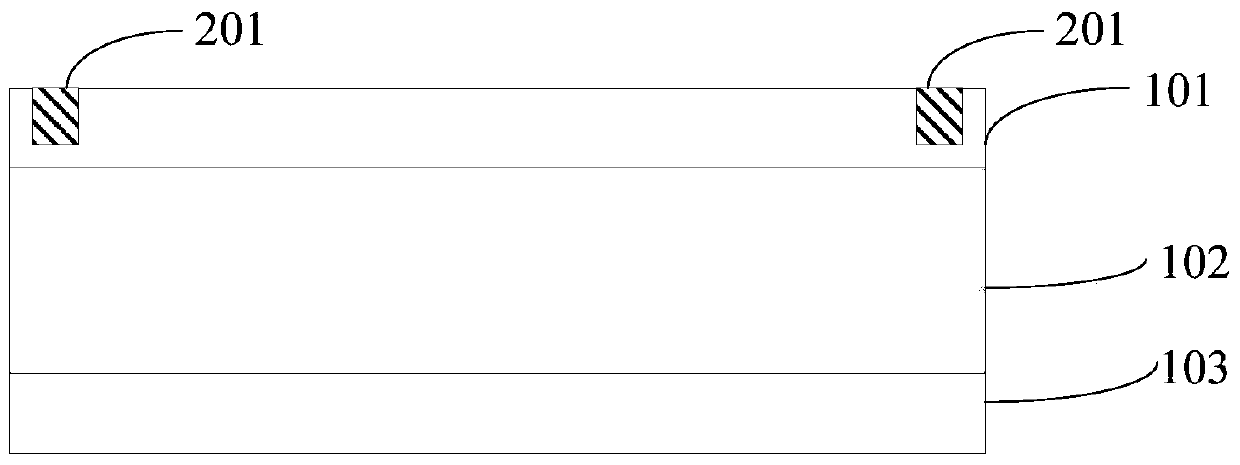

The invention provides a tunneling field effect transistor and a preparation method thereof. The preparation method at least comprises the following steps that an SOI substrate provided with top layer silicon, an oxygen buried layer and bottom layer silicon is provided, and ion injection is conducted on the two sides of the top layer silicon to form a source electrode and a drain electrode respectively; an intrinsic silicon layer, and a grid medium layer and a grid layer are sequentially formed on the surface of the SOI substrate from bottom to top; a stacking structure is formed by etching the intrinsic silicon layer, the grid medium layer and the grid layer through the photoetching and etching technologies, the stacking structure is partially overlapped with the source electrode and is preset distance away from the drain electrode in the horizontal direction. According to the tunneling field effect transistor and the preparation method of the tunneling field effect transistor, the stacking structure is overlapped with the source electrode so that the tunneling area can be increased, and further a driving current is increased. In addition, the stacking structure is preset distance away from the drain electrode in the horizontal direction, and the bipolar effect in the tunneling field effect transistor can be suppressed through the preset distance, and a subthreshold current is reduced.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

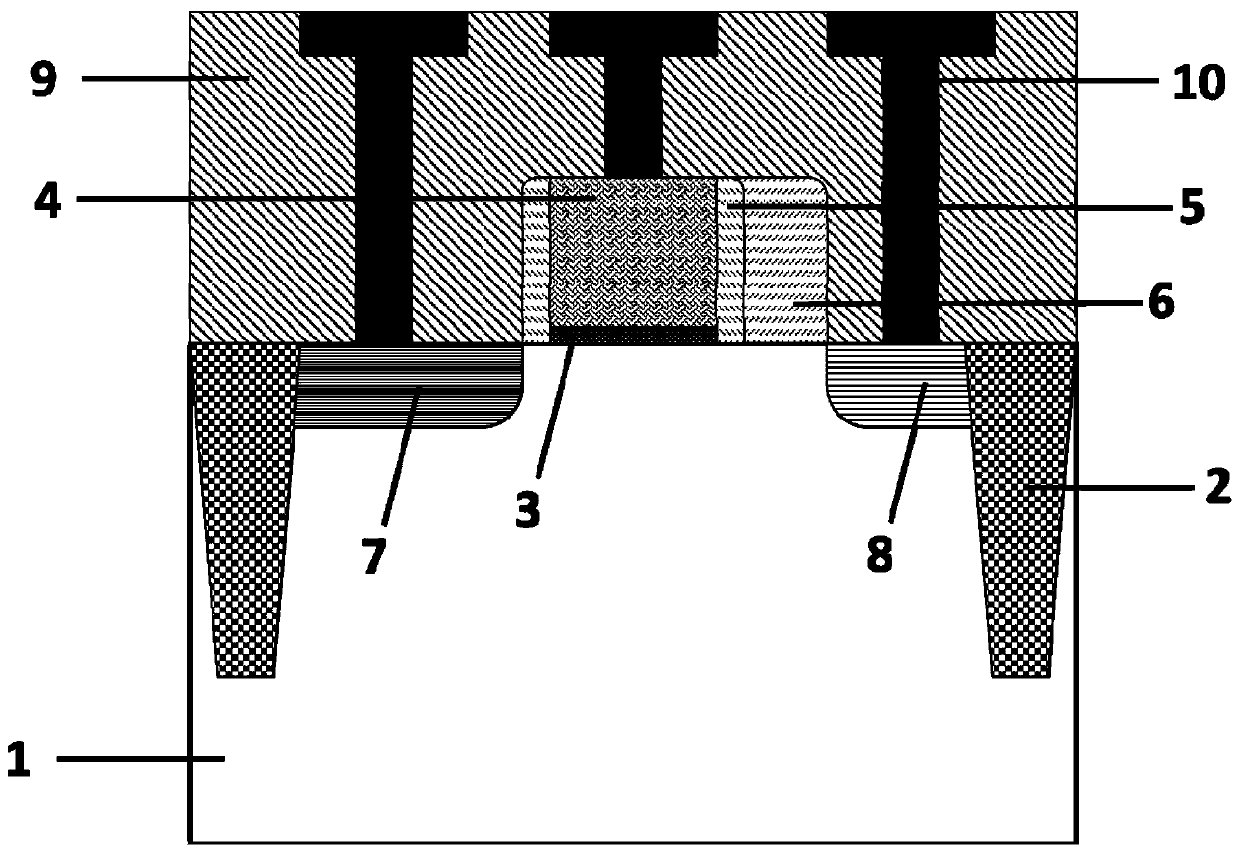

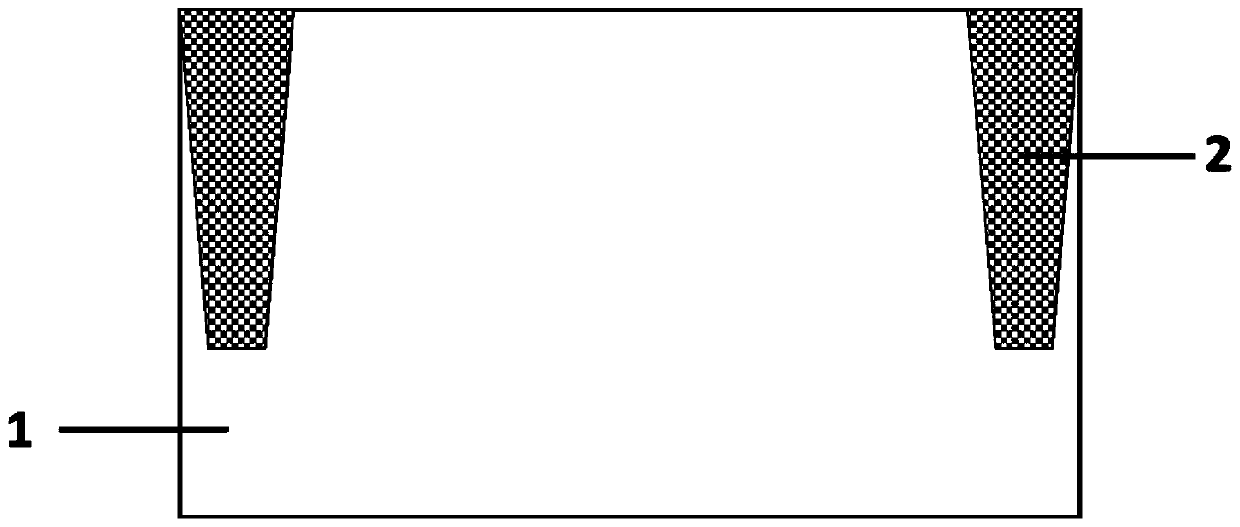

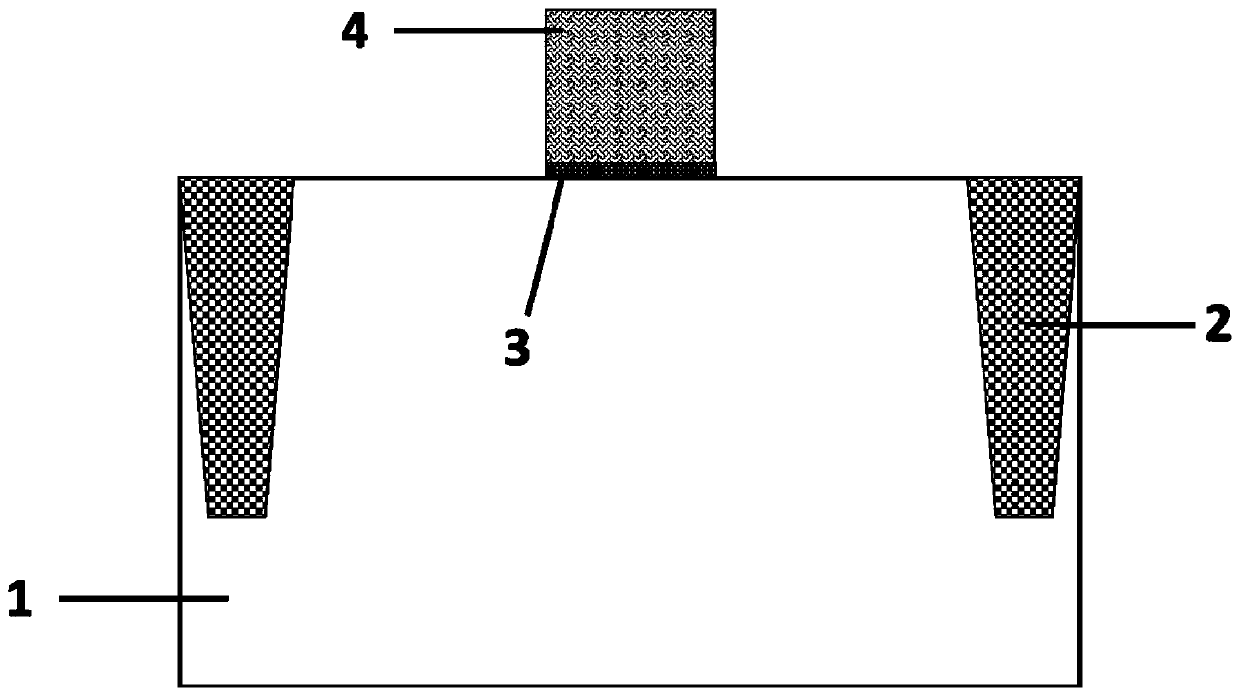

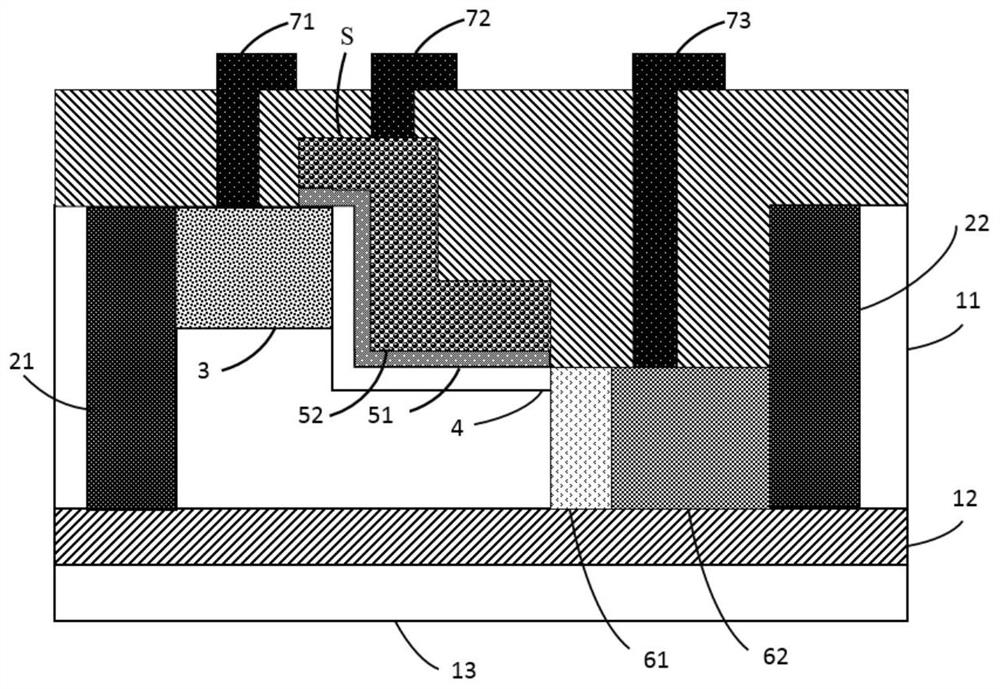

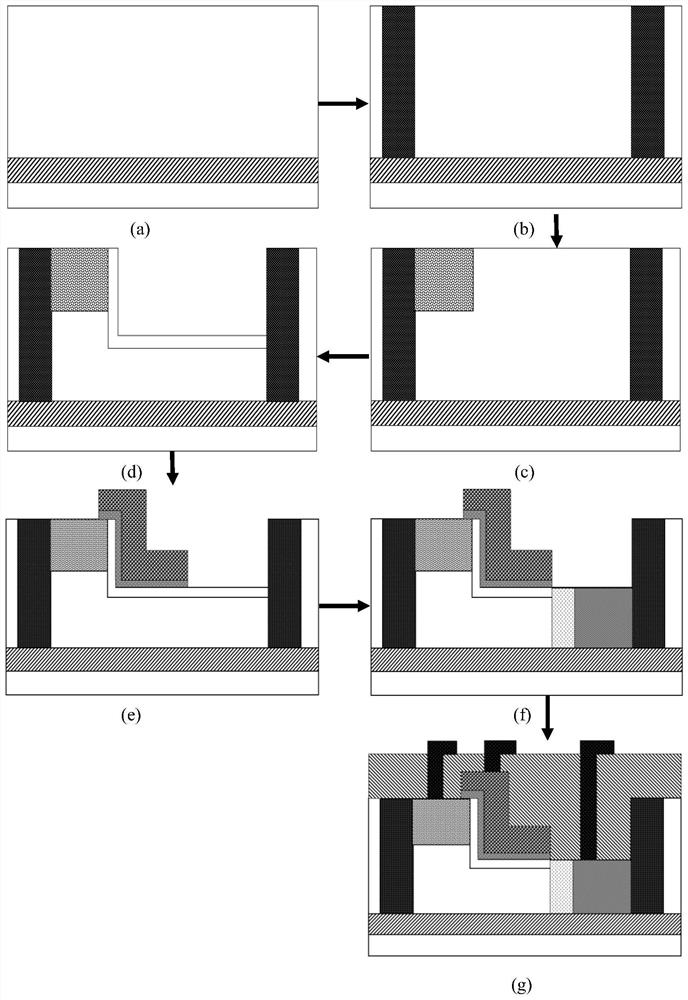

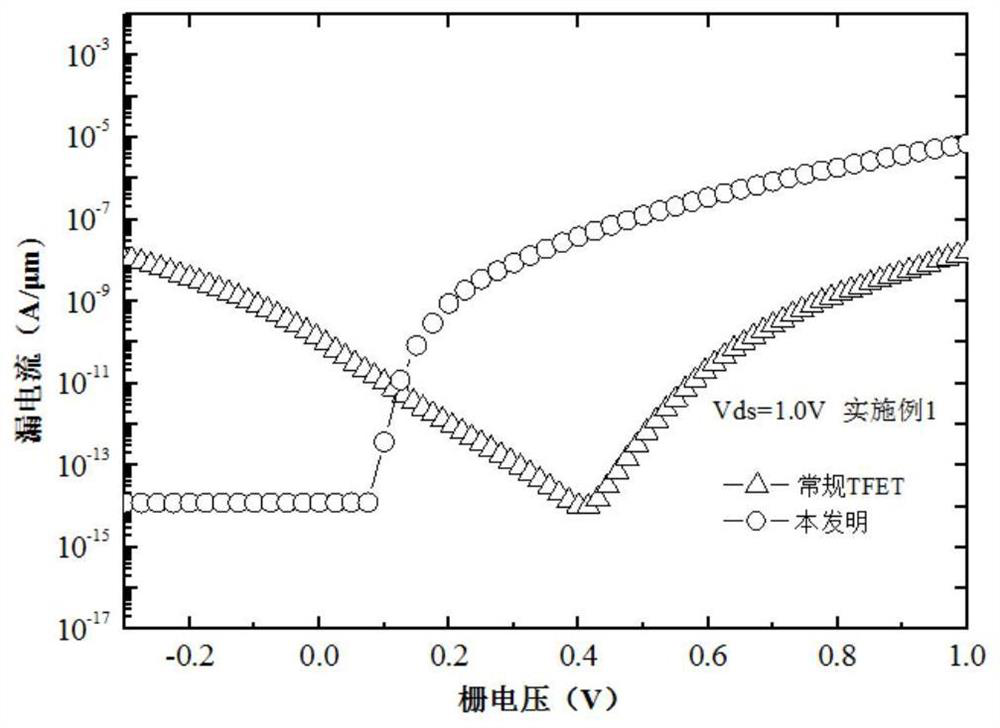

Optimized L-type tunneling field effect transistor and preparation method thereof

ActiveCN108538911AShorten tunneling distanceIncrease drive currentSemiconductor/solid-state device manufacturingDiodeDriving currentSemiconductor materials

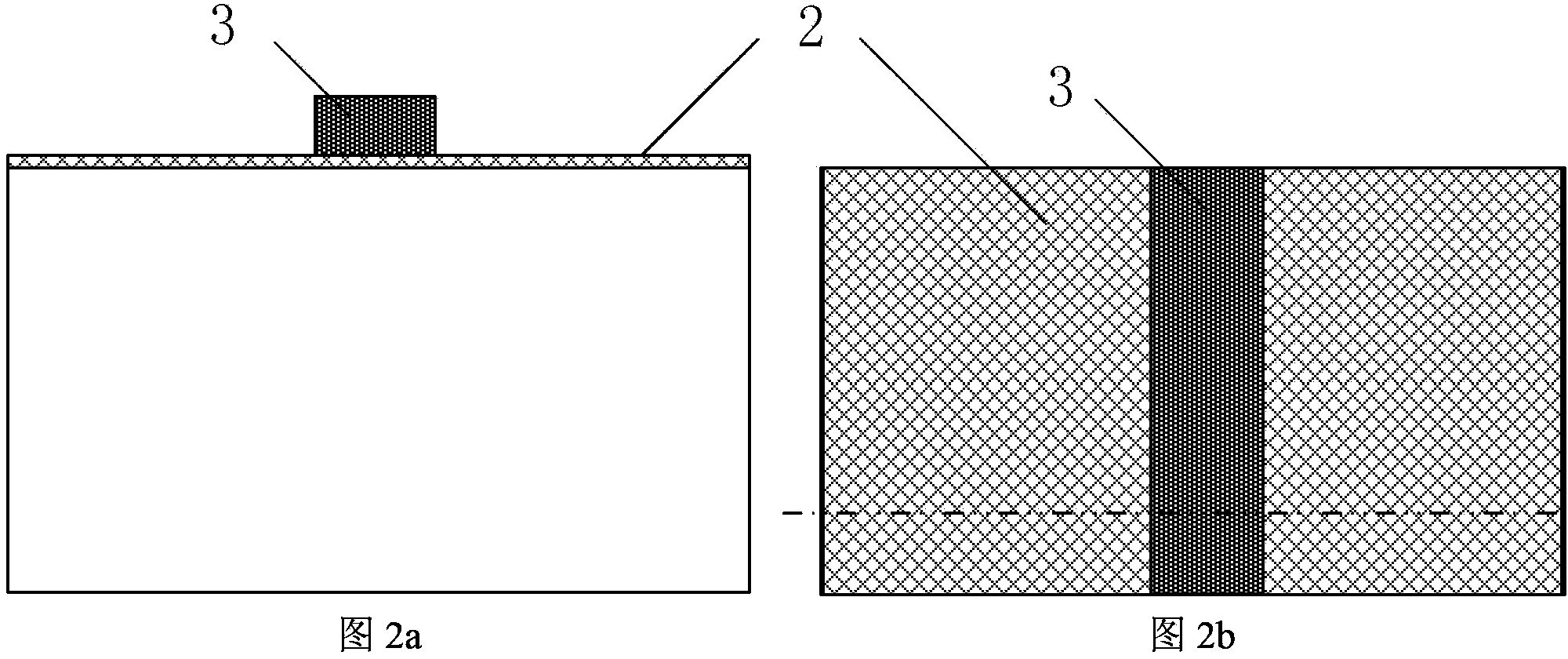

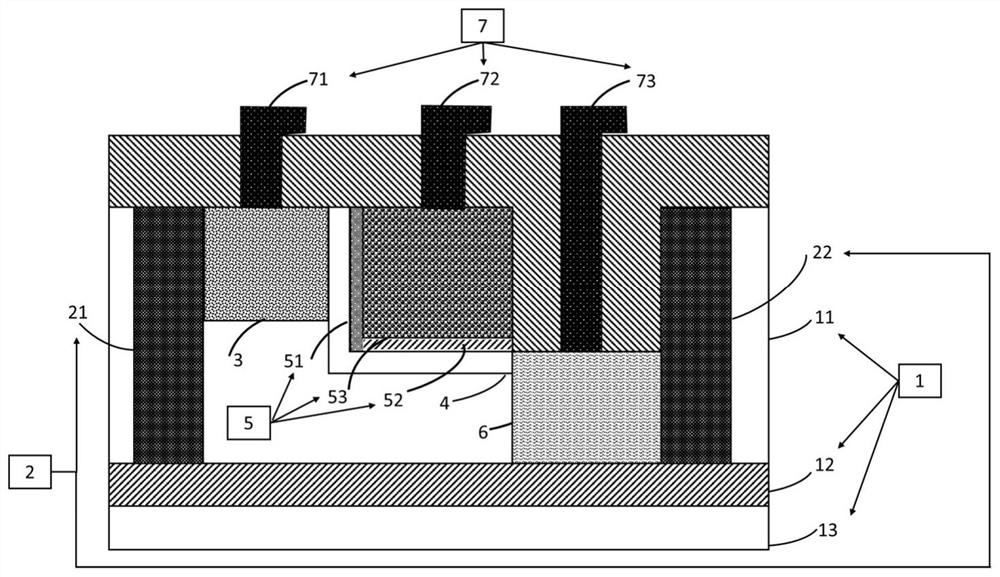

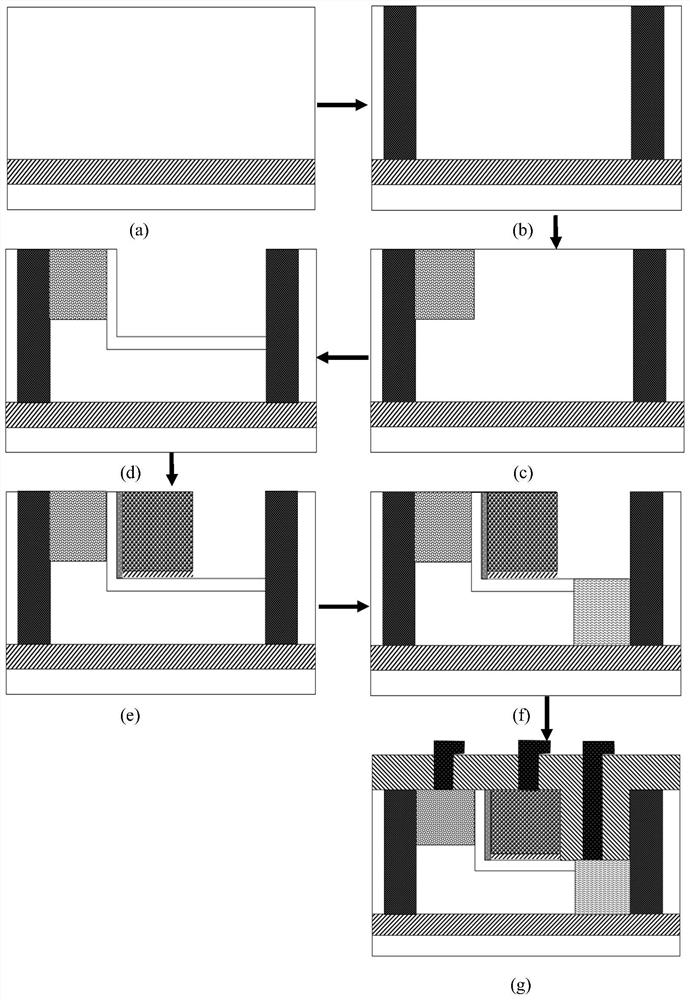

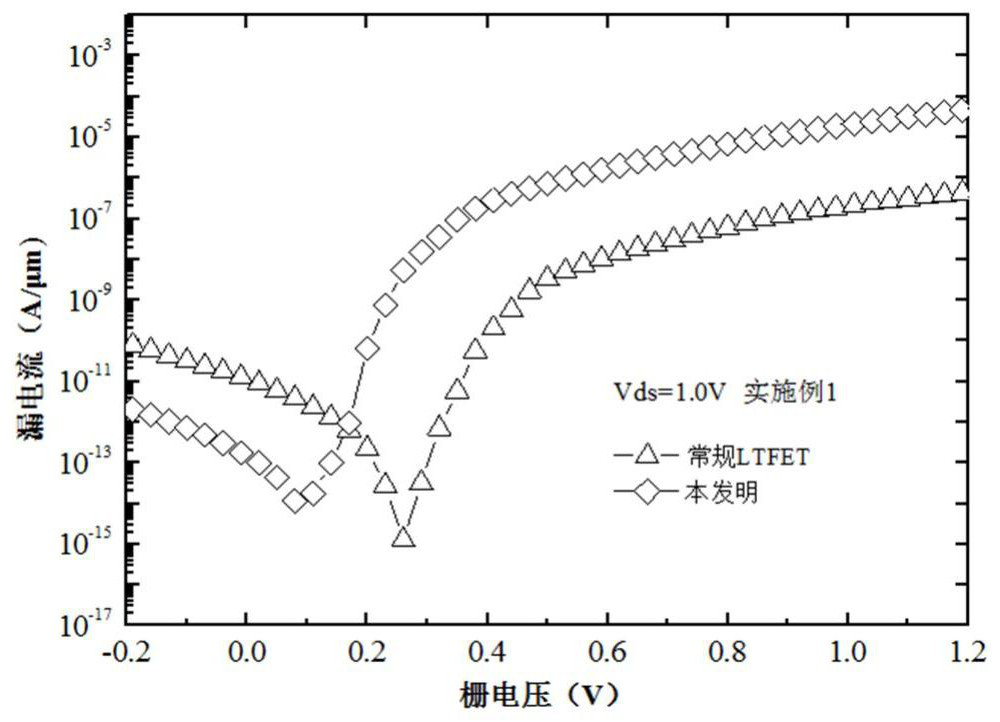

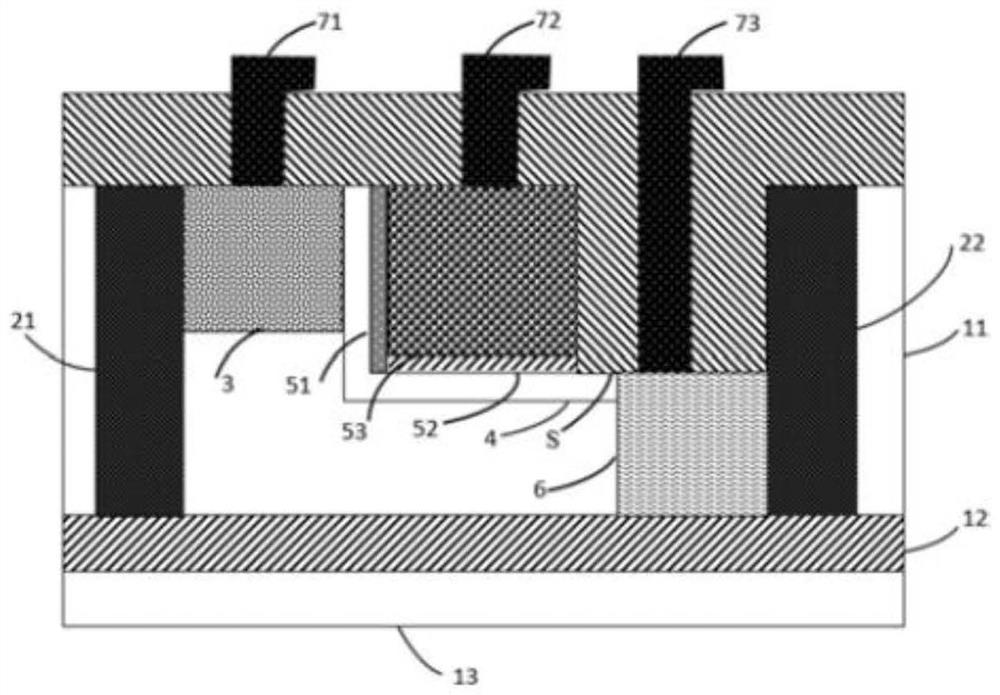

The invention discloses an optimized L-type tunneling field effect transistor and a preparation method thereof and mainly solves the problems of low on state current and severe bipolar effect of an existing device. The optimized L-type tunneling field effect transistor comprises an SOI (silicon on insulator) substrate (1), isolation grooves (2), a source region (3), a channel region (4), a drain region (6), a gate region (5) and a conducting layer (7), wherein the isolation grooves (2) are located on two sides of the SOI substrate (1), and the source region (3), the channel region (4) and thedrain region (6) are located on the upper surface of the SOI substrate; the gate region (5) is located on the upper side of the channel region (4); the source region (3) is made of a germanium semiconductor material, the gate region (5) is of a hetero-gate dielectric structure, a high-k dielectric material is adopted on one side close to the source region, and a low-k dielectric material is adopted on one side close to the drain region; a space S is formed between the drain region (6) and the right margin of the gate region (5). The optimized L-type tunneling field effect transistor can effectively inhibit the bipolar effect, increases drive current and can be applied to manufacture of large-scale integrated circuits.

Owner:西安电子科技大学重庆集成电路创新研究院

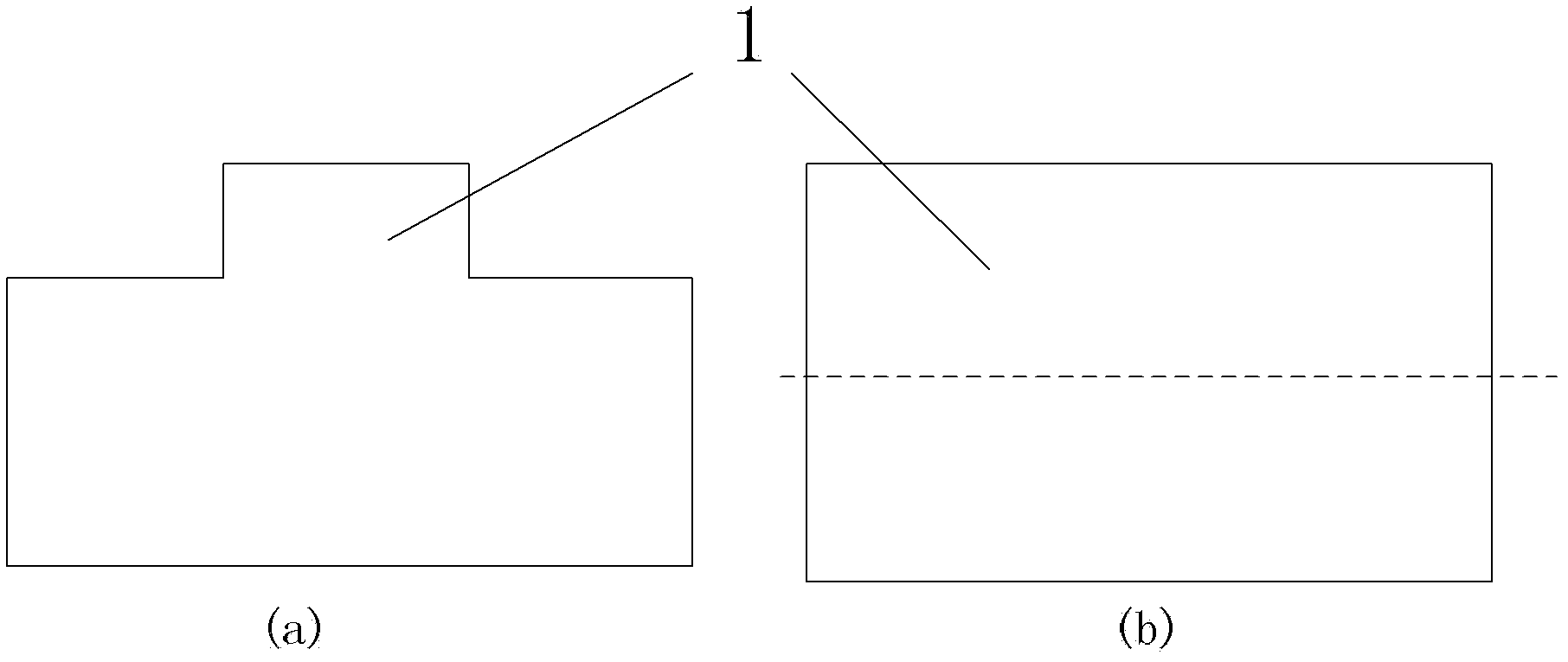

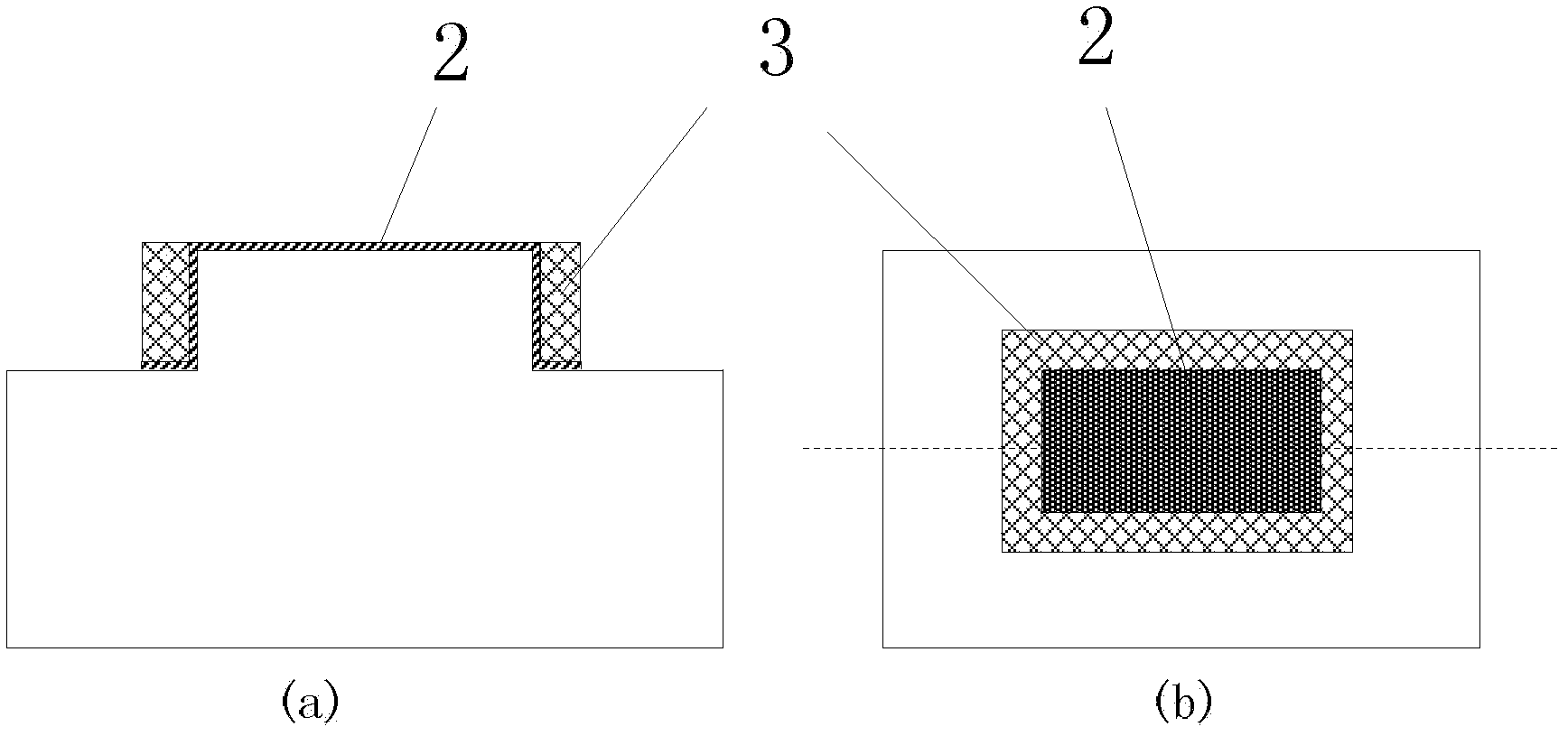

Schottky barrier metal oxide semiconductor (MOS) transistor and preparation method thereof

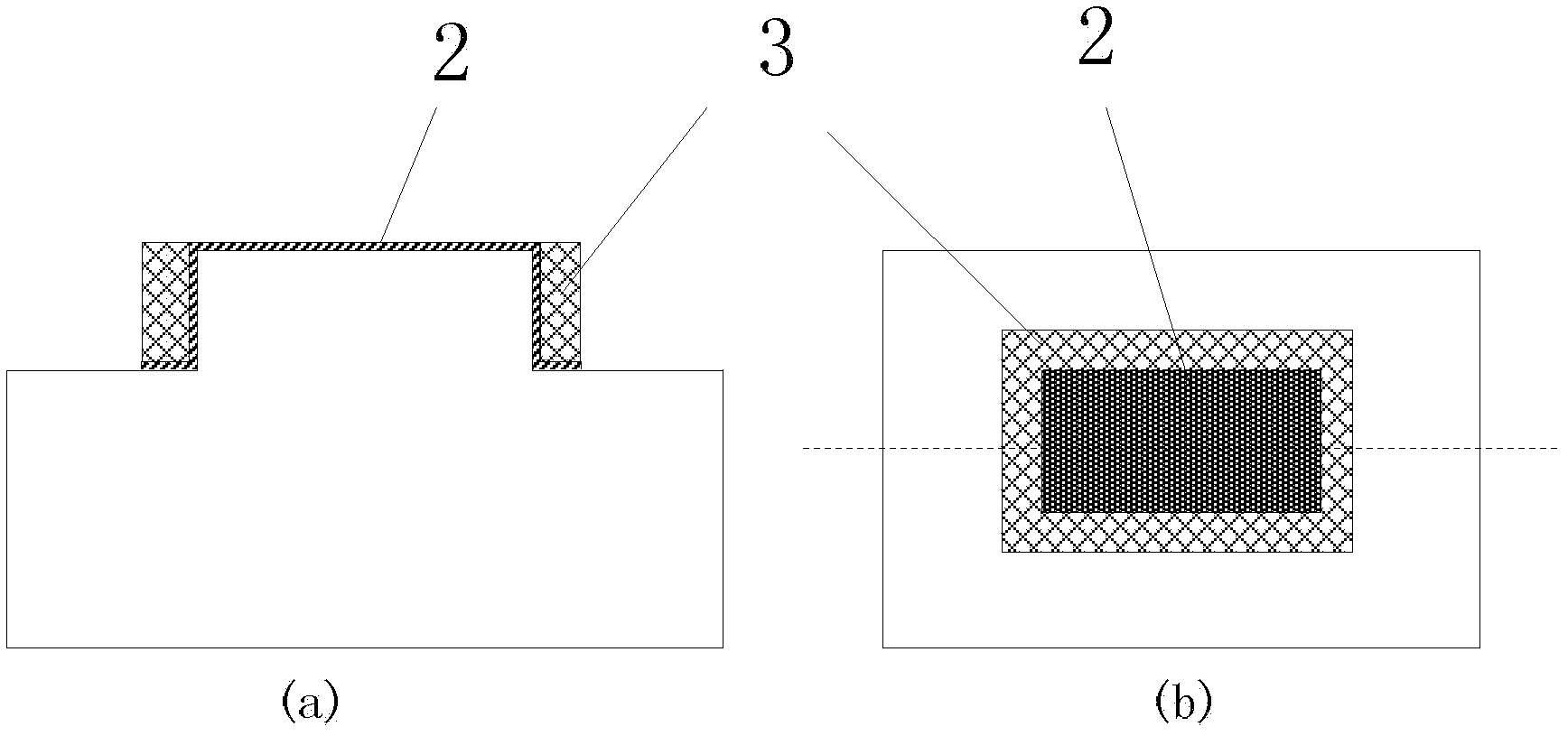

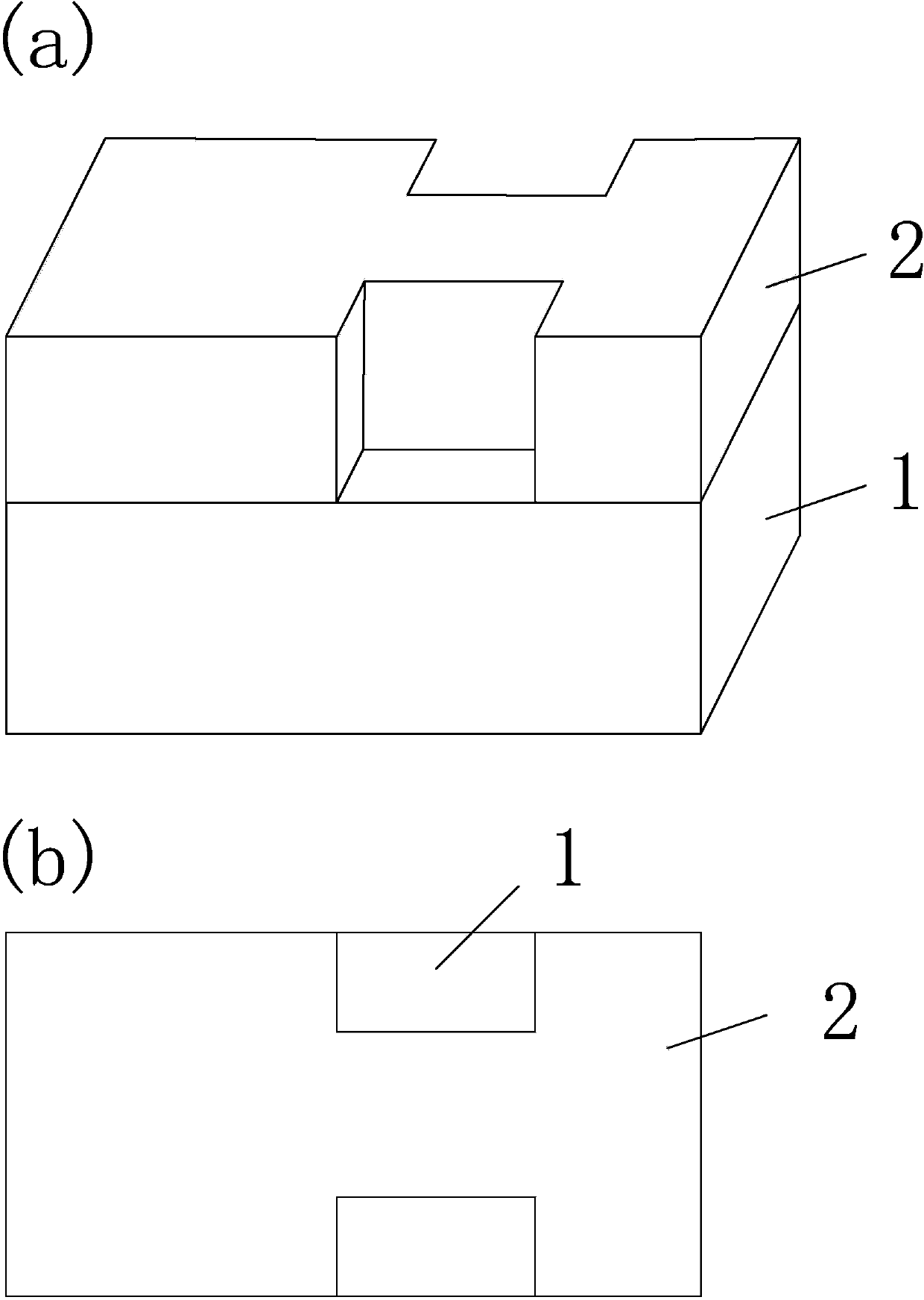

ActiveCN102324434AReduce parasitic resistanceEliminate uncovered areasSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate dielectric

The invention discloses a Schottky barrier metal oxide semiconductor (MOS) transistor, which comprises a ring-shaped gate electrode (3), a ring-shaped gate dielectric layer (2), a ring-shaped gate electrode side wall (4), a semiconductor substrate, a source region (5) and a ring-shaped drain region (6). The Schottky barrier MOS transistor is characterized in that: the semiconductor substrate is provided with a convex step structure; the source region is positioned on a high plane of a convex step; the ring-shaped drain region surrounds the convex step and is positioned on a low plane; the gate dielectric layer and the gate electrode are positioned at a corner of the convex step, surrounds the step and is raised into a ring shape; and the gate electrode side wall is ring-shaped, surrounds on the outer side of the gate electrode and has a certain thickness to serve as a shelter to form an underlap structure of a drain terminal. The Schottky barrier MOS transistor adopts a step structurecombining a ring-shaped gate structure and an asymmetric source / drain structure, so on the basis of inheriting advantages of traditional SB-MOSFET, the on-state conduction current is improved, a dipolar effect is inhibited, and the process is simplified.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Tunneling field-effect transistor with composite-mechanism strip-type grid and preparation method of tunneling field-effect transistor

ActiveCN103474464AIncrease the on-state currentIncrease subthreshold slopeSemiconductor/solid-state device manufacturingDiodeCMOSPunching

The invention discloses a tunneling field-effect transistor with a composite-mechanism strip-type grid and a preparation method of the tunneling field-effect transistor and belongs to the field of logic devices and circuits of field-effect transistors in CMOS (Complementary Metal Oxide Semiconductor) ultra-large-scale integrated (ULSI) circuits. The tunneling field-effect transistor has the advantages that the energy band of surface channels under the grid can be improved by changing the shape of the grid and utilizing a depletion effect of PN nodes on the two sides of the strip-type grid, and the subthreshold characteristic of the device is improved; since a composite mechanism is introduced into double-doped source areas, an ON state current of the device is improved; due to an I-shaped design of an active area, body leakage currents, including a source-drain direct tunneling current and a punching current, between the two doped source areas to a doped drain area can be greatly inhibited, and a short-channel effect is inhibited, so that the device with small size can be applied.

Owner:PEKING UNIV

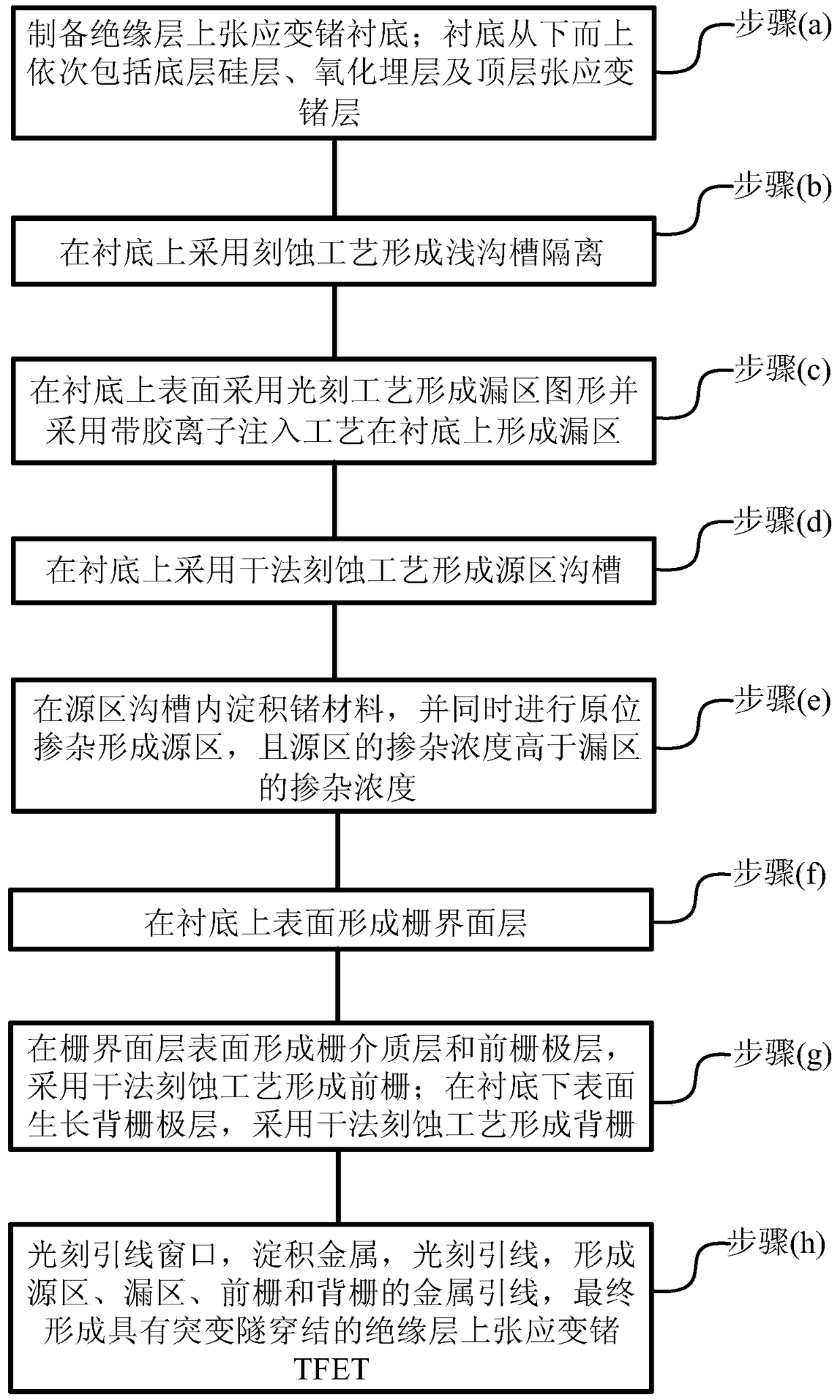

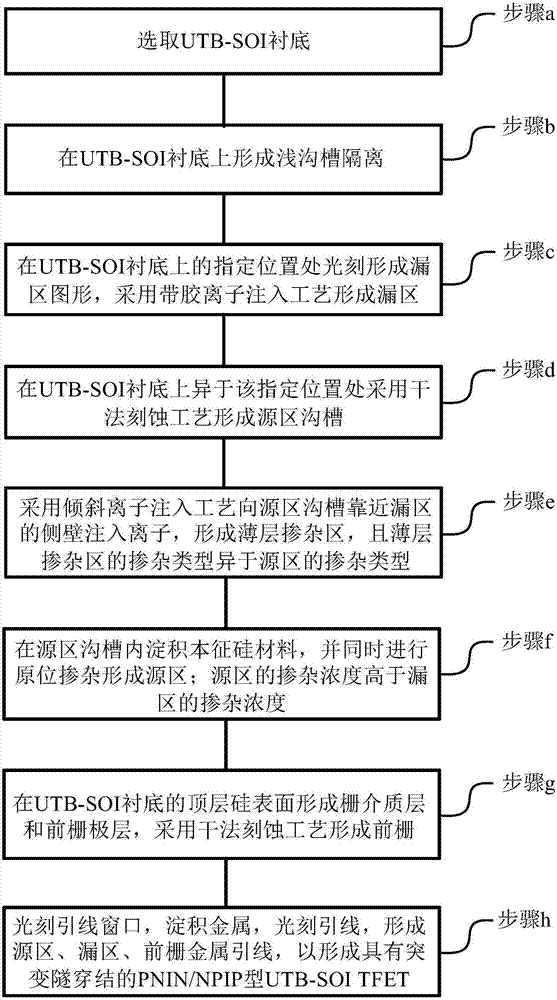

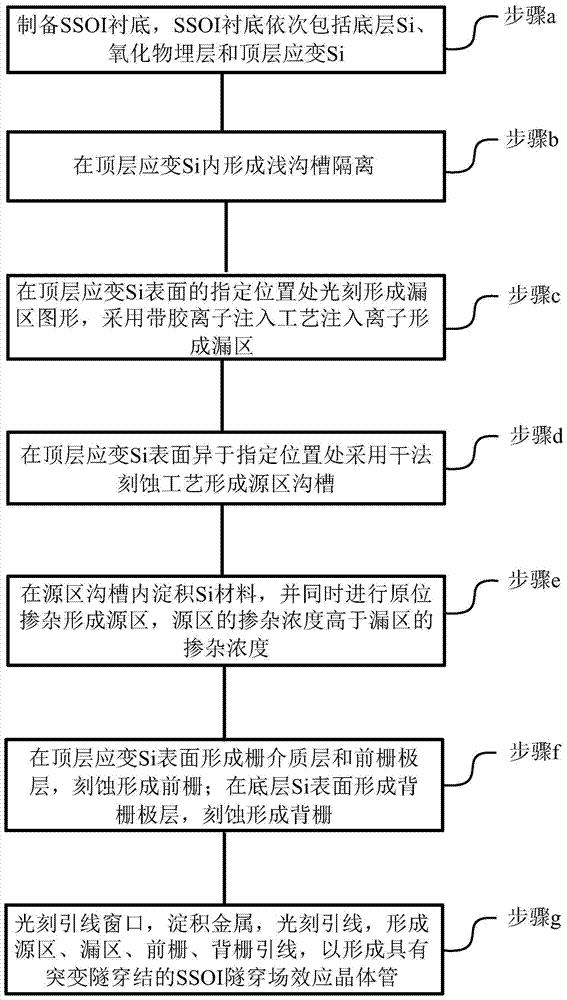

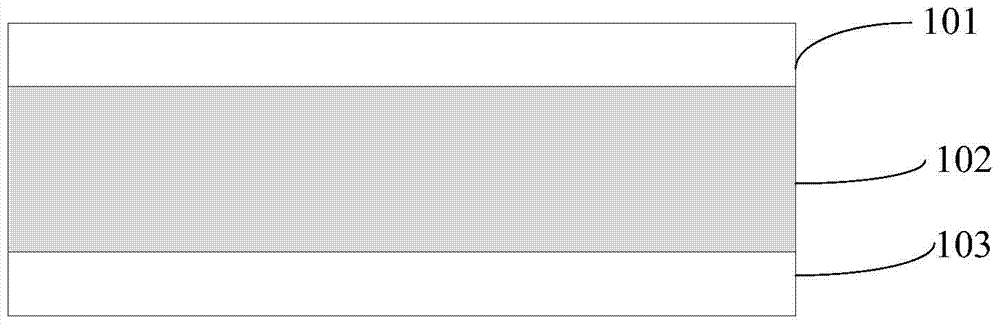

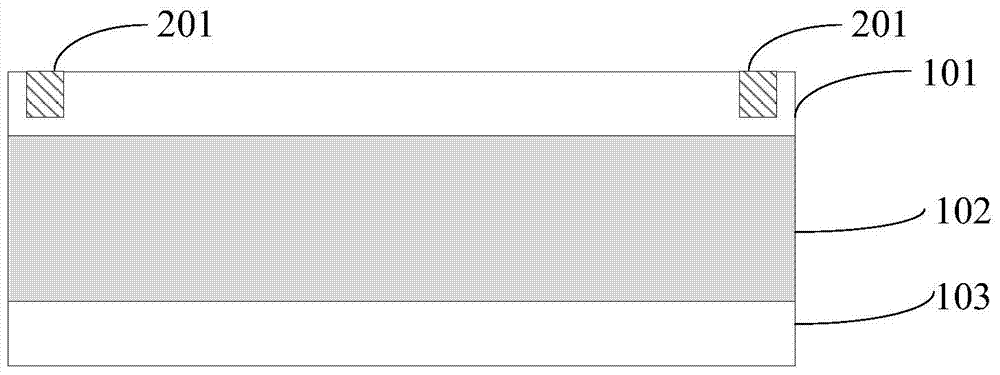

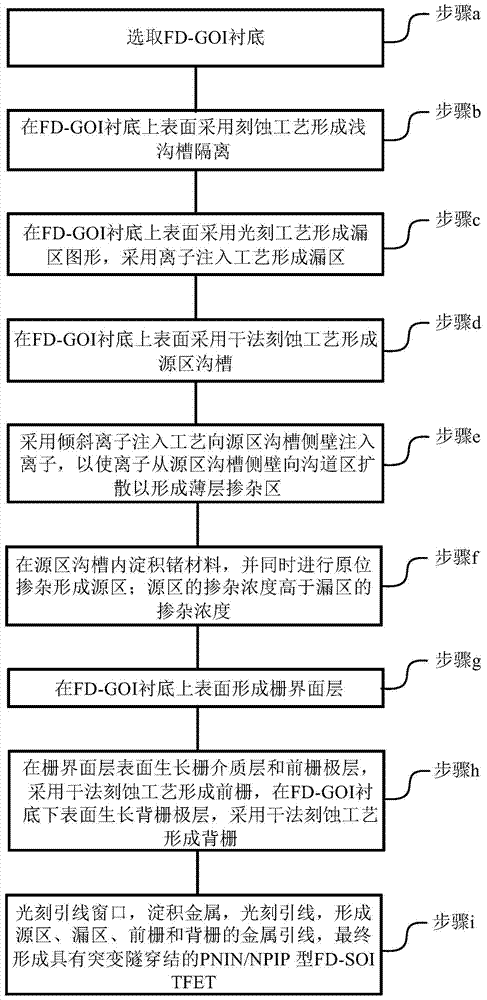

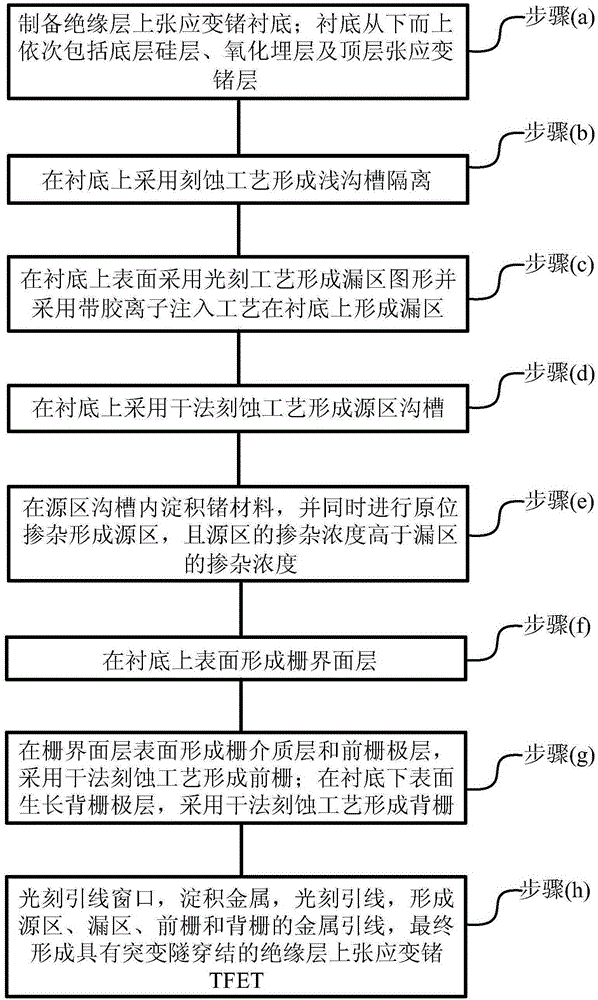

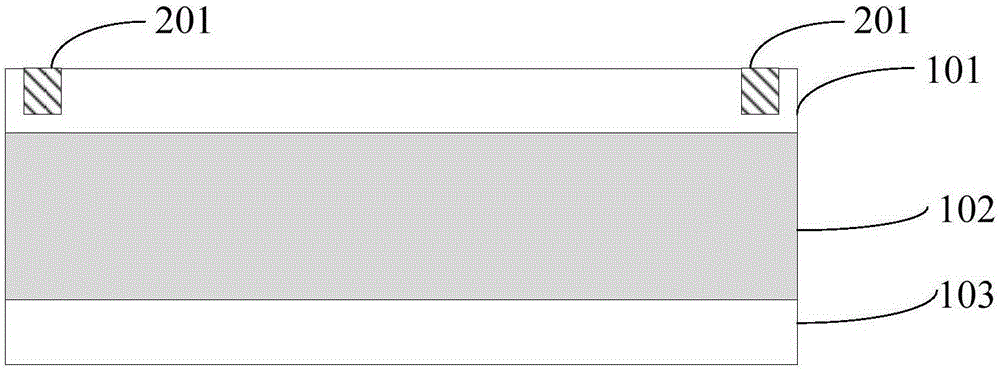

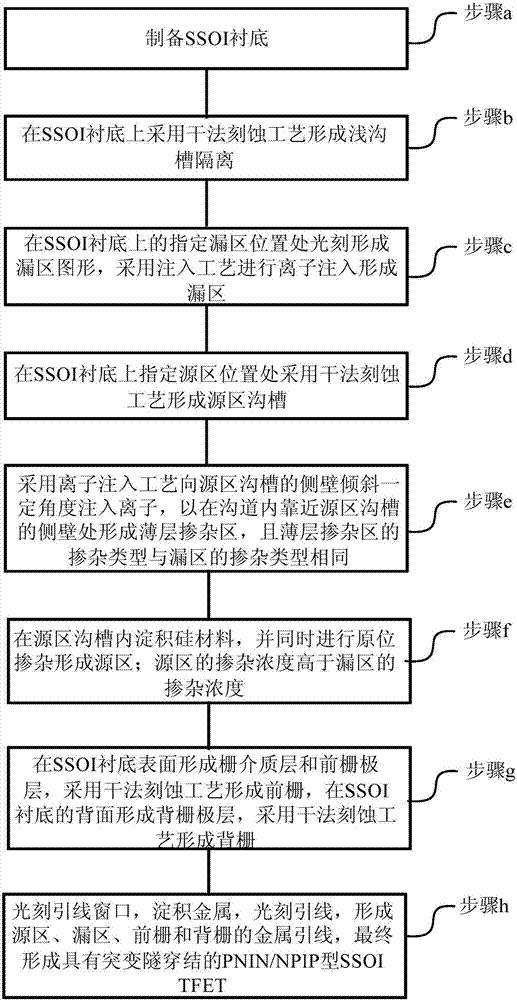

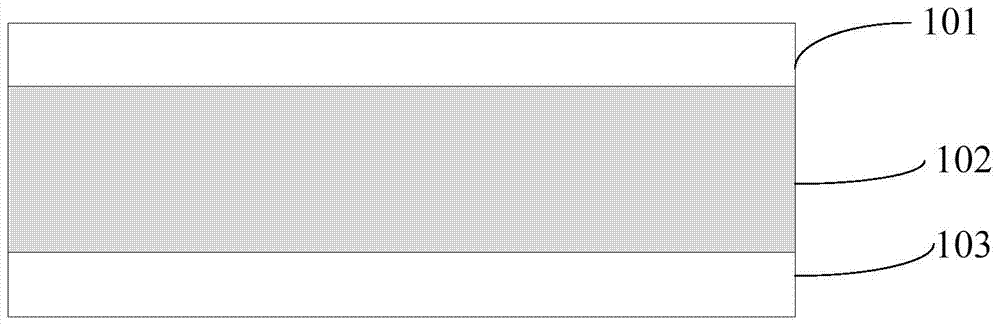

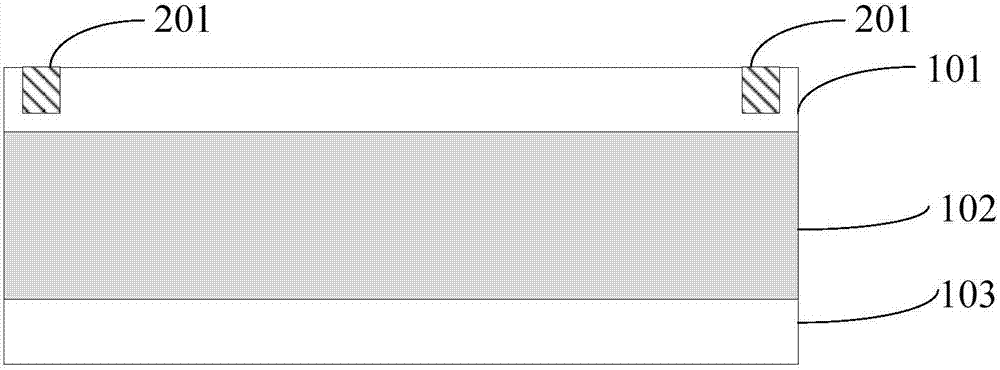

PNIN/NPIP type SSOI TFET with abrupt tunneling junctions and preparation method thereof

InactiveCN105244375APrevent proliferationImprove performanceSemiconductor/solid-state device manufacturingDiodeDriving currentGate dielectric

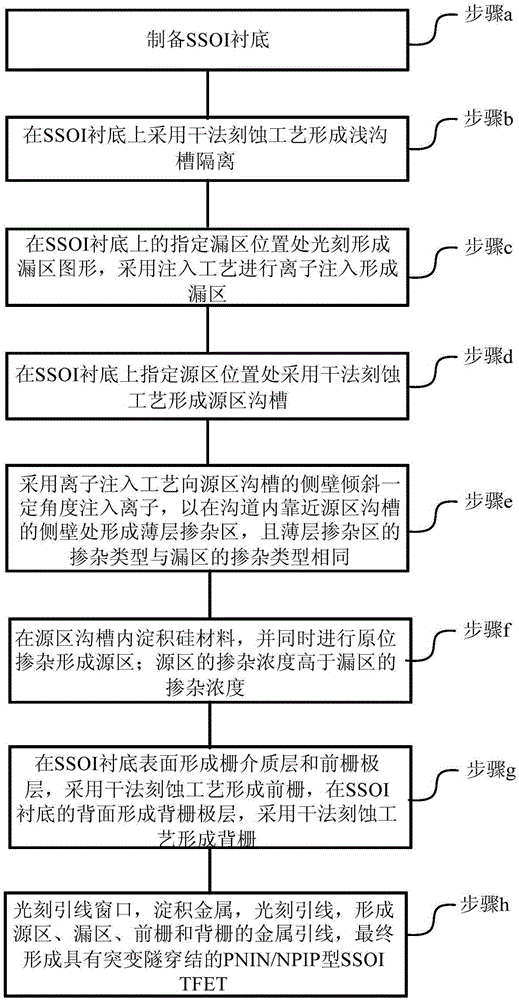

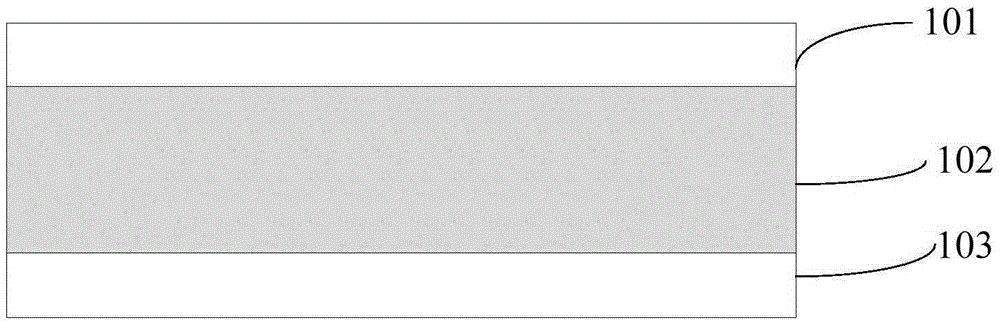

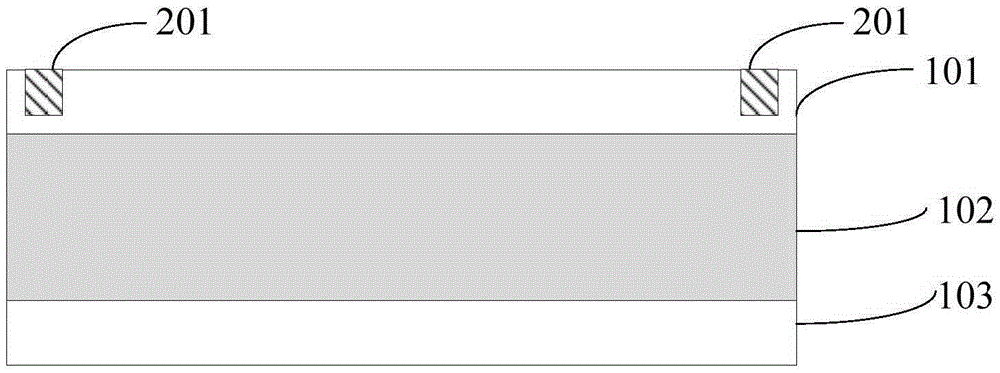

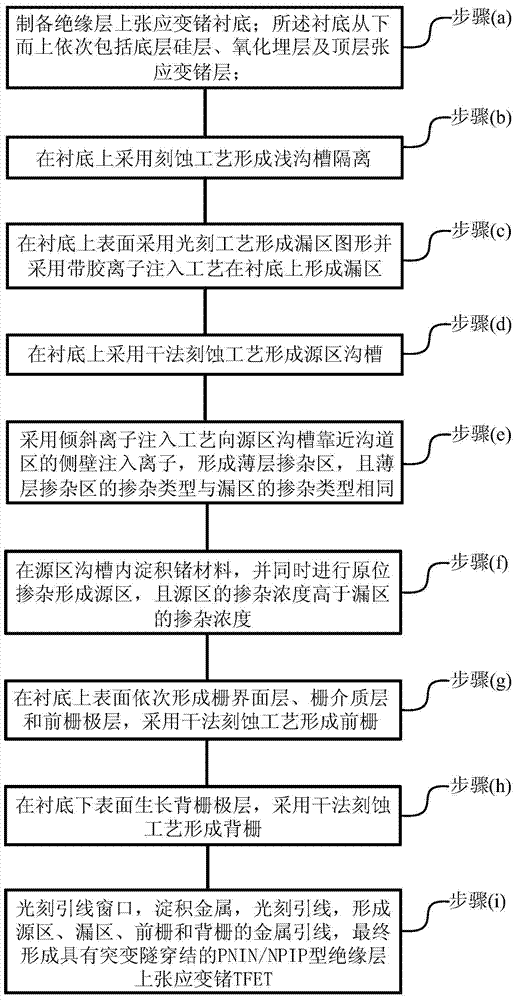

The invention relates to a PNIN / NPIP type SSOI TFET with abrupt tunneling junctions and a preparation method thereof. The preparation method comprises the steps that an SSOI substrate is prepared; shallow trench isolation is formed; a drain region pattern is formed through photoetching, and adhesive ions are injected so that a drain region is formed; a source region trench is formed through dry etching; the ions are injected in the side wall of the source region trench at a certain inclined angle by adopting an ion injection technology, Si material is deposited in the source region trench, and in-situ doping is performed so that a source region is formed; a gate dielectric layer and a front gate layer are formed on the upper surface of the substrate, a front gate is formed through etching, a back gate layer is formed on the lower surface of the substrate, and a back gate is formed through etching; and a lead-wire window is photoetched, metal is deposited and a lead-wire is photoetched so that source / drain and front / back gate lead-wires are formed. Drive current of the TFET can be effectively enhanced and subthreshold slope of the TFET can be reduced.

Owner:XIAN UNIV OF SCI & TECH

Self-adaptive composite tunneling field effect transistor and method for fabricating the same

InactiveUS9171944B2Increase currentSteeper subthreshold characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSMOSFET

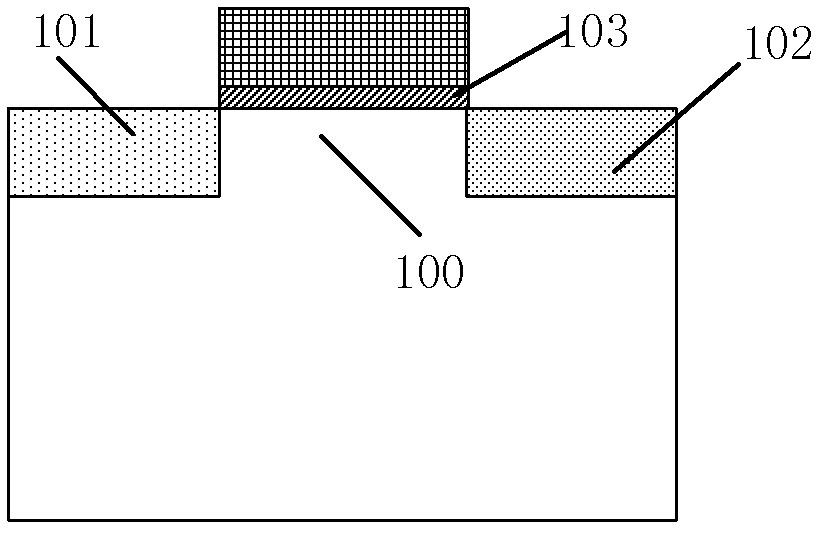

The present invention provides a tunneling field effect transistor and a method for fabricating the same which refer to a field effect transistor logic device and circuit in a CMOS ultra-large integrated circuit (ULSI). The inventive concept of the invention lies in that, in a case of an N-type transistor, a side portion of a doped source region adjacent to an edge of the control gate is further implanted with P+ impurities on a basis of the doped source region being initially doped N− impurities, so that the initial N− impurities in the implanted portion are completely compensated by the P+ impurities, and in a case of a P-type transistor, a side portion of the doped source region adjacent to an edge of the control gate is implanted with N+ impurities on a basis of the doped source region being initially doped P− impurities, so that the initial P− impurities in the implanted portion are completely compensated by the N+ impurities. In the transistor, the source region is implanted twice with different doping concentrations, such that a large current characteristic of the MOSFET can be effectively combined to increase an on-state current of the transistor, and also, the threshold adjustment for the MOSFET portion and the TFET portion of the transistor can be achieved in a self-adaptive way.

Owner:PEKING UNIV

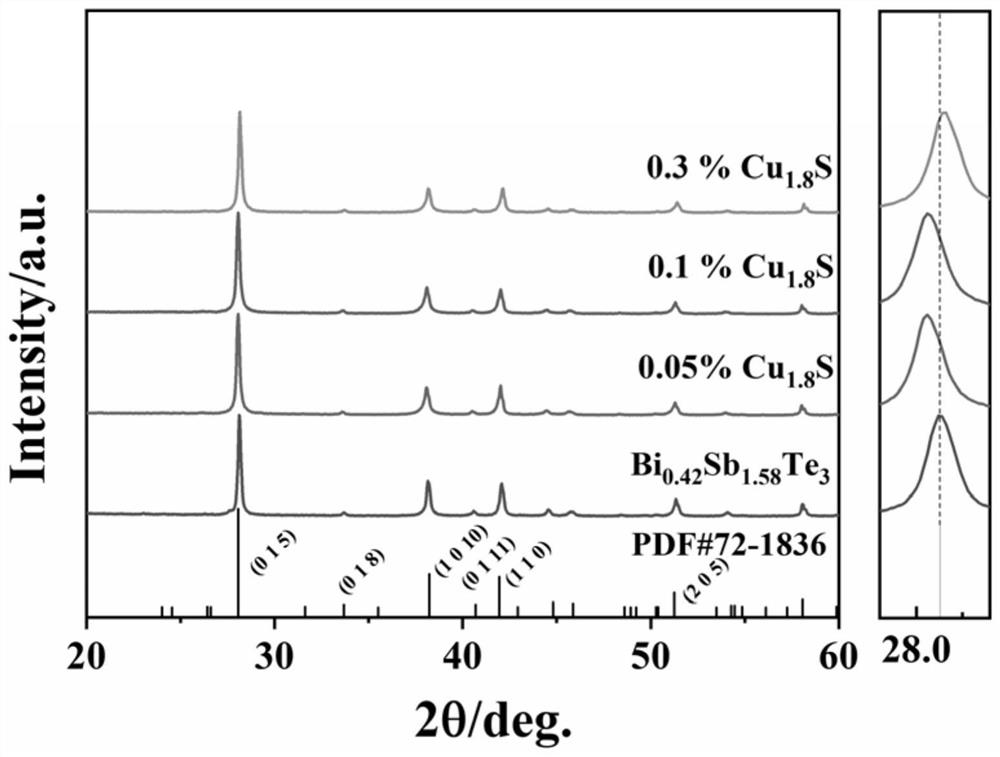

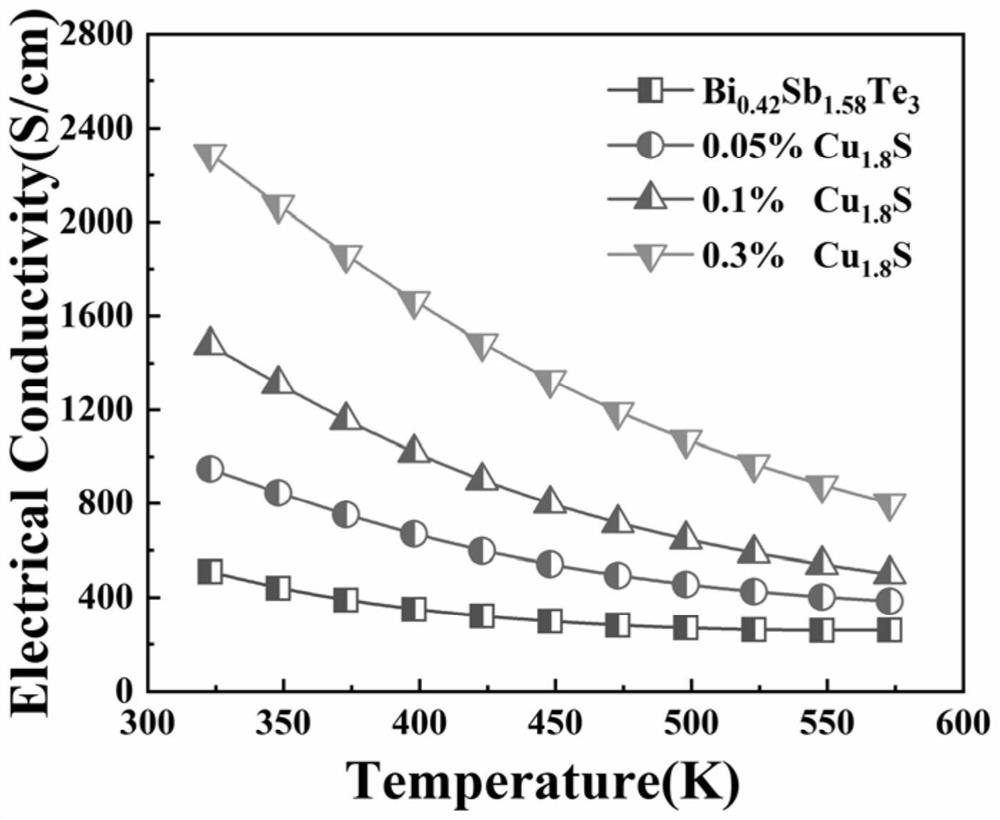

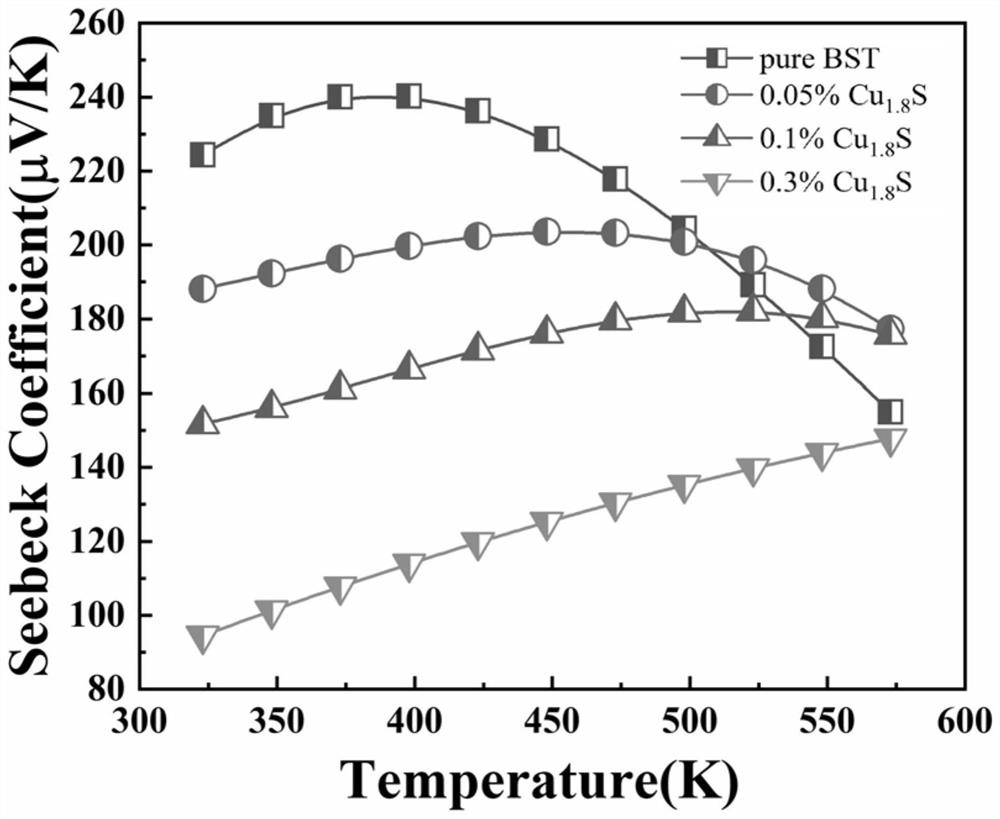

Method for improving performance of Bi-Sb-Te-based thermoelectric material

ActiveCN112397634AOptimizing electrical transport propertiesLow thermal conductivityThermoelectric device manufacture/treatmentThermoelectric device junction materialsThermoelectric materialsVertical tube

The invention relates to the technical field of thermoelectric materials, and particularly discloses a method for improving the performance of a BiSbTe-based thermoelectric material. The method comprises the following steps: weighing Te particles, Sb particles, Bi powder and Cu1.8S powder according to a chemical general formula Bi0.42Sb1.58Te3(Cu1.8S)x, filling a quartz tube with the Te particles,the Sb particles, the Bi powder and Cu1.8S powder, and performing vacuumizing, wherein x is greater than 0 and less than or equal to 0.3%; putting the quartz tube into a vertical tube furnace, carrying out heat preservation for 15-20 hours at the temperature of 900-1,000 DEG C, and carrying out furnace cooling to obtain an initial cast ingot; grinding the cast ingot by adopting a high-energy ballmill to obtain powder; and performing heat preservation of the powder for 4-8 min at the temperature of 410-450 DEG C and the sintering pressure of 40-60 MPa through a spark plasma sintering process,and obtaining the BiSbTe-based thermoelectric material, wherein the material has high conductivity, the bipolar effect is remarkably inhibited, the ZT value is increased, and the temperature for obtaining the highest ZT value is regulated and controlled.

Owner:KUNMING UNIV OF SCI & TECH

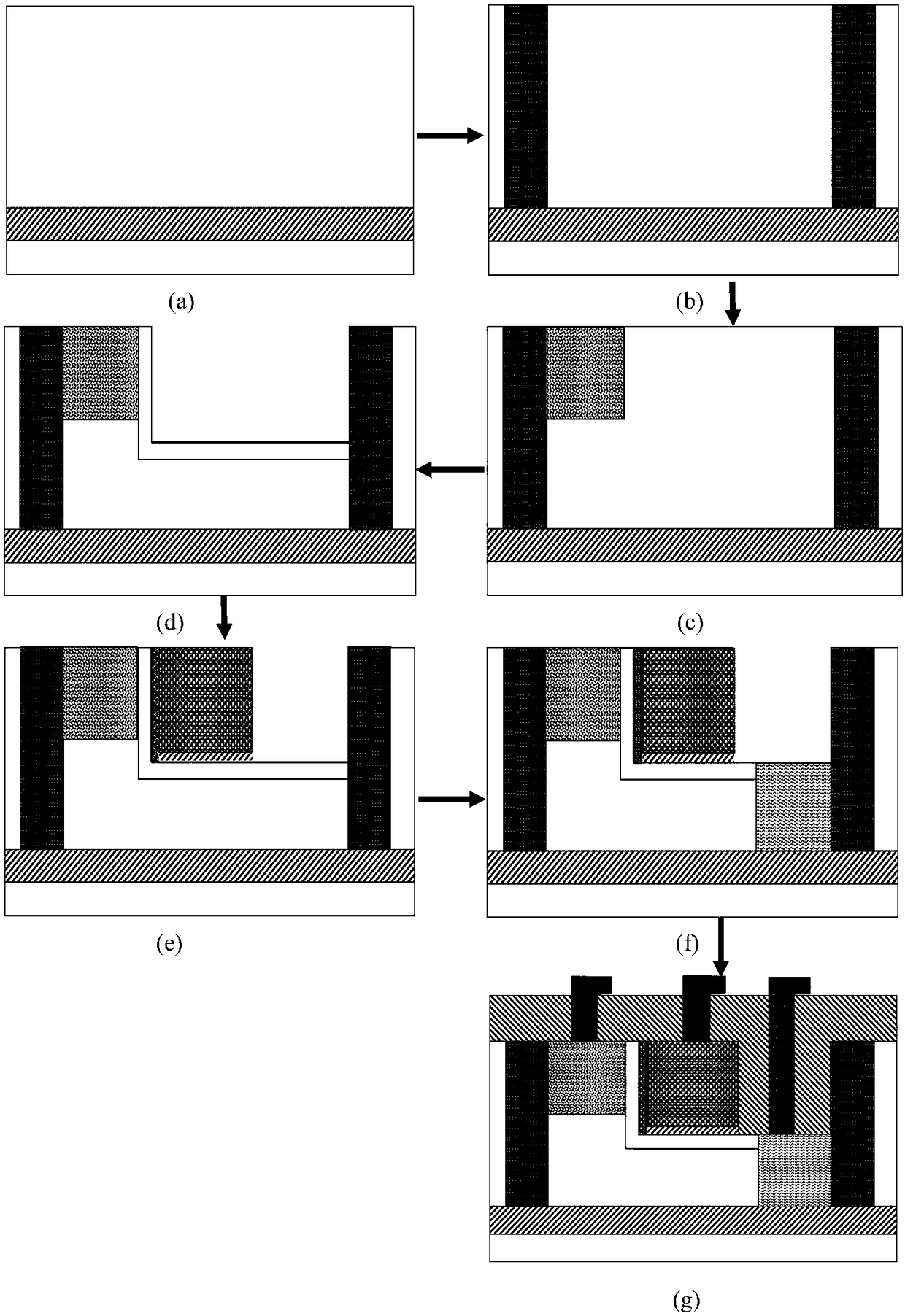

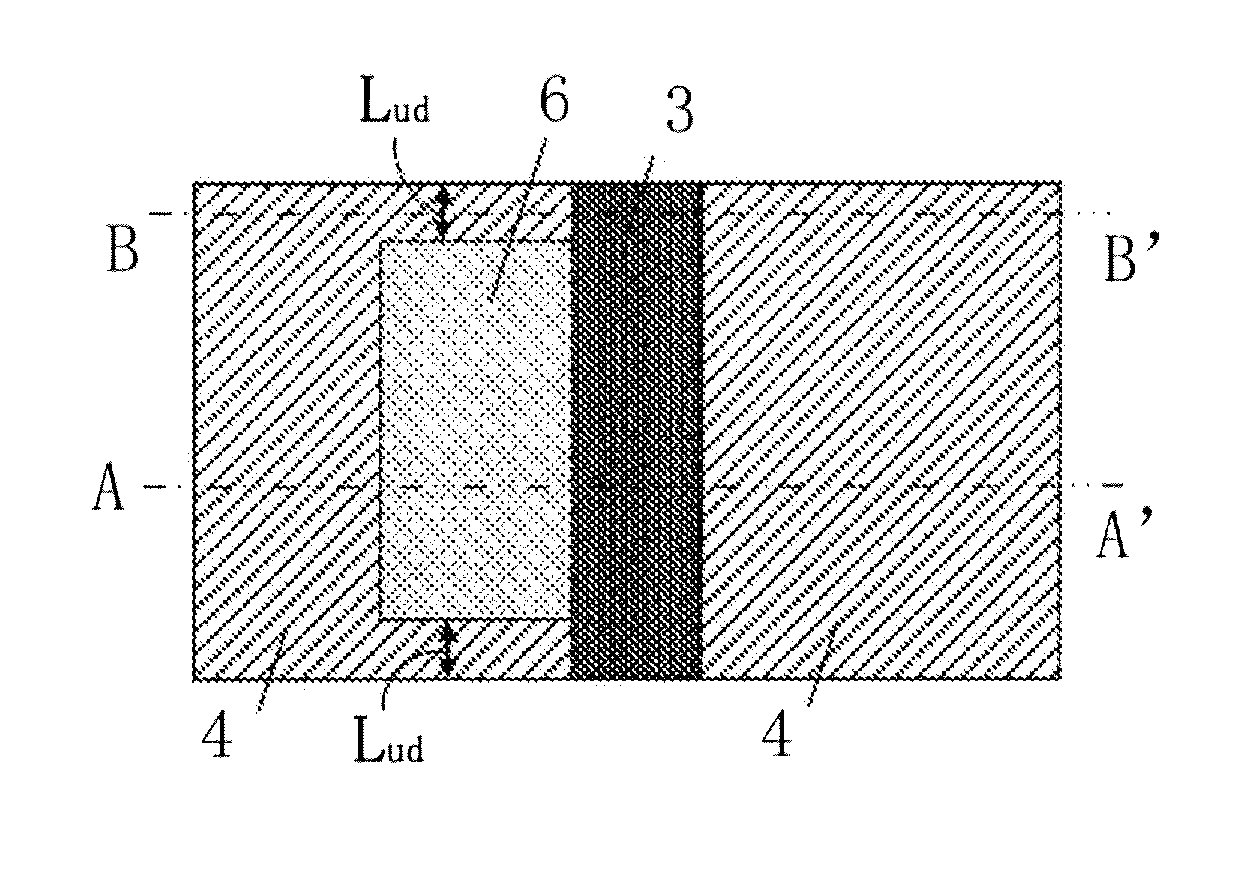

Self-alignment preparation method of drain terminal negative overlapping region of tunneling transistor

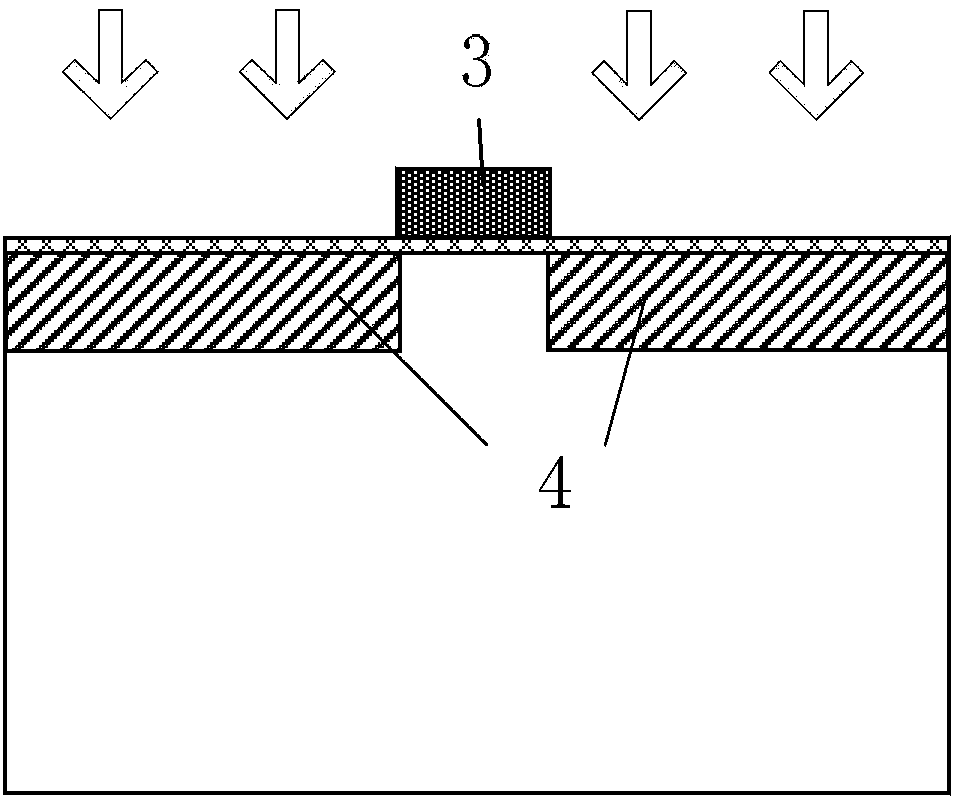

InactiveCN111564498AGuaranteed mixed-chip integrationComplex multiple circuit functionsTransistorSemiconductor/solid-state device manufacturingHemt circuitsEngineering

The invention discloses a self-alignment preparation method for a self-alignment gate-drain negative overlapping region of a tunneling field effect transistor, and belongs to the field of field effecttransistor logic devices and circuits in a CMOS ultra-large integrated circuit (ULSI). According to the method, asymmetric side wall structures are designed on the two sides of a tunneling transistorgate, the side, close to a source end, of the gate is a thin side wall, and the side, close to a drain end, of the gate is a thick side wall. According to the invention, by reasonably utilizing the thin side wall and the thick side wall in the standard CMOS process, the thin side wall at the source end is used as a hard mask for transistor source region injection, and the thick side wall at the drain end is used as a hard mask for transistor drain region injection, so that special materials and special processes are not introduced, the bipolar effect of a tunneling field effect transistor (TFET) is inhibited, the fluctuation characteristic of the device is optimized, it can be guaranteed that the TFET can be mixed and integrated with a standard CMOS device, and complex and diversified circuit functions are achieved.

Owner:PEKING UNIV

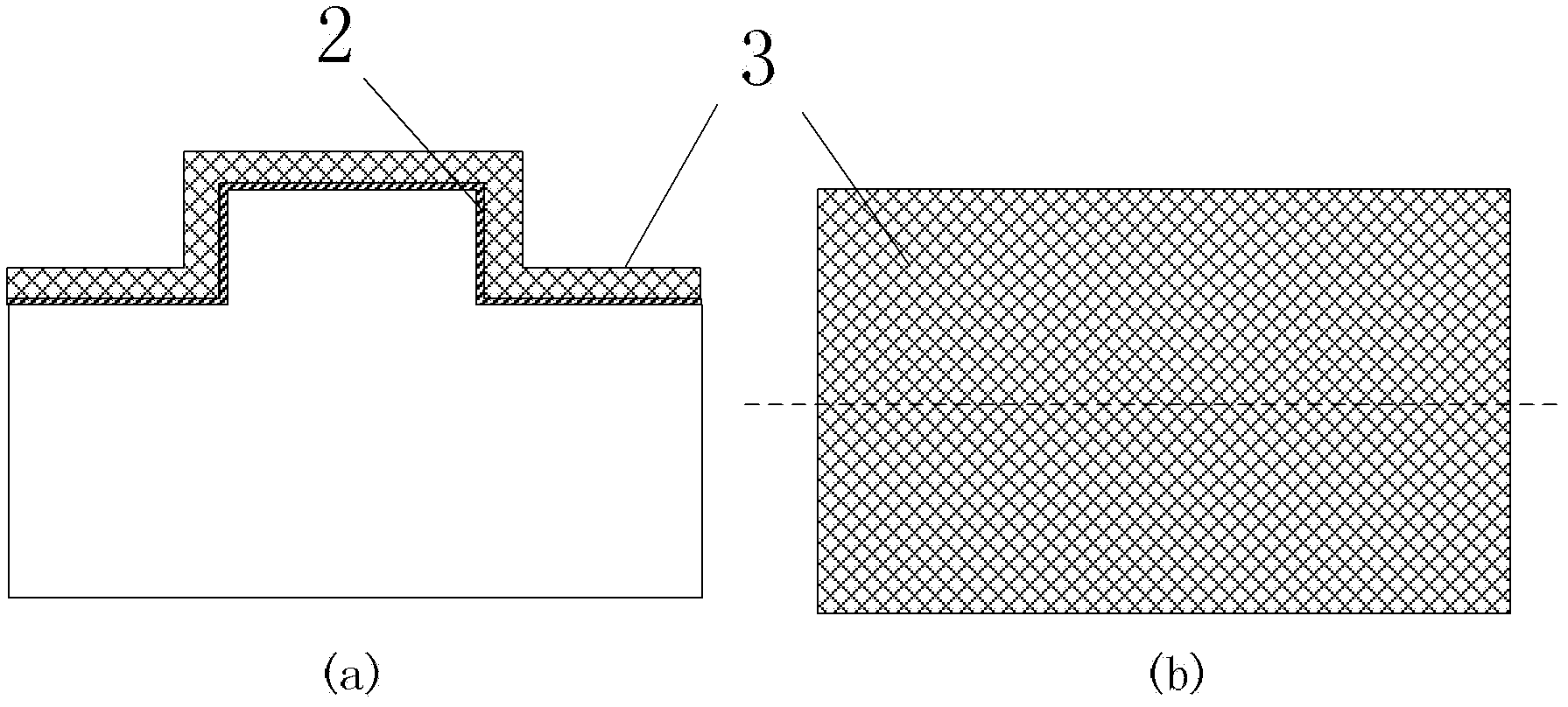

Z-type heterojunction tunneling field effect transistor with lightly doped drain structure and preparation method thereof

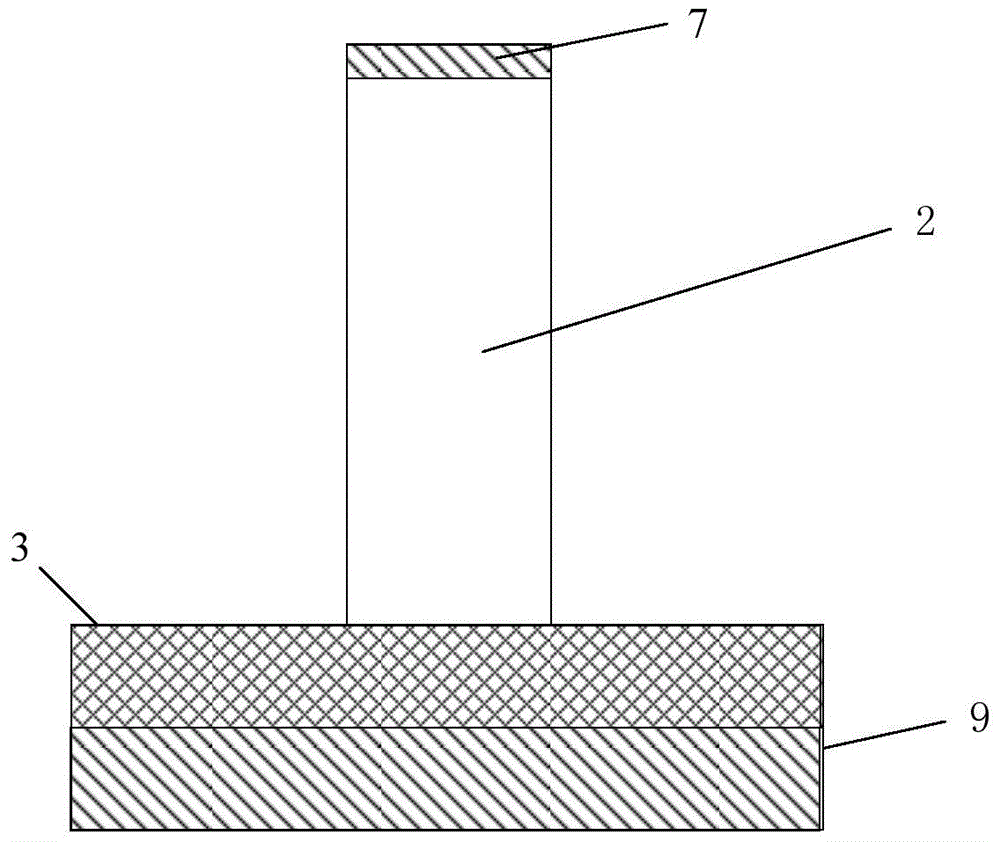

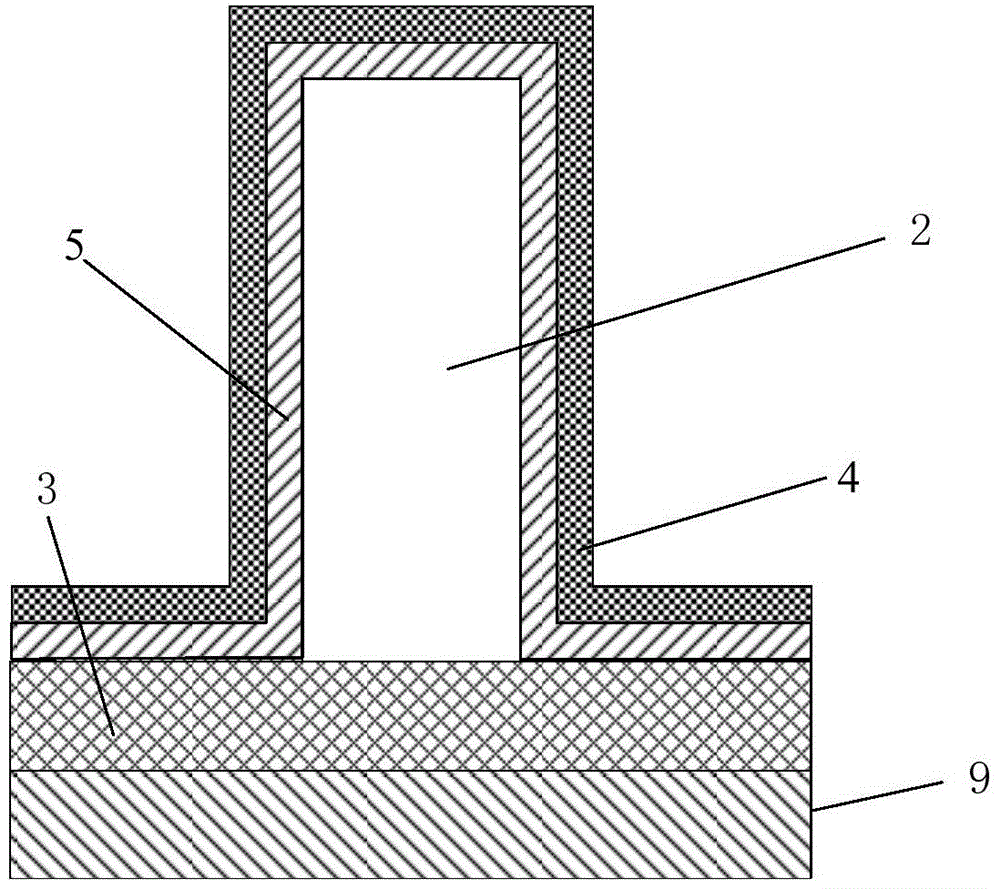

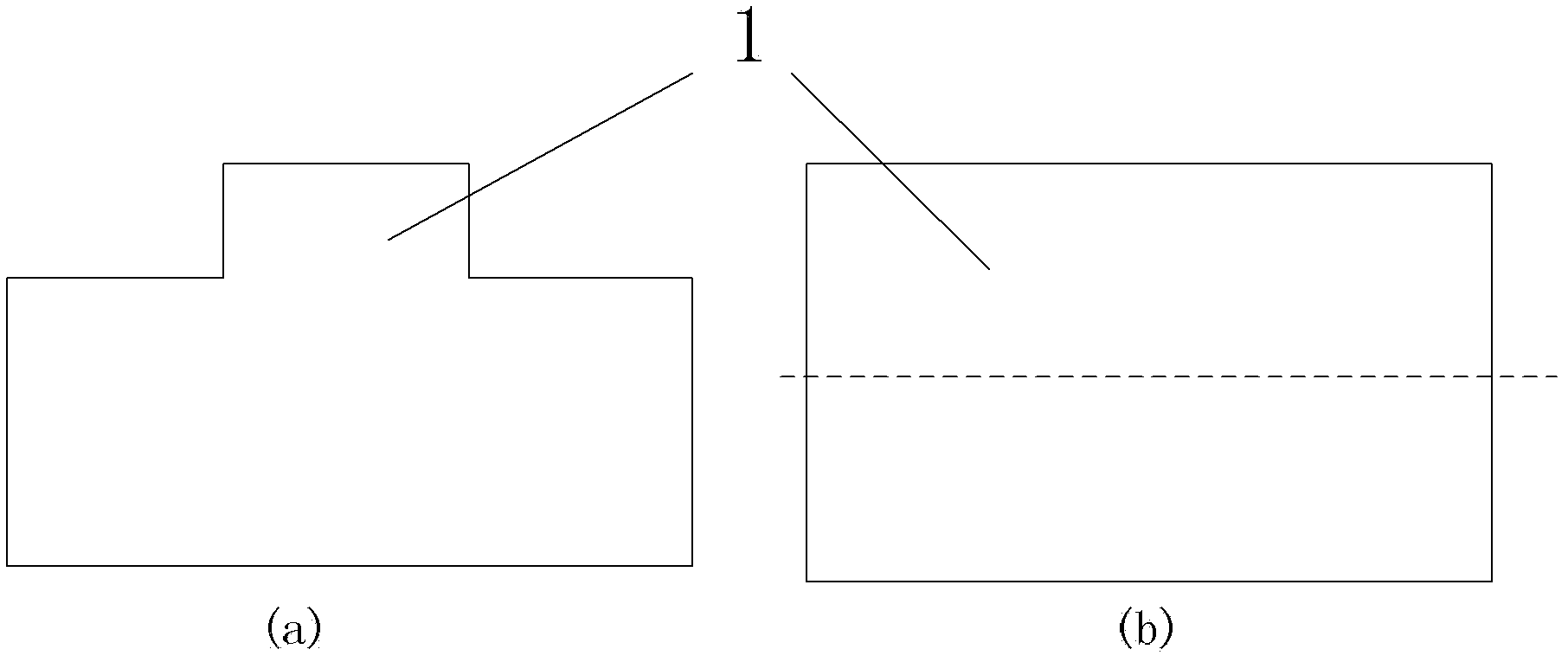

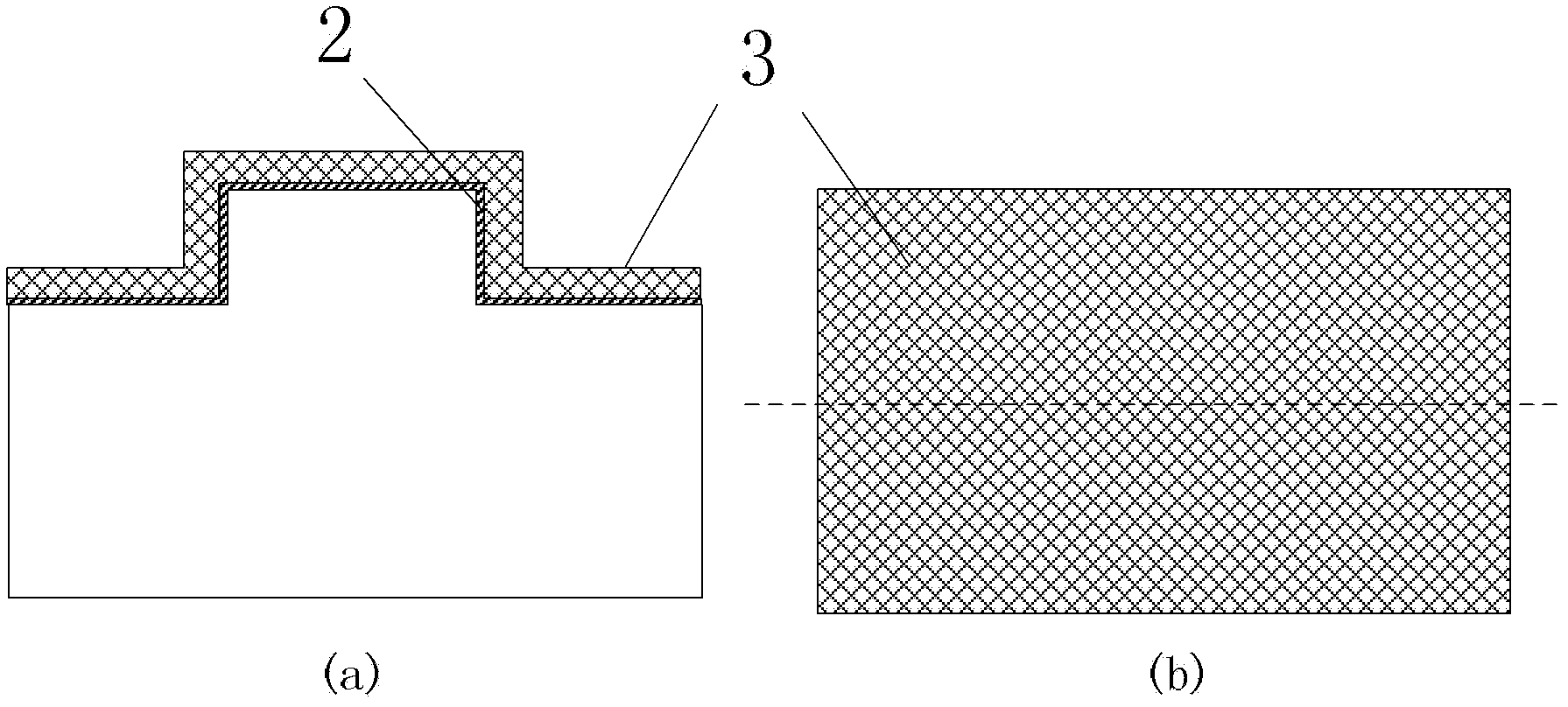

ActiveCN108493240BShorten tunneling distanceIncrease drive currentSemiconductor/solid-state device manufacturingDiodeHeterojunctionSemiconductor materials

The invention discloses a Z-type heterojunction tunneling field effect transistor having a lightly-doped drain structure and a preparation method thereof, and mainly solves the problems of low on-state current and severe bipolar effect of an existing device. The Z-type heterojunction tunneling field effect transistor comprises an SOI substrate (1), isolation grooves (2), a source region (3), a channel region (4), a drain region (6), a gate region (5) and a conductive layer (7). The isolation grooves (2) are arranged at the two sides of the SOI substrate (1); the source region (3), the channelregion (4) and the drain region (6) are arranged on the upper surface of the SOI substrate; the gate region (5) is arranged on the upper side of the channel region (4); the source region (3) adopts agermanium semiconductor; the gate region (5) adopts a Z-type structure, and gates with the length of 3nm-9nm are covered on the source region; and the side, close to the gate region (5), of the drainregion (6) is provided with a lightly-doped drain region. The Z-type heterojunction tunneling field effect transistor can effectively suppress the bipolar effect and improve driving current, and can be used for manufacturing of a large-scale integrated circuit.

Owner:西安电子科技大学重庆集成电路创新研究院

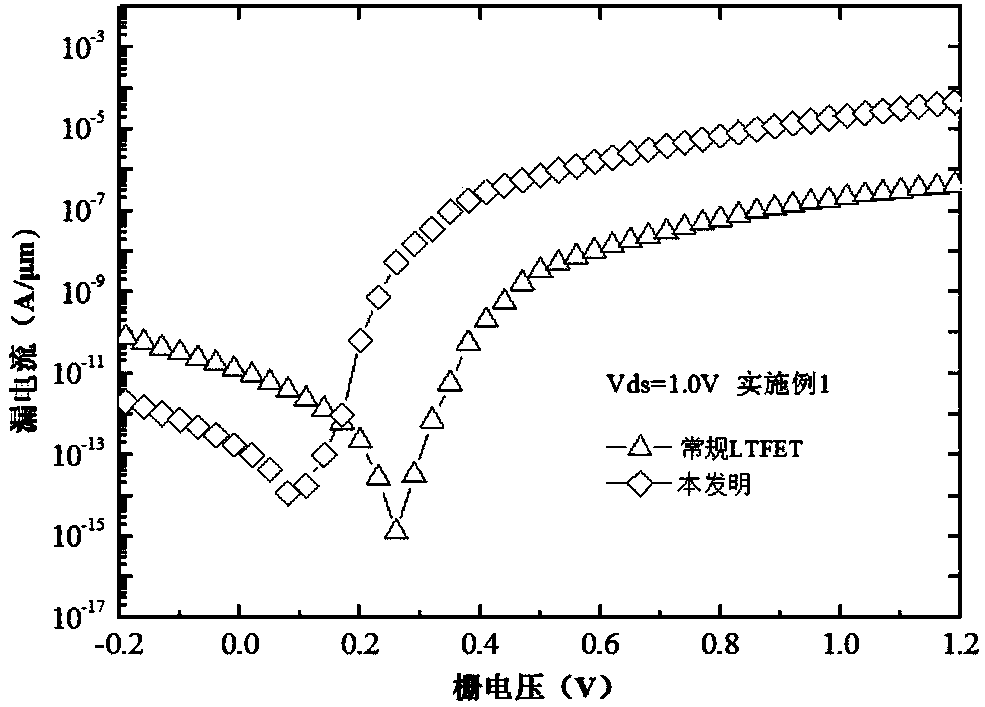

Self-adaptive composite mechanism tunneling field effect transistor (TFET) and preparation method thereof

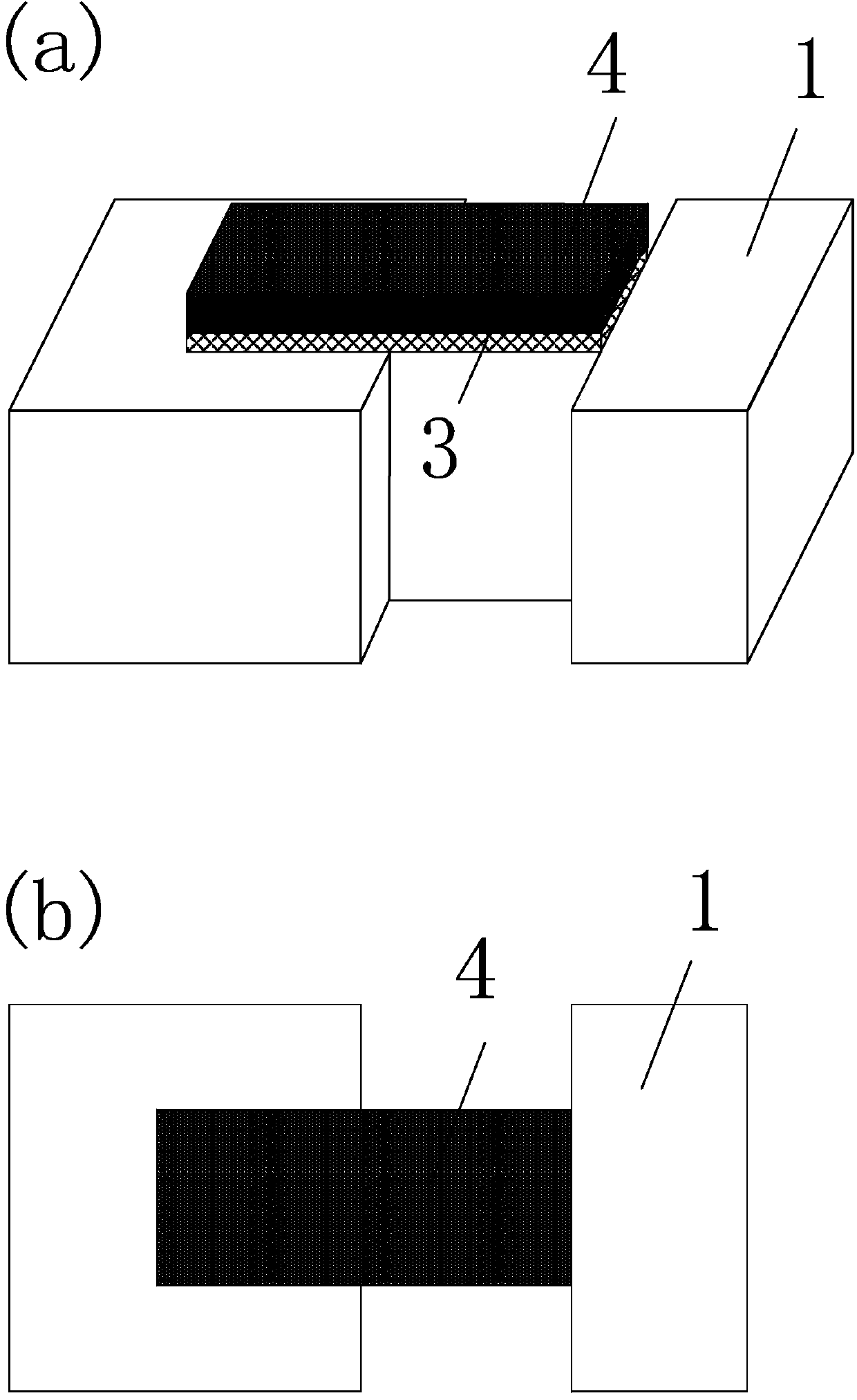

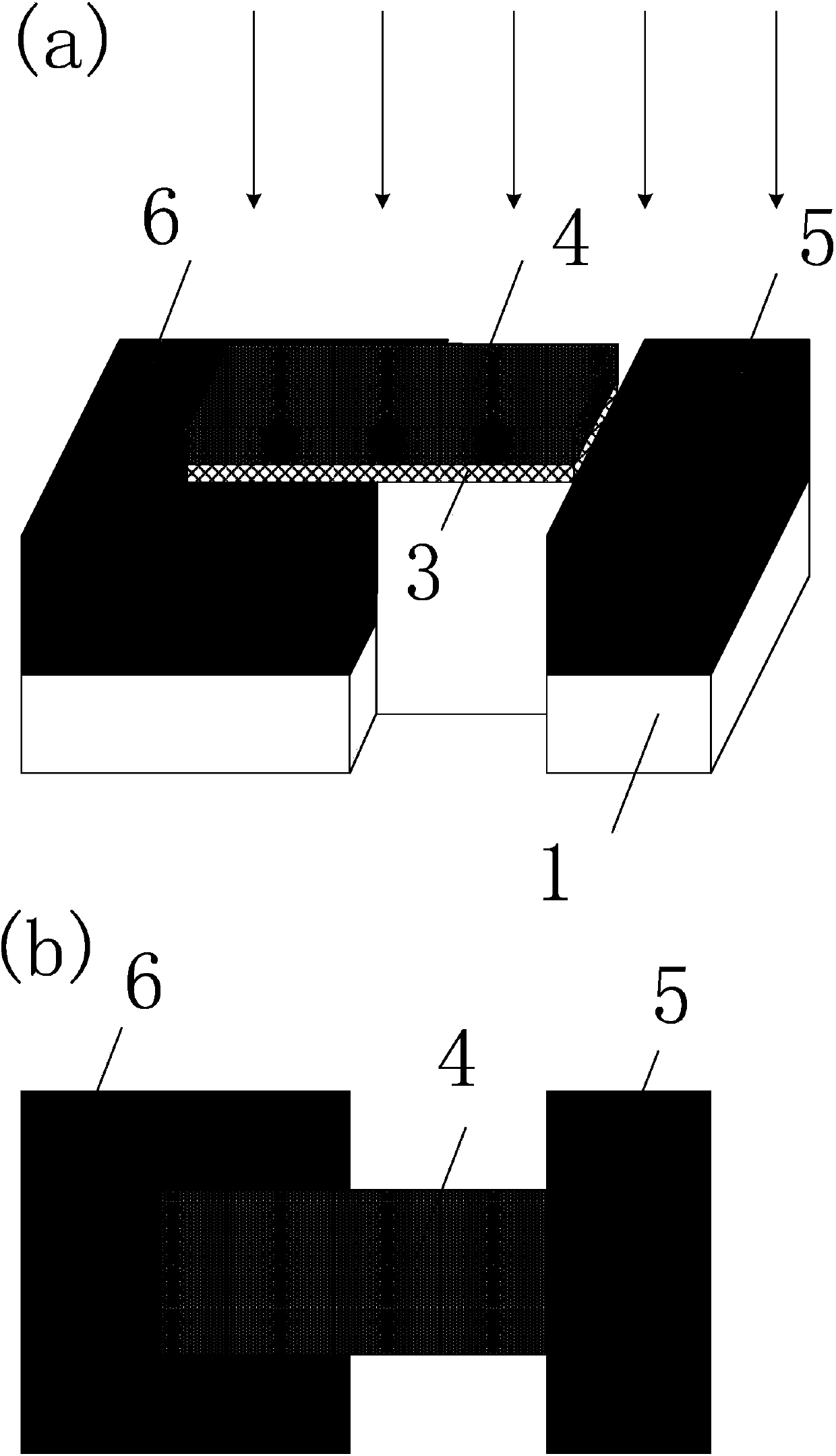

ActiveCN102664192BSuppression of bipolar effectsSteep Subthreshold CharacteristicSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSMOSFET

The present invention relates to the field of tunneling field effect transistor logic devices and circuits in a CMOS ultra large scale integrated (ULSI) circuit. Disclosed are a tunneling field effect transistor and manufacturing method thereof. The tunneling field effect transistor is: for an N type transistor, P+ is injected, on the basis of doping N-, into one side of a doped source area close to the edge of a control gate (3), so that the original doped N- of the injected part is completely compensated as P+; and for a P type transistor, N+ is injected, on the basis of doping P-, into one side of the doped source area close to the edge of the control gate (3), so that the original doped P- of the injected part is completely compensated as N+. Through the doped injection twice of different concentrations into the source area, the device structure of the tunneling field effect transistor effectively combines the characteristics of large conducting current of an MOSFET, thus improving the on-state current of the device, and self-adaptively achieving threshold adjustment of the MOSFET and TFET parts of the device.

Owner:PEKING UNIV

Tunneling field-effect transistor for inhibiting bipolar effect and preparation method thereof

ActiveCN102412302BOptimize subthreshold characteristicsReduced subthreshold slopeSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowSemiconductor materials

The invention discloses a tunneling field-effect transistor for inhibiting the bipolar effect and a preparation method thereof. In the tunneling field-effect transistor, a drain region and a channel region adopt different semiconductor materials; and the width of a forbidden band of the drain region is larger than that of the forbidden band of the channel region, so that the bipolar effect can be effectively inhibited, the subthreshold leakage current of the device is reduced and simultaneously the on-state current of the device is not influenced. Therefore, the on-state current ratio of the device can be increased, the subthreshold slope of the device is also reduced and the performance of the device is very obviously improved.

Owner:PEKING UNIV

Optimized l-type tunneling field effect transistor and its preparation method

ActiveCN108538911BShorten tunneling distanceIncrease drive currentSemiconductor/solid-state device manufacturingDiodeDriving currentGate dielectric

Owner:西安电子科技大学重庆集成电路创新研究院

A kind of tunneling field effect transistor and its preparation method

ActiveCN103560153BLarge tunneling areaIncrease drive currentSemiconductor/solid-state device manufacturingDiodeDriving currentPower flow

The invention provides a tunneling field effect transistor and a preparation method thereof. The preparation method at least comprises the following steps that an SOI substrate provided with top layer silicon, an oxygen buried layer and bottom layer silicon is provided, and ion injection is conducted on the two sides of the top layer silicon to form a source electrode and a drain electrode respectively; an intrinsic silicon layer, and a grid medium layer and a grid layer are sequentially formed on the surface of the SOI substrate from bottom to top; a stacking structure is formed by etching the intrinsic silicon layer, the grid medium layer and the grid layer through the photoetching and etching technologies, the stacking structure is partially overlapped with the source electrode and is preset distance away from the drain electrode in the horizontal direction. According to the tunneling field effect transistor and the preparation method of the tunneling field effect transistor, the stacking structure is overlapped with the source electrode so that the tunneling area can be increased, and further a driving current is increased. In addition, the stacking structure is preset distance away from the drain electrode in the horizontal direction, and the bipolar effect in the tunneling field effect transistor can be suppressed through the preset distance, and a subthreshold current is reduced.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

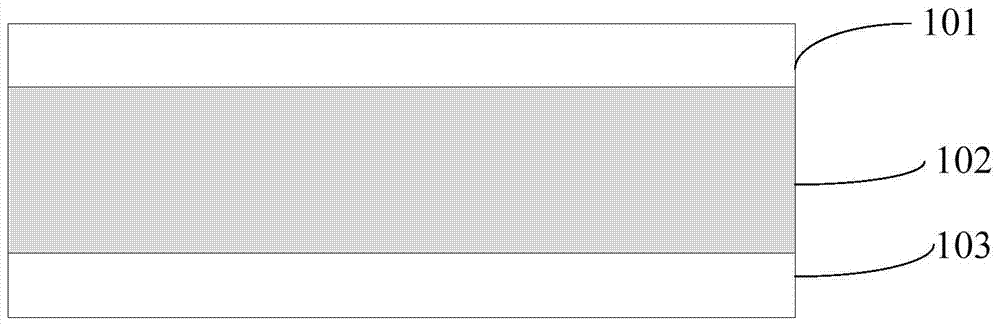

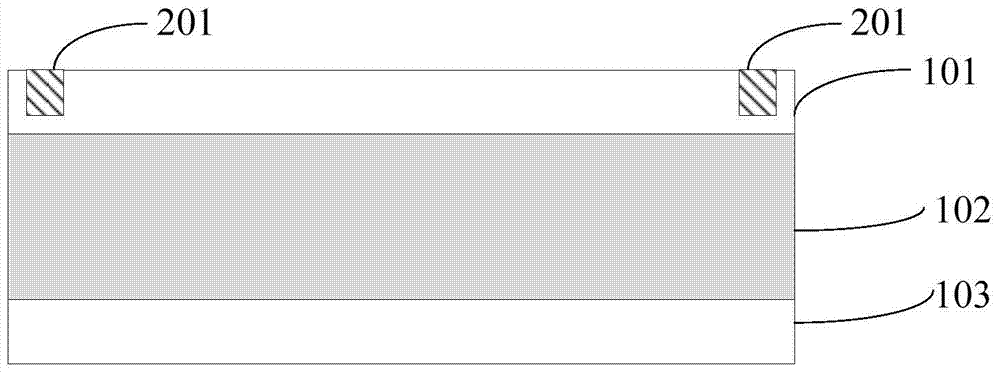

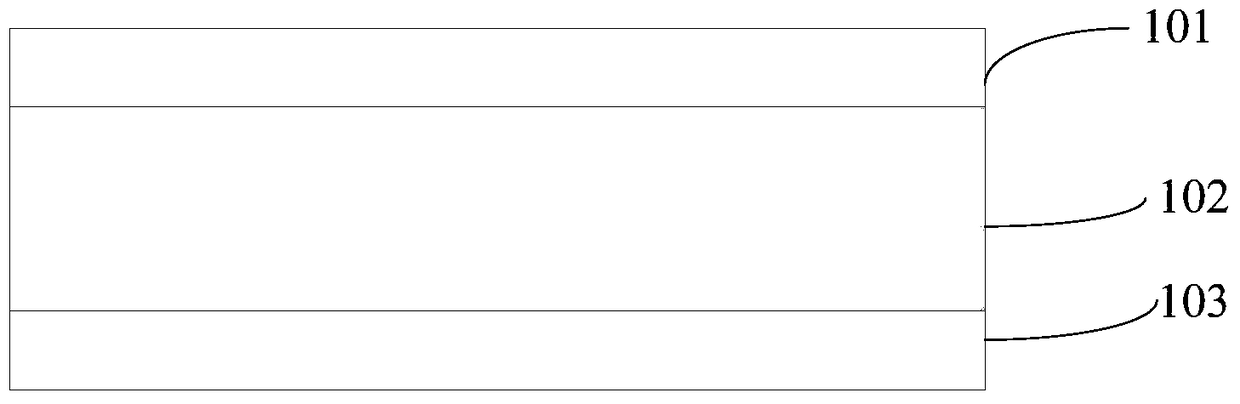

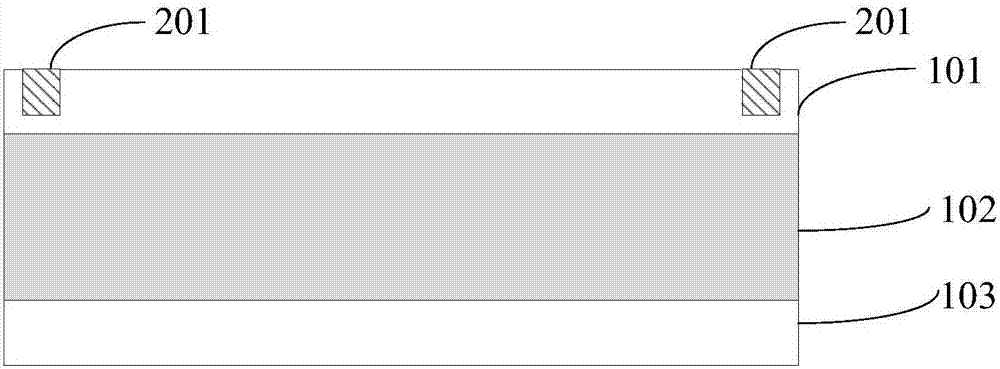

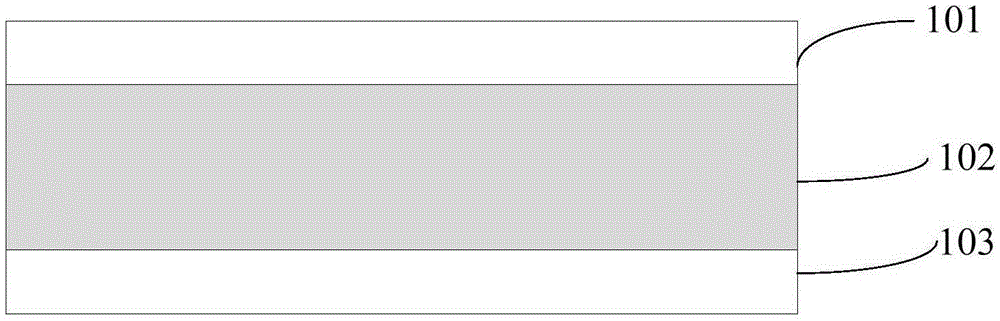

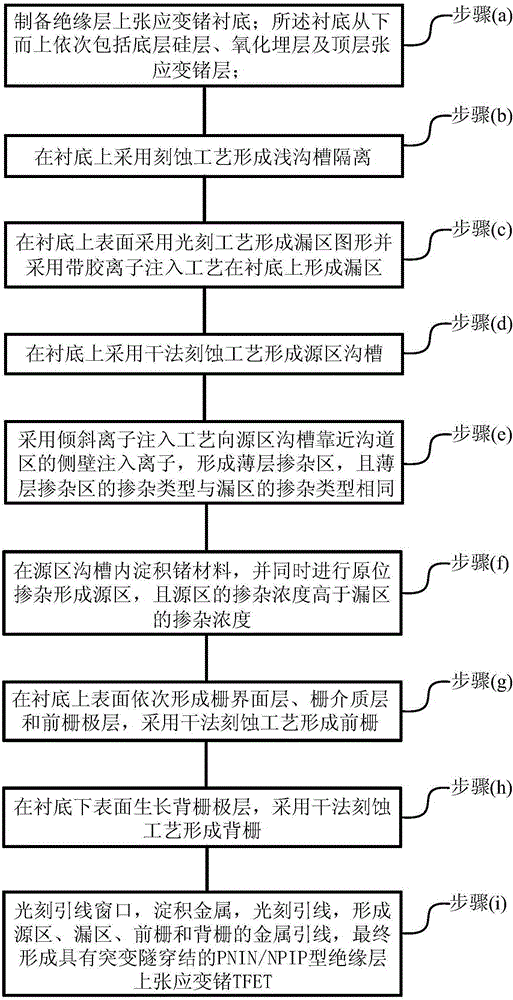

Tensionally strained germanium tfet on pnin/npip type insulating layer with abrupt tunneling junction and preparation method

InactiveCN105244275BIncrease drive currentFast switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesTensile strainIn situ doping

The invention relates to a PNIN / NPIP type tensile strained germanium on insulator TFET with abrupt tunneling junctions and a preparation method thereof. The preparation method comprises the steps that a tensile strained germanium on insulator substrate is prepared; shallow trench isolation is formed by adopting an etching technology; a drain region pattern is formed on the upper surface of the substrate by adopting a photoetching technology and a drain region is formed by adopting an adhesive ion injection technology; a source region trench is formed on the substrate by adopting the etching technology; ions are injected in the side wall of the source region trench close to a channel region by adopting an inclined ion injection technology so that a thin layer doped region is formed; germanium material is deposited in the source region trench and in-situ doping is performed so that a source region is formed; a gate interface layer, a gate dielectric layer and a front gate layer are formed on the upper surface of the substrate in turn, and a front gate is formed by adopting the etching technology; a back gate layer is grown on the lower surface of the substrate, and a back gate is formed by adopting the etching technology; and a lead-wire window is photoetched, metal is deposited and a lead-wire is photoetched so that a metal lead-wire of the source region, the drain region, the front gate and the back gate is formed, and finally the PNIN / NPIP type tensile strained germanium on insulator TFET with the abrupt tunneling junctions is formed.

Owner:XIAN UNIV OF SCI & TECH

Tensionally strained germanium tfet on insulating layer with abrupt tunneling junction and preparation method thereof

InactiveCN105226087BSuppression of bipolar effectsIncrease drive currentSemiconductor/solid-state device manufacturingDiodeInsulation layerIn situ doping

The invention relates to an insulation layer upwards-expanded strained germanium tunneling field effect transistor (TFET) with an abrupt tunneling junction and a preparation method. The preparation method comprises the following steps of: preparing an insulation layer upwards-expanded strained germanium substrate; forming shallow groove isolation by an etching process; forming a drain region pattern on the upper surface of the substrate by the etching process, and forming a drain region on the substrate by a glued ion implantation technology; forming a source region groove on the substrate by a dry etching process; depositing a germanium material in the source region groove, and simultaneously carrying out in-situ doping to form a source region; forming a grid interface layer, a grid dielectric layer and a front grid layer on the upper surface of the substrate, and forming a front grid by the dry etching process; growing a back grid layer on the lower surface of the substrate, and forming a back grid by the dry etching process; and carrying out photoetching of a lead window, metal deposition and lead photoetching, forming metal leads of the source region, the drain region, the front grid and the back grid, and finally forming the insulation layer upwards-expanded strained TFET with the abrupt tunneling junction.

Owner:XIAN UNIV OF SCI & TECH

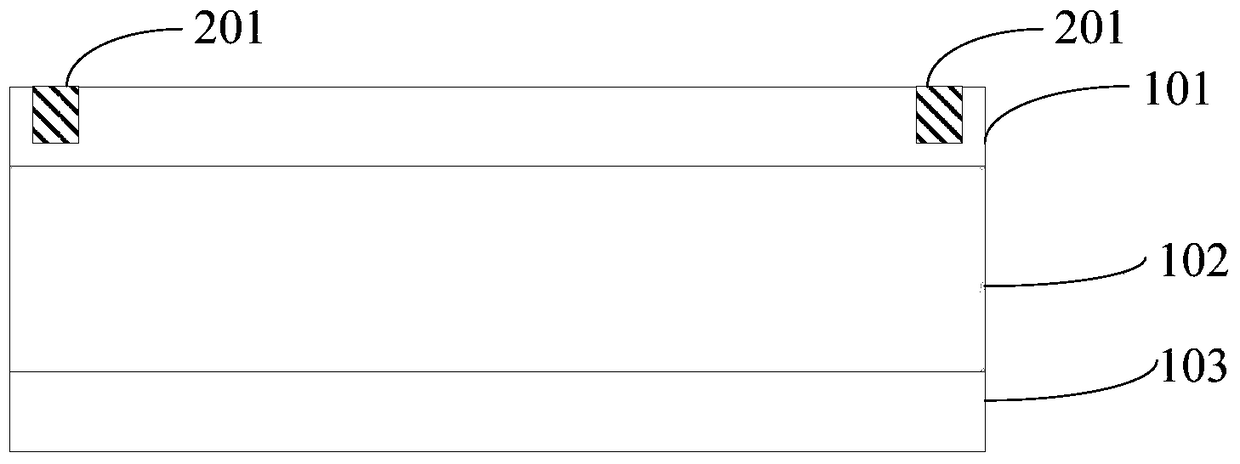

Pnin/npip type utb-soi TFET with abrupt tunneling junction and preparation method

InactiveCN105140127BSuppression of bipolar effectsIncrease drive currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricLow leakage

Owner:XIAN UNIV OF SCI & TECH

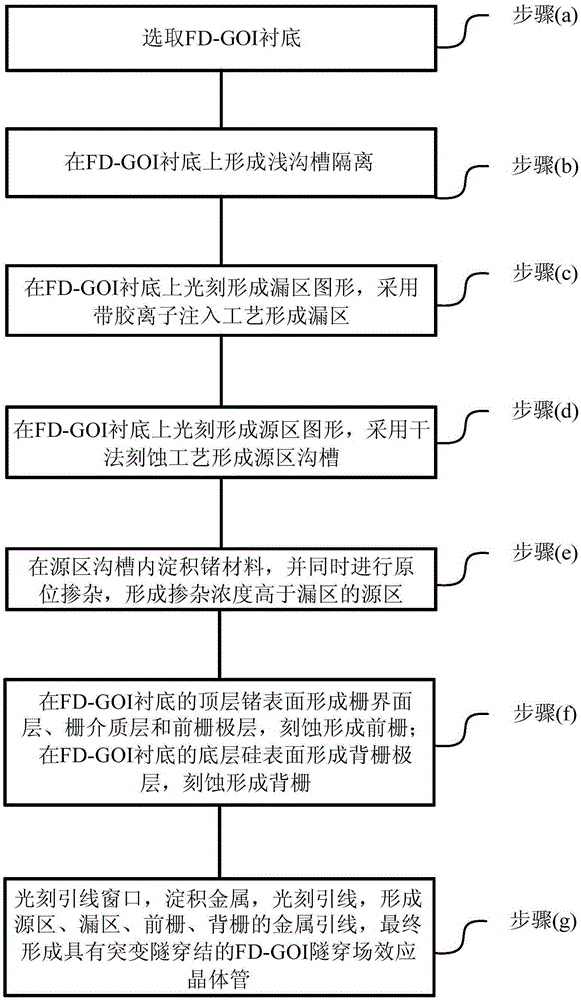

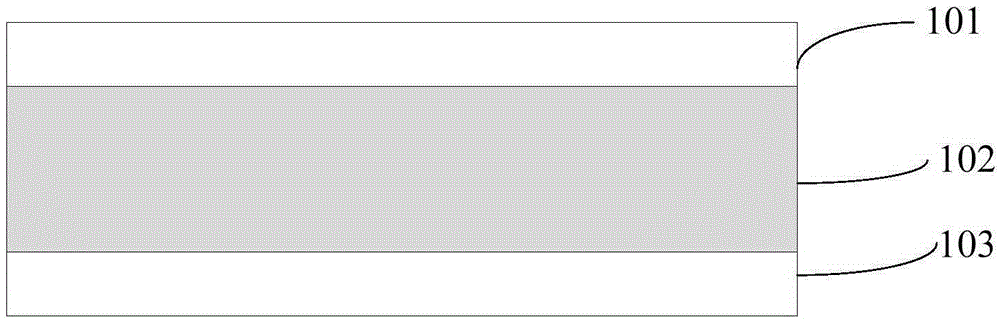

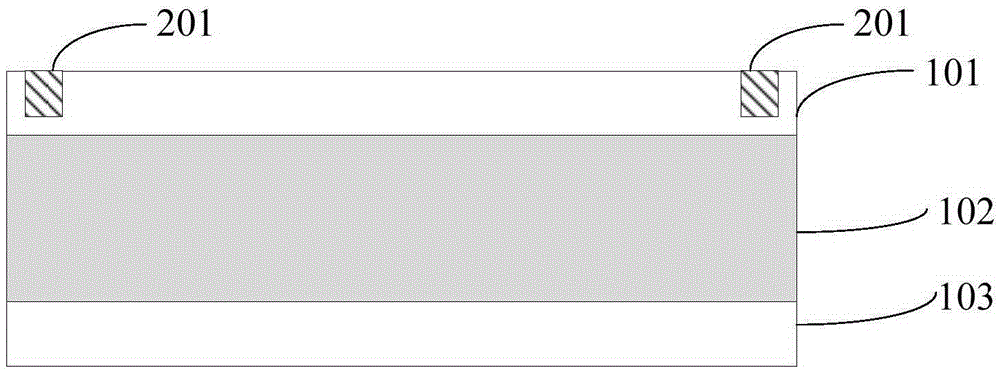

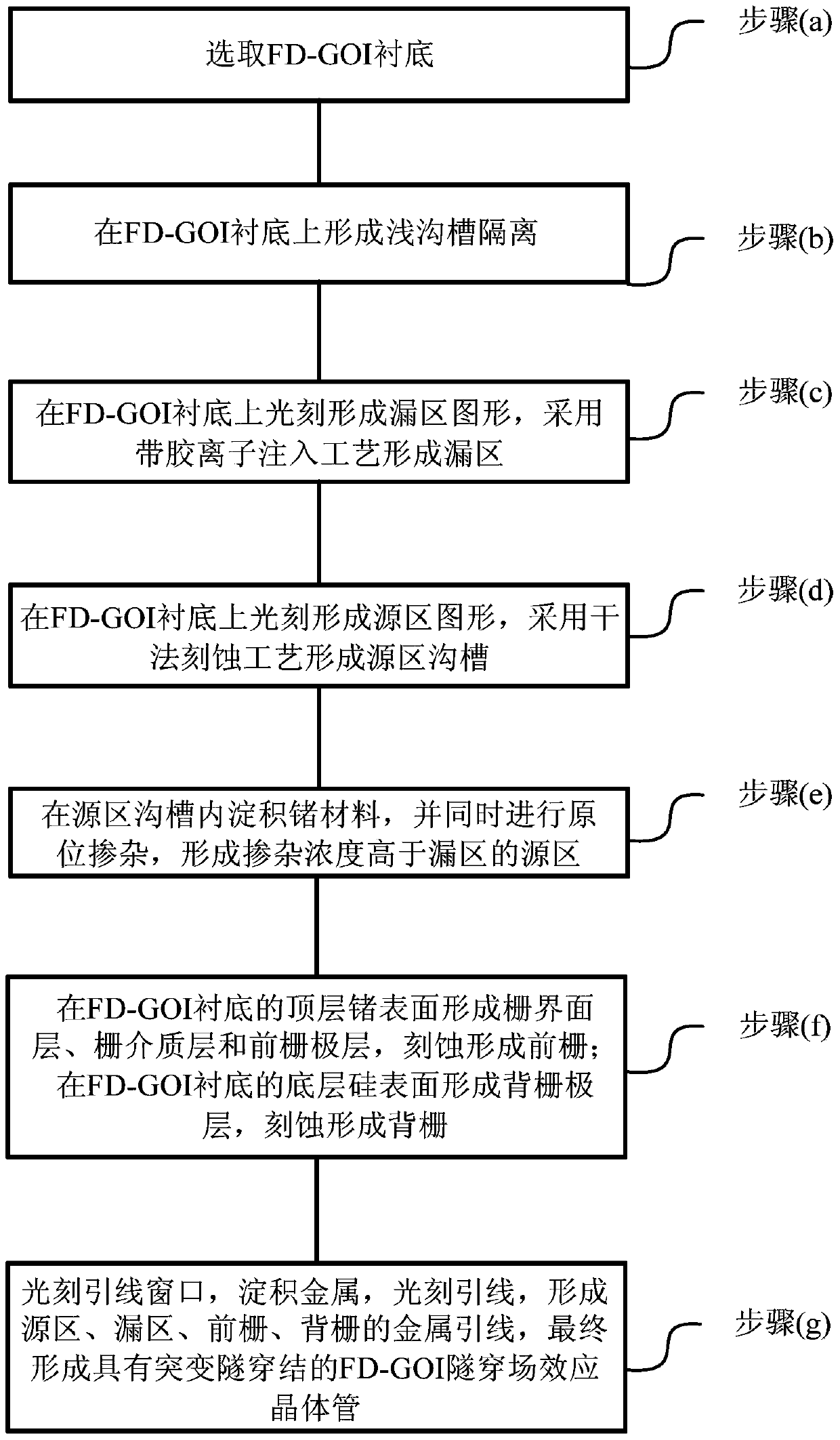

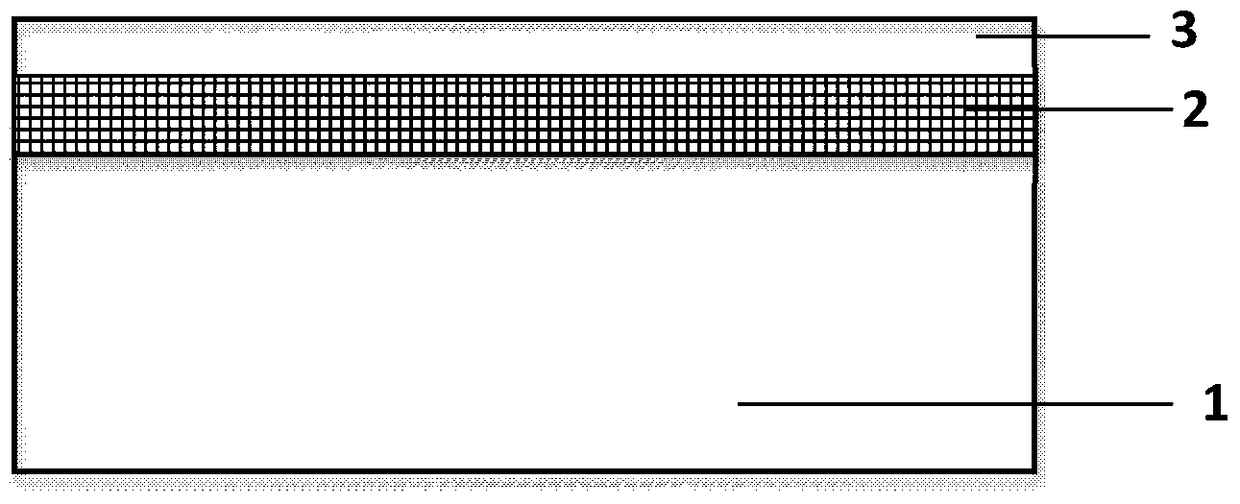

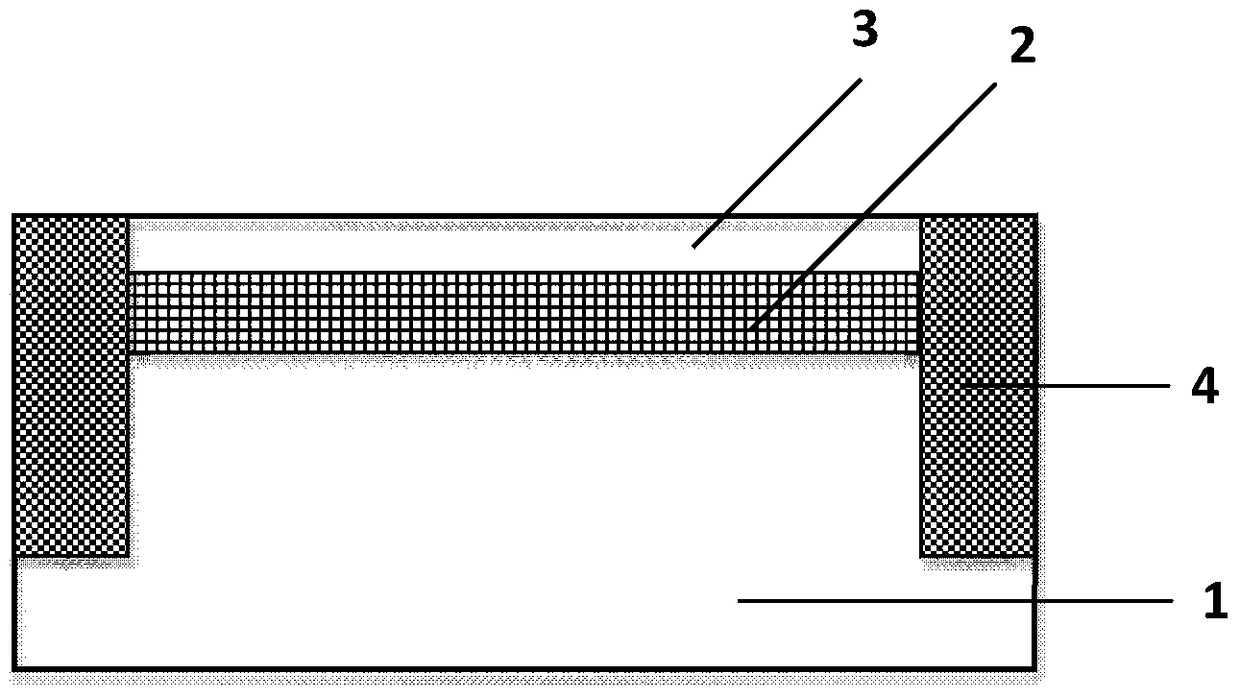

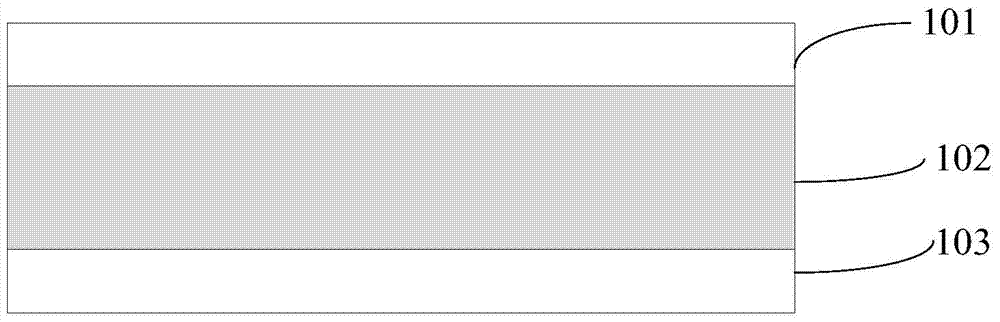

FD-GOI tunneling field effect transistor with abrupt tunneling junction and manufacturing method

InactiveCN105261563AImprove isolationIncrease drive currentSemiconductor/solid-state device manufacturingDiodeIn situ dopingInterface layer

The invention relates to an FD-GOI tunneling field effect transistor with an abrupt tunneling junction and a manufacturing method. The manufacturing method comprises: selecting an FD-GOI substrate; forming shallow trench isolation with an etching process; performing photoetching on the FD-GOI substrate to form a drain region graph and forming a drain region with an adhesive ion implantation process; step (d), performing photoetching on the FD-GOI substrate to form a source region graph and forming a source region trench with a dry etching process; step (e), depositing a germanium material in the source region trench and performing in-situ doping at the same time to form a source region with the doping concentration higher than that of the drain region; step (f), forming a gate interface layer, a gate medium layer and a normal gate layer on a top-layer germanium surface of the FD-GOI substrate, and performing etching to form a normal gate; forming a back gate layer on a bottom-layer silicon surface of the FD-GOI substrate, and performing etching to form a back gate; and step (g), photoetching lead windows, depositing metal, and photoetching leads to form metal leads of the source region, the drain region, the normal gate and the back gate, thereby finally forming the FD-GOI tunneling field effect transistor with the abrupt tunneling junction.

Owner:XIAN UNIV OF SCI & TECH

Fd-goi tunneling field-effect transistor with abrupt tunneling junction and preparation method thereof

InactiveCN105261563BImprove isolationIncrease drive currentSemiconductor/solid-state device manufacturingDiodeIn situ dopingInterface layer

The invention relates to an FD-GOI tunneling field effect transistor with an abrupt tunneling junction and a manufacturing method. The manufacturing method comprises: selecting an FD-GOI substrate; forming shallow trench isolation with an etching process; performing photoetching on the FD-GOI substrate to form a drain region graph and forming a drain region with an adhesive ion implantation process; step (d), performing photoetching on the FD-GOI substrate to form a source region graph and forming a source region trench with a dry etching process; step (e), depositing a germanium material in the source region trench and performing in-situ doping at the same time to form a source region with the doping concentration higher than that of the drain region; step (f), forming a gate interface layer, a gate medium layer and a normal gate layer on a top-layer germanium surface of the FD-GOI substrate, and performing etching to form a normal gate; forming a back gate layer on a bottom-layer silicon surface of the FD-GOI substrate, and performing etching to form a back gate; and step (g), photoetching lead windows, depositing metal, and photoetching leads to form metal leads of the source region, the drain region, the normal gate and the back gate, thereby finally forming the FD-GOI tunneling field effect transistor with the abrupt tunneling junction.

Owner:XIAN UNIV OF SCI & TECH

Doped-free l-shaped tunneling field-effect transistor and its preparation method

ActiveCN109935631BReduce trap concentrationReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricField effect

The invention discloses an un-doped L-shaped tunneling field effect transistor and a preparation method thereof, which mainly solve the problems of large off-state current, serious bipolar effects andhigh preparation cost of the existing device. The un-doped L-shaped tunneling field effect transistor comprises an SOI substrate (1), a heterogeneous gate dielectric layer (5), a metal layer (6) anda conductive layer (8), wherein two sides of the SOI substrate are provided with isolation grooves (2); the upper surface of the SOI substrate is provided with a source region (3), a channel region (4) and a drain region (7); the heterogeneous gate dielectric layer and the metal layer are located at the upper side of the channel region; the source region, the channel region and the drain region are all made of un-doped intrinsic materials; the gate dielectric layer adopts a heterogeneous gate dielectric material, one side close to the source region adopts a high-K dielectric material and one side close to the drain region adopts a low-K dielectric material; and the metal layer is divided to an upper layer and a lower layer with different work functions, and the two metal layers are isolated by silicon dioxide. The off-state current is reduced, the bipolar effects are suppressed, the preparation cost is saved, and the un-doped L-shaped tunneling field effect transistor can be applied topreparation of a large-scale integrated circuit.

Owner:XIDIAN UNIV

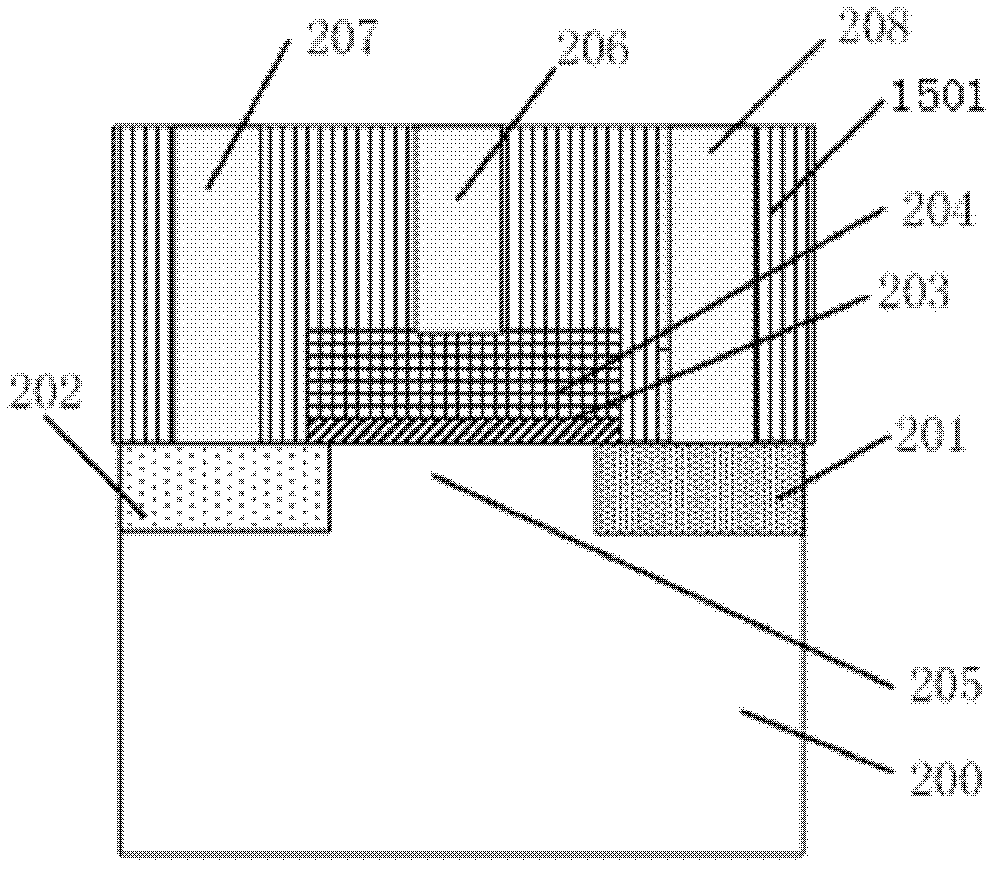

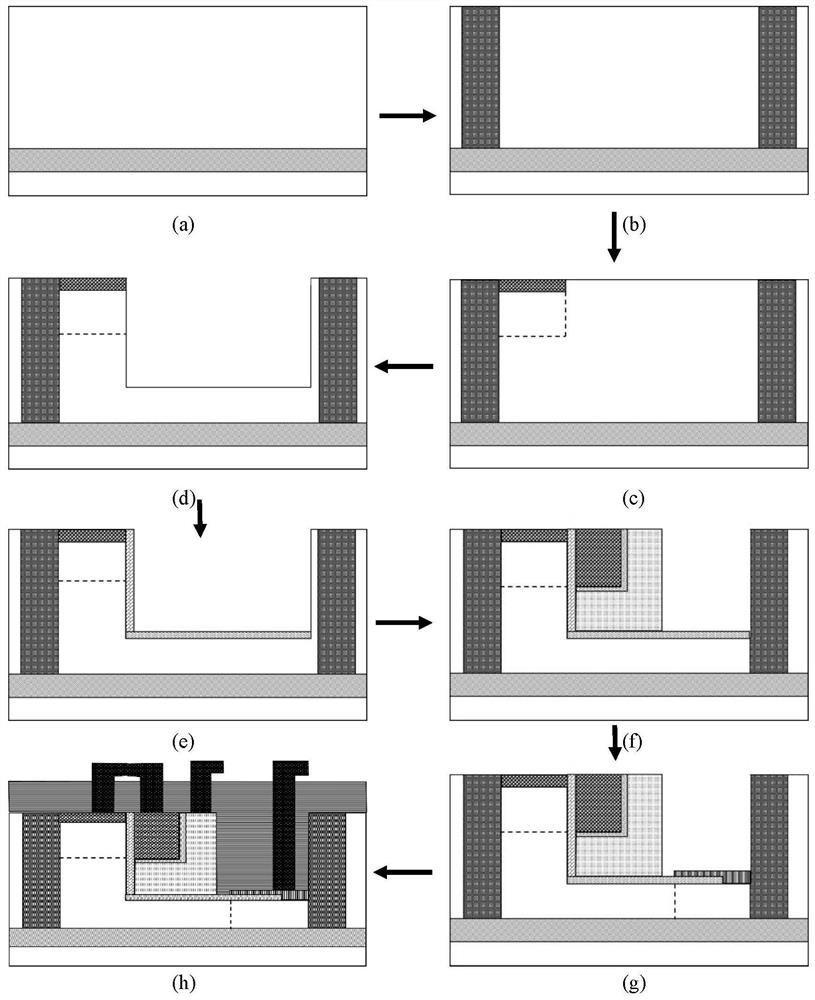

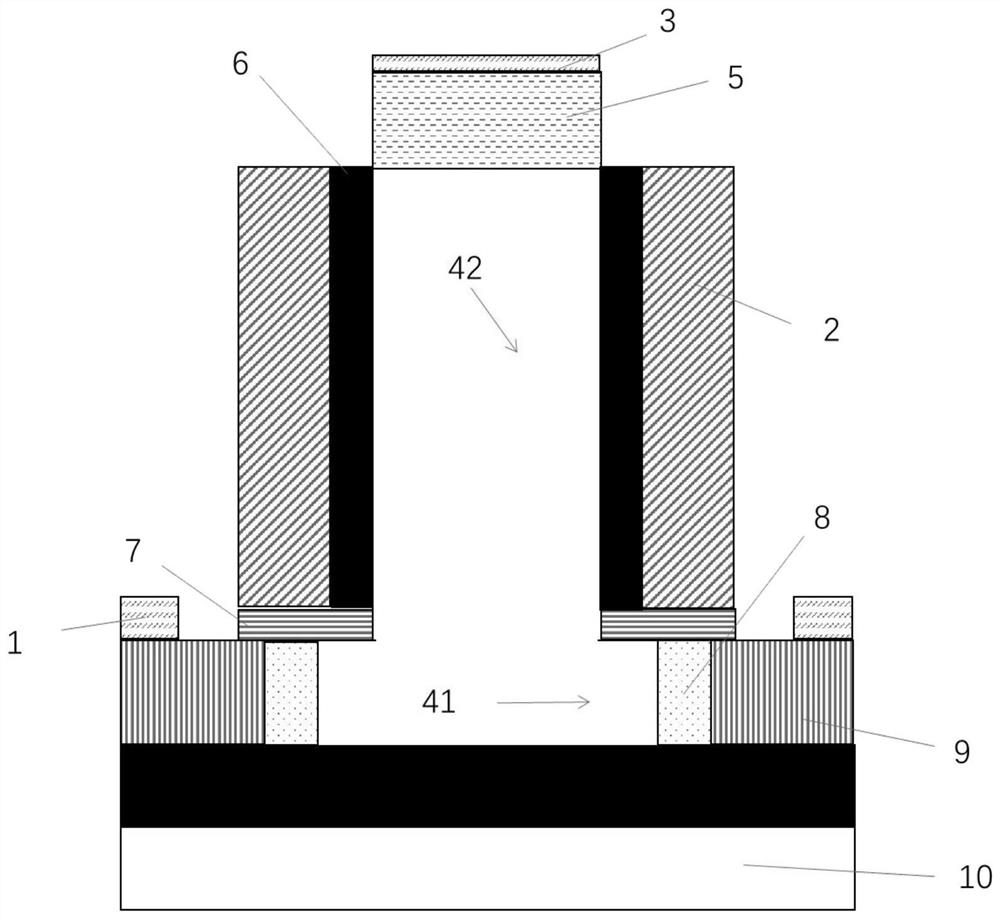

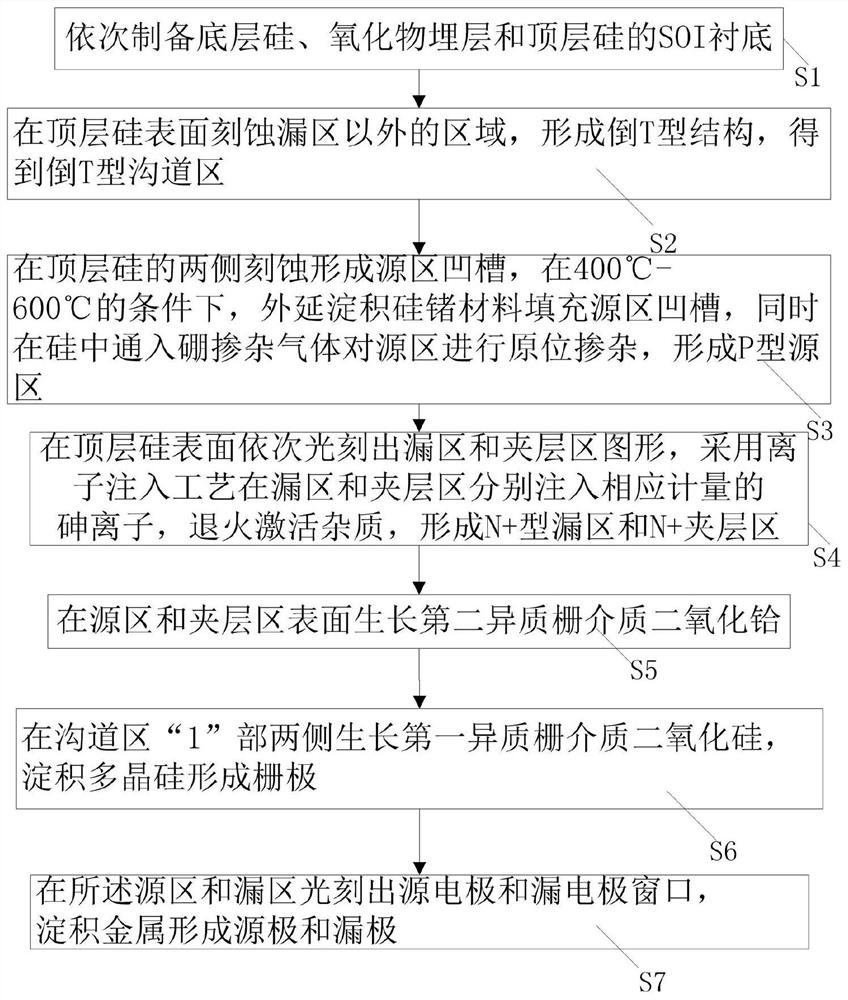

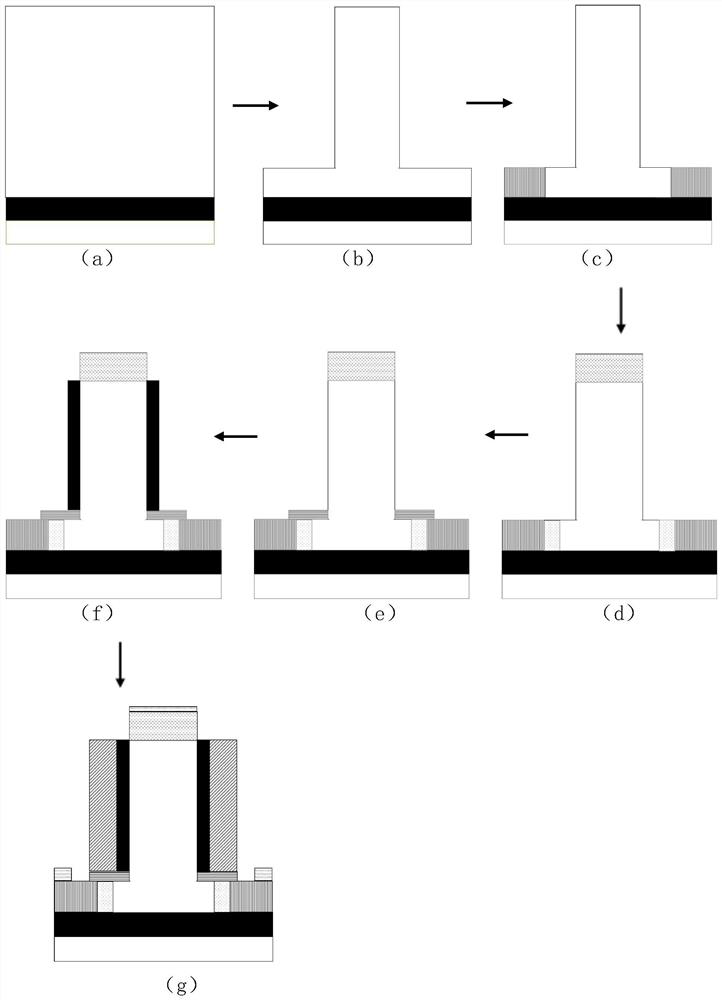

Heterojunction tunneling field effect transistor with heterogeneous gate dielectric and manufacturing method thereof

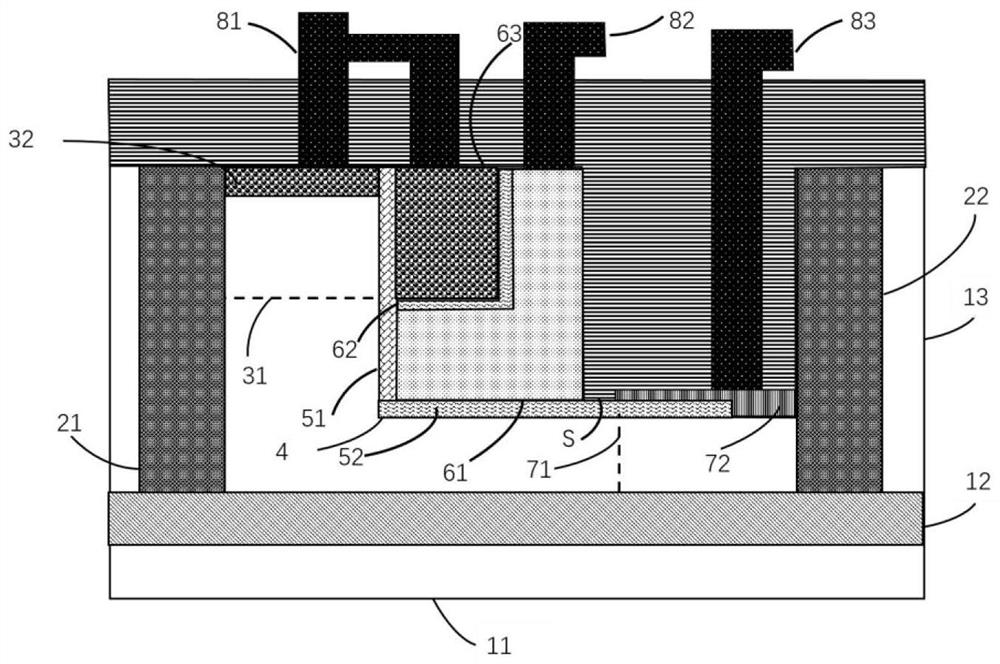

ActiveCN113571589BSuppression of bipolar effectsIncrease the on-state currentSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionDielectric

The invention discloses a heterojunction tunneling field effect transistor with a heterogeneous gate dielectric and a manufacturing method thereof, and mainly solves the problems of small on-state current and serious bipolar effect of the existing tunneling field effect transistor. It includes source, gate, drain, source region, channel region and drain region. Carriers enter the channel region through the source and leave the channel region through the drain. The channel region includes "a" part and " 1", the "1" part includes a first connection end connected to the "one" part, and a second connection end opposite to the first connection end, the second connection end is connected to the drain through the drain region, and the "1" part Two gates are arranged on both sides of the two gates, and two first heterogeneous dielectrics are respectively arranged between the two gates and the "1" part, the gates and the first heterogeneous medium are arranged perpendicular to the second heterogeneous medium, and The sum of the heights of the first heterogeneous medium and the second heterogeneous medium is equal to the "1" part, the height of the gate is equal to that of the first heterogeneous medium, and two sources are respectively arranged on both sides of the "1" part.

Owner:XIDIAN UNIV

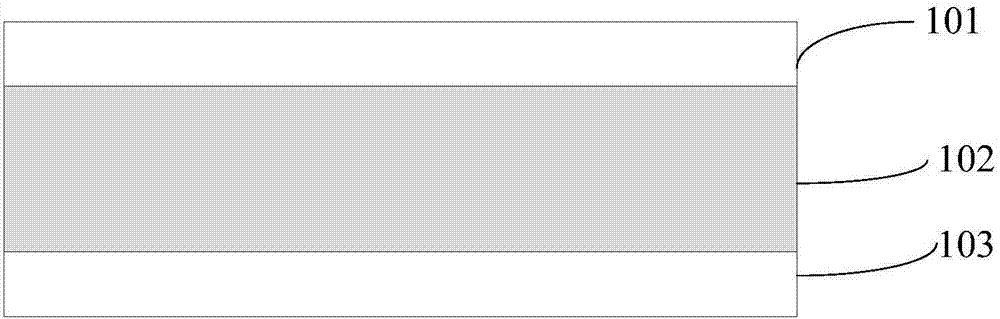

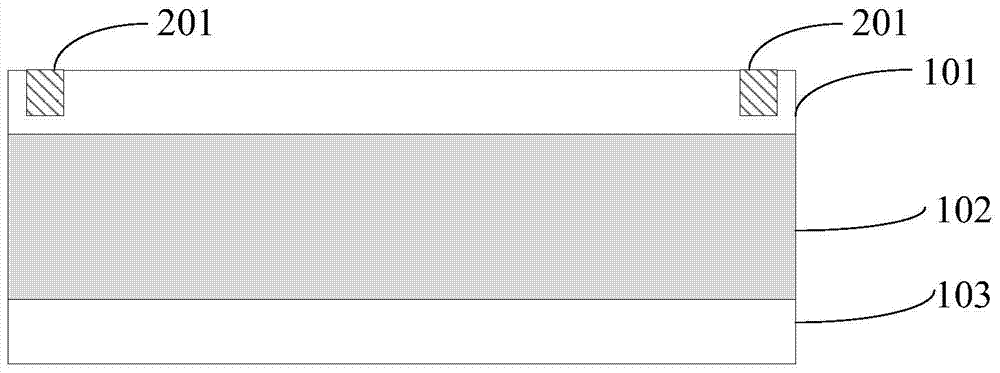

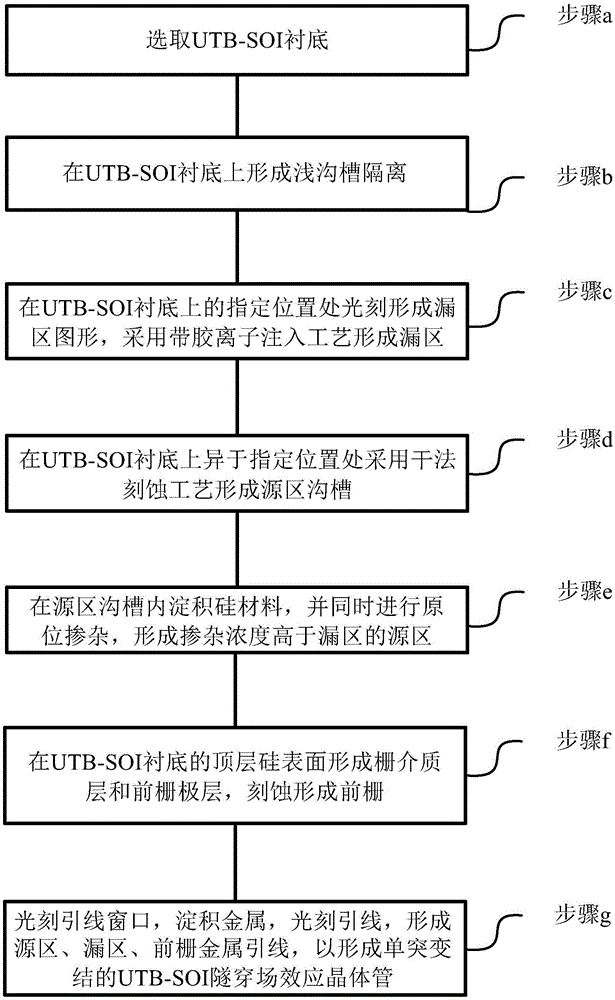

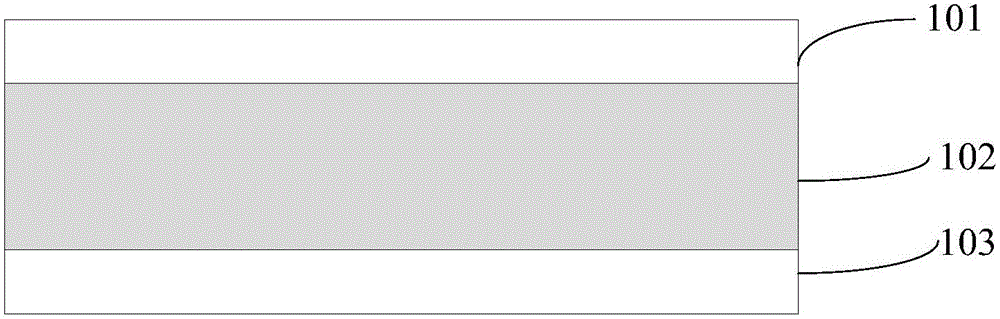

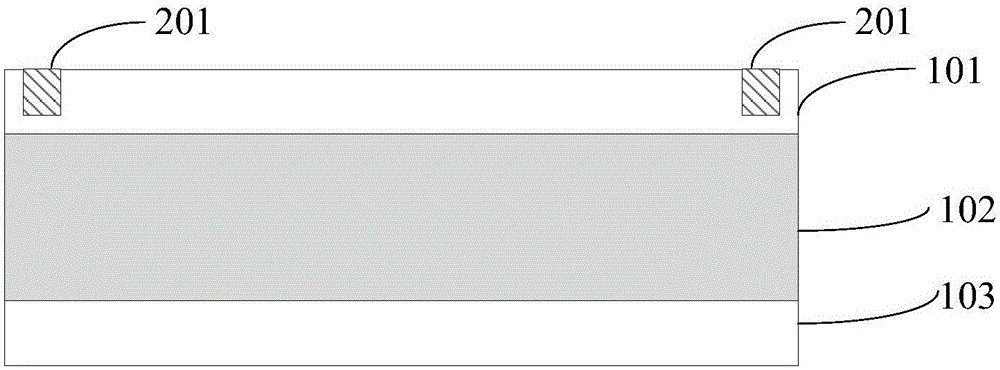

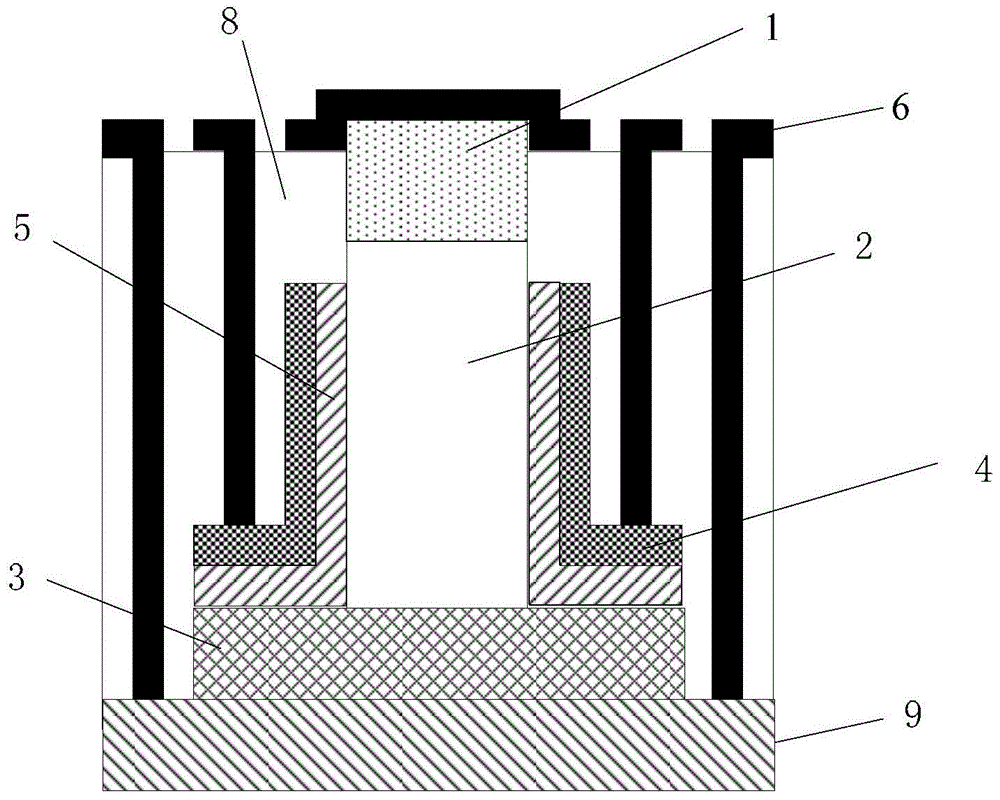

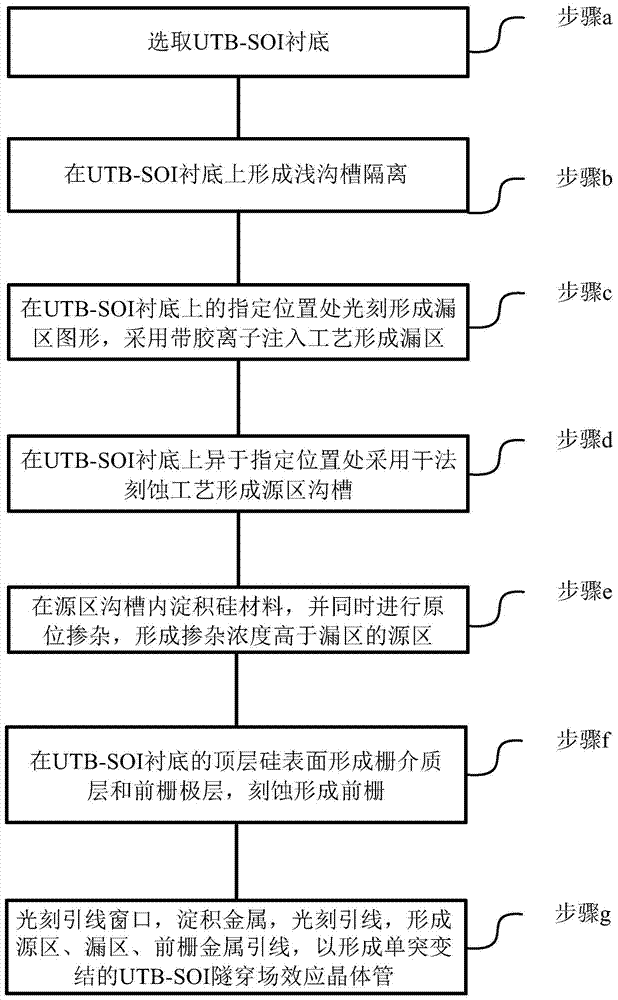

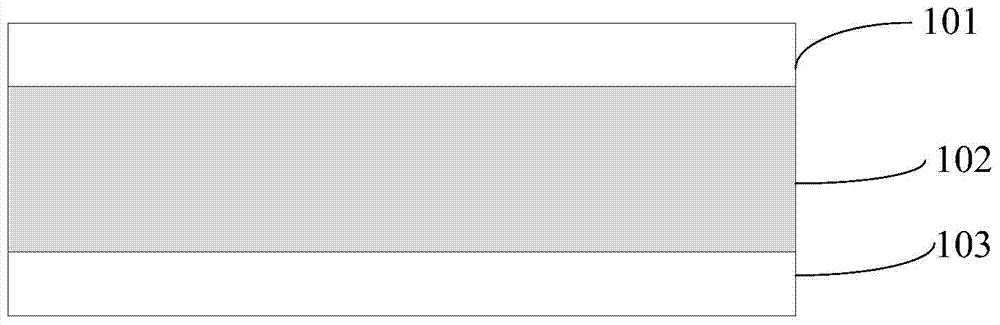

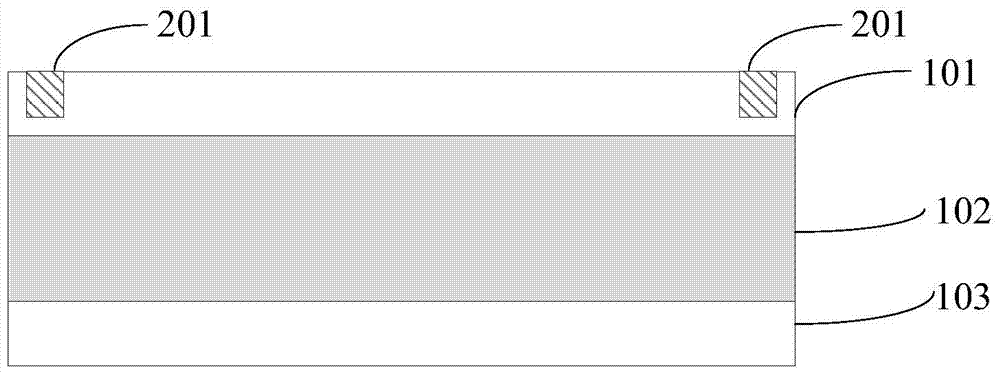

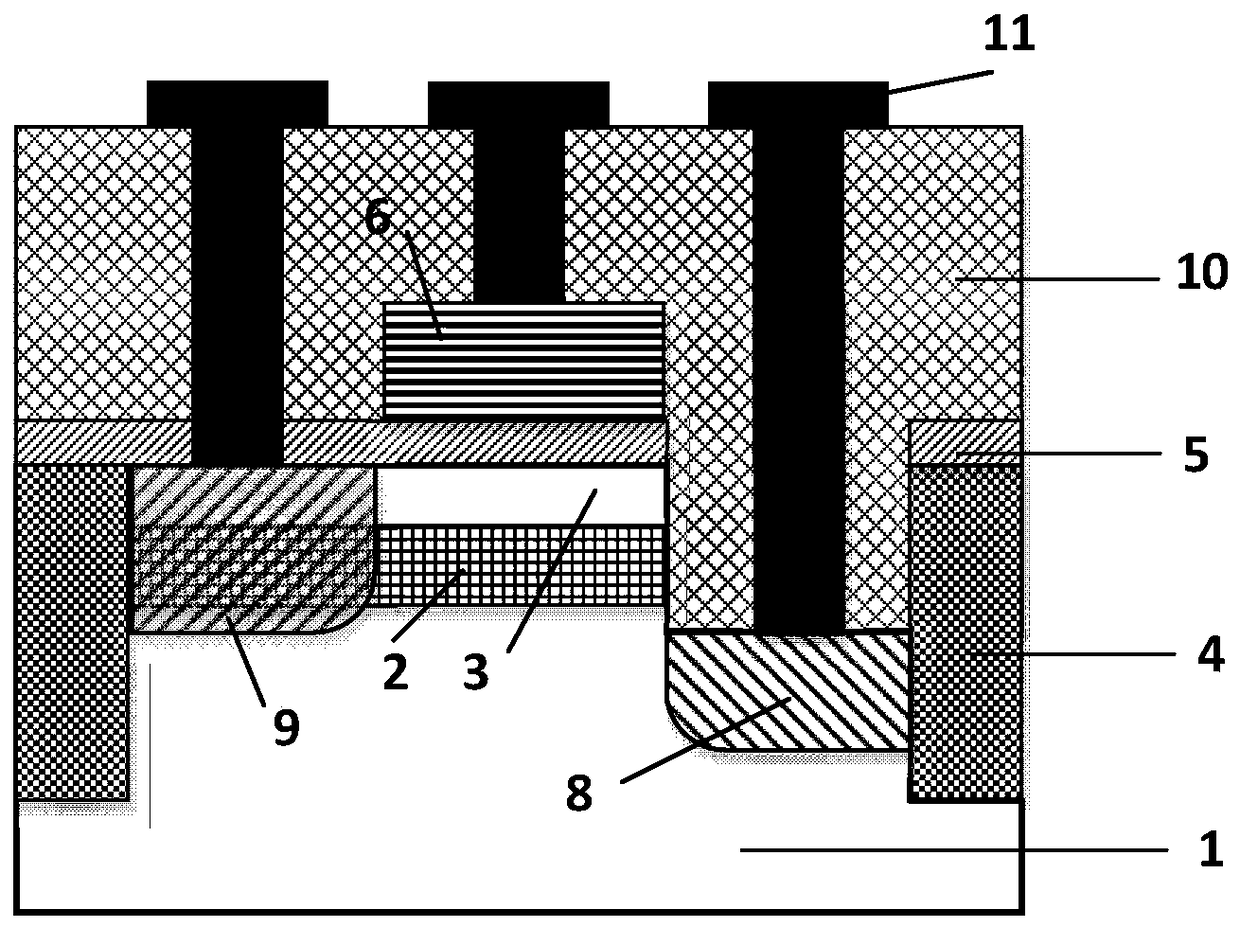

UTB-SOI tunneling field effect transistor with abrupt tunnel junction and preparation method

InactiveCN105118784ASuppression of bipolar effectsIncrease drive currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricConcentration gradient

The invention relates to an ultra-thin-body-silicon-on-insulator (UTB-SOI) tunneling field-effect transistor with an abrupt tunneling junction and a preparation method. The preparation method comprises: selecting a UTB-SOI substrate; forming a shallow trench isolation unit; carrying out photoetching to form a drain region graph and carrying out adhesive ion implantation to form a drain region; carrying out dry etching to form a source region trench; carrying out silicon material deposition in the source region trench and carrying out in-situ doping to form a source region; forming a gate dielectric layer and a front gate layer, and carrying out etching to form a front gate; and carrying out lead window photoetching, metal deposition, and lead photoetching to form source / drain and front gate leads. According to the invention, ion implantation is carried out on the drain region by using an ion implantation process, so that an intrinsic region / drain region junction with the gradually-changed doping concentration gradient can be formed well and the bipolar effect of the tunneling field effect transistor can be effectively inhibited; with the technique and preparation of trench etching and selective epitaxy deposition and filling at the source region, the tunnel junction area can be limited precisely; and on the basis of in-situ doping, the tunnel junction with the steep doping concentration gradient can be formed well and the driving current of the device can be effectively improved and the sub-threshold slope can be reduced.

Owner:XIAN UNIV OF SCI & TECH

Vertical channel dual-mechanism conduction nanowire tunneling transistor and preparation method

ActiveCN103996713BRaise the potentialLower the barrierSemiconductor/solid-state device manufacturingSemiconductor devicesNanowireDual mechanism

The invention provides a vertical-channel double-mechanism conduction nano-wire tunneling transistor and a preparation method. The tunneling transistor comprises a hot electron emission source region, a tunneling source region, a channel region, a tunneling drain region and a gate of a nano-wire. The gate is controlled to encircle the channel; band-to-band tunneling happens at the interface of the tunneling source region and the channel region; the hot electron emission source region, the doping type of which is opposite to that of the tunneling source region, is arranged under the tunneling source region; and the electric potential of the tunneling source region is in floating arrangement, and the source terminal potential of a device is added to the hot electron emission source region. Compared with a conventional TFET, the vertical-channel double-mechanism conduction nano-wire tunneling transistor introduces a hot electron emission mechanism besides a tunneling mechanism through the structure design of the device, thereby enlarging the conduction current of the device effectively, meanwhile, keeping steep subthreshold slope, and improving the characteristics of the device substantially. The vertical-channel double-mechanism conduction nano-wire tunneling transistor is simple in preparation process, reduces the production cost greatly, and simplifies the process flow.

Owner:PEKING UNIV

Schottky barrier metal oxide semiconductor (MOS) transistor and preparation method thereof

ActiveCN102324434BReduce parasitic resistanceEliminate uncovered areasSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETSchottky barrier

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

SSOI Tunneling Field Effect Transistor with Abrupt Tunneling Junction and Preparation Method

InactiveCN105118782BPrevent proliferationImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricTunnel junction

The invention relates to a strained-silicon-on-insulator (SSOI) tunneling field effect transistor with an abrupt tunnel junction and a preparation method thereof. The preparation method comprises: preparing an SSOI substrate; forming a shallow trench isolation unit; carrying out photoetching to form a drain region graph; carrying out adhesive ion implantation to form a drain region; carrying out dry etching to form a source region trench; depositing a Si material in a source region trench and carrying out in-situ doping to form a source region; forming a gate dielectric layer and a front gate layer on the upper surface of the substrate, carrying out etching to form a front gate, forming a back gate layer on the lower surface of the substrate, and carrying out etching to form a back gate; carrying out lead window photoetching, metal deposition, and lead photoetching to form source / drain and front / back leads. According to the invention, the drive current of the tunneling field effect transistor can be effectively improved and the sub-threshold slope can be reduced.

Owner:XIAN UNIV OF SCI & TECH

Utb-soi tunneling field-effect transistor with abrupt tunneling junction and preparation method thereof

InactiveCN105118784BSuppression of bipolar effectsIncrease drive currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricConcentration gradient

The invention relates to an ultra-thin-body-silicon-on-insulator (UTB-SOI) tunneling field-effect transistor with an abrupt tunneling junction and a preparation method. The preparation method comprises: selecting a UTB-SOI substrate; forming a shallow trench isolation unit; carrying out photoetching to form a drain region graph and carrying out adhesive ion implantation to form a drain region; carrying out dry etching to form a source region trench; carrying out silicon material deposition in the source region trench and carrying out in-situ doping to form a source region; forming a gate dielectric layer and a front gate layer, and carrying out etching to form a front gate; and carrying out lead window photoetching, metal deposition, and lead photoetching to form source / drain and front gate leads. According to the invention, ion implantation is carried out on the drain region by using an ion implantation process, so that an intrinsic region / drain region junction with the gradually-changed doping concentration gradient can be formed well and the bipolar effect of the tunneling field effect transistor can be effectively inhibited; with the technique and preparation of trench etching and selective epitaxy deposition and filling at the source region, the tunnel junction area can be limited precisely; and on the basis of in-situ doping, the tunnel junction with the steep doping concentration gradient can be formed well and the driving current of the device can be effectively improved and the sub-threshold slope can be reduced.

Owner:XIAN UNIV OF SCI & TECH

A kind of tunneling field effect transistor and its preparation method

ActiveCN104810405BReduce thicknessWide band gapSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSSemiconductor materials

The invention discloses a tunneling field effect transistor and a preparation method, and belongs to the field of a field effect transistor logic device of a CMOS (Complementary Metal Oxide Semiconductor) ultra-large scale integrated circuit (ULSI). A tunneling source region and a channel region of the tunneling field effect transistor are of heterogeneous structures in the vertical direction of the device; the upper layer is made of a semiconductor material with larger forbidden bandwidth; the middle layer is made of a semiconductor material with smaller forbidden bandwidth; the lower layer is a semiconductor substrate with the larger forbidden bandwidth. Compared with the prior art, the transistor and the method have the advantages that the degradation phenomenon of sub-threshold slope in device transfer characteristic can be effectively inhibited, meanwhile the average sub-threshold slope of the tunneling field effect transistor is obviously reduced, and steep minimum sub-threshold slope is kept.

Owner:PEKING UNIV

Pnin/npip type fd-goi TFET with abrupt tunneling junction and preparation method thereof

InactiveCN105118783BSuppression of bipolar effectsIncrease drive currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricIn situ doping

The invention relates to a PNIN / NPIP type fully-depleted-silicon-on-insulator (FD-GOI) TFET with an abrupt tunnel junction and a preparation method thereof. The preparation method comprises: an FD-GOI substrate is selected; an etching process is carried out to form a shallow-trench isolation unit; a photoetching process is carried out form a drain region graph and an ion implantation technology is used for forming a drain region; a source region trench is formed in the upper surface of the substrate; ion implantation is carried out on the side wall of the source region trench by using an angled ion implantation technology to form a thin-layer doping region; germanium material deposition is carried out on the source region trench and in-situ doping is carried out simultaneously to form a source region; the doping concentration of the source region is higher than that of the drain region; a gate interface layer is formed on the upper surface of the substrate; a gate dielectric layer and a front gate layer grow on the surface of the gate interface layer and a dry etching process is used for forming a front gate, a back gate layer grows on the lower surface of the substrate, and a dry etching process is used for forming a back gate; lead window photoetching, metal deposition, and lead photoetching are carried out to form metal leads of the source region, the drain region, the front gate, and the back gate, thereby forming the PNIN / NPIP type FD-GOI TFET with an abrupt tunnel junction.

Owner:XIAN UNIV OF SCI & TECH

Insulation layer upwards-expanded strained germanium tunneling field effect transistor (TFET) with abrupt tunneling junction and preparation method

InactiveCN105226087ASuppression of bipolar effectsIncrease drive currentSemiconductor/solid-state device manufacturingDiodeInsulation layerIn situ doping

The invention relates to an insulation layer upwards-expanded strained germanium tunneling field effect transistor (TFET) with an abrupt tunneling junction and a preparation method. The preparation method comprises the following steps of: preparing an insulation layer upwards-expanded strained germanium substrate; forming shallow groove isolation by an etching process; forming a drain region pattern on the upper surface of the substrate by the etching process, and forming a drain region on the substrate by a glued ion implantation technology; forming a source region groove on the substrate by a dry etching process; depositing a germanium material in the source region groove, and simultaneously carrying out in-situ doping to form a source region; forming a grid interface layer, a grid dielectric layer and a front grid layer on the upper surface of the substrate, and forming a front grid by the dry etching process; growing a back grid layer on the lower surface of the substrate, and forming a back grid by the dry etching process; and carrying out photoetching of a lead window, metal deposition and lead photoetching, forming metal leads of the source region, the drain region, the front grid and the back grid, and finally forming the insulation layer upwards-expanded strained TFET with the abrupt tunneling junction.

Owner:XIAN UNIV OF SCI & TECH

Pnin/npip type ssoi TFET with abrupt tunneling junction and preparation method thereof

InactiveCN105244375BPrevent proliferationImprove performanceSemiconductor/solid-state device manufacturingDiodeDriving currentGate dielectric

The invention relates to a PNIN / NPIP type SSOI TFET with abrupt tunneling junctions and a preparation method thereof. The preparation method comprises the steps that an SSOI substrate is prepared; shallow trench isolation is formed; a drain region pattern is formed through photoetching, and adhesive ions are injected so that a drain region is formed; a source region trench is formed through dry etching; the ions are injected in the side wall of the source region trench at a certain inclined angle by adopting an ion injection technology, Si material is deposited in the source region trench, and in-situ doping is performed so that a source region is formed; a gate dielectric layer and a front gate layer are formed on the upper surface of the substrate, a front gate is formed through etching, a back gate layer is formed on the lower surface of the substrate, and a back gate is formed through etching; and a lead-wire window is photoetched, metal is deposited and a lead-wire is photoetched so that source / drain and front / back gate lead-wires are formed. Drive current of the TFET can be effectively enhanced and subthreshold slope of the TFET can be reduced.

Owner:XIAN UNIV OF SCI & TECH

PNIN/NPIP type tensile strained germanium on insulator TFET with abrupt tunneling junctions and preparation method thereof

InactiveCN105244275AIncrease drive currentFast switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricIon implantation

The invention relates to a PNIN / NPIP type tensile strained germanium on insulator TFET with abrupt tunneling junctions and a preparation method thereof. The preparation method comprises the steps that a tensile strained germanium on insulator substrate is prepared; shallow trench isolation is formed by adopting an etching technology; a drain region pattern is formed on the upper surface of the substrate by adopting a photoetching technology and a drain region is formed by adopting an adhesive ion injection technology; a source region trench is formed on the substrate by adopting the etching technology; ions are injected in the side wall of the source region trench close to a channel region by adopting an inclined ion injection technology so that a thin layer doped region is formed; germanium material is deposited in the source region trench and in-situ doping is performed so that a source region is formed; a gate interface layer, a gate dielectric layer and a front gate layer are formed on the upper surface of the substrate in turn, and a front gate is formed by adopting the etching technology; a back gate layer is grown on the lower surface of the substrate, and a back gate is formed by adopting the etching technology; and a lead-wire window is photoetched, metal is deposited and a lead-wire is photoetched so that a metal lead-wire of the source region, the drain region, the front gate and the back gate is formed, and finally the PNIN / NPIP type tensile strained germanium on insulator TFET with the abrupt tunneling junctions is formed.

Owner:XIAN UNIV OF SCI & TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com