Insulation layer upwards-expanded strained germanium tunneling field effect transistor (TFET) with abrupt tunneling junction and preparation method

A technology of straining germanium on an insulating layer, which is applied in semiconductor/solid-state device manufacturing, electrical components, diodes, etc., can solve the problems of subthreshold slope theoretical value degradation and small driving current, so as to suppress bipolar effect and improve mobility , Improve the effect of driving current and switching speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

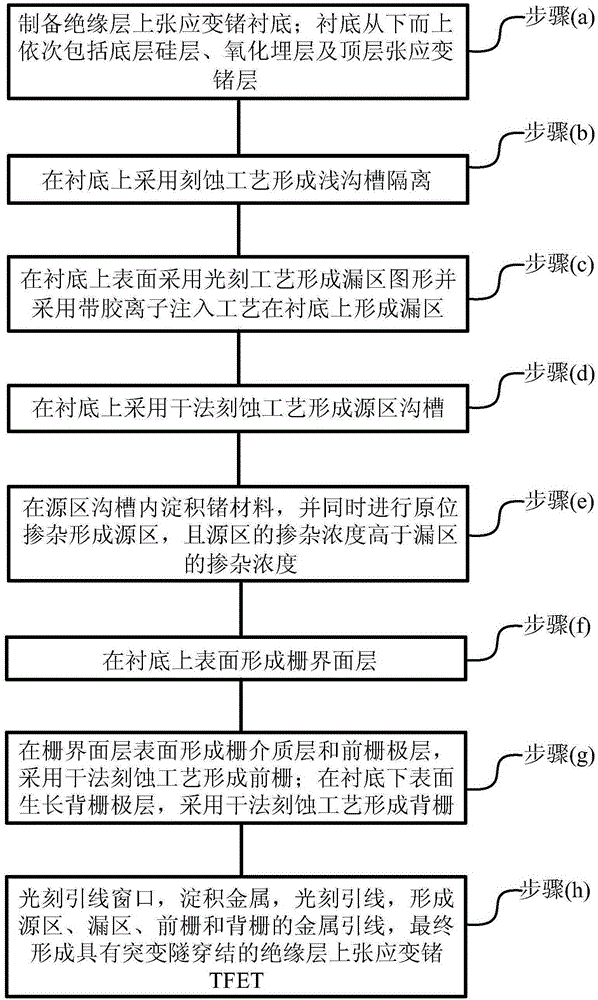

[0027] See figure 1 , figure 1 It is a flowchart of a method for preparing a tensile strained germanium TFET on an insulating layer with an abrupt tunnel junction according to an embodiment of the present invention, and the method includes the following steps:

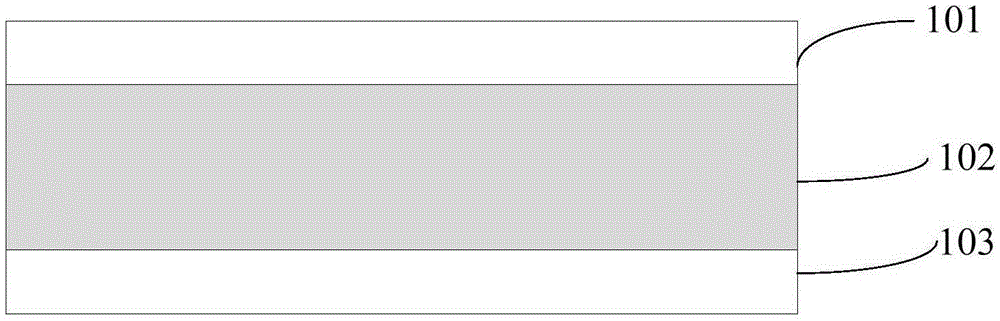

[0028] (a) preparing a tensile-strained germanium substrate on an insulating layer; the substrate sequentially includes a bottom silicon layer, a buried oxide layer and a top tensile-strained germanium layer from bottom to top;

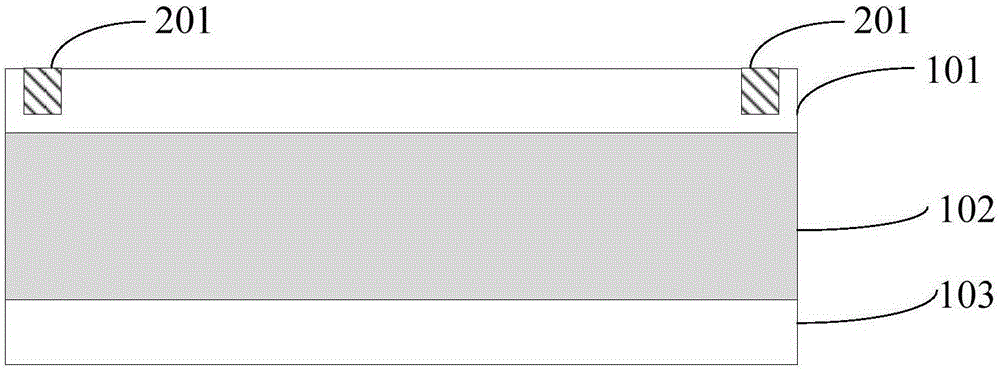

[0029] (b) forming shallow trench isolation on the substrate by an etching process;

[0030] (c) forming a drain region pattern on the upper surface of the substrate by a photolithography process and forming a drain region on the substrate by using an ion implantation process with glue;

[0031] (d) forming source region trenches on the substrate by a dry etching process;

[0032] (e) Depositing a germanium material in the trench of the source region, and simultaneously performing in-situ...

Embodiment 3

[0112] See image 3 , image 3 It is a schematic flow chart of a method for preparing a tensile-strained germanium-on-insulator TFET with an abrupt tunneling junction according to an embodiment of the present invention. To prepare an N-type tensile-strained germanium-on-insulator TFET with an abrupt tunneling junction with a channel length of 45 nm is An example is described in detail, and the specific steps are as follows:

[0113] 1. Preparation of strained germanium substrate on insulating layer

[0114] 1.1 Epitaxial growth.

[0115] Using molecular beam epitaxy (Molecular Beam Epitaxy, MBE) technology or metal organic chemical vapor deposition (MetalOrganic Chemical Vapour Deposition, MOCVD) technology, at the temperature of 400 ℃ to 450 ℃, epitaxial growth of 30nm to 120nm In composition graded In on the GaAs substrate x Ga 1-x As layer, where x is gradually changed from 0 to 0.3 or 0.35, and then a layer of In with fixed In composition is epitaxially grown at a temp...

Embodiment 4

[0175] See Figure 4 , Figure 4 It is a schematic diagram of the device structure of a tensile-strained germanium-on-insulator TFET with an abrupt tunneling junction according to an embodiment of the present invention. The tensile-strained germanium-on-insulator TFET with an abrupt tunneling junction of the present invention includes a fully depleted top-layer tensile-strained germanium layer, buried oxide layer, underlying silicon layer, high-K gate interface layer, high-K gate dielectric layer, front gate, back gate, highly doped source region and low doped drain region.

[0176] Specifically, the thickness of the fully depleted top tensile strained germanium layer can be selected from 20 to 30 nm, preferably 20 nm, and the doping concentration is less than 10 17 cm -3 .

[0177] Specifically, the gate interface layer is preferably yttrium oxide (Y 2 o 3 ) material, the high-K material layer can be selected from hafnium-based materials (a class of high dielectric constan...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More