Pnin/npip type fd-goi TFET with abrupt tunneling junction and preparation method thereof

A tunneling junction and dry etching technology, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc., can solve the problems of small driving current, reduced sub-threshold slope, and degradation of the theoretical value of sub-threshold slope. Bipolar effect, the effect of reducing the difficulty of the process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

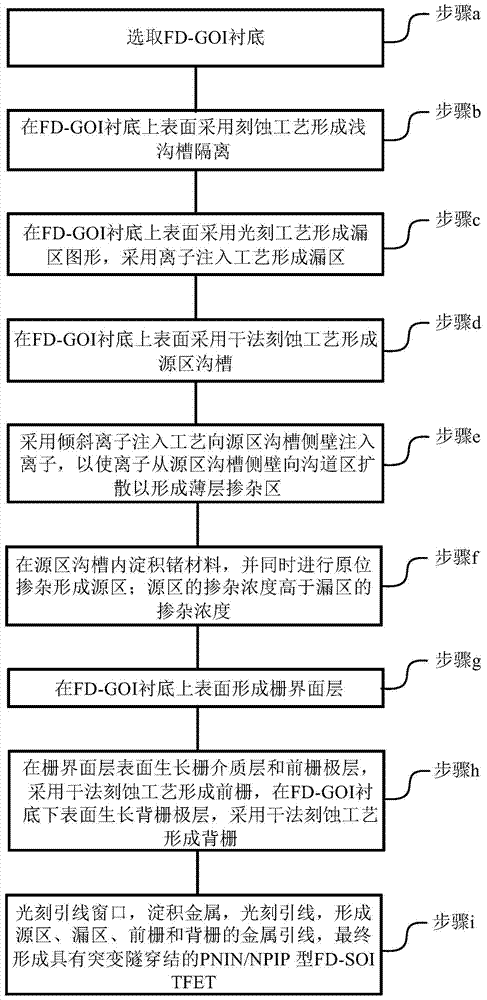

[0026] See figure 1 , figure 1 It is a flow chart of a preparation method of a PNIN / NPIP type FD-GOITFET with a sudden tunnel junction according to an embodiment of the present invention, and the preparation method includes the following steps:

[0027] (a) Select a fully depleted germanium-on-insulator (Fully Depleted Germanium-On-Insulator, referred to as FD-GOI) substrate;

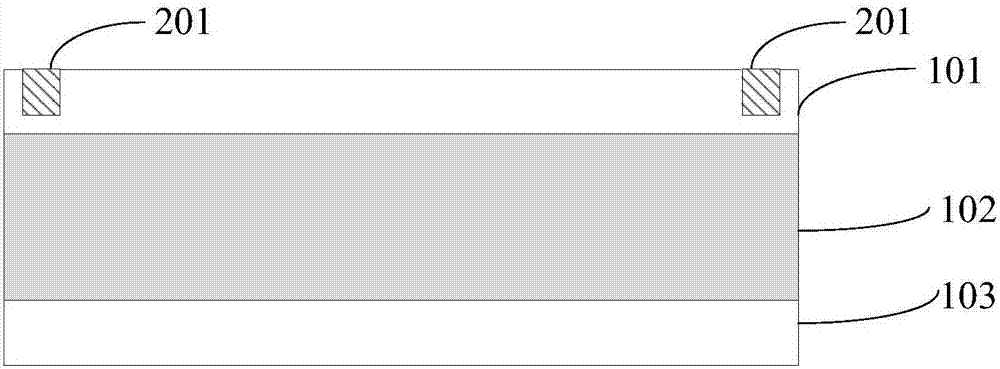

[0028] (b) Form shallow trench isolation on the upper surface of the FD-GOI substrate by etching;

[0029] (c) forming a drain region pattern on the upper surface of the FD-GOI substrate by photolithography, and forming a drain region by ion implantation;

[0030] (d) forming a source region trench on the upper surface of the FD-GOI substrate by a dry etching process;

[0031] (e) implanting ions into the sidewall of the trench in the source region by using an inclined ion implantation process, so that the ions diffuse from the sidewall of the trench in the source region to the channel region to fo...

Embodiment 2

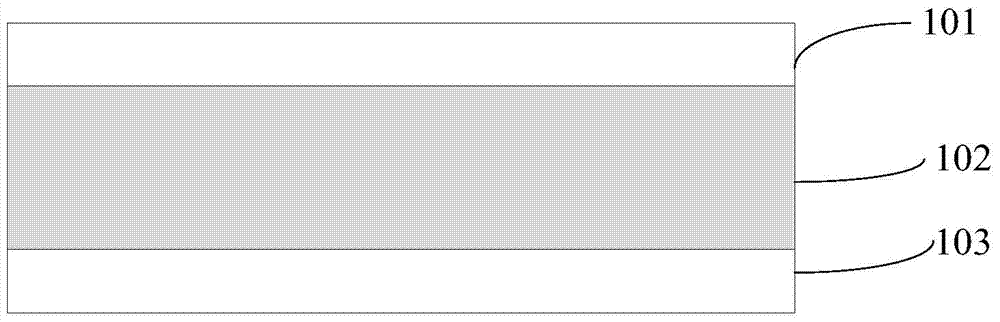

[0076] See Figure 2a-2i , Figure 2a-Figure 2i It is a schematic diagram of the preparation method of a PNIN / NPIP type FD-GOI TFET with an abrupt tunneling junction according to an embodiment of the present invention, taking the preparation of a PNIN type FD-GOI TFET with an abrupt tunneling junction with a channel length of 45 nm as an example for detailed description. Instructions, the specific steps are as follows:

[0077] 1. Select the FD-GOI substrate.

[0078] Such as Figure 2a , the FD-GOI substrate includes a top layer of germanium 101, an oxide buried layer 102 such as a silicon dioxide layer buried layer, and a bottom layer of silicon 103, and the crystal orientation of the FD-GOI substrate 101 can be (100) or (110) or ( 111), without any limitation here, in addition, the doping type of the FD-GOI substrate 101 can be N-type or P-type, and the doping concentration is, for example, 10 14 ~10 17 cm -3 The thickness of the top layer Si is, for example, 20-100 n...

Embodiment 3

[0135] See image 3 , image 3 It is a schematic structural diagram of a PNIN / NPIP type FD-GOITFET with an abrupt tunneling junction according to an embodiment of the present invention. The PNIN / NPIP FD-GOITFET with an abrupt tunneling junction of the present invention includes a fully depleted top germanium layer, a buried Oxygen layer, underlying silicon layer, gate interface layer, gate dielectric layer, front gate, back gate, heavily doped source region, low doped drain region and N-type / P-type thin layer.

[0136] Specifically, the thickness of the fully depleted top germanium layer can be selected from 20 to 100 nm, preferably 20 nm, and the doping concentration is less than 10 17 cm -3 .

[0137] Specifically, the gate interface layer is preferably yttrium oxide (Y 2 o 3 ) material, the high-K material layer can be selected from hafnium-based materials (a class of high dielectric constant materials), such as HfO 2 , HfSiO, HfSiON, HfTaO, HfTiO or HfZrO or a combinat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More