A kind of tunneling field effect transistor and its preparation method

A tunneling field effect and transistor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of high subthreshold slope of devices and unfavorable application of TFET devices, etc., and achieve large-band tunneling current increase The effect of reducing the minimum subthreshold slope and reducing the production cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

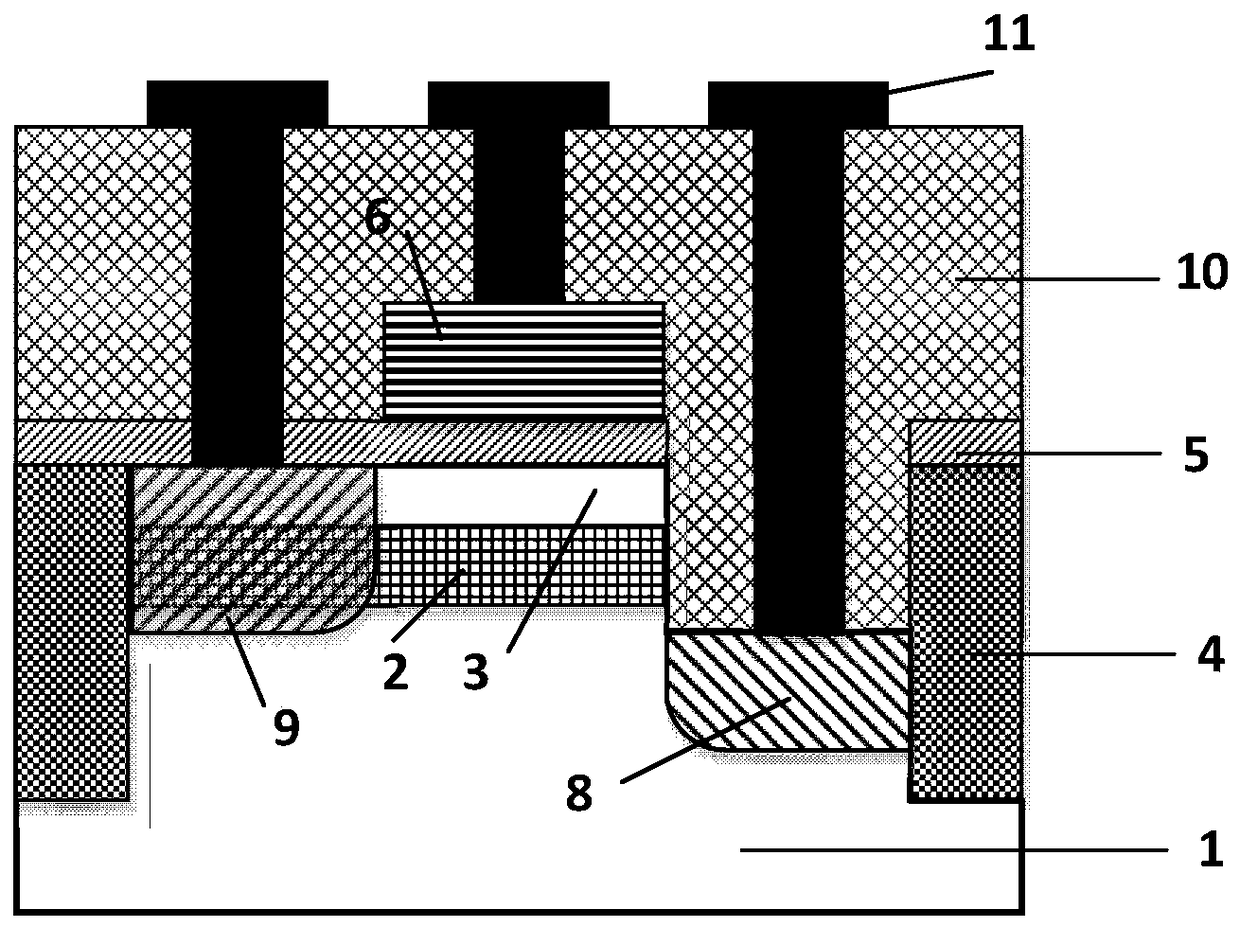

[0040] The implementation method of the heterostructure tunneling field effect transistor in the vertical channel direction of the present invention will be further described through specific embodiments below in conjunction with the accompanying drawings.

[0041] The specific implementation steps are as Figure 2-Figure 6 Shown: (This example takes N-type devices as an example, and P-type devices can be deduced by analogy)

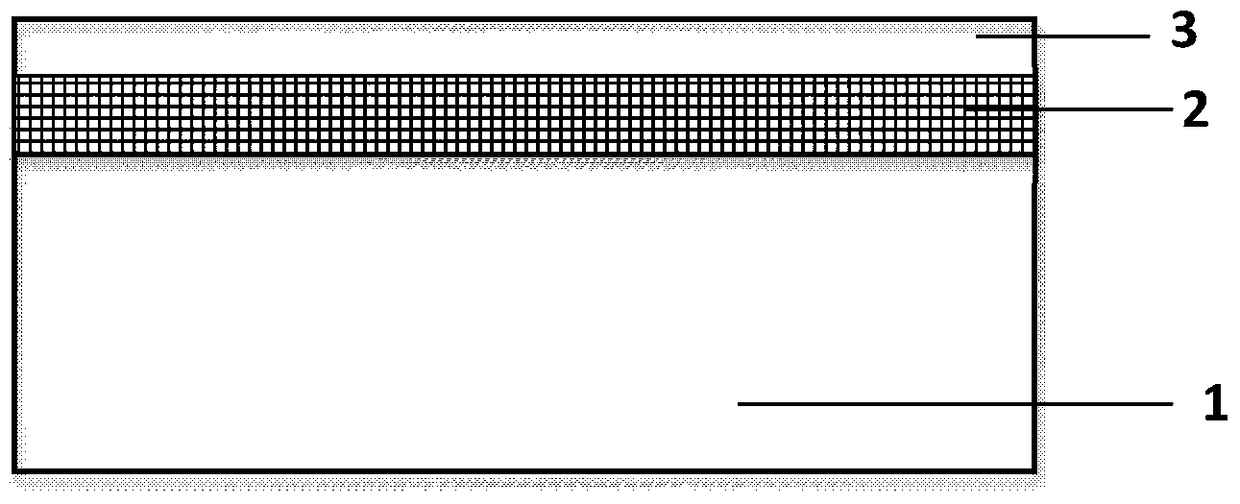

[0042] 1. The substrate doping concentration is lightly doped (about 1E13cm -3 -1E15cm -3 ), an InAs intermediate layer 2 is epitaxially grown on a GaAs substrate 1 with a crystal orientation of and lightly doped in situ (about 1E13cm -3 -1E15cm -3 ), with a thickness of about 15nm; then epitaxially grow a layer of GaAs upper layer 3 material and perform in-situ light doping (about 1E13cm -3 -1E15cm -3 ), the thickness is about 6nm; if figure 1 shown.

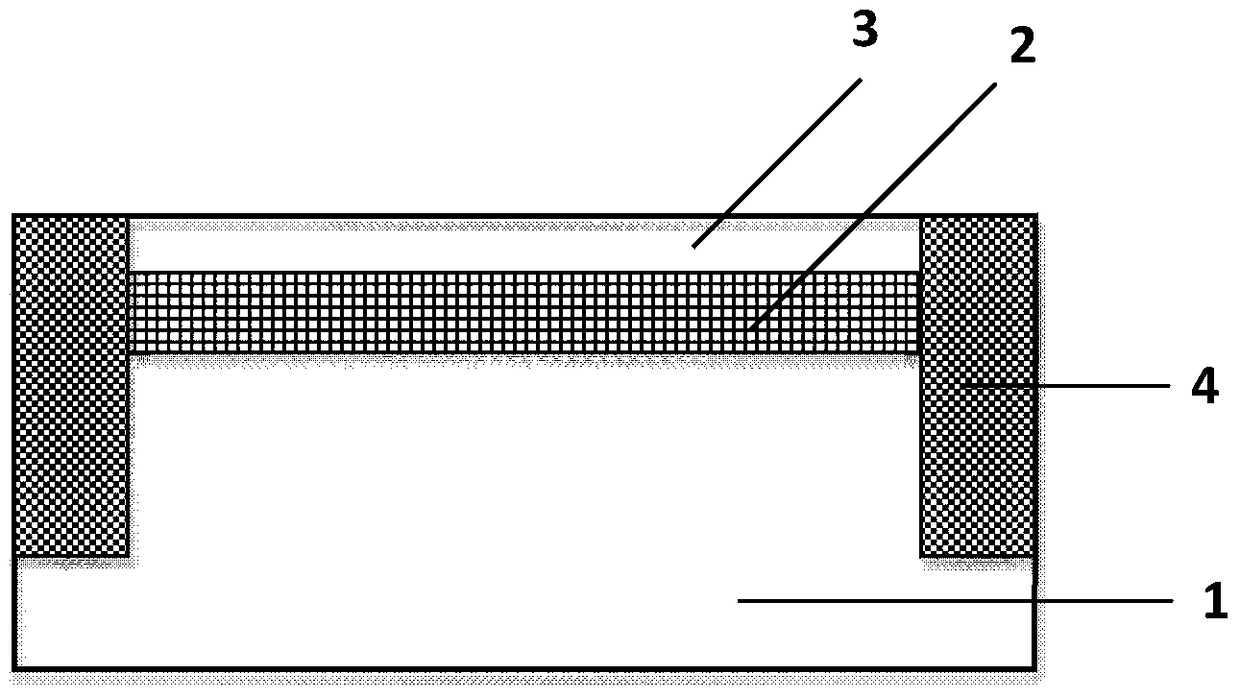

[0043] 2. Deposit a layer of silicon dioxide with a thickness of about 10nm, and deposit a lay...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More