Utb-soi tunneling field-effect transistor with abrupt tunneling junction and preparation method thereof

A technology of UTB-SOI and tunneling field effect, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc. It can solve the problems of small driving current and degradation of theoretical value of sub-threshold slope, so as to improve performance and suppress dual Extreme effect, high practical value effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

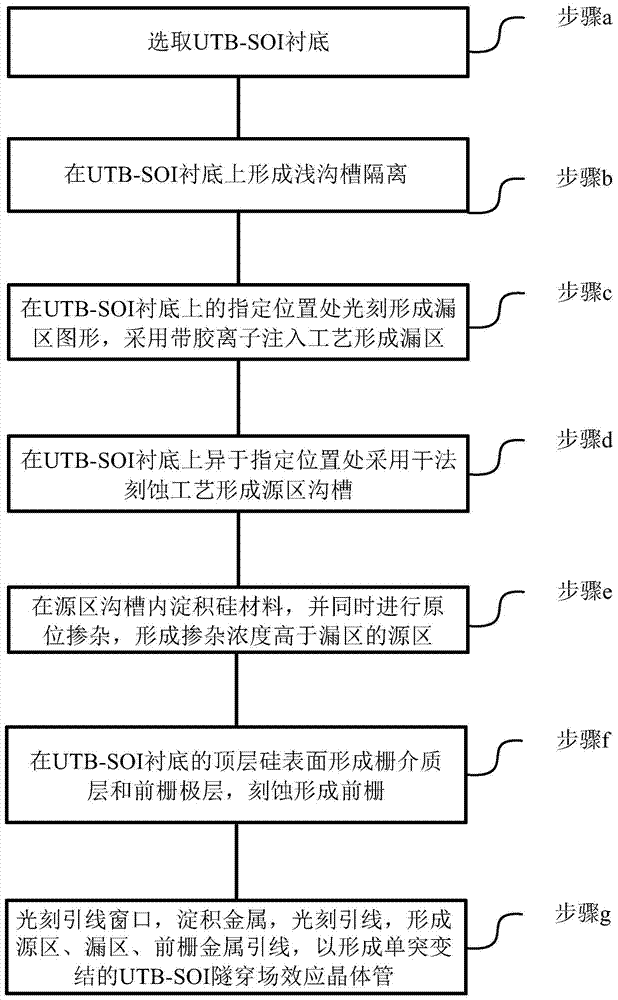

[0046] See figure 1 , figure 1 It is a flowchart of a method for preparing a UTB-SOI tunneling field effect transistor with an abrupt tunnel junction according to an embodiment of the present invention, and the method includes the following steps:

[0047] Step a, select UTB-SOI substrate;

[0048] Step b, forming shallow trench isolation on the UTB-SOI substrate;

[0049] Step c, photolithographically forming a drain region pattern at a specified position on the UTB-SOI substrate, and forming a drain region by using an ion implantation process with glue;

[0050] Step d, forming source region trenches on the UTB-SOI substrate at positions different from the designated positions by dry etching;

[0051] Step e, depositing silicon material in the trench of the source region, and performing in-situ doping at the same time, forming a source region with a higher doping concentration than the drain region;

[0052] Step f, forming a gate dielectric layer and a front gate layer ...

Embodiment 2

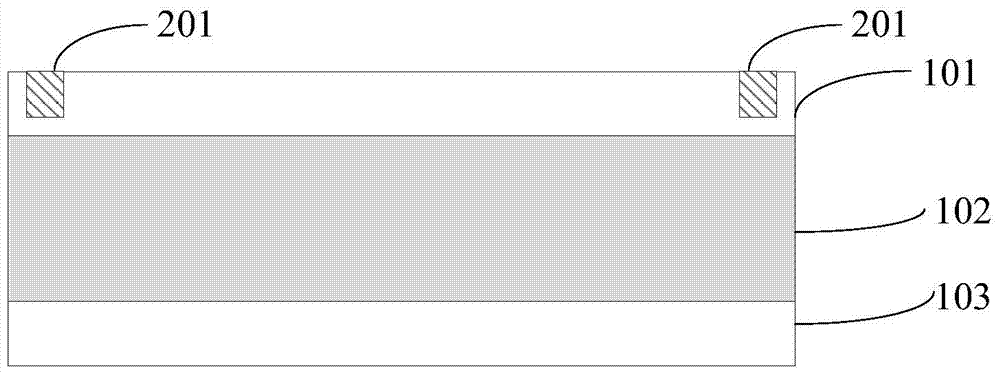

[0076] See Figure 2a-Figure 2h It is a schematic diagram of a method for preparing a UTB-SOI tunneling field-effect transistor with an abrupt tunneling junction according to an embodiment of the present invention; this embodiment takes the preparation of a UTB-SOI tunneling field-effect transistor with an abrupt tunneling junction as an example to illustrate, Specific steps are as follows:

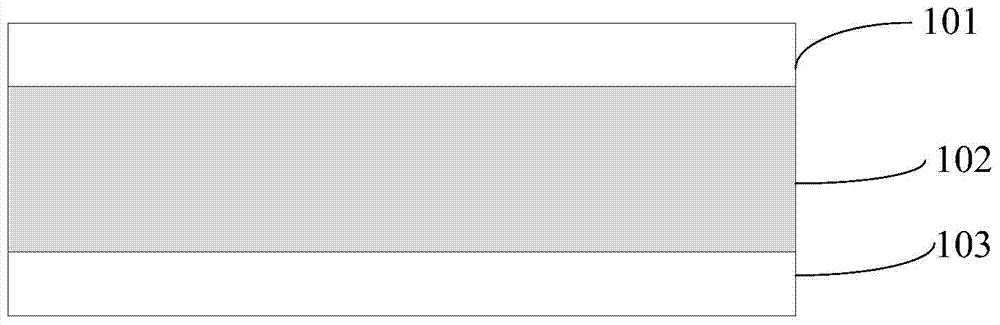

[0077] (1) Select the UTB-SOI substrate. Such as Figure 2a As shown, the UTB-SOI substrate includes a top layer of silicon 101 , a buried oxide layer 102 such as a buried layer of silicon dioxide, and a bottom layer of silicon 103 . The reason for using the UTB-SOI substrate is that the semiconductor device formed on the UTB-SOI substrate has low power consumption, high speed, high integration density, strong anti-interference ability, strong anti-radiation ability, simple process, and can completely eliminate the bulk The advantages of the parasitic latch-up effect of Si devices can ...

Embodiment 3

[0105] See image 3 , image 3 It is a schematic flow chart of a method for preparing a UTB-SOI tunneling field effect transistor with an abrupt tunneling junction according to an embodiment of the present invention, so as to prepare an N-type UTB-SOI tunneling field effect transistor with an abrupt tunneling junction with a channel length of 45 nm. Taking the transistor as an example to describe in detail, the specific steps are as follows:

[0106] 1. Select UTB-SOI substrate

[0107] The crystal orientation of the UTB-SOI substrate 101 may be (100) or (110) or (111), without any limitation here. In addition, the doping type of the UTB-SOI substrate 101 may be N type, or It can be P-type, and the doping concentration is, for example, 10 14 ~10 17 cm -3 , the thickness of the top layer Si is, for example, 10-20 nm.

[0108] 2. Shallow trench isolation formation

[0109] 2.1 Form a first protective layer on the UTB-SOI substrate.

[0110] First, two layers of materials...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More