Pnin/npip type ssoi TFET with abrupt tunneling junction and preparation method thereof

A technology of tunneling junction and dry etching, which is applied in semiconductor/solid-state device manufacturing, electrical components, diodes, etc., can solve the problems of limiting the tunneling probability of TFET devices, reducing the average sub-threshold slope, and small driving current, etc., to achieve Effects of suppressing bipolar effects, increasing the probability of tunneling, and reducing the forbidden band width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

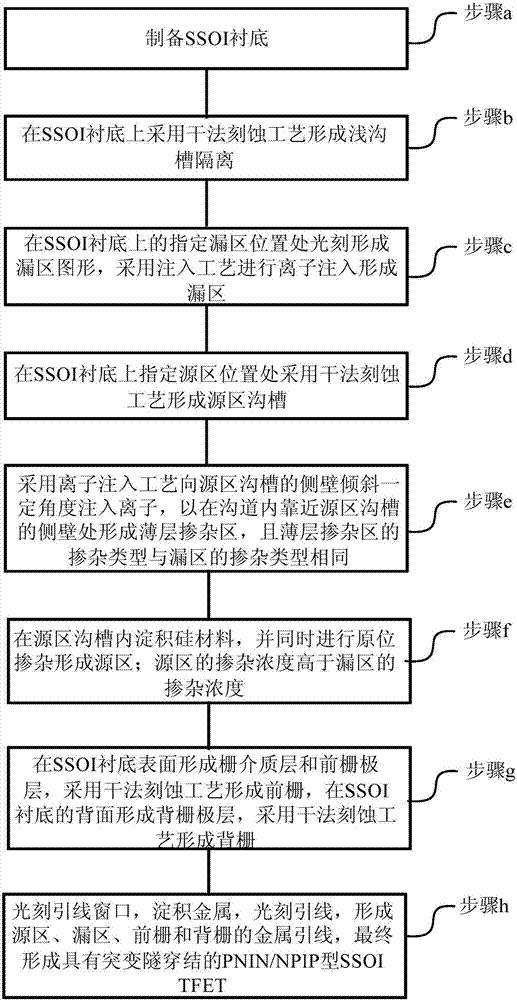

[0026] See figure 1 , figure 1 It is a flow chart of a preparation method of a PNIN / NPIP type SSOI TFET with an abrupt tunneling junction according to an embodiment of the present invention. The preparation method includes the following steps:

[0027] (a) Preparation of SSOI substrate;

[0028] (b) Using a dry etching process to form shallow trench isolation on the SSOI substrate;

[0029] (c) Forming a drain region pattern by photolithography at a designated drain region position on the SSOI substrate, and performing ion implantation using an implantation process to form the drain region;

[0030] (d) Using a dry etching process to form a source region trench at a designated source region location on the SSOI substrate;

[0031] (e) Using an ion implantation process to implant ions at an oblique angle to the sidewall of the source region trench to form a thin doped region in the trench near the sidewall of the source region trench, and the thin layer The doping type of the doped re...

Embodiment 2

[0076] See Figure 2a-2i , Figure 2a-Figure 2i It is a schematic diagram of the preparation method of a PNIN / NPIP type SSOI TFET with abrupt tunneling junction according to an embodiment of the present invention, taking the preparation of a PNIN type SSOITFET with a sudden tunneling junction with a channel length of 45nm as an example for detailed description. The specific steps are as follows :

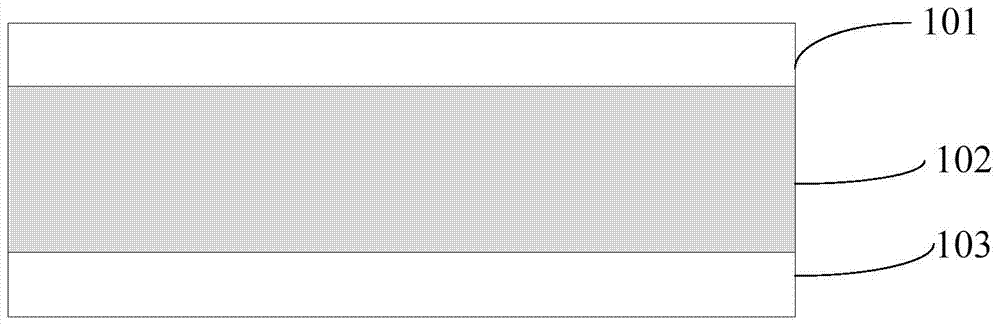

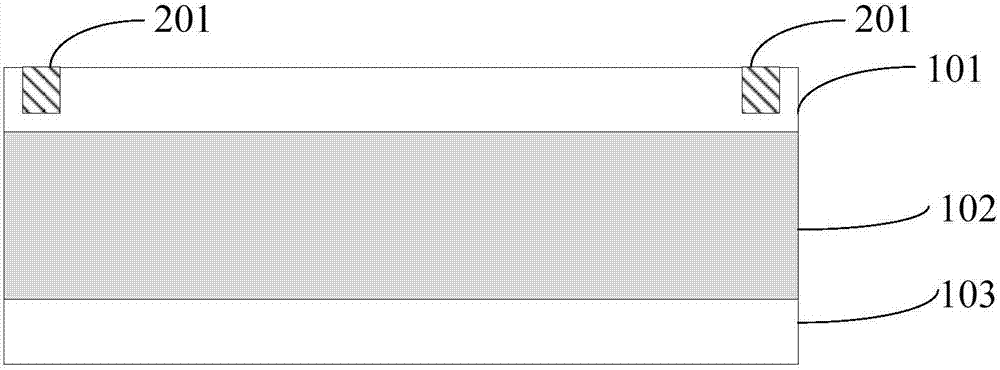

[0077] 1. Prepare SSOI substrate, such as Figure 2a Shown:

[0078] 1.1 Epitaxial growth.

[0079] Using selective epitaxy technology, a graded SiGe layer is epitaxially grown on a Si wafer at a high temperature of 800°C to 900°C, by dynamically adjusting the gas phase precursor GeH during the epitaxial growth process 4 And SiH 2 Cl 2 To control the Ge composition of the graded SiGe layer to increase the Ge composition of the relaxed SiGe layer from 0 to a fixed composition, and then epitaxially grow a fixed composition at a high temperature of 800°C to 900°C Relaxed Si 1-x Ge x Layer, w...

Embodiment 3

[0140] See image 3 , image 3 It is a schematic structural diagram of a PNIN / NPIP type SSOITFET with abrupt tunneling junction according to an embodiment of the present invention. The PNIN / NPIP SSOI TFET with abrupt tunneling junction of the present invention includes a top strained Si layer, a buried oxide layer, and a bottom Si layer , Gate dielectric layer, front gate, back gate, highly doped source region, low doped drain region and N-type / P-type thin layer.

[0141] Specifically, the SSOI substrate is prepared by smart stripping technology, the Ge component of the strain-inducing layer SiGe layer is preferably 0.4, the strained Si layer is directly on the insulating layer, and there is no strain-inducing layer SiGe layer under it, and the thickness of the strained Si layer is preferably 10-20nm, the thickness is less than the critical thickness of strained Si when the Ge composition is 0.4, and the doping concentration is less than 10 17 cm -3 .

[0142] Specifically, the gate ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More