Tunneling field effect transistor and preparation method thereof

A tunneling field effect, transistor technology, applied in semiconductor/solid-state device manufacturing, diodes, semiconductor devices, etc., can solve problems such as low bipolar effect of driving current, suppress bipolar effect, increase driving current, The effect of reducing the subthreshold current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

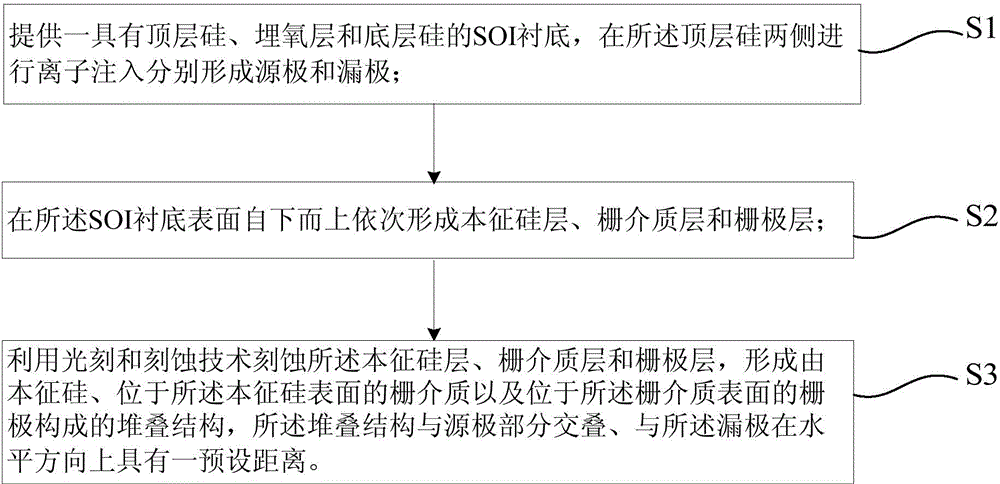

[0044] The invention provides a method for preparing a tunneling field effect transistor, such as figure 1 As shown in the flowchart of the preparation method, the preparation method of the tunneling field effect transistor at least includes the following steps:

[0045] S1, providing an SOI substrate with a top layer of silicon, a buried oxide layer and a bottom layer of silicon, performing ion implantation on both sides of the top layer of silicon to form a source and a drain respectively;

[0046] S2, sequentially forming an intrinsic silicon layer, a gate dielectric layer and a gate layer on the surface of the SOI substrate from bottom to top;

[0047] S3, using photolithography and etching techniques to etch the intrinsic silicon layer, gate dielectric layer, and gate layer to form intrinsic silicon, a gate dielectric on the surface of the intrinsic silicon, and a gate electrode on the surface of the gate dielectric. A stacked structure composed of electrodes, the stacke...

Embodiment 2

[0068] The present invention also provides a tunneling field effect transistor, which is made by using the preparation method provided in Embodiment 1, and the tunneling field effect transistor at least includes:

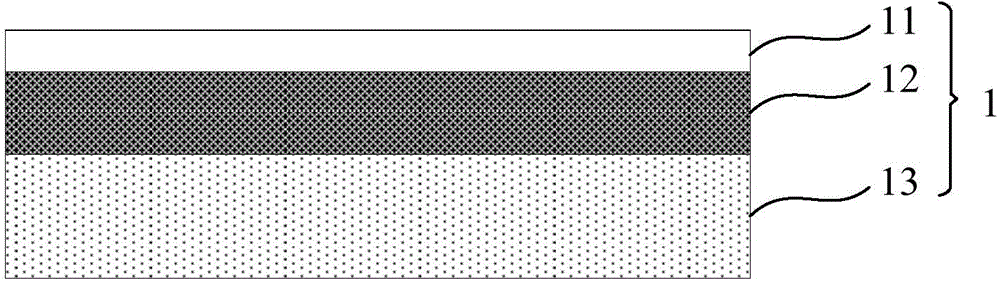

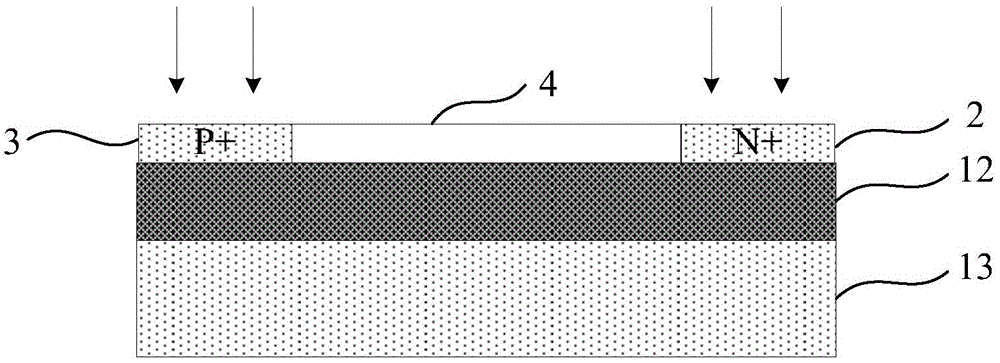

[0069] SOI substrate 1, said SOI substrate 1 comprises top layer silicon 11, buried oxide layer 12 and bottom layer silicon 13;

[0070] The source 3 and the drain 2 are respectively formed on both sides of the top layer silicon 11;

[0071] A stacked structure, formed on the SOI substrate 1, the stacked structure includes intrinsic silicon 8, a gate dielectric 9 located on the surface of the intrinsic silicon 8, and a gate 10 located on the surface of the gate dielectric 9; The stacked structure partially overlaps the source 3 and has a predetermined distance from the drain 2 in the horizontal direction.

[0072] The stacked structure formed is as Figure 5 As shown, the stacked structure partially overlaps with the source 3 and has a predetermined distance from ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More