Patents

Literature

36results about How to "Large tunneling area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Tunneling field effect transistor with T-shaped grid structure and low power consumption

ActiveCN102005481AIncrease the on-currentLarge tunneling areaSemiconductor devicesEngineeringTunnel field-effect transistor

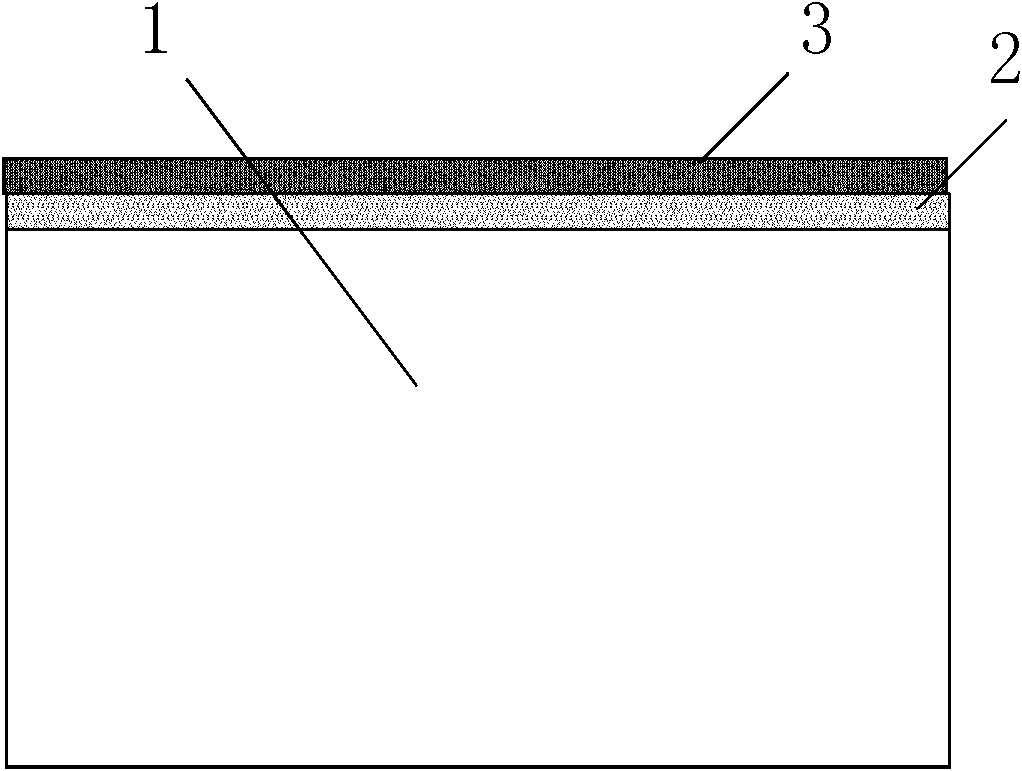

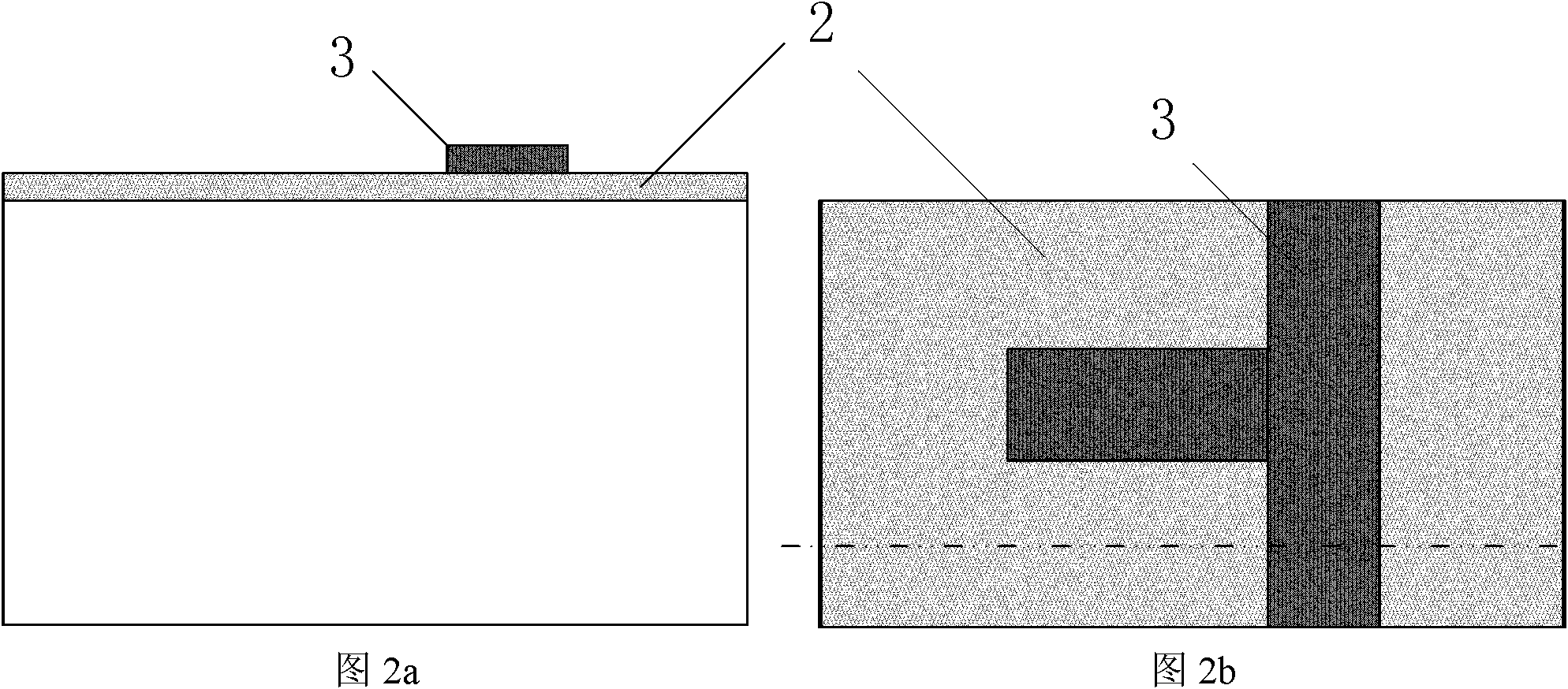

The invention provides a tunneling field effect transistor (TFET) with a T-shaped grid structure and low power consumption, and belongs to the field of field effect transistor logic devices and circuits in complementary metal oxide semiconductor (CMOS) ultra large scale integrated circuits (ULSI). The TFET comprises a source electrode, a drain electrode and a control grid, wherein the control grid extends toward the end of the source electrode to form a T shape; the T-shaped control grid consists of an extending grid region and the original control grid region; and an active region covered below the extending grid region is a channel region and is made of a substrate material. By using the T-shaped grid structure, the source region of the TFET encircles a channel, so that the conduction current of a device is improved. Compared with the conventional planar TFET, the TFET can achieve higher conduction current and steeper subthreshold slope under the same process conditions and the same size of the active region.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

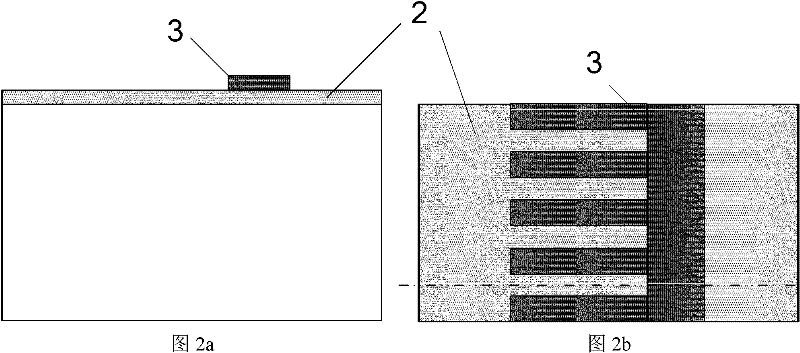

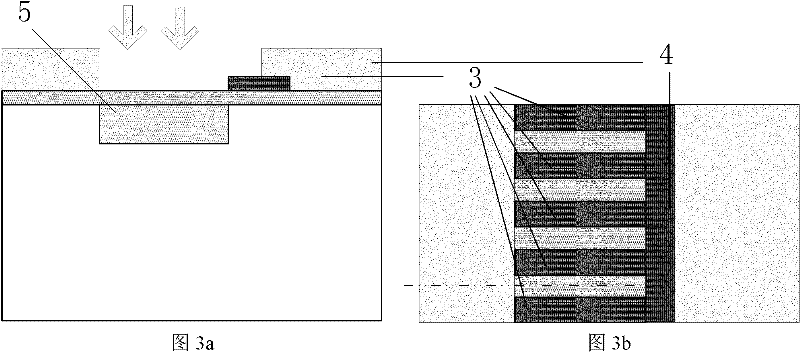

Low-power consumption tunneling field effect transistor (TFET) of fork-structure grid structure

ActiveCN102157559AEnhanced source junction electric field strengthIncrease the on-currentSemiconductor devicesCMOSEngineering

The invention provides a low-power consumption tunneling field effect transistor (TFET), belonging to the field of a field effect transistor logic device and a circuit of CMOS (complementary metal oxide semiconductors) ultra large scale integrated circuit (ULSI). The TFET provided by the invention comprises a source, a drain and a control grid, wherein the control grid extends towards a source electrode end into a fork structure, and the fork-structure control grid is composed of an extended grid region and an original control grid region; and the active region which is covered below the extended grid region is similarly a channel region and is made of a substrate material. According to the invention, the channel is enclosed by the source region of the TFET, and the conduction current of the device is improved; and compared with the existing panel TFET, the TFET has provided by the invention has the advantage that under the conditions of the same technology and the same active region size, higher conduction current and a steep subthreshold gradient can be obtained.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

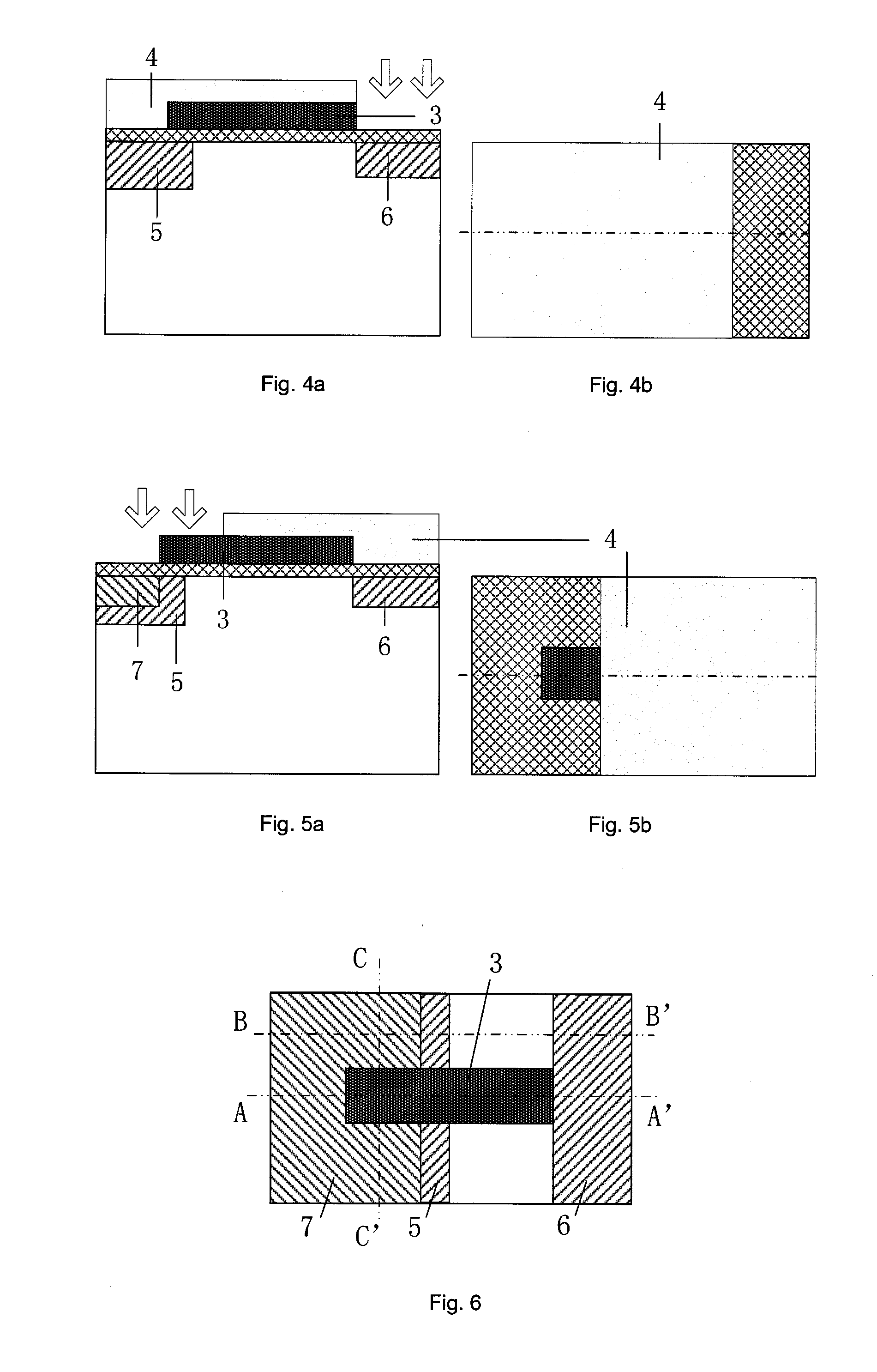

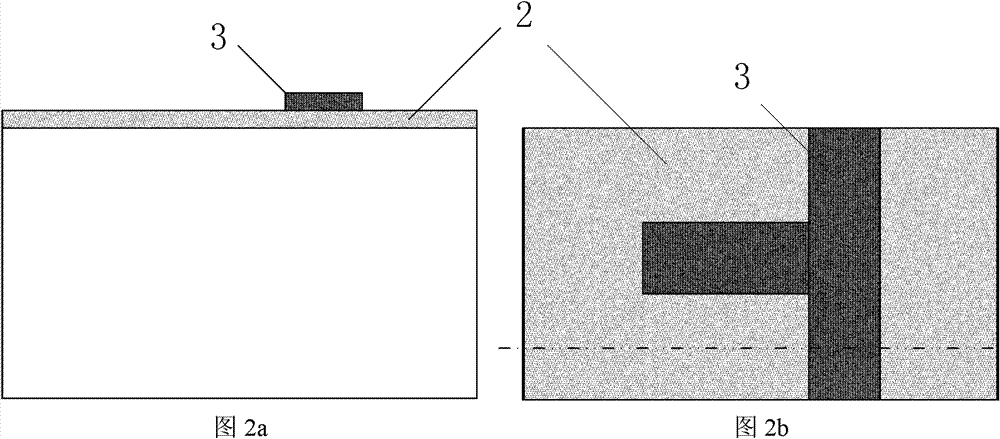

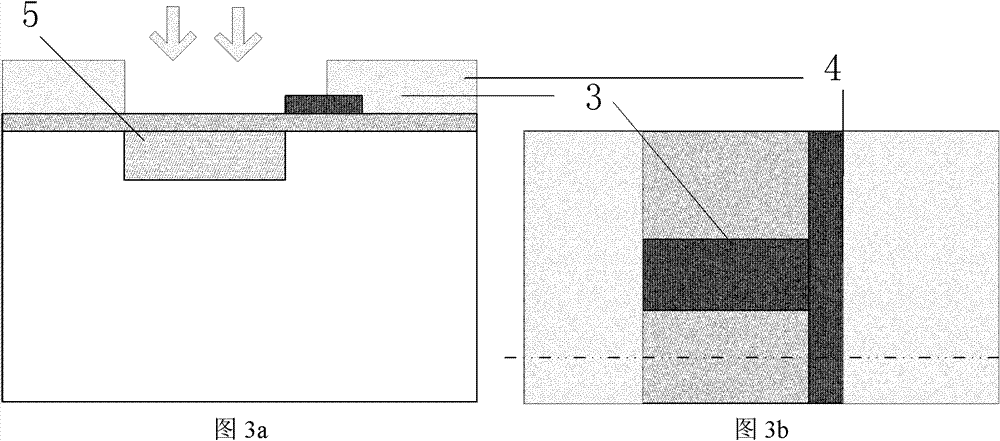

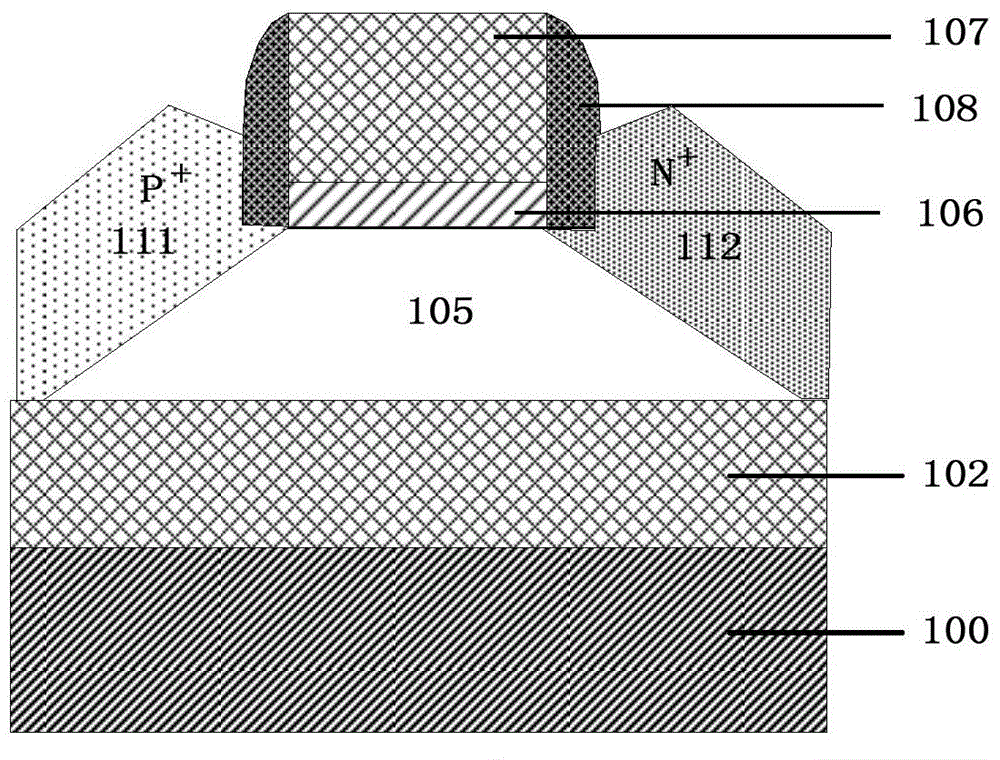

Tunneling transistor structure and manufacturing method thereof

ActiveCN104201198AIncrease the on-state currentLarge tunneling areaSemiconductor/solid-state device manufacturingDiodeGate dielectricDielectric layer

The invention provides a tunneling transistor structure. The tunneling transistor structure comprises a substrate, a silicon strip, a drain electrode area, a source electrode area, a gate dielectric layer and a grid electrode, wherein the silicone strip is formed on the substrate; the drain electrode area is formed at one side of the silicon strip; the source electrode area is equipped with a first groove in which the silicon strip is contained; the grate dielectric layer is formed on the source electrode area and partially covers the source electrode area; the grid electrode is equipped with a second groove in which the gate dielectric layer is contained; the cross section of the second groove is the same as that of the first groove; when in tunneling, the first groove tunnels under the effect of the second groove to form a tunneling current. The invention also provides a manufacturing method of the tunneling transistor structure. According to the tunneling transistor structure, the structures of the source electrode area and the grid electrode are changed; when in tunneling, the tunneling area of the source electrode area is expanded under the effect of the grid electrode, and point tunneling and line tunneling occur in the first groove; therefore, both the tunneling area and the tunneling portability are raised through the structure, and as a result, the on-state current of the whole device can be improved.

Owner:HUAWEI TECH CO LTD

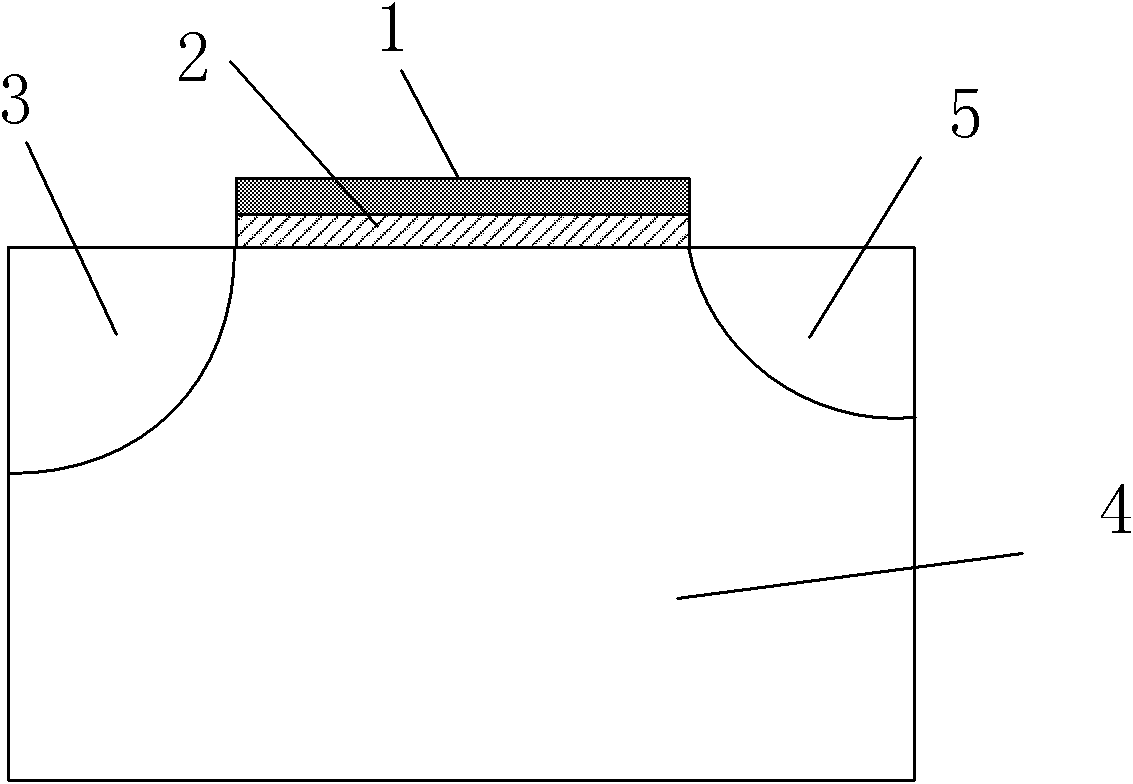

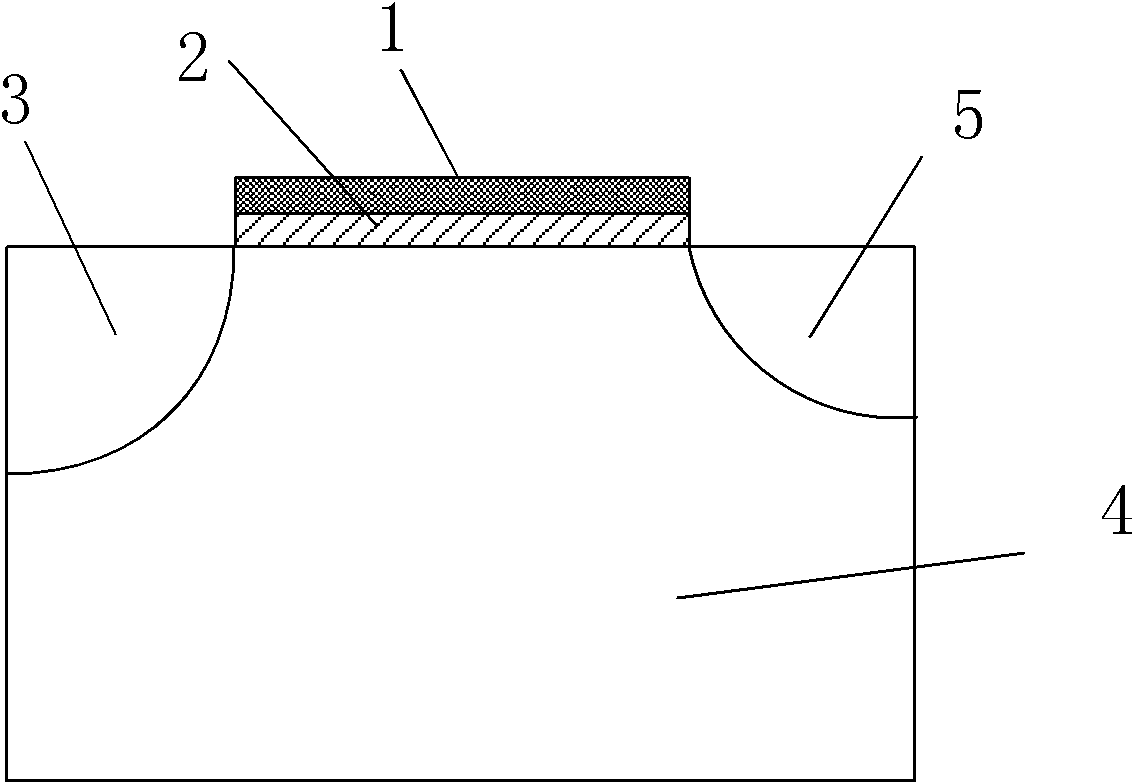

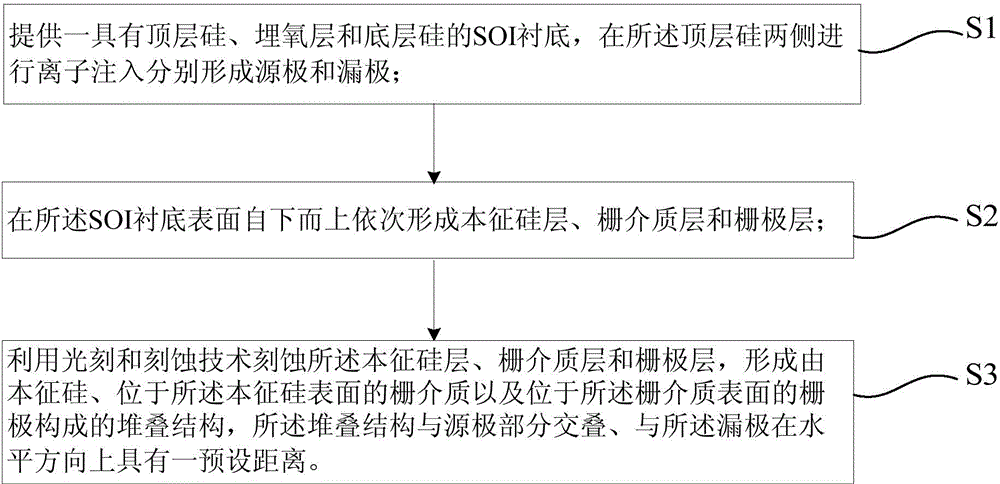

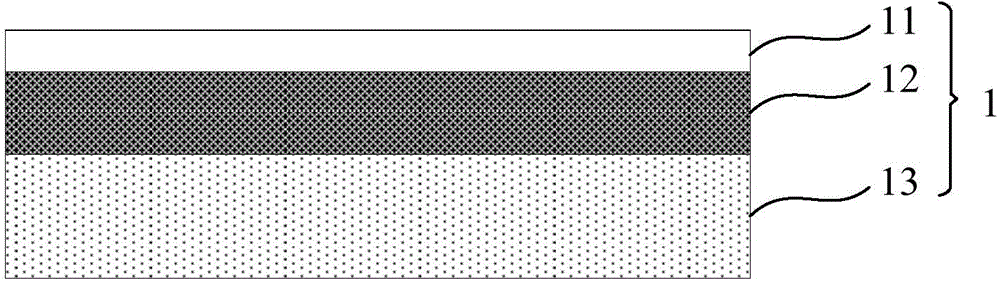

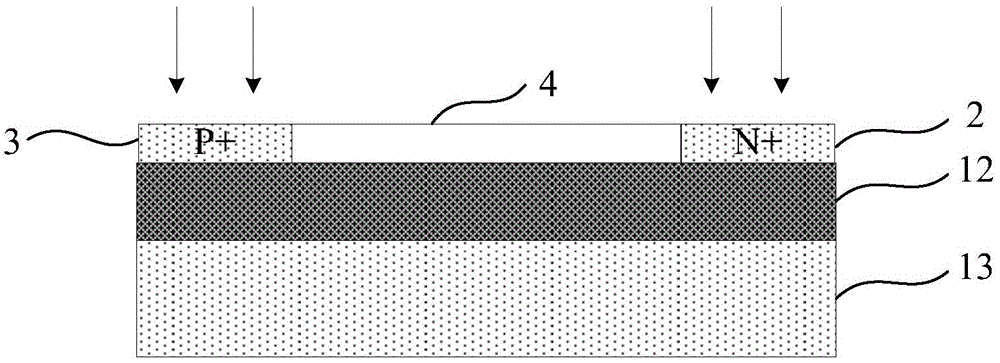

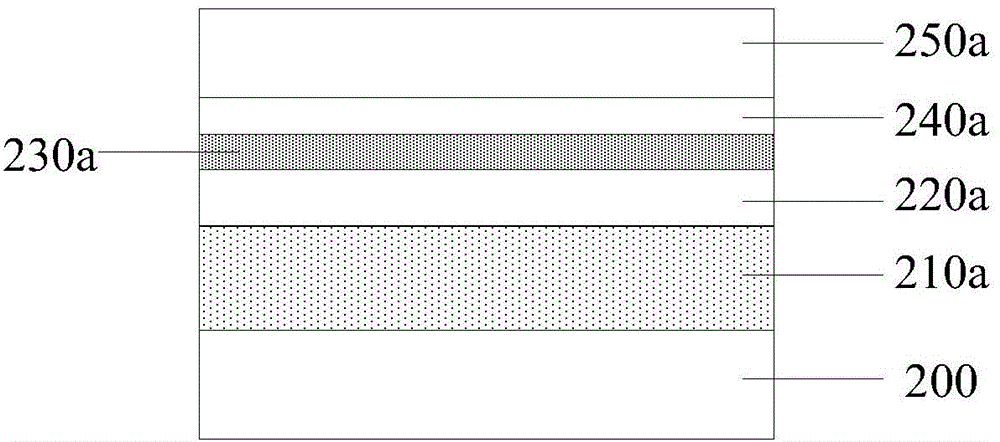

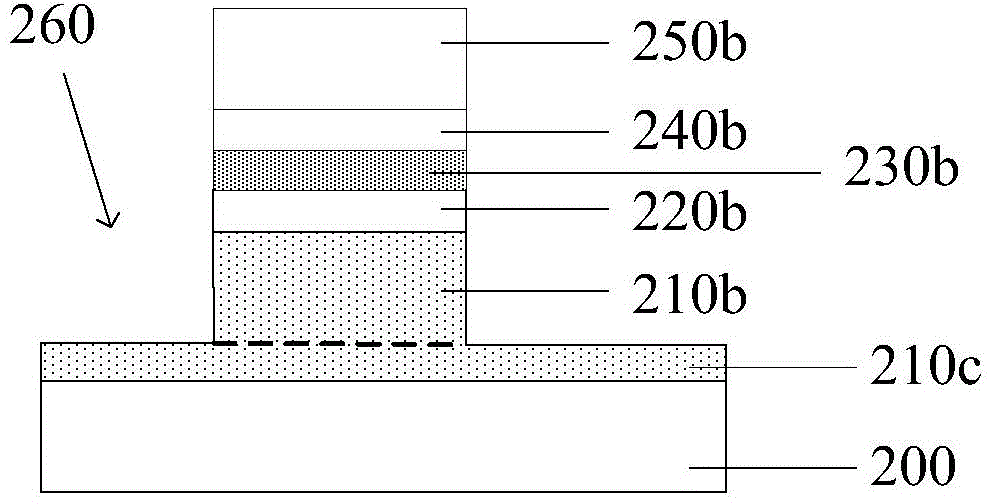

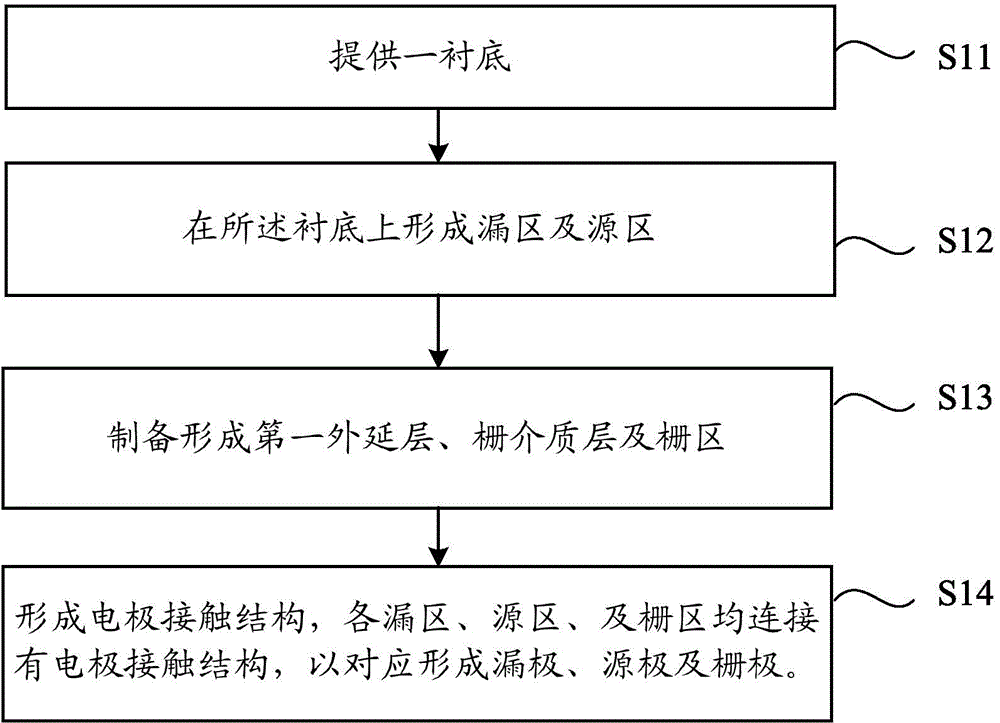

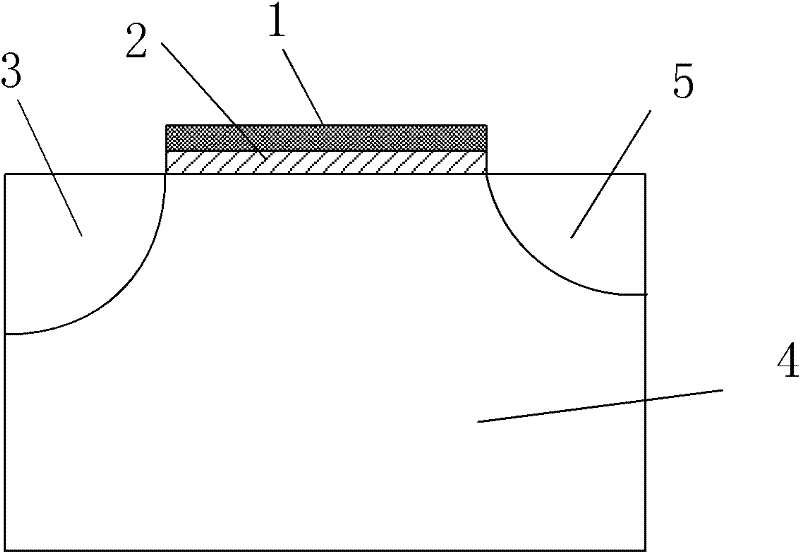

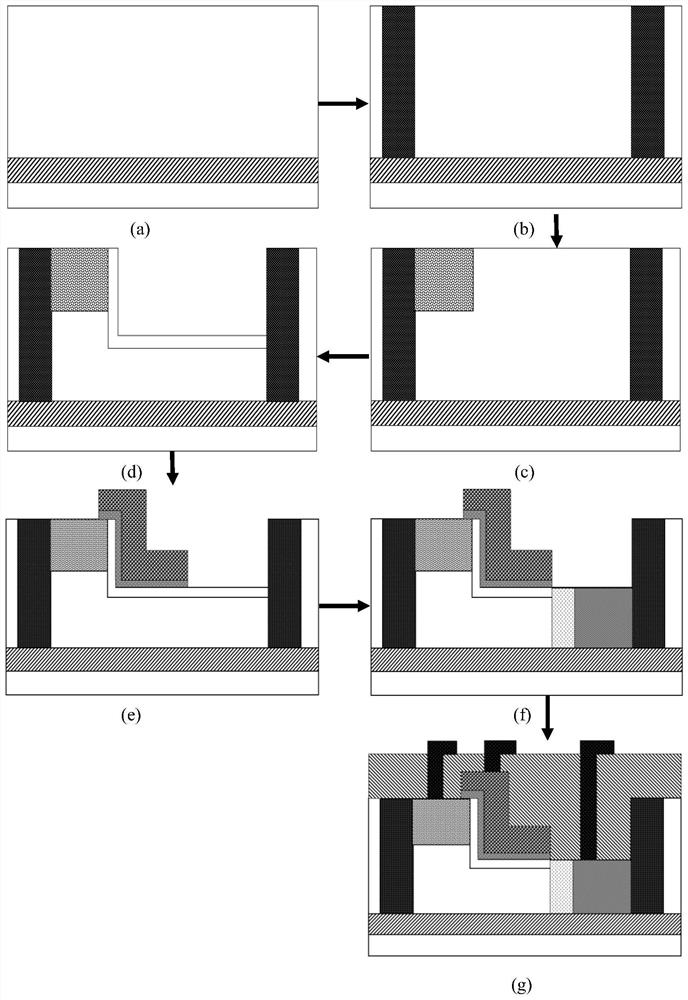

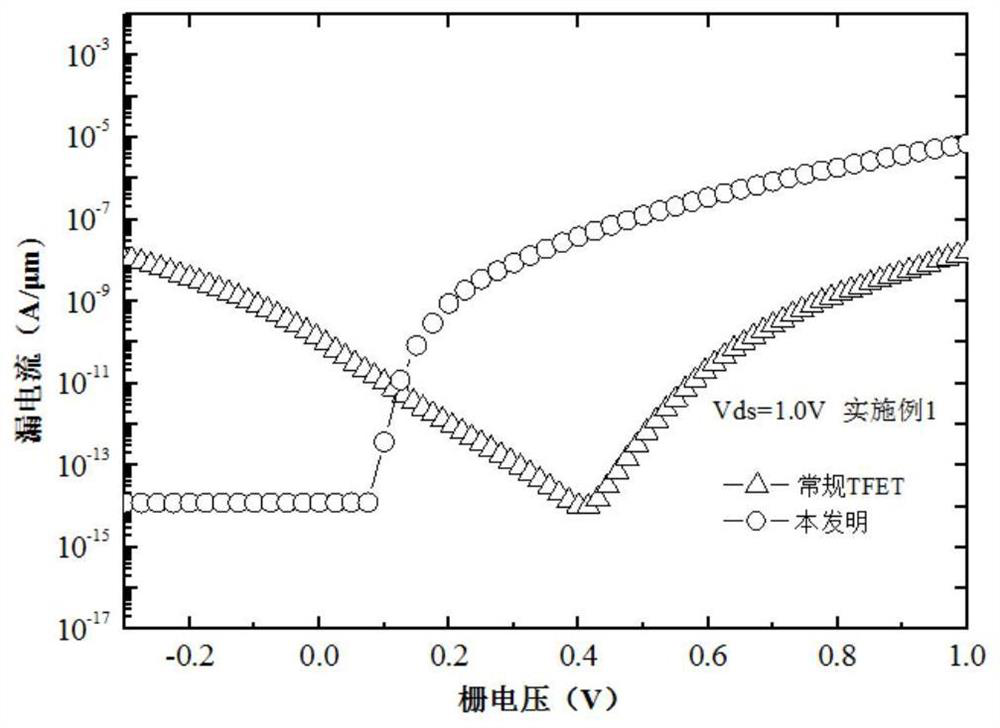

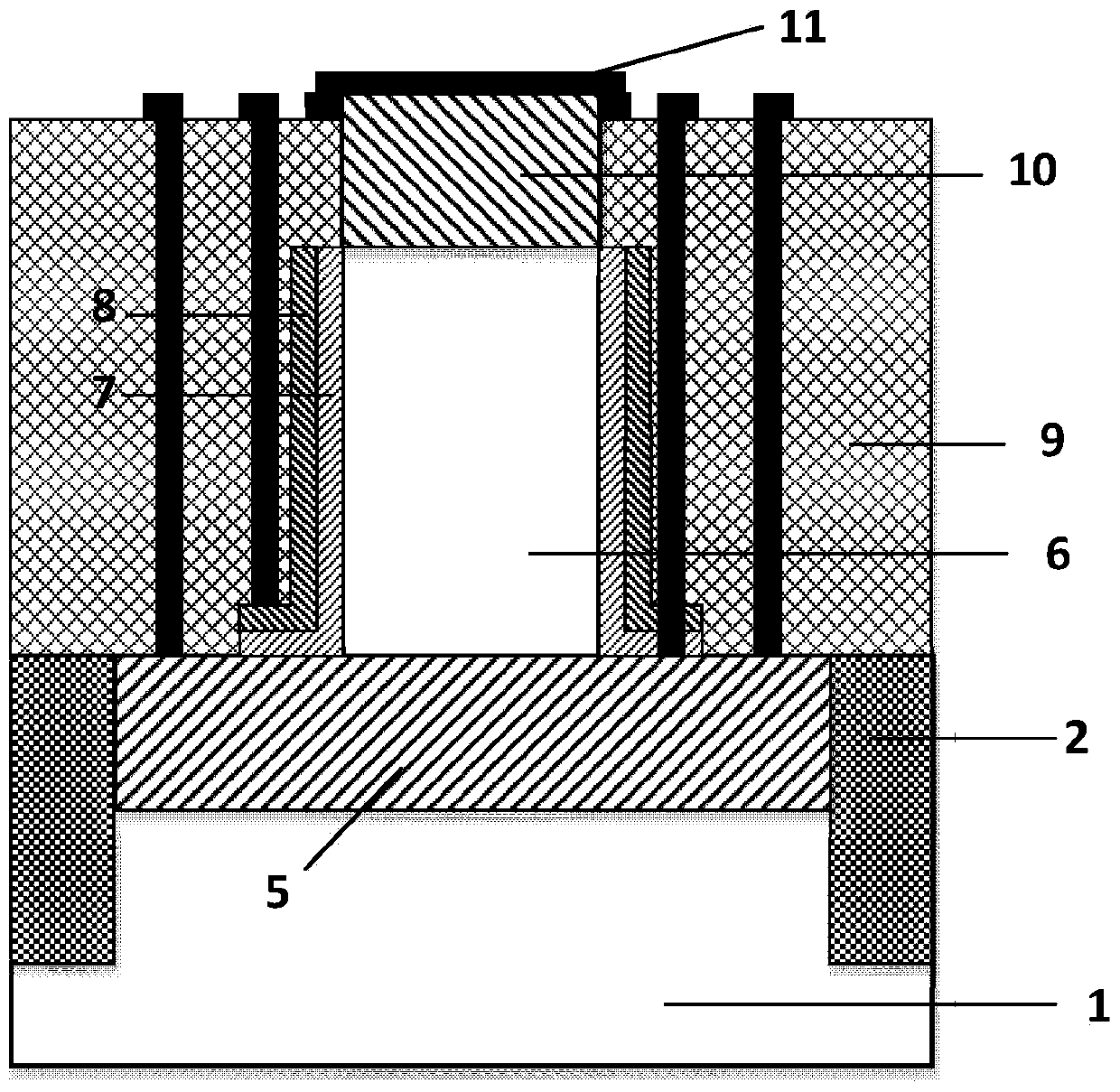

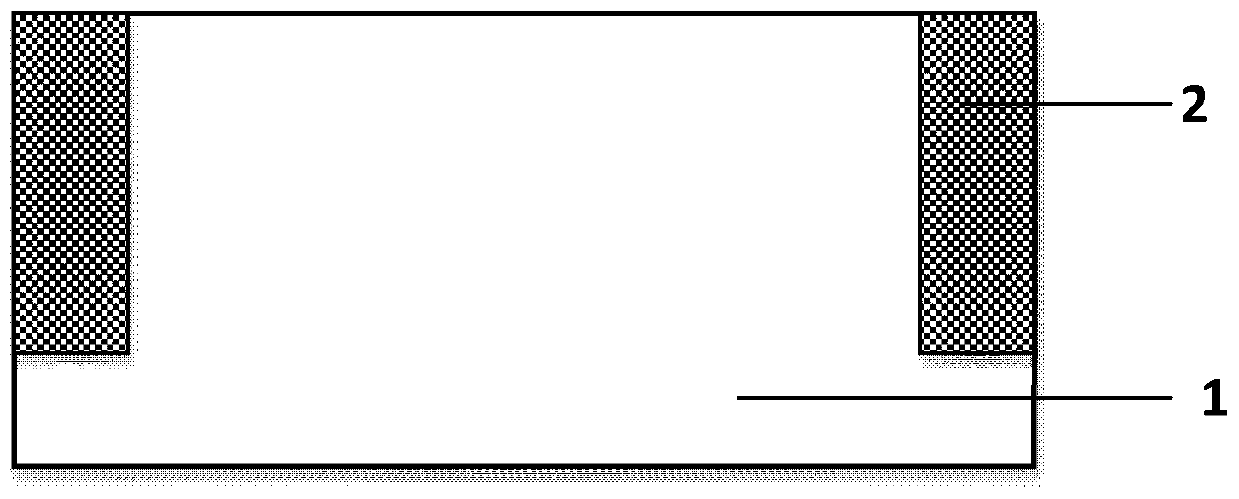

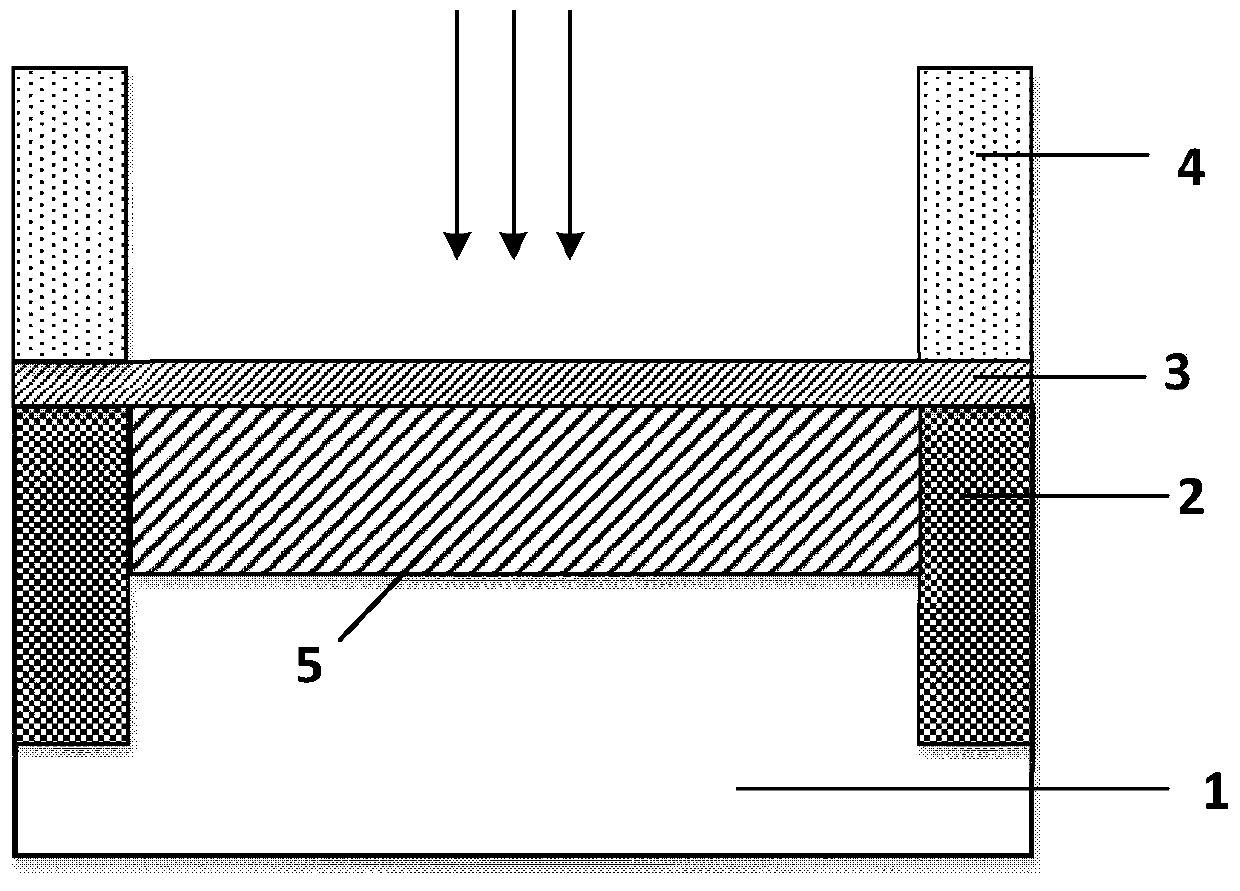

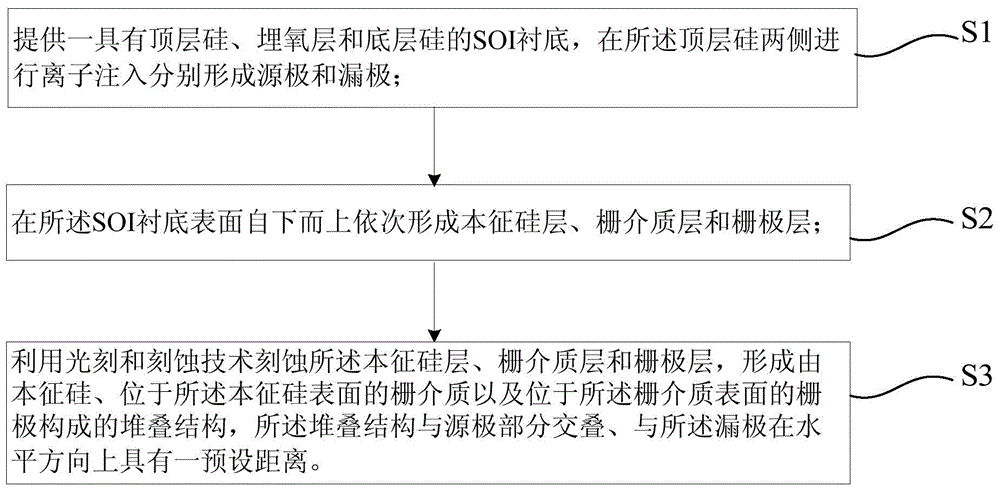

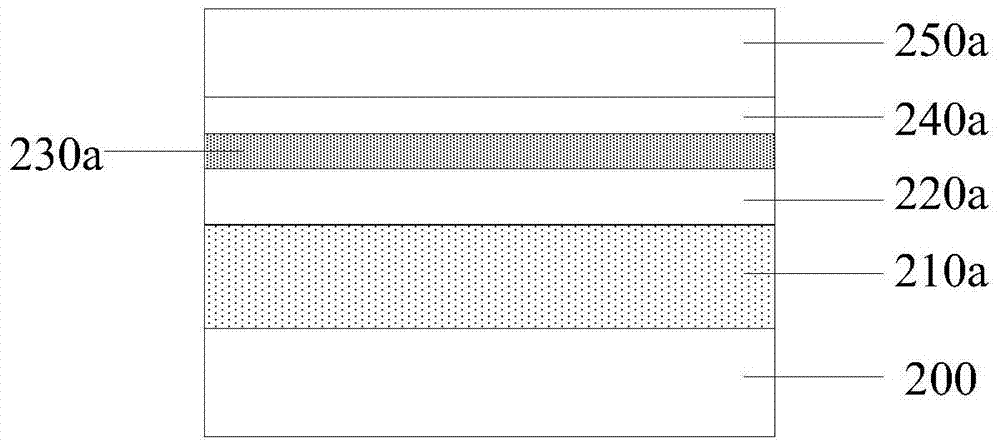

Tunneling field effect transistor and preparation method thereof

ActiveCN103560153ALarge tunneling areaIncrease drive currentSemiconductor/solid-state device manufacturingDiodeDriving currentPower flow

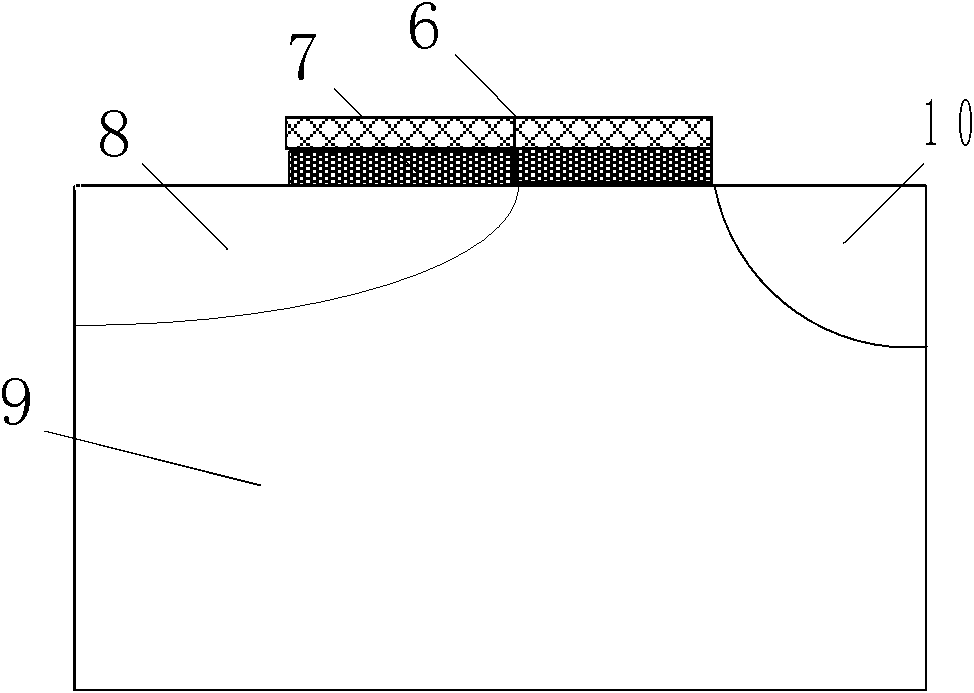

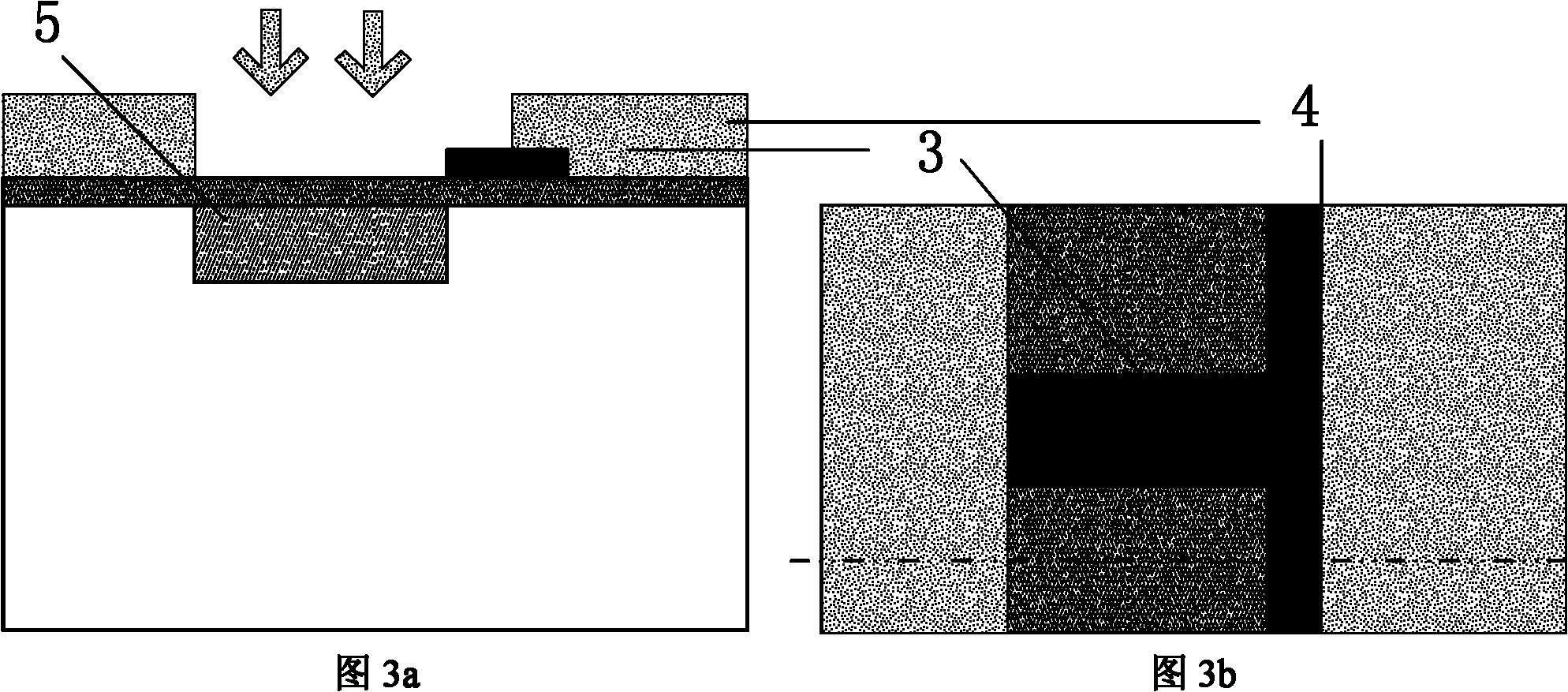

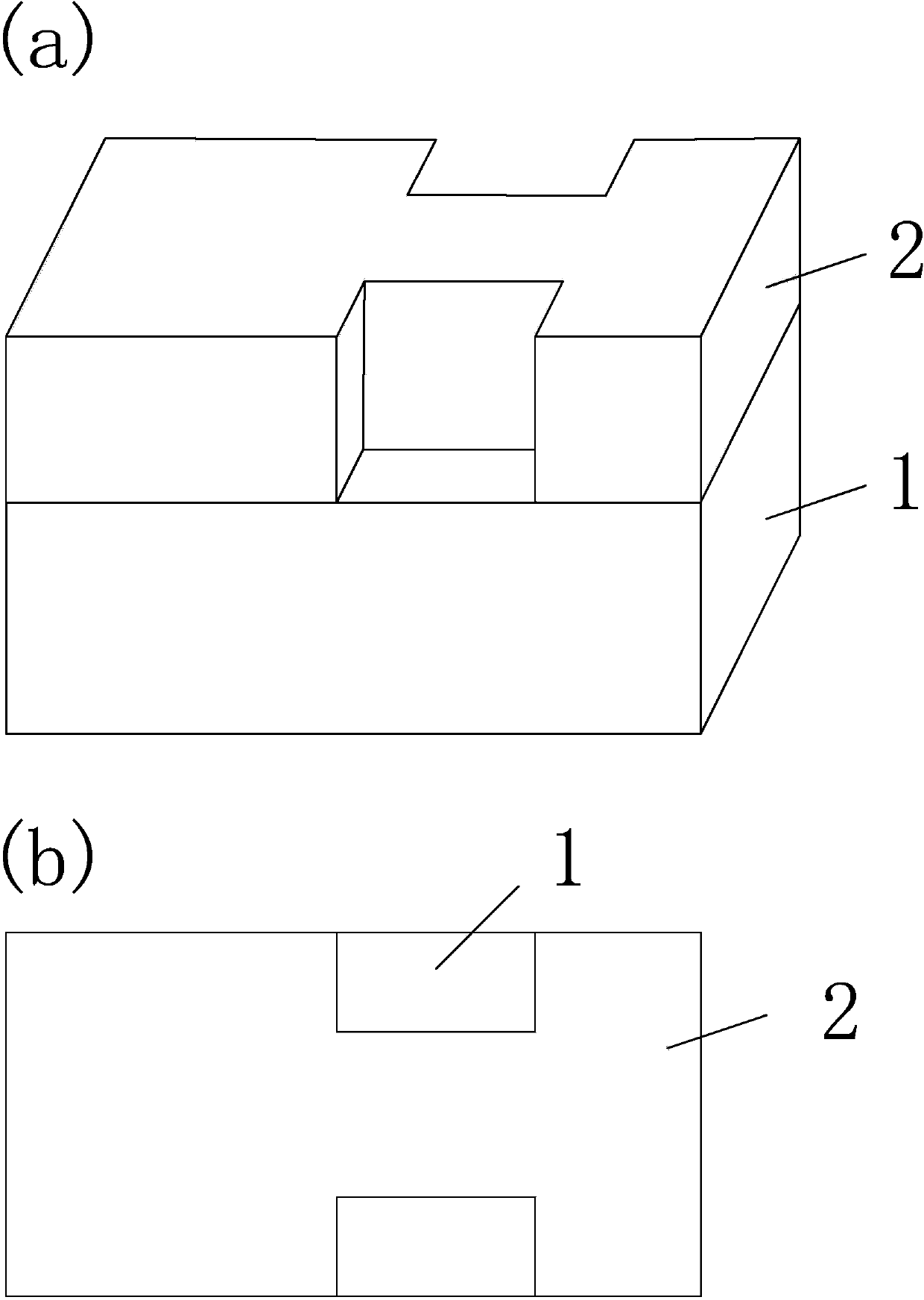

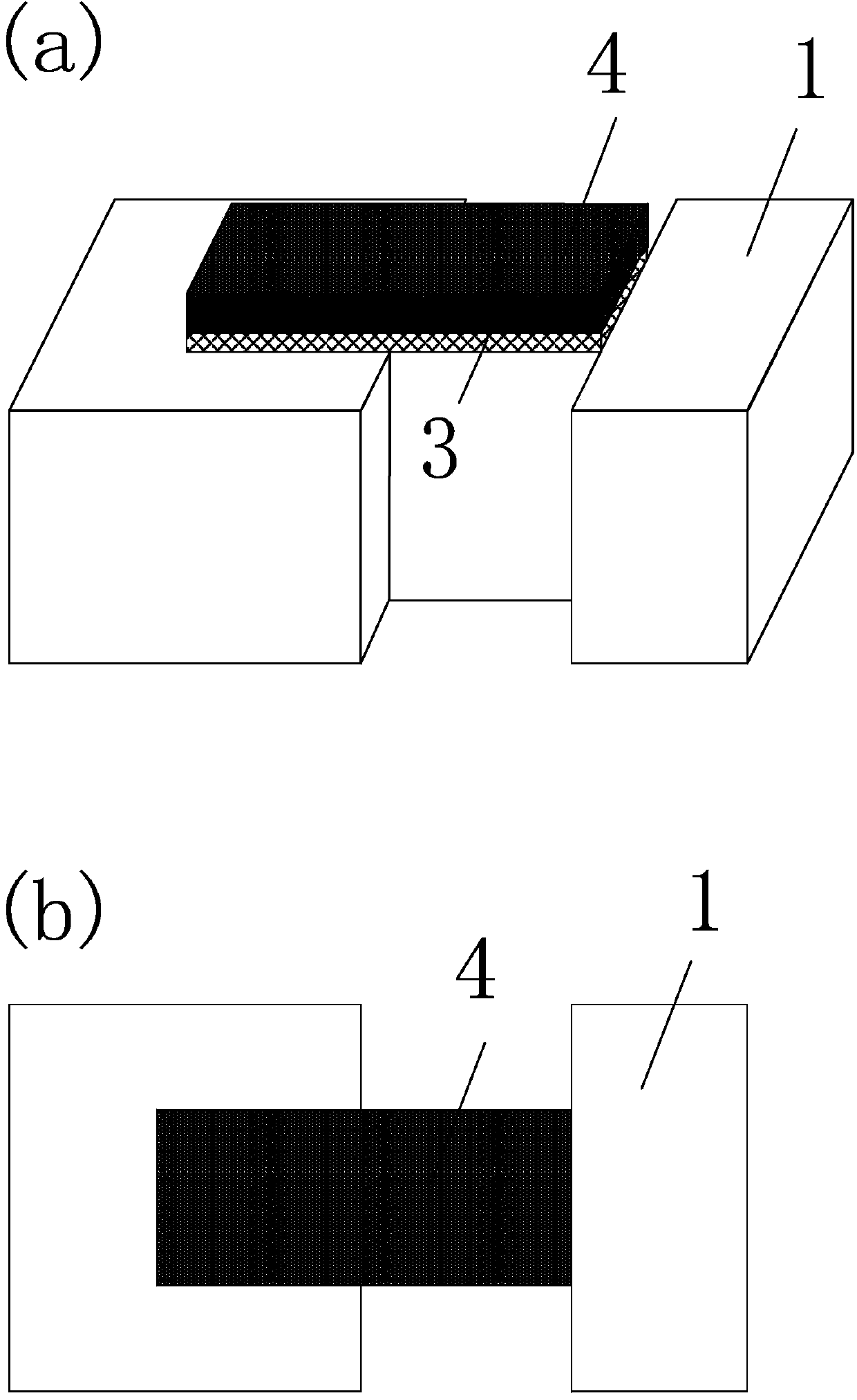

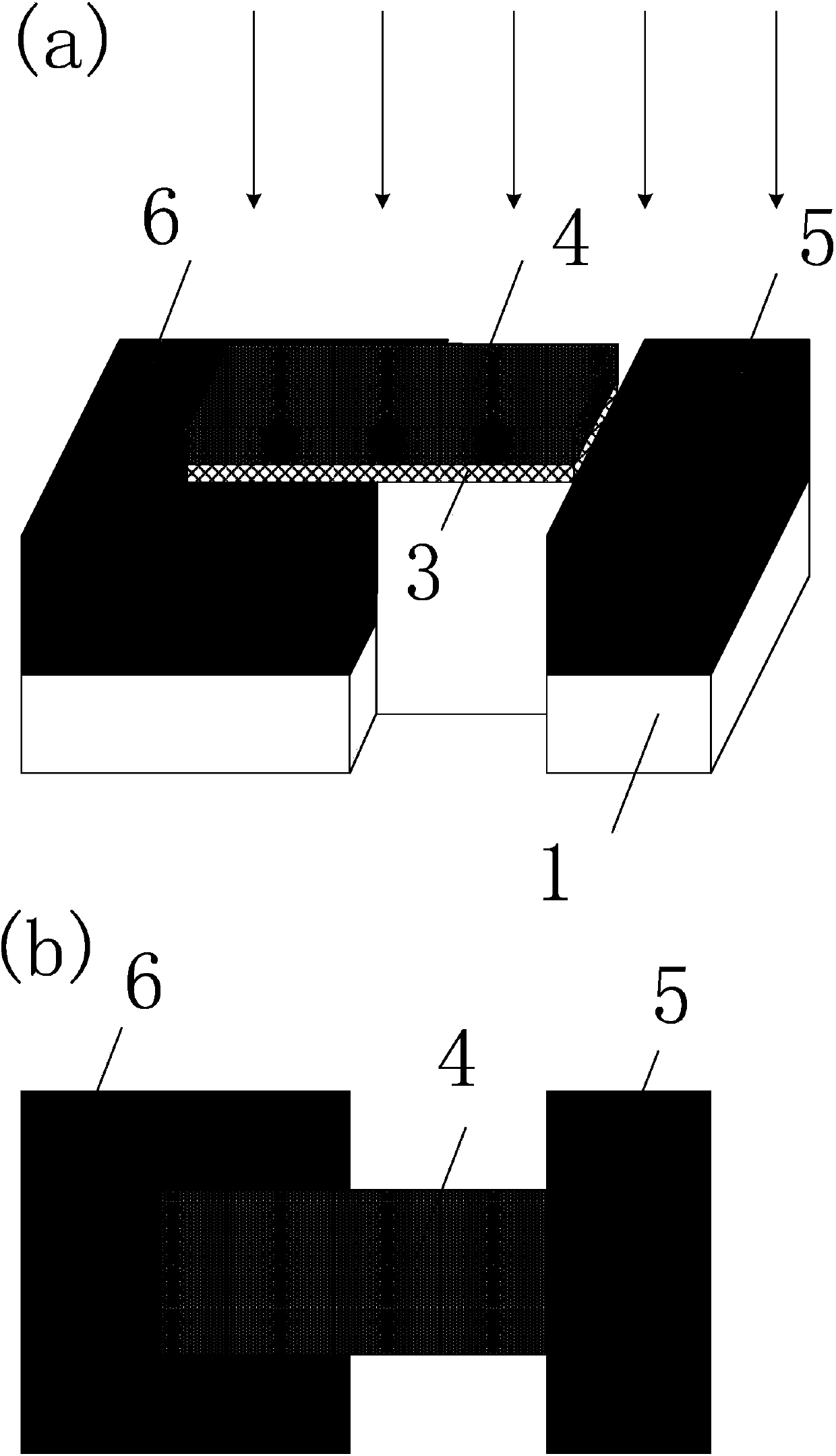

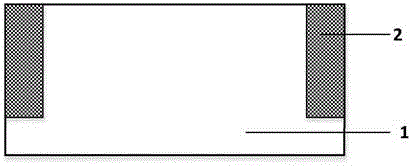

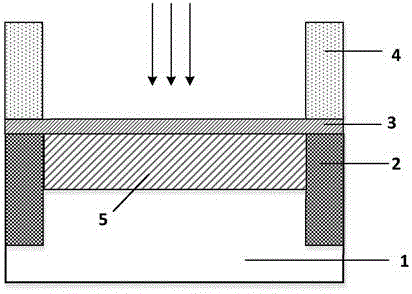

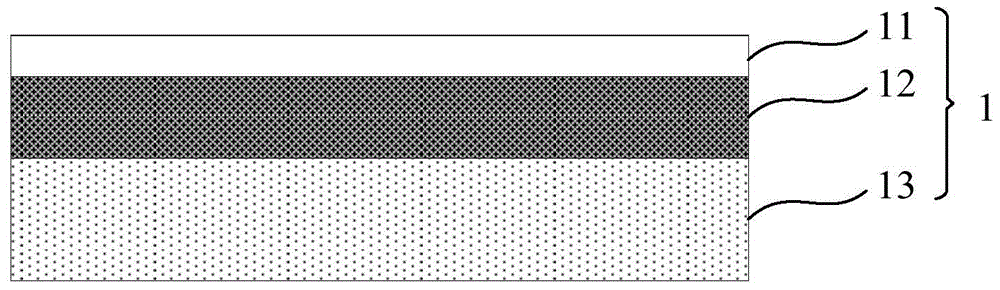

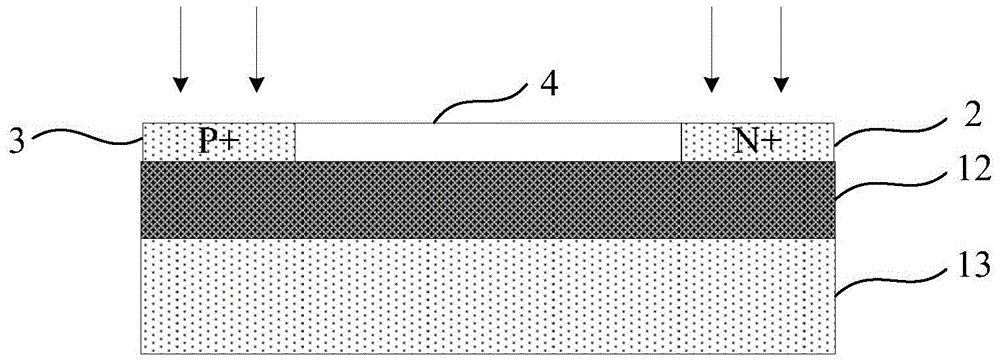

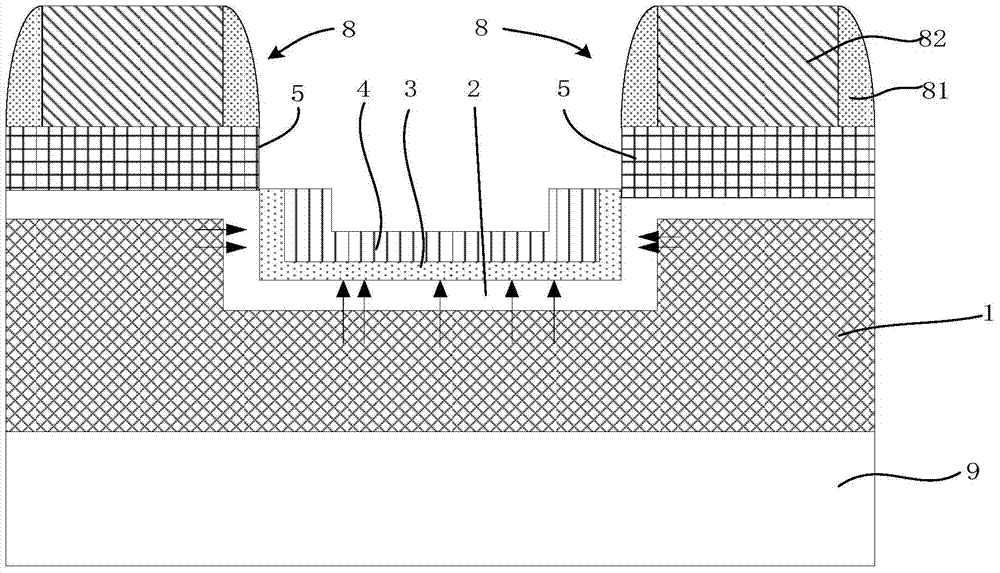

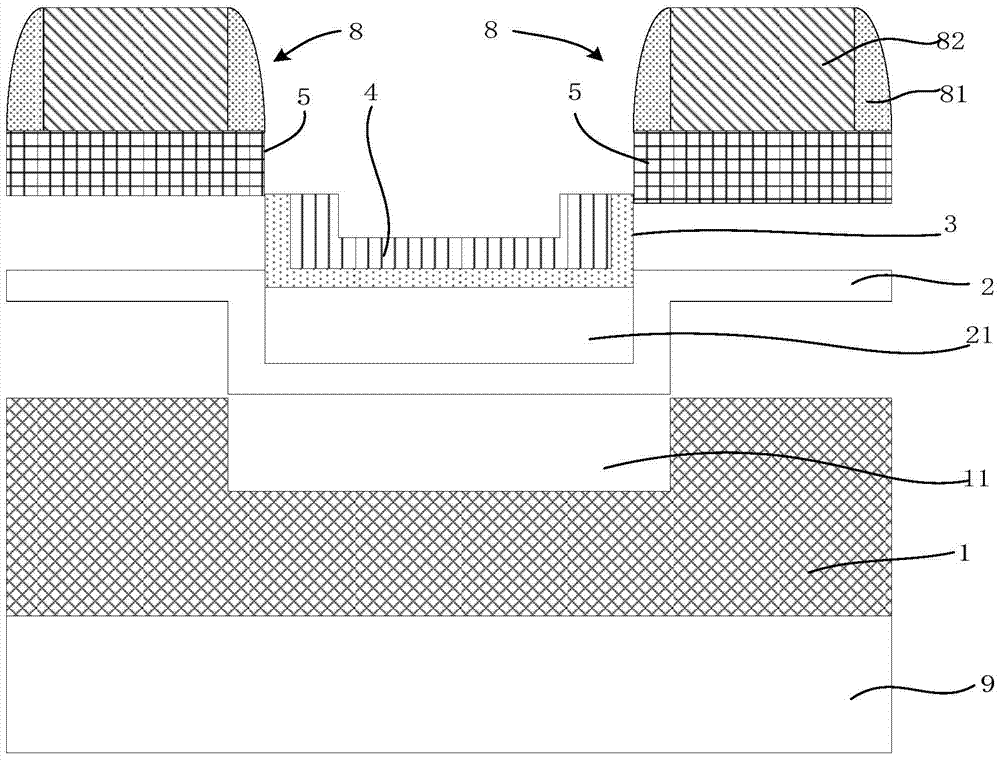

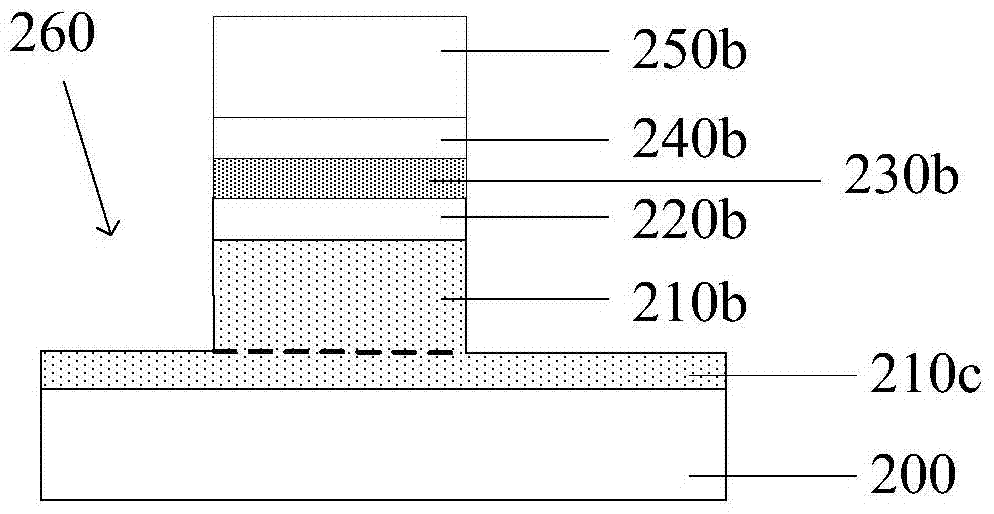

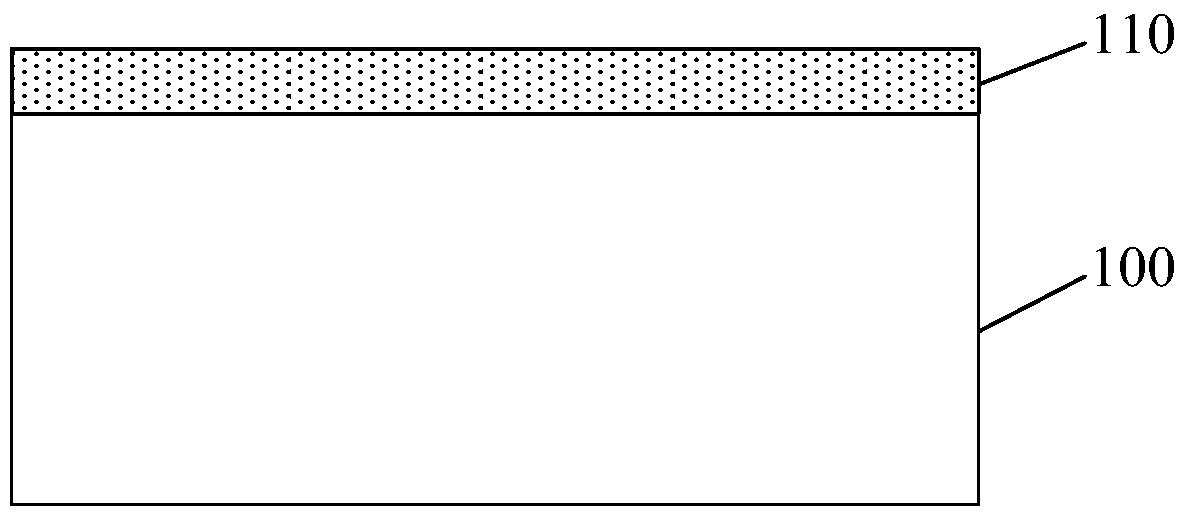

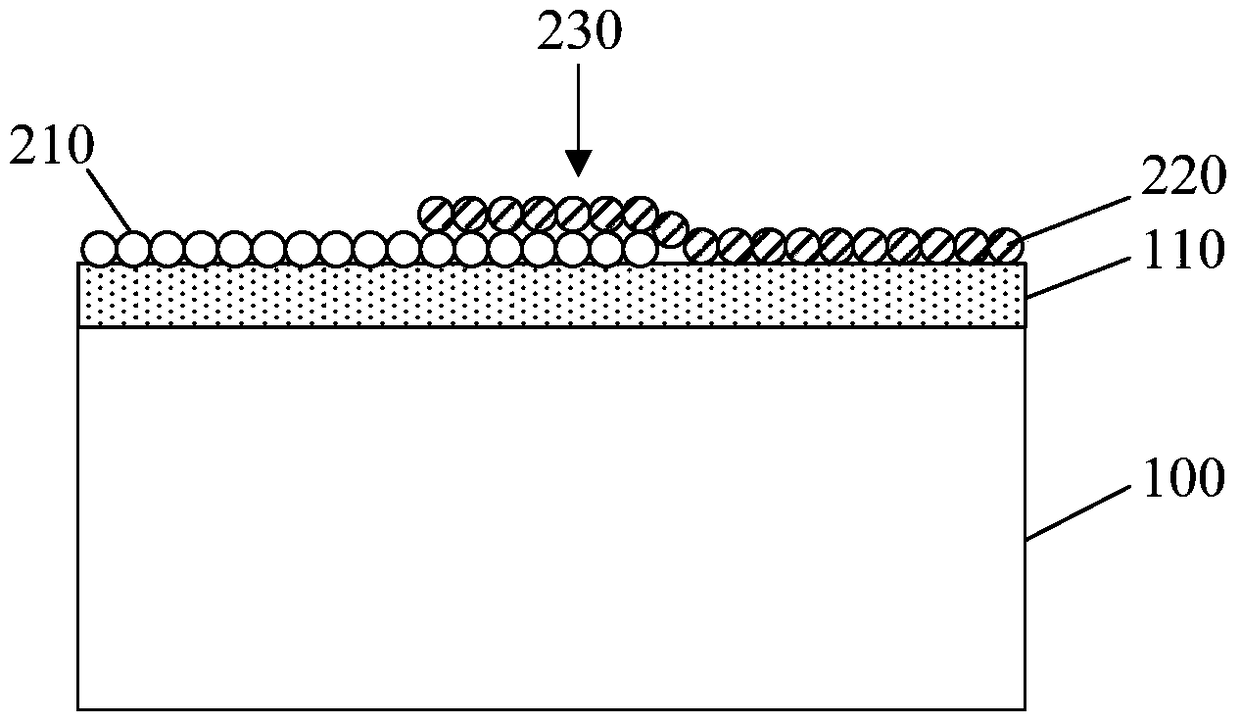

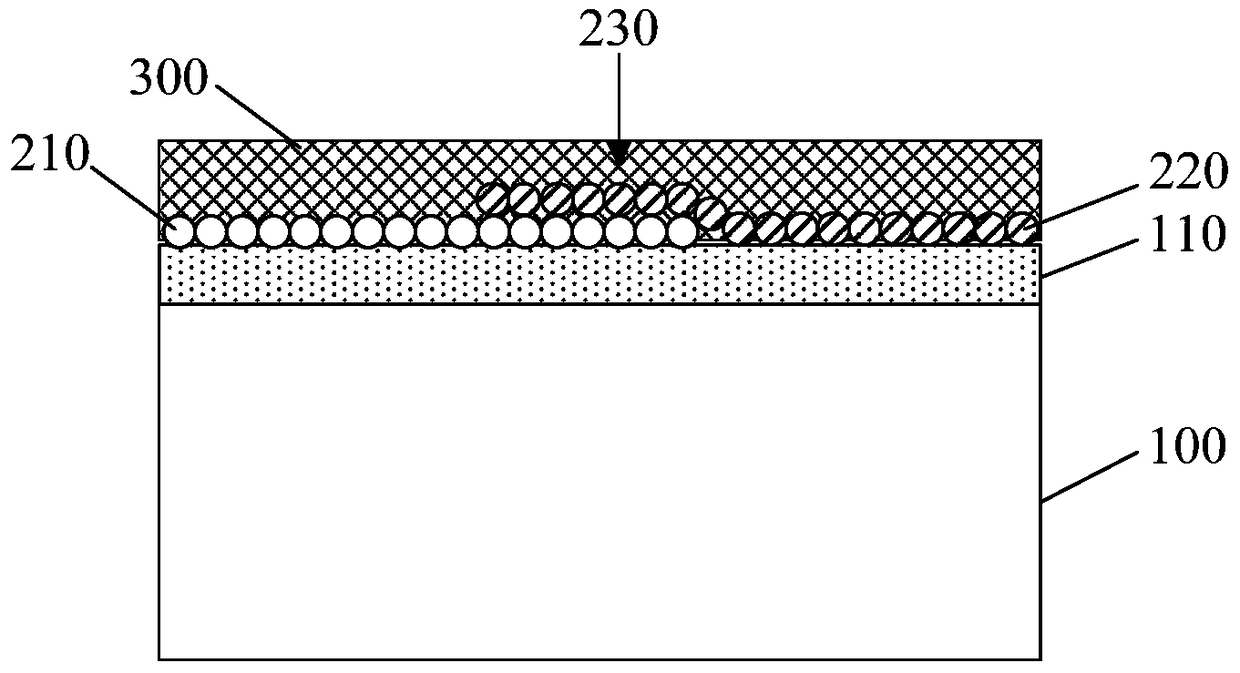

The invention provides a tunneling field effect transistor and a preparation method thereof. The preparation method at least comprises the following steps that an SOI substrate provided with top layer silicon, an oxygen buried layer and bottom layer silicon is provided, and ion injection is conducted on the two sides of the top layer silicon to form a source electrode and a drain electrode respectively; an intrinsic silicon layer, and a grid medium layer and a grid layer are sequentially formed on the surface of the SOI substrate from bottom to top; a stacking structure is formed by etching the intrinsic silicon layer, the grid medium layer and the grid layer through the photoetching and etching technologies, the stacking structure is partially overlapped with the source electrode and is preset distance away from the drain electrode in the horizontal direction. According to the tunneling field effect transistor and the preparation method of the tunneling field effect transistor, the stacking structure is overlapped with the source electrode so that the tunneling area can be increased, and further a driving current is increased. In addition, the stacking structure is preset distance away from the drain electrode in the horizontal direction, and the bipolar effect in the tunneling field effect transistor can be suppressed through the preset distance, and a subthreshold current is reduced.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Multiple source MOS transistor with impurity segregation and production method thereof

ActiveCN102117834AControl channel surface potentialControl potentialSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

The invention provides a multiple source MOS (metal oxide semiconductor) transistor with impurity segregation and a production method thereof. The multiple source MOS transistor comprises a control gate electrode layer, a gate dielectric layer, a semiconductor substrate, a highly-doped source region and a highly-doped drain region; one end of a control gate extends towards the highly-doped sourceregion to form a T shape; the extended gate region is used as an extension gate; an original control gate region is a main gate; the highly-doped source region is formed by highly doping a semiconductor and is positioned on two sides of the extension gate along the width direction of the source region; and one side of the highly-doped region, which is away from the channel direction, is connectedwith a Schottky source region with impurity segregation. Compared with the present MOSFET (metal-oxide-semiconductor field-effect transistor), under the same process condition and the same size of the active region, higher conducting current, lower leakage current and steeper sub-threshold slope can be obtained.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Tunneling field effect transistor and forming method thereof

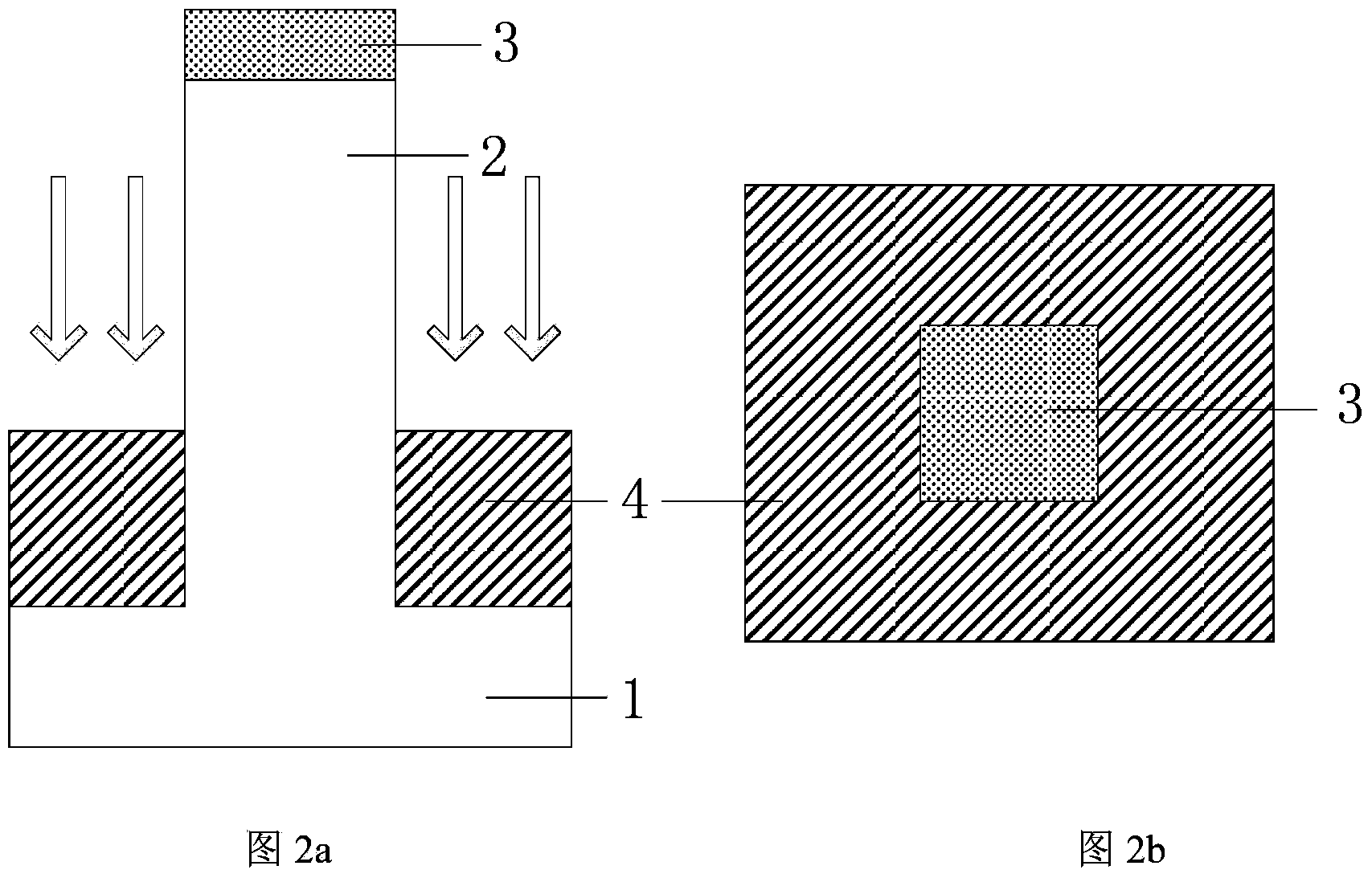

ActiveCN104701374AAdd tunnel pathIncrease the areaSemiconductor/solid-state device manufacturingSemiconductor devicesDielectric layerCondensed matter physics

Disclosed are a tunneling field effect transistor and a forming method thereof. The tunneling field effect transistor comprises a semiconductor substrate, a first semiconductor layer, an annular groove, a first doping region, a first channel region, a second doping region, second channel regions, a grid electrode and a grid dielectric layer, the first semiconductor layer is positioned on the semiconductor substrate and has a first doping type, the annular groove is positioned in the first semiconductor layer, the first doping region is positioned on the first semiconductor layer and surrounded by the annular groove and has a first doping type, the first channel region is positioned on the first doping region, the second doping region is positioned on the first channel region and has a second doping type, the second channel regions are positioned on the side faces of the second doping region, the first channel region and the first doping region and at the bottom of the annular groove, the grid electrode is positioned in the annular groove, and the grid dielectric layer is positioned between the second channel regions and the grid electrode. Tunneling path and tunneling area are increased, so that performance of the tunneling field effect transistor is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Comb-shaped gate composite source MOS (Metal Oxide Semiconductor) transistor and manufacturing method thereof

ActiveCN102117833AReduce parasitic resistanceReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierGate dielectric

The invention provides a composite source MOS (Metal Oxide Semiconductor) transistor with schottky barrier and comb-shaped gate structures and a manufacturing method thereof. The composite source MOS transistor comprises a control gate electrode layer, a gate dielectric layer, a semiconductor substrate, a high doped source region and a high doped drain region, wherein one side far away from the channel direction of the high doped source region is connected with a schottky source region; one end of a control gate extends towards the high doped source region; the extended gate region is an extension gate shaped like a comb; the original control gate region is a main gate; the active region covered by the extension gate is likewise a channel region with the substrate material; the high doped source region is formed by the high doping of semiconductor and is located on the two sides of each comb of the extension gate; and a schottky junction is formed at the channel under the schottky source region and the extension gate. Compared with the traditional MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor), the composite source MOS transistor can obtain a higher conduction current, a lower leakage current and a steeper subthreshold slope under a same technological condition and a same active region size.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Junction-modulated type tunneling field effect transistor and manufacturing method thereof

ActiveCN103594376AImproved subthreshold characteristicsSubthreshold characteristic steepSemiconductor/solid-state device manufacturingDiodePower flowEngineering

The invention discloses a junction-modulated type tunneling field effect transistor and a manufacturing method of the junction-modulated type tunneling field effect transistor, and belongs to the field of field effect transistor logic devices and circuits in CMOS ultra large scale integration (ULSI) circuits. According to the junction-modulated type tunneling field effect transistor, a PN junction provided by a highly-doped source region enclosed on three sides in a vertical channel region is utilized so that the channel region can be effectively used up, a surface channel energy band below a grid can be increased, a device can obtain a steeper energy band and a smaller tunneling barrier width compared with a traditional TFET when subjected to band-band tunneling, the effect of a steep tunnel junction doping density gradient is achieved equivalently, as a result, the subthreshold property of the traditional TFET is improved substantially, and breakover currents of the device are increased at the same time. According to the junction-modulated type tunneling field effect transistor and the manufacturing method of the junction-modulated type tunneling field effect transistor, under the condition that the junction-modulated type tunneling field effect transistor is compatible with an existing CMOS process, the bipolar breakover effect of the device is restrained effectively, parasitic tunneling currents at corners of a source junction with a small size also can be restrained, and the effect of steep source junction doping density can be achieved equivalently.

Owner:PEKING UNIV

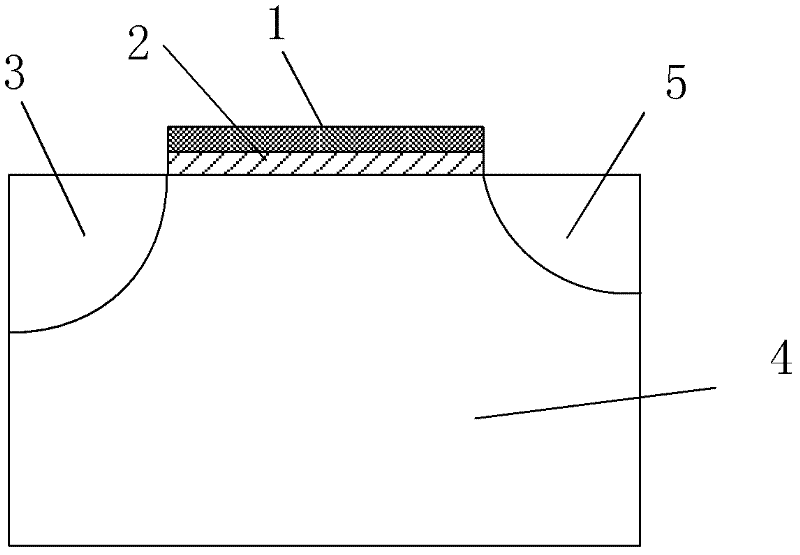

Schottky barrier metal oxide semiconductor (MOS) transistor and preparation method thereof

ActiveCN102324434AReduce parasitic resistanceEliminate uncovered areasSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate dielectric

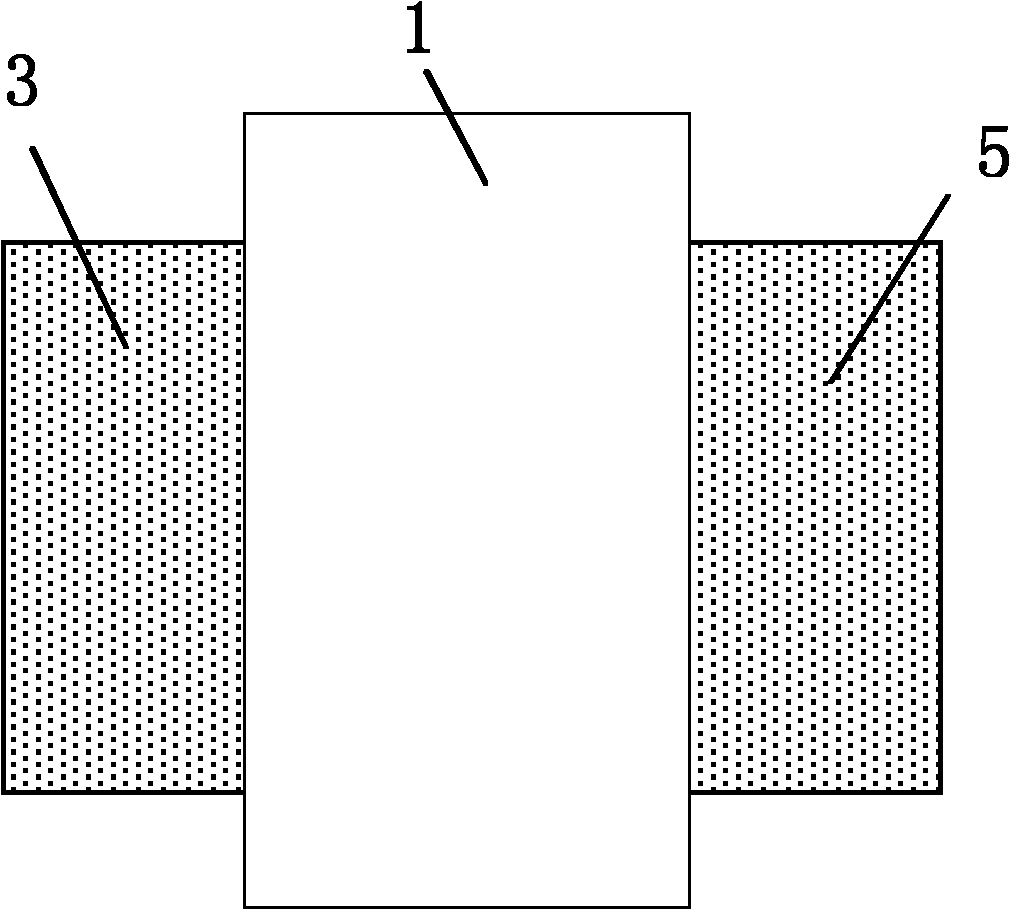

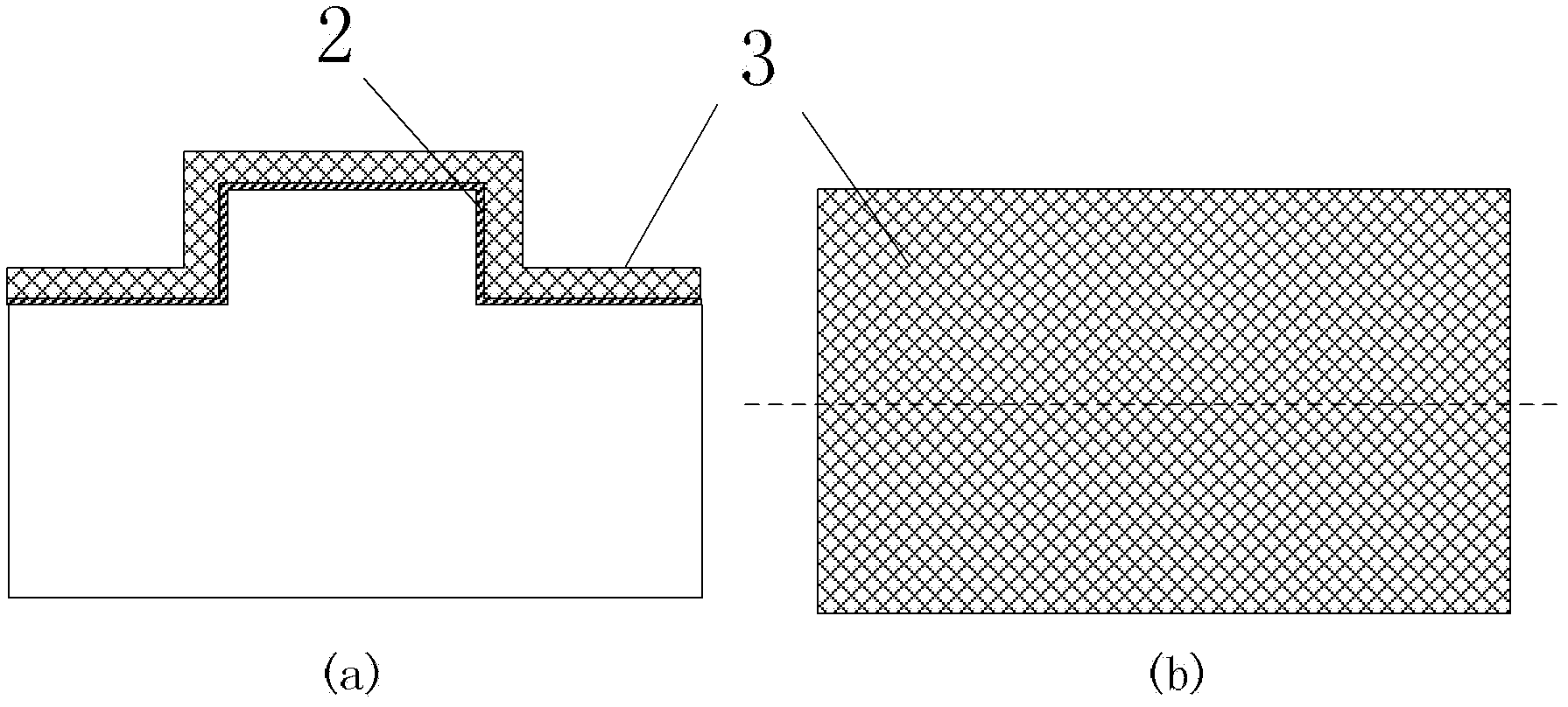

The invention discloses a Schottky barrier metal oxide semiconductor (MOS) transistor, which comprises a ring-shaped gate electrode (3), a ring-shaped gate dielectric layer (2), a ring-shaped gate electrode side wall (4), a semiconductor substrate, a source region (5) and a ring-shaped drain region (6). The Schottky barrier MOS transistor is characterized in that: the semiconductor substrate is provided with a convex step structure; the source region is positioned on a high plane of a convex step; the ring-shaped drain region surrounds the convex step and is positioned on a low plane; the gate dielectric layer and the gate electrode are positioned at a corner of the convex step, surrounds the step and is raised into a ring shape; and the gate electrode side wall is ring-shaped, surrounds on the outer side of the gate electrode and has a certain thickness to serve as a shelter to form an underlap structure of a drain terminal. The Schottky barrier MOS transistor adopts a step structurecombining a ring-shaped gate structure and an asymmetric source / drain structure, so on the basis of inheriting advantages of traditional SB-MOSFET, the on-state conduction current is improved, a dipolar effect is inhibited, and the process is simplified.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

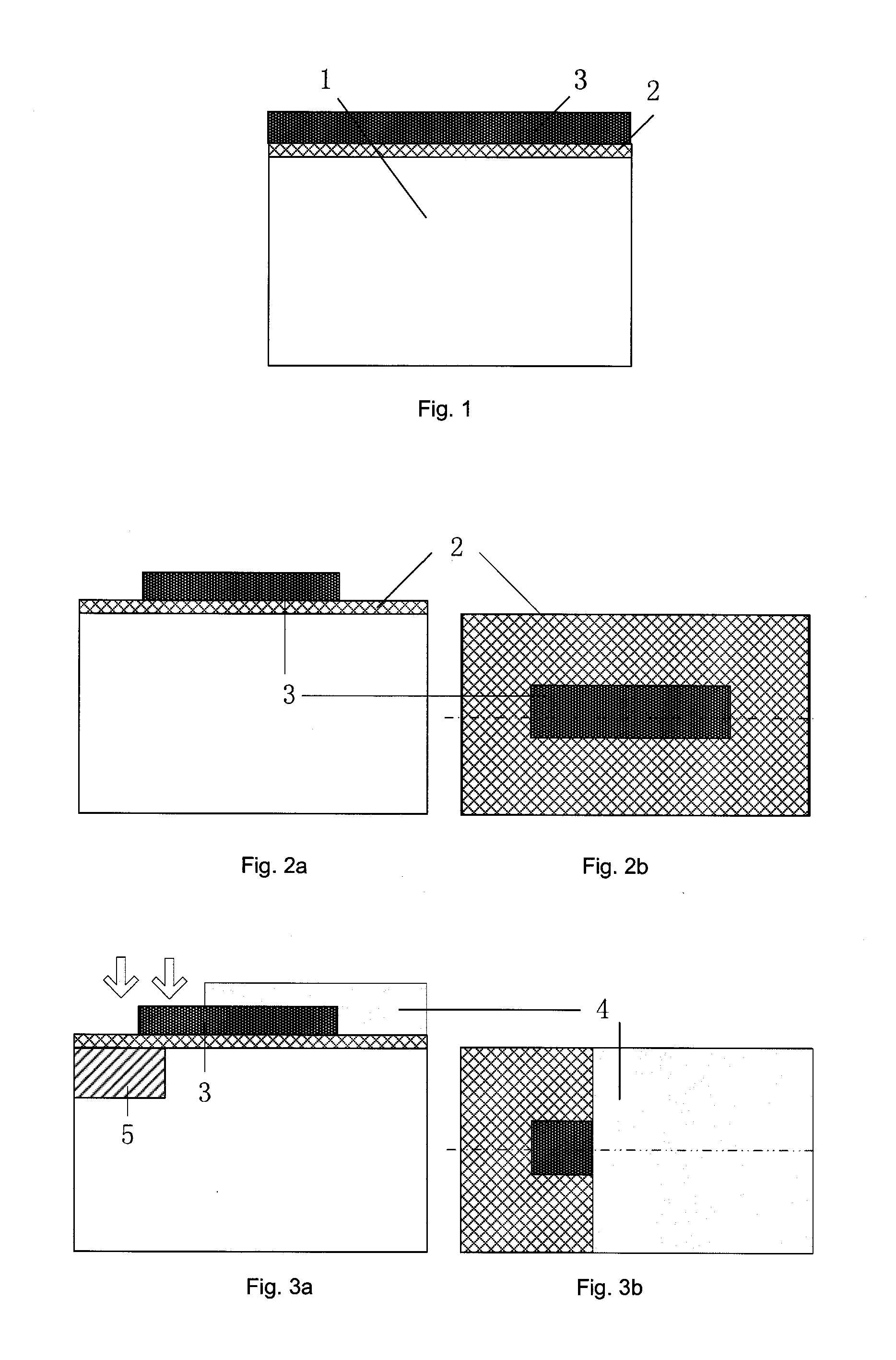

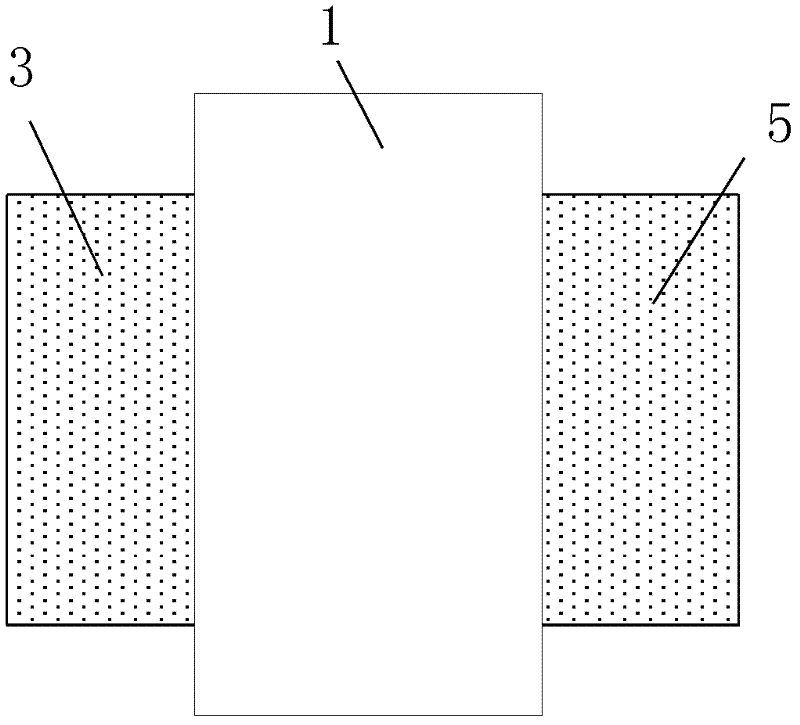

Tunneling field effect transistor and preparation method thereof

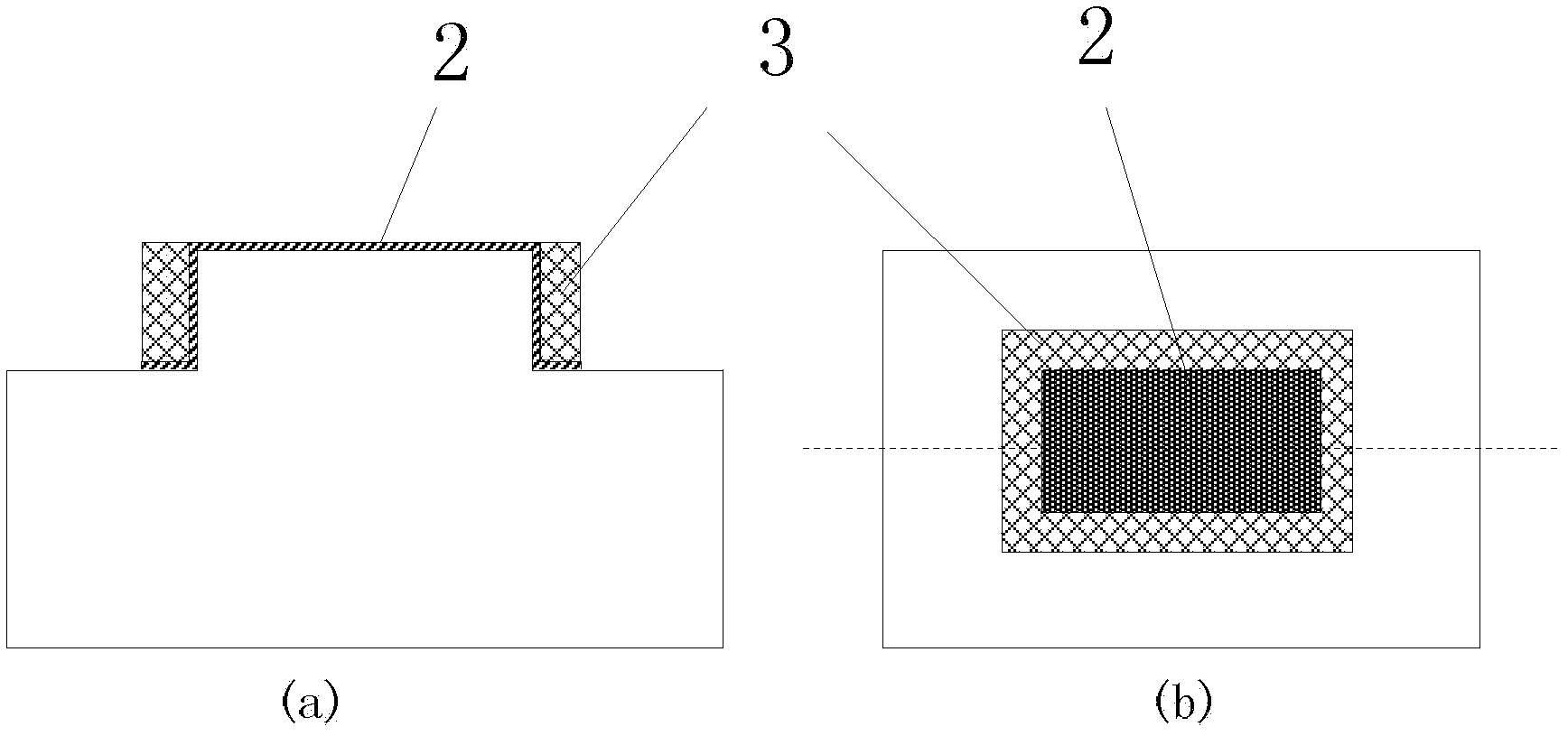

ActiveCN104617138ALarge tunneling areaIncrease chance of tunnelingSemiconductor/solid-state device manufacturingDiodeMedia layerElectron

Disclosed is a tunneling field effect transistor. The tunneling field effect transistor comprises a source region, two drain regions and two grid regions. The two drain regions are arranged on opposite two sides of the source region in a first direction; the two grid regions are arranged on opposite two sides of the source region; first extension layers and grid medium layers are arranged between the source region and the two grid regions, wherein the first extension layers are arranged between the source region and the grid medium layers and form tunneling junction with the source region; the two drain regions and the two grid regions are arranged around the source region, so that the source region can be completely under the control of the two grid regions, and current carrying electrons in the overlapped regions of the source region and the grid regions can tunnel under the action of the electric field of the grid regions; the first extension layers are arranged between the source region and the grid medium layers and is of a linear tunneling mode, thereby being large in tunneling area; the direction of the electric field of the grid regions and the tunneling direction of the electrons of the source region are on the same line, so that high tunneling probability can be achieved, and tunneling current can be increased. Besides, the invention also provides a preparation method of the tunneling field effect transistor.

Owner:HUAWEI TECH CO LTD

Tunneling field-effect transistor with composite-mechanism strip-type grid and preparation method of tunneling field-effect transistor

ActiveCN103474464AIncrease the on-state currentIncrease subthreshold slopeSemiconductor/solid-state device manufacturingDiodeCMOSPunching

The invention discloses a tunneling field-effect transistor with a composite-mechanism strip-type grid and a preparation method of the tunneling field-effect transistor and belongs to the field of logic devices and circuits of field-effect transistors in CMOS (Complementary Metal Oxide Semiconductor) ultra-large-scale integrated (ULSI) circuits. The tunneling field-effect transistor has the advantages that the energy band of surface channels under the grid can be improved by changing the shape of the grid and utilizing a depletion effect of PN nodes on the two sides of the strip-type grid, and the subthreshold characteristic of the device is improved; since a composite mechanism is introduced into double-doped source areas, an ON state current of the device is improved; due to an I-shaped design of an active area, body leakage currents, including a source-drain direct tunneling current and a punching current, between the two doped source areas to a doped drain area can be greatly inhibited, and a short-channel effect is inhibited, so that the device with small size can be applied.

Owner:PEKING UNIV

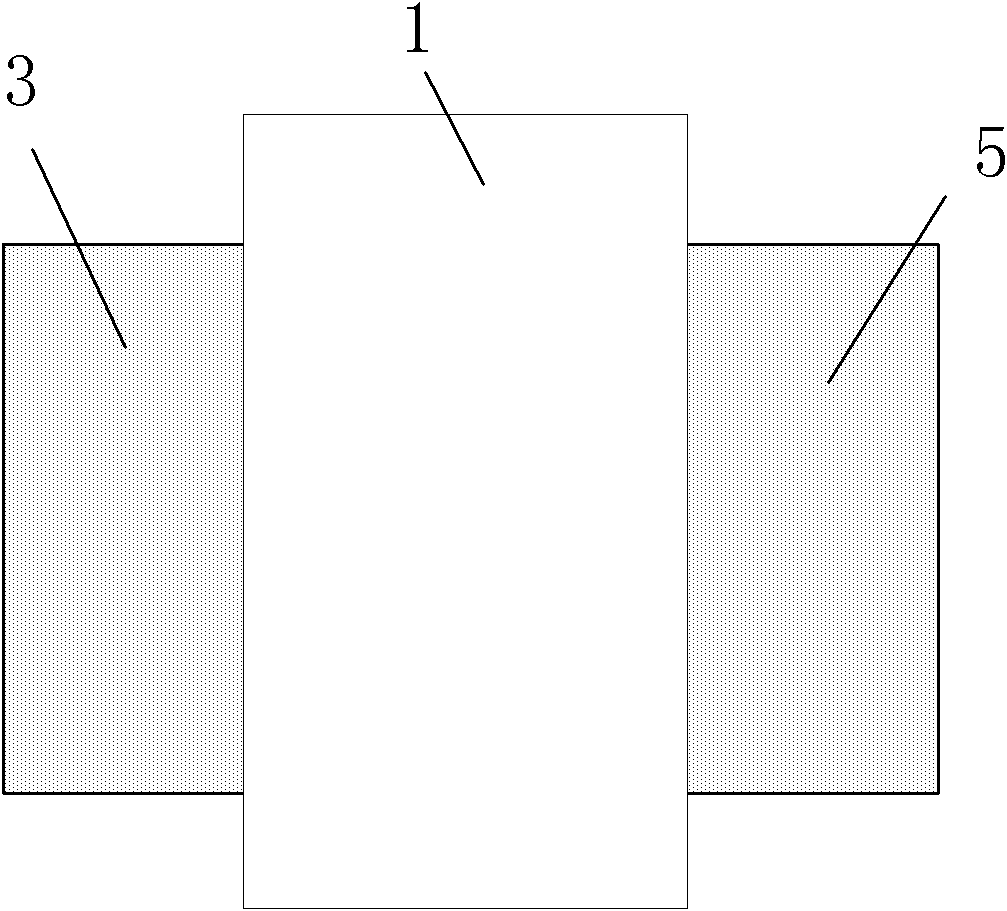

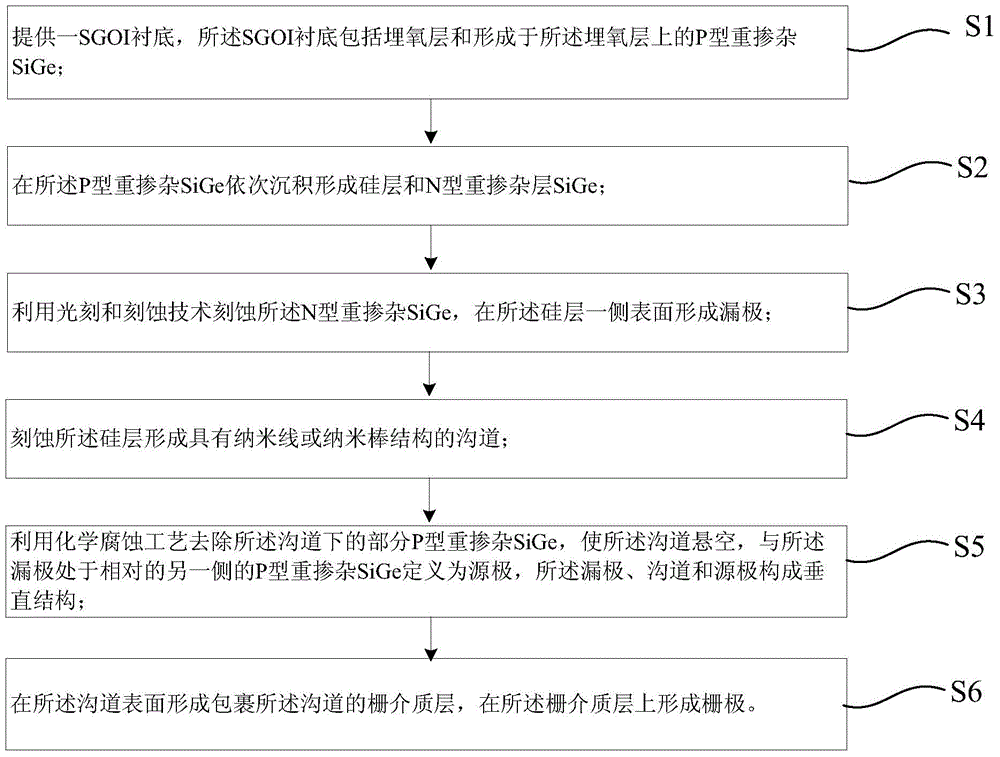

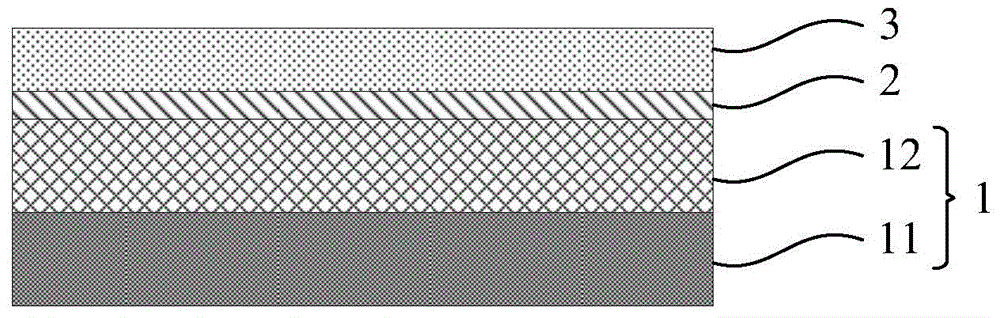

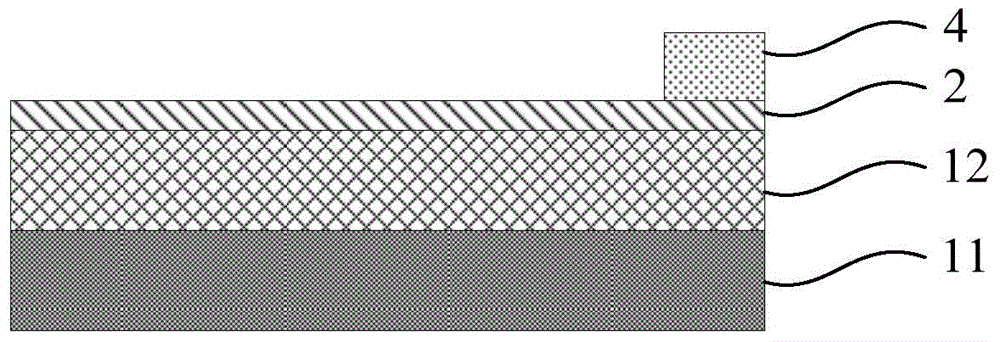

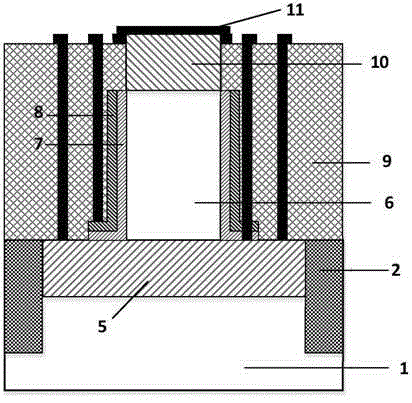

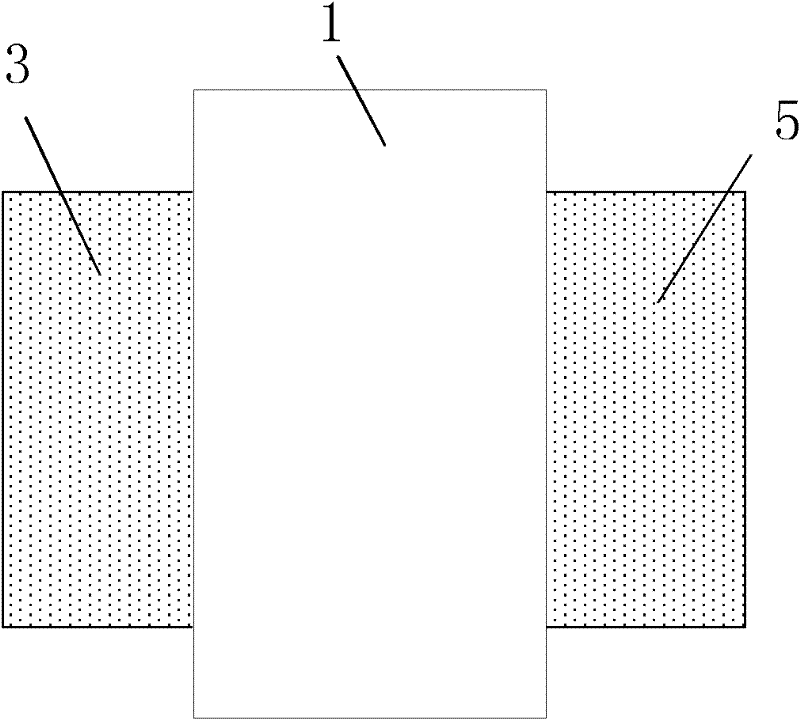

Tunneling field effect transistor of vertical structure and preparation method thereof

ActiveCN103560152ALarge tunneling areaIncrease drive currentSemiconductor/solid-state device manufacturingSemiconductor devicesPhotolithographyEngineering

The invention provides a tunneling field effect transistor of a vertical structure and a preparation method thereof. The preparation method at least comprises the steps of providing an SGOI substrate which comprises an oxygen buried layer and P-type heavy dopping SiGe; sequentially sedimenting to form a silicon layer and N-type heavy dopping SiGe on the P-type heavy dopping SiGe; utilizing the photoetching and etching technology to etch the N-type heavy dopping SiGe so as to form a drain electrode on one side surface of the silicon layer; etching the silicon layer to form a ditch of a nanometer line structure or a nanometer bar structure; utilizing the chemical erosion technology to remove a part of P-type heavy dopping SiGe under the ditch so as to enable the ditch to be hung in the air, defining the P-type heave dopping SiGe on the other side opposite to the drain electrode to be a source electrode. The drain electrode, the ditch and the source electrode form a vertical structure. According to the tunneling field effect transistor of the vertical structure, the drain electrode, the ditch and the source electrode form the vertical structure, so that a tunneling area can be increased, and drive currents of elements can be improved. Further, the formed ditch hung in the air can further restrict leaked currents of elements.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

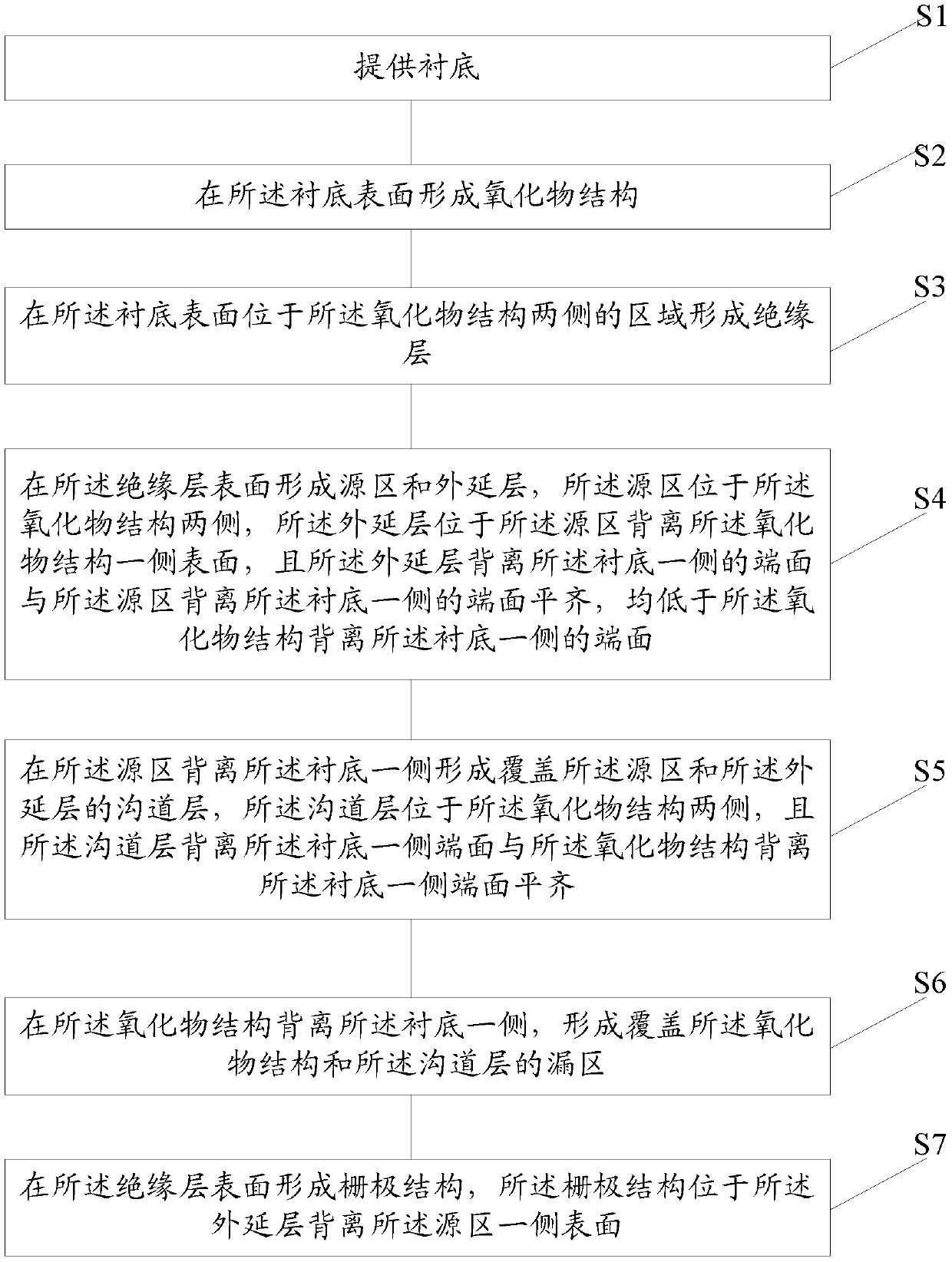

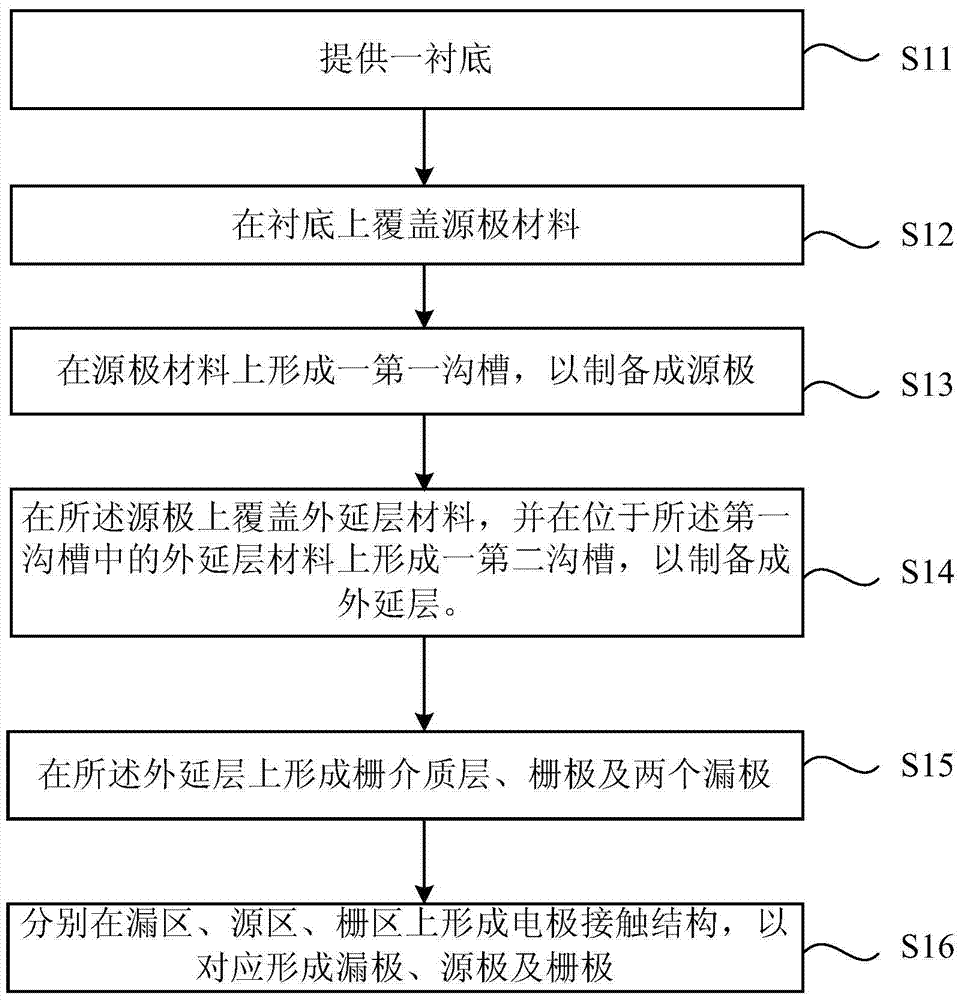

Method for preparing tunneling field effect transistor

The present invention discloses a method for preparing a tunneling field effect transistor, belonging to the field of field effect transistor logic devices in a CMOS super-large-scale integration (ULSI) circuit. The tunneling field effect transistor of an ultra-steep source junction is realized through preparation process design. The device characteristic can be improved significantly, at the same time, the preparation method is compatible with standard CMOS IC technology, TFET devices can be effectively integrated in a CMOS integrated circuit, a low power consumption integrated circuit formed by TFET can be prepared by using standard process, the production cost is greatly reduced, and the process flow is simplified.

Owner:PEKING UNIV

Strip-shaped gate tunneling field effect transistor with double-diffusion and a preparation method thereof

InactiveUS20150048313A1Large tunneling areaSteeper energy band bendingSemiconductor/solid-state device manufacturingDiodeCMOSDouble diffusion

The present invention discloses a strip-shaped gate-modulated tunneling field effect transistor with double-diffusion and a preparation method thereof, belonging to a field of CMOS field effect transistor logic device and the circuit. The tunneling field effect transistor includes a semiconductor substrate, a highly-doped source region, a highly-doped drain region, a double-diffusion source region, a gate dielectric layer, and a control gate, wherein the control gate has a strip-shaped structure with a gate length greater than a gate width, and at one side thereof is connected to the highly-doped drain region and at the other side thereof extends laterally into the highly-doped source region; a region located below the control gate is a channel region; the gate width of the control gate is less than twice width of a source depletion layer; the double-diffusion region has the same doping region as the highly-doped source region and the double-diffusion region has the same doping type as the highly-doped drain region; and the channel region located below a portion of the control gate portion in the highly-doped source region has double-diffusion source doped impurities. The TFET device according to the invention improves its performance, and the preparation method thereof is simple.

Owner:PEKING UNIV

Tunneling field effect transistor with T-shaped grid structure and low power consumption

ActiveCN102005481BEnhanced source junction electric field strengthIncrease the on-currentSemiconductor devicesEngineeringTunnel field-effect transistor

The invention provides a tunneling field effect transistor (TFET) with a T-shaped grid structure and low power consumption, and belongs to the field of field effect transistor logic devices and circuits in complementary metal oxide semiconductor (CMOS) ultra large scale integrated circuits (ULSI). The TFET comprises a source electrode, a drain electrode and a control grid, wherein the control grid extends toward the end of the source electrode to form a T shape; the T-shaped control grid consists of an extending grid region and the original control grid region; and an active region covered below the extending grid region is a channel region and is made of a substrate material. By using the T-shaped grid structure, the source region of the TFET encircles a channel, so that the conduction current of a device is improved. Compared with the conventional planar TFET, the TFET can achieve higher conduction current and steeper subthreshold slope under the same process conditions and the samesize of the active region.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Low-power consumption tunneling field effect transistor (TFET) of fork-structure grid structure

ActiveCN102157559BEnhanced source junction electric field strengthIncrease the on-currentSemiconductor devicesCMOSEngineering

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

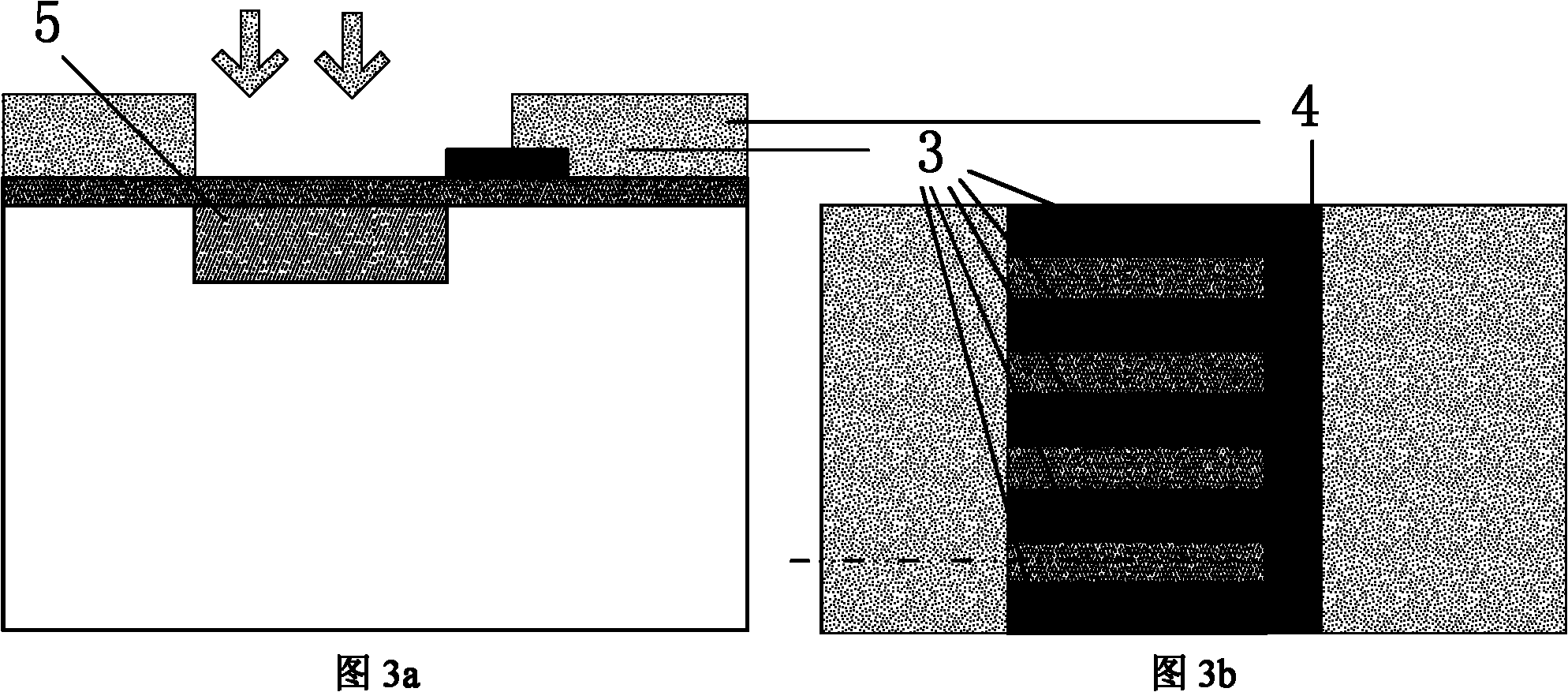

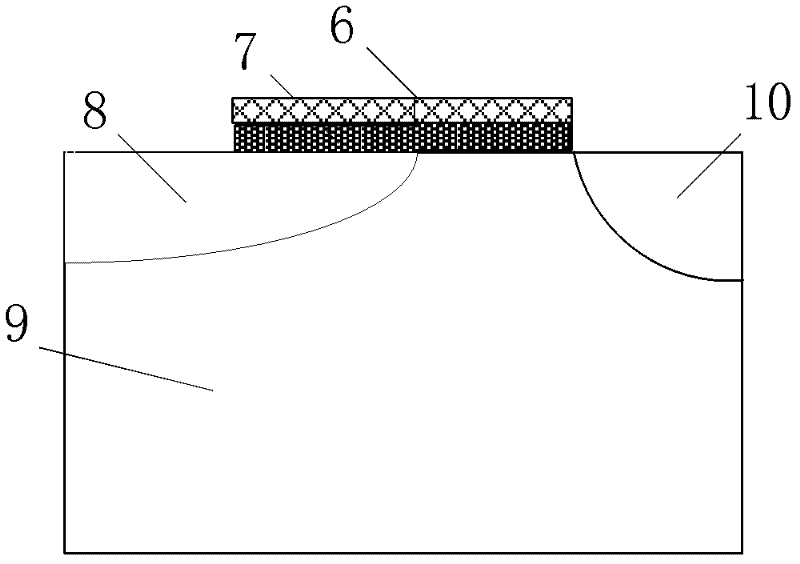

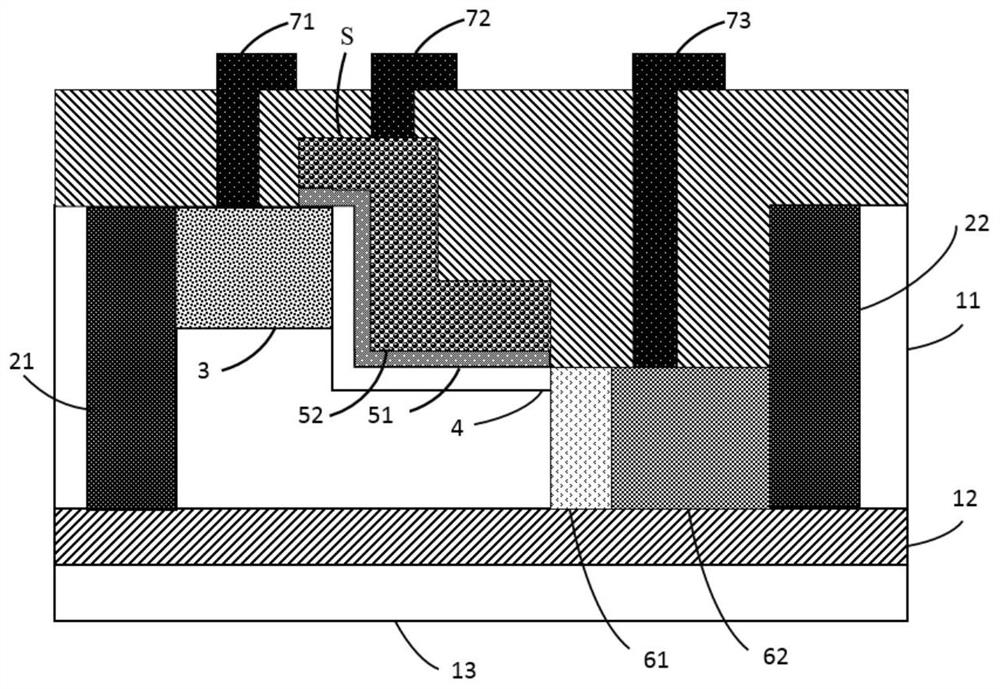

Z-type heterojunction tunneling field effect transistor with lightly doped drain structure and preparation method thereof

ActiveCN108493240BShorten tunneling distanceIncrease drive currentSemiconductor/solid-state device manufacturingDiodeHeterojunctionSemiconductor materials

The invention discloses a Z-type heterojunction tunneling field effect transistor having a lightly-doped drain structure and a preparation method thereof, and mainly solves the problems of low on-state current and severe bipolar effect of an existing device. The Z-type heterojunction tunneling field effect transistor comprises an SOI substrate (1), isolation grooves (2), a source region (3), a channel region (4), a drain region (6), a gate region (5) and a conductive layer (7). The isolation grooves (2) are arranged at the two sides of the SOI substrate (1); the source region (3), the channelregion (4) and the drain region (6) are arranged on the upper surface of the SOI substrate; the gate region (5) is arranged on the upper side of the channel region (4); the source region (3) adopts agermanium semiconductor; the gate region (5) adopts a Z-type structure, and gates with the length of 3nm-9nm are covered on the source region; and the side, close to the gate region (5), of the drainregion (6) is provided with a lightly-doped drain region. The Z-type heterojunction tunneling field effect transistor can effectively suppress the bipolar effect and improve driving current, and can be used for manufacturing of a large-scale integrated circuit.

Owner:西安电子科技大学重庆集成电路创新研究院

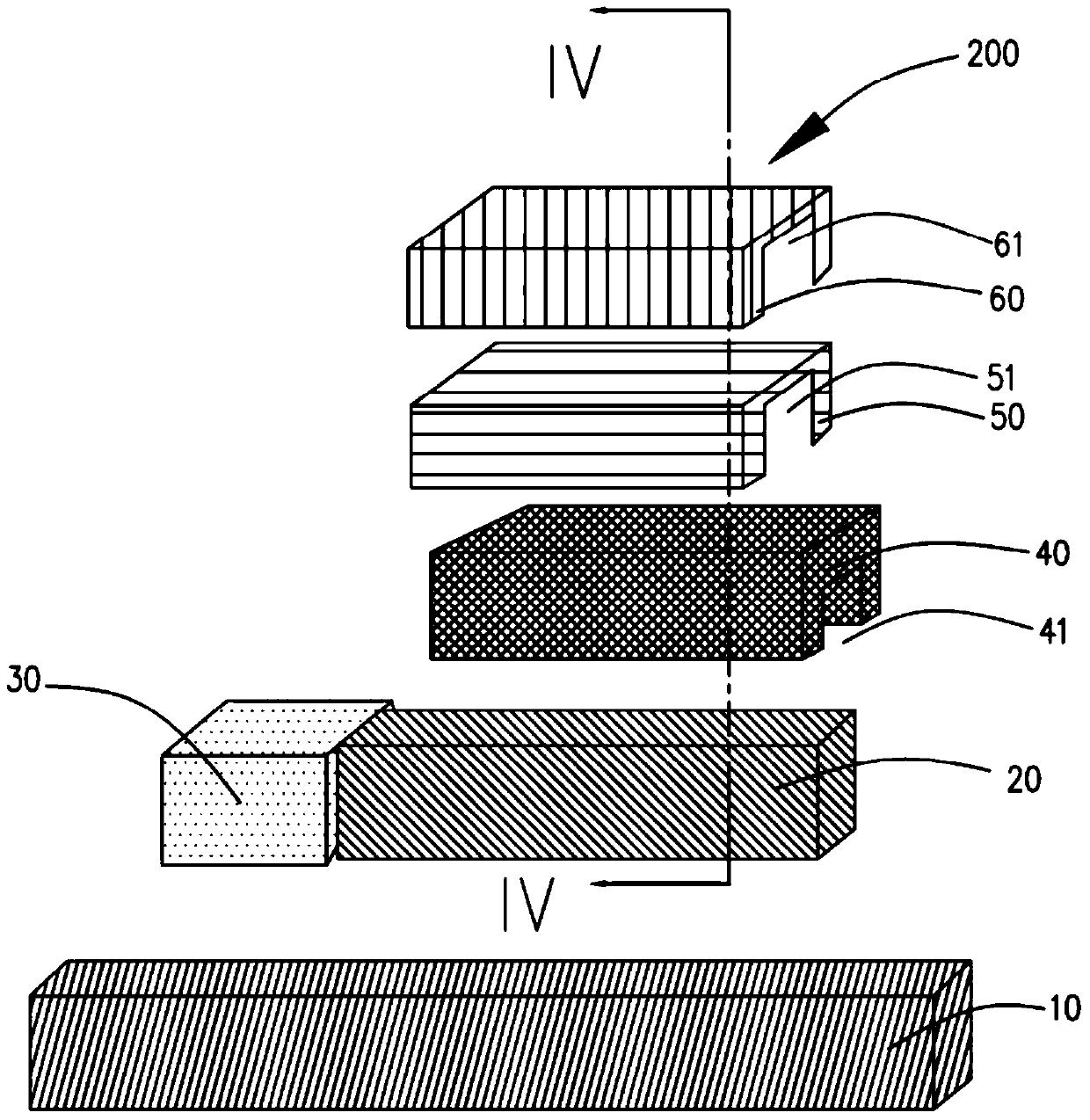

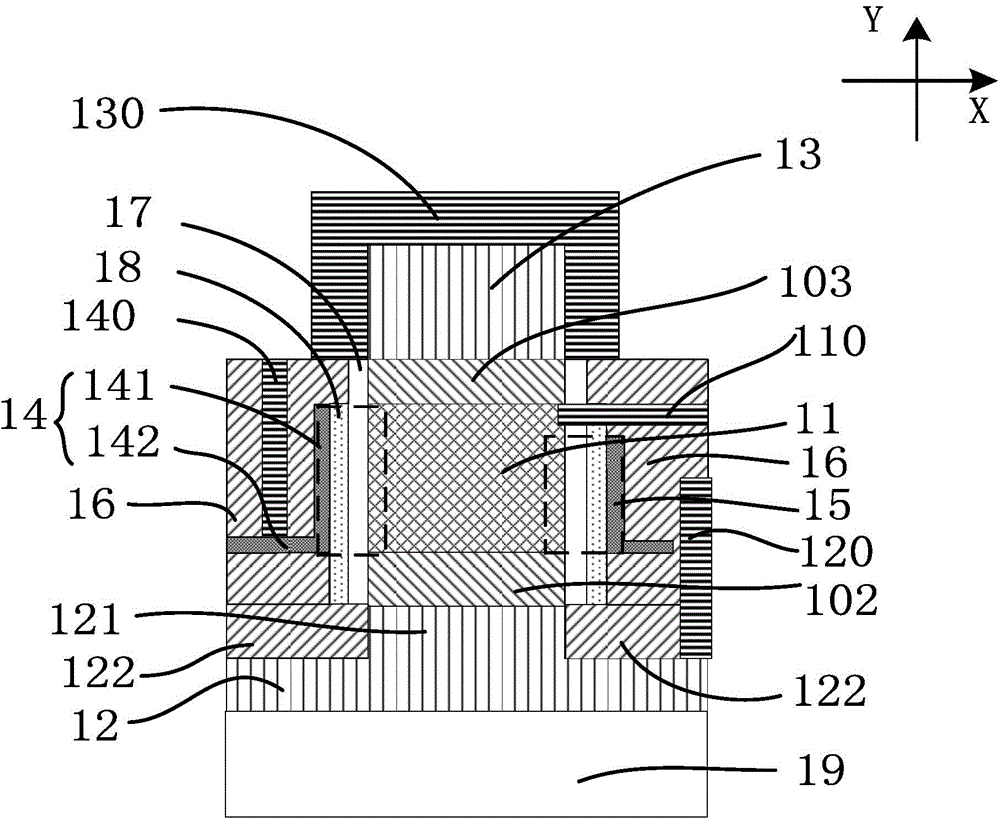

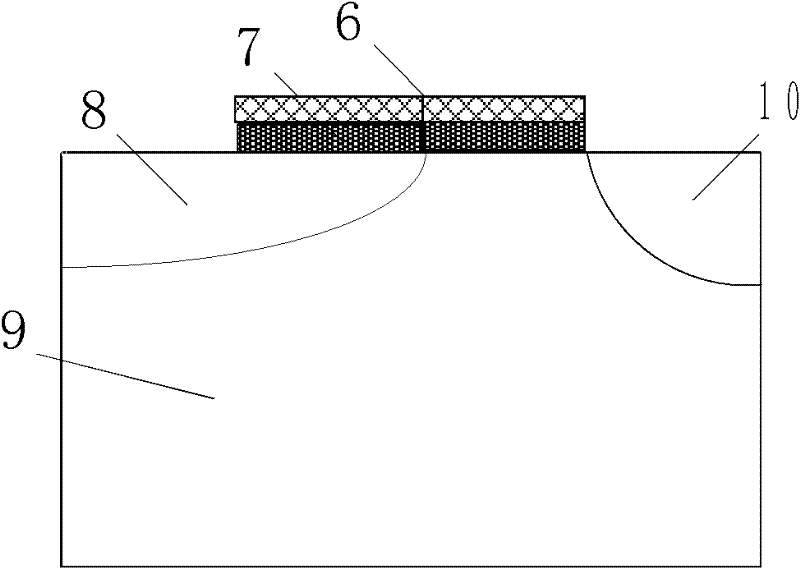

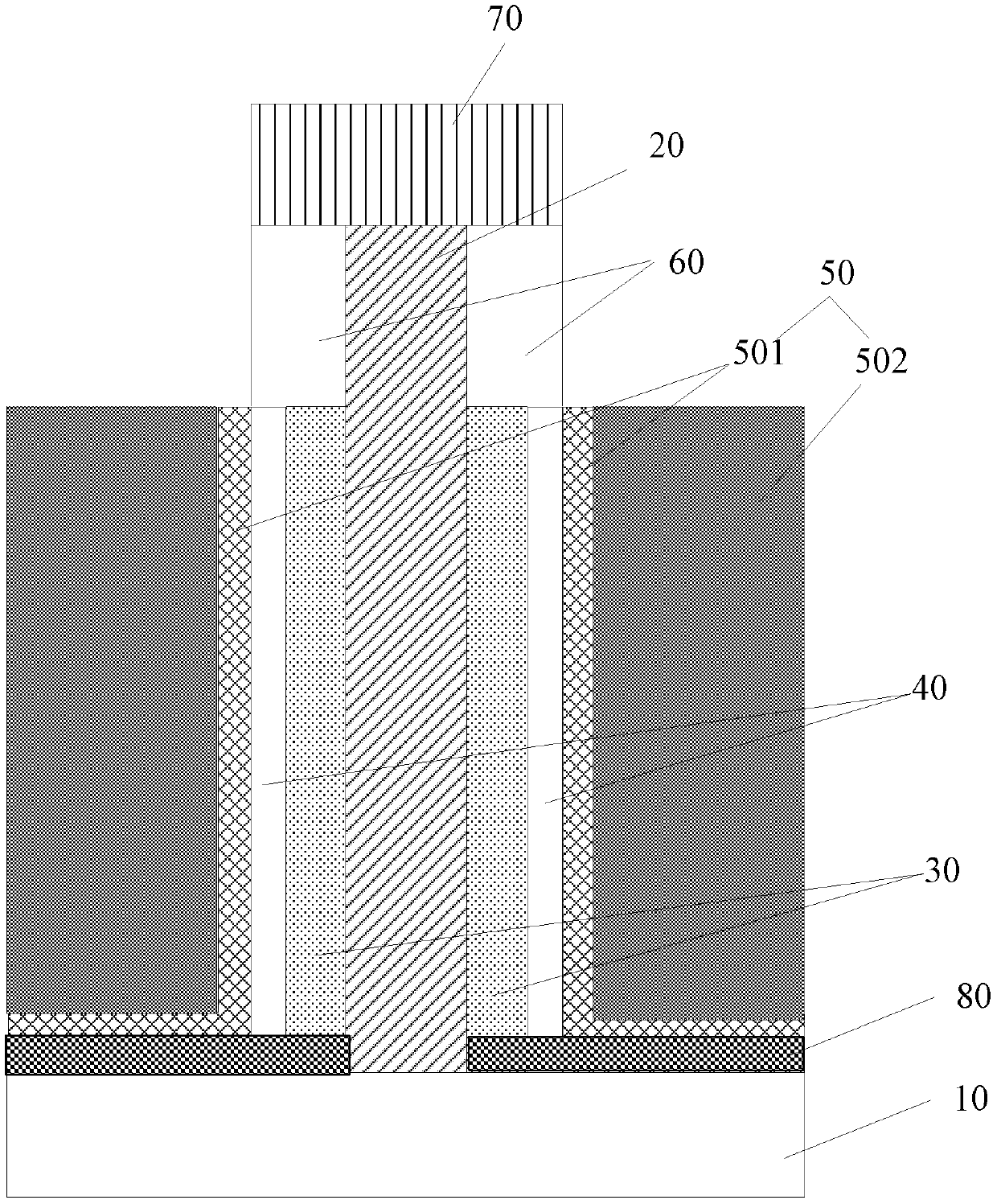

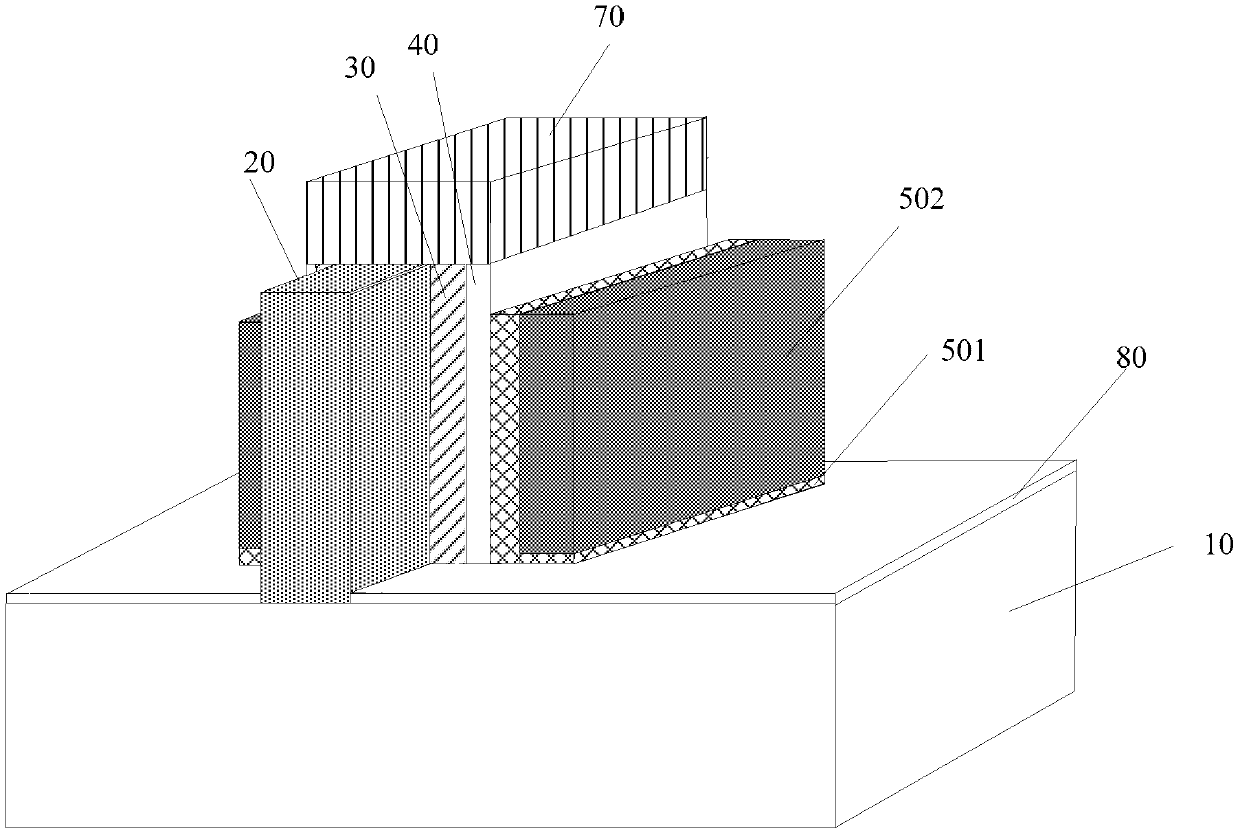

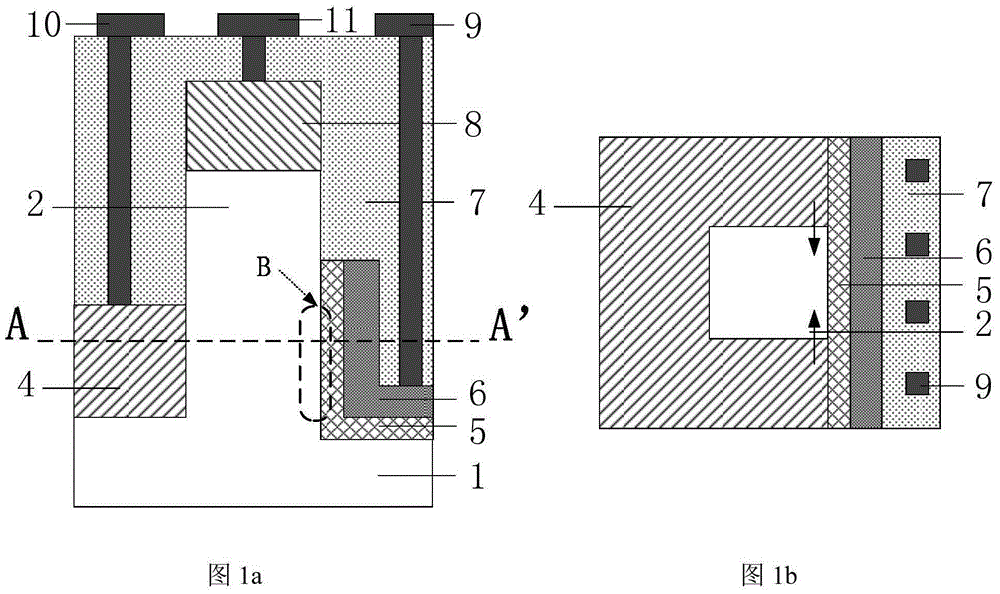

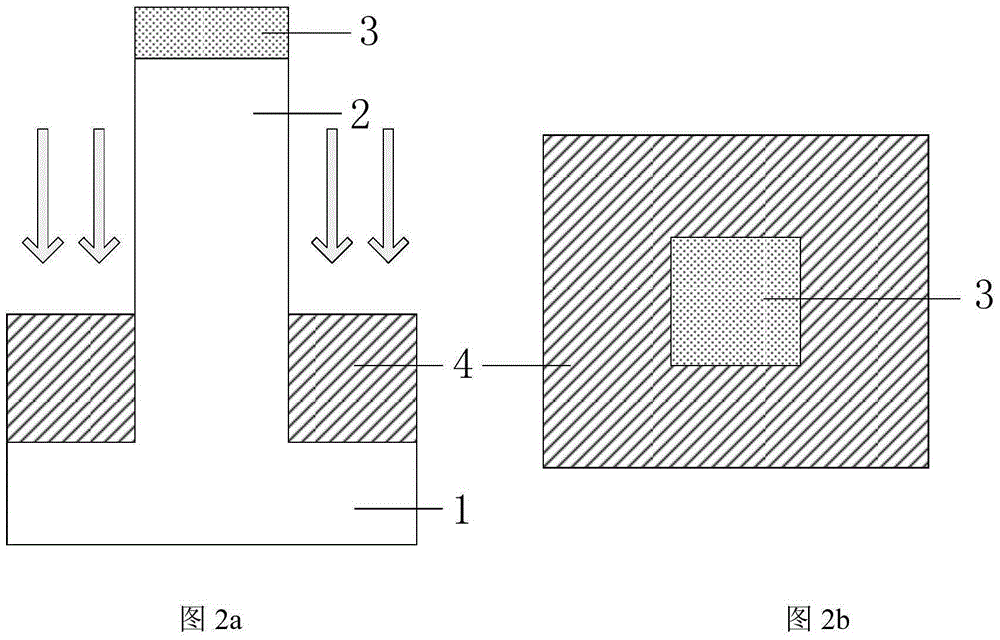

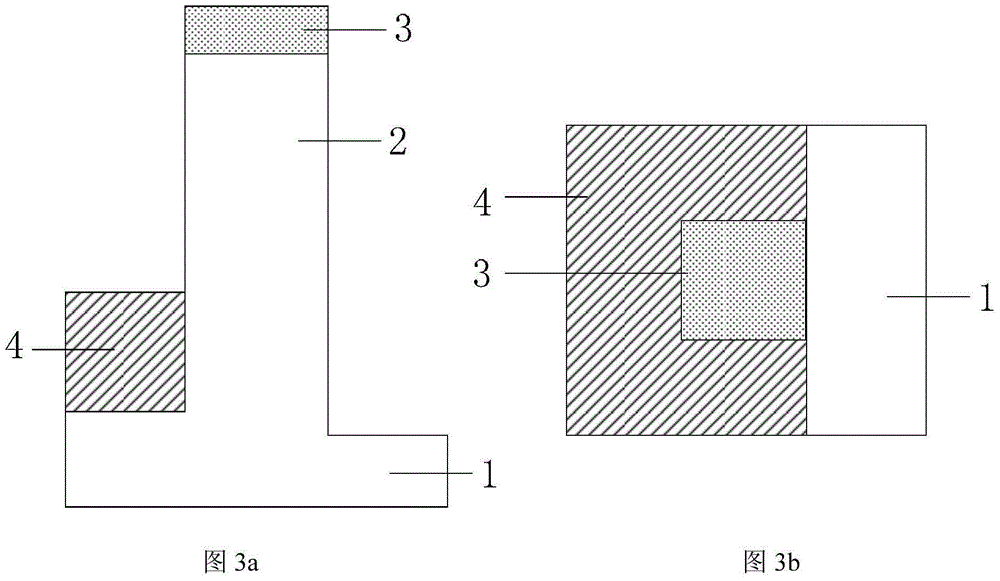

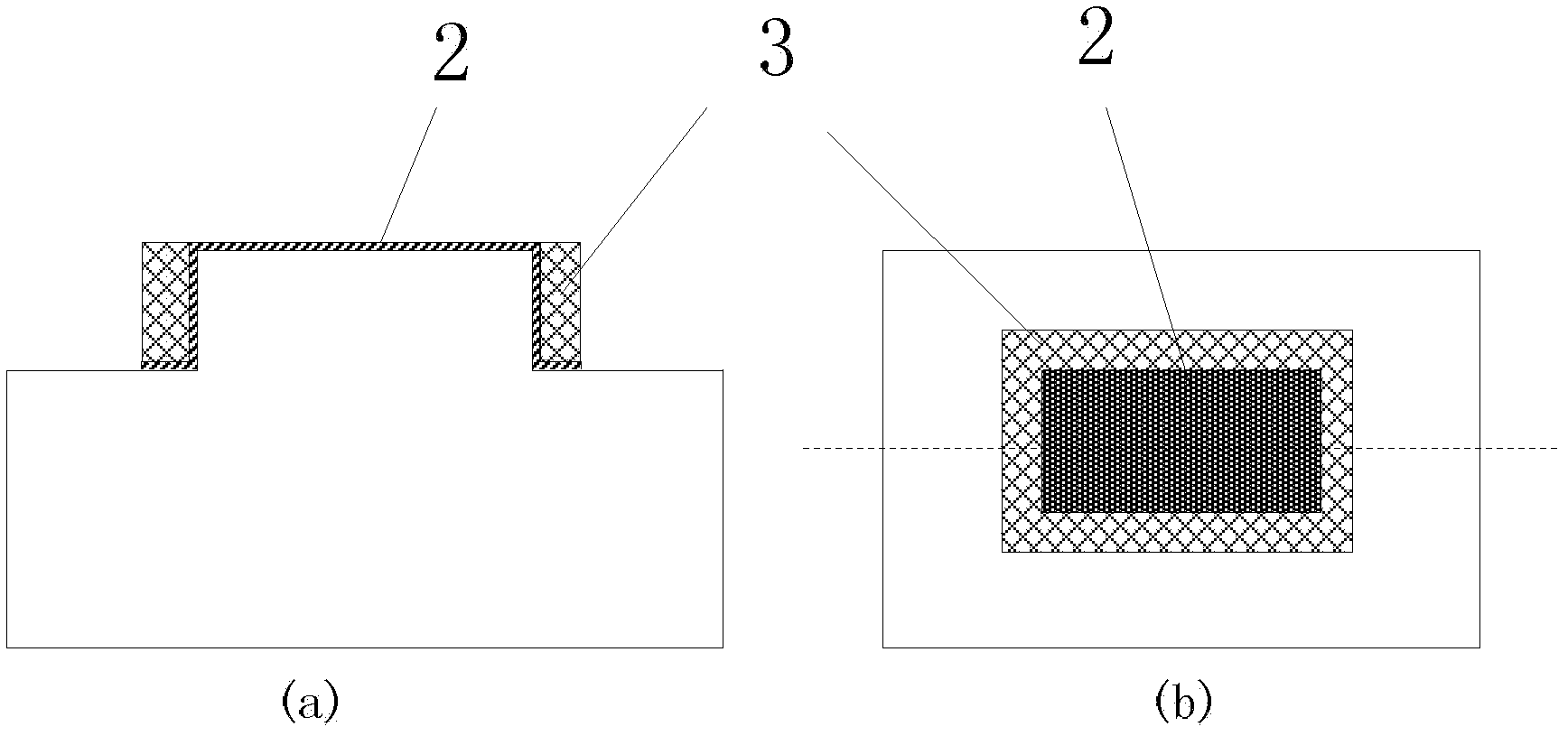

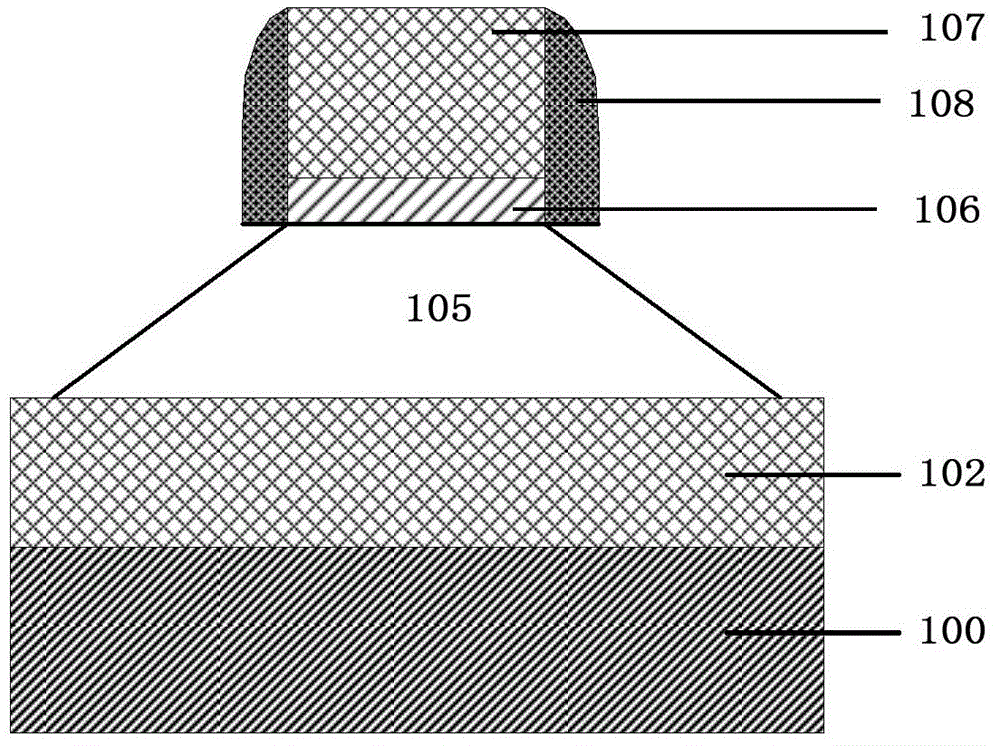

A tunneling field effect transistor and its manufacturing method

ActiveCN108140672BReduced subthreshold swingReduce power consumptionNanoinformaticsSemiconductor/solid-state device manufacturingValence bandSubthreshold swing

A tunneling field effect transistor and a manufacturing method thereof, in which the source region (30) is located on both sides of an oxide structure (20), and the epitaxial layer (40) is located on the source region (30) away from the oxide structure ( 20) On one surface, the gate structure (50) is located on the surface of the epitaxial layer (40) away from the source region (30), so that the electric field direction of the gate of the tunneling field effect transistor is consistent with the electron tunneling direction, and the value of the source region The tunneling efficiency of the carriers in the band to the conduction band of the epitaxial layer is high, which can generate a steep sub-threshold swing, which in turn makes the sub-threshold swing of the tunneling field effect transistor lower than 60mV / dec, and the power consumption smaller. Moreover, in the embodiment of the present invention, the epitaxial layer (40) is entirely located between the gate structure (50) and the source region (30), which increases the tunneling area between the epitaxial layer (40) and the source region (30), The subthreshold characteristic of the tunneling field effect transistor is further improved, and the subthreshold swing value of the tunneling field effect transistor is reduced.

Owner:HUAWEI TECH CO LTD

A junction-modulated tunneling field-effect transistor and its manufacturing method

ActiveCN103594376BImproved subthreshold characteristicsSubthreshold characteristic steepSemiconductor/solid-state device manufacturingDiodeSub thresholdConcentration gradient

The invention discloses a junction modulation type tunneling field effect transistor and a preparation method thereof, belonging to the field of field effect transistor logic devices and circuits in CMOS ultra large integrated circuits (ULSI). The tunneling field effect transistor utilizes the PN junction provided by the highly doped source region surrounded on three sides of the vertical channel region to effectively deplete the channel region, so that the channel energy band on the lower surface of the gate is increased, and when the device undergoes band tunneling, it can obtain The steeper energy band and narrower tunneling barrier width than traditional TFETs equivalently realize the effect of steep tunneling junction doping concentration gradient, thereby greatly improving the subthreshold characteristics of traditional TFETs and improving the conductance of the device at the same time. Pass current. Under the condition of being compatible with the existing CMOS technology, the present invention effectively suppresses the bipolar conduction effect of the device on the one hand, and at the same time suppresses the parasitic tunneling current at the corner of the source junction in a small size, and can equivalently realize steep The effect of straight source-junction doping concentration.

Owner:PEKING UNIV

A kind of preparation method of tunneling field effect transistor

Owner:PEKING UNIV

A kind of tunneling field effect transistor and its preparation method

ActiveCN103560153BLarge tunneling areaIncrease drive currentSemiconductor/solid-state device manufacturingDiodeDriving currentPower flow

The invention provides a tunneling field effect transistor and a preparation method thereof. The preparation method at least comprises the following steps that an SOI substrate provided with top layer silicon, an oxygen buried layer and bottom layer silicon is provided, and ion injection is conducted on the two sides of the top layer silicon to form a source electrode and a drain electrode respectively; an intrinsic silicon layer, and a grid medium layer and a grid layer are sequentially formed on the surface of the SOI substrate from bottom to top; a stacking structure is formed by etching the intrinsic silicon layer, the grid medium layer and the grid layer through the photoetching and etching technologies, the stacking structure is partially overlapped with the source electrode and is preset distance away from the drain electrode in the horizontal direction. According to the tunneling field effect transistor and the preparation method of the tunneling field effect transistor, the stacking structure is overlapped with the source electrode so that the tunneling area can be increased, and further a driving current is increased. In addition, the stacking structure is preset distance away from the drain electrode in the horizontal direction, and the bipolar effect in the tunneling field effect transistor can be suppressed through the preset distance, and a subthreshold current is reduced.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

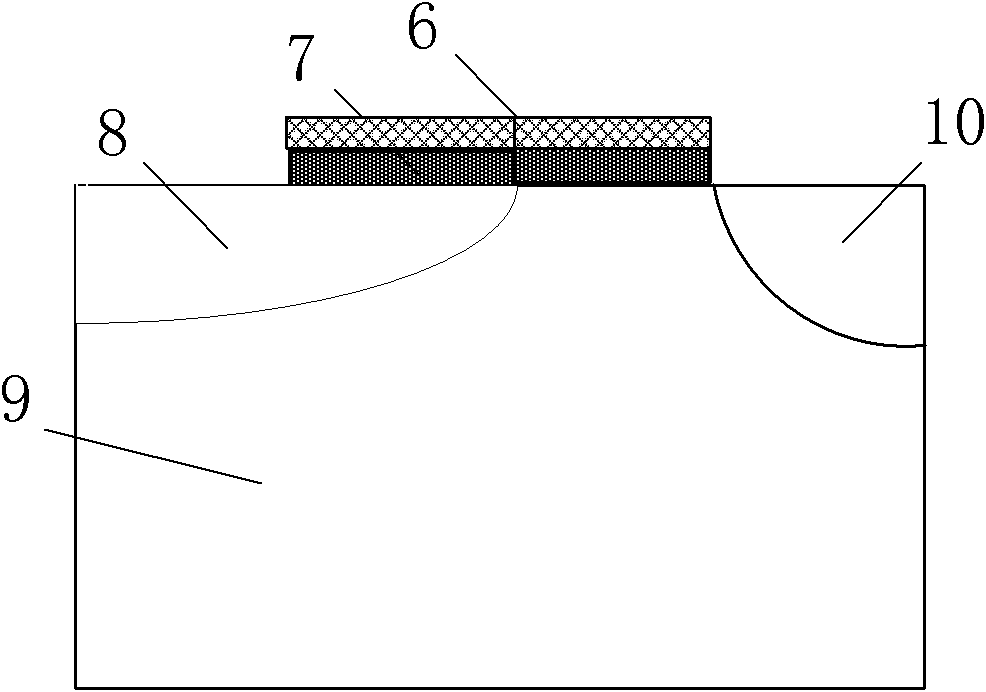

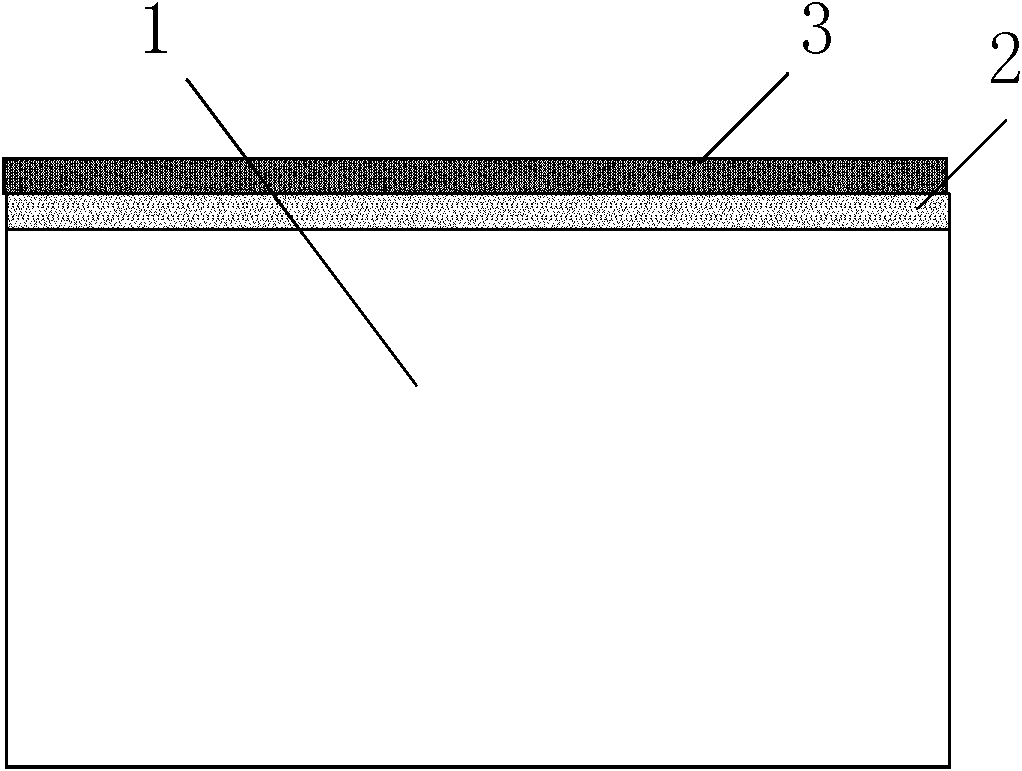

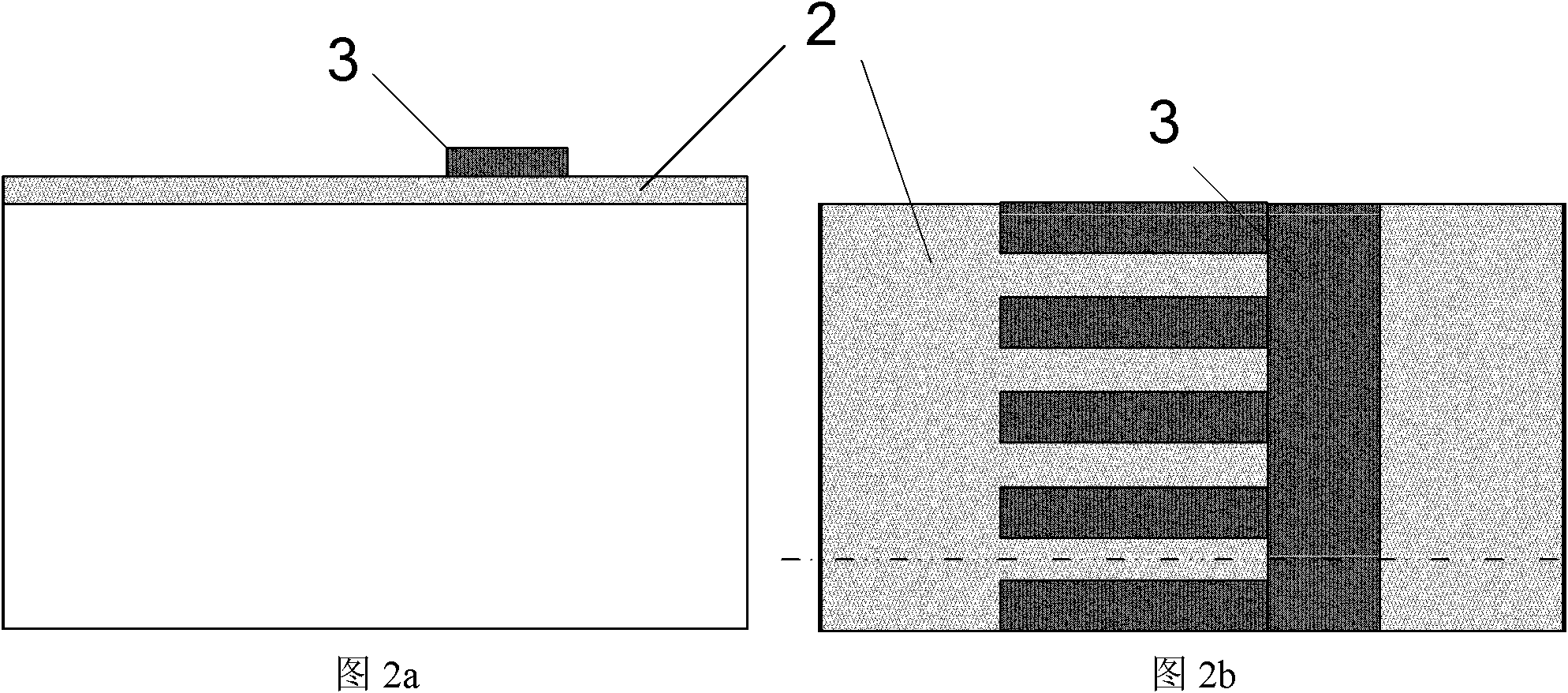

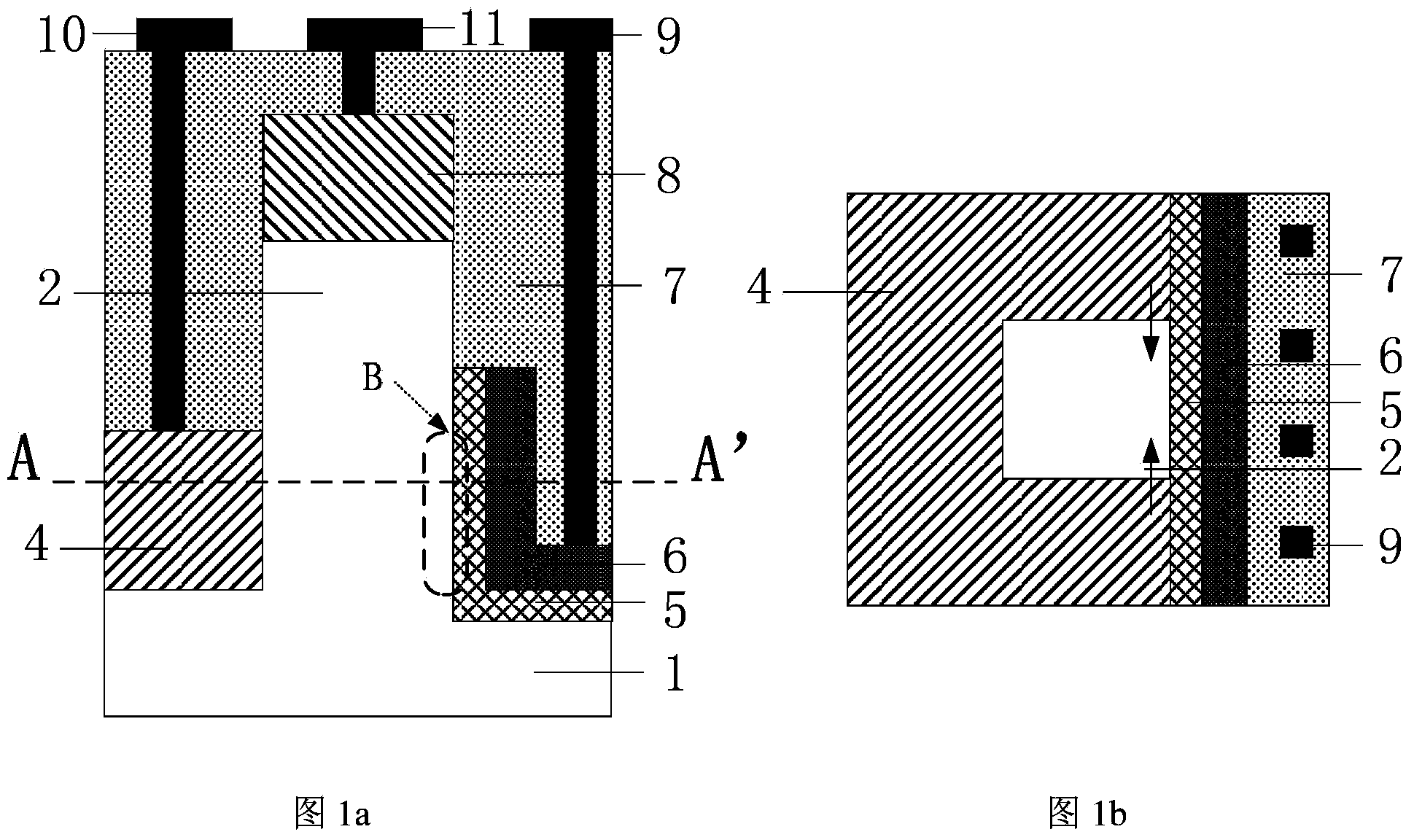

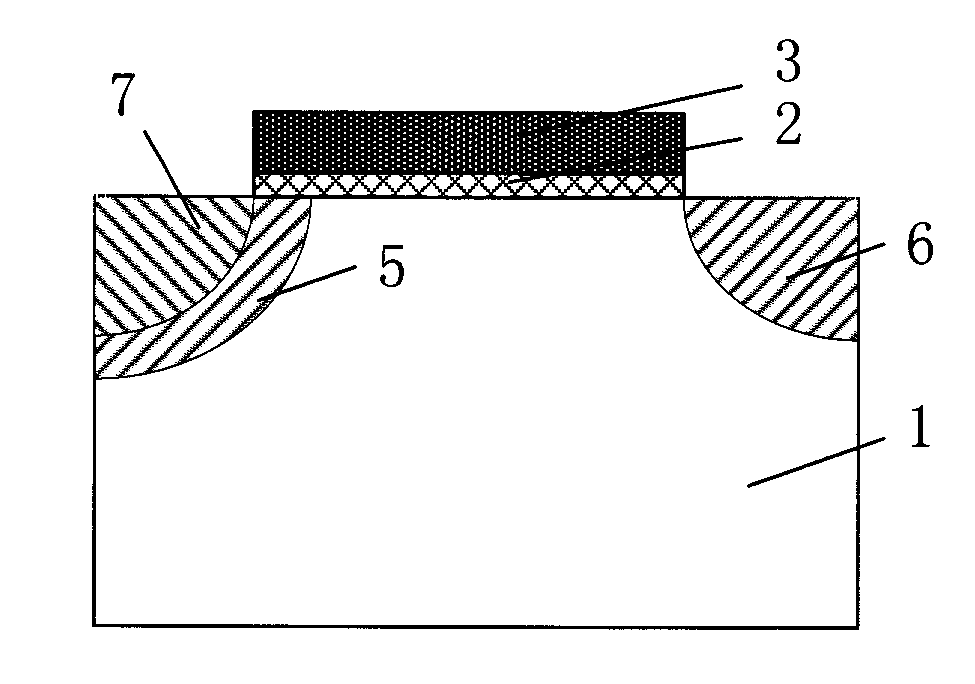

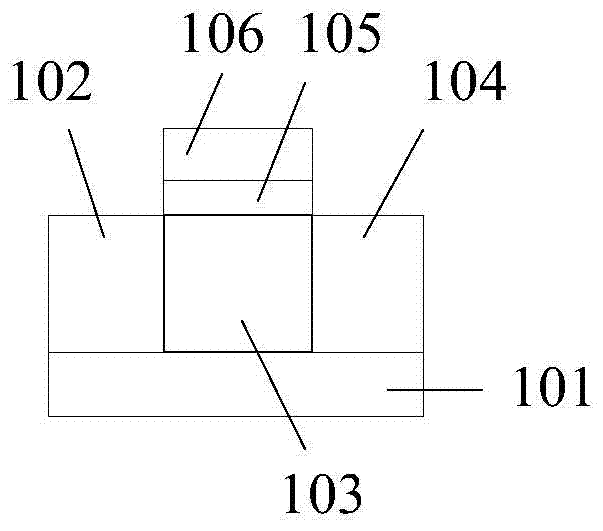

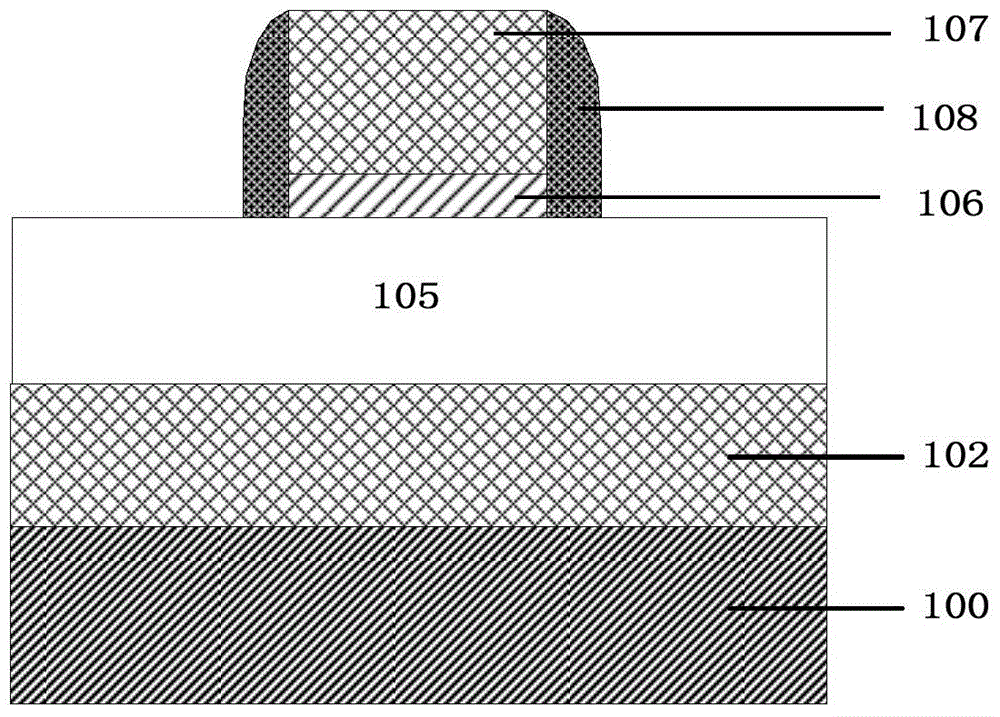

Vertical tunneling field effect transistor and its manufacturing method

ActiveCN104659099BIncrease the overlapping areaLarge tunneling areaSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricField-effect transistor

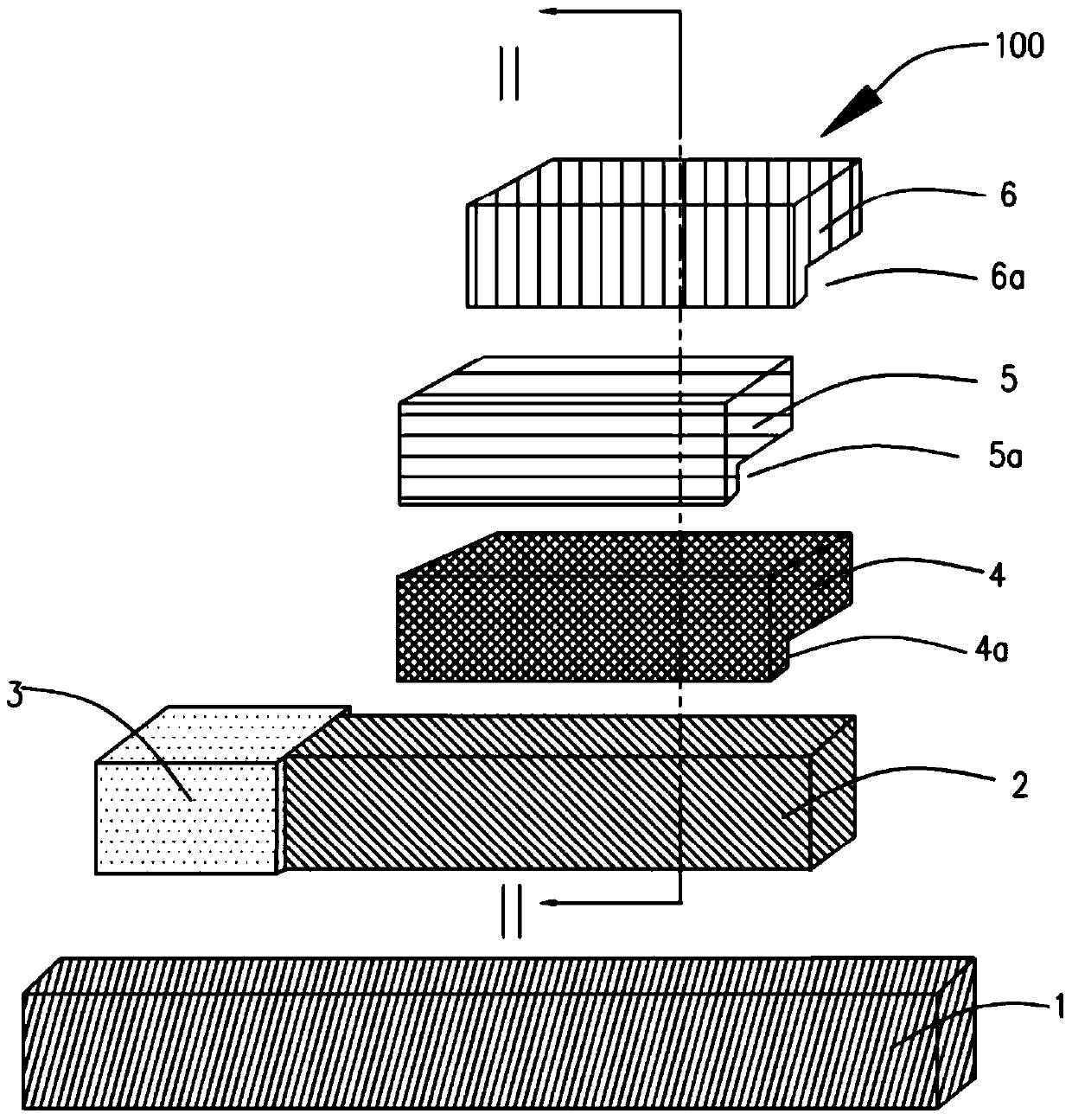

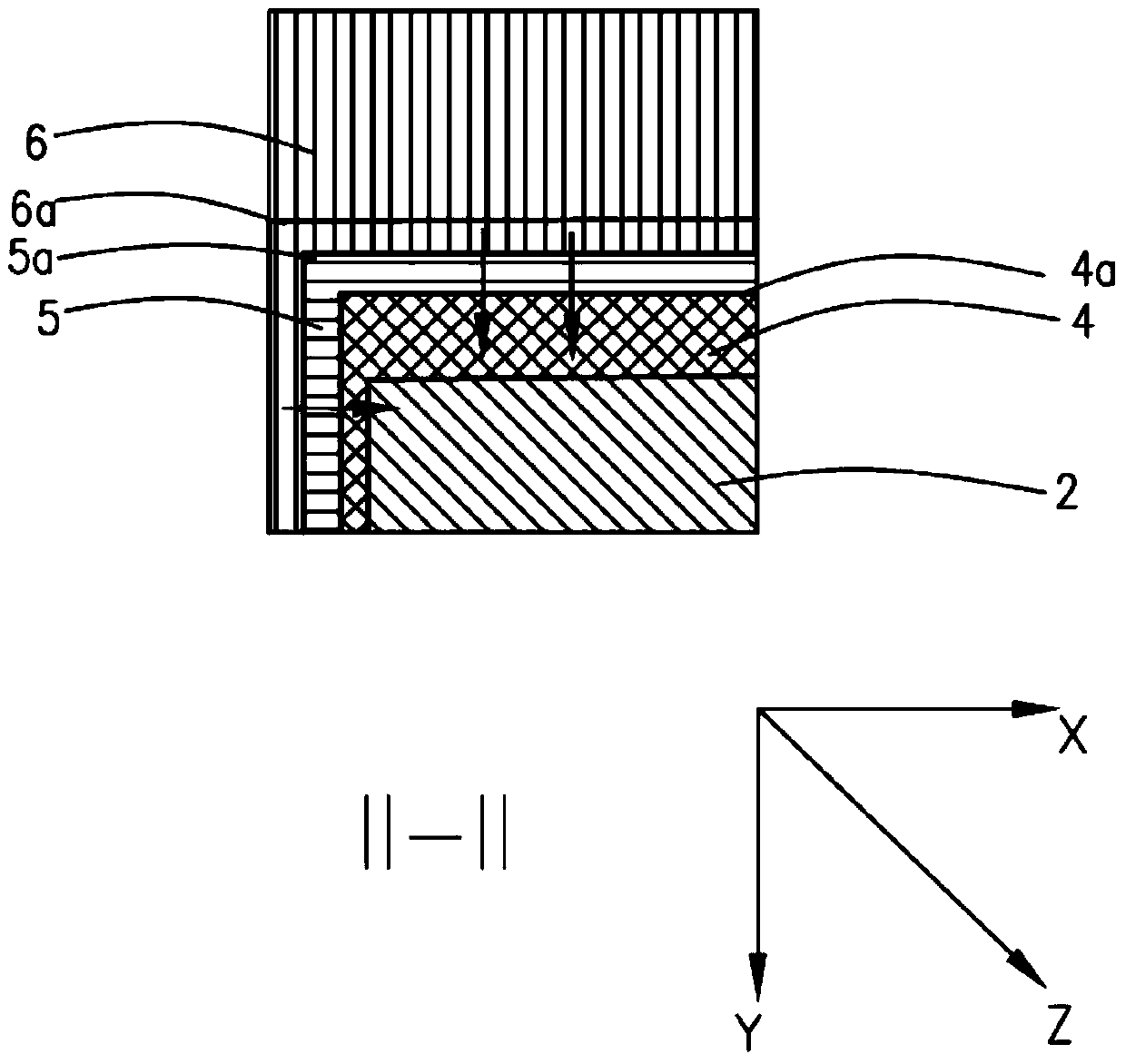

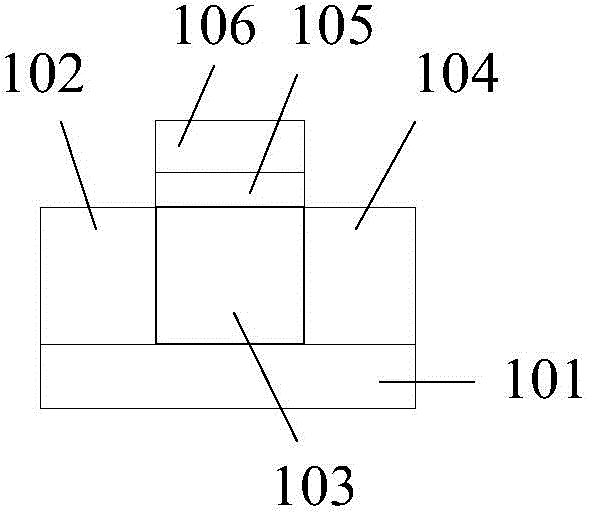

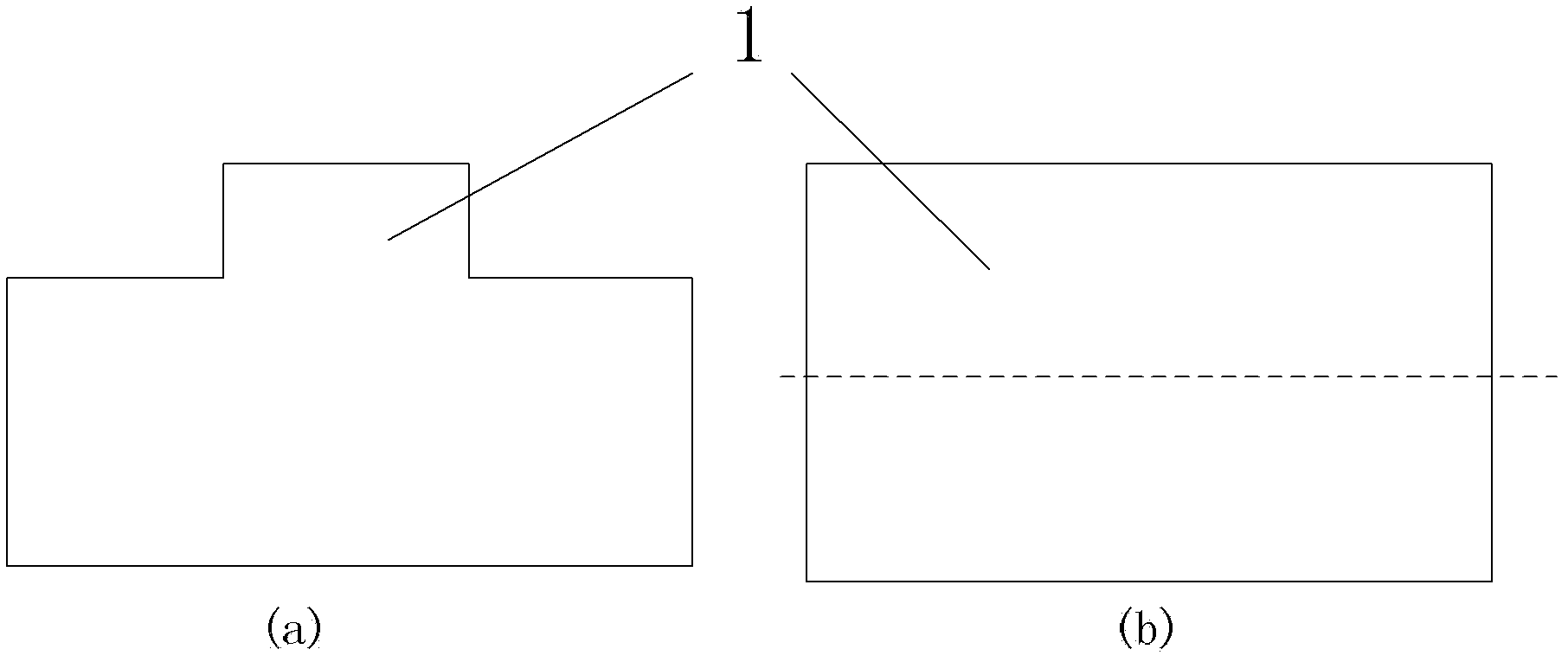

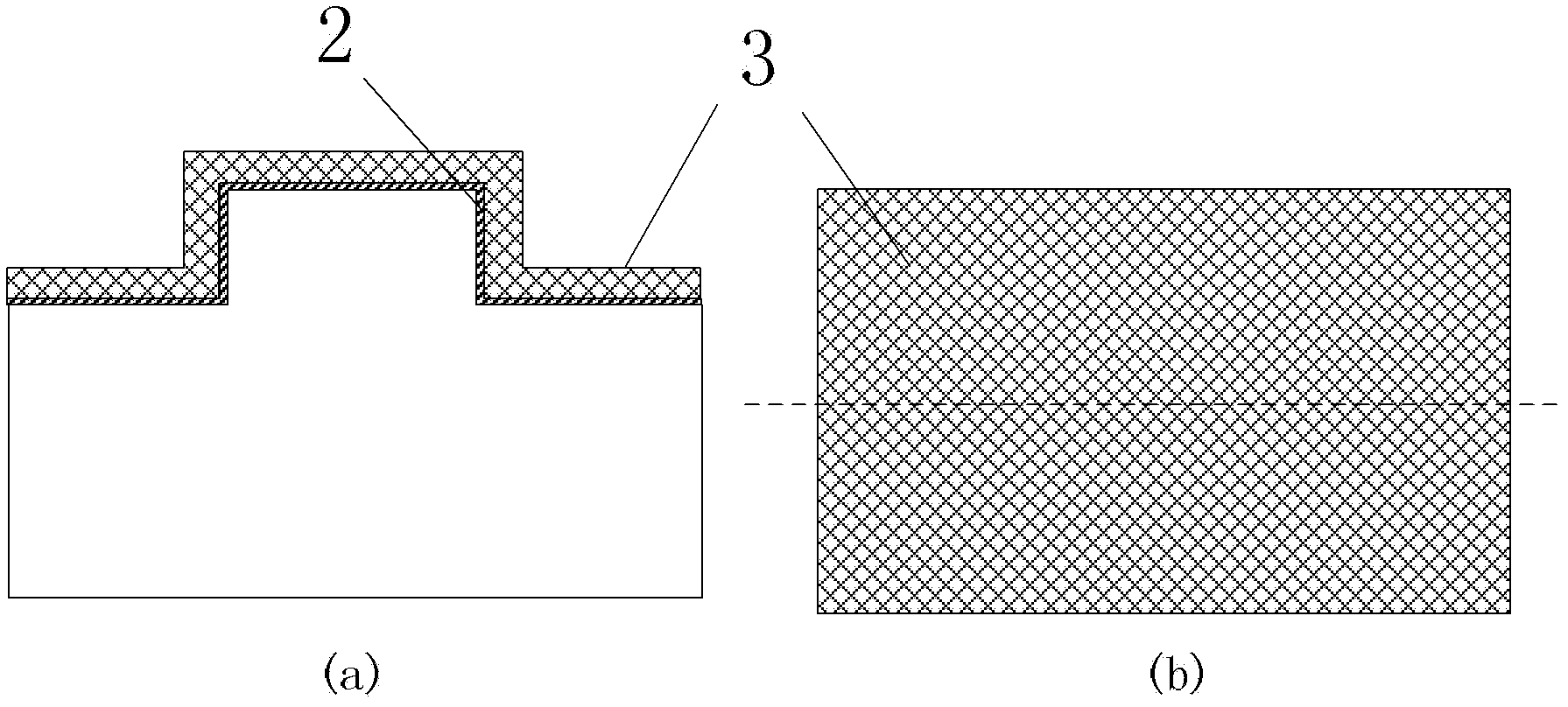

Provided are a vertical tunnelling field-effect transistor and a preparation method therefor. The vertical tunnelling field-effect transistor comprises: a source region (1), a first epitaxial layer (2), a gate dielectric layer (3), a gate region (4) and two drain regions (5). A first groove (11) is provided in the source region. A second groove (21) is provided on the first epitaxial layer, and the first epitaxial layer forms a tunnelling channel between the gate region and the source region. Both the gate dielectric layer and the gate region are provided in the second groove. The two drain regions are respectively provided at two opposite sides outside the second groove. Tunnelling can occur in conduction electrons in an area, overlapped with the gate region, of the first groove of the source region, i.e. an overlapping area between the source region and the gate region is enlarged using the first groove, so that a tunnelling area is enlarged. The first epitaxial layer can form the channel between the gate region and the source region, which involves linear tunnelling, and when the electric field direction of the gate region and the electron tunnelling direction of the source region are on the same line, the tunnelling probability is high, thereby improving a tunnelling current.

Owner:HUAWEI TECH CO LTD

Schottky barrier metal oxide semiconductor (MOS) transistor and preparation method thereof

ActiveCN102324434BReduce parasitic resistanceEliminate uncovered areasSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETSchottky barrier

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Tunneling field effect transistor and method of making the same

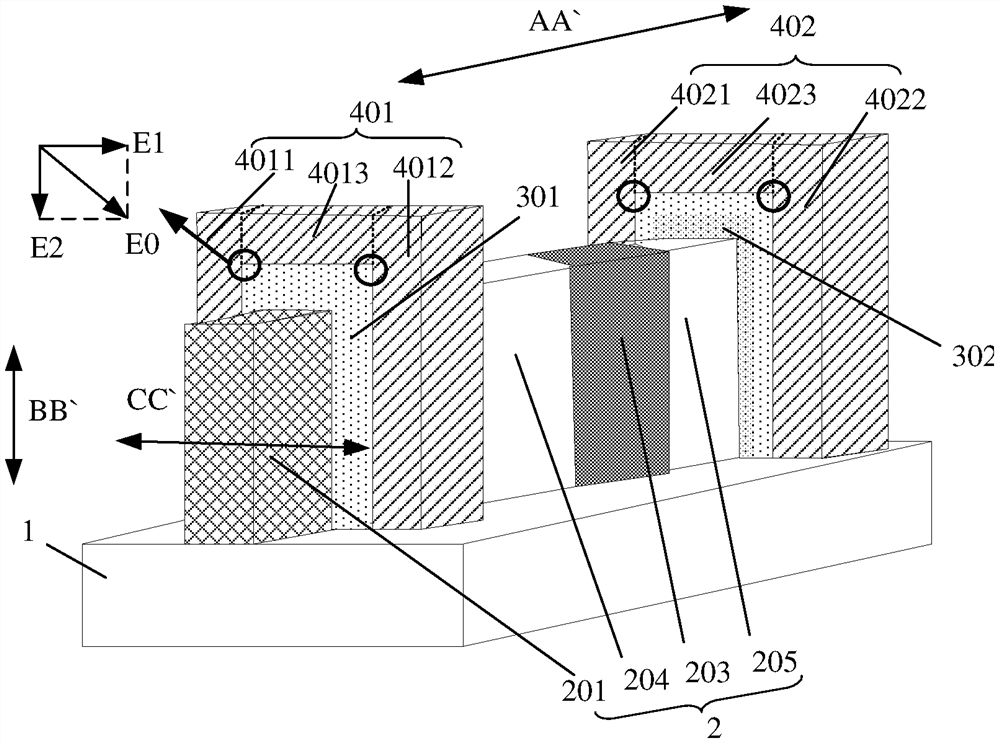

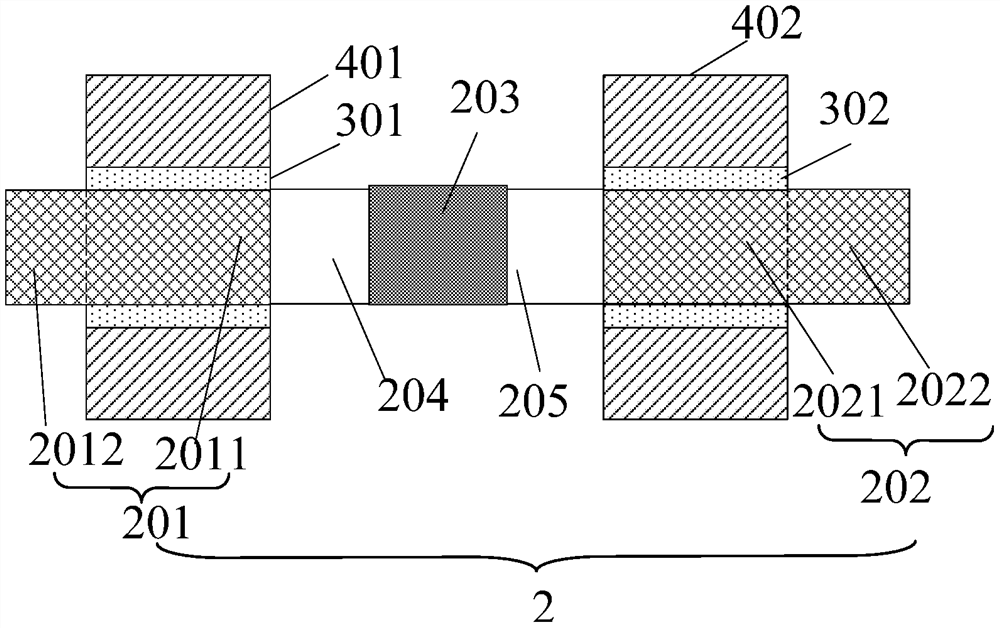

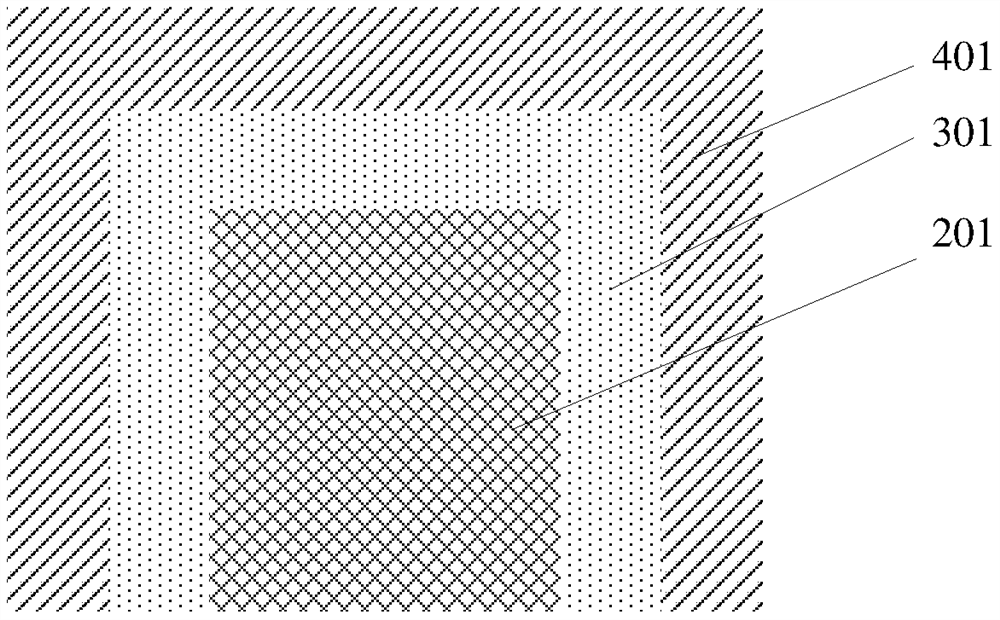

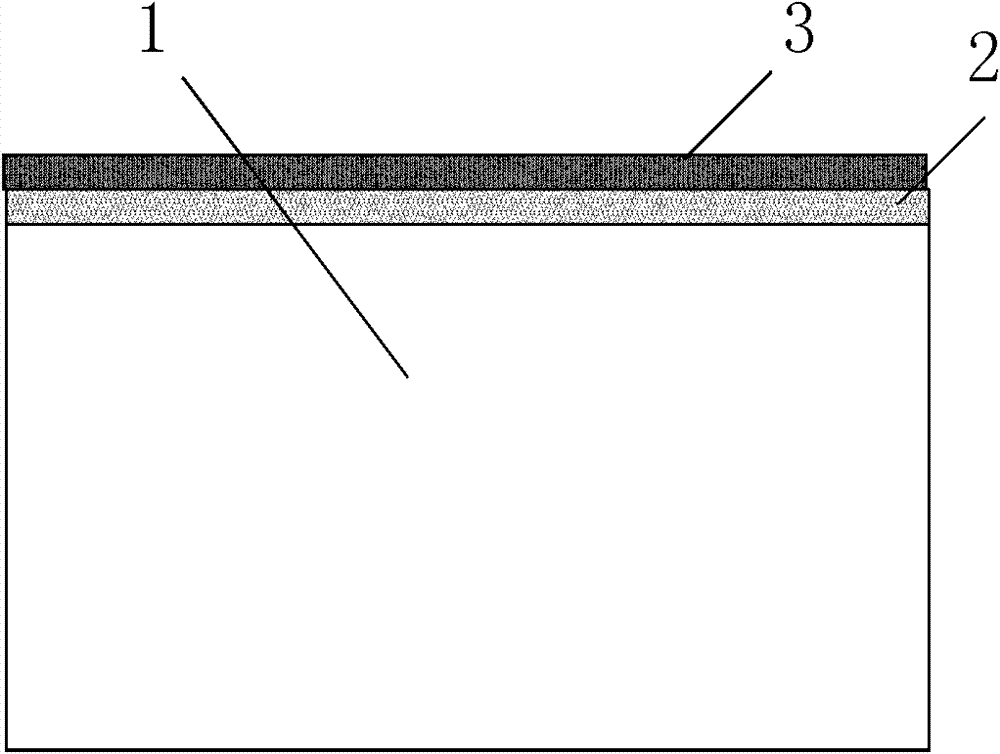

ActiveCN108780812BLarge tunneling areaIncrease chance of tunnelingNanoinformaticsSolid-state devicesElectric fieldEngineering

A tunneling field effect transistor and a method for preparing the same, comprising: a substrate layer (1); a rectangular semiconductor strip (2) formed on an upper surface of the substrate layer, the rectangular semiconductor strip being sequentially provided with first source regions (201 along a first direction) ), a first channel region (204), a drain region (203), a second channel region (205) and a second source region (202); covering the first portion (2011) and the second source region of the first source region The first gate dielectric layer (301) and the second gate dielectric layer (302) on the outer surface of the third part (2021) of the region; the first gate region (401) covering the outer surface of the first gate dielectric layer, the first gate The direction of the electric field applied to the region points to the first source region; the second gate region (402) covering the outer surface of the second gate dielectric layer, the direction of the electric field applied to the second gate region points to the second source region. The design of dual source regions increases the tunneling area of carriers in the source region, and the direction of the electric field applied in the gate region is consistent with the tunneling direction of carriers in the source region, which increases the tunneling probability. The penetration area is proportional to the tunneling probability, so the tunneling current is larger.

Owner:HUAWEI TECH CO LTD

Multiple source MOS transistor with impurity segregation and production method thereof

ActiveCN102117834BControl channel surface potentialControl potentialSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSub threshold

The invention provides a multiple source MOS (metal oxide semiconductor) transistor with impurity segregation and a production method thereof. The multiple source MOS transistor comprises a control gate electrode layer, a gate dielectric layer, a semiconductor substrate, a highly-doped source region and a highly-doped drain region; one end of a control gate extends towards the highly-doped sourceregion to form a T shape; the extended gate region is used as an extension gate; an original control gate region is a main gate; the highly-doped source region is formed by highly doping a semiconductor and is positioned on two sides of the extension gate along the width direction of the source region; and one side of the highly-doped region, which is away from the channel direction, is connectedwith a Schottky source region with impurity segregation. Compared with the present MOSFET (metal-oxide-semiconductor field-effect transistor), under the same process condition and the same size of the active region, higher conducting current, lower leakage current and steeper sub-threshold slope can be obtained.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Tunneling Field Effect Transistor and Method of Forming the Same

ActiveCN104701374BAdd tunnel pathIncrease the areaSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricCondensed matter physics

Owner:SEMICON MFG INT (SHANGHAI) CORP

Tunnel Field Effect Transistor and Manufacturing Method

ActiveCN104979385BImprove tunneling efficiencyHigh electron mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesContact formationSilylene

The present invention provides a tunnel field effect transistor and a manufacturing method thereof. The tunnel field effect transistor comprises a substrate; a P-type silylene layer and an N-type silylene layer which form a lamination structure; a grid structure located on the lamination structure; electrodes located on the P-type silylene layer and the N-type silylene layer at the two sides of the grid structure and used for forming a source or a drain with the P-type silylene layer and the N-type silylene layer. The present invention also provides a manufacturing method of the tunnel field effect transistor. The manufacturing method of the tunnel field effect transistor comprises the steps of providing the substrate; forming the P-type silylene layer and the N-type silylene layer to thereby enable the P-type silylene layer and the N-type silylene layer to overlap and contact at the intersection position mutually to form the lamination structure; forming the grid structure on the lamination structure; forming the electrodes on the P-type silylene layer and the N-type silylene layer at the two sides of the grid structure, wherein the electrodes are used to form the source or drain with the P-type silylene layer and the N-type silylene layer. The tunnel field effect transistor of the present invention has a larger tunneling area, and enables the performance to be improved to a certain extent.

Owner:SEMICON MFG INT (SHANGHAI) CORP

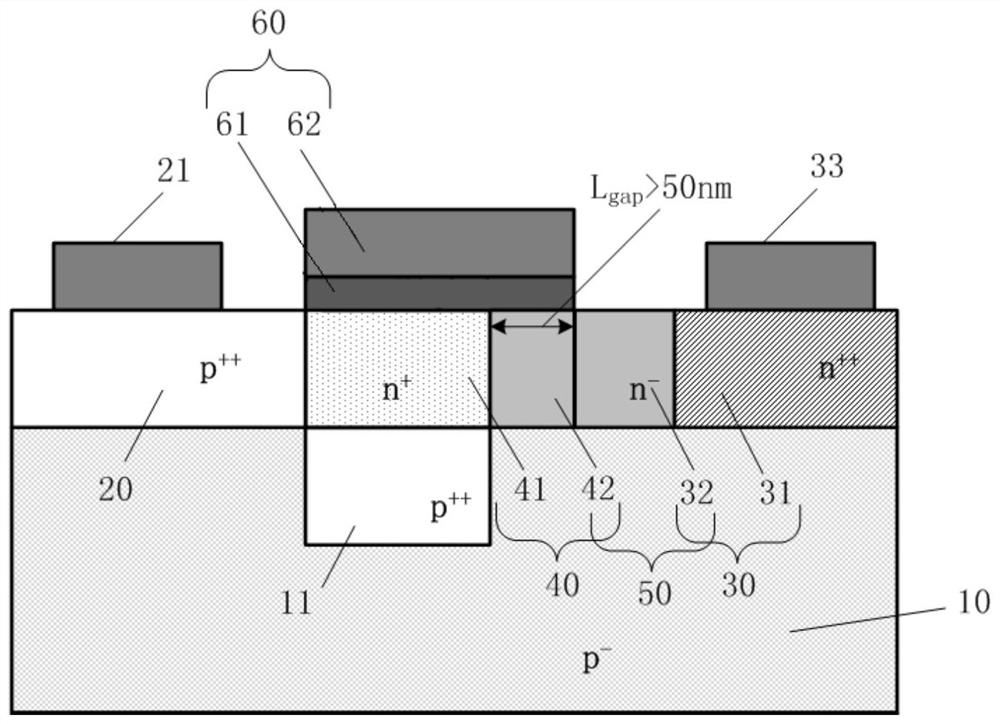

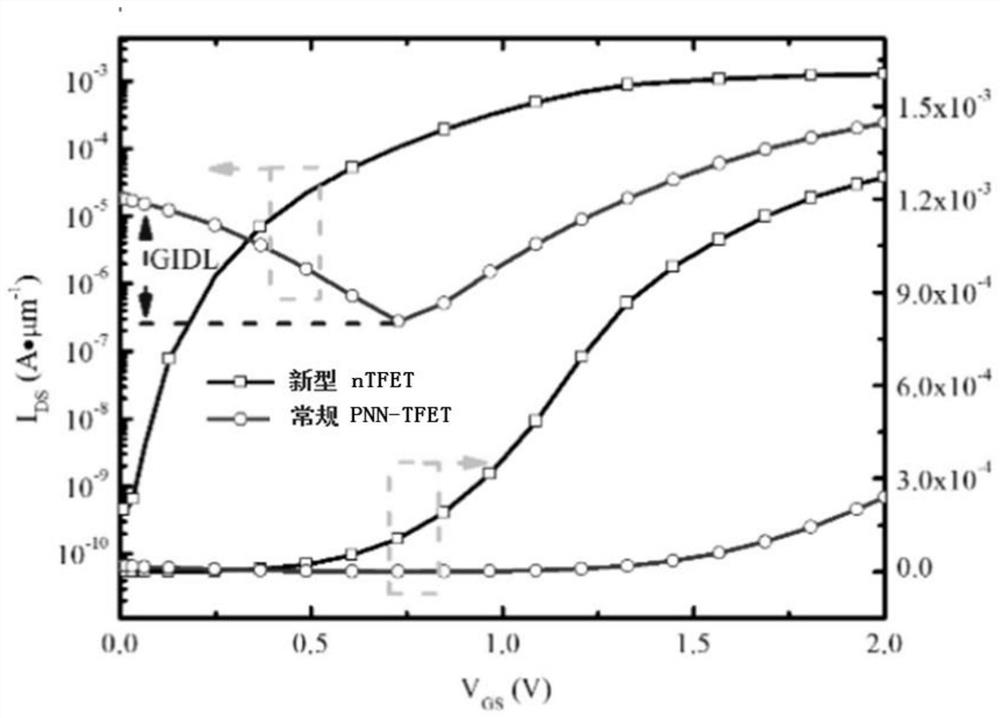

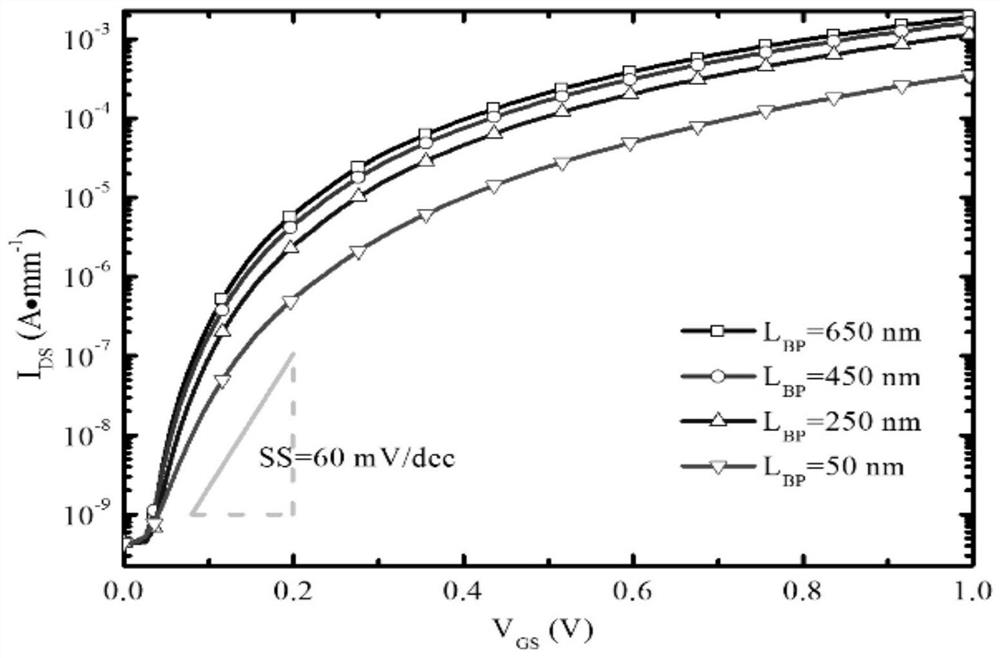

Novel high-current n-type TFET device with buried layer structure and preparation method thereof

ActiveCN111863937ALower threshold voltageAchieve pinch offSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

The invention discloses a novel high-current n-type TFET device with a buried layer structure and a preparation method of the novel high-current n-type TFET device. The n-type TFET device comprises asubstrate, wherein a source region, a drain region and a channel region are arranged on the surface of the substrate, the source region and the drain region are located at the two ends of the channelregion respectively; a buried layer is arranged below the channel region, the buried layer starts from the junction of the channel region and the source region, and the length of the buried layer is smaller than that of the channel region; a gate structure is arranged above the channel region, the gate structure comprises a gate electrode and a gate dielectric layer located between the gate electrode and the channel region; and a source electrode and a drain electrode are correspondingly arranged on the source region and the drain region respectively. According to the n-type TFET device provided by the invention, the requirement on a gate metal work function is reduced, so that the threshold voltage of the device is reduced, and the GIDL effect is inhibited; meanwhile, due to the introduction of a substrate tunneling junction, the tunneling area of the device is increased, the on-state current is improved, and the performance of the device is improved.

Owner:XIDIAN UNIV

Comb-shaped gate composite source MOS (Metal Oxide Semiconductor) transistor and manufacturing method thereof

ActiveCN102117833BControl channel surface potentialEnhanced source junction electric field strengthSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierGate dielectric

The invention provides a composite source MOS (Metal Oxide Semiconductor) transistor with schottky barrier and comb-shaped gate structures and a manufacturing method thereof. The composite source MOS transistor comprises a control gate electrode layer, a gate dielectric layer, a semiconductor substrate, a high doped source region and a high doped drain region, wherein one side far away from the channel direction of the high doped source region is connected with a schottky source region; one end of a control gate extends towards the high doped source region; the extended gate region is an extension gate shaped like a comb; the original control gate region is a main gate; the active region covered by the extension gate is likewise a channel region with the substrate material; the high dopedsource region is formed by the high doping of semiconductor and is located on the two sides of each comb of the extension gate; and a schottky junction is formed at the channel under the schottky source region and the extension gate. Compared with the traditional MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor), the composite source MOS transistor can obtain a higher conduction current,a lower leakage current and a steeper subthreshold slope under a same technological condition and a same active region size.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Field effect transistor, semiconductor device and method for manufacturing same

ActiveCN104638002ALarge tunneling areaImprove performanceTransistorSolid-state devicesPower semiconductor deviceField-effect transistor

Owner:SEMICON MFG INT (SHANGHAI) CORP