Patents

Literature

42results about How to "Steep subthreshold slope" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

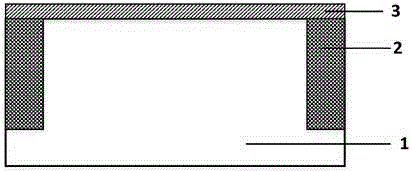

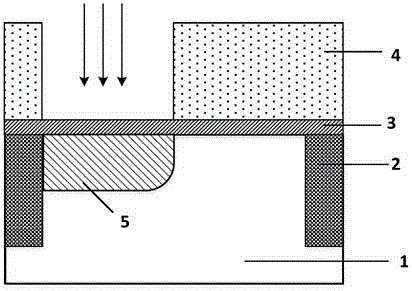

Biosensor based on tunneling field effect transistor and preparation method of biosensor

InactiveCN103558280ASteep subthreshold slopeSensitiveMaterial analysis by electric/magnetic meansGate dielectricOxygen

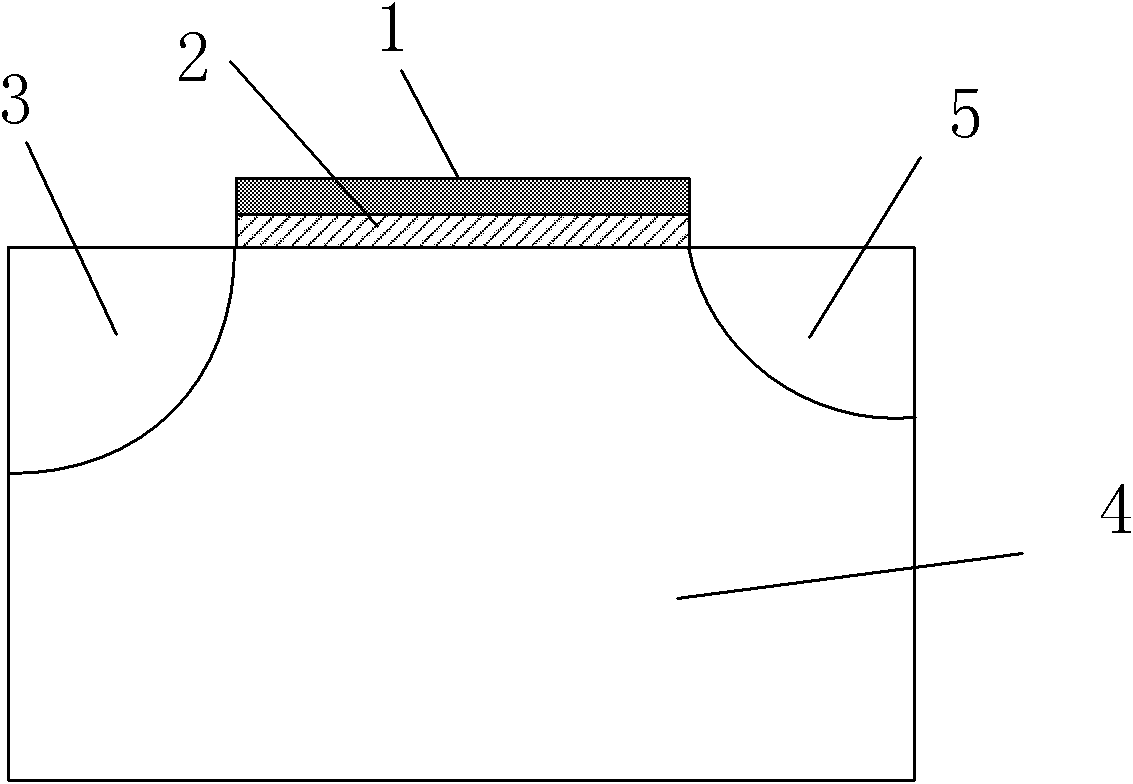

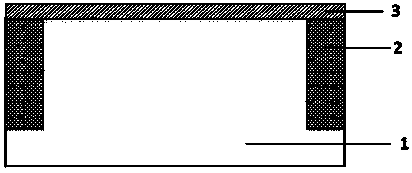

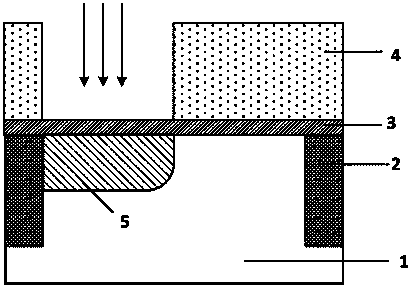

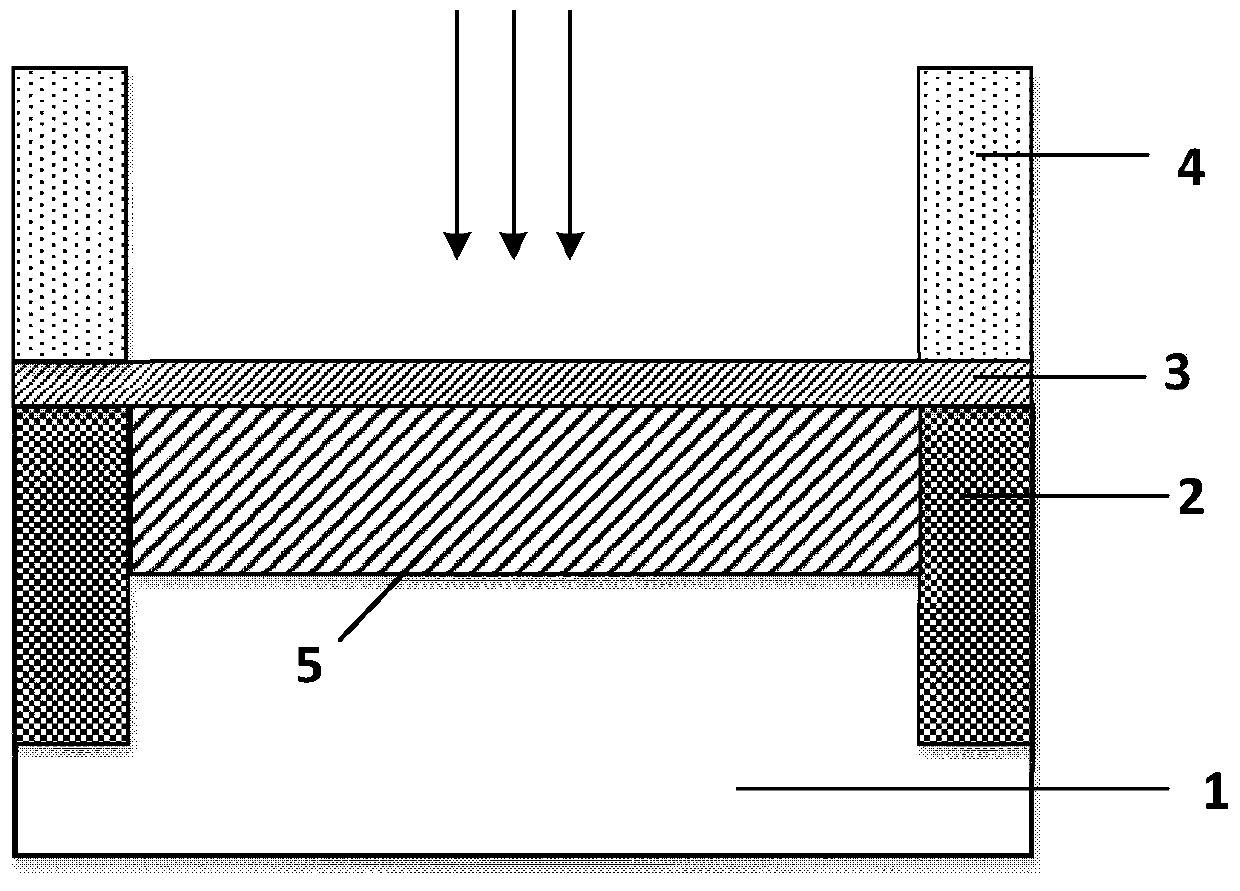

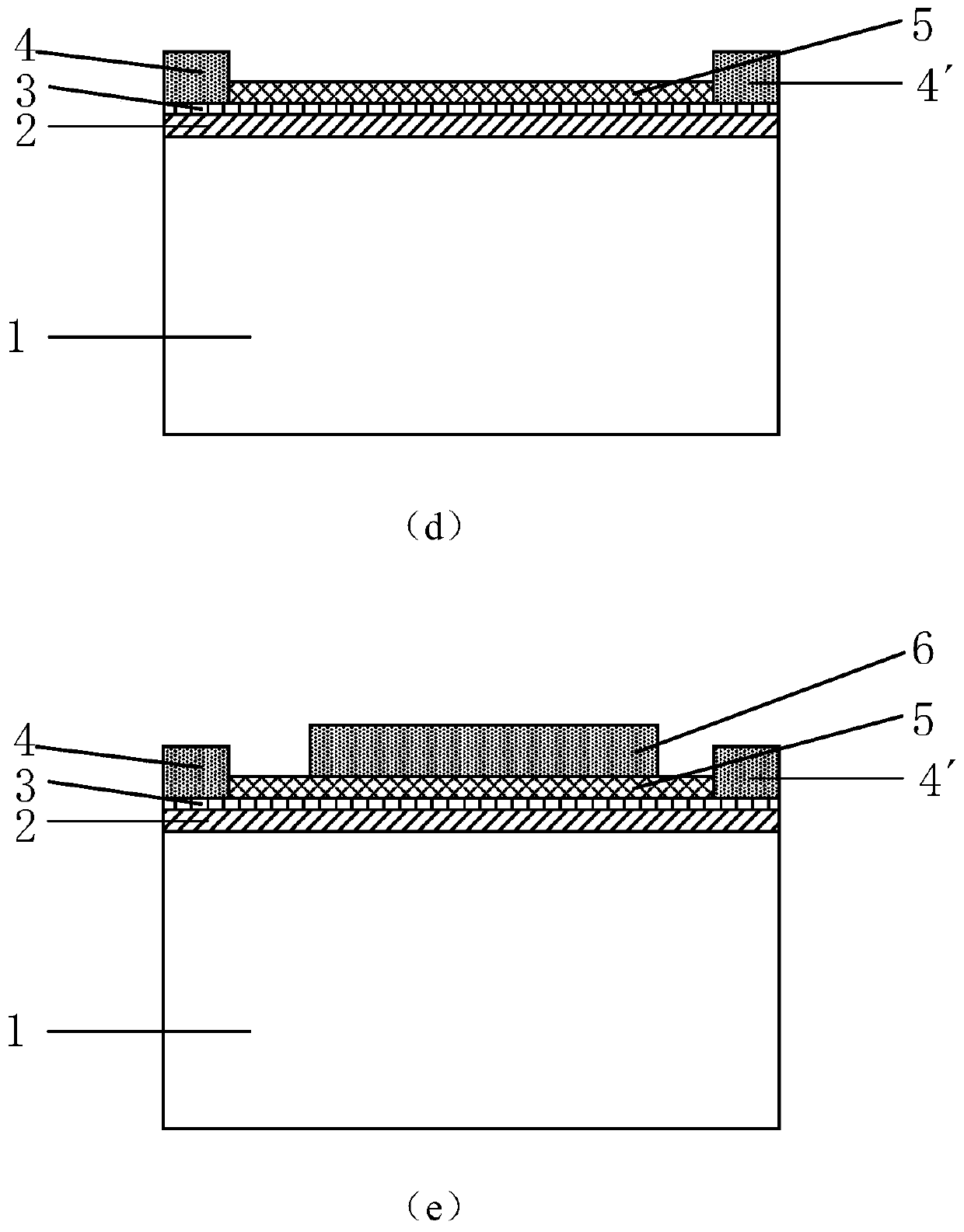

The invention provides a biosensor based on a tunneling field effect transistor and a preparation method of the biosensor. The preparation method of the biosensor at least comprises the steps of firstly, preparing a tunneling field effect transistor as a converter; and then carrying out activated modification on the surface of a channel in the tunneling field effect transistor by adopting a surface modification agent, wherein the step of preparing the tunneling field effect transistor specifically comprises the procedures of providing an SOI (Silicon On Insulator) substrate, wherein the SOI substrate comprises a top layer silicon, a buried oxygen layer and a bottom layer silicon; forming a gate dielectric layer on the surface of the top layer silicon; carrying out ion injection on the top layer silicon at two sides of the gate dielectric layer by adopting an ion injection process to form a source electrode and a leak electrode, defining the top layer silicon of the gate dielectric layer, which is not subjected to the ion injection, as a channel; and forming a back gate on the surface of the bottom layer silicon. The tunneling field effect transistor provided by the invention is abrupt in sub-threshold slope, and is sensitive in change of charges on the surface of the channel, thereby enabling the biosensor to be capable of detecting a biomolecule at high sensitivity.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

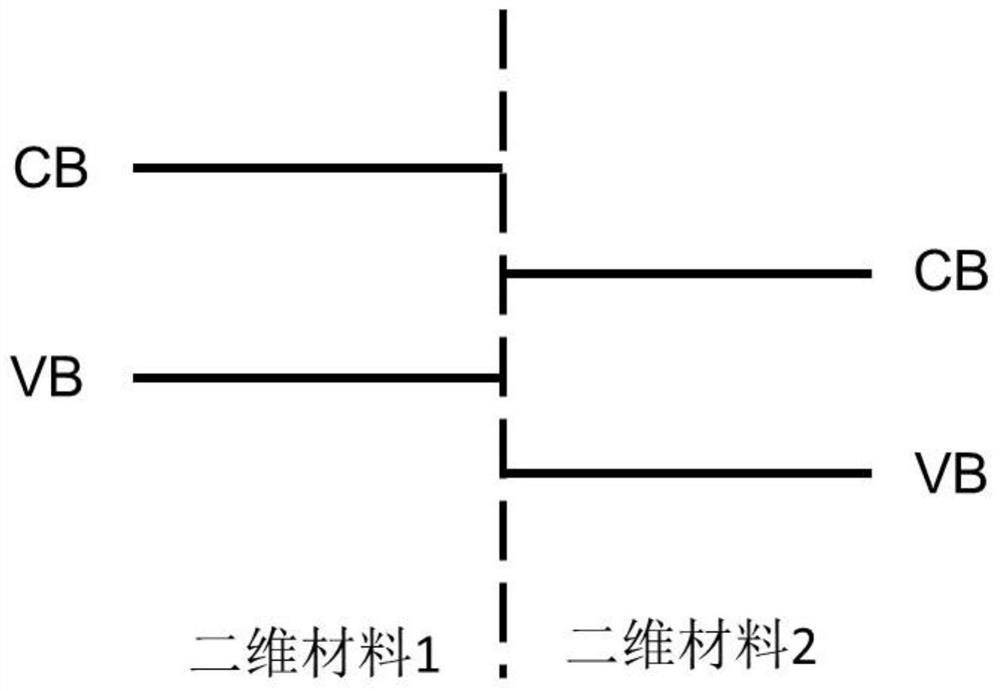

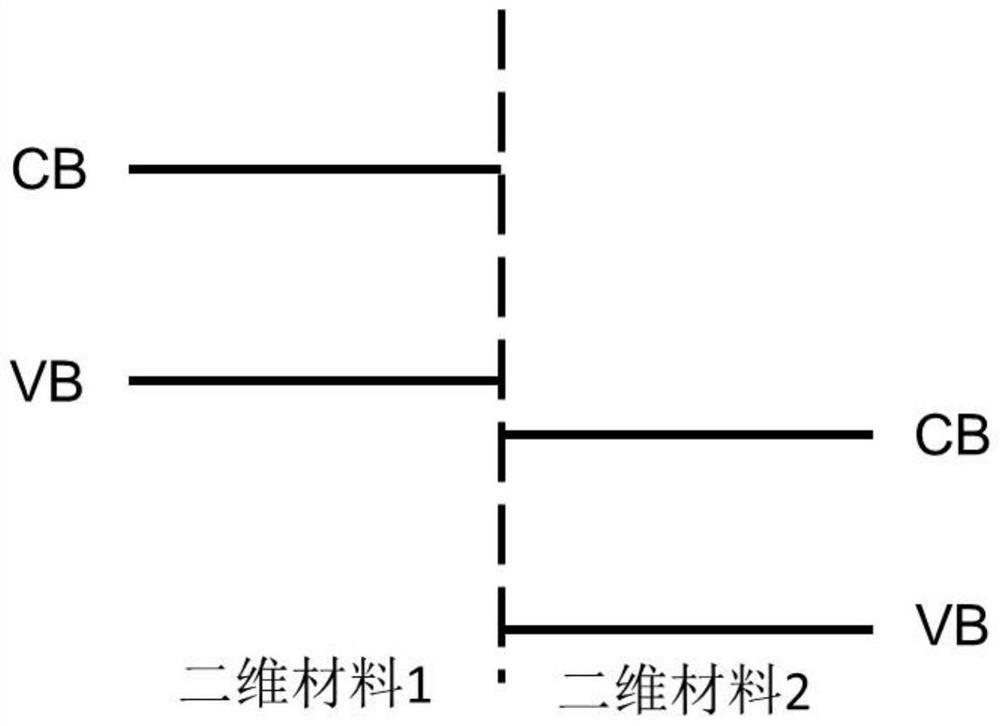

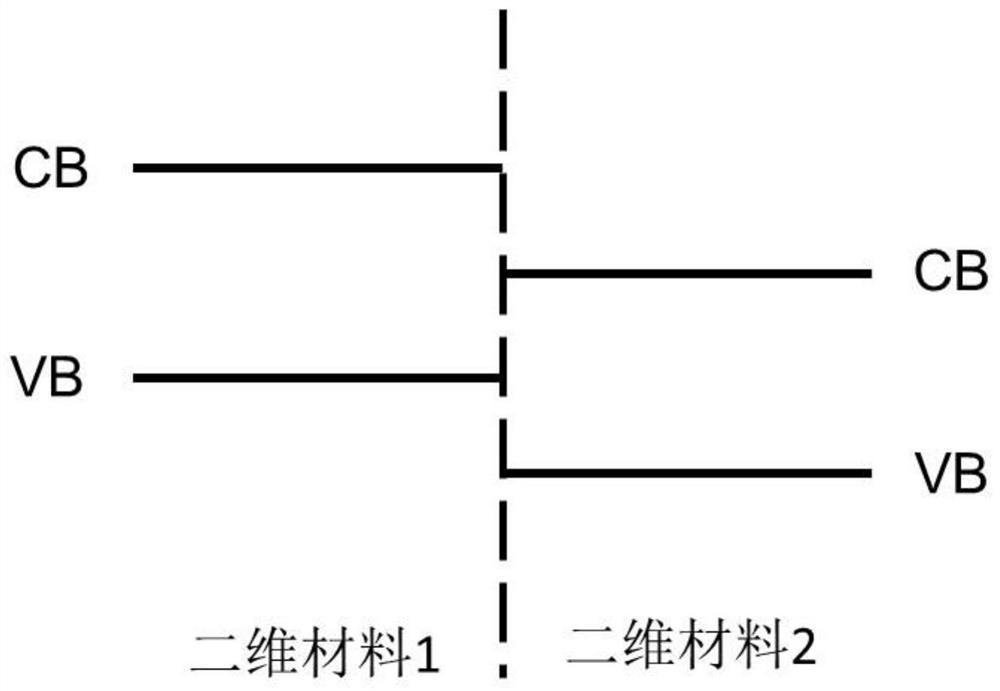

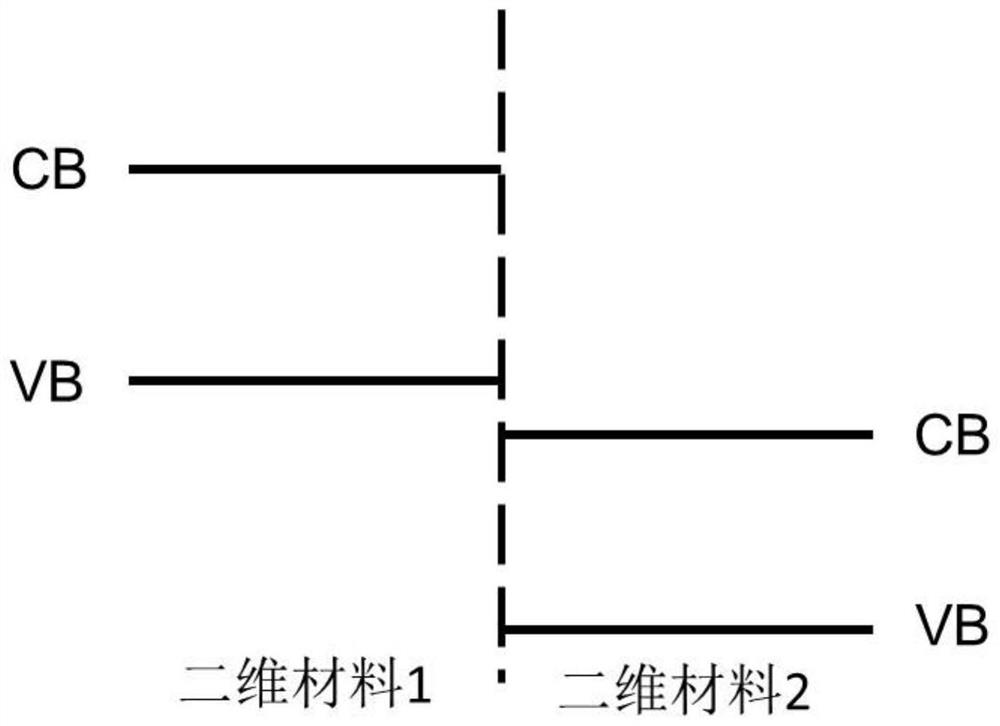

Two-dimensional material/semiconductor hetero-junction tunneling transistor and preparation method thereof

ActiveCN107104140AEffective tunnelingDirect tunnelingSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsPower flow

The invention discloses a tunneling field effect transistor based on a two-dimensional material / semiconductor hetero-junction and a preparation method thereof. A device forms an interleaved energy band structure in the off state through the energy band design, namely, a tunneling window is inexistent between the two-dimensional material and the semiconductor material, and the ultra-low off-state current can be acquired; the grid voltage can be applied to regulate an energy band alignment way at the two-dimensional material / semiconductor hetero-junction so that the device can form the staggered energy band structure in the on-state, and the effective tunneling barrier height is a negative value; and meanwhile, the current carrier tunnels to a channel region from a source region to realize the direct tunneling, thereby acquiring large on-state current. The device adopts the highly-doped three-dimensional semiconductor material as the source region material, and the three-dimensional semiconductor material and the metal source electrode are unipotential; since the thickness of the two-dimensional material is ultra-thin, the grid voltage can regulate the two-dimensional material and the energy band at the two-dimensional material / semiconductor hetero-junction interface, thereby acquiring an ideal grid control capacity. The tunneling field effect transistor disclosed by the invention is simple in process, and large in compatibility with the traditional semiconductor process.

Owner:PEKING UNIV

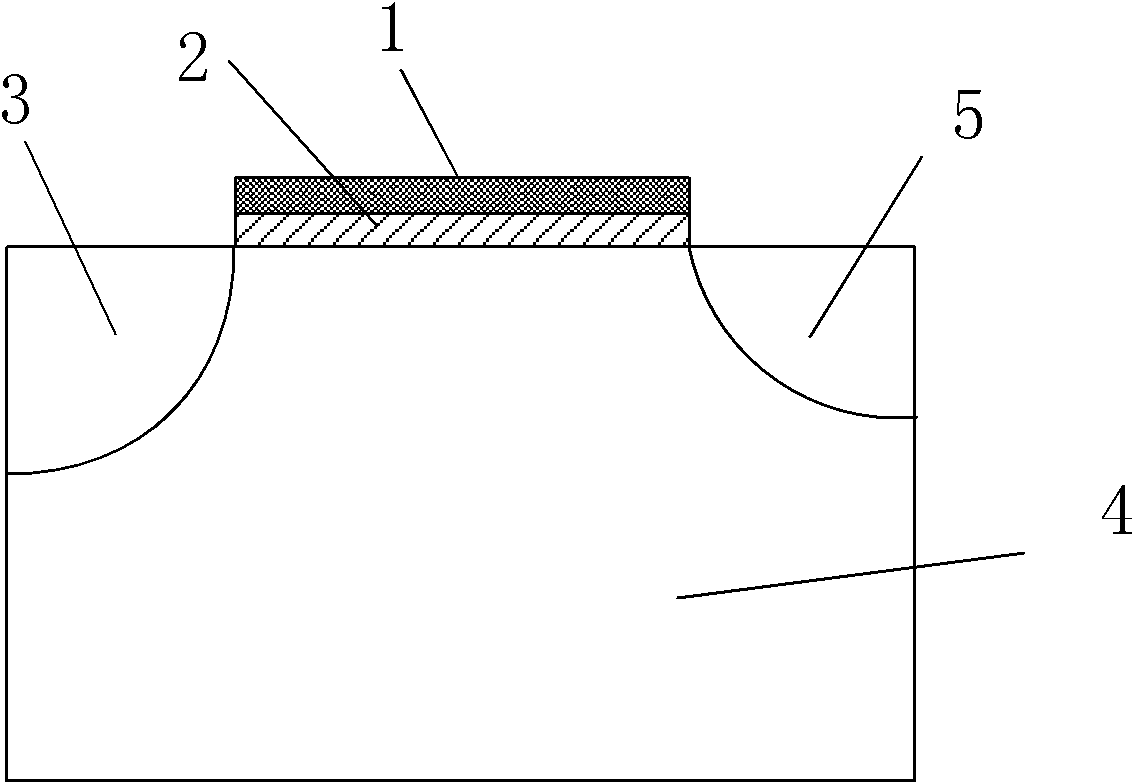

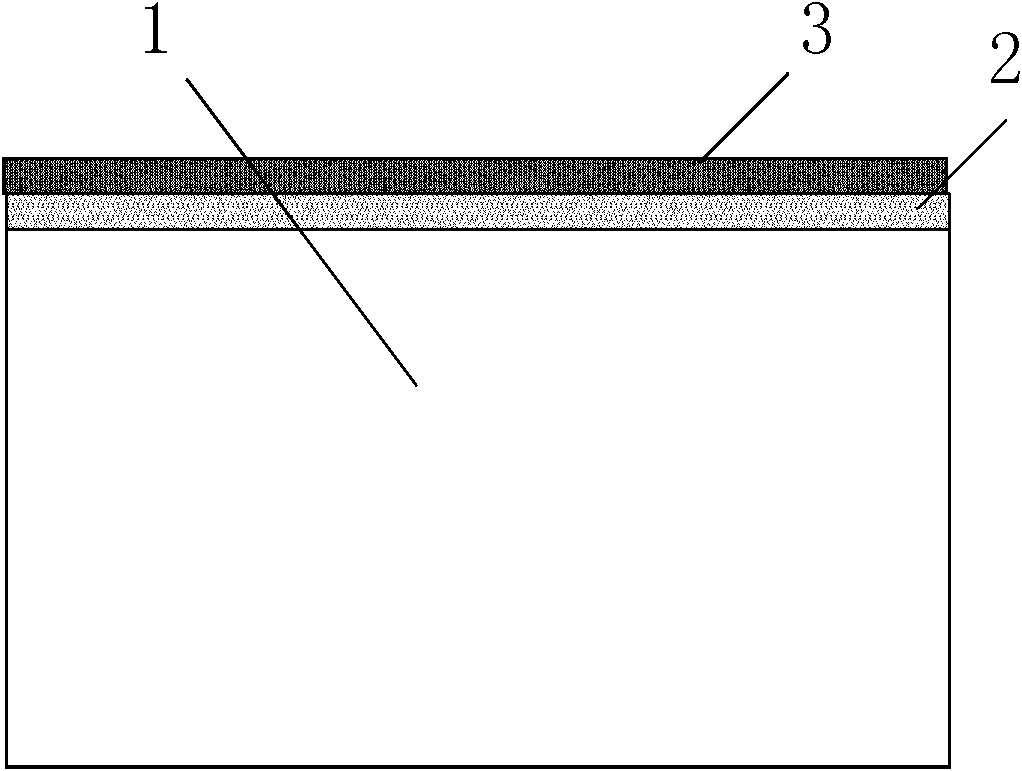

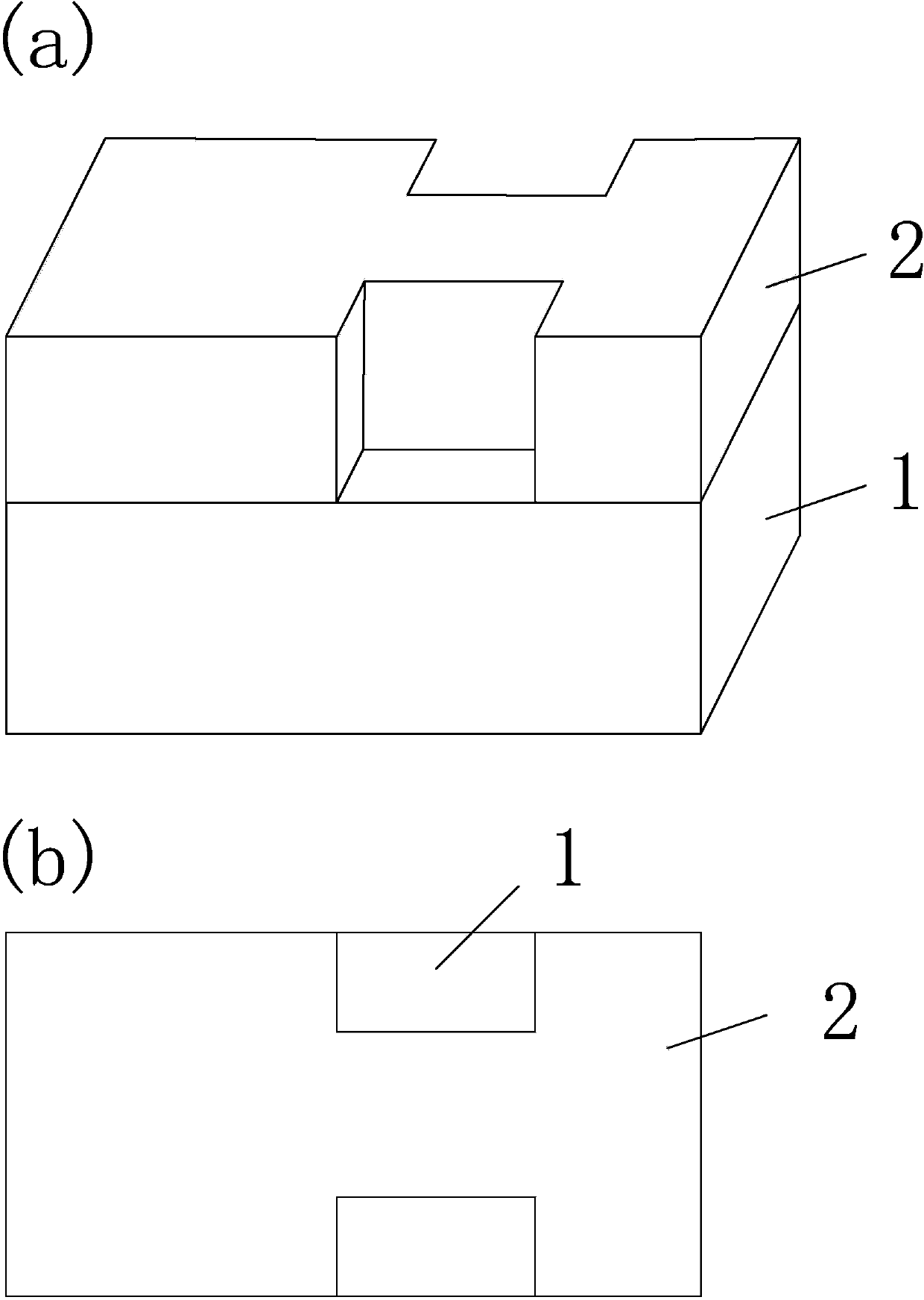

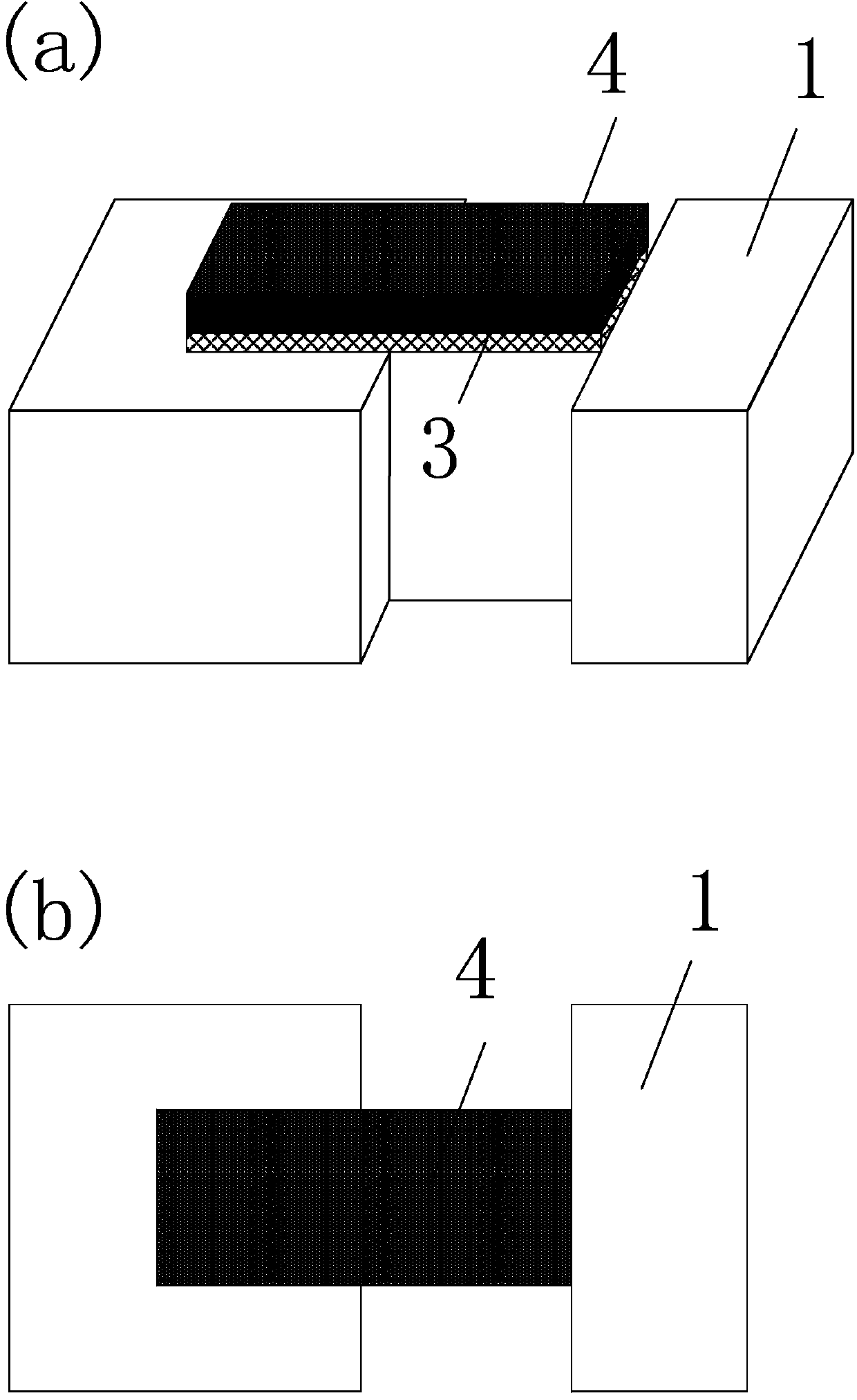

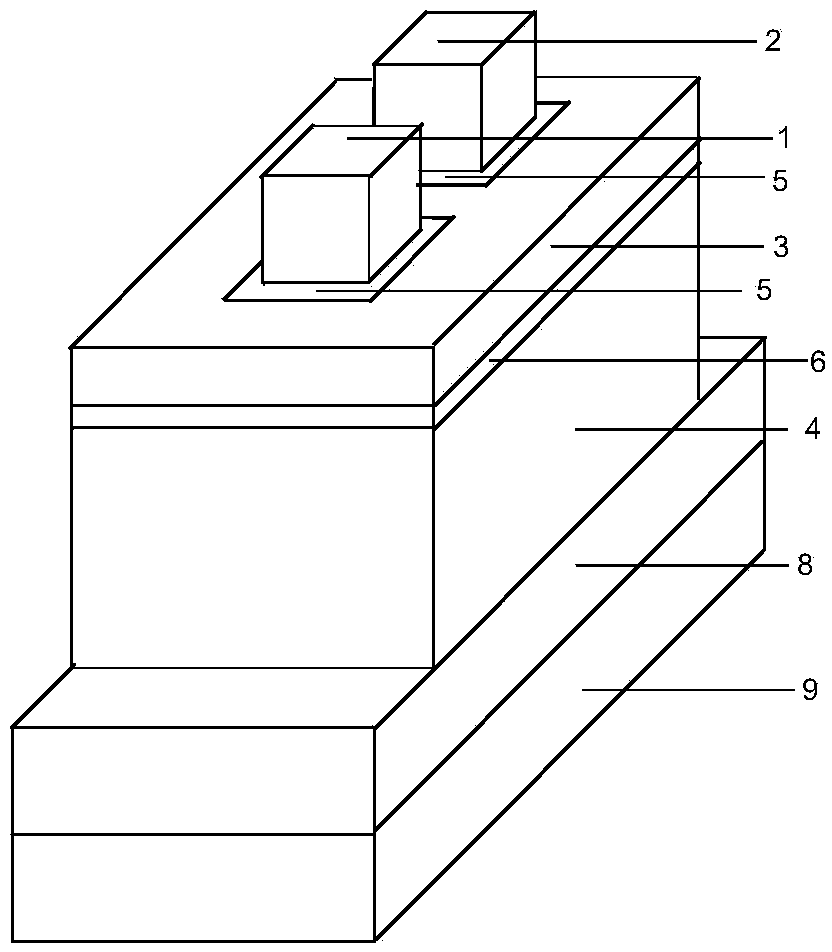

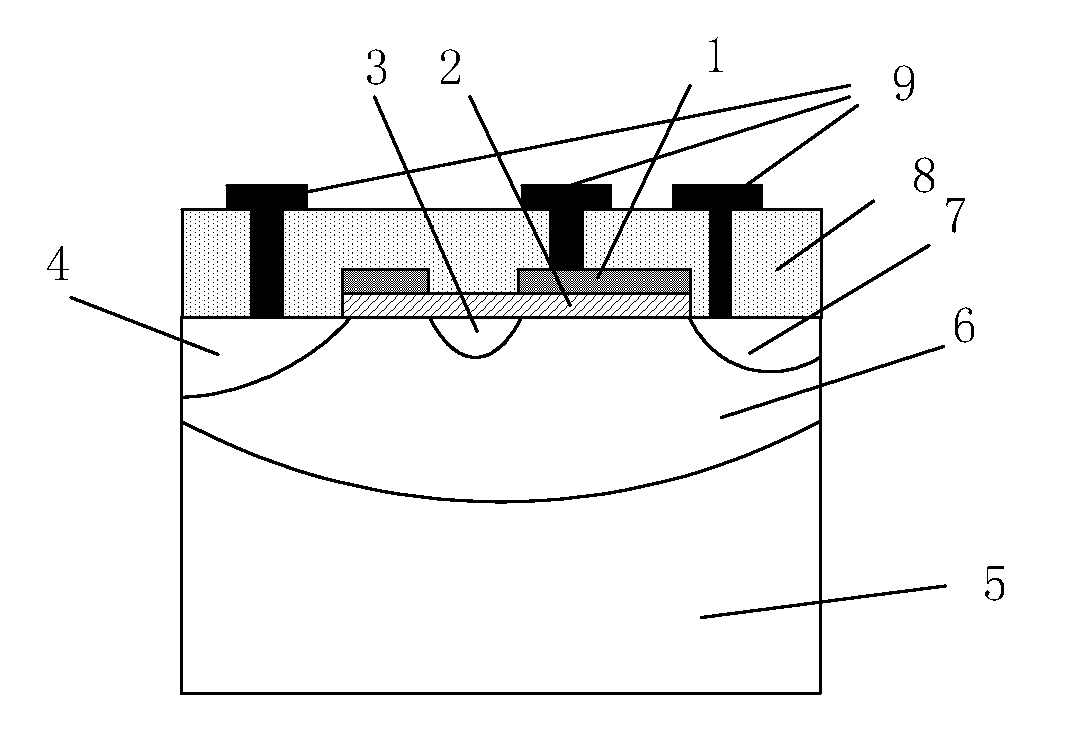

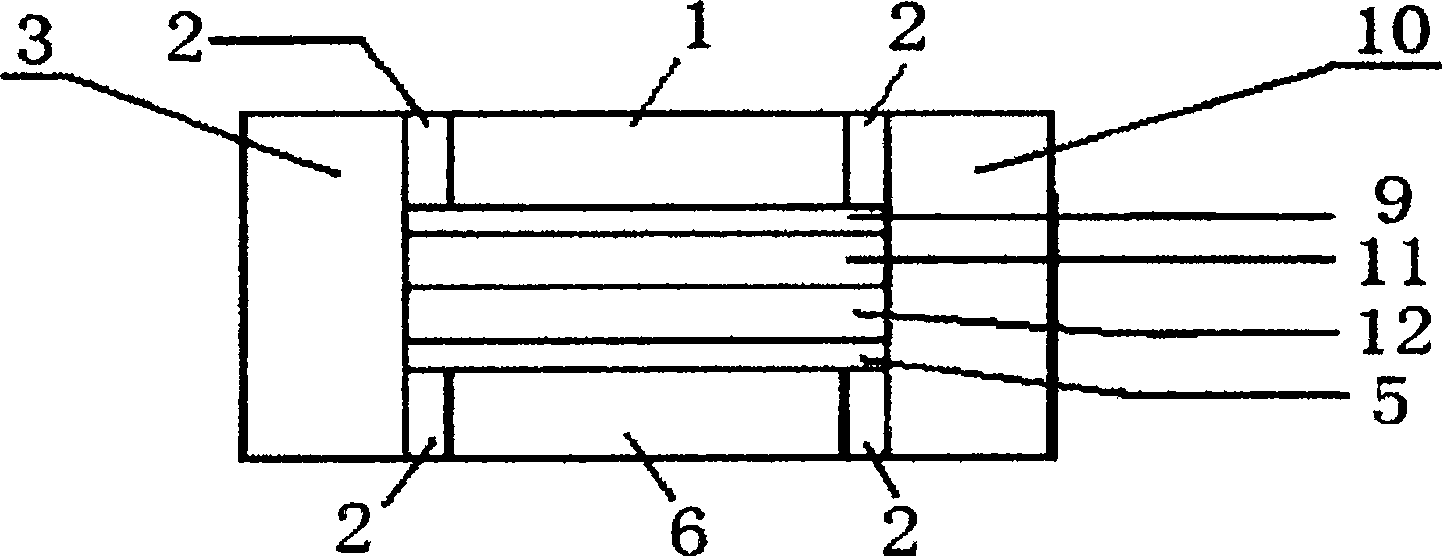

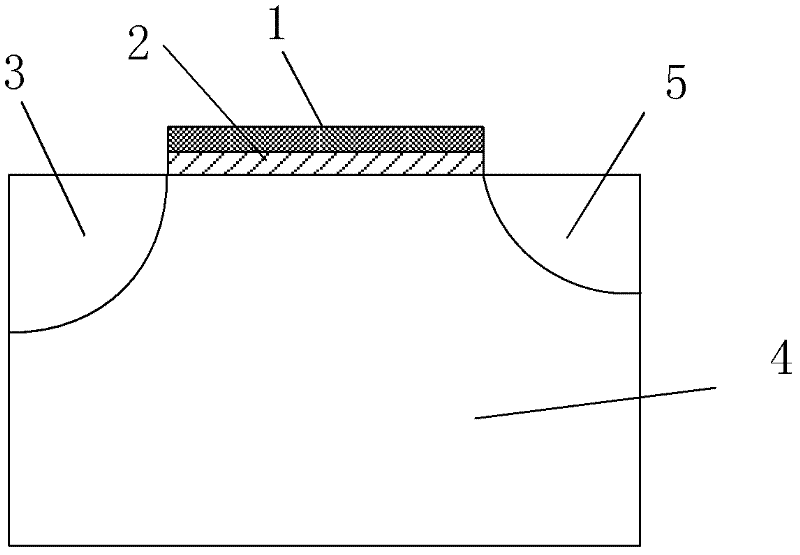

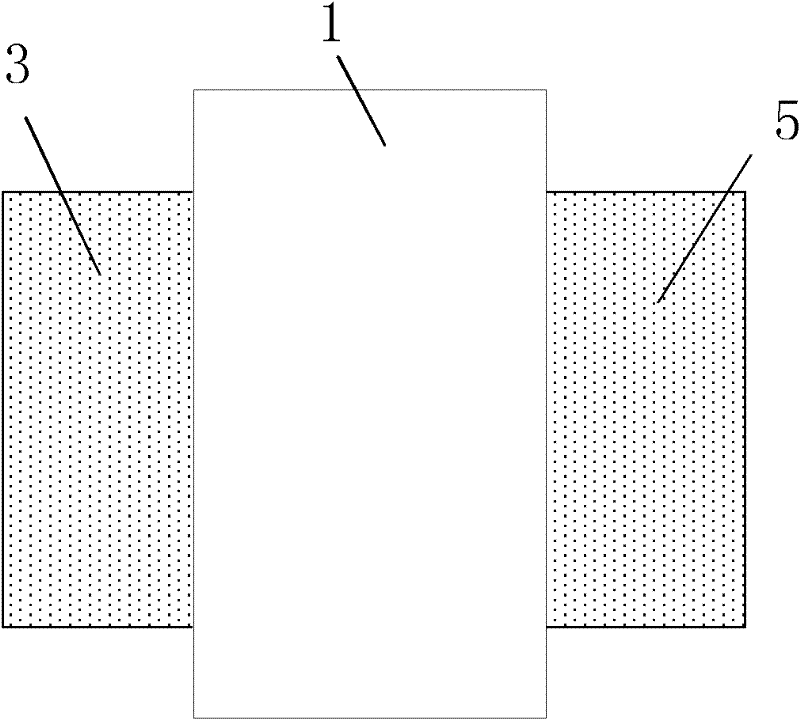

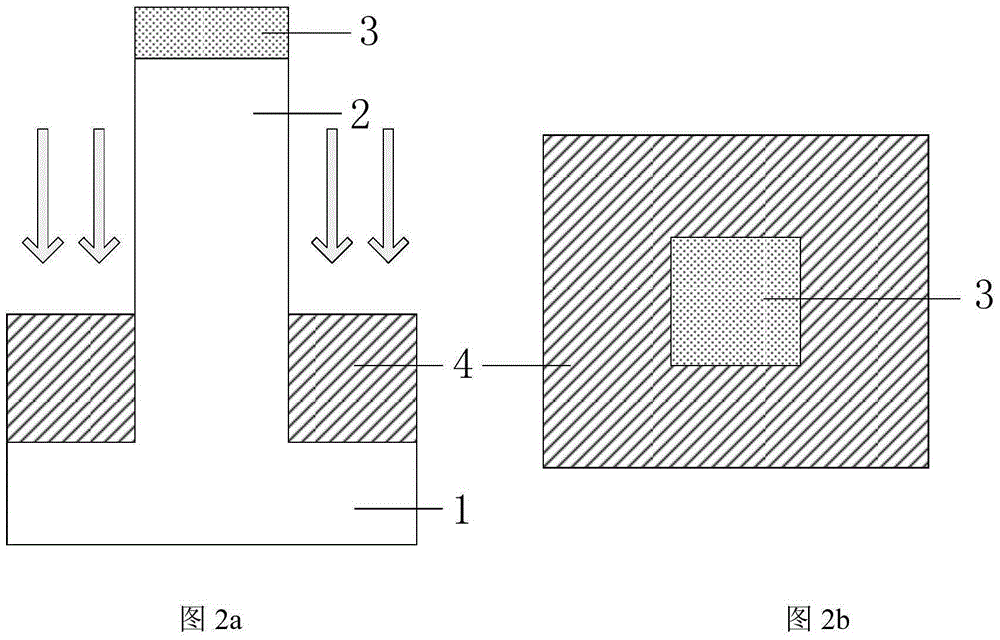

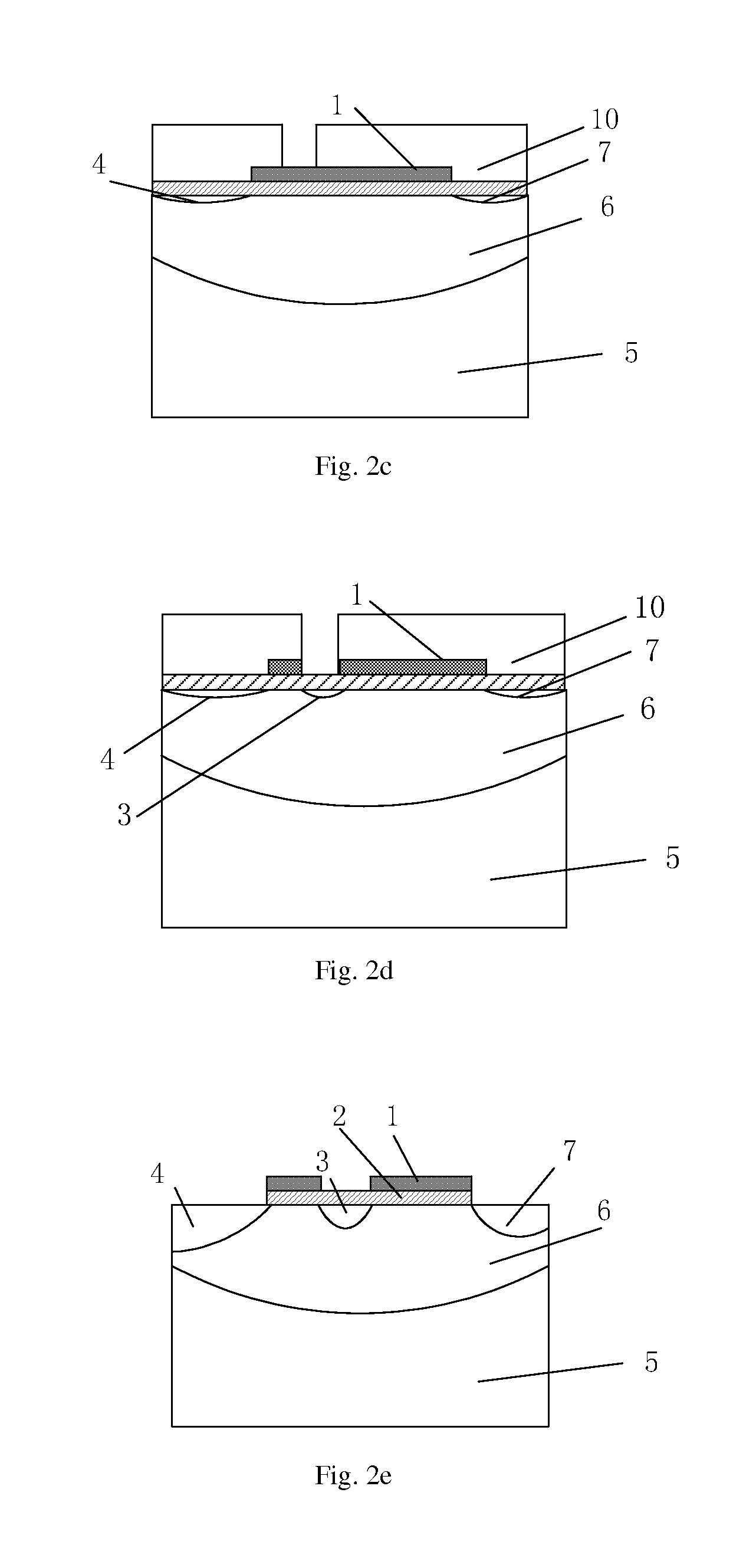

Tunneling field effect transistor with T-shaped grid structure and low power consumption

ActiveCN102005481AIncrease the on-currentLarge tunneling areaSemiconductor devicesEngineeringTunnel field-effect transistor

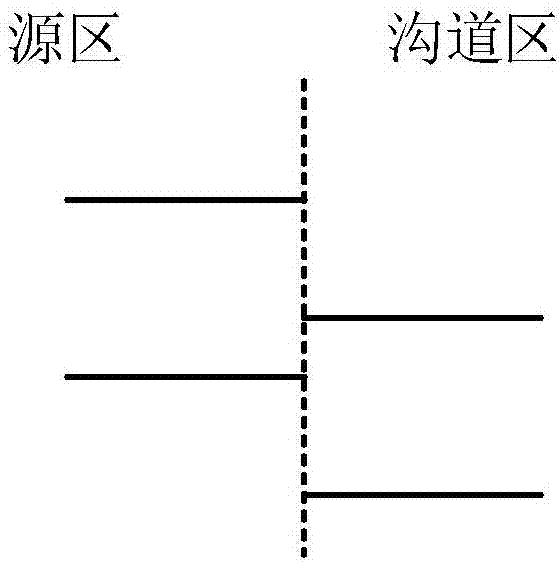

The invention provides a tunneling field effect transistor (TFET) with a T-shaped grid structure and low power consumption, and belongs to the field of field effect transistor logic devices and circuits in complementary metal oxide semiconductor (CMOS) ultra large scale integrated circuits (ULSI). The TFET comprises a source electrode, a drain electrode and a control grid, wherein the control grid extends toward the end of the source electrode to form a T shape; the T-shaped control grid consists of an extending grid region and the original control grid region; and an active region covered below the extending grid region is a channel region and is made of a substrate material. By using the T-shaped grid structure, the source region of the TFET encircles a channel, so that the conduction current of a device is improved. Compared with the conventional planar TFET, the TFET can achieve higher conduction current and steeper subthreshold slope under the same process conditions and the same size of the active region.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

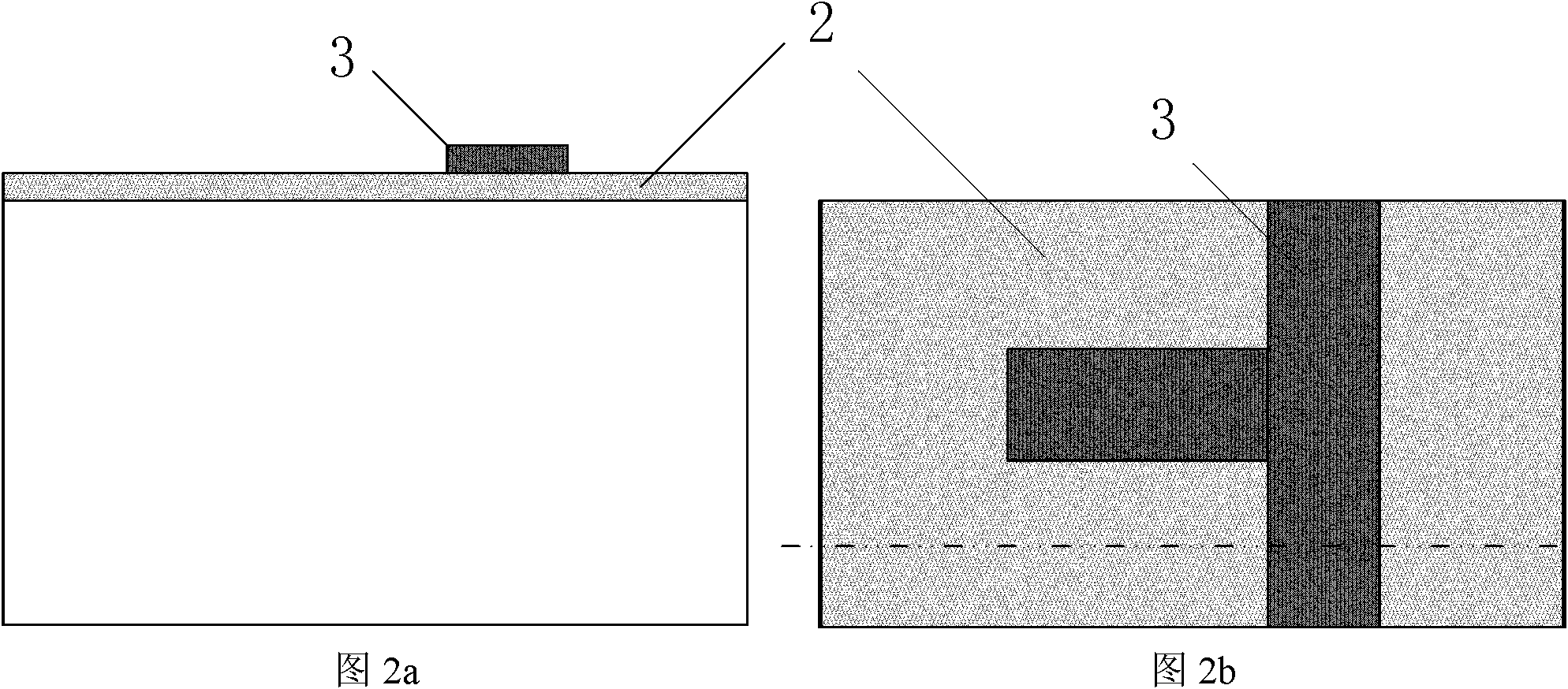

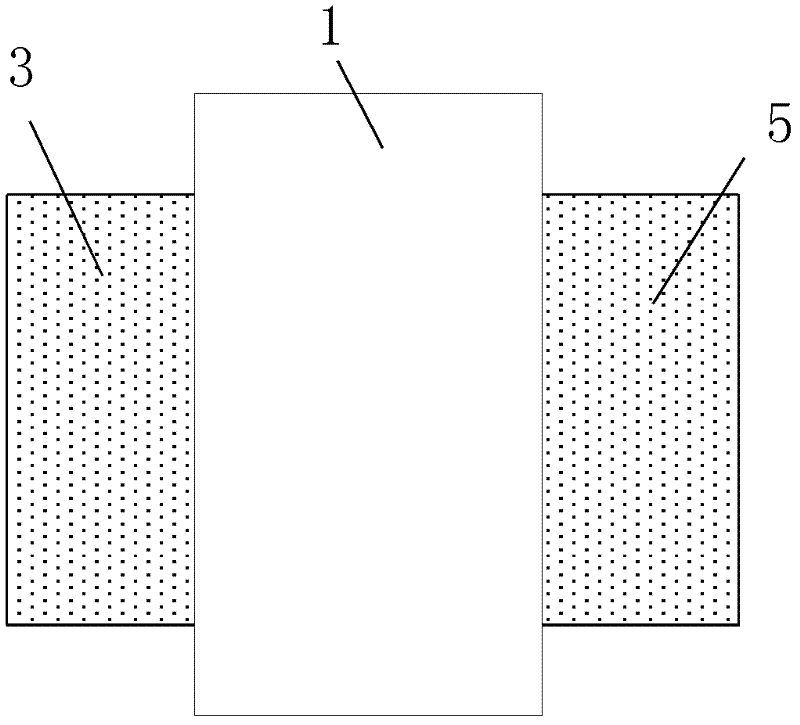

Low-power consumption tunneling field effect transistor (TFET) of fork-structure grid structure

ActiveCN102157559AEnhanced source junction electric field strengthIncrease the on-currentSemiconductor devicesCMOSEngineering

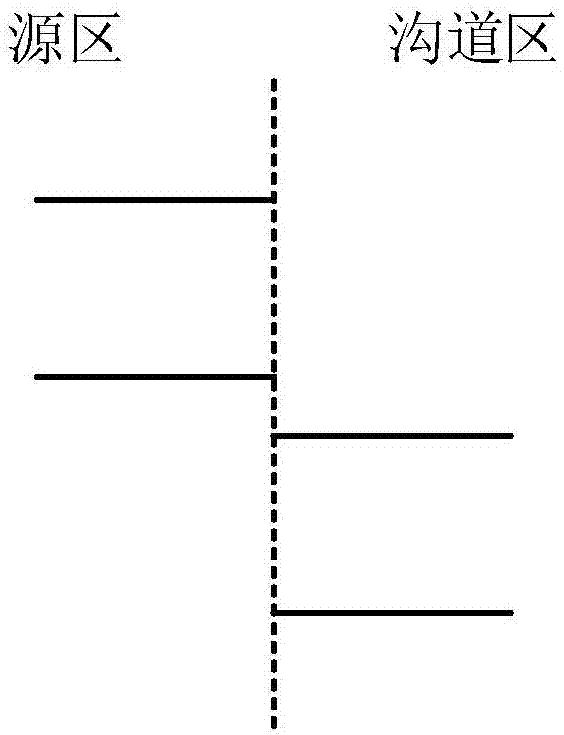

The invention provides a low-power consumption tunneling field effect transistor (TFET), belonging to the field of a field effect transistor logic device and a circuit of CMOS (complementary metal oxide semiconductors) ultra large scale integrated circuit (ULSI). The TFET provided by the invention comprises a source, a drain and a control grid, wherein the control grid extends towards a source electrode end into a fork structure, and the fork-structure control grid is composed of an extended grid region and an original control grid region; and the active region which is covered below the extended grid region is similarly a channel region and is made of a substrate material. According to the invention, the channel is enclosed by the source region of the TFET, and the conduction current of the device is improved; and compared with the existing panel TFET, the TFET has provided by the invention has the advantage that under the conditions of the same technology and the same active region size, higher conduction current and a steep subthreshold gradient can be obtained.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

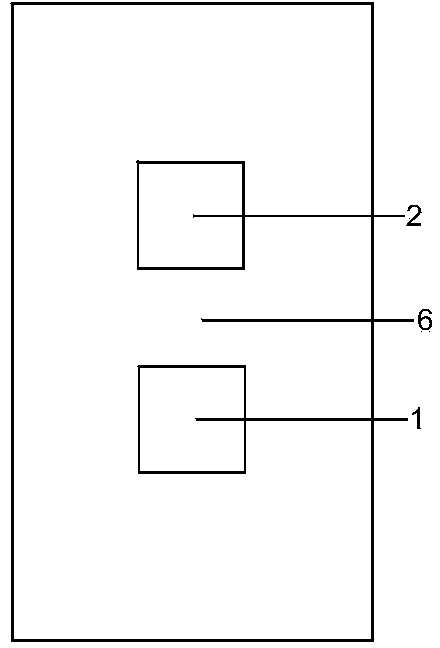

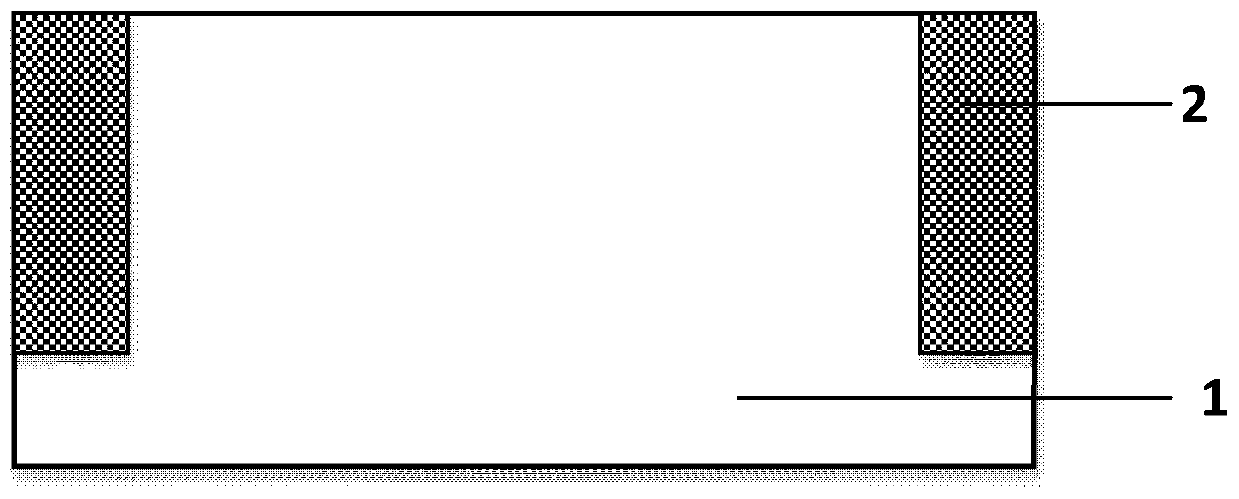

SOI dynamic threshold transistor

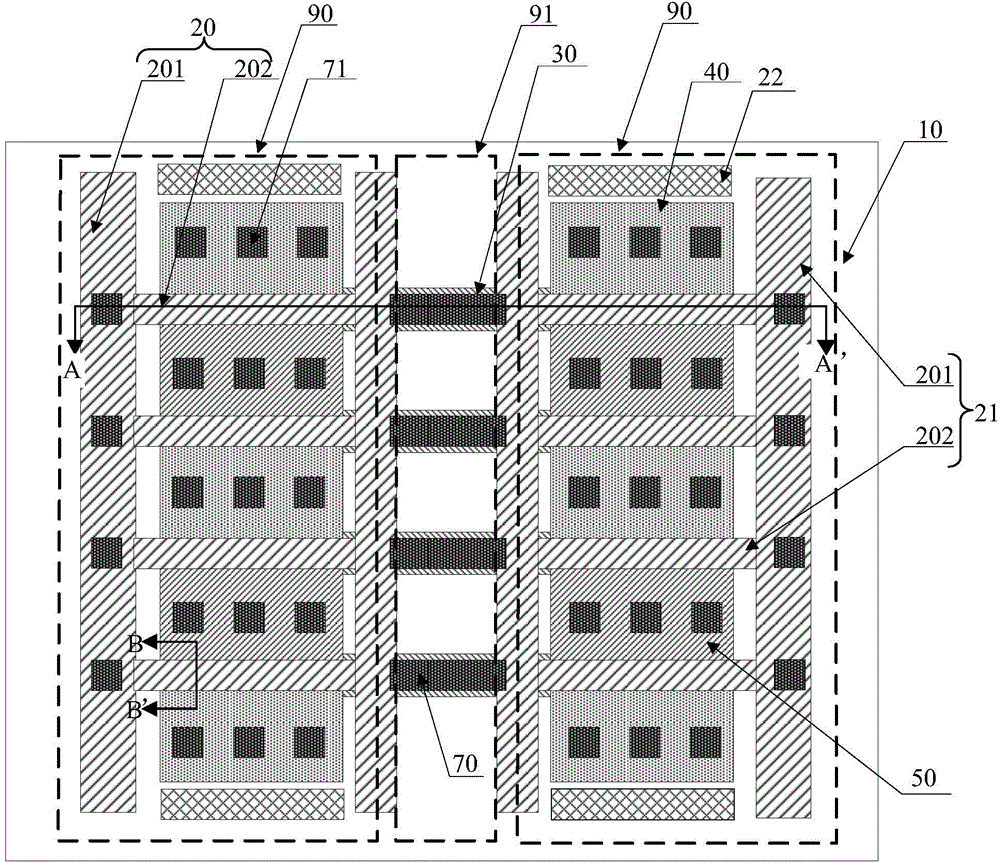

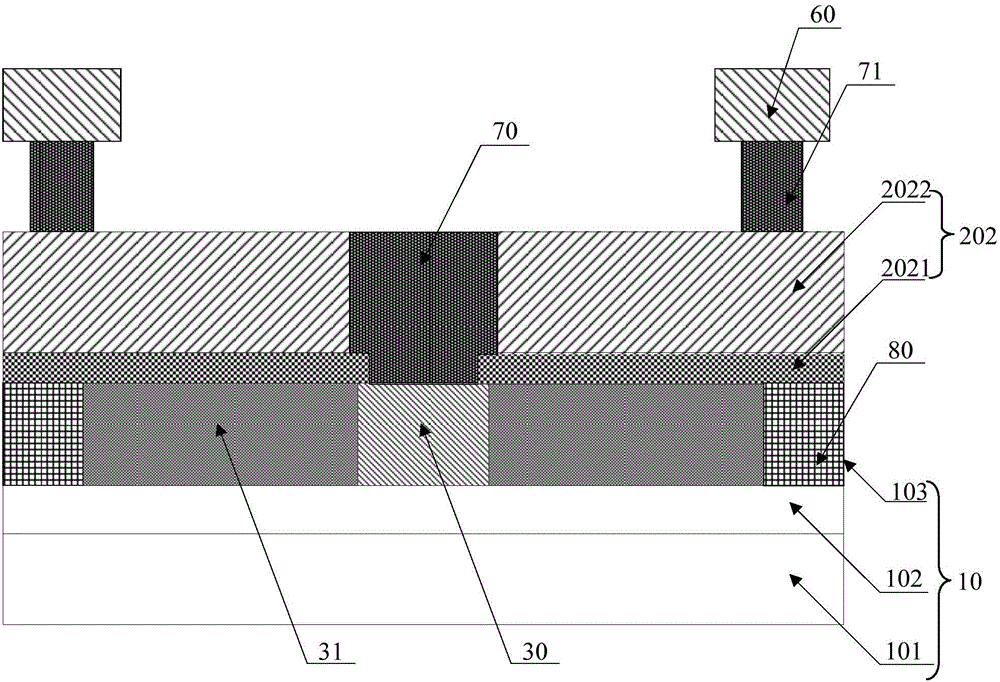

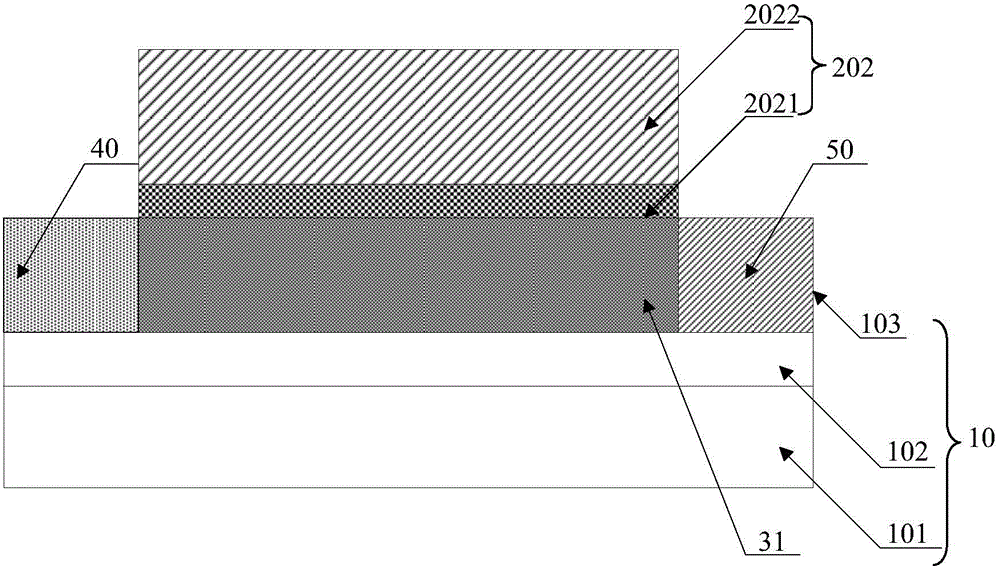

ActiveCN104362174AImprove RF performanceReduce areaSemiconductor devicesParasitic capacitorCapacitance

The invention provides an SOI dynamic threshold transistor which comprises a semiconductor substrate, a first multi-interdigital gate structure, a second multi-interdigital gate structure, a body contact region, a source region, a drain region and a first contact hole. A grid electrode is connected with the body contact region through the first contact hole. By the adoption of a body contact region sharing method, the utilization rate of the body contact region can be increased, and parasitic capacitance can be lowered; meanwhile, by the adoption of a multilateral connection mode, low gate resistance can be obtained. When a device is in a cut-off state, the threshold of the device is high, and the leaked current is low; when the device is in an on state, the threshold voltage of the device is lowered and the current is increased under the influence of the bulk effect. As a result, the device can have a steep sub-threshold slope and a large saturation current; meanwhile, the working voltage of the device is low, and the device is quite suitable for application at low power consumption. By the adoption of the design method, a parasitic resistor and a parasitic capacitor can be improved, and the SOI dynamic threshold transistor has certain application value in the radio frequency application field.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Tunneling field effect transistor inhibiting output non-linear opening and preparing method of tunneling field effect transistor

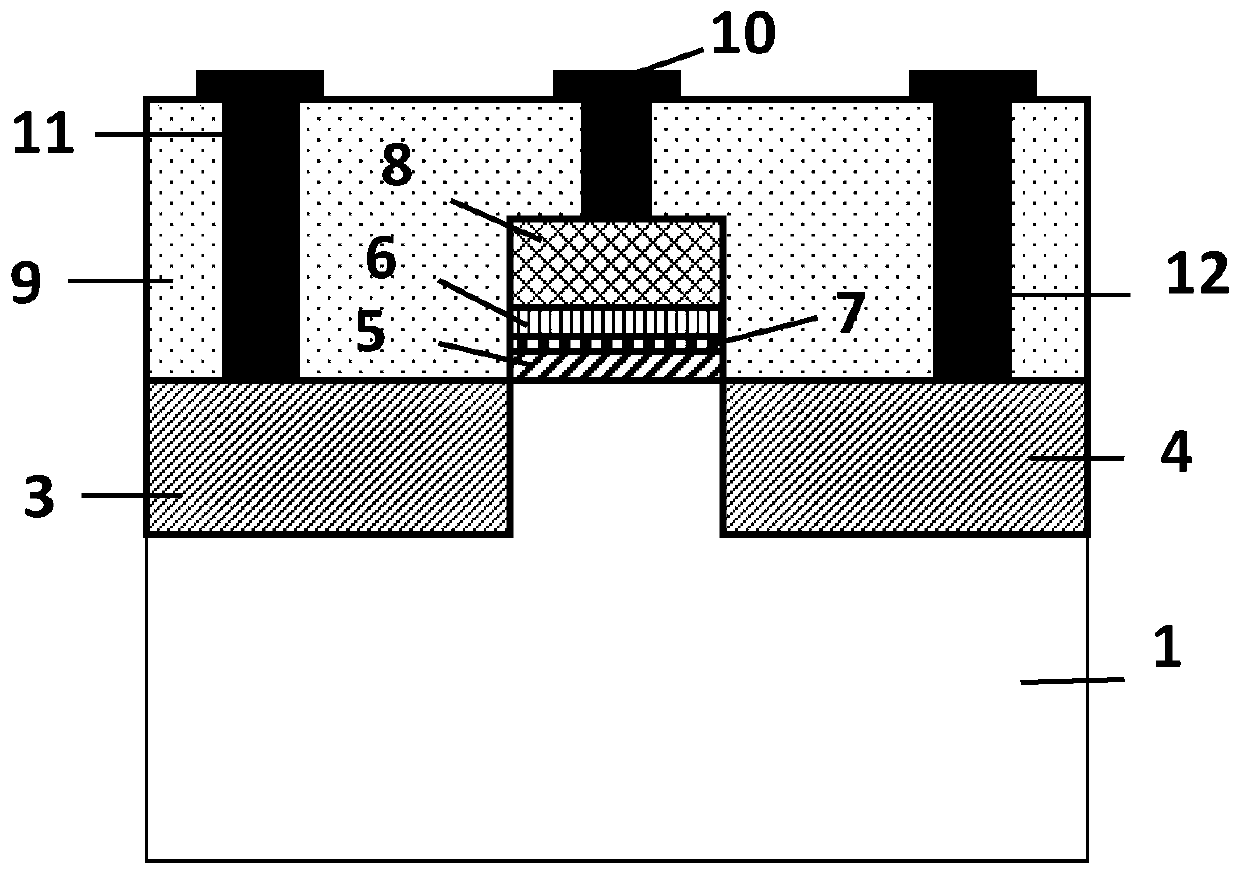

ActiveCN104347692ASteep subthreshold slopeSuppression of non-linear turn-on phenomenaSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor materials

The invention provides a tunneling field effect transistor inhibiting output non-linear opening. The tunneling field effect transistor comprises a tunneling source region, a channel region, a drain region, a semiconductor substrate region, a gate dielectric layer and a control gate, wherein the gate dielectric layer is positioned above the channel region, the control gate is positioned above the gate dielectric layer, the channel region is positioned above the channel source region, in addition, the position of the channel region is partially overlapped with the tunneling source region, a tunneling junction is formed at the interface part of the channel region and the tunneling source region, the drain region is parallel to the channel region and is positioned at the other side of the channel region, the control gate is positioned above the overlapping part of the channel region and the tunneling source region, a control-gate-free region is arranged in the channel region near the drain region, and in addition, the channel region adopts semiconductor materials with the energy state density being lower than 1E18cm<-3>. The tunneling field effect transistor has the advantages that the nonlinear opening phenomenon in the device output characteristics can be effectively inhabited, and in addition, the steeper and straighter sub-threshold slope is maintained.

Owner:PEKING UNIV

Tunneling field effect transistor (TFET) and manufacturing method thereof

ActiveCN102364690AGood subthreshold characteristicsSimple preparation processSemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorPower consumption

The invention discloses a tunneling field effect transistor (TFET) and a manufacturing method thereof, which belong to the fields of logic devices and circuits of field effect transistors. A high-doping source region of the TFET consists of a P<+> high-doping region and an N<+> high-doping region, and threshold values of a metal-oxide semiconductor field effect transistor (MOSFET) part and a TFET part of a device can be adjusted through ingenious layout variation, so that the performance of a TFET device is improved, and the manufacturing method is simple. Compared with the conventional TFET, the TFET has the advantages that: higher switch-on current can be obtained and a steep subthreshold gradient can be kept by the device under the condition of the same process and the same active region size, so that the TFET is expected to be used in a low power consumption field and has higher practical value.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

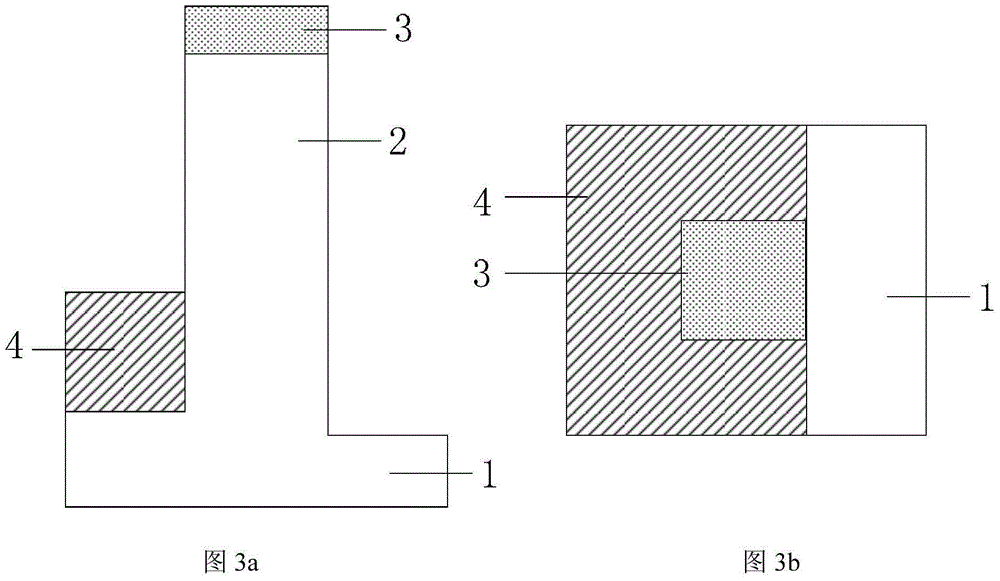

Multiple source MOS transistor with impurity segregation and production method thereof

ActiveCN102117834AControl channel surface potentialControl potentialSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

The invention provides a multiple source MOS (metal oxide semiconductor) transistor with impurity segregation and a production method thereof. The multiple source MOS transistor comprises a control gate electrode layer, a gate dielectric layer, a semiconductor substrate, a highly-doped source region and a highly-doped drain region; one end of a control gate extends towards the highly-doped sourceregion to form a T shape; the extended gate region is used as an extension gate; an original control gate region is a main gate; the highly-doped source region is formed by highly doping a semiconductor and is positioned on two sides of the extension gate along the width direction of the source region; and one side of the highly-doped region, which is away from the channel direction, is connectedwith a Schottky source region with impurity segregation. Compared with the present MOSFET (metal-oxide-semiconductor field-effect transistor), under the same process condition and the same size of the active region, higher conducting current, lower leakage current and steeper sub-threshold slope can be obtained.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Two-dimensional semiconductor material negative capacitance field effect transistor and preparation method thereof

ActiveCN108831928AReduce deteriorationMetal Contact Fermi Pinning ImprovementSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceFerroelectricity

The invention discloses a two-dimensional semiconductor material negative capacitance field effect transistor and a preparation method thereof; a two-dimensional alloy semiconductor material HfZrSe2 is adopted as a channel material, and the surface of the channel material is oxidized in air to generate HfZrO2, and then annealing is carried out to obtain an HfZrO2 dielectric layer with a ferroelectric property; a high-k gate dielectric layer is deposited on the dielectric layer, and a gate dielectric with a mixed structure is formed. By means of the device structure, high gate dielectric and channel two-dimensional semiconductor material interfaces can be obtained, the deterioration of the interface state on the sub-threshold characteristic is reduced, and the super-steep sub-threshold slope is easily obtained; meanwhile, the high-k gate dielectric on the upper layer can protect the HfZrO2 dielectric of the ferroelectric characteristics below, so that the dielectric is isolated from theair, and the stability of the device is greatly improved. The device is simple in preparation process and large-scale production can be realized.

Owner:PEKING UNIV

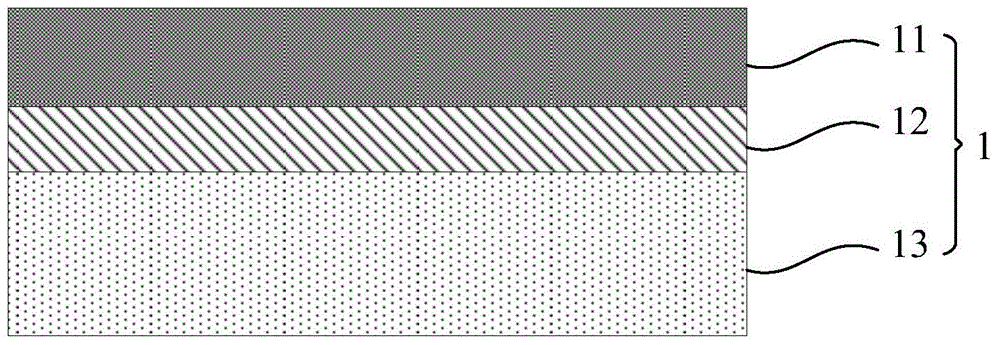

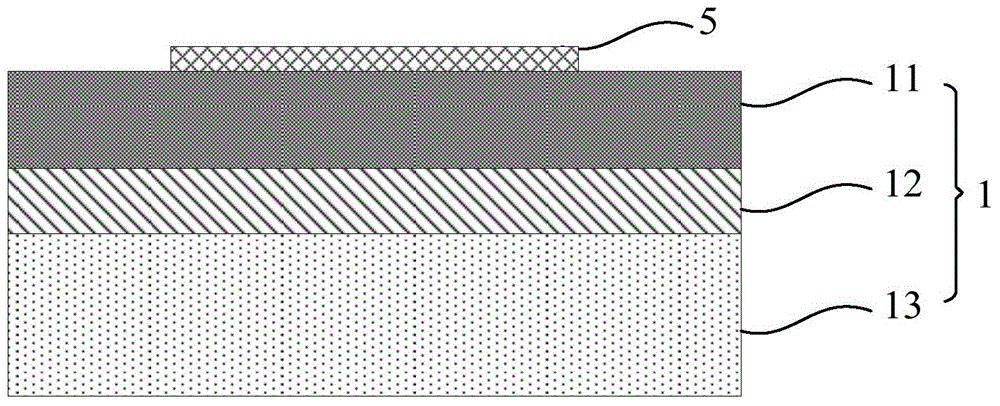

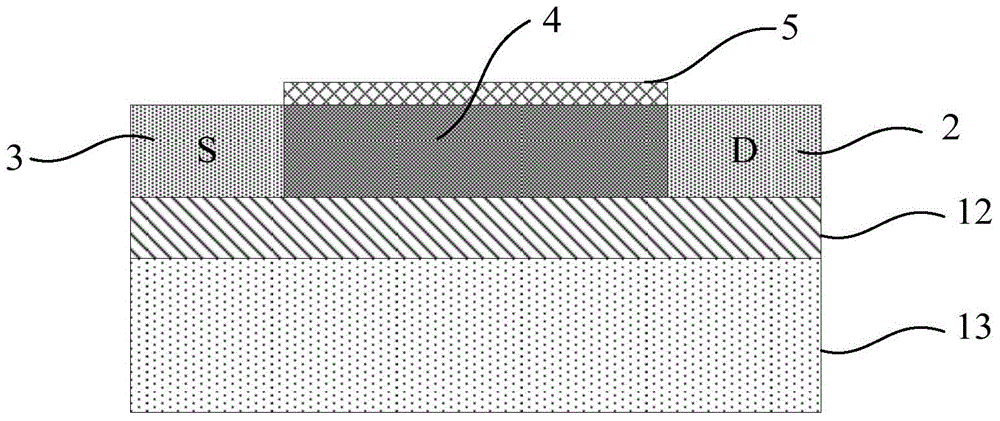

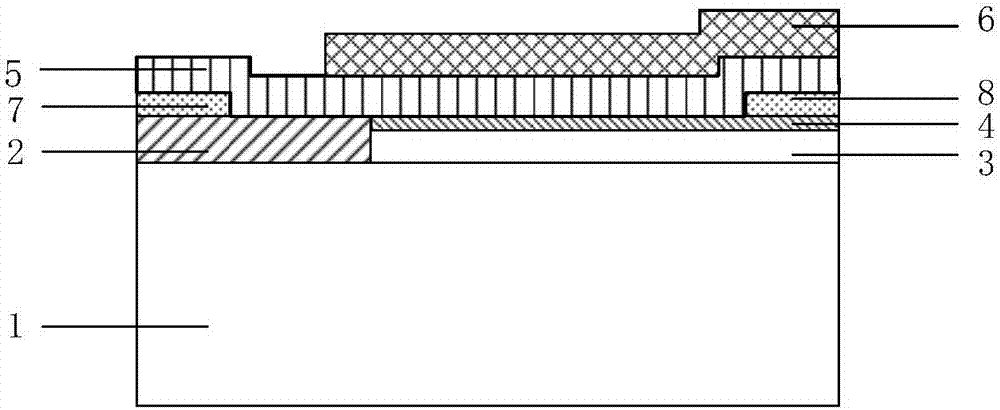

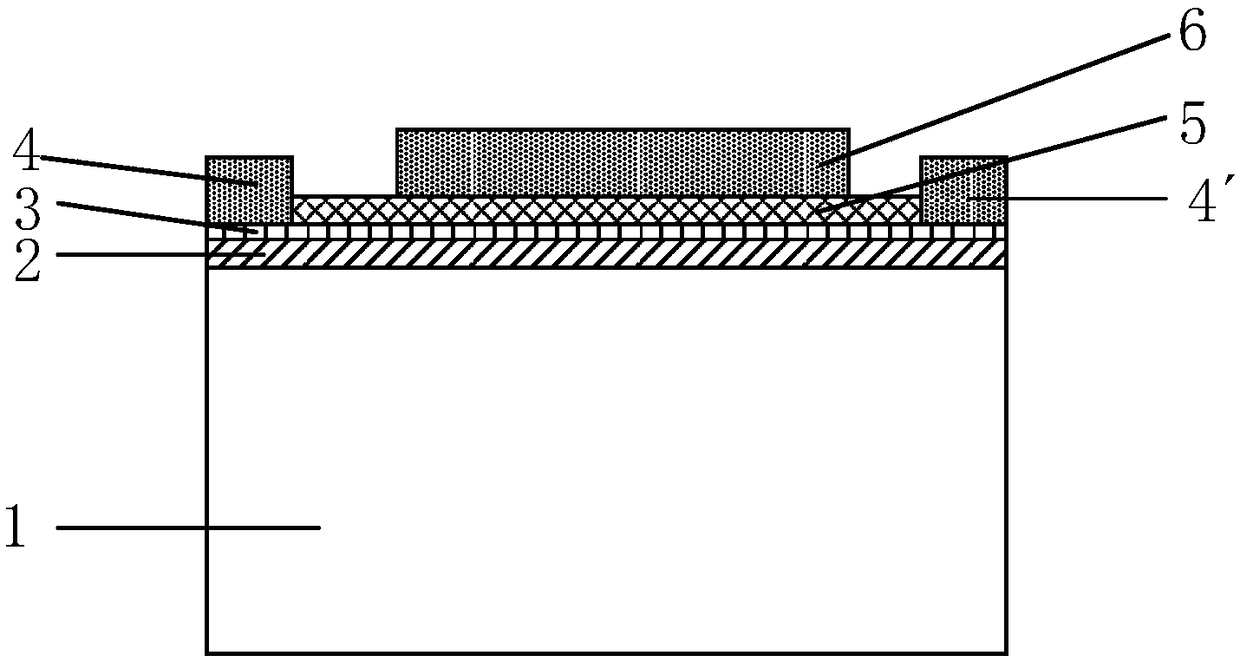

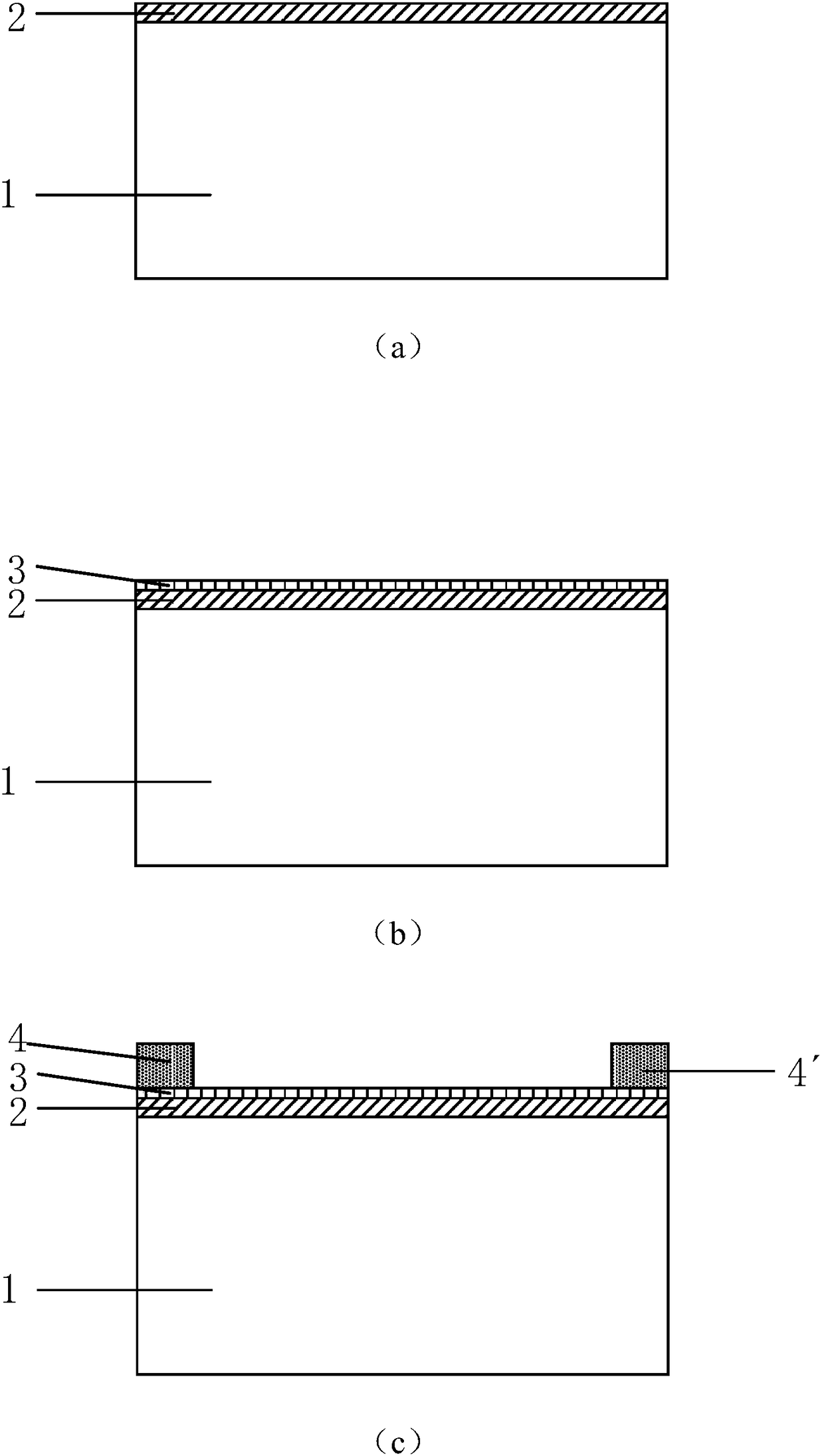

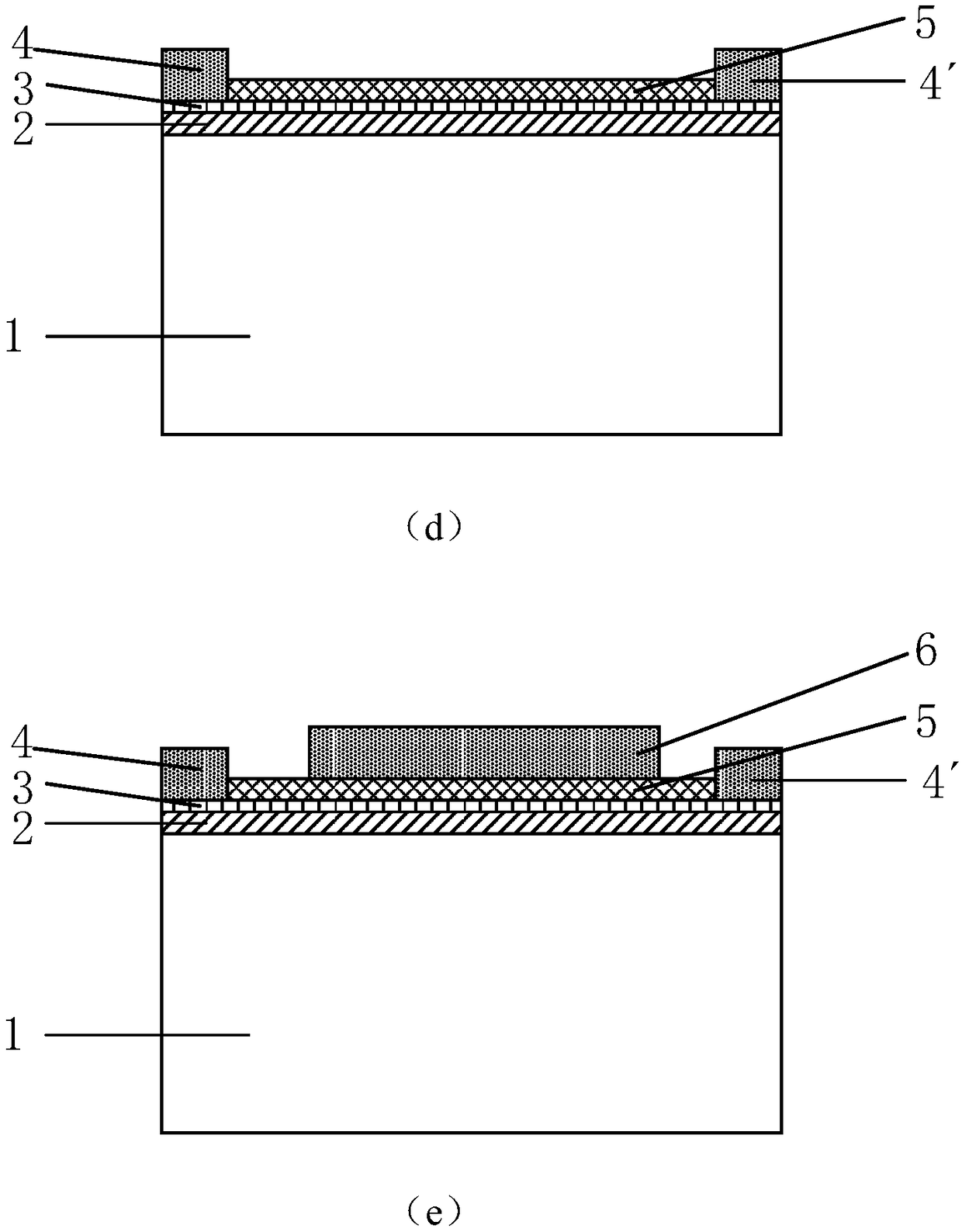

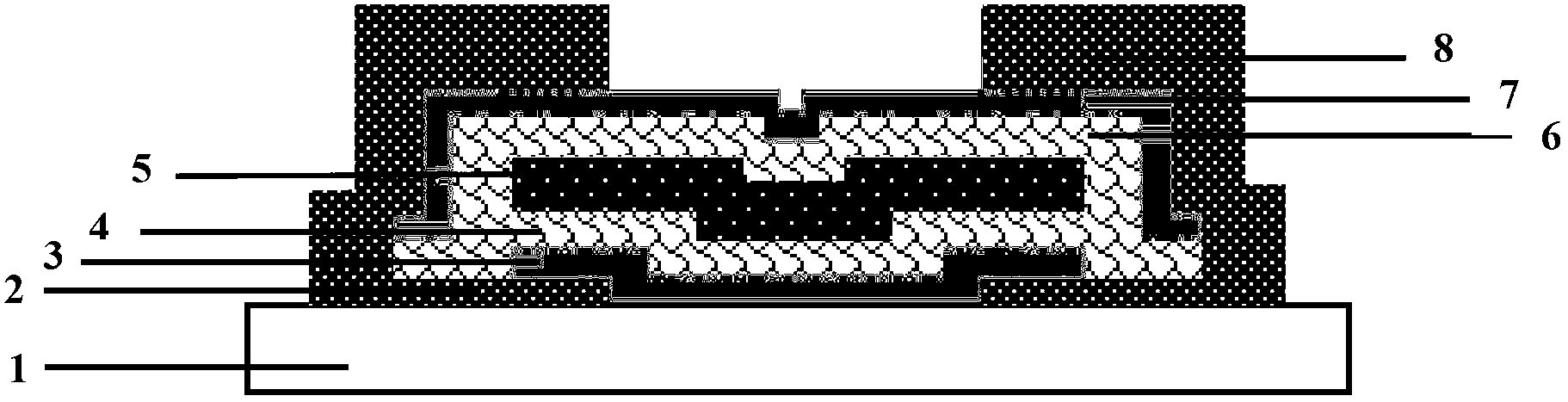

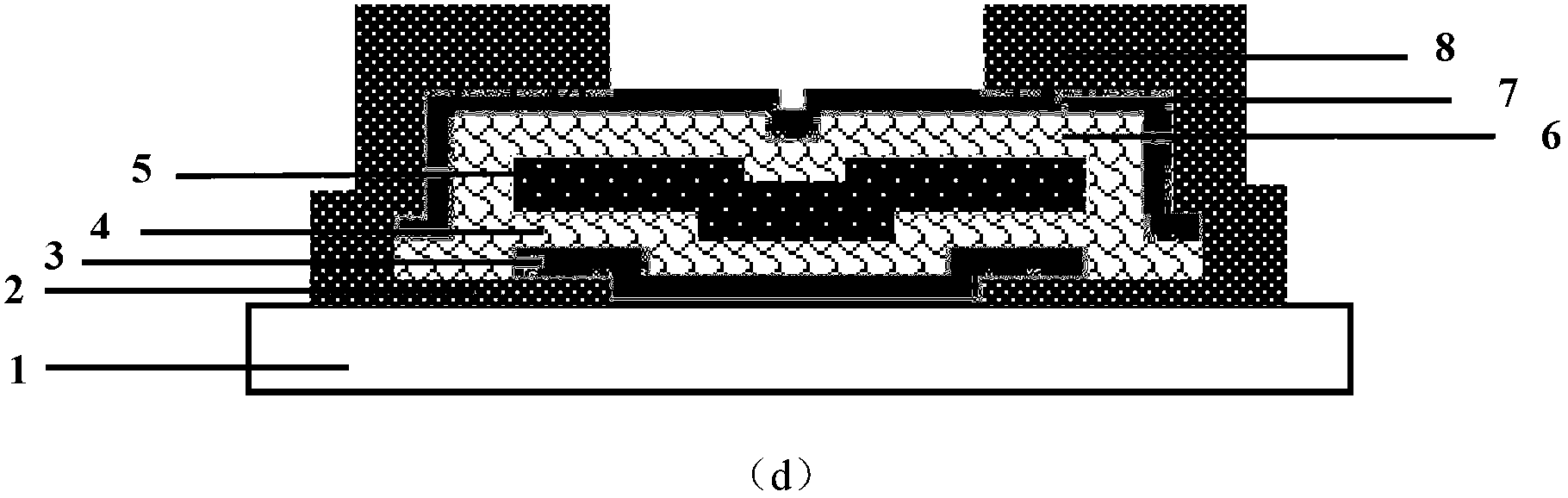

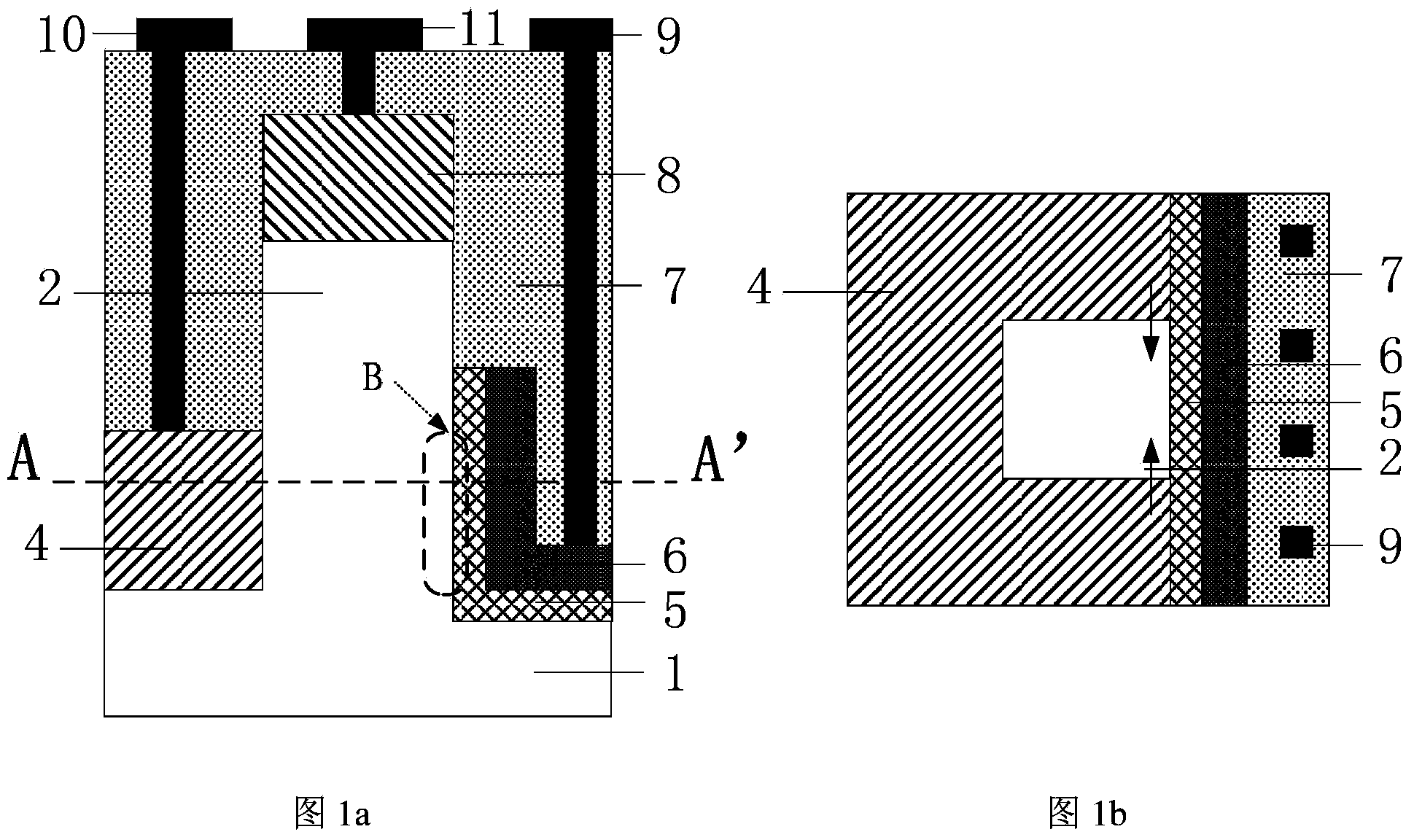

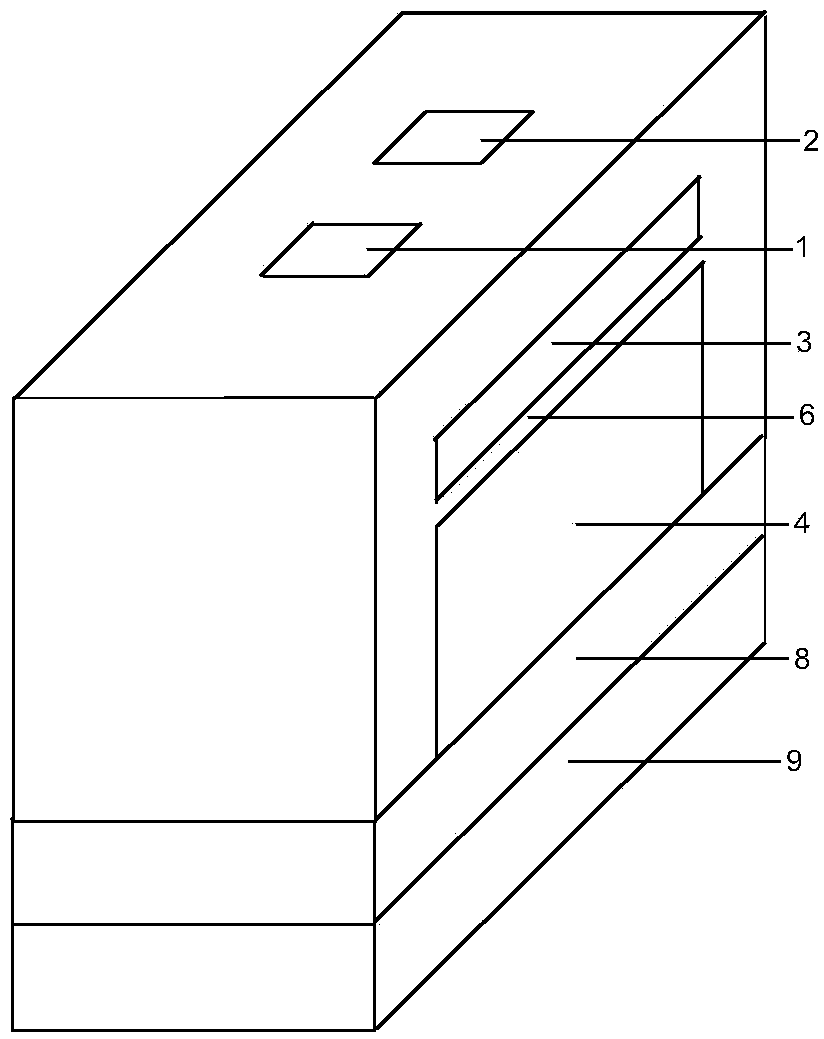

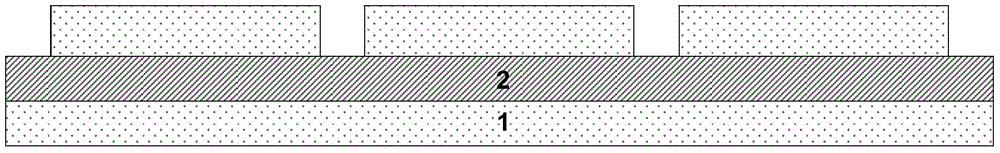

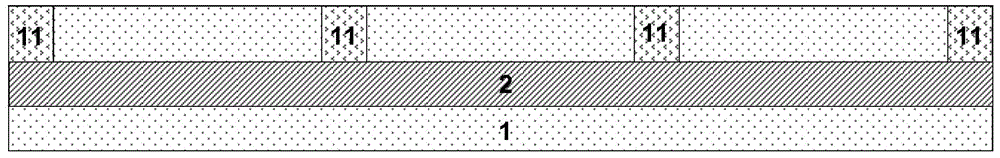

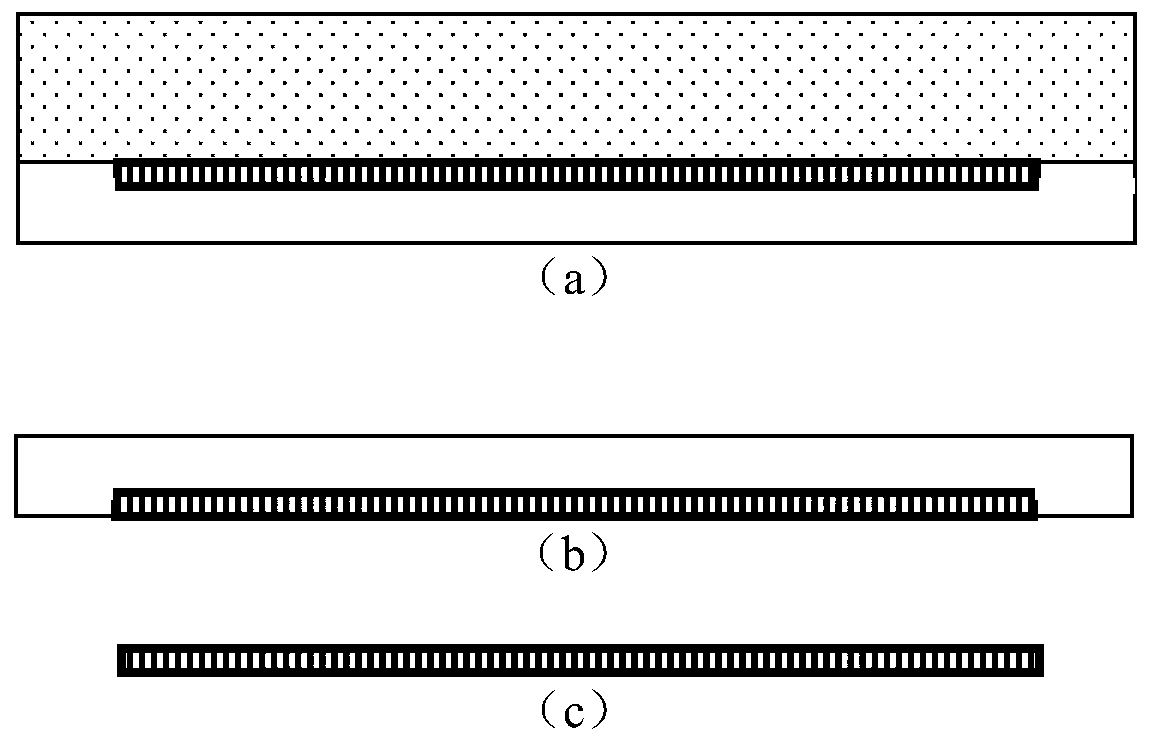

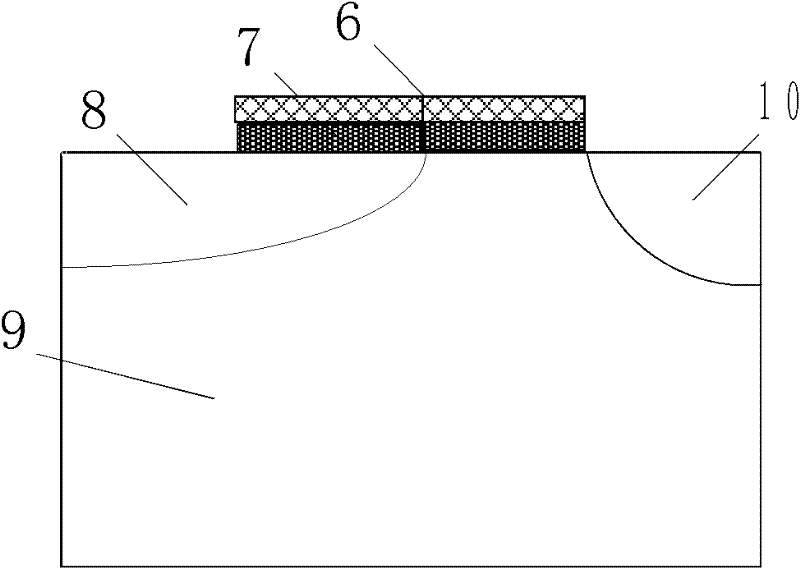

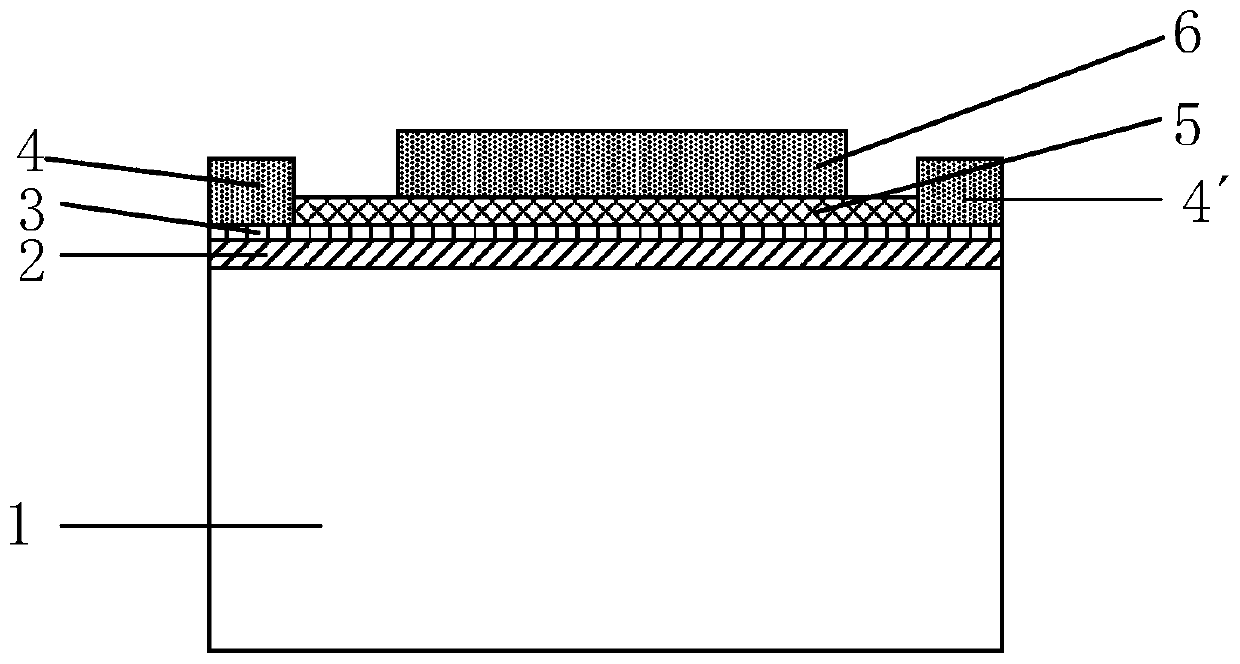

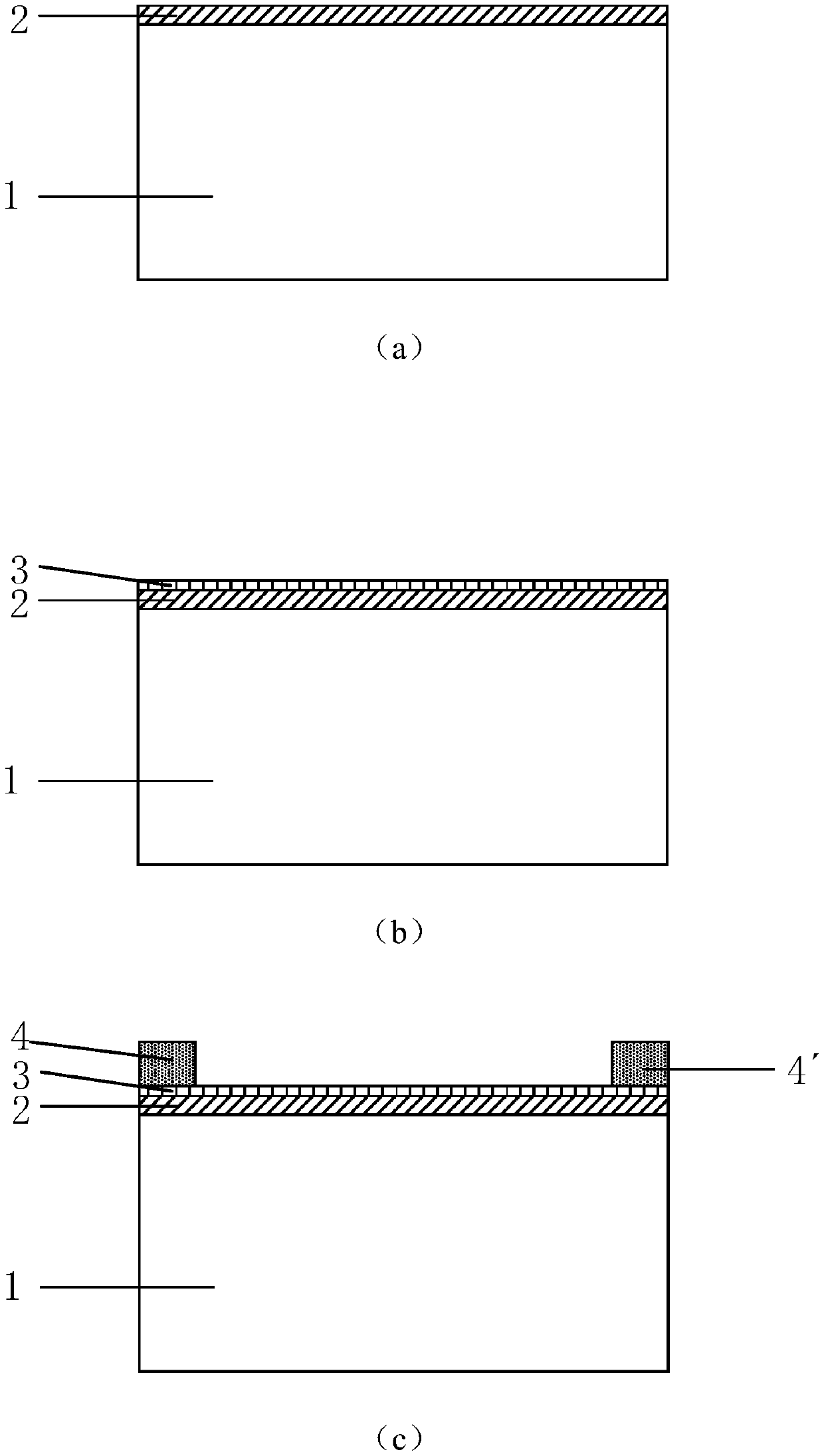

Three-dimensional (3D) oxide semiconductor thin film transistor and preparation method thereof

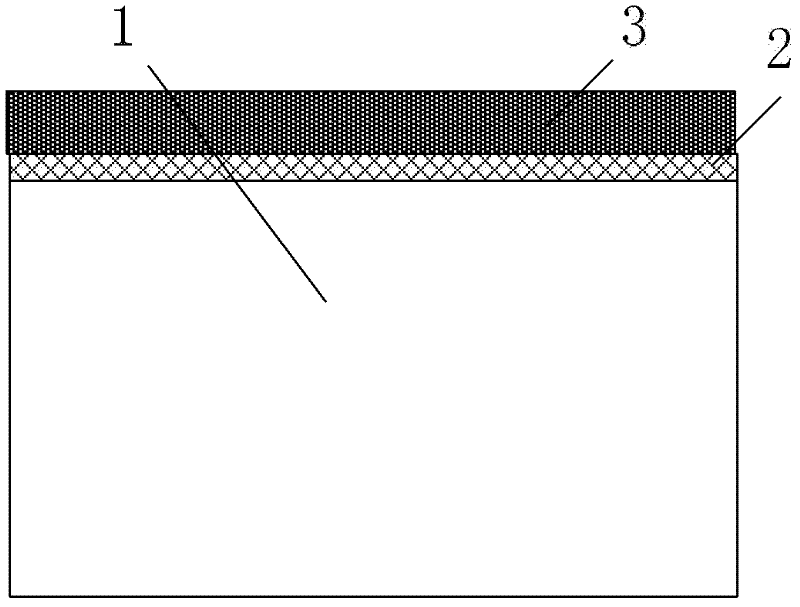

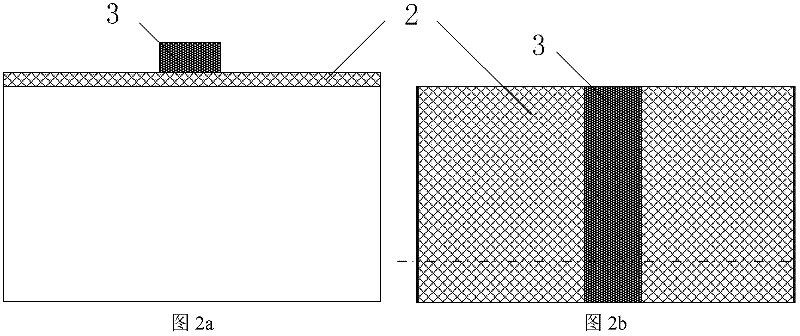

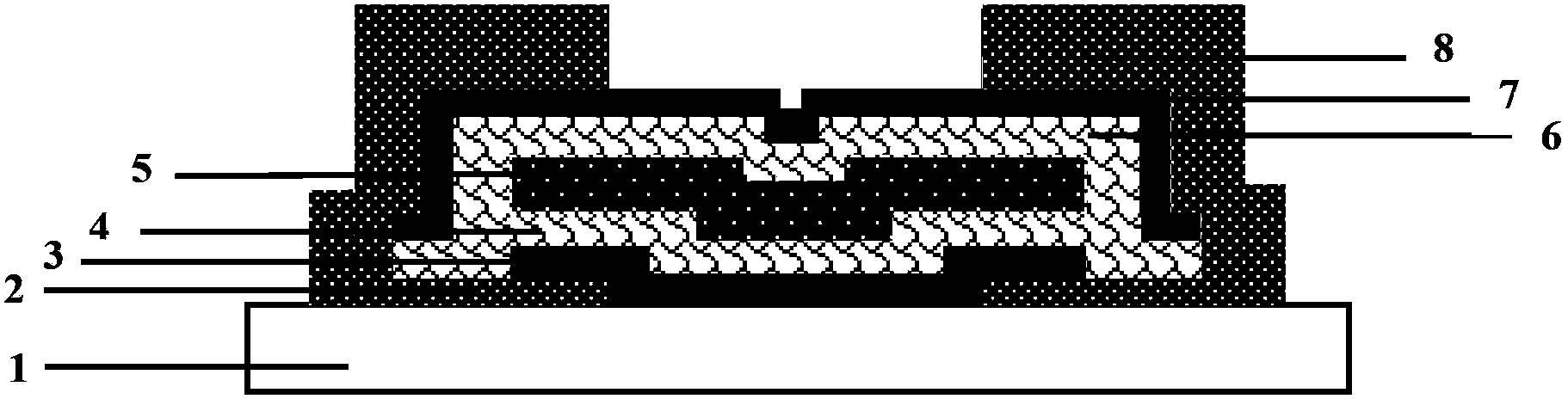

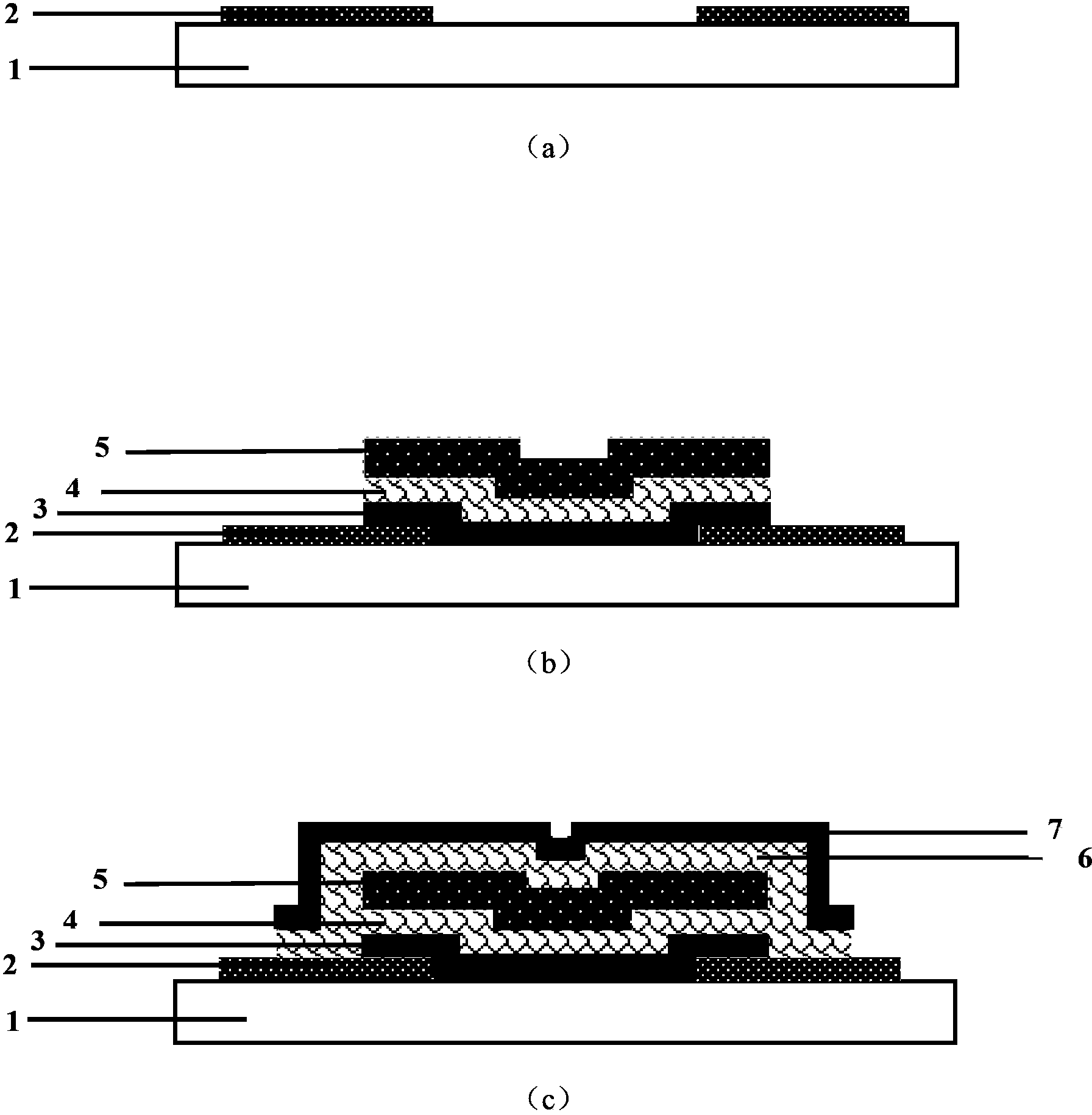

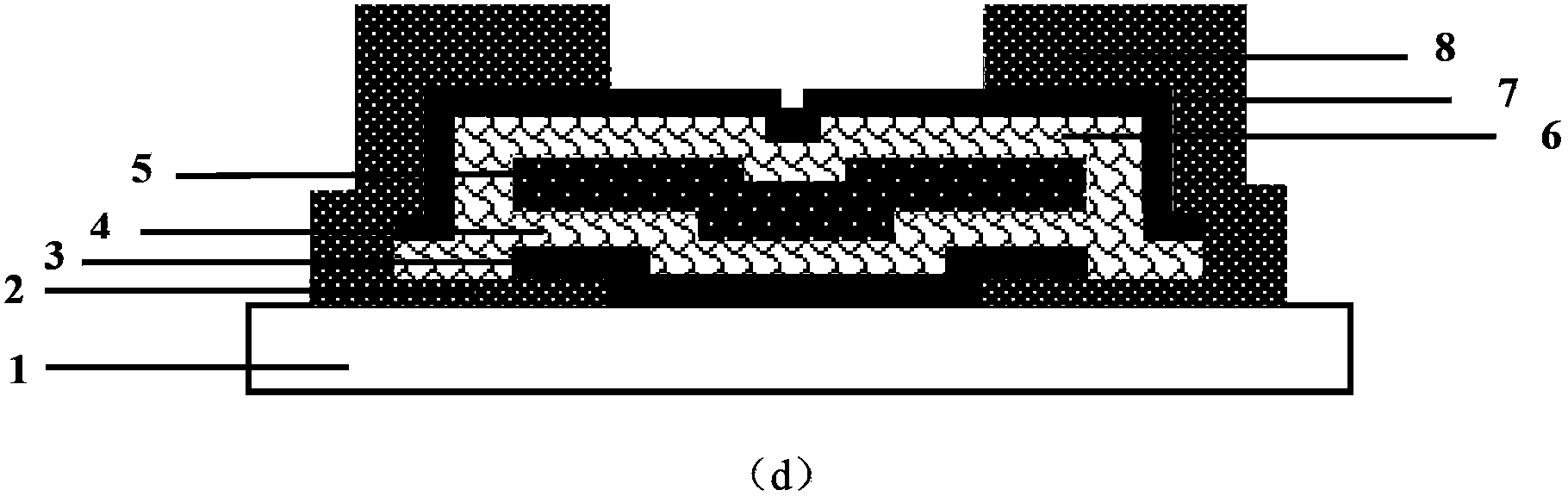

ActiveCN102709316AImprove driving abilityReduce interface defect statesTransistorSemiconductor/solid-state device manufacturingGate dielectricSub threshold

The invention discloses a three-dimensional (3D) oxide semiconductor thin film transistor (TFT) and a preparation method thereof. According to the TFT, the continuous growth of a lower-layer active area, a lower-layer gate dielectric and a gate electrode and the continuous growth of an upper-layer gate dielectric and an upper-layer active area are adopted, so that the interface deficiency state of an active layer and the gate dielectric can be greatly reduced to greatly improve the driving capability of the (TFT). Moreover, the same gate electrode can simultaneously control the upper-layer and lower-layer active areas, so that the driving capability of the TFT is further improved. The TFT prepared by the method has the good characteristics of high switch ratio, high on-state current, abrupt sub-threshold slope and the like. Therefore, the TFT and the preparation method thereof have high practical value, and are expected to be widely used for microelectronic and flat panel display industries. Furthermore, if the upper-layer and lower-layer active areas are controlled by different threshold voltages, a multi-threshold technology can be integrated into the same TFT, and the integration of the multi-threshold technology into the TFT is expected to widely used for pixel driving unit circuits.

Owner:BOE TECH GRP CO LTD

Comb-shaped gate composite source MOS (Metal Oxide Semiconductor) transistor and manufacturing method thereof

ActiveCN102117833AReduce parasitic resistanceReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierGate dielectric

The invention provides a composite source MOS (Metal Oxide Semiconductor) transistor with schottky barrier and comb-shaped gate structures and a manufacturing method thereof. The composite source MOS transistor comprises a control gate electrode layer, a gate dielectric layer, a semiconductor substrate, a high doped source region and a high doped drain region, wherein one side far away from the channel direction of the high doped source region is connected with a schottky source region; one end of a control gate extends towards the high doped source region; the extended gate region is an extension gate shaped like a comb; the original control gate region is a main gate; the active region covered by the extension gate is likewise a channel region with the substrate material; the high doped source region is formed by the high doping of semiconductor and is located on the two sides of each comb of the extension gate; and a schottky junction is formed at the channel under the schottky source region and the extension gate. Compared with the traditional MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor), the composite source MOS transistor can obtain a higher conduction current, a lower leakage current and a steeper subthreshold slope under a same technological condition and a same active region size.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

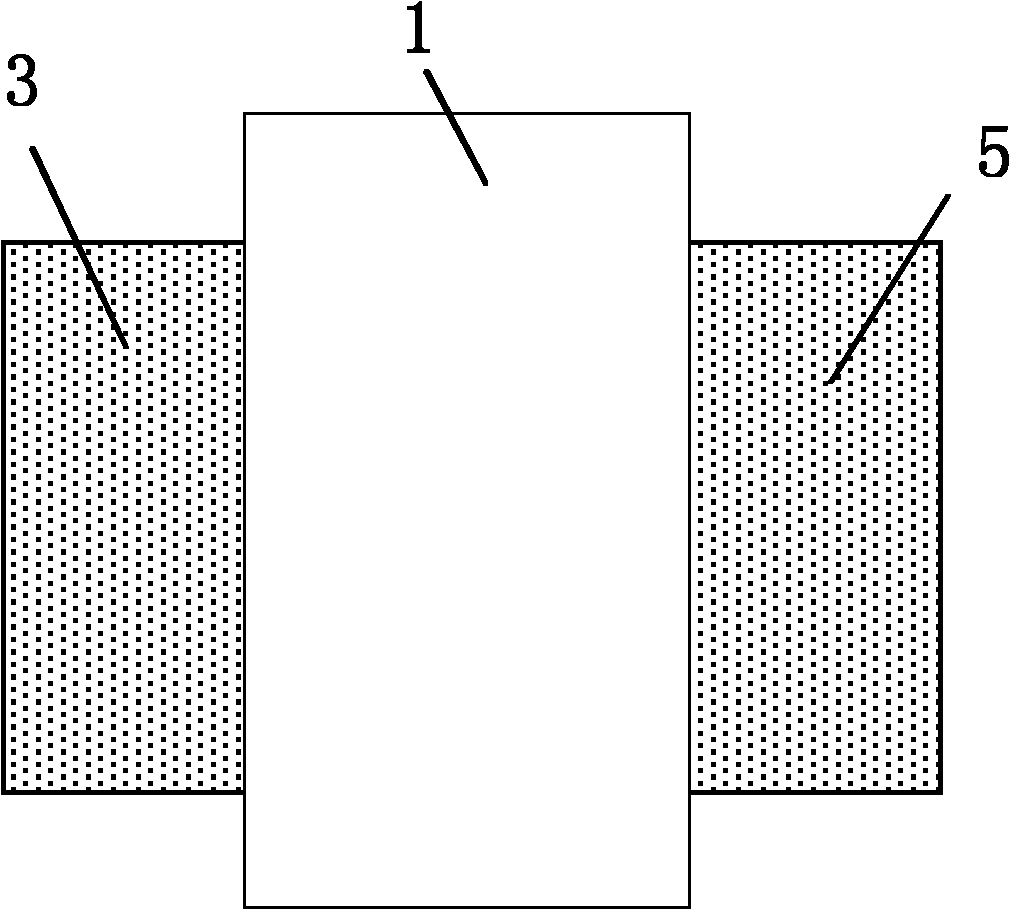

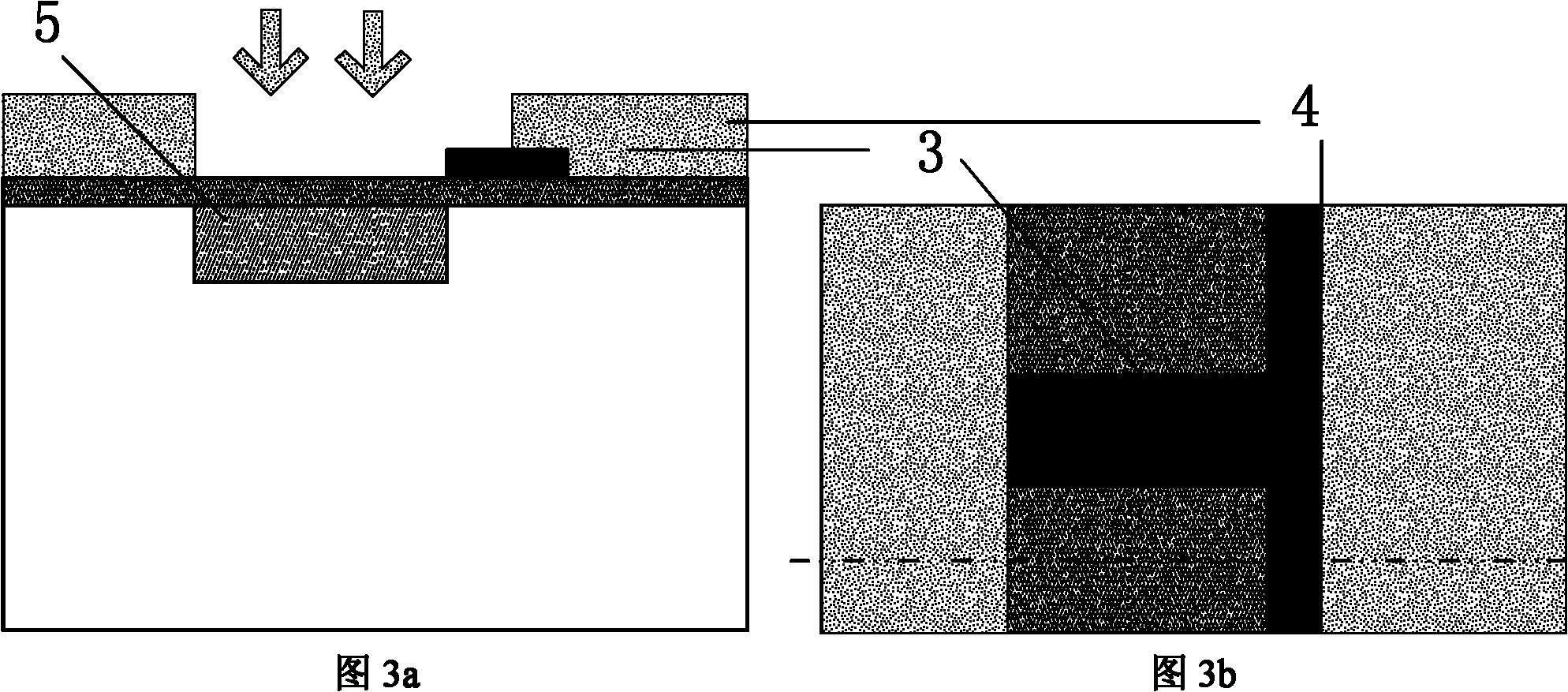

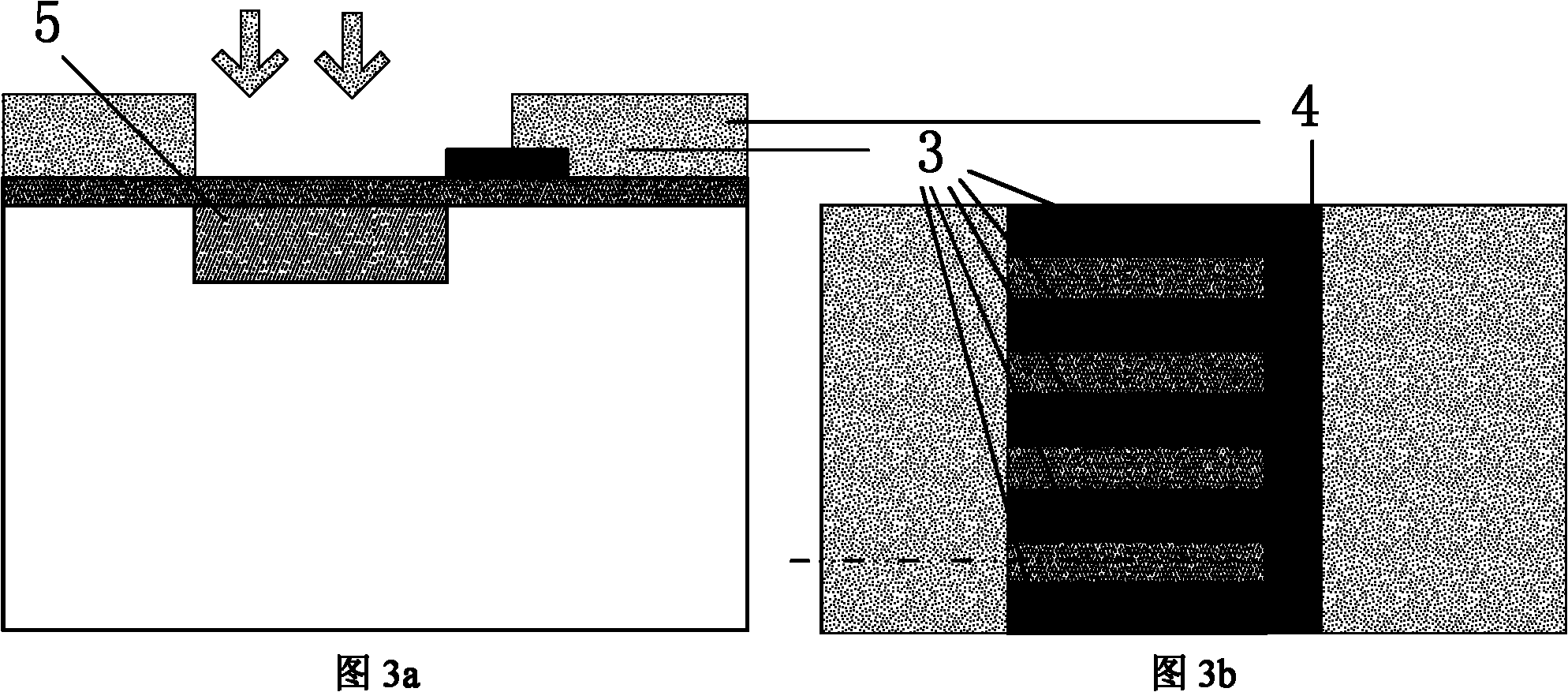

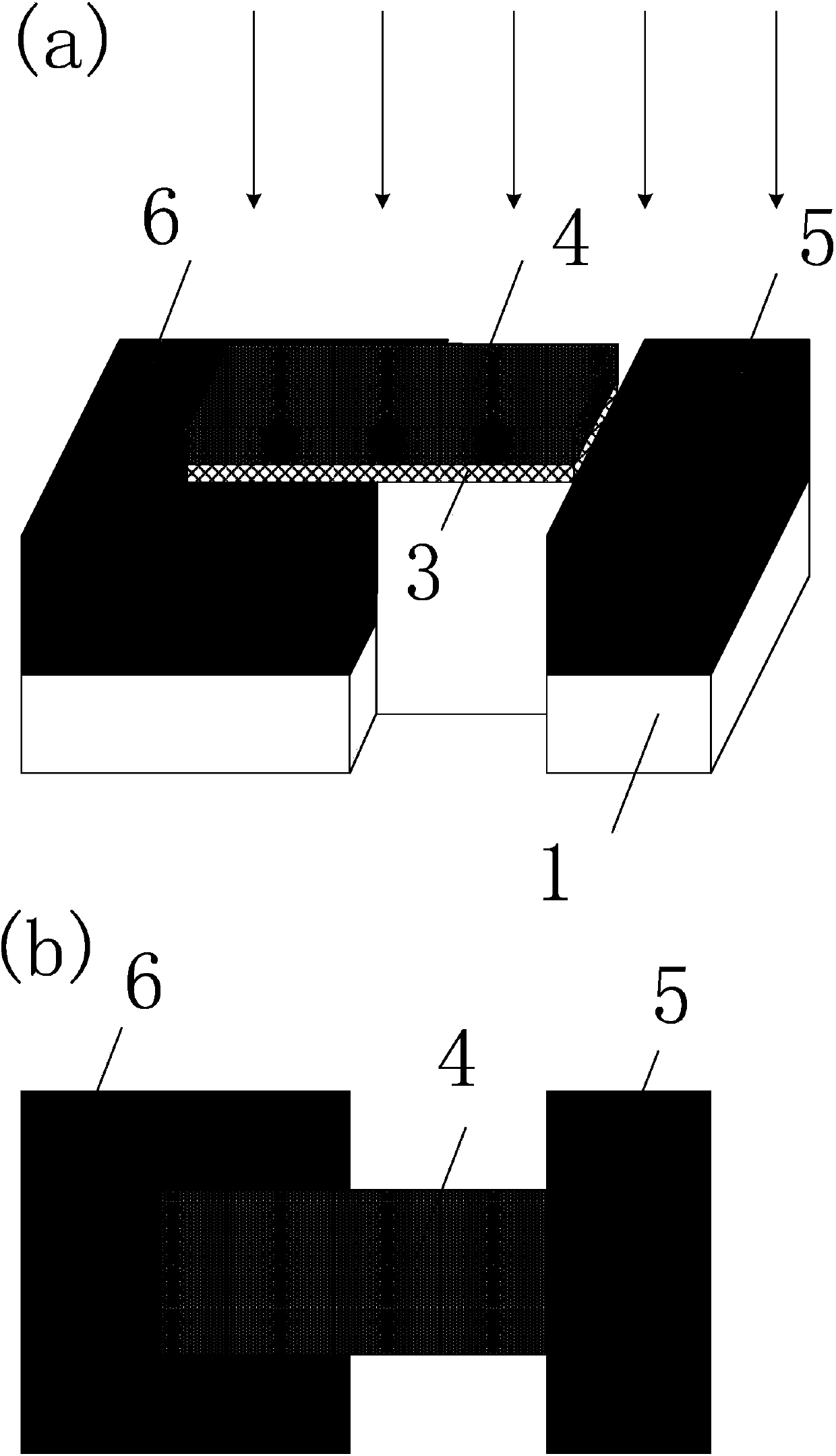

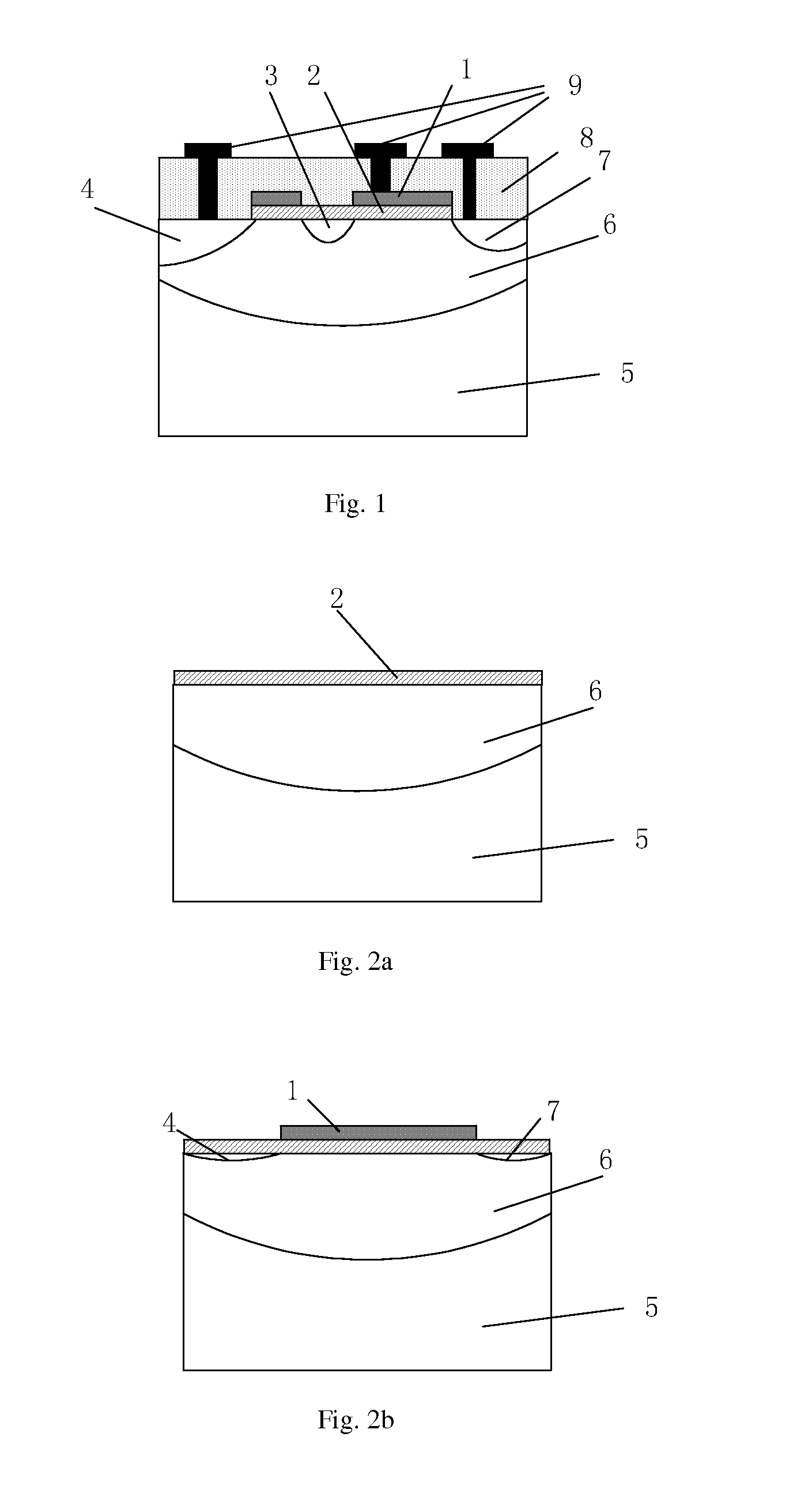

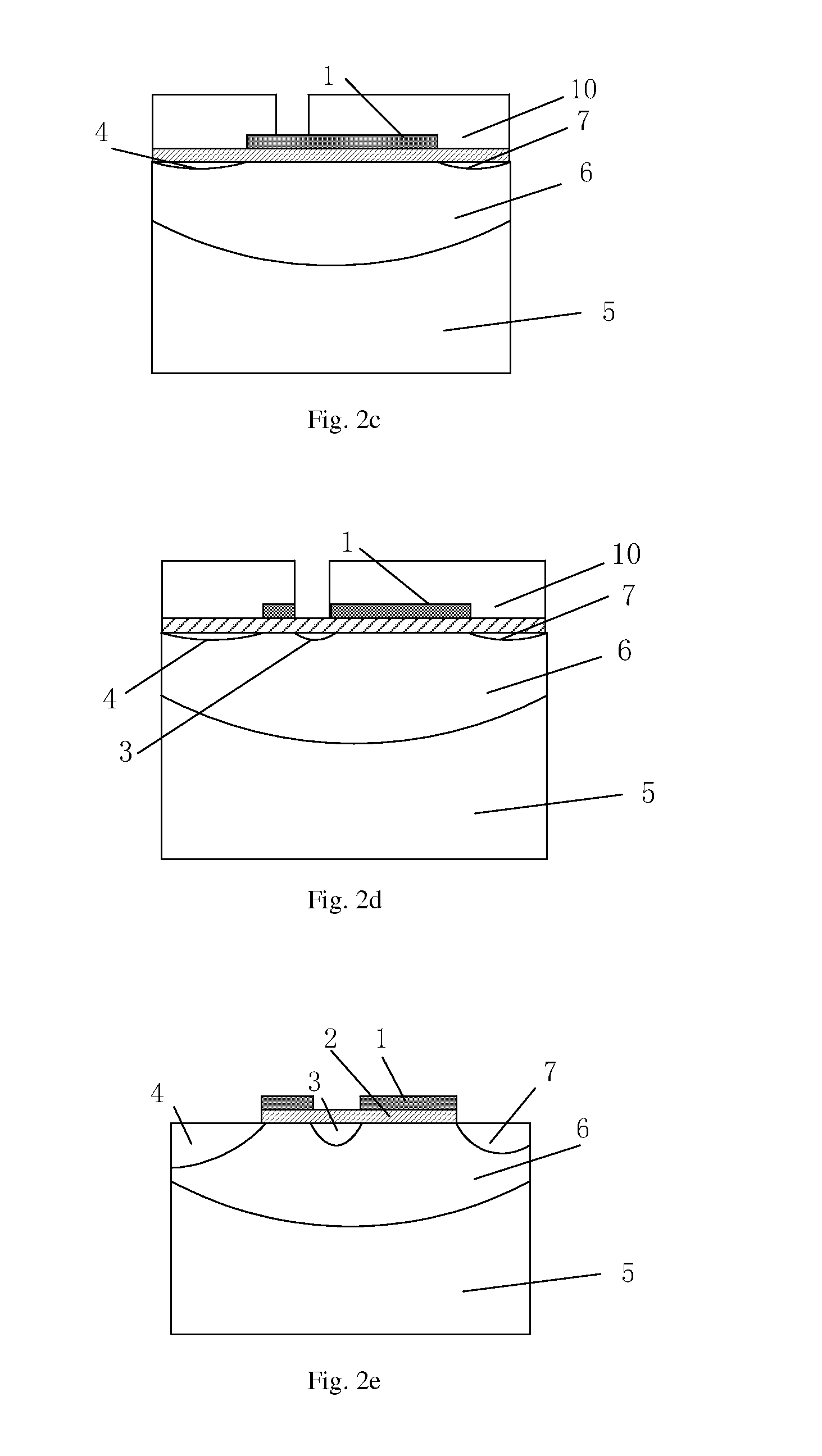

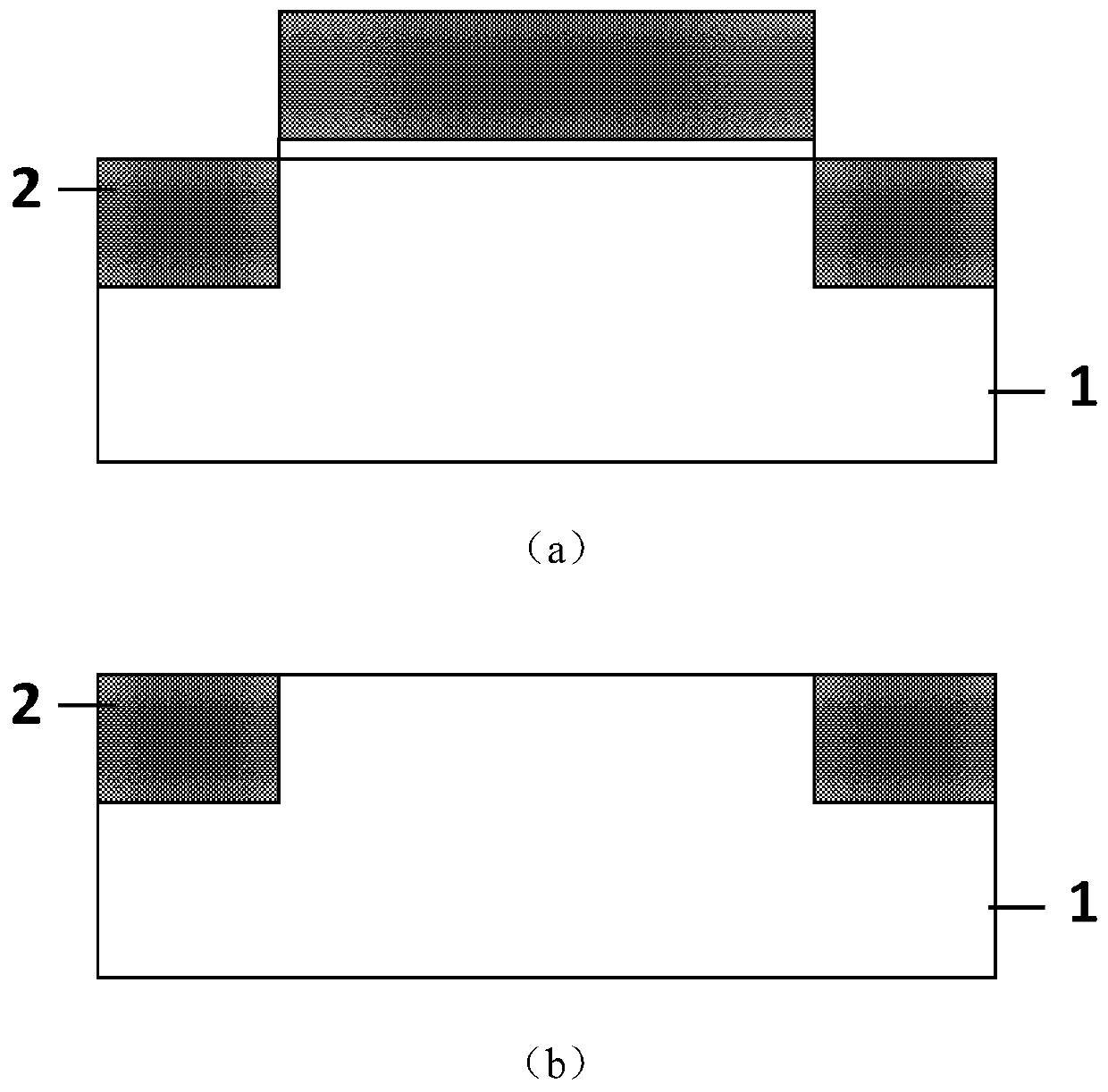

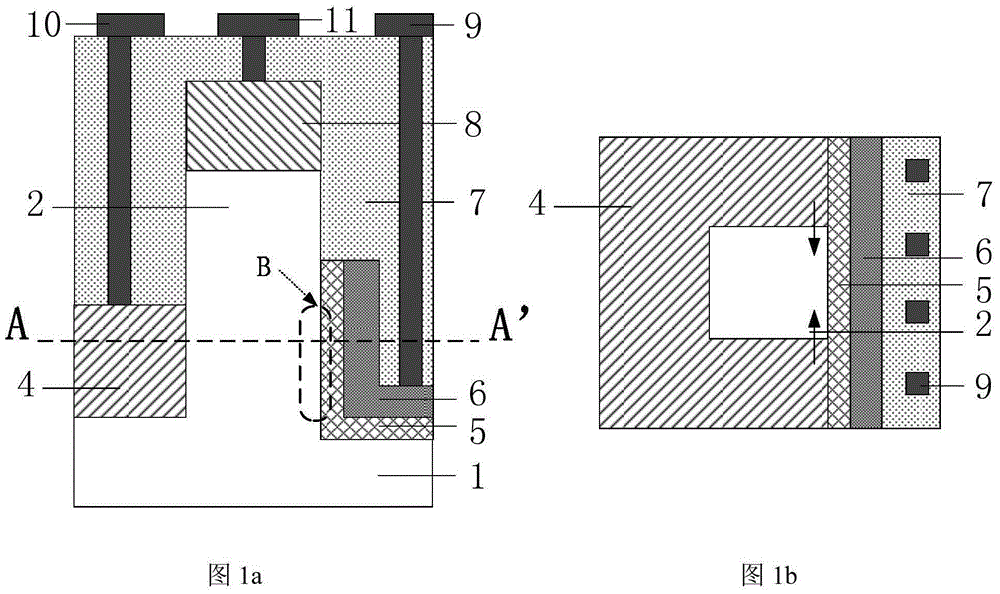

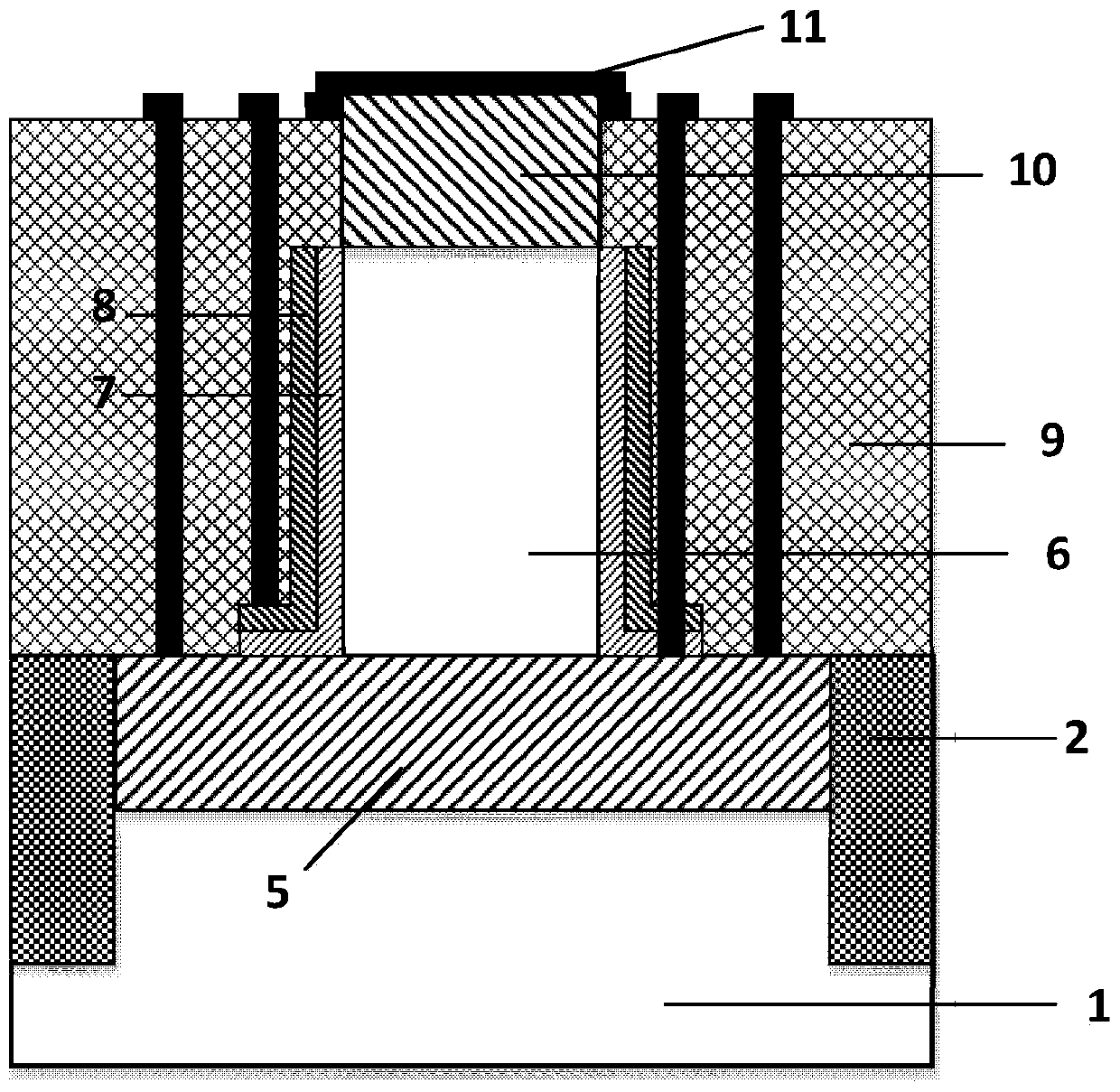

Junction-modulated type tunneling field effect transistor and manufacturing method thereof

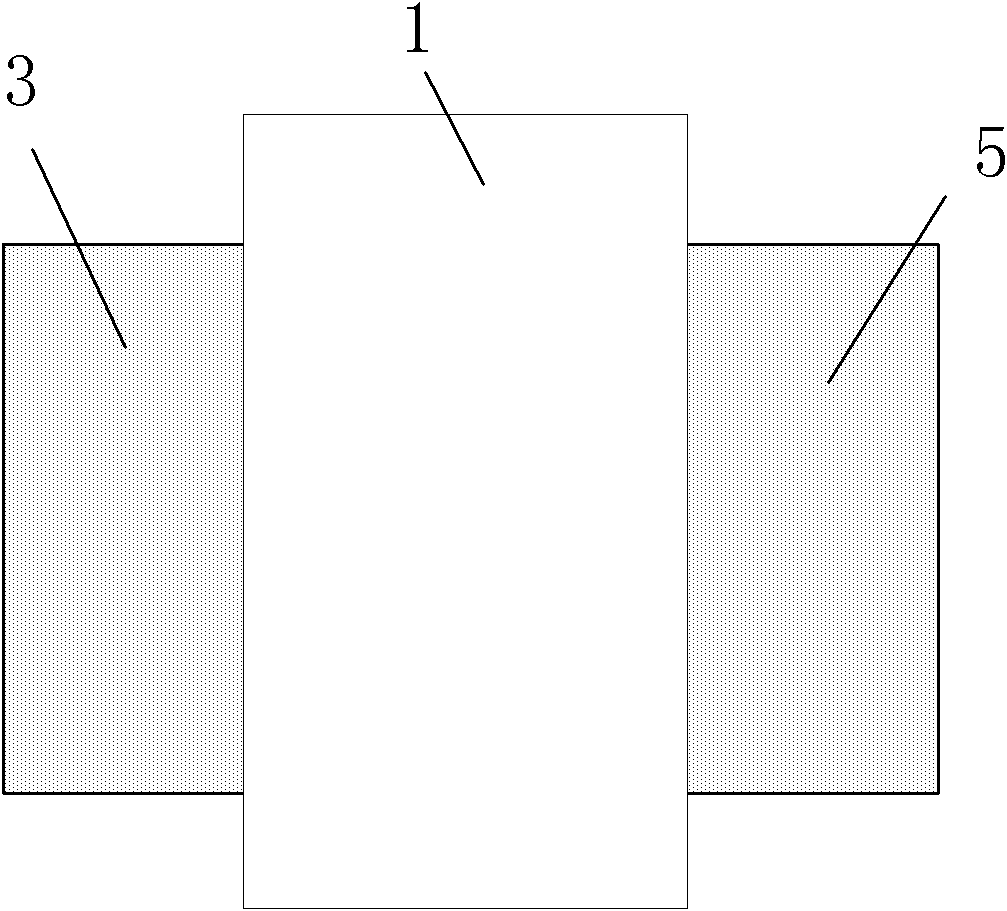

ActiveCN103594376AImproved subthreshold characteristicsSubthreshold characteristic steepSemiconductor/solid-state device manufacturingDiodePower flowEngineering

The invention discloses a junction-modulated type tunneling field effect transistor and a manufacturing method of the junction-modulated type tunneling field effect transistor, and belongs to the field of field effect transistor logic devices and circuits in CMOS ultra large scale integration (ULSI) circuits. According to the junction-modulated type tunneling field effect transistor, a PN junction provided by a highly-doped source region enclosed on three sides in a vertical channel region is utilized so that the channel region can be effectively used up, a surface channel energy band below a grid can be increased, a device can obtain a steeper energy band and a smaller tunneling barrier width compared with a traditional TFET when subjected to band-band tunneling, the effect of a steep tunnel junction doping density gradient is achieved equivalently, as a result, the subthreshold property of the traditional TFET is improved substantially, and breakover currents of the device are increased at the same time. According to the junction-modulated type tunneling field effect transistor and the manufacturing method of the junction-modulated type tunneling field effect transistor, under the condition that the junction-modulated type tunneling field effect transistor is compatible with an existing CMOS process, the bipolar breakover effect of the device is restrained effectively, parasitic tunneling currents at corners of a source junction with a small size also can be restrained, and the effect of steep source junction doping density can be achieved equivalently.

Owner:PEKING UNIV

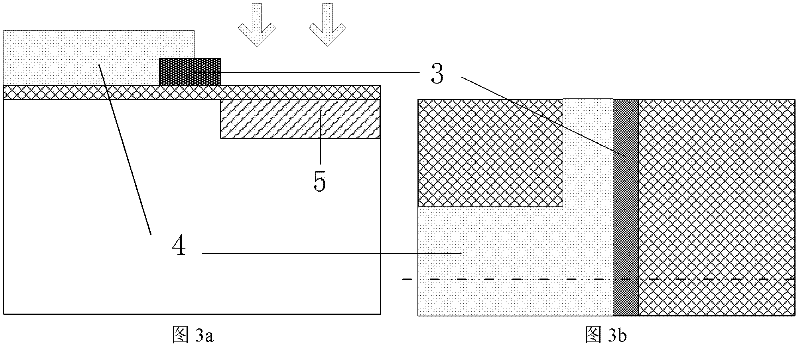

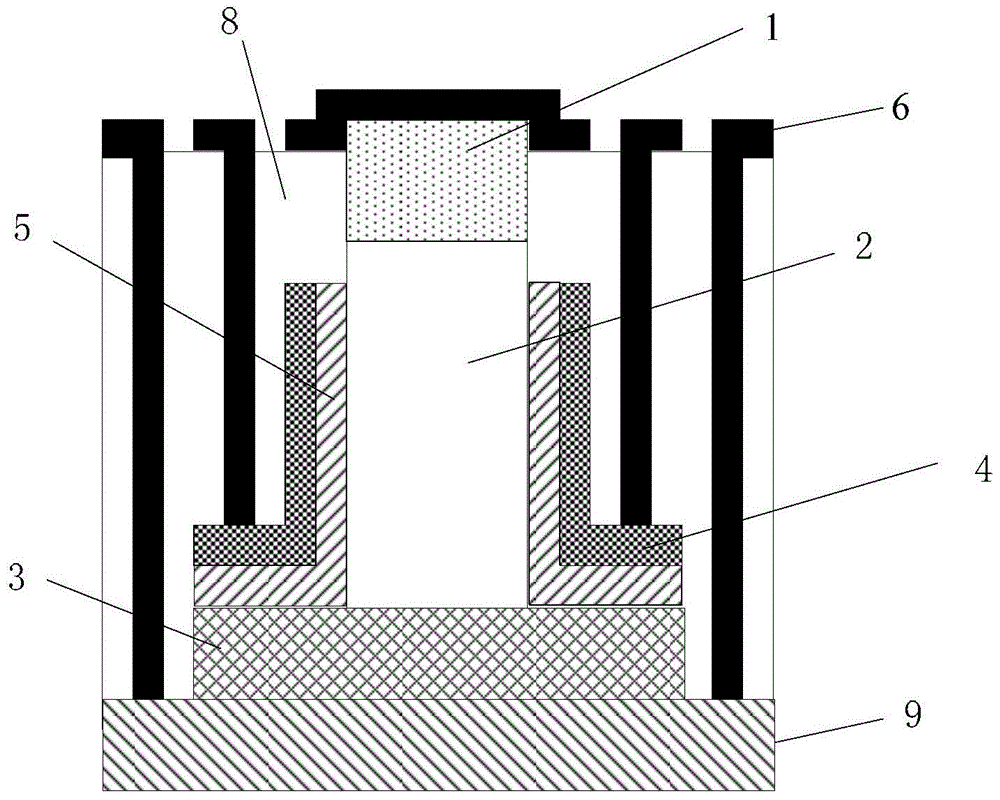

Tunneling field-effect transistor with composite-mechanism strip-type grid and preparation method of tunneling field-effect transistor

ActiveCN103474464AIncrease the on-state currentIncrease subthreshold slopeSemiconductor/solid-state device manufacturingDiodeCMOSPunching

The invention discloses a tunneling field-effect transistor with a composite-mechanism strip-type grid and a preparation method of the tunneling field-effect transistor and belongs to the field of logic devices and circuits of field-effect transistors in CMOS (Complementary Metal Oxide Semiconductor) ultra-large-scale integrated (ULSI) circuits. The tunneling field-effect transistor has the advantages that the energy band of surface channels under the grid can be improved by changing the shape of the grid and utilizing a depletion effect of PN nodes on the two sides of the strip-type grid, and the subthreshold characteristic of the device is improved; since a composite mechanism is introduced into double-doped source areas, an ON state current of the device is improved; due to an I-shaped design of an active area, body leakage currents, including a source-drain direct tunneling current and a punching current, between the two doped source areas to a doped drain area can be greatly inhibited, and a short-channel effect is inhibited, so that the device with small size can be applied.

Owner:PEKING UNIV

High-integration-level source, drain and gate auxiliary control U-shaped channel high-mobility-ratio junction-free transistor shaped like Chinese character 'ri'

InactiveCN104282753ALow source-drain resistanceImprove mobilitySemiconductor devicesElectrical resistance and conductanceChinese characters

The invention relates to a high-integration-level source, drain and gate auxiliary control U-shaped channel high-mobility-ratio junction-free transistor shaped like the Chinese character 'ri'. Two independently-controlled gate electrodes including the auxiliary control gate electrode shaped like the Chinese character 'ri' and the gate electrode are adopted, it is guaranteed that the dosing concentration of the device is reduced to improve the mobility ratio, and the device mobility ratio reduction and the device stability reduction caused by strengthening of the random scattering effect under the high doping concentration are avoided; meanwhile, the resistance of source and drain areas is effectively reduced through the auxiliary control gate electrode shaped like the Chinese character 'ri', so that the contradictions that the source and drain resistance will be increased if the doping concentration of a channel of a common junction-free transistor is excessively low, and the device mobility ratio reduction and the device stability reduction will be caused if the doping concentration is excessively high are overcome; meanwhile, U-shaped monocrystalline silicon serves a channel part of the device; compared with a common plane structure, on the premise that the chip area is not additionally increased, the effective channel length is obviously increased to reduce the short channel effect of the device under the deep nanoscale, and therefore the high-integration-level source, drain and gate auxiliary control U-shaped channel high-mobility-ratio junction-free transistor shaped like the Chinese character 'ri' is suitable for application and popularization.

Owner:SHENYANG POLYTECHNIC UNIV

Tunneling current amplification transistor

InactiveUS20120267700A1Improve device performanceReduce leakage currentTransistorCMOSGate dielectric

The present invention discloses a tunneling current amplification transistor, which relates to an area of field effect transistor logic devices in CMOS ultra large scale semiconductor integrated circuits (ULSI). The tunneling current amplification transistor includes a semiconductor substrate, a gate dielectric layer, an emitter, a drain, a floating tunneling base and a control gate, wherein the drain, the floating tunneling base and the control gate forms a conventional TFET structure, and a doping type of the emitter is opposite to that of the floating tunneling base. A position of the emitter is at the other side of the floating tunneling base with respect to the drain. A type of the semiconductor between the emitter and the floating tunneling base is the same as that of the floating tunneling base. As compared with the conventional TFET, the tunneling current amplification transistor of the present invention can increase the on-current of the device effectively and increase the driving capability of the device.

Owner:PEKING UNIV

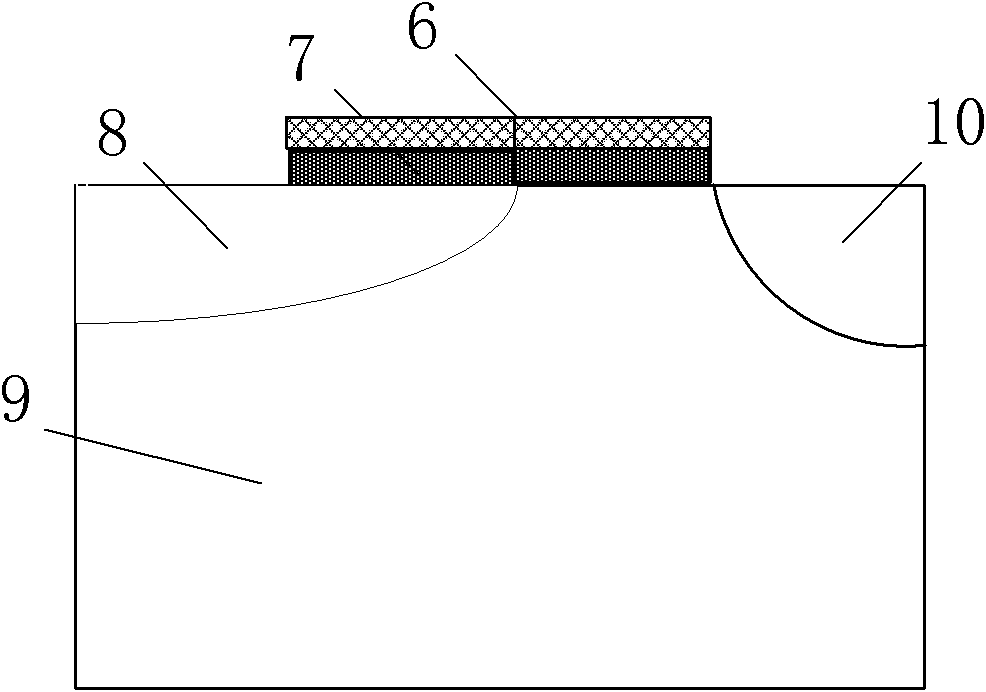

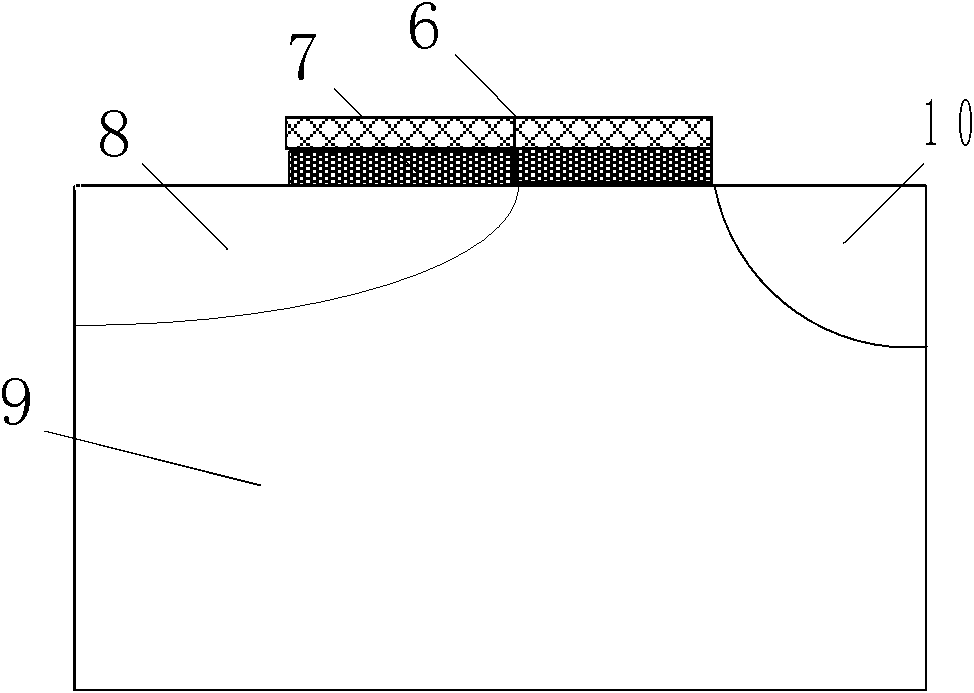

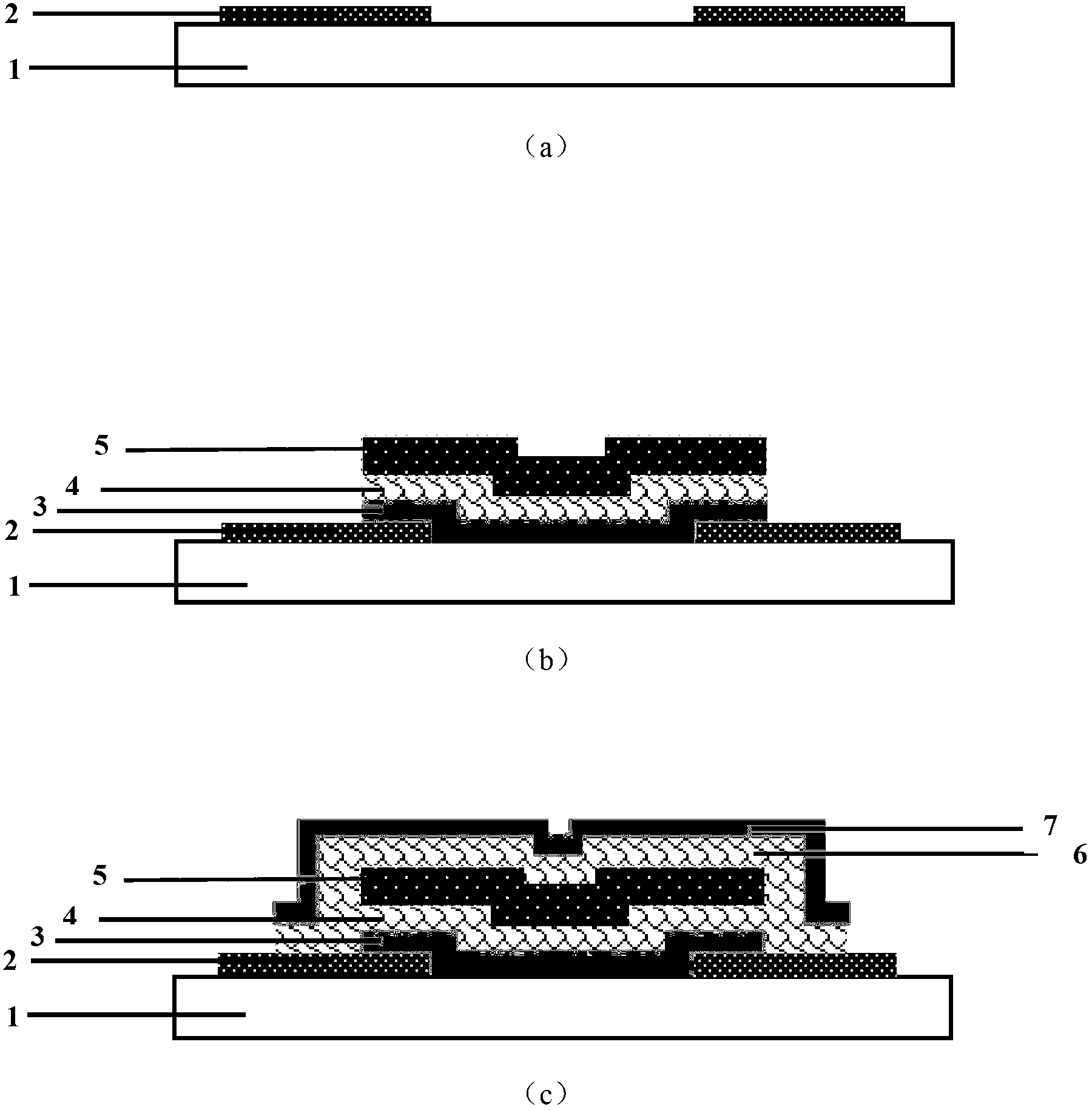

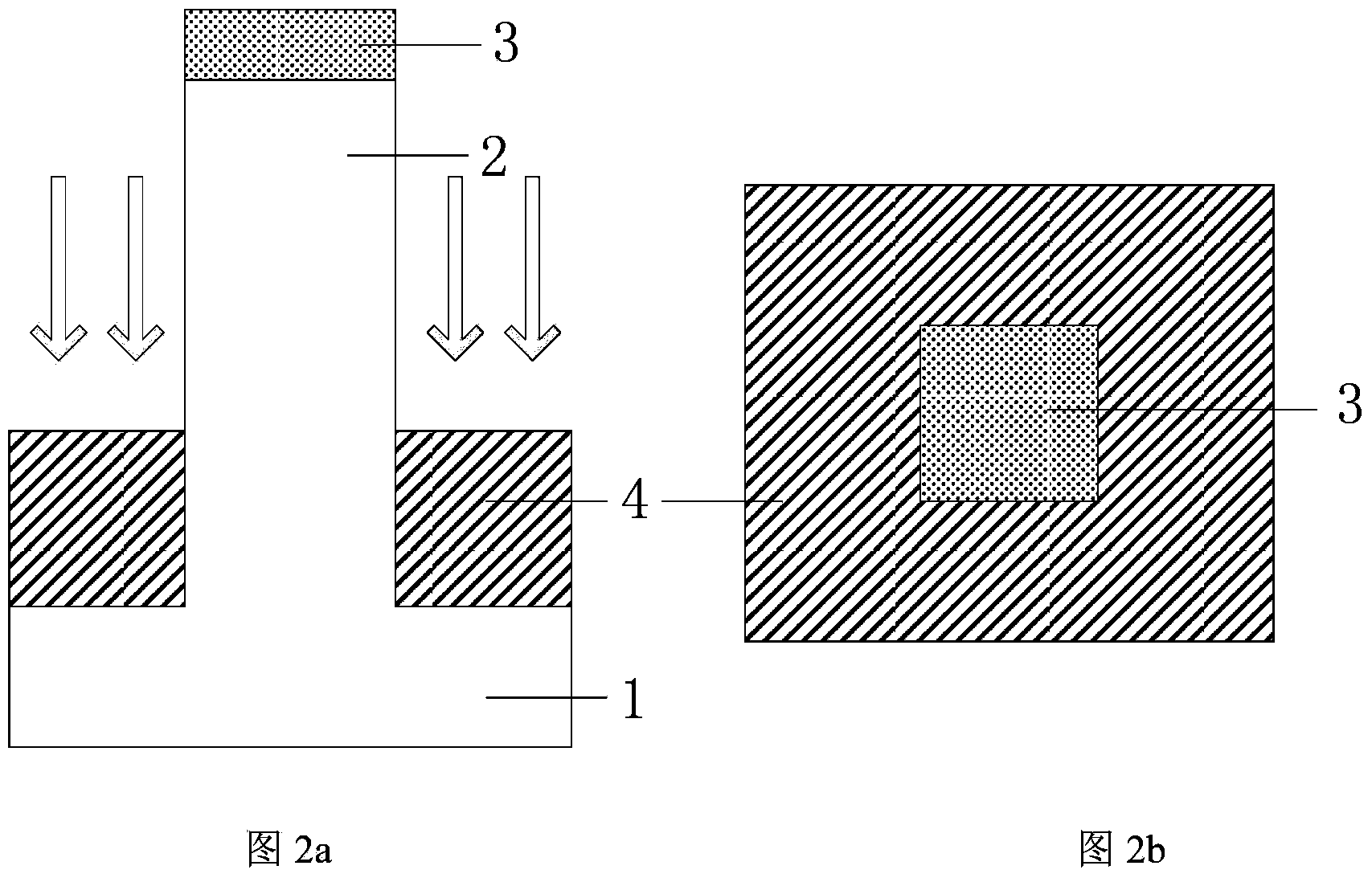

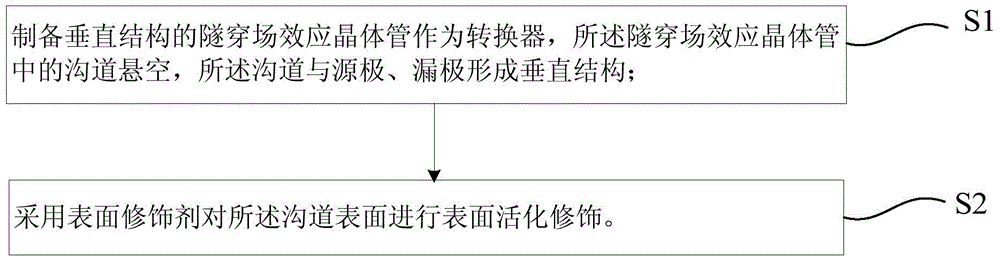

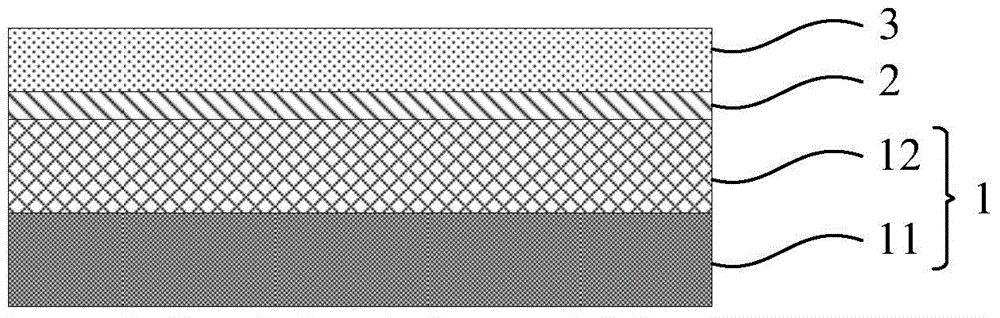

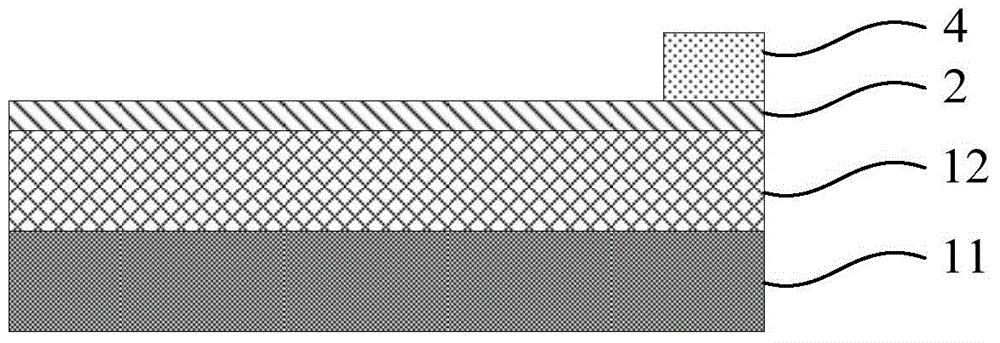

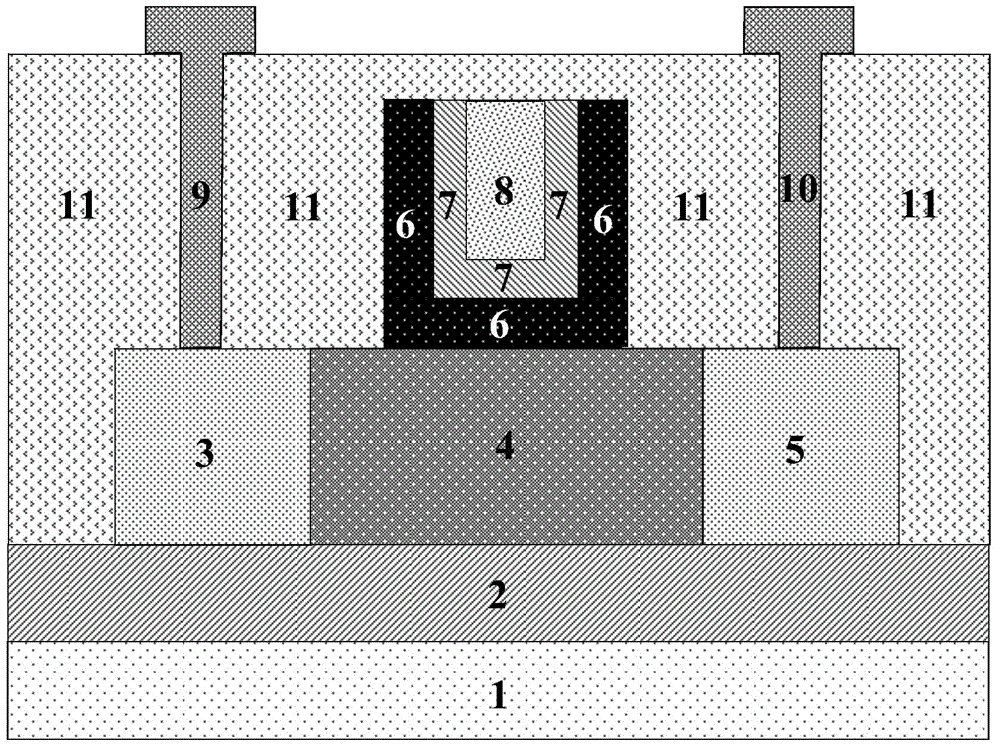

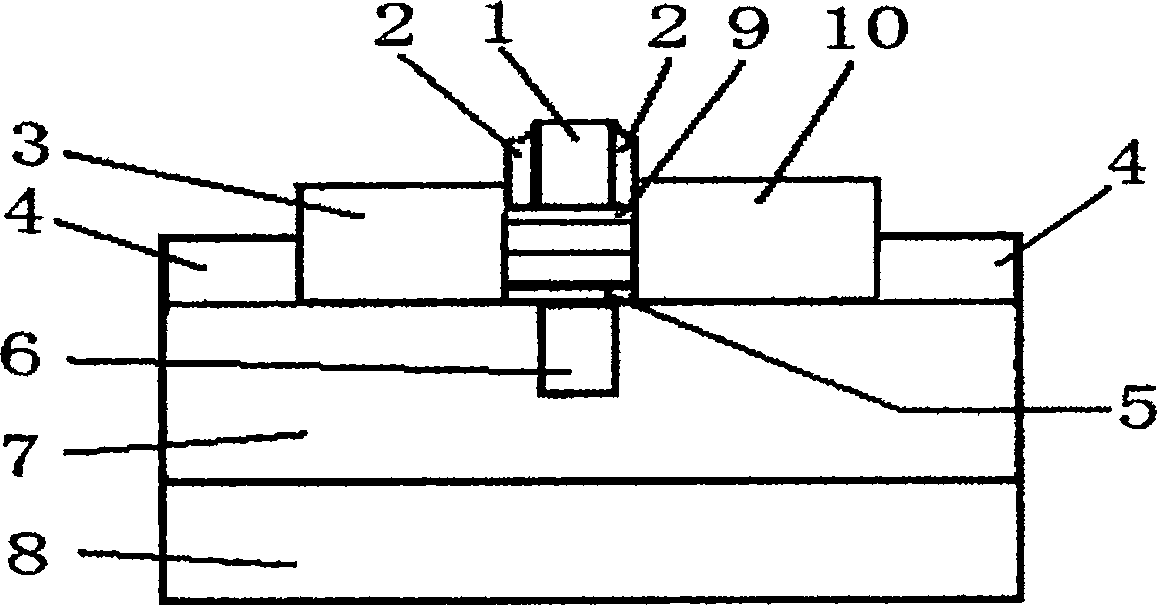

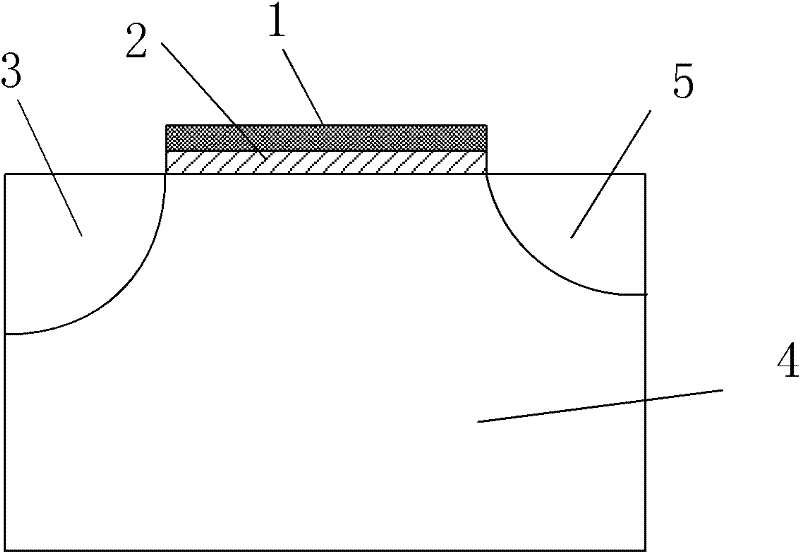

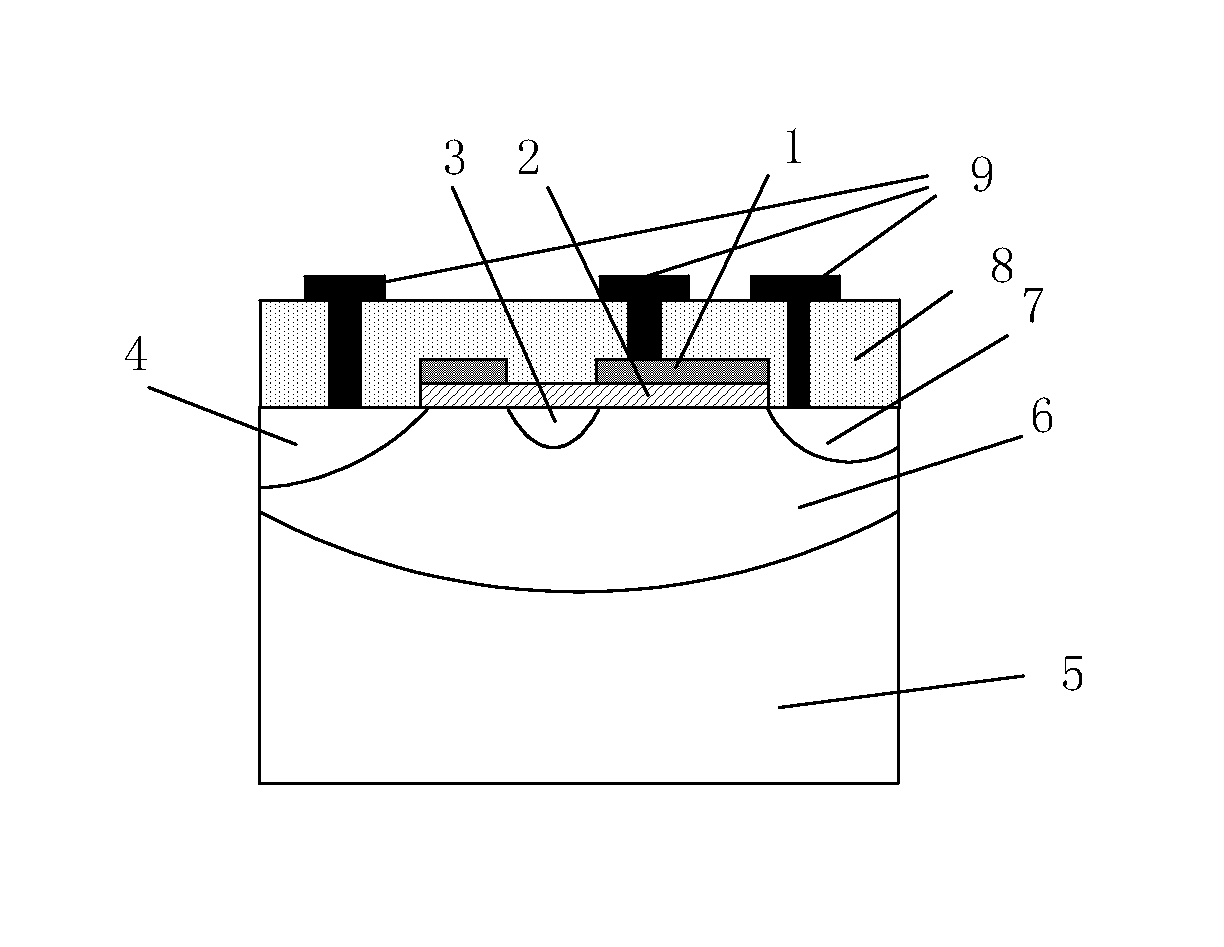

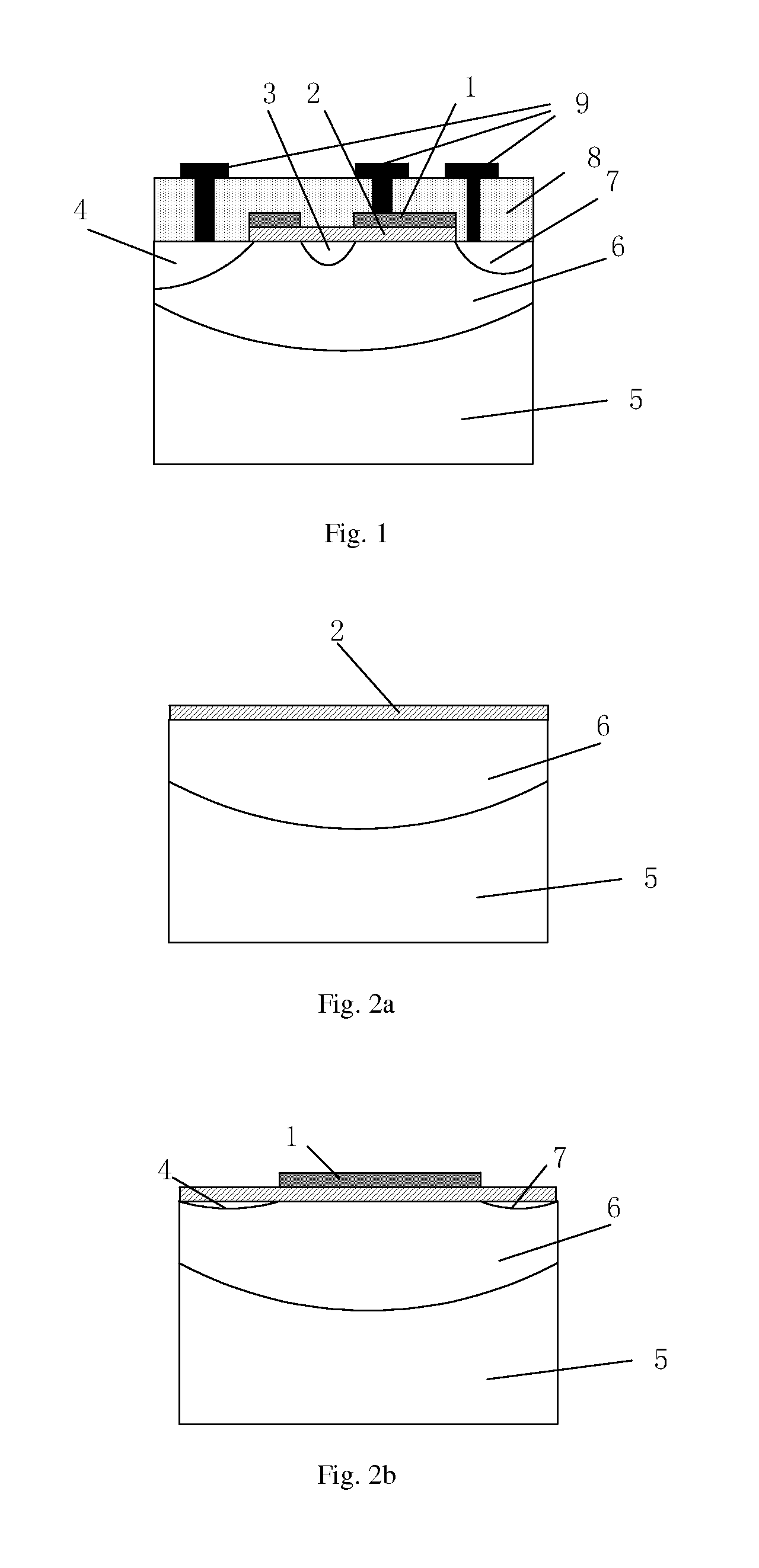

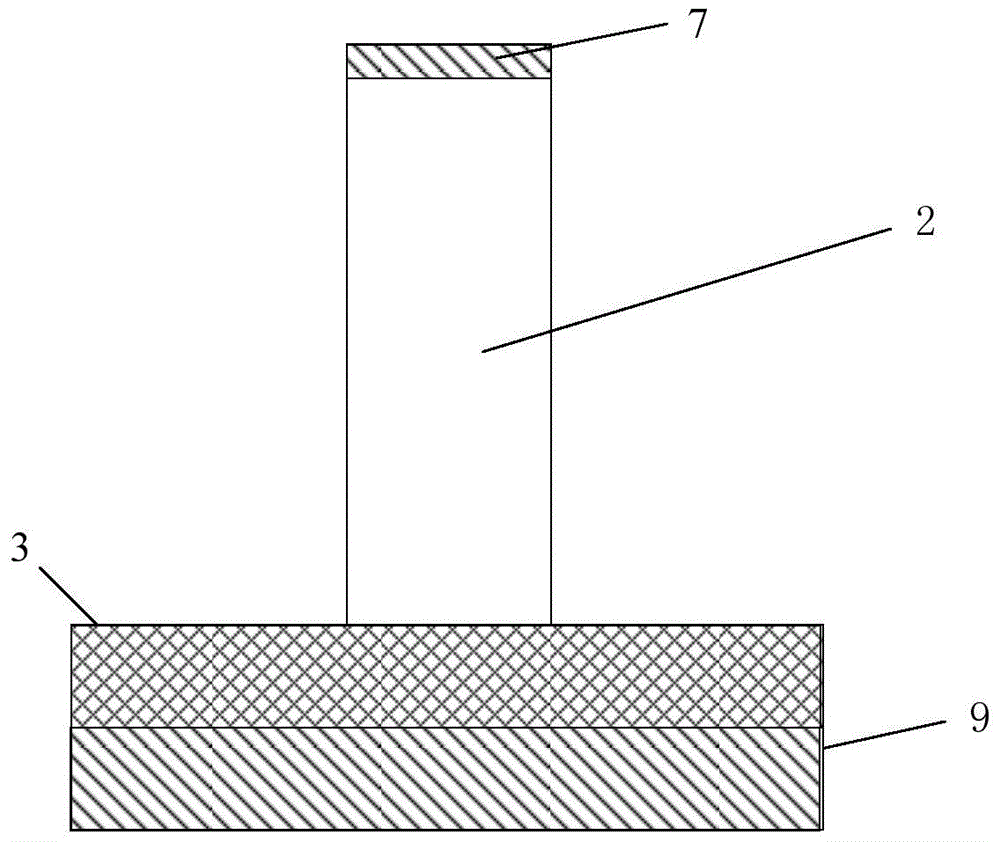

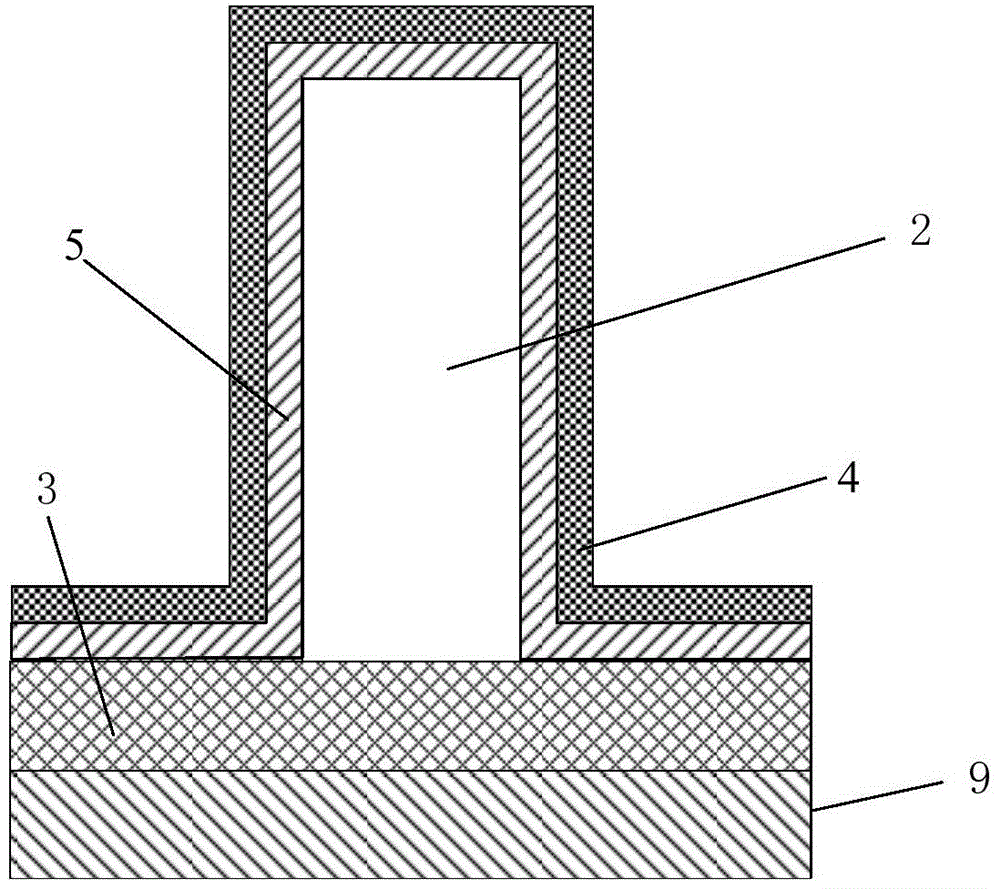

Biosensor based on vertical-structure tunneling field effect transistor and preparation method thereof

ActiveCN103558254AImprove work performanceSteep subthreshold slopeMaterial analysis by electric/magnetic meansSemiconductor/solid-state device manufacturingWork performanceBiological activation

The invention provides a biosensor based on a vertical-structure tunneling field effect transistor and a preparation method thereof. The preparation method at least comprises the following steps: step one, preparing the vertical-structure tunneling field effect transistor as a converter, wherein a channel inside the tunneling field effect transistor is suspended, and a vertical structure is formed by the channel, a source electrode and a drain electrode; and step two, carrying out surface activation modification on the surface of the channel by a surface modifying agent. According to the biosensor provided by the invention, the source electrode, the channel and the drain electrode inside the tunneling field effect transistor as the converter adopt the vertical structure, and the channel is in a suspended structure, so that the subthreshold slope of the device is steep; therefore, the induction of the device to the change of surface charges of the channel is sensitive, and the working performance of the biosensor is further improved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

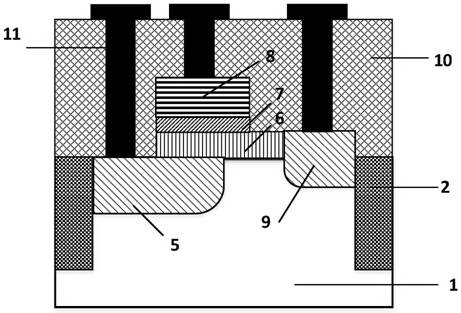

Insulated gate tunneling bipolar transistor with U-shaped tunneling insulating layer and manufacturing process

InactiveCN104485353AImprove switching characteristicsIncrease the forward conduction currentSemiconductor/solid-state device manufacturingSemiconductor devicesUltimate tensile strengthElectric field

The invention relates to an insulated gate tunneling bipolar transistor with a U-shaped tunneling insulating layer. A gate electrode tunneling current is generated by the U-shaped tunneling insulating layer, and the very sensitive mutual relation between impedance of the tunneling insulating layer and intensity of an internal electric field of the tunneling insulating layer is utilized to enable the U-shaped tunneling insulating layer to implement conversion between a high impedance state and a low impedance state in a very short electric potential change interval of a gate electrode, and thus, compared with the prior art, the insulated gate tunneling bipolar transistor can realize a better switching characteristic; by bipolar amplification, the positive conduction characteristic of a nanoscale insulated gate transistor is obviously improved. The invention also discloses a specific manufacturing method of the insulated gate tunneling bipolar transistor with the U-shaped tunneling insulating layer. Therefore, the working characteristic of a nanoscale integrated circuit unit is obviously improved, and the insulated gate tunneling bipolar transistor and the manufacturing method are suitable for being popularized and applied.

Owner:SHENYANG POLYTECHNIC UNIV

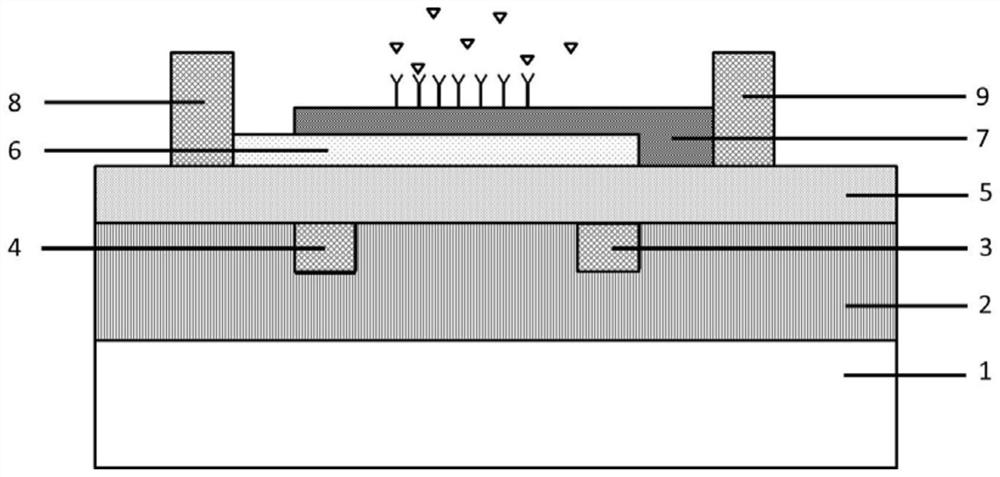

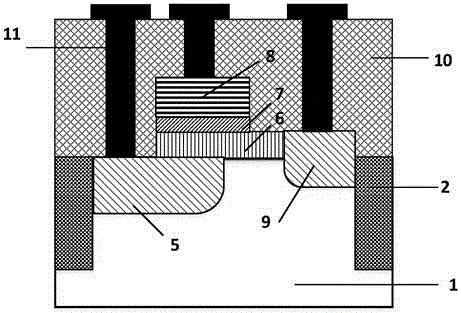

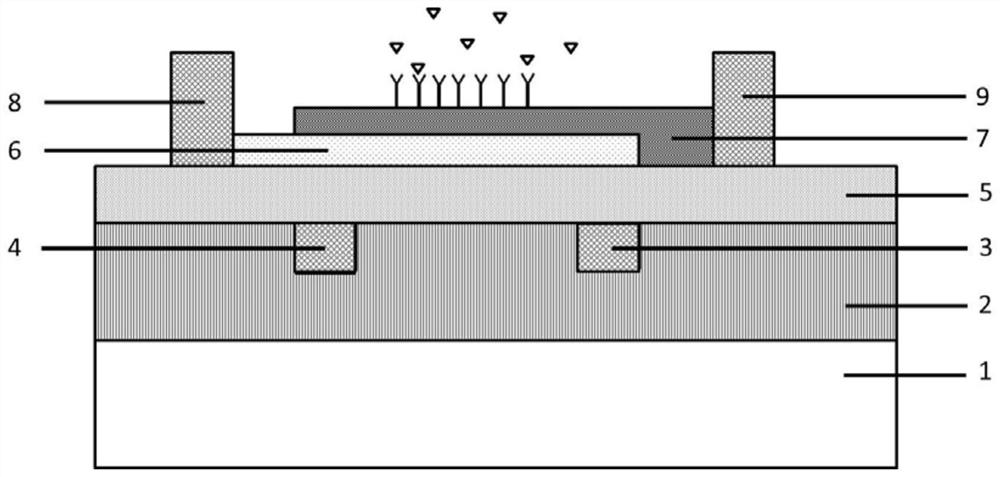

Two-dimensional heterojunction tunneling field effect transistor immunosensor and preparation method thereof

ActiveCN112186036AEasy to detectEasy to controlTransistorSemiconductor/solid-state device manufacturingHeterojunctionDielectric

The invention discloses a two-dimensional heterojunction tunneling field effect transistor immunosensor and a preparation method thereof. A two-dimensional material with a specific band gap is selected and stacked into a vertical heterojunction as a channel layer, and the energy band structures of the device in an on state and an off state are respectively in staggered arrangement and staggered arrangement through gate voltage control, low current in the off state is realized, and in an on state, large current is obtained due to inter-band tunneling. A buried gate structure is used, and specific antibody protein molecules are used for surface modification on the surface of the heterojunction modulated by gate voltage. A heterojunction is used as an effective detection area and has ideal grid control capability. The dielectric regulation and control of a detection area is detected along with a detection sample by utilizing a plurality of electrical parameters. The sensor provided by theinvention has a steeper subthreshold slope, can realize ultra-high sensitivity detection of biomolecules and save precious clinical specimens, and meanwhile, because the thickness of a two-dimensional material is ultra-thin, the sensor has great advantages in size reduction and is convenient for energy band regulation and control.

Owner:XI AN JIAOTONG UNIV

Tunneling Field Effect Transistor with Suppressed Output Nonlinear Turn-on and Preparation Method thereof

ActiveCN104347692BSteep subthreshold slopeSuppression of non-linear turn-on phenomenaSemiconductor/solid-state device manufacturingSemiconductor devicesSub thresholdGate dielectric

The invention provides a tunneling field effect transistor inhibiting output non-linear opening. The tunneling field effect transistor comprises a tunneling source region, a channel region, a drain region, a semiconductor substrate region, a gate dielectric layer and a control gate, wherein the gate dielectric layer is positioned above the channel region, the control gate is positioned above the gate dielectric layer, the channel region is positioned above the channel source region, in addition, the position of the channel region is partially overlapped with the tunneling source region, a tunneling junction is formed at the interface part of the channel region and the tunneling source region, the drain region is parallel to the channel region and is positioned at the other side of the channel region, the control gate is positioned above the overlapping part of the channel region and the tunneling source region, a control-gate-free region is arranged in the channel region near the drain region, and in addition, the channel region adopts semiconductor materials with the energy state density being lower than 1E18cm<-3>. The tunneling field effect transistor has the advantages that the nonlinear opening phenomenon in the device output characteristics can be effectively inhabited, and in addition, the steeper and straighter sub-threshold slope is maintained.

Owner:PEKING UNIV

Negative electron compressibility-ultrasteep subthreshold slope field effect transistor and its preparation method

ActiveCN106887460BSteep Subthreshold SlopeQuick responseSemiconductor/solid-state device manufacturingNanotechnologyHysteresisCapacitance

The present invention discloses a negatron compression rate-ultra-steep sub-threshold slope field effect transistor and a preparation method thereof. According to the technical scheme of the invention, in the sub-threshold region of a device, a first conventional gate dielectric layer and a second conventional gate dielectric layer form a conventional gate dielectric capacitor. A negatron compression-rate gate dielectric layer forms an NEC capacitor. In this way, the capacitance value of the conventional gate dielectric capacitor is larger than the absolute value of the NEC capacitor, so that the above two series capacitors are negative in value. The gate control coefficient is less than 1 and the gate leakage current is inhibited. As a result, the gate voltage has an exceptional control capability over the surface of a channel, so that the device is ultra-steep in sub-threshold slope. Meanwhile, considering the variation at the electronic scale, the NEC capacitor of the device enables the macroscopic properties of the device to be free of the hysteresis and the material fatigue resistance any more. Therefore, on the basis that the power consumption of the device is reduced, the NCFET problem of the traditional ferroelectric material is solved. For the industry development of low-power-consumption integrated circuits in the future, the negatron compression rate-ultra-steep sub-threshold slope field effect transistor and the preparation method thereof have a wide application prospect.

Owner:PEKING UNIV

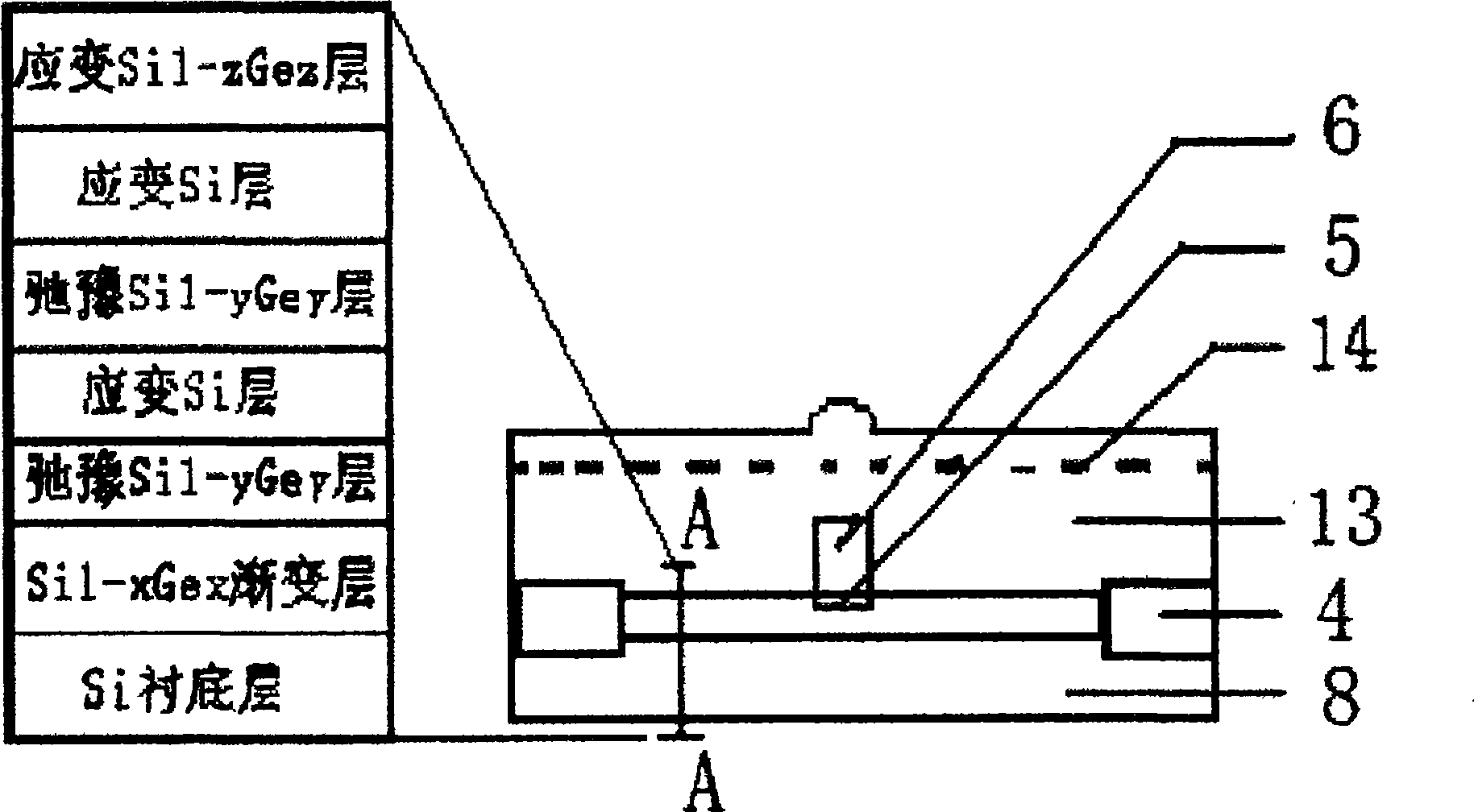

Dual bar and dual stress channel-changing full consumption SOI MOSFETs part structure

InactiveCN100505314CResolve incompatibilitiesImprove driving abilityTransistorBottom gateEngineering

Owner:XIAN UNIV OF TECH

Tunneling field effect transistor with T-shaped grid structure and low power consumption

ActiveCN102005481BEnhanced source junction electric field strengthIncrease the on-currentSemiconductor devicesEngineeringTunnel field-effect transistor

The invention provides a tunneling field effect transistor (TFET) with a T-shaped grid structure and low power consumption, and belongs to the field of field effect transistor logic devices and circuits in complementary metal oxide semiconductor (CMOS) ultra large scale integrated circuits (ULSI). The TFET comprises a source electrode, a drain electrode and a control grid, wherein the control grid extends toward the end of the source electrode to form a T shape; the T-shaped control grid consists of an extending grid region and the original control grid region; and an active region covered below the extending grid region is a channel region and is made of a substrate material. By using the T-shaped grid structure, the source region of the TFET encircles a channel, so that the conduction current of a device is improved. Compared with the conventional planar TFET, the TFET can achieve higher conduction current and steeper subthreshold slope under the same process conditions and the samesize of the active region.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

A two-dimensional heterojunction tunneling field effect transistor immunosensor and its preparation method

ActiveCN112186036BEasy to detectEasy to controlTransistorSemiconductor/solid-state device manufacturingHeterojunctionBio molecules

The invention discloses a two-dimensional heterojunction tunneling field effect transistor immunosensor and a preparation method thereof. A two-dimensional material with a specific band gap is selected to be stacked into a vertical heterojunction as a channel layer. The energy band structures in the on-state and off-state are staggered arrangement and staggered arrangement respectively, achieving low current in the off-state and high current due to inter-band tunneling in the on-state. Using buried gate structure, surface modification with specific antibody protein molecules on the heterojunction surface modulated by gate voltage. As an effective detection area, the heterojunction has the ability to obtain ideal gate control. The detection is realized by using multiple electrical parameters to control the dielectric of the detection area along with the detection sample. The sensor of the present invention has a steeper sub-threshold slope, which can realize ultra-high sensitivity detection of biomolecules and save precious clinical specimens. At the same time, due to the ultra-thin thickness of the two-dimensional material, the device has a great advantage in size reduction, which is convenient for energy saving. With regulation.

Owner:XI AN JIAOTONG UNIV

Low-power consumption tunneling field effect transistor (TFET) of fork-structure grid structure

ActiveCN102157559BEnhanced source junction electric field strengthIncrease the on-currentSemiconductor devicesCMOSEngineering

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

A junction-modulated tunneling field-effect transistor and its manufacturing method

ActiveCN103594376BImproved subthreshold characteristicsSubthreshold characteristic steepSemiconductor/solid-state device manufacturingDiodeSub thresholdConcentration gradient

The invention discloses a junction modulation type tunneling field effect transistor and a preparation method thereof, belonging to the field of field effect transistor logic devices and circuits in CMOS ultra large integrated circuits (ULSI). The tunneling field effect transistor utilizes the PN junction provided by the highly doped source region surrounded on three sides of the vertical channel region to effectively deplete the channel region, so that the channel energy band on the lower surface of the gate is increased, and when the device undergoes band tunneling, it can obtain The steeper energy band and narrower tunneling barrier width than traditional TFETs equivalently realize the effect of steep tunneling junction doping concentration gradient, thereby greatly improving the subthreshold characteristics of traditional TFETs and improving the conductance of the device at the same time. Pass current. Under the condition of being compatible with the existing CMOS technology, the present invention effectively suppresses the bipolar conduction effect of the device on the one hand, and at the same time suppresses the parasitic tunneling current at the corner of the source junction in a small size, and can equivalently realize steep The effect of straight source-junction doping concentration.

Owner:PEKING UNIV

A kind of preparation method of tunneling field effect transistor

Owner:PEKING UNIV

Three-dimensional (3D) oxide semiconductor thin film transistor and preparation method thereof

ActiveCN102709316BImprove driving abilityReduce interface defect statesTransistorSemiconductor/solid-state device manufacturingGate dielectricSub threshold

The invention discloses a three-dimensional (3D) oxide semiconductor thin film transistor (TFT) and a preparation method thereof. According to the TFT, the continuous growth of a lower-layer active area, a lower-layer gate dielectric and a gate electrode and the continuous growth of an upper-layer gate dielectric and an upper-layer active area are adopted, so that the interface deficiency state of an active layer and the gate dielectric can be greatly reduced to greatly improve the driving capability of the (TFT). Moreover, the same gate electrode can simultaneously control the upper-layer and lower-layer active areas, so that the driving capability of the TFT is further improved. The TFT prepared by the method has the good characteristics of high switch ratio, high on-state current, abrupt sub-threshold slope and the like. Therefore, the TFT and the preparation method thereof have high practical value, and are expected to be widely used for microelectronic and flat panel display industries. Furthermore, if the upper-layer and lower-layer active areas are controlled by different threshold voltages, a multi-threshold technology can be integrated into the same TFT, and the integration of the multi-threshold technology into the TFT is expected to widely used for pixel driving unit circuits.

Owner:BOE TECH GRP CO LTD

Tunneling current amplification transistor

InactiveUS8895980B2Reduce leakage currentSteep subthreshold slopeTransistorSolid-state devicesCMOSGate dielectric

The present invention discloses a tunneling current amplification transistor, which relates to an area of field effect transistor logic devices in CMOS ultra large scale semiconductor integrated circuits (ULSI). The tunneling current amplification transistor includes a semiconductor substrate, a gate dielectric layer, an emitter, a drain, a floating tunneling base and a control gate, wherein the drain, the floating tunneling base and the control gate forms a conventional TFET structure, and a doping type of the emitter is opposite to that of the floating tunneling base. A position of the emitter is at the other side of the floating tunneling base with respect to the drain. A type of the semiconductor between the emitter and the floating tunneling base is the same as that of the floating tunneling base. As compared with the conventional TFET, the tunneling current amplification transistor of the present invention can increase the on-current of the device effectively and increase the driving capability of the device.

Owner:PEKING UNIV

Vertical channel dual-mechanism conduction nanowire tunneling transistor and preparation method

ActiveCN103996713BRaise the potentialLower the barrierSemiconductor/solid-state device manufacturingSemiconductor devicesNanowireDual mechanism

The invention provides a vertical-channel double-mechanism conduction nano-wire tunneling transistor and a preparation method. The tunneling transistor comprises a hot electron emission source region, a tunneling source region, a channel region, a tunneling drain region and a gate of a nano-wire. The gate is controlled to encircle the channel; band-to-band tunneling happens at the interface of the tunneling source region and the channel region; the hot electron emission source region, the doping type of which is opposite to that of the tunneling source region, is arranged under the tunneling source region; and the electric potential of the tunneling source region is in floating arrangement, and the source terminal potential of a device is added to the hot electron emission source region. Compared with a conventional TFET, the vertical-channel double-mechanism conduction nano-wire tunneling transistor introduces a hot electron emission mechanism besides a tunneling mechanism through the structure design of the device, thereby enlarging the conduction current of the device effectively, meanwhile, keeping steep subthreshold slope, and improving the characteristics of the device substantially. The vertical-channel double-mechanism conduction nano-wire tunneling transistor is simple in preparation process, reduces the production cost greatly, and simplifies the process flow.

Owner:PEKING UNIV