Patents

Literature

36results about How to "Improved subthreshold characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

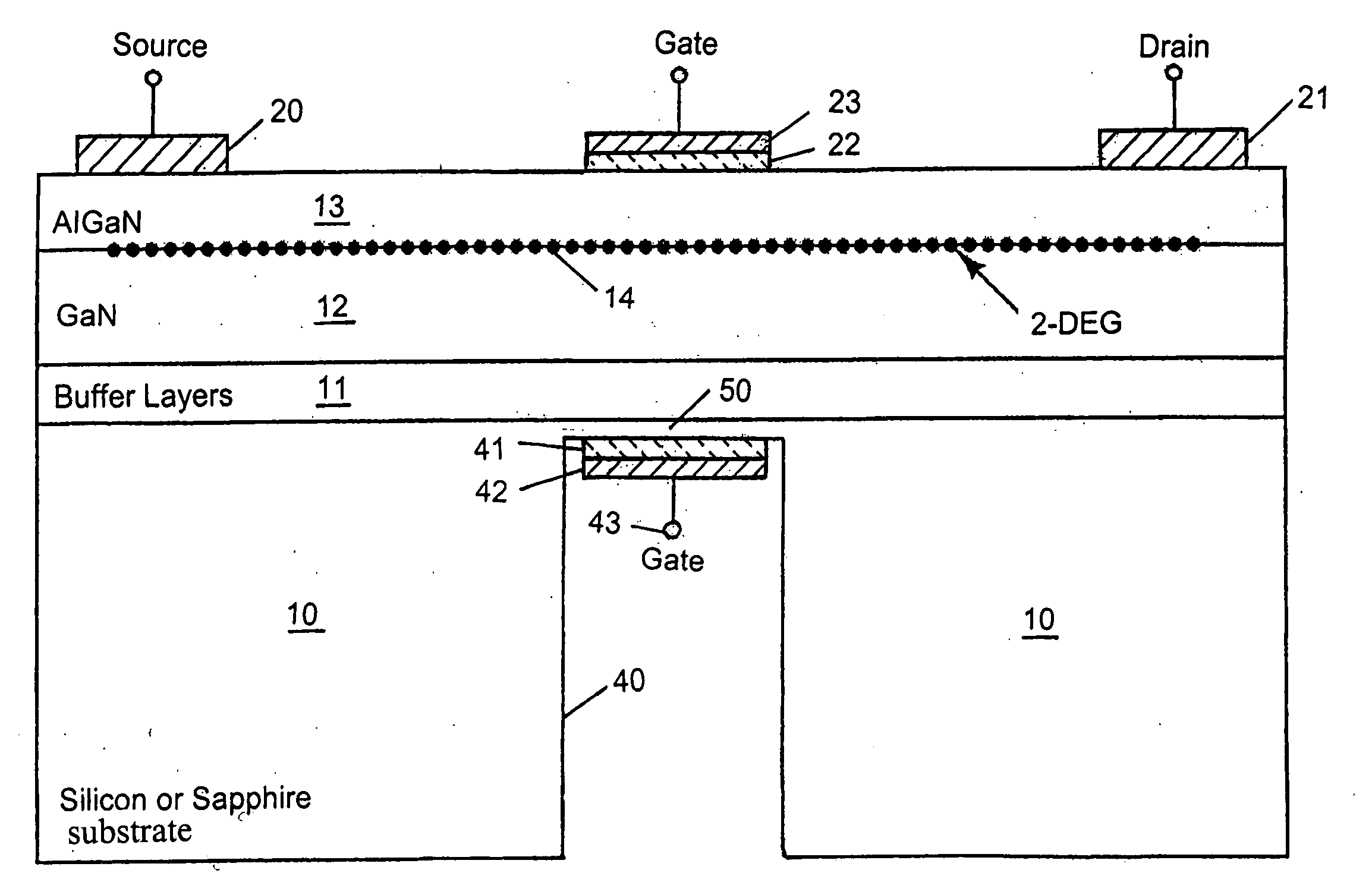

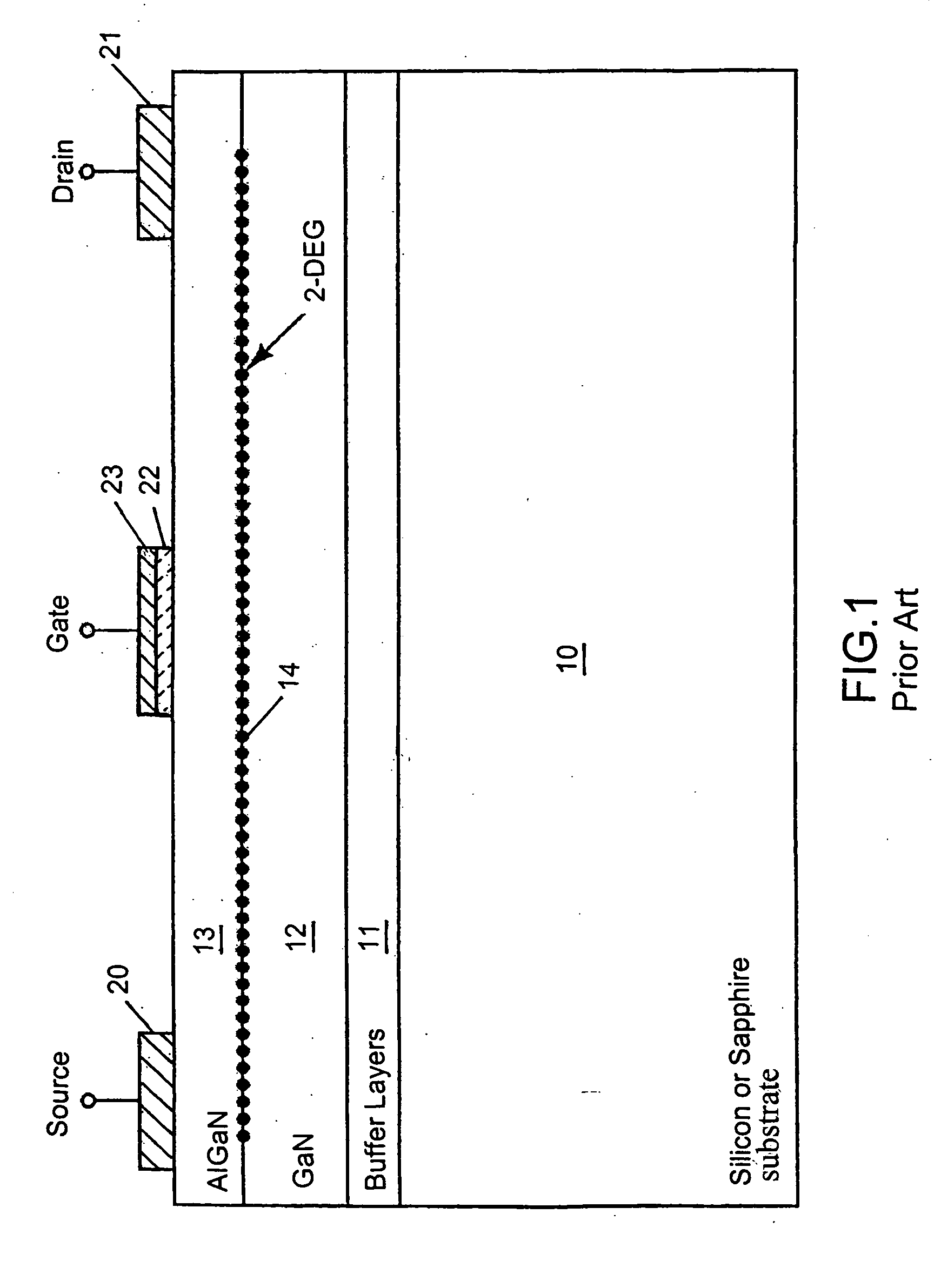

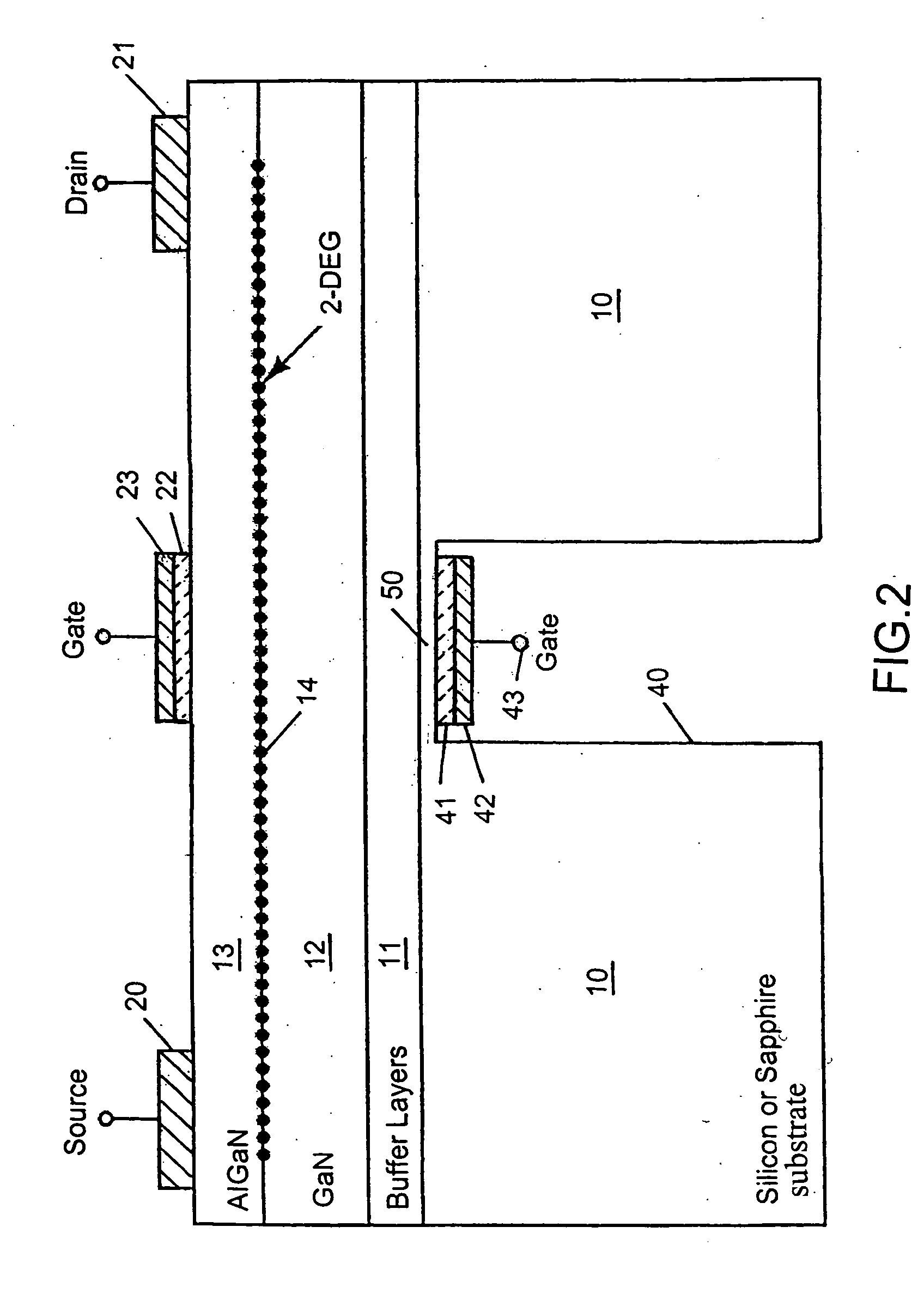

Iii-nitride device with back-gate and field plate and process for its manufacture

InactiveUS20100065923A1Reduce conductivityImproved subthreshold characteristicsBulk negative resistance effect devicesSemiconductor devicesElectrical and Electronics engineeringElectrode

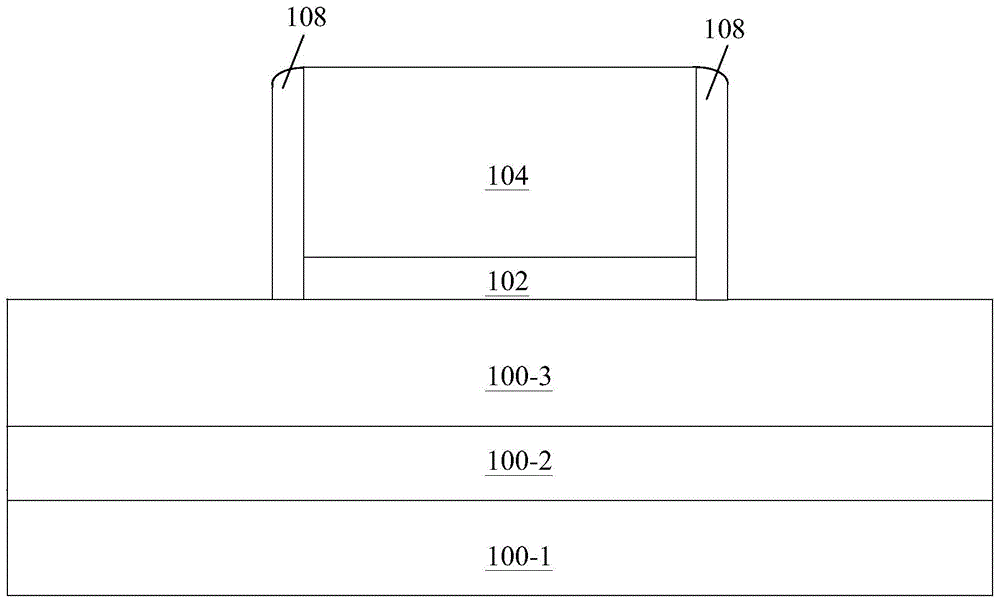

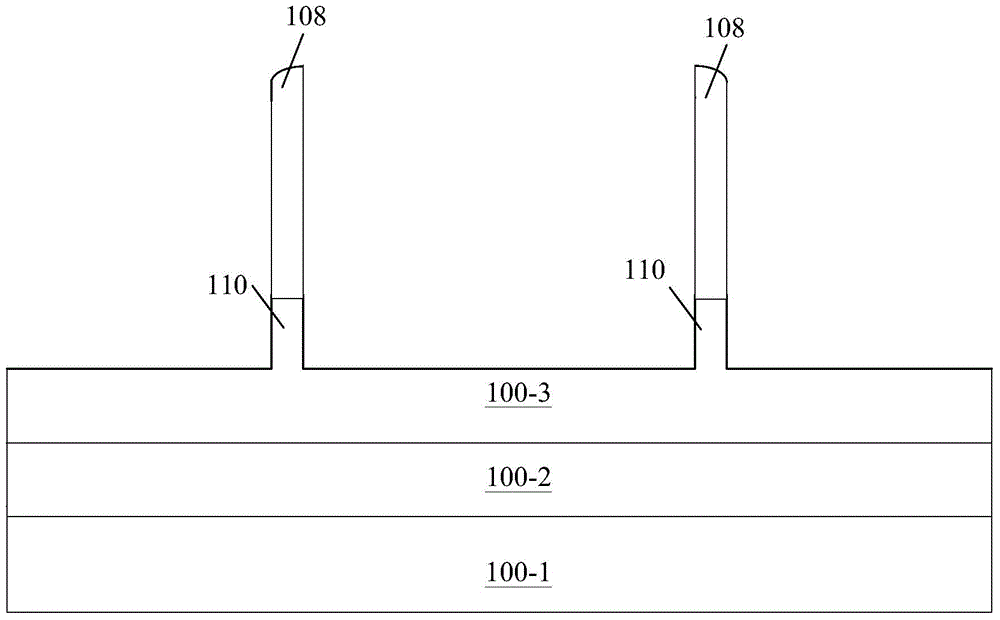

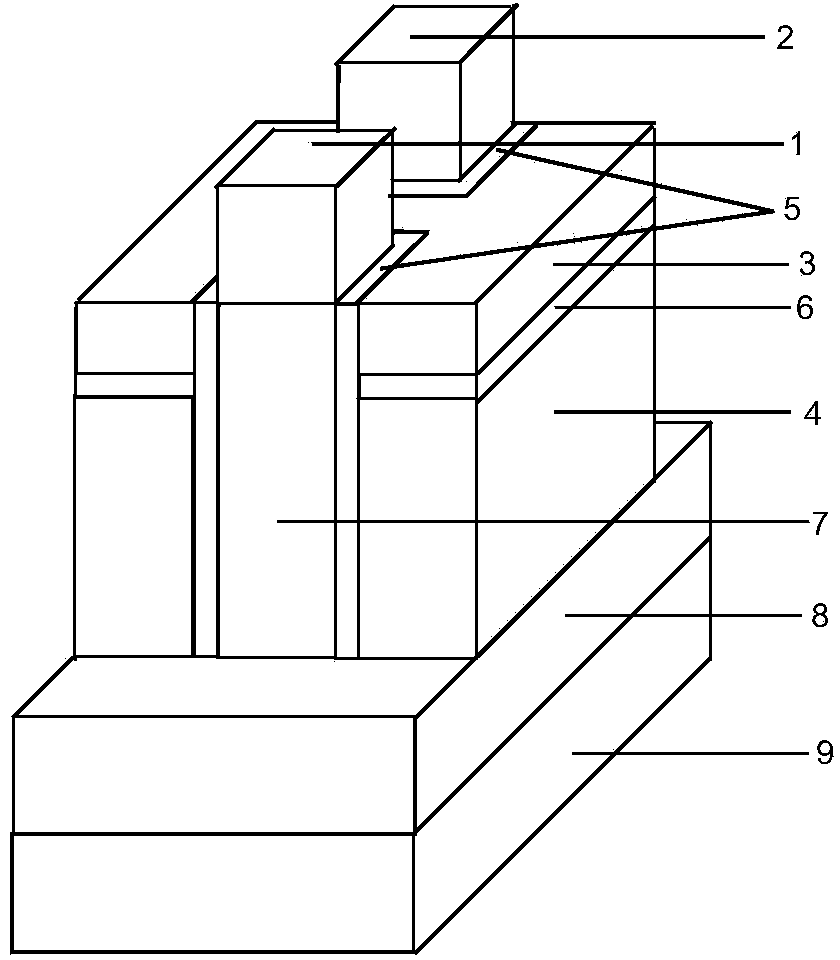

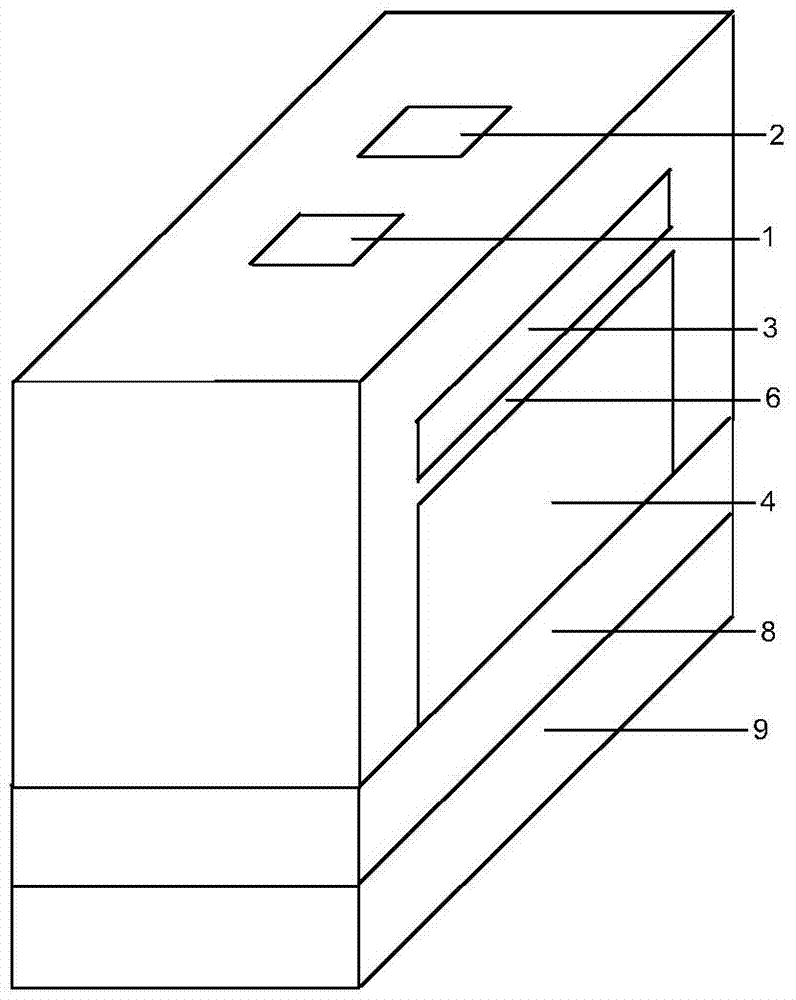

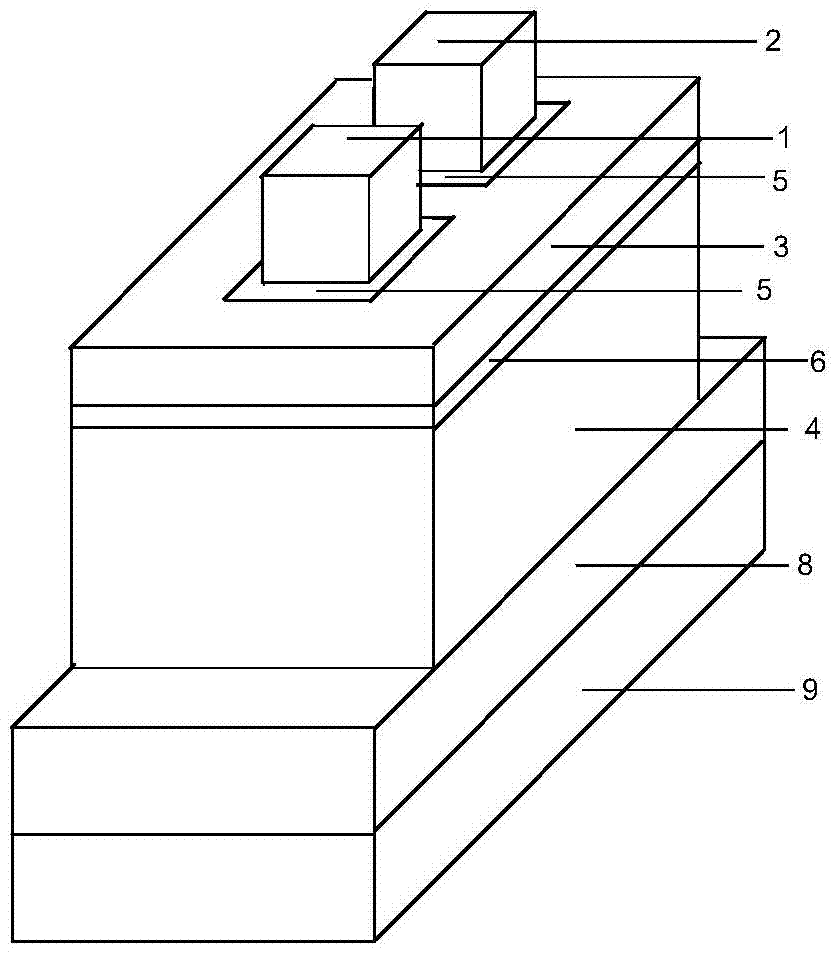

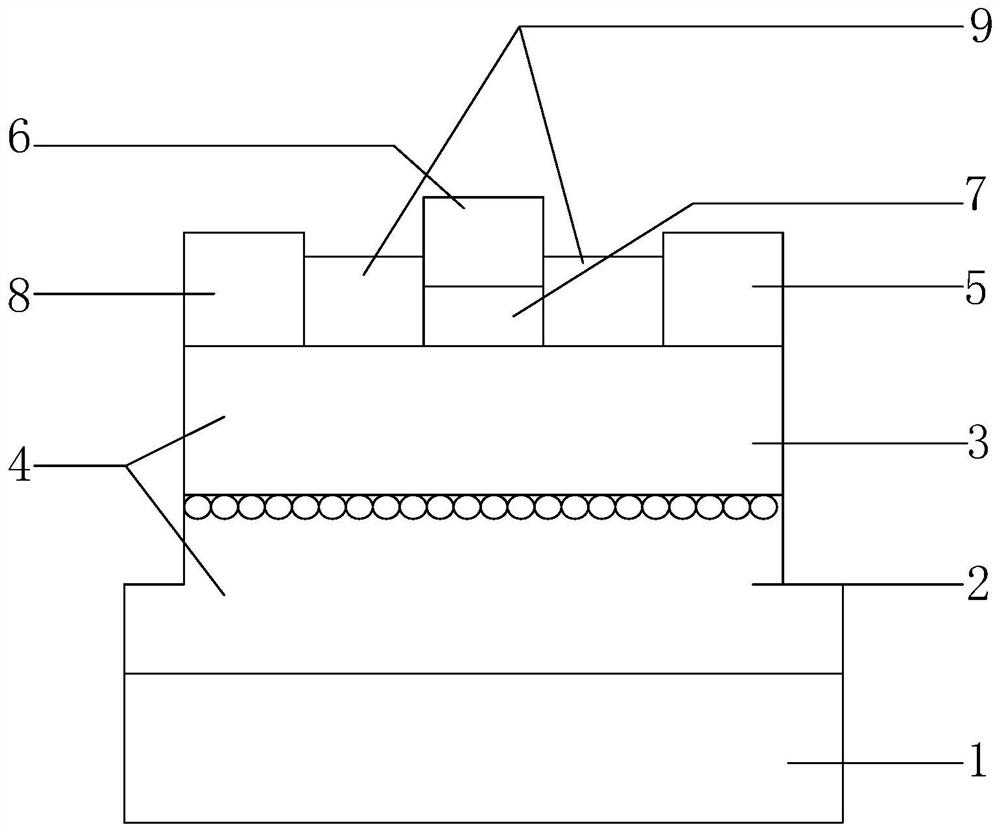

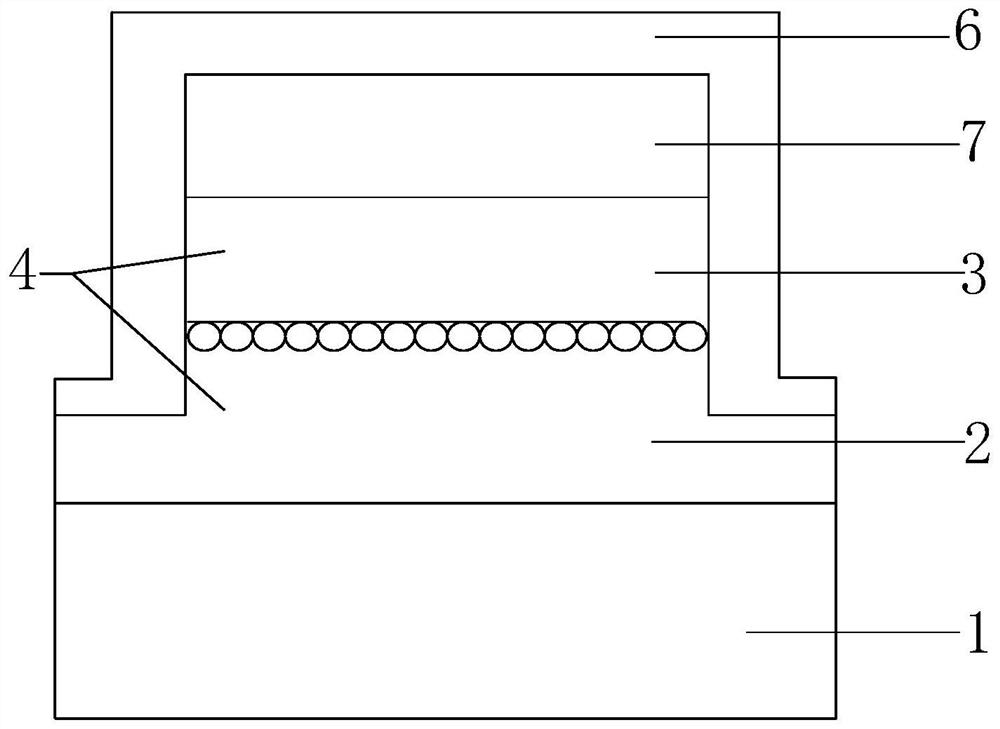

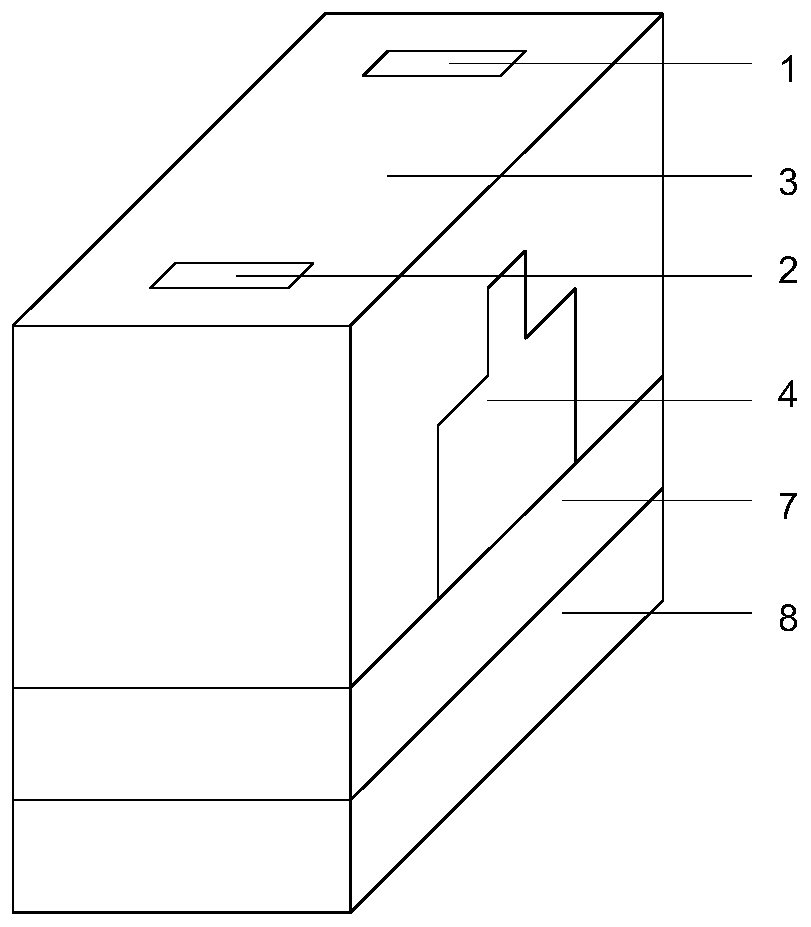

A III-Nitride device has a back-gate disposed in a trench and under and in close proximity to the 2 DEG layer and in lateral alignment with the main gate of the device. A laterally disposed trench is also disposed in a trench and under and in close proximity to the drift region between the gate and drain electrodes of the device. The back-gate is connected to the main gate and the field plate is connected to the source electrode. The back-gate can consist of a highly conductive silicon substrate.

Owner:INTERNATIONAL RECTIFIER COEP

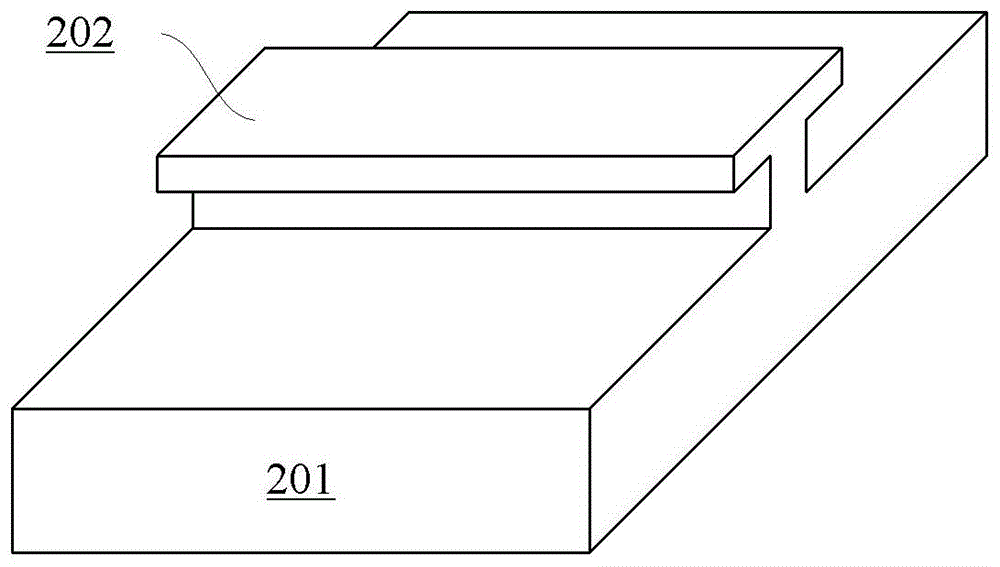

Tunneling field effect transistor (TFET) and manufacturing method thereof

ActiveCN102364690AGood subthreshold characteristicsSimple preparation processSemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorPower consumption

The invention discloses a tunneling field effect transistor (TFET) and a manufacturing method thereof, which belong to the fields of logic devices and circuits of field effect transistors. A high-doping source region of the TFET consists of a P<+> high-doping region and an N<+> high-doping region, and threshold values of a metal-oxide semiconductor field effect transistor (MOSFET) part and a TFET part of a device can be adjusted through ingenious layout variation, so that the performance of a TFET device is improved, and the manufacturing method is simple. Compared with the conventional TFET, the TFET has the advantages that: higher switch-on current can be obtained and a steep subthreshold gradient can be kept by the device under the condition of the same process and the same active region size, so that the TFET is expected to be used in a low power consumption field and has higher practical value.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

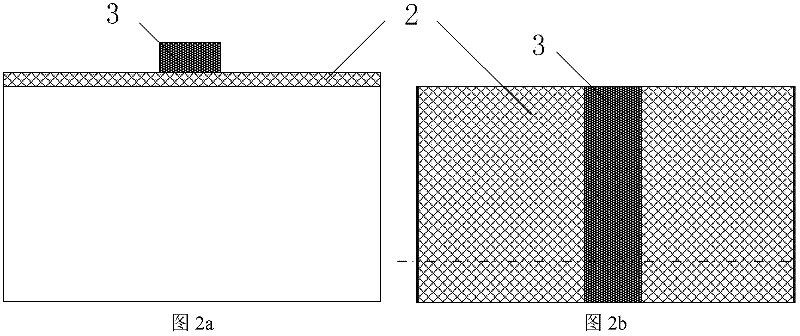

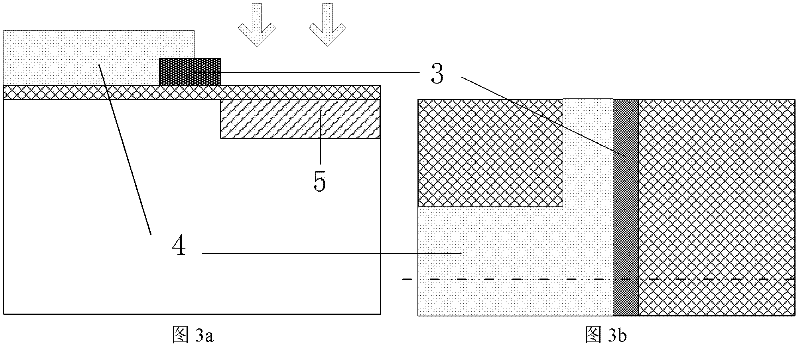

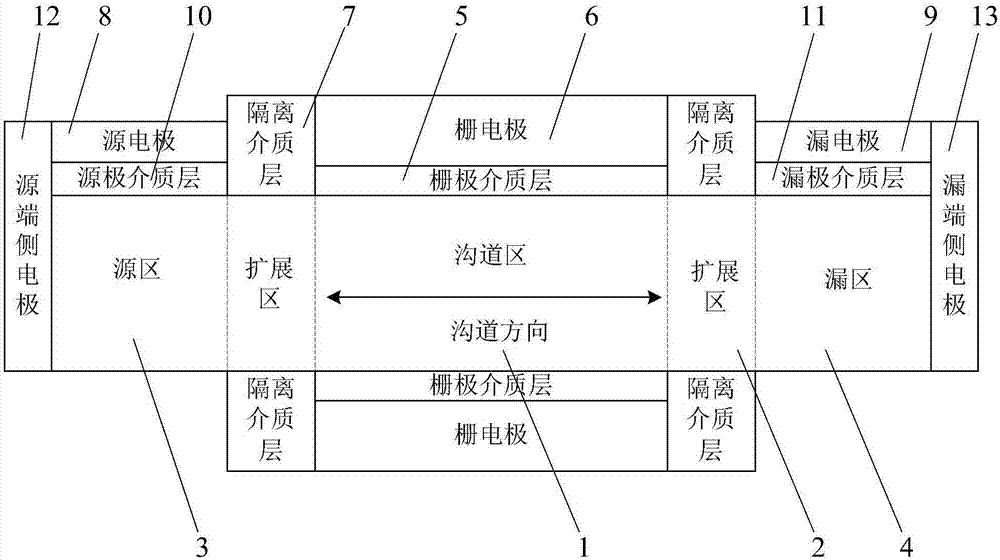

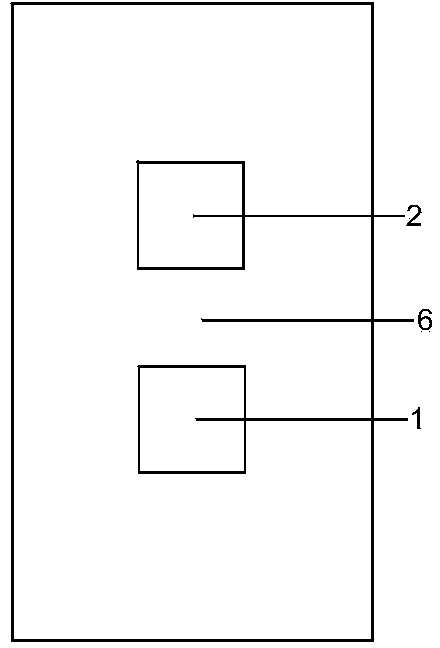

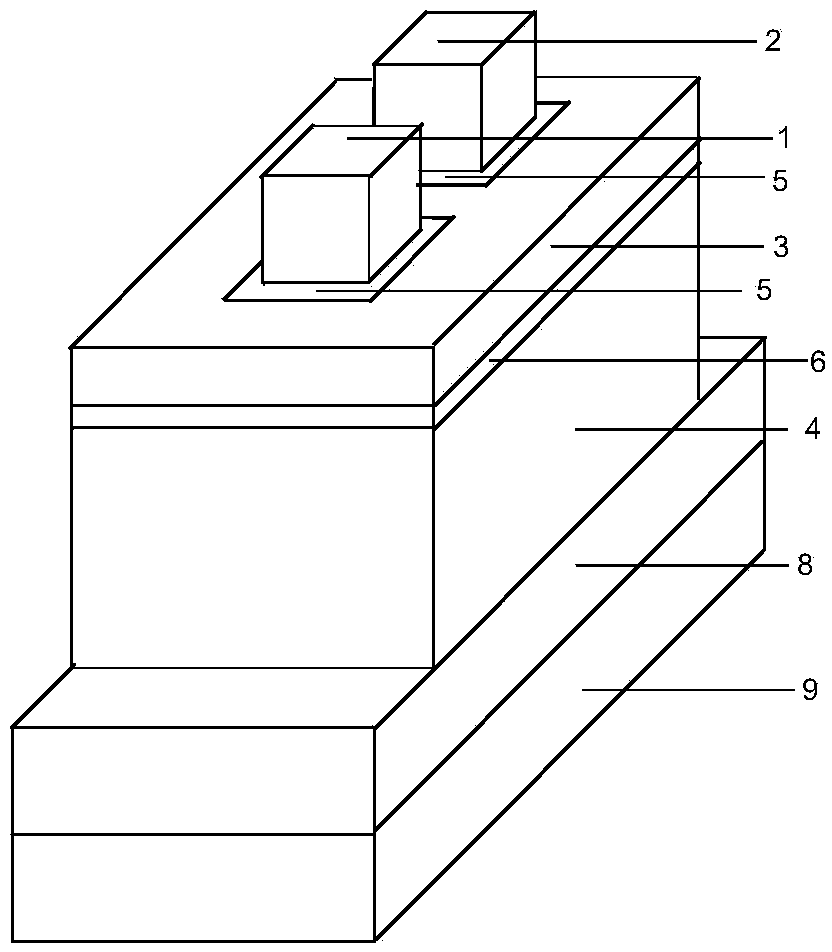

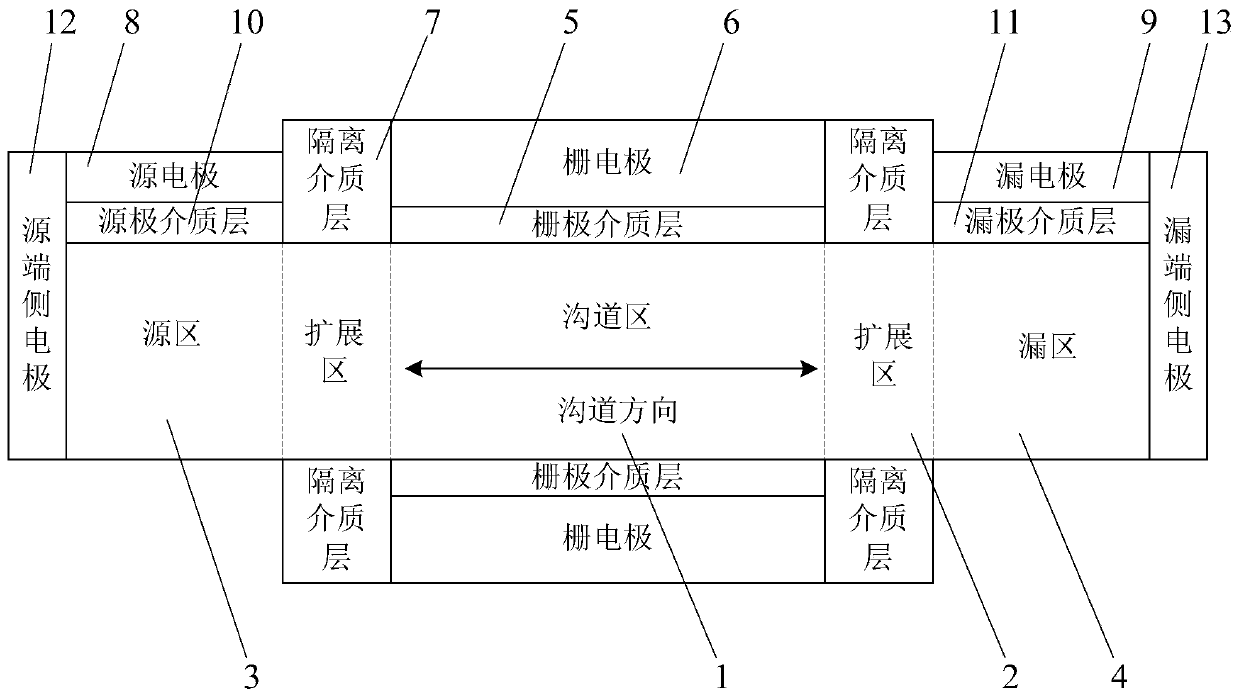

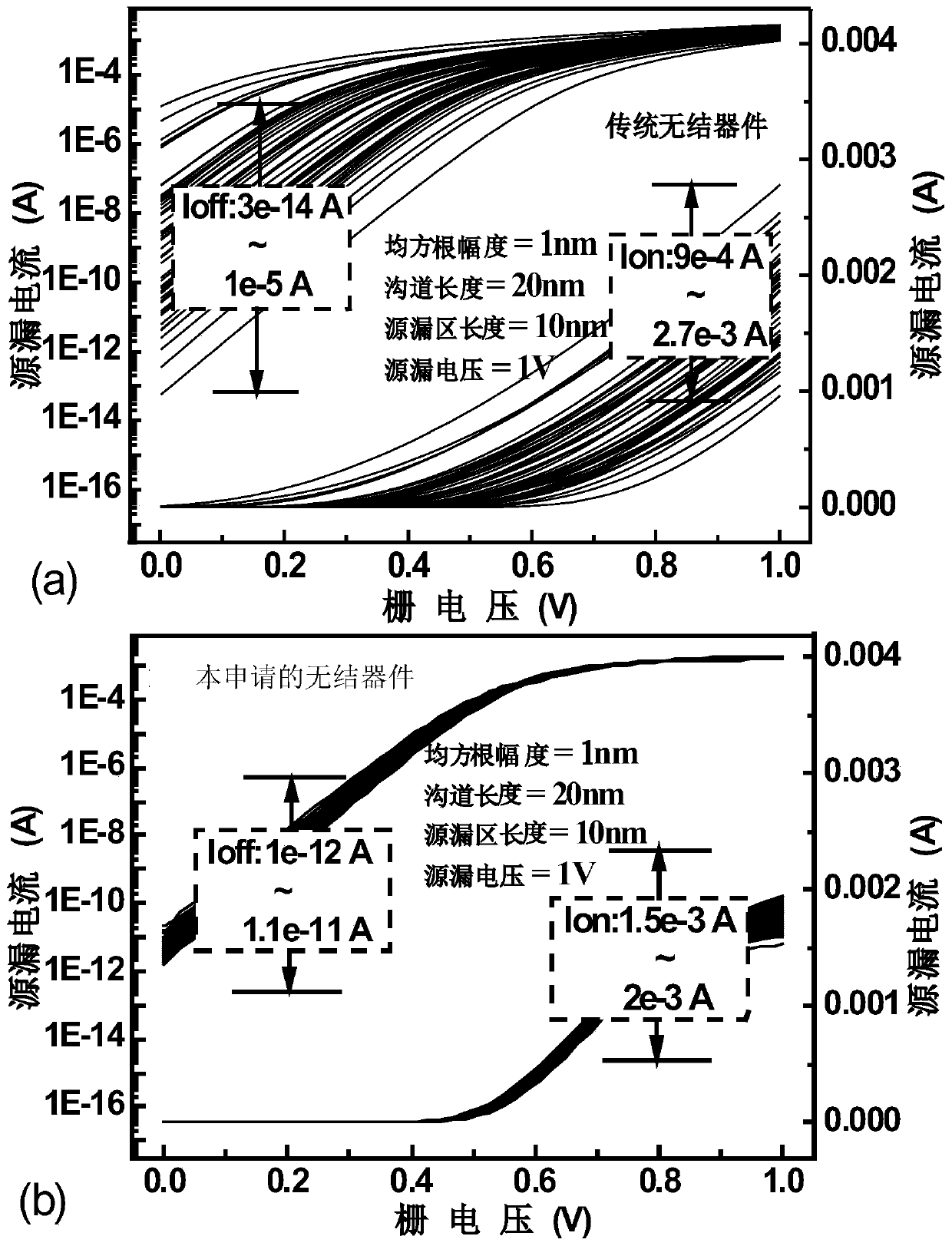

Non-junction field-effect transistor

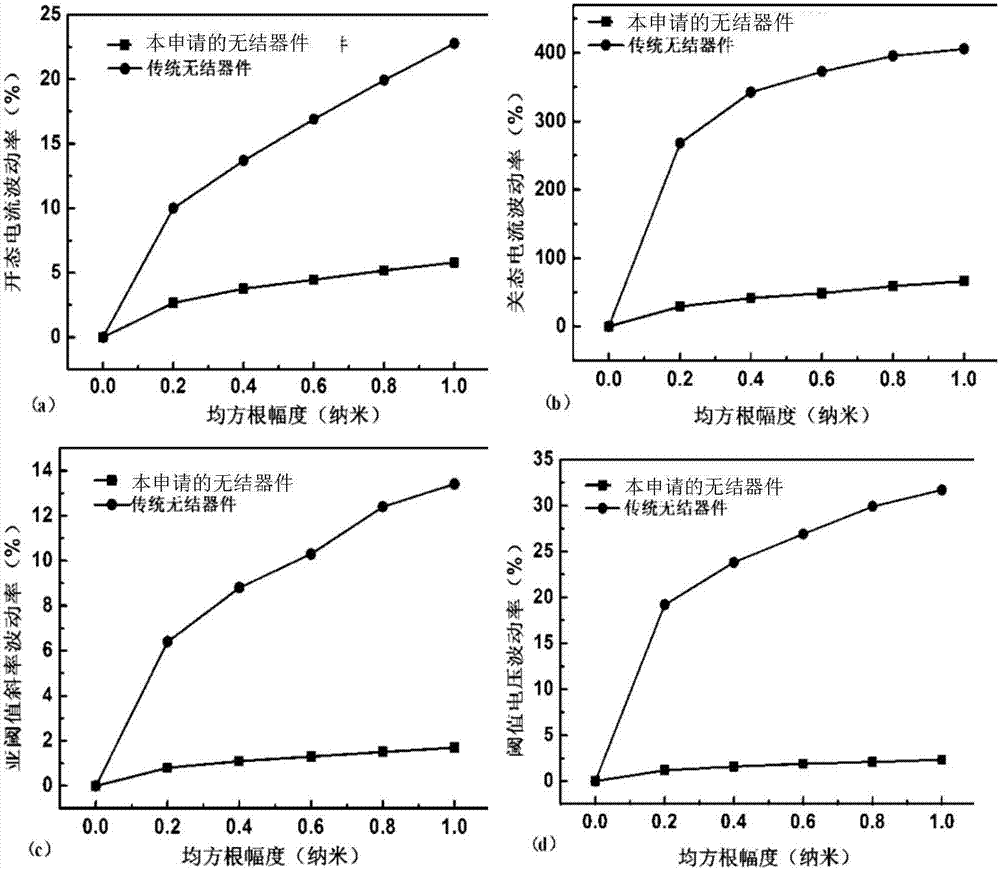

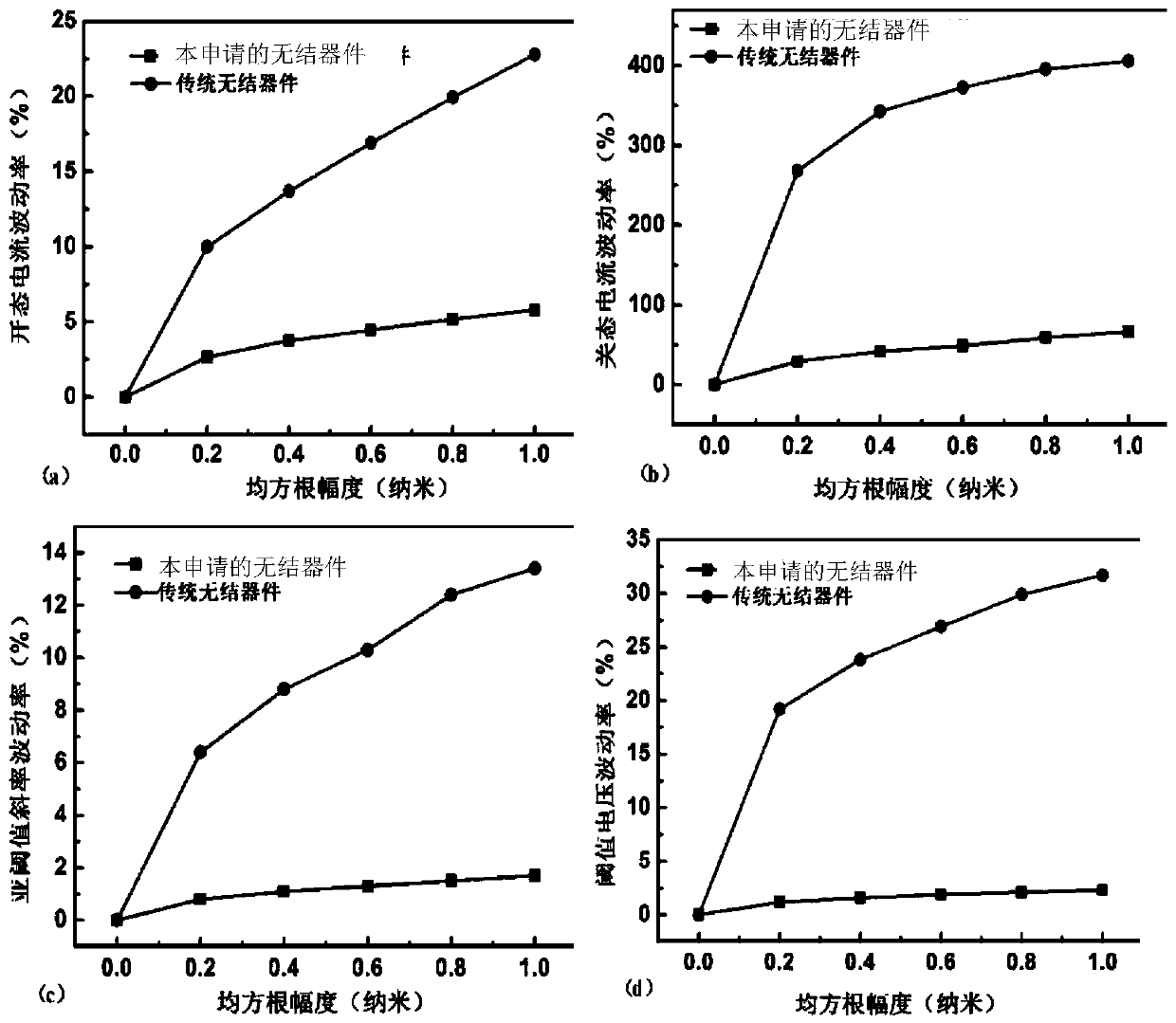

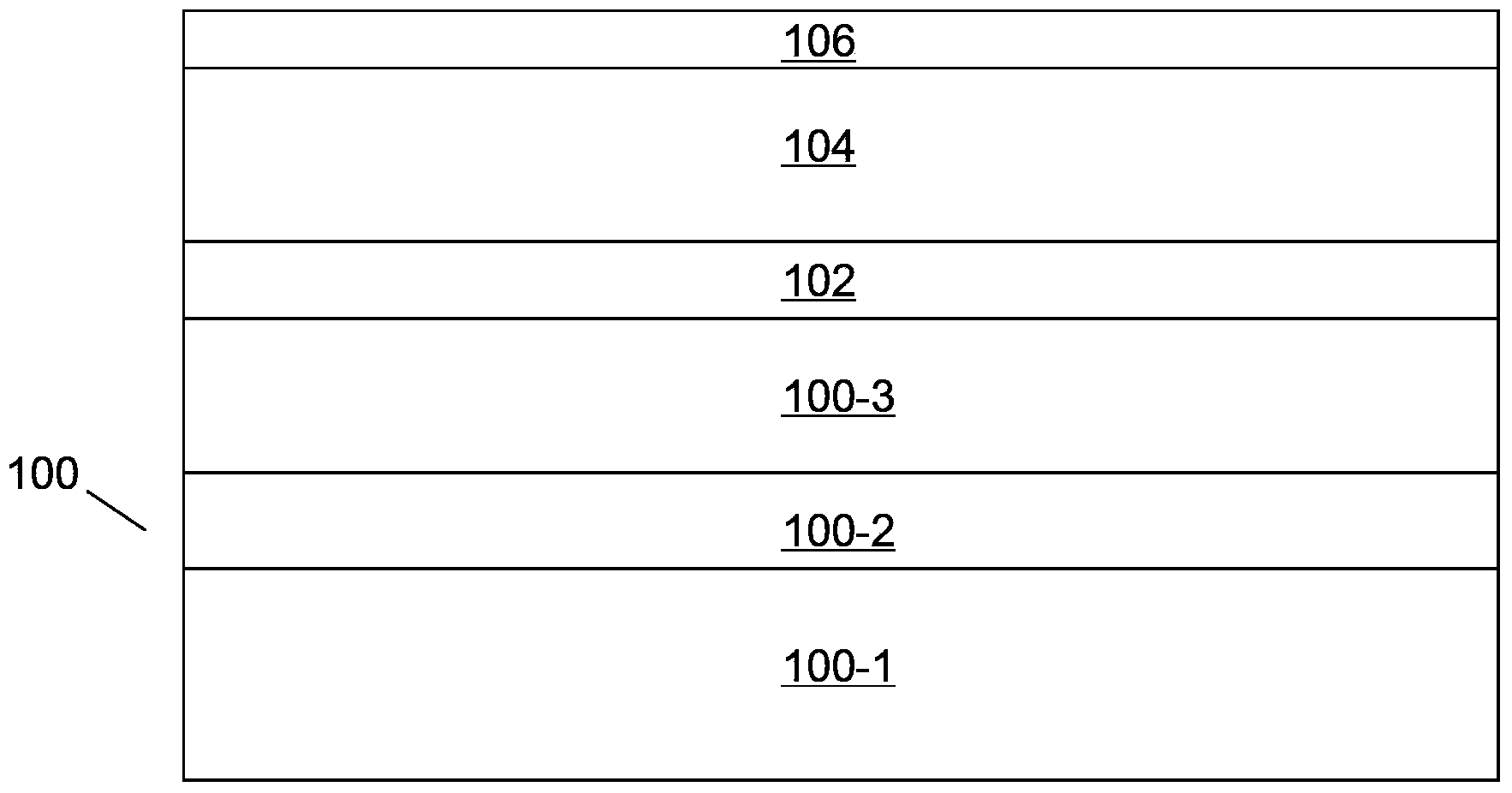

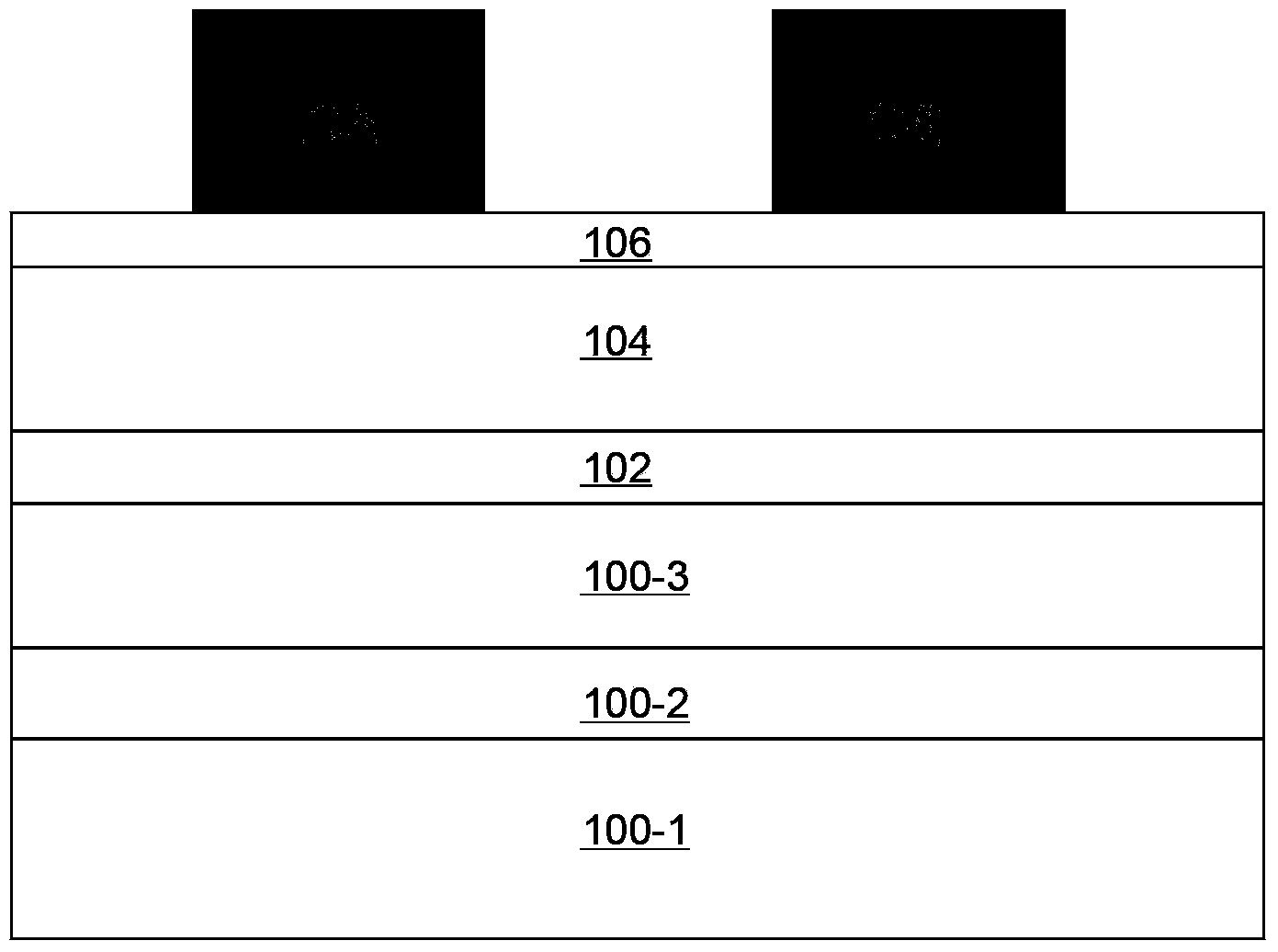

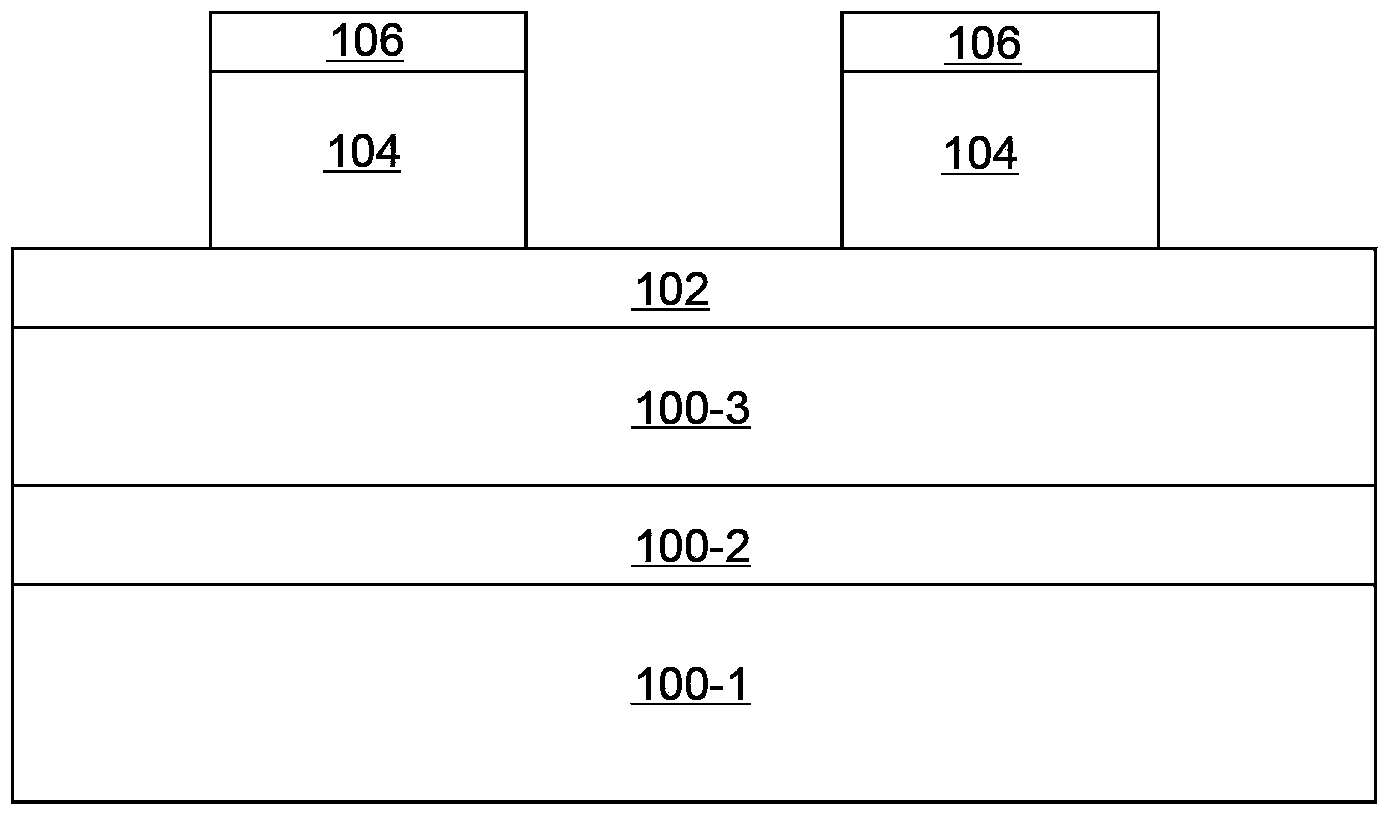

ActiveCN107068734APerformance impactImprove stabilitySemiconductor devicesGate dielectricCharge carrier

The invention provides a non-junction field-effect transistor. The non-junction field-effect transistor includes a source region and a drain region, wherein the source region and the drain region are arranged at two sides of a channel region in a central symmetry manner; the channel region, the source region and the drain region are the same in the doping type and the doping concentration; the channel region is provided with a gate dielectric layer and a gate electrode which is arranged on the gate dielectric layer; the source region and the drain region are respectively provided with a source electrode dielectric layer, a source electrode, a source end side electrode, a drain electrode dielectric layer, a drain electrode and a drain end side electrode; isolating dielectric layers isolate the source electrode from the gate electrode; and the work functions of the source electrode and the drain electrode are the work functions which are determined according to the doping type so as to form a conductive carrier layer on the surface of the source region and the surface of the drain region. The non-junction field-effect transistor can accumulate the corresponding type of carriers on the source region and the drain region to perform current transportation by adjusting the metal work functions of the source electrode and the drain electrode. The structure of the non-junction field-effect transistor can restrain the influence of rough edge of a technological fluctuation line on the device performance, can maintain the current driving capability of a non-junction device, and can optimize the subthreshold feature of the non-junction device so as to improve the stability of device.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

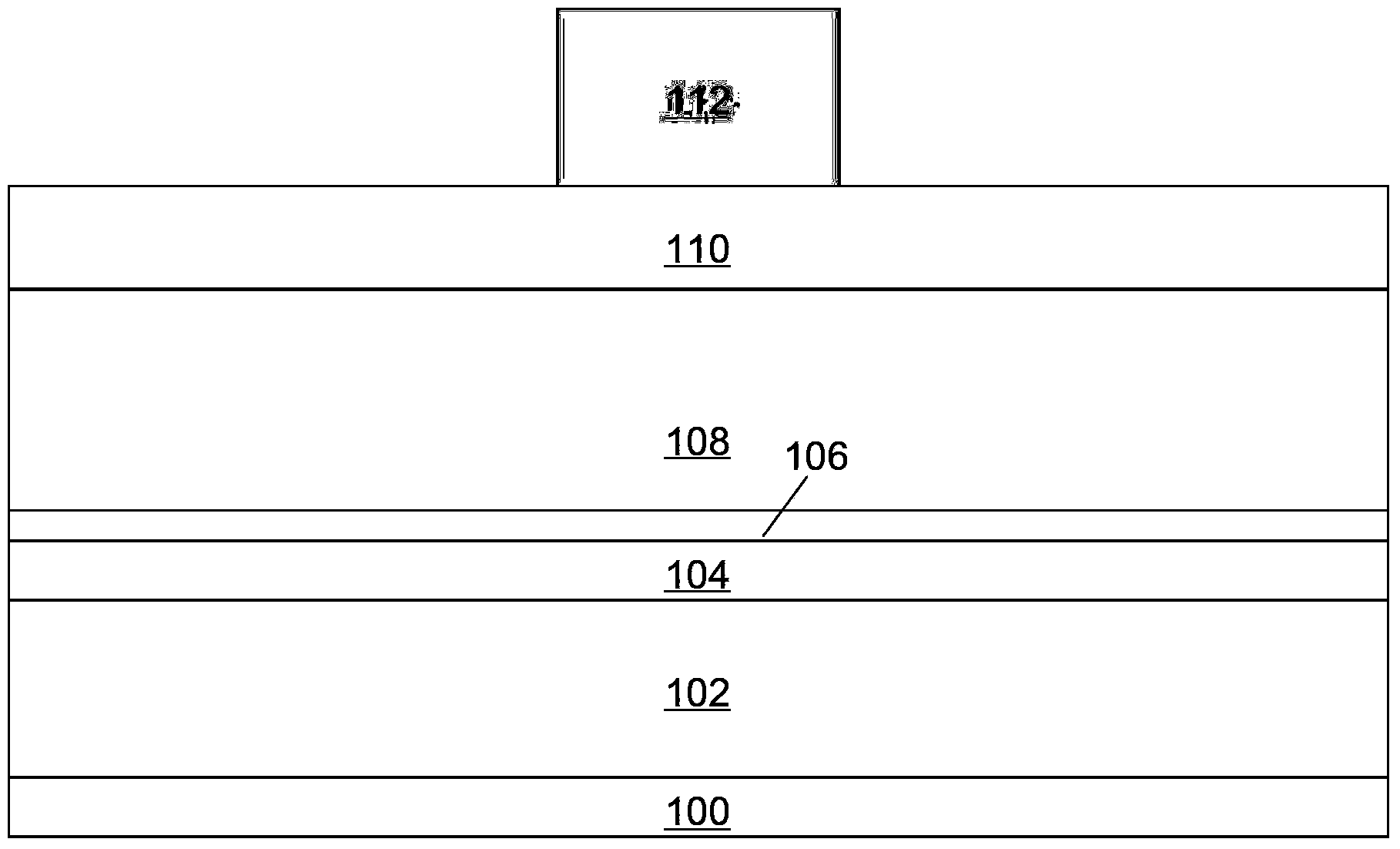

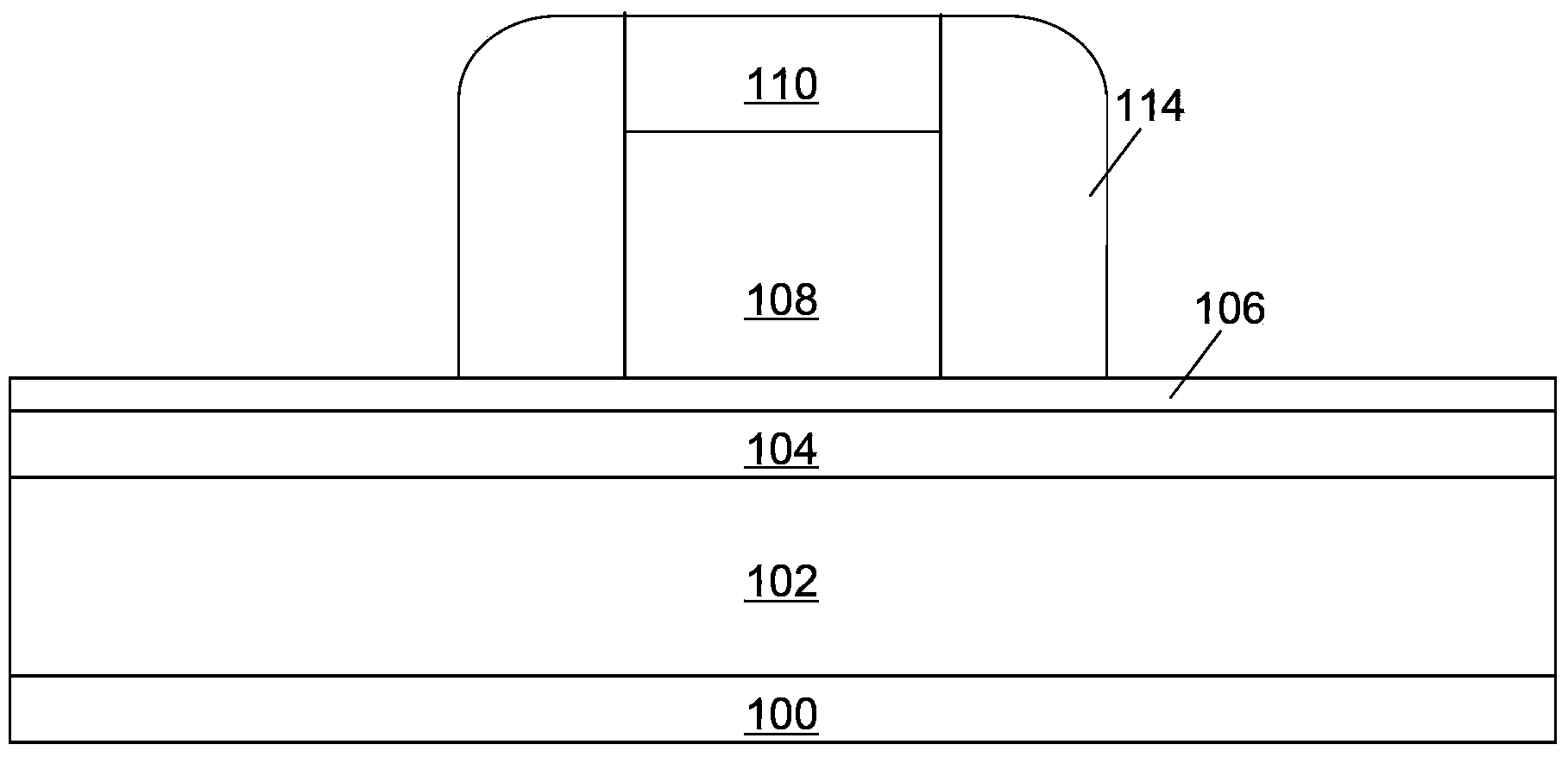

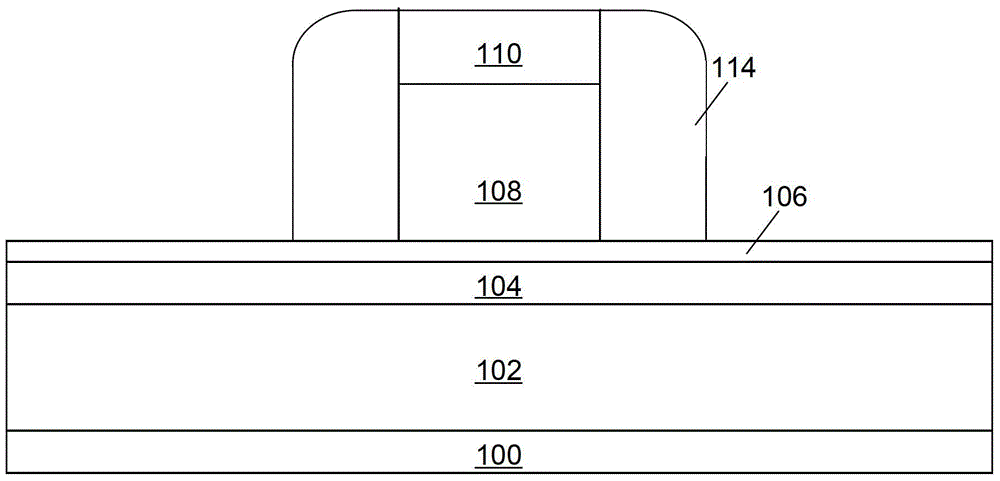

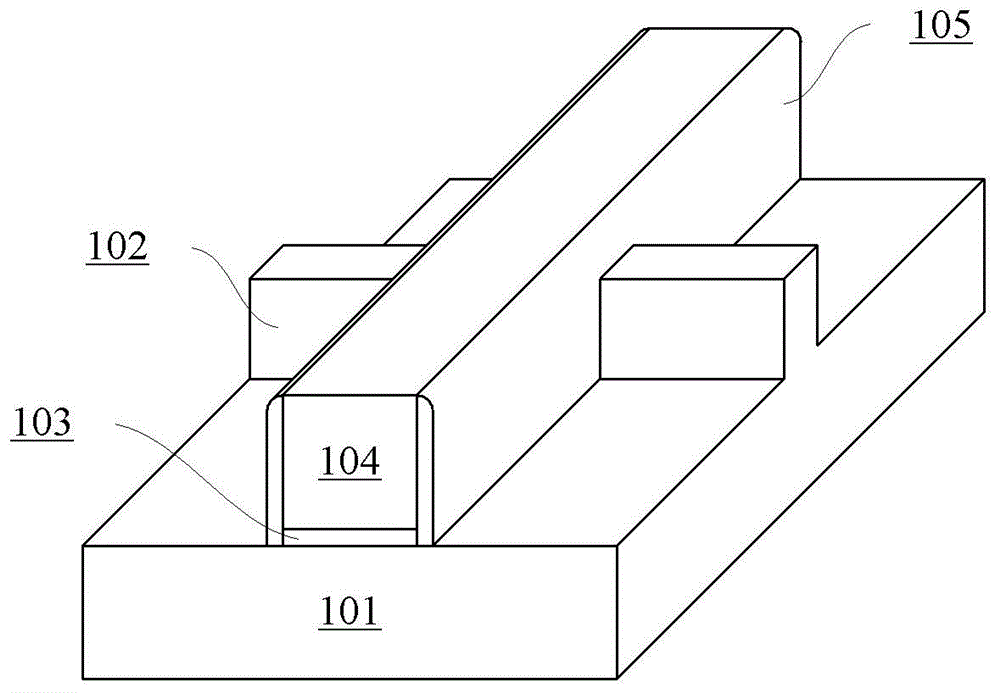

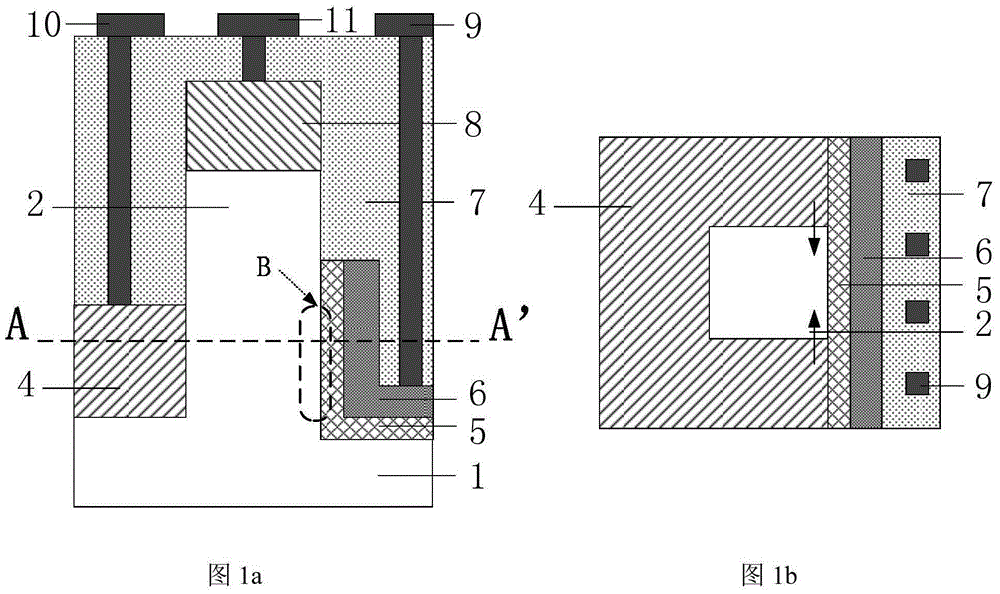

Tunneling field effect transistor and manufacturing method thereof

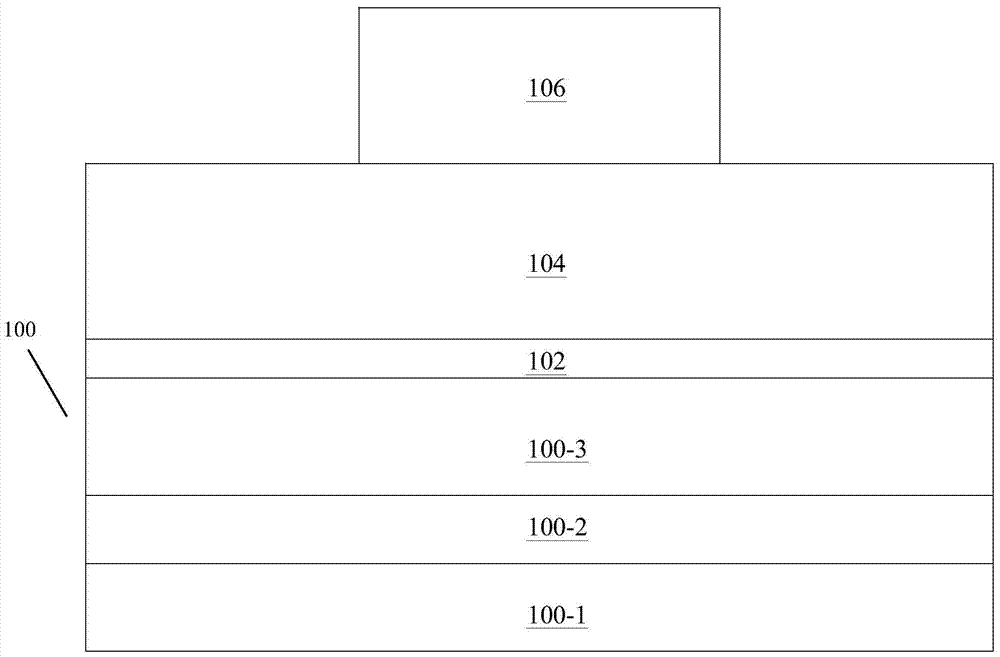

ActiveCN104347725AImproved subthreshold characteristicsAchieve shutdownTransistorSemiconductor/solid-state device manufacturingSub thresholdSemiconductor package

The invention provides a tunneling field effect transistor. The tunneling field effect transistor comprises a semiconductor layer, a first gate medium layer and a second gate medium layer which are respectively arranged two opposite surfaces of the semiconductor layer, a source electrode region and a drain electrode region which have different doping types, are respectively arranged at two sides of the semiconductor layer and contact with the semiconductor layer, and a first grid electrode and a second grid electrode which are respectively arranged on the first gate medium layer and the second gate medium layer. According to the tunneling field effect transistor, tunneling junctions are controlled through thickness of a channel region, a larger effective tunneling area is realized, the conduction current is further enhanced, moreover, tunneling is generated in the semiconductor layer, namely, the channel; tunneling layers are non-doped or low-doped tunneling layers, so a leakage current caused by defects can be reduced, and thereby sub-threshold characteristics of devices can be improved; dual-gate control is employed, so bipolar conduction characteristics can be better controlled, and on and off control on the devices can be realized.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

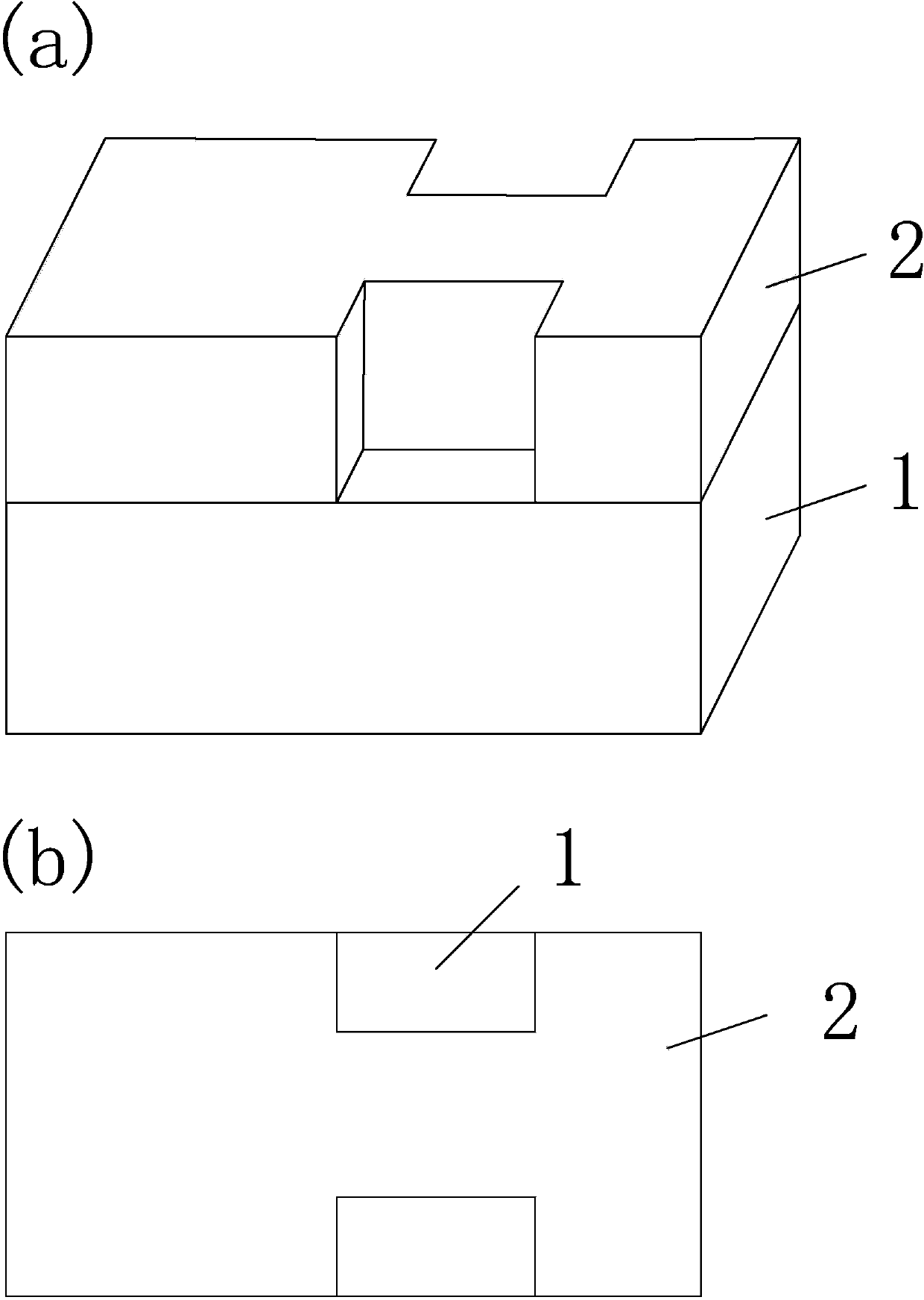

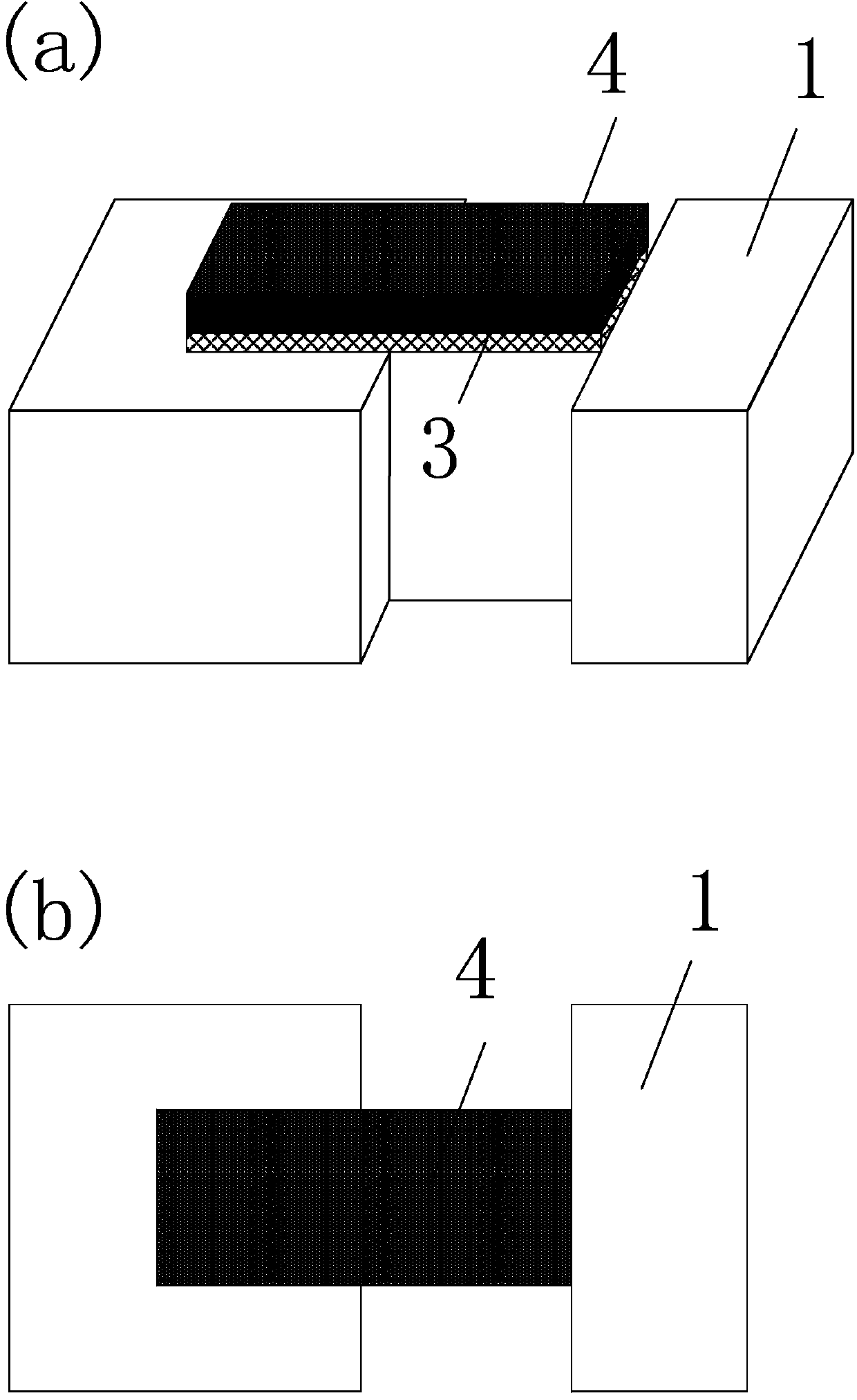

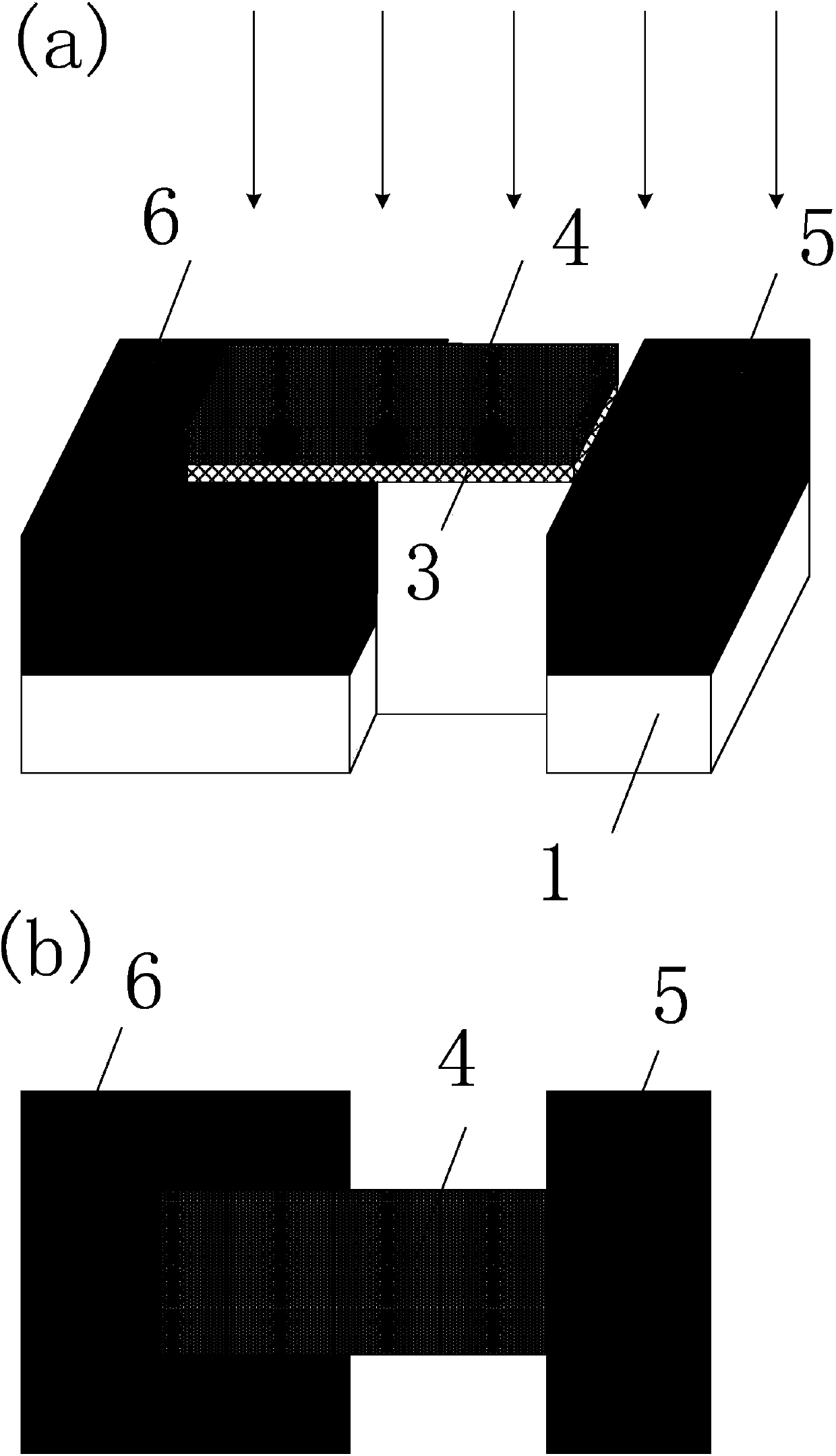

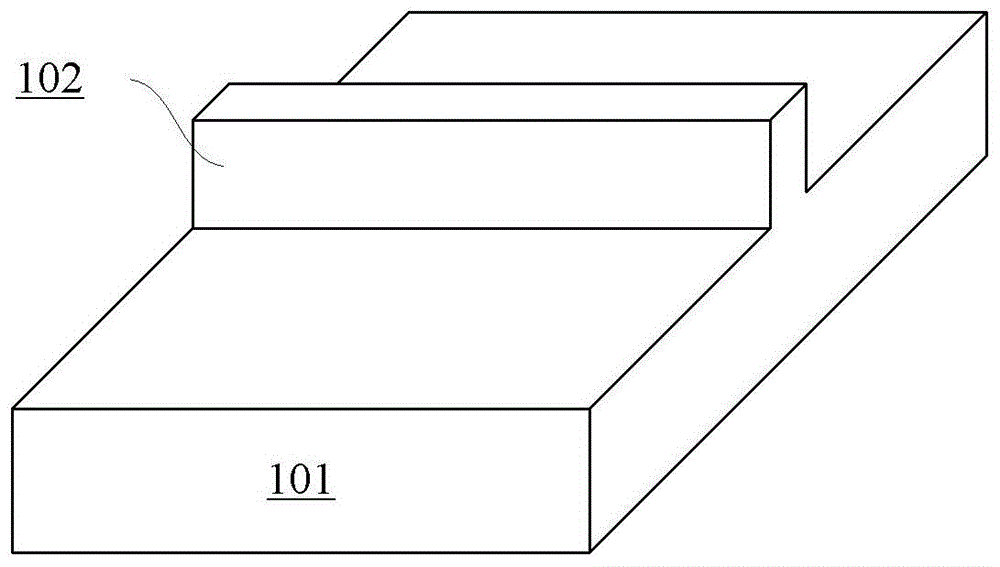

Junction-modulated type tunneling field effect transistor and manufacturing method thereof

ActiveCN103594376AImproved subthreshold characteristicsSubthreshold characteristic steepSemiconductor/solid-state device manufacturingDiodePower flowEngineering

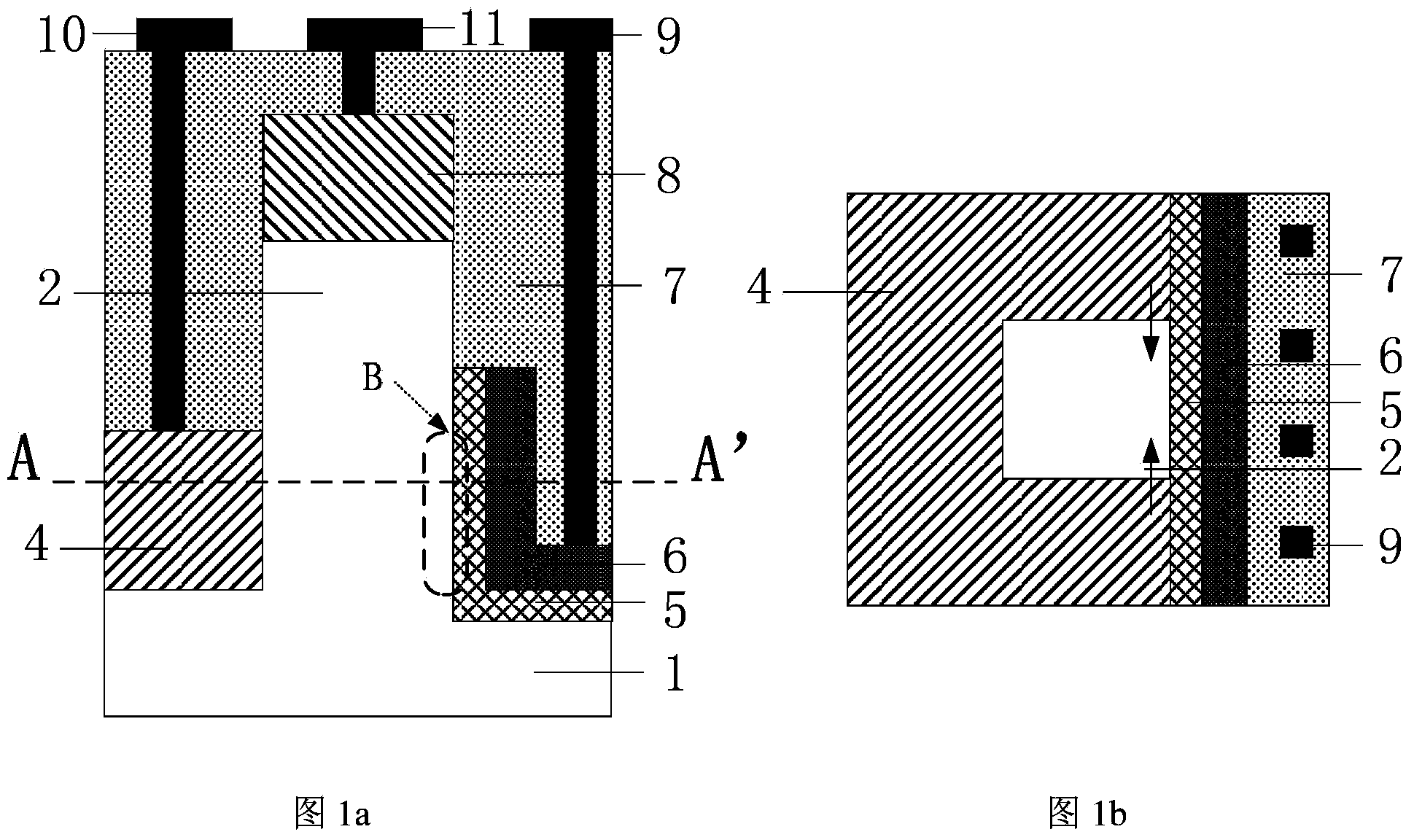

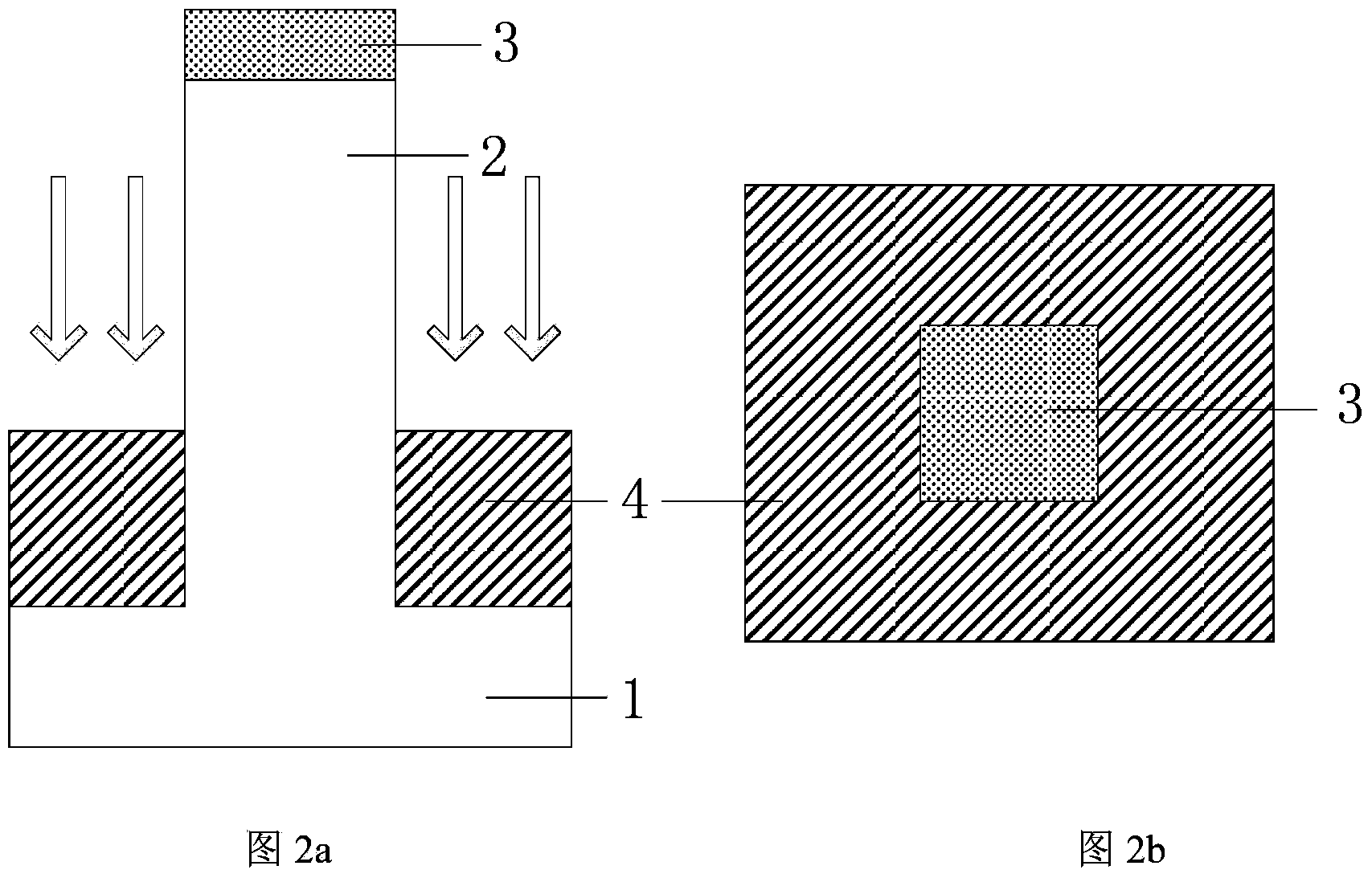

The invention discloses a junction-modulated type tunneling field effect transistor and a manufacturing method of the junction-modulated type tunneling field effect transistor, and belongs to the field of field effect transistor logic devices and circuits in CMOS ultra large scale integration (ULSI) circuits. According to the junction-modulated type tunneling field effect transistor, a PN junction provided by a highly-doped source region enclosed on three sides in a vertical channel region is utilized so that the channel region can be effectively used up, a surface channel energy band below a grid can be increased, a device can obtain a steeper energy band and a smaller tunneling barrier width compared with a traditional TFET when subjected to band-band tunneling, the effect of a steep tunnel junction doping density gradient is achieved equivalently, as a result, the subthreshold property of the traditional TFET is improved substantially, and breakover currents of the device are increased at the same time. According to the junction-modulated type tunneling field effect transistor and the manufacturing method of the junction-modulated type tunneling field effect transistor, under the condition that the junction-modulated type tunneling field effect transistor is compatible with an existing CMOS process, the bipolar breakover effect of the device is restrained effectively, parasitic tunneling currents at corners of a source junction with a small size also can be restrained, and the effect of steep source junction doping density can be achieved equivalently.

Owner:PEKING UNIV

Surrounding gate nanowire field effect transistor and preparation method thereof

InactiveCN108288647AImprove gate control abilityReduce parasitic resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSub thresholdNanowire

The invention provides a surrounding gate nanowire field effect transistor and a preparation method thereof. The preparation method comprises the following steps of S1, forming a first fin body isolated from a substrate on the substrate, wherein the first fin body consists of a first region, a second region and a third region which are connected in sequence in the length direction; S2, forming a nanowire structure in the second region of the first fin body; and S3, forming an interface oxide layer, a ferroelectric layer and a gate which are laminated around the exposed surface of the nanowirestructure in sequence, wherein the preparation method also comprises the following steps of forming a source / drain in the first region and the third region, wherein the source / drain is connected withthe two ends of the nanowire structure. By virtue of the preparation method, the gate control capability of the device is improved, electric leakage of the device is lowered, source / drain parasitic resistance of the device is lowered, and the sub threshold value slope of the device can be greatly lower than 60mV / dec.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

Method and corresponding device for restraining tunneling transistor from leaking current and method for manufacturing corresponding device

ActiveCN103560144AImproved subthreshold characteristicsSuppresses tunneling leakage currentSemiconductor/solid-state device manufacturingDiodeCMOSHemt circuits

The invention discloses a method and corresponding device for restraining a tunneling transistor from leaking a current and a method for manufacturing the corresponding device and belongs to the field of field effect transistors and currents in a ULSI of a CMOS. According to the method for restraining the tunneling transistor from leaking the current, an insulating layer is inserted between a source zone and a body zone below a tunnel junction, an insulating layer is not inserted in the portion, between the source zone and a tunnel, of the tunnel junction, so that the source zone and a drain zone in a small-size TFET device are effectively prevented from being directly tunneled and leaking the current, and meanwhile the slope of a subthreshold value can be effectively improved. The method for manufacturing the corresponding device is compatible with the existing CMOS technology.

Owner:PEKING UNIV

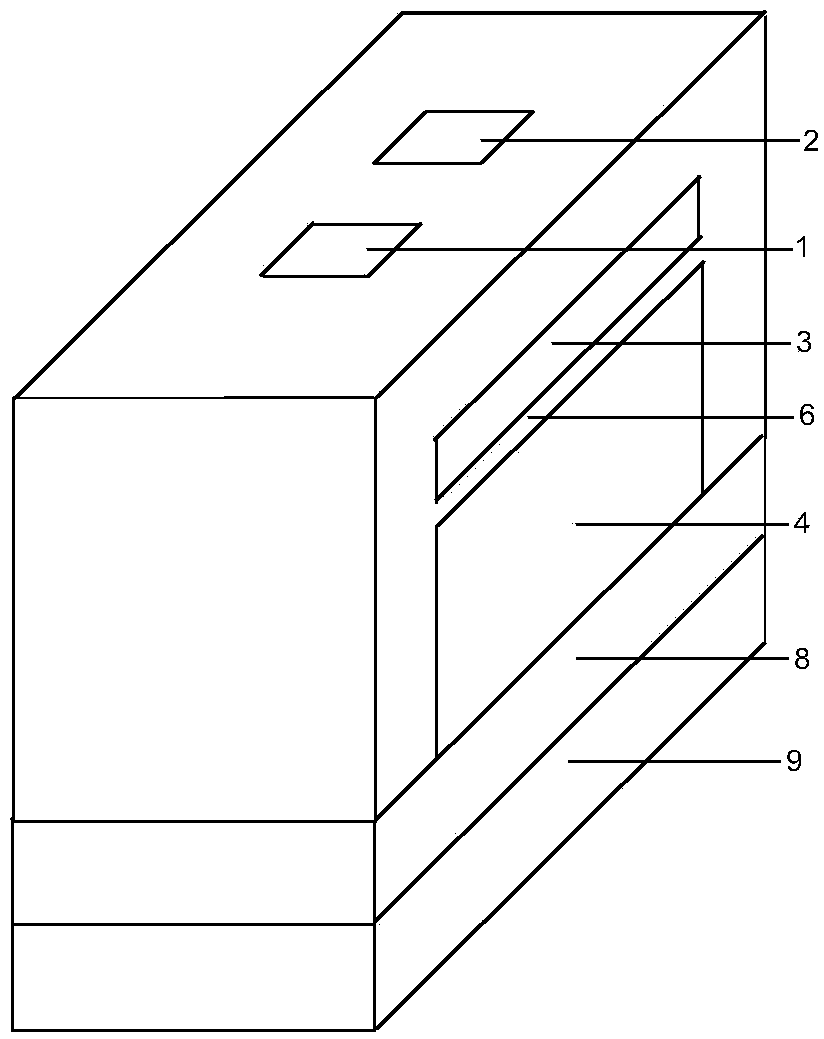

Tunneling field-effect transistor with composite-mechanism strip-type grid and preparation method of tunneling field-effect transistor

ActiveCN103474464AIncrease the on-state currentIncrease subthreshold slopeSemiconductor/solid-state device manufacturingDiodeCMOSPunching

The invention discloses a tunneling field-effect transistor with a composite-mechanism strip-type grid and a preparation method of the tunneling field-effect transistor and belongs to the field of logic devices and circuits of field-effect transistors in CMOS (Complementary Metal Oxide Semiconductor) ultra-large-scale integrated (ULSI) circuits. The tunneling field-effect transistor has the advantages that the energy band of surface channels under the grid can be improved by changing the shape of the grid and utilizing a depletion effect of PN nodes on the two sides of the strip-type grid, and the subthreshold characteristic of the device is improved; since a composite mechanism is introduced into double-doped source areas, an ON state current of the device is improved; due to an I-shaped design of an active area, body leakage currents, including a source-drain direct tunneling current and a punching current, between the two doped source areas to a doped drain area can be greatly inhibited, and a short-channel effect is inhibited, so that the device with small size can be applied.

Owner:PEKING UNIV

High-integration-level source, drain and gate auxiliary control U-shaped channel high-mobility-ratio junction-free transistor shaped like Chinese character 'ri'

InactiveCN104282753ALow source-drain resistanceImprove mobilitySemiconductor devicesElectrical resistance and conductanceChinese characters

The invention relates to a high-integration-level source, drain and gate auxiliary control U-shaped channel high-mobility-ratio junction-free transistor shaped like the Chinese character 'ri'. Two independently-controlled gate electrodes including the auxiliary control gate electrode shaped like the Chinese character 'ri' and the gate electrode are adopted, it is guaranteed that the dosing concentration of the device is reduced to improve the mobility ratio, and the device mobility ratio reduction and the device stability reduction caused by strengthening of the random scattering effect under the high doping concentration are avoided; meanwhile, the resistance of source and drain areas is effectively reduced through the auxiliary control gate electrode shaped like the Chinese character 'ri', so that the contradictions that the source and drain resistance will be increased if the doping concentration of a channel of a common junction-free transistor is excessively low, and the device mobility ratio reduction and the device stability reduction will be caused if the doping concentration is excessively high are overcome; meanwhile, U-shaped monocrystalline silicon serves a channel part of the device; compared with a common plane structure, on the premise that the chip area is not additionally increased, the effective channel length is obviously increased to reduce the short channel effect of the device under the deep nanoscale, and therefore the high-integration-level source, drain and gate auxiliary control U-shaped channel high-mobility-ratio junction-free transistor shaped like the Chinese character 'ri' is suitable for application and popularization.

Owner:SHENYANG POLYTECHNIC UNIV

A junctionless field effect transistor

ActiveCN107068734BPerformance impactImprove stabilitySemiconductor devicesGate dielectricEngineering

The invention provides a non-junction field-effect transistor. The non-junction field-effect transistor includes a source region and a drain region, wherein the source region and the drain region are arranged at two sides of a channel region in a central symmetry manner; the channel region, the source region and the drain region are the same in the doping type and the doping concentration; the channel region is provided with a gate dielectric layer and a gate electrode which is arranged on the gate dielectric layer; the source region and the drain region are respectively provided with a source electrode dielectric layer, a source electrode, a source end side electrode, a drain electrode dielectric layer, a drain electrode and a drain end side electrode; isolating dielectric layers isolate the source electrode from the gate electrode; and the work functions of the source electrode and the drain electrode are the work functions which are determined according to the doping type so as to form a conductive carrier layer on the surface of the source region and the surface of the drain region. The non-junction field-effect transistor can accumulate the corresponding type of carriers on the source region and the drain region to perform current transportation by adjusting the metal work functions of the source electrode and the drain electrode. The structure of the non-junction field-effect transistor can restrain the influence of rough edge of a technological fluctuation line on the device performance, can maintain the current driving capability of a non-junction device, and can optimize the subthreshold feature of the non-junction device so as to improve the stability of device.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

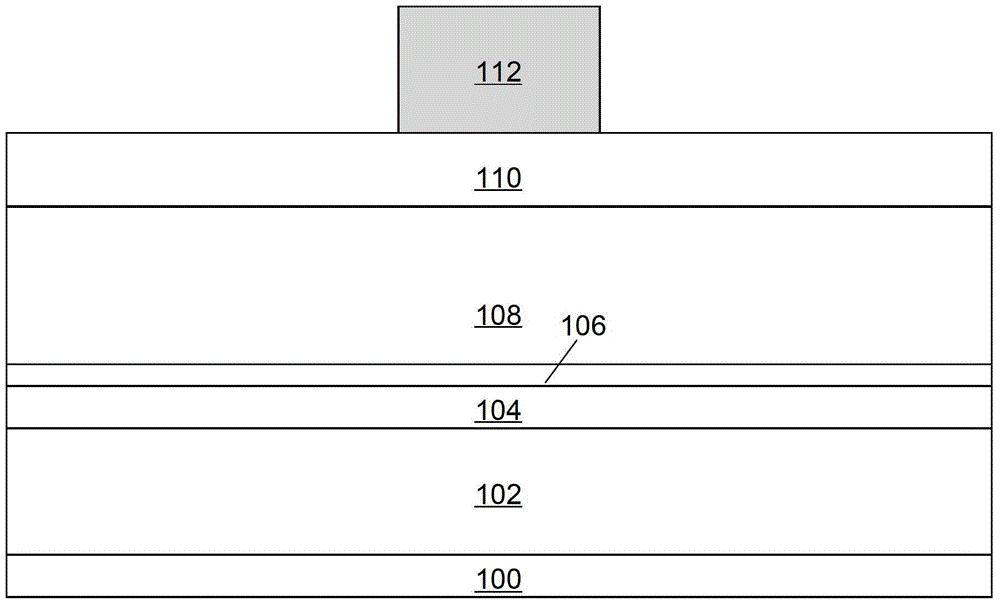

Tunneling field-effect transistor and manufacturing method thereof

ActiveCN104347704AImproved subthreshold characteristicsAchieve shutdownSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSub threshold

The invention provides a tunneling field-effect transistor. The tunneling field-effect transistor includes a substrate, a first gate dielectric layer and a second gate dielectric layer, a first gate and a second gate as well as a first doped region and a second doped region; the substrate is provided with a fin; the fin is provided with a first side surface and a second side surface which are opposite to each other as well as a third side surface and a fourth side surface which are opposite to each other; the first gate dielectric layer and the second gate dielectric layer are formed on the first side surface and the second side surface respectively; the first gate and the second gate are formed on the substrate and are connected with the first gate dielectric layer and the second gate dielectric layer respectively; the first doped region and the second doped region are formed on the substrate and are connected with the third side surface and the fourth side surface respectively; and the first doped region and the second doped region have different doping types. According to the tunneling field-effect transistor of the invention, the width of a tunneling junction is controlled through the width of a fin channel region, and a larger and more effective tunneling area can be provided, and thus, conduction current can be increased; tunneling occurs in a semiconductor layer, namely in a channel, and a tunneling layer is un-doped or lowly-doped, and therefore, leakage current can be reduced, and the sub threshold characteristics of the device can be improved; and double-gate control is adopted, so that bipolar conduction characteristics can be better controlled, and the on-off of the device can be realized.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

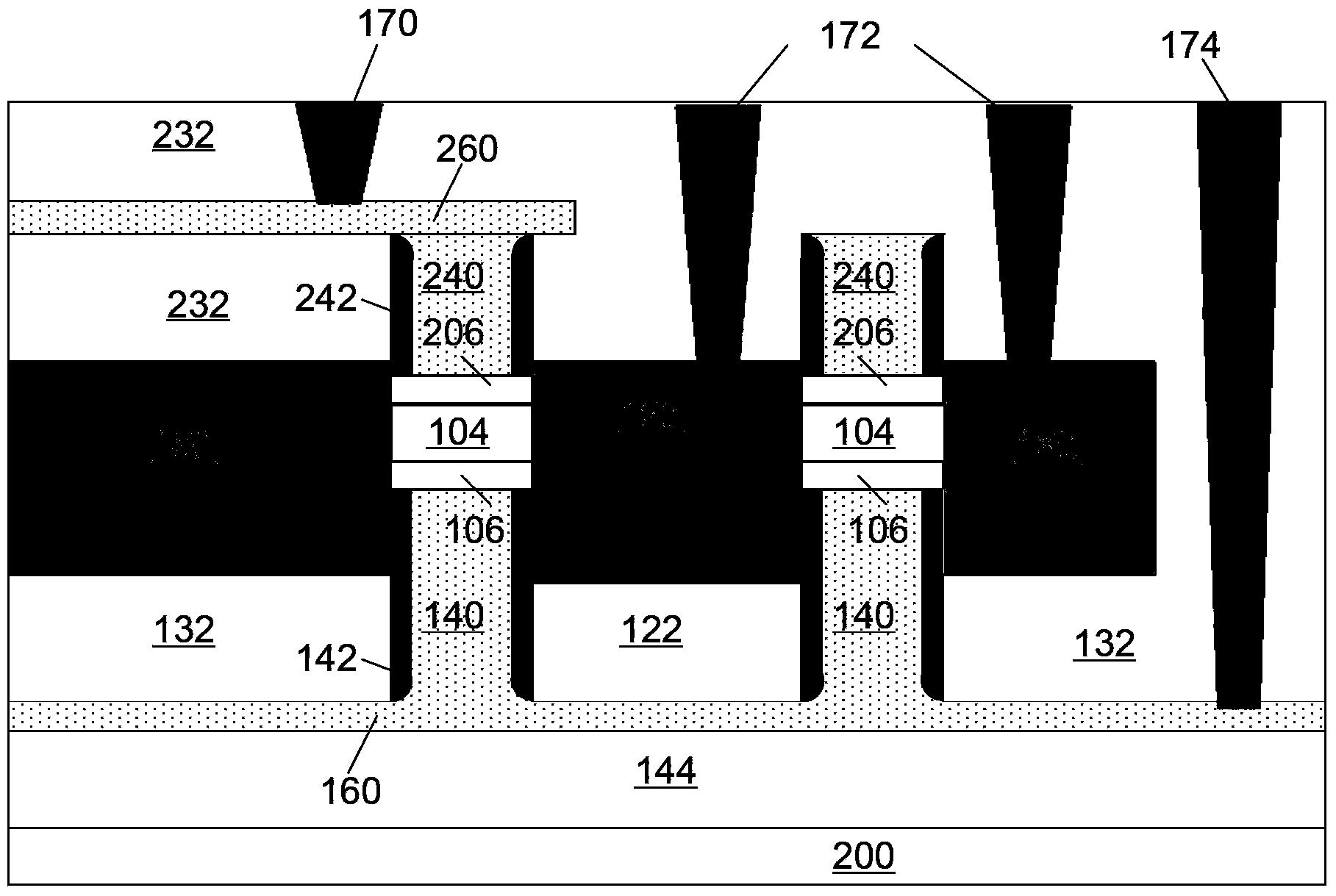

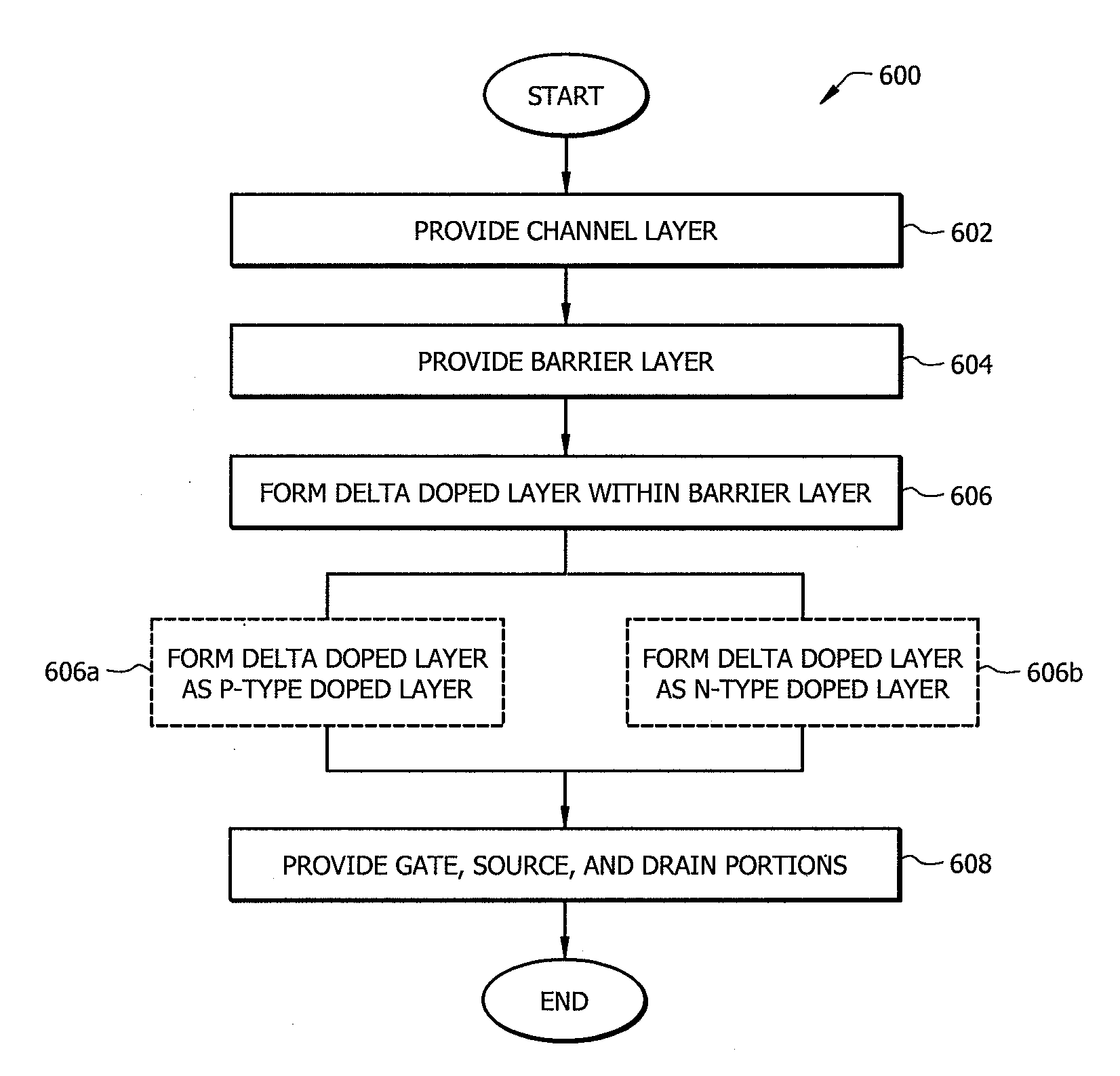

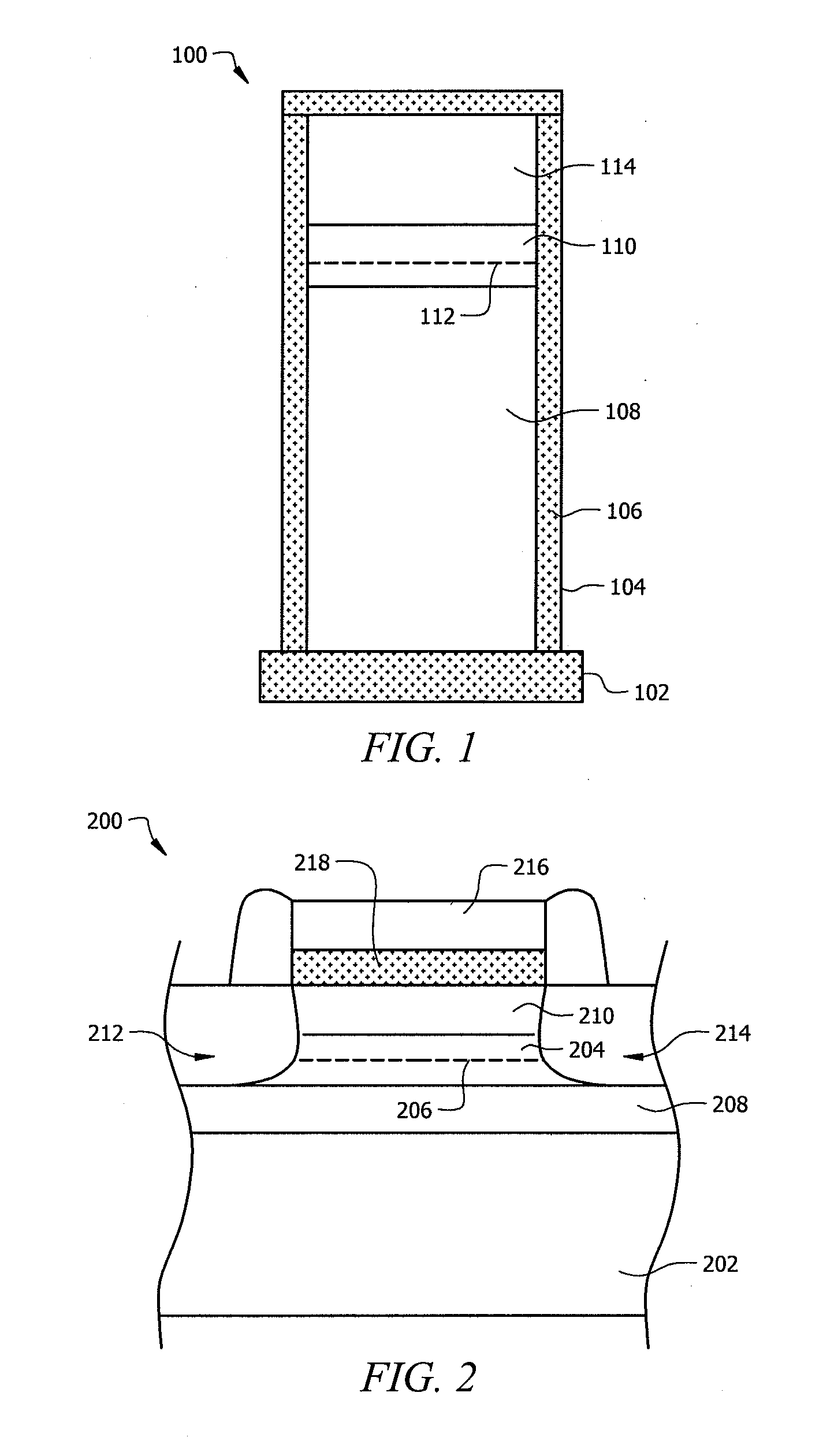

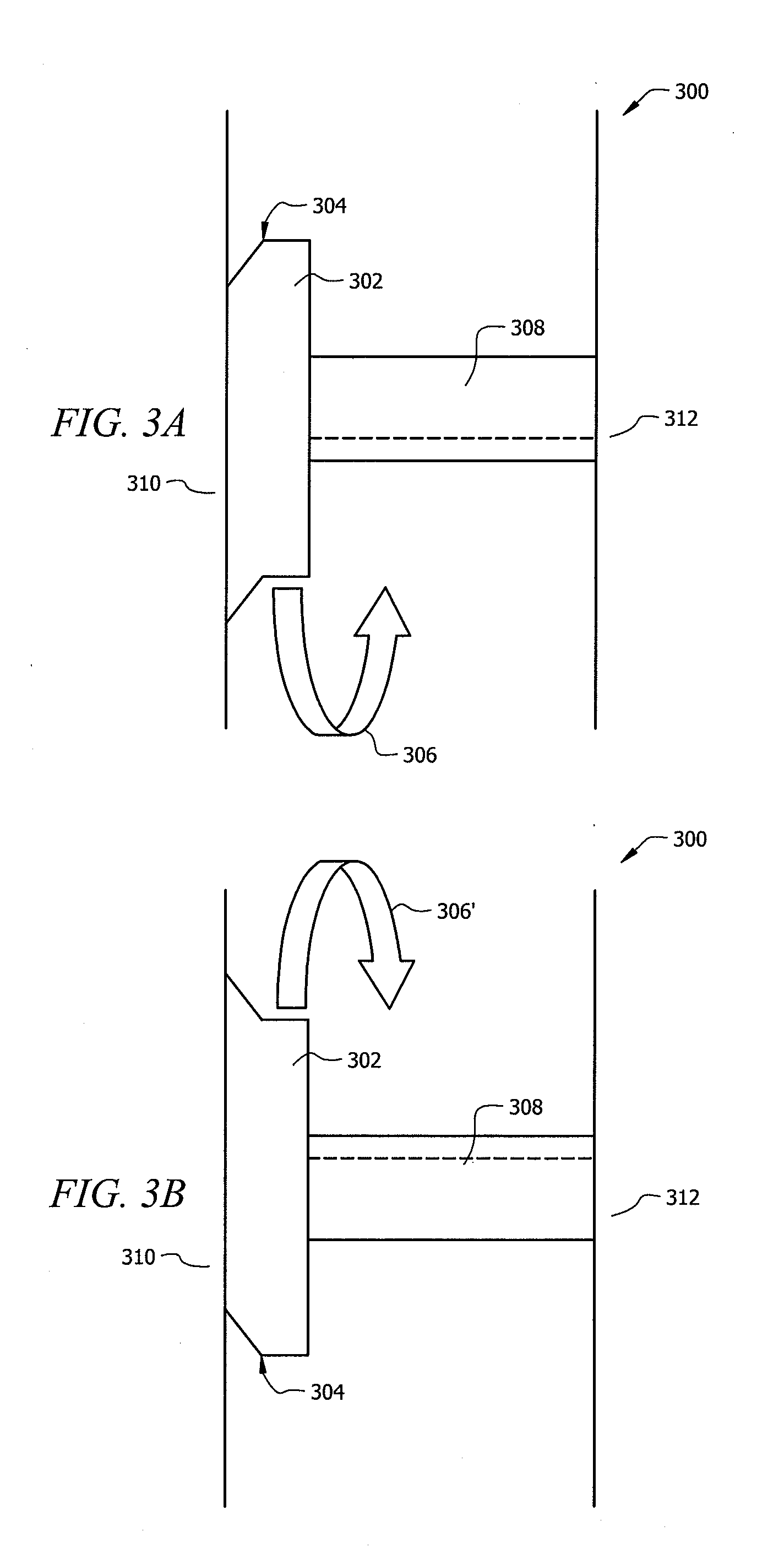

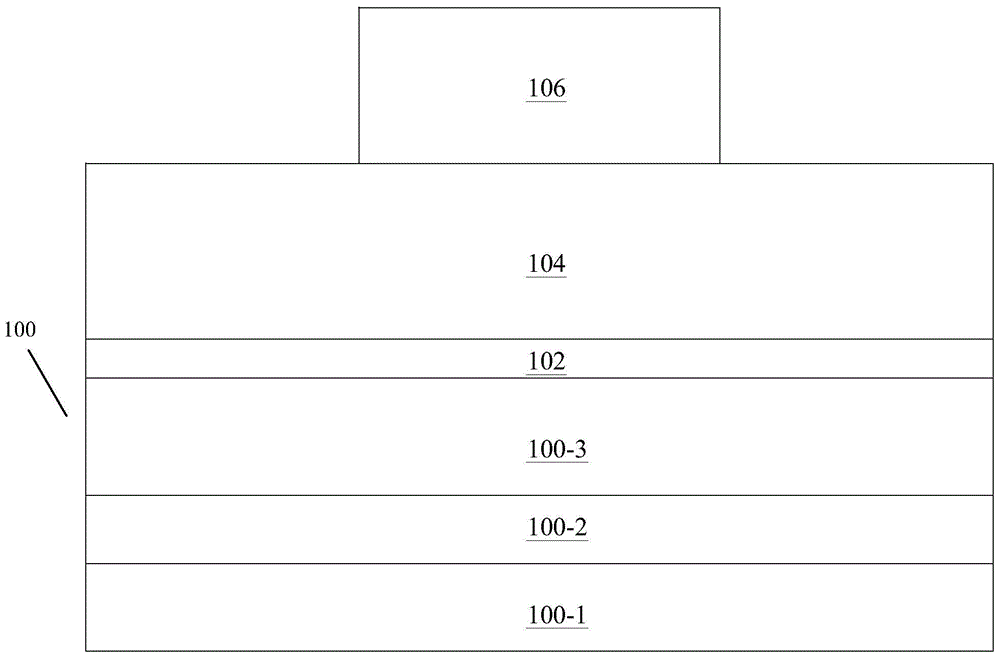

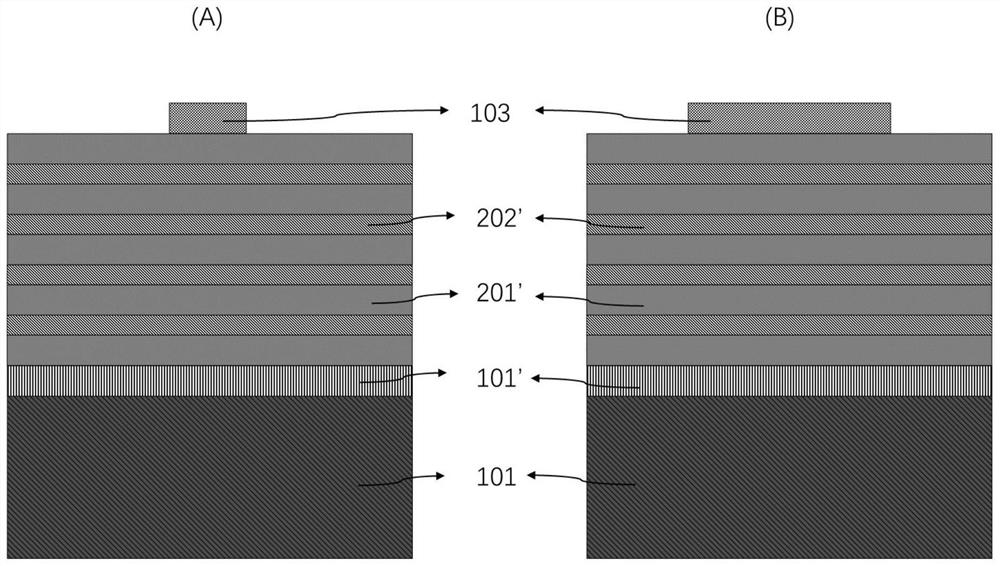

Remote Doped High Performance Transistor Having Improved Subthreshold Characteristics

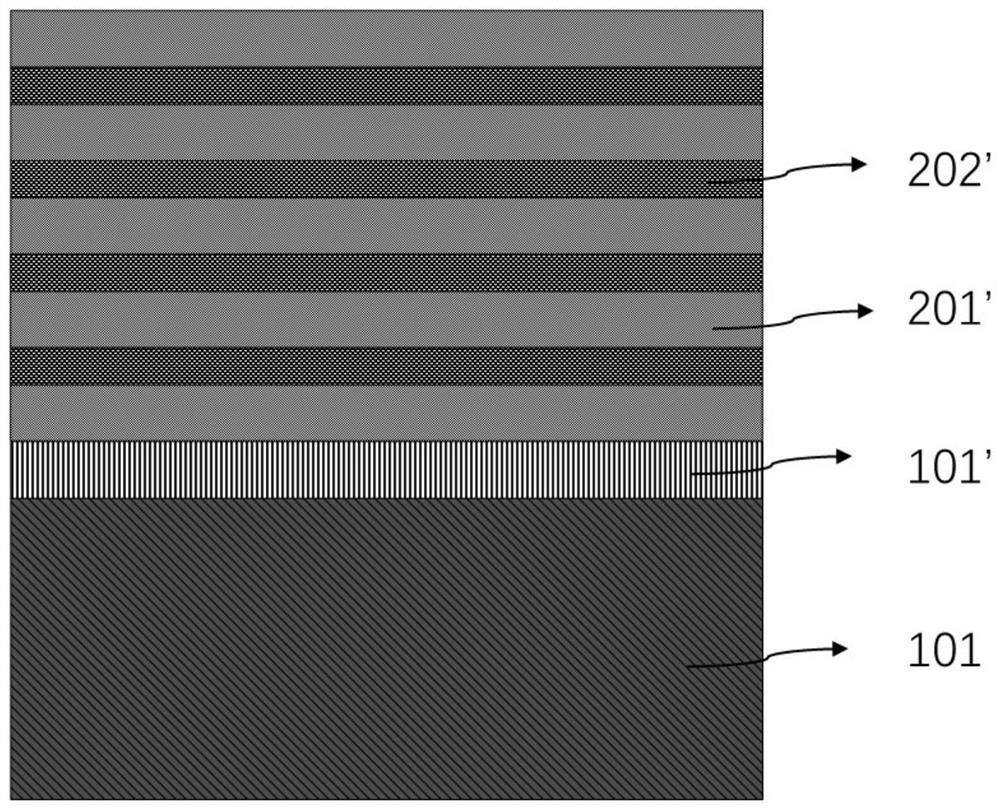

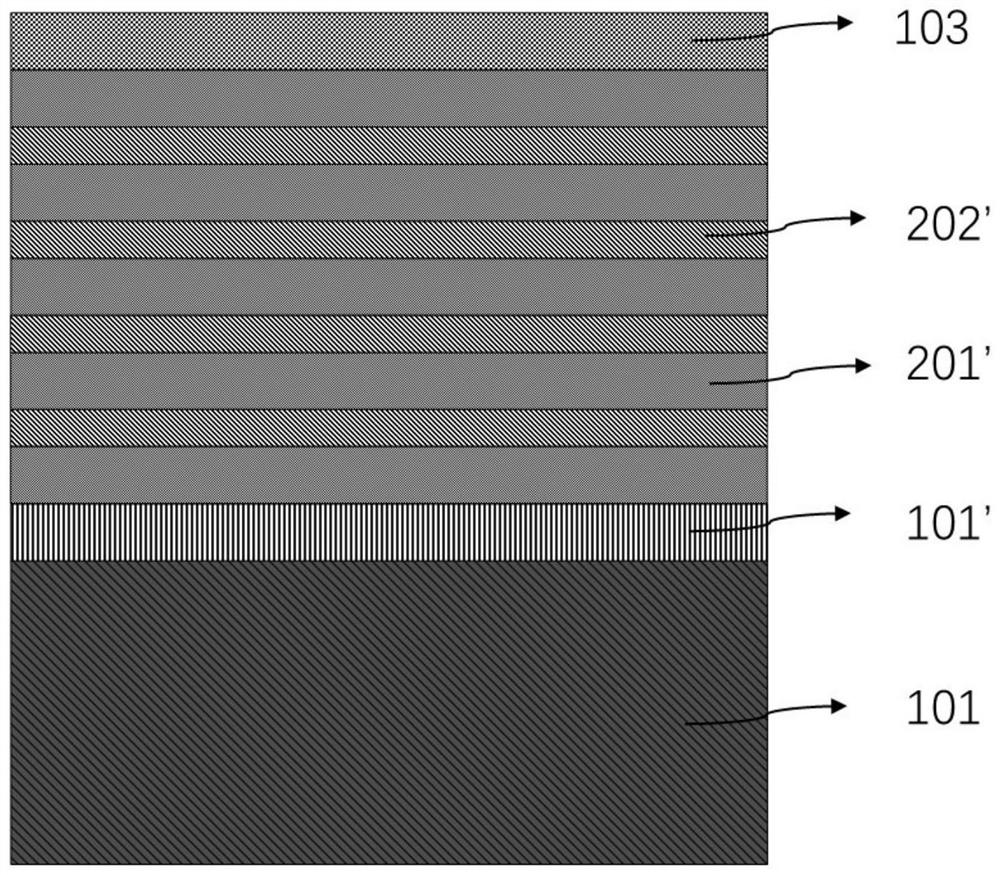

InactiveUS20110147845A1Improve mobilityShort channel characteristic of channelSemiconductor/solid-state device detailsNanoinformaticsDopantDelta doping

Devices comprising, and a method for fabricating, a remote doped high performance transistor having improved subthreshold characteristics are disclosed. In one embodiment a field-effect transistor includes a channel layer configured to convey between from a source portion and a drain portion of the transistor when the transistor is in an active state. Further, the field-effect transistor includes a barrier layer adjacent to the channel layer. The barrier layer comprises a delta doped layer configured to provide carriers to the channel layer of the transistor, while preferably substantially retaining dopants in said delta-doped layer.

Owner:INTEL AMERICAS INC +1

Tunneling field effect transistor and forming method thereof

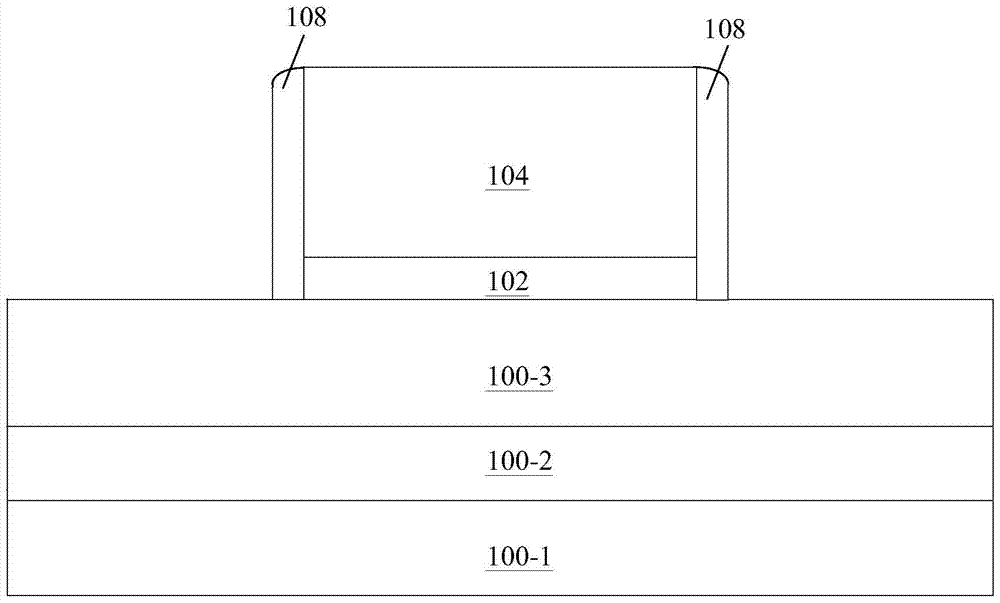

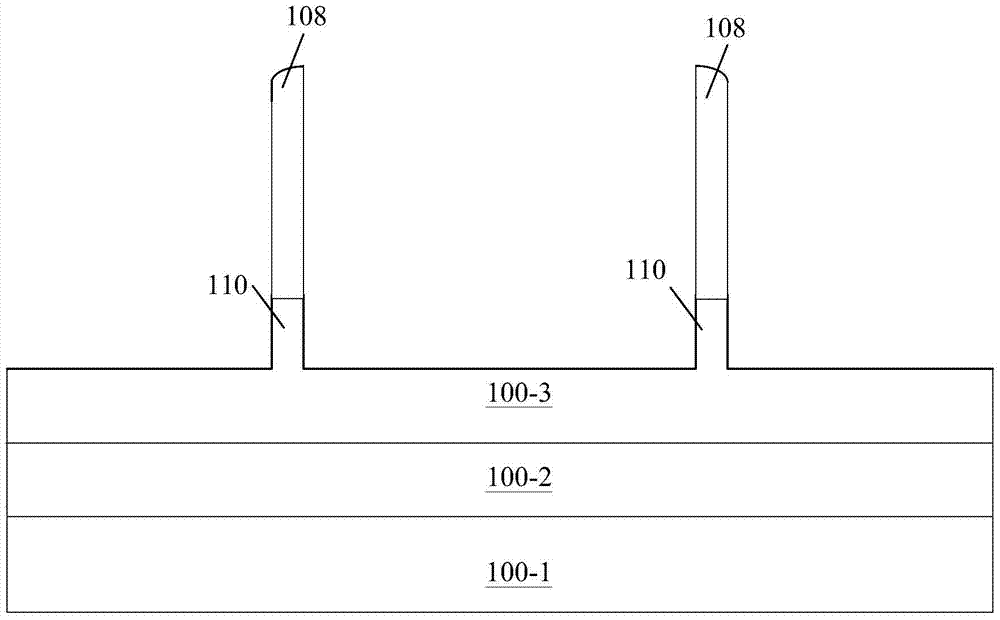

ActiveCN104600110AImproved subthreshold characteristicsAchieve shutdownSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSub threshold

The invention provides a tunneling field effect transistor comprising a semiconductor substrate, first gates, second gates, first doped regions, and second doped regions. Fins are formed on the semiconductor substrate. Each first gate and the corresponding second gate are respectively formed on the semiconductor substrate at the two sides of the corresponding fin. A gate dielectric layer is formed among each first gate, a first side of the corresponding fin and the semiconductor substrate, and a gate dielectric layer is formed among each second gate, a second side of the corresponding fin and the semiconductor substrate. The first doped regions and the second doped regions are respectively disposed in the semiconductor substrate at one side of the first gates and at one side of the second gates. A narrow tunneling junction is realized by controlling the width of the fins, the tunneling current is increased, and the conduction current is further improved by increasing the effective tunneling area. In addition, defect-related leakage current can be inhibited, and the sub threshold characteristic of devices can be improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Oxide semiconductor device and production method thereof

PendingCN113471295AImprove subthreshold characteristicsSuppression of short channel effectsTransistorNanoinformaticsPhysicsOxide semiconductor

The invention relates to an oxide semiconductor device which includes an insulating substrate; a source electrode and a drain electrode are oppositely arranged on the insulating substrate; a nanosheet stack part is included and is arranged on the substrate to form a plurality of conducting channels; the nanosheet stack part comprises a plurality of metal oxide semiconductor nanosheets which are vertically stacked to form the nanosheet stack part, and the two ends of the metal oxide semiconductor nanosheets are embedded into the source electrode and the drain electrode respectively; and a surrounding type grid electrode is included and surrounds the periphery of the plurality of metal oxide semiconductor nanosheets in the nanometer stack part. The design of the novel structure gate-all-around OS-TFT (GAA OS-TFT) can significantly improve the sub-threshold characteristic, the current switch ratio and the short channel effect of the device; the working current of the device can be obviously improved by utilizing the design of combining the multiple layers of nanosheets and the supporting structure; the preparation process of the device is compatible with a mainstream CMOS process and is simple; and through the structure design of the surrounding type grid device, the channel carrier mobility can be remarkably improved, the electrical performance of the device is increased, and the reliability and the stability of the device can also be improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Manufacturing method of tunneling field effect transistor

ActiveCN104347725BImproved subthreshold characteristicsAchieve shutdownTransistorSemiconductor/solid-state device manufacturingEngineeringField effect

The invention provides a tunneling field effect transistor. The tunneling field effect transistor comprises a semiconductor layer, a first gate medium layer and a second gate medium layer which are respectively arranged two opposite surfaces of the semiconductor layer, a source electrode region and a drain electrode region which have different doping types, are respectively arranged at two sides of the semiconductor layer and contact with the semiconductor layer, and a first grid electrode and a second grid electrode which are respectively arranged on the first gate medium layer and the second gate medium layer. According to the tunneling field effect transistor, tunneling junctions are controlled through thickness of a channel region, a larger effective tunneling area is realized, the conduction current is further enhanced, moreover, tunneling is generated in the semiconductor layer, namely, the channel; tunneling layers are non-doped or low-doped tunneling layers, so a leakage current caused by defects can be reduced, and thereby sub-threshold characteristics of devices can be improved; dual-gate control is employed, so bipolar conduction characteristics can be better controlled, and on and off control on the devices can be realized.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

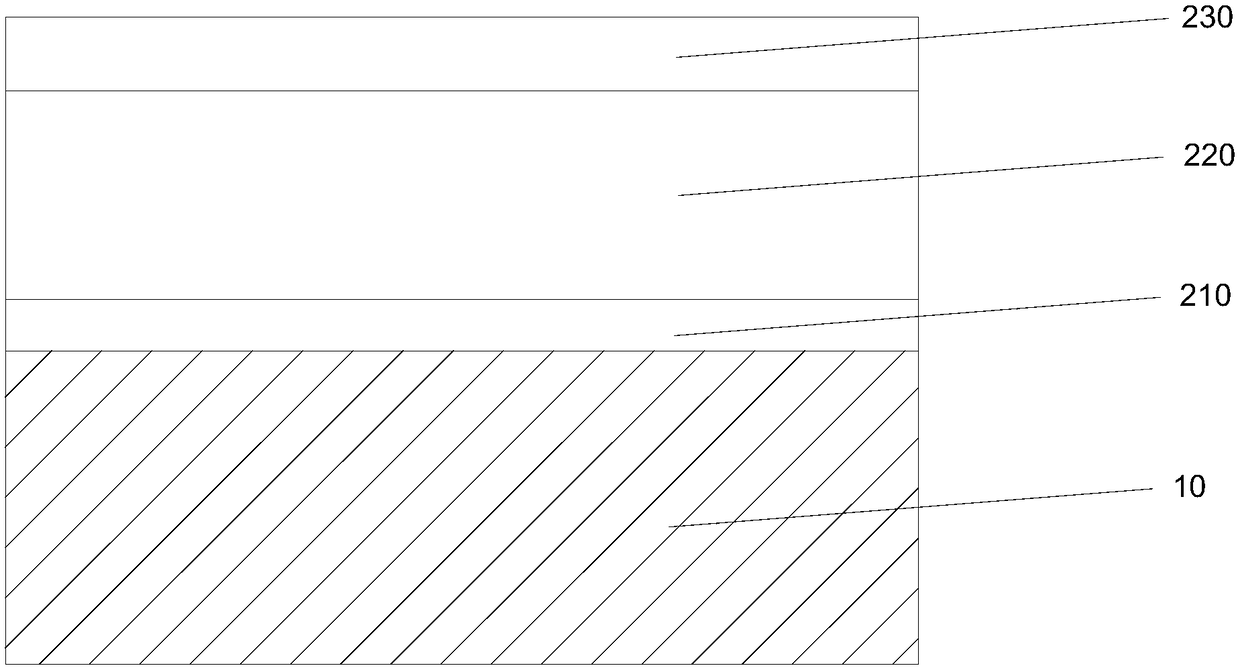

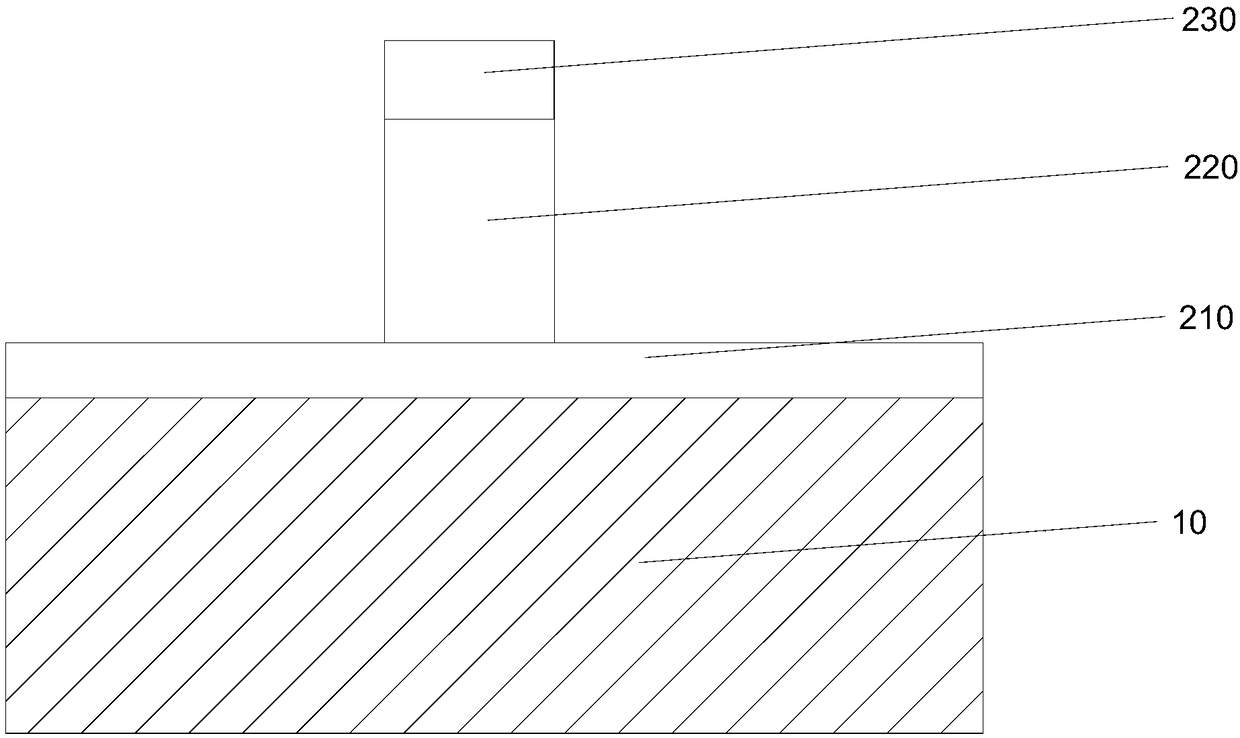

Semiconductor device and manufacturing method thereof

ActiveCN104347681BImproved subthreshold characteristicsShort channel effect is well controlledSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

Provided are a semiconductor configuration and a method for manufacturing the same. The semiconductor configuration may comprise: a substrate (301); and a fin. The fin comprises a first portion (302-1) and a second portion (302-2) formed sequentially on the substrate, and the first portion and the second portion are T shaped as a whole. The second portion has a reduced thickness at a region corresponding to the first portion.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

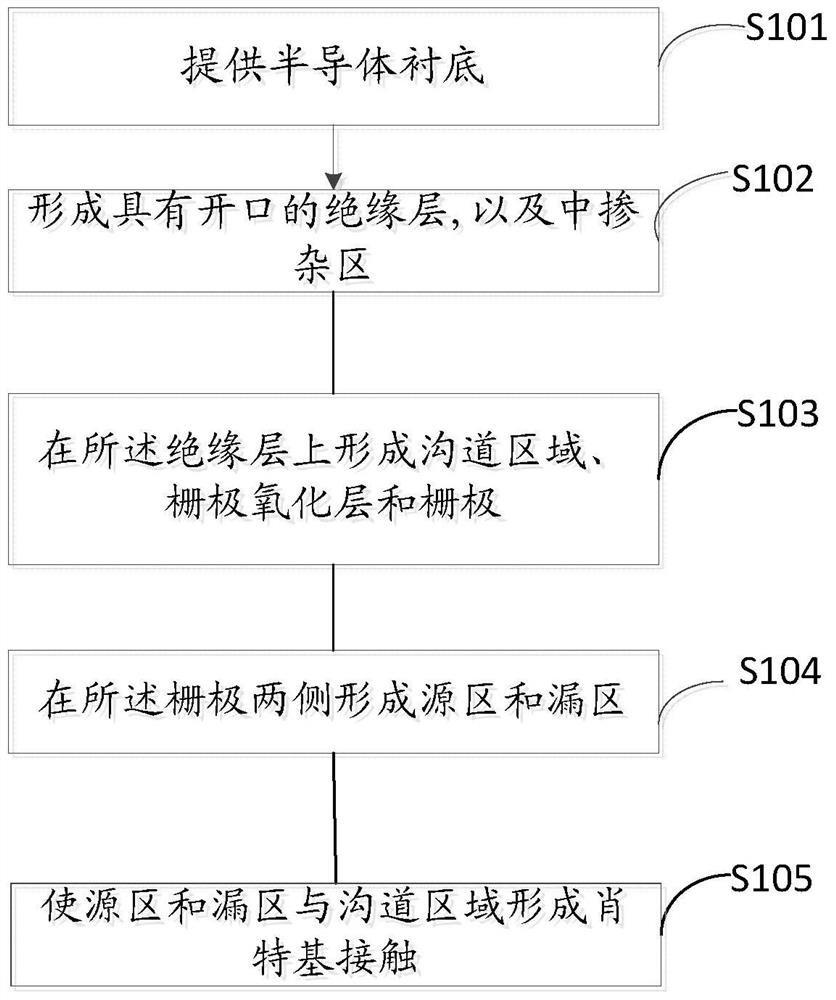

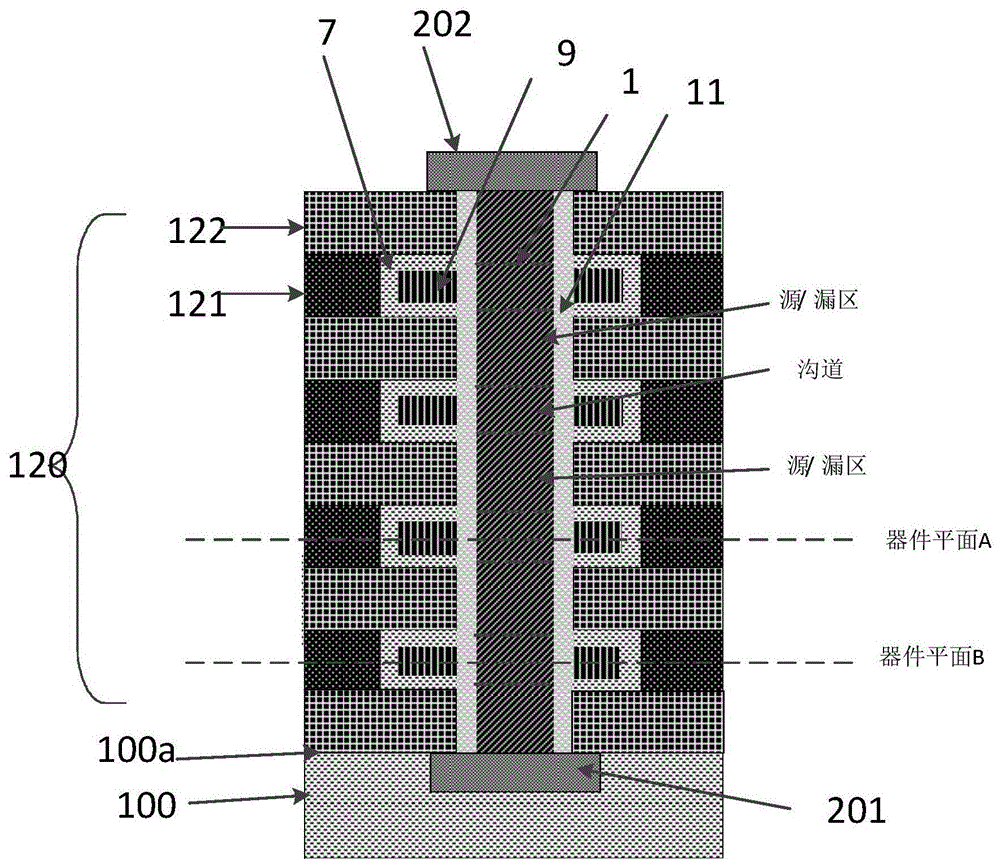

A kind of semiconductor device and its manufacturing method, electronic device

ActiveCN105990144BReduce self-heating effectInhibition of mobility degradationSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialHeating effect

The present invention provides a method for manufacturing a semiconductor device, the method comprising: step a: providing a semiconductor substrate; step b: forming an insulating layer having an opening and a silicon layer located in the opening on the semiconductor substrate; Forming a heavily doped region in the opening region and the surface layer of the semiconductor substrate below the opening region; step c: forming a channel region, a gate oxide layer and a gate on the insulating layer; step d: forming a gate on the gate A source region and a drain region are formed on both sides; wherein, the source region and the drain region form a Schottky contact with the channel region. Through the manufacturing method of the semiconductor device of the invention, the self-heating effect, leakage-induced potential barrier lowering effect and subthreshold characteristics of the device can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

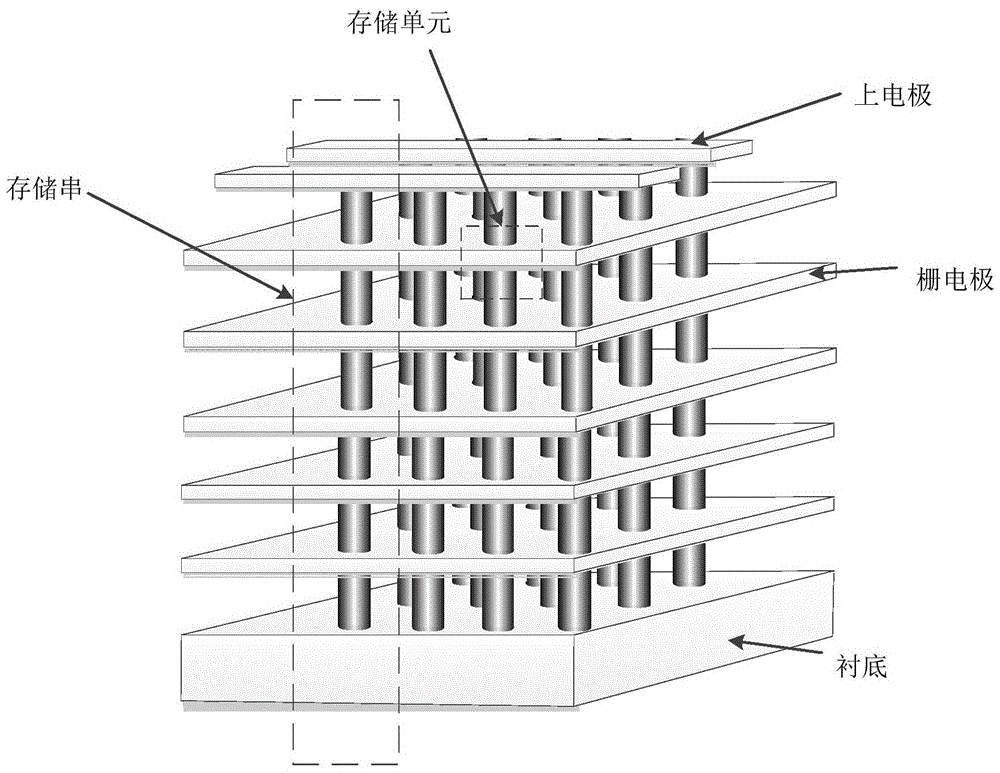

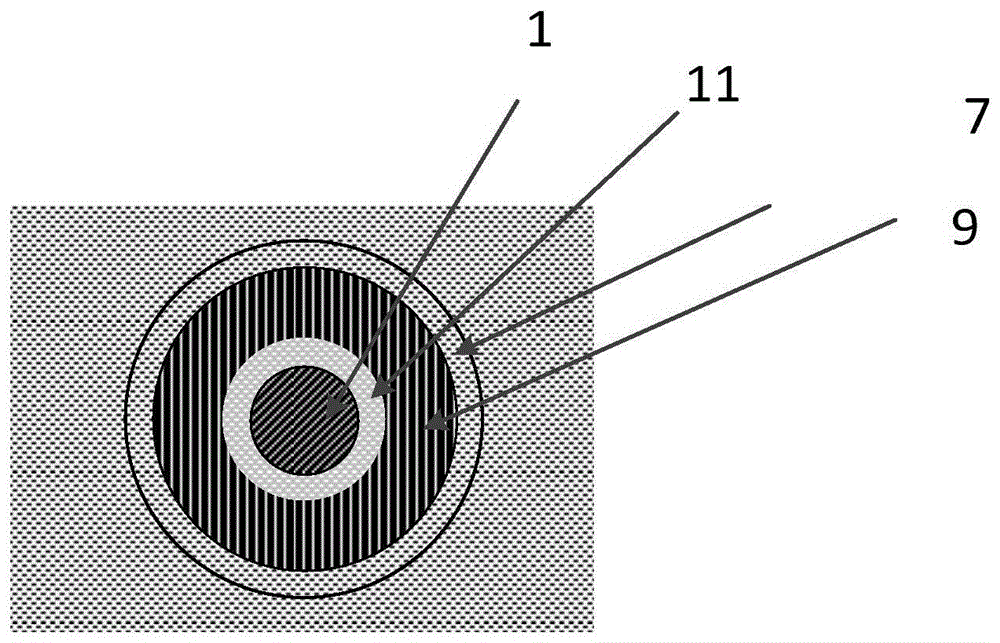

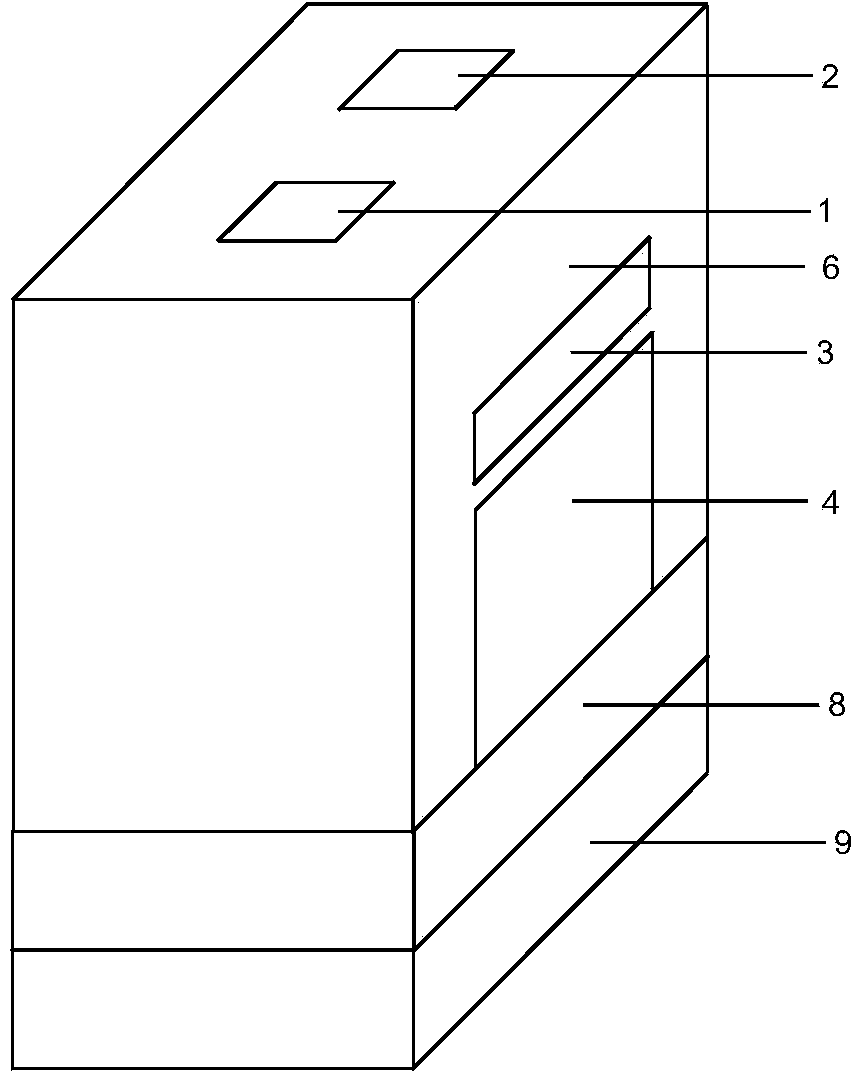

A kind of non-volatile three-dimensional semiconductor memory and its preparation method

ActiveCN104241294BChange the way you workAvoid dopingSolid-state devicesSemiconductor devicesMemory cellDielectric layer

The invention discloses a non-volatile three-dimensional semiconductor memory and a preparation method thereof, comprising a plurality of vertical three-dimensional NAND storage strings, each three-dimensional NAND storage string including a horizontal substrate, a cylindrical semiconductor region perpendicular to the substrate, The second electrode and the first electrode respectively located on the top and bottom of the semiconductor region, the tunneling dielectric surrounding the cylindrical semiconductor region, a plurality of discrete charge storage layers are distributed above and below the tunneling dielectric, the tunneling dielectric is wrapped and multiple The blocking dielectric layer of the charge storage layer, the control gate electrode stacked with the insulating layer; the cylindrical semiconductor region includes the source region, the drain region and the channel of a plurality of memory cells. The present invention adopts a floating gate transistor as a storage unit, uses a chalcogenide compound as a channel material, and the storage unit adopts a surrounding gate structure, and the channel region and the source and drain regions use the same material to form a junction-free structure, which well avoids short circuits. ditch effect.

Owner:HUAZHONG UNIV OF SCI & TECH

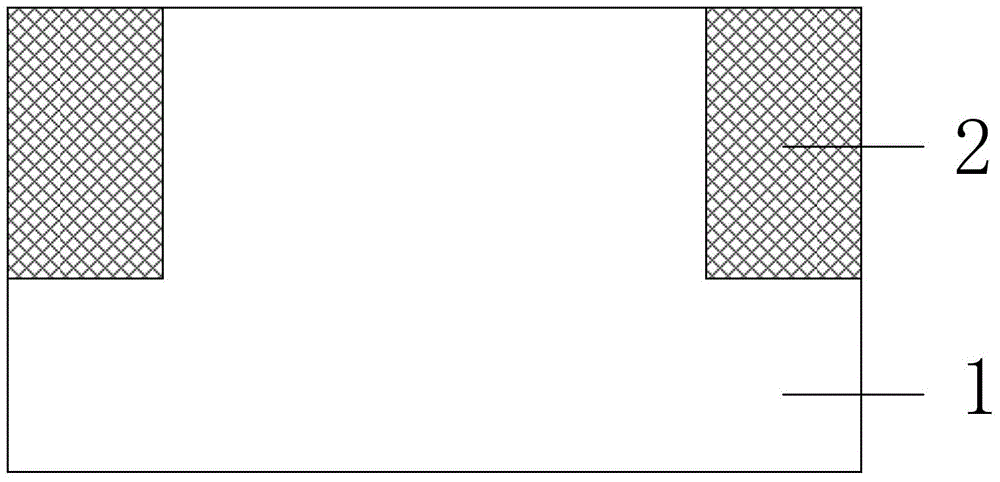

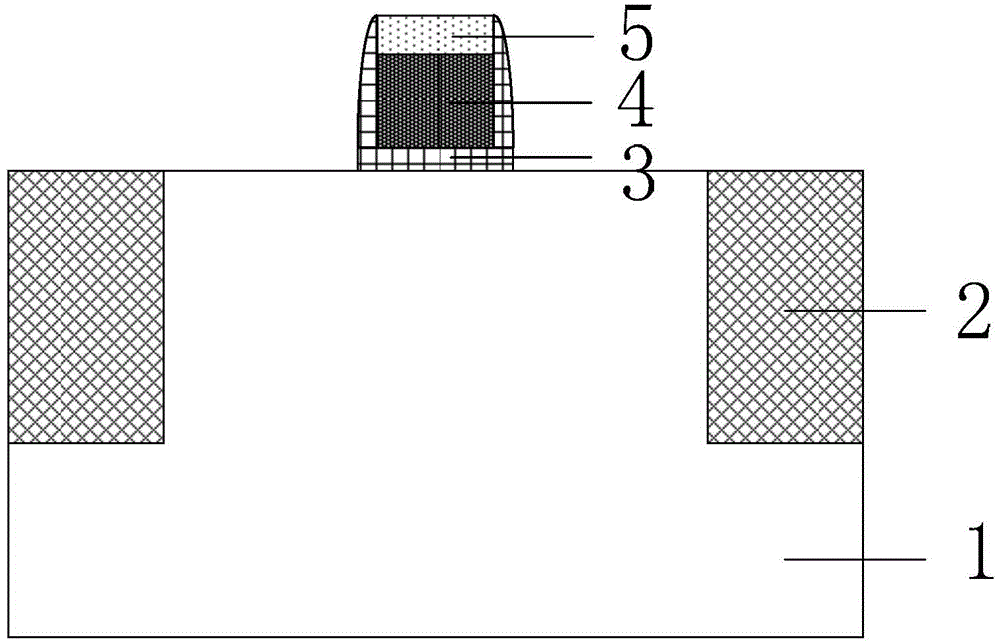

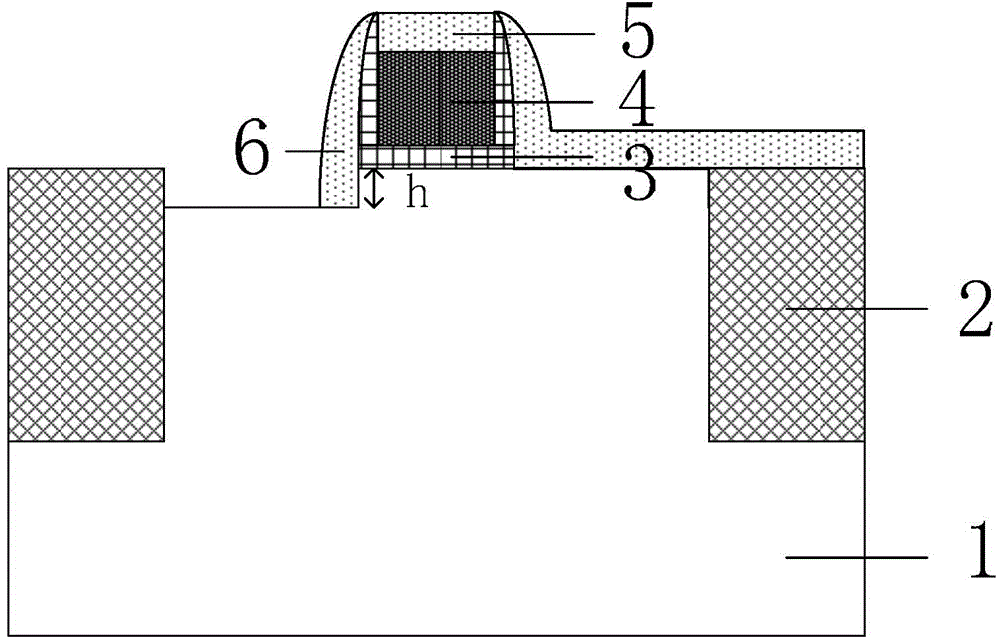

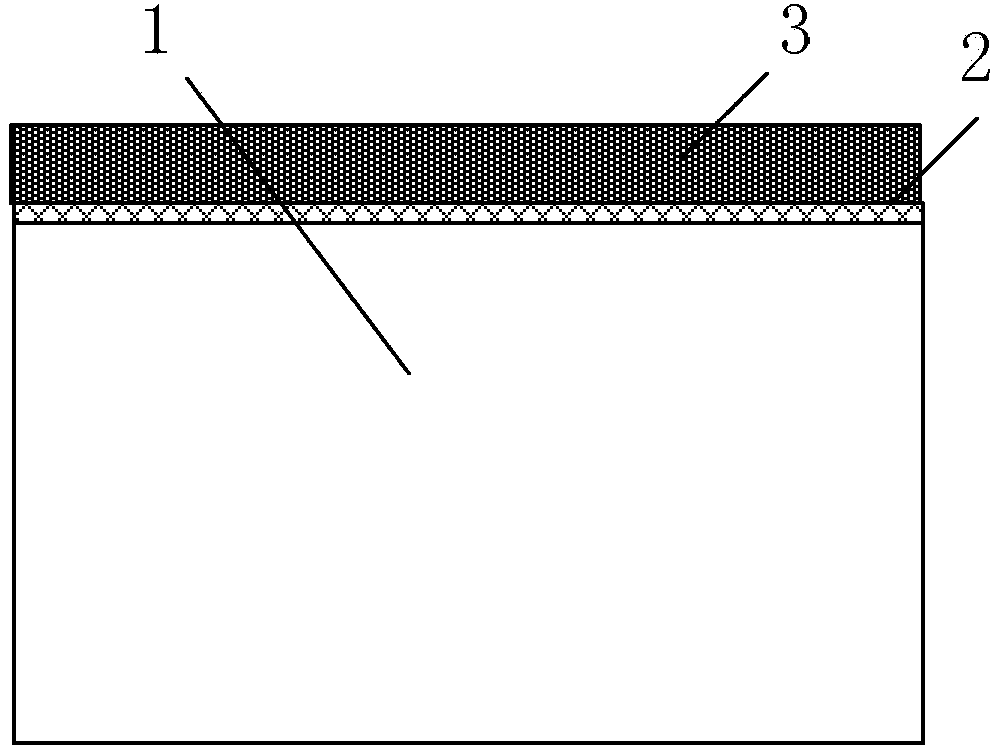

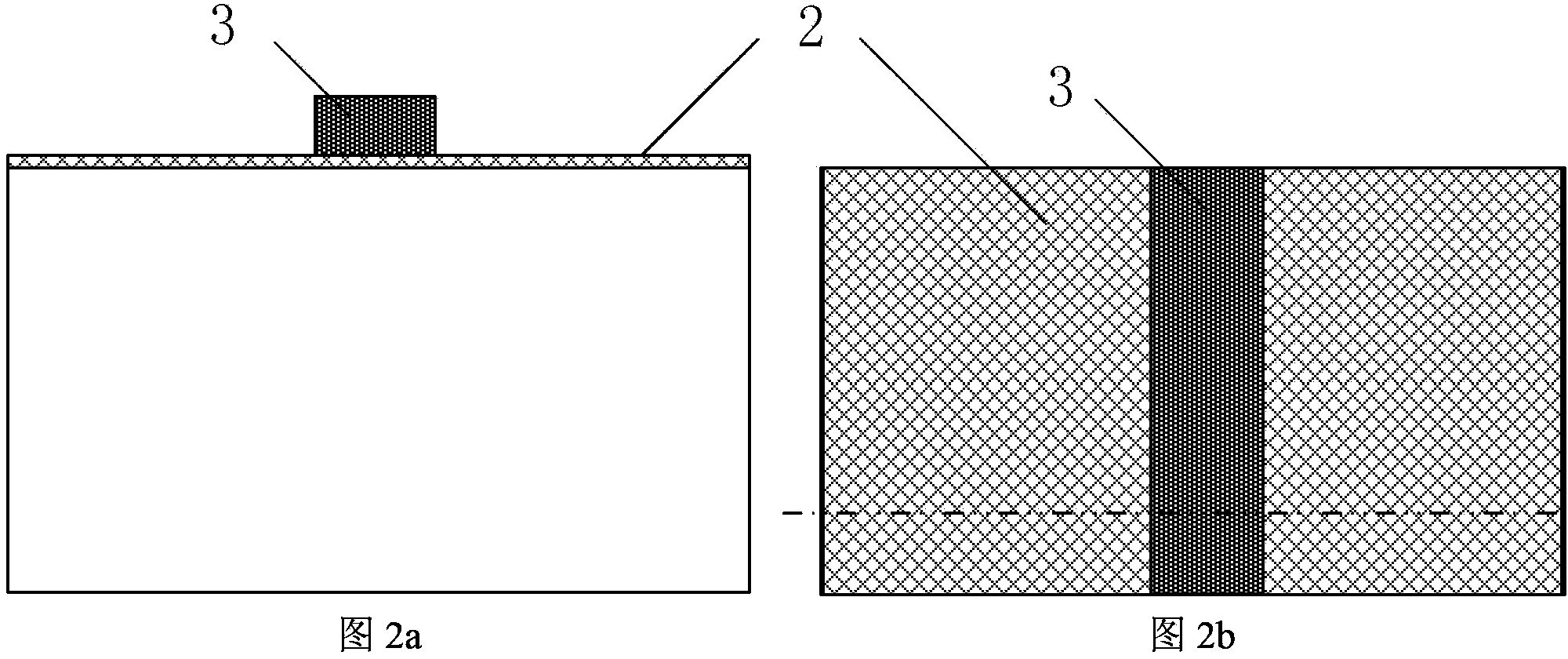

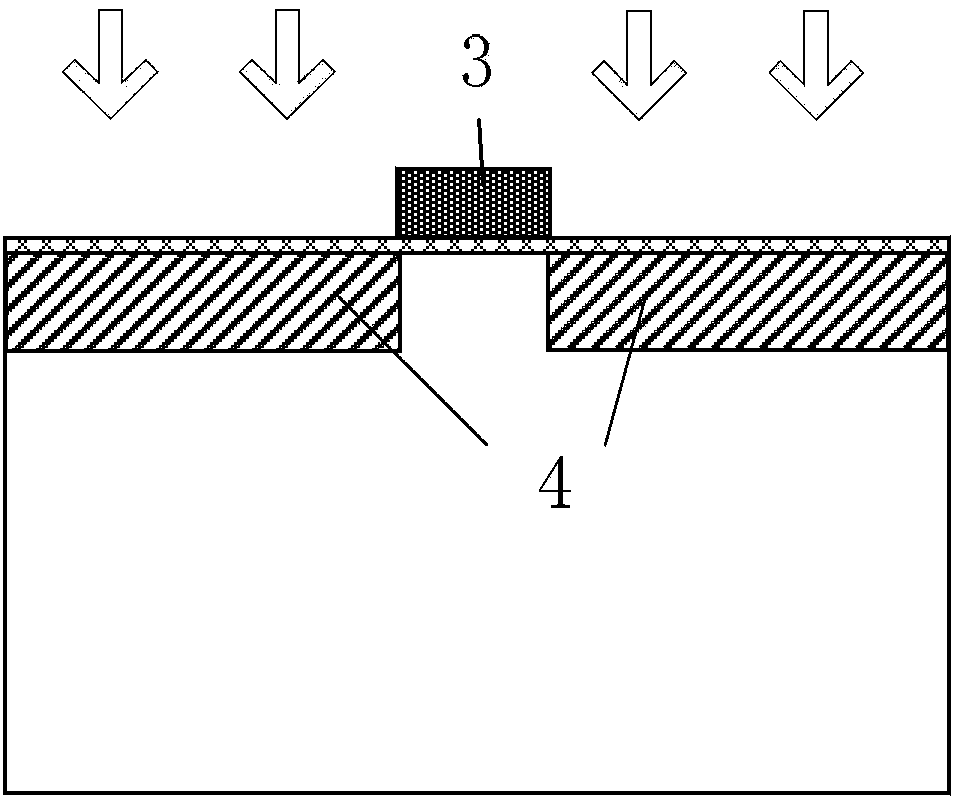

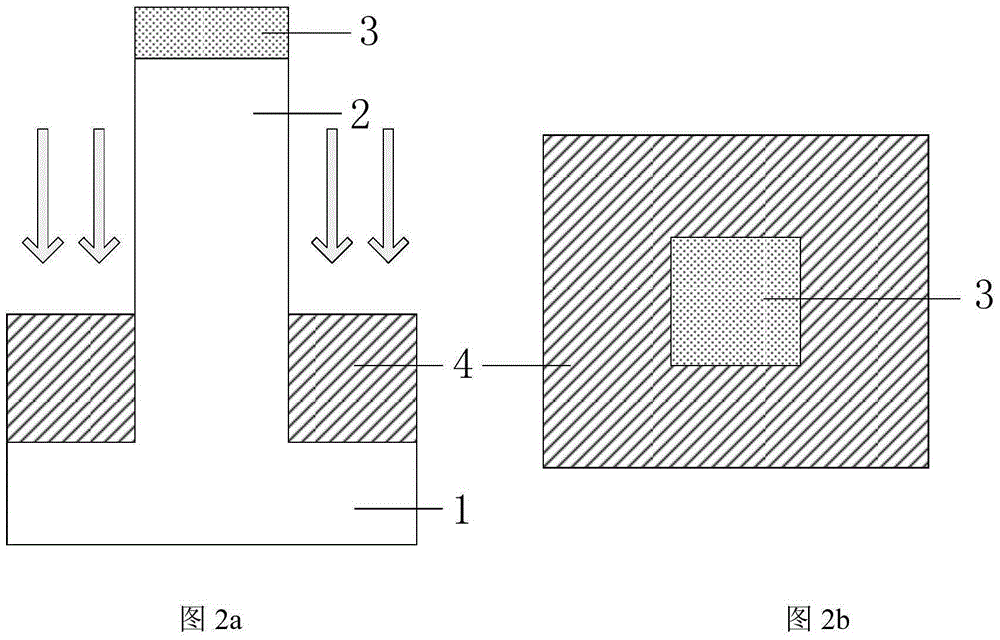

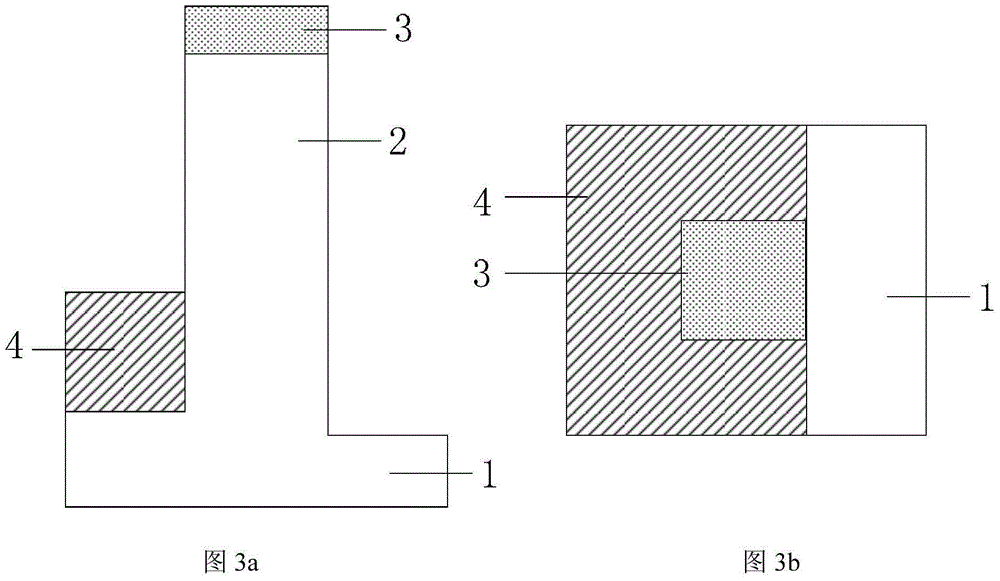

Self-adaptive composite mechanism tunneling field effect transistor (TFET) and preparation method thereof

ActiveCN102664192BSuppression of bipolar effectsSteep Subthreshold CharacteristicSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSMOSFET

The present invention relates to the field of tunneling field effect transistor logic devices and circuits in a CMOS ultra large scale integrated (ULSI) circuit. Disclosed are a tunneling field effect transistor and manufacturing method thereof. The tunneling field effect transistor is: for an N type transistor, P+ is injected, on the basis of doping N-, into one side of a doped source area close to the edge of a control gate (3), so that the original doped N- of the injected part is completely compensated as P+; and for a P type transistor, N+ is injected, on the basis of doping P-, into one side of the doped source area close to the edge of the control gate (3), so that the original doped P- of the injected part is completely compensated as N+. Through the doped injection twice of different concentrations into the source area, the device structure of the tunneling field effect transistor effectively combines the characteristics of large conducting current of an MOSFET, thus improving the on-state current of the device, and self-adaptively achieving threshold adjustment of the MOSFET and TFET parts of the device.

Owner:PEKING UNIV

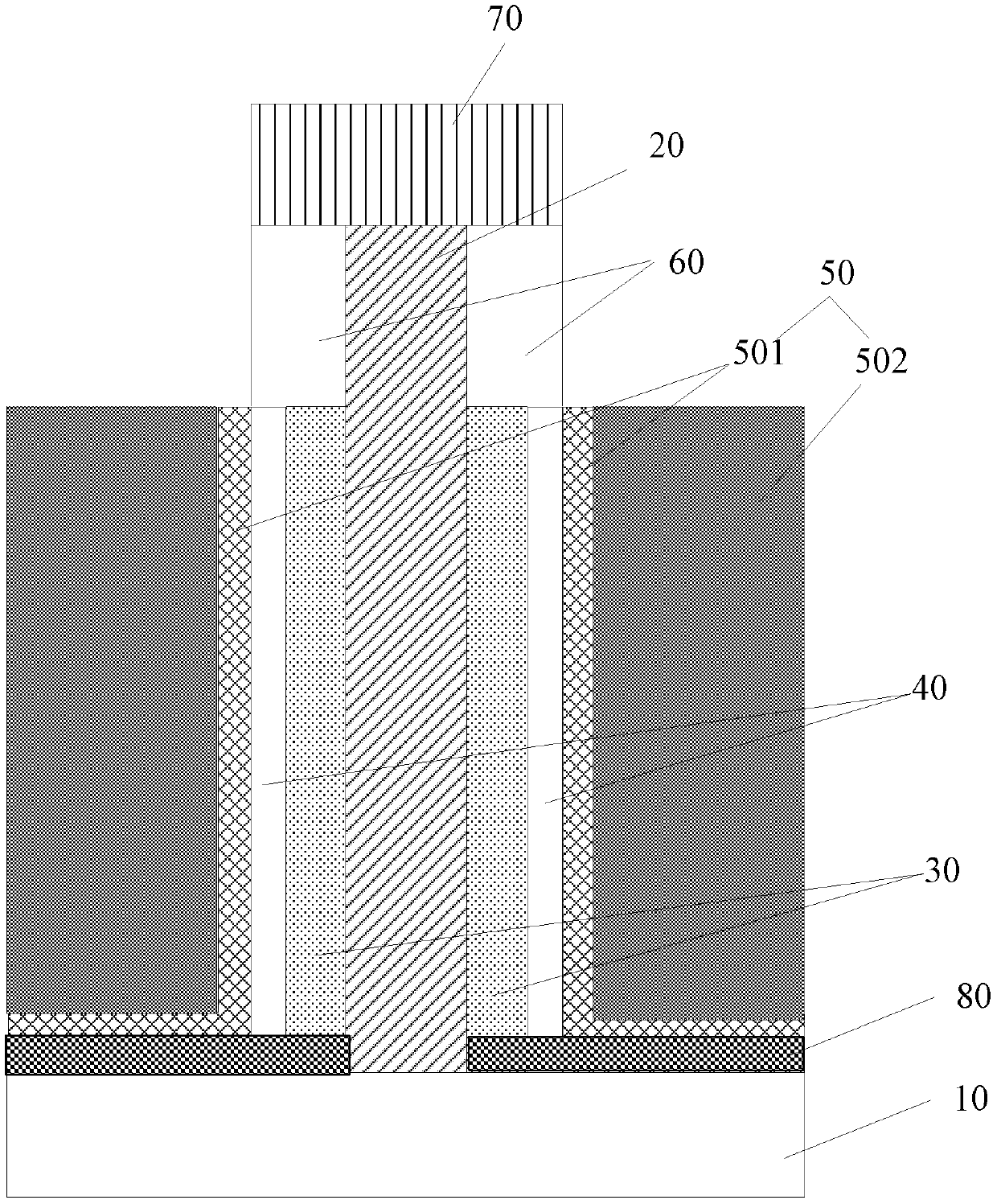

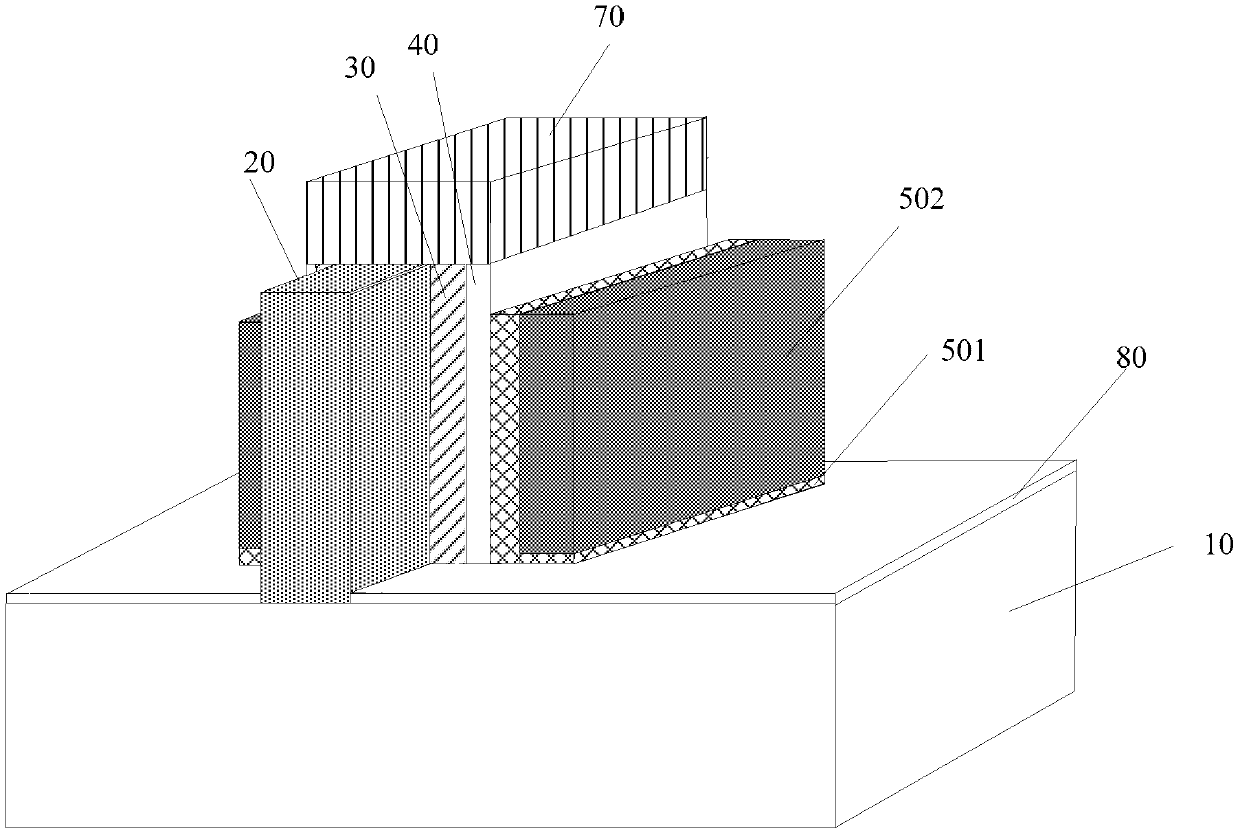

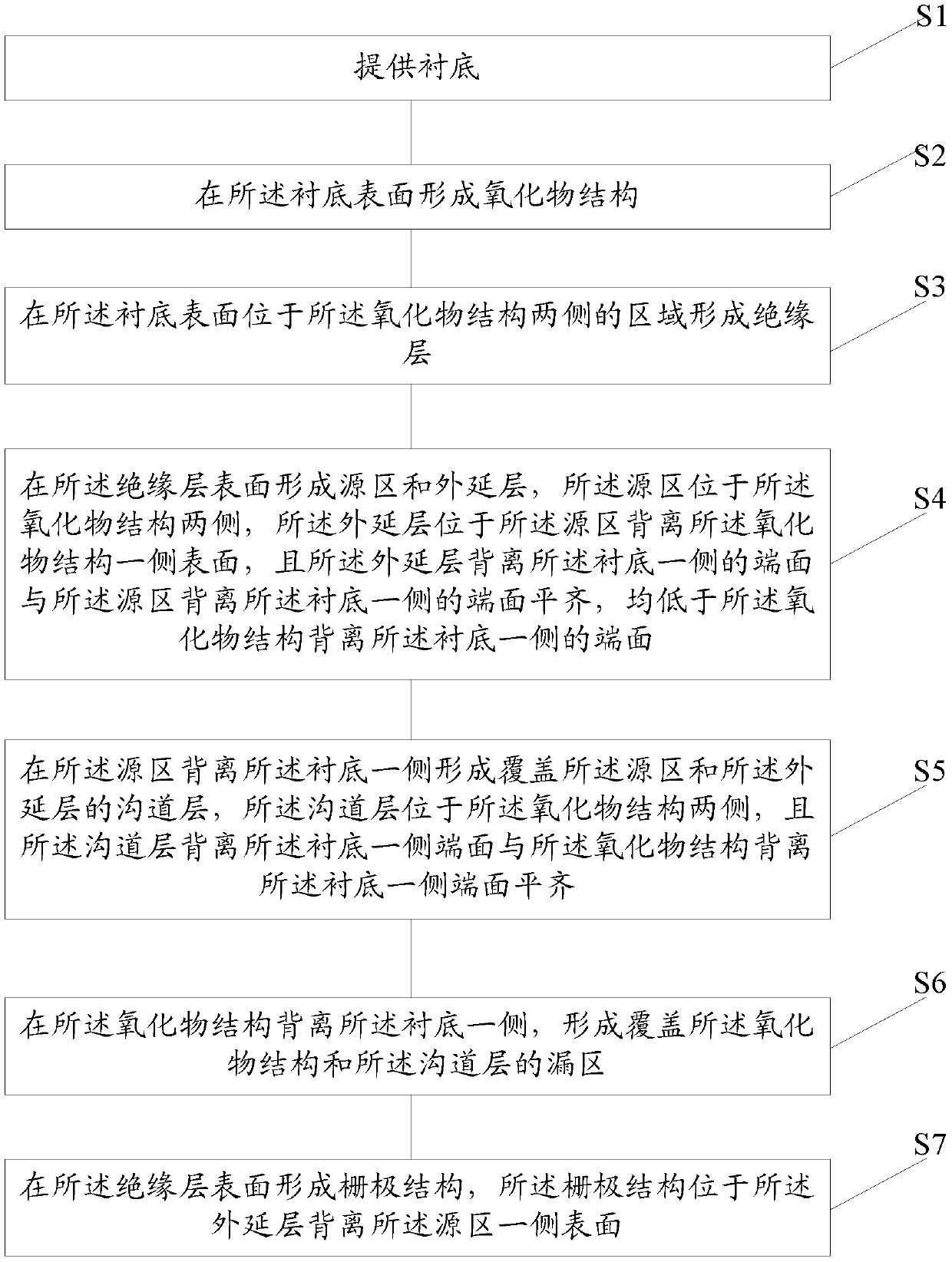

A tunneling field effect transistor and its manufacturing method

ActiveCN108140672BReduced subthreshold swingReduce power consumptionNanoinformaticsSemiconductor/solid-state device manufacturingValence bandSubthreshold swing

A tunneling field effect transistor and a manufacturing method thereof, in which the source region (30) is located on both sides of an oxide structure (20), and the epitaxial layer (40) is located on the source region (30) away from the oxide structure ( 20) On one surface, the gate structure (50) is located on the surface of the epitaxial layer (40) away from the source region (30), so that the electric field direction of the gate of the tunneling field effect transistor is consistent with the electron tunneling direction, and the value of the source region The tunneling efficiency of the carriers in the band to the conduction band of the epitaxial layer is high, which can generate a steep sub-threshold swing, which in turn makes the sub-threshold swing of the tunneling field effect transistor lower than 60mV / dec, and the power consumption smaller. Moreover, in the embodiment of the present invention, the epitaxial layer (40) is entirely located between the gate structure (50) and the source region (30), which increases the tunneling area between the epitaxial layer (40) and the source region (30), The subthreshold characteristic of the tunneling field effect transistor is further improved, and the subthreshold swing value of the tunneling field effect transistor is reduced.

Owner:HUAWEI TECH CO LTD

A junction-modulated tunneling field-effect transistor and its manufacturing method

ActiveCN103594376BImproved subthreshold characteristicsSubthreshold characteristic steepSemiconductor/solid-state device manufacturingDiodeSub thresholdConcentration gradient

The invention discloses a junction modulation type tunneling field effect transistor and a preparation method thereof, belonging to the field of field effect transistor logic devices and circuits in CMOS ultra large integrated circuits (ULSI). The tunneling field effect transistor utilizes the PN junction provided by the highly doped source region surrounded on three sides of the vertical channel region to effectively deplete the channel region, so that the channel energy band on the lower surface of the gate is increased, and when the device undergoes band tunneling, it can obtain The steeper energy band and narrower tunneling barrier width than traditional TFETs equivalently realize the effect of steep tunneling junction doping concentration gradient, thereby greatly improving the subthreshold characteristics of traditional TFETs and improving the conductance of the device at the same time. Pass current. Under the condition of being compatible with the existing CMOS technology, the present invention effectively suppresses the bipolar conduction effect of the device on the one hand, and at the same time suppresses the parasitic tunneling current at the corner of the source junction in a small size, and can equivalently realize steep The effect of straight source-junction doping concentration.

Owner:PEKING UNIV

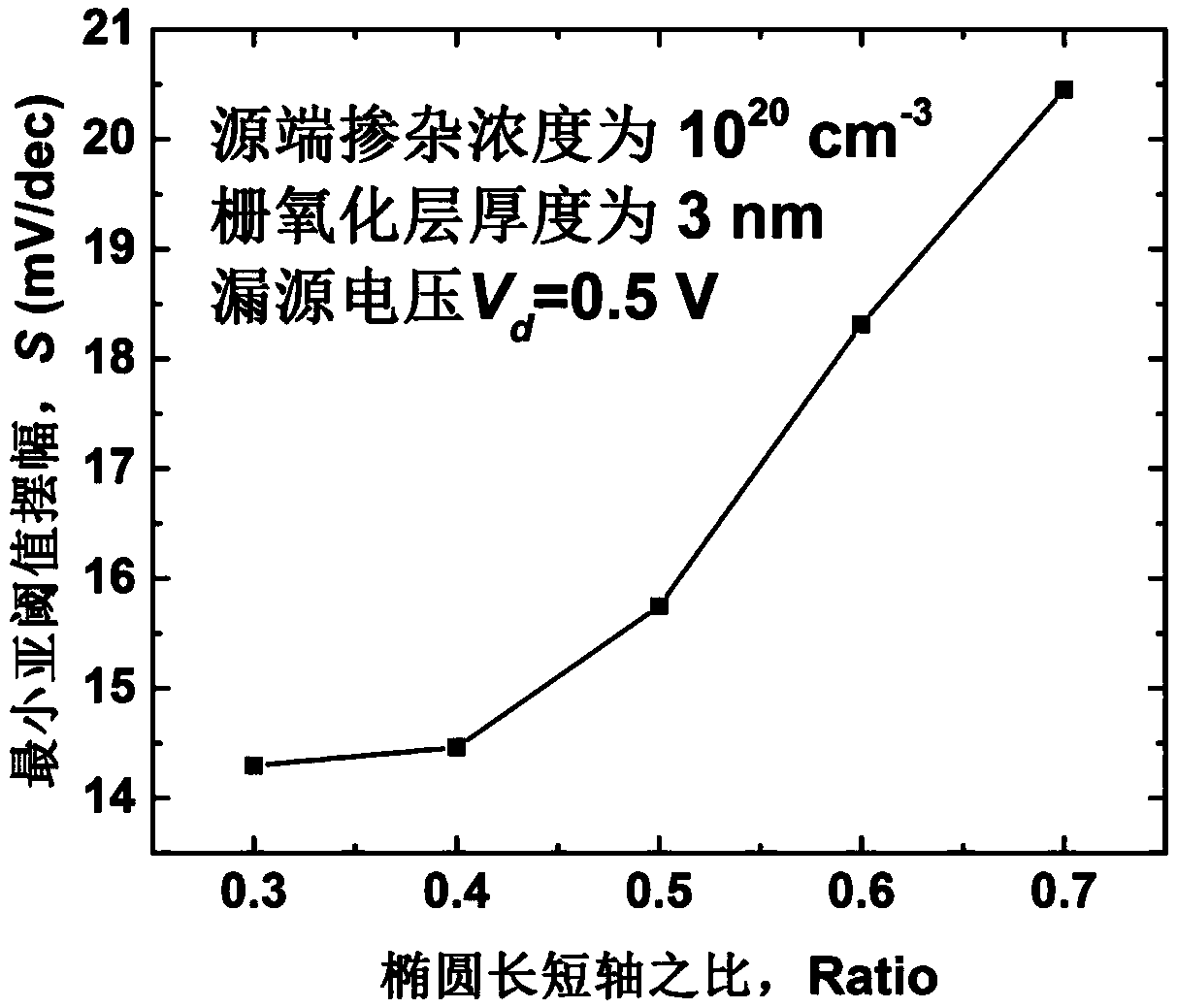

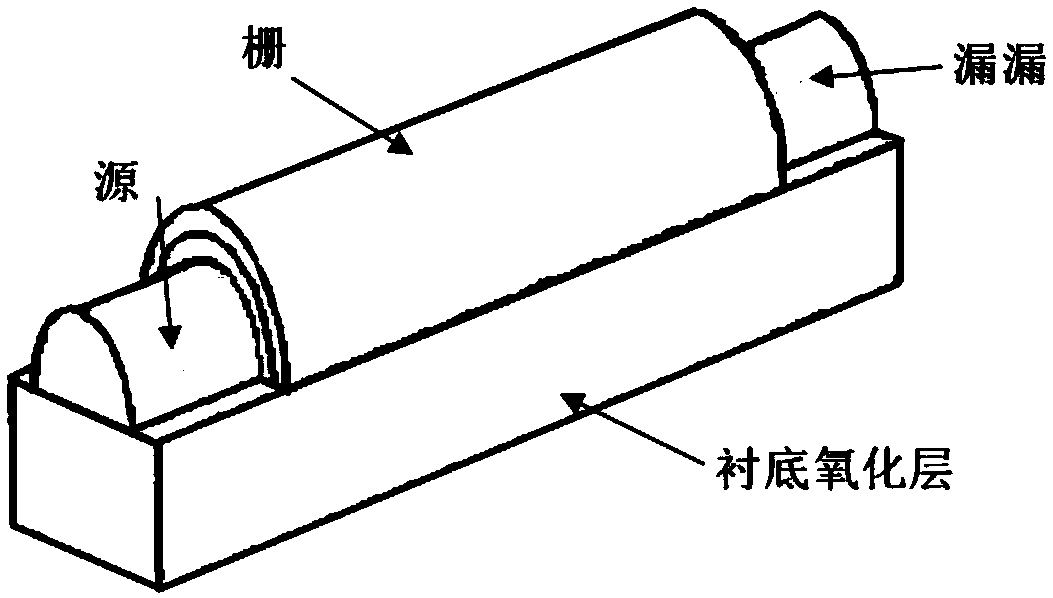

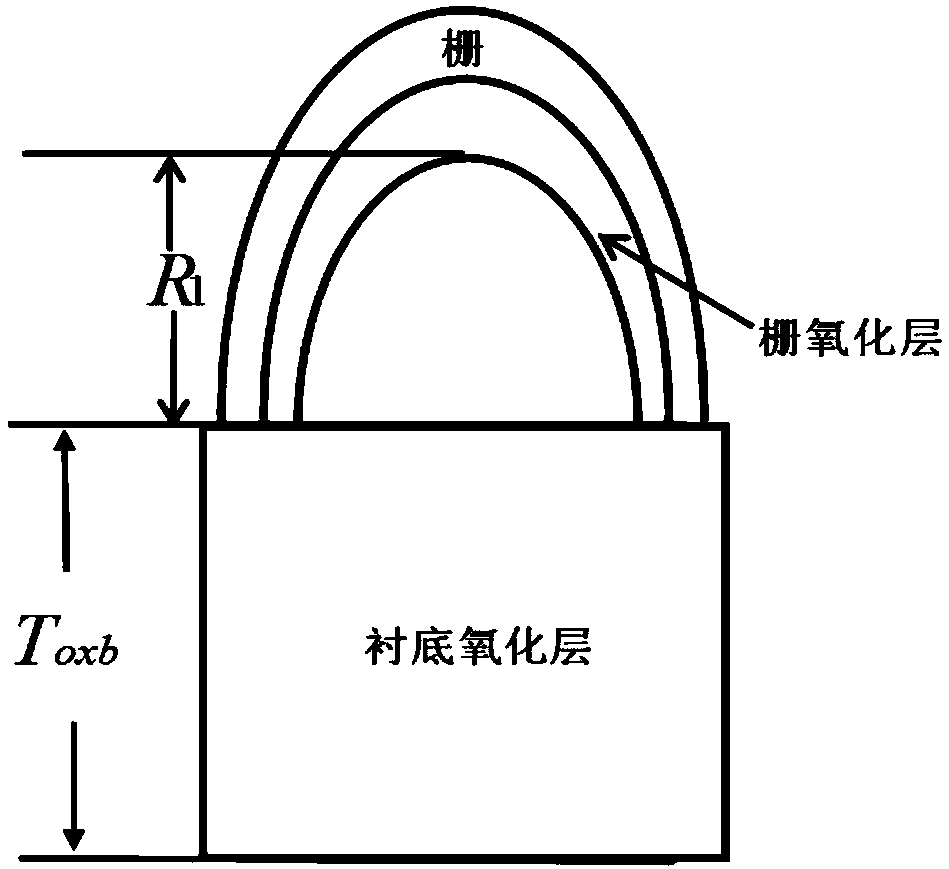

High-performance silicon-based elliptical gate tunneling field effect transistor

ActiveCN108733940AImproved subthreshold characteristicsSpecial data processing applicationsMOSFETHigh concentration

The invention belongs to the technical field of integrated circuit semiconductors, and particularly relates to a high-performance silicon-based elliptical gate tunneling field effect transistor. According to the structure, hafnium oxide is used as a substrate oxidation layer; semi-elliptic column type silicon serving as a channel and source-drain is arranged above the hafnium oxide; and an elliptic ring type hafnium oxide gate oxidation layer and a metal gate which have the same length-diameter ratio as the channel cover the channel. The p-type high-concentration boron doping is carried out onthe source end; the light n doping is carried out on the channel; and the n-type high-concentration phosphorus doping is carried out on the drain end. The field effect transistor takes transverse tunneling as a main tunneling mechanism, and can be regarded as a grid-controlled p-i-n junction. The simulation of simulation software shows that the tunneling field effect transistor has a good sub-threshold characteristic; the minimum sub-threshold swing can be as low as 20mV / dec and is smaller than the minimum sub-threshold swing, which is 60mV / dec, of a traditional MOSFET by three times; and a good design foundation is provided for practical development and application of tunneling devices.

Owner:FUDAN UNIV

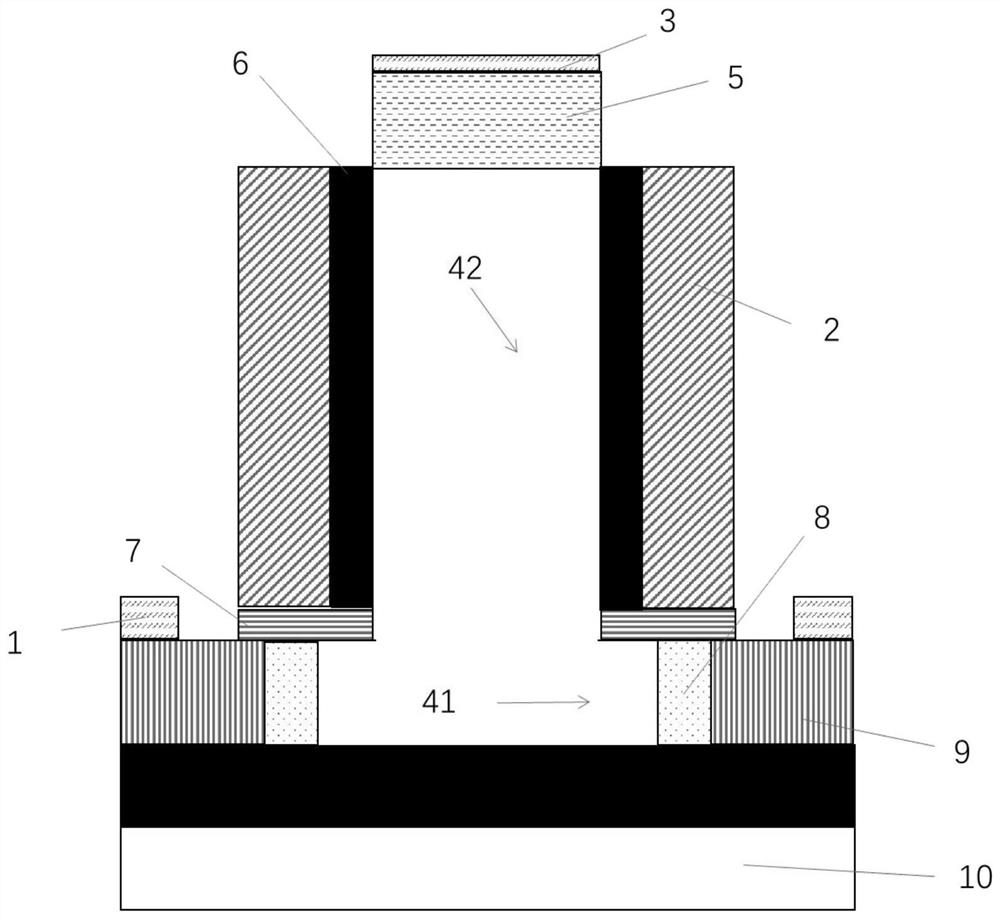

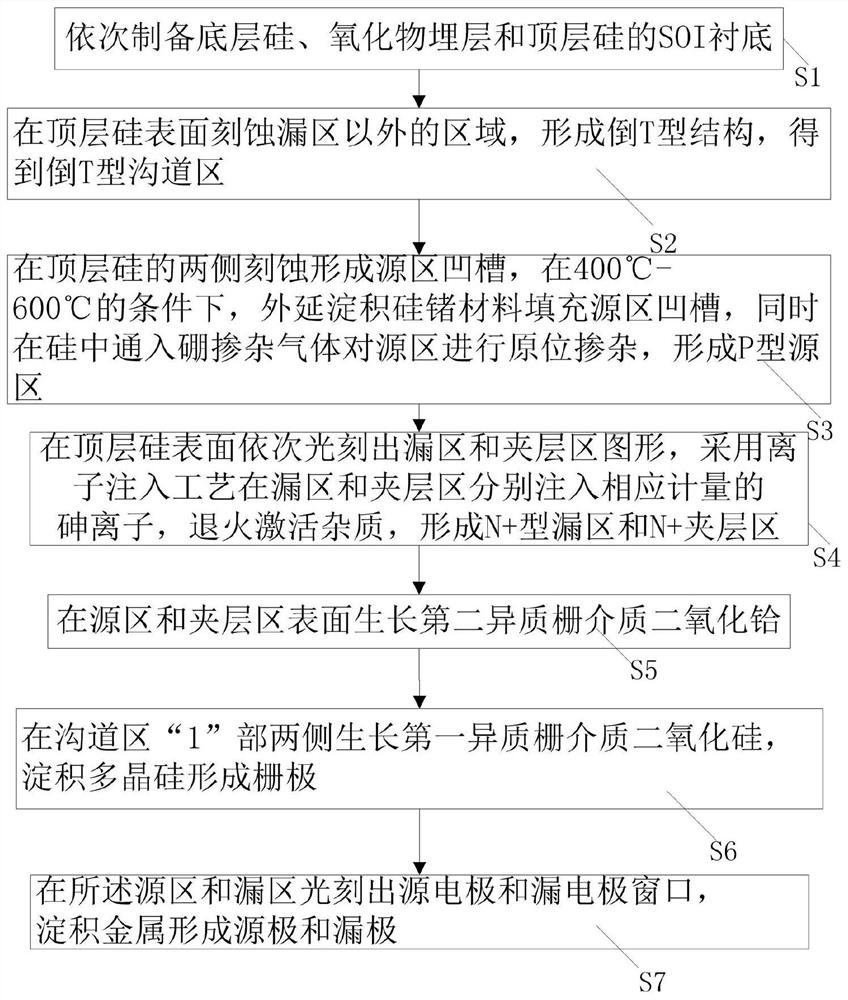

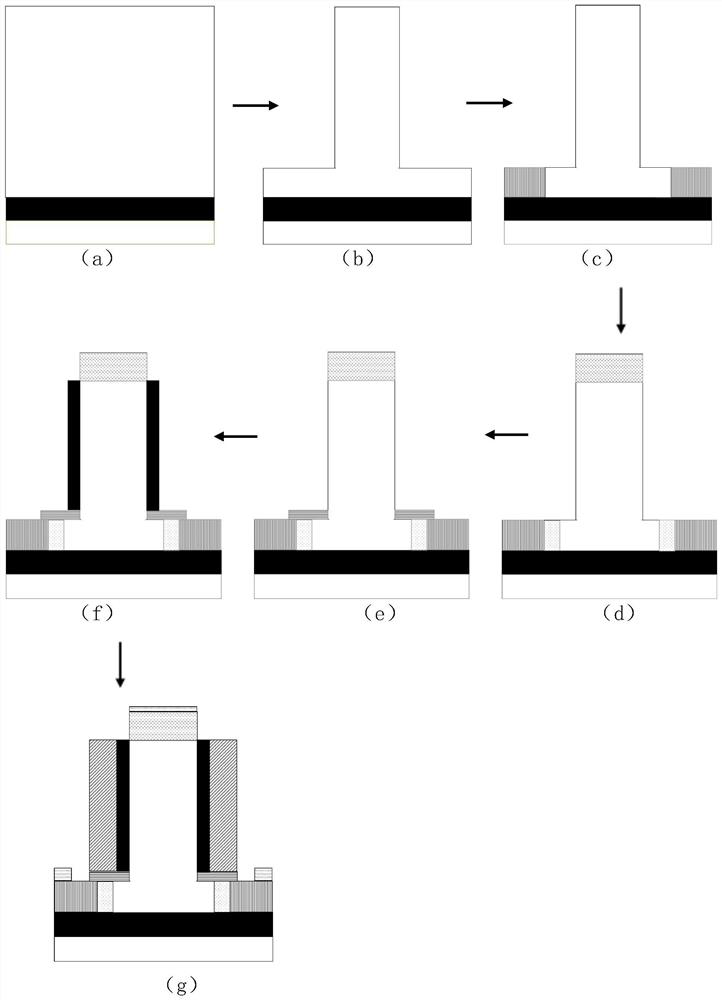

Heterojunction tunneling field effect transistor with heterogeneous gate dielectric and manufacturing method thereof

ActiveCN113571589BSuppression of bipolar effectsIncrease the on-state currentSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionDielectric

The invention discloses a heterojunction tunneling field effect transistor with a heterogeneous gate dielectric and a manufacturing method thereof, and mainly solves the problems of small on-state current and serious bipolar effect of the existing tunneling field effect transistor. It includes source, gate, drain, source region, channel region and drain region. Carriers enter the channel region through the source and leave the channel region through the drain. The channel region includes "a" part and " 1", the "1" part includes a first connection end connected to the "one" part, and a second connection end opposite to the first connection end, the second connection end is connected to the drain through the drain region, and the "1" part Two gates are arranged on both sides of the two gates, and two first heterogeneous dielectrics are respectively arranged between the two gates and the "1" part, the gates and the first heterogeneous medium are arranged perpendicular to the second heterogeneous medium, and The sum of the heights of the first heterogeneous medium and the second heterogeneous medium is equal to the "1" part, the height of the gate is equal to that of the first heterogeneous medium, and two sources are respectively arranged on both sides of the "1" part.

Owner:XIDIAN UNIV

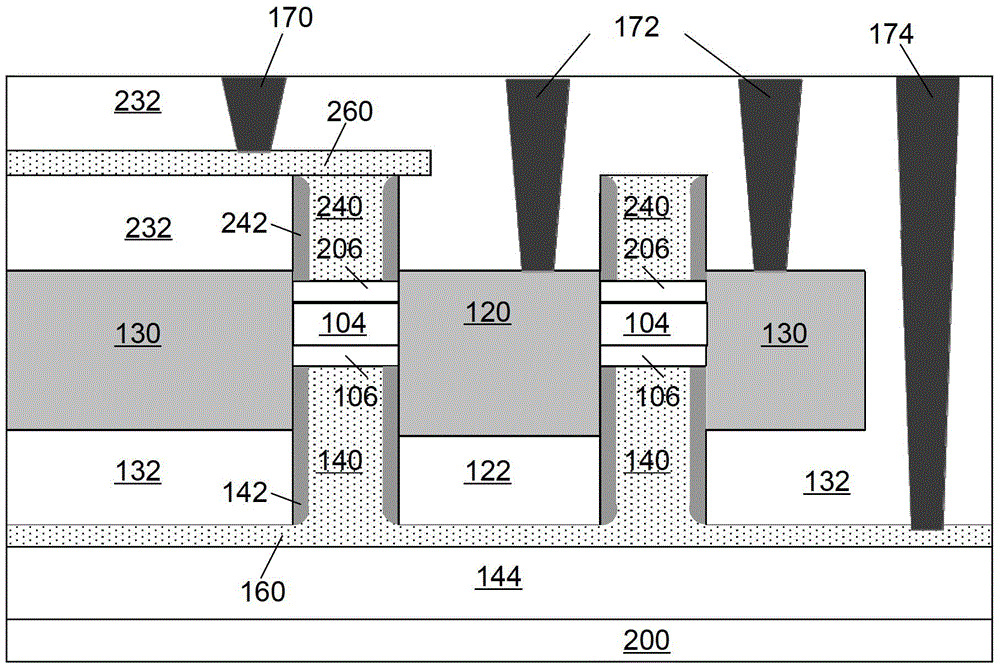

Tunneling Field Effect Transistor and Method of Forming the Same

ActiveCN105990410BImproved subthreshold characteristicsAchieve shutdownSemiconductor/solid-state device manufacturingDiodeGate dielectricImpurity

The invention provides a tunneling field effect transistor which comprises a substrate with the formation of a fin with an epitaxial, first and second grids formed on opposite side walls of the fin, a first gate dielectric layer which is formed between the first grid and the side wall of the fin and the bottom surface of the first grid, a second gate dielectric layer which is formed between the second grid and the side wall of the fin and the bottom surface of the second grid, and source and drain regions which are formed at one side of the first grid and one side of the second grid. According to the tunneling field effect transistor with the structure, through controlling the width of the fin, a narrow tunneling junction without the limitation of impurity injection diffusion is realized, the tunneling current is increased, and the conduction current is further raised through increasing an effective tunneling area.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

High-integration-level H-shaped source, drain and gate auxiliary control U-shaped channel high-mobility-ratio junction-free transistor

InactiveCN104282737ALow source-drain resistanceImprove mobilitySemiconductor devicesElectrical resistance and conductanceEngineering

The invention relates to a high-integration-level H-shaped source, drain and gate auxiliary control U-shaped channel high-mobility-ratio junction-free transistor. Two independently-controlled gate electrodes including the H-shaped auxiliary control gate electrode and the gate electrode are adopted, the doping concentration of a device is guaranteed to improve the mobility ratio, the device mobility ratio reduction and the device stability reduction caused by strengthening of the random scattering effect under the high doping concentration is avoided, and meanwhile the resistance of source and drain areas is effectively reduced through the H-shaped auxiliary control gate electrode, so that the contradictions that the source and drain resistance will be increased if the doping concentration of a channel of a common junction-free transistor is excessively low, and the device mobility ratio reduction and the device stability reduction will be caused if the doping concentration is excessively high are overcome; meanwhile, U-shaped monocrystalline silicon serves a channel part of the device; compared with a common plane structure, on the premise that the chip area is not increased additionally, the effective channel length is obviously increased to reduce the short channel effect of the device under the deep nanoscale, and therefore the high-integration-level H-shaped source, drain and gate auxiliary control U-shaped channel high-mobility-ratio junction-free transistor is suitable for application and popularization.

Owner:SHENYANG POLYTECHNIC UNIV

Highly integrated u-shaped channel high-mobility junctionless transistor with source-drain-gate assisted control

InactiveCN104282753BLow source-drain resistanceImprove mobilitySemiconductor devicesReverse short-channel effectScattering effect

The invention relates to a high-integration sun-shaped source-drain gate auxiliary-controlled U-shaped channel high-mobility junctionless transistor, which adopts two independently controlled gate electrodes, such as a sun-shaped auxiliary control gate electrode and a gate electrode. The doping concentration is used to improve the mobility and avoid the decrease in the mobility and stability of the device caused by the enhanced random scattering effect under high doping concentration. It solves the contradiction between the low doping concentration of ordinary junctionless transistors, which will increase the source-drain resistance, and the high doping concentration, which will reduce the mobility and stability of the device. Crystal silicon is used as the channel part of the device. Compared with the ordinary planar structure, the effective channel length is significantly increased without increasing the chip area to reduce the short channel effect of the device at the deep nanometer scale, so it is suitable for popularization and application. .

Owner:SHENYANG POLYTECHNIC UNIV

Tunneling Field Effect Transistor and Method of Forming the Same

ActiveCN104600110BImproved subthreshold characteristicsAchieve shutdownSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSub threshold

The invention provides a tunneling field effect transistor comprising a semiconductor substrate, first gates, second gates, first doped regions, and second doped regions. Fins are formed on the semiconductor substrate. Each first gate and the corresponding second gate are respectively formed on the semiconductor substrate at the two sides of the corresponding fin. A gate dielectric layer is formed among each first gate, a first side of the corresponding fin and the semiconductor substrate, and a gate dielectric layer is formed among each second gate, a second side of the corresponding fin and the semiconductor substrate. The first doped regions and the second doped regions are respectively disposed in the semiconductor substrate at one side of the first gates and at one side of the second gates. A narrow tunneling junction is realized by controlling the width of the fins, the tunneling current is increased, and the conduction current is further improved by increasing the effective tunneling area. In addition, defect-related leakage current can be inhibited, and the sub threshold characteristic of devices can be improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Adulation method for MOS transistor body area

InactiveCN100561692CGood short channel characteristicsHigh carrier mobilitySemiconductor/solid-state device manufacturingManufacturing technologyCharge carrier mobility

The invention provides a method for doping a body region of a MOS transistor, belonging to the technical field of semiconductor integrated circuits and its manufacture. In the method, slits are formed on both sides of the gate electrode, and the ion implantation doping of the body region is performed through the slits. In the present invention, since the heavy doping of the body region is carried out through the slits on both sides of the gate electrode, the heavily doped region is strip-shaped on both sides of the channel region, and the strip-shaped heavily doped region can effectively shield the leakage electric field from affecting The influence of the channel and the source makes the device have good short channel characteristics. Moreover, the strip-shaped heavily doped region is on both sides of the channel, and the impurity concentration in the channel region can be very low, so that the device has high carrier mobility and good subthreshold characteristics. The invention can effectively avoid or alleviate the problems caused by the current conventional body region doping method.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

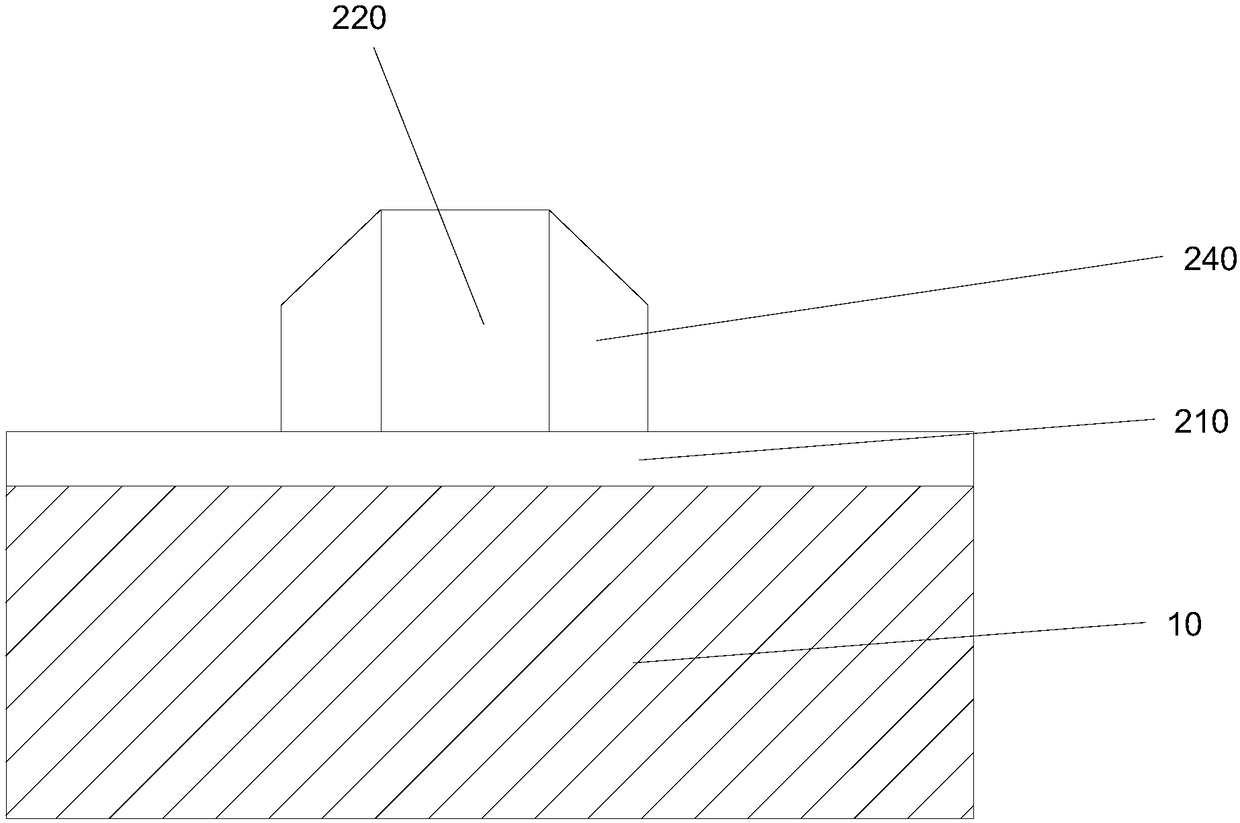

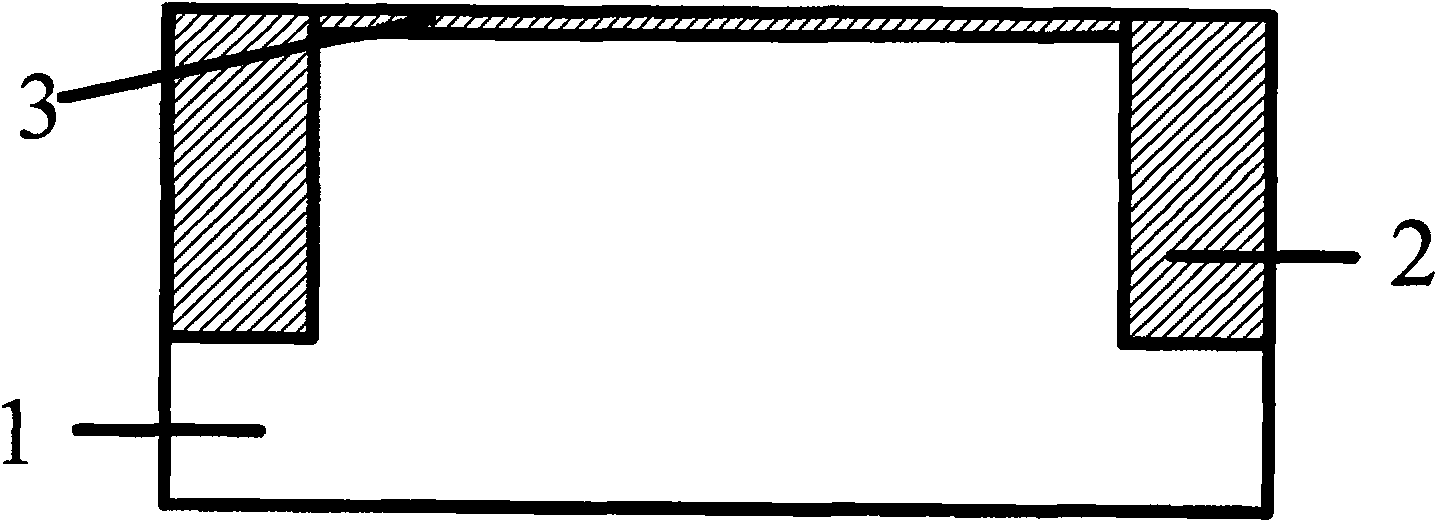

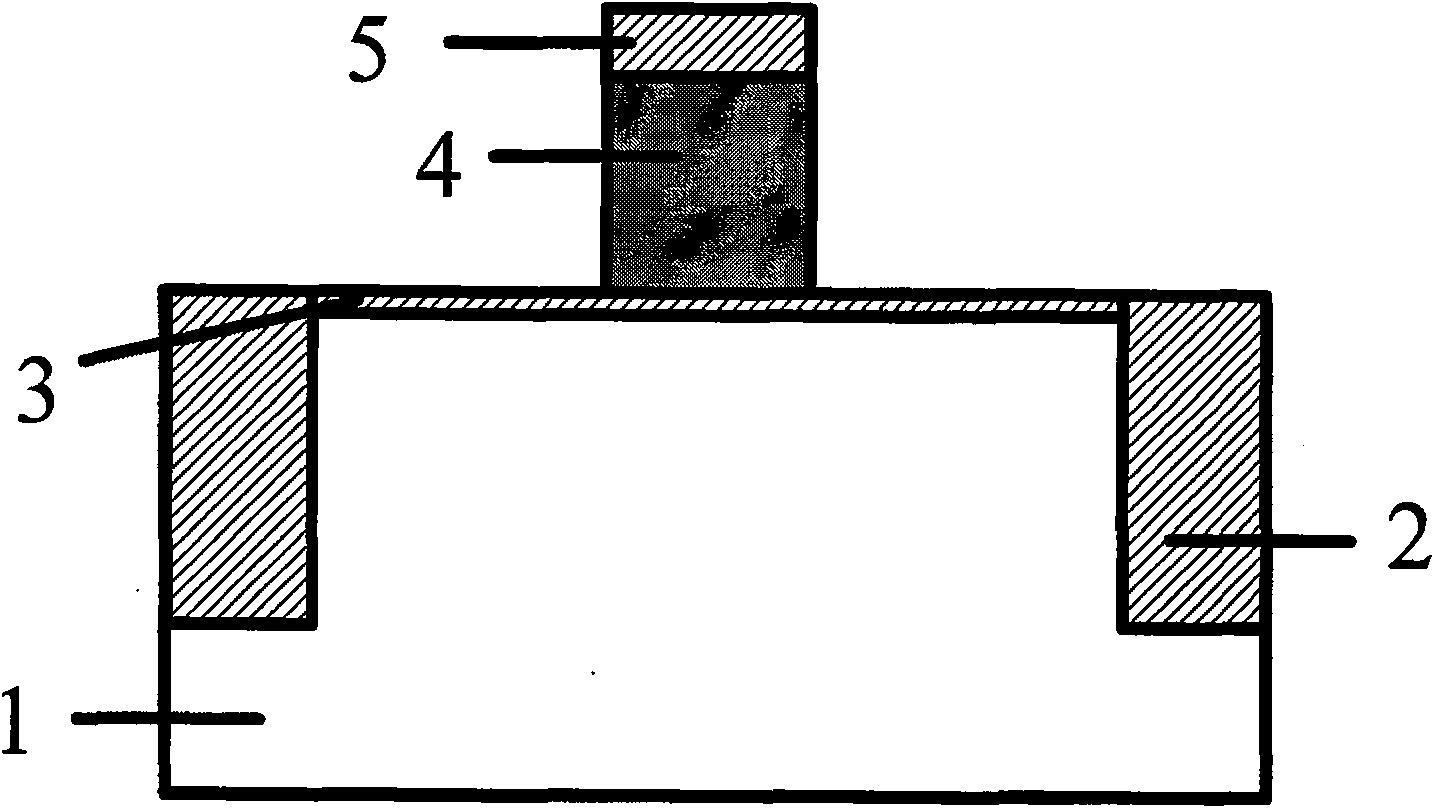

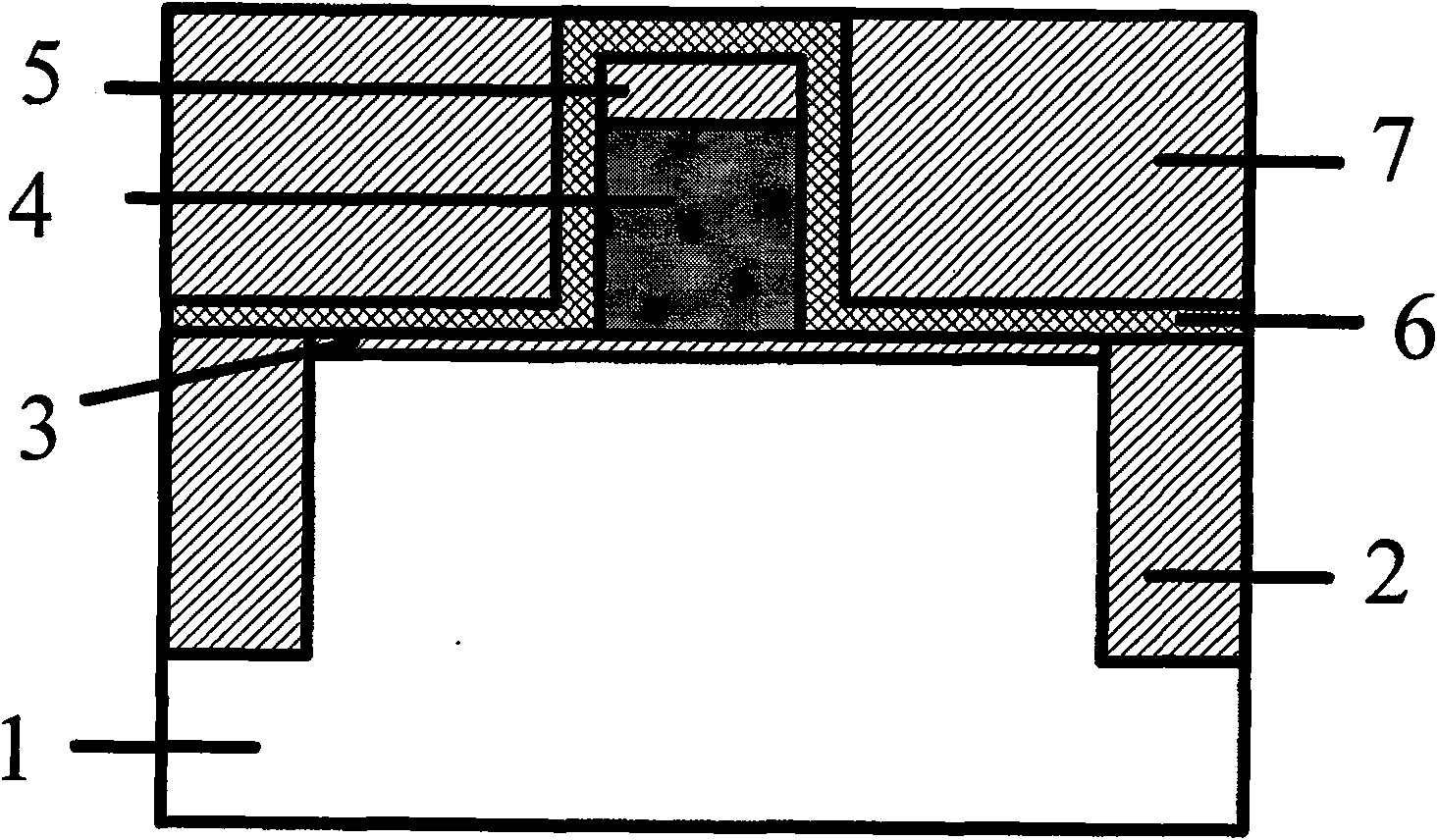

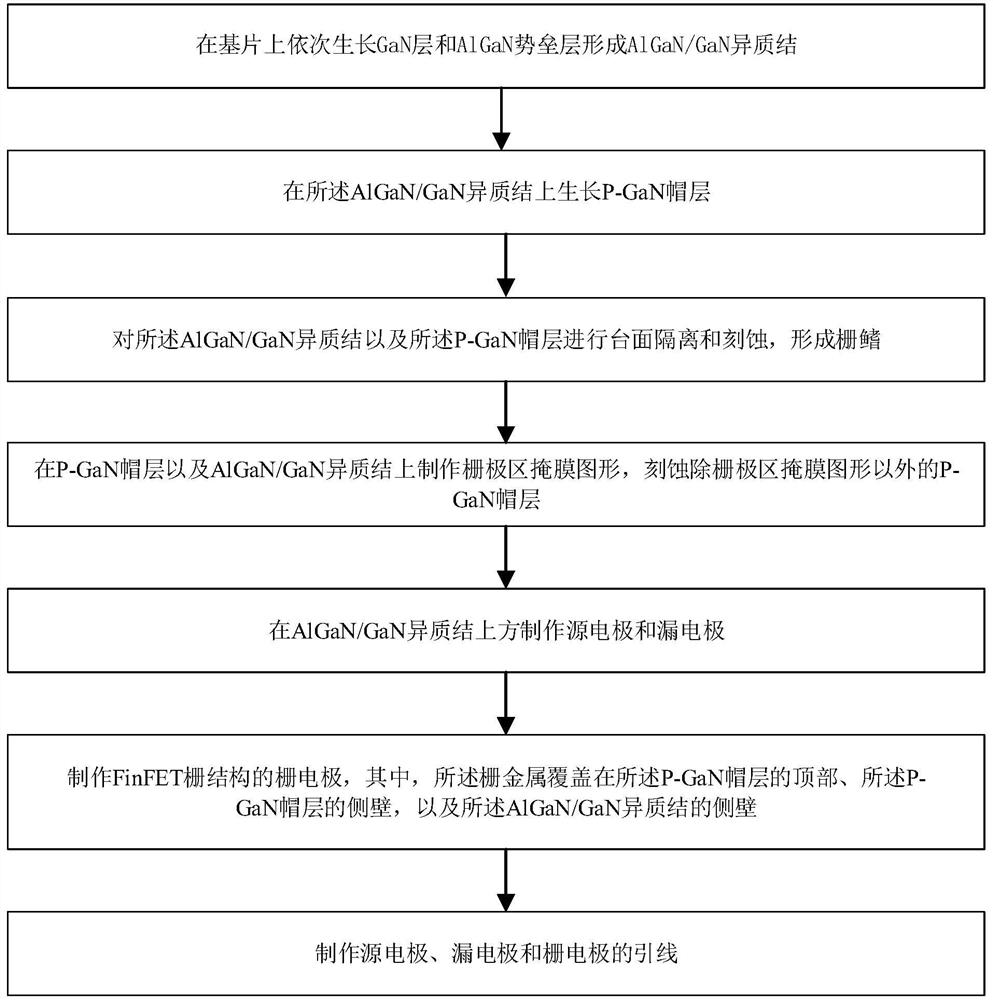

Finfet enhanced device and manufacturing method of p-gan cap layer

ActiveCN110676166BHigh Forward Threshold VoltageImprove gate control abilitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionTransconductance

The invention relates to a FinFET enhanced device of a P-GaN cap layer and a manufacturing method. The manufacturing method comprises the steps of enabling a GaN layer and an AlGaN barrier layer sequentially to grow on a substrate to form an AlGaN / GaN heterojunction; enabling a P-GaN cap layer to grow on the heterojunction; performing mesa isolation and etching on the heterojunction to form a gatefin; forming a gate region mask pattern on the surfaces of the P-GaN cap layer and the heterojunction, and etching the P-GaN cap layer except the gate region mask pattern; manufacturing a source electrode and a drain electrode on two sides of the heterojunction; depositing gate metal in the region of the P-GaN cap layer to form a FinFET gate structure gate electrode, the gate metal covering the top and the sidewall of the P-GaN cap layer and covering the sidewall of the heterojunction; manufacturing an electrode lead. According to the device and the manufacturing method, a P-GaN cap layer structure is adopted, and a three-dimensional grid-controlled FinFET structure is combined, so that the transconductance and grid-control capabilities of the device are enhanced, and the threshold voltage and stability of the device are improved.

Owner:XIDIAN UNIV

Junctionless Folded I-Gate Field Effect Transistor with Low Leakage Current

ActiveCN106653853BGood gating abilitySuppression of short channel effectsSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerGate dielectric

The invention relates to a non-junction folded I-shaped gate field effect transistor with low leakage current, which comprises a silicon substrate of an SOI wafer. An insulation layer of the SOI wafer is arranged above the silicon substrate of the SOI wafer; monocrystalline silicon is arranged above the insulation layer of the SOI wafer; a gate dielectric insulation layer is attached to the surface of the monocrystalline silicon; a folded I-shaped gate electrode is attached to the surface of the gate dielectric insulation layer; the gate electrode is closely attached to the gate dielectric insulation layer; two ends of the upper surface of the monocrystalline silicon are respectively a source electrode and a drain electrode; adjacent monocrystalline silicon and the source electrode and the drain electrode are separated by insulation dielectric layers; and metal is injected to through holes formed after the insulation dielectric layers attached to the upper surface of the monocrystalline silicon and close to the two ends are etched to generate the source electrode and the drain electrode respectively. A low reverse leakage current characteristic can be provided in a condition of ensuring the positive characteristic not to be influenced almost, the power consumption of the device is reduced, and promotion and applications are facilitated.

Owner:宿松新驱光电科技有限公司