Manufacturing method of tunneling field effect transistor

A technology of tunneling field effect and manufacturing method, which is applied in transistors, semiconductor/solid-state device manufacturing, diodes, etc., can solve problems such as difficult to realize narrow tunneling junctions, destroy sub-threshold swings, and difficult to turn off devices, and achieve Improve subthreshold characteristics, reduce leakage current, and increase the effect of on-current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

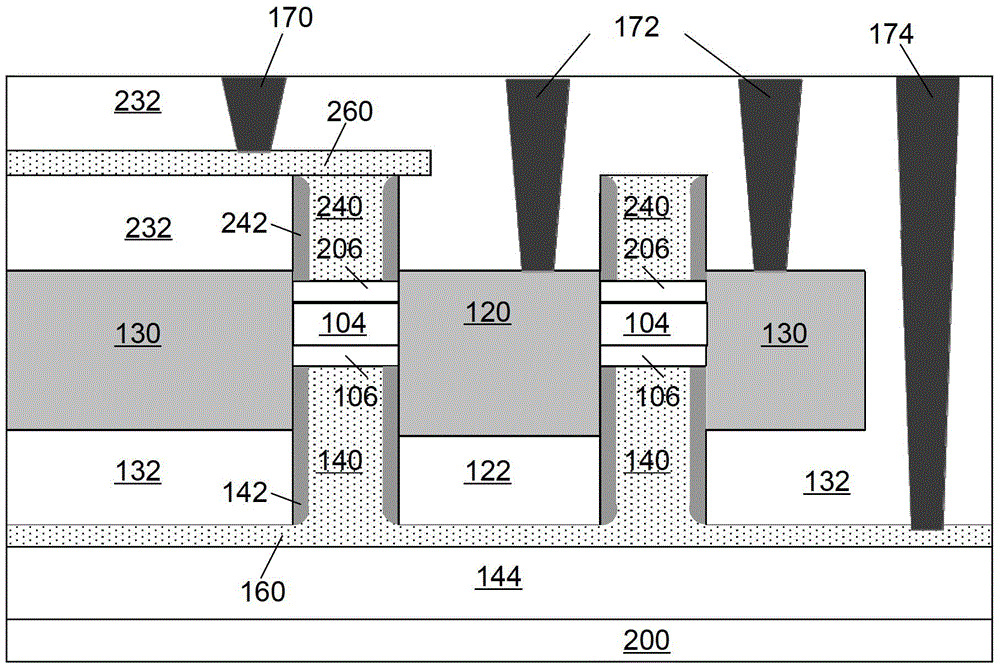

[0040] Embodiments of the present invention are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals designate the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary only for explaining the present invention and should not be construed as limiting the present invention.

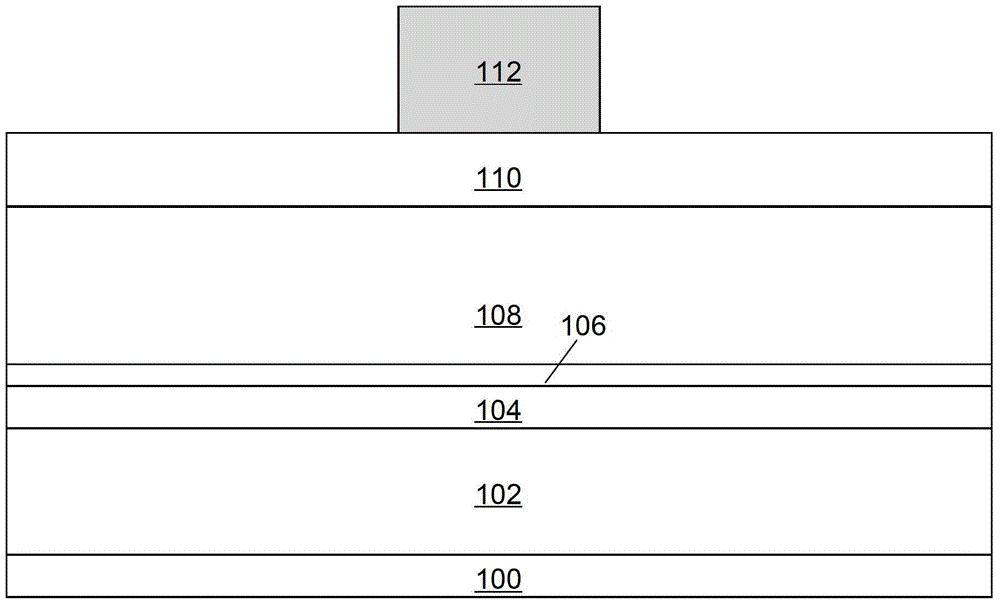

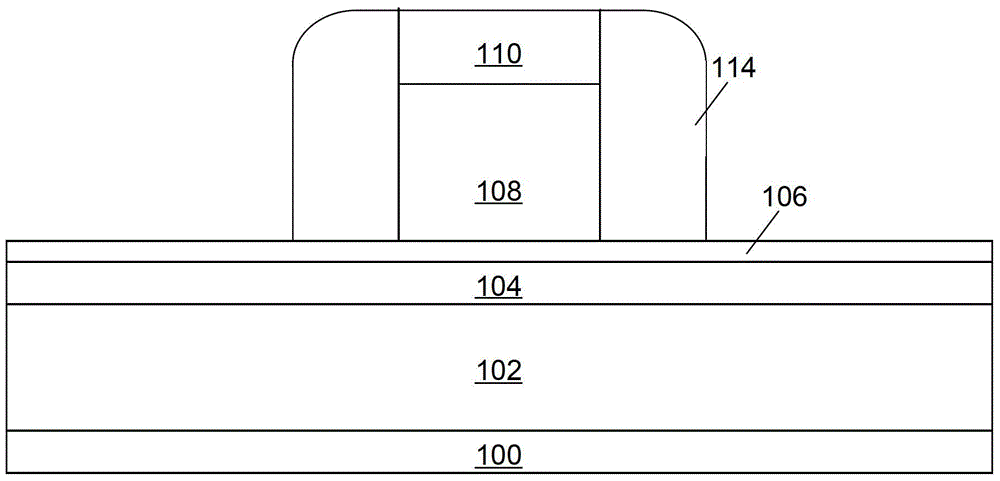

[0041] The present invention aims to propose a new tunneling field effect transistor structure to overcome the difficulty in realizing narrow tunneling junctions in existing tunneling field effect transistor structures. Refer to figure 1 As shown, the tunneling field effect transistor includes:

[0042] semiconductor layer 104;

[0043] The first gate dielectric layer 106 and the second gate dielectric layer 206 are respectively located on two opposite surfaces of the semiconductor layer 104;

[0044] The source region 120 and the drai...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More