Junctionless Folded I-Gate Field Effect Transistor with Low Leakage Current

A field-effect transistor and low-leakage technology, applied in circuits, electrical components, semiconductor devices, etc., can solve the problems of increased static power consumption of devices, reduce static power consumption, increase effective channel length, and reduce manufacturing costs Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

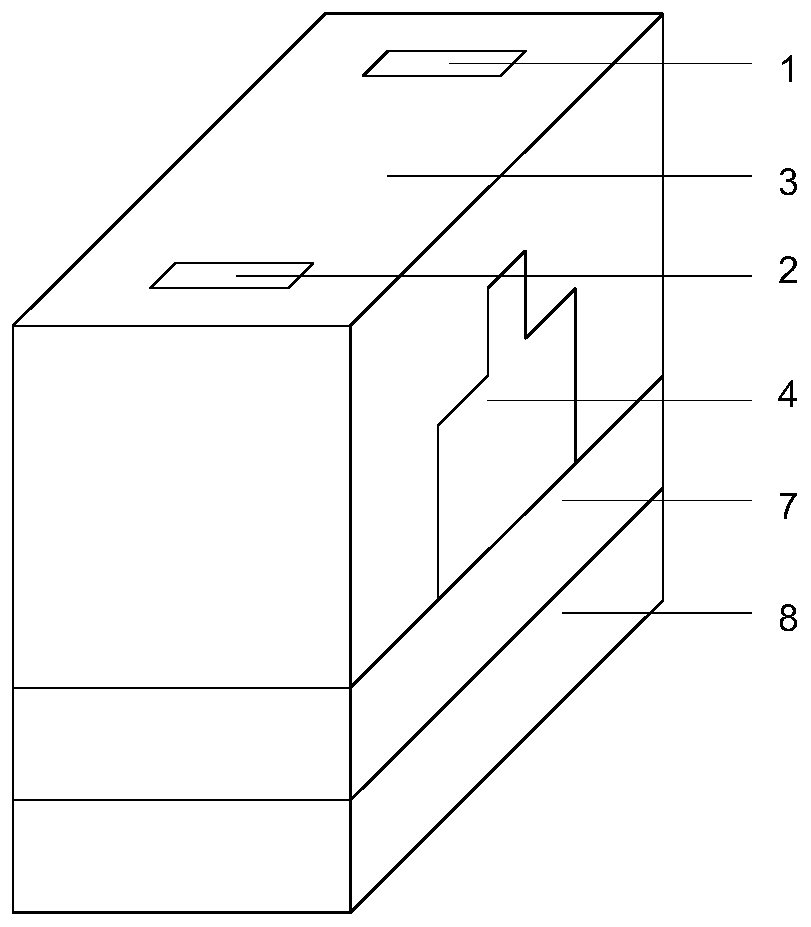

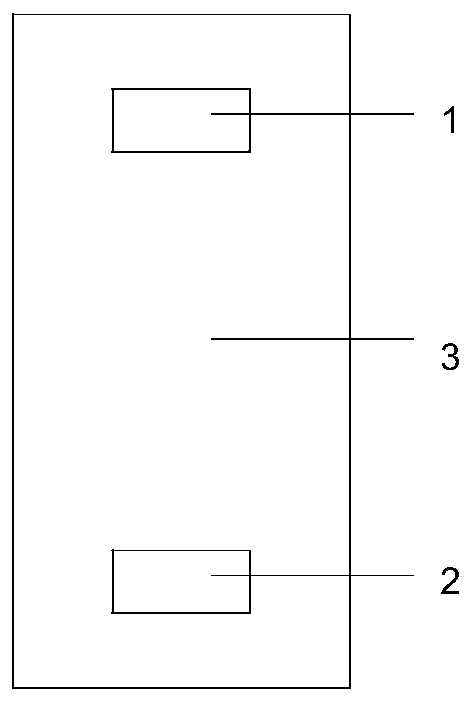

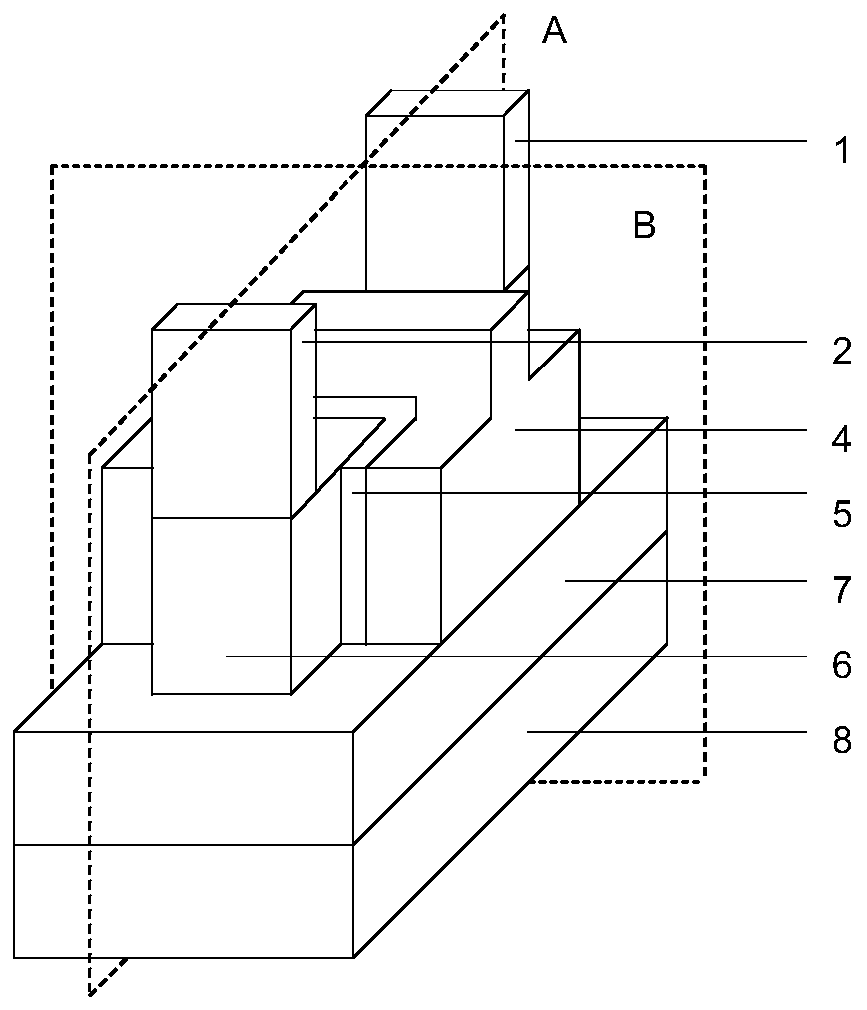

[0044] Below in conjunction with accompanying drawing, the present invention will be further described:

[0045]The present invention provides a junctionless folded I-shaped gate field effect transistor with low leakage current. The low leakage current property is realized through the control of carrier distribution in single crystal silicon by the I-shaped gate electrode 4 . Applying a positive voltage to the gate electrode 4 places the device in a conducting state. The folded I-shaped gate electrode 4 located on both sides of the single crystal silicon 6 respectively constitutes the upper and lower "horizontal" parts of the letter "I", and its length is longer, which mainly controls the carrier distribution in the single crystal silicon Function; while the folded I-shaped gate electrode 4 is located above the monocrystalline silicon 6 to form the middle "vertical" part of the letter "I", its length is relatively short, and it is located in the center of the monocrystalline s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More