A vertical gate-around tunneling transistor and its manufacturing method

A transistor and field effect transistor technology, applied in the field of gate-all-around transistors and their preparation, can solve the problems of complex GAA source-drain design, and achieve the effects of solving thermal stability problems, reducing thermal budget, and small sub-threshold slope.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

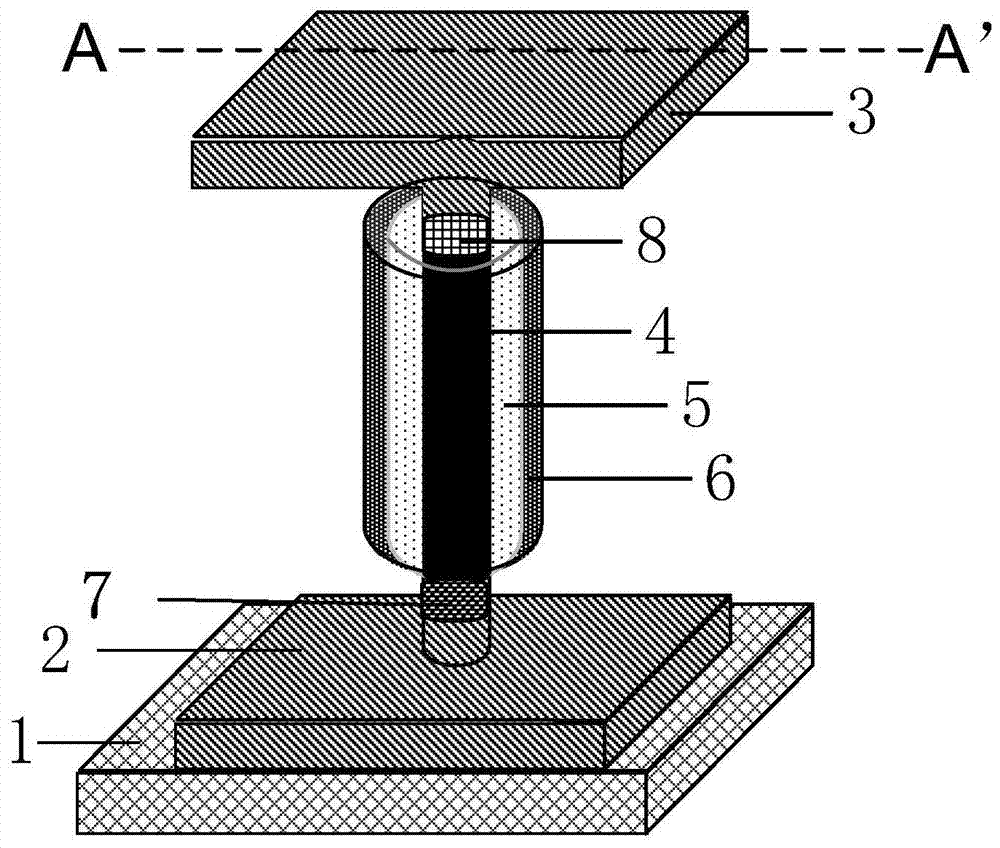

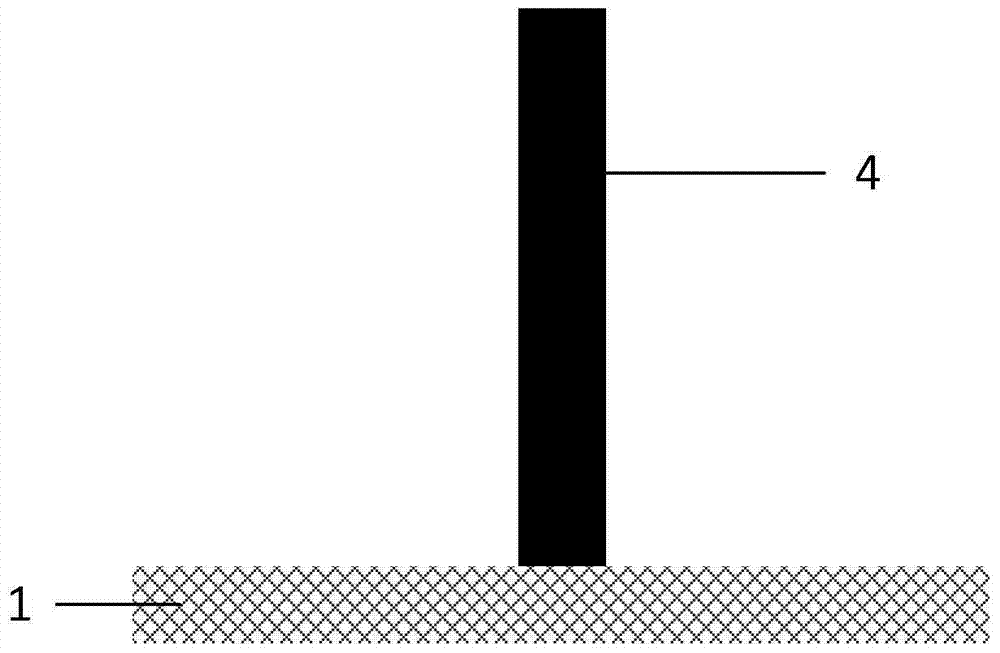

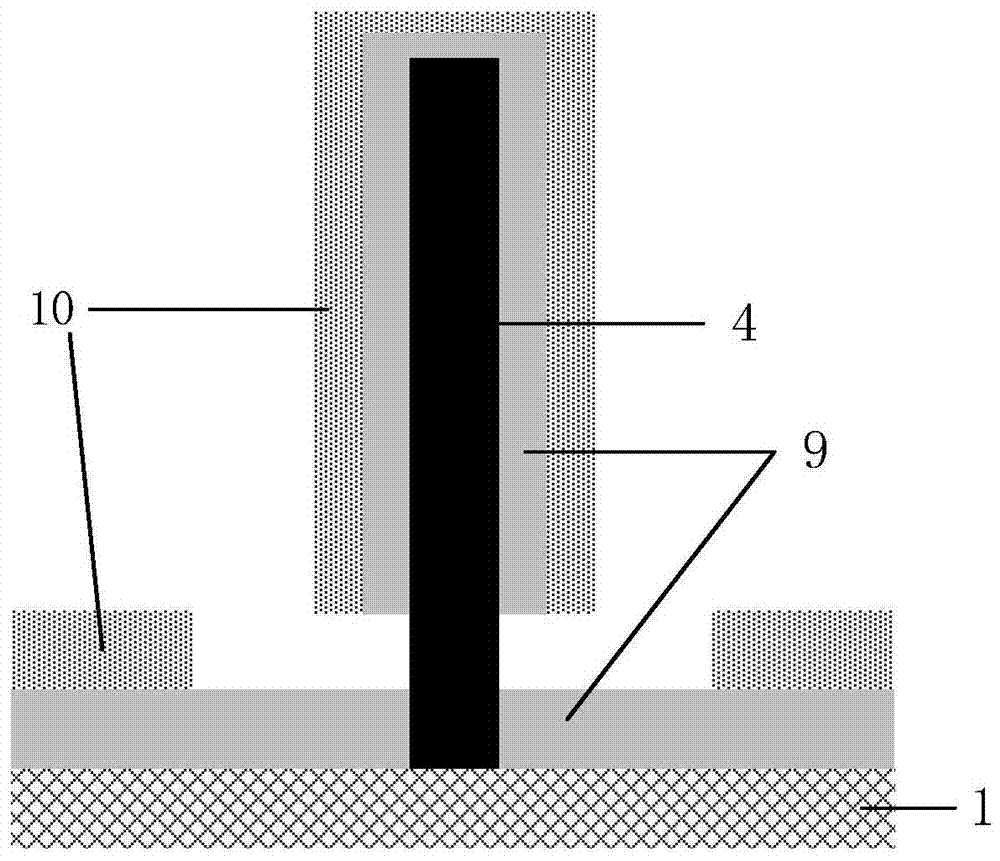

[0045] The present invention provides a field effect transistor with a novel structure, specifically a gate-all-around MOS transistor (such as figure 1 shown), including a ring-shaped semiconductor channel 4 in a vertical direction, a ring-shaped gate electrode 6, a ring-shaped gate dielectric layer 5, a source region 2, an impurity segregation region 7 (such as n-type), and a drain Region 3, an impurity segregation region 8 (different from the source region, such as p-type), a semiconductor substrate 1; wherein, the source region 2 is located at the bottom of the vertical channel 4, connected to the substrate 1, and the impurity segregation Region 7 is between source region 2 and vertical channel 4; drain region 3 is located at the top of vertical channel 4, impurity segregation region 8 is between drain region 3 and vertical channel 4; gate dielectric layer 5 and gate The electrode 6 surrounds the vertical channel 4 in a ring shape; the source region 2 and the drain region 3...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More