Patents

Literature

33results about How to "Small subthreshold slope" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

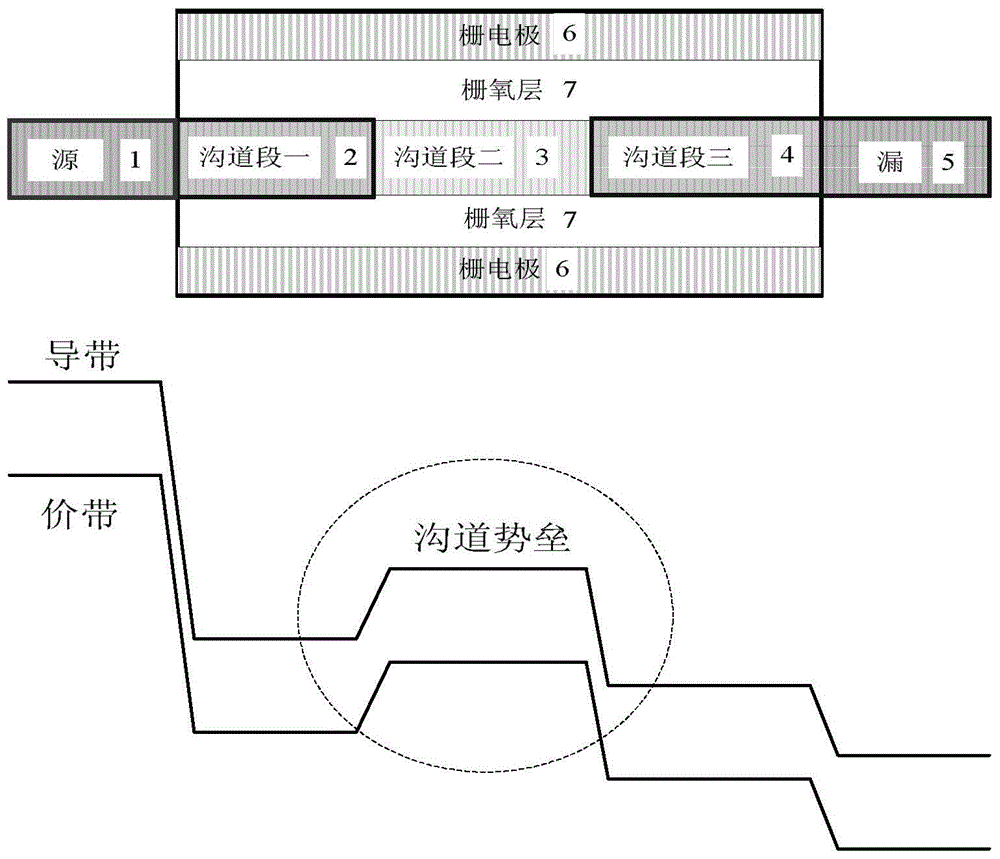

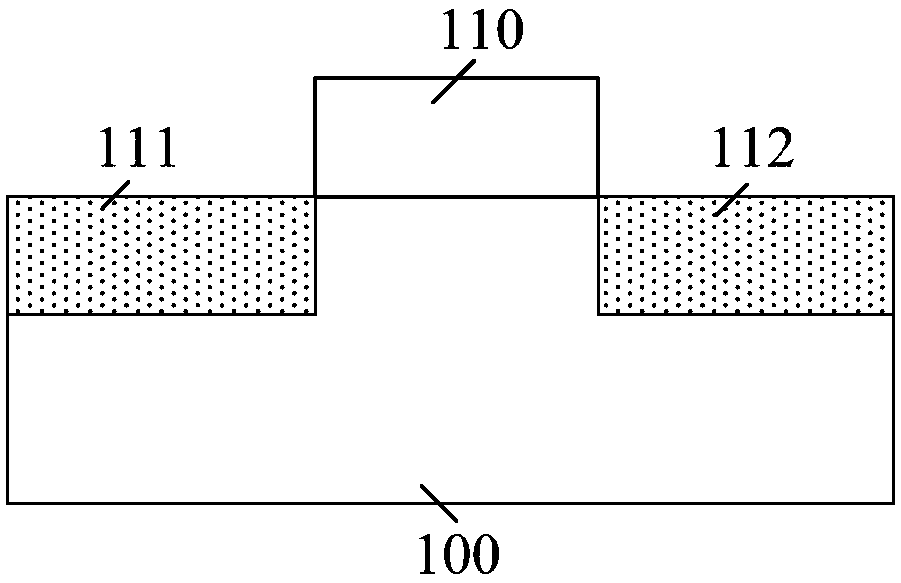

Tunneling field effect transistor having heterogeneous grid work function and formation method thereof

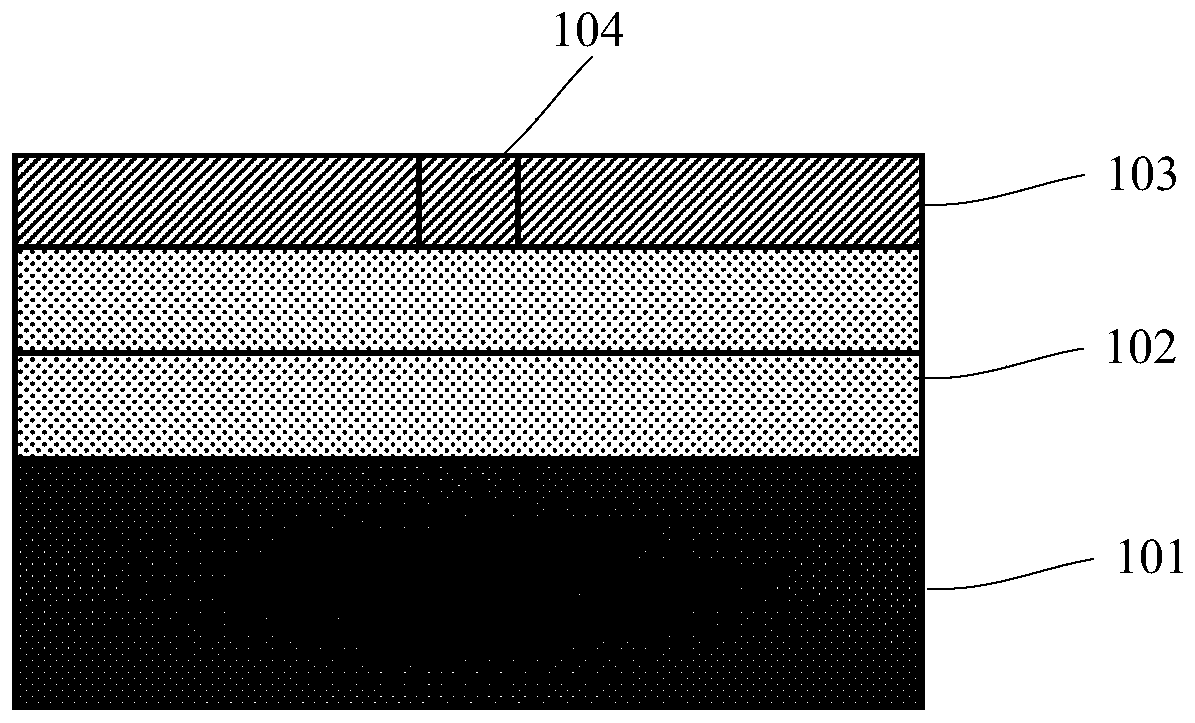

ActiveCN102169901ASmall subthreshold slopeIncrease drive currentSemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentEngineering

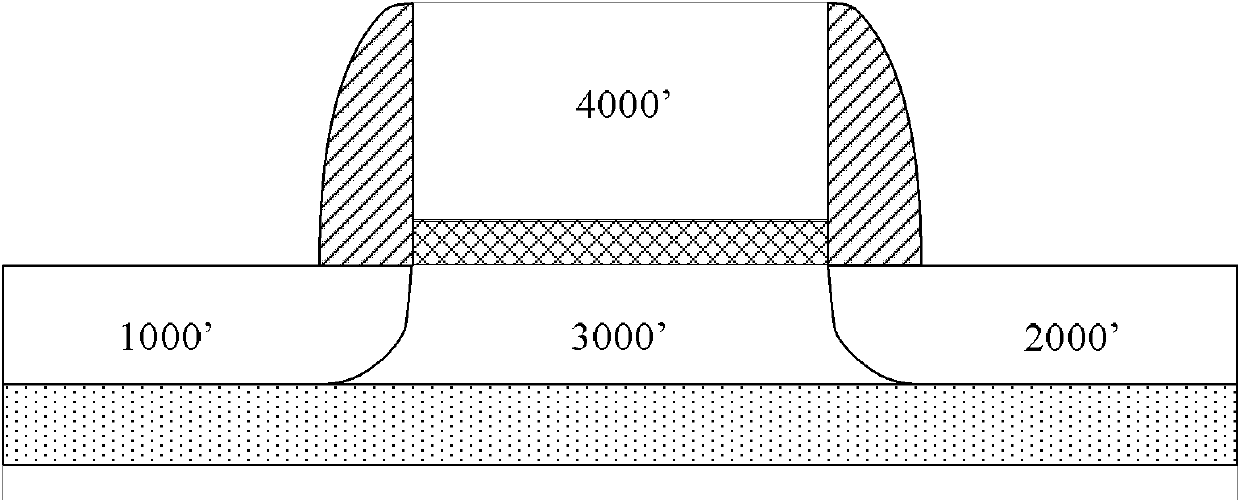

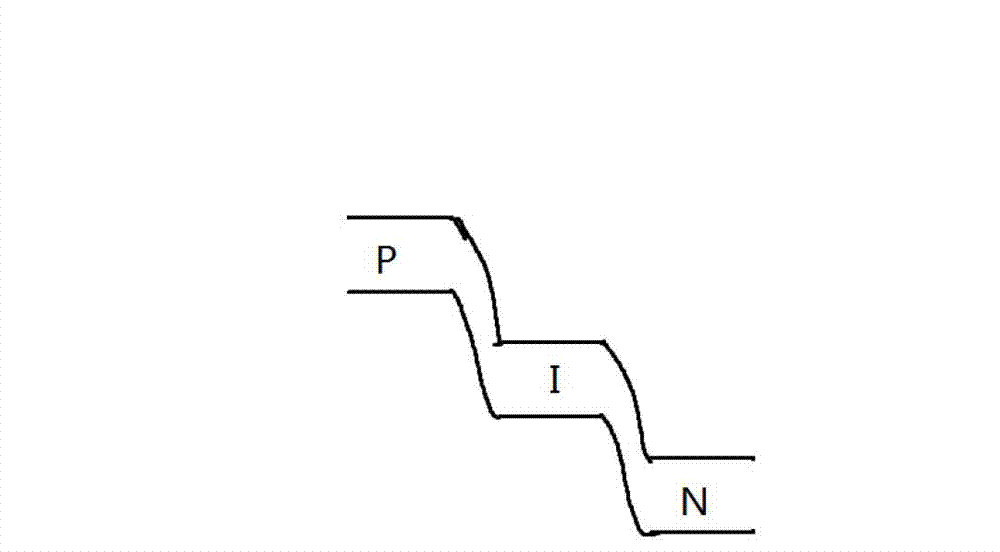

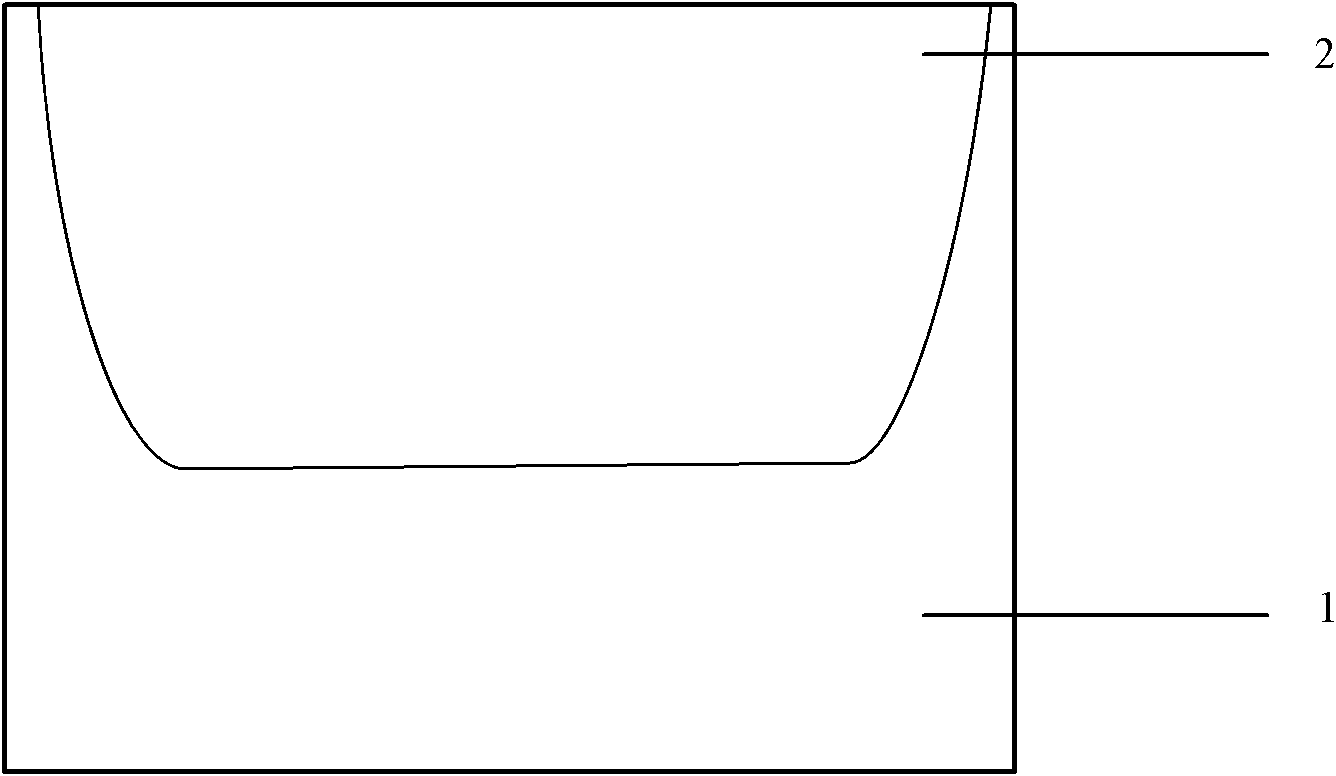

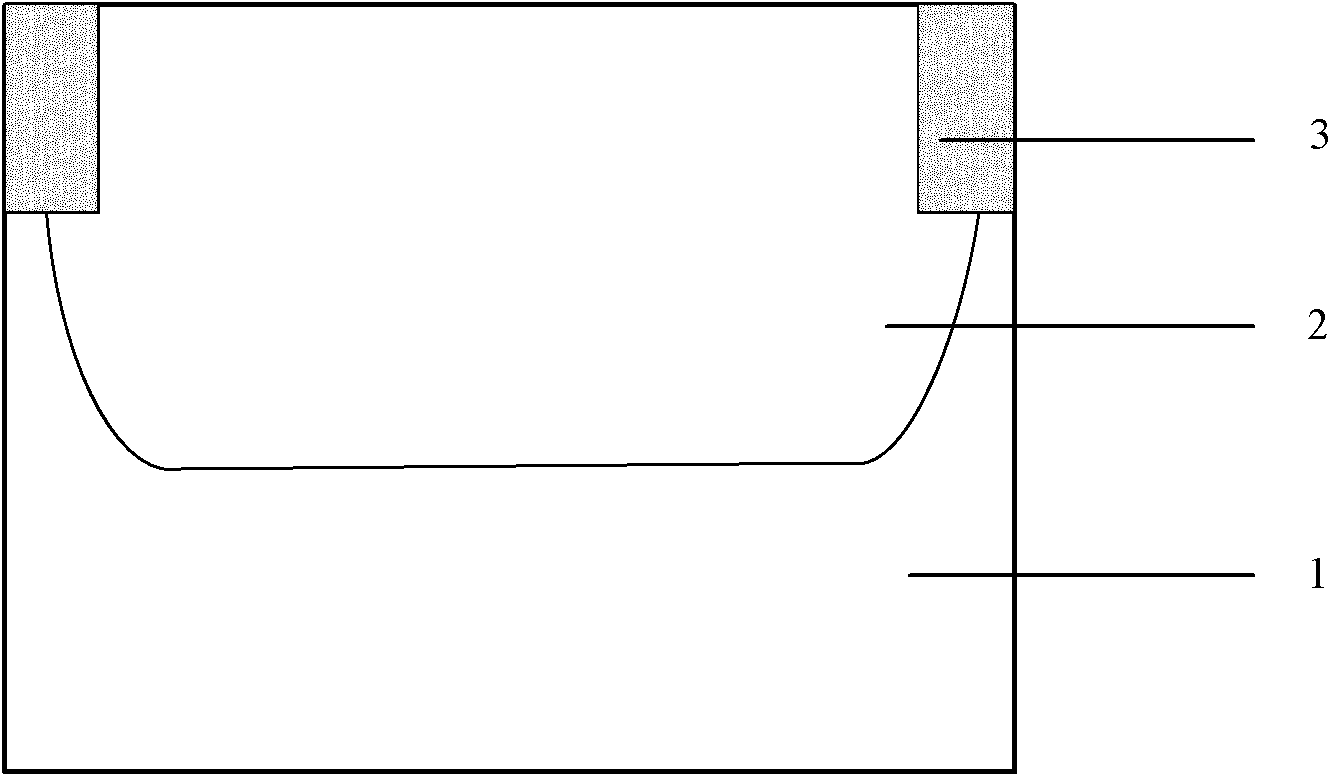

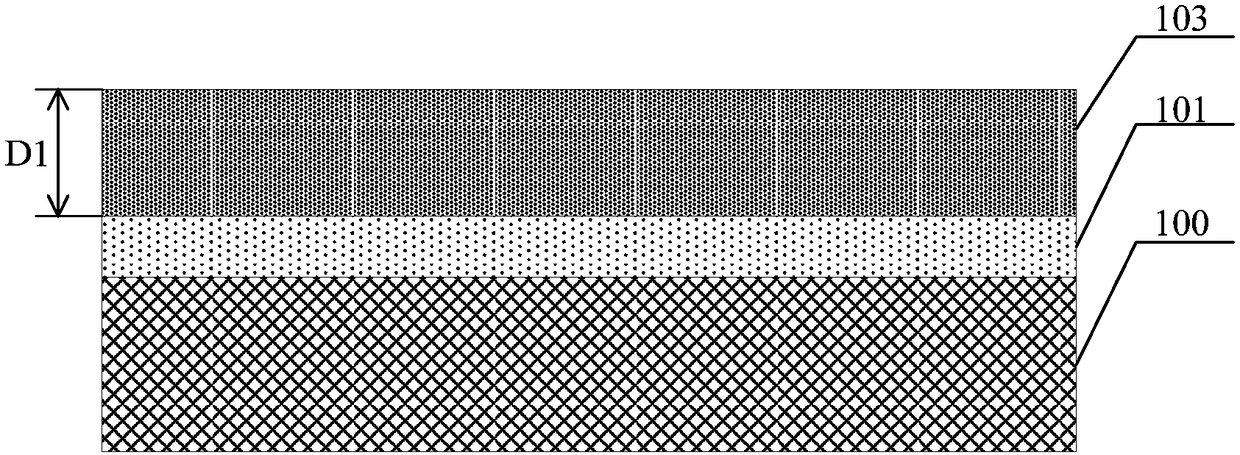

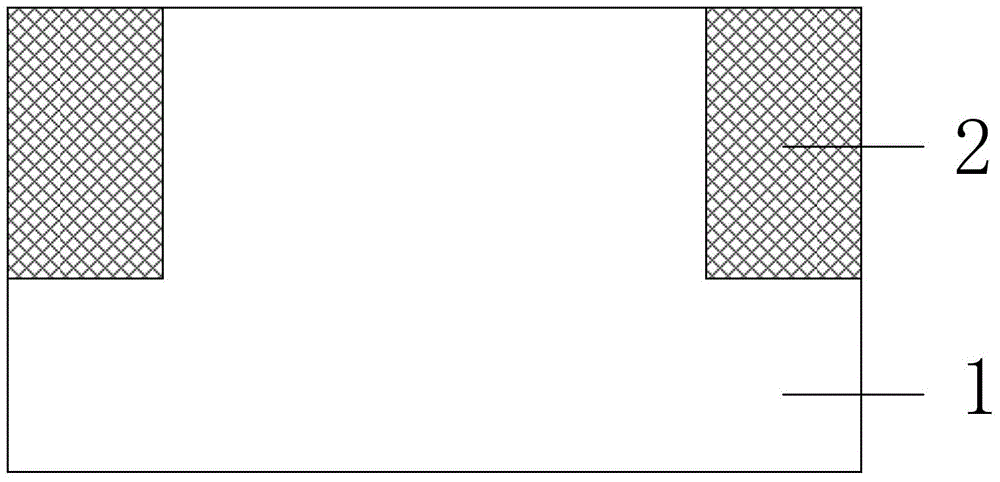

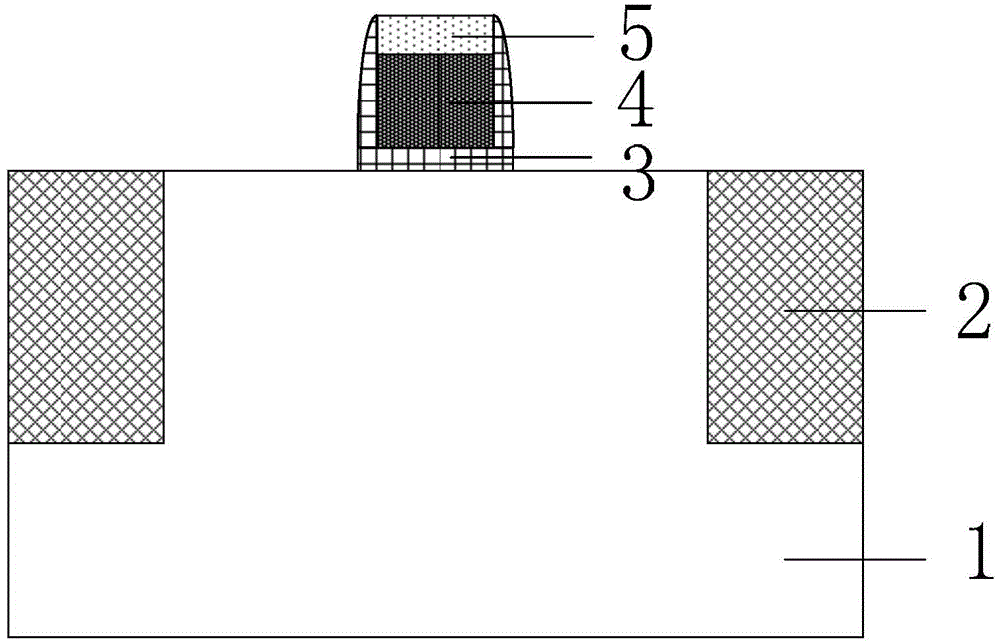

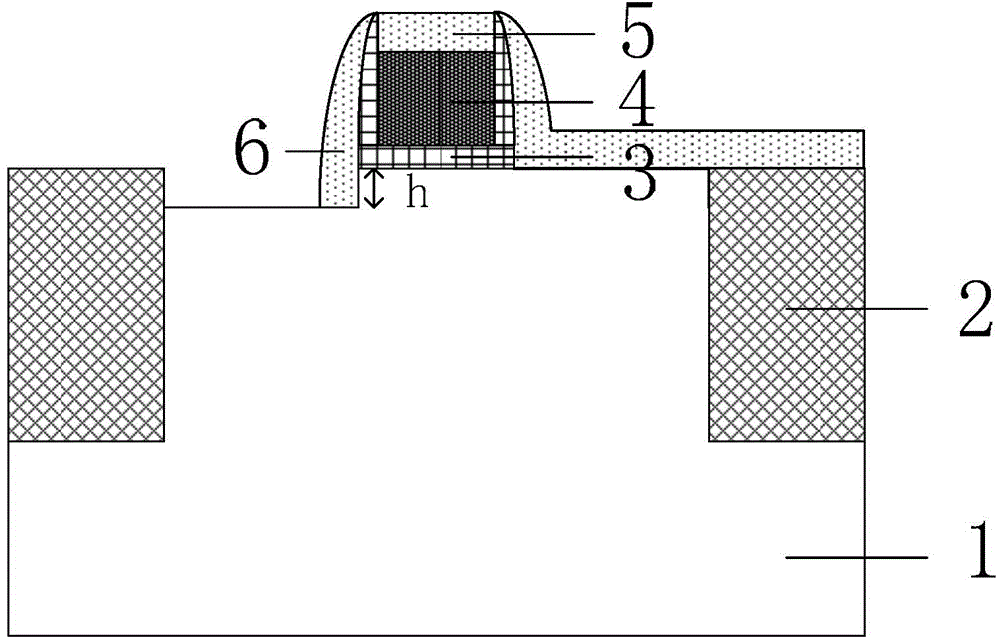

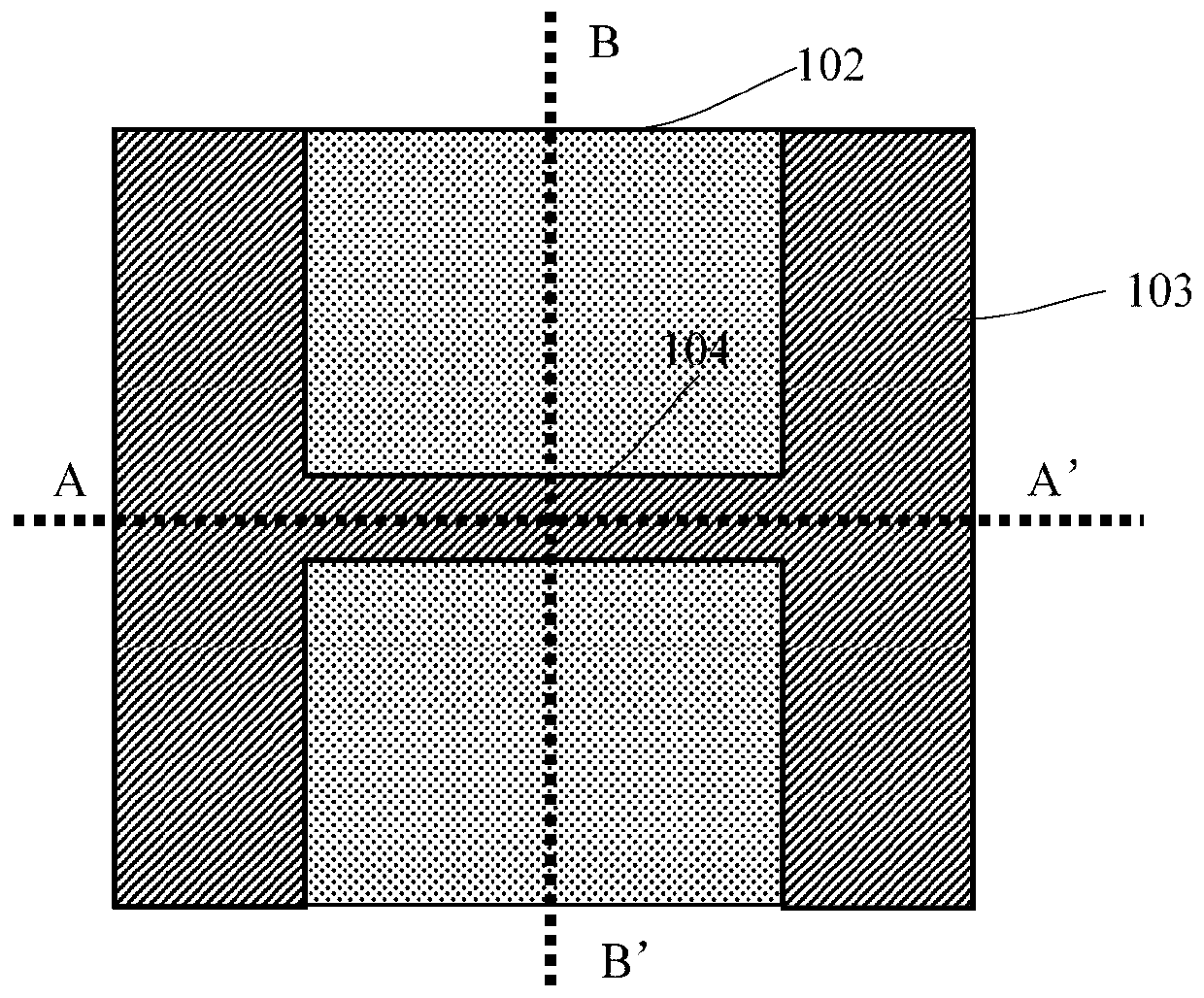

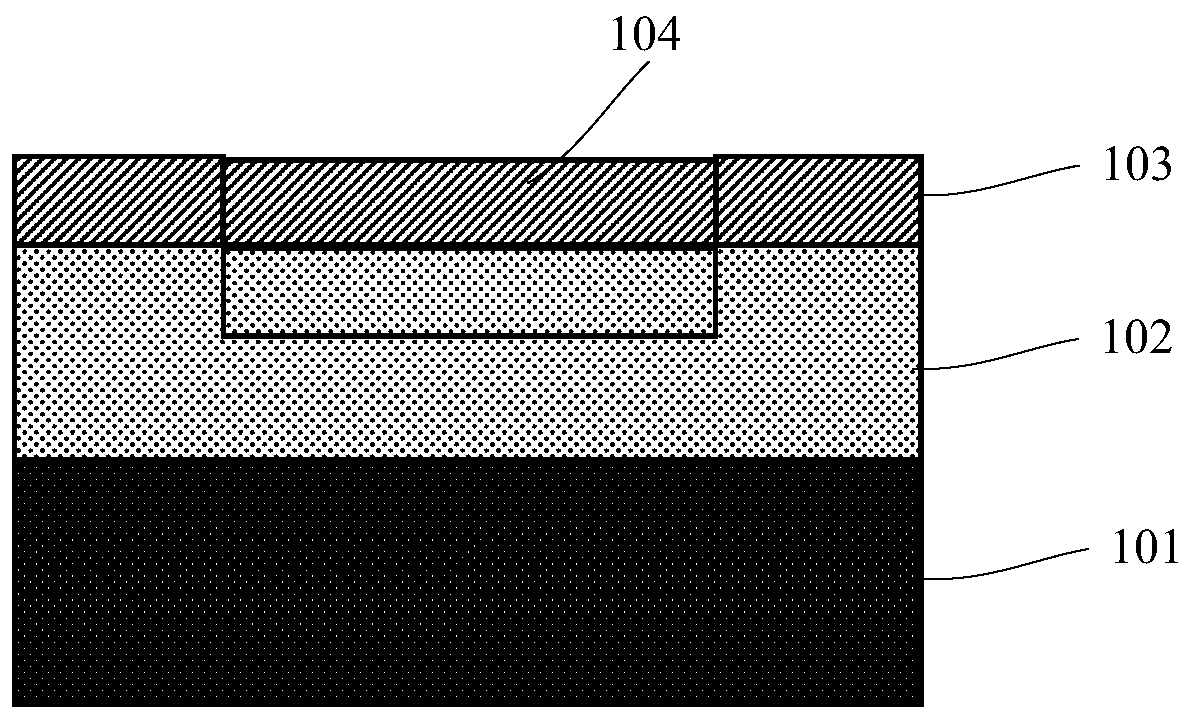

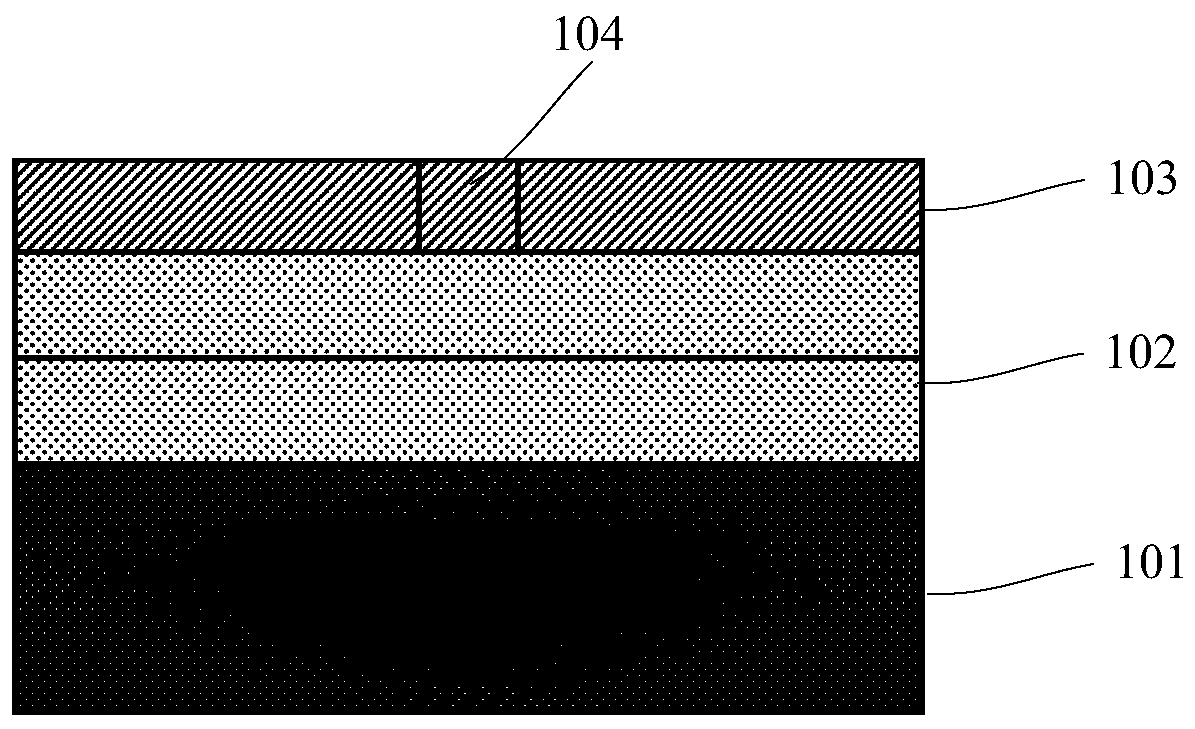

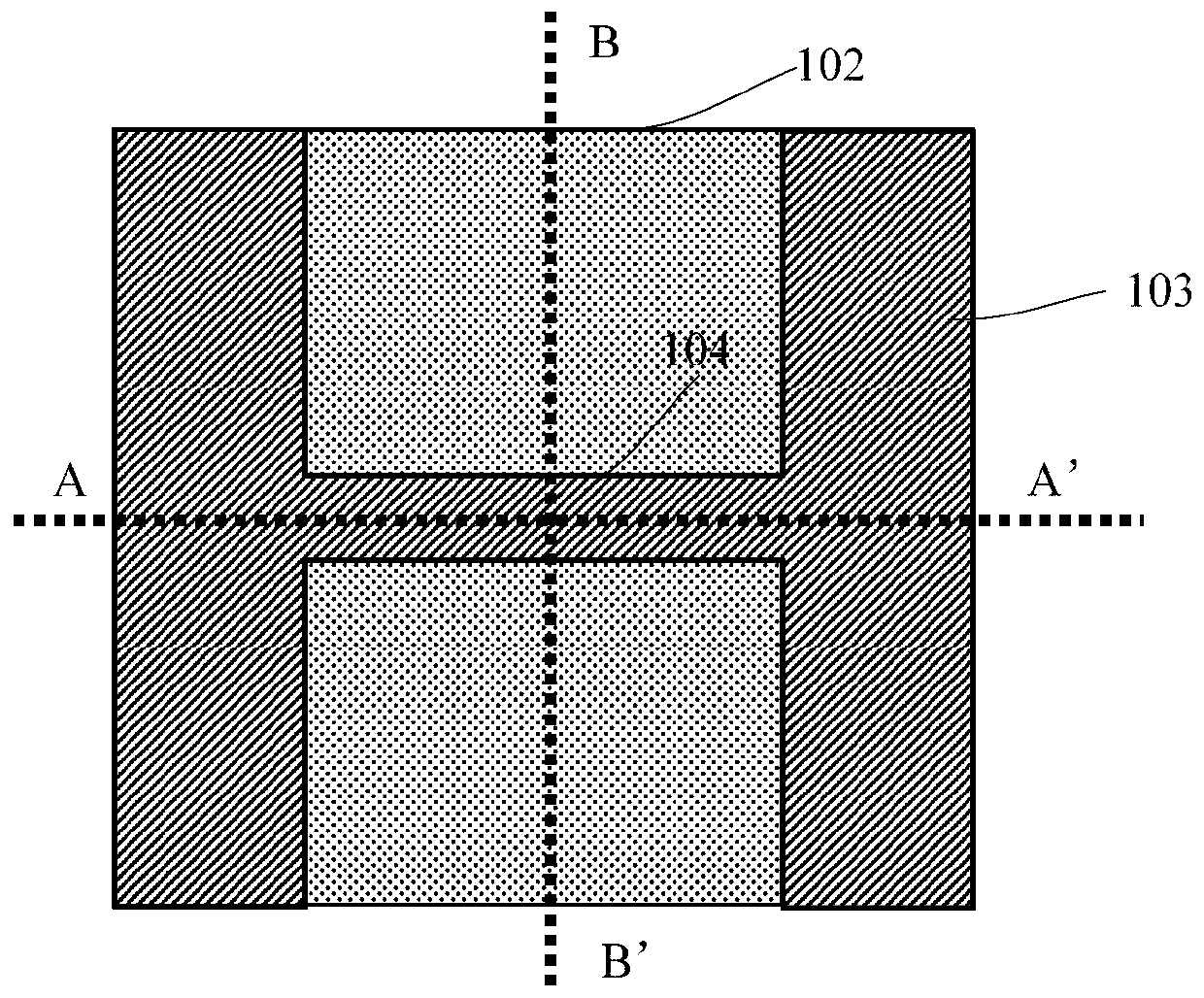

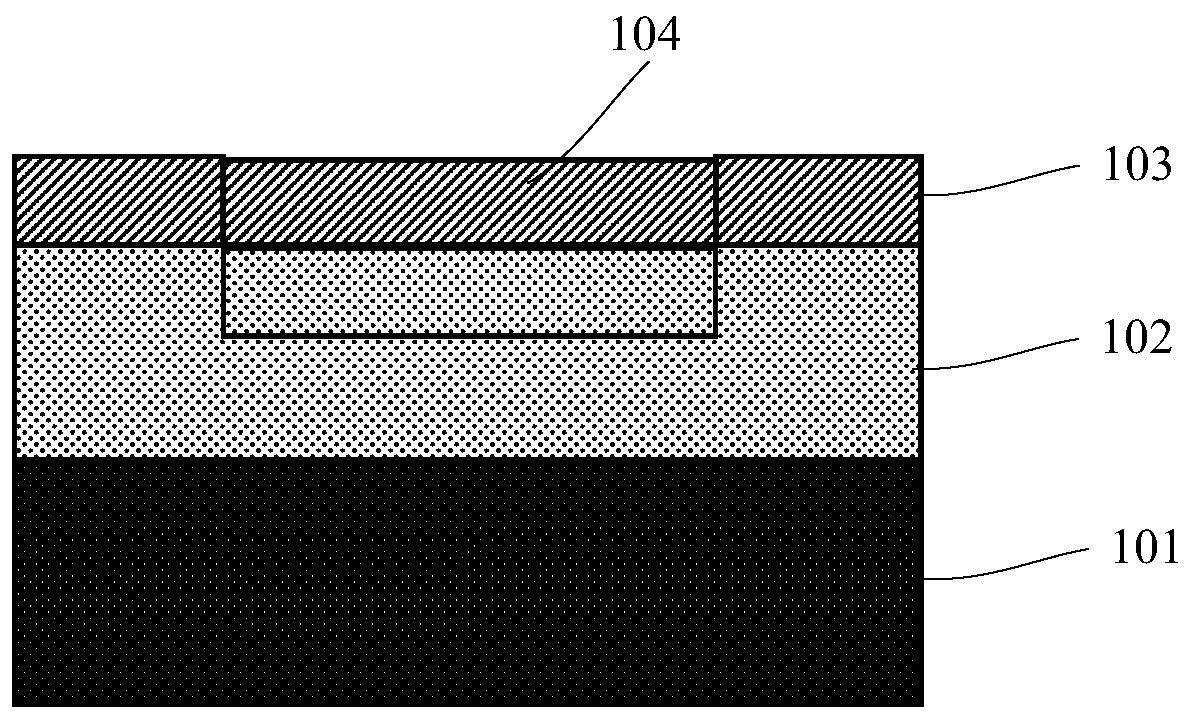

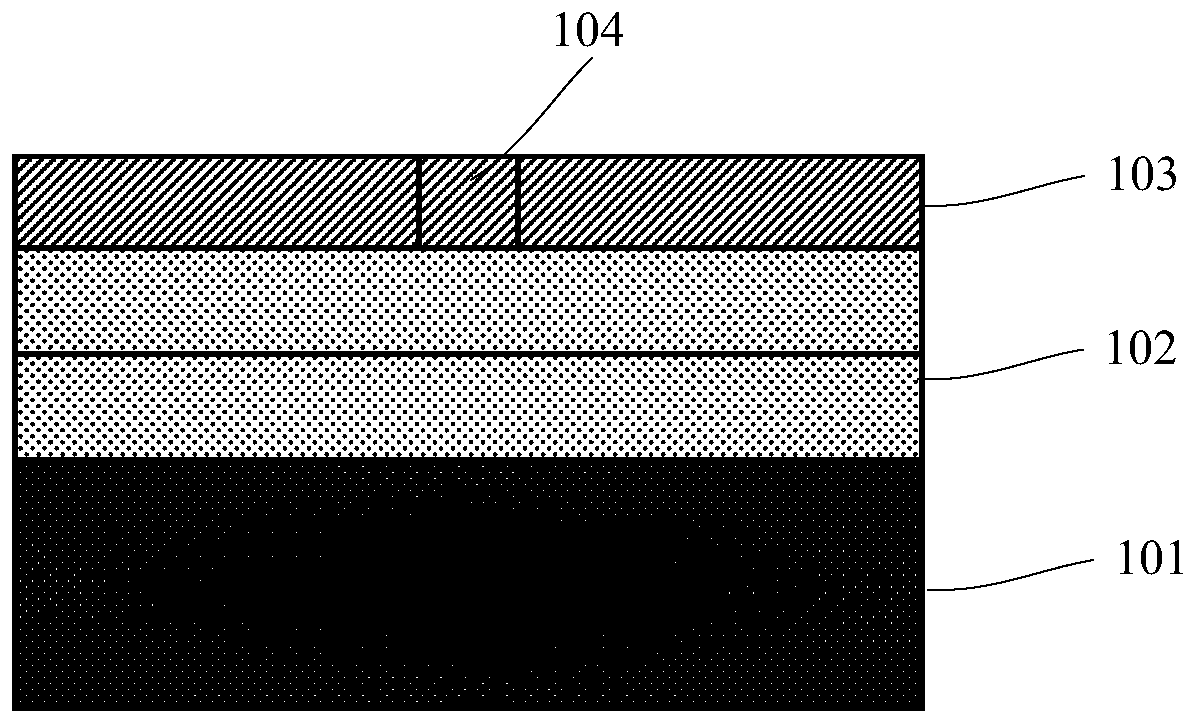

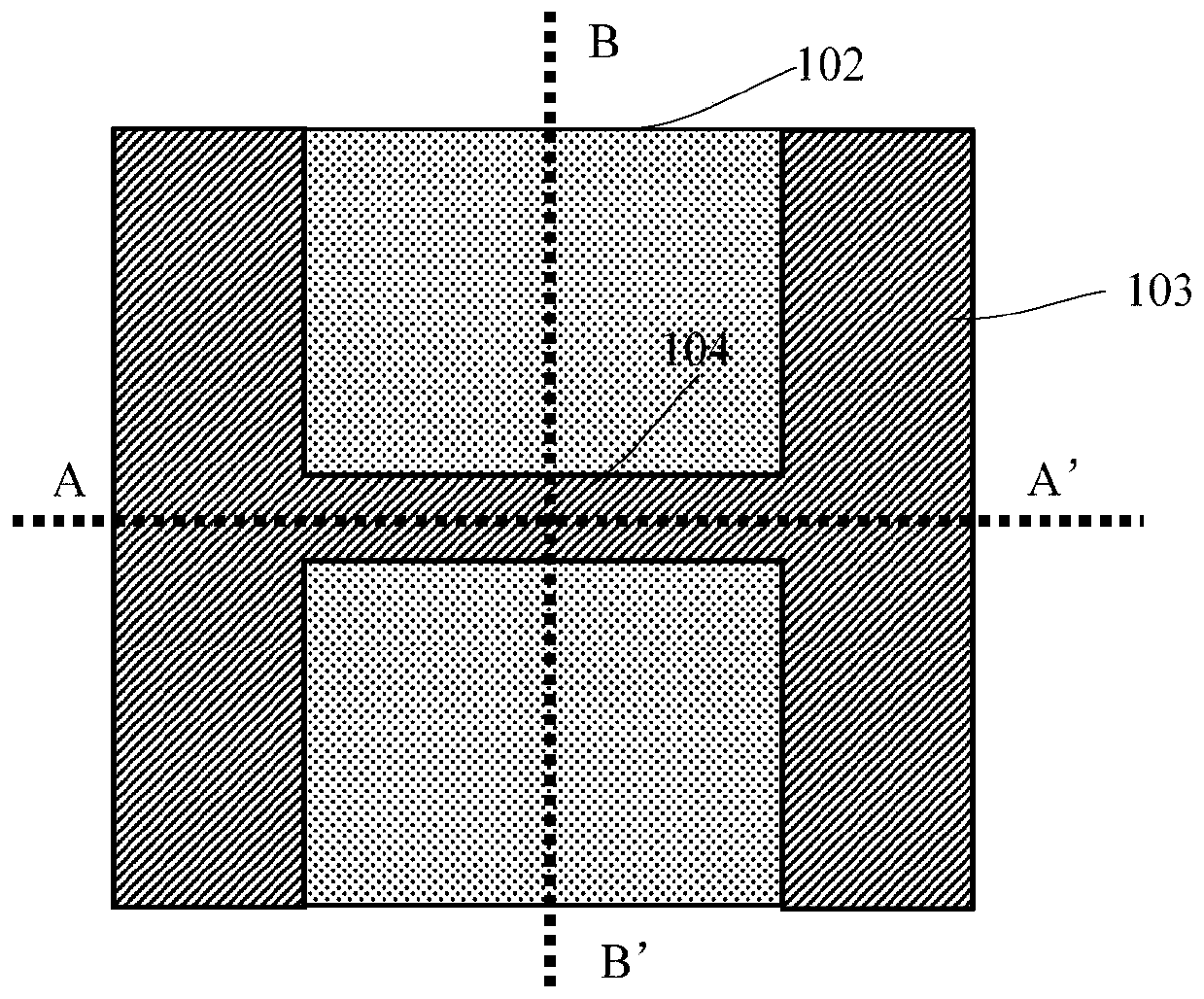

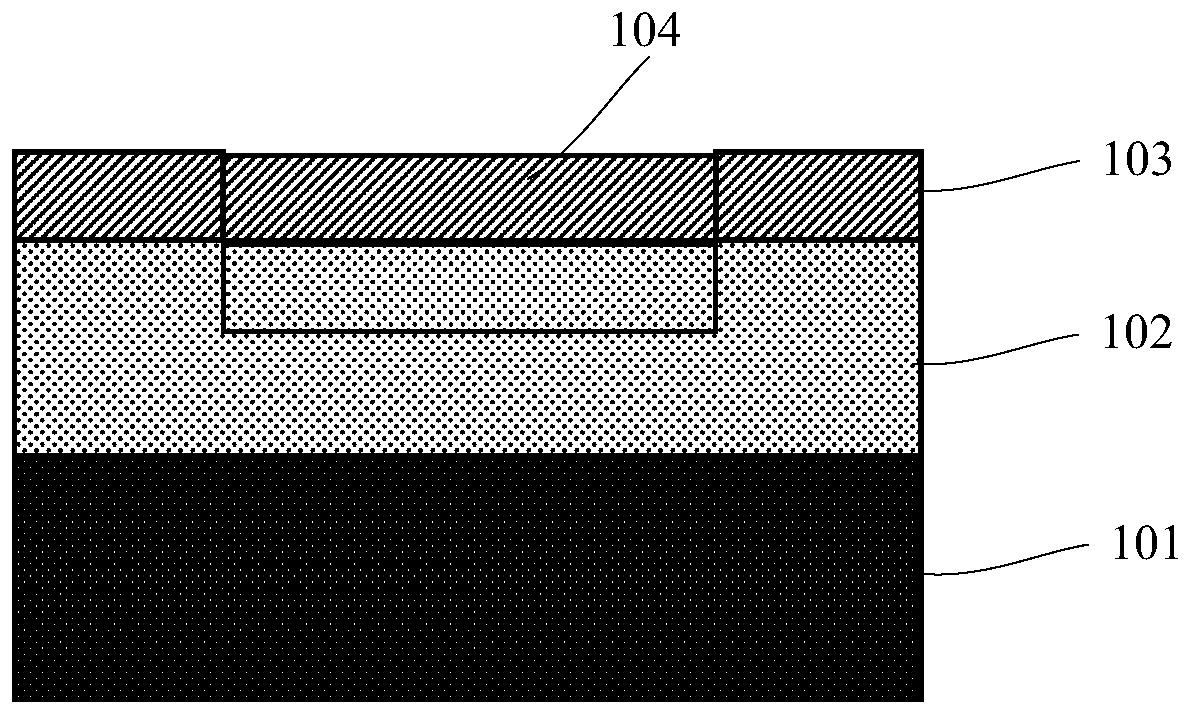

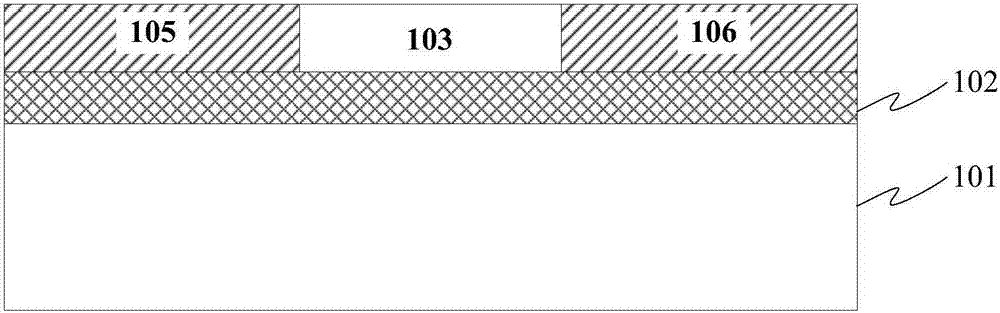

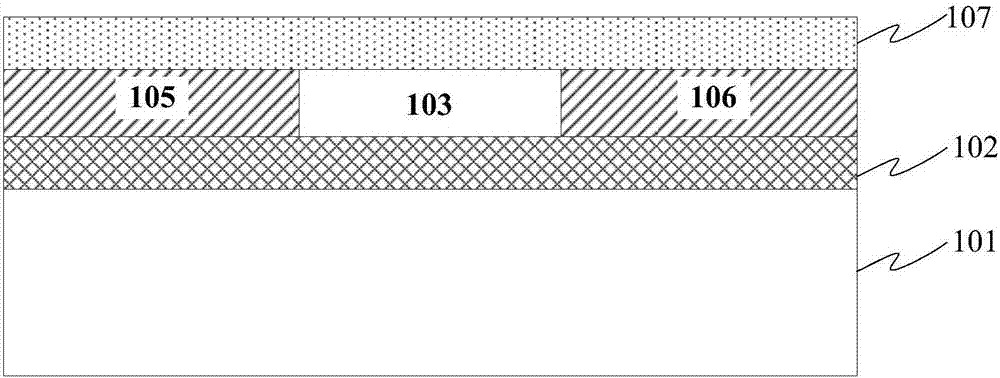

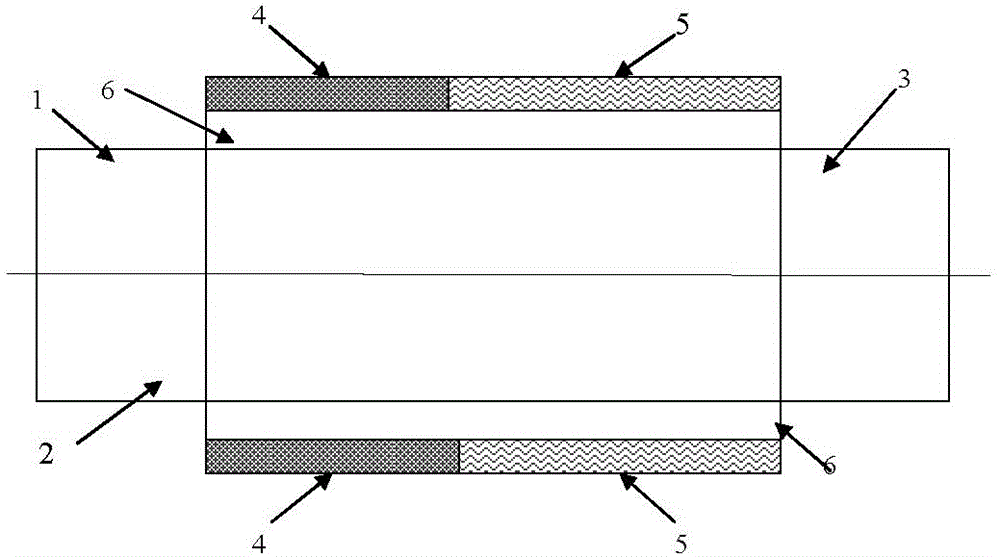

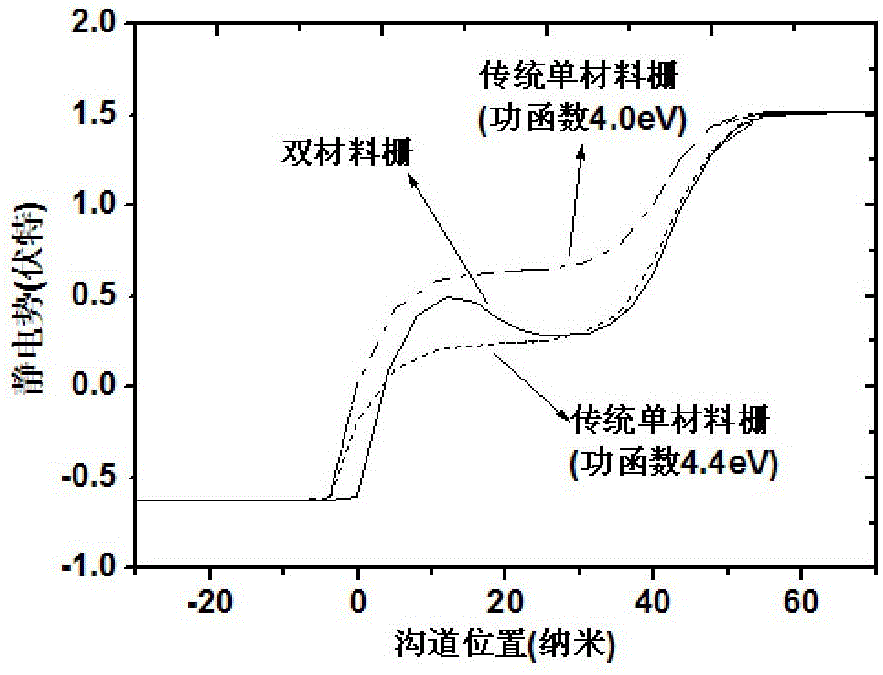

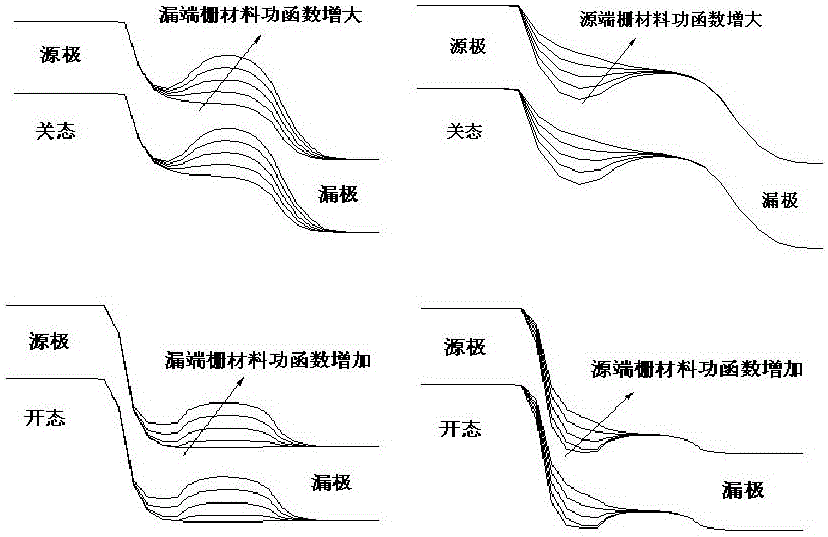

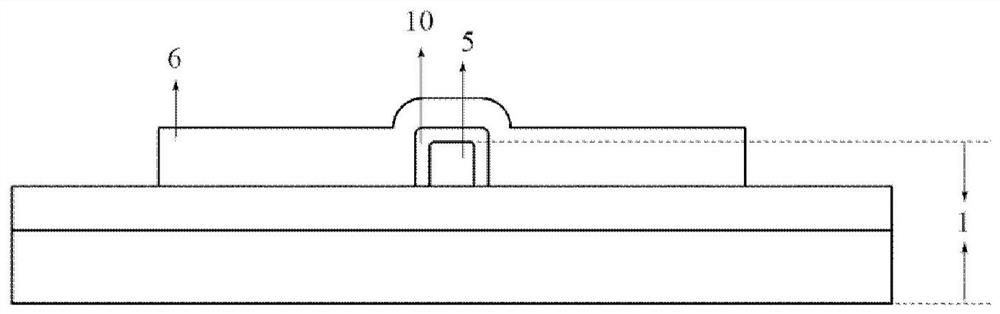

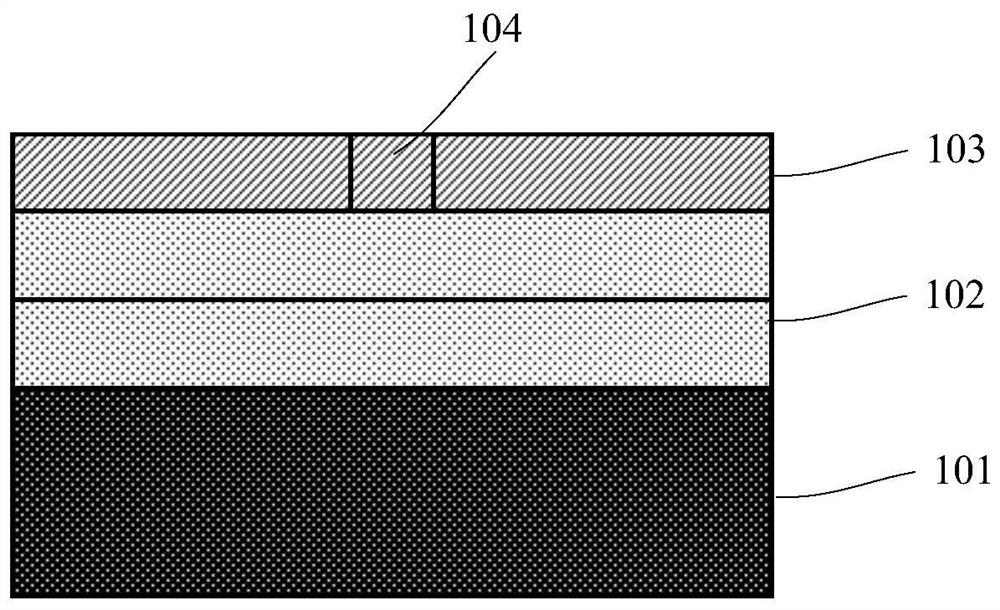

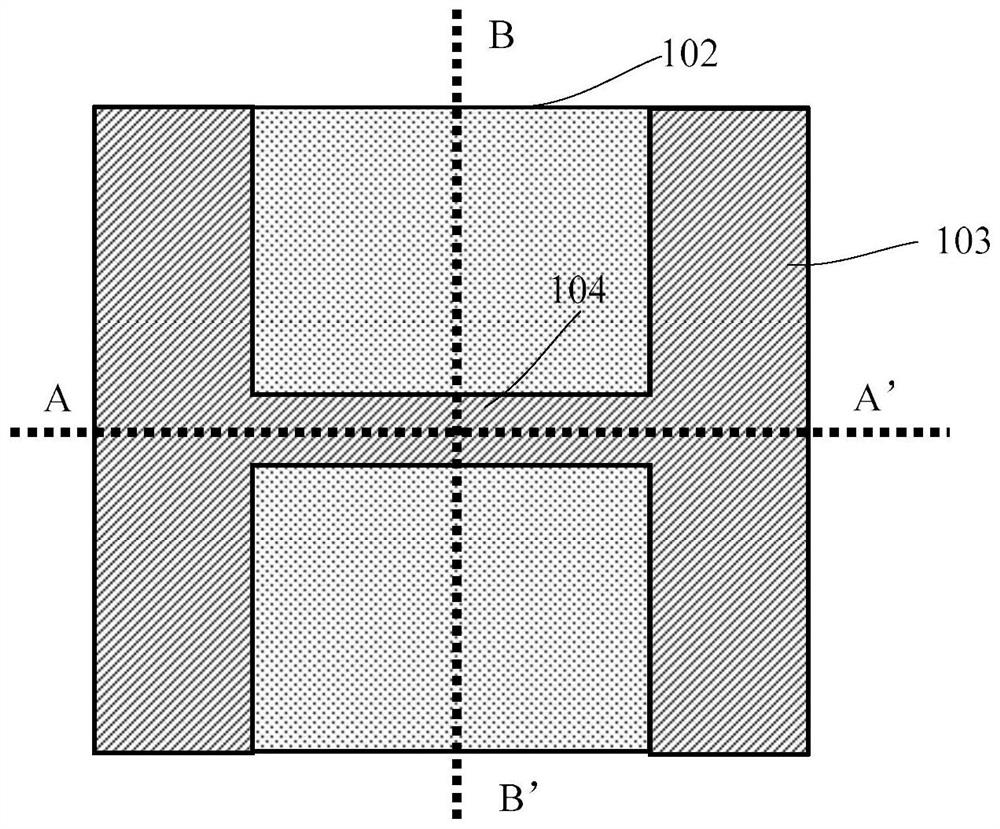

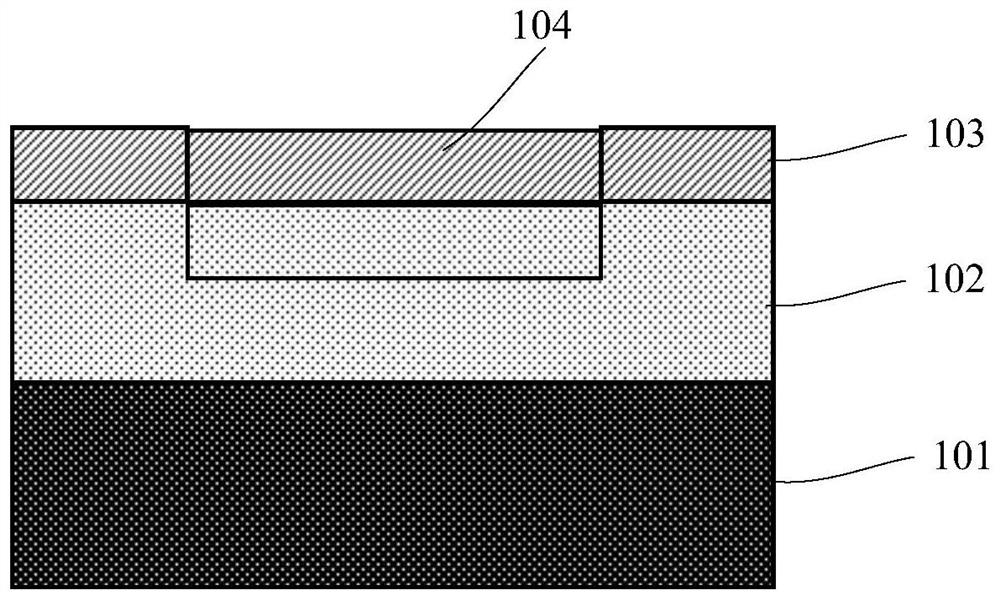

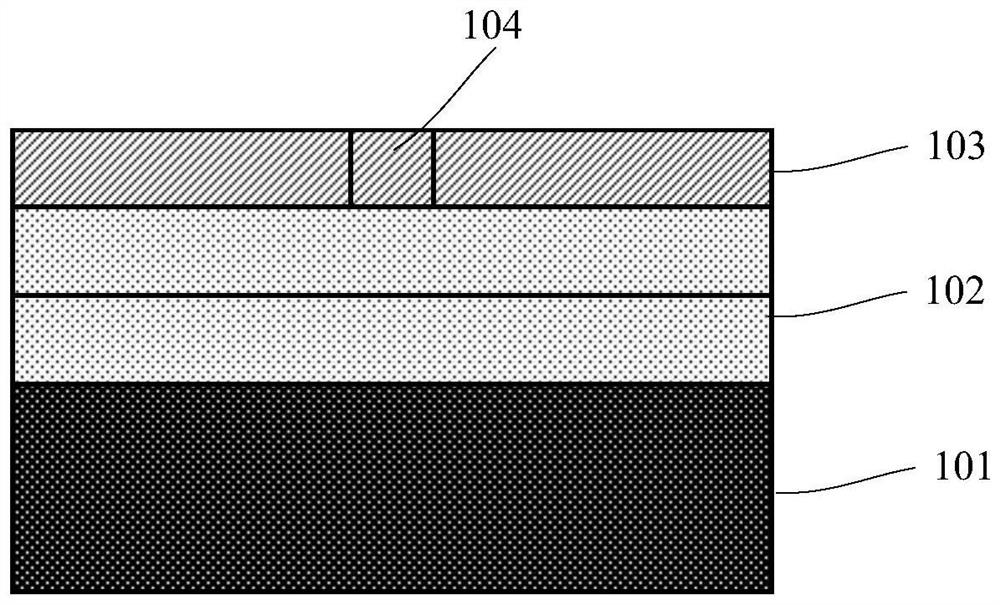

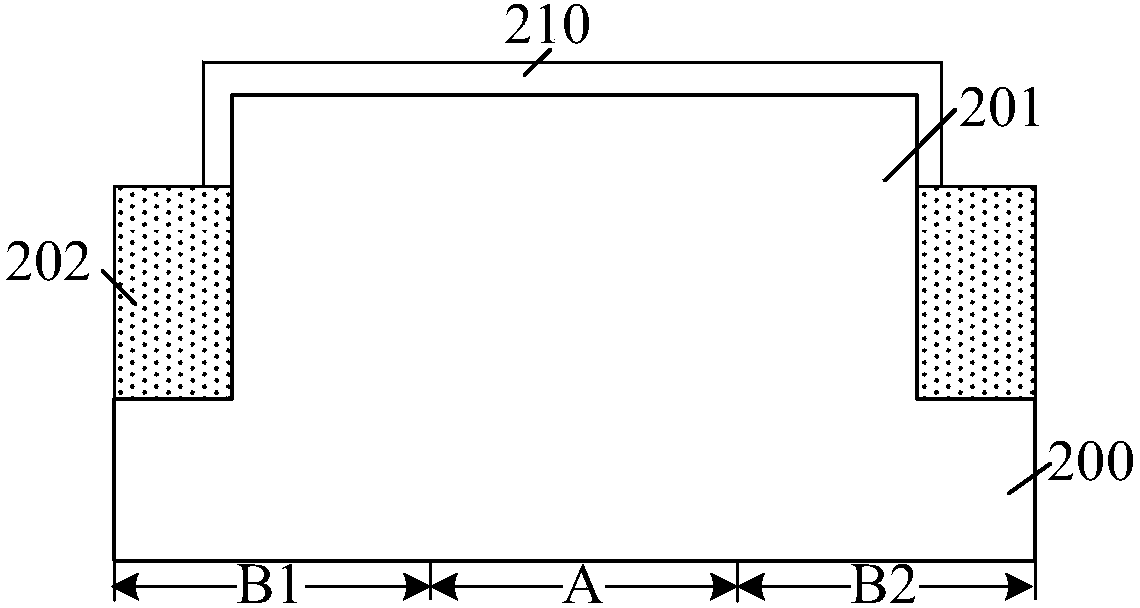

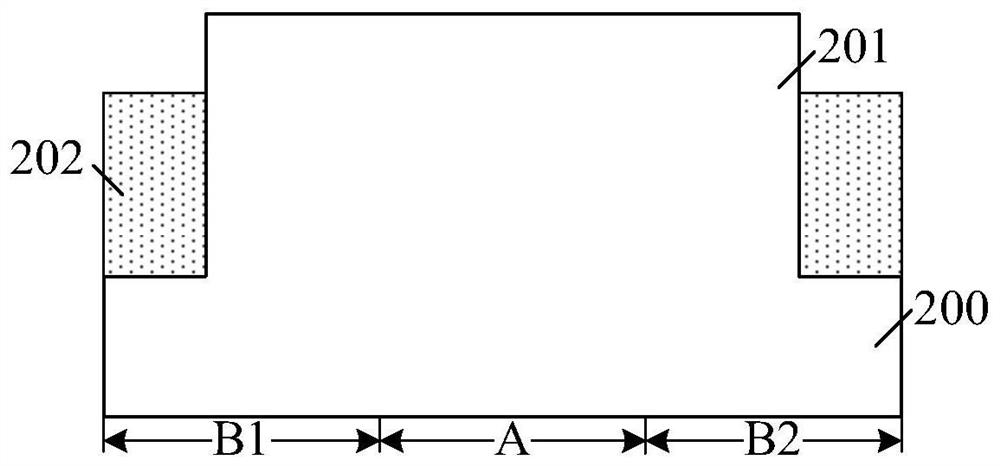

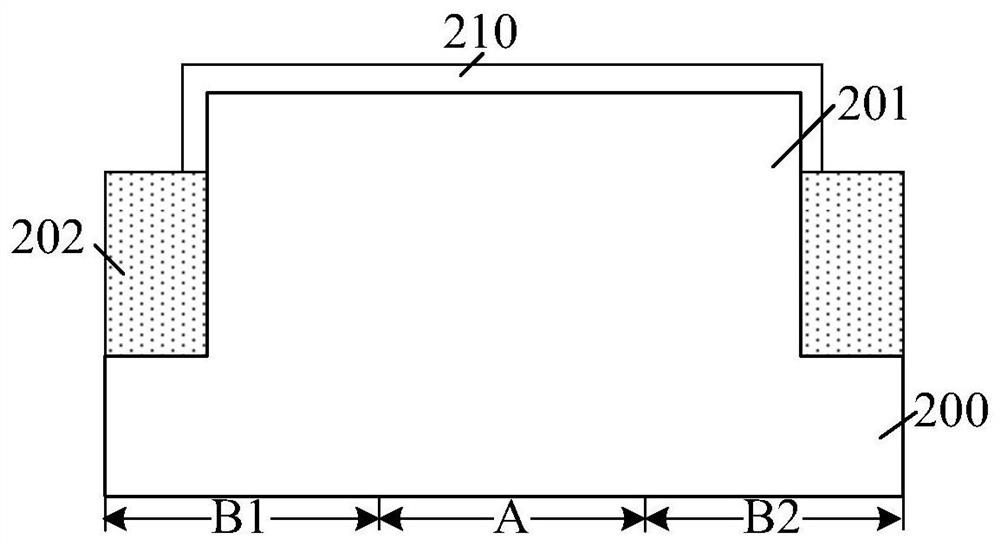

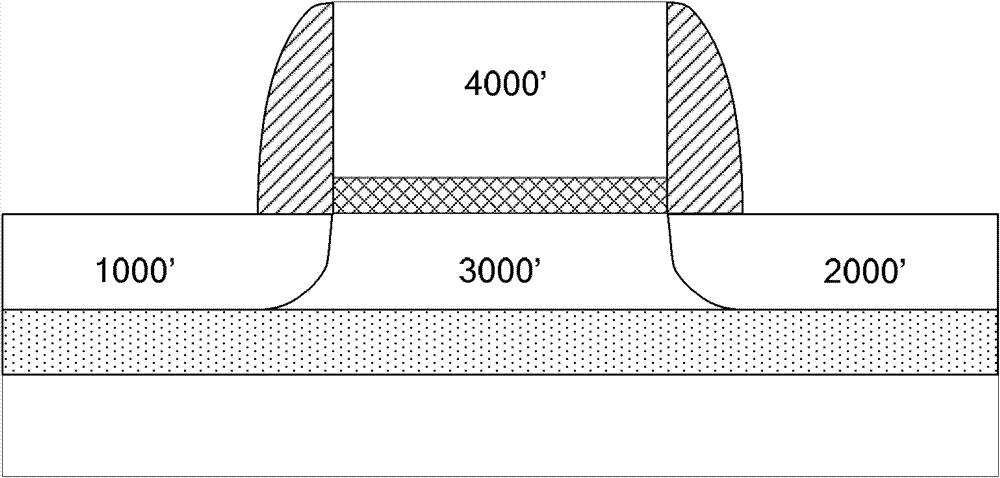

The invention provides a tunneling field effect transistor having heterogeneous grid work function, which comprises a substrate, a channel zone formed in the substrate, a source zone and a drain zone formed at two sides of the channel zone, and a grid stack, wherein the doping type of the source zone is opposite to that of the drain zone; the grid stack comprises a grid dielectric layer and further comprises a first grid electrode and a second grid electrode located on the grid dielectric layer and distributed along the direction from the source zone to the drain zone, and a first side wall and a second side wall located on the grid dielectric layer and respectively formed at a side of the first grid electrode and a side of the second grid electrode; and the first grid electrode and the second grid electrode have different work functions. In the embodiment of the invention, a structure of transverse heterogeneous grid work function is introduced to the tunneling field effect transistor, so the energy zone distribution of the channel zone is adjusted, the sub-threshold gradient of the transistor is substantially decreased, meanwhile, the driving current is greatly improved.

Owner:TSINGHUA UNIV

Germanium-based NMOS (N-metal-oxide-semiconductor) device and preparation method thereof

ActiveCN102222687AHigh switching current ratioSmall subthreshold slopeSemiconductor/solid-state device manufacturingSemiconductor devicesHafniumOxygen

The invention provides a germanium-based NMOS (N-metal-oxide-semiconductor) device and a preparation method thereof, belonging to the technical field of ultra large scale integration (ULSI) circuit manufacturing. Two layers of insulation medium material are inserted among metal source and drain electrodes and a substrate of the germanium based-NMOS device, and the bottom layer is S medium material with high pinning coefficient, such as hafnium oxide, silicon nitride or hafnium silica, and the upper layer of medium material is delta EC medium material with low conduction band offset, such as titanium dioxide, gallium oxide or strontium titanium oxygen. According to the invention, the fermi energy level pinning effect can be weakened, the electronic potential barrier is reduced, and furtherthe performances of a germanium-based schottky NMOS device are improved; and compared with the traditional method in which a single layer of insulation medium material such as AL2O3 is adopted, the preparation method can be used for effectively reducing the schottky potential barrier and maintaining lower source and drain resistance, therefore, the performances of the device are improved to a large extent.

Owner:SEMICON MFG INT (BEIJING) CORP +1

Tunneling field effect transistor

InactiveCN102832256AImprove performanceIncrease the on-state currentTransistorSub thresholdCondensed matter physics

The invention relates to the technical field of field effect transistors and discloses a tunneling field effect transistor. The tunneling field effect transistor comprises a source region, a channel region and a drain region, wherein the source region and the drain region are respectively formed on the two sides of the channel region, and a contact region between the source region and the channel region is made of extrinsic materials and different from the doping type of the source region. According to the invention, the contact area between the source region and the channel region is doped differently from the source region, so that the device is relatively narrow in a tunneling layer from the source end to the channel in an ON state, and the ON-state current is increased. As the thickness of a tunneling layer from the source end to the drain end in an OFF state is not changed with the method, a relatively low OFF-state current can be kept, as a result, a higher switch ratio and a relatively low sub-threshold slope can be acquired with the method, so that a better device performance can be acquired.

Owner:PEKING UNIV

Preparation method of germanium-based Schottky N-type field effect transistor

ActiveCN102136428ADoes not significantly increase parasitic resistanceIncrease the current switch ratioSemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorSchottky transistor

The invention provides a preparation method of a germanium-based Schottky N-type field effect transistor, belonging to the technical field of technical manufacturing of ultra large scale integrations (ULSI). In the preparation method, a high-k medium thin layer is formed among a germanium substrate, a metal source and a metal drain. On one hand, the thin layer can prevent an electron wave function in metal from introducing an MIGS (Metal Induction Gap Strip) interface state into a semiconductor forbidden band and can passivate a dangling bond of a germanium interface; and on the other hand, an insulating medium layer is very thin and electrons can freely pass through the insulating medium layer basically, so that the parasitic resistances of the source and the drain cannot be increased remarkably. By adopting the method, the Fermi level pinning effect can be wakened, the Fermi level is close to the conduction band position of germanium, and the electronic barrier is lowered, therefore, the electric current on-off ratio of the germanium-based Schottky transistor is increased, and the performance of an NMOS (Negative Channel Metal Oxide Semiconductor) device is improved.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

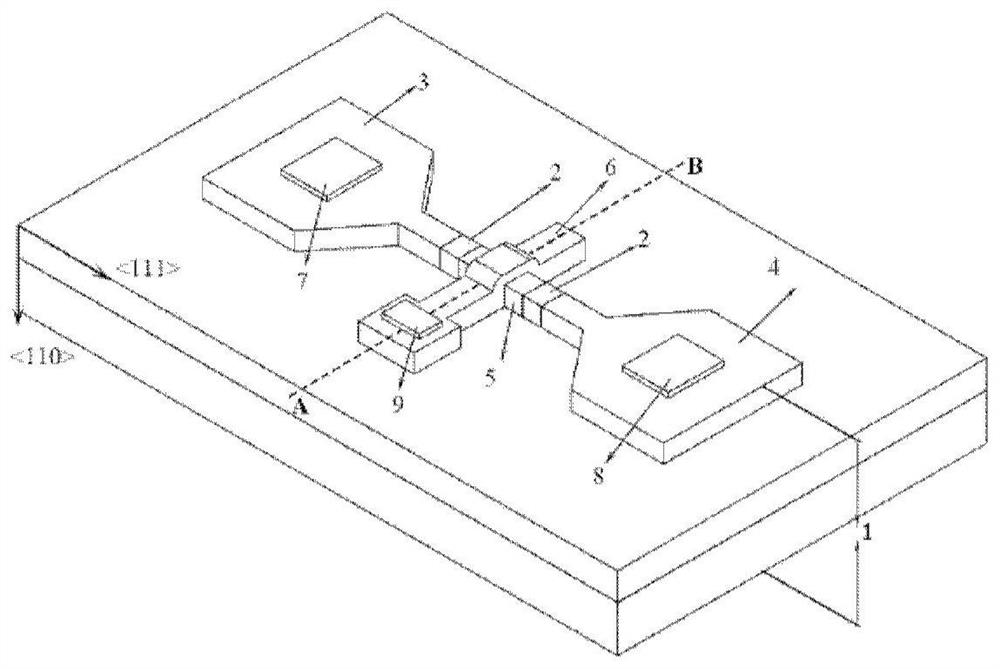

Junction-modulated type tunneling field effect transistor and manufacturing method thereof

ActiveCN103594376AImproved subthreshold characteristicsSubthreshold characteristic steepSemiconductor/solid-state device manufacturingDiodePower flowEngineering

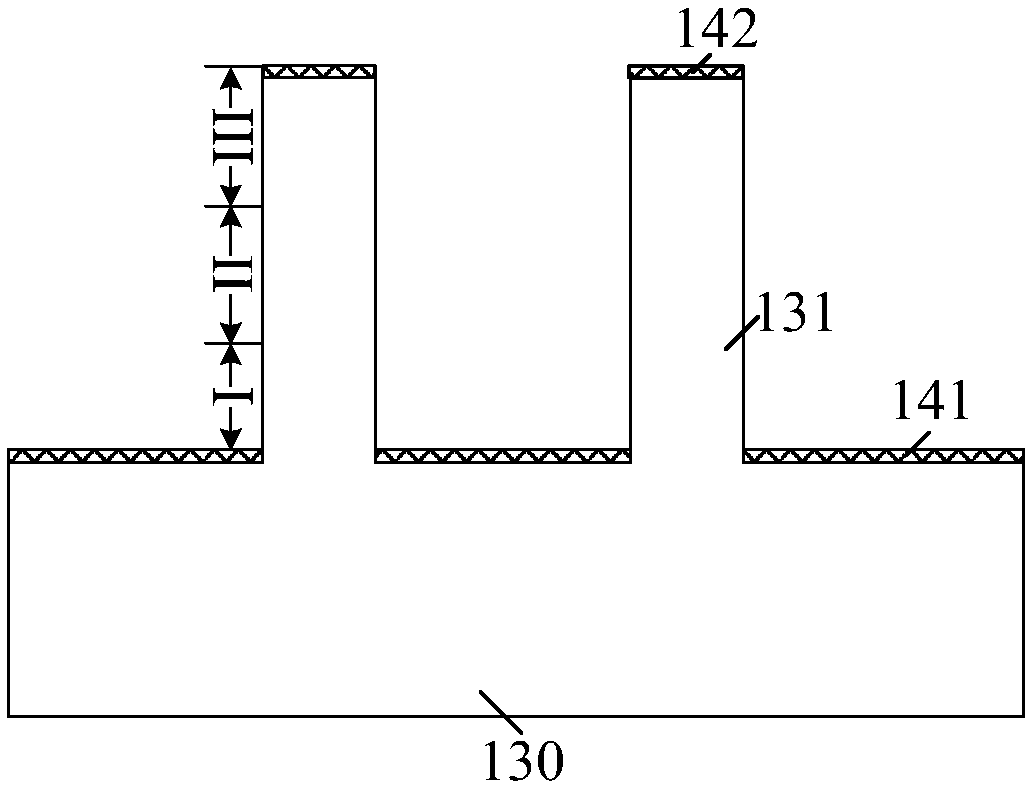

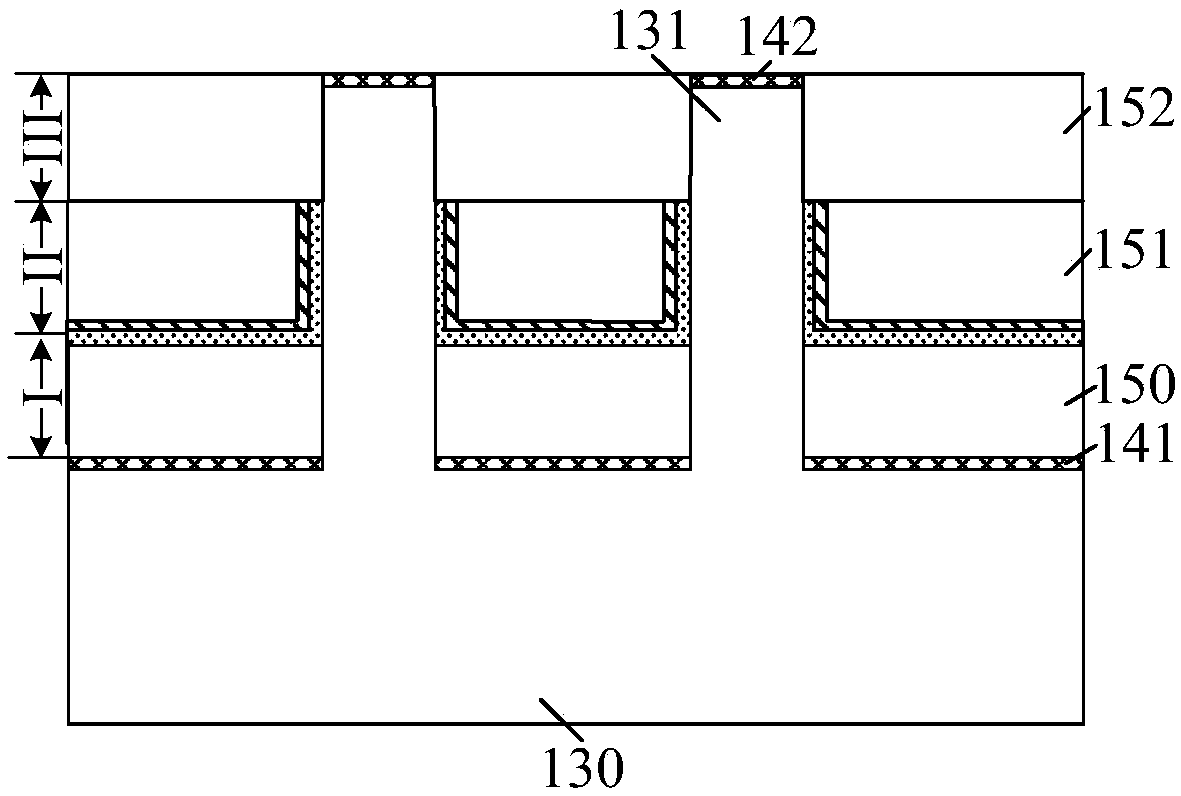

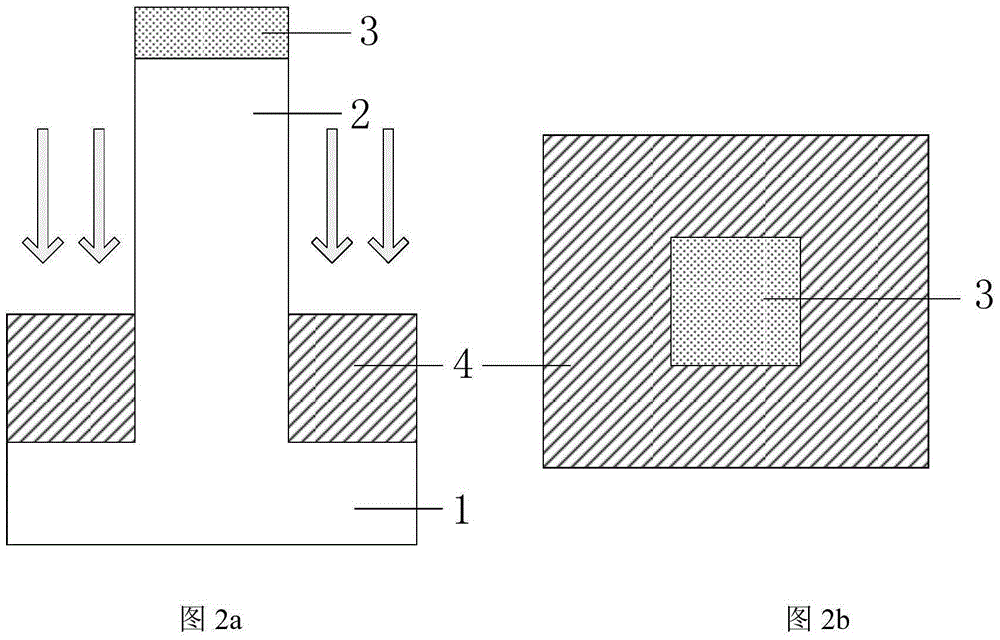

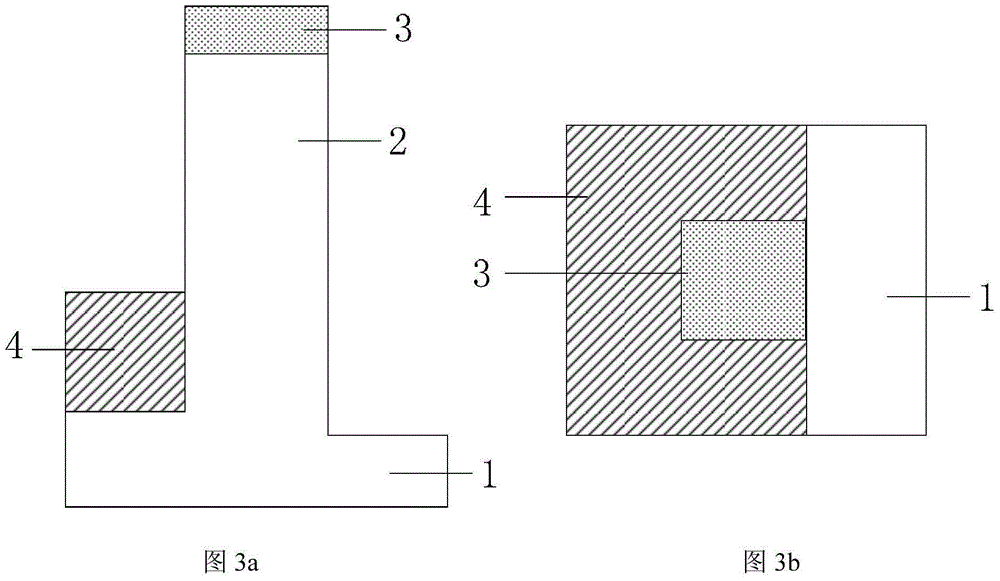

The invention discloses a junction-modulated type tunneling field effect transistor and a manufacturing method of the junction-modulated type tunneling field effect transistor, and belongs to the field of field effect transistor logic devices and circuits in CMOS ultra large scale integration (ULSI) circuits. According to the junction-modulated type tunneling field effect transistor, a PN junction provided by a highly-doped source region enclosed on three sides in a vertical channel region is utilized so that the channel region can be effectively used up, a surface channel energy band below a grid can be increased, a device can obtain a steeper energy band and a smaller tunneling barrier width compared with a traditional TFET when subjected to band-band tunneling, the effect of a steep tunnel junction doping density gradient is achieved equivalently, as a result, the subthreshold property of the traditional TFET is improved substantially, and breakover currents of the device are increased at the same time. According to the junction-modulated type tunneling field effect transistor and the manufacturing method of the junction-modulated type tunneling field effect transistor, under the condition that the junction-modulated type tunneling field effect transistor is compatible with an existing CMOS process, the bipolar breakover effect of the device is restrained effectively, parasitic tunneling currents at corners of a source junction with a small size also can be restrained, and the effect of steep source junction doping density can be achieved equivalently.

Owner:PEKING UNIV

Field effect transistor based on vertical tunneling, biosensor and preparation methods thereof

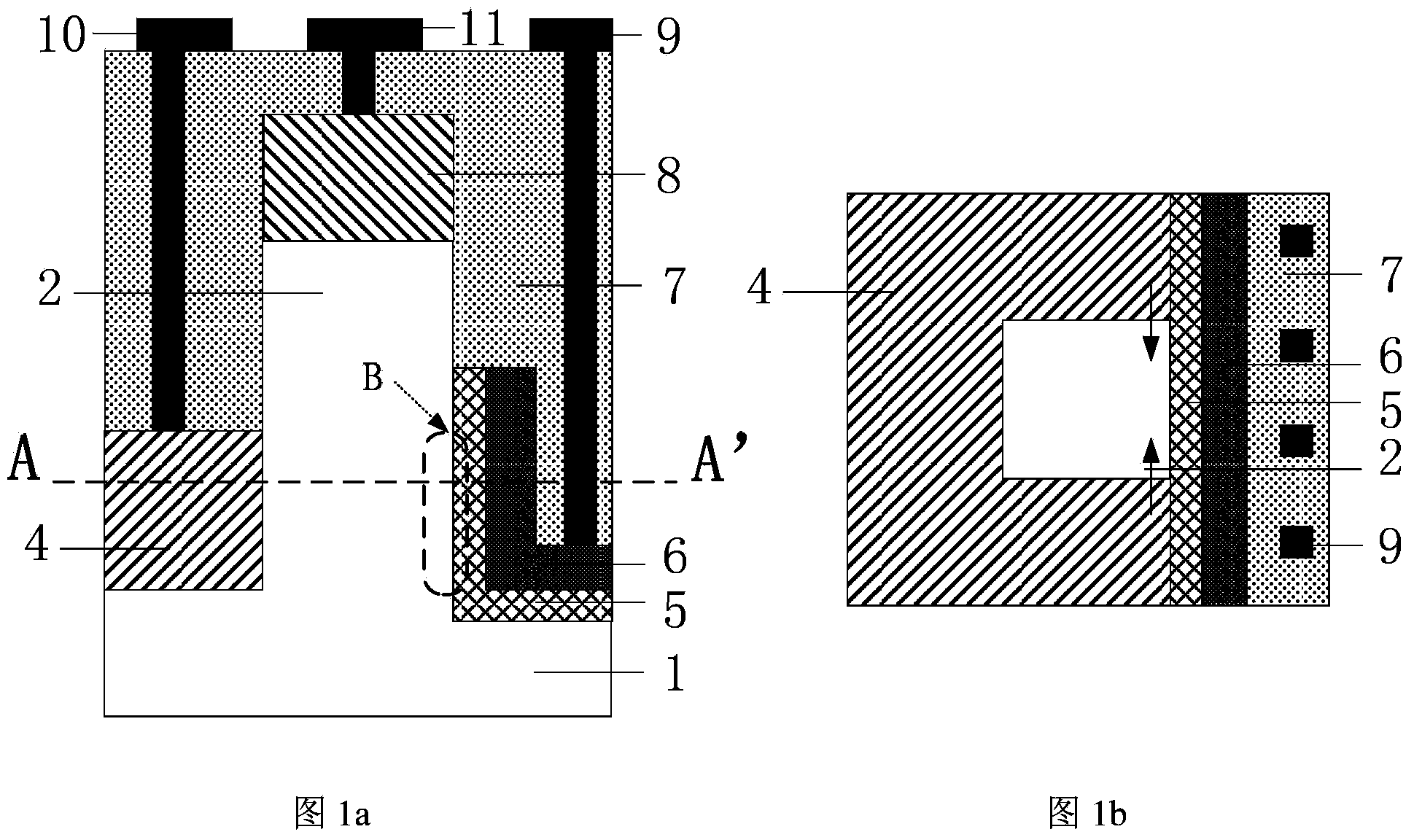

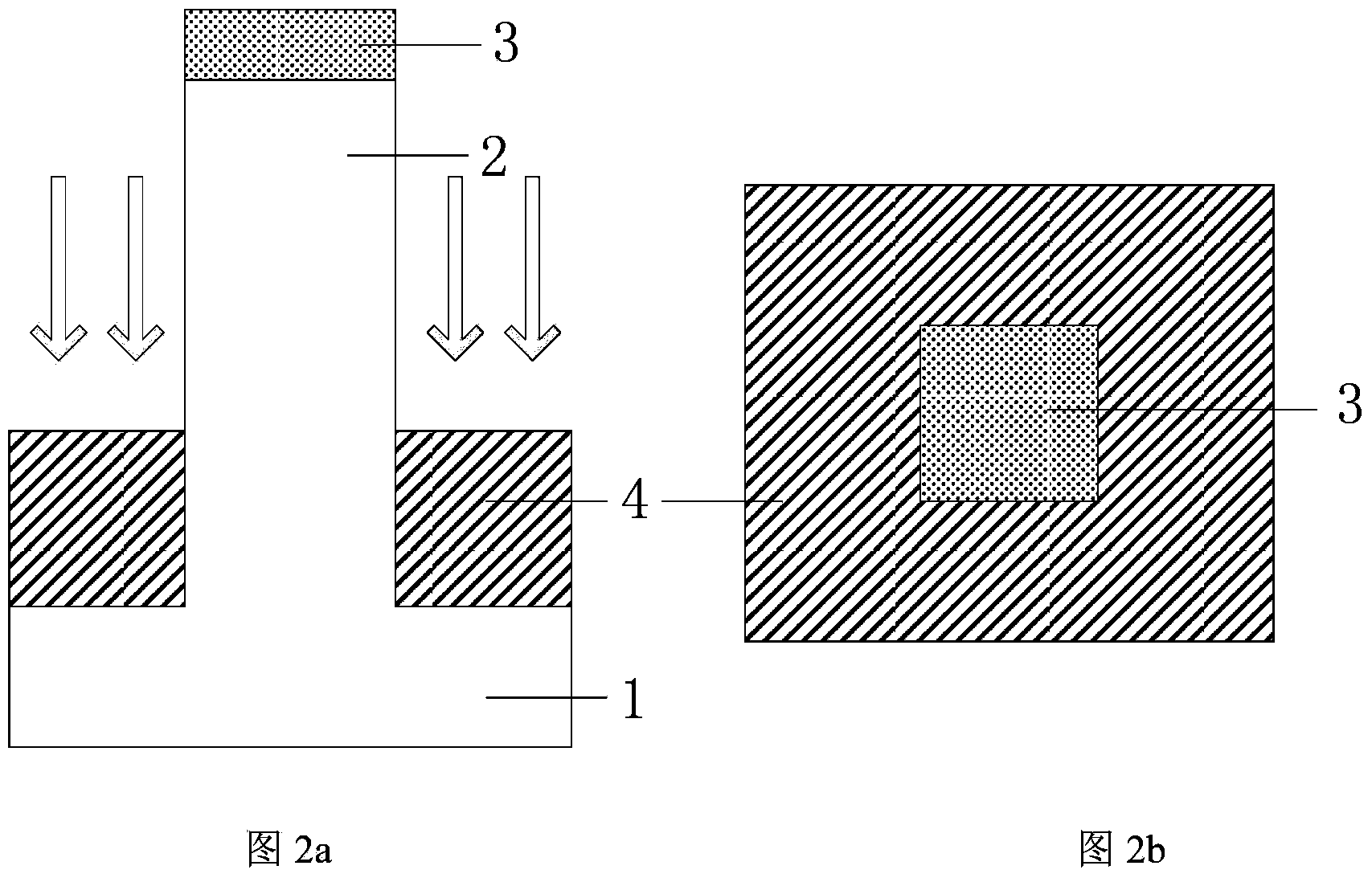

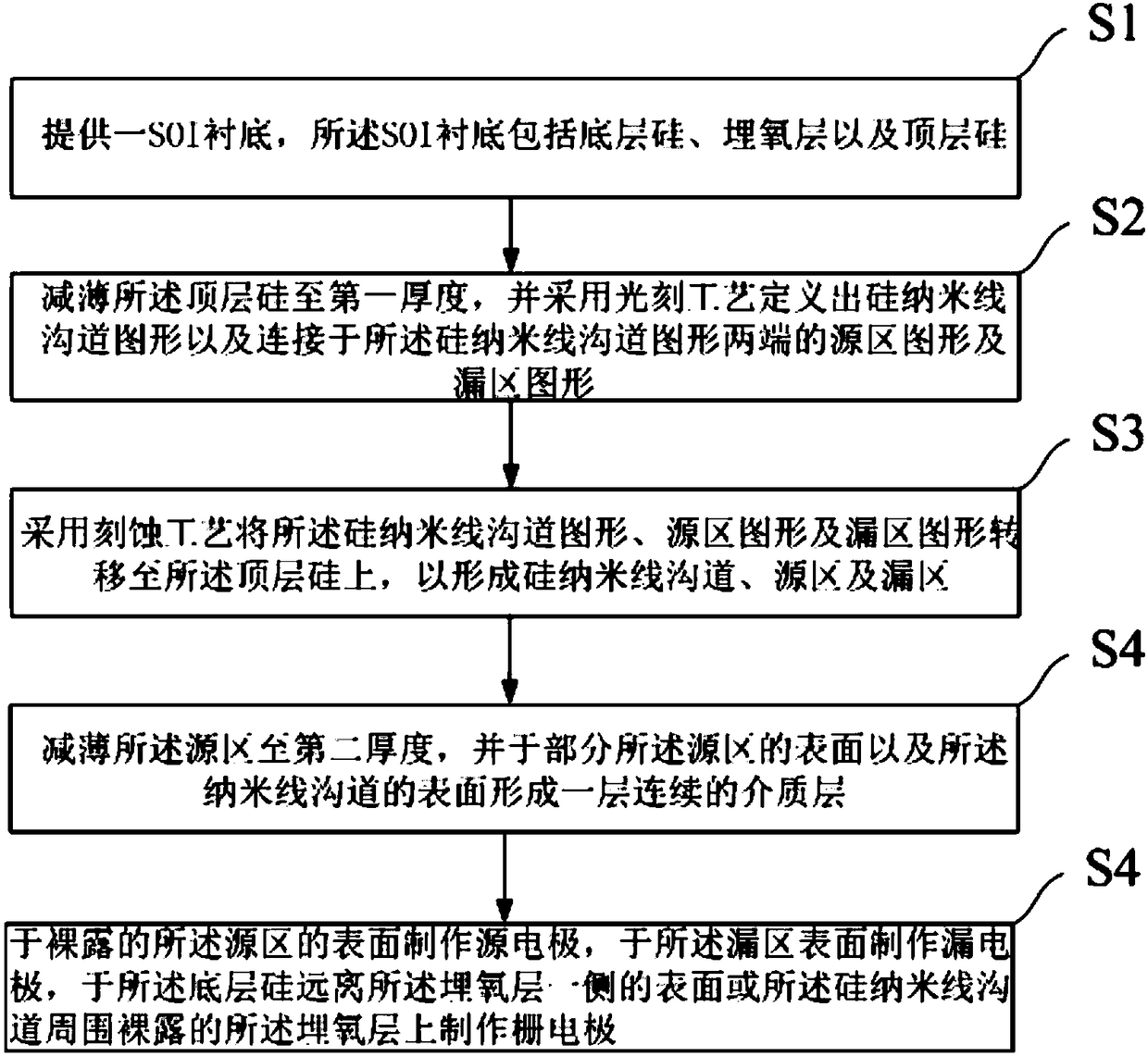

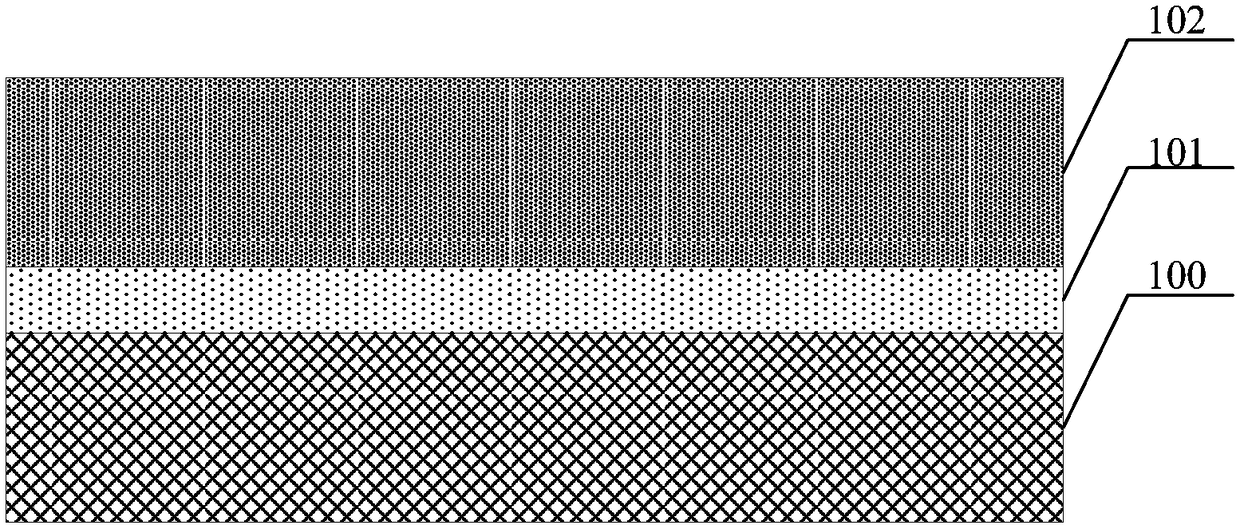

InactiveCN108074979AImprove stabilityImprove responsivenessMaterial analysis by electric/magnetic meansSemiconductor/solid-state device manufacturingSub thresholdSilicon nanowires

The invention provides a field effect transistor based on vertical tunneling, a biosensor and preparation methods thereof. The preparation method of the field effect transistor comprises the followingsteps: providing an SOI substrate; thinning top silicon, and defining a silicon nanowire channel pattern and a source region pattern and a drain region pattern connected at the two ends; transferringthe patterns above to the top silicon, and carrying out ion implantation to form a silicon nanowire channel, a source region and a drain region; thinning the source region, and forming a dielectric layer on a part of source region surface and nanowire channel surface; and preparing a source electrode on the surface of the source region, preparing a drain electrode on the surface of the drain region, and preparing a gate electrode on bottom silicon or a buried oxide layer. Through the scheme above, the transistor based on vertical tunneling comprises point tunneling and line tunneling, has lower sub-threshold slope, can be used for high-sensitivity biochemical molecular detection, has bipolar characteristics, can carry out comparison on bidirectional detection results and ensures detectionaccuracy; and through the high-K dielectric layer material, detection stability is enhanced and response capability for biomolecule is improved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Surrounding gate nanowire field effect transistor and preparation method thereof

InactiveCN108288647AImprove gate control abilityReduce parasitic resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSub thresholdNanowire

The invention provides a surrounding gate nanowire field effect transistor and a preparation method thereof. The preparation method comprises the following steps of S1, forming a first fin body isolated from a substrate on the substrate, wherein the first fin body consists of a first region, a second region and a third region which are connected in sequence in the length direction; S2, forming a nanowire structure in the second region of the first fin body; and S3, forming an interface oxide layer, a ferroelectric layer and a gate which are laminated around the exposed surface of the nanowirestructure in sequence, wherein the preparation method also comprises the following steps of forming a source / drain in the first region and the third region, wherein the source / drain is connected withthe two ends of the nanowire structure. By virtue of the preparation method, the gate control capability of the device is improved, electric leakage of the device is lowered, source / drain parasitic resistance of the device is lowered, and the sub threshold value slope of the device can be greatly lower than 60mV / dec.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

Method and corresponding device for restraining tunneling transistor from leaking current and method for manufacturing corresponding device

ActiveCN103560144AImproved subthreshold characteristicsSuppresses tunneling leakage currentSemiconductor/solid-state device manufacturingDiodeCMOSHemt circuits

The invention discloses a method and corresponding device for restraining a tunneling transistor from leaking a current and a method for manufacturing the corresponding device and belongs to the field of field effect transistors and currents in a ULSI of a CMOS. According to the method for restraining the tunneling transistor from leaking the current, an insulating layer is inserted between a source zone and a body zone below a tunnel junction, an insulating layer is not inserted in the portion, between the source zone and a tunnel, of the tunnel junction, so that the source zone and a drain zone in a small-size TFET device are effectively prevented from being directly tunneled and leaking the current, and meanwhile the slope of a subthreshold value can be effectively improved. The method for manufacturing the corresponding device is compatible with the existing CMOS technology.

Owner:PEKING UNIV

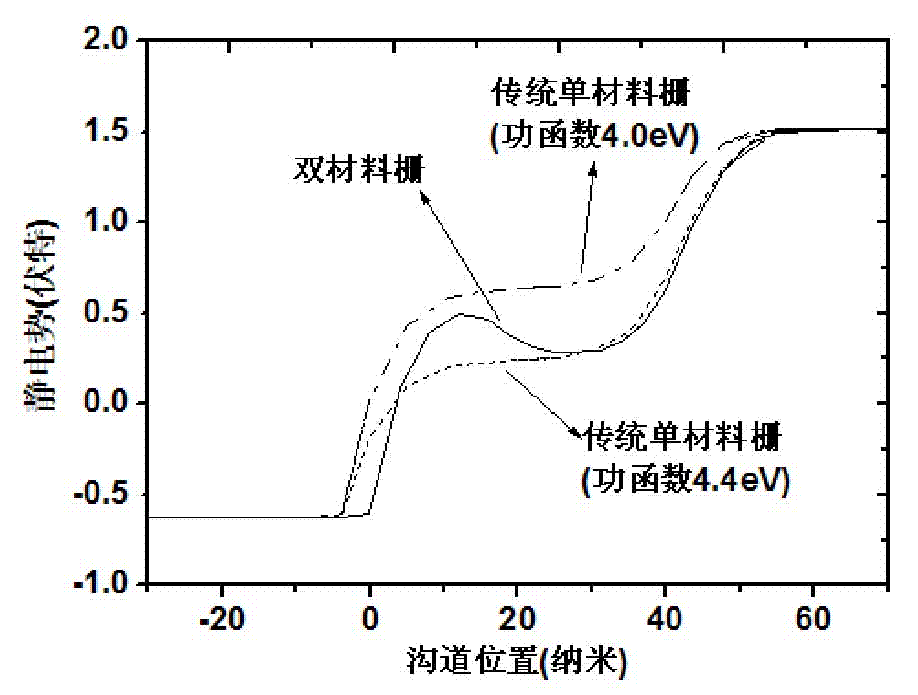

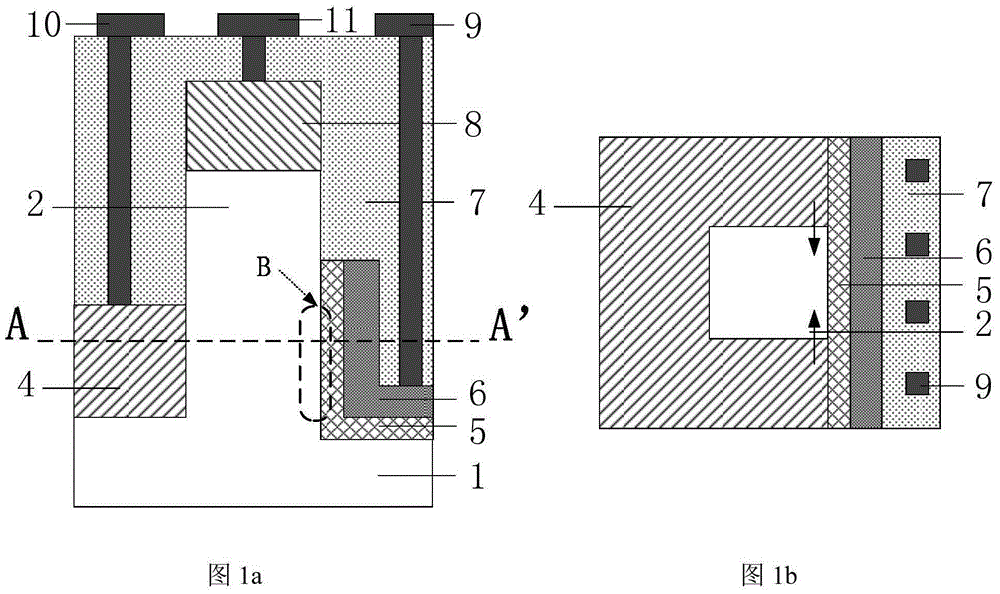

Bi-material railing nanowire tunneling field effect device and manufacturing method thereof

ActiveCN102956709AReduces off-state leakage currentHigh switching current ratioSemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorPhysics

The invention relates to a bi-material railing nanowire tunneling field effect device and a manufacturing method thereof. According to the bi-material railing nanowire tunneling field effect device, a channel is arranged at the center, and a source region and a drain region are respectively arranged at two ends, and an oxide and a gate electrode are covered at the periphery of the channel in sequence. The manufacturing method comprises the steps: SF6 etching a silicon column on a silicon wafer by using a round silicon nitride hard mask; conducting high-temperature oxidation, corroding and reducing the size of the silicon column to be a set diameter value of 6nm-30nm with HF aqueous solution, and conducting high-temperature oxidation to form a silicon column coated by an oxidation layer with set thickness; completing the preparation of a bi-material railing structure by adopting deposition and photoetching technology; and injecting boron and phosphorus of 1*10<20>cm<-2> / 10keV and 5*10<18>cm<-2> / 10keV at 120-150 DEG C respectively, and annealing at 900 DEG C / 10s-1100 DEG C / 10s to prepare the source region and the drain region; completing preparation of a metal electrode by CMOS (Complementary Metal-Oxide-Semiconductor) process; and manufacturing the bi-material railing nanowire tunneling field effect device.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

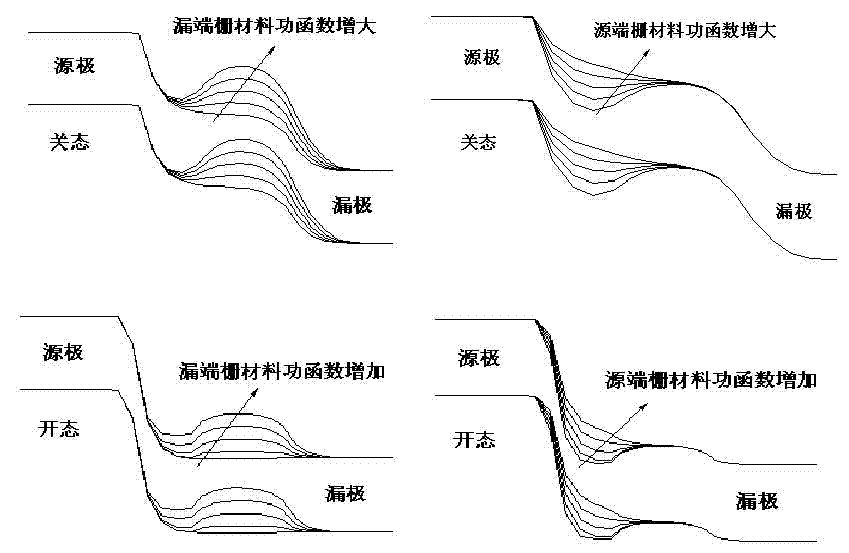

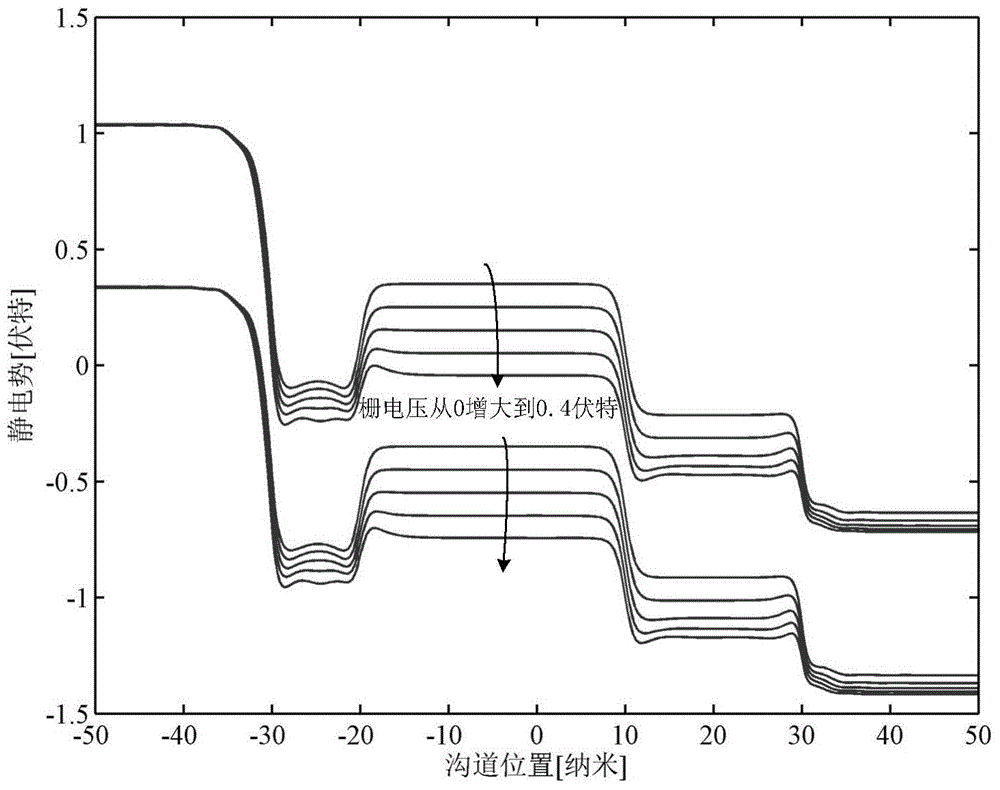

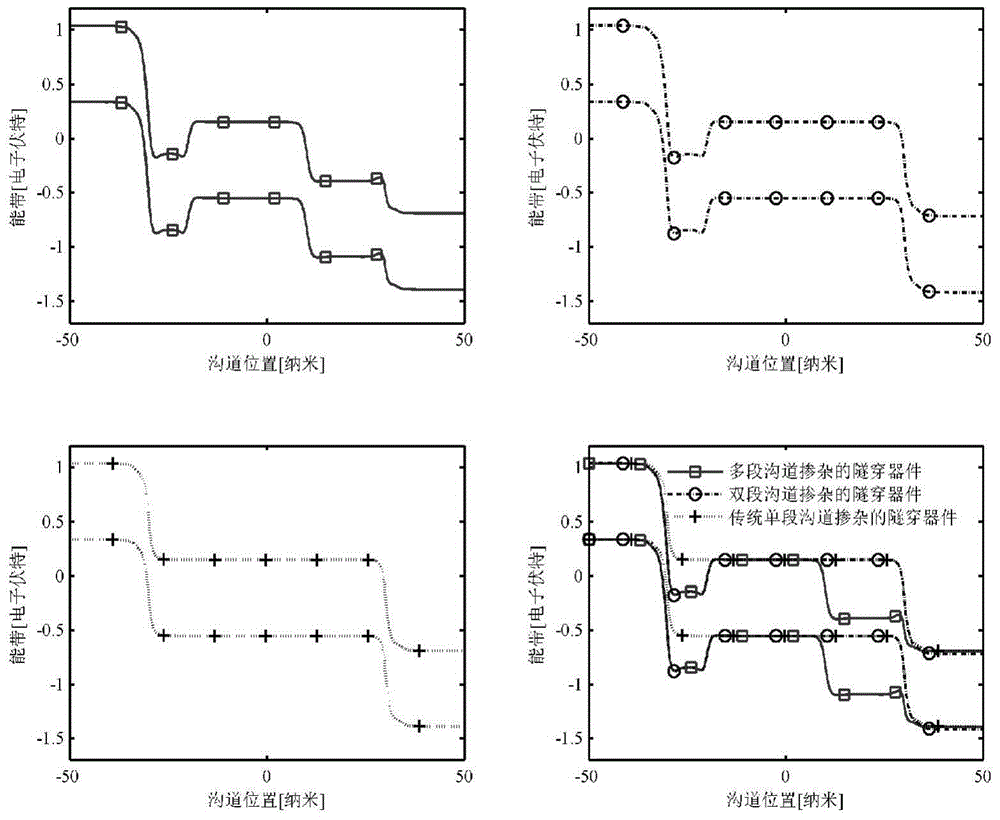

Tunneling field effect device for channel potential barrier height control

InactiveCN104882484AMaterial adjustableAdjustable thicknessSemiconductor devicesSub thresholdGate oxide

The invention belongs to the field of semiconductor integrated circuits, and specifically relates to a tunneling field effect device for channel potential barrier height control. The center of the device is provided with a channel, two ends of the channel are provided with a source terminal and a drain terminal of different conductive types, a tunneling junction is formed between the source terminal and the channel, the channel is formed by the adoption of three or more than three potential barrier areas, the energy band of the potential barrier area at the middle section is higher than the energy bands of the channel close to the drain terminal and the source terminal, the device also comprises a gate oxide layer fully covering the channel, and the gate oxide layer is fully covered by a gate electrode. The portion of the channel of the device employs materials of different doping concentrations or types, and three sections or more sections of the potential barrier structures are formed in the channel. According to the simulation research result of the tunneling device structure for channel potential barrier height control, the off-state leakage current of the device can be effectively reduced, the sub-threshold slope is reduced, the short-channel effect and the DIBL effect are suppressed, the transconductance characteristic is good, and comprehensive optimization of the performance of the device is realized.

Owner:WUHAN UNIV

Nanowire transistor based on resonant tunneling and preparation method thereof

InactiveCN110491940AImprove gate control abilitySmall subthreshold slopeSemiconductor/solid-state device manufacturingSemiconductor devicesBuried oxideConduction current

The invention discloses a nanowire transistor based on resonance tunneling. The nanowire transistor comprises an SOI substrate, a tunneling barrier structure, a source region, a drain region, nanowires, a grid electrode, a source electrode, a drain electrode, a grid electrode and an insulating dielectric layer. The tunneling barrier structure is located on the buried oxide layer of the SOI substrate. The source region, the drain region and the nanowire are formed by etching top silicon of the SOI substrate; the nanowire is positioned between the source region and the drain region; wherein thesource region, the drain region and the nanowire are not directly connected and are connected through a tunneling barrier structure, the insulating dielectric layer is formed on the surfaces of the source region, the drain region and the nanowire, the grid electrode is formed on the insulating dielectric layer above the nanowire, the source electrode is formed on the source region, the drain electrode is formed on the drain region, and the grid electrode is formed on the grid electrode. According to the nanowire transistor structure based on resonance tunneling and the preparation method of the nanowire transistor structure, the sub-threshold slope is reduced, and large conduction current and small source-drain contact resistance can be achieved.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Preparation method of gate-all-around transistor

ActiveCN111435678ABroaden your optionsAchieve performance requirementsSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricNanowire

The invention provides a preparation method for a gate-all-around transistor, and the method comprises the steps: 1), providing an SOI substrate, and forming a groove in an insulating layer of the SOIsubstrate; 2) forming a semiconductor nanowire structure which is suspended and stretches across the groove; 3) rounding and thinning the semiconductor nanowire structure; 4) forming an injection barrier layer on the surface of the channel region, wherein the injection barrier layer exposes the preparation regions of the source region and the drain region; 5) performing an ion implantation process to form the source region and the drain region; 6) forming a fully-surrounded gate dielectric layer and a gate electrode layer on the surface of the semiconductor nanowire, and performing patterningto form a gate structure; and 7) forming a source electrode and a drain electrode. The gate-all-around transistor is prepared by adopting a gate-last process, so that the selection range of gate materials can be effectively widened, different device performance requirements are met, isotropic wet etching is not needed when the semiconductor nanowire is prepared, and a concave cavity can be effectively prevented from being generated.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Multichannel gate-all-around transistor

InactiveCN111435682AAvoid overlapReduce parasitic capacitanceTransistorNanoinformaticsGate dielectricNanowire

The invention provides a multichannel gate-all-around transistor. The multichannel gate-all-around transistor comprises: a semiconductor substrate; an insulating layer which is provided with a groovewhich does not penetrate through the insulating layer; a semiconductor nanowire structure which is suspended in the air, stretches across the groove and comprises semiconductor bosses located on the two sides of the groove and a plurality of semiconductor nanowires connected to the bosses; a gate dielectric layer and a gate electrode layer which surround the semiconductor nanowires; a source region and a drain region which are formed at the end parts of the semiconductor nanowires, wherein the plurality of semiconductor nanowires between the semiconductor bosses form a multichannel channel region together; and a source electrode and a drain electrode. The width of the groove below the multichannel gate-all-around transistor is smaller than that of the semiconductor nanowires, so that an unnecessary overlapping region between the bottom gate and the source drain can be effectively avoided, the scattering of carriers in a channel is reduced, the parasitic capacitance of the source drainis reduced, and the high-frequency characteristic of the device is improved. The gate-all-around transistor is provided with a plurality of channels, the driving power of the transistor can be greatlyimproved, and the integration level of a device is improved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Three-dimensional stacked gate-all-around transistor and preparation method thereof

ActiveCN111435641AImprove processing stabilityImprove process precisionNanoinformaticsSemiconductor/solid-state device manufacturingGate dielectricNanowire

The invention provides a three-dimensional stacked gate-all-around transistor and a preparation method thereof, and the method comprises the steps: 1), providing an SOI substrate, and forming a groovein the insulating layer of the SOI substrate; 2) forming a semiconductor nanowire structure which is suspended, stretches across the groove and is stacked upwards; 3) rounding and thinning the semiconductor nanowire structure; 4) forming a fully-enclosed gate dielectric layer and a gate electrode layer on the surface of the semiconductor nanowire; 5) taking the gate electrode layer as a mask, andperforming ion implantation to form a source region and a drain region; 6) removing the gate dielectric layer outside the gate electrode layer; and 7) forming a source electrode and a drain electrodein the source region and the drain region. According to the invention, the gate electrode layer is used as a mask to carry out self-aligned injection of the source region and the drain region, so that the process stability and the injection precision can be effectively improved. When the semiconductor nanowire is prepared, isotropic wet etching is not needed, and the generation of a concave cavity can be effectively avoided. The integration level of the device can be effectively improved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

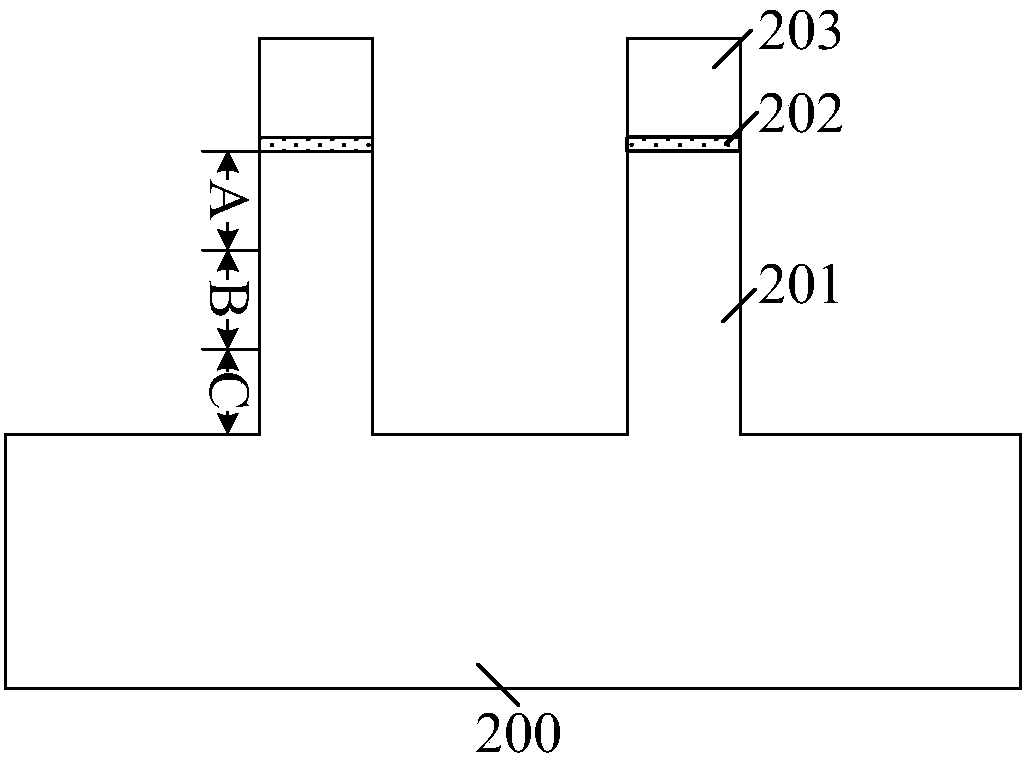

Semiconductor structure and method of forming the same

ActiveCN109962105BHighly integratedAffect performanceSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureEngineering physics

A semiconductor structure and a method for forming the same, wherein the forming method includes: forming a sidewall covering a channel region of a fin pillar and a sidewall of a top region; using the sidewall as a mask, forming on the surface of the sidewall of the bottom region a first conductive structure; after the first conductive structure is formed, the spacer is removed; after the spacer is removed, a gate structure is formed on top of the first conductive structure, and the gate structure is located in the fin pillar trench the surface of the channel region; after the gate structure is formed, a second conductive structure is formed on the top of the gate structure, and the second conductive structure is located on the surface of the top region of the fin column. The forming method can improve the integration degree of the formed semiconductor structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

A high-dielectric gate dielectric material for flexible low-voltage driving organic thin film transistors and its preparation method and application

ActiveCN106058047BImprove mobilityHigh on/off ratioSolid-state devicesSemiconductor/solid-state device manufacturingOrganic filmGate dielectric

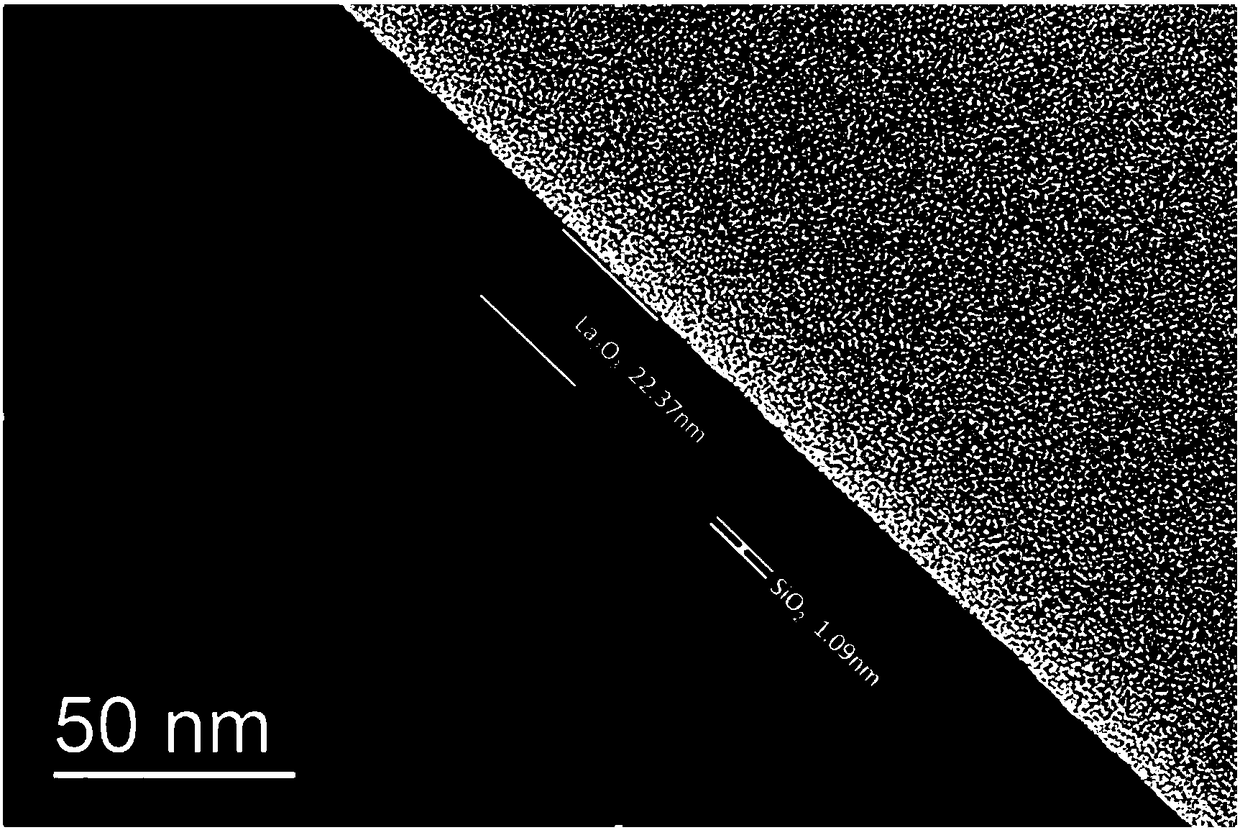

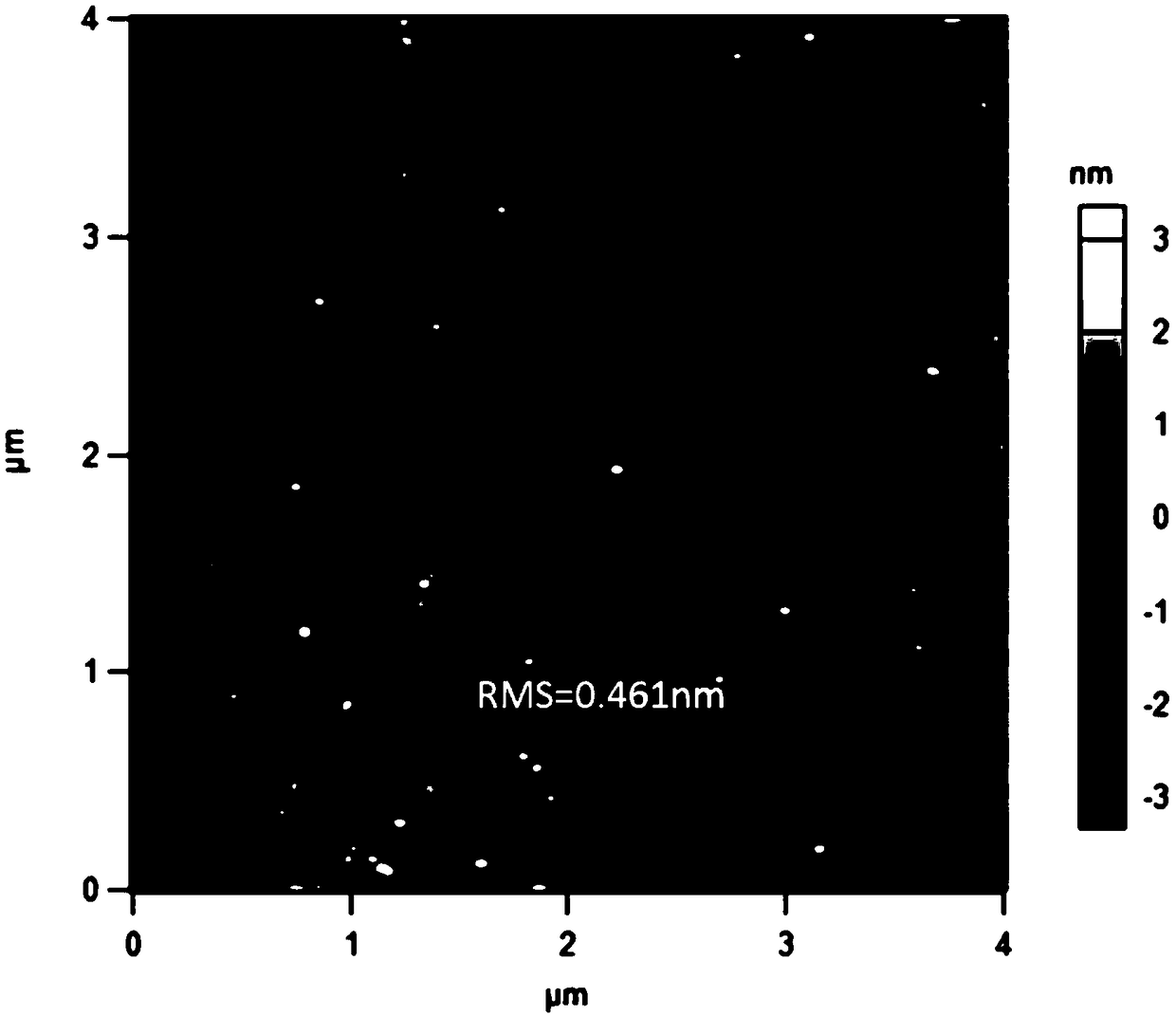

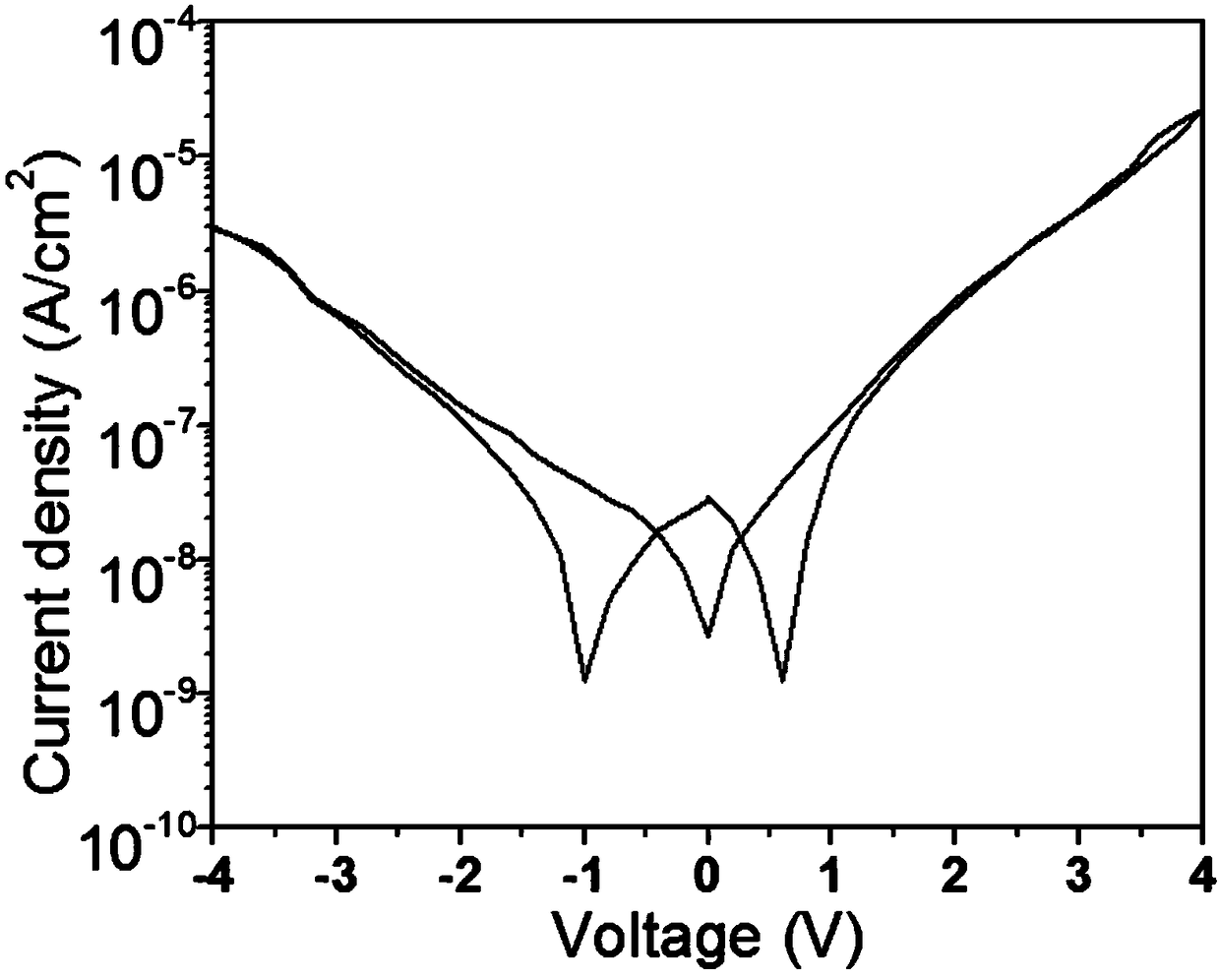

The invention relates to a high-dielectric gate dielectric material for flexible low-voltage driving organic thin film transistors and a preparation method thereof, comprising the following steps: 1) preparing a lanthanum oxide precursor solution; 2) preparing a lanthanum oxide dielectric layer film: combining step 1) After the obtained lanthanum oxide precursor solution is filtered, the lanthanum oxide precursor solution is spin-coated on the substrate to obtain a lanthanum oxide precursor film; 3) the samples obtained in step 2) are sequentially subjected to pre-annealing treatment, heat treatment and ozone activation treatment Finally, a lanthanum oxide dielectric layer is obtained, that is, a high dielectric gate dielectric material is obtained. The high-dielectric gate dielectric material lanthanum oxide dielectric layer of the present invention has a high dielectric constant and a wide energy band, which can effectively reduce the working voltage required by the device; and it is prepared by a solution method, and can form a dense Non-toxic thin film, simple process and low cost. The invention also provides a flexible low-voltage driving organic thin film transistor using the high-dielectric gate dielectric material as a dielectric layer and a preparation method thereof.

Owner:SOUTH CHINA NORMAL UNIVERSITY

Biosensor based on ssoi MOSFET and preparation method thereof

ActiveCN104713931BSmall subthreshold slopeImprove mobilityMaterial analysis by electric/magnetic meansBiological activationDielectric layer

The invention provides a biosensor based on sSOI MOSFET and a preparation method of the biosensor. The preparation method comprises the following steps: 1) providing an sSOI substrate, wherein the thickness of top strain silicon of the sSOI substrate is 10nm-50nm; 2) manufacturing a device region; 3) forming an N+ source region, an N+ drain region and a strain channel region; 4) forming a dielectric layer on the surface of the sSOI substrate; 5) forming a metal contact opening hole and manufacturing a metal contact electrode; 6) manufacturing an electrode protective layer and exposing a grid sensing region; 7) manufacturing a back grid on the back of the body silicon substrate; and 8) performing surface activation modification on the surface of the grid sensing region. Through the adoption of the preparation method, the strain silicon is used as the channel, and a high signal to noise ratio is obtained since the migration rate of the channel material is increased through the strain technology; the channel is in a full exhaustion state along with the thinning of the channel material, the subthreshold slope of the corresponding device is reduced, and the high sensitivity is obtained; therefore, the biosensor provided by the invention can be used for detecting biomolecules with high sensitivity.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

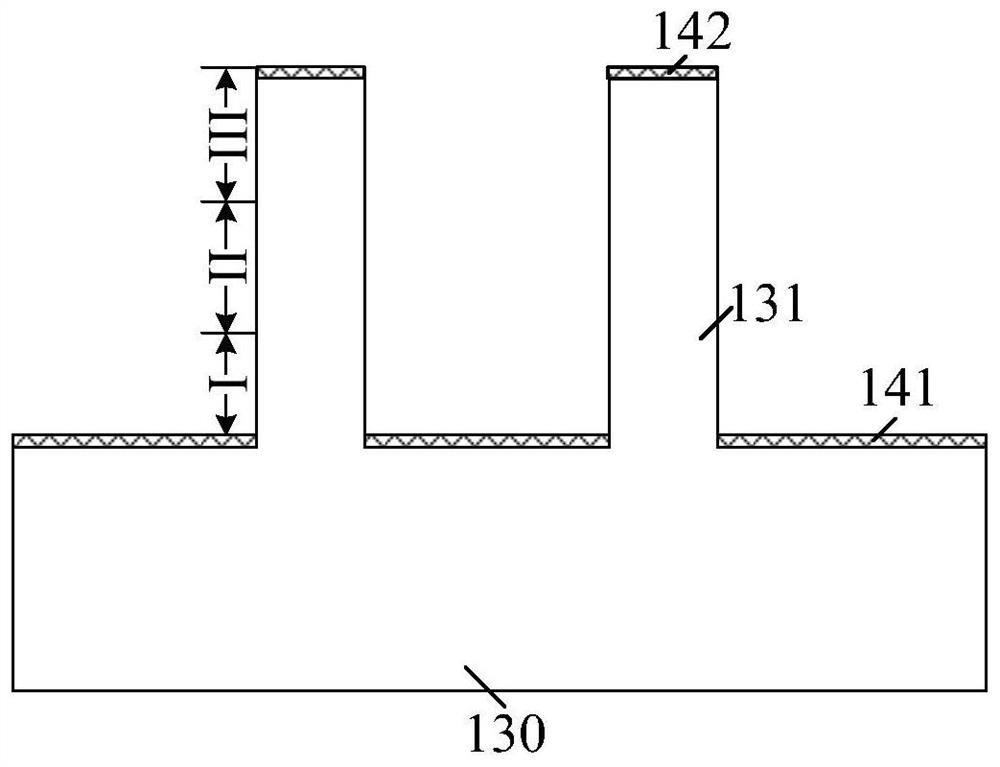

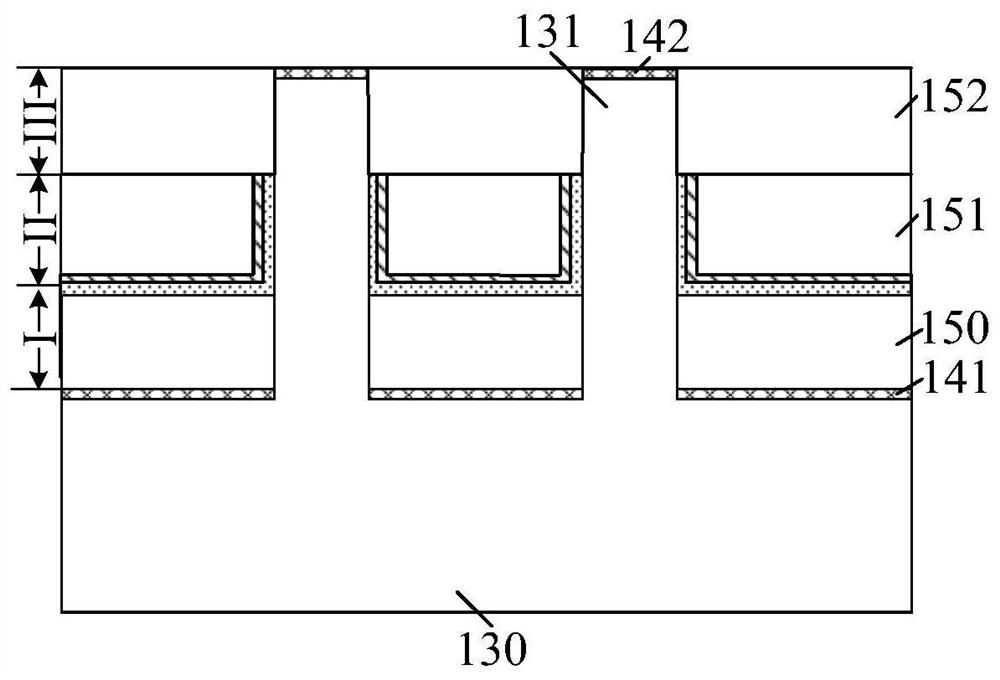

Semiconductor structure and forming method thereof

ActiveCN109962105AHighly integratedAffect performanceSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureEngineering

A semiconductor structure and a forming method thereof are provided. The forming method comprises the following steps: forming a spacer covering the side walls of a channel region and a top region ofeach fin column; forming a first conductive structure on the side wall surface of each bottom region with the spacers as masks; removing the spacers after forming the first conductive structures; forming a gate structure on the top of each first conductive structure after removing the spacers, wherein the gate structures are located on the surfaces of the channel regions of the fin columns; and forming a second conductive structure on the top of each gate structure after forming the gate structures, wherein the second conductive structures are located on the surfaces of the top regions of thefin columns. The forming method can improve the integration degree of the formed semiconductor structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

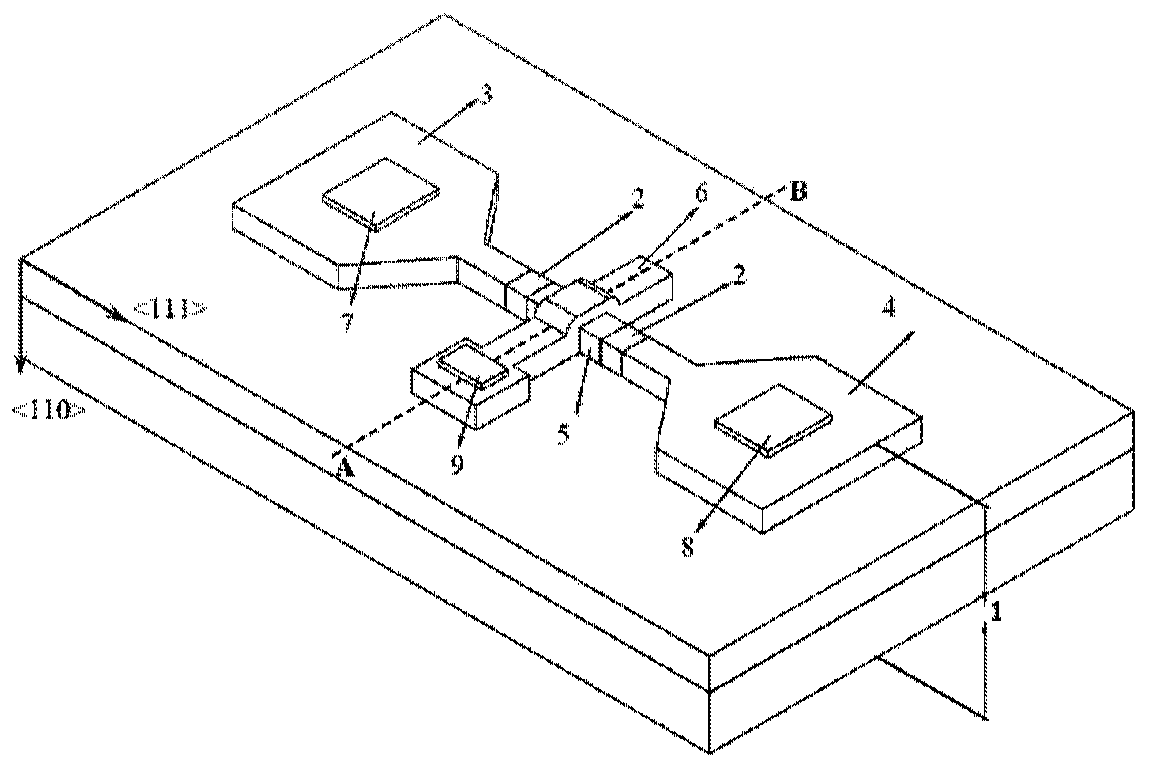

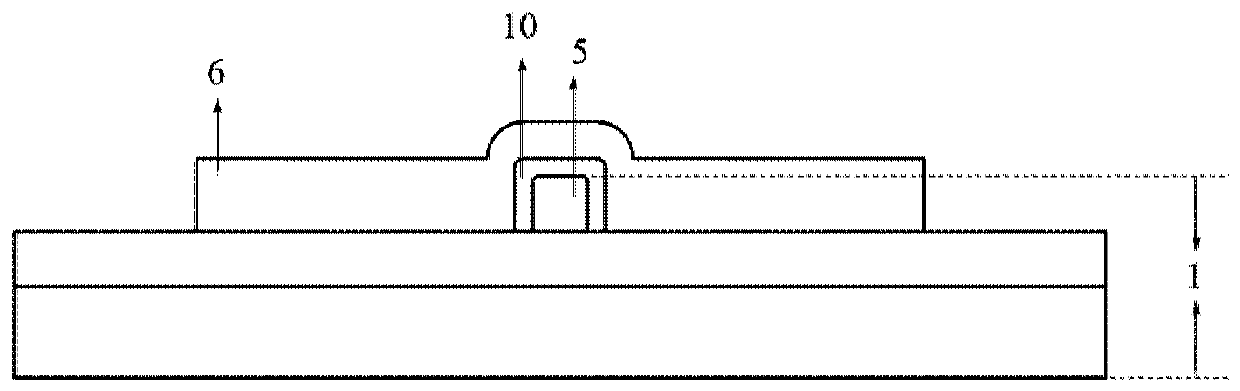

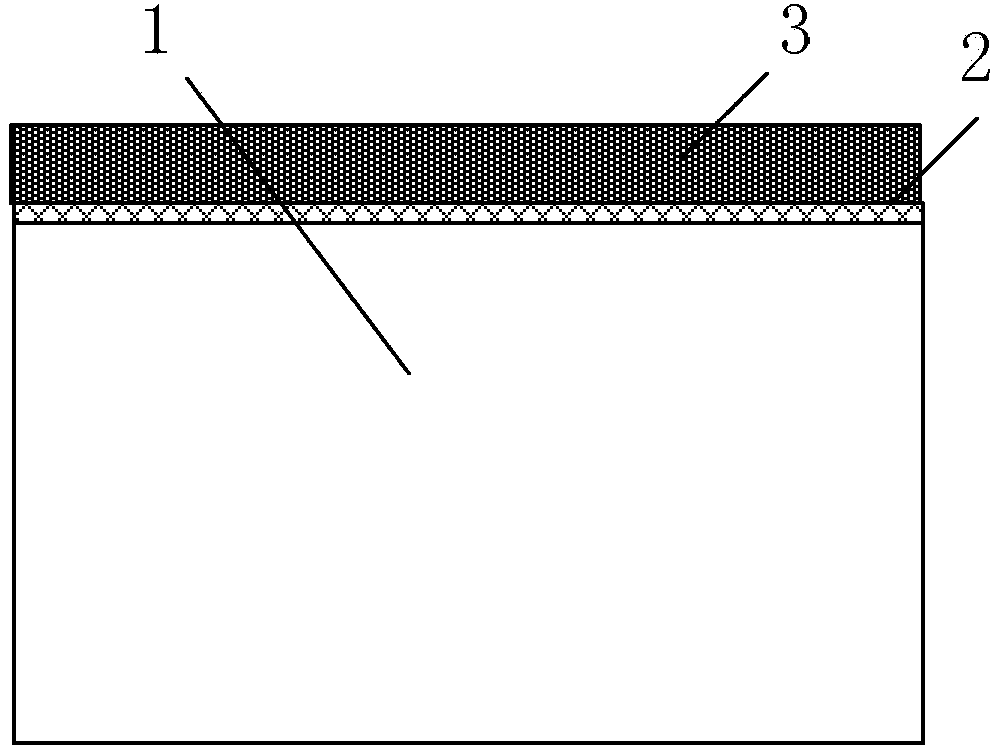

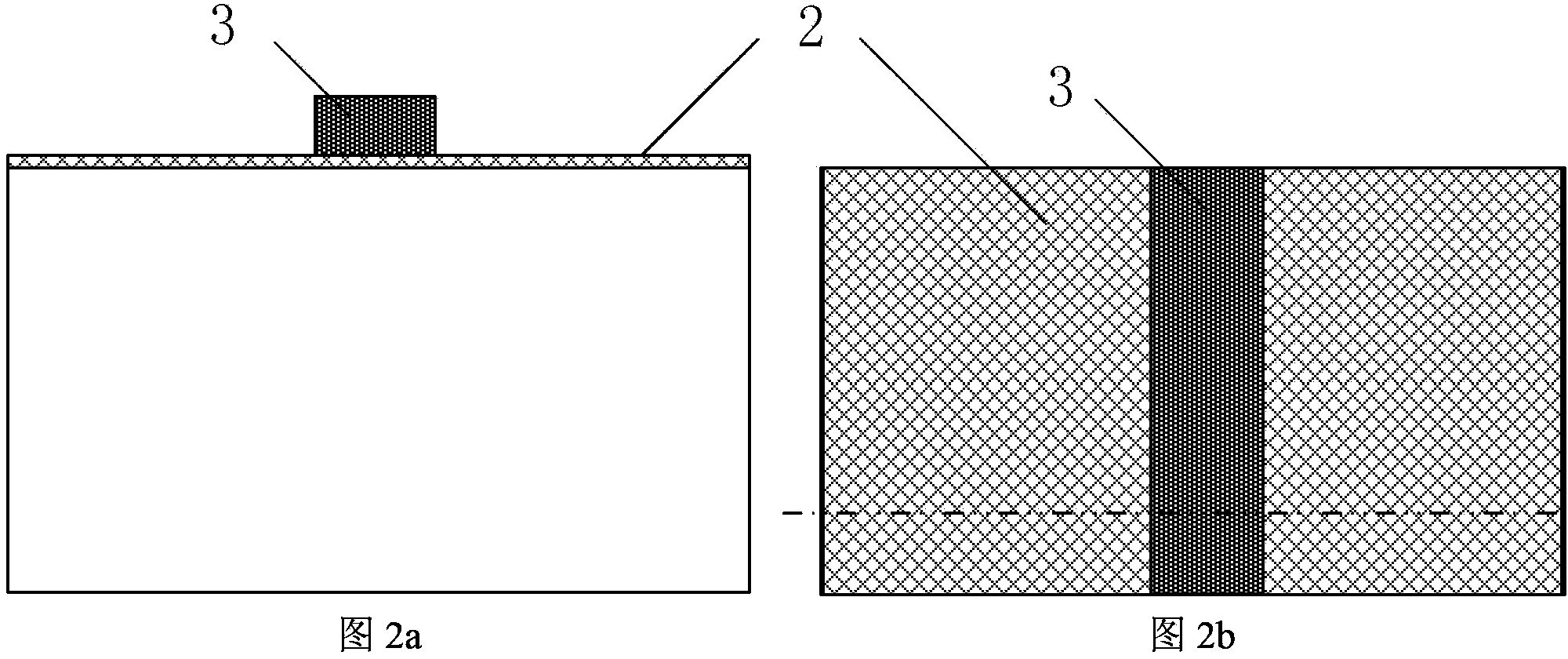

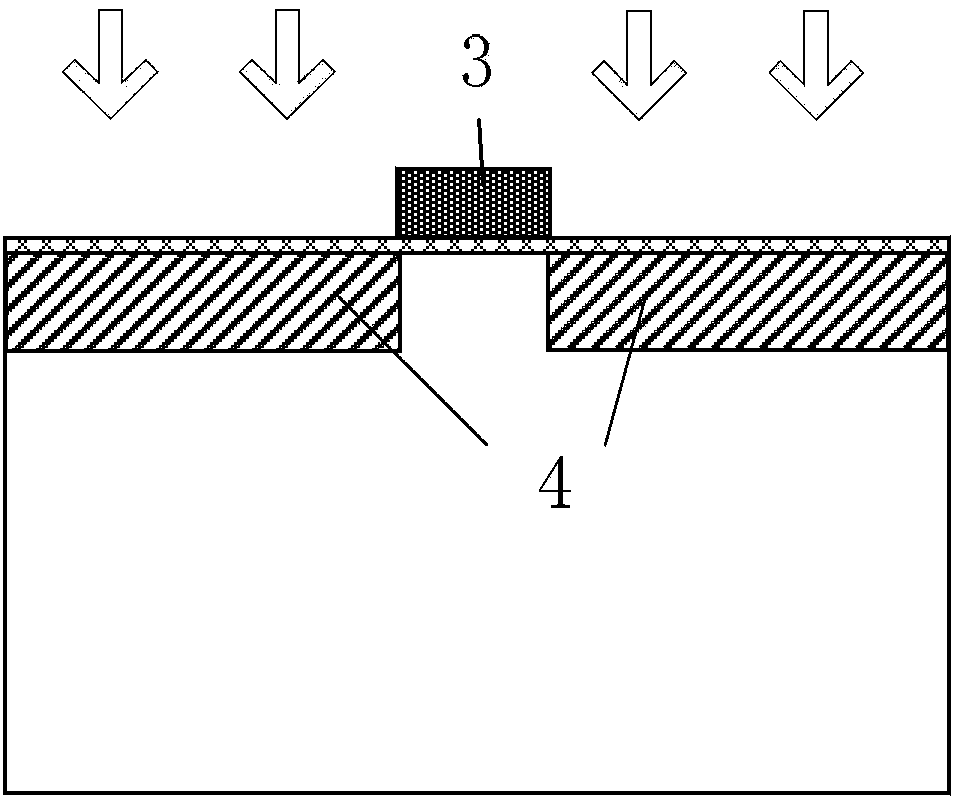

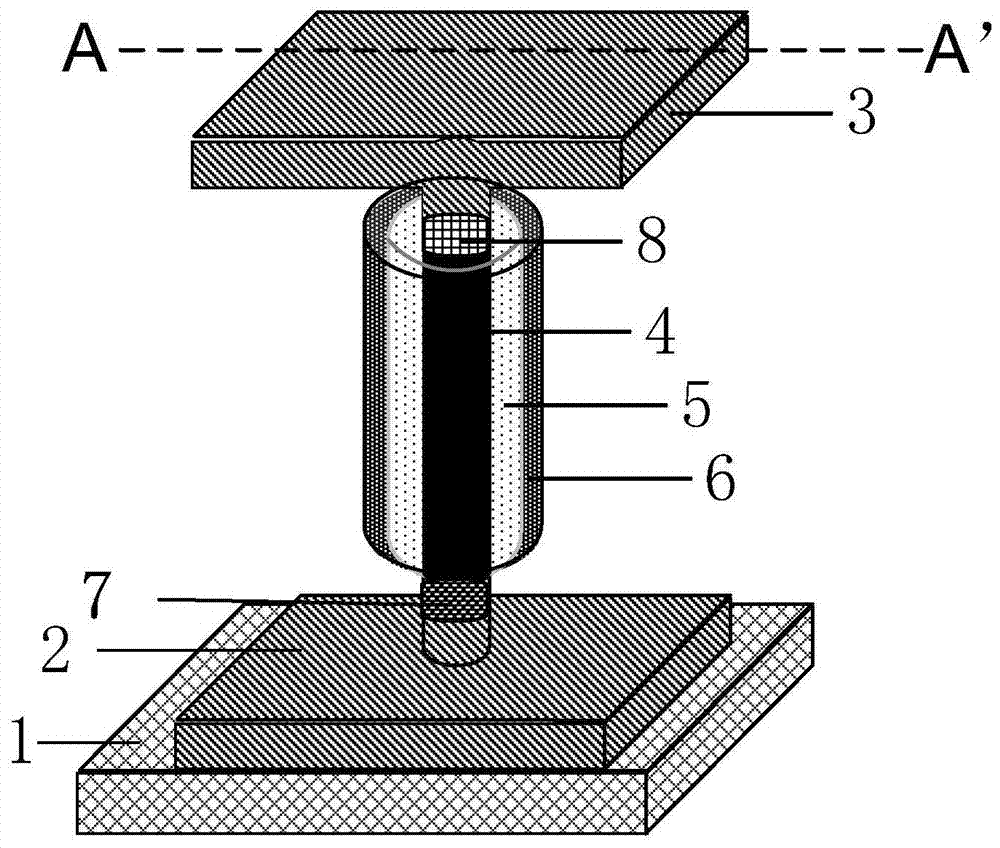

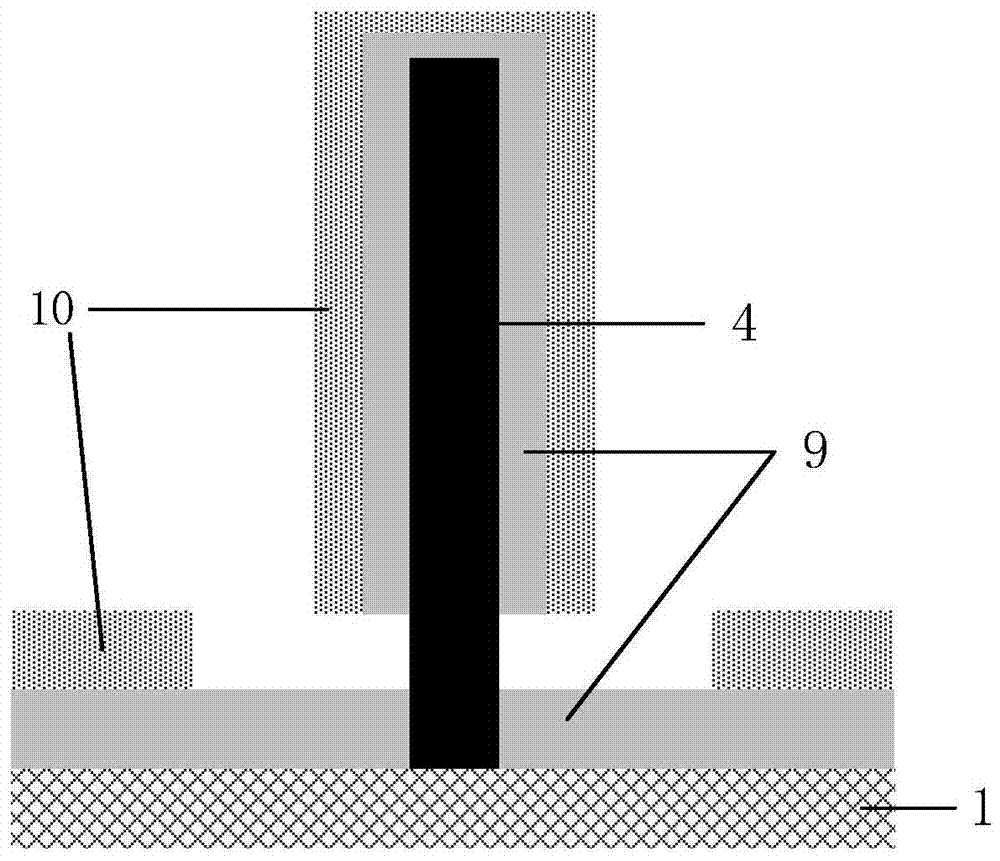

Self-adaptive composite mechanism tunneling field effect transistor (TFET) and preparation method thereof

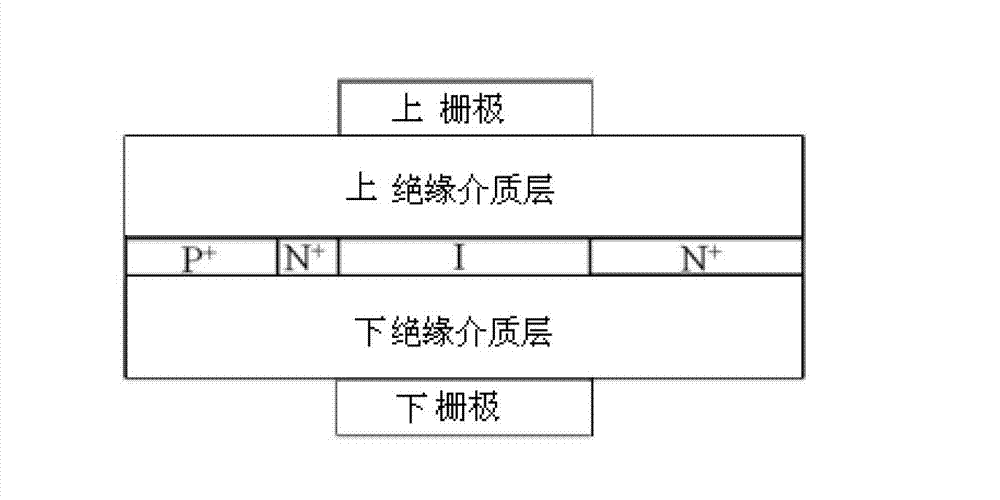

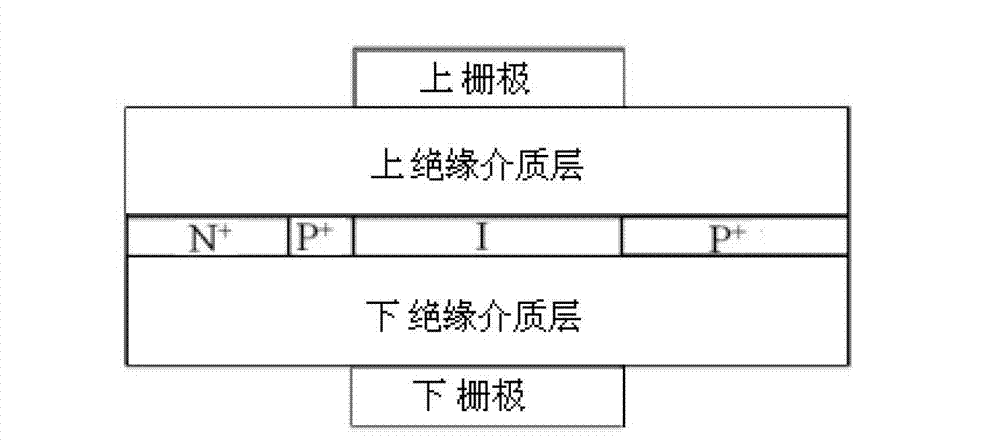

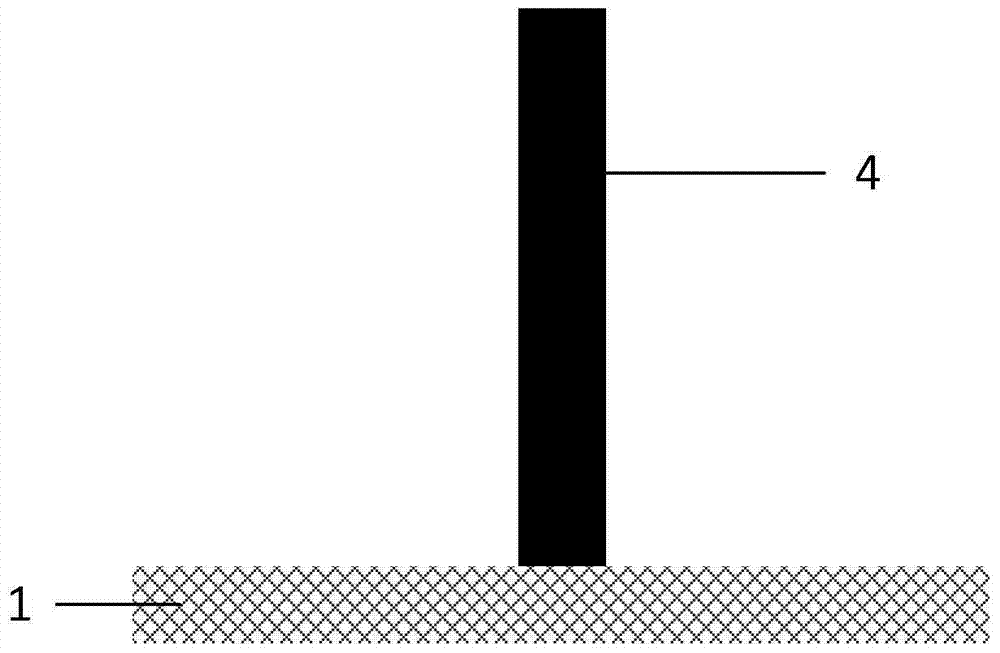

ActiveCN102664192BSuppression of bipolar effectsSteep Subthreshold CharacteristicSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSMOSFET

The present invention relates to the field of tunneling field effect transistor logic devices and circuits in a CMOS ultra large scale integrated (ULSI) circuit. Disclosed are a tunneling field effect transistor and manufacturing method thereof. The tunneling field effect transistor is: for an N type transistor, P+ is injected, on the basis of doping N-, into one side of a doped source area close to the edge of a control gate (3), so that the original doped N- of the injected part is completely compensated as P+; and for a P type transistor, N+ is injected, on the basis of doping P-, into one side of the doped source area close to the edge of the control gate (3), so that the original doped P- of the injected part is completely compensated as N+. Through the doped injection twice of different concentrations into the source area, the device structure of the tunneling field effect transistor effectively combines the characteristics of large conducting current of an MOSFET, thus improving the on-state current of the device, and self-adaptively achieving threshold adjustment of the MOSFET and TFET parts of the device.

Owner:PEKING UNIV

Double material gate nanowire tunneling field effect device and manufacturing method thereof

ActiveCN102956709BReduces off-state leakage currentHigh switching current ratioSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSNanowire

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

A junction-modulated tunneling field-effect transistor and its manufacturing method

ActiveCN103594376BImproved subthreshold characteristicsSubthreshold characteristic steepSemiconductor/solid-state device manufacturingDiodeSub thresholdConcentration gradient

The invention discloses a junction modulation type tunneling field effect transistor and a preparation method thereof, belonging to the field of field effect transistor logic devices and circuits in CMOS ultra large integrated circuits (ULSI). The tunneling field effect transistor utilizes the PN junction provided by the highly doped source region surrounded on three sides of the vertical channel region to effectively deplete the channel region, so that the channel energy band on the lower surface of the gate is increased, and when the device undergoes band tunneling, it can obtain The steeper energy band and narrower tunneling barrier width than traditional TFETs equivalently realize the effect of steep tunneling junction doping concentration gradient, thereby greatly improving the subthreshold characteristics of traditional TFETs and improving the conductance of the device at the same time. Pass current. Under the condition of being compatible with the existing CMOS technology, the present invention effectively suppresses the bipolar conduction effect of the device on the one hand, and at the same time suppresses the parasitic tunneling current at the corner of the source junction in a small size, and can equivalently realize steep The effect of straight source-junction doping concentration.

Owner:PEKING UNIV

A vertical gate-around tunneling transistor and its manufacturing method

ActiveCN104157687BHighly integratedGood gating abilitySemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierGate dielectric

The invention provides an around-gate field effect transistor which combines a vertical channel, heterogeneous impurity segregation and a schottky barrier source / drain structure. The around-gate field effect transistor comprises an annular semiconductor channel in the vertical direction, an annular gate electrode, an annular gate dielectric layer, a source region, an impurity segregation region (7), a drain region, an impurity segregation region (8), and a semiconductor substrate, wherein the source region is located at the bottom part of the vertical channel and connected with the substrate, and the impurity segregation region (7) is located between eth source region and the vertical channel; the drain region is located at the top part of the vertical channel, and the impurity segregation region (8) is located between the drain region and the vertical channel; the gate dielectric layer and the gate electrode surround the vertical channel; schottky contact is formed respectively between the source region and the drain region and the channel; and impurities of the impurity segregation region (7) and the impurity segregation region (8) choose heterogeneous impurities, that is, impurities of the impurity segregation region (7) choose p-type material, and impurities of the impurity segregation region (8) choose n-type material; and impurities of the impurity segregation region (7) choose n-type material, and impurities of the impurity segregation region (8) choose p-type material.

Owner:PEKING UNIV

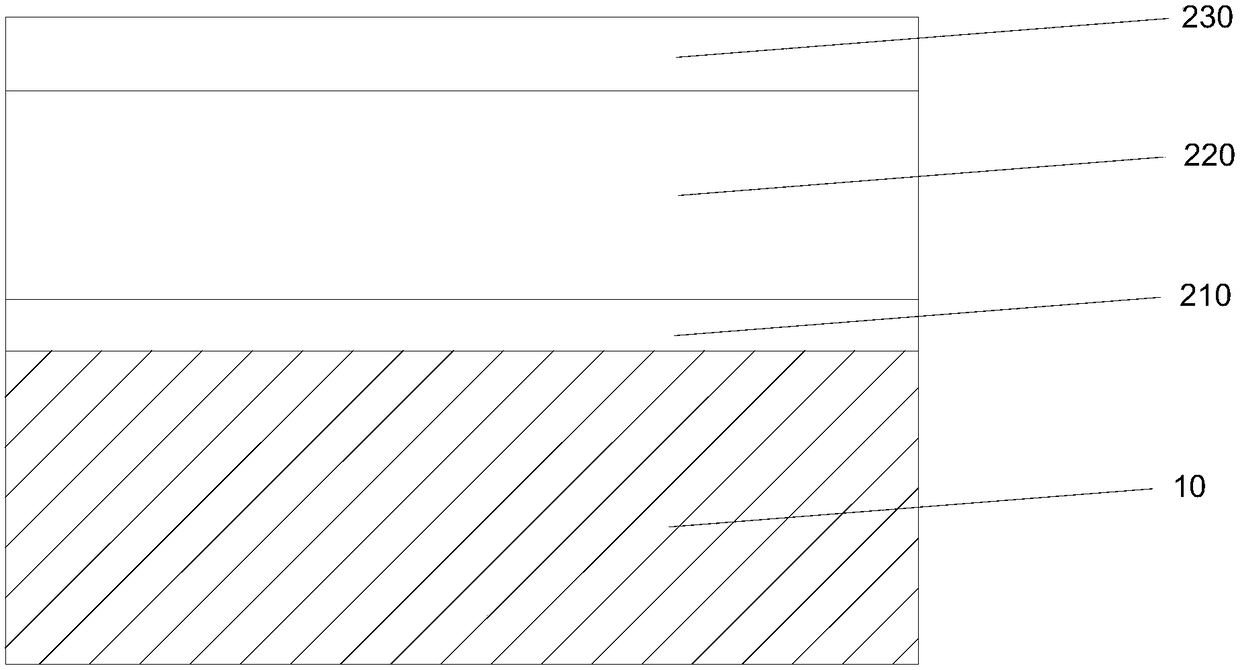

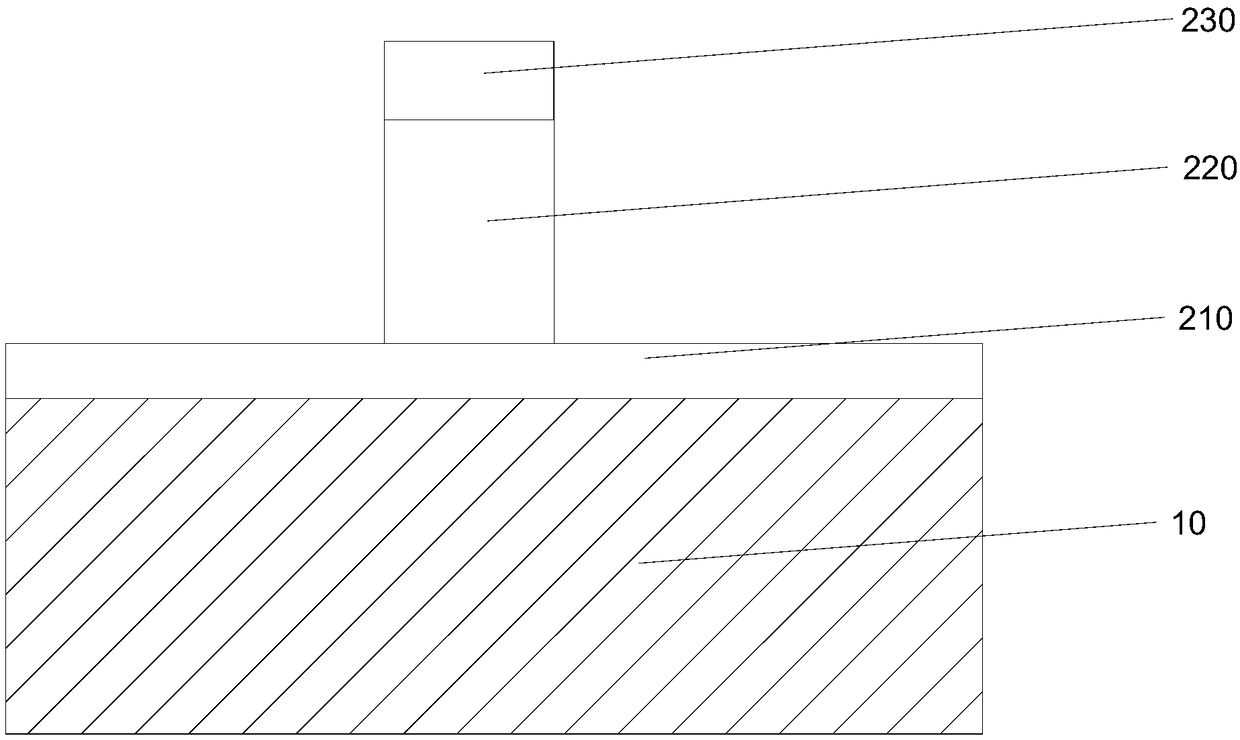

Fin type field effect transistor and preparation method thereof

InactiveCN108288646AImprove gate control abilitySuppress leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesSub thresholdEngineering

The invention provides a fin type field effect transistor and a preparation method thereof. The preparation method comprises the following steps of S1, forming a first fin body isolated from a substrate on the substrate, wherein the first fin body consists of a first region, a second region and a third region which are connected in sequence in the length direction; and S2, forming an interface oxide layer, a ferroelectric layer and a gate which are laminated around the exposed surface of the second region in sequence, wherein the preparation method also comprises the following steps of forminga source / drain in the first region and the third region, wherein the source / drain is connected with the two ends of the second region. By virtue of the preparation method, the gate control capabilityof the device is improved, electric leakage of the device is lowered, and the sub threshold value slope of the device can be greatly lower than 60mV / dec.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

A nanowire transistor based on resonant tunneling and its preparation method

InactiveCN110491940BImprove gate control abilityTunneling transportSemiconductor/solid-state device manufacturingSemiconductor devicesNanowireContact resistance

The invention discloses a nanowire transistor based on resonance tunneling. The nanowire transistor comprises an SOI substrate, a tunneling barrier structure, a source region, a drain region, nanowires, a grid electrode, a source electrode, a drain electrode, a grid electrode and an insulating dielectric layer. The tunneling barrier structure is located on the buried oxide layer of the SOI substrate. The source region, the drain region and the nanowire are formed by etching top silicon of the SOI substrate; the nanowire is positioned between the source region and the drain region; wherein thesource region, the drain region and the nanowire are not directly connected and are connected through a tunneling barrier structure, the insulating dielectric layer is formed on the surfaces of the source region, the drain region and the nanowire, the grid electrode is formed on the insulating dielectric layer above the nanowire, the source electrode is formed on the source region, the drain electrode is formed on the drain region, and the grid electrode is formed on the grid electrode. According to the nanowire transistor structure based on resonance tunneling and the preparation method of the nanowire transistor structure, the sub-threshold slope is reduced, and large conduction current and small source-drain contact resistance can be achieved.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Gate-all-around transistor and manufacturing method thereof

ActiveCN111435644BImprove processing stabilityImprove process precisionSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricNanowire

The present invention provides a gate-all-around transistor and a preparation method thereof, the method comprising: 1) providing an SOI substrate with grooves formed in its insulating layer; 2) forming a semiconductor nanowire structure suspended and straddling the grooves; 3) ) rounding and thinning the semiconductor nanowire structure; 4) forming a fully enclosed gate dielectric layer on the surface of the semiconductor nanowire, and forming a gate electrode layer on the surface of the gate dielectric layer; 5) using the gate electrode layer as a mask to perform An ion implantation process to form a source region and a drain region; 6) removing the gate dielectric layer outside the gate electrode layer; 7) forming a source electrode and a drain electrode in the source region and the drain region. The invention adopts the gate electrode layer as a mask to carry out the self-alignment implantation of the source region and the drain region, which can effectively improve the process stability and implantation precision, and can effectively reduce the process cost. The invention does not need isotropic wet etching when preparing semiconductor nanowires, and can effectively avoid the generation of concave cavities.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Three-dimensional stacked gate-all-around transistor and its preparation method

ActiveCN111435641BImprove processing stabilityImprove process precisionNanoinformaticsSemiconductor/solid-state device manufacturingGate dielectricNanowire

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Manufacturing method of gate-all-around transistor

ActiveCN111435678BBroaden your optionsAchieve performance requirementsSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricNanowire

The invention provides a method for preparing a gate-all-around transistor, the method comprising: 1) providing an SOI substrate with a groove formed in its insulating layer; 2) forming a semiconductor nanowire structure suspended and straddling the groove; 3) Rounding and thinning the semiconductor nanowire structure; 4) forming an implantation barrier layer on the surface of the channel region, the implantation barrier layer reveals the preparation area of the source region and the drain region; 5) performing an ion implantation process to form the source region and drain region; 6) forming a fully-enclosed gate dielectric layer and a gate electrode layer on the surface of the semiconductor nanowire, and patterning to form a gate structure; 7) forming a source electrode and a drain electrode. The gate-all-round transistor of the present invention is prepared by a gate-last process, which can effectively increase the selection range of gate materials, thereby realizing different device performance requirements. The invention does not need isotropic wet etching when preparing semiconductor nanowires, and can effectively avoid the generation of concave cavities.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Semiconductor device and formation method thereof

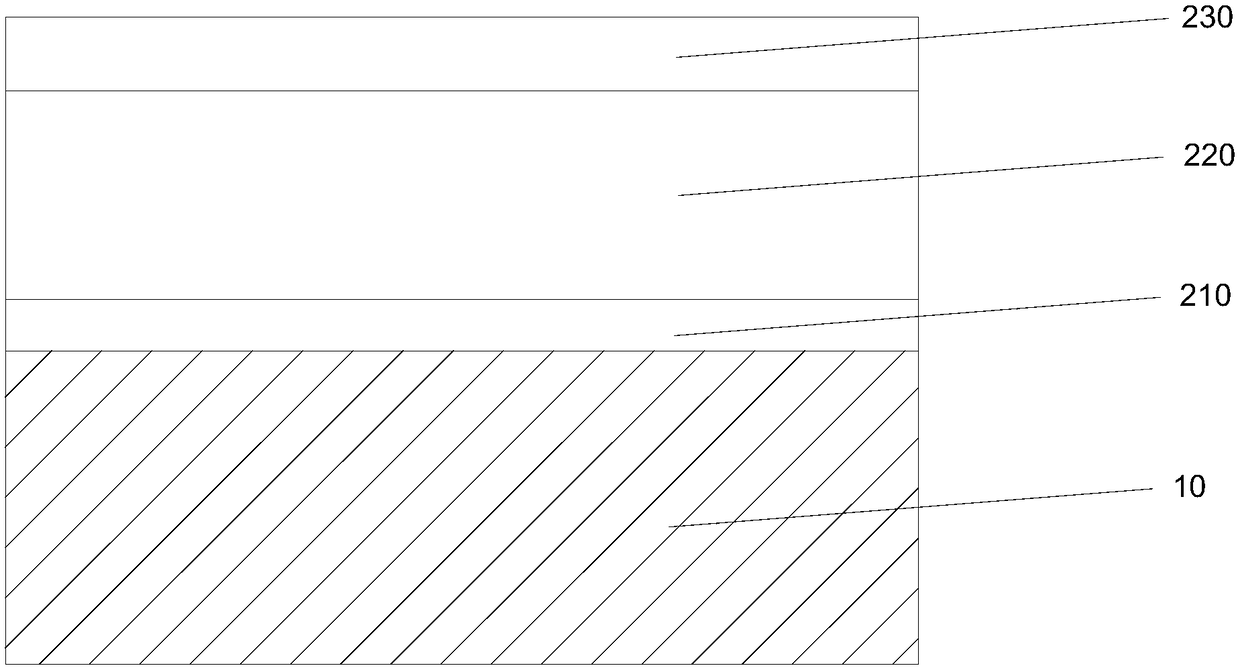

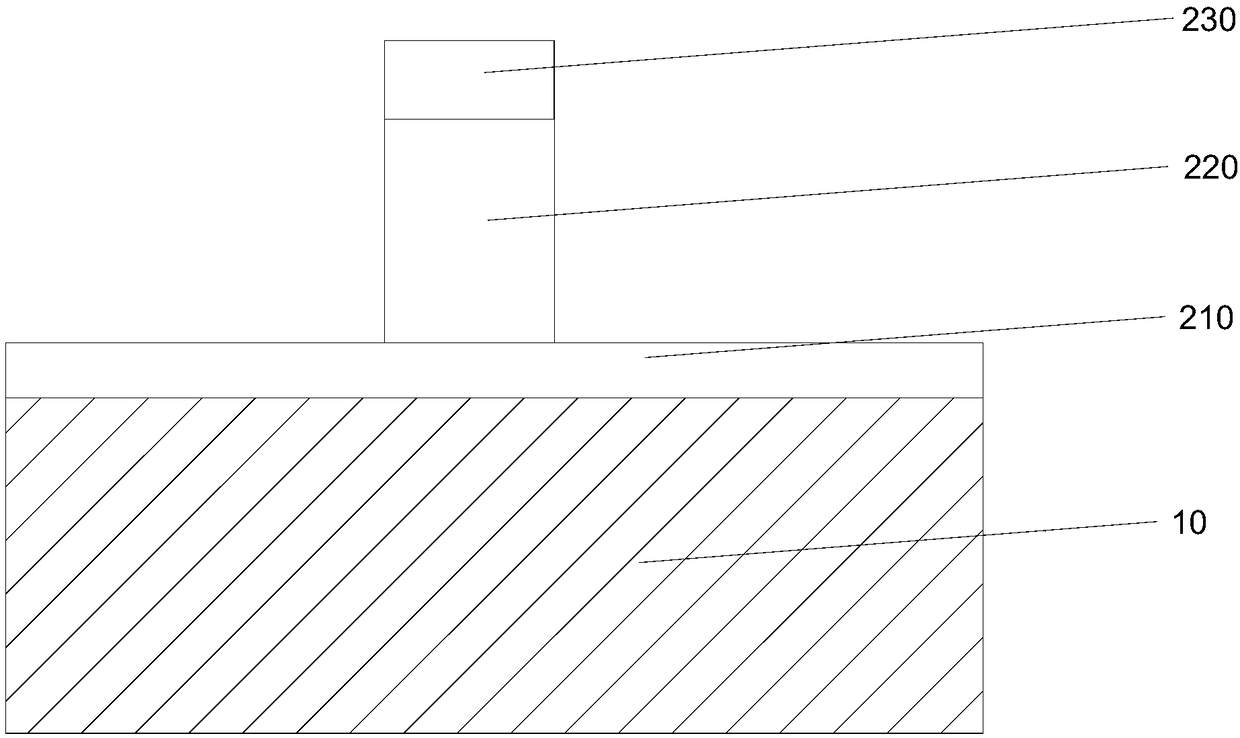

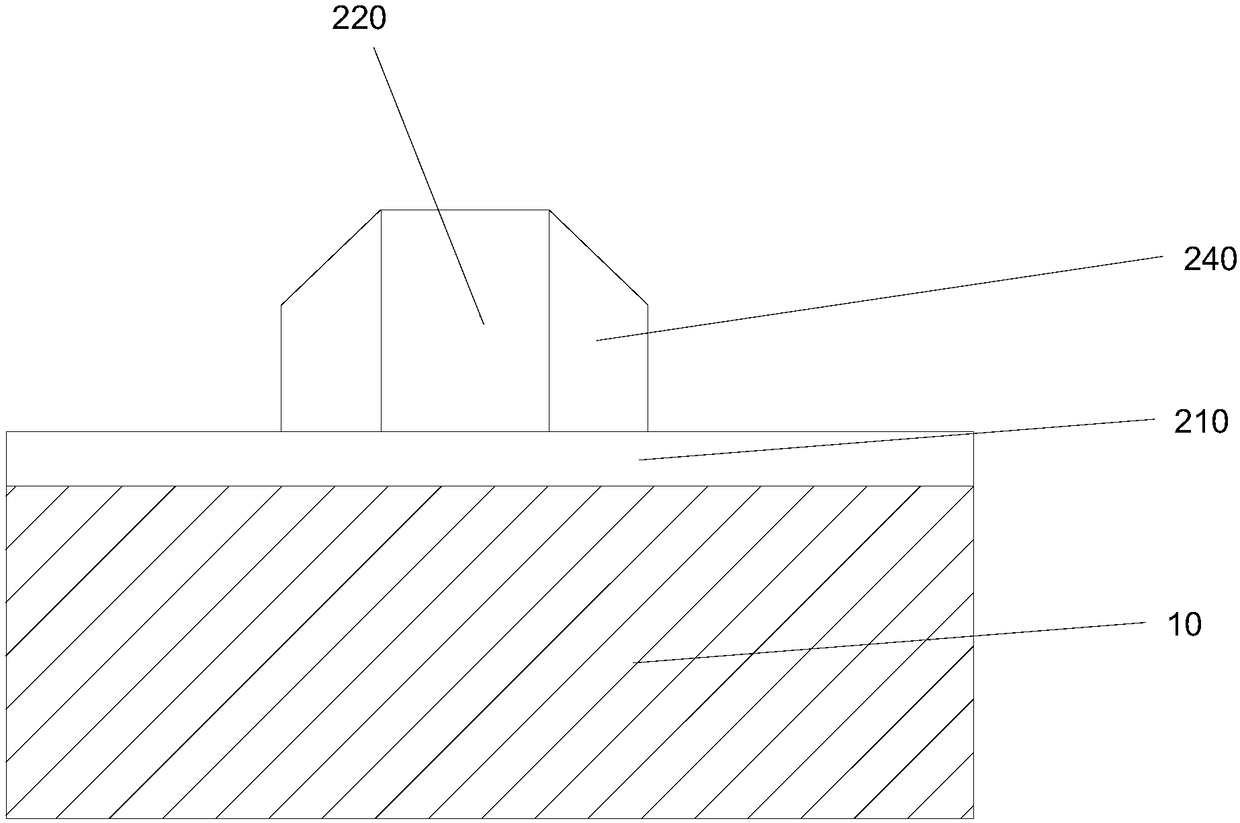

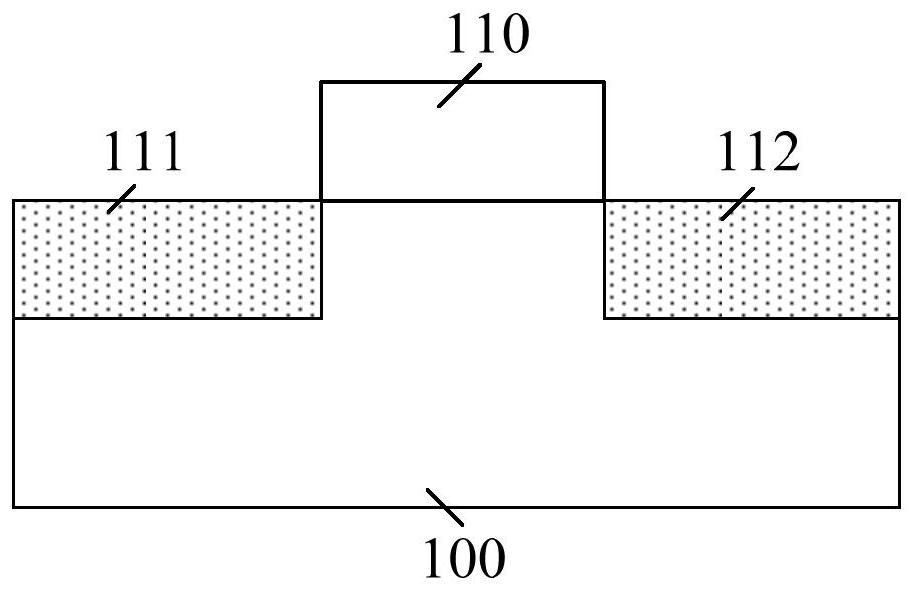

ActiveCN108735807AHigh currentSmall subthreshold slopeSemiconductor/solid-state device manufacturingDiodePower semiconductor deviceSemiconductor

The invention provides a semiconductor device and a formation method thereof. The method comprises the steps of forming a semiconductor substrate, wherein the semiconductor substrate comprises a gateregion, a first region and a second region, the first region and the second region are respectively arranged at two sides of the gate region, an epitaxial layer is arranged in the semiconductor substrate at the first region, and the energy gap of the epitaxial layer is smaller than the energy gap of the semiconductor substrate; forming a first doping region in the epitaxial layer at the first region, wherein first doping ions are arranged in the first doping region; forming a gate structure on the semiconductor substrate at the gate region; and forming a second doping region in the semiconductor substrate at the second region, wherein second doping ions are arranged in the second doping region, and the conductive type of the second doping ions is opposite to the conductive type of the first doping ions. The bandgap of the epitaxial layer is smaller than the bandgap of the semiconductor substrate, the barrier width of a contact surface of the first doping region and a channel region isrelatively small, and thus, the subthreshold slope of the formed semiconductor device can be reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor device and method of forming the same

ActiveCN108735807BHigh currentSmall subthreshold slopeSemiconductor/solid-state device manufacturingDiodeDevice materialSemiconductor

The present invention provides a semiconductor device and a method for forming the same, wherein the method includes: forming a semiconductor substrate, the semiconductor substrate including a gate region and a first region and a second region respectively located on both sides of the gate region, There is an epitaxial layer in the semiconductor substrate in the first region, and the energy gap of the epitaxial layer is smaller than the energy gap of the semiconductor substrate; a first doped region is formed in the epitaxial layer in the first region, and the first There are first doping ions in the doping region; a gate structure is formed on the semiconductor substrate in the gate region; a second doping region is formed in the semiconductor substrate in the second region, and the second doping region There are second dopant ions in which the conductivity type of the second dopant ions is opposite to that of the first dopant ions. If the bandgap of the epitaxial layer is smaller than that of the semiconductor substrate, the barrier width on the contact surface between the first doped region and the channel region will be smaller. Therefore, the forming method can reduce the Formation of subthreshold slopes for semiconductor devices.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

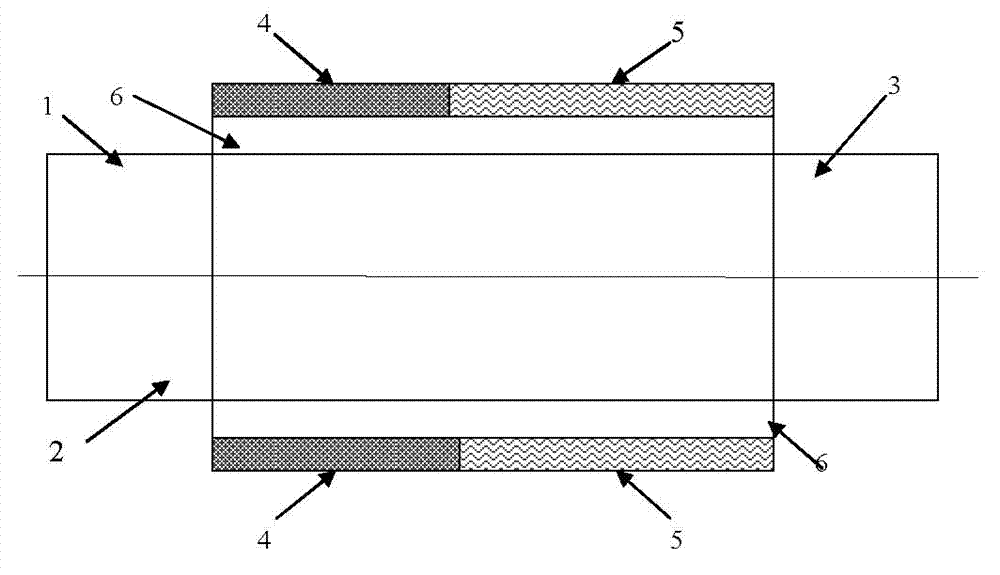

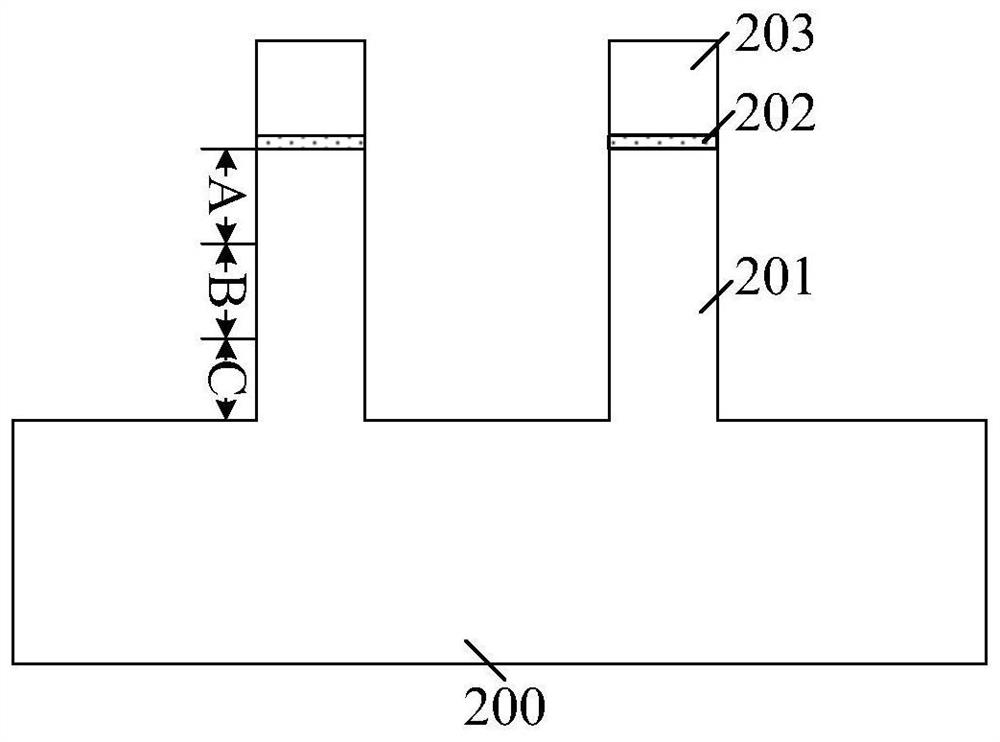

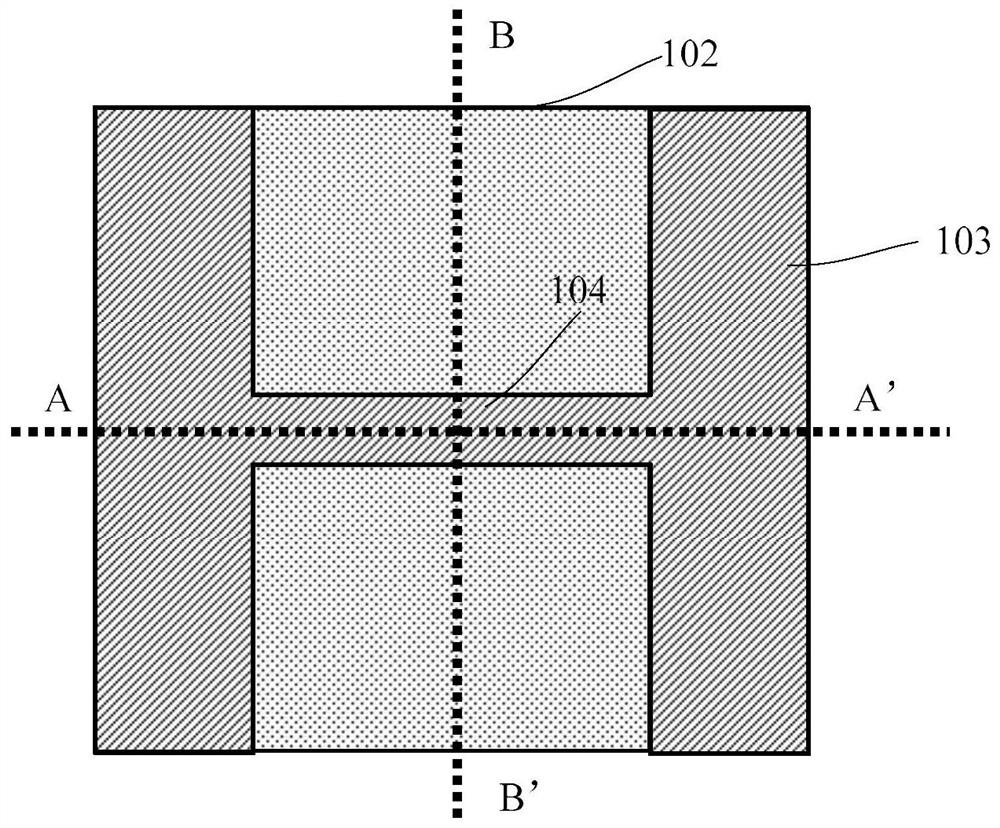

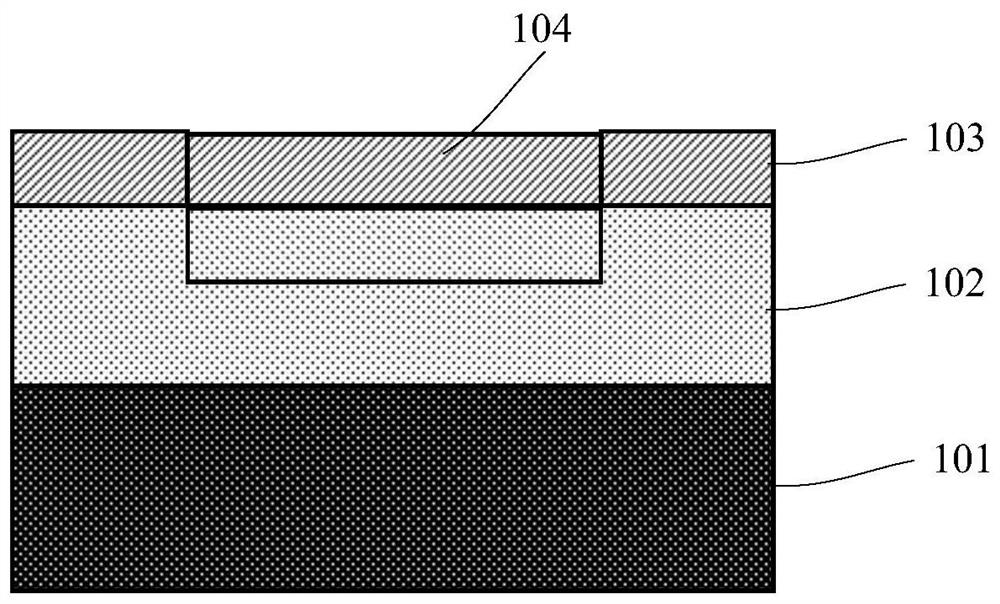

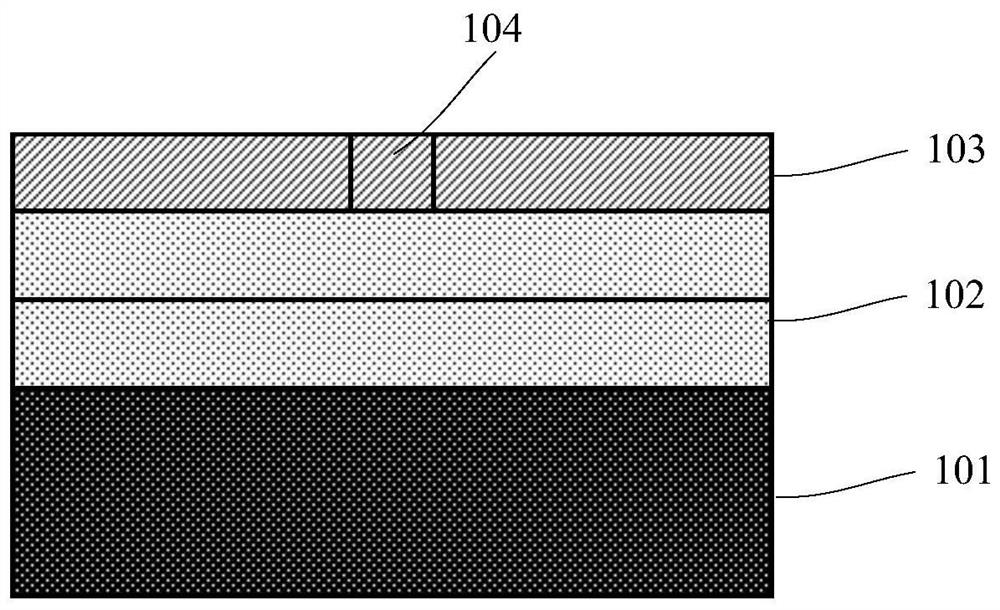

Tunnelling field effect transistor based on work function of heterogeneous gate and forming method of tunnelling field effect transistor

ActiveCN102169900BSmall subthreshold slopeIncrease drive currentSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowGate dielectric

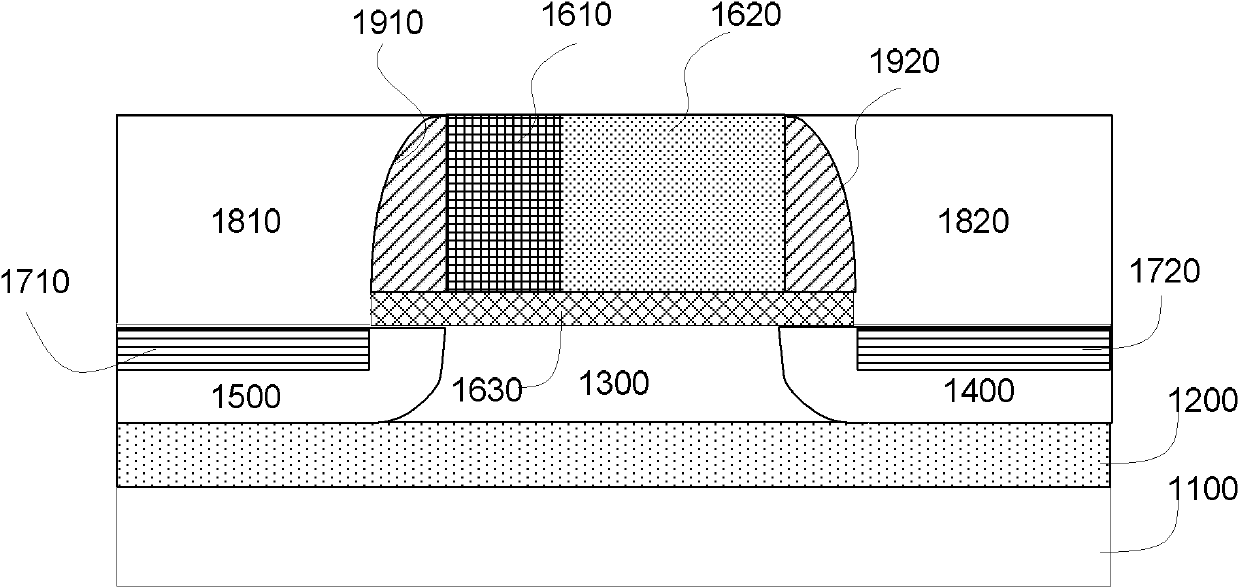

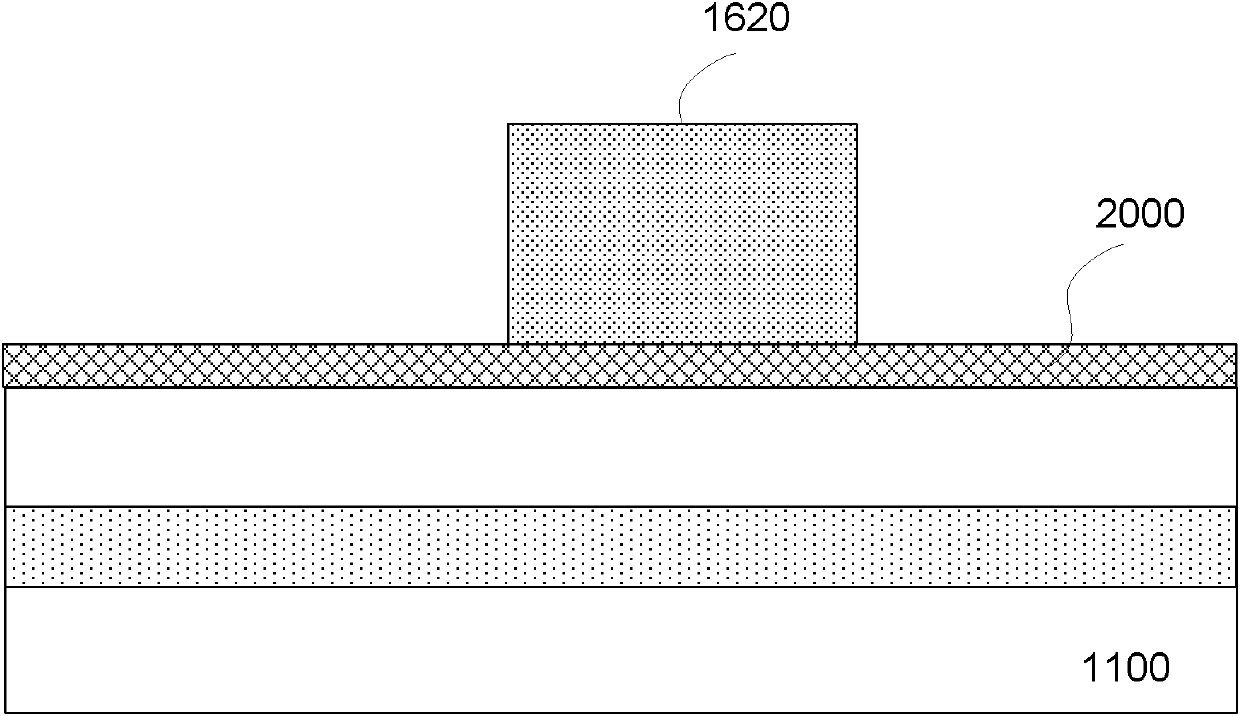

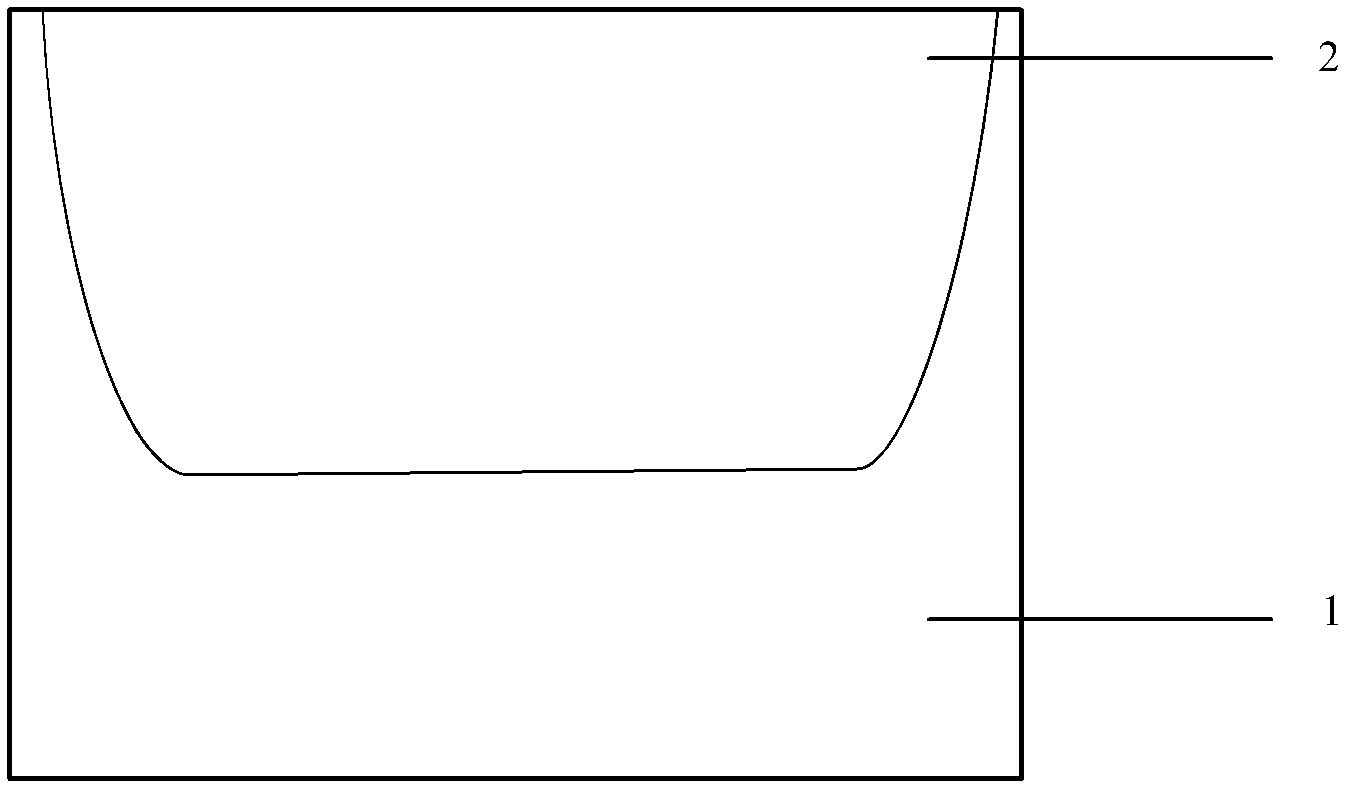

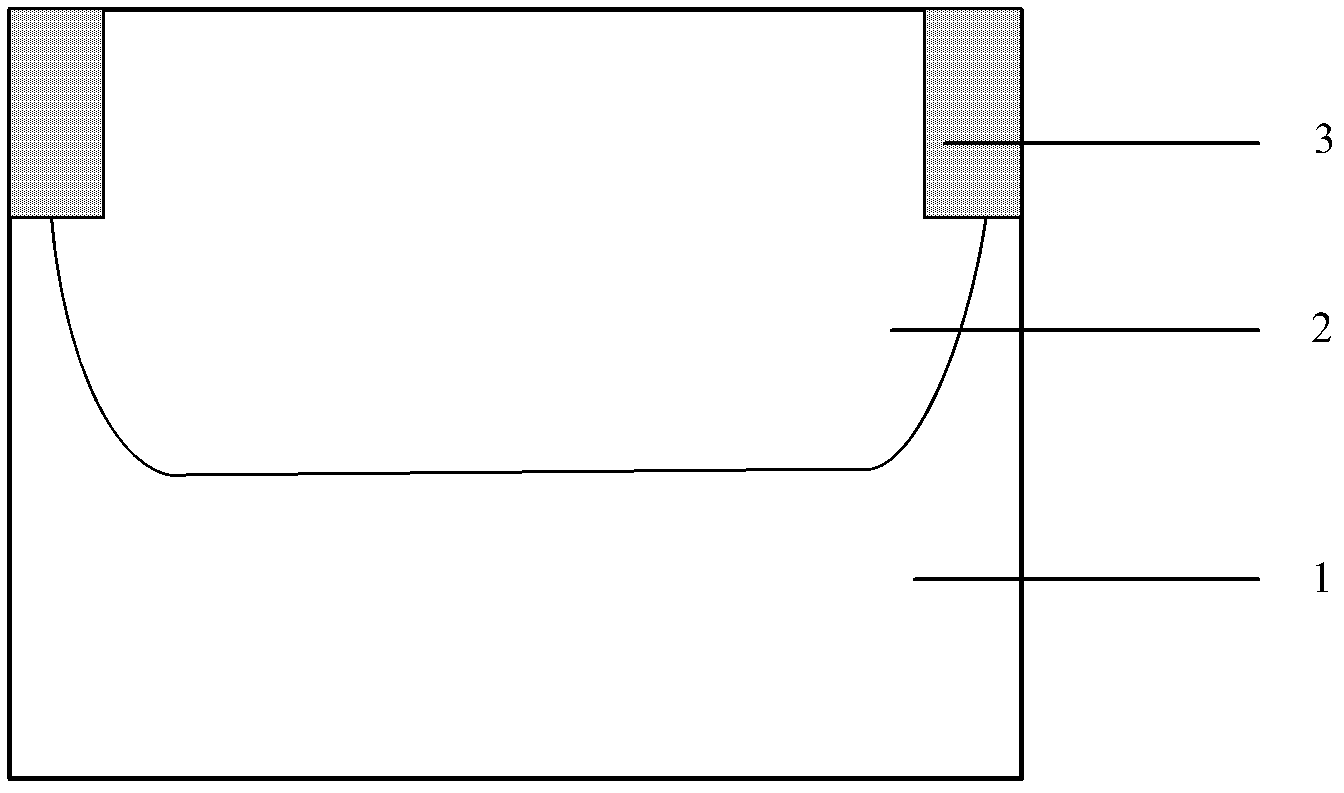

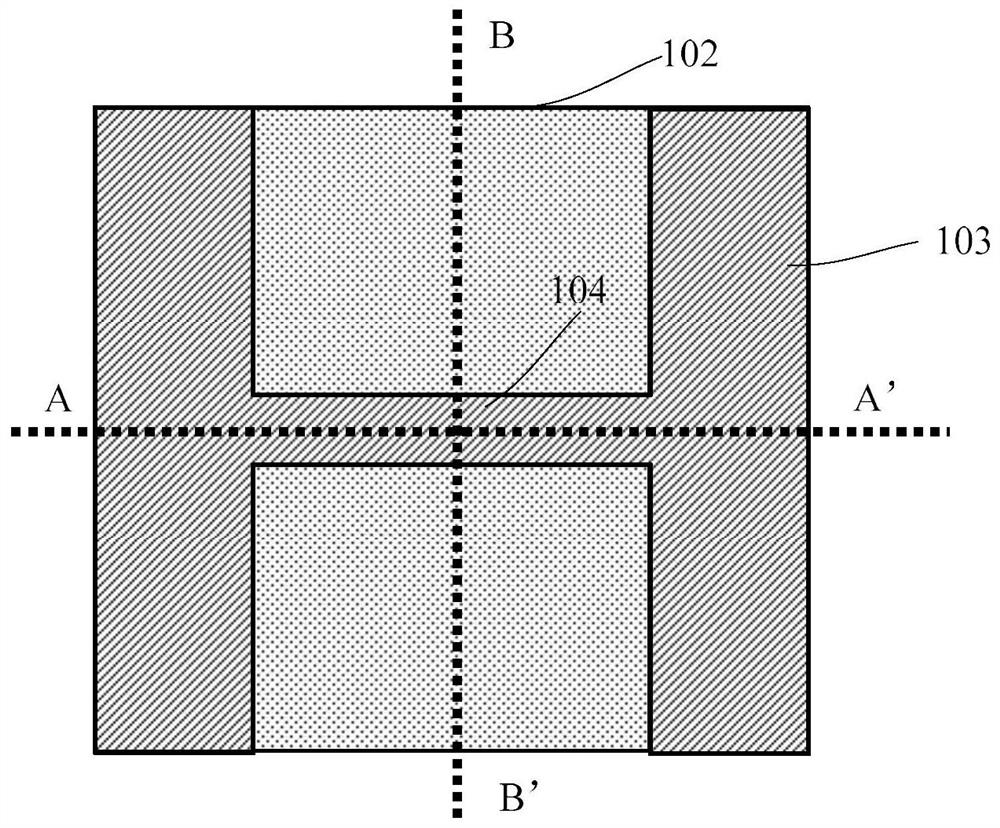

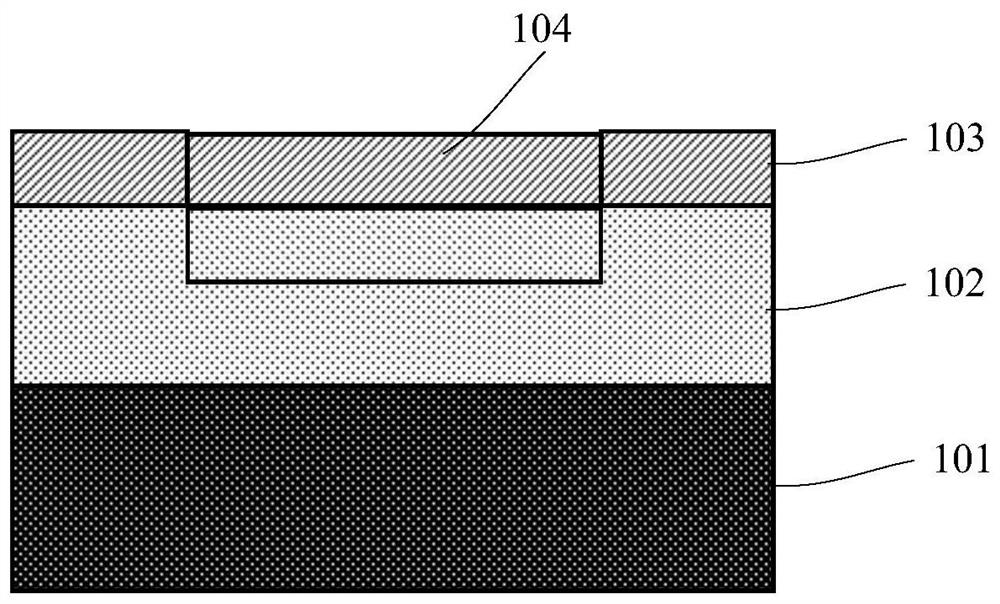

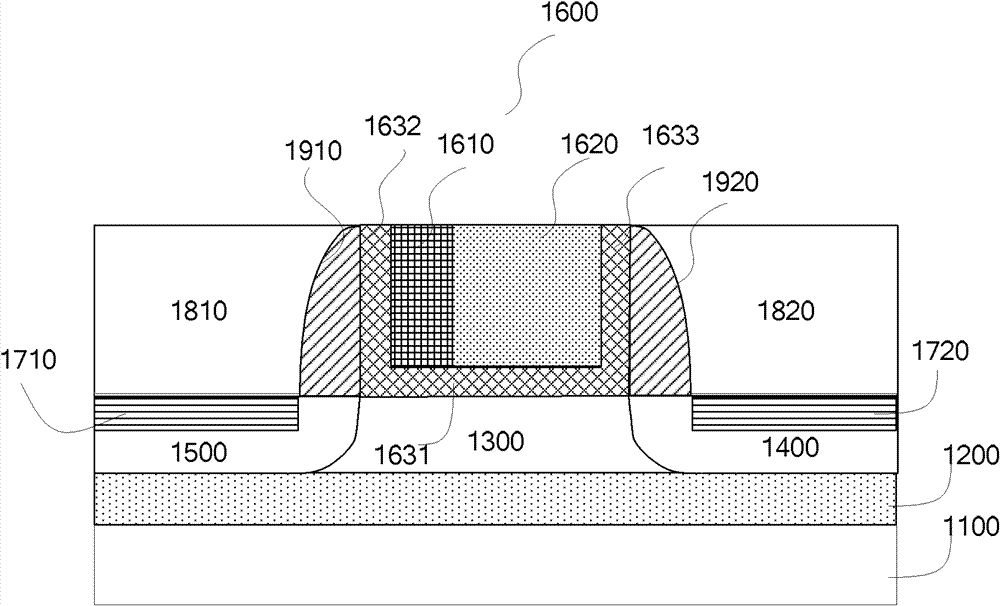

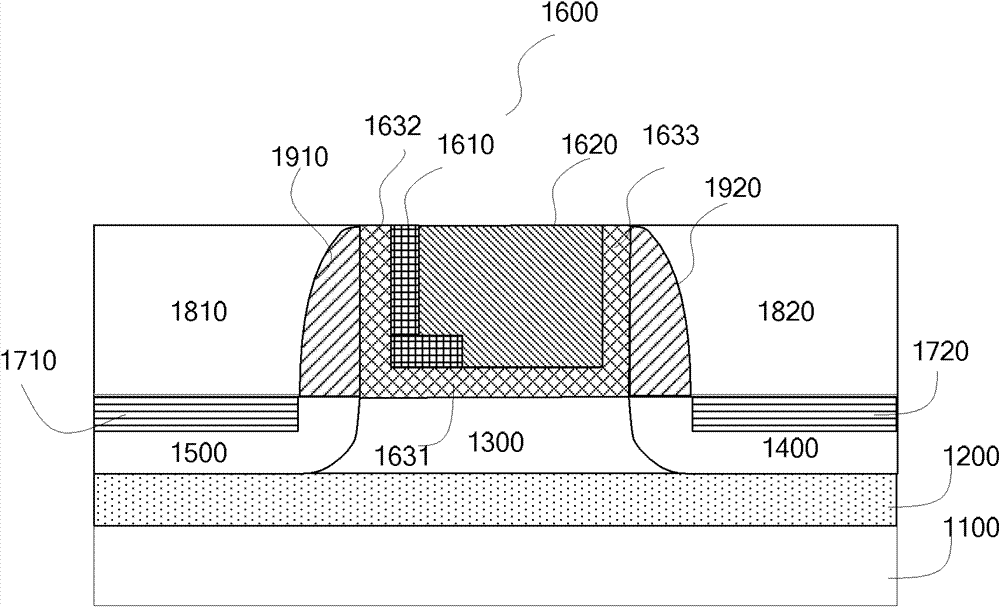

The present disclosure provides a tunneling device, which comprises: a substrate (1100); a channel region (1300) formed in the substrate, and a source region (1500) and a drain region (1400) formed on two sides of the channel region (1300); and a gate stack (1600) formed on the channel region (1300) and a first side wall (1910) and a second side wall (1920) formed on two sides of the gate stack (1600), wherein the gate stack (1600) comprises: a first gate dielectric layer (1631); at least a first gate electrode (1610) and a second gate electrode (1620) formed on the first gate dielectric layer (1631); a second gate dielectric layer (1632) formed between the first gate electrode (1610) and the first side wall (1910); and a third gate dielectric layer (1633) formed between the second gate electrode (1620) and the second side wall (1920).

Owner:TSINGHUA UNIV