A nanowire transistor based on resonant tunneling and its preparation method

A resonant tunneling and nanowire technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as difficulty in meeting the requirements of smaller technology nodes, nanowire transistors that have not been reported, and increased static power consumption. , to achieve low requirements for ion implantation process and annealing process, reduce sub-threshold slope, and facilitate popularization and application

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

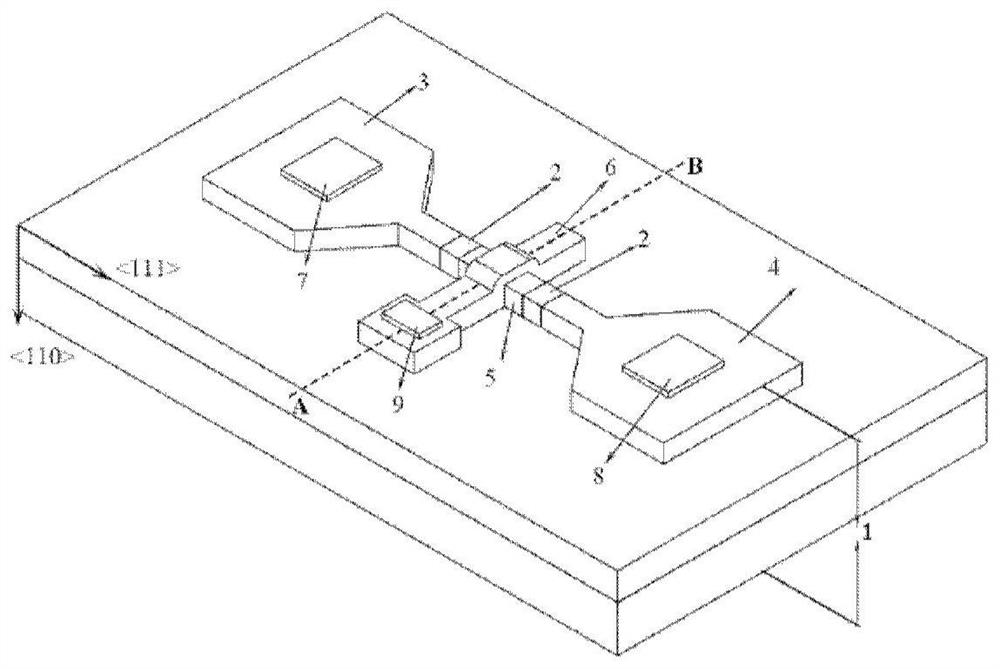

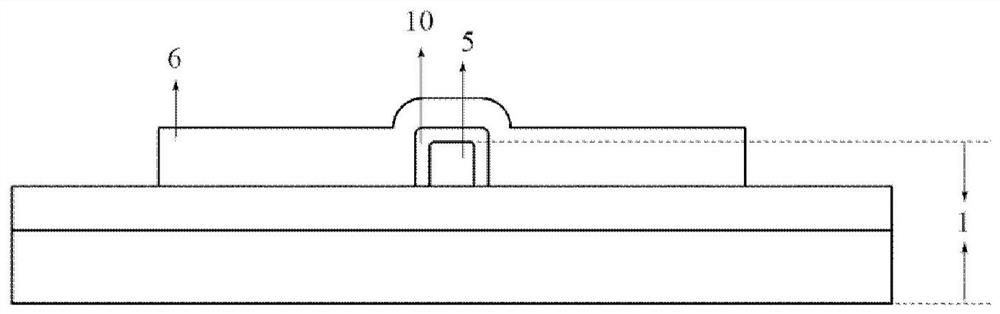

[0042] Such as figure 1 as shown, figure 1 is a three-dimensional schematic diagram of a nanowire transistor based on resonant tunneling according to an embodiment of the present invention, figure 2 It is a nanowire transistor based on resonant tunneling according to an embodiment of the present invention in figure 1 The cross-sectional view taken along the line AB. combine figure 1 and figure 2 As shown, the nanowire transistor includes: SOI substrate 1 except for the source region 3, the drain region 4, the part of the nanowire 5, the double barrier structure 2, the source region 3, the drain region 4, the nanowire 5, the gate electrode 6, source electrode 7, drain electrode 8, gate electrode 9 and insulating die...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More