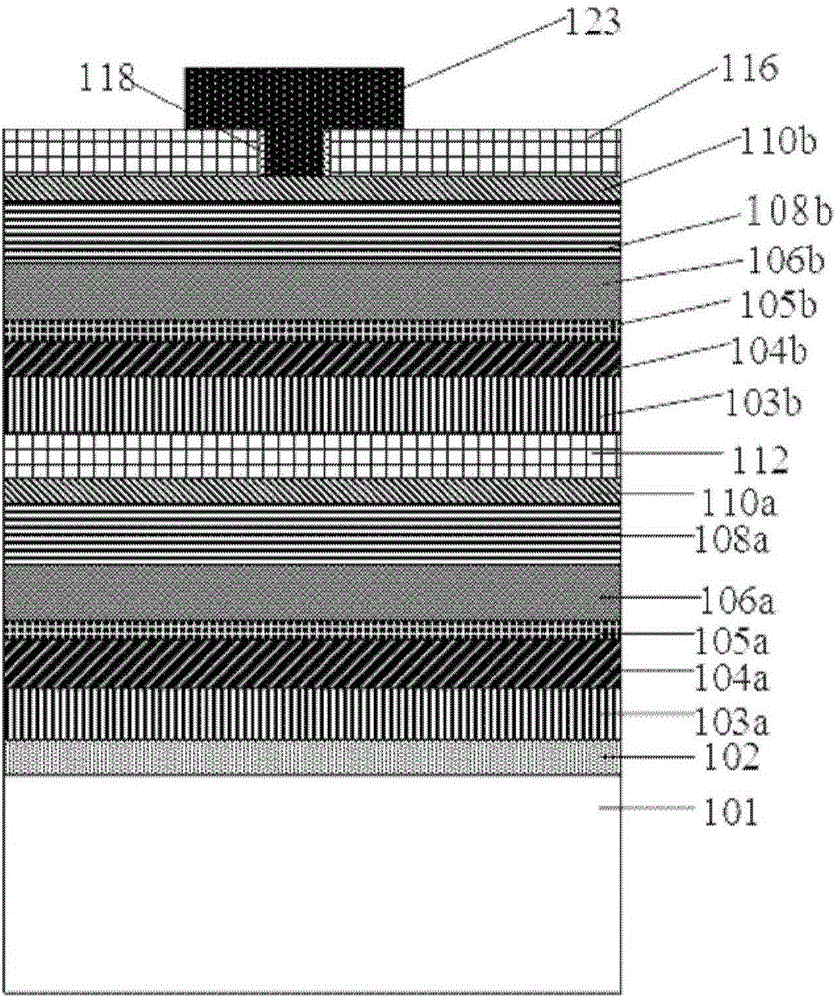

Vertically-integrated double-gate MOSFET structure and preparation method therefor

A technology of metal gate and gate dielectric layer, which is used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc. Small parasitic capacitance, the effect of shortening the length

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

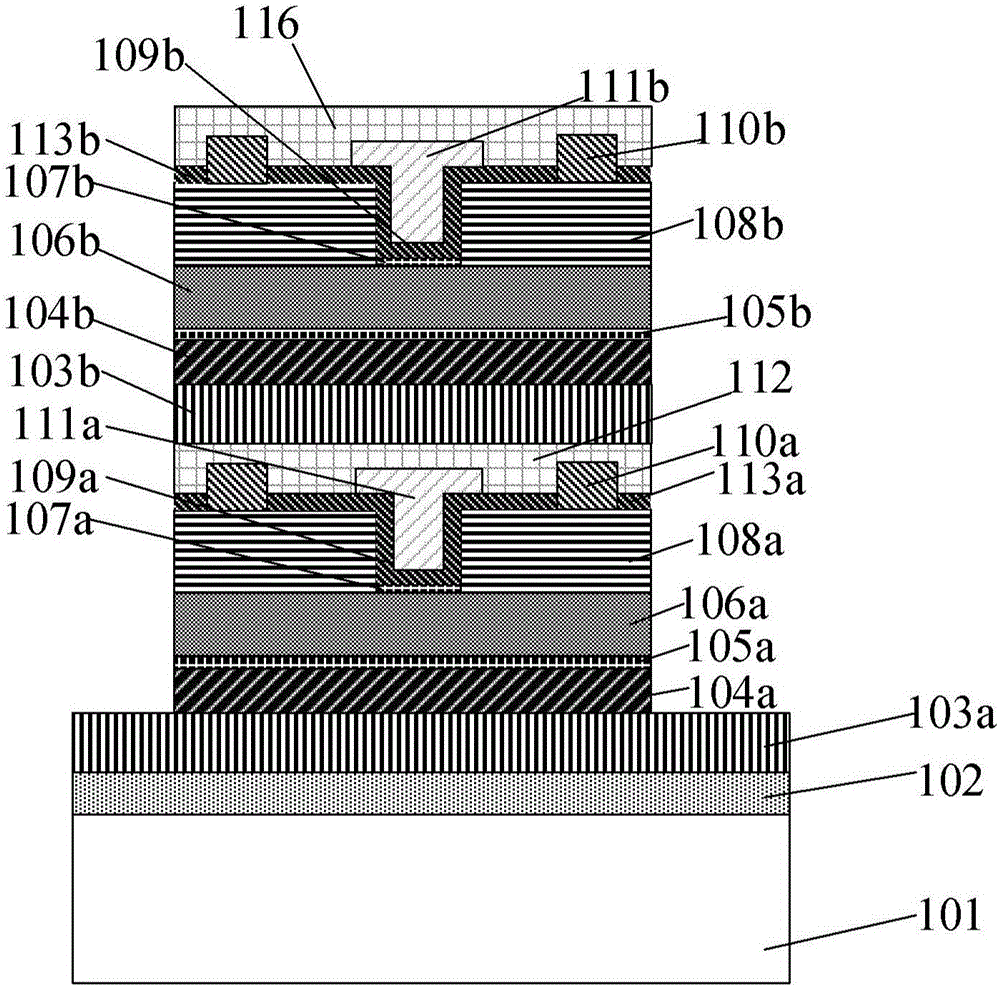

[0067] The invention also discloses a method for preparing a vertically integrated double-gate MOSFET structure, which includes the following steps:

[0068] Step 1. Depositing a first gate metal layer on the isolation layer formed by the substrate to form a first bonding sheet;

[0069] Step 2, forming a second bonding sheet and a third bonding sheet;

[0070] Step 3, bonding the first bonding sheet and the second bonding sheet together;

[0071] Step 4, bonding the second bonding sheet and the third bonding sheet together;

[0072] Step 5, respectively forming the first metal gate electrode 117, the second metal gate electrode 119, the third metal gate electrode 120, the fourth metal gate electrode 121, the first metal source-drain electrode 122 and the second metal source-drain electrode 123;

[0073] Step 6, lead out the source-drain metal and the gate metal to form the first metal source-drain electrode 122, the second metal source-drain electrode 123, the first metal g...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More