Preparation method of germanium-based Schottky N-type field effect transistor

A field effect transistor, MOS transistor technology, applied in the field of VLSI process manufacturing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

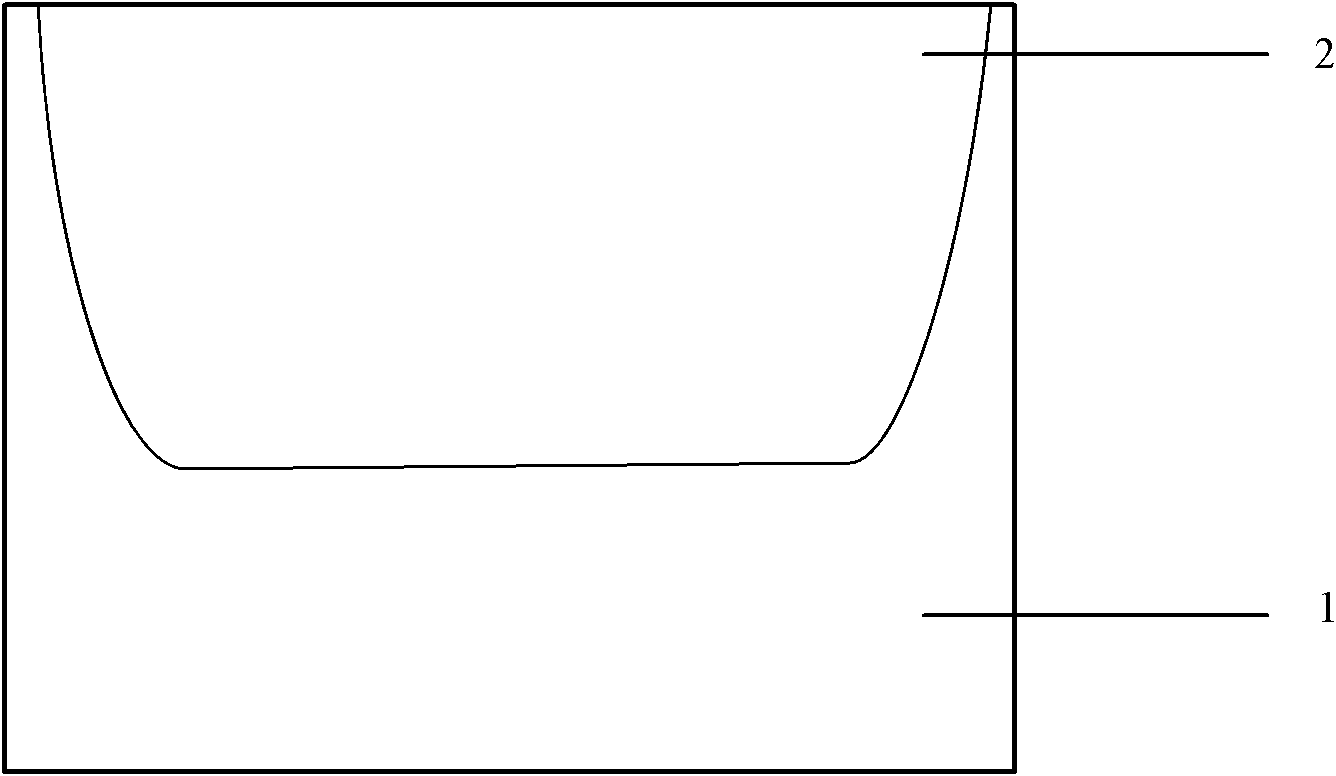

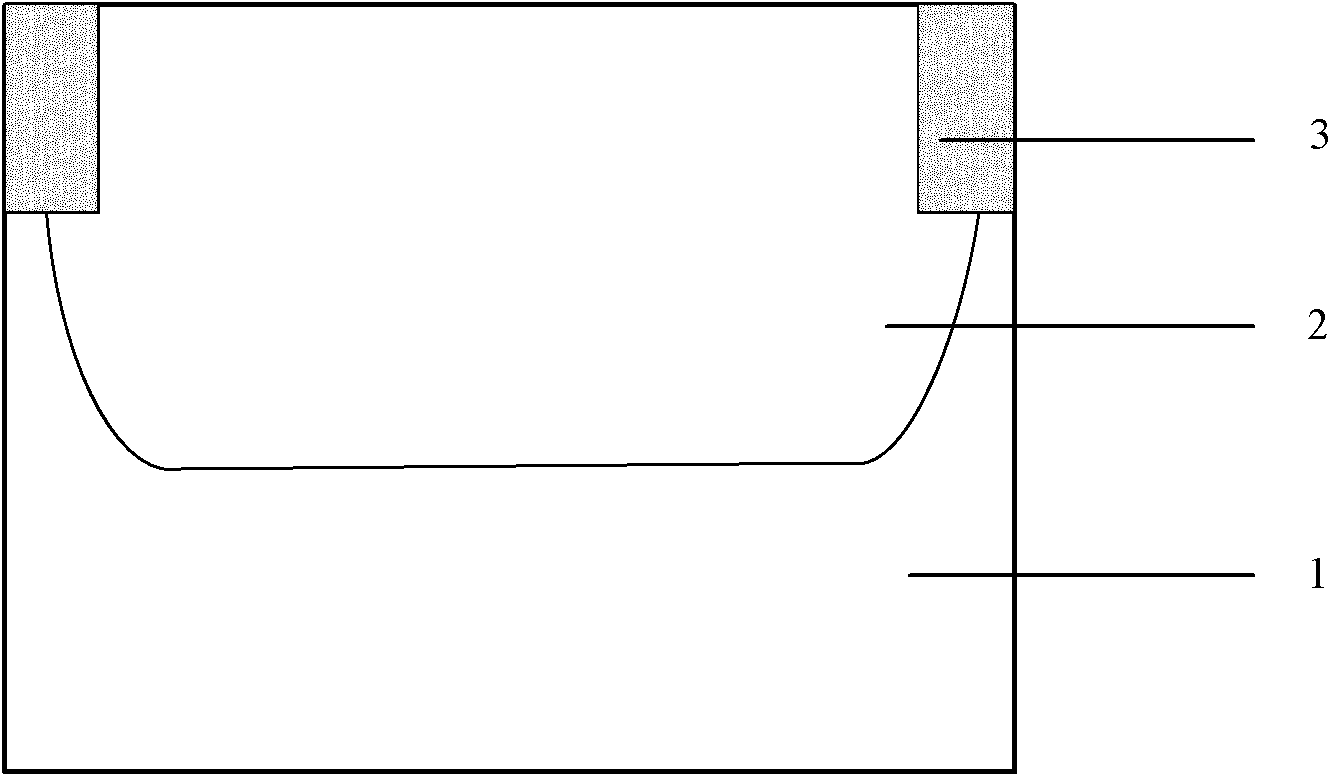

[0027] With reference to Fig. 1, the present invention provides a preferred embodiment to illustrate the preparation method of germanium-based Schottky NMOS transistor of the present invention, and this method comprises the steps:

[0028] Step 1: Provide a germanium-based substrate. As shown in FIG. 1(a), a P-type semiconductor germanium substrate 1, wherein the semiconductor germanium substrate 1 can be a bulk germanium substrate, a germanium-on-insulator (GOI) substrate, or an epitaxial germanium substrate.

[0029] Step 2: Fabricate the N-well region. Deposit a silicon oxide layer and a silicon nitride layer on the germanium substrate, define the N well region by photolithography, reactive ion etch away the silicon nitride in the N well region, and ion implant N-type impurities, such as phosphorus, and then Annealing is driven in to make N...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More