An Asymmetric Reconfigurable Field Effect Transistor

A field-effect transistor, asymmetric technology, applied in the field of reconfigurable field-effect transistors, can solve the problems of shortening the operation delay of logic gates, low open-state driving current of reconfigurable transistors, etc., and achieves strong logic processing capability and clock frequency improvement. , the effect of shortening the switching delay time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

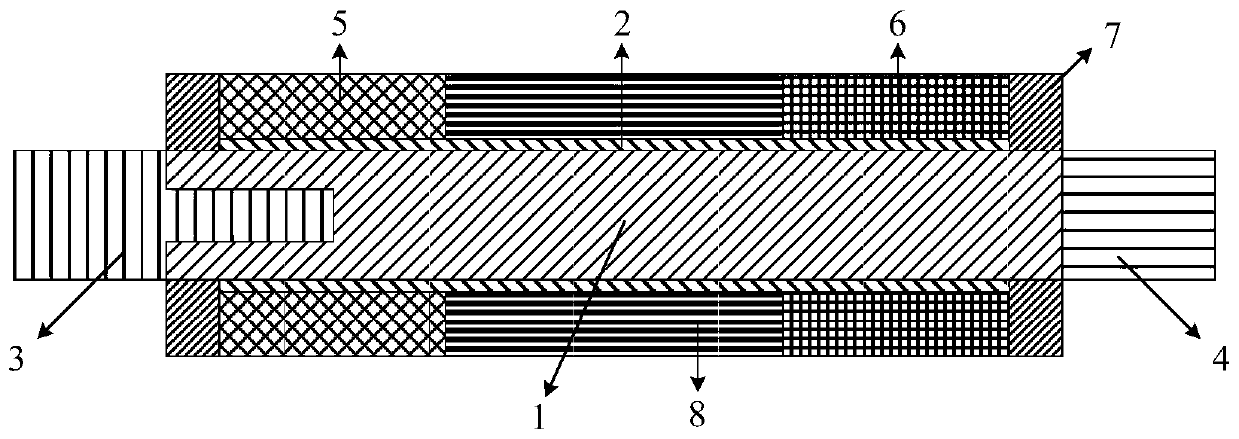

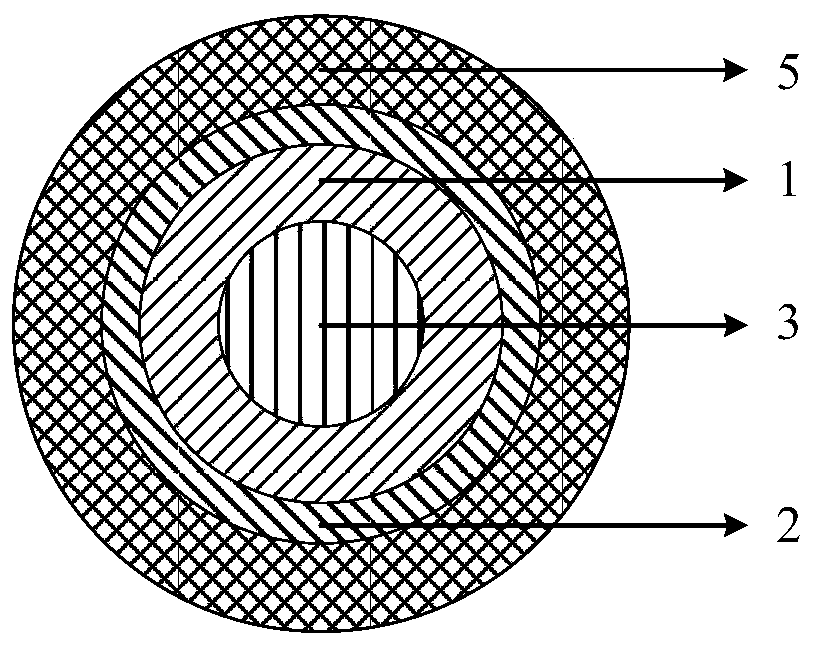

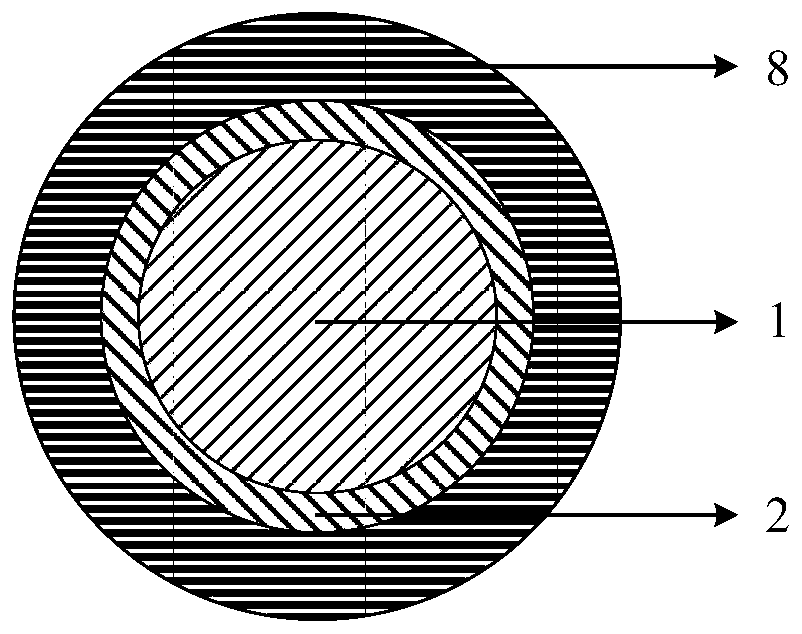

[0029] refer to Figure 1-2 , the present invention includes a nanowire channel 1, a gate oxide 2, a source 3 extending to the inside of the channel 1, a drain 4, a control gate 5, a polarity gate 6, a side wall 7 and a gate isolation 8 , in the nanowire channel 1 near one end of the control gate (Control Gate) 5, the source electrode 3 composed of metal silicide continues to extend a certain length toward the inside of the channel 1, and the diameter of the source electrode in the extension part should be less than or equal to the nanowire diameter.

[0030] An asymmetrical reconfigurable field effect transistor, which includes a drain 4 arranged at one end of the channel 1 and a source 3 extending to the inside of the channel 1 at the other end of the channel 1, and a drain 4 arranged outside the channel 1 Gate oxide 2, control gate 5 and polarity...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More