Patents

Literature

574results about How to "Increase write speed" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

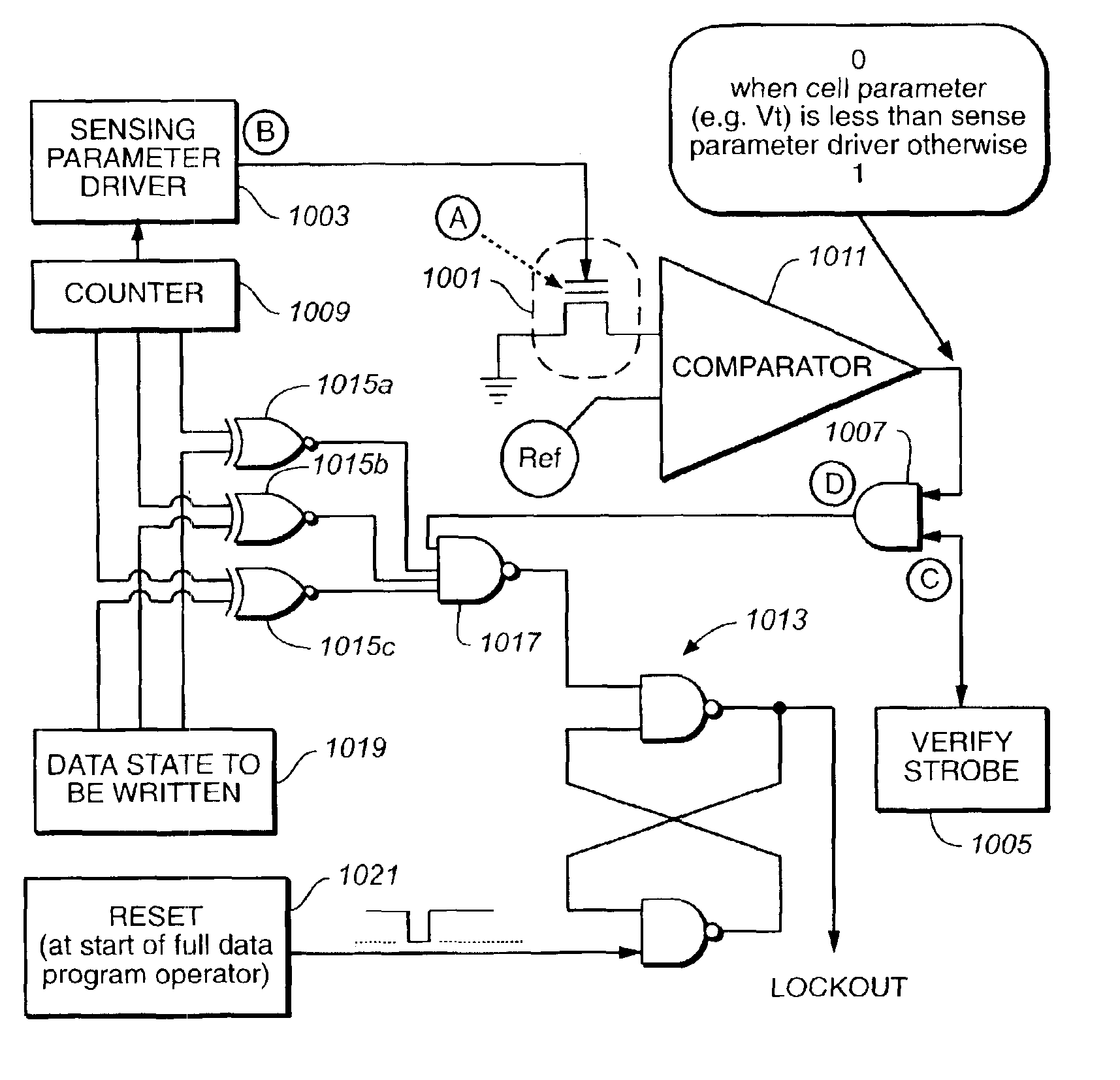

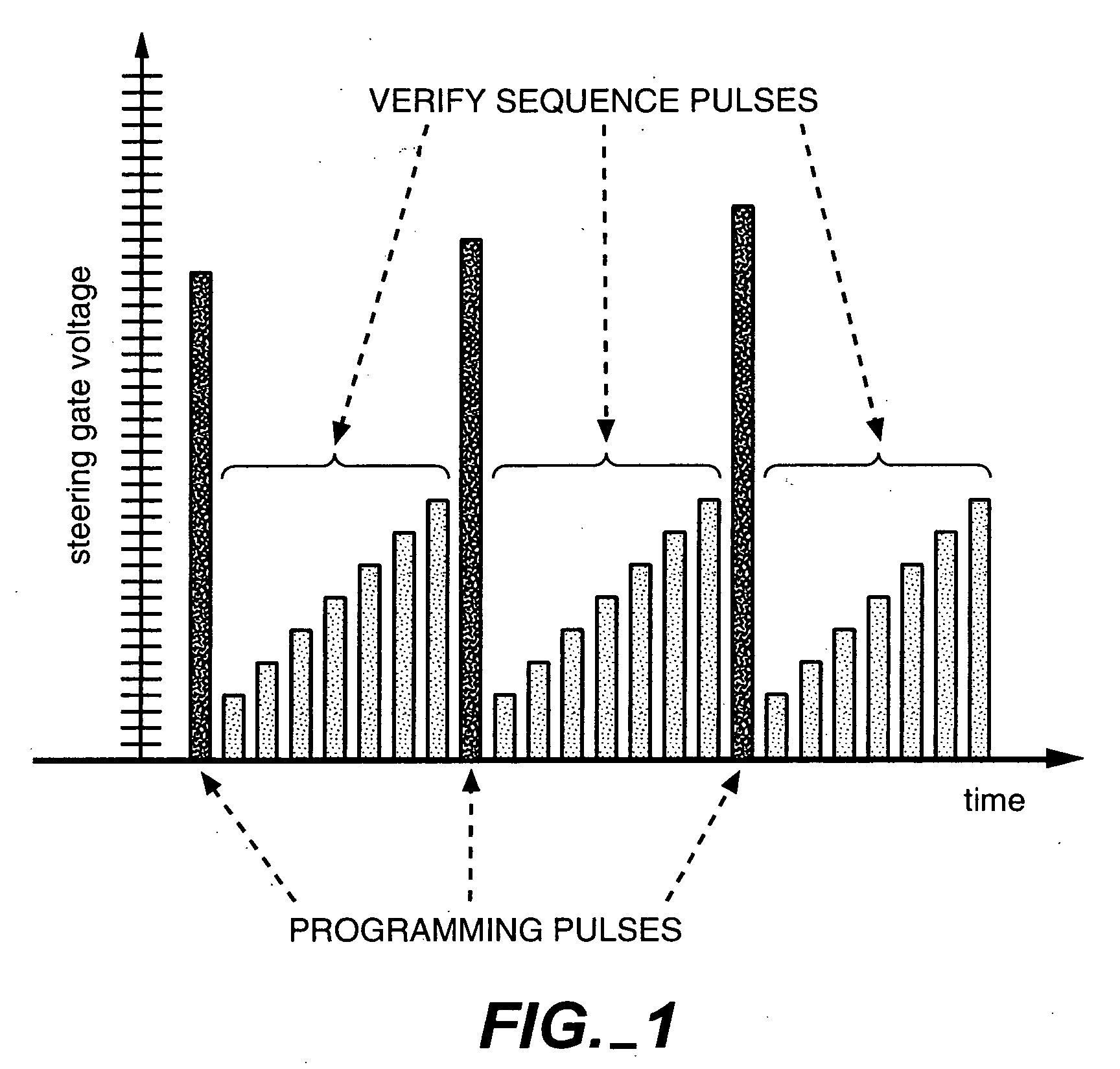

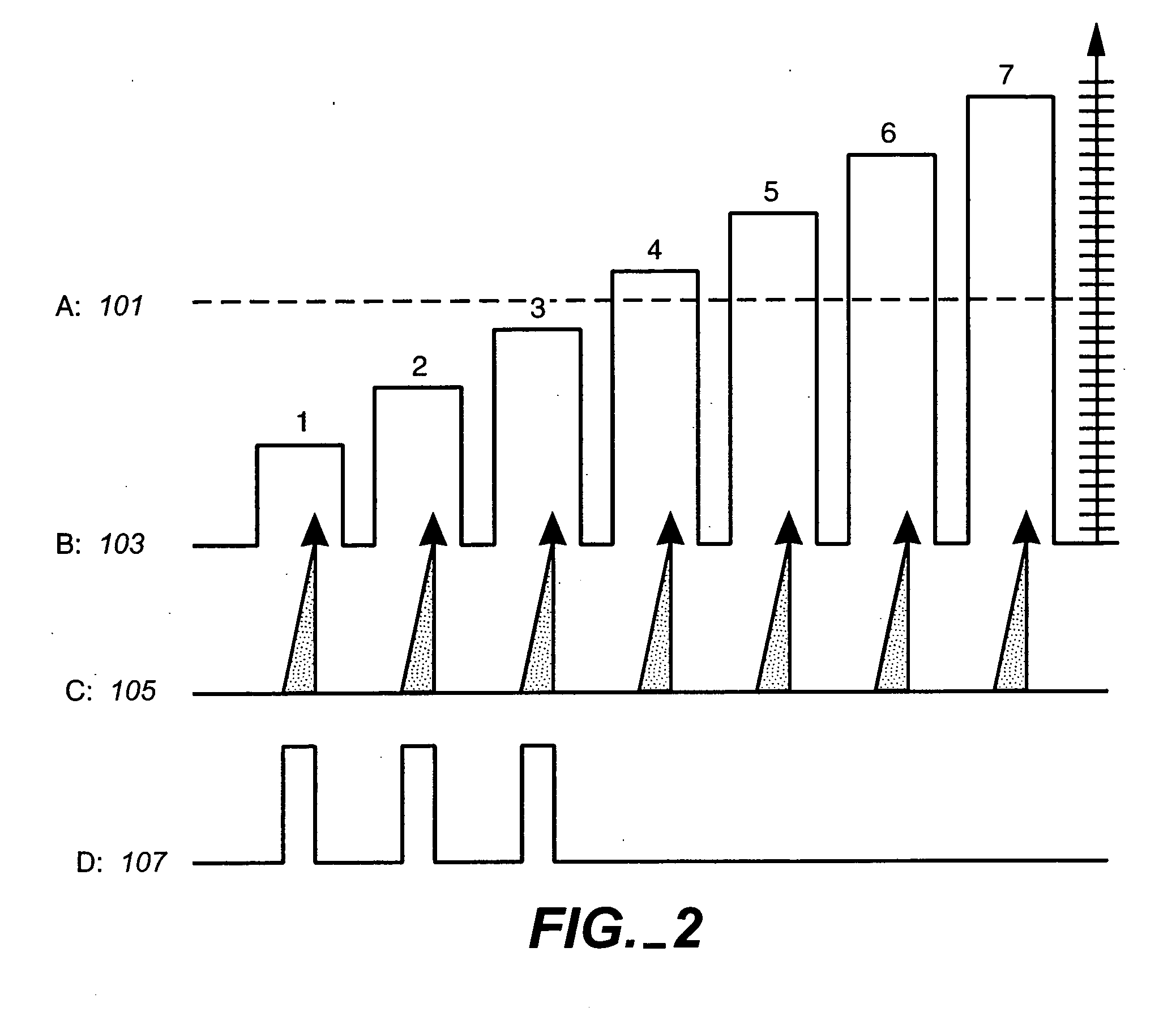

Smart verify for multi-state memories

ActiveUS7073103B2Minimize the numberIncrease write speedRead-only memoriesDigital storageComputer engineeringIntelligent verification

Owner:WODEN TECH INC

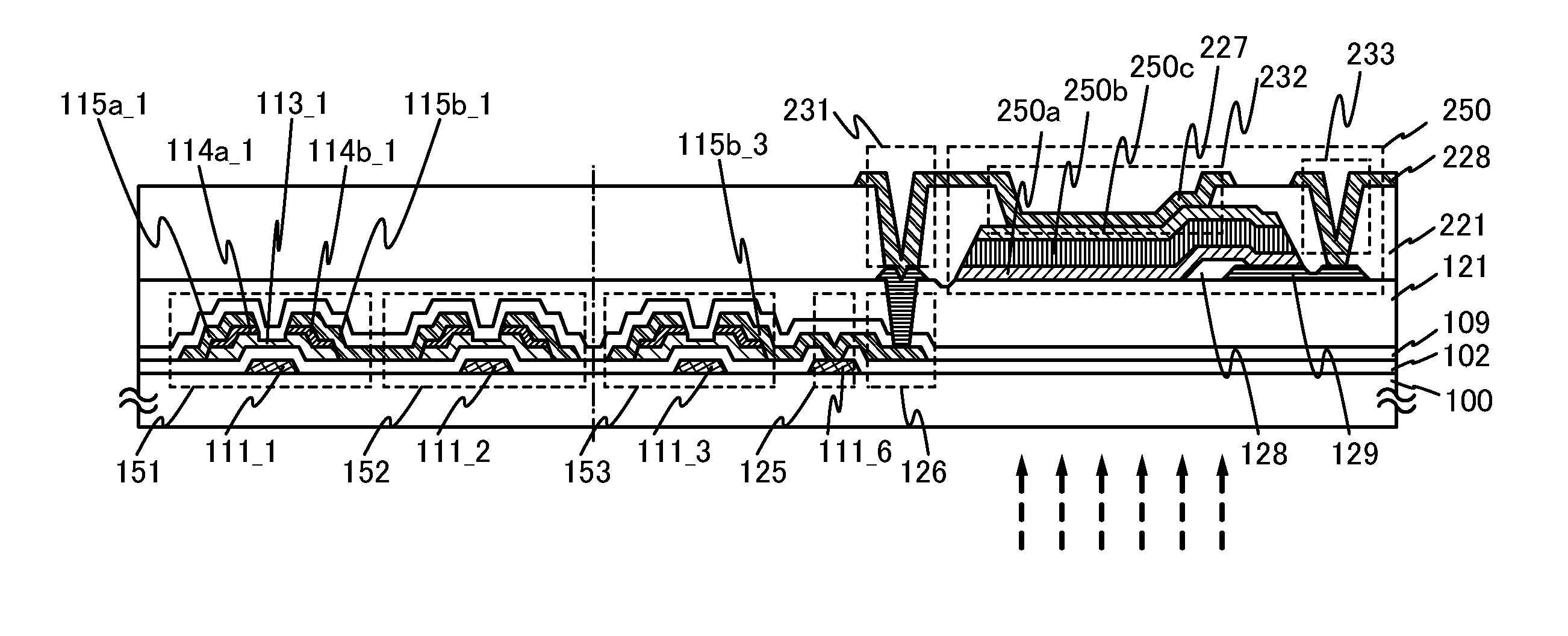

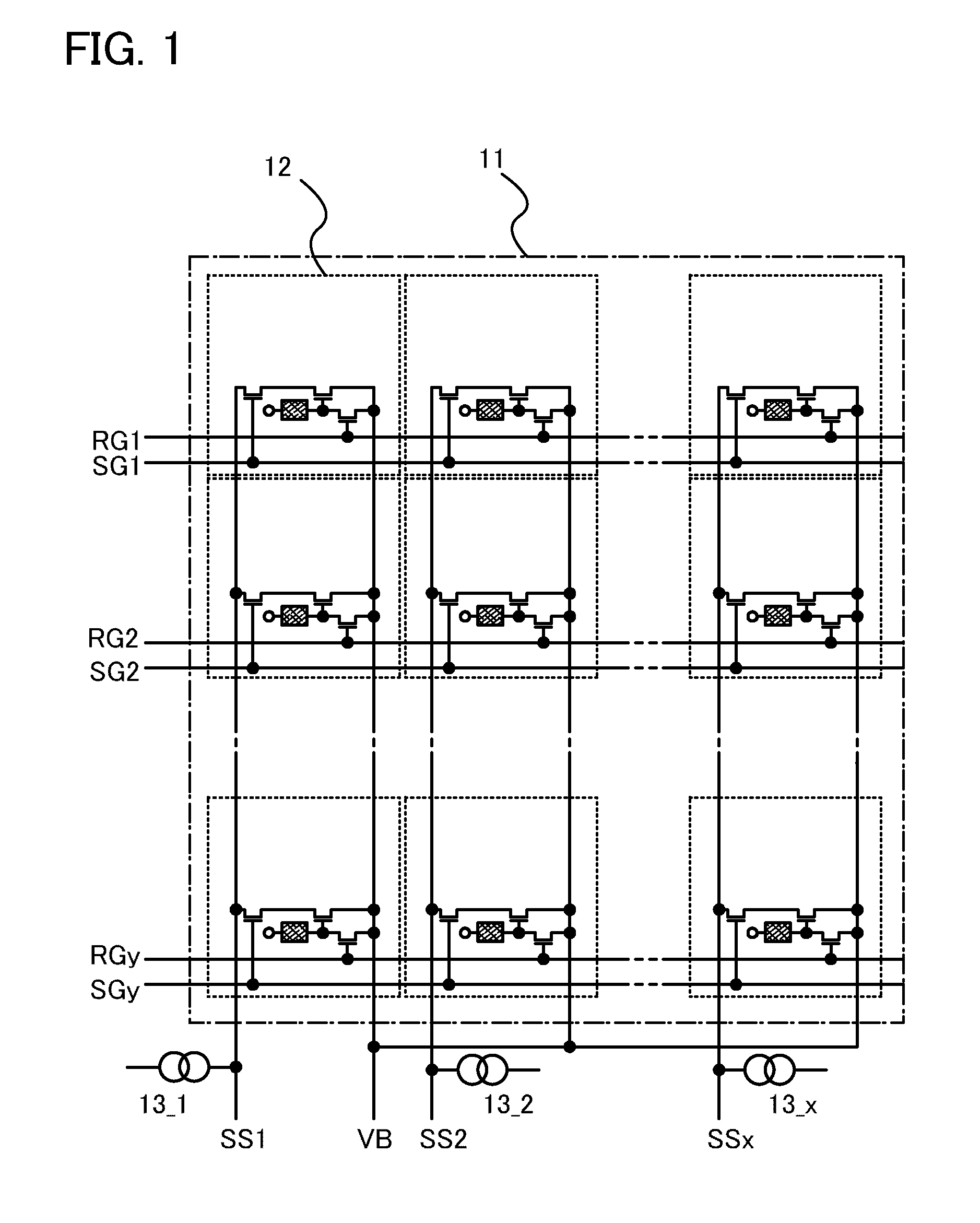

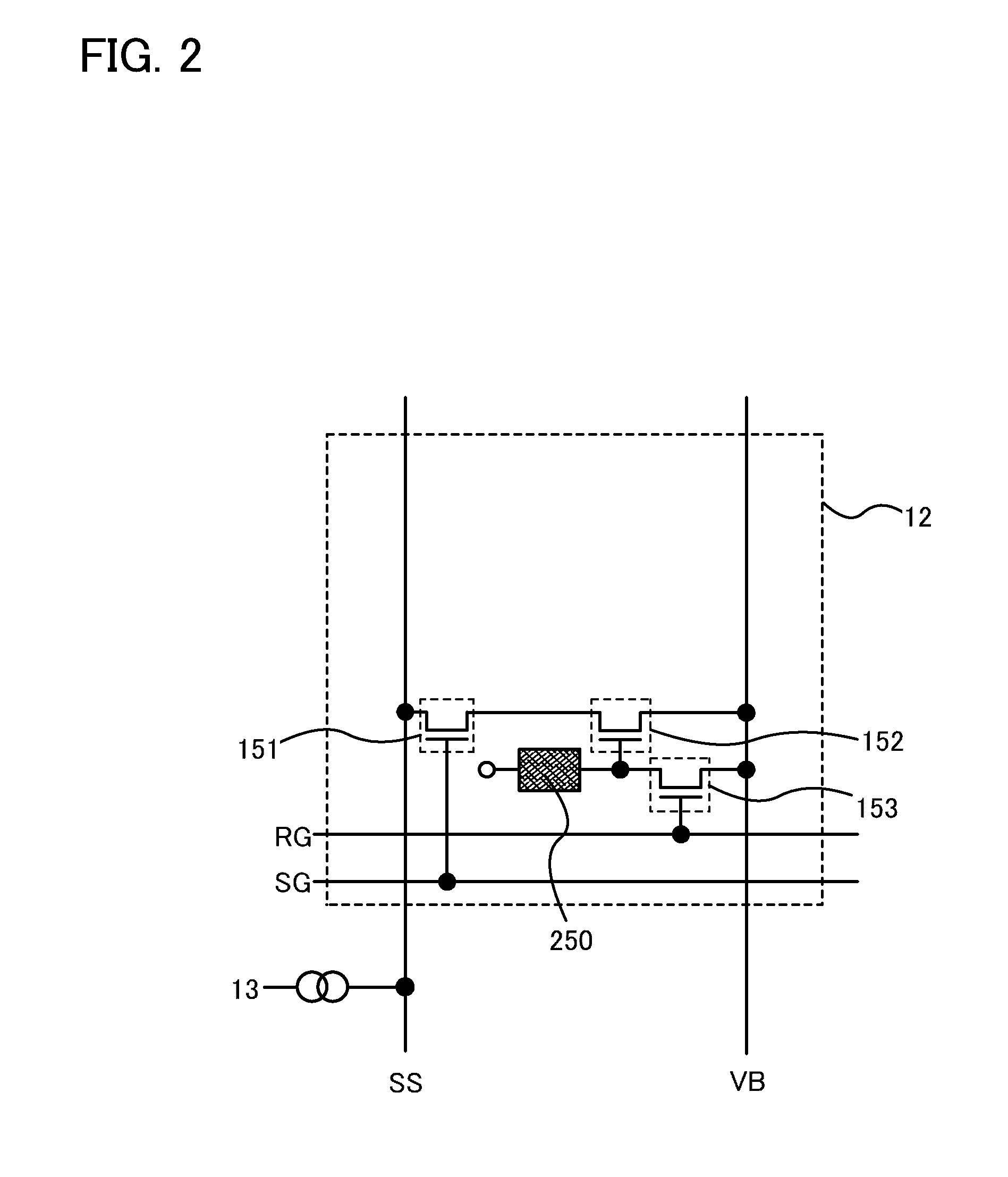

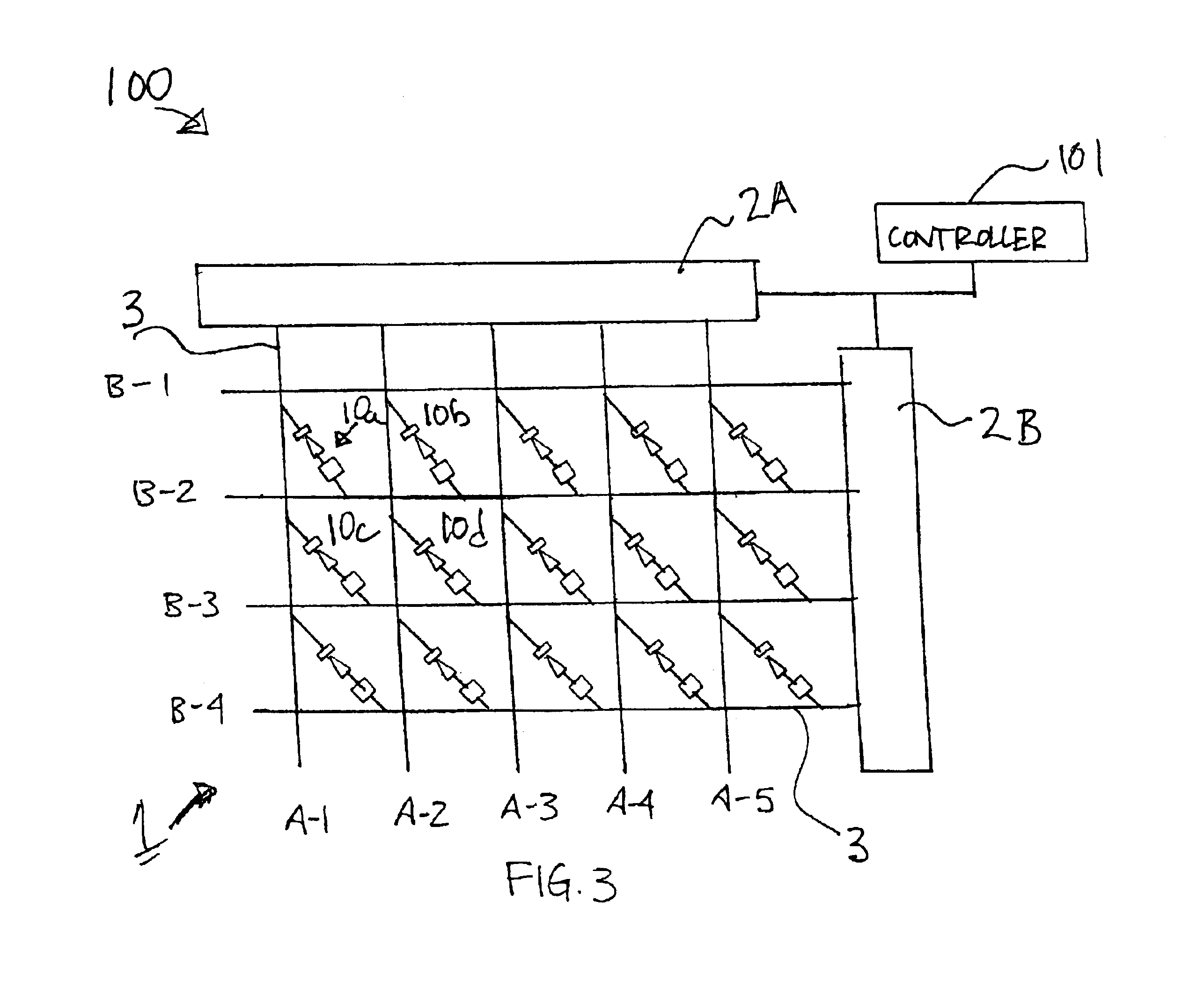

Photosensor and display device

ActiveUS20100134735A1Good reproducibilitySmall display unevennessTransistorStatic indicating devicesDriver circuitIndium

Thin film transistors including an oxide semiconductor containing indium, gallium, and zinc are easily arranged in a matrix over a large substrate and have small characteristic variations. With amplifier circuits and driver circuits of display elements which include the thin film transistors including an oxide semiconductor containing indium, gallium, and zinc with small characteristic variations, intensity distribution of light received by the photodiodes arranged in a matrix is converted into electrical signals with high reproducibility and output, and the display elements arranged in a matrix can be uniformly driven.

Owner:SEMICON ENERGY LAB CO LTD

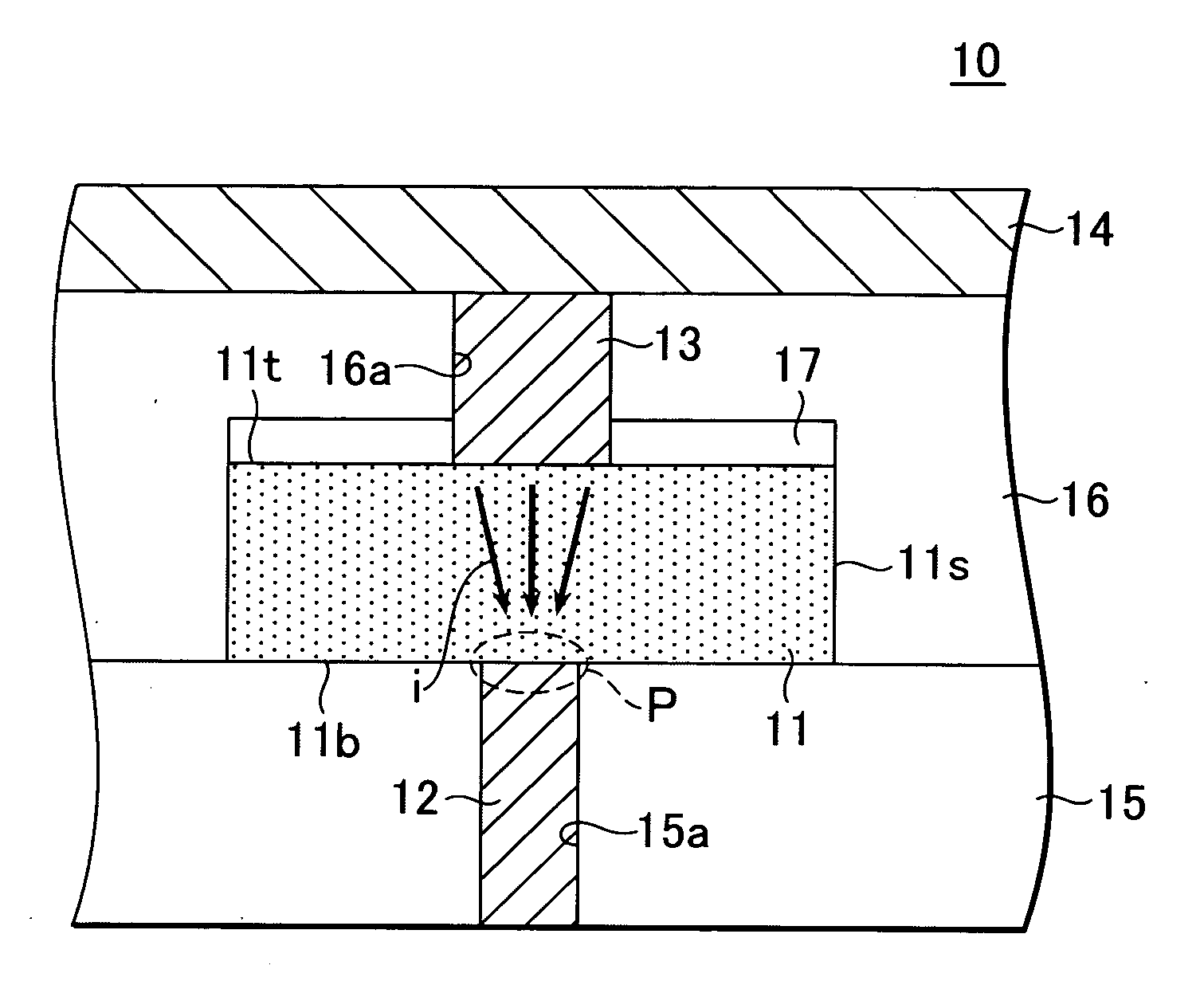

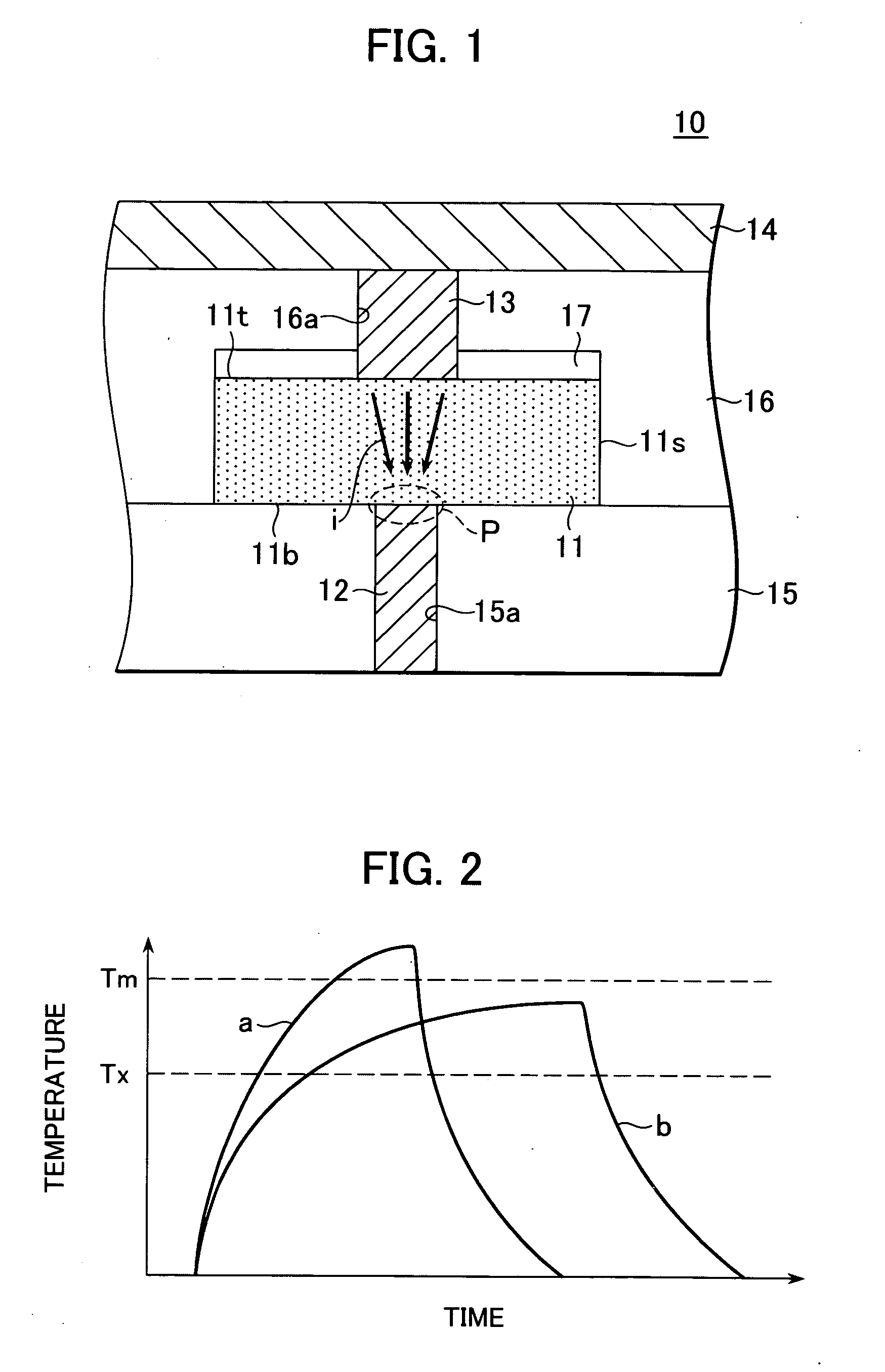

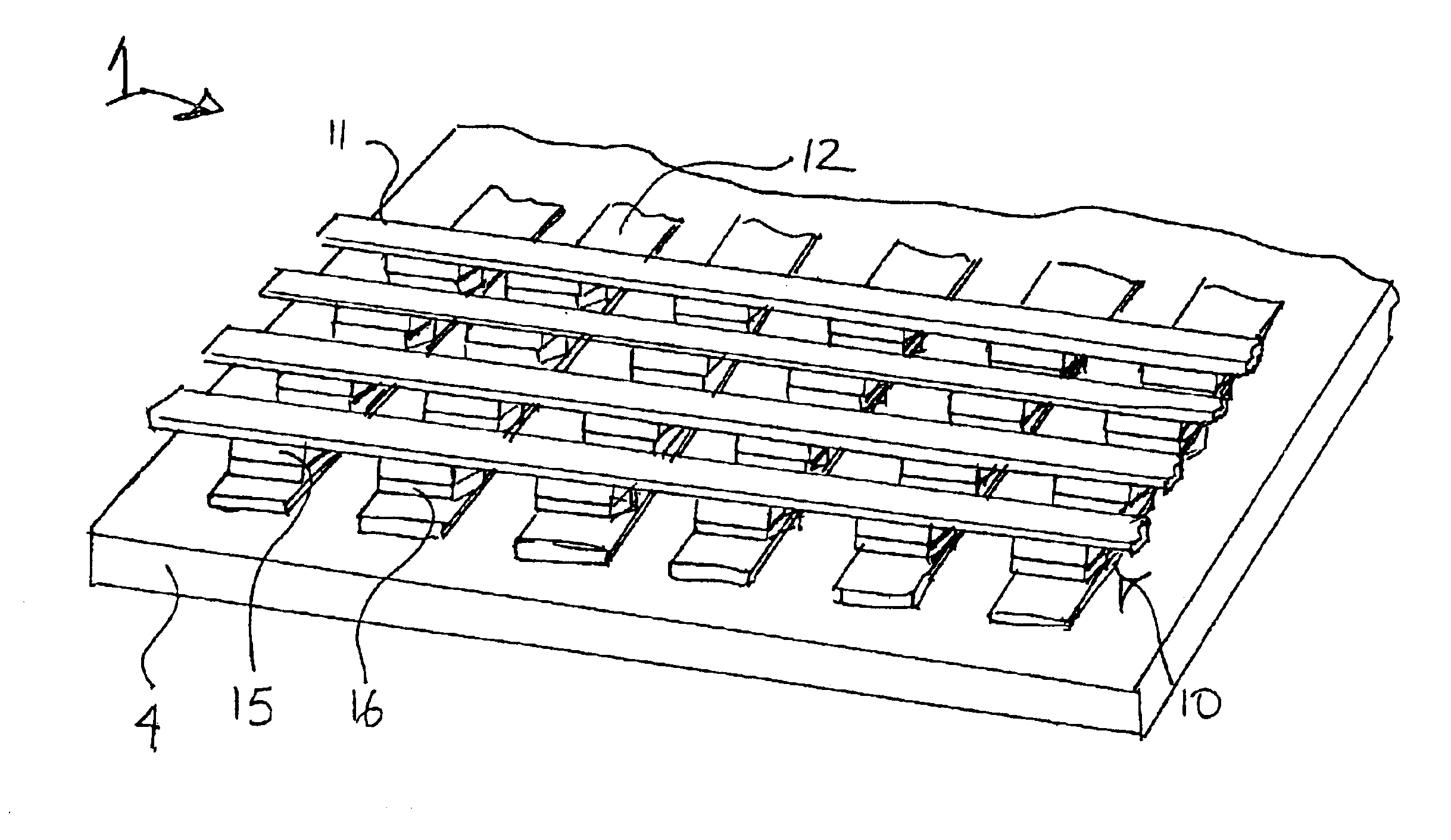

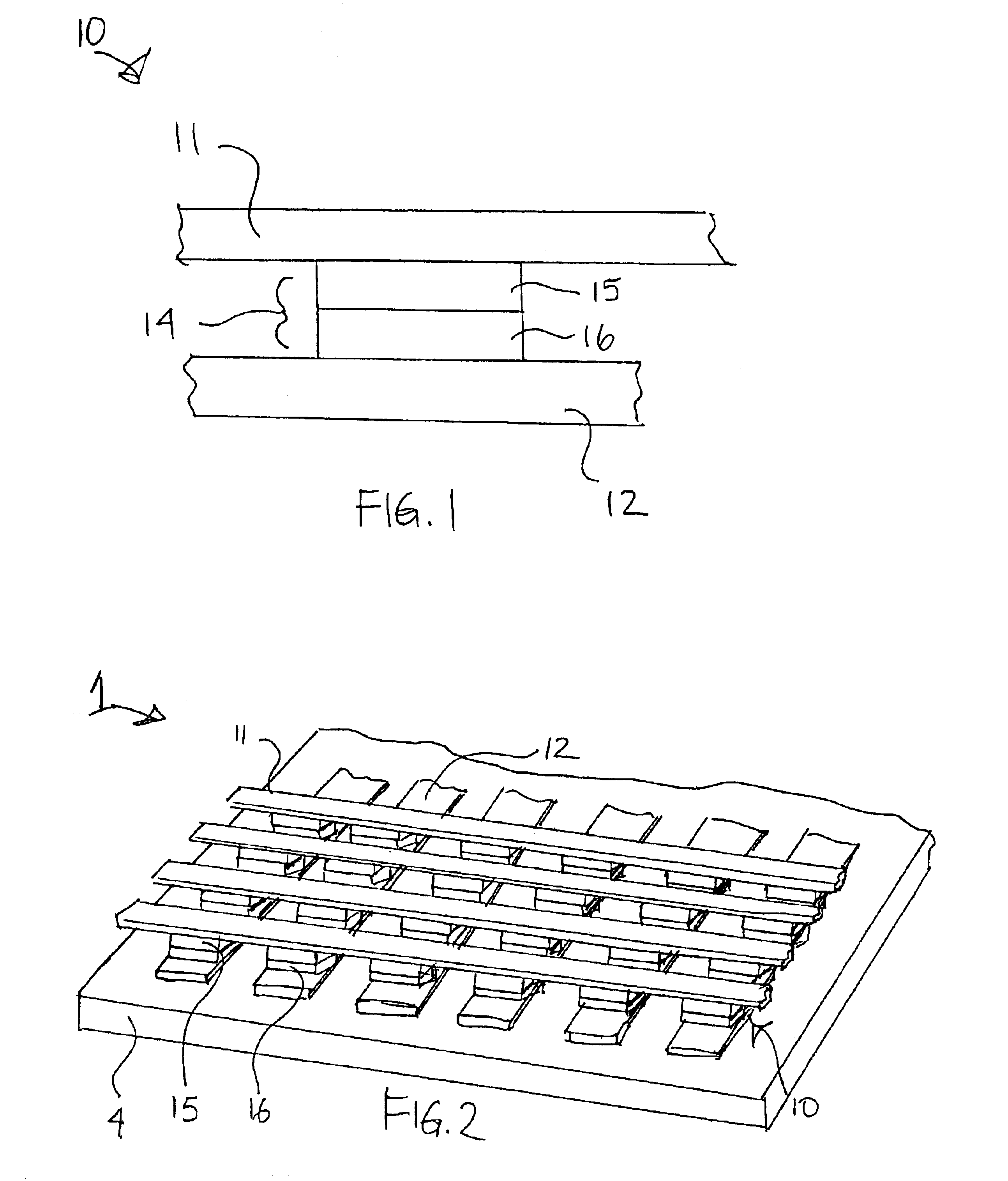

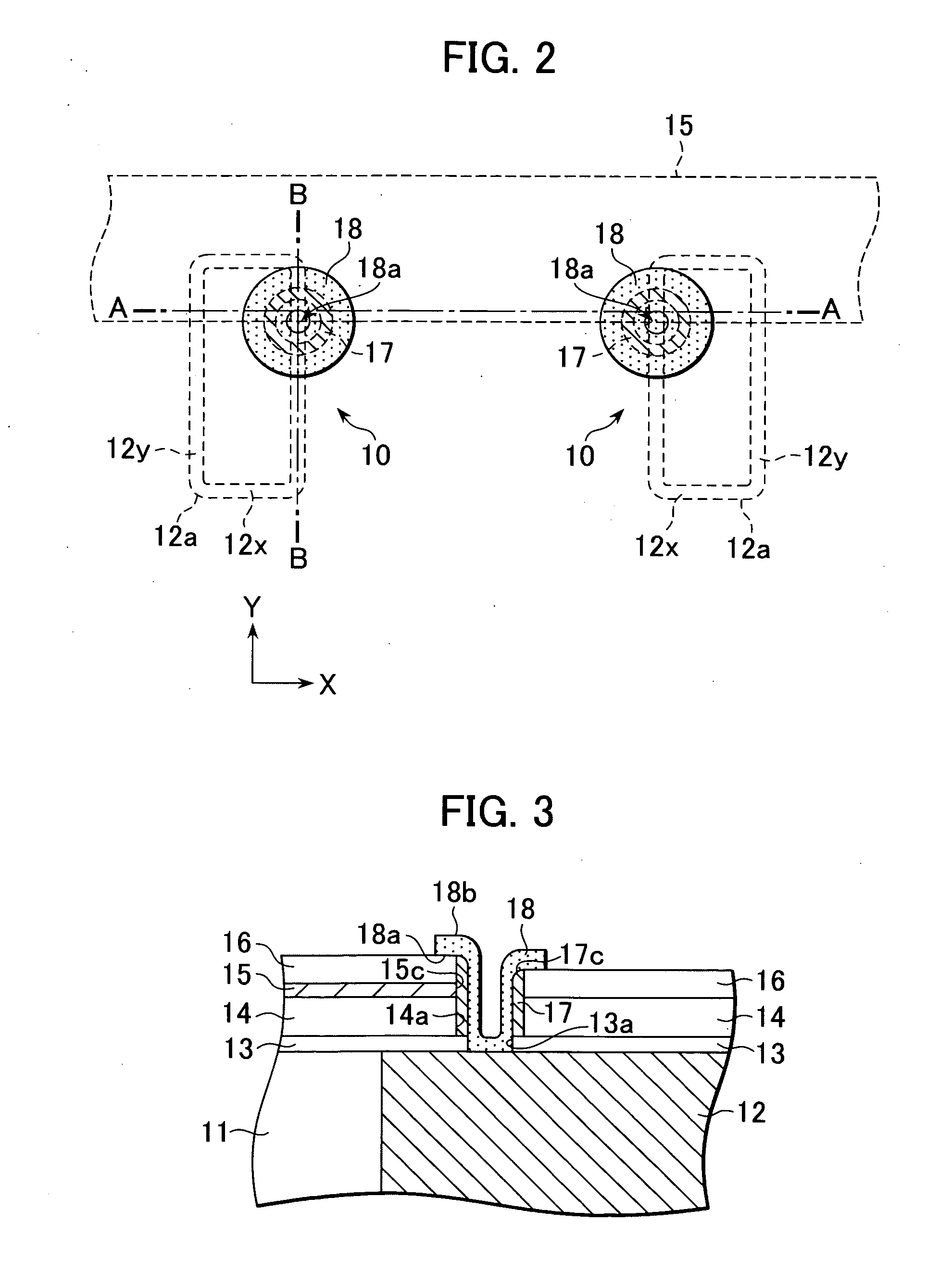

Electrically rewritable non-volatile memory element and method of manufacturing the same

InactiveUS20070063180A1Minimizing damageImprove thermal efficiencySolid-state devicesBulk negative resistance effect devicesEngineeringRecording layer

A non-volatile memory element includes a recording layer that includes a phase change material, a lower electrode provided in contact with the recording layer, an upper electrode provided in contact with a portion of the upper surface of the recording layer, a protective insulation film provided in contact with the other portion of the upper surface of the recording layer, and an interlayer insulation film provided on the protective insulation film. High thermal efficiency can thereby be obtained because the size of the area of contact between the recording layer and the upper electrode is reduced. Providing the protective insulation film between the interlayer insulation film and the upper surface of the recording layer makes it possible to reduce damage sustained by the recording layer during patterning of the recording layer or during formation of the through-hole for exposing a portion of the recording layer.

Owner:ELPIDA MEMORY INC

Memory device with active and passive layers

InactiveUS6858481B2Improve reading speedIncrease write speedNanoinformaticsSolid-state devicesAmount of substanceElectron mobility

A memory including memory cells having active and passive layers may store multiple information bits. The active layer may include an organic polymer that has a variable resistance based on the movement of charged species (ions or ions and electrons) between the passive layer and the active layer. The passive layer may be a super-ionic material that has high ion and electron mobility. The active layer may be self-assembled from a monomer in a liquid or gas.

Owner:SPANSION LLC

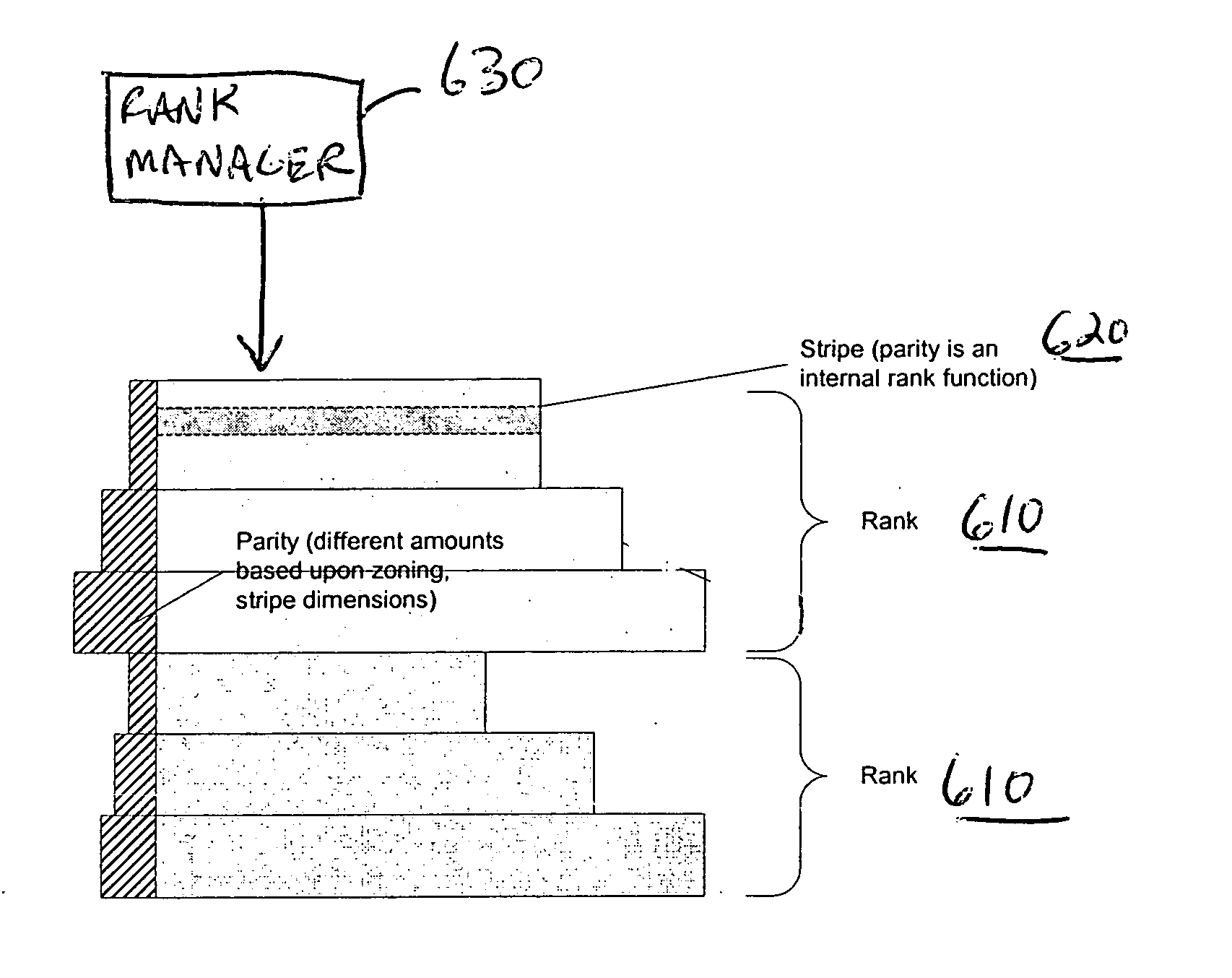

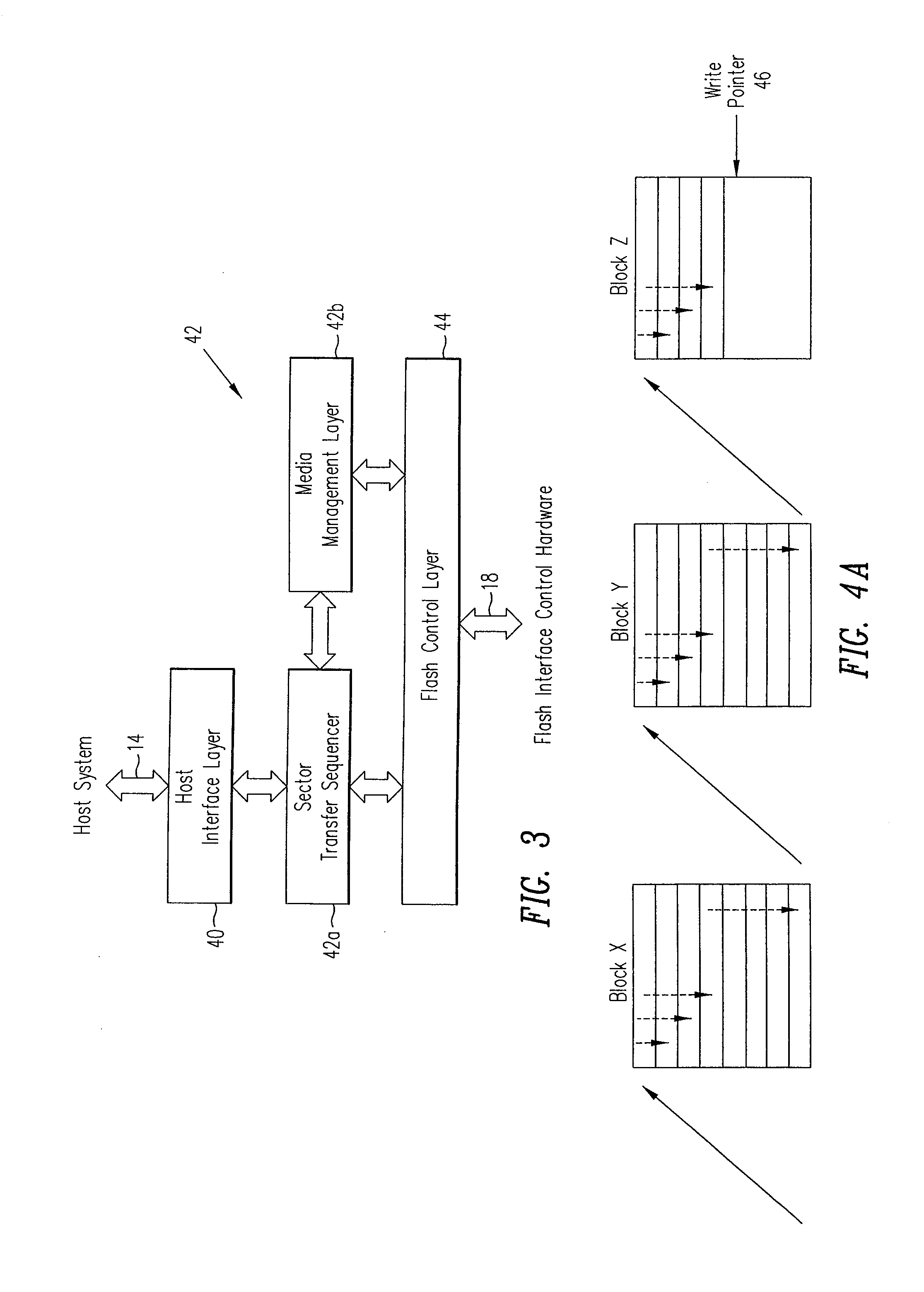

Transaction-based storage system and method that uses variable sized objects to store data

ActiveUS20050257083A1Increase write speedImprove reading speedMemory loss protectionError detection/correctionExtendible hashingBinary tree

The present invention provides a storage system for storing variable sized objects. The storage system is preferably a transaction-based system that uses variable sized objects to store data. The storage system is preferably implemented using arrays disks that are arranged in ranks. Each rank includes multiple stripes. Each stripe may be read and written as a convenient unit for maximum performance. A rank manager is able to dynamically configure the ranks to adjust for failed and added disks by selectively shortening and lengthening the stripes. The storage system may include a stripe space table that contains entries describing the amount of space used in each stripe. An object map provides entries for each object in the storage system describing the location (e.g., rank, stripe and offset values), the length and version of the object. A volume index translates regions of logical storage into object identifiers. The storage system may implement various types of formats such as I-node, binary tree and extendible hashing formats.

Owner:COUSINS ROBERT E

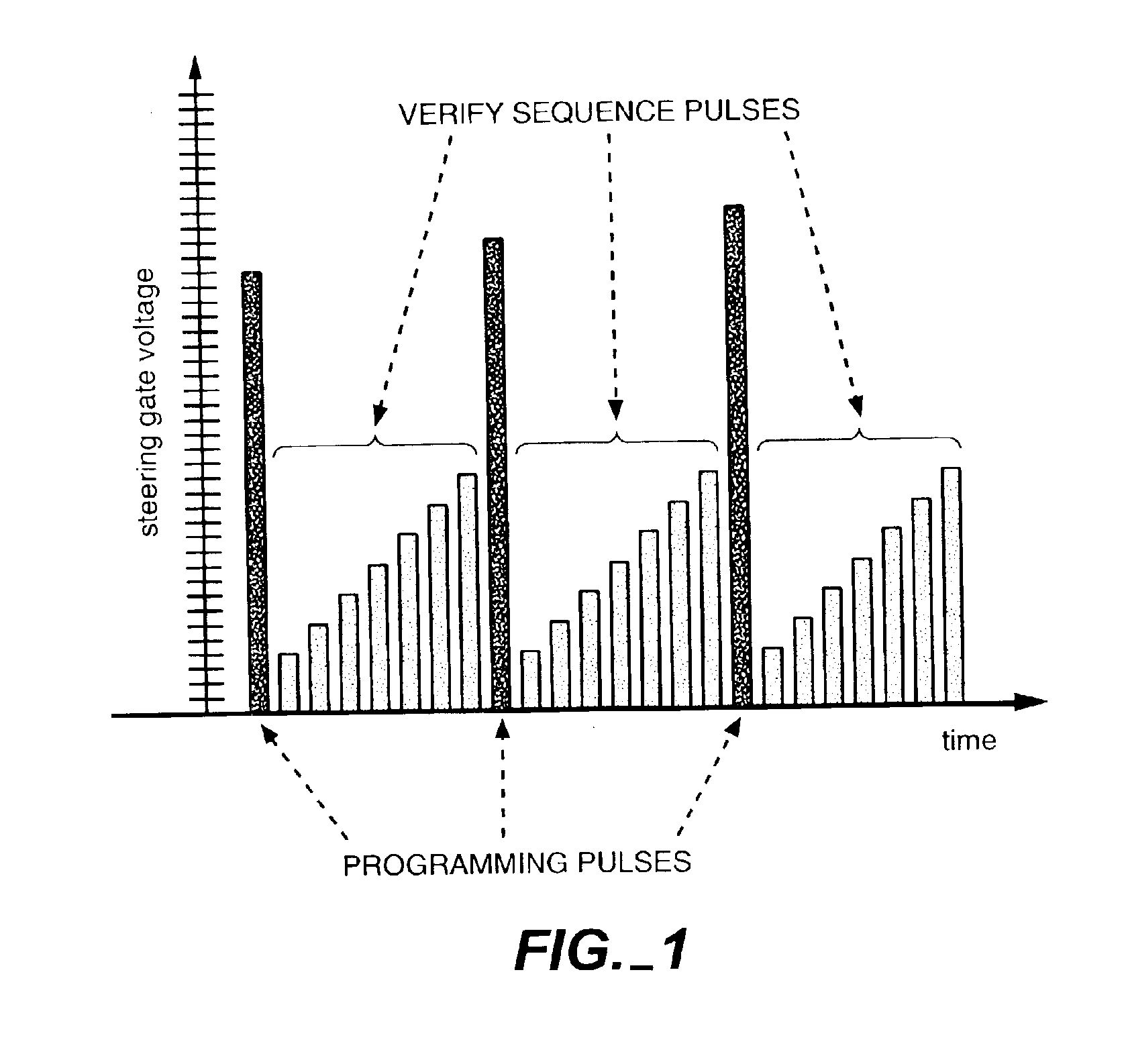

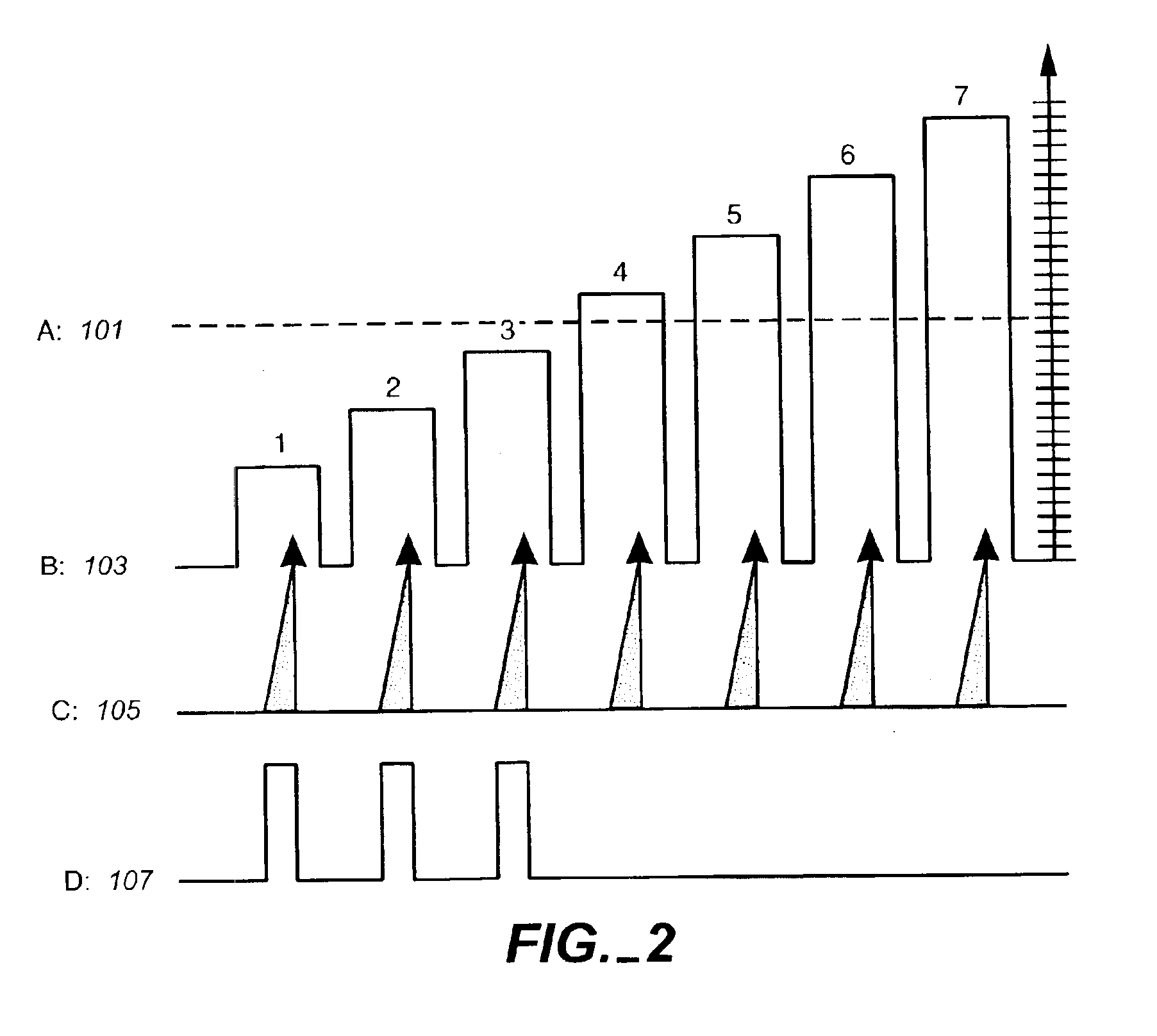

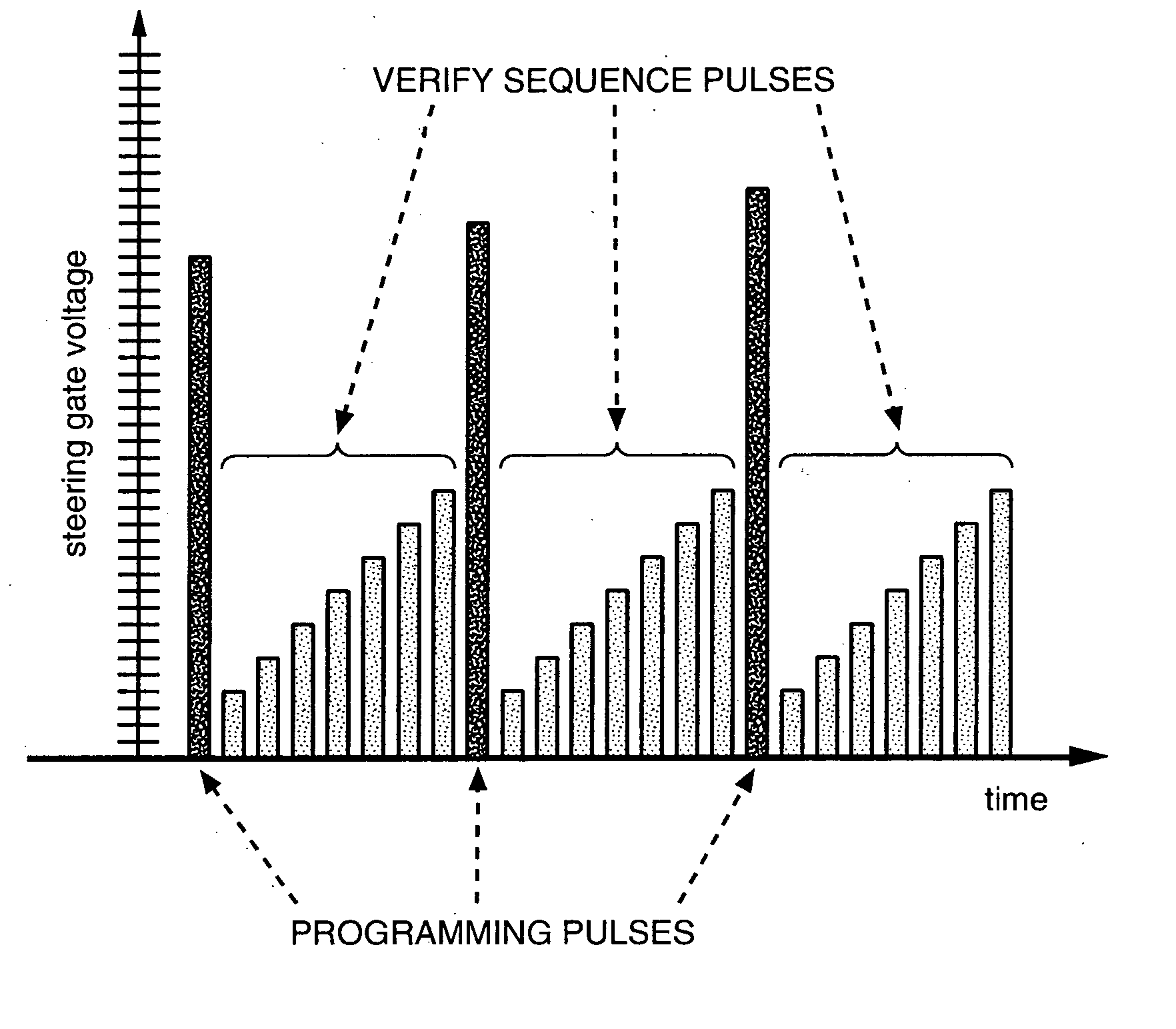

Smart verify for multi-state memories

InactiveUS20060107136A1Increase multi-state write speedMinimizes numberRead-only memoriesDigital storageMulti stateIntelligent verification

The present invention presents a “smart verify” technique whereby multi-state memories are programmed using a verify-results-based dynamic adjustment of the multi-states verify range for sequential-state-based verify implementations. This technique can increase multi-state write speed while maintaining reliable operation within sequentially verified, multi-state memory implementations. It does so by providing “intelligent” means to minimize the number of sequential verify operations for each program / verify / lockout step of the write sequence. In an exemplary embodiment of the write sequence for the multi-state memory during a program / verify cycle sequence of the selected storage elements, at the beginning of the process only the lowest state of the multi-state range to which the selected storage elements are being programmed is checked during the verify phase. Once the first storage state is reached by one or more of the selected elements, the next state in the sequence of multi-states is added to the verify process. This next state can either be added immediately upon the fastest elements reaching this preceding state in the sequence or after a delay of several program cycles. The adding of states to the set being checked in the verify phase continues through the rest of the set of multi-states in sequence, until the highest state has been added. Additionally, lower states can be removed from the verify set as all of the selected storage elements bound for these levels verify successfully to those target values and are locked out from further programming.

Owner:WODEN TECH INC

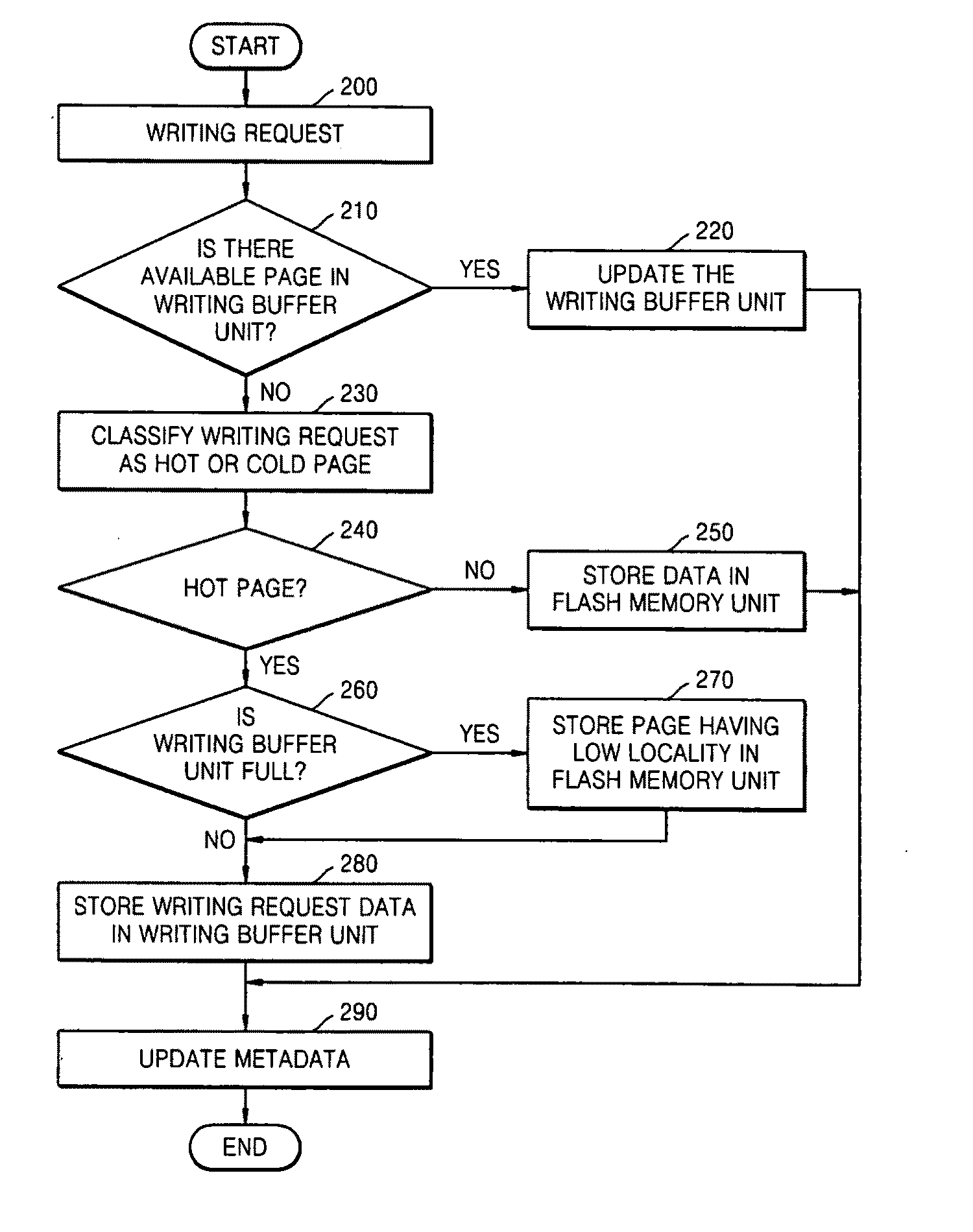

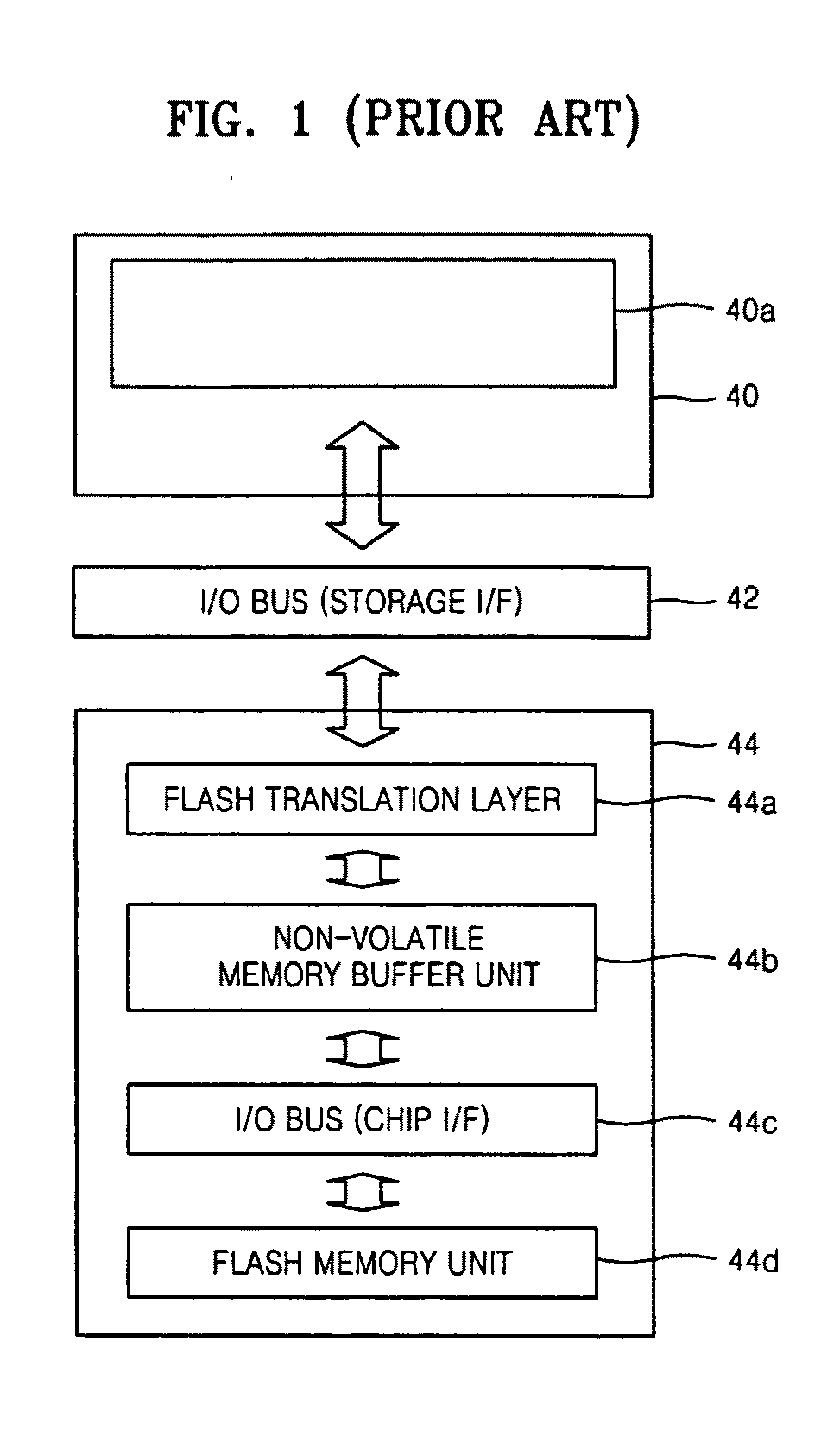

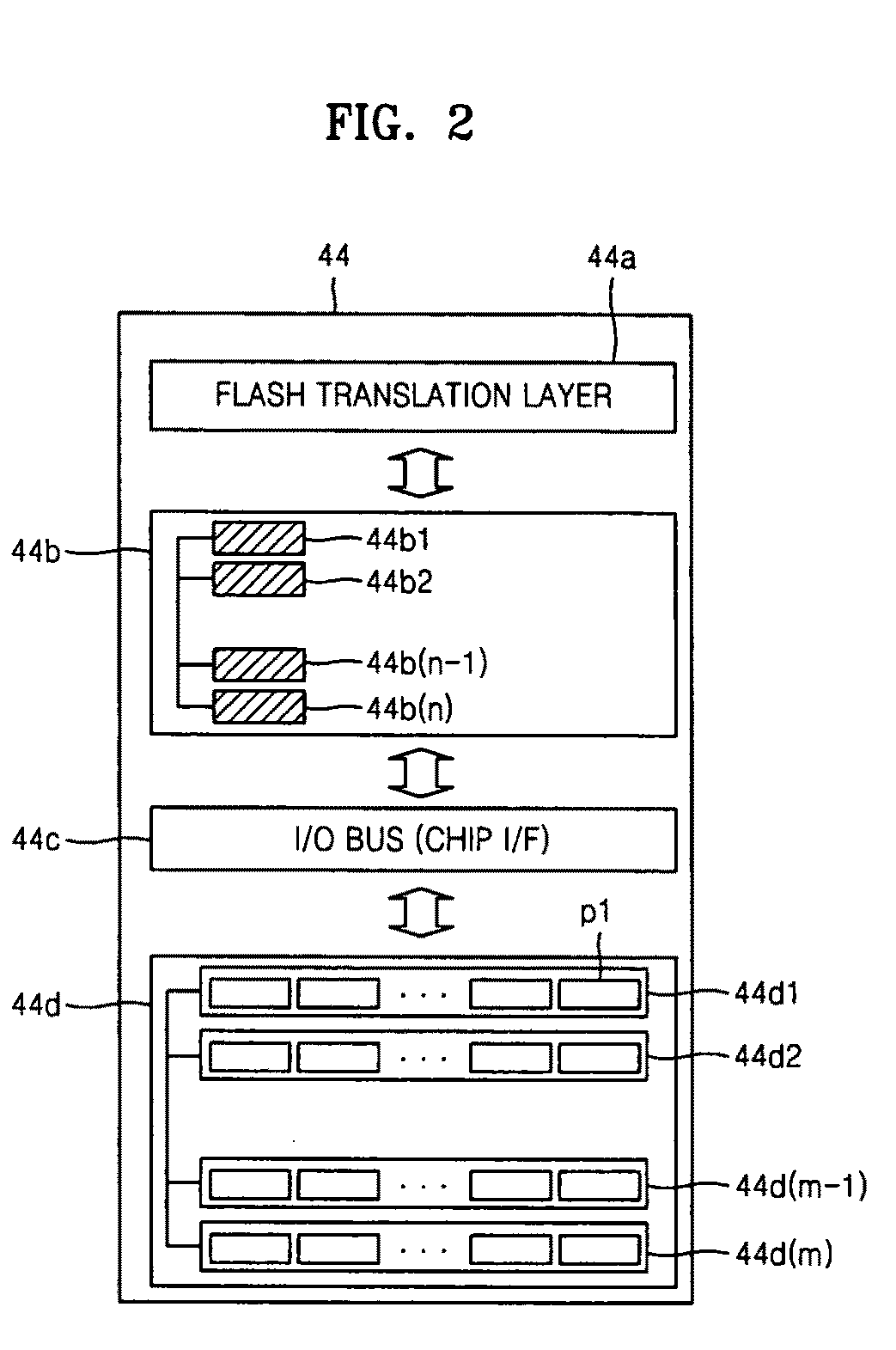

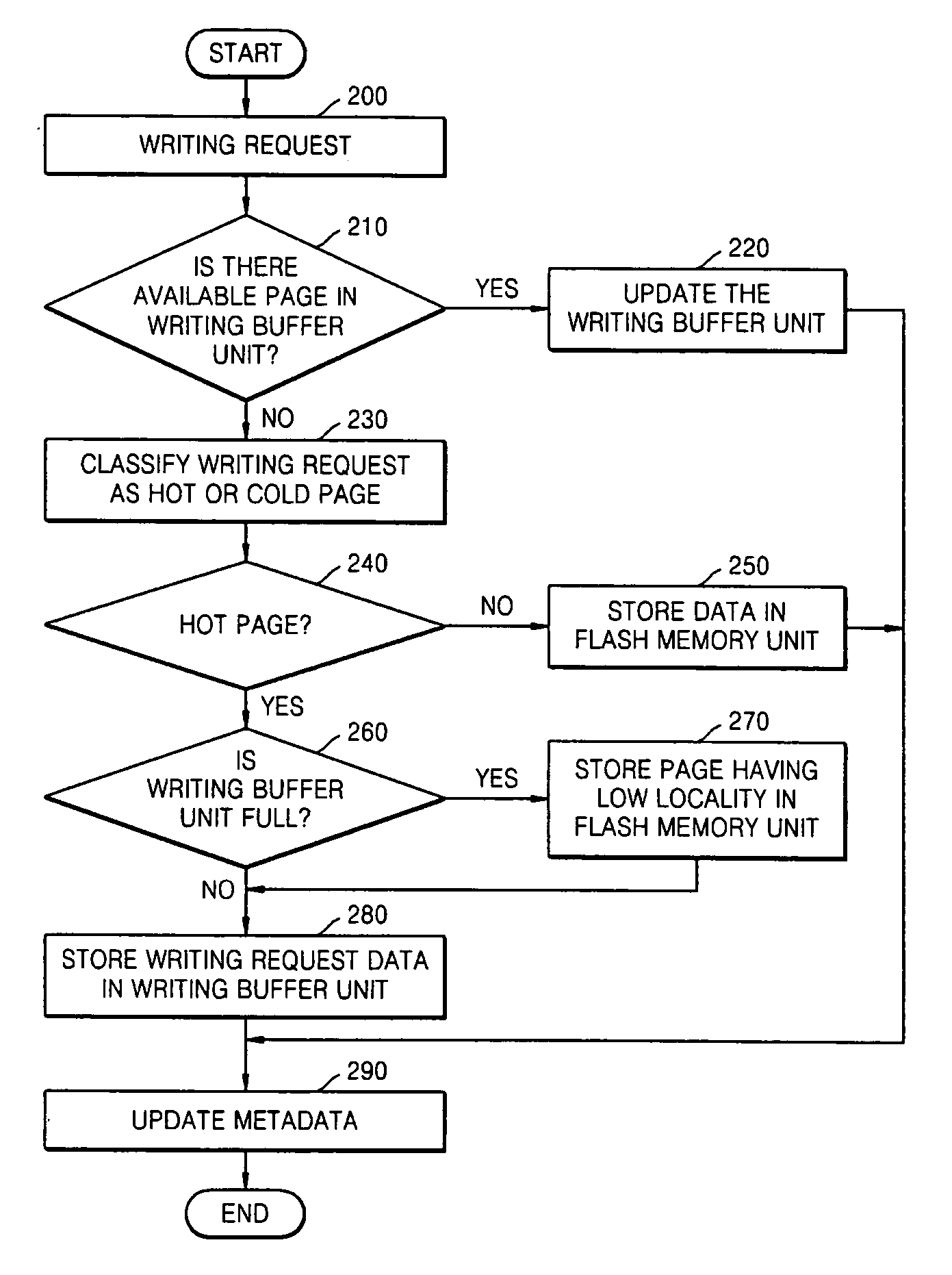

Data storage system with complex memory and method of operating the same

InactiveUS20090144501A2Increase write speedReduce in quantityMemory architecture accessing/allocationStatic storageData storingData store

Owner:SAMSUNG ELECTRONICS CO LTD

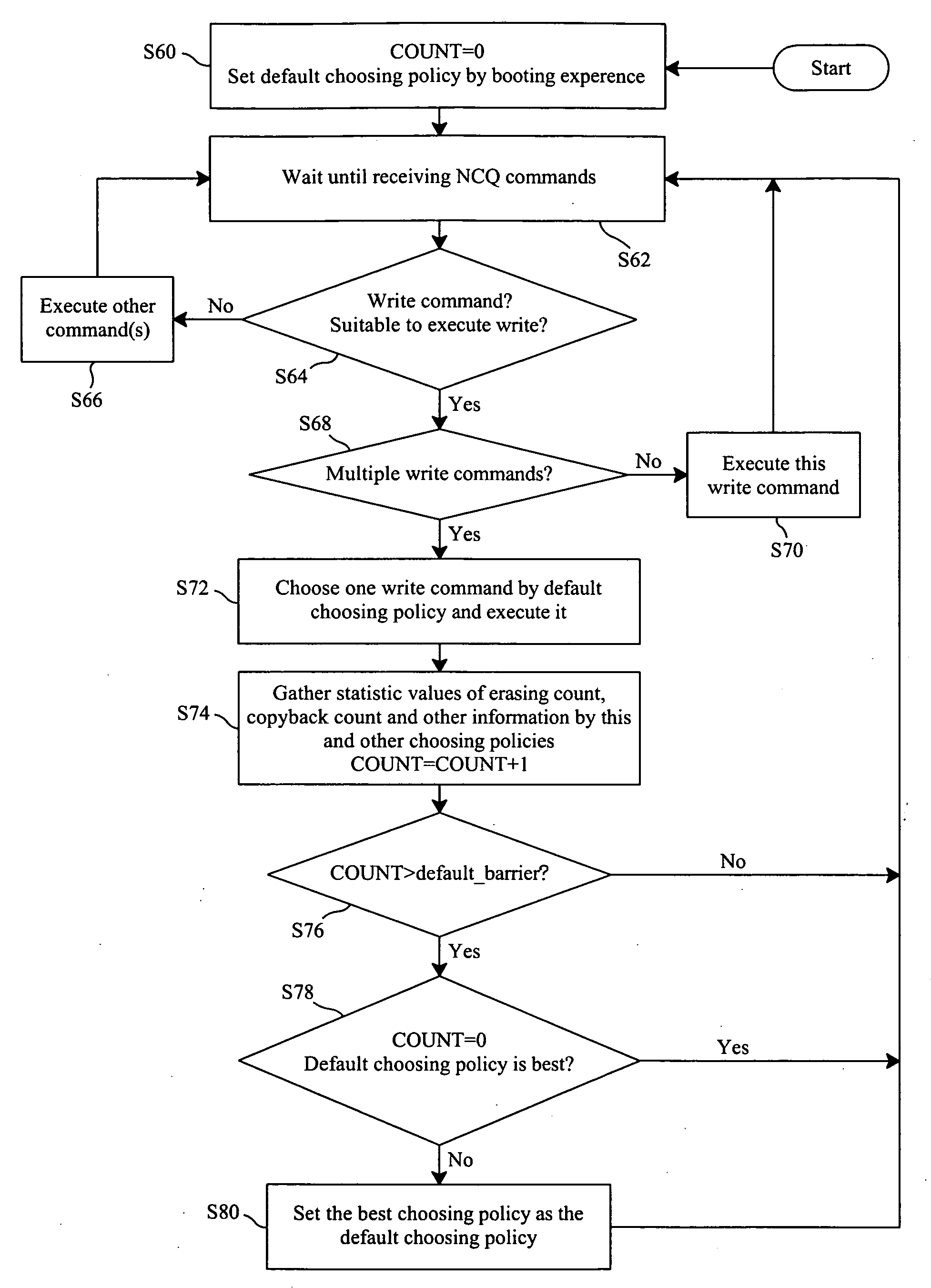

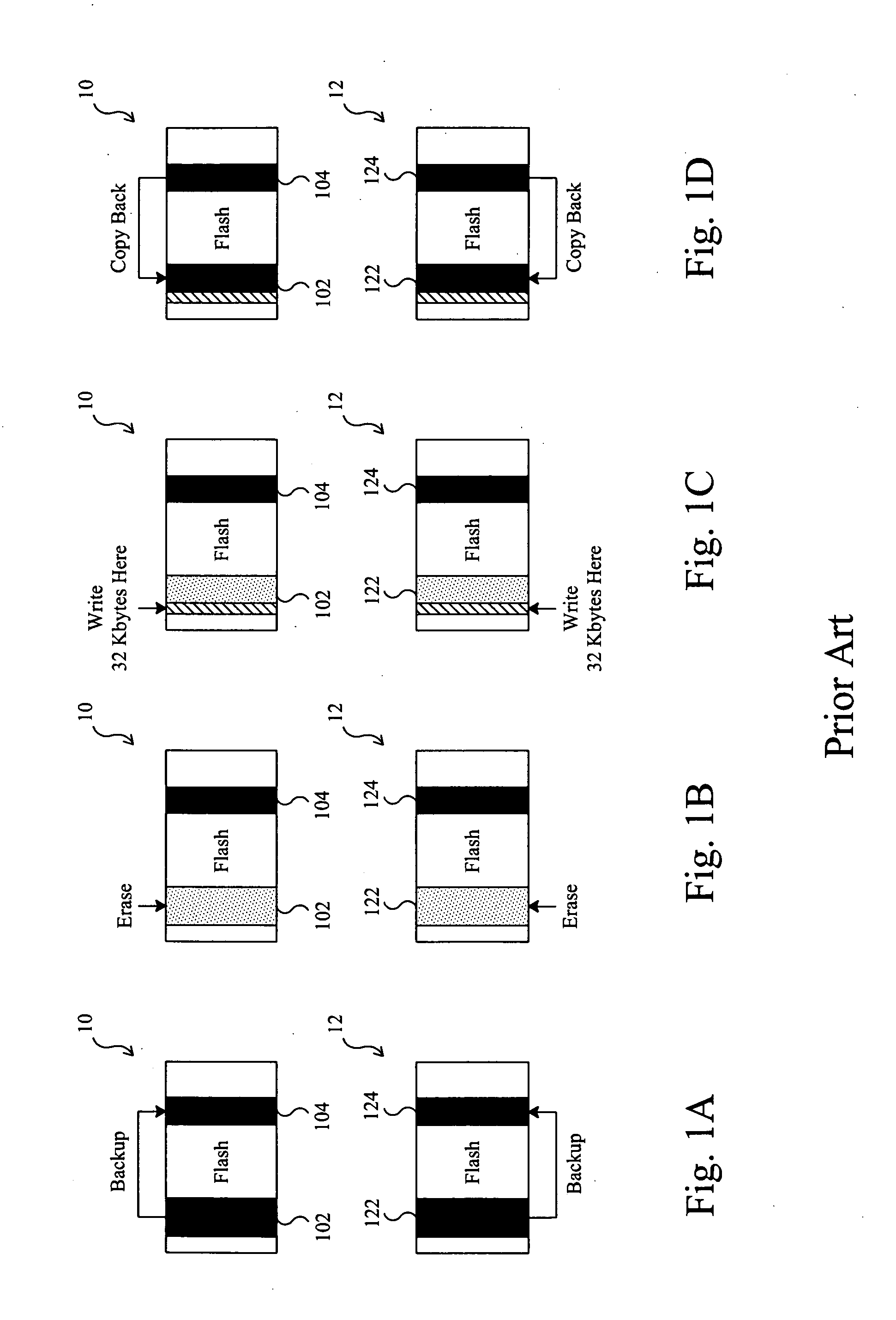

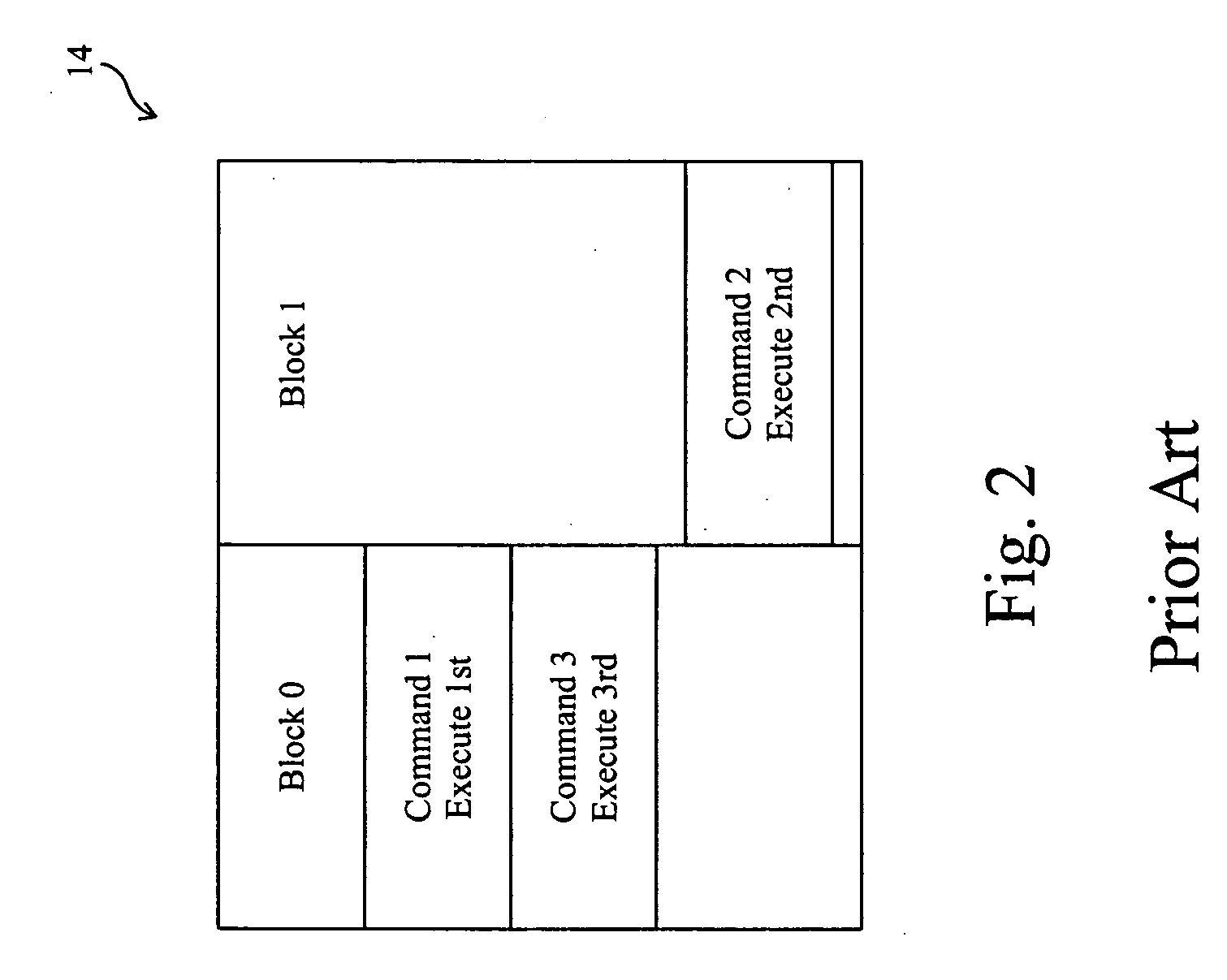

Nonvolatile storage device with NCQ supported and writing method for a nonvolatile storage device

ActiveUS20090164698A1Increase write speedExtended service lifeRead-only memoriesMemory systemsComputer hardwareBackup

A nonvolatile storage device buffers multiple write commands and selects one or more therefrom according to a choosing policy to execute in priority, so as to increase the probability of continuously executing write commands corresponding to an identical smallest erasable unit, thereby reducing the frequency of backup, erasing and copyback operations and improving the efficiency of the nonvolatile storage device.

Owner:SKYMEDI CORPORATION

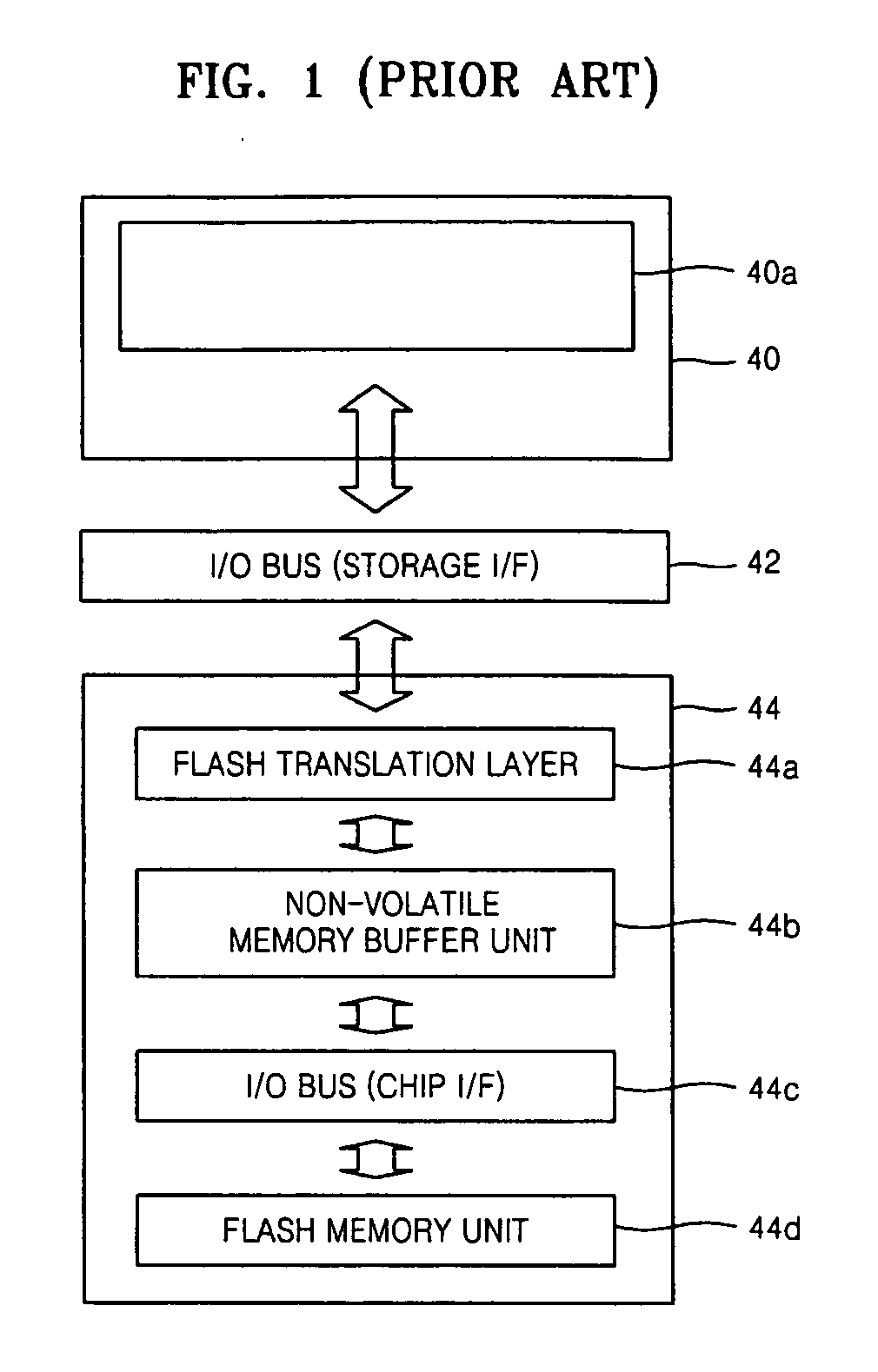

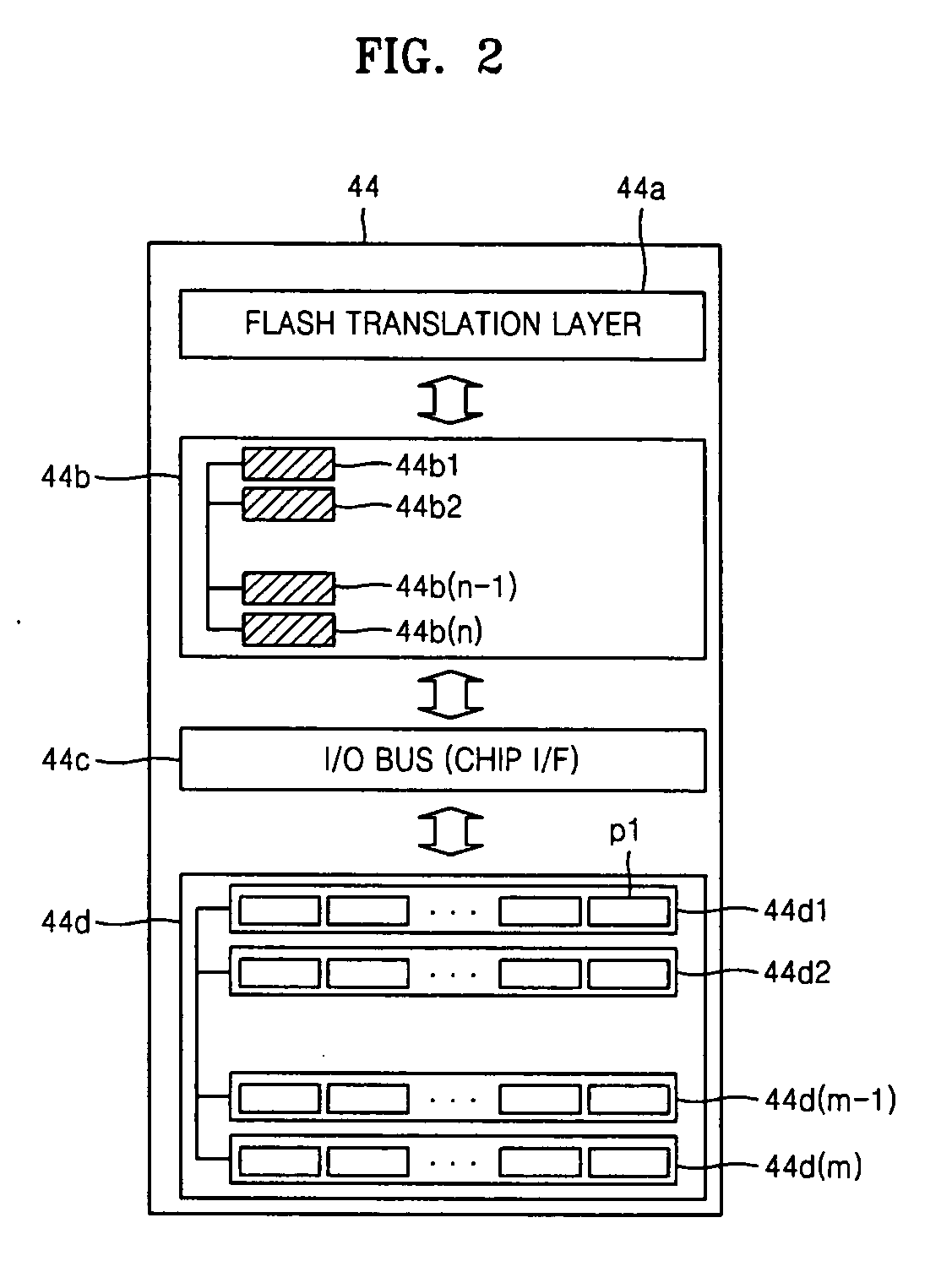

Data storage system with complex memory and method of operating the same

InactiveUS20070038808A1Increase write speedReduce in quantityMemory architecture accessing/allocationStatic storageEngineeringData storing

A data storage system and a data storing method for the data storage system are provided. The data storage system includes a host unit, a storage unit, and a first input / output bus functioning as an interface between the host unit and the storage unit. The storage unit includes a non-volatile memory buffer unit and a flash memory unit. The non-volatile memory buffer unit includes a plurality of buffers arranged in parallel. The flash memory unit includes a plurality of data storage devices arranged in parallel to input and output data using a parallel method. In the method, a writing request is first classified into one of a plurality of grades according to a writing request frequency when there is a writing request and the writing requested data is stored in one of the non-volatile memory buffer unit and the flash memory unit according to the writing request frequency.

Owner:SAMSUNG ELECTRONICS CO LTD

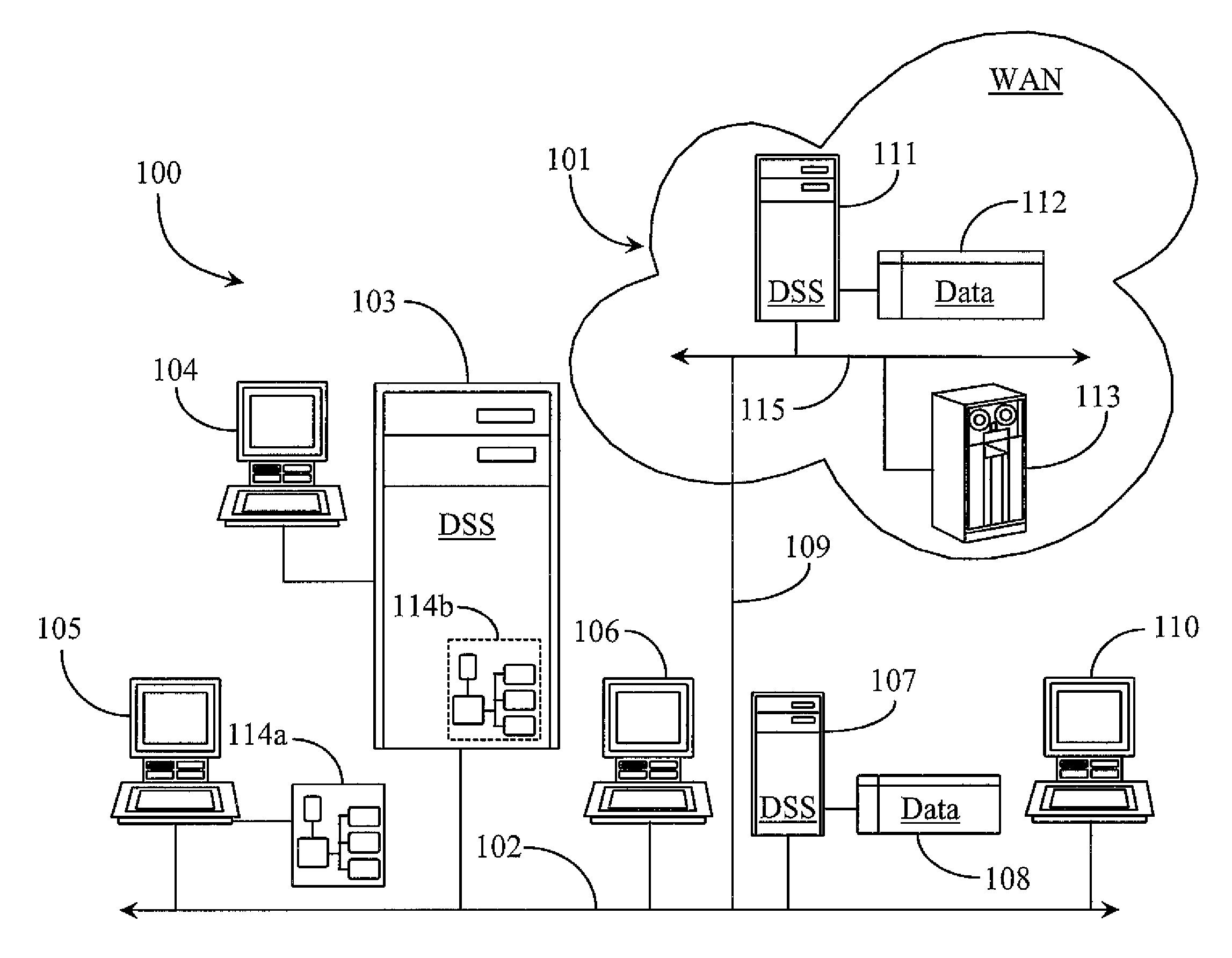

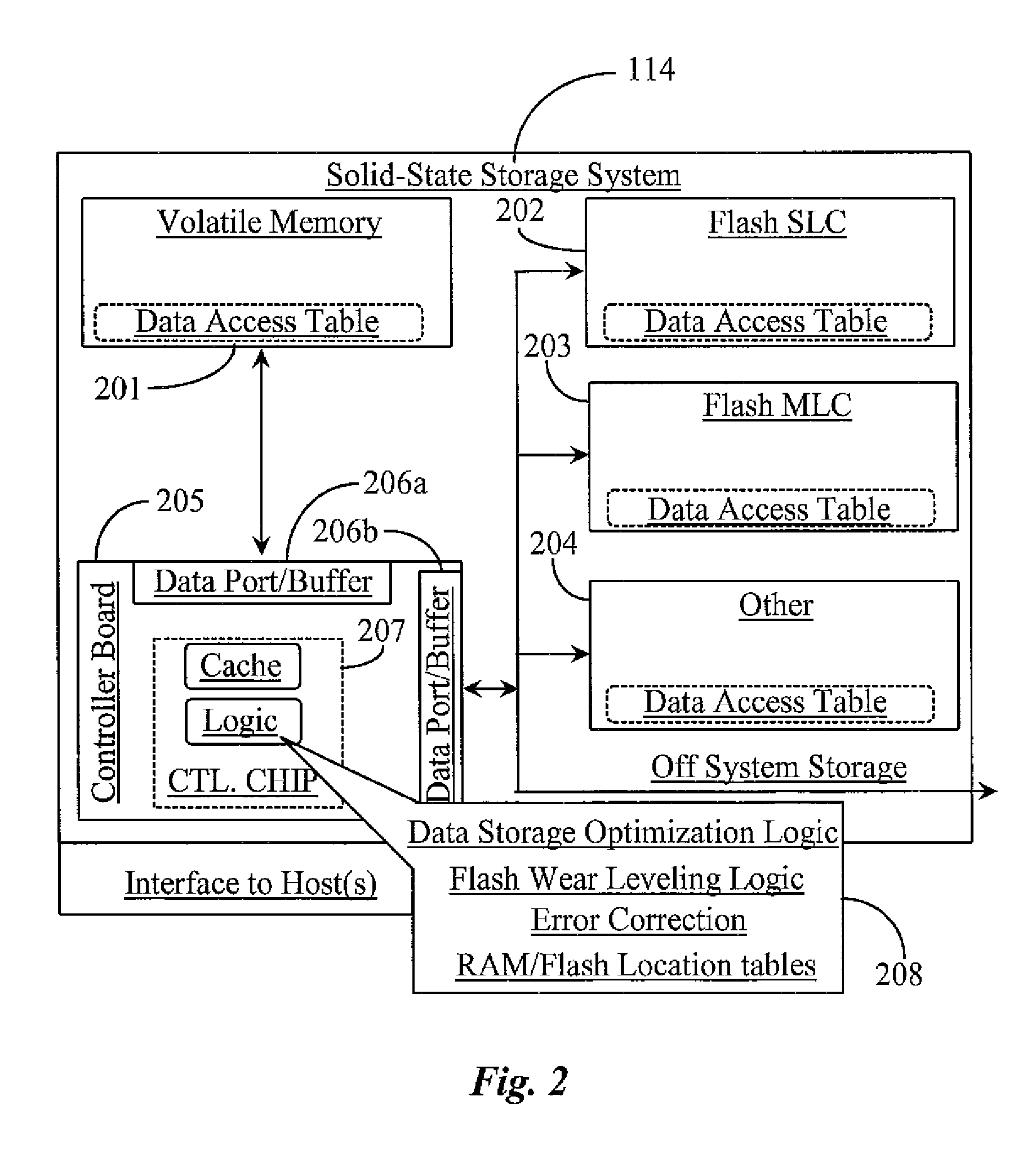

Priority Ordered Multi-Medium Solid-State Storage System and Methods for Use

InactiveUS20110191523A1Low costIncrease write speedMemory architecture accessing/allocationMemory adressing/allocation/relocationSolid-state storageTracking data

A hierarchical data-storage system has a volatile storage medium, a first non-volatile storage medium, and a controller including a ranking engine tracking data writes to each of the memory mediums. Each medium is associated with a pre-set capacity threshold, and the controller, upon the volatile medium reaching its pre-set threshold, identifies one or more blocks of data as least-frequently written to the volatile medium, copies the data in those blocks to the non-volatile medium, and marks those blocks as available for new data writes, and the controller, upon the non-volatile medium reaching its pre-set threshold, identifies one or more blocks of data as least-frequently written to the non-volatile medium, and marks those blocks as available for new data writes from the volatile medium.

Owner:DATARAM MEMORY

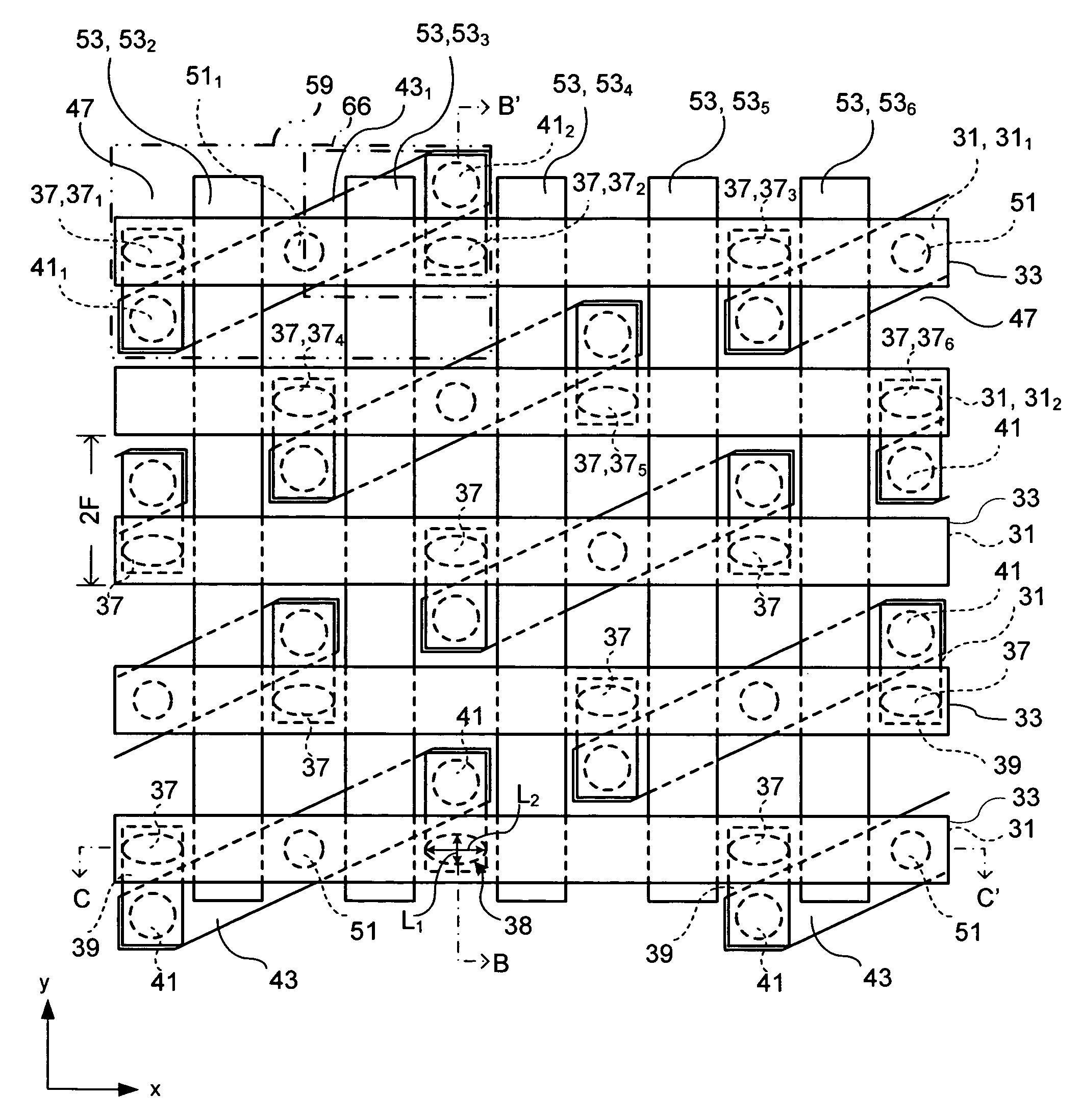

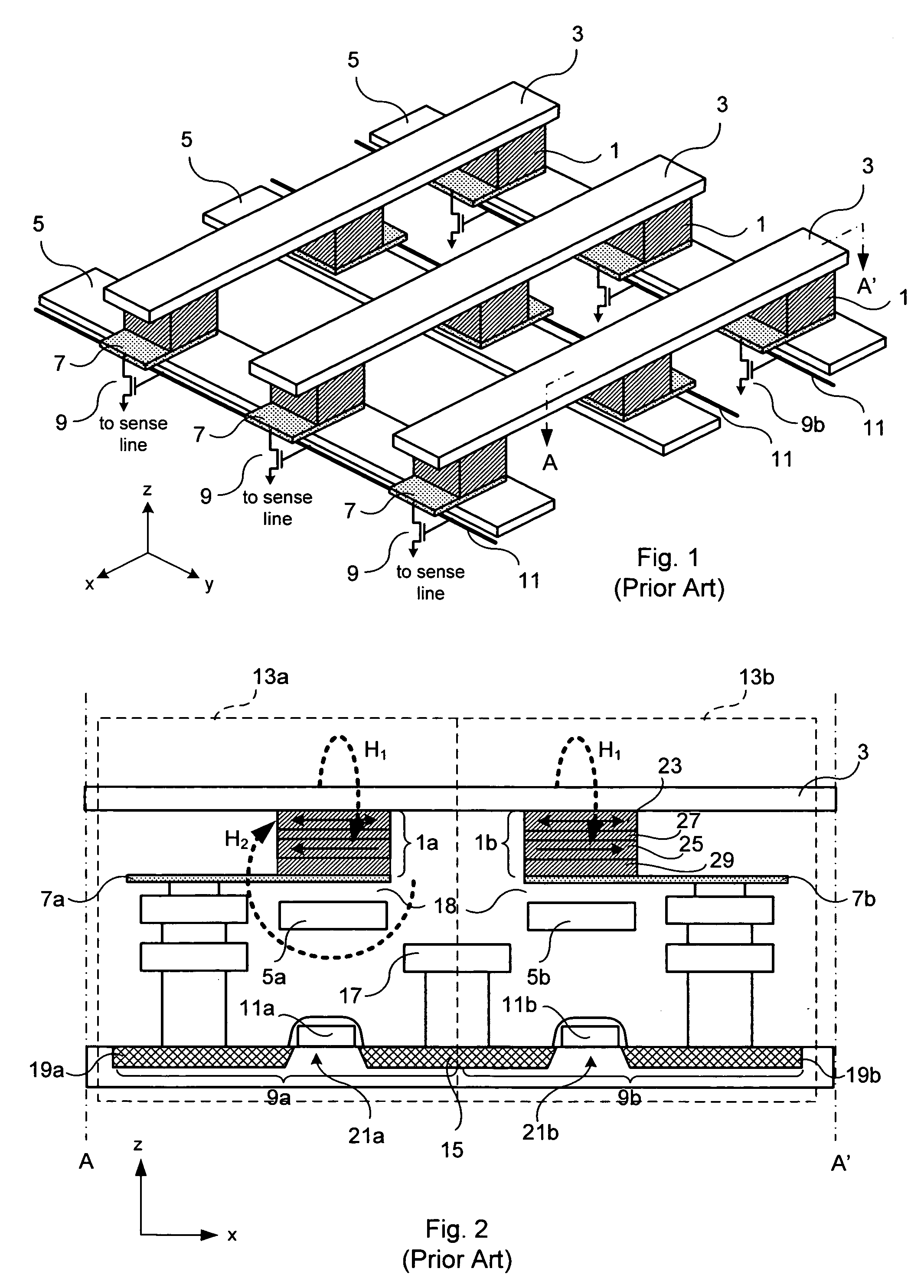

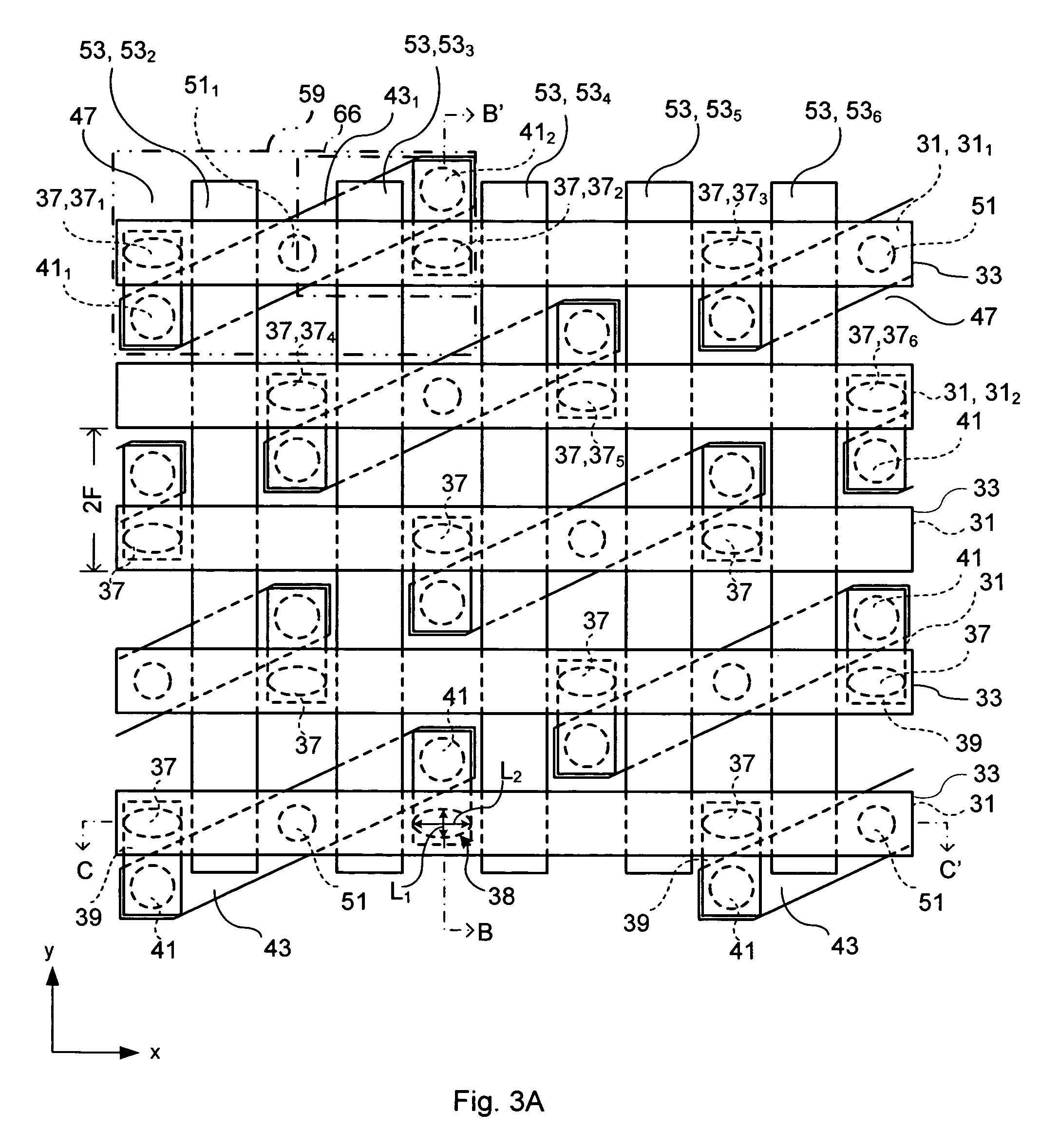

Magnetic memory device

InactiveUS20080037179A1High resistance stateIncrease write speedNanotechRecord information storageHigh resistanceBit line

A magnetic memory device comprises a magnetic tunnel junction (MTJ) connecting to a bit line to a sense line through an isolation transistor. The MTJ includes a ferromagnetic layer having a magnetic hard axis. An assist current line overlies the bit line and is insulated from the bit line. The MTJ is switchable between a first, relatively high resistance state and a second, relatively low resistance state. The assist current line applies a magnetic field along the magnetic hard axis in the ferromagnetic layer, independently of current flow through the MTJ for assisting switching of the MTJ between the first and second states.

Owner:CENT NAT DE LA RECHERCHE SCI +2

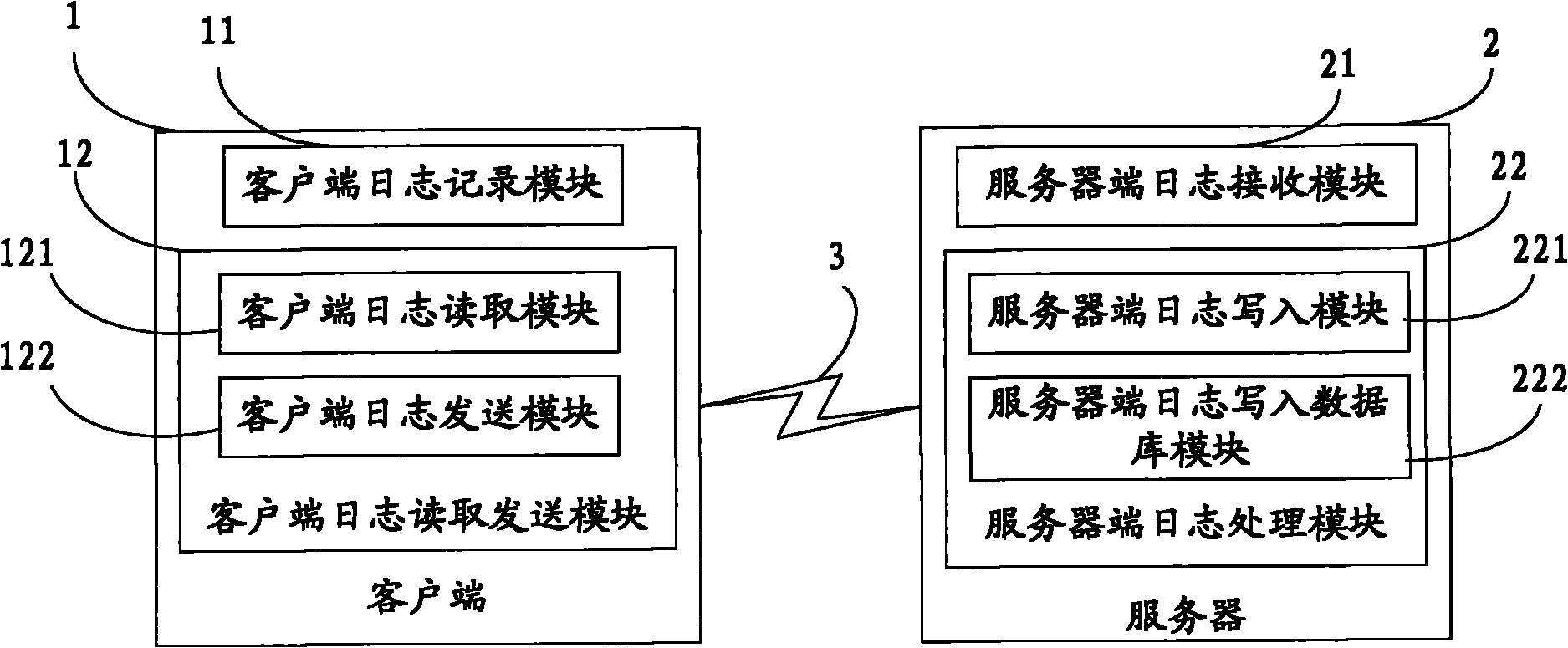

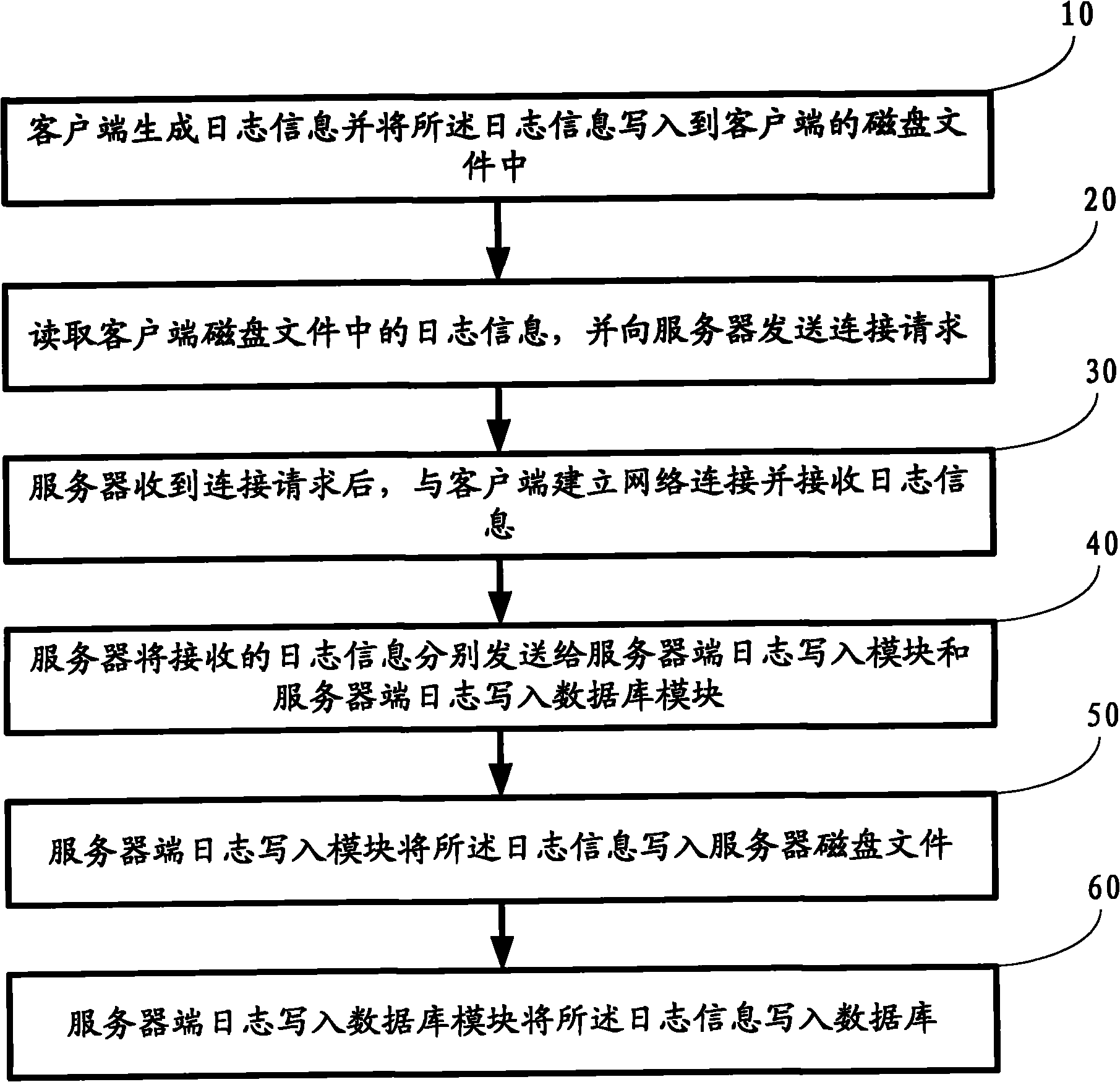

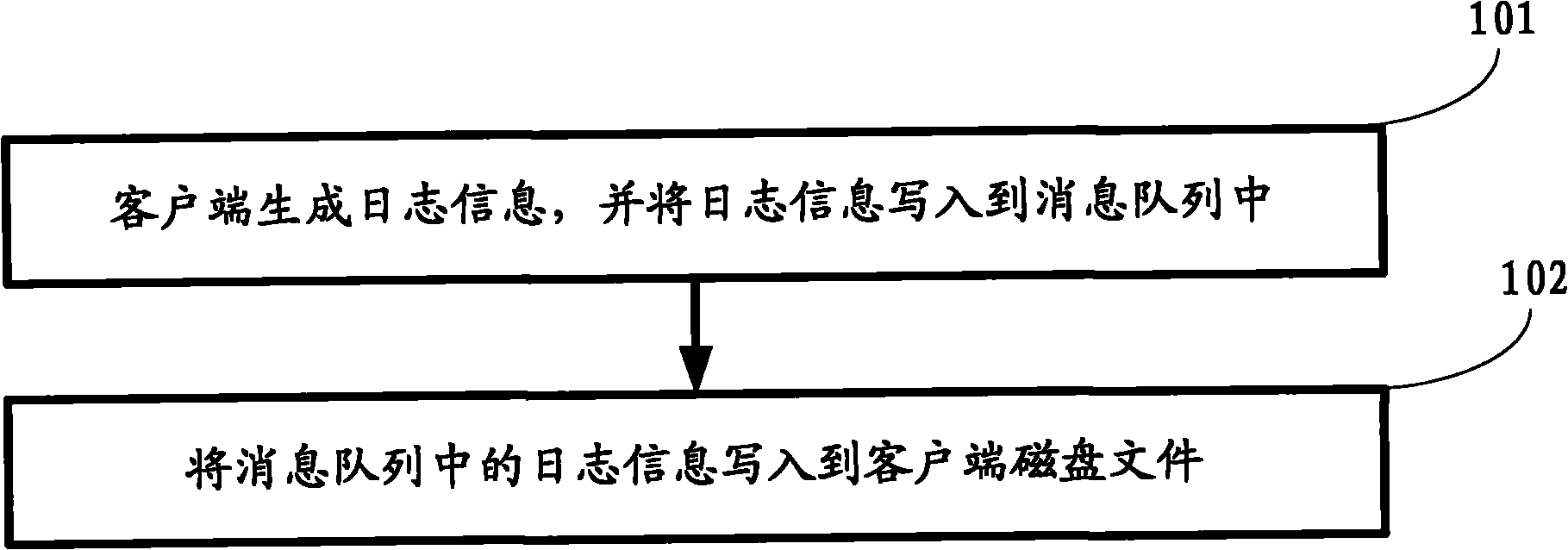

Log acquisition device and log acquisition method

InactiveCN101969386AReal-time deliveryRealize distributed collectionData switching networksServer logNetwork connection

The invention relates to a log acquisition device and a log acquisition method. The device comprises at least one client for collecting logs and at least one server for recording the logs, wherein log information is transmitted between the client and the server through a network in real time. The method comprises that: the client generates the log information, writes the log information into a disk file of the client, reads the log information from the disk file of the client, and sends a connection request to the server; after receiving the request, the server establishes network connection with the client and receives the log information; the server sends the received log information to a server log writing module and a server log writing database module; the server log writing module writes the log information into the disk file of the server; and the server log writing database module writes the log information into the database. When the device and the method of the invention are used, the data analysis is more real-time, and the distributed acquisition of the logs is realized.

Owner:道有道科技集团股份公司 +1

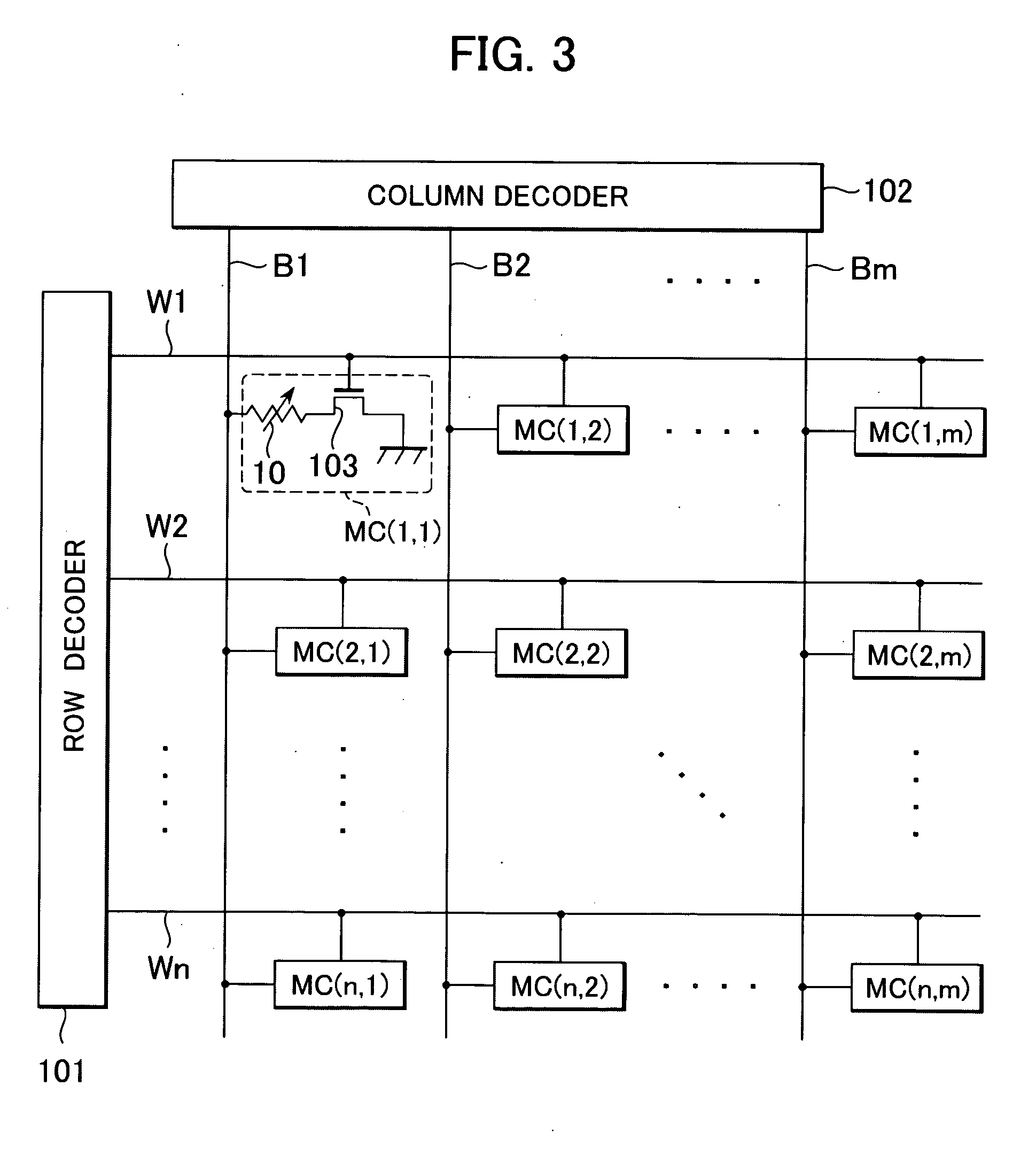

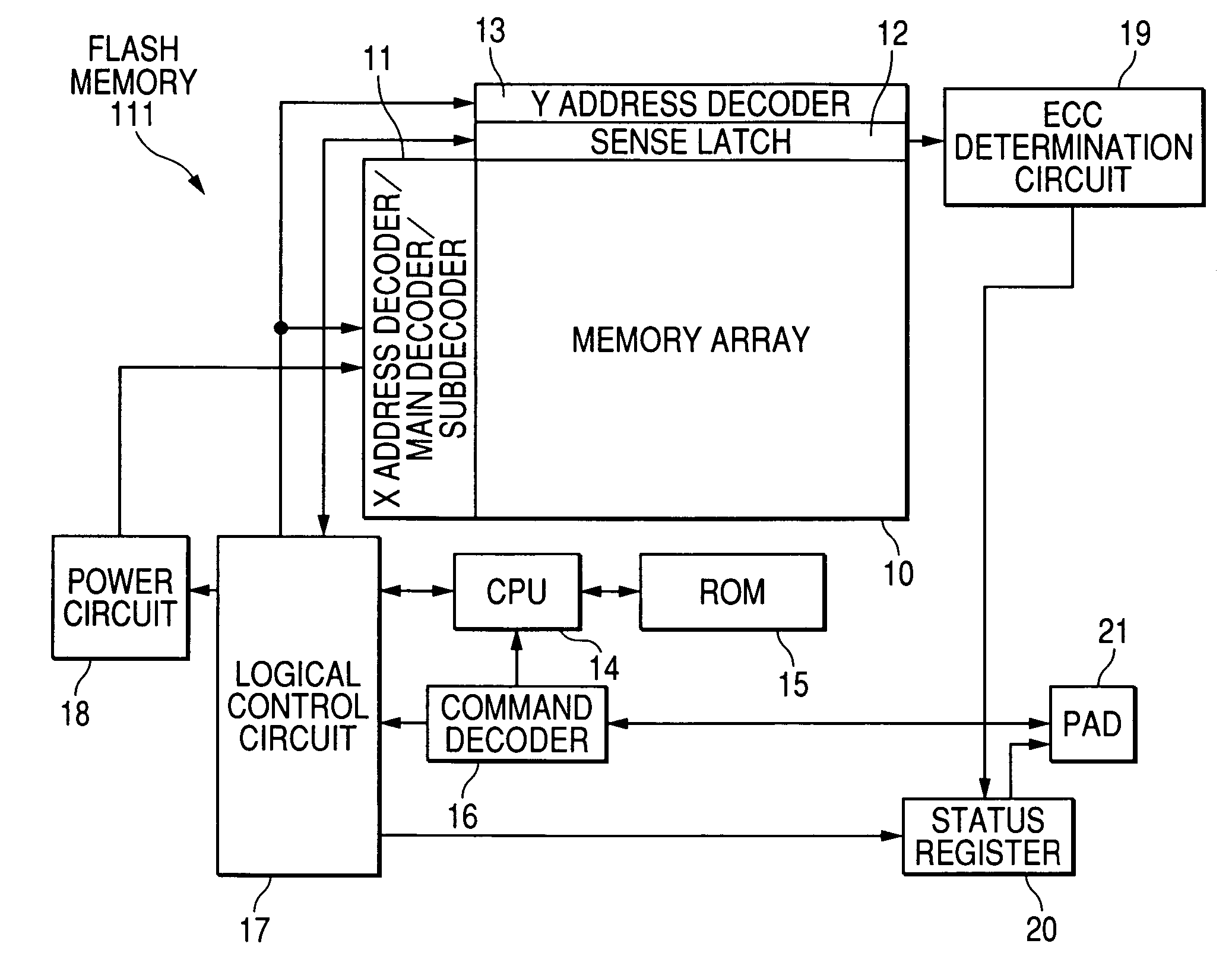

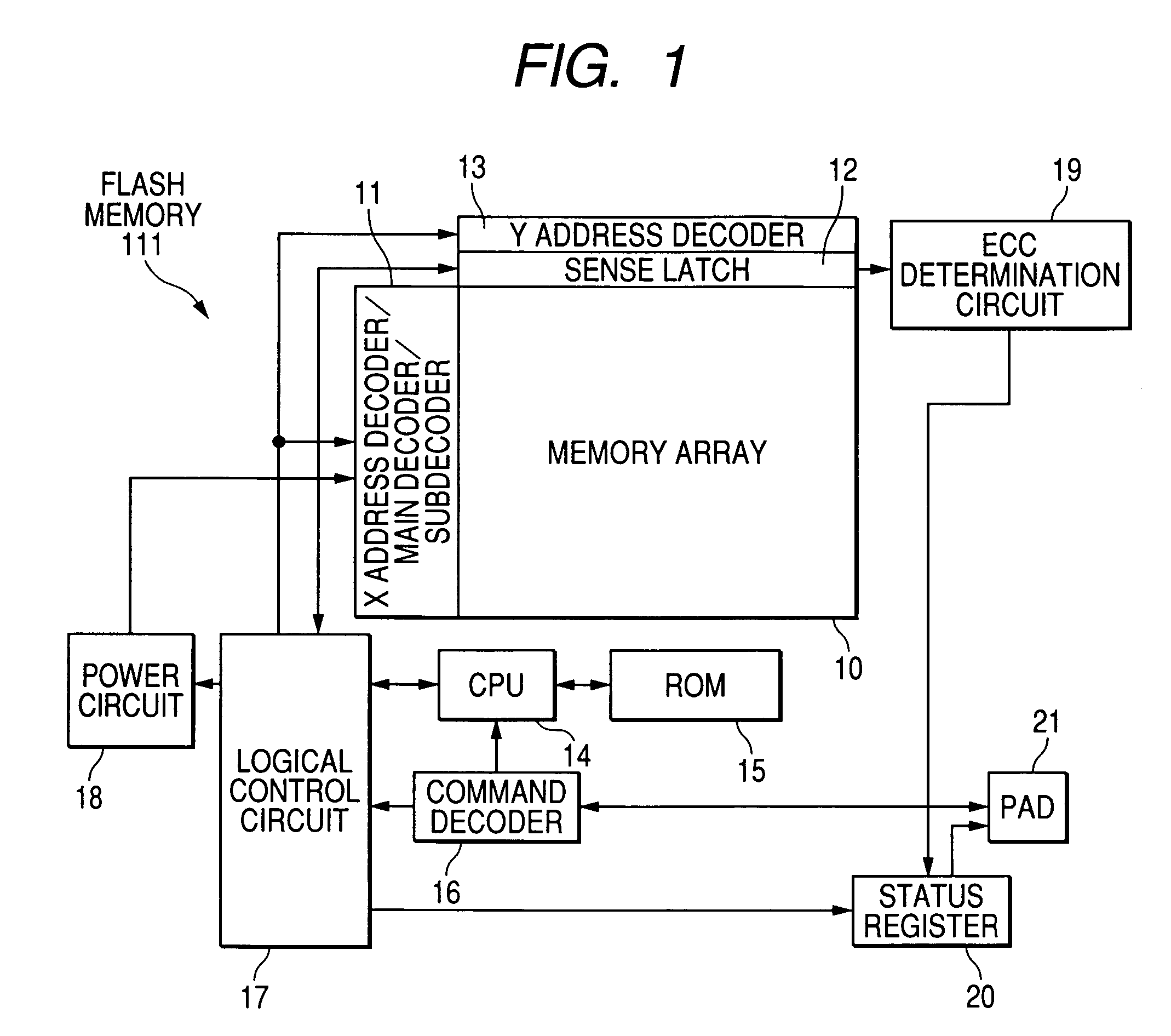

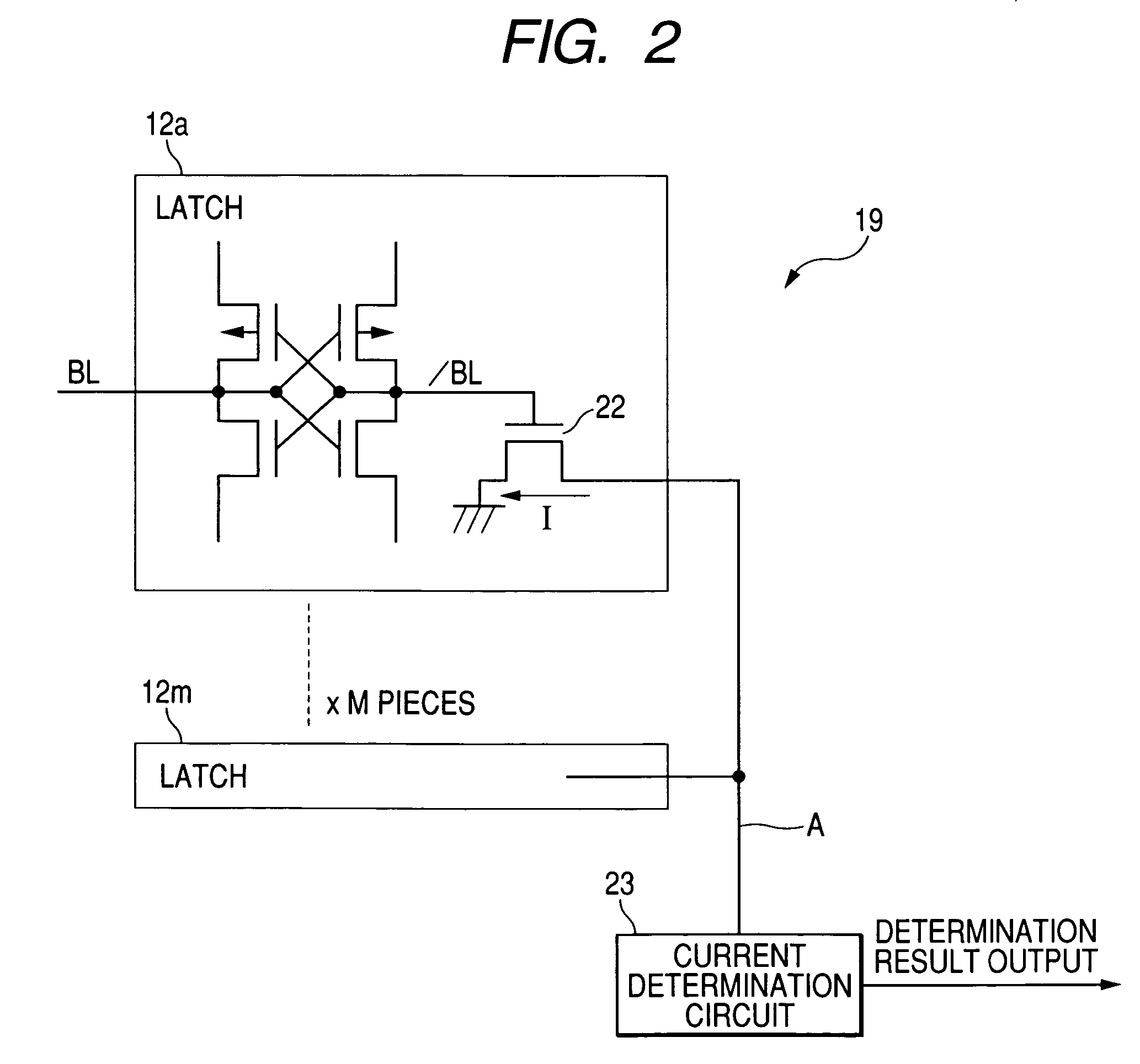

Nonvolatile memory and nonvolatile memory apparatus

ActiveUS7305596B2Reduce loadRapidly detecting n-bit errorsError preventionTransmission systemsComputer scienceNon-volatile memory

To provide a technique which enables a load on a controller to be reduced by rapidly detecting n-bit errors during writing / erasing on a chip in ECC in a nonvolatile memory. A flash memory of the present invention, which is a nonvolatile memory that includes plural electrically erasable and writable nonvolatile memory cells and performs write-and-verify processing in a write operation on the nonvolatile memory cells, includes an ECC determination circuit that counts the number of bits of write error detected in the write-and-verify processing, and outputs the information, and a status register for holding pass / fail information of the write operation and the information about the number of bits of write error outputted from the ECC determination circuit.

Owner:RENESAS ELECTRONICS CORP

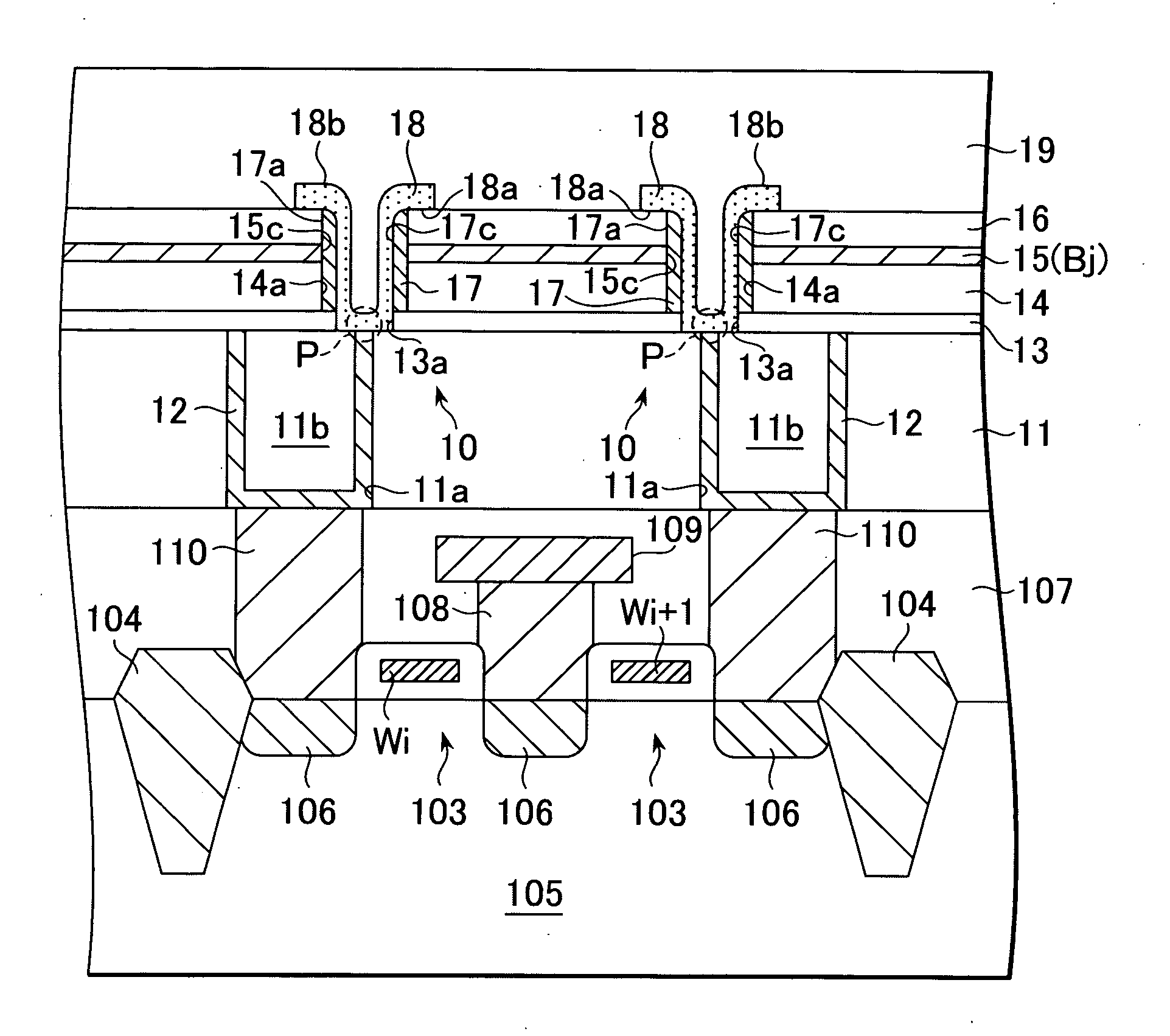

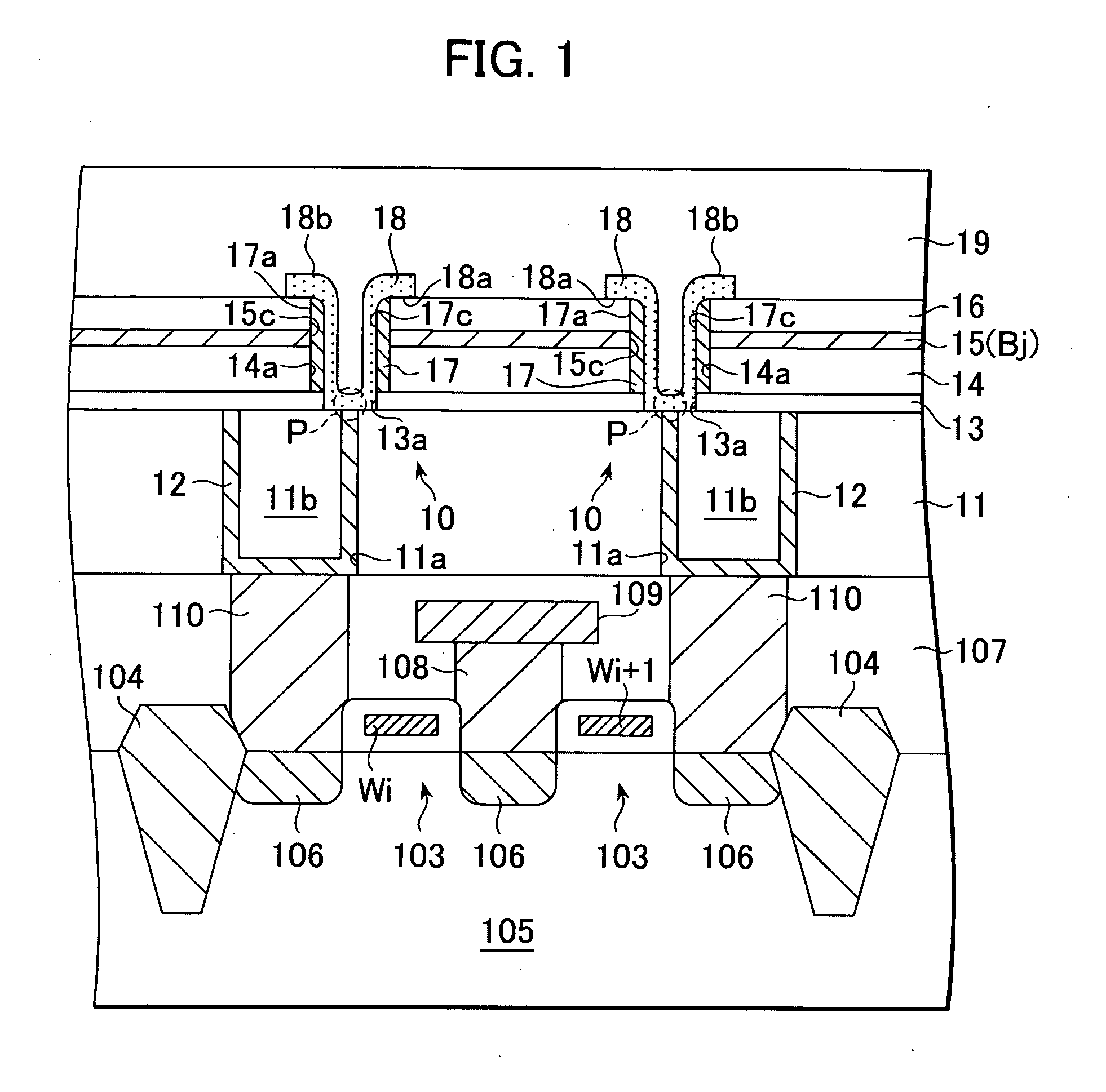

Electrically rewritable non-volatile memory element and method of manufacturing the same

ActiveUS20070097738A1Improve heating efficiencyTotal current dropElectrical apparatusDigital storageBit lineEngineering

A non-volatile memory element comprising a bottom electrode 12, a top electrode 17 provided on the bottom electrode 12, and a recording layer 18 containing phase change material connected between the bottom electrode 12 and the top electrode 17. In accordance with this invention, the top electrode 17 is in contact with a growth initiation surface 18a of the recording layer 17. This structure can be obtained by forming the top electrode 17 before the recording layer 18, resulting in a three-dimensional structure. This decreases heat dissipation to the bit line without increasing the thickness of the recording layer 18.

Owner:MICRON TECH INC

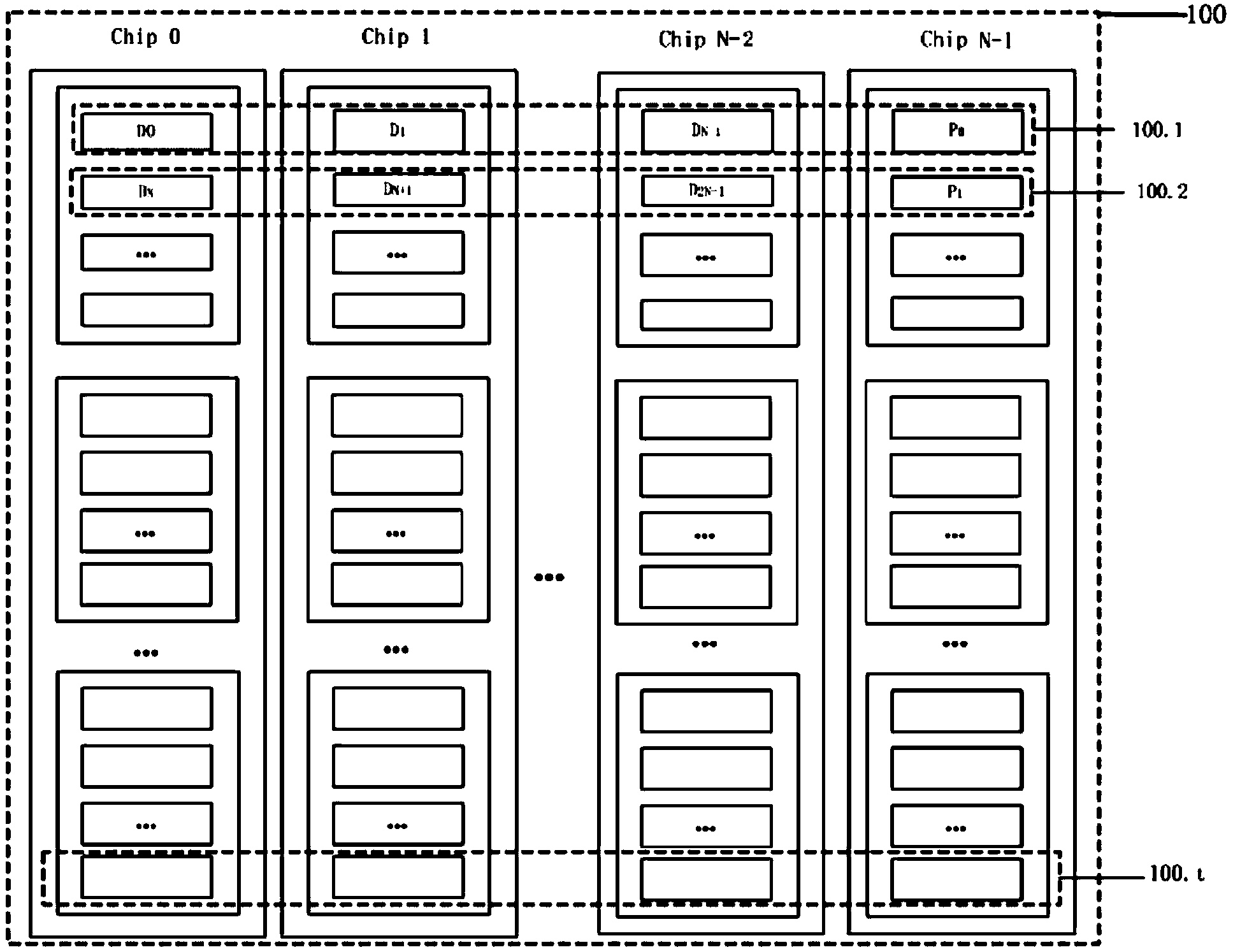

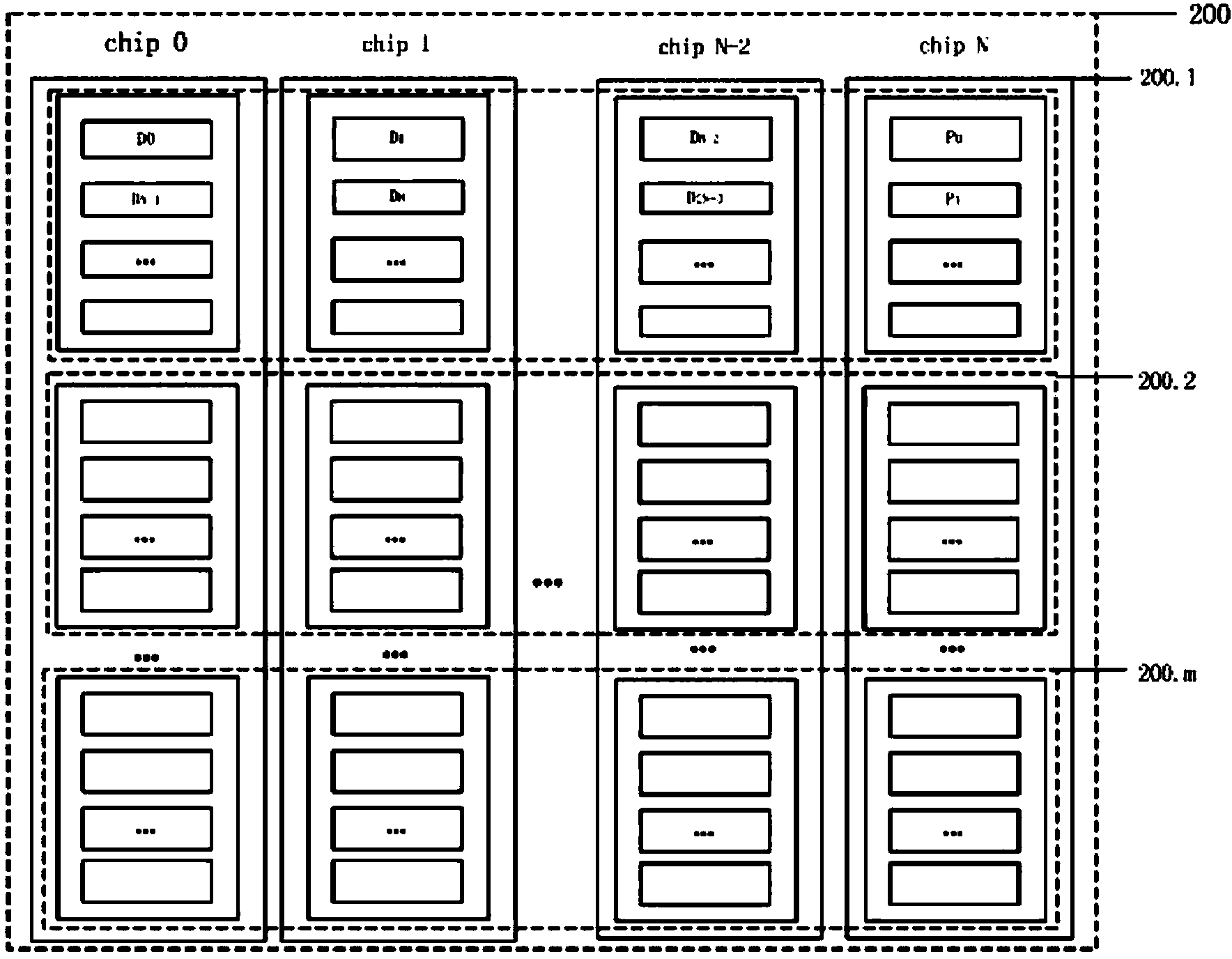

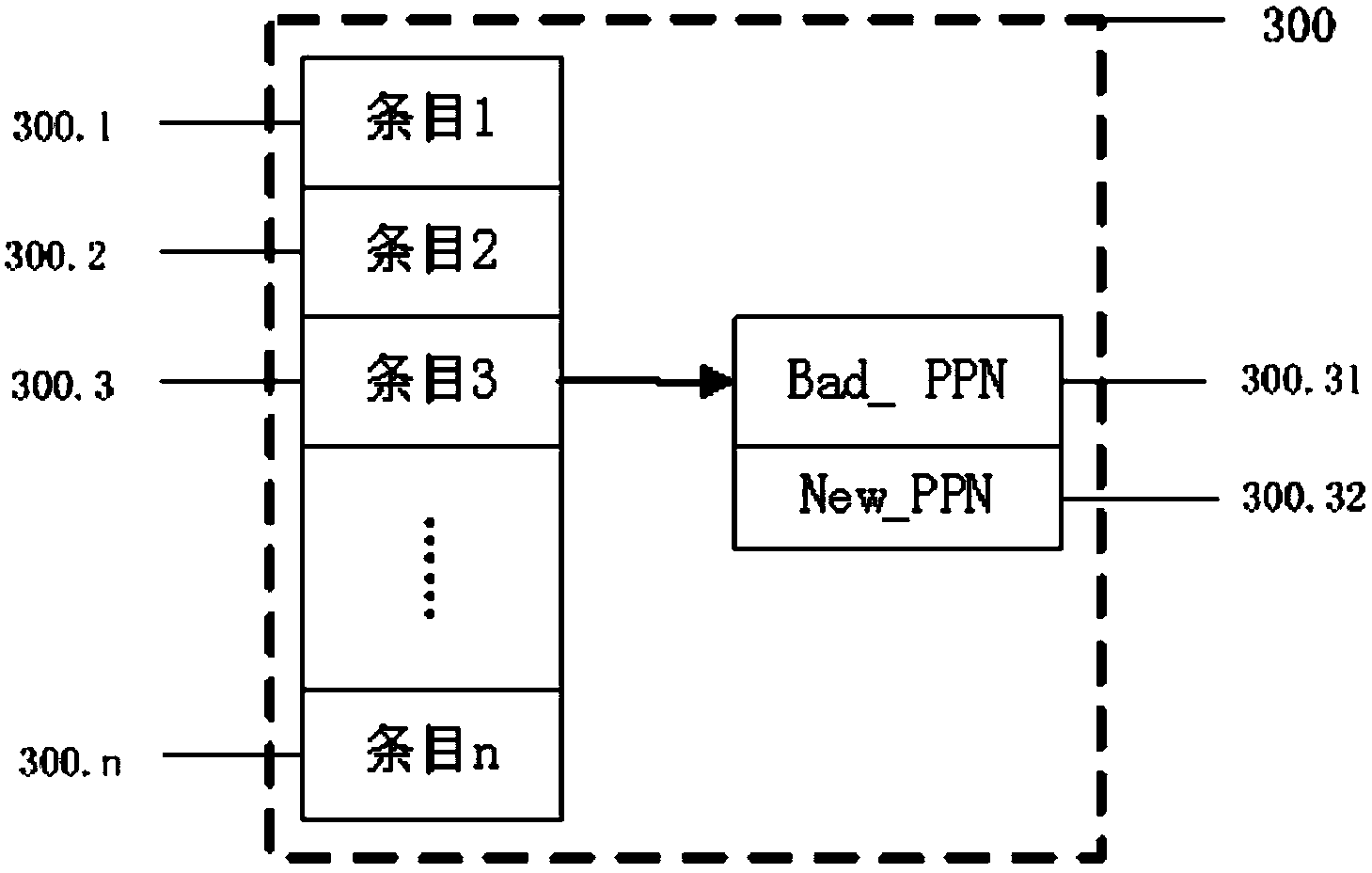

High-performance reliable solid-state disk realizing method

ActiveCN103488583AImprove performanceImprove reliabilityInput/output to record carriersMemory adressing/allocation/relocationRAIDData error

The invention provides a high-performance reliable solid-state disk realizing method. The method includes: (1), dividing all flash memory chips in a solid-state disk into groups and forming an RAID (redundant array of independent disks) 4-level flash array in each group by N successive flash chips; (2), receiving and storing data through a cache; (3), judging whether the cache is filled up or not, if yes, entering the step (4), and if not, returning to the step (2); (4), extracting N-1 data blocks from the cache and computing check values of the N-1 data blocks; making up the N-1 data blocks and the check values into filled stripe data and writing back the flash array; returning to the step (2). The flash chips in the solid-state disk are used for establishing the RAID4-level physical array to assure data reliability. Faults at different levels including page level, block level, or even chip level can be processed. Besides, writing-in performance is improved by writing of filled stripes and sequence, and spatial and performance loss resulted from data errors can be reduced to the utmost.

Owner:HUAZHONG UNIV OF SCI & TECH

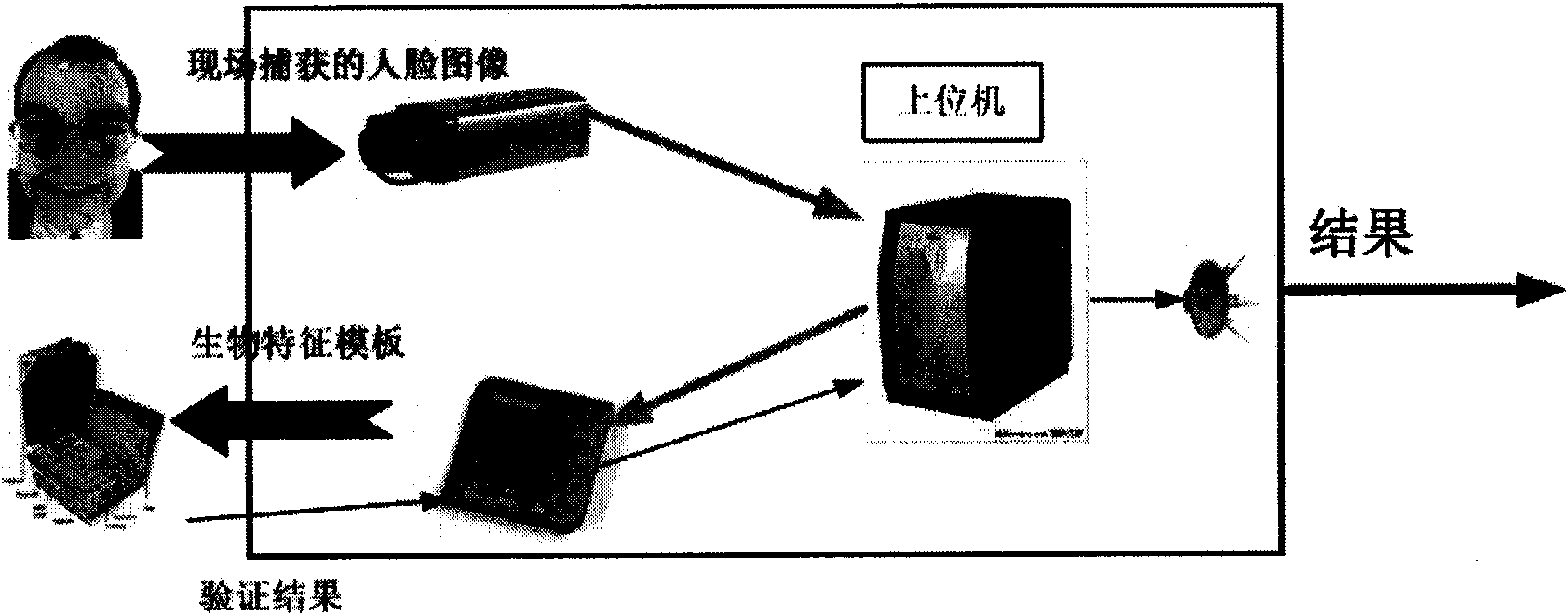

Face recognition system and face recognition method based on intelligent card

InactiveCN101661557AEliminate attitude deviationImprove recognition ratePerson identificationCharacter and pattern recognitionFace verificationRecognition system

The invention discloses a face recognition method based on an intelligent card, which comprises the following steps: acquiring and transmitting face data; judging the quality of the face data; adjusting the brightness for the face data with qualified quality; extracting face features, and transmitting the face features to the intelligent card by an encrypted way; and comparing the face images, anddetermining whether the identification passes or not. The invention also discloses a face recognition system which comprises a face detection module, a data safety communication module, a face imagequality judging module, a face image brightness adjusting module, a face feature extracting module and a face verification module. By adopting the system and the method of the invention, the defect ofthe reduction of the recognition effect caused by attitude deviation is eliminated, and the recognition rate is greatly improved. In addition, in the process of comparing the face images, the writingspeed, the reading speed and the operating speed of the compressed face image data are quick, thereby meeting the requirements of various real-time application conditions.

Owner:SHANGHAI INST OF APPLIED PHYSICS - CHINESE ACAD OF SCI

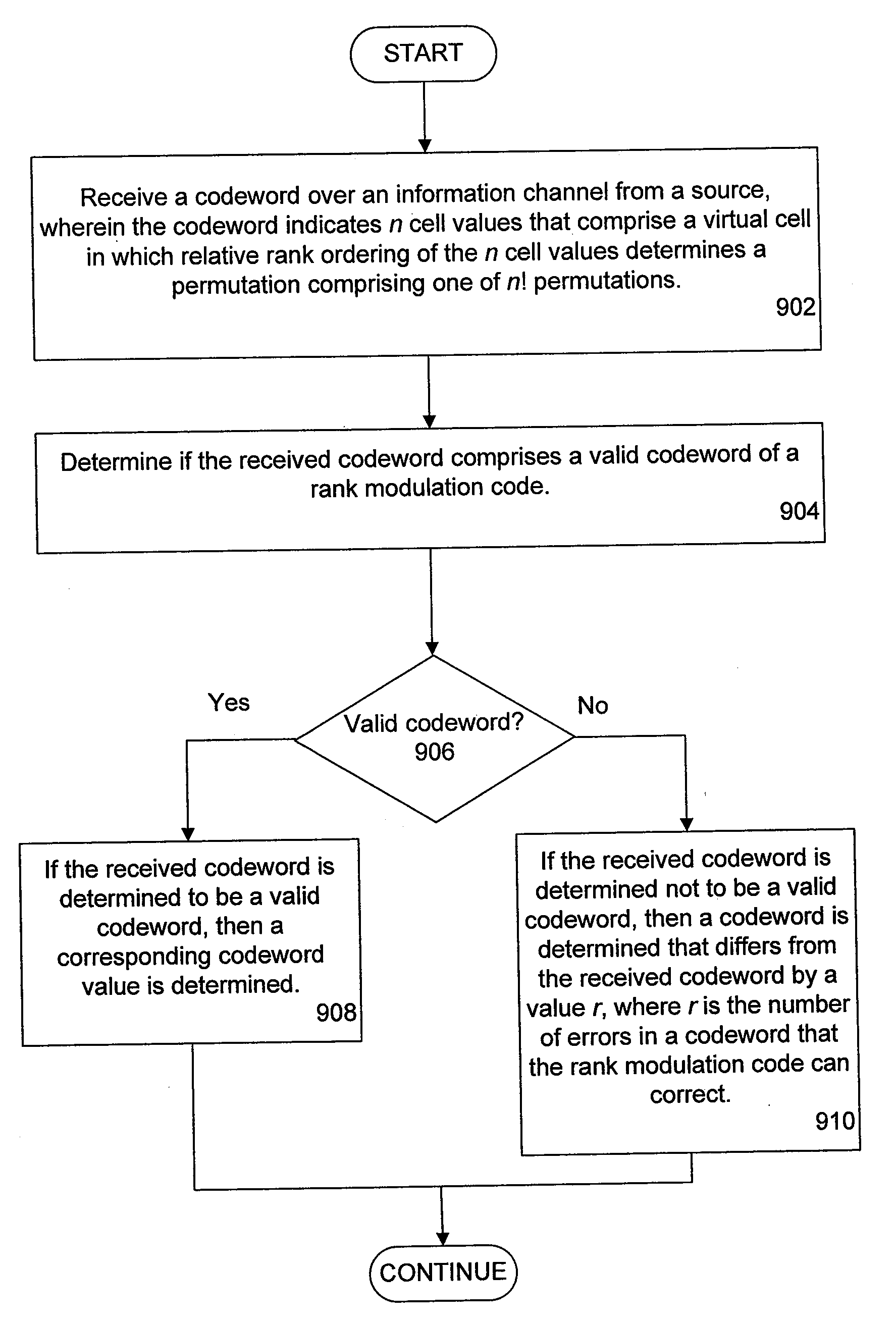

Error correcting codes for rank modulation

ActiveUS20090132895A1Eliminate riskReduce the impactError preventionRead-only memoriesArray data structureTheoretical computer science

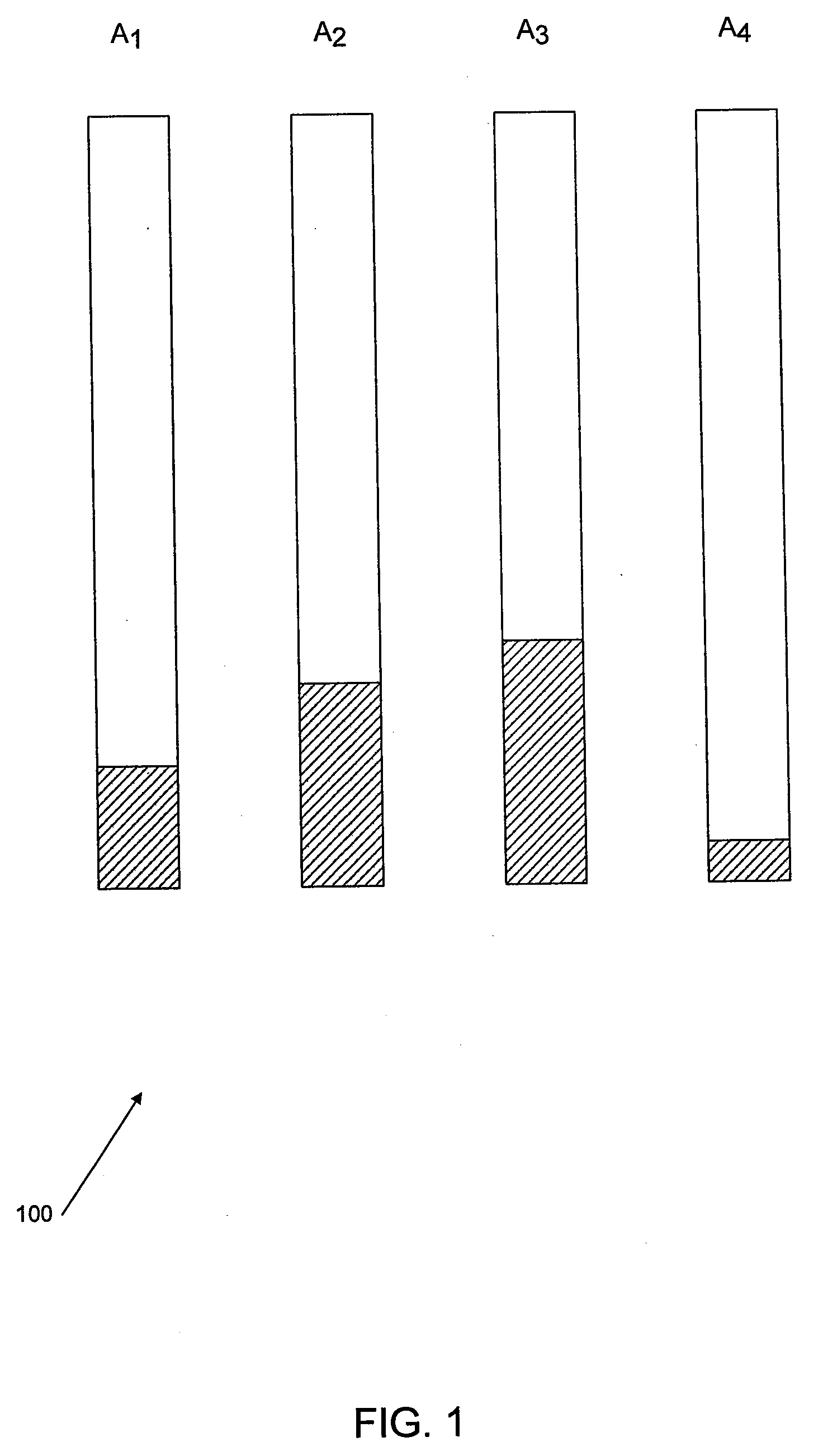

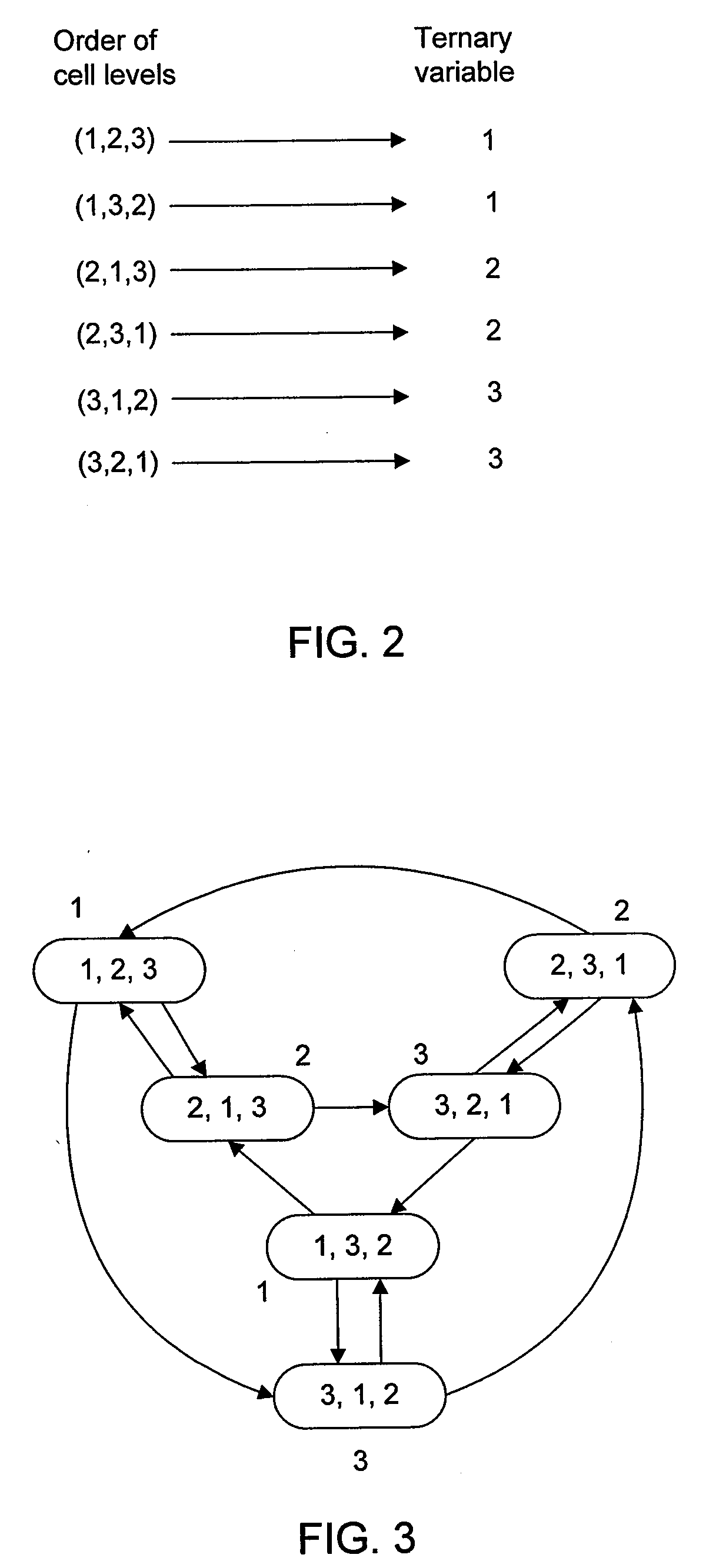

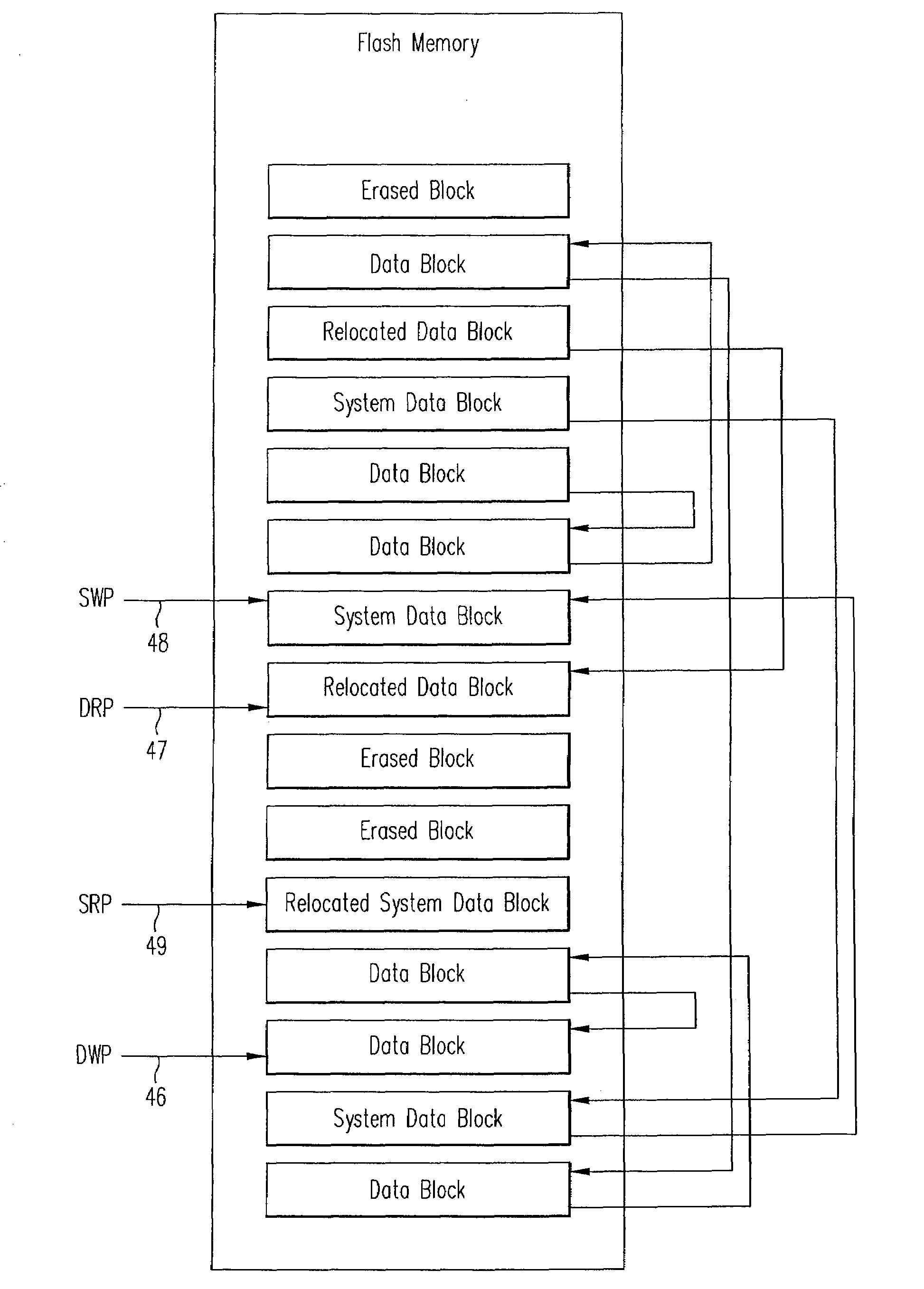

We investigate error-correcting codes for a novel storage technology, which we call the rank-modulation scheme. In this scheme, a set of n cells stores information in the permutation induced by the different levels of the individual cells. The resulting scheme eliminates the need for discrete cell levels, and overshoot errors when programming cells (a serious problem that reduces the writing speed), as well as mitigates the problem of asymmetric errors. In this discussion, the properties of error correction in rank modulation codes are studied. We show that the adjacency graph of permutations is a subgraph of a multi-dimensional array of a special size, a property that enables code designs based on Lee-metric codes and L1-metric codes. We present a one-error-correcting code whose size is at least half of the optimal size. We also present additional error-correcting codes and some related bounds.

Owner:TEXAS A&M UNIVERSITY

Methods and apparatus for writing data to non-volatile memory

ActiveUS20080155184A1Reduce in quantityIncrease write speedMemory architecture accessing/allocationInput/output to record carriersOperating systemVolatile memory

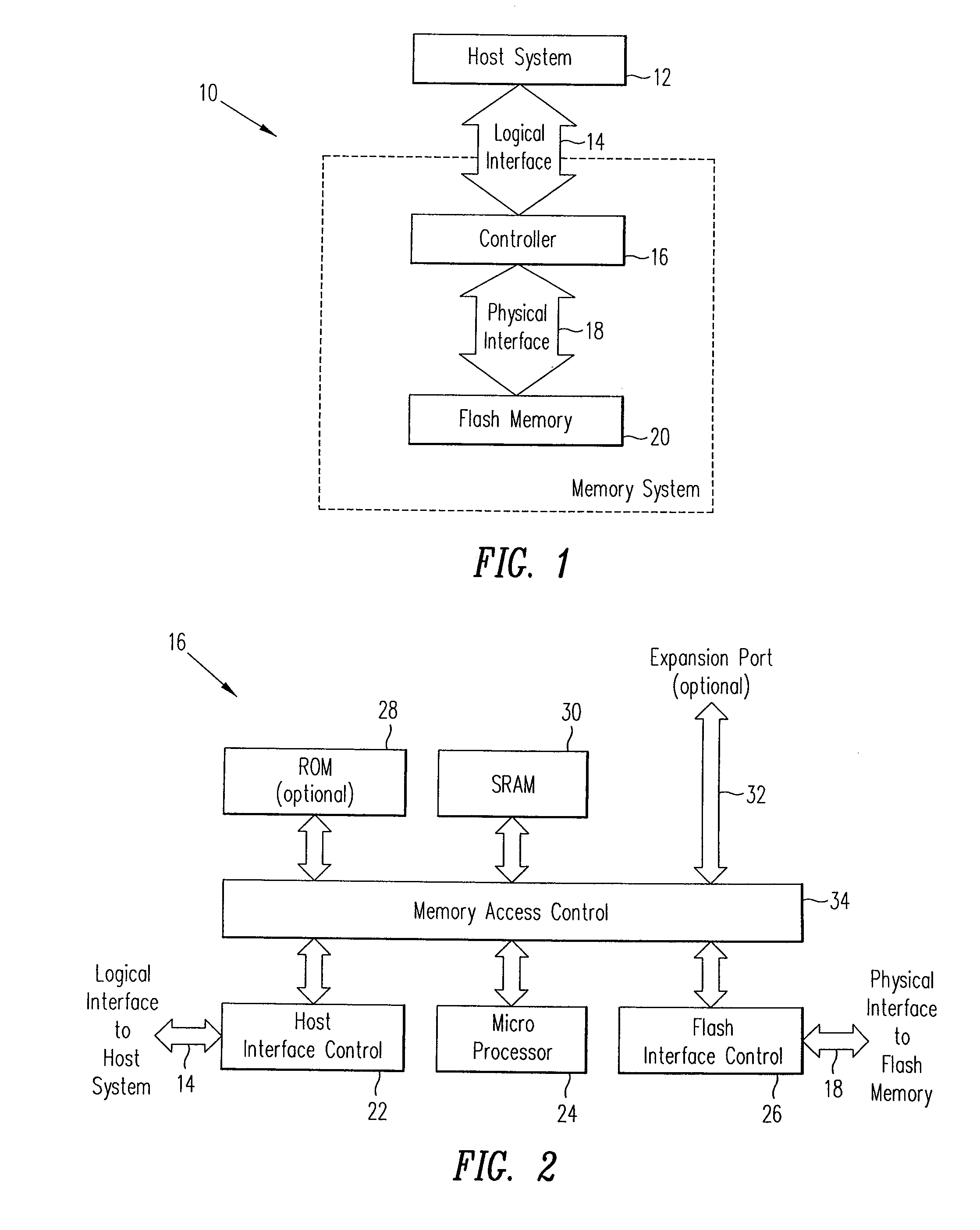

Methods and apparatus for writing data to non-volatile memory include maintaining one or more lists of obsolete blocks of the non-volatile memory and limiting the lists to a predetermined value. If a write operation would result in a list exceeding its predetermined value, a block erase operation is performed on one of the obsolete blocks. Valid data contained in an obsolete block selected for erasure is relocated prior to erasure.

Owner:MICRON TECH INC

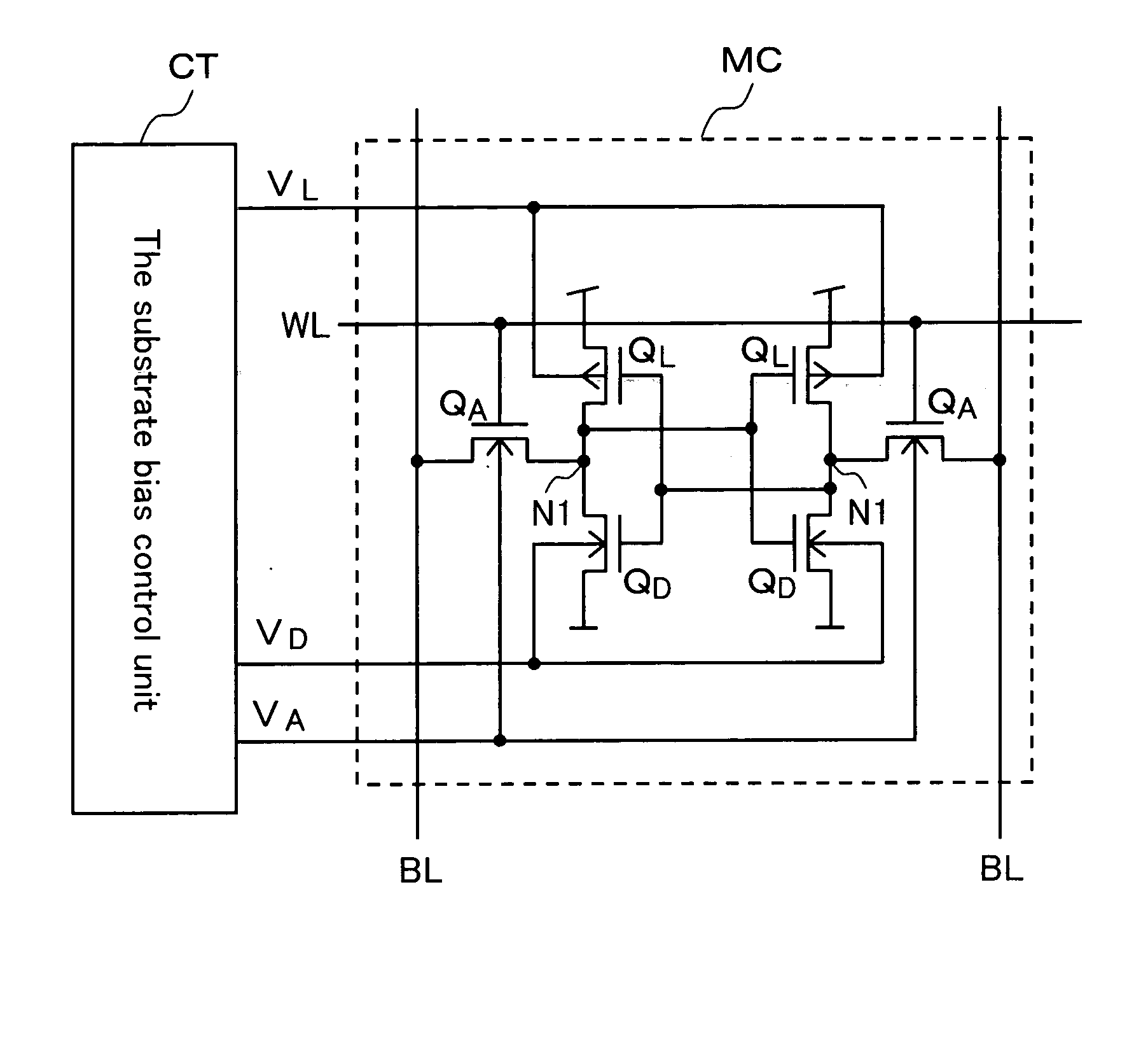

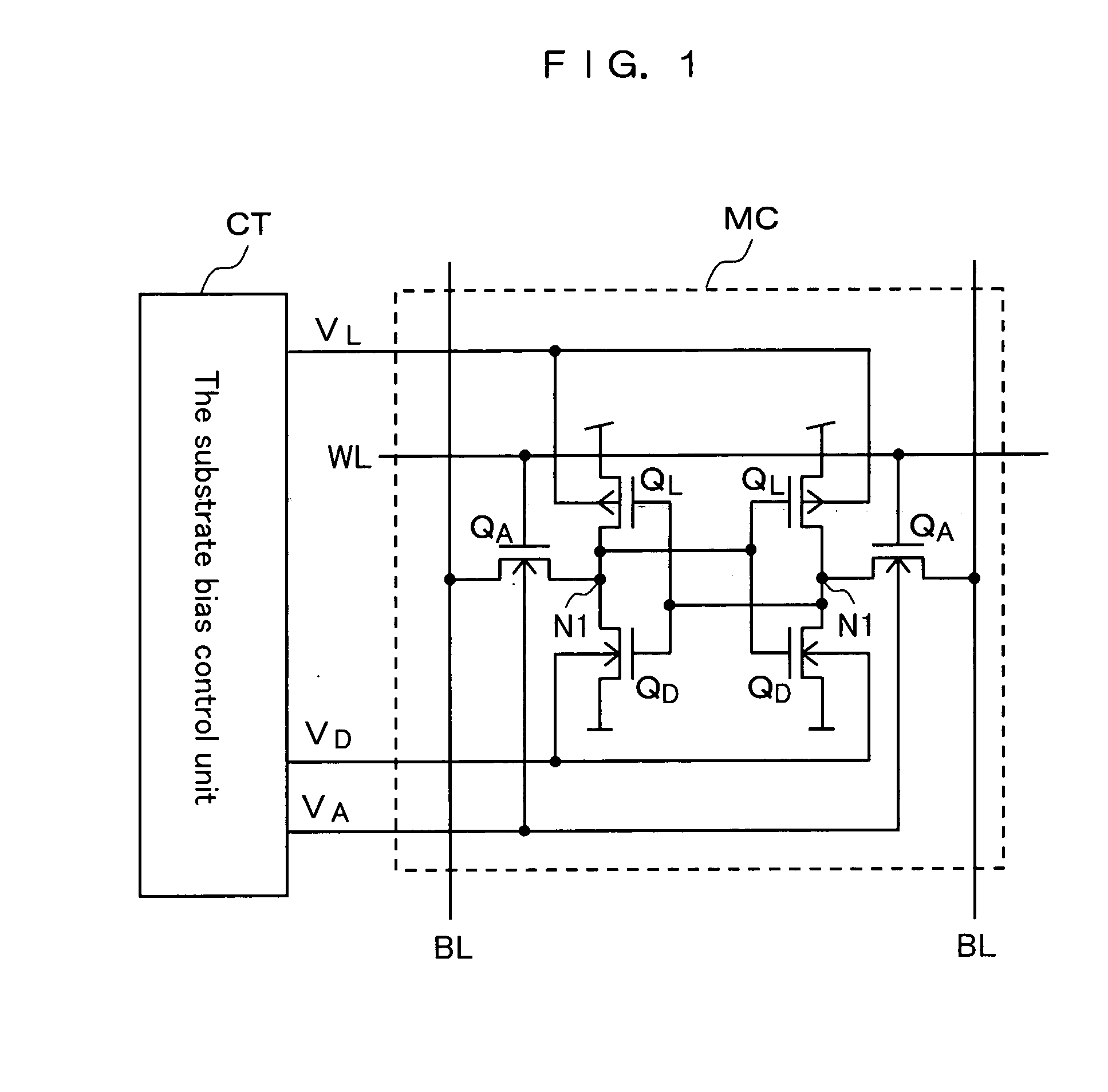

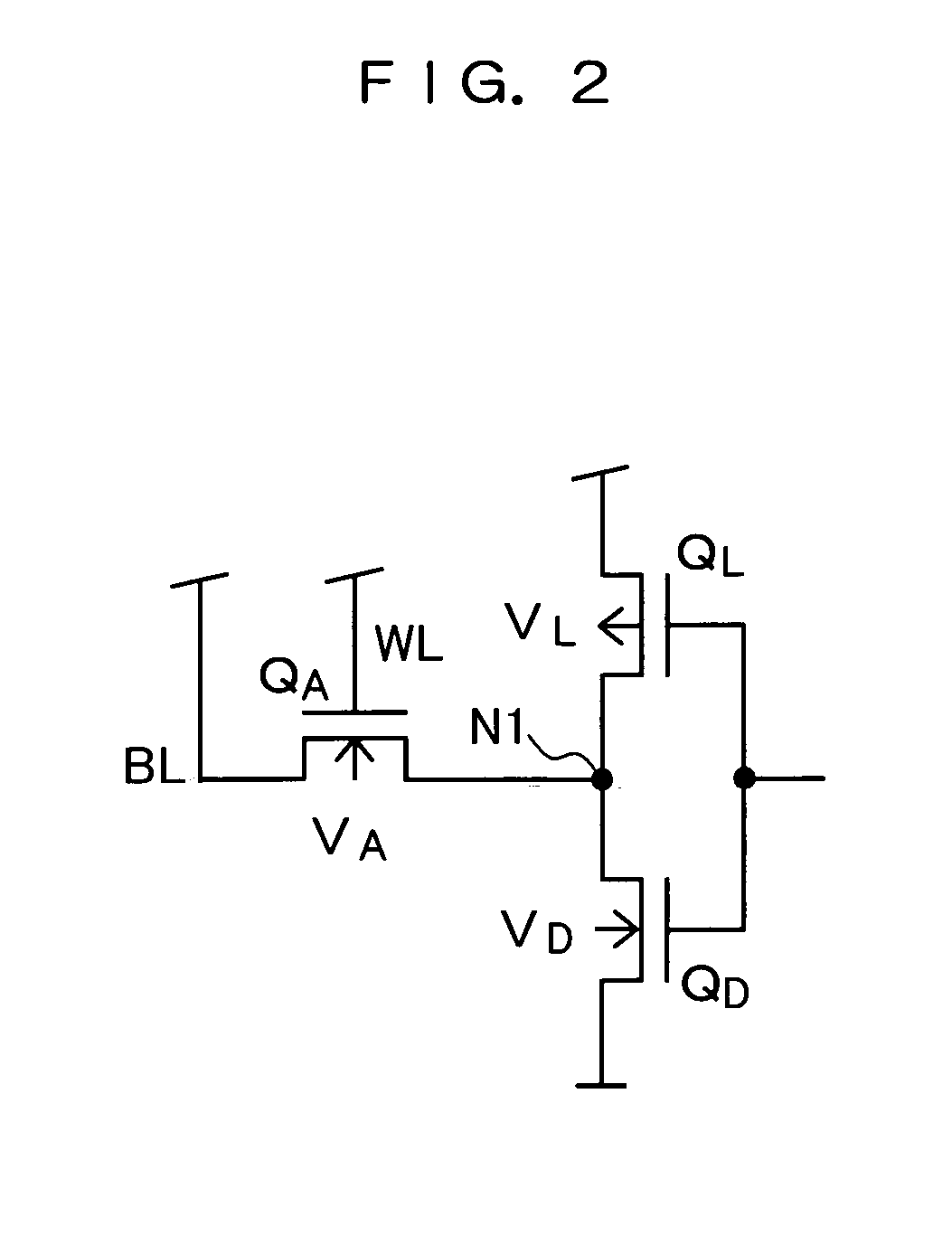

Semiconductor memory

InactiveUS20050068824A1Improve caching capacityImprove performanceDigital storageEngineeringJunction point

A semiconductor memory of the present invention comprises: a static-type memory cell constituted of a pair of access transistors formed with NMOS transistors, a pair of drive transistors formed with NMOS transistors, and a pair of load transistors formed with PMOS transistors. Further, it comprises a substrate bias control unit which applies bias for increasing access speed to a substrate of any of the transistors when making access to the memory cell through adjusting electric current flown to a memory storage node in a common junction point of the three types of transistors. A substrate potential which is appropriate for reading-out, writing, memory-storing operation and low leak is applied.

Owner:PANASONIC CORP

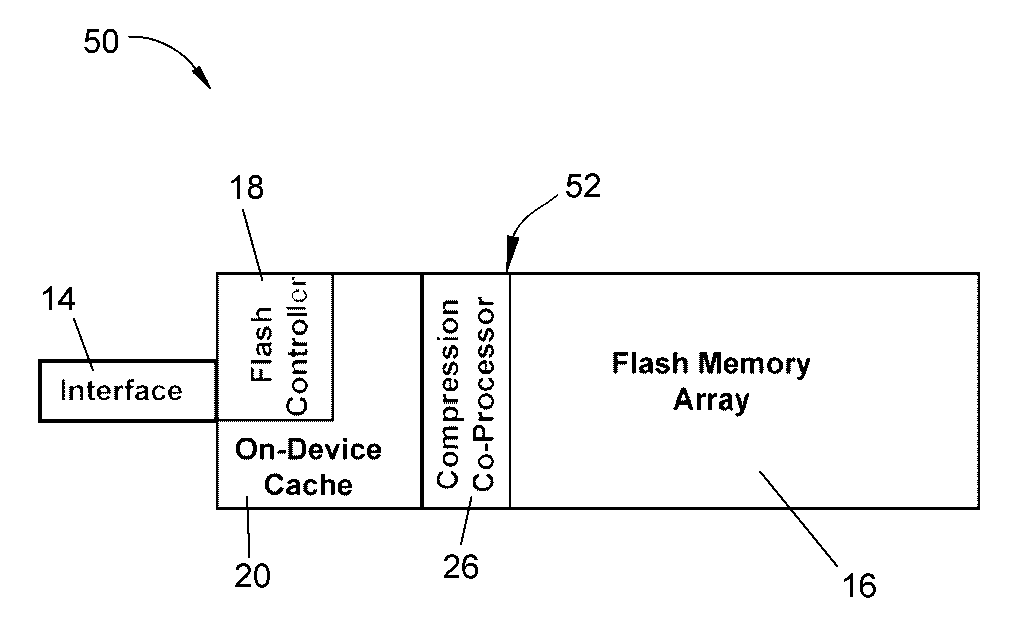

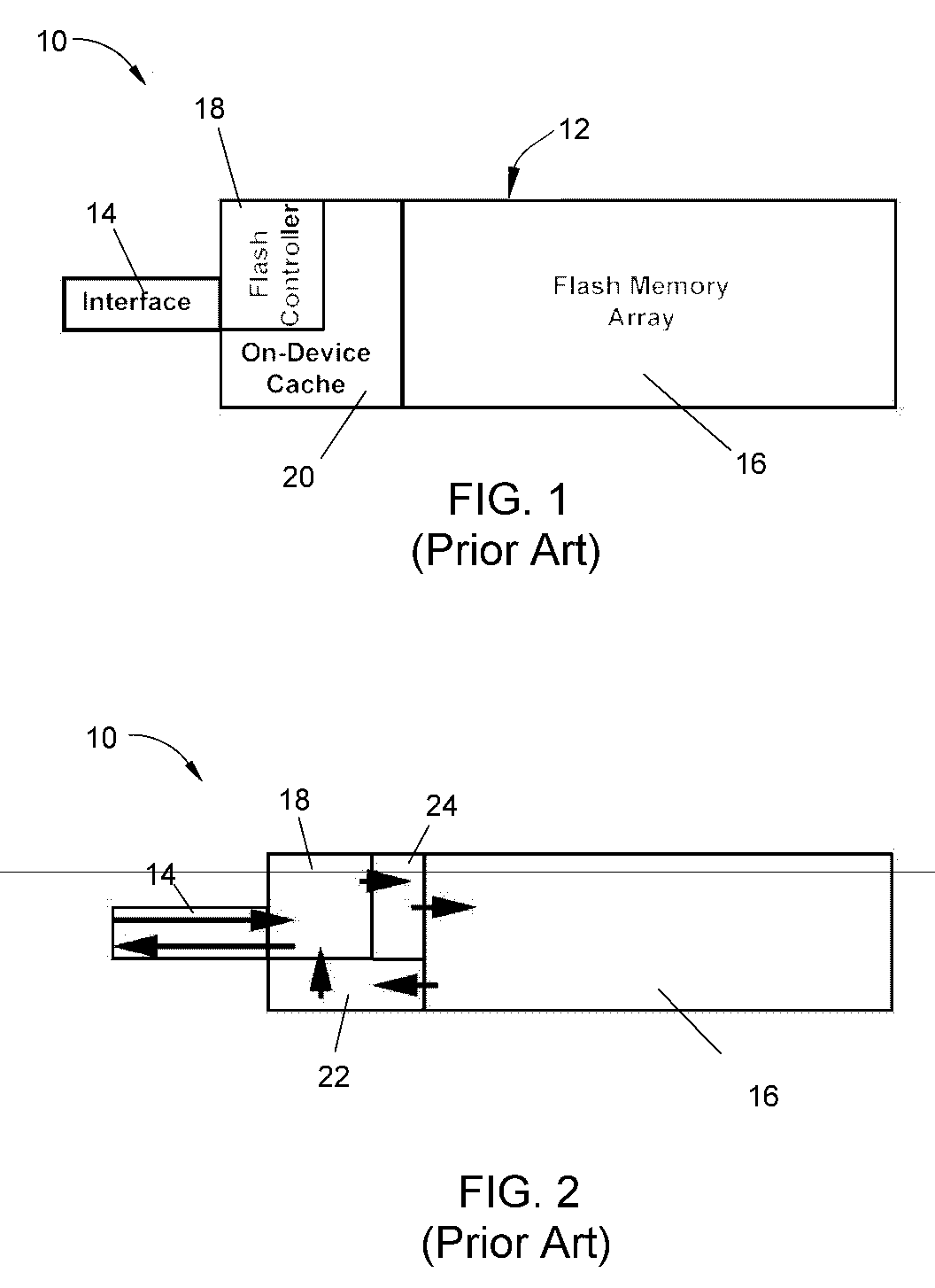

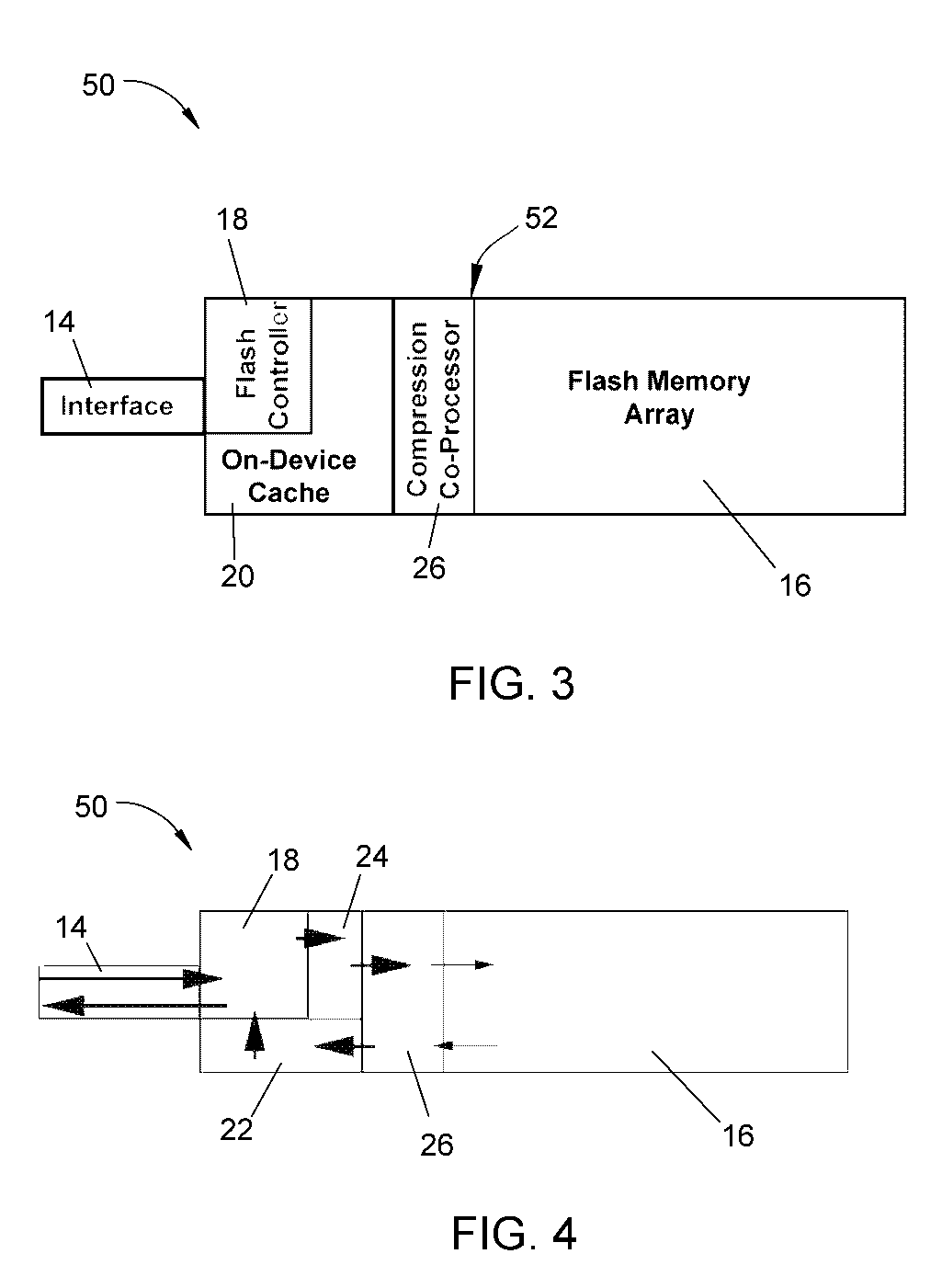

On-device data compression to increase speed and capacity of flash memory-based mass storage devices

ActiveUS20060212645A1High data densityIncrease write speedMemory architecture accessing/allocationMemory systemsData compressionMass storage

A mass storage device having at least one flash memory device and DRAM or SRAM-based cache within a package, and which comprises co-processor means within the package for performing compression and decompression of cached data before writing the cached data to the flash memory device.

Owner:KIOXIA CORP

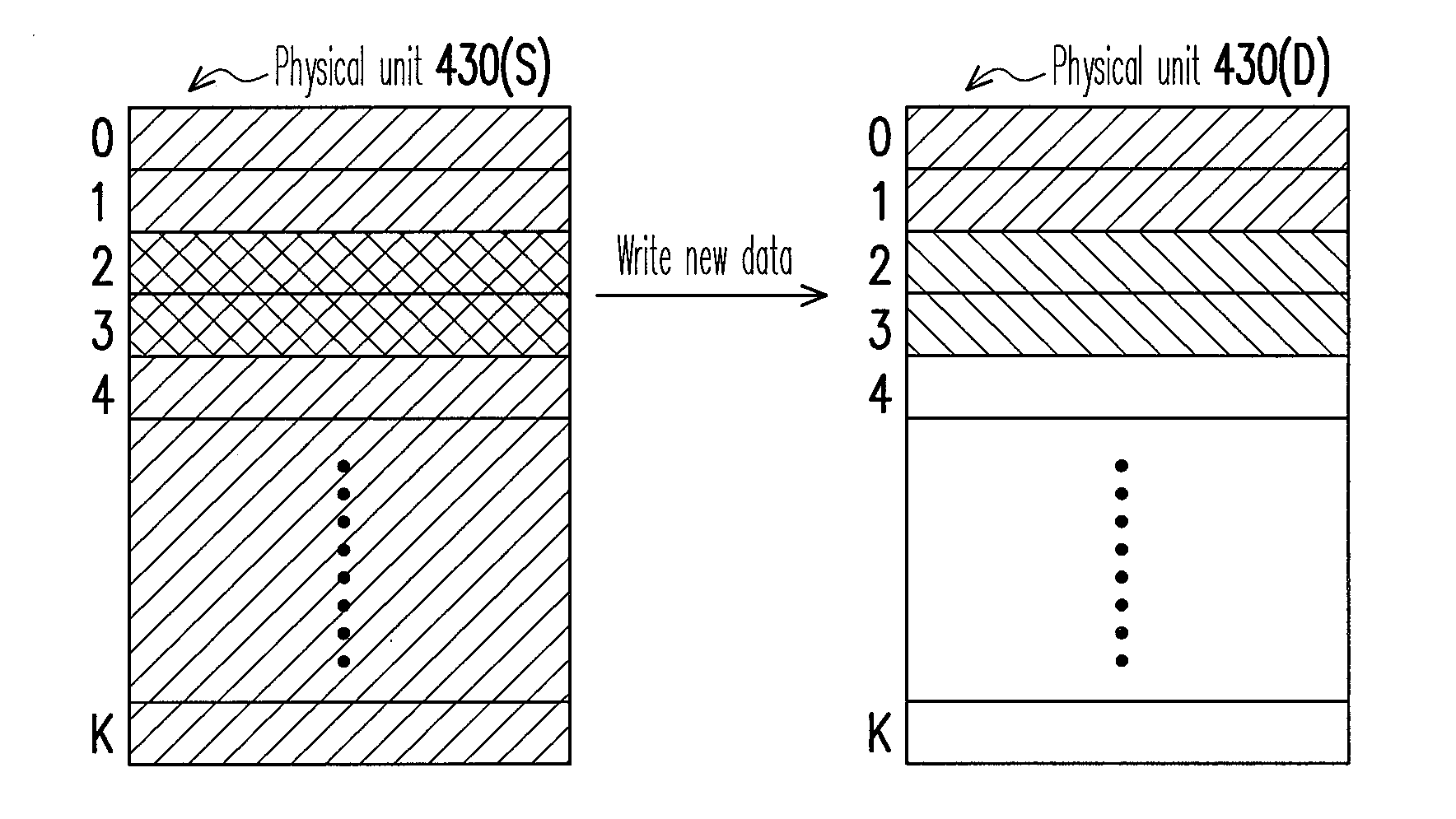

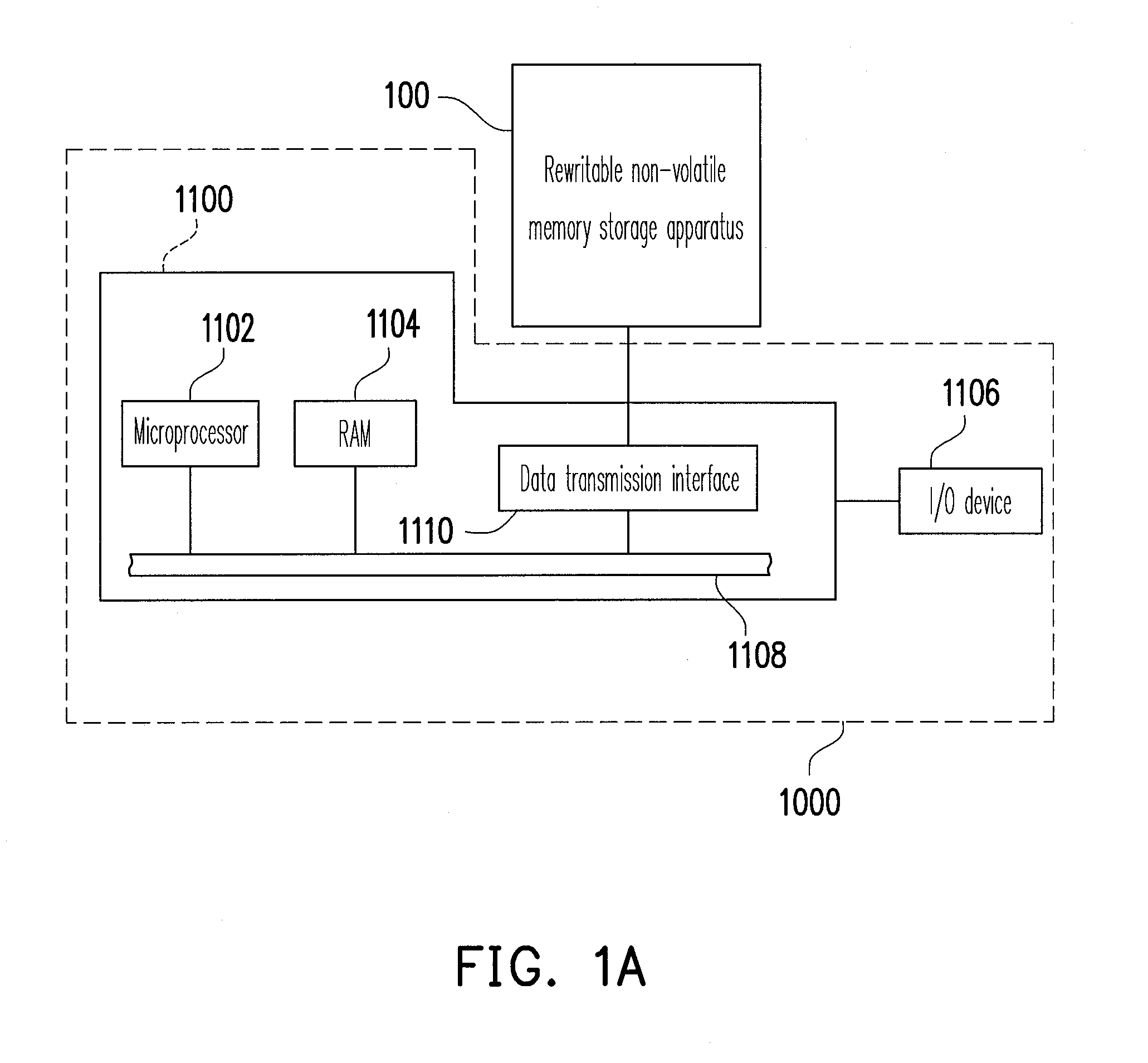

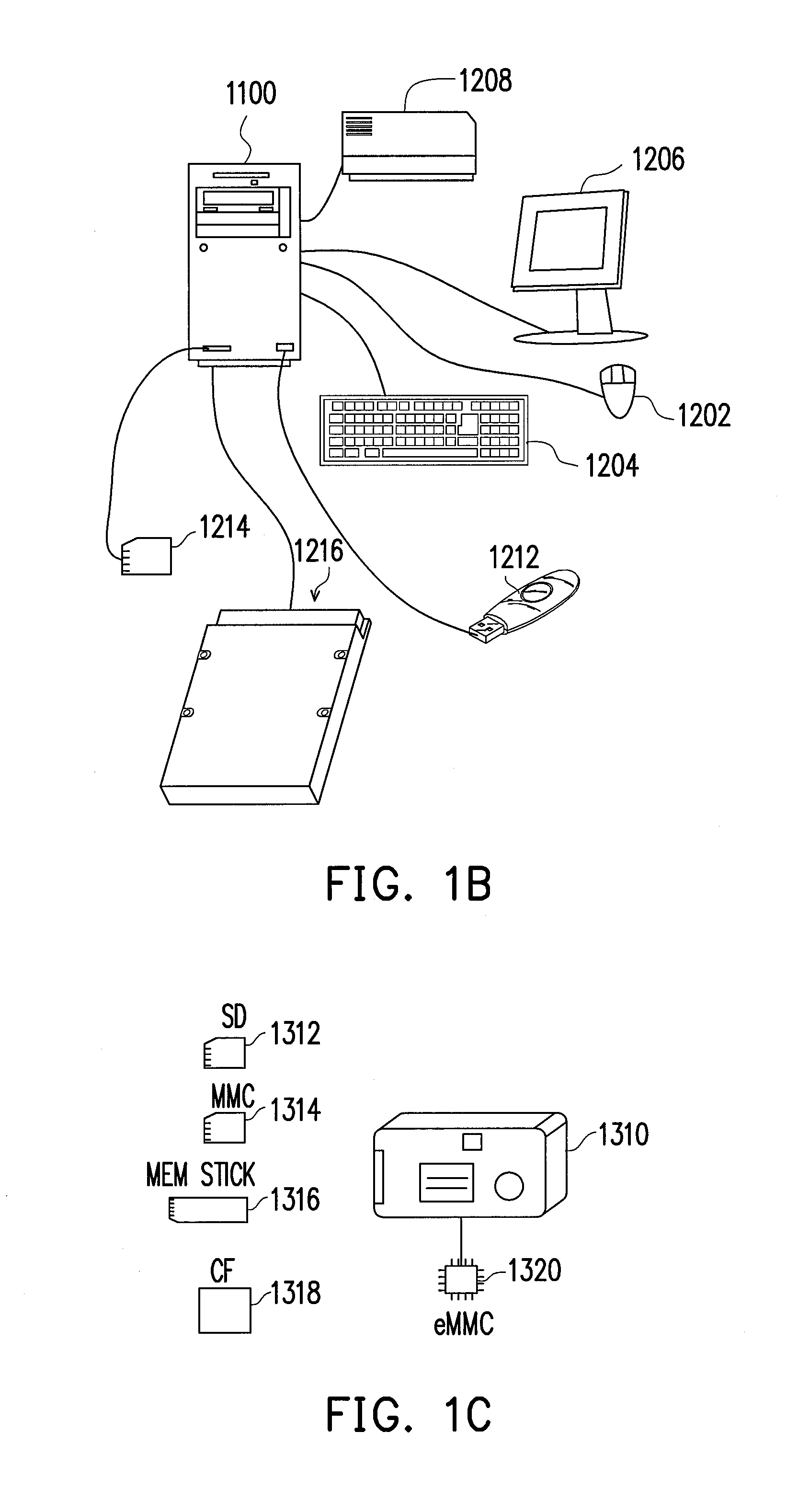

Memory management and writing method and rewritable non-volatile memory controller and storage system using the same

ActiveUS20110197014A1Increase speedExtend your lifeMemory architecture accessing/allocationMemory loss protectionMemory chipComputer architecture

A memory management and writing method for managing a plurality of physical units of a memory chip is provided. The present method includes grouping the physical units into a first physical unit group and a second physical unit group, recording and calculating a first erase count of the first physical unit group and a second erase count of the second physical unit group, and calculating an erase count difference between the first erase count and the second erase count. The present method also includes determining whether the erase count difference is larger than an erase count difference threshold when a write command is received. The method further includes executing a switched writing procedure to write data corresponding to the write command into the memory chip when the erase count difference is larger than the erase count difference threshold. Thereby, the lifespan of the memory chip is effectively prolonged.

Owner:PHISON ELECTRONICS

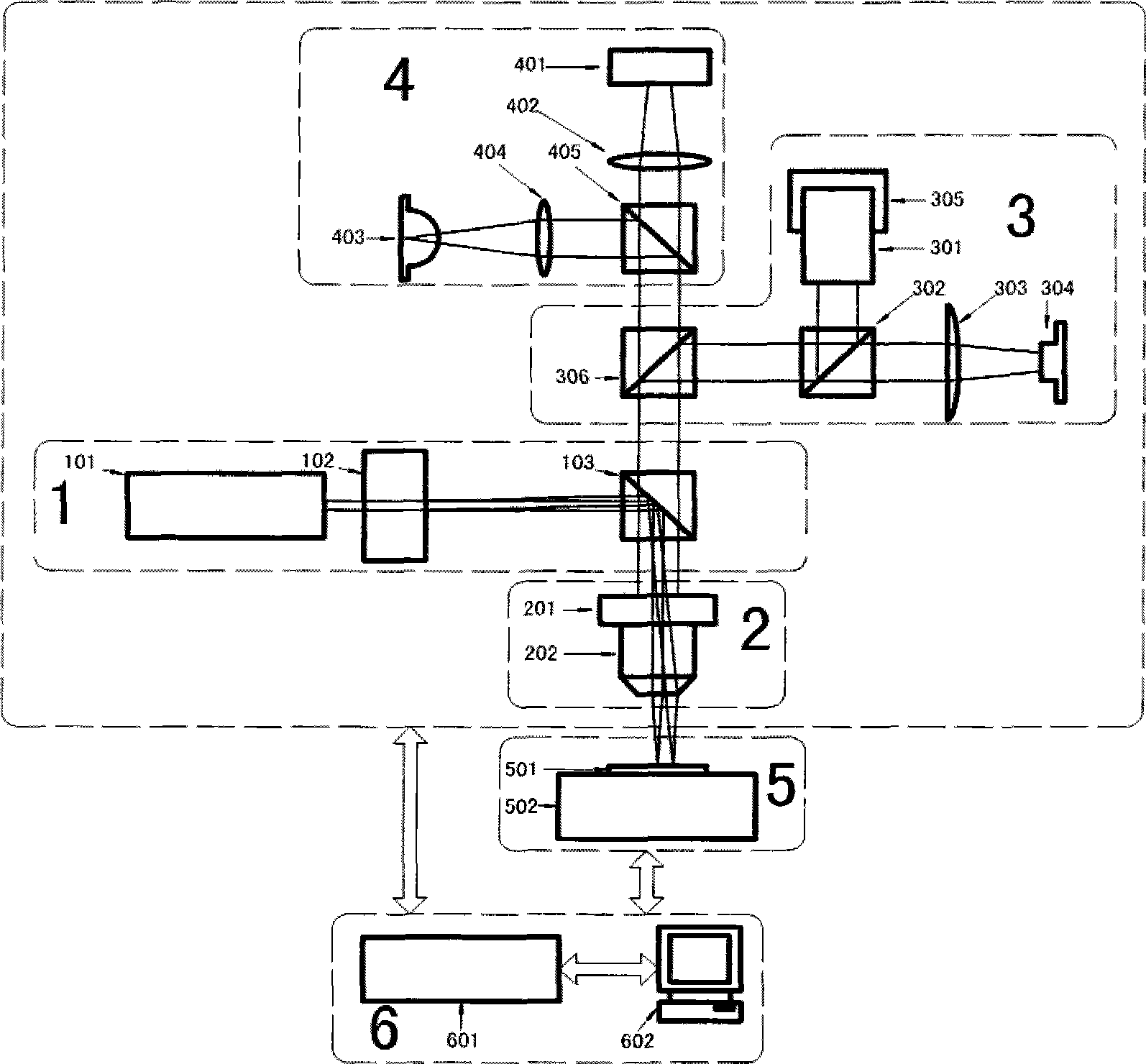

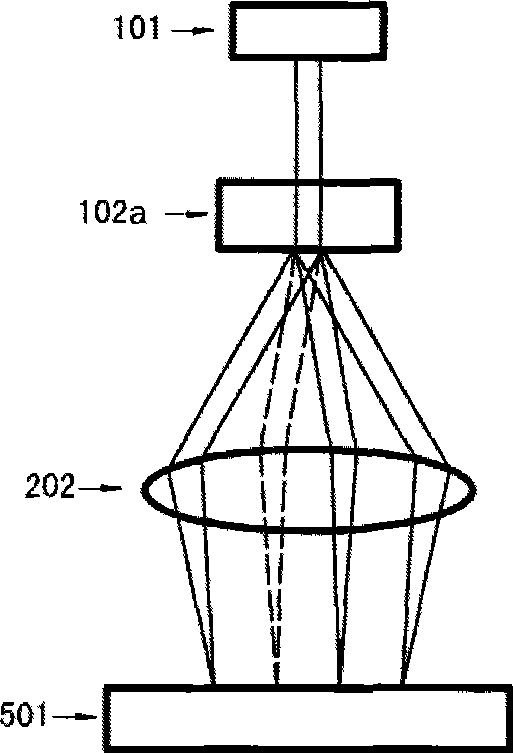

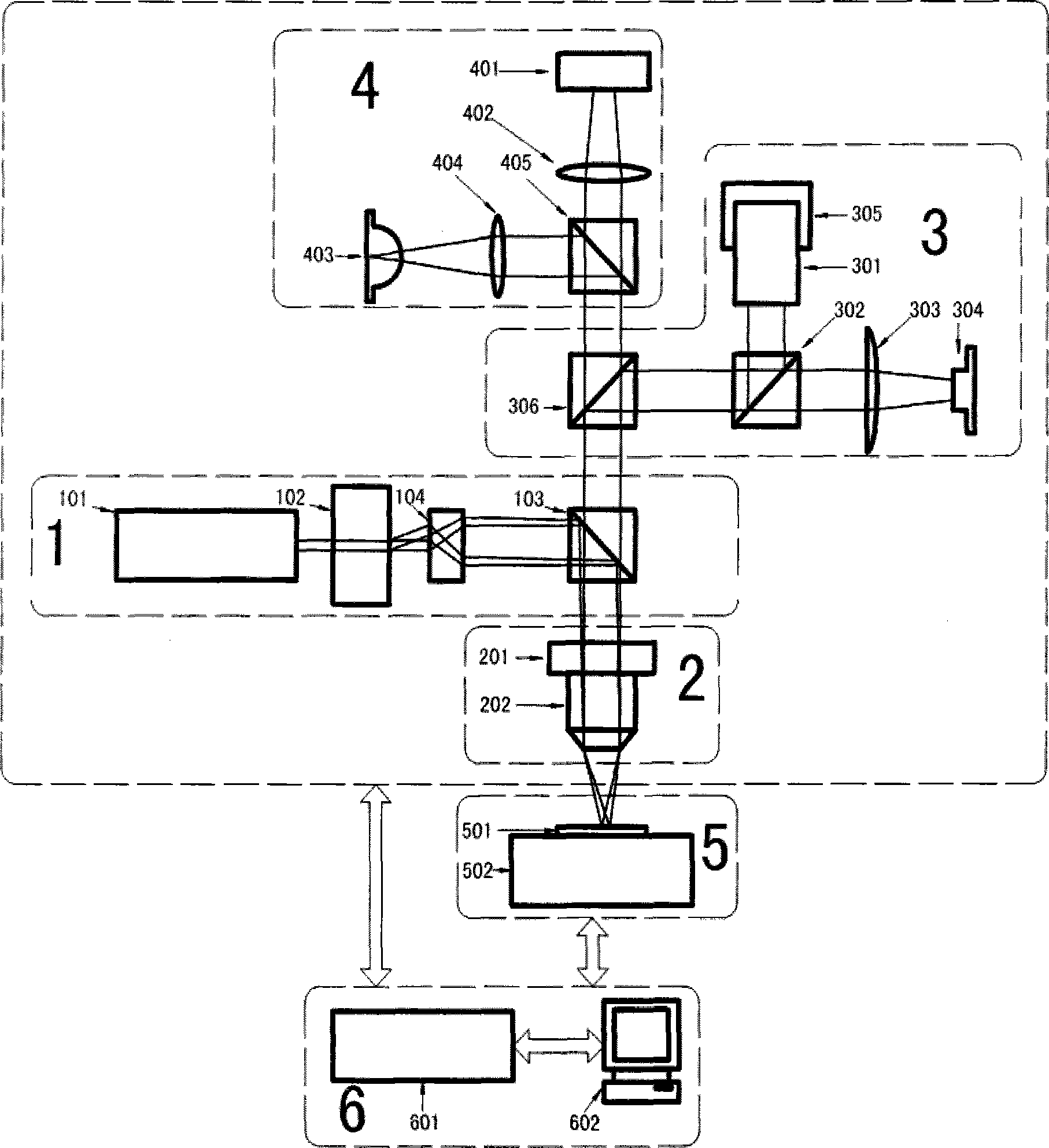

High-speed multi-beam parallel laser direct-writing device

ActiveCN101477306AImprove writing speedThe Impact of Clothing ClipsPhotomechanical exposure apparatusMicrolithography exposure apparatusMicro nanoLight beam

The invention provides a high-speed multi-beam parallel laser direct-writing device applying to micro-nano processing. The device consists of an inscribing light source modulation module, an inscribing optical header, an out-of-focus detection module, an illuminating and monitoring module, a sample displacement table and a master control module. The device greatly improves inscribing speed by multi-beam laser parallel high-speed inscribing. A multi-beam inscribing sub-system can be combined with sample tables with different motion modes to form inscribing devices with different functions according to the requirement of actual application.

Owner:安徽中科春谷激光产业技术研究院有限公司

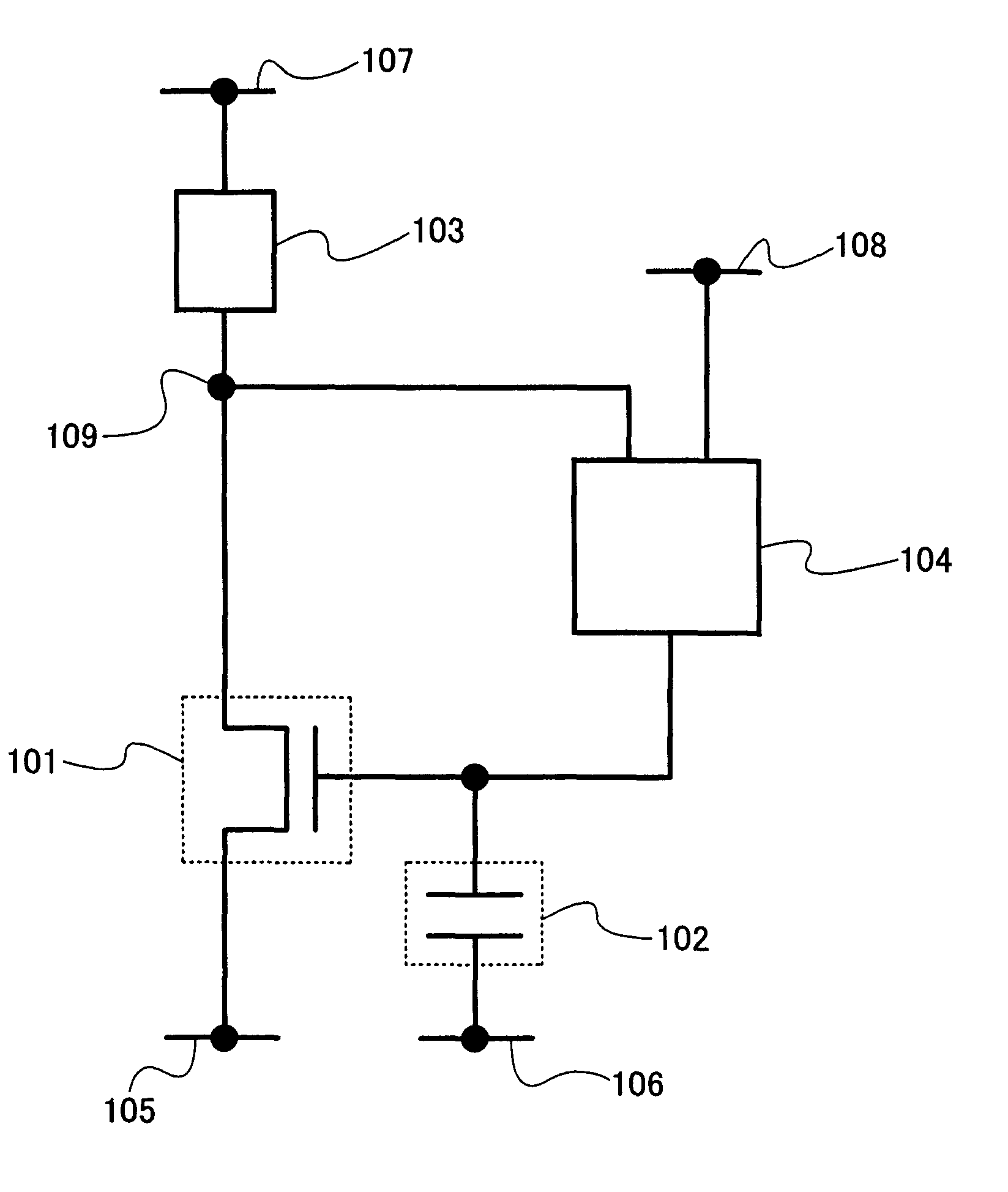

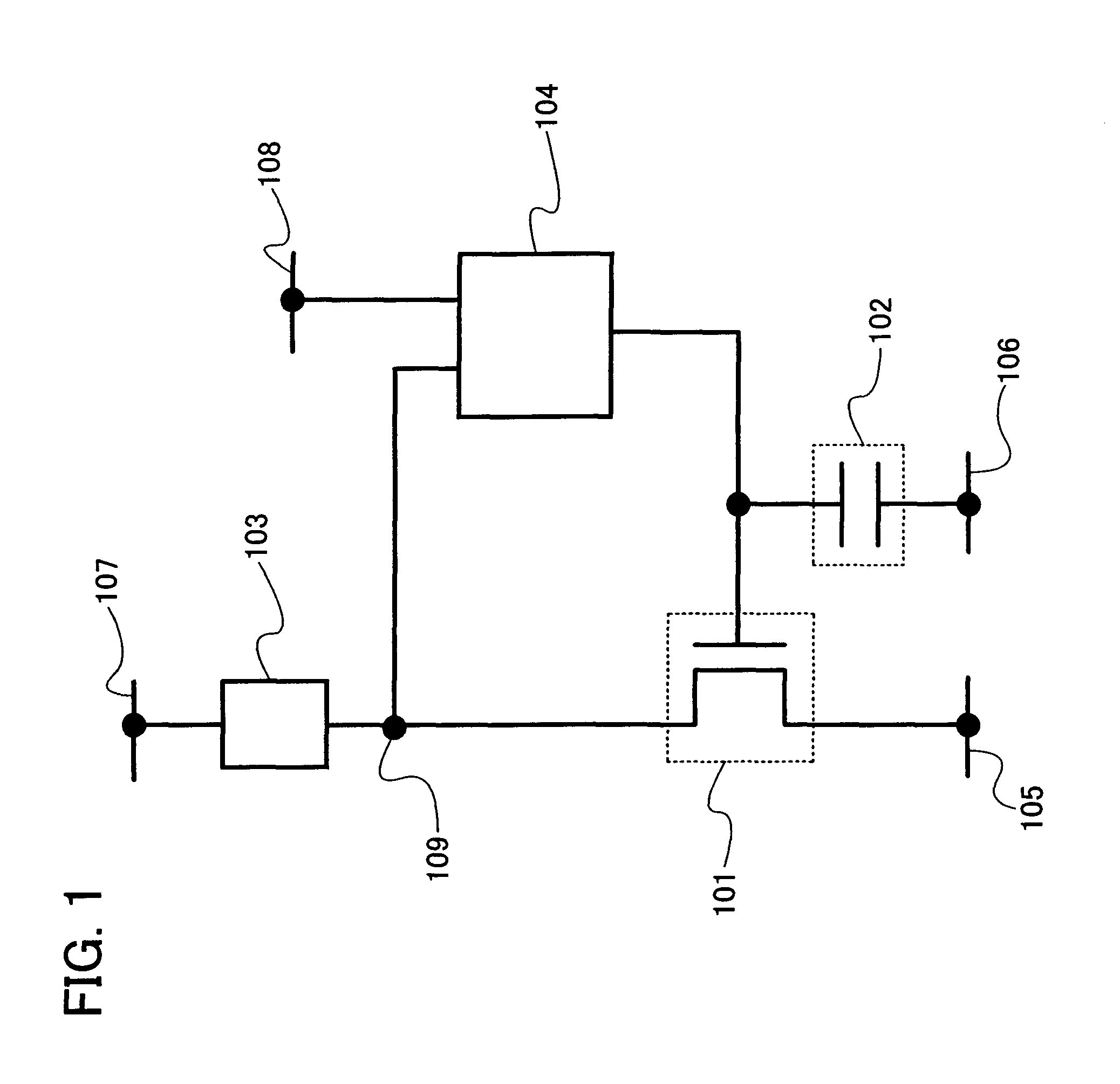

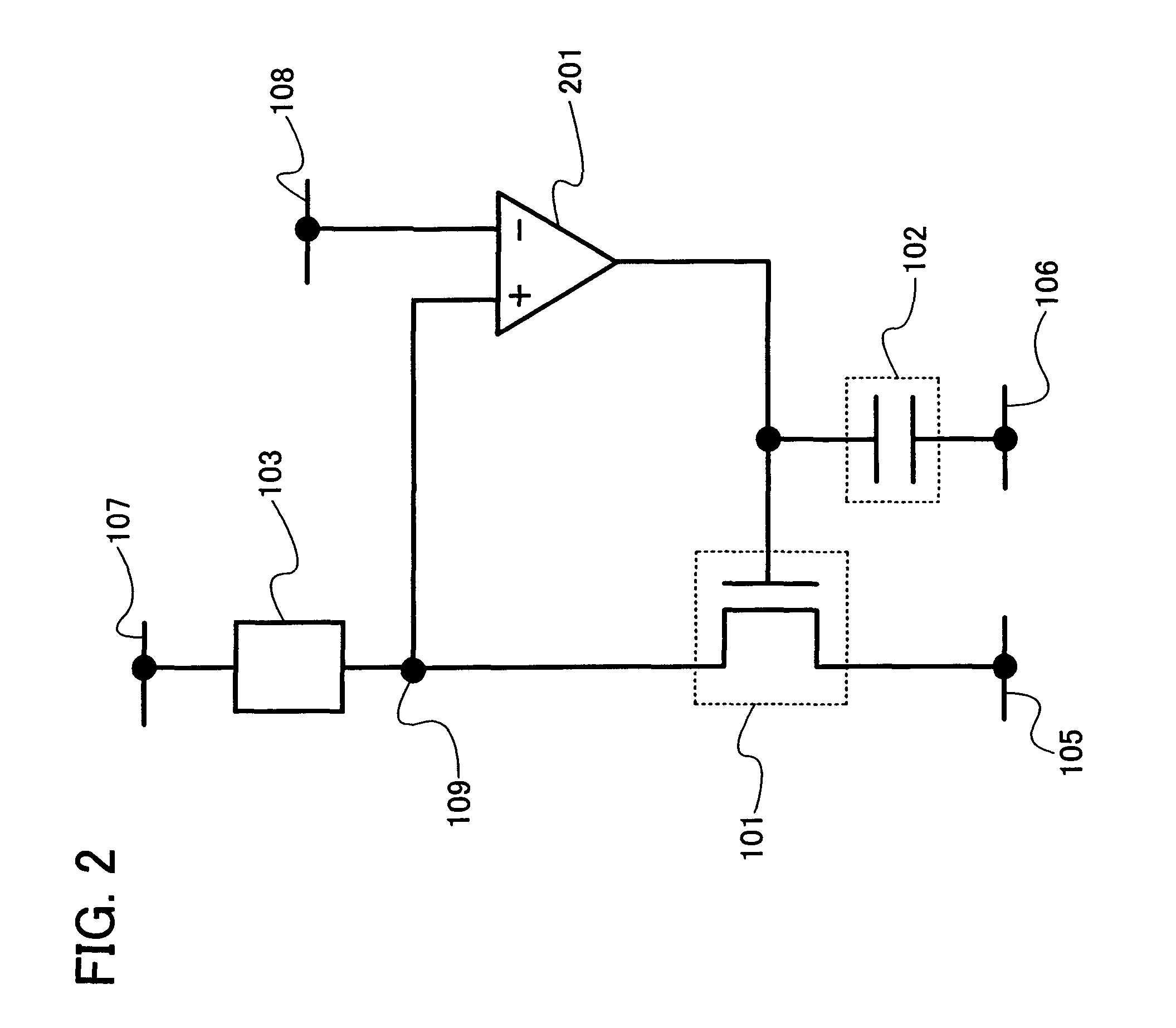

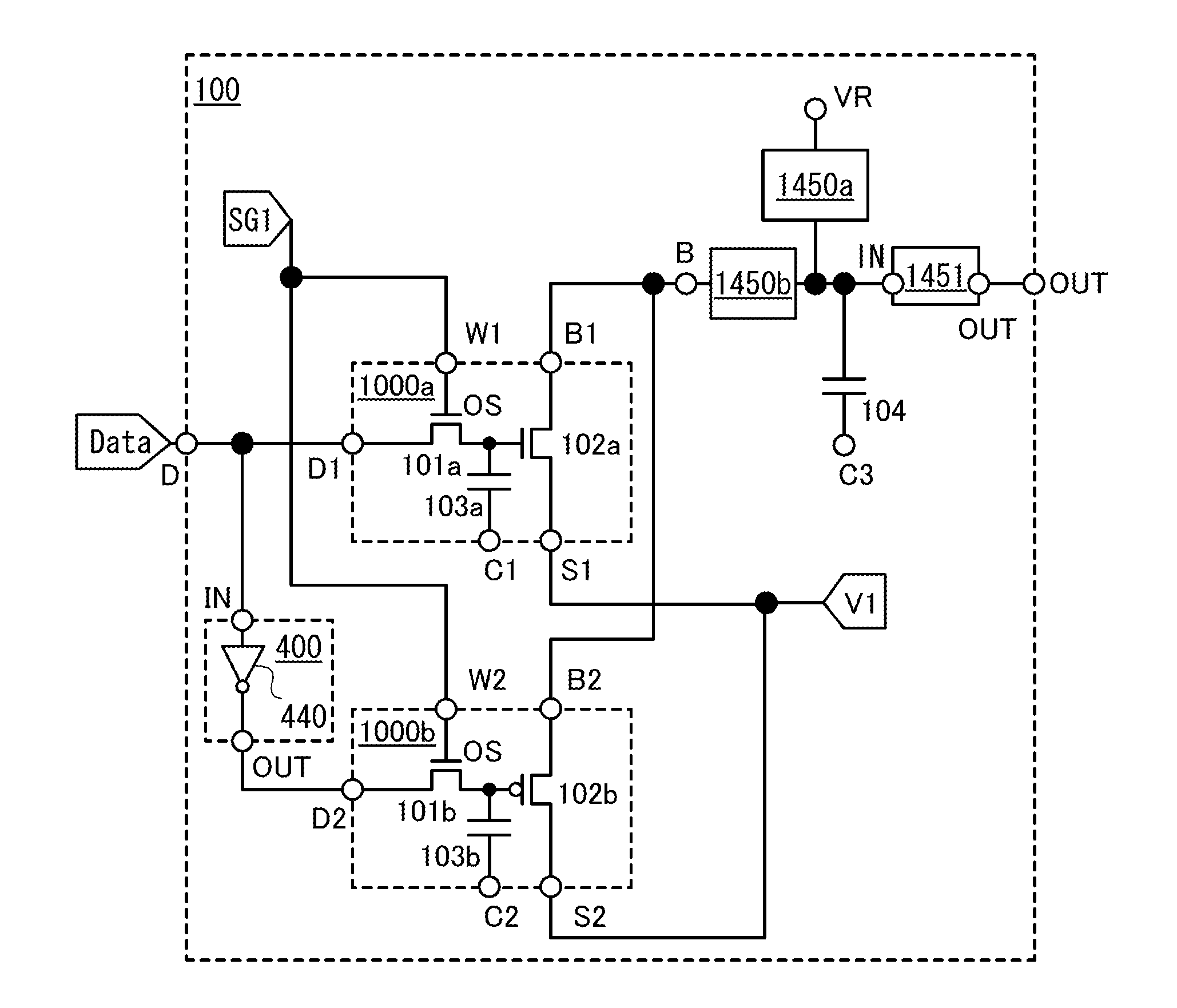

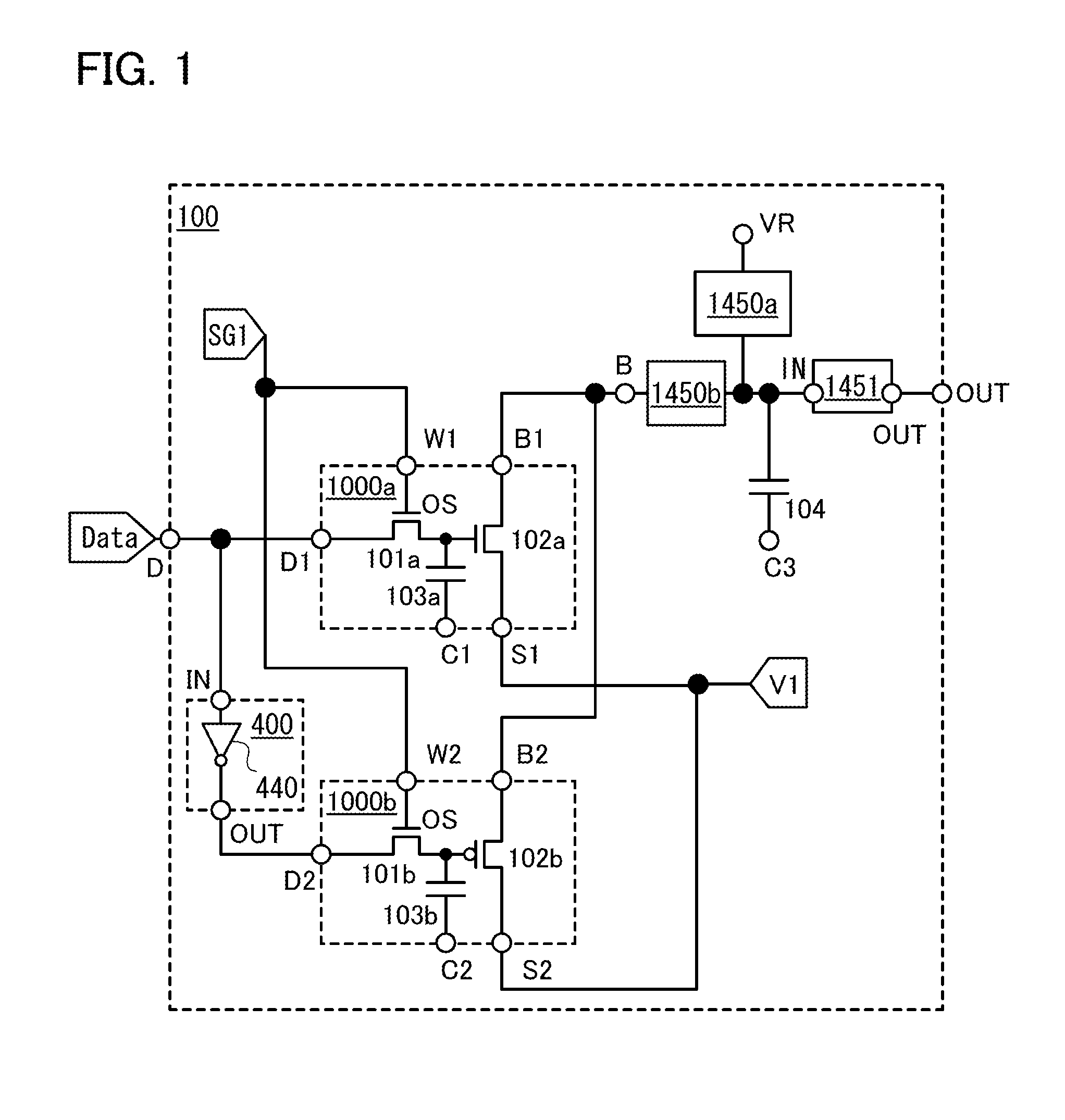

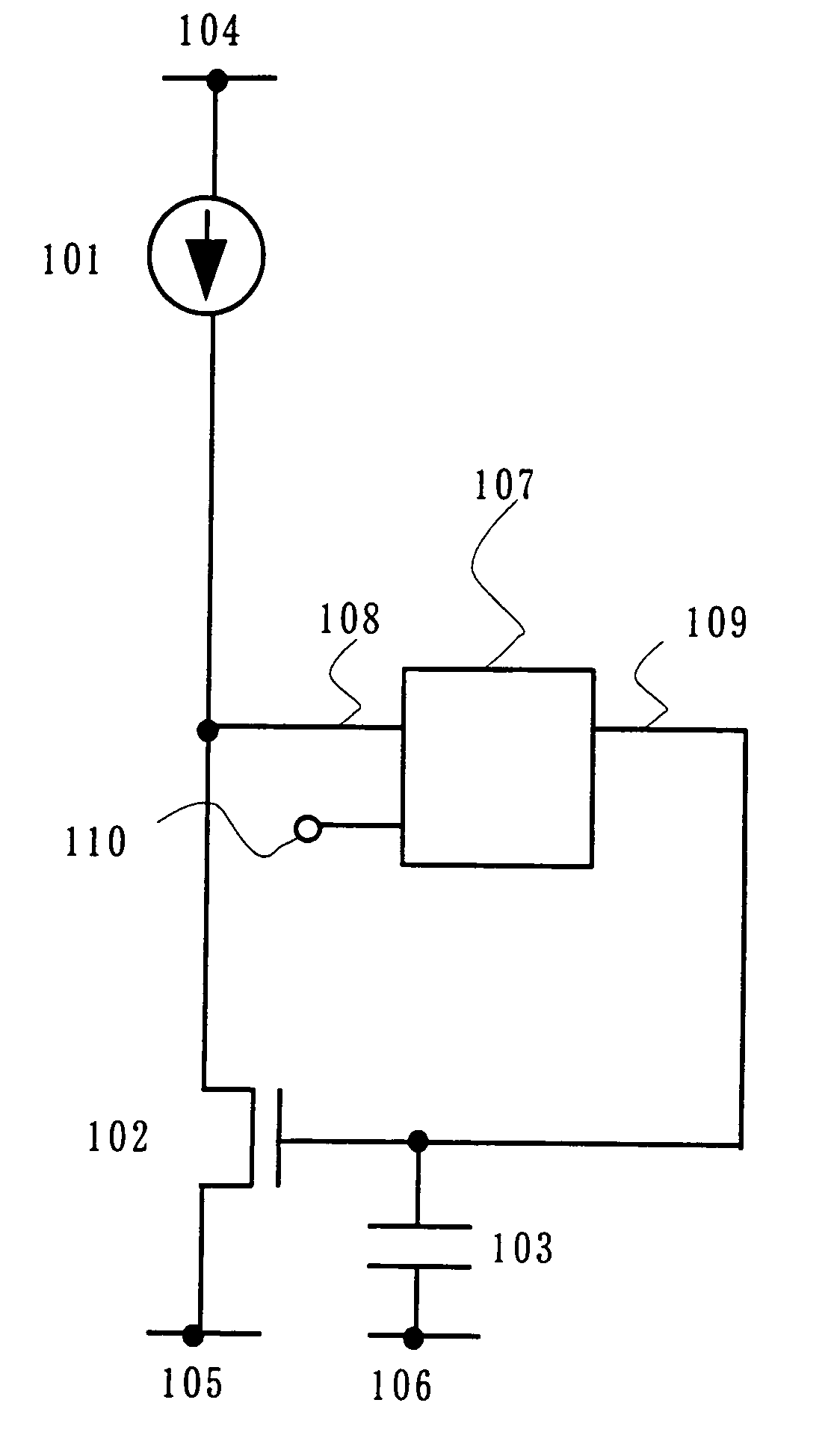

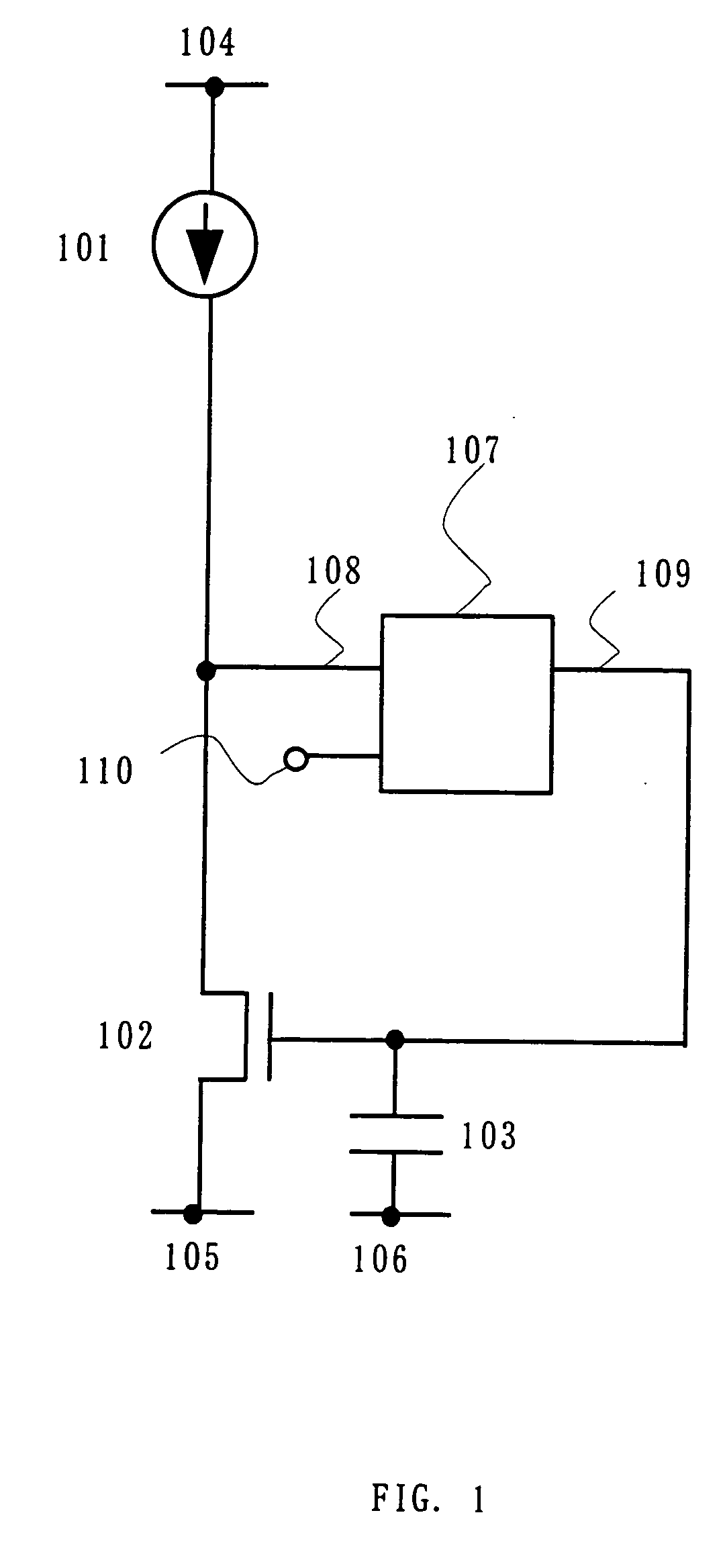

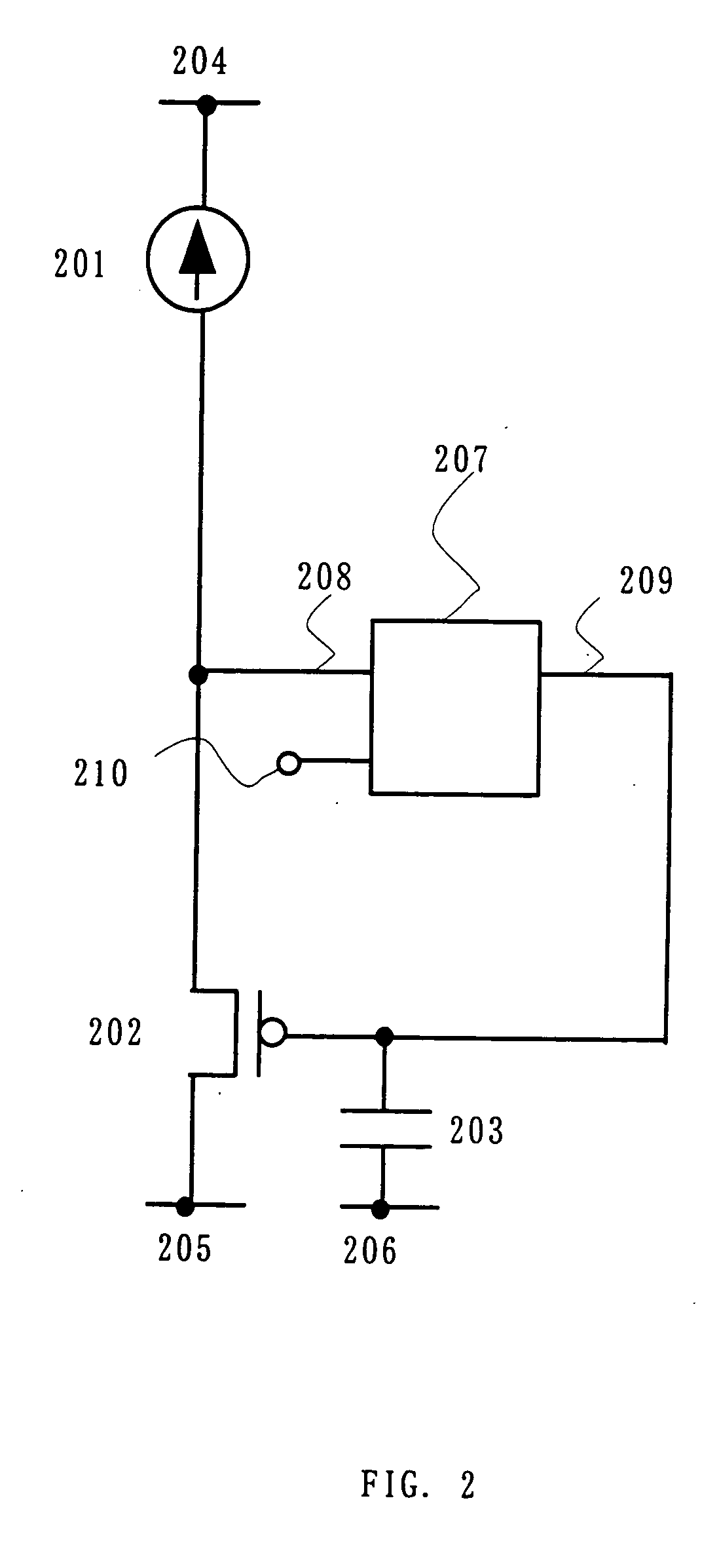

Semiconductor device

ActiveUS20070126668A1Image degradationIncrease write speedElectrical apparatusStatic indicating devicesAudio power amplifierDevice material

The invention provides a semiconductor device which is capable of decreasing an effect of a variation in characteristics of transistors, supplying a predetermined current even when voltage-current characteristics of a load change, and improving a write speed of a signal sufficiently even when the amount of a signal current is small. In the semiconductor device, a current-voltage converting element and a transistor are connected in series; and an amplifier circuit detects a voltage which is applied when a current flows to the current-voltage converting element, and sets a gate-source voltage of the transistor depending on the voltage. Therefore, since the amplifier circuit has low output impedance, a write speed of a signal can be improved sufficiently even when the amount of a signal current is small.

Owner:SEMICON ENERGY LAB CO LTD

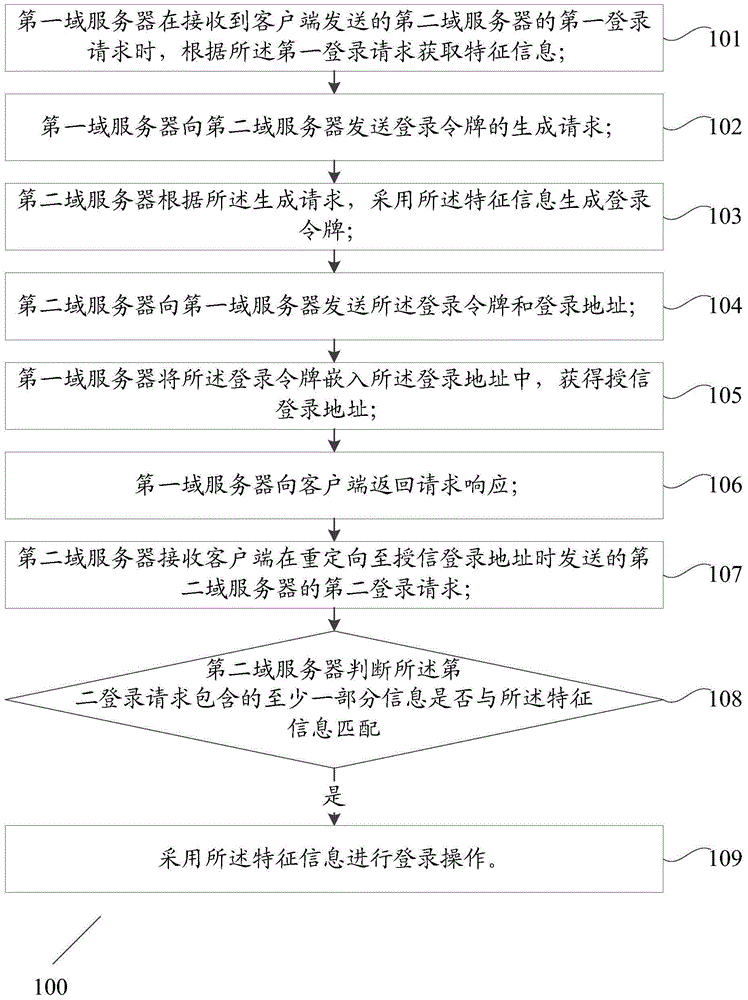

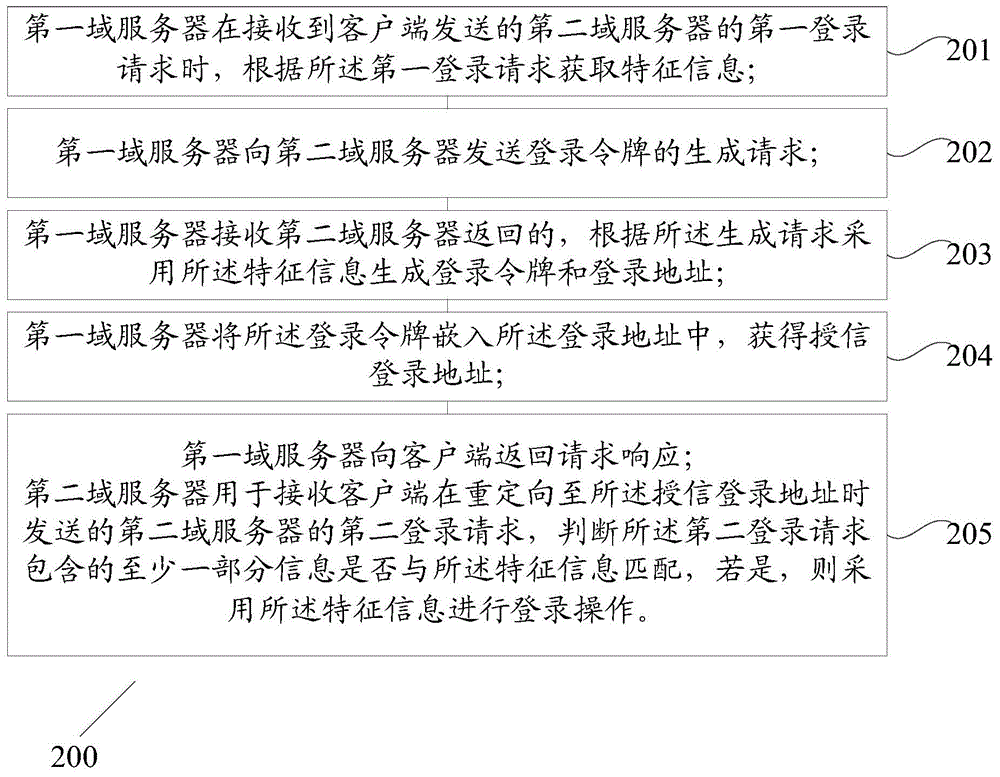

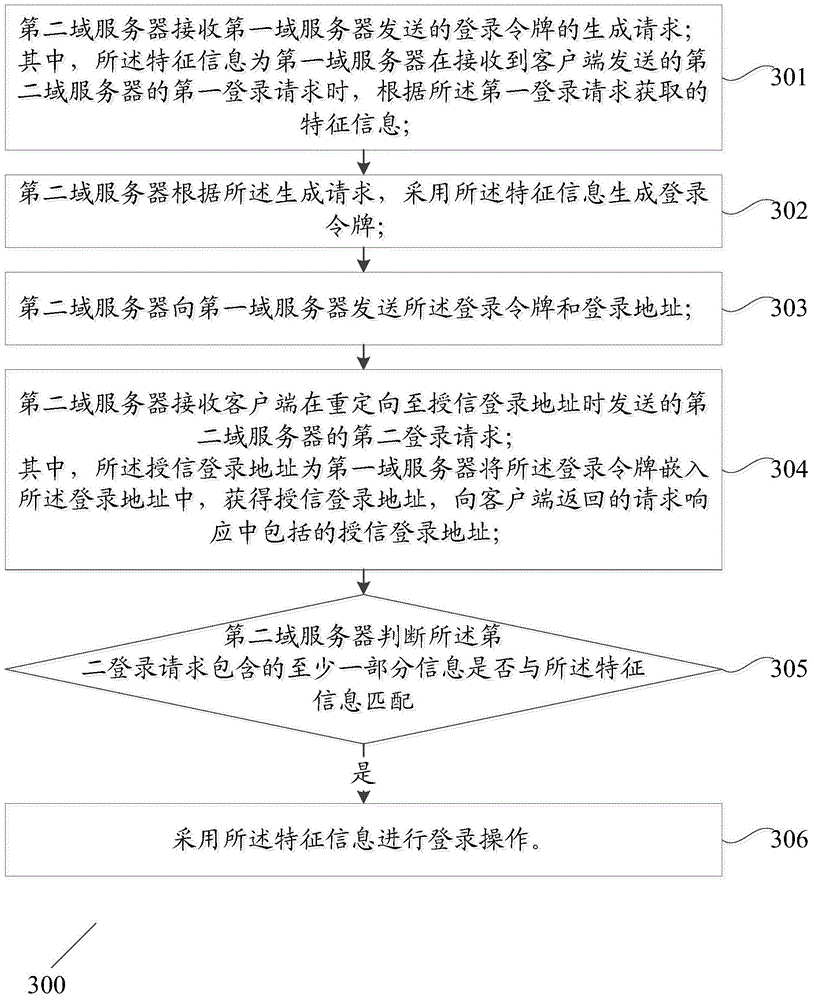

Login method and system of cross-domain server

The embodiment of the invention provides a login method and a login system of a cross-domain server. The login method comprises the steps that: a first domain server obtains feature information according to a first login request when receiving the first login request of a second domain server sent by a client; the first domain server sends a login token generation request to the second domain server; the second domain server generates a login token by utilizing the feature information according to the generation request; the second domain server sends the login token and a login address to the first domain server; the first domain server embeds the login token into the login address to obtain a credit login address; the first domain server returns a request response to the client; the second domain server receives a second login request of the second domain server sent by the client when redirecting to the credit login address; and the second domain server adopts the feature information to perform login operation when judging that at least part of information contained in the second login request matches with the feature information. The login method and the login system enlarge the range of application.

Owner:ALIBABA GRP HLDG LTD

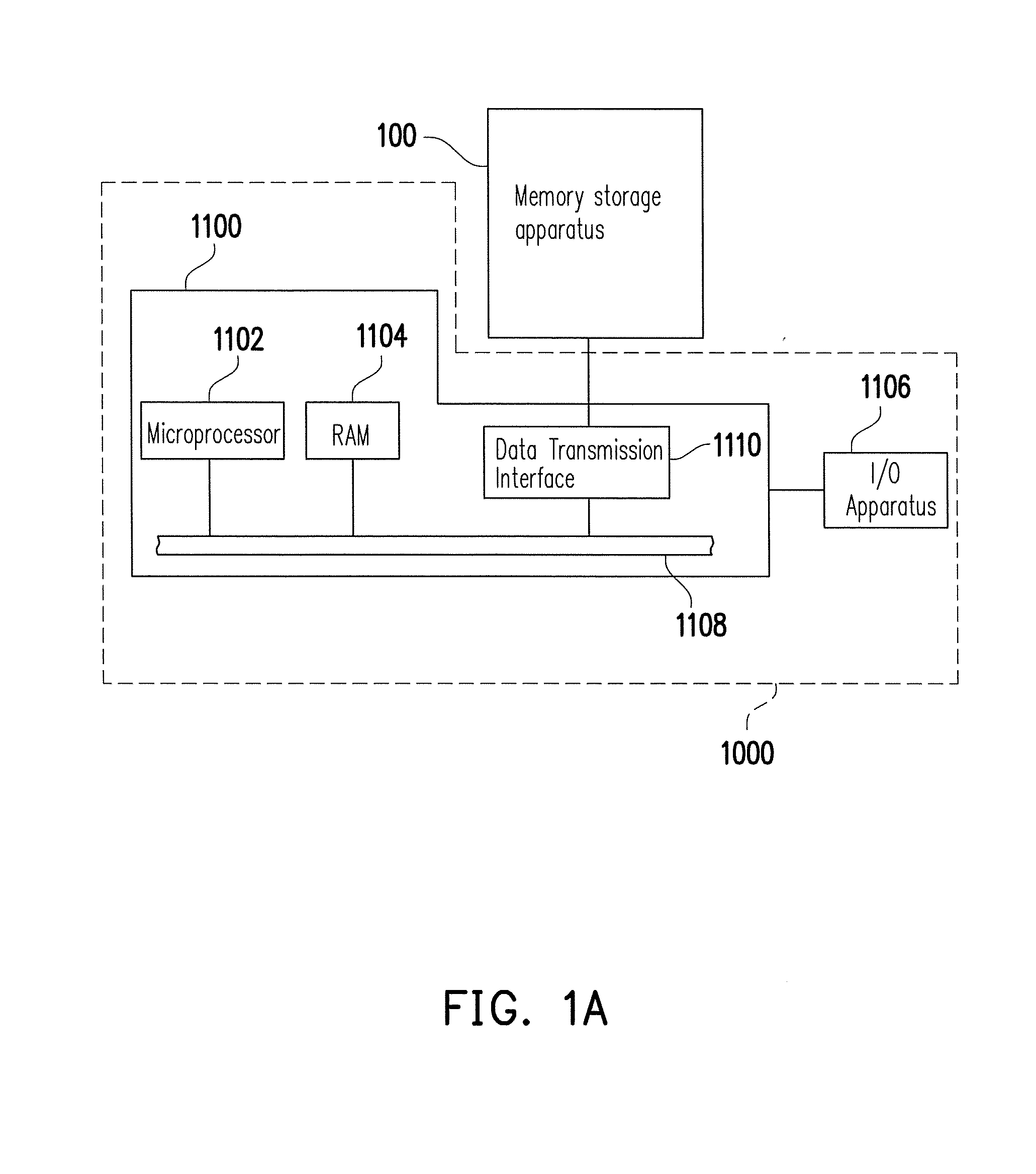

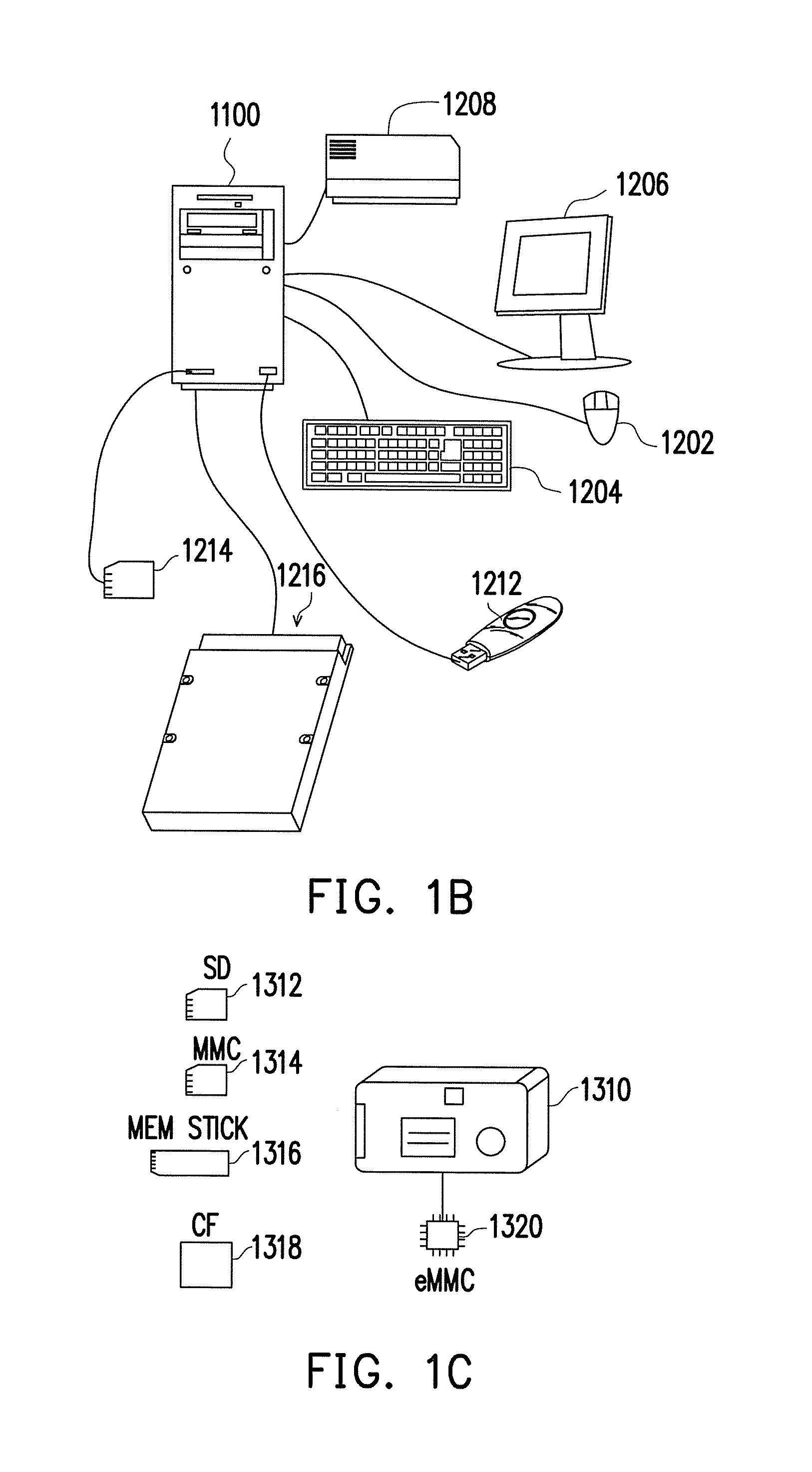

Method of programming memory cells and reading data, memory controller and memory storage apparatus using the same

ActiveUS20130246732A1Increase speedUnnecessary write operationMemory architecture accessing/allocationMemory adressing/allocation/relocationMemory controllerComputer science

Owner:PHISON ELECTRONICS

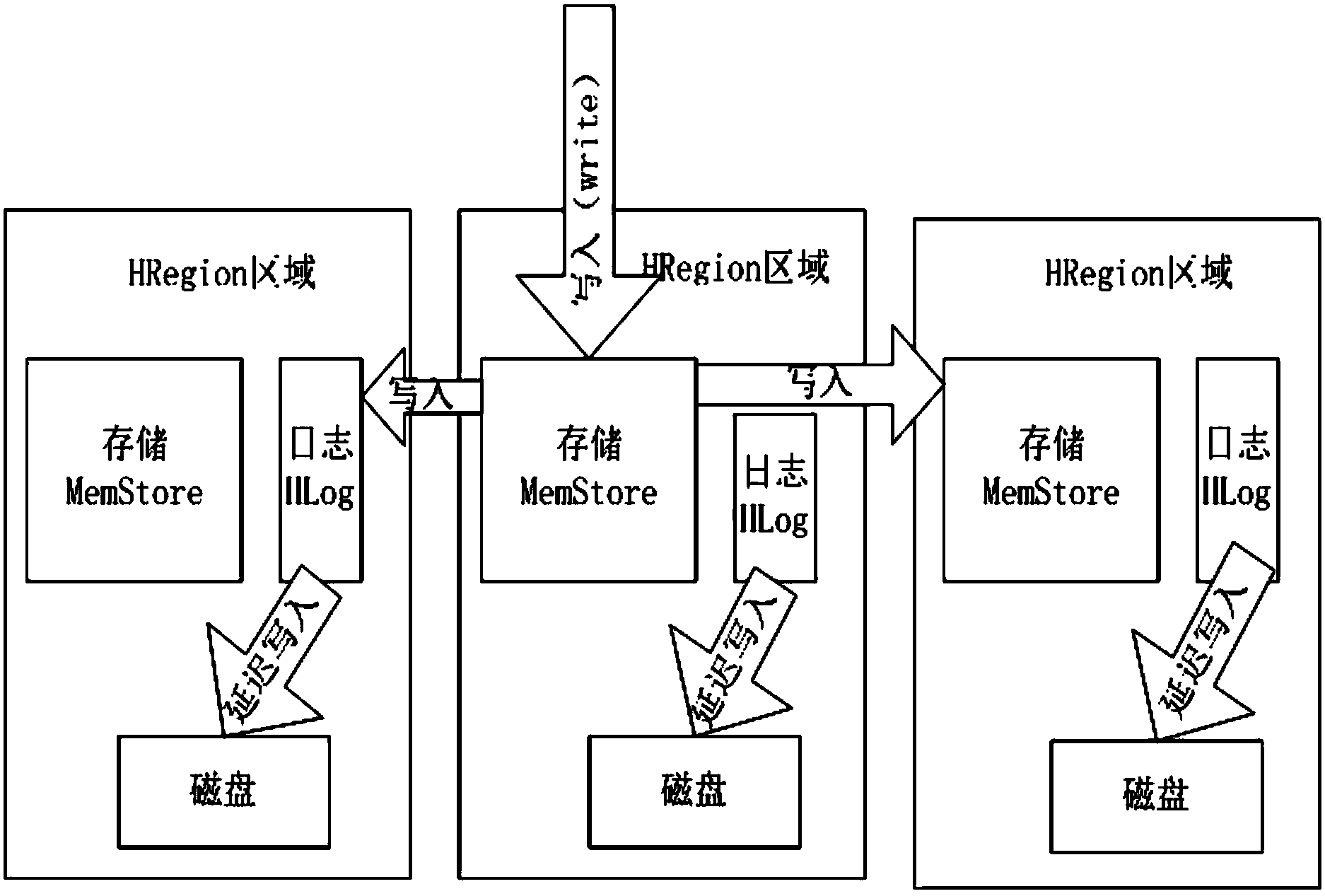

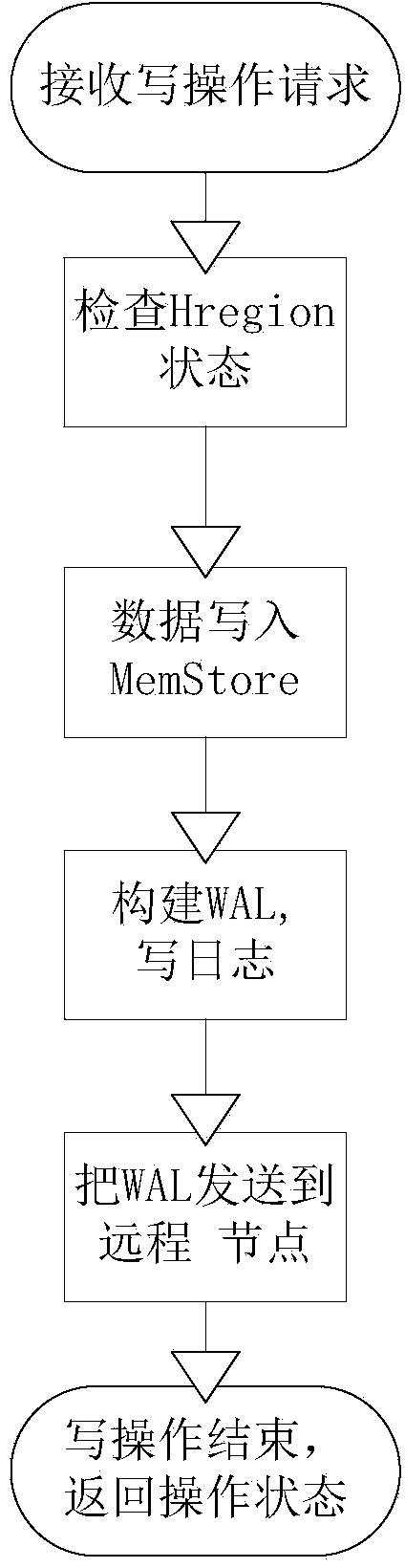

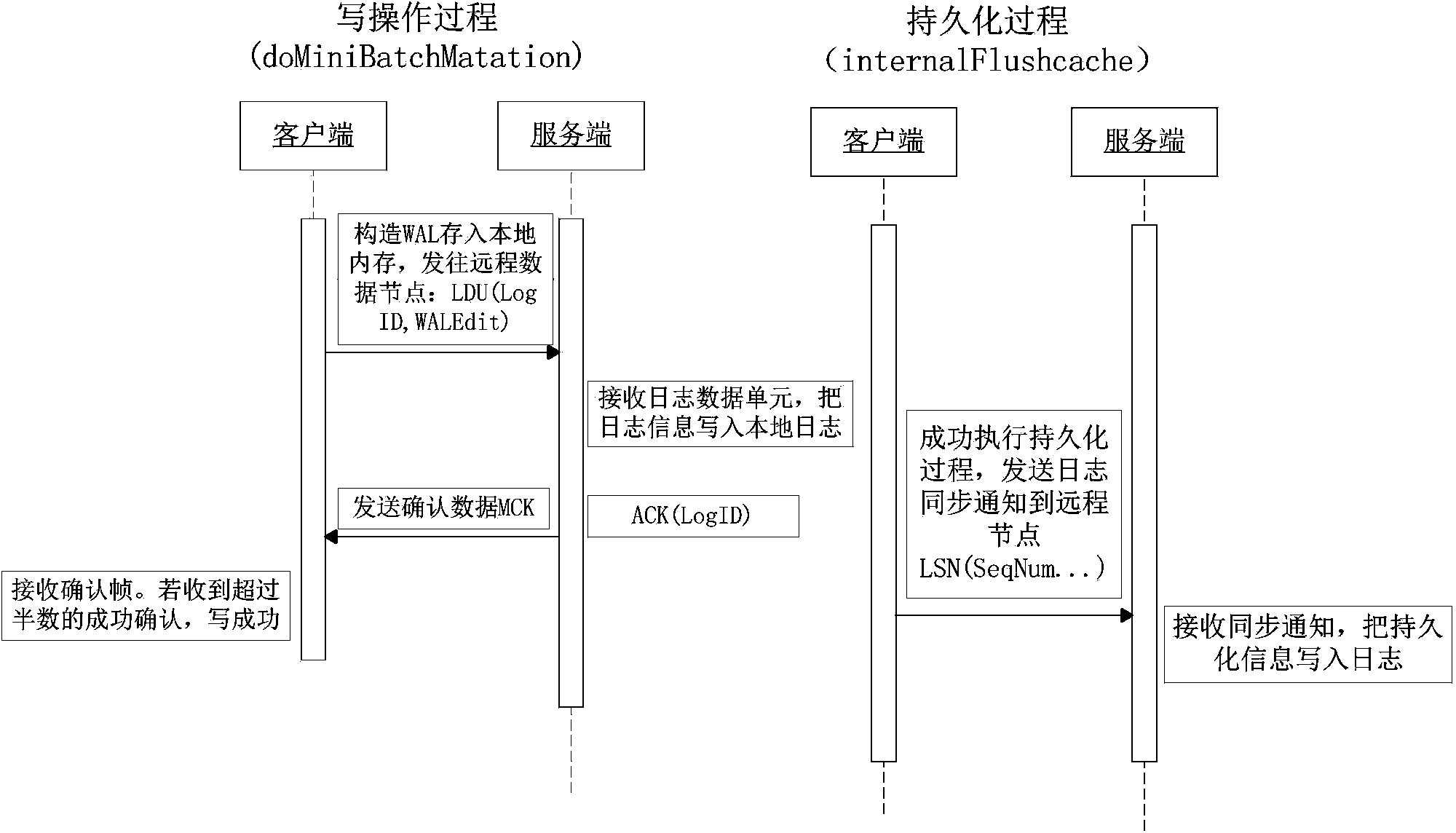

HBase (Hadoop database) data usability and durability method based on remote log backup

ActiveCN103870570AGuaranteed availabilityGuaranteed persistenceHardware monitoringSpecial data processing applicationsFile systemData node

The invention discloses an HBase (hadoop database) data usability and durability method based on remote log backup. The method is characterized in that when a data node of the HBase is written, the log record is first encapsulated through a distributive system, the log is backed up to a preliminarily-designated remote node through a network, the usability and durability of the data can be guaranteed, on the basis of the data, a great amount of user data and log record are temporarily stored in a memory, and the data persisting process in the data processing process is reduced; when the data node of the HBase is idle, the data in the memory is persisted to a file system, the storage pressure of the memory can be alleviated, the frequency of the persistence process in the writing process can be reduced, and the data writing time performance can be improved. By adopting the method, the usability and durability of the data can be guaranteed, the data writing speed can be greatly increased, and the system performance is improved.

Owner:上海艾讯云计算有限公司

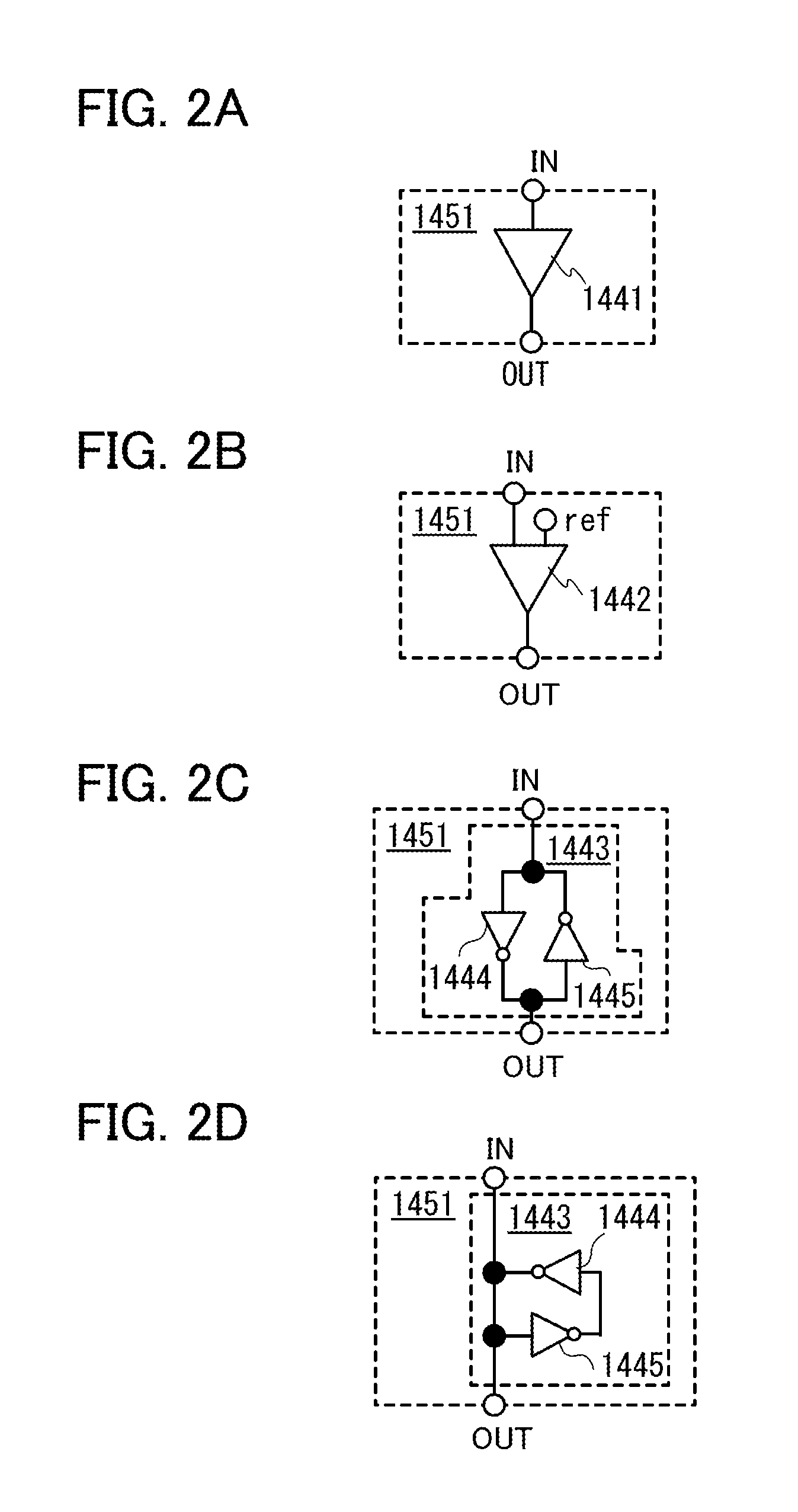

Memory element and signal processing circuit

ActiveUS20120230138A1Reduce the refresh rateIncrease number of rewritable timeDigital data processing detailsRead-only memoriesSignal processing circuitsHemt circuits

A memory element having a novel structure and a signal processing circuit including the memory element are provided. A first circuit, including a first transistor and a second transistor, and a second circuit, including a third transistor and a fourth transistor, are included. A first signal potential and a second signal potential, each corresponding to an input signal, are respectively input to a gate of the second transistor via the first transistor in an on state and to a gate of the fourth transistor via the third transistor in an on state. After that, the first transistor and the third transistor are turned off. The input signal is read out using both the states of the second transistor and the fourth transistor. A transistor including an oxide semiconductor in which a channel is formed can be used for the first transistor and the third transistor.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

InactiveUS20050168905A1Accurate currentAddressing slow performanceCathode-ray tube indicatorsRelaysSignal linesFeedback circuits

A semiconductor device is provided in which a transistor which supplies a current to a load (an EL pixel and a signal line) can supply an accurate current without being affected by a variation. A voltage of each terminal of a transistor is controlled by using a feedback circuit using an amplifier circuit. A current Idata is inputted from a current source circuit to a transistor and a gate-source voltage (a source potential) required for the transistor to flow the current Idata is set by using the feedback circuit. The feedback circuit is controlled to operate so that a drain potential of the transistor becomes a predetermined potential. Then, a gate voltage required to flow the current Idata is set. By using the set transistor, an accurate current can be supplied to the load (an EL element and a signal line). As a drain potential can be controlled, the kink effect can be reduced.

Owner:SEMICON ENERGY LAB CO LTD

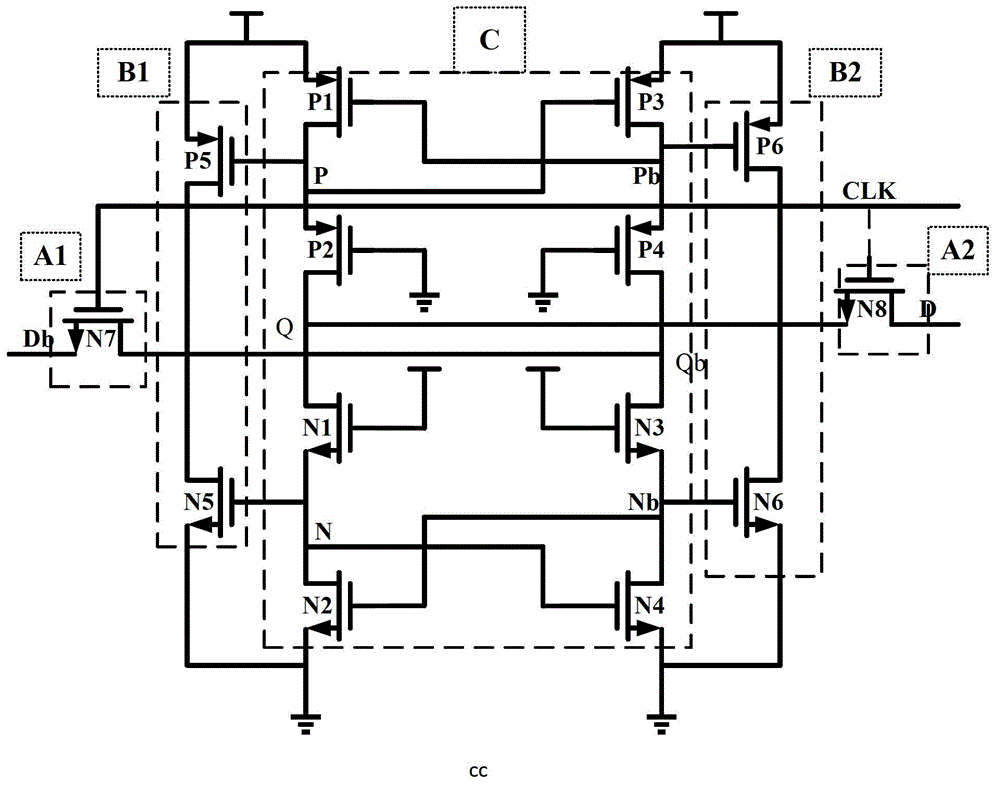

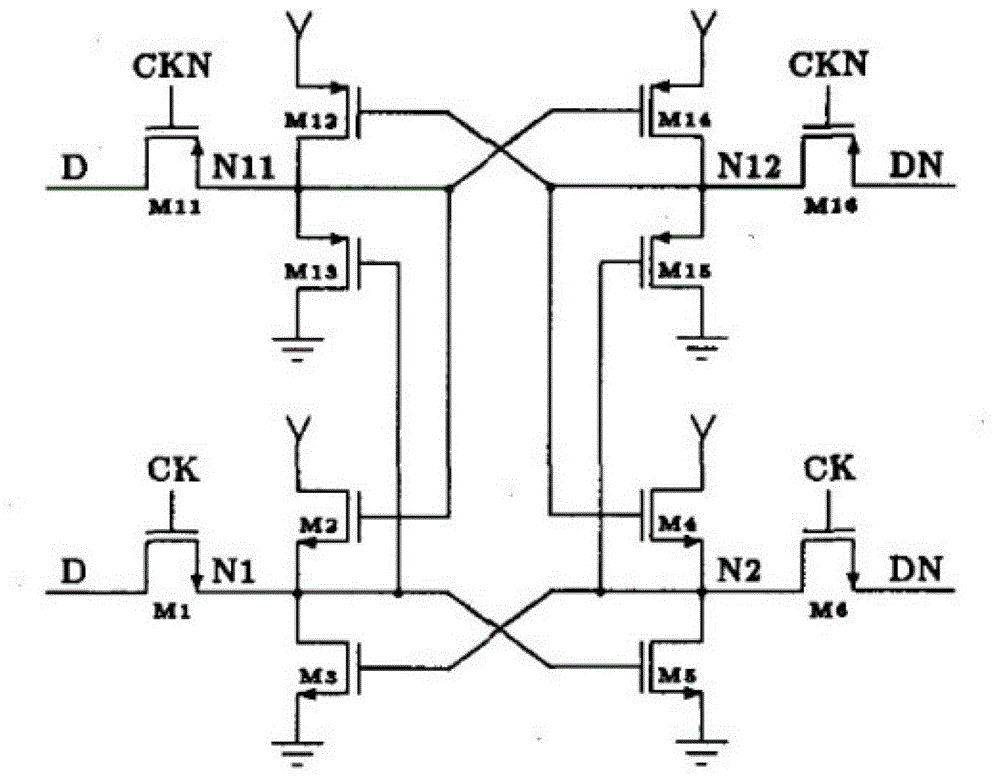

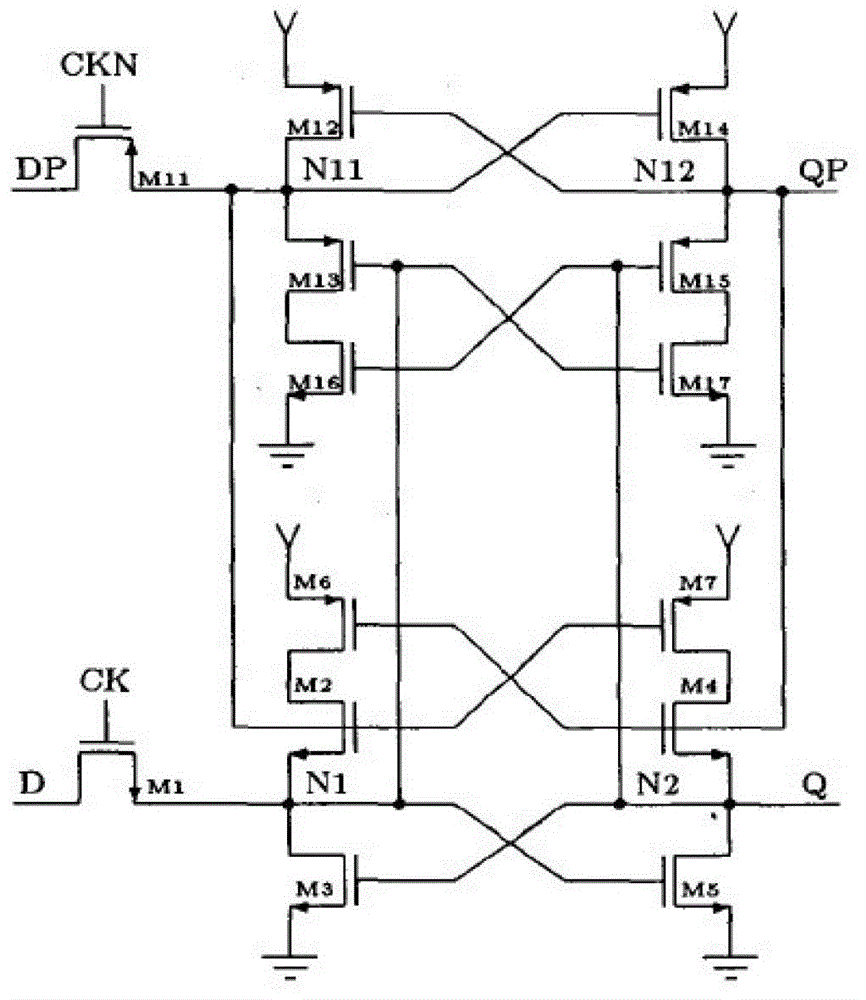

Novel static random access memory (SRAM) storage unit preventing single particle from turning

ActiveCN102723109ARealize the ability of flip reinforcementReduce rollover recovery timeDigital storageStatic random-access memoryClock network

The invention discloses a novel static random access memory (SRAM) storage unit preventing a single particle from turning. The storage unit comprises a first input / output port, a first potential turning recovery driving circuit, a voltage retaining circuit, a second potential turning recovery driving circuit and a second input / output port which are connected in series with one another sequentially. An automatic recovery function for voltage turning when a sensitive node is impacted by a high-energy particle can be realized; according to a simulation result of a TSMC 0.18 mu_m process, a turning threshold value LETth is more than 500 MeV / (mg.cm<2>); compared with the conventional storage unit preventing the single particle from turning, the SRAM storage unit has the characteristic of high writing speed; the recovery time can be effectively shortened; by adopting a unidirectional clock and a small-clock amplitude, a clock network is relatively simple and relatively high in reliability; the clock is only connected with the gate of a read-write transistor, and the clock load is relatively small; and the sensitive node can be used for reinforcing multi-node turning of the single particle, which is caused by drains positioned on a P-type tube and an N-type tube..

Owner:XI AN JIAOTONG UNIV

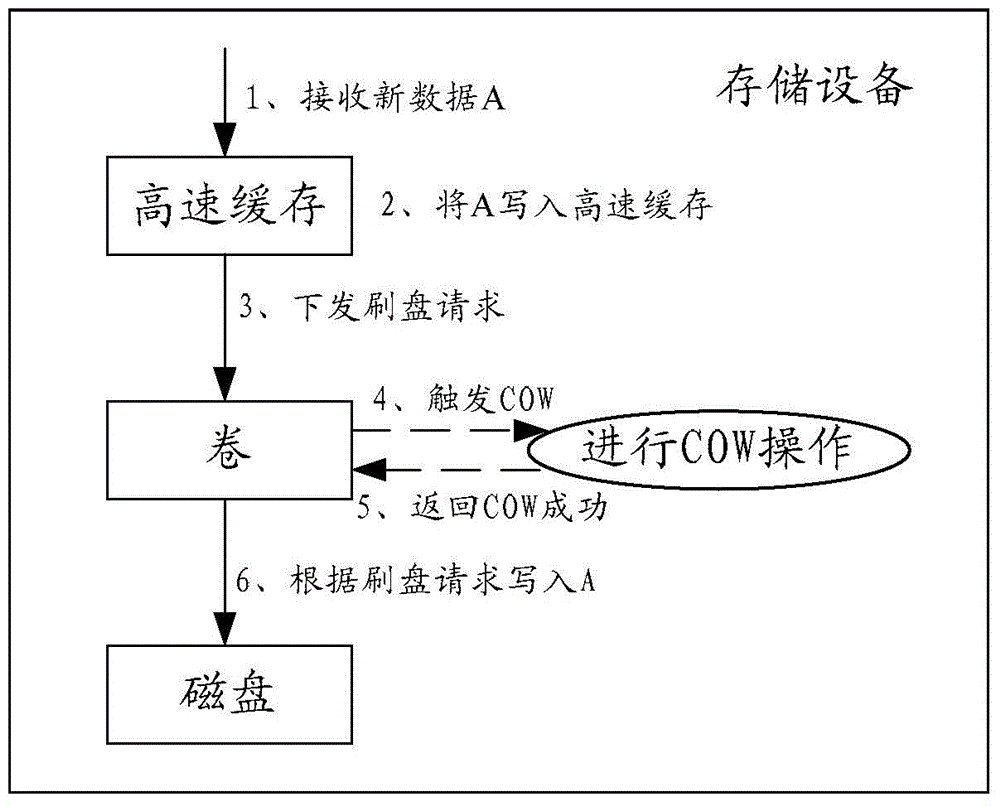

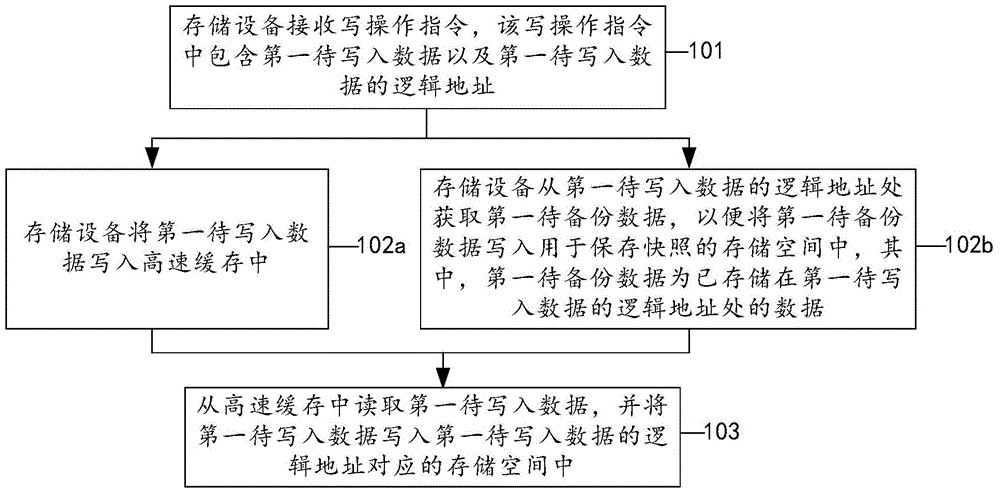

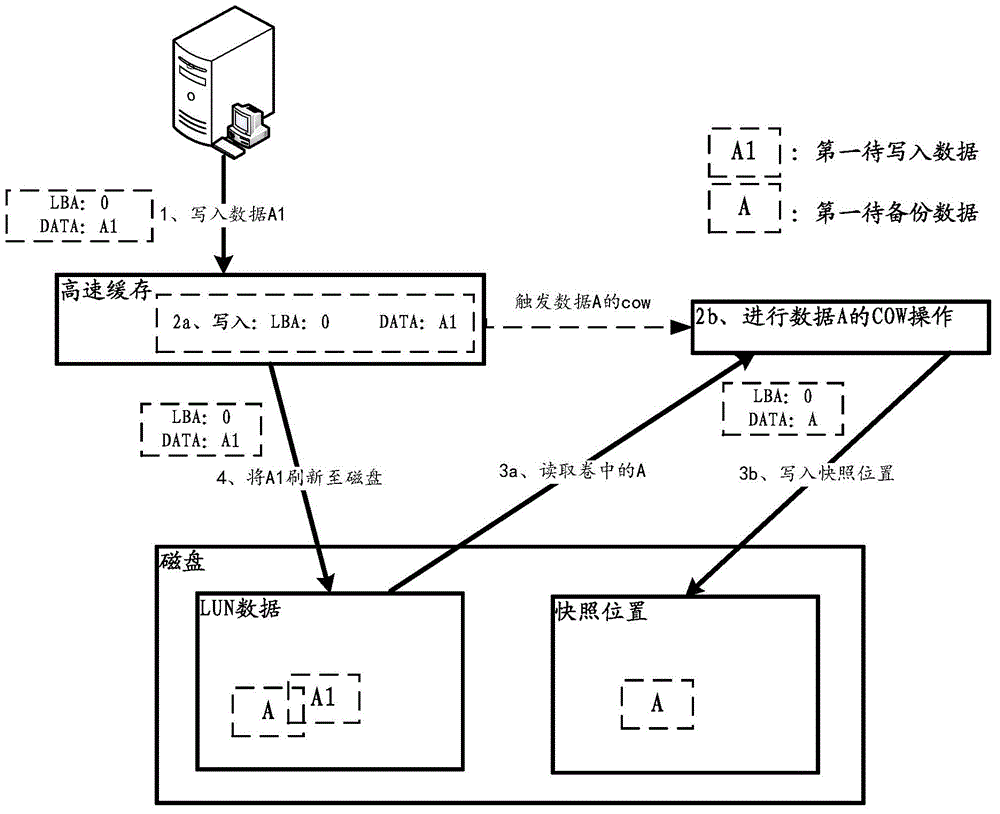

Data backup method and device

ActiveCN104407933AIncrease write speedIncrease profitMemory adressing/allocation/relocationRedundant operation error correctionLogical addressCopy-on-write

The embodiment of the invention provides a data backup method and device, and relates to the field of data storage. The method and the device solve the problem of I / O (input / output) performance reduction due to COW (copy on write) processing in the prior art, and have the advantage that the data write-in speed is accelerated. The method adopting the scheme comprises the following steps that a write operation instruction is received, wherein the write operation instruction includes first data to be written in and a logic address of the first data to be written in; the first data to be written in is written into a high-speed cache; when the first data to be written in is written into the high-speed cache, first data to be backed up is obtained from the logic address of the first data to be written in, so that the first data to be backed up is written into a storage space used for storing a snapshot, wherein the first data to be written in is read from the high-speed cache, the first data to be written in is written into the storage space corresponding to the logic address of the first data to be written in.

Owner:HUAWEI TECH CO LTD