Patents

Literature

994 results about "Multi state" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

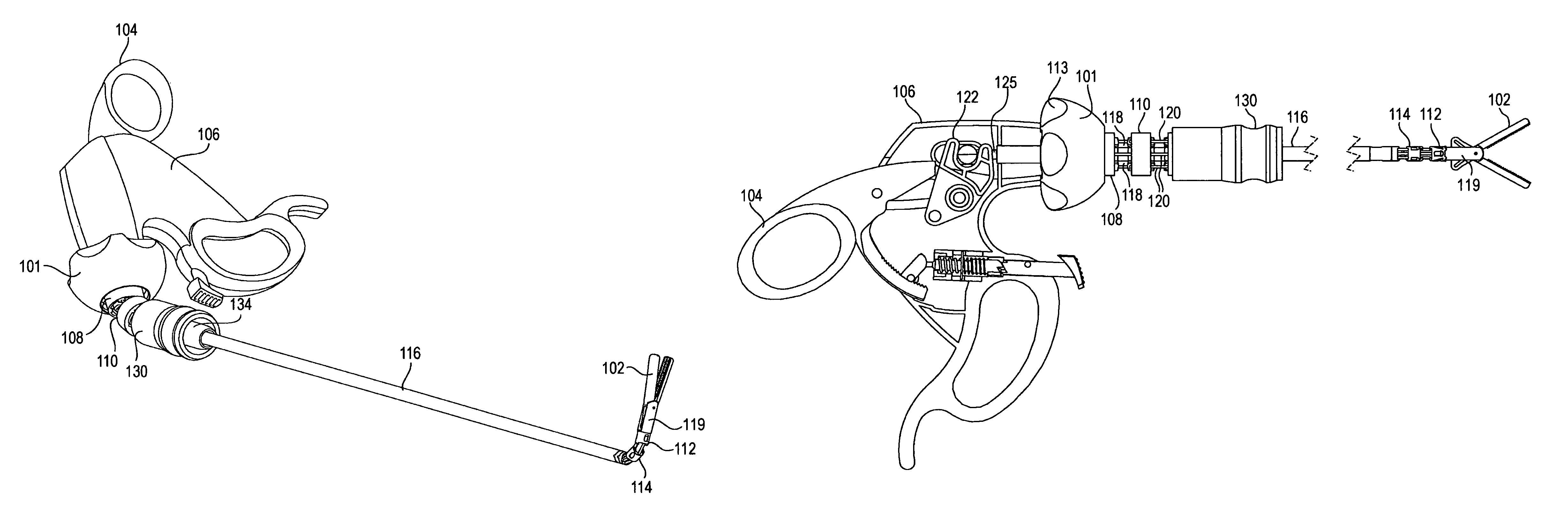

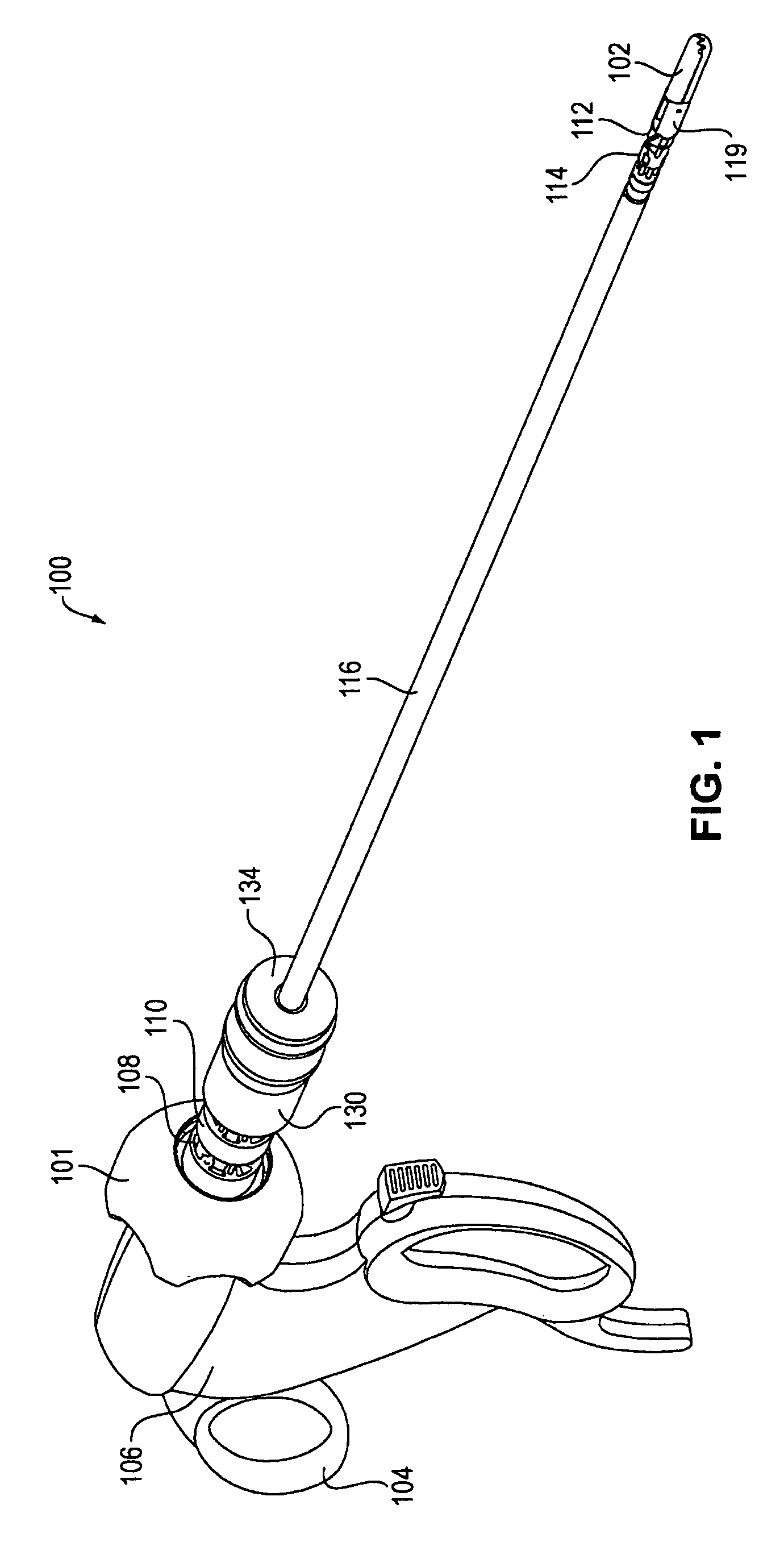

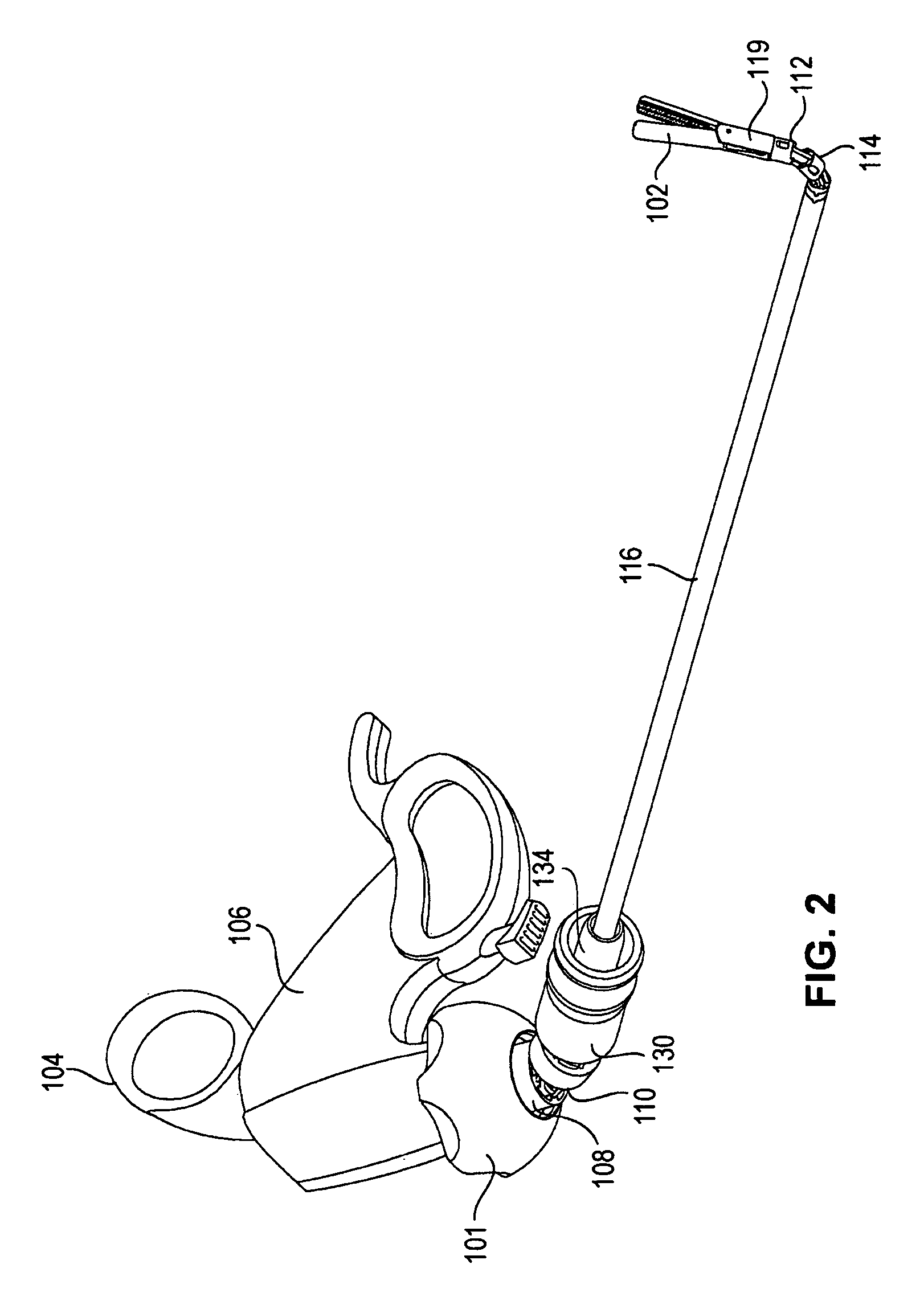

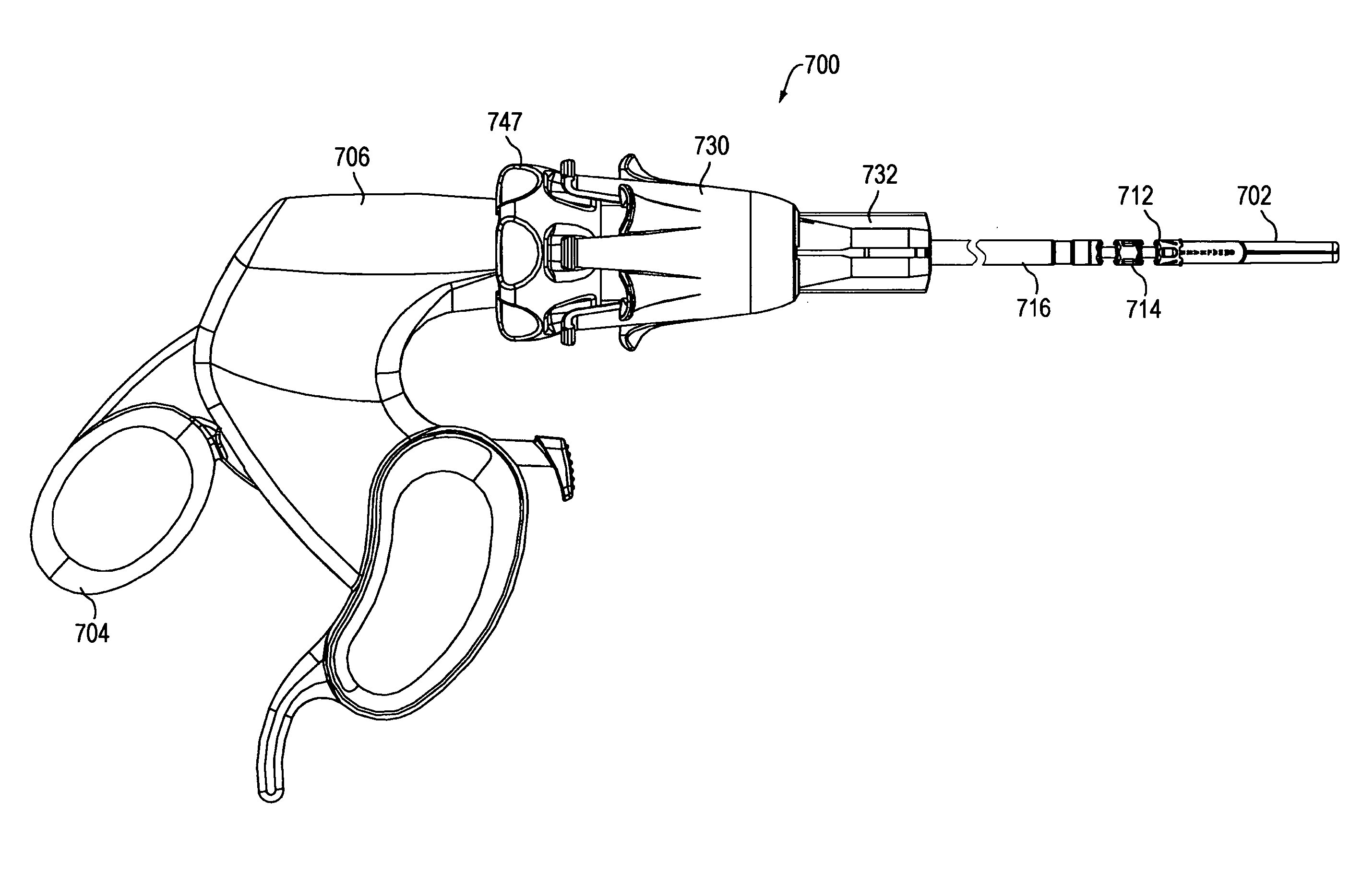

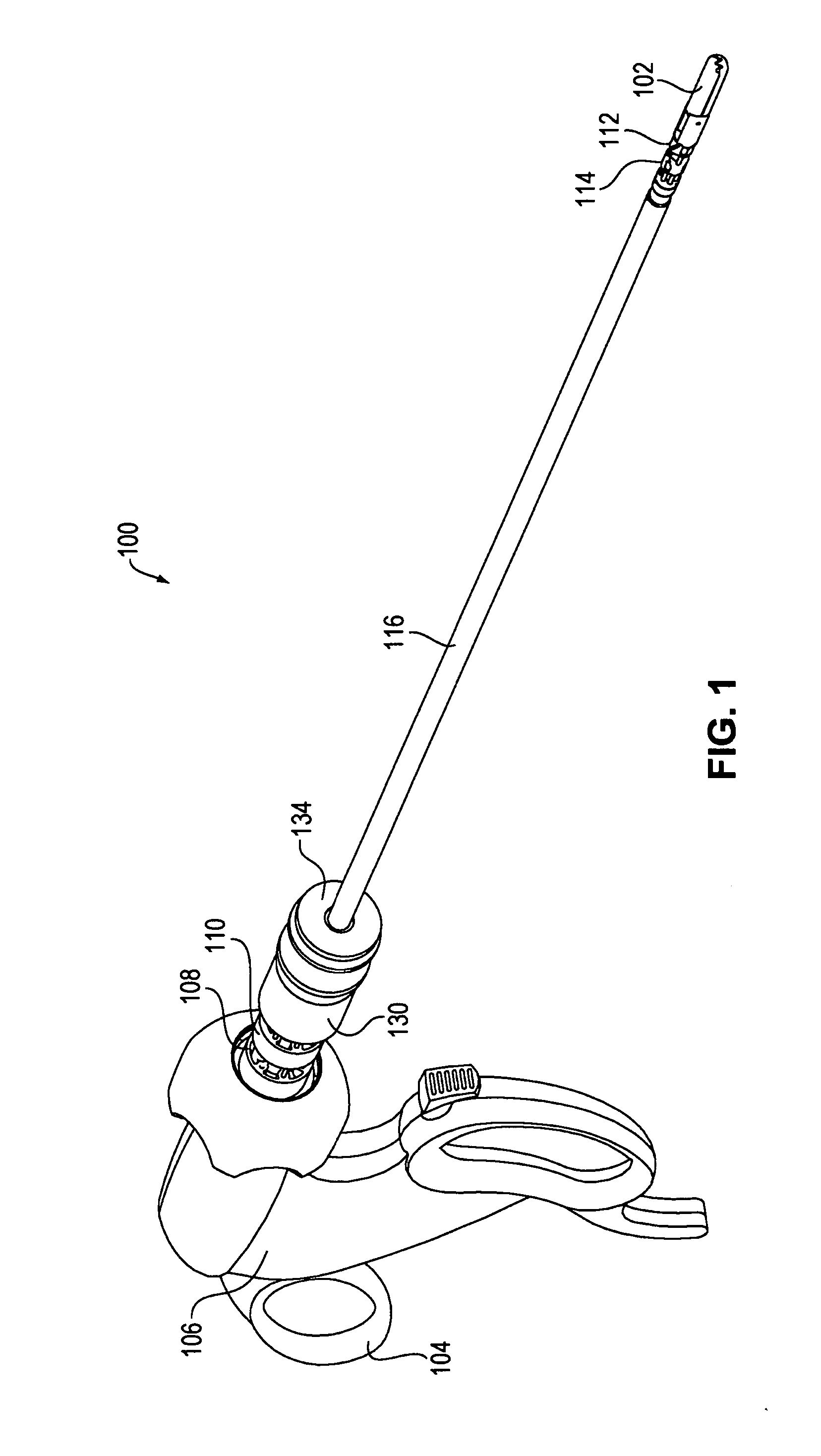

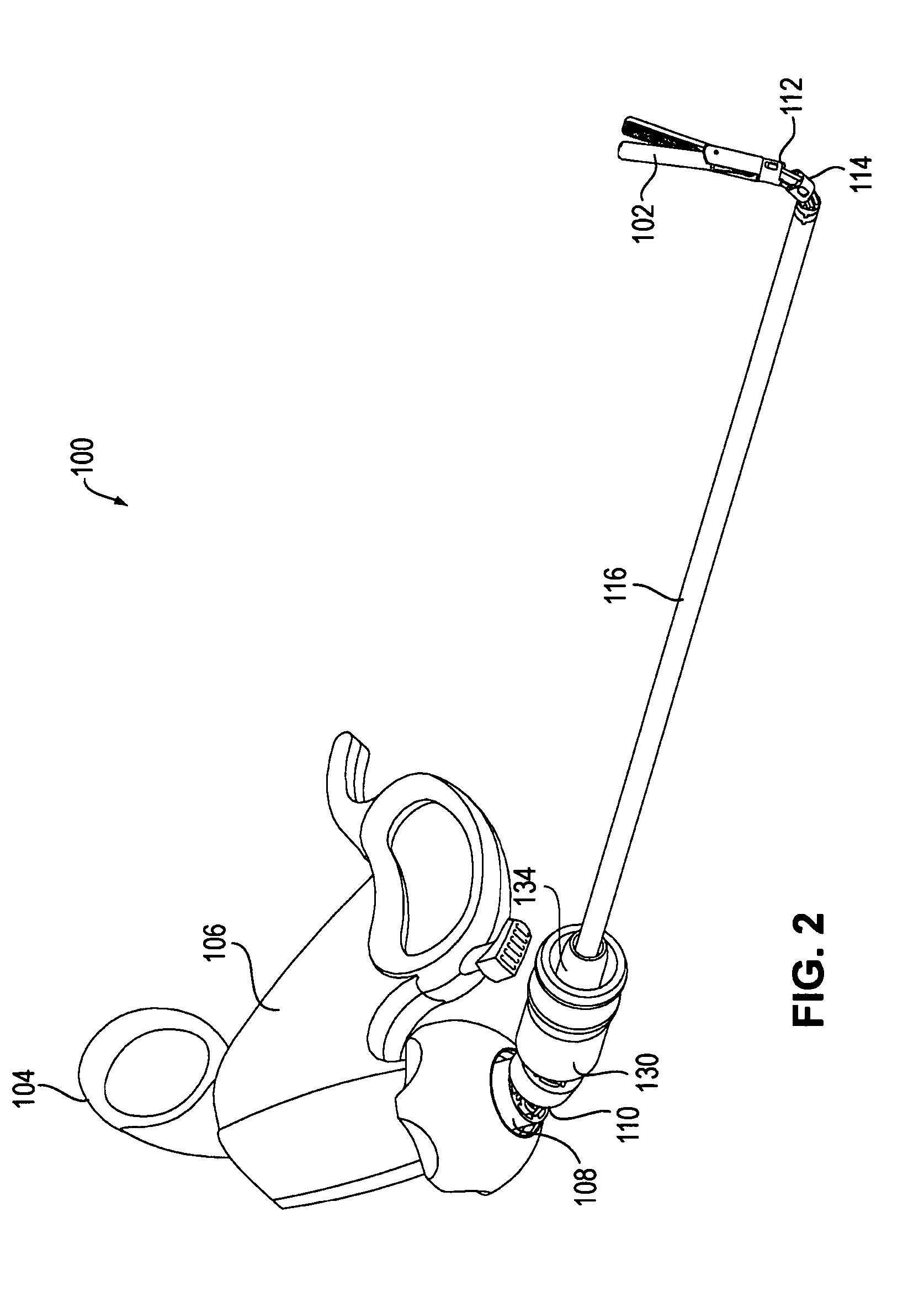

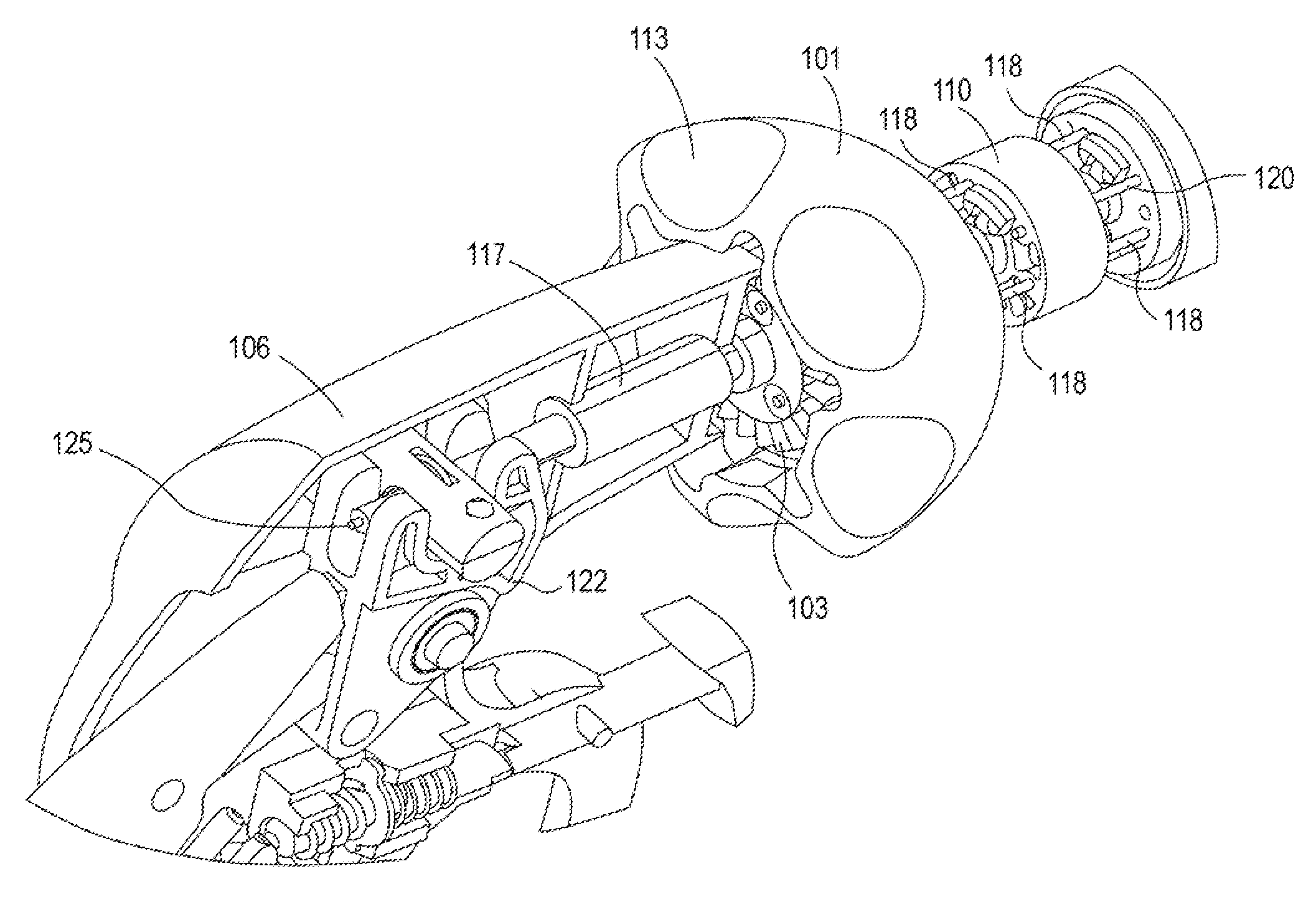

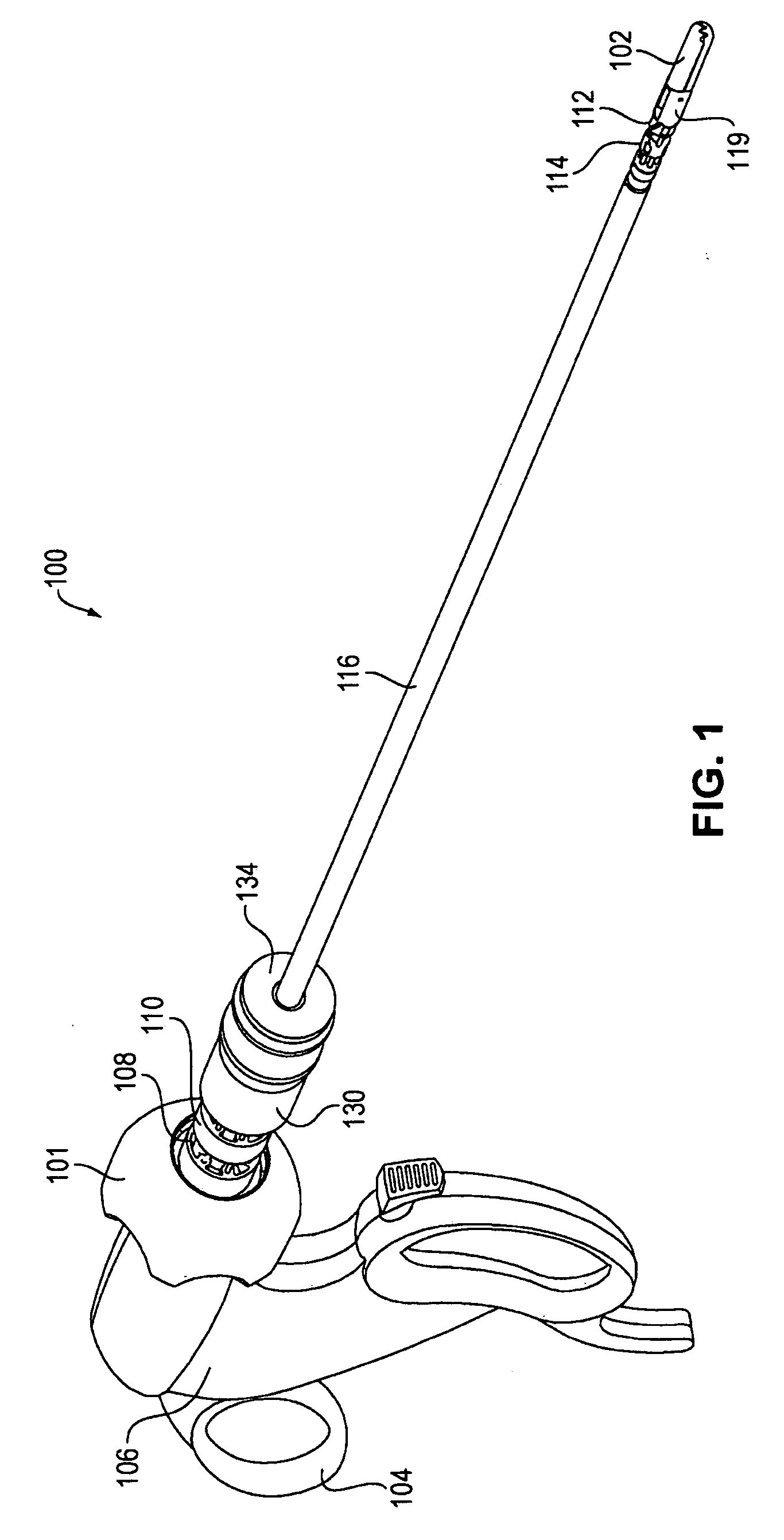

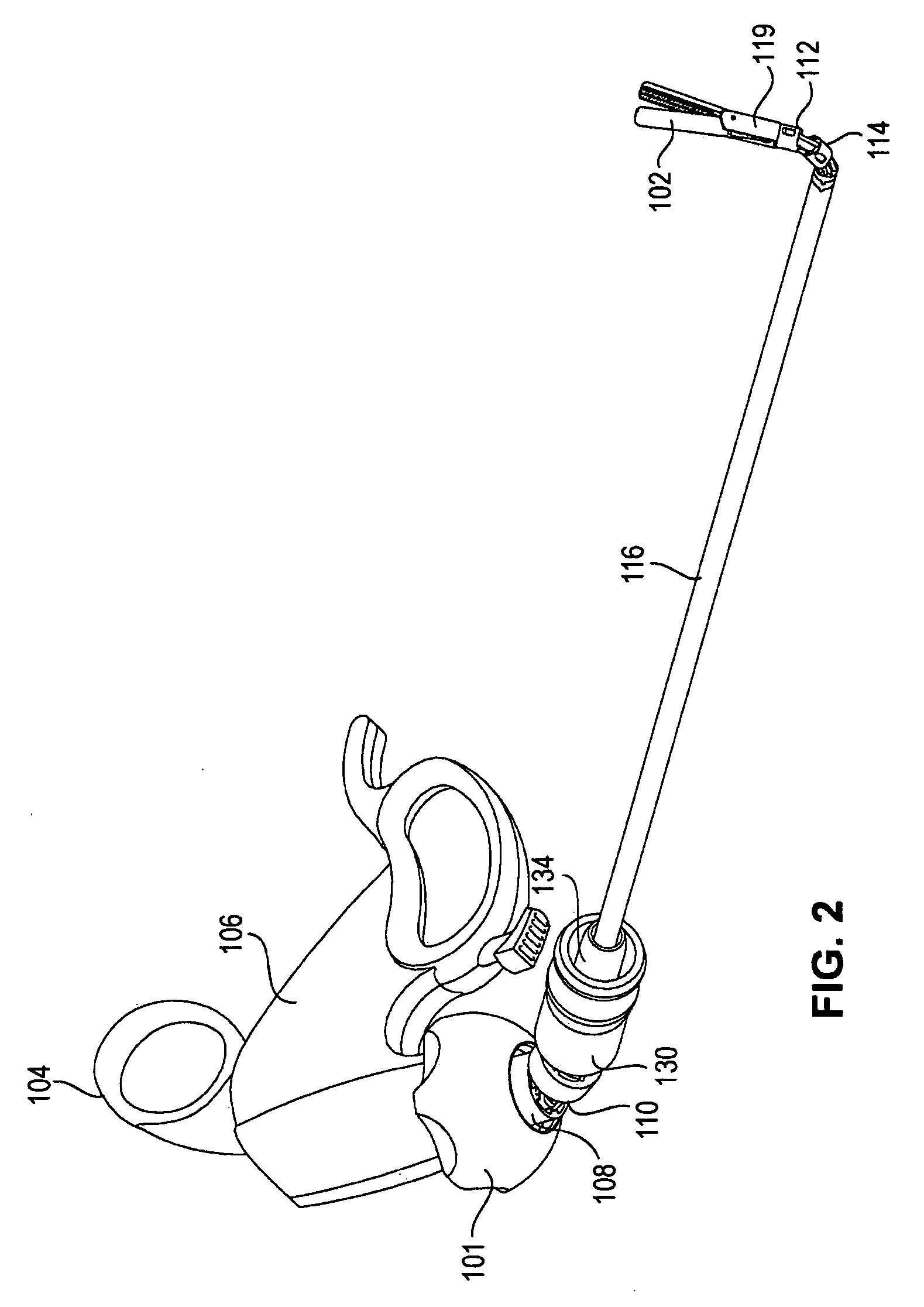

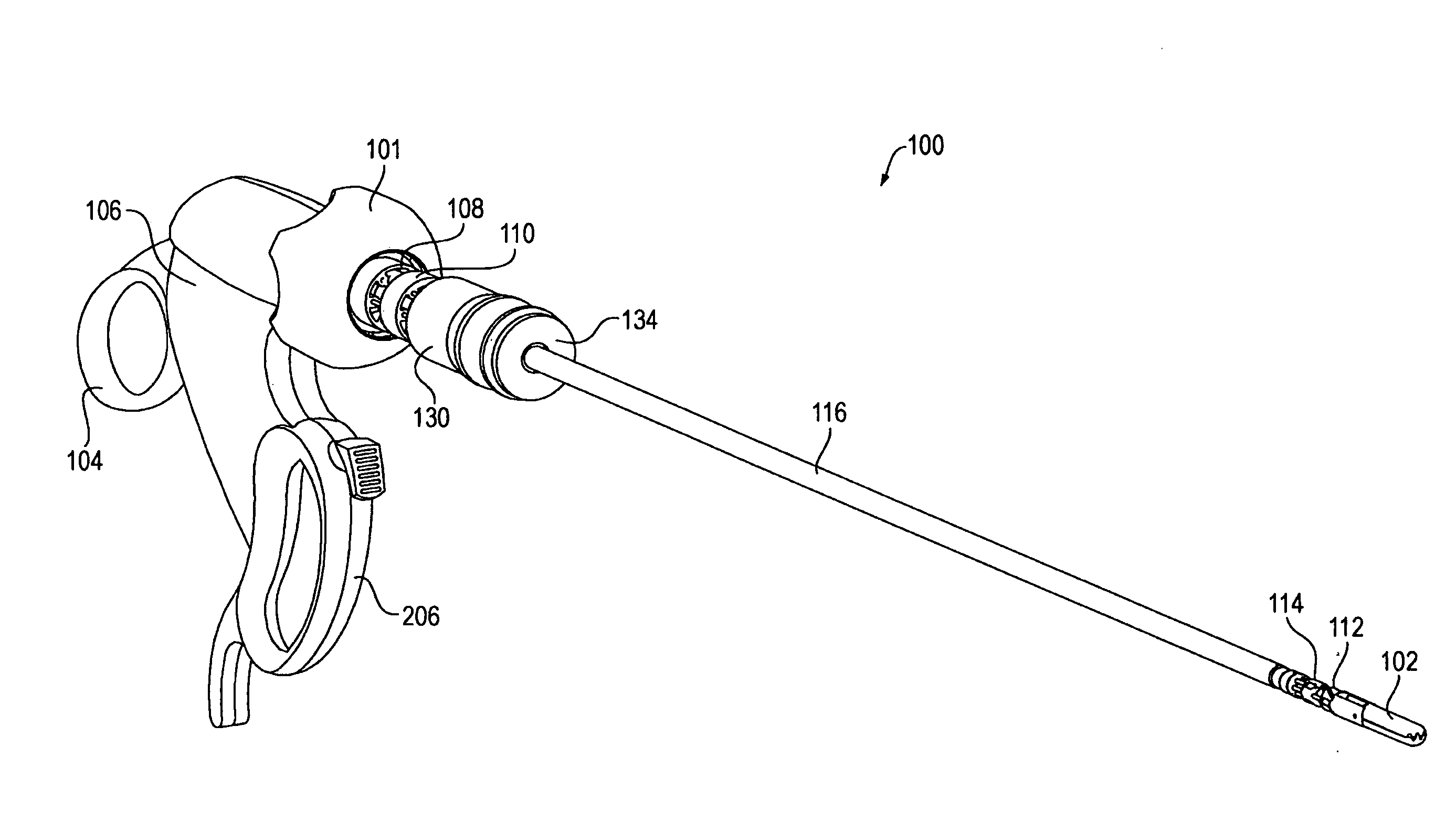

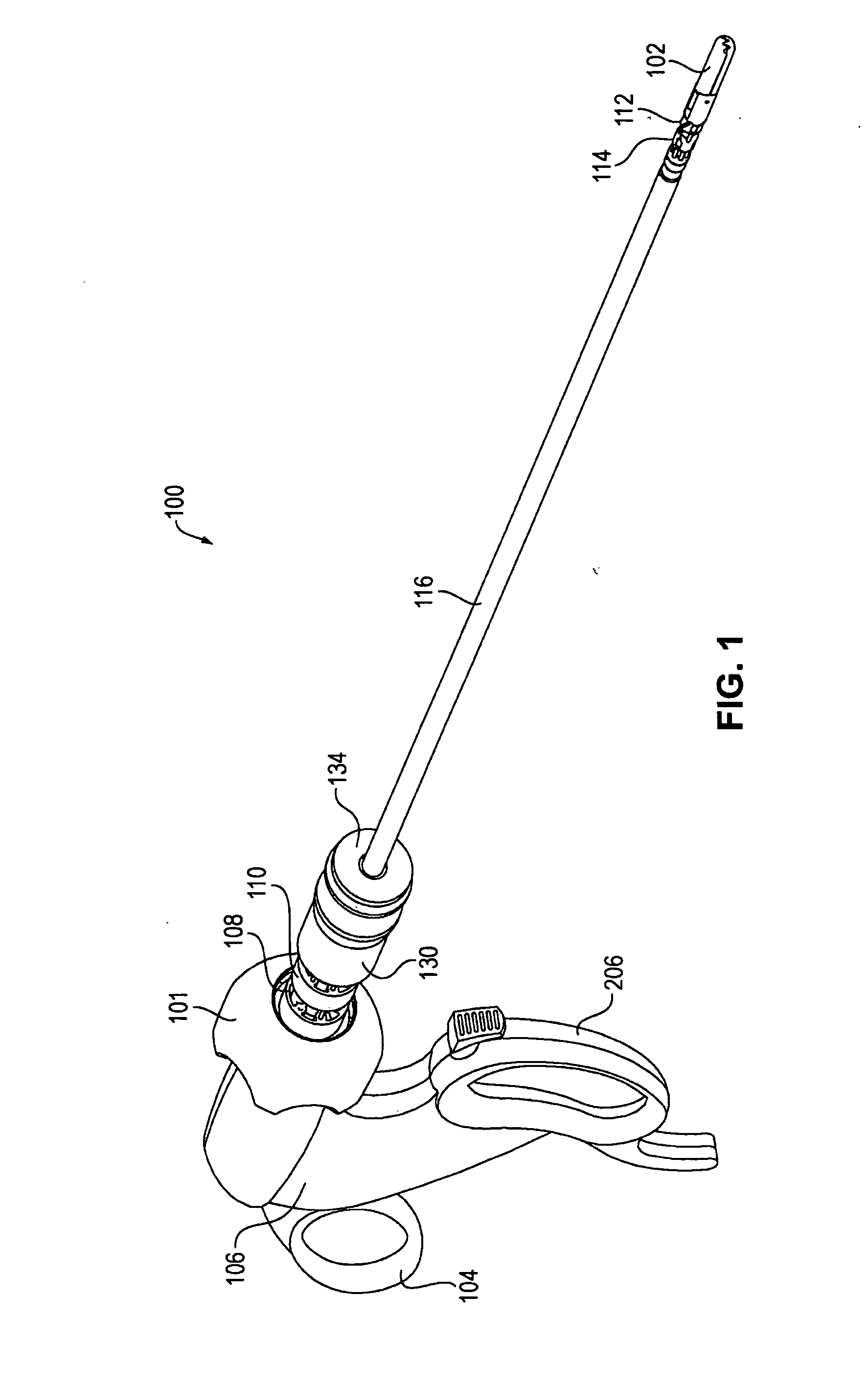

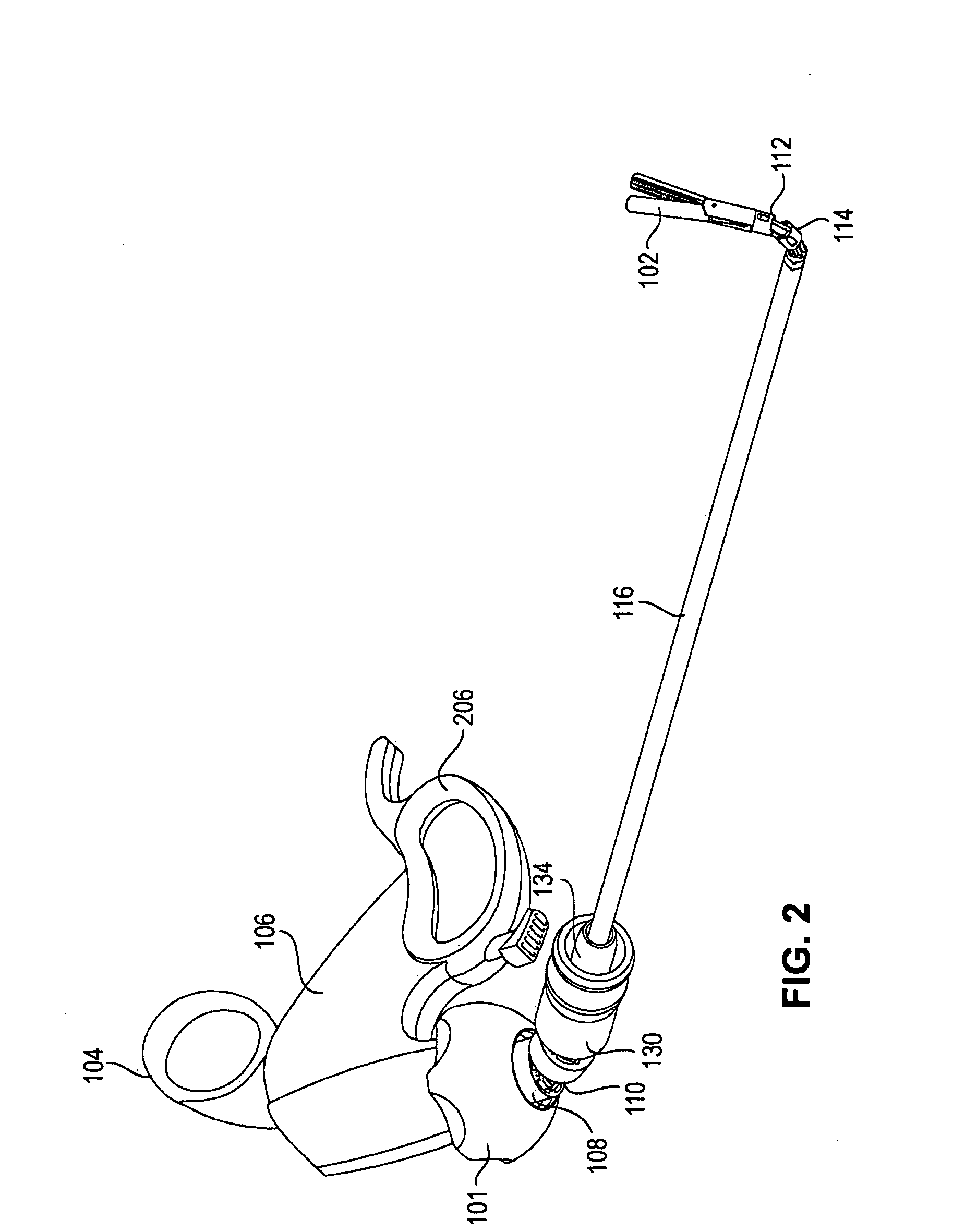

Tool with rotation lock

The invention provides surgical or diagnostic tools and associated methods that offer improved user control for operating remotely within regions of the body. These tools include a proximally-located actuator for the operation of a distal end effector, as well as proximally-located actuators for articulational and rotational movements of the end effector. Control mechanisms and methods refine operator control of end effector actuation and of these articulational and rotational movements. A rotation lock provides for enablement and disablement of rotatability of the end effector. The tool may also include other features. A multi-state ratchet for end effector actuation provides enablement-disablement options with tactile feedback. A force limiter mechanism protects the end effector and manipulated objects from the harm of potentially excessive force applied by the operator. An articulation lock allows the fixing and releasing of both neutral and articulated configurations of the tool and of consequent placement of the end effector.

Owner:INTUITIVE SURGICAL OPERATIONS INC

Tool with articulation lock

ActiveUS8100824B2Increase frictionMovement is blocked and preventedEndoscopesSubstation equipmentEngineeringActuator

The invention provides surgical or diagnostic tools and associated methods that offer user control for operating remotely within regions of the body. These tools include a proximally-located actuator for the operation of a distal end effector, as well as proximally-located actuators for articulational and rotational movements of the end effector. Control mechanisms and methods refine operator control of end effector actuation and of these articulational and rotational movements. An articulation lock allows the fixing and releasing of both neutral and articulated configurations of the tool and of consequent placement of the end effector. The tool may also include other features. A multi-state ratchet for end effector actuation provides enablement-disablement options with tactile feedback. A force limiter mechanism protects the end effector and manipulated objects from the harm of potentially excessive force applied by the operator. A rotation lock provides for enablement and disablement of rotatability of the end effector.

Owner:INTUITIVE SURGICAL OPERATIONS INC

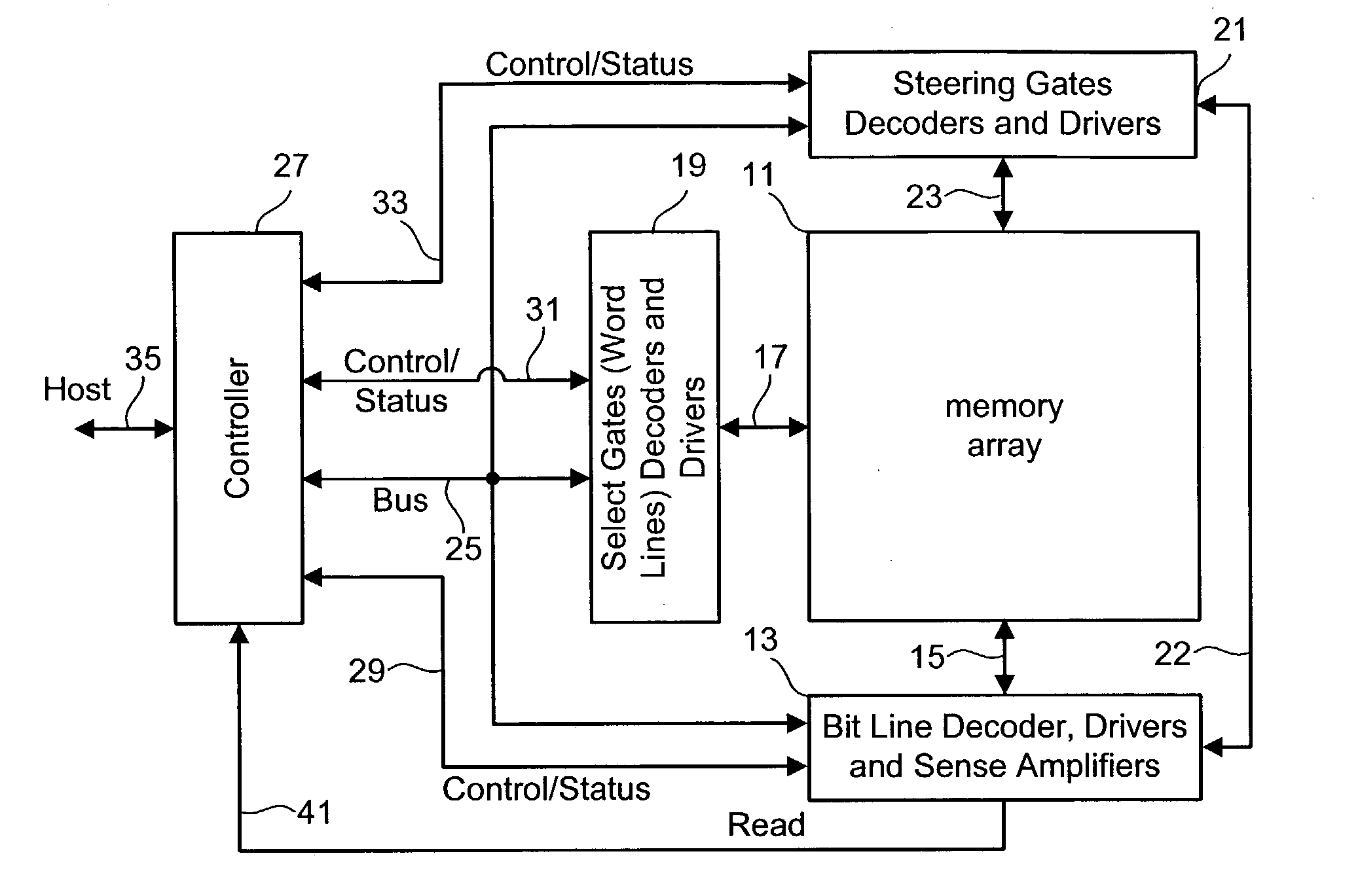

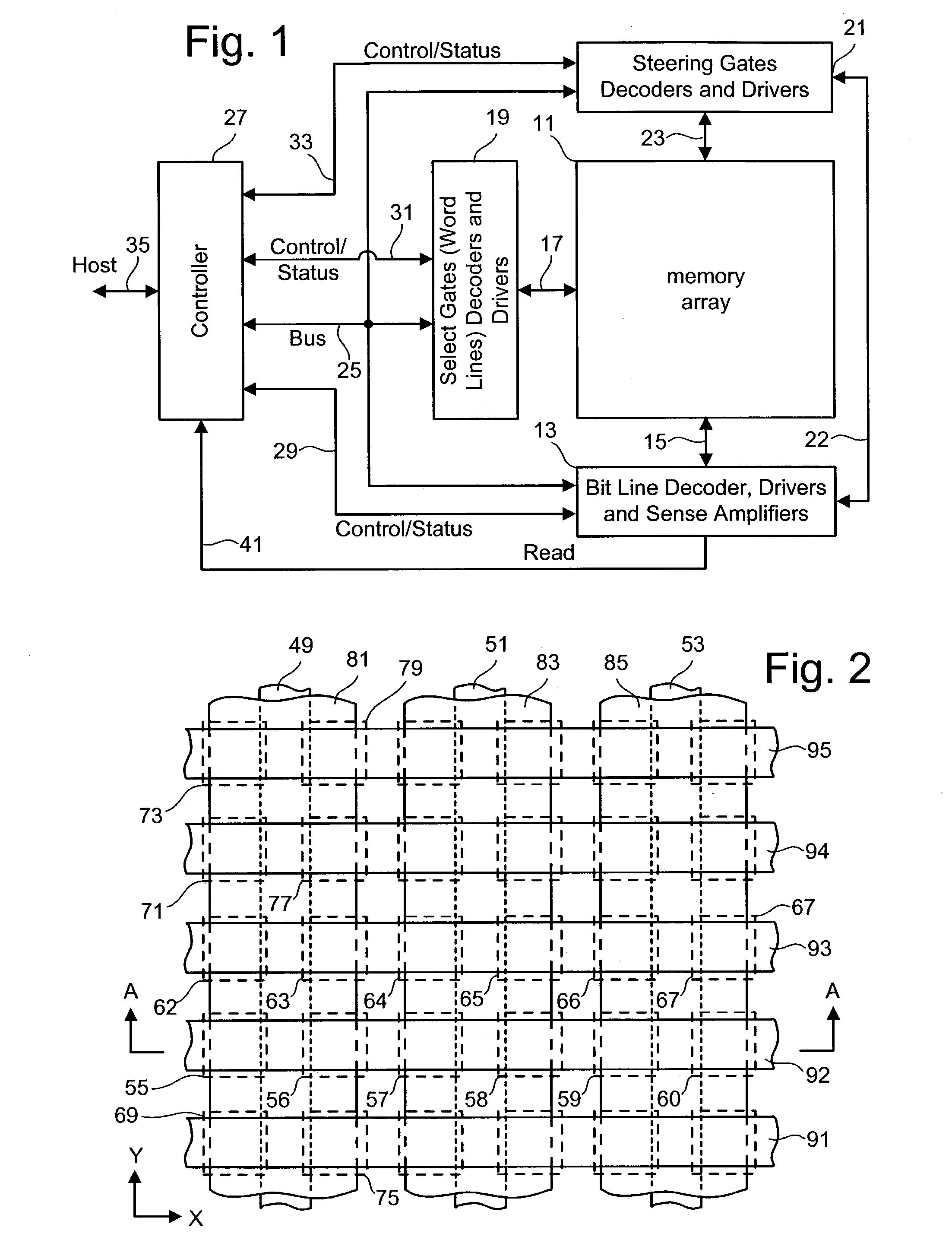

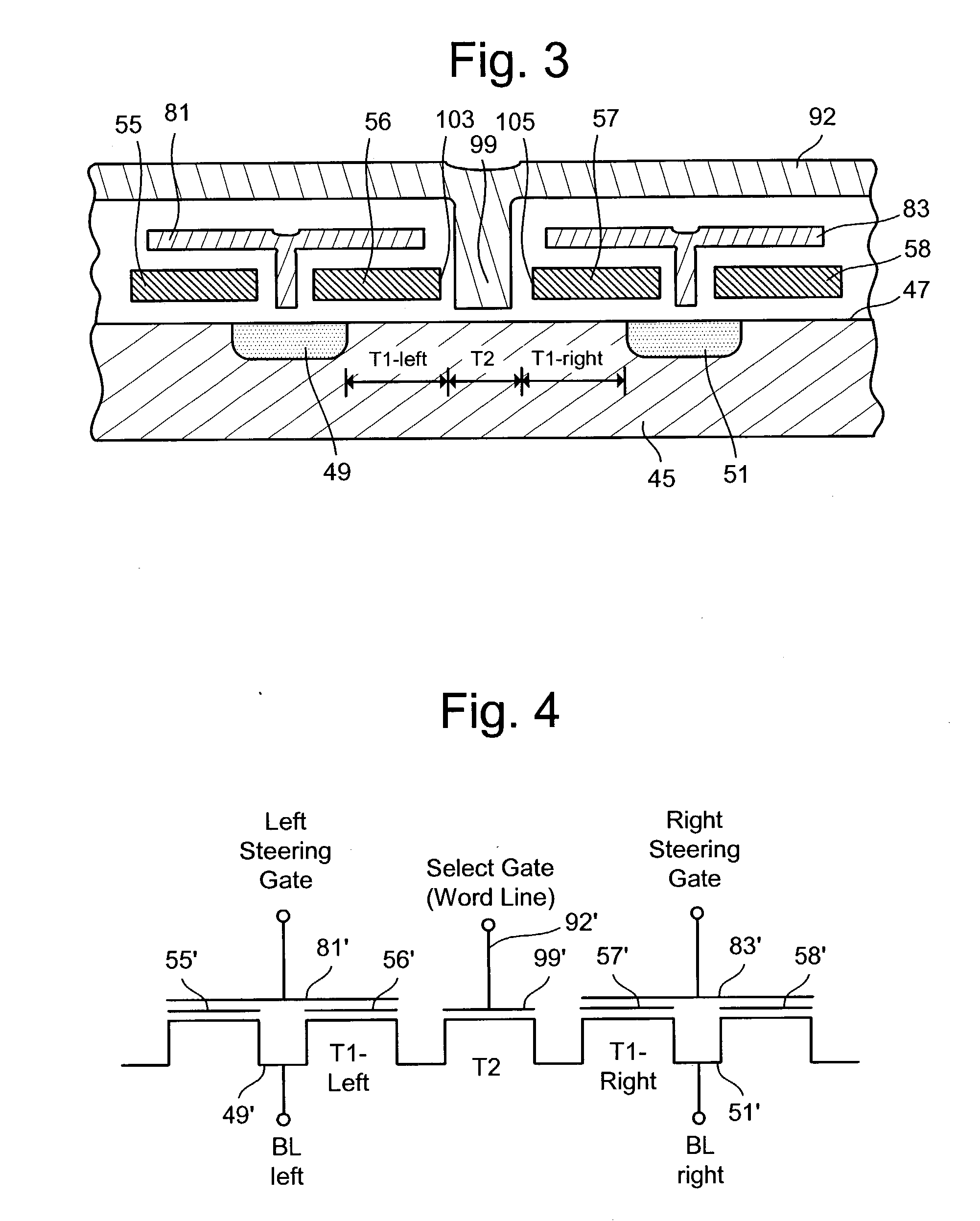

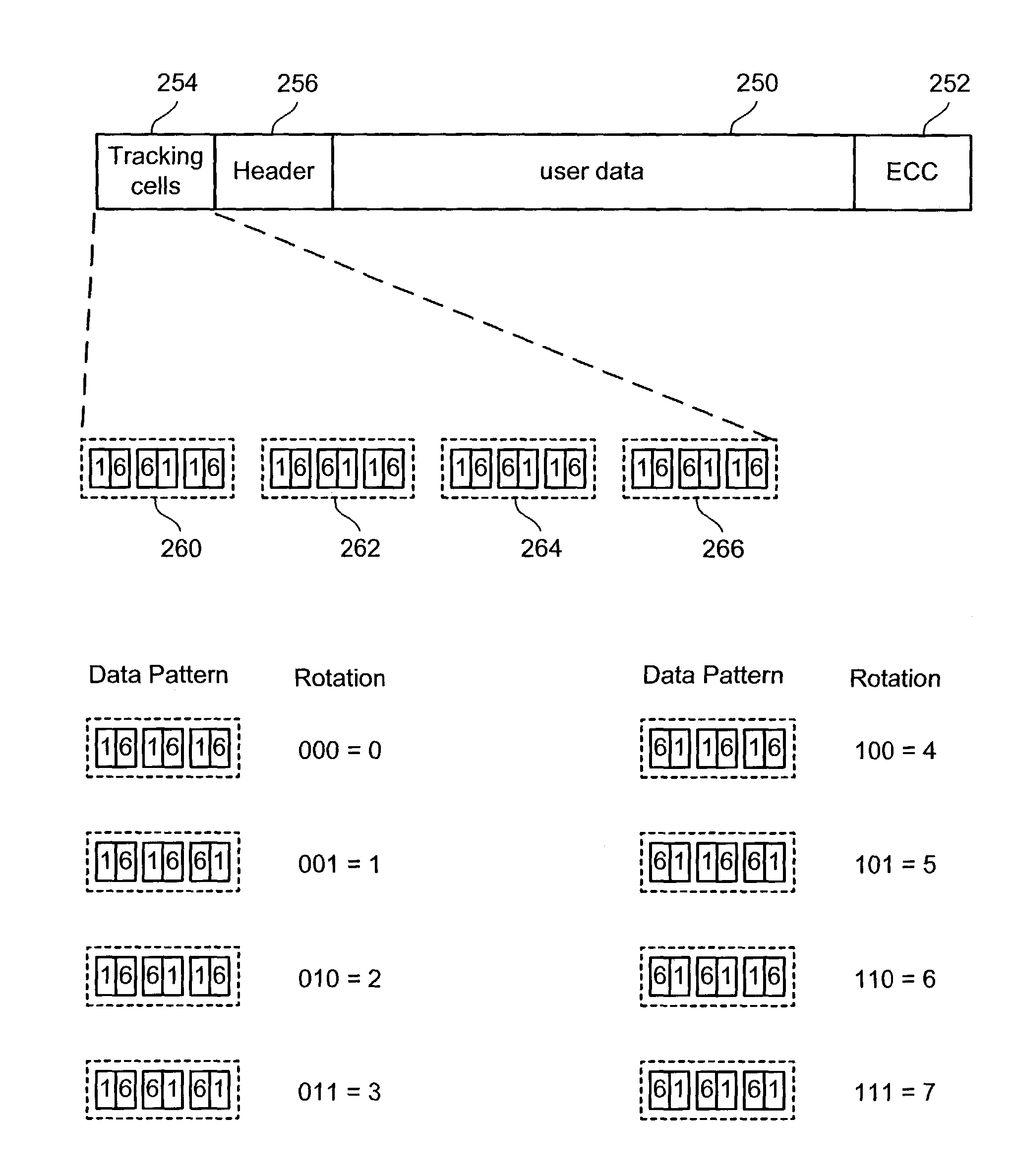

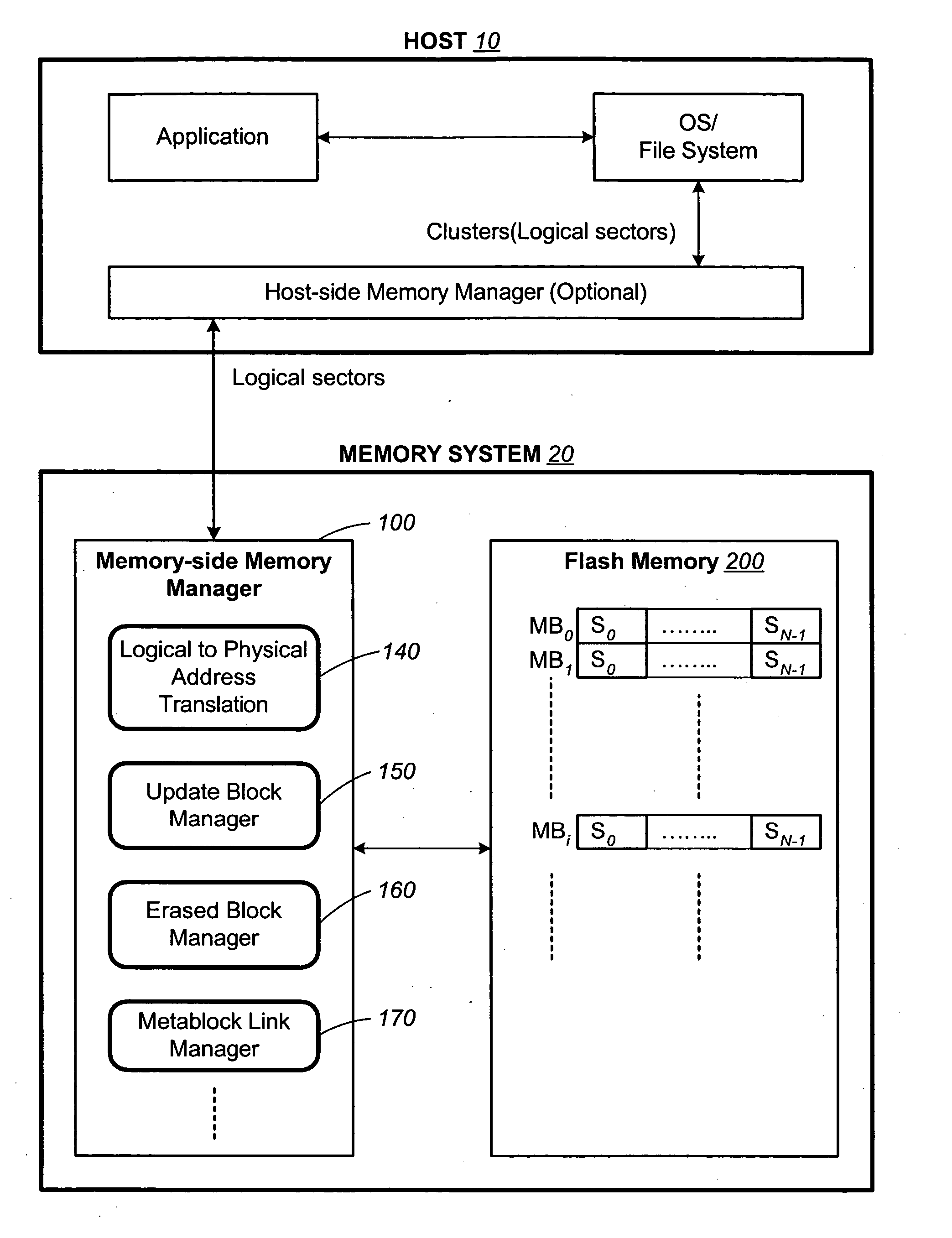

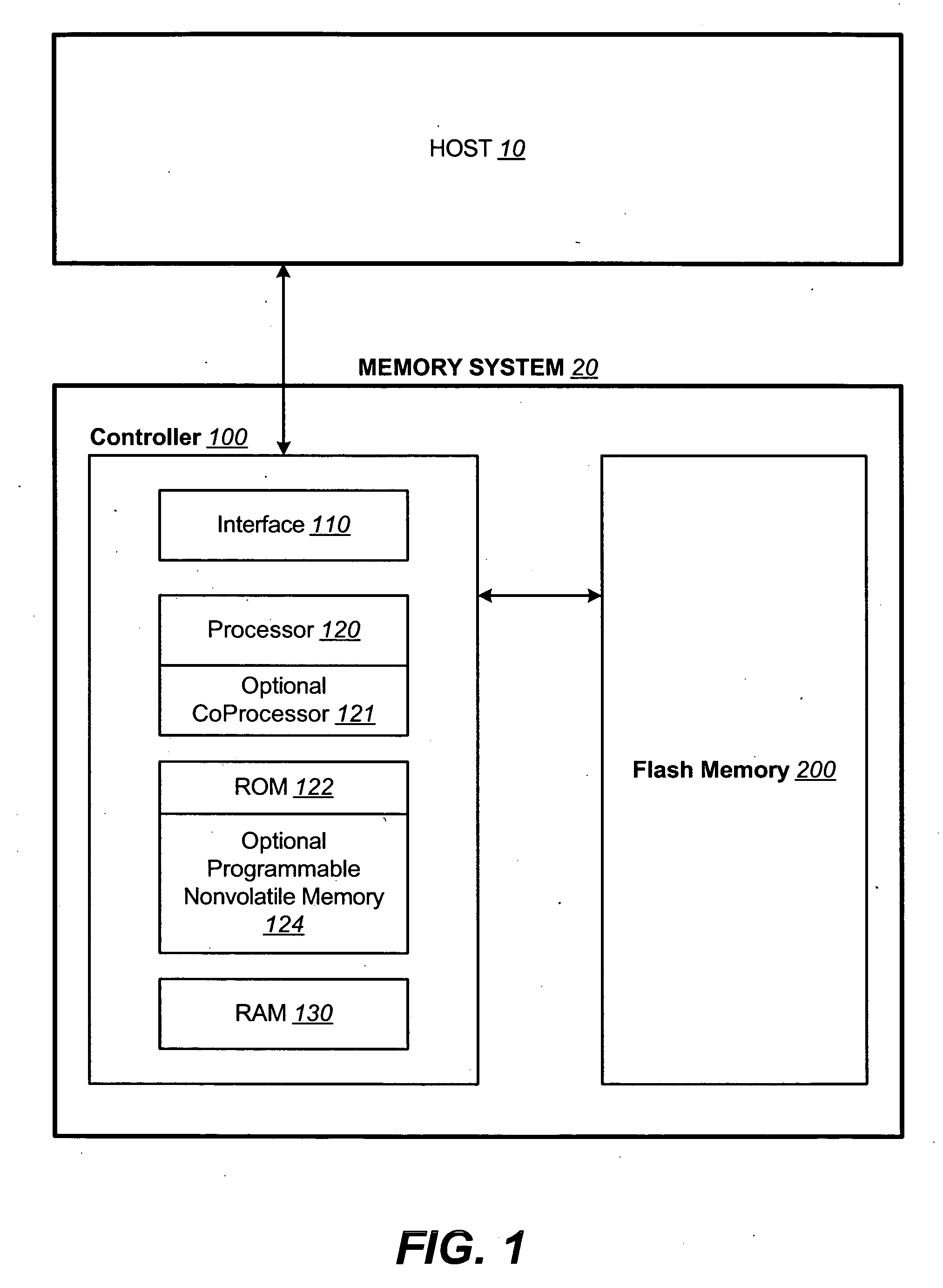

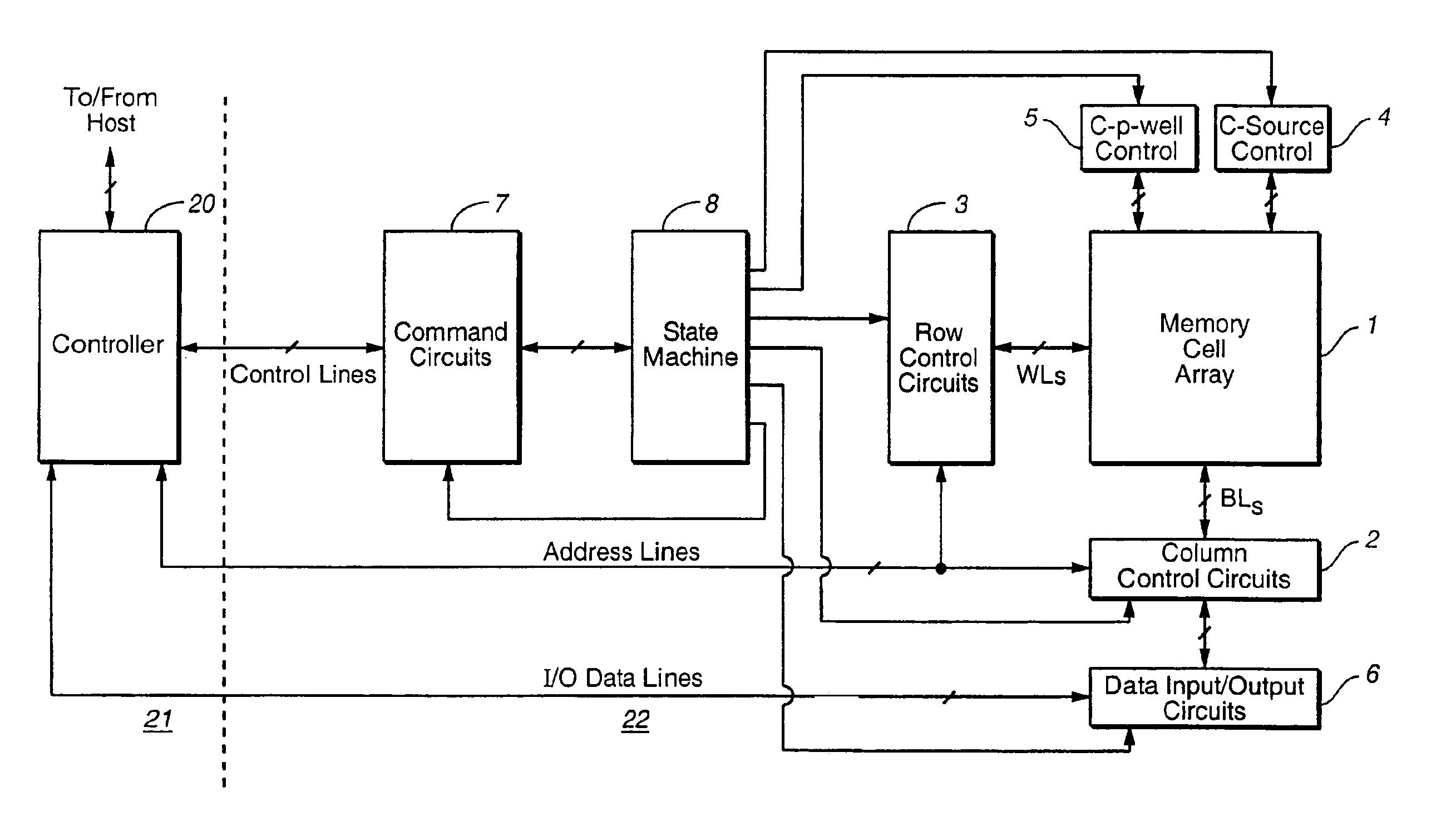

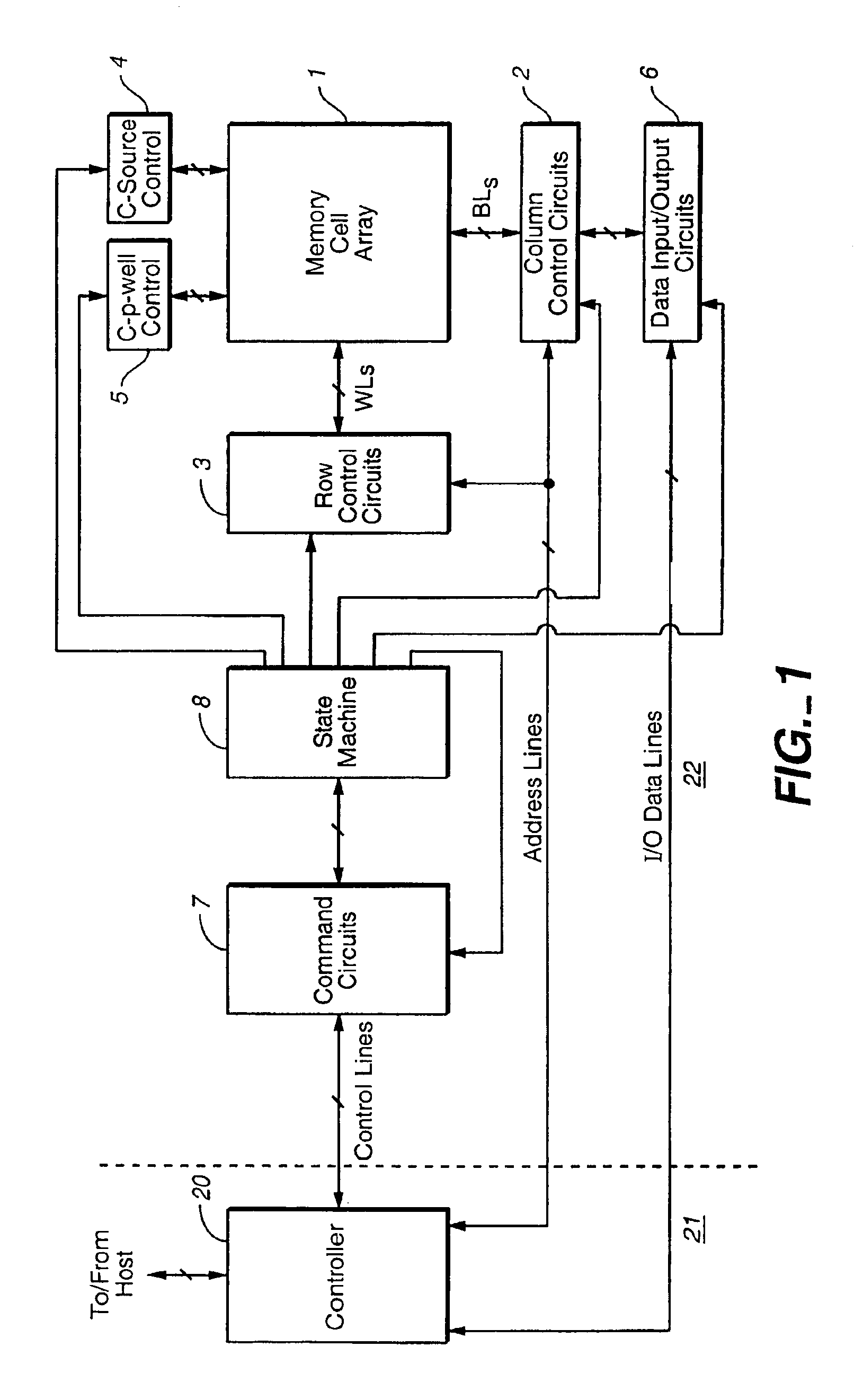

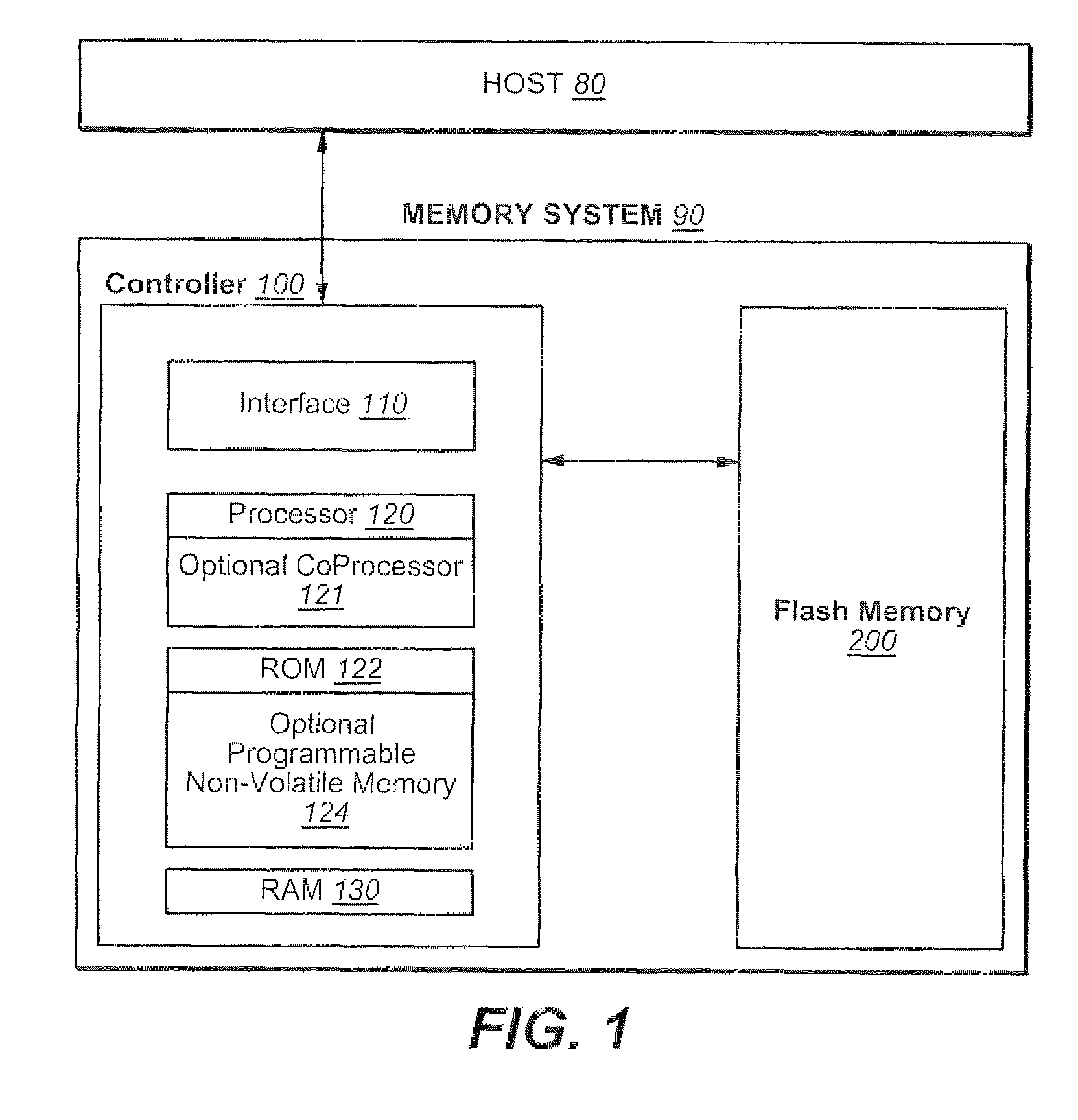

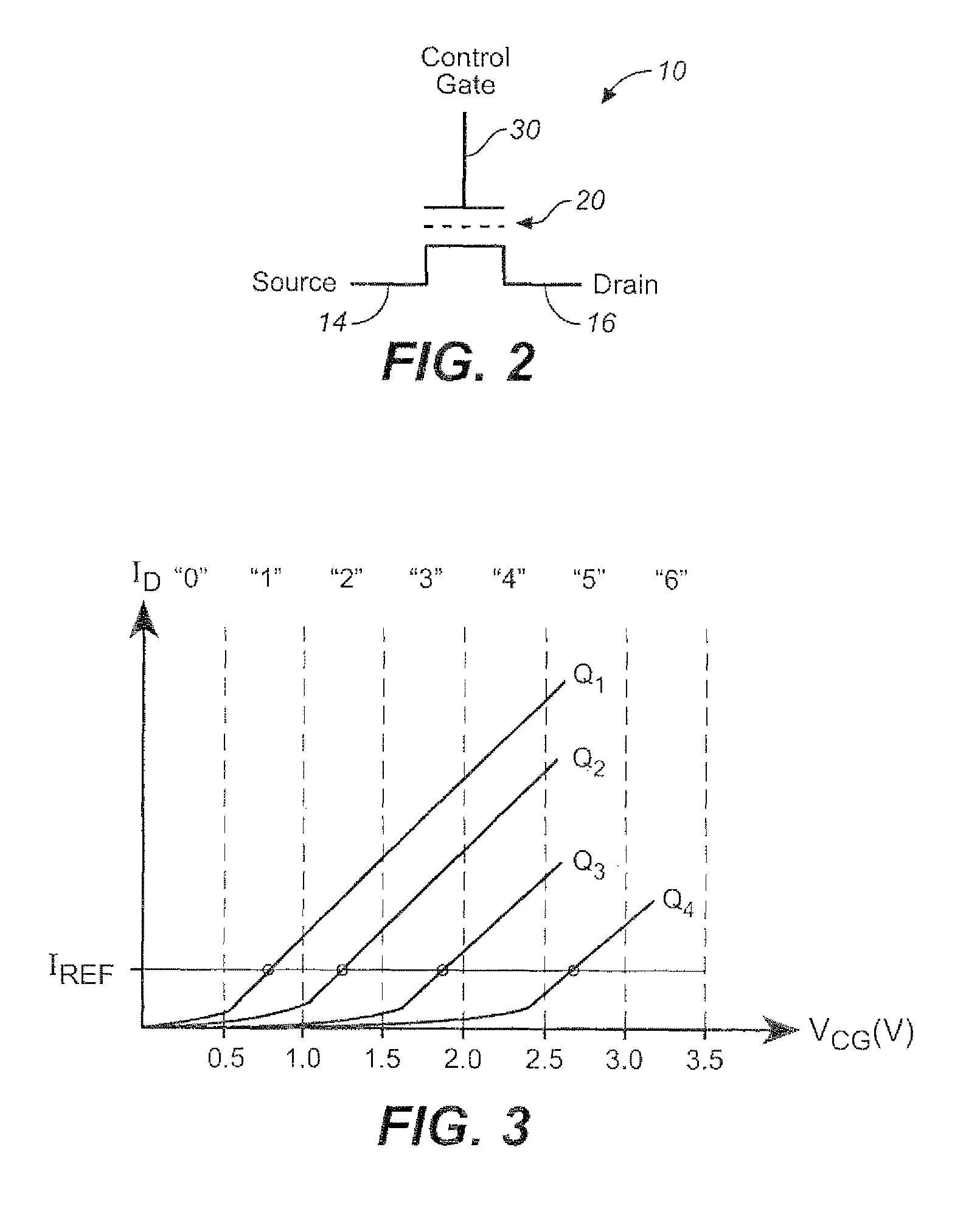

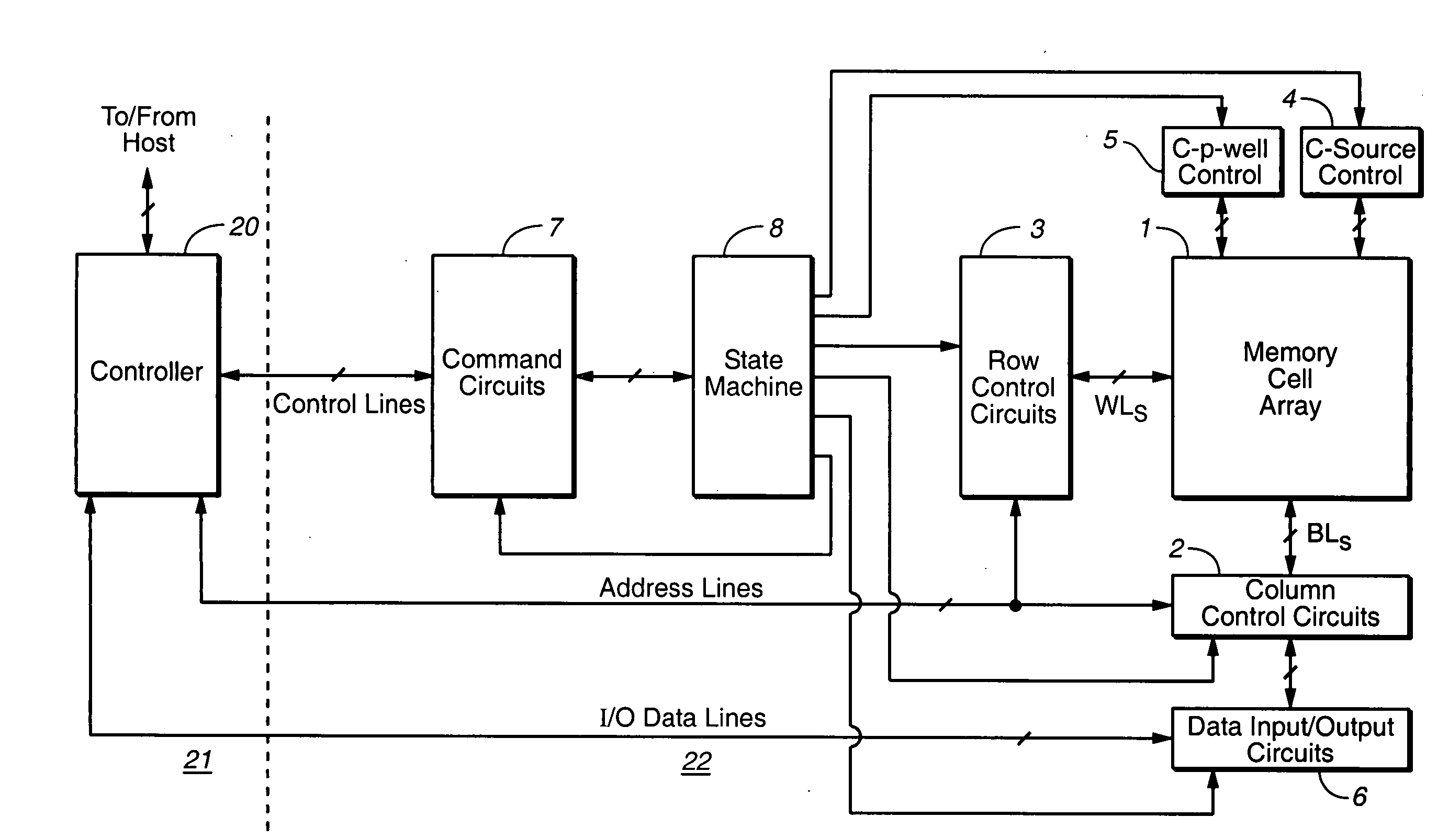

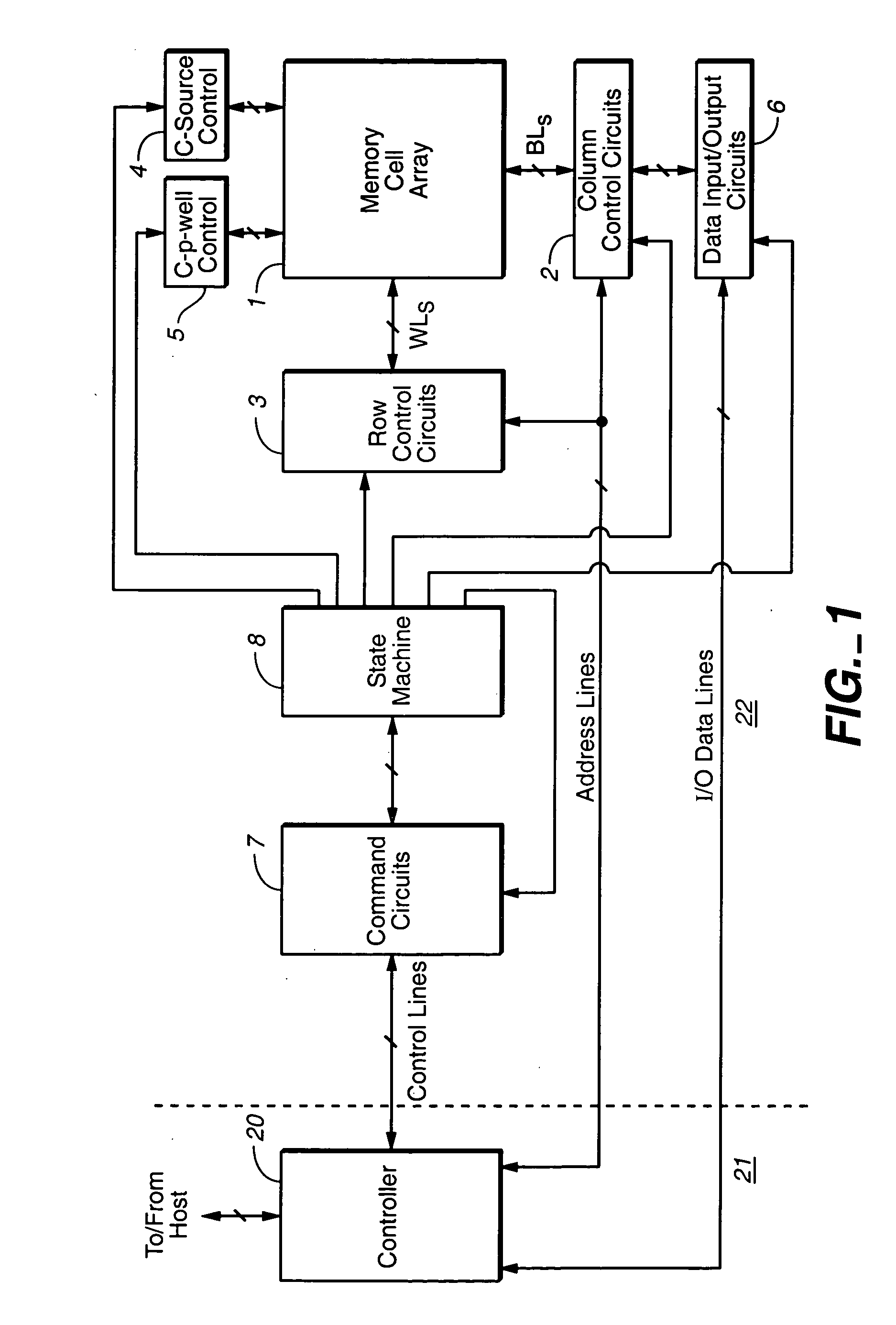

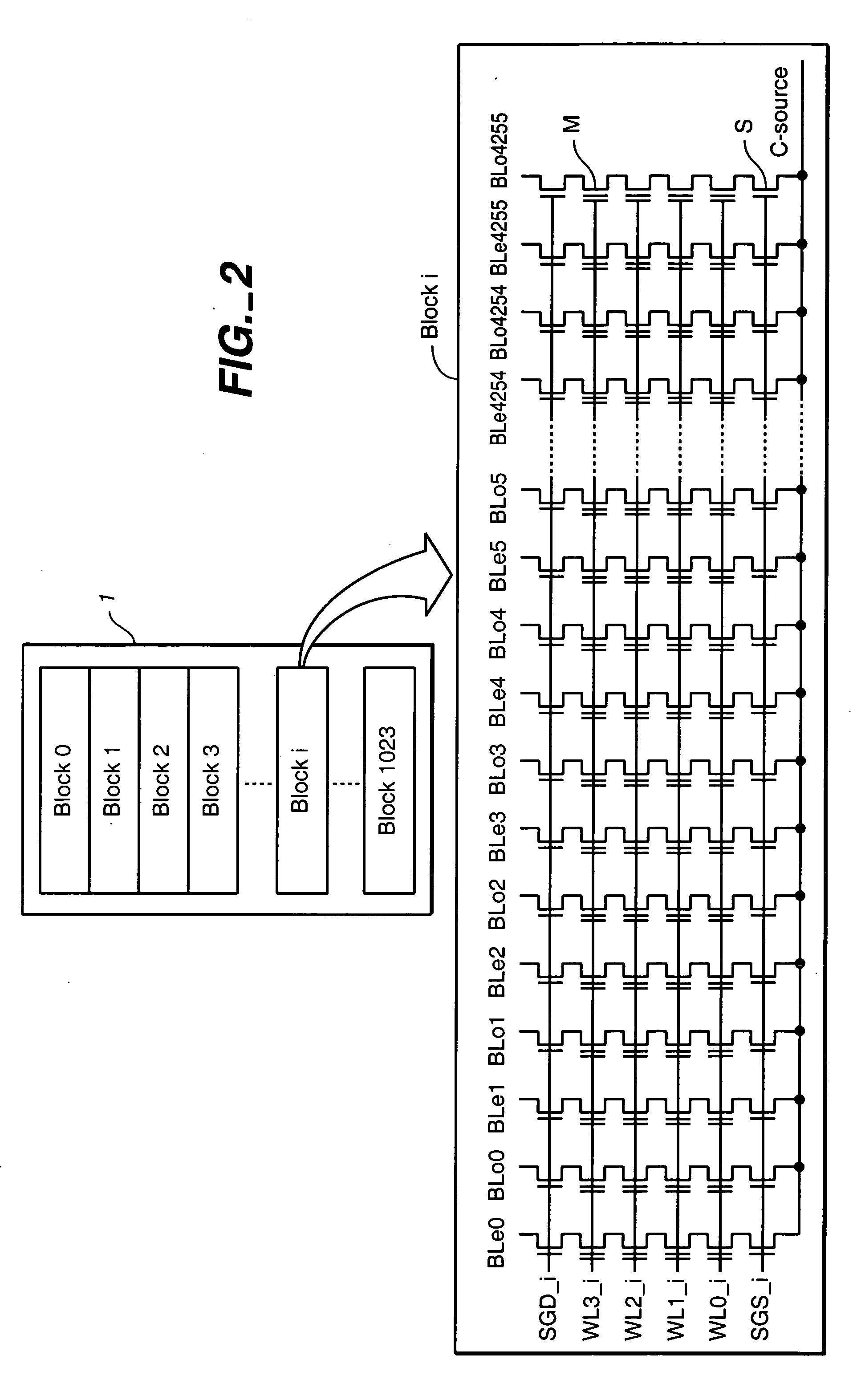

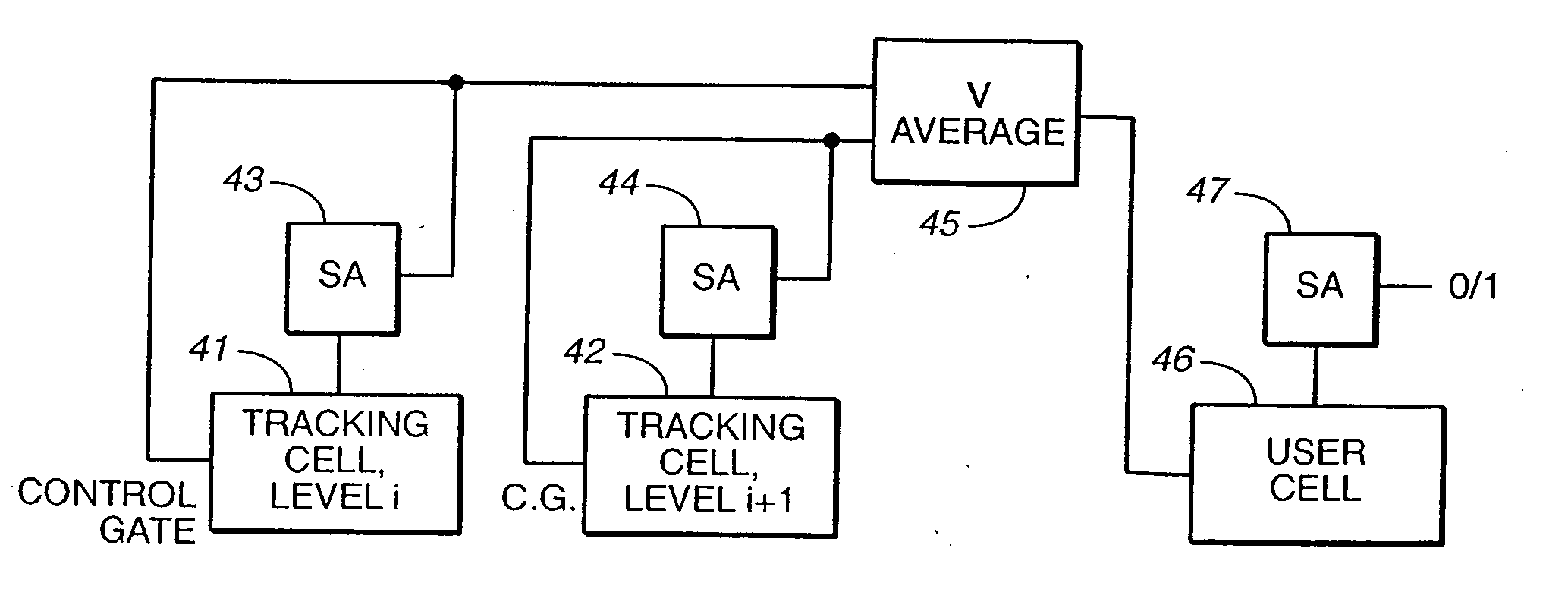

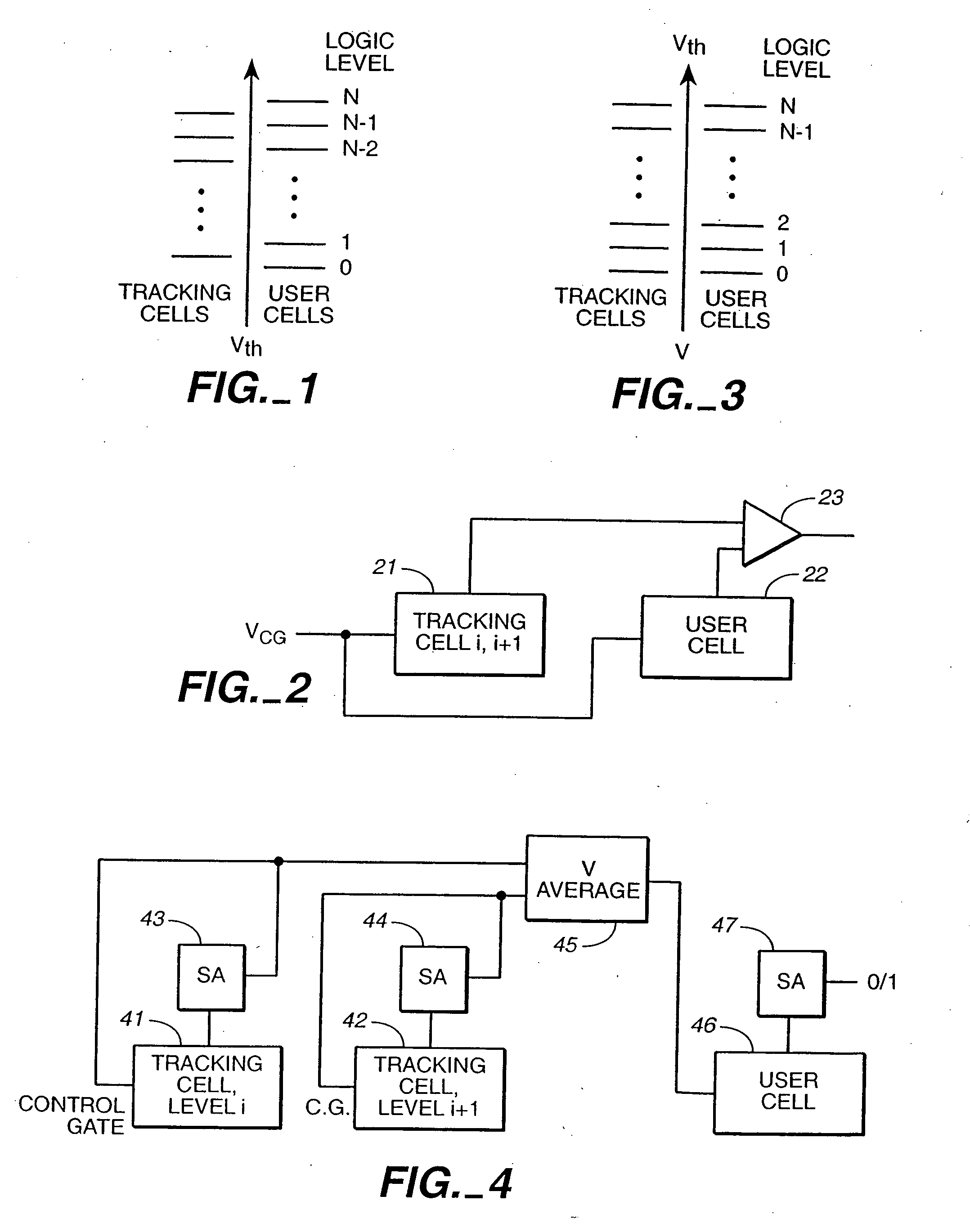

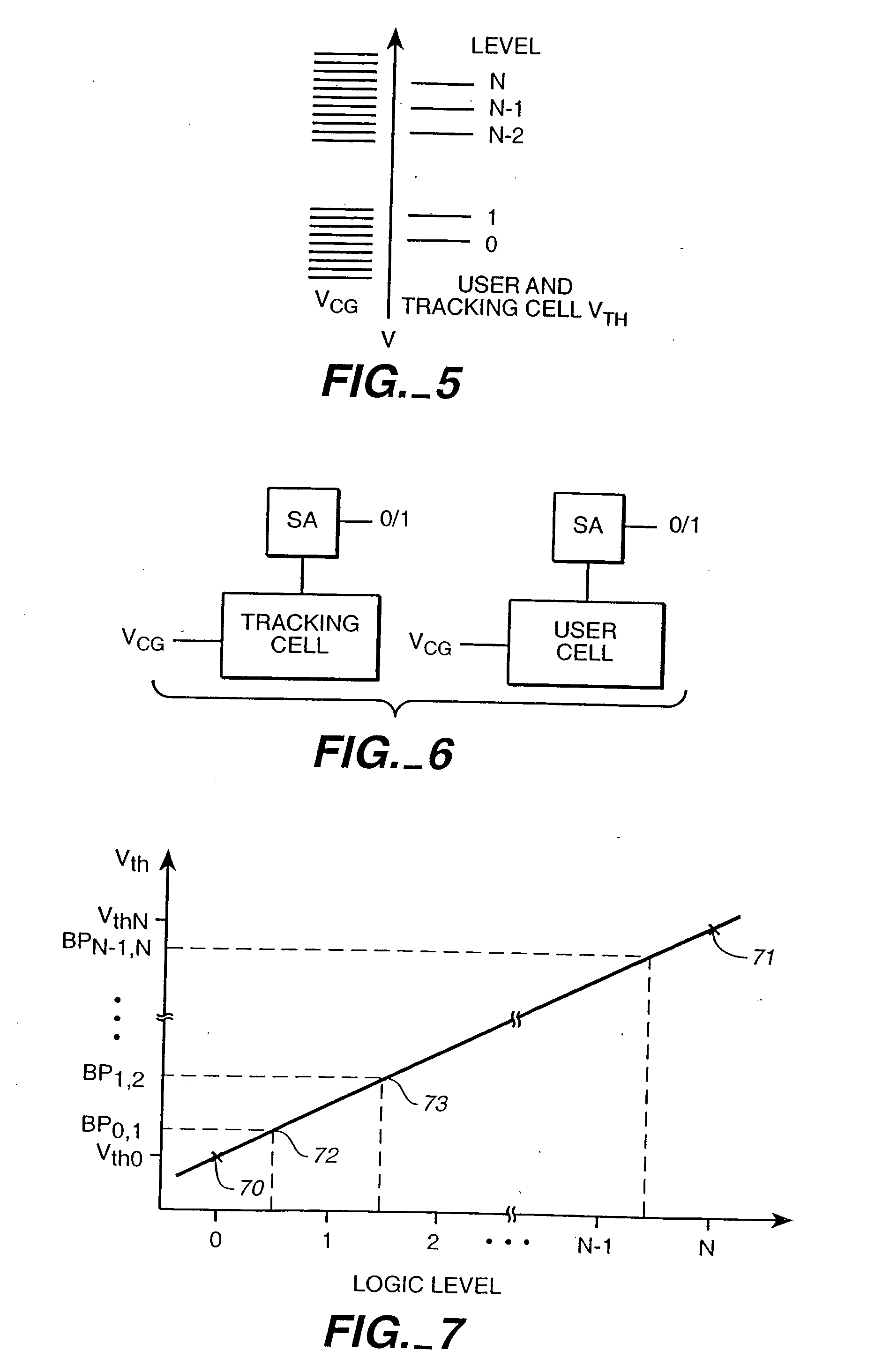

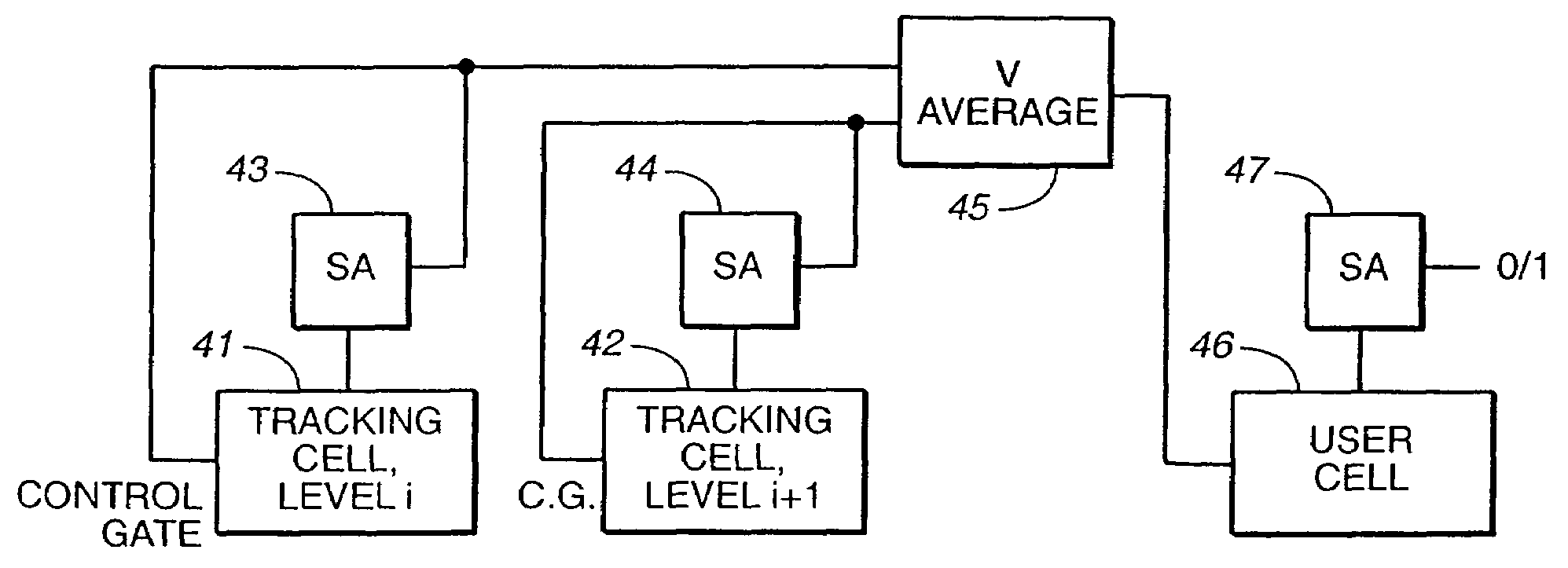

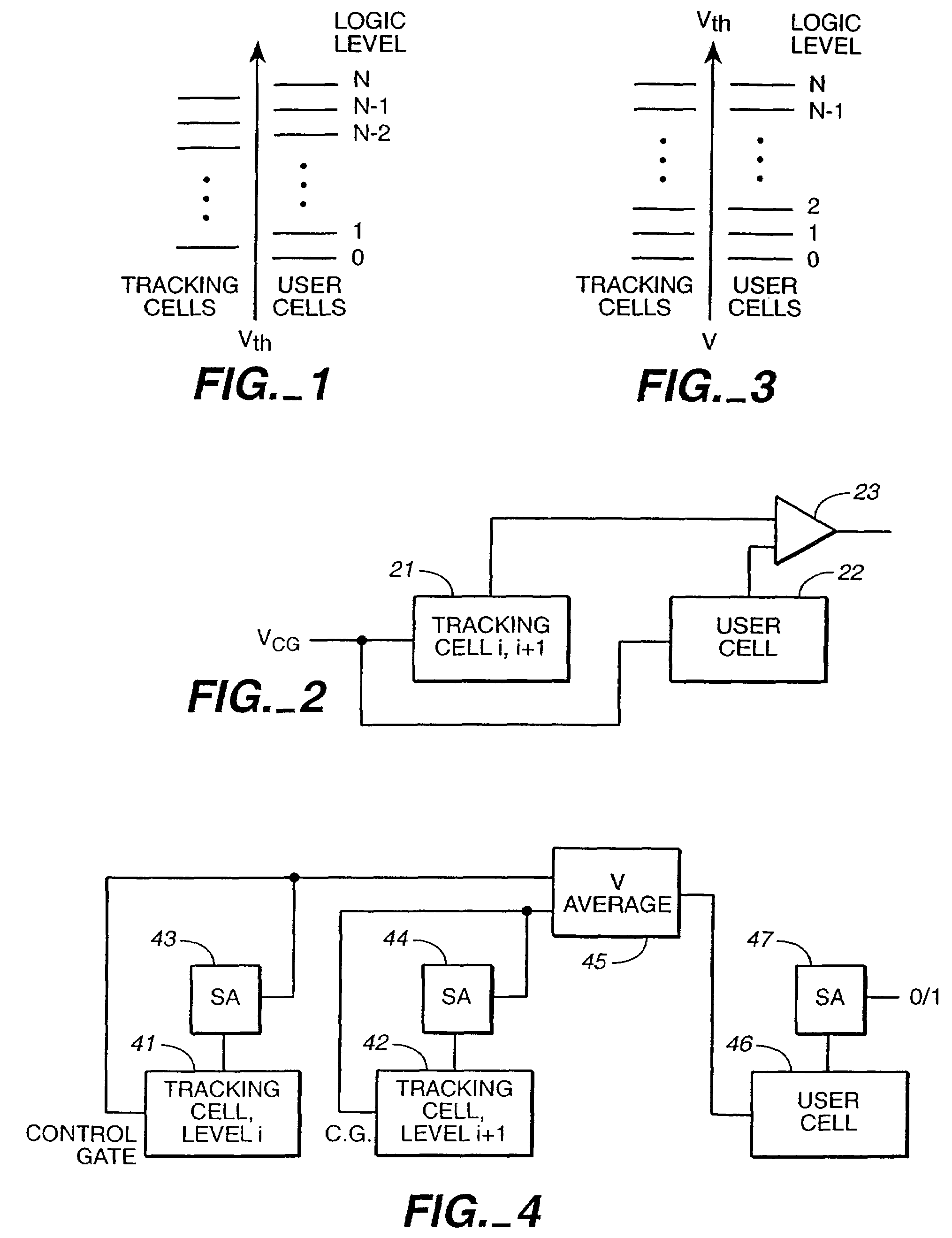

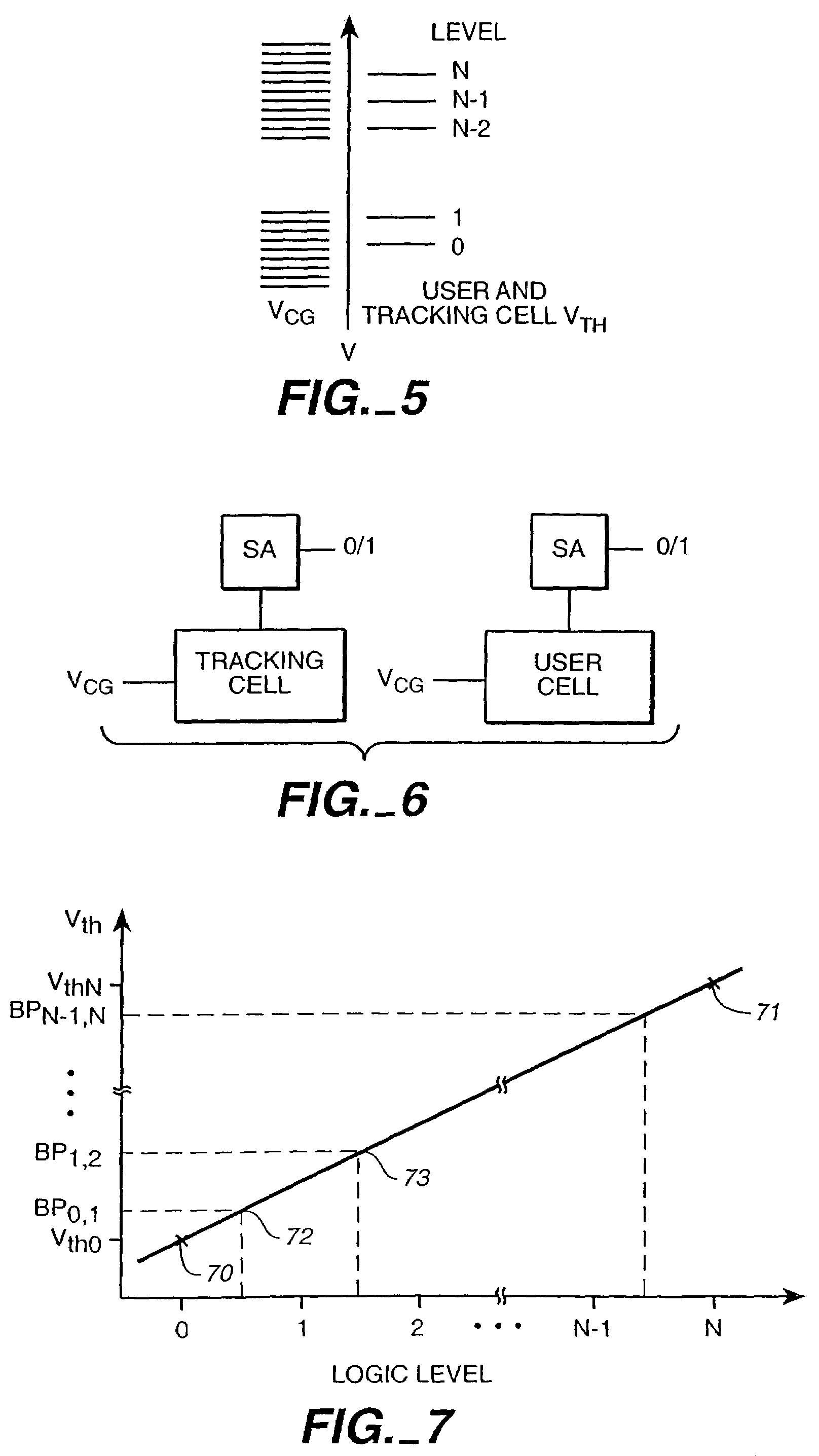

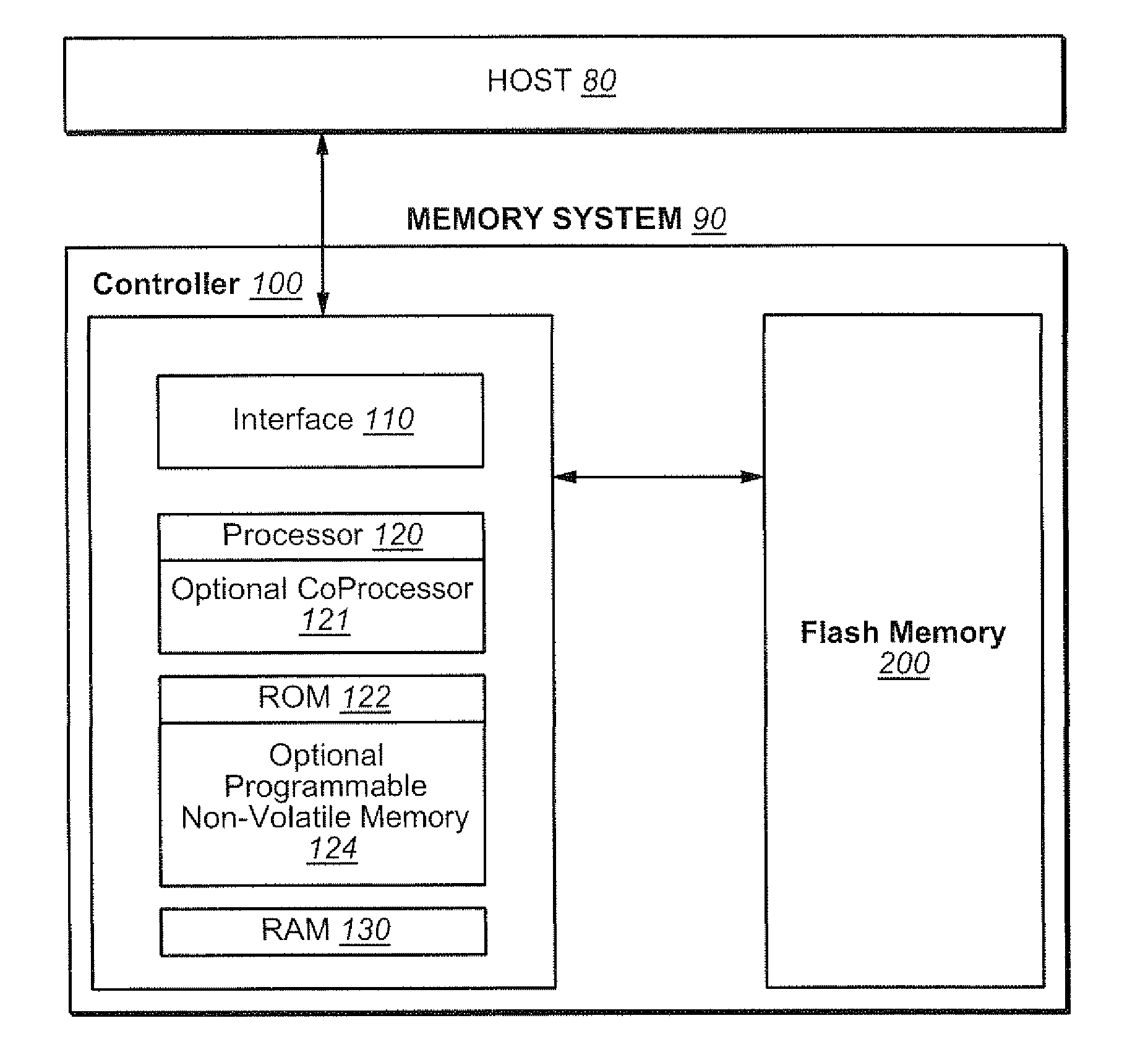

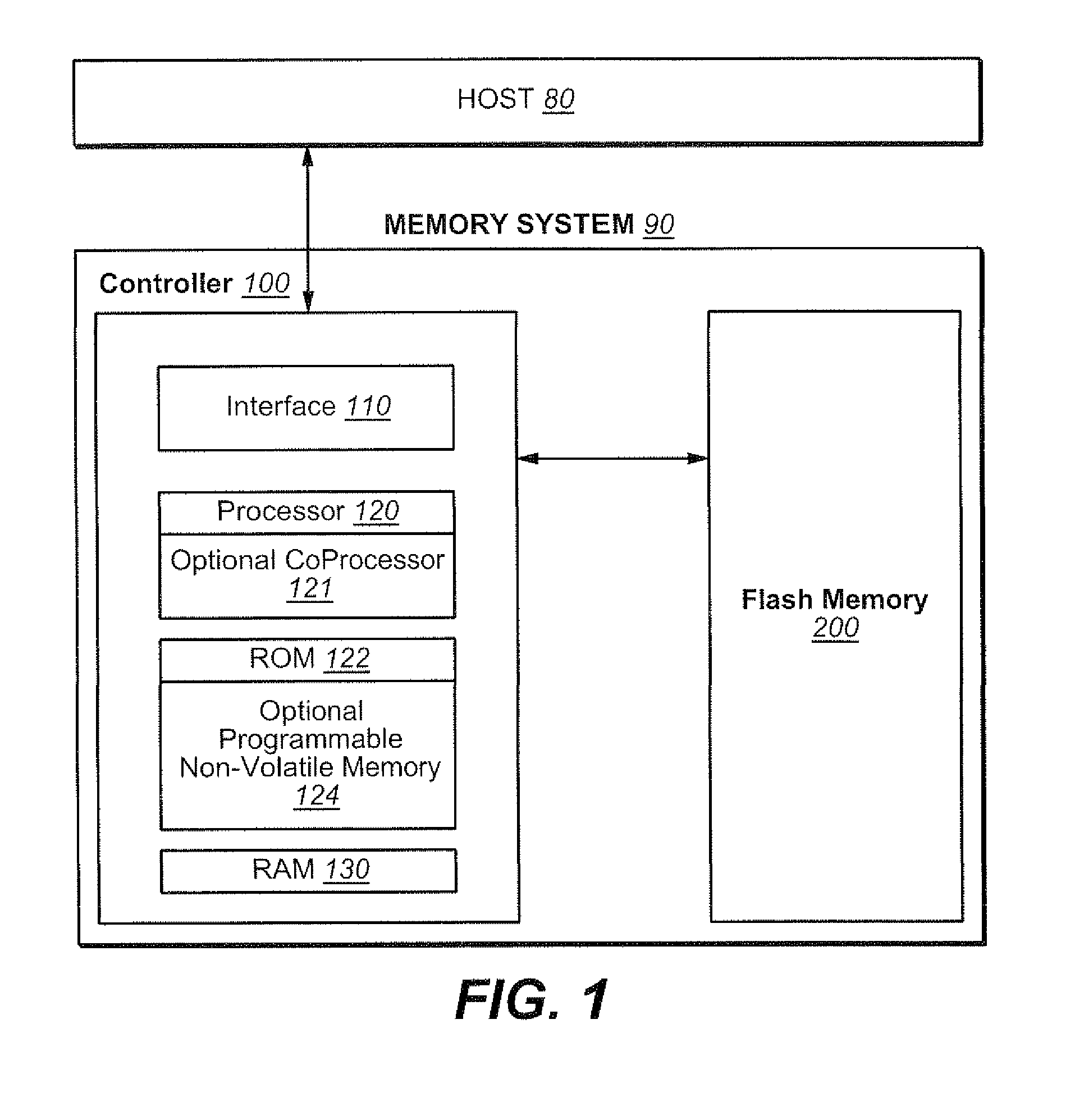

Tracking cells for a memory system

Tracking cells are used in a memory system to improve the read process. The tracking cells can provide an indication of the quality of the data and can be used as part of a data recovery operation if there is an error. The tracking cells provide a means to adjust the read parameters to optimum levels in order to reflect the current conditions of the memory system. Additionally, some memory systems that use multi-state memory cells will apply rotation data schemes to minimize wear. The rotation scheme can be encoded in the tracking cells based on the states of multiple tracking cells, which is decoded upon reading.

Owner:SANDISK TECH LLC

Tool with rotation lock

The invention provides surgical or diagnostic tools and associated methods that offer improved user control for operating remotely within regions of the body. These tools include a proximally-located actuator for the operation of a distal end effector, as well as proximally-located actuators for articulational and rotational movements of the end effector. Control mechanisms and methods refine operator control of end effector actuation and of these articulational and rotational movements. A rotation lock provides for enablement and disablement of rotatability of the end effector. The tool may also include other features. A multi-state ratchet for end effector actuation provides enablement-disablement options with tactile feedback. A force limiter mechanism protects the end effector and manipulated objects from the harm of potentially excessive force applied by the operator. An articulation lock allows the fixing and releasing of both neutral and articulated configurations of the tool and of consequent placement of the end effector.

Owner:INTUITIVE SURGICAL OPERATIONS INC

Tracking cells for a memory system

Tracking cells are used in a memory system to improve the read process. The tracking cells can provide an indication of the quality of the data and can be used as part of a data recovery operation if there is an error. The tracking cells provide a means to adjust the read parameters to optimum levels in order to reflect the current conditions of the memory system. Additionally, some memory systems that use multi-state memory cells will apply rotation data schemes to minimize wear. The rotation scheme can be encoded in the tracking cells based on the states of multiple tracking cells, which is decoded upon reading.

Owner:SANDISK TECH LLC

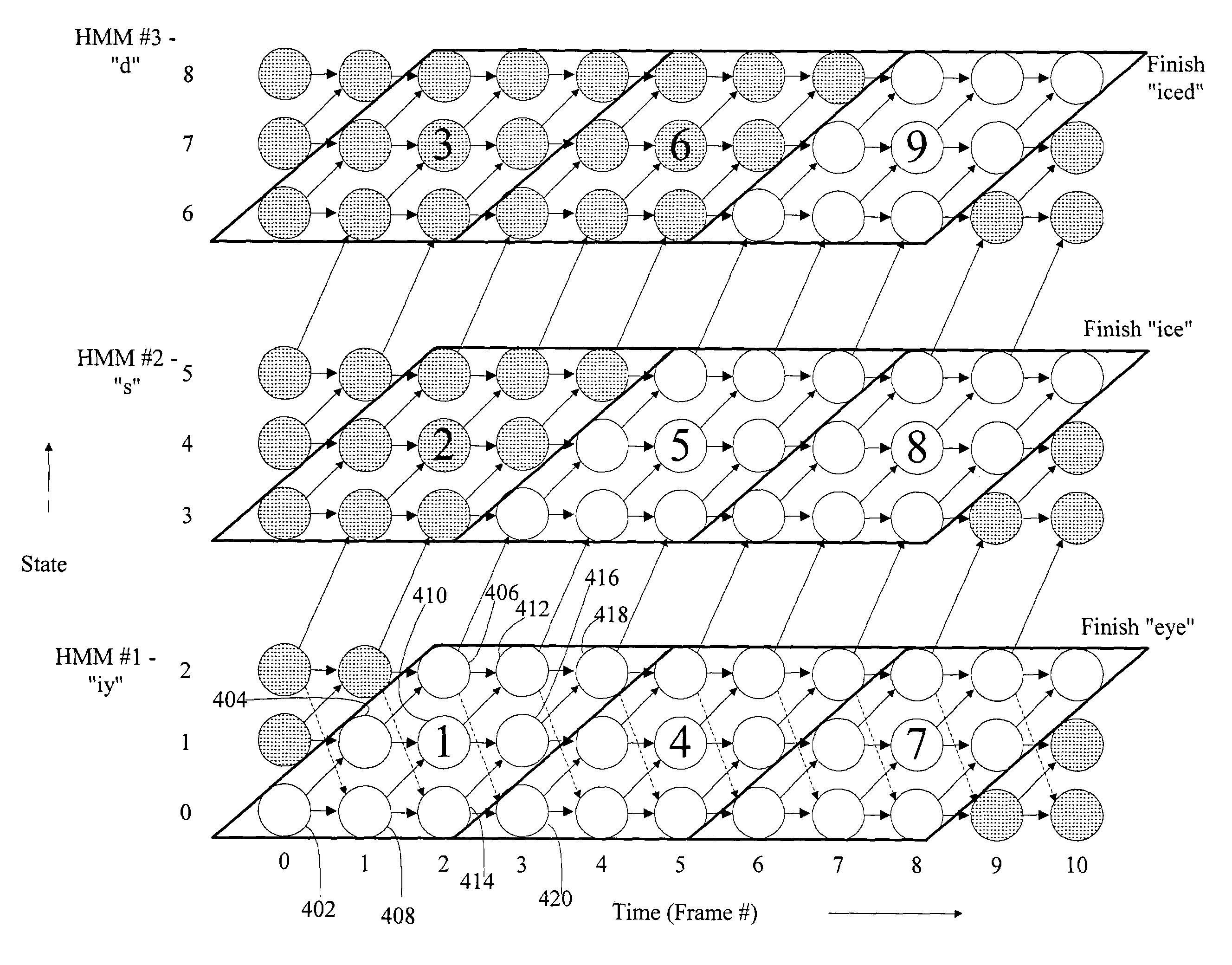

Block synchronous decoding

InactiveUS7529671B2Improved pattern recognition speedImprove cache localityKitchenware cleanersGlovesHide markov modelCache locality

A pattern recognition system and method are provided. Aspects of the invention are particularly useful in combination with multi-state Hidden Markov Models. Pattern recognition is effected by processing Hidden Markov Model Blocks. This block-processing allows the processor to perform more operations upon data while such data is in cache memory. By so increasing cache locality, aspects of the invention provide significantly improved pattern recognition speed.

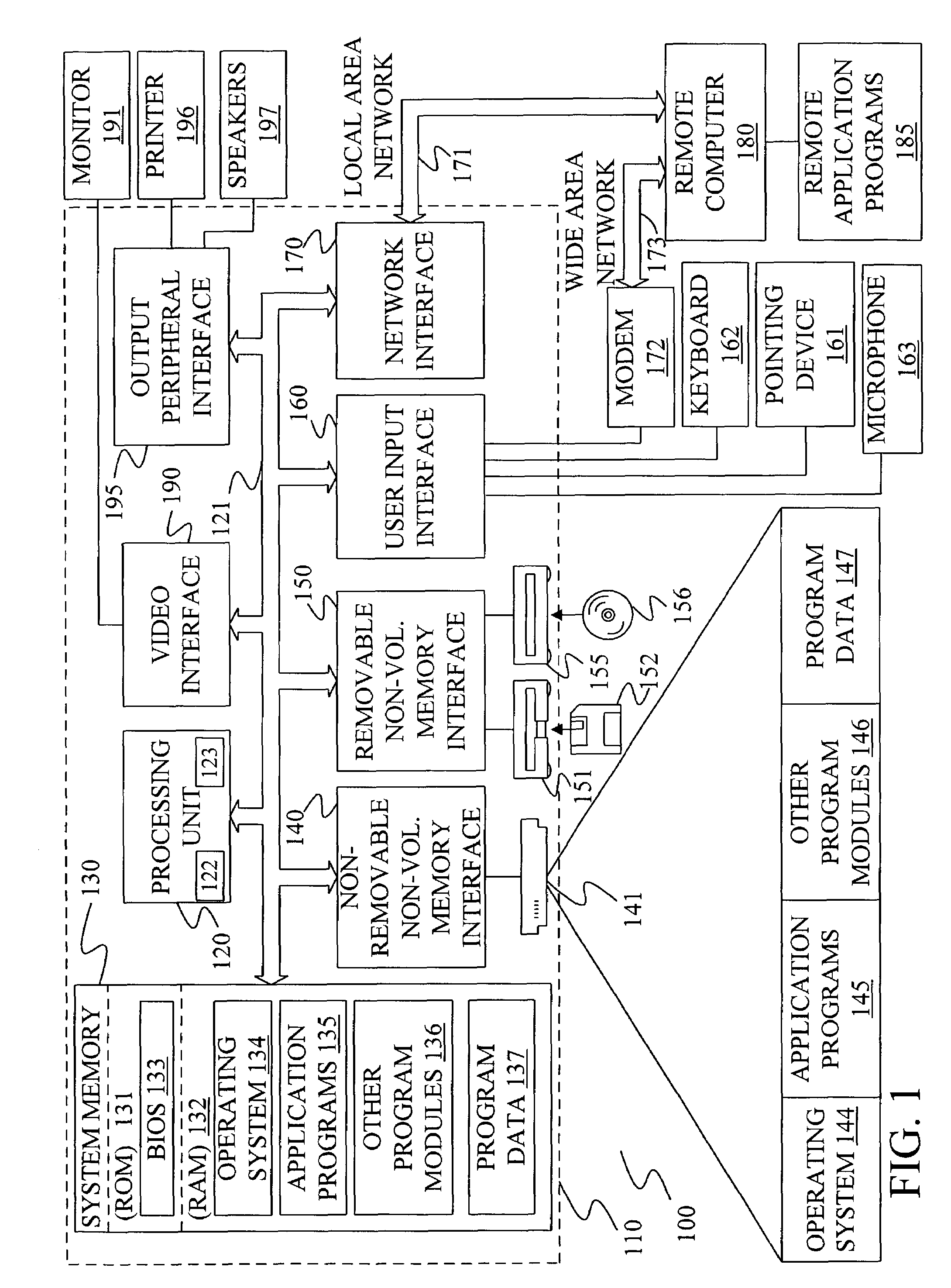

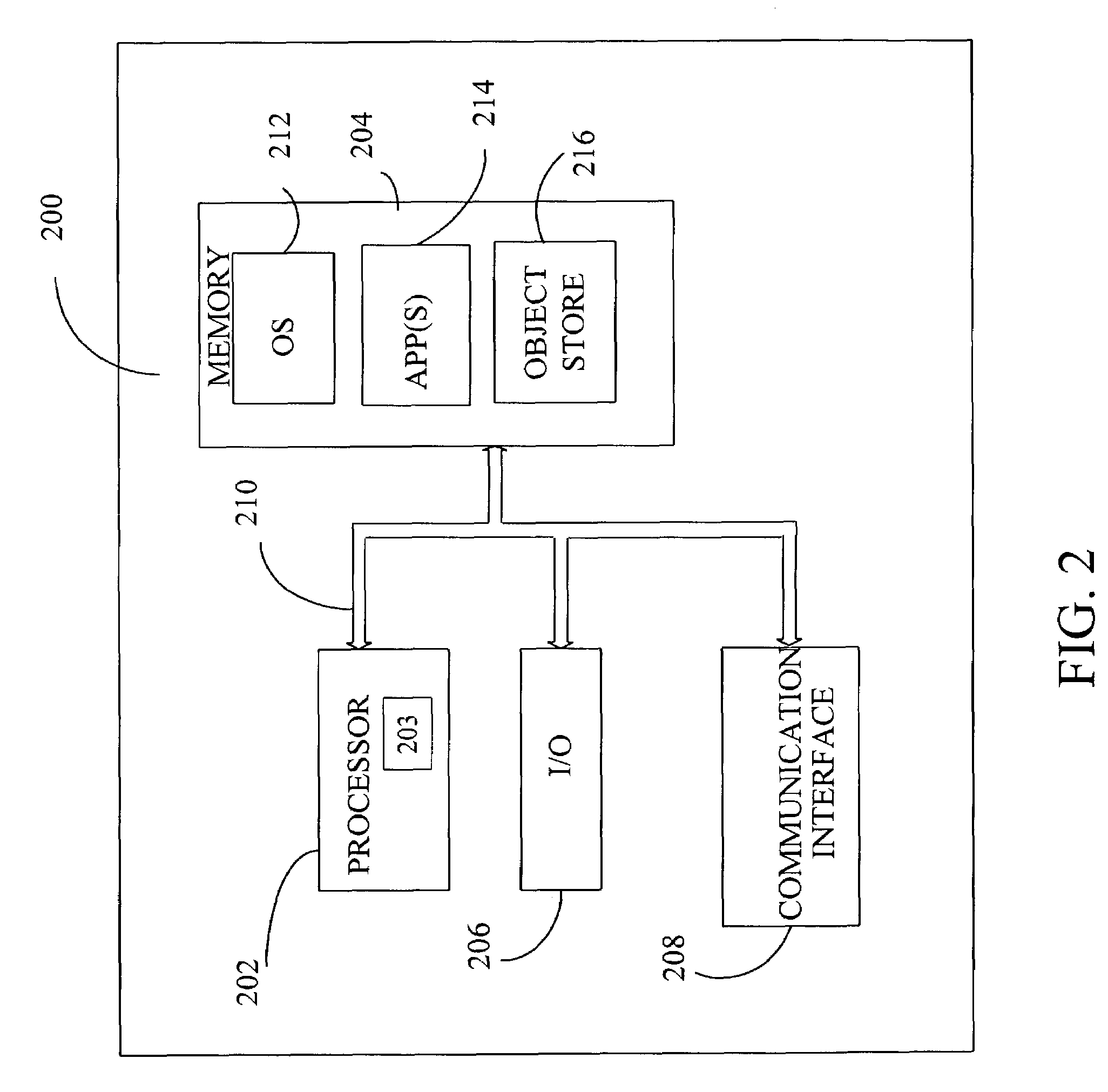

Owner:MICROSOFT TECH LICENSING LLC

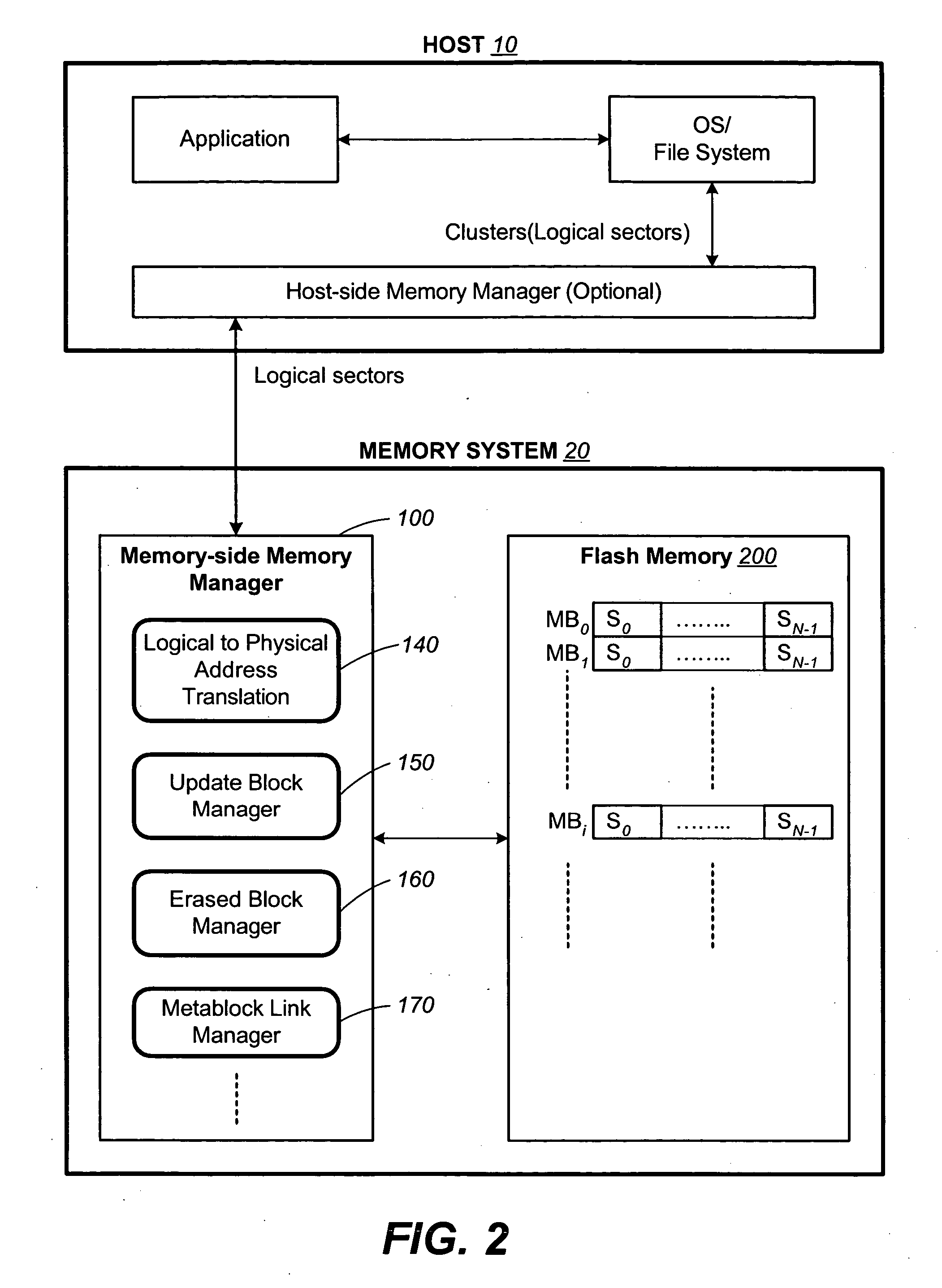

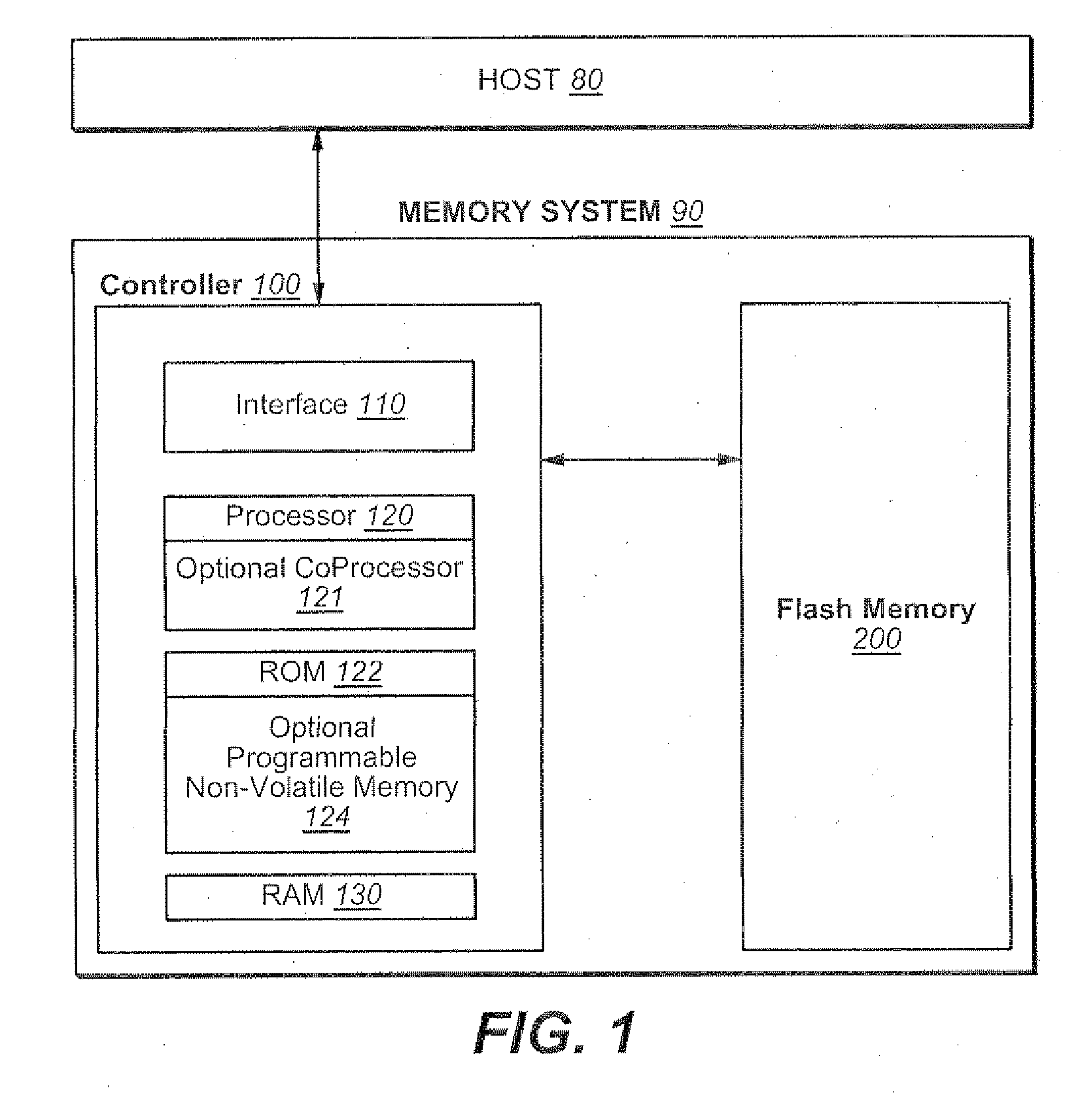

Non-volatile memory and method with control data management

ActiveUS20050144365A1Good ECCExtra level of reliabilityMemory architecture accessing/allocationMemory adressing/allocation/relocationManagement systemMulti state

In a nonvolatile memory with block management system, critical data such as control data for the block management system is maintained in duplicates. Various methods are described for robustly writing and reading two copies of critical data in multi-state memory. In another aspect of the invention, a preemptive garbage collection on memory block containing control data avoids an undesirable situation where a large number of such memory blocks need be garbage collected at the same time.

Owner:SANDISK TECH LLC

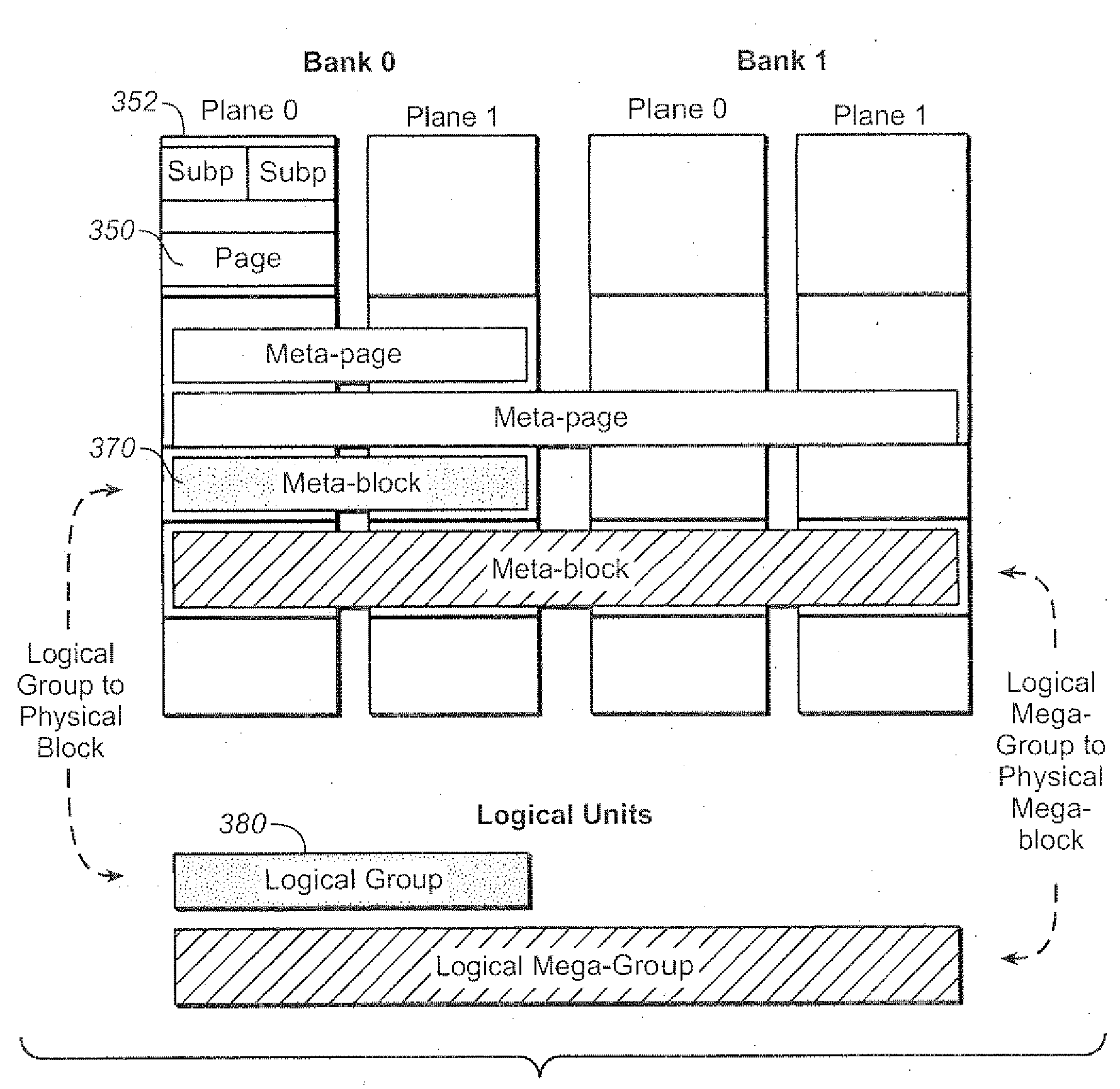

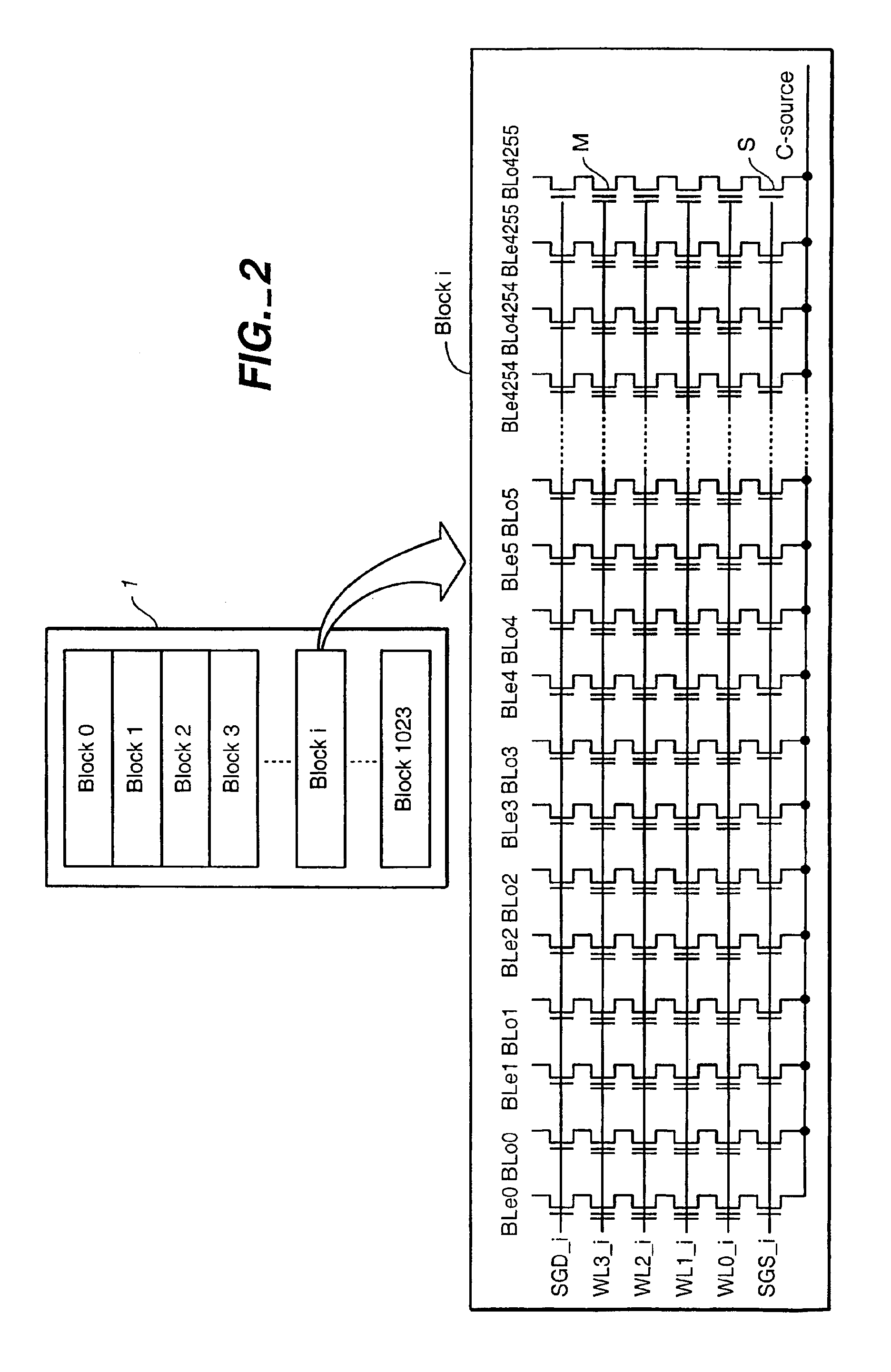

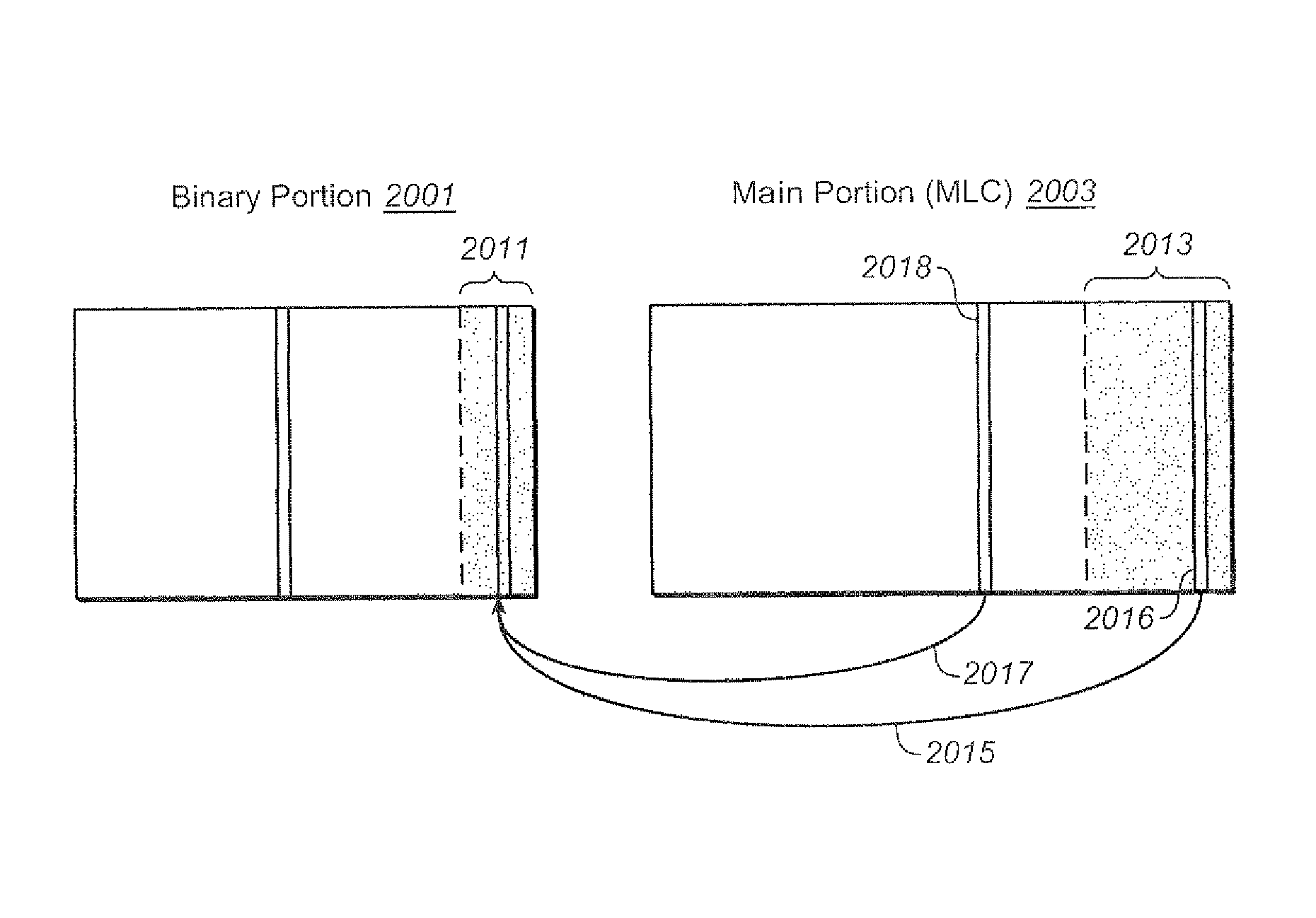

Spare Block Management of Non-Volatile Memories

ActiveUS20100172179A1Improve staminaMemory architecture accessing/allocationRead-only memoriesNon-volatile memoryLogical address

Techniques for the management of spare blocks in re-programmable non-volatile memory system, such as a flash EEPROM system, are presented. In one set of techniques, for a memory partitioned into two sections (for example a binary section and a multi-state section), where blocks of one section are more prone to error, spare blocks can be transferred from the more error prone partition to the less error prone partition. In another set of techniques for a memory partitioned into two sections, blocks which fail in the more error prone partition are transferred to serve as spare blocks in the other partition. In a complementary set of techniques, a 1-bit time stamp is maintained for free blocks to determine whether the block has been written recently. Other techniques allow for spare blocks to be managed by way of a logical to physical conversion table by assigning them logical addresses that exceed the logical address space of which a host is aware.

Owner:SANDISK TECH LLC

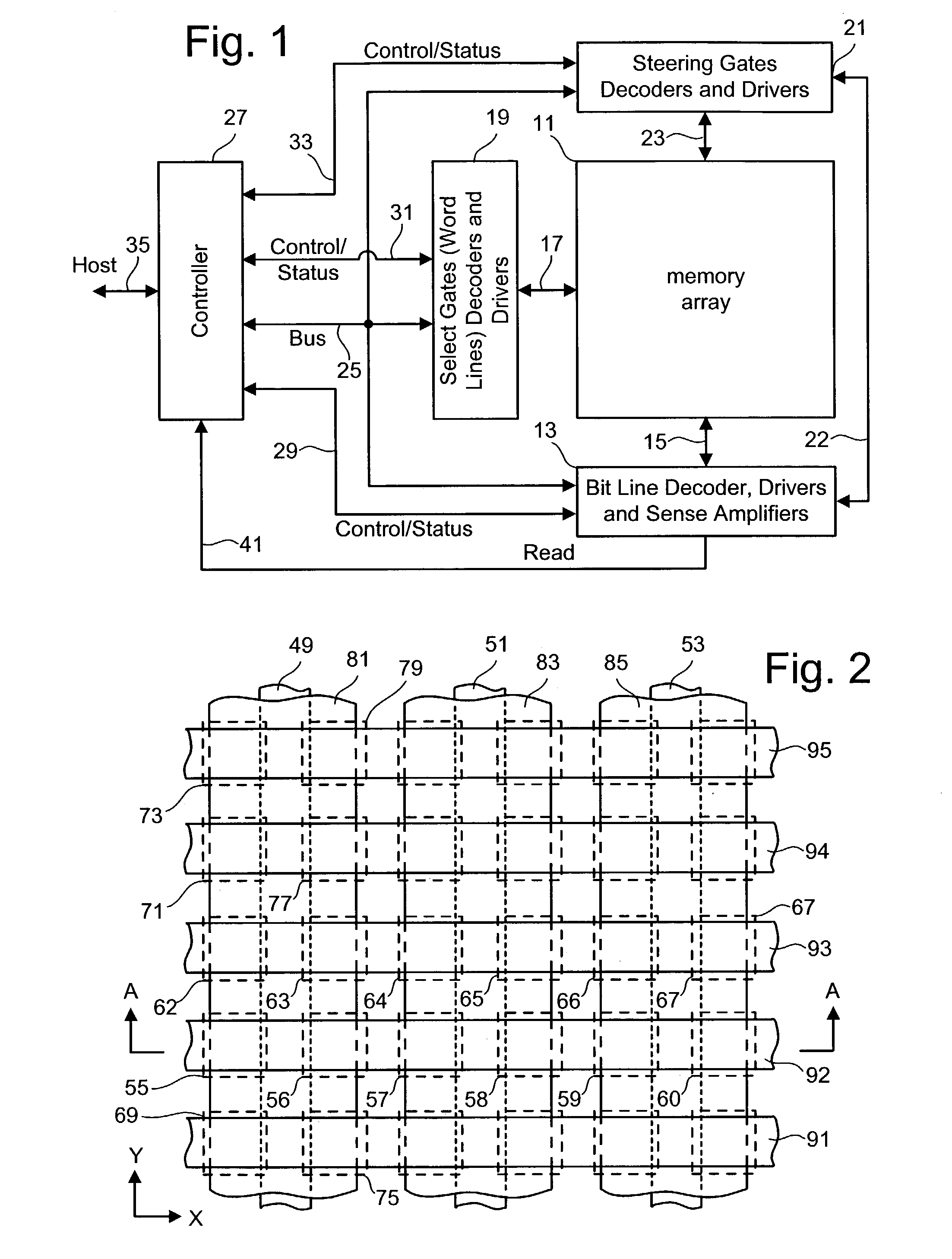

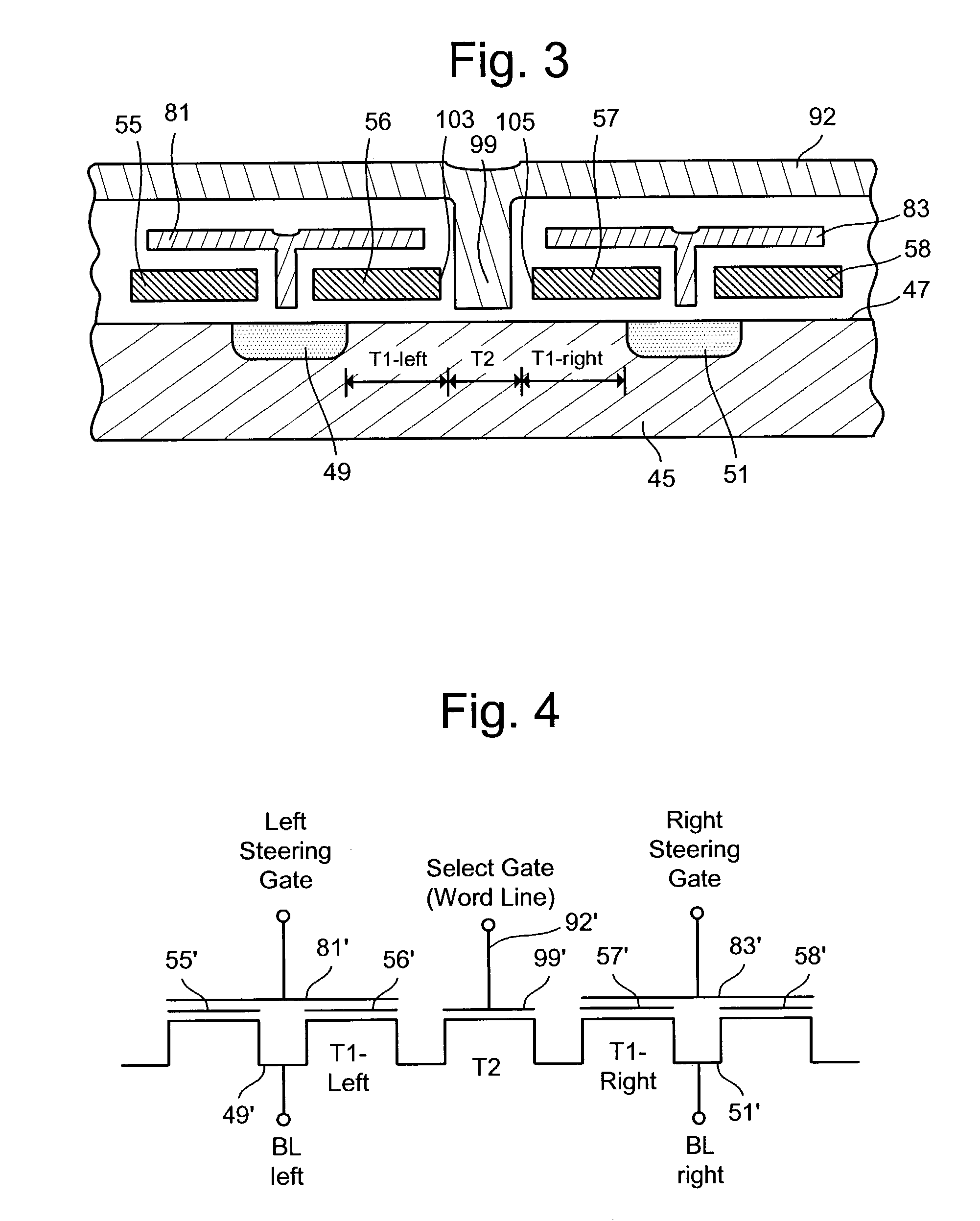

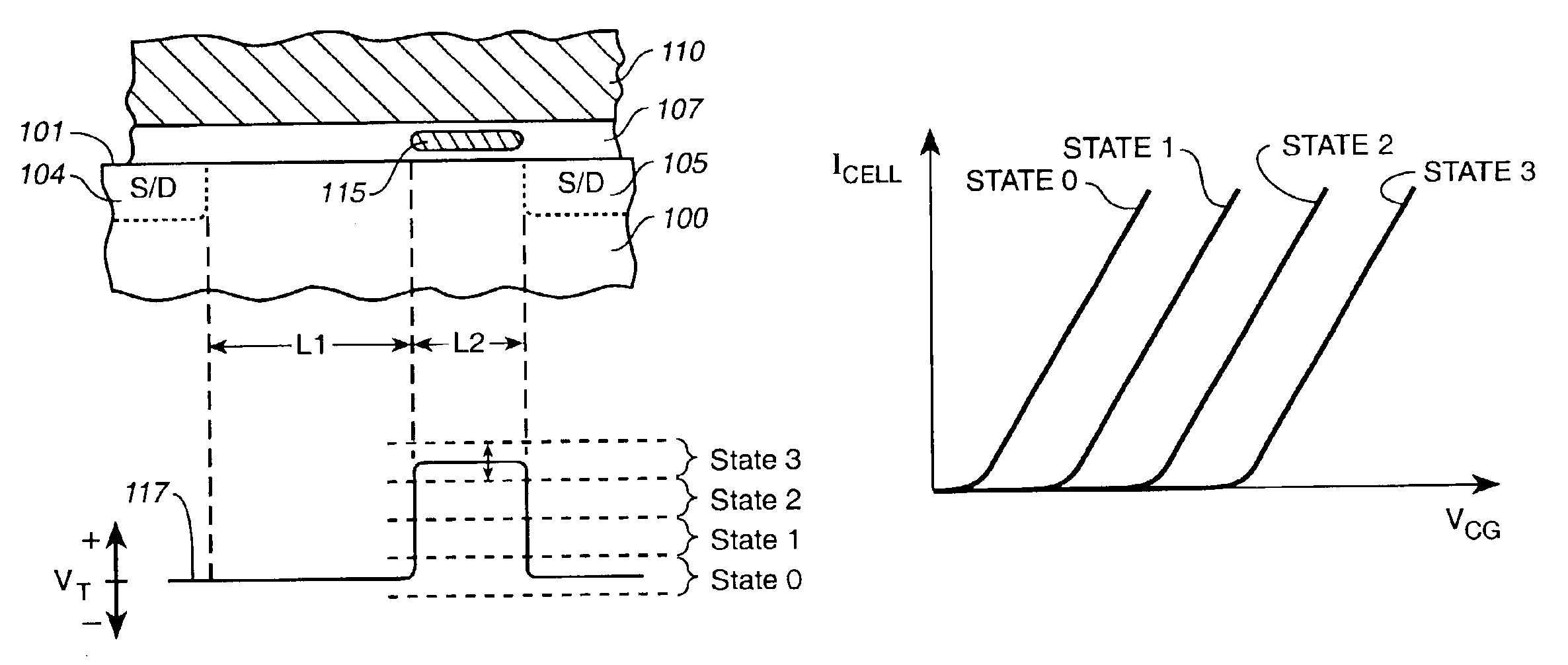

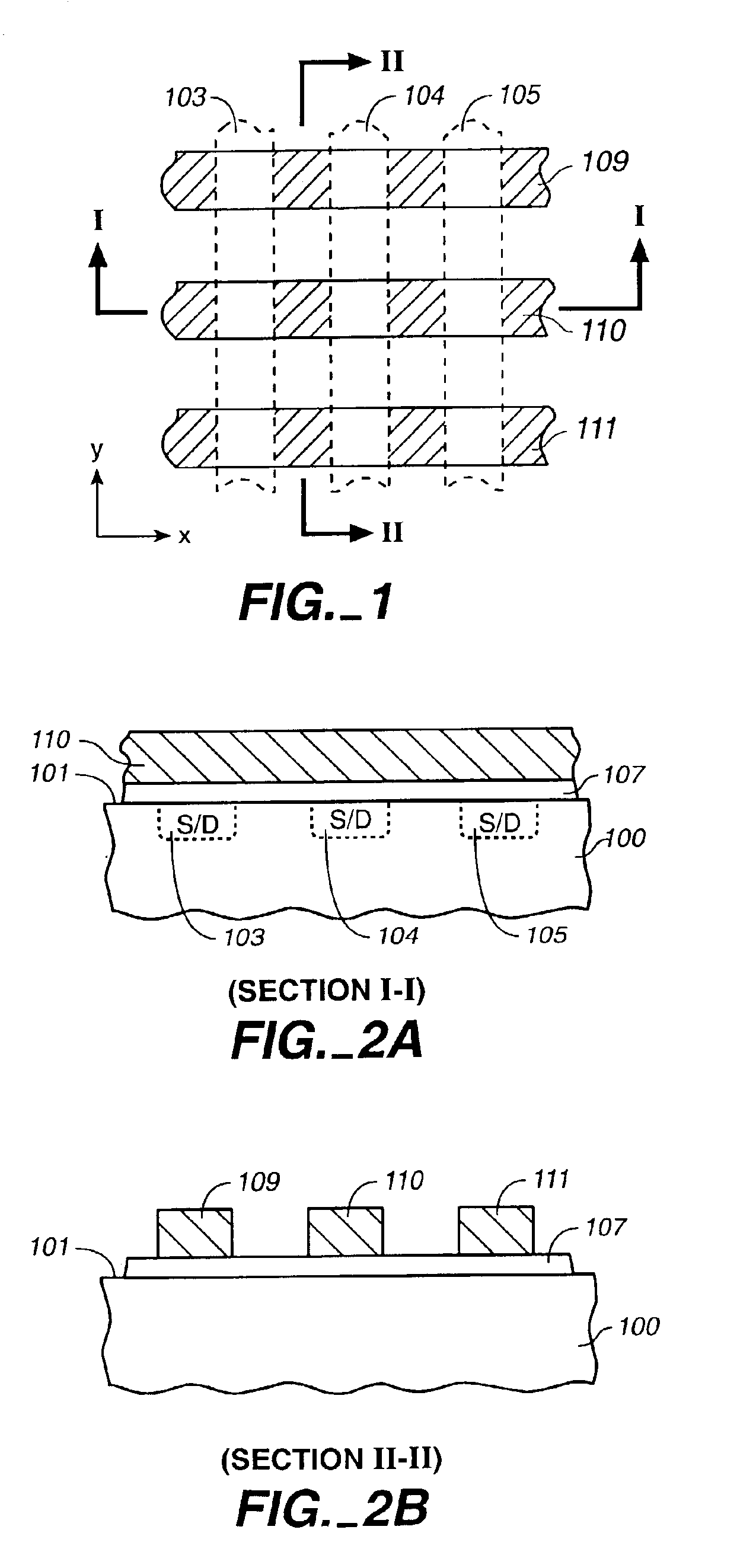

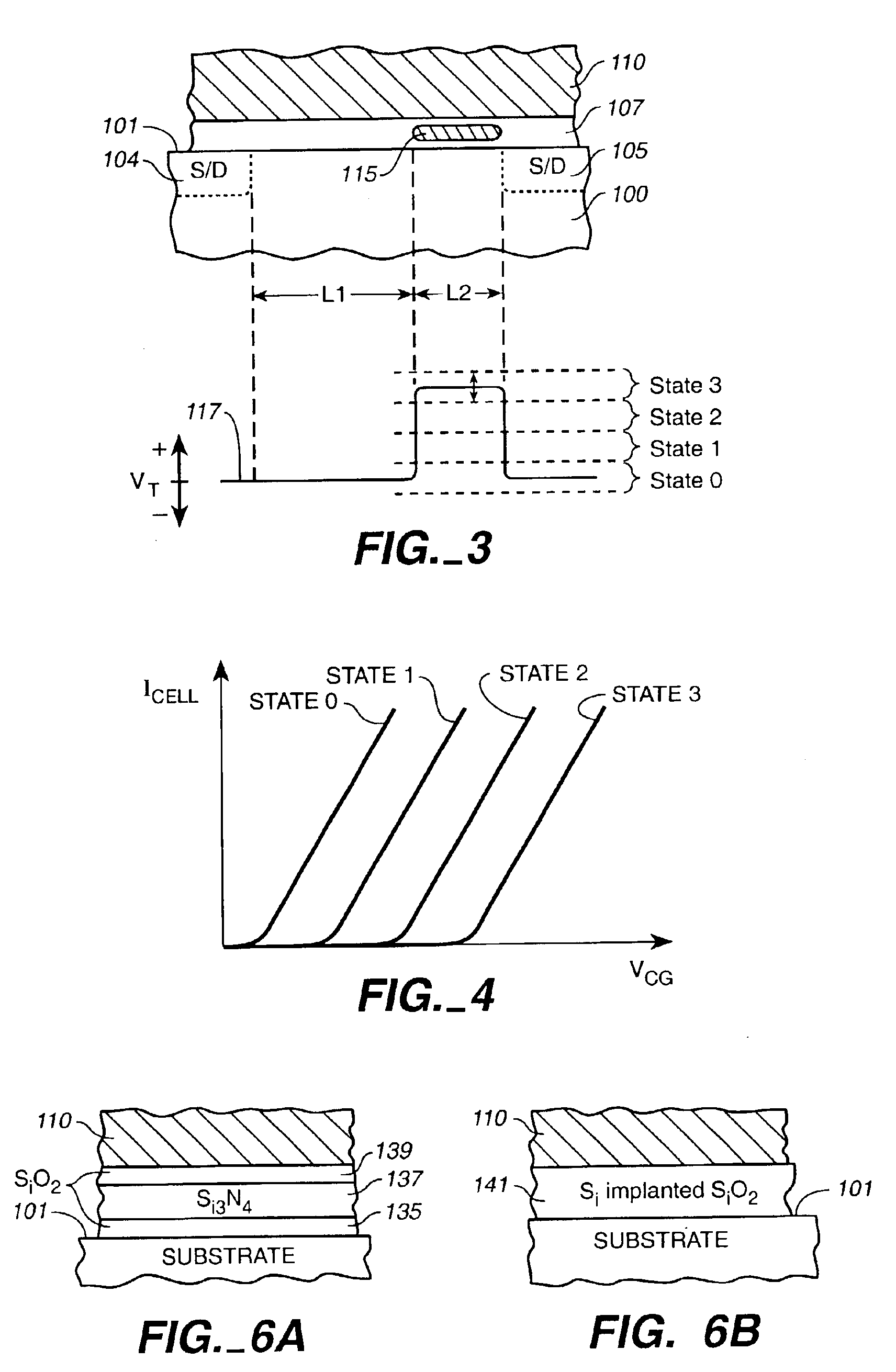

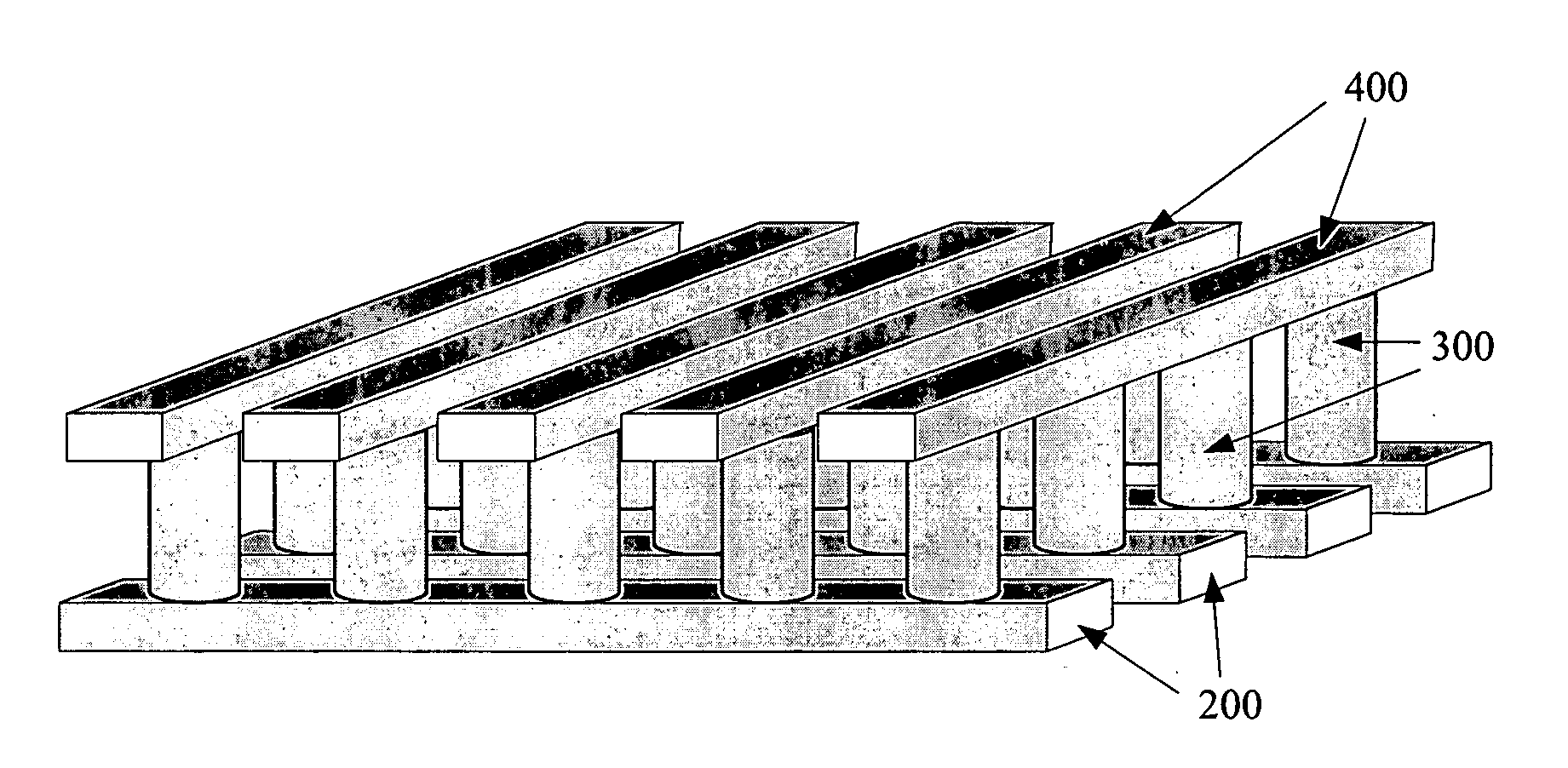

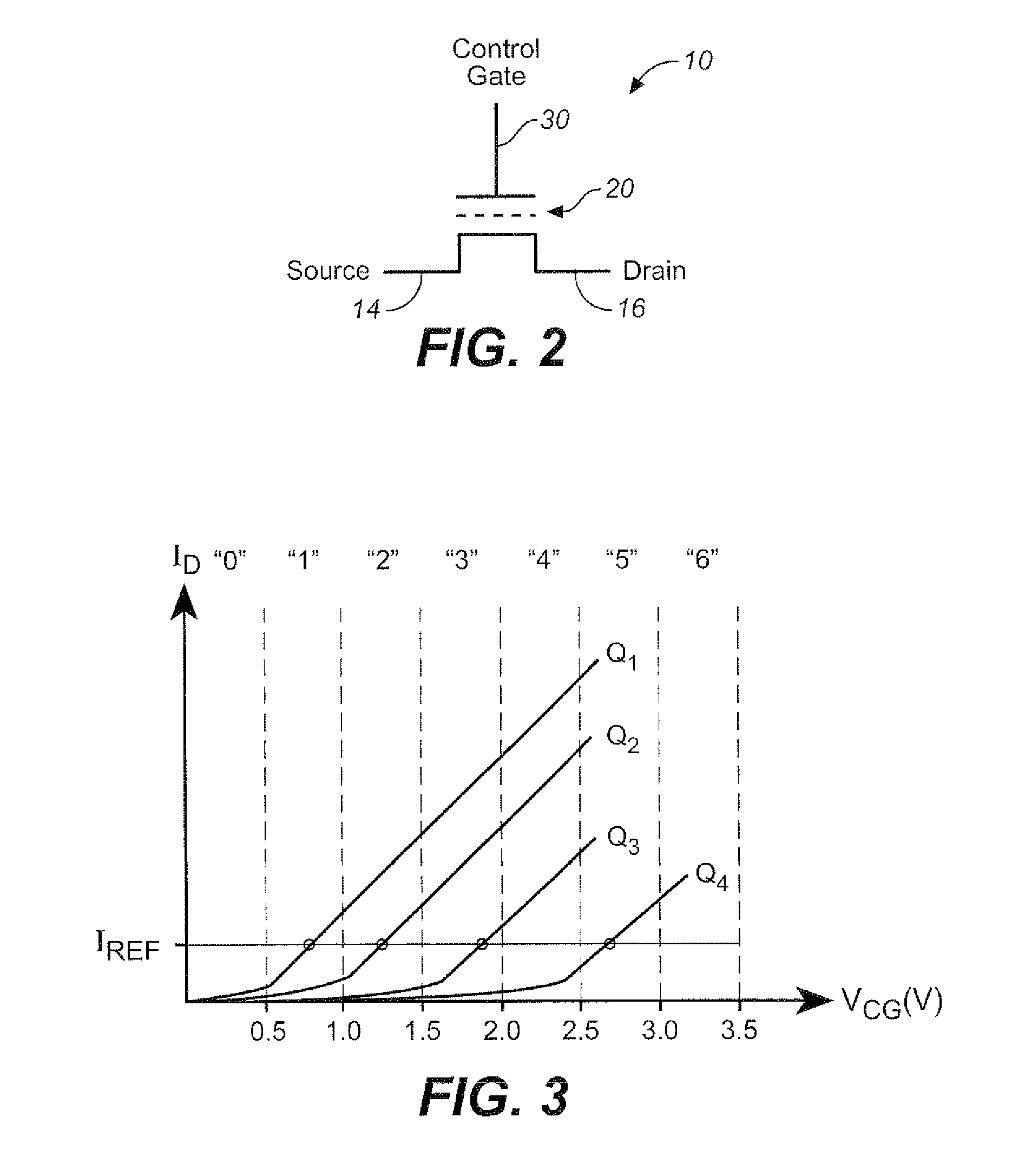

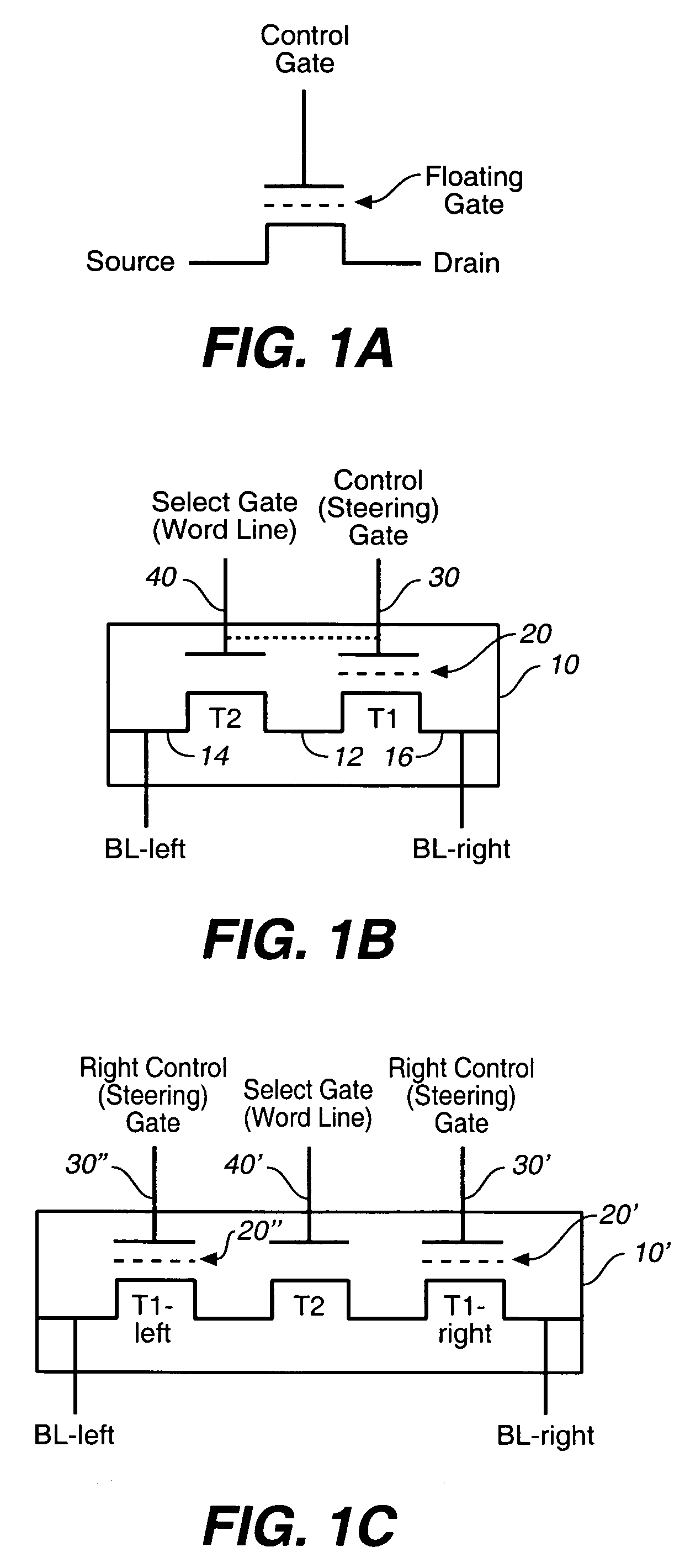

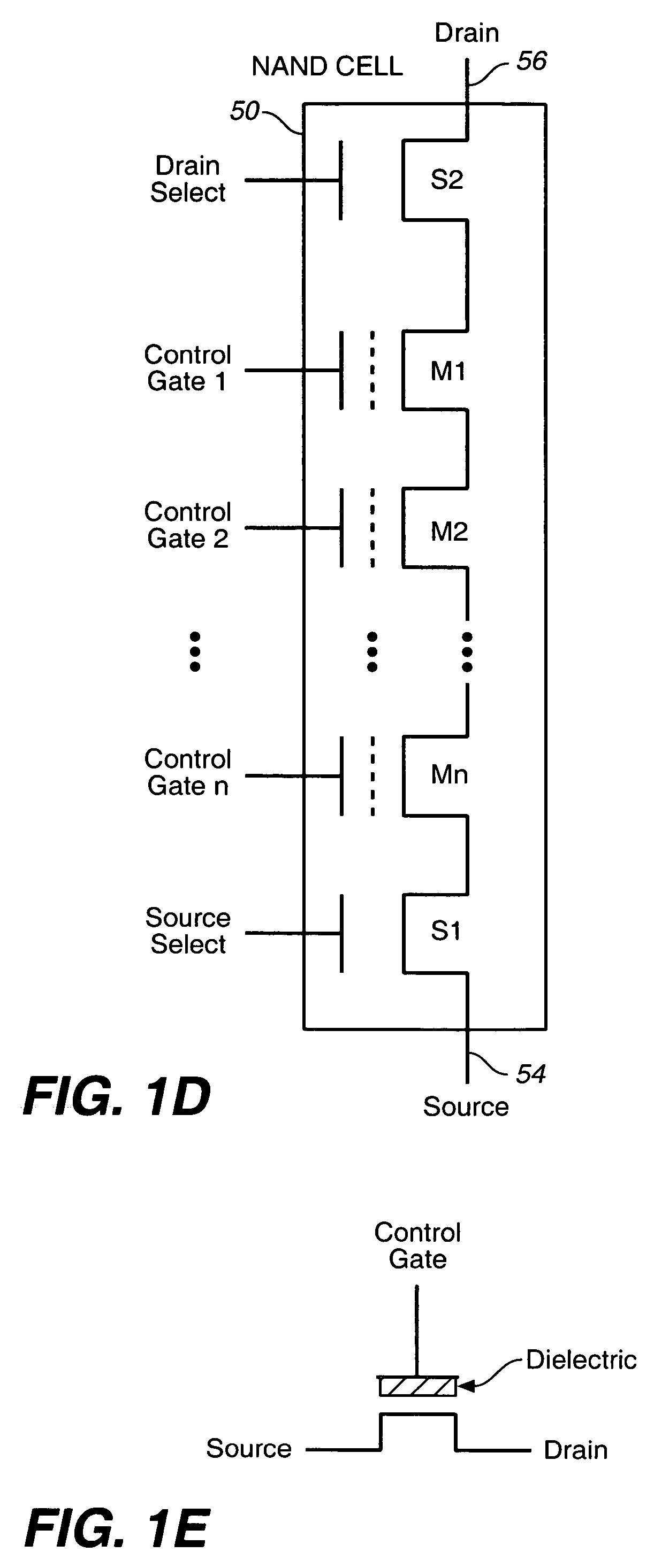

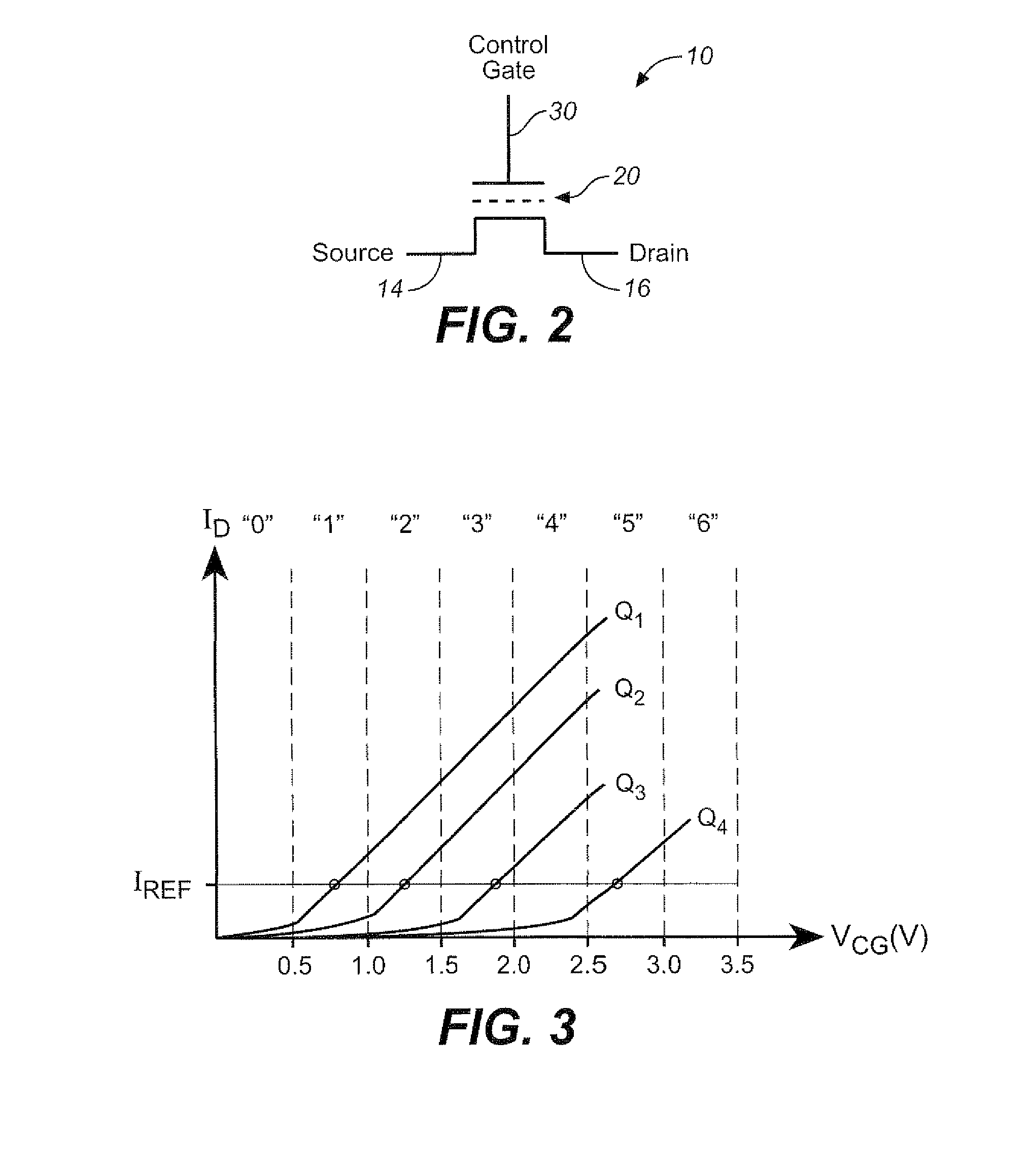

Multi-state non-volatile integrated circuit memory systems that employ dielectric storage elements

InactiveUS6925007B2Increase the number ofExtend effective lifeTransistorNanoinformaticsEngineeringDielectric layer

Non-volatile memory cells store a level of charge corresponding to the data being stored in a dielectric material storage element that is sandwiched between a control gate and the semiconductor substrate surface over channel regions of the memory cells. More than two memory states are provided by one of more than two levels of charge being stored in a common region of the dielectric material. More than one such common region may be included in each cell. In one form, two such regions are provided adjacent source and drain diffusions in a cell that also includes a select transistor positioned between them. In another form, NAND arrays of strings of memory cells store charge in regions of a dielectric layer sandwiched between word lines and the semiconductor substrate.

Owner:SANDISK TECH LLC

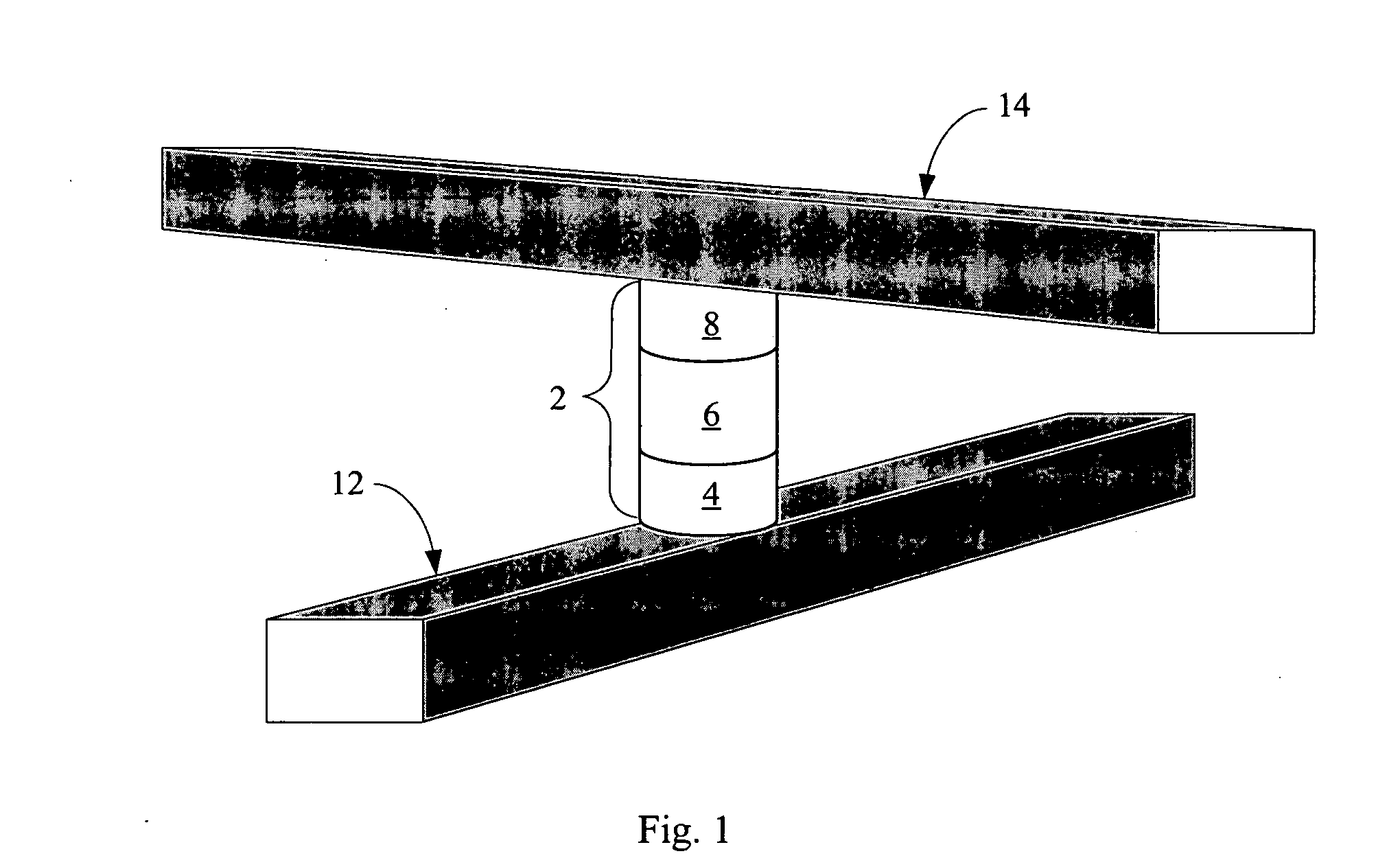

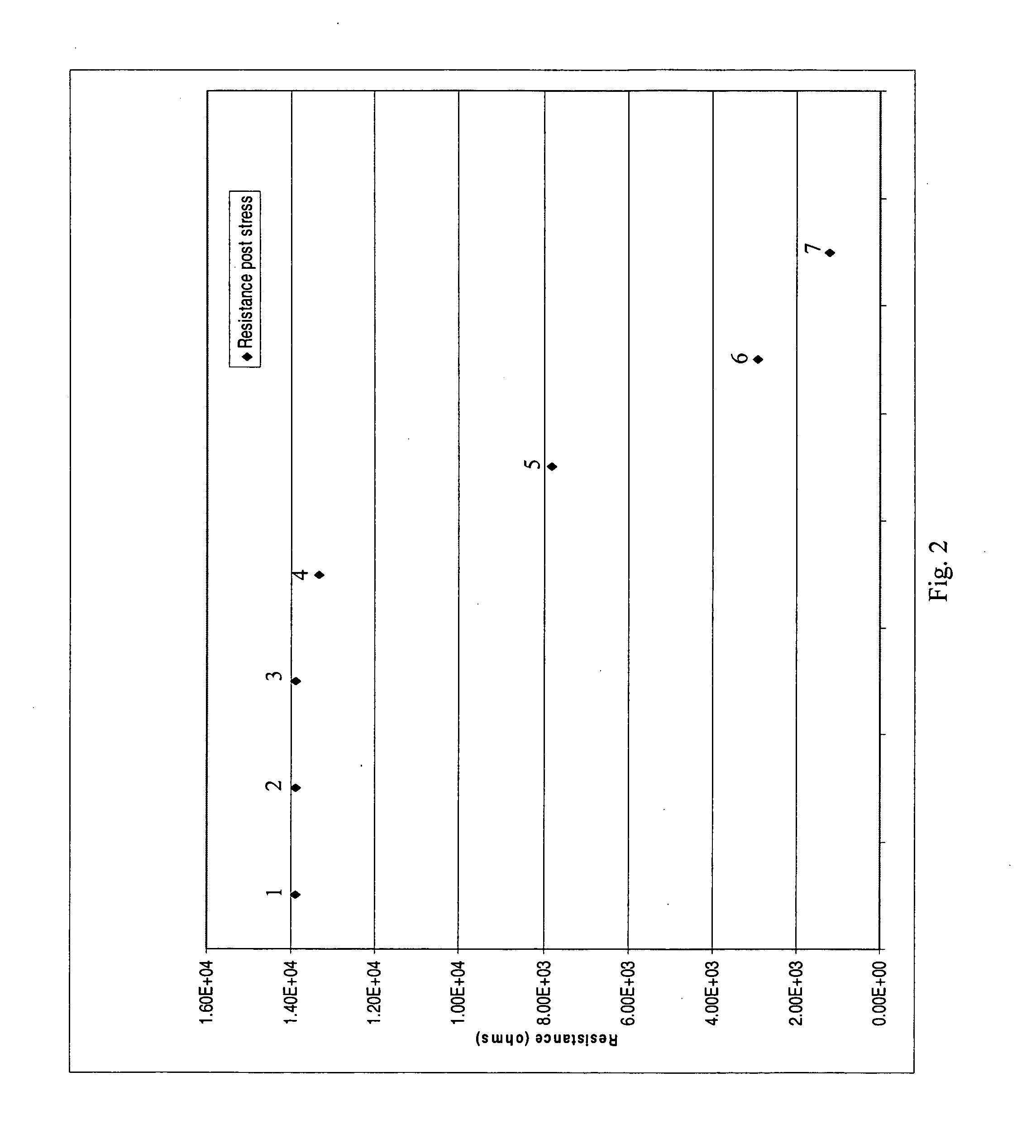

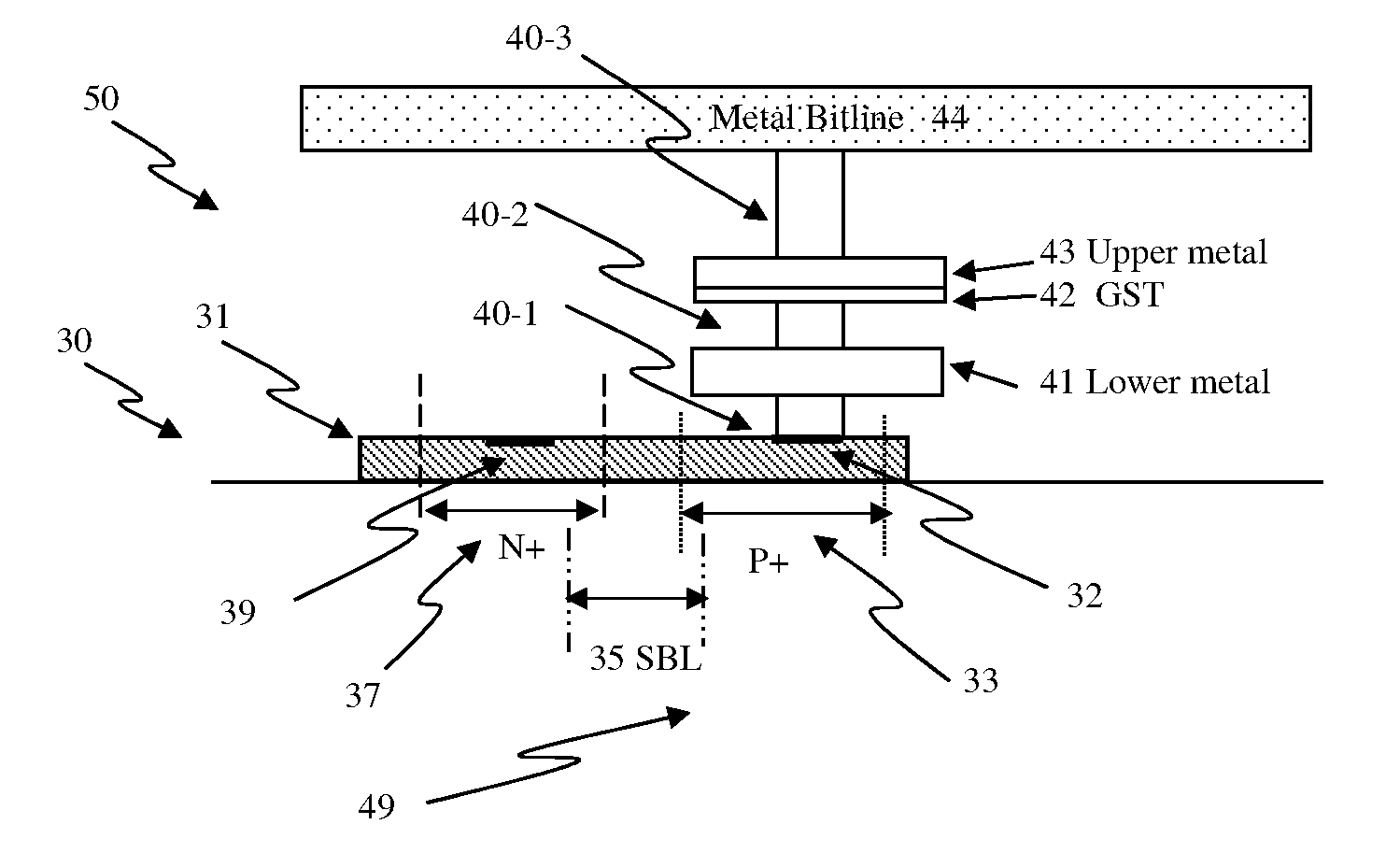

Memory cell comprising switchable semiconductor memory element with trimmable resistance

ActiveUS20070090425A1Solid-state devicesRead-only memoriesHigh resistanceElectrical resistance and conductance

A nonvolatile memory cell comprising doped semiconductor material and a diode can store memory states by changing the resistance of the doped semiconductor material by application of a set pulse (decreasing resistance) or a reset pulse (increasing resistance.) Set pulses are of short duration and above a threshold voltage, while reset pulses are longer duration and below a threshold voltage. In some embodiments multiple resistance states can be achieved, allowing for a multi-state cell, while restoring a prior high-resistance state allows for an rewriteable cell. In some embodiments, the diode and a switchable memory formed of doped semiconductor material are formed in series, while in other embodiments, the diode itself serves as the semiconductor switchable memory element.

Owner:WODEN TECH INC

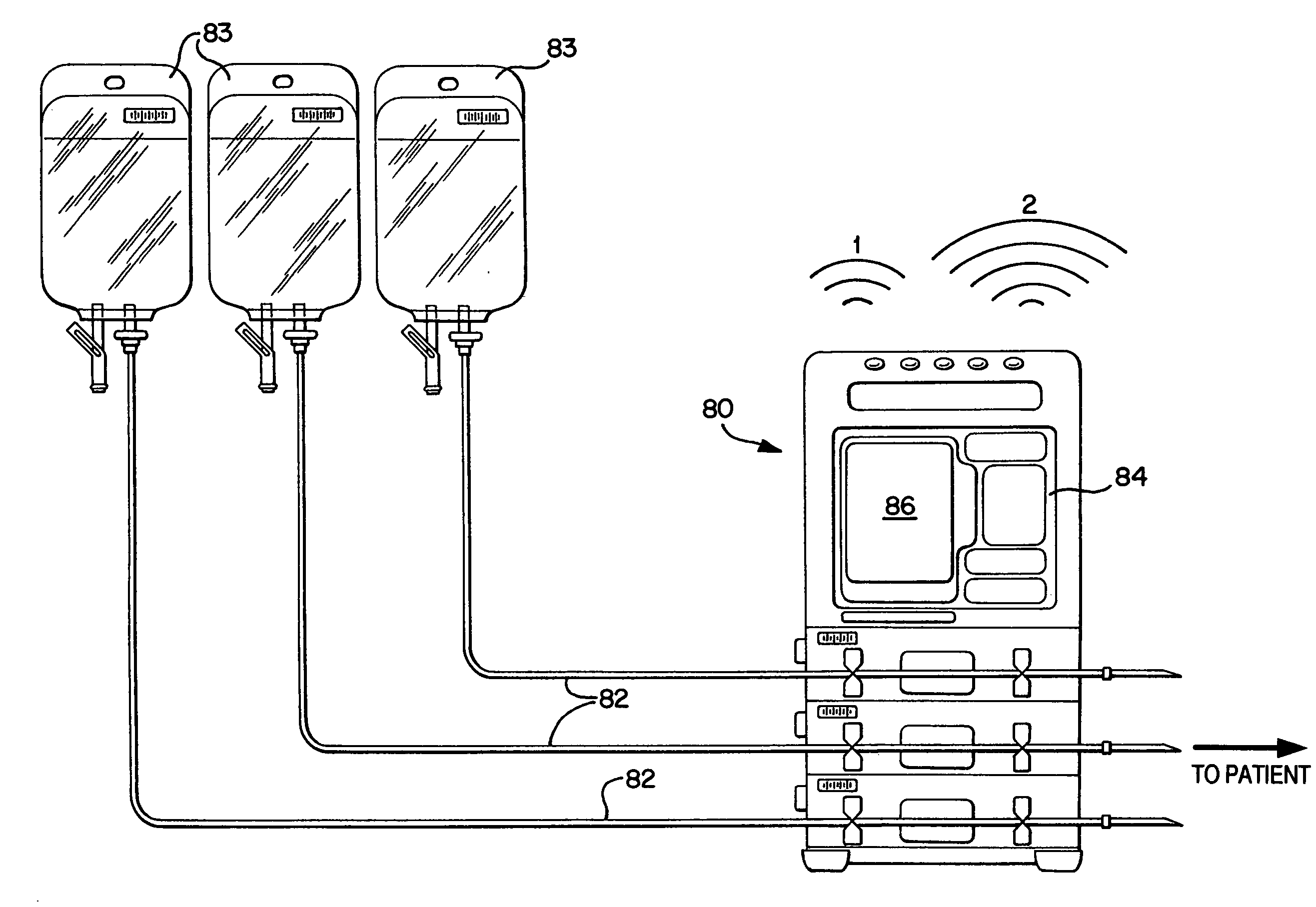

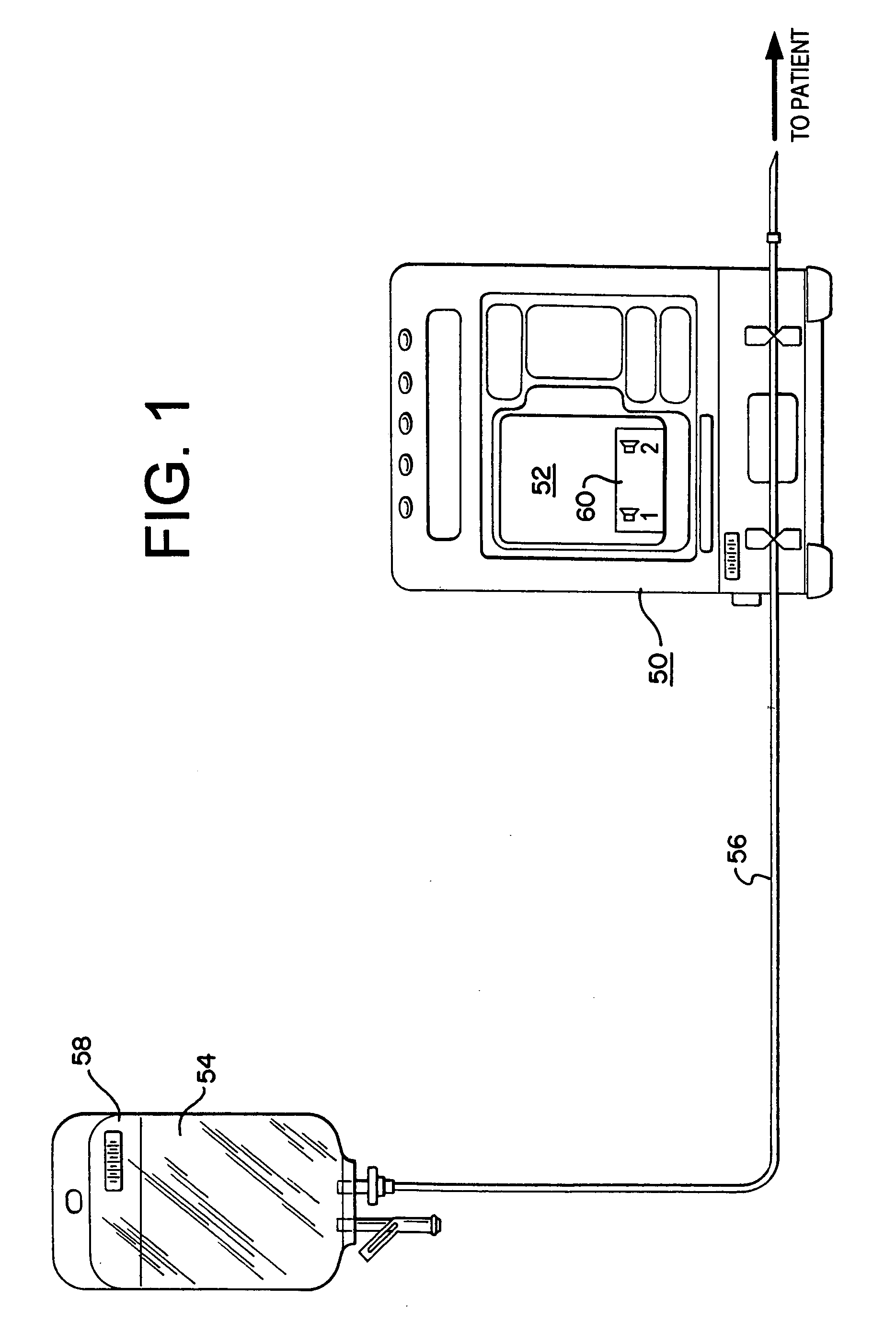

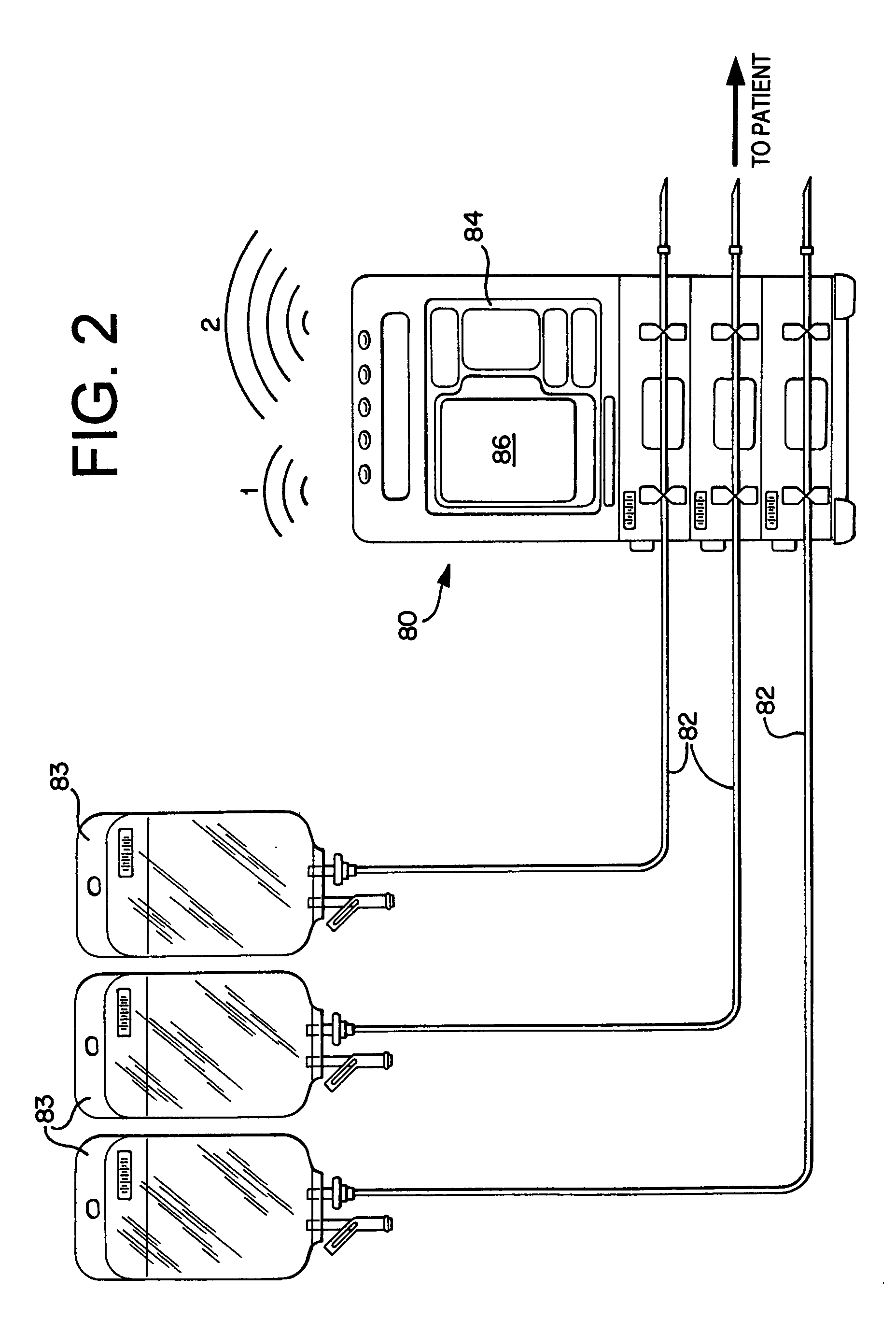

Multi-state alarm system for a medical pump

An alarm system (52) for a medical pump (50) associated with delivering a fluid (54) to a patient in connection with treatment of the patient is provided. The alarm system (52) comprises an alarm (60) associated with at least one treatment parameter. The alarm (60) includes a first alarm state (1) associated with a first event relating to the treatment parameter and a second alarm state (2) associated with a second event. The second alarm state (2) is discernable from the first alarm state (1), which will allow each of the events to be treated differently by a caregiver.

Owner:BAXTER INT INC

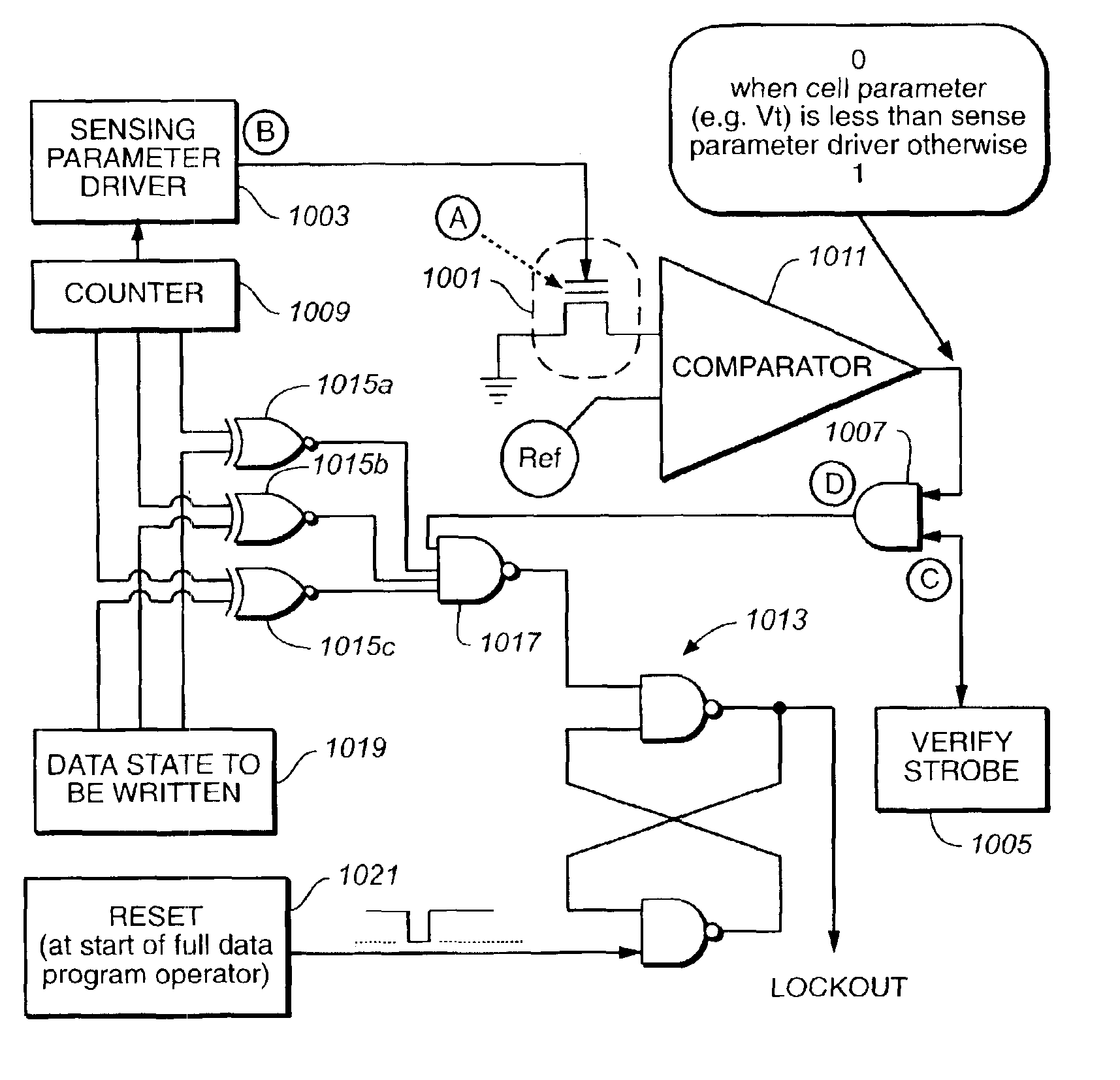

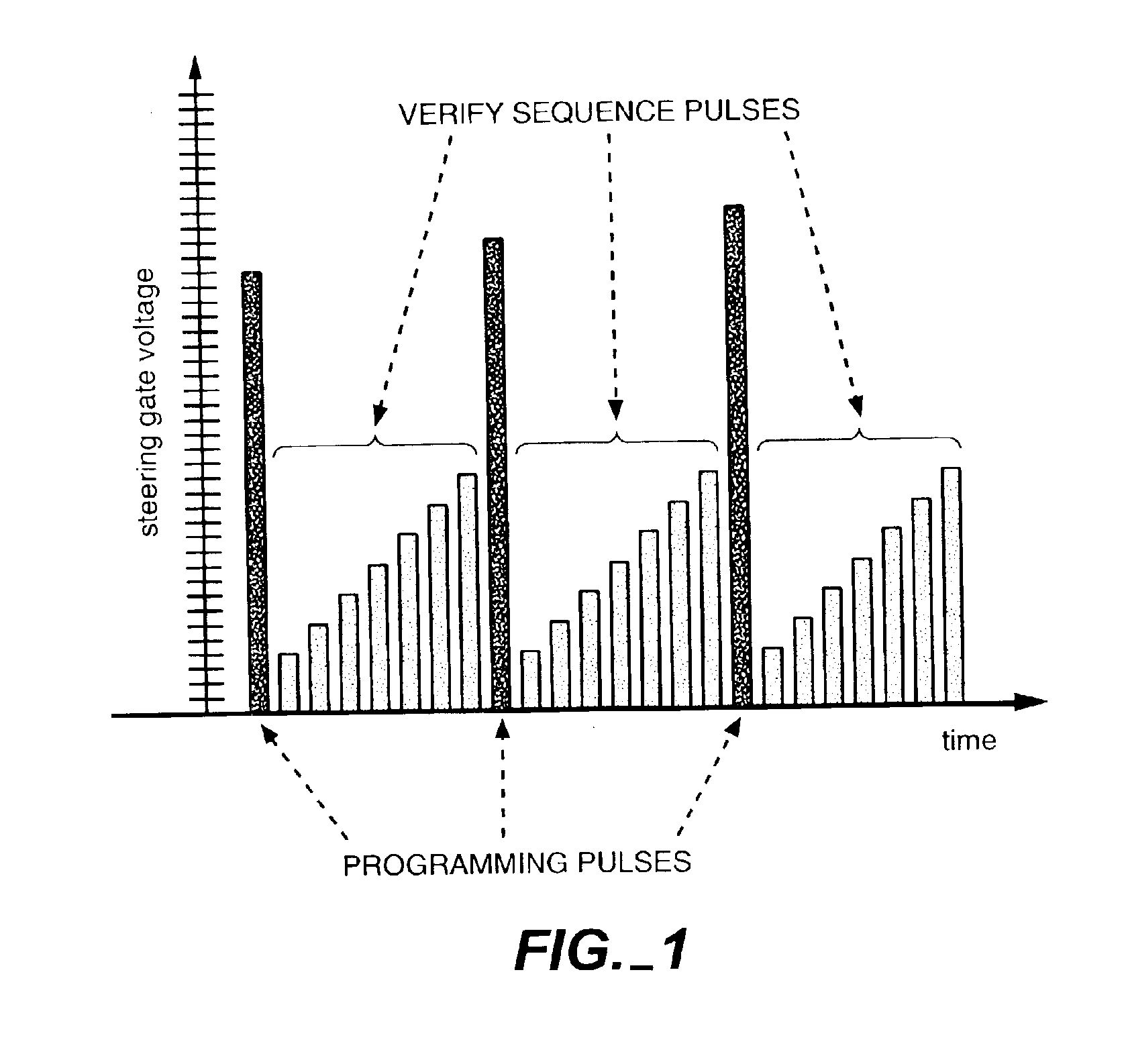

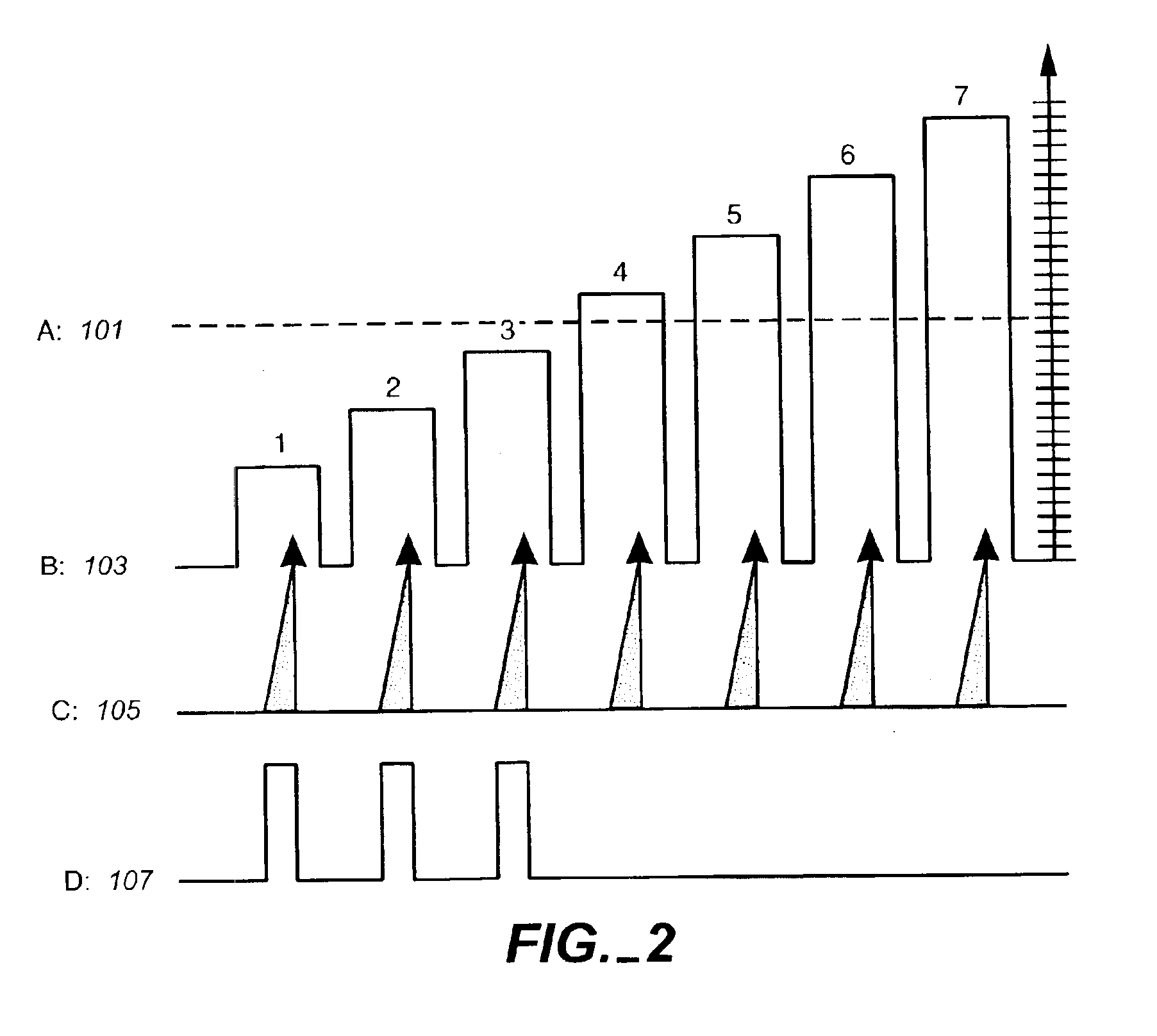

Smart verify for multi-state memories

ActiveUS7073103B2Minimize the numberIncrease write speedRead-only memoriesDigital storageComputer engineeringIntelligent verification

Owner:WODEN TECH INC

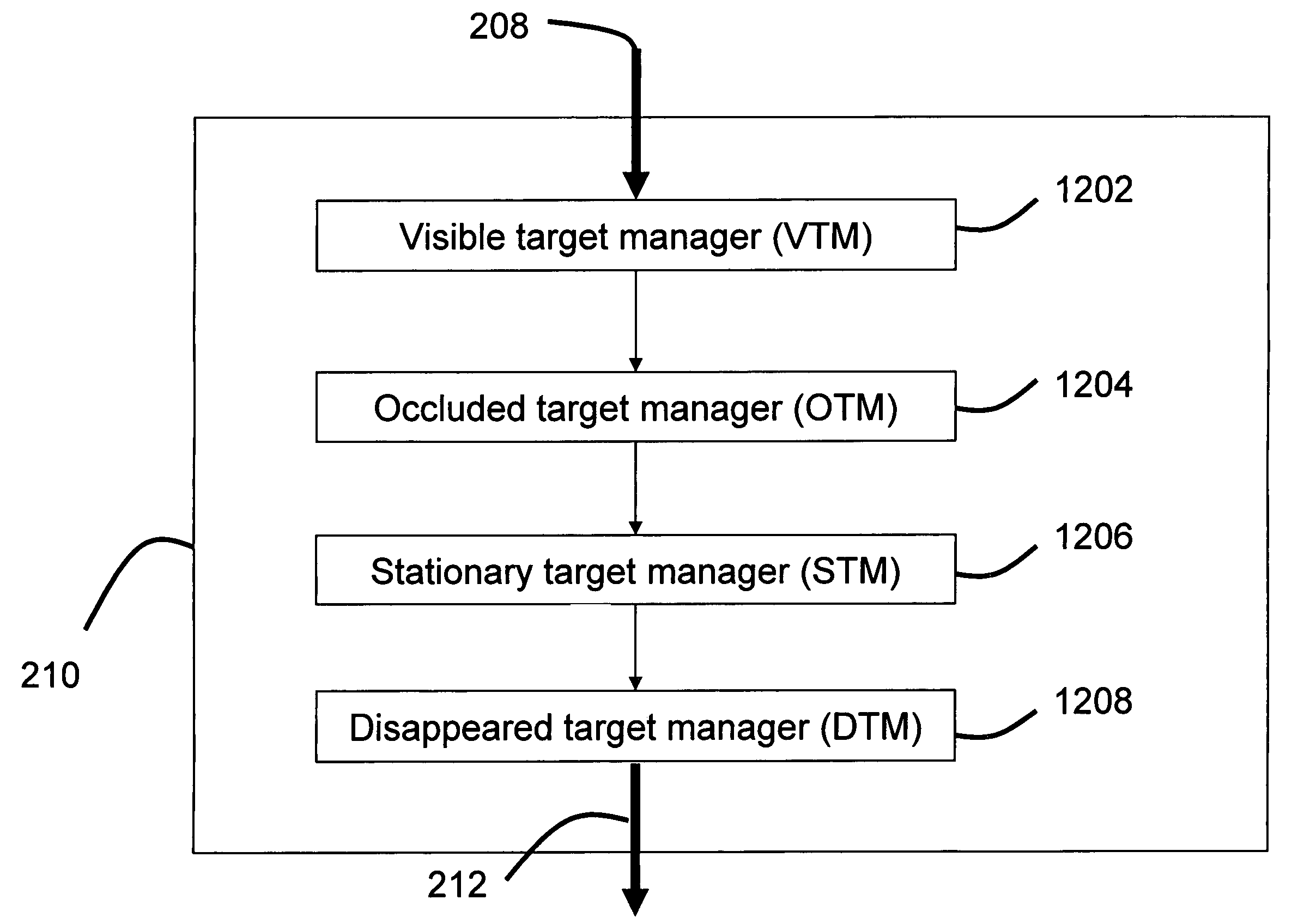

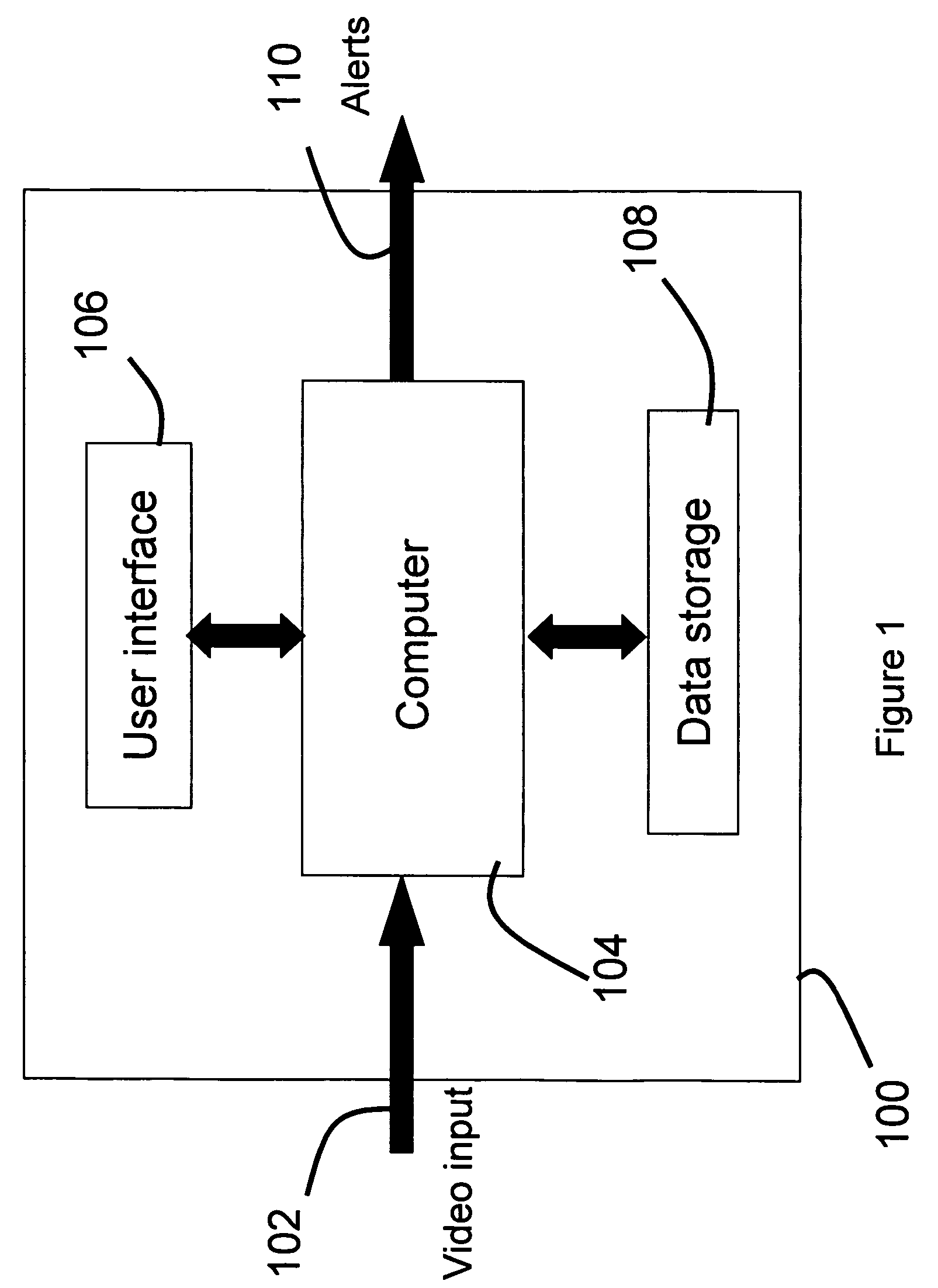

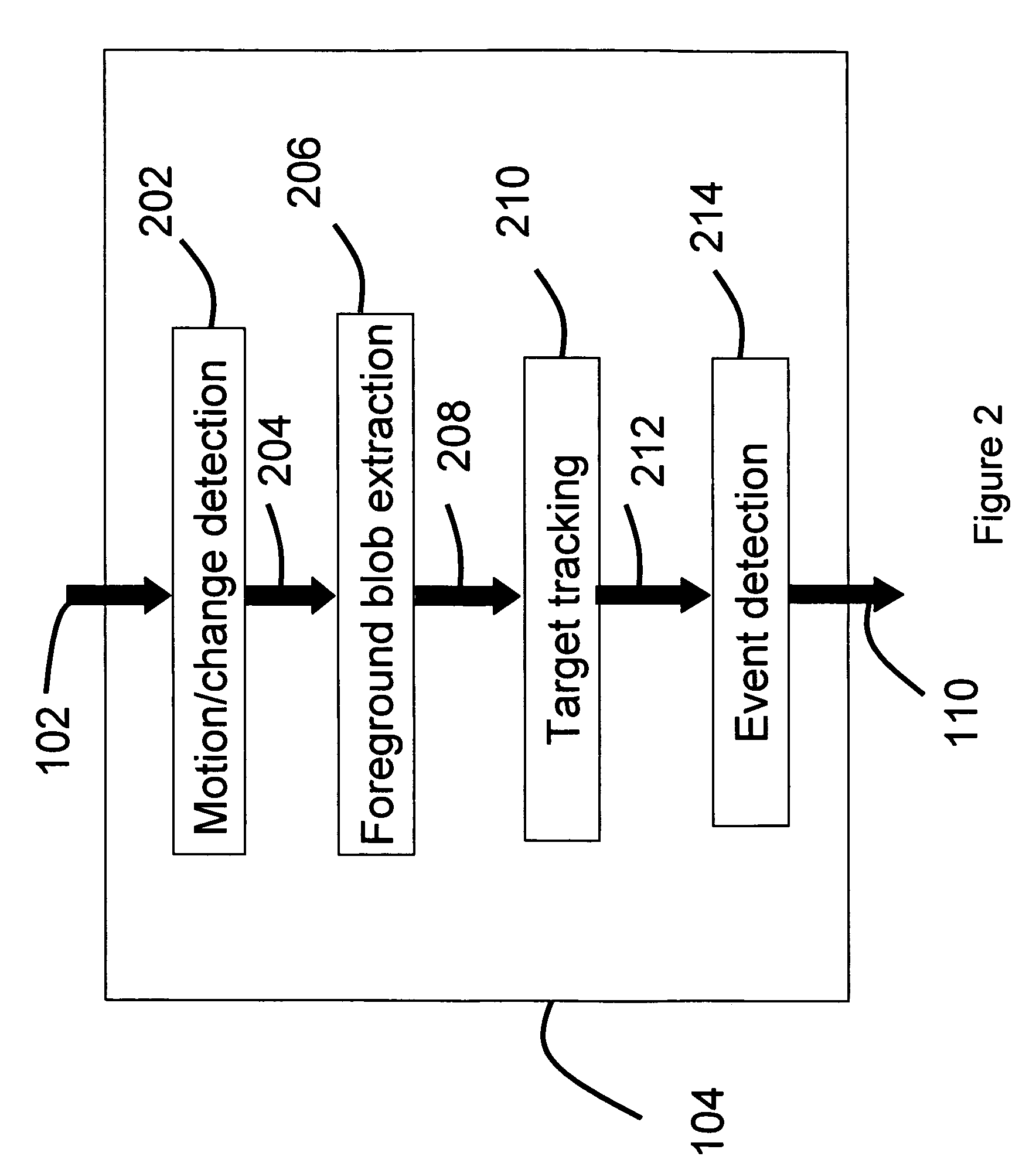

Multi-state target tracking

ActiveUS7825954B2Television system detailsCharacter and pattern recognitionComputer graphics (images)Multiple frame

A method of video analysis may comprise tracking a state of each target in a video through multiple frames of said video, each state indicating a visibility condition of a target.

Owner:MOTOROLA SOLUTIONS INC

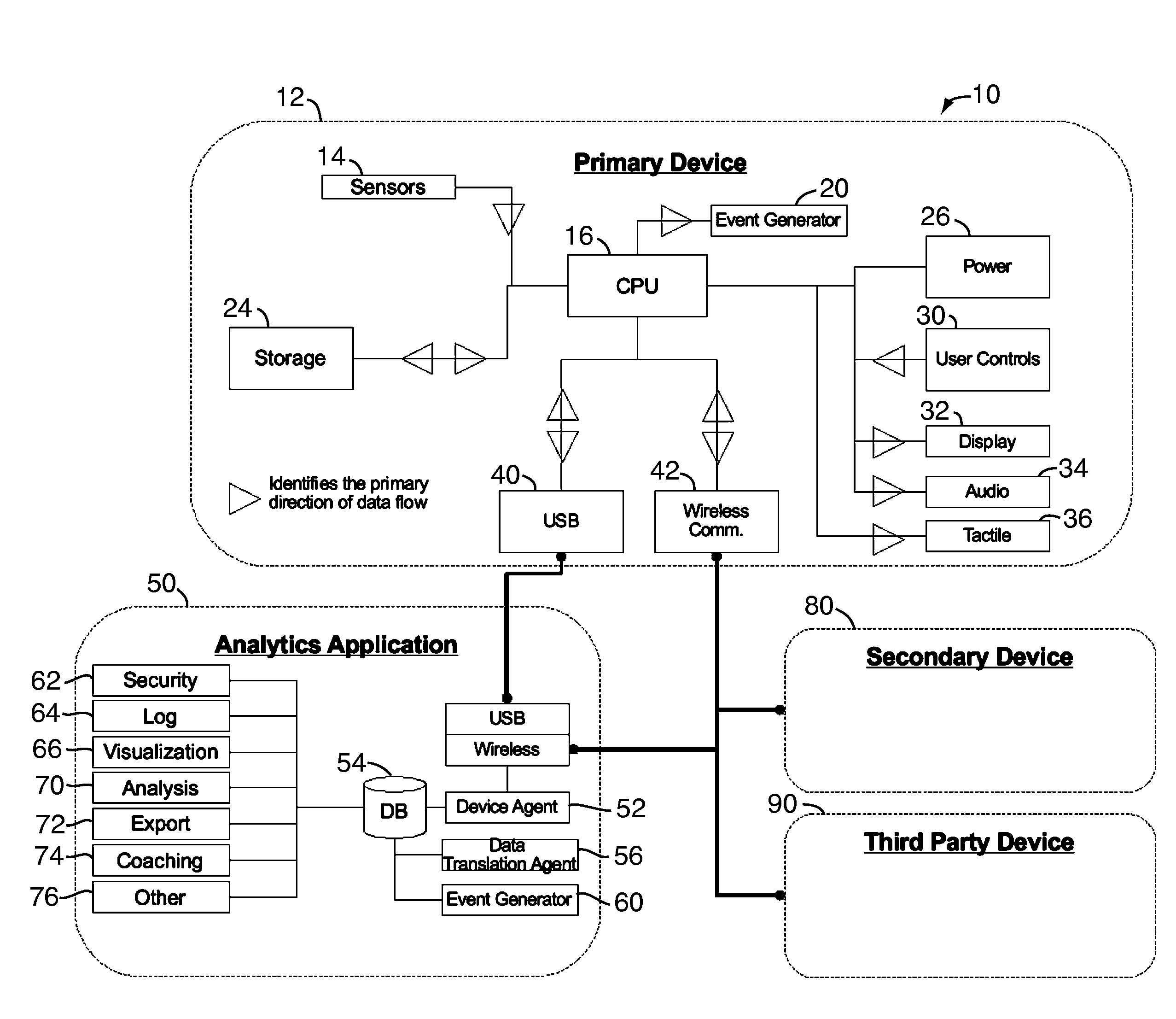

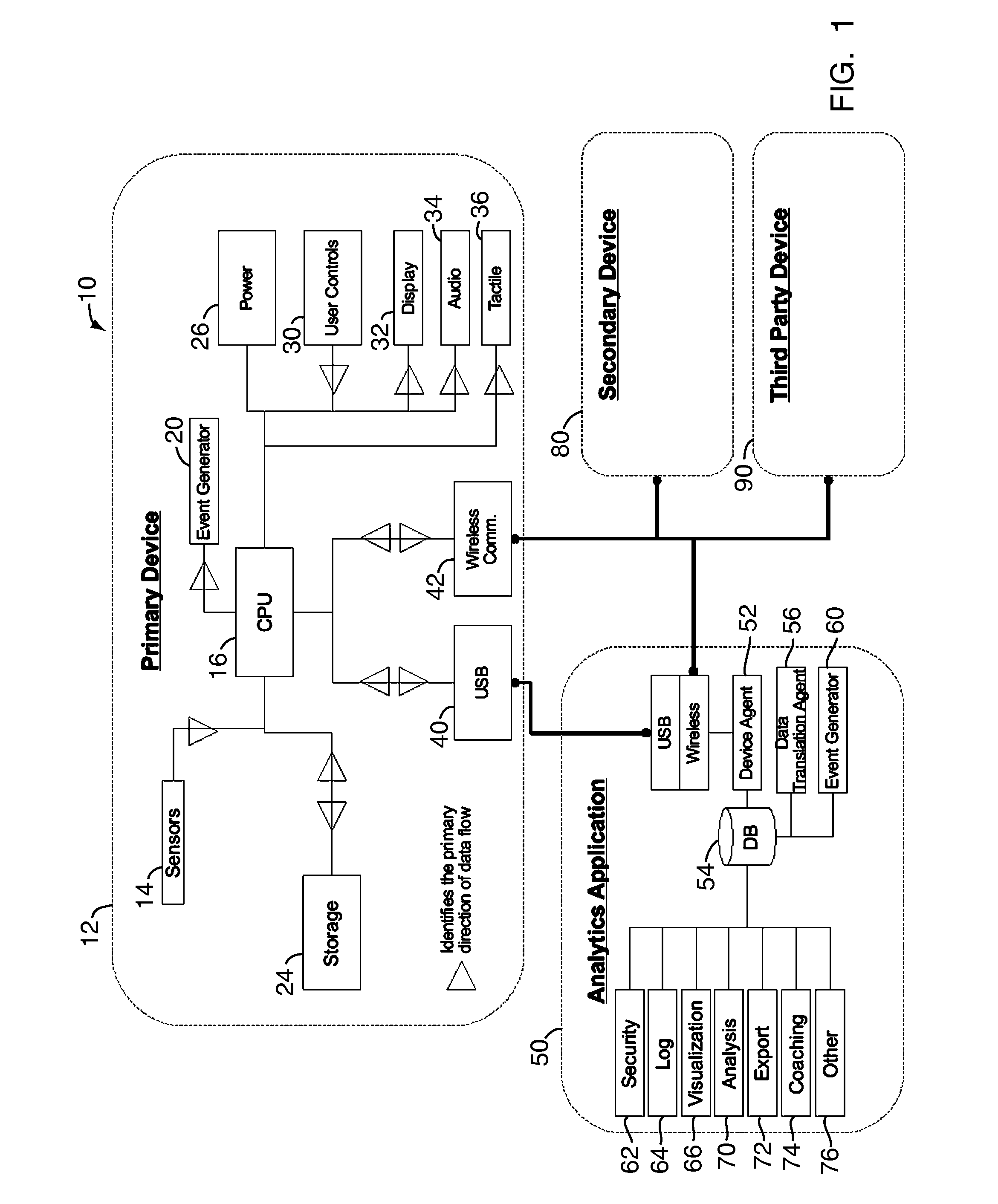

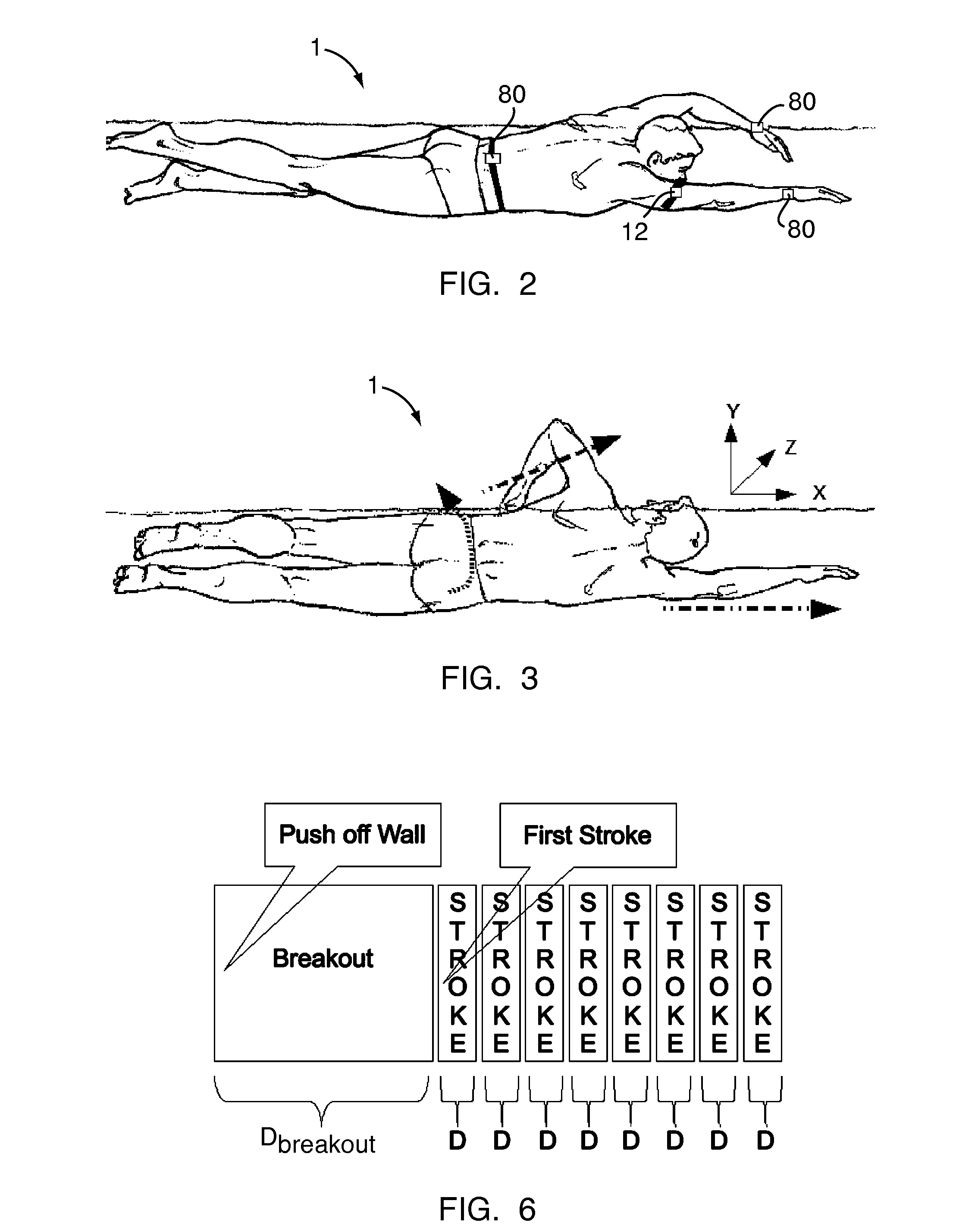

Multi-state performance monitoring system

InactiveUS20100210975A1Provide real-time feedbackCapturing performance metrics in a wide variety of activitiesPerson identificationInertial sensorsThird partyAccelerometer

Owner:SWIMSENSE

Selective operation of a multi-state non-volatile memory system in a binary mode

InactiveUS7177184B2Improve programming performanceProlong lifeTransistorSolid-state devicesComputer architectureMode selection

A flash non-volatile memory system that normally operates its memory cells in multiple storage states is provided with the ability to operate some selected or all of its memory cell blocks in two states instead. The two states are selected to be the furthest separated of the multiple states, thereby providing an increased margin during two state operation. This allows faster programming and a longer operational life of the memory cells being operated in two states when it is more desirable to have these advantages than the increased density of data storage that multi-state operation provides.

Owner:SANDISK TECH LLC

Spare block management of non-volatile memories

ActiveUS8040744B2Memory architecture accessing/allocationRead-only memoriesBit timeNon-volatile memory

Techniques for the management of spare blocks in re-programmable non-volatile memory system, such as a flash EEPROM system, are presented. In one set of techniques, for a memory partitioned into two sections (for example a binary section and a multi-state section), where blocks of one section are more prone to error, spare blocks can be transferred from the more error prone partition to the less error prone partition. In another set of techniques for a memory partitioned into two sections, blocks which fail in the more error prone partition are transferred to serve as spare blocks in the other partition. In a complementary set of techniques, a 1-bit time stamp is maintained for free blocks to determine whether the block has been written recently. Other techniques allow for spare blocks to be managed by way of a logical to physical conversion table by assigning them logical addresses that exceed the logical address space of which a host is aware.

Owner:SANDISK TECH LLC

Fixed Position Multi-State Interactive Advertisement

Owner:MICROSOFT TECH LICENSING LLC

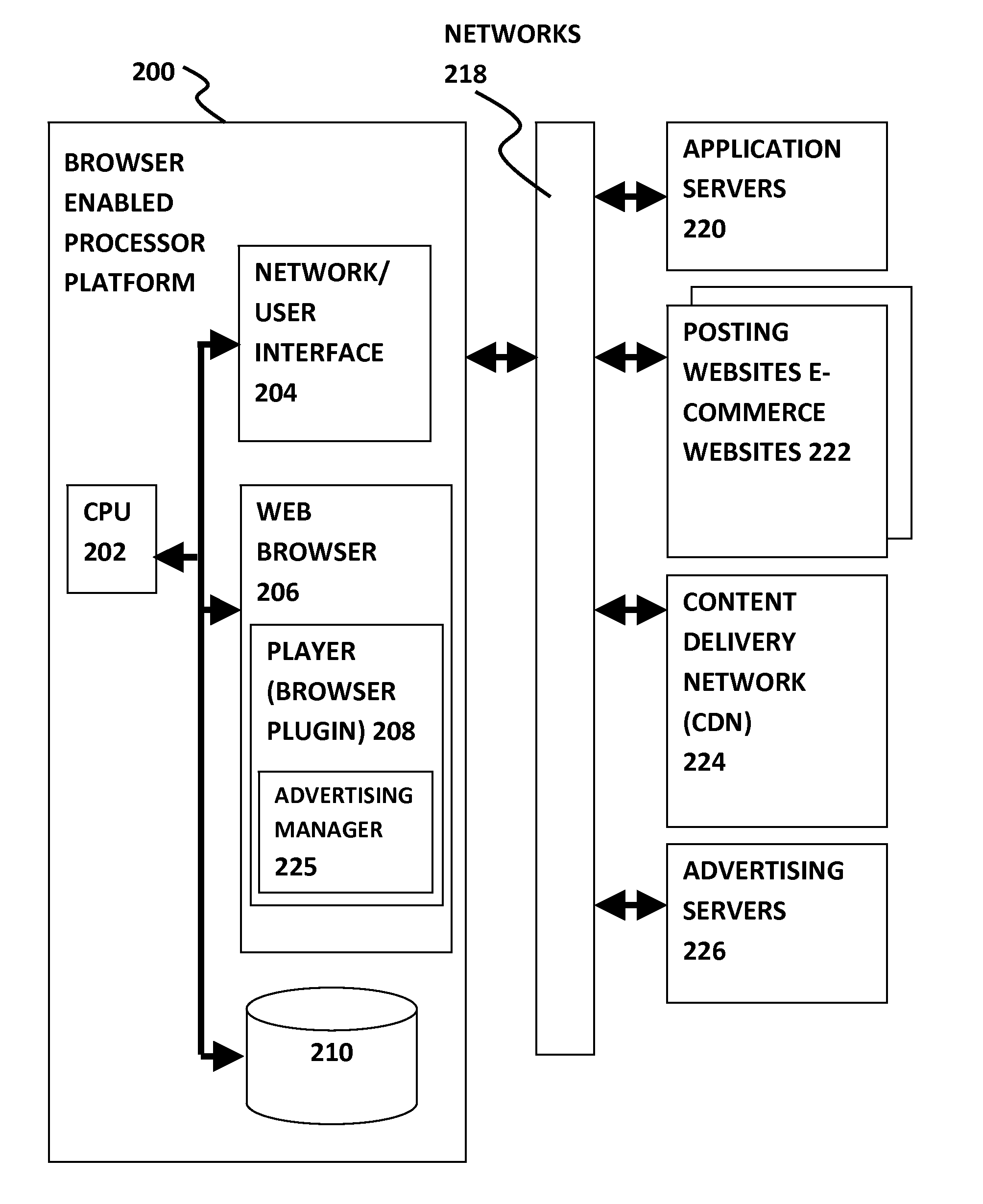

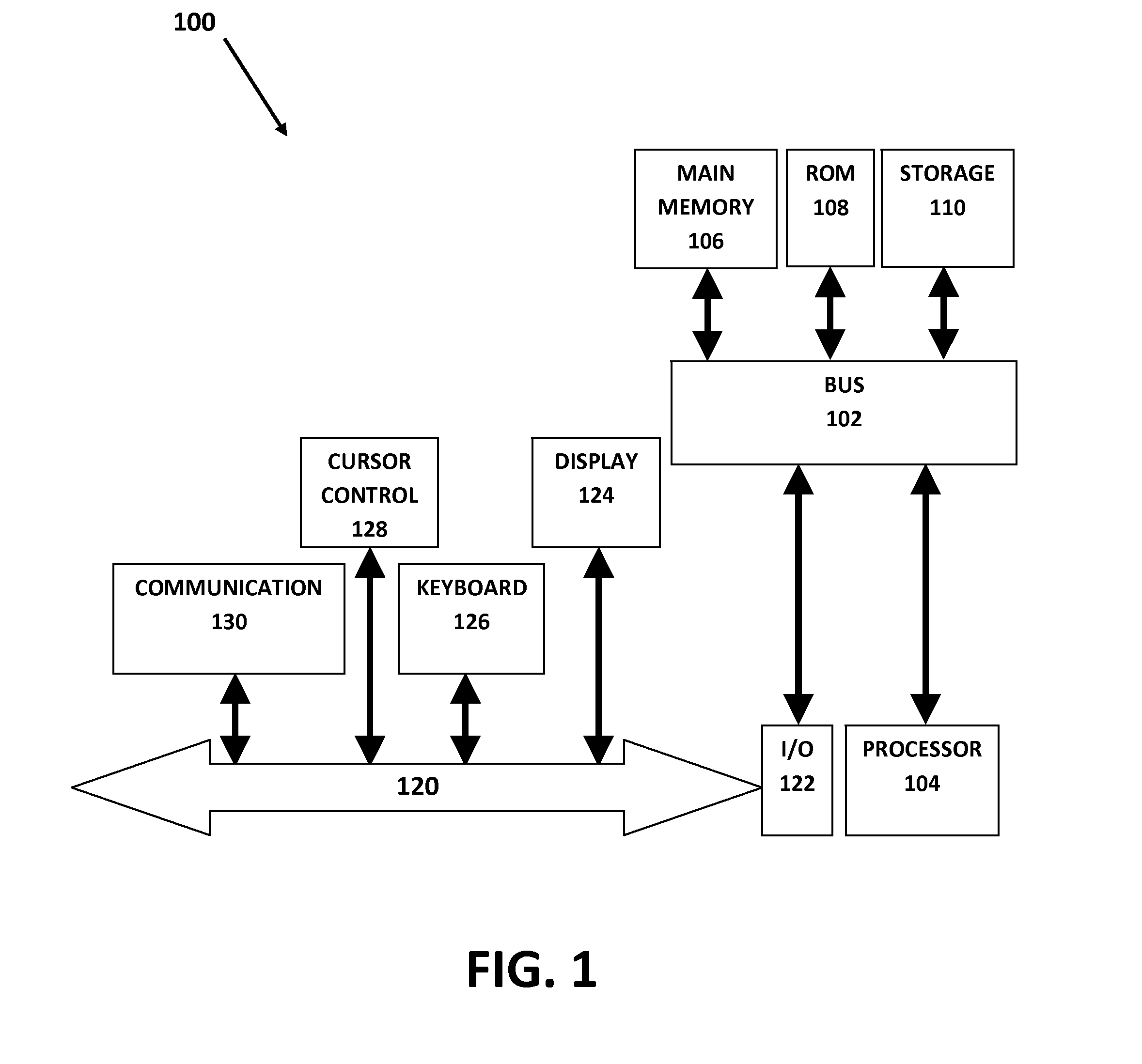

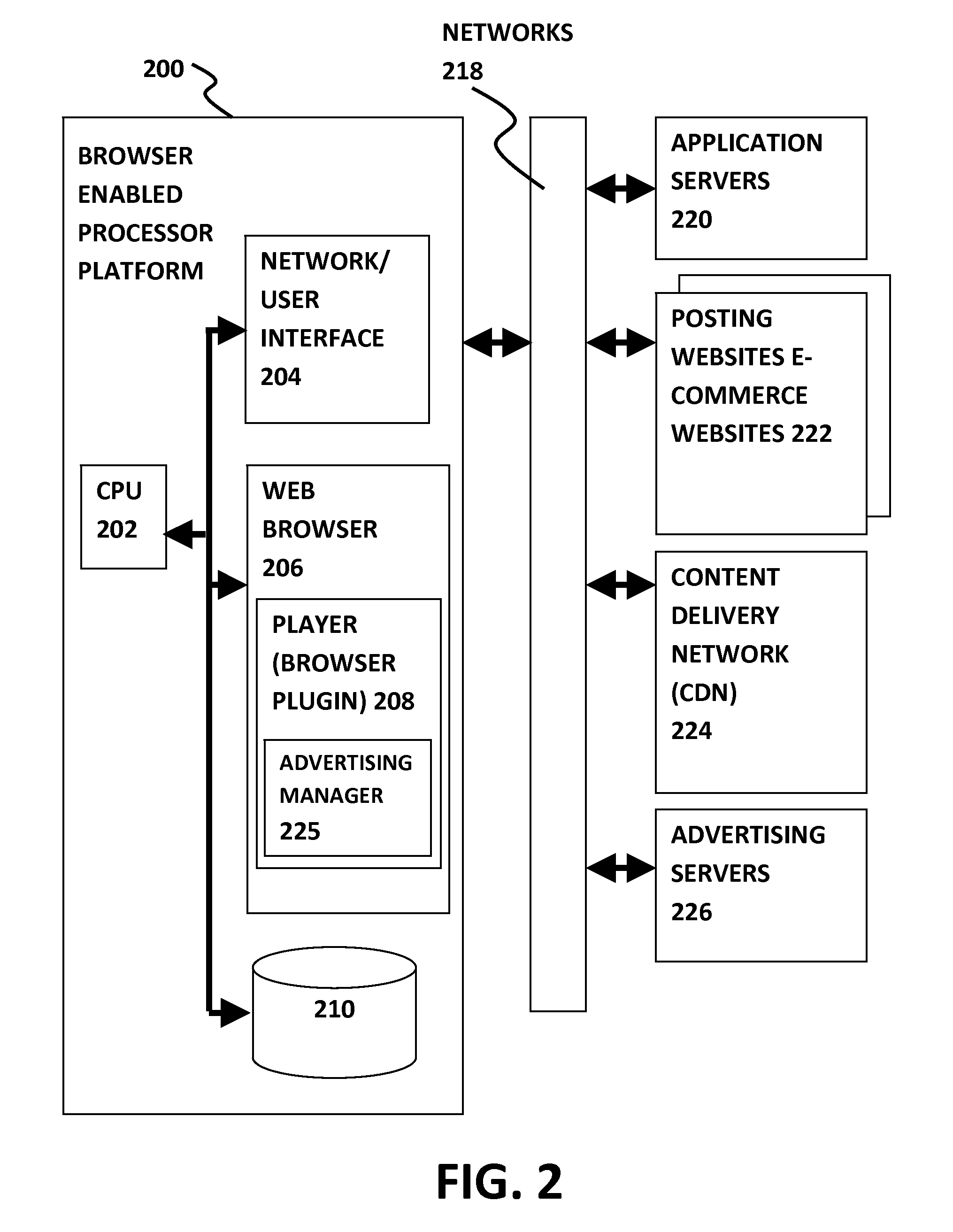

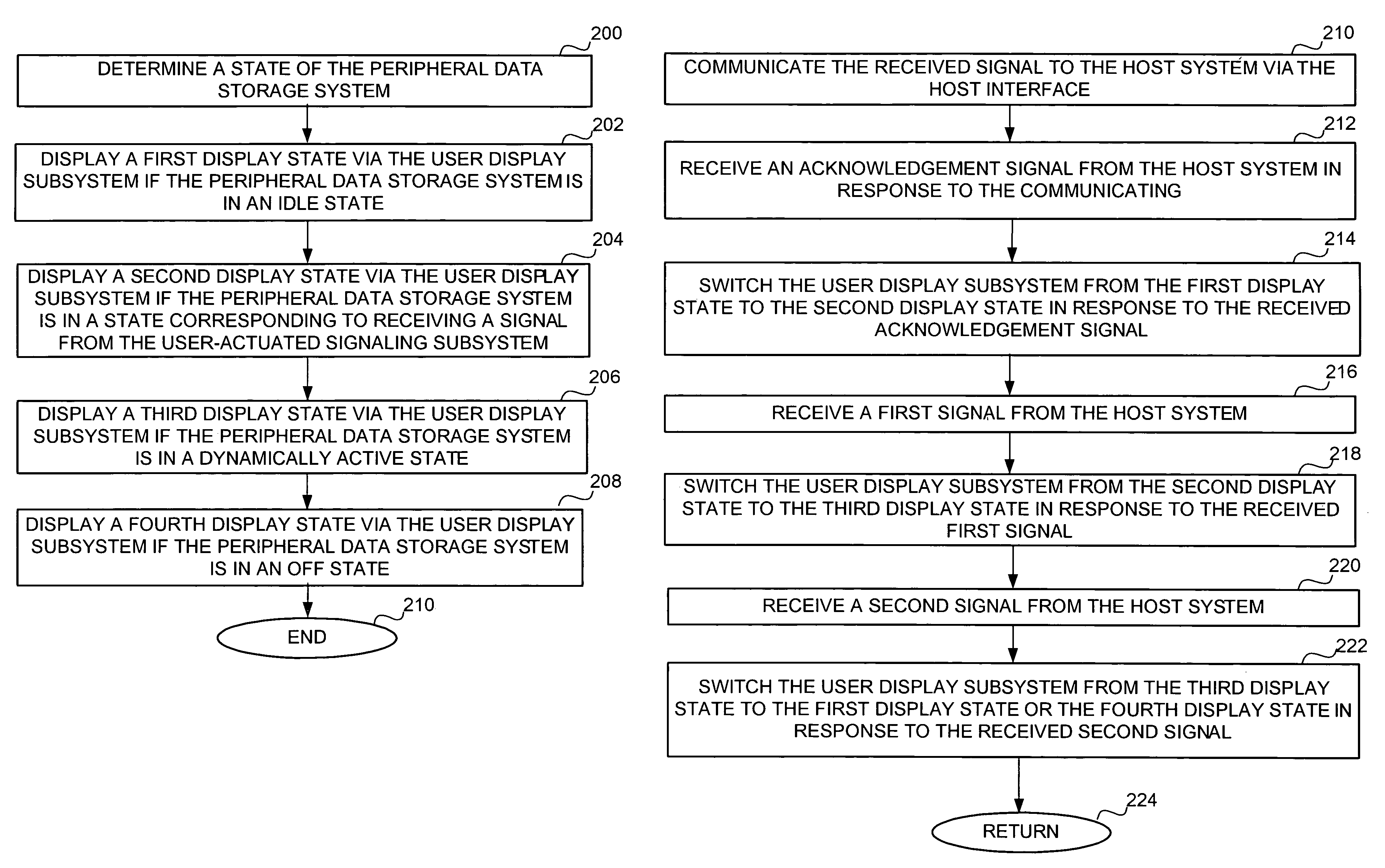

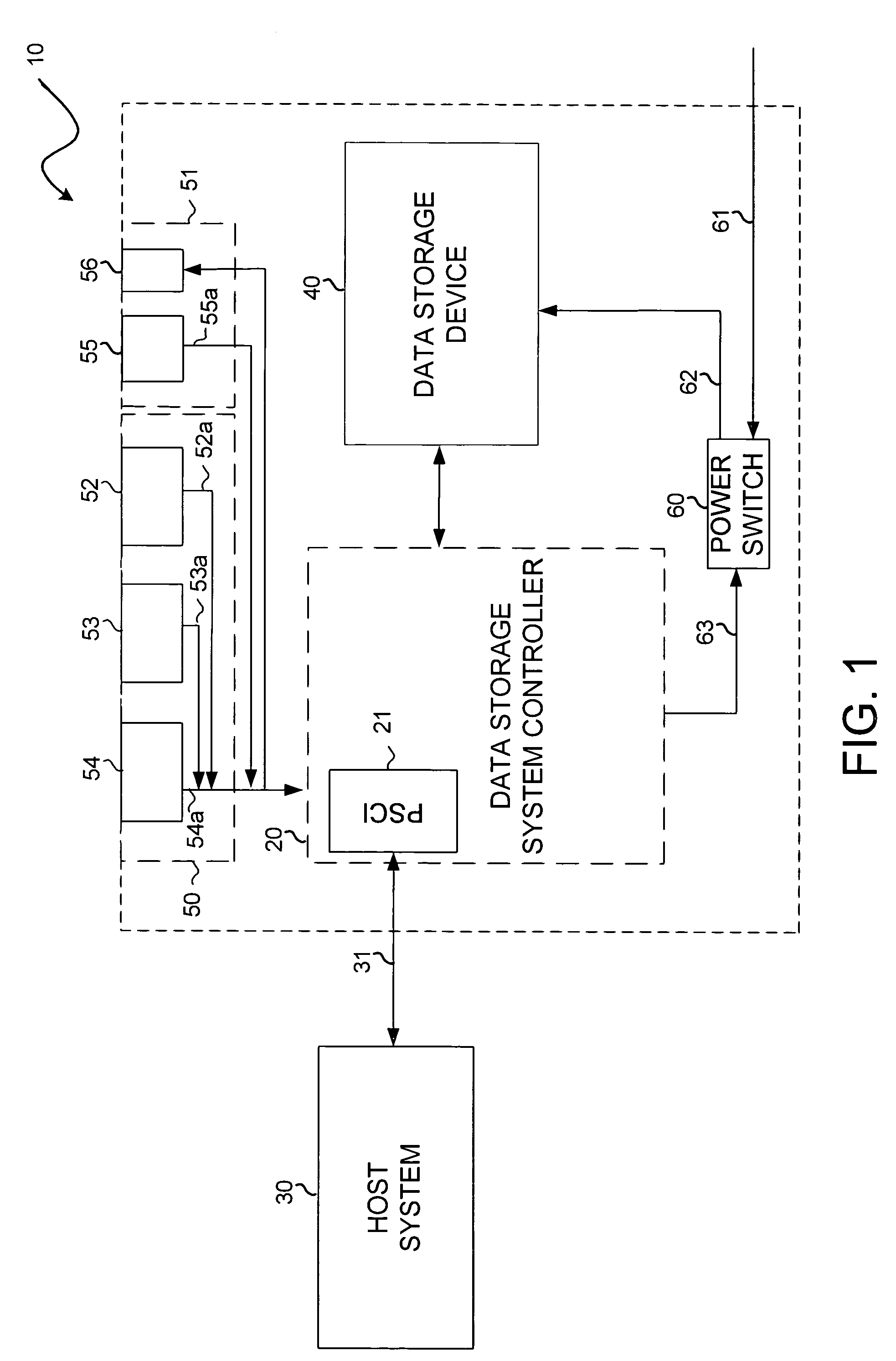

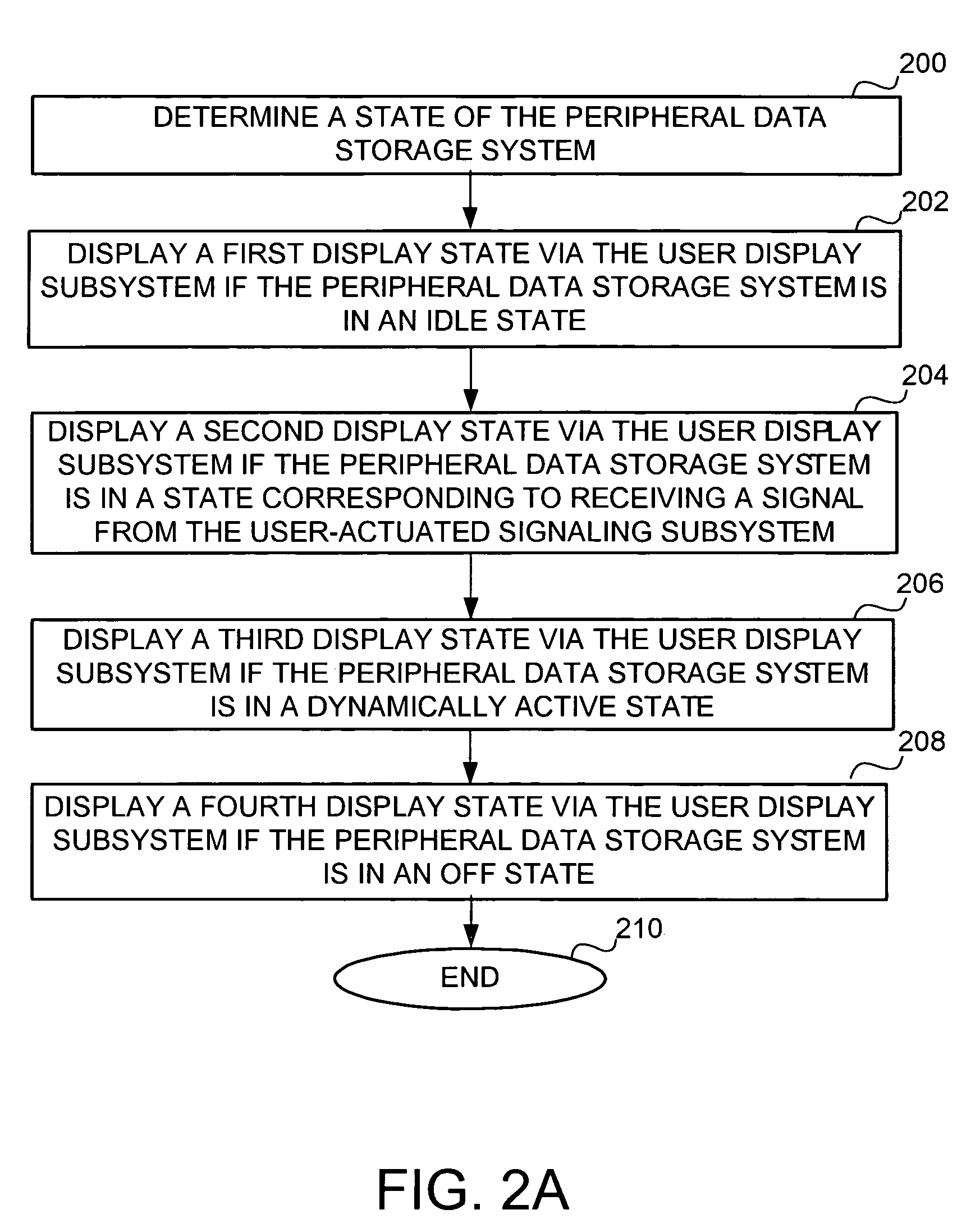

Peripheral data storage system with multi-state user display

InactiveUS7302501B1Error detection/correctionInput/output processes for data processingComputer hardwareActive state

A method of displaying states of a peripheral data storage system (PDSS) comprising a data storage device, a data storage system controller, a user-actuated signaling subsystem, a user display subsystem adapted to display the states, and a peripheral data storage controller host interface adapted for communication with a host system. The method includes determining a state of the PDSS; displaying a first display state via the user display subsystem if the PDSS is in an idle state; displaying a second display state via the user display subsystem if the PDSS is in a state corresponding to receiving a signal from the user-actuated signaling subsystem; displaying a third display state via the user display subsystem if the PDSS is in a dynamically active state; and displaying a fourth display state via the user display subsystem if the PDSS is in an off state.

Owner:WESTERN DIGITAL TECH INC

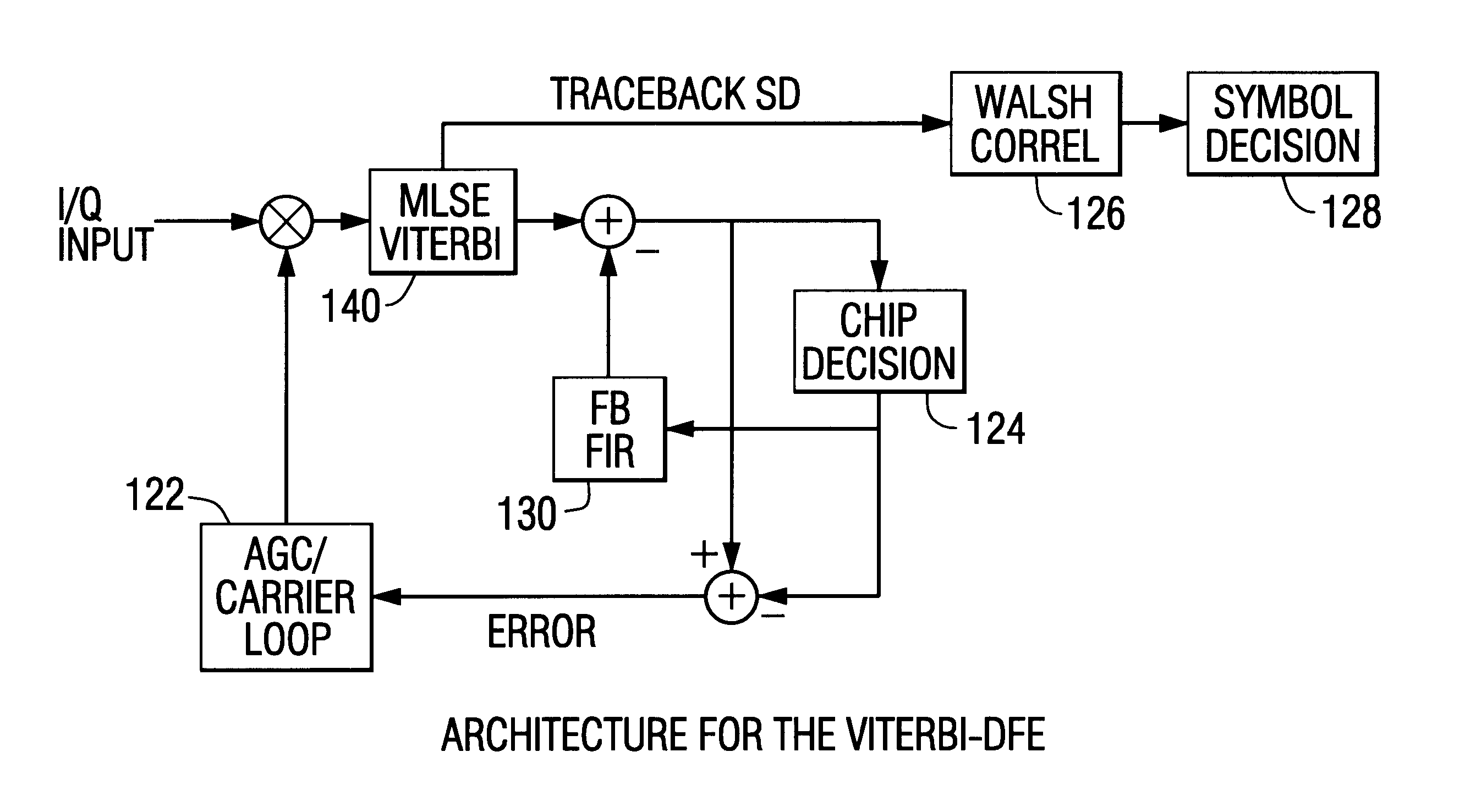

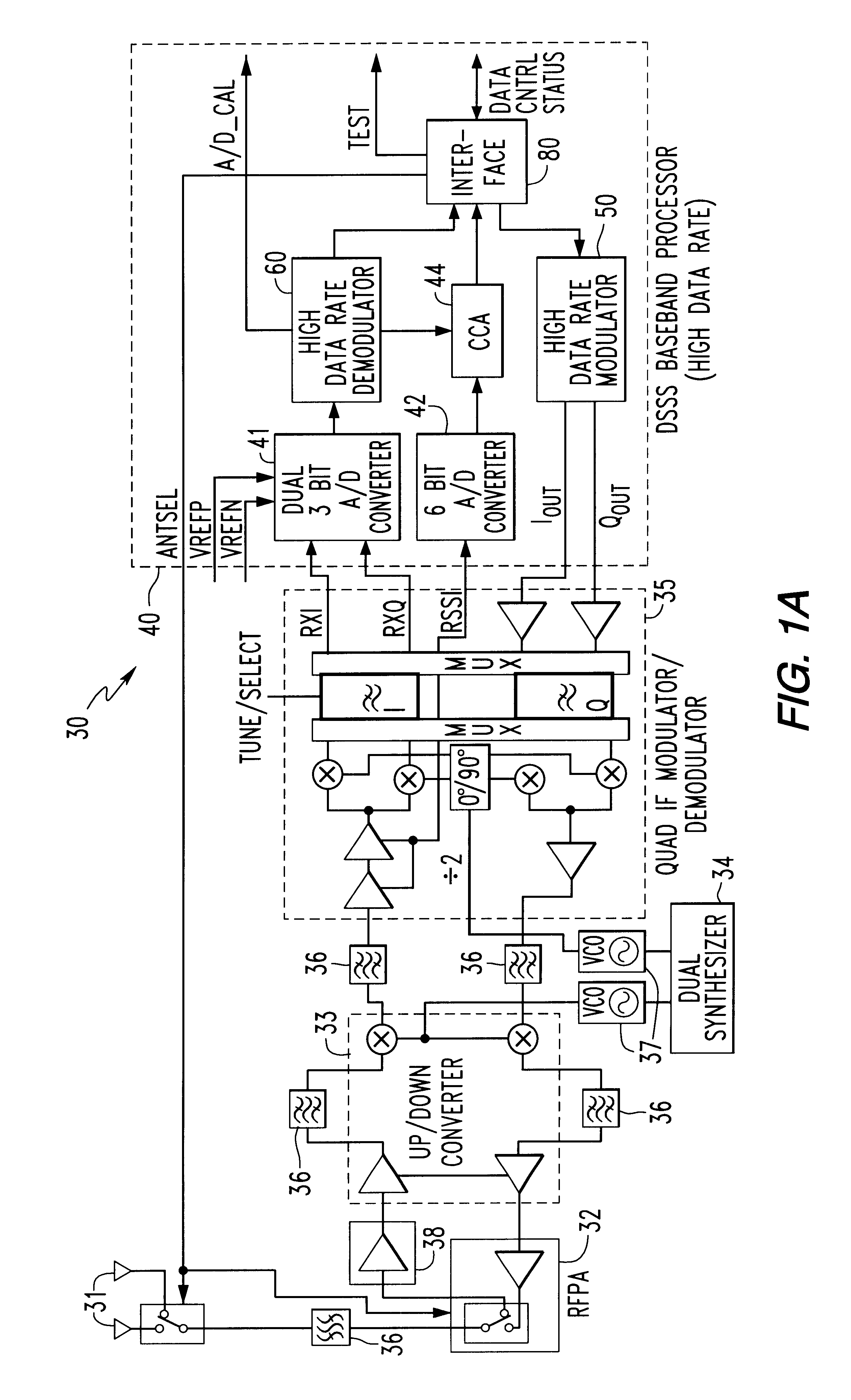

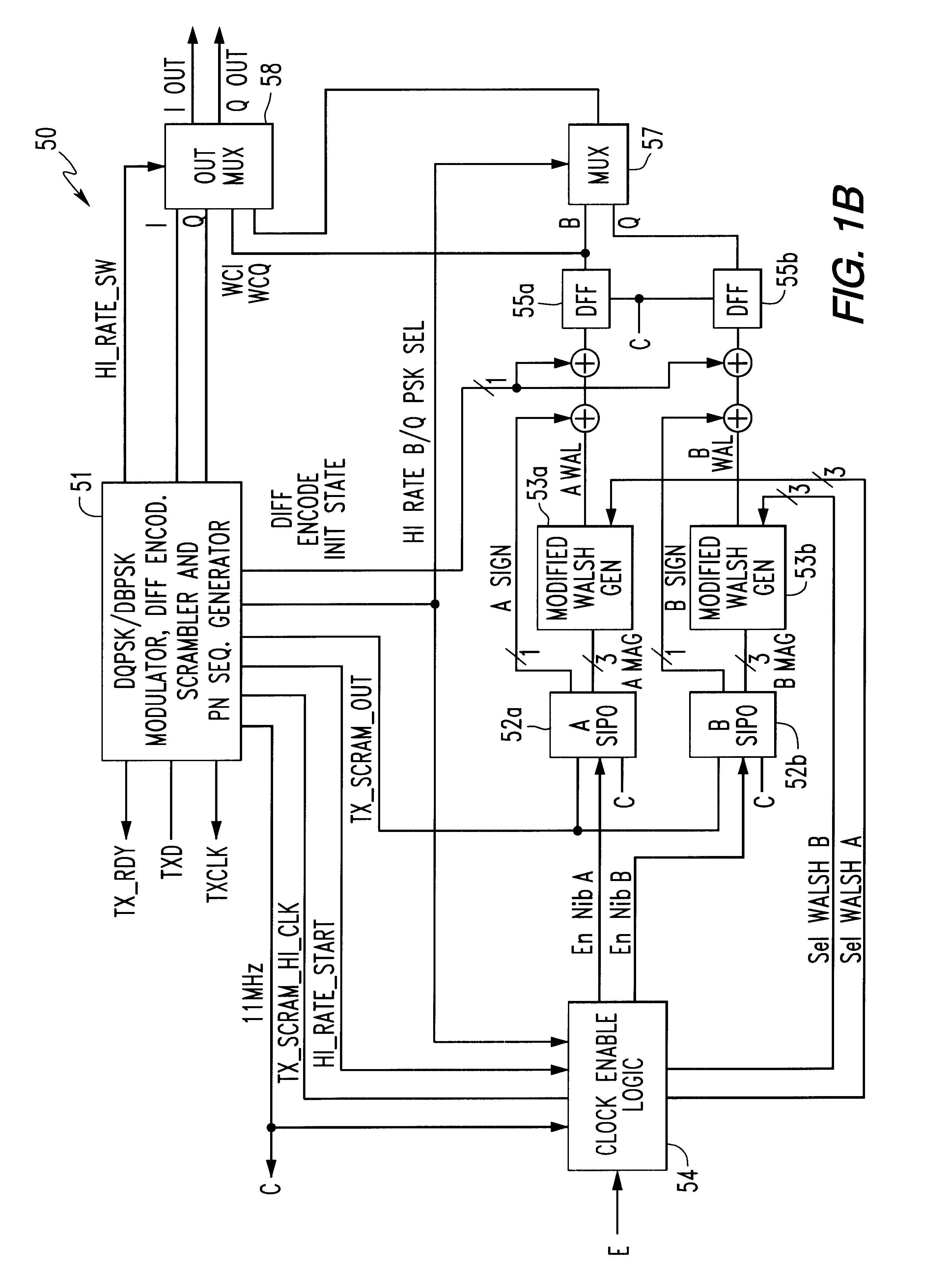

Spread spectrum transceiver for use in wireless local area network and having multipath mitigation

InactiveUS6603801B1Good diversity selection metricGood energySpatial transmit diversityNetwork topologiesFinite impulse responseTransceiver

A method and spread spectrum transceiver for demodulating a spread spectrum signal is disclosed. A spread spectrum phase shift keyed (PSK) modulated information signal is received within a demodulator of a spread spectrum receiver on a signal channel. The information signal includes a sequence of data symbols formed from a plurality of high rate mode chips. A precursor portion of the signal channel is Viterbi detected. A multi-state trellis is formed having a predetermined number of states. A post-cursor portion of the signal channel is feedback equalized with a finite impulse response filter having feedback taps operatively connected to a chip detection circuit that tracks high rate mode chips and a carrier loop circuit for phase and frequency tracking. The information signal is despread within a spread spectrum code function correlator.

Owner:INTELLECTUAL VENTURES I LLC +1

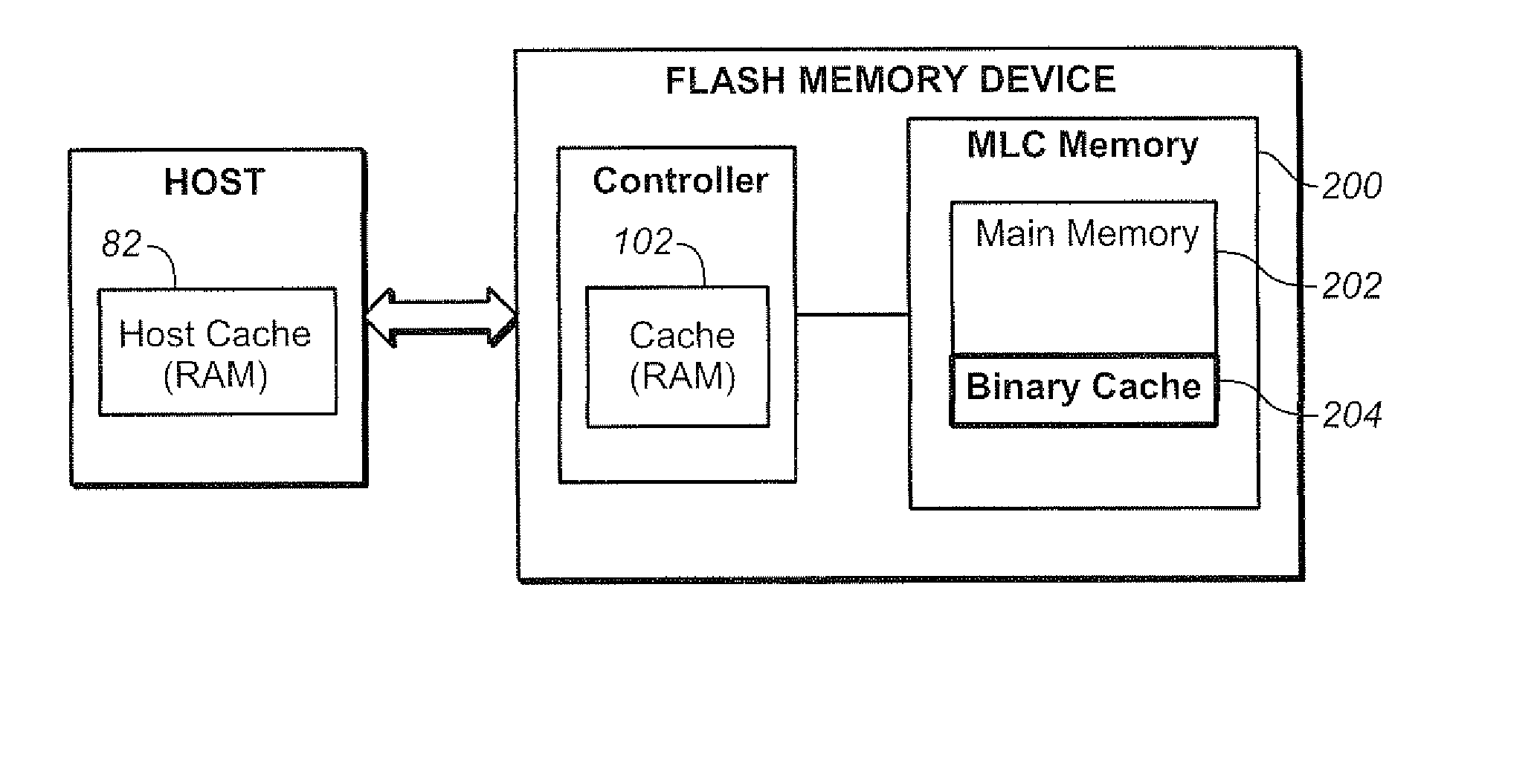

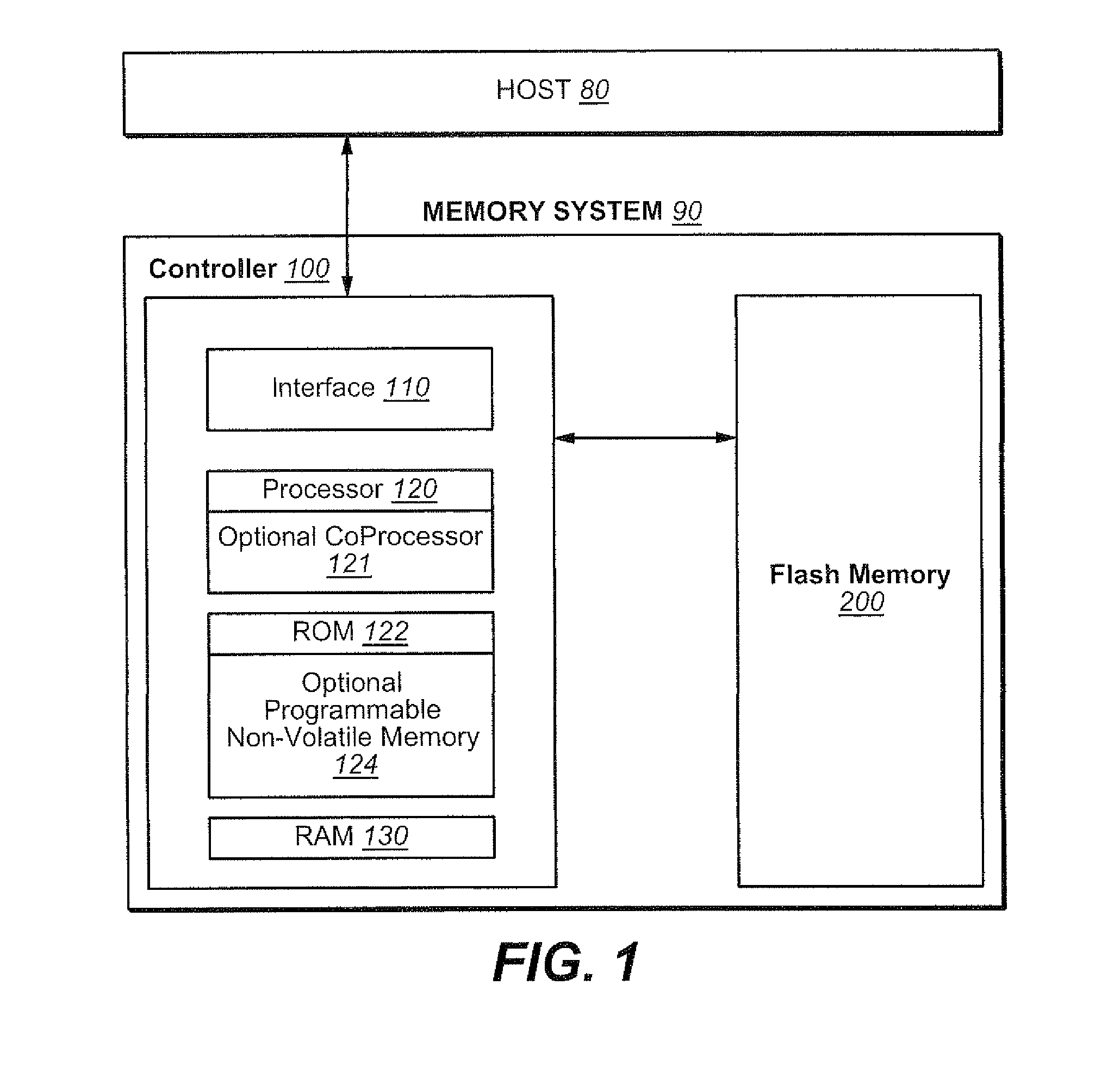

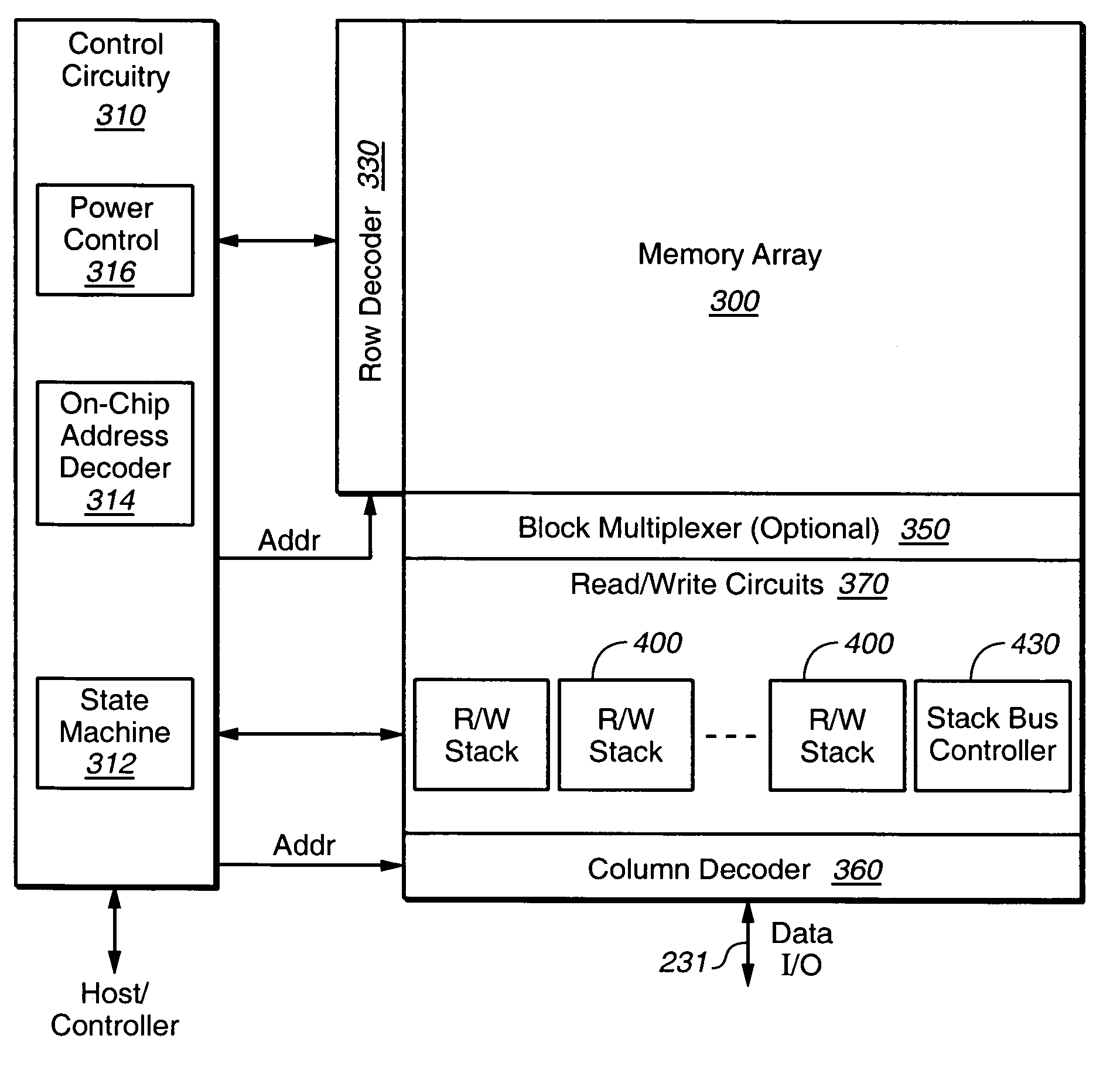

Data transfer flows for on-chip folding

ActiveUS8144512B2Memory architecture accessing/allocationRead-only memoriesProcessor registerParallel computing

A memory system and methods of its operation are presented. The memory system includes a volatile buffer memory and a non-volatile memory circuit, where the non-volatile memory circuit has a first section, where data is stored in a binary format, and a second section, where data is stored in a multi-state format. When writing data to the non-volatile memory, the data is received from a host, stored in the buffer memory, transferred from the buffer memory to into read / write registers of the non-volatile memory circuit, and then written from the read / write registers to the first section of the non-volatile memory circuit using a binary write operation. Portions of the data and then subsequently folded from the first section of the non-volatile memory to the second section of the non-volatile memory, where a folding operation includes reading the portions of the data from multiple locations in the first section into the read / write registers and performing a multi-state programming operation of the portions of the data from the read / write registers into a location the second section of the non-volatile memory. The multi-state programming operations include a first phase and a second phase and one or more of the binary write operations are performed between the phases of the multi-state programming operations.

Owner:SANDISK TECH LLC

Multi-state memory having data recovery after program fail

ActiveUS7420847B2Reduce the amount requiredMaintain integrityRead-only memoriesDigital storageComputer scienceData recovery

A non-volatile memory device includes the ability to recover data in event of a program failure without having to maintain a copy of the data until the write is completed. As the integrity of the data can thus be maintained with having to save a copy, buffers can be freed up for other data or even eliminated, reducing the amount of controller space that needs to devoted data buffering. In exemplary embodiments, the data is recovered by logically combining the verify data for the (failed) write process maintained in data latches with the results of one or more read operations to reconstitute the data. The exemplary embodiments are for memory cells storing multi-state data, both in the format of independent upper page, lower page form, as well as in 2-bit form. This can be accomplished by a state machine and data latches in the sense amp area on the memory, without use of the controller.

Owner:SANDISK TECH LLC

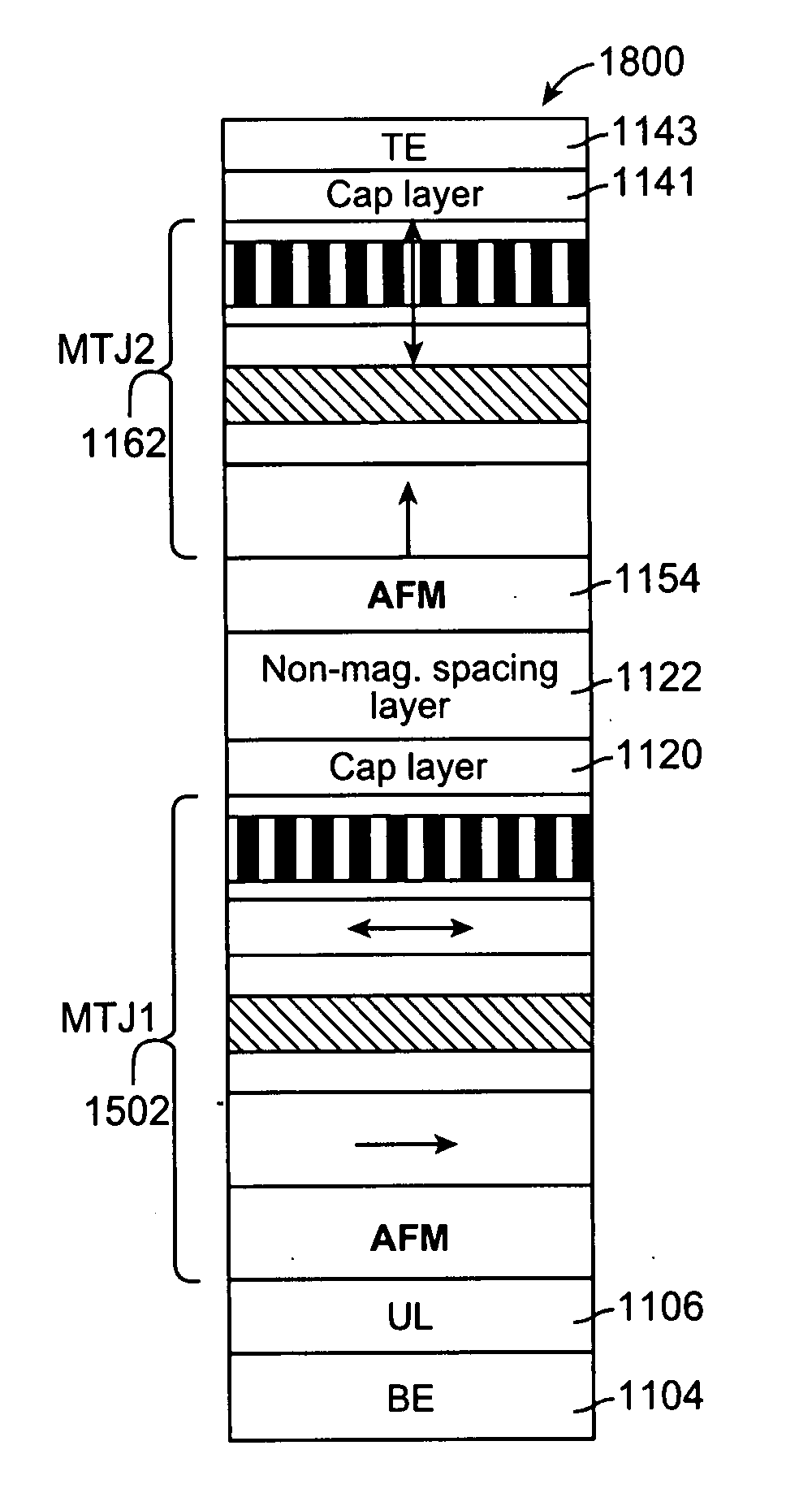

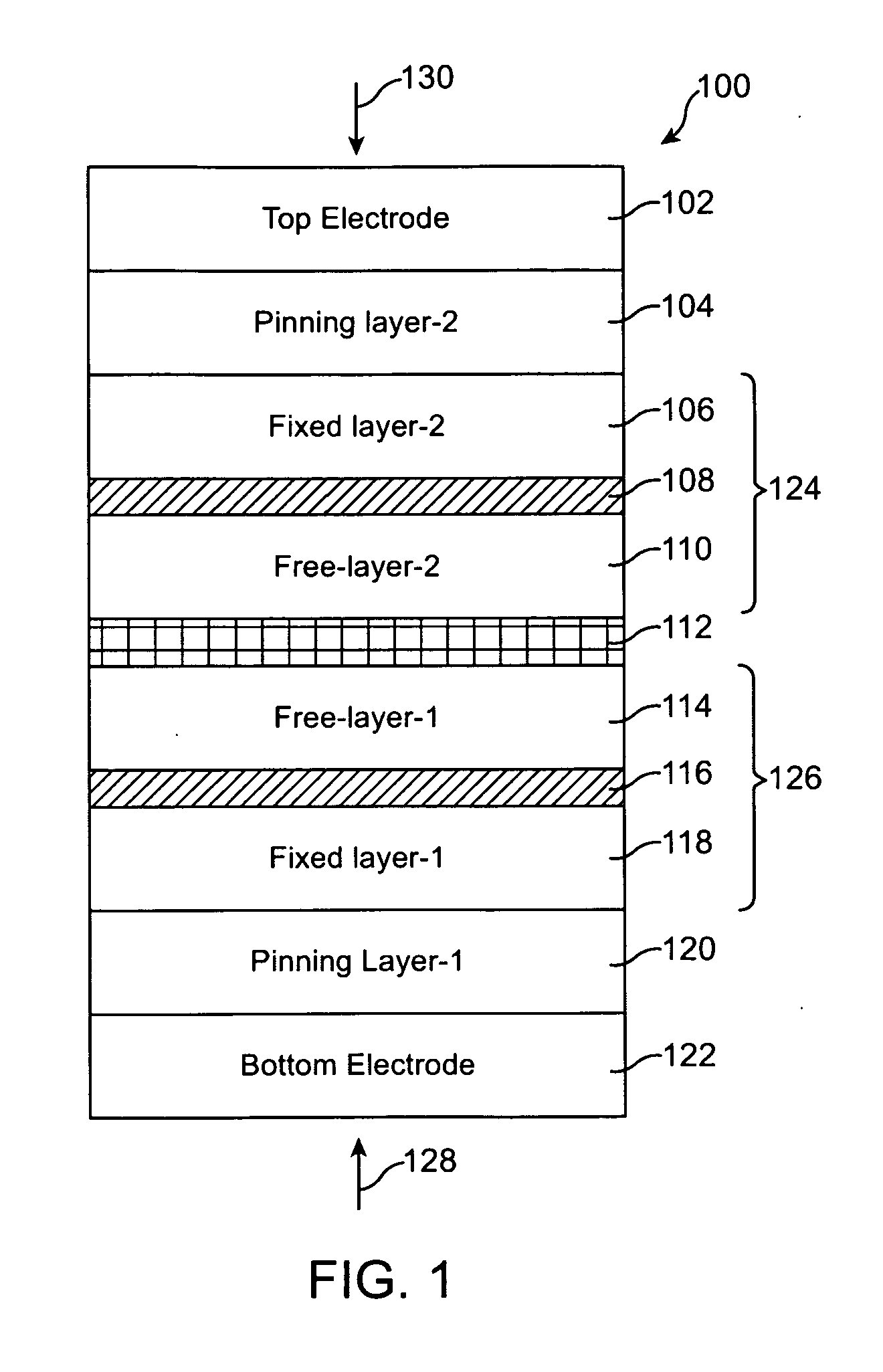

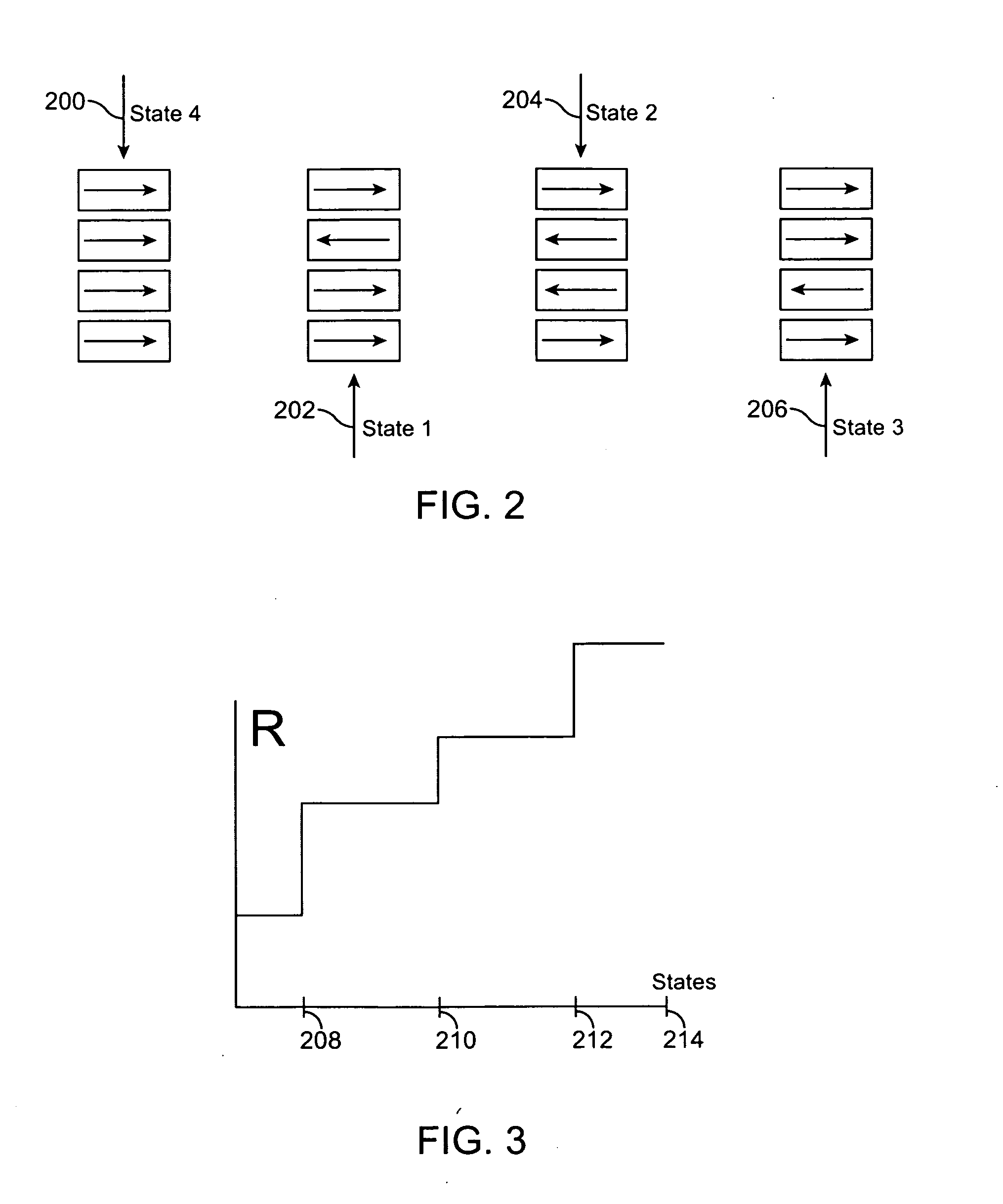

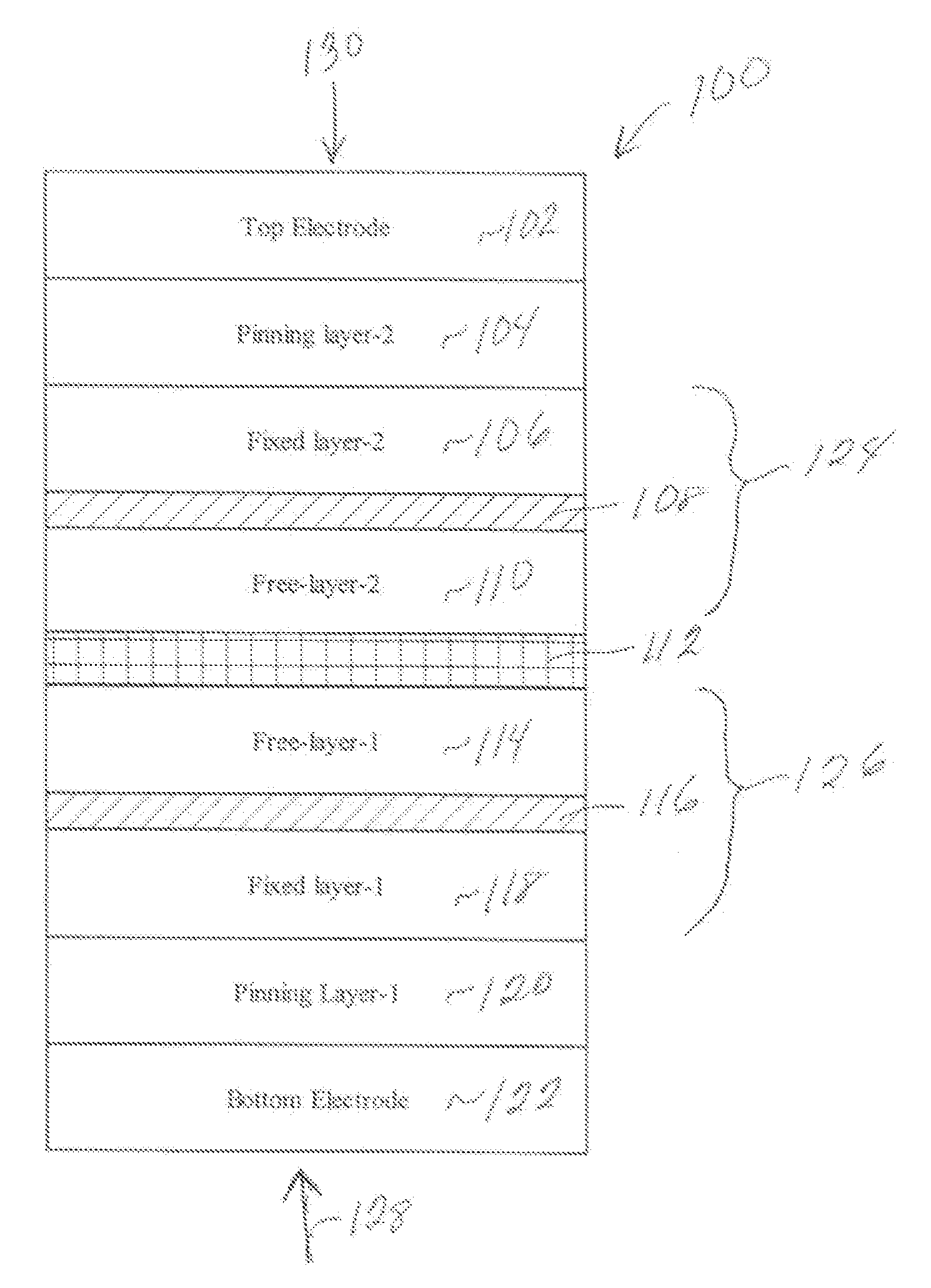

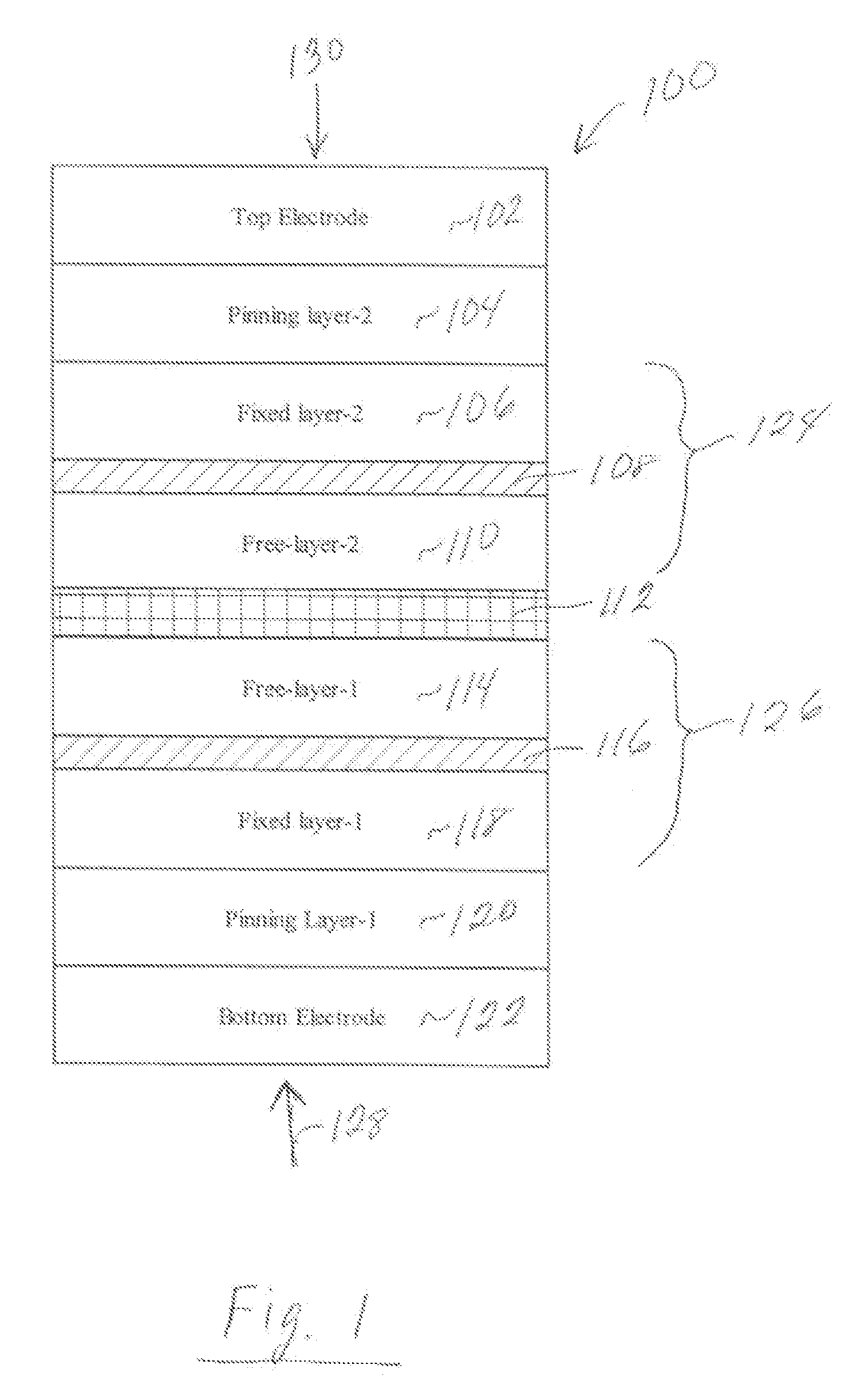

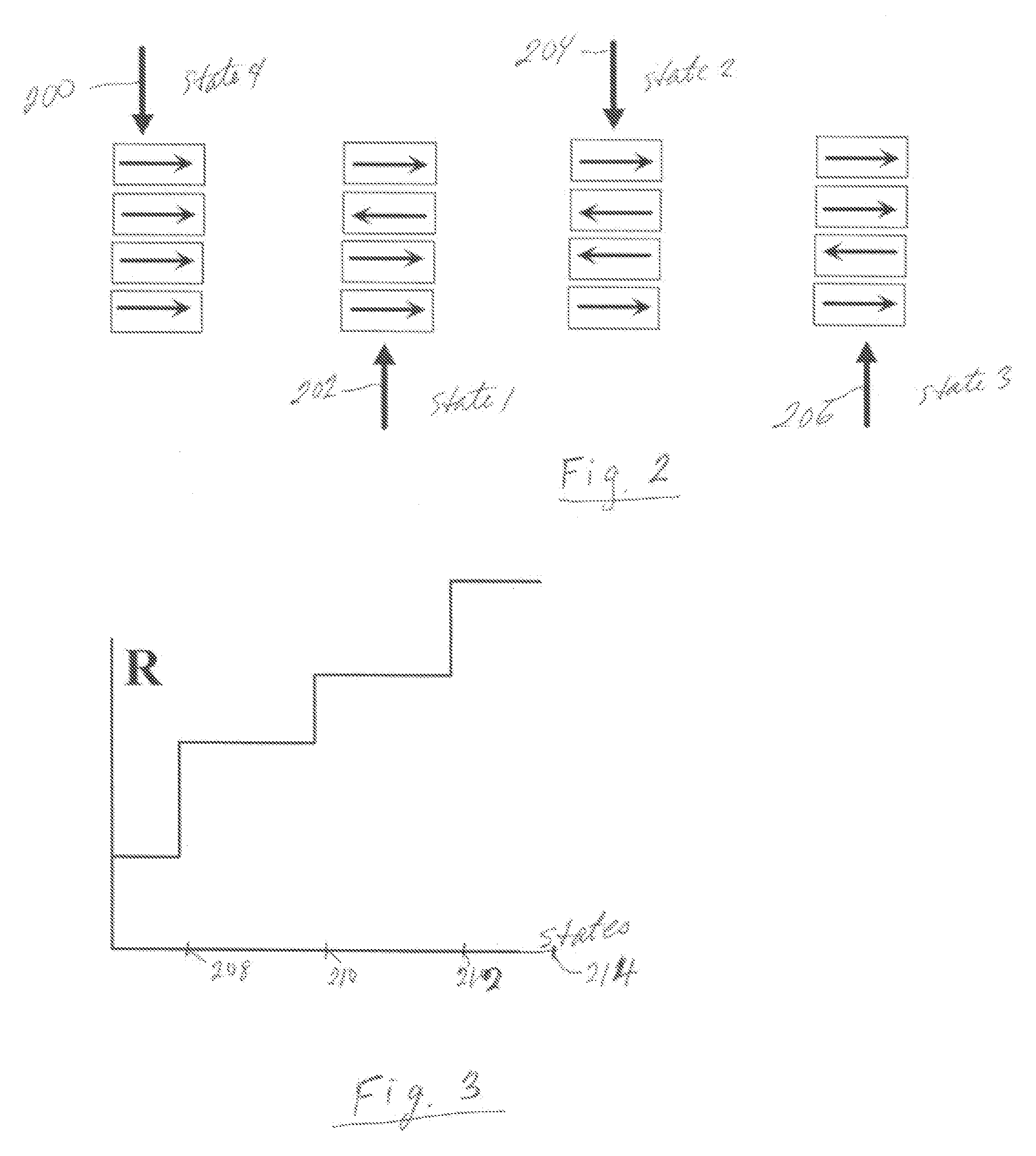

Multi-state spin-torque transfer magnetic random access memory

InactiveUS20090218645A1Reduced switching currentImprove thermal stabilityNanotechMagnetic-field-controlled resistorsMagnetic anisotropyRandom access memory

A multi-state spin-torque transfer magnetic random access memory (STTMRAM) is formed on a film and includes a first magnetic tunneling junctions (MTJ) having a first fixed layer, a first sub-magnetic tunnel junction (sub-MTJ) layer and a first free layer. The first fixed layer and first free layer each have a first magnetic anisotropy. The STTMRAM further includes a non-magnetic spacing layer formed on top of the first MTJ layer and a second MTJ formed on top of the non-magnetic spacing layer. The second MTJ has a second fixed layer, a second sub-MTJ layer and a second free layer. The second fixed and second free layers each have a second magnetic anisotropy, wherein at least one of the first or second magnetic anisotropy is perpendicular to the plane of the film.

Owner:AVALANCHE TECH

Multi-purpose non-volatile memory card

A flash non-volatile memory system that normally operates its memory cells in multiple storage states is provided with the ability to operate some selected or all of its memory cell blocks in two states instead. The two states are selected to be the furthest separated of the multiple states, thereby providing an increased margin during two state operation. This allows faster programming and a longer operational life of the memory cells being operated in two states when it is more desirable to have these advantages than the increased density of data storage that multi-state operation provides. An exemplary embodiment is as a memory card where the user can choice between two state and multi-state operation.

Owner:SANDISK TECH LLC

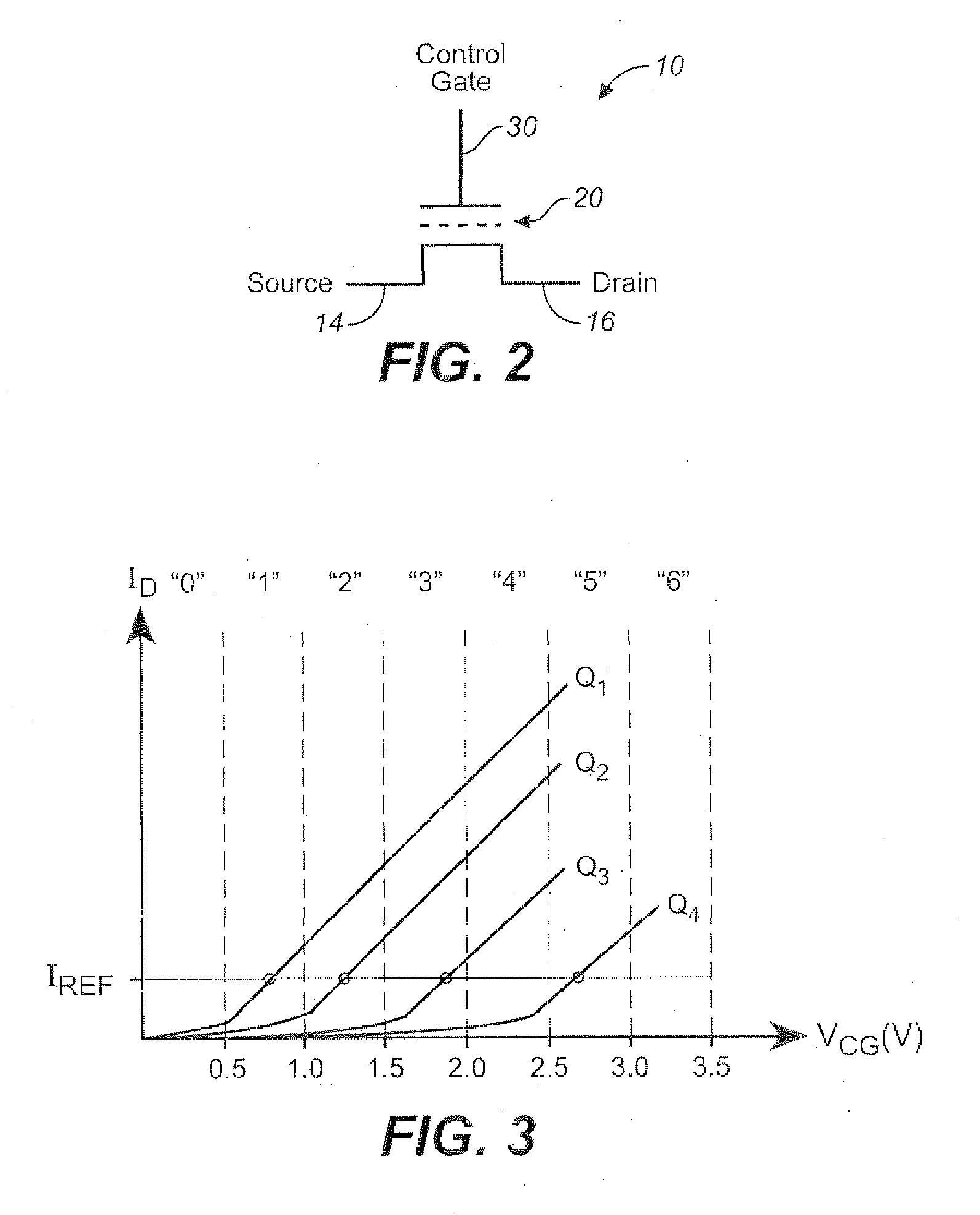

Writable tracking cells

ActiveUS20050169051A1Less uncertaintyReduce reference cell threshold uncertaintyElectric analogue storesRead-only memoriesComputer scienceThreshold voltage

The present invention presents several techniques for using writable tracking cells. Multiple tracking cells are provided for each write block of the memory. These cells are re-programmed each time the user cells of the associated write block are written, preferably at the same time, using the same fixed, global reference levels to set the tracking and user cell programmed thresholds. The threshold voltages of the tracking cells are read every time the user cells are read, and these thresholds are used to determine the stored logic levels of the user cells. In one set of embodiments, populations of one or more tracking cells are associated with different logic levels of a multi-state memory. These tracking cell populations may be provided for only a subset of the logic levels. The read points for translating the threshold voltages are derived for all of the logic levels based upon this subset. In one embodiment, two populations each consisting of multiple tracking cells are associated with two logic levels of the multi-bit cell. In an analog implementation, the user cells are read directly using the analog threshold values of the tracking cell populations without their first being translated to digital values. A set of alternate embodiments provide for using different voltages and / or timing for the writing of tracking cells to provide less uncertainty in the tracking cells' final written thresholds.

Owner:SANDISK TECH LLC

Writable tracking cells

InactiveUS7301807B2Less uncertaintyReduced referenceElectric analogue storesRead-only memoriesComputer scienceThreshold voltage

The present invention presents several techniques for using writable tracking cells. Multiple tracking cells are provided for each write block of the memory. These cells are re-programmed each time the user cells of the associated write block are written, preferably at the same time, using the same fixed, global reference levels to set the tracking and user cell programmed thresholds. The threshold voltages of the tracking cells are read every time the user cells are read, and these thresholds are used to determine the stored logic levels of the user cells. In one set of embodiments, populations of one or more tracking cells are associated with different logic levels of a multi-state memory. These tracking cell populations may be provided for only a subset of the logic levels. The read points for translating the threshold voltages are derived for all of the logic levels based upon this subset. In one embodiment, two populations each consisting of multiple tracking cells are associated with two logic levels of the multi-bit cell. In an analog implementation, the user cells are read directly using the analog threshold values of the tracking cell populations without their first being translated to digital values. A set of alternate embodiments provide for using different voltages and / or timing for the writing of tracking cells to provide less uncertainty in the tracking cells' final written thresholds.

Owner:SANDISK TECH LLC

Tool with end effector force limiter

ActiveUS20080255608A1Increase strainIncrease pressureDiagnosticsSurgical instrument detailsSurgical operationEngineering

The invention provides surgical or diagnostic tools and associated methods that offer improved user control for operating remotely within regions of the body. In some embodiments these tools include a proximally-located actuator for the operation of a distal end effector, as well as proximally-located actuators for articulational and rotational movements of the end effector. Control mechanisms and methods refine operator control of end effector actuation and of these articulational and rotational movements. A force limiter mechanism protects the end effector and manipulated objects from the harm of potentially excessive force applied by the operator. The tool may also include other features. A multi-state ratchet for end effector actuation provides enablement-disablement options with tactile feedback. An articulation lock allows the fixing and releasing of both neutral and articulated configurations of the tool and of consequent placement of the end effector. A rotation lock provides for enablement and disablement of rotatability of the end effector.

Owner:INTUITIVE SURGICAL OPERATIONS INC

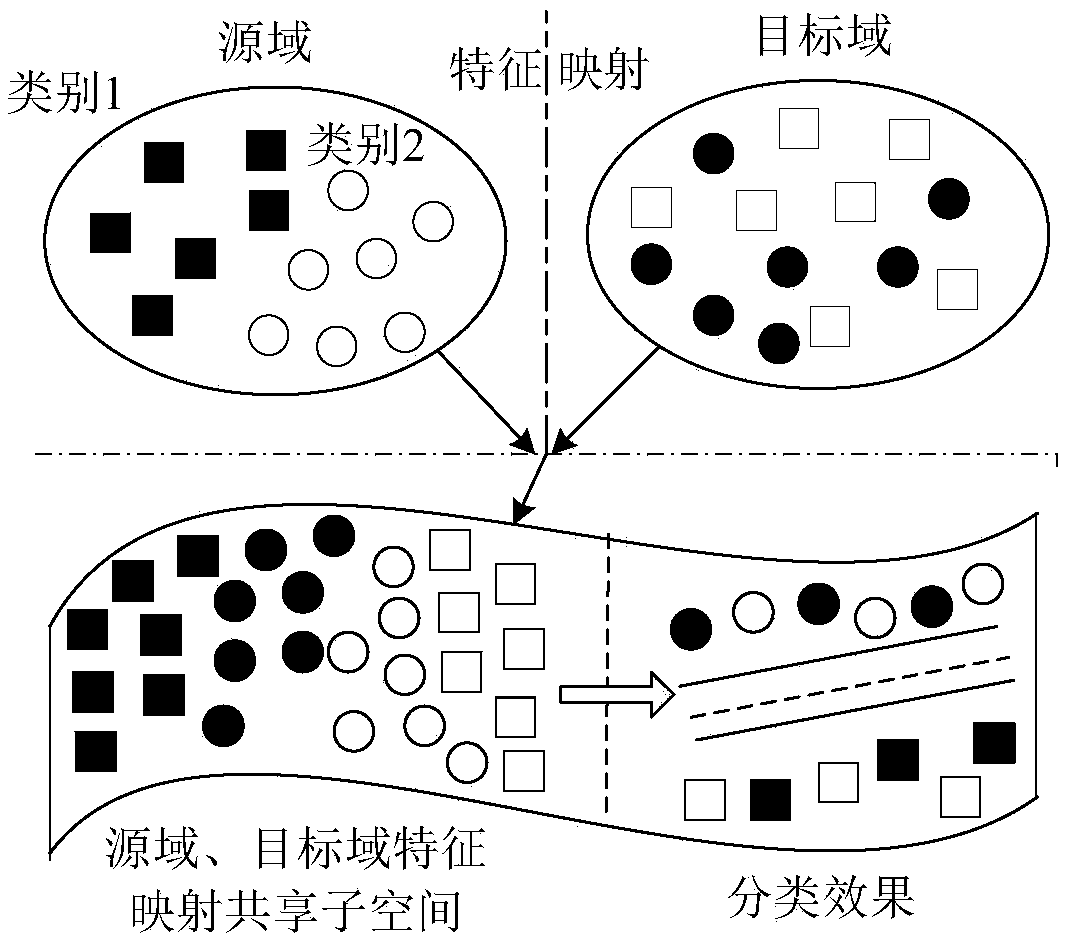

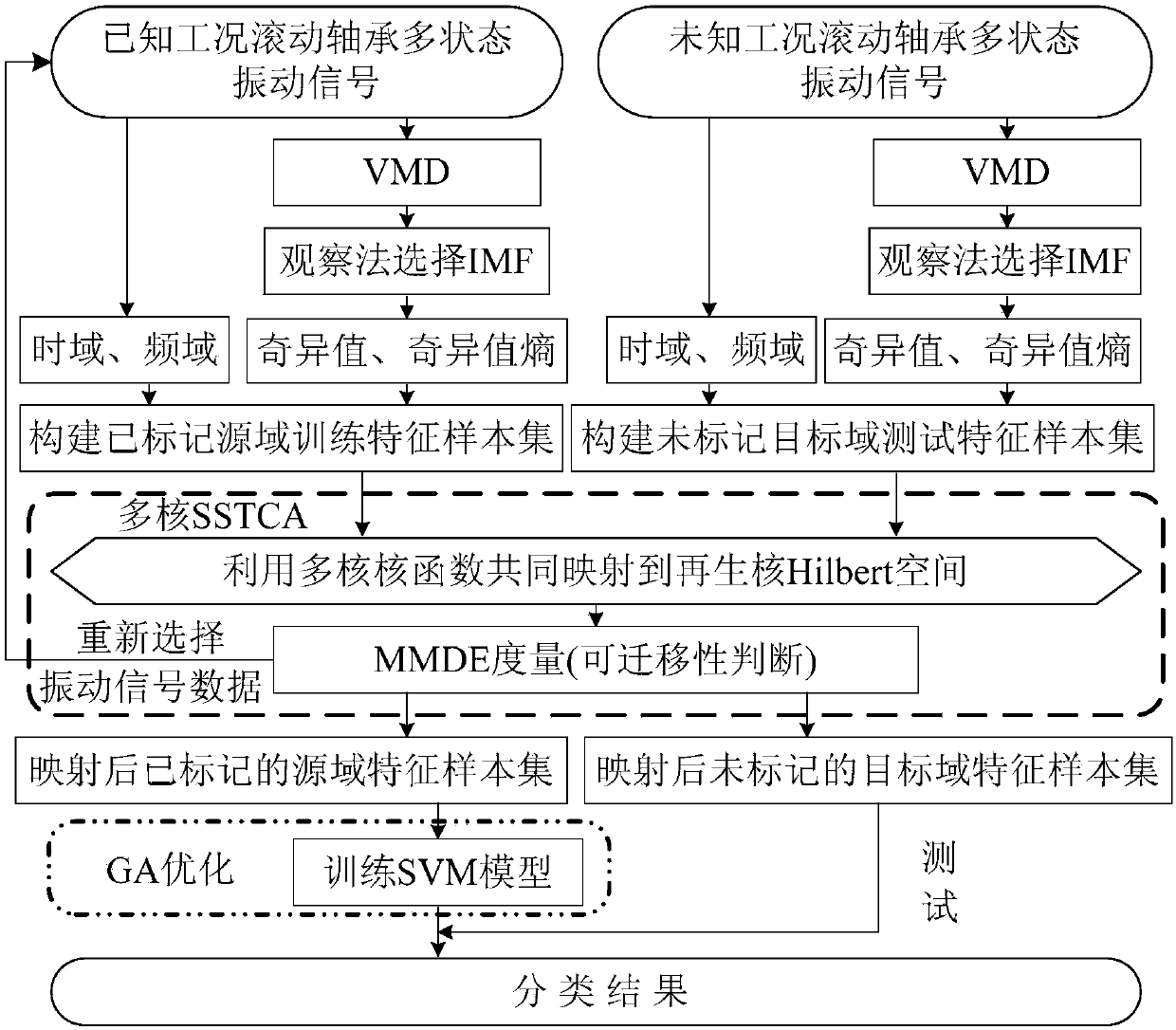

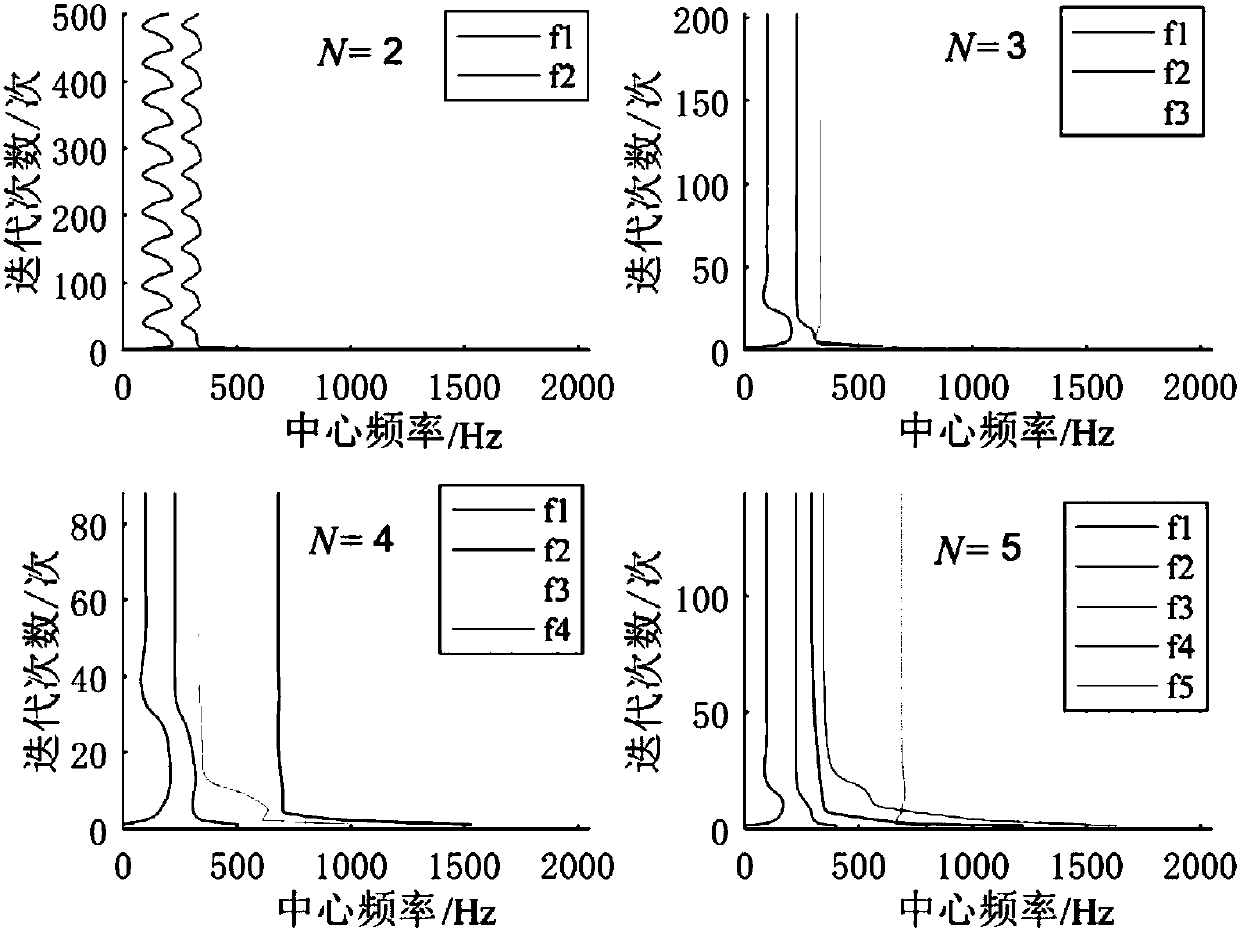

Rolling bearing fault diagnosis method in various working conditions based on feature transfer learning

ActiveCN108414226ABest mapped kernel matrixImprove accuracyMachine bearings testingSingular value decompositionDecomposition

The present invention provides a rolling bearing fault diagnosis method in various working conditions based on feature transfer learning, and relates to the field of fault diagnosis. The objective ofthe invention is to solve the problem that a rolling bearing, especially to various working conditions, is low in accuracy of diagnosis. The method comprise the steps of: employing a VMD (VariationalMode Decomposition) to perform decomposition of vibration signals of a rolling bearing in each state to obtain a series of intrinsic mode functions, performing singular value decomposition of a matrixformed by the intrinsic mode functions to solve a singular value or a singular value entropy, combining time domain features and frequency domain features of the vibration signals to construct a multi-feature set; introducing a semisupervised transfer component analysis method to perform multinuclear construction of a kernel function thereof, sample features of different working conditions are commonly mapped to a shared reproducing kernel Hilbert space so as to improve the data intra-class compactness and the inter-class differentiation; and employing the maximum mean discrepancy embedding to select more efficient data as a source domain, inputting source domain feature samples into a SVM (Support Vector Machine) for training, and testing target domain feature samples after mapping. Therolling bearing fault diagnosis method in various working conditions has higher accuracy in the rolling bearing multi-state classification in various working conditions.

Owner:HARBIN UNIV OF SCI & TECH

Maintaining Updates of Multi-Level Non-Volatile Memory in Binary Non-Volatile Memory

InactiveUS20110153912A1Memory adressing/allocation/relocationDigital storageData setData transmission

A method of operating a memory system is presented. The memory system includes a controller and a non-volatile memory circuit, where the non-volatile memory circuit has a first portion, where data is stored in a binary format, and a second portion, where data is stored in a multi-state format. The controller manages the transfer of data to and from the memory system and the storage of data on the non-volatile memory circuit. The method includes receiving a first set of data and storing this first set of data in a first location in the second portion of the non-volatile memory circuit. The memory system subsequently receives updated data for a first subset of the first data set. The updated data is stored in a second location in the first portion of the non-volatile memory circuit, where the controller maintains a logical correspondence between the second location and the first subset of the first set of data.

Owner:SANDISK TECH LLC

High capacity low cost multi-state magnetic memory

One embodiment of the present invention includes a multi-state current-switching magnetic memory element having a stack of magnetic tunneling junction (MTJ) separated by a non-magnetic layer for storing more than one bit of information, wherein different levels of current applied to the memory element cause switching to different states.

Owner:AVALANCHE TECH

Multiple-State One-Time Programmable (OTP) Memory to Function as Multi-Time Programmable (MTP) Memory

ActiveUS20120314473A1Small cell sizeLow costRead-only memoriesDigital storageOne time programmableComputer science

A circuit, method, and system for using multiple-state One-Time Programmable (OTP) memory to function as a multiple-bit programmable (MTP) memory are disclosed. The OTP memory can have N(N>2) distinct resistance states, that can be differentiated by at least N−1 reference resistances, can be functionally equivalent programmed N−1 times. The multiple-state OTP memory can have a plural of multiple-state OTP cells that can be selectively programmed to a resistance state. The reference resistance can be set to determine a state of the from the programmed multiple-state OTP cells.

Owner:ATTOPSEMI TECH CO LTD