Patents

Literature

114results about How to "Reduce the refresh rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor device

ActiveUS20110134683A1Easily multivaluedNovel structureTransistorSolid-state devicesPower semiconductor deviceDriver circuit

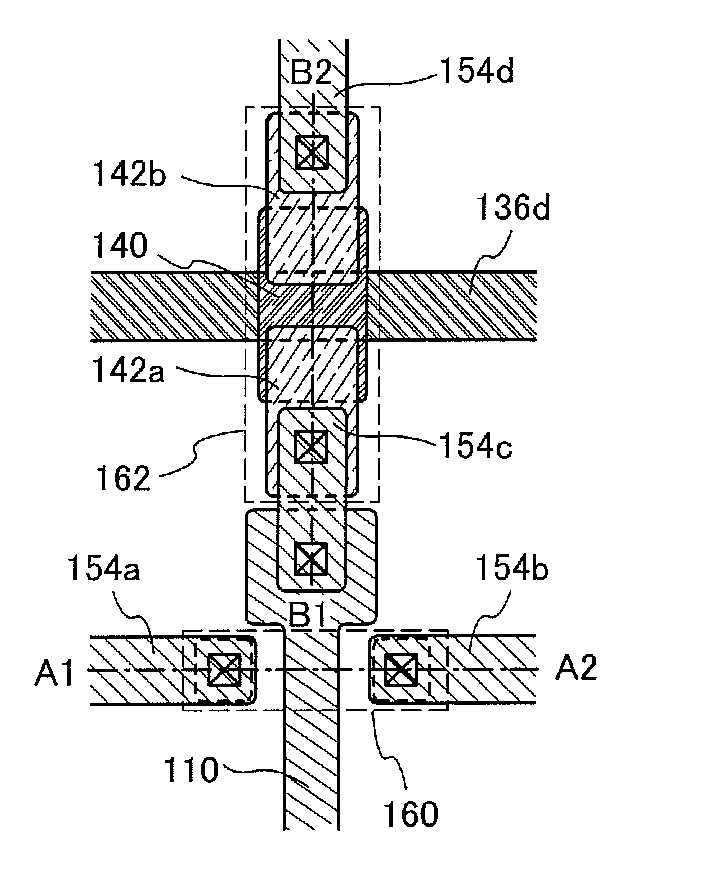

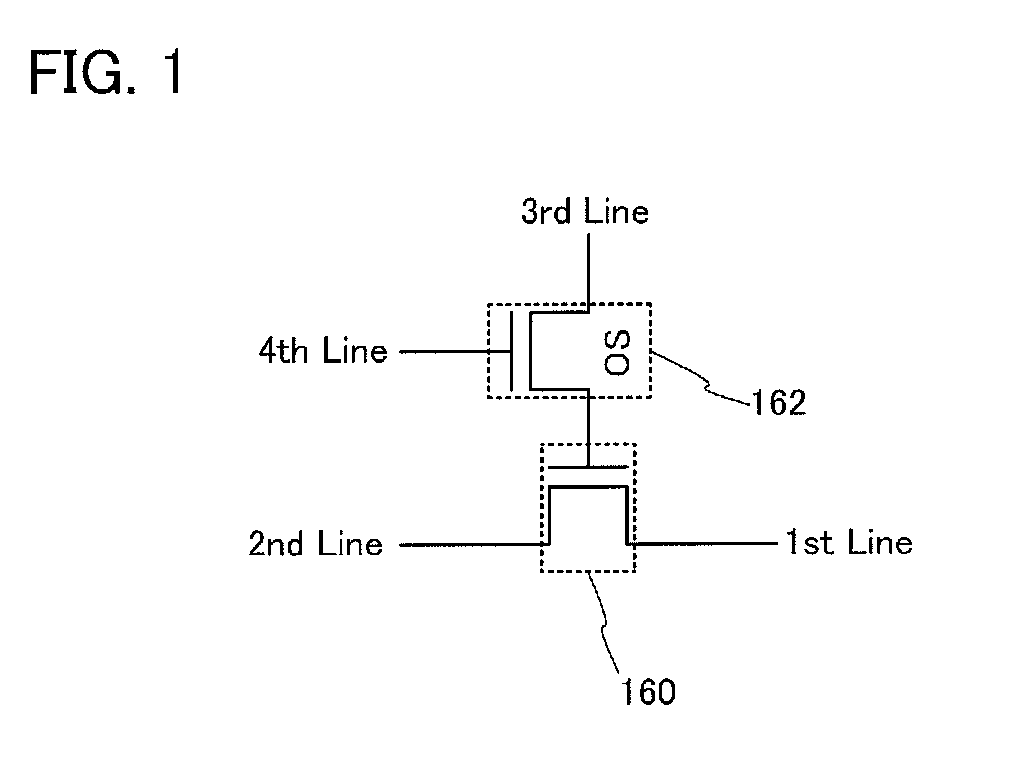

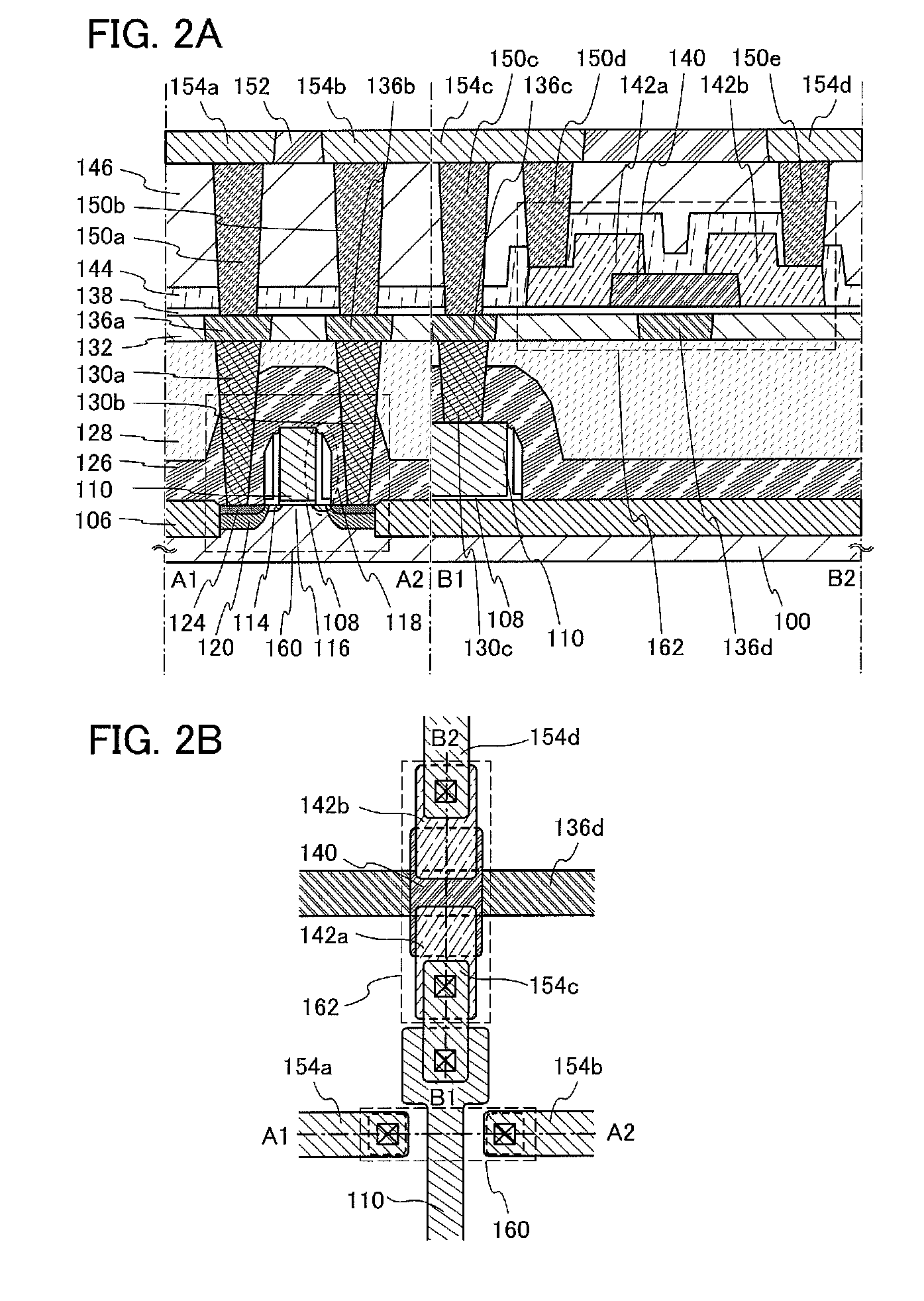

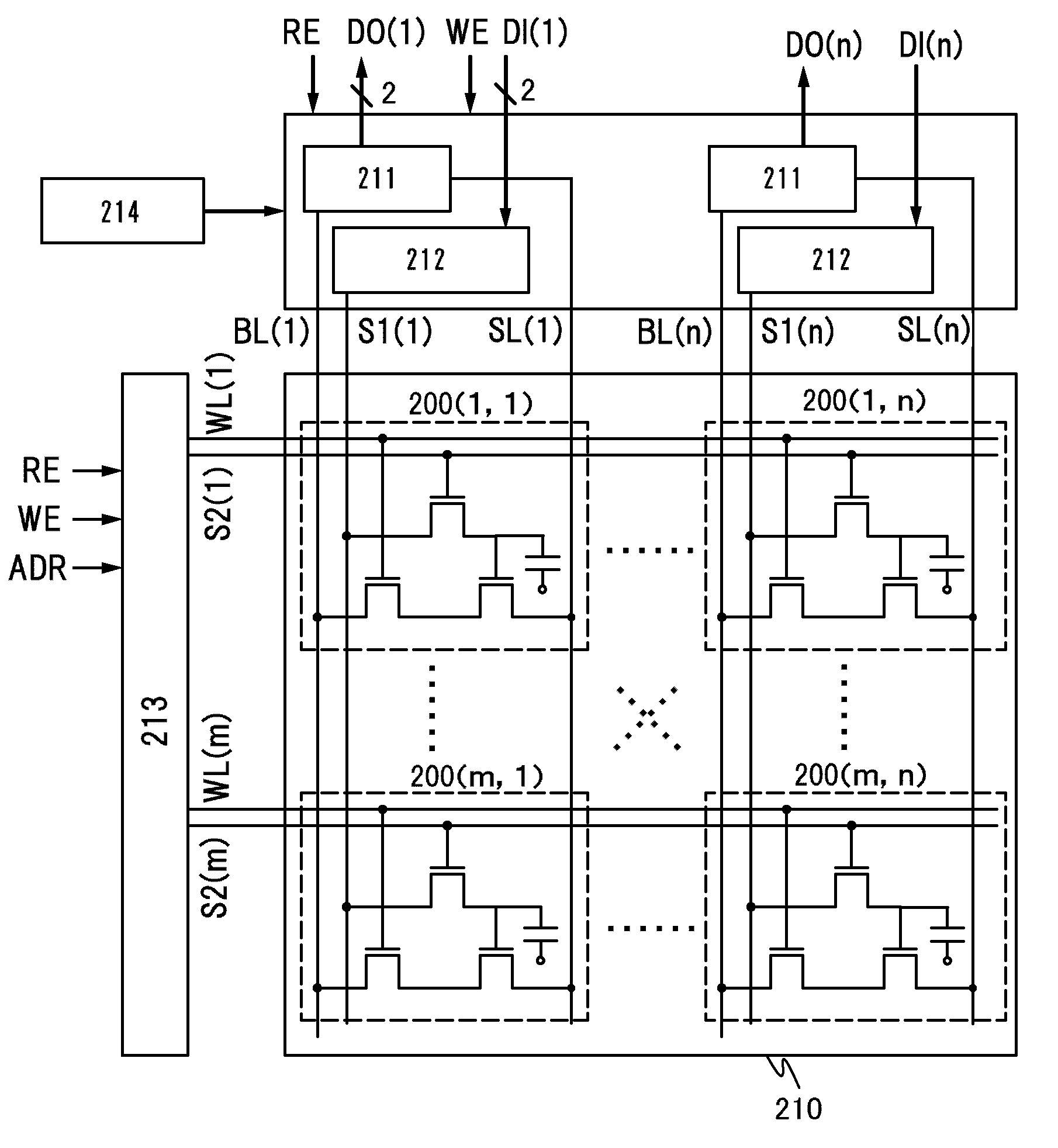

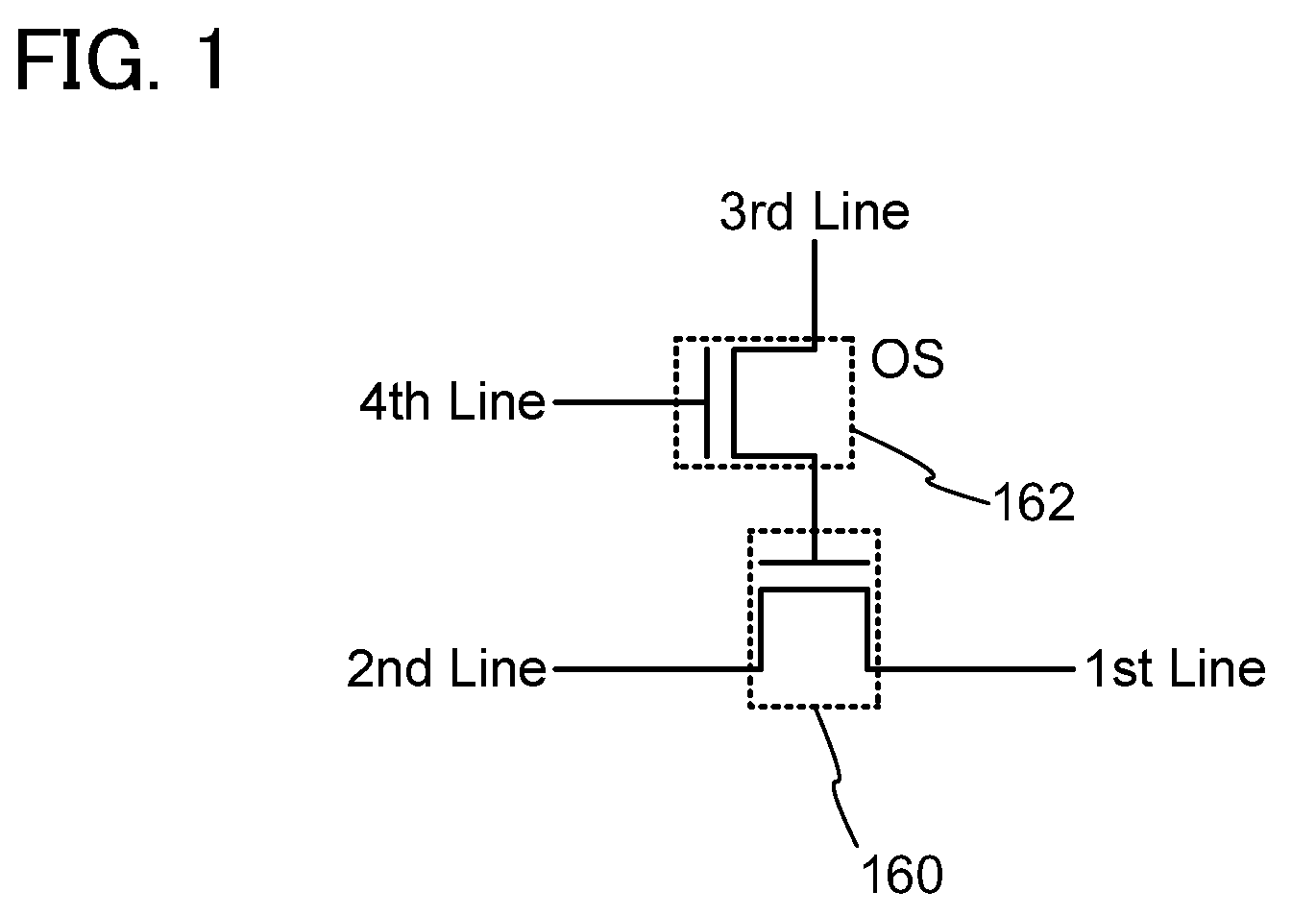

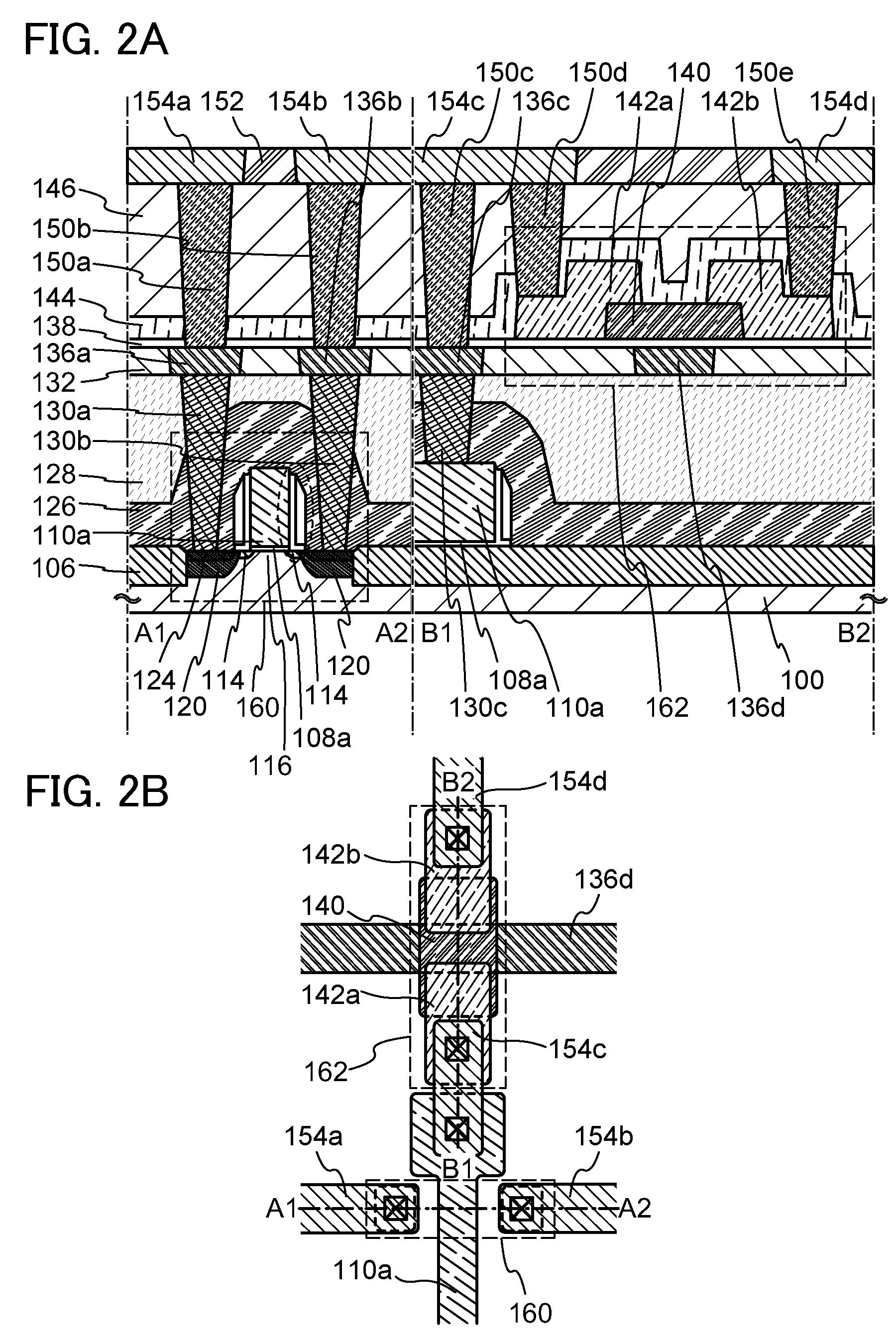

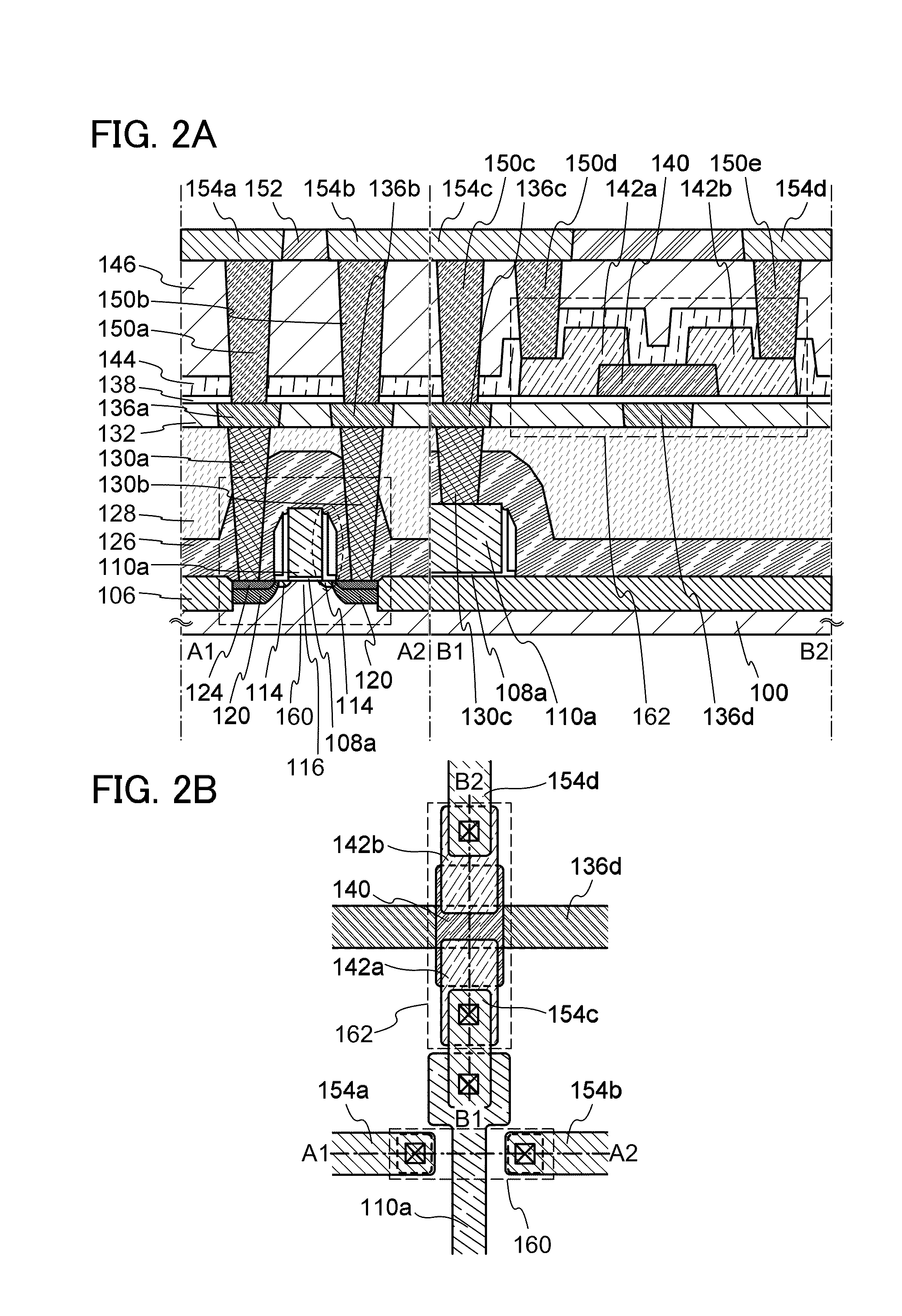

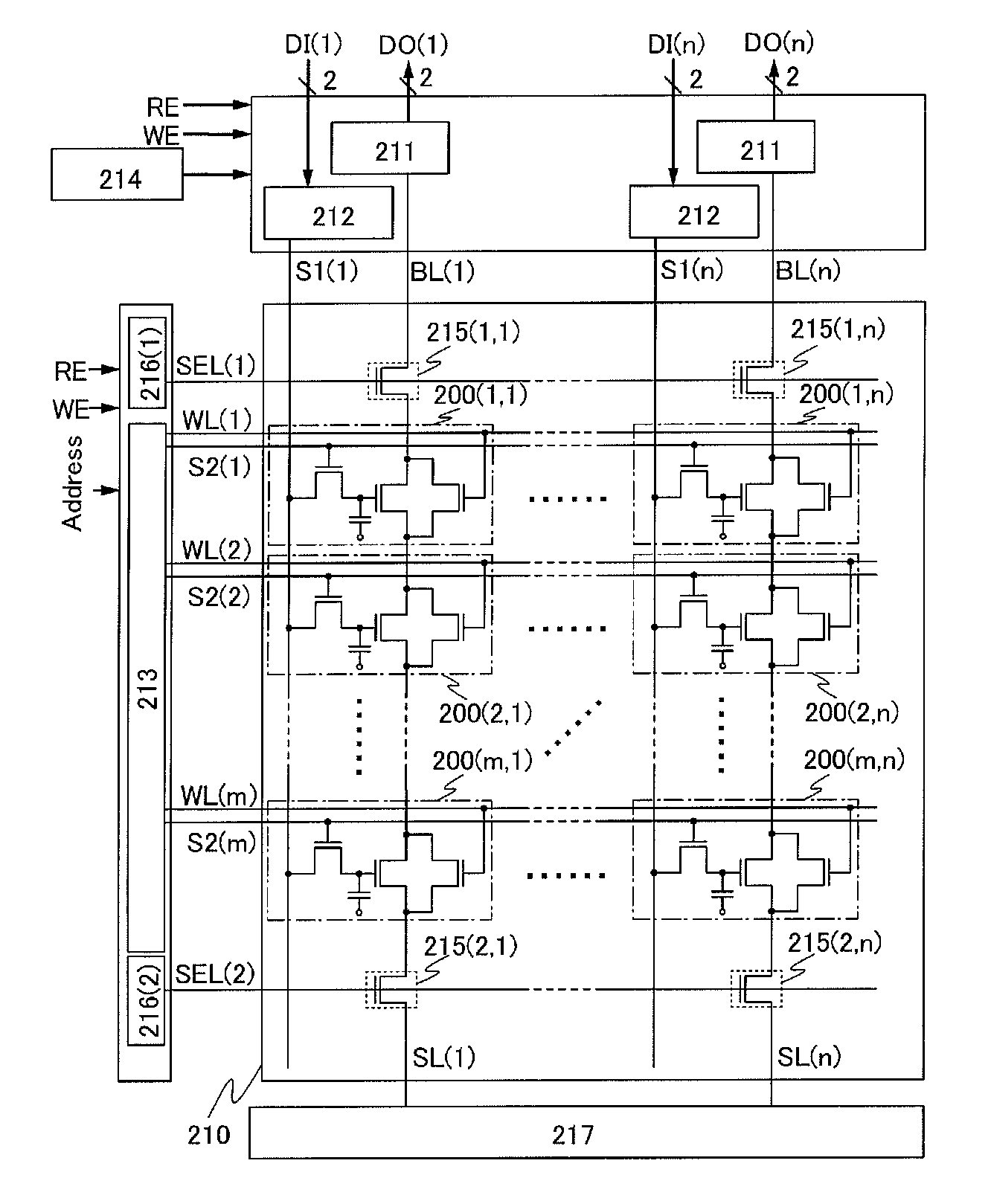

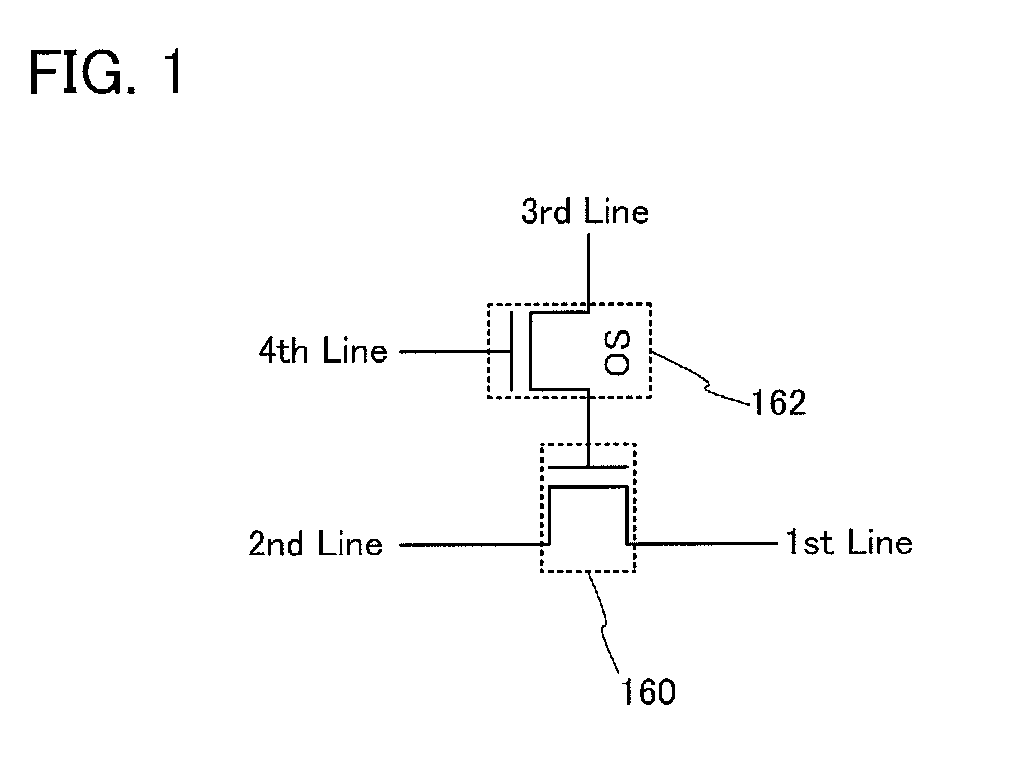

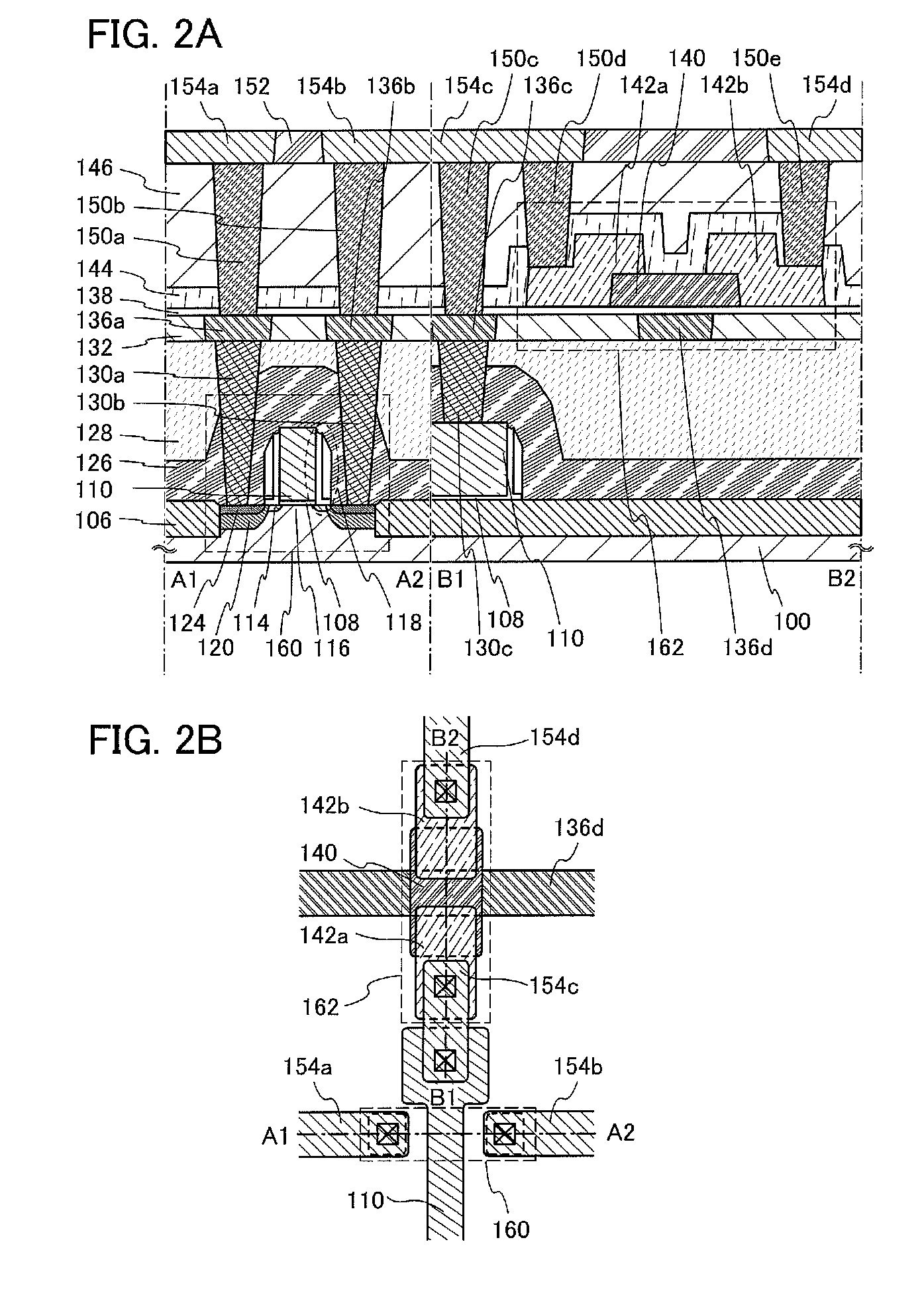

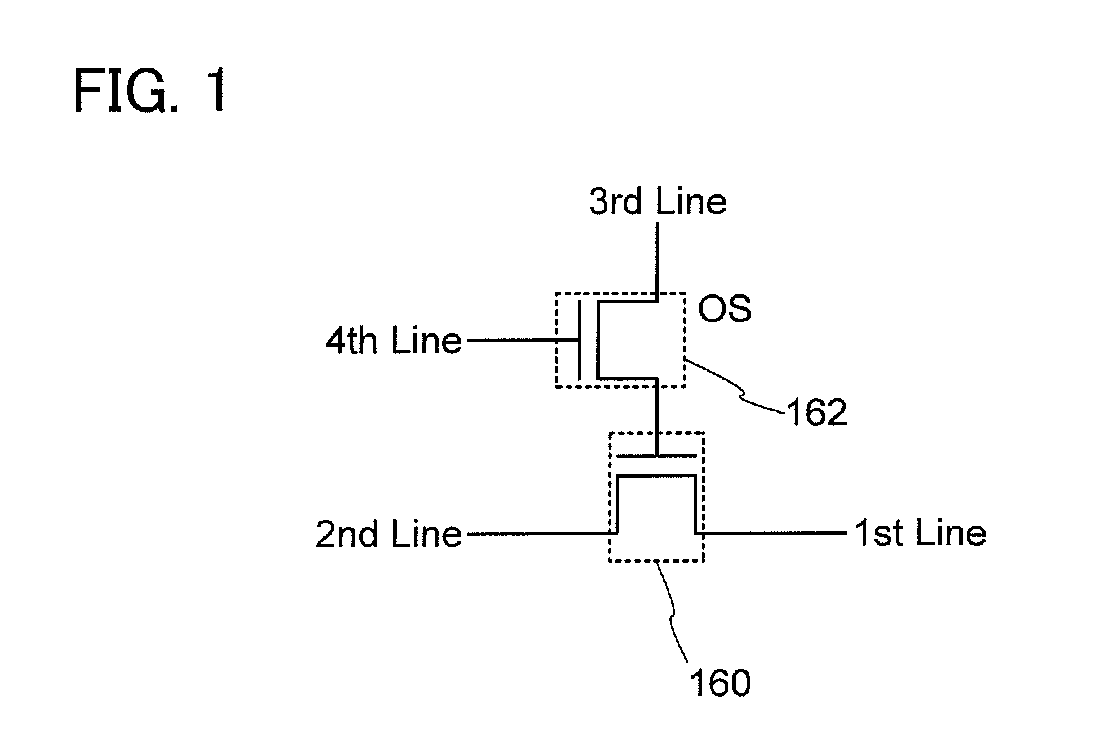

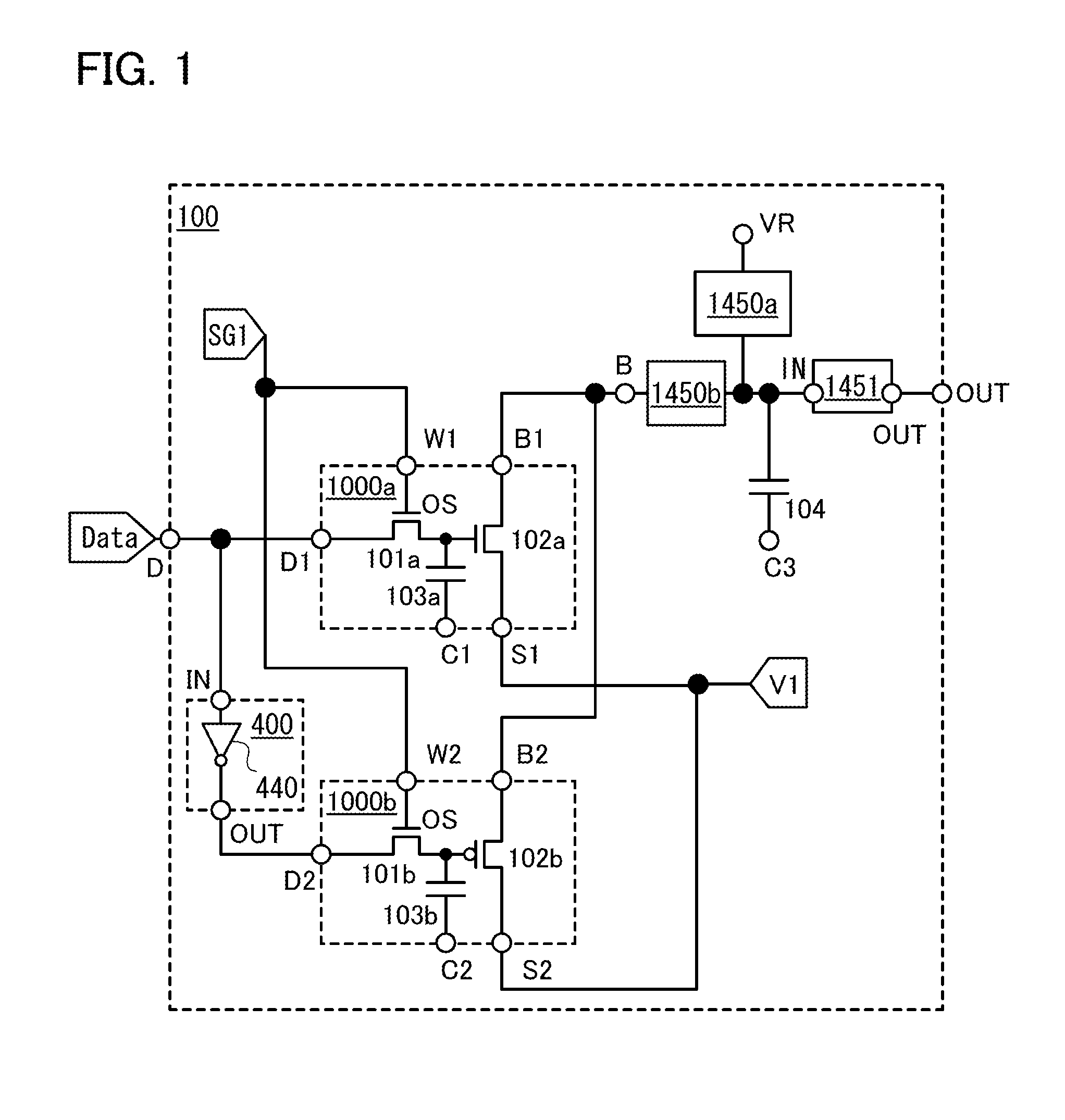

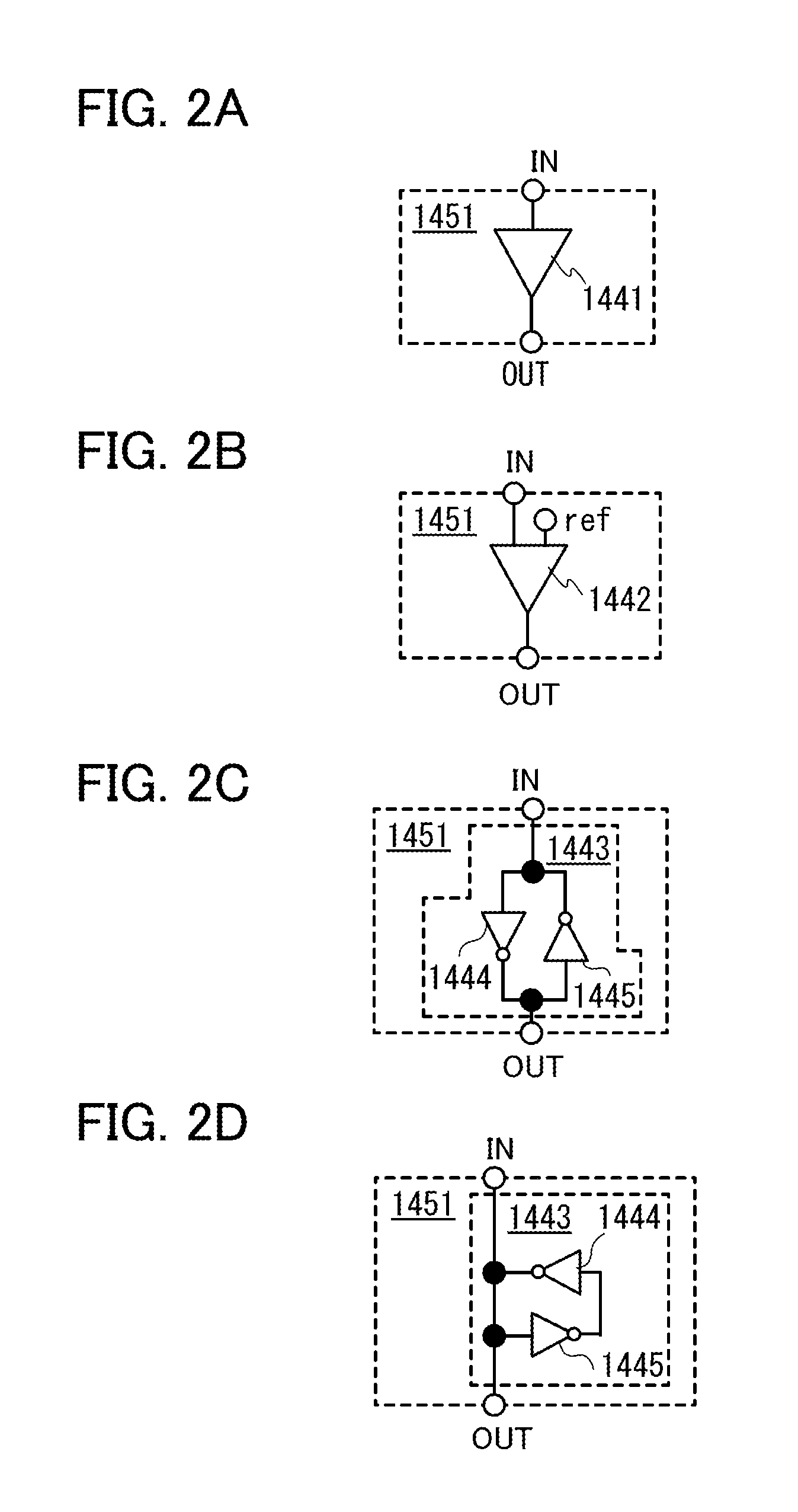

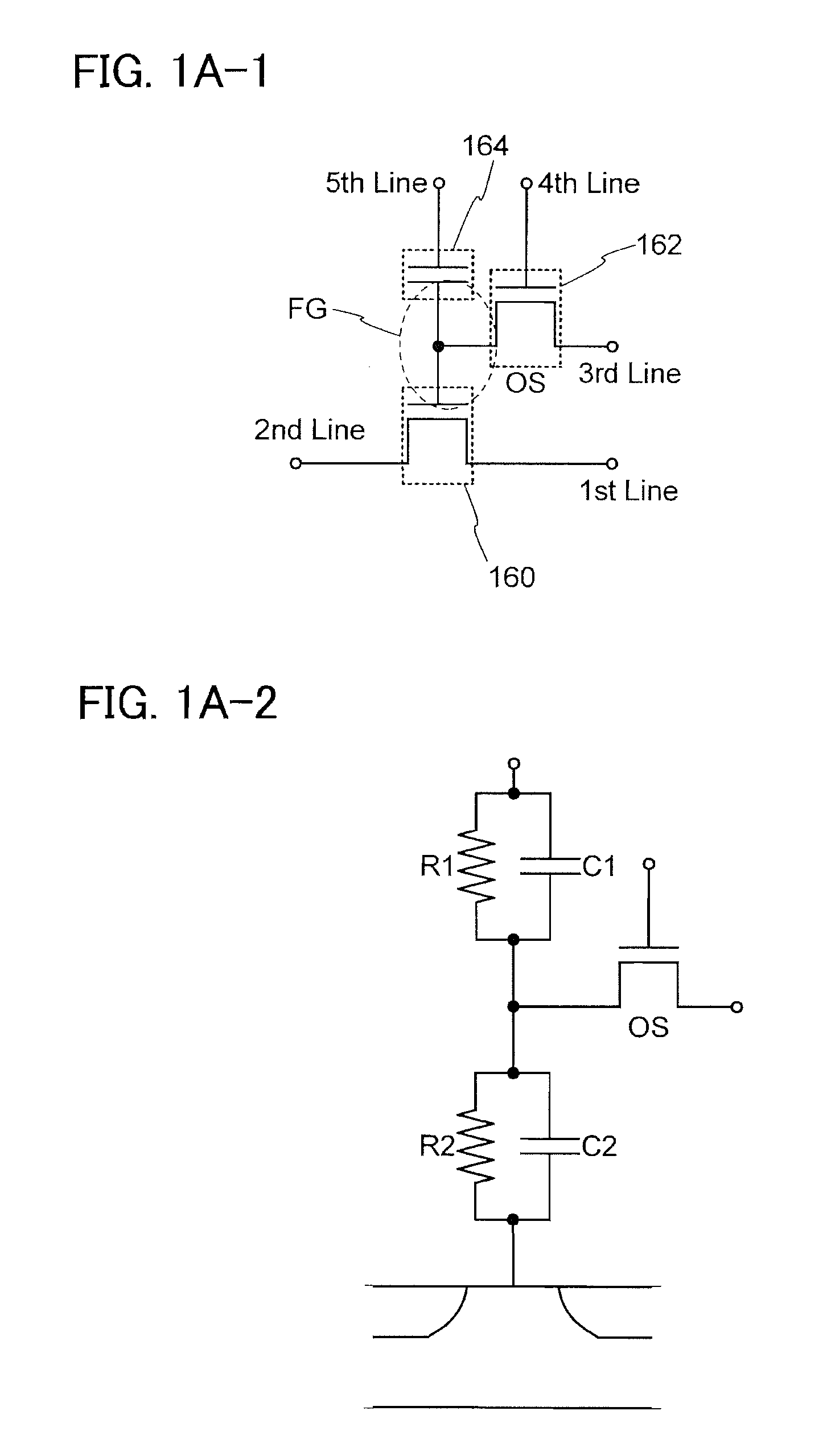

Disclosed is a semiconductor device functioning as a multivalued memory device including: memory cells connected in series; a driver circuit selecting a memory cell and driving a second signal line and a word line; a driver circuit selecting any of writing potentials and outputting it to a first signal line; a reading circuit comparing a potential of a bit line and a reference potential; and a potential generating circuit generating the writing potential and the reference potential. One of the memory cells includes: a first transistor connected to the bit line and a source line; a second transistor connected to the first and second signal line; and a third transistor connected to the word line, bit line, and source line. The second transistor includes an oxide semiconductor layer. A gate electrode of the first transistor is connected to one of source and drain electrodes of the second transistor.

Owner:SEMICON ENERGY LAB CO LTD

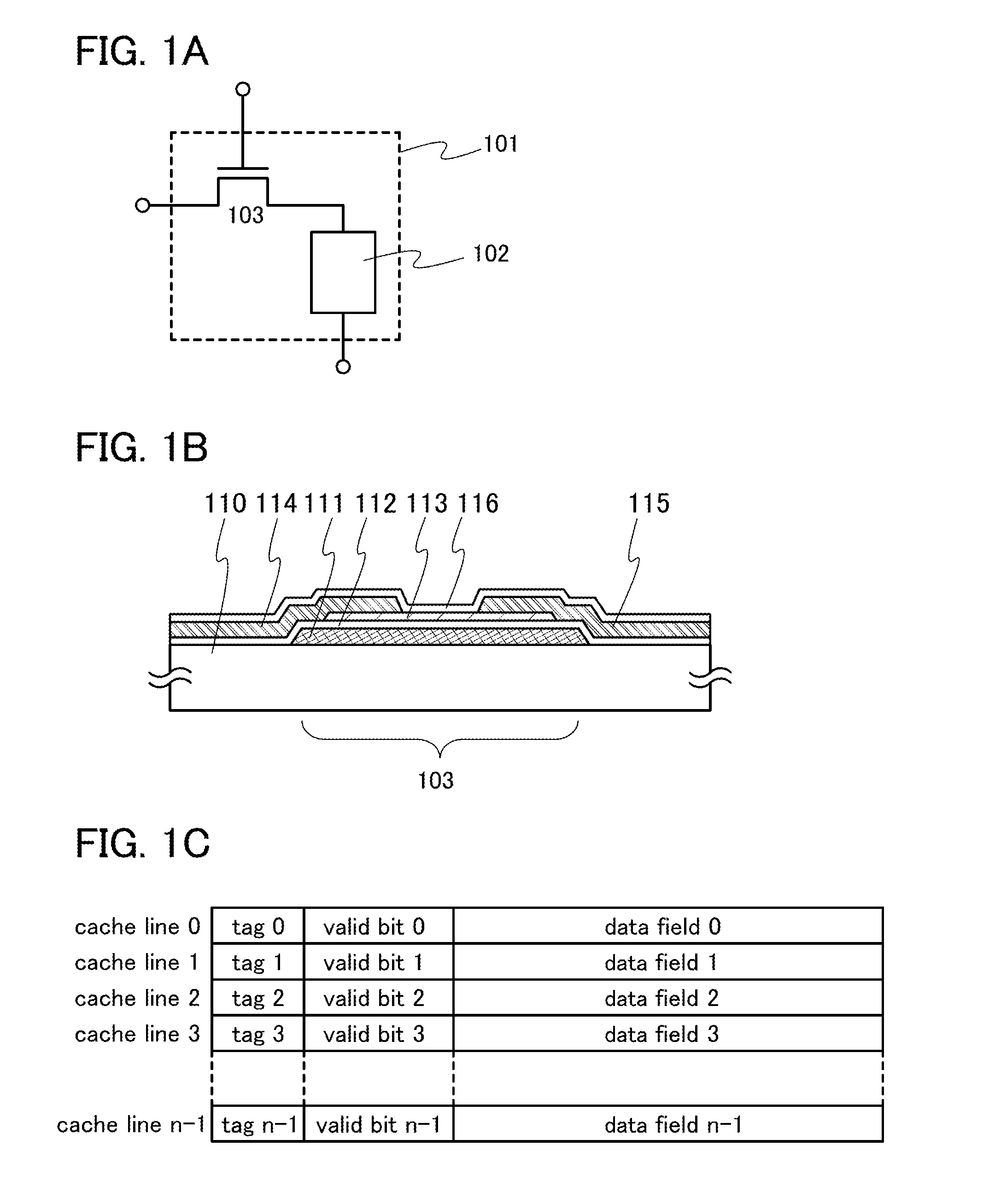

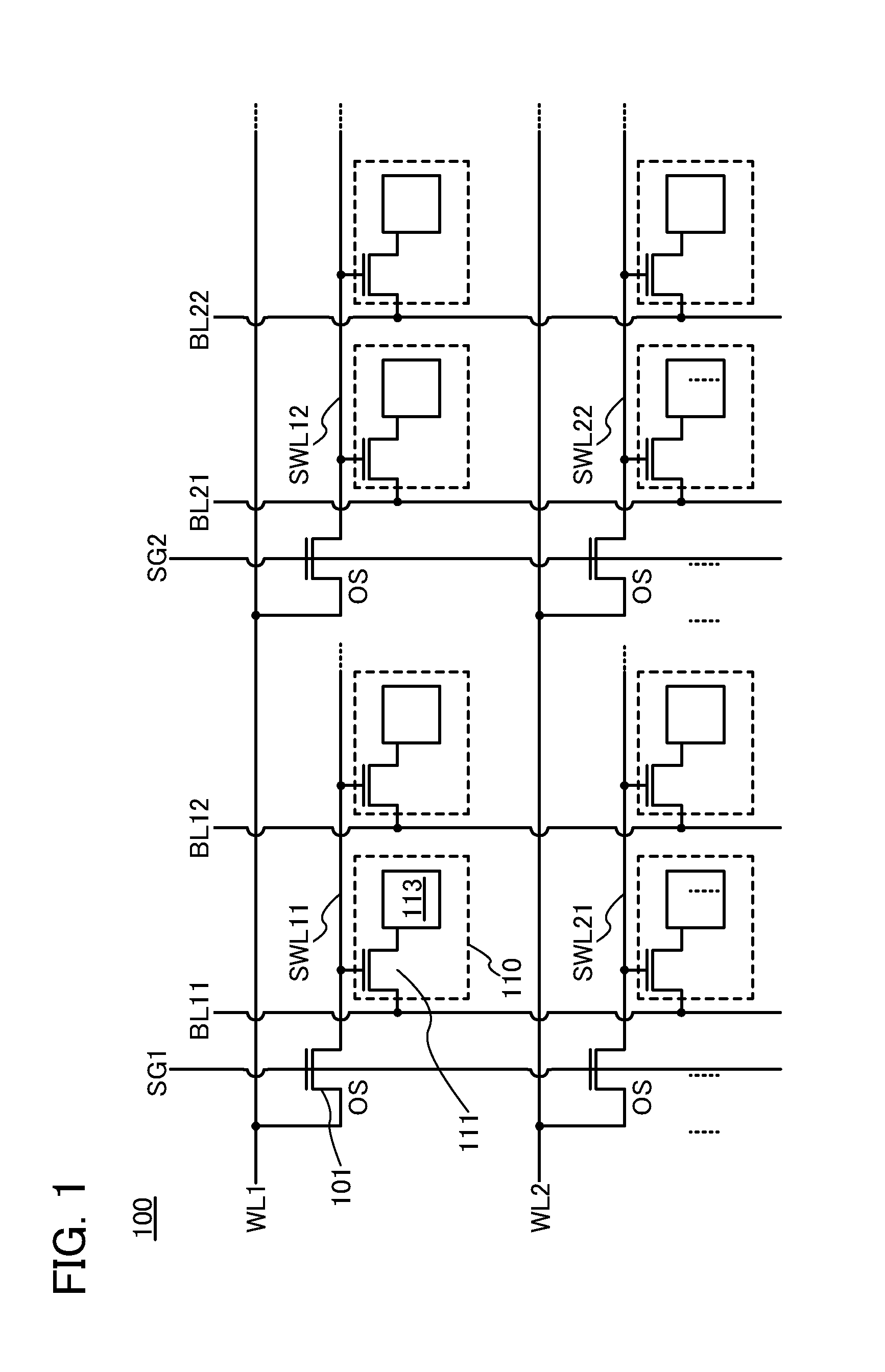

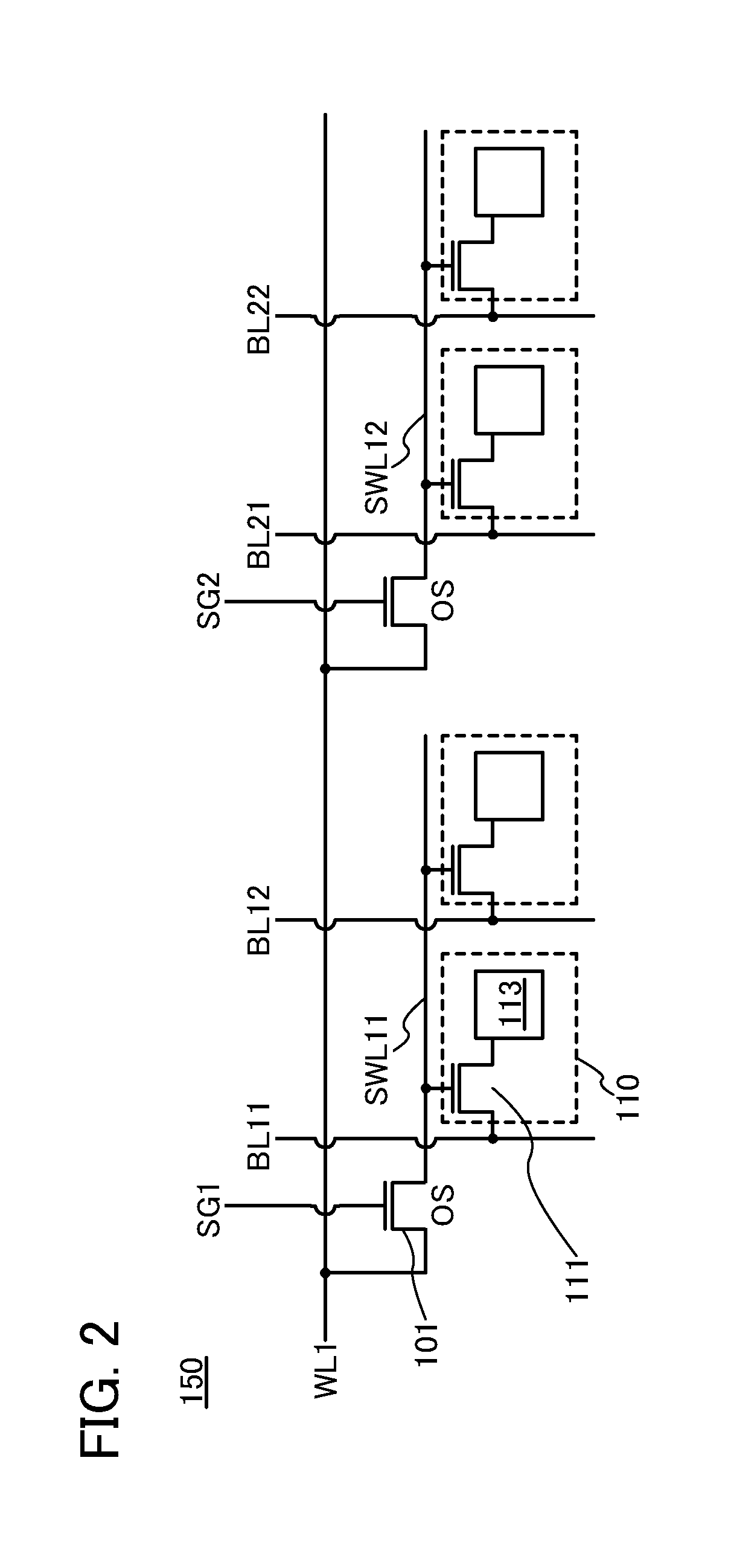

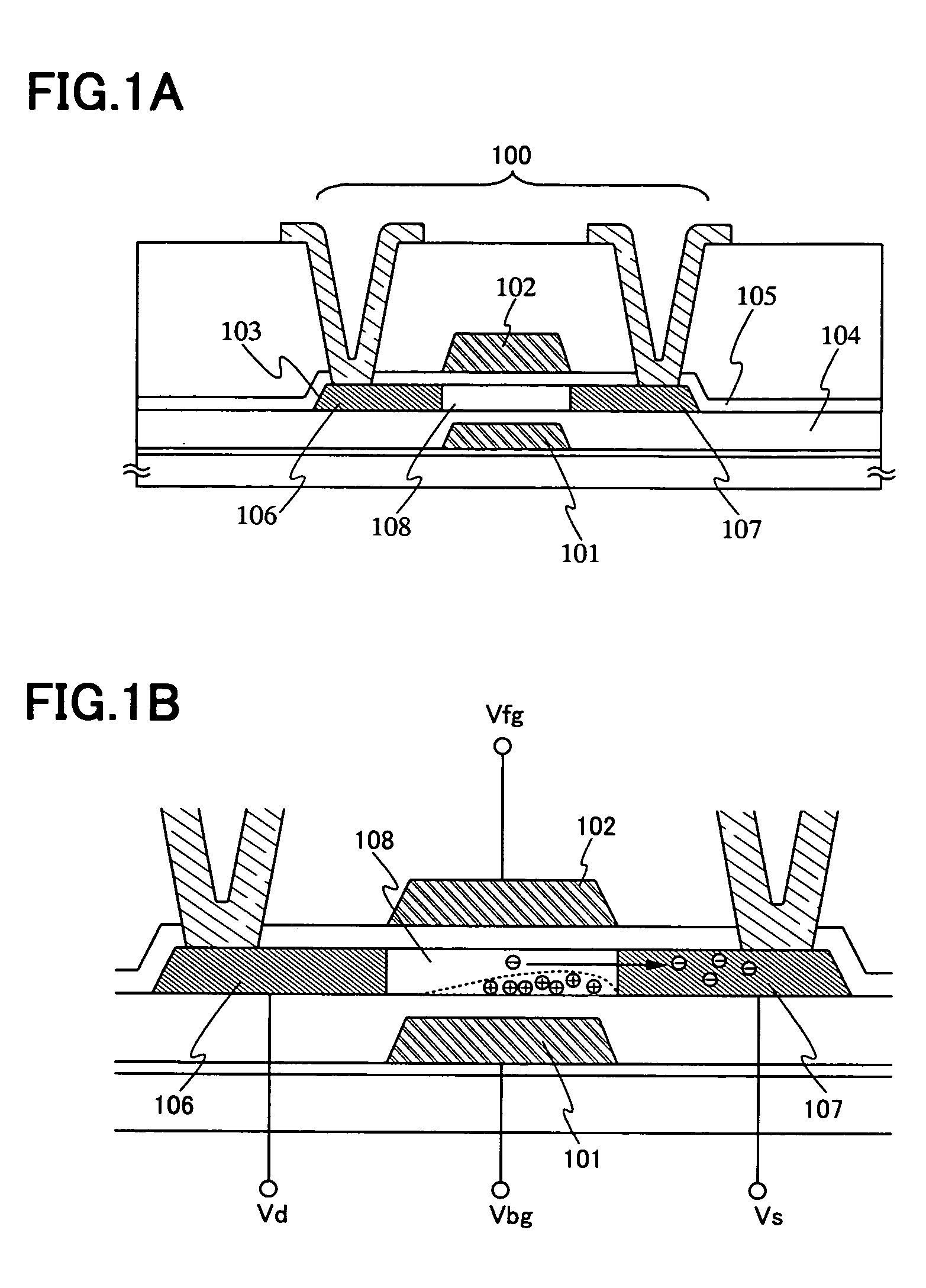

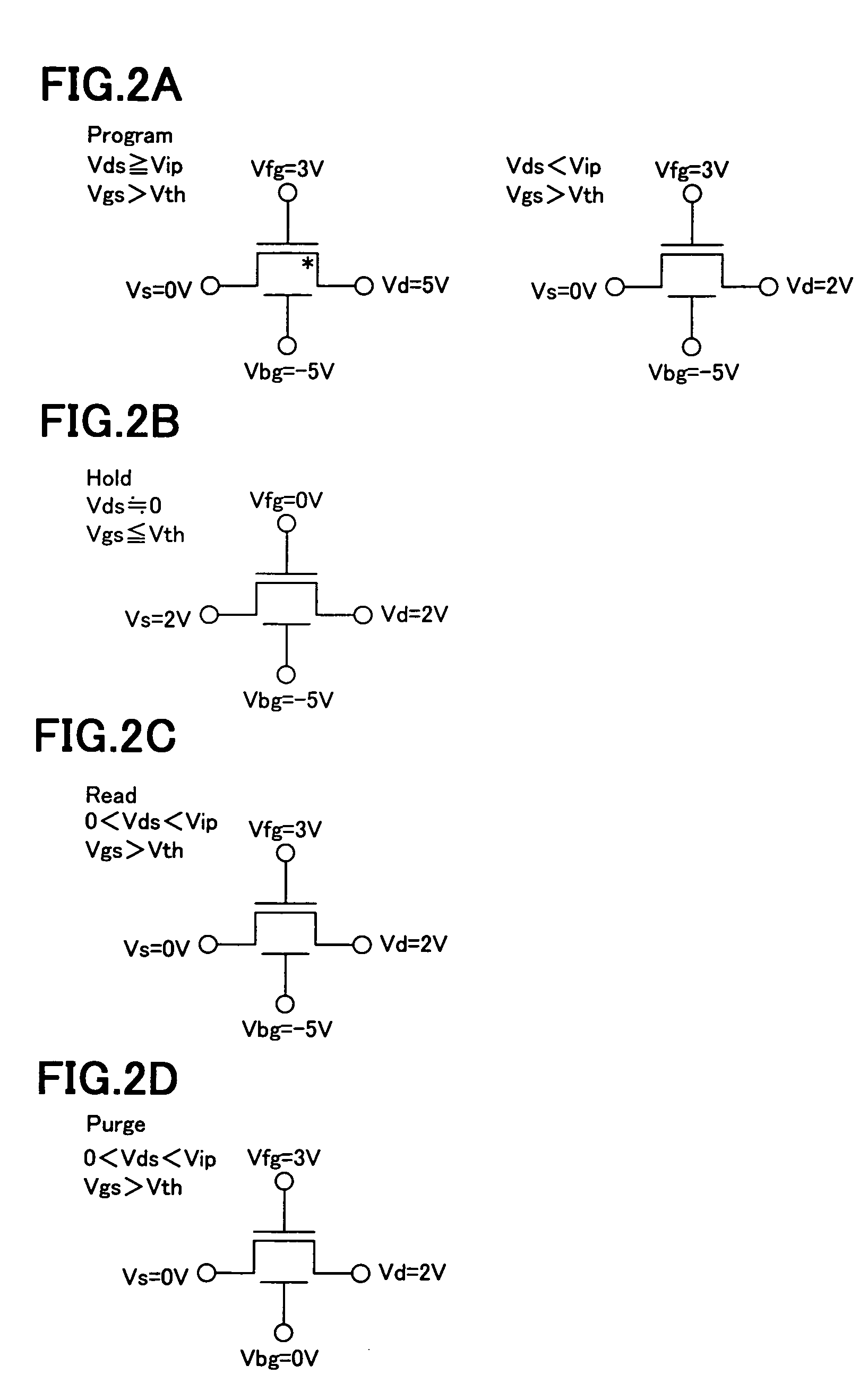

Semiconductor device

ActiveUS20110122670A1Limitation number of operationEasily multivalued informationTransistorSemiconductor/solid-state device detailsHemt circuitsSemiconductor

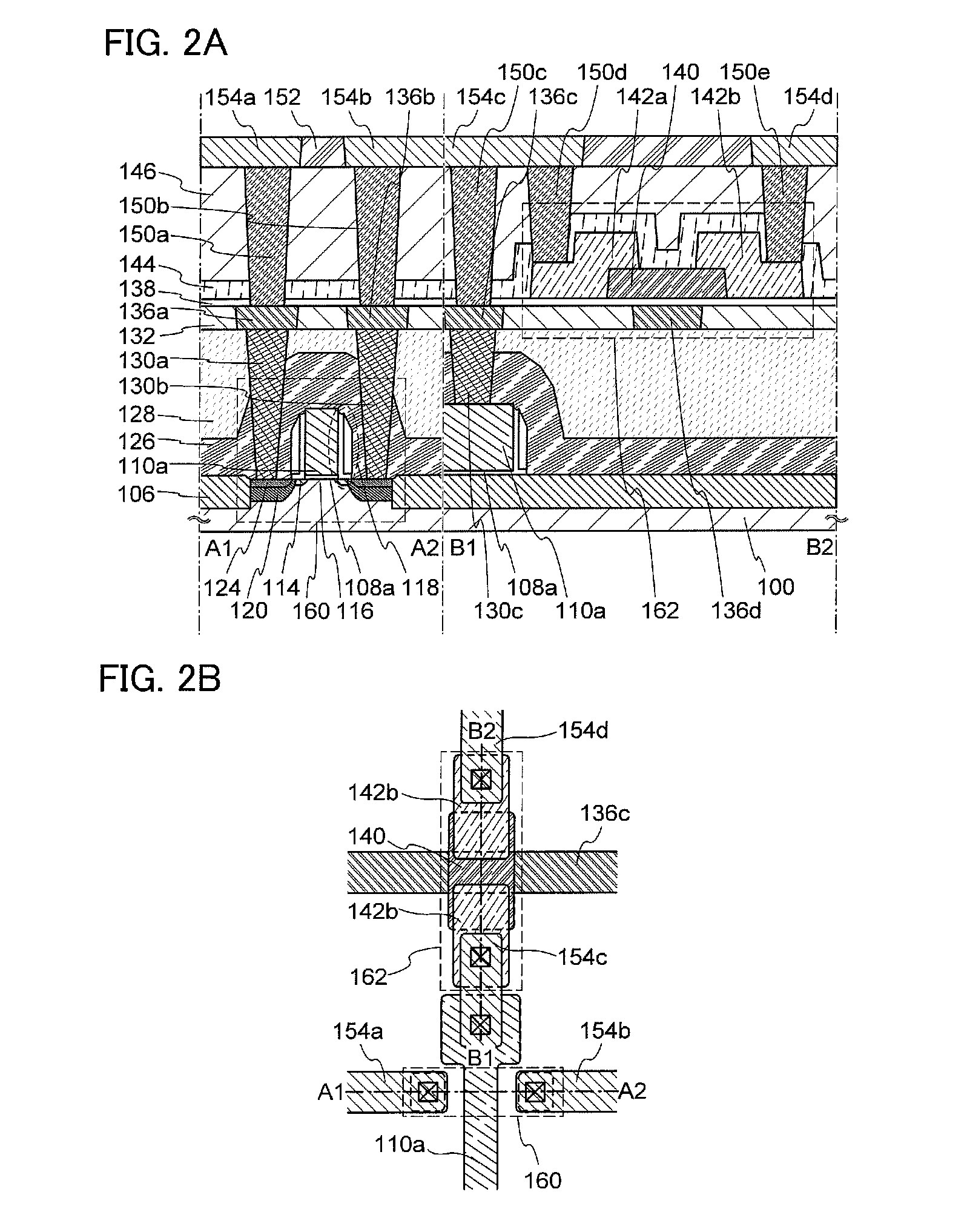

An object of the present invention is to provide a semiconductor device combining transistors integrating on a same substrate transistors including an oxide semiconductor in their channel formation region and transistors including non-oxide semiconductor in their channel formation region. An application of the present invention is to realize substantially non-volatile semiconductor memories which do not require specific erasing operation and do not suffer from damages due to repeated writing operation. Furthermore, the semiconductor device is well adapted to store multivalued data. Manufacturing methods, application circuits and driving / reading methods are explained in details in the description.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

ActiveUS8339828B2Limitation number of operationEasily multivalued informationTransistorSemiconductor/solid-state device detailsPower semiconductor deviceSemiconductor

An object of the present invention is to provide a semiconductor device combining transistors integrating on a same substrate transistors including an oxide semiconductor in their channel formation region and transistors including non-oxide semiconductor in their channel formation region. An application of the present invention is to realize substantially non-volatile semiconductor memories which do not require specific erasing operation and do not suffer from damages due to repeated writing operation. Furthermore, the semiconductor device is well adapted to store multivalued data. Manufacturing methods, application circuits and driving / reading methods are explained in details in the description.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

ActiveUS8363452B2Easily multivaluedNovel structureTransistorSolid-state devicesBit lineDriver circuit

Disclosed is a semiconductor device functioning as a multivalued memory device including: memory cells connected in series; a driver circuit selecting a memory cell and driving a second signal line and a word line; a driver circuit selecting any of writing potentials and outputting it to a first signal line; a reading circuit comparing a potential of a bit line and a reference potential; and a potential generating circuit generating the writing potential and the reference potential. One of the memory cells includes: a first transistor connected to the bit line and a source line; a second transistor connected to the first and second signal line; and a third transistor connected to the word line, bit line, and source line. The second transistor includes an oxide semiconductor layer. A gate electrode of the first transistor is connected to one of source and drain electrodes of the second transistor.

Owner:SEMICON ENERGY LAB CO LTD

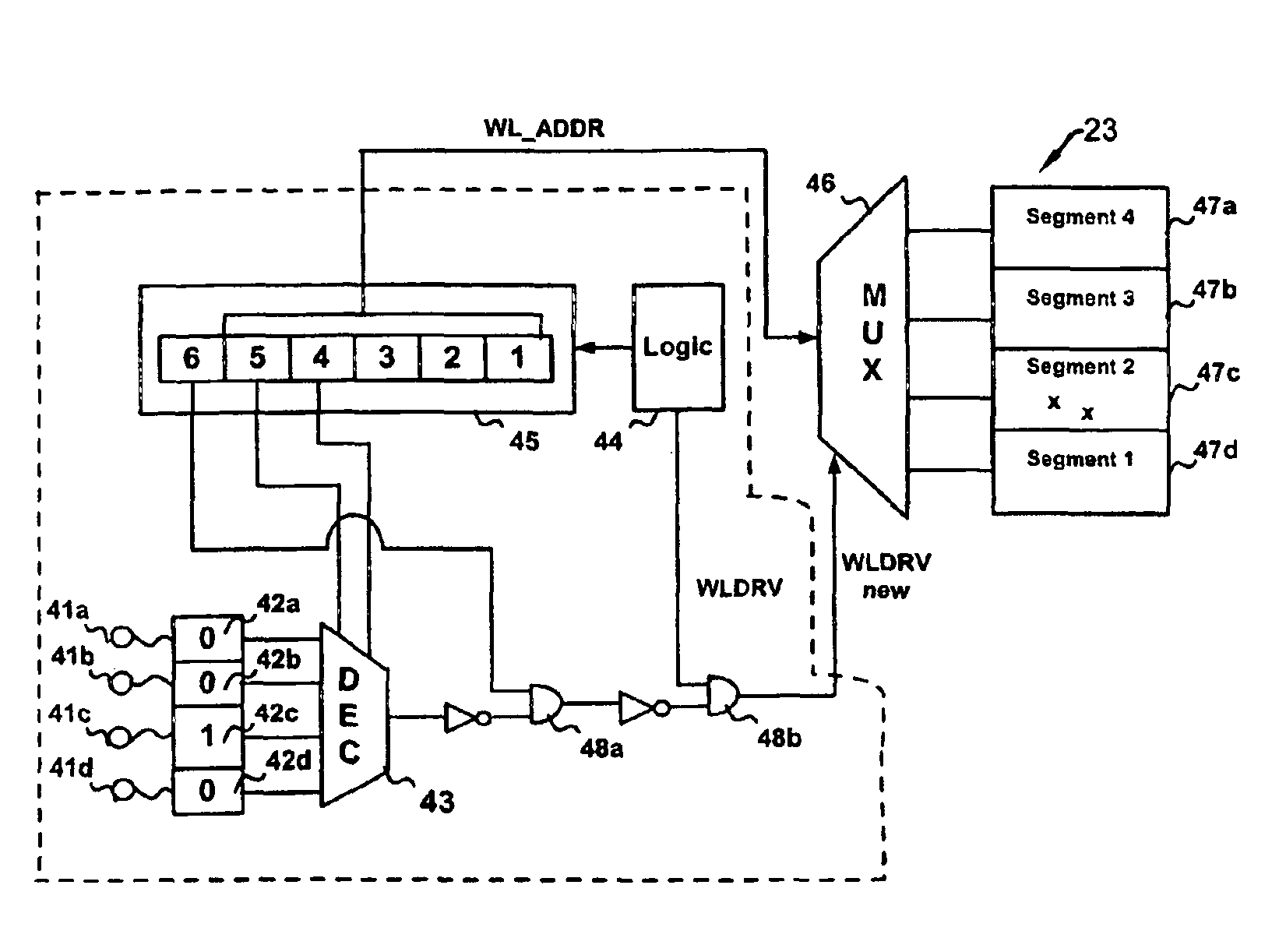

Method and system for manufacturing DRAMs with reduced self-refresh current requirements

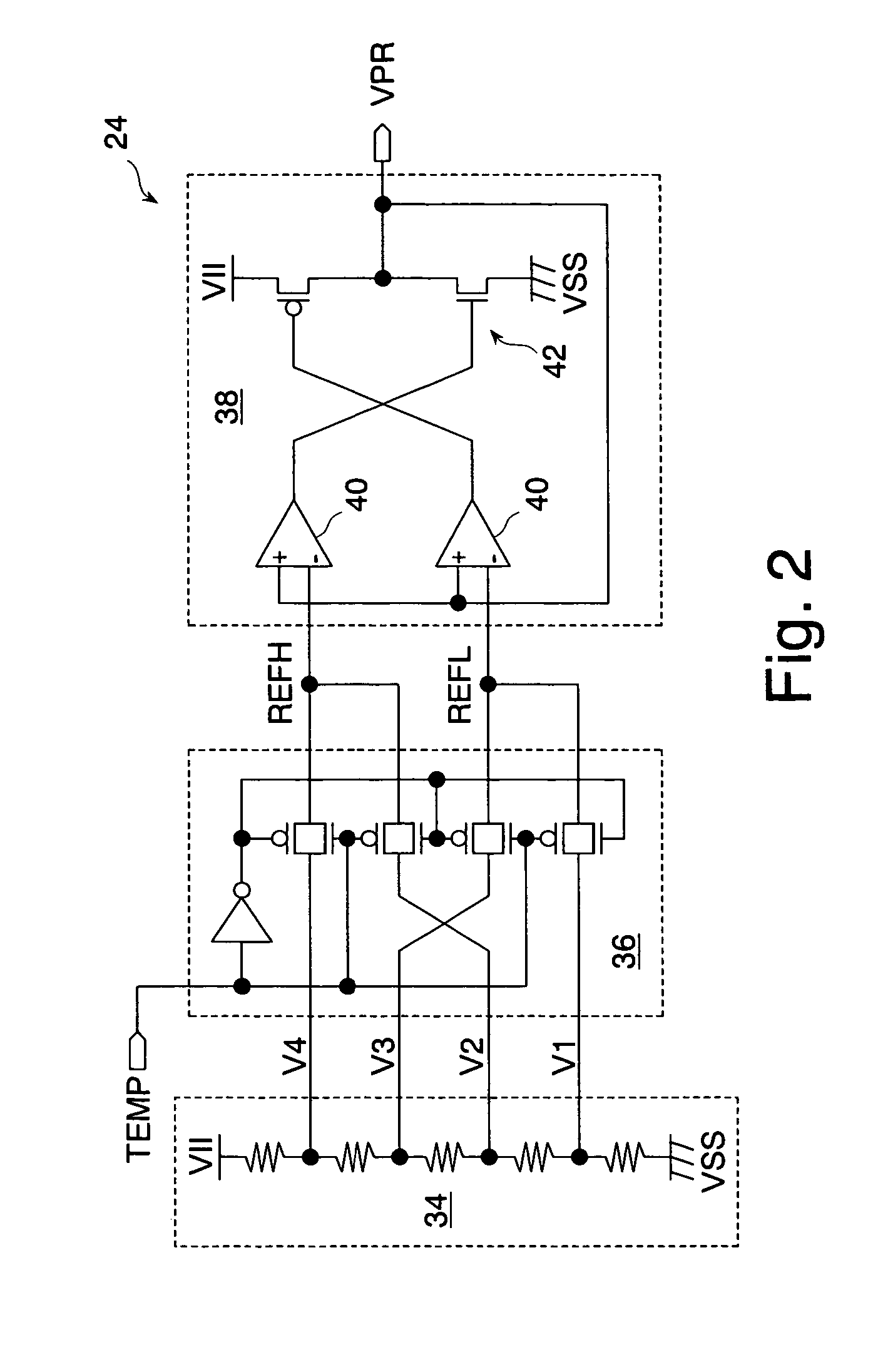

InactiveUS6940773B2Reducing self-refresh current requirementConserving current required can be drawnRead-only memoriesDigital storageRefresh rateRefresh cycle

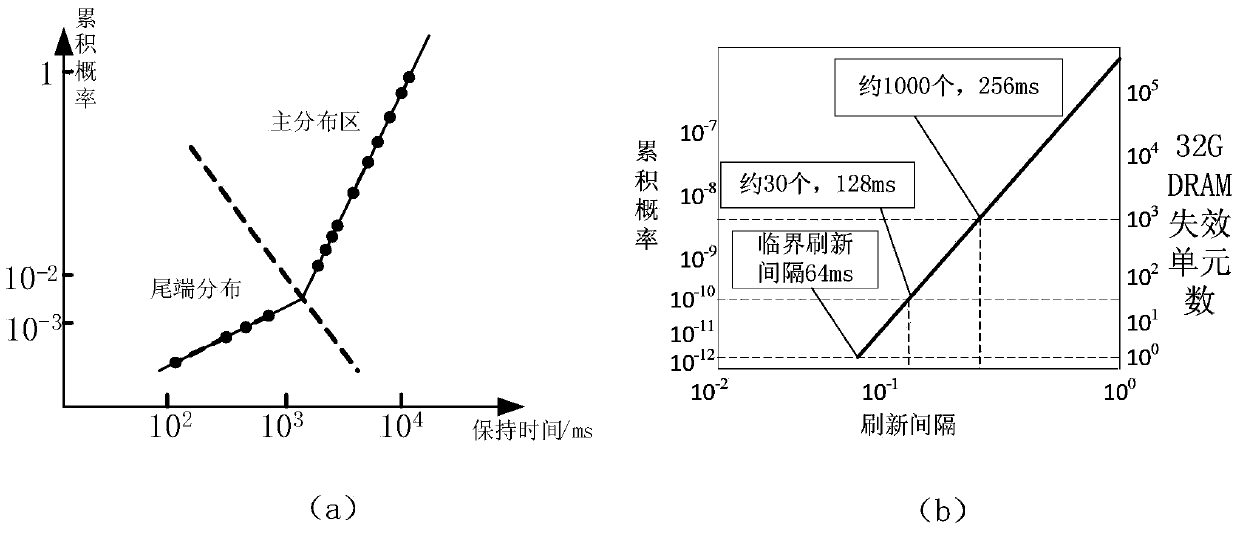

A method and system for reducing self-refresh current requirements in a includes a DRAM chip that is sectioned into a number of segments. The entire DRAM chip is tested upon manufacture to determine the relative decay rates for each cell in the DRAM. For each segment, the refresh rate for that segment is selected based on the fastest decay rate for a DRAM cell in the segment. The DRAM is configured for refreshing memory cells during a self-refresh at different refresh rates for different segments. The refresh period is controlled for individual segments using techniques, such as programmable logic or fuses, to skip certain self-refresh cycles for those segments capable of operating at lower refresh rates. The refresh period in memory segments with strong memory cells can be reduced, thereby conserving current required to be drawn.

Owner:POLARIS INNOVATIONS

Semiconductor device

ActiveUS8289753B2Reduced shutdown currentReduce the refresh rateTransistorSolid-state devicesSemiconductor materialsEngineering

Owner:SEMICON ENERGY LAB CO LTD

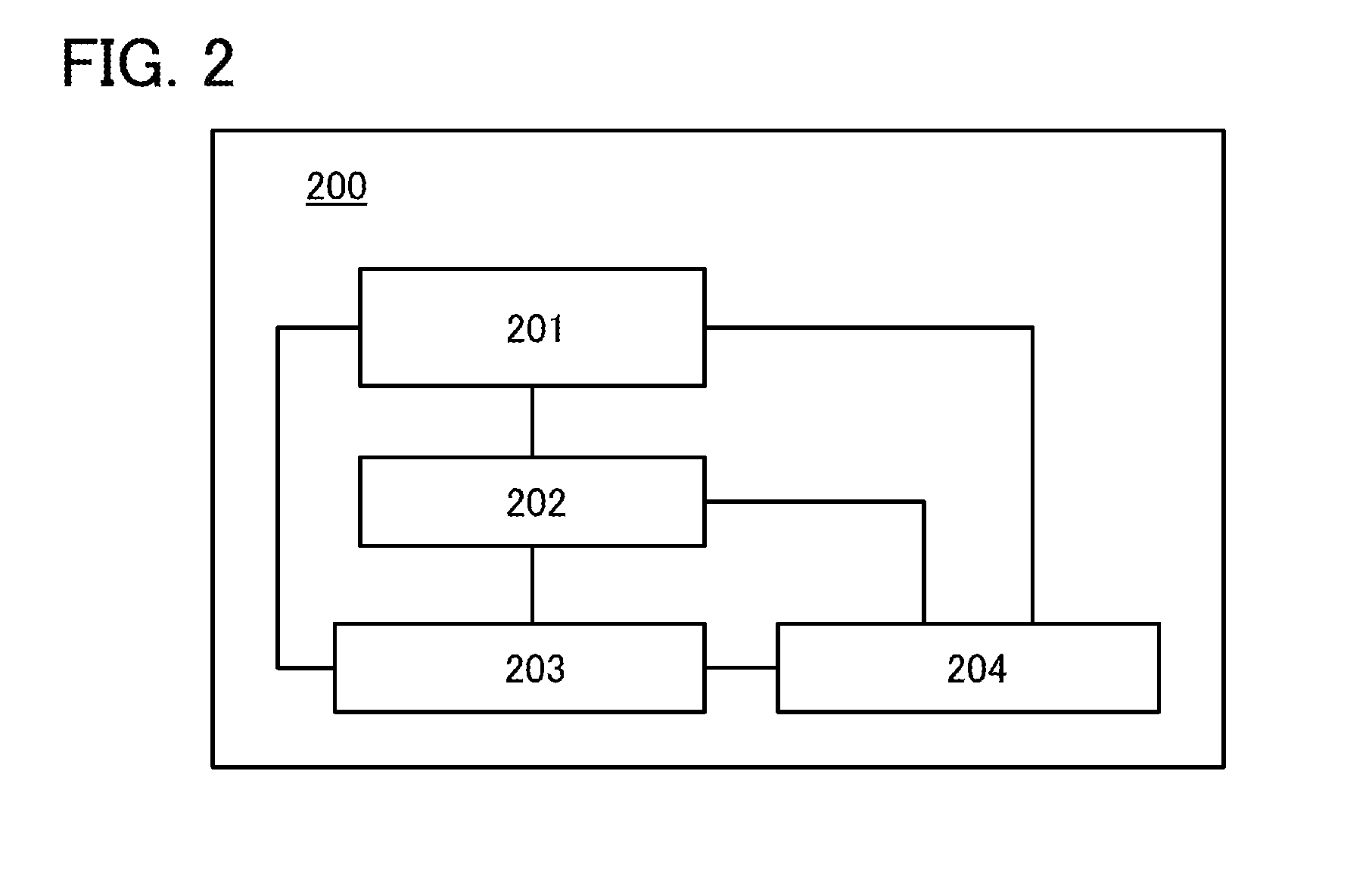

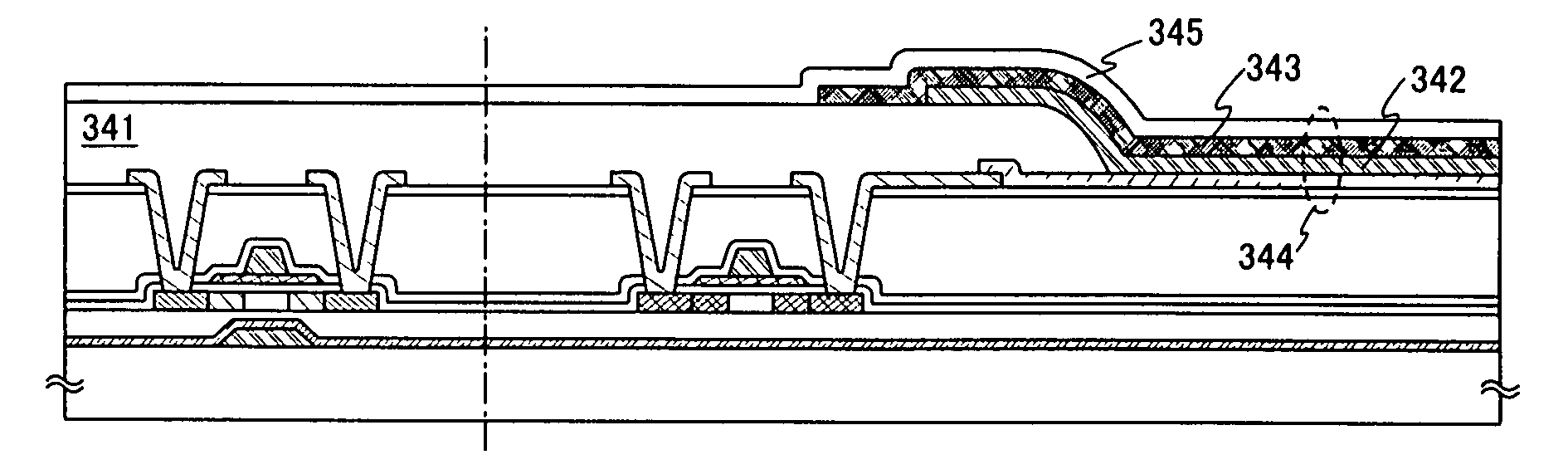

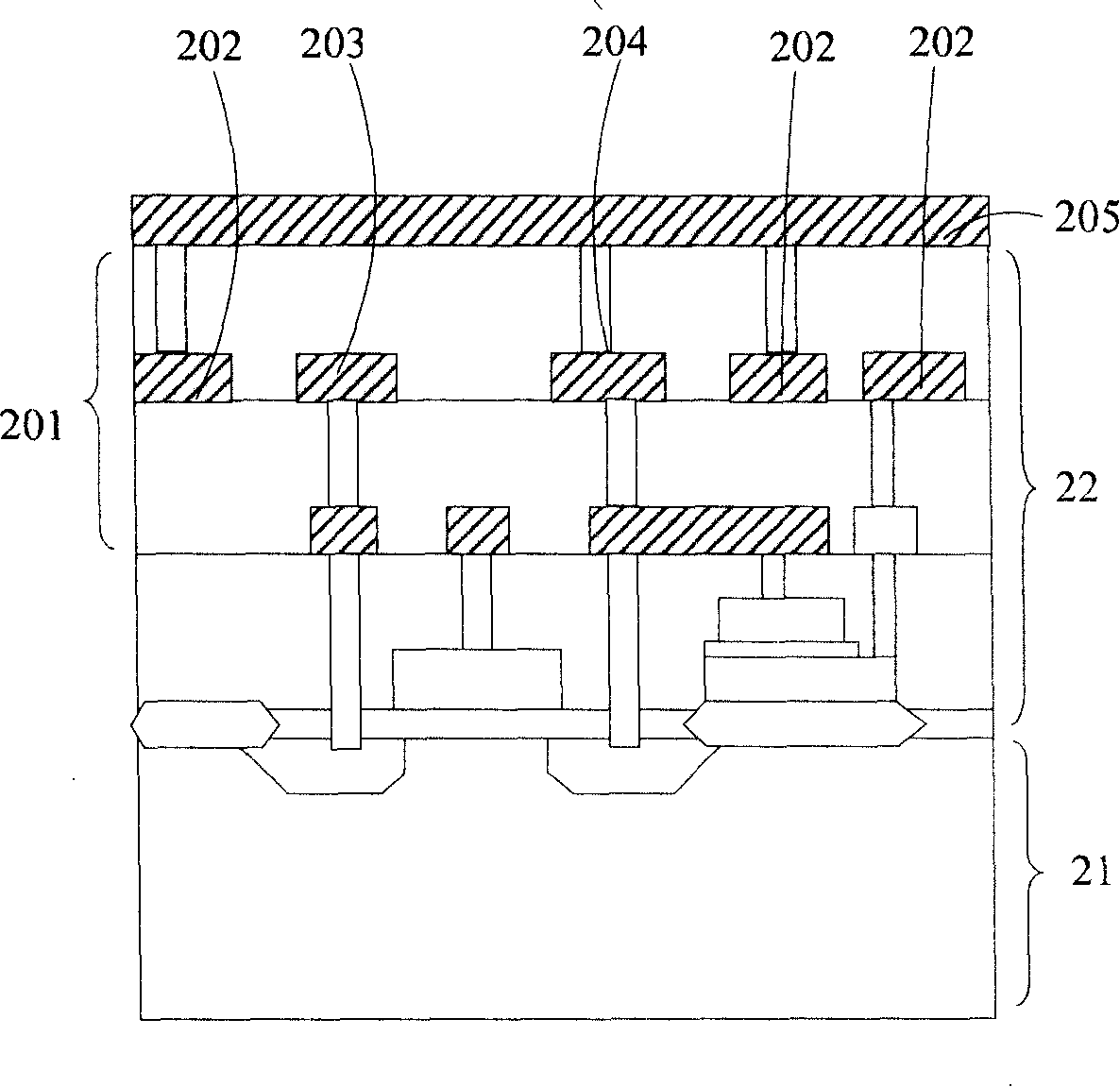

Semiconductor device and driving method of semiconductor device

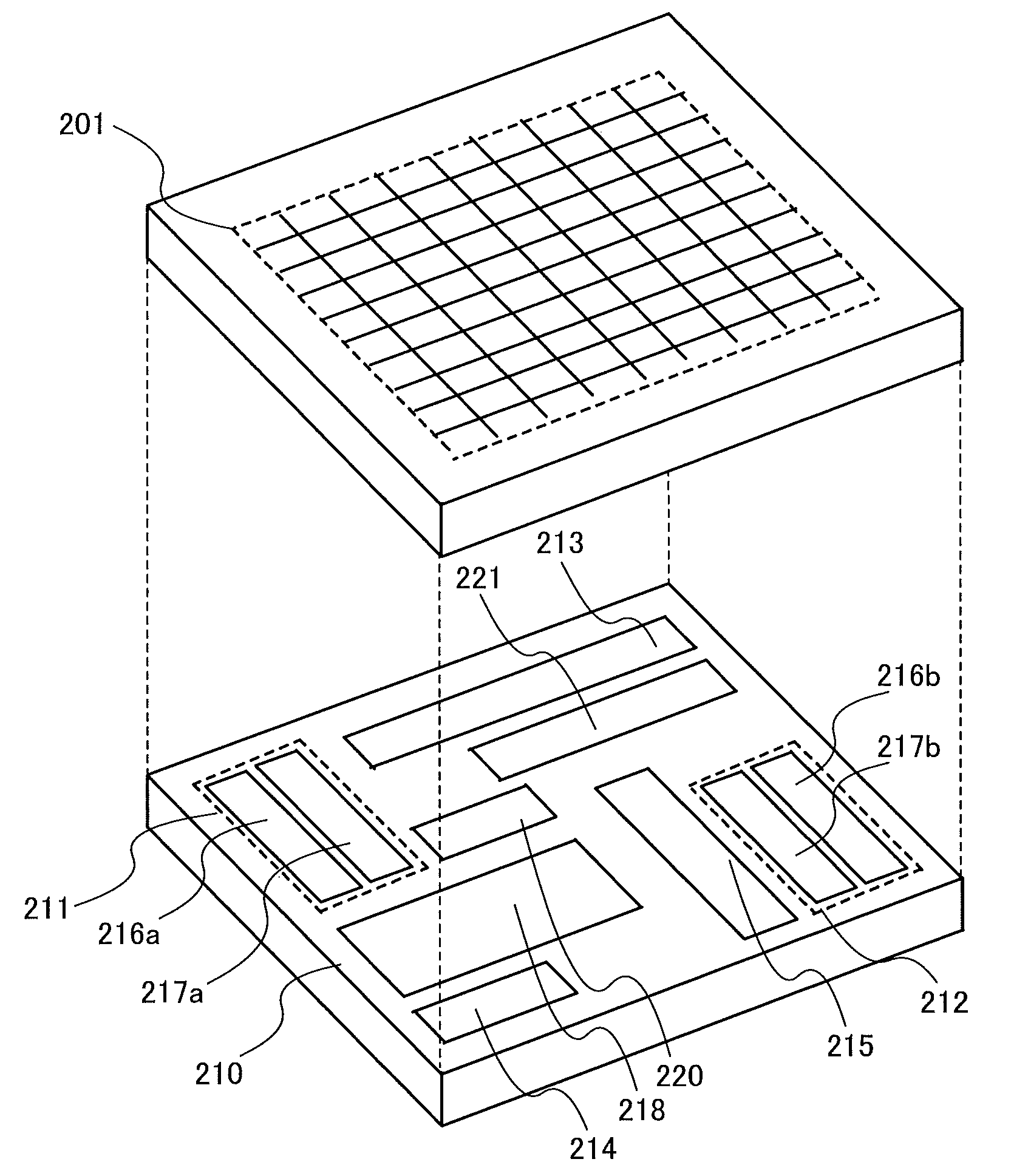

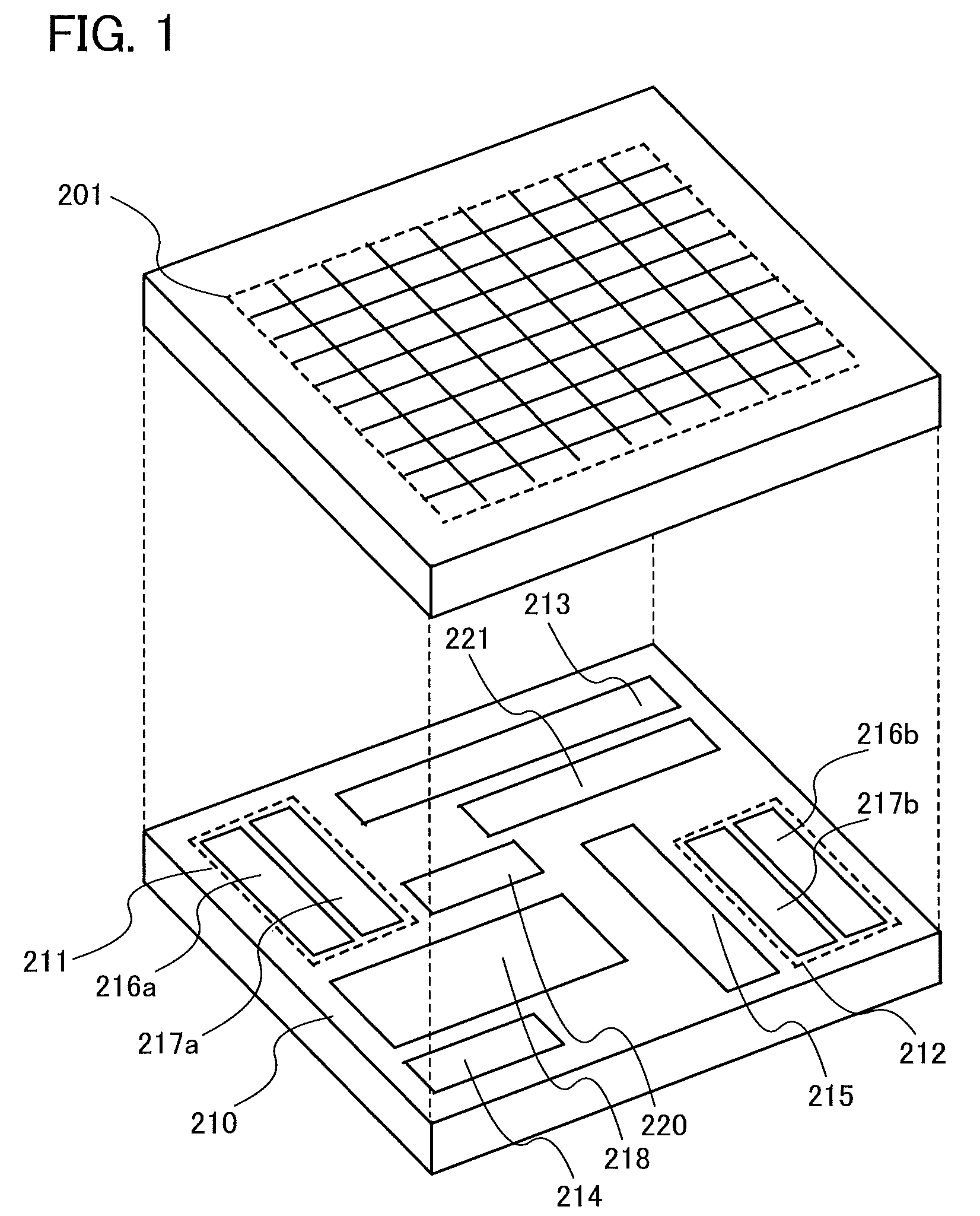

ActiveUS8508967B2Total current dropReduce the refresh rateDigital storageDriver circuitPower semiconductor device

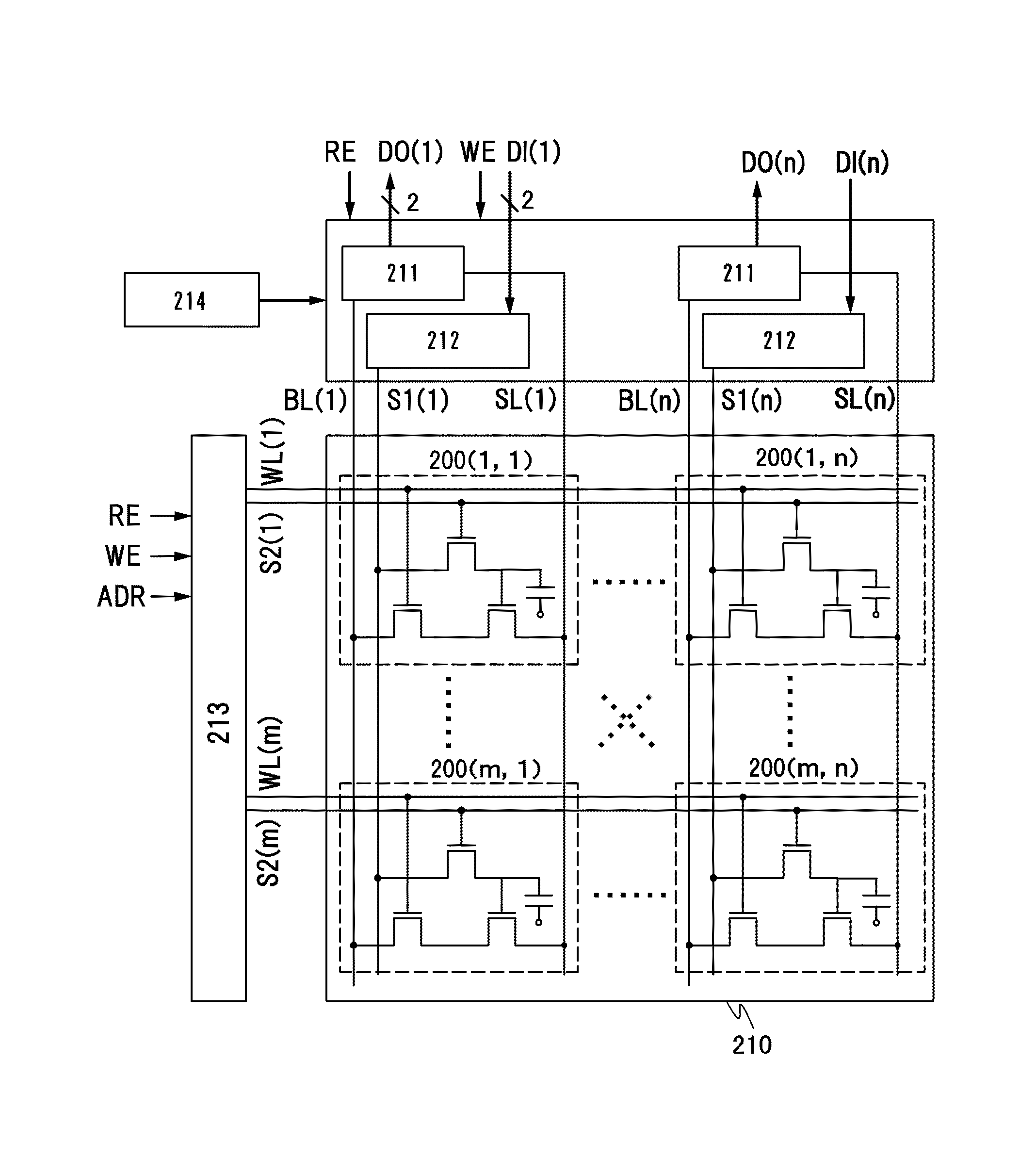

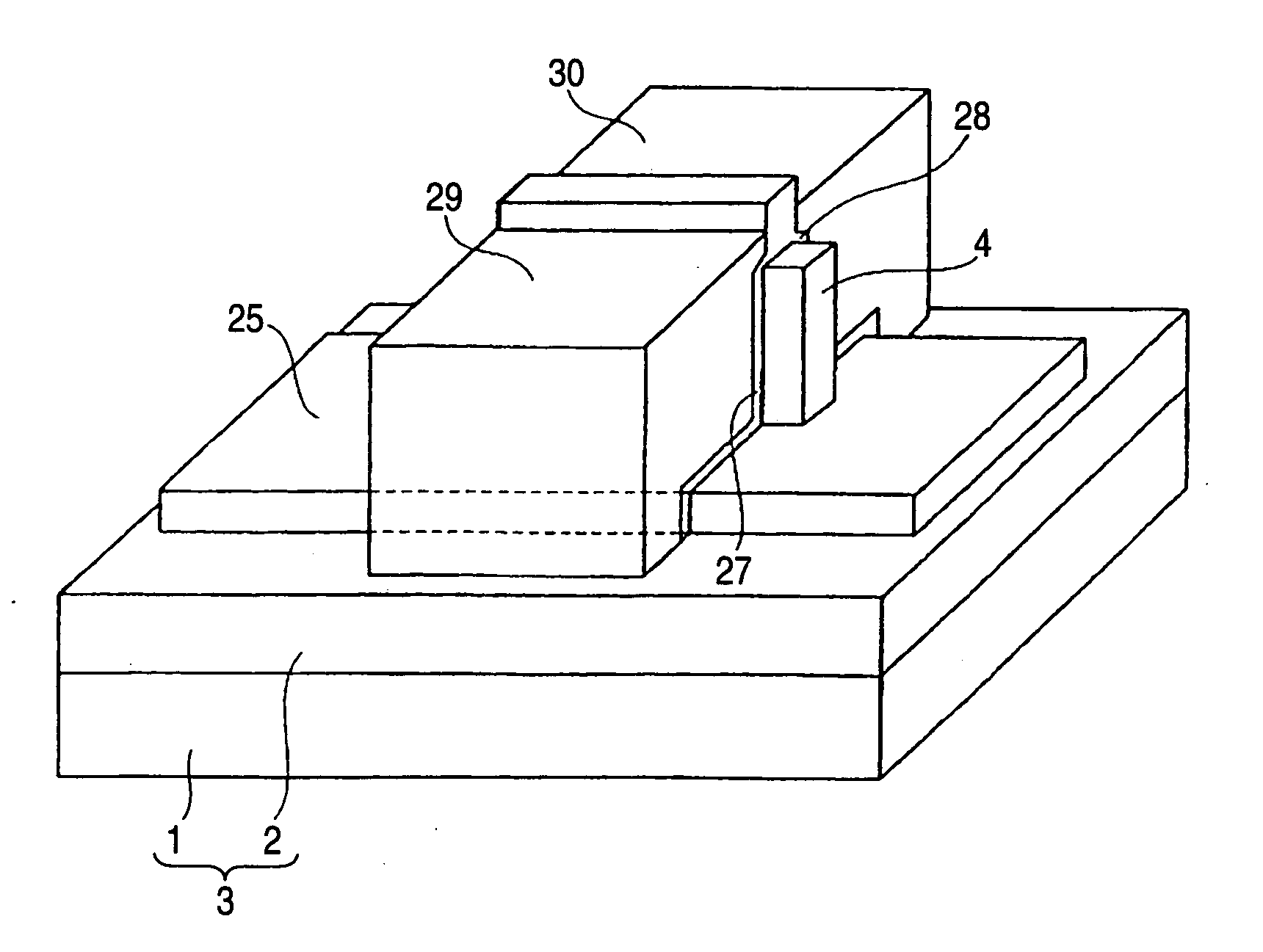

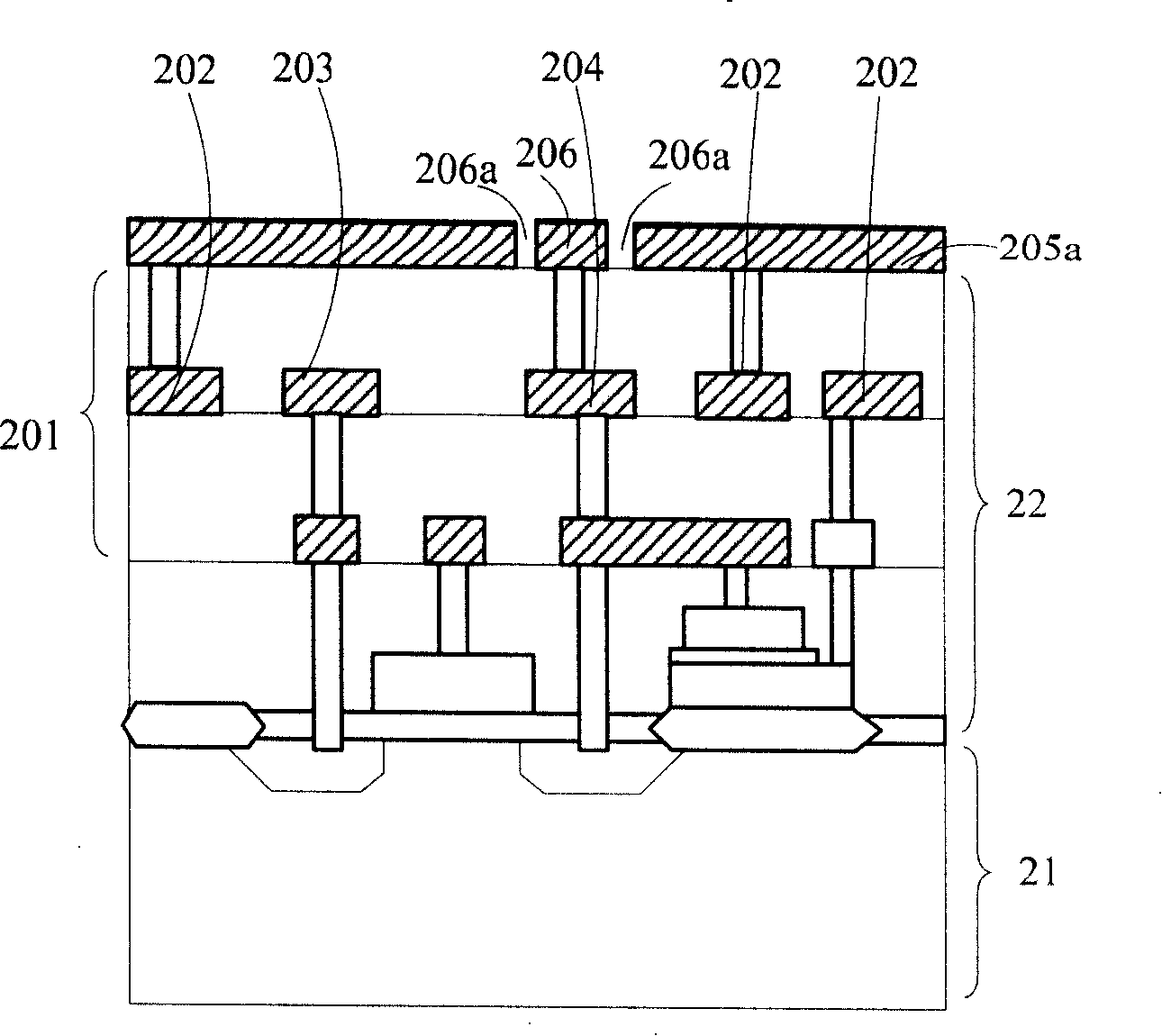

An object is to provide a semiconductor device having a novel structure, which can hold stored data even when not powered and which has an unlimited number of write cycles. A semiconductor device is provided with both a memory circuit including a transistor including an oxide semiconductor (in a broader sense, a transistor whose off-state current is sufficiently small) and a peripheral circuit such as a driver circuit including a transistor including a material other than an oxide semiconductor (in other words, a transistor capable of operating at sufficiently high speed). The peripheral circuit is provided in a lower portion and the memory circuit is provided in an upper portion; thus, the area and size of the semiconductor device can be decreased.

Owner:SEMICON ENERGY LAB CO LTD

Display method of E-ink electronic paper screen

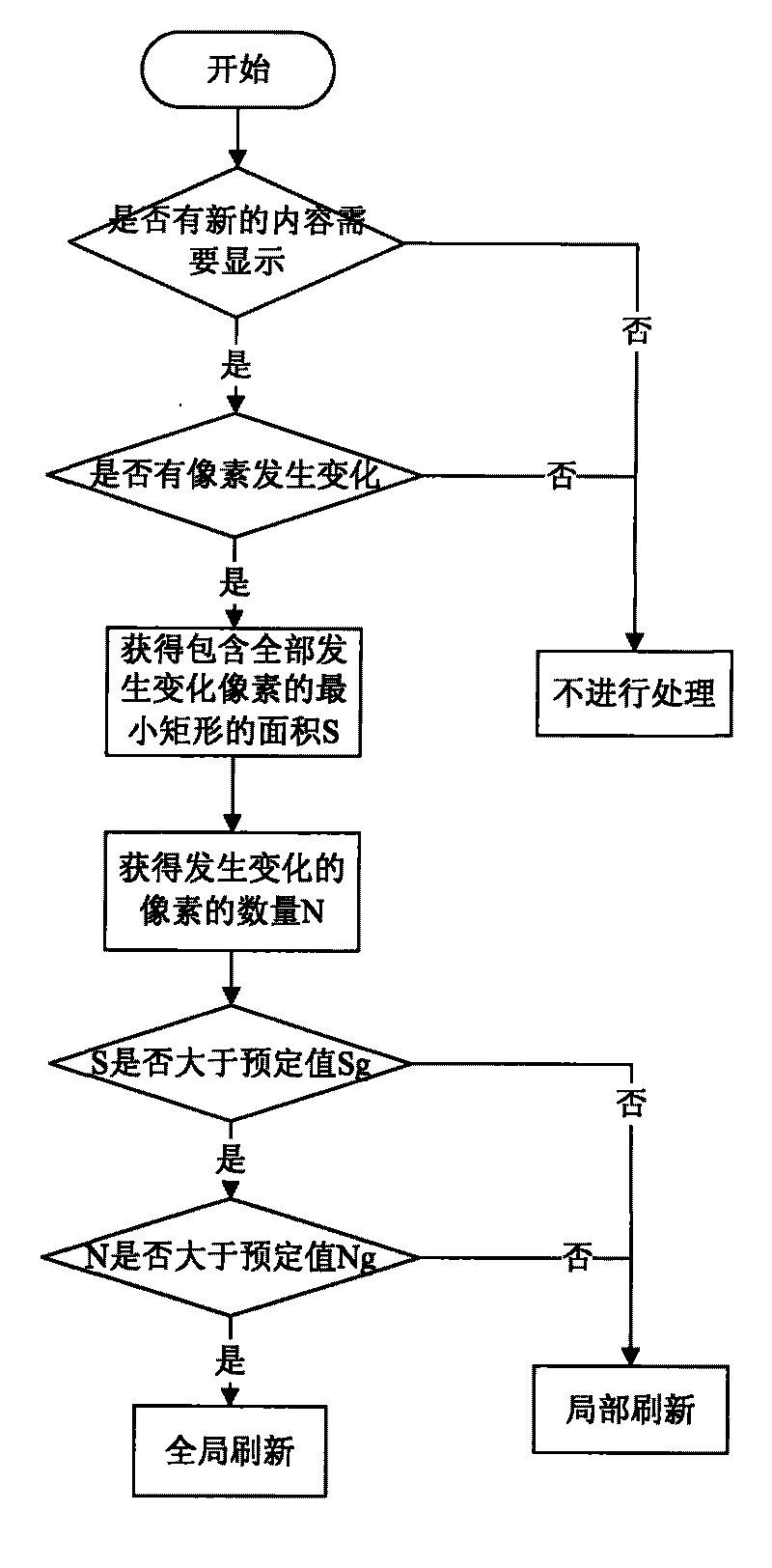

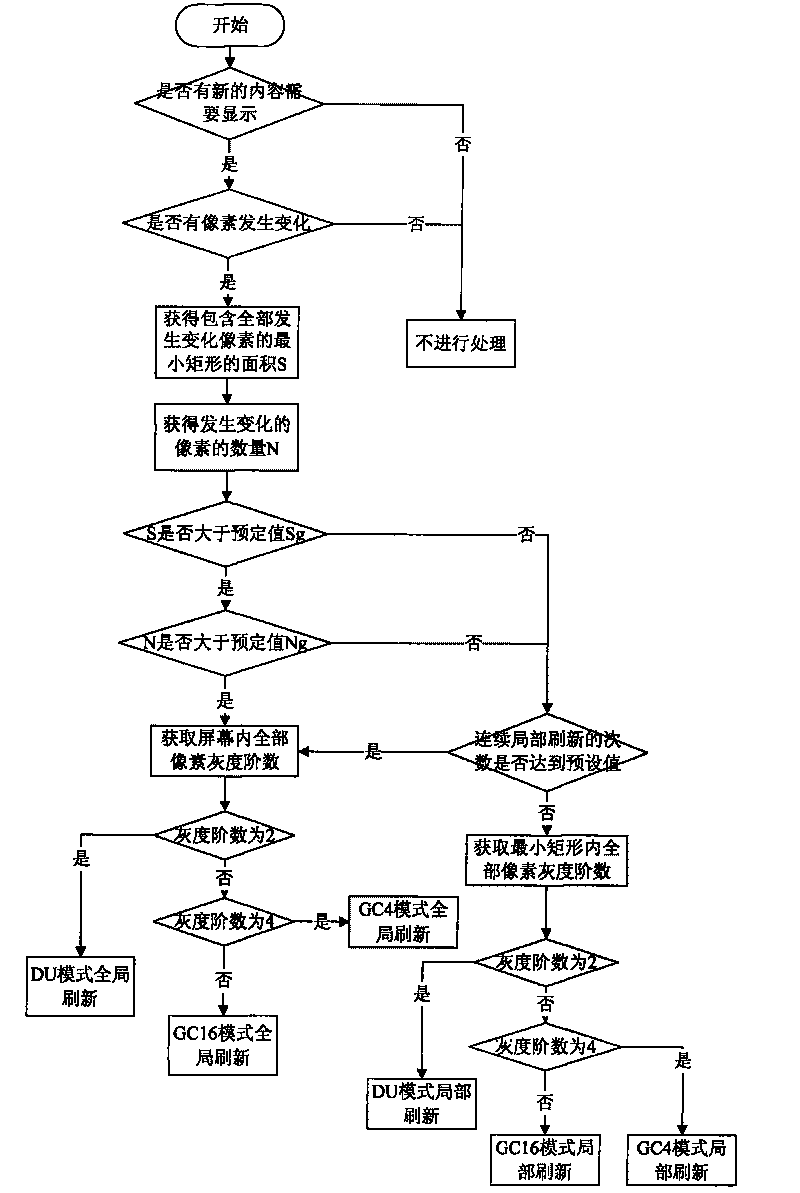

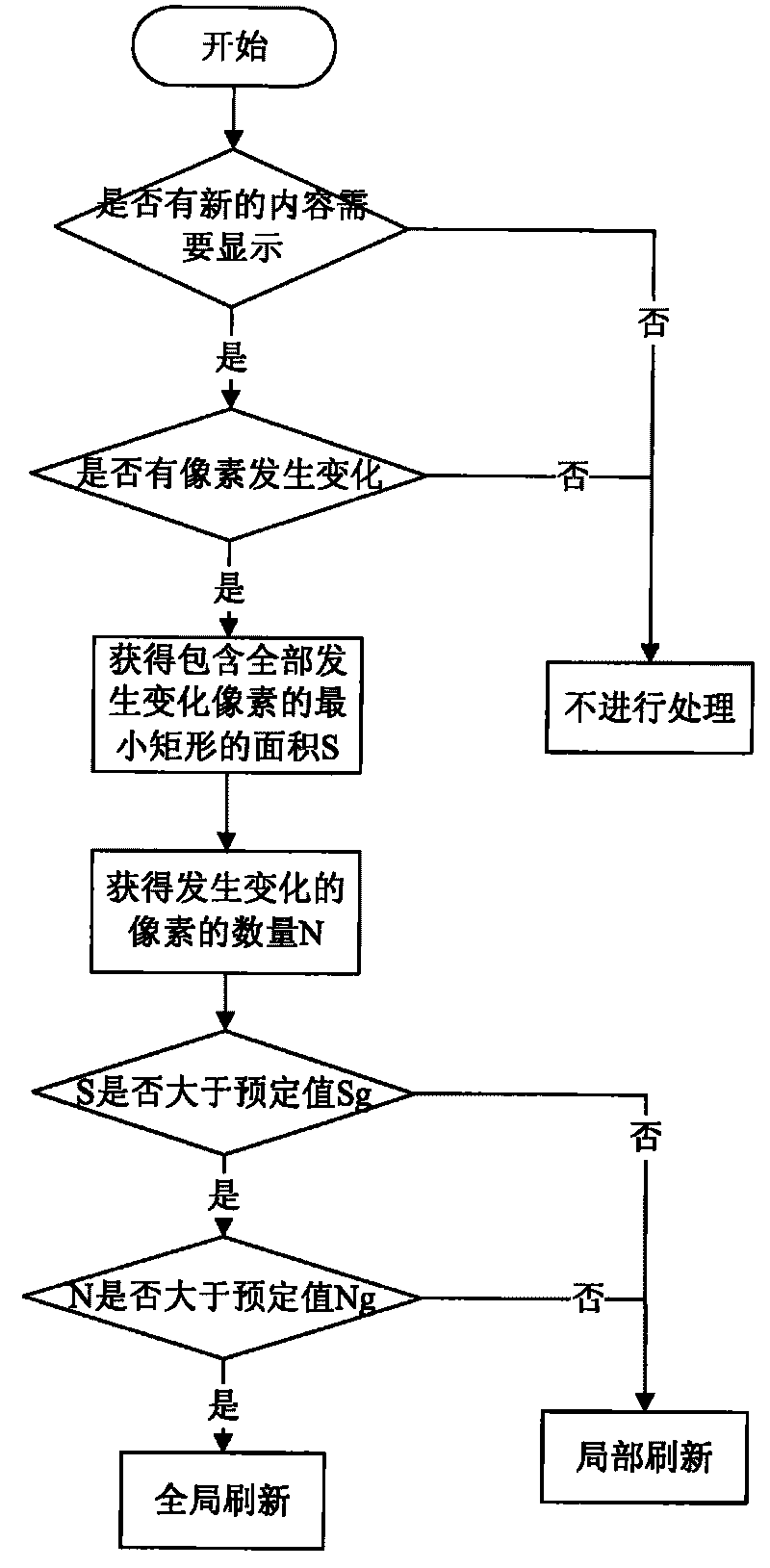

InactiveCN101727836AReduce the refresh rateReduce flickerStatic indicating devicesComputer scienceElectronic paper

In order to solve the problem of frequent flashing when an E-ink electronic paper screen is used in the prior art, the invention provides a display method of the E-ink electronic paper screen, which comprises the steps of: when new content needs to be displayed in the E-ink electronic paper screen, comparing the content displayed in the current E-ink electronic paper screen with the new content; if the change of pixels occurs, computing a minimum rectangle containing all changed pixels in the E-ink electronic paper screen; if the number of the changed pixels is greater than the number of the preset pixels and the area of the minimum rectangle is greater than the area of the preset rectangle, carrying out the globally refreshing process in the range of the E-ink electronic paper screen; and otherwise, carrying out the locally refreshing process. The invention can effectively solve the problem of flashing of the E-ink electronic paper screen.

Owner:北京登合科技有限公司

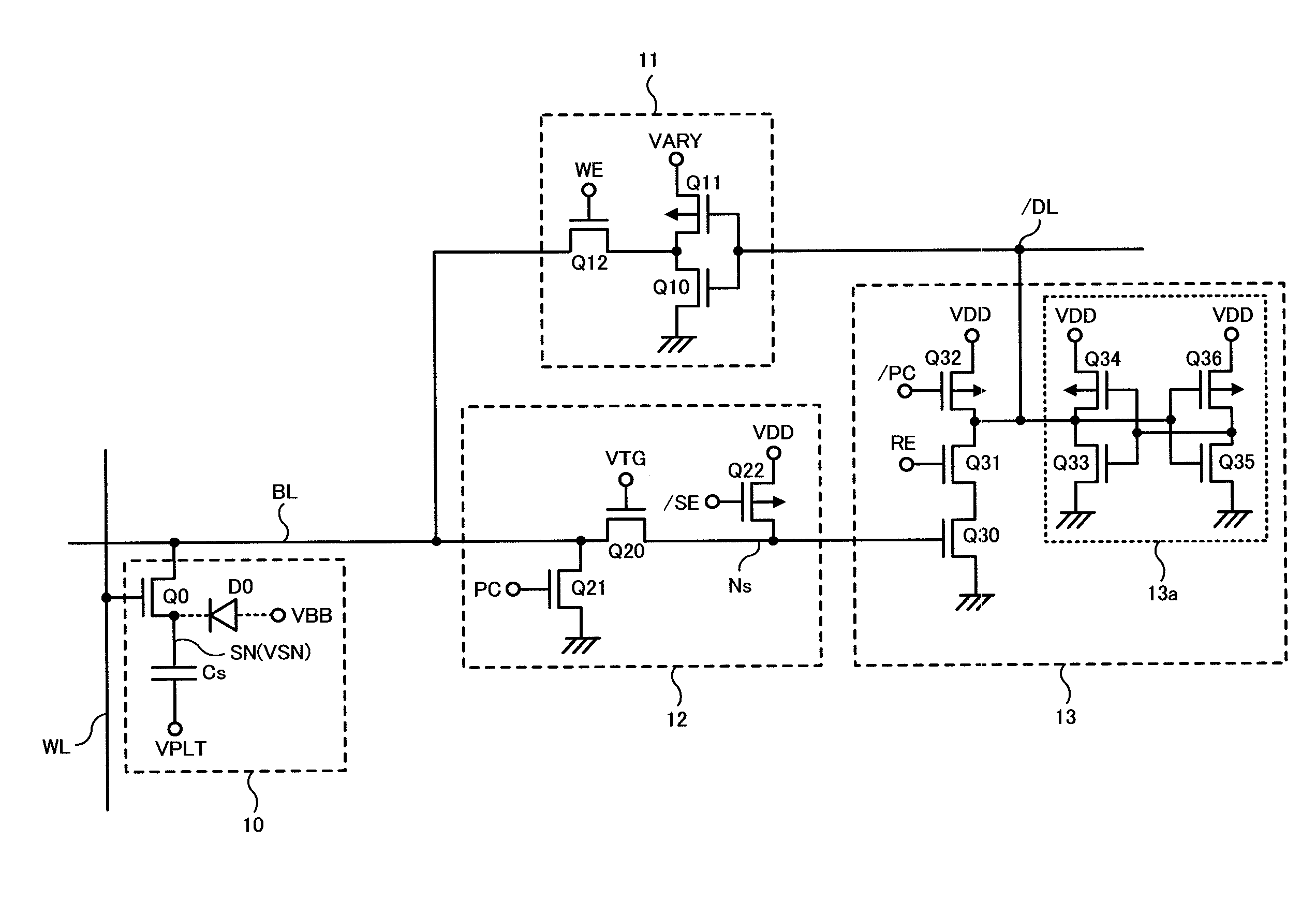

Semiconductor memory

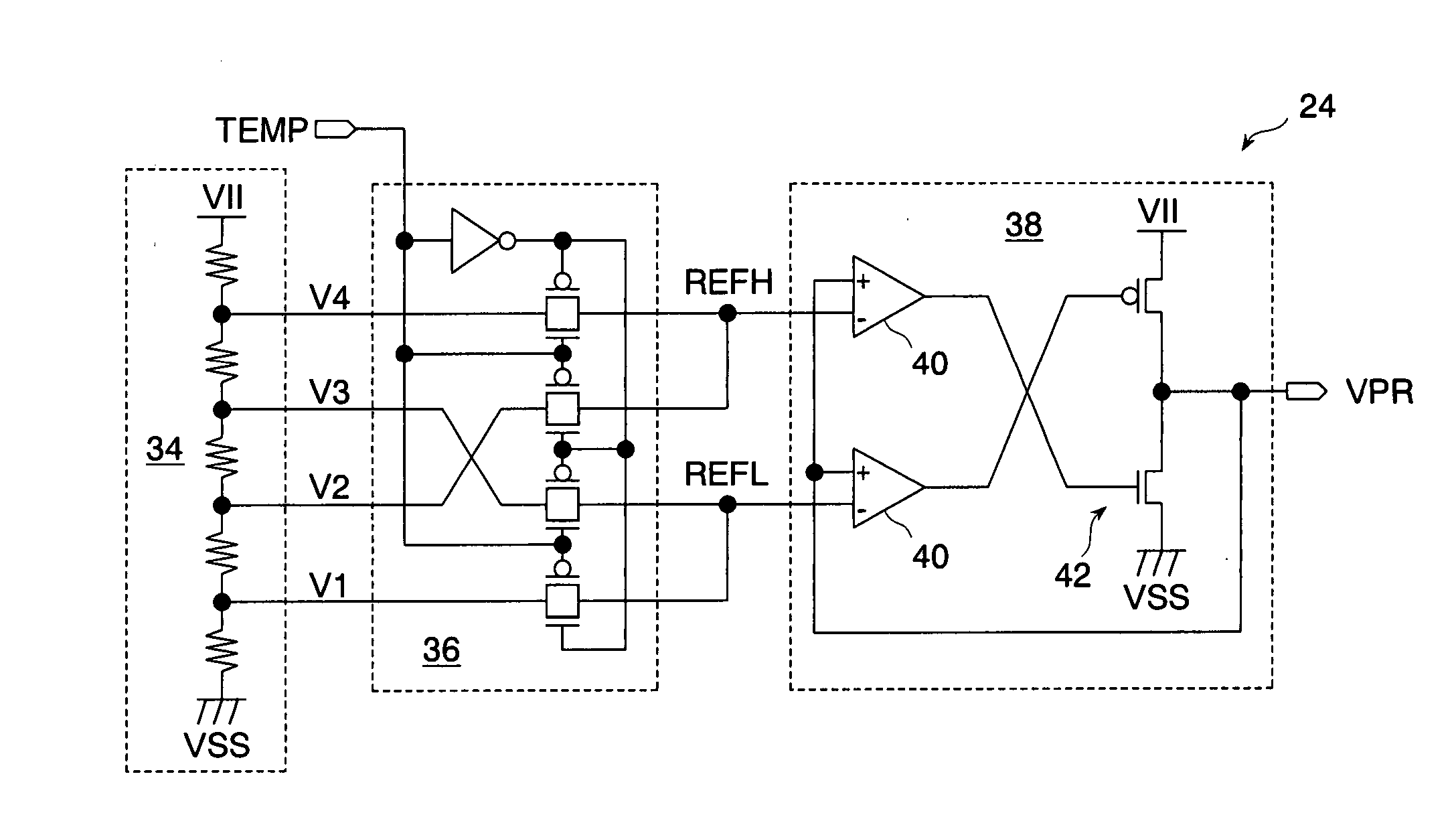

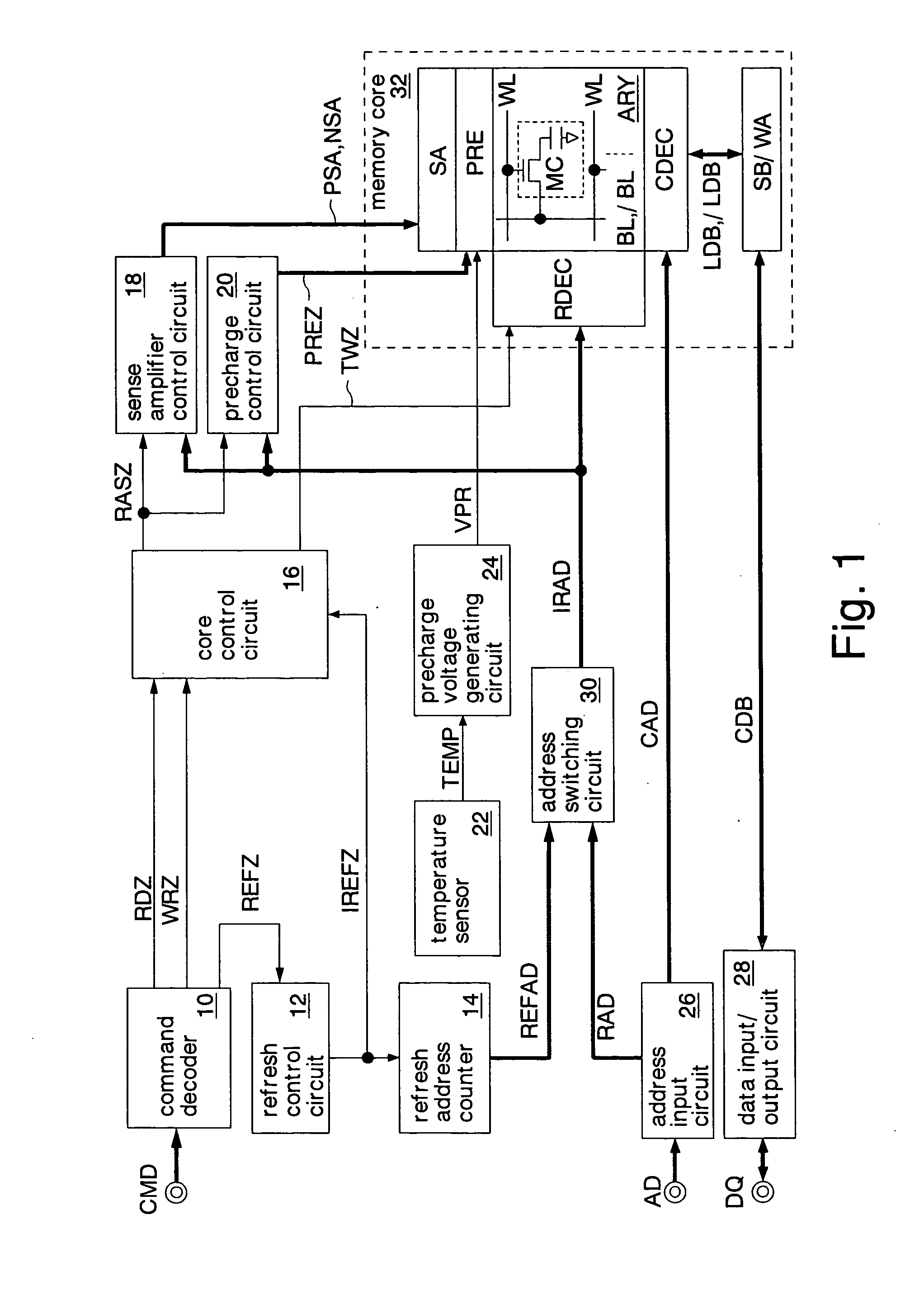

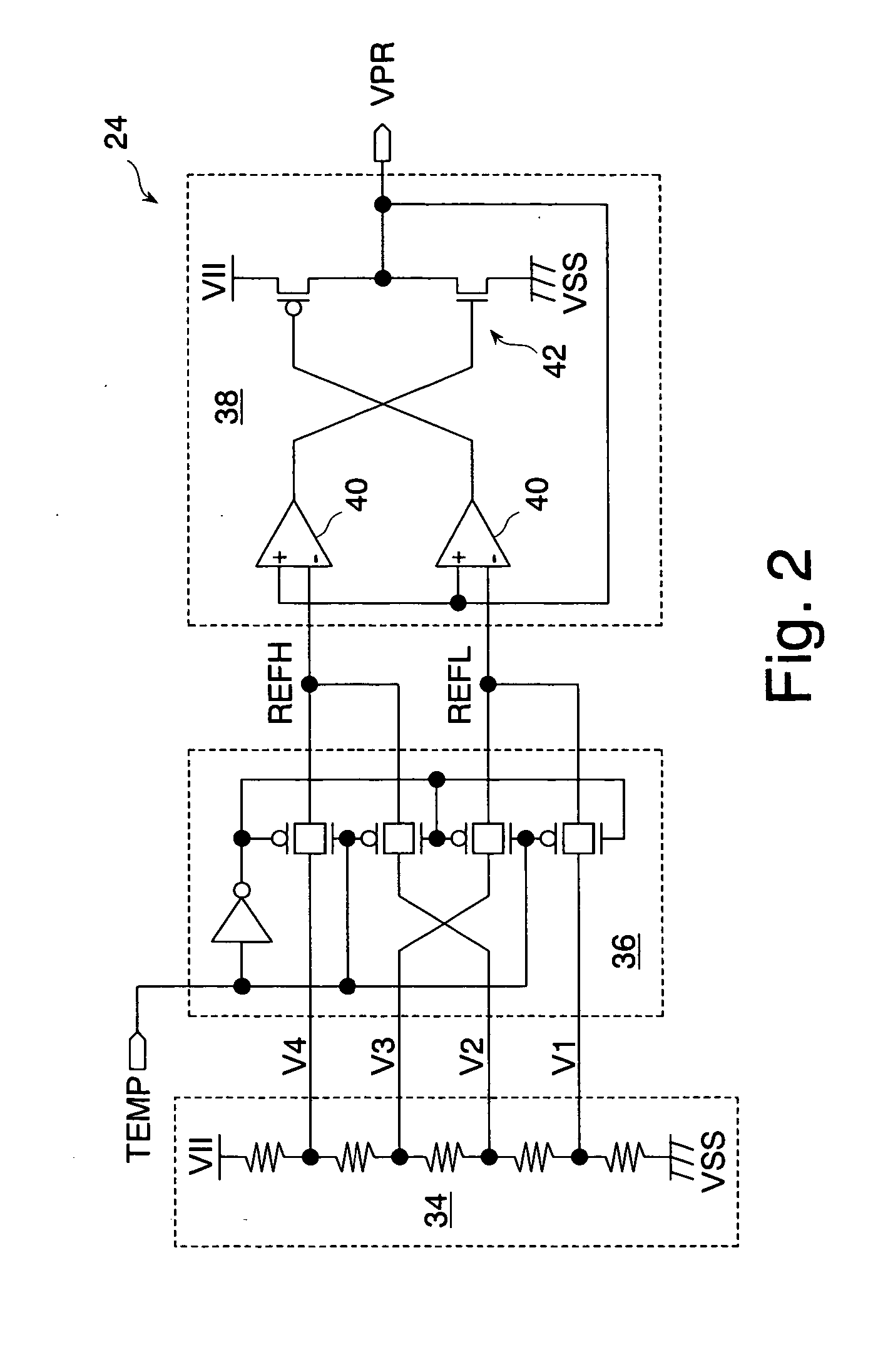

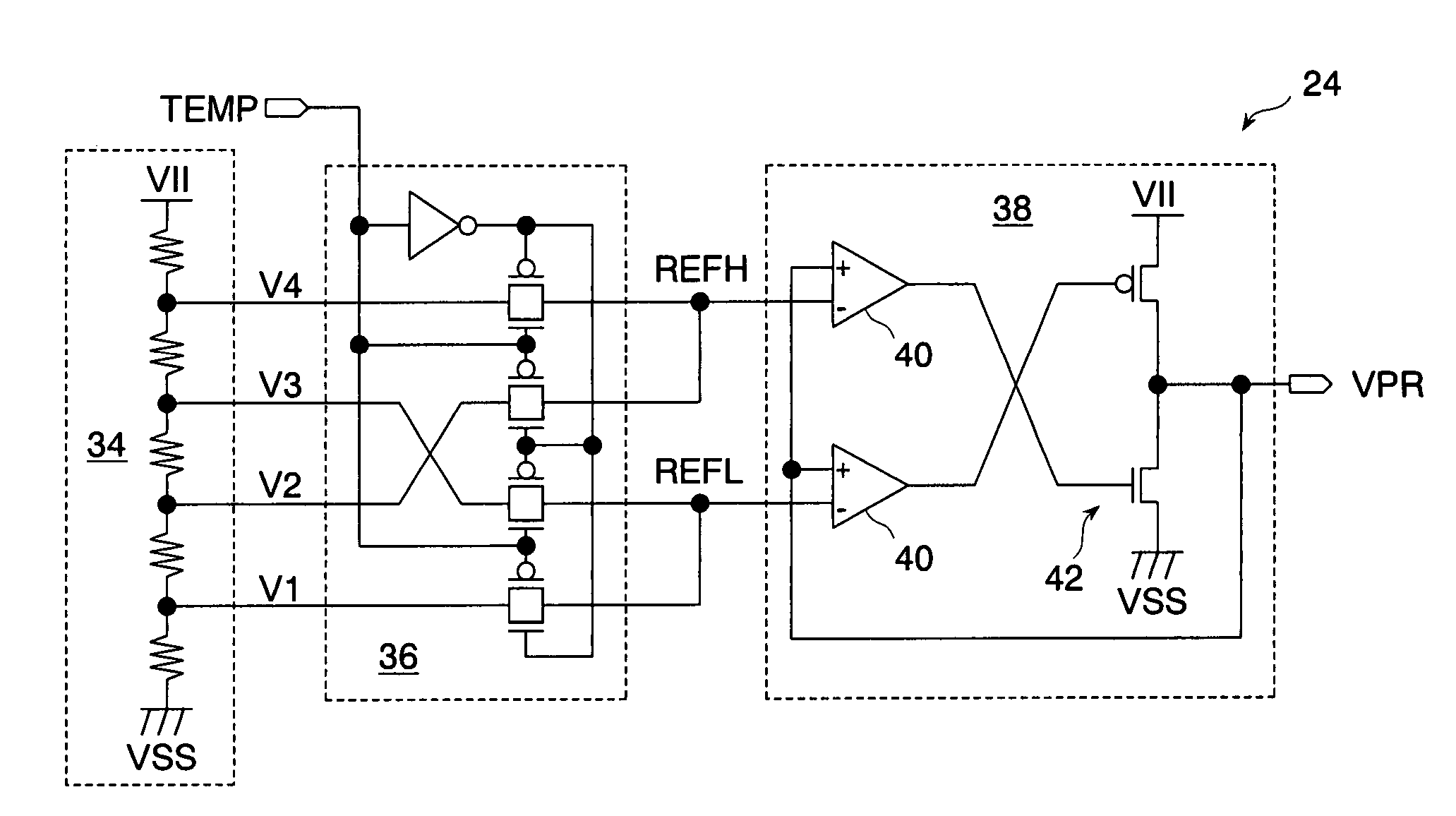

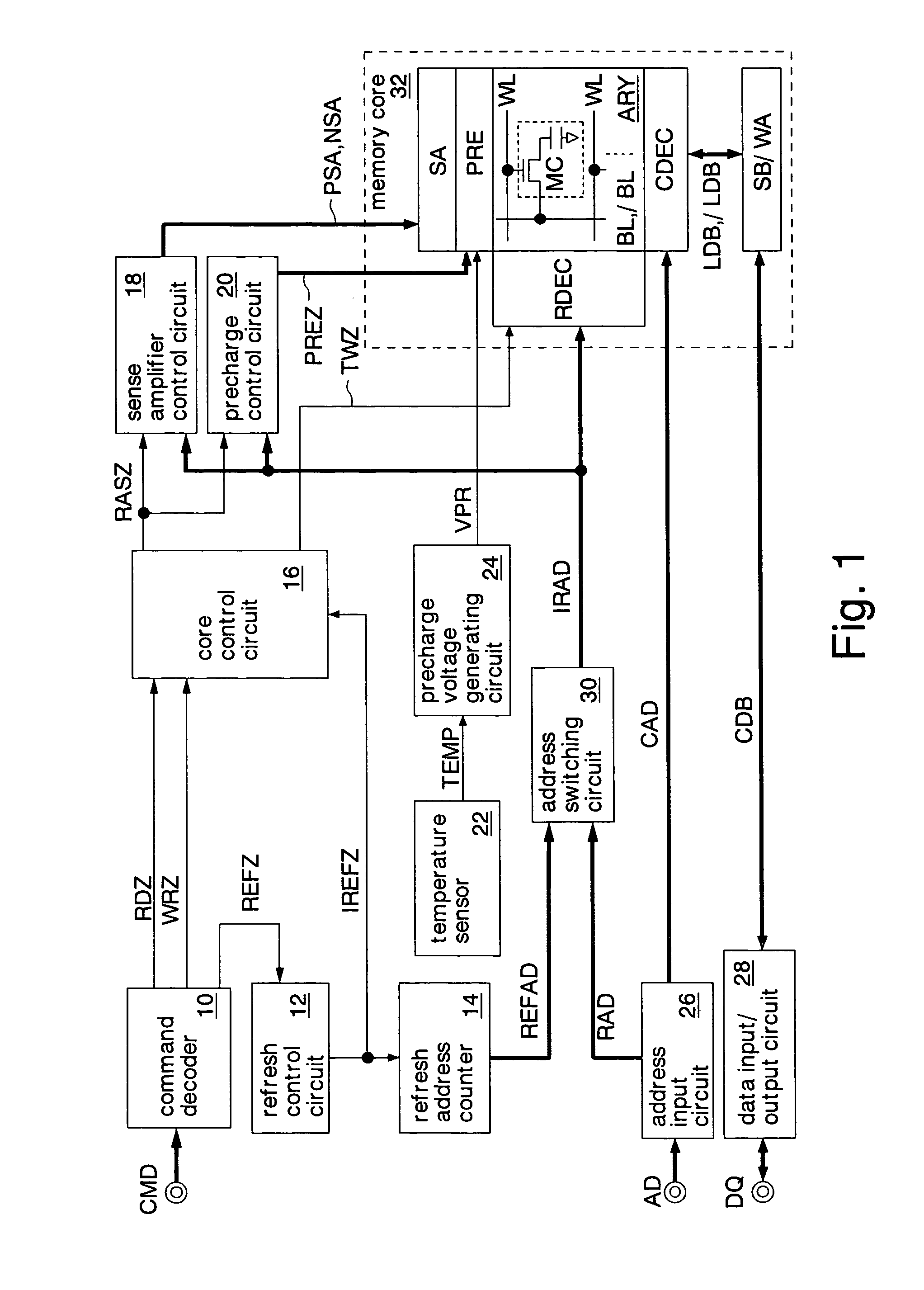

ActiveUS20070091703A1Easy switch controlPrevent circuit scaleDigital storageBit lineAudio power amplifier

A precharge voltage generating circuit outputs any of a plurality of kinds of precharge voltages in accordance with an ambient temperature. A precharge circuit supplies the precharge voltage to a bit line during the nonaccess of a dynamic memory cell. A sense amplifier amplifies a difference between the voltage of a data signal read from the dynamic memory cell onto the bit line and the supplied precharge voltage. The precharge voltage is altered in accordance with the ambient temperature, whereby the read margin of the sense amplifier can be changed, and the worst value of the data retaining time of the memory cell can be improved. As a result, the frequency of refreshing of the memory cell can be lowered, reducing power consumption and a standby current.

Owner:SOCIONEXT INC

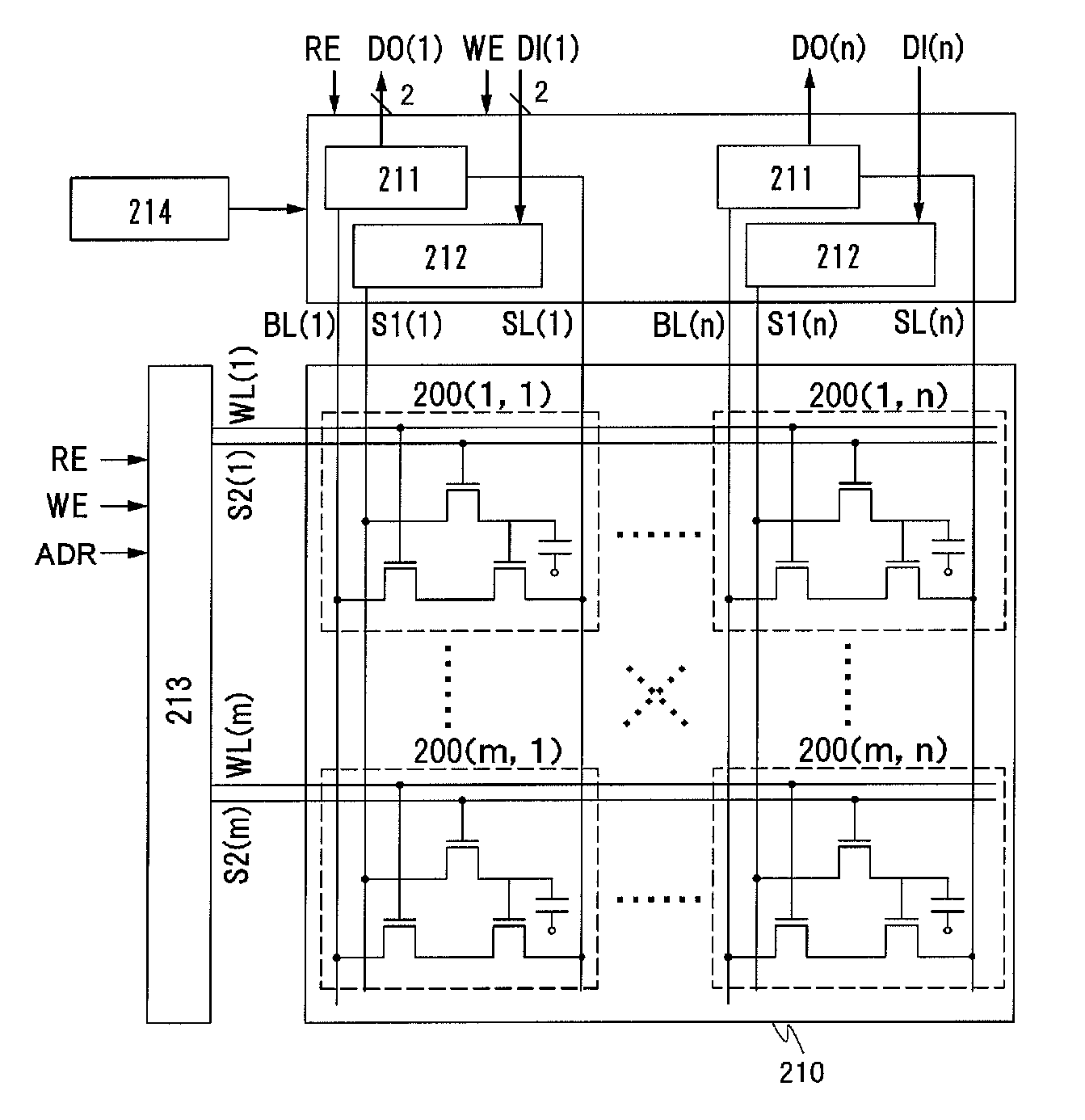

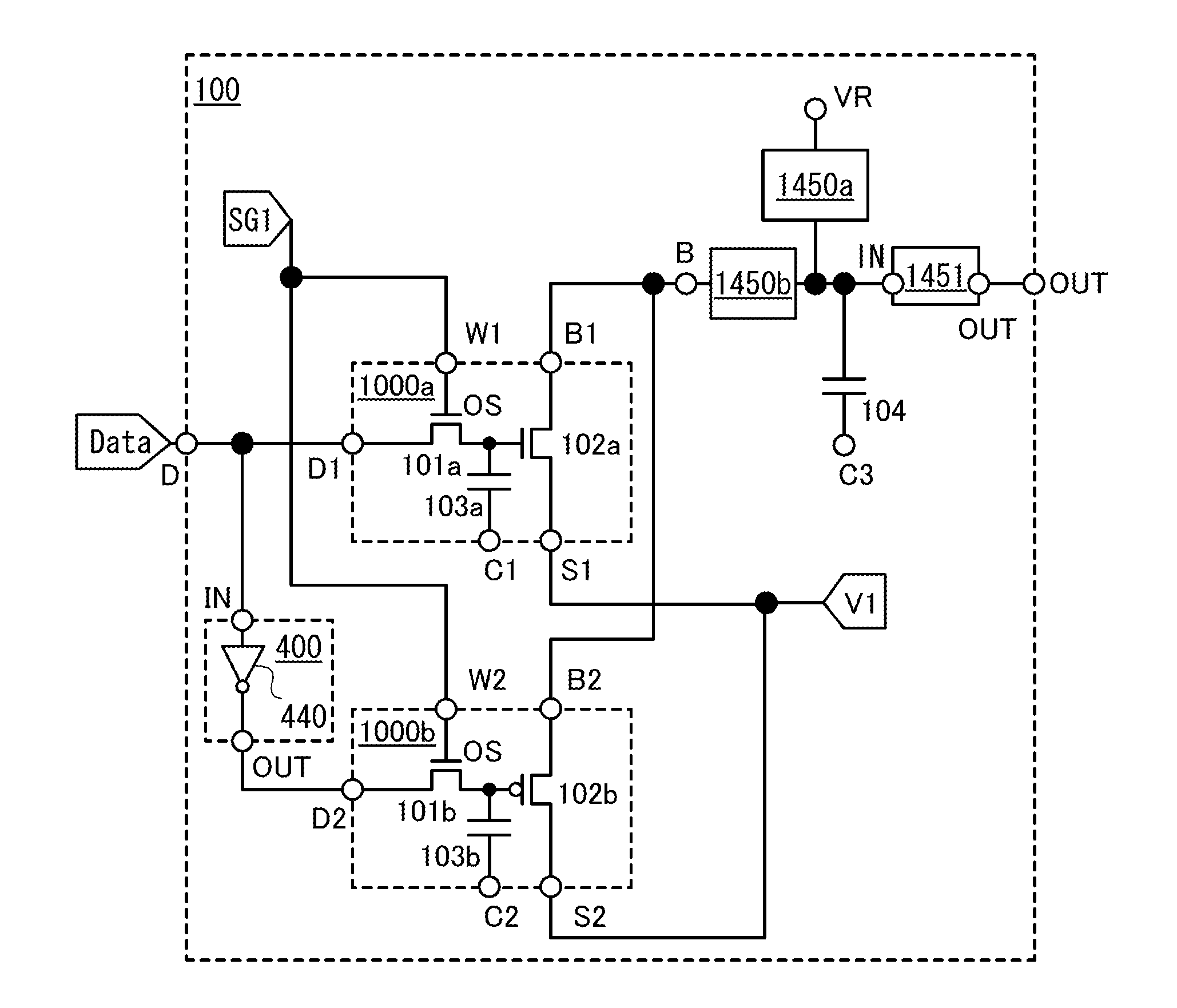

Memory element and signal processing circuit

ActiveUS20120230138A1Reduce the refresh rateIncrease number of rewritable timeDigital data processing detailsRead-only memoriesSignal processing circuitsHemt circuits

A memory element having a novel structure and a signal processing circuit including the memory element are provided. A first circuit, including a first transistor and a second transistor, and a second circuit, including a third transistor and a fourth transistor, are included. A first signal potential and a second signal potential, each corresponding to an input signal, are respectively input to a gate of the second transistor via the first transistor in an on state and to a gate of the fourth transistor via the third transistor in an on state. After that, the first transistor and the third transistor are turned off. The input signal is read out using both the states of the second transistor and the fourth transistor. A transistor including an oxide semiconductor in which a channel is formed can be used for the first transistor and the third transistor.

Owner:SEMICON ENERGY LAB CO LTD

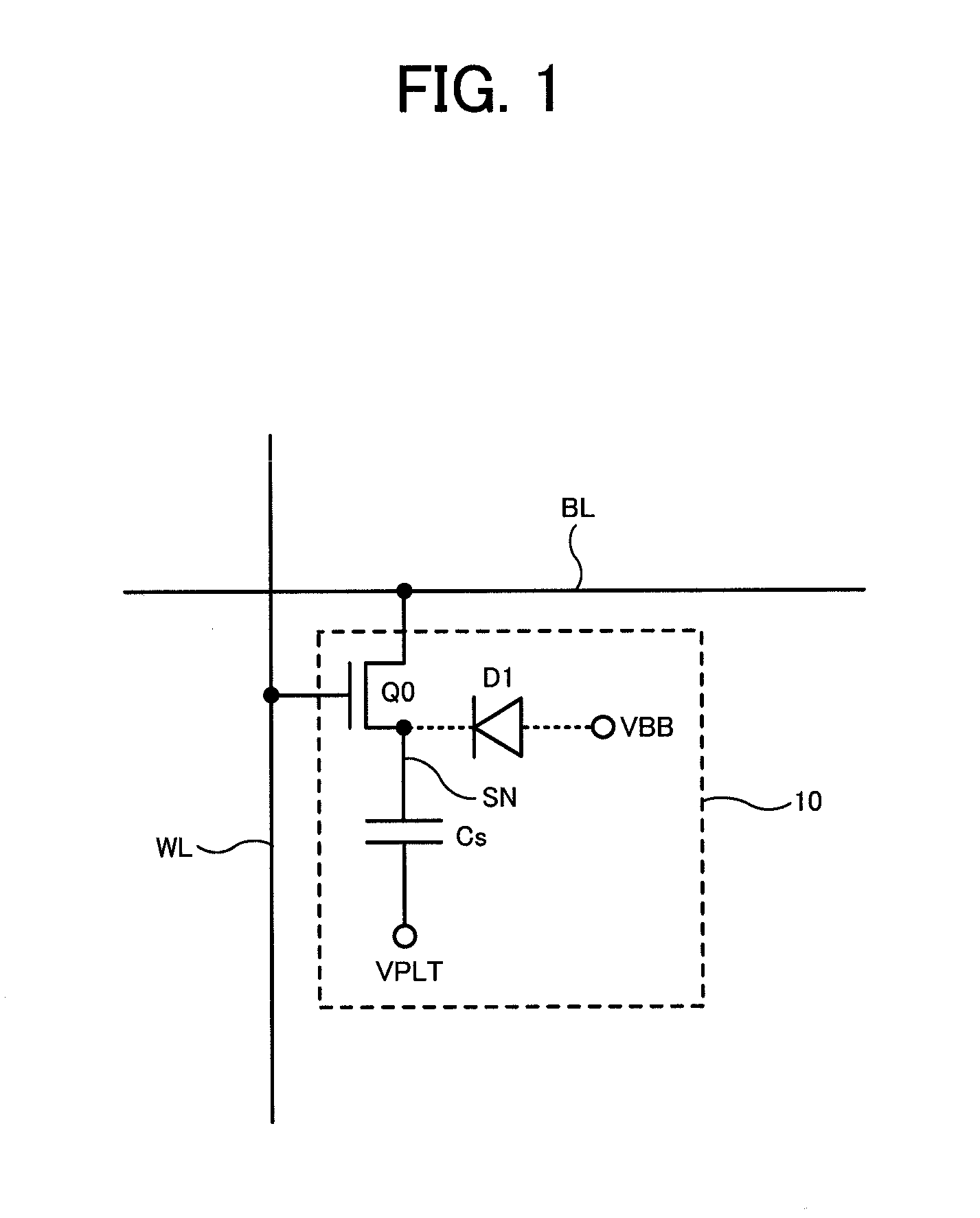

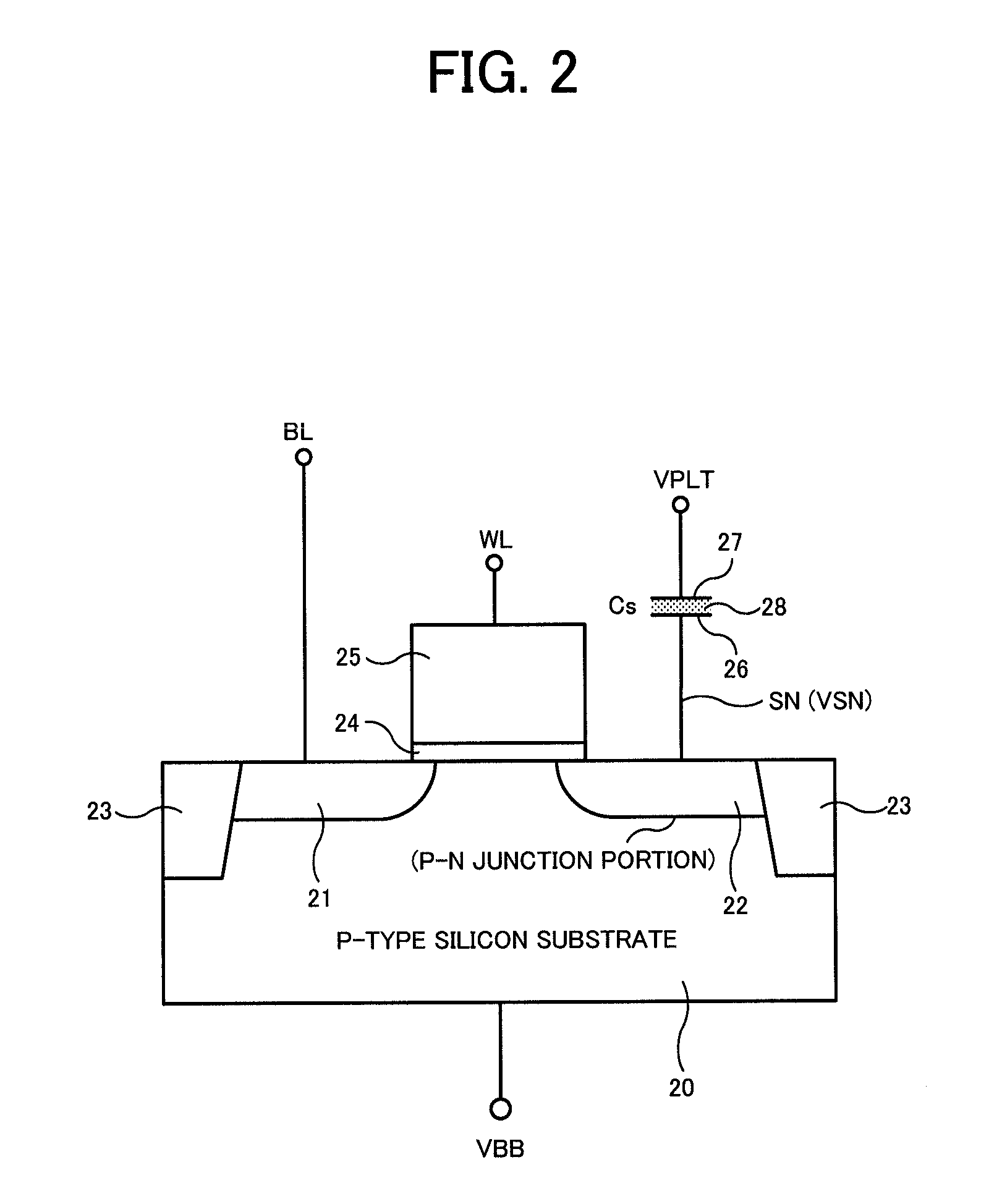

Semiconductor memory device

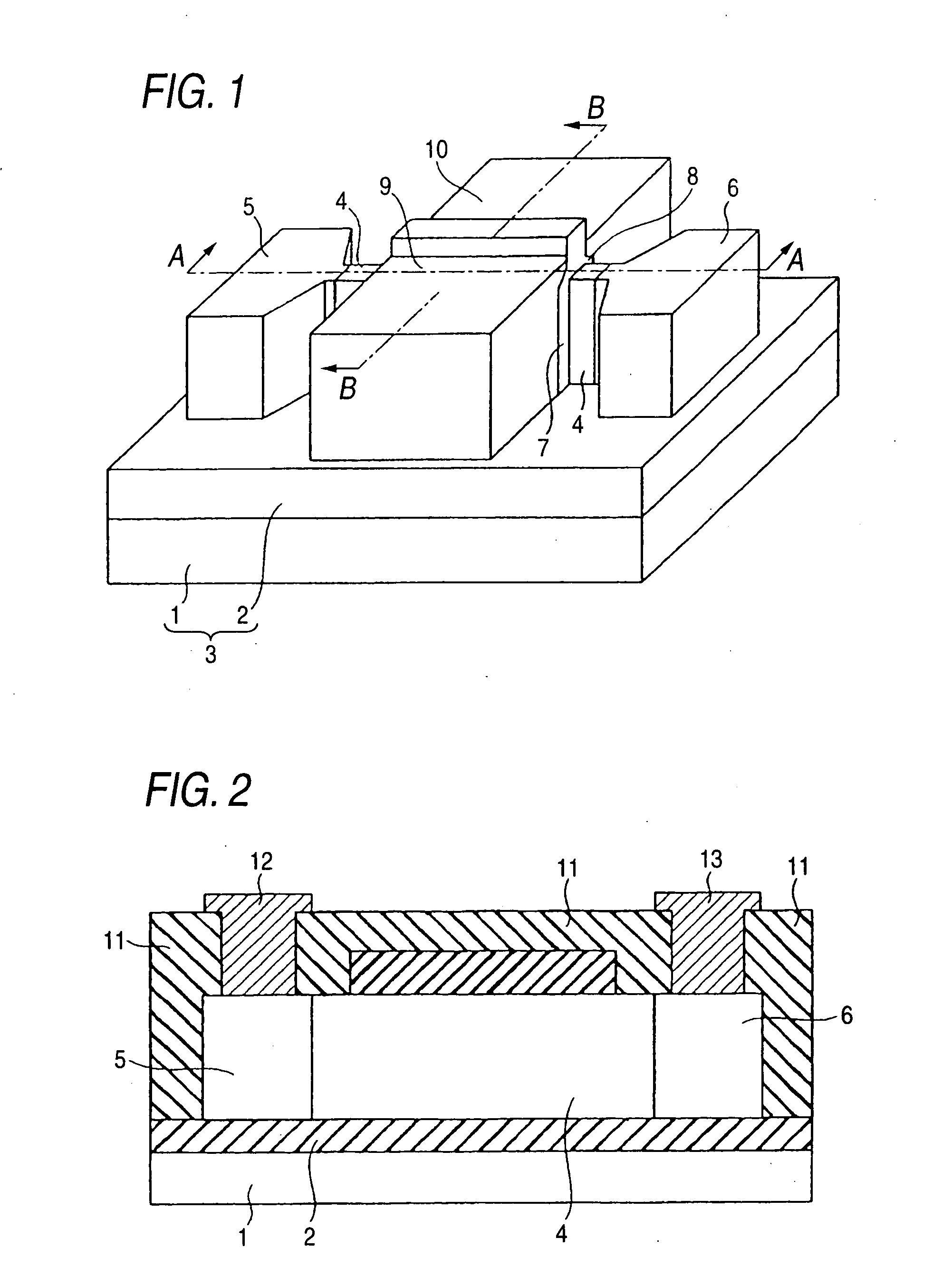

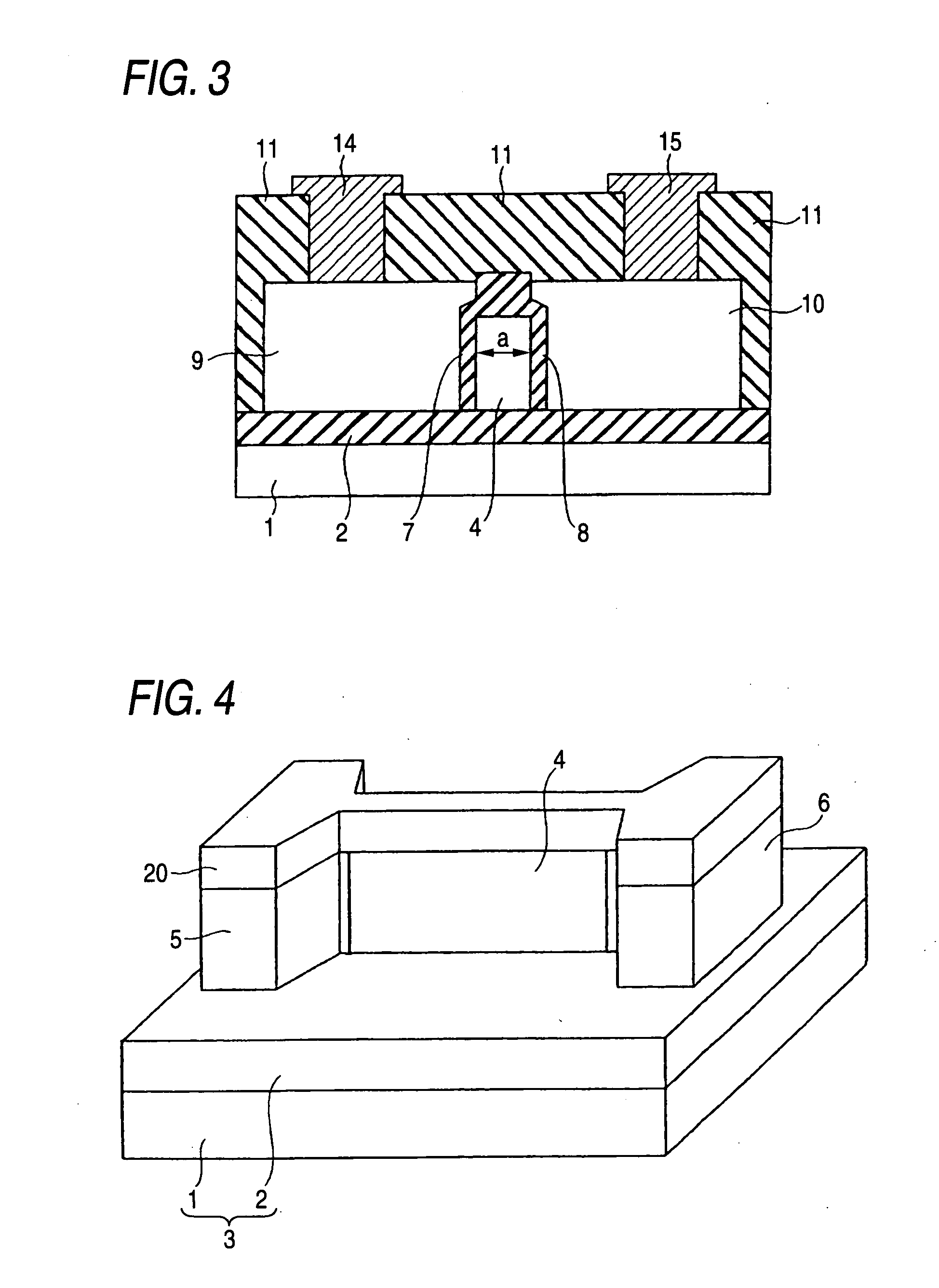

InactiveUS20060081851A1Reduce the refresh rateRun at high speedTransistorSolid-state devicesSemiconductorPhysics

A semiconductor memory device includes a semiconductor substrate, a semiconductor layer, a source / drain layer, first and second insulating films, and first and second gate electrodes. The semiconductor layer of one conductivity type is formed on a principal surface of the semiconductor substrate. The source / drain layer is formed on the principal surface with being in contact with one end of the semiconductor layer, and has a conductivity type opposite to the one conductivity type. The first insulating film is formed on one side surface of the semiconductor layer. The second insulating film is formed on another side surface of the semiconductor layer. The first gate electrode is formed on the one side surface via the first insulating film. The second gate electrode is formed on the other side surface of the semiconductor layer via the second insulating film, and is opposed to the first gate electrode.

Owner:KK TOSHIBA

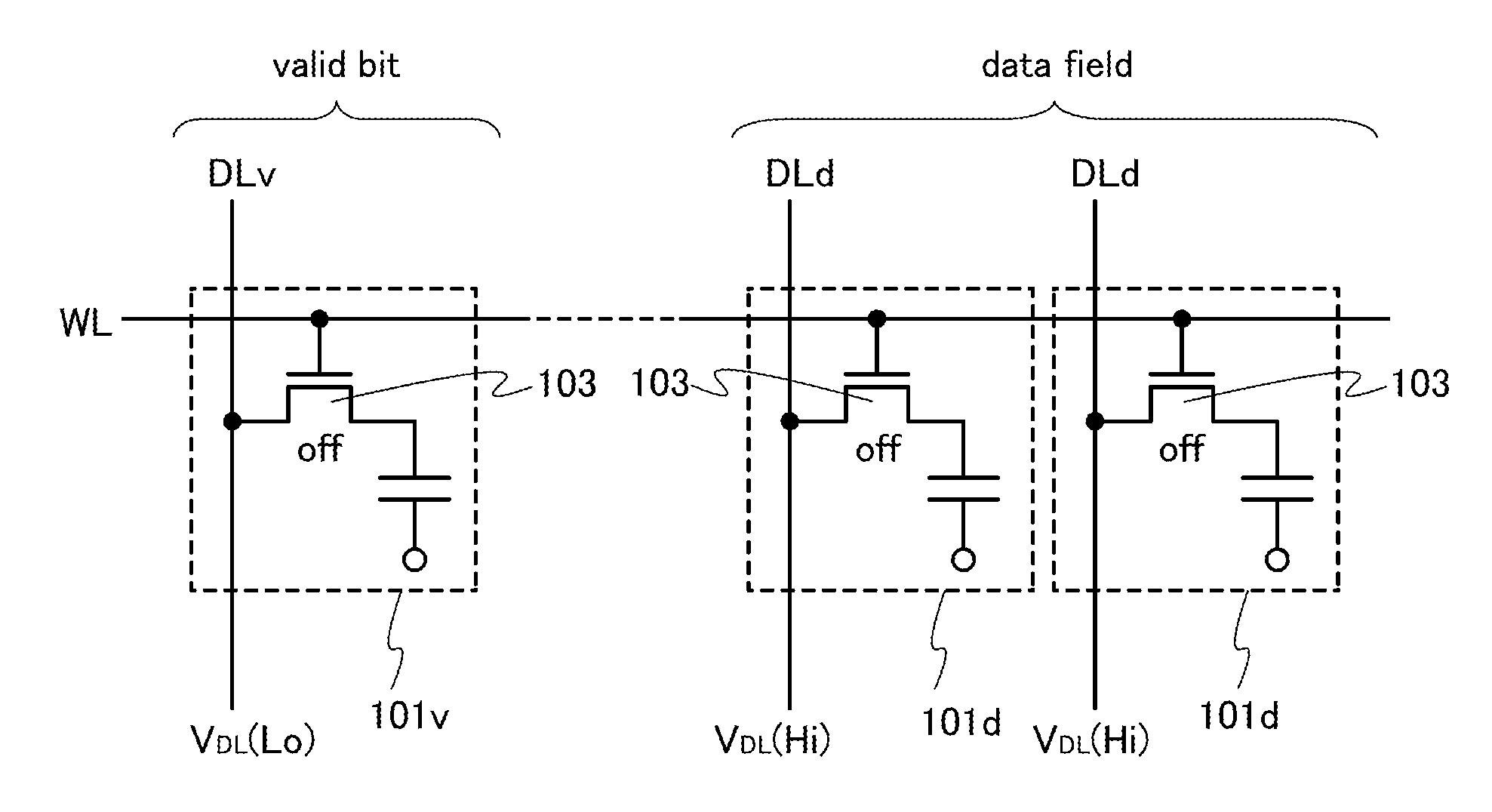

Memory device and semiconductor device using the same

InactiveUS20120257439A1Reduce the refresh rateReduce the numberDigital storageOxide semiconductorSemiconductor components

A memory device whose speed at the time of operation such as writing or reading is high and whose number of semiconductor elements per memory cell is small is provided. The memory device includes a control unit, an arithmetic unit, and a buffer memory device. The buffer memory device stores data sent from a main memory device and / or the arithmetic unit, in accordance with an instruction from the control unit. The buffer memory device includes a plurality of memory cells. The memory cells each include a transistor including a channel formation region including an oxide semiconductor, and a memory element to which charge with an amount in accordance with a value of the data is supplied through the transistor. Further, a data retention time of the memory cell corresponding to a valid bit is shorter than a data retention time of the memory cell corresponding to a data field.

Owner:SEMICON ENERGY LAB CO LTD

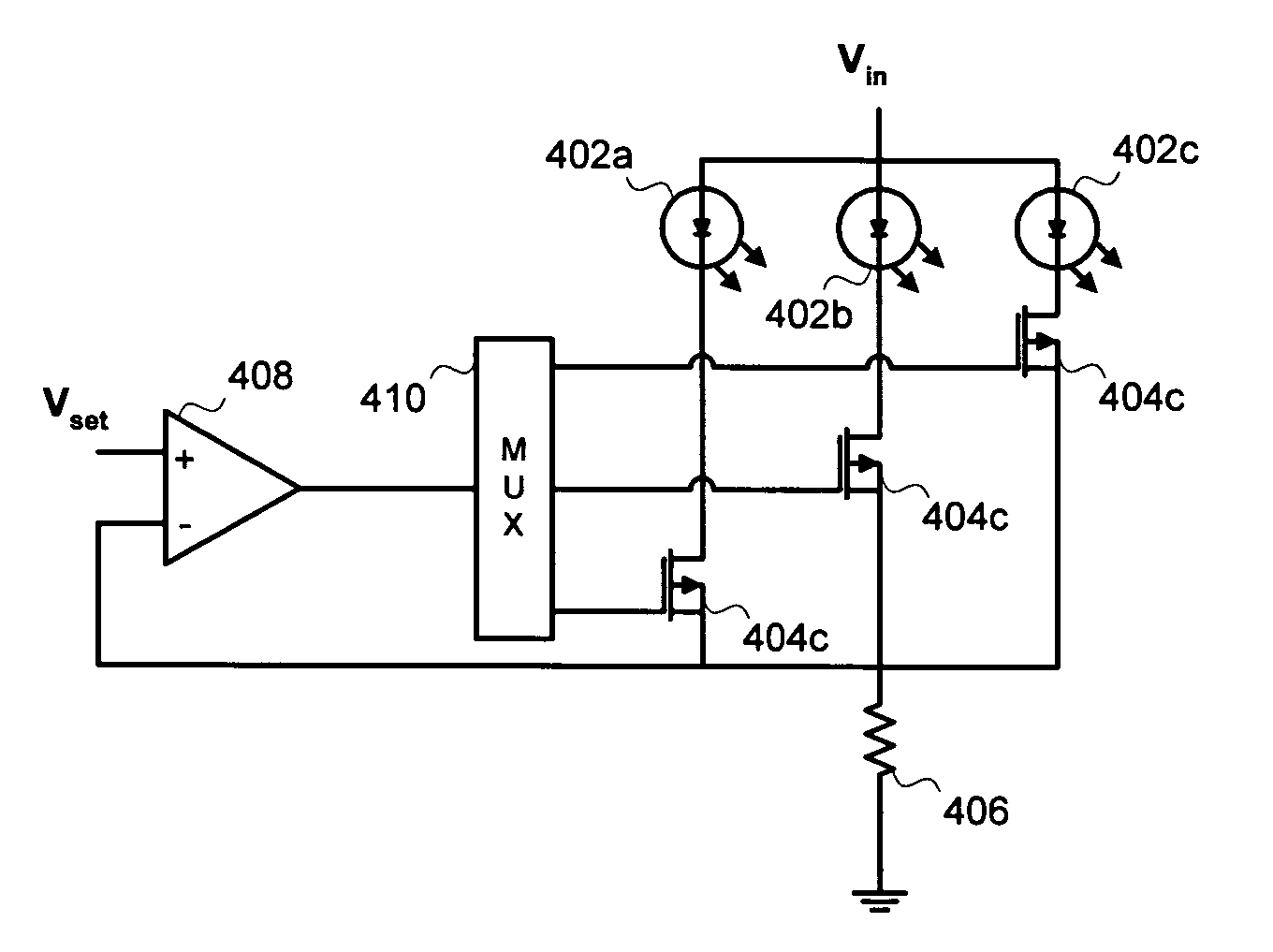

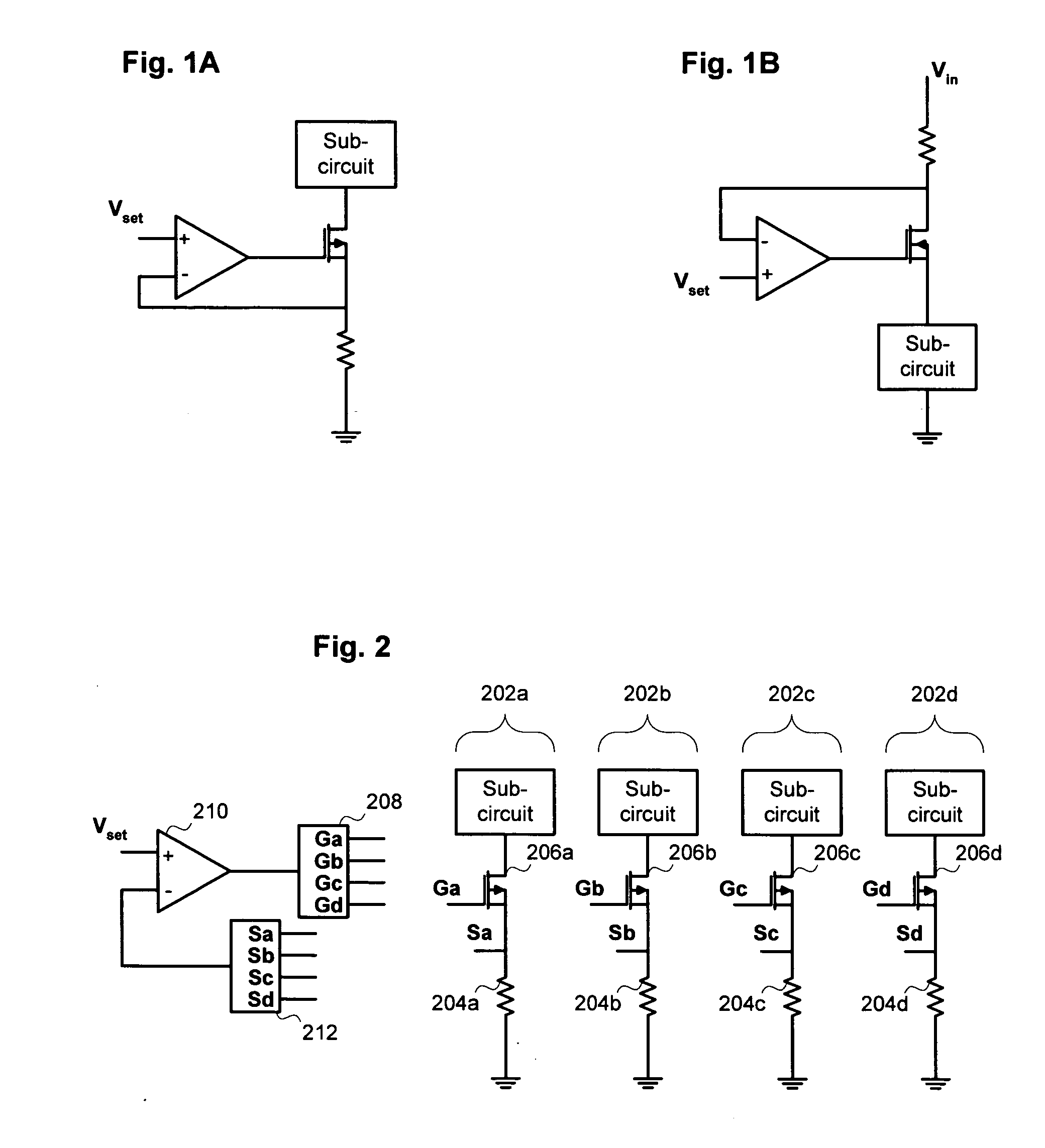

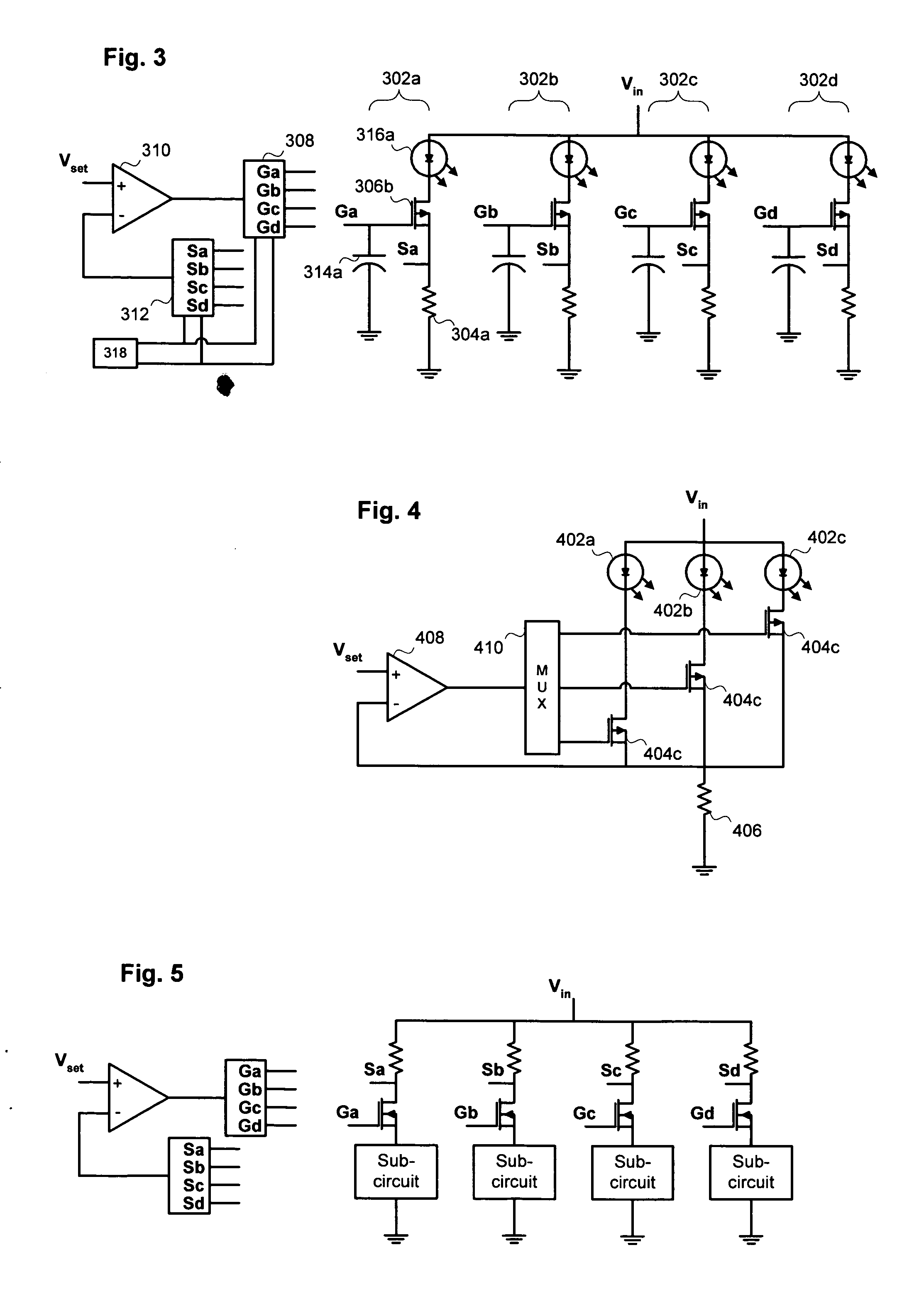

Single, multiplexed operational amplifier to improve current matching between channels

InactiveUS20060082412A1Reduce the refresh rateMaintaining regulationElectric variable regulationCapacitanceMultiplexing

A multi-channel current regulator includes two or more channels, each channel acting as a current source or sink for a respective load. Each channel regulates its load current so that the load current is proportional to an input voltage supplied to the channel. Each channel also generates a feedback voltage that is proportional to the load current of the channel. The current regulator also includes an operational amplifier. The amplifier is connected, using two multiplexors to drive one channel at a time. Each channel is selected in a rotating sequence for connection to the amplifier. Internal gate capacitance maintains each channel not connected to the amplifier at its previously set load current.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

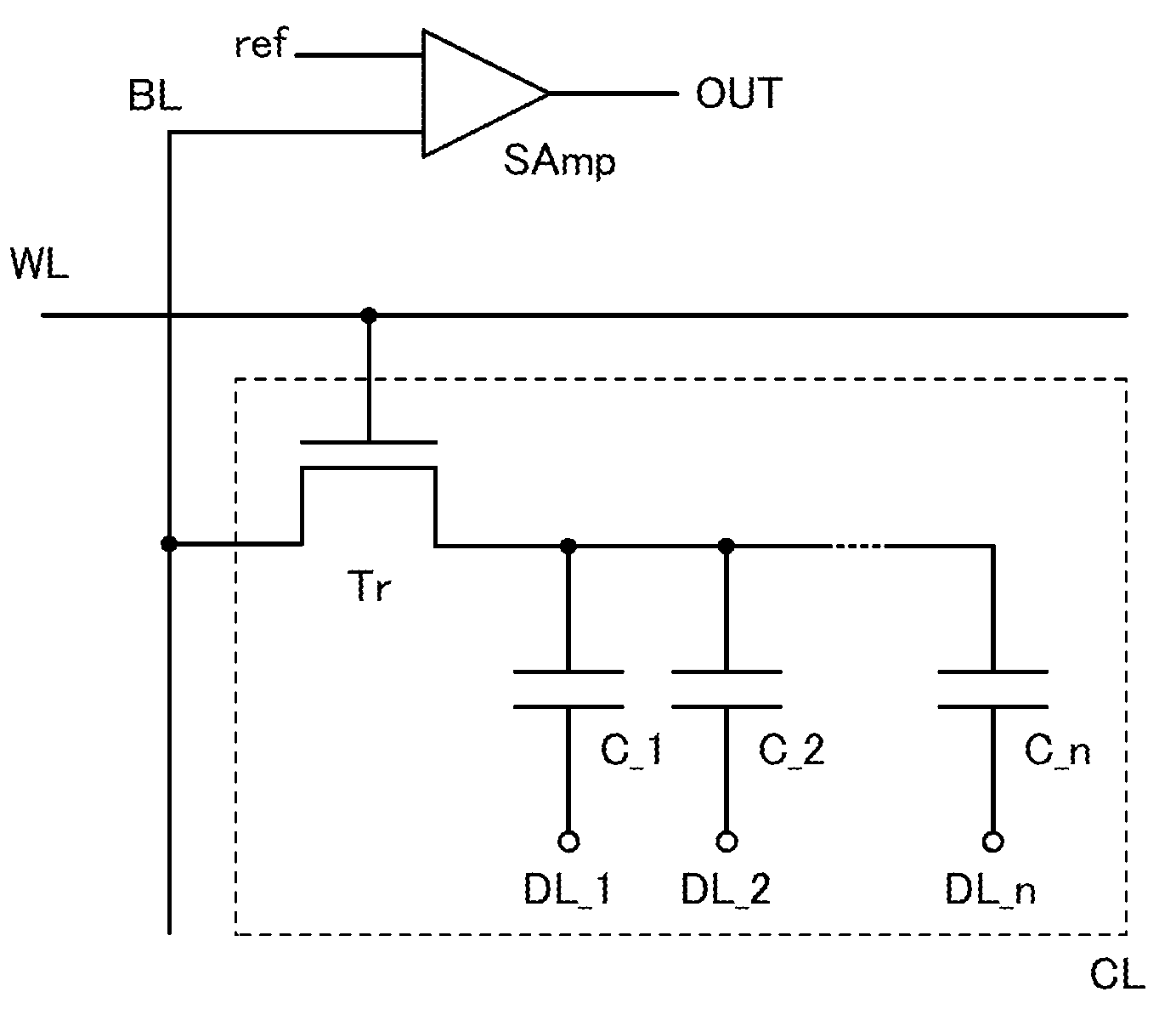

Semiconductor memory device

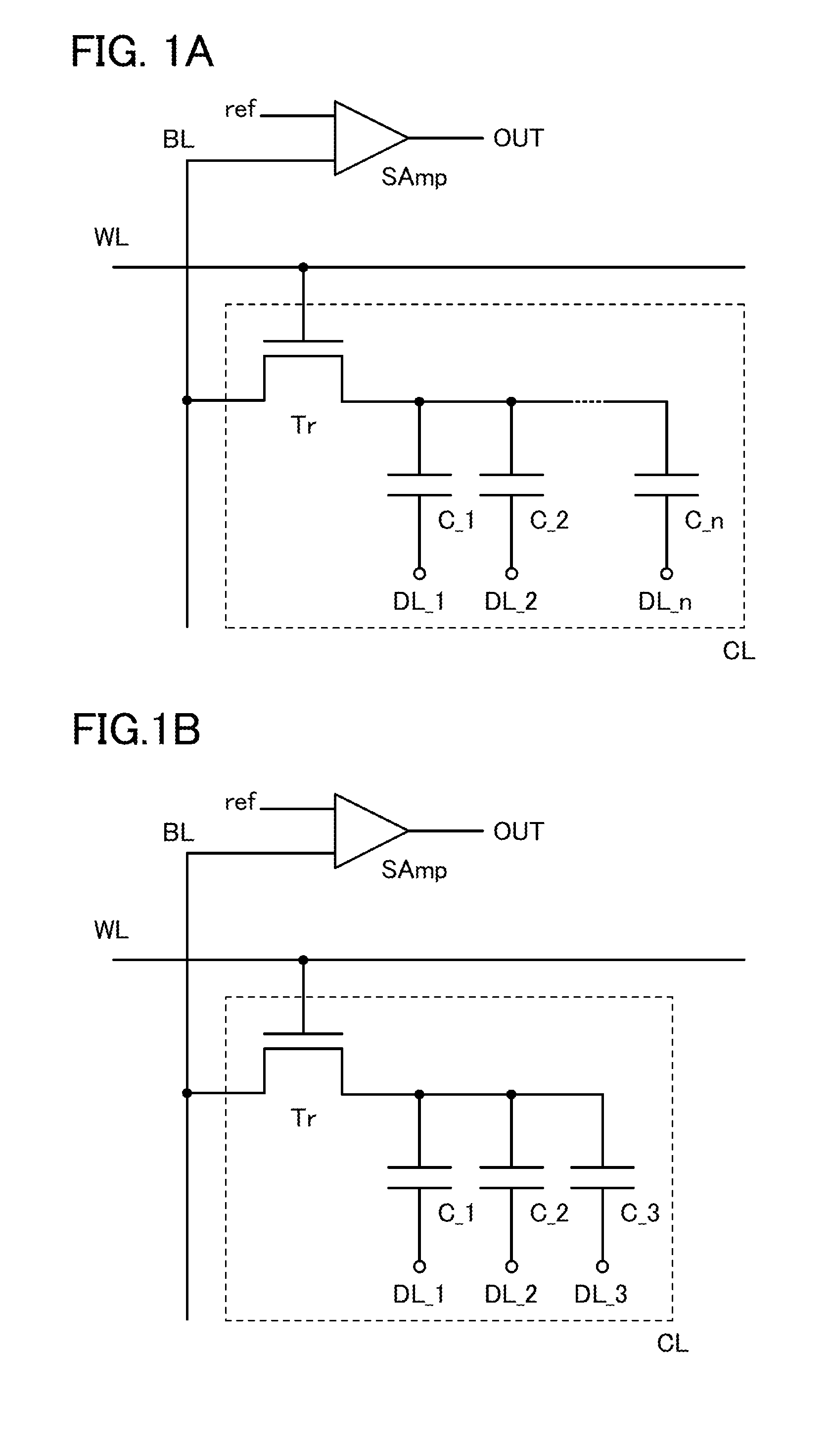

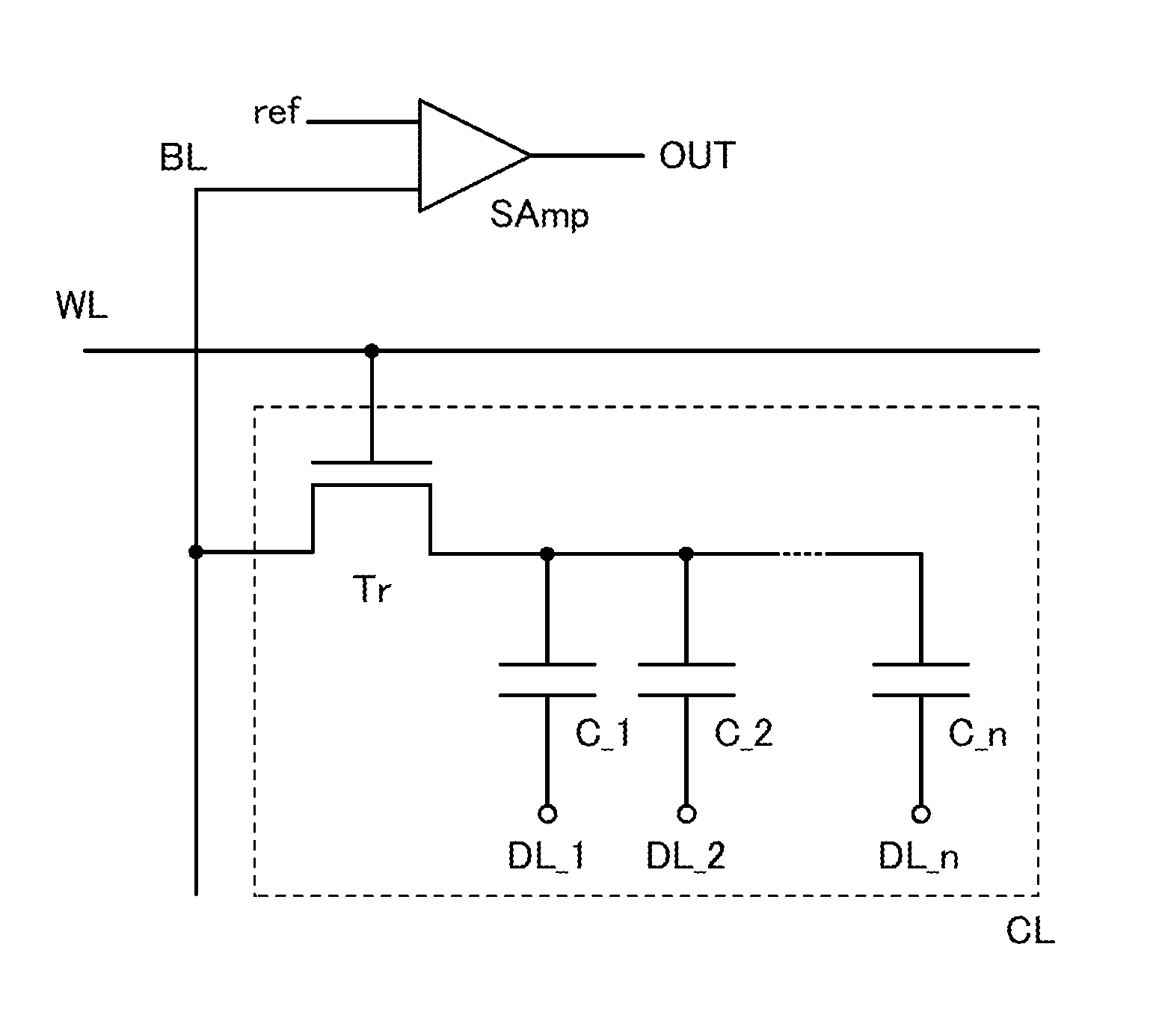

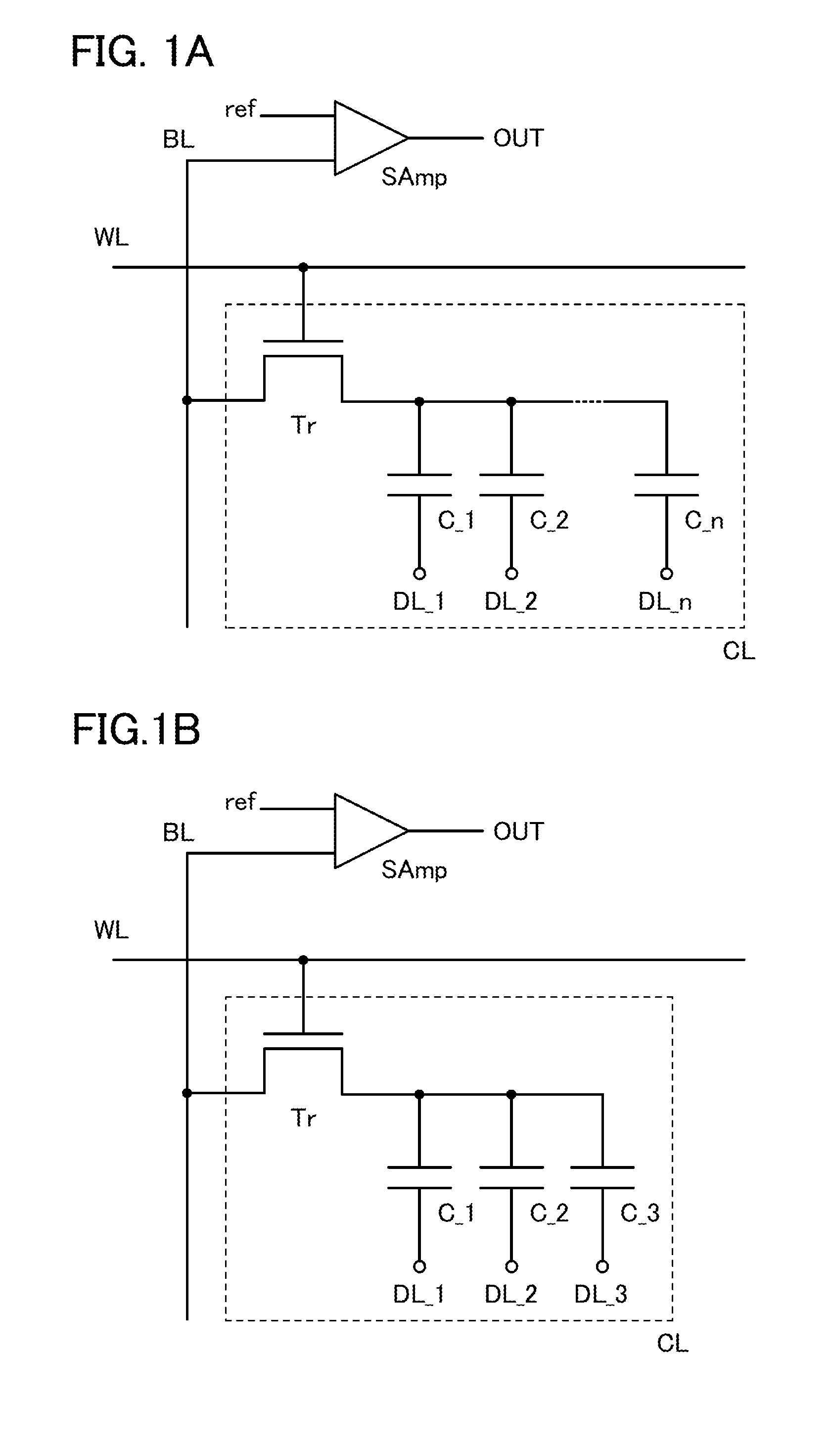

InactiveUS20120127781A1More memory capacityIncrease storage capacityTransistorSolid-state devicesCapacitanceRetention period

To increase a storage capacity of a memory module per unit area, and to provide a memory module with low power consumption, a transistor formed using an oxide semiconductor film, a silicon carbide film, a gallium nitride film, or the like, which is highly purified and has a wide band gap of 2.5 eV or higher is used for a DRAM, so that a retention period of potentials in a capacitor can be extended. Further, a memory cell has n capacitors with different capacitances and the n capacitors are each connected to a corresponding one of n data lines, so that a variety of the storage capacitances can be obtained and multilevel data can be stored. The capacitors may be stacked for reducing the area of the memory cell.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor memory having a precharge voltage generation circuit for reducing power consumption

ActiveUS7580303B2Reduce power consumptionData Retention Time EnhancementDigital storageBit lineAudio power amplifier

A precharge voltage generating circuit outputs any of a plurality of kinds of precharge voltages in accordance with an ambient temperature. A precharge circuit supplies the precharge voltage to a bit line during the nonaccess of a dynamic memory cell. A sense amplifier amplifies a difference between the voltage of a data signal read from the dynamic memory cell onto the bit line and the supplied precharge voltage. The precharge voltage is altered in accordance with the ambient temperature, whereby the read margin of the sense amplifier can be changed, and the worst value of the data retaining time of the memory cell can be improved. As a result, the frequency of refreshing of the memory cell can be lowered, reducing power consumption and a standby current.

Owner:SOCIONEXT INC

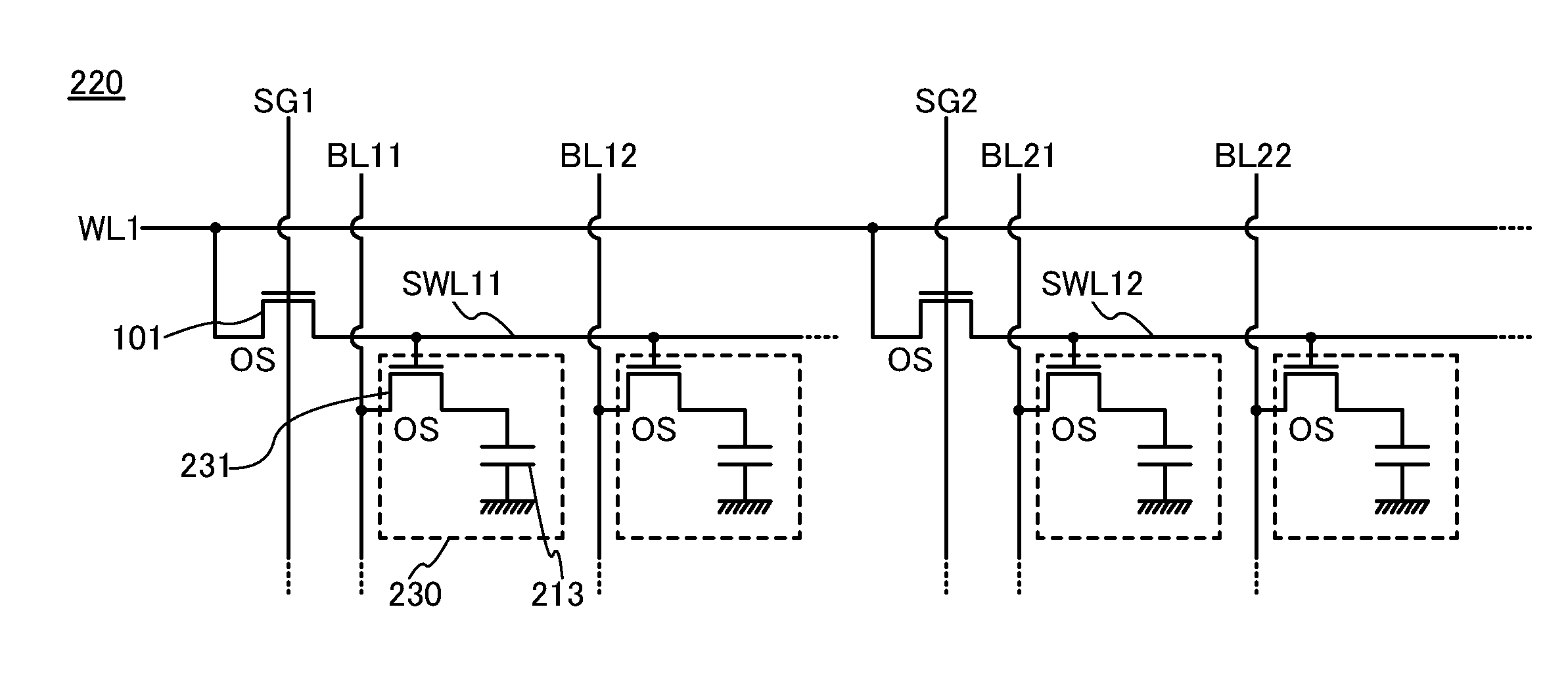

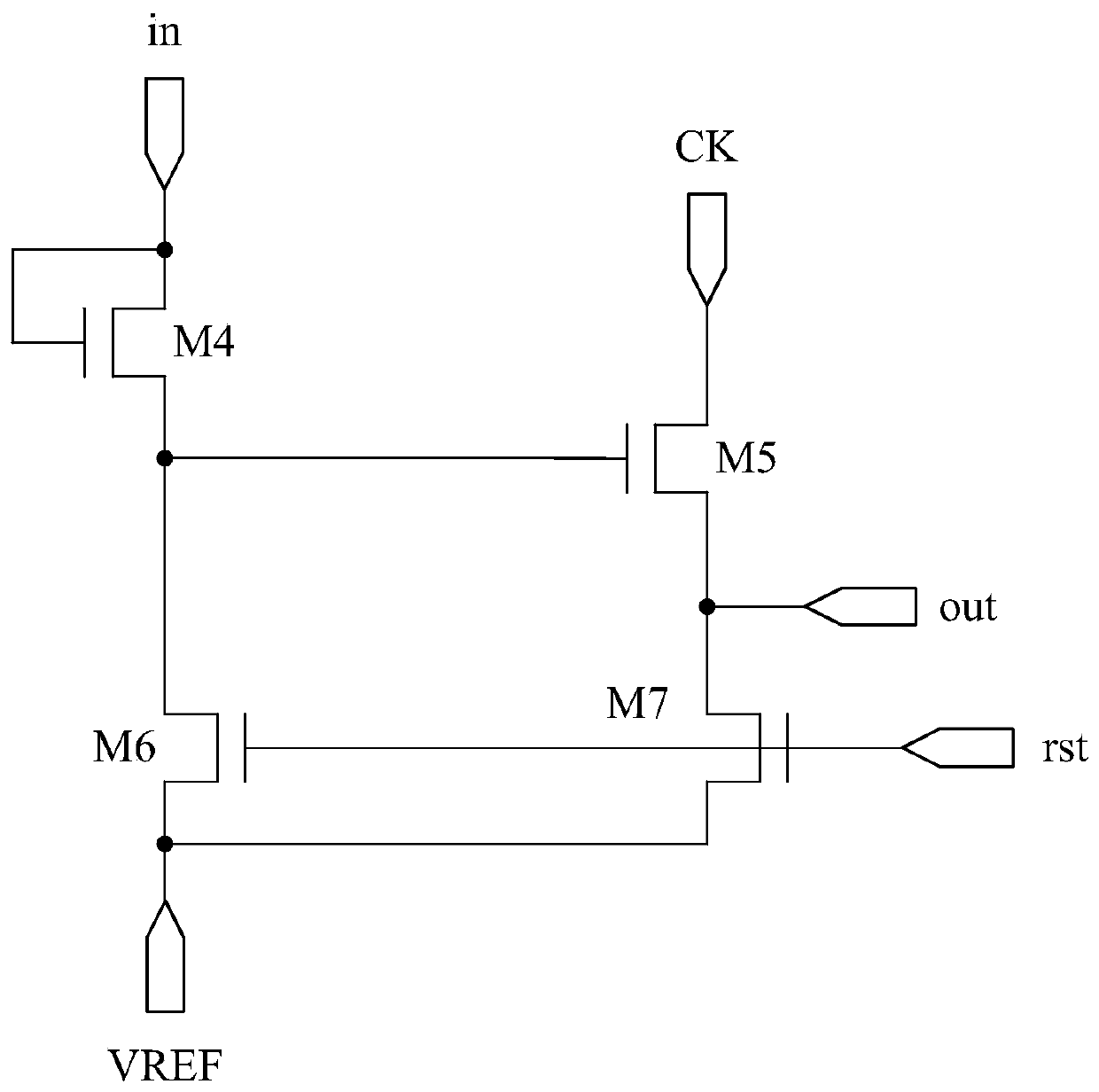

Word line divider and storage device

InactiveUS20120294061A1Simple circuit structureGuaranteed uptimeDigital storageSemiconductor packageHemt circuits

A word line divider which has a simplified circuit structure and can operate stably is provided. A storage device which has a simplified circuit structure and can operate stably is provided. A transistor whose leakage current is extremely low is connected in series with a portion between a word line and a sub word line so that the word line divider is constituted. The transistor can include an oxide semiconductor for a semiconductor layer in which a channel is formed. Such a word line divider whose circuit structure is simplified is used in the storage device.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor memory device

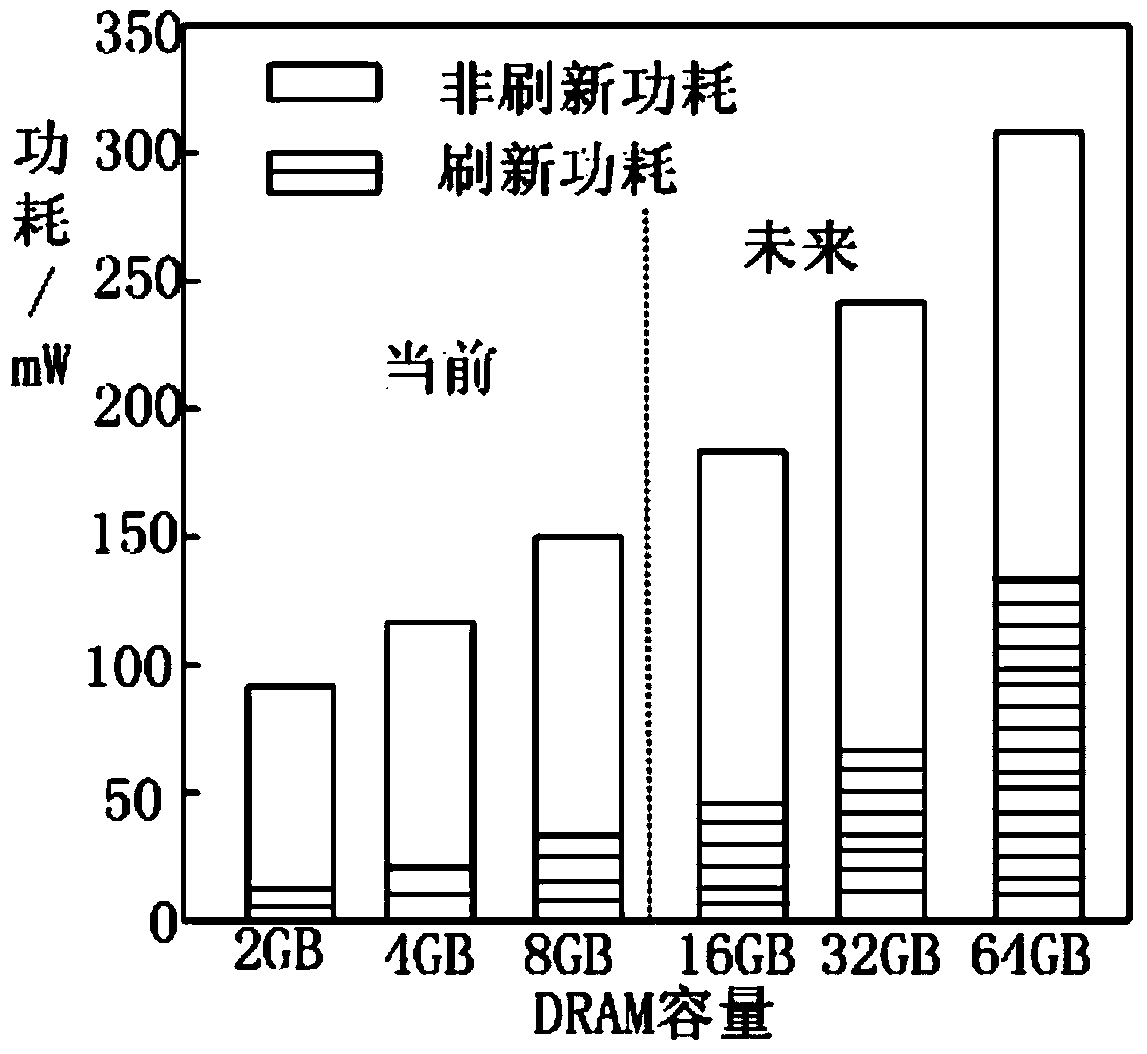

InactiveUS8854865B2Solve the large power consumptionReduce the refresh rateTransistorSolid-state devicesRetention periodCapacitance

To increase a storage capacity of a memory module per unit area, and to provide a memory module with low power consumption, a transistor formed using an oxide semiconductor film, a silicon carbide film, a gallium nitride film, or the like, which is highly purified and has a wide band gap of 2.5 eV or higher is used for a DRAM, so that a retention period of potentials in a capacitor can be extended. Further, a memory cell has n capacitors with different capacitances and the n capacitors are each connected to a corresponding one of n data lines, so that a variety of the storage capacitances can be obtained and multilevel data can be stored. The capacitors may be stacked for reducing the area of the memory cell.

Owner:SEMICON ENERGY LAB CO LTD

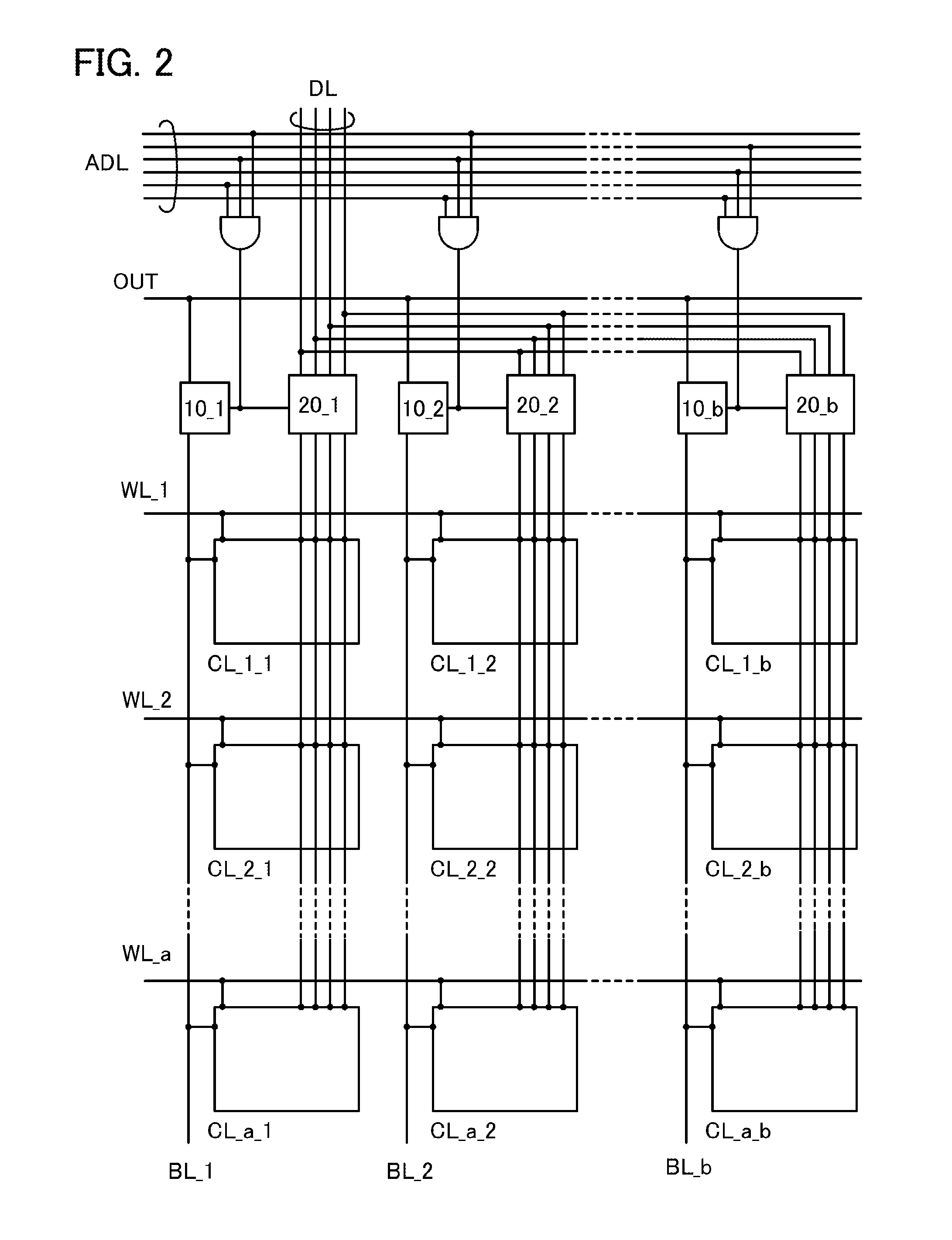

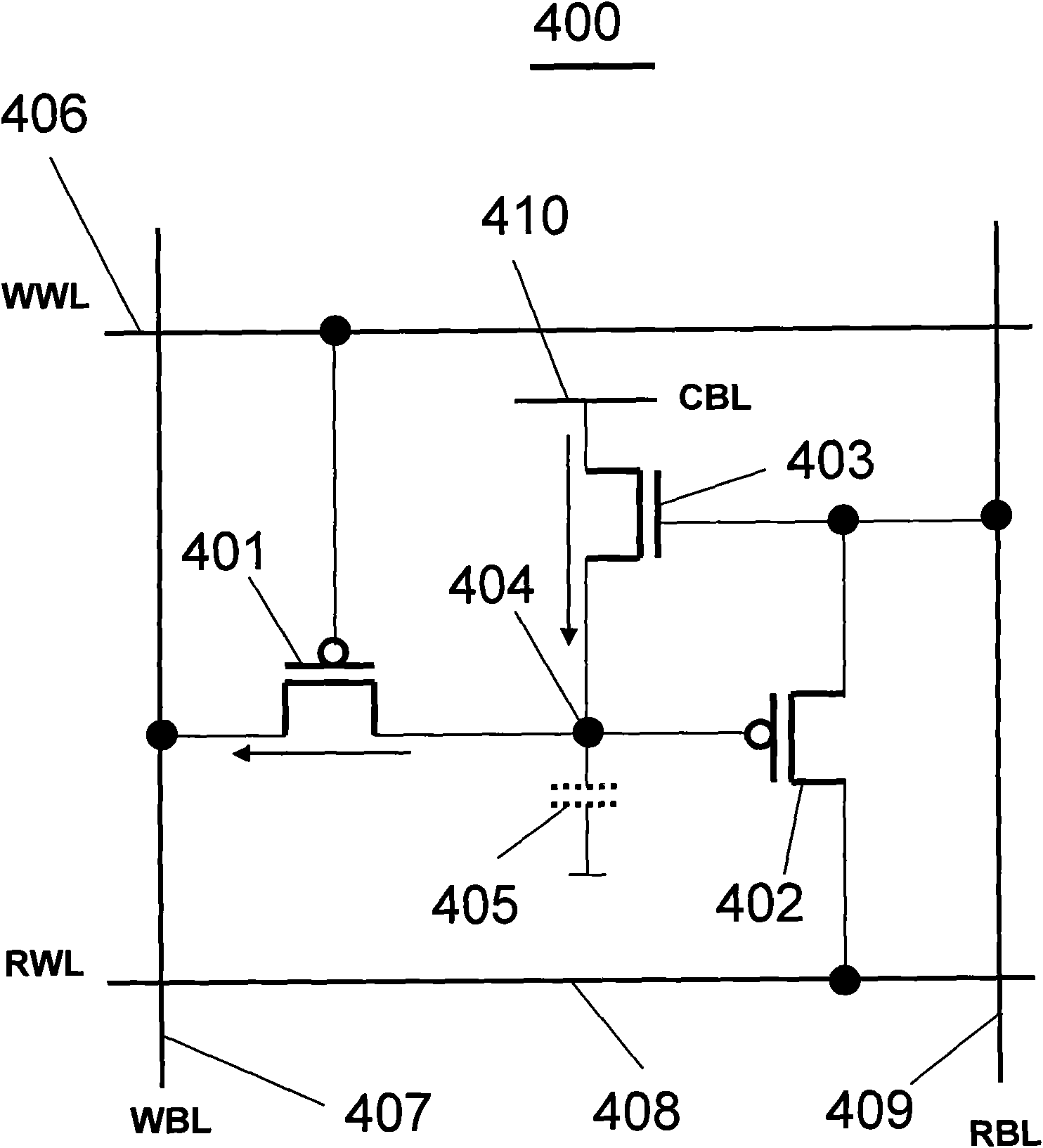

Semiconductor device

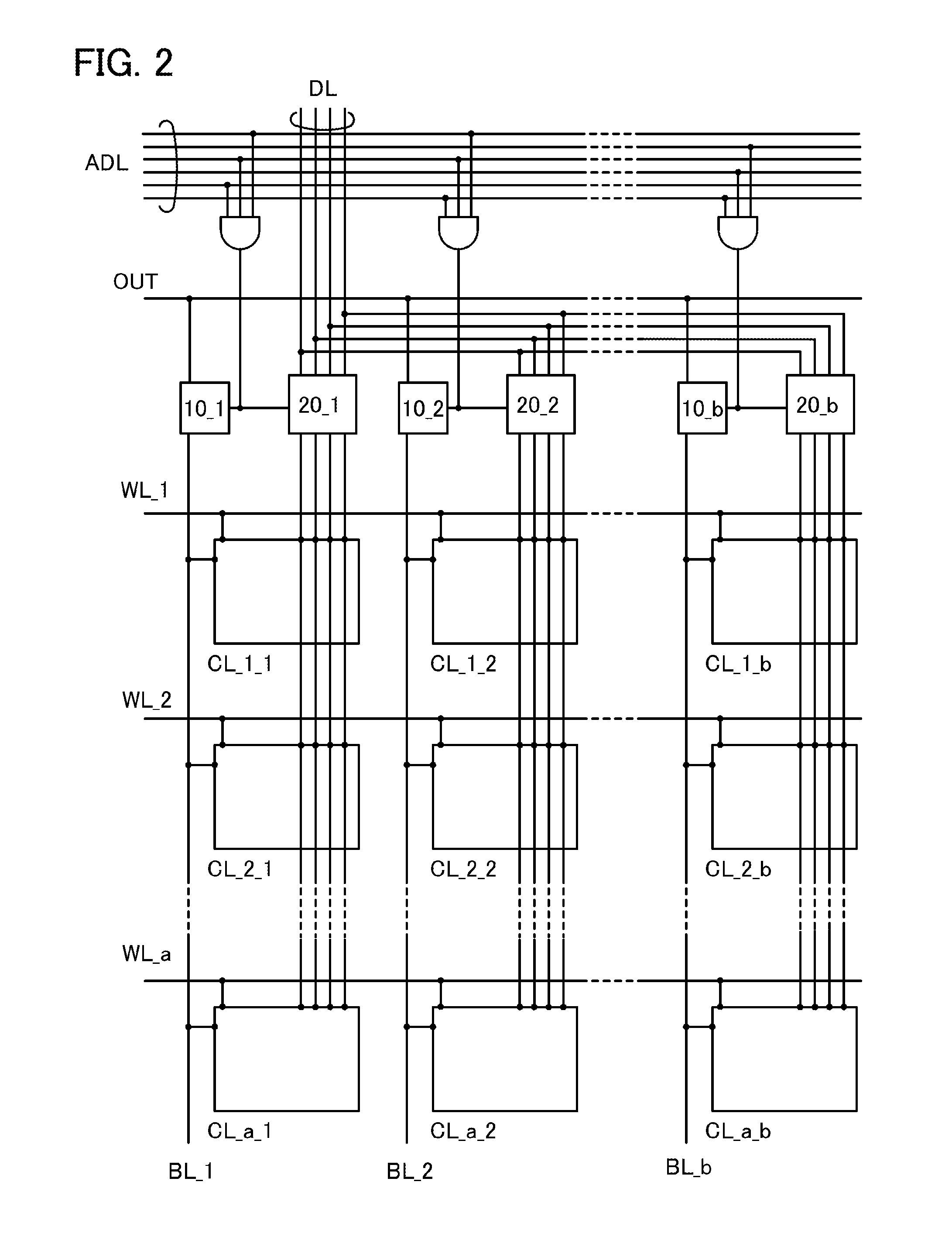

InactiveUS20120014157A1Reduce power consumptionData read performance of be improveSolid-state devicesRead-only memoriesEngineeringDevice material

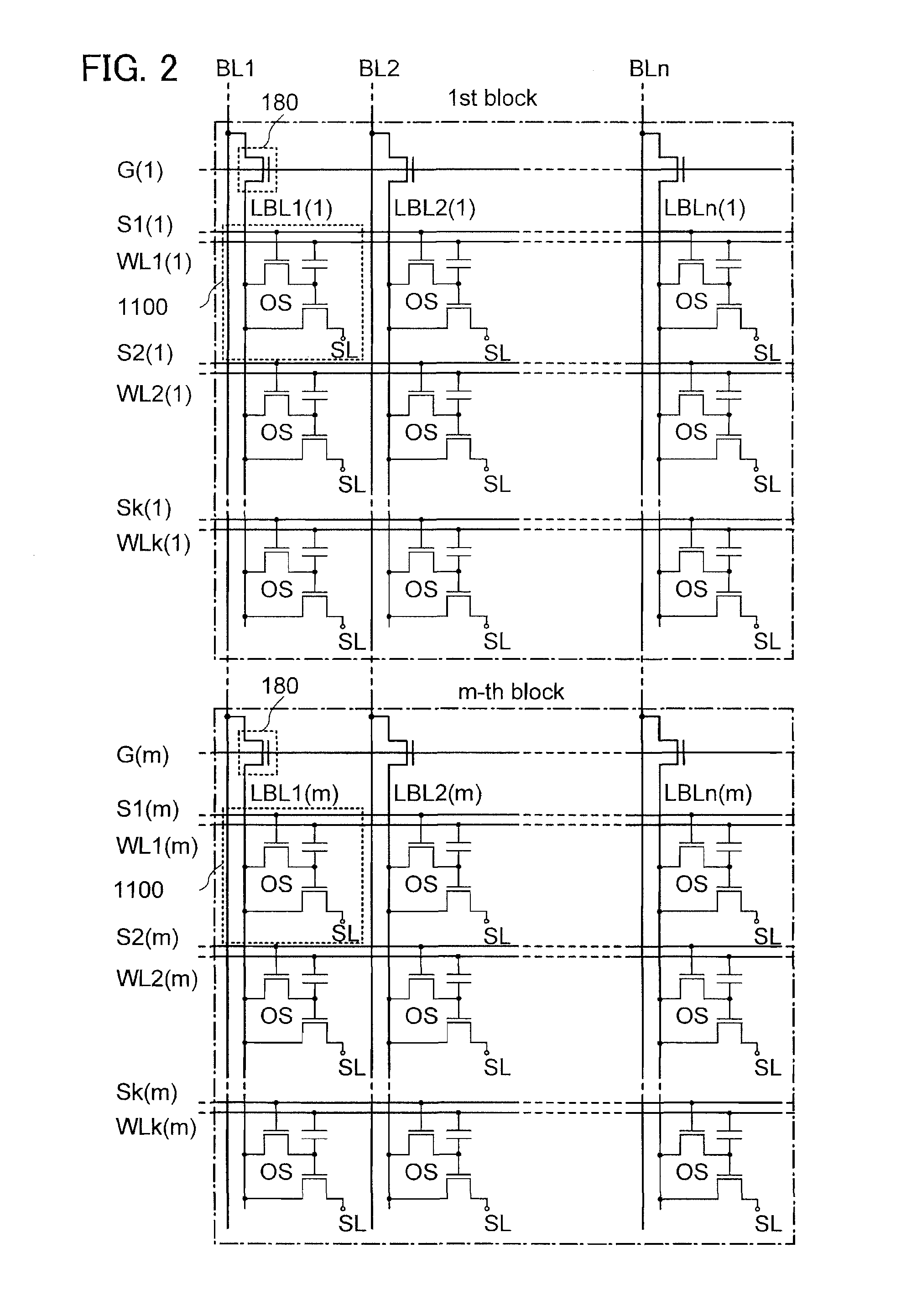

A plurality of memory cells included in a memory cell array are divided into a plurality of blocks every plural rows. A common bit line is electrically connected to the divided bit lines through selection transistors in the blocks. One of the memory cells includes a first transistor, a second transistor, and a capacitor. The first transistor includes a first channel formation region. The second transistor includes a second channel formation region. The first channel formation region includes a semiconductor material different from the semiconductor material of the second channel formation region.

Owner:SEMICON ENERGY LAB CO LTD

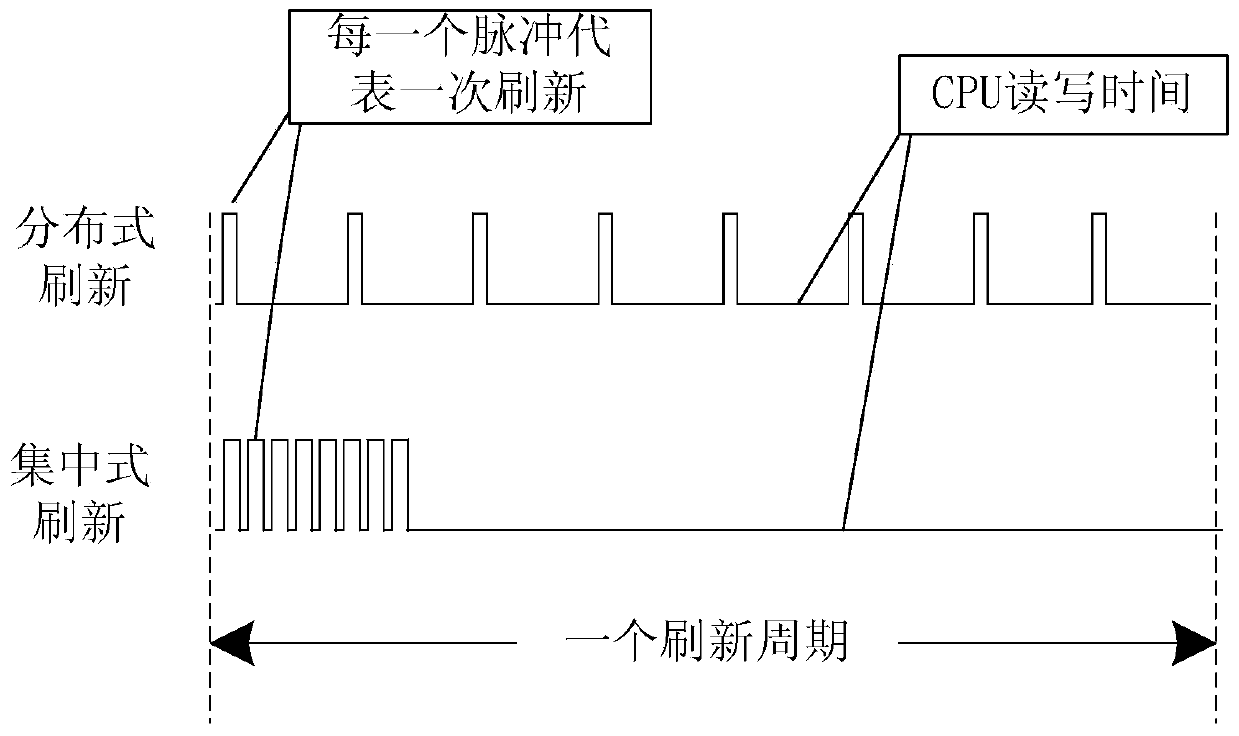

Low power consumption refresh method of hybrid memory structure

ActiveCN103811048ADoes not affect access performanceReduce the refresh rateDigital storageRefresh cycleLow power dissipation

The invention provides a low power consumption refresh method of a hybrid memory structure. When a DRAM (Dynamic Random Access Memory) is in a very busy state, a temperature sensitive mode is selected, a storage unit in a nonvolatile memory takes the place of a worst storage unit detected within a present temperature range to reconfigure the DRAM refresh cycle; when the condition that the present temperature is changed to another temperature range at one moment is detected, the information of the worst storage unit is updated, and the refresh cycle is updated; if the DRAM is operated in a temperature non-sensitive mode, the storage unit in the nonvolatile memory takes the place of the detected worst storage unit to reconfigure the refresh cycle of the DRAM; if the operation temperature of the DRAM exceeds a provided value at one moment, the DRAM is switched back to an ordinary refresh mode for a low power consumption refresh mode. By adopting the technical scheme of the invention, the improvement of the refresh cycle is achieved, the refresh power consumption is saved, and the original storage and reading performance of the DRAM is generally not affected.

Owner:SHANGHAI XINCHU INTEGRATED CIRCUIT

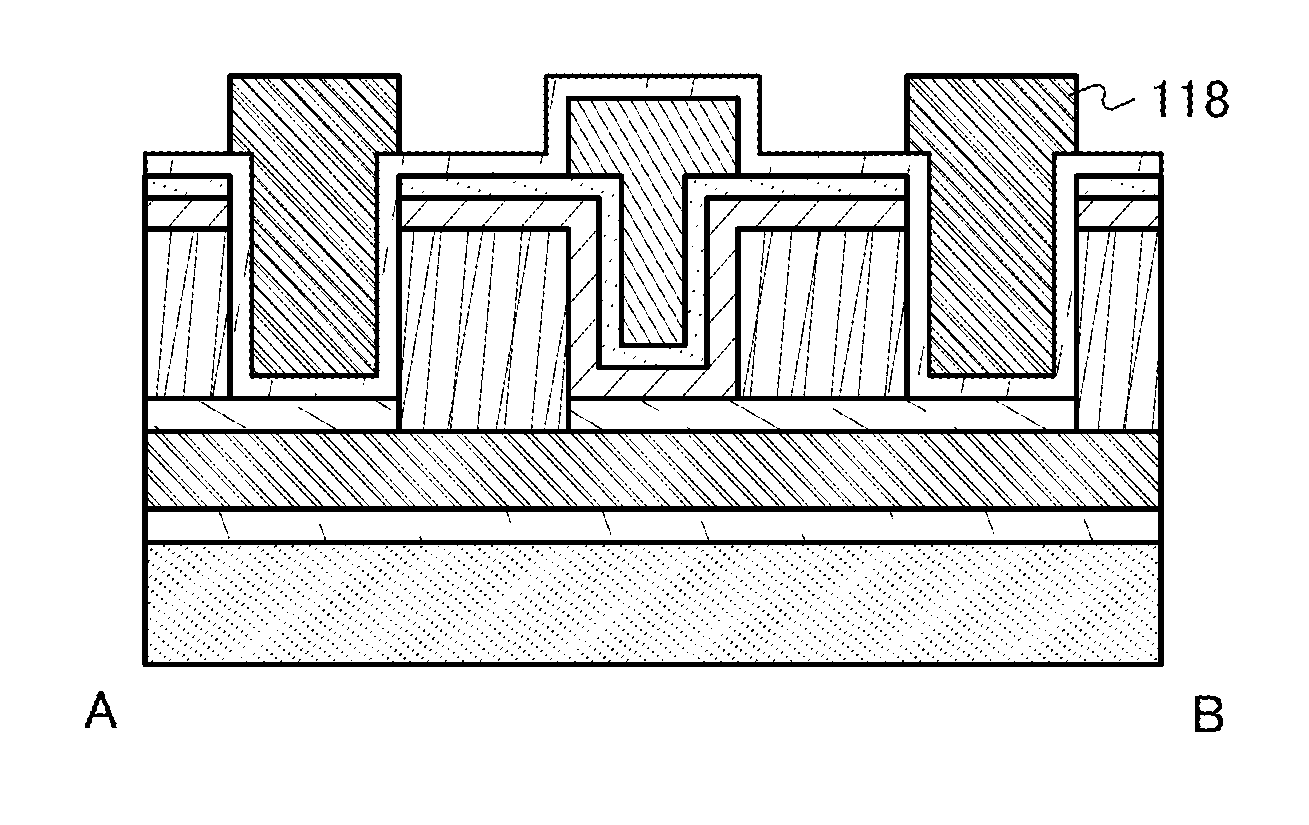

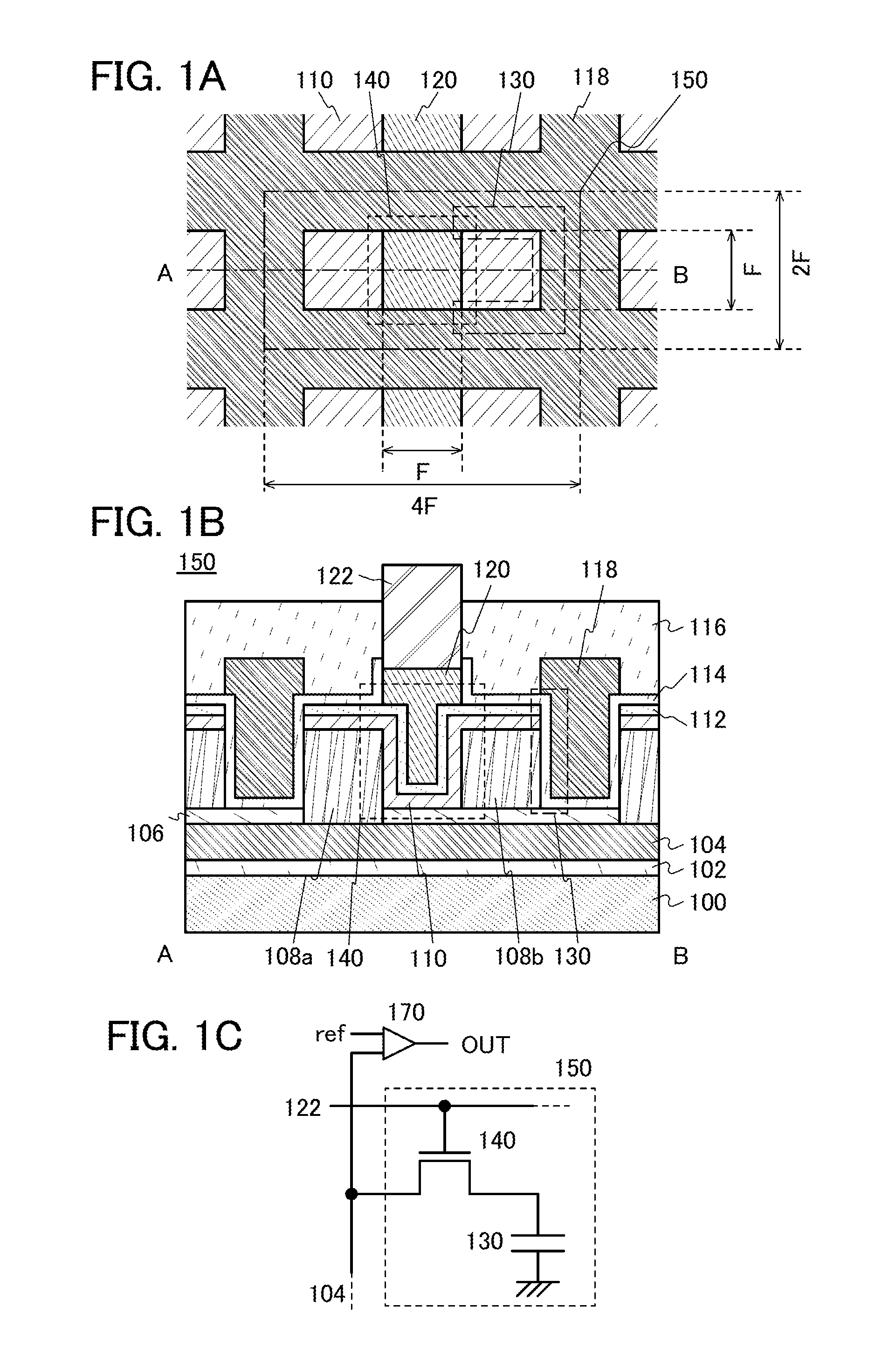

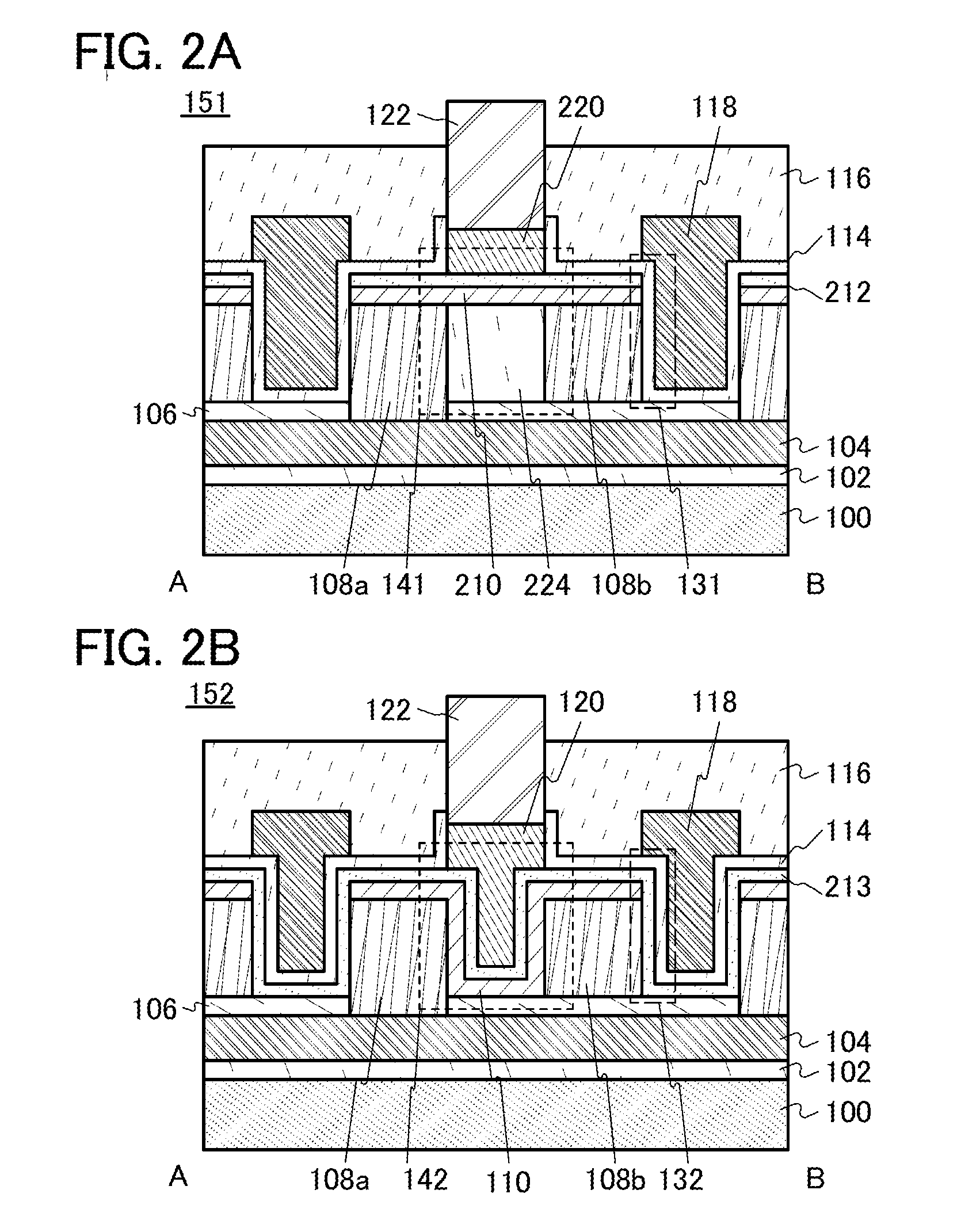

Semiconductor memory device

InactiveUS20120261664A1Improve charging characteristicsReduce the refresh rateTransistorSolid-state devicesBit lineSemiconductor storage devices

A semiconductor memory device including a bit line, a word line, a transistor, and a capacitor is provided. The transistor includes source and drain electrodes; an oxide semiconductor film in contact with at least both top surfaces of the source and drain electrodes; a gate insulating film in contact with at least a top surface of the oxide semiconductor film; a gate electrode which overlaps with the oxide semiconductor film with the gate insulating film provided therebetween; and an insulating film covering the source and drain electrodes, the gate insulating film, and the gate electrode. The transistor is provided in a mesh of a netlike conductive film when seen from the above. Here, the drain electrode and the netlike conductive film serve as one and the other of a pair of capacitor electrodes of the capacitor. A dielectric film of the capacitor includes at least the insulating film.

Owner:SEMICON ENERGY LAB CO LTD

Integrated circuit, semiconductor device comprising the same, electronic device having the same, and driving method of the same

InactiveUS7541614B2Large memory capacityReduce the refresh rateTransistorSolid-state devicesData controlActive layer

An integrated circuit mounting a DRAM which can realize high integration without complicated manufacturing steps. The integrated circuit according to the invention comprises a DRAM in which a plurality of memory cells each having a thin film transistor are disposed. The thin film transistor comprises an active layer including a channel forming region, and first and second electrodes overlapping with each other with the channel forming region interposed therebetween. By controlling a drain voltage of the thin film transistor according to data, it is determined whether to accumulate holes in the channel forming region or not, and data is read out by confirming whether or not holes are accumulated.

Owner:SEMICON ENERGY LAB CO LTD

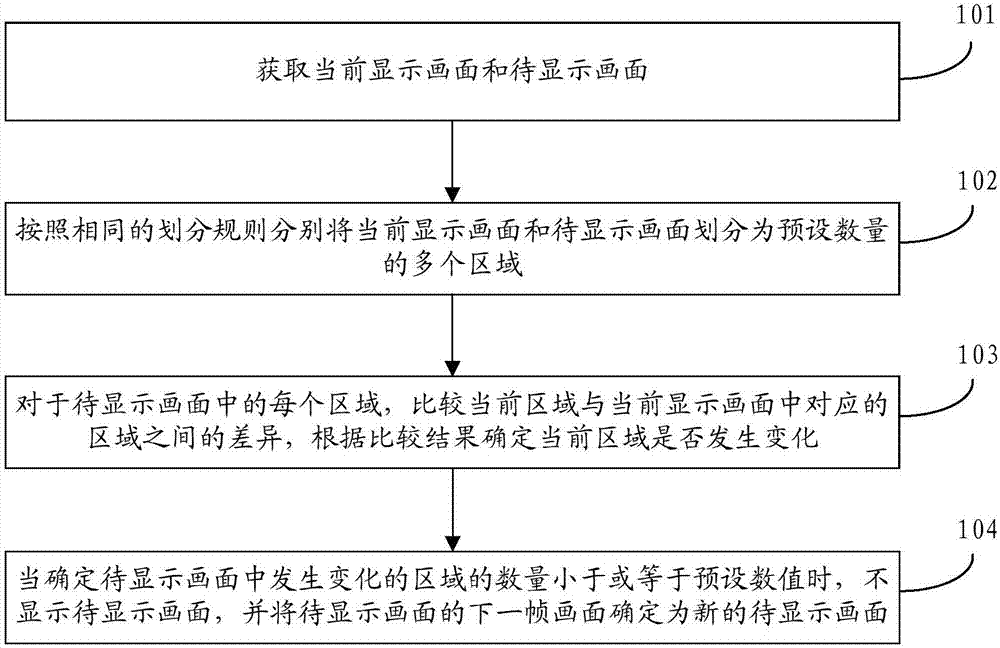

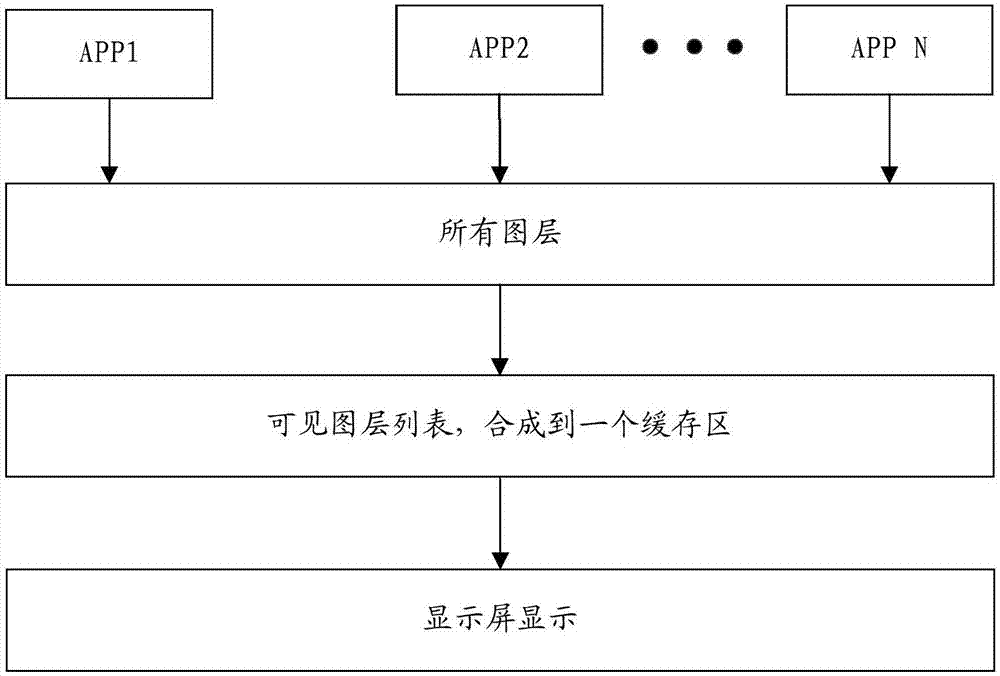

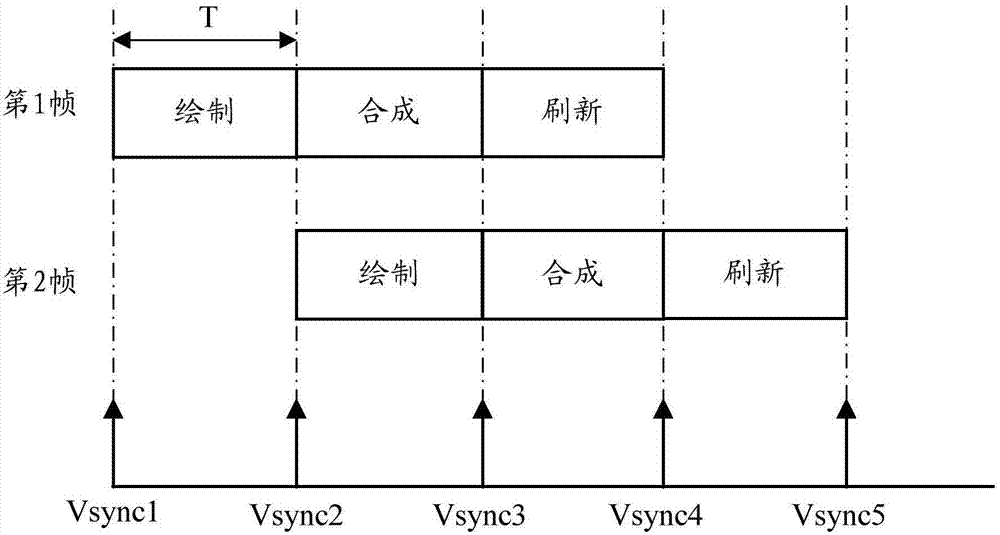

Display control method and device for mobile terminal and mobile terminal

InactiveCN106933527AReduce power consumptionReduce the refresh ratePower supply for data processingDigital output to display deviceComputer hardwareEmbedded system

The embodiment of the invention discloses a display control method and device for a mobile terminal and the mobile terminal. The method comprises the steps that a currently-displayed picture and a to-be-displayed picture are acquired; the currently-displayed picture and the to-be-displayed picture are divided into multiple regions in a preset number according to the same dividing rules; the difference between the current region of all the regions in the to-be-displayed picture and a corresponding region in the currently-displayed picture is obtained through comparison; and when it is determined that the number of changed regions in the to-be-displayed picture is smaller than or equal to a preset value, the to-be-displayed picture is not displayed, and a frame of picture following the to-be-displayed picture is determined as a new to-be-displayed picture. According to the embodiment, by the adoption of the technical scheme, the to-be-displayed picture can be displayed selectively, screen refresh efficiency can be lowered, and therefore system power consumption of the mobile terminal is reduced.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

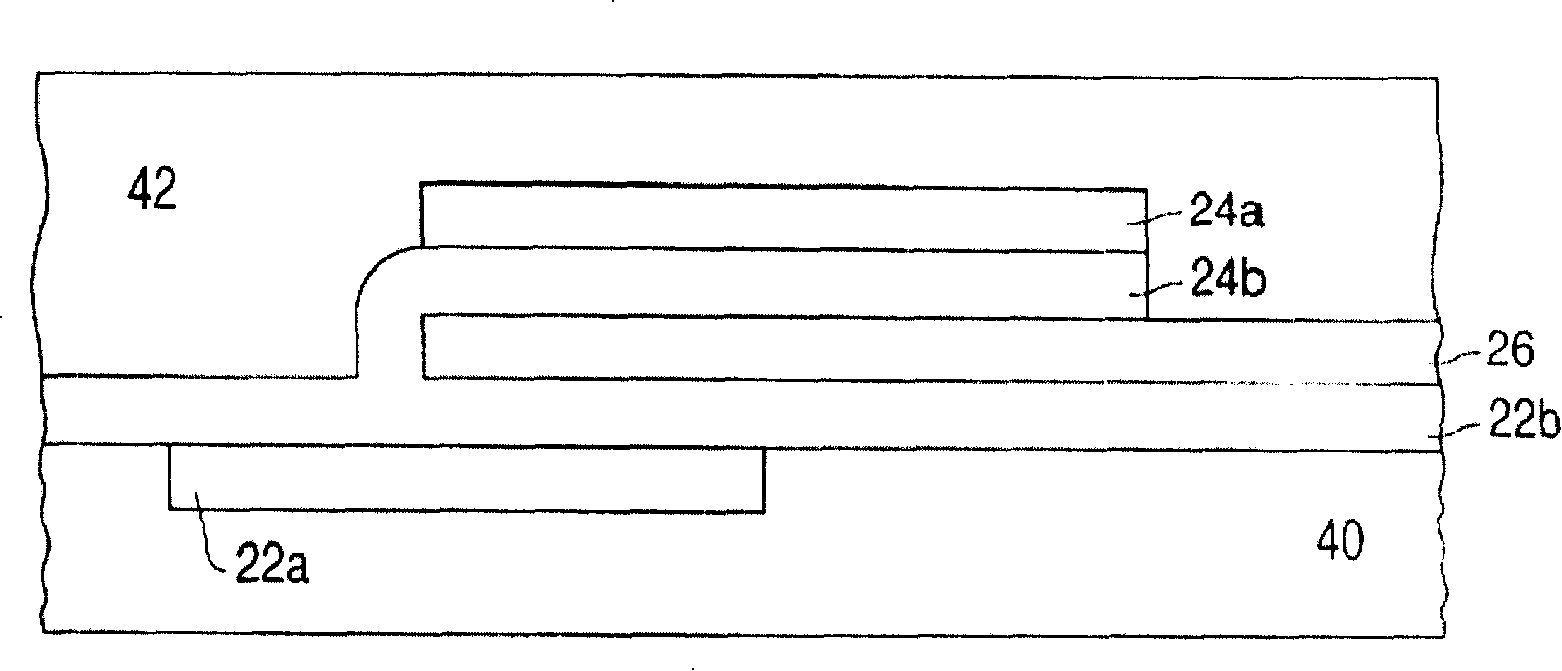

Silicon based LCD unit and method for forming the same

ActiveCN101196656AIncrease capacitanceReduce the refresh rateSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceLiquid-crystal display

A silicon-based liquid crystal display unit is provided, by grounding a light shielding layer located on a pixel switch circuit layer, a metal-insulating layer-metal (MIM) second capacitor composed by micro reflection micro reflecting mirror layer-insulating later-light shielding layer is formed, the second capacitance is connected with a first capacitance of the pixel switch circuit layer in parallel to be the capacitance of the pixel switch circuit layer together; the invention also provides a forming method of the silicon-based liquid crystal display unit. By fully utilizing the entire pixel area, the invention enlarges the capacitance, lowers the refresh rate of the silicon-based liquid crystal display unit. Simultaneously, the invention enlarges the design area of the switch circuit, designs high performance switch circuit according to different requirements and increases the design flexibility of the switch circuit. The invention also simplifies procedure of capacitance manufacture, so as to lower the total chip manufacture cost.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

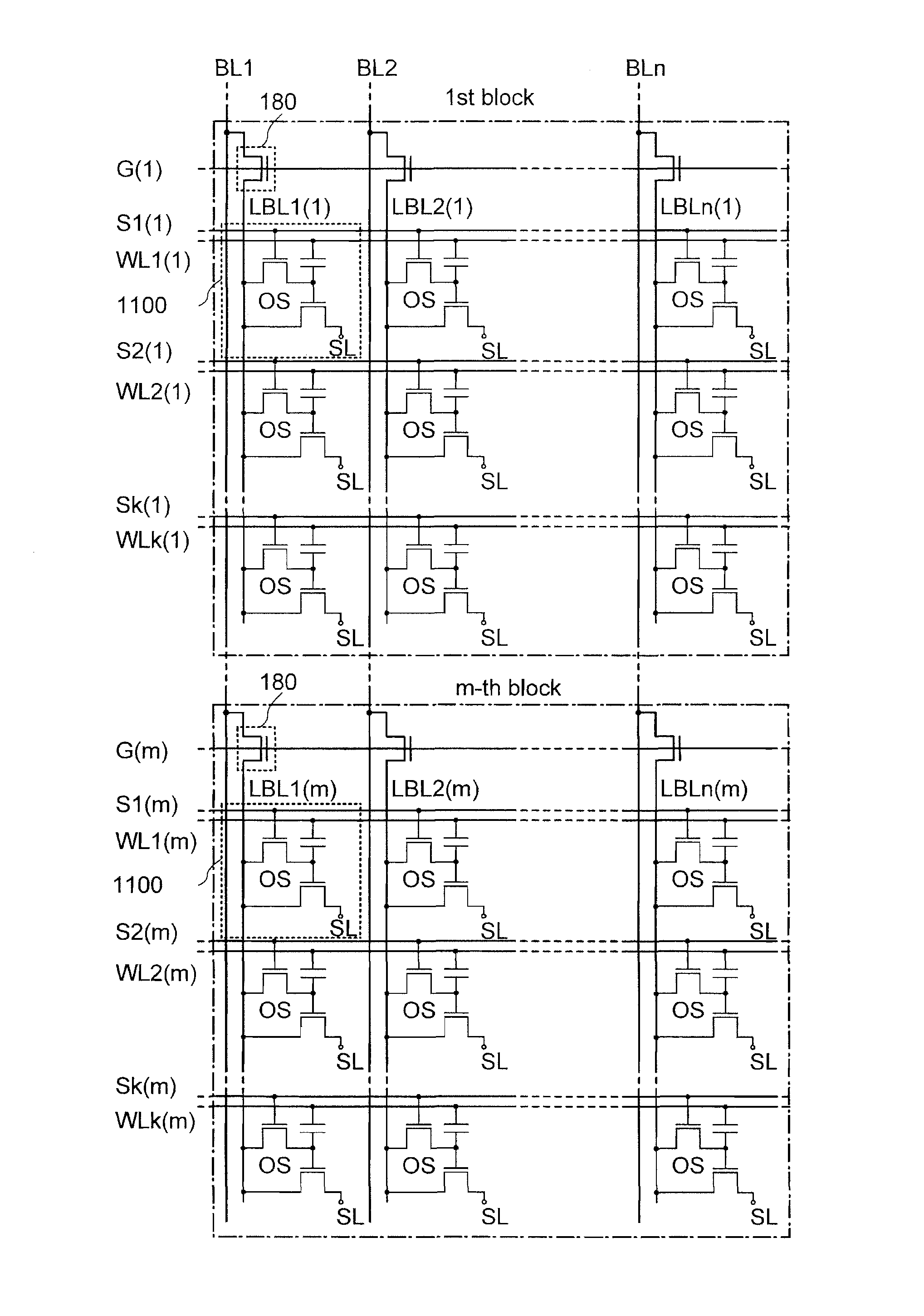

Semiconductor device and driving method thereof

ActiveUS9001563B2Reduce power consumptionReduce the refresh rateTransistorSolid-state devicesEngineeringP channel

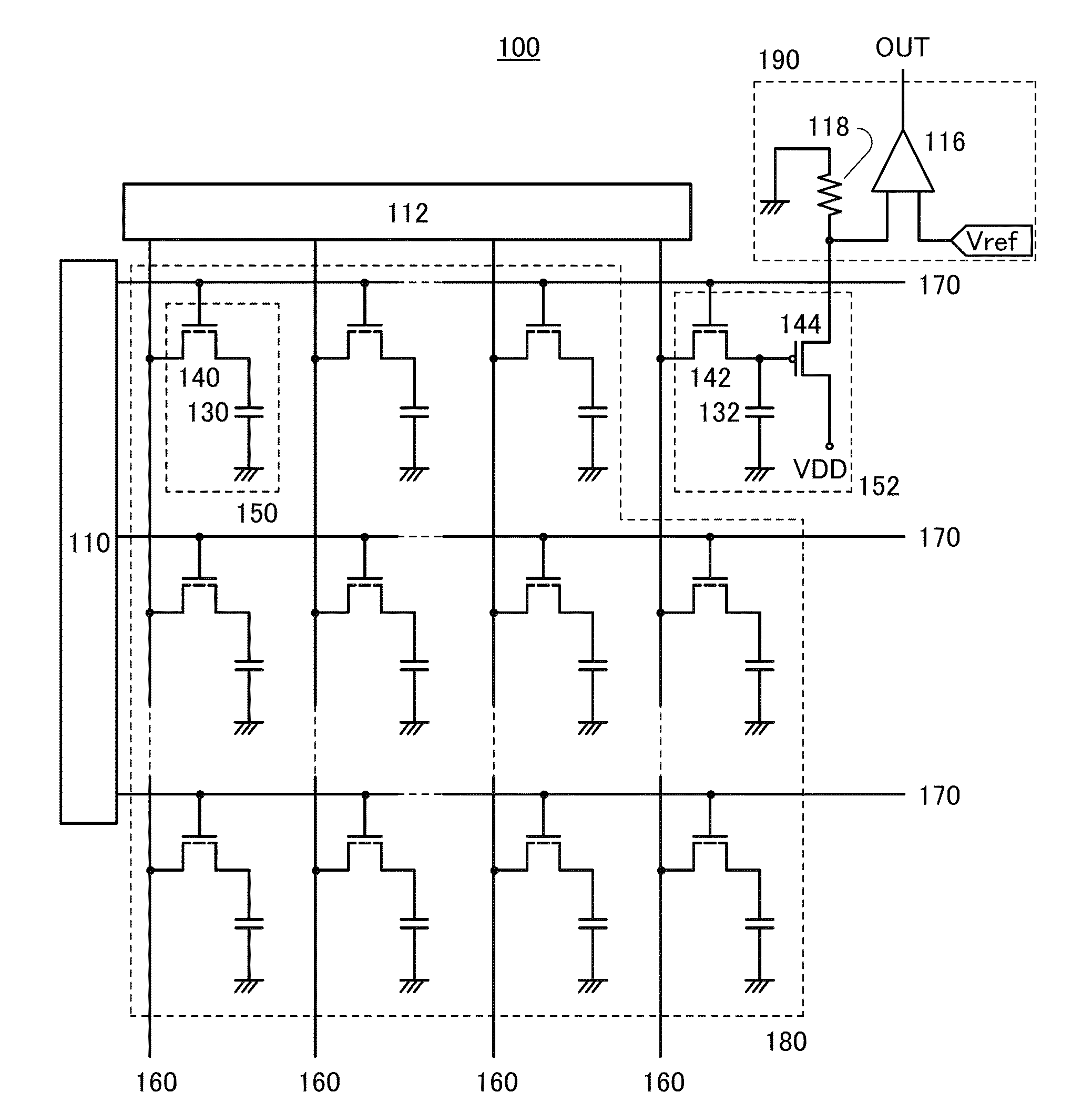

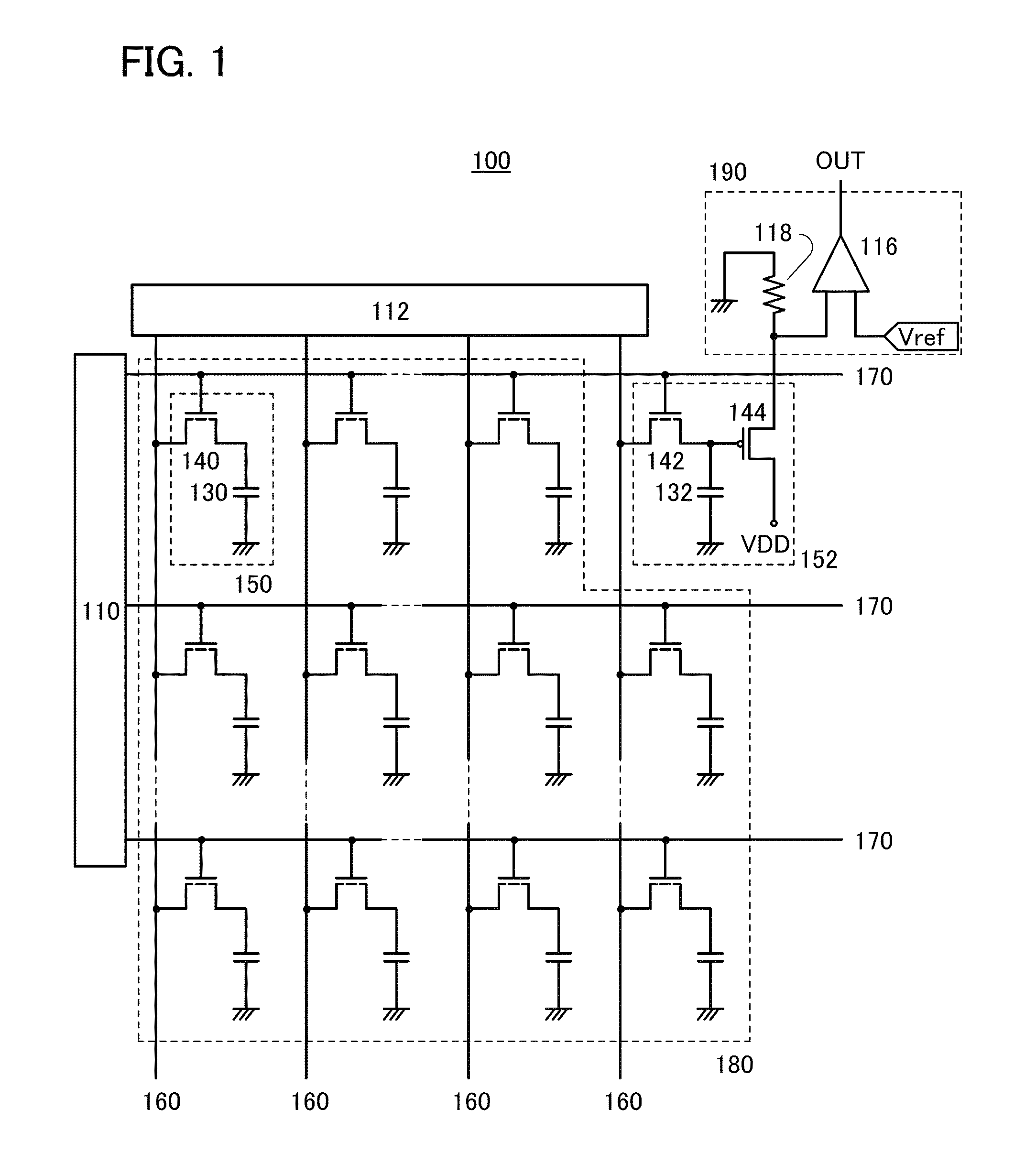

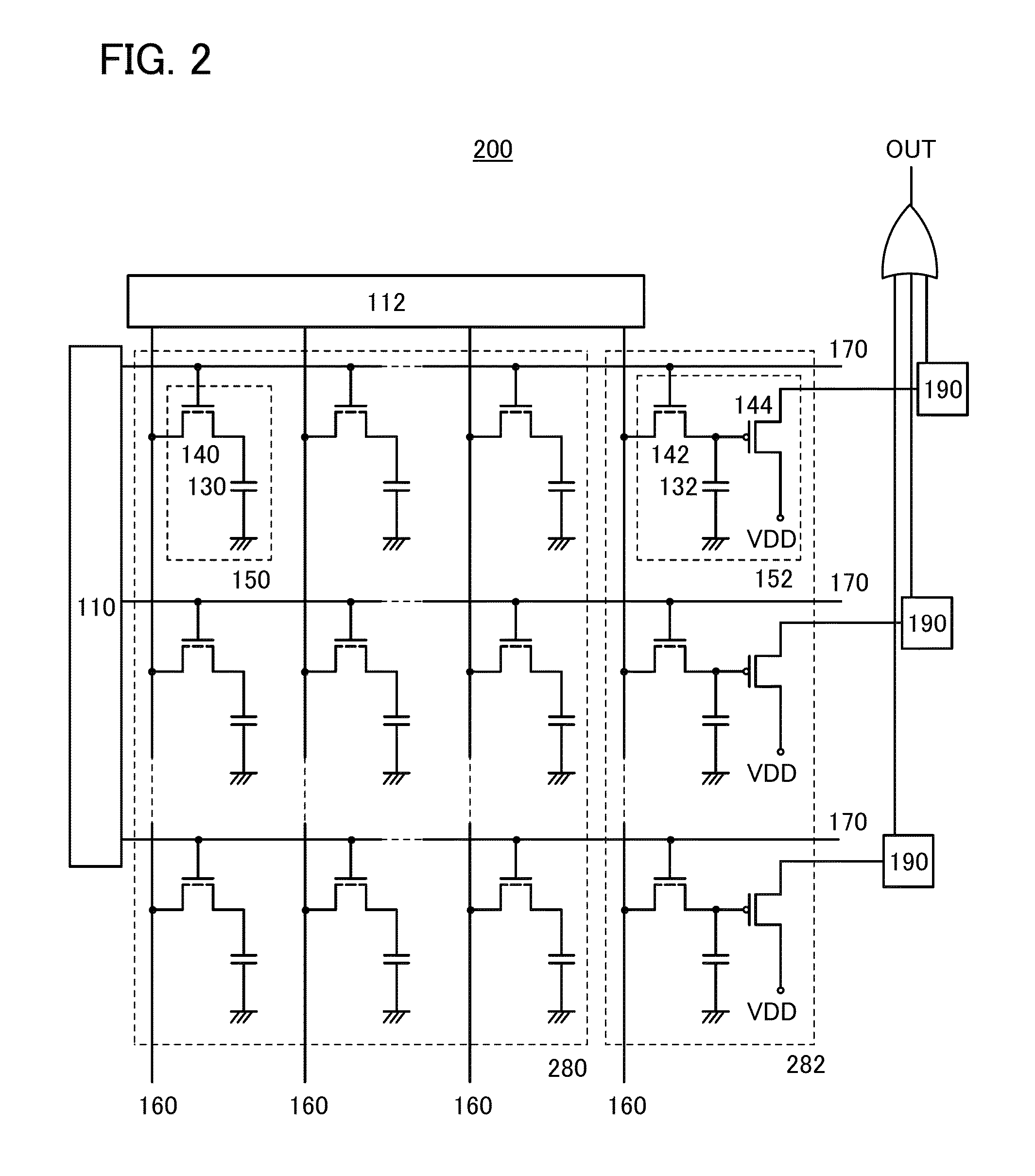

In a memory module including a memory cell array including memory cells arranged in matrix, each including a first transistor using an oxide semiconductor and a first capacitor; a reference cell including a p-channel third transistor, a second capacitor, and a second transistor using an oxide semiconductor; and a refresh timing detection circuit including a resistor and a comparator, wherein when a potential is supplied to the first capacitor through the first transistor, a potential is supplied to the second capacitor through the second transistor, wherein a drain current value of the third transistor is changed in accordance with the potential stored in the second capacitor, and wherein when the drain current value of the third transistor is higher than a given value, a refresh operation of the memory cell array and the reference cell are performed.

Owner:SEMICON ENERGY LAB CO LTD

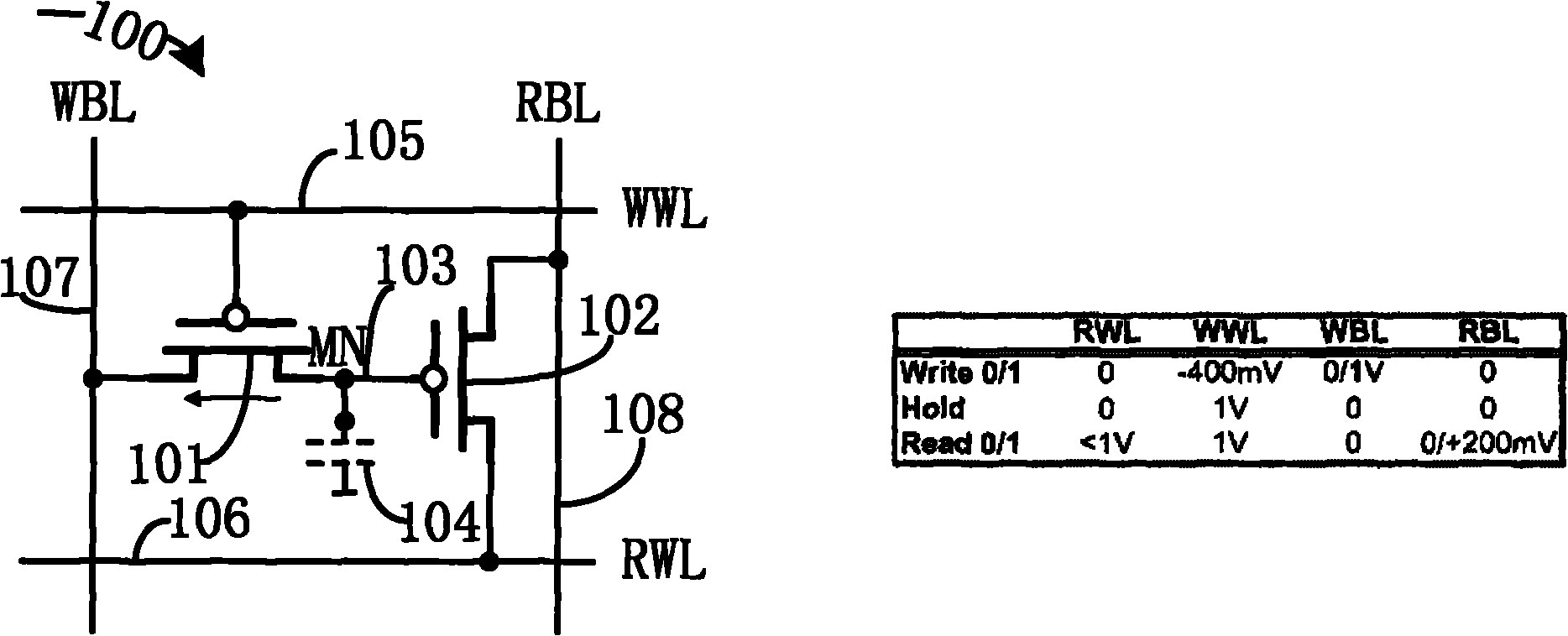

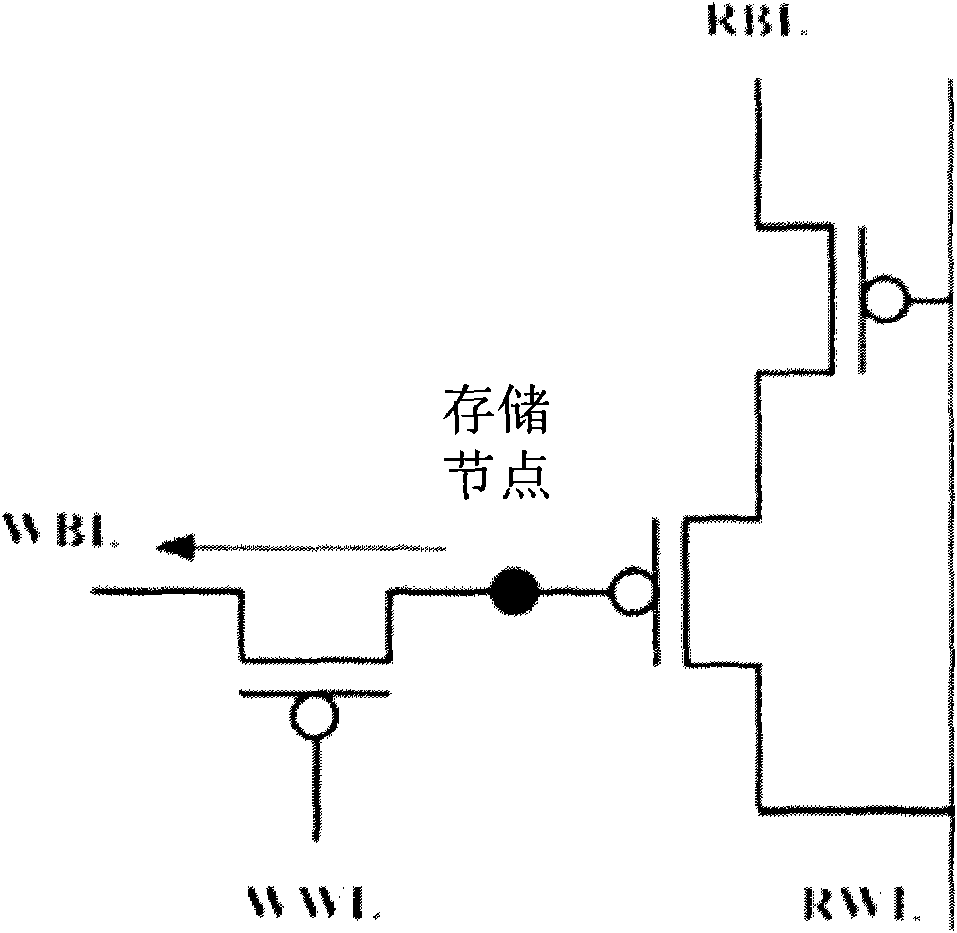

EDRAM (Enhanced Dynamic Random Access Memory) unit of gain unit, memory and operating method

InactiveCN102081962AImprove reading speedData retention time is longDigital storageWrite bitHigh Readings

The invention belongs to the technical field of dynamic random access memories and in particular relates to an EDRAM (Enhanced Dynamic Random Access Memory) unit of a gain unit, a memory and an operating method thereof. Based on a writing MOS (Metal Oxide Semiconductor) transistor, a reading MOS transistor, a writing word line, a writing bit line, a reading word line, a reading bit line and an equivalent parasitic capacitor, the EDRAM unit of the gain unit provided by the invention is obtained by increasing a coupling complementary MOS transistor and a shared bit line which is connected to a fixed voltage such that the EDRAM unit of the gain unit has the characteristics of long data retention time and low refreshing frequency; and the memory formed by the EDRAM unit of the gain unit has the characteristics of high reading speed and low power consumption.

Owner:FUDAN UNIV

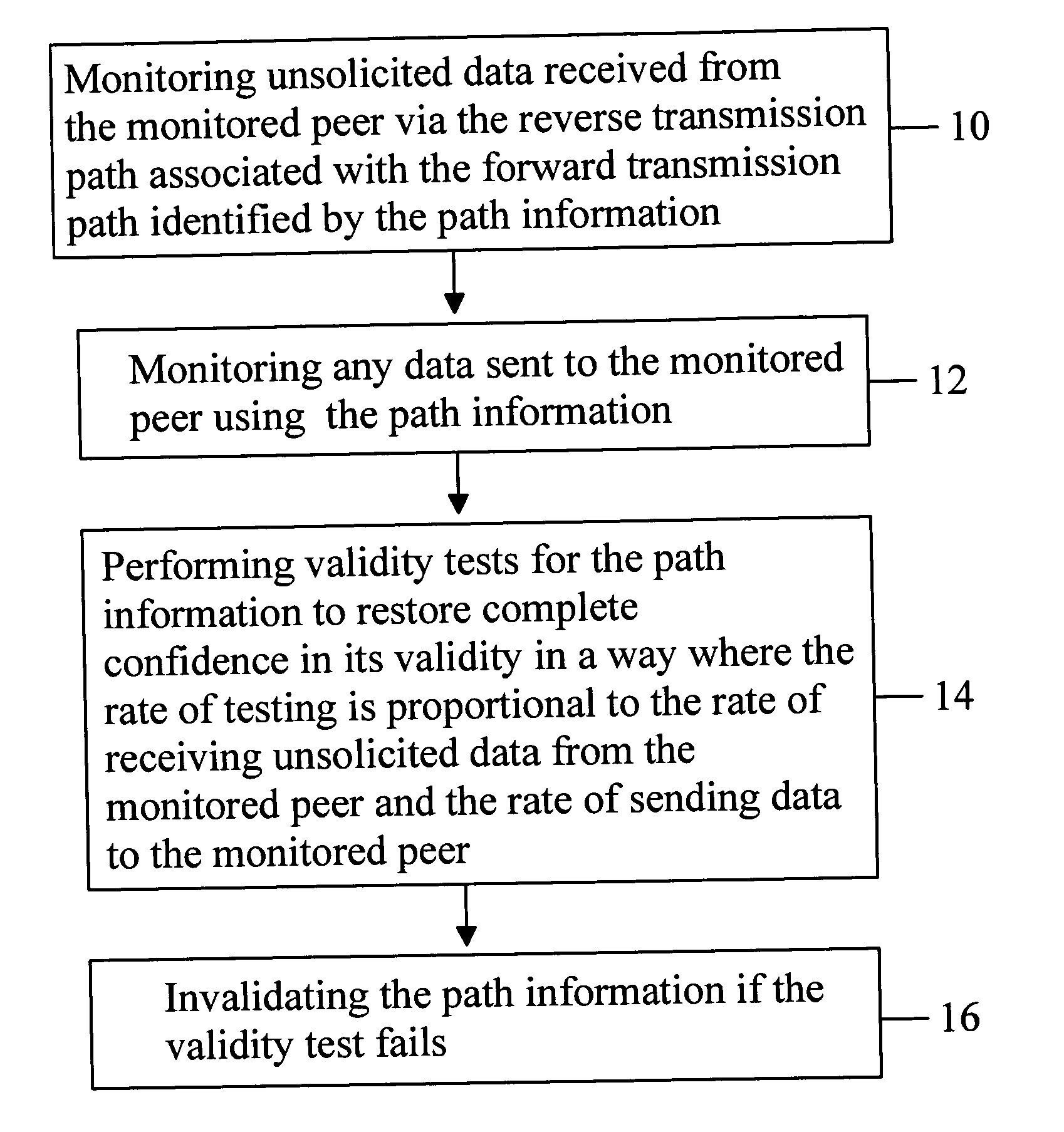

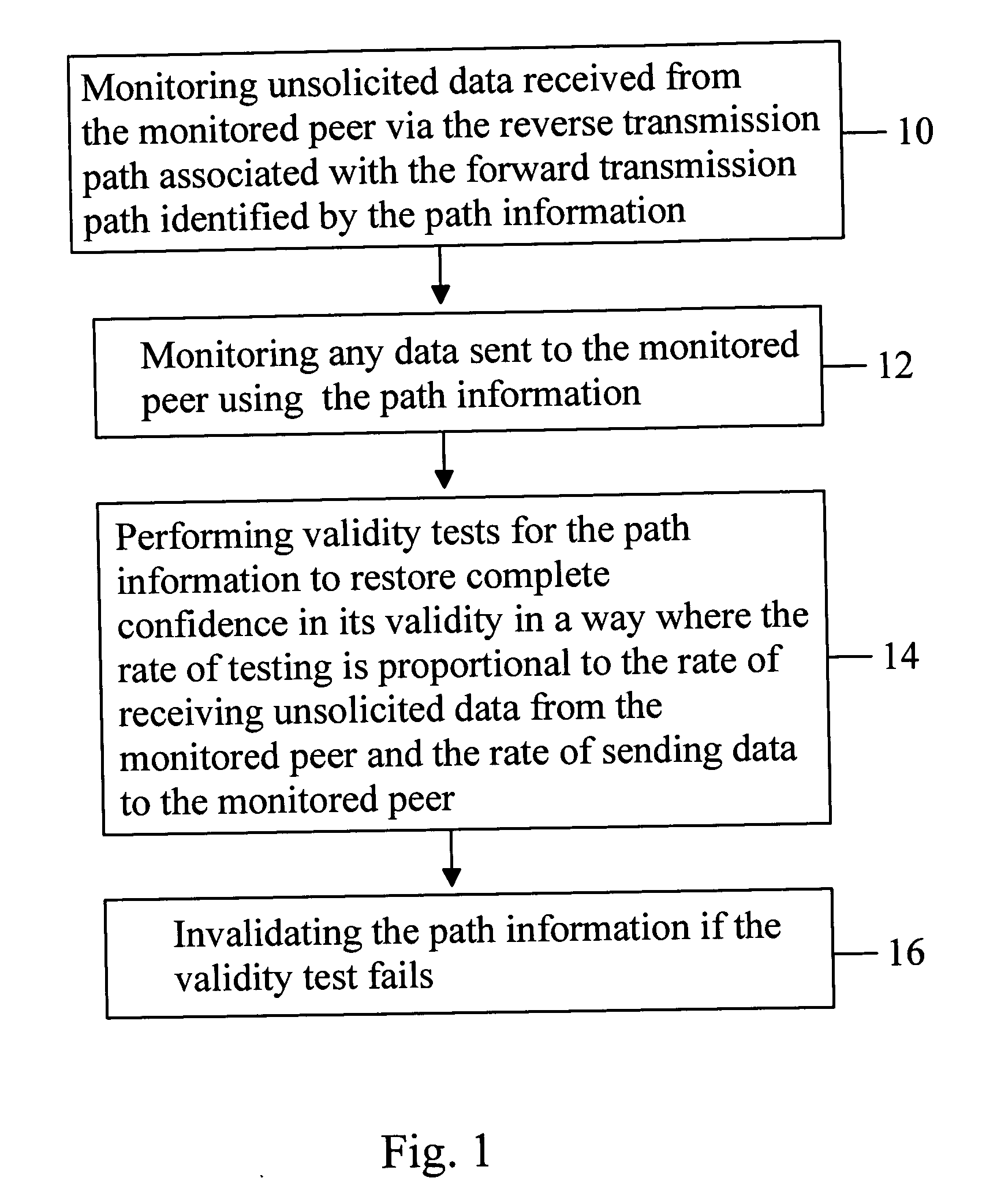

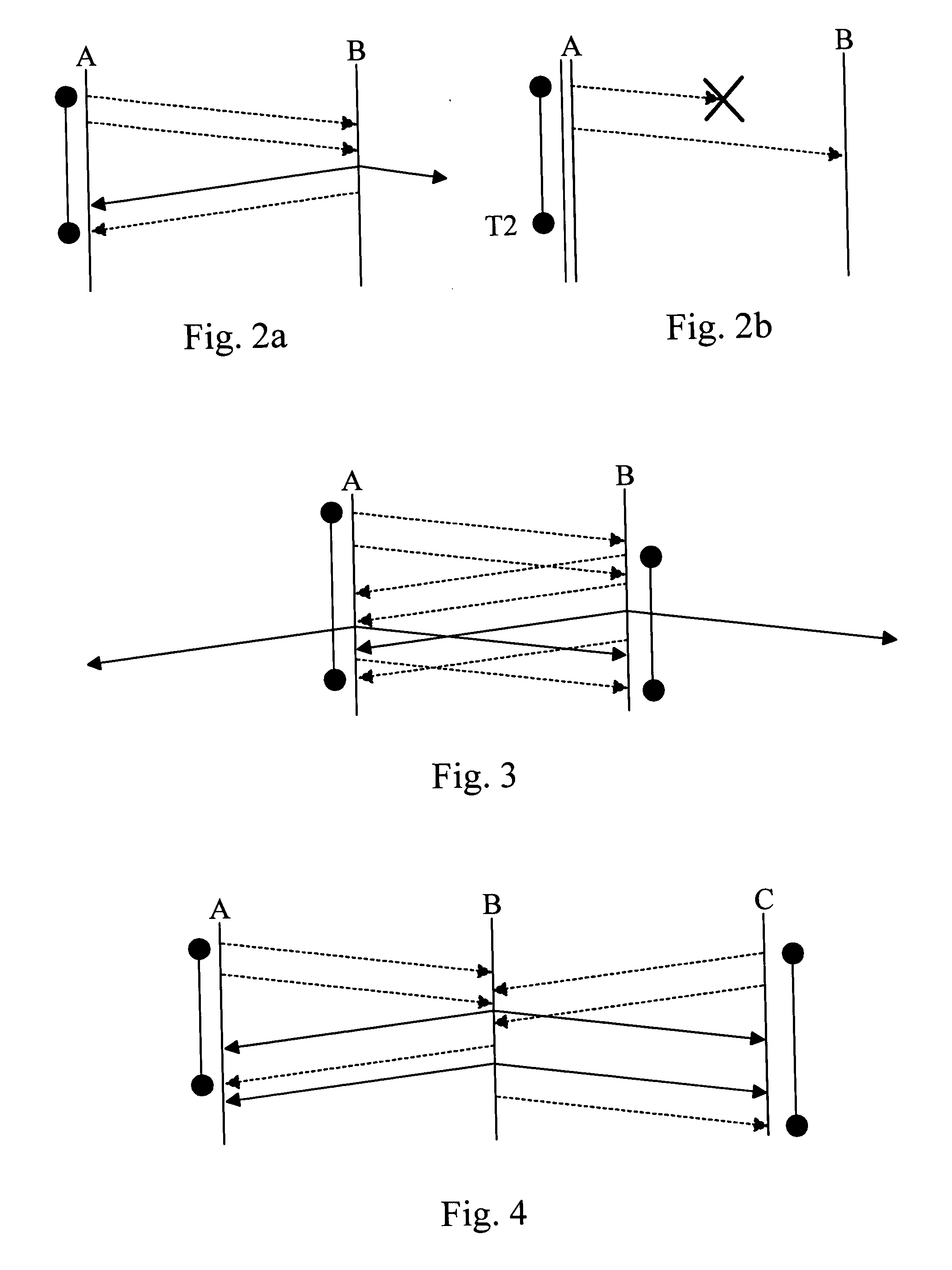

Failure detection of path information corresponding to a transmission path

InactiveUS20060002306A1Eliminate redundancyInterfere with dataError preventionTransmission systemsComputer programReal-time computing

A method, system, peers and computer programs determine validity of path information corresponding to a transmission path between a monitoring peer and a monitored peer in a data communication network. The monitoring peer monitors unsolicited data received from the monitored peer via the reverse transmission path identified by the path information and further monitors any data sent to the monitored peer using the path information. Validity tests are performed by the monitoring peer for the path information to restore complete confidence in its validity in a way where the rate of testing is proportional to the rate of receiving unsolicited data from the monitored peer and to the rate of sending data to the monitored peer. The monitoring peer invalidates the path information if the validity test fails.

Owner:SPYDER NAVIGATIONS L L C

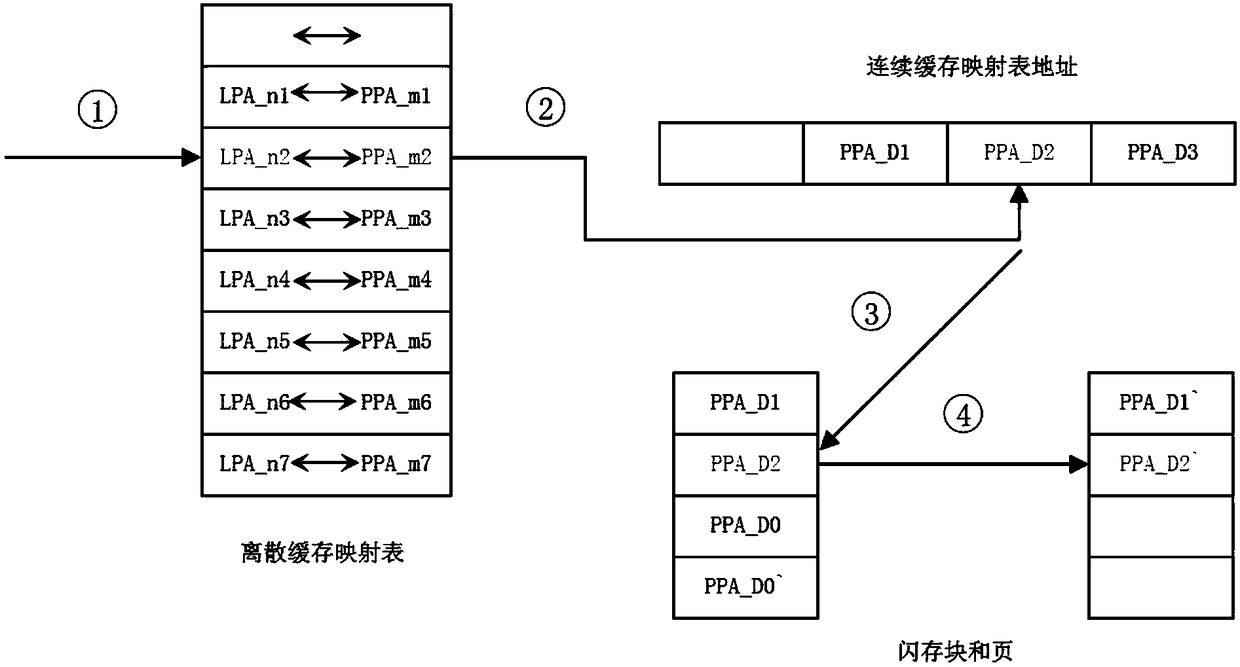

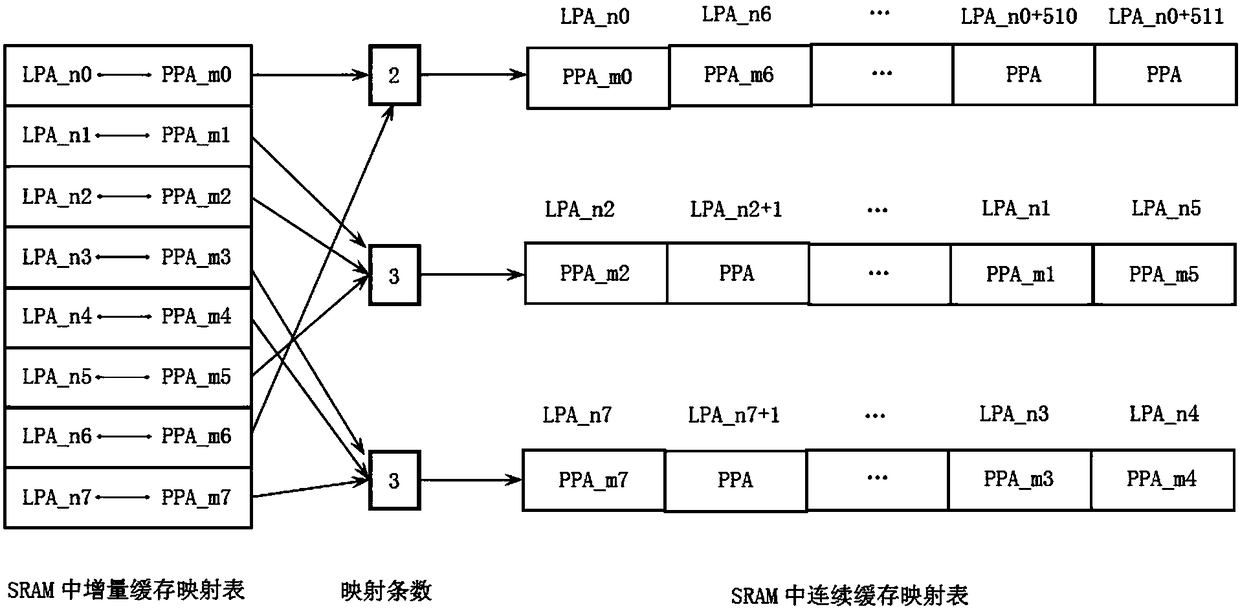

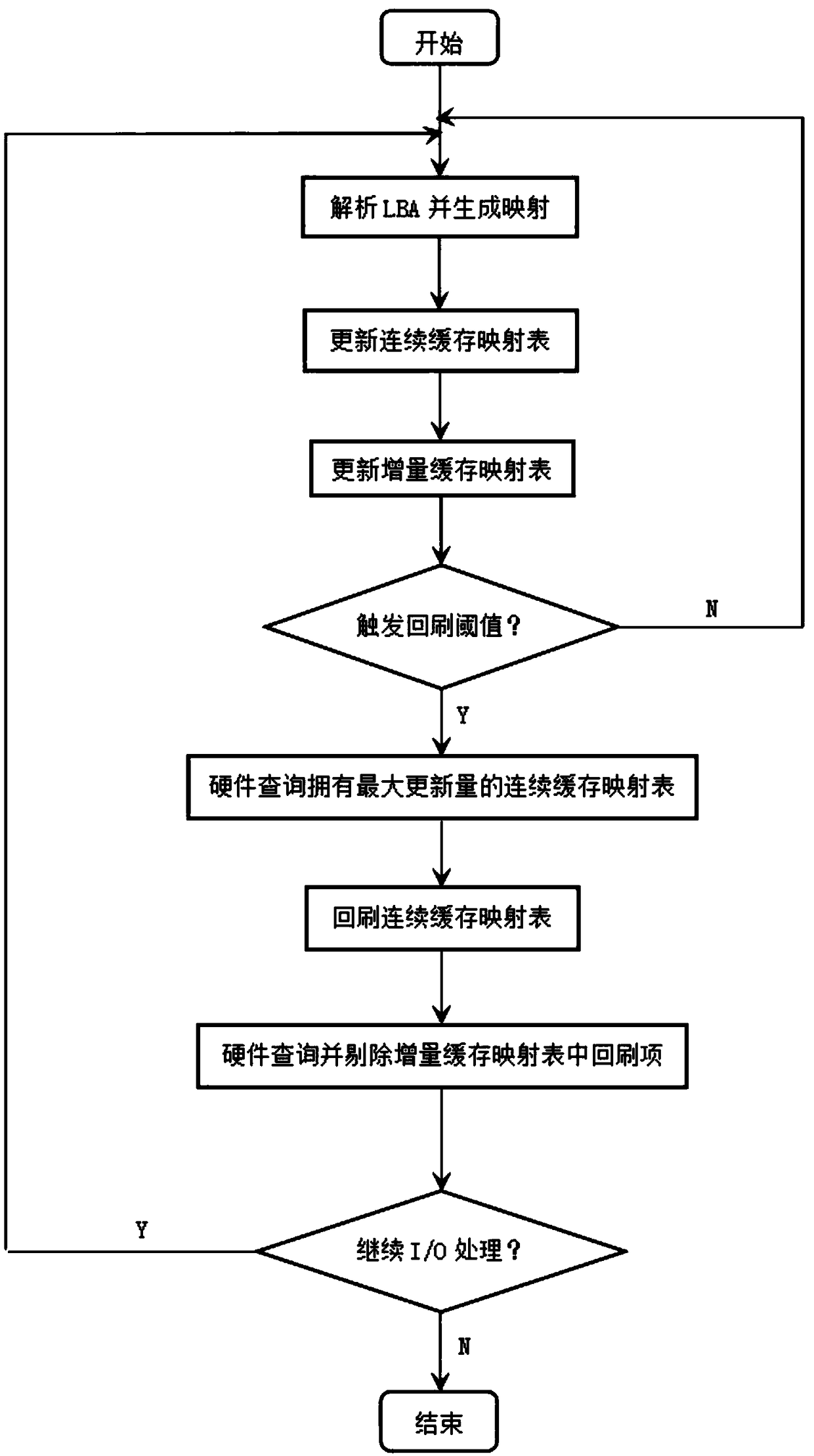

Mapping method for decreasing solid state disk metadata refreshing frequency

ActiveCN108121670AReduce the refresh rateReduce the number of brushbacksEnergy efficient computingMemory systemsElectricityTheoretical computer science

The invention provides a mapping method for decreasing the solid state disk metadata refreshing frequency so as to decrease the metadata refreshing frequency. The method comprises the steps that a caching mapping table is divided into an increment caching mapping table and a continuous caching mapping table, all updated maps which are not refreshed to Nand Flash are saved in the increment cachingmapping table; if the mapping amount in the increment caching mapping table in the read-write process reaches a preset threshold value, the operation for refreshing the continuous caching mapping table is triggered, if the phenomenon that only a small number of increment mapping tables are saved due to abnormal power failure happens, the overall mapping table is updated after power is on, and rebuilding is completed. The table refreshing frequency in the read-write process is lowered, the metadata refreshing quantity during abnormal failure is decreased, and meanwhile the requirement for the rebuilding time of a solid state disk is met.

Owner:HONGQIN (BEIJING) TECHNOLOGY CO LTD

Semiconductor device, semiconductor memory device and data processing system comprising semiconductor system

ActiveUS20110063891A1Excellent operating marginRun at high speedDigital storageData processing systemBit line

A semiconductor device comprises a memory cell, a bit line, a sense amplifier operating between a first voltage and a second voltage higher than the first voltage, a transfer control circuit including a transfer transistor, and a write circuit writing data into the memory cell through the bit line based on the first voltage and a third voltage. The sense amplifier receives and amplifiers the signal voltage at a sense node when the transfer transistor controls the connection between the bit line and the sense node in response to a transfer control voltage. The third voltage is set to a voltage lower than the second voltage and higher than the transfer control voltage, and the sense node is set to a voltage higher than the transfer control voltage in an initial period of a read operation before the data of the memory cell is read out to the bit line.

Owner:PS4 LUXCO SARL

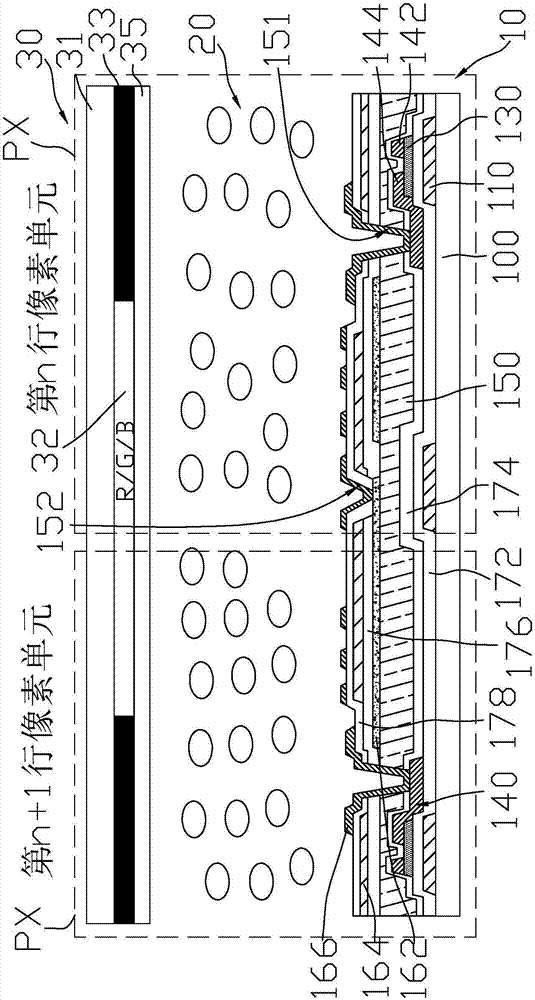

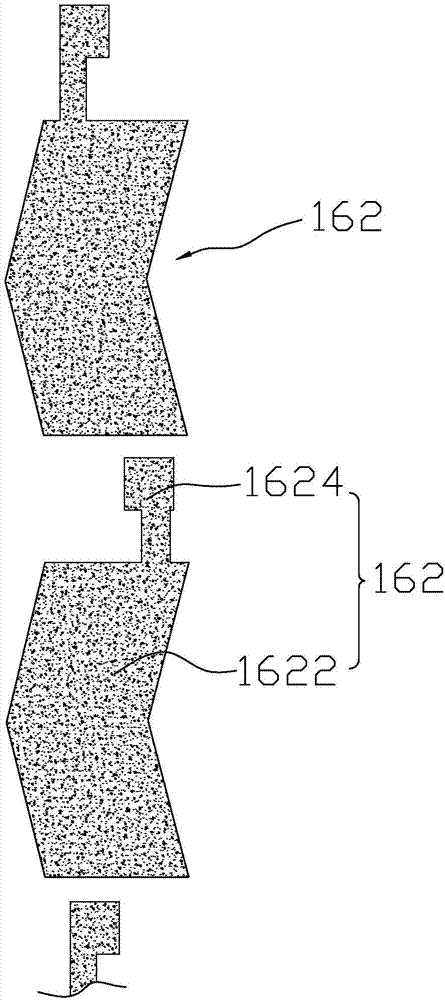

Array substrate and repairing method thereof, and liquid crystal display device

ActiveCN107991796AReduce power consumptionThe display effect is not affectedNon-linear opticsLiquid-crystal displayAuxiliary electrode

The invention discloses an array substrate. The array substrate includes a gate layer, a source-drain electrode layer, common electrodes, a plurality of pixel electrodes and a plurality of auxiliary electrodes. The pixel electrodes, the common electrodes and the pixel electrodes are arranged at intervals, the auxiliary electrodes are located below the pixel electrodes, the common electrodes are located between the pixel electrodes and the auxiliary electrodes, a plurality of pixel units are arranged in arrays on an array substrate, and each pixel unit is internally provided with one auxiliaryelectrode and one pixel electrode; the source-drain electrode layer includes an source electrode and a drain electrode which are separated, and the pixel electrode in each pixel unit is electrically connected with the corresponding drain electrode in the pixel unit through a first contact hole; in the two pixel units located up and down in the same column, the pixel electrode in one pixel unit iselectrically connected with the auxiliary electrode in the next pixel unit through a second contact hole. The invention further discloses a repairing method of the array substrate and a liquid crystaldisplay device.

Owner:KUSN INFOVISION OPTOELECTRONICS

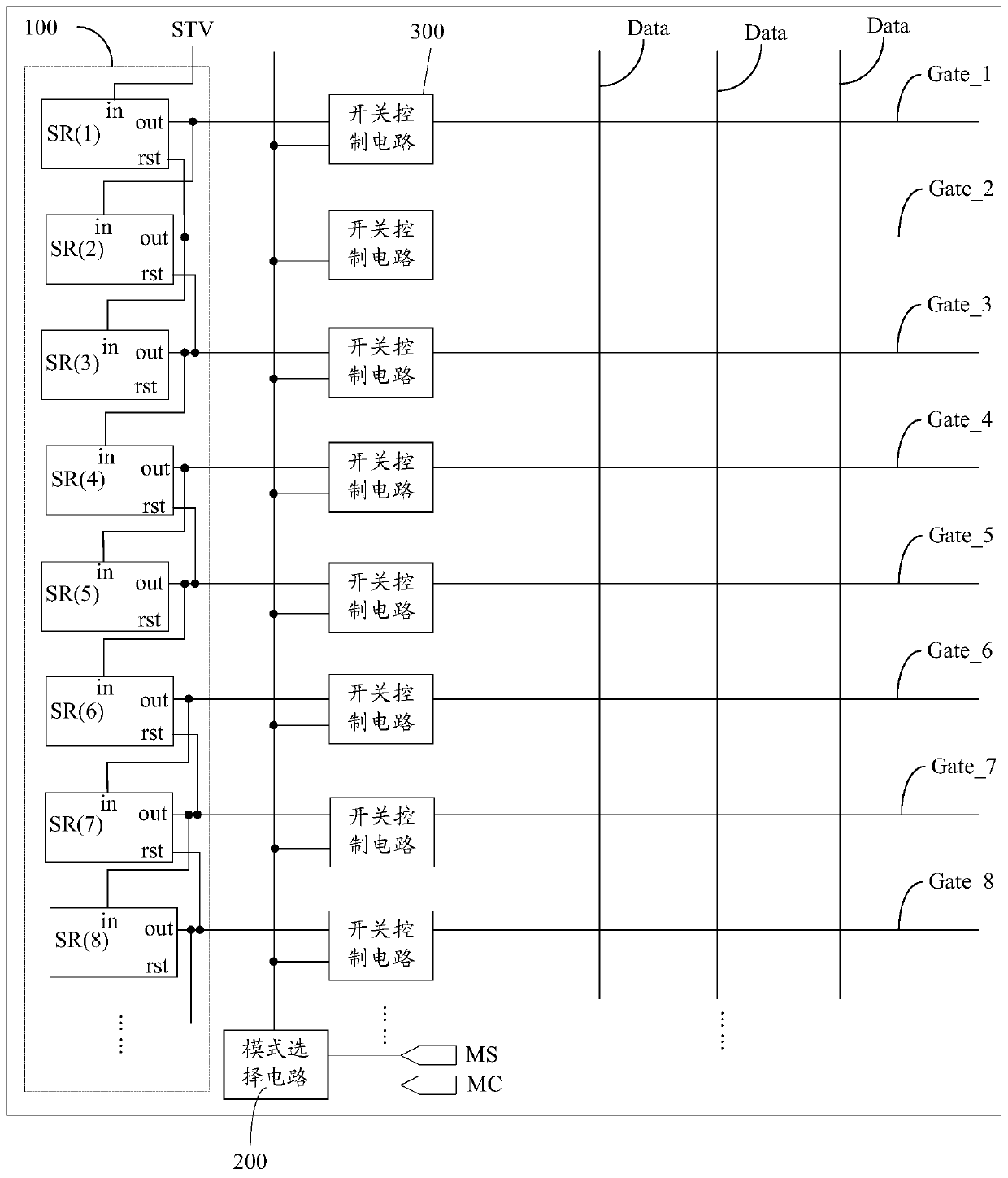

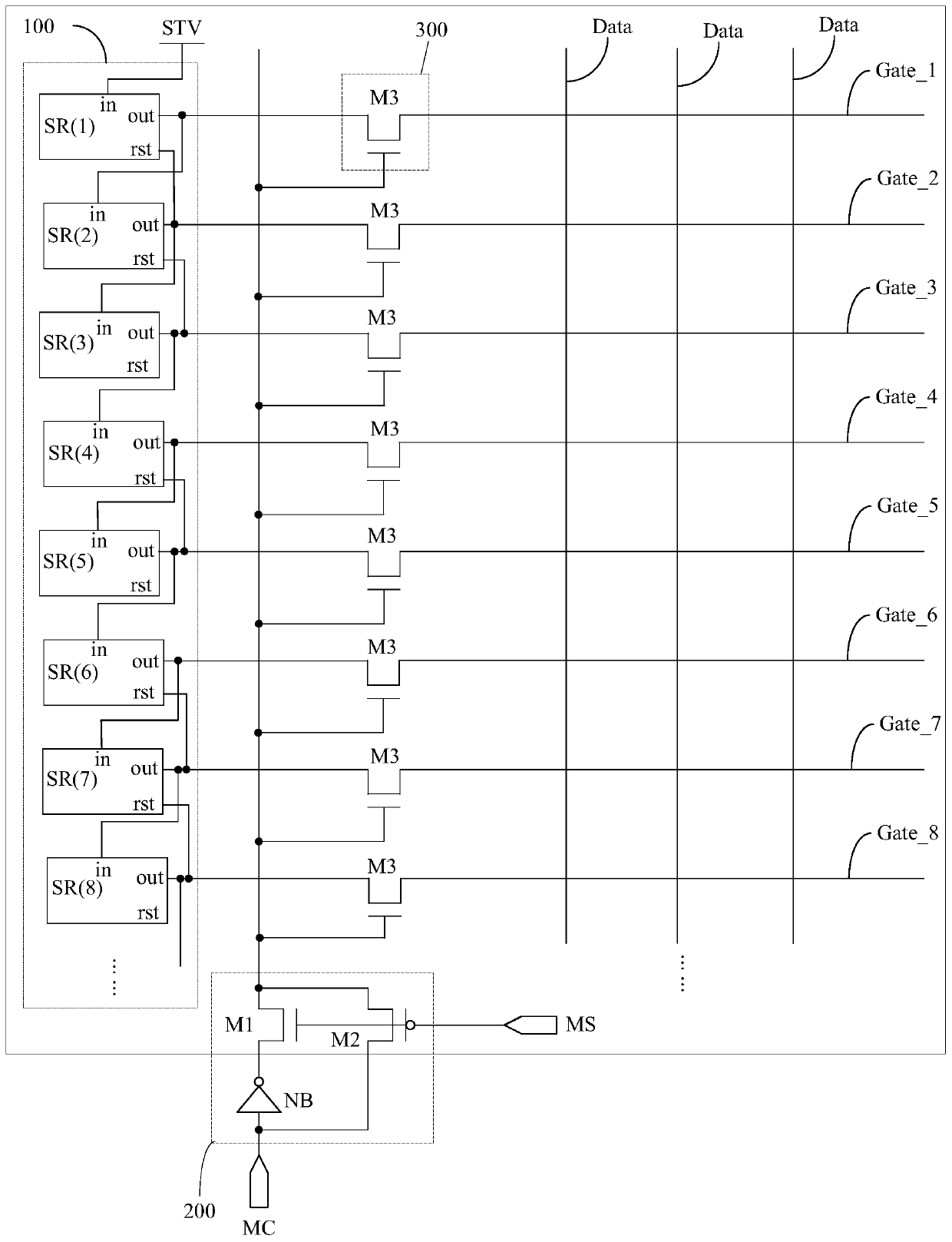

Display panel, driving method thereof and display device

ActiveCN110491331AReduce the refresh rateReduce power consumptionStatic indicating devicesDigital storageElectricityShift register

The invention discloses a display panel, a driving method of the display panel and a display device. By arranging a mode selection circuit and switch control circuits in one-to-one correspondence withshift registers, the output signal ends of the shift registers can be electrically connected with corresponding grid lines through the corresponding switch control circuits. In this way, the mode selection circuit is controlled by the signal of the mode selection signal end; according to signals of the gating control signal ends, signals are provided for the control ends of all the switch controlcircuits so as to control connection and disconnection of the switch control circuits, and therefore when the switch control circuits are connected, the output signal ends of the shifting registers can be connected with the grid lines correspondingly connected with the output signal ends. When the switch control circuit is cut off, the output signal end of the shift register can be disconnected from the correspondingly connected grid line, so that the refreshing frequency of the display panel can be reduced, and the effect of reducing power consumption is achieved.

Owner:BOE TECH GRP CO LTD +1