Patents

Literature

13176results about How to "Reduce size" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

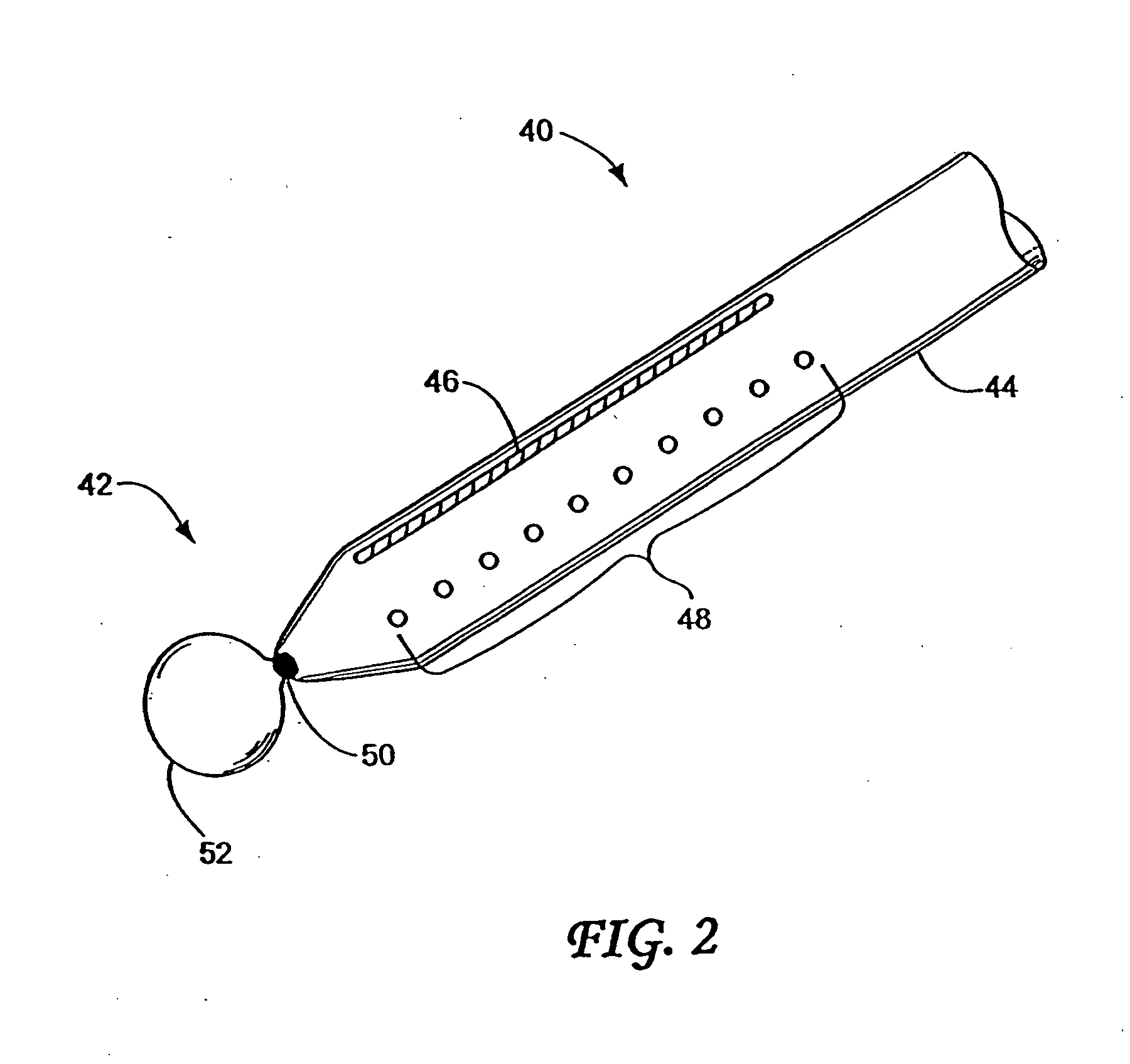

Surgical tools for use in minimally invasive telesurgical applications

This invention provides surgical tools or instruments for use in minimally invasive telesurgical applications. The instruments typically include a base whereby the instrument is removably mountable on a robotically controlled articulated arm. An elongate shaft extends from the base. A working end of the shaft is disposed at an end of the shaft remote from the base. A wrist member is pivotally mounted on the working end. At least one end effector element mounting formation is pivotally mounted on an opposed end of the wrist member. A plurality of elongate elements, e.g., cables, extend from the end effector element mounting formation and the wrist member to cause selective angular displacement of the wrist member and end effector mounting formation in response to selective pulling of the elongate elements.

Owner:PENN STATE RES FOUND +1

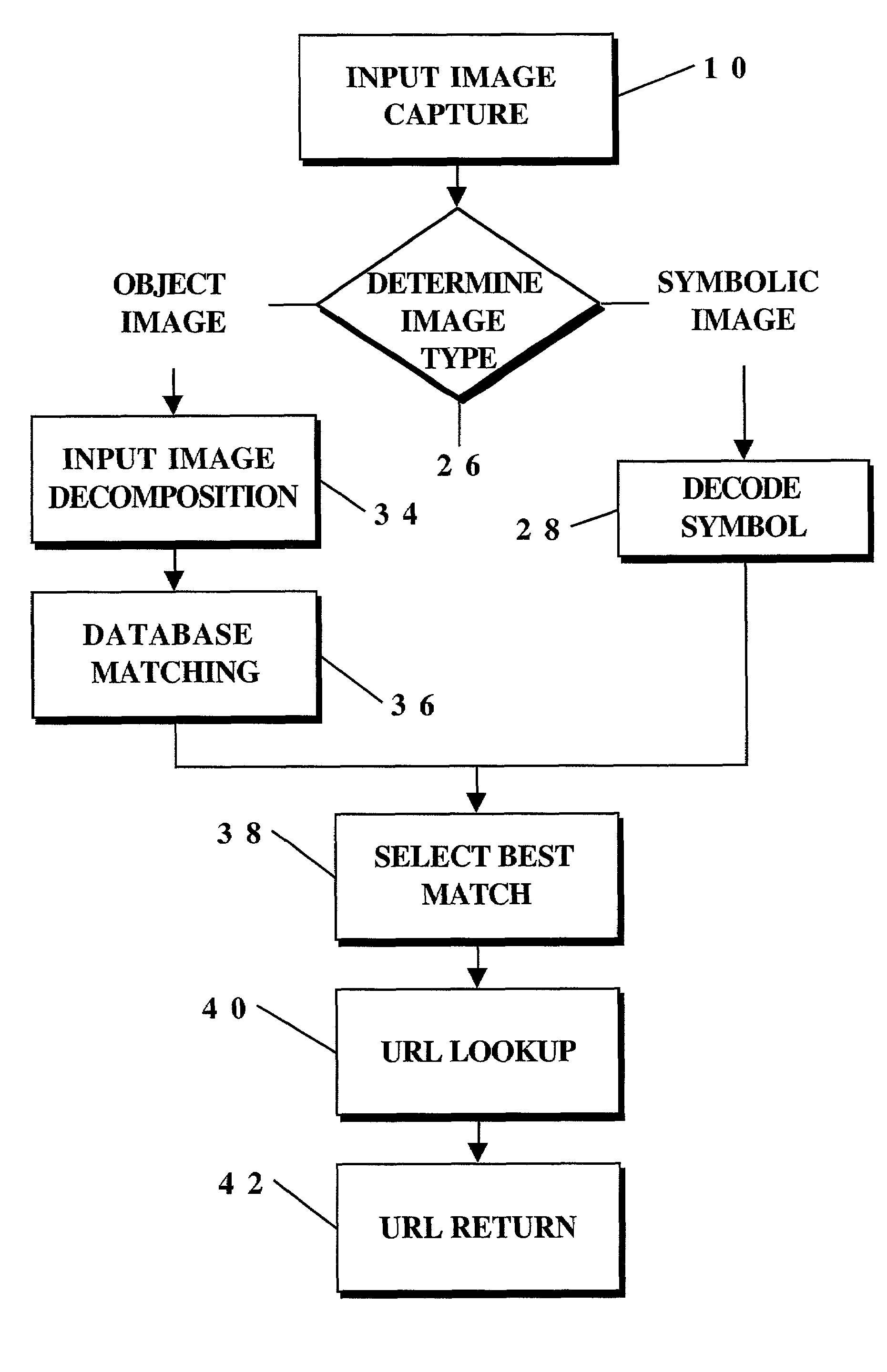

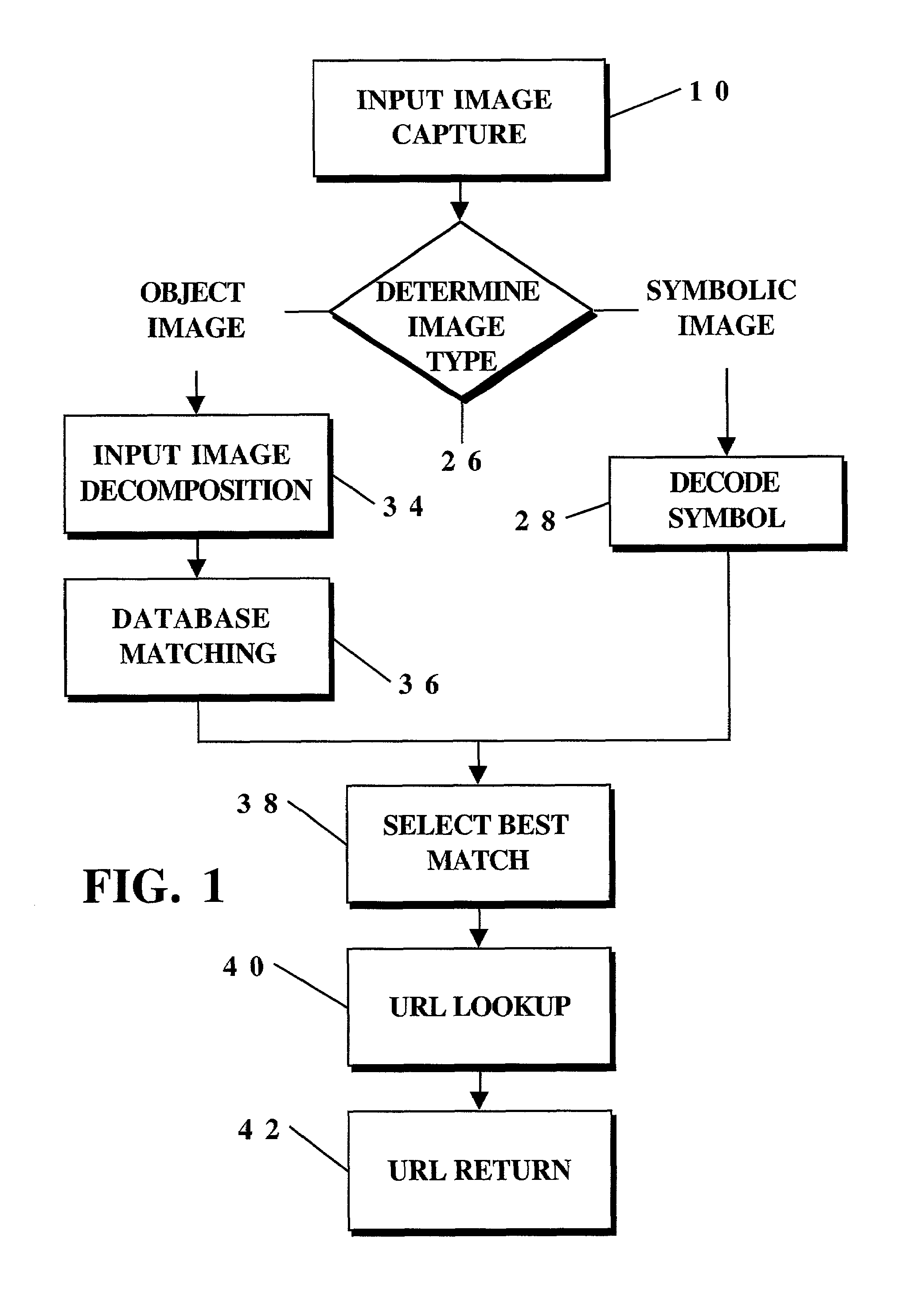

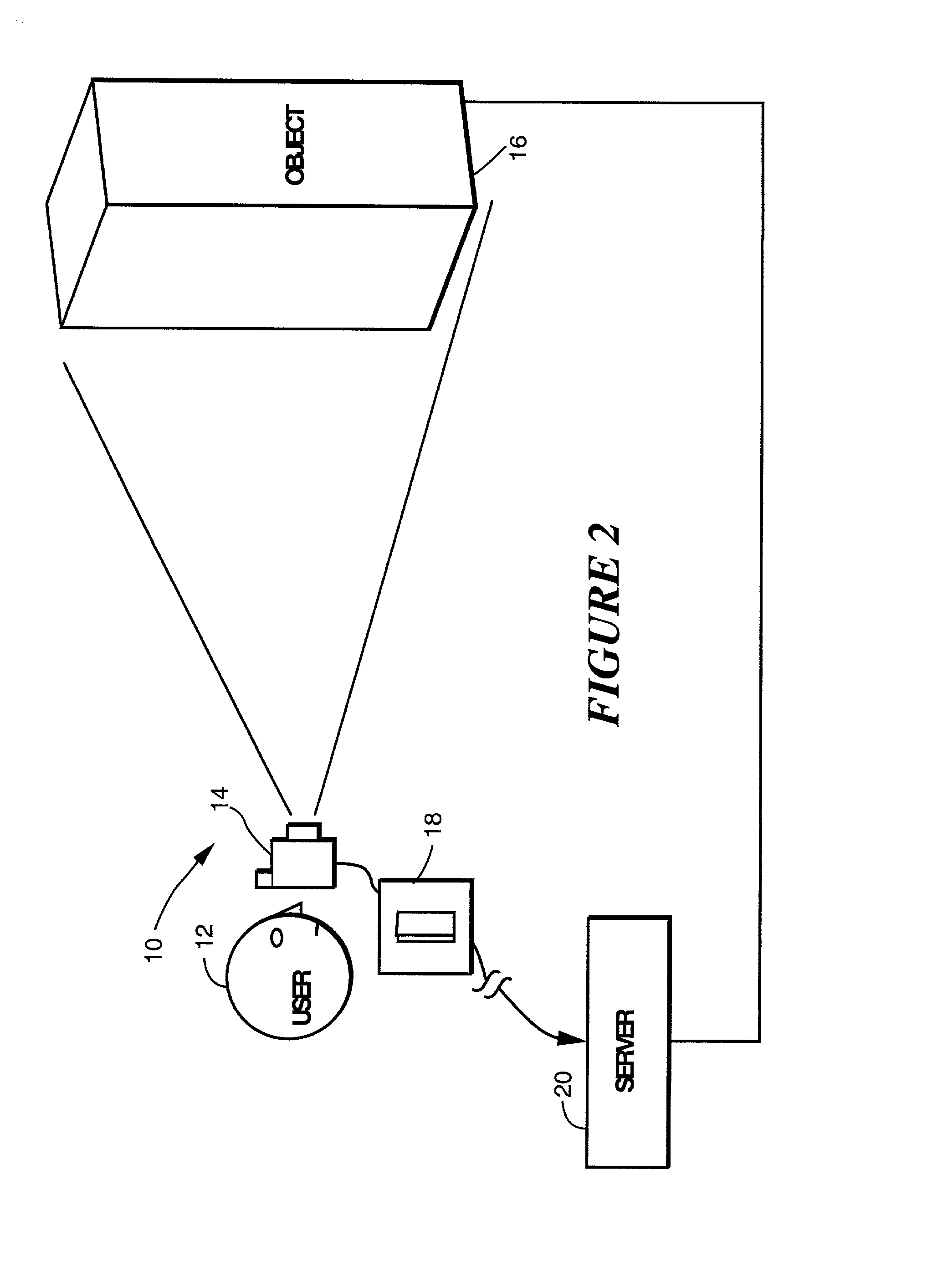

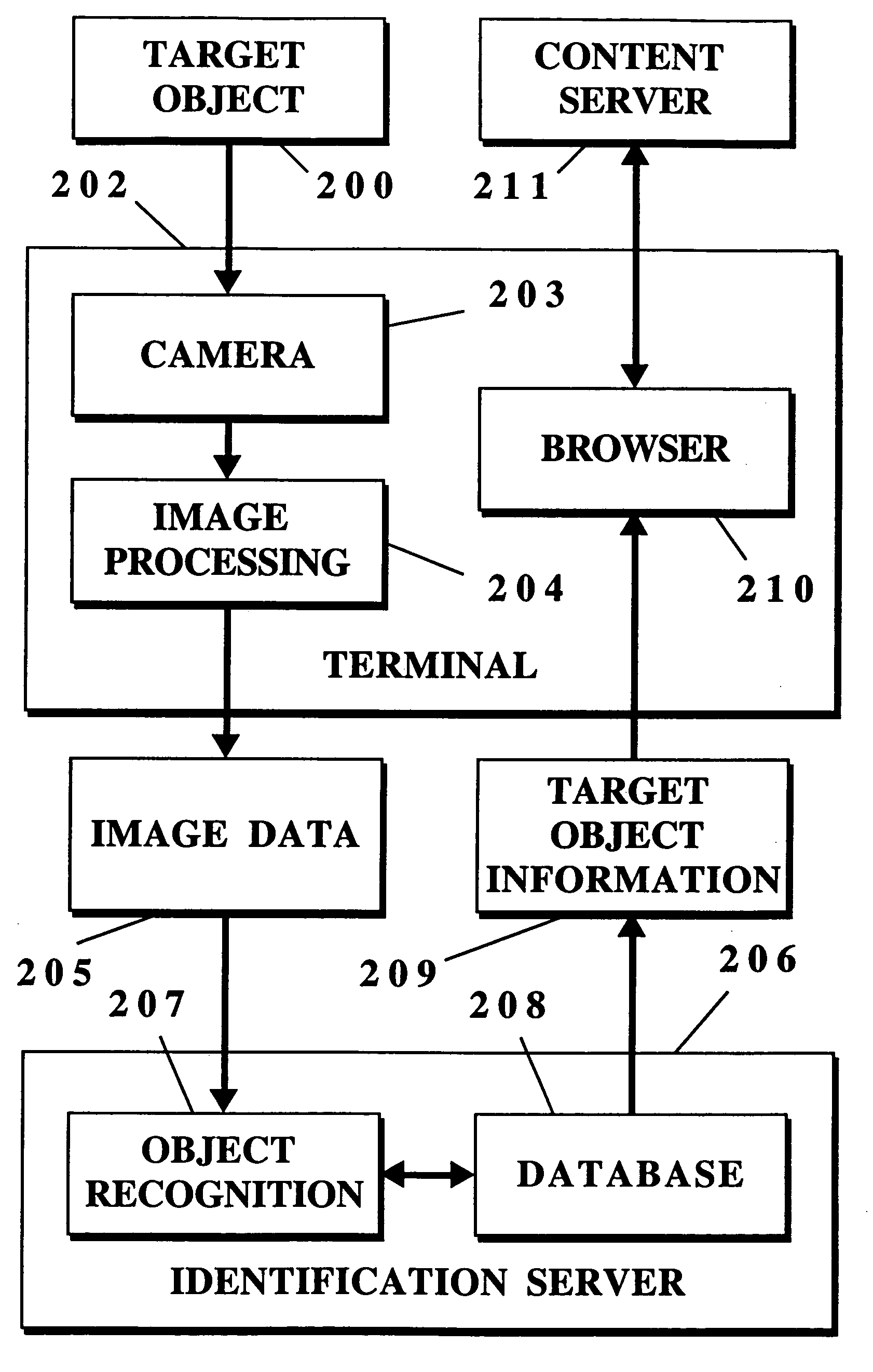

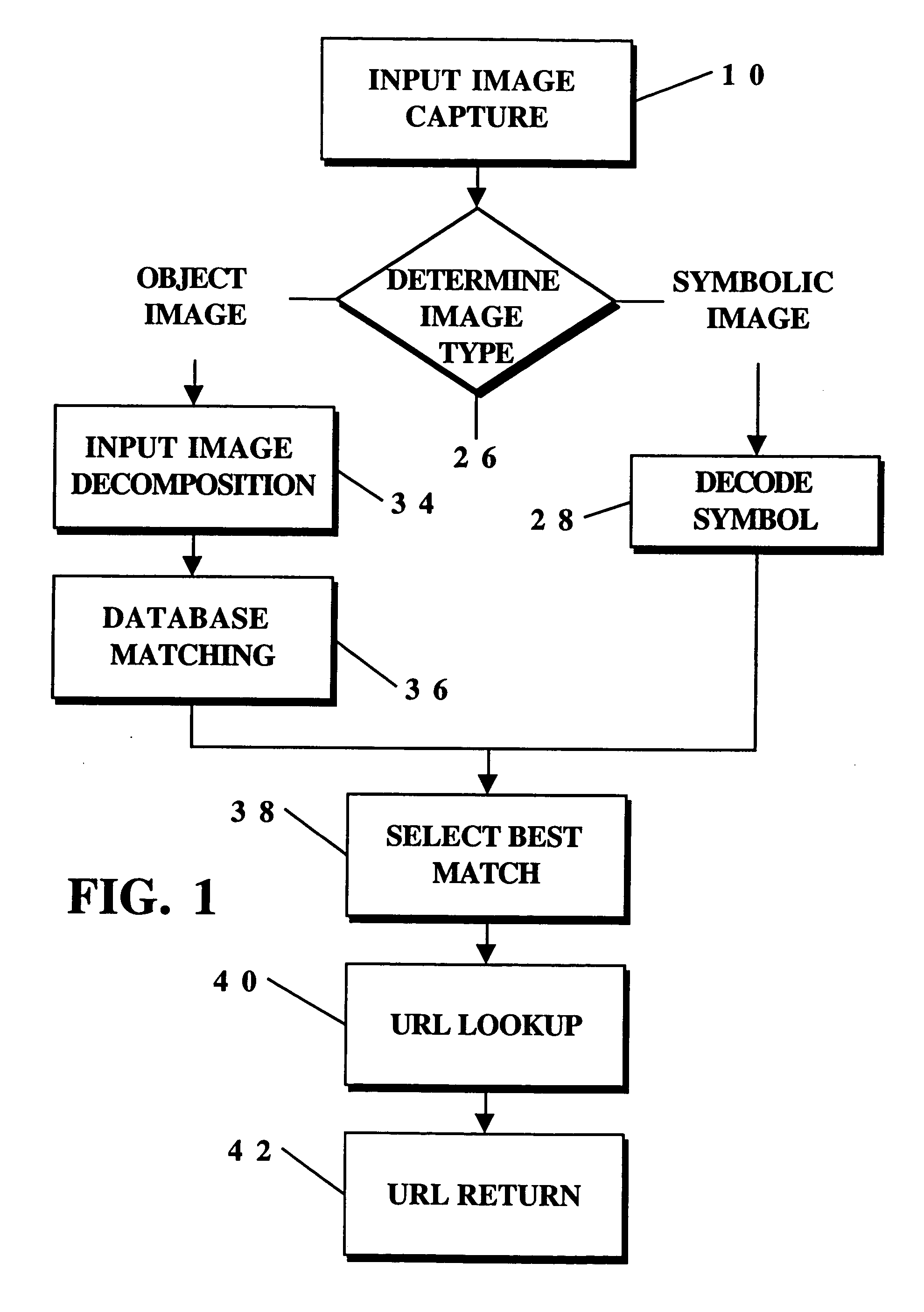

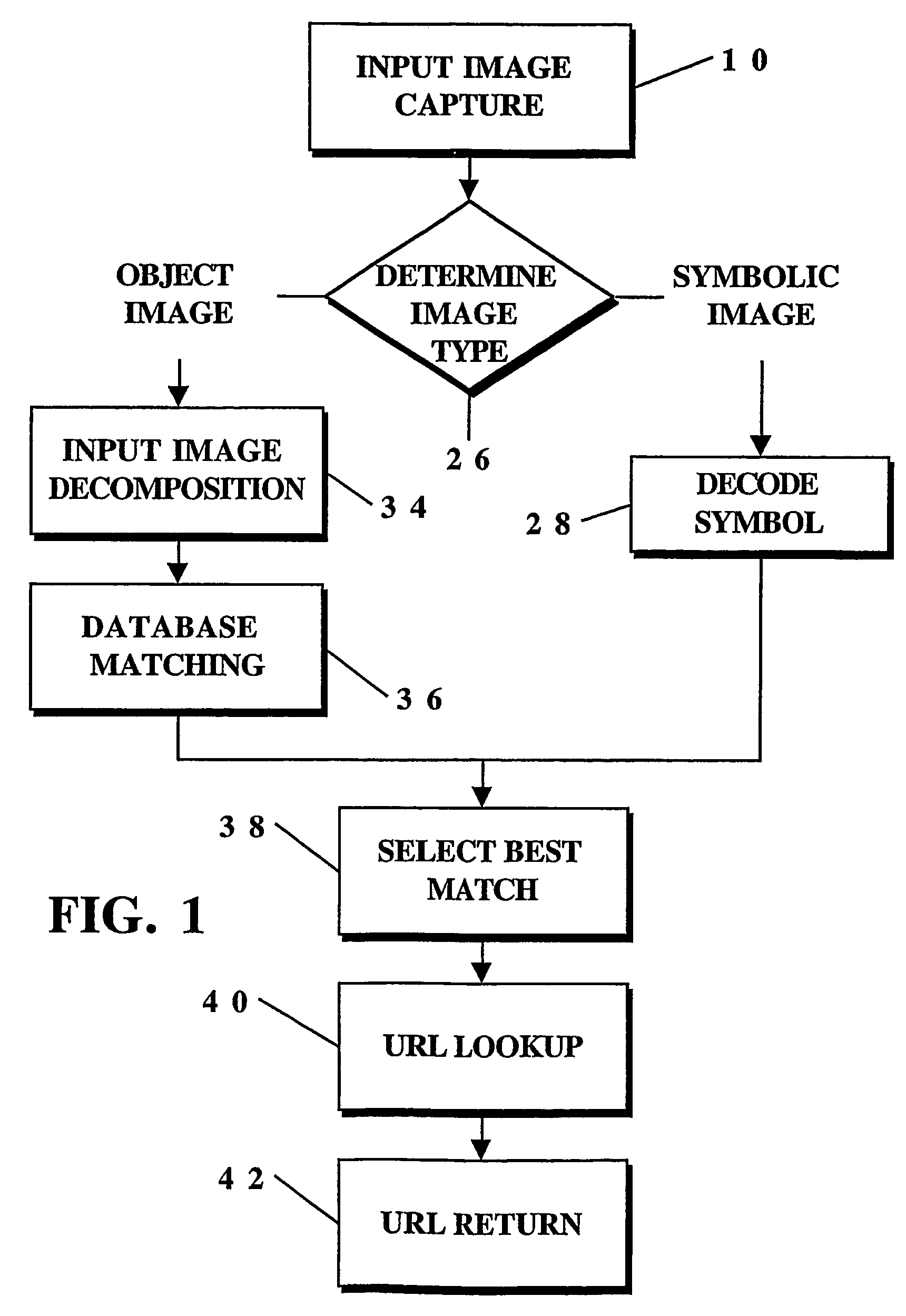

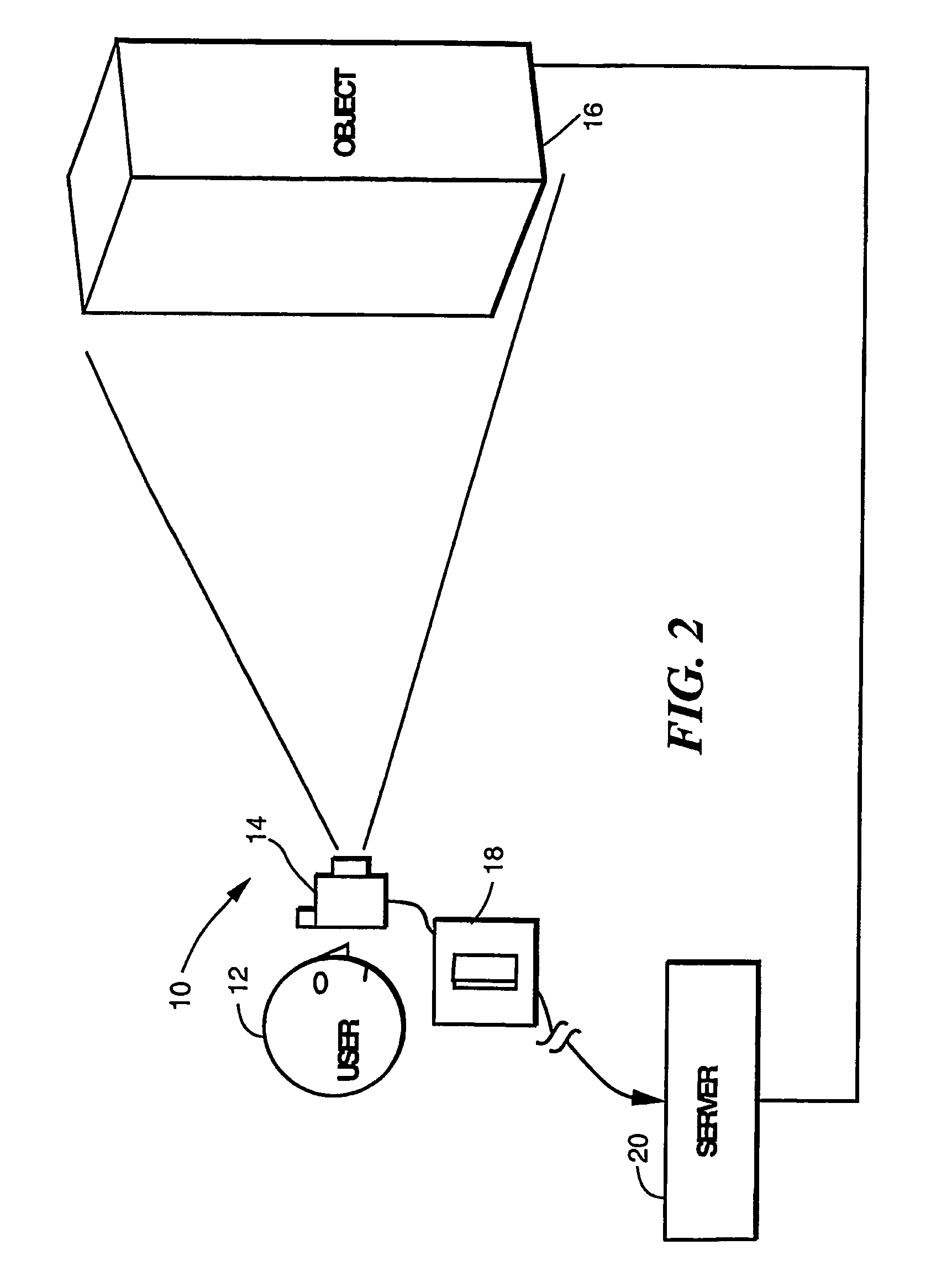

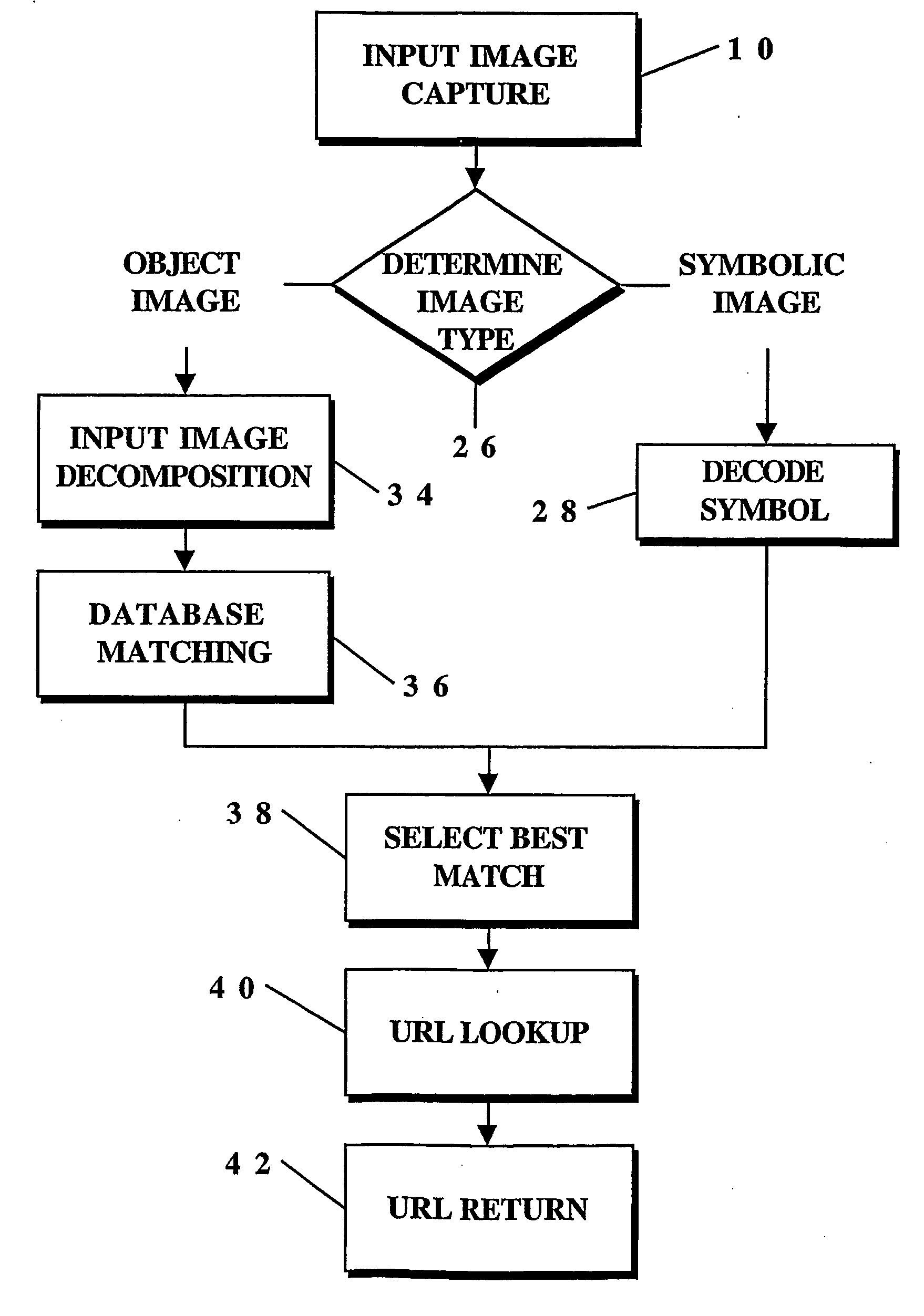

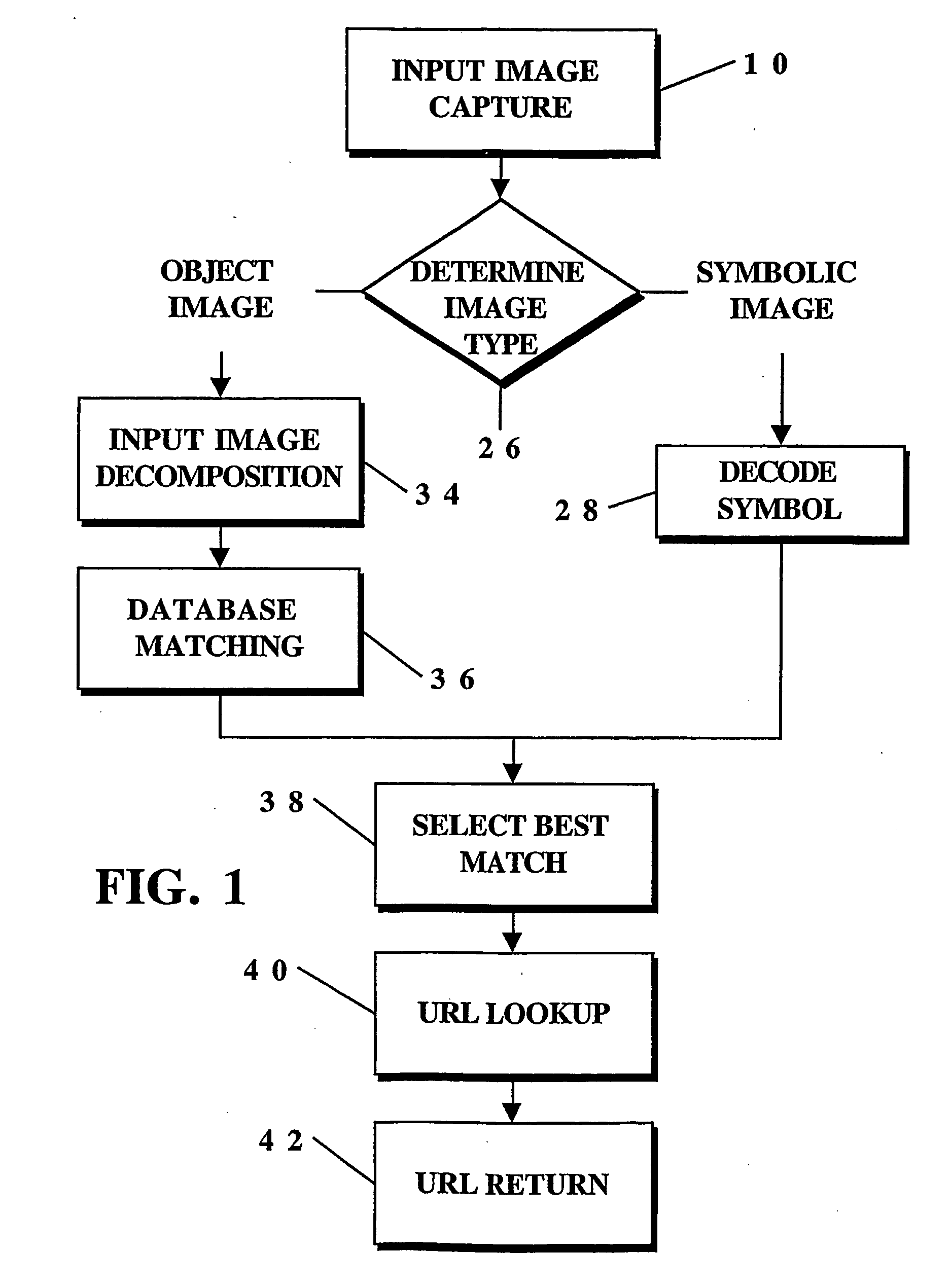

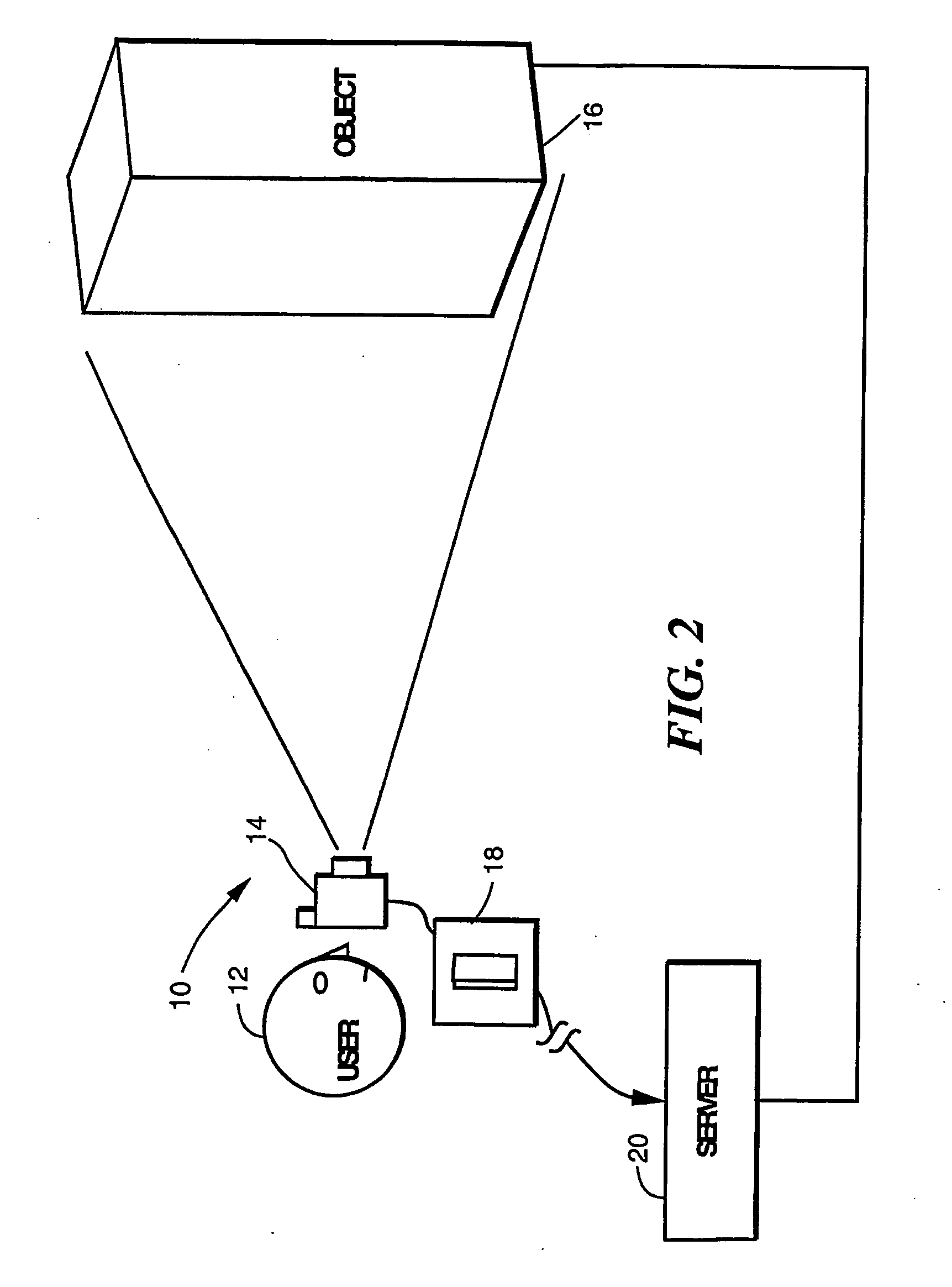

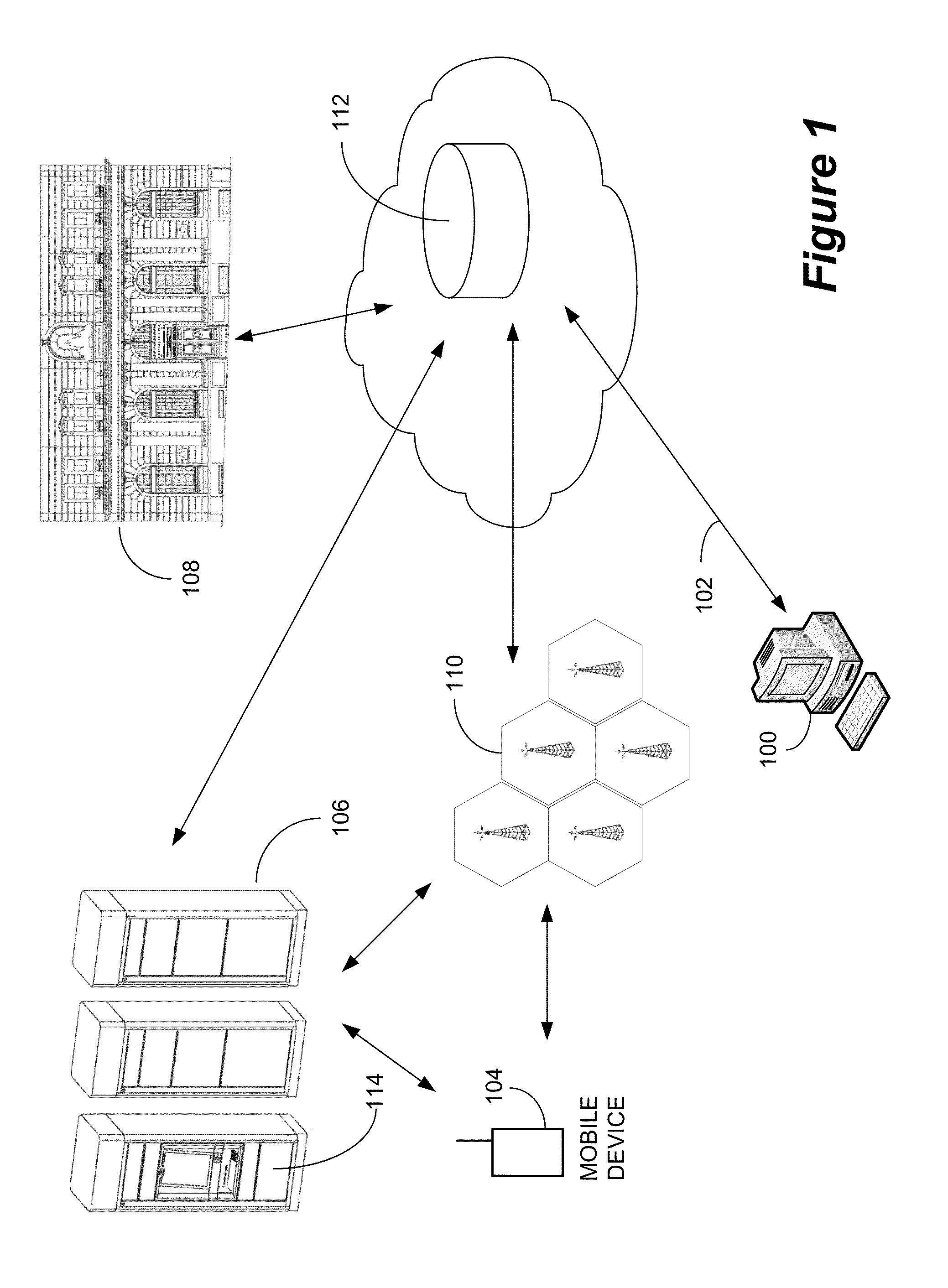

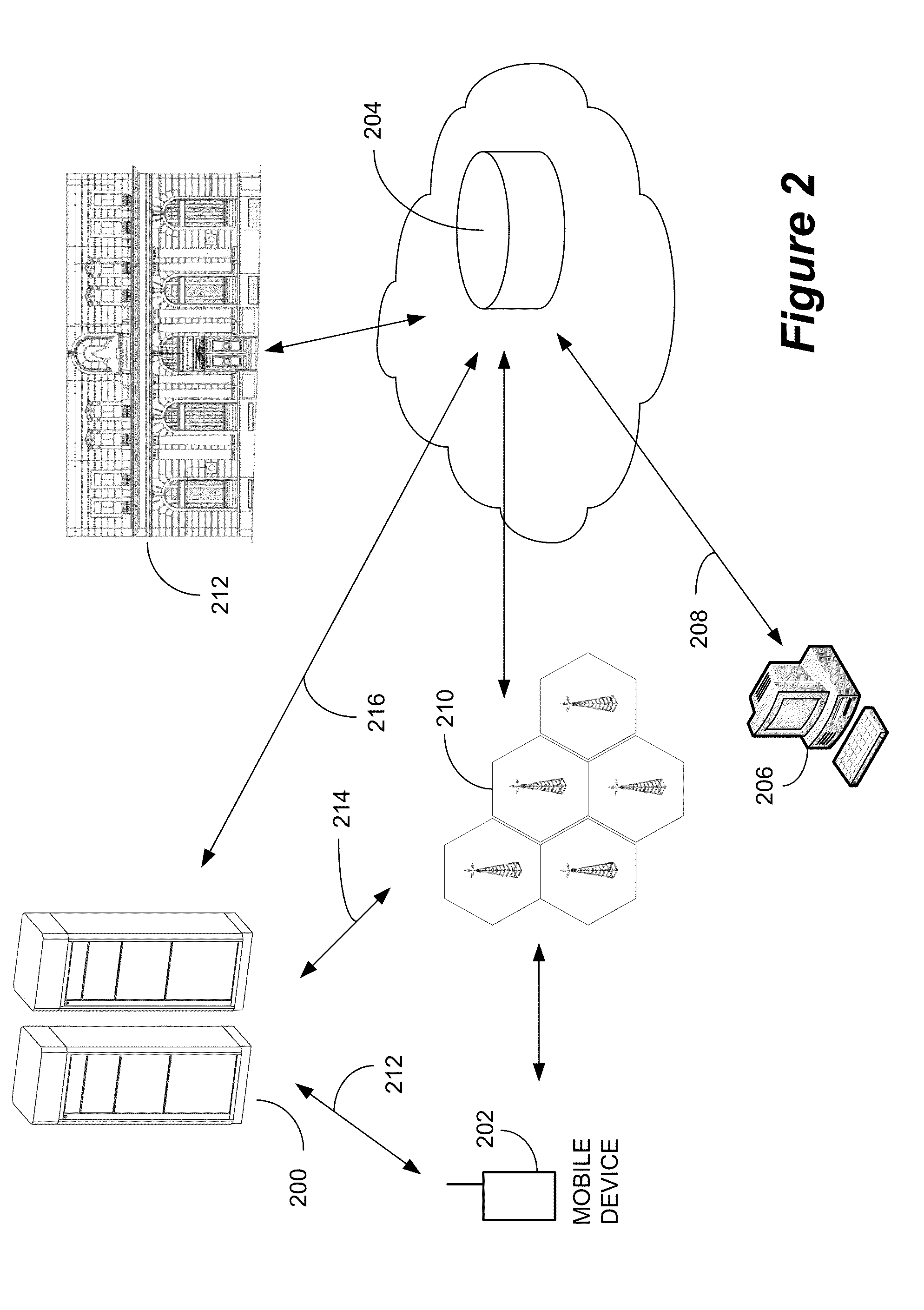

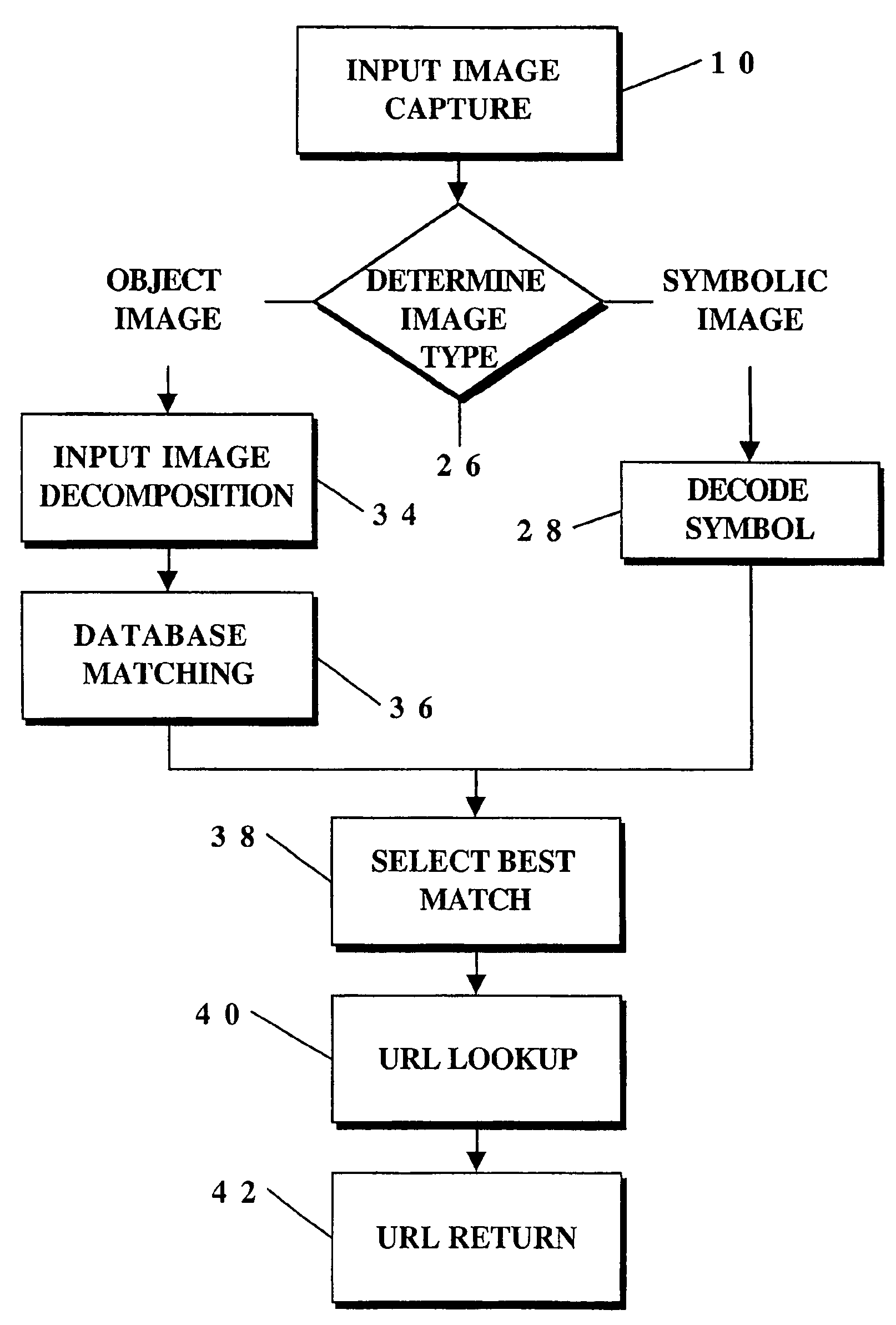

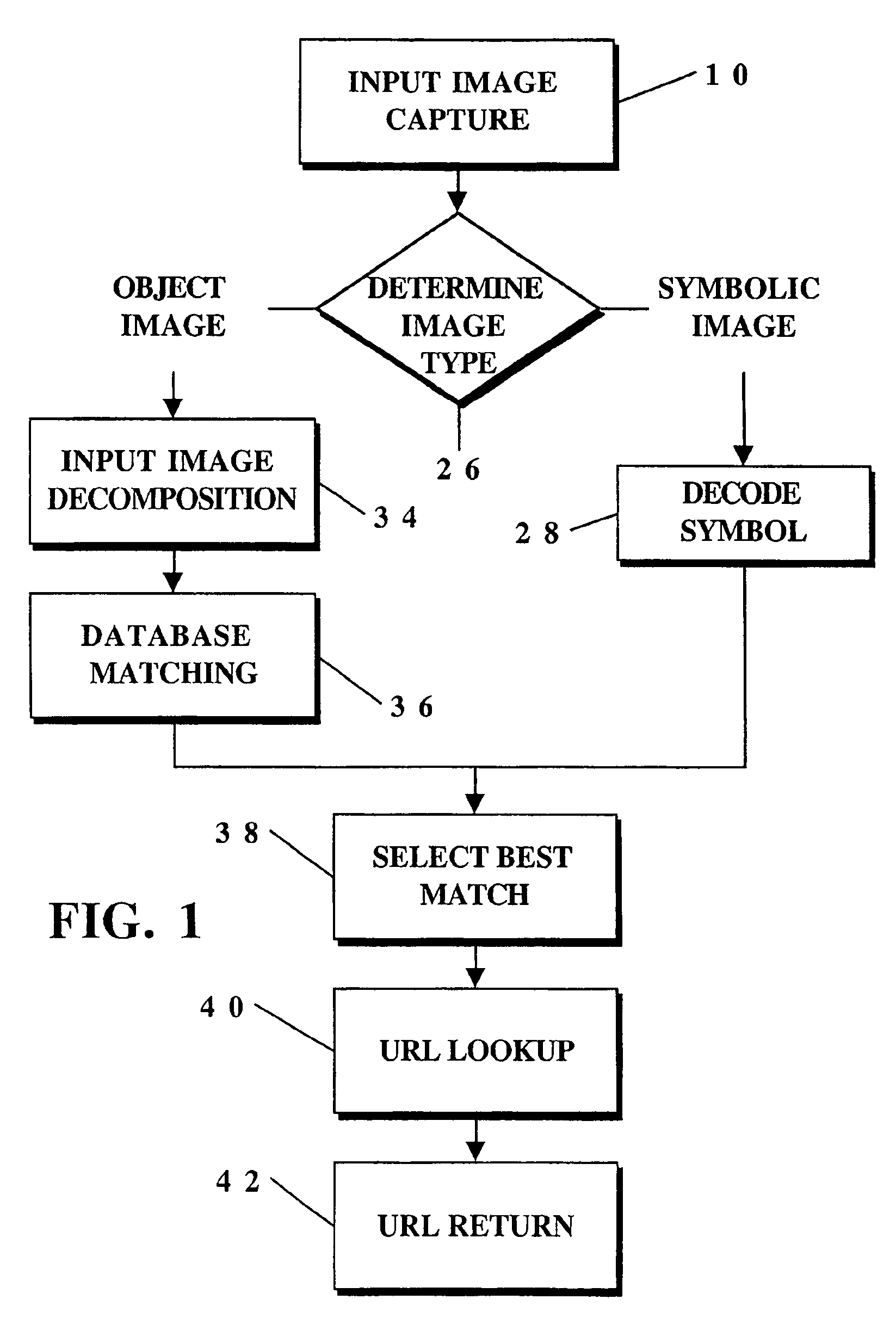

Image capture and identification system and process

InactiveUS7016532B2Fast and reliable detection and recognitionReduce sizeDigital data information retrievalImage analysisDigital imageImage capture

An identification method and process for objects from digitally captured images thereof that uses image characteristics to identify an object from a plurality of objects in a database. The image is broken down into parameters such as a Shape Comparison, Grayscale Comparison, Wavelet Comparison, and Color Cube Comparison with object data in one or more databases to identify the actual object of a digital image.

Owner:NANT HLDG IP LLC

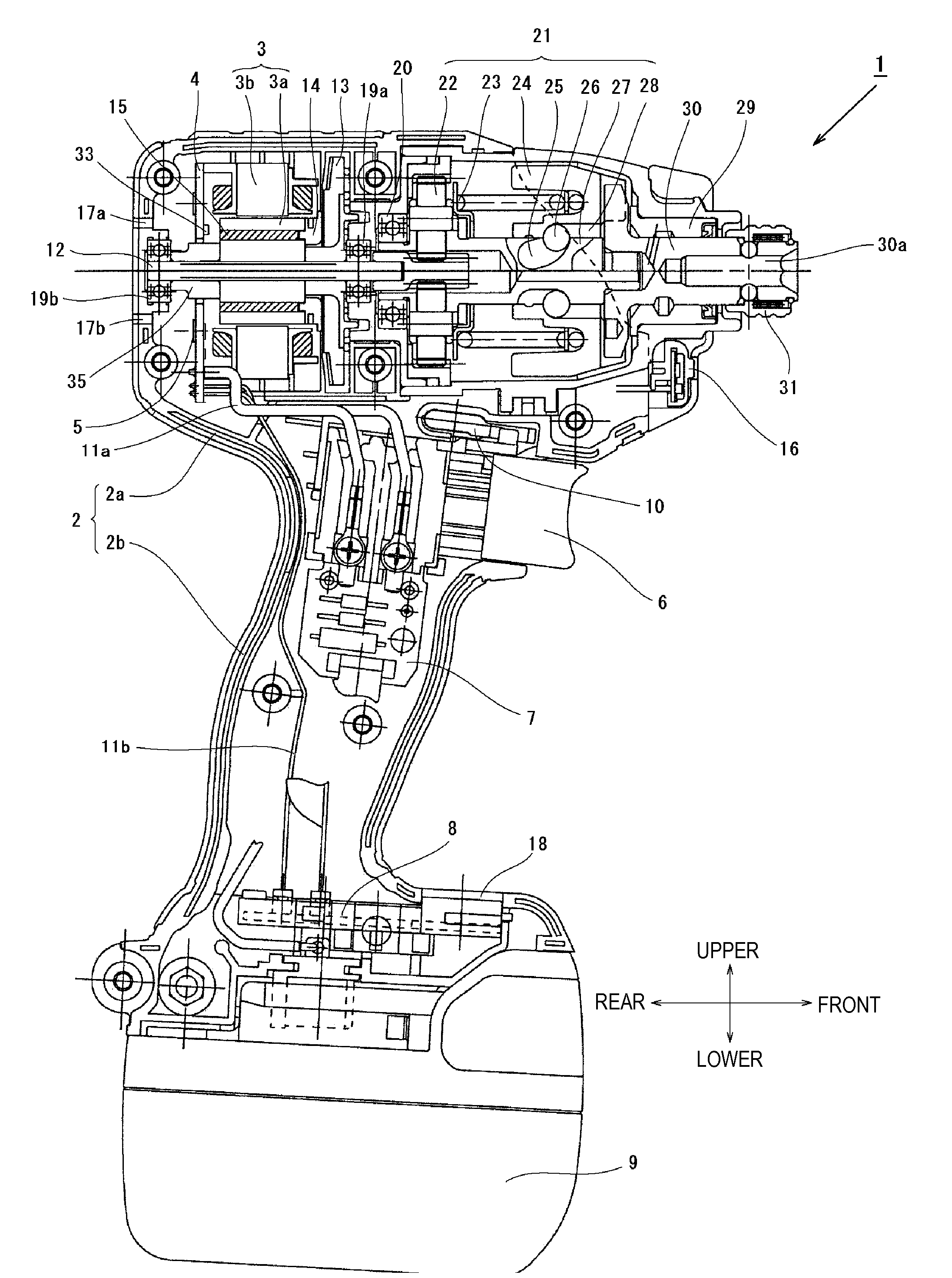

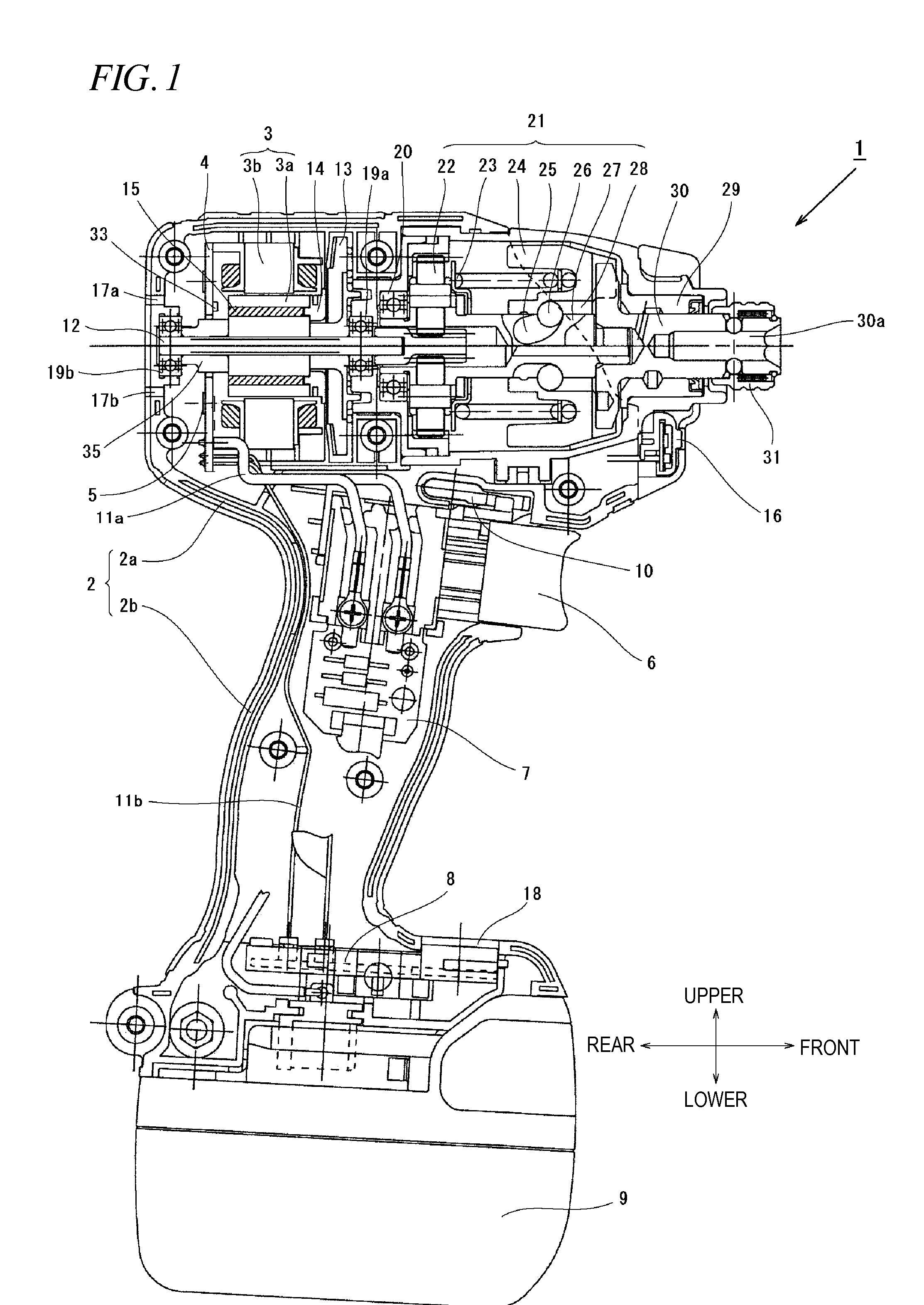

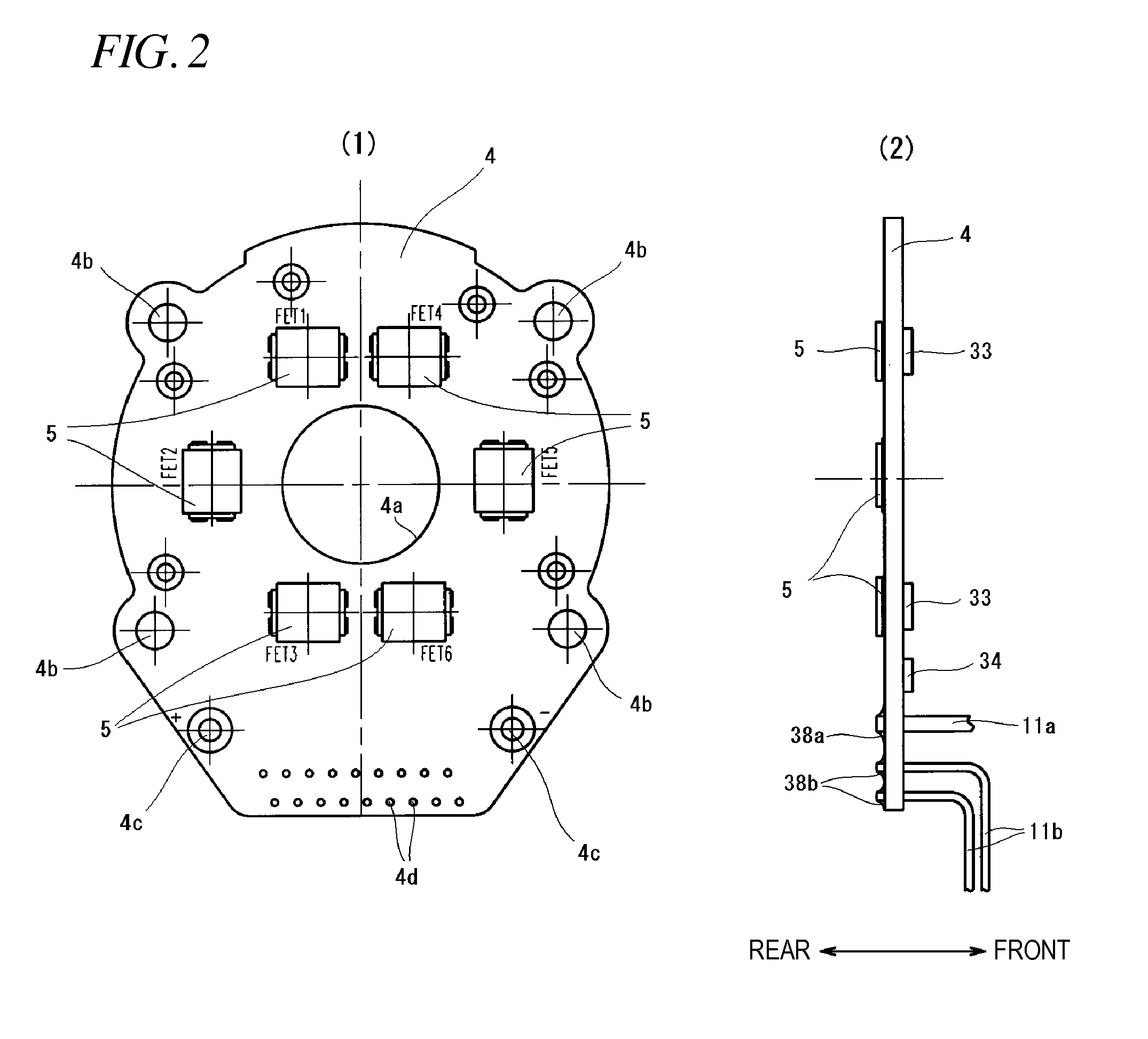

Impact tool and method of controlling impact tool

An impact tool includes: a motor; a trigger; a controller configured to control driving power supplied to the motor using a semiconductor switching element according to an operation of the trigger; a striking mechanism configured to drive a tip tool continuously or intermittently by rotation force of the motor, the striking mechanism including a hammer and an anvil. The controller drives the semiconductor switching element at a high duty ratio when the trigger is manipulated. The motor is driven so that the duty ratio is lowered before a first striking of the hammer on the anvil is performed and the first striking is performed at a low duty ratio lower than the high duty ratio.

Owner:HITACHI KOKI CO LTD

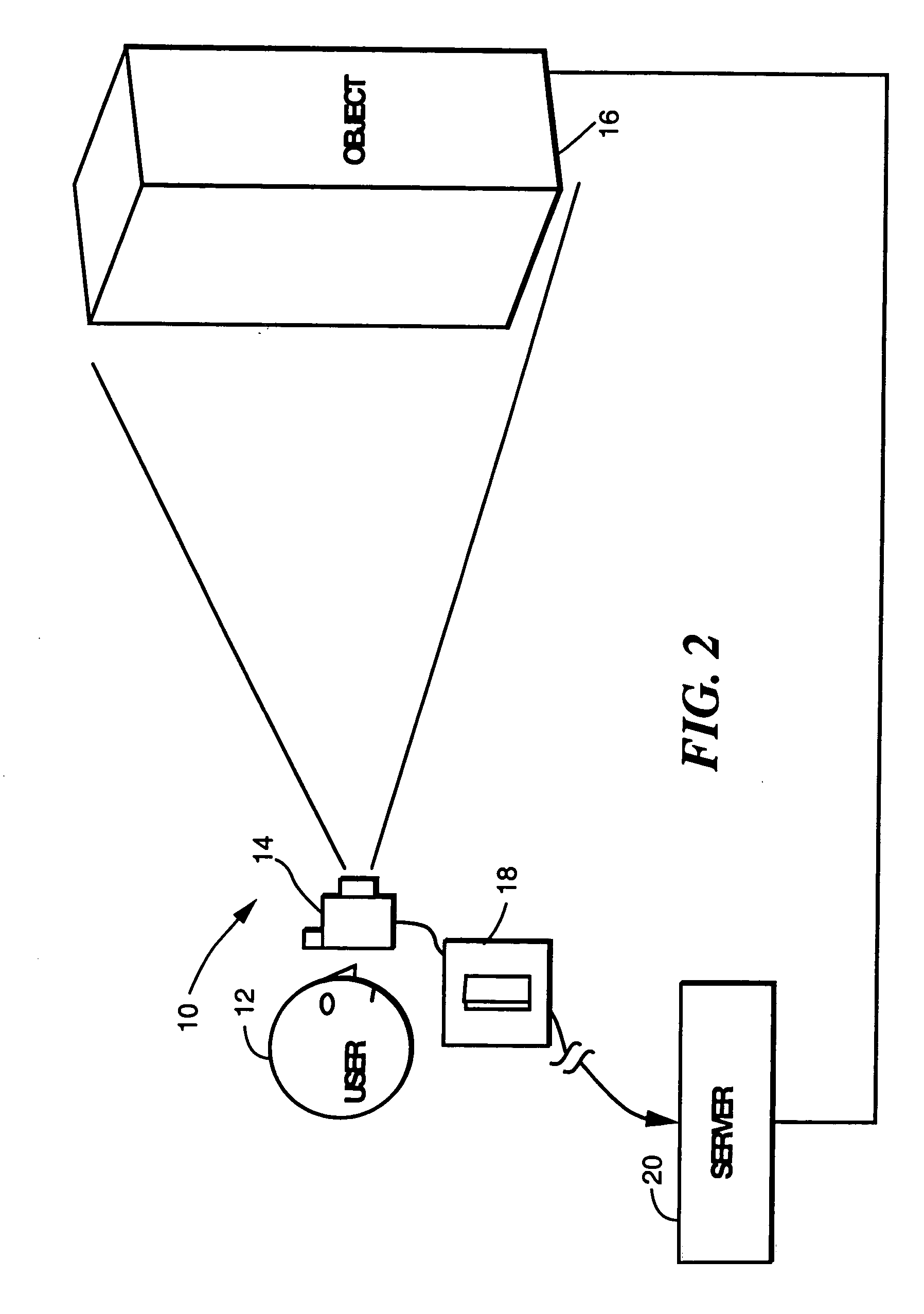

Image capture and identification system and process

ActiveUS20040208372A1Fast and reliable detection and recognitionReduce sizeImage analysisDigital data information retrievalDigital imageImage capture

The invention is a method by which information and communication pertinent to an object is provided based on imagery of the object. A digital image of the object is captured and the object is recognized from a plurality of objects in a database. An information address corresponding to the object is then used to access information and initiate communication pertinent to the object.

Owner:NANT HLDG IP LLC

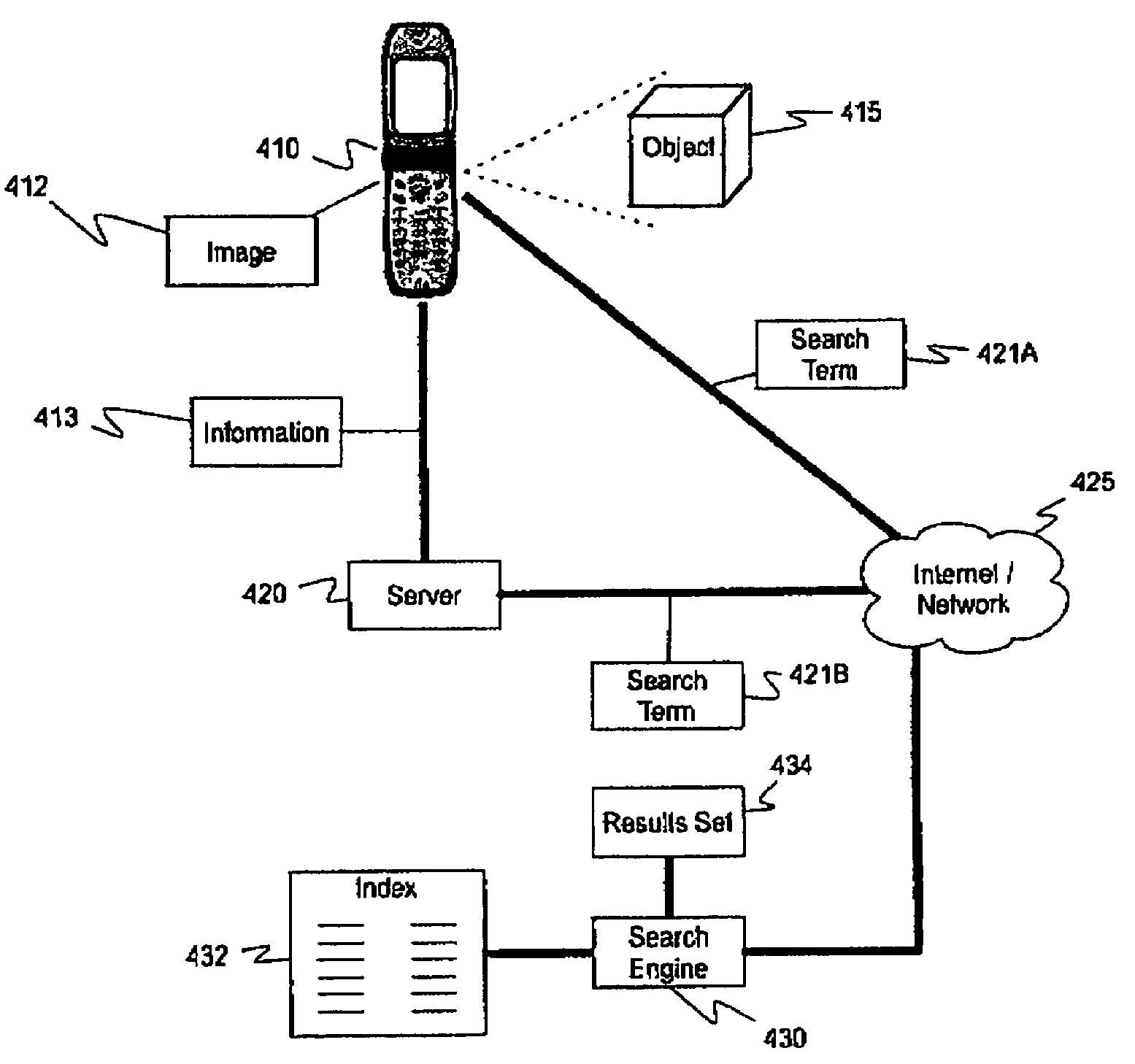

Use of image-derived information as search criteria for internet and other search engines

ActiveUS7680324B2Reduce sizeFaster and accurate algorithmStill image data retrievalTelevision system detailsHuman search engineThe Internet

Search terms are derived automatically from images captured by a camera equipped cell phone, PDA, or other image capturing device, submitted to a search engine to obtain information of interest, and at least a portion of the resulting information is transmitted back locally to, or nearby, the device that captured the image.

Owner:NANT HLDG IP LLC

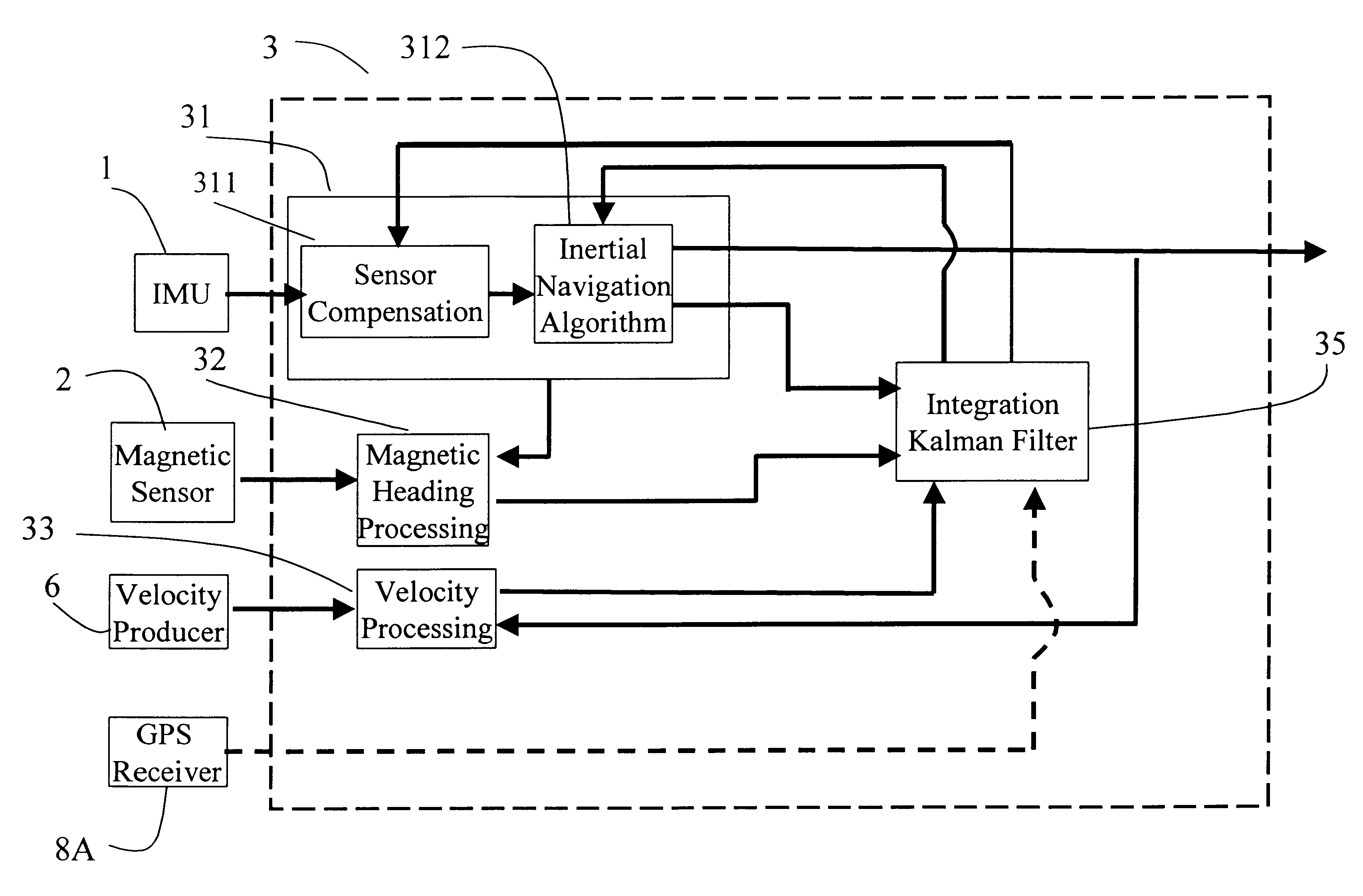

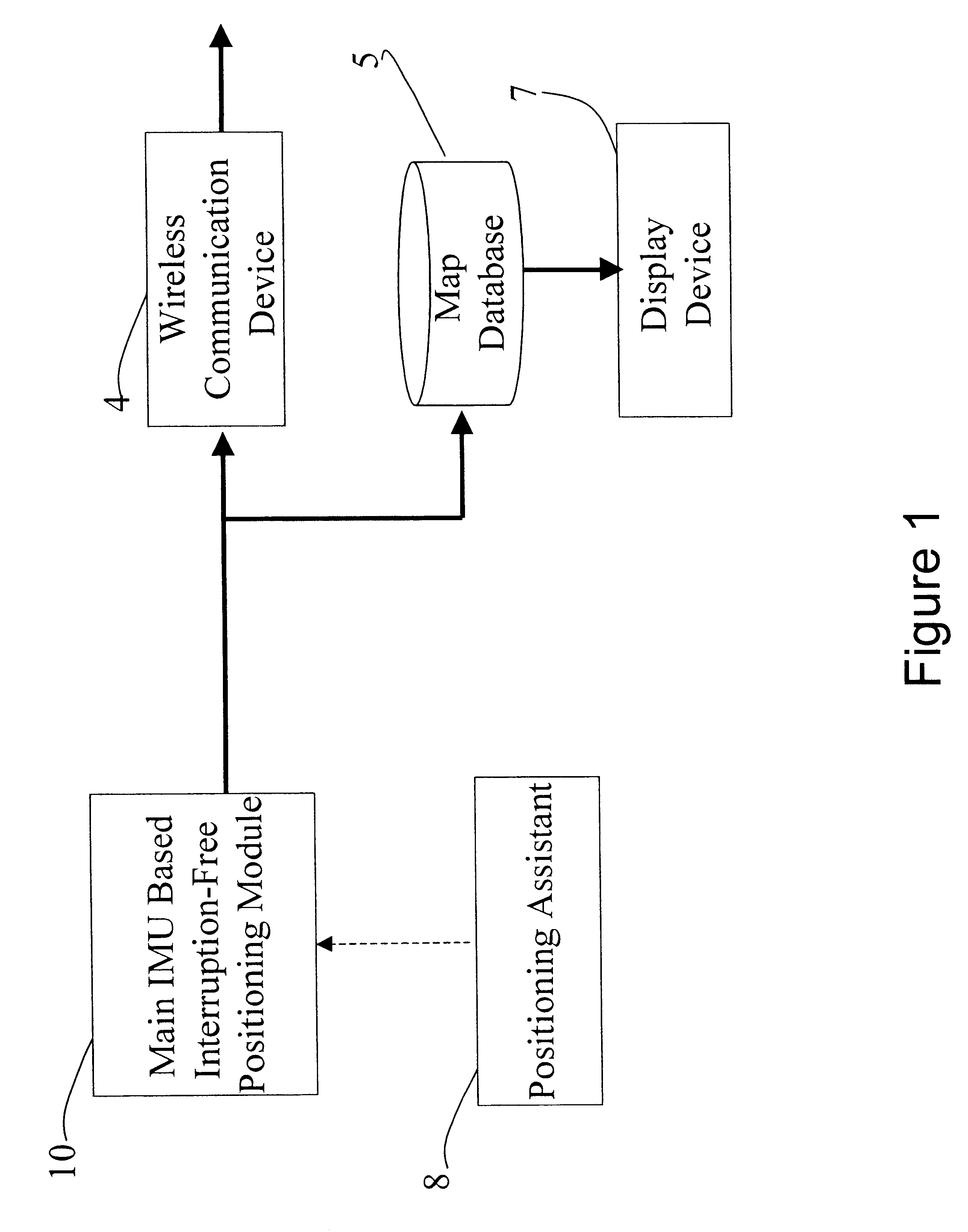

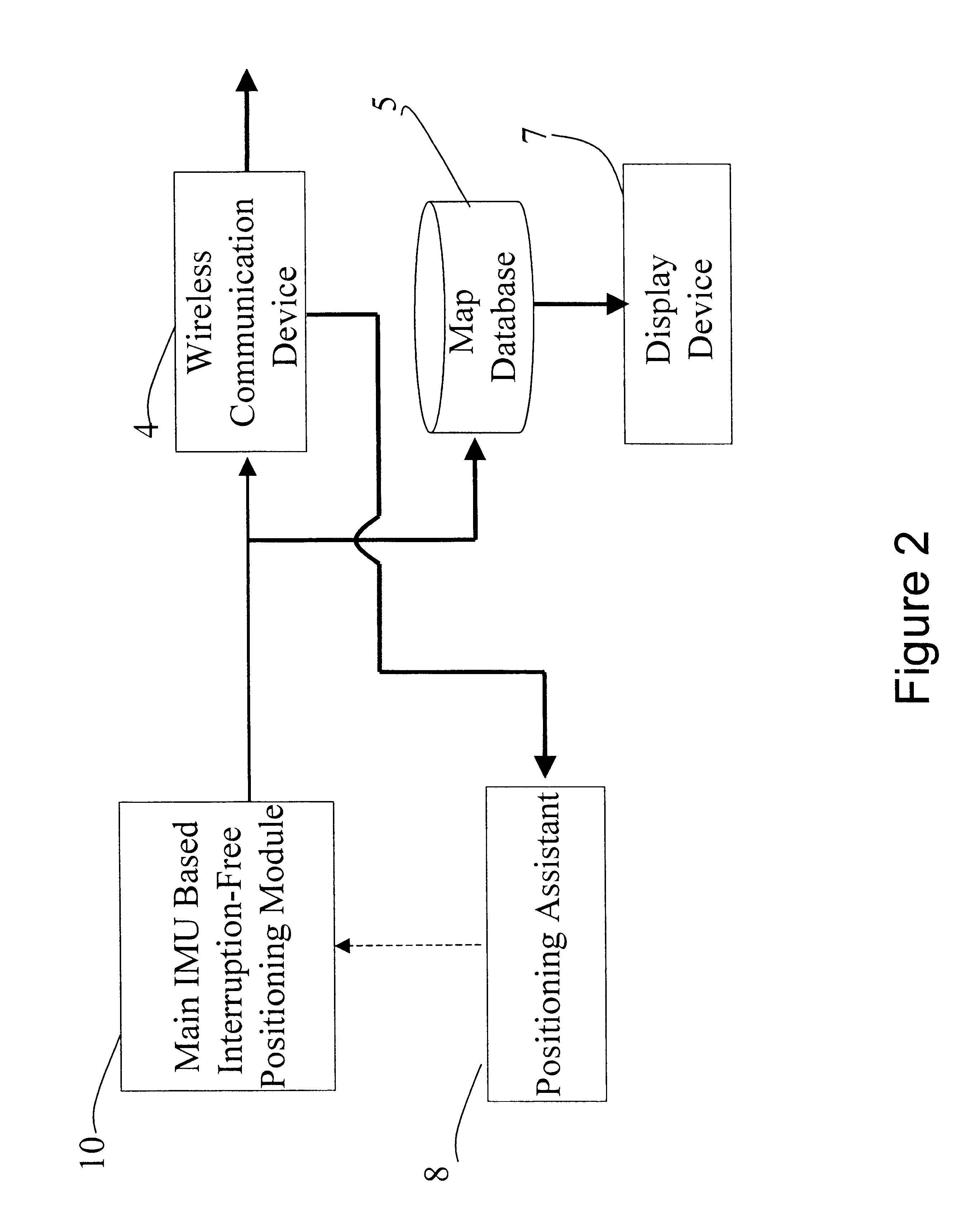

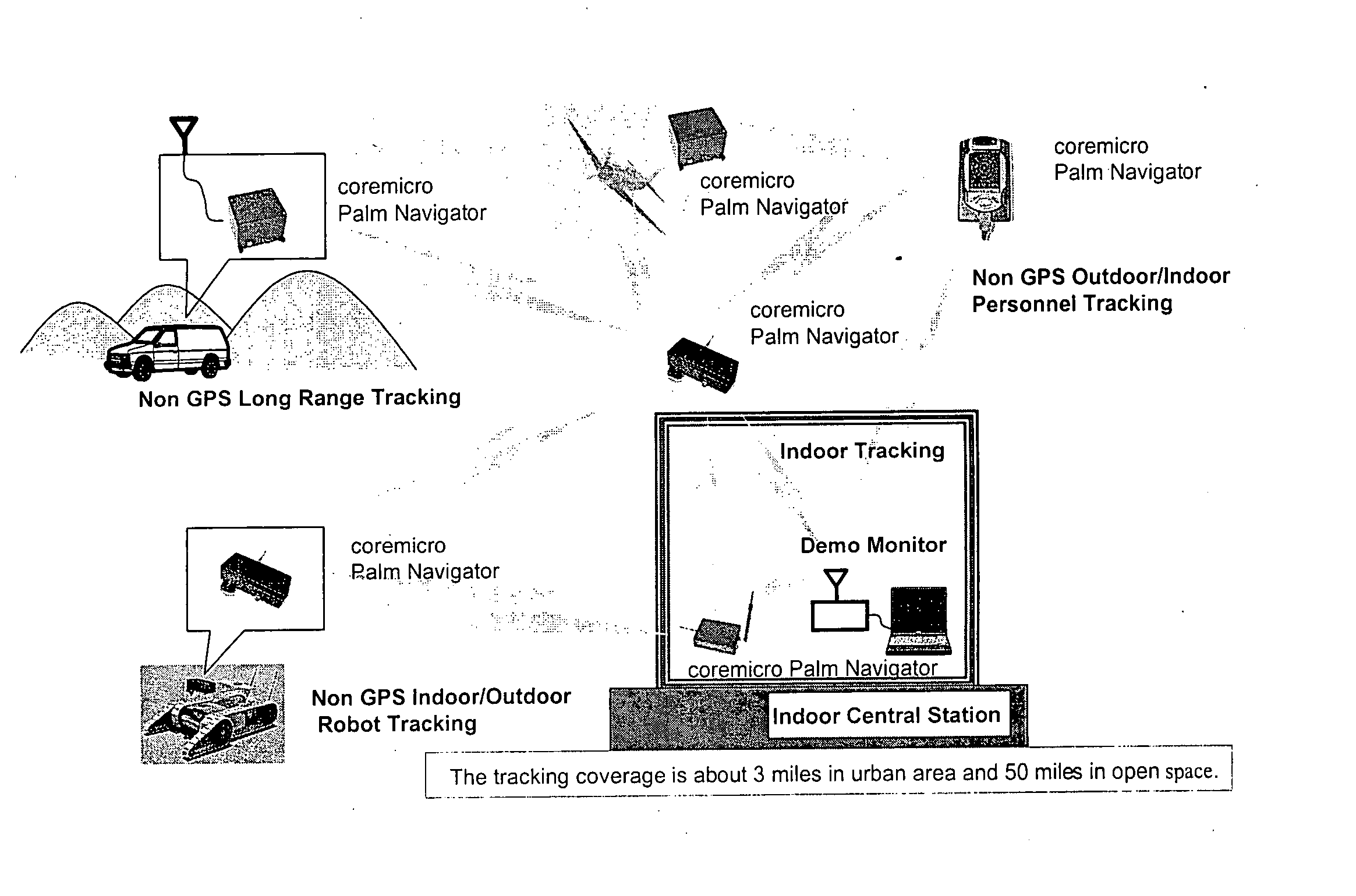

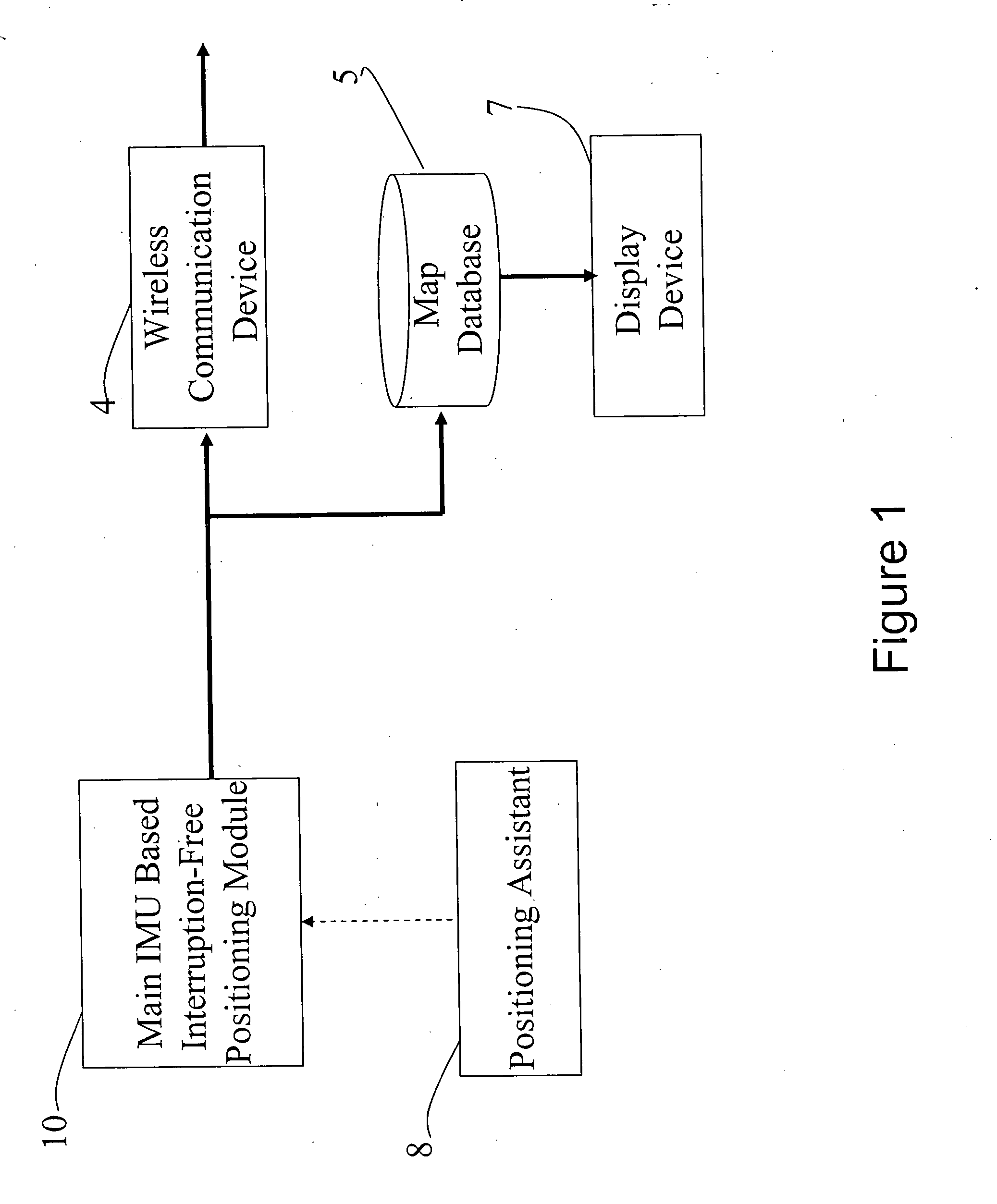

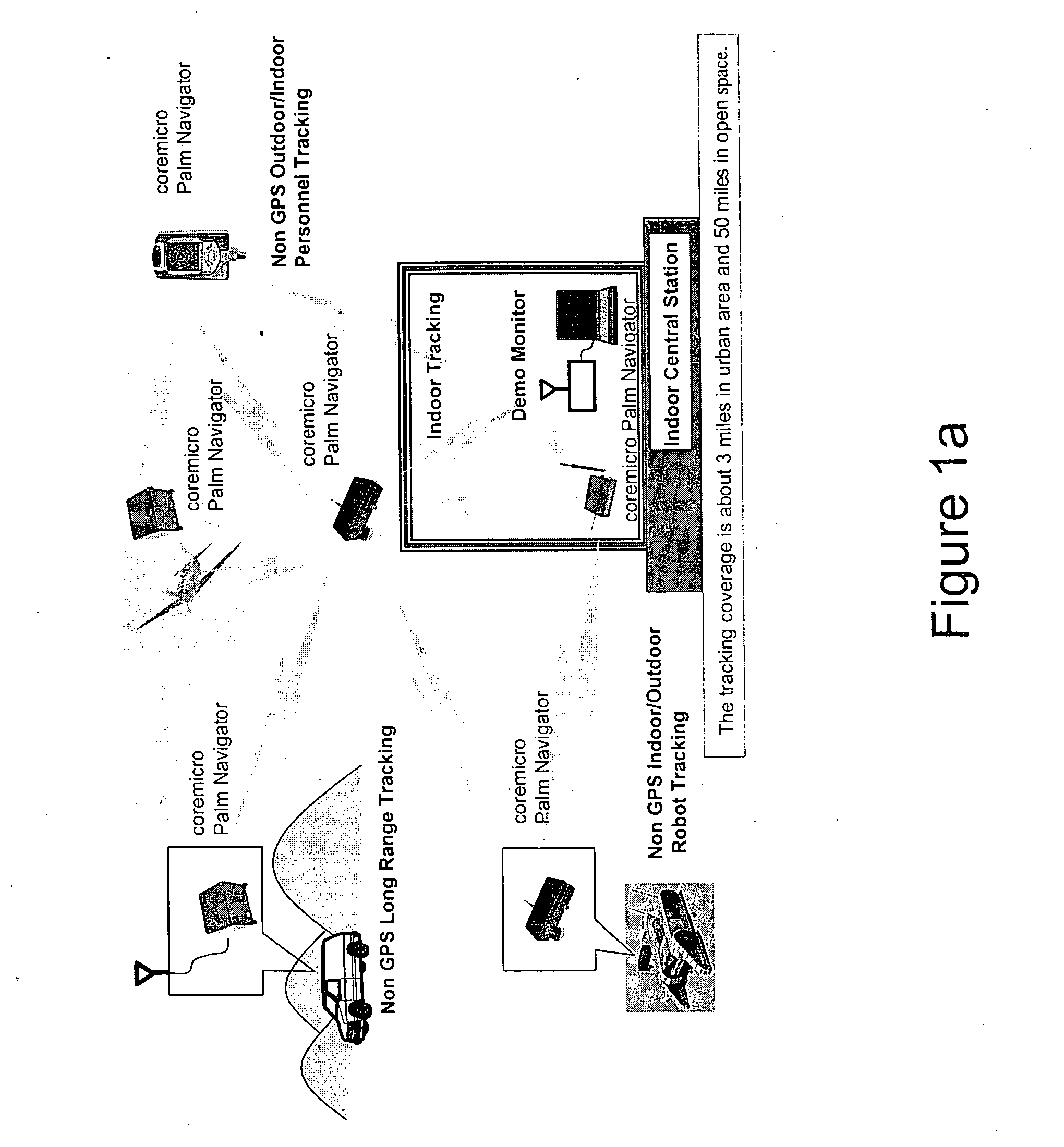

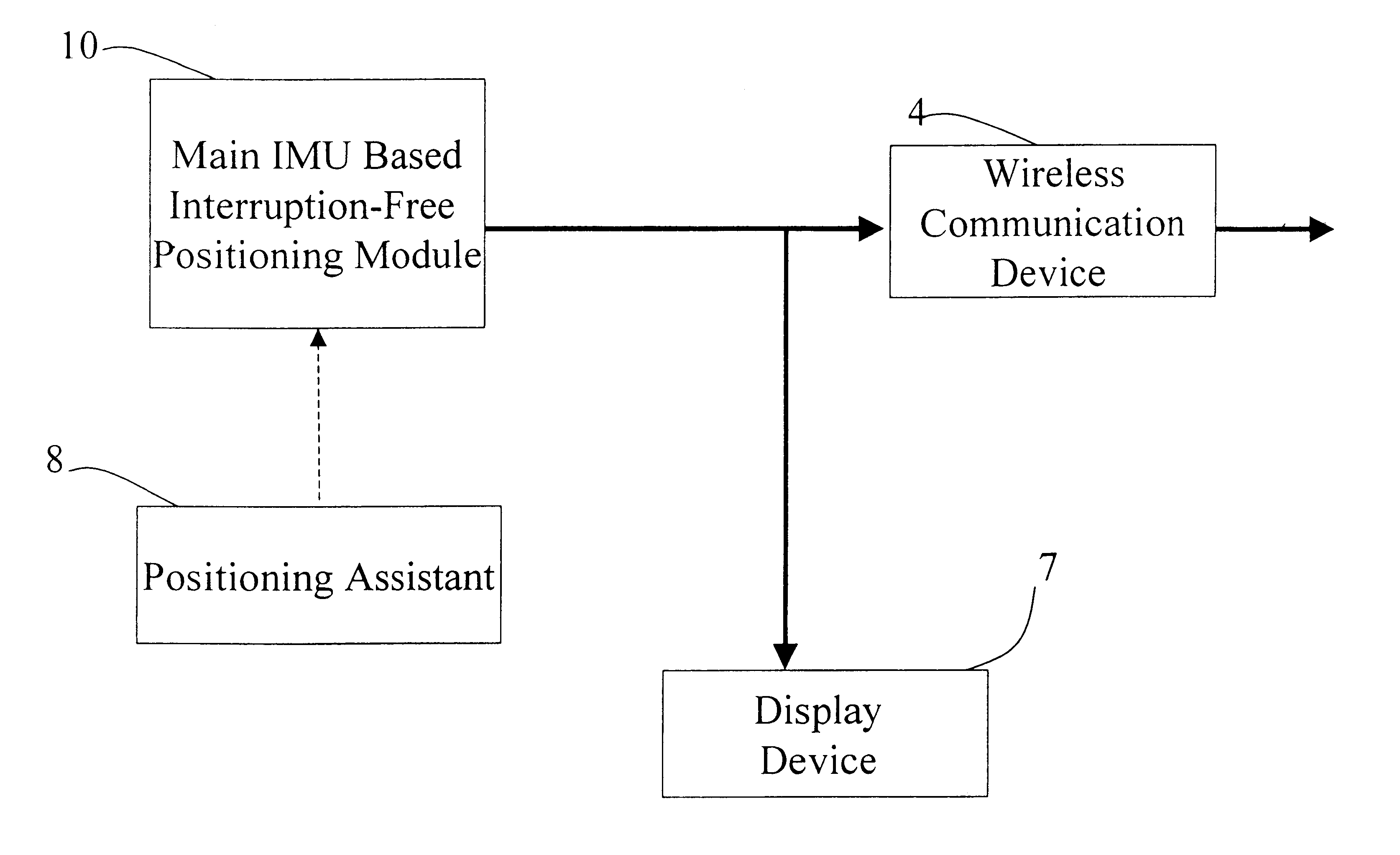

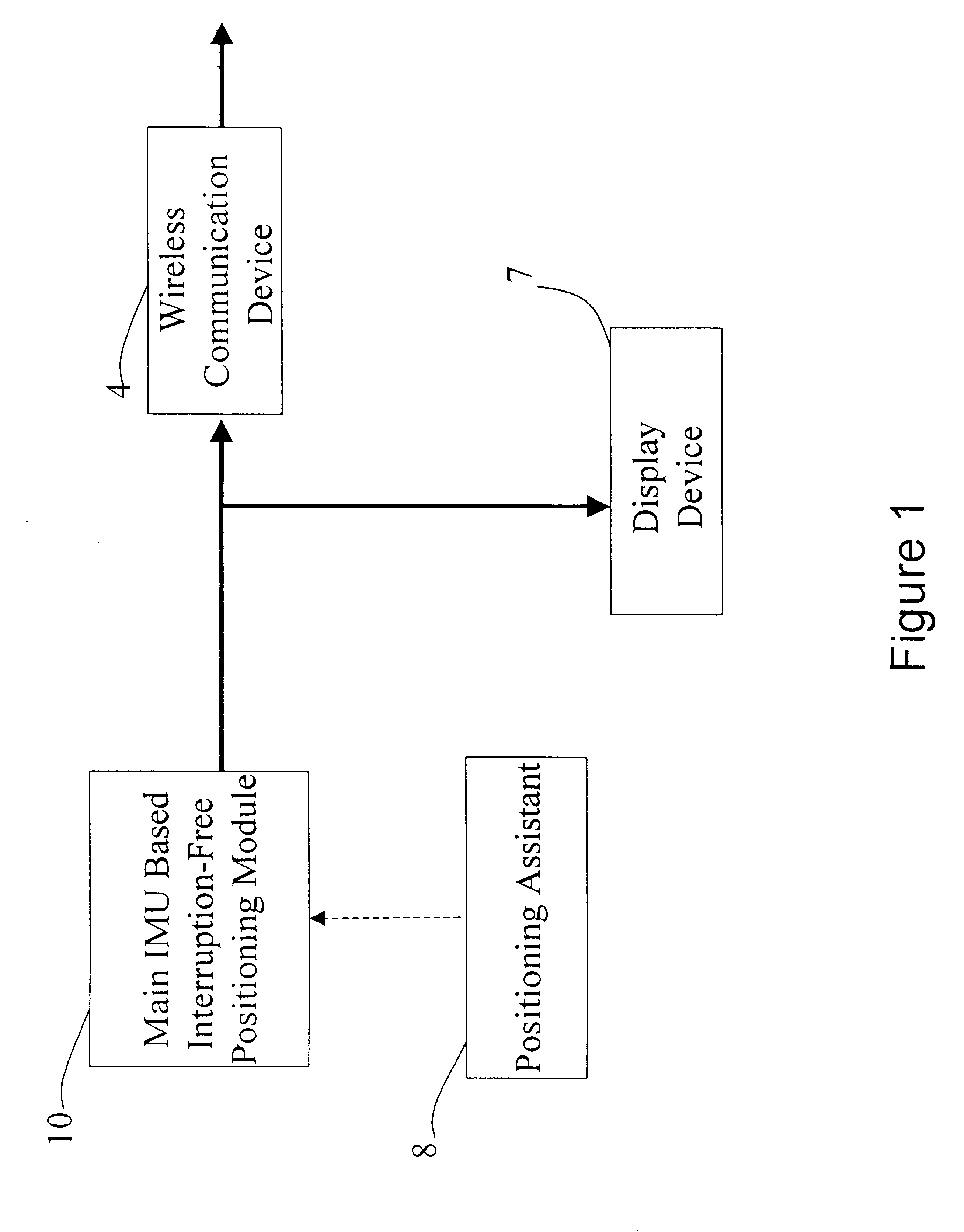

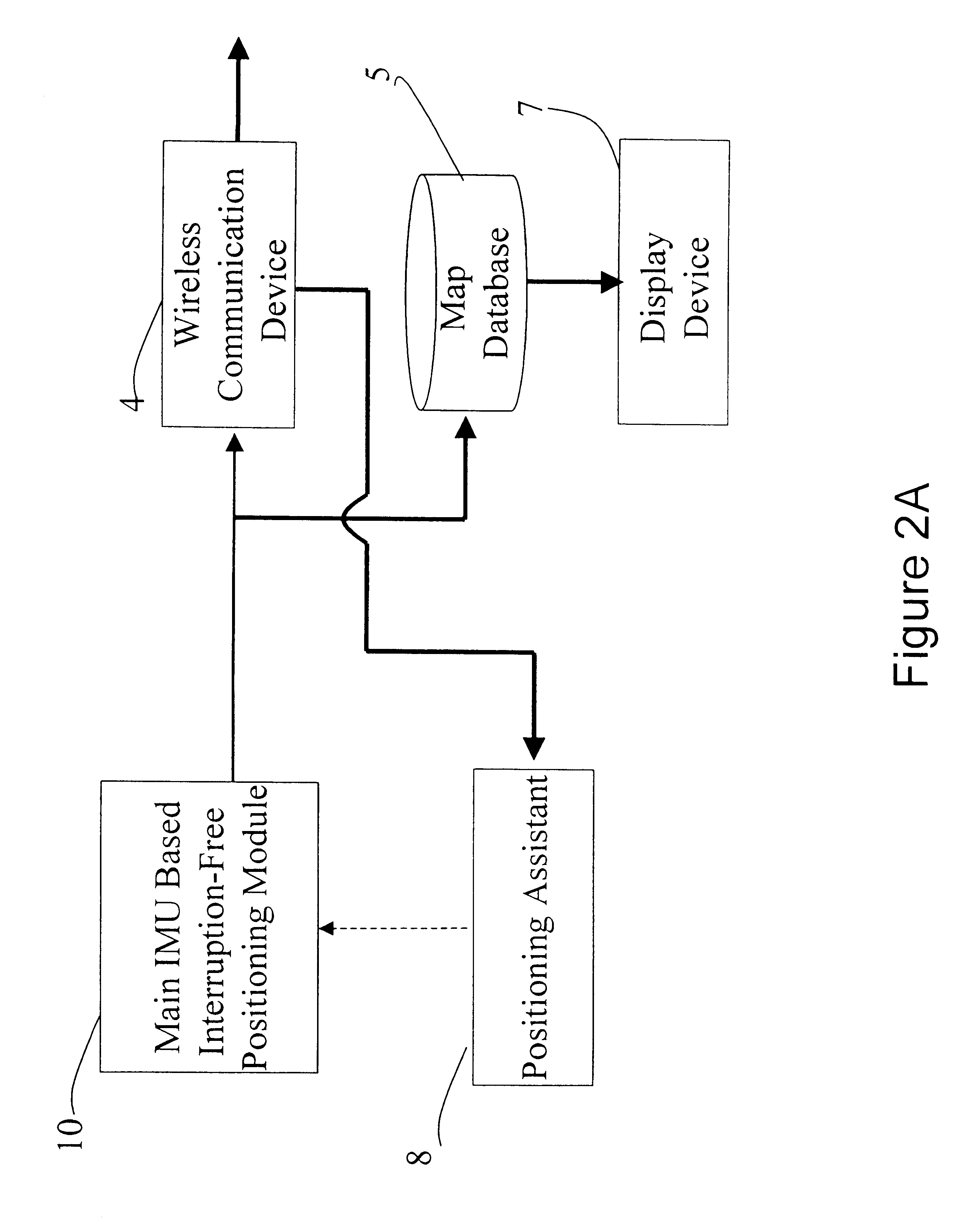

Interruption-free hand-held positioning method and system thereof

InactiveUS6415223B1Low costReduce power consumptionInstruments for road network navigationDirection finders using radio wavesDisplay deviceHand held

An interruption-free hand-held positioning method and system, carried by a person, includes an inertial measurement unit, a north finder, a velocity producer, a positioning assistant, a navigation processor, a wireless communication device, and a display device and map database. Output signals of the inertial measurement unit, the velocity producer, the positioning assistant, and the north finder are processed to obtain highly accurate position measurements of the person. The user's position information can be exchanged with other users through the wireless communication device, and the location and surrounding information can be displayed on the display device by accessing a map database with the person position information.

Owner:AMERICAN GNC

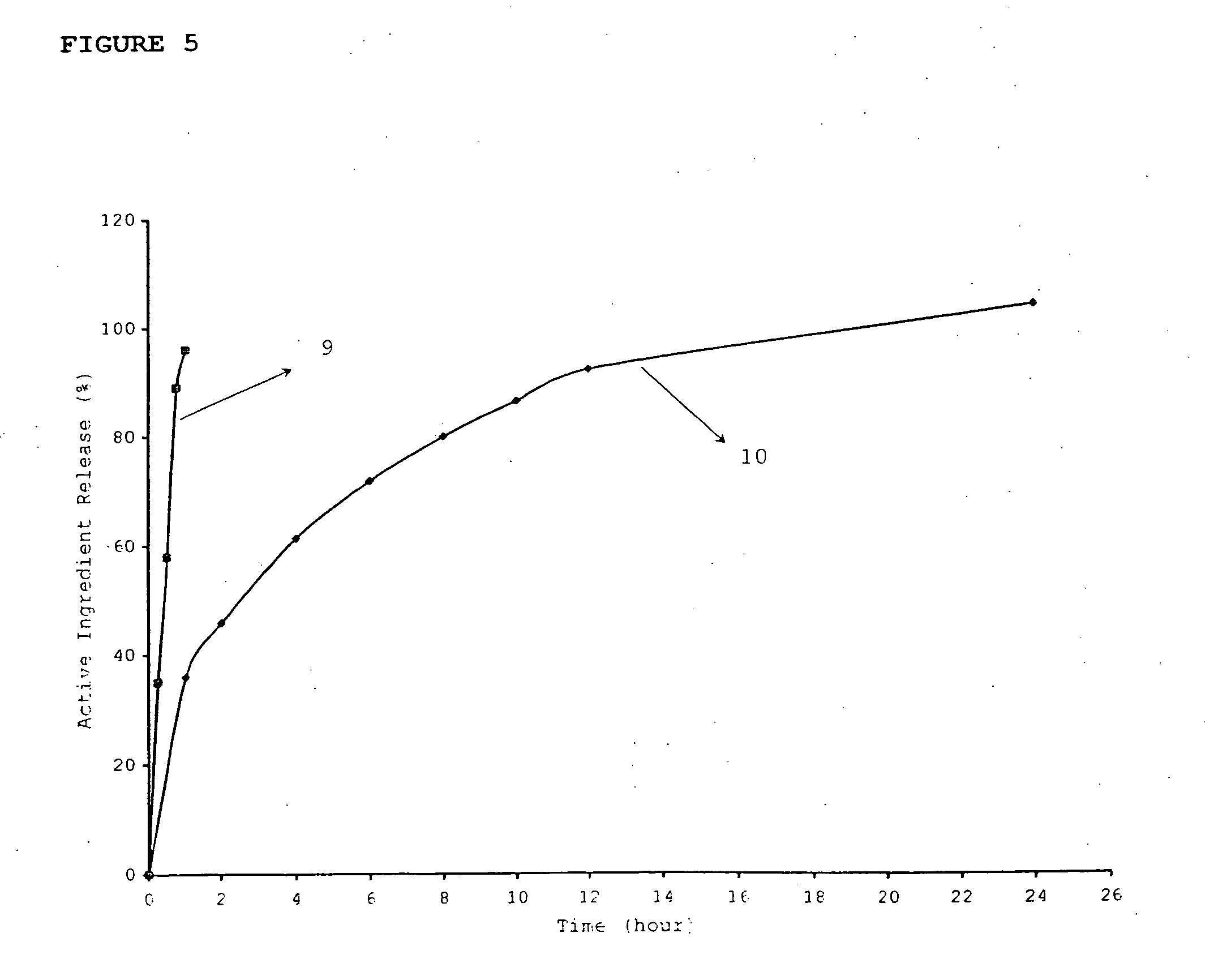

Novel dosage form

ActiveUS20060024365A1Effectively control release rateReduce sizePill deliveryEster active ingredientsHigh dosesSolubility

A dosage form comprising of a high dose, high solubility active ingredient as modified release and a low dose active ingredient as immediate release where the weight ratio of immediate release active ingredient and modified release active ingredient is from 1:10 to 1:15000 and the weight of modified release active ingredient per unit is from 500 mg to 1500 mg; a process for preparing the dosage form.

Owner:TORRENT PHARMA LTD

Use of image-derived information as search criteria for internet and other search engines

ActiveUS20060002607A1Reduce sizeFaster and accurate algorithmStill image data retrievalTelevision system detailsThe InternetComputer science

Search terms are derived automatically from images captured by a camera equipped cell phone, PDA, or other image capturing device, submitted to a search engine to obtain information of interest, and at least a portion of the resulting information is transmitted back locally to, or nearby, the device that captured the image.

Owner:NANT HLDG IP LLC

Coded Molecules for Detecting Target Analytes

InactiveUS20070190543A1Easy to detectHigh sensitivityBioreactor/fermenter combinationsBiological substance pretreatmentsAnalytePhysics

Owner:APPL BIOSYSTEMS INC

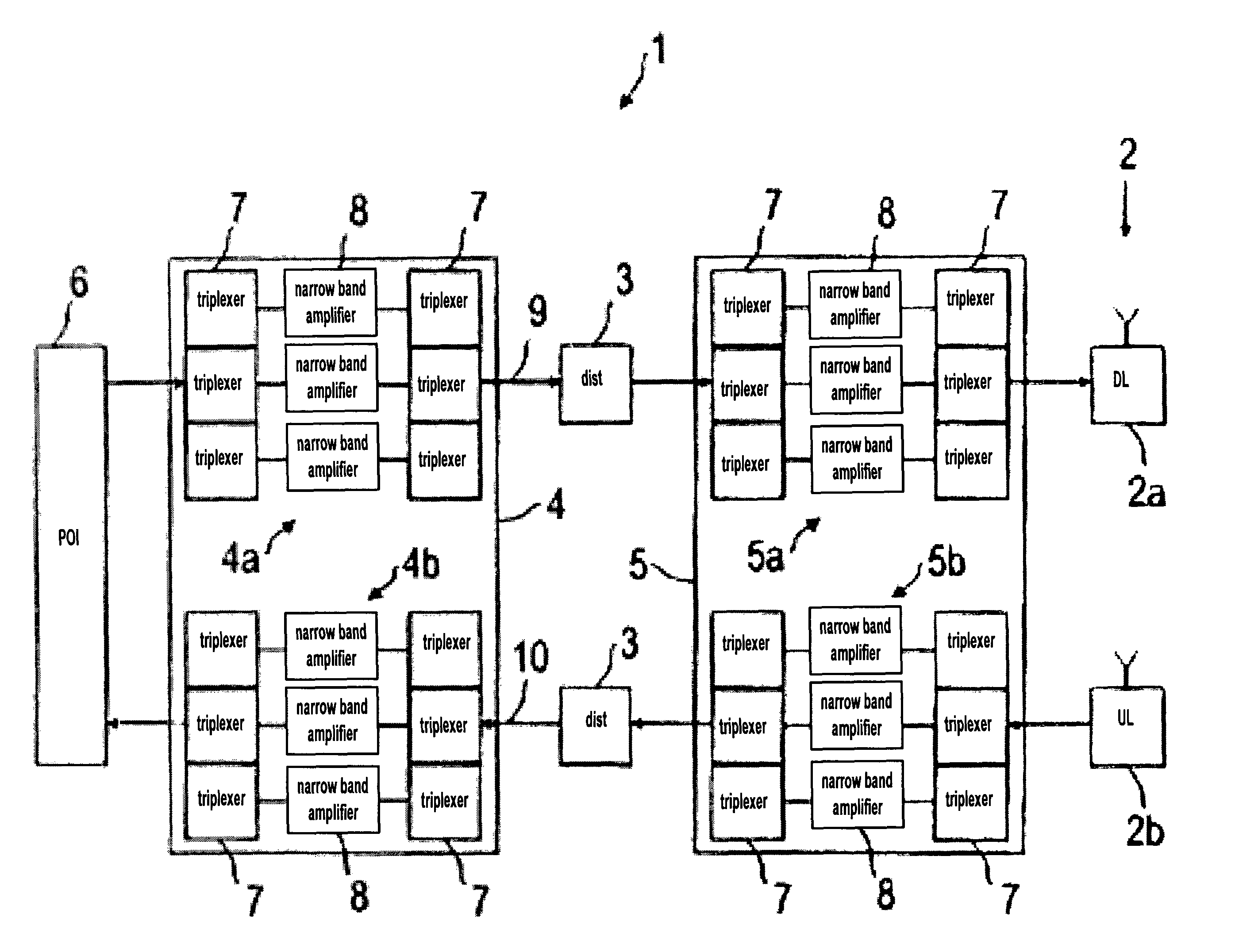

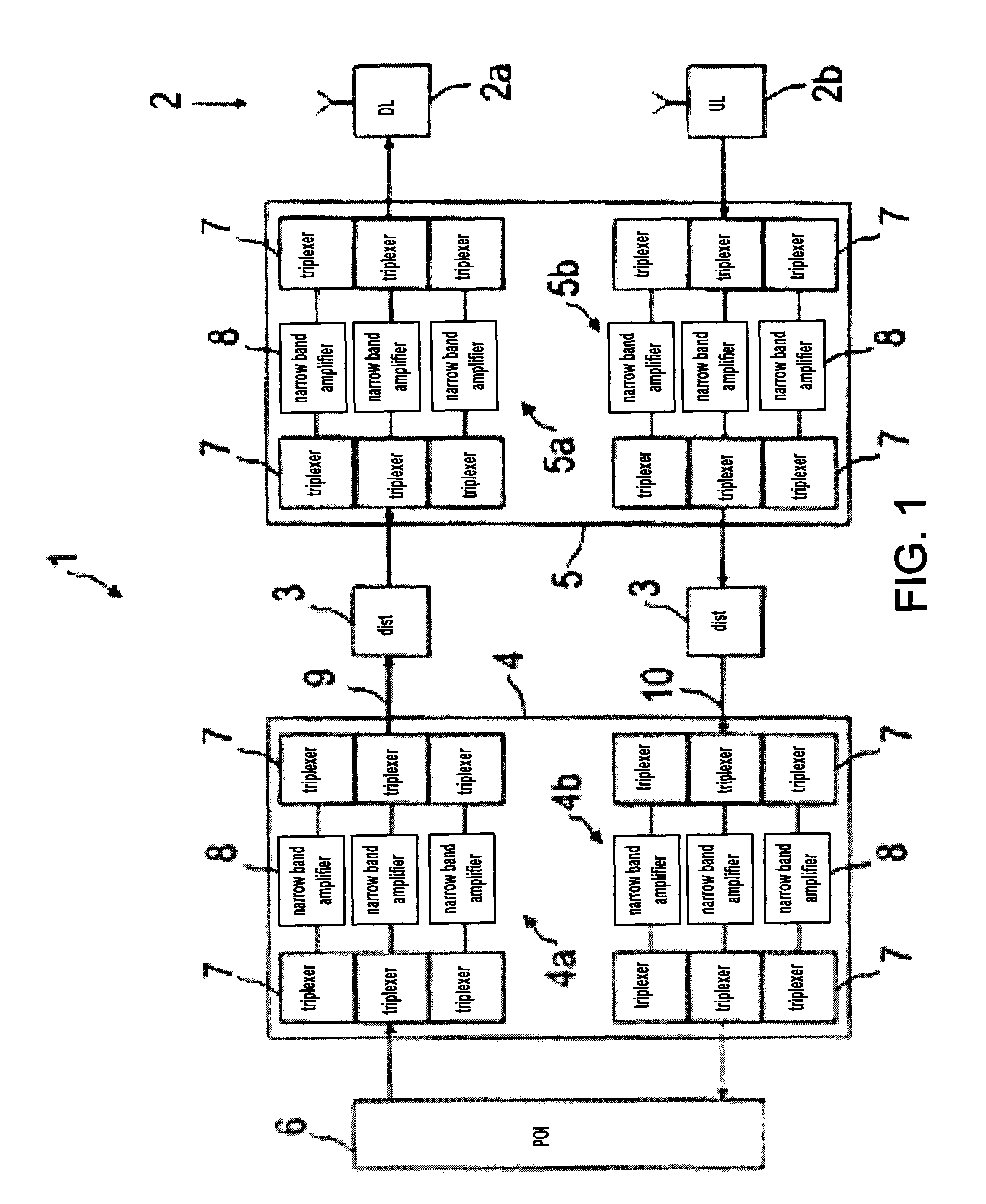

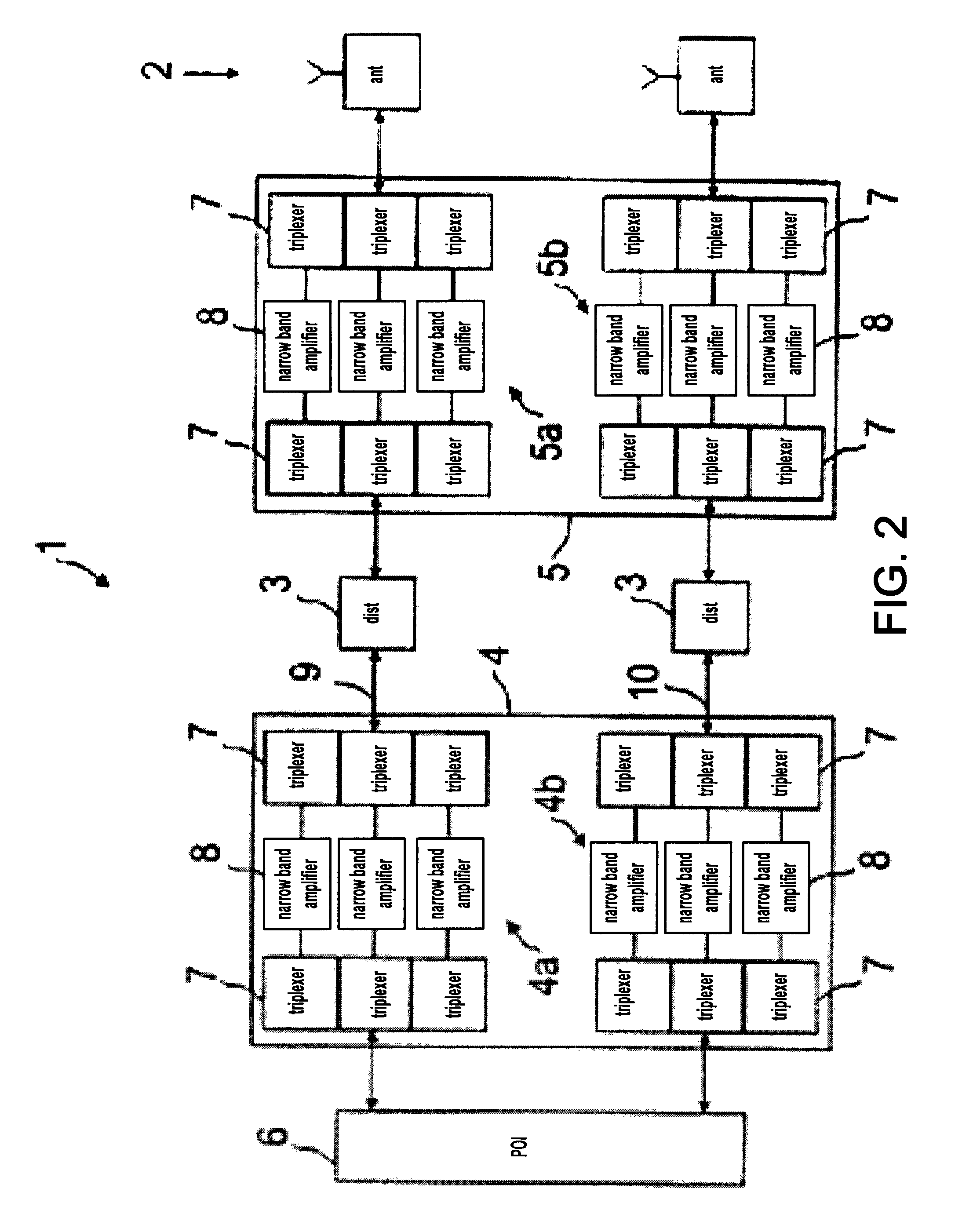

Radio frequency network

ActiveUS8428033B2Avoid intermodulationsReduce sizeFrequency-division multiplexWireless commuication servicesAudio power amplifierDistributed antenna system

Owner:RFS TECH INC

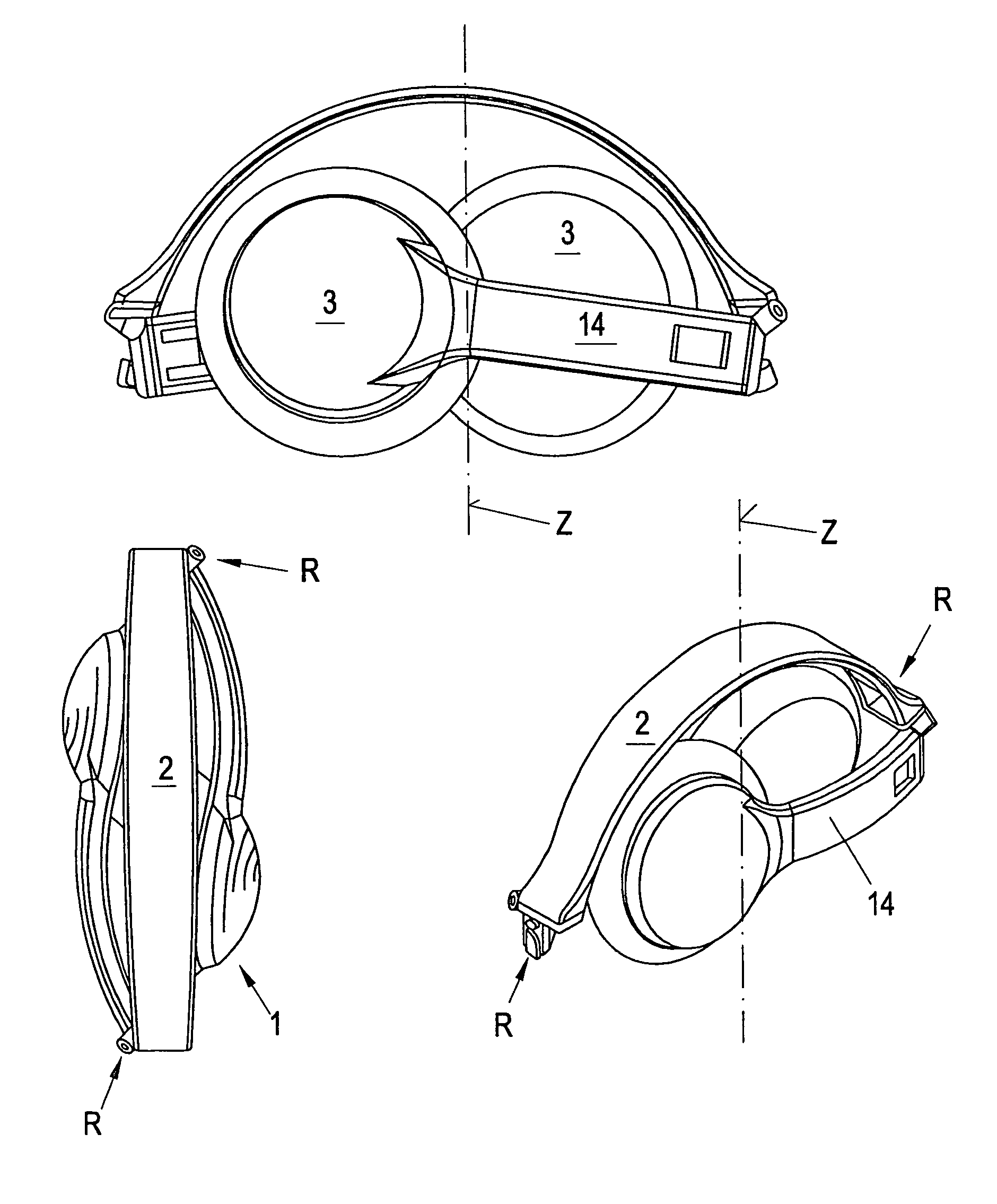

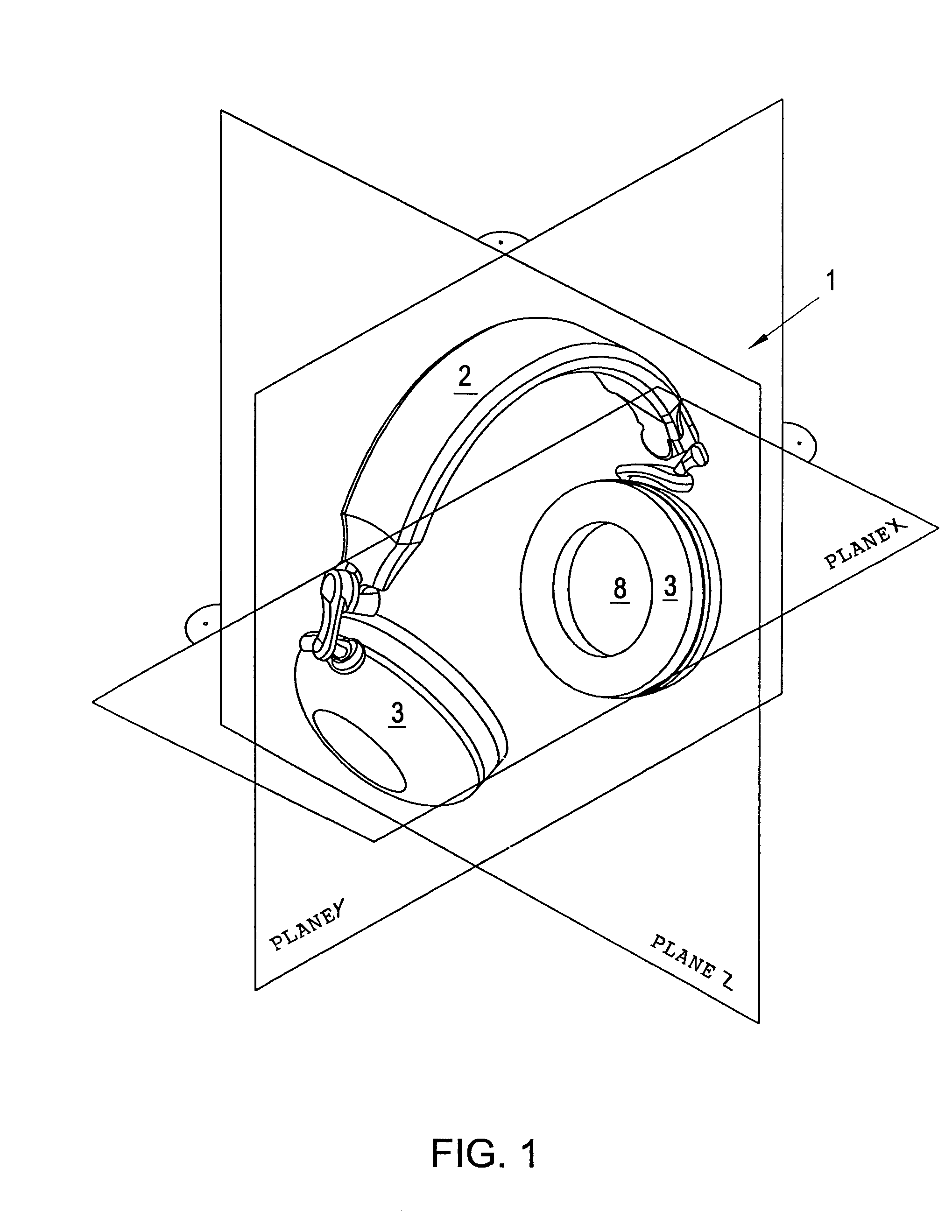

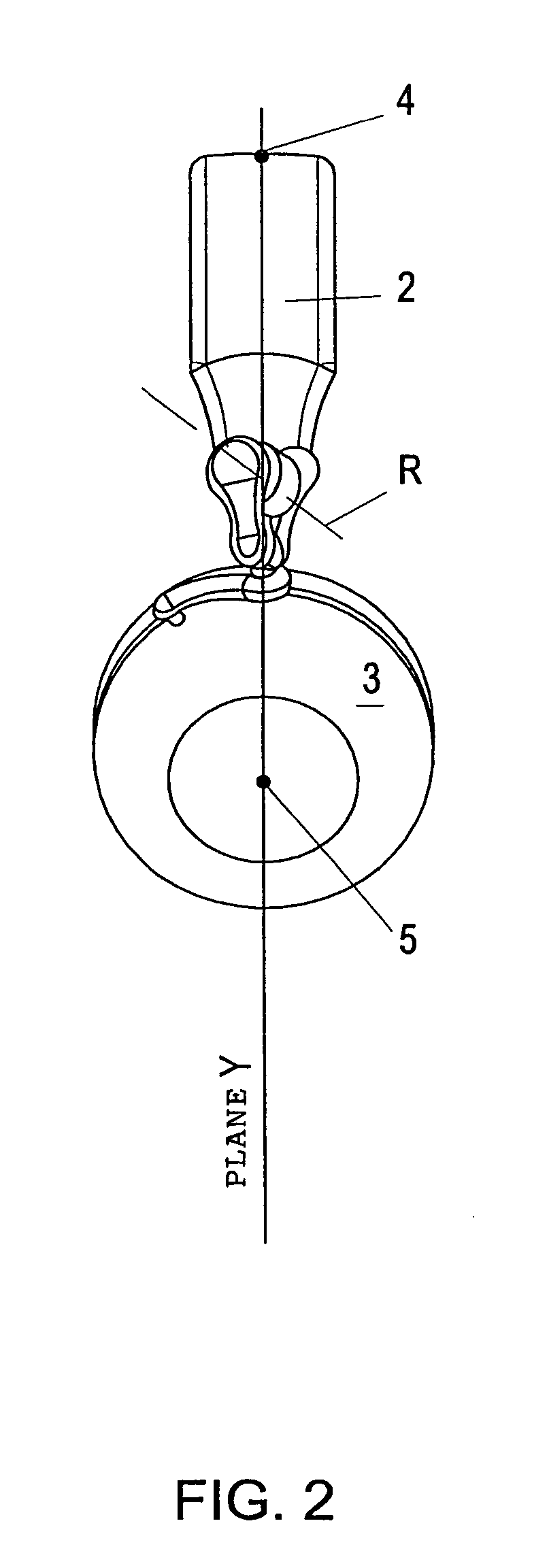

Headphone

ActiveUS7072483B2Small sizeImprove wearing comfortHeadphones for stereophonic communicationSupra/circum aural earpiecesEngineeringHeadphones

A headphone has a headband and two earpieces each connected to the headband so as to be pivotable relative thereto. When assuming a Cartesian coordinate system having a Z plane that is a symmetry plane of the headphone, having a Y plane that is positioned perpendicularly to the Z plane and extends through a center of the headband, and having an X plane that is positioned perpendicularly to the Z and Y planes at any desired height, a pivot axis is provided between the headband and the earpiece, respectively, wherein the pivot axis is positioned at an angle of at least 10° relative to the X, Y, and Z planes, respectively.

Owner:AKG ACOUSTICS

Interruption free navigator

InactiveUS20060287824A1Improve accuracyAccurate dataNavigational calculation instrumentsPosition fixationDisplay devicePerson location

An interruption free navigator includes an inertial measurement unit, a north finder, a velocity producer, a positioning assistant, a navigation processor, an altitude measurement, an object detection system, a wireless communication device, and a display device and map database. Output signals of the inertial measurement unit, the velocity producer, the positioning assistant, the altitude measurement, the object detection system, and the north finder are processed to obtain highly accurate position measurements of the person. The user's position information can be exchanged with other users through the wireless communication device, and the location and surrounding information can be displayed on the display device by accessing a map database with the person position information.

Owner:AMERICAN GNC

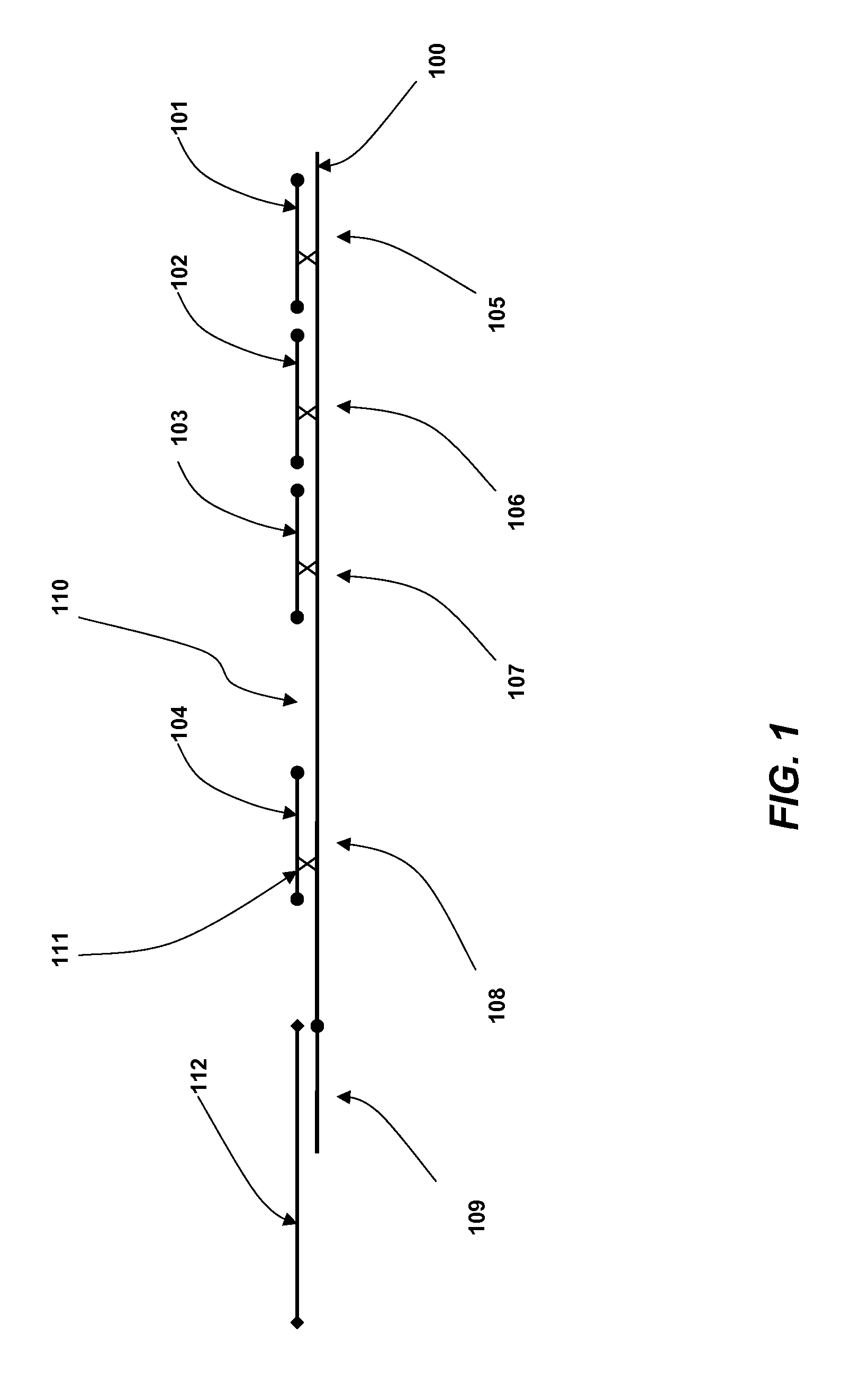

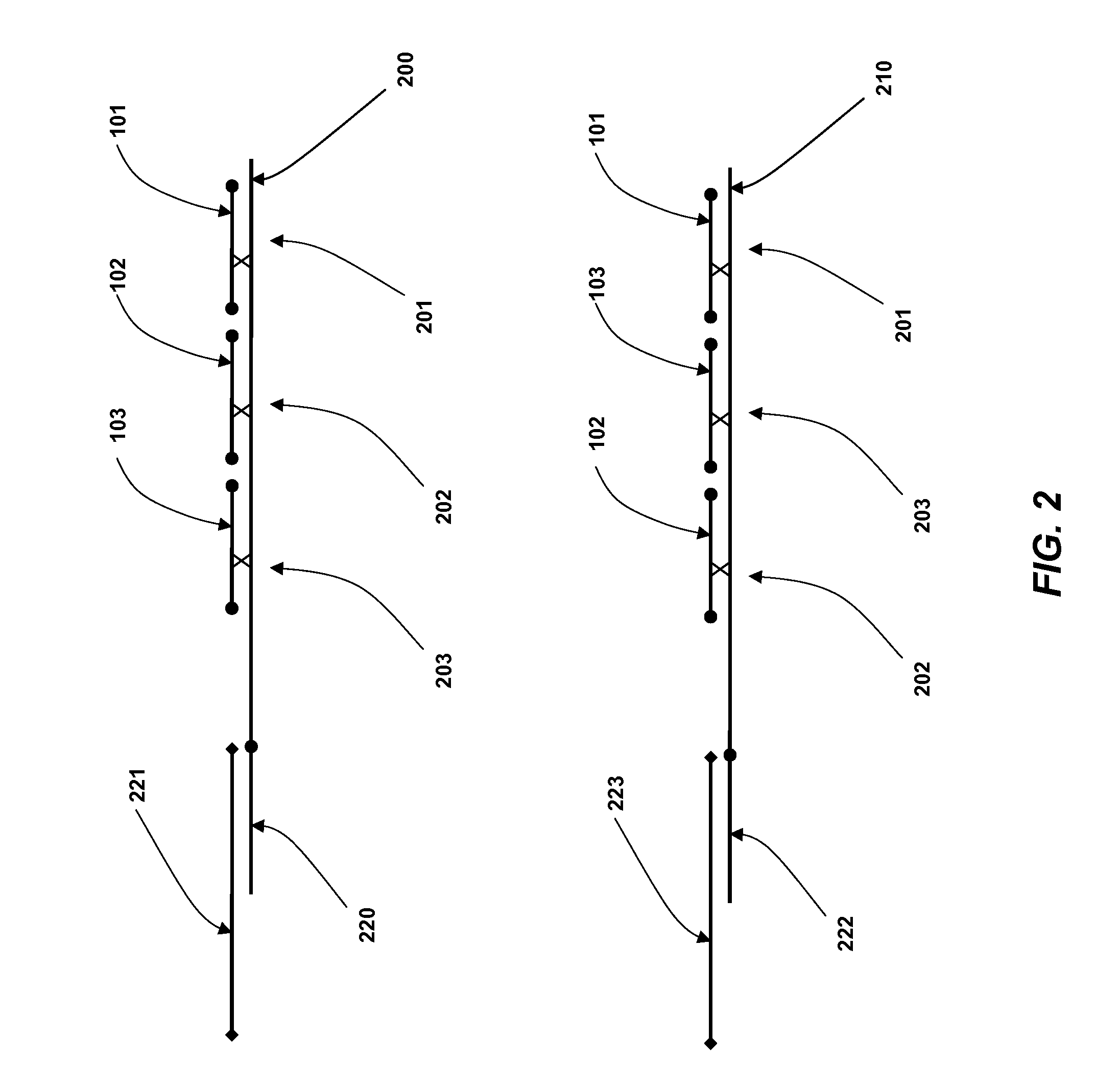

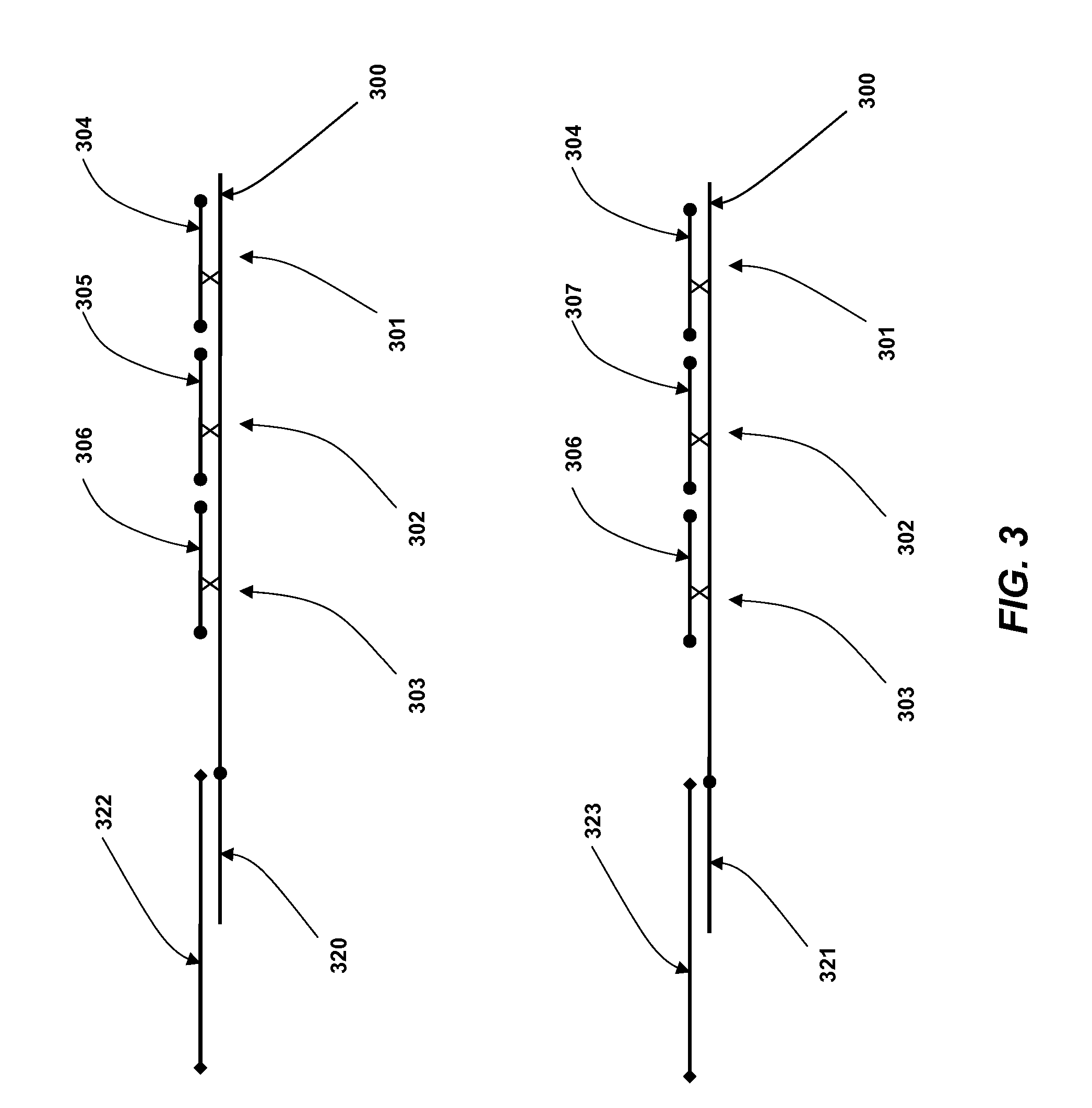

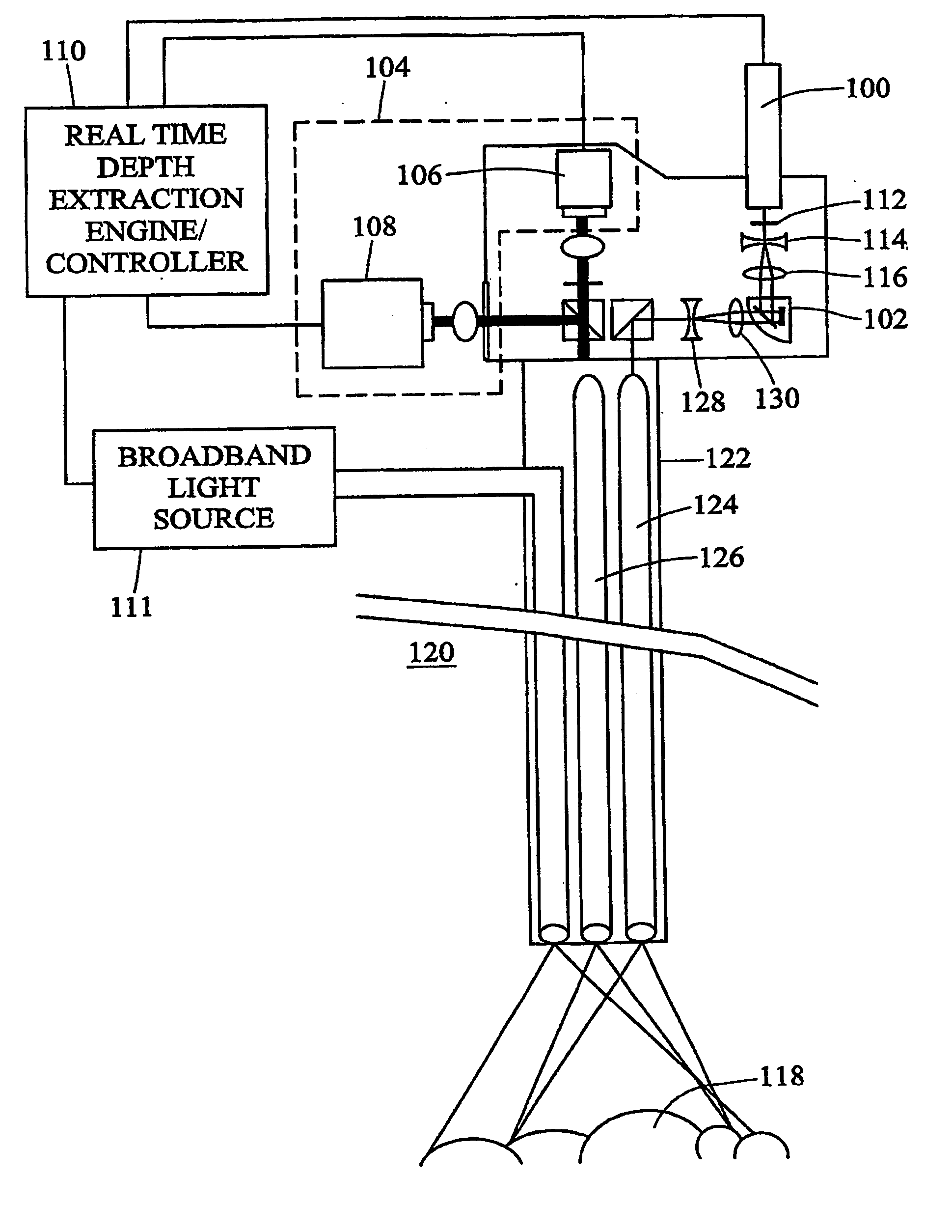

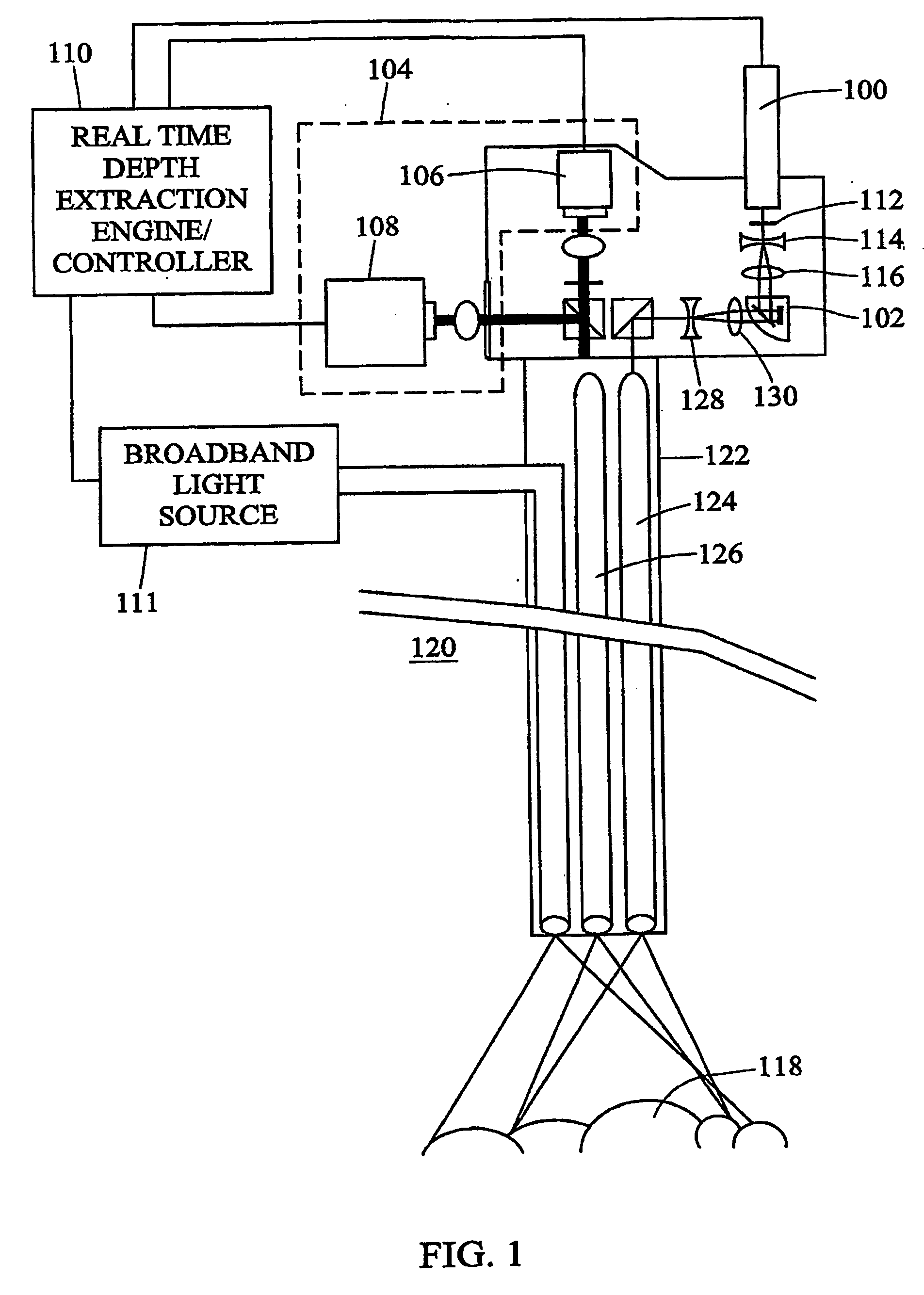

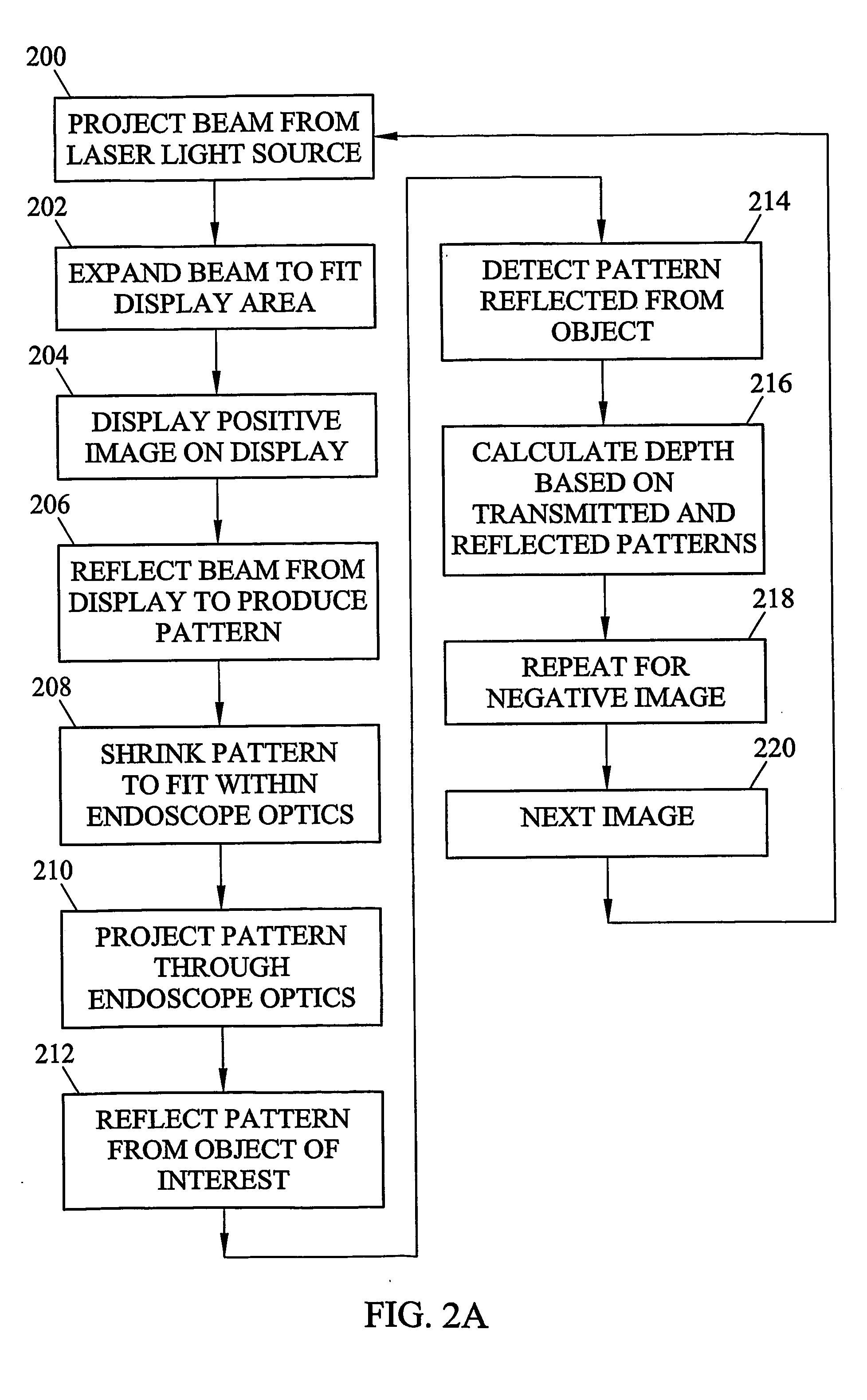

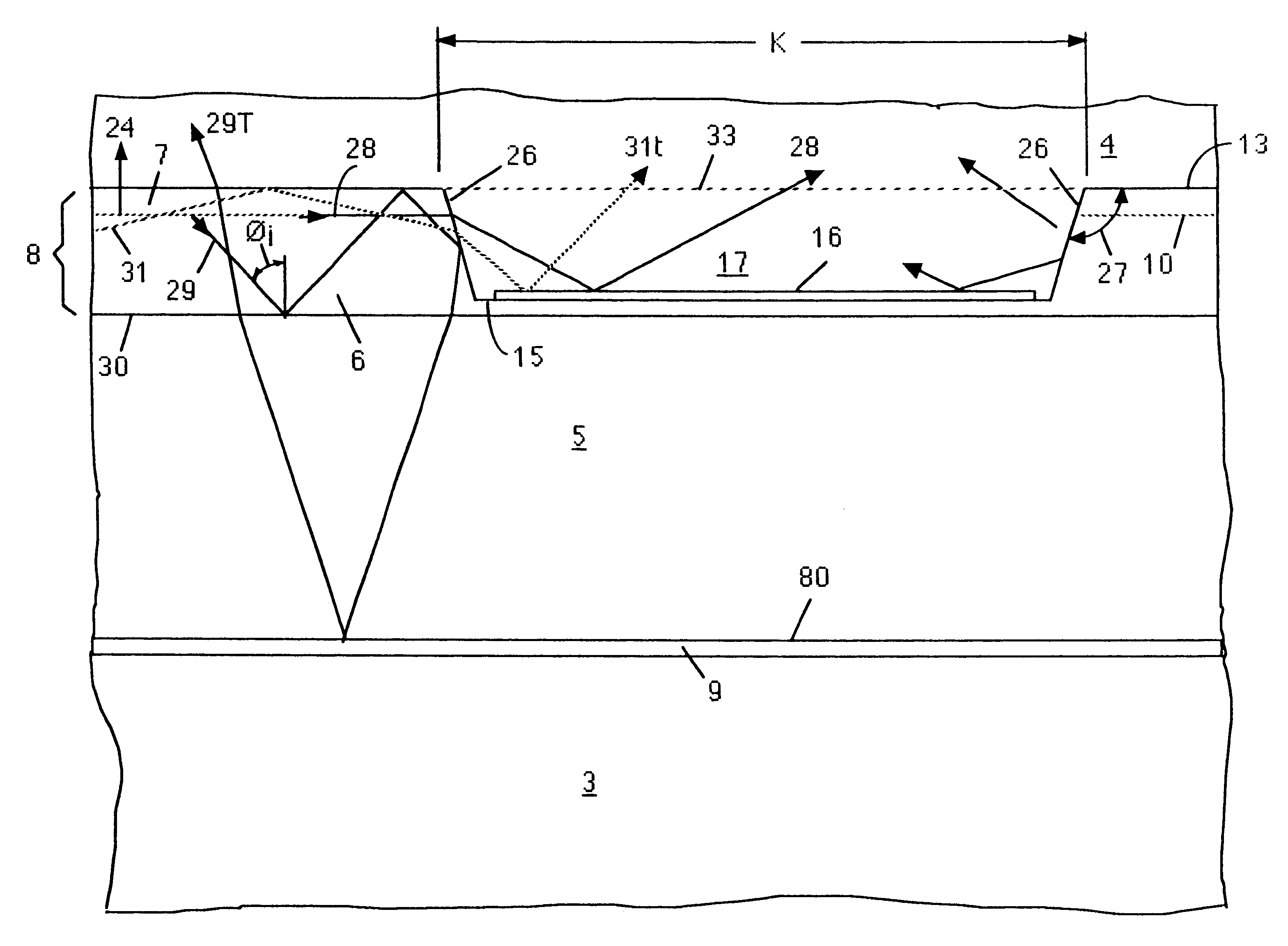

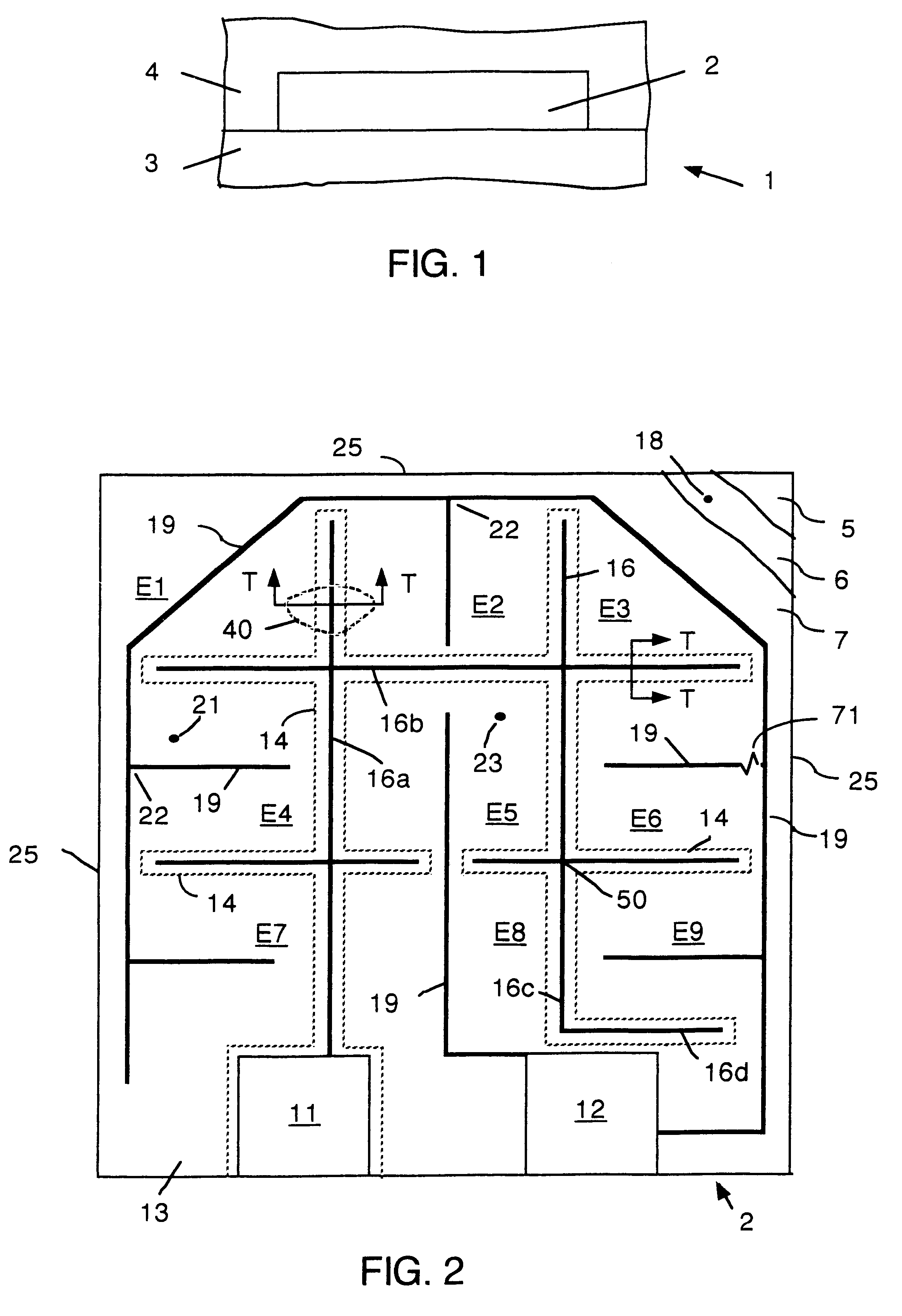

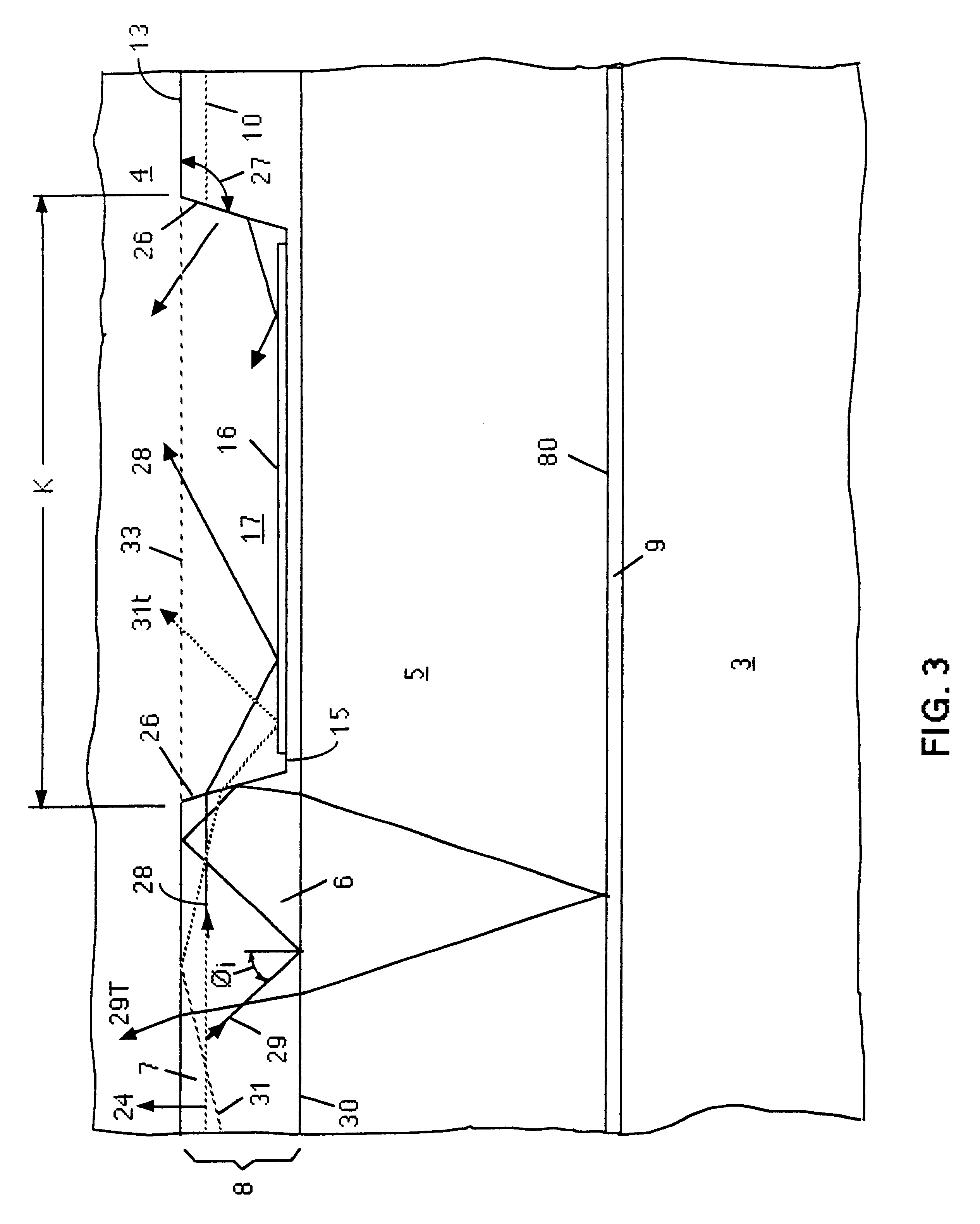

Methods and systems for laser based real-time structured light depth extraction

InactiveUS20050219552A1Photonic efficiencyImprove efficiencyImage analysisSurgeryLow speedImage resolution

Laser-based methods and systems for real-time structured light depth extraction are disclosed. A laser light source (100) produces a collimated beam of laser light. A pattern generator (102) generates structured light patterns including a plurality of pixels. The beam of laser light emanating from the laser light source (100) interacts with the patterns to project the patterns onto the object of (118). The patterns are reflected from the object of interest (118) and detected using a high-speed, low-resolution detector (106). A broadband light source (111) illuminates the object with broadband / light, and a separate high-resolution, low-speed detector (108) detects broadband light reflected from the object (118). A real-time structured light depth extraction engine / controller (110) based on the transmitted and reflected patterns and the reflected broadband light.

Owner:THE UNIV OF NORTH CAROLINA AT CHAPEL HILL

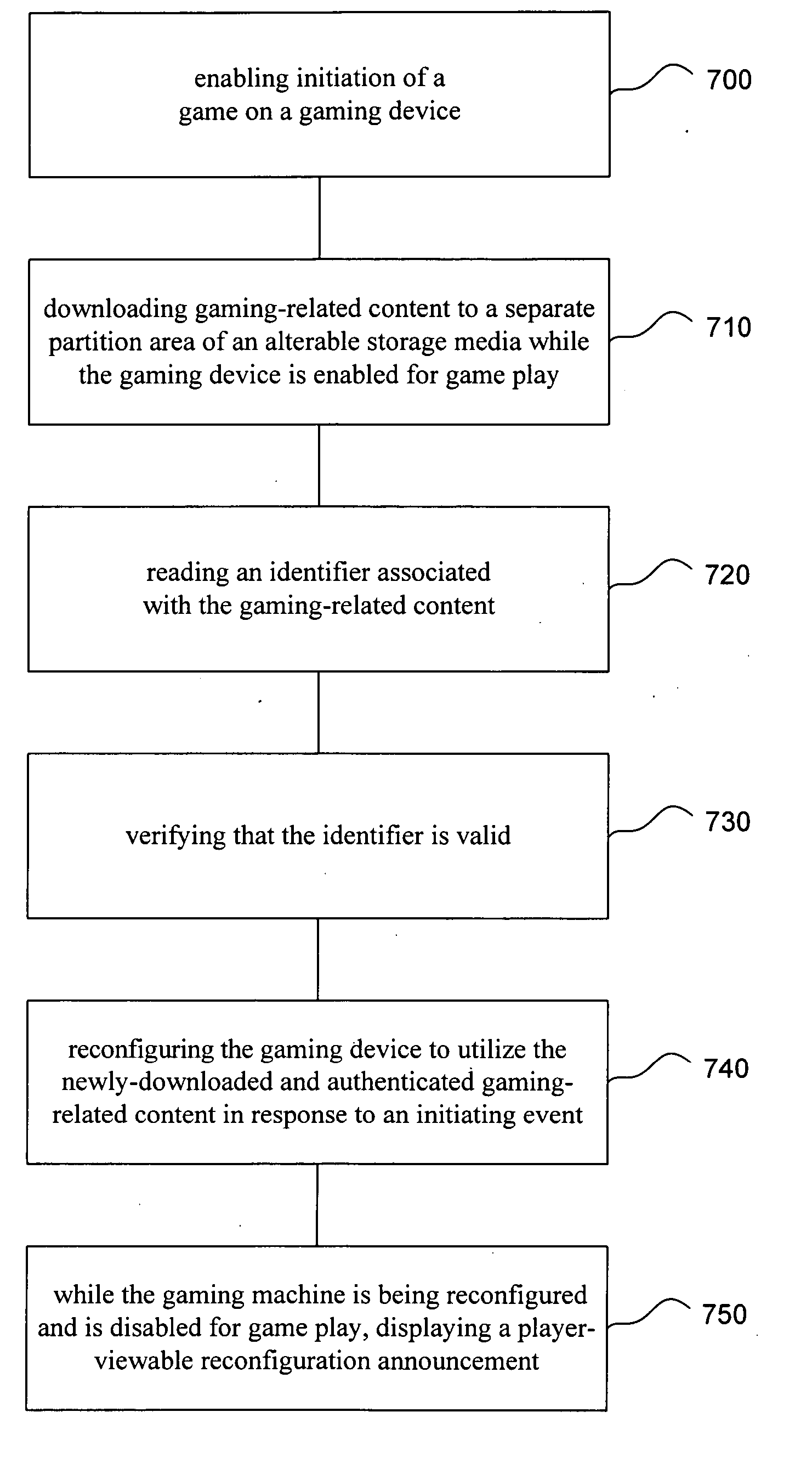

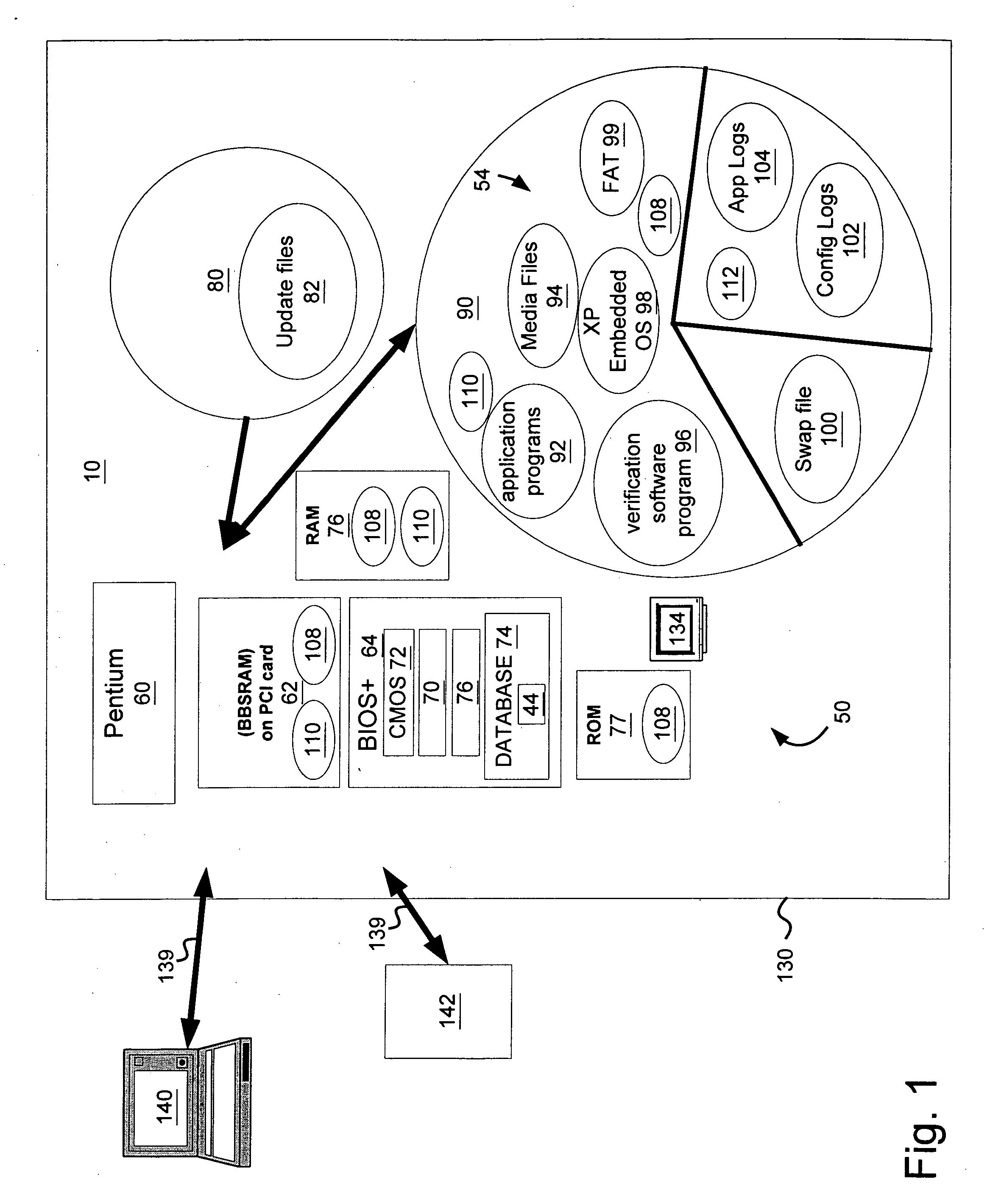

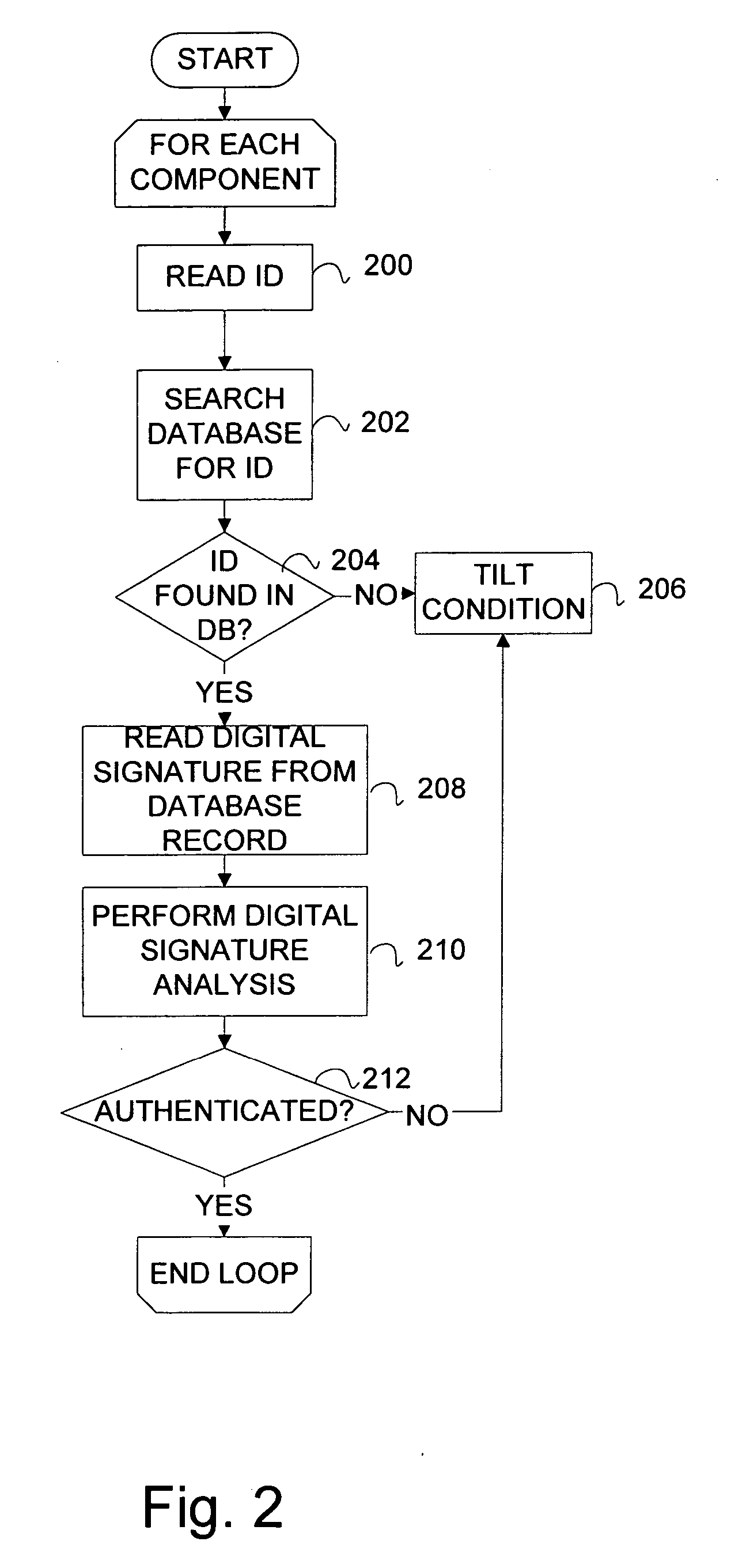

System and method for an alterable storage media in a gaming machine

InactiveUS20060079333A1Easy accessLess instructionDetecting faulty hardware by configuration testDetecting faulty hardware by remote testHard disc driveIdenticon

A system for verifying one or more downloaded components 54 of a gaming device 10 that includes the gaming device, which has an alterable hard drive 80 (or other persistent storage media 90), and the downloaded components that further include gaming-related content 92-96. A related method includes: enabling initiation of a game on the gaming device 10; downloading the gaming-related content 92-96 to the alterable hard drive 80 while the gaming device 10 is enabled for game play; reading an identifier associated with the gaming-related content 92-96; verifying that the identifier is valid (using verification software 70); and reconfiguring the gaming device 10 to utilize the newly-downloaded, gaming-related content 92-96 in response to an initiating event.

Owner:BALLY GAMING INC

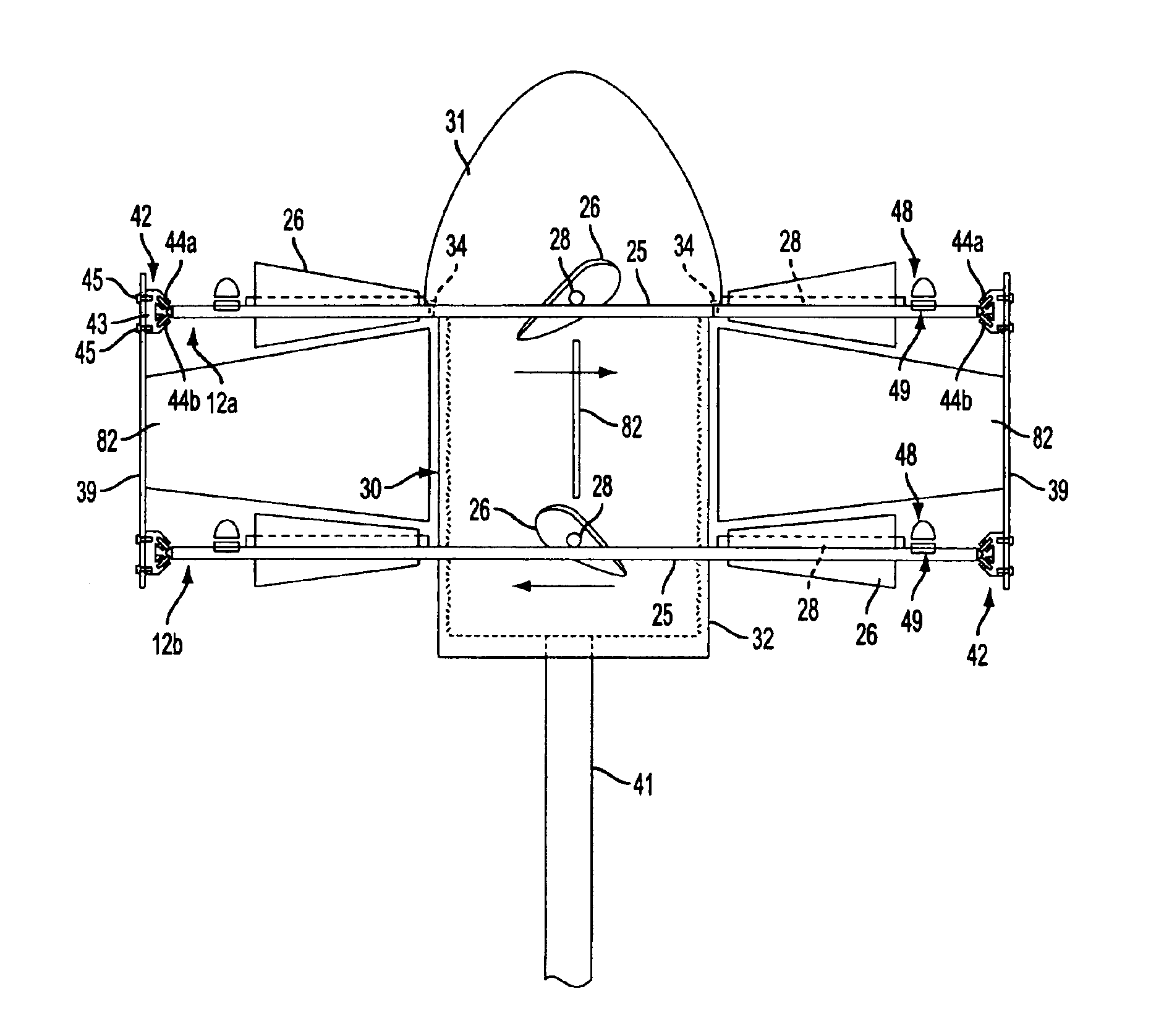

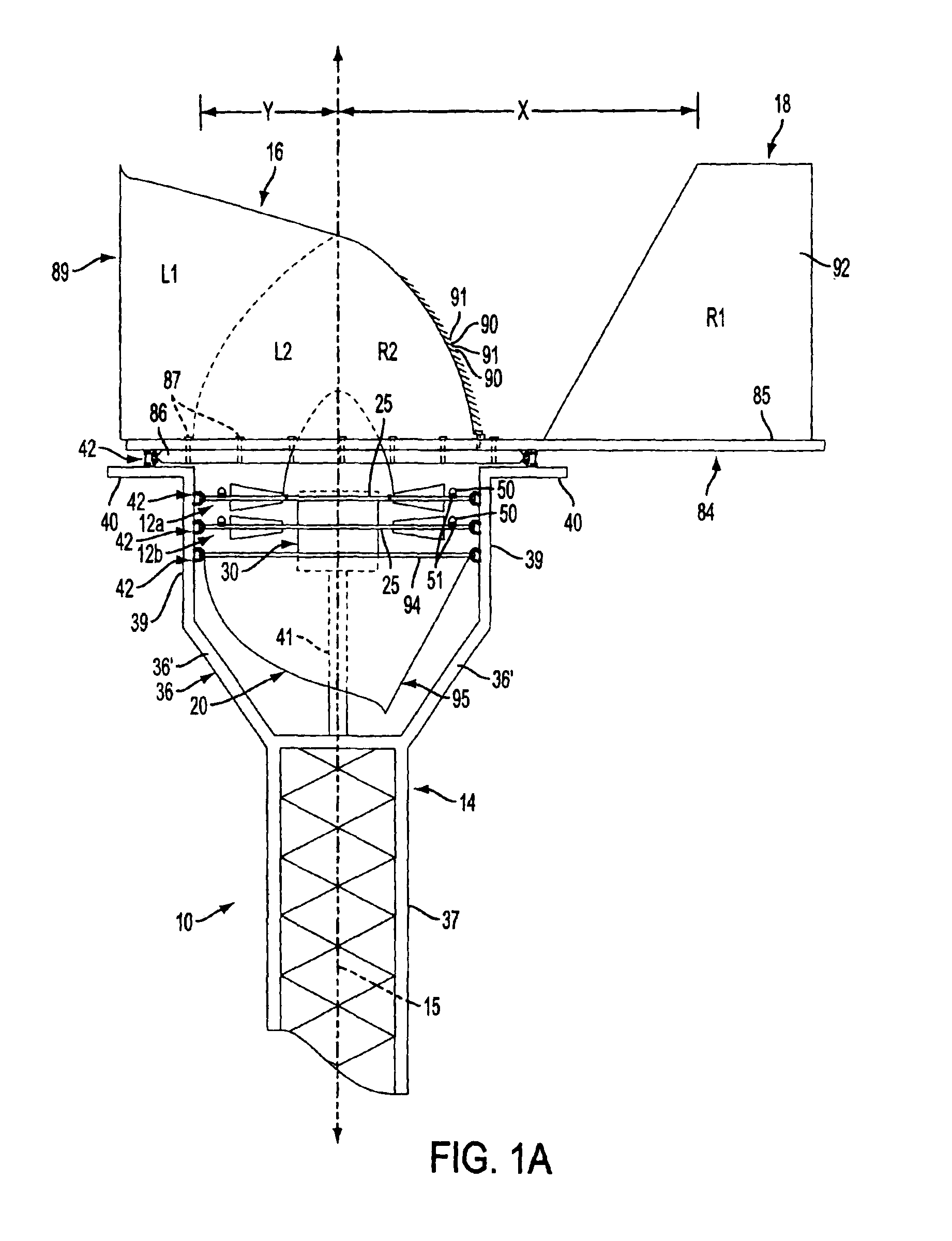

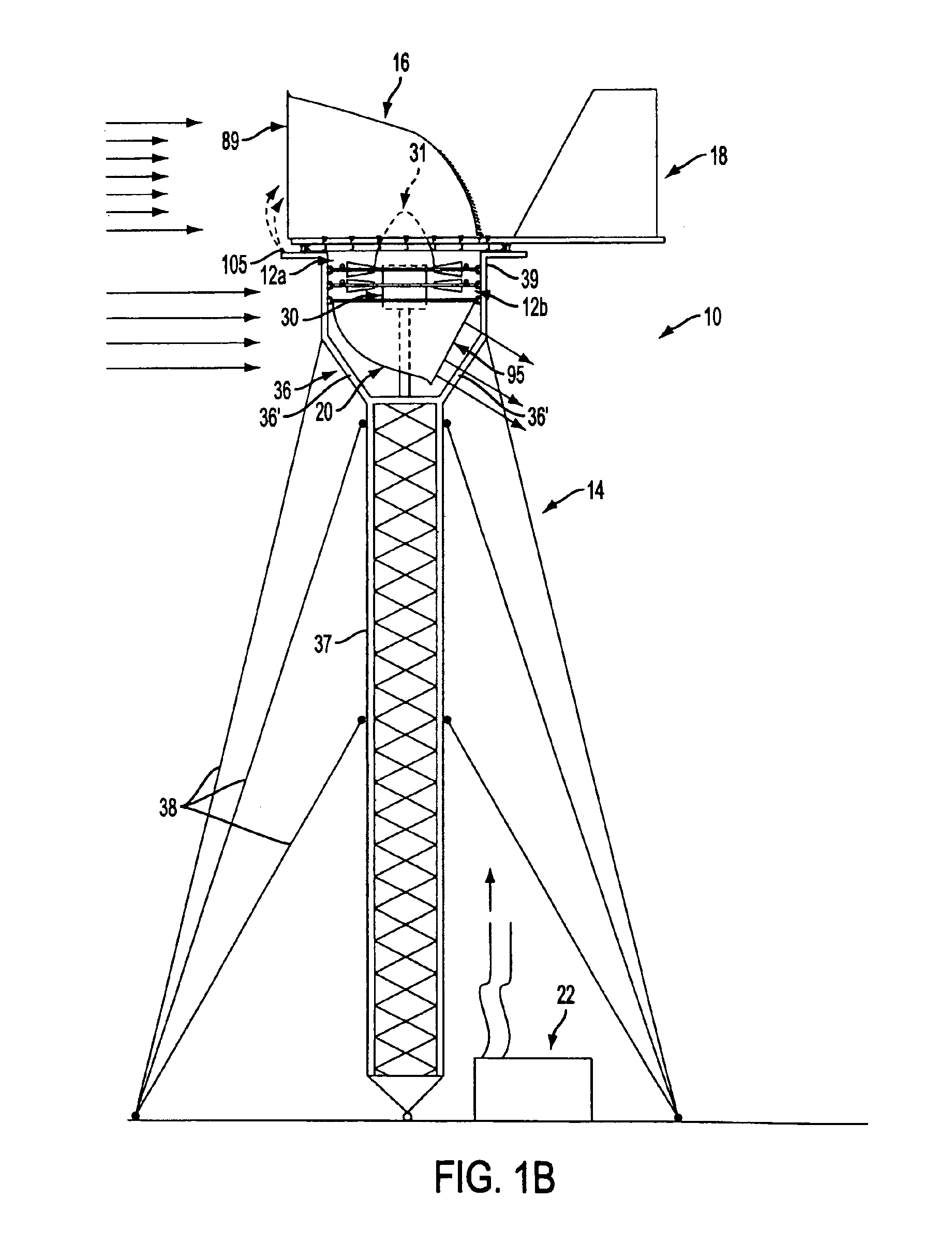

Wind energy conversion system

InactiveUS6952058B2Reduced weight and mass and costAdjustable sizePropellersWind motor supports/mountsWind energy conversionEngineering

A wind energy conversion system includes upper and lower wind turbines having counter-rotating blade assemblies supported for rotation about a vertical rotation axis, with each blade assembly carrying a rotor for rotation past a stator to produce an electrical output. The wind turbines are supported by a tower at an elevated position above the ground. Each wind turbine produces torque, and the wind energy conversion system provides for balancing the torques to avoid a net torque on the tower. Adjustment mechanisms are provided for adjusting blade pitch and for adjusting the size of an air gap between a stator and a rotor that comes into alignment with the stator as the rotor rotates therepast. The wind energy conversion system provides a hood for supplying intake air to a wind turbine and an exhaust plenum for exhausting air from the wind turbine, with the hood and the exhaust plenum being directionally positionable.

Owner:WECS

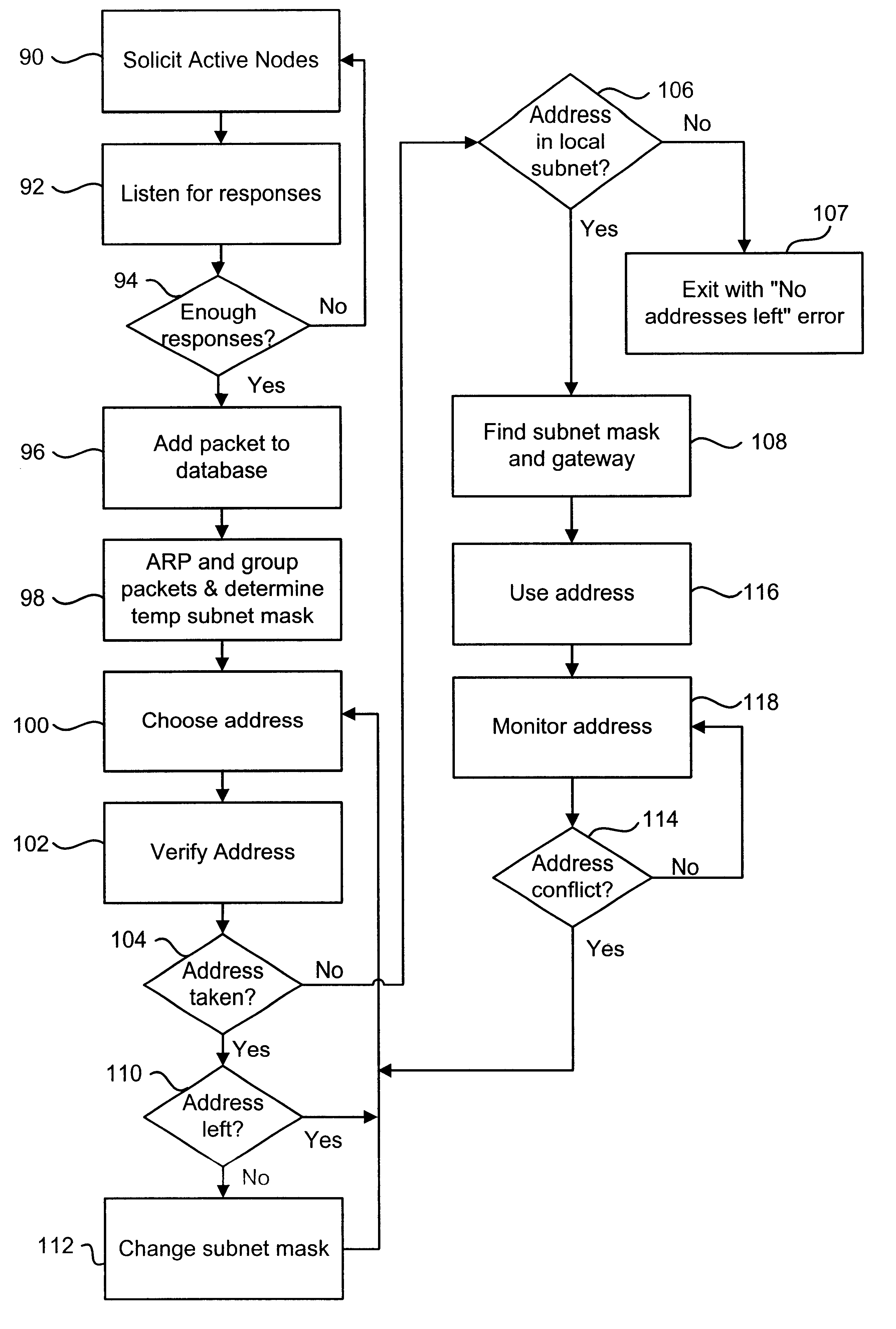

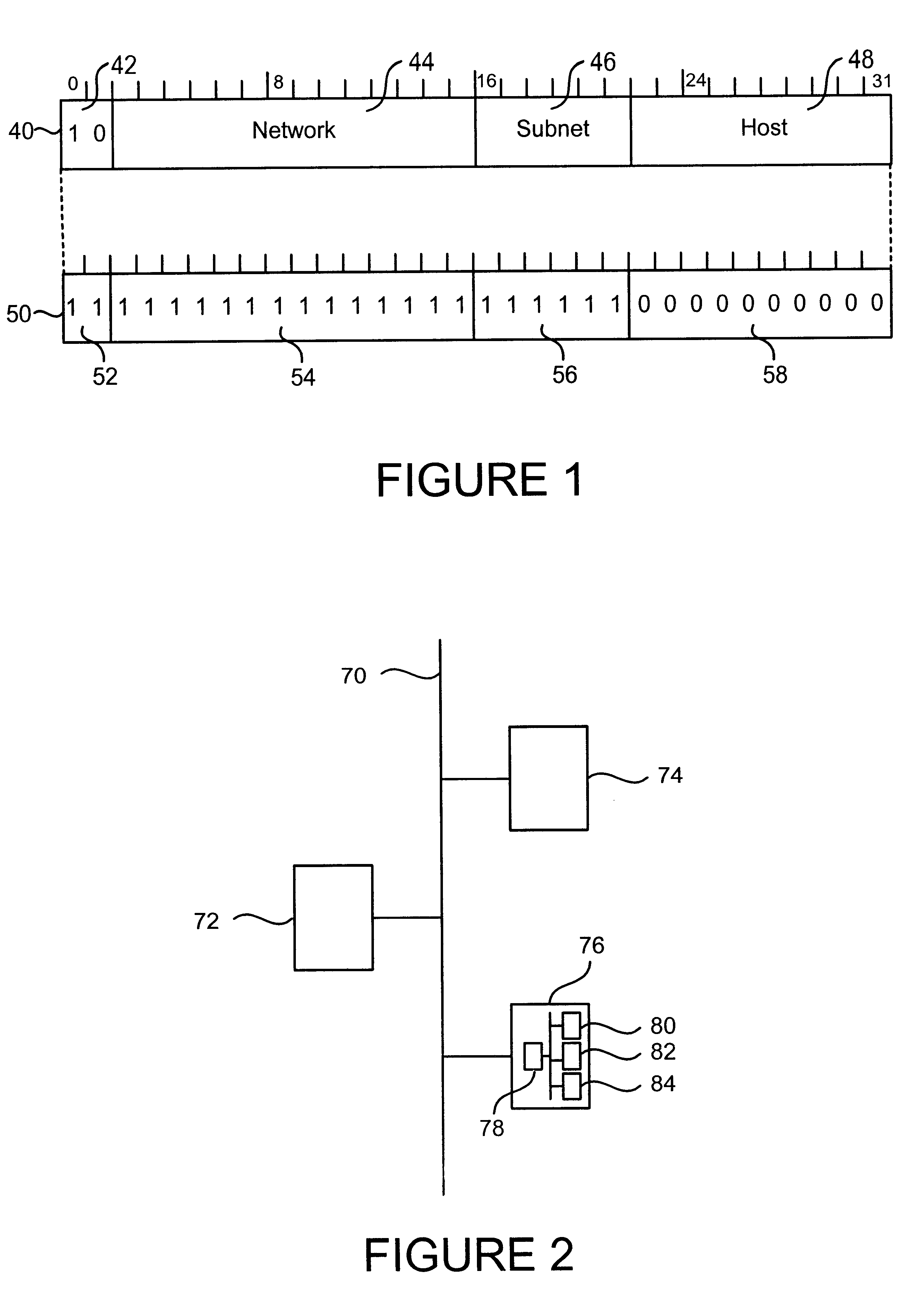

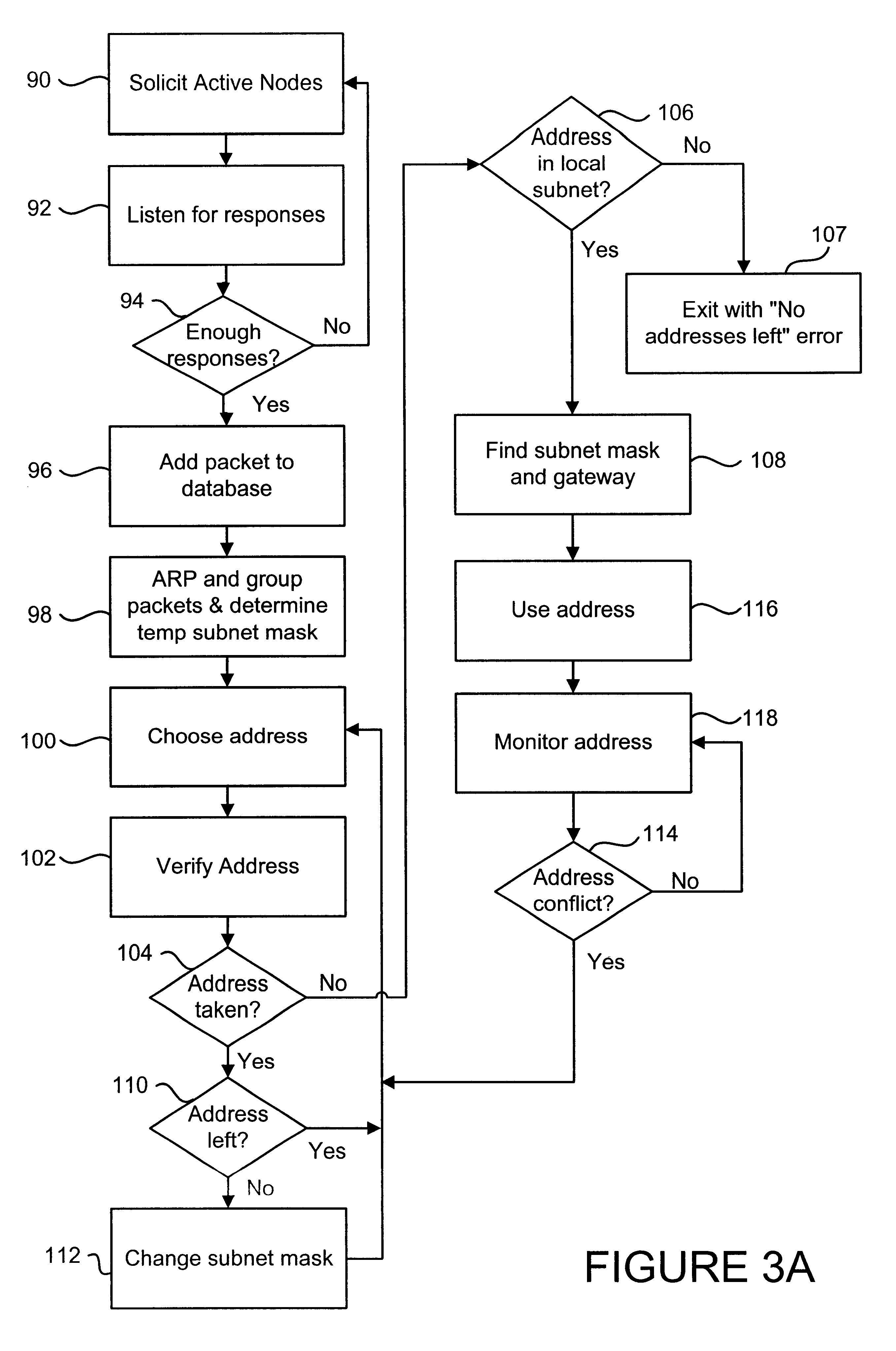

System for automatically determining a network address

InactiveUS6532217B1Reduce sizeSmall sizeError preventionTransmission systemsNetwork addressWorld Wide Web

The present invention provides for a system for automatically determining a network address. A new node starting on the network will solicit addresses from other nodes on the subnet. The addresses received are stored in a database. The address stored in the database will be reviewed in order to determine a subnet mask. The new node will choose a host number, based on the subnet mask, that is unique among the addresses in the database: The chosen unique host number is combined with the subnet number to form the new node's network address. One example of a network address is an IP version 4 address.

Owner:HANGER SOLUTIONS LLC

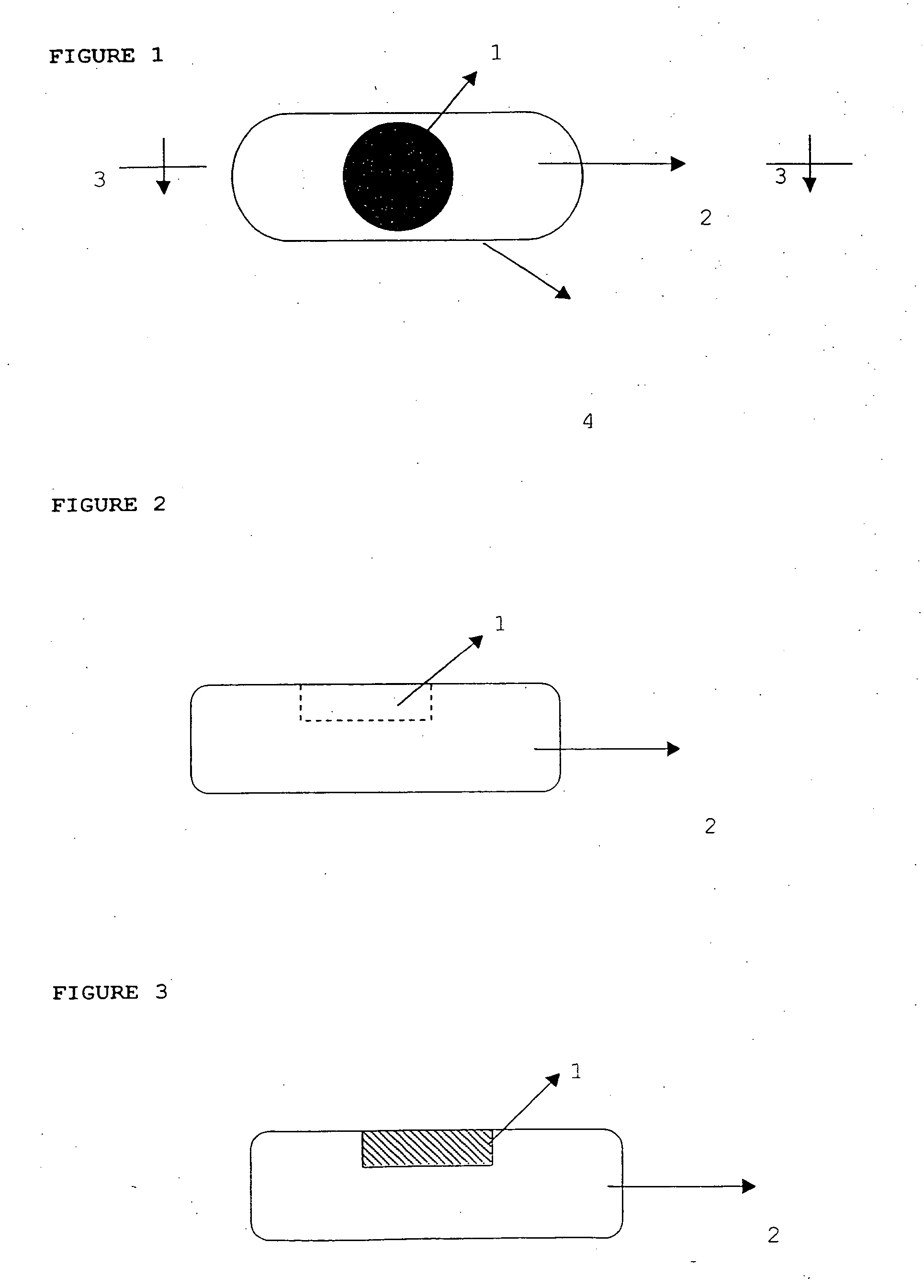

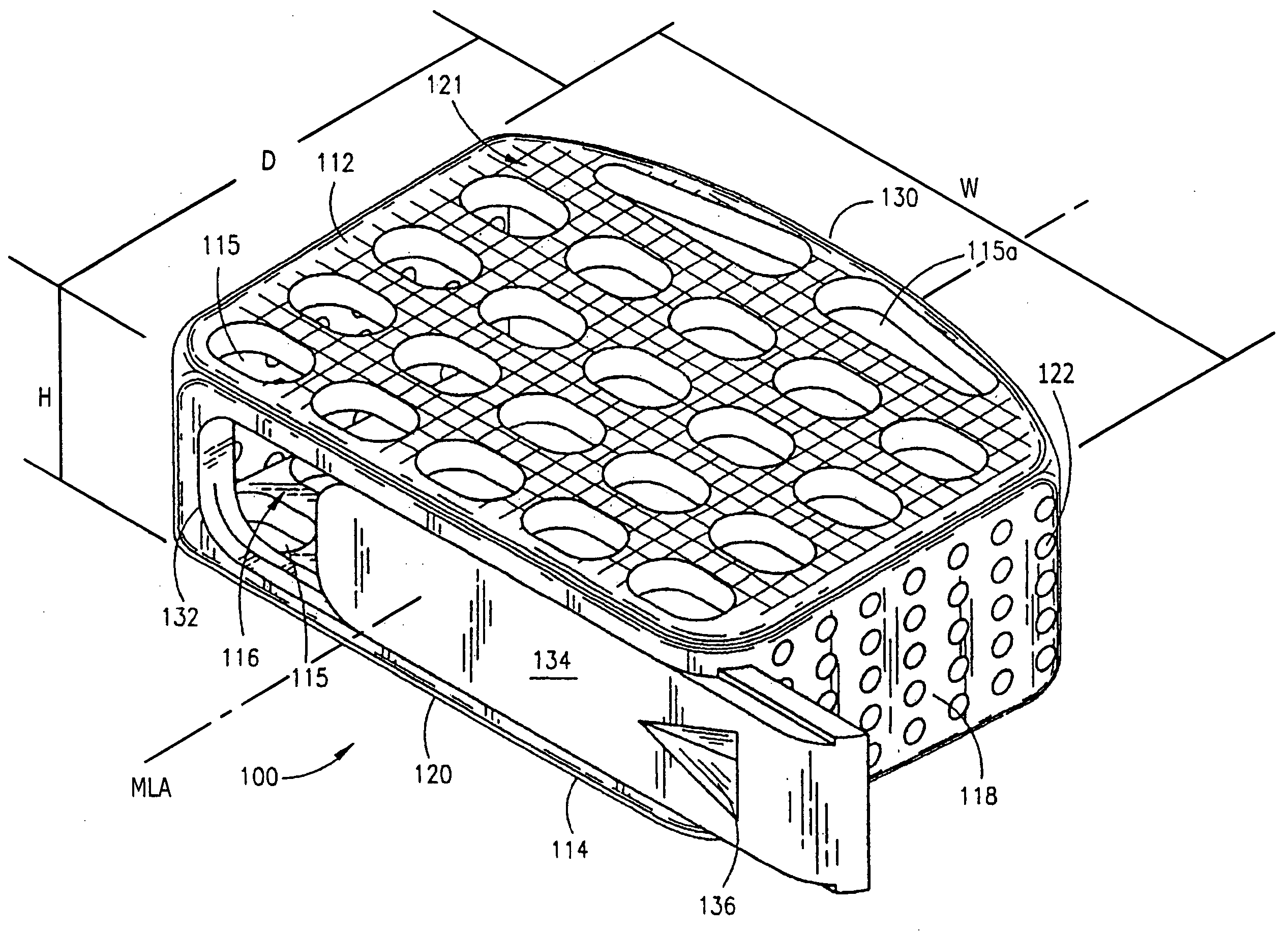

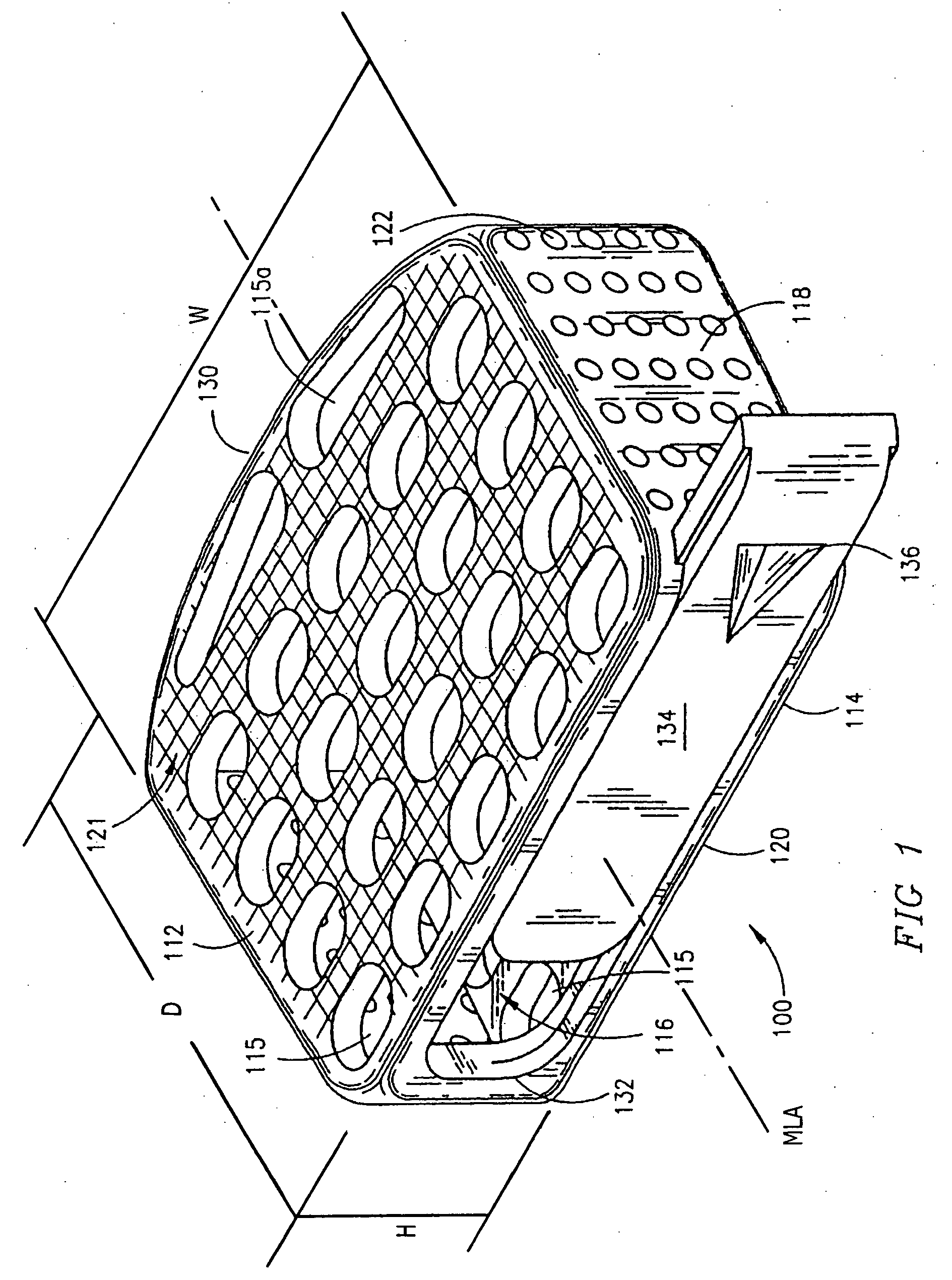

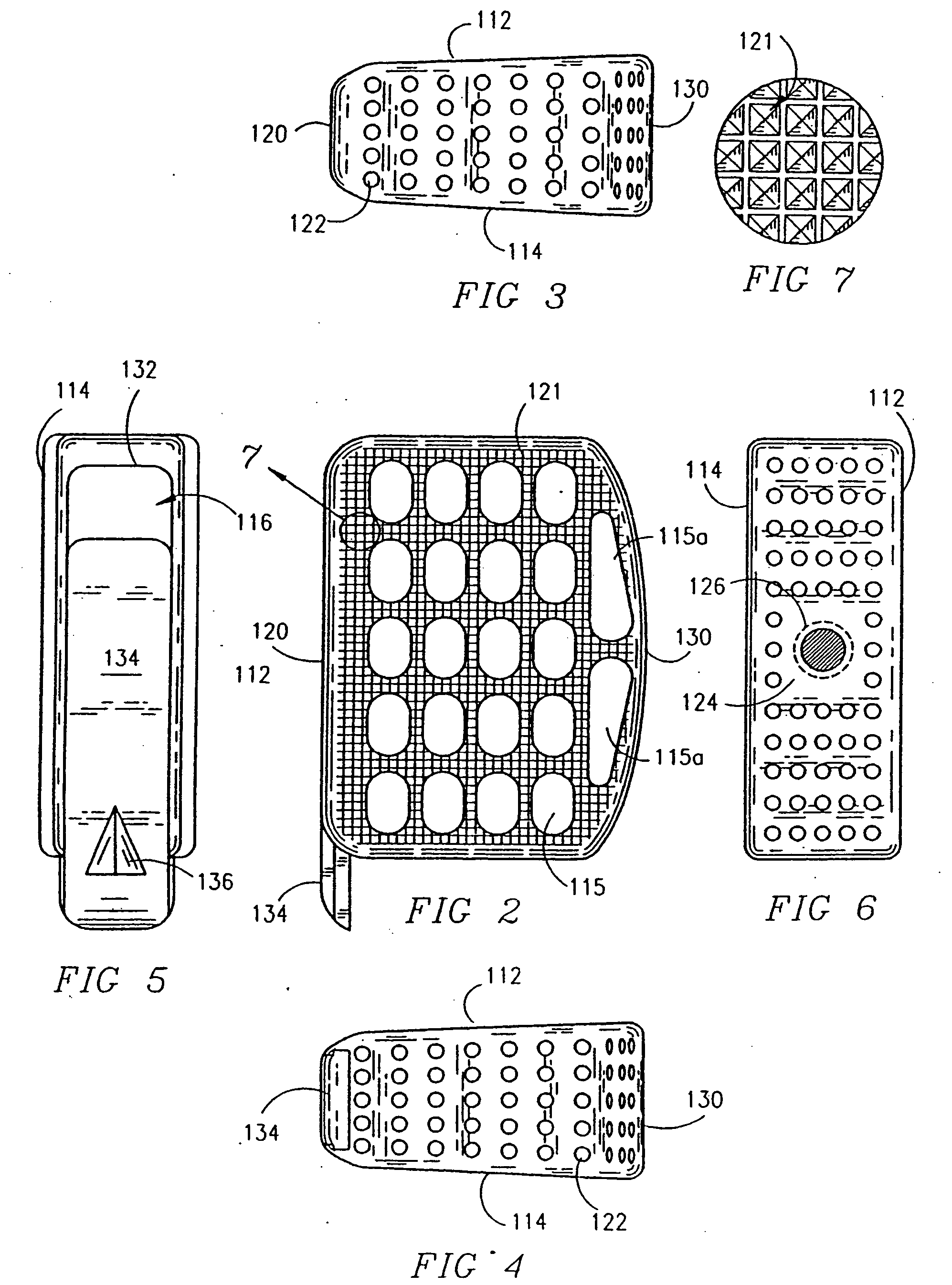

Implant having arcuate upper and lower bearing surfaces along a longitudinal axis

The present application is directed to interbody spinal fusion implants having a structural configuration that provides for the maintaining and creating of the normal anatomic angular relationship of two adjacent vertebrae of the spine to maintain and create spinal lordosis. The spinal fusion implants are sized to fit within the disc space created by the removal of disc material between two adjacent vertebrae and conform wholly or in part to the disc space created. The spinal fusion implants of the present invention have upper and lower surfaces that form a support structure for bearing against the end plates of the adjacent vertebrae. The upper and lower surfaces are disposed in a converging angular relationship to each other such that the implants have an overall “wedged-shape” in an elevational side view. The angular relationship of the upper and lower surfaces places and maintains the vertebrae adjacent to those surfaces in an angular relationship to each other, creating and maintaining the desired lordosis.

Owner:WARSAW ORTHOPEDIC INC

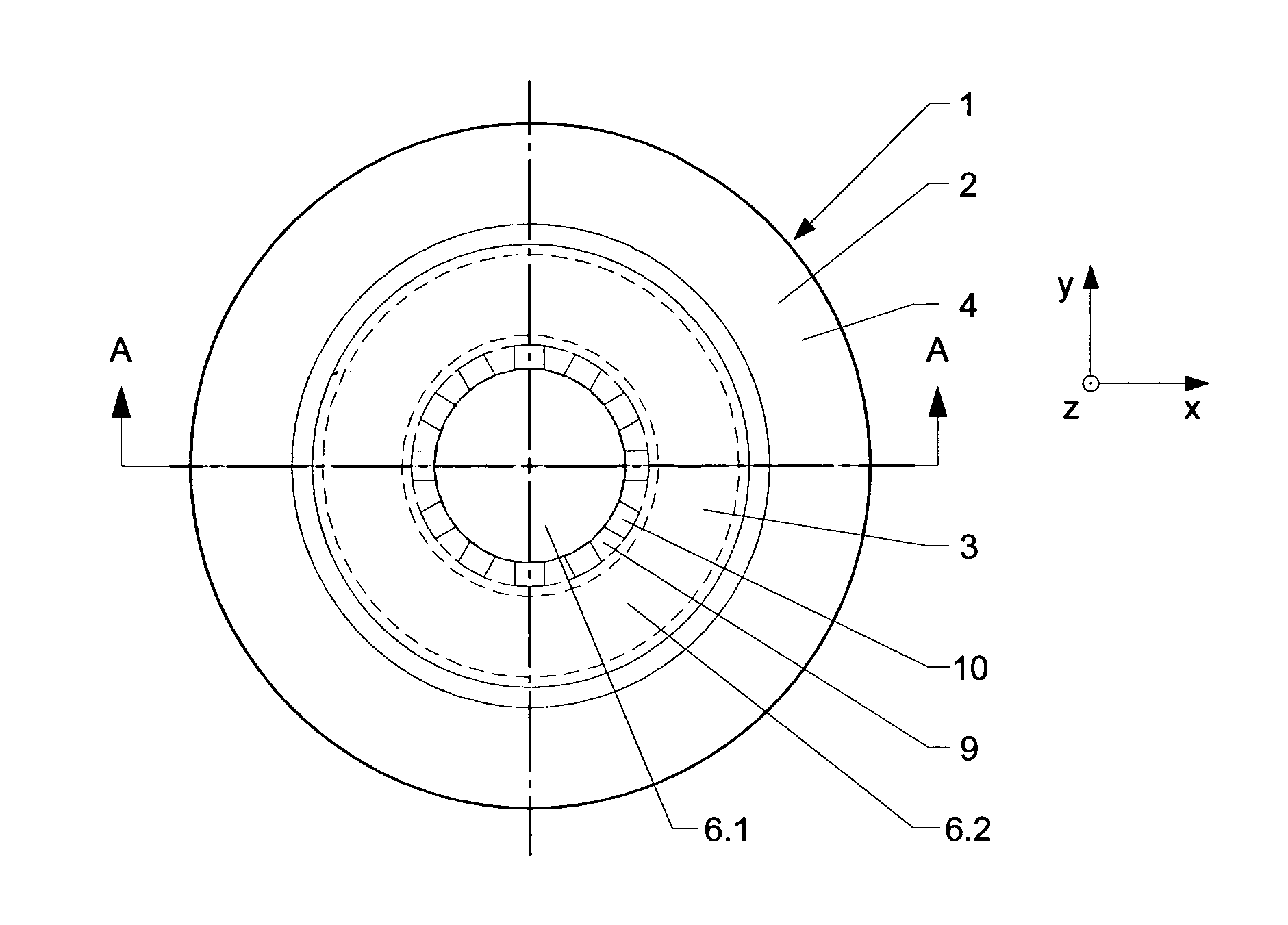

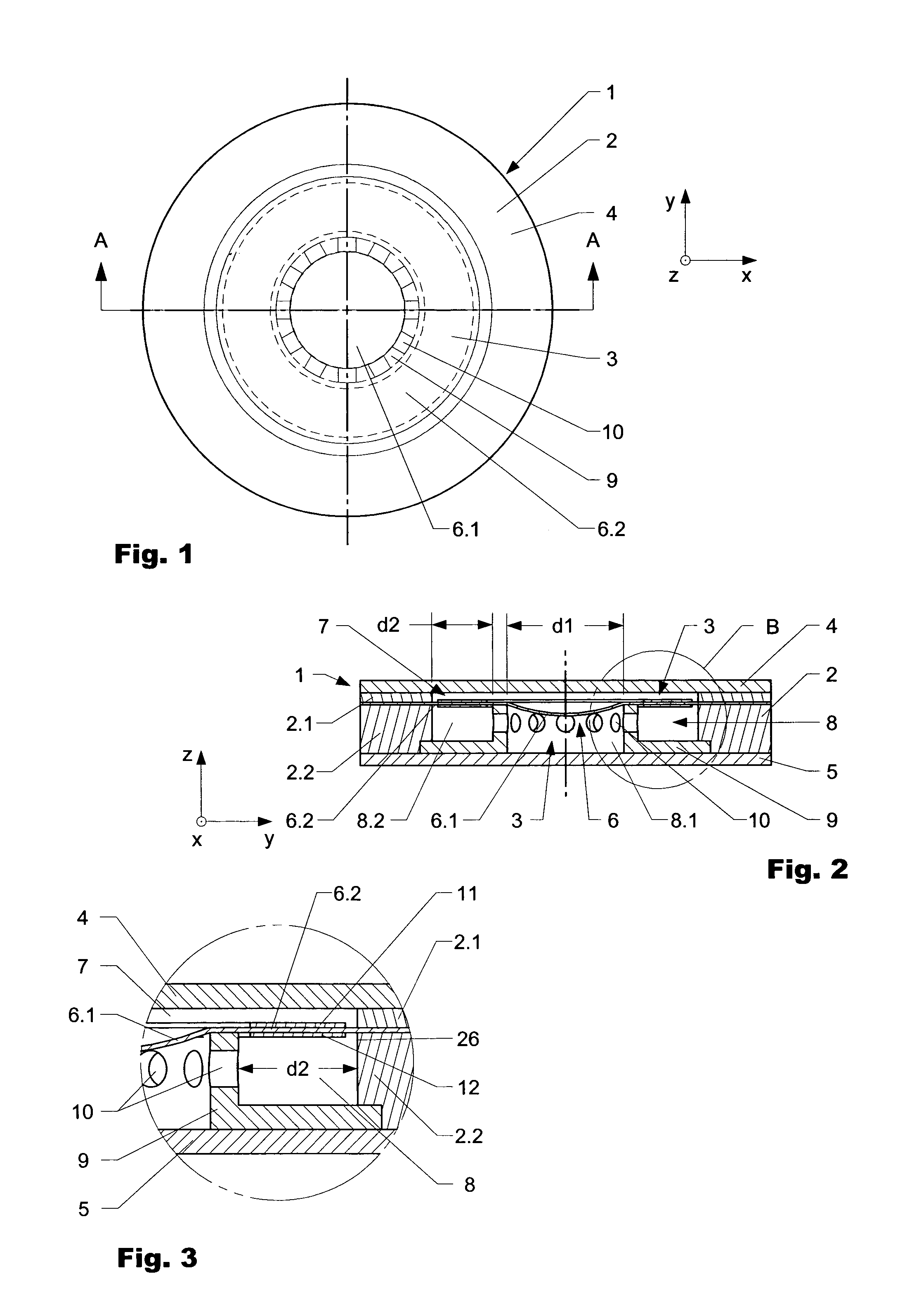

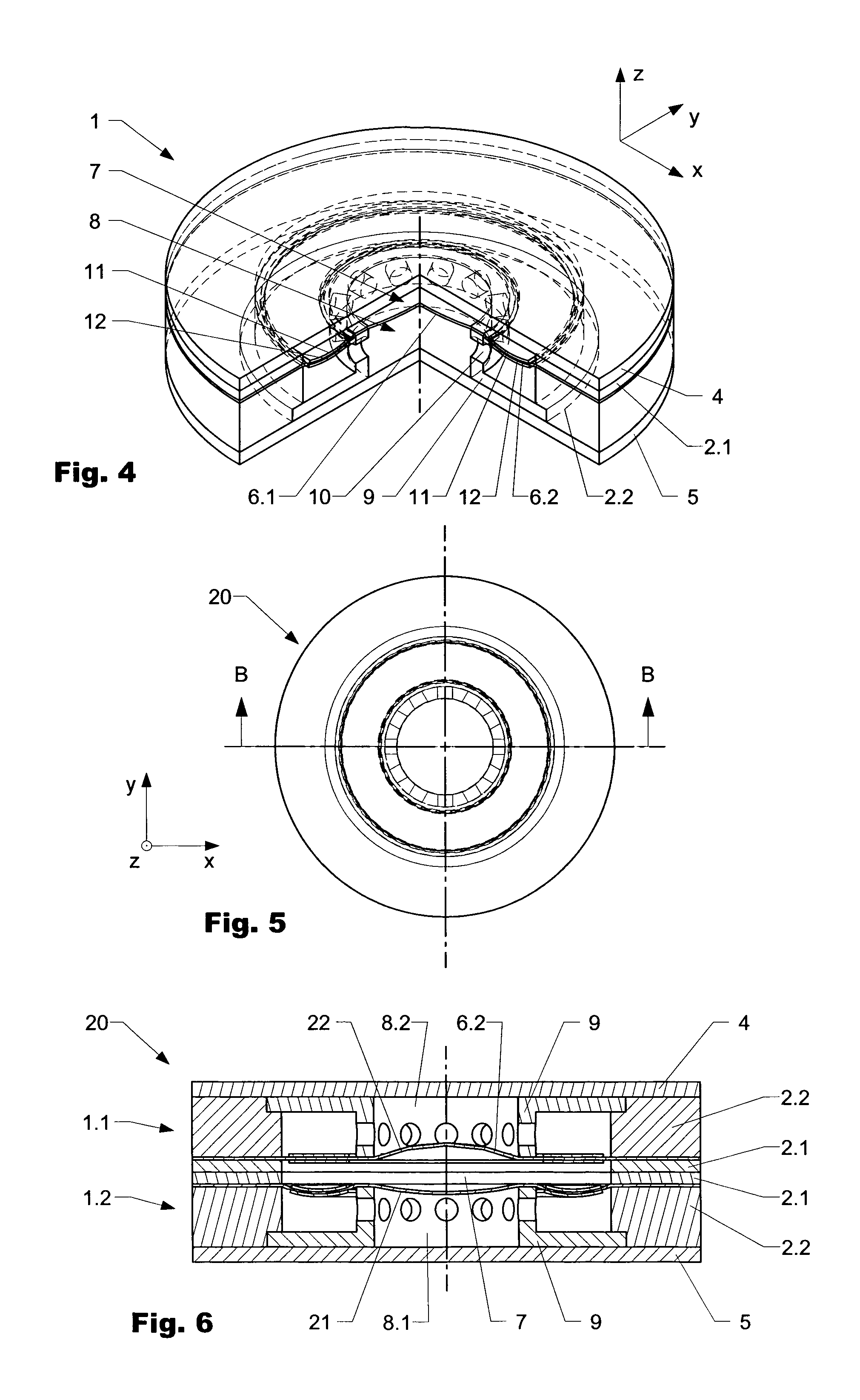

Liquid Lens System

ActiveUS20100202054A1Change shapeGood effectDiffusing elementsDiffraction gratingsEngineeringActuator

The invention is directed to an optical system (1). The optical system (1) has a housing (2) with an opening (3) extending through the housing (2) encompassing an in general constant volume (V). A membrane (6) with two or more membrane sections is arranged across the opening separating the volume (V) in a first and a second chamber (7, 8) filled with at least one fluid. The membrane is attached to an annular holding frame (9). An actuator is interconnected to the membrane (6) directly or indirectly to change the optical behaviour of the membrane.

Owner:OPTOTUNE AG

Interruption free navigator

InactiveUS6658354B2Improve accuracyHighly accurate positioning solutionRoad vehicles traffic controlPosition fixationDisplay deviceMarine navigation

An interruption free navigator includes an inertial measurement unit, a north finder, a velocity producer, a positioning assistant, a navigation processor, an altitude measurement, an object detection system, a wireless communication device, and a display device and map database. Output signals of the inertial measurement unit, the velocity producer, the positioning assistant, the altitude measurement, the object detection system, and the north finder are processed to obtain highly accurate position measurements of the person. The user's position information can be exchanged with other users through the wireless communication device, and the location and surrounding information can be displayed on the display device by accessing a map database with the person position information.

Owner:AMERICAN GNC

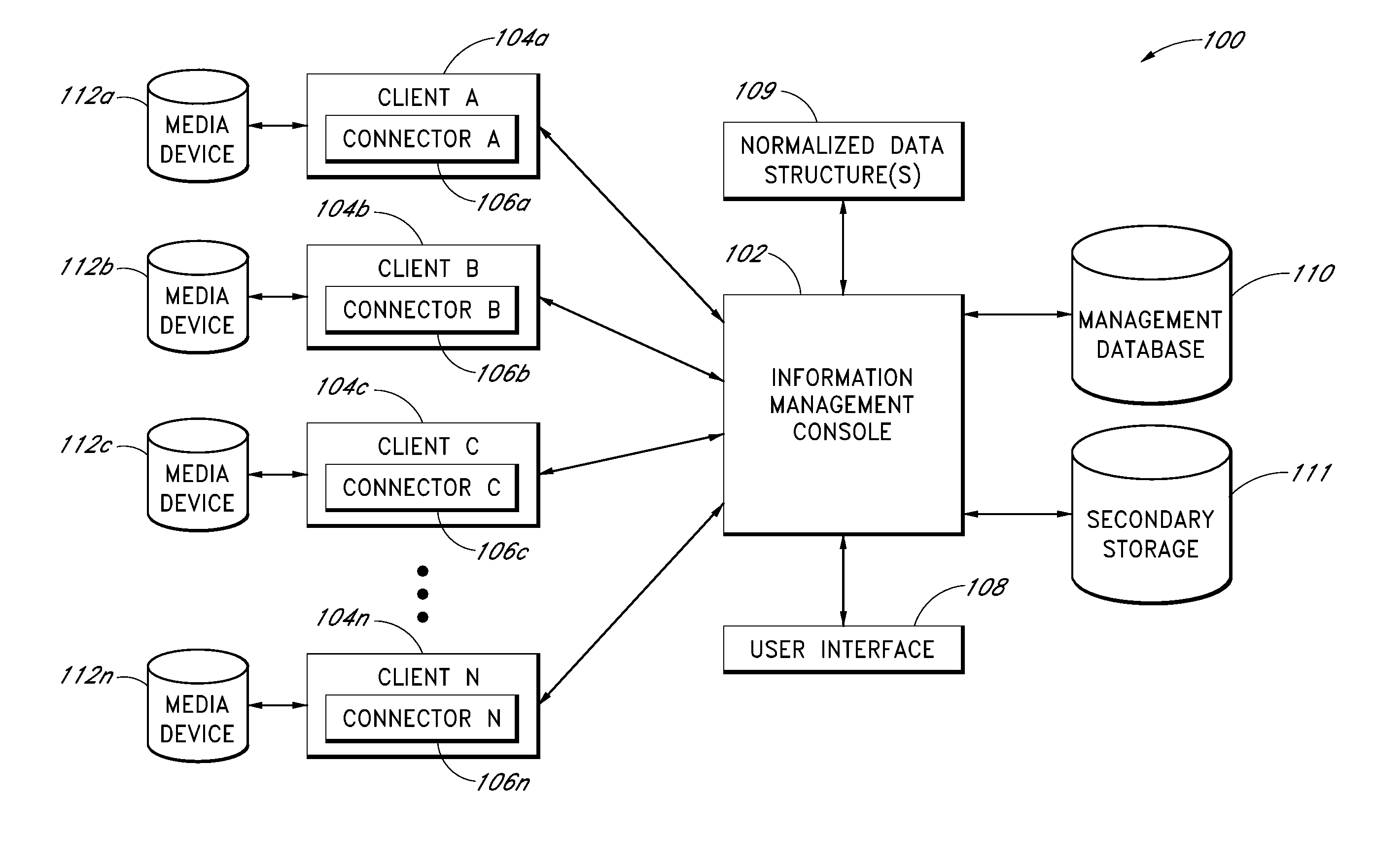

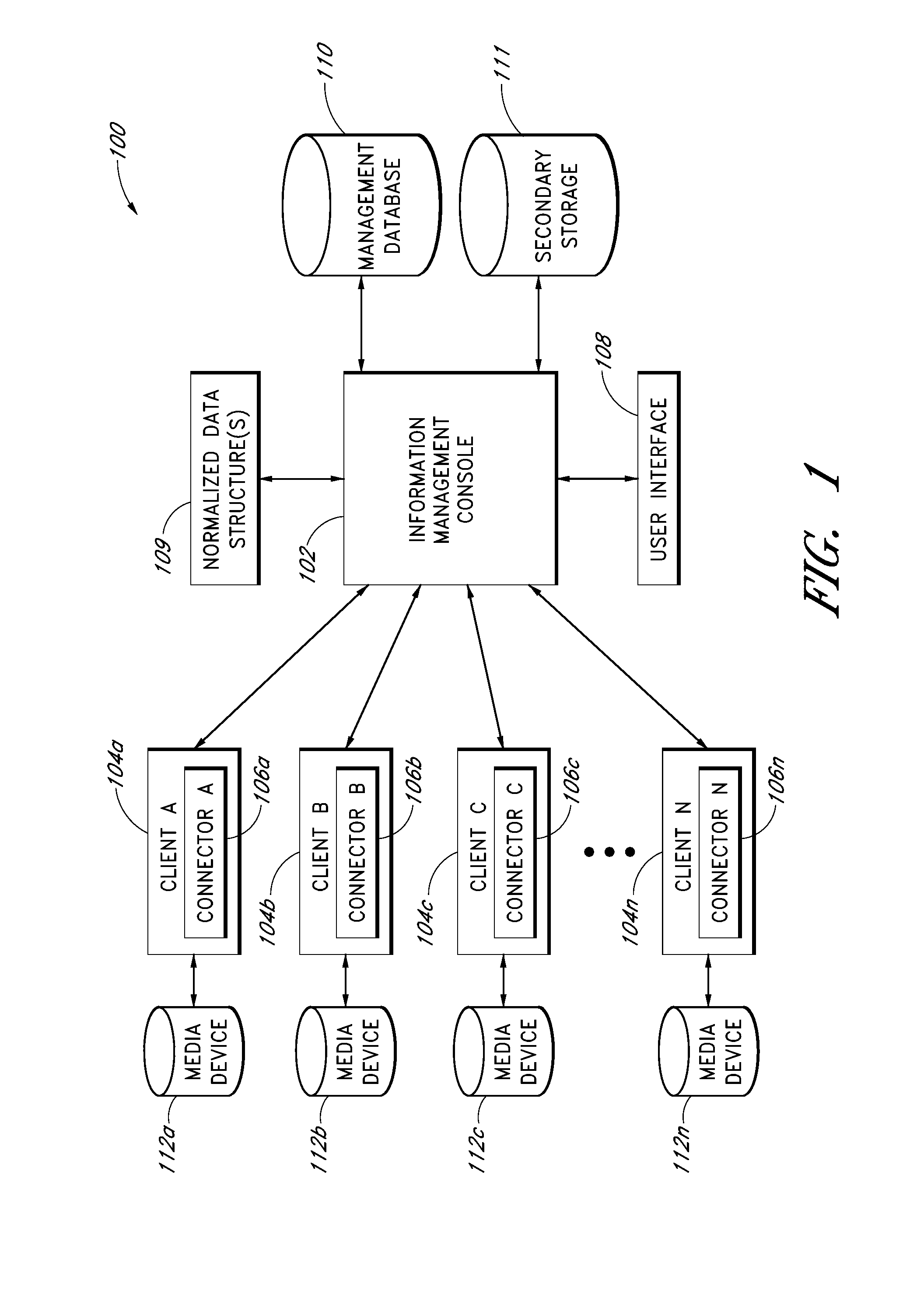

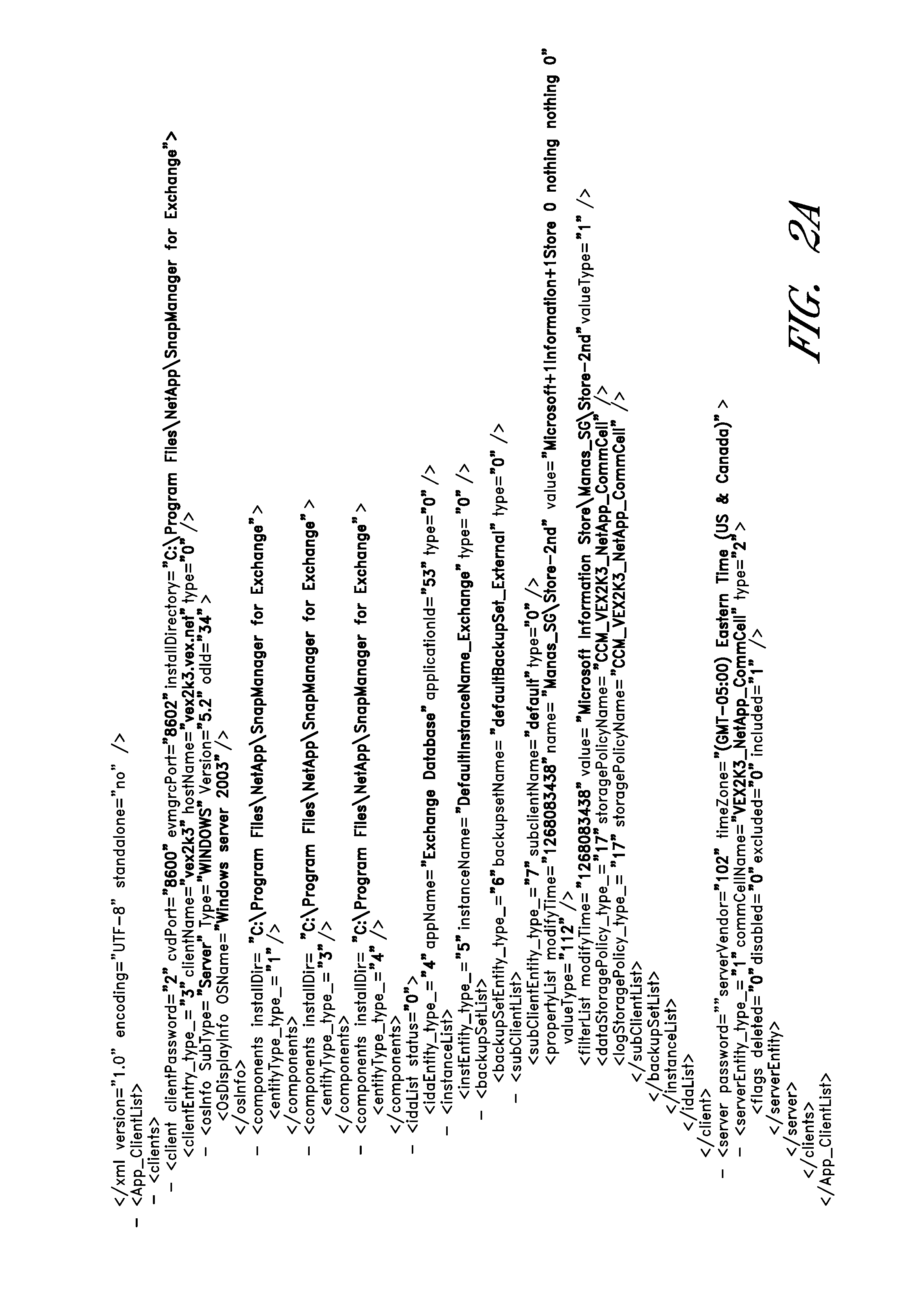

Data mining systems and methods for heterogeneous data sources

ActiveUS20100332453A1Reduce sizeReduce needDigital data processing detailsError detection/correctionData sourceData management

Systems and methods integrate disparate backup devices with a unified interface. In certain examples, a management console manages data from various backup devices, while retaining such data in its native format. The management console can display a hierarchical view the client devices and / or their data and can further provide utilities for processing the various data formats. A data structure including fields for storing both metadata common to the client device data and value-added metadata can be used to mine or process the data of the disparate client devices. The unified single platform and interface reduces the need for multiple data management products and / or customized data utilities for each individual client device and provides a single pane of glass view into data management operations. Integrating the various types of storage formats and media allows a user to retain existing storage infrastructures and further facilitates scaling to meet long-term management needs.

Owner:COMMVAULT SYST INC

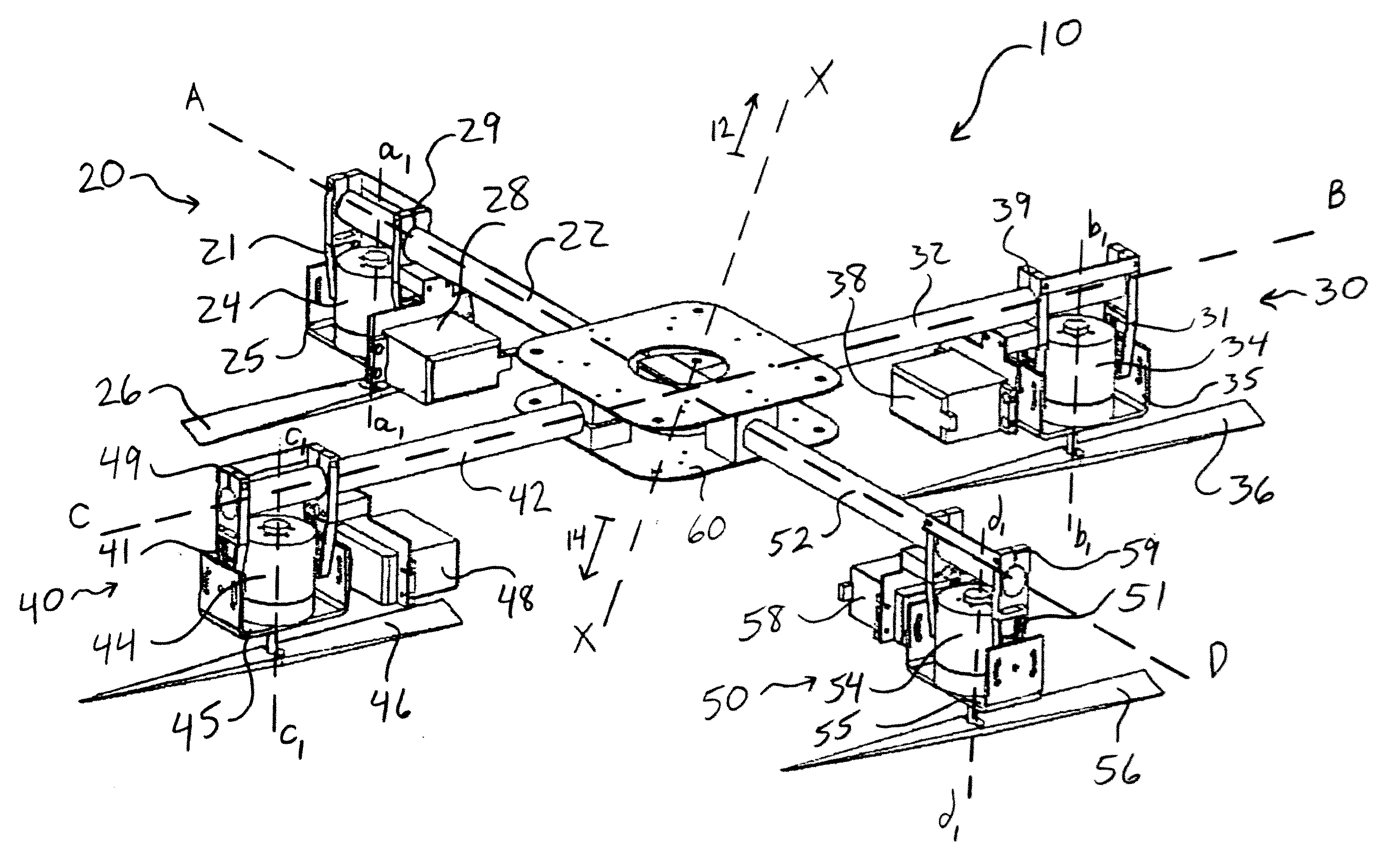

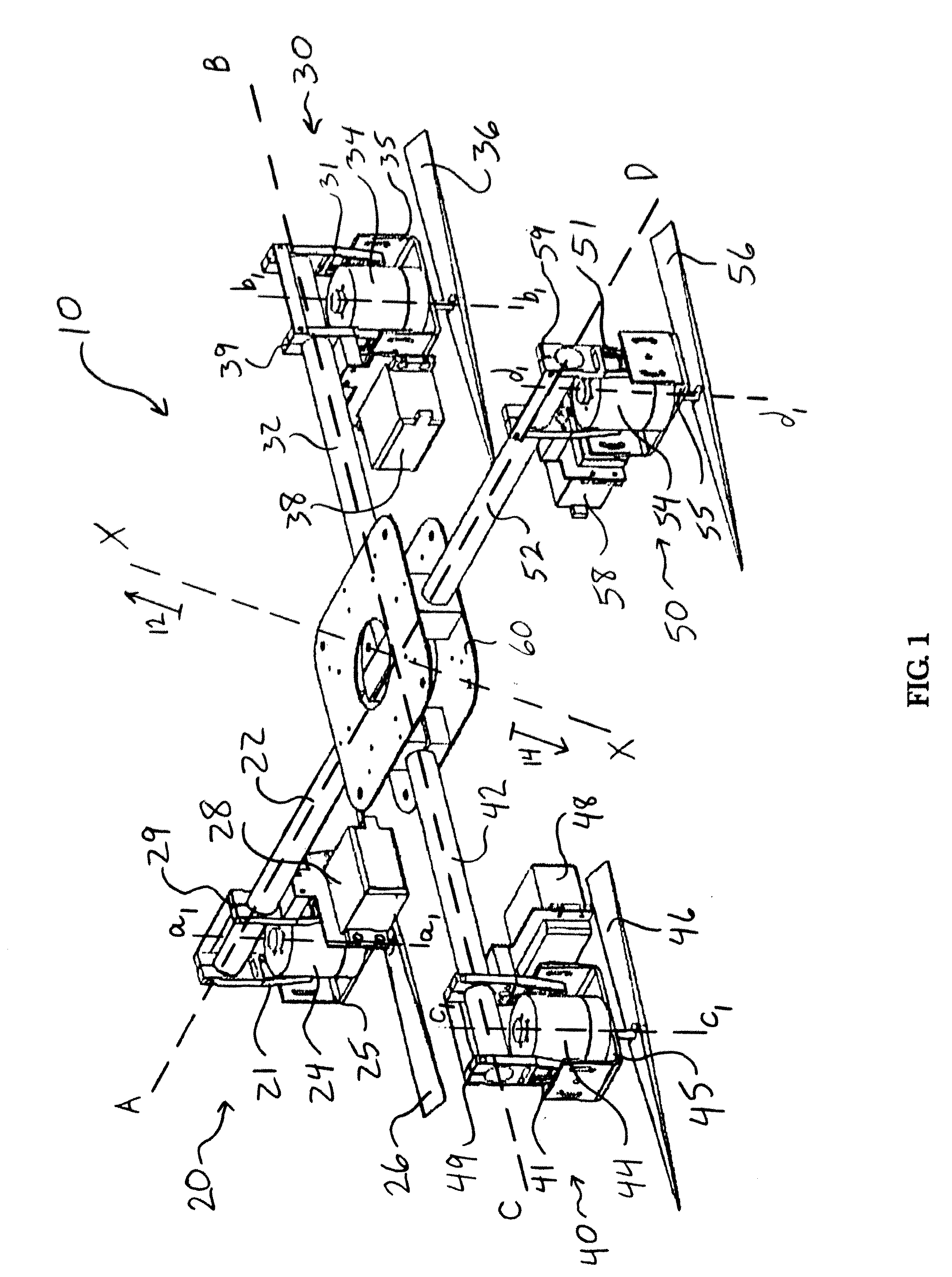

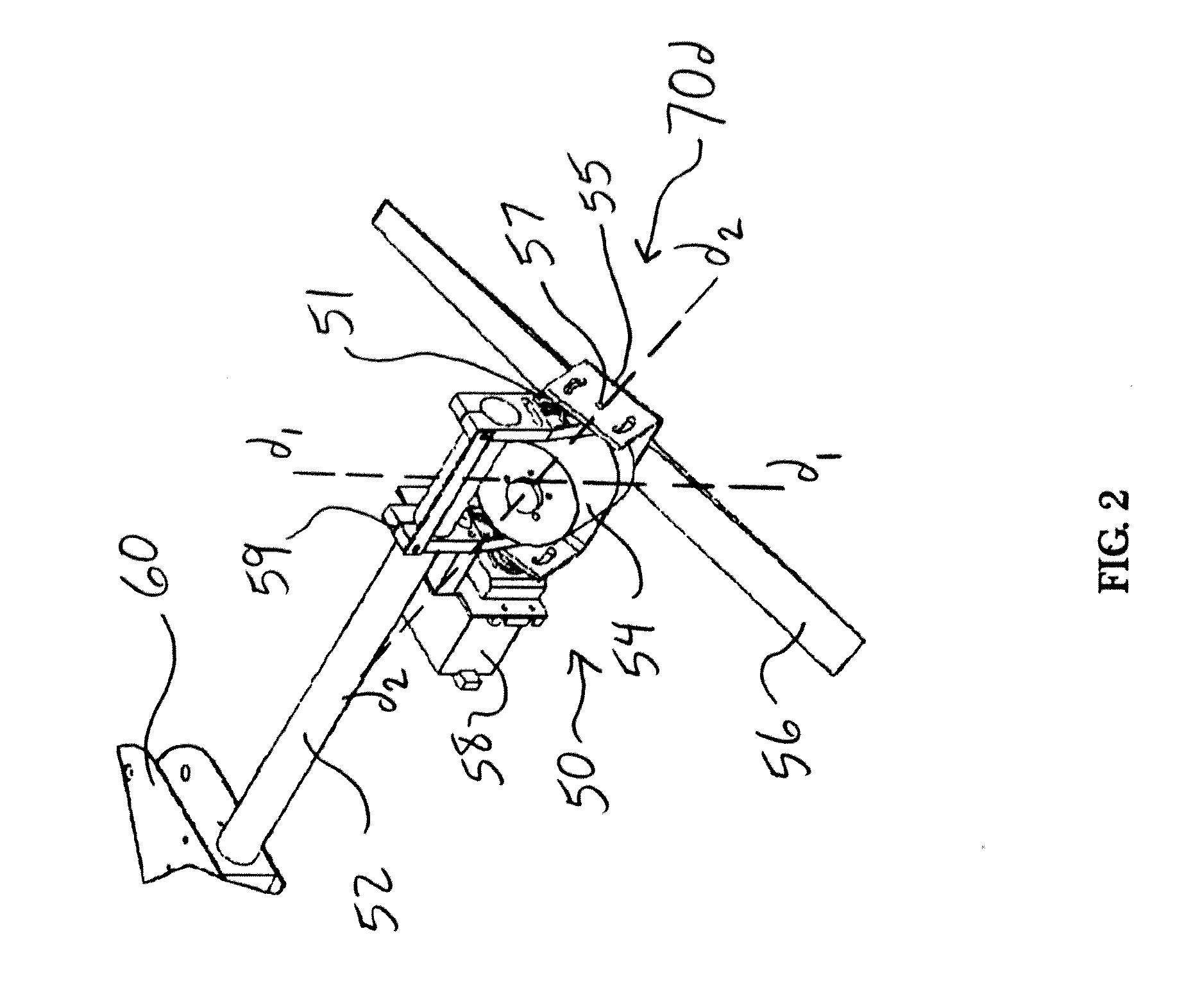

Quad tilt rotor vertical take off and landing (VTOL) unmanned aerial vehicle (UAV) with 45 degree rotors

InactiveUS20130105635A1Maintain balance and stabilityIncreased payload capacityUnmanned aerial vehiclesRemote controlled aircraftFlight vehicleClassical mechanics

A system and method to control the stability and direction of a quad tilt vertical takeoff and landing (VTOL) unmanned aerial vehicle (UAV) by manipulating the rotational speed of propellers at each rotor while simultaneously tilting the rotors in a 45 degree configuration related to a central axis for directional control. Each rotor is attached to a tilting mechanism configured to be symmetrically aligned at a 45 degree angle from a central axis to manipulate a directional angle of each rotor along a first and second axis. The first and fourth rotors are aligned on the first axis while the second and third rotors are aligned on the second axis. A controller includes a first control loop for manipulating the rotational speed of the propellers to control the aircraft balance and a second control loop for controlling lateral movement by tilting the rotors along the first and second axis.

Owner:KING ABDULLAH II DESIGN & DEV BUREAU

Intelligent Reconfigurable Locker System

InactiveUS20140330603A1OptimizationQuick and simple setupComputer controlResourcesModularityE-commerce

This invention involves the configuration of locker sizes during installation that can be reconfigured periodically to conform to the packages that arrive at the locker location. Locker control software can enable the efficient selection of locker size so that the locker bank can be optimized to the size of the packages that are delivered to the locker location. The reconfigurable lockers also may include a modular locker control module that can assist in the easy facilitation of changing the locker size. Also, the locker software can be flexible enough so that customers can have a direct communication link to the locker software that would allow the customer's mobile device to input authentication and access codes that would open up locker door(s). The locker software could also be enabled on the cloud providing an e-commerce goods seller, shipper or locker operator with information about goods that are shipped to locker locations and when customers stop by to pick up their goods or to return their goods to the e-commerce seller.

Owner:AIRLOCKER INC

Data capture and identification system and process

InactiveUS7565008B2Fast and reliable detection and recognitionReduce sizeStill image data indexingCharacter and pattern recognitionRadiologyData acquisition

An identification method and process for objects from digitally captured images thereof that uses data characteristics to identify an object from a plurality of objects in a database. The data is broken down into parameters such as a Shape Comparison, Grayscale Comparison, Wavelet Comparison, and Color Cube Comparison with object data in one or more databases to identify the actual object of a digital image.

Owner:NANT HLDG IP LLC

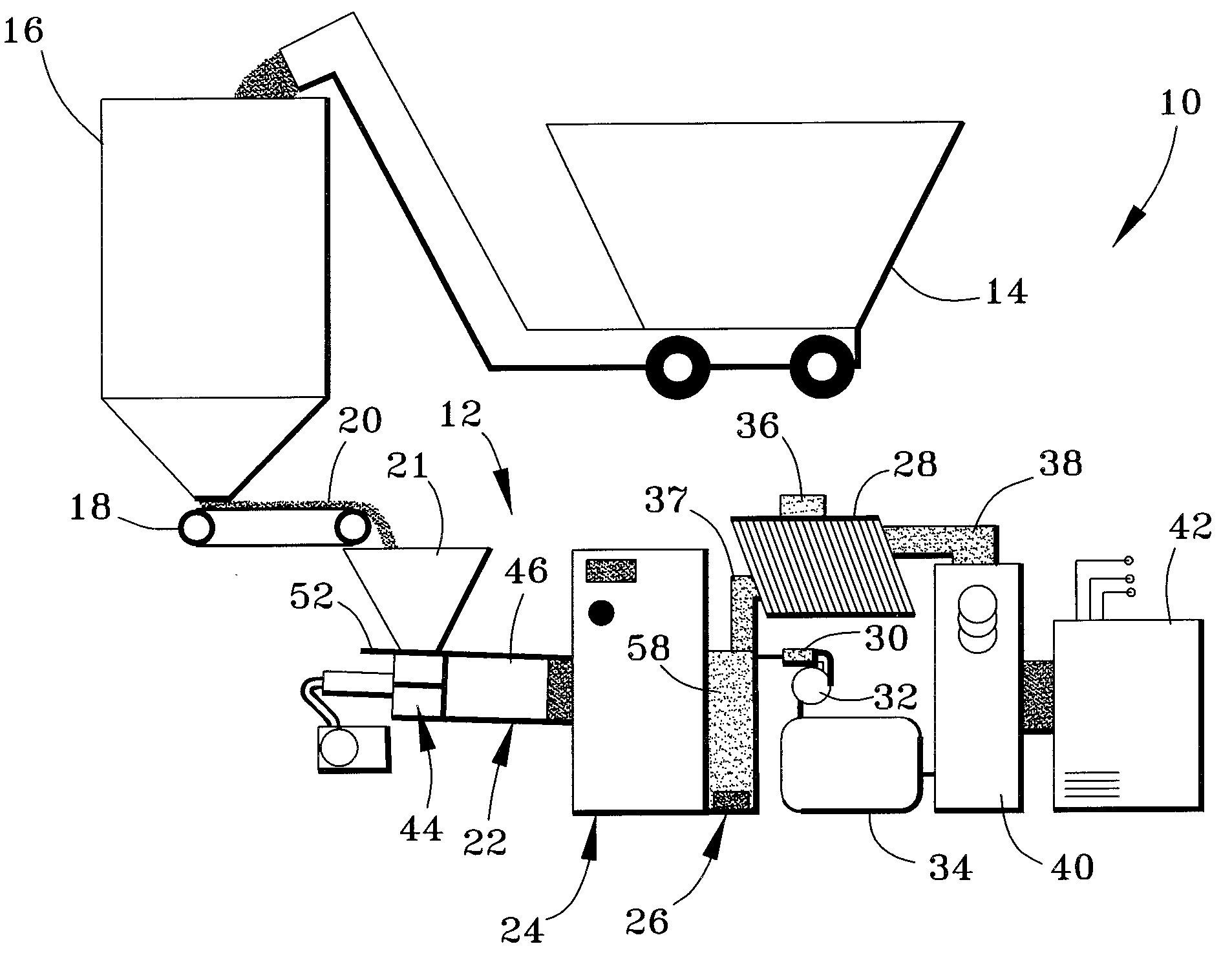

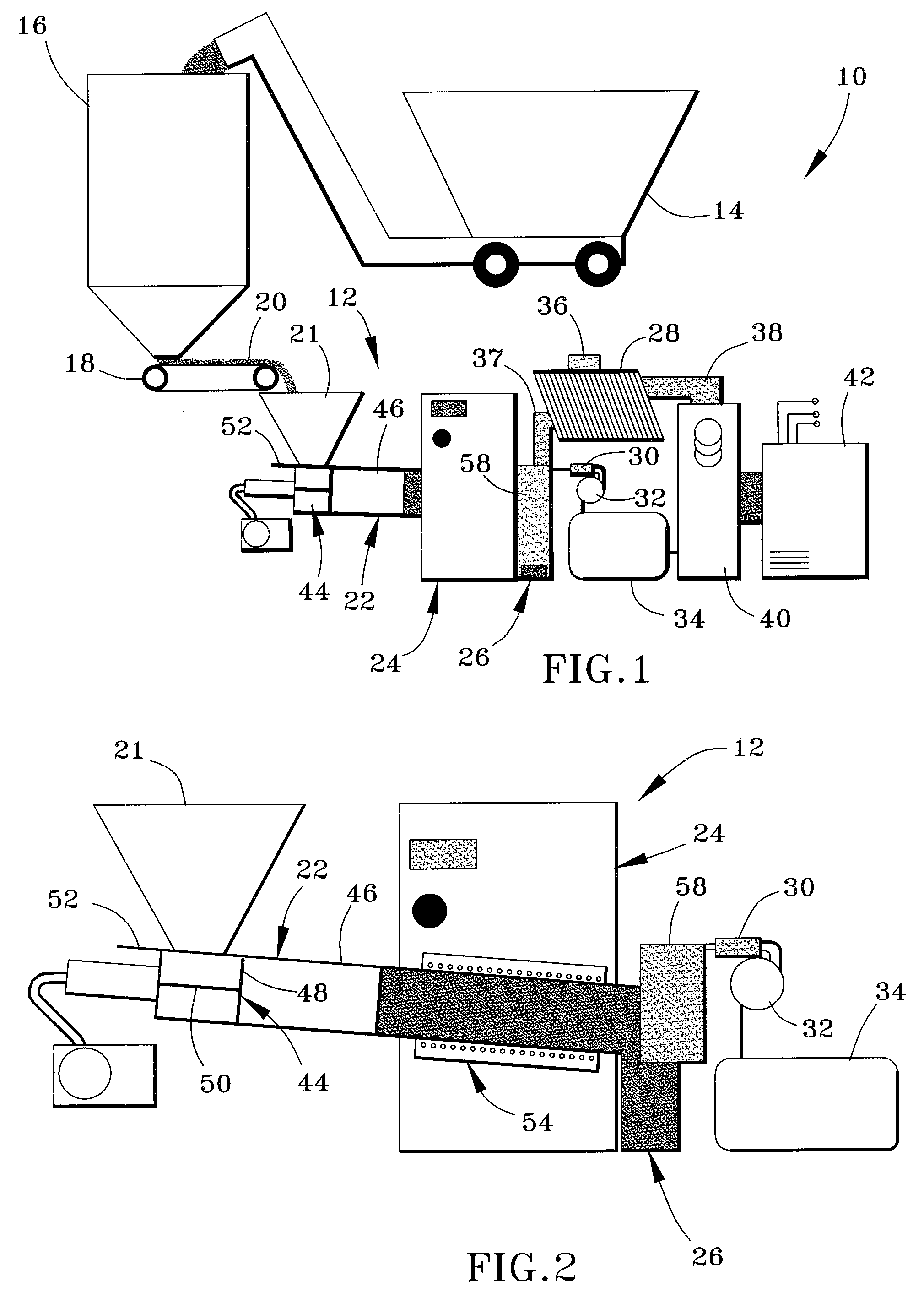

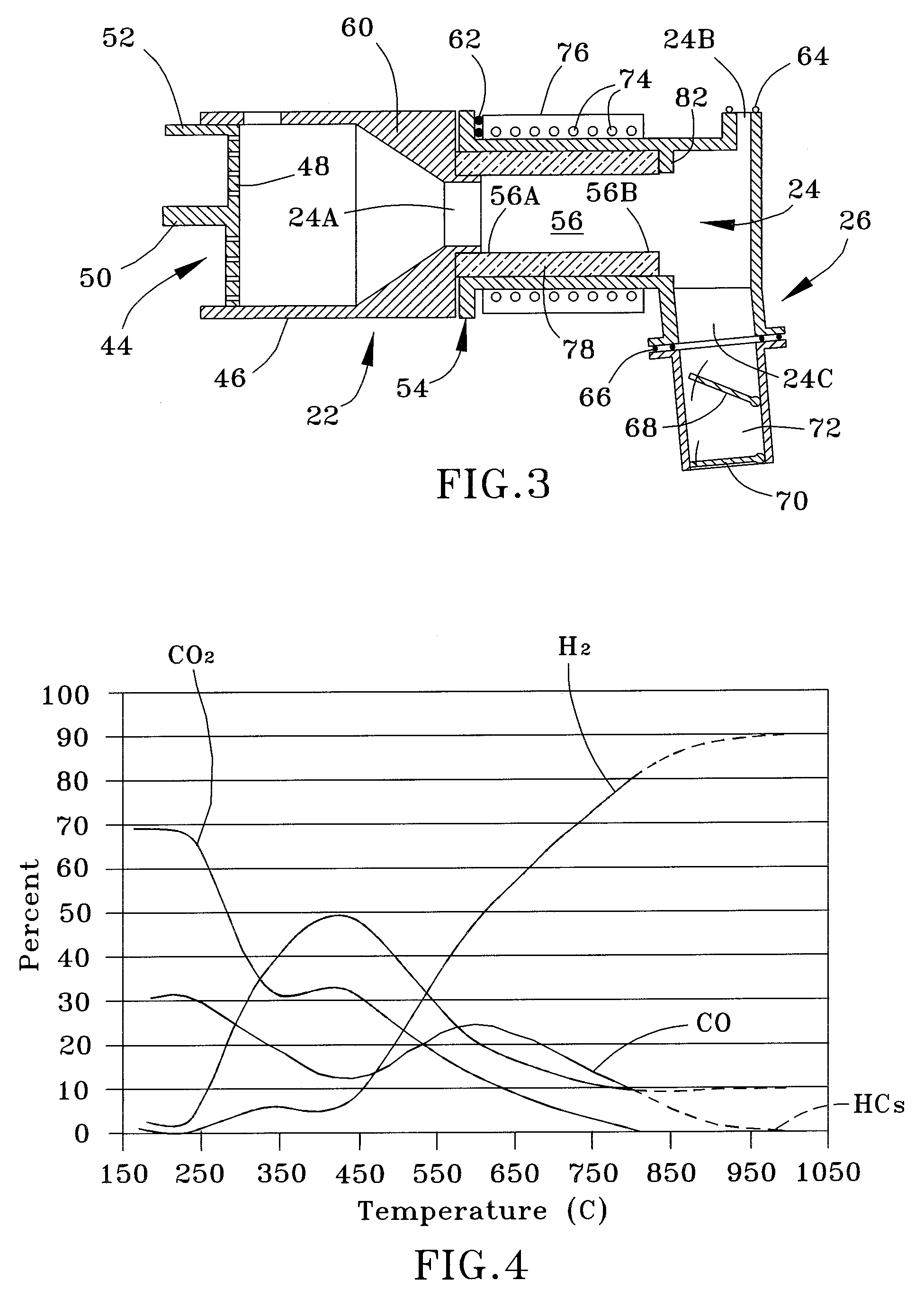

Process and system for syngas production from biomass materials

A process and system suitable for producing syngas from biomass materials. The process and system entail the compaction of a loose biomass material to remove air therefrom and form a compacted biomass material. The compacted biomass material is then introduced into a reactor and heated in the substantial absence of air so as not to combust the compacted biomass material. Instead, the compacted biomass material is heated to a temperature at which organic molecules within the compacted biomass material break down to form ash and gases comprising carbon monoxide and hydrogen gas. Thereafter, the carbon monoxide and hydrogen gas are released from the reactor, and the ash is removed from the reactor.

Owner:GREEN FORTRESS ENG INC

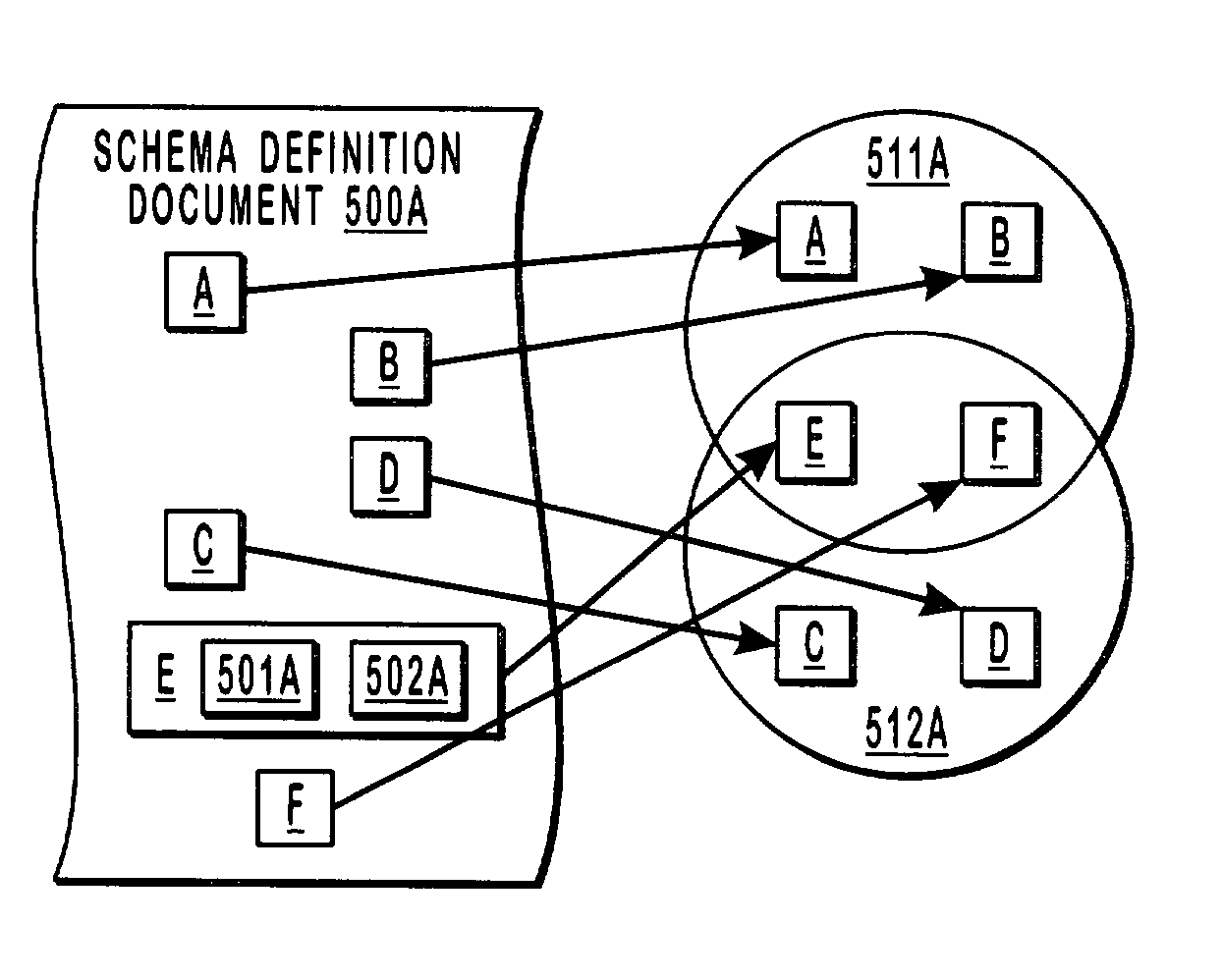

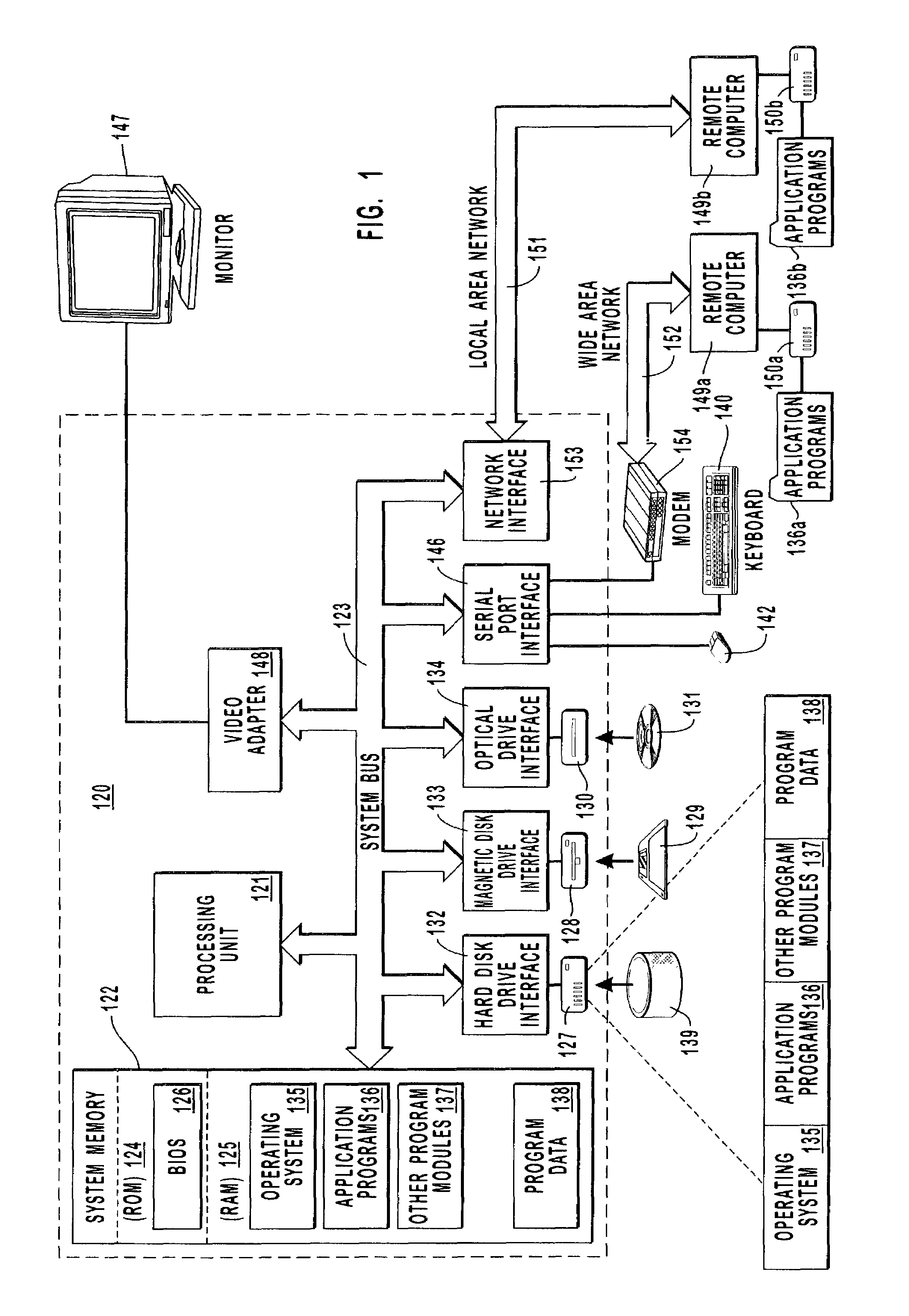

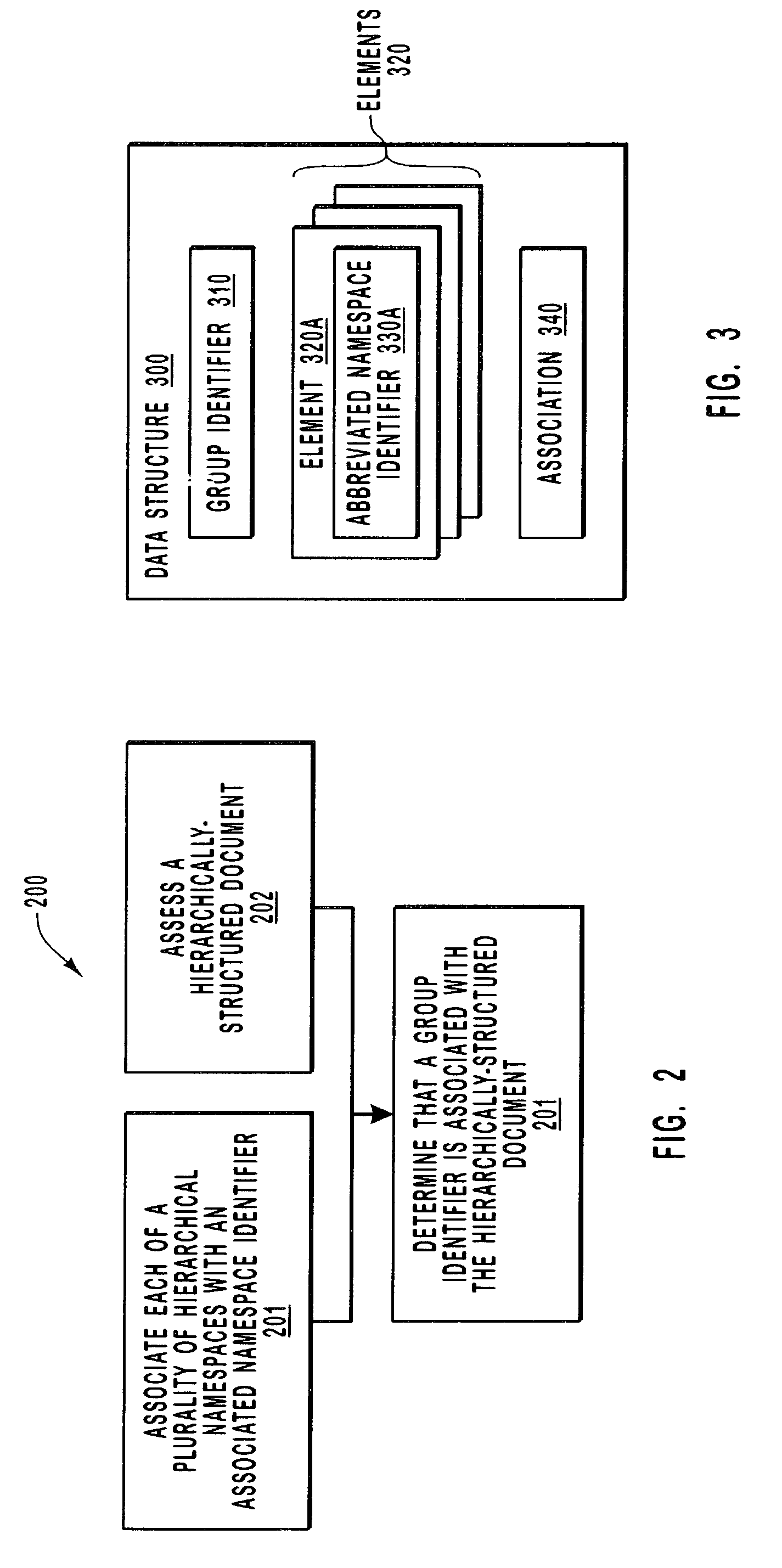

Grouping and nesting hierarchical namespaces

InactiveUS6993714B2Reduce sizeDigital data information retrievalDigital computer detailsXML namespaceIdenticon

A group identifier represents an association between each of a number of different abbreviated namespace identifiers with a corresponding hierarchical namespace (e.g., an XML namespace). A hierarchically-structured document (e.g., an XML document) is accessed by a computing system that determines that the group identifier is associated with the hierarchically-structured document. Hence, when using the abbreviated namespace identifiers in the hierarchically-structured document, the computing system knows that the corresponding namespace is associated with the designated portions of the hierarchically-structured document. Also, a schema description language document (e.g., an XSD document) may specify multiple target namespaces for a single element. Accordingly, groupings of elements may be included in different namespaces to creating overlapping or even nested namespaces.

Owner:MICROSOFT TECH LICENSING LLC

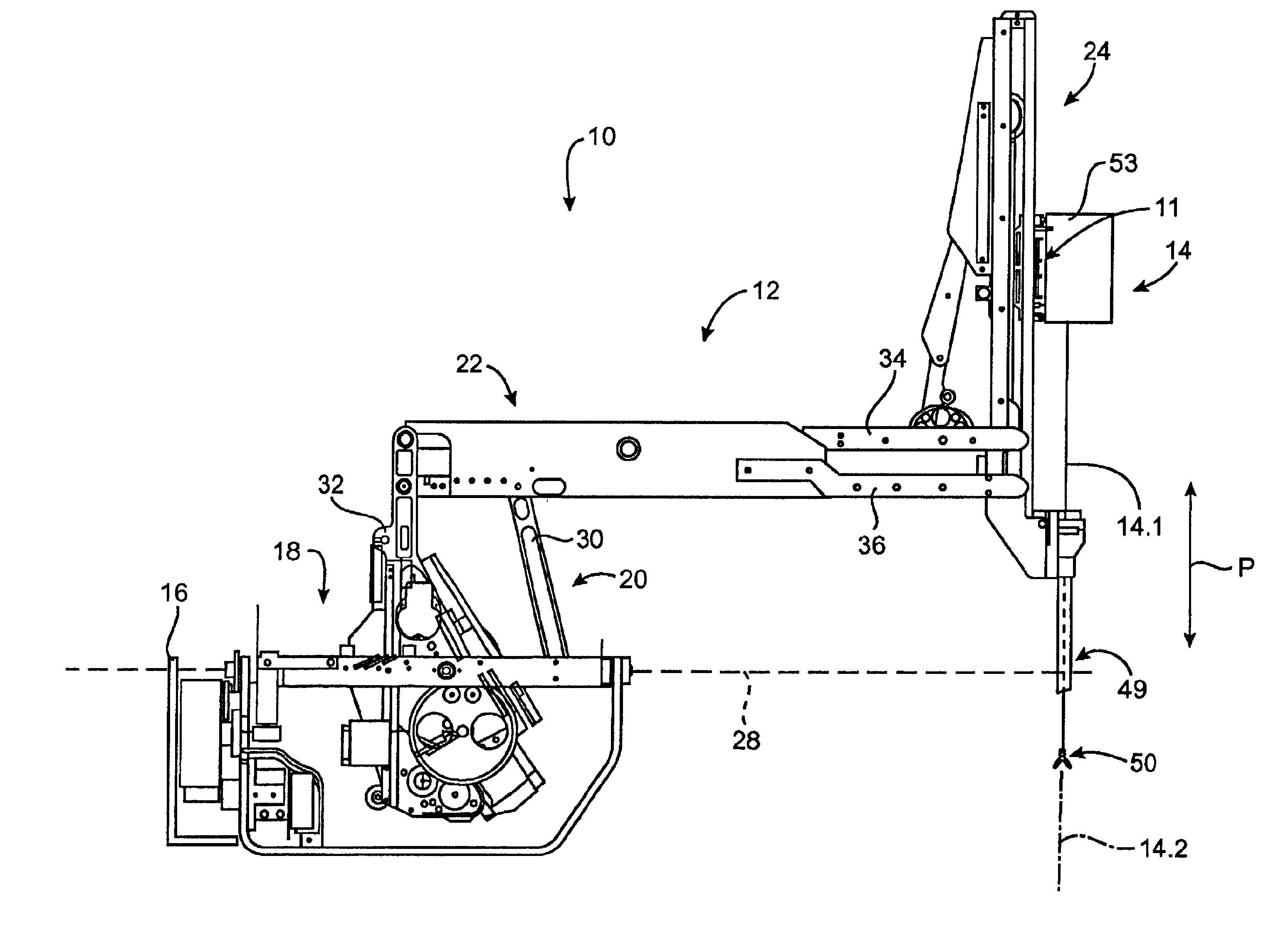

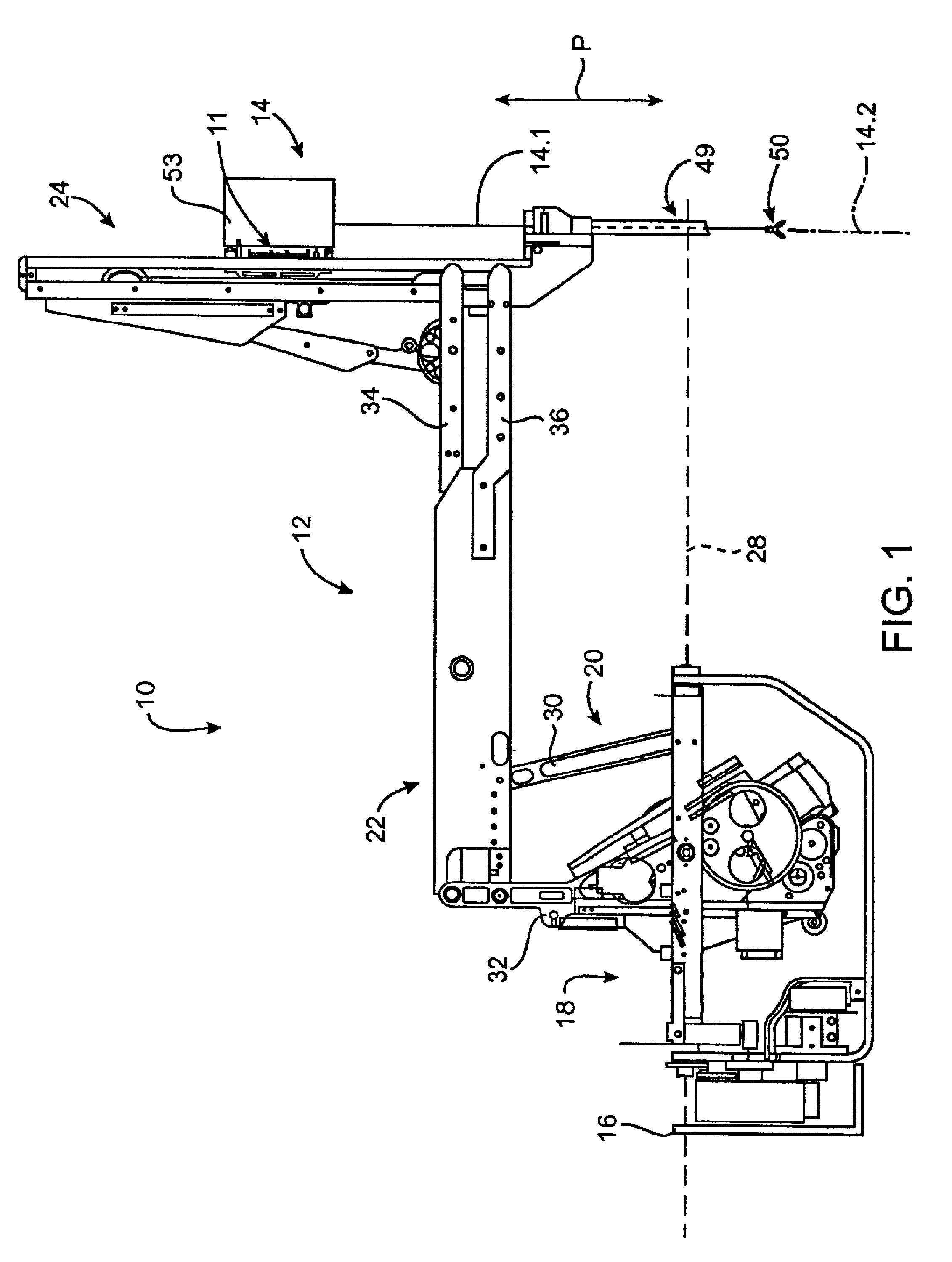

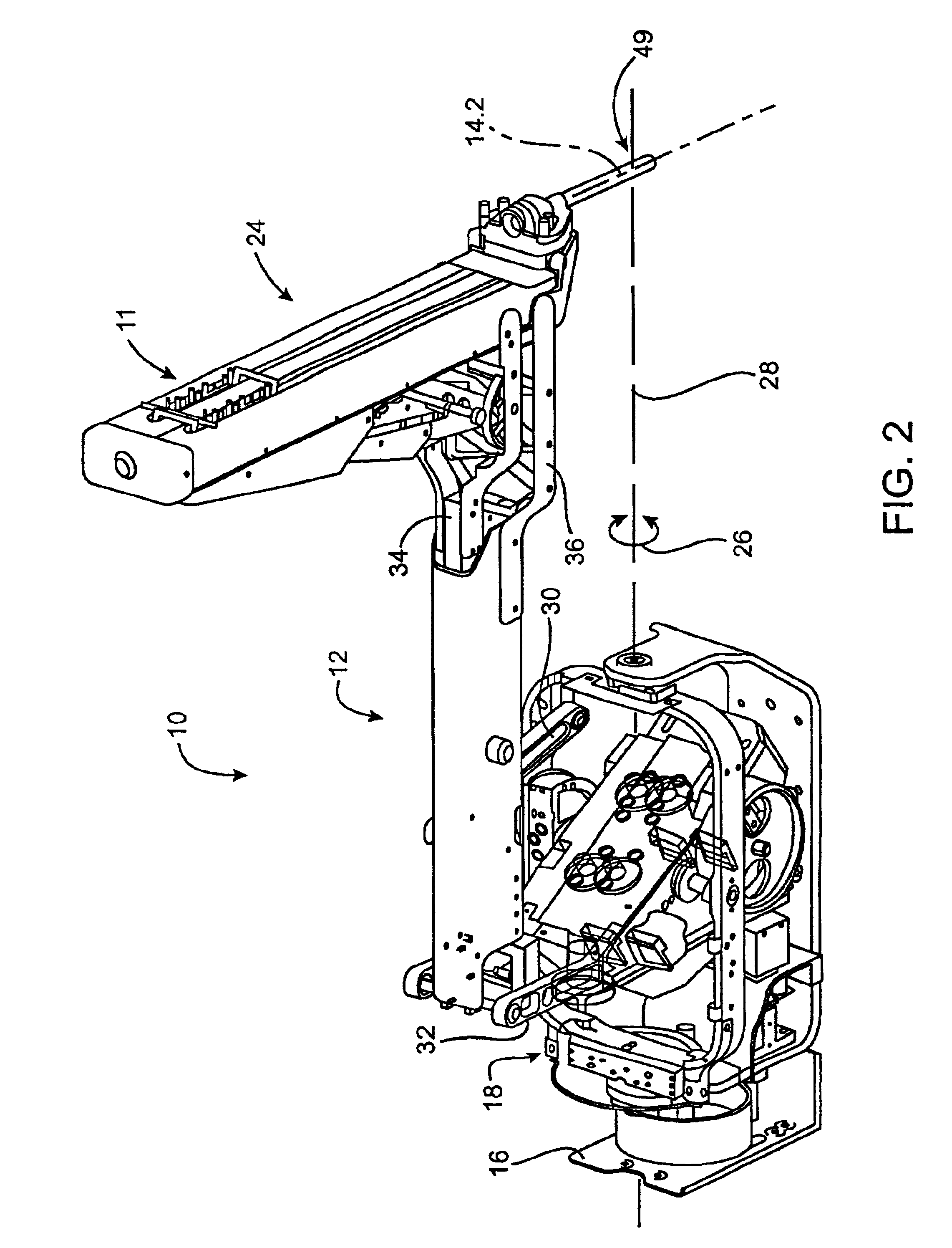

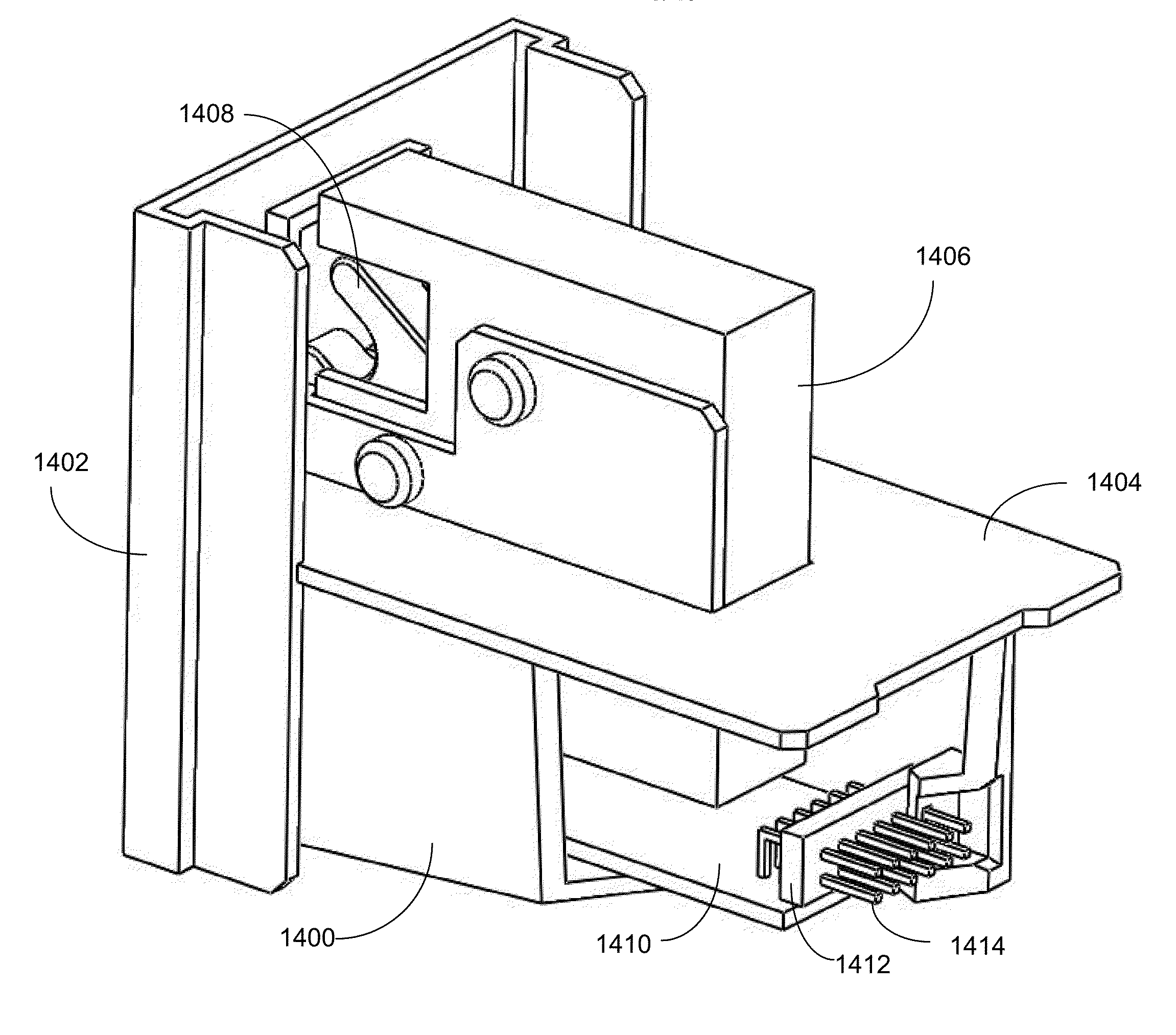

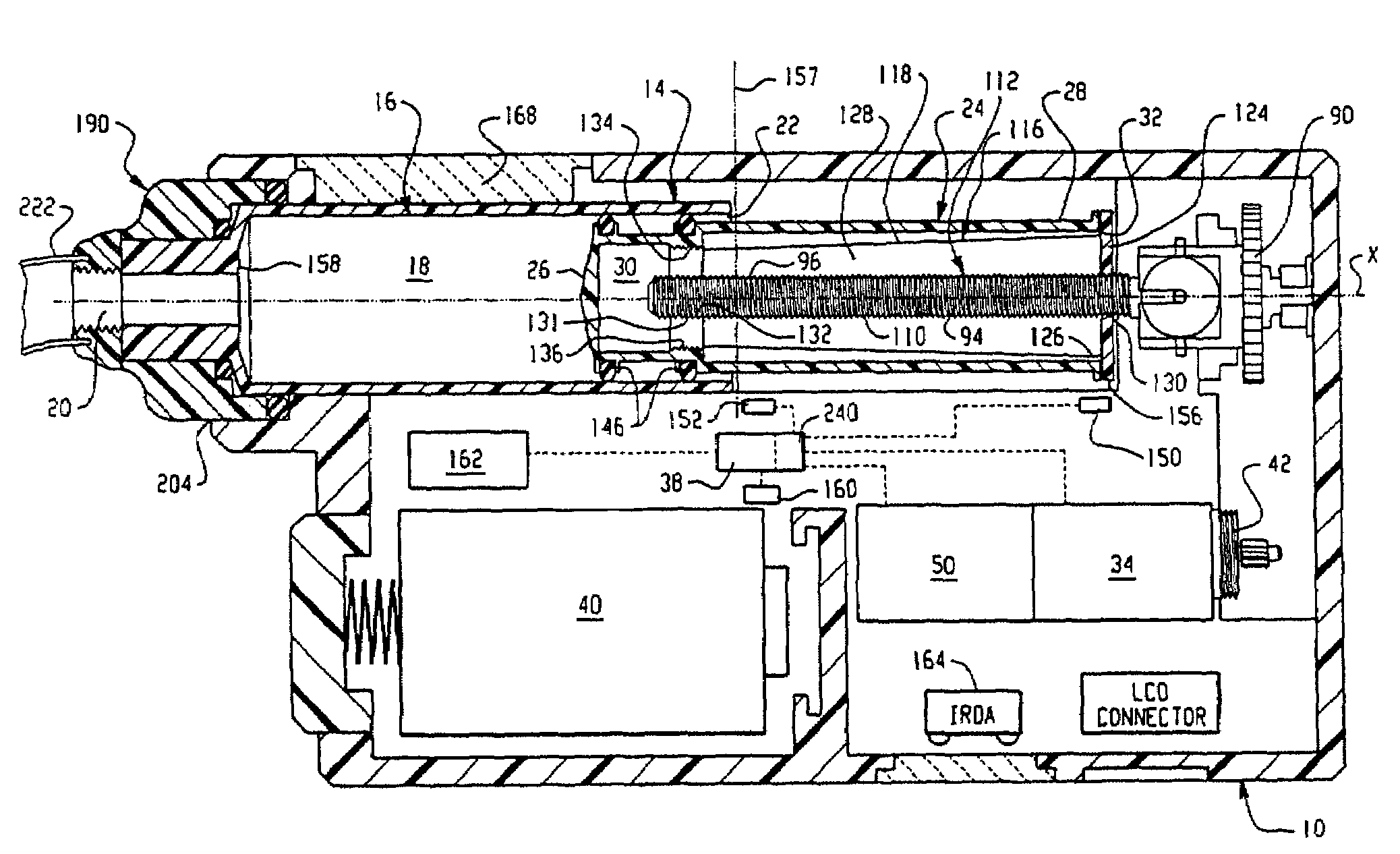

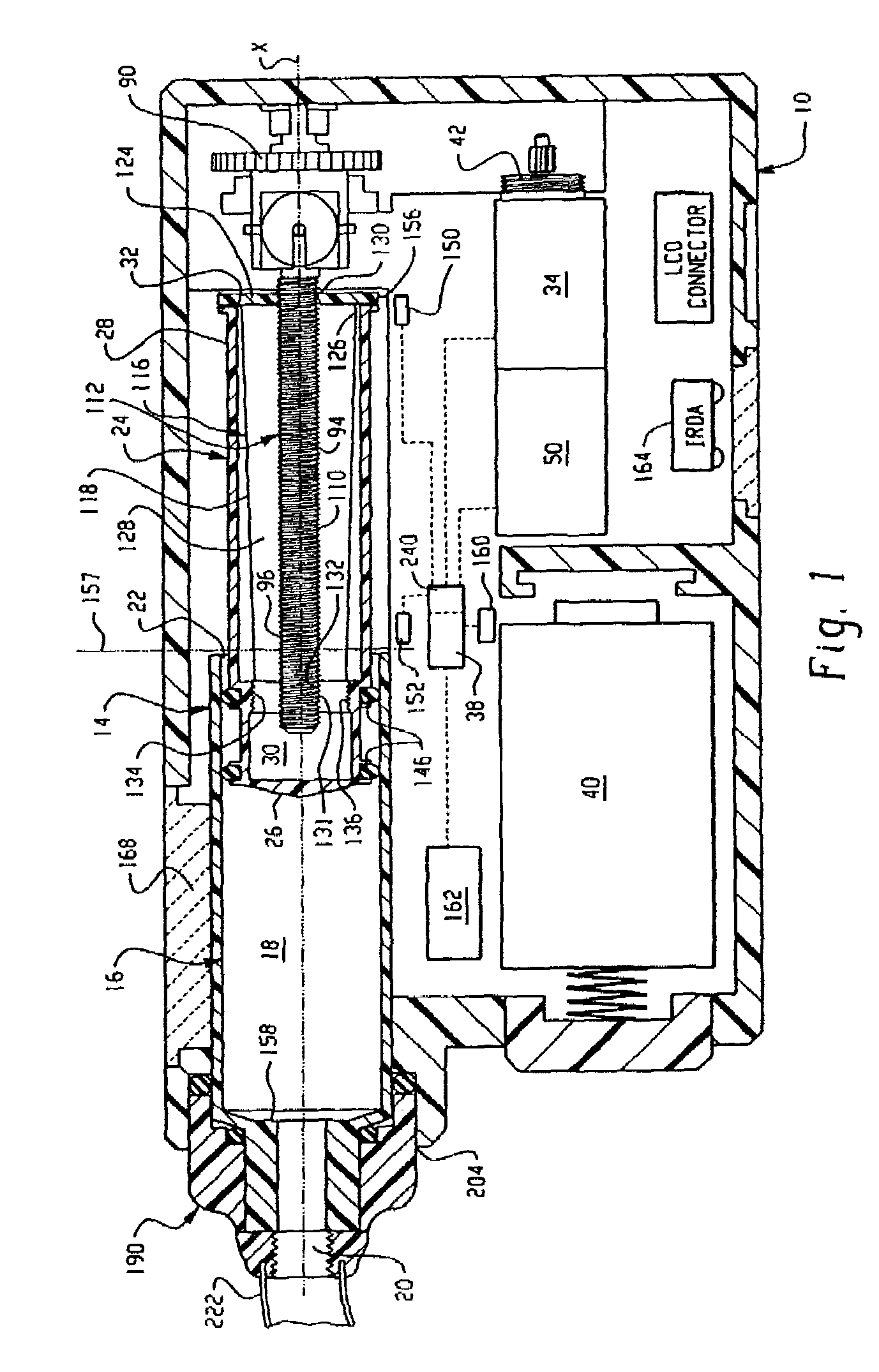

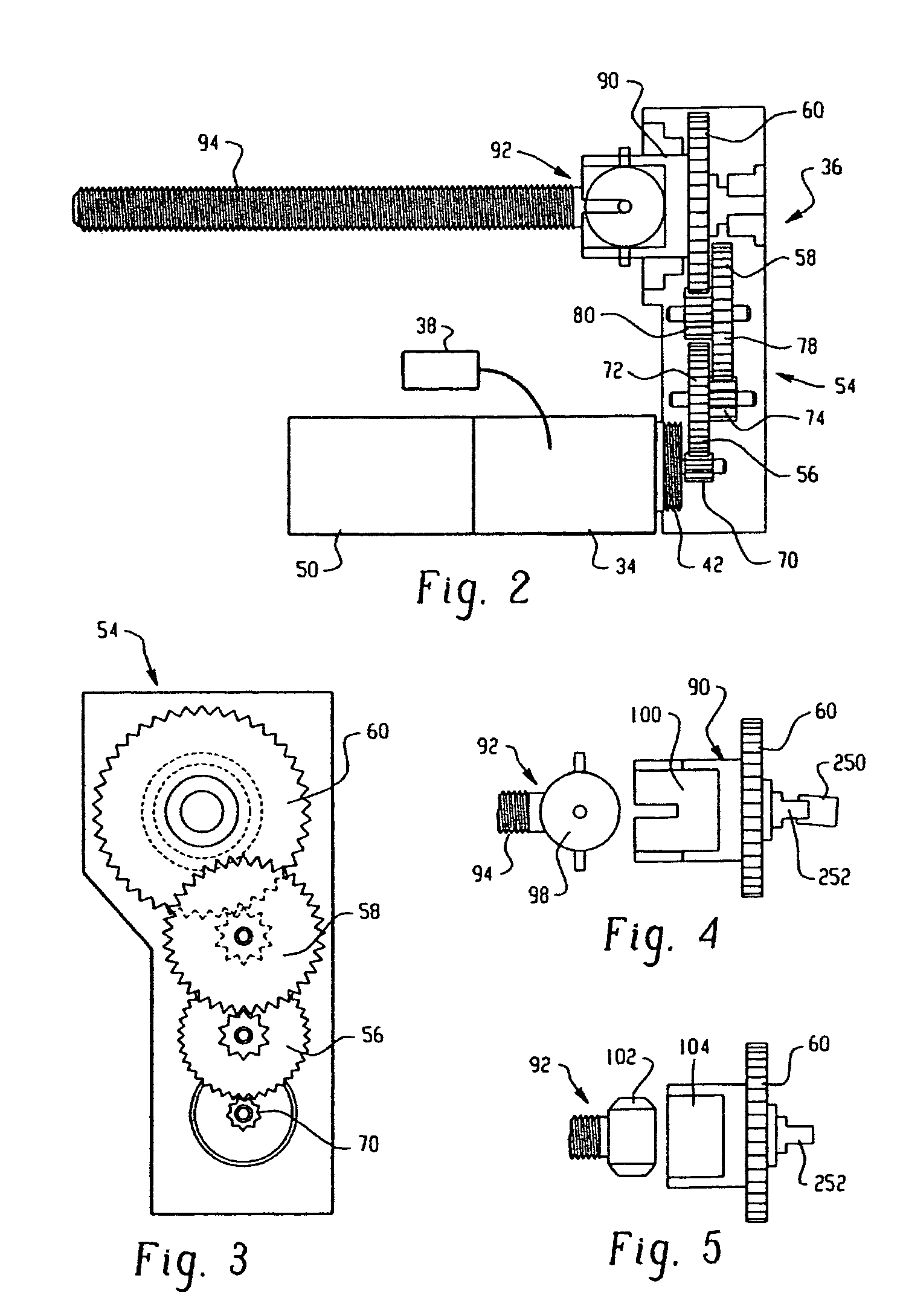

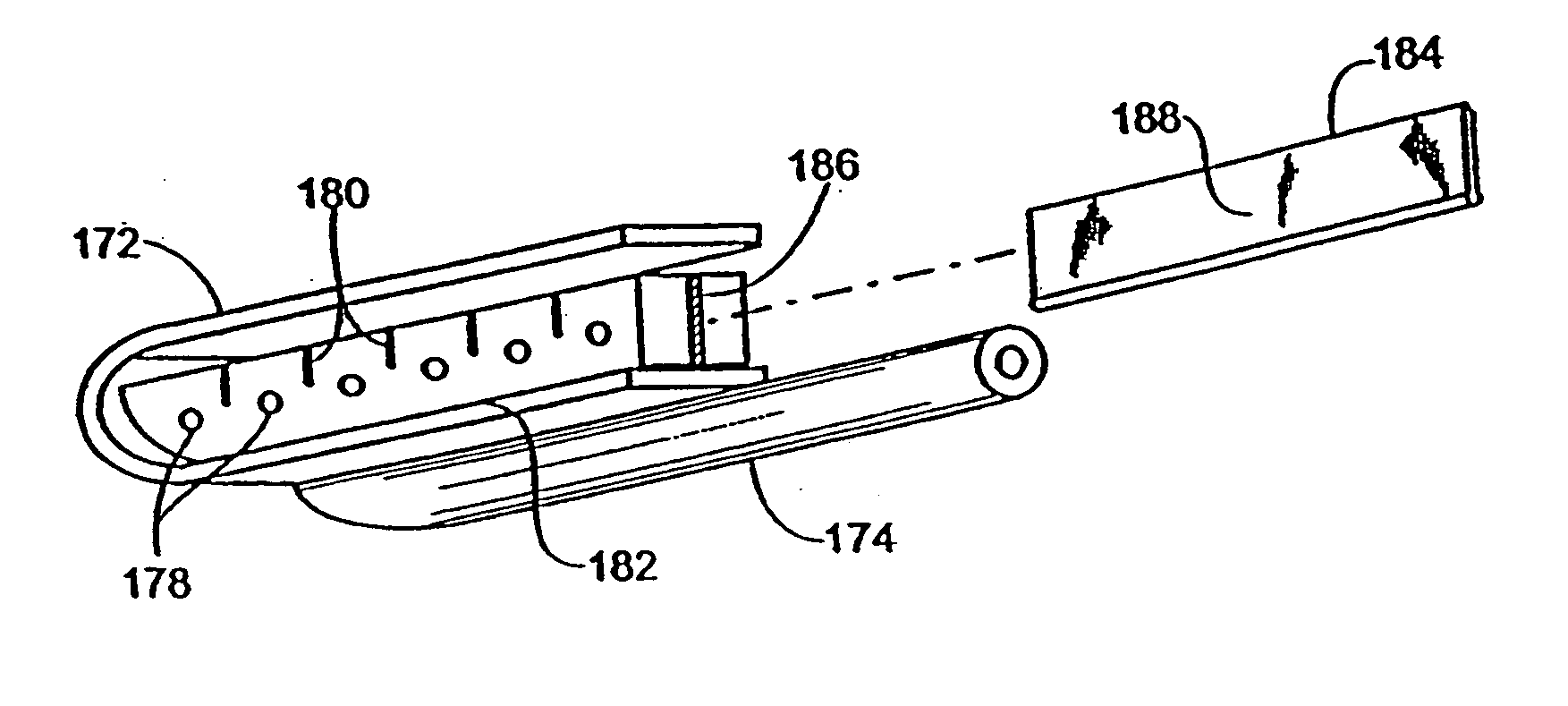

Drive system for an infusion pump

InactiveUS7025226B2Reduce sizeImprove portabilityOpening closed containersPower operated devicesLinear motionProximity sensor

A pump system for an infusion system includes a linear drive (36, 36′) which minimizes the space occupied by the pump components in a portable housing (10, 10′). A motor (34) and a motor drive shaft (42) are arranged in parallel with, and adjacent to a syringe (14, 14′) and lead screw (94, 94′). A gear box (54) connects the drive shaft and lead screw to transfer rotational movements between them. A piston driving member, such as a cone (116) or drive nut (116′) converts the rotational movement of the lead screw into linear motion of a syringe piston (24). Sensors (150, 152) detect when the piston or cone is in a “home” position and in an “end” position, respectively. Optionally, a proximity sensor (170) is used to ensure that the cone and the piston (24) are abutting during dispensing. Alternatively, a clamping member (350) selectively clamps the lead screw (94′) against linear motion in at least a dispensing direction.

Owner:TRIVIDIA HEALTHCARE SYST LLC

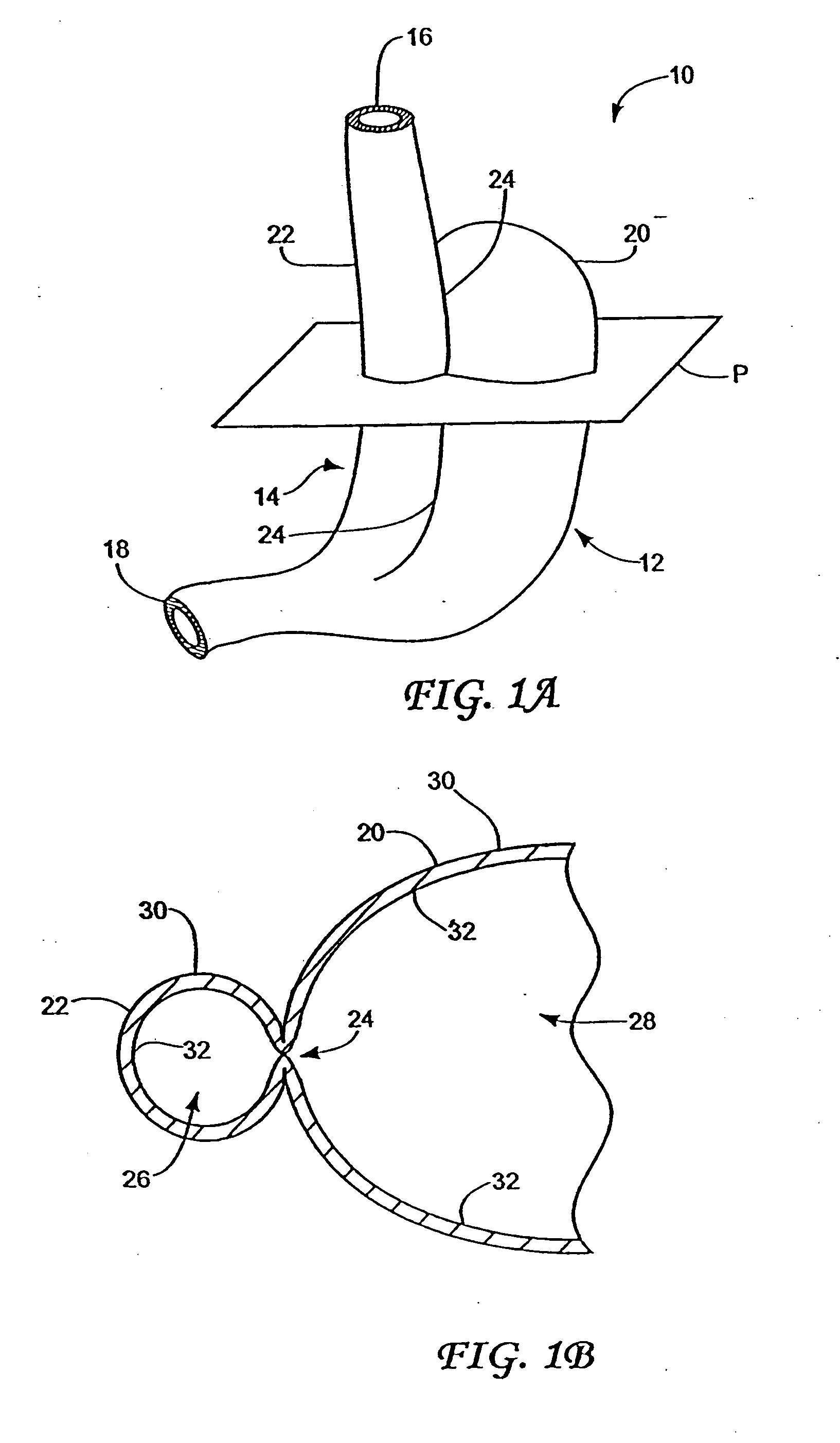

Obesity treatment tools and methods

Various obesity treatment tools and methods are described herein, as well as treatments for other gastric-related diseases, e.g., GERD. Treatment includes reducing the size of the stomach pouch to limit the caloric intake as well as to provide an earlier feeling of satiety. This may be done by creating a smaller gastric pouch within the stomach directly from the interior of the stomach itself. The smaller pouches may be made through the use of individual anchoring devices, rotating probes, or volume reduction devices. A pyloroplasty procedure may also be performed to render the pyloric sphincter incompetent. A gastric bypass procedure may additionally be performed using atraumatic magnetic anastomoses devices so that sugars and fats are passed directly to the bowel while bypassing the stomach. Many of these procedures may be done in a variety of combinations. Treatment may create enforced behavioral modifications by discouraging the ingestion of high-caloric foods.

Owner:ETHICON ENDO SURGERY INC

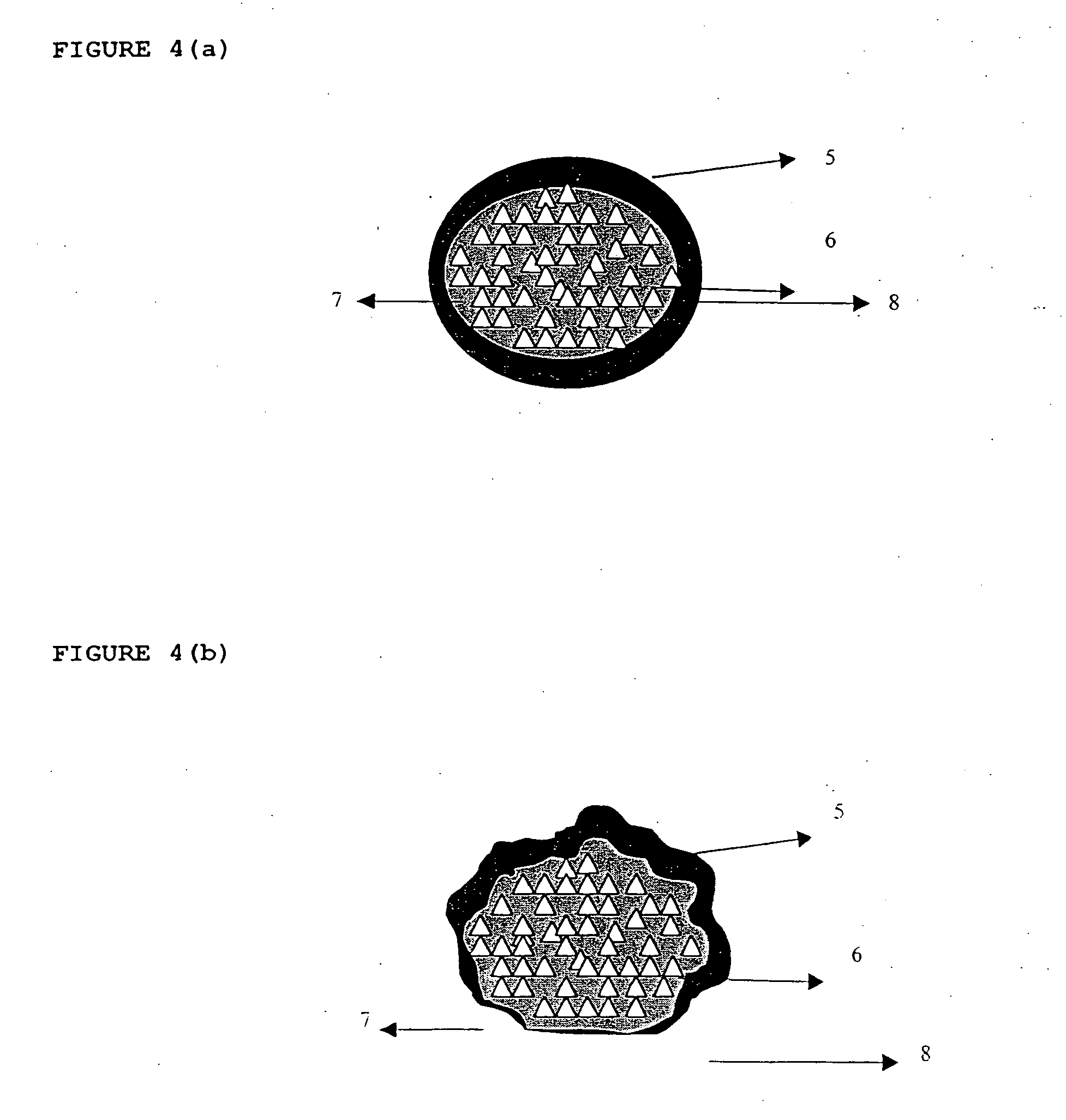

High power led lamp

InactiveUS6346771B1Improve uniformityReduce chip sizeDischarge tube luminescnet screensLamp detailsEngineeringLED lamp

A high-power LED lamp uses an LED chip that can be larger than 1mm square. The chip has trenches that can convert light trapped in the semiconductor into light that passes through a major surface of the chip. The trenches include light-reflecting tracks joined to a chip terminal and feeding a semiconductor layer. The chip can have triangular light emitting elements that improve light extraction from the semiconductor. The elements can be fused, resulting in improved manufacture yield of chips. A 25 watt single chip lamp with a heat sink very close to the active region is described.

Owner:EPISTAR CORP

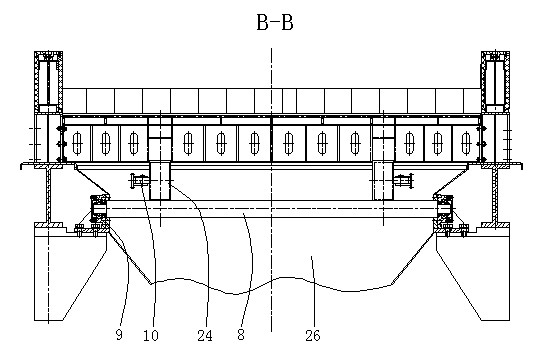

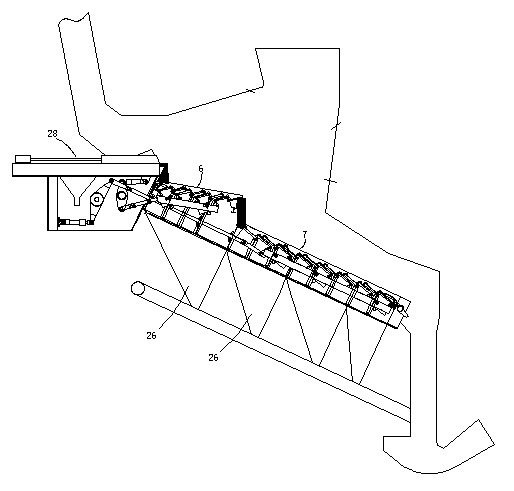

Two-stage garbage incinerator

ActiveCN101922715AGuaranteed incineration effectFully dryInclined grateIncinerator apparatusLoss rateCombustion

A two-stage garbage incinerator is characterized in that secondary air supply holes are arranged on front and rear arches of a furnace body and an ignition combustion-supporting hole is arranged on the rear arch; a grate in the furnace body is divided into two stages from top to bottom; the upper stage is a forward pushing stage and the lower stage is a backward pushing stage; an independent primary air chamber is arranged below each stage; the heads of the grates on the forward pushing stage face the low point direction of the grates; the heads of the grates on the backward pushing stage face the high point direction of the grates; moving beams of the grates on the same stage are equipped with left and right draw bars arranged side by side; the left and right draw bars are supported by supporting roller devices and are connected with the moving beams to form draw bar frames; and the ends of the draw bar frames are connected with front rocker arm driving mechanisms, lateral rocker arm driving mechanisms or front straight driving mechanisms. The incinerator can realize full drying of the whole garbage material, ensure complete combustion and ensure the garbage incineration effect and hot ignition loss rate. At the same time, the incinerator has less spare parts and spare part specifications, good quick-wear part interchangeability and low manufacture and maintenance costs.

Owner:CHONGQING SANFENG ENVIRONMENTAL IND GRP

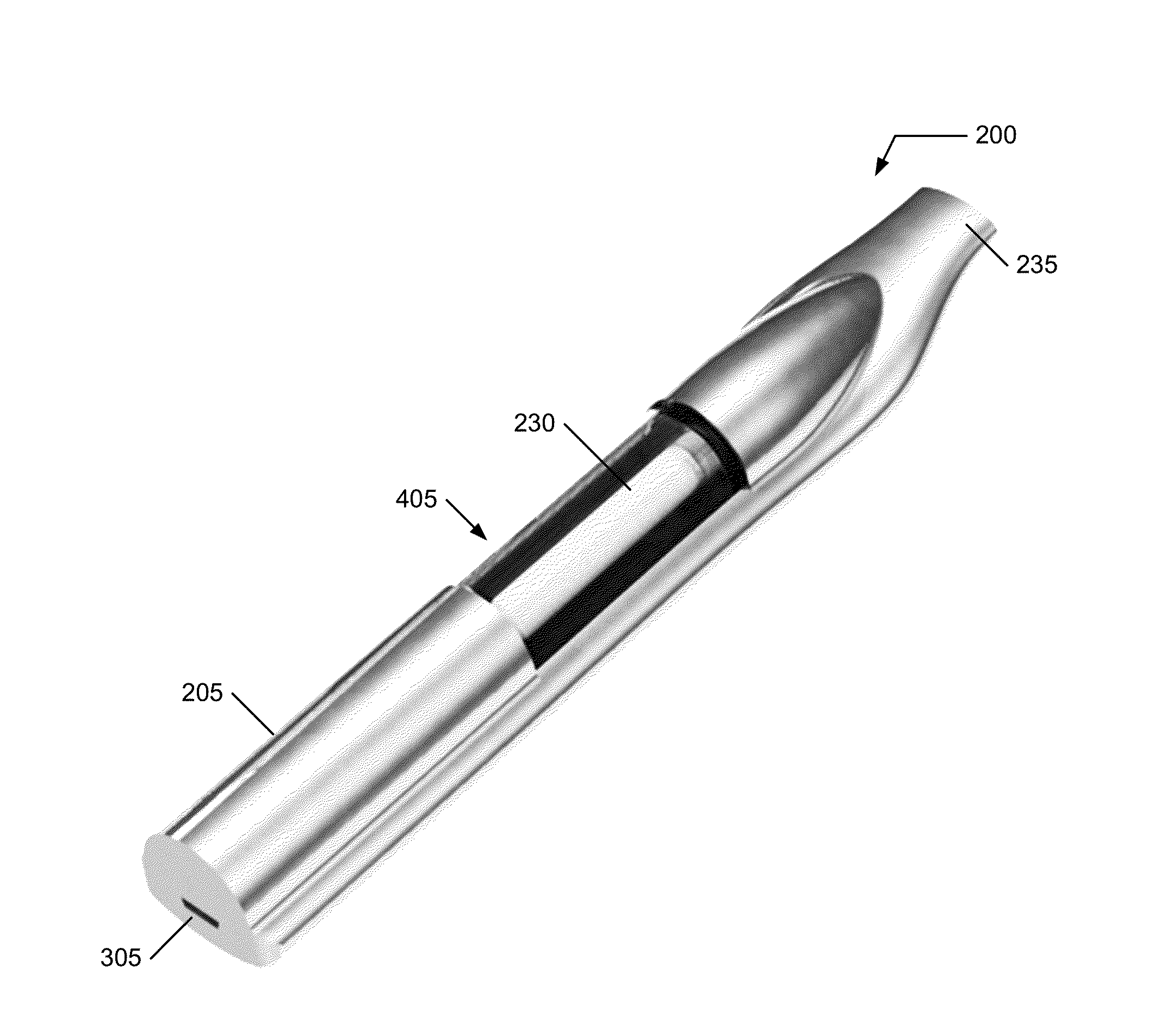

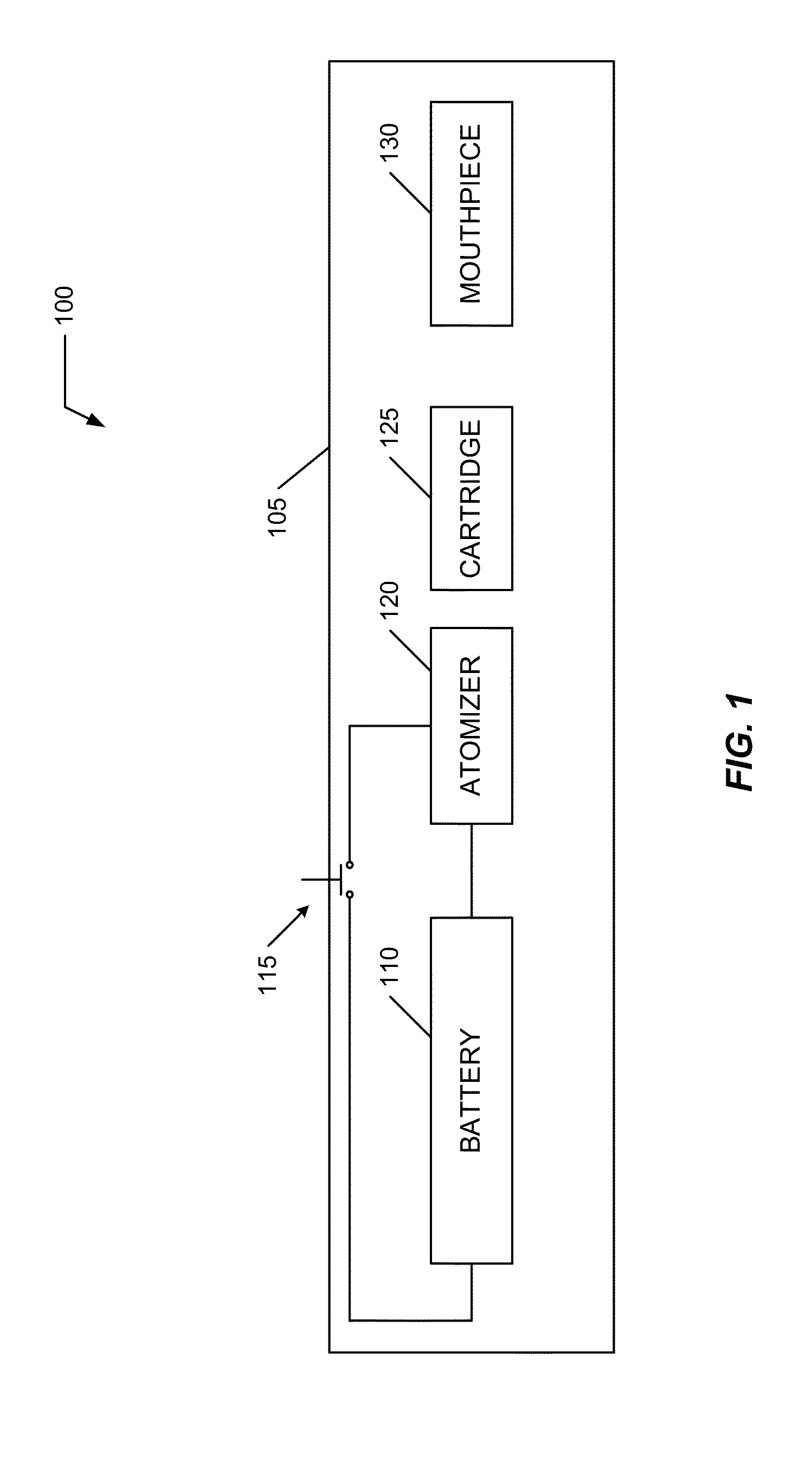

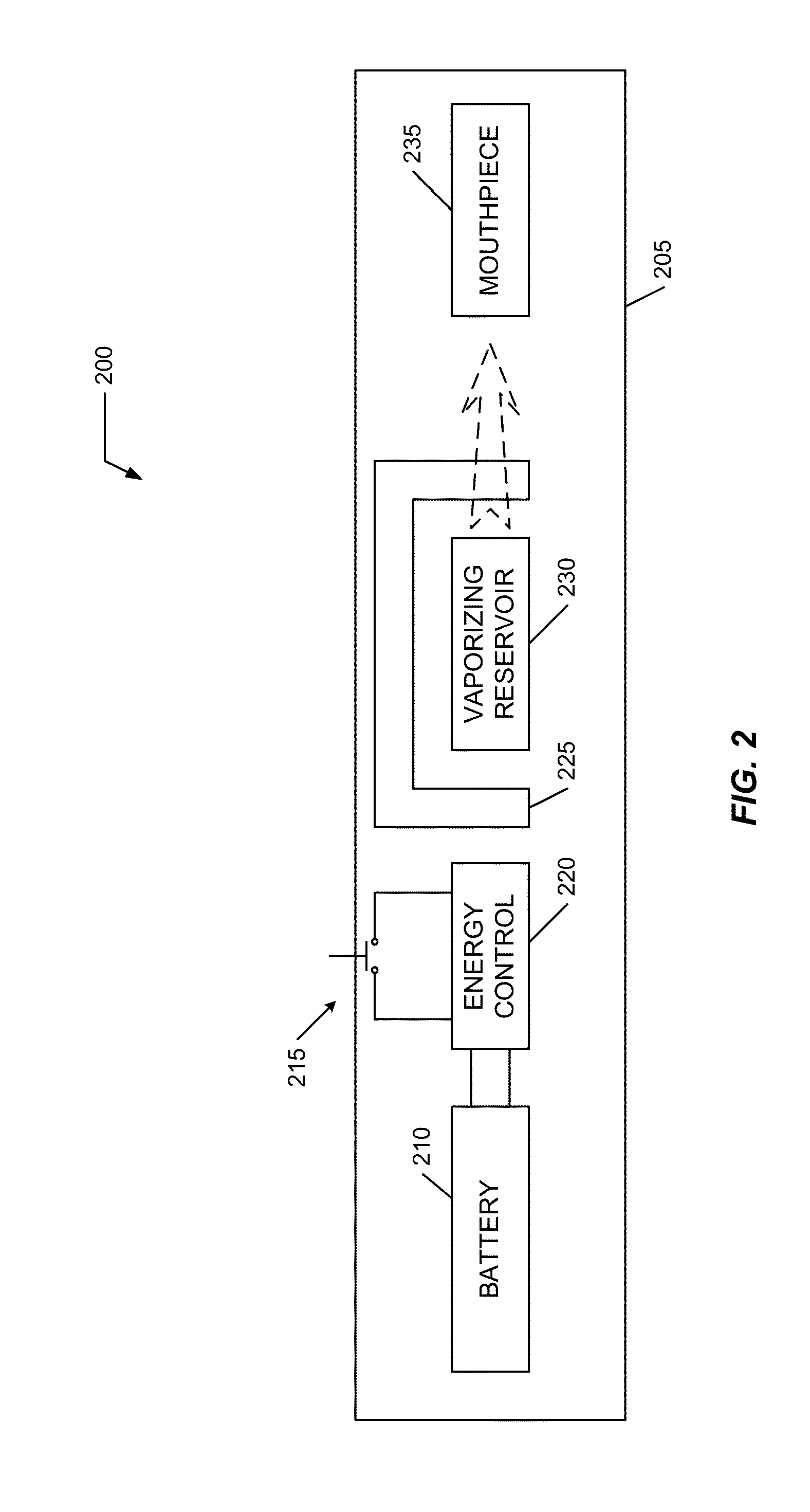

Vaporizing reservoir

InactiveUS20160150828A1Less-prone to leakingEasy to change out flavorSpace heating and ventilationTobacco devicesElectricityEngineering

A vaporizing reservoir including a containment vessel having a first shaft port exposed to ambient and one or more sidewalls defining a body portion having an interior cavity and a vaporizing portion communicated to the interior cavity; an inductive coil disposed within the vaporizing portion, the inductive coil electrically disconnected outside of the containment vessel and configured for inductive heating; and an air shaft communicated to the vaporizing portion and extending to the first shaft port. Fluid or solid material may be present in the interior cavity for vaporization. For fluid material, a wick may be included with the inductive coil to facilitate communication of the material to the inductive coil. An exterior inductive coil heats the inductive coil within the vaporizing portion and vaporizes the material communicated to the interior inductive coil. Vapor from the heated interior inductive coil is extracted through the air shaft.

Owner:GOLDSTEIN GABRIEL MARC