Multichannel gate-all-around transistor

A multi-channel, transistor technology, used in transistors, semiconductor devices, electrical components, etc., can solve the problems of easy breakdown driving power, large parasitic capacitance, etc., and achieve good radiation resistance, small off-state current density, good resistance to radiation. The effect of total dose-response capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

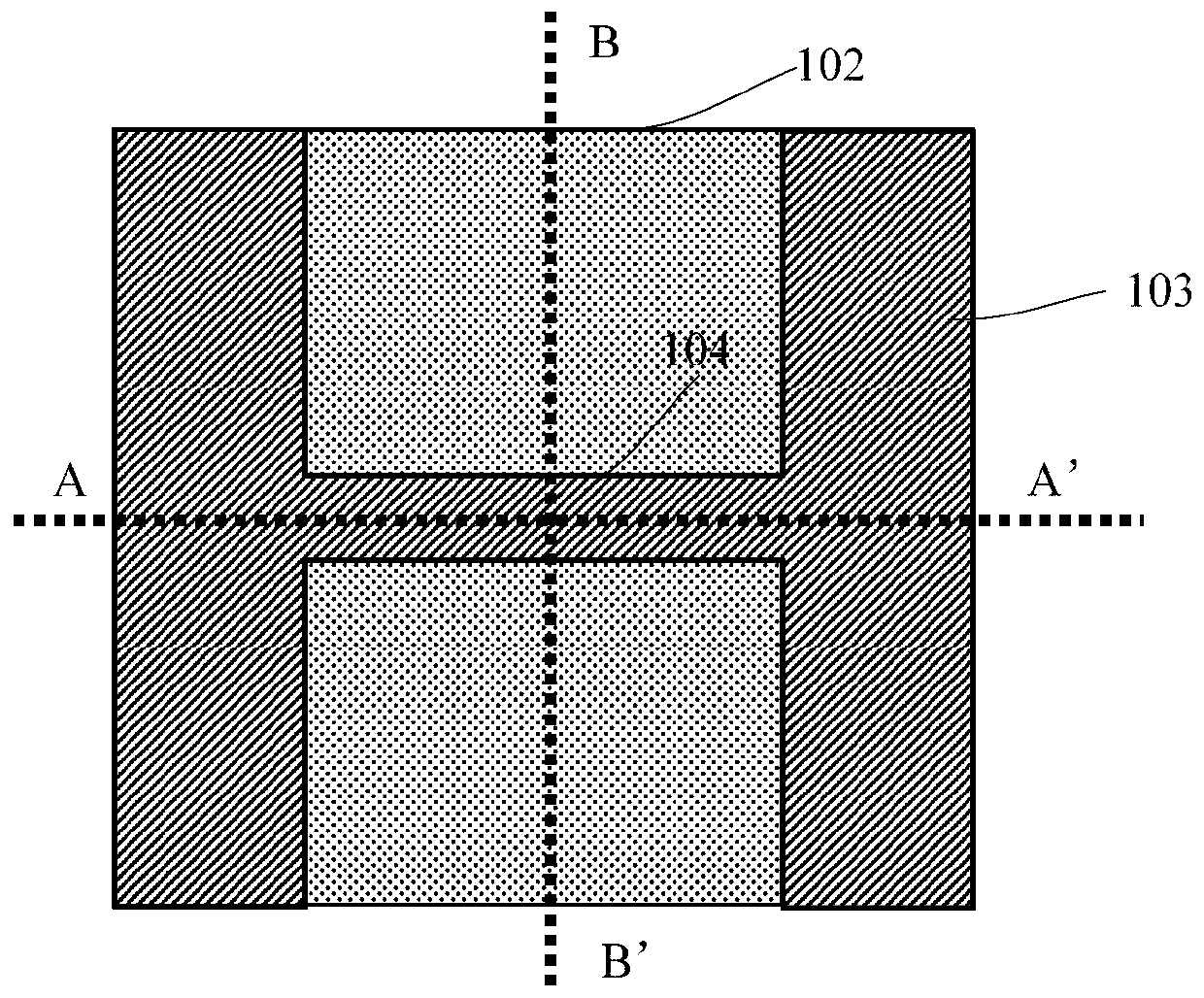

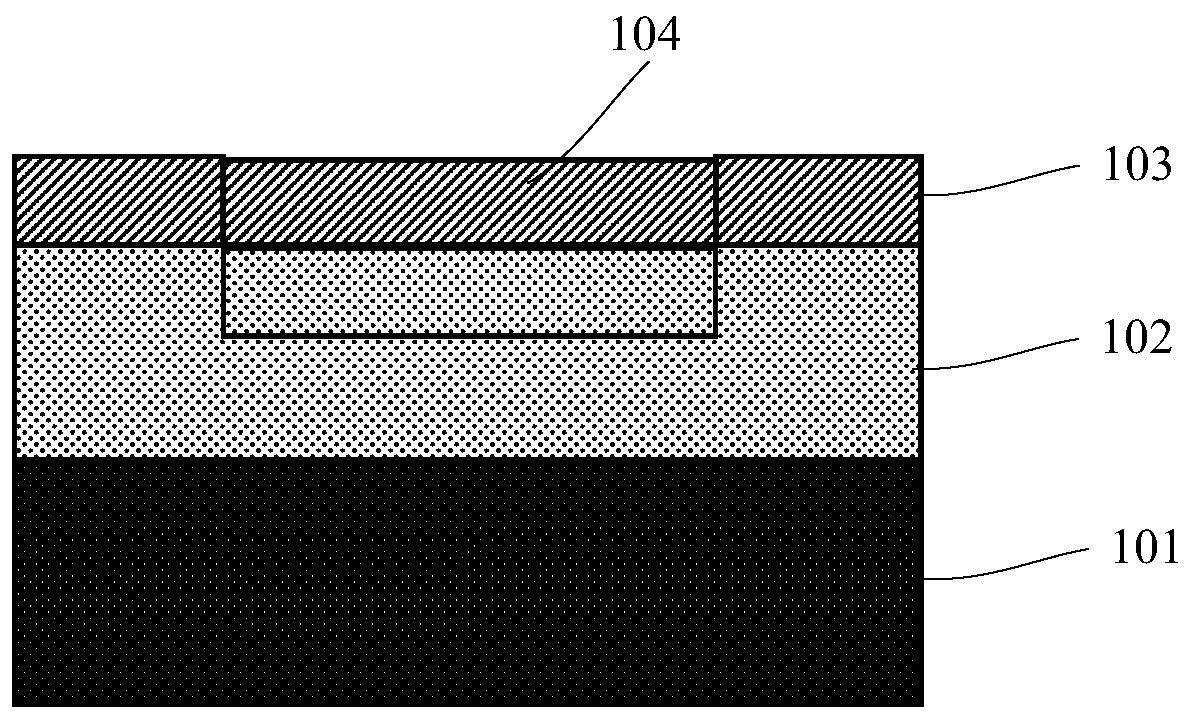

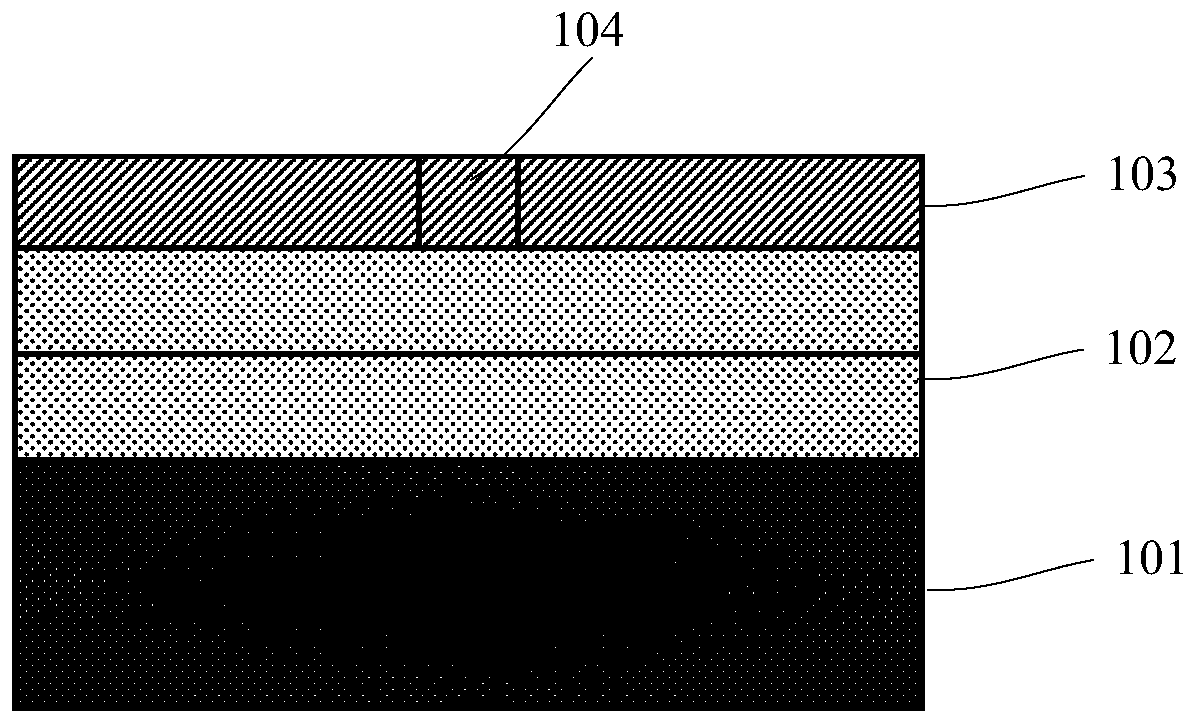

[0051] Such as Figure 15 ~ Figure 17 As shown, among them, Figure 16 shown as Figure 15 The schematic diagram of the cross-sectional structure at A-A' in the middle, Figure 17 shown as Figure 15 Schematic diagram of the cross-sectional structure at B-B' in the middle. This embodiment provides a multi-channel gate-all-round transistor, including: a semiconductor substrate 201, an insulating layer 202, a semiconductor nanowire structure, a gate dielectric layer 601, a gate electrode layer 602, a source region 603 and a drain region 604, a source electrode 605 and Drain electrode 606 .

[0052] The semiconductor substrate 201 may be a silicon substrate, a silicon carbide substrate, a gallium nitride substrate, or the like.

[0053] There is a groove in the insulating layer 202 , and the groove does not penetrate through the insulating layer 202 . As an example, the thickness of the insulating layer 202 is not greater than 150 nanometers, and the depth of the groove is ...

Embodiment 2

[0068] Such as Figure 19 ~ Figure 22 As shown, this embodiment provides a three-dimensional stacked multi-channel gate-around transistor, wherein, Figure 19 shown as Figure 18 The schematic diagram of the cross-sectional structure at A-A' in the middle, Figure 20 shown as Figure 18 Schematic diagram of the cross-sectional structure at B-B' in the middle. The basic structure of the multi-channel gate-all-around transistor of this embodiment is the same as that of Embodiment 1, wherein the difference from Embodiment 1 is that the gate-all-round transistor comprises a plurality of semiconductor nanowire structures stacked upwards, and the nanowire structure It includes semiconductor protrusions located on both sides of the groove and a plurality of semiconductor nanowires connected to the semiconductor protrusions, and two adjacent semiconductor protrusions are separated by sacrificial layer protrusions 608, so that the upper and lower There is an interval between two ad...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More