Adulation method for MOS transistor body area

A MOS transistor and body region technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of reduced carrier mobility, increased parasitic capacitance and leakage current, and poor subthreshold characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The preferred embodiment of the present invention is described in more detail below with reference to the accompanying drawings of the present invention.

[0039] (1) The substrate is a bulk silicon wafer

[0040] A specific example of the integrated silicon MOS transistor prepared by the manufacturing method is as follows: Figure 1 to Figure 6 shown, including the following steps:

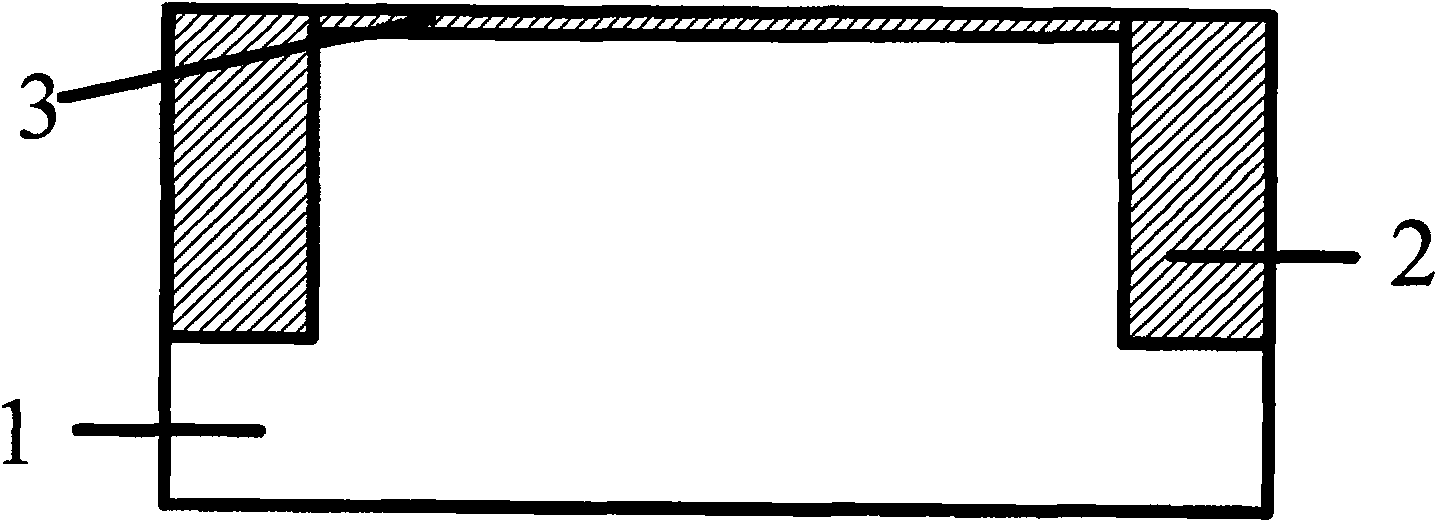

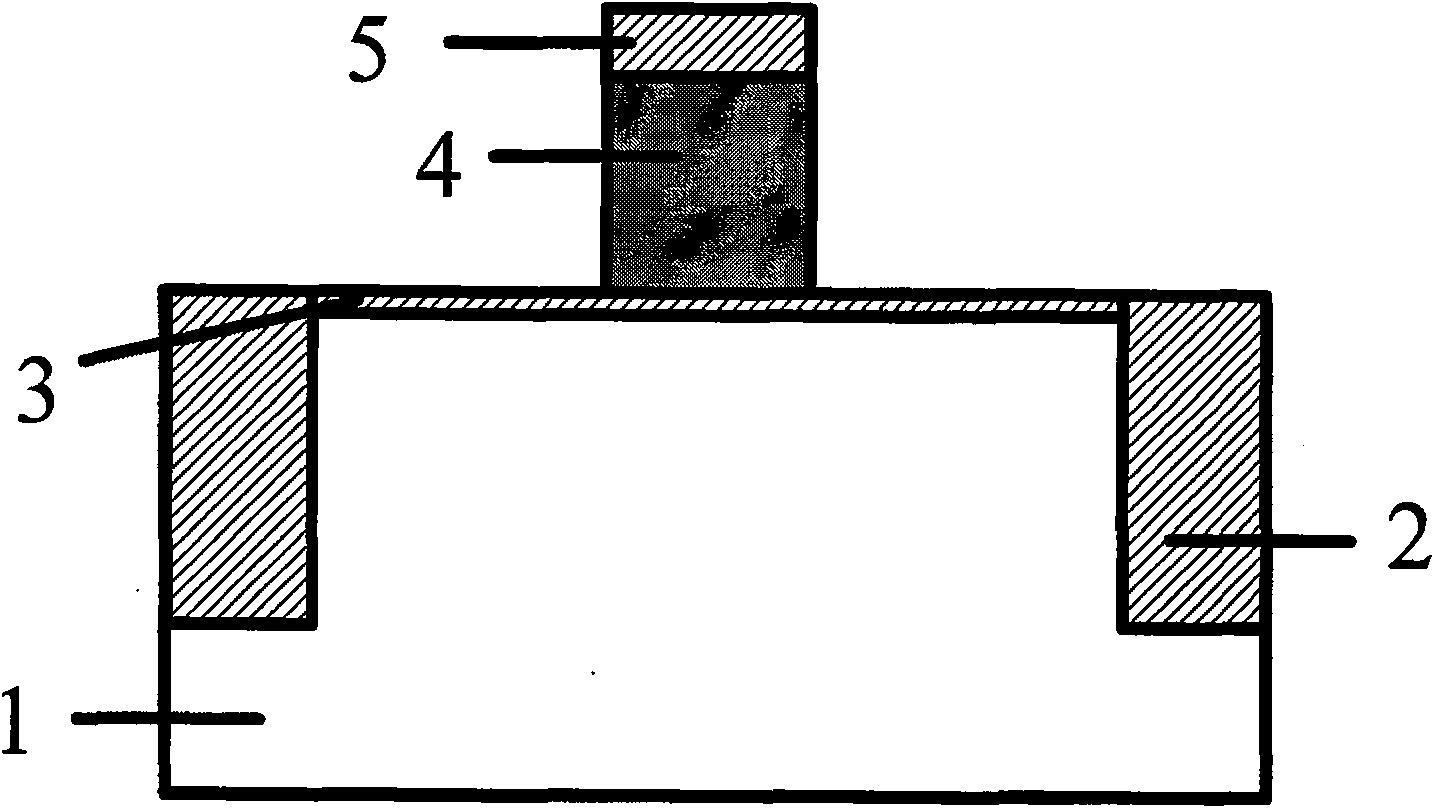

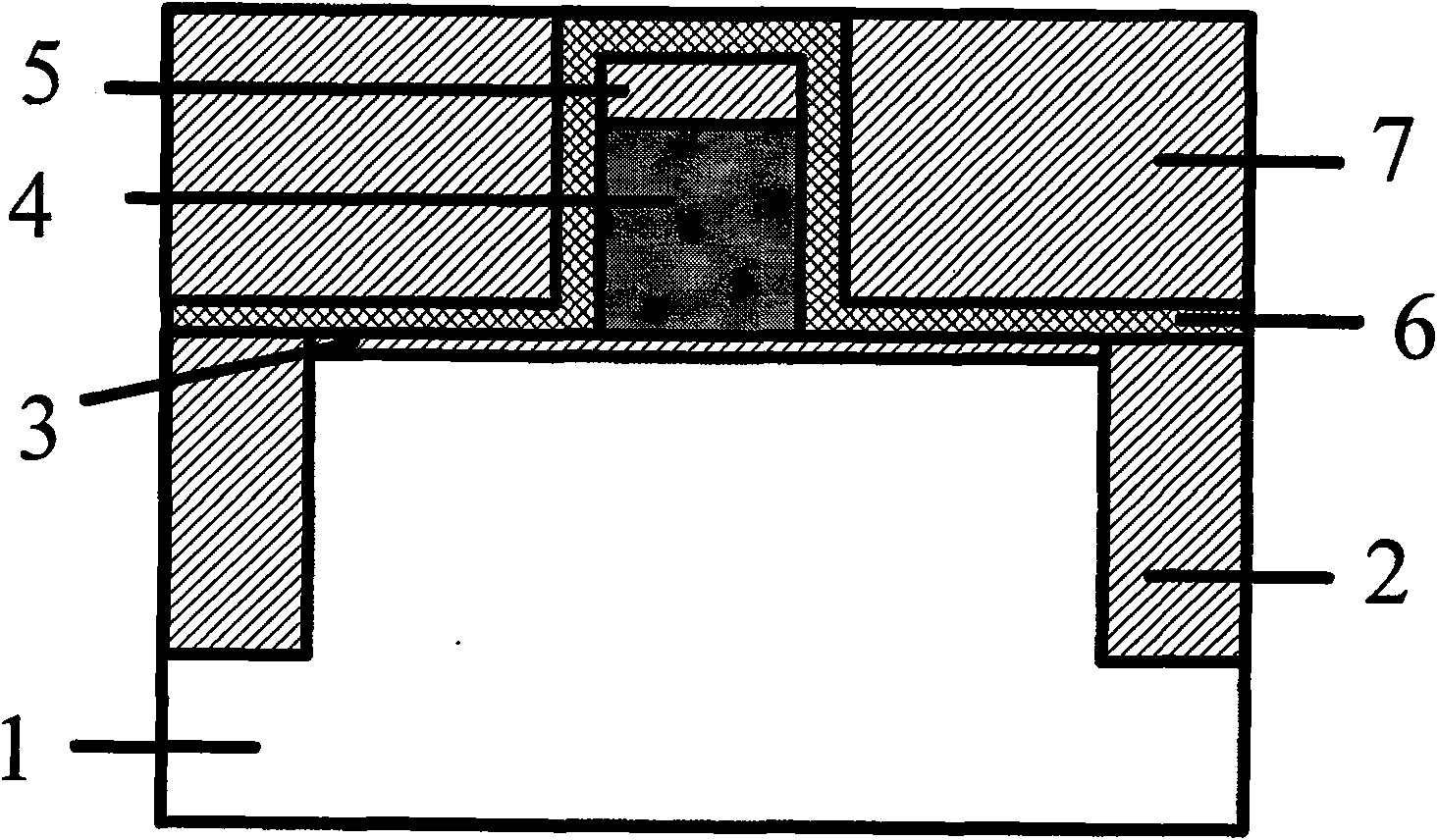

[0041] 1) if figure 1 As shown, the crystal orientation of the single crystal silicon substrate used is (100), and for n-type MOS transistors, the body region 1 is initially lightly doped with p-type. For p-type MOS transistors, body region 1 is initially lightly doped with n-type. The active region isolation layer 2 is fabricated by using conventional CMOS shallow trench isolation technology. Next, a gate dielectric layer 3 is grown. The gate dielectric layer 3 is silicon dioxide with a thickness of 0.5-3 nm. The gate dielectric can also be formed by one of the following methods: c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More