A Tunneling Field Effect Transistor for Suppressing Off-state Current

A technology of tunneling field effect and off-state current, applied in circuits, electrical components, semiconductor devices, etc., can solve the problems of high carrier concentration and increase of off-state current, achieve simple process, reduce off-state current, Realize the effect of on-state current and low off-state current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

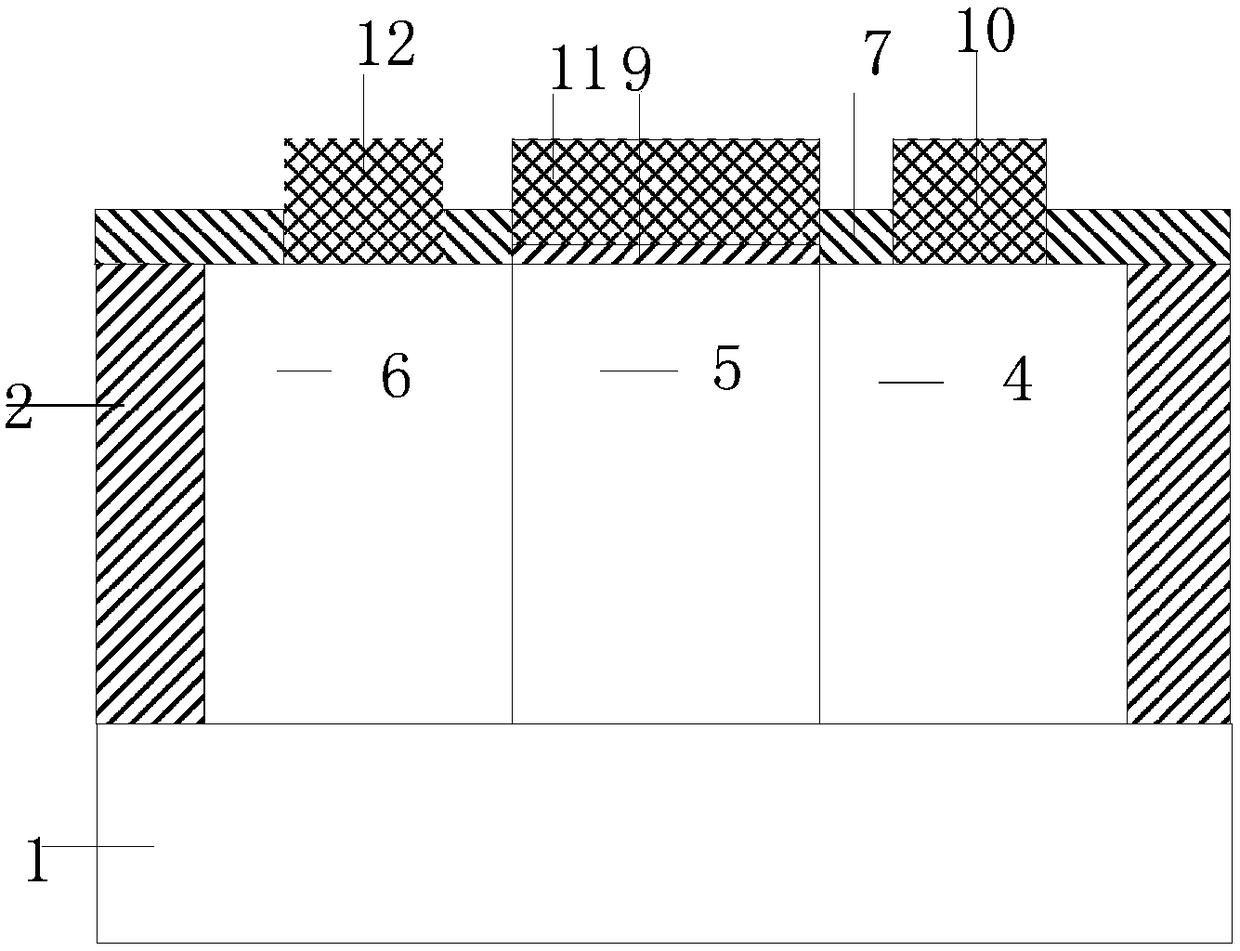

[0033] This example is for Figure 4 The structure of the off-state current suppressing TFET device is shown as an example of an N-type TFET fabricated on a P-type substrate. The N-type buried layer is in contact with the PIN structure above, and the thickness of the N-type buried layer is not less than 200nm.

[0034] The embodiment includes high-resistance P-type substrate 1, deep trench isolation 2, N-type buried layer 3, drain region 4, intrinsic region 5, source region 6, electrode isolation structure 7, thin epitaxial intrinsic region 8, gate oxide Layer 9, metal drain electrode 10, metal gate electrode 11, metal source electrode 12. The N-type buried layer is between the PIN structure and the P-type buried layer. First select the bulk silicon of the (100) crystal plane for epitaxy to obtain the required N-type buried layer. The N-type buried layer has the same doping level as the substrate and is also low-doped, and then make a PIN structure; or directly on the P Type...

Embodiment 2

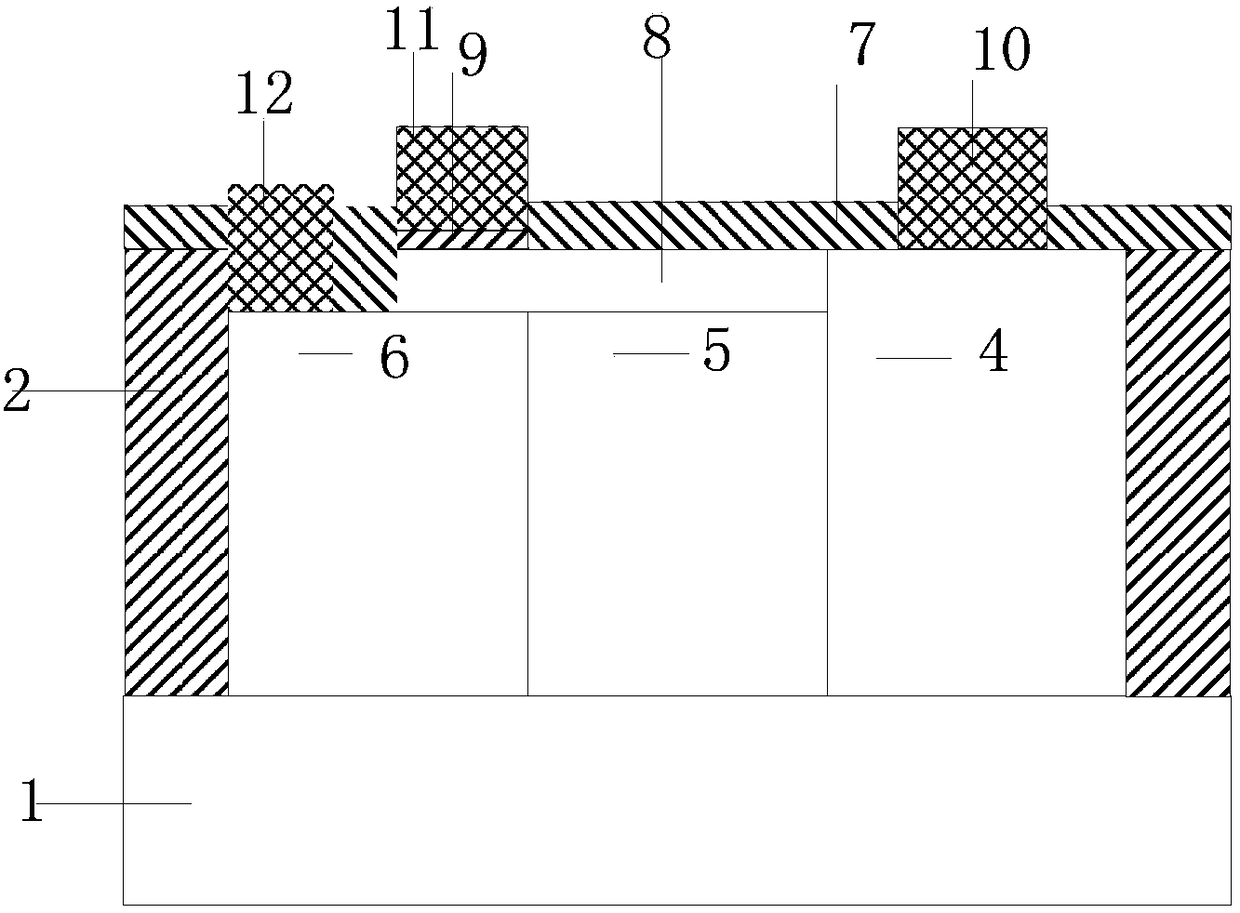

[0039] Figure 4 Although the shown N-type TFET structure can suppress the off-state current of the device, since the drain region is in contact with the buried layer, the parasitic capacitance of the drain increases, which is not conducive to the high-frequency characteristics of the device. It is modified to make it suitable for the high-frequency field, and the contact between the drain region and the buried layer of the N-type TFET is disconnected, and the area between the drain region and the buried layer is an intrinsic region, and at the same time, the buried layer is separately drawn out.

[0040] Figure 5 In order to suppress the off-state current TFET device structure applicable to the high frequency field, this embodiment is Figure 5 The shown N-type TFET device structure in which the buried layer is disconnected from the drain region, the embodiment includes a P-type substrate 1, a deep trench isolation 2, an N-type buried layer 3, a drain region 4, an intrinsic...

Embodiment 3

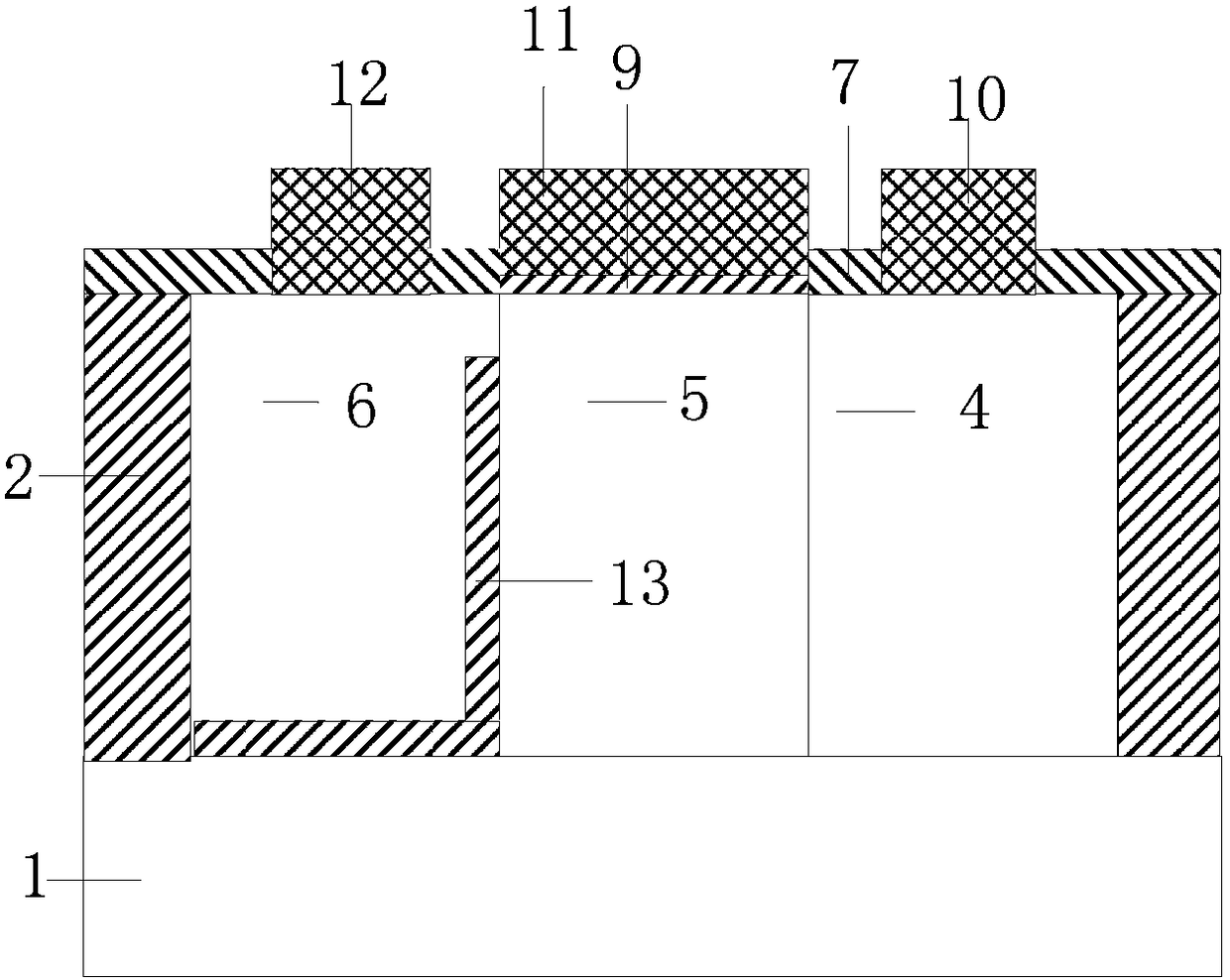

[0043] This example is for Figure 6 Shown is a lateral TFET employing the present invention to suppress off-state current. Taking an N-type TFET fabricated on a P-type substrate as an example, the N-type buried layer is in contact with the PIN structure above, and the thickness of the N-type buried layer is not less than 200nm.

[0044] The embodiment includes P-type substrate 1, deep trench isolation 2, N-type buried layer 3, drain region 4, intrinsic region 5, source region 6, electrode isolation structure 7, gate oxide layer 9, metal drain electrode 10, metal Gate electrode 11, metal source electrode 12. In the manufacturing process of the device structure in this example, the bulk silicon of the (100) crystal plane is first selected for epitaxy to obtain the required N-type buried layer. The N-type buried layer has the same doping level as the substrate and is also low-doped, and then fabricated PIN structure; or directly epitaxially sufficiently thick I layer on the P-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More