Patents

Literature

31results about How to "Increase the electric field" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

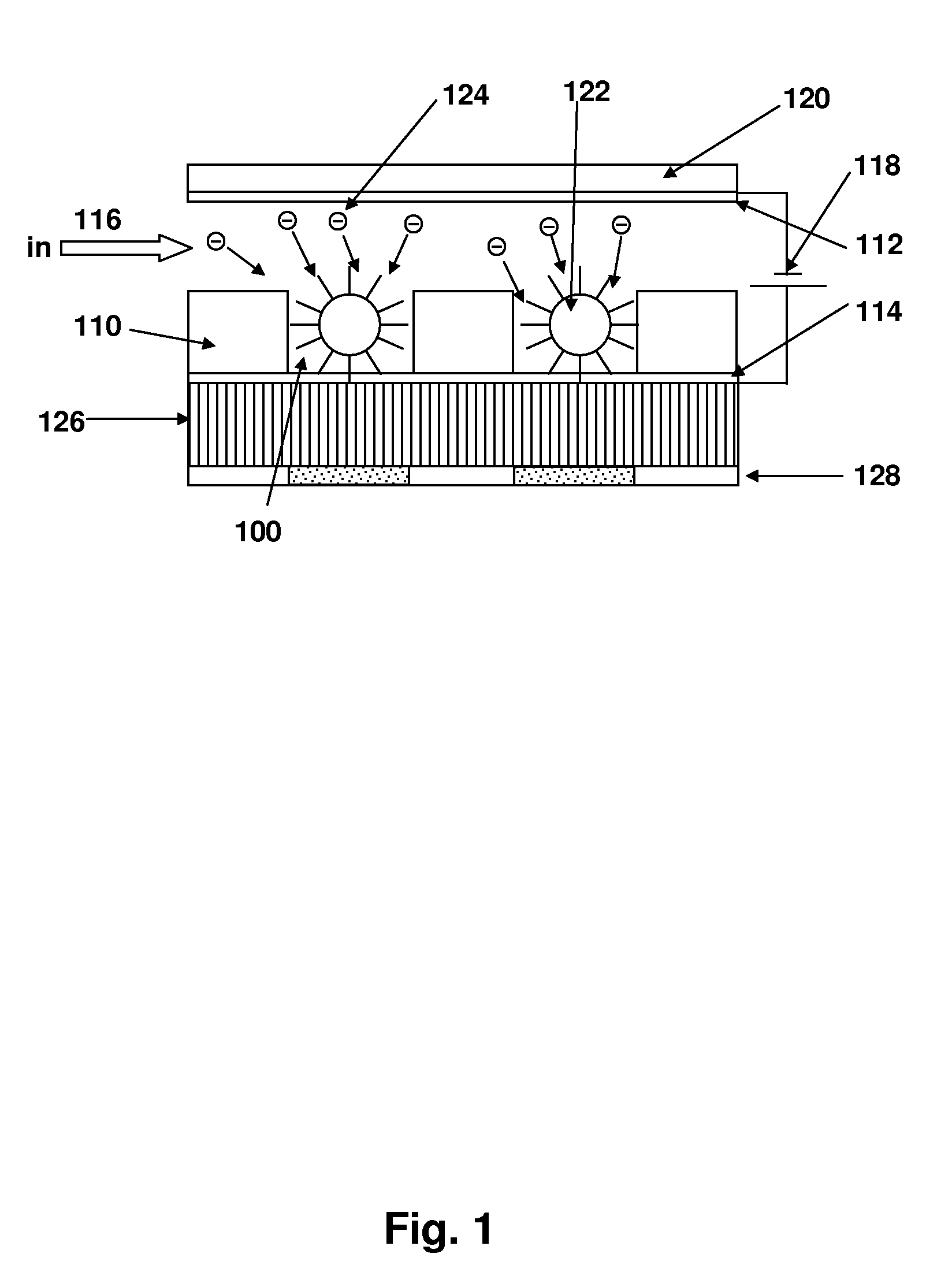

Method and Apparatus Using Electric Field for Improved Biological Assays

ActiveUS20090032401A1Avoid corrosionIncrease electric fieldElectrostatic separatorsSludge treatmentPresent methodEngineering

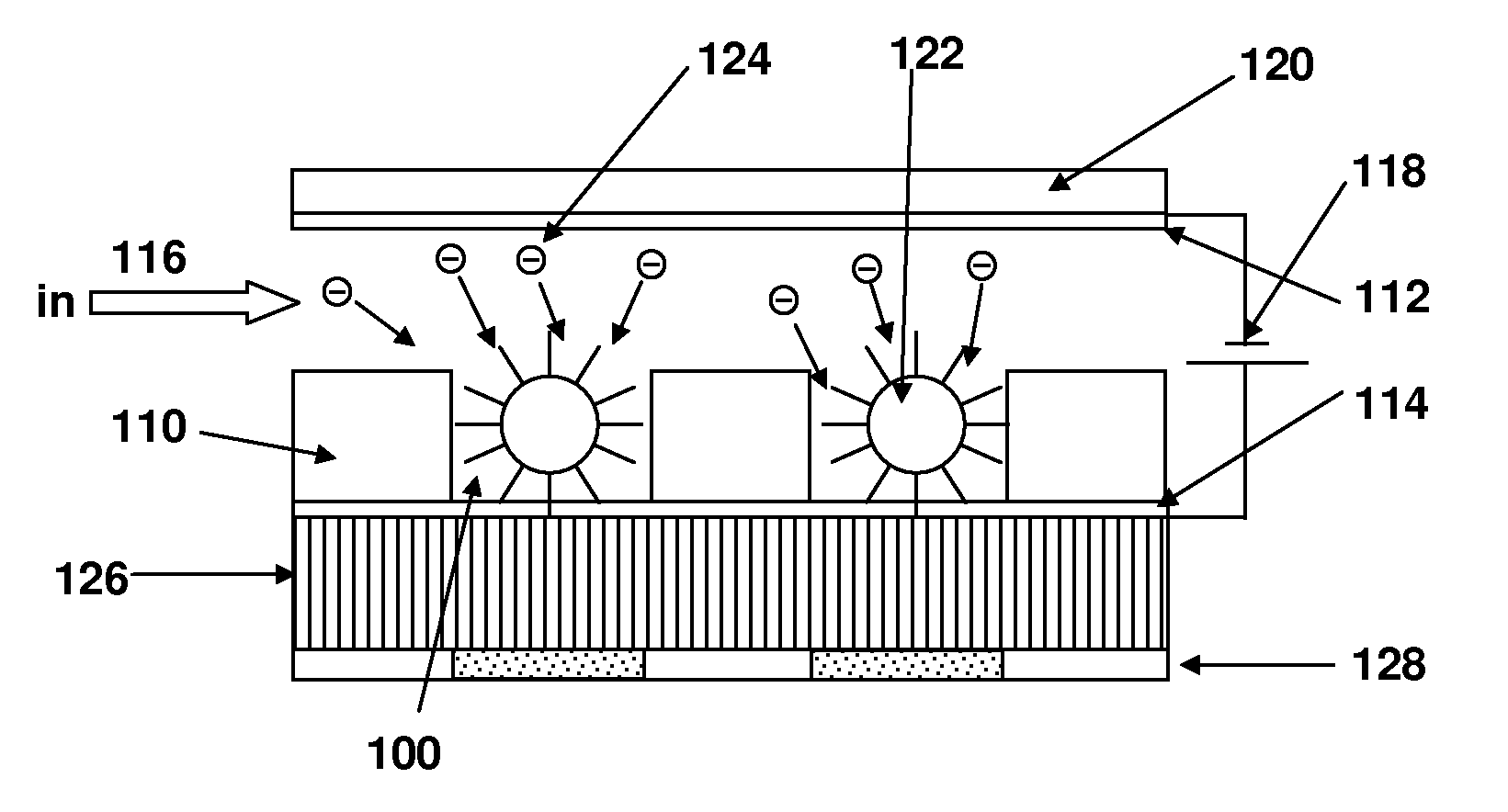

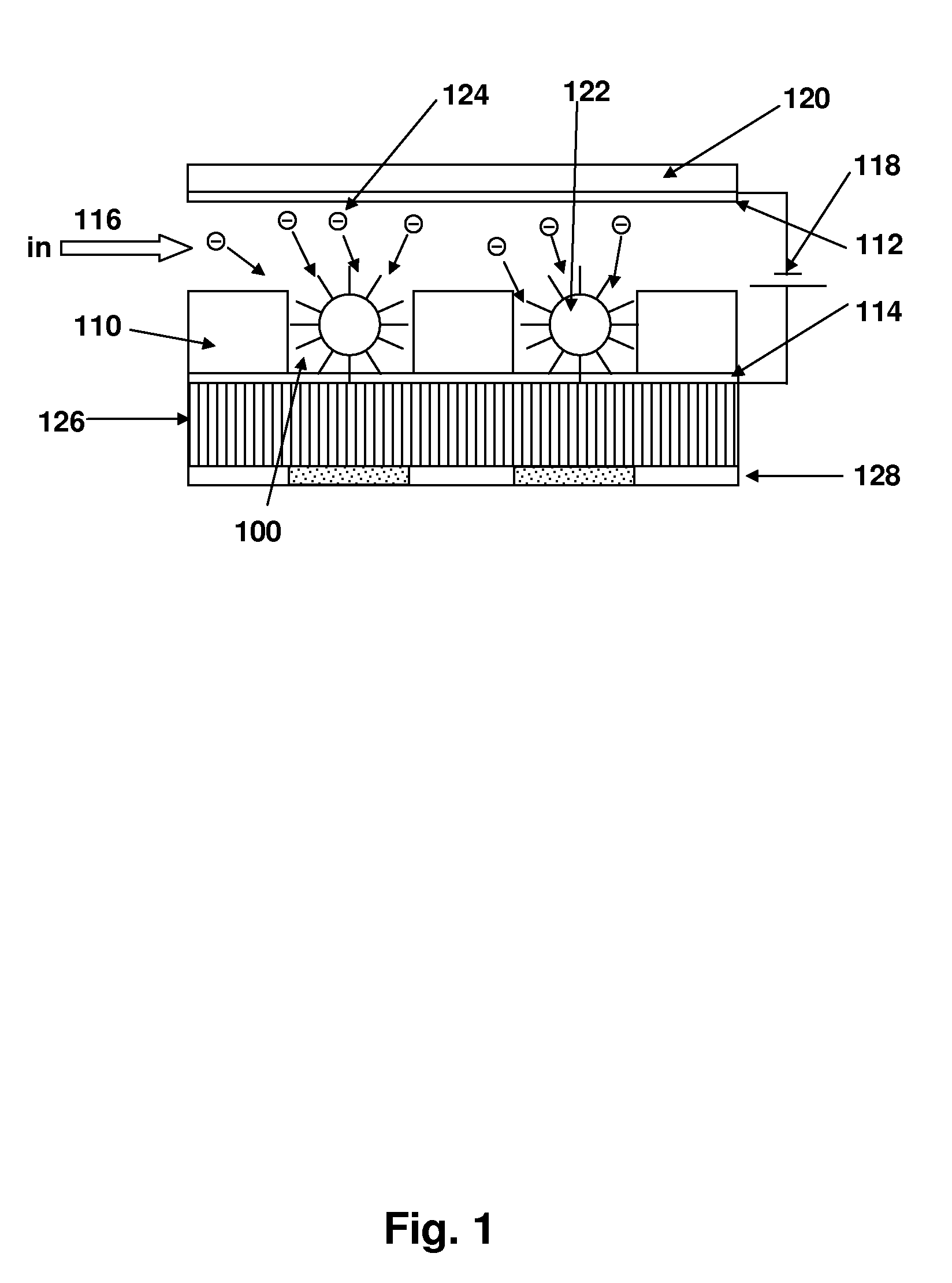

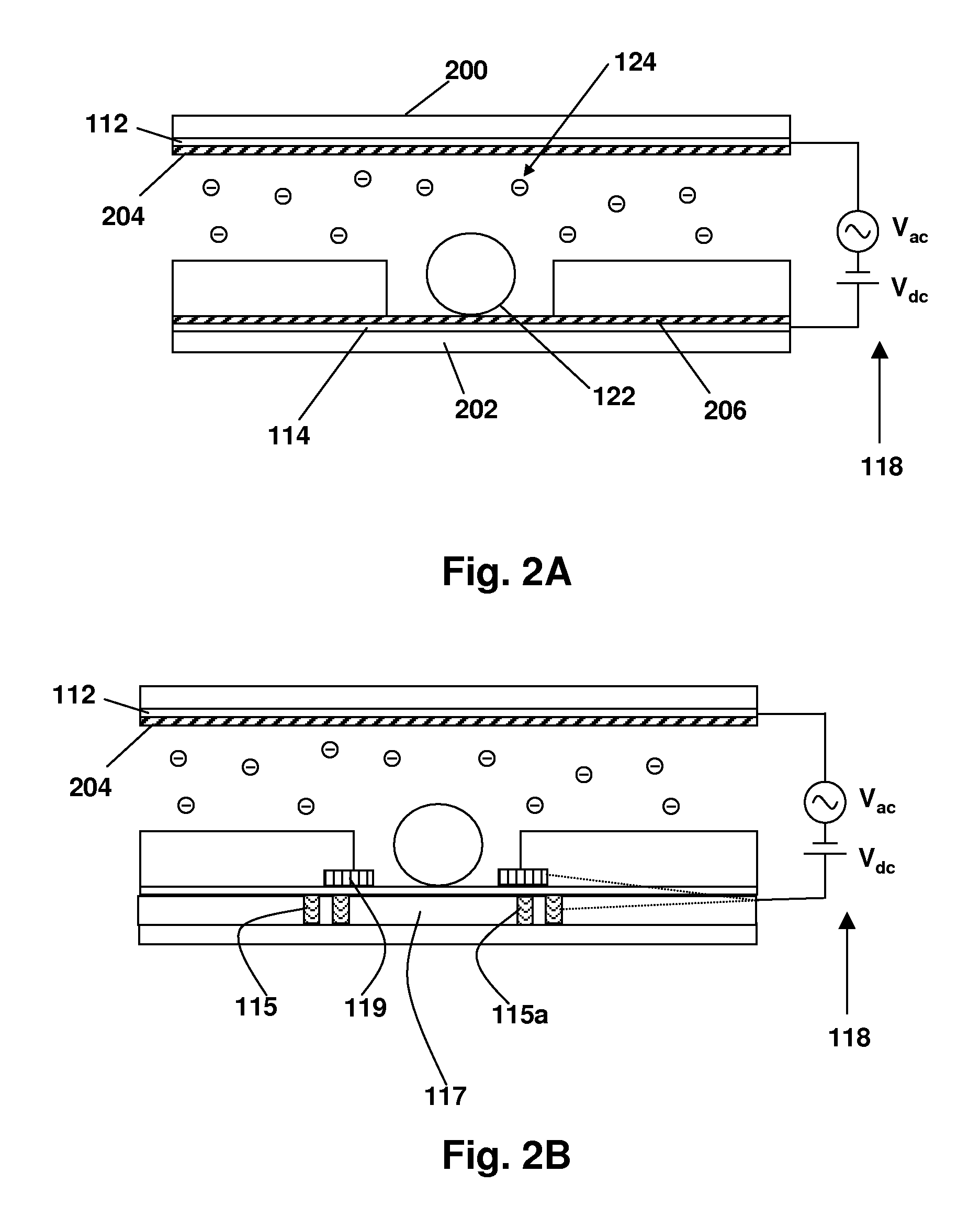

Disclosed are a method and apparatus that use an electric field for improved biological assays. The electric field is applied across a device having wells, which receive reactants, which carry a charge. The device thus uses a controllable voltage source between the first and second electrodes, which is controllable to provide a positive charge and a negative charge to a given electrode. By controlled use of the electric field charged species in a fluid in a fluid channel are directed into or out of the well by an electric field between the electrodes. The present method involves the transport of fluids, as in a microfluidic device, and the electric field-induced movement of reactive species according to various assay procedures, such as DNA sequencing, synthesis or the like.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

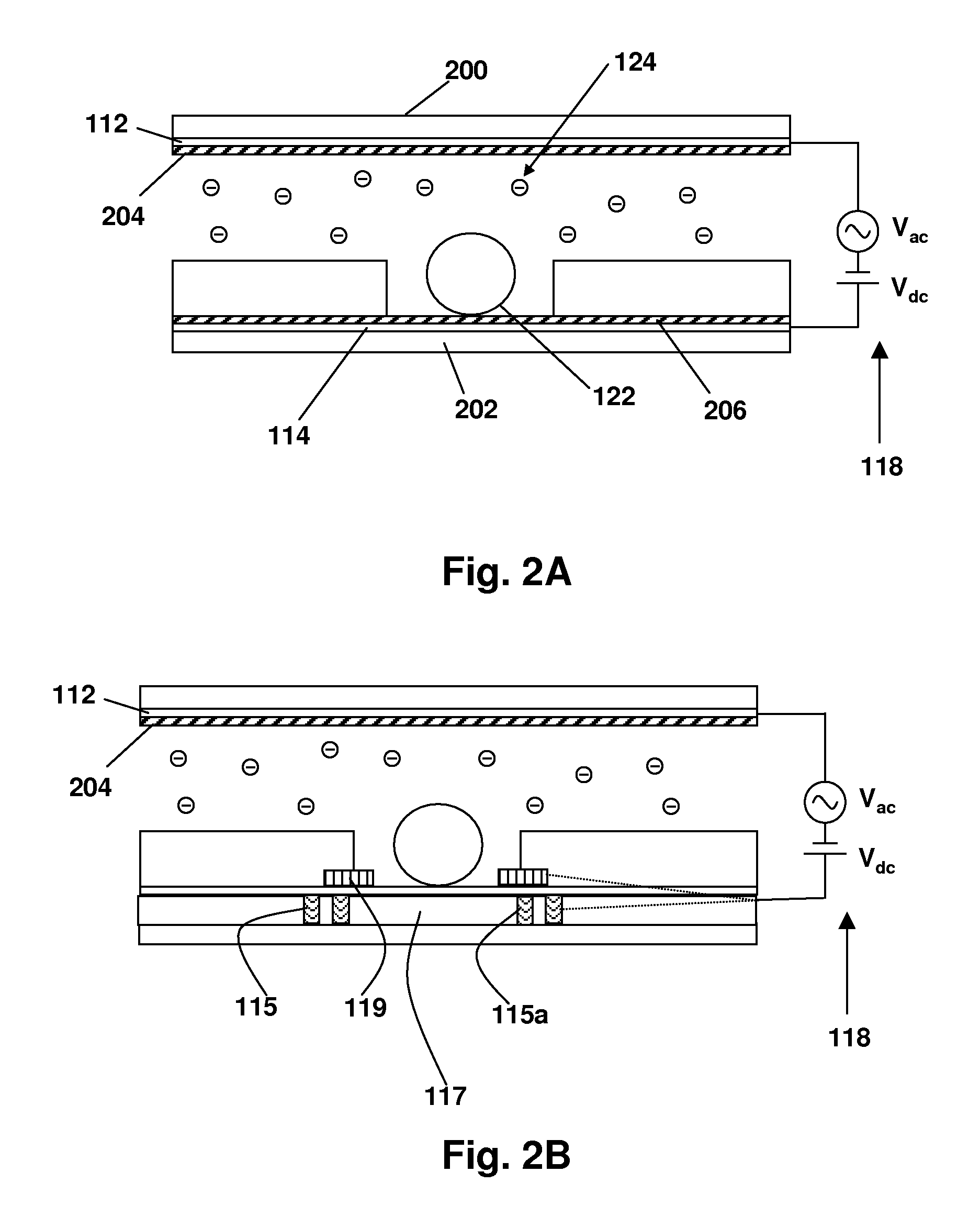

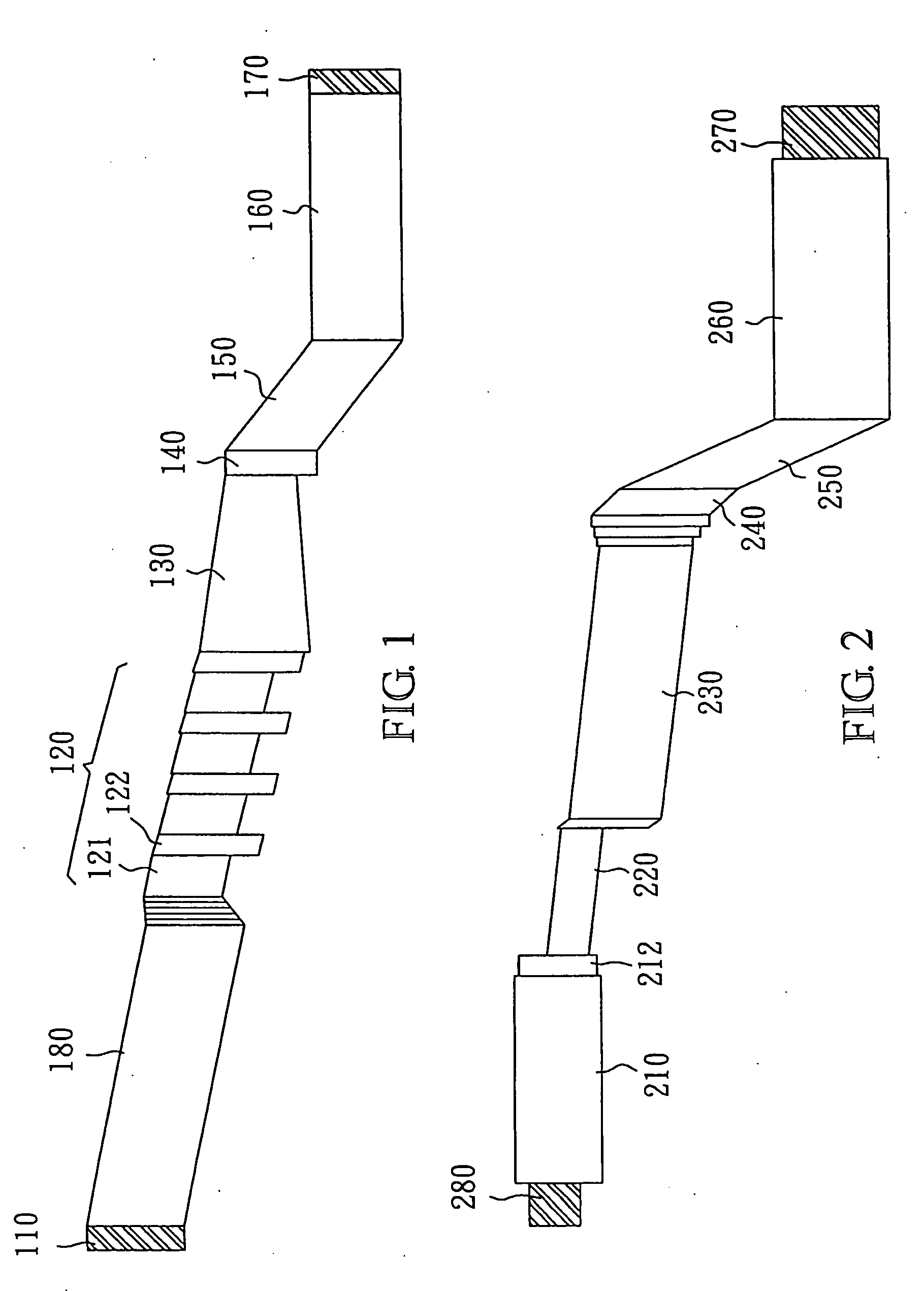

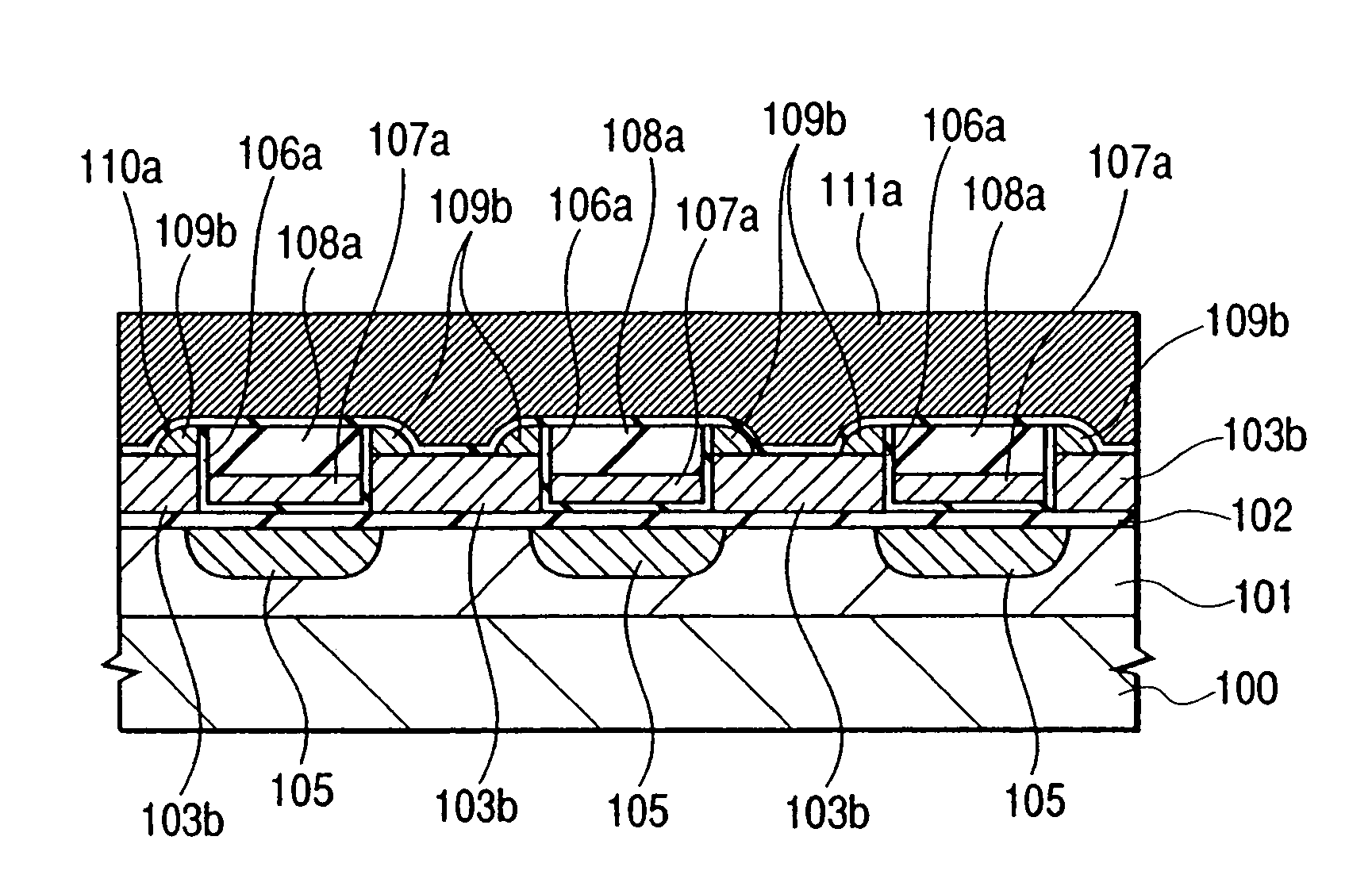

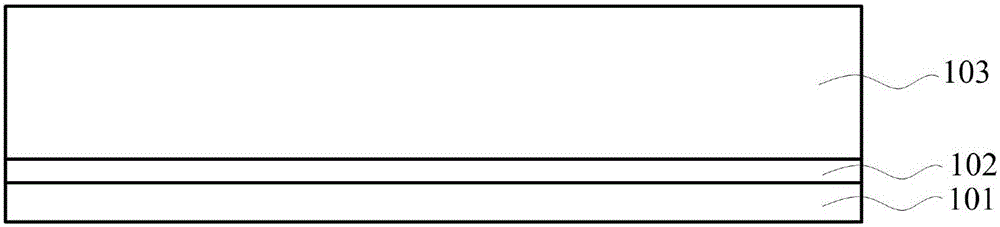

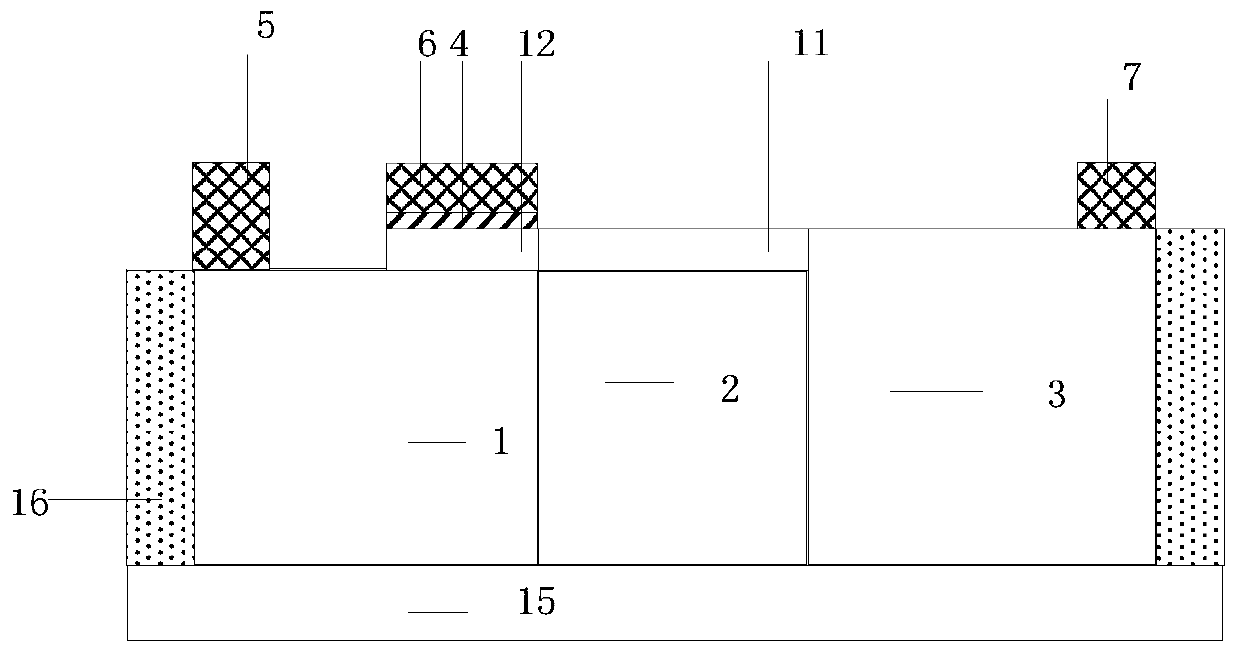

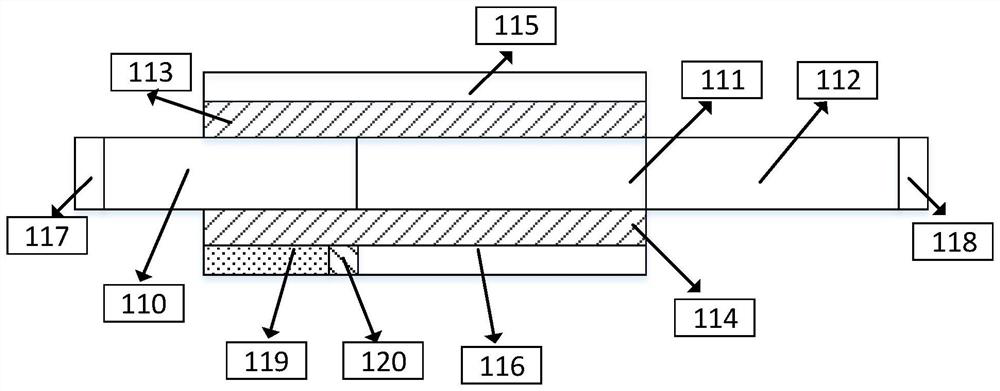

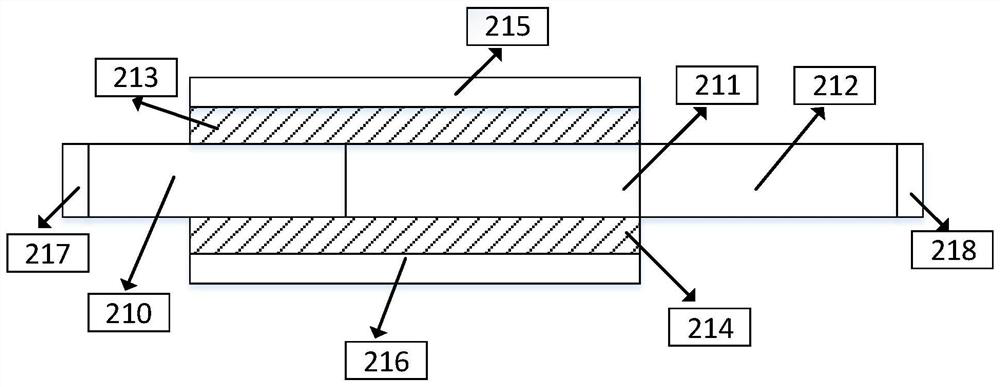

Avalanche photo-detector with high saturation power and high gain-bandwidth product

InactiveUS20050051861A1Reduce operating voltageReducing carrier transport timeNanoinformaticsSolid-state devicesLow noiseCapacitance

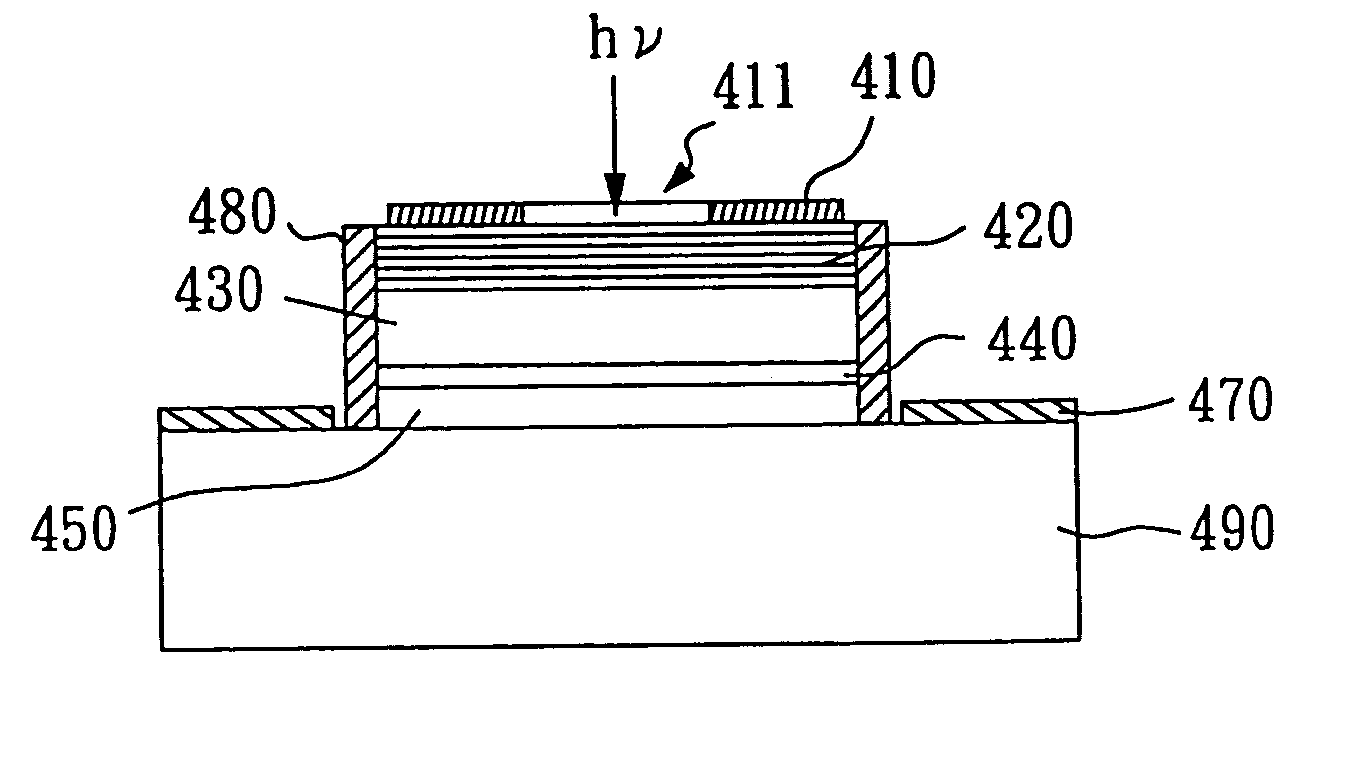

An avalanche photo-detector (APD) is disclosed, which can reduce device capacitance, operating voltage, carrier transport time and dark current as well as increasing response speed and output power. Thus, an avalanche photo-detector (APD) with high saturation power, high gain-bandwidth product, low noise, fast response, low dark current is achieved. The APD includes an absorption layer with graded doping for converting an incident light into carriers, an undoped multiplication layer for multiplying current by means of receiving carriers, a doped field buffer layer sandwiched between the absorption layer and the multiplication layer for concentrating an electric field in the multiplication layer when a bias voltage is applied, and an undoped drift layer sandwiched between the absorption layer and the field buffer layer for capacitance reduction.

Owner:IND TECH RES INST

Method and apparatus using electric field for improved biological assays

ActiveUS8277628B2Quality improvementEfficient removalElectrostatic separatorsSludge treatmentPresent methodEngineering

Disclosed are a method and apparatus that use an electric field for improved biological assays. The electric field is applied across a device having wells, which receive reactants, which carry a charge. The device thus uses a controllable voltage source between the first and second electrodes, which is controllable to provide a positive charge and a negative charge to a given electrode. By controlled use of the electric field charged species in a fluid in a fluid channel are directed into or out of the well by an electric field between the electrodes. The present method involves the transport of fluids, as in a microfluidic device, and the electric field-induced movement of reactive species according to various assay procedures, such as DNA sequencing, synthesis or the like.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

Avalanche photo-detector with high saturation power and high gain-bandwidth product

InactiveUS6963089B2Reduce capacitanceReduce voltageNanoinformaticsSolid-state devicesLow noiseCapacitance

An avalanche photo-detector (APD) is disclosed, which can reduce device capacitance, operating voltage, carrier transport time and dark current as well as increasing response speed and output power. Thus, an avalanche photo-detector (APD) with high saturation power, high gain-bandwidth product, low noise, fast response, low dark current is achieved. The APD includes an absorption layer with graded doping for converting an incident light into carriers, an undoped multiplication layer for multiplying current by means of receiving carriers, a doped field buffer layer sandwiched between the absorption layer and the multiplication layer for concentrating an electric field in the multiplication layer when a bias voltage is applied, and an undoped drift layer sandwiched between the absorption layer and the field buffer layer for capacitance reduction.

Owner:IND TECH RES INST

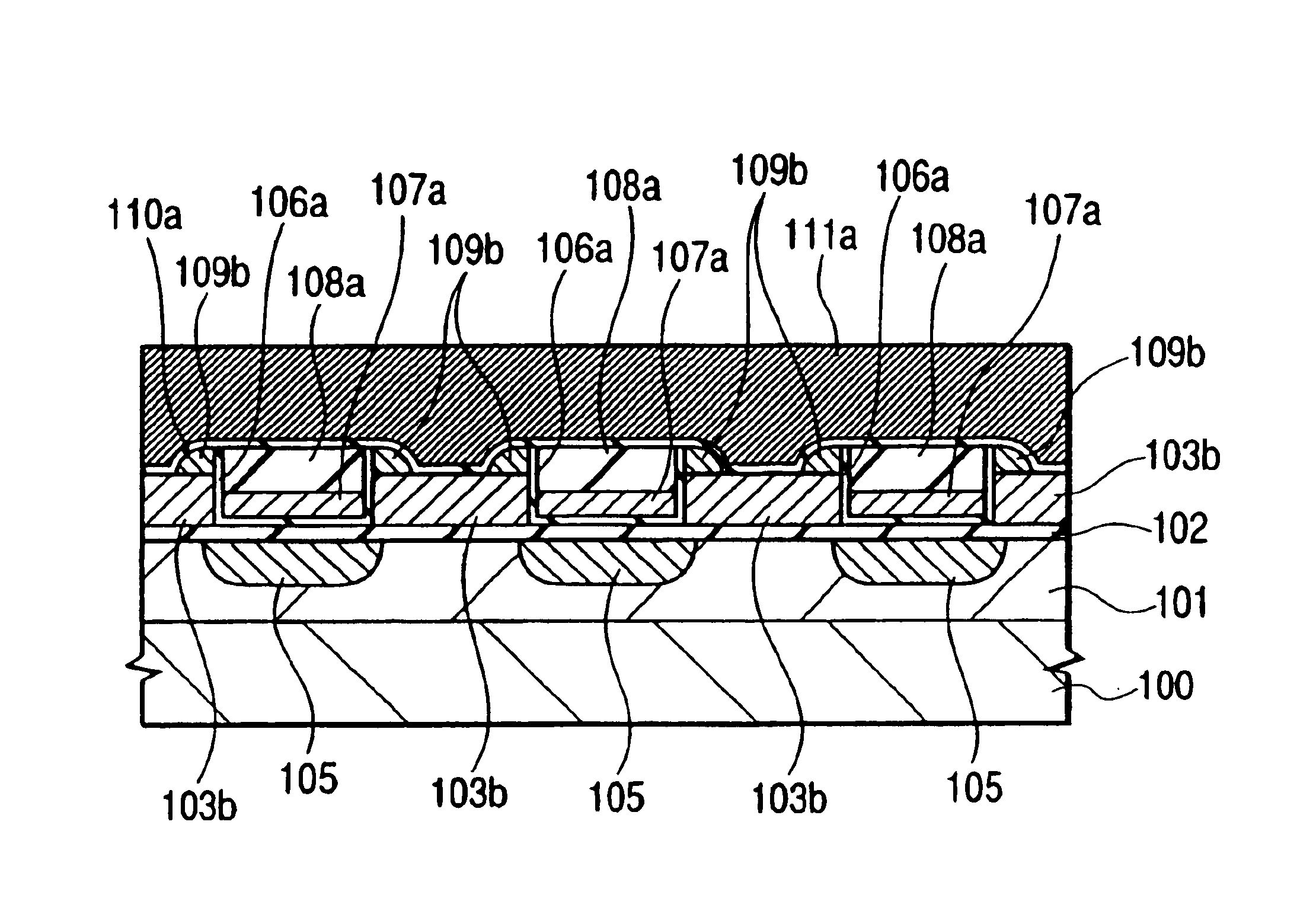

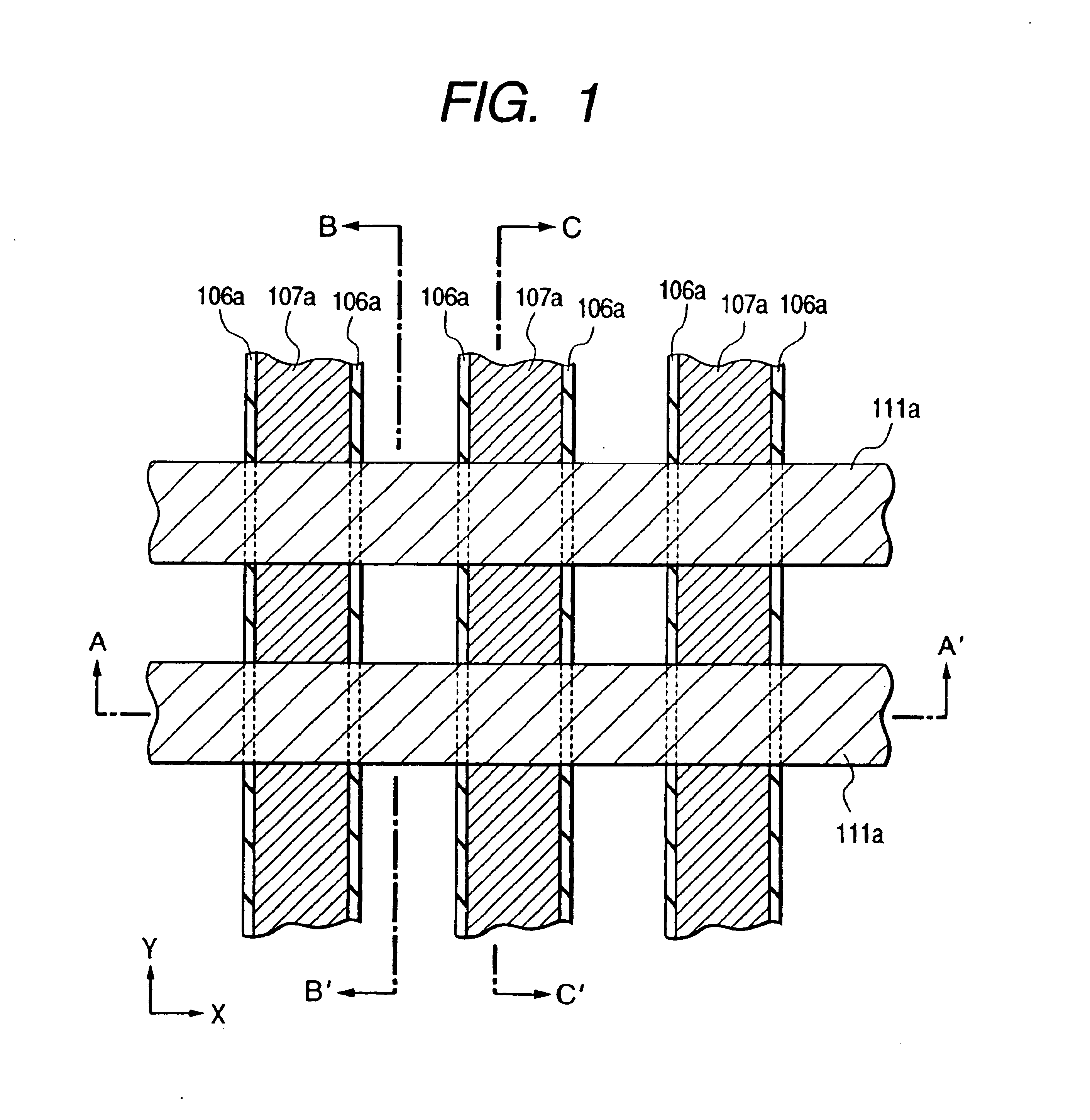

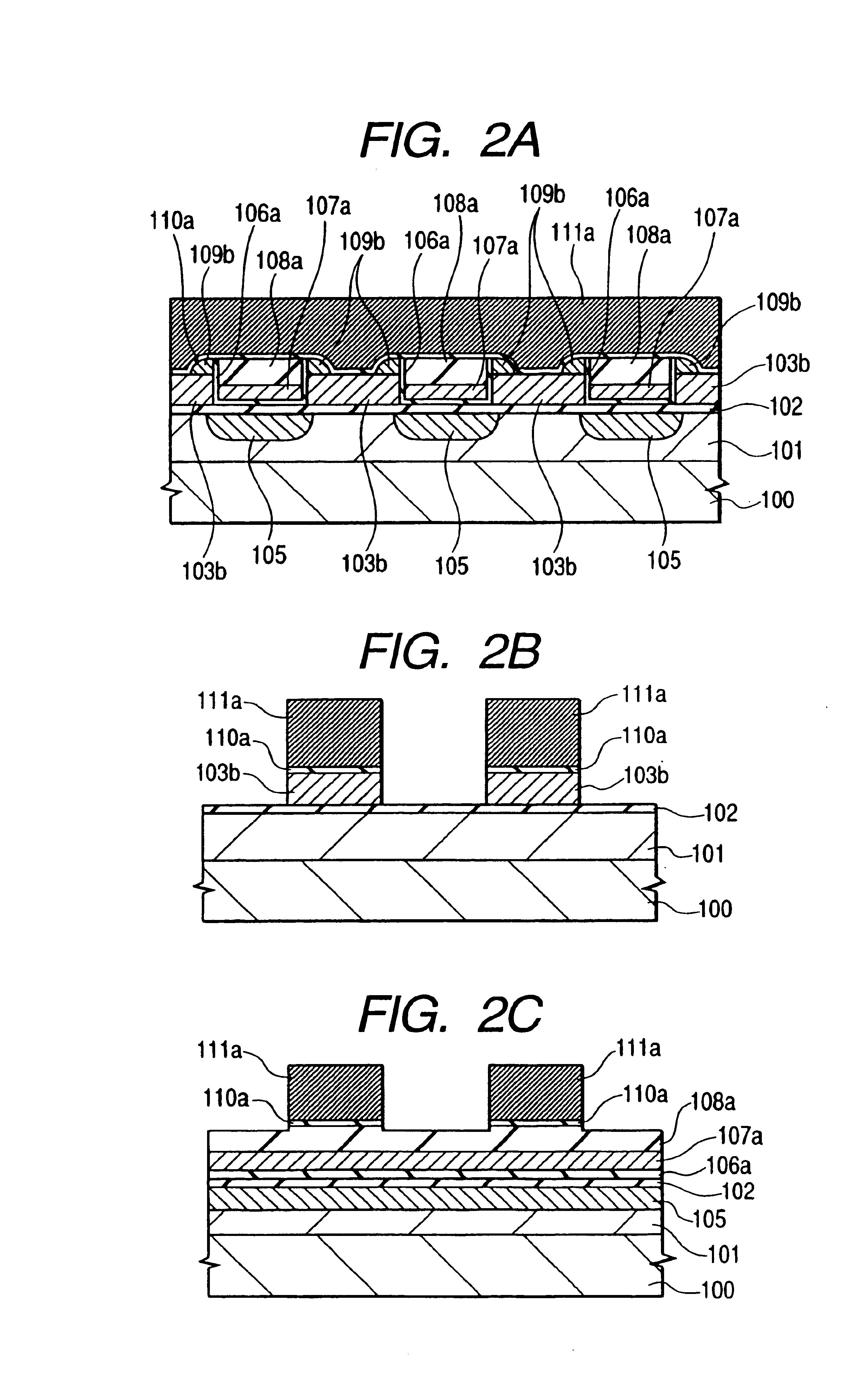

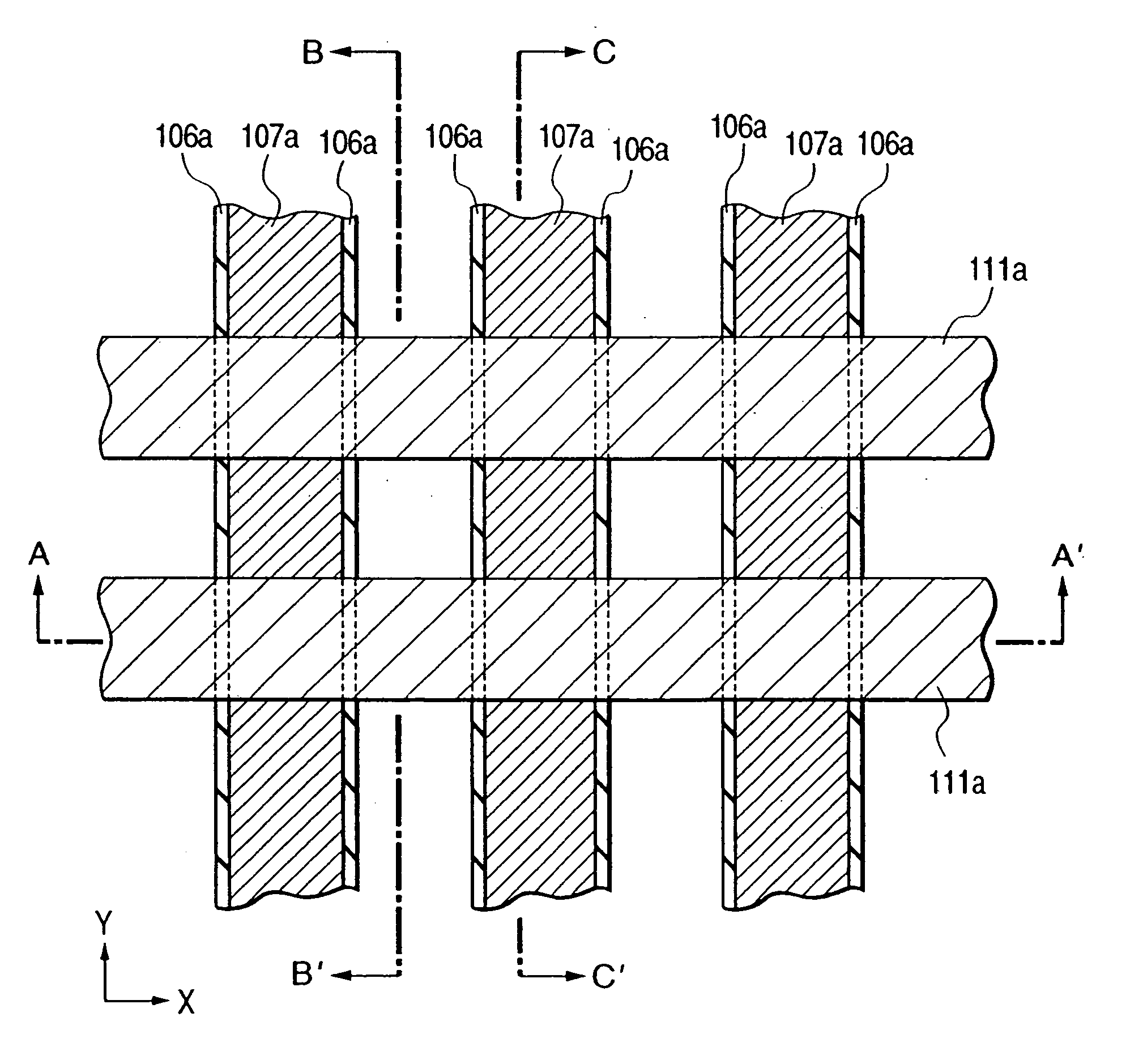

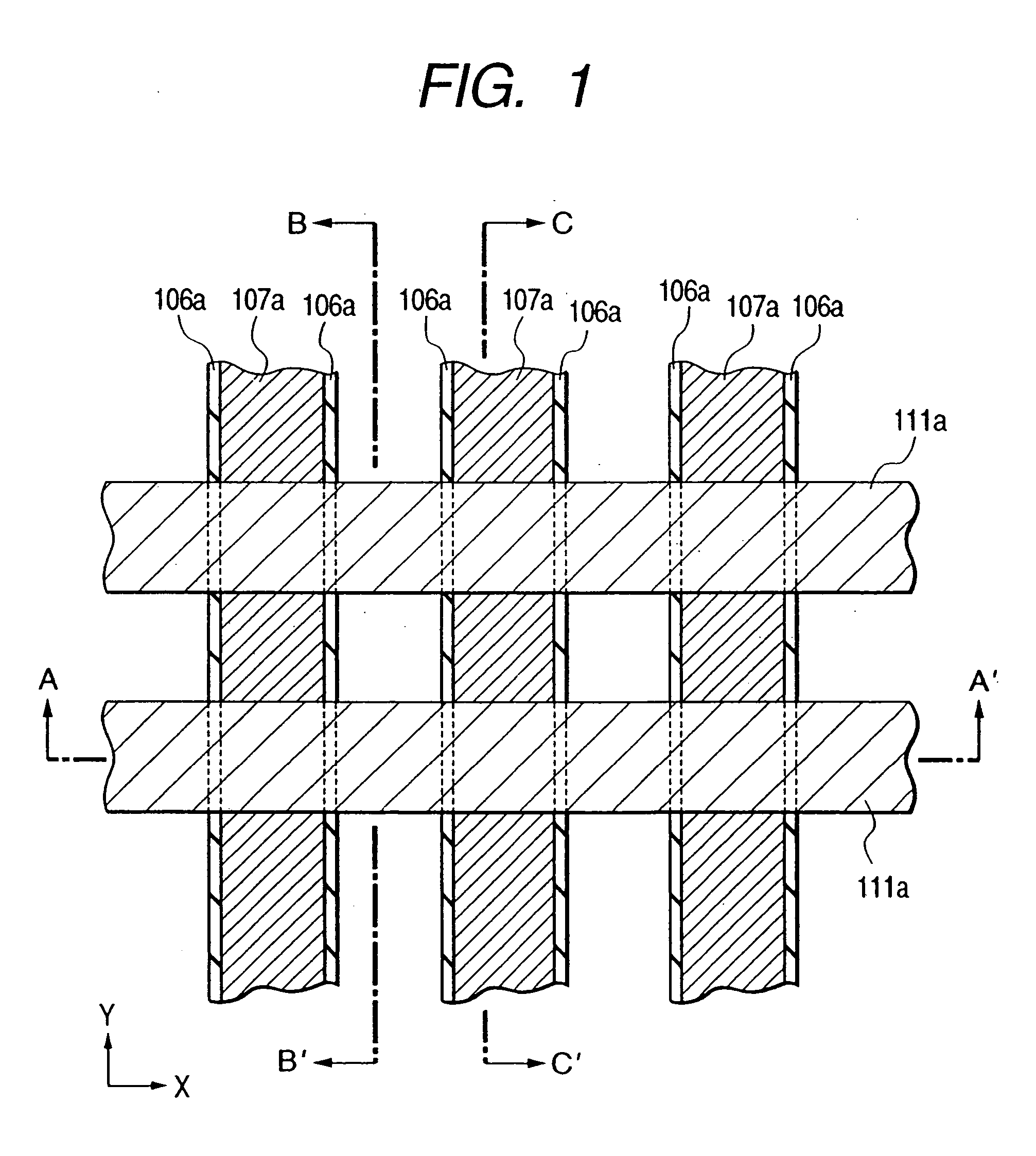

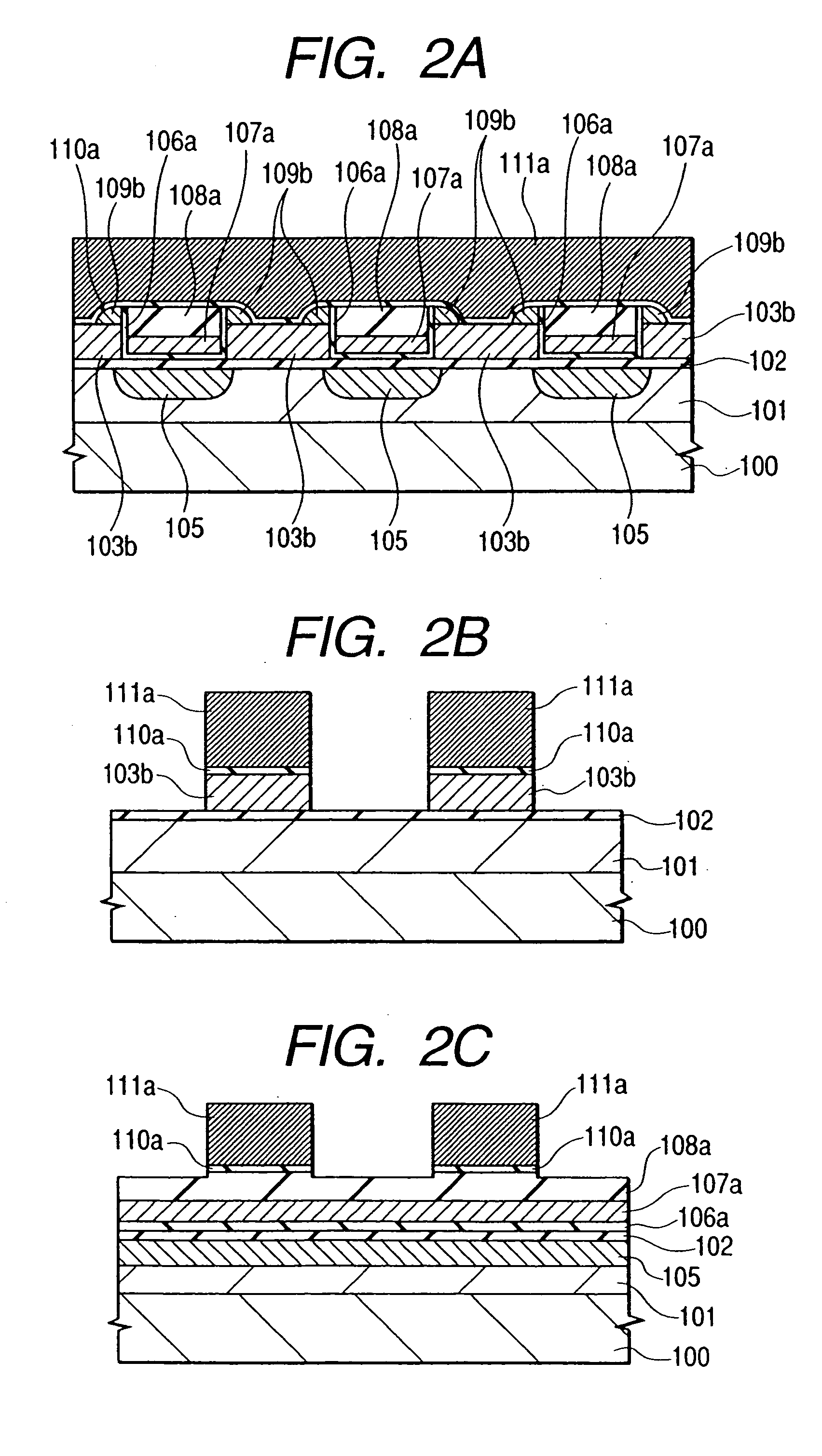

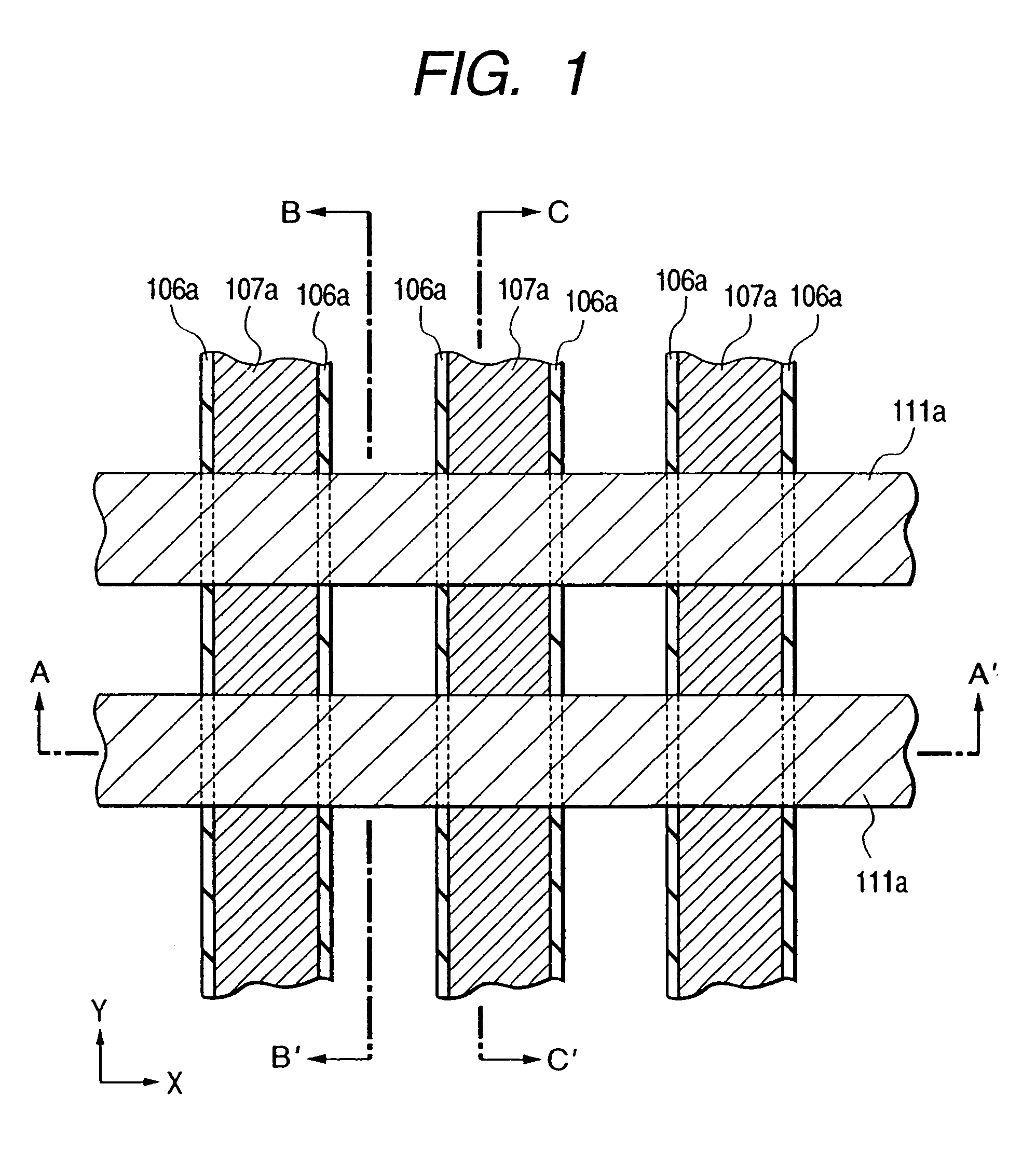

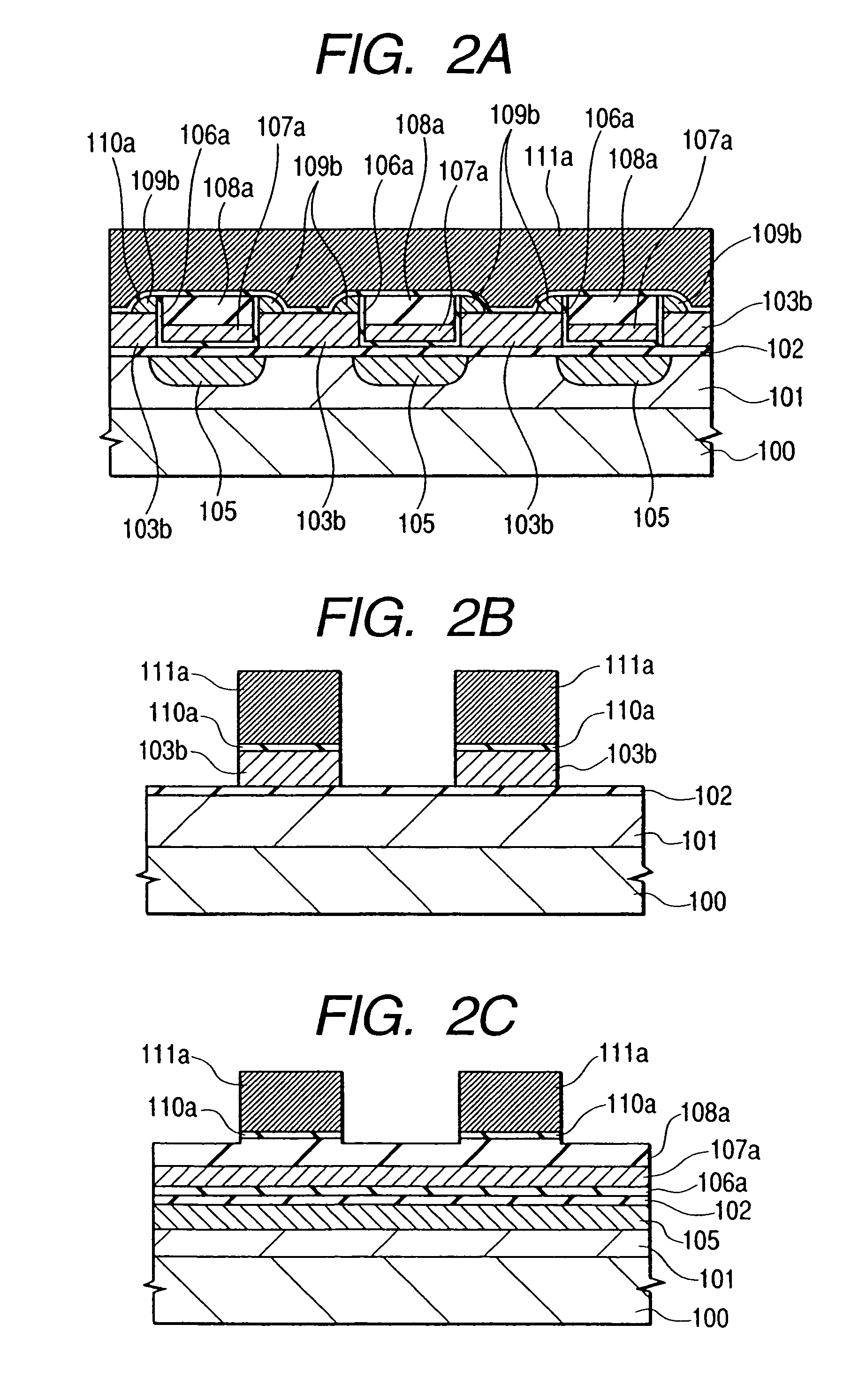

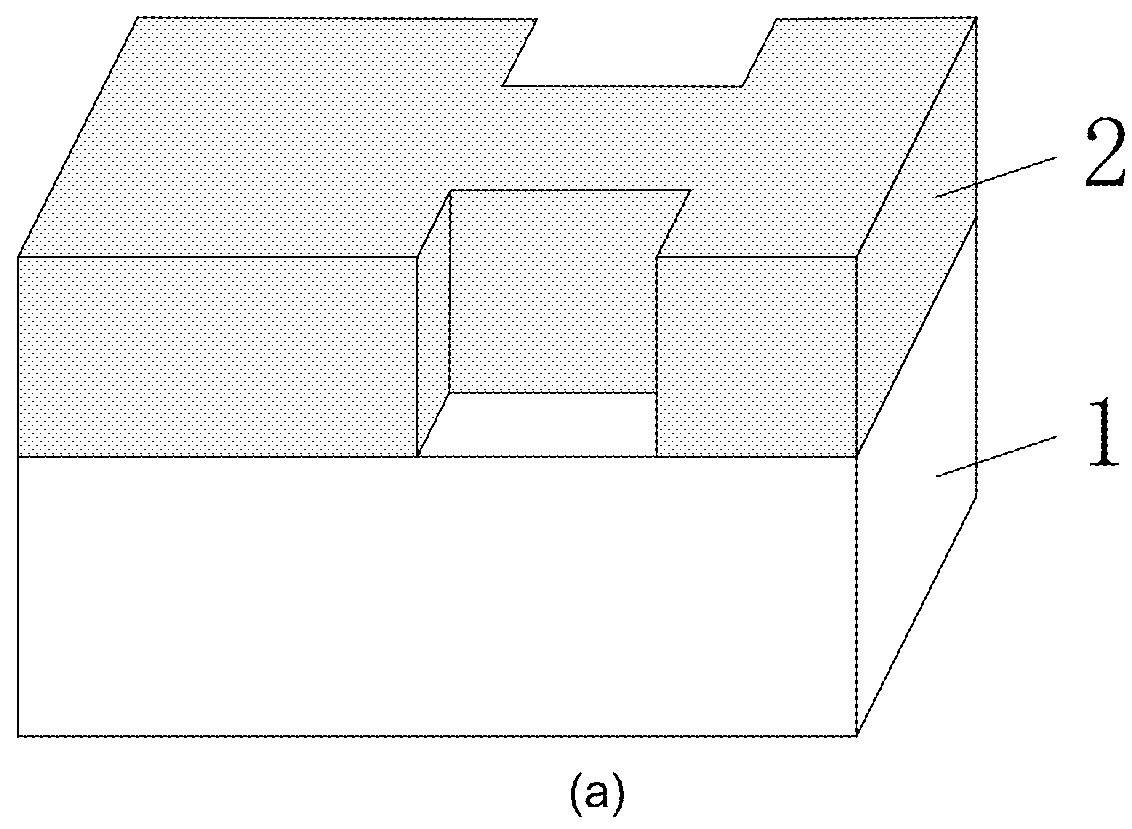

Semiconductor integrated circuit device including first, second and third gates

InactiveUS6901006B1Increase computing speedReduce defect densityTransistorSolid-state devicesMiniaturizationConnection control

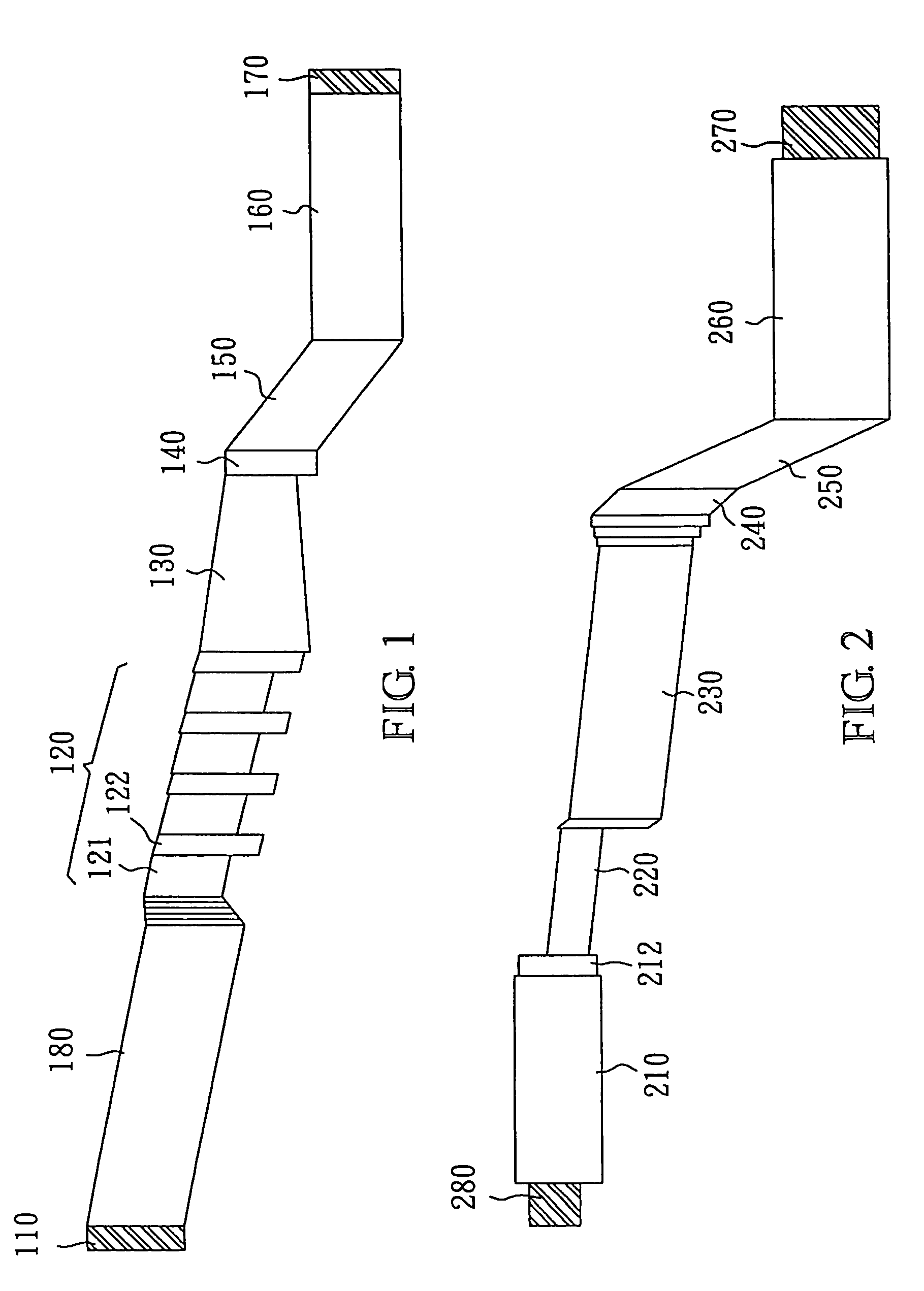

In a semiconductor integrated circuit device including a third gate, the present invention improves miniaturization and operation speed and reduces a defect density of an insulator film. In a semiconductor integrated circuit device including a well of a first conductivity type formed in a semiconductor substrate, a source / drain diffusion layer of a second conductivity type inside the well, a floating gate formed over the semiconductor substrate through an insulator film, a control gate formed and isolated from the floating gate through an insulator film, word lines formed by connecting the control gates and a third gate formed and isolated from the semiconductor substrate, the floating gate and the control gate through an insulator film and different from the floating gate and the control gate, the third gate is buried into a space of the floating gates existing in a direction vertical to the word line and a channel.

Owner:RENESAS ELECTRONICS CORP

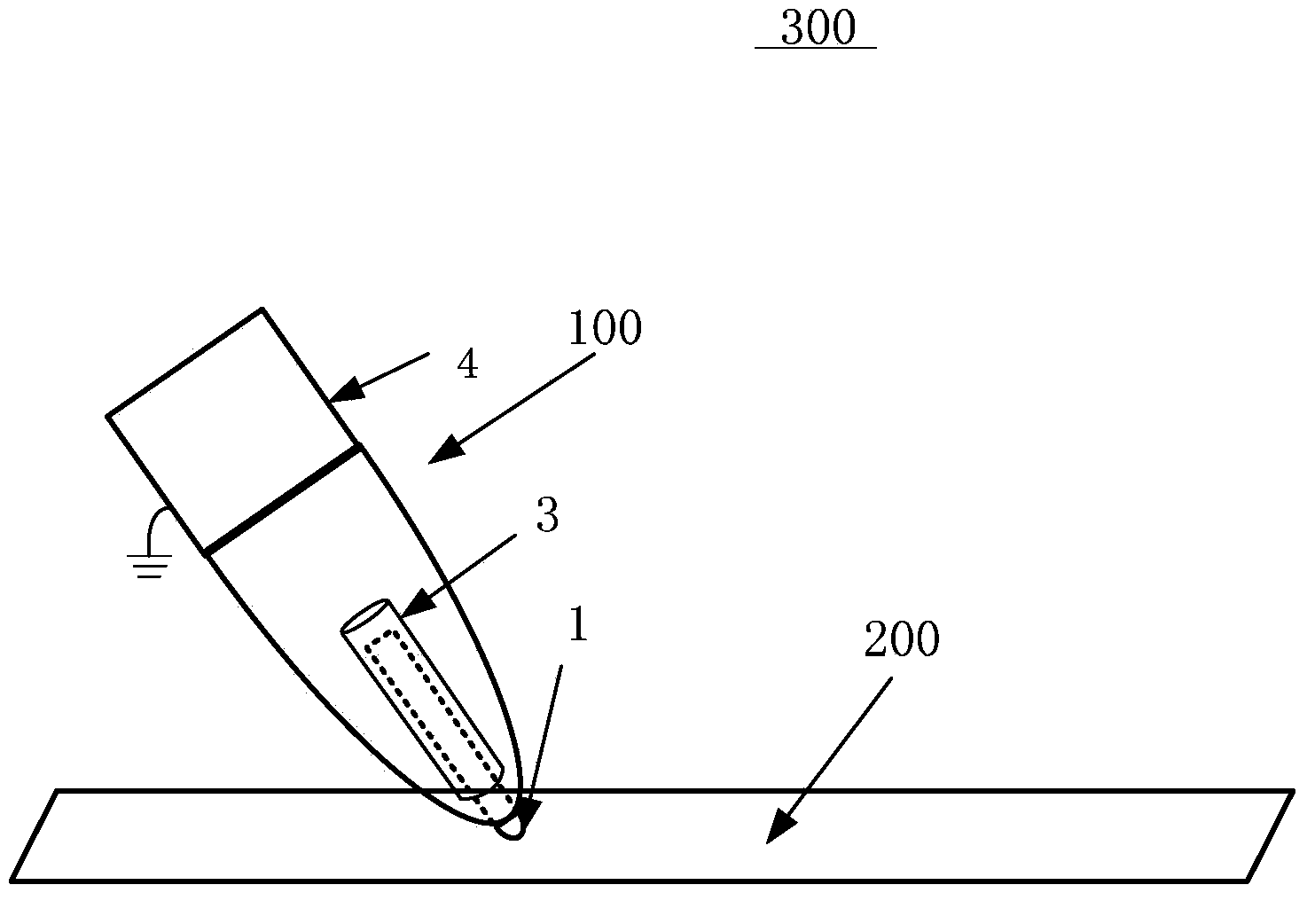

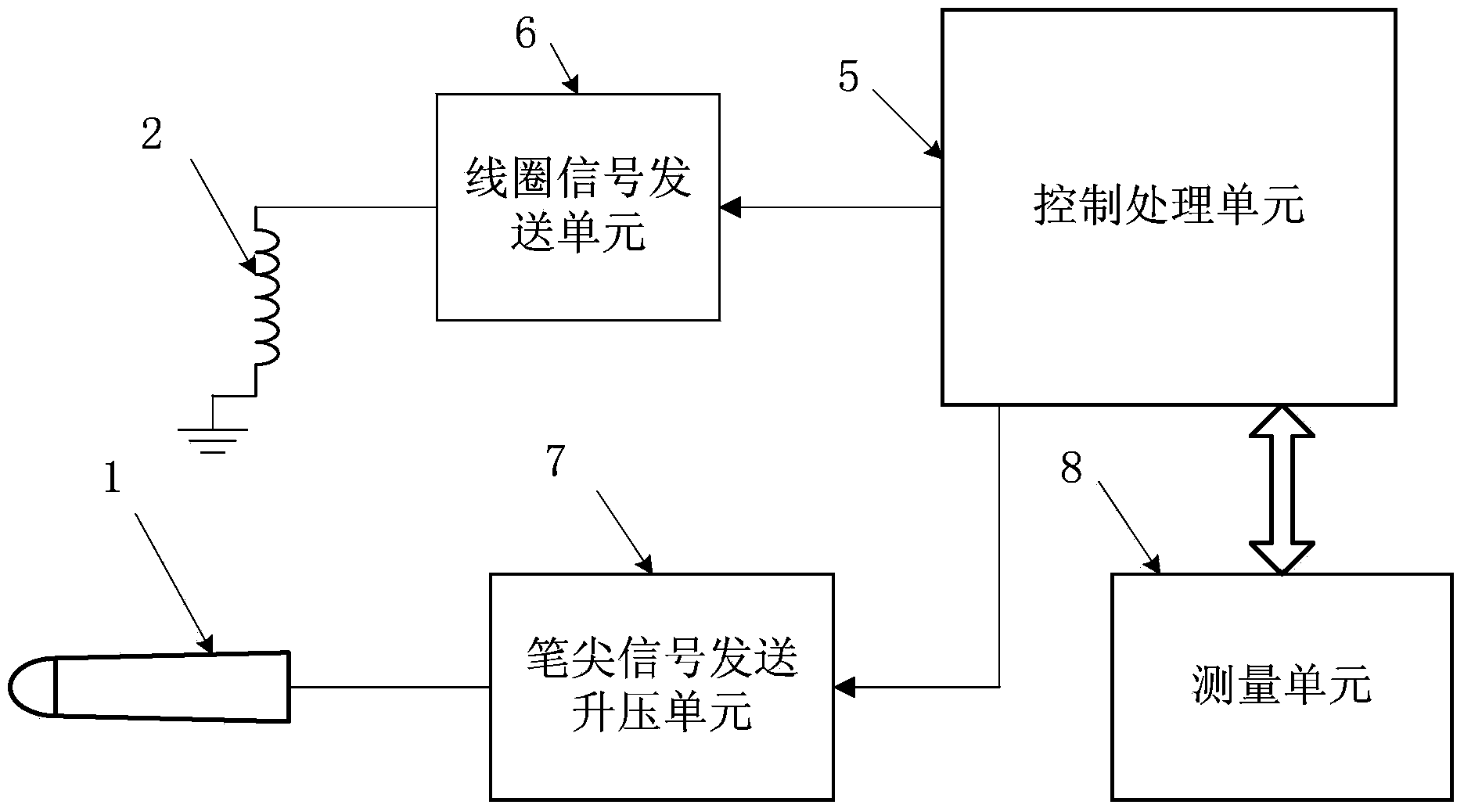

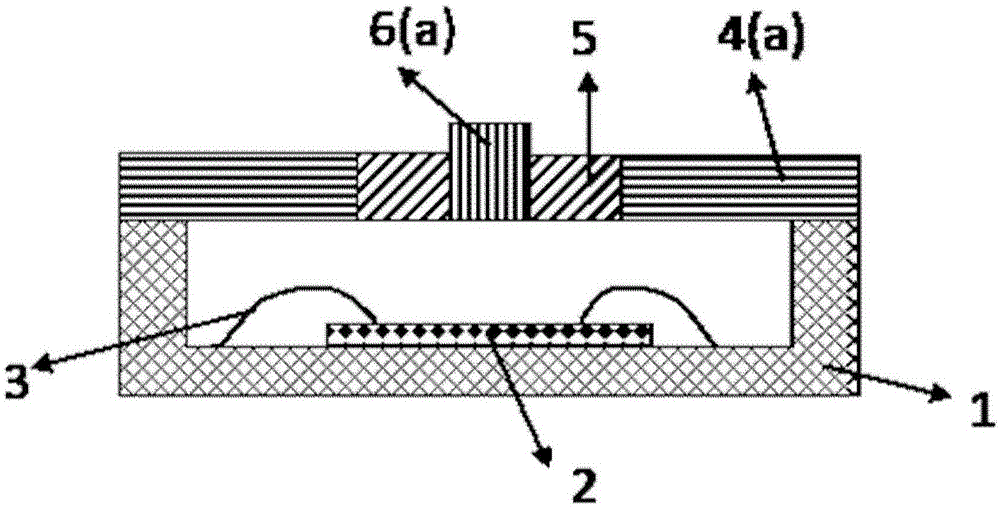

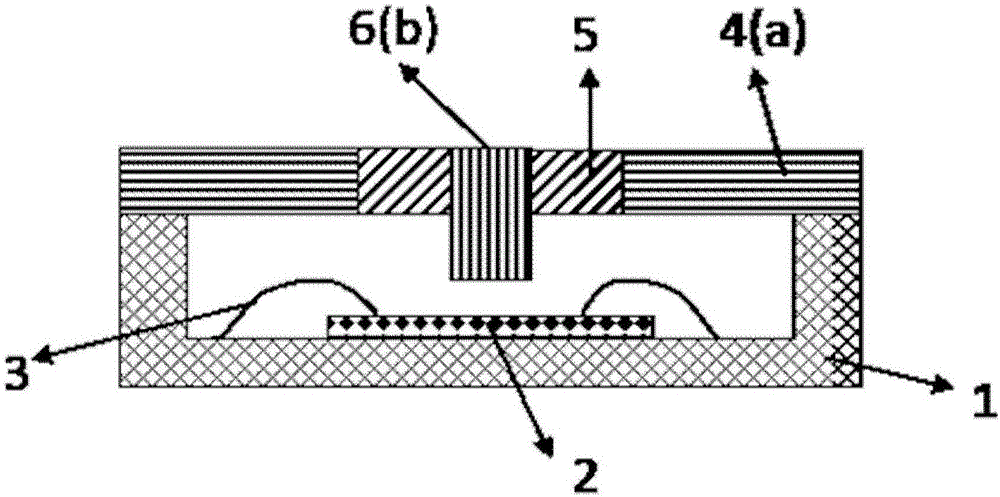

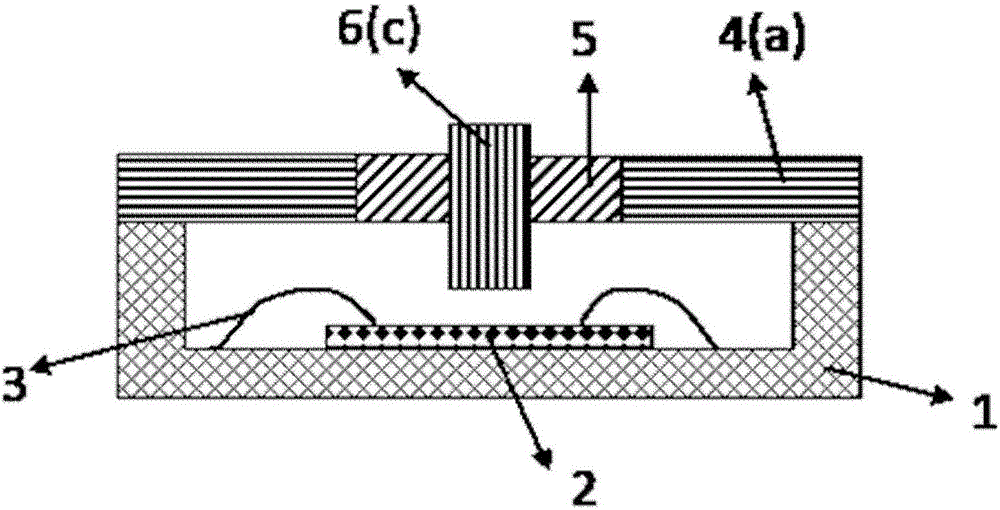

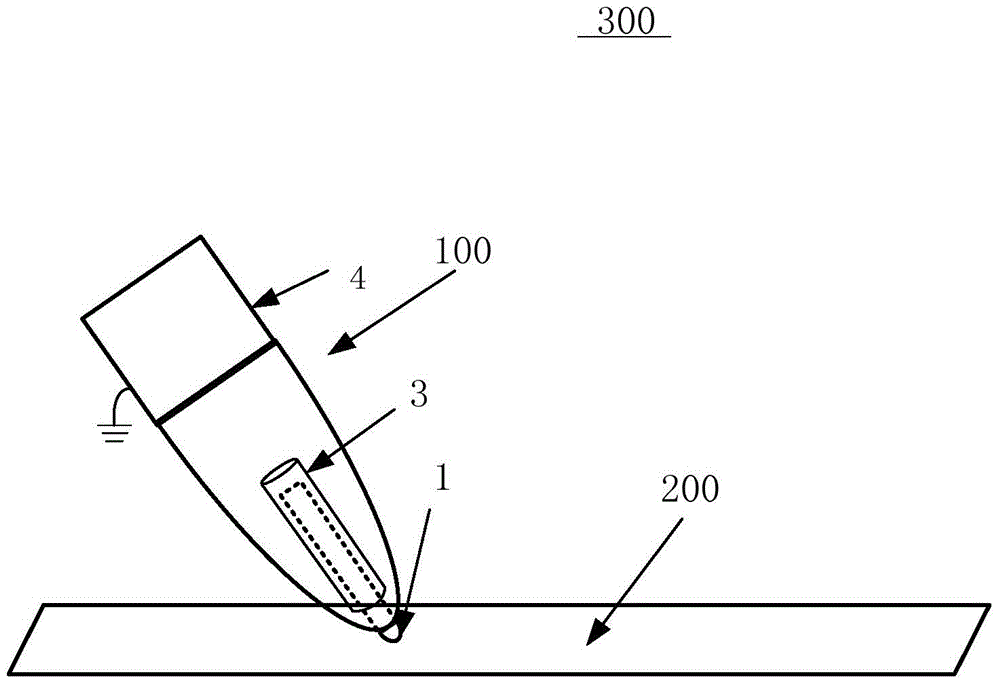

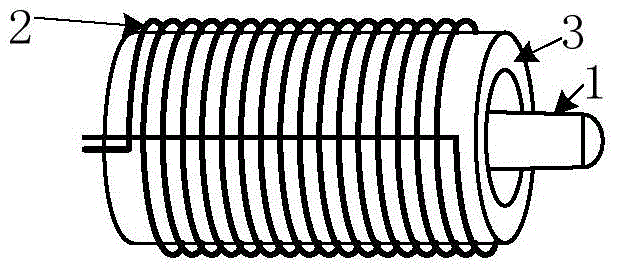

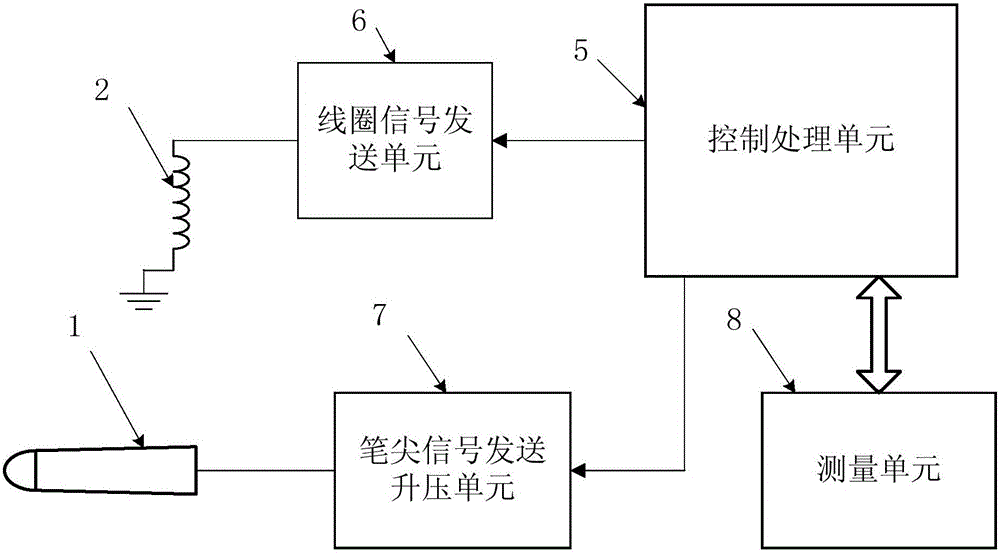

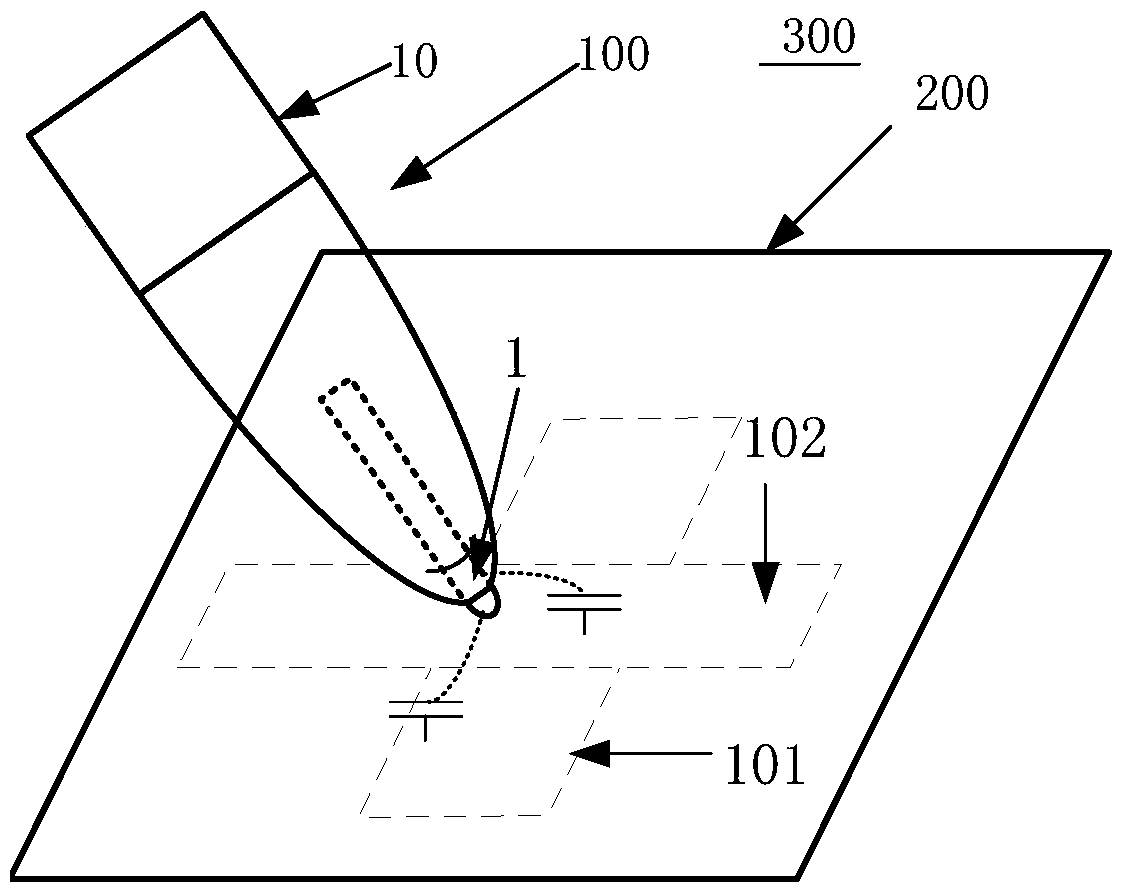

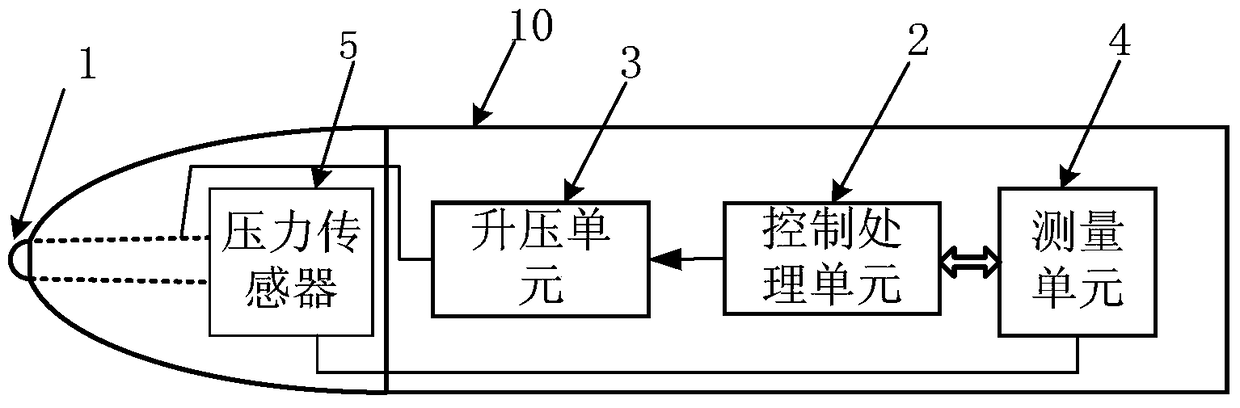

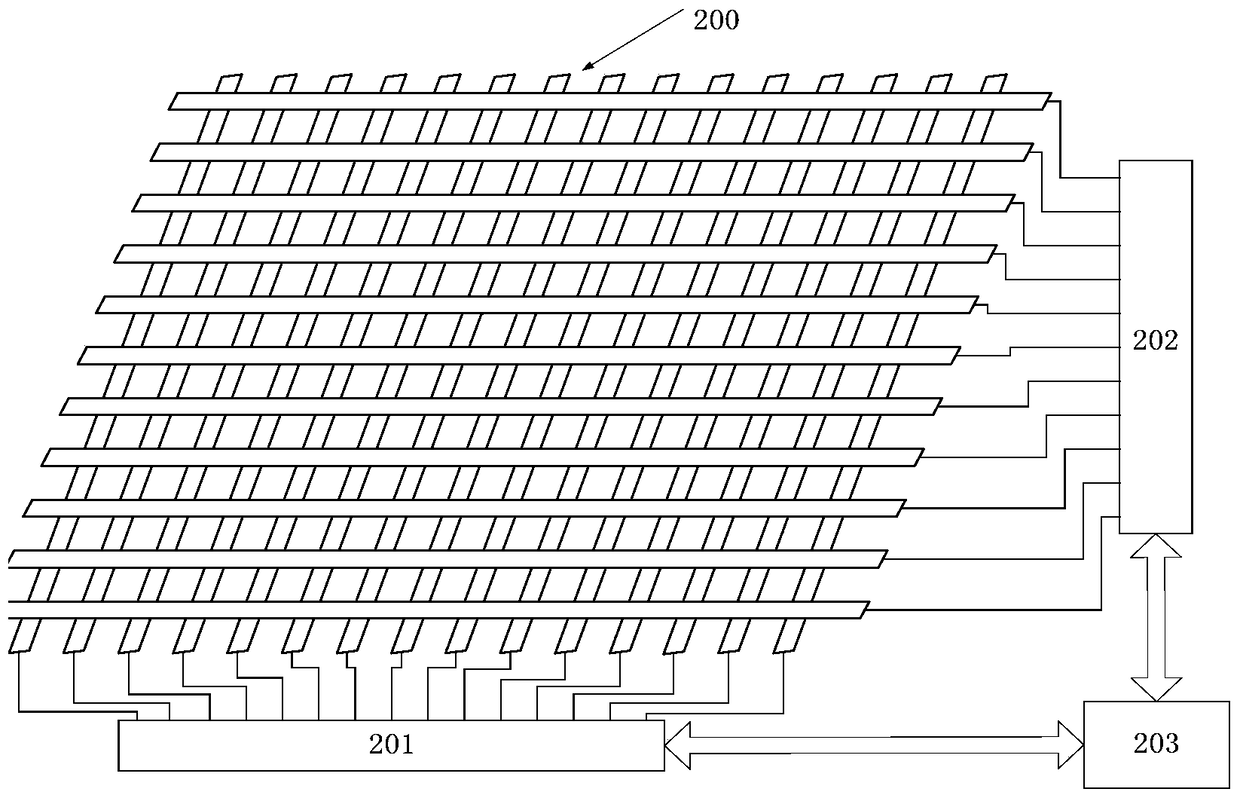

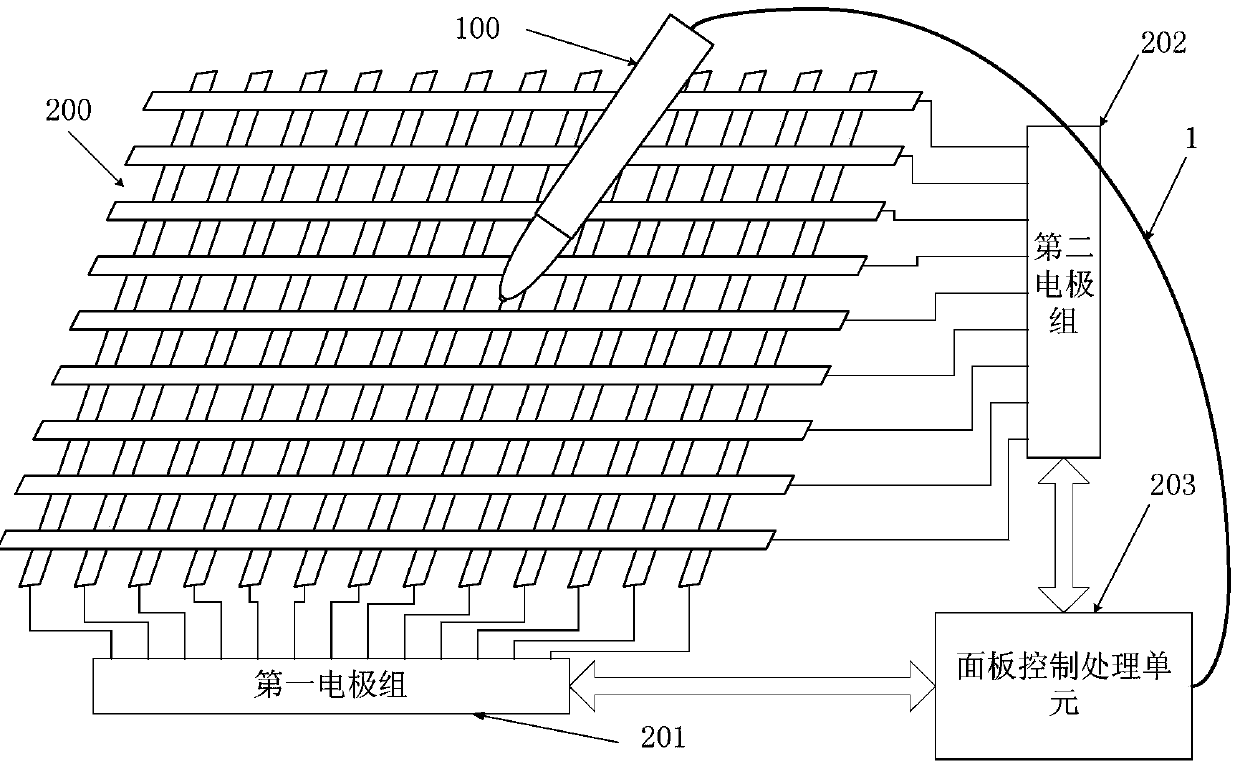

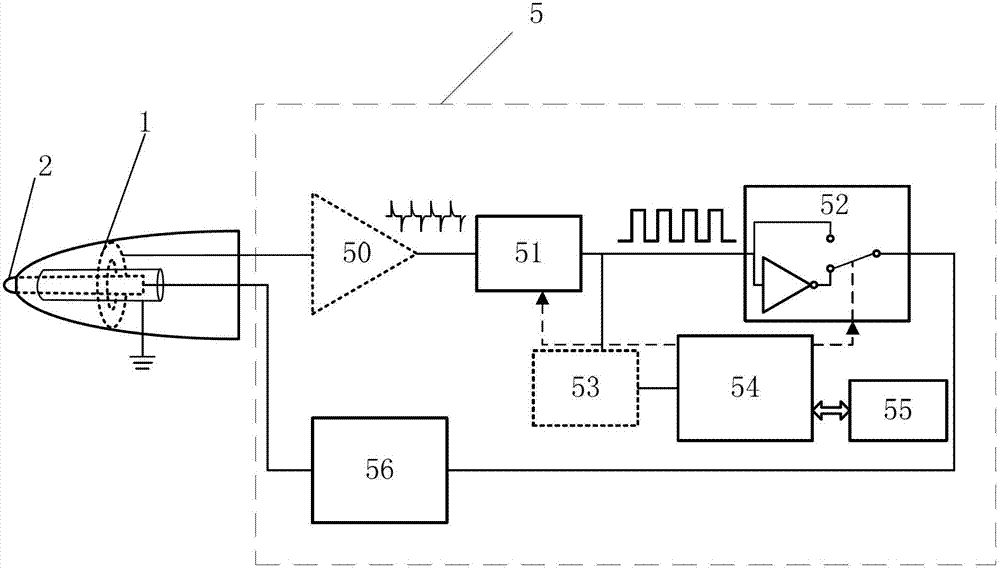

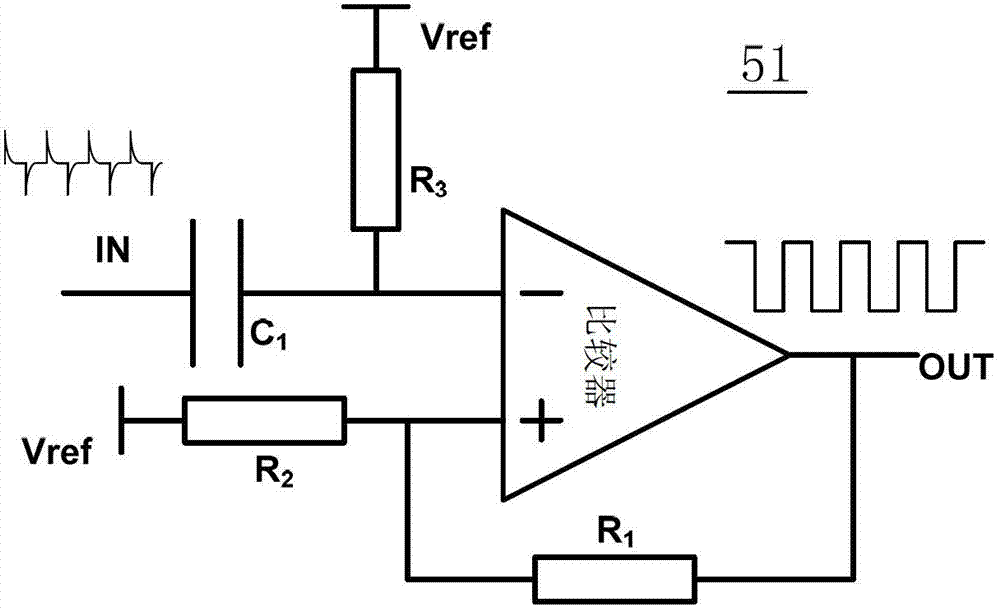

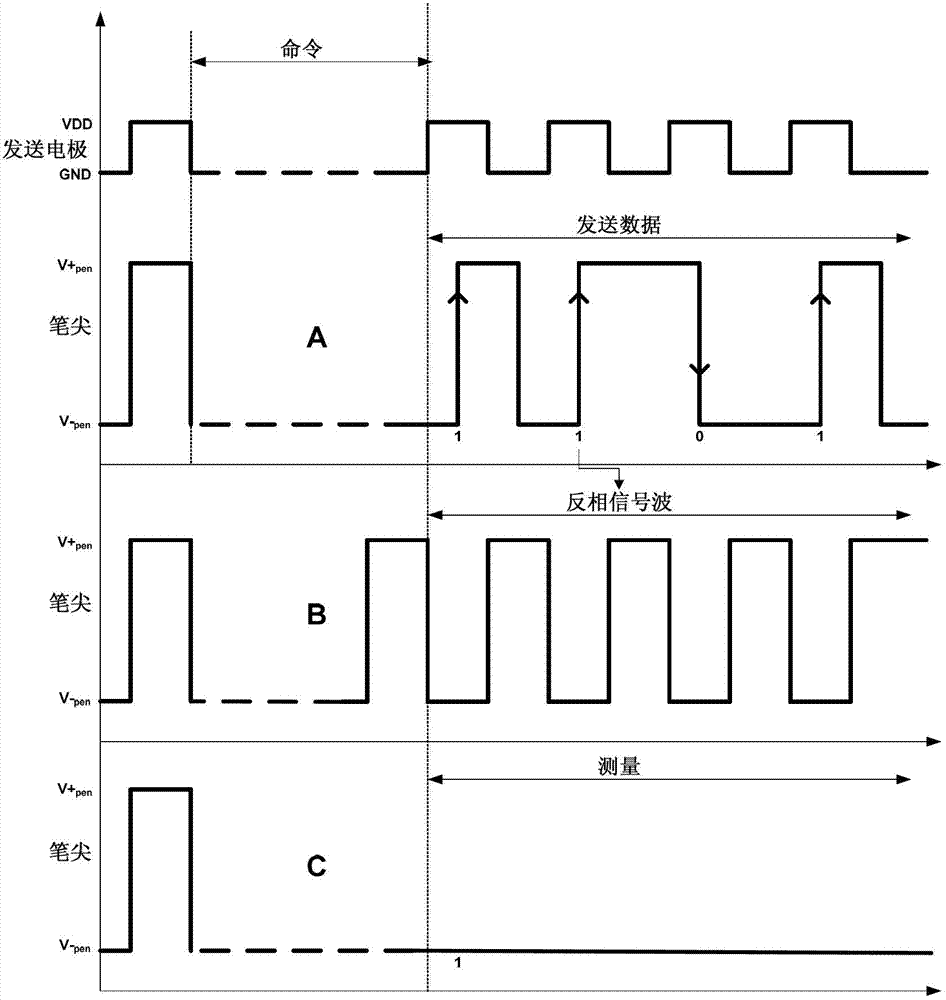

Active capacitance pen, capacitance touch panel and touch device

ActiveCN103440055AHigh strengthAchieve coordinationInput/output processes for data processingCapacitanceEngineering

The invention provides an active capacitance pen which is used for operation on a capacitance touch panel (200). The active capacitance pen comprises a first sending unit (1), a second sending unit (2) and a control processing unit (5). The first sending unit (1) sends high-voltage signals to the capacitance touch panel (200). The second sending unit (2) sends order signals to the capacitance touch panel (200) and informs the capacitance touch panel (200) of the fact that the first sending unit (1) sends the high-voltage signals to the capacitance touch panel (200), so that the capacitance touch panel (200) generates measuring signals which are synchronous with the high-voltage signals. The control processing unit (5) generates the high-voltage signals and the order signals and sends the high-voltage signals and the order signals to the capacitance touch panel (200) respectively through the first sending unit (1) and the second sending unit (2), so that the capacitance touch panel (200) obtains the position information of the capacitance pen (100). According to the capacitance pen, the intensity of the signals received by the capacitance touch panel can be improved, locating accuracy is improved, mutual harmony between the capacitance pen and the capacitance touch panel can be improved, and the capacitance pen and the capacitance touch panel conduct timely response.

Owner:HANVON CORP

Semiconductor integrated circuit device including first, second and third gates

InactiveUS20050243603A1Lower resistanceLimiting riseSolid-state devicesRead-only memoriesEngineeringSemiconductor

A semiconductor integrated device having a plurality of memory cells, each including a floating gate, a control gate and an auxiliary gate formed over a side surface of the floating gate through an insulator film. Auxiliary gates coupled to selected memory cells function to generate hot electrons and are alternately arranged with other auxiliary gates functioning to prevent write errors in the non-selected memory cells.

Owner:RENESAS ELECTRONICS CORP

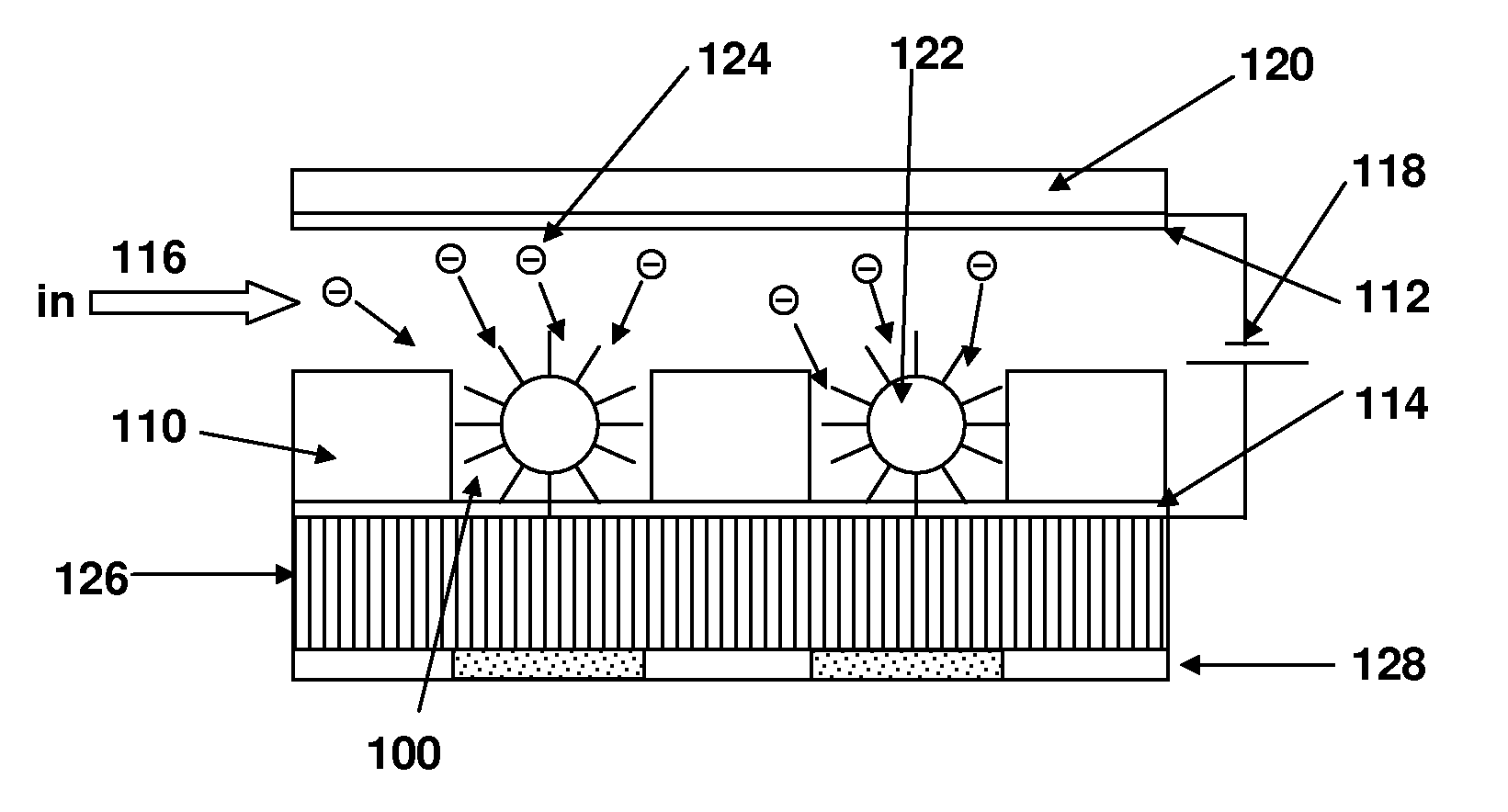

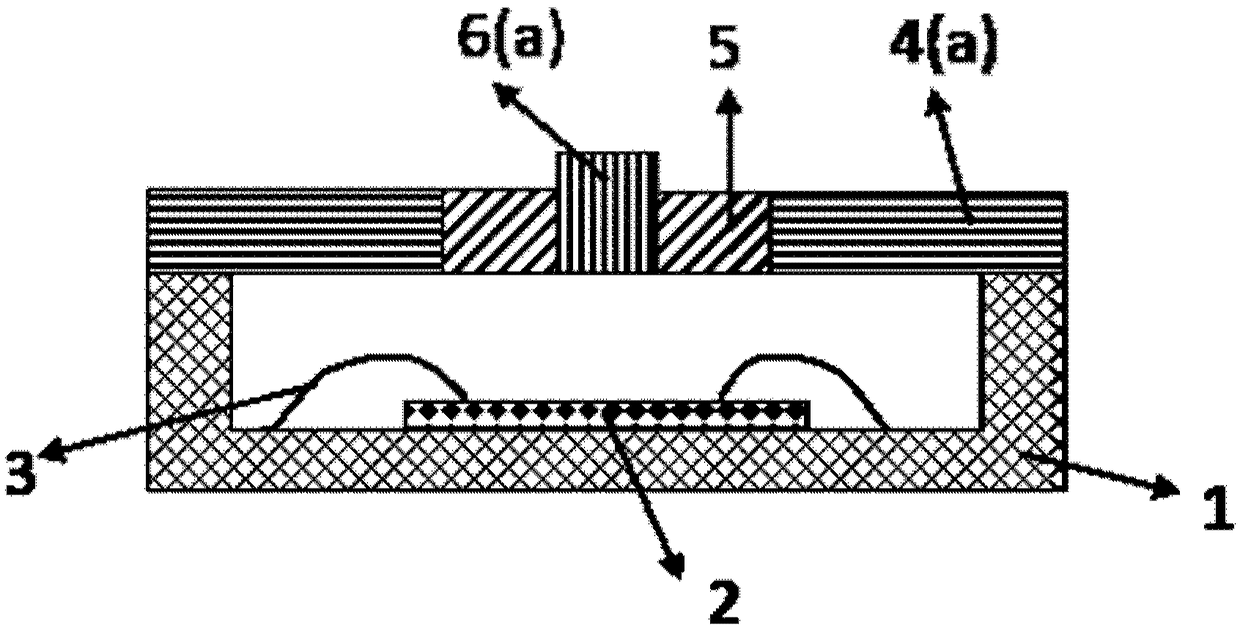

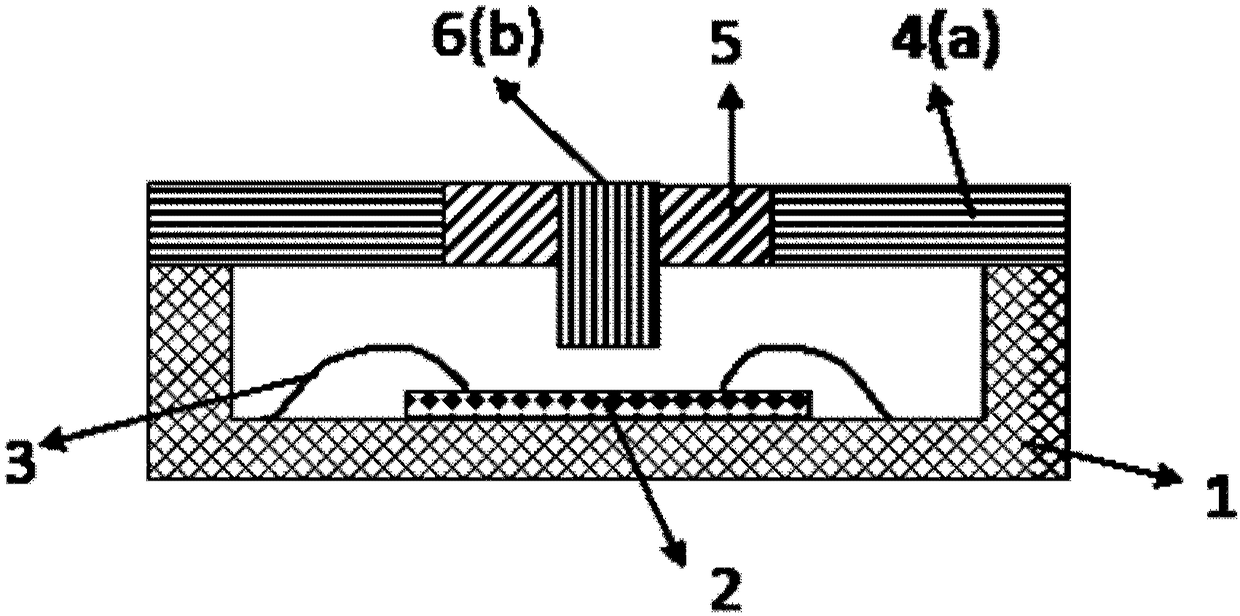

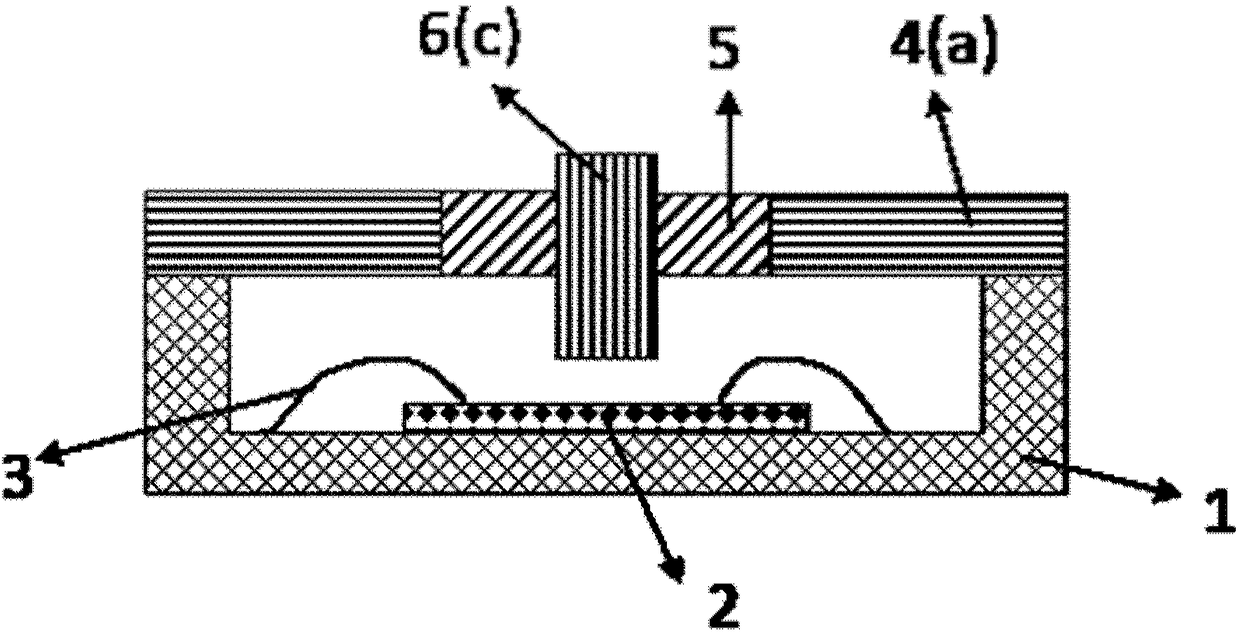

Packaging cover plate of sensitivity-strengthened electric field sensor and packaging method

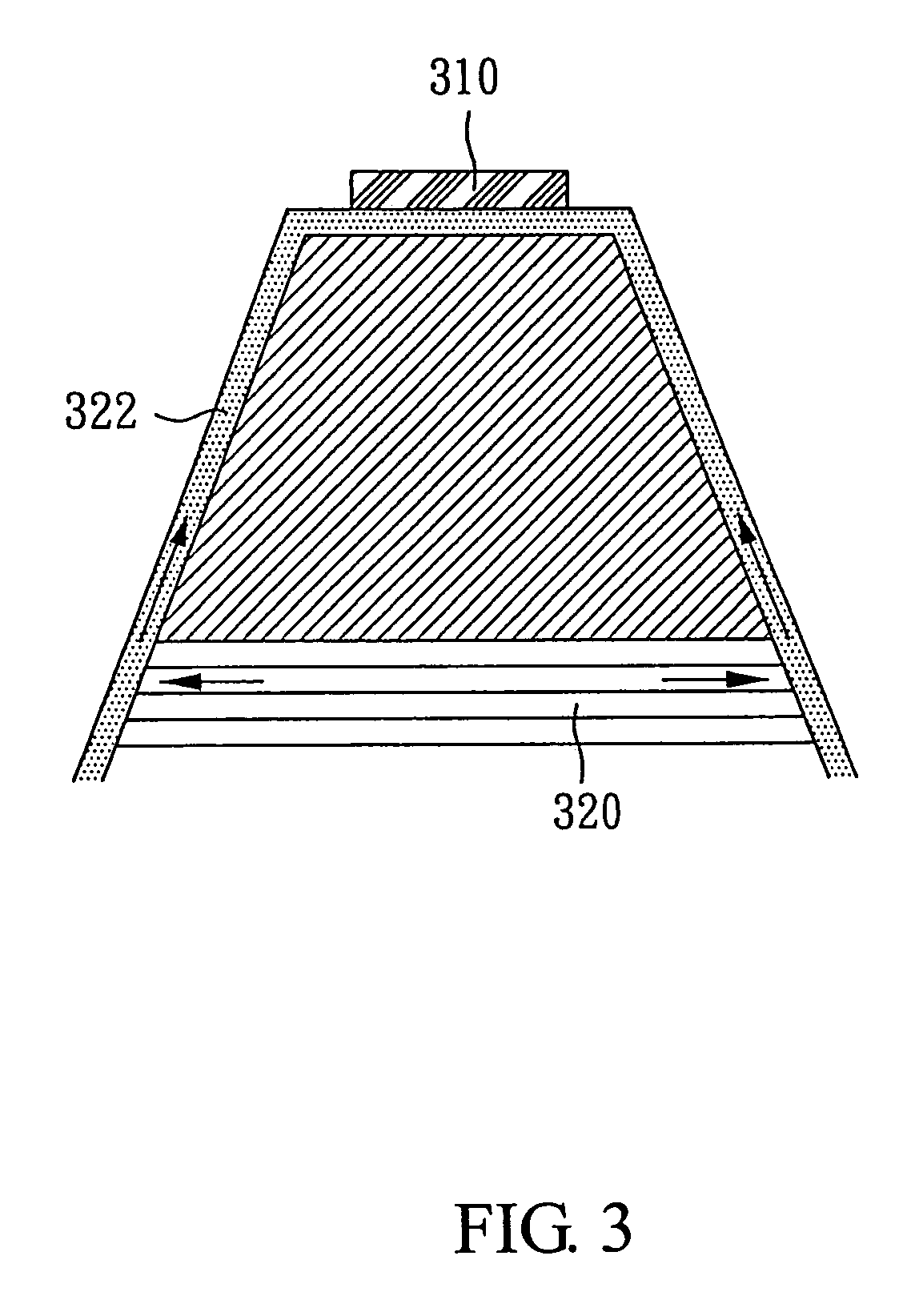

ActiveCN106672890AEnhanced surface electric field strengthHigh sensitivitySolid-state devicesFluid speed measurementIsolation effectElectric field sensor

The invention discloses a packaging cover plate of a sensitivity-strengthened electric field sensor and a packaging method and relates to the technical field of electric field detection. The packaging cover plate comprises an inner core, a cover plate edge and an isolation ring, wherein the inner core is located in the middle of the cover plate and above the sensitive face of the packaged electric field sensor, and the sensitivity of the electric field sensor is effectively strengthened. The cover plate edge is used for connecting a packaging pipe housing. The isolation ring is located between the cover plate edge and the inner core to play supporting and isolation effects. In addition, the packaging convenience is further increased by adopting the structure. Correspondingly, the structure is successively prepared by adopting the packaging method of the corresponding electric field sensor.

Owner:BEIJING TFLYING TRANSDUCER TECH CO LTD

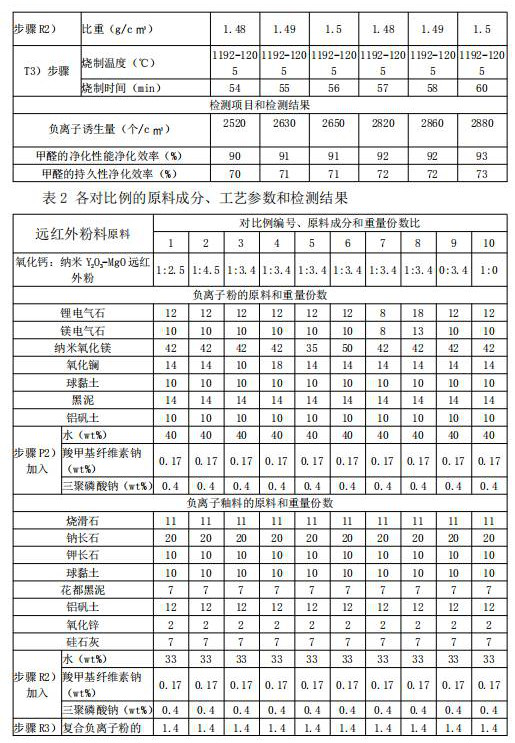

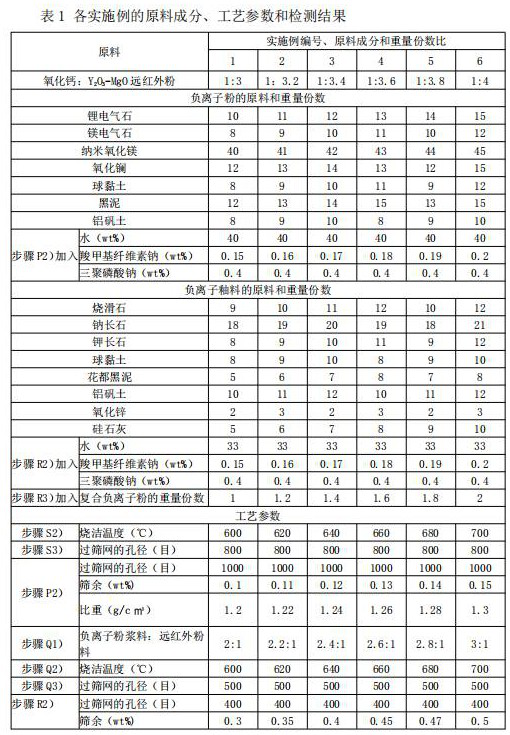

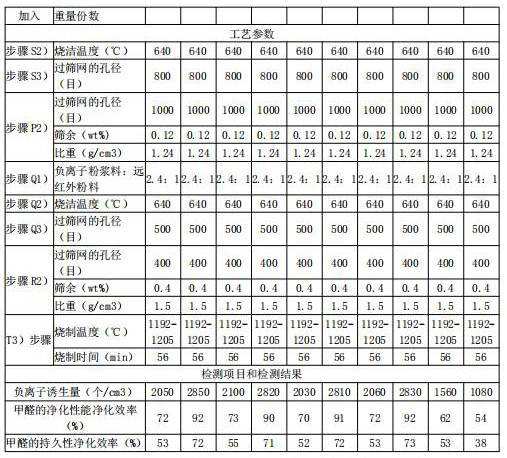

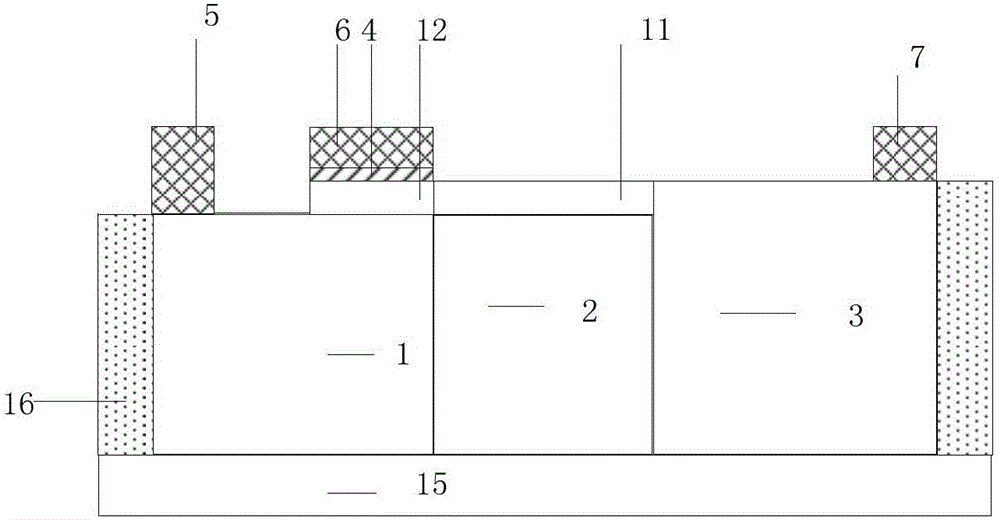

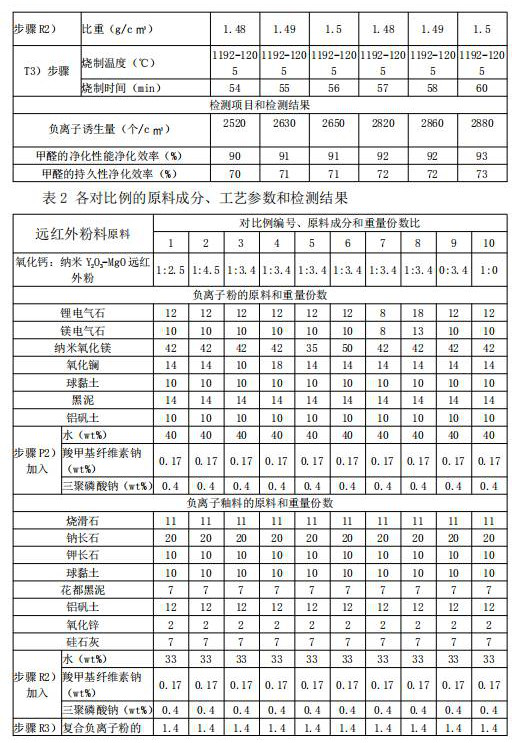

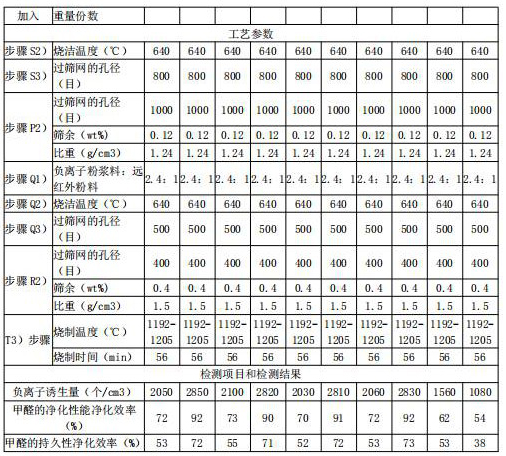

Ceramic tile with far infrared composite air purification function, and preparation process thereof

ActiveCN112010672AWith far-infrared composite air purification functionImprove purification effectGlazePhysical chemistry

The invention relates to the technical field of ceramics and functional decorative materials, and especially relates to a ceramic tile with a far infrared composite air purification function, and a preparation process thereof. The ceramic tile comprises a ceramic tile blank and a glaze layer, the glaze layer is prepared from far-infrared powder and negative ion powder, and the far-infrared powderis prepared from calcium oxide and nano-Y2O3-MgO far-infrared powder; the outer surface of the nano-Y2O3-MgO far infrared powder is wrapped by the negative ion powder and is sintered; the nano-Y2O3-MgO far infrared powder is adsorbed on the surfaces of the calcium oxide particles; the mixing ratio of the calcium oxide to the nano-Y2O3-MgO far infrared powder in parts by weight is 1: (3-4); and theweight part ratio of the far infrared powder to the negative ion powder is 1: (2-3). According to the ceramic tile with the far infrared composite air purification function, the activity of negativeion inducing substances in the negative ion powder can be activated, so more negative ions are induced to be generated for air purification.

Owner:佛山市东鹏陶瓷发展有限公司 +1

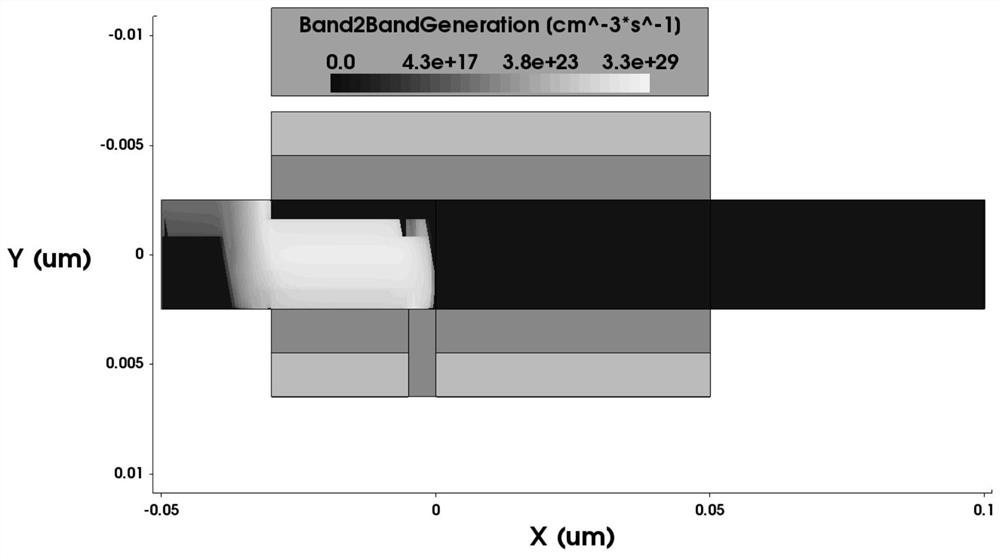

Tunneling field effect transistor capable of increasing current switching ratio

ActiveCN106098765AGood offMitigate bipolar effectsSemiconductor devicesVery large scale integrated circuitsCMOS

The invention belongs to the logic device and circuit field in the super-large scale integrated circuit field and relates to a tunneling field effect transistor capable of increasing a current switching ratio. According to the tunneling field effect transistor, a low-K dielectric region is arranged between a source region and a drain region, so that an electric field between the source region and an intrinsic region can be increased, and therefore, on-state current can be improved, and off-state current can be suppressed; a doped layer is adopted, so that a reversely biased PN junction can be formed based on the substrate, and therefore, the contact of a source region-low-K dielectric region-drain region structure with the substrate can be isolated, and the off-state current of the tunneling field effect transistor (TFET) can be decreased. An on-state current increasing mode and an off-state current suppressing mode can be combined and overlapped with each other. Thus, the tunneling field effect transistor of the invention can improve the on-state current, is compatible with conventional CMOS technologies, is low in cost and can achieve a high current switching ratio.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

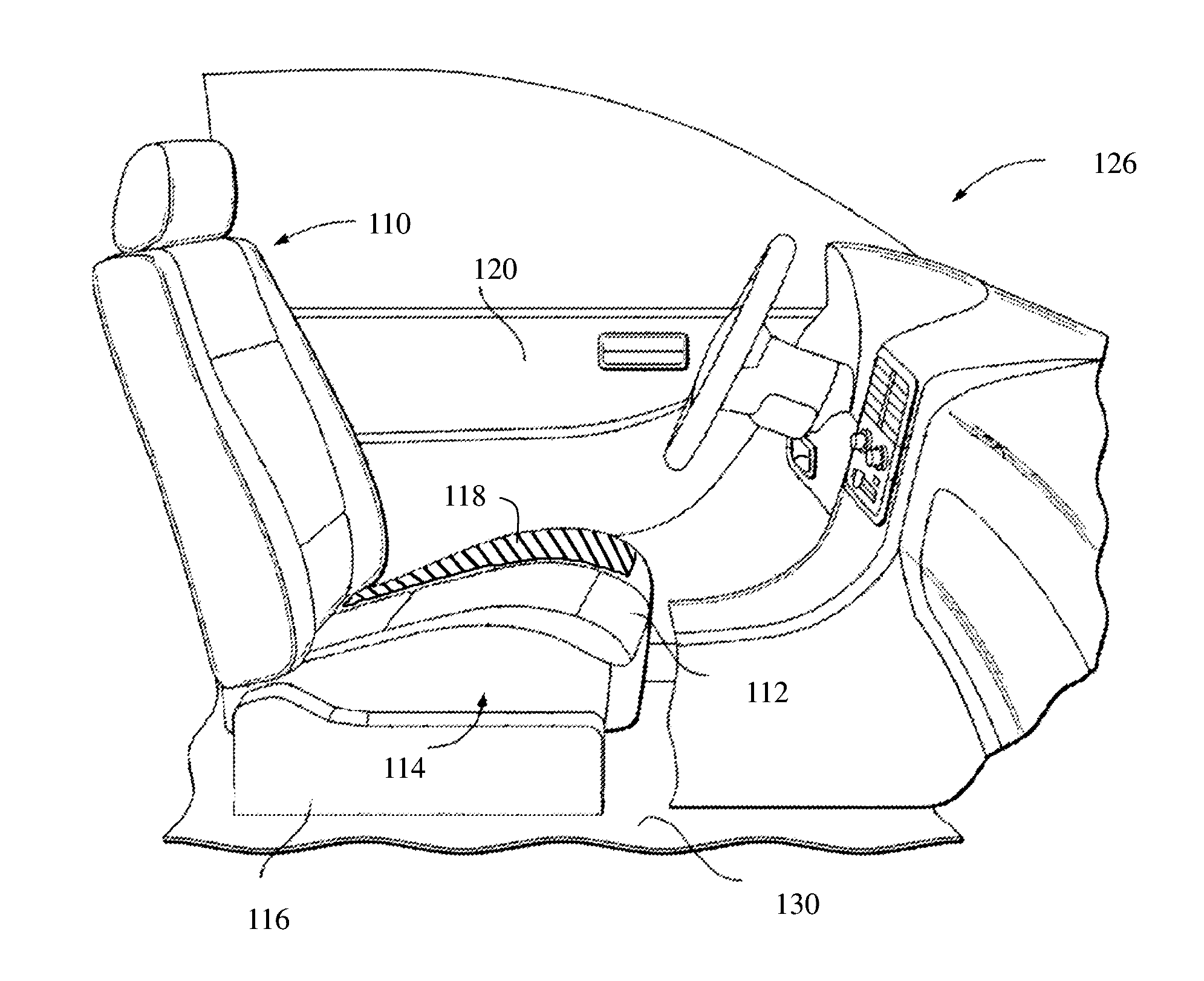

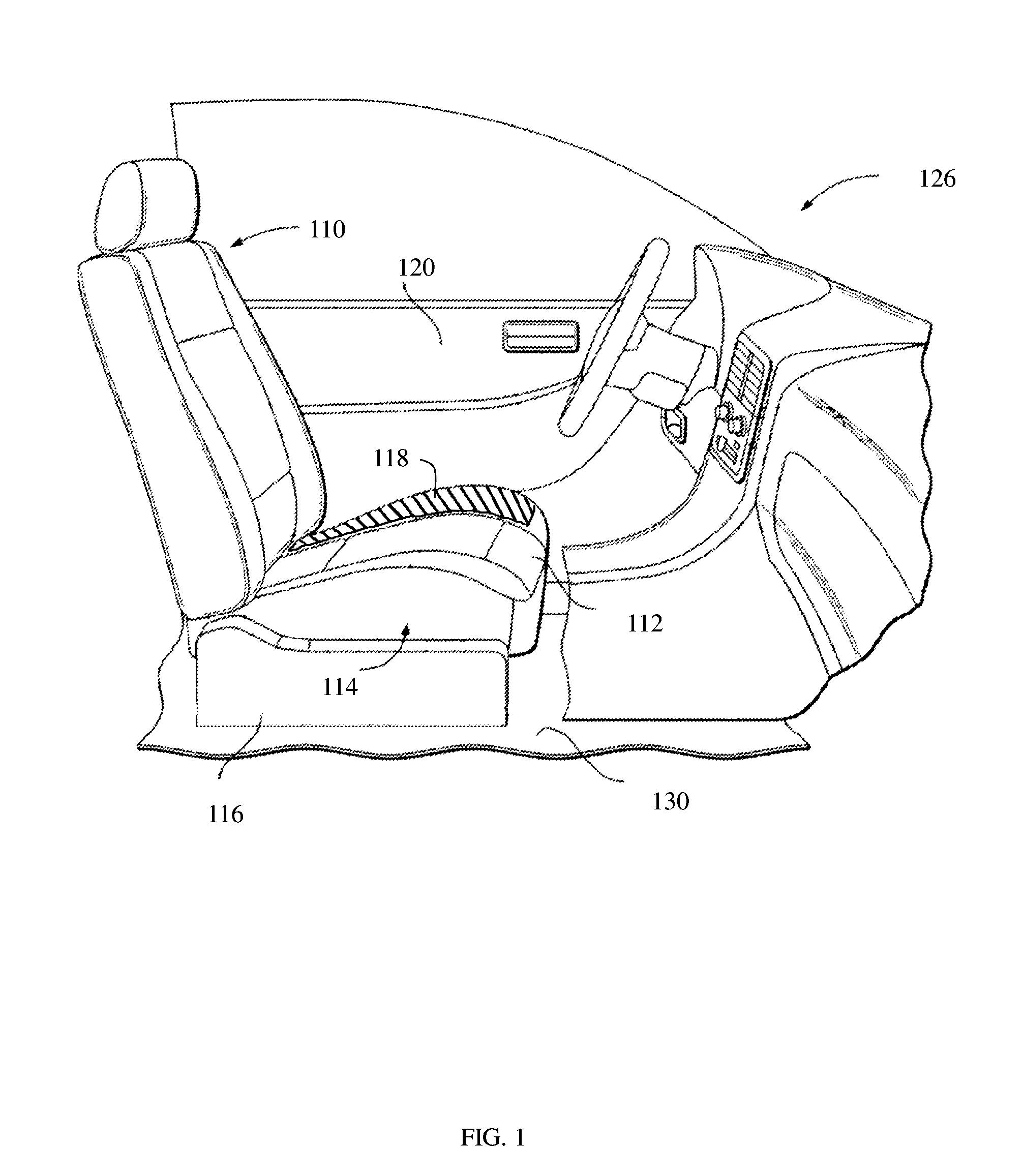

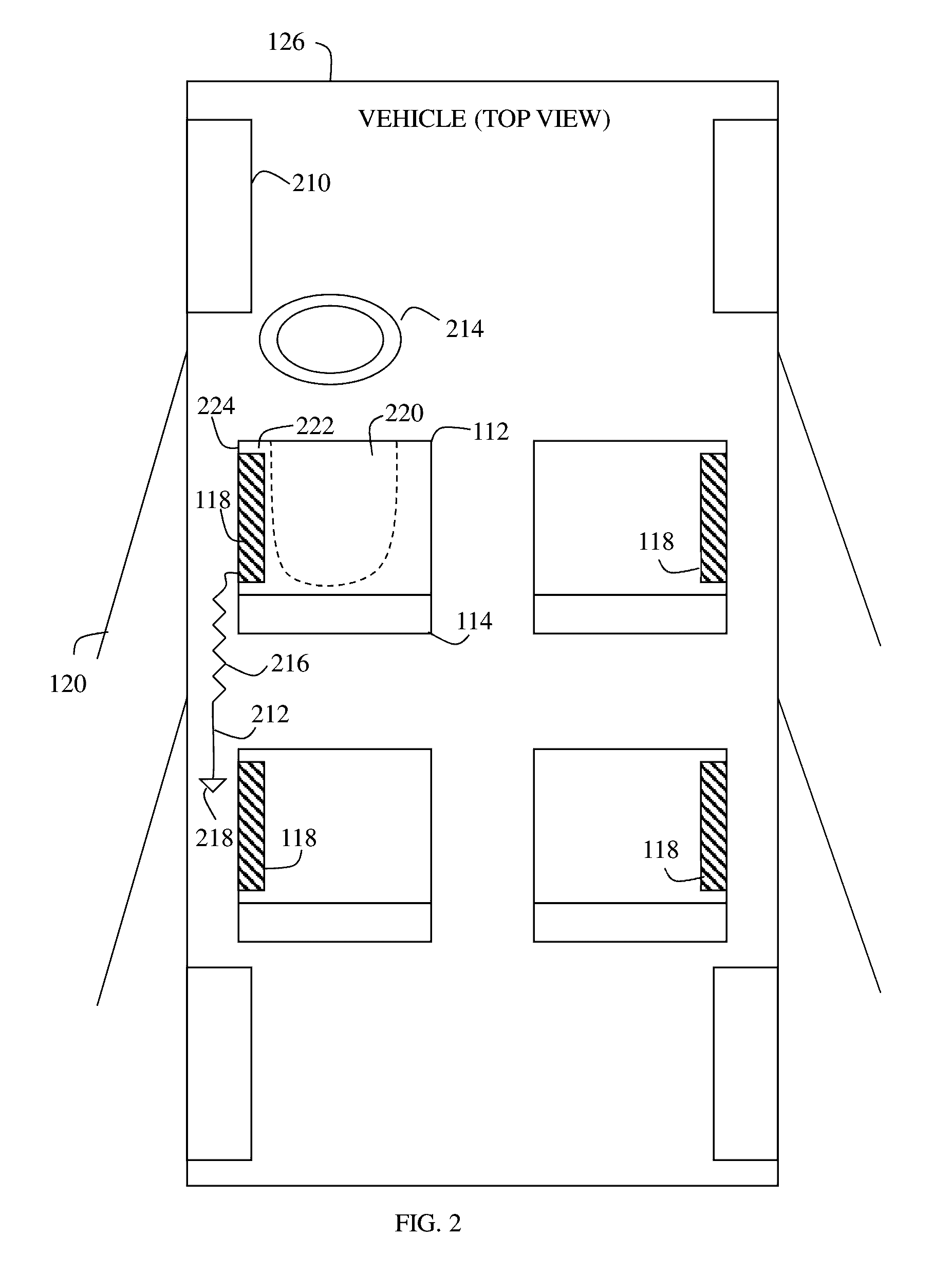

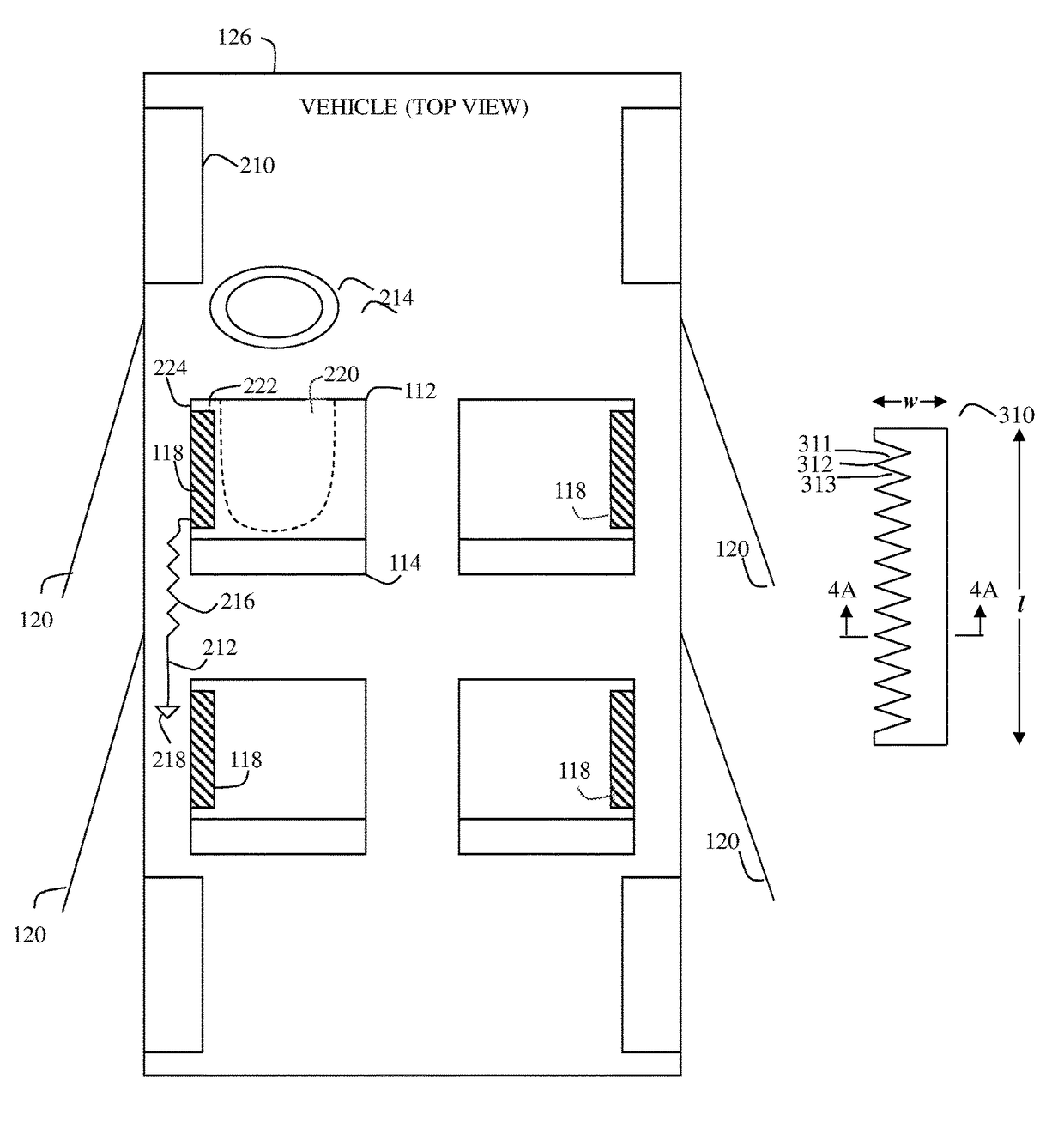

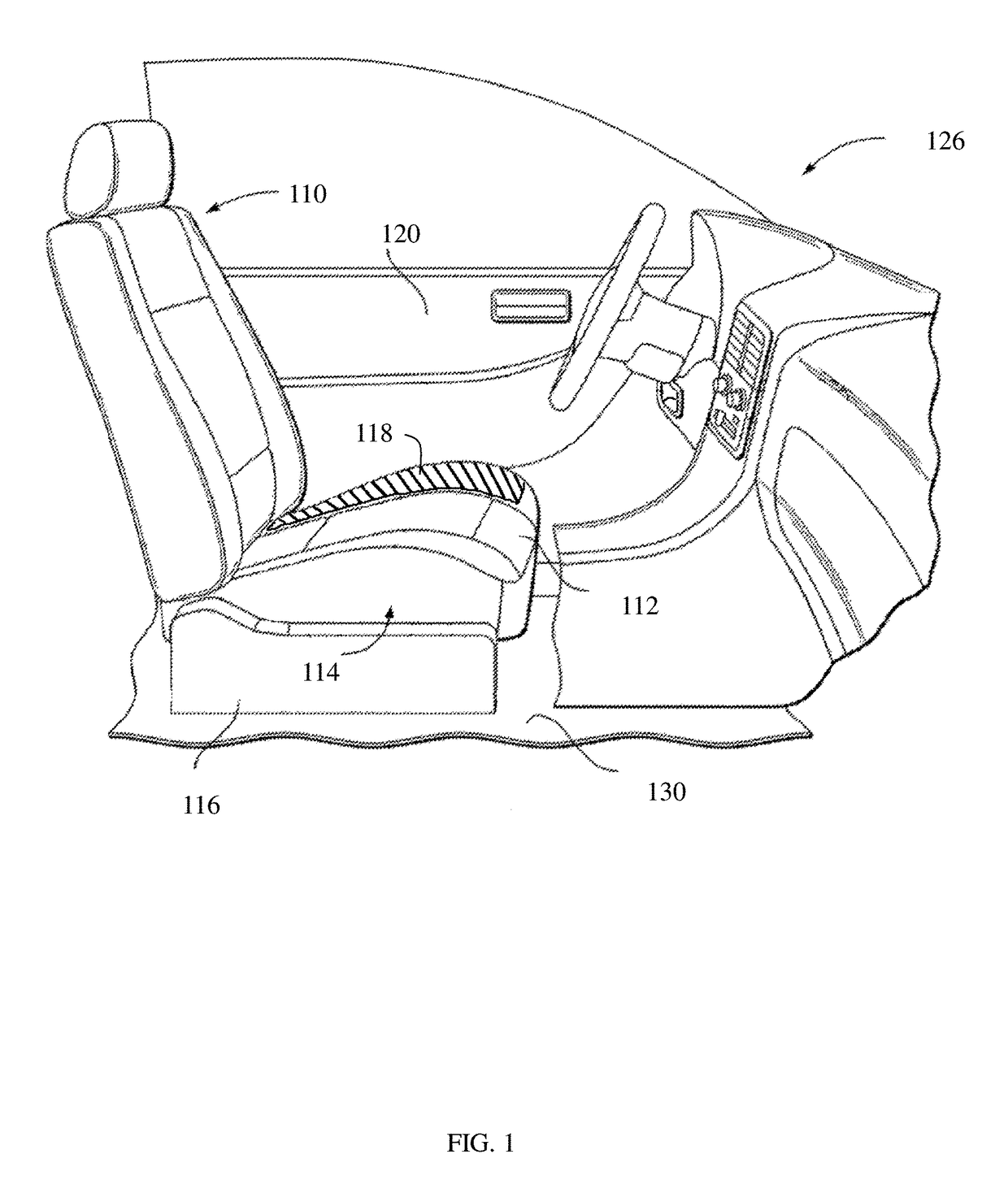

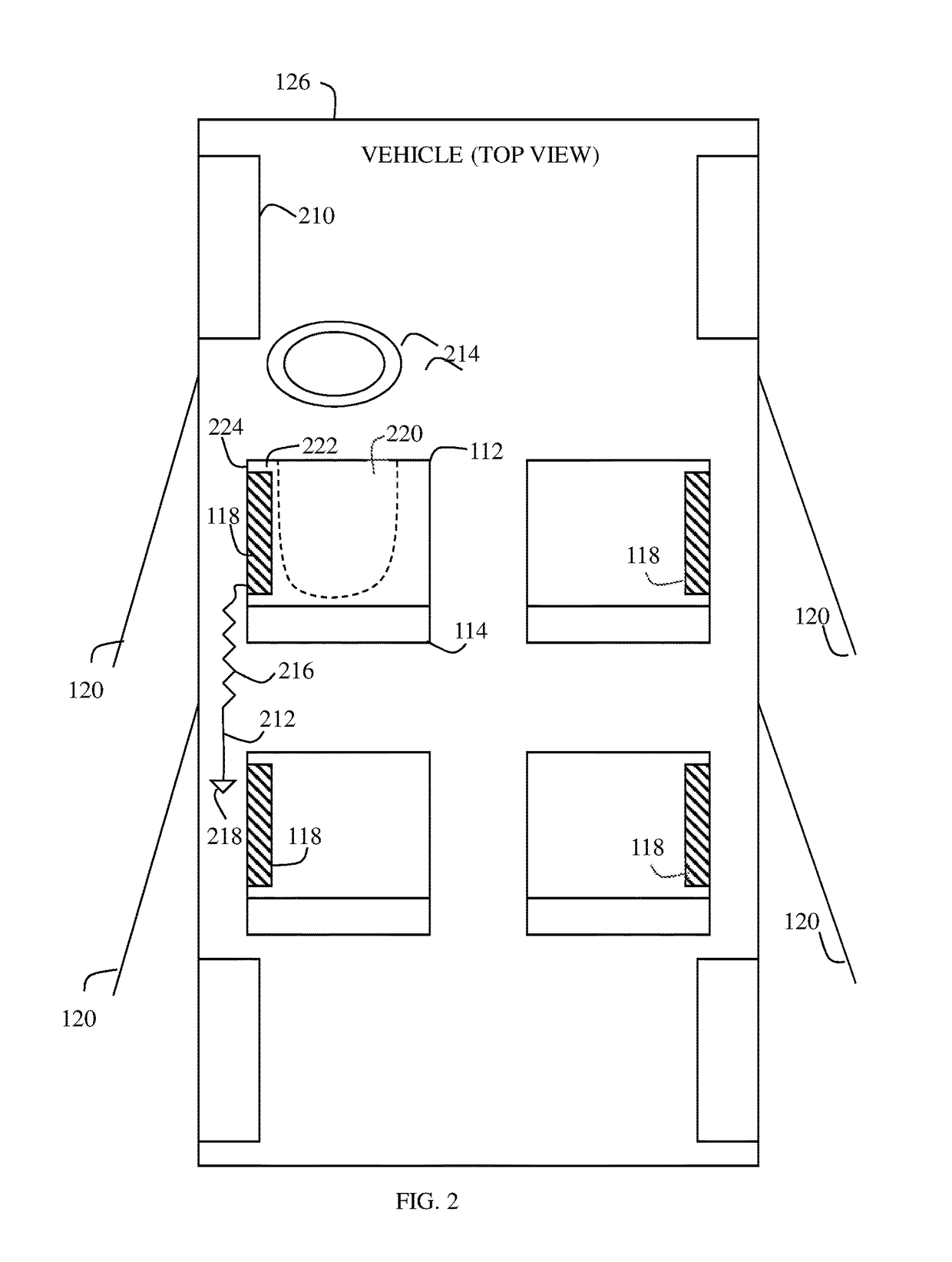

Electrostatic discharge mitigator for vehicles

ActiveUS20170057389A1Efficient dischargeEasy to modifySeat coveringsElectric/fluid circuitElectricityEngineering

An improved, low-cost system for mitigating electrostatic discharge (ESD) that may occur during egress from vehicles is provided. One embodiment comprises a narrow conductive electrode that is galvanically connected to the vehicle chassis, and that is applied to that one edge of a seat which is next to the door nearest that seat. For example, in the U.S., this edge will normally be the left edge of the driver's seat, or the right edge of the front passenger's seat. The electrode is substantially located on a normally unoccupied surface of the seat cushion. Other embodiments further include pointed shapes on the electrode to increase the electric field intensity, which may promote more complete discharging. Certain embodiments may allow a manufacturer to easily retrofit an existing seat design with an electrode by simply adding a manufacturing step. The system is simpler, less expensive, and more effective than prior art ESD mitigators.

Owner:DICKERMAN ROBERT LEON

A packaging cover plate and packaging method of a sensitivity-enhanced electric field sensor

ActiveCN106672890BHigh sensitivityReduce distanceSolid-state devicesFluid speed measurementIsolation effectElectric field sensor

The invention discloses a packaging cover plate of a sensitivity-strengthened electric field sensor and a packaging method and relates to the technical field of electric field detection. The packaging cover plate comprises an inner core, a cover plate edge and an isolation ring, wherein the inner core is located in the middle of the cover plate and above the sensitive face of the packaged electric field sensor, and the sensitivity of the electric field sensor is effectively strengthened. The cover plate edge is used for connecting a packaging pipe housing. The isolation ring is located between the cover plate edge and the inner core to play supporting and isolation effects. In addition, the packaging convenience is further increased by adopting the structure. Correspondingly, the structure is successively prepared by adopting the packaging method of the corresponding electric field sensor.

Owner:BEIJING TFLYING TRANSDUCER TECH CO LTD

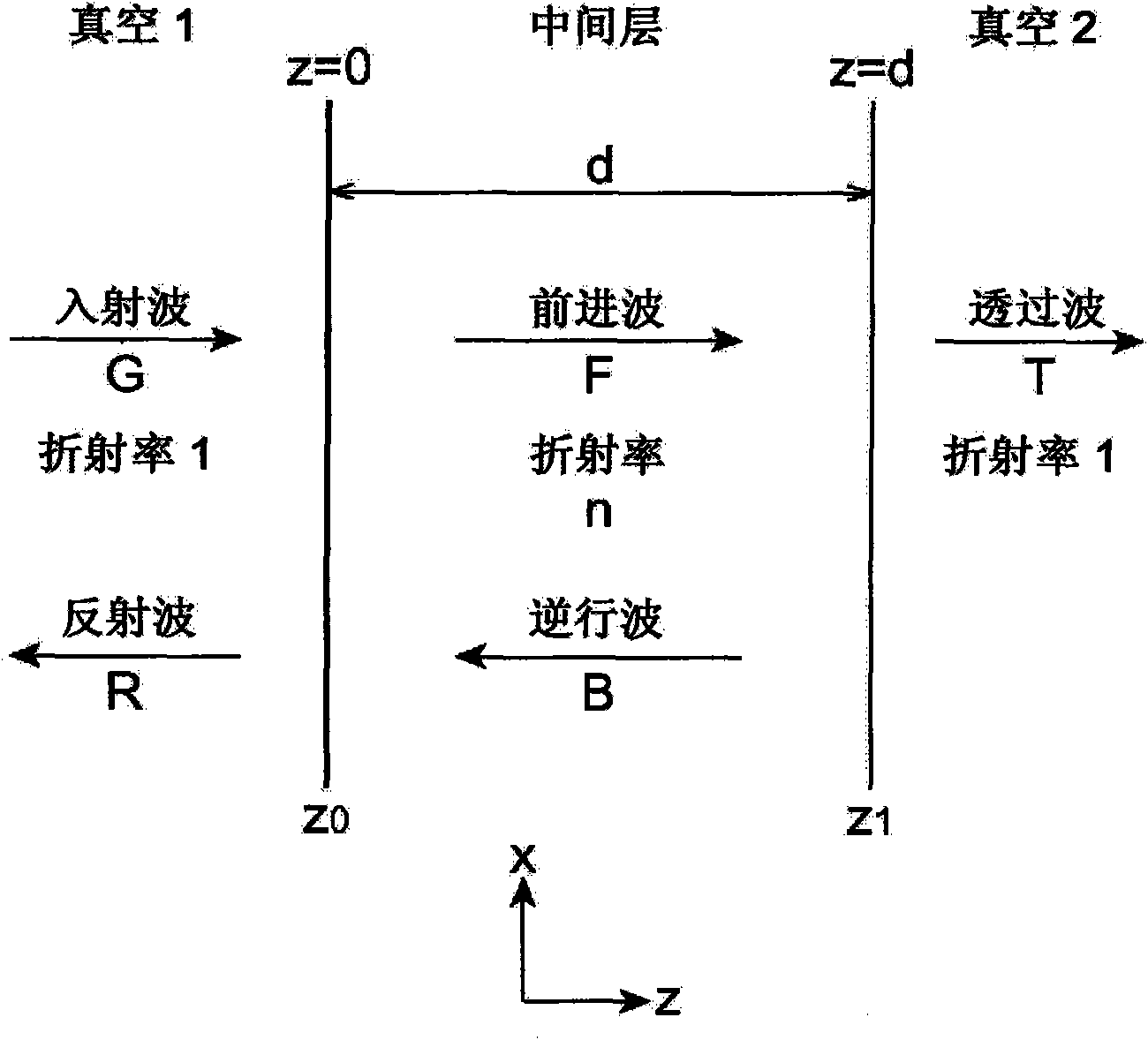

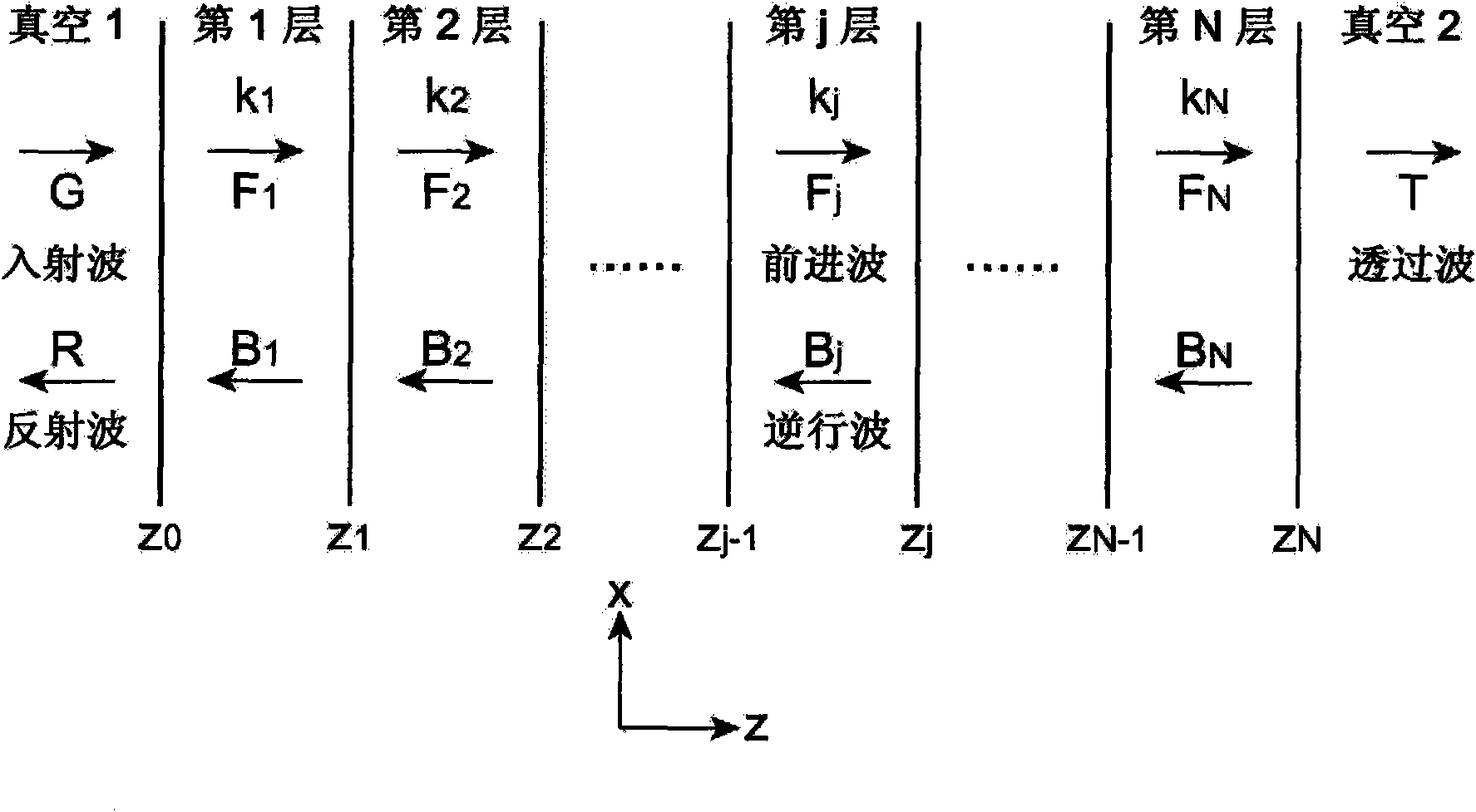

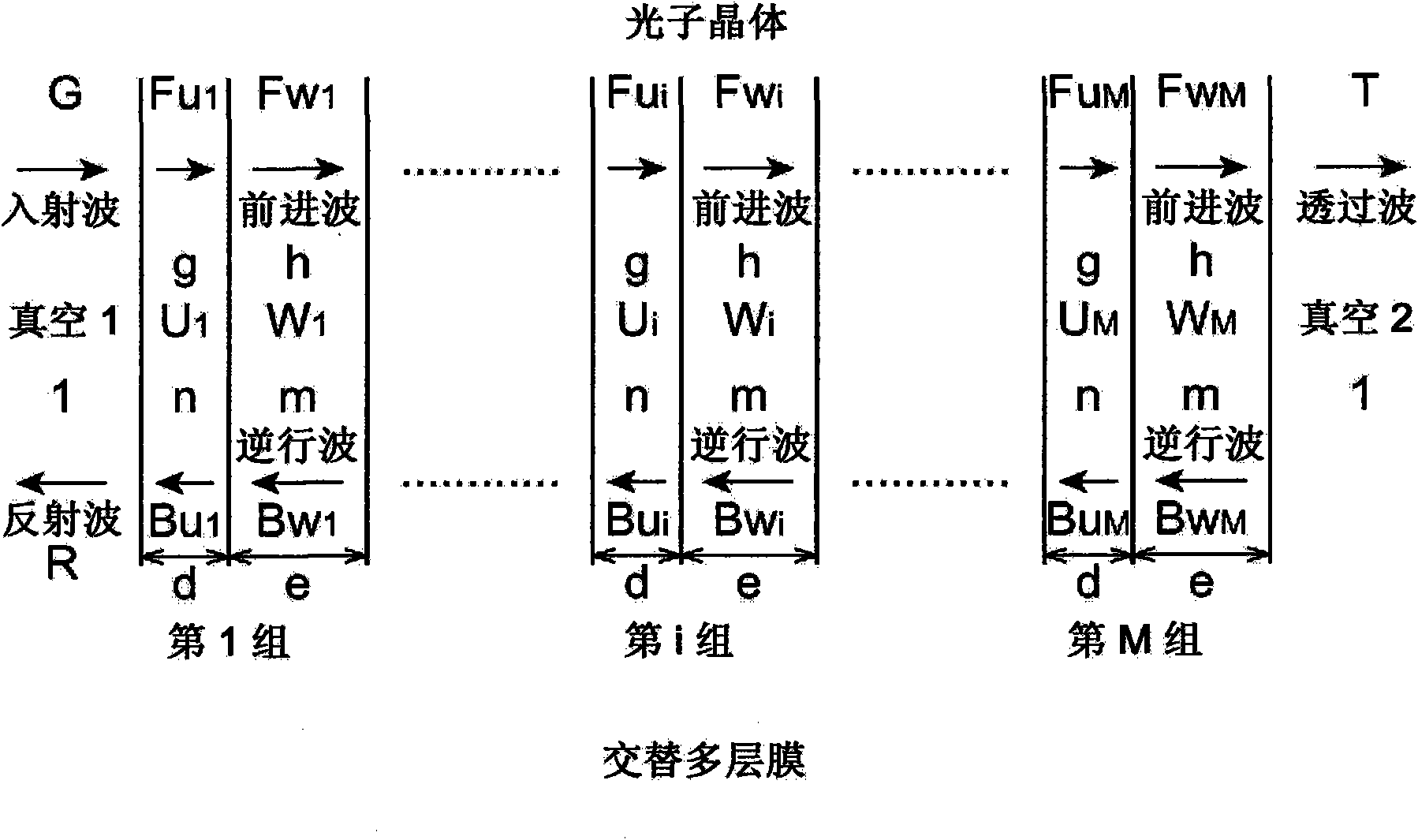

Composite photonic structure element, surface emitting laser using the composite photonic structure element, wavelength conversion element, and laser processing device using the wavelength conversion element

InactiveCN101918890AElectric field multiplicationSecond harmonic largeNanoopticsNon-linear opticsPhotonic bandgapPhotonics

A composite photonic structure element includes a photonic crystal and a multi-layer film. The photonic crystal is formed by alternately laying an active layer having a nonlinear effect for converting a fundamental wave into a second higher harmonic and an inactive layer having no nonlinear effect, so that the energy of the fundamental wave coincides with the photonic band gap end. The multi-layer film is formed by layering a plurality of sets of two types of thin films having different refractive indexes so as to reflect the fundamental wave. The multi-layer film is connected to both ends of the photonic crystal. The fundamental wave comes into one of the end faces and the fundamental wave is reciprocally reflected between resonators having a multi-layer film so that the intensity of the fundamental wave in the photonic crystal is increased. The fundamental wave is converted into a second higher harmonic in the active layer and the second higher harmonic is extracted outside from the other end face.

Owner:PUBLIC UNIVERSITY CORPORATION OSAKA CITY UNIVERSITY +2

Tunnel field effect transistor with increased on state current

InactiveCN106206703ASuppresses part of the off-state leakage pathSuppresses off-state leakage pathsSemiconductor/solid-state device manufacturingDiodeVery large scale integrated circuitsCMOS

The invention belongs to the field of a logic device and circuit in the field of a super-large-scale integrated circuit, specifically a tunnel field effect transistor with an increased on state current. According to the tunnel field effect transistor, a low K dielectric area is arranged between a source area and a drain area, thereby isolating the source area and the drain area; an intrinsic area is arranged on the source area; a layer of conductive channel is arranged between the intrinsic area and the drain area; and the conductive channel is located on the low K dielectric area. According to the structure of the tunnel field effect transistor, the bipolar effect of a traditional transverse TFET is weakened. Through utilization of a low K dielectric, the contact between the drain area and the intrinsic area is reduced and the bipolar effect is weakened, thereby facilitating thorough switch-off of a device. An electric field of a tunnel junction area is increased by employing the low K dielectric and a high K side wall. The on state current of the TFET is increased through adoption of the side wall (a passivation layer) made of a high dielectric material. According to the tunnel field effect transistor, the bipolar effect is weakened, the on state current is increased, the tunnel field effect transistor is compatible with a CMOS technology and the cost is low.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

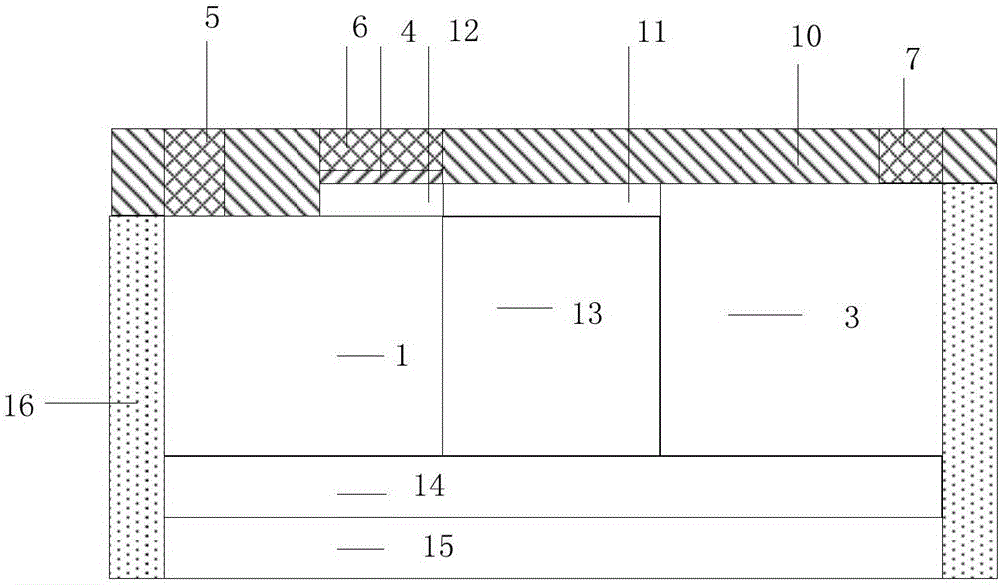

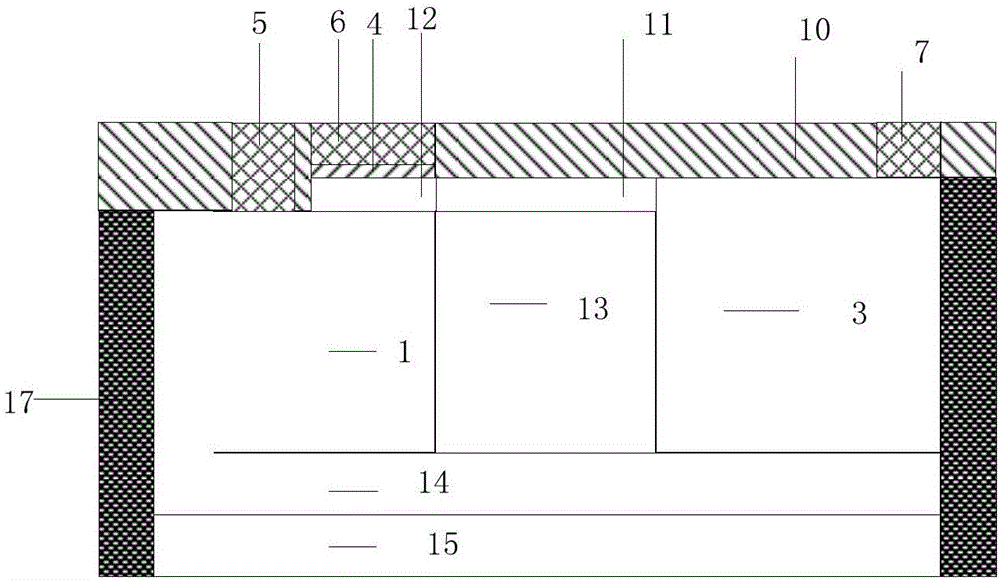

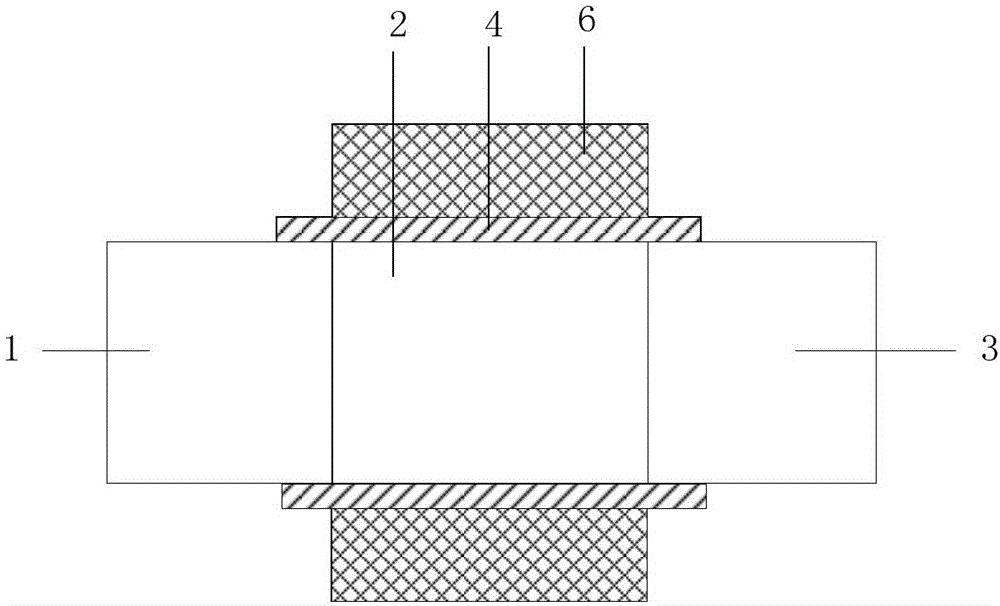

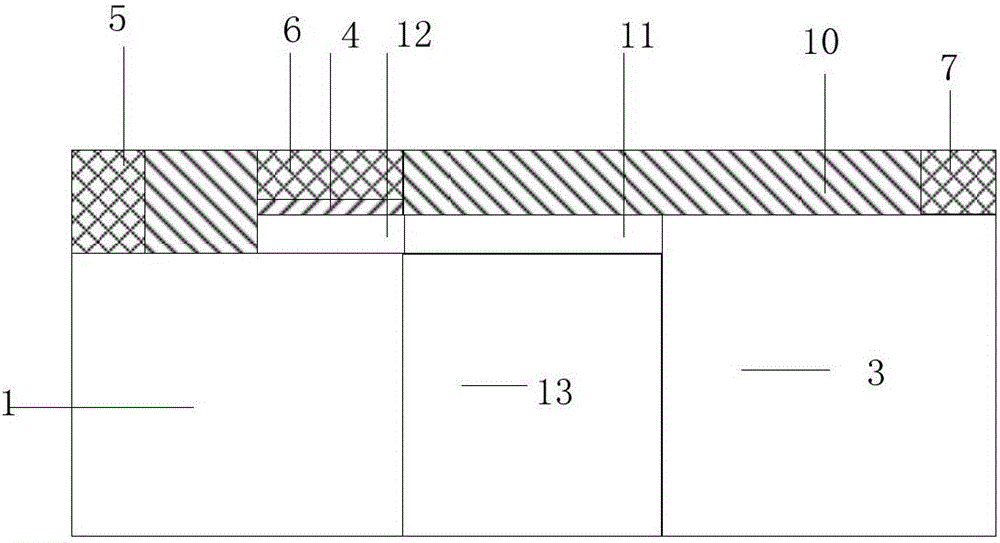

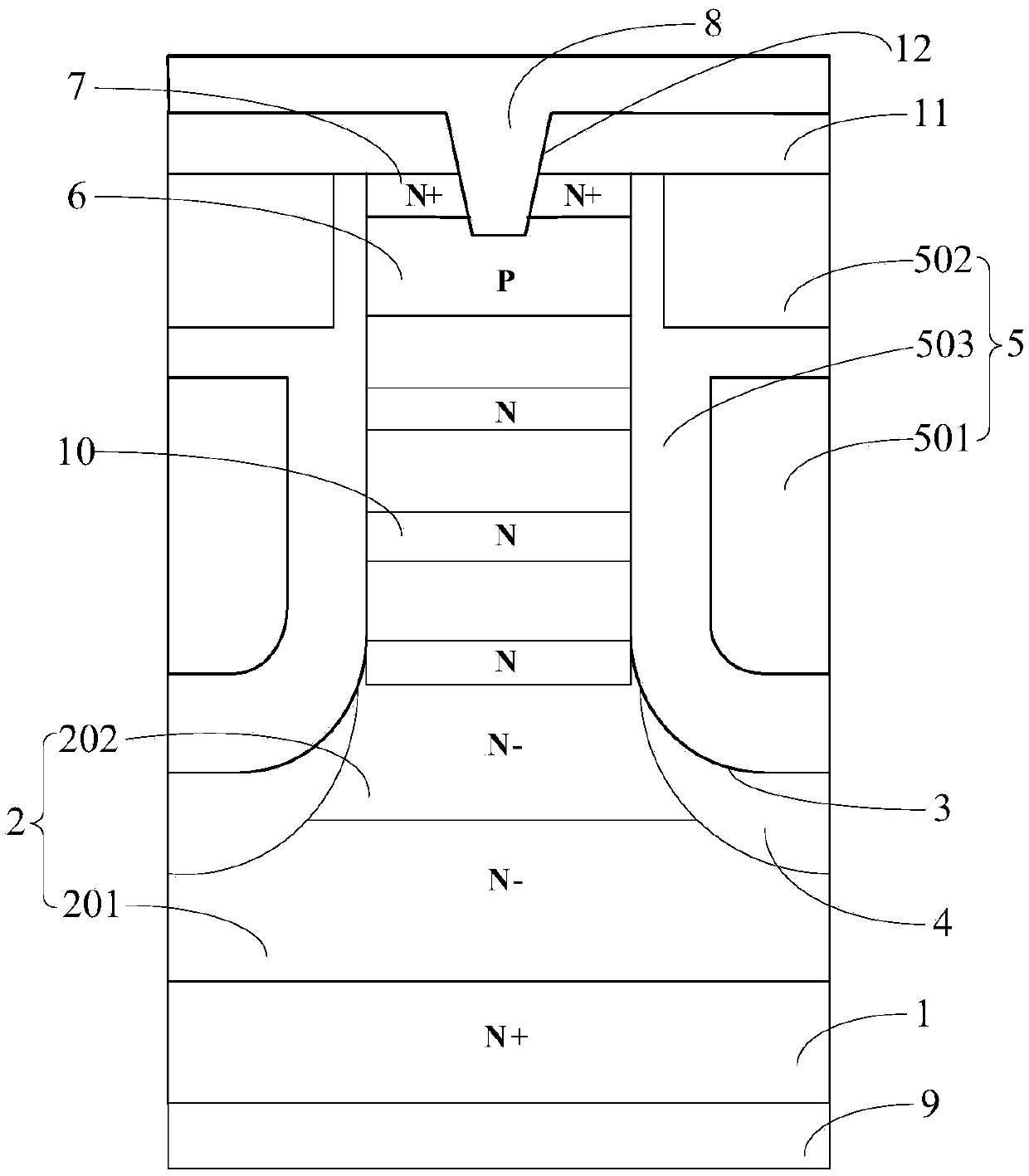

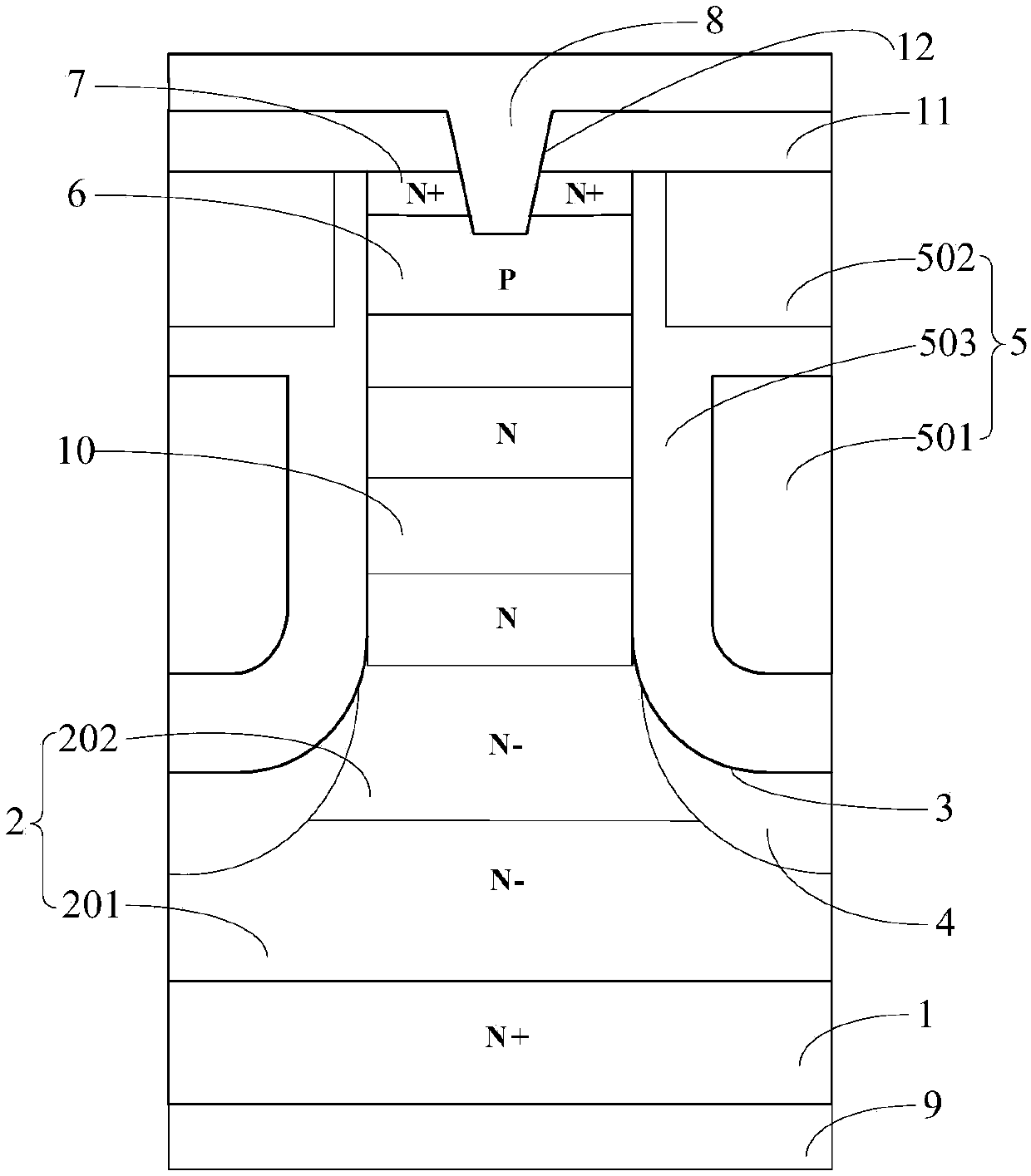

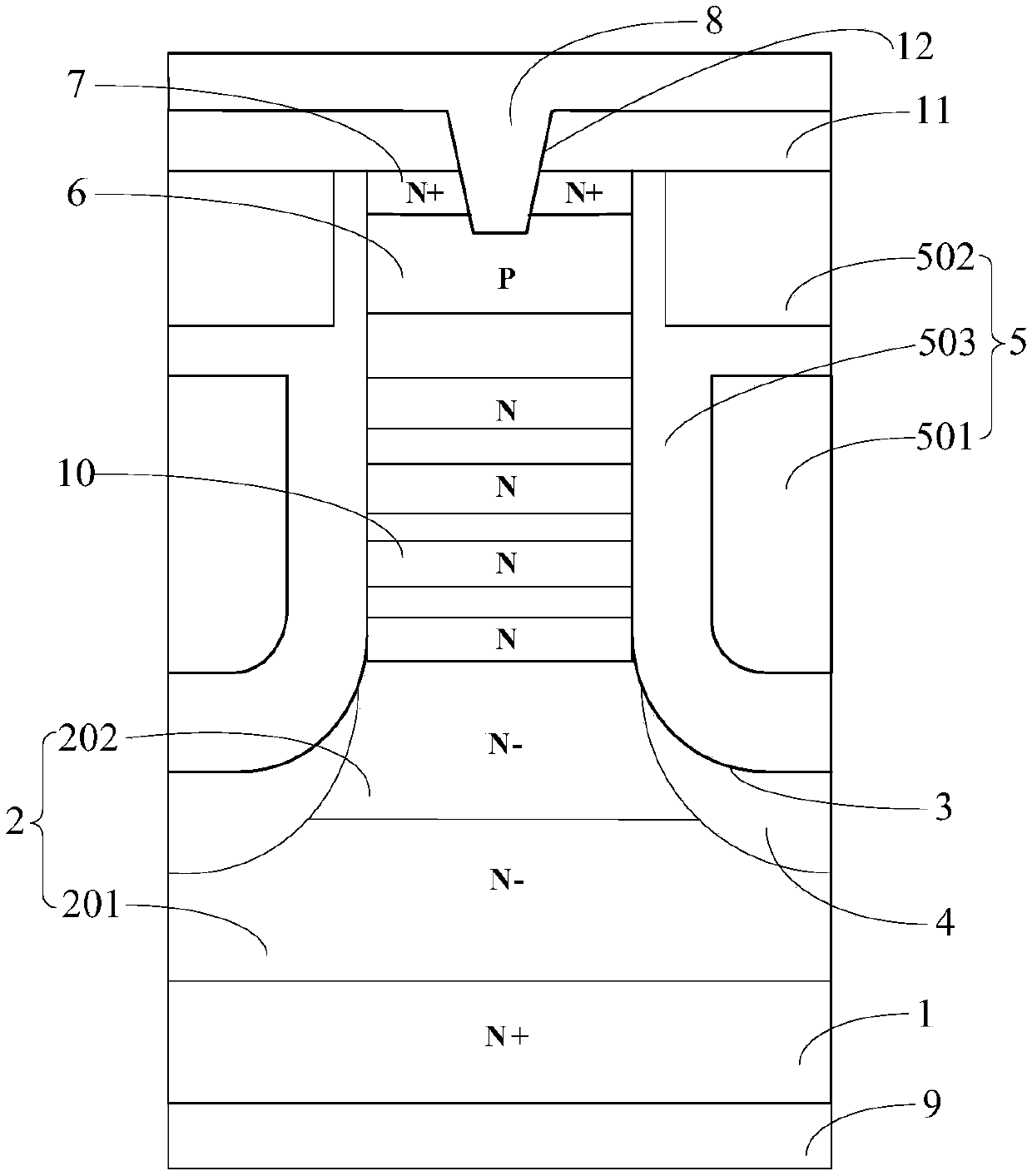

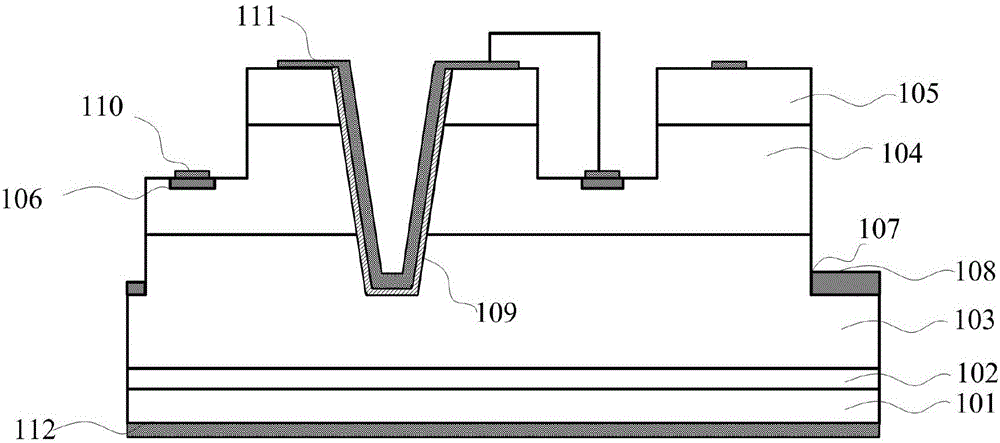

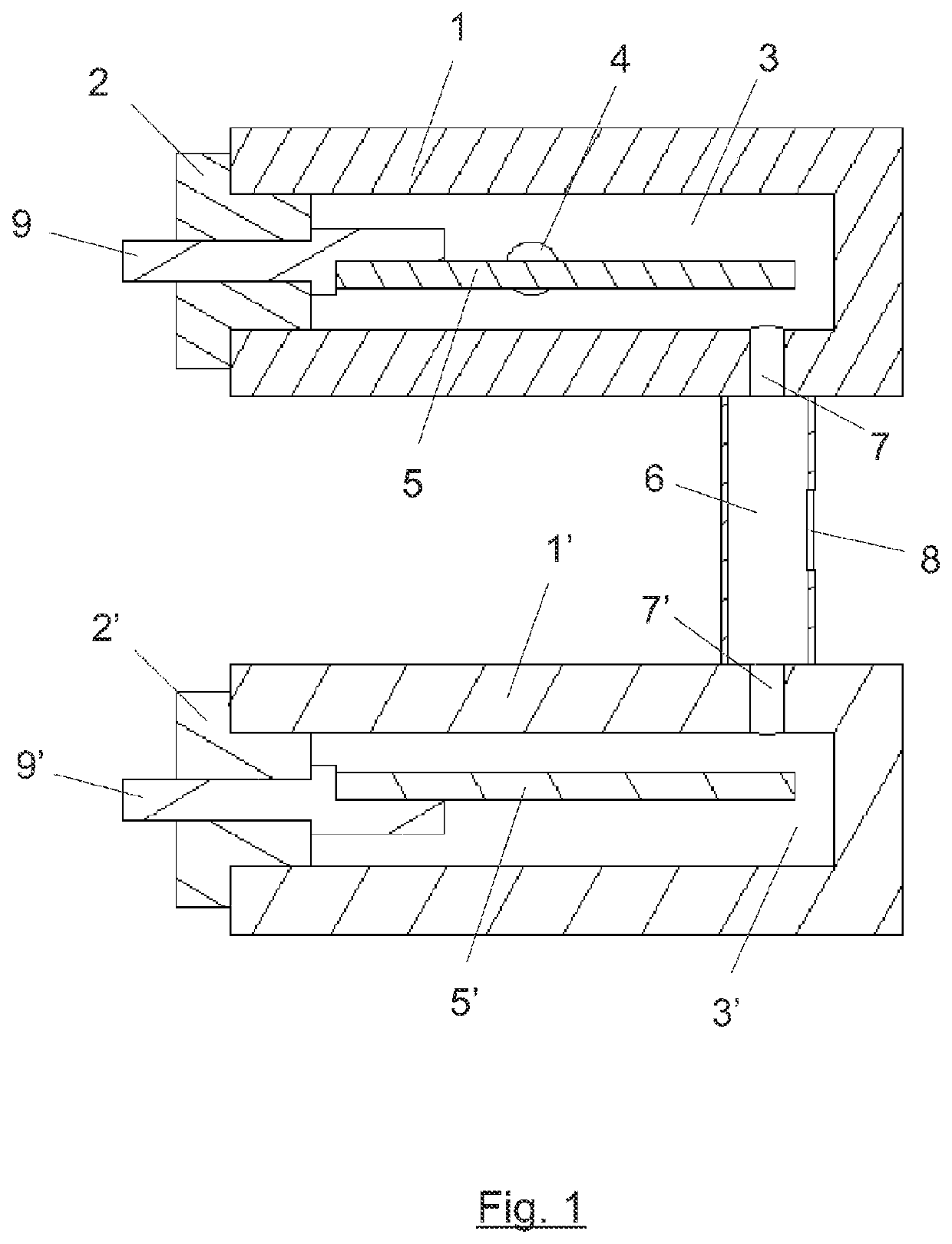

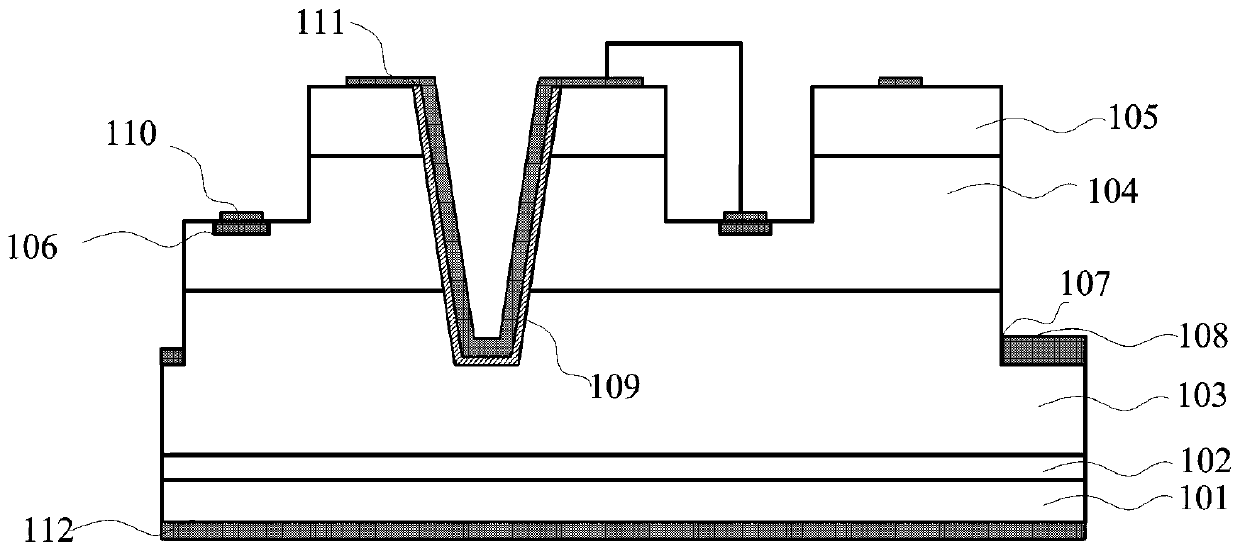

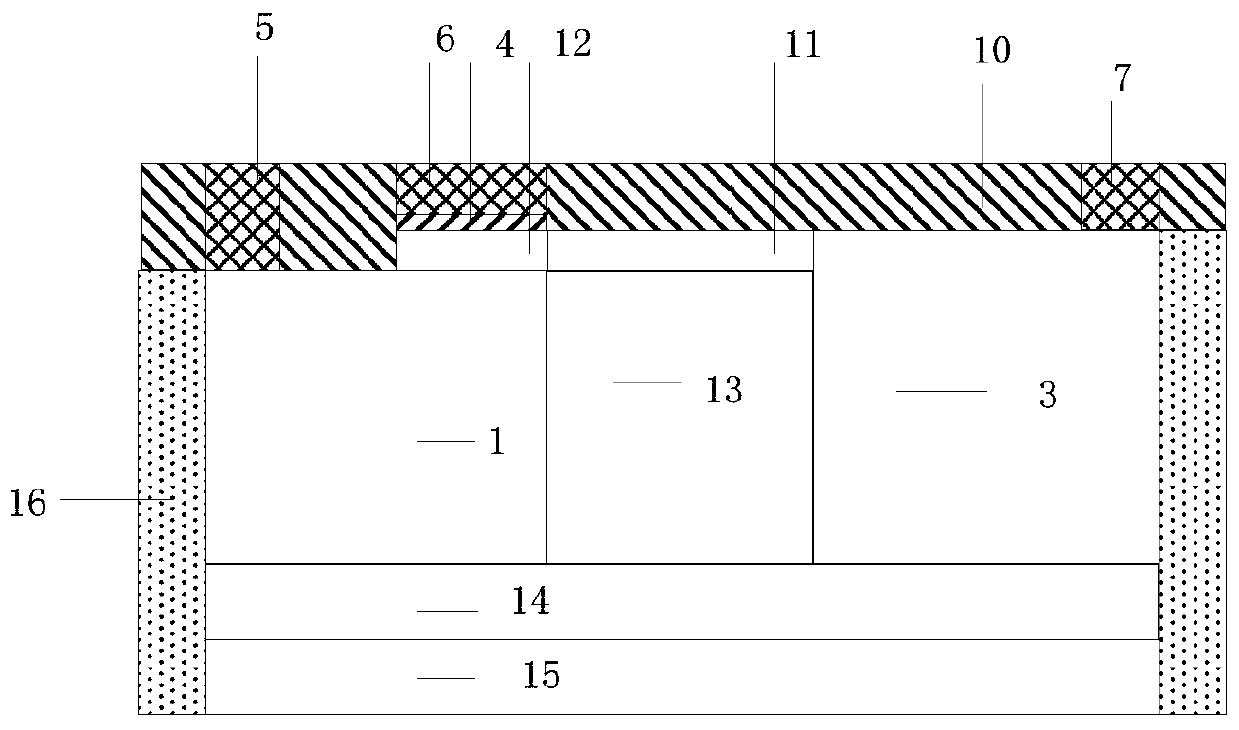

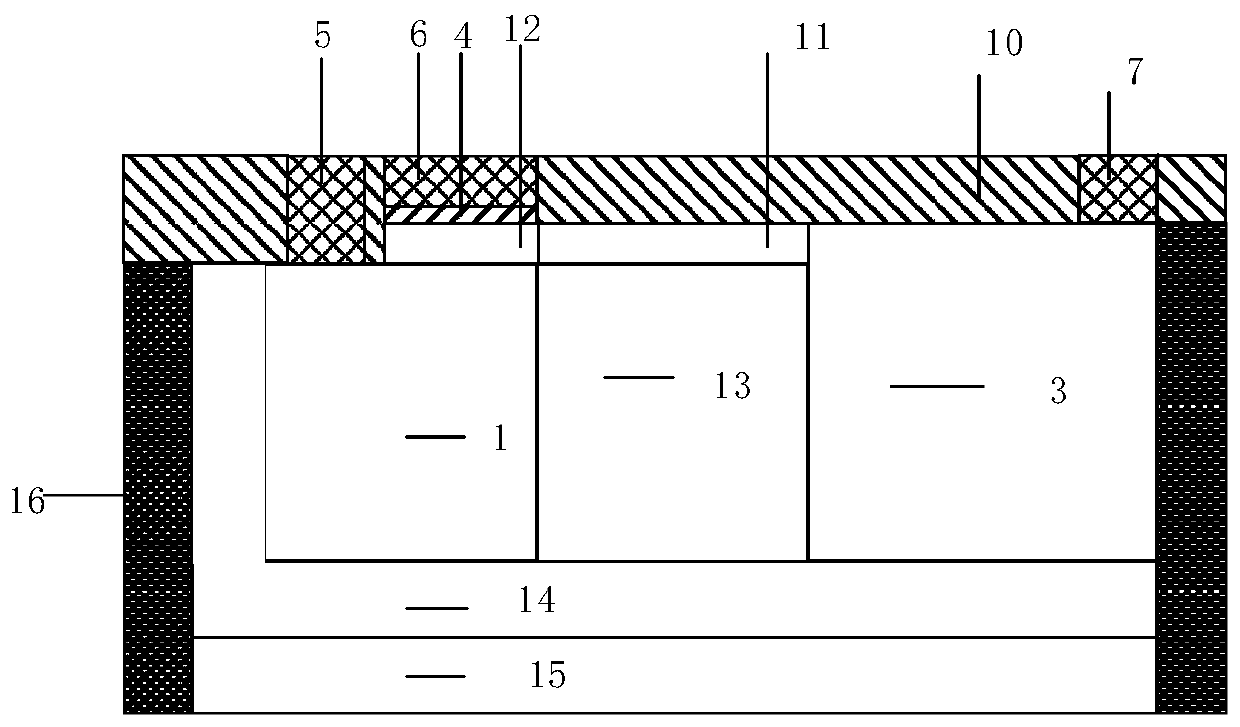

Trench MOSFET and manufacturing method thereof

PendingCN110676320AImprove pressure resistanceLower specific on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetDielectric layer

The invention provides a trench MOSFET and a manufacturing method thereof. The trench MOSFET comprises: a substrate having a first conductivity type; an epitaxial layer formed on the substrate and having a first conductivity type, the doping concentration of the epitaxial layer being lower than that of the substrate; a trench formed in the epitaxial layer; a buried layer formed below the trench and having a second conductivity type; a gate structure filled in the trench and comprising a shielding gate electrode, a control gate electrode positioned above the shielding gate electrode and a dielectric layer which covers the shielding gate electrode and is filled in the side part of the control gate electrode; a body region having a second conductivity type and formed in the epitaxial layer; and a source region formed in the epitaxial layer, positioned above the body region and having a first conductivity type, the doping concentration of the source region being greater than that of the body region.

Owner:WUXI CHINA RESOURCES HUAJING MICROELECTRONICS

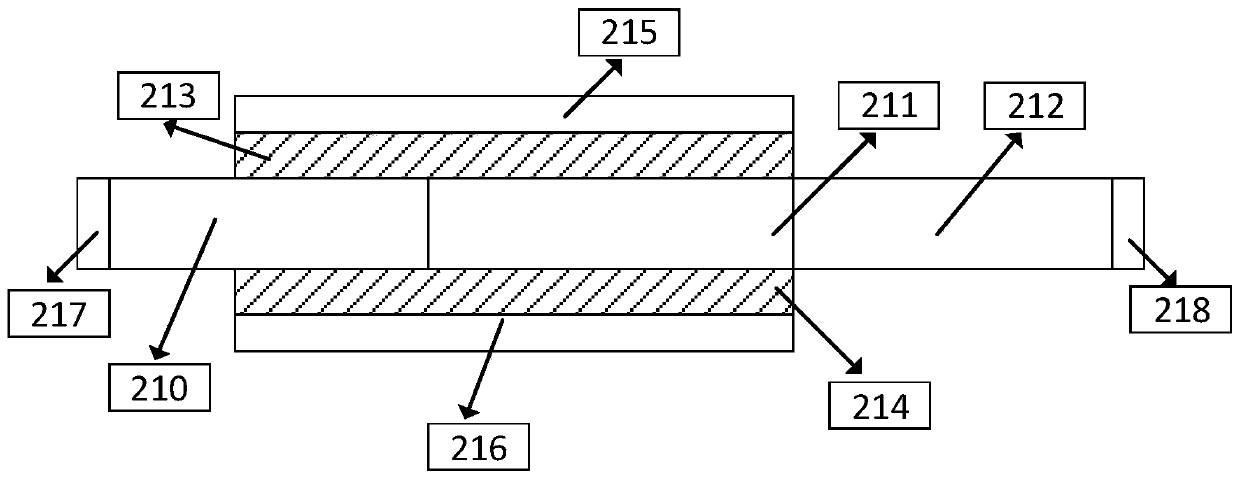

Tunneling field effect transistor capable of effectively increasing on-state current

ActiveCN109980015AIncrease the on-state currentHigh strengthSemiconductor devicesNon symmetricGate dielectric

The invention discloses a tunneling field effect transistor capable of effectively increasing the on-state current, which belongs to the field of semiconductor devices and is used for increasing the on-state current of the tunneling field effect transistor. According to the invention, upper and lower gate dielectric layers of the tunneling field effect transistor extend to a source region and partially cover the source region, the surface of the gate dielectric layer at one side of the source region is covered with a metal gate, the surface of the gate dielectric layer at the other side of thesource region is covered with a bias electrode, the bias electrode is isolated from a metal gate at the side by an isolation wall so as to form a vertically asymmetrical structure, the electric fieldperpendicular to the channel direction on the upper and lower sides of the source region covered by the gate electrode is enhanced through externally applying bias voltage to the bias electrode or utilizing the difference of a metal work function between the bias electrode and the metal gate, the intensity of carrier line tunneling is improved, and the total carrier tunneling area and tunneling probability are increased, so that the on-state current of the device is effectively increased.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Electrostatic discharge mitigator for vehicles

ActiveUS9751444B2Efficient dischargeEasy to modifySeat coveringsElectric/fluid circuitElectricityEngineering

A system for mitigating electrostatic discharge (ESD) that may occur during egress from vehicles is provided. One embodiment comprises a narrow conductive electrode that is galvanically connected to the vehicle chassis, and that is applied to that one edge of a seat which is next to the door nearest that seat. For example, in the U.S., this edge will normally be the left edge of the driver's seat, or the right edge of the front passenger's seat. The electrode is substantially located on a normally unoccupied surface of the seat cushion. Other embodiments further include pointed shapes on the electrode to increase the electric field intensity, which may promote more complete discharging.

Owner:DICKERMAN ROBERT LEON

Semiconductor integrated circuit device including first, second and third gates

InactiveUS7180774B2Lower resistanceLimiting riseSolid-state devicesRead-only memoriesSemiconductorStorage cell

A semiconductor integrated device having a plurality of memory cells, each including a floating gate, a control gate and an auxiliary gate formed over a side surface of the floating gate through an insulator film. Auxiliary gates coupled to selected memory cells function to generate hot electrons and are alternately arranged with other auxiliary gates functioning to prevent write errors in the non-selected memory cells.

Owner:RENESAS ELECTRONICS CORP

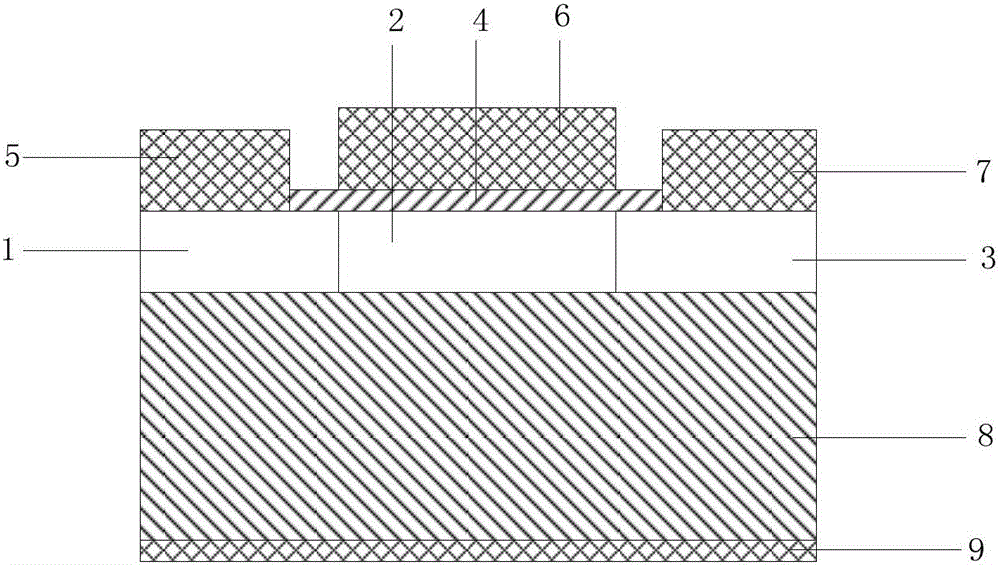

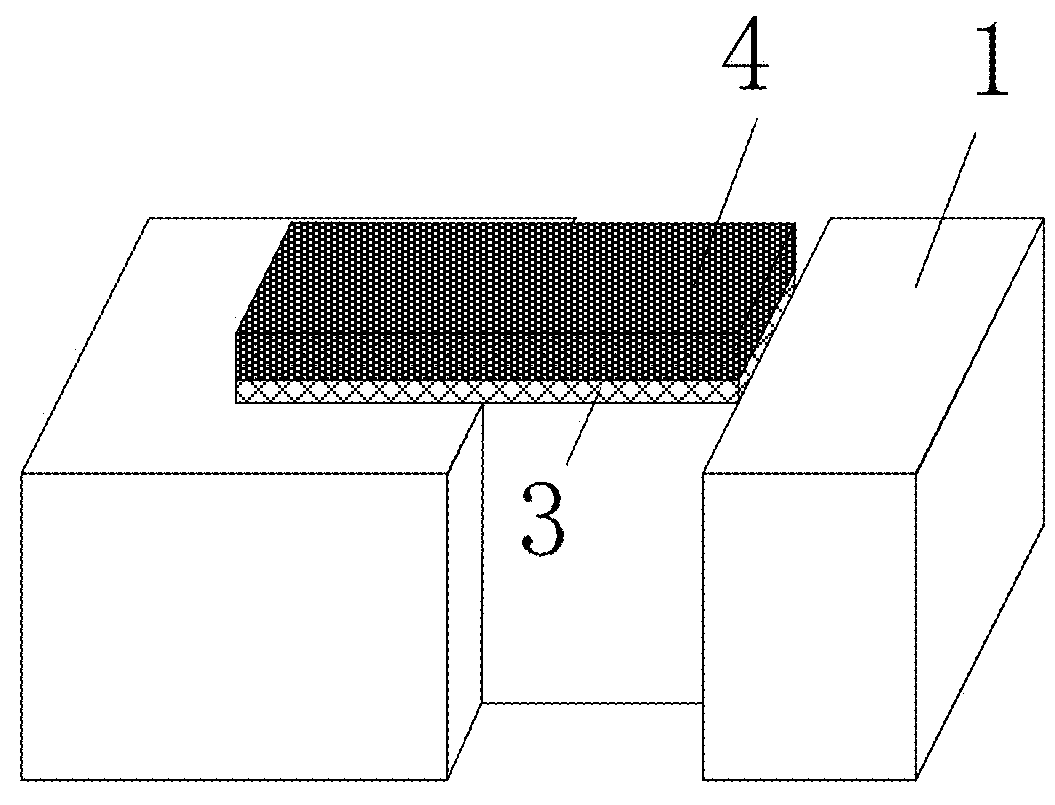

Integrated silicon carbide Darlington transistor and manufacturing method thereof

ActiveCN106601734AIncrease the electric fieldIncrease current gainTransistorSemiconductor/solid-state device manufacturingPower flowManufacturing technology

The invention discloses an integrated silicon carbide Darlington transistor and a manufacturing method thereof, and belongs to the technical field of micro-electronics, aiming at addressing the problems of small capability of driving tube current handling, complex manufacturing technologies, and high cost of current silicon carbide Darlington transistors. The integrated silicon carbide Darlington transistor includes: a N+emitting region which is arranged on the upper surface of a base region and includes a device slot which assumes the shape of a tilted slot, a device isolation region which assumes the shape of a vertical slot and an emitting region table which assumes the shape of a vertical slot; a base region P+ injection region which is arranged on a lower surface of the emitting region table and is disposed within the base region, wherein the device slot is arranged in the N+emitting region and extends to the upper portion of a N-collector region, the device isolation region is arranged in the N+emitting region and extends to the upper portion of the N-collector region; and an isolation injection layer which is arranged on the upper surface of the bottom portion of the device isolation region.

Owner:XIDIAN UNIV

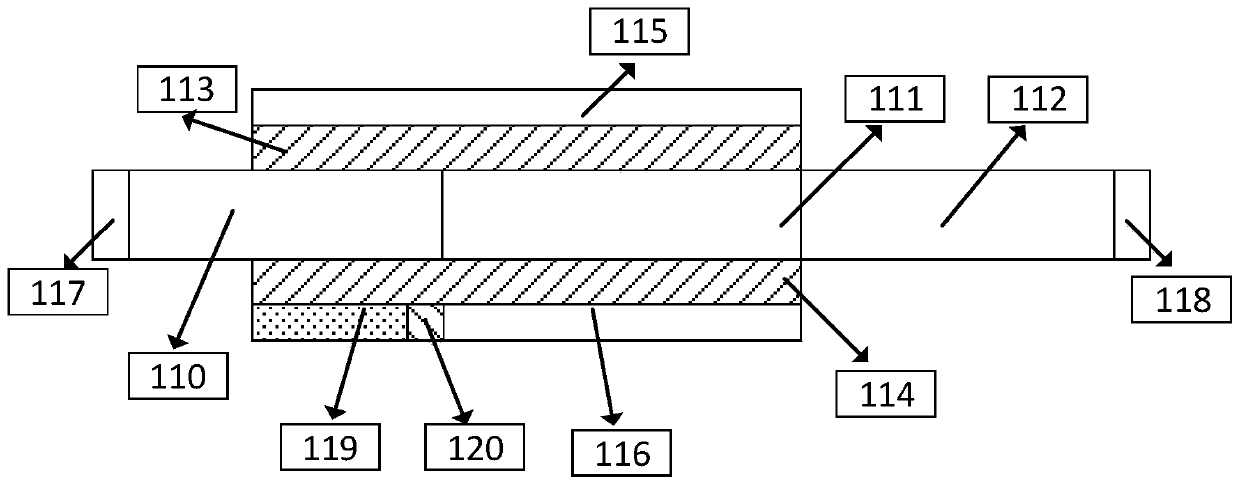

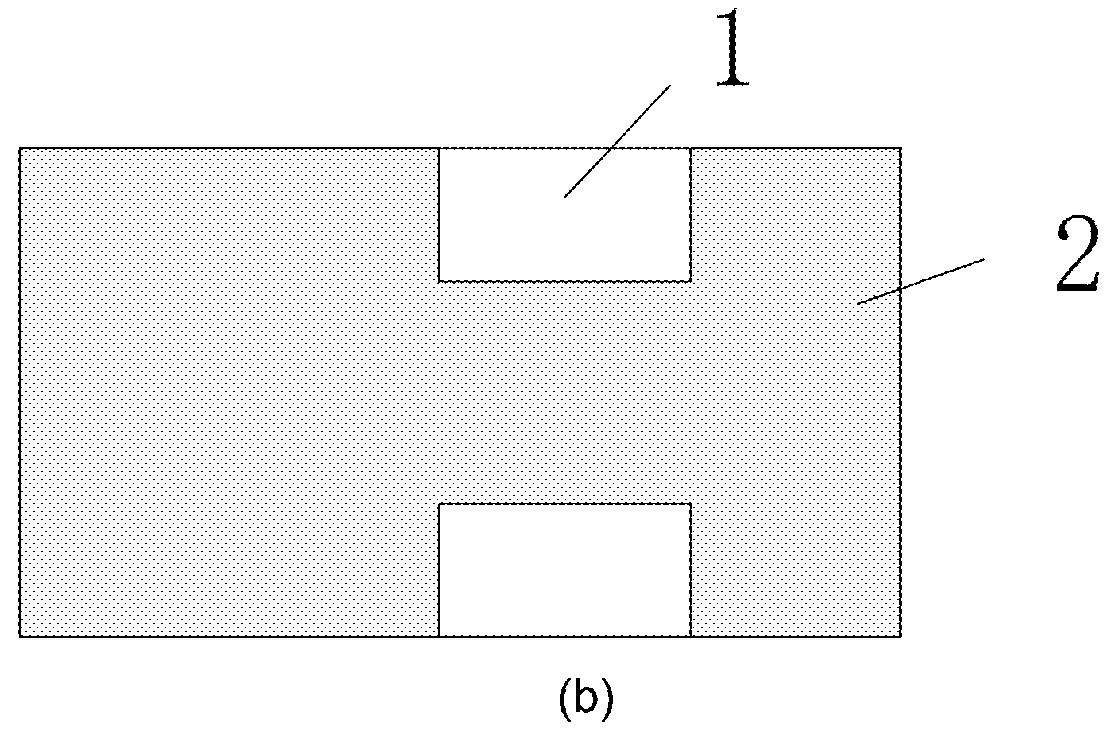

Strip-shaped gate tunneling field effect transistor using composite mechanism and fabrication method thereof

InactiveUS20160035889A1Increase the on-currentSteeper band bendingSemiconductor/solid-state device manufacturingDiodeCMOSVery large scale integrated circuits

The present invention discloses a strip-shaped gate tunneling field effect transistor using composite mechanism and a fabrication method thereof, which belongs to a field of field effect transistor logic devices and circuits in the CMOS ultra large scale integrated circuit (ULSI). According to the tunneling field effect transistor, the energy band of the channel underneath the gate is elevated by means of a change of the gate morphology and the PN junction depletion effect occurred at both sides of the strip-shaped gate, so that the sub-threshold characteristics of the transistor are improved. Meanwhile, the on-state current of the transistor is effectively increased by means of the composite mechanism introduced by the two parts of the doped source region. Moreover, the bulk leakage current, including a source-to-drain direct tunneling current and a punching through current, which comes from the two parts of the doped source region to the doped drain region can be greatly suppressed through the design of the ‘’-shaped active region, so that the short channel effect is inhibited and thus the transistor can be applied with a smaller size.

Owner:PEKING UNIV

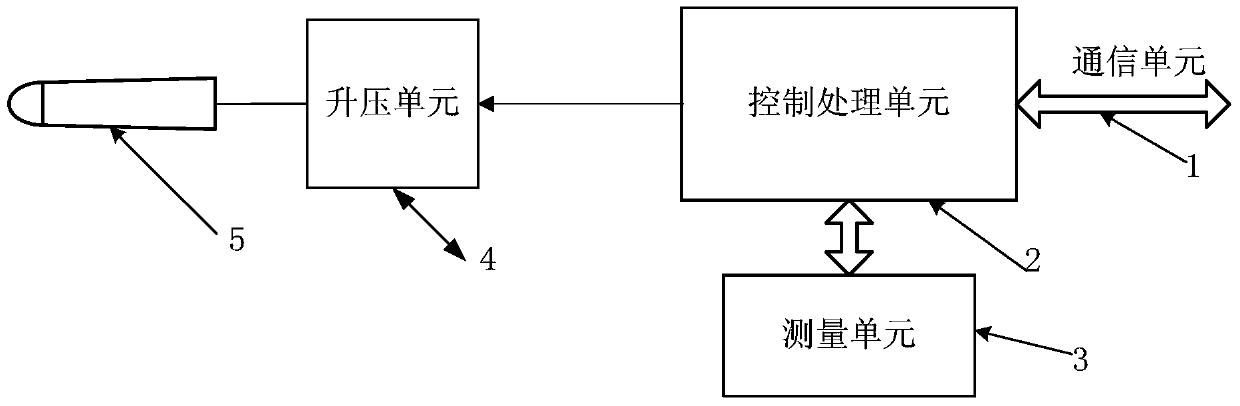

Active capacitive pens, capacitive touch panels and touch devices

ActiveCN103440055BHigh strengthAchieve coordinationInput/output processes for data processingCapacitanceHigh pressure

The invention provides an active capacitance pen which is used for operation on a capacitance touch panel (200). The active capacitance pen comprises a first sending unit (1), a second sending unit (2) and a control processing unit (5). The first sending unit (1) sends high-voltage signals to the capacitance touch panel (200). The second sending unit (2) sends order signals to the capacitance touch panel (200) and informs the capacitance touch panel (200) of the fact that the first sending unit (1) sends the high-voltage signals to the capacitance touch panel (200), so that the capacitance touch panel (200) generates measuring signals which are synchronous with the high-voltage signals. The control processing unit (5) generates the high-voltage signals and the order signals and sends the high-voltage signals and the order signals to the capacitance touch panel (200) respectively through the first sending unit (1) and the second sending unit (2), so that the capacitance touch panel (200) obtains the position information of the capacitance pen (100). According to the capacitance pen, the intensity of the signals received by the capacitance touch panel can be improved, locating accuracy is improved, mutual harmony between the capacitance pen and the capacitance touch panel can be improved, and the capacitance pen and the capacitance touch panel conduct timely response.

Owner:HANVON CORP

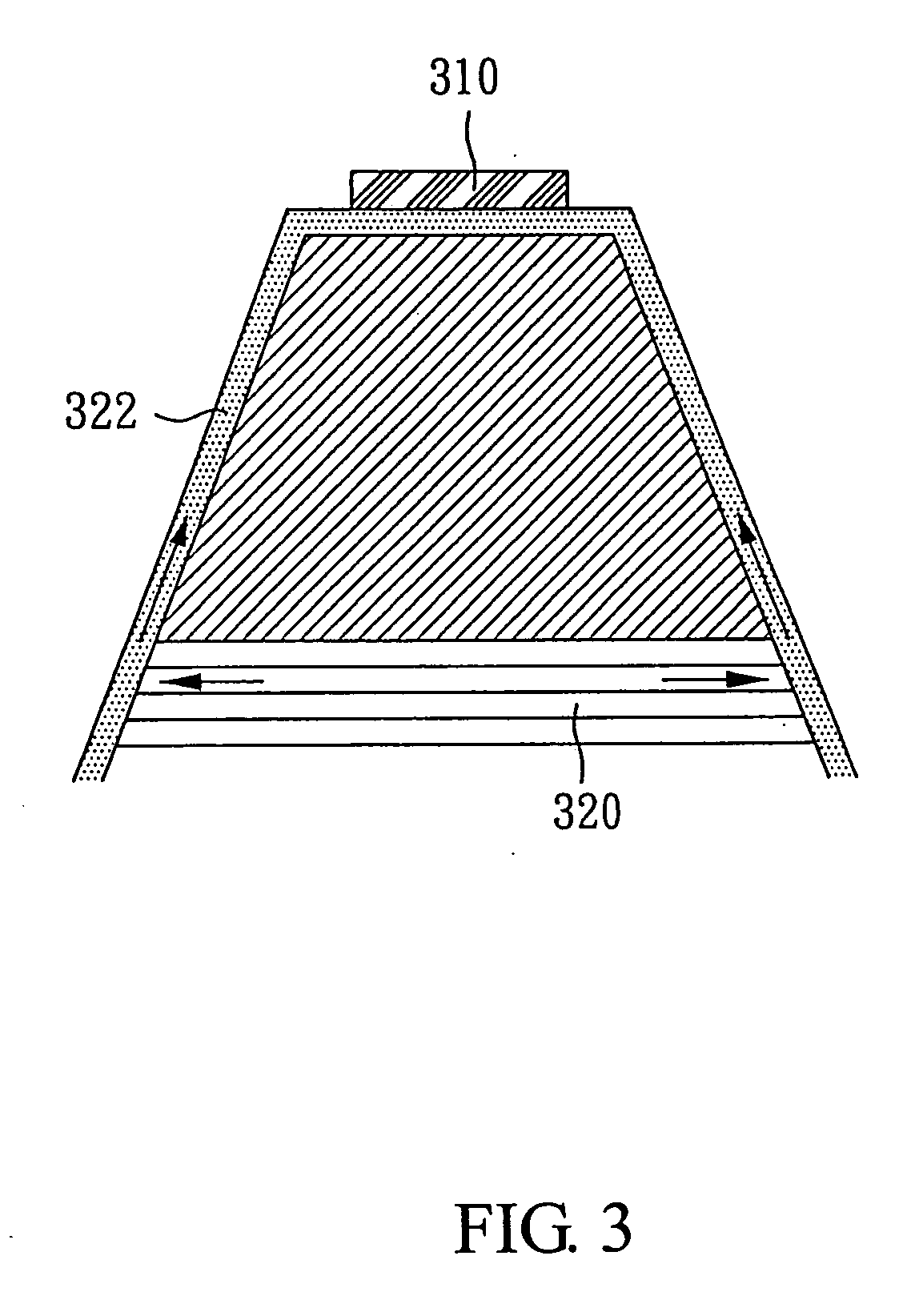

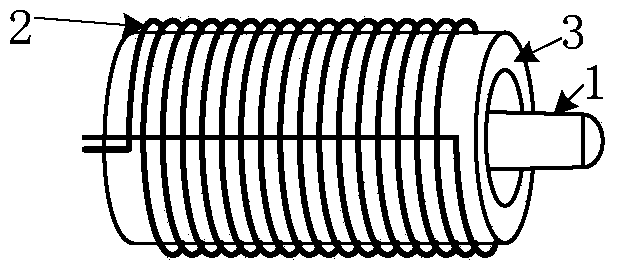

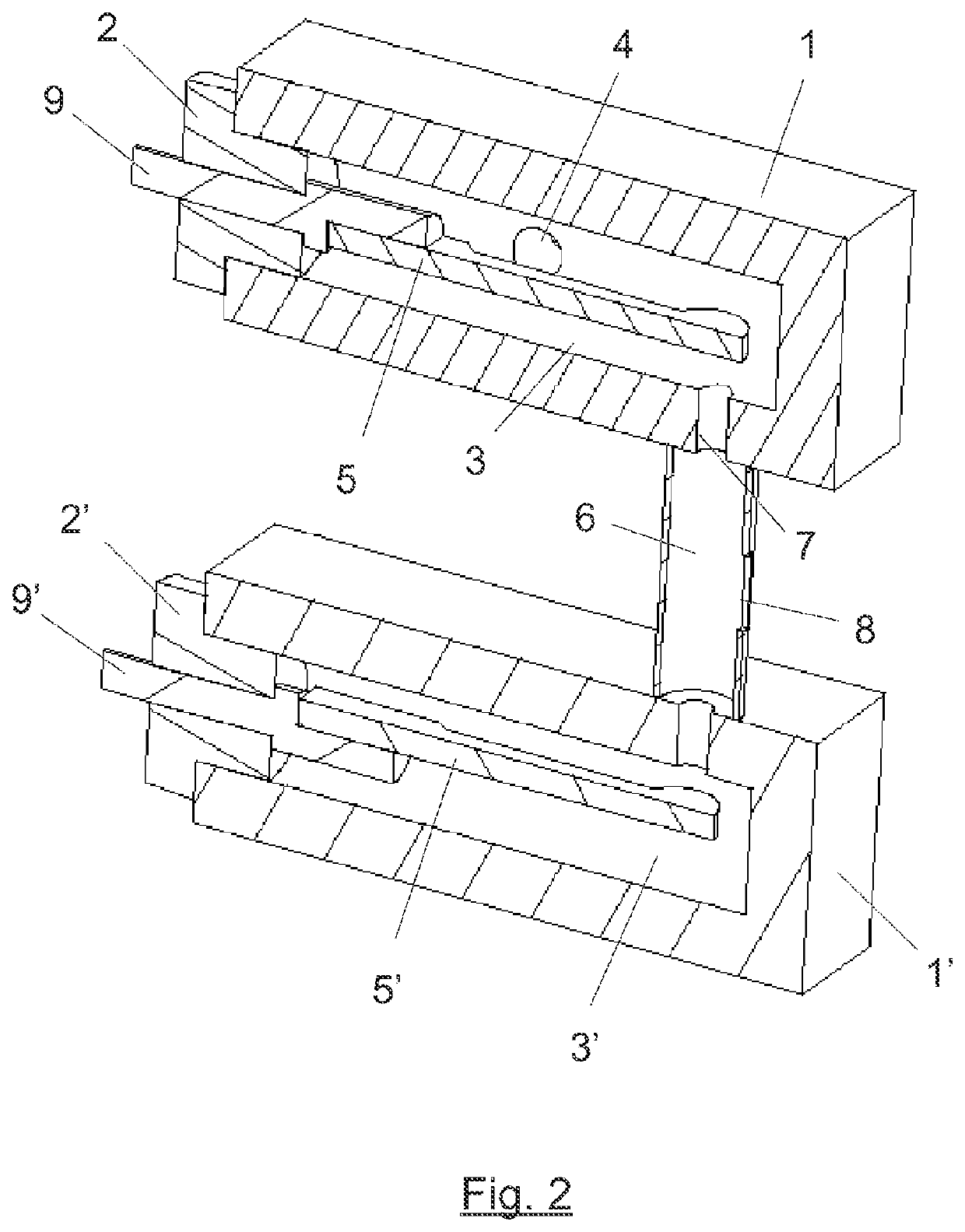

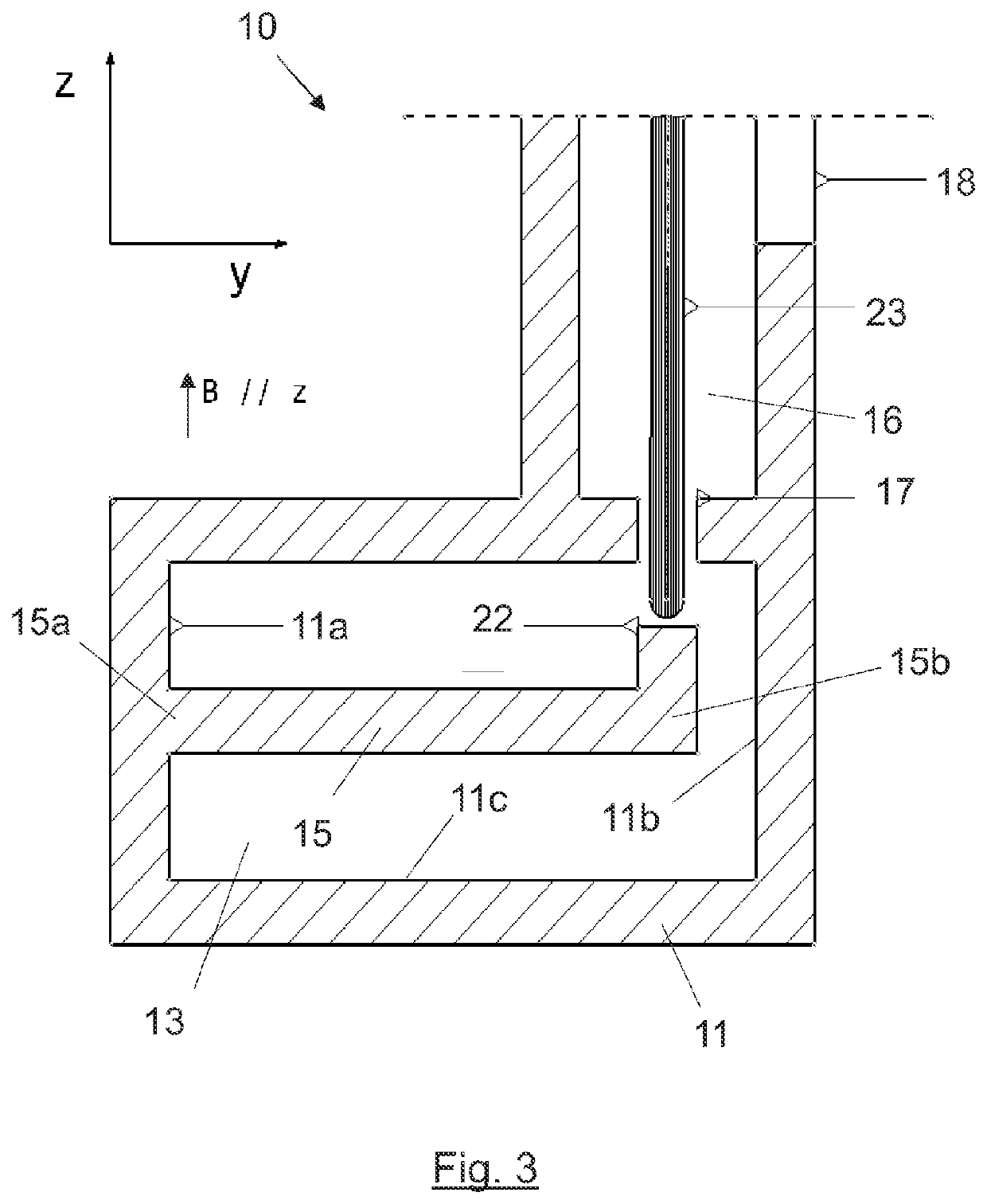

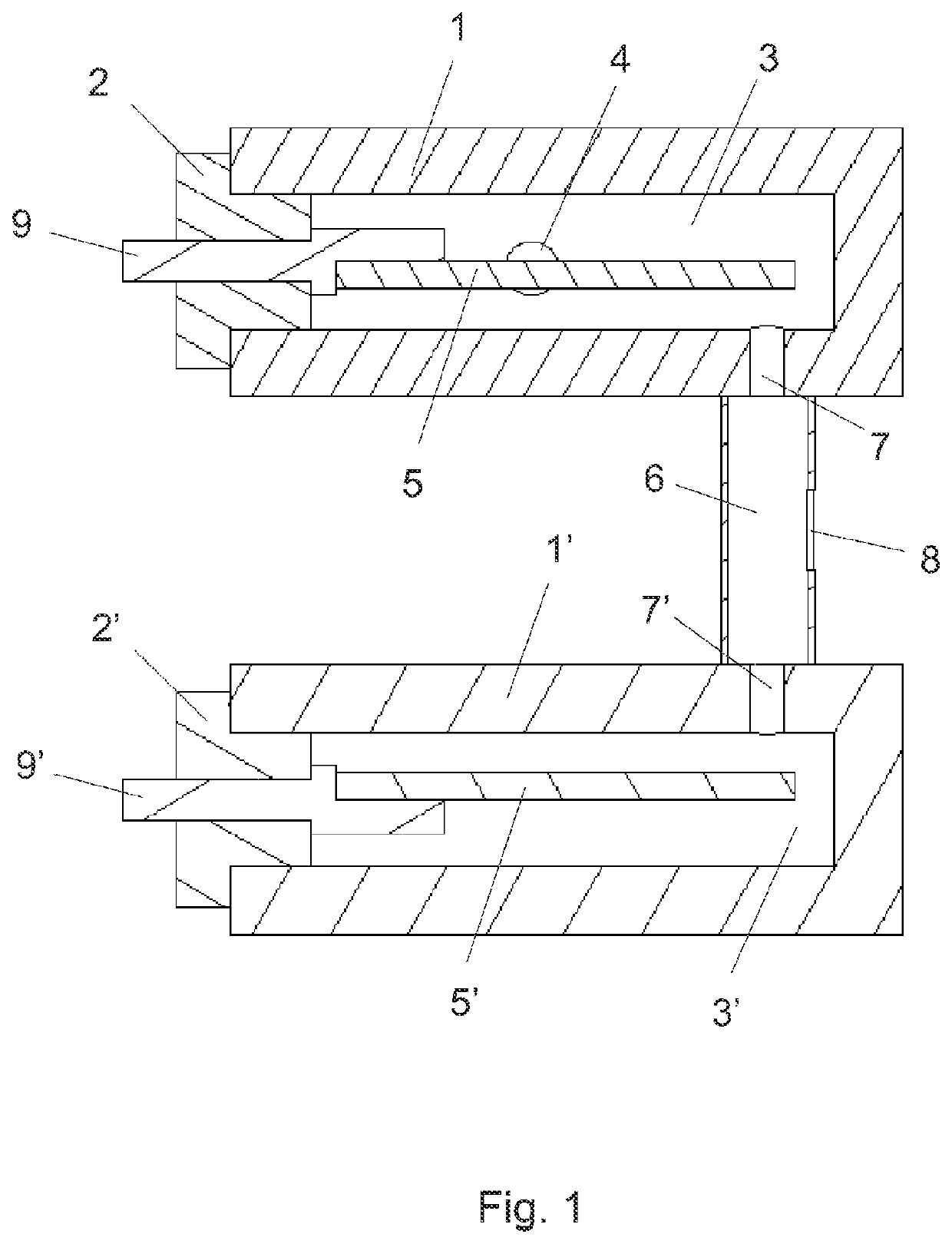

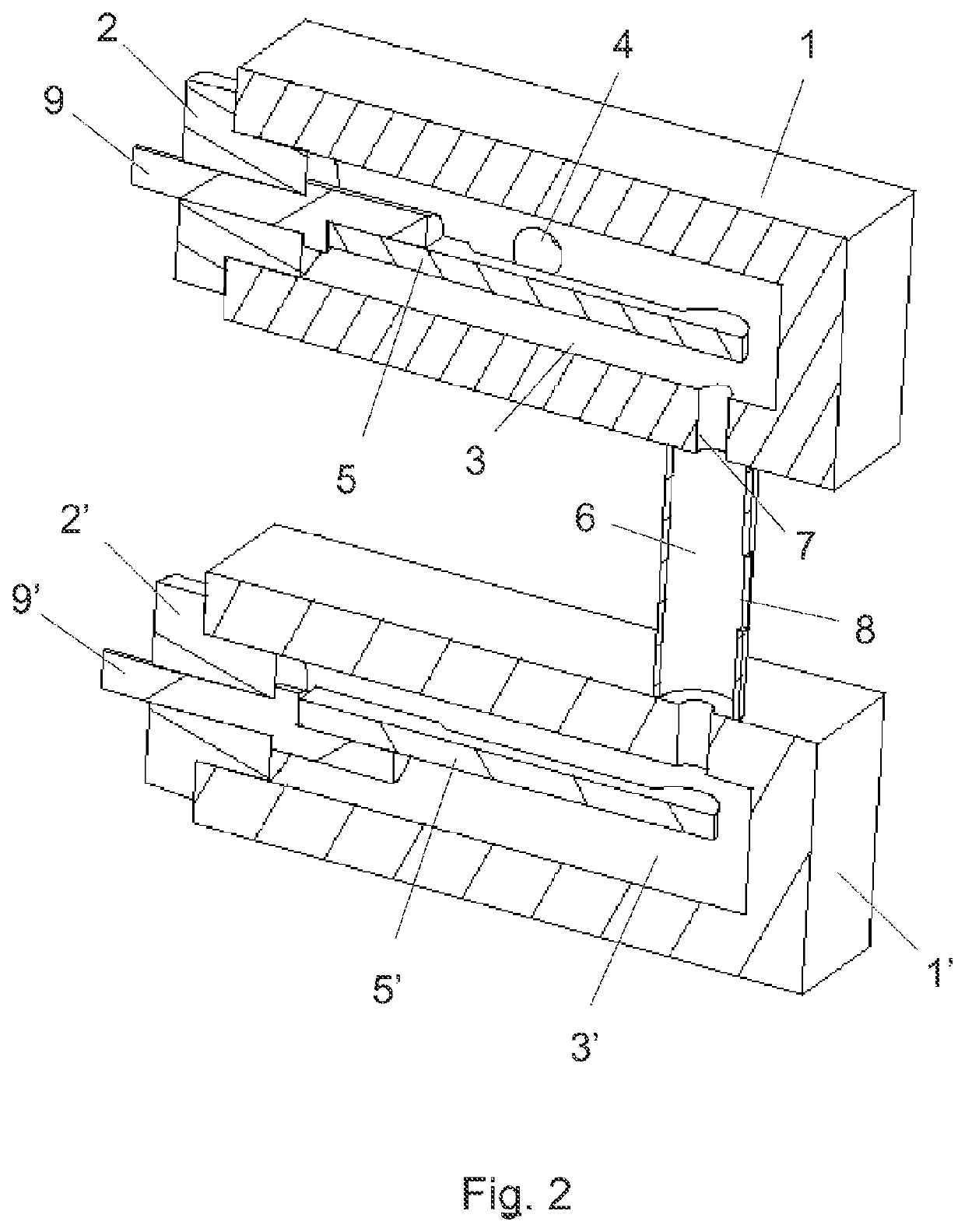

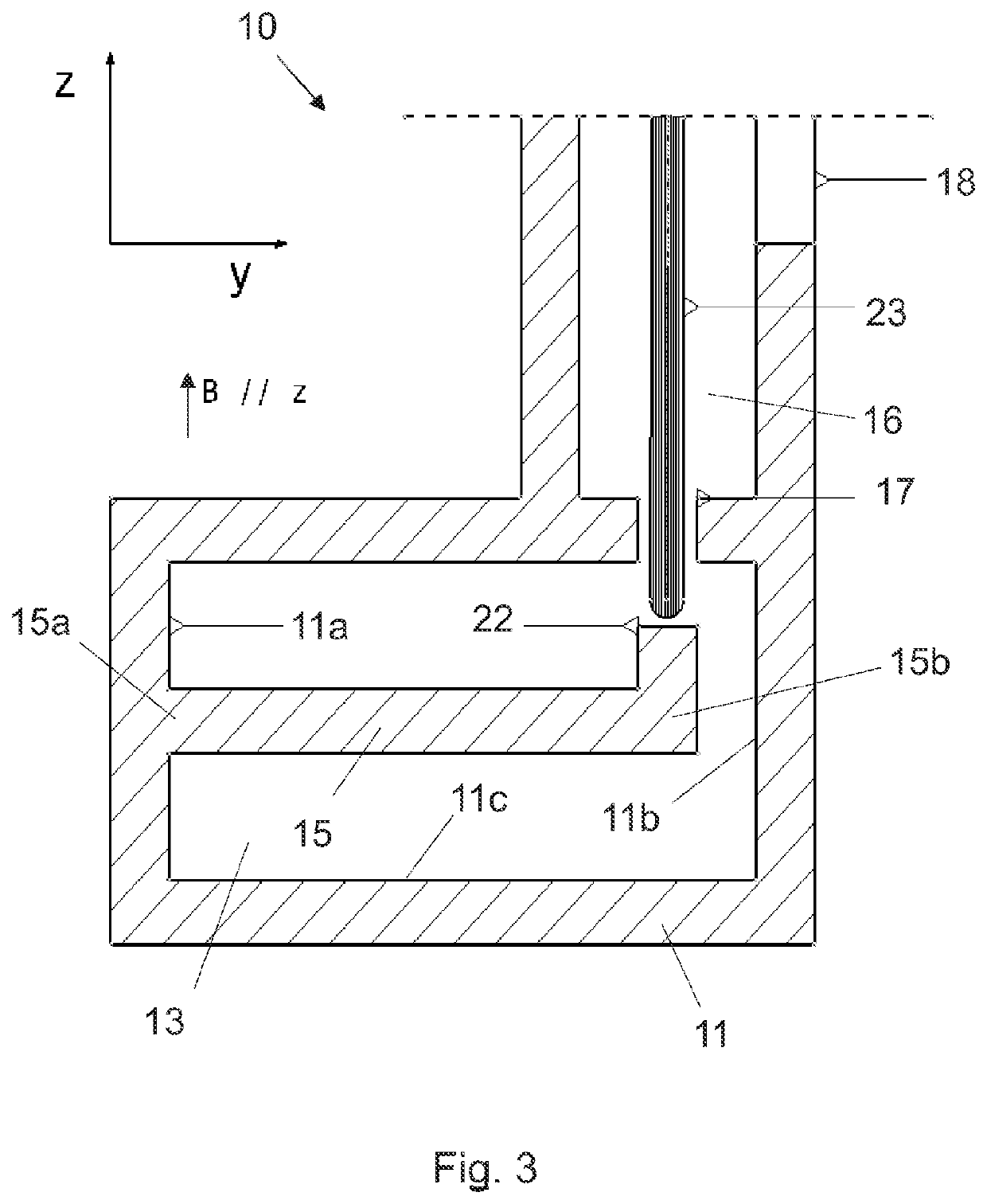

Low-erosion internal ion source for cyclotrons

ActiveUS20210274632A1Increase the electric fieldEasy to igniteMagnetic resonance acceleratorsIon beam tubesResonant cavityRadio frequency energy

A low-erosion radio frequency ion source is disclosed having a hollow body with conductive interior walls that define a cylindrical cavity, with a gas supply inlet for plasma-forming gases and a power supply inlet for injecting radio frequency energy into the cavity; an expansion chamber connected to the cavity by means of a plasma outlet hole; an ion-extraction aperture in contact with the expansion chamber; coaxial conductor disposed in the cavity, parallel to the longitudinal axis thereof, one or both ends of the coaxial conductor being in contact with a circular interior wall of the body, forming a coaxial resonant cavity; the coaxial conductor having a conductive protuberance opposite the plasma outlet hole and which extends radially into the cavity. It substantially reduces the erosion of the conductive materials.

Owner:CENT DE INVESTIGACIONES ENERGETICAS MEDIO AMBIENTALLES Y TECNOLOGICAS (C I E M A T)

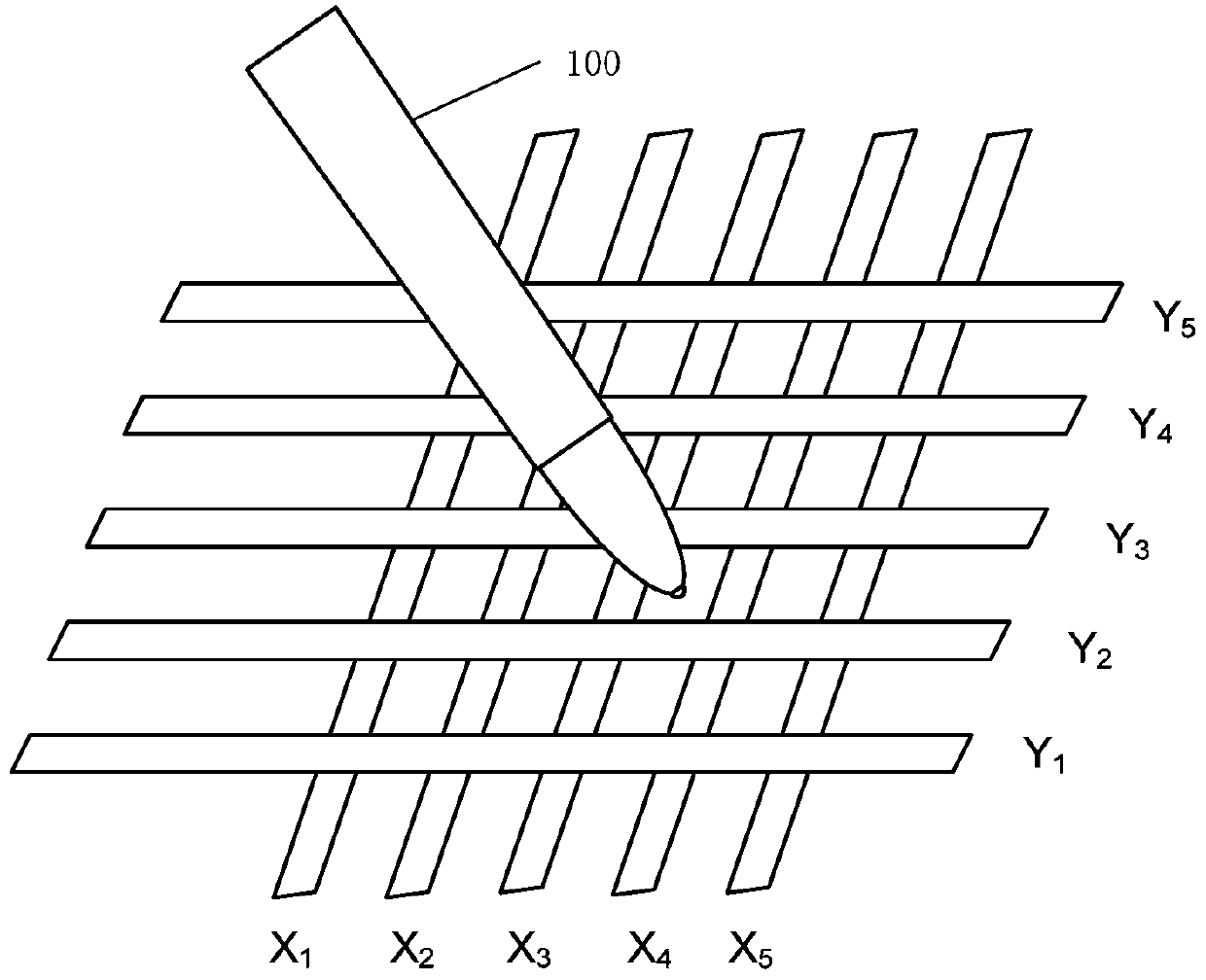

Capacitive pen, capacitive touch panel and touch device

ActiveCN103488316BAdd supportAchieve precise positioningInput/output processes for data processingCapacitanceSignal-to-noise ratio (imaging)

The present invention provides a capacitive pen for operating on a capacitive touch panel (200), which includes: a sending unit (1), which sends a high-voltage AC signal to the capacitive touch panel (200); the capacitive pen controls A processing unit (2), which generates the high-voltage AC signal, and sends the high-voltage signal to the capacitive touch panel (200) through the sending unit (1), so that the capacitive touch panel (200 ) measuring the position information of the capacitive pen (100) according to the high voltage AC signal. The capacitive stylus provided by the present invention sends a high-voltage AC signal to the capacitive touch panel so that the capacitive touch panel can be positioned according to the high-voltage AC signal. Since the high-voltage AC signal is strong, the signal-to-noise ratio and positioning accuracy can be improved.

Owner:HANVON CORP

An integral silicon carbide Darlington tube and its manufacturing method

ActiveCN106601734BIncrease the electric fieldIncrease current gainTransistorSemiconductor/solid-state device manufacturingManufacturing technologyDarlington transistor

The invention discloses an integrated silicon carbide Darlington transistor and a manufacturing method thereof, and belongs to the technical field of micro-electronics, aiming at addressing the problems of small capability of driving tube current handling, complex manufacturing technologies, and high cost of current silicon carbide Darlington transistors. The integrated silicon carbide Darlington transistor includes: a N+emitting region which is arranged on the upper surface of a base region and includes a device slot which assumes the shape of a tilted slot, a device isolation region which assumes the shape of a vertical slot and an emitting region table which assumes the shape of a vertical slot; a base region P+ injection region which is arranged on a lower surface of the emitting region table and is disposed within the base region, wherein the device slot is arranged in the N+emitting region and extends to the upper portion of a N-collector region, the device isolation region is arranged in the N+emitting region and extends to the upper portion of the N-collector region; and an isolation injection layer which is arranged on the upper surface of the bottom portion of the device isolation region.

Owner:XIDIAN UNIV

Active capacitive pens, capacitive touch panels and touch devices

ActiveCN103455176BSimple processLow costInput/output processes for data processingCapacitanceCommunication unit

The invention provides an active capacitance pen, which is used for operating on a capacitance touch panel (200). The active capacitance pen comprises a communication unit (1), a control processing unit (2) and a sending unit (5), wherein the communication unit (1) is connected with a capacitance pen (100) and the capacitance touch panel (200) and is used for receiving a synchronizing signal synchronous with a measurement signal sent by the capacitance touch panel (200); the control processing unit (2) is communicated with the communication unit (1) and is used for generating a high-voltage signal synchronous with the measurement signal according to the received synchronizing signal; the sending unit (5) sends the high-voltage signal to the capacitance touch panel (200) to enable the capacitance touch panel (200) to obtain the touch information and / or position information of the capacitance pen (100). According to the capacitance pen provided by the invention, the synchronizing high-voltage signal is sent to enhance the induction signal of the touch panel, the touch panel can be used for sensing a small-area electric conductor, the function of the pen is expanded on the basis of finger touch, and the user experience is greatly improved.

Owner:HANVON CORP

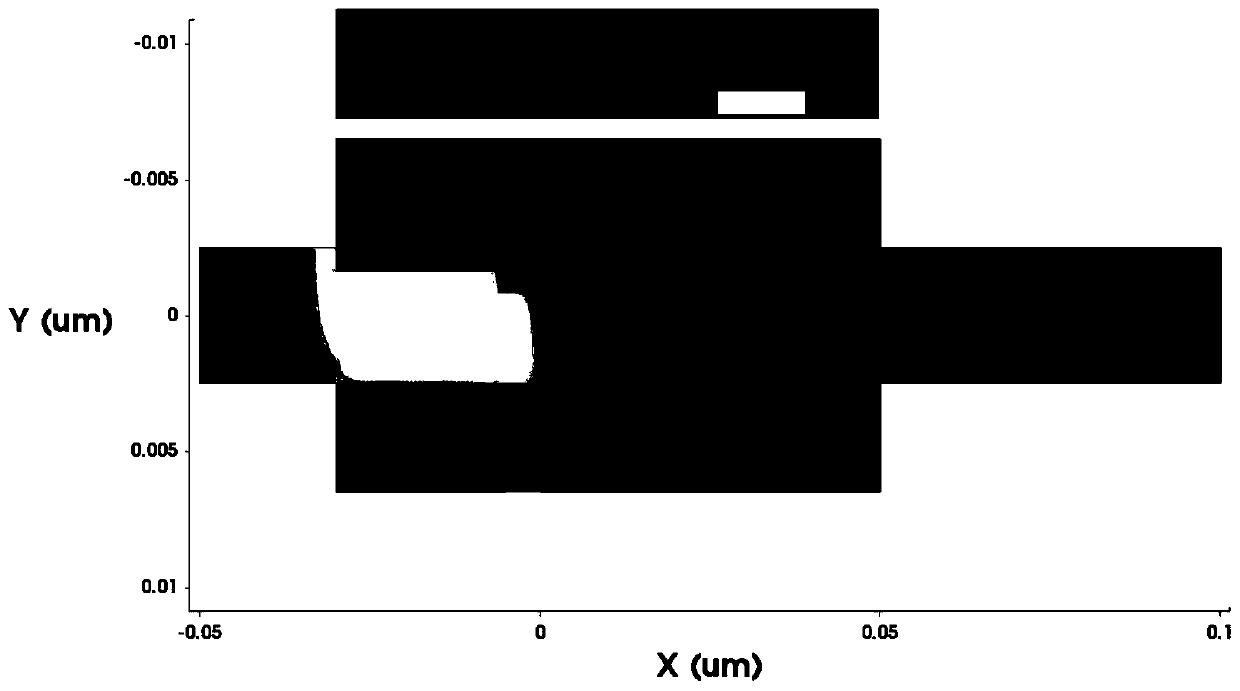

A Tunneling Field Effect Transistor with Increased Current Switching Ratio

ActiveCN106098765BIncrease the electric fieldMitigate bipolar effectsSemiconductor devicesCMOSVery large scale integrated circuits

The invention belongs to the field of logic devices and circuits in the field of ultra-large-scale integrated circuits, and specifically relates to a tunneling field-effect transistor with an increased current switching ratio. In the present invention, the electric field between the source region and the intrinsic region is increased by setting a low-K dielectric region between the source region and the drain region, thereby increasing the on-state current and suppressing the off-state current. The doped layer and the substrate are set to form a reverse-biased PN junction, and the contact between the source region-low-K dielectric region-drain region and the substrate is isolated, and the off-state current of the TFET is reduced. The above methods of increasing the on-state current and suppressing the off-state can be combined and superimposed on each other. Furthermore, the invention improves the on-state current, is compatible with the traditional CMOS technology, has low cost, and realizes a high current switching ratio.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Capacitive pen, capacitive touch panel and touch device

ActiveCN103984422BAdd supportAchieve precise positioningInput/output processes for data processingEngineeringHigh pressure

Provided in the present disclosure is a capacitive pen for operating on a capacitive touch-control panel (200), comprising: a receiving unit (1) for receiving a measurement signal transmitted by the capacitive touch-control panel (200), a signal processing unit (5) for generating a high voltage signal synchronous with the measurement signal according to the signal received by the receiving unit (1), and a transmitting unit (2) for transmitting the high voltage signal to the capacitive touch-control panel (200) such that the capacitive touch-control panel (200) obtains the information of a capacitive pen (100). The capacitive pen of the present disclosure transmits a synchronous high voltage signal to enhance the sensing signal of a touch-control panel, such that the touch-control panel can sense a small-area conductor, thus expanding the function of the pen on the basis of finger touch control, and greatly improving user experience. In addition, the circuit is easy to realize, and has low cost and good compatibility.

Owner:HANVON CORP

A Tunneling Field Effect Transistor Effectively Increases On-state Current

ActiveCN109980015BIncrease the on-state currentHigh strengthSemiconductor devicesGate dielectricDevice material

The invention discloses a tunneling field effect transistor for effectively increasing the on-state current, which belongs to the field of semiconductor devices and is used for increasing the on-state current of the tunneling field effect transistor. In the present invention, the upper and lower gate dielectric layers of the tunneling field effect transistor are extended to the source region and partly covered to the source region, the surface of the gate dielectric layer on one side of the source region is covered with a metal gate, and the surface of the gate dielectric layer on the other side of the source region is covered with a bias electrode , the bias electrode and the metal grid on this side are separated by a partition wall to form an up-and-down asymmetric structure. By applying a bias voltage to the bias electrode, or using the metal work function difference between the bias electrode and the metal grid, the gate electrode is enhanced. The electric field perpendicular to the channel direction on the upper and lower sides of the covered part of the source region increases the strength of the carrier line tunneling, and the total carrier tunneling area and tunneling probability increase, thereby effectively increasing the device's on-state current.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Low-erosion internal ion source for cyclotrons

ActiveUS11497111B2Increase the electric fieldEasy to igniteMagnetic resonance acceleratorsIon beam tubesResonant cavityRadio frequency energy

A low-erosion radio frequency ion source is disclosed having a hollow body with conductive interior walls that define a cylindrical cavity, with a gas supply inlet for plasma-forming gases and a power supply inlet for injecting radio frequency energy into the cavity; an expansion chamber connected to the cavity by means of a plasma outlet hole; an ion-extraction aperture in contact with the expansion chamber; coaxial conductor disposed in the cavity, parallel to the longitudinal axis thereof, one or both ends of the coaxial conductor being in contact with a circular interior wall of the body, forming a coaxial resonant cavity; the coaxial conductor having a conductive protuberance opposite the plasma outlet hole and which extends radially into the cavity. It substantially reduces the erosion of the conductive materials.

Owner:CENT DE INVESTIGACIONES ENERGETICAS MEDIO AMBIENTALLES Y TECNOLOGICAS (C I E M A T)

Ceramic brick with far-infrared composite air purification function and its preparation process

ActiveCN112010672BWith far-infrared composite air purification functionImprove purification effectGlazeAir purification

The invention relates to the technical field of ceramics and functional decorative materials, in particular to a ceramic brick with far-infrared composite air purification function and a preparation process thereof. It includes ceramic tiles and a glaze layer. The raw materials of the glaze layer include far-infrared powder and negative ion powder. The raw materials of the far-infrared powder include calcium oxide and nano Y 2 o 3 ‑MgO far-infrared powder; the nano Y 2 o 3 ‑The outer surface of the MgO far-infrared powder is wrapped and sintered by the anion powder; the nano Y 2 o 3 ‑MgO far-infrared powder is adsorbed on the surface of calcium oxide particles; the calcium oxide and nano Y 2 o 3 The mixing ratio of the parts by weight of the MgO far-infrared powder is 1:3-4; the ratio of the parts by weight of the far-infrared powder and the anion powder is 1:2-3. The ceramic brick with the far-infrared composite air purification function of the present invention can activate the activity of the negative ion inducing substances in the negative ion powder, thereby inducing more negative ions to purify the air.

Owner:佛山市东鹏陶瓷发展有限公司 +1