A Tunneling Field Effect Transistor Effectively Increases On-state Current

A technology of tunneling field effect and on-state current, which is applied in the direction of circuits, electrical components, semiconductor devices, etc., can solve the problems of limiting tunneling current, electric field limitation, and line tunneling cannot occur, so as to increase the on-state current, The effect of increasing the electric field and increasing the intensity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

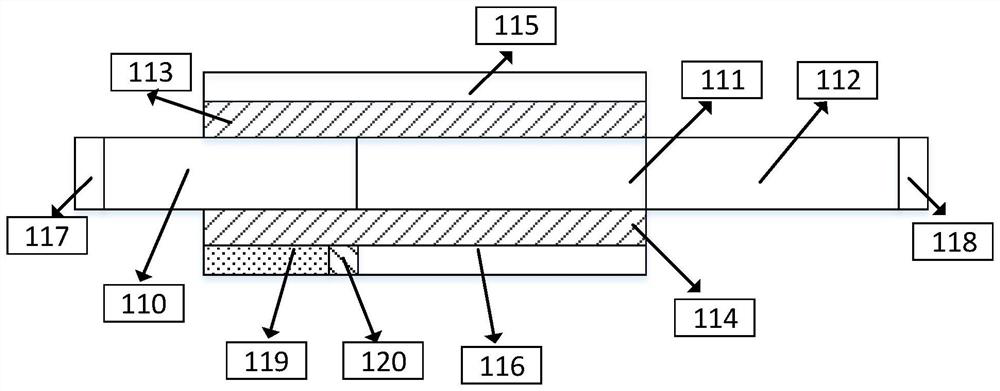

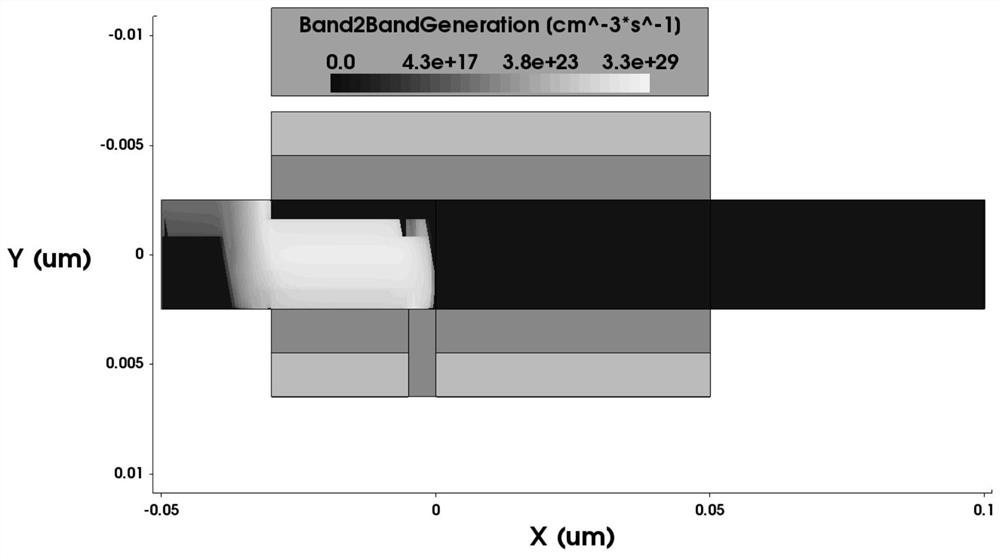

[0020] In Example 1, the thickness of the source region, the channel region and the drain region are all 5nm, and the doping concentration is 1E20cm -3 P-type doping, 1E15cm -3 N-type doping and 5E18cm -3 N-type doping. The metal gate and the bias electrode partially covered by the source region enhance the electric field in the vertical direction of the source region, so that the carriers in the source region can undergo line tunneling, thereby effectively increasing the on-state current.

Embodiment 2

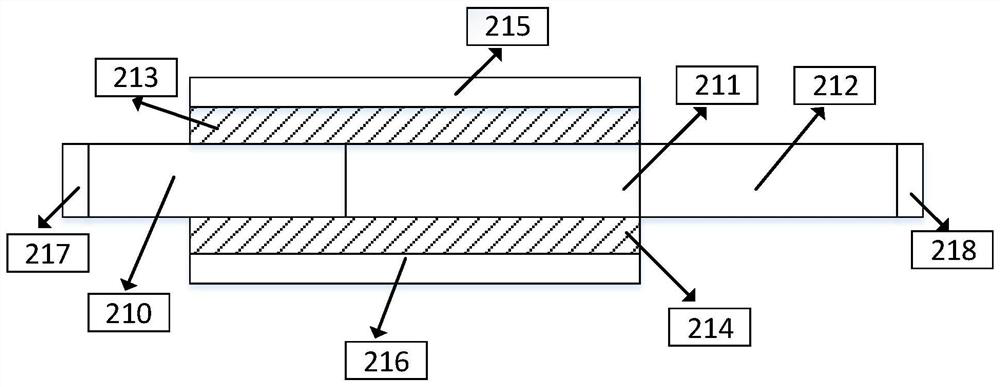

[0021] In Example 2, the thickness of the source region, the channel region and the drain region are all 7nm, and the doping concentration is 1E20cm -3 P-type doping, 1E15cm -3 N-type doping and 5E18cm -3 N-type doping. It is used to illustrate the ability of the present invention to increase the on-state current under different channel thicknesses.

Embodiment 3

[0022] In Example 3, the thickness of the source region, the channel region and the drain region are all 5nm, and the doping concentration is 1E20cm -3 P-type doping, 1E15cm -3 N-type doping and 5E18cm -3 N-type doping. The material of the bias electrode in Example 3 is gold, and its work function difference is larger than that of the gate electrode, which is used to illustrate that the difference in metal work function between electrode materials can be used to achieve the same effect as an external bias voltage.

[0023] figure 1 It is a structural schematic diagram of a tunneling field effect transistor that effectively increases the on-state current provided in the first embodiment. The transistor comprises a source region (110), a channel region (111), a drain region (112), a top gate dielectric layer (113) and a bottom gate dielectric layer (114), a top metal gate (115) and a bottom metal gate (116 ), a bias electrode (119), a source electrode (117), a drain electrod...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More