Patents

Literature

54results about How to "Increased tunneling current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

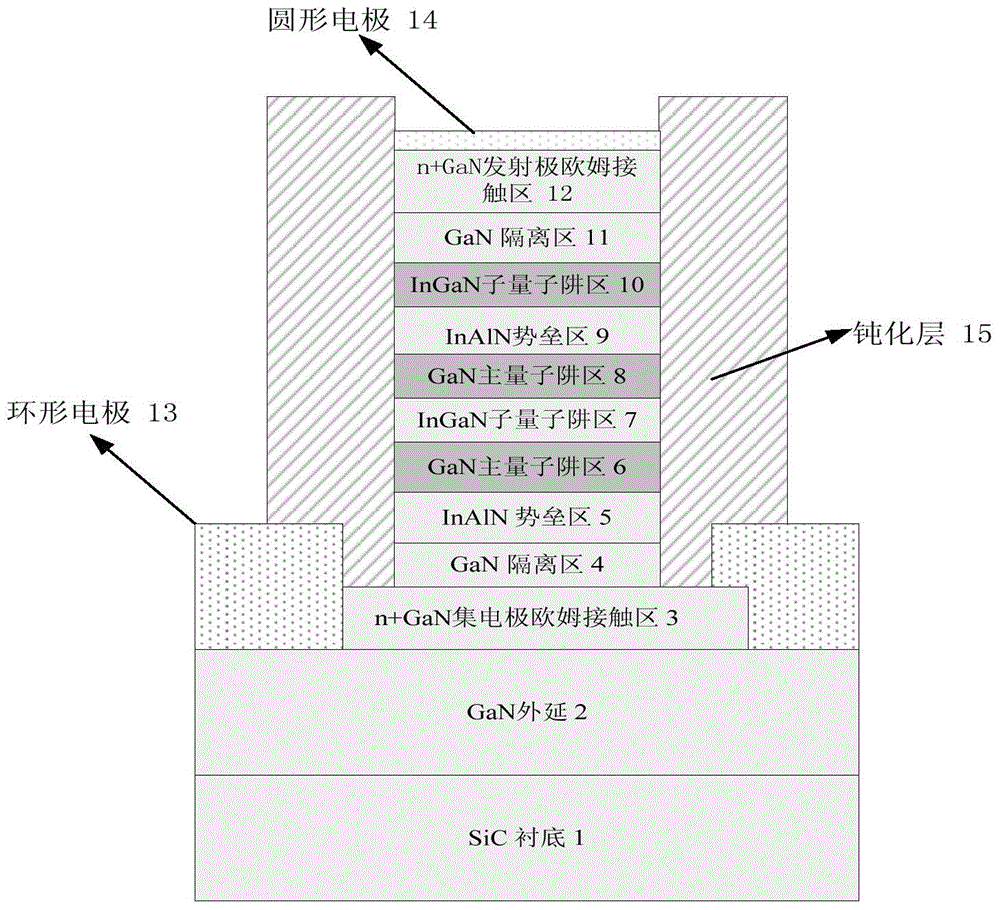

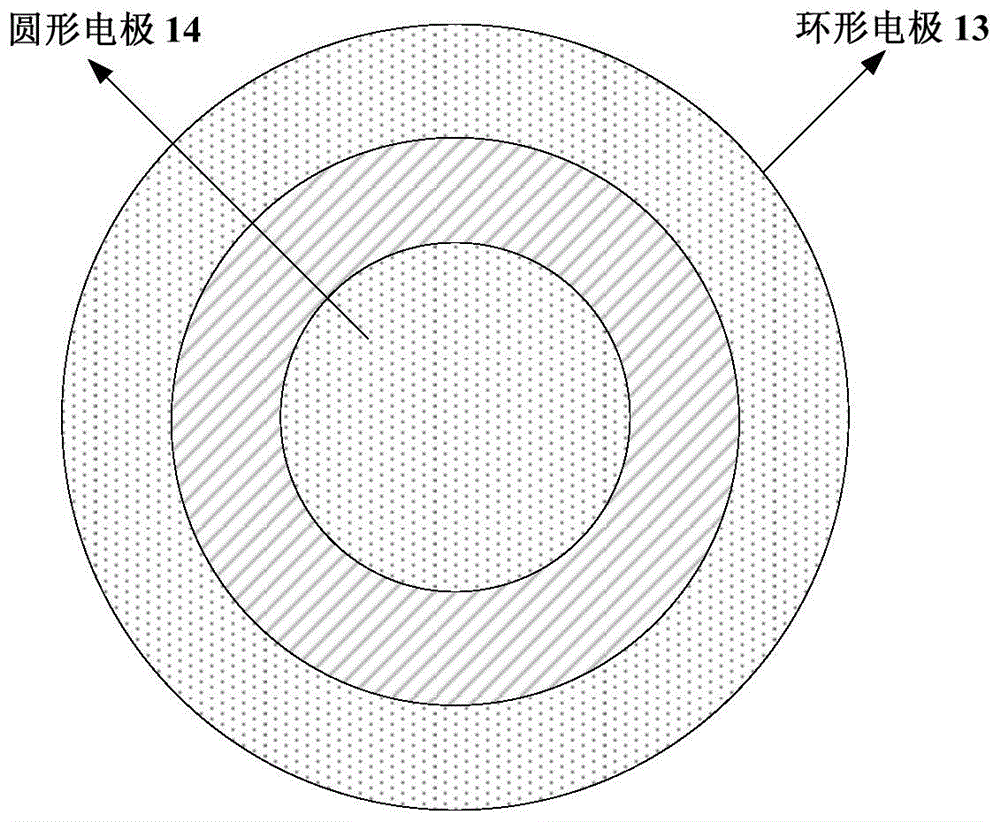

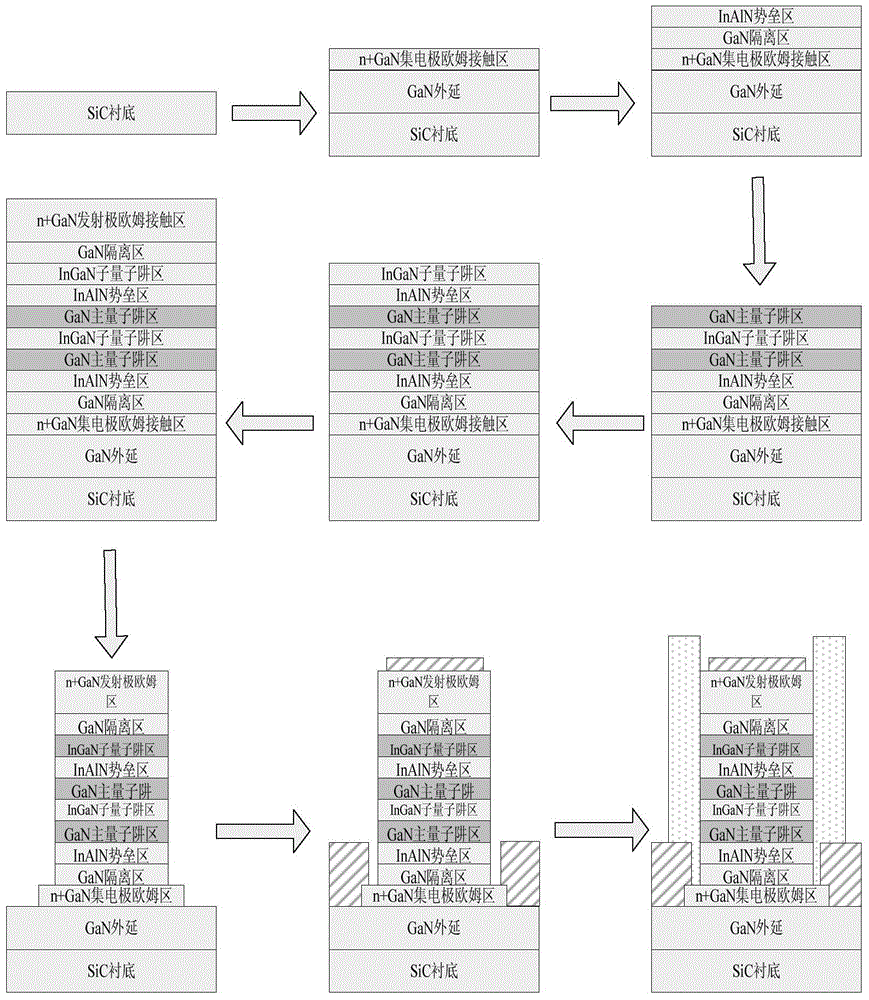

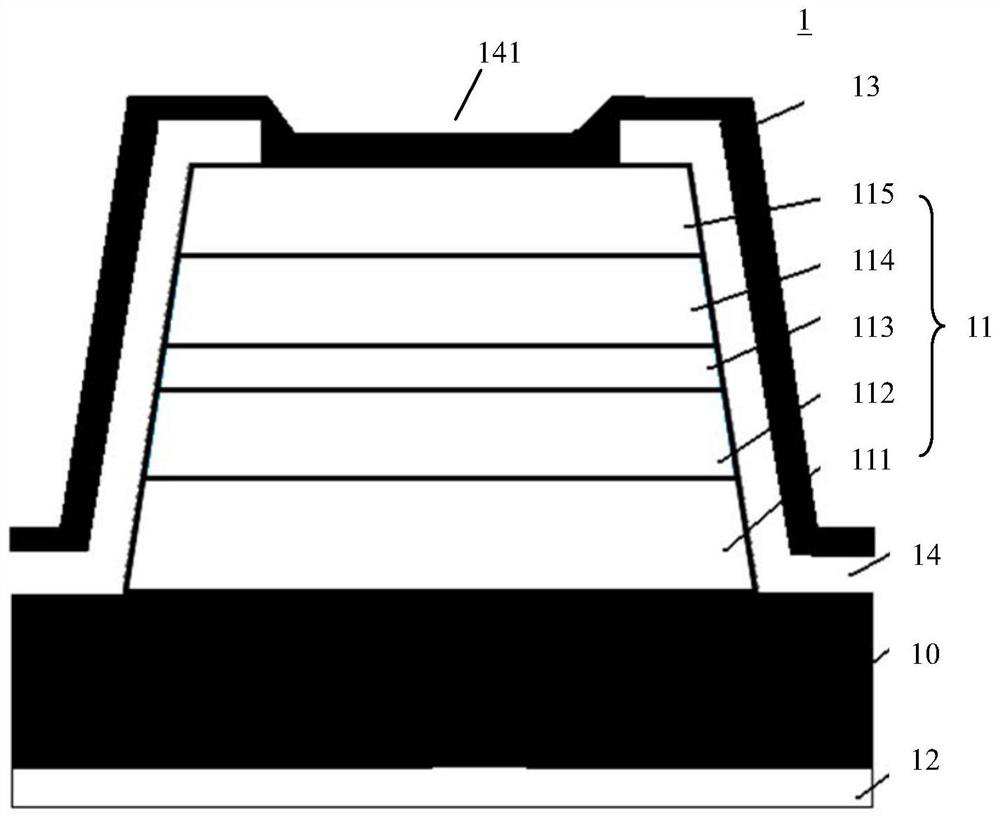

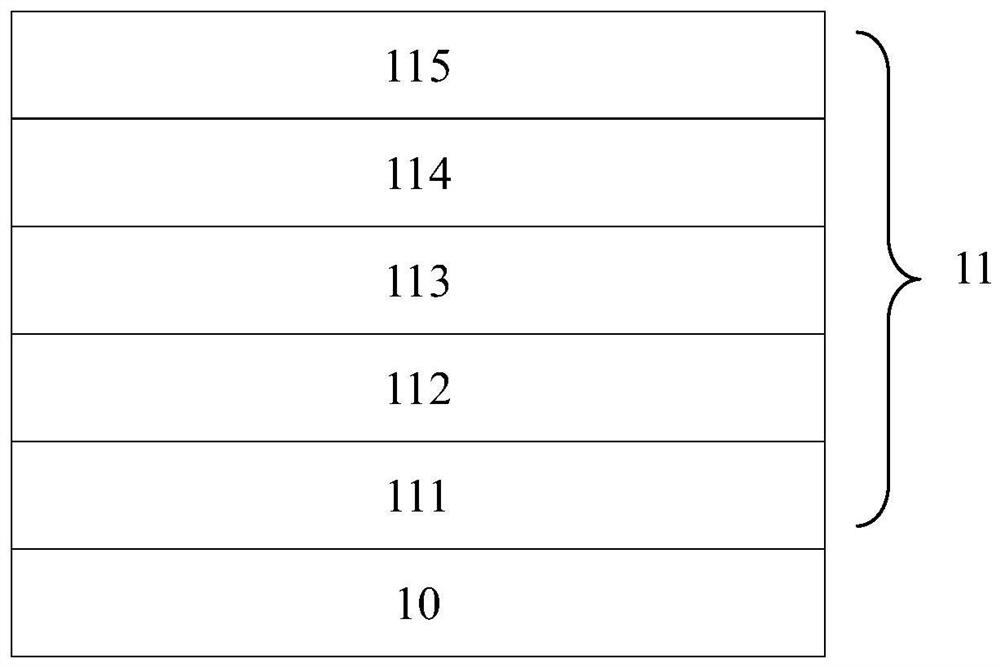

Resonance tunneling diode with double InGaN sub quantum wells and manufacturing method thereof

ActiveCN104465913AIncrease peak currentReduce power consumptionSemiconductor devicesPower flowTerahertz radiation

The invention discloses a resonance tunneling diode with double InGaN sub quantum wells. The resonance tunneling diode mainly solves the problems that an existing device is small in tunneling current and poor in I-V character repeatability. The resonance tunneling diode comprises a main body and an auxiliary body, the main body is divided into a SiC substrate layer, a GaN epitaxial layer, an n+GaN collector ohmic contact layer, a first GaN isolating layer, a first InAlN barrier layer, a first GaN main quantum well layer, a second GaN main quantum layer, a second InAlN barrier layer, a second GaN isolating layer and an n+GaN emitter diode ohmic contact layer from bottom to top, and the auxiliary part is provided with an annular electrode, a round electrode and a passivation layer. The annular electrode is arranged above the n-GaN collector ohmic contact layer, the round electrode is arranged above the n+GaN emitter ohmic contact layer, and the passivation layer is arranged above the annular electrode and the round electrode. The resonance tunneling diode can effectively improve the power of the device, reduce power consumption and improve the repeatability and is suitable for the terahertz radiation frequency band work.

Owner:晋江三伍微电子有限公司

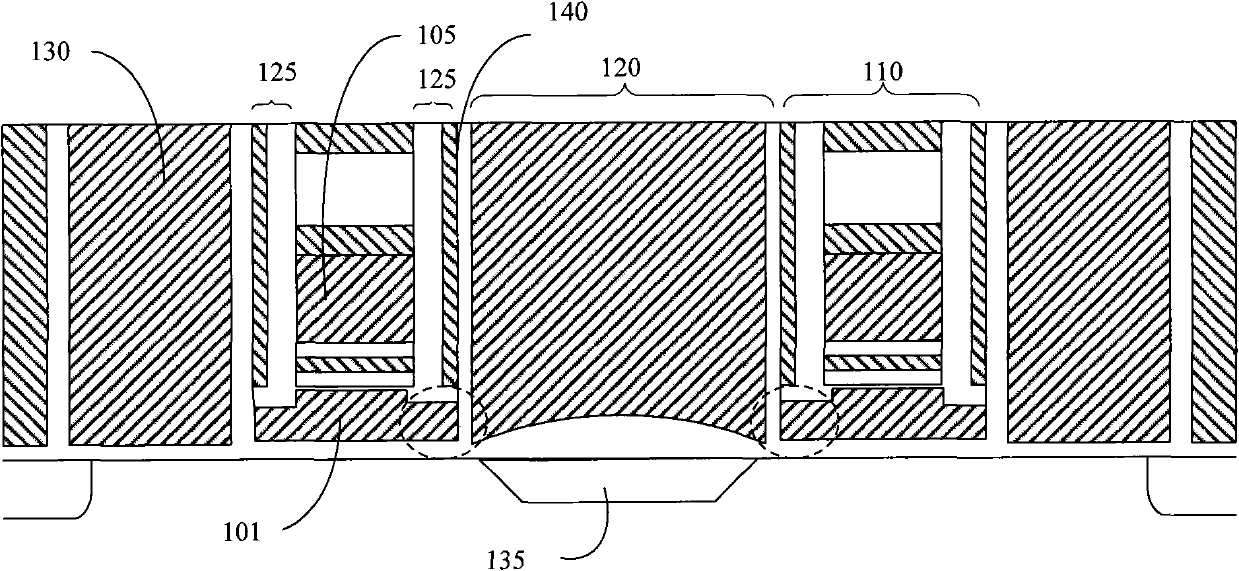

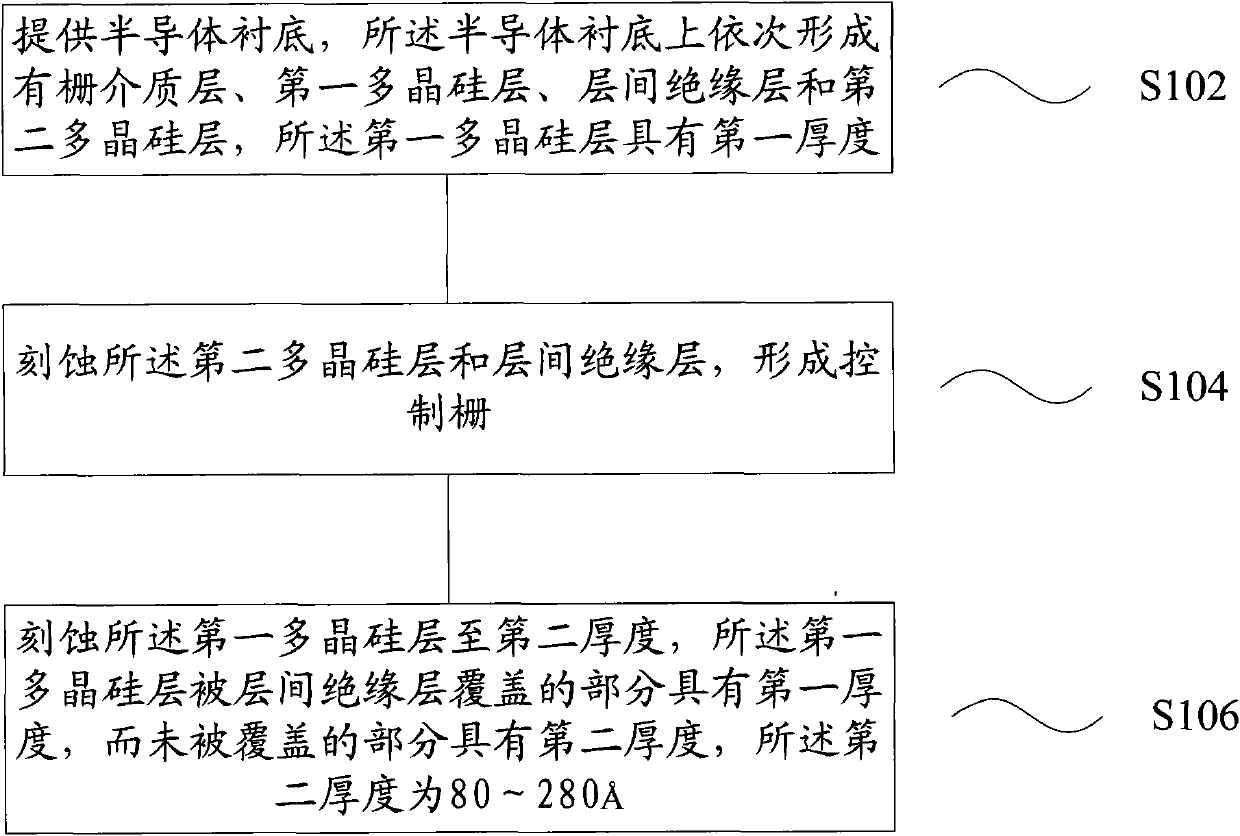

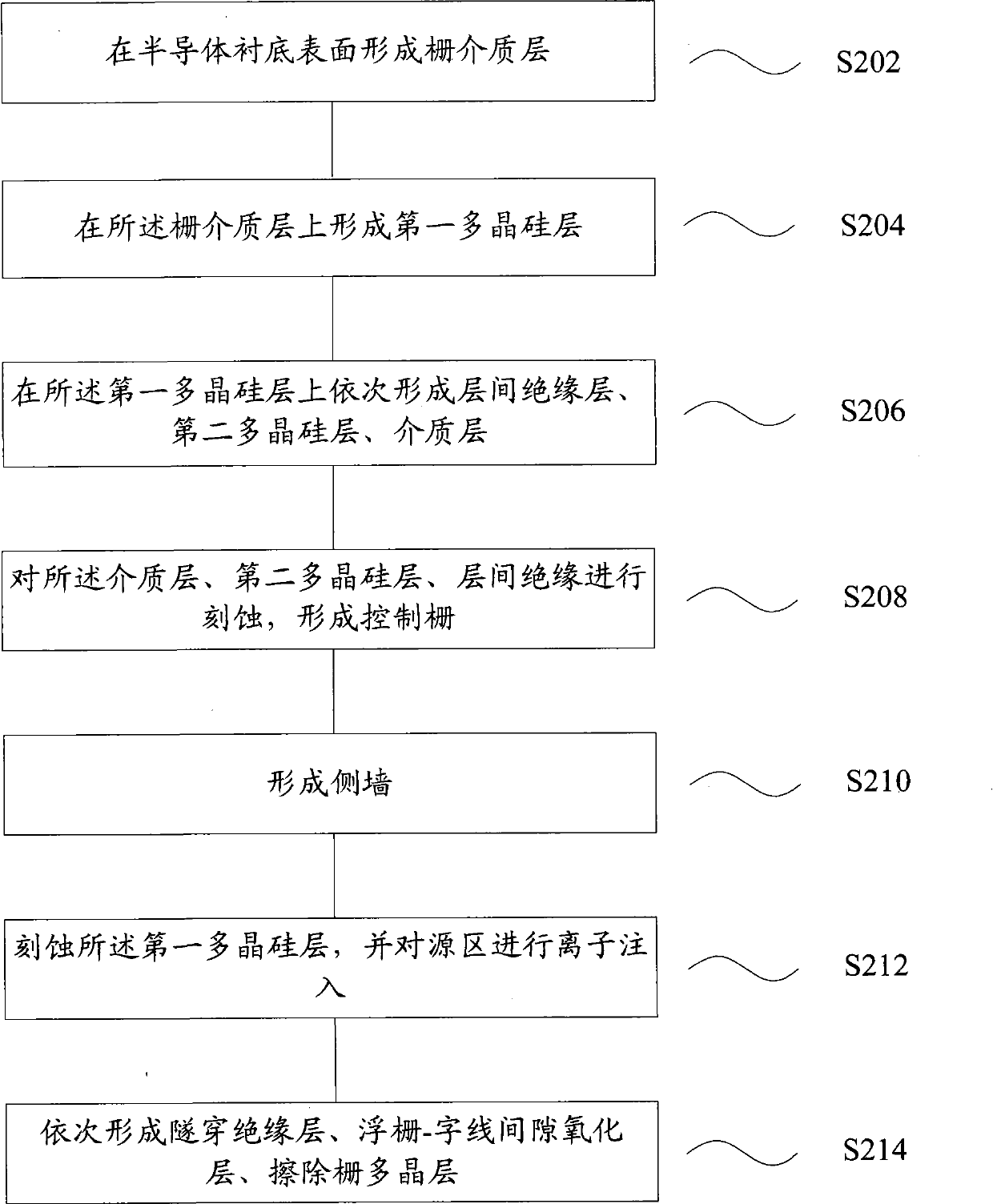

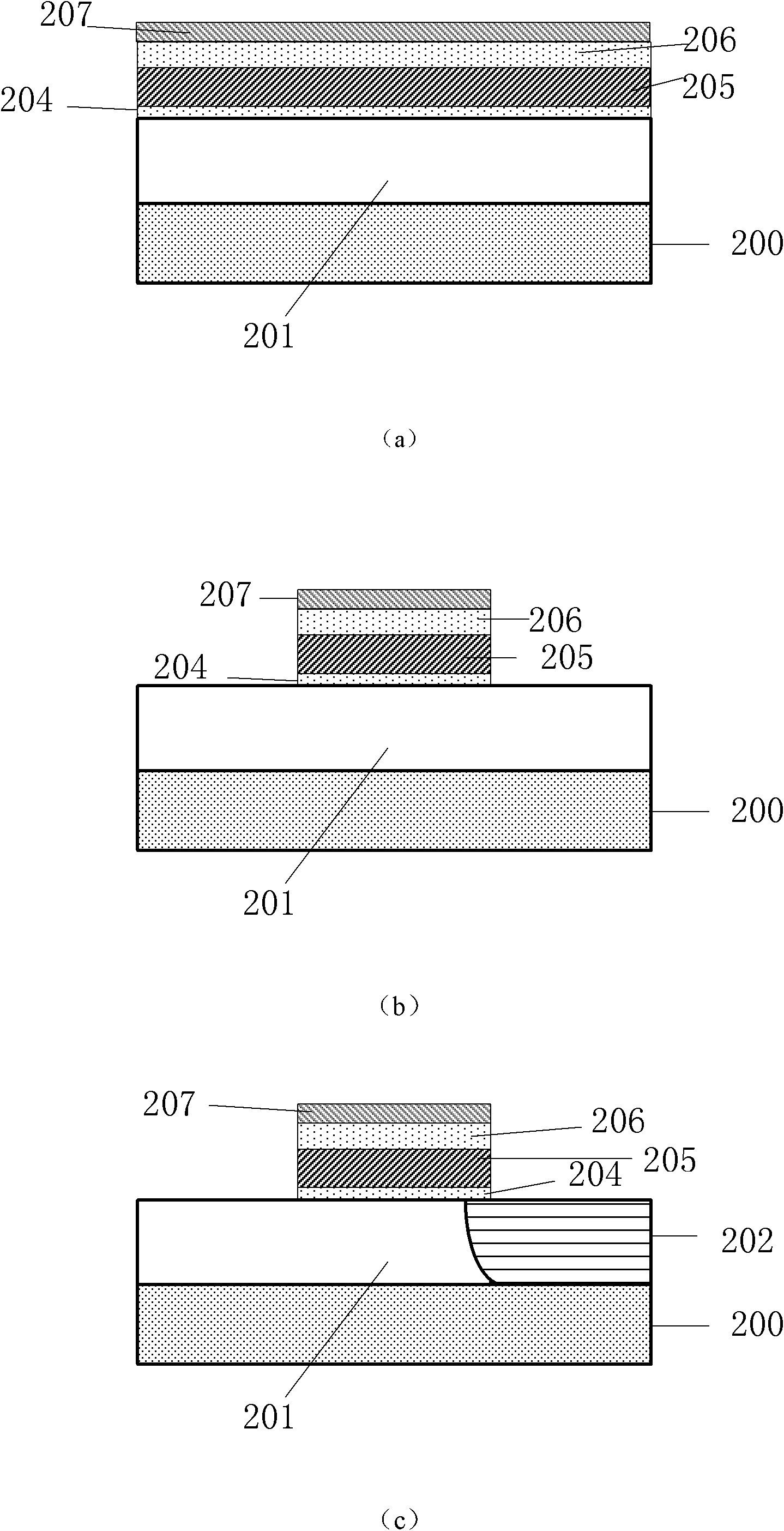

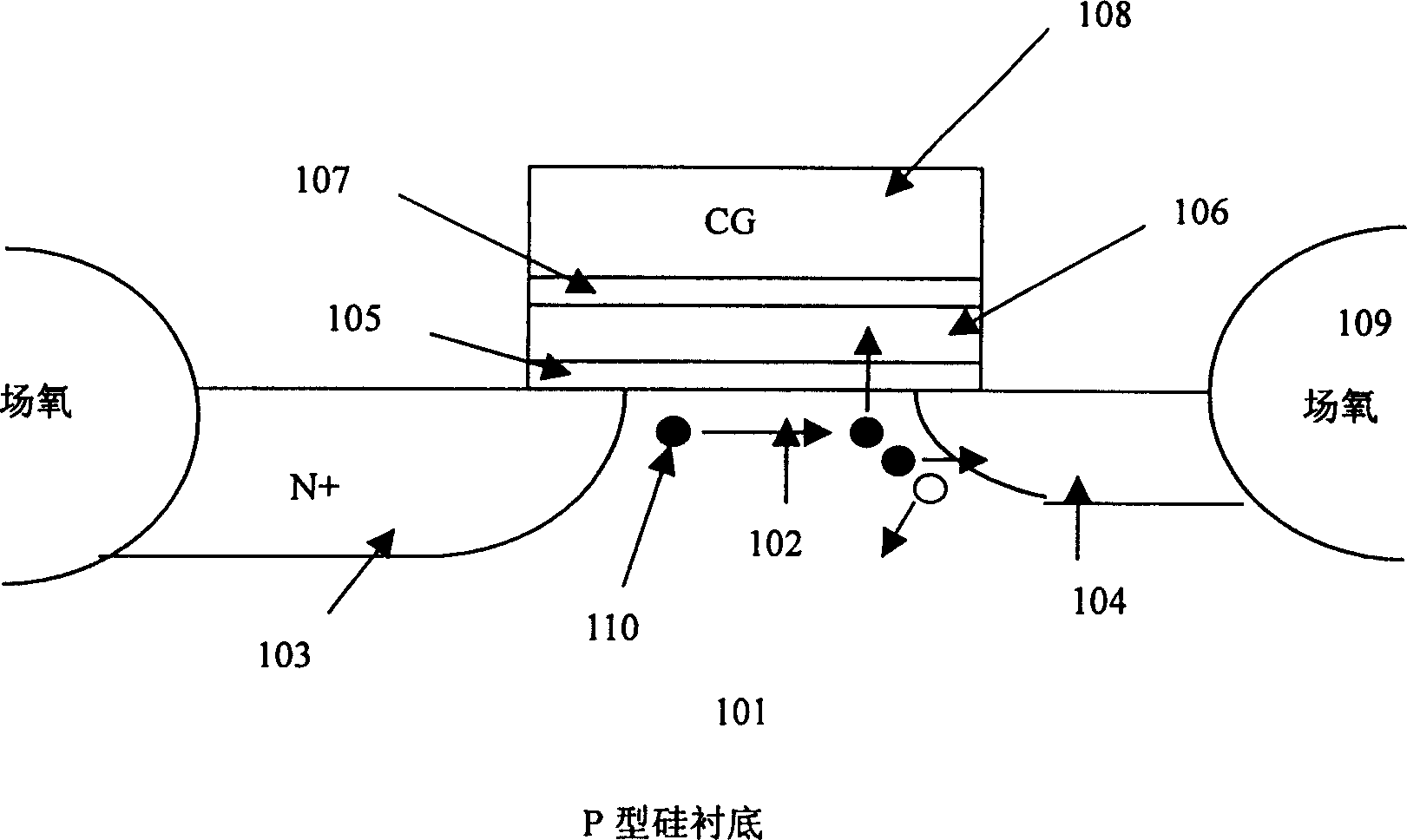

Method for forming discrete gate memory device

ActiveCN102044497AControl process precisionIncreased tunneling currentSolid-state devicesSemiconductor/solid-state device manufacturingInter layerGate dielectric

The invention relates to a method for forming a discrete gate memory device, which comprises the steps of: providing a semiconductor substrate, wherein a gate dielectric layer, a first polycrystalline silicon layer, an inter-layer insulating layer and a second polycrystalline silicon layer are formed on the semiconductor substrate in sequence, the first polycrystalline silicon layer has a first thickness; etching the second polycrystalline silicon layer and the insulating layer to form a control gate; and etching the first polycrystalline silicon layer to a second thickness, wherein the part of first polycrystalline silicon layer, which is covered by the inter-layer insulating layer, has the first thickness while the part not covered by the inter-layer insulating layer has the second thickness in a range of 80-280. The invention improves the tip shape of a floating gate polycrystal layer by reducing the rest thickness of the floating gate polycrystalline silicon layer by means of smile effect in following technical process and can be suitable for a device in smaller characteristic size and is beneficial to the increase of the erasing speed of the device.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

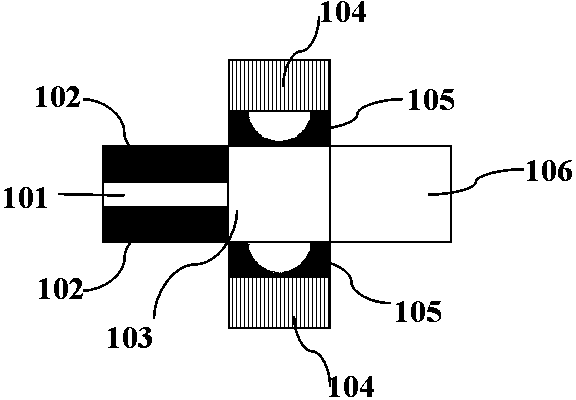

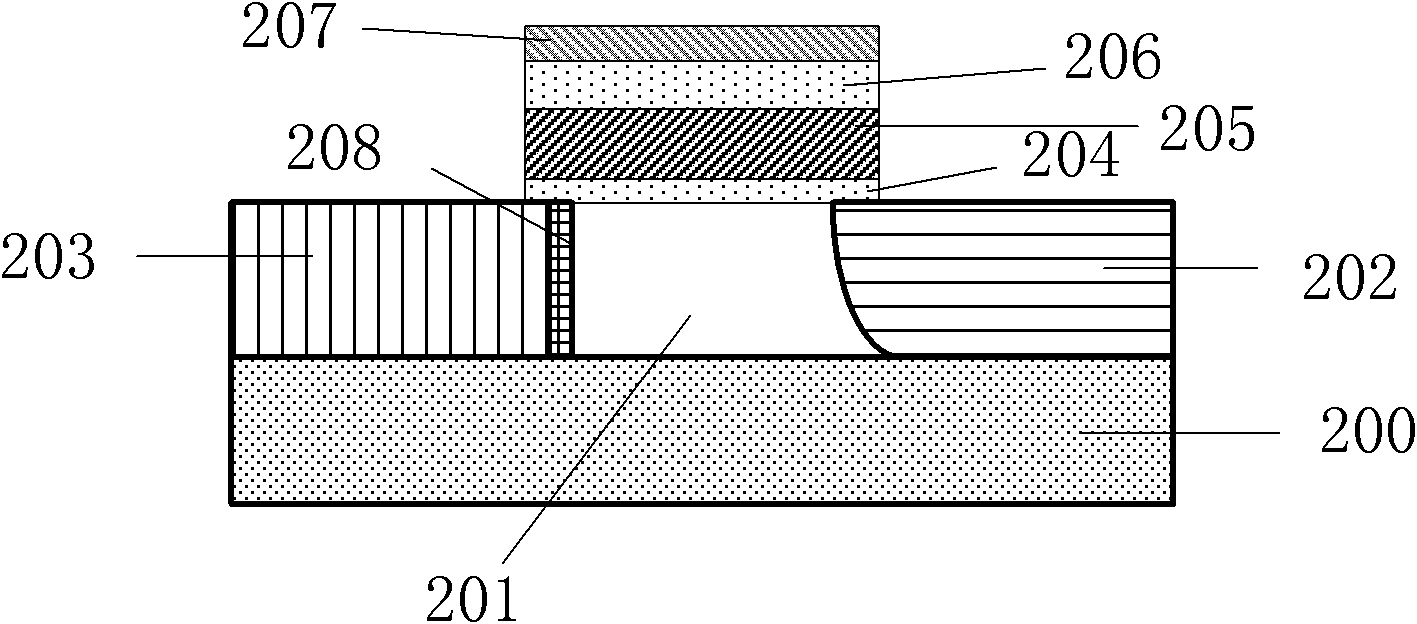

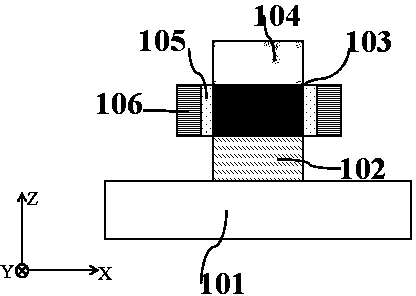

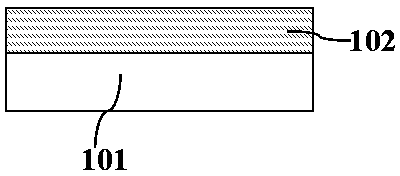

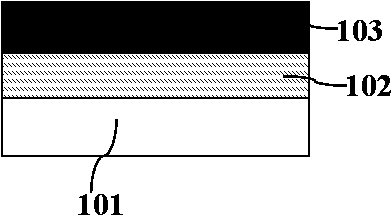

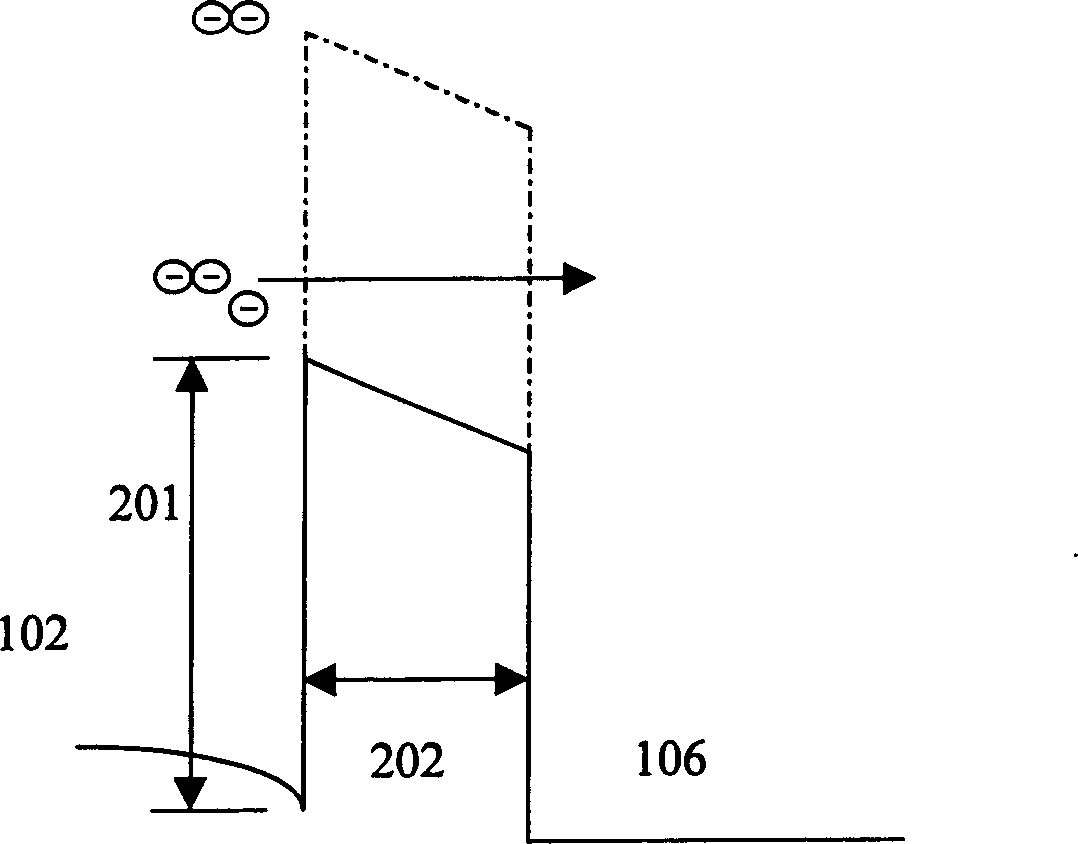

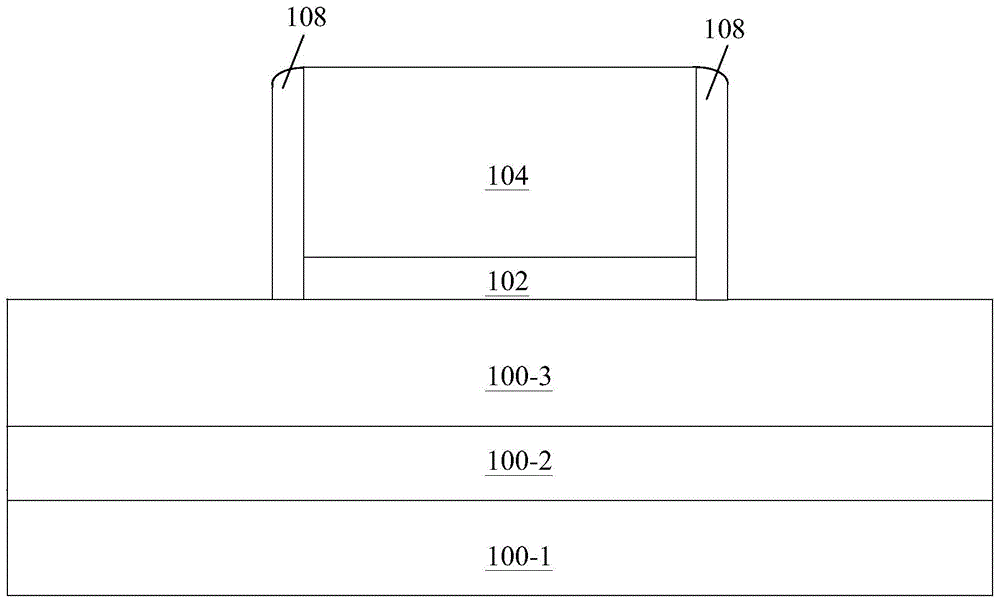

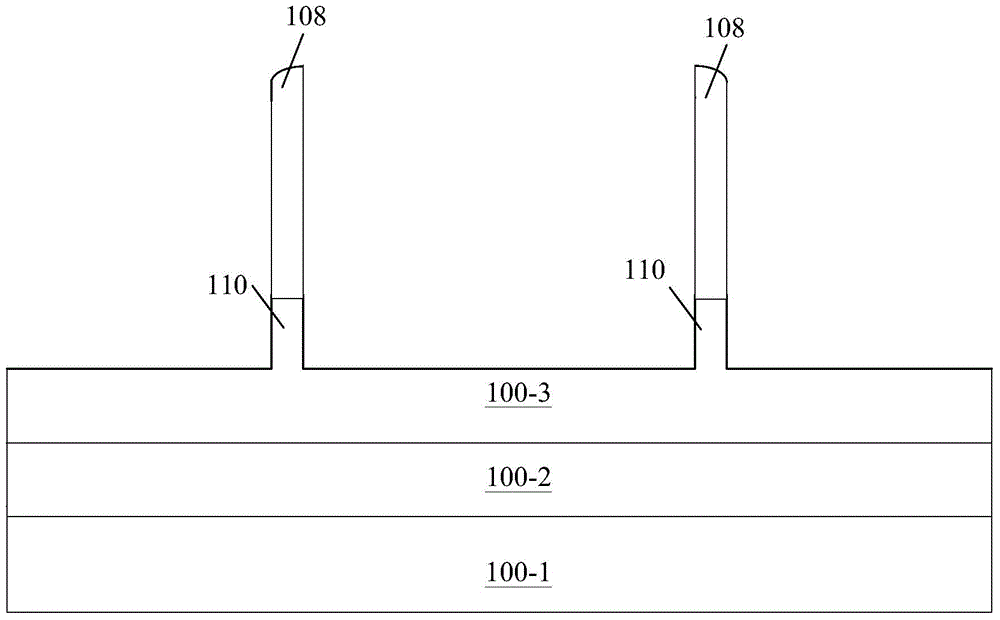

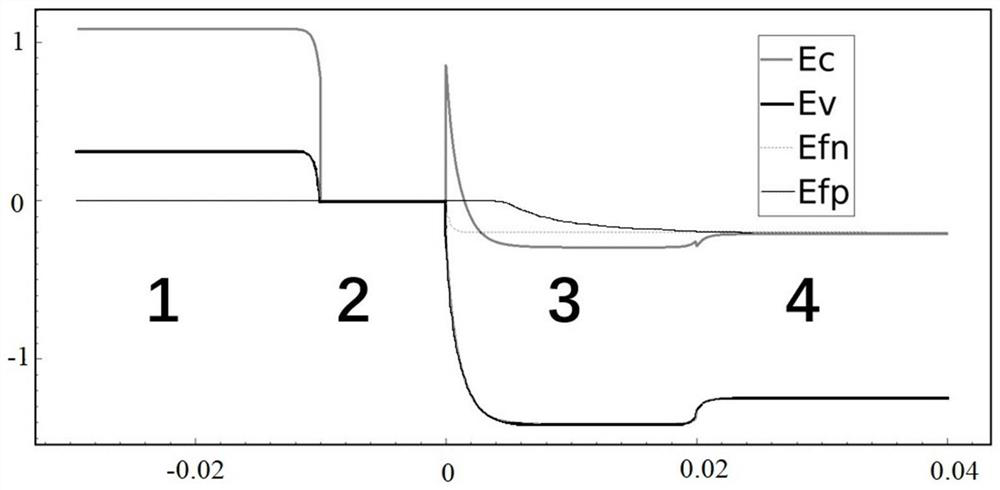

GeSnn channel tunneling field effect transistor with source strain source

The invention provides a GeSnn channel tunneling field effect transistor (10) with a source strain source. The GeSnn channel tunneling field effect transistor structurally comprises a GeSnn channel, a source electrode, a drain electrode, the source strain source, an insulating dielectric film and a gate electrode. The source strain source (102) grows in a source electrode area (101), the insulating dielectric film (105) grows on the GeSnn channel, and the insulating dielectric film is covered with a layer of gate (104). The lattice constant of the source strain source (102) is larger than that of the source electrode area (101), the strain on a channel area is formed, the strain is double-axis tensile strain in the yz-plane, and the strain is single-axis compression strain in the x direction. The strain enables n channel GeSn to be changed into a direct band gap from an indirect band gap, therefore, direct quantum tunneling is formed, tunneling currents are increased, and then the performance of the TFET is improved.

Owner:CHONGQING UNIV

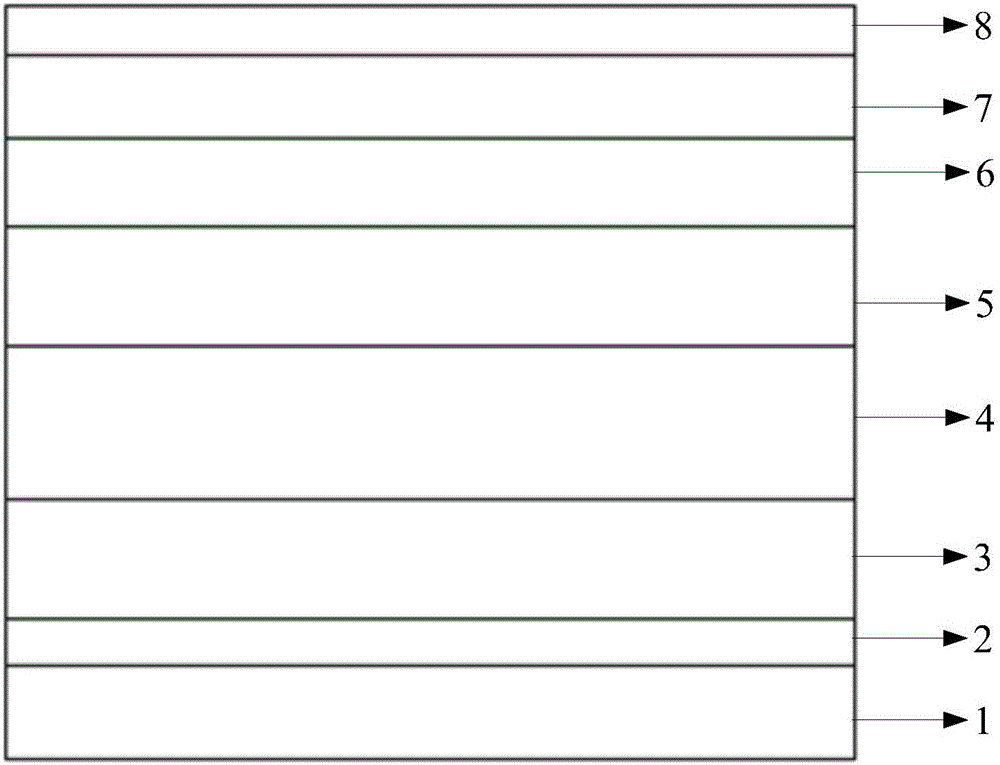

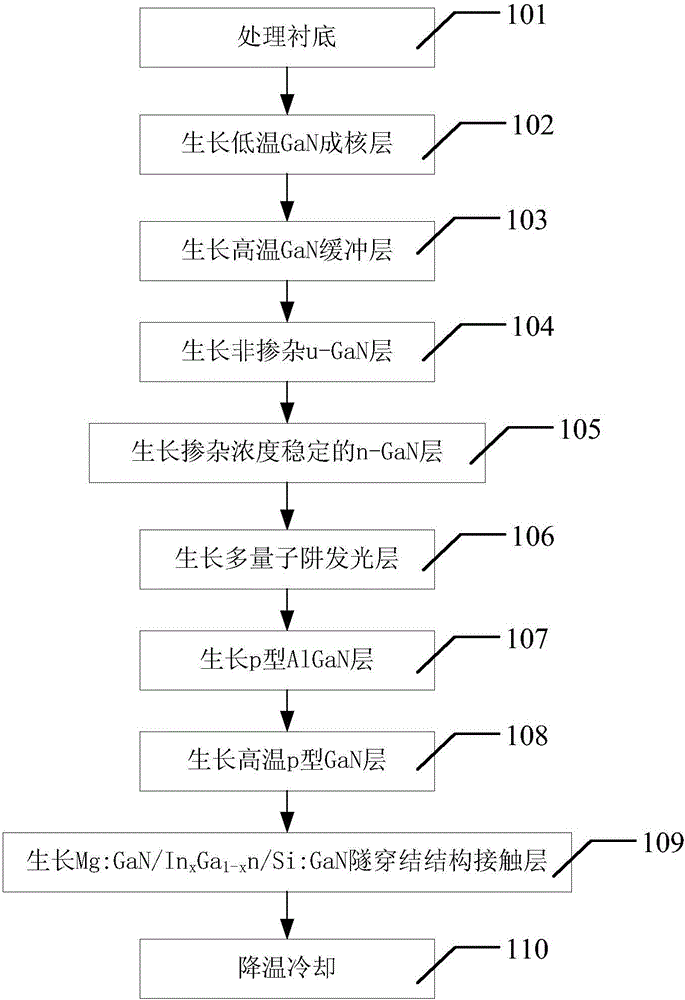

Growth method of LED epitaxial contact layer

ActiveCN106098870ALow working voltageIncreased tunneling currentSemiconductor devicesQuantum wellContact layer

The application discloses a growth method of an LED epitaxial contact layer. The method comprises: processing a substrate; a growing a low-temperature GaN nucleating layer; growing a high-temperature GaN buffer layer; growing a non-doping u-GaN layer; growing a n-GaN layer with stable doping concentration; growing a multi-quantum-well light-emitting layer; growing a p type AlGaN layer; growing a high-temperature p type GaN layer; growing a Mg:GaN / InxGa(1-x)n / Si:GaN tunneling structure contact layer; and carrying out temperature-reducing cooling. According to the technical scheme, the contact layer of LED epitaxy is designed to have a Mg:GaN / InxGa(1-x)n / Si:GaN tunneling structure, so that the contact resistance is reduced effectively and thus the working voltage of the LED chip is reduced.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

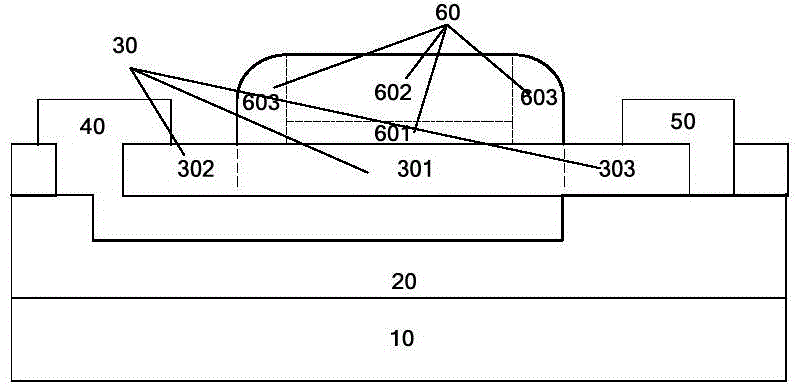

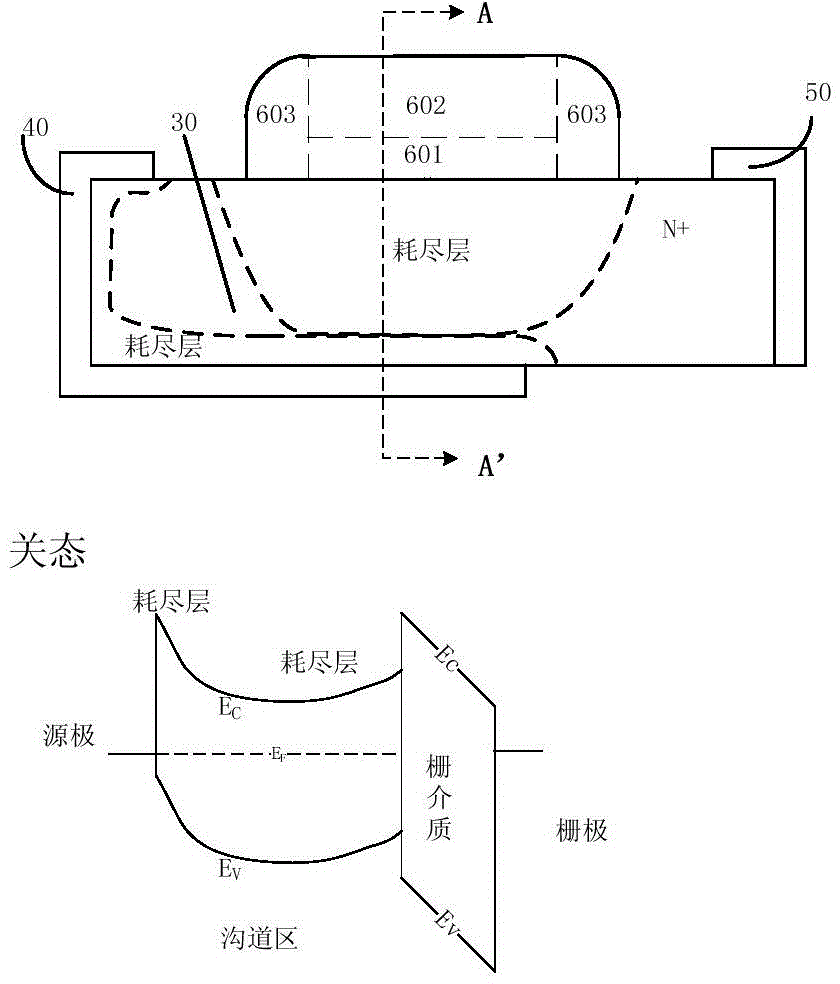

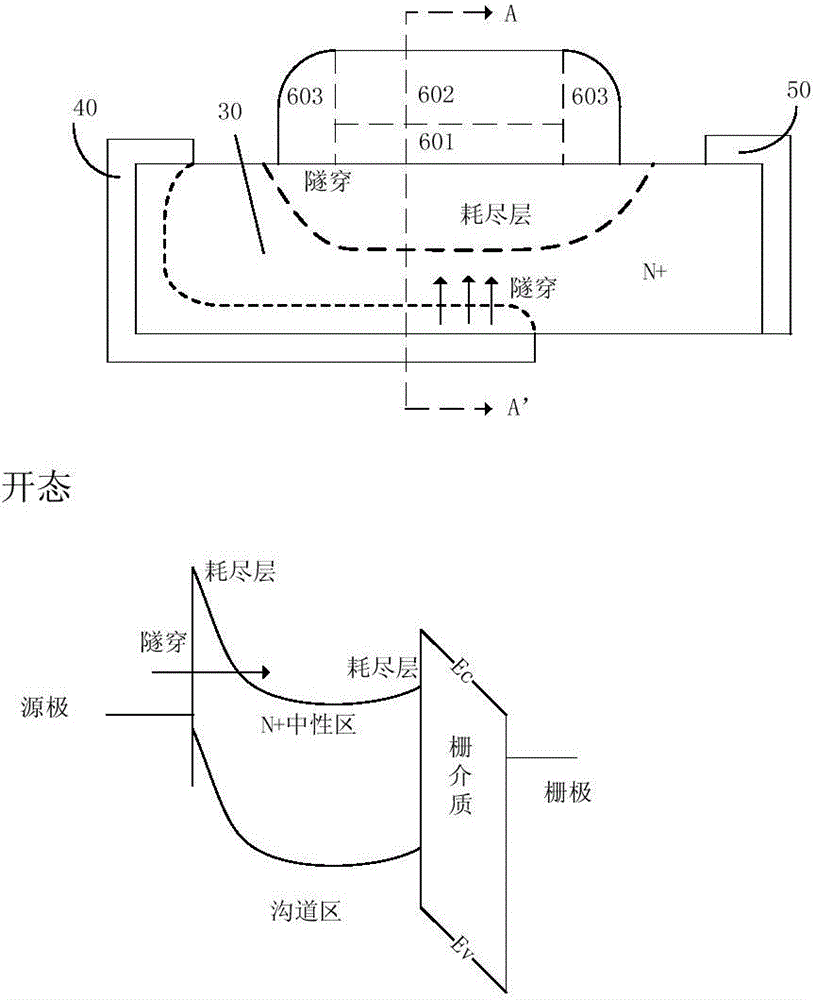

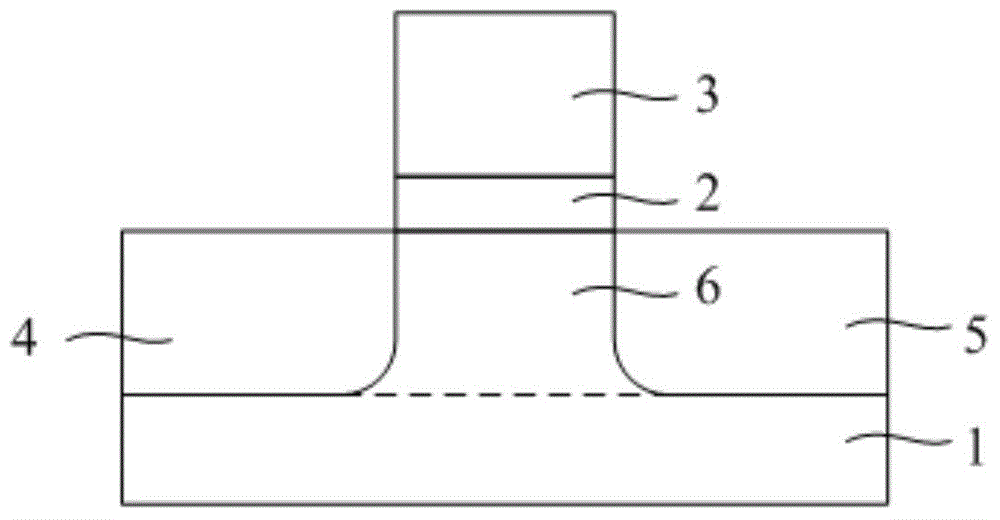

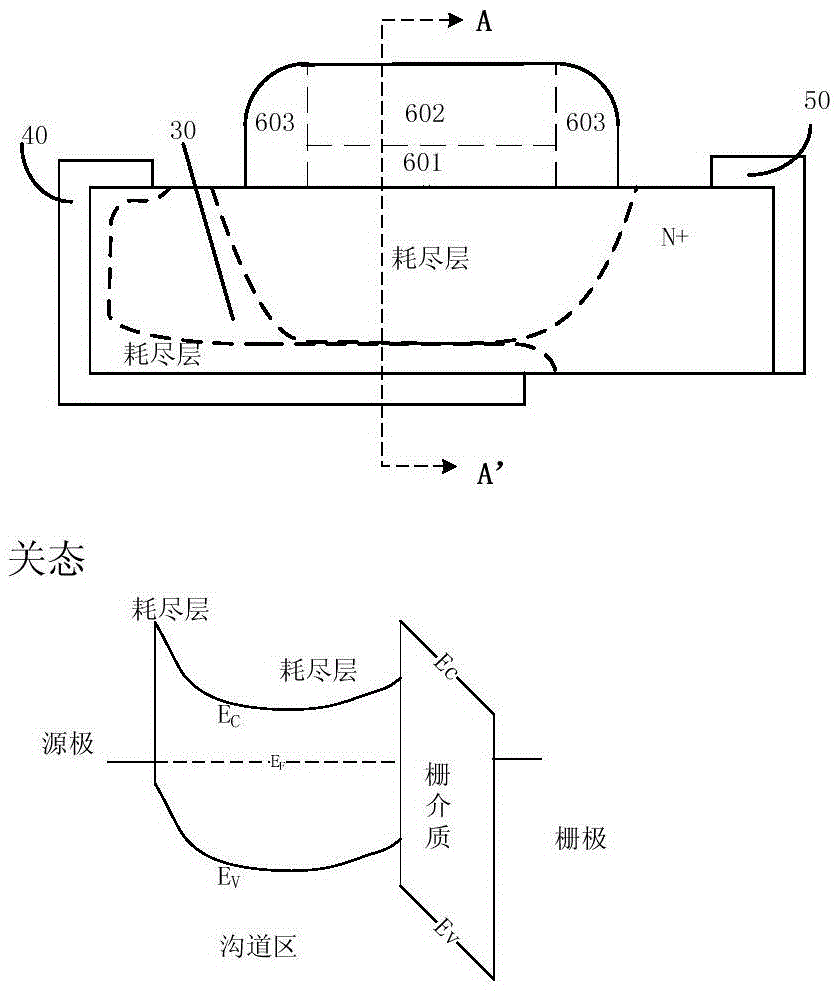

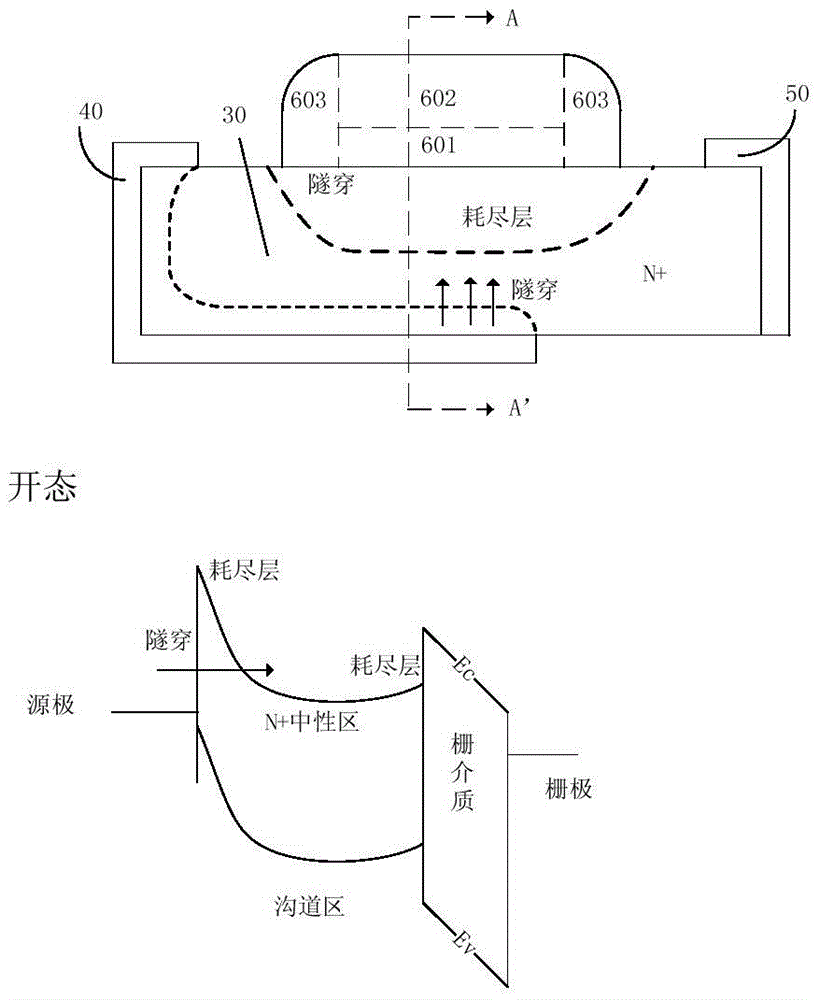

Junctionless tunneling field effect transistor and formation method thereof

ActiveCN103606563AIncreased tunneling currentIncrease the on-state currentTransistorSemiconductor/solid-state device manufacturingGate stackCondensed matter physics

The invention provides a junctionless tunneling field effect transistor and a formation method thereof. The junctionless tunneling field effect transistor includes the following components of: a substrate; a liner layer arranged on the substrate; a channel layer which is arranged on the liner layer and includes a channel region arranged in the middle as well as a source region and a drain region arranged at two sides of the channel region, wherein the channel region, the source region and the drain region have the same doping type; a source which coats on the upper surface, a side surface and the lower surface of the source region and coats the lower surface of the channel region, and is in Schottky contact with the channel region; a drain which coats the upper surface and a side surface of the drain region; and a gate stack structure which is located on the channel region. The junctionless tunneling field effect transistor has the advantages of simple structure, large tunneling current, capability of effectively suppressing a short channel effect and the like. The invention also provides a formation method of the junctionless tunneling field effect transistor.

Owner:TSINGHUA UNIV

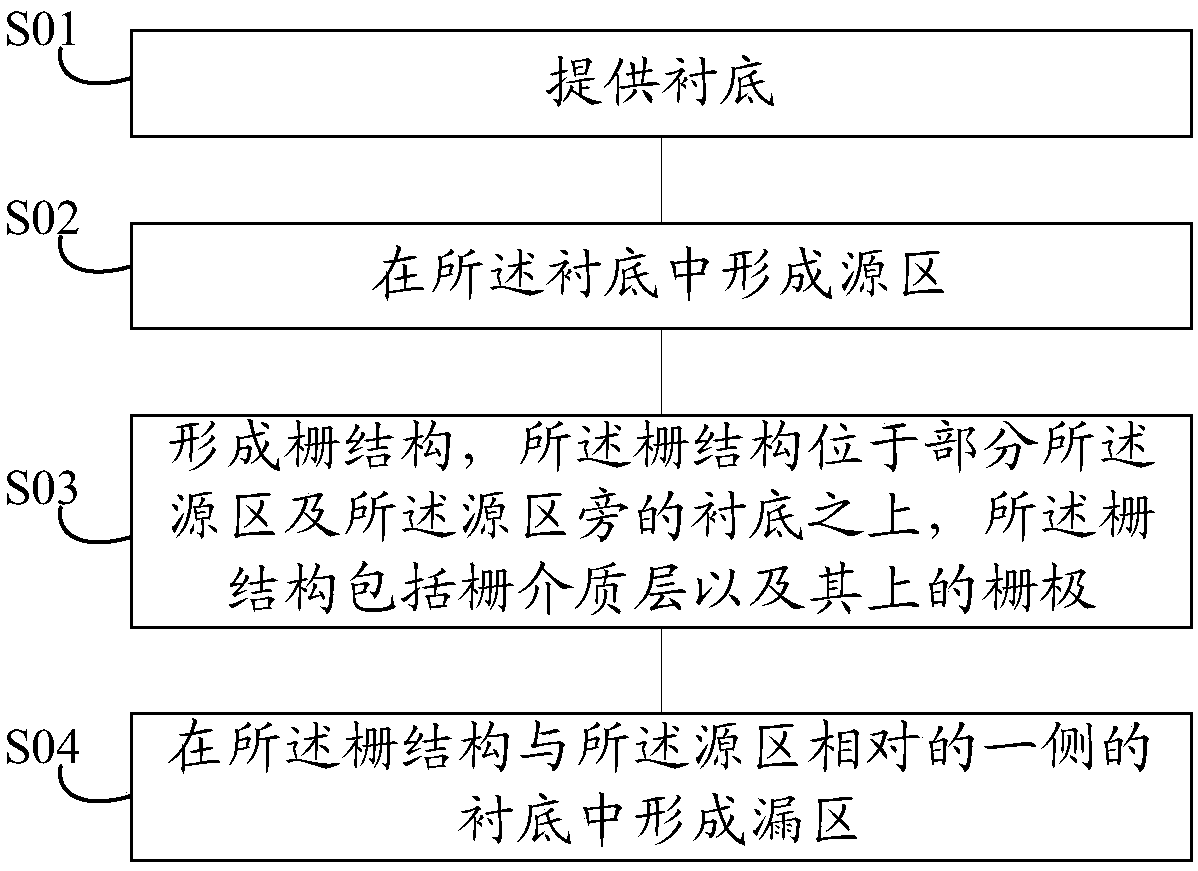

Tunneling field effect transistor and manufacturing method thereof

InactiveCN108321197AImproved Potential Control CapabilityIncrease the on-state currentSemiconductor/solid-state device manufacturingDiodeCapacitancePower flow

The present invention provides a tunneling field effect transistor and a manufacturing method thereof. A formed source region is located below part of a gate structure and in a substrate of the side of the gate structure, that is to say, the gate structure alternately covers part of the source region, so that the potential control capacity of a gate voltage on a device source region / channel regionis improved, further, the area of the source region is larger than the area of a drain region, the dosage concentration of the source region is higher than the dosage concentration of the drain region to allow the carrier concentration of the source region to be higher than the carrier concentration of the drain region as a whole, the finally formed gate electrode with a ferroelectric gate layerhas a negative capacitance effect to amplify the gate electrode surface potential, and therefore, the tunneling probability of a device can be increased, and an ON state current of the device can be integrally improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

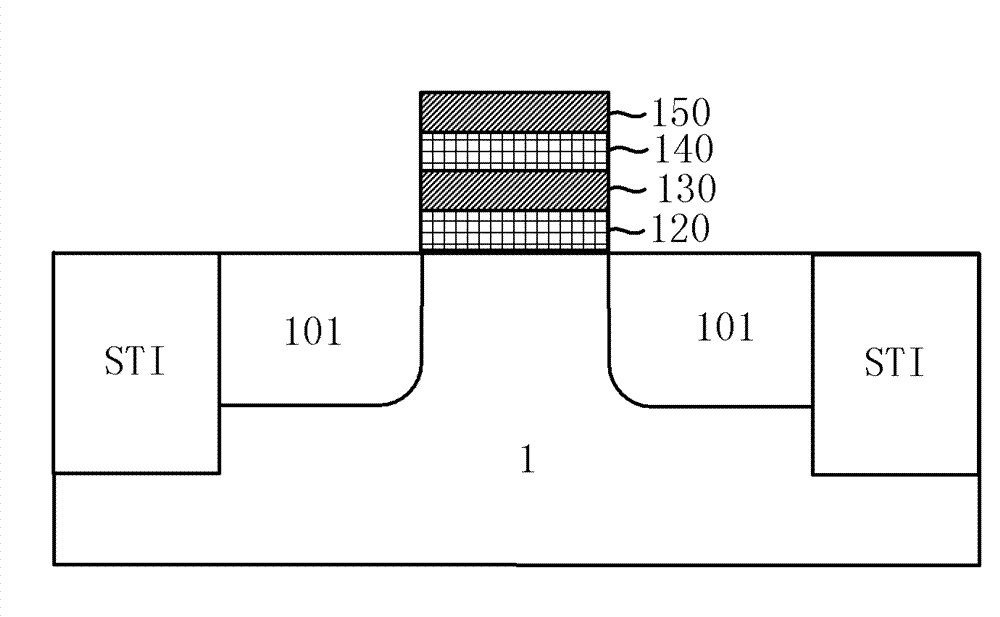

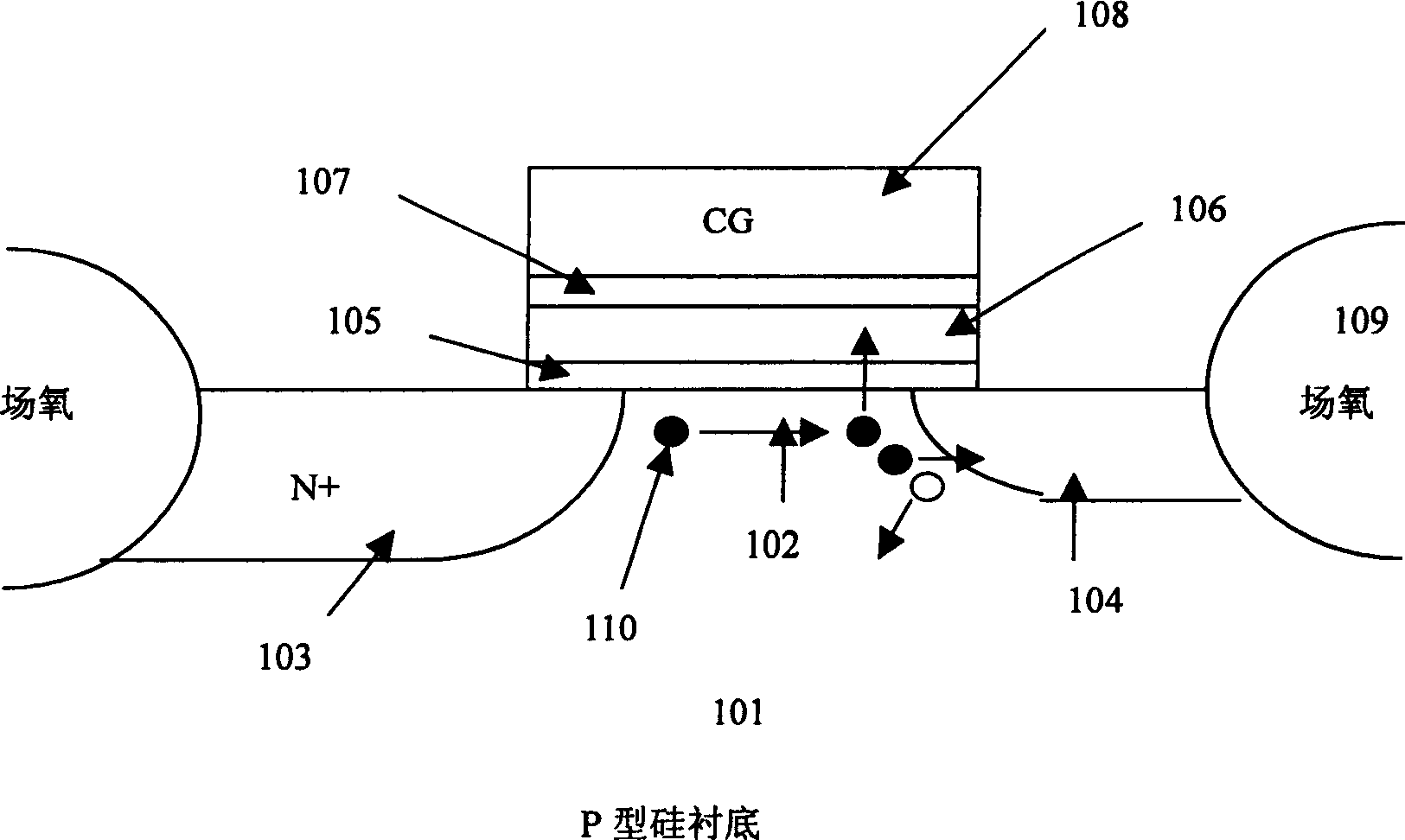

Flash memory and manufacturing method thereof

InactiveCN102738169ASuppression of punch-through effectImprove programming efficiencyTransistorSolid-state devicesGate stackEngineering

The invention discloses a flash memory and a manufacturing method thereof, belonging to the technology field of a semiconductor memory. The flash memory includes a buried oxide layer on which a source terminal, a channel and a drain terminal are arranged. The channel locates between the source terminal and the drain terminal. A tunnel oxide layer, a polysilicon floating gate, a barrier oxide layer and a polysilicon controlling gate are arranged on the channel in order. A thin silicon nitride layer is arranged between the source terminal and the channel. The manufacturing method comprises the following steps of: (1) providing an SOI silicon substrate with shallow trench isolation and forming an active area; (2) growing the tunnel oxide layer and a first polysilicon layer on the silicon substrate in order and preparing the polysilicon floating gate, and growing the barrier oxide layer and a second polysilicon layer and preparing the polysilicon controlling gate; (3) etching and forming a gate stacking structure; (4) preparing the drain terminal on one side of the gate stacking structure, etching a thin silicon film on the other side of the gate stacking structure, growing the thin silicon nitride layer, then backfilling a material of silicon, and preparing the source terminal. The flash memory and the method have the advantages of high programming efficiency, low power consumption, and capability of inhibiting a source-drain punch-through effect effectively.

Owner:PEKING UNIV

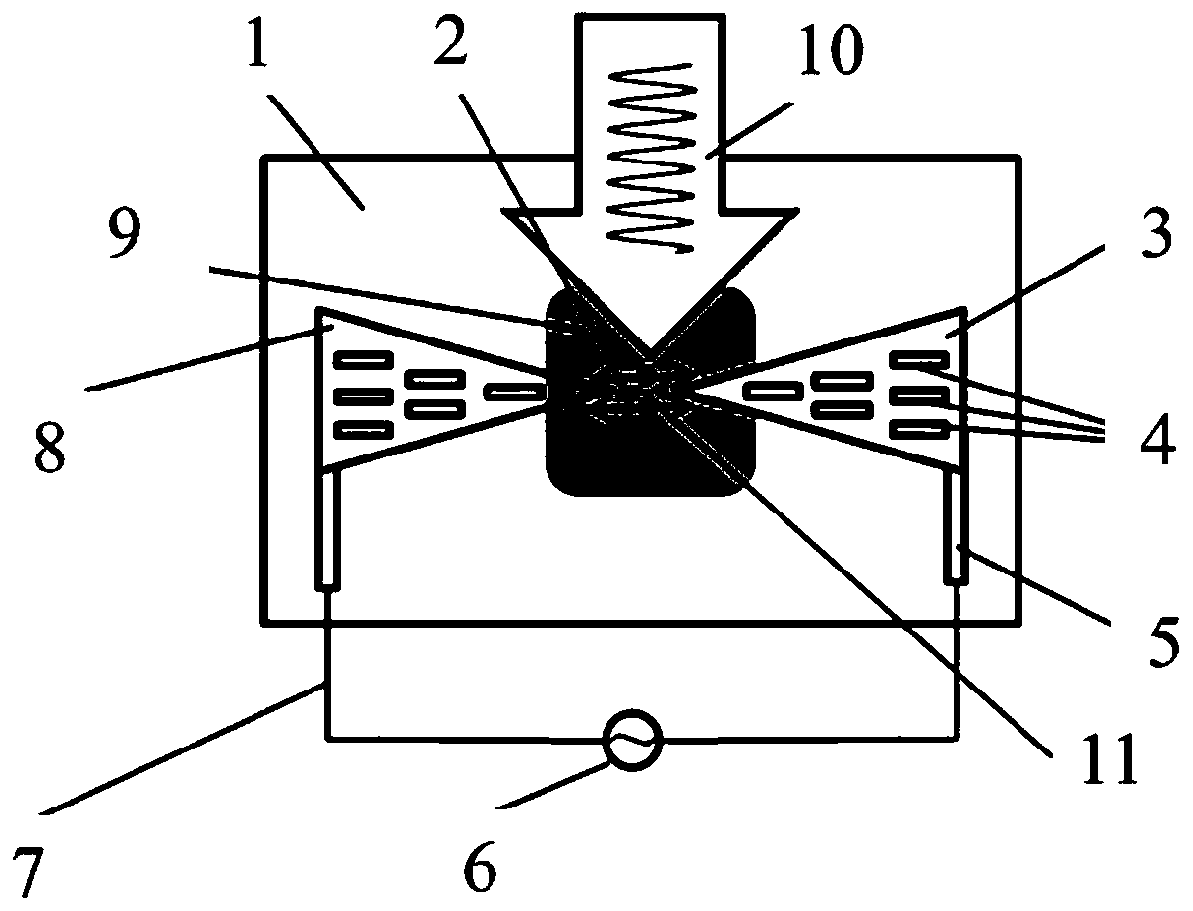

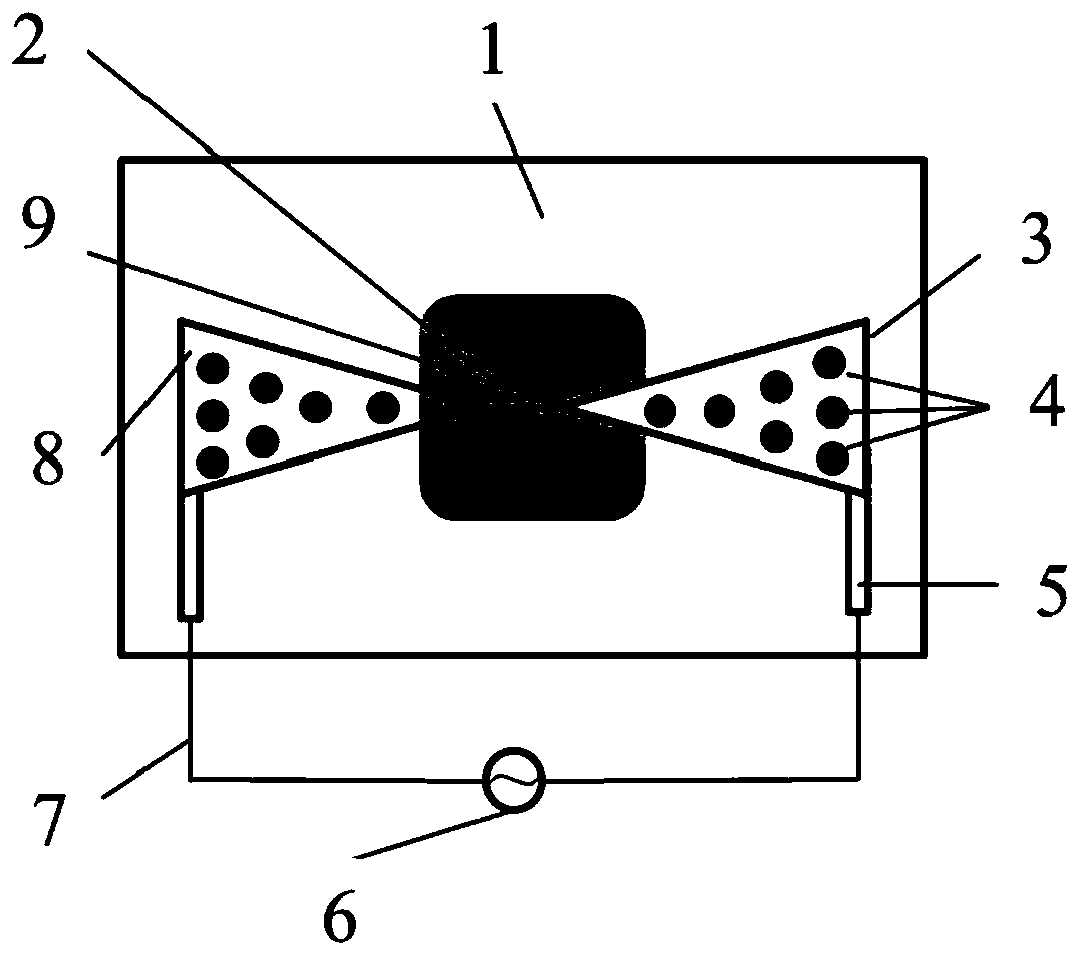

TFET (Tunneling Field Effect Transistor) and forming method thereof

ActiveCN104425606AIncrease working currentHigh currentSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowElectron mobility

The invention discloses a TFET (Tunneling Field Effect Transistor) and forming method thereof. The TFET comprises a substrate, a bottom-layer fin part, a channel fin part, a gate structure, a source electrode and a drain electrode, wherein the bottom-layer fin part is positioned on the substrate and is provided with a first type of doping; the channel fin part is positioned on the upper surface of the bottom-layer fin part and is provided with a second type of doping, the second type of doping is different from the first type of doping, and the electron mobility of the channel fin part is greater than that of the bottom-layer fin part; the gate structure stretches across the channel fin part; the source electrode is provided with the first type of doping; the drain electrode is provide with the second type of doping. The TFET provided by the invention has high working current and low power consumption.

Owner:SEMICON MFG INT (SHANGHAI) CORP

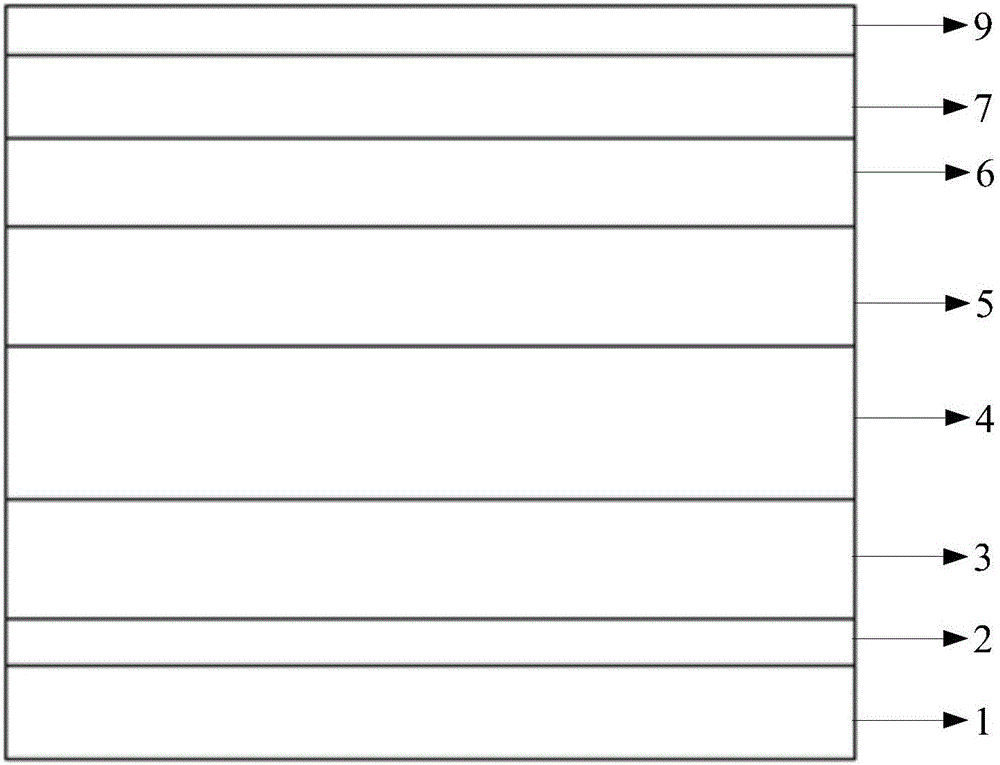

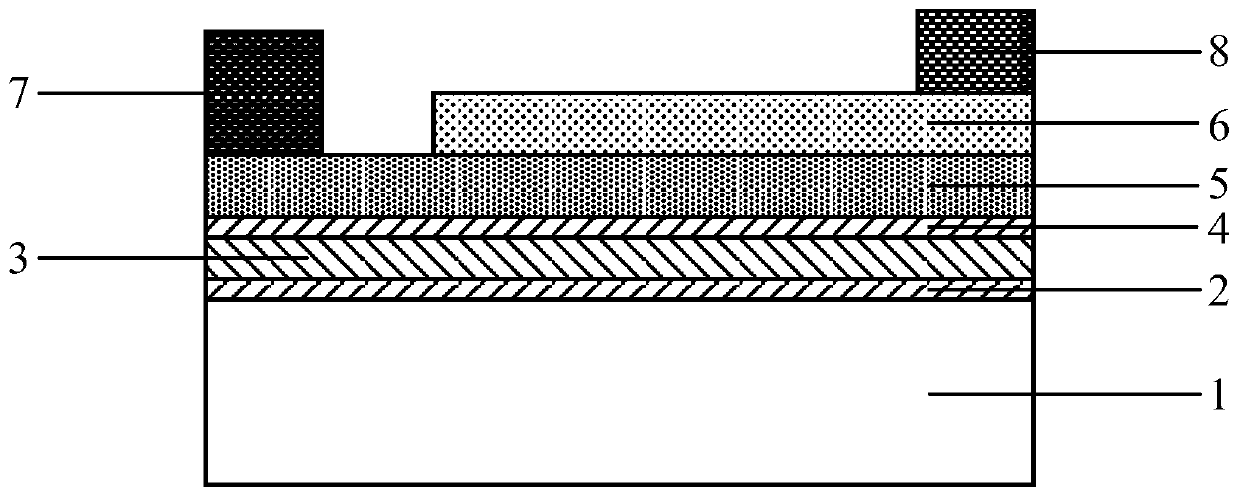

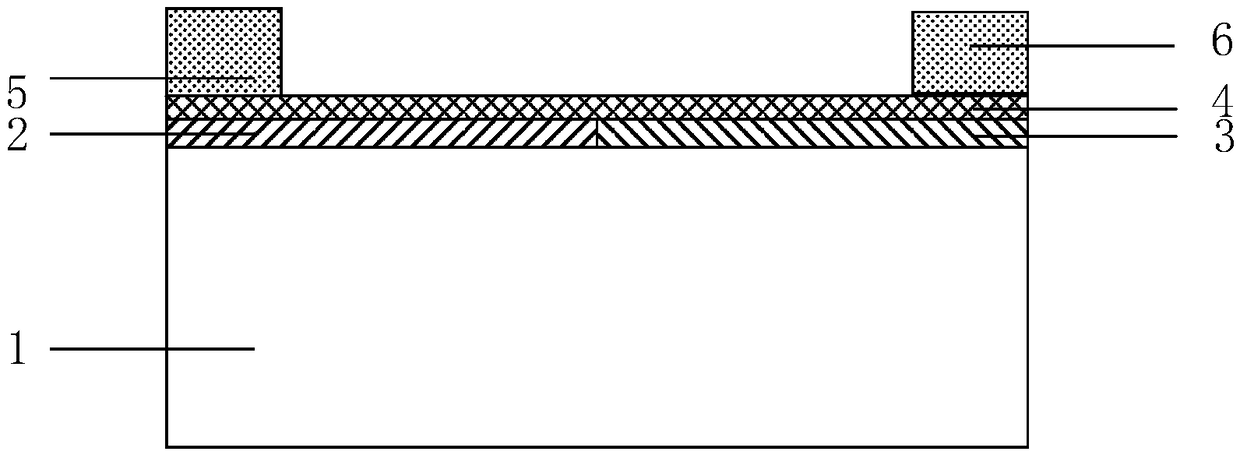

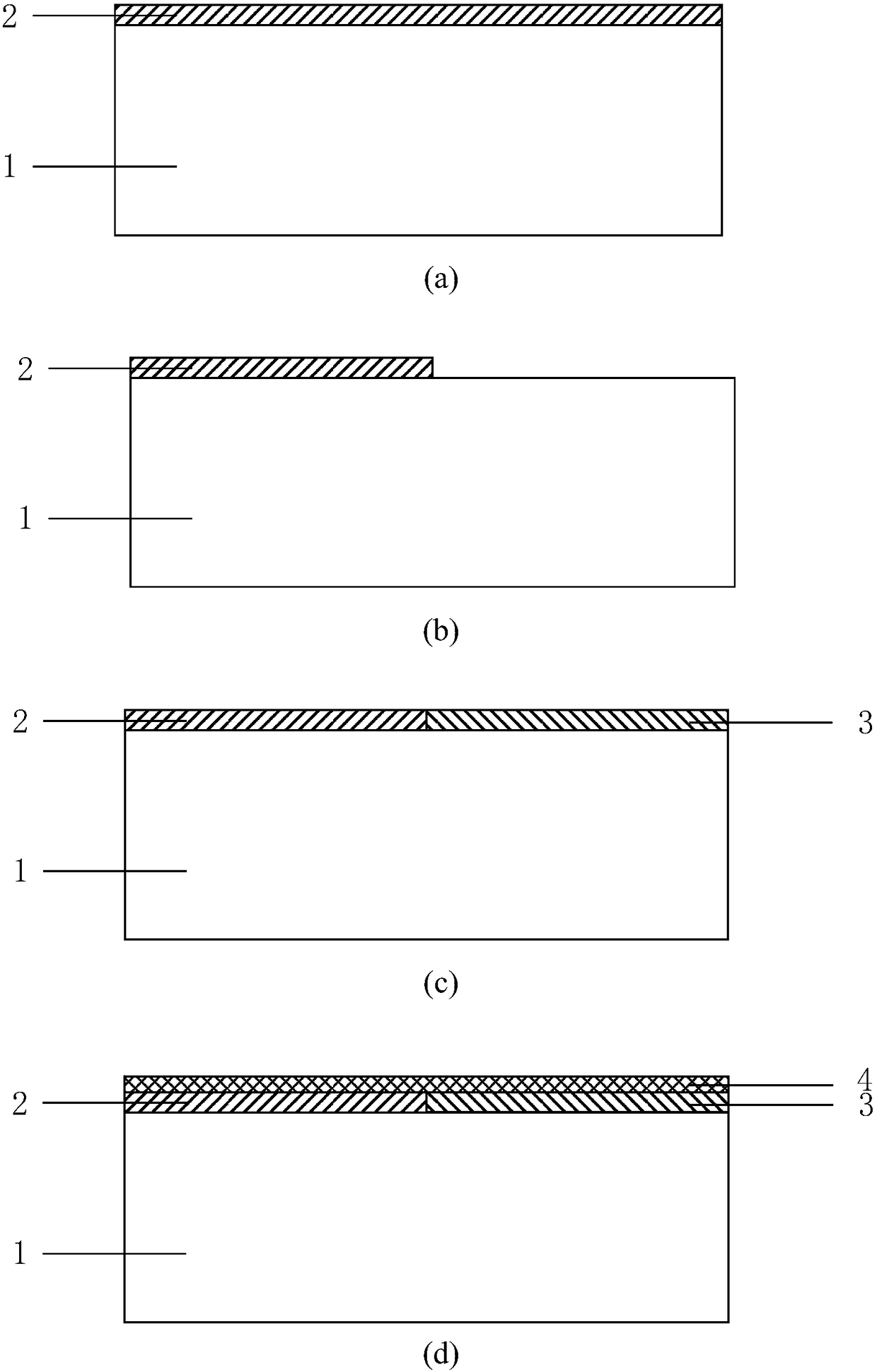

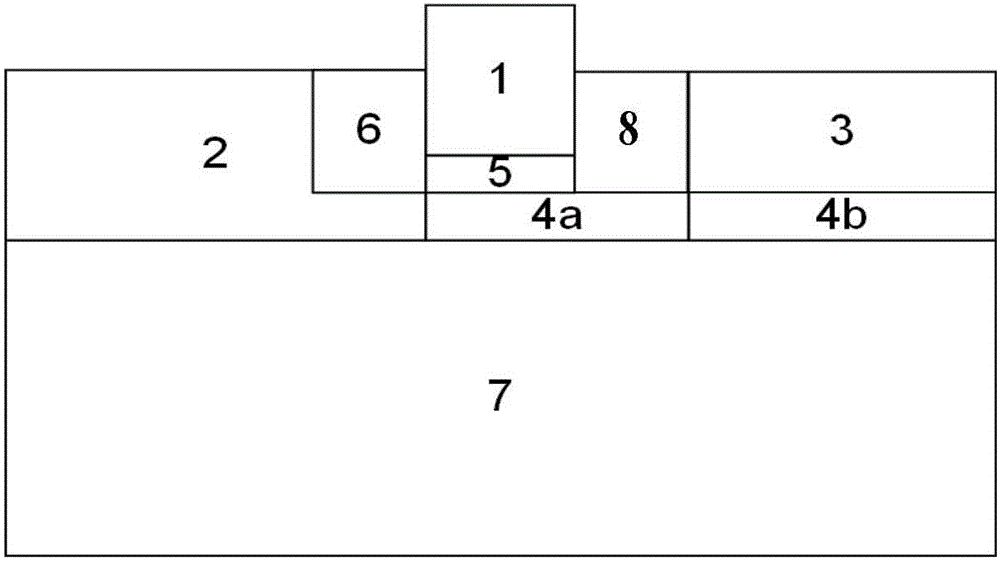

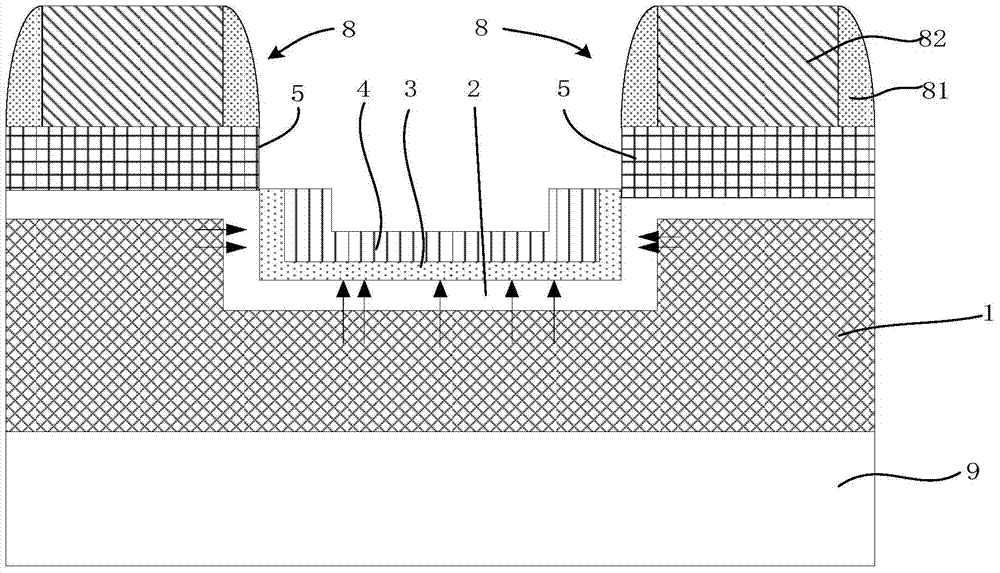

Two-dimensional material heterojunction back gate negative capacitance tunneling transistor and preparation method thereof

InactiveCN110649092AIncrease the on-state currentLow open currentSemiconductor/solid-state device manufacturingDiodeCapacitanceHeterojunction

The invention relates to the technical field of semiconductor devices, and particularly discloses a two-dimensional material heterojunction back gate negative capacitance tunneling transistor. The transistor comprises a semiconductor substrate (1), a first high-k dielectric layer (2), a ferroelectric material layer (3), a second high-k dielectric layer (4), a first two-dimensional material layer (5), a second two-dimensional material layer (6), a metal source electrode (7) and a metal drain electrode (8). The advantages of the negative capacitance and the two-dimensional material are brought into full play, the on-state current of the tunneling field effect transistor is improved, and the off-state current of the tunneling field effect transistor is reduced. A preparation method of the two-dimensional material heterojunction back gate negative capacitance tunneling transistor is also disclosed, which comprises the growth of all the material layers. Because of the adoption of aback gatestructure, the device is simple in preparation process and compatible with a traditional semiconductor process.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

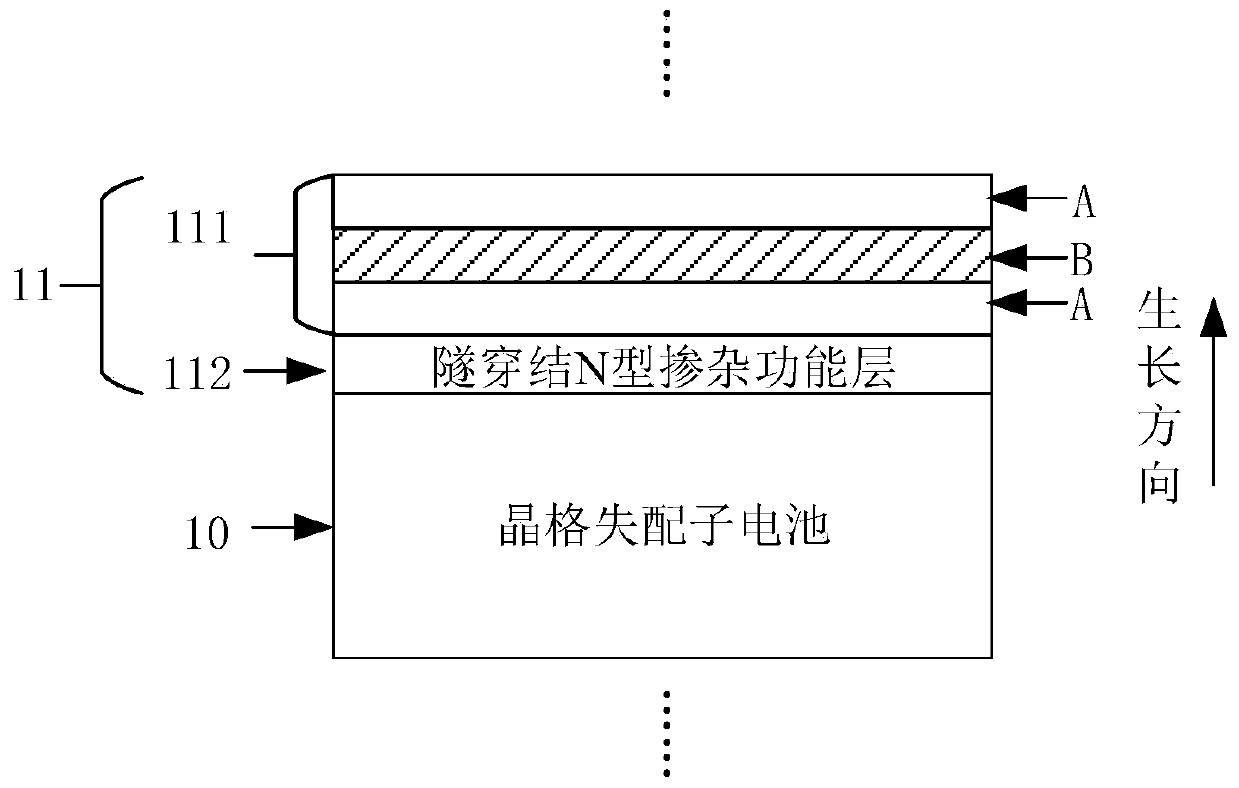

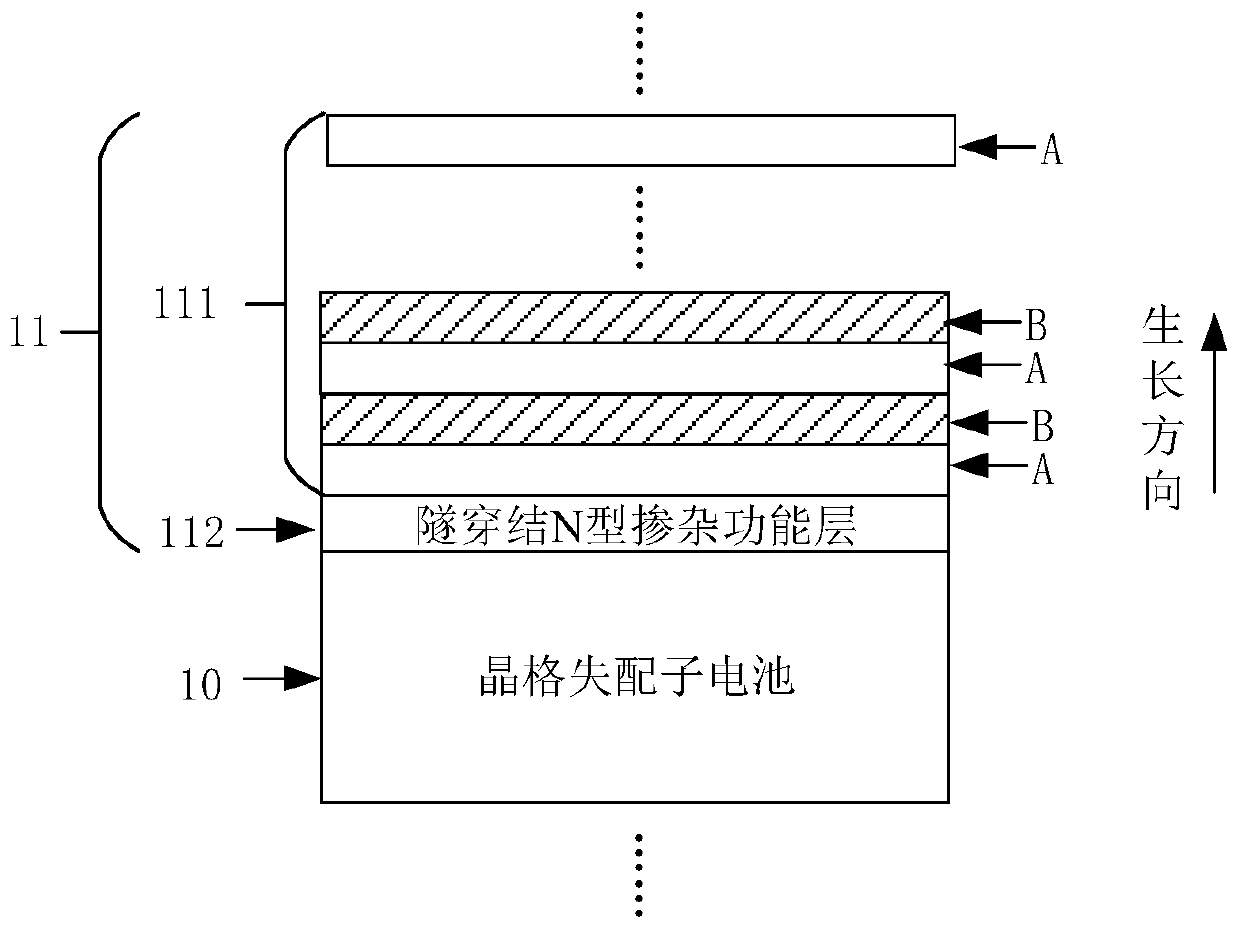

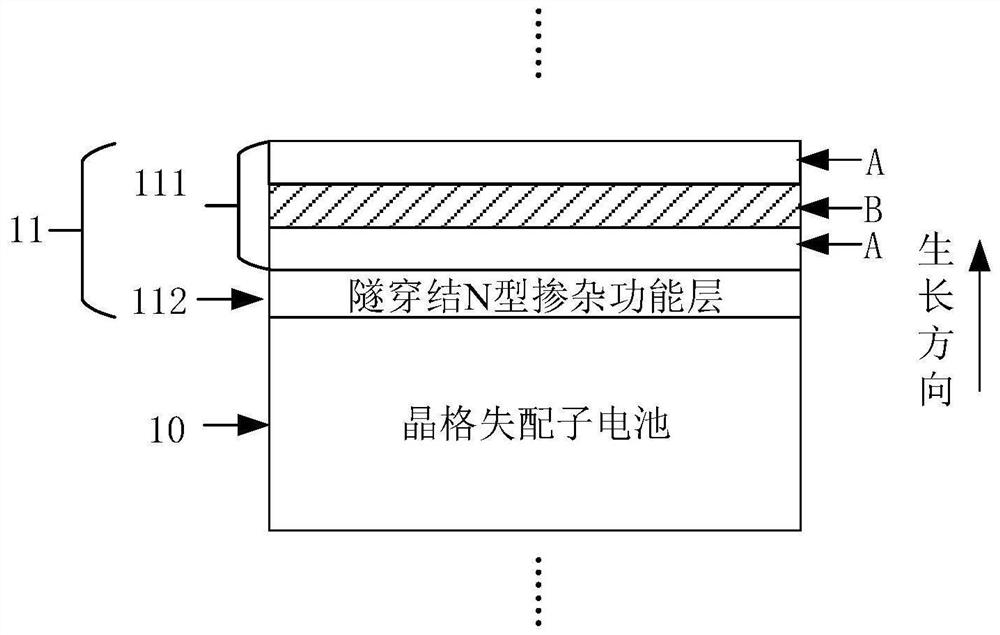

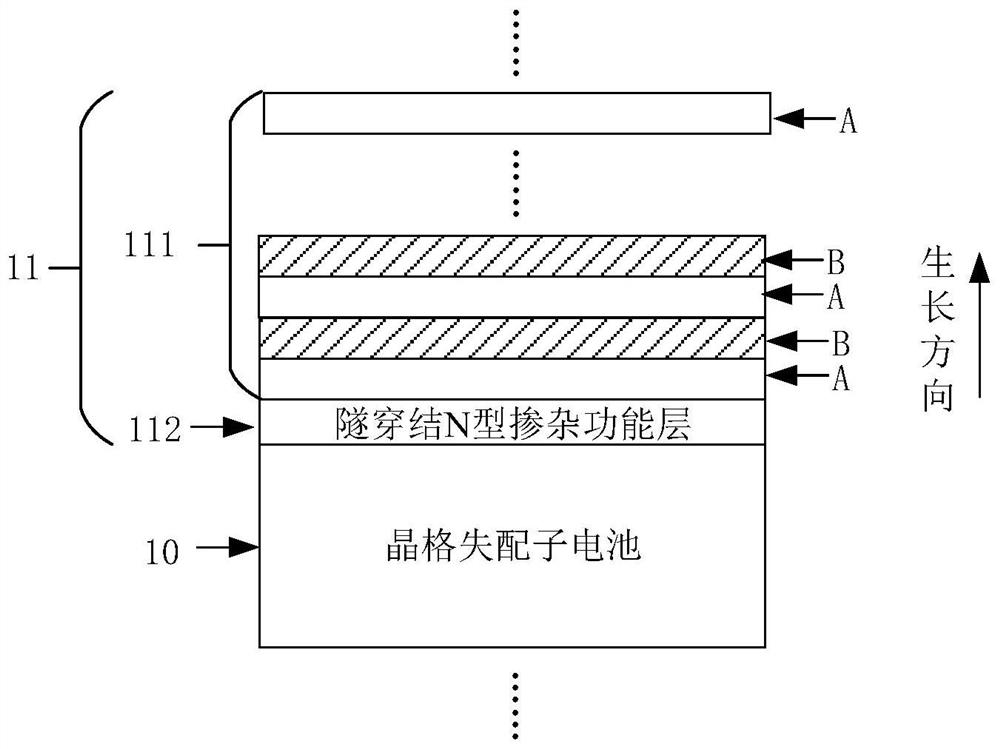

Lattice mismatch multi-junction solar cell

ActiveCN110224036AAvoid mismatchInhibited DiffusionNanotechnologyPhotovoltaic energy generationP type dopingLattice mismatch

The invention provides a lattice mismatch multi-junction solar cell. The lattice mismatch multi-junction solar cell comprises at least one crystal lattice mismatch sub cell and a tunneling junction grown on the crystal lattice mismatch sub cell; the P-type doping functional layer of the tunneling junction is a C-doped p-type AlxGaAs layer / Zn-doped p type AlyInGaAs layer / C-doped p-type AlxGaAs layer, or after the C-doped p-type AlxGaAs layer / Zn-doped p type AlyInGaAs layer alternately grow for N periods, and then the superlattice structure of the C-doped p-type AlxGaAs is grown. A new structureis adopted to replace the C-doped p type (Al) InGaAs layer in the prior art, so that the problem of InGaAs lattice mismatch with the body material in the solar cell caused by suppression of In component access due to the doped reaction source halogen in the p type AlyInGaAs, so that the photoelectric conversion efficiency of the solar cell is improved.

Owner:YANGZHOU CHANGELIGHT

Homogenous PN (positive-negative) junction on basis of two-dimensional semiconductor materials and method for preparing homogenous PN junction

ActiveCN108807553AImprove stabilityEnhanced tunneling electric fieldSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsWork function

The invention discloses a homogenous PN (positive-negative) junction on the basis of two-dimensional semiconductor materials and a method for preparing the homogenous PN junction. By the aid of the homogenous PN junction and the method, the problems of N-type doping on semiconductor materials with low Fermi energy levels and P-type doping on semiconductor materials with high Fermi energy levels due to the fact that electrons can be transferred to the materials with the low Fermi energy levels from the existing two-dimensional semiconductor materials with the high Fermi energy levels when the two types of semiconductor materials with different work functions are perpendicularly stacked can be solved. The homogenous PN junction and the method have the advantages that the homogenous abrupt PNjunction can be formed in the two-dimensional semiconductor materials by the aid of the doping method, band tails can be prevented from being led into forbidden bands, and the homogenous PN junctionand the method have important significance in electronic device application; the doping method is free of crystal lattice damage due to ion collision, the stability can be greatly enhanced, processesfor preparing the homogenous PN junction are simple, and the homogenous PN junction and the method are easy to popularize to large-scale production.

Owner:PEKING UNIV

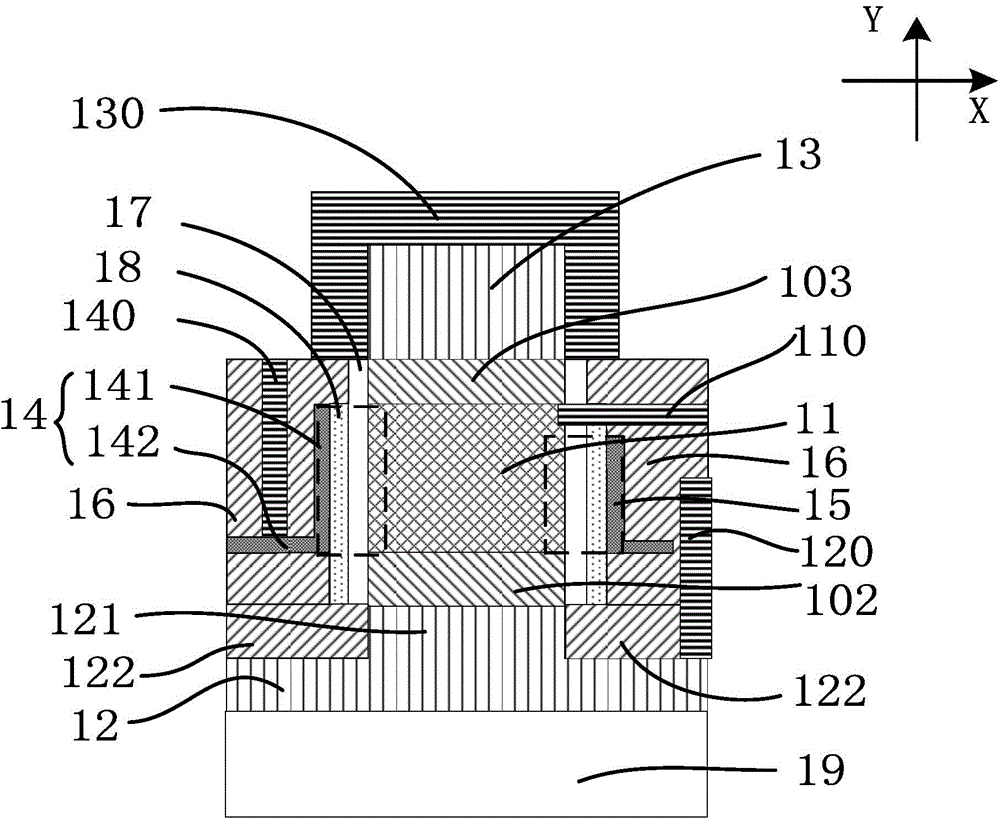

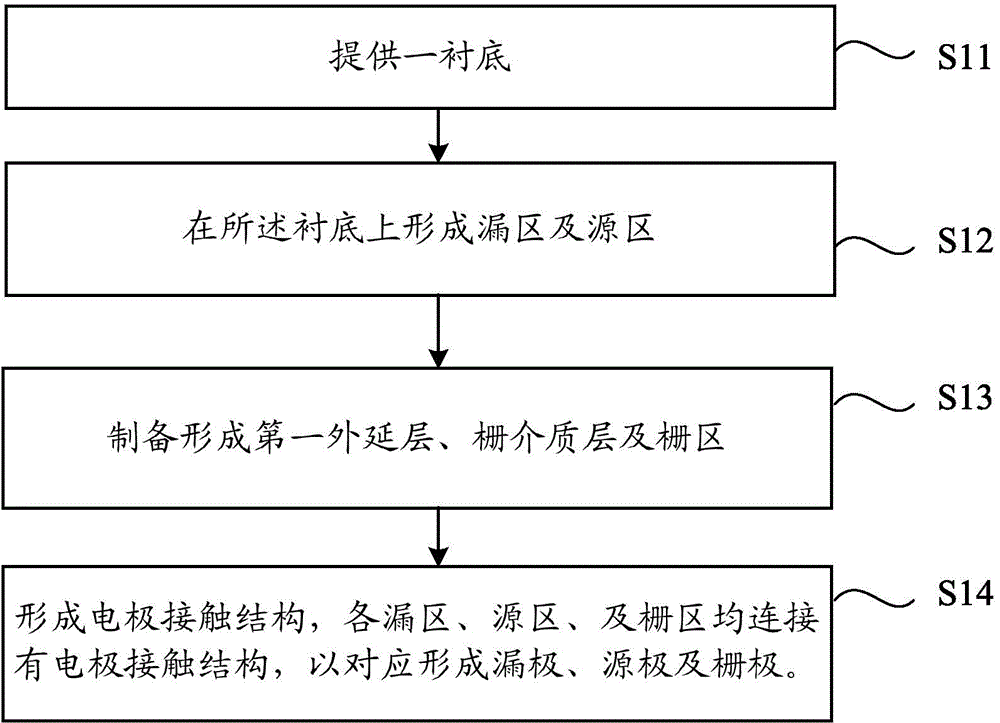

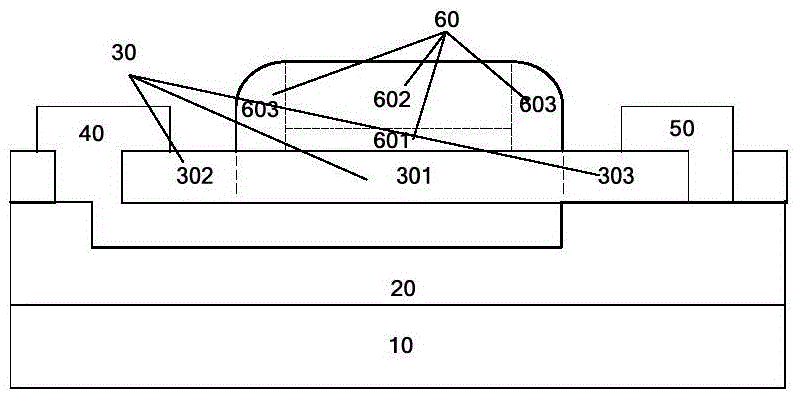

Tunneling field effect transistor and preparation method thereof

ActiveCN104617138ALarge tunneling areaIncrease chance of tunnelingSemiconductor/solid-state device manufacturingDiodeMedia layerElectron

Disclosed is a tunneling field effect transistor. The tunneling field effect transistor comprises a source region, two drain regions and two grid regions. The two drain regions are arranged on opposite two sides of the source region in a first direction; the two grid regions are arranged on opposite two sides of the source region; first extension layers and grid medium layers are arranged between the source region and the two grid regions, wherein the first extension layers are arranged between the source region and the grid medium layers and form tunneling junction with the source region; the two drain regions and the two grid regions are arranged around the source region, so that the source region can be completely under the control of the two grid regions, and current carrying electrons in the overlapped regions of the source region and the grid regions can tunnel under the action of the electric field of the grid regions; the first extension layers are arranged between the source region and the grid medium layers and is of a linear tunneling mode, thereby being large in tunneling area; the direction of the electric field of the grid regions and the tunneling direction of the electrons of the source region are on the same line, so that high tunneling probability can be achieved, and tunneling current can be increased. Besides, the invention also provides a preparation method of the tunneling field effect transistor.

Owner:HUAWEI TECH CO LTD

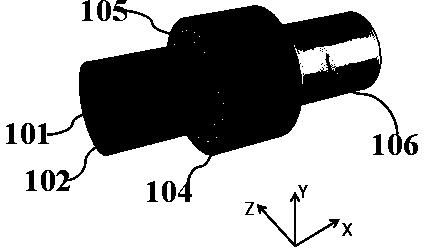

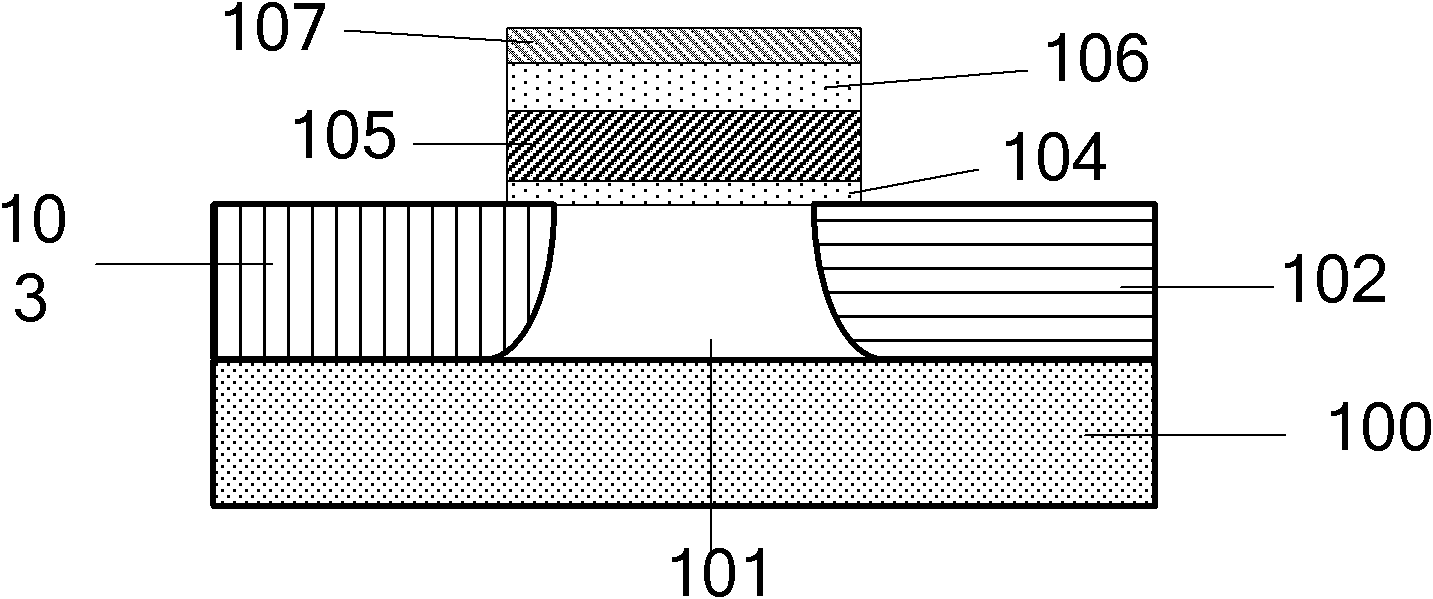

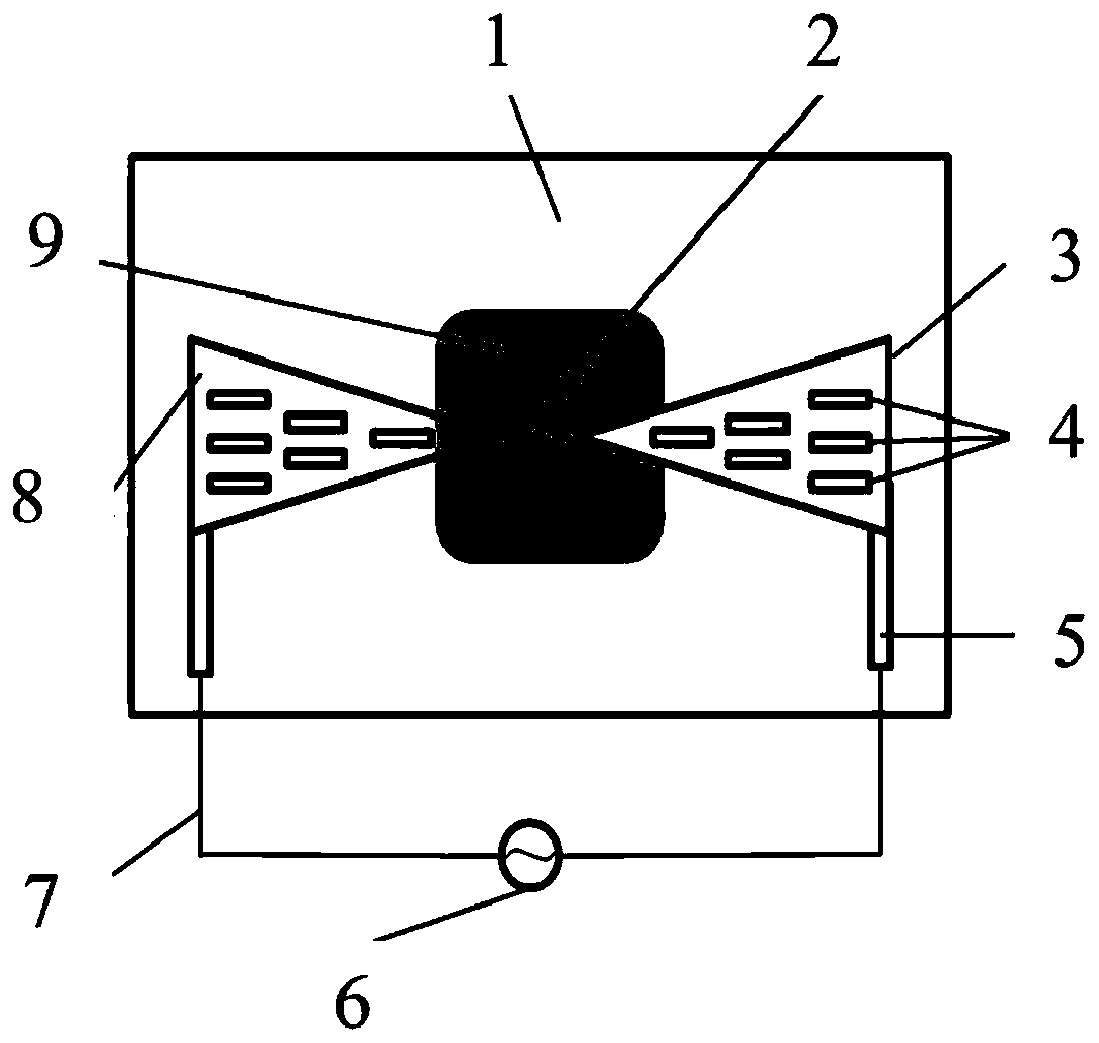

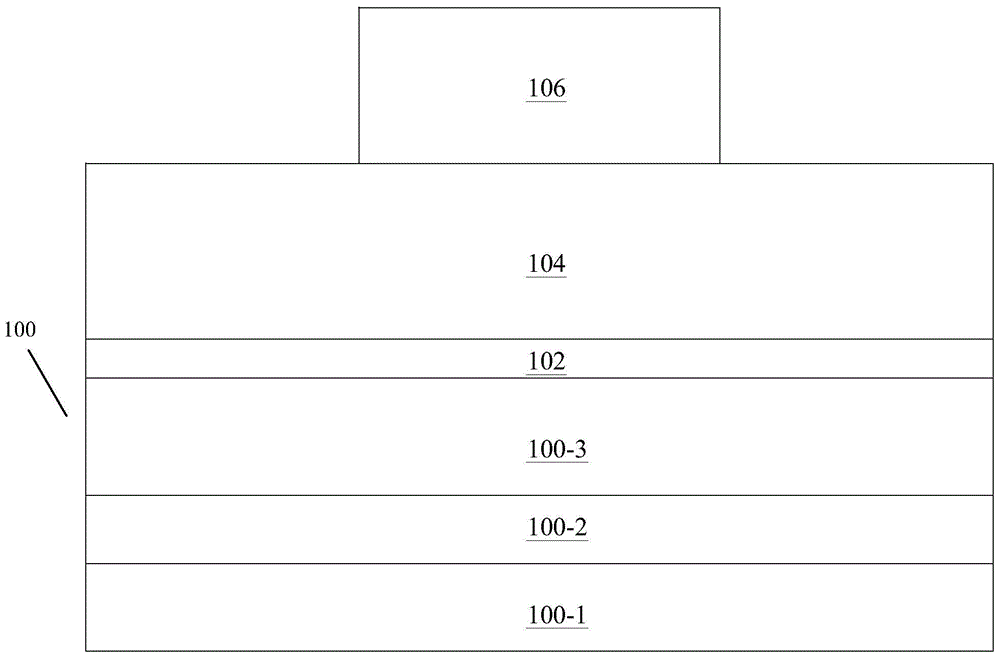

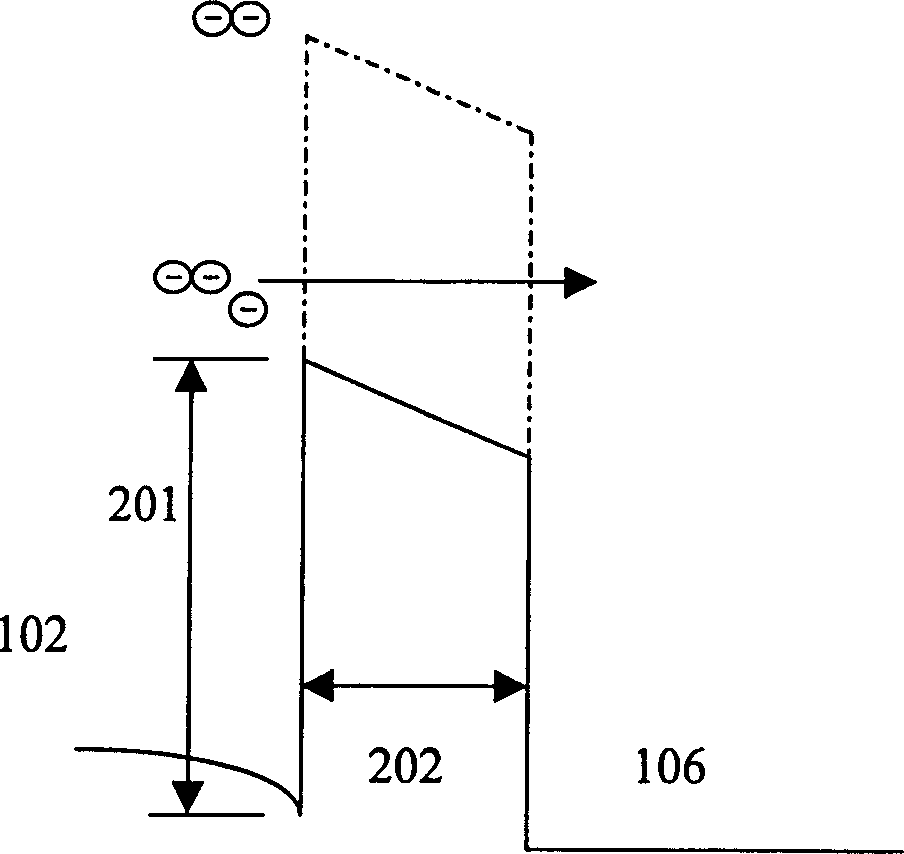

Dual-axis tensile strain GeSn n channel tunneling field effect transistor

InactiveCN103824880AImprove performanceIncreased tunneling currentSemiconductor devicesTensile strainLattice constant

The invention provides a dual-axis tensile strain GeSn n channel tunneling field effect transistor (10) which structurally comprises a substrate (101), a source electrode (102), a drain electrode (104), a GeSn n channel (103), an insulation dielectric substance film (105) and a grid electrode (106). The source electrode, the n channel and the drain electrode form a vertical device structure. The lattice constant of a regional material of the source electrode is larger than that of the GeSn n channel (103). The GeSn n channel forms dual-axis tensile strain in the X face and the Y face, and the strain facilitates conversion of GeSn of the channel from an indirect band gap into a direct band gap, so that direct quantum tunneling happens, tunneling currents are increased, and device performance is improved.

Owner:CHONGQING UNIV

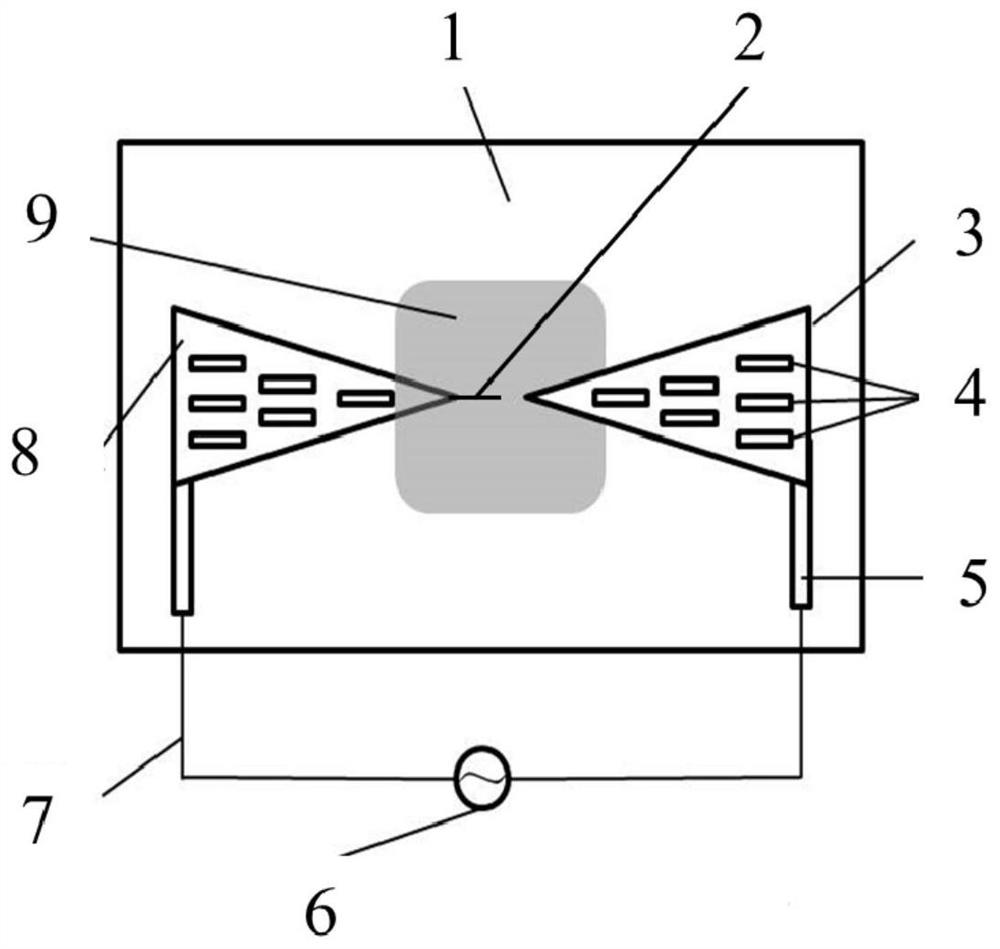

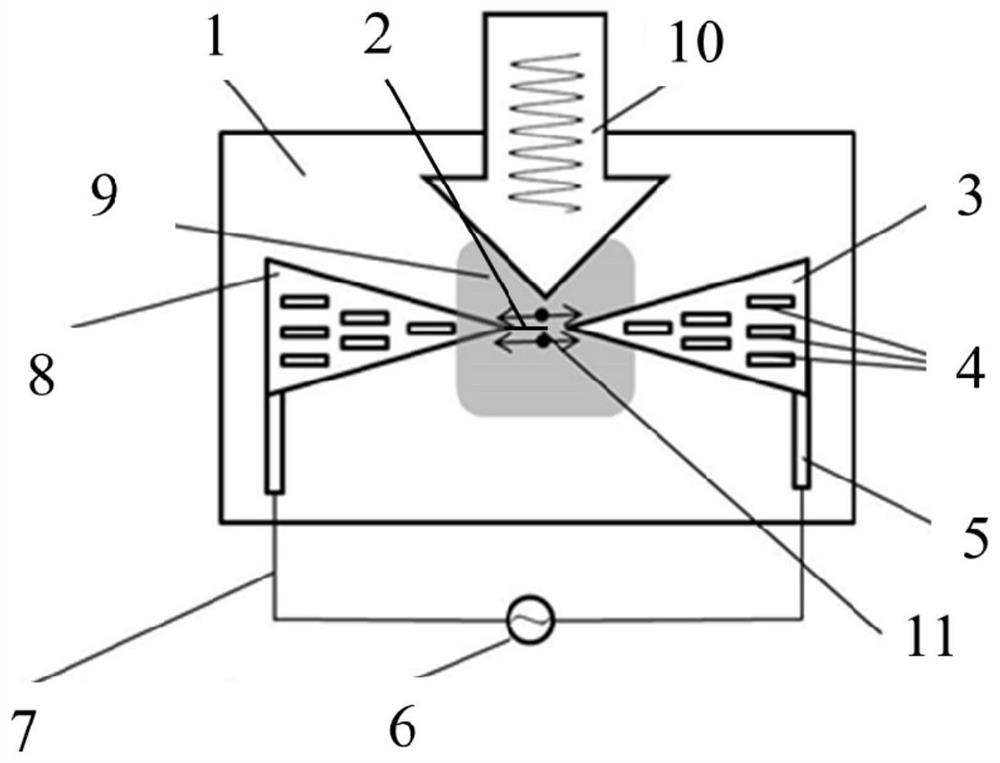

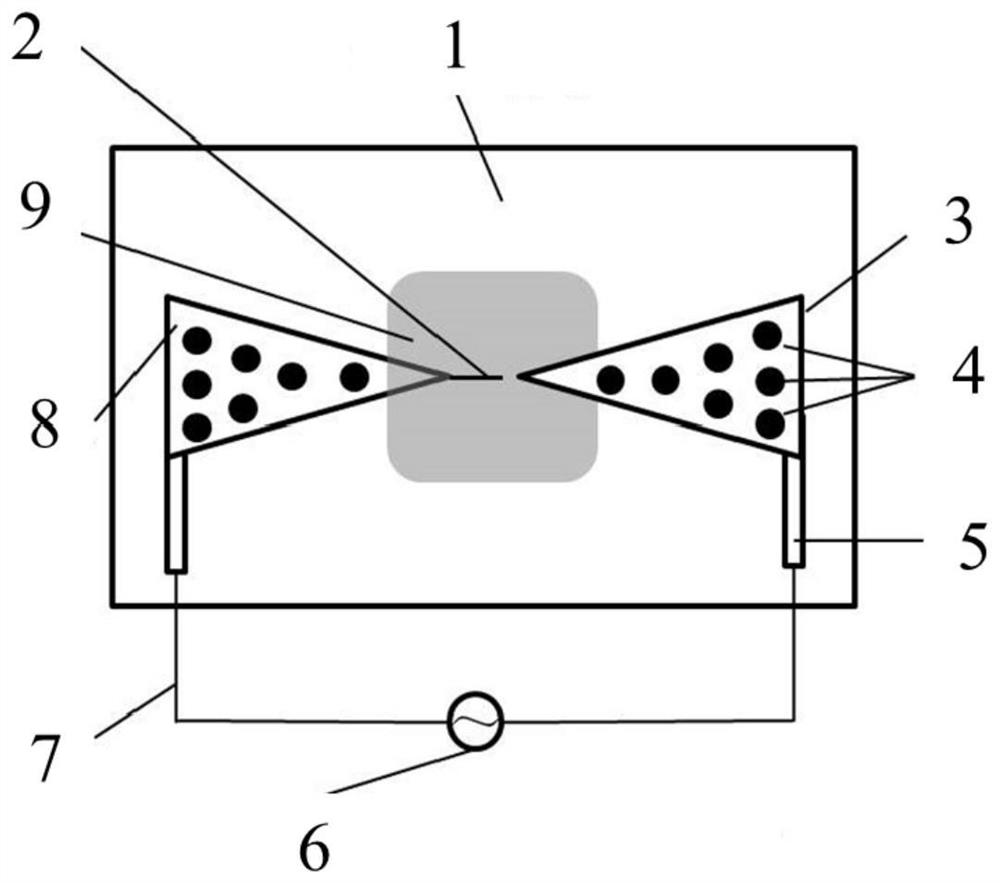

Optical frequency response electron tunneling structure as well as preparation method and application thereof

ActiveCN110993719AEasy to detectEnabling Energy HarvestingFinal product manufactureSolid-state devicesWave bandQuantum electrodynamics

The invention relates to an optical frequency response electron tunneling structure and a preparation method and application thereof. According to the invention, the time required by an electron tunneling nano insulating layer is at the femtosecond magnitude, and a nano enhanced structure is utilized to improve the optical frequency electromagnetic wave radiation absorption energy of an antenna, so that the detection and energy collection of the optical frequency signals are realized, the optical frequency response efficiency is enhanced, meanwhile, the optical frequency response of infrared,visible or ultraviolet bands can be realized, and the response speed can exceed that of an existing commercial photoelectric device. The optical frequency response electron tunneling structure has theadvantages that the response time is short, the pixel area is in the nanoscale magnitude, and the structure can be widely applied to the fields of optical frequency detection, radiation energy collection, high-resolution imaging and the like.

Owner:THE NAT CENT FOR NANOSCI & TECH NCNST OF CHINA

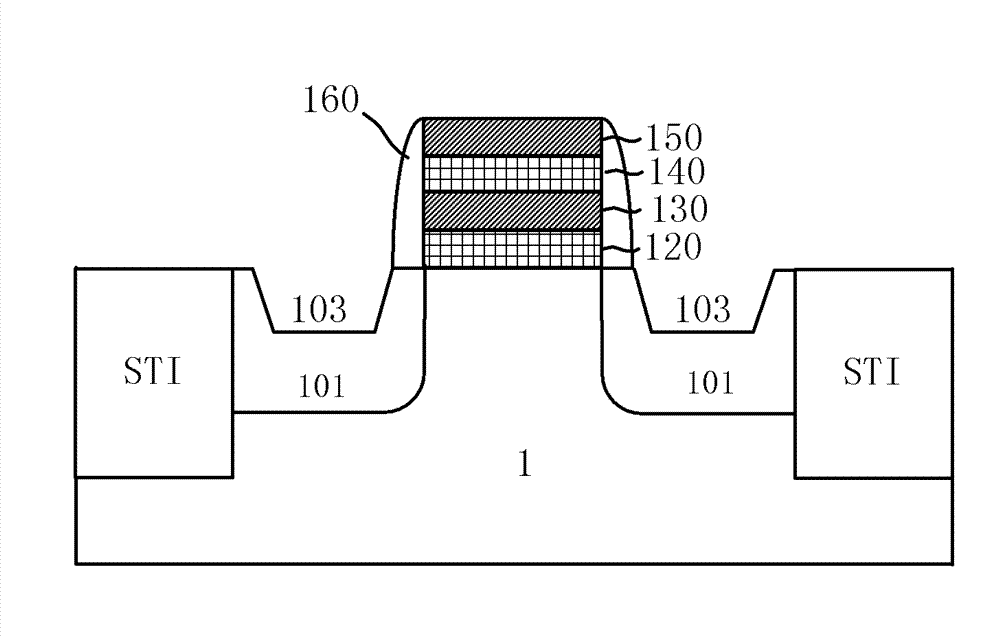

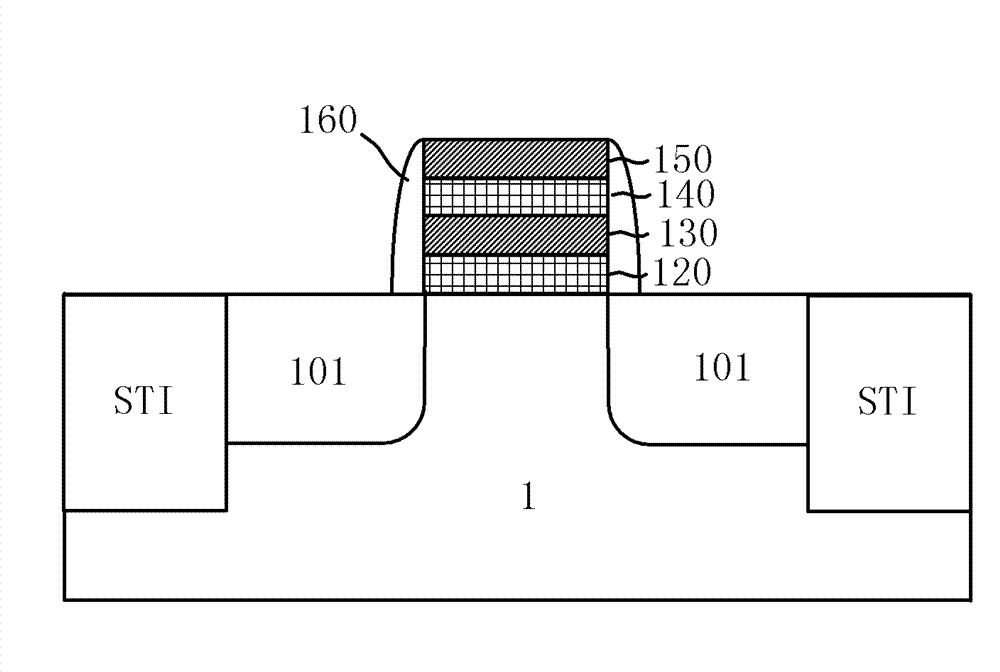

Semiconductor device and manufacturing method thereof

ActiveCN102903638AEasy to storeIncreased tunneling currentTransistorSemiconductor/solid-state device manufacturingSemiconductor materialsGate dielectric

The invention relates to a manufacturing method of a semiconductor device, which comprises a tunneling dielectric layer, a memory dielectric layer, a gate dielectric layer and a gate layer which are sequentially formed on a semiconductor substrate of a first semiconductor material; patterning the tunneling dielectric layer, memory dielectric layer, gate dielectric layer and gate layer to form a gate lamination body; forming trenches in the semiconductor substrate on both sides of the gate lamination body; and filling a second semiconductor material, which is different from the first semiconductor material, in the trenches, and meanwhile, covering the dielectric layer on the whole device. The surface energy level is changed through the stress generated by the second semiconductor material and the covering dielectric layer, thereby enhancing the tunneling current and improving the memory effect of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

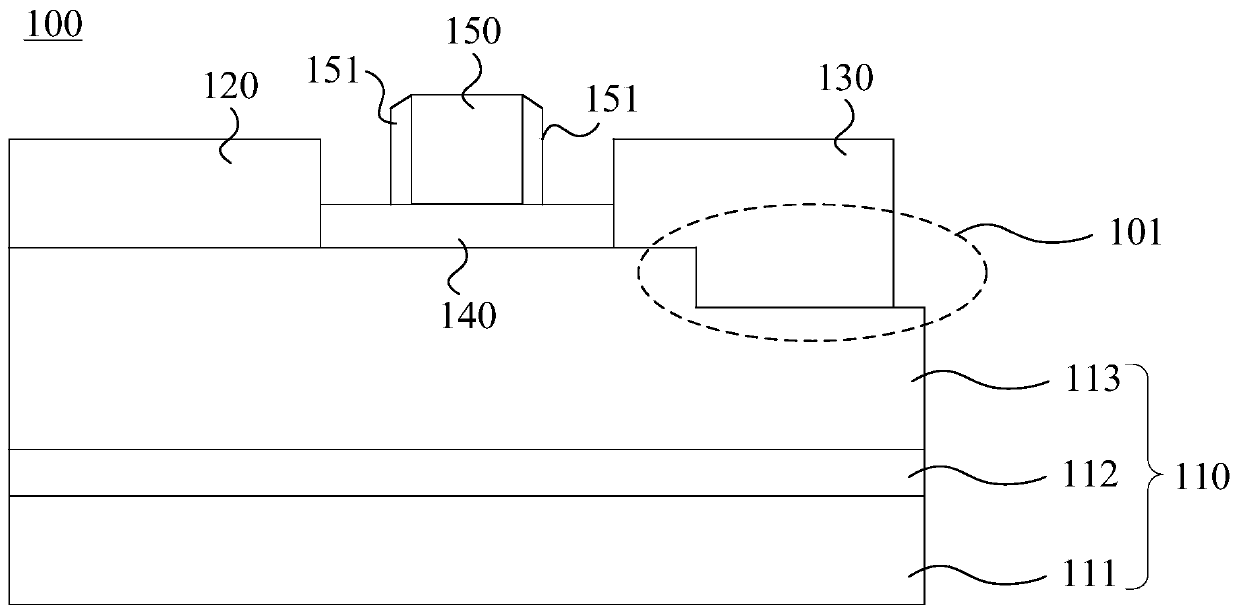

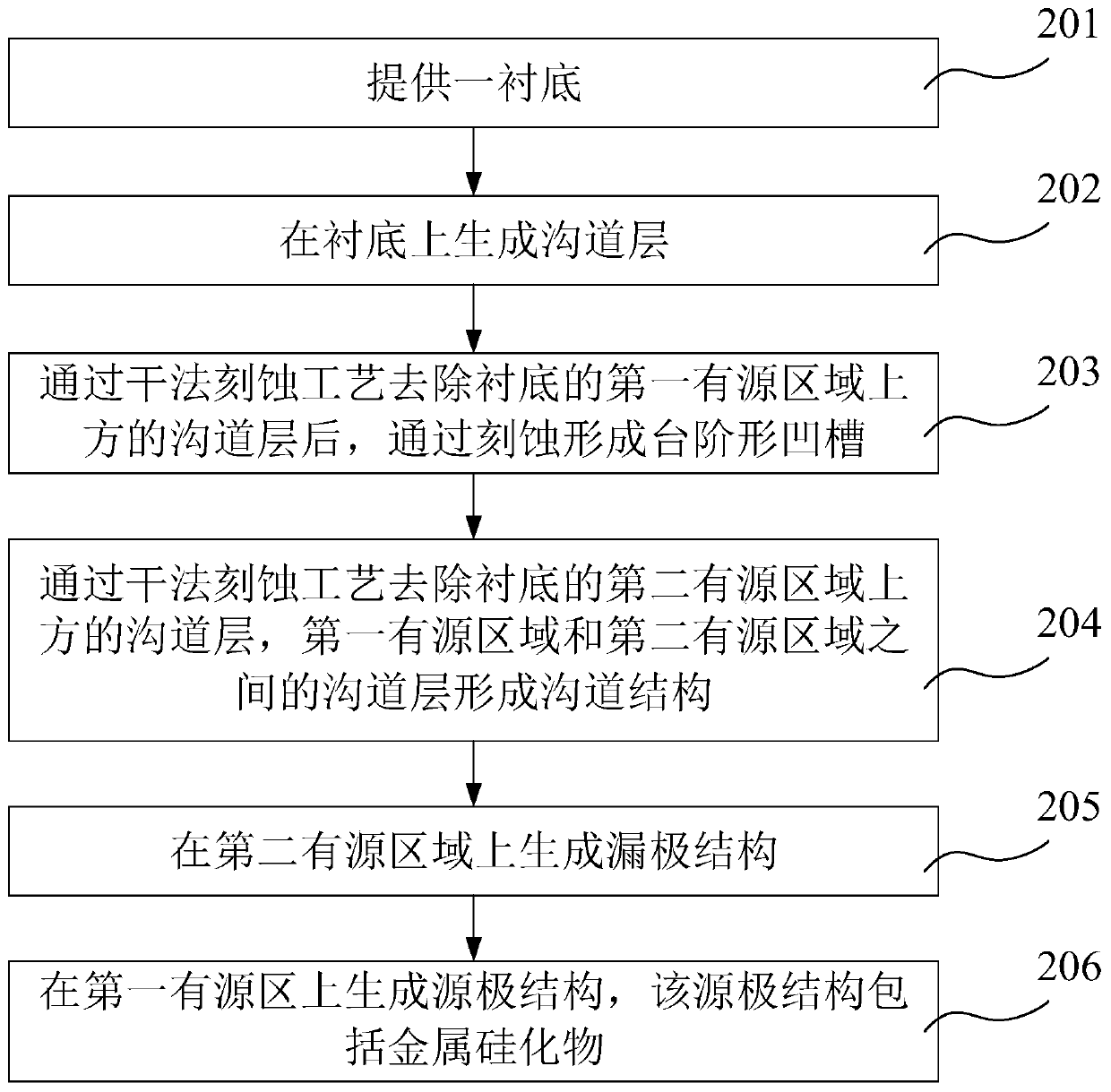

Schottky field effect transistor and manufacturing method thereof

ActiveCN110391300AIncreased tunneling currentSmall barrier widthSemiconductor/solid-state device manufacturingSemiconductor devicesMetal silicideField-effect transistor

The invention discloses a Schottky field effect transistor and a manufacturing method thereof, which belong to the technical field of semiconductors. The Schottky field effect transistor comprises a substrate. The first end part of the substrate is a stepped groove. The Schottky field effect transistor further comprises a drain structure arranged on the second end part of the substrate, a source structure which is arranged on the first end part and comprises a metal silicide, a channel structure which is arranged above the substrate and between the source structure and the drain structure, anda gate structure arranged on the channel structure. According to the invention, the first end part of the substrate is the stepped recess; the source structure is arranged in the stepped recess; thedrain structure is arranged on the second end part of the substrate; the gate structure is arranged on the channel structure between the source structure and the drain structure; due to the fact thatthe source structure is arranged in the stepped groove of the substrate, the barrier width at the source structure becomes smaller when the Schottky field effect transistor is turned on; the tunnelingcurrent of the device is increased; and the channel current of the device in on-state is increased.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

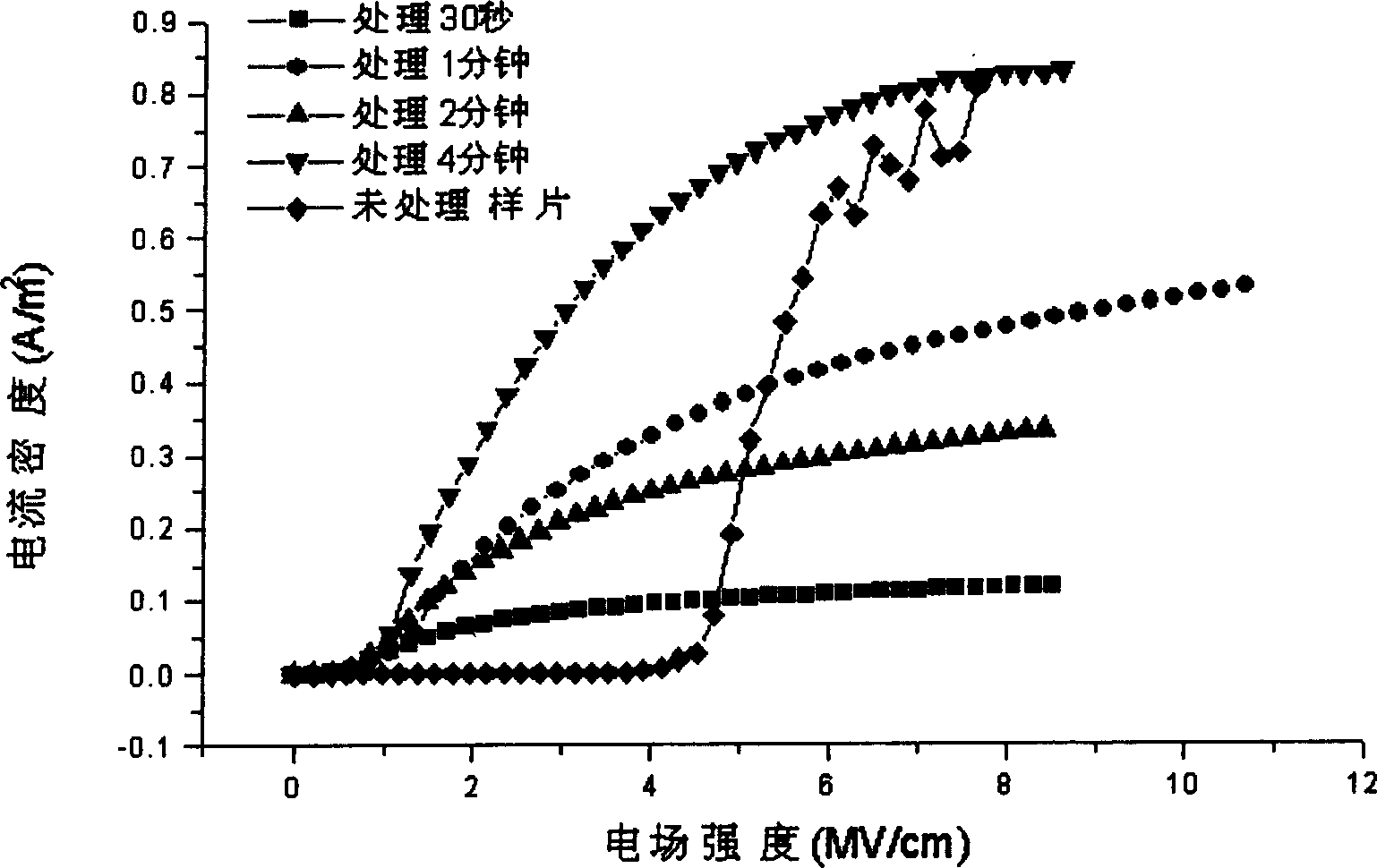

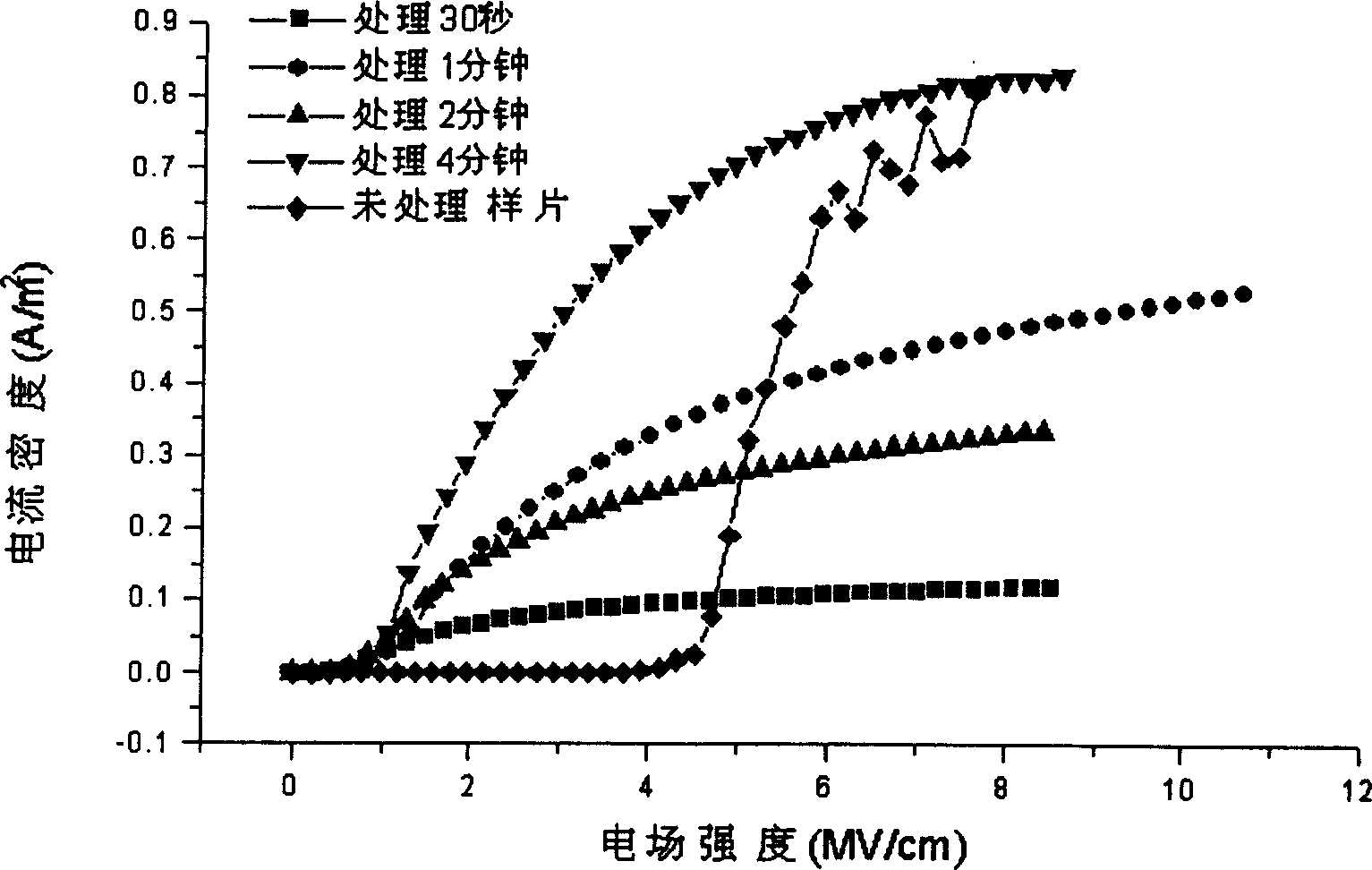

Preparation method of tunnelling oxidized layer in imbedded type quick flash storage

InactiveCN1459833AReduce gate operating voltageLower the barrierSemiconductor/solid-state device manufacturingEngineeringSilicon chip

A process for preparing the tunnelling oxidized layer in embedded flash memory includes such steps as washing the silicon chip, using dry etching machine to fluorinate it, conventional washing, washing it in the solution of isopropanol for 1 min, and high-temp oxidizing.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

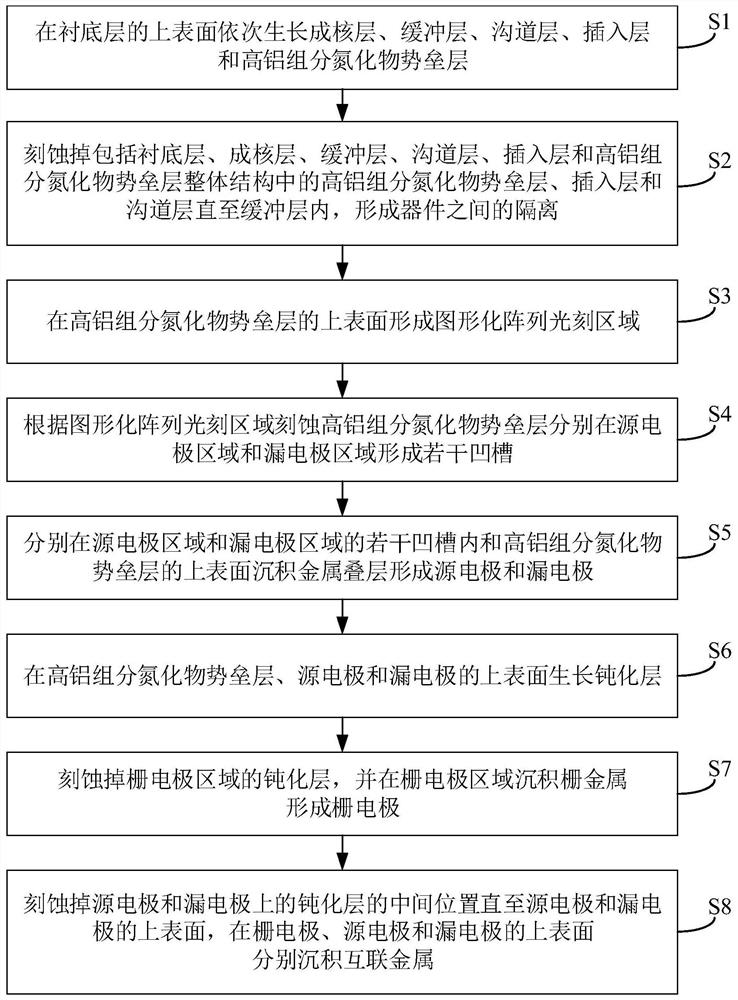

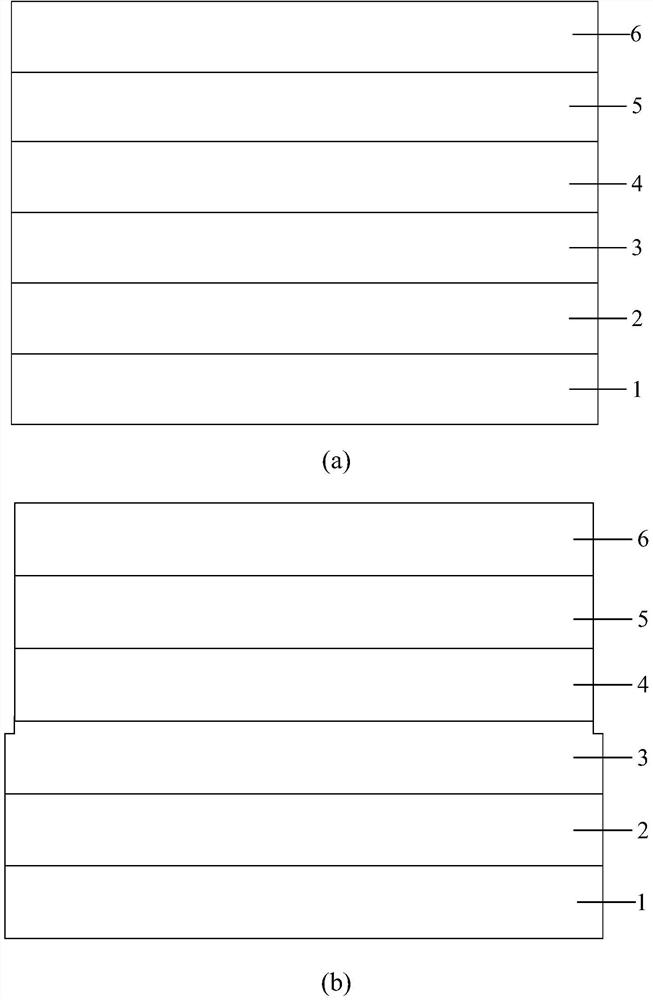

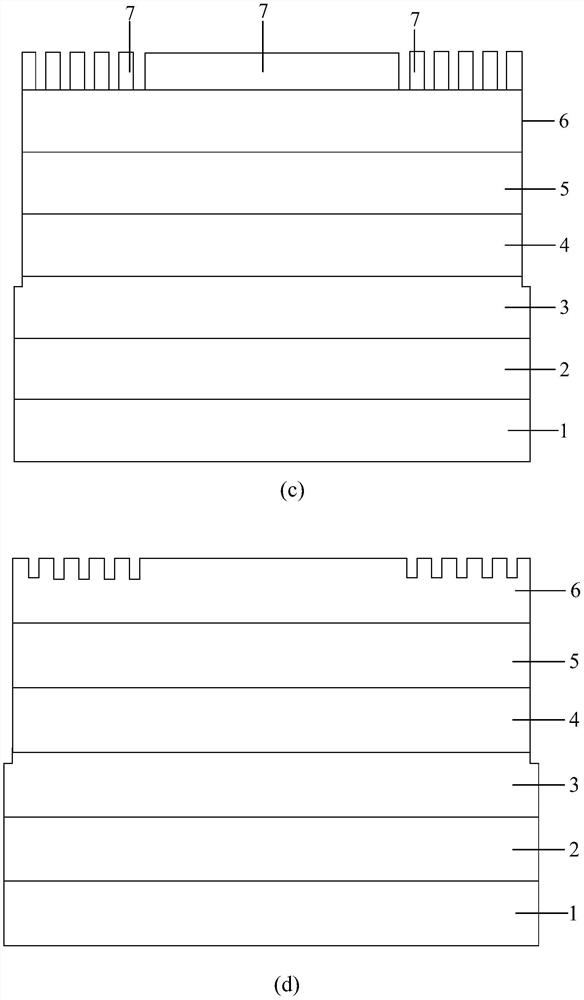

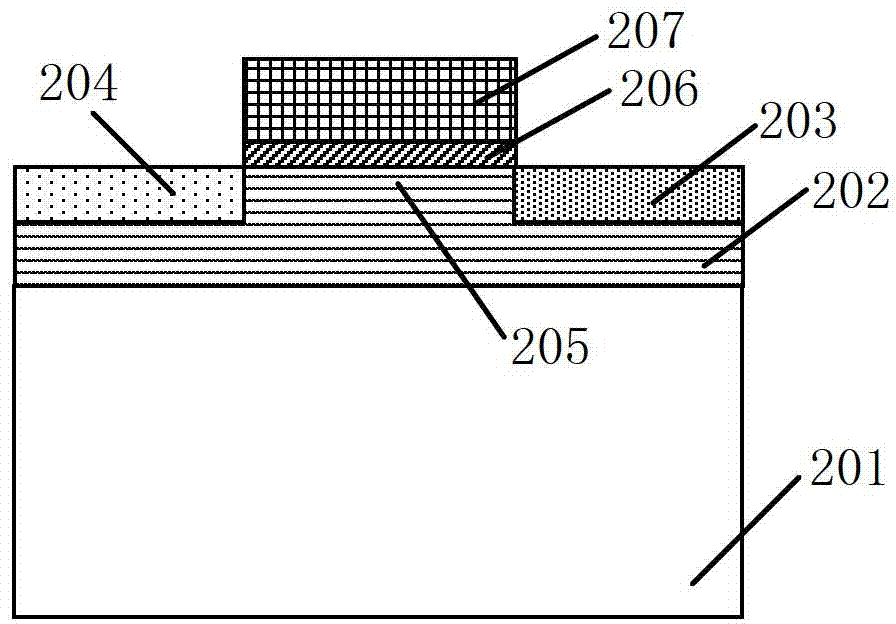

High-aluminum-component nitride ohmic contact device and preparation method thereof

PendingCN113808942AAvoid introducingAvoid dissociationSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactElectric resistivity

The invention discloses a high-aluminum-component nitride ohmic contact device and a preparation method thereof. The preparation method comprises the following steps: sequentially growing a nucleating layer, a buffer layer, a channel layer, an insertion layer and a high-aluminum-component nitride barrier layer on a substrate layer; etching a part of the high aluminum component nitride barrier layer, a part of the insertion layer and a part of the channel layer into the buffer layer; forming a graphical array photoetching region on the high-aluminum component nitride barrier layer; etching the high-aluminum component nitride barrier layer according to the patterned array photoetching region to form a plurality of grooves; forming a source electrode and a drain electrode in the plurality of grooves of the source electrode region and the drain electrode region and the high-aluminum-component nitride barrier layer respectively; growing a passivation layer on the high-aluminum-component nitride barrier layer, the source electrode and the drain electrode; etching the passivation layer in the gate electrode region, and forming a gate electrode in the gate electrode region; and depositing interconnection metal on the gate electrode, the source electrode and the drain electrode respectively. The process is simple, and the ohmic contact device with low contact resistivity is prepared.

Owner:XIDIAN UNIV

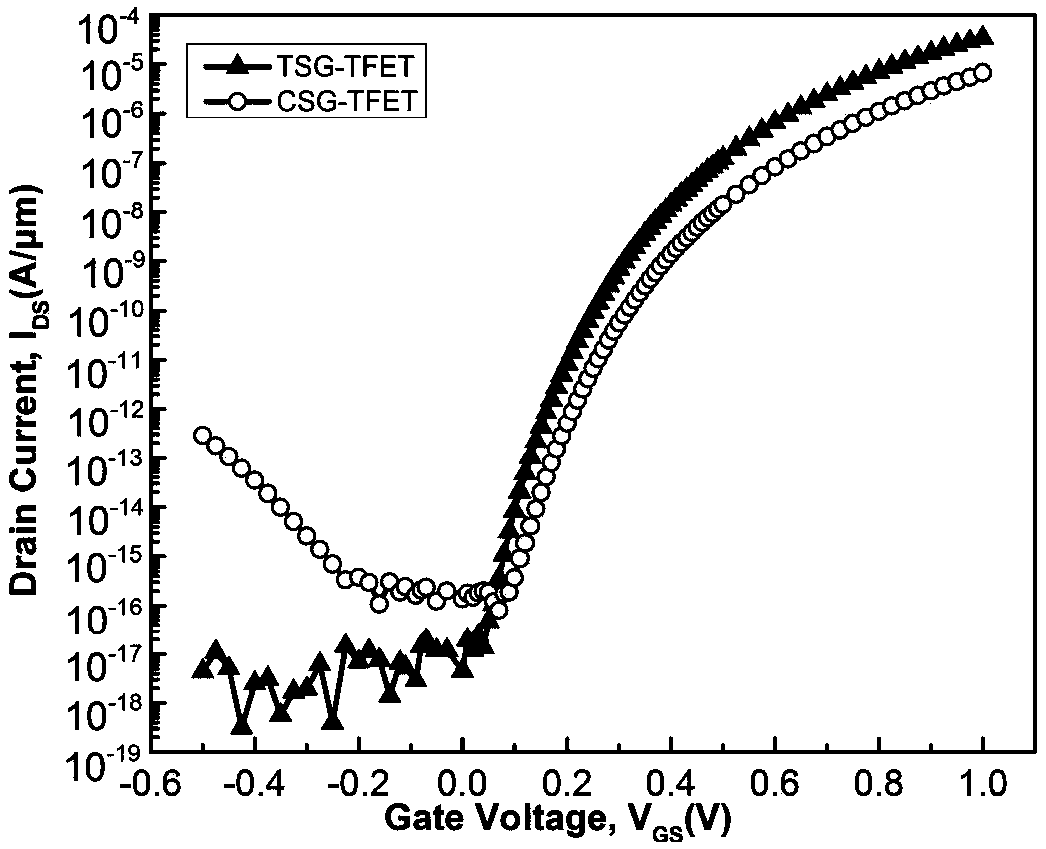

Tunneling field effect transistor and forming method thereof

ActiveCN104600110AImproved subthreshold characteristicsAchieve shutdownSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSub threshold

The invention provides a tunneling field effect transistor comprising a semiconductor substrate, first gates, second gates, first doped regions, and second doped regions. Fins are formed on the semiconductor substrate. Each first gate and the corresponding second gate are respectively formed on the semiconductor substrate at the two sides of the corresponding fin. A gate dielectric layer is formed among each first gate, a first side of the corresponding fin and the semiconductor substrate, and a gate dielectric layer is formed among each second gate, a second side of the corresponding fin and the semiconductor substrate. The first doped regions and the second doped regions are respectively disposed in the semiconductor substrate at one side of the first gates and at one side of the second gates. A narrow tunneling junction is realized by controlling the width of the fins, the tunneling current is increased, and the conduction current is further improved by increasing the effective tunneling area. In addition, defect-related leakage current can be inhibited, and the sub threshold characteristic of devices can be improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

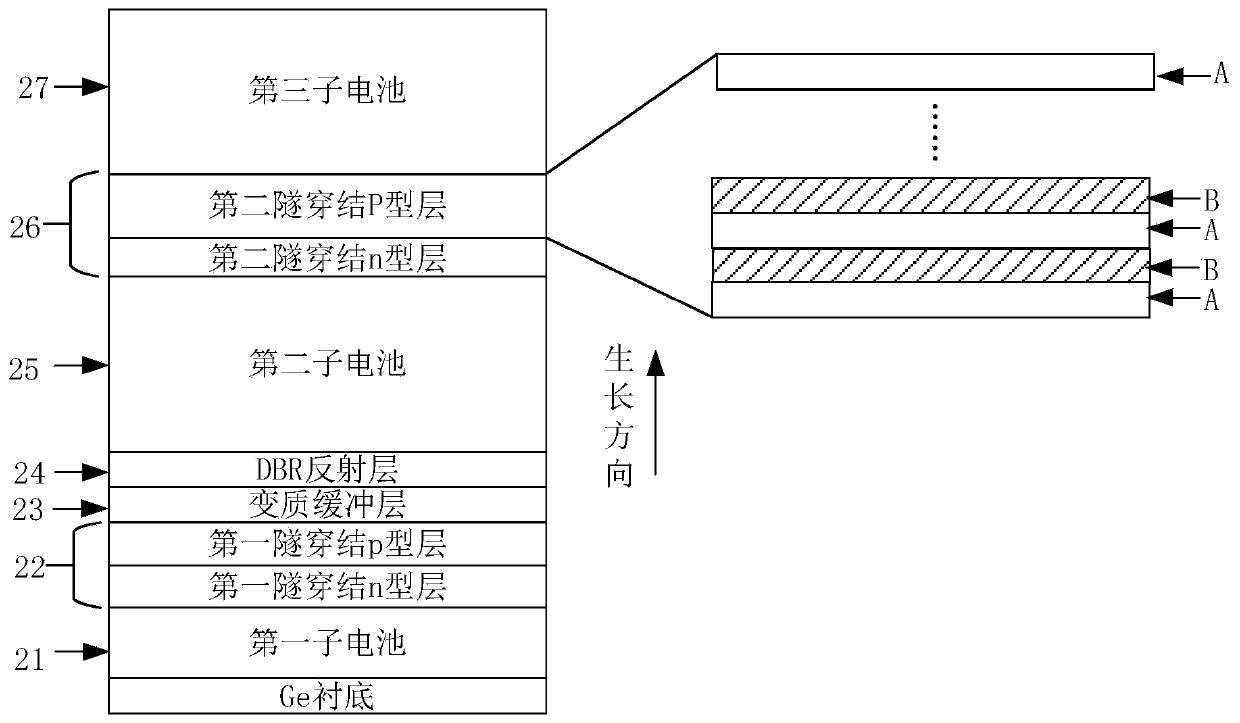

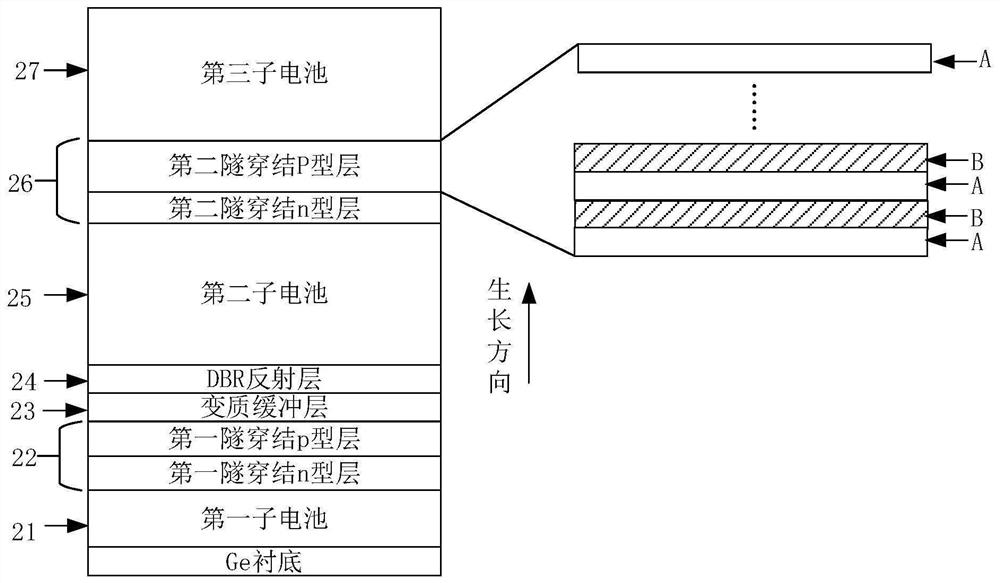

Lattice-mismatched multi-junction solar cell structure

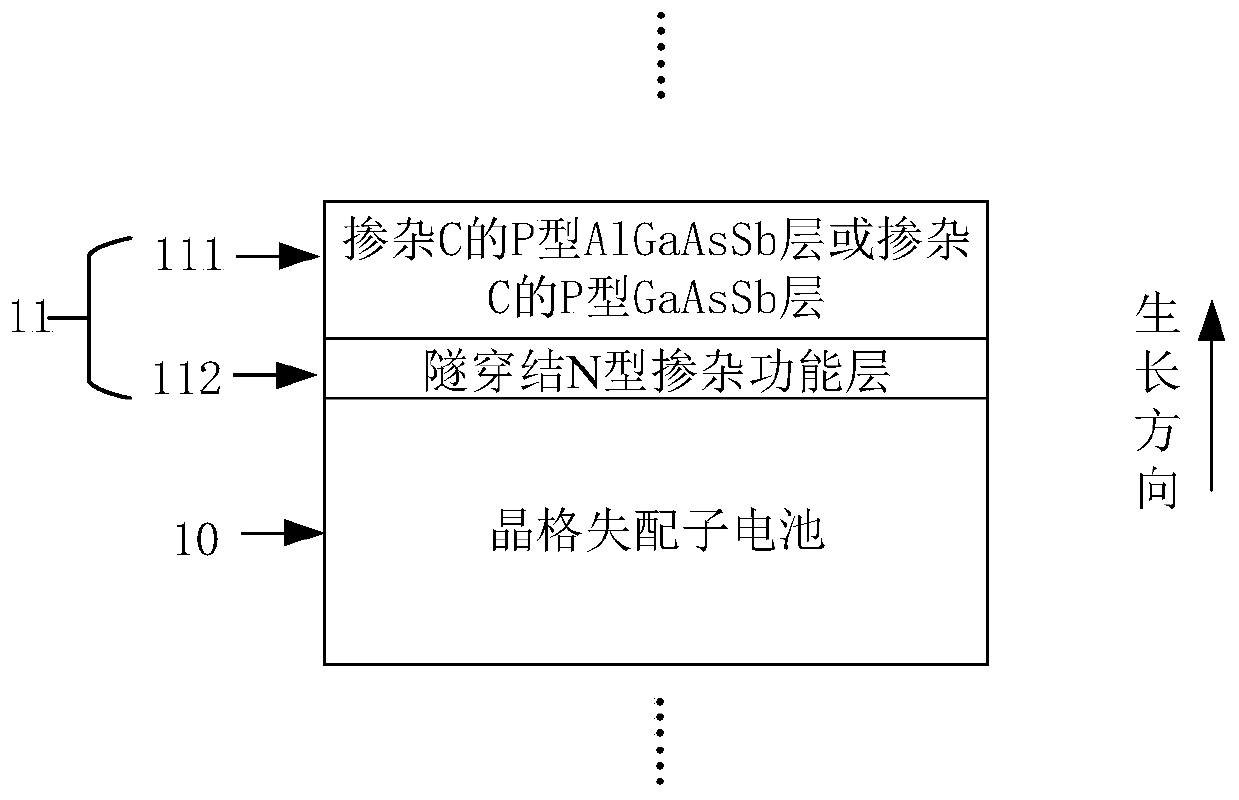

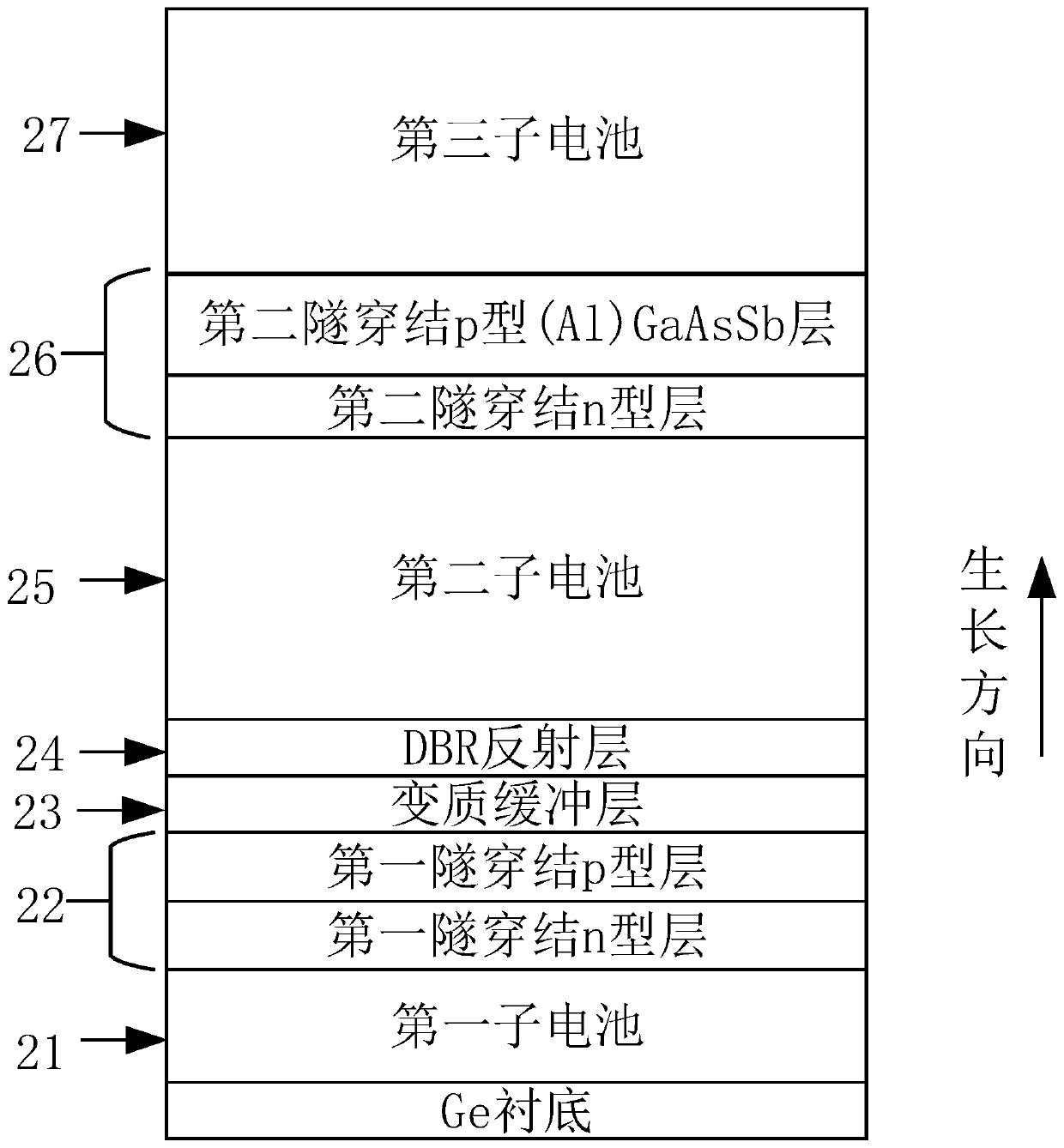

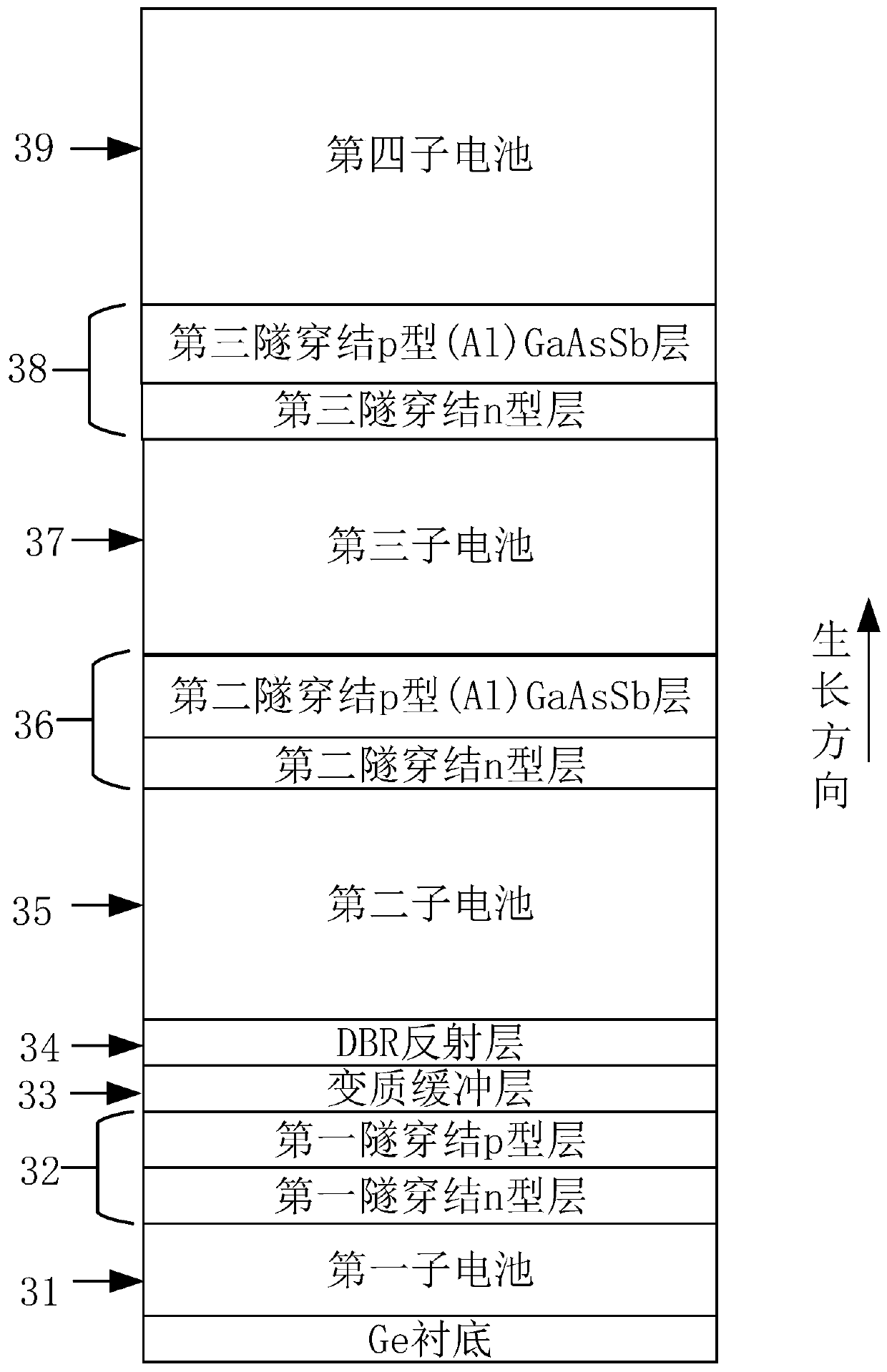

ActiveCN110233187AIncreased tunneling currentAvoid mismatchPhotovoltaic energy generationSemiconductor devicesHalogenP type doping

The invention provides a lattice-mismatched multi-junction solar cell structure which comprises a substrate, a lattice-mismatched sub-battery and a tunnel junction growing on the lattice-mismatched sub-battery, wherein at least one junction of the lattice-mismatched sub-battery is mismatched with a lattice constant of the substrate; the tunnel junction comprises a P-type doping function layer andan N-type doping function layer; and the P-type doping function layer is a C doping P-type AlGaAsSb layer or a C doping P-type GaAsSb layer. The solar cell structure replaces a C doping P-type (Al)InGaAs layer in the prior art with the C doping P-type AlGaAsSb layer or the C doping P-type GaAsSb layer as a P-type doping function layer of a tunnel junction structure of a lattice-mismatched solar cell. The P-type layer does not contain an In component, so that the problem of lattice mismatch with a body material InGaAs in the solar cell caused by inhibition of In component incorporation by source halogen gas due to C doping reaction of the P-type layer can be effectively avoided.

Owner:YANGZHOU CHANGELIGHT

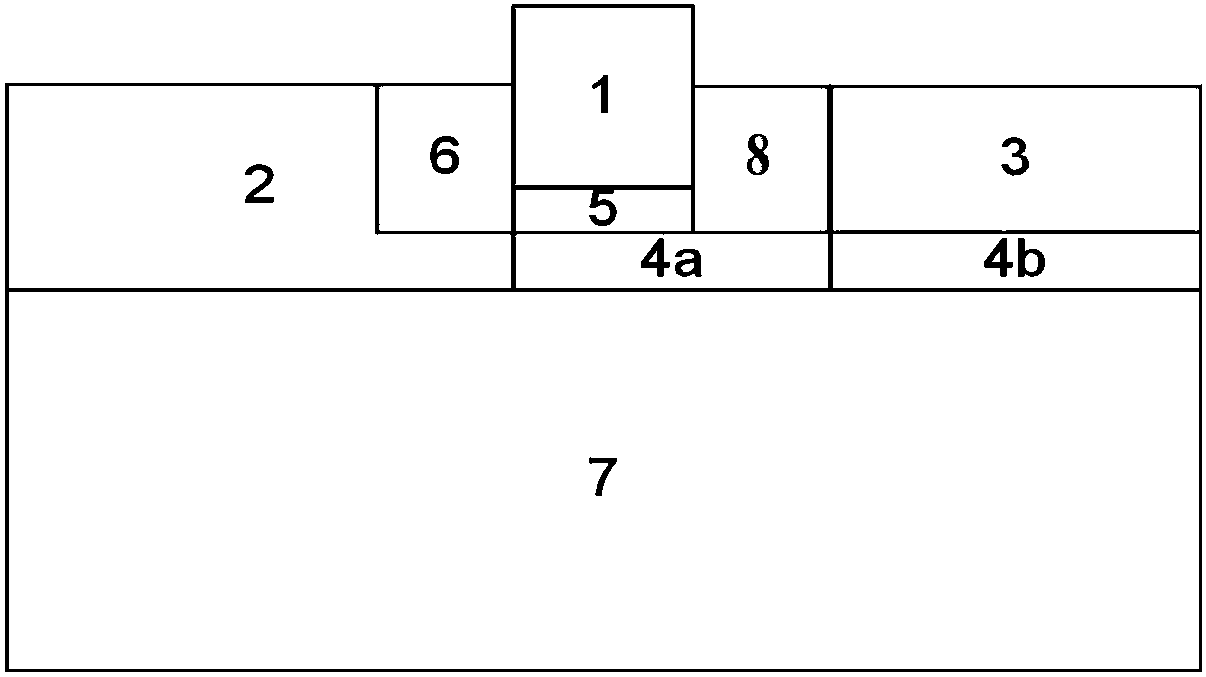

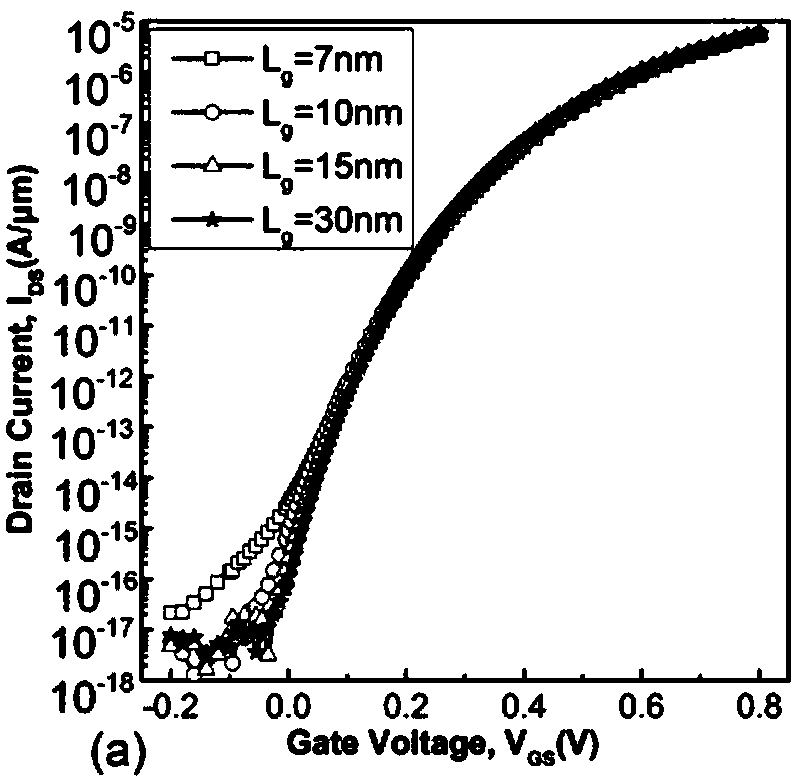

Ultrathin channel groove tunneling field effect transistor

The invention discloses an ultrathin channel groove tunneling field effect transistor which is composed of a grid electrode, a source region, a drain region, a first channel region, a second channel region, a grid dielectric layer, a first isolating layer, a second isolating layer and buried oxide layer, wherein the grid electrode and the grid dielectric layer arranged on the position of the channel regions, and the isolation layers are arranged at the two sides of the grid electrode. The new structure has an ultrathin channel so that coupling of the grid electrode and the channel can be enhanced, and thus control capability of the grid electrode can be enhanced and tunneling current of a device can be increased. Another characteristic of the structure is that the intrinsic region (low-doped region) of the channel extends to the drain region. In a word, compared with conventional tunneling transistors, the device of the structure is obviously improved in the aspects of the electrical characteristics of subthreshold swing and switching current ratio and stability.

Owner:HANGZHOU DIANZI UNIV

Cold source Schottky transistor and preparation process thereof

PendingCN114512546AThermal current reductionReduce off-state currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSubthreshold swing

The invention provides a cold source Schottky transistor and a preparation process thereof. The cold source Schottky transistor comprises a substrate, a source region, a channel region, a source electrode, a drain electrode and a grid electrode, the source region is arranged on the substrate and comprises a first source region and a metal region connected with the first source region, and the first source region is a heavily doped region; the drain region is arranged on the substrate, the drain region is a heavily doped region, and the doping type of the drain region is opposite to that of the first source region; the channel region is arranged on the substrate, the channel region is located between the metal region and the drain region, and the upper side and / or the lower side of the channel region are / is provided with a gate dielectric; the source electrode is arranged on the source region; the drain electrode is arranged on the drain region; the grid electrode is arranged on the grid electrode medium. Under the condition of certain source-drain bias voltage, in the process of increasing the gate voltage, the Schottky barrier between the channel region and the metal region is lowered, the Schottky barrier is thinned until the Schottky barrier of the low-energy region is thin enough, the tunneling current is increased rapidly, electrons of the low-energy region of the source region tunnel the Schottky barrier, and the tunneling current is increased rapidly. Therefore, the subthreshold swing can be lower than 60mV / dec.

Owner:PEKING UNIV

An ultra-thin channel trench tunneling field effect transistor

The invention discloses an ultrathin channel groove tunneling field effect transistor which is composed of a grid electrode, a source region, a drain region, a first channel region, a second channel region, a grid dielectric layer, a first isolating layer, a second isolating layer and buried oxide layer, wherein the grid electrode and the grid dielectric layer arranged on the position of the channel regions, and the isolation layers are arranged at the two sides of the grid electrode. The new structure has an ultrathin channel so that coupling of the grid electrode and the channel can be enhanced, and thus control capability of the grid electrode can be enhanced and tunneling current of a device can be increased. Another characteristic of the structure is that the intrinsic region (low-doped region) of the channel extends to the drain region. In a word, compared with conventional tunneling transistors, the device of the structure is obviously improved in the aspects of the electrical characteristics of subthreshold swing and switching current ratio and stability.

Owner:HANGZHOU DIANZI UNIV

Optical frequency response electron tunneling structure, preparation method and use thereof

ActiveCN110993719BEasy to detectEnabling Energy HarvestingFinal product manufactureSolid-state devicesParticle physicsFrequency detection

The invention relates to an optical frequency response electron tunneling structure, its preparation method and application. The invention utilizes the characteristic that the time required for electron tunneling through the nano-insulation layer is on the femtosecond level, and uses a nano-enhanced structure to enhance the energy absorption of the optical frequency electromagnetic wave radiation by the antenna, thereby realizing the detection and energy collection of the optical frequency signal and enhancing the optical frequency. Response efficiency, at the same time, can realize the optical frequency response of infrared, visible or ultraviolet bands, and the response speed can exceed the existing commercial optoelectronic devices. The optical frequency responsive electronic tunneling structure of the present invention has the advantages of fast response time and a pixel area in the order of nanometer size, and can be widely used in fields such as optical frequency detection, radiation energy collection, and high-resolution imaging.

Owner:THE NAT CENT FOR NANOSCI & TECH NCNST OF CHINA

Preparation method of tunnelling oxidized layer in imbedded type quick flash storage

InactiveCN1225772CReduce gate operating voltageLower the barrierSemiconductor/solid-state device manufacturingEngineeringSilicon chip

A process for preparing the tunnelling oxidized layer in embedded flash memory includes such steps as washing the silicon chip, using dry etching machine to fluorinate it, conventional washing, washing it in the solution of isopropanol for 1 min, and high-temp oxidizing.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Junctionless tunneling field effect transistor and method of forming same

ActiveCN103606563BIncreased tunneling currentIncrease the on-state currentTransistorSemiconductor/solid-state device manufacturingGate stackCondensed matter physics

The invention provides a junctionless tunneling field effect transistor and a formation method thereof. The junctionless tunneling field effect transistor includes the following components of: a substrate; a liner layer arranged on the substrate; a channel layer which is arranged on the liner layer and includes a channel region arranged in the middle as well as a source region and a drain region arranged at two sides of the channel region, wherein the channel region, the source region and the drain region have the same doping type; a source which coats on the upper surface, a side surface and the lower surface of the source region and coats the lower surface of the channel region, and is in Schottky contact with the channel region; a drain which coats the upper surface and a side surface of the drain region; and a gate stack structure which is located on the channel region. The junctionless tunneling field effect transistor has the advantages of simple structure, large tunneling current, capability of effectively suppressing a short channel effect and the like. The invention also provides a formation method of the junctionless tunneling field effect transistor.

Owner:TSINGHUA UNIV

A kind of semiconductor device and manufacturing method

ActiveCN111628021BImprove performanceIncrease the doping concentrationFinal product manufacturePhotovoltaic energy generationDevice materialPeak current

The invention discloses a semiconductor device and relates to the field of semiconductor optoelectronic devices. The semiconductor device disclosed in the present invention includes: a first conductivity type semiconductor layer; an insertion layer arranged on the first conductivity type semiconductor layer, the insertion layer is silicon-tellurium co-doped indium gallium arsenic; a second conductivity type is arranged on the insertion layer type semiconductor layer; wherein the first conductivity type and the second conductivity type are different conductivity types. The semiconductor device disclosed by the invention can realize higher tunneling peak current and can meet higher tunneling current requirement.

Owner:SUZHOU EVERBRIGHT PHOTONICS CO LTD +1

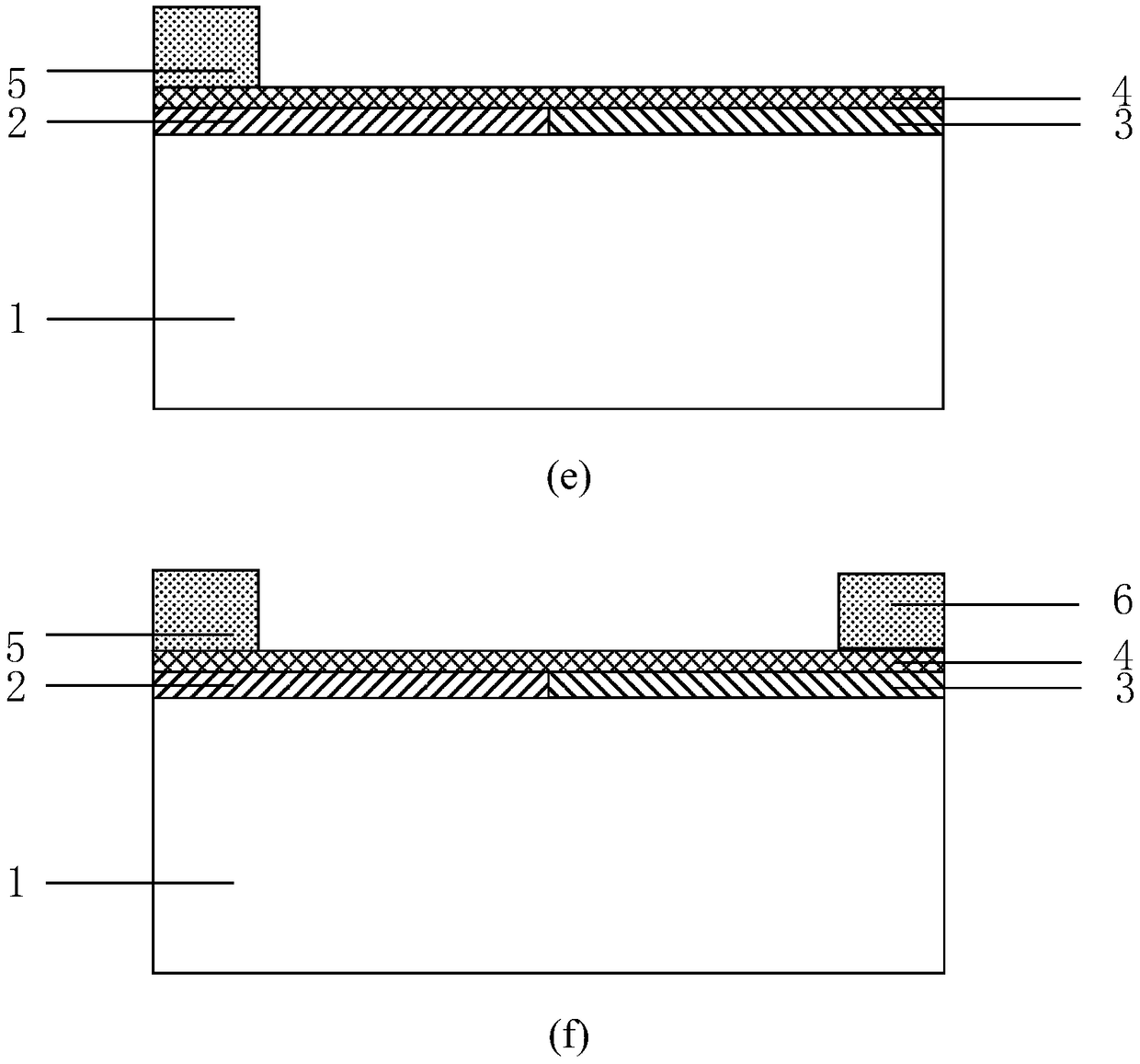

Vertical tunneling field effect transistor and its manufacturing method

ActiveCN104659099BIncrease the overlapping areaLarge tunneling areaSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricField-effect transistor

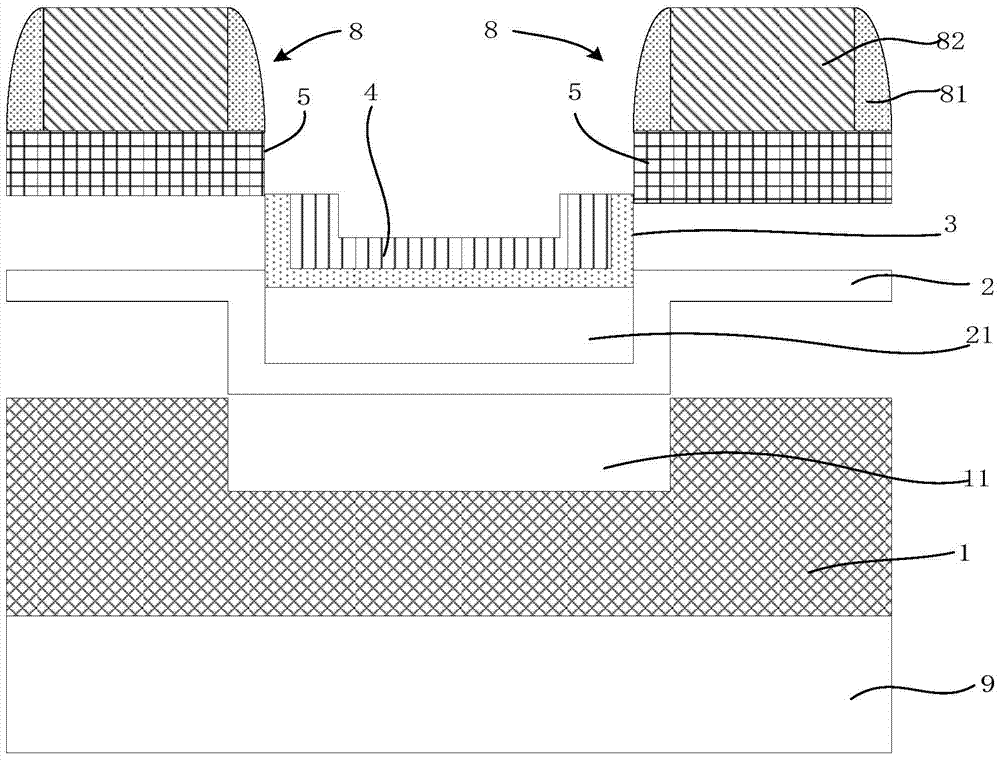

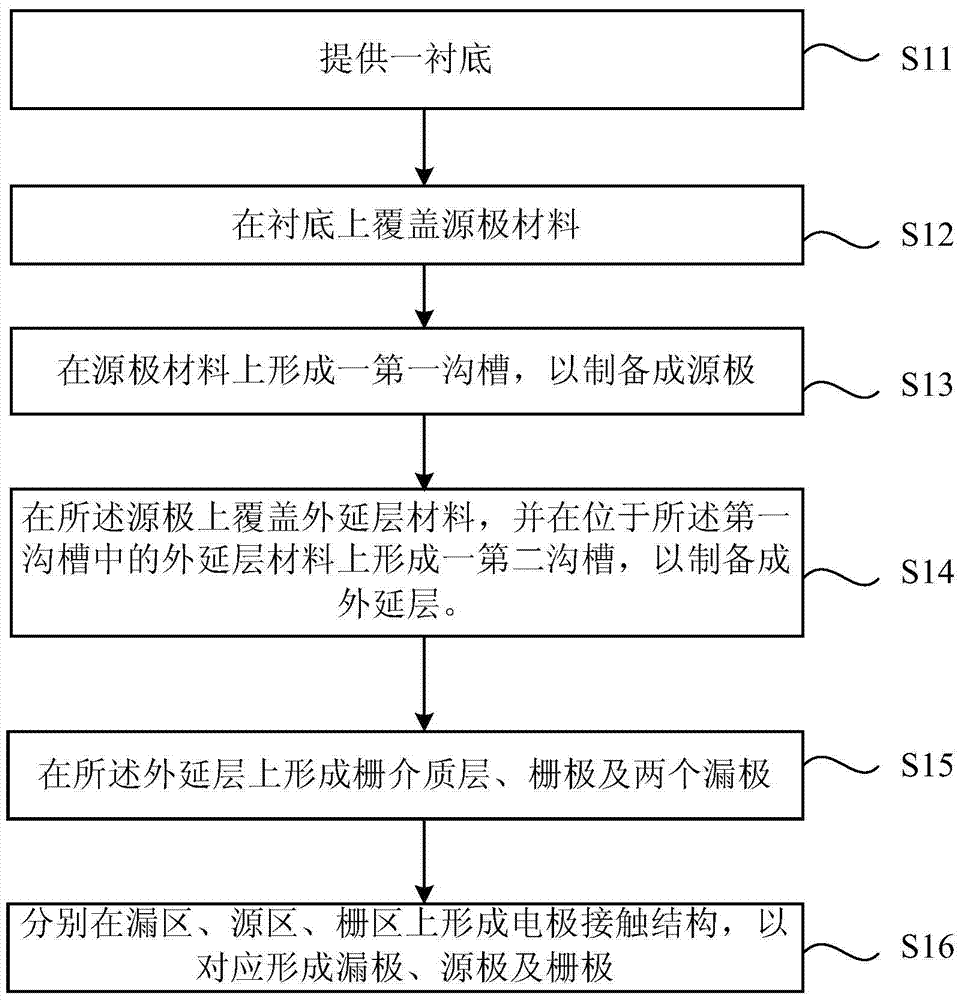

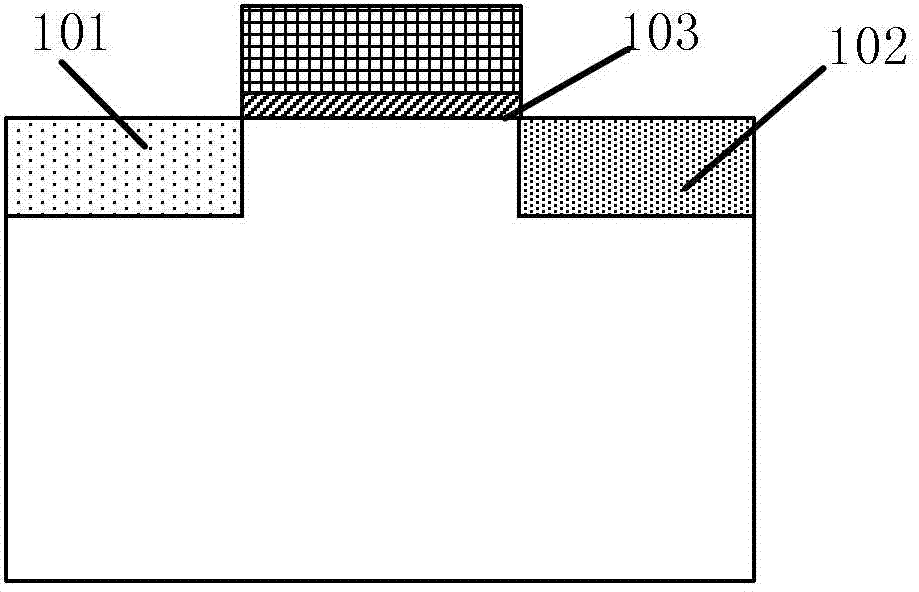

Provided are a vertical tunnelling field-effect transistor and a preparation method therefor. The vertical tunnelling field-effect transistor comprises: a source region (1), a first epitaxial layer (2), a gate dielectric layer (3), a gate region (4) and two drain regions (5). A first groove (11) is provided in the source region. A second groove (21) is provided on the first epitaxial layer, and the first epitaxial layer forms a tunnelling channel between the gate region and the source region. Both the gate dielectric layer and the gate region are provided in the second groove. The two drain regions are respectively provided at two opposite sides outside the second groove. Tunnelling can occur in conduction electrons in an area, overlapped with the gate region, of the first groove of the source region, i.e. an overlapping area between the source region and the gate region is enlarged using the first groove, so that a tunnelling area is enlarged. The first epitaxial layer can form the channel between the gate region and the source region, which involves linear tunnelling, and when the electric field direction of the gate region and the electron tunnelling direction of the source region are on the same line, the tunnelling probability is high, thereby improving a tunnelling current.

Owner:HUAWEI TECH CO LTD

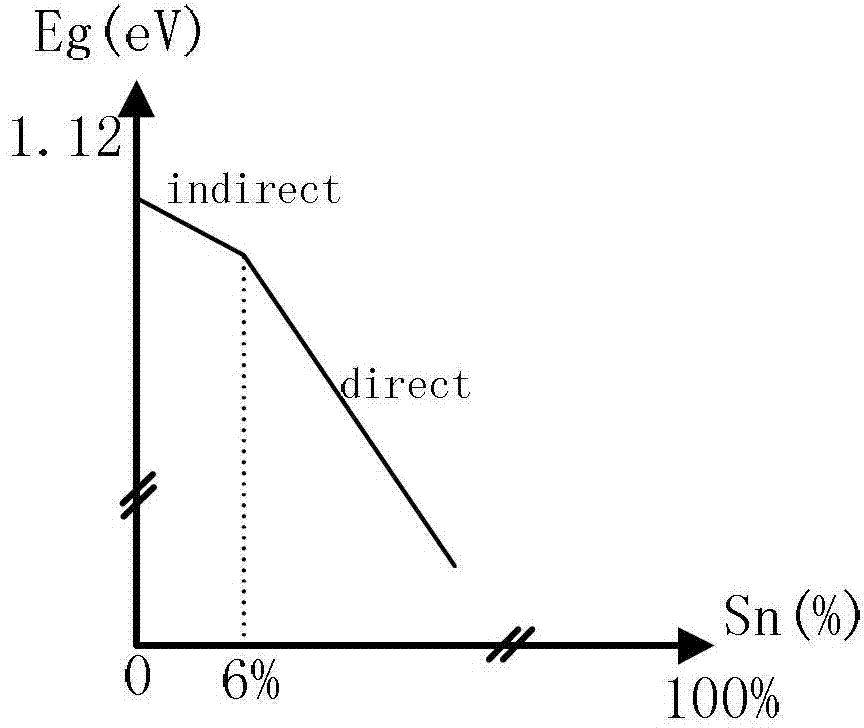

Germanium tin tunneling field effect transistor and preparation method thereof

InactiveCN102810555BSolve the problem of insufficient drive currentIncrease drive currentSemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentPower flow

The invention discloses a germanium tin tunneling field effect transistor and a preparation method thereof. The germanium tin tunneling field effect transistor comprises a germanium tin film layer, a source region, a drain region, a channel region and a grid stack region which are formed on a substrate of a germanium semiconductor, and the substrate of the germanium semiconductor. The germanium tin tunneling field effect transistor is prepared on the germanium tin film layer growing on the substrate of the germanium semiconductor; the tin content of the germanium tin film layer is regulated in the growing process, and along with increase of the tin content, the forbidden bandwidth of the germanium tin film layer decreases all the time; due to decrease of the forbidden bandwidth of the germanium tin film layer, the tunneling width decreases and the tunneling current obviously increases; and conversion of an indirect band gap into a direct band gap (about 6% of tin) also increases the tunneling current, so that the germanium tin tunneling field effect transistor can increase the driving current significantly, thereby effectively solving the problem of insufficient driving current of the conventional tunneling field effect transistor.

Owner:PEKING UNIV

A lattice mismatched multijunction solar cell

ActiveCN110224036BAvoid mismatchInhibited DiffusionNanotechnologyPhotovoltaic energy generationLattice mismatchParticle physics

The invention provides a lattice mismatch multi-junction solar cell. The lattice mismatch multi-junction solar cell comprises at least one crystal lattice mismatch sub cell and a tunneling junction grown on the crystal lattice mismatch sub cell; the P-type doping functional layer of the tunneling junction is a C-doped p-type AlxGaAs layer / Zn-doped p type AlyInGaAs layer / C-doped p-type AlxGaAs layer, or after the C-doped p-type AlxGaAs layer / Zn-doped p type AlyInGaAs layer alternately grow for N periods, and then the superlattice structure of the C-doped p-type AlxGaAs is grown. A new structureis adopted to replace the C-doped p type (Al) InGaAs layer in the prior art, so that the problem of InGaAs lattice mismatch with the body material in the solar cell caused by suppression of In component access due to the doped reaction source halogen in the p type AlyInGaAs, so that the photoelectric conversion efficiency of the solar cell is improved.

Owner:YANGZHOU CHANGELIGHT