An ultra-thin channel trench tunneling field effect transistor

A tunneling field effect and transistor technology, which is applied in the direction of transistors, semiconductor devices, electrical components, etc., can solve the problems of reducing the short channel effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] In order to make the purpose, technical solution and advantages of the present invention clearer, the present invention will be described in detail below in conjunction with the accompanying drawings.

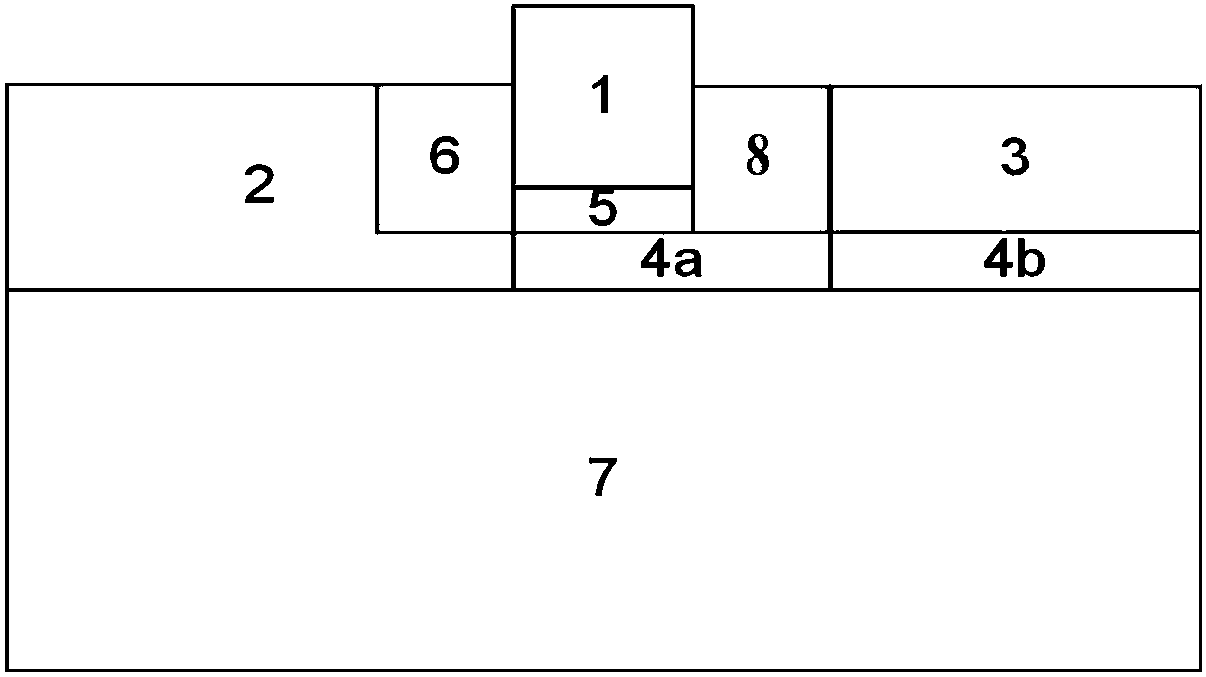

[0017] Such as figure 1 As shown, an ultra-thin channel groove tunneling field effect transistor is characterized in that it includes a gate 1, a source region 2, a drain region 3, a first channel region 4a, a second channel region 4b, and a gate dielectric layer 5. The first isolation layer 6 and the buried oxide layer 7; the gate dielectric layer 5 is provided under the gate 1, the gate 1 and the gate dielectric layer 5 are located on the first channel region 4a, and the first isolation layer 6 will The gate 1 is isolated from the source region 2, and the second isolation layer 8 isolates the gate 1 from the drain region 3; the thickness of the first isolation layer 6 and the second isolation layer 8 is not less than the thickness of the gate dielectric layer 5; the se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More