Tunnel field effect transistor with increased on state current

A technology of tunneling field effect and on-state current, which is applied in circuits, diodes, electrical components, etc., can solve the problems of high cost and incompatibility, and achieve the effect of low cost, large off-state current, and increased on-state current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

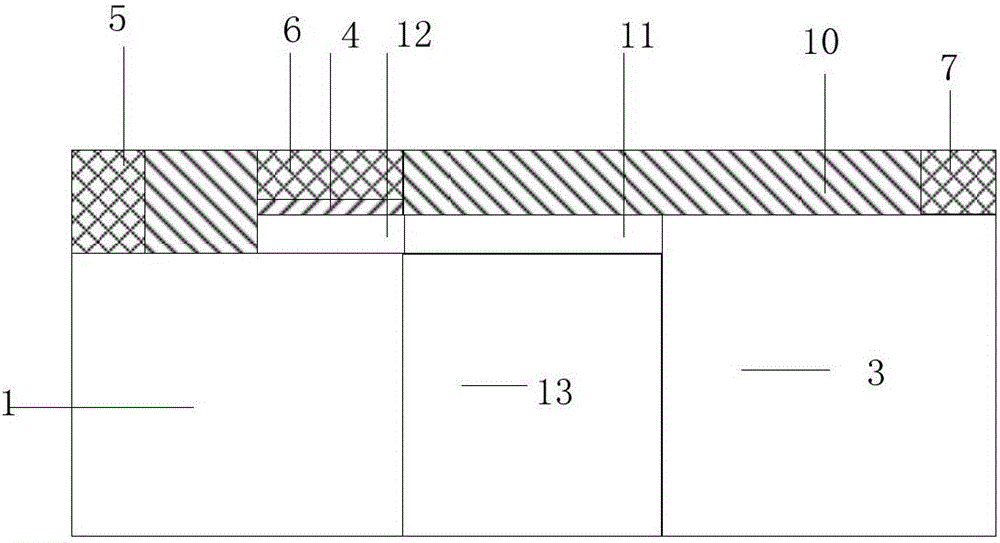

[0030] This example is for image 3 The structure of the TFET device with increased on-state current is shown, taking the N-type TFET fabricated on Si material as an example, and the insulating low-K dielectric is made of SiO 2 , Si, and vacuum N-type TFETs with three structures, the relative dielectric constants are 3.9, 11.5, and 1, respectively, and the high-K sidewalls use HfO with a relative dielectric constant of 22. 2 . Figure 5 Given the corresponding transfer characteristic curves under these three different dielectric constants, it can be known that the smaller the dielectric constant, the larger the on-state current, that is, the low-K insulating medium can significantly increase the on-state current of the TFET.

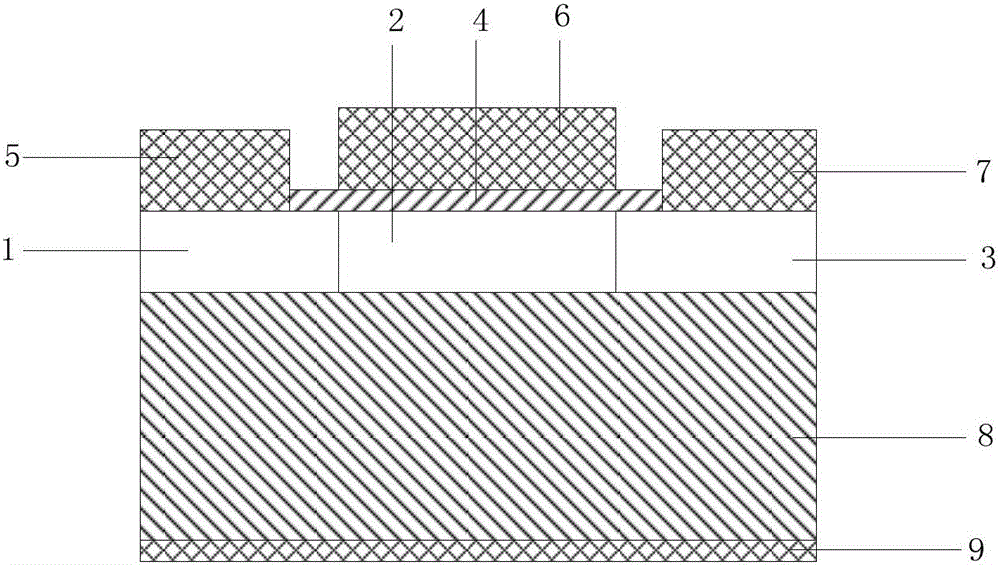

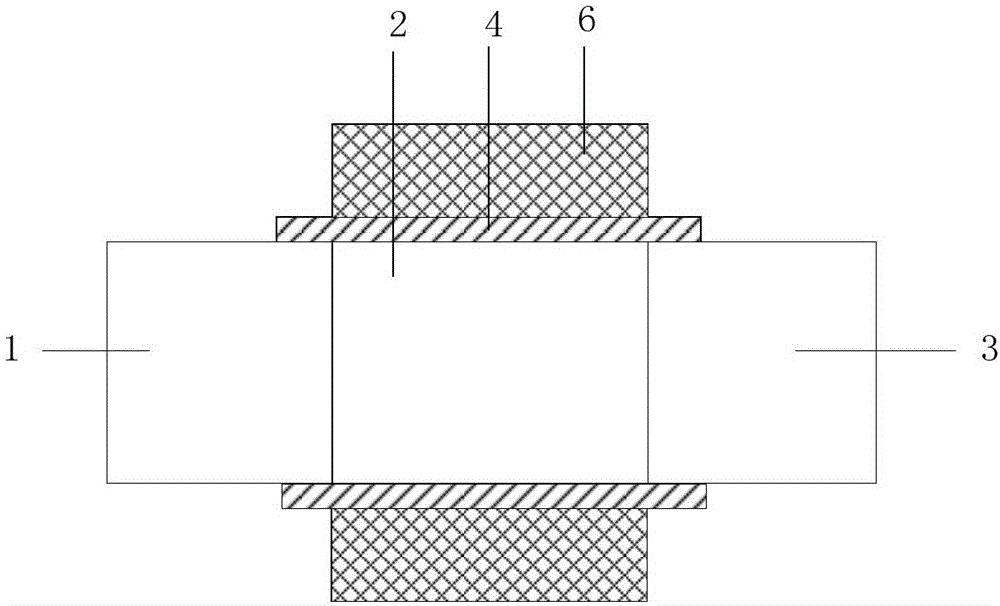

[0031] The embodiment includes source region 1 , drain region 3 , gate oxide layer 4 , source electrode 5 , gate electrode 6 , drain electrode 7 , spacer 10 , polysilicon 11 , intrinsic region 12 , and low-K dielectric region 13 . Firstly, bulk silicon...

Embodiment 2

[0036] This example is for Figure 4 The structure of the TFET device with increased on-state current shown is taken as an example of an N-type TFET fabricated on Si material. The insulating low-K medium adopts vacuum, and the relative permittivity is 1. To study the influence of the dielectric constant of the high-K sidewall (passivation film) on the on-state current, Example 2 produced three kinds of TFETs including sidewalls with different dielectric constants, and the sidewalls were SiO 2 、Si 3 N 4 , HfO 2 , and the dielectric constants are 3.9, 7.5, and 22, respectively.

[0037] Image 6 It uses Sentaurus software to use three different dielectric constants Figure 4 Structural simulation results. It can be seen that the greater the dielectric constant of the sidewall material, the greater the on-state current can be obtained.

[0038] The embodiment includes source region 1 , drain region 3 , gate oxide layer 4 , source electrode 5 , gate electrode 6 , drain elec...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More